## OEM BOARDS AND SYSTEMS DATA CATALOG

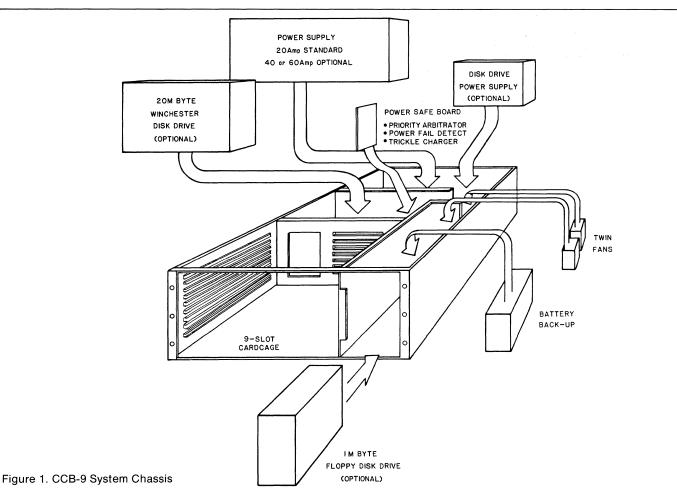

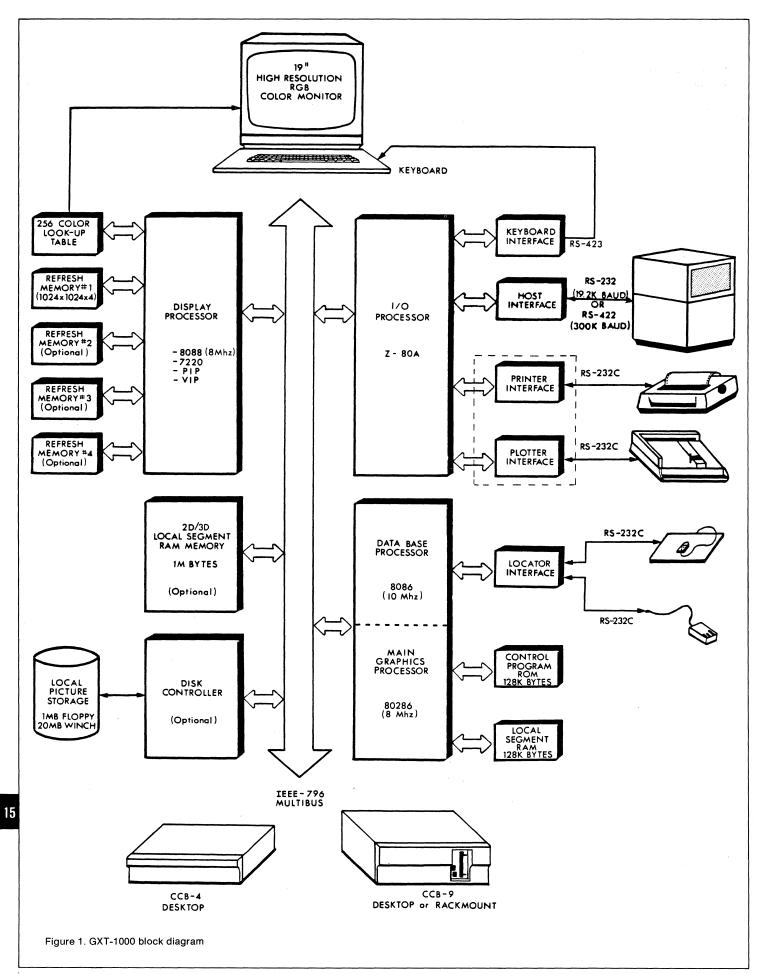

PRICE: \$25

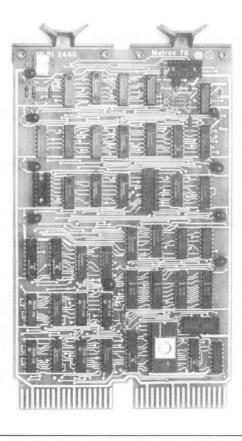

CAT-01-01 JUNE 1983

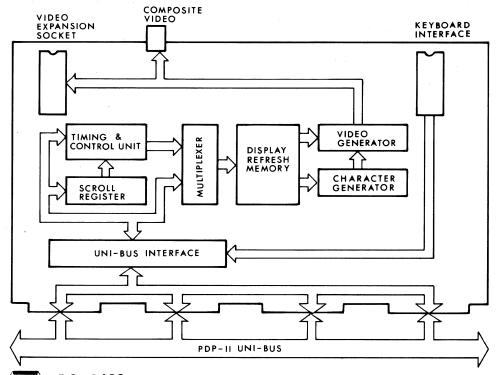

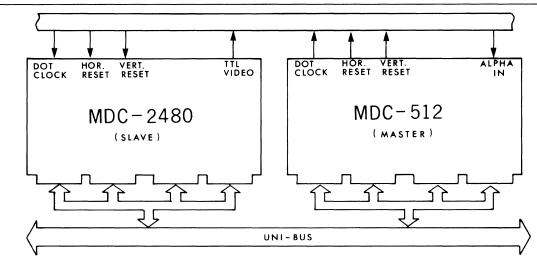

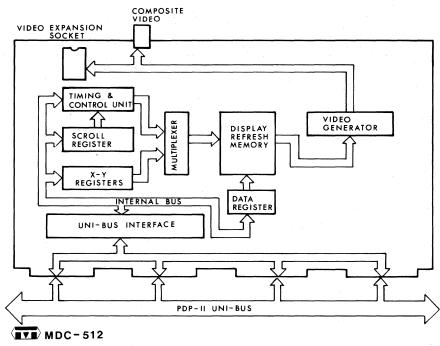

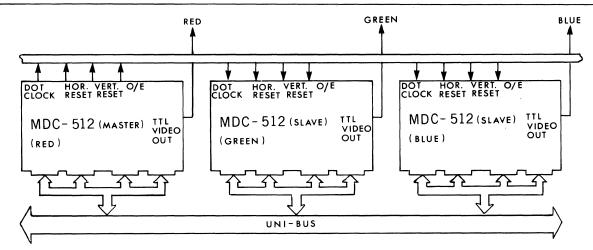

Matrox Electronic Systems Ltd reserves the right to make changes in specifications at any time and without notice. The information furnished by Matrox Electronic Systems Ltd in this publication is believed to be accurate and reliable. However, no responsibility is assumed by Matrox Electronic Systems Ltd for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of Matrox Electronic Systems Ltd.

## TABLE OF CONTENTS

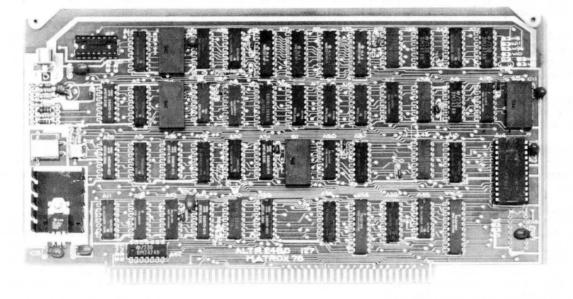

| QUALITY ASSURANCE                                                      | SECTION      | , i |

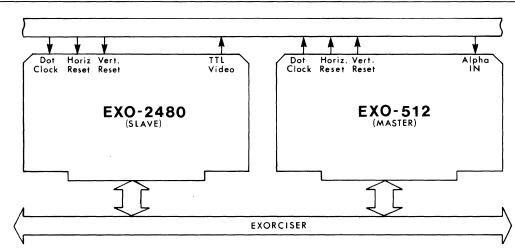

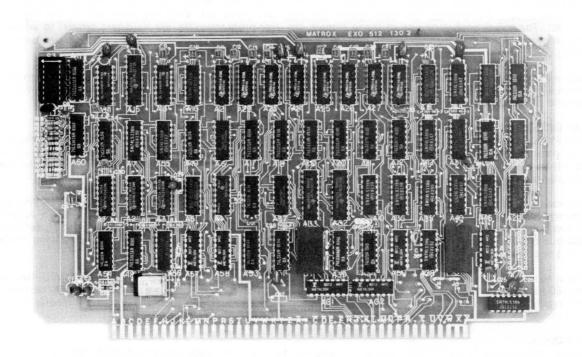

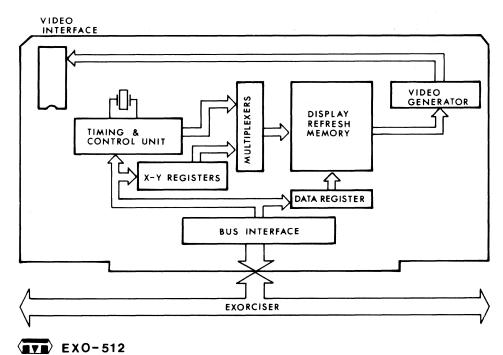

|------------------------------------------------------------------------|--------------|-----|

| CUSTOM CAPABILITY                                                      | SECTION      | ii  |

| PRODUCT INDEX                                                          | SECTION      | ĨĬĬ |

| MULTIBUS VIDEO BOARDS                                                  | SECTION      | 1   |

| Q-BUS (LSI-11) VIDEO BOARDS                                            | SECTION      | 2   |

| UNIBUS (PDP-11) VIDEO BOARDS                                           | SECTION      | 3   |

| STD-BUS VIDEO BOARDS                                                   | SECTION      | 4   |

| S-100 BUS VIDEO BOARDS                                                 | SECTION      | 5   |

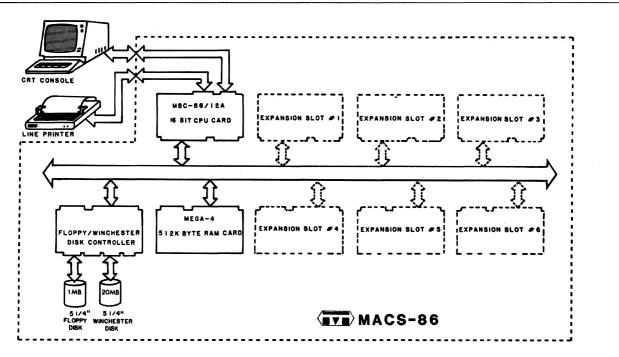

| EXORCISER BUS VIDEO BOARDS                                             | ···· SECTION | 6   |

| SPECIAL PURPOSE VIDEO BOARDS                                           | ··· SECTION  | 7   |

| VIDEO CONTROLLER MODULES                                               |              | 8   |

| SINGLE CHIP LED DISPLAY CONTROLLERS                                    | SECTION      | 9   |

| CRT MONITORS AND VIDEO ACCESSORIES                                     | SECTION      | 10  |

| MULTIBUS CPU BOARDS                                                    | SECTION      | 11  |

| MULTIBUS MEMORY, DISK CONTROLLER, COMMUNICATIONS, AND ACCESSORY BOARDS | SECTION      | 12  |

| CARDCAGES, DISK DRIVES, AND KEYBOARDS                                  | SECTION      | 13  |

| OEM COMPUTER SYSTEMS                                                   | SECTION      | 14  |

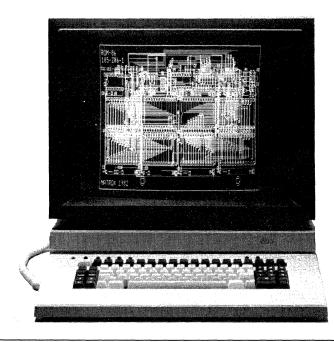

| GRAPHICS TERMINALS                                                     | SECTION      | 15  |

| GRAPHICS SOFTWARE                                                      | SECTION      | 16  |

| APPLICATION NOTES                                                      | APPENDIX     | A   |

| ORDERING INFORMATION                                                   | APPENDIX     | В   |

Figure 1. Matrox 27,000 square foot production facility in Montreal, Canada.

### INTRODUCTION

Matrox is a world leader in the design and manufacture of computer graphics boards and systems. The company is one of the pioneers in raster scan graphics, having been manufacturing video and computer systems for OEM's for over seven years.

### PRODUCTS

The original Matrox product offering consisted of a series of Video RAM modules providing simple inexpensive displays for OEM applications. These video modules were so successful, that they still remain as viable products today.

With the introduction of standardized bus architectures in the late 70's, the Matrox product line grew to include several "board" level offerings. Matrox video boards are available for a number of industrial buses including Multibus, Q-Bus, Uni-Bus, STD-Bus, S-100 bus and Exorcisor bus.

As the company's expertise in graphics developed, marketing opportunities for complete graphics systems led Matrox to expand the Multibus product line to include CPU boards, memory boards, communication controllers, disk controllers, and Multibus cardcages.

Matrox currently markets a complete line of boards, cardcages, color monitors, keyboards and complete turnkey color graphics terminals and systems.

Future growth for the company will come from new products. Matrox will continue to set the pace in the development of high resolution high performance video boards and systems, and will expand its software and service offerings to support the future needs of a growing base of customers.

#### FACILITIES

Matrox was founded in 1976. The company currently employs about 200 people in two Montreal based plants and a New York based distribution centre. A 22,000 square foot facility houses sales, R & D and administration. A second 27,000 square foot plant houses production, and production engineering.

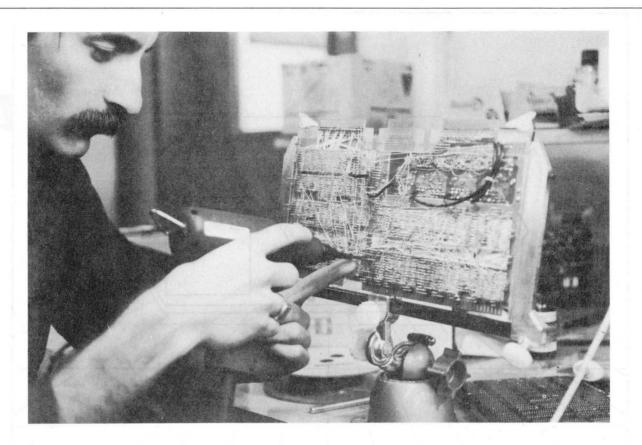

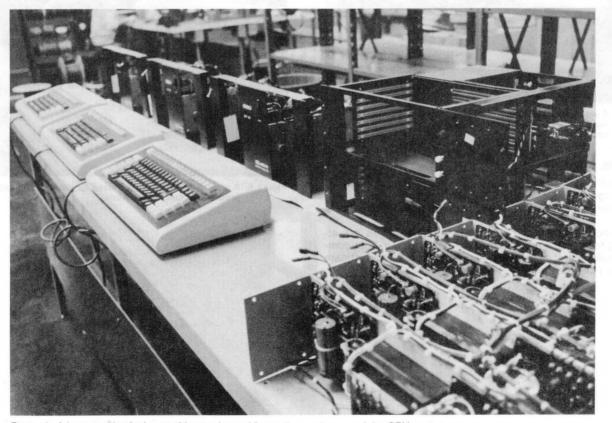

Figure 2. Board assembly area.

i

i-1

Figure 3. Matrox 22,000 square foot administration and engineering facility in Montreal, Canada.

### DISTRIBUTION

Matrox products are sold world wide through a network of representatives and distributors. Over 95% of the company's production is shipped to export markets including the United States, Europe, Australia and Japan.

Matrox is dedicated to serving the world marketplace, and will continue to emphasize solid relationships with the company's distributors in order to provide strong local support for its clients.

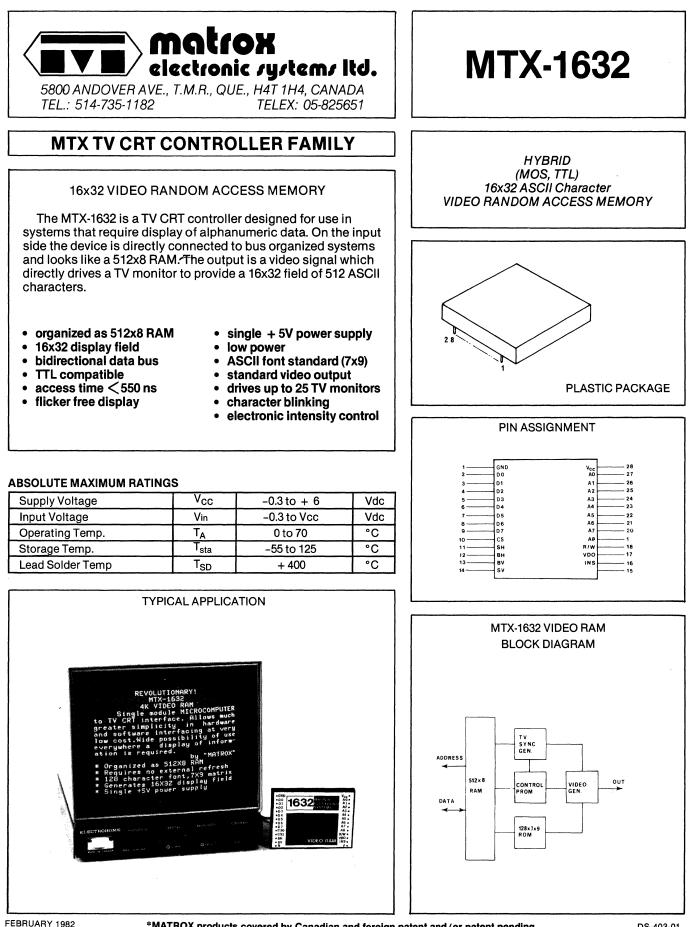

# Figure 4. Matrox MTX-1632 Video RAM is used in the console of this industrial robotics system. (photo courtesy of Graco Robotics Inc.)

### APPLICATIONS

Matrox products have provided a cost effective solution for a wide and varied number of applications. Some of the larger industries served by the company include:

- Process control

- CAD/CAM

- Medical Electronics

- Robotics

- Computer Aided Instruction

- Financial Displays

- Engineering Work Stations

- Geophysical/Seismic Displays

- Military Electronics

- Presentation Graphics

- Business Graphics

- Public Information Displays

Matrox typically manufactures board or system level products for OEM customers. OEM's incorporate additional hardware and applications software to suit their particular requirements.

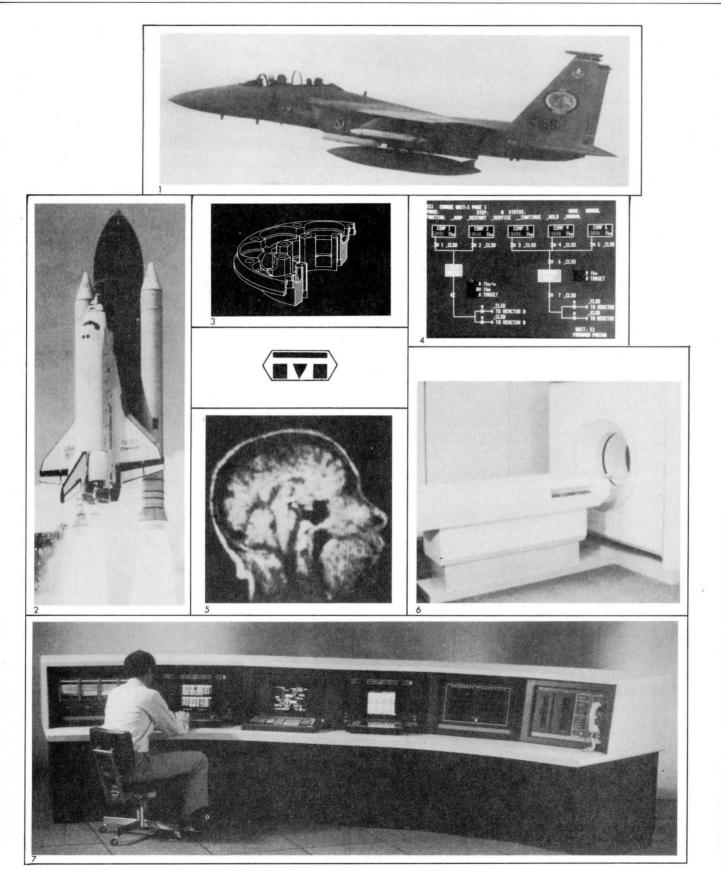

### Matrox OEM customers use Matrox products in a wide range of applications

- Matrox OEM customers use matrox products in a wide range of applications

1 & 2 Matrox products are used in a number of applications in the Aerospace Industry.

3 Matrox display controllers are capable of generating very high resolution color CAD/CAM images.

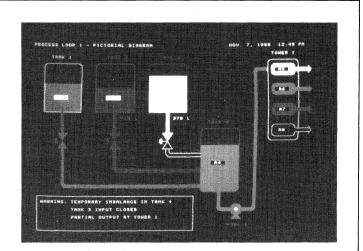

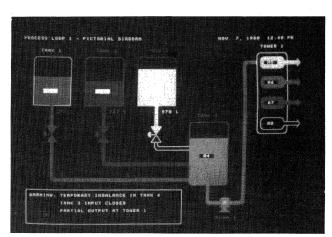

4 Process control displays can be generated using high resolution bit-mapped graphics or low cost character graphics with Matrox display controllers.

5 & 6 Matrox is a major supplier of graphic display controllers to the OEM Medical Electronics Industry.

7 Process control workstations use several computer controlled graphic displays.

## QUALITY ASSURANCE

Quality assurance means conforming to specifications.

### QUALITY IN DESIGN

Performance, reliability, and quality are all important considerations in the design process. Quality must be woven into the design fabric, not added to the finished design. A good designer considers the customer, the service technician, and the manufacturing staff when developing a new product.

At Matrox, we are strongly committed to excellence in design. Our component library lists all Q.A. approved parts and approved sources for those parts. Much emphasis is placed on second source components. All new engineering designs are tested, at the prototype level, with complete sets of integrated circuits from several manufacturers. Engineering prototypes are submitted to an extensive series of tests which include: functional, temperature, and humidity testing, as well as a full 200 hour dynamic burn-in at 60°C.

### QUALITY IN PROCUREMENT

To ensure the reliability of our products, we must demand quality from our suppliers. Matrox works closely with reputable vendors to set up long term stable sources of supply. In the case of critical items, such as multilayer circuit boards, each approved vendor is visited at least once a year to ensure that their quality control measures are up to our standards.

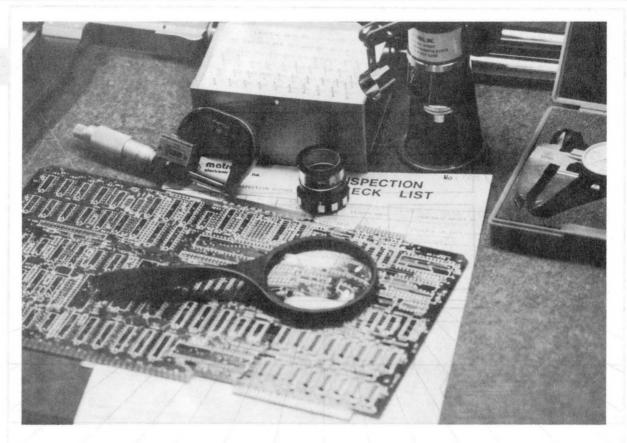

### **INCOMING INSPECTION**

Occasionally, vendors do slip up. It is the role of the Matrox Incoming Inspection Group to ensure that all supplies entering the manufacturing area do conform to specifications. All items are subjected to thorough electrical and mechanical analysis. Bare circuit boards are 100% checked for warpage, twists, size, registration, revision level, silkscreen, and proper plating before being allowed into the raw materials inventory. All digital integrated circuits are 100% inspected on a go/no-go GENRAD "hot-rail" IC tester which performs a complete electrical test at an elevated temperature.

Any rejected materials are clearly tagged, logged, and turned over to a Management Review Board (MRB) for disposition. If one vendor consistently has rejects, the situation is flagged, and corrective action can be taken.

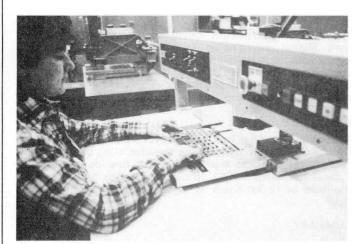

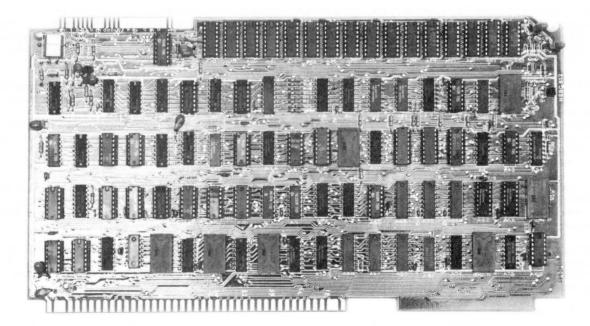

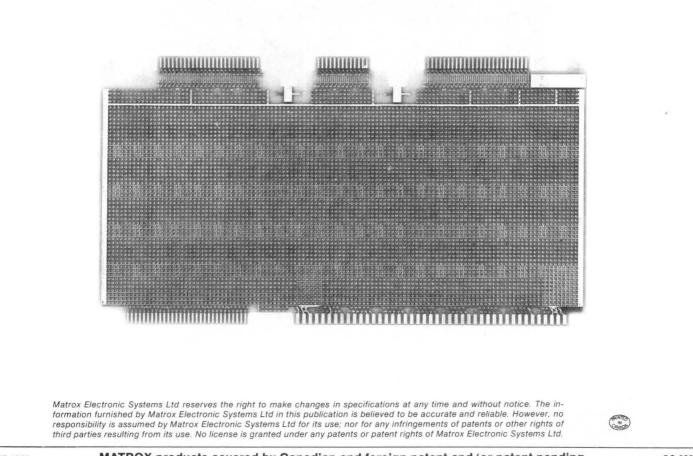

Figure 1. All digital ICs are tested at an elevated temperature on a "hot-rail tester" before entering raw materials inventory.

### QUALITY AS AN ATTITUDE

Quality in a manufacturing environment requires more than a series of inspection stations. Quality starts with people, and their attitude towards their work.

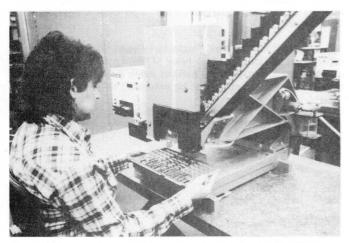

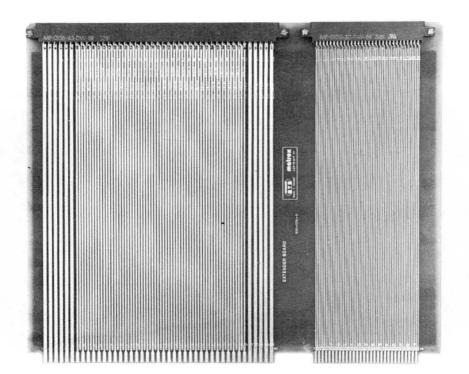

Figure 2. Semi-automatic insertion equipment simplifies assembly and reduces assembly errors.

Taking a lesson from the Japanese, the company has set up a Quality Circles program, whereby every worker has an opportunity to introduce improvements that pertain to his particular job in the manufacturing process.

Quality circles get people involved in their work, and allow them to see tangible results from their efforts. Quality products and pride in workmanship are closely correlated. Attitudes are an important factor in ensuring that products conform to specifications.

### QUALITY IN ASSEMBLY

Matrox has an enviable production record from the standpoint of quality control. A meticulous set of checks and balances between assembly and inspection has resulted in almost zero reworks, and a defective goods return rate of less than 1%.

Figure 3; DIP inserter automatically inserts, bends, and clips IC leads to the proper length.

Our excellent quality record is due in part to a substantial investment in automatic assembly equipment including: DIP insertors, component insertors, lead forming equipment, pin insertors and a wave soldering machine. The automatic equipment is ideal for manufacturing large quantities of product.

Soldering is a very important stage in the manufacturing process. Matrox technicians thoroughly inspect the wave solder machine daily and measure solder contaminant levels on a monthly basis. Wave soldering consistently turns out excellent soldering results because every board is preheated to the correct temperature, and passed through a flux bath just prior to entering the wave. After soldering, all boards are cleaned in a freon bath and carefully inspected for flaws.

All of the production personnel involved with soldering are required to attend and pass a comprehensive course on soldering techniques. Also, each assembler is provided with a "workmanship standards" manual which identifies, using large color pictures, what is and is not acceptable for a solder joint. The workmanship manual is based on the Martin Marrietta standards for the aerospace industry.

Figure 4: All Matrox boards pass through a wave solder machine which turns out consistent excellent results.

### INSPECTION

After each step in the assembly procedure, all products are fully inspected by an inspector who must stamp the board and the routing sheet with his unique marker. Boards are 100% inspected after insertion, after wave soldering, after touch-up, after test and after system test. Boards are assigned a serial number immediately after wave soldering, thus allowing complete inspection and test records to be maintained throughout the manufacturing process.

### QUALITY IN TEST

Every Matrox product undergoes two extensive functional tests and a 48 to 72 hour dynamic burn-in at 60°C. Every board is functionally tested against a comprehensive set of minimal performance specifications, which include normal, low voltage, and high voltage checks.

Initial testing is performed on a Zentehl "bed of nails" tester which provides a diagnostic printout for every board. The Zentehl tester identifies 95% of all faults on all cards. After the initial test, any faults are repaired, the board is retested, and is then sent to burn-in.

After burn-in, a comprehensive systems test is performed to identify any infant mortality problems. If a fault is found, the card is again burned-in and recycled through the systems test.

### DOCUMENTATION AND TRACEABILITY

Despite an extremely rigorous test and inspection program, some number of products do reach the customer with a problem. It is extremely important that problems discovered both in the field and in the plant be properly identified, so that remedial action can be taken. To ensure traceability of problems, Matrox keeps comprehensive records on each individual product shipped (referenced by serial number). These records provide a log of all of the assemblers, inspectors, and test technicians who worked on the product, as well as a listing of any faults found in the production of that product. A summary of field repairs its analyzed every month, so that any trends can be identified. If a large number of faults appear to be associated with a particular assembler or a particular test jig, corrective action is taken.

Similarly, for all batches of new materials coming into the plant, records are maintained for the incoming inspection test results. If a problem appears to be associated with a particular batch of components, that batch and the supplier of the parts can be identified.

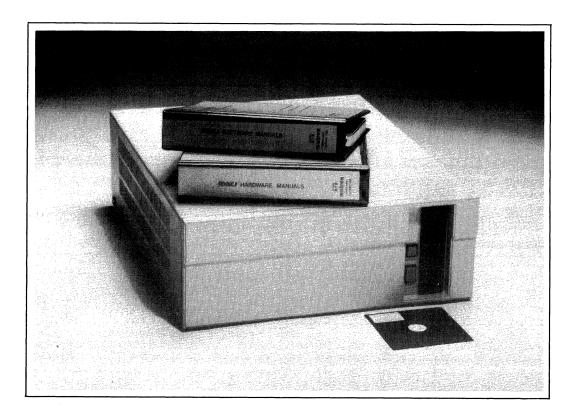

Another important quality consideration is the standard product documentation shipped with every production unit. Each product is accompanied by a comprehensive manual and a shematic diagram reflecting the proper ECO revision level. If any interim PMB's (product modification bulletins) have been implemented, a copy of the PMB is also shipped with the unit. Every product is clearly identified as to both ECO revision level and PMB level.

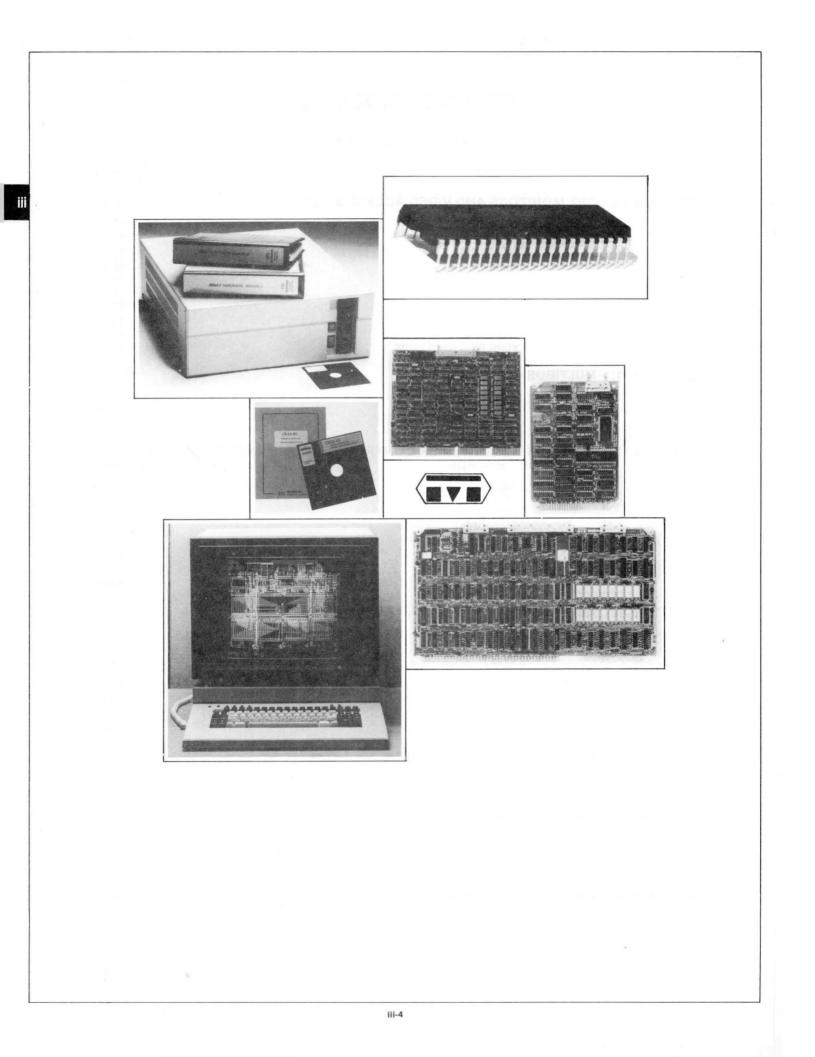

Figure 5: Matrox product documentation is complete and accurate. All documentation is controlled in-house.

### WARRANTY

Matrox guarantees the functionality of every manufactured item with a six month all inclusive parts and labor warranty. This warranty can be extended to one or even two full years for volume OEM customers.

### AFTER SALES SUPPORT

To assist customers in integrating our products into their systems, Matrox maintains an Applications Engineering Group. These applications engineers work with customers in setting up, testing, and trouble shooting Matrox products. Over 50% of all perceived quality problems can usually be isolated and corrected over the telephone.

### RELIABILITY

Reliability is another important aspect of Quality Assurance. Careful attention to detail in the manufacturing cycle assures that Matrox products enjoy a long fault-free life in the field. Typical calculated MTBFs on complex Matrox boards are on the order of 12,000 hours. MTTRs are typically less then one hour.

### SUMMARY

Quality assurance means conforming to specifications.

Matrox has an excellent quality record which boasts less than a 1% return rate of defective goods. This performance is achieved by people, who are dedicated to precision and perfection in what they do.

Quality can be achieved only by careful attention to detail at all stages of the manufacturing process. At Matrox, quality is a primary consideration in the design process, in parts procurement, in incoming inspection, in assembly, in inspection, and in test. Every product shipped by Matrox is required to pass two independent comprehensive sets of functional tests and a 48-72 hour burn-in at 60°C. When a product is allowed into finished goods inventory, we guarantee that it fully conforms to specifications.

In order to correct problems on that fraction of a per cent of units that do fail in the field, Matrox maintains comprehensive records at all stages of the manufacturing process. These records provide the traceability necessary for proper feedback to the production group. Also, a well staffed Applications Engineering Group is employed to assist in fault diagnosis and field repairs.

The realiability of Matrox products is born out both by theoretical calculations (12,000 hour MTBF typical) and by field experience. Matrox stands behind every product with a comprehensive warranty that can be extended to two full years.

Quality does not stop when the product is shipped. Customer support ensures that Matrox products continue to meet specifications, in the field, for many years.

İİ

# **CUSTOM CAPABILITY**

## **CUSTOM CAPABILITY**

Matrox has extensive engineering expertise in both hardware and software for computer graphics systems. The company has done custom systems work for several Fortune 500 companies including McDonnell Douglas, General Electric, Philips, and Xerox. Our design ability, our experience, and our solid manufacturing capability permit Matrox to undertake complex projects with tight delivery schedules. Many of the company's

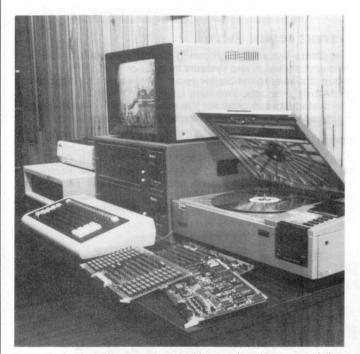

Figure 1. GF-18 graphics terminal is a custom product developed for McDonnell Douglas Corp. standard products were originally developed as custom designs for large customers. Where new designs are undertaken for products with a significant market beyond the immediate requirements of a single customer, Matrox will share the development costs, or forego completely any engineering charges.

An engineering staff of over 80 people are organized by function into 6 engineering groups; Hardware, Software, Systems, Production, Applications and Research & Development (R & D) Groups. Additional engineering support groups include Drafting and Technical Documentation. Matrox's strong committment to R & D has contributed substantially to the company's role as a technological leader in the computer graphics industry.

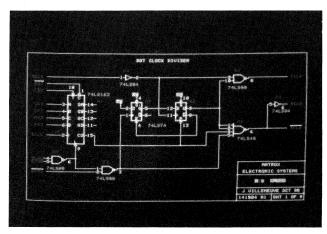

Figure 2. Matrox can generate complex multilayer board designs in 4 to 6 months.

### HARDWARE DESIGN

Matrox has a hardware design staff of over 30 experienced engineers. The company can develop entirely new board designs in about 4 to 6 months for prototypes, and 9 to 12 months for volume production.

For major contracts, a design team headed by a project manager is assigned to develop and maintain a schedule for the system. The schedule, which identifies all significant milestones and critical path items, is reviewed on a weekly basis in order to keep any deviations in check.

Matrox has considerable expertise in graphics design, CPU design, communications, and distributed processing systems.

### SOFTWARE DESIGN

Over ten experienced software engineers are employed in the Matrox Software Engineering Group. The company has extensive experience in assembly language programming for most popular microprocessors, as well as high level language programming in Fortran, C, and Pascal using a variety of operating systems including CP/M, CP/M-86, UNIX, RT-11, and VMS. Over 90% of all program development is done on a VAX-11/750 running under a VMS operating system.

At the heart of the company's new high resolution graphics system is a real-time multi-tasking operating system which supports multiple processors. The ROM-based MRTOS software was developed, in-house, in response to a need for realtime interactive system performance.

Much of the graphics systems work that Matrox has done has required that the software be compatible with the emerging CORE and GKS graphics standards. Matrox has also been involved in the proposed VDI (Virtual Device Interface), VDM (Virtual Device Metafile), and NAPLPS (North American Presentation Level Protocol Syntax) standards.

Figure 3. A VAX-11/750 is used for software development for most of the company's ROM and disk based software packages.

### SYSTEMS DESIGN

A separate Systems Engineering Group is responsible for all mechanical design and systems integration work. The systems group is also responsible for securing all regulatory approvals for Matrox products, including UL, CSA, DIN, VDE, and FCC. The systems group provides the experienced project management capabilities required for complex systems products.

### **PRODUCTION ENGINEERING**

A large well equipped Production Engineering Group is responsible for overseeing the introduction of new engineering designs to the production assembly line. The production engineering group designs all of the test fixtures and test procedures used in assembling, testing, trouble-shooting, and burning-in Matrox products.

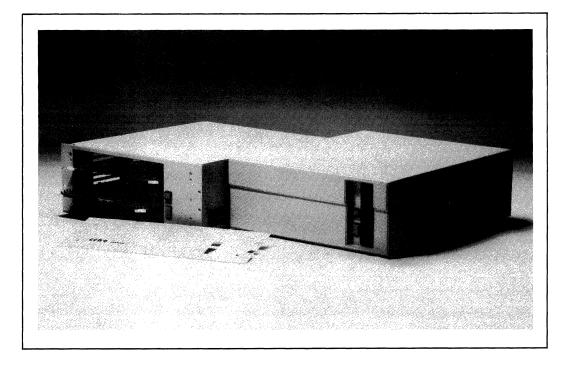

Figure 4. A large mechanical assembly area is used for custom systems work for OEM customers.

T

### APPLICATIONS ENGINEERING

An independent Application Engineering Group handles dayto-day technical liason with customers. This group is responsible for working with clients having special product requirements, to determine if these requirements can be satisfied by modifying a standard product. The applications group also provides customer training and trouble-shooting support.

### RESEARCH AND DEVELOPMENT

Matrox has maintained its technological leadership in the graphics business because of a strong committment to research and development. A separate R & D Engineering Group is responsible for the investigation of new developments in VLSI technology, video disk technology, new CPUs, graphics controllers, etc. New product designs can be done quickly and economically because the strengths and weaknesses of new technologies have already been identified through the R & D effort.

Figure 5. A video disk research project has produced a commercially viable 1.2 gigabyte archival storage system for picture, text, and audio data.

### MAKE VS. BUY

Many successful companies who have manufacturing capability are eager to build new products "in-house" if they cannot find an existing product that exactly meets their requirements.

The ''in-house'' approach is not always best. If you are attempting to source a product that is not generally in your company's main line of business, it is probably best to investigate outside custom designs. Matrox's graphics experience and capability have been built up over a long period of time, and the costs associated with acquiring this expertise have been substantial. Typically the overhead costs associated with in-house designs far outweigh the benefits of lower direct costs, unless significant quantities of the product can be guaranteed.

### SUMMARY

Matrox has extensive experience in custom board and system design. Many Fortune 500 companies have come to Matrox for custom products because of the company's engineering know-how, experience, and manufacturing capability to design, integrate, and produce top quality products in a short amount of time.

Most of the major products introduced by Matrox have originated as custom designs for our customers. This type of approach to product development has several benefits for both parties; the vendor is guaranteed at least one major customer for the product, and the customer is guaranteed a stable source of supply and minimal engineering costs.

Separate engineering groups are employed in hardware design, software design, systems work, production, applications, and R & D. Because of our strong engineering capability and our consistent product excellence, Matrox is regarded as a technological leader in the computer graphics field.

Matrox has the capability, the experience, and the resources to undertake custom graphics and microprocessor products. Talk to us about your special requirements before you commit to a Make/Buy decision.

Figure 6. A manual assembly area is used for low-volume standard products or custom products.

iif

# **PRODUCT INDEX**

|                    | PRODUCT INDEX                                                                                                                                           |                                                                                             |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| SECTION 1.         | MULTIBUS VIDEO BOARDS                                                                                                                                   | 1-1                                                                                         |

|                    | GXB-1000<br>RGB-GRAPH<br>VAF-512<br>RGB-ALPHA<br>BW-ALPHA<br>MSBC-QV3<br>MSBC-QV2<br>MSBC-2480<br>MSBC-2480<br>MSBC-512<br>NSBC-512<br>RGB-256<br>FG-01 | 1-3<br>1-15<br>1-23<br>1-31<br>1-35<br>1-39<br>1-47<br>1-51<br>1-55<br>1-59<br>1-63<br>1-67 |

| <b>SECTION 2</b> . | Q-BUS (LSI-11) VIDEO BOARDS                                                                                                                             | 2-1                                                                                         |

|                    | QRGB-GRAPH<br>QVAF-512<br>QRGB-ALPHA<br>QBW-ALPHA<br>MLSI-2480<br>MLSI-512<br>QRGB-256<br>QFG-01                                                        | 2-3<br>2-11<br>2-19<br>2-23<br>2-27<br>2-31<br>2-35<br>2-39                                 |

| <b>SECTION 3.</b>  | UNI-BUS (PDP-11) VIDEO BOARDS                                                                                                                           | 3-1                                                                                         |

|                    | MDC-2480<br>MDC-512                                                                                                                                     | 3-3<br>3-7                                                                                  |

| <b>SECTION 4.</b>  | STD-BUS VIDEO BOARDS                                                                                                                                    | 4-1                                                                                         |

|                    | STD-ALPHA<br>STD-2480<br>STD-256<br>STD-800                                                                                                             | 4-3<br>4-11<br>4-15<br>4-19                                                                 |

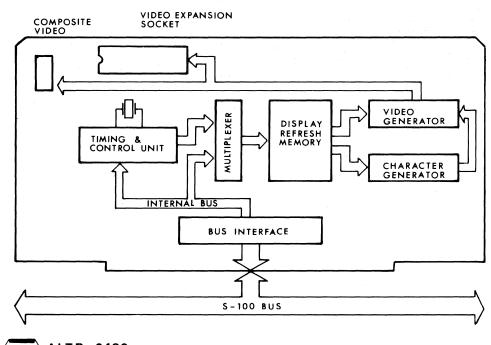

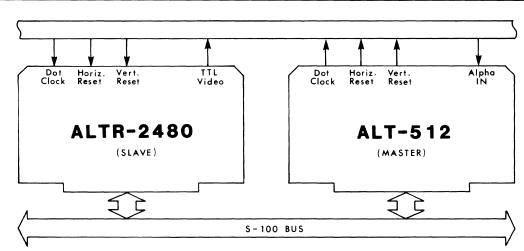

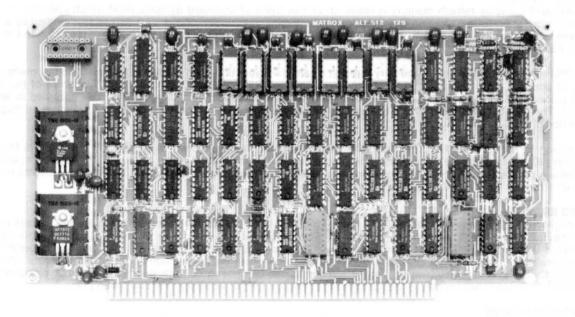

| SECTION 5.         | S-100 BUS VIDEO BOARDS                                                                                                                                  | 5-1                                                                                         |

|                    | ALTR-2480<br>ALT-512                                                                                                                                    | 5-3<br>5-7                                                                                  |

| SECTION 6.         | EXORCISER BUS VIDEO BOARDS                                                                                                                              | 6-1                                                                                         |

|                    | EXO-2480<br>EXO-512                                                                                                                                     | 6-3<br>6-7                                                                                  |

| SECTION 7.         | SPECIAL PURPOSE VIDEO BOARDS                                                                                                                            | 7-1                                                                                         |

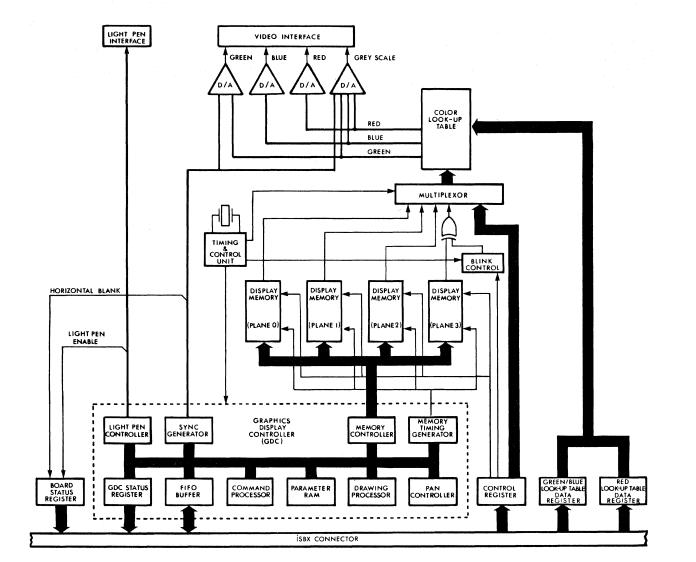

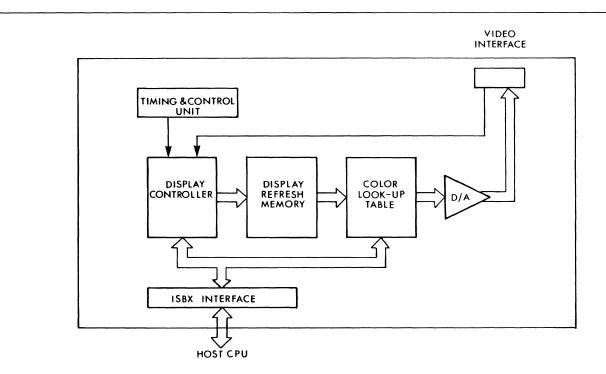

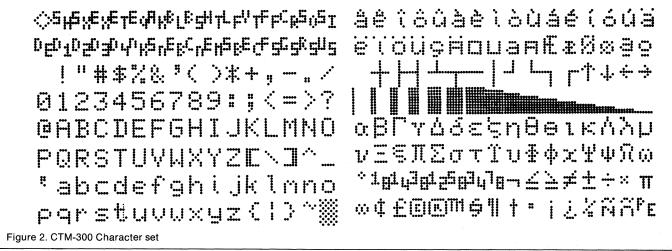

|                    | GT-600A<br>CTM-300/BRD<br>MSBX-800                                                                                                                      | 7-3<br>7-7<br>7-11                                                                          |

| <b>SECTION 8.</b>  | VIDEO CONTROLLER MODULES                                                                                                                                | 8-1                                                                                         |

|                    | MTX-816<br>MTX-1632<br>MTX-1632SL<br>PV-1<br>MTX-2064<br>MMD-2480<br>MMD-256                                                                            | 8-3<br>8-7<br>8-11<br>8-15<br>8-19<br>8-23<br>8-27                                          |

, iii

|             | PRODUCT INDEX Cont'd.                                                                                           |   |

|-------------|-----------------------------------------------------------------------------------------------------------------|---|

| SECTION 9.  | SINGLE CHIP LED DISPLAY CONTROLLERS                                                                             |   |

|             | MTX-A1<br>MTX-B1                                                                                                |   |

| SECTION 10. | CRT MONITORS AND VIDEO ACCESSORIES                                                                              | 1 |

|             | MCM-2000L<br>MCM-1000L<br>MCM-1014L<br>MCM-19L<br>MCM-14L<br>MEC-12A<br>MCRT-9/14<br>LP-600<br>PLL-01<br>CABLES |   |

| SECTION 11. | MULTIBUS CPU BOARDS                                                                                             | 1 |

|             | MBC-86/12A<br>PBC-80<br>ZBC-80                                                                                  |   |

| SECTION 12. | MULTIBUS MEMORY, DISK CONTROLLER, COMMUNICATIONS AND ACCESSORY BOARDS                                           | 1 |

|             | MEGA-4<br>FFD-1<br>COM-1<br>MSBX-423<br>MSBX-422<br>ROM-86<br>PTB-2<br>BEX-1                                    |   |

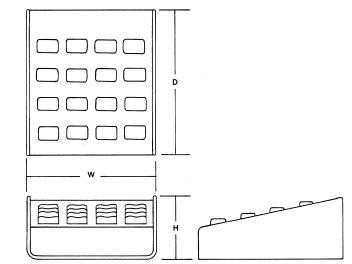

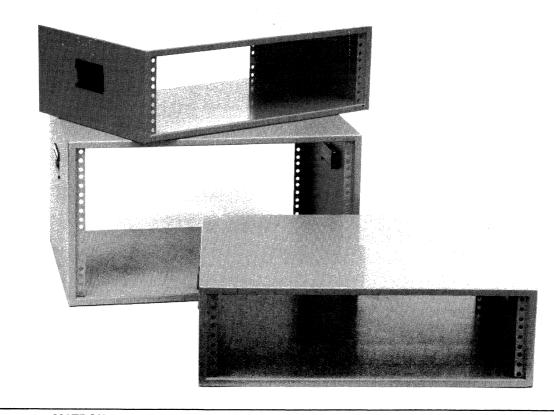

| SECTION 13. | CARDCAGES, DISK DRIVES, AND KEYBOARDS                                                                           | 1 |

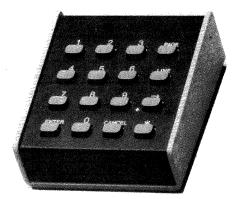

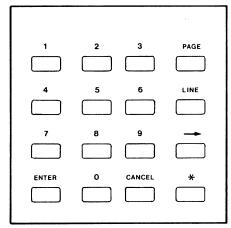

|             | CCB-9<br>CCB-4<br>CCB-7<br>KB-100<br>KB-300<br>KB-16<br>DF-28<br>SYS-CAB                                        |   |

| SECTION 14. | OEM COMPUTER SYSTEMS                                                                                            | 1 |

|             | MACS-86<br>MACS-10                                                                                              |   |

| SECTION 15. | GRAPHICS TERMINALS                                                                                              | 1 |

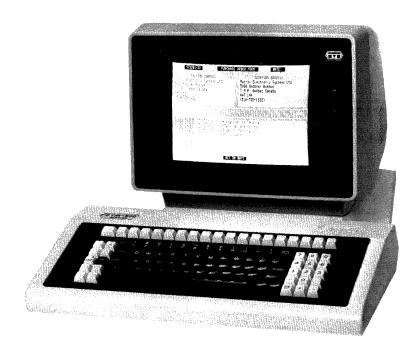

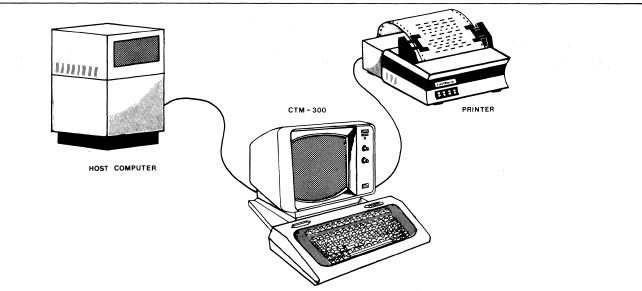

|             | GXT-1000<br>CTM-300<br>CTM-300/R                                                                                |   |

| SECTION 16. | GRAPHICS SOFTWARE                                                                                               | 1 |

|             | GRAS-80<br>QUARTO<br>PLOT-512                                                                                   |   |

iii

1

# **MULTIBUS VIDEO BOARDS**

### SECTION 1 MULTIBUS VIDEO BOARDS

| GXB-1000<br>2K x 2K Superhigh Resolution Color Graphics Board System for Multibus   | 1-3  |

|-------------------------------------------------------------------------------------|------|

| RGB-GRAPH<br>Vector Plot 512 x 512 Color Graphics Display Controller for Multibus   | 1-15 |

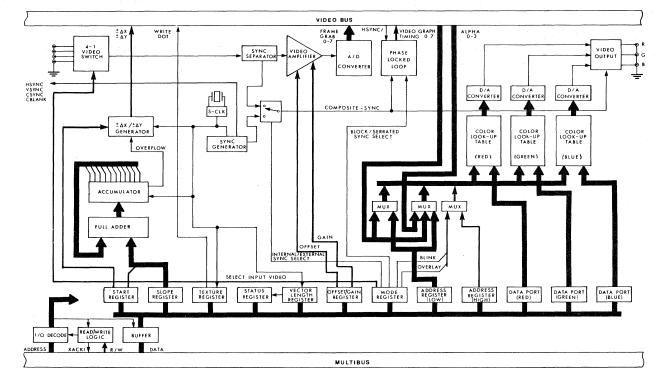

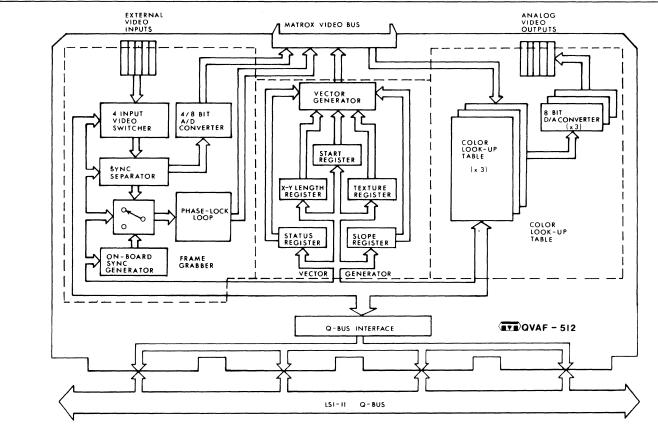

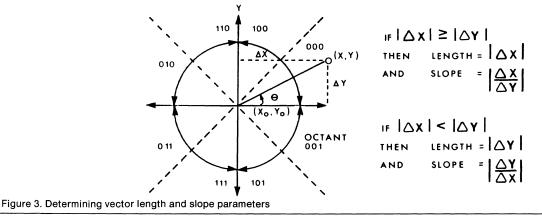

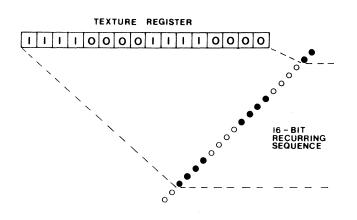

| VAF-512<br>RGB-GRAPH Video Input/Output Processor for Multibus                      | 1-23 |

| <b>RGB-ALPHA</b><br>Programmable Color Alphanumeric Display Controller for Multibus | 1-31 |

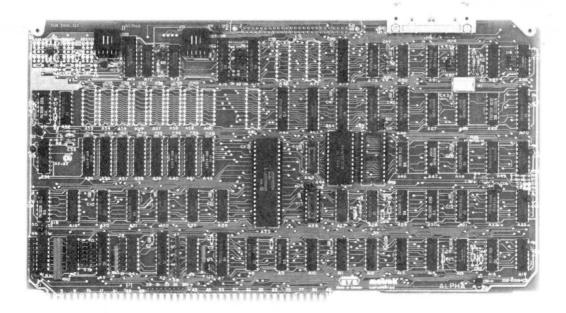

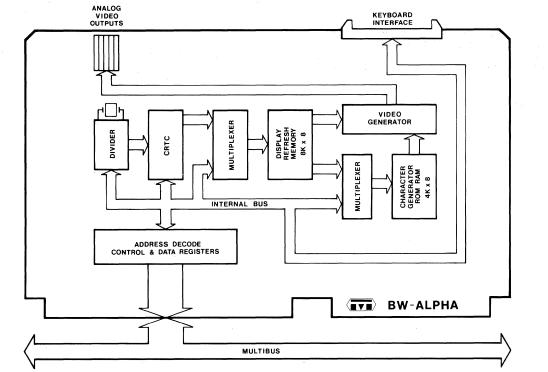

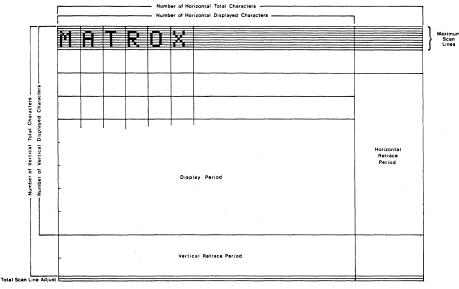

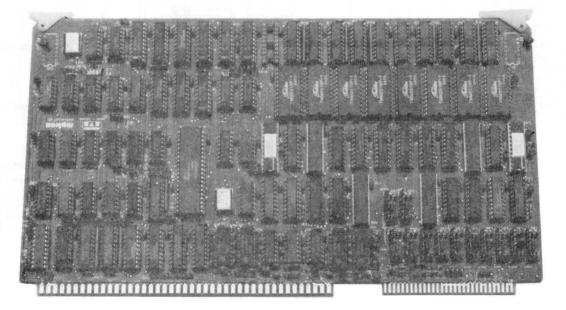

| <b>BW-ALPHA</b><br>Programmable B/W Alphanumeric Display Controller for Multibus    | 1-35 |

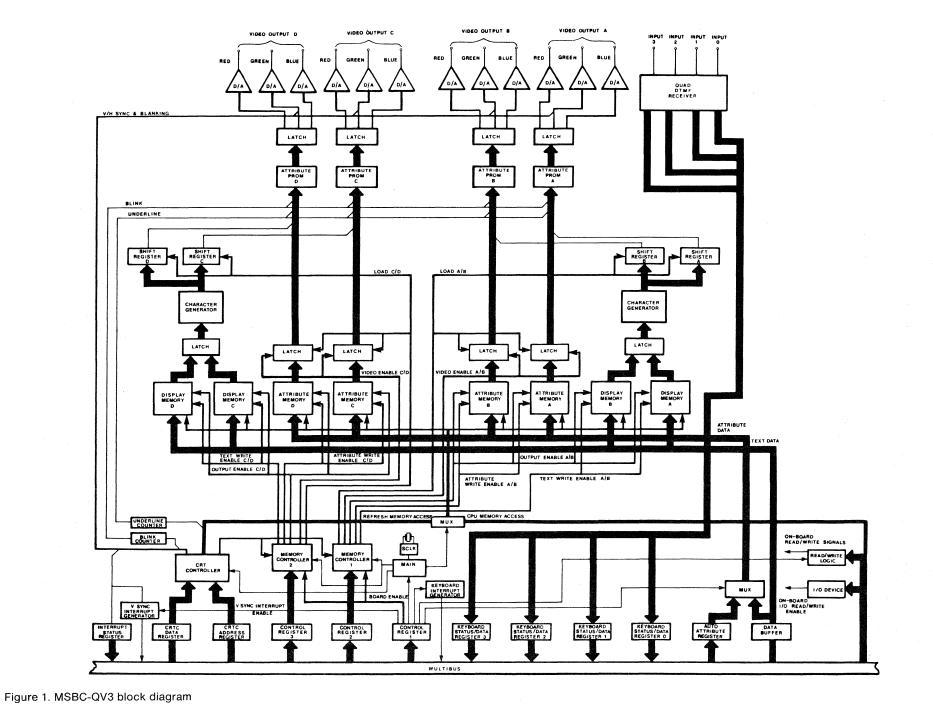

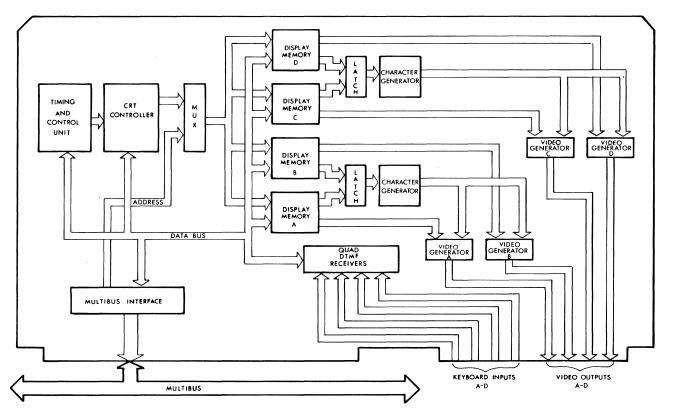

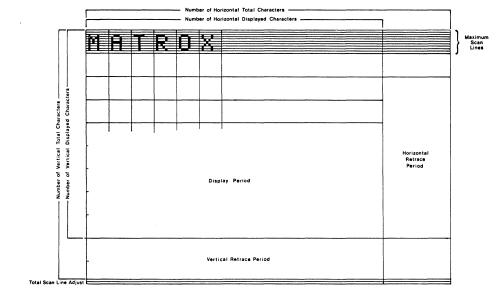

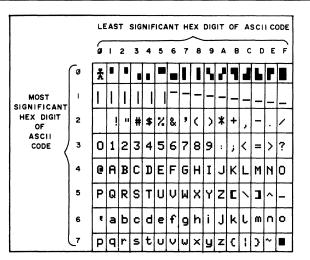

| MSBC-QV3<br>Quad Color Alphanumeric Display Controller for Multibus                 | 1-39 |

| MSBC-QV2<br>Quad Programmable B/W Alphanumeric Display Controller for Multibus      | 1-47 |

| MSBC-2480<br>24 x 80 Alphanumeric Display Controller for Multibus                   | 1-51 |

| MSBC-512<br>512 x 512 Graphics Display Controller for Multibus                      | 1-55 |

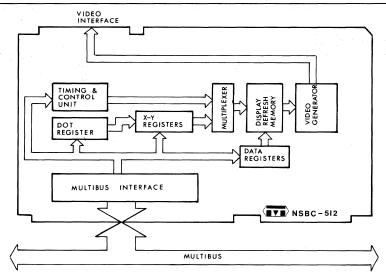

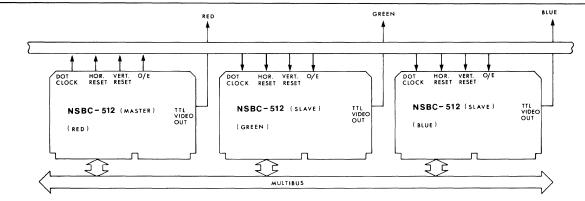

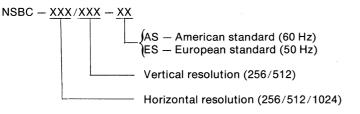

| NSBC-512<br>Vector Plot 512 x 512 Graphics Display Controller for Multibus          | 1-59 |

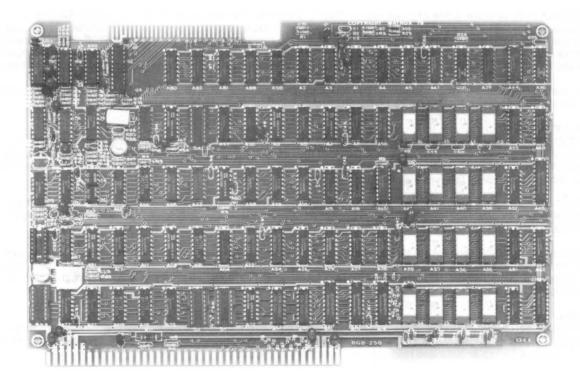

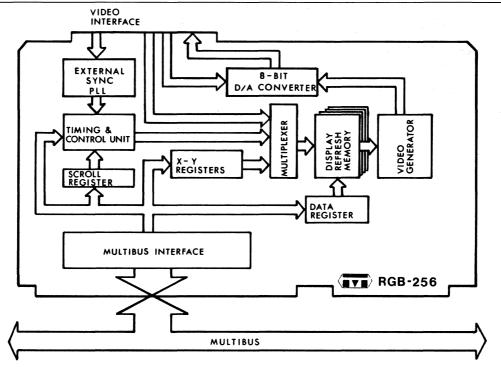

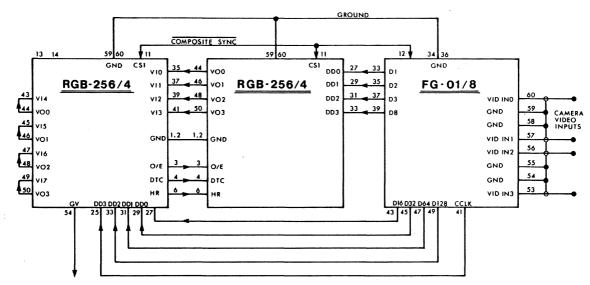

| <b>RGB-256</b><br>256 x 256 Color Graphics Display Controller for Multibus          | 1-63 |

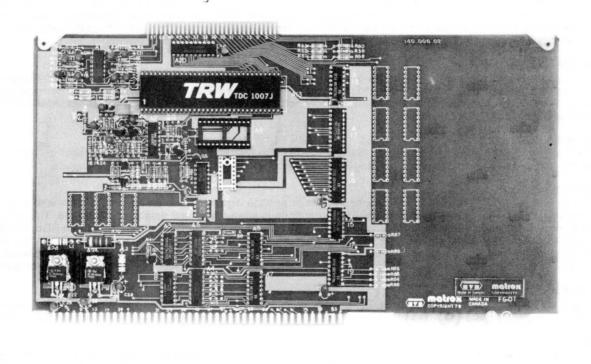

| FG-01<br>High Speed Video A/D Converter for Multibus                                | 1-67 |

5800 ANDOVER AVE., T.M.R., QUE., H4T 1H4, CANADA

TEL.:

514-735-1182

TELEX: 05-825651

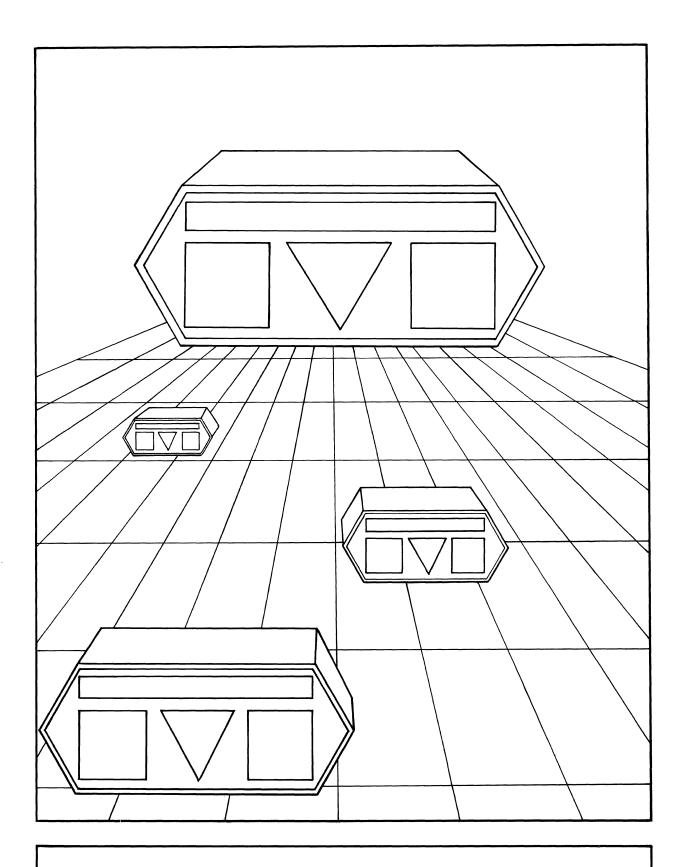

# **GXB-1000**

### 2K x 2K SUPERHIGH RESOLUTION COLOR GRAPHICS BOARD SYSTEM FOR MULTIBUS

- 2K x 2K read/write area

- 1600 x 1200 and 1024 x 768 display resolution

- 60 Hz noninterlaced/interlaced refresh

- 4, 8, 12, or 16 image planes (bits/pixel)

- Hardware vector generator (800 nsec/ pixel)

- 256 color look-up table

- Four pipelined on-board processors

- On-board 16 bit CPU (8088/5MHz)

- 32K byte graphics interpreter

- 2D primitives plus segments

- Flash preset, clear, pan, blink, pixel processor, raster ops, flash load

- Modular design

- Fully Multibus compatible

- Single +5V power supply

- Bus Master or Slave modes

The GXB-1000 is a two board Multibus based graphics system. The GXB-1000 provides the highest performance raster scan color graphics for an extremely low cost. By adding a simple custom software instruction translator in a high level language (C, Pascal, Fortran), the GXB-1000 can be used to build a powerful high resolution color system capable of interpreting any graphics terminal communications protocol. This feature enables the CAD/CAM user to upgrade his existing installation with the GXB-1000 color graphics display controller without changing existing data bases or application software.

Over 6 programmer years of Matrox software effort have gone into the development of the resident graphics interpreter, which recognizes over 256 graphics commands.

The latest state-of-the-art color raster graphics hardware and software are incorporated into the GXB-1000 boards. Advanced features include: 1600 x 1200 resolution, 60 Hz noninterlaced refresh, hardware vector and circle generators (800 nsec/pixel), on-board 16 bit CPU, look-up table, pixel processor, etc. A combination of the highest possible raster display resolution with ultrafast drawing speed yields the top performance required for CAD/CAM applications at the lowest possible cost.

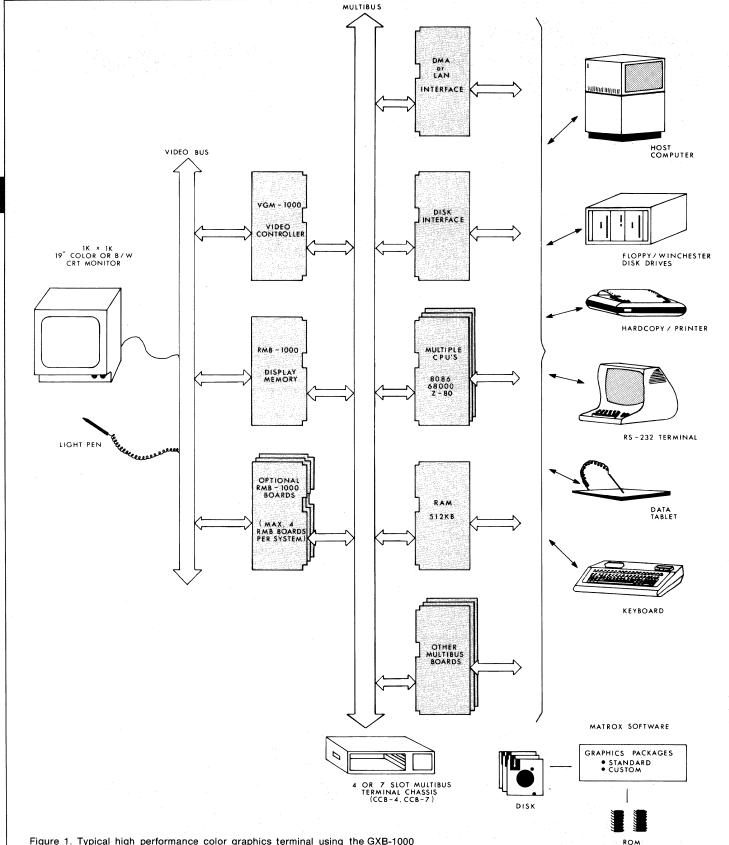

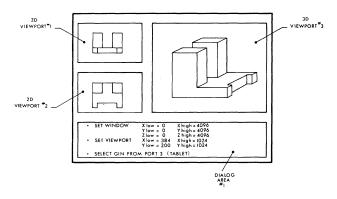

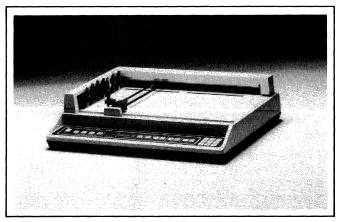

Figure 1. Typical high performance color graphics terminal using the GXB-1000

The GXB-1000 video board set is the basis of an extremely powerful and versatile graphics display system. Using additional boards available off-the-shelf from Matrox such as 8 or 16 bit CPUs (ZBC-80 [Z-80A], MBC-86/12 [8086/87], MRC-68K [68000]), 512K byte RAM (MEGA-4), floppy disk interface (FFD-1), plus DMA, ETHERNET, and other Multibus boards from other suppliers, the user can assemble a high perform-ance graphics system with minimal engineering effort, short development time, and low cost. Matrox supplied graphics software and accessories (CRT monitors, light pen, etc.) enable the OEM user to tailor system performance for a wide range of applications.

## **GXB-1000 FEATURES**

| Resolution:            | 1024 x 768 standard<br>1600 x 1200 optional<br>1280 x 1024<br>1024 x 1024                                                                                                                                                                                 | Multibus<br>Interface:                                                                                               | Memory board takes only +5V power<br>from the Multibus. VGM board fully con-<br>forms to Multibus specs.                                                                                                                                                      |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits/Pixel:            | (other resolutions are user-selectable)<br>4 bits/pixel standard<br>8, 12, and 16 bits/pixel optional                                                                                                                                                     | Metabus:                                                                                                             | The two boards are interconnected via three 50-pin ribbon cables at the top of each board (supplied).                                                                                                                                                         |

| R/W Area:              | Read/write memory is 1K x 1K standard<br>2K x 2K optional                                                                                                                                                                                                 | Pipeline<br>Processors:                                                                                              | Four on-board processors include 16 bit<br>CPU, pixel processor, video ECL proc-                                                                                                                                                                              |

| Refresh Rate:          | Noninterlaced or interlaced (50/60 Hz) all resolutions except 1600 x 1200 which is interlaced only.                                                                                                                                                       | On-Board CPU:                                                                                                        | essor, and hardware vector generator.<br>5MHz 8088 CPU with 32K of ROM, 4K                                                                                                                                                                                    |

| Figure Draw<br>Speed:  | 800 nsec/pixel min. (''snow'')<br>3.2 $\mu$ sec/pixel min. (retrace only)<br>includes vectors, arcs, circles, area fills,<br>and character draws.                                                                                                         |                                                                                                                      | RAM, and Multibus interface. Interprets<br>off-board display file through on-board<br>ROM interpreter (graphics mode). Can<br>also be used as system CPU executing<br>8088 code (direct mode).                                                                |

| Flash Preset<br>Speed: | 12 nsec/pixel. All pixels (on single or mul-<br>tiple surfaces) are preset to a fixed value<br>in one field (16 msec).                                                                                                                                    | Multibus Mode:                                                                                                       | On-board CPU executes graphics instruc-<br>tions as either Bus Master or Slave. In<br>Master mode, the 8088 CPU fetches in-                                                                                                                                   |

| Slice Draw<br>Speed:   | 50 nsec/pixel. 16 pixel horizontal (slices)<br>segments are written in one 800 nsec<br>write cycle. Used in alphanumeric mode<br>for character draws, window clear, fill,<br>marker, etc.                                                                 |                                                                                                                      | structions from an off-board RAM display<br>file. In Slave mode, the host transfers the<br>instructions from the display file to the<br>8088 CPU via an on-board FIFO buffer<br>through an on-board I/O port. Byte by<br>byte or 256 byte block transfers are |

| Flash Load<br>Speed:   | 12 nsec/pixel. 16 succesive horizontal<br>pixels in one bit plane are loaded in one<br>200 nsec memory cycle. Synchronous with<br>the display refresh. Used for high speed<br>load from external sources via Metabus.                                     | Pixel<br>Processor (PIP):                                                                                            | supported.<br>100 nsec cycle time processor for process-<br>ing pixel values. Used for pixel com-<br>plement, color offset, load, shift, etc. Pro-                                                                                                            |

| Raster OP<br>Speed:    | 6 $\mu$ sec/pixel for direct raster operations<br>(Bit Blitz) on raster rectangles. 2D trans-<br>form (translation, rotation, zoom/scale,<br>and reflection) and logic/arithmetic oper-<br>ations between source and destination<br>pixels are supported. | Video<br>Processor (VIP):                                                                                            | gram for PIP loaded by local 8088 CPU or<br>the user's CPU.<br>16 x 8 high speed ECL look-up RAM used<br>for color mapping and video processing.<br>Program for the VIP is loaded by the local                                                                |

| Preset Mask:           | Individual control of each bit plane by plane mask.                                                                                                                                                                                                       | Vector                                                                                                               | 8088 CPU or by the user's CPU.<br>High speed VLSI graphics processor gen-                                                                                                                                                                                     |

| Scroll:                | Smooth vertical scroll (by 1 pixel).                                                                                                                                                                                                                      | Generator:                                                                                                           | erates vectors, circles, arcs, rectangles,<br>characters, etc. at 800 nsec/pixel. Pro-<br>gram for the graphics generator is loaded                                                                                                                           |

| Shift:                 | Horizontal shift by 4 pixels.                                                                                                                                                                                                                             |                                                                                                                      | by the local 8088 CPU.                                                                                                                                                                                                                                        |

| Pan:                   | Scroll and Shift can be combined for a smooth two dimensional pan within the 2K x 2K area.                                                                                                                                                                | SOFTWARE SUPP                                                                                                        | ORT                                                                                                                                                                                                                                                           |

| Look-Up Table:         | 256 color look-up table for each 4 bit/<br>pixel surface.                                                                                                                                                                                                 | MIG-1<br>Graphics                                                                                                    | Local CPU with resident MIG-1 inter-<br>preter recognizes approximately 256 high                                                                                                                                                                              |

| Overlay Video:         | Any bit plane can be used for overlay func-<br>tions such as blink, alpha, cursors, etc.                                                                                                                                                                  | Package:                                                                                                             | level graphics commands. Included are<br>various figure draw commands, video ef-<br>fects, pan, clear, control, etc. The MIG-1                                                                                                                                |

| Cursors:               | Cross-hair or user-defined cursor for graphics. Underline cursor for alphanumer-<br>ics and dialog areas.                                                                                                                                                 | for interpreter is stored in El<br>accessed either by MA<br>from a data file or direct<br>a library table. MIG-1 sou | interpreter is stored in EPROM and can be<br>accessed either by MACRO commands<br>from a data file or directly by the CPU via<br>a library table. MIG-1 source code is avail-                                                                                 |

| Light Pen:             | Built-in interface detects the light pen<br>position to one pixel accuracy in<br>100 msec.                                                                                                                                                                |                                                                                                                      | able separately.                                                                                                                                                                                                                                              |

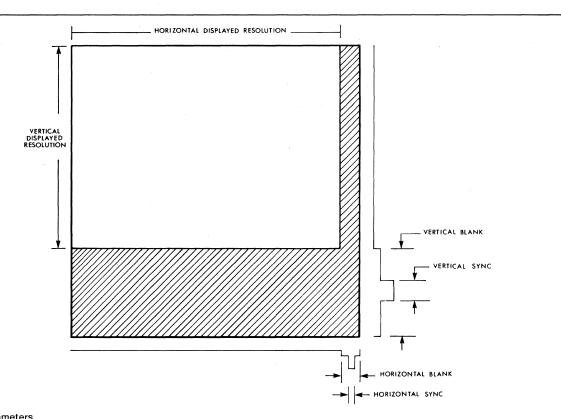

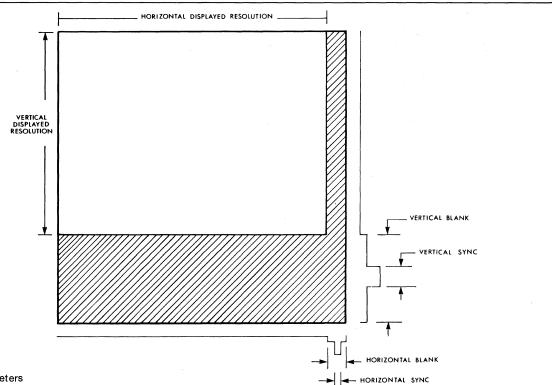

| Video<br>Baramotore:   | All video parameters including horizontal<br>and vertical syncs, blanks, frequency, and                                                                                                                                                                   | ACCESSORIES                                                                                                          |                                                                                                                                                                                                                                                               |

| Parameters:            | display format are user software program-<br>mable.                                                                                                                                                                                                       | CRT Monitors:                                                                                                        | Matrox supports a full line of 19" color<br>monitors for 1K x 1K resolution displays<br>with periodection displays                                                                                                                                            |

| Video Outputs:         | R,G,B color signals $1Vpp$ , $75\Omega$ with composite sync on green. Separate video signal connector.                                                                                                                                                    | Light Pen:                                                                                                           | with noninterlaced or interlaced refresh.<br>High speed ligh pen (LP-600).                                                                                                                                                                                    |

|                        |                                                                                                                                                                                                                                                           |                                                                                                                      |                                                                                                                                                                                                                                                               |

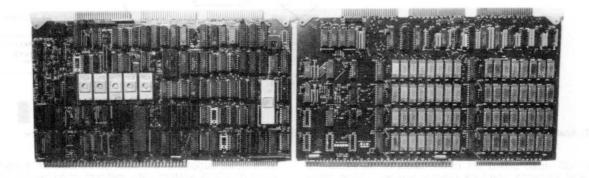

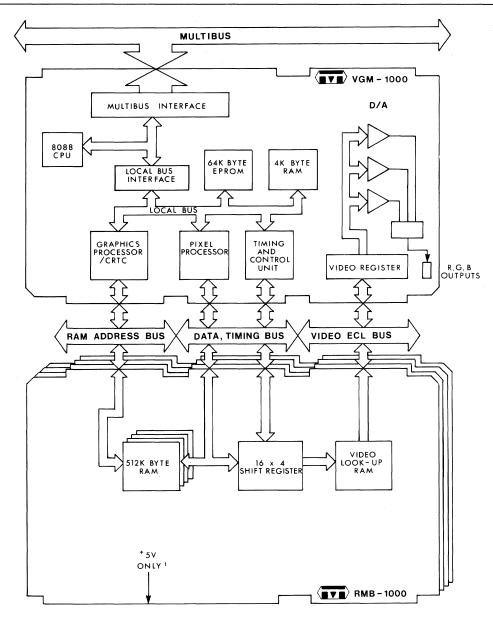

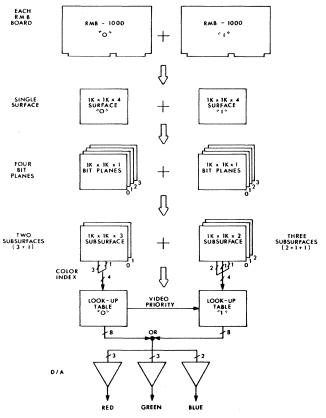

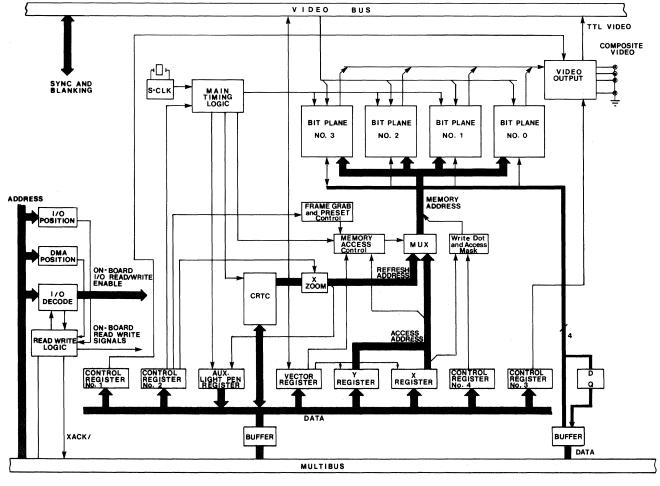

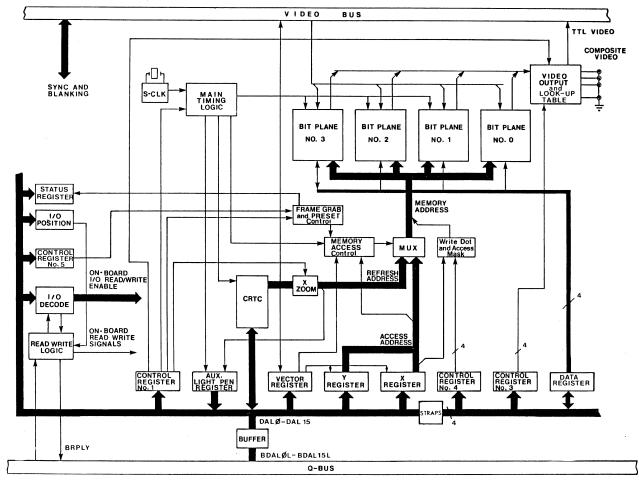

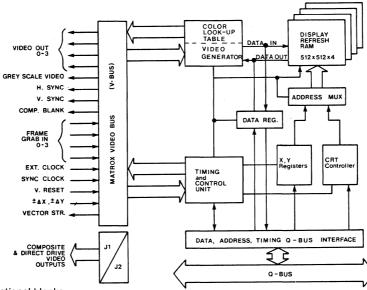

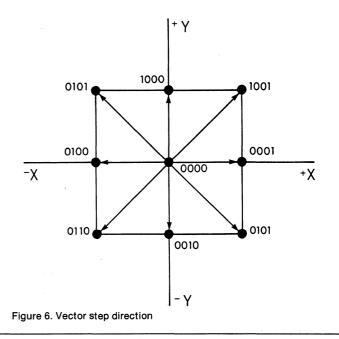

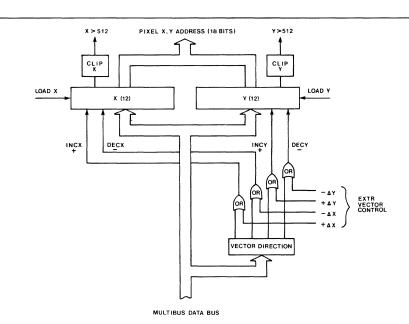

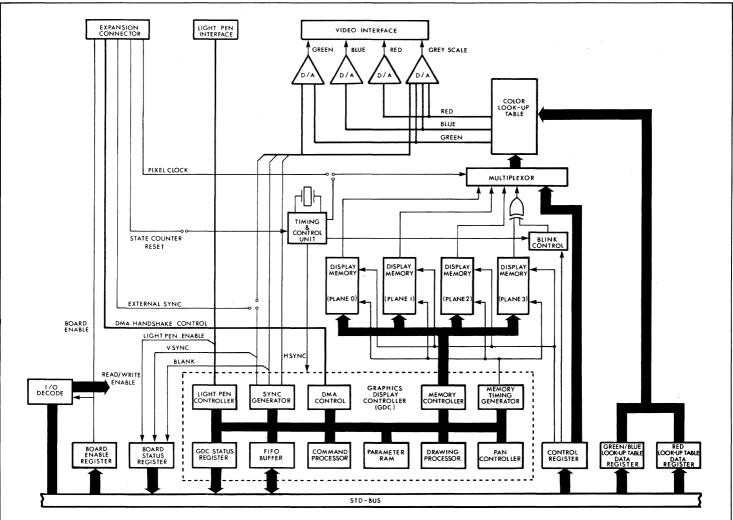

Figure 2. GXB-1000 functional blocks

### **FUNCTIONAL DESCRIPTION**

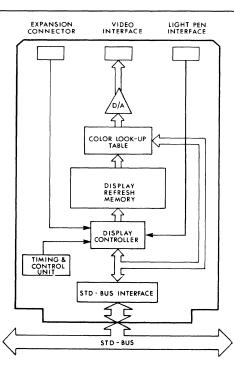

The GXB-1000 board set is a complex high speed digital graphics system. By using the latest state-of-the-art VLSI circuits together with high speed ECL logic and advanced software, Matrox can offer the highest performance in color raster graphics. A board level product means lower cost, higher reliability, easier system design, and faster product introduction.

The system consists of two boards; VGM-1000 (Virtual Graphics Machine) and RMB-1000 (Refresh Memory Board). The VGM-1000 generates all of the video timing signals and provides local intelligence with an on-board graphics interpreter executed by an 8088 CPU. The RMB-1000 contains 512K bytes of high speed RAM for four bit plane storage. The memory is organized as 1024 x 1024 x 4 pixels. The system has also been designed to accommodate 256K RAMs. When these parts become available a single RMB-1000 memory board can hold 2M bytes of RAM organized as 2048 x 2048 x 4 pixels.

The VGM-1000 and the RMB-1000 boards are connected via three 50 pin ribbon cables at the top of each board (Me-

tabus). Both boards require only +5V power from the Multibus. The VGM-1000 board appears to the system bus as an 8088 master CPU with full bus arbitration logic.

The user can configure the RMB-1000 memory board for a variety of different display formats and memory configurations through a combination of software programming, jumper changes, and crystal clock changes.

A minimal configuration consists of two boards; one VGM-1000 and one RMB-1000. This system can be structured for any display format within 1 Mega pixels, with each pixel being 4 bits deep. Examples are 1024 x 1024, 1024 x 768, 640 x 480, 800 x 600 landscape and portrait displays.

For displays requiring more bits per pixel (up to 16 bits per pixel) or more resolution (up to  $2K \times 2K$ ) additional RMB-1000 memory boards can be used. A maximum of four RMB-1000s can be "stacked" together with one VGM-1000. For example, a display of 1600 x 1200 x 4 requires two RMB memory boards configured for serial operation. A display of 1024 x 768 x 16 requires four RMBs configured to operate in parallel.

### **VIRTUAL GRAPHICS MACHINE**

The GXB-1000 design incorporates the concept of pipelined distributed processors. The four GXB-1000 processors represent the lowest level of the pipeline (as far as the actual picture generation is concerned). The higher level CPU (on-bus or off-bus via a data link) loads a display file containing the picture description (data and instructions) into off-board RAM memory on the Multibus (there can be multiple display files in the off-board RAM). The display file can be up to 16 million bytes long. Multiple display files can also exist anywhere in the 24 bit Multibus address space.

The user can think of the GXB-1000 board set as a graphics processor which executes its own instruction set. The internal CPU together with local resources (ROM, RAM, graphics processor, VIP, PIP, refresh memory, etc.) can be thought of as a single graphics CPU with microcode stored in on-board ROM. A particular graphics instruction is performed by executing microcode (actually 8088 machine language).

The display file containing the graphics instructions can be interpreted by the VGM in either Multibus Master or Slave mode (selected by jumper).

In the Master mode, the host computer has to transfer only the starting address of the display file to the VGM's I/O Command Input Port (3 byte transfer). The host then issues a Run Display File (CONTINUE) command, after which the VGM fetches successive bytes starting from the starting address by becoming the Bus Master for every fetch.

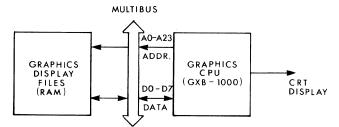

Figure 3. GXB-1000 Bus Master mode configuration.

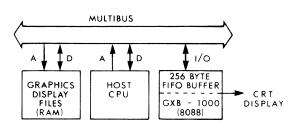

In the Slave mode, the host must transfer every byte from the display file to the VGM's internal FIFO buffer via the Command Input Port. Up to 256 bytes of the display file commands can be stored in the buffer. Commands can be loaded sequentially or in a single 256 byte block transfer. At the end of a transfer, the VGM's 8088 CPU will fetch instructions from the FIFO buffer until the buffer is empty. At that time the VGM will issue an interrupt to the host. The Slave mode is used for Multibus systems that do not support multimasters.

Figure 4. GXB-1000 Bus Slave mode configuration.

The local CPU executes instructions using on-board resources; vector generator, VIP, and PIP. The instruction execution time varies from slow (milliseconds) for long vectors, clear screen, area fills, etc. to very fast (nanoseconds) for control instructions. During execution the Multibus is not used, thereby freeing it for higher level CPU communications. After execution of the complete display file, the local CPU (8088) sends an interrupt signal to the host, notifying it that the display file has been finished. Alternately, multiple display files can be linked so that at the completion of one file the on-board 8088 will jump to the beginning of the next file. Nesting of display files is also supported.

The same byte (fetched from off-board RAM or internal FIFO buffer) can be interpreted by the 8088 as either 8088 instruction opcode or as graphics instruction opcode. The mode is determined by executing the instructions "Switch to Graphics Mode" or "Switch to 8088 Mode". This feature enables the programmer to combine the full 8088 instruction set (at full speed) with Matrox graphics instructions, in the same or different files.

### **TYPICAL APPLICATIONS**

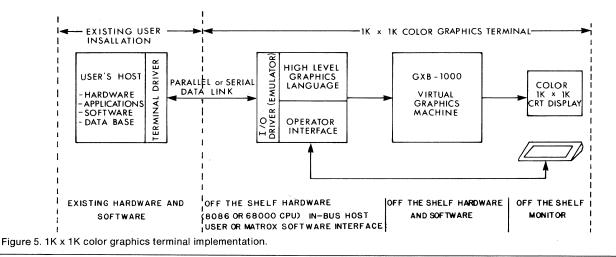

The GXB-1000 graphics board set is a powerful video display driver that represents the state of the art in raster graphics equipment. The Matrox building block approach to both hardware and software allows the system designer to implement a new graphics terminal, or emulate an existing terminal, with considerable savings in development effort, cost, and time.

By writing the terminal's high level graphics software in a high level language (C, Fortan, Pascal), executed by the inbus user CPU, any graphics terminal can be designed (Matrox offers both 8086/87 or 68000 based Multibus CPU cards as in-bus host processors). The Matrox graphics commands are treated as user macrocommands and are defined as such to the user's high level language assembler. The programmer does not have to be concerned with the display hardware, and can therefore write high level terminal programs on the CPU of his choice to generate display files. These display files are in turn executed by the Virtual

Graphics Machine in a pipelined fashion, providing the high throughput required for interactive graphics.

This approach significantly simplifies the design of a graphics terminal and enables the user to construct a custom terminal or emulate and upgrade any existing terminal in the shortest possible time. All of the existing user application software and hardware can be used without any change.

As an example of this philosophy, Matrox has developed a Tektronix 4113 emulator software package in "C" which runs on the Matrox MBC-86/12 (8086/87) Multibus CPU board. The package uses a real-time kernel, written in "C", which supports multitasking.

The software is available in "C" source code for the user wanting to add special functions.

### **USER MODEL OF THE GXB-1000**

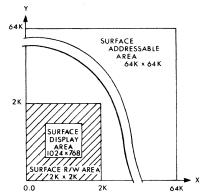

The GXB-1000 display appears to the user as a series of 4 plane read/write surfaces. One RMB board represents a single 1K x 1K x 4 bit surface. Up to four RMB boards can be combined serially to provide a larger surface (2K x 2K x 4 bits), or, they can be combined in parallel to provide up to four 1K x 1K x 4 surfaces.

Two bytes are required to define a unique X address, and two bytes are required to define a unique Y address within a read/write surface (64K x 64K addressable area). The graphics interpreter uses only the first 11 address bits (2K x 2K read/write area) and ignores the upper five bits (wraparound). The actual displayed area may be less than the full read/write area (i.e. 1024 x 768 display area). The display area can be panned to any position within the read/write area.

Figure 6. Surface addressable, read/write, and display area definitions.

Each surface can be organized into subsurfaces, with each subsurface consisting of one to four planes. The number of planes used for each subsurface determines the maximum number of colors that can be displayed by that subsurface. Up to 16 one-plane subsurfaces can be defined if four RMB boards are used.

Every surface has its own color look-up table (LUT). As each pixel is displayed, its color index (the four bit binary value stored in the display memory) addresses one of sixteen positions in the look-up table. The output from the look-up table is an 8-bit binary number which, after D/A conversion, defines one of 256 possible display colors. When more than one display surface is used the outputs of the look-up tables can be combined in a "logical OR" or a priority manner (figure 6).

Each subsurface produces its own graphics image. These various images are combined to create a single display, according to the user's overlay and priority commands; "Surface Video Combination", "Set Surface Priority", "Set Surface Visibility", etc. (see GRAPHICS INSTRUCTION

SET). If a given subsurface uses a transparent background the next lower priority subsurface will be seen. If, on the other hand, the background is opaque, all other lower priority subsurfaces will be hidden.

Once a subsurface has been specified, the graphics processor can draw various figures, patterns, or characters. The primitives include: point, vector, arc, circle, marker, rectangle, polygon, filled window, and filled character cell. Figures and figure attributes (thickness, texture, addressing and data modes, etc.) are specified by the figure drawing instructions.

There are three possible drawing speeds selectable by the user (Set Drawing Speed instruction). The highest speed is 64 clock cycles per pixel (800 nsec with an 80 MHz clock, or 1.25 million pixels/sec). However, in this mode the display is blanked when accessed by the graphics processor resulting in a "snow" effect on the screen. If the drawing is limited to the retrace period only (i.e. when the display is blanked), to avoid "snow" on the screen, the resulting drawing speed is 3.2  $\mu$ sec/pixel or over 300,000 pixels/sec. The third speed, obtained by using a wider display blanking signal, is 1.2  $\mu$ sec/pixel or 830,000 pixels/sec. The user can switch at any time between these drawing speeds depending on the desired effect and the amount of data to be drawn.

A complete surface can be preset to any color by a hardware flash preset command which loads each pixel in the surface at 12.5 nsec/pixel or one field for the complete surface (16 million pixels in 16.6 msec).

Figure 7. Five subsurface/two surface display example.

In the Alphanumerics display mode, the GXB-1000 works as a color alphanumerics terminal, supporting commands such as carriage return, line feed, back space, etc. Either the full screen or up to four rectangular display areas (Dialog Areas) can be specified for writing text. Alphanumerics Mode and Dialog Area instructions are used for text manipulation. Any 1-bit subsurface on each surface can be designated for pixel blink control. Setting the pixel bit "on" will result in an on/off blink rate of 4 Hz for all the pixels with the same X,Y address on the same surface. A designated subsurface can also be used as an overlay plane, a graphics cursor plane, or an alphanumerics plane.

### **GRAPHICS INSTRUCTION SET**

The instruction set has been organized into 10 different functional groups:

- 1. Flow Control Instructions

- 2. Context Switching Instructions

- 3. Configuration and Initialization Instructions

- 4. Command Instructions

- 5. Direct Raster Instructions (Raster Op)

- 6. Figure Drawing Instructions

- 7. Alphanumeric Terminal Mode Instructions

- 8. Dialog Area Instructions

- 9. Miscellaneous Instructions

- **10. Input Function Support Instructions**

The execution times shown in the following tables apply only to the "worst case" mode, where only one instruction is executed at a time. Normally execution times are much shorter (approaching zero) due to the pipelined architechture of the GXB-1000. For example, when drawing polygons, the execution time is a function of the pixel drawing speed only, since the graphics processor and the 8088 CPU operate in the pipelined fashion; i.e. one draws the vector while the other calculates the parameters for the next vector.

The instruction set shown is a superset of all available instructions for the virtual graphics machine. Actual versions of available MIG-XX interpreters execute a subset of the GXB-1000 superset, since not all users require all the instructions. For information on the MIG-XX implementations currently available, consult the factory.

**Flow Control Instructions** — These instructions are used for various housekeeping functions related to the display file and program flow control.

| INSTRUCTION          | #<br>BYTES | EXECUTION<br>TIME (µs) | DESCRIPTION                                                                                                      |

|----------------------|------------|------------------------|------------------------------------------------------------------------------------------------------------------|

| Go To                | 4          | 100                    | Loads graphics program<br>counter with address of next<br>instruction (24 bits).                                 |

| Go Sub               | 4          | 100                    | Loads graphics program<br>counter with address of next<br>instruction and stores the<br>current PC on the stack. |

| Return               | 1          | 100                    | Return to main program from the subroutine.                                                                      |

| Stop                 | 1          | 60                     | Stops program execution requires an I/O command to restart.                                                      |

| NOP                  | 1          | 100                    | Dummy instruction. No operation.                                                                                 |

| ldie                 | 1          | 50                     | Wait loop, 8088 fetches the<br>same instruction byte,<br>looping conditional on code<br>change.                  |

| Reset                | 1          | 50,000                 | Resets and initializes all<br>local resources after<br>executing self-test.                                      |

| Load Status          | 1          | 100                    | Loads current status of local<br>resources (stored in VGM<br>RAM) to shared buffer.                              |

| Interrupt            | 1          | 60                     | Sends interrupt to Host CPU.                                                                                     |

| Fetch<br>Single/Page | 2          | 60                     | Sets subsequent fetches<br>from file as single byte or<br>256 bytes (stored in cache).                           |

**Context Switching Instructions** — Data fetched from the display file can be interpreted as direct 8088 op code, or as graphics op code. After a power-up or reset, the VGM defaults to "native 8088 mode". In this mode all instructions are interpreted as 8088 commands. The user can operate in this mode, or can select the "graphics interpreter mode" by executing a CALL instruction to the starting address of the on-board graphics interpreter (switch to graphics instructions. When operating in the graphics mode, an instruction is provided to return to the native 8088 mode (Switch to 8088 Mode).

| INSTRUCTION                | #<br>BYTES | EXECUTION<br>TIME (μs) | DESCRIPTION                                         |

|----------------------------|------------|------------------------|-----------------------------------------------------|

| Switch to<br>8088 Mode     | 5          | 120                    | Disengages the graphics interpreter (display file). |

| Switch to<br>Graphics Mode | 5          | 120                    | Engages the graphics interpreter.                   |

Table 2. Command Instructions.

**Configuration and Initializing Instructions** — This group of instructions defines and initializes display parameters such as; number of horizontal and vertical pixels, drawing speed, pan, syncs, blanking, and refresh rate.

| INSTRUCTION                            | #<br>BYTES | EXECUTION<br>TIME (µs) | DESCRIPTION                                                                                                                          |

|----------------------------------------|------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Set Video<br>Format                    | 2          | 100                    | Selects standard video<br>display formats: 1024 x 768,<br>1024 x 1024, 1600 x 1200.                                                  |

| Set Drawing<br>Speed                   | 2          | 100                    | Selects drawing in<br>retrace only (4 $\mu$ sec/pixel),<br>all the time (800 nsec/pixel),<br>or 50% video (1.2 $\mu$ sec/<br>pixel). |

| Pan Display                            | 5          | 100                    | Positions display within 2K x 2K area.                                                                                               |

| Surfaces<br>Video<br>Combination       | 2          | 100                    | Define combination function<br>for multiple surfaces<br>(visibility, priority/OR<br>overlay).                                        |

| Select<br>Surface                      | 2          | 100                    | Selects one of four surfaces for read/write operations.                                                                              |

| Subsurface<br>Priority<br>Set          | 2          | 400                    | Define overlay function for<br>multiple subsurfaces on a<br>surface (priority/OR overlay).                                           |

| Select<br>Subsurface                   | 2          | 400                    | Select one of several subsurfaces on a surface for read/write operations.                                                            |

| Define<br>Subsurfaces                  | 2          | 400                    | Defines one to four<br>subsurfaces on a four plane<br>surface.                                                                       |

| Set<br>Subsurface<br>Color             | 2          | 400                    | Defines foreground color for subsurface write operations.                                                                            |

| Set<br>Subsurface<br>Combination       | 2          | 400                    | Defines background color<br>and combined subsurface<br>display color.                                                                |

| Set<br>Subsurface<br>Visibility        | 2          | 400                    | Enables/disables subsurface visibility.                                                                                              |

| Load Surface<br>LUT Directly           | 17         | 200                    | Loads 16 byte Look-Up Table<br>directly.                                                                                             |

| Load Surface<br>UCS Start<br>Address   | 5          | 100                    | Loads start address of user<br>character set file (file =<br>$256 \times 16 \times 16 = 8K$ bytes).                                  |

| Load Shared<br>Buffer Start<br>Address | 5          | 100                    | Loads off-board RAM buffer start address (8 bytes long).                                                                             |

| Define Video                           | 9          | 200                    | Defines special video display<br>formats (sync, blanks, no. of<br>lines, etc.).                                                      |

Table 3. Configuration and Initializing Instructions.

**Commands** — This group of instructions provide the highest priority control of the on-board 8088 by the host. These are the only instructions that are transfered directly to the I/O port on the VGM-1000 board, and are not fetched from external Multibus RAM (Master mode). The I/O port address is hardware selectable by the user.

| INSTRUCTION           | #<br>BYTES | EXECUTION<br>TIME (µs) | DESCRIPTION                                                                                              |

|-----------------------|------------|------------------------|----------------------------------------------------------------------------------------------------------|

| Load Start<br>Address | 4          | 200                    | Loads internal graphics<br>24-bit program counter (start<br>address of display file in<br>Multibus RAM). |

| Reset                 | 1          | 50,000                 | Resets and initializes all<br>local resources after<br>executing self-test.                              |

| Load Status           | 4          | 200                    | Load current status of local<br>resources (stored in VGM<br>RAM) to Multibus memory.                     |

| Stop                  | 1          | 100                    | Suspends all 8088<br>operations, no Multibus<br>access.                                                  |

| Continue              | 1          | 100                    | Resumes program execution after a stop command.                                                          |

**Direct Raster Instructions** — This group of instructions works directly on a rectangular area of the raster. Both run length and bit by bit encoding can be used. Execution speed is a function of the number of pixels in the rectangle, N, and the pixel op speed (3  $\mu$ sec/pixel).

The instructions; Read Back Raster, Write to Raster, and Set Data Packing Mode, are used for the transfer of raster data to/from off-board RAM.

The Raster Operations work on pixels inside a specified raster rectangle. First a 2D transformation is performed on each "source" pixel, then each transformed pixel is combined with the corresponding pixel at the new destination on the same or different subsurface.

The available 2D transforms and raster operations are described below:

| Source/Destination - | Defines size | , initial X/Y | position, and |

|----------------------|--------------|---------------|---------------|

| Raster Rectangle     | destination  | subsurface    | of the raster |

|                      | rectangle or | the current   | subsurface.   |

2D Transform – Defines the 2D transformation Parameters performed on each source pixel before combination with the destination pixel.

- Translation -X, Y translation offset for each pixel.

- Rotation Rotates each source pixel about the Z-axis with the lower left corner of the rectangle at the origin (8 angles in multiples of 45°).

- Zoom/Scale Source raster is multiplied by 1, 2, 4, or 8 (zoom by pixel replication) or divided by 1, 2, 4, or 8 (scaling by pseudo random dither sampling).

- Reflection Source raster can be reflected about any one of four axes (X, Y, Y = X, Y = -X).

- Raster Operations After the 2D transformation, the source raster is combined with the destination raster pixel by pixel. Source pixels can be complemented before the operation. Logic operation (AND, OR, X–OR), arithmetic operations (ADD, SUBTRACT), copy and user-defined pixel functions can also be specified. Operations with a constant are also supported.

| INSTRUCTION              | #<br>BYTES | EXECUTION<br>TIME (µs) | DESCRIPTION                                                                      |

|--------------------------|------------|------------------------|----------------------------------------------------------------------------------|

| Read Back<br>Raster      | 13         | 100 + N×3              | Reads raster rectangle to off-board RAM.                                         |

| Write to<br>Raster       | 13         | 100 + NX3              | Write raster rectangle from off-board RAM.                                       |

| Set Data<br>Packing Mode | 2          | 100                    | Defines data packing; bit x bit, run length.                                     |

| Raster Op                | 14         | 100 + 2NX3             | Moves raster rectangle from<br>one screen location to<br>another with operation. |

Table 5. Direct Raster Instructions.

**Figure Drawing Instructions** — The VGM-1000 draws graphics primitives at a rate of 800 nsec/pixel. The nine primitives include line draw commands (point, vector, arc, circle, marker, rectangle, and polygon) and area draw commands (window and character cell). Several attributes are associated with each figure to be drawn:

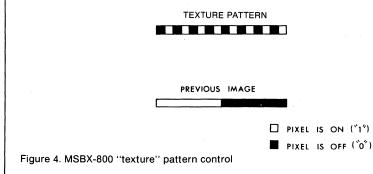

- Texture Write/skip pixel pattern (16 x 1 bit). Used to define texture of a line primitive.

- Fill Pattern Write/skip pixel pattern (8 x 8 bits). Used to define the fill pattern of an area primitive.

- Thickness Defines the "pen size" to be used in line drawing operations: 1 x 1 pixels, 2 x 2 pixels, 3 x 3 pixels, up to 16 x 16 pixels.

- Chain Specifies the number of times the figure is to be drawn in succession.

- Addressing The coordinates can be specified in one of three ways: Absolute - 2 bytes for each X,Y

|                | coordinate.<br>range = 0 — 65,535                                                   |

|----------------|-------------------------------------------------------------------------------------|

| Relative       | <ul> <li>2 bytes for each coordi-<br/>nate relative to the cur-<br/>sor.</li> </ul> |

|                | range = $\pm$ 32,767                                                                |

| Short Relative | - 1 byte for each coordi-<br>nate relative to the cur-<br>sor.<br>range = $\pm 127$ |

- PIP Function Specifies the pixel data to be written to the addressed pixel. Five possible functions can be defined:

- Complement Pixel complements each pixel bit Color Index – defines 1 of 16 colors Offset to Index – reads value and offsets by 0 – 15 User PIP Function – user defined truth table

- ser PIP Function user defined truth table used for pixel transformation

- Chromakey Switch used for user defined chromakey outline fill or hardware clipping (used only with window command).

The texture, fill pattern, thickness, and PIP are each selected through separate explicit instructions. The figure, chain, and addressing mode are selected implicitly by the figure draw instruction op code.

| INSTRUCTION               | #<br>BYTES | EXECUTION<br>TIME (µs) | DESCRIPTION                                                                      |

|---------------------------|------------|------------------------|----------------------------------------------------------------------------------|

| Set Texture               | 3          | 100                    | Loads 16 bit write/skip pixel pattern.                                           |

| Set Fill<br>Pattern       | 9          | 200                    | Loads 8 x 8 bit fill pattern<br>(organized as 8 bytes).                          |

| Set<br>Thickness          | 2          | 100                    | Selects 1 of 16 pen sizes from 1 x 1 to 16 x 16.                                 |

| Set<br>Chromakey<br>Index | 2          | 100                    | Selects chromakey index<br>0-15 for fill and clip<br>functions.                  |

| Select PIP<br>Function    | 2          | 100                    | Selects 1 of 5 PIP functions<br>(complement, color, offset,<br>chromakey, user). |

| Load User<br>PIP          | 9          | 100                    | Loads user PIP, pixel<br>in / pixel out table — 16 x 4<br>organized as 8 bytes.  |

| Select<br>Marker          | 2          | 100                    | Selects 1 of 16 Matrox defined markers.                                          |

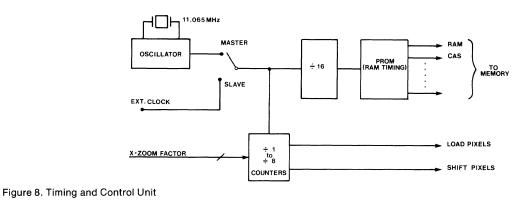

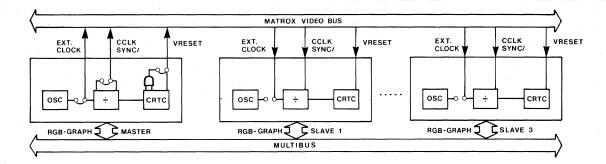

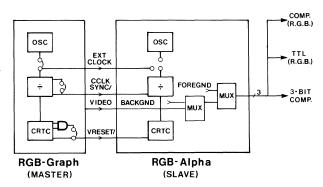

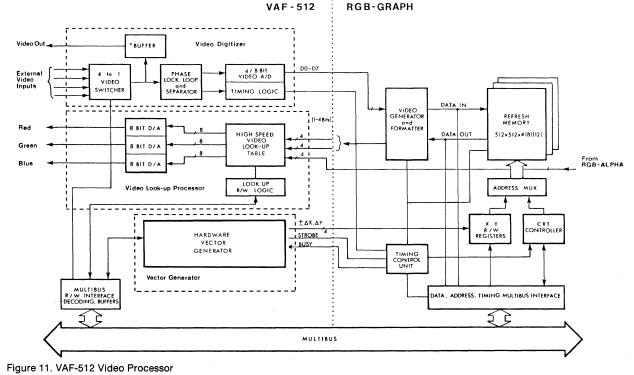

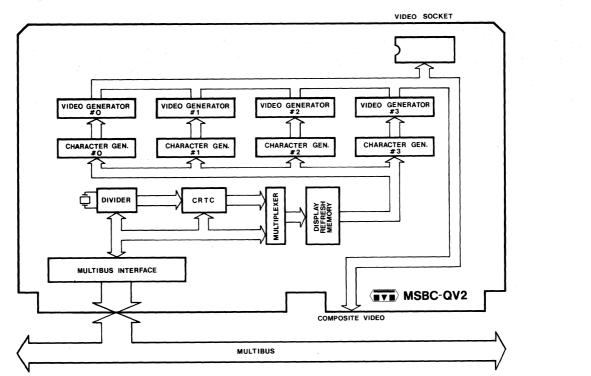

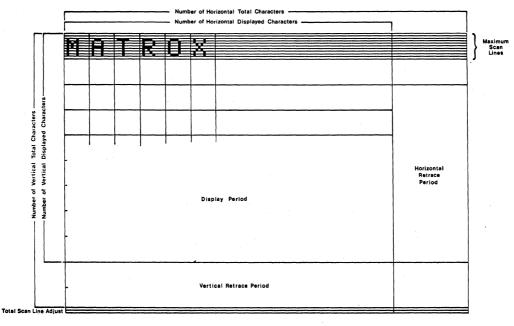

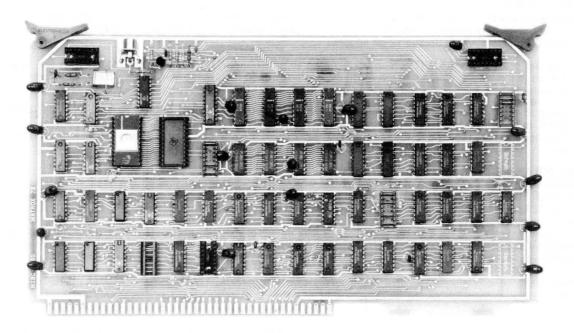

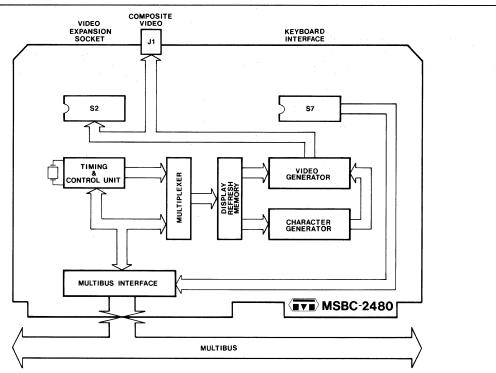

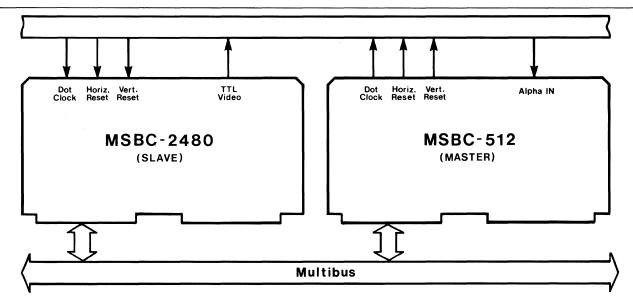

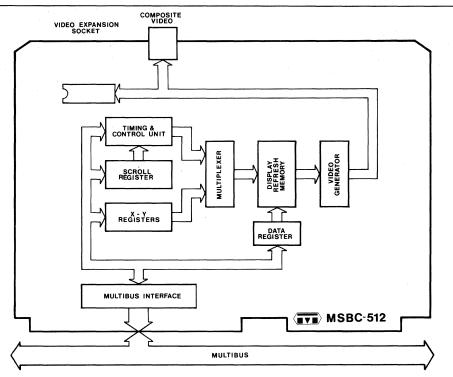

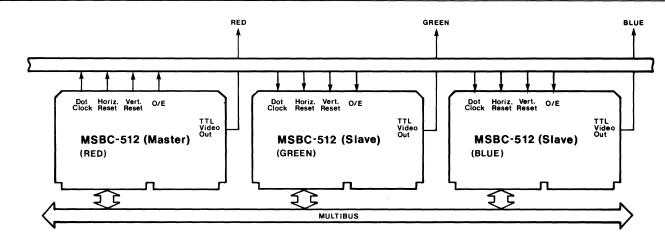

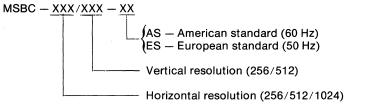

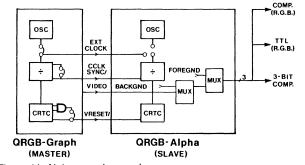

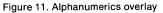

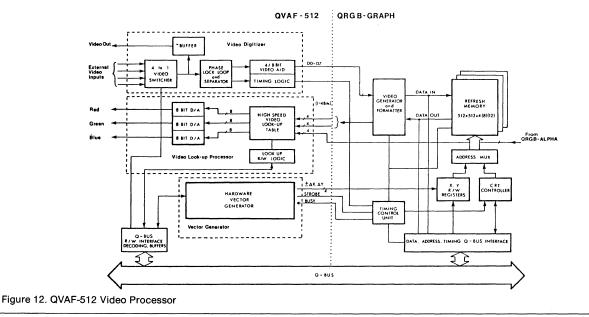

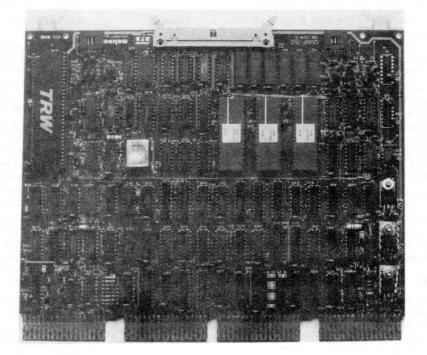

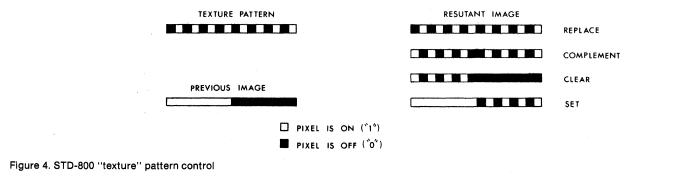

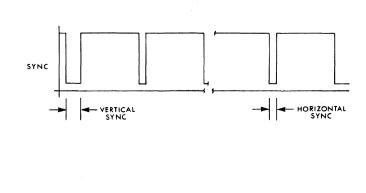

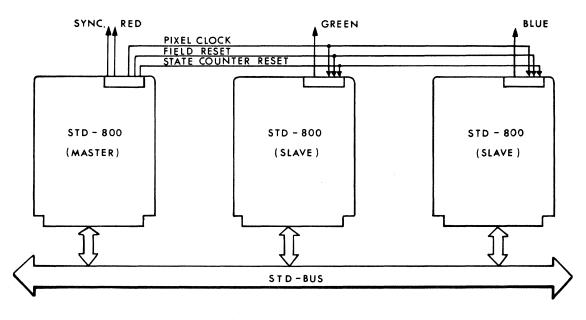

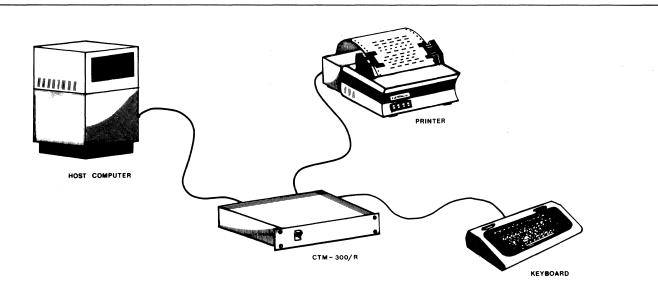

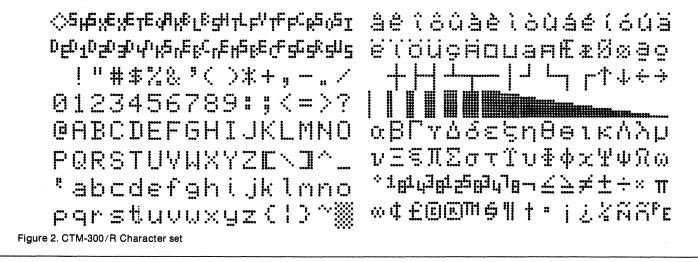

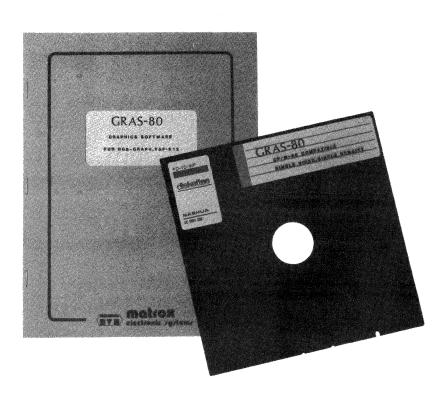

| Select User<br>Marker     | 4          | 100                    | Selects user defined 8 x 8<br>bit marker located in<br>Multibus RAM.             |