## GENERAL SYSTEM BULLETIN

# PROCESSOR INSTRUCTION SET

GB13020009103

G3

#### SUE PROCESSOR INSTRUCTION SET

GENERAL SYSTEM BULLETIN G3

Third Edition

This bulletin supercedes SUE Processor Instruction Set General System Bulletin G3, Rev. A dated June 1972

Bulletin GB13020009103 May 1973

©Copyright 1973 by Lockheed Electronics Company Los Angeles, California All rights reserved

#### EFFECTIVE PAGES

New pages introduced in this third edition include Processor Instruction Sets for SUE 1110A/B, 1111A/B, 1112A/B, and Appendices D and E.

Changes in the second edition, which included Processor Instruction Set SUE 1110, and Appendices A through C, are indicated by a heavy line in the outer margin of the changed page.

.

## CONTENTS

## <u>Title</u>

## Page

SUE 1110 INSTRUCTION SET

| Introduction 1                                                                              |             |

|---------------------------------------------------------------------------------------------|-------------|

| Word Formats                                                                                |             |

| Data Words • • • • • • • • • • • • • • • • • • •                                            |             |

| Address Words 3                                                                             |             |

| Instruction Words · · · · · · · · · · · · · · · · · · ·                                     | :           |

| $\mathbf{Fields}  \cdots  \cdots  \cdots  \cdots  \cdots  \cdots  \cdots  \cdots  \cdots  $ | ,           |

| Addressing                                                                                  | ;           |

| Byte-Word Addressing · · · · · · · · · · · · · · · · · · ·                                  | <b>;</b> .  |

| Absolute and Relative Addressing                                                            | ;           |

| Extended Addressing                                                                         | ;           |

| Indexing                                                                                    | •           |

| Auto Incrementing and Decrementing                                                          | •           |

| Indirect Addressing                                                                         | •           |

| Register, Immediate and Literal Operands                                                    | 1           |

| Combination Addressing Modes                                                                | i i         |

| Special Addresses 10                                                                        | )           |

| Status Indicators                                                                           |             |

| Instruction Descriptions 12                                                                 | }           |

| General Register Instructions 12                                                            | :<br>:<br>: |

| General Operations 12                                                                       | }           |

| General Register Instruction Word Formats 13                                                | ŀ           |

| General Register Instruction Times                                                          | 1           |

| Branch Conditional Instructions 20                                                          | )           |

| Branch Conditions 21                                                                        | -           |

| Branch Instruction Word Formats 22                                                          | F.          |

| Branch Instruction Times                                                                    |             |

## CONTENTS (continued)

## Title

## Page

| Shift Instructions               | <b>24</b>  |

|----------------------------------|------------|

| Shift Instruction Word Formats   | 25         |

| Shift Instruction Timing         | 2 <b>7</b> |

| Control Instructions             | 28         |

| Control Instruction Word Formats | 28         |

| Control Instruction Times        | 33         |

| Unimplemented Instructions       | 34         |

| Input/Output Instructions        | 34         |

| SUE 1110A INSTRUCTION SET        |            |

| Introduction                     | 35         |

| Store Key Instruction            | 35         |

| SUE 1110B INSTRUCTION SET        |            |

| Introduction                     | 37         |

| Fetch and Clear Instructions     | 37         |

| Fetch and Clear Operation        | 38         |

| SUE 1111A INSTRUCTION SET        |            |

| Introduction                     | 39         |

| Temporary Storage                | 39         |

| Instruction Format               | 40         |

| Decimal Data Format              | 41         |

| Character Data Format            | 41         |

| Symbolic Coding for Operands     | 42         |

| Instructions                     | 42         |

| SUE 1111B INSTRUCTION SET        |            |

| Introduction                     | 46         |

| Fetch and Clear Instructions     | 46         |

| Fetch and Clear Operations       | 46         |

į

## CONTENTS (continued)

## <u>Title</u>

## Page

| SUE 1112A INSTRUCTION SET                           |            |

|-----------------------------------------------------|------------|

| Introduction                                        | 49         |

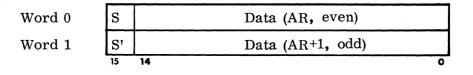

| Double Precision Data Format                        | 49         |

| Instruction Times                                   | 50         |

| Bit Manipulation Instructions                       | 50         |

| Bit Manipulation Instruction Formats                | 51         |

| Bit Manipulation Operations                         | 52         |

| Move Instructions                                   | 52         |

| Move Instruction Format                             | 52         |

| Move Operations                                     | 53         |

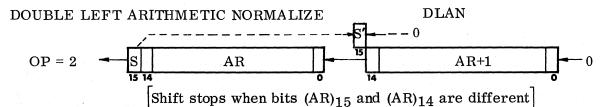

| Normalize and Count Instructions                    | 53         |

| Normalize and Count Instruction Format              | 53         |

| Normalize and Count Operations                      | 53         |

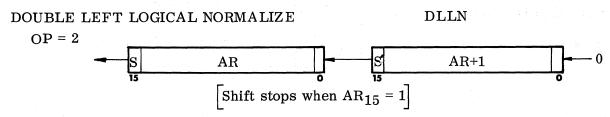

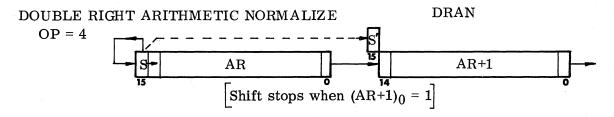

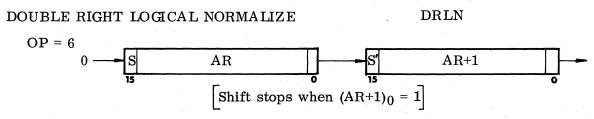

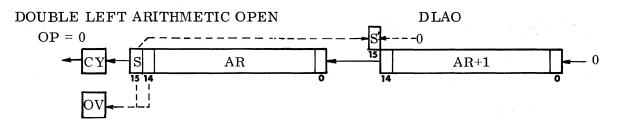

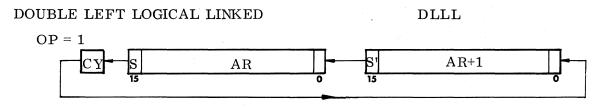

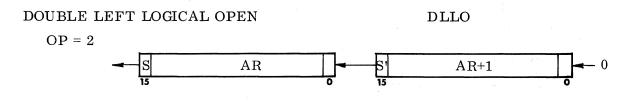

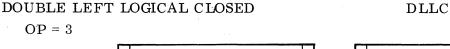

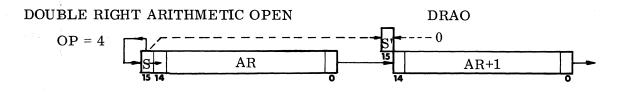

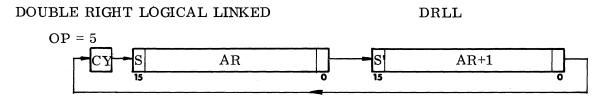

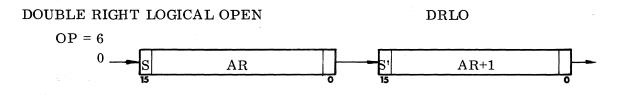

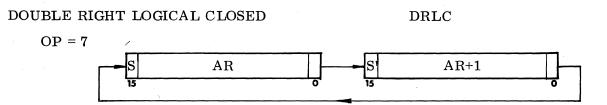

| Double Length Shift Instructions                    | 56         |

| Double Length Shift Instruction Format <sup>,</sup> | 5 <b>7</b> |

| Double-Length Shift Operations                      | 57         |

| Class B Instruction Set                             | 60         |

| Class B Instruction Format                          | 60         |

| Accumulator Registers                               | 60         |

| Single-Precision Fixed Point Instructions           | 60         |

| Addressing Modes                                    | 60         |

| One-Word Operand Format                             | 61         |

| Single Precision Fixed-Point Operations             | 61         |

| Double Precision Fixed-Point Instructions           | 62         |

| Addressing Modes                                    | 62         |

| Double Precision Fixed Point Operations             | 63         |

| Control Instructions                                | 63         |

| Control Instruction Formats                         | 64         |

v

#### CONTENTS (continued)

## <u>Title</u>

Page

| SUE 1112B INSTRUCTION SET                                                       |      |

|---------------------------------------------------------------------------------|------|

| Introduction                                                                    | 65   |

| Fetch and Clear Instructions                                                    | 65   |

| Fetch and Clear Operation                                                       | 66   |

| APPENDIX A, INSTRUCTION TIMES                                                   |      |

| Single Shift Instruction Timing for SUE 1110 (Basic), 1110A/B, 1111A/B, 1112A/B | A-3  |

| SUE 1111A/B CLASS C INSTRUCTION TIMES<br>DECIMAL AND CHARACTER INSTRUCTIONS     |      |

| Decimal Add and Subtract Timing                                                 | A-5  |

| Decimal Shift Timing                                                            | A-10 |

| Move Timing                                                                     | A-11 |

| Compare-Field Timing                                                            | A-11 |

| Decimal Compare Timing                                                          | A-13 |

| APPENDIX B, INSTRUCTION SUMMARY AND INDEX                                       |      |

| SUE 1110 (Basic) Instructions Summary                                           | B-1  |

| SUE 1110 (Basic) Instruction Index                                              | B-2  |

|                                                                                 |      |

#### APPENDIX C, INPUT/OUTPUT ADDRESSES

#### APPENDIX D, SELF-INTERRUPT AND SYSTEM INTERRUPT EXECUTIVE SPACE

## APPENDIX E, USASCII CHARACTER SET AND HEXADECIMAL CODES

G

## LIST OF TABLES

| Table       | Title                                                                       |     | Page |

|-------------|-----------------------------------------------------------------------------|-----|------|

| 1           | Combination Addressing Modes                                                | •   | 9    |

| 2           | Special Addresses                                                           | •   | 10   |

| 3           | General Register Instruction Word Formats                                   | •   | 14   |

| 4           | SUE 1110 (Basic) General Register Instruction Times                         | •   | 19   |

| 5           | Branch Instruction Times                                                    | •   | 24   |

| 6           | SUE 1110 (Basic) Control Instruction Times                                  | •   | 33   |

| A-1         | SUE 1110 (Basic) General Register Instruction Times                         |     | A-1  |

| A-2         | SUE 1110A/B, 1111A/B, and 1112A/B General Register<br>Instruction Times     | ••• | A-2  |

| A-3         | SUE 1110 (Basic), 1110A/B, 1111A/B and 1112A/B<br>Control Instruction Times |     | A-3  |

| A-4         | SUE 1110 (Basic) Branch Instruction Times                                   |     | A-4  |

| A-5         | SUE 1110A/B, 1111A/B and 1112A/B Branch Instruction<br>Times                |     | A-4  |

| A-6         | Decimal Shift Timing Chart                                                  | • • | A-10 |

| A-7         | SUE 1112A/B Instruction Times                                               |     | A-18 |

| <b>A-</b> 8 | SUE 1112A/B Single- and Double-Precision Fixed-Point<br>Instruction Times   | • • | A-20 |

| C-1         | Input-Output Device Addresses                                               | • • | C-1  |

#### PREFACE

This bulletin contains instructions to program seven types of SUE processors:

|                                        | Number of Instructions |

|----------------------------------------|------------------------|

| SUE 1110 (basic)                       | 108                    |

| SUE 1110A                              | 109                    |

| SUE 1110B                              | 111                    |

| SUE 1111A, Decimal Arithmetic          | 118                    |

| SUE 1111B, Decimal Arithmetic          | 120                    |

| SUE 1112A, Scientific Double Precision | 144                    |

| SUE 1112B, Scientific Double Precision | 146                    |

SUE 1110 basic is the first instruction set described in this bulletin. SUE 1110A performs the basic instruction set and one additional instruction, Store Key (SKEY). Both SUE 1111A and 1112A processors have the speed and capabilities of SUE 1110A, and each has an extended instruction set. Descriptions of these extended instructions follow the description of the SUE 1110B. Instruction times for all instructions are summarized in Appendix A.

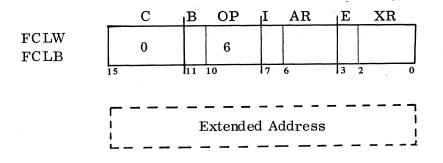

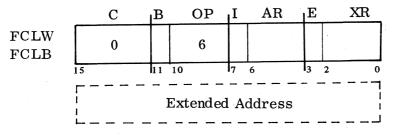

Processors SUE 1110B, 1111B, and 1112B perform the same instructions as the respective A-series processors, and two additional instructions Fetch and Clear Word (FCLW), and Fetch and Clear Byte (FCLB). These two instructions can be used in multiprocessor systems as a synchronizing mechanism.

Instructions in this bulletin are described in machine language for the system user possessing a background in digital computer terminology and operation. Additional information on the basic instruction set is contained in the LAP-2 Assembler manual. Operation and maintenance of SUE processors is contained in the respective reference and maintenance bulletins designated by the processor model number.

#### SUE 1110 INSTRUCTION SET

#### INTRODUCTION

SUE 1110 instruction set includes 108 basic instructions exclusive of 16 addressing modes. Many of these instructions operate on either 16-bit data or 8-bit byte formats. Other instructions test one or more of the 16 status indicator bits. This bulletin presents a detailed description of word formats, addressing modes, and status indicators followed by a definition of each instruction operation.

The 108 instructions are divided into eleven classes according to type of instruction function. Seven of these classes are grouped as general register instructions. They contain arithmetic, logical, move, compare and test functions that involve the eight general registers of the processor. Two classes represent the branch instructions. They contain unconditional and conditional branch functions on the true or false condition of status indicators. The shift class contains full 15-bit shift capabilities with eight different operations and two address modes. The control class contains system control functions such as load/store of all general registers, load/store of status indicators and control of interrrupt operations.

The eleven instruction classes are:

Class Code

#### Description

| 1 Accumulator to Memory with Auto Decrement  |       |

|----------------------------------------------|-------|

| 2 Accumulator to Memory with Auto Incremen   | it    |

| 3 Accumulator to Memory                      |       |

| 4 Data to Accumulator, Jump to Subroutine, J | lump, |

| and Register to Register                     |       |

| 5 Memory to Accumulator with Auto Decrement  | nt    |

| 6 Memory to Accumulator with Auto Incremen   | nt    |

| 7 Memory to Accumulator                      |       |

GB13020009103

SUE G3

| 8<br>9 | Branch False and No Operation<br>Branch True and Unconditional |

|--------|----------------------------------------------------------------|

| А      | Shift                                                          |

| 0      | Control                                                        |

Class codes are specified in the instruction word format by the four-bit C field. (Fields are defined later under instruction words in this bulletin). Five class codes are not defined for the basic instruction set. They have been reserved for specification of additional general purpose instructions in the SUE 1111A, B and 1112A, B Processors; or, for special purpose instructions in future SUE processors with expanded ROM control memories.

SUE 1110 Processor contains eight, 16-bit general registers including the program counter. Seven of these registers may be used as accumulators or index registers. The arithmetic-logic unit processes 16-bit operands but memory data may be 8-bit bytes or 16-bit words.

Memory addresses are 16-bit numbers that select up to 60k (k = 1024) bytes. Addresses 60k to 64k are used to directly address registers within system modules other than program memory modules.

#### WORD FORMATS

Bit positions within a word are numbered right to left starting with 0. Bit 0 is the least significant bit of the word and bit 15 is the most significant.

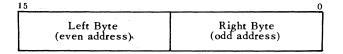

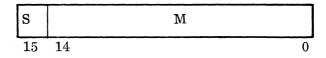

#### DATA WORDS

Two data word formats can be processed, an 8-bit byte and a 16-bit word. The most significant bit (15) represents the algebraic sign of numeric data. A ONE in bit position 15 represents a negative number, and a ZERO represents a positive number. Negative numbers are in twos complement form.

#### Byte Format

#### Word Format

$\frac{5}{1} \frac{51\text{gm}}{\text{negative (-)}}$ 0 positive (+)

In byte operations, the entire selected 16-bit register is used in the operation with the byte operand. In register-to-memory instructions (byte mode), the right byte of the register operates on the designated byte in memory. In memory-to-register instructions (byte mode), the designated byte in memory operates on the full 16-bit register as though the memory operand has a left byte equal to ZERO attached to it. In either type of operation, arithmetic operations occur in a 16-bit register and carry and overflow are detected out of a 16-bit register.

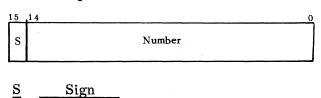

#### ADDRESS WORDS

The 16-bit address represents a byte address. Bit zero selects the left or right byte of a 16-bit word. On word addresses, bit zero is used to specify more than one level of indirect addressing.

Byte Address

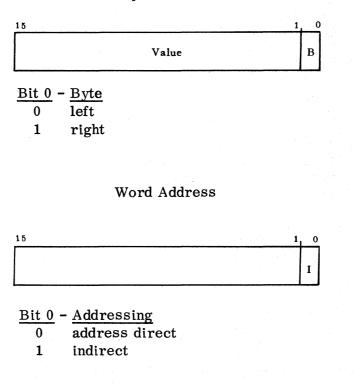

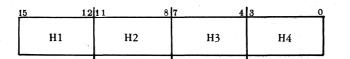

#### INSTRUCTION WORDS

4

Instruction words are constructed to facilitate encoding and decoding of the machine language code. The words are defined so that the fields of the instruction do not overlap the four hexadecimal digits represented by H1, H2, H3, and H4. Those fields that are subsets of a hexadecimal digit are right-justified, with the high-order bit used to indicate the less common condition.

Digit

- H1 Class Designation 0 through 15

- H2 Operation Designator (usually)

- H3 Accumulator Designator (usually)

- H4 Index Designator (usually)

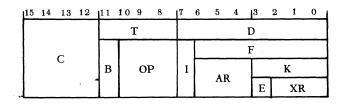

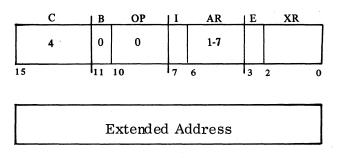

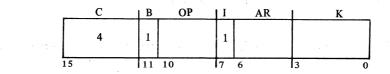

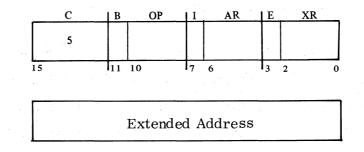

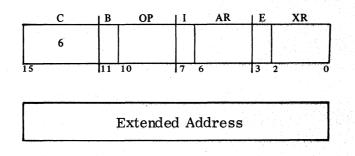

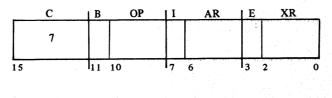

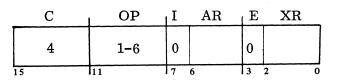

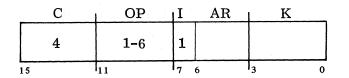

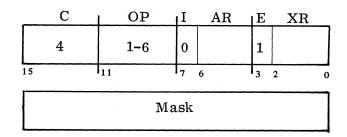

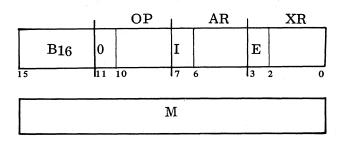

FIELDS. - A variety of word formats are interpreted by the processor. All of the fields used, and their positions, are defined below in a composite drawing. Functions of a given field may vary according to the instruction.

NOTE: Several fields have more than one function depending on the instruction that contains them. In the field definitions below, any function common to several instructions is defined. For descriptions of other functions, refer to corresponding instruction descriptions.

#### Field Definitions

#### Symbol

#### Description

- C Class Indicator (4 bits) Specifies 1 of 16 classes or divisions of the instruction set. Classes indicate the type of function.

- T Test Operation (4 bits) Defines operation codes for the Control and Branch classes.

- D Displacement Address (8 bits) Direct address (+ or -) to words relative to the address of the instruction. May be expressed as P (Program Counter) +D, where D is the range, -128 through +127. An exception, if the absolute-address mode of a Control instruction is specified, then D directly addresses the first 256 words in memory.

- B Byte Indicator (1 bit) Specifies whether the memory operand is a word (B=0) or a byte (B=1). Field of a Control instruction specifies the Relative (B=1) or Absolute (B=0) address mode.

- OP Operation Indicator (3 bits) Defines 1 of 8 operations available to certain classes. Several classes use the same set of operations, as explained in greater detail under Instruction Descriptions.

- I Indirect Addressing Indicator (1 bit) Specifies first level of indirect addressing if I=1.

- AR Accumulator Register Designator (3 bits) Designates 1 of 8 general registers as an A-Register during instruction execution.

- E Extended-Address Indicator (1 bit) Indicates (when 1) that the word following the instruction will be accessed as an extended-address part of the instruction.

- XR Index Register Designator (3 bits) Designates 1 of 7 general registers as an X-Register during instruction execution.

- K Constant (4 bits) Designates length of a Shift command, or an immediate constant. Also used to enable interrupts.

- F Status Bit-Pattern (7 bits) Comprises the bit pattern for changing control states for certain Control instructions.

#### ADDRESSING

SUE 1110 Processor develops a 16-bit operand address based on the mode that is selected by the instruction class code and other fields of the instruction word format.

#### BYTE-WORD ADDRESSING

A bit (B) in the instruction word specifies if the operand is to be a byte (8 bits) or a word (16 bits) in general register instructions. If B = 1 and bit zero of the effective operand address is ZERO, the left byte (bits 15 through 8) is used; the right byte (bits 7 through 0) is used if bit zero is ONE. If B = 0, a word operand is requested and the address of the word is treated as an even-numbered byte address.

#### ABSOLUTE AND RELATIVE ADDRESSING

Branch instructions use the relative displacement method to develop the branch address. The D field of the instruction is an 8-bit (7 bits plus sign) number that specifies a branch within +127 or -128 words (not bytes) from the current location. Negative numbers are represented in twos complement form.

Control instructions use the relative displacement as well as the absolute addressing modes. Bit B of the instruction word, when set to a ONE, selects the relative mode and, when ZERO, selects the absolute mode. In the absolute address mode the D field of the instruction is an 8 bit number that specifies direct address of the first 256 words (not bytes) of memory.

#### EXTENDED ADDRESSING

6

When the E bit of the instruction is a ONE, the word following the instruction becomes the base address and is used to develop the operand address. When E = 0 the base address is ZERO.

GB13020009103

#### INDEXING

Content of one of the seven general registers may be selected as an index register. The XR field of the instruction selects the register. When the XR field is all zeros, no indexing is specified. If neither extended addressing nor indexing is called for (i.e. bits 3-0 all ZEROs) then no address is specified and an unimplemented instruction trap is generated.

Two types of indexing are used:

Base Relative Indexing (indexing relative to the base address of the computer or user program). - In this type of indexing, the index register contains the complete address of the desired memory location. Base relative indexing together with autoincrement or autodecrement provide generalized push down and pop up stack processing capabilities.

Table Indexing (indexing relative to the base address of a table). - In this type of indexing the index register contains the variable n to fetch the quantity located at TABLE + n.

#### AUTO INCREMENTING AND DECREMENTING

Within the general register instructions, separate class codes are used to provide the option for automatic increment or decrement of the index register selected by the XR field of the instruction. When autodecrement is specified, the content of the index register is decremented before the operand address is generated. When autoincrement is specified, the content of the selected index register is incremented after the operand address is generated.

ONE is subtracted or added to the content of the index register when the instruction specifies a byte operand with autodecrement or autoincrement. TWO is subtracted or added when the instruction specifies a word operand with autodecrement or autoincrement.

#### INDIRECT ADDRESSING

If indirect bit I of the instruction is set to a ONE, the address developed by the processor points to the address of the operand.

Multi-level indirect addressing is provided in the word mode only. The processor tests the least significant bit of the indirect address. If this bit is a ONE, and the word mode is specified, the word pointed-to is also treated as an indirect address. If the least significant bit of the address is a ZERO, the processor stops the multi-level indirect addressing for this instruction. If the processor counts up to 16 levels of indirect addressing, an unimplemented instruction self-interrupt is generated and the instruction is trapped.

Only single level indirect addressing is available in the byte mode because the least significant bit of the operand address specifies left or right byte.

#### REGISTER, IMMEDIATE AND LITERAL OPERANDS

The data-to-accumulator (class code 4) general instruction provides for selection of register, literal or immediate operands. The register operand is the register specified by the XR field, and can be the program counter if XR=0. The literal operand may be the 16-bit word following the instruction or the 16-bit word following the instruction plus the contents of XR. An immediate operand is the 4-bit value in the instruction's K field.

#### COMBINATION ADDRESSING MODES

8

In most general register instructions, combinations of addressing modes may be specified to yield fourteen useful functions for memory operand selection. The processor develops addresses in combinations of the following in the sequence shown:

> Extended Address Autodecrement the Index Indexed Indirect Autoincrement the Index

Autodecrement and autoincrement functions apply to the contents of the general register selected by the XR field of the instruction.

On autodecrement the content of the index register is decremented by one for byte addresses or by two for word addresses before the index register contents is used as an index value. On autoincrement the content of the index register is incremented by one or two after it is used as an index value.

If the XR field of an instructions is all ZEROs, no indexing is specified. However, auto-increment or auto-decrement specified with a ZERO XR field affects the program counter.

Table 1 contains a summary of the fourteen combinational addressing modes.

| Address Mode                                         | M<br>Effective<br>Address | XR<br>Index<br>Register | Assembler<br>Mnemonic |  |

|------------------------------------------------------|---------------------------|-------------------------|-----------------------|--|

| Extended                                             | Α                         | -                       | А                     |  |

| Extended, Indexed                                    | A + X                     |                         | A(R)                  |  |

| Extended, Indexed, Autoincrement                     | A + X                     | X + e                   | A(R+)                 |  |

| Extended, Autodecrement, Indexed                     | A + X - e                 | Х-е                     | A(-R)                 |  |

| Indexed                                              | X                         | -                       | (R)                   |  |

| Indexed, Autoincrement                               | X                         | X + e                   | (R+)                  |  |

| Autodecrement, Indexed                               | Х-е                       | Х-е                     | ( <b>-</b> R)         |  |

| Extended, Indirect                                   | [A]                       |                         | *A                    |  |

| Extended, Indexed, Indirect                          | [A + X]                   | <u>-</u>                | *A(R)                 |  |

| Extended, Indexed, Autoincrement, Indirect           | [A + X]                   | X + e                   | *A(R+)                |  |

| Extended, Autodecrement, Indexed, Indirect           | $\left[A + X - e\right]$  | Х-е                     | *A(-R)                |  |

| Indexed, Indirect                                    | [x]                       | -                       | *(R)                  |  |

| Indexed, Autoincrement, Indirect                     | [x]                       | X + e                   | *(R+)                 |  |

| Autodecrement, Indexed, Indirect                     | [X - e]                   | Х-е                     | *(-R)                 |  |

| NOTES: A - 16-bit word following instruction         | 1n                        | L                       | 1                     |  |

| X - Content of General register selected by XR field |                           |                         |                       |  |

| e - A ONE if byte address, a TWO if word address     |                           |                         |                       |  |

| [] - 16-bit word at address specified                | l in b <b>rac</b> kets    | •                       | •<br>•                |  |

| Table 1. | Com | bination | Addressi | ng | Modes |

|----------|-----|----------|----------|----|-------|

|          |     |          |          |    |       |

#### SPECIAL ADDRESSES

Even addresses 61,440 to 65,534 (hexadecimal F000 to FFFE) are reserved for addressing of system hardware registers within SUE system modules. The odd numbered addresses in this range are not used. Each system module is assigned a set of even (word) addresses as shown in table 2.

Addressing a system register for either a read or write function is allowed by master modules. The slave module always transmits or receives 16 data bits. If the selected register is less than 16 bits in length, the data is transmitted in the least significant bit positions and the most significant, unused, bit positions are ZEROS.

| _ |                            |                                                                   |

|---|----------------------------|-------------------------------------------------------------------|

|   | Addresses<br>(Hexadecimal) | Module Assignment                                                 |

|   | F000-F7FE                  | Reserved for special memory assignments                           |

| Γ | F800                       | I/O Device Controller #1, Status Register                         |

|   | F802                       | I/O Device Controller #1, BTA Address Register                    |

|   | F804                       | I/O Device Controller #1, BTA Block Length Register               |

|   | F806                       | I/O Device Controller #1, Control Register                        |

|   | F808                       | I/O Device Controller #1, Data Register                           |

|   | F80A-F80E                  | Reserved for I/O Device Controller #1                             |

|   | F810-F81E                  | I/O Device Controller #2 as in #1                                 |

|   | F820-FAFE                  | Reserved for I/O Device Controllers as in #1.<br>(see Appendix C) |

| F | FB00-FBFE                  | Auto Load Memory                                                  |

|   | FC00-FEFE                  | Reserved for Auto Load                                            |

|   | FF00                       | Central Processor (#0) Register 0, (Program<br>Counter)           |

|   | FF02-FF0E                  | Central Processor (#0), General Registers 1-7                     |

|   | FF10                       | Central Processor (#0), Status Indicators                         |

|   | <b>FF12</b>                | Central Processor (#0), Instruction Register                      |

|   | FF14-FF1C                  | Reserved for Central Processor #0                                 |

|   | FF1E                       | Central Processor (#0), Control Flip-Flops                        |

|   | FF20-FF3E                  | Processor #1, same set as #0                                      |

|   | FF40-FF5E                  | Processor #2, same set as #0                                      |

|   | FF60-FF7E                  | Processor #3, same set as #0                                      |

|   | FF80                       | Control Panel #1 Address Register-Attention Interrupt             |

|   | FF82                       | Control Panel #1 Data Register                                    |

|   | FF84-FF86                  | Control Panel #2 as in #1                                         |

|   | FF88-FF8A                  | Control Panel #3 as in #1                                         |

|   | FF8C-FF8E                  | Control Panel #4 as in #1                                         |

|   | FF90-FFFF                  | Reserved for other System Modules to be assigned.                 |

|   |                            |                                                                   |

#### Table 2. Special Addresses

#### STATUS INDICATORS

SUE 1110 Processor has a 16-bit status indicator register. Status indicators may be affected by execution of general register and shift instructions. This is indicated by their symbol in INSTRUCTION DESCRIPTIONS. The status indicators may also be set or reset with special control instructions.

The status bit position within the status register, symbol, name, and description are as follows:

| Bit            | Symbol         | Name and Description                                                                                                                                                                                                        |

|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | EQ             | Equal - In a compare operation, the source operand equals the target operand.                                                                                                                                               |

| 1              | GT             | Greater-Than - In a compare operation, the source operand is greater than the target operand.                                                                                                                               |

| 2              | OV             | Overflow - Set during Add, Subtract, or Arithmetic<br>Left Shift if the Carry out of bit 15 is different than<br>the Carry in to bit 15. If the set condition is not<br>caused, V remains unchanged.                        |

| 3              | CY .           | Carry – Receives the Carry out of bit 15 during an<br>Add, Subtract, Arithmetic Left Shift, or Left Linked<br>Shift. Reset during an Arithmetic Right Shift.<br>Receives bit 0 shifted out from a Right Linked Shift.       |

| 4              | F1             |                                                                                                                                                                                                                             |

| 5              | F2             | Flags 1, 2, or 3 - Programmable flag bits.                                                                                                                                                                                  |

| 6              | F3)            |                                                                                                                                                                                                                             |

| 7<br>          | LP             | Loop Complete – Set if content of register selected<br>by XR field equals ZERO at the completion of an<br>Autoincrement or Autodecrement instruction. Reset<br>if content of XR is NOT ZERO.                                |

| · 8            | OD             | Odd - For all general register instructions except<br>Compare, the Odd indicator receives the least signi-<br>ficant bit of the result.                                                                                     |

| 9              | ZE             | Zero – For all general register instructions except<br>Compare, set if the result is ZERO and reset if<br>NOT ZERO.                                                                                                         |

| 10             | NG             | Negative – Receives the most significant bit of the result of any general register instruction except Compare.                                                                                                              |

| 11             | <b>A</b>       | Active - Indicates that the processor is executing<br>instructions. A is set unless the processor is<br>quiescent.                                                                                                          |

| 12<br>13<br>14 | M1<br>M2<br>M3 | Interrupt Mask - Bits M1 through M4 correspond to<br>system interrupts 1 through 4. When any bit is set<br>or reset, respectively, the Bus Controller is requested<br>to ignore or allow interrupt requests for the corres- |

| 15             | M4 )           | ponding vector.                                                                                                                                                                                                             |

#### GB13020009103

#### INSTRUCTION DESCRIPTIONS

#### GENERAL REGISTER INSTRUCTIONS

Class codes 1 through 7 specify the general register instructions. They are all two-operand instructions with one set of eight general operations. In the definitions of these operations, the terms target (T) and source (S) are used. The target is the register or memory cell to be modified, the source is the register or memory cell used as an operand that is to remain unchanged.

GENERAL OPERATIONS. - The OP field of the instruction selects the operation for each class of general register instruction as follows:

| OP Code<br>(Hexadecimal | Operation       | Description                                                                                                                               | Status<br>Indicators<br>Affected |

|-------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 0                       | MOVe            | Transfer the source operand to the target operand.<br>(S) $\rightarrow$ (T)                                                               | NG, ZE, OD                       |

| 1                       | SUBtract        | Subtract the source operand from<br>the target operand and store the<br>result in the target operand.<br>$-(S) + (T) \rightarrow (T)$     | CY,OV,NG;ZE,<br>OD               |

| 2                       | ADD             | Form the sum of the source (S)<br>and target (T) operands and<br>store in (T).<br>(S) + (T) $\rightarrow$ (T)                             | CY, OV, NG, ZE,<br>OD            |

| 3                       | AND             | Form the logical product of the source and target operands and store the result in the target operand.<br>(S). AND. (T) $\rightarrow$ (T) | NG, ZE, OD                       |

| 4                       | Inclusive<br>OR | Form the logical sum of the source and target operands and store in the target operand.<br>(S).OR. (T) $\rightarrow$ (T)                  | NG,ZE,OD                         |

NG, ZE, OD

5

6

7

| Exclusive | Form the logical difference of the |

|-----------|------------------------------------|

| OR        | source and target operands and     |

|           | store in the target operand.       |

|           | (S). EOR. (T) $\rightarrow$ (T)    |

CoMPare Compare logical, the source operand to the target operand. Register contents and memory contents are not affected. GT, EQ

|                | $\overline{\mathrm{GT}}$ | EQ |

|----------------|--------------------------|----|

| If $(S) < (T)$ | 0                        | 0  |

| If $(S) = (T)$ | 0                        | 1  |

| If $(S) > (T)$ | 1                        | 0  |

#### NOTE

Bit 15 of each word is considered a magnitude bit, not a sign bit. The compare result is unsigned based on the 16-bit magnitude.

TeST

Form the logical product of the NG, ZE, OD source and target operands. Register and memory contents are not affected. If (S). AND. (T) = 0, SET ZE, RESET NG, OD

If (S).AND. (T)  $\neq$  0, RESET ZE

If (S) .AND. (T) is odd, SET OD (odd implies bit 0 is set)

If (S) .AND. (T) is negative, SET NG (negative implies bit 15 is set)

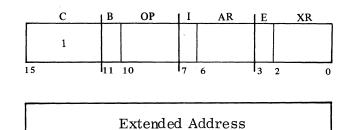

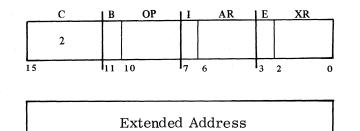

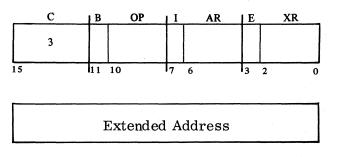

GENERAL REGISTER INSTRUCTION WORD FORMATS. - The instruction word formats used for the general register instructions is shown in table 3.

| General Register Classes*                                                                                                                                                                                                                                              |                                                                                                                                          | <sup>H</sup> 1                   |              | $H_2$                |     | $^{ m H}_{ m 3}$ | H <sub>4</sub> |       |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------|----------------------|-----|------------------|----------------|-------|--|--|--|

|                                                                                                                                                                                                                                                                        |                                                                                                                                          | $15 \ 14 \ 13 \ 12$              | 11           | 10 9 8               | 7   | 654              | 3              | 2 1 0 |  |  |  |

| Accumulator                                                                                                                                                                                                                                                            | Auto Decrement                                                                                                                           | C=1                              | В            | OP                   | I   | AR               | Е              | XR    |  |  |  |

| То                                                                                                                                                                                                                                                                     | Auto Increment                                                                                                                           | C=2                              | B            | OP                   | Ι   | AR               | Ε              | XR    |  |  |  |

| Memory                                                                                                                                                                                                                                                                 |                                                                                                                                          | C=3                              | В            | OP                   | Ι   | AR               | Ε              | XR    |  |  |  |

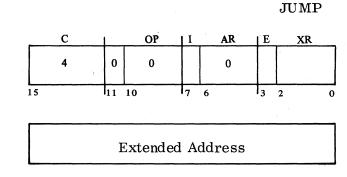

| Jump to Subro                                                                                                                                                                                                                                                          | outine                                                                                                                                   | C=4                              | 0            | 0                    | Ι   | AR               | Ε              | XR    |  |  |  |

| Jump                                                                                                                                                                                                                                                                   |                                                                                                                                          | C=4                              | 0            | 0                    | Ι   | 0                | Ε              | XR    |  |  |  |

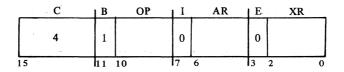

| Data to                                                                                                                                                                                                                                                                | <u>{Literal/Register</u>                                                                                                                 | C=4                              | 1            | OP                   | 0   | AR               | E              | XR    |  |  |  |

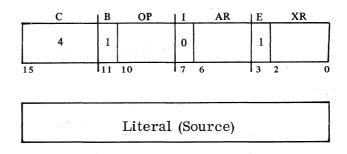

| Accumulator                                                                                                                                                                                                                                                            |                                                                                                                                          | C=4                              | 1            | OP                   | 1   | AR               |                | K     |  |  |  |

| Memory                                                                                                                                                                                                                                                                 | (Auto Decrement                                                                                                                          | C=5                              | B            | OP                   | Ι   | AR               | E              | XR    |  |  |  |

| То                                                                                                                                                                                                                                                                     | Auto Increment                                                                                                                           | <u>C=6</u>                       | B            | OP                   | I   | AR               | E              | XR    |  |  |  |

| Accumulator                                                                                                                                                                                                                                                            | (                                                                                                                                        | C=7                              | В            | OP                   | Ι   | AR               | Ε              | XR    |  |  |  |

| NOTES:<br>C                                                                                                                                                                                                                                                            | Class Codes 1-7                                                                                                                          |                                  |              |                      |     |                  |                |       |  |  |  |

| OP                                                                                                                                                                                                                                                                     | Operation Code:0MOVMove1SUBSubtraction2ADDAddition3ANDLogical Product4IORLogical Inclusive OR5EORLogical Exclusive OR6CMPCompare7TSTTest |                                  |              |                      |     |                  |                |       |  |  |  |

| В                                                                                                                                                                                                                                                                      | Word when 0, Byte when 1                                                                                                                 |                                  |              |                      |     |                  |                |       |  |  |  |

| Ι                                                                                                                                                                                                                                                                      | Indirect when 1                                                                                                                          |                                  |              |                      |     |                  |                |       |  |  |  |

| AR                                                                                                                                                                                                                                                                     | Accumulator Regis                                                                                                                        | ster designator                  | c (0-        | -7)                  |     |                  |                |       |  |  |  |

| E                                                                                                                                                                                                                                                                      | Extended or two-w                                                                                                                        | ord instructio                   | n wł         | nen 1                |     |                  |                |       |  |  |  |

| XR                                                                                                                                                                                                                                                                     | Index Register des                                                                                                                       | ignator (0-7),                   | no           | indexing             | ç N | hen 0            |                |       |  |  |  |

| К                                                                                                                                                                                                                                                                      | 4-bit Immediate da                                                                                                                       | ata constant                     |              |                      |     |                  |                |       |  |  |  |

| register is se<br>for class 4, F                                                                                                                                                                                                                                       | XR≠0, XR provides<br>lected (XR=0), and<br>Register, where the                                                                           | E=0, an instru<br>PC is the sour | ictio<br>rce | on trap c<br>operand | •   | curs, ex         | cep            | ot    |  |  |  |

| For E=1, XR=0, the next word provides the entire operand address. If E=1 and XR $\neq 0$ , indexing operation is specified. In this case, the content of (XR) is added to the next word to produce the effective address of the memory operand or an indirect address. |                                                                                                                                          |                                  |              |                      |     |                  |                |       |  |  |  |

| Table 3. Ge | neral Registe | r Instruction | Word | Formats |

|-------------|---------------|---------------|------|---------|

|-------------|---------------|---------------|------|---------|

\*SUE 1112 Instruction Set contains more instructions in class code 4.

L

SUE G3

The following additional symbols are used in the instruction definitions:

- () Contents of

- M effective operand address

- PC Program Counter, general register 0.

- P Current instruction address

#### General Register Instruction Definitions

ACCUMULATOR TO MEMORY, AUTO DECREMENT

(AR) operates on (M). (XR) is decremented before use.

ACCUMULATOR TO MEMORY, AUTO INCREMENT

(AR) operates on (M). (XR) is incremented after use.

ACCUMULATOR TO MEMORY

(AR) operates on (M). (XR) is not affected.

JUMP TO SUBROUTINE

#### JS BR

P + 2 replaces (AR) for E = 0 and P + 4 replaces (AR) for E = 1. (M) operates on PC (content of general register 0). Thus, the return address is stored in AR and PC is set to the jump-location address.

(M) operates on PC, setting it to the jump-location address. The jump function is the same as a MOV (M) to PC, but does not affect status indicators.

#### DATA TO ACCUMULATOR, INDEX REGISTER

A register-to-register instruction. (XR) operates on (AR).

DATA TO ACCUMULATOR, LITERAL

The word following the instruction is the literal source operand. It operates on (AR). If XR is not 0, then (XR) is added to the literal before operating on (AR).

#### DATA TO ACCUMULATOR, IMMEDIATE

K operates on (AR). K is the 4-bit immediate constant operand.

MEMORY TO ACCUMULATOR, AUTO DECREMENT

(M) operates on (AR). (XR) is decremented before use.

## MEMORY TO ACCUMULATOR, AUTO INCRÉMENT

(M) operates on (AR). (XR) is incremented after use.

MEMORY TO ACCUMULATOR

Extended Address

(M) operates on (AR). (XR) is not affected.

GENERAL REGISTER INSTRUCTION TIMES. - Instruction execution times depend on:

Operand addressing modes General operation code Program memory access and cycles INFIBUS availability

Table 4 contains a summary of typical general register instruction times assuming the INFIBUS is available to the processor and a SUE 3311 Core Memory is used for instruction and data storage. A memory cycle time of 850 nanoseconds, read access time of 750 nanoseconds, and a write access time of 550 nanoseconds is used. Access is the total time to access both the bus scheduler and memory. Microprogram steps of 160 nanoseconds are used for arithmetic operations and 130 nanoseconds for non-arithmetic operations.

| Table 4. SUE 1110 | (Basic) General | l Register | Instruction | Times |

|-------------------|-----------------|------------|-------------|-------|

|-------------------|-----------------|------------|-------------|-------|

| Indexed<br>3<br>3.94<br>4.03<br>3.70<br>3.35<br>, | Auto-<br>Increment<br>2<br>4.81<br>4.90<br>4.57<br>4.22 | Auto-<br>Decrement<br>1<br>4.81<br>4.90<br>4.57<br>4.22 |

|---------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|

| 3.94<br>4.03<br>3.70<br>3.35                      | 4.81<br>4.90<br>4.57                                    | 4.81<br>4.90<br>4.57                                    |

| 4.03<br>3.70<br>3.35                              | 4.90<br>4.57                                            | 4.90<br>4.57                                            |

| 3.70<br>3.35                                      | 4.57                                                    | 4.57                                                    |

| 3.35                                              |                                                         |                                                         |

|                                                   | 4.22                                                    | 4.22                                                    |

| 4                                                 |                                                         |                                                         |

| 4                                                 |                                                         |                                                         |

|                                                   |                                                         |                                                         |

| 2.79                                              | _                                                       | -                                                       |

| 2.85                                              | _                                                       |                                                         |

| 3.93                                              | -                                                       |                                                         |

| 4.12                                              |                                                         | · _                                                     |

| 4                                                 | -                                                       | 2 -                                                     |

| 2.50                                              |                                                         |                                                         |

| 2.69                                              | -                                                       | - <sup>1</sup>                                          |

| 2.50                                              | -                                                       | -                                                       |

|                                                   |                                                         |                                                         |

| 7                                                 | 6                                                       | 5.                                                      |

| 3.35                                              | 4.09                                                    | 4.09                                                    |

| 3.64                                              | 4.38                                                    | 4.38                                                    |

| 3.67                                              | 4.41                                                    | 4.41                                                    |

| 3.35                                              | 4.09                                                    | 4.09                                                    |

|                                                   |                                                         |                                                         |

|                                                   | 2.79<br>2.69<br>2.50<br>7<br>3.35<br>3.64<br>3.67       | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$   |

To compute the actual instruction execution time, it is necessary to add the time increments shown in Table 4 for each selected addressing mode. The minimum times shown in the table assume an indexed addressing mode. A more complete table of general instruction times is given in Appendix A.

For example, an ADD register-to-register instruction requires 2.79 microseconds with the SUE core memory. An ADD memory-to-accumulator instruction requires 3.64 microseconds when the operand address is held in an index register. If the address is located in the next word location (extended instruction mode), the time is 3.77 microseconds. Indexing the extended address does not add time to the instruction. Indirect addressing adds 1.14 microseconds for the first level and 1.01 for each subsequent level.

#### BRANCH CONDITIONAL INSTRUCTIONS

Thirteen conditions can be tested by branch conditional (TRUE or FALSE) instructions. Each condition can be tested to produce a branch or a fallthrough to the next instruction for either state (TRUE for class code 9 and FALSE for class code 8). The condition status is determined by testing the status indicators and programmable flags affected by the last operation.

GB13020009103

BRANCH CONDITIONS. – Following is a list of the 13 branch conditions and their meaning when TRUE.

| <u>T Field</u> | Condition        | Symbol        | Meaning (TRUE Condition)                                                                                                                              |

|----------------|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0              | Unconditional    | UN            | The branch is made unconditionally.                                                                                                                   |

| 1              | Equal            | EQ            | The latest compare operation found the two operands to be equal to each other.                                                                        |

| 2              | Greater-Than     | GT            | The latest compare operation found the source operand to be greater than the target operand.                                                          |

| 3              | Overflow         | OV            | An add, subtract, or shift operation produced a result outside of the range $-2^{15} \le R \le + (2^{15} - 1)$ since overflow was last reset.         |

| 4              | Carry            | СҮ            | The latest add, subtract, or shift opera-<br>tion produced a carry out of the most<br>significant end of the arithmetic unit.                         |

| 5              | Flag 1           | F1            | These three programmable flags can be                                                                                                                 |

| 6<br>7         | Flag 2<br>Flag 3 | F2<br>F3      | set or reset by a set or reset status indicator instruction.                                                                                          |

| 8              | Loop Complete    | LP            | This indicator is set if the result of the<br>latest autoincrement or autodecrement<br>of any index register equals zero; other-<br>wise it is reset. |

| 9              | Odd              | OD            | The result of the latest general operation (except compare), or shift operation is an odd number (Bit $0 = 1$ ).                                      |

| А              | Zero             | ZE            | The latest general operation (except compare), or shift operation results in all zeros.                                                               |

| В              | Negative         | NG            | Result of the latest general operation<br>(except compare), or shift operation is<br>a negative number (Bit 15 = 1).                                  |

| С              | Less-Than        | $\mathbf{LT}$ | In the latest compare operation, the source operand was less than the target operand.                                                                 |

| D, E, F        |                  |               | Cause an unimplemented instruction trap.                                                                                                              |

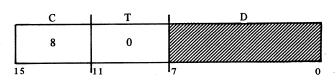

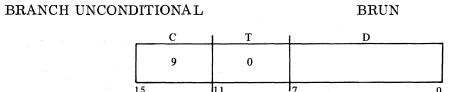

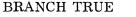

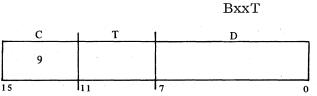

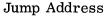

#### BRANCH INSTRUCTION WORD FORMATS. -

|                      | Н1          | H <sub>2</sub> | H <sub>3</sub> | H <sub>4</sub> |

|----------------------|-------------|----------------|----------------|----------------|

|                      | 15 14 13 12 | 11 10 9 8      | 7 6 5 4        | 3 2 1 0        |

| No Operation         | C= 8        | 0              |                |                |

| Branch Unconditional | C= 9        | 0              | I              | )              |

| Branch False         | C= 8        | Т              | I              | )              |

| Branch True          | C= 9        | Т              | I              | )              |

- D Displacement word address in twos complement form.

- T The T-Field specifies each Branch test. That is, which processor status indicator (if any) is to be tested. A list of each indicator, the corresponding value for T, and the operator assembler-mnemonics follows (z = T for true and F for false):

| T<br>(hexadecimal) | Indicator            | Assembler<br>Mnemonic |

|--------------------|----------------------|-----------------------|

|                    |                      | XX                    |

|                    |                      |                       |

| 1                  | Equal                | BÉQz                  |

| 2                  | Greater Than         | BGTz                  |

| 3                  | Overflow             | BOVz                  |

| 4                  | Carry                | BCYz                  |

| 5                  | Flag 1               | BF1z                  |

| 6                  | Flag 2               | BF2z                  |

| 7                  | Flag 3               | BF3z                  |

| 8                  | Loop Complete        | BLPz                  |

| 9                  | Odd                  | BODz                  |

| Α                  | Zero                 | BZEz                  |

| В                  | Negative             | BNGz                  |

| C                  | Less Than            | BLTz                  |

| D, E, F,           | (Instruction is trap | oped)                 |

#### **Branch Instruction Definitions**

#### NO OPERATION

NOPR

A one-word NO-OP which does not affect status indicators.

May 73

An unconditional (no testing) branch is made to the relative address specified by D.  $PC + 2 \times D$  replaces PC. D is in twos complement form with sign extended to represent a 16 bit number.

BRANCH FALSE BxxF

A Branch is made to the relative address specified by D if the indicator specified by T is false, or 0; otherwise, the next instruction in sequence is accessed.

A Branch is made to the relative address specified by D if the indicator specified by T is true, or 1; otherwise, the next instruction in sequence is accessed.

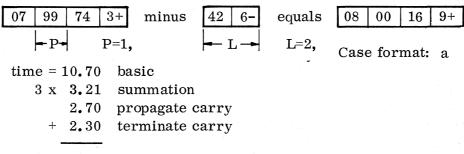

BRANCH INSTRUCTION TIMES. – Branch instruction execution times depend on whether or not the branch occurs, or the next instruction in sequence is executed. The branch-on-less-than operation (T = C) has different timing than the branch on other status bits. The branch instruction times are shown in Table 5.

| Word<br>All<br>Others**<br>1.75                                                                                 | Bra<br>1110<br>Basic | All<br>Others** |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|----------------------|-----------------|--|--|--|--|--|--|--|--|

| Others**                                                                                                        |                      |                 |  |  |  |  |  |  |  |  |

| 1.75                                                                                                            |                      |                 |  |  |  |  |  |  |  |  |

| the second se | <b>–</b> 1           | -               |  |  |  |  |  |  |  |  |

| -                                                                                                               | 2.72                 | 2.82            |  |  |  |  |  |  |  |  |

| 1.75                                                                                                            | 2.72                 | 2.82            |  |  |  |  |  |  |  |  |

| 1.75                                                                                                            | 2.72                 | 2.82            |  |  |  |  |  |  |  |  |

| 1.75                                                                                                            | 3.08                 | 3.21            |  |  |  |  |  |  |  |  |

| 1.88                                                                                                            | 3.08                 | 3.21            |  |  |  |  |  |  |  |  |

|                                                                                                                 |                      |                 |  |  |  |  |  |  |  |  |

Table 5. Branch Instruction Times

#### SHIFT INSTRUCTIONS

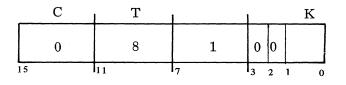

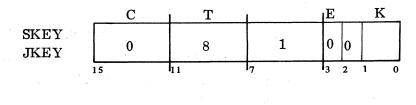

Class code A (hexadecimal) specifies a shift instruction. Up to 15 bit-position shifts may be specified in a single shift instruction. Two formats are provided to allow an option on the location of the shift count. When bit 7 of the instruction is a ZERO, the least significant four bits of the general register selected by XR, contains the shift count. When bit 7 is a ONE, the K field of the instruction word specifies the shift count.

#### SHIFT INSTRUCTION WORD FORMATS. -

Two single-word formats are used. The formats illustrated are for the shift count defined by (XR) or K, respectively.

|                 | н1              |    |    | H <sub>2</sub> |    |    |    | H <sub>3</sub> |   |   |   | H <sub>4</sub> |   |   |   |   |

|-----------------|-----------------|----|----|----------------|----|----|----|----------------|---|---|---|----------------|---|---|---|---|

|                 | 15              | 14 | 13 | 12             | 11 | 10 | 9  | 8              | 7 | 6 | 5 | 4              | 3 | 2 | 1 | 0 |

| Shift Indexed   | A <sub>16</sub> |    | 0  | OP             |    | 0  | AR |                |   | 0 |   | XR             |   |   |   |   |

| Shift Immediate | A <sub>16</sub> |    | 0  | OP             |    | 1  | AR |                |   | К |   |                |   |   |   |   |

- AR Accumulator Register designator (to be shifted).

- K Shift Count

XR Shift Count Source Register.

OP Shift Operation Code:

| <u>OP</u> |                                          | Bits<br>9 | 8 | Operation                    |

|-----------|------------------------------------------|-----------|---|------------------------------|

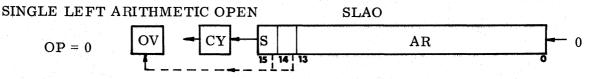

| 0         | 0                                        | 0         | 0 | Single Left Arithmetic Open  |

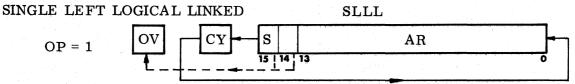

| 1         | n an | 0         | 1 | Single Left Logical Linked   |

| 2         | 0<br>1                                   | 1         | 0 | Single Left Logical Open     |

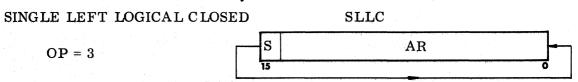

| 3         | 0                                        | 1         | 1 | Single Left Logical Closed   |

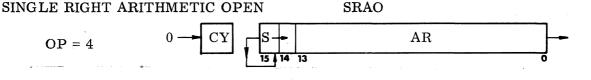

| 4         | 1                                        | 0         | 0 | Single Right Arithmetic Open |

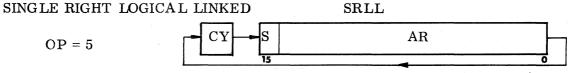

| 5         |                                          | 0         | 1 | Single Right Logical Linked  |

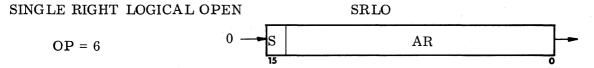

| 6         | 1                                        | 1         | 0 | Single Right Logical Open    |

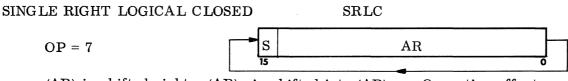

| 7         | 1                                        | 1         | 1 | Single Right Logical Closed  |

#### NOTE

SUE 1112 Processor provides double length shifts and also normalize instructions in addition to these basic single shifts.

Shift Instruction Definitions

(AR) bits are shifted left out of  $(AR)_{15}$  to the carry (CY) and zeros are shifted to  $(AR)_0$ . If any  $(AR)_{14}$  bit is different than  $(AR)_{15}$  preceding a shift, then the overflow indicator, OV, is set. Operation affects status indicators: CY, OV, NG, ZE, OD.

Carry (CY) is shifted into  $(AR)_0$  and  $(AR)_{15}$  is shifted into CY. If any  $(AR)_{14}$  bit is different than  $(AR)_{15}$  preceding a shift, then the overflow indicator, OV, is set. Operation affects status indicators: CY, OV, NG, ZE, OD.

(AR) is shifted left. For each bit shifted,  $(AR)_{15}$  is lost and  $(AR)_0$  equals 0. Operation affects status indicators: NG, ZE, OD.

(AR) is shifted left.  $(AR)_{15}$  is shifted into  $(AR)_0$ . Operation affects status indicators; NG, ZE, OD.

(AR) is shifted right. (AR)<sub>15</sub>, the sign bit, remains the same and is shifted into  $(AR)_{14}$ .  $(AR)_0$  bits shifted out are lost. Carry (CY) is reset. Operation affects status indicators: CY, NG, ZE, OD.

Carry (CY) is shifted into  $(AR)_{15}$ , and  $(AR)_0$  is shifted into CY. Operation affects status indicators: CY, NG, ZE, OD.

(AR) is shifted right. For each bit shifted,  $(AR)_0$  is lost and  $(AR)_{15}$  equals 0. Operation affects status indicators: NG, ZE, OD.

(AR) is shifted right.  $(AR)_0$  is shifted into  $(AR)_{15}$ . Operation affects status indicators: NG, ZE, OD.

SHIFT INSTRUCTION TIMING. - Shift instruction execution times depend on the number of single bit shifts (N) specified in either the K field (immediate) or the selected register, XR. The time is calculated by the formula:

$$T_{s} = 2.76 + (0.26)N$$

where N = 0, 1, ..., 15.

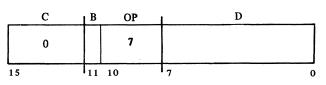

#### CONTROL INSTRUCTIONS

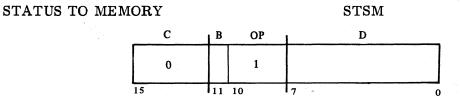

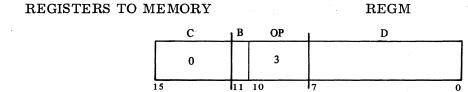

Class code  $0^1$  specifies a group of instructions that provide control of processor operation in a system. The instructions provide control of system interrupts, and storing and restoring status indicators and general registers.

#### CONTROL INSTRUCTION WORD FORMATS. -

|     |                |          | For    | mats           |                                          | Assembler<br>Mnemonic | Instructions                         |

|-----|----------------|----------|--------|----------------|------------------------------------------|-----------------------|--------------------------------------|

|     | H <sub>1</sub> | '        | н2     | H <sub>3</sub> | H <sub>4</sub>                           |                       |                                      |

| ſ   | 15 14 13 12    | 11       | 10 9 8 | 7 6 5 4        | 3 2 1 0                                  |                       |                                      |

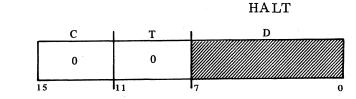

| Ī   | C= 0           |          | 0      |                |                                          | HALT                  | Halt                                 |

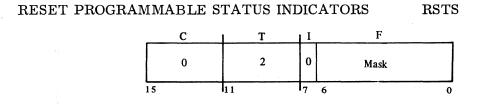

| Γ   | C= 0           |          | 2      | 0              | F                                        | RSTS                  | Reset Programmable Status Indicators |

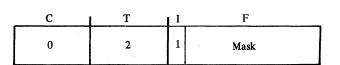

| Γ   | C= 0           |          | 2      | 1              | F                                        | SETS                  | Set Programmable Status Indicators   |

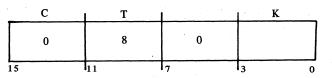

|     | C= 0           |          | 8      | 0              | K                                        | ENBL                  | Enable Interrupts                    |

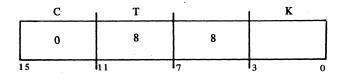

| ſ   | C= 0           | <b>—</b> | 8      | 4              | K                                        | ENBW                  | Enable and Wait                      |

| ſ   | C= 0           | Γ        | 8      | 8              | K                                        | DSBL                  | Disable Interrupt                    |

| Γ   | C= 0           |          | 8      | С              | K                                        | DSBW                  | Disable and Wait                     |

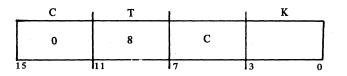

| ſ   | C= 0           | 1        | 8      | 4/C            | 0                                        | WAIT                  | Wait                                 |

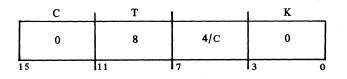

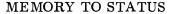

| ſ   | C= 0           | В        | 1      | D              |                                          | STSM                  | Status to Memory                     |

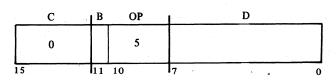

| ſ   | C= 0           | В        | 3      | D              |                                          | REGM                  | Registers to Memory                  |

| - 1 | C= 0           | B        | 4      | D              | an a | RETN                  | Return from Interrupt                |

| ſ   | C= 0           | В        | 5      | D              |                                          | MSTS                  | Memory to Status                     |

| ľ   | C= 0           | B        | 7      | D              |                                          | MREG                  | Memory to Registers                  |

#### Notes:

Shaded areas are ignored.