## INTERSIL IM6100 CMOS 12 BIT MICROPROCESSOR

# INNERSIL

# CONTENTS

| Introduction 3                                         |

|--------------------------------------------------------|

| Section I: Intersil IM6100 CMOS                        |

| 12 Bit Microprocessor 5                                |

| Introduction 6                                         |

| Pin Assignments 8                                      |

| Specifications                                         |

| Architecture 10                                        |

| Memory and Processor Instructions                      |

| Operate Instructions 14                                |

| Input/Output Transfer Instructions                     |

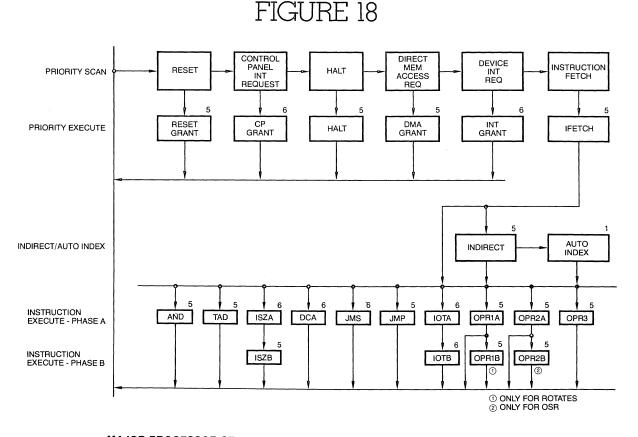

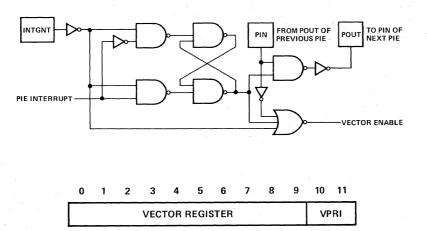

| Internal Priority Structure 23                         |

| PDP-8/E Compatibility 25                               |

| Applications 26                                        |

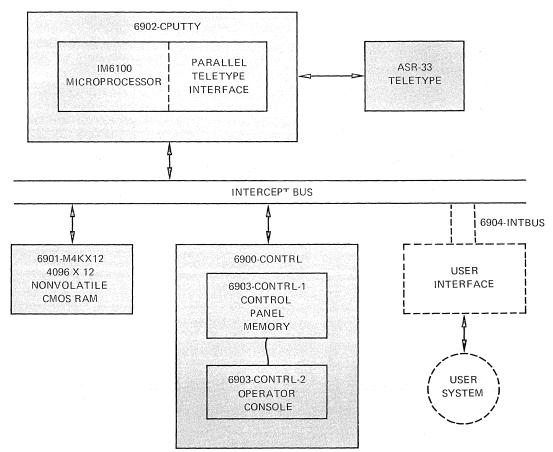

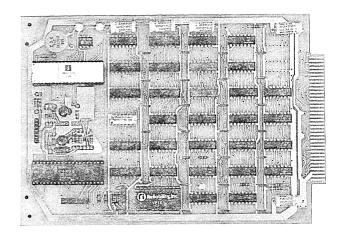

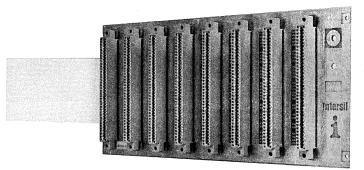

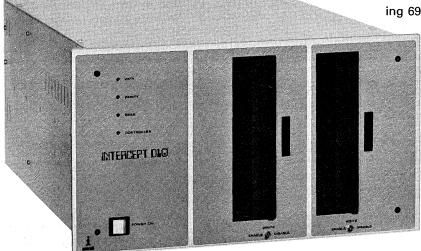

| Section II: Intercept Prototyping System               |

| Introduction                                           |

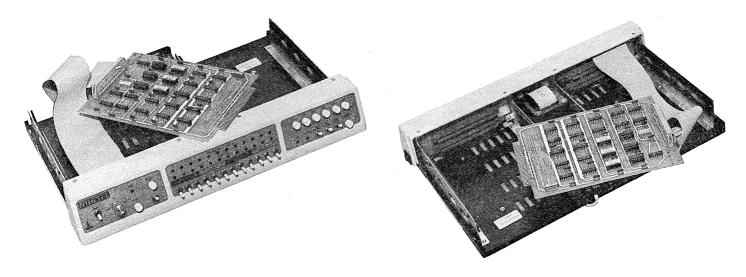

| Specifications 31                                      |

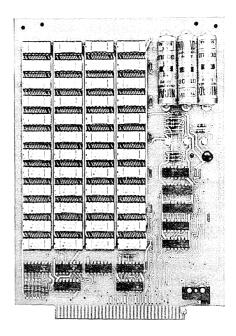

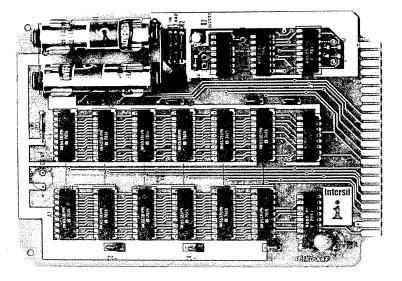

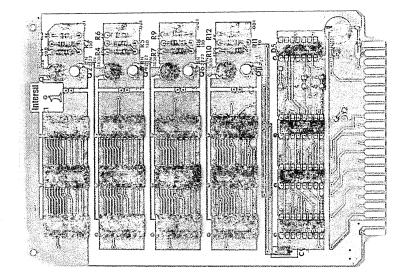

| Intercept Modules 32                                   |

| Software and Hardware Options                          |

| Appendix I—Edge Connector Pin Assignments 36           |

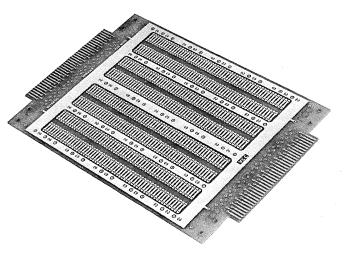

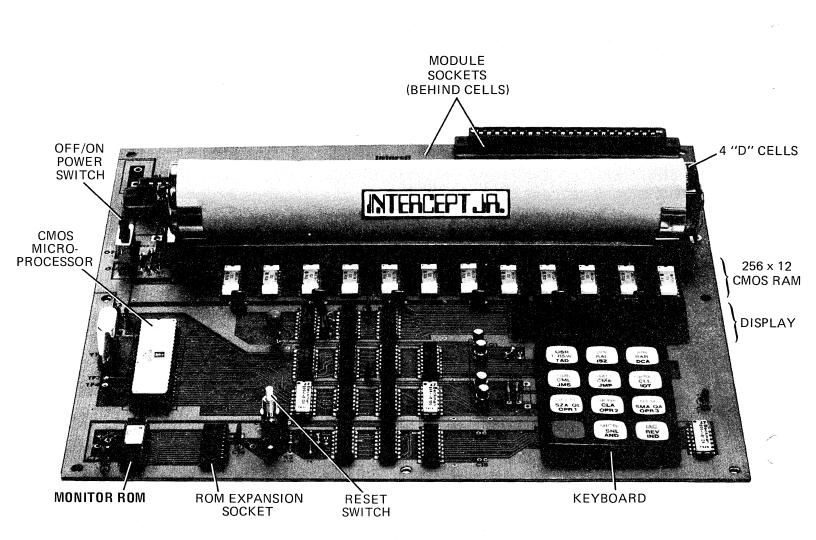

| Section III: Intercept Jr. Tutorial System             |

| Section IV: Intersil Data Sheets 43                    |

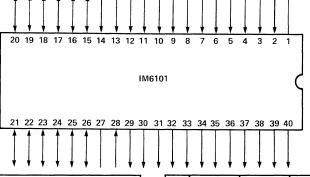

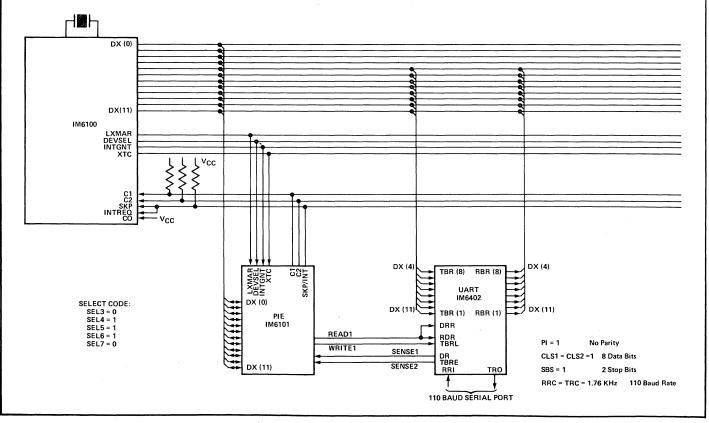

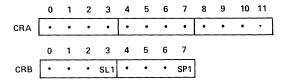

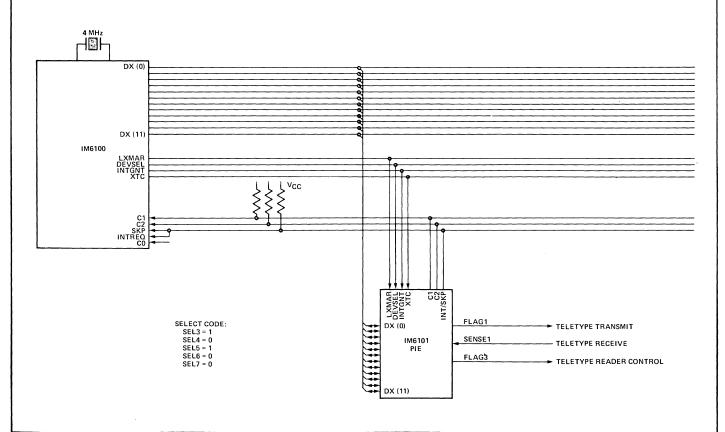

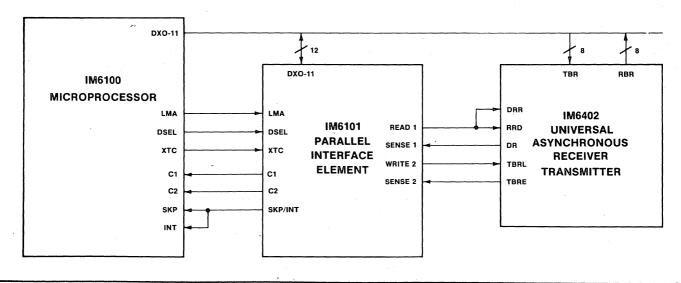

| IM6101/6101A CMOS Parallel Interface Element 44        |

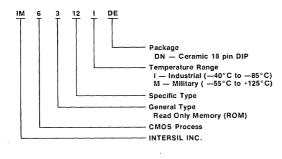

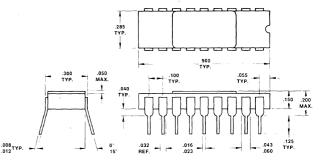

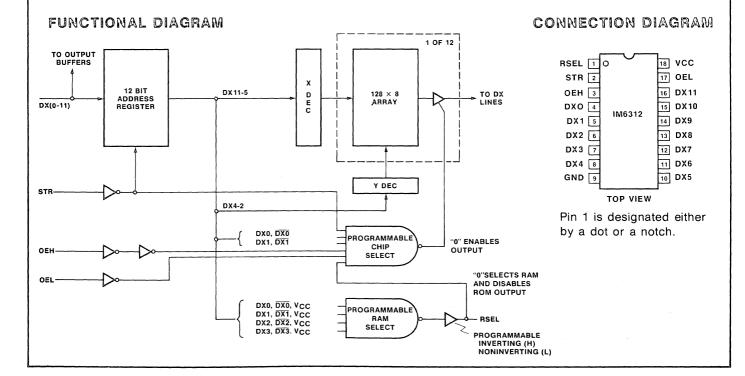

| IM6312/6312A CMOS ROM, 1024 Word x 12 Bit 59           |

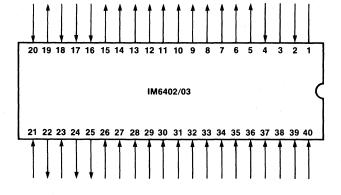

| IM6402/6403 CMOS/LSI UART63                            |

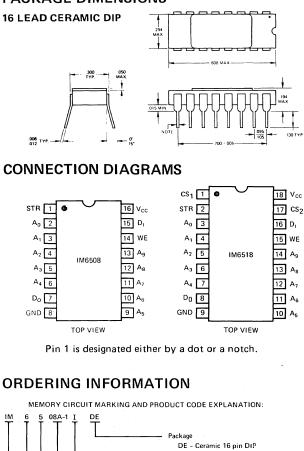

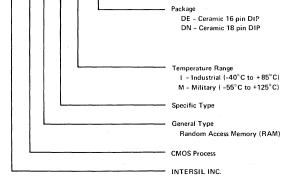

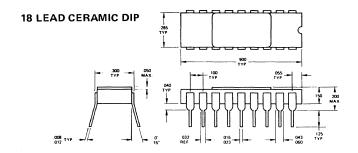

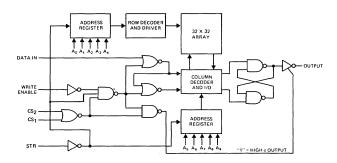

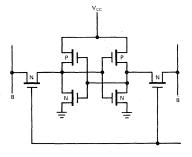

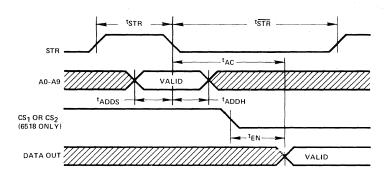

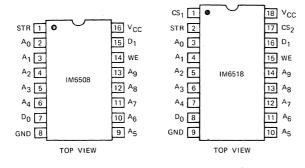

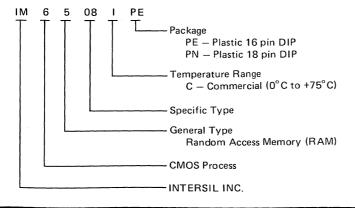

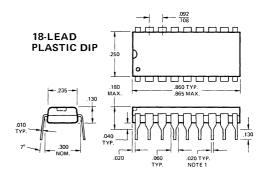

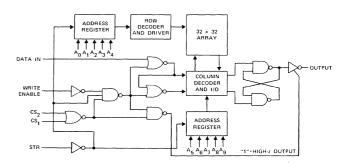

| IM6508/6518 CMOS RAM, 1024 Bit                         |

| IM6508C/6518C CMOS RAM, 1024 Bit                       |

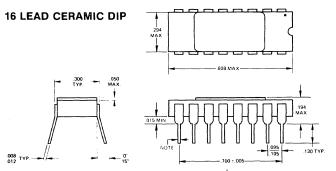

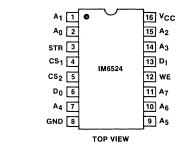

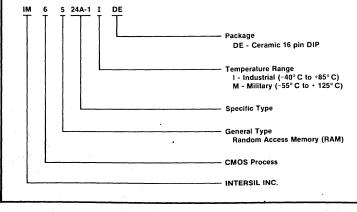

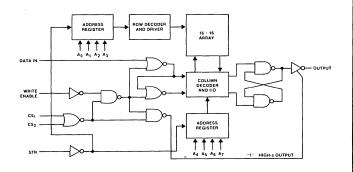

| IM6524/6524-1 CMOS RAM, 256 Bit                        |

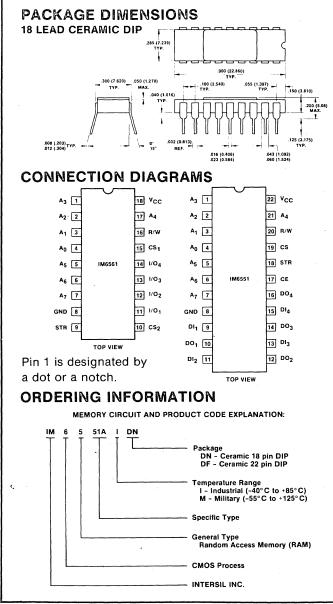

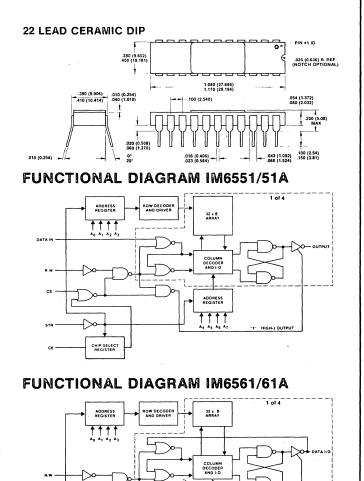

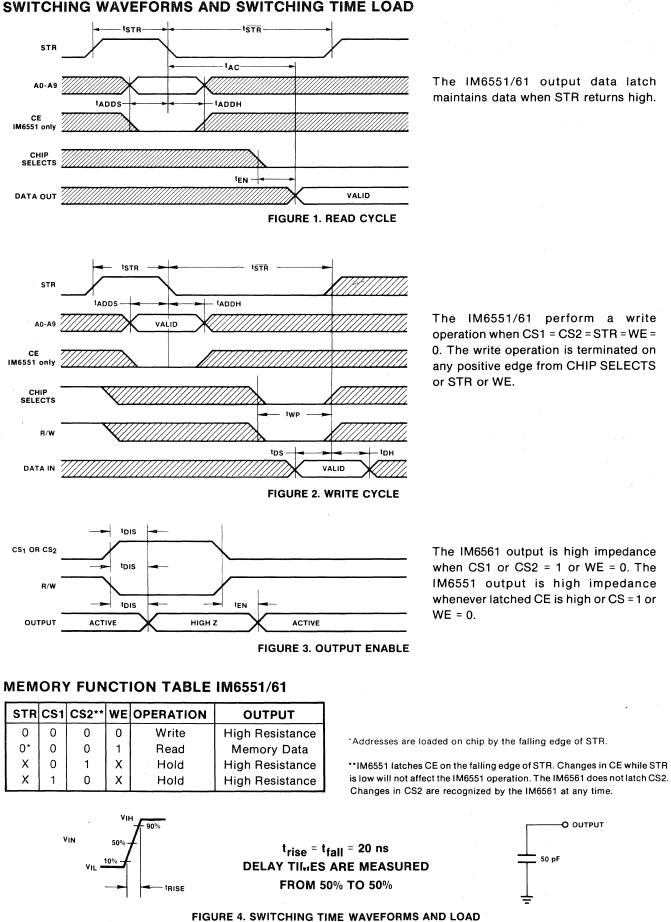

| IM6551/6561 CMOS RAM, 1024 Bit                         |

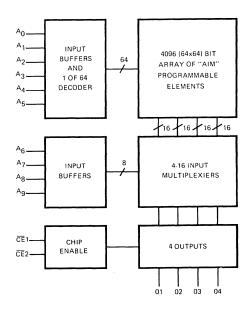

| IM56S06/56S26 Electronically Programmable              |

| ROM 4096 Bit 87                                        |

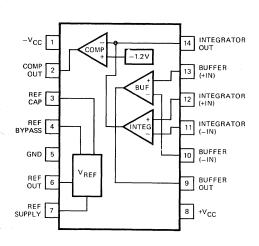

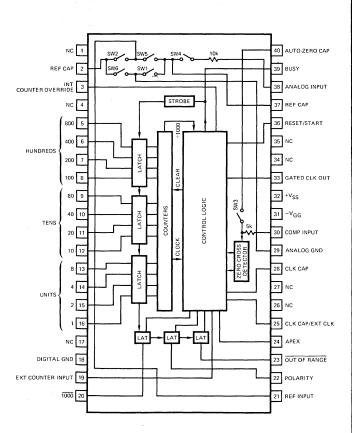

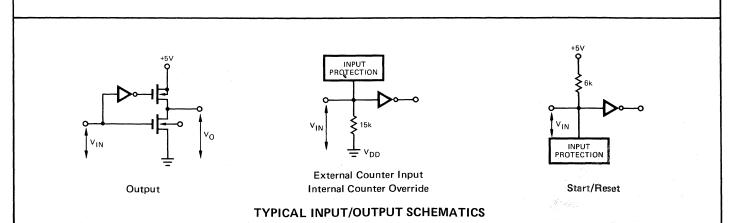

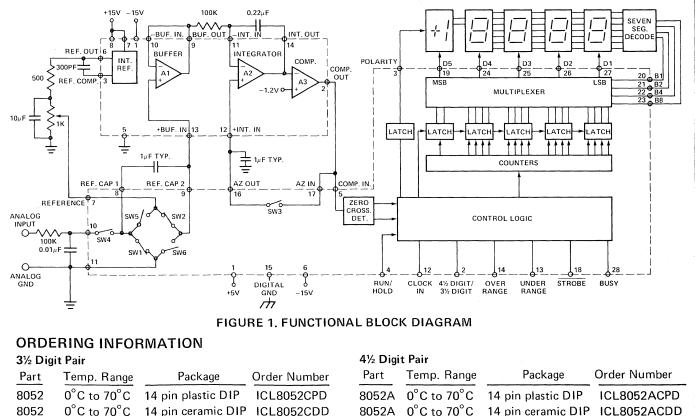

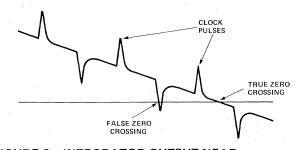

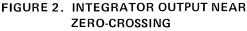

| 8052/7101 3 <sup>1</sup> / <sub>2</sub> Digit A/D Pair |

| 8052A/7103A 4½ Digit Pair 97                           |

| Section V: CMOS RAM Reliability Report105              |

1

• . . . .

2

## INTRODUCTION

Since its founding on July 26, 1967, Intersil, Inc. has become a company of many products and processes.

In addition to the digital CMOS devices covered in detail in this publication, Intersil has developed and markets a line of advanced linear products and semiconductor memories. TTL bipolar, MOS, metal-gate CMOS and silicon-gate CMOS processes are all represented in Intersil's line, with the significant design advantage that, because they were developed by a single forwardthinking company, many of the different kinds of devices and technologies produced by Intersil will work together for enhanced performance and greater efficiency and flexibility of the final developed product.

The Silicon Gate CMOS process, which was developed at Intersil over two years ago, offers a semiconductor structure resulting in packing densities which surpass the conventional metal gate process 3:1. Additionally, circuit performance is improved 2:1.

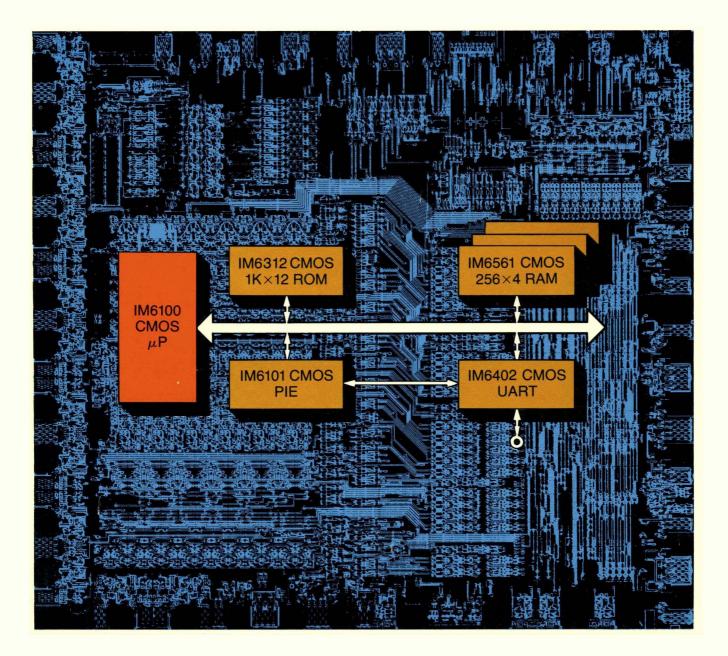

Mass production experience with the Silicon Gate CMOS process, through previously announced 256 and 1024 bit CMOS RAMs, has lead to the practicality of introducing the IM6100 microprocessor.

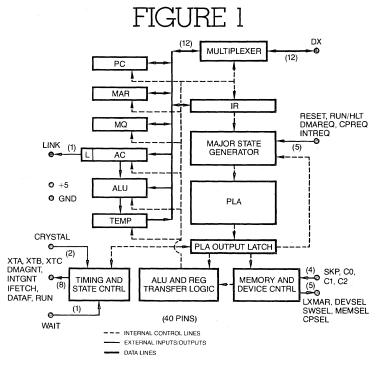

The IM6100 and IM6100A are single address, fixed word length, parallel transfer microprocessors using 12-bit, two's complement arithmetic. The processors recognize the instruction set of Digital Equipment Corporation's PDP8/E minicomputer. The internal circuitry is completely static and is designed to operate at any speed between DC and the maximum operating frequency. Two pins are available to allow for an external crystal thereby eliminating the need for clock generators and level translators. The crystal can be removed and the processor clocked by an external clock generator. A 12-bit memory-accumulator ADD instruction is performed in 5 $\mu$ sec by the IM6100 using a +5 volt supply and in 2.5 $\mu$ sec by the IM6100A using a +10 volt supply. The device design is optimized to minimize the number of external components required for interfacing with standard memory and peripheral devices.

Intersil cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an Intersil product. No other circuit patent licenses are implied. Intersil reserves the right to change without notice at any time the circuitry and specifications of any Intersil product represented in this document.

## SECTION I: INTERSIL IM6100 CMOS 12 BIT MICROPROCESSOR

# INTRODUCTION

## IM6100 MICROPROCESSOR

Since its founding on July 26, 1967, INTERSIL INC. has offered its customers advanced products utilizing the semiconductor industry's most technologically sophisticated processes for the manufacture of practical, economical devices.

The Silicon Gate CMOS process, which was developed at Intersil in 1972, offers a semiconductor structure resulting in packing densities which surpass the conventional metal gate process 3:1. Additionally, circuit performance is improved 2:1.

Mass production experience with the Silicon Gate CMOS process, through previously announced 256 and 1024 bit CMOS RAMs, has lead to the practicality of introducing the IM6100 microprocessor. The IM6100 is a single address, fixed word length, parallel transfer microprocessor using 12-bit, two's complement arithmetic. The processors recognize the instruction set of Digital Equipment Corporation's PDP8/E minicomputer. The internal circuitry is completely static and is designed to operate at any speed between DC and the maximum operating frequency. Two pins are available to allow for an external crystal thereby eliminating the need for clock generators and level translators. The crystal can be removed and the processor clocked by an external clock generator. A 12-bit memoryaccumulator ADD instruction, using a +5 volt supply, is performed in  $5\mu$ sec by the IM6100, in  $6\mu$ sec by the IM6100C and in 2.5 $\mu$ sec by the IM6100A using a +10 volt supply. The device design is optimized to minimize the number of external components required for interfacing with standard memory and peripheral devices.

## FEATURES

#### DESIGN

- Silicon Gate Complementary MOS ο

- Fully Static-0 to 8 MHz ο

- Single Power Supply ο

- $\begin{array}{c} \text{IM6100/C} \quad \text{V}_{\text{cc}} = 5 \text{ volts} \\ \text{IM6100A} \quad \text{V}_{\text{cc}} = 10 \text{ volts} \end{array}$

- Crystal Controlled On Chip Timing 0

- Low Power Dissipation < 10 mW @ 4 MHz @ 5 volts 0

- Single Power Supply  $4V \le V_{cc} \le 11V$ 0

- TTL Compatible at 5 Volts 0

- Excellent Noise Immunity 0

- -55°C to +125°C Operation 0

#### INTERFACE

- Memory—Any Speed

Control Panel

- Switch Register 0

- Asynchronous CPU-Memory and CPU-Device 0 Communication

- 64 I/O Devices with PDP-8/E Compatible Interface 0

- **Device Controlled Input-Output** 0

- All Control Signals Produced By The CPU 0

- Power-on Initialize 0

#### ARCHITECTURAL

- Executes PDP-8/E, Instruction Set

- Direct, Indirect, and Autoindexed Memory Addressing 0

- 12-Bit Memory Accumulator ADD Instruction 0 IM6100 5µsec @ +5 volts/4.0 MHz IM6100A 2.5µsec @ +10 volts/8.0 MHz IM6100C 6µsec @+5 volts/3.3 MHz

- Input-Output Instruction 0 IM6100 8.5µsec @ +5 volts/4.0 MHz IM6100A 4.25µsec @ +10 volts/8 MHz IM6100C 10.2µsec @ +5 volts/3.3 MHz

- Single-Clock, Single-Instruction Capability

- 0 Direct Memory Access (DMA) ο

- 0 Interrupt

- **Dedicated Control Panel Features** 0

## APPLICATIO

- Intelligent Computer Terminals 0

- POS Terminals 0

- Portable Terminals ο

- Aerospace/Satellite System 0

- Automotive Systems 0

- Remote Data Acquisition Systems 0

- Process Control 0

- Instrumentation 0

- Medical Electronics 0

- Displays 0

- Traffic Control 0

- Navigation 0

7

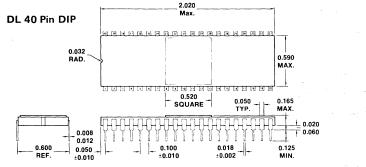

# PINASSIGNMENTS

| PIN    | SYMBOL          | ACTIVE<br>LEVEL   | DESCRIPTION                                                                                                       | PIN | SYMBOL          | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                               |

|--------|-----------------|-------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|

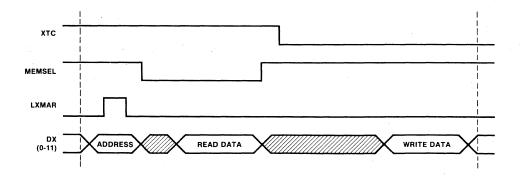

| 1<br>2 | V<br>RUN        | Н                 | Supply voltage.<br>The signal indicates the runstate of the<br>CPU and may be used to power down                  | 10  | LXMAR           | Н               | The Load External Address Register is used to store memory and peripheral address externally.                             |

| 3      | DMAGNT          | H                 | the external circuitry<br>Direct Memory Access Grant—DX lines<br>are three-state.                                 | 11  | WAIT            | L               | Indicates that peripherals or external<br>memory is not ready to transfer data.<br>The CPU state gets extended as long as |

| 4      | DMAREQ          |                   | Direct Memory Access Request—DMA is granted at the end of the current in-                                         |     |                 |                 | WAIT is active. The CPU is in the lowest power state with clocks running.                                                 |

|        |                 |                   | struction. Upon DMA grant, the CPU<br>suspends program execution until the<br>DMAREQ line is released.            | 12  | ХТ <sub>в</sub> | Н               | External coded minor cycle timing—<br>signifies output transfers from the<br>IM6100.                                      |

| 5      | CPREQ           | Logical<br>Sector | Control Panel Request—a dedicated in-<br>terrupt which bypasses the normal<br>device interrupt request structure. | 13  | ХТ <sub>с</sub> | H               | External coded minor cycle timing—<br>used in conjunction with the Select Lines<br>to specify read or write operations.   |

| 6      | RUN/HLT         | L                 | Pulsing the Run/Halt line causes the CPU to alternately run and halt by                                           | 14  | OSC OUT         |                 | Crystal input to generate the internal timing (also external clock input).                                                |

|        |                 |                   | changing the state of the internal RUN/HLT flip flop.                                                             | 15  | OSC IN          |                 | See Pin 14—OSC OUT (also external clock ground)                                                                           |

| 7      | RESET           | L                 | Clears the AC and loads 7777 <sub>8</sub> into the PC, CPU is halted.                                             | 16  | DXo             |                 | DataX—multiplexed data in, data out<br>and address lines.                                                                 |

| 8      | INTREQ          | L                 | Peripheral device interrupt request.                                                                              | 17  | DX <sub>1</sub> |                 | See Pin 16—DX <sub>o</sub> .                                                                                              |

| 9      | XT <sub>A</sub> | Н                 | External coded minor cycle timing-                                                                                | 18  | DX <sub>2</sub> |                 | See Pin 16—DX <sub>o</sub> .                                                                                              |

|        |                 |                   | signifies input transfers to the IM6100.                                                                          | 19  | DX3             |                 | See Pin 16—DX <sub>o</sub> .                                                                                              |

| No.    |                 | 122               |                                                                                                                   | 20  | DX₄             |                 | See Pin 16—DX <sub>o</sub> .                                                                                              |

| 20 19 18 | 17 16 |      | I I   | 12 11 |        |      | 7  | 6  | 5  | 4  | 3  | 2  | 1  |

|----------|-------|------|-------|-------|--------|------|----|----|----|----|----|----|----|

|          |       |      |       | IM    | 6100   |      |    |    |    |    |    |    | (  |

| 21 22 23 | 24 25 | 26 2 | 27 28 | 29 30 | ) 31 3 | 2 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

| PIN  | SYMBOL                                                                                                          | ACTIVE<br>LEVEL | DESCRIPTION                                                                                                                                   | PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SYMBOL                                                                                                                                                                                                                              | ACTIVE<br>LEVEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DESCRIPTION                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21   | DX <sub>5</sub>                                                                                                 |                 | See Pin 16—DX <sub>o</sub> .                                                                                                                  | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C <sub>1</sub>                                                                                                                                                                                                                      | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | See Pin 32—Co.                                                                                                                                                  |

| 22   | DX <sub>6</sub>                                                                                                 |                 | See Pin 16—DX <sub>0</sub> .                                                                                                                  | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C <sub>2</sub>                                                                                                                                                                                                                      | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | See Pin 32Co.                                                                                                                                                   |

| 23   | DX <sub>7</sub>                                                                                                 | 1000            | See Pin 16-DX <sub>0</sub> .                                                                                                                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SKP                                                                                                                                                                                                                                 | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Skips the next sequential instruction if                                                                                                                        |

| 24   | DX <sub>8</sub>                                                                                                 |                 | See Pin 16—DX <sub>o</sub> .                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     | and the second sec | active during an I/O instruction.                                                                                                                               |

| 25   | DX <sub>9</sub>                                                                                                 |                 | See Pin 16—DX <sub>o</sub> .                                                                                                                  | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IFETCH                                                                                                                                                                                                                              | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Instruction Fetch Cycle                                                                                                                                         |

| 26   | GND                                                                                                             |                 | Ground                                                                                                                                        | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MEMSEL                                                                                                                                                                                                                              | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Memory Select for memory transfers.                                                                                                                             |

| 27   | DX <sub>10</sub>                                                                                                |                 | See Pin 16—DX <sub>o</sub> .                                                                                                                  | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CPSEL                                                                                                                                                                                                                               | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | The Control Panel Memory Select be-                                                                                                                             |

| 28   | DX <sub>11</sub>                                                                                                |                 | See Pin 16—DX <sub>o</sub> .                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | comes active, instead of the MEMSEL,                                                                                                                            |

| 29   | LINK                                                                                                            | Н               | Link flip flop.                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | for control panel routines. Signal may be                                                                                                                       |

| 30   | DEVSEL                                                                                                          | L               | Device Select for I/O transfers.                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | used to distinguish between control                                                                                                                             |

| 31   | SWSEL                                                                                                           | L               | Switch Register Select for the OR THE                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | panel and main memories.                                                                                                                                        |

| 1999 |                                                                                                                 |                 | SWITCH REGISTER INSTRUCTION                                                                                                                   | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INTGNT                                                                                                                                                                                                                              | н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Peripheral device Interrupt Grant                                                                                                                               |

|      |                                                                                                                 |                 | (OSR). OSR is a Group 2 Operate<br>Instruction which reads a 12 bit external<br>switch register and OR's it with the con-<br>tents of the AC. | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DATAF                                                                                                                                                                                                                               | Н                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data Field pin indicates the execute<br>phase of indirectly addressed AND,<br>TAD, ISZ and DCA instructions so that<br>the data transfers are controlled by the |

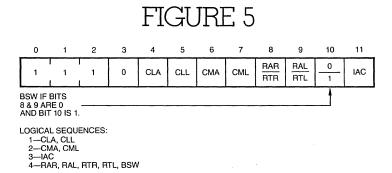

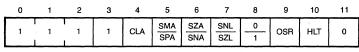

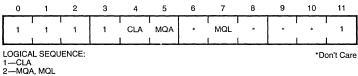

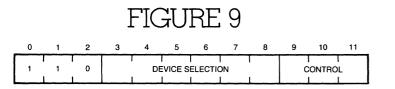

| 32   | Co                                                                                                              | L               | Control line inputs from the peripheral                                                                                                       | and the second sec |                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Data Field, DF, and not the Instruction                                                                                                                         |