# V/SCSI-2 4220 Cougar II and 4220W Cougar Wide User's Guide

Document No.: UG4220W-001,REVA Release Date: April, 1994

> © Copyright 1994 Interphase Corporation All Rights Reserved

# Overview

The V/SCSI-2 4220 Cougar II is available as a Fast or Fast and Wide SCSI-2 controller. The Cougar II is capable of controlling any combination of up to 14 SCSI-2 devices, seven on the primary SCSI channel and seven more if the optional secondary SCSI channel is installed. The Cougar II Wide is capable of controlling any combination of up to 15 Fast or Fast and Wide devices per channel.

If you have the Cougar II Wide product, the extensions to the MACSI SCSI interface necessary to support

fast and wide SCSI operations are defined throughout this manual (identified with a W in the left margin). These extensions are defined to be fully upward compatible with existing drivers, therefore no changes are required to maintain the current level of functionality.

## System Interface

The host processor communicates with the Cougar through 256, 512, 1K, or 2K bytes of onboard RAM. All commands and responses pass through this memory space which is referred to as *Short I/O* because it is mapped into the Short I/O space of the VMEbus.

Each command to the Cougar is specified using a host-generated software structure called an Input/Output Parameter Block (IOPB). IOPBs can be built in either the Cougar's Short I/O space or offboard in system memory. In the latter case, command completions may optionally be posted to both onboard and offboard data structures.

The system-level interface, referred to as *MACSI* (Multiple Active Command Software Interface), is implemented in Short I/O. In addition to supporting command queuing, MACSI enables multiple commands to be active simultaneously. The Cougar accepts commands from the host and queues them internally. It then acts on each command as soon as possible within the confines of the SCSI bus. As commands are completed, the board notifies the host of each command's completion as well as the completion status.

# Issuing Commands

The host submits commands to the Cougar by making an entry into a circular queue called the Command Queue. Each Command Queue entry is a 12-byte block containing a pointer to the IOPB and other control information.

The host may build IOPBs either onboard (in the Cougar's Host Usable Space in Short I/O) or offboard in system memory. Once it builds an IOPB, the host creates an entry for the IOPB in the next available slot in the Command Queue.

## Work Gueues

The concept of work queues is integral to the way that MACSI allows multiple commands to be active simultaneously. Information in the Command Queue entry determines the work queue into which a particular command is placed. At any time, there is an *In Progress* command for each work queue that has at least one entry. The *Next* command waits for the *In Progress* command from that work queue to complete.

The Cougar II accommodates up to 14 work queues and the Cougar II Wide up to 255 work queues. This is not counting a special queue called *Work Queue 0*. Work queue 0 is intended for issuing special commands such as initialize controller or error recovery, etc. Cougar II Wide supports up to 255 work queues, numbered 0 through 255. Work queues are intended to be dedicated to a specific SCSI-2 device. Multiple work queues may be dedicated to the same device. The host sets the parameters of each work queue when it initializes the queue.

Since the SCSI bus allows many tasks to overlap on multiple devices, the MACSI interface allows for commands from all work queues to be interspersed. Assuming that the SCSI devices support overlapped activity on the SCSI bus (using Disconnect/Reconnect), one *In Progress* command for each attached SCSI device can be simultaneously active, resulting in overlapped data streams. Since the Cougar can have two fully independent SCSI buses, it can support two truly simultaneous data streams. If some devices do not support overlapped activity, they can be relegated to the optional second channel, allowing fully functioning devices on the primary channel unrestricted operation. Both channels can, of course, support full SCSI functionality.

## **Executing Commands**

The Cougar reads the Command Queue, determines which entry to execute next, and moves the appropriate Command Queue entry and IOPB into one of its internal work queues. Commands intended for a specific device are sent to the work queue dedicated to that device.

After the Command Queue entry and IOPB are placed into a work queue, the slot in the Command Queue formerly filled by the command becomes available for re-use by the host. Even in the unlikely case that the Command Queue is full when the host tries to enter a command, the Cougar provides efficient operation by optionally interrupting the host when an entry becomes available in the Command Queue.

Once the command is moved to the appropriate work queue, it is executed at the first opportunity. The Cougar then posts command completion to the Command Response Block (CRB) in either Short I/O or system memory, and generates an optional interrupt. The host acknowledges the command completion by writing a word to the CRB, releasing it for further use.

## Master Command Entry and Work Gueue 0

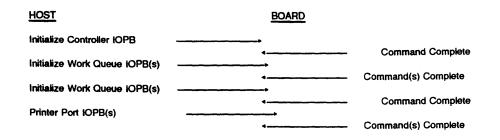

In order to initialize the board, as well as to execute high priority commands, the Cougar provides two autoinitialized facilities: the Master Command Entry and the Work Queue 0.

The Master Command Entry and Work Queue 0 allow a single command to be issued and the host to poll for its completion before issuing the next one. This mechanism is used, upon power-up, to initialize the rest of the work queues for normal SCSI operations, and in error recovery operations.

\_

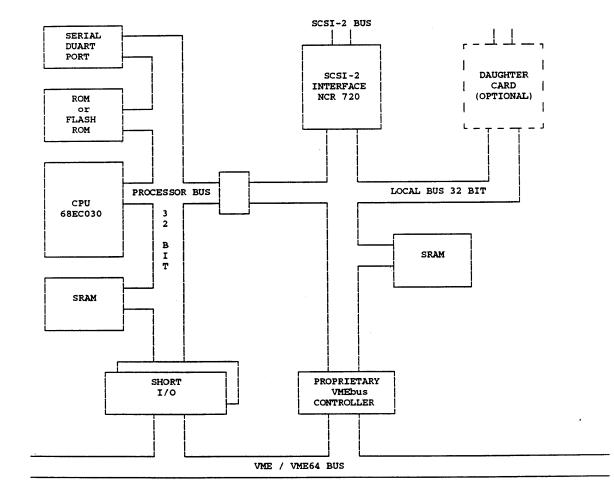

Figure 1-1. V/SCSI-2 Cougar II Block Diagram

1-5

.

4

# Chapter 2 Installation

# Overview

To insure safe installation, read this chapter thoroughly before attempting installation of either the V/SCSI-2 4220 Cougar II motherboard or the V/SCSI-2 4220 Cougar II Wide motherboard into your system. If you have any questions regarding installation which are not answered in this chapter, please contact Interphase Customer Service at (214) 919-9111.

The boards are installed into the VMEbus system using the following steps:

- 1. Visual Inspection

- 2. Fuse And Diagnostic LEDs

- 3. Set Motherboard Jumpers

- 3a. Cougar II

- 3b. Cougar II Wide

- 4. Set Motherboard Termination

- 5. Set Daughter Card Jumpers And Termination

- 5a. Single-Ended SCSI-2 Daughter Card

- 5b. Differential SCSI-2 Daughter Card

- 5c. Differential SCSI-2 Wide Daughter Card

- 5d. Printer (Short Line)

- 5e. Printer (Long Line)

- 6. Cabling Procedure

- 7. Installing the Board

# WARNING

- 1. Catastrophic DAMAGE can result from improper connections. Therefore, those planning to connect power sources to the VMEbus to feed the user-defined 96 pins of P2 (Rows A and C) should FIRST CHECK to ensure that all boards installed are compatible with those connections.

- 2. Do NOT install or apply power to a damaged board. Failure to observe this warning could result in extensive damage to the board and/or system.

- 3. **Caution!** The controller is extremely sensitive to electrostatic discharge (ESD), and the board could be damaged if handled improperly. Interphase ships the board enclosed in a special antistatic bag. Upon receipt of the board, take the proper measures to eliminate board damage due to ESD (i.e., wear a wrist ground strap or other grounding device).

The installation procedure will vary depending on the desired configuration. Variables include:

- One or two SCSI channels (up to 7 devices per channel for a Fast SCSI-2 channel, and up to 15 devices for a Fast and Wide SCSI-2 channel).

- Single-ended vs. differential SCSI operation for each channel.

- Fast SCSI-2 vs. Fast and Wide SCSI-2 I/O for the SCSI daughter card, if any.

- Use of a printer port daughter card instead of a second SCSI channel.

Table 2-1 summarizes the 4220 Cougar II board products available from Interphase to implement various combinations of the above functions. The SCSI Bus drivers on the above products are not convertible. That is, a board with single-ended SCSI drivers cannot be converted to differential, and vice versa. However, a single-ended motherboard can have a differential daughter card, and a differential motherboard can have a single-ended daughter card.

**NOTE:** The jumper designations differ on the Cougar II and the Cougar II Wide board layouts. Refer to page 2-28 for the Cougar II and page 2-19 for The Cougar II Wide.

-

| PRODUCT                                               | DESCRIPTION                                                                                                        |  |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| Single-ended V/SCSI-2 4220 Cougar II Motherboard      | Provides one single-ended SCSI channel with 8-bit<br>SCSI I/O. Signals are routed off P8.                          |  |  |

| Differential V/SCSI-2 4220 Cougar II Motherboard      | Provides one differential SCSI channel with 8-bit SCSI<br>I/O. Signals are routed off P8.                          |  |  |

| Single-ended V/SCSI-2 4220 Cougar II Wide Motherboard | Provides one single-ended SCSI channel with 16-bit SCSI I/O. Signals are routed off P8.                            |  |  |

| Differential V/SCSI-2 4220 Cougar II Wide Motherboard | Provides one differential SCSI channel with 16-bit SCSI<br>I/O. Signals are routed off P8.                         |  |  |

| Fast and Wide Single-ended SCSI-2 Daughter Card       | Adds one single-ended SCSI channel with 16-bit SCSI<br>I/O to any 4220 motherboard. Signals are routed off<br>P13. |  |  |

| Fast and Wide Differential SCSI-2 Daughter Card       | Adds one differential SCSI channel with 16-bit SCSI I/O to any 4220 motherboard. Signals are routed off P13.       |  |  |

| Fast Single-ended SCSI-2 Daughter Card                | Adds one single-ended SCSI channel with 8-bit SCSI<br>I/O to any 4220 motherboard. Signals are routed off<br>P13.  |  |  |

| Fast Differential SCSI-2 Daughter Card                | Adds one differential SCSI channel with 8-bit SCSI I/O to any 4220 motherboard. Signals are routed off P13.        |  |  |

| Centronics/Short Line Daughter Card                   | Adds one Centronics Short Line Printer Port to any 4220 motherboard. Signals are routed off P9.                    |  |  |

| Dataproducts Long Line Daughter Card                  | Adds one Dataproducts Long Line Printer Port to any 4220 motherboard. Signals are routed off P9.                   |  |  |

# Table 2-1 4220 Cougar II Wide Products

12

Chapter

P8 is a 68-pin micro D "P" connector P7 is a 50-pin ribbon "A" connector

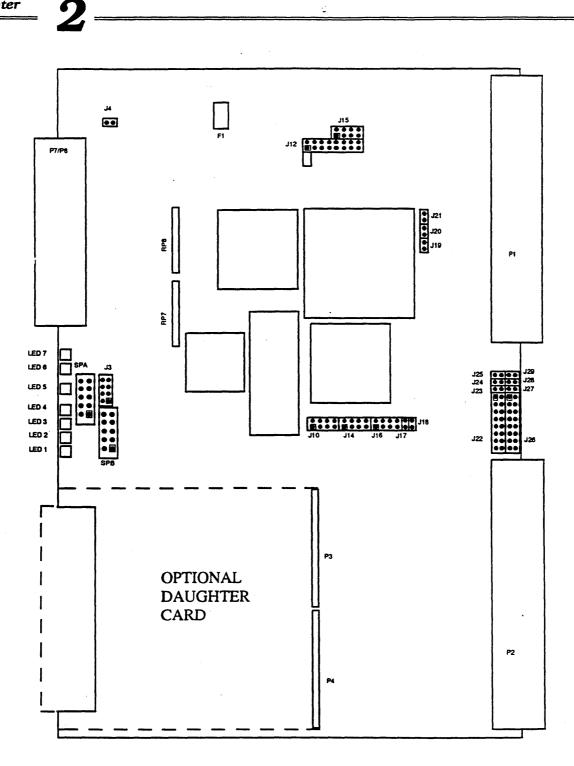

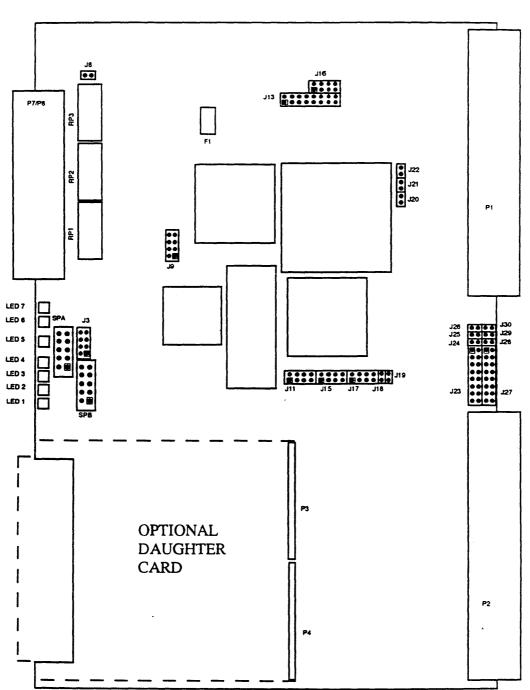

Figure 2-1 V/SCSI-2 4220 Cougar II Single-Ended Board Layout

NOTE: RP7 and RP9 (not pictured) are not SCSI Terminators. Do not remove. P8 is a 68-pin micro D "P" connector P7 is a 50-pin ribbon "A" connector

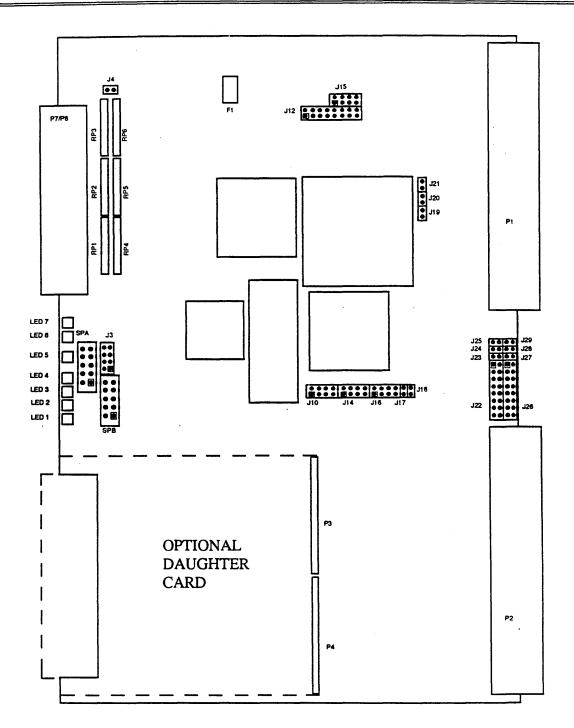

Figure 2-2 V/SCSI-2 4220 Cougar II Differential Board Layout

Chapter

·\_\_

NOTE: P8 is a 68-pin micro D "P" connector P7 is a 50-pin ribbon "A" connector

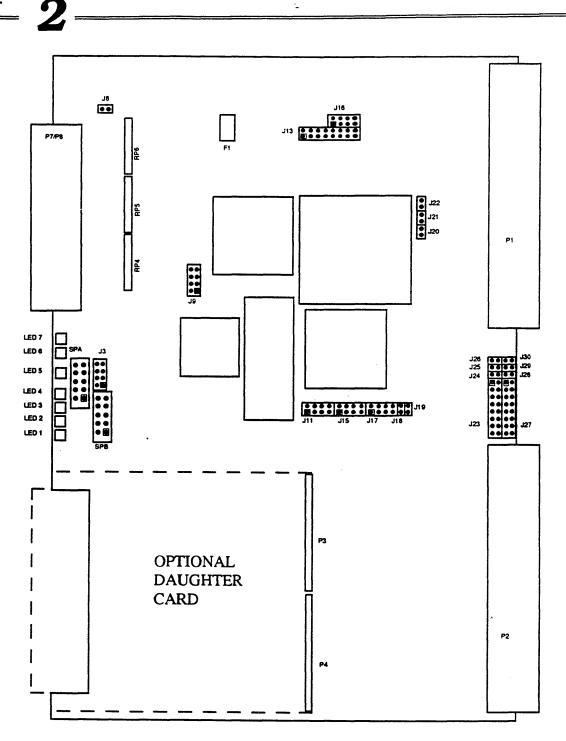

Figure 2-3 V/SCSI-2 4220 Cougar II Wide Single-Ended Board Layout

NOTE: P8 is a 68-pin micro D "P" connector P7 is a 50-pin ribbon "A" connector

Figure 2-4 V/SCSI-2 4220 Cougar II Wide Differential Board Layout

COUGAR II & COUGAR II WIDE

COUGAR II & COUGAR II WIDE

# Installation Procedure: V/SCSI-2 4220 Cougar II Motherboard

Proper installation of the Cougar II motherboard (hereafter referred to as the *Cougar II*) requires the following seven step procedure. Follow step 3a for the Cougar II and step 3b for the Cougar II Wide motherboard. Skip step 5 if you do not have a daughter board.

# Step 1. Visual Inspection

Always wear an anti-static or grounding device before attempting the installation of this board. Remove the board from the anti-static bag, and visually inspect it to ensure no damage has occurred during shipment. A visual inspection is usually sufficient, since Interphase thoroughly checks each board just prior to shipment. After verifying the presence of all parts and the condition of the board, proceed with the installation.

# Step 2. Fuse And Diagnostic LEDs

## Fuse

The Cougar II board uses a 1.5A fuse (part number LITTELFUSE 273-01.5) (F1) to protect the SCSI terminator power when provided by the Cougar. Refer to the board layout to determine the location of the fuse on the board.

# Diagnostic LEDs

This motherboard has 7 board status LEDs mounted on the component side of the board. Refer to the board layout illustrations (Figures 2-1 and 2-2) on pages 2-4 and 2-5 for the location and identification of the LEDs. Table 2-2 summarizes the function of these LEDs.

#### COUGAR II & COUGAR II WIDE

#### COUGAR II & COUGAR II WIDE

| DESIGNATOR | FUNCTION                              |  |

|------------|---------------------------------------|--|

| LED1       | Board Status 0 (LSB)                  |  |

| LED2       | Board Status 1                        |  |

| LED3       | Board Status 2                        |  |

| LED4       | Board Status 3 (MSB)                  |  |

| LED5       | Board OK (Red/Green) Green = Board OK |  |

| LED6       | Term Power (On = OK)                  |  |

| LED7       | SCSI Bus Busy (On = Busy)             |  |

## Table 2-2 V/SCSI-2 4220 LEDs

## **Board Status LEDs**

LEDs 1, 2, 3 and 4 are Board Status LEDs providing the following functions:

- Power On Self Test (POST) Mode

- Monitor Mode

- Run Mode

**POST Mode:** Provides diagnostics for the CPU and Buffer. Refer to Table 2-3 for a list of diagnostics performed while in this mode. The time required for the board to complete normal power-up diagnostics is approximately 200 milliseconds.

## COUGAR II & COUGAR II WIDE

COUGAR II & COUGAR II WIDE

| HEX CODE | DIAGNOSTICS             | DEFINITION  | TYPE OF TEST            |

|----------|-------------------------|-------------|-------------------------|

| 0x01     | CPU Register Test       | CPUFAIL     | CPU Core Test           |

| 0x02     | ROM Checksum Test       | ROMFAIL     | CPU Core Test           |

| 0x03     | Walking 1's SRAM        | STAT1FAIL   | CPU Core Test           |

| 0x04     | Walking 0's SRAM        | STATOFAIL   | CPU Core Test           |

| 0x05     | Decrementing Longwords  | STATLFAIL   | CPU Core Test           |

| 0x06     | Word Access             | STATWFAIL   | CPU Core Test           |

| 0x07     | Byte Access             | STATBFAIL   | CPU Core Test           |

| 0x08     | Reserved                | RESERVED    | CPU Core Test           |

| 0x09     | Walking 1's In Buffer   | BUFFERFAIL1 | Static Buffer Test      |

| 0x0a     | Walking 0's In Buffer   | BUFFERFAILO | Static Buffer Test      |

| 0x0b     | Decrementing Longwords  | BUFFERFAIL  | Static Buffer Test      |

| OxOc     | Walking 1's,0's VME DMA | VMEFAIL     | Control Register Access |

| 0x0d     | Motherboard FEC Tests   | FEC0 & 1    | Control Register Access |

| OxOe     | Daughter Card FEC Tests | FEC2 & 3    | Control Register Access |

Table 2-3 Board Status Diagnostics Used In POST Mode

·\_\_

Monitor Mode: LEDs sequentially flicker when Serial Port A is active and On-Board monitor controls the board.

**Run Mode:** The board accepts commands from the host. If all LEDs are extinguished, no commands are on the Cougar and the board is completely idle. Refer to table 2-4 for a complete definition of the Board Status LEDs in the Run Mode.

| LED1 | LED2 | LED3 | LED4 | FUNCTION                     |  |

|------|------|------|------|------------------------------|--|

| ON   | OFF  | OFF  | OFF  | 1-4 Commands On Board        |  |

| ON   | ON   | OFF  | OFF  | 5-16 Commands On Board       |  |

| ON   | ON   | ON   | OFF  | F 17-64 Commands On Board    |  |

| ON   | ON   | ON   | ON   | 65 or More Commands On Board |  |

COUGAR II

# Step 3a. Check Cougar II Board Jumpers

Check all onboard, user-configurable jumpers for proper configuration for your system. The motherboard layouts on pages 2-4 and 2-5 show the jumper locations for the Cougar II Single-Ended and Differential motherboards. (For Cougar II Wide jumper settings, skip to step 3B).

# Motherboard Jumper Settings

The following are jumpers and the default settings used on the motherboard.

**NOTE:** Jumpers which are not described are not user-configurable and should remain as set at the factory.

J3 REMOTE LED CONNECTOR: Used to cable LEDs to a 9U front panel (Optional).

| 8• | •7 |     |

|----|----|-----|

| •  | •  | J3  |

| •  | •  | 0.5 |

| 2• | •1 |     |

| PIN | DESCRIPTION   |  |  |

|-----|---------------|--|--|

| 1   | LED 3         |  |  |

| 2   | LED 2         |  |  |

| 3   | LED 4         |  |  |

| 4   | LED 1         |  |  |

| 5   | LED 5 (Green) |  |  |

| 6   | LED 5 (Red)   |  |  |

| 7   | +5V           |  |  |

| 8   | LED 5 ANODE   |  |  |

## Table 2-5 J3 Remote LED Connector Pinout

| Chap <i>ter</i> |  |

|-----------------|--|

|                 |  |

COUGAR II

## J4 Terminator Power to Primary SCSI Bus:

Connects terminator power to the primary SCSI bus. Placing a jumper on J4 connects the power. The Cougar II is shipped with the jumper installed on J4 (Default is **ON**).

4

# J10 Firmware Options:

| • 2 | • | • | • 8 | J10 |

|-----|---|---|-----|-----|

| •1  | • | • | •7  | 010 |

(Pins 1-2) 16-Bit Block Mode Enabled (Default is OFF) ON : 16-Bit Block Mode Disabled OFF: 16-Bit Block Mode Enabled

(Pins 3-4) SysFail (Default is OFF)

ON : Clear SysFail after passing Power-up Diagnostics

OFF: Clear SysFail before running Power-up Diagnostics

(Pins 5-6) Reset SCSI Bus on Powerup (Default is OFF) ON : Disabled OFF: Enabled

(Pins 7-8) GDB Debugger Enabled (Default is OFF) ON : Debugger Enabled OFF: Debugger Disabled

J12 SCSI ID & VME Bus Grant Level

| 2• | • | • | • | • | • | • | •16  |

|----|---|---|---|---|---|---|------|

| 1• | • | • | • | • | • | • | • 15 |

Primary SCSI Channel ID (J12 Pins 1-6)

| Table 2-6 Primary SCSI Channel ID |       |           |     |  |  |

|-----------------------------------|-------|-----------|-----|--|--|

| PRIMARY                           |       | J12 PIN # |     |  |  |

| SCSI ID                           | 1-2   | 3-4       | 5-6 |  |  |

| 0                                 | 0     | 0         | 0   |  |  |

| 1                                 | 0     | 0         | F   |  |  |

| 2                                 | 0 F 0 |           |     |  |  |

| 3                                 | O F F |           |     |  |  |

| 4                                 | F     | 0         | 0   |  |  |

| 5                                 | F O F |           |     |  |  |

| 6                                 | F F O |           |     |  |  |

| 7*                                | F*    | F*        | F*  |  |  |

-\_\_\_\_

\* = Factory Default O = On F = Off

# Secondary SCSI Channel ID (J12 Pins 7-12)

| SECONDARY | J12 PIN # |      |       |  |  |

|-----------|-----------|------|-------|--|--|

| SCSI ID   | 7-8       | 9-10 | 11-12 |  |  |

| 0         | 0         | 0    | 0     |  |  |

| 1         | 0         | 0    | F     |  |  |

| 2         | 0         | F    | 0     |  |  |

| 3         | 0         | F    | F     |  |  |

| 4         | F         | 0    | 0     |  |  |

| 5         | F         | 0    | F     |  |  |

| 6         | F         | F    | 0     |  |  |

| 7*        | F*        | F*   | F*    |  |  |

\*Factory Default O = On

F = Off

COUGAR II

## VME Bus Grant (J12 Pins 13-16)

| BUS GRANT | J12 PIN # |       |  |  |  |

|-----------|-----------|-------|--|--|--|

|           | 13-14     | 15-16 |  |  |  |

| 0         | 0         | 0     |  |  |  |

| 1         | 0         | F     |  |  |  |

| 2         | F         | 0     |  |  |  |

| 3*        | F*        | F*    |  |  |  |

Table 2-8 VME Bus Grant Settings

÷\_\_\_\_

\*Factory Default O = On

F = Off

## J14 Firmware Options/Secondary Short I/O Size

| •2 | •4  | • 6 | • 8 | J14 |

|----|-----|-----|-----|-----|

| •1 | • 3 | • 5 | •7  | 014 |

# Firmware Options (J14 Pins 1-4)

(Pins 1-2) Load Firmware (Default is OFF) ON : Load Firmware from on-board buffer OFF: Load Firmware from EPROM

(Pins 3-4) On-board Monitor Enable (Default is OFF) ON : Stop in monitor after loading firmware OFF: Normal Run mode

**COUGAR II**

## Secondary Short I/O Size (J14 Pins 5-8)

## Table 2-9 Secondary Short I/O Size

| J14 F | PIN # | SIZE (BYTES)                           |

|-------|-------|----------------------------------------|

| 5-6   | 7-8   |                                        |

| F     | F     | 256 bytes of Secondary Short I/O space |

| F     | 0     | 512 bytes of Secondary Short I/O space |

| 0     | F     | 1K bytes of Secondary Short I/O space  |

| 0*    | 0*    | 2K bytes of Secondary Short I/O space  |

\* = Factory Default

O = ONF = OFF

#### **J15 Firmware Options:**

| •2 | •4 | • 6 | • 8 | J15 |

|----|----|-----|-----|-----|

| •1 | •3 | •5  | •7  | 015 |

- (Pins 1-2) Delayed Initialization of SCSI Bus (Default is OFF) ON : Initialize only after IOPB Command (0x41) OFF: Initialize after power-up self-test

- (Pins 3-4) Memory Test Enabled (Default is OFF) ON : Disabled OFF: Enabled

- (Pins 5-6) Console Message Disable (Default is OFF) ON : Disabled OFF: Enabled

- (Pins 7-8) GDB Enable Point (Default is OFF) ON : GDB Initialized on Exit OFF: GDB Initialized on Reset

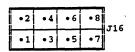

# J16 Primary Short I/O Size/Reset Enable

# Primary Short I/O Size (J16 Pins 1-4)

# Table 2-10 Primary Short I/O Size

4

| J16 I | PIN # | SIZE (BYTES)                           |

|-------|-------|----------------------------------------|

| 1-2   | 3-4   |                                        |

| F     | F     | 256 bytes of Secondary Short I/O space |

| F     | 0     | 512 bytes of Secondary Short I/O space |

| 0     | F     | 1K bytes of Secondary Short I/O space  |

| 0*    | 0*    | 2K bytes of Secondary Short I/O space* |

\* = Factory Default O = ON F = OFF

## Reset Enable (J16 Pins 5-8)

(Pins 5-6) Secondary Master Control Register (Default is OFF)

(Pins 7-8) Primary Master Control Register (Default is ON)

# J17 Secondary Channel Address Modifiers:

ON : Secondary Channel Address Modifiers 29 or 2D OFF: Secondary Channel Address Modifiers 2D only (Default is OFF)

## J18 Primary Channel Address Modifiers:

ON : Primary Channel Address Modifiers 29 or 2D OFF: Primary Channel Address Modifier 2D only (Default is **ON**)

COUGAR II

## J19 VME Bus Grant Input Level 2 Disable

ON : Enabled OFF: Disabled (Default is **ON**)

#### J20 VME Bus Grant Input Level 0 Disable

ON : Enabled OFF: Disabled (Default is **OFF)**

#### J21 VME Bus Grant Input Level 1 Disable

ON : Enabled OFF: Disabled (Default is **OFF**)

#### J22/J23/J24/J25 Primary Short I/O Base Address

Table 2-11 shows the jumper settings for the Primary Short I/O base address for the default 2K Short I/O size. The tables for the other sizes are in Appendix E, *Primary Base Addresses for J22/J23/J24/J25*, page E-1.

**NOTE:** Setting jumper J22 pins 15-16 to ON (O) and all other pins to OFF (F) will disable Primary Short I/O.

#### J26/27/28/29 Secondary Short I/O Base Address

The factory default for these jumpers is J26 pins 15-16 ON, and all others OFF. Secondary Short I/O is disabled.

# Chapter

2 -

COUGAR II

=

COUGAR II

.

.

•

-----

1

| ADDRESS | J22 PIN SETTINGS |       |       |      |     |     |     |     |     |     |     |

|---------|------------------|-------|-------|------|-----|-----|-----|-----|-----|-----|-----|

|         | 15-16            | 13-14 | 11-12 | 9-10 | 7-8 | 5-6 | 3-4 | 1-2 | J23 | J24 | J25 |

| 0000    | F                | F     | F     | 0    | 0   | 0   | 0   | 0   | F   | F   | F   |

| 0800    | F                | F     | F     | F    | 0   | 0   | 0   | 0   | F   | F   | F   |

| 1000    | F                | F     | F     | 0    | F   | 0   | 0   | 0   | F   | F   | F   |

| 1800    | F                | F     | F     | F    | F   | 0   | 0   | 0   | F   | F   | F   |

| 2000    | F                | F     | F     | 0    | 0   | F   | 0   | 0   | F   | F   | F   |

| 2800    | F                | F     | F     | F    | 0   | F   | 0   | 0   | F   | F   | F   |

| 3000    | F                | F     | F     | 0    | F   | F   | 0   | 0   | F   | F   | F   |

| 3800    | F                | F     | F     | F    | F   | F   | 0   | 0   | F   | F   | F   |

| 4000    | F                | F     | F     | 0    | 0   | 0   | F   | 0   | F   | F   | F   |

| 4800    | F                | F     | F     | F    | 0   | 0   | F   | 0   | F   | F   | F   |

| 5000    | F                | F     | F     | 0    | F   | 0   | F   | 0   | F   | F   | F   |

| 5800    | F                | F     | F     | F    | F   | 0   | F   | 0   | F   | F   | F   |

| 6000    | F                | F     | F     | 0    | 0   | F   | F   | 0   | F   | F   | F   |

| 6800    | F                | F     | F     | F    | 0   | F   | F   | 0   | F   | F   | F   |

| 7000    | F                | F     | F     | 0    | F   | F   | F   | 0   | F   | F   | F   |

| 7800    | F                | F     | F     | F    | F   | F   | F   | 0   | F   | F   | F   |

| 8000    | F                | F     | F     | 0    | . 0 | 0   | 0   | F   | F   | F   | F   |

| 8800    | F                | F     | F     | F    | 0   | 0   | 0   | F   | F   | F   | F   |

| 9000    | F                | F     | F     | 0    | F   | 0   | 0   | F   | F   | F   | F   |

| 9800    | F                | F     | F     | F    | F   | 0   | 0   | F   | F   | F   | F   |

| A000    | F                | F     | F     | 0    | 0   | F   | 0   | F   | F   | F   | F   |

| A800    | F                | F     | F     | F    | 0   | F   | 0   | F   | F   | , F | F   |

| B000    | F                | F     | F     | 0    | F   | F   | 0   | F   | F   | F   | F   |

| - B800  | F                | F     | F     | F    | F   | F   | 0   | F   | F   | F   | F   |

| C000    | F                | F     | F     | 0    | 0   | 0   | F   | F   | F   | F   | F   |

| C800    | F                | F     | F     | F    | 0   | 0   | F   | F   | F   | F   | F   |

| D000    | F                | F     | F     | 0    | F   | 0   | F   | F   | F   | F   | F   |

| D800    | F                | F     | F     | F    | F   | 0   | F   | F   | F   | F   | F   |

| E000    | F                | F     | F     | 0    | 0   | F   | F   | F   | F   | F   | F   |

| E800    | F                | F     | F     | F    | 0   | F   | F   | F   | F   | F   | F   |

| F000    | F                | F     | F     | 0    | F   | F   | F   | F   | F   | F   | F   |

| F800    | F                | F     | F     | F    | F   | F   | F   | F   | F   | F   | F   |

| Table 2-11 | Primary | Base | Address | for | 2K | Short I/O |

|------------|---------|------|---------|-----|----|-----------|

÷

**NOTE**: O = ON, F = OFF

2-18

COUGAR II WIDE

# W Step 3b. Check Cougar II Wide Motherboard Jumpers

Check all onboard user-configurable jumpers for proper configuration for operation within your system. The location of the jumpers is shown on the Cougar II motherboard layouts, Figure 2-3 (page 2-6) and Figure 2-4 (page 2-7).

# **Motherboard Jumper Settings**

The following are jumpers and the default settings used on the motherboards.

**NOTE**: Jumpers which are not described are not user-configurable and should remain as set at the factory.

J3 Remote LED Connector: Used to cable LEDs to a 9U front panel (Optional).

J5 (Default is OFF)

J6 (Default is OFF)

J7 (Default is OFF)

J8 TERMINATOR POWER:

ON : Supply SCSI terminator power to SCSI Bus (Default is ON) OFF: Does not supply SCSI terminator power to SCSI bus

# Chapter

COUGAR II WIDE

COUGAR II WIDE

# J9 Primary SCSI Channel ID

2

# Table 2-12 Primary SCSI Channel ID

·\_\_\_\_

| SCSI ID | J9 PIN # |     |     |     |  |  |

|---------|----------|-----|-----|-----|--|--|

|         | 1-2      | 3-4 | 5-6 | 7-8 |  |  |

| 0       | 0        | 0   | 0   | 0   |  |  |

| 1       | 0        | 0   | 0   | F   |  |  |

| 2       | 0        | 0   | F   | 0   |  |  |

| 3       | 0        | 0   | F   | F   |  |  |

| 4       | 0        | F   | 0   | 0   |  |  |

| 5       | 0        | F   | 0   | F   |  |  |

| 6       | 0        | F   | F   | 0   |  |  |

| 7*      | 0*       | F*  | F*  | F*  |  |  |

| 8       | F        | 0   | 0   | 0   |  |  |

| 9       | F        | 0   | 0   | F   |  |  |

| 10      | F        | 0   | F   | 0   |  |  |

| 11      | F        | 0   | F   | F   |  |  |

| 12      | F        | F   | 0   | 0   |  |  |

| 13      | F        | F   | 0   | F   |  |  |

| 14      | F        | F   | F   | 0   |  |  |

| 15      | F        | F   | F   | F   |  |  |

\* = Factory Default

O = On

F = Off

\_\_\_\_

.

COUGAR II WIDE

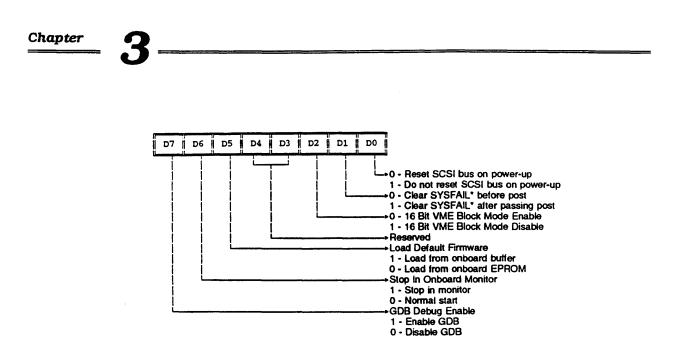

#### J11 Firmware Options

| •2 | • | • | • 8 | J11 |

|----|---|---|-----|-----|

| •1 | • | • | •7  |     |

(Pins 1-2) 16-Bit Block Mode Enabled (Default is OFF) ON : 16-Bit Block Mode Disabled OFF: 16-Bit Block Mode Enabled

(Pins 3-4) SysFail (Default is **OFF**) ON : Clear SysFail after passing Diagnostics OFF: Clear SysFail before running Power-up Diagnostics

(Pins 5-6) Reset SCSI Bus on Power-up (Default is OFF) ON : Reset Disabled OFF: Reset Enabled

(Pins 7-8) GDB Debugger Enabled (Default is OFF) ON : Debugger Enabled OFF: Debugger Disabled

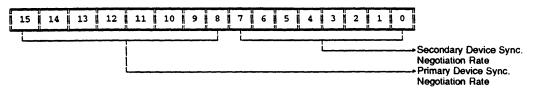

## J13 Secondary SCSI ID/VME Bus Grant for SCSI-2 Fast Daughter card ONLY

|   | 2 | • | • | • | • | • | • | • 16 |

|---|---|---|---|---|---|---|---|------|

| - | 1 | • | • | • | • | • | • | •15  |

(Pins 1-7) Reserved

(Pins 7-12) Secondary SCSI ID for SCSI-2 Fast daughter card

**NOTE:** Not used for SCSI-2 Wide daughter cards. If a Wide daughter card is used, do not populate pins 7-12.

2

COUGAR II WIDE

| SCSI ID | J13 PIN # |      |       |  |  |

|---------|-----------|------|-------|--|--|

|         | 7-8       | 9-10 | 11-12 |  |  |

| 0       | 0         | 0    | 0     |  |  |

| 1       | 0         | 0    | F     |  |  |

| 2       | 0         | F    | 0     |  |  |

| 3       | 0         | F    | F     |  |  |

| 4       | F         | 0    | 0     |  |  |

| 5       | F         | 0    | F     |  |  |

| 6       | F         | F    | 0     |  |  |

| *7      | *F        | *F   | •F    |  |  |

Table 2-13 Secondary SCSI Channel ID for SCSI-2 Fast Daughter Card

4

\* = Factory Default

O = OnF = Off

Table 2-14 VME Bus Grant

,

| SCSI ID | J13 PIN # |       |  |

|---------|-----------|-------|--|

|         | 13-14     | 15-16 |  |

| 0       | 0         | 0     |  |

| 1       | 0         | F     |  |

| 2       | F         | 0     |  |

| 3*      | F*        | F*    |  |

\* = Factory Default

O = OnF = Off

**COUGAR II WIDE**

J15 Firmware Options/Secondary Short I/O Size:

| •2 | • 4 | • 6 | • 8 | J15 |

|----|-----|-----|-----|-----|

| •1 | • 3 | • 5 | •7  |     |

(Pins 1-2) Load firmware (Default is OFF) ON : Load firmware from onboard buffer OFF: Load firmware from EPROM

(Pins 3-4) Onboard monitor enable (Default is OFF) ON : Stop in monitor after loading firmware OFF: Normal run mode

(Pins 5-8) Secondary Short I/O size

Table 2-15 Secondary Short I/O Size

| . J15 F | Pin# | Size (Bytes) |

|---------|------|--------------|

| 5-6     | 7-8  |              |

| F       | F    | 256          |

| F       | 0    | 512          |

| 0       | F    | 1K           |

| 0*      | 0*   | 2K*          |

\* = Factory Default

O = On

F = OFF

Chapter

**COUGAR II WIDE**

COUGAR II WIDE

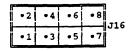

J16 Firmware Options:

(Pins 1-2) Delayed initiation of SCSI Bus (Default is **OFF**) ON : Initialize only after IOPB Command (0x41) OFF: Initialize after power-up self test

2

(Pins 3-4) Memory test enable (Default is **OFF**) ON : Disable OFF: Enable

(Pins 5-6) Console message disable (Default is OFF) ON : Disable OFF: Enable

(Pins 7-8) GDB enable point (Default is OFF) ON : GDB initialized on exit OFF: GDB initialized on reset

.

#### COUGAR II WIDE

#### J17 Primary Short I/O Size/Reset Enable

|   | •2 | • 4 | •6  | • 8 | <br> <br> J17 |

|---|----|-----|-----|-----|---------------|

| 1 | •1 | • 3 | • 5 | •7  | 017           |

| J17 F | Pin # | Size (Bytes) |

|-------|-------|--------------|

| 1-2   | 3-4   |              |

| F     | F     | 256          |

| F     | 0     | 512          |

| 0     | F     | 1K           |

| 0*    | 0*    | 2K*          |

Table 2-16 Primary Short I/O Size

\* = Factory Default O = On F = OFF

- (Pins 5-6) Secondary Master Control Register reset enable (Default is OFF) ON : Reset enabled OFF: Reset disabled

- (Pins 7-8) Primary Master Control Register reset enable (Default is ON) ON : Reset enabled OFF: Reset disabled

J18 Secondary Channel Address Modifiers (Default is OFF):

ON : Secondary Channel Address Modifiers 29 or 2D OFF: Secondary Channel Address Modifiers 2D only

J19 Primary Channel Address Modifiers (Default is OFF):

ON : Primary Channel Address Modifiers 29 or 2D OFF: Primary Channel Address Modifiers 2D only

COUGAR II WIDE

J20/J21/J22 VME Bus Grant IN:

J20 (Default is OFF)

ON : VME Bus Grant IN 2 enabled OFF: VME Bus Grant IN 2 disabled

J21 (Default is OFF)

ON : VME Bus Grant IN 1 enabled OFF: VME Bus Grant IN 1 disabled

J22 (Default is OFF)

ON : VME Bus Grant IN 0 enabled OFF: VME Bus Grant IN 0 disabled

#### J23/J24/J25/26 Primary Short I/O Base Address

Table 2-20 shows the base address jumper settings for the default 2K Short I/O size. The tables for the other sizes are in Appendix F, *Primary Base Address for J/23/J24/J25/J26*, page ?.

NOTE: Setting jumper J23 pins 15-16 to ON (O) and all other pins to OFF (F) will disable the Primary Short I/O.

#### J27/J28/J29/J30 Secondary Short I/O Base Address

The factory default for these jumpers is J27 pins 15-16 ON and all others OFF. Secondary Short I/O is disabled.

## COUGAR II WIDE

-

| Table 2-20 Primary Base Address for 2K Short I/O |                  |       |       | 7                |     |     |     |     |     |     |     |

|--------------------------------------------------|------------------|-------|-------|------------------|-----|-----|-----|-----|-----|-----|-----|

| ADDRESS                                          | J23 PIN SETTINGS |       |       |                  |     |     |     |     |     |     |     |

|                                                  | 15-16            | 13-14 | 11-12 | <del>9</del> -10 | 7-8 | 5-6 | 3-4 | 1-2 | J24 | J25 | J26 |

| 0000                                             | F                | F     | F     | 0                | 0   | 0   | 0   | 0   | F   | F   | F   |

| 0800                                             | F                | F     | F     | F                | 0   | 0   | 0   | 0   | F   | F   | F   |

| 1000                                             | F                | F     | F     | 0                | F   | 0   | 0   | 0   | F   | F   | F   |

| 1800                                             | F                | F     | F     | F                | F   | 0   | 0   | 0   | F   | F   | F   |

| 2000                                             | F                | F     | F     | 0                | 0   | F   | 0   | 0   | F   | F   | F   |

| 2800                                             | F                | F     | F     | F                | 0   | F   | 0   | 0   | F   | F   | F   |

| 3000                                             | F                | F     | F     | 0                | F   | F   | 0   | 0   | F   | F   | F   |

| 3800                                             | F                | F     | F     | F                | F   | F   | 0   | 0   | F   | F   | F   |

| 4000                                             | F                | F     | F     | 0                | 0   | 0   | F   | 0   | F   | F   | F   |

| 4800                                             | F                | F     | F     | F                | 0   | 0   | F   | 0   | F   | F   | F   |

| 5000                                             | F                | F     | F     | 0                | F   | 0   | F   | 0   | F   | F   | F   |

| 5800                                             | F                | F     | F     | F                | F   | 0   | F   | 0   | F   | F   | F   |

| 6000                                             | F                | F     | F     | 0                | 0   | F   | F   | 0   | F   | F   | F   |

| 6800                                             | F                | F     | F     | F                | 0   | F   | F   | 0   | F   | F   | F   |

| 7000                                             | F                | F     | F     | 0                | F   | F   | F   | 0   | F   | F   | F   |

| 7800                                             | F                | F     | F     | F                | F   | F   | F   | 0   | F   | F   | F   |

| 8000                                             | F                | F     | F     | 0                | 0   | 0   | 0   | F   | F   | F   | F   |

| 8800                                             | F                | F     | F     | F                | 0   | 0   | 0   | F   | F   | F   | F   |

| 9000                                             | F                | F     | F     | 0                | F   | 0   | 0   | F   | F   | F   | F   |

| 9800                                             | F                | F     | F     | F                | F   | 0   | 0   | F   | F   | F   | F   |

| A000                                             | F                | F     | F     | 0                | 0   | F   | 0   | F   | F   | F   | F   |

| A800                                             | F                | F     | F     | F                | 0   | F   | 0   | F   | F   | F   | F   |

| B000                                             | F                | F     | F     | 0                | F   | F   | 0   | F   | F   | Ę   | F   |

| B800                                             | F                | F     | F     | F                | F   | F   | 0   | F   | F   | F   | F   |

| C000                                             | F                | F     | F     | 0                | 0   | 0   | F   | F   | F   | F   | F   |

| C800                                             | F                | F     | F     | F                | 0   | 0   | F   | F   | F   | F   | F   |

| D000                                             | F                | F     | F     | 0                | F   | 0   | F   | F   | F   | F   | F   |

| D800                                             | F                | F     | F     | F                | F   | 0   | F   | F   | F   | F   | F   |

| E000                                             | F                | F     | F     | 0                | 0   | F   | F   | F   | F   | F   | F   |

| E800                                             | F                | F     | F     | F                | 0   | F   | F   | F   | , F | F   | F   |

| F000                                             | F                | F     | F     | 0                | F   | F   | F   | F   | F   | F   | F   |

| F800                                             | F                | F     | F     | F                | F   | F   | F   | F   | F   | F   | F.  |

Table 2-20 Primary Base Address for 2K Short I/O

NOTE: O = ON, F = OFF

Chapter

**COUGAR II WIDE**

COUGAR II WIDE

# Step 4. Set Motherboard Termination

The SCSI specification requires the bus to be terminated at both ends of the SCSI cable. It does not allow any other termination; otherwise, a bus impedance mismatch occurs.

The primary channel (Channel 0) and optional secondary SCSI channel (Channel 1) are each provided with separate terminating resistors. The following statement applies to either channel: If the port is at either end of the SCSI cable, the channel's terminating resistors should be left in place. If the port is not at the end of the cable, the termination should be removed.

All versions of the 4220 Cougar II are shipped with termination installed. These resistors provide termination for Channel 0. If Channel 0 is not at one end of the SCSI cable, remove the indicated terminating resistors from the motherboard (Table 2-18).

| Cougar II Single-ended      | RP7,RP8 |                        |

|-----------------------------|---------|------------------------|

| Cougar II Differential      | RP1-RP6 | Do Not Remove RP7, RP9 |

| Cougar II Wide Single-ended | RP4-RP6 |                        |

| Cougar II Wide Differential | RP1-RP3 |                        |

| Table 2-18 Motherboard Terminal |

|---------------------------------|

|---------------------------------|

# Step 5. Set Daughter Card Jumpers And Termination

If your setup includes a daughter card, it may be necessary to set the card's jumpers and/or termination. Skip to Step 6 if you do not have a daughter card.

| DESIGNATOR | FUNCTION  | DESCRIPTION                                                                        |

|------------|-----------|------------------------------------------------------------------------------------|

| LED1       | SCSI BUSY | When illuminated, indicates BSY is asserted on the secondary SCSI bus (channel 1). |

| LED2       | TERMPWR   | When illuminated, indicates TERMPWR is OK.                                         |

# SINGLE-ENDED DAUGHTER CARD

SINGLE-ENDED DAUGHTER CARD

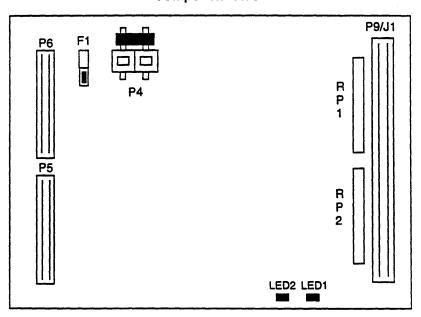

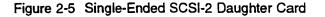

# 5a. Single-Ended SCSI-2 Daughter Card

# Jumpers Used On Single-Ended SCSI-2 Daughter Card

**Component Side**

## P4 - Terminator Power to Secondary Bus:

P4 is used to connect terminator power to the secondary SCSI bus. Placing a jumper in P4 connects the power. The card is shipped with a jumper installed in P4 (Factory Default Setting).

#### **DIFFERENTIAL DAUGHTER CARD**

DIFFERENTIAL DAUGHTER CARD

# Termination On Single-Ended SCSI-2 Daughter Card

On the Single-Ended Daughter Card, the SIP terminating resistors are labelled RP1 and RP2. If channel 1 is not at the end of the SCSI cable, **REMOVE THESE TERMINATORS** from the daughter card.

2

# Fuse

The daughter card has a 1.5A fuse (F1) (part number LITTELFUSE 273-01.5), used to protect the SCSI terminator power when provided by the card.

# LEDs on Single-Ended SCSI-2 Daughter Card

The Single-Ended Daughter Card has 2 LEDs. Refer to Table 2-20 for a description of the LEDs.

| DESIGNATOR | FUNCTION  | DESCRIPTION                                                  |

|------------|-----------|--------------------------------------------------------------|

| LED1       | TERMPWR   | When illuminated, indicates TERMPWR is OK                    |

| LED2       | SCSI BUSY | When illuminated, indicates BSY is asserted on the SCSI bus. |

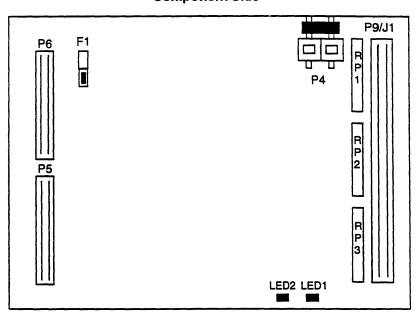

# 5b. Differential SCSI-2 Daughter Card

# Jumpers Used On Differential SCSI-2 Daughter Card

**Component Side**

Figure 2-6 Differential SCSI-2 Daughter Card

## P4 - Terminator Power to Secondary Bus:

P4 is used to connect terminator power to the secondary SCSI bus. Placing a jumper in P4 connect the power. The card is shipped with a jumper installed in P4.

| P4 |  |

|----|--|

DIFFERENTIAL DAUGHTER CARD

DIFFERENTIAL DAUGHTER CARD

# Termination On Differential SCSI-2 Daughter Card

On the Differential Daughter Card, the terminating resistors are labelled RP1, RP2, and RP3. If channel 1 is not at the end of the SCSI cable, **REMOVE THESE TERMINATORS** from the daughter card.

4

# Fuse

The daughter card has a 1.5A fuse (F1) (part number LITTELFUSE 273-01.5), used to protect the SCSI terminator power when provided by the card.

# LEDs on Differential Daughter Card

The Differential Daughter Card has 2 LEDs. Refer to Table 2-23 for a description of the LEDs.

| DESIGNATOR | FUNCTION  | DESCRIPTION                                                  |

|------------|-----------|--------------------------------------------------------------|

| LED1       | TERMPWR   | When illuminated, indicates TERMPWR is OK                    |

| LED2       | SCSI BUSY | When illuminated, indicates BSY is asserted on the SCSI bus. |

Table 2-21 Differential Daughter Card LEDs

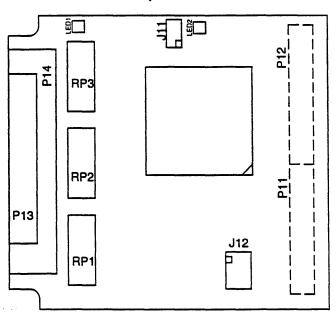

#### 5c. Differential Wide SCSI-2 Daughter Card

# Jumpers Used On Differential Wide SCSI-2 Daughter Card

If your setup includes a Wide differential daughter card, it may also be necessary to set some jumpers on the card. To determine the location of the jumpers, refer to Figure 2-7.

#### **Component Side**

Figure 2-7 Differential Wide SCSI-2 Daughter Card

#### J11 - Terminator Power to Differential Wide Secondary Bus:

J11 is used to connect terminator power to the secondary SCSI bus. Placing a jumper in J11 connects the power. The daughter card is shipped with a jumper installed in J11.

#### J12 - SCSI ID of Differential Wide Secondary Bus

| 1        |   |   | 1   |     |

|----------|---|---|-----|-----|

| 12.      | • | • | • 8 |     |

| И        | i |   |     | J12 |

|          |   |   |     |     |

| 1.       | • | • | •7  |     |

| <u> </u> |   |   | L   | 1   |

**DIFFERENTIAL WIDE DAUGHTER CARD**

DIFFERENTIAL WIDE DAUGHTER CARD

#### J12 - SCSI ID of Differential Wide Secondary Bus

| 2• | • | • | •8 | J12 |

|----|---|---|----|-----|

| 1• | • | • | •7 | 012 |

#### Pins 1-2: (Jumper must be IN. Factory Default Do Not Alter)

Table 2-22 Secondary SCSI Channel ID (Differential Wide Channel)

1

| SCSI ID |     | PIN # |     |

|---------|-----|-------|-----|

|         | 3-4 | 5-6   | 7-8 |

| 0       | 0   | 0     | 0   |

| 1       | 0   | 0     | F   |

| 2       | 0   | F     | 0   |

| 3       | 0   | F     | F   |

| 4       | F   | 0     | 0   |

| 5       | F   | 0     | F   |

| 6       | F   | F     | 0   |

| *7      | ۴F  | *F    | *F  |

\* = Factory Default O = On F = Off

# Termination On Differential Wide SCSI-2 Daughter Card

On the Differential Wide Daughter Card, the DIP terminating resistors are labelled RP1-RP3. If channel 1 is not at the end of the SCSI cable, **REMOVE THESE TERMINATORS** from the daughter card.

## Fuse

The daughter card has a 1.5A fuse (F1) (part number LITTELFUSE 273-01.5), used to protect the SCSI terminator power when provided by the card.

## LEDs on Differential Wide SCSI-2 Daughter Card

The Differential Wide Daughter Card has 2 LEDs, as shown in Figure 2-7. For a description of the LEDs, refer to Table 2-23.

| DESIGNATOR | FUNCTION  | DESCRIPTION                                                                        |

|------------|-----------|------------------------------------------------------------------------------------|

| LED1       | SCSI BUSY | When illuminated, indicates BSY is asserted on the secondary SCSI bus (channel 1). |

| LED2       | TERMPWR   | When illuminated, indicates TERMPWR is OK.                                         |

Table 2-23 Differential Wide Daughter Card LEDs

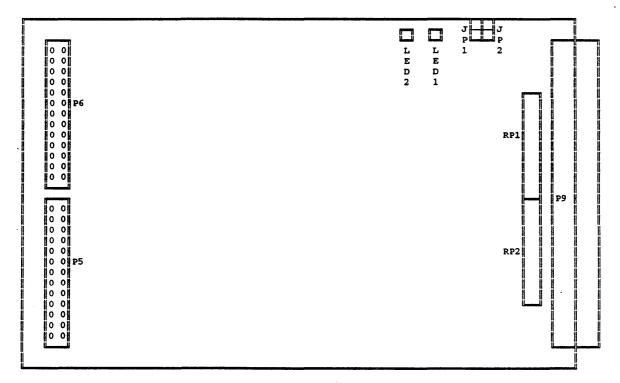

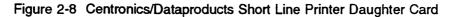

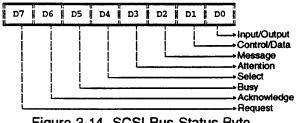

# 5d. Centronics/Dataproducts Short Line Printer Daughter Card

# Jumpers Used On Centronics/Dataproducts Printer Daughter Card

2

If your setup includes a Centronics/Dataproducts Short Line daughter card, it may also be necessary to set some jumpers on the card.

#### COMPONENT SIDE

#### JP1 and JP2 - Printer Type Selection:

Jumpers JP1 and JP2 are used to select the desired interface -- Centronics or Dataproducts Short Line Printer.

**CENTRONICES/DATAPRODUCTS**

The valid settings for JP1 and JP2 are as follows:

| Centronics Printer:              | JP1:<br>JP2: |           |

|----------------------------------|--------------|-----------|

| Dataproducts Short Line Printer: |              | IN<br>OUT |

## Termination On Centronics/Dataproducts Printer Daughter Card

Be sure to set the termination appropriately for the printer selected using jumpers JP1 and JP2.

Centronics Printer: RP1 = 470 Ohms RP2 = Not Installed

Dataproducts Short Line Printer: RP1 = 390 Ohms RP2 = 390 Ohms

# LEDs on Centronics/Dataproducts Printer Daughter Card

| DESIGNATOR | FUNCTION            | DESCRIPTION                                                                                       |

|------------|---------------------|---------------------------------------------------------------------------------------------------|

| LED1       | GOT_LBUS            | When illuminated, indicates the printer daughter card is driving the Local Bus.                   |

| LED2       | COMMAND_IN_PROGRESS | When illuminated, indicates the printer daughter card is executing commands from the motherboard. |

Table 2-24

Centronics/Dataproducts

Short

Line

LEDs

**CENTRONICS/DATAPRODUCTS**

# 5e. Dataproducts Long Line Printer Daughter Card

# Jumpers Used On Dataproducts Long Line Printer Daughter Card

12

**COMPONENT SIDE**

Figure 2-9 Long Line Printer Daughter Card

## JP1 and JP2 - Printer Type Selection:

JP1 and JP2 are used to select the desired interface. Dataproducts Long Line Printer: JP1: IN JP2: IN

## Termination On Dataproducts Long Line Daughter Card

No termination is required for the Dataproducts Long Line printer daughter card.

# LEDs on Dataproducts Long Line Daughter Card

Table 2-25 Dataproducts Long Line Daughter Card LEDs

12

| DESIGNATOR | FUNCTION            | DESCRIPTION                                                                                       |

|------------|---------------------|---------------------------------------------------------------------------------------------------|

| LED1       | GOT_LBUS            | When illuminated, indicates the printer daughter card is driving the Local Bus.                   |

| LED2       | COMMAND_IN_PROGRESS | When illuminated, indicates the printer daughter card is executing commands from the motherboard. |

2-39

**CENTRONICS/DATAPRODUCTS**

# Step 6. Cabling Procedure

The cabling procedure depends on which 4220 Cougar II motherboard and optional daughter card (if installed) you are using. Refer to the Appendix discussion on, *Connector Printouts and Cabling* for details on the required cables.

# CAUTION

System power and peripheral power must be turned OFF before attempting to install the controller. Failure to do so may result in severe damage to the board and/or system.

Once the board is configured, ensure that the host system and peripherals are turned OFF.

# SCSI-2 Cabling Instructions

Table 2-26 summarizes the various SCSI-2 configurations of the 4220 Cougar II.

| To implement:                                                                                                        | Cable the Board as Follows:                                                    |

|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| A Single-ended SCSI bus on the primary SCSI channel                                                                  | Connect a single-ended SCSI "A cable" to the motherboard's P7 connector.       |

| A Differential SCSI bus on the primary SCSI channel                                                                  | Connect a differential SCSI "A cable" to the motherboard's P7 connector.       |

| A Single-Ended Wide SCSI bus on the primary SCSI channel                                                             | Connect a single-ended SCSI "P cable" to the motherboard's P8 connector.       |

| A Differential Wide SCSI bus on the primary SCSI channel                                                             | Connect a differential SCSI "P cable" to the motherboard's P8 connector.       |

| A Single-Ended Wide SCSI bus on the secondary SCSI<br>channel card                                                   | Connect a single-ended SCSI 'P cable' to the daughter card's P13 connector.    |

| A Differential Wide SCSI bus on the secondary SCSI channel                                                           | Connect a differential SCSI "P cable" to the<br>daughter card's P13 connector. |

| A Single-ended SCSI bus on the secondary SCSI channel                                                                | Connect a single-ended SCSI "A cable" to the daughter card's P14 connector.    |

| A Differential SCSI bus on the secondary SCSI channel<br>(provided by Fast differential daughter card, if installed) | Connect a differential SCSI "A cable" to the<br>daughter card's P14 connector. |

Table 2-26 SCSI-2 Cable Variations

For a description of the "A" cable and "P" cable, refer to the appendices.

# **Printer Cabling Instructions**

Table 2-27 summarizes printer cabling requirements.

| TO IMPLEMENT                                         | CABLING INSTRUCTIONS                                                                                                      |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| A Centronics Printer using the Printer Daughter Card | Connect a Centronics Printer cable to P9 on the Printer Daughter<br>Card. Refer to the Appendices for the cable pinout.   |

| A Dataproducts Short Line Printer                    | Connect a Dataproducts Printer cable to P9 on the Printer<br>Daughter Card. Refer to the Appendices for the cable pinout. |

| A Dataproducts Long Line Printer                     | Connect a Dataproducts Printer cable to P9 on the Printer<br>Daughter Card. Refer to the Appendices for the cable pinout. |

# **RS232 Connectors And Cables**

There are two 10 pin connectors (2x5 headers) used as the RS232 port cable connectors. These connectors are the same type used for the second serial port I/O Extension-X.2 of PC compatible machines.

The connectors are labeled "SPA" and "SPB" for Serial Port A and Serial Port B respectively. Refer to either motherboard layout in the front of this chapter for location. Both RS232 ports on the board are configured as Data Terminal Equipment (DTE).

As an option, a terminal may be connected to SPA to view debug information provided by the Cougar II. See Firmware Options jumper settings, in this chapter, to enable/disable the console messages. SPB is used for advanced debug operations, with factory assistance.

# Step 7. Installing the Board

- 1. Carefully slide the board into the VMEbus card slot. It should slide all the way in without any difficulty. If it doesn't, pull it out and check to make sure that there are no cables in the way.

- 2. Once the board is properly seated in the slot, tighten the captive mounting screws on each end of the front panel.

- 3. Connect the SCSI devices to the SCSI cable(s), following the directions given by the device manufacturers.

1

#### **CENTRONICES/DATAPRODUCTS**

-

4. Apply power to the system and peripherals. The board OK LED on the Cougar II should change from **red** to **green** when the power-on self test is complete and the board enters **Run** mode.

4

# Chapter 3 System Interface

#### Overview

The host communicates with the board through the onboard *Short I/O* space, mapped into the Short I/O space of the VMEbus. The MASCI system-level interface allows the board to reset and initialize the board, set up multiple work queues, queue multiple commands internally, read command responses and board configuration, and status information. Every location can be physically both written to and read from by the host at any time, but the protocol of the MACSI System Interface puts some restrictions upon when certain areas should be accessed. Also, some areas are logically write only or read only.

## NOTE

When issuing commands or otherwise interacting with the board via the MACSI interface, the host must clear all bits and fields marked "RESERVED" to 0. For performance reasons, the board does not execute a sanity check on all reserved fields. Clearing these reserved fields helps avoid driver problems that may otherwise occur when a later firmware implementation is released.

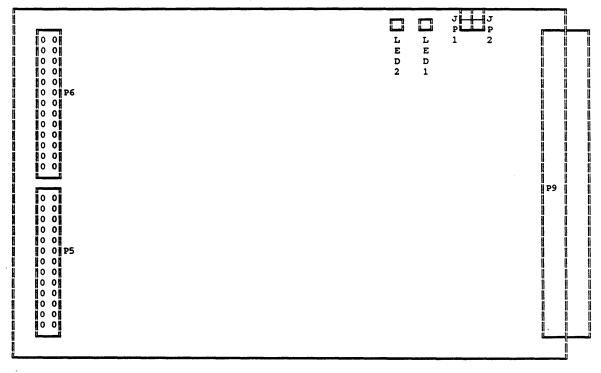

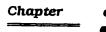

MACSI partitions the Short I/O space into six major sections:

- Master Control/Status Block (MCSB)

- Master Command Entry (MCE)

- Command Queue (CQ)

- Host Usable Space (HUS)

- Command Response Block (CRB)

- Controller Specific Space (CSS)

Figure 3-1 Typical Memory Map of 2K Short I/O Space

## Master Control/Status Block (MCSB)

Chapter

The Master Control/Status Block (MCSB) is used to exchange information relative to the overall operation of the board. The 16-byte MCSB consists of the Master Status Register (MSR), the Master Control Register (MCR), the Interrupt on Queue Available Register (IQAR), the Queue Head Pointer (QHP), and the Thaw Work Queue Register (TWQR).

| Word #           | 15 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |      |   |      |       |      |   |  | 0    |  |  |

|------------------|----|---------------------------------------|--|--|--|------|---|------|-------|------|---|--|------|--|--|

| 0x0              |    | MASTER STATUS REGISTER                |  |  |  |      |   |      |       |      |   |  |      |  |  |

| 0x1              |    |                                       |  |  |  | MAST |   | ONTR | OL RE | GIST | R |  | <br> |  |  |

| 0x2              |    | INTERRUPT ON QUEUE AVAILABLE REGISTER |  |  |  |      |   |      |       |      |   |  |      |  |  |

| 0x3              |    | QUEUE HEAD POINTER                    |  |  |  |      |   |      |       |      |   |  |      |  |  |

| 0x4              |    | THAW WORK QUEUE REGISTER              |  |  |  |      |   |      |       |      |   |  |      |  |  |

| 0x5<br>To<br>0x7 |    |                                       |  |  |  |      | R | ESER | VED   |      |   |  |      |  |  |

## Table 3-1 Master Control/Status Block (MCSB)

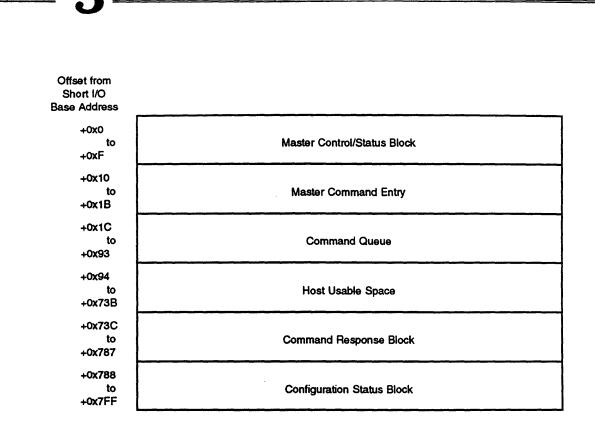

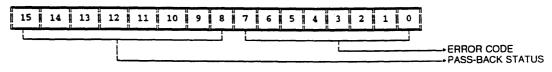

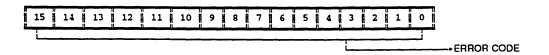

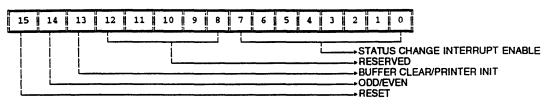

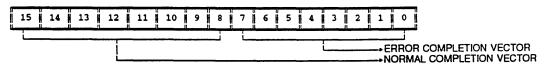

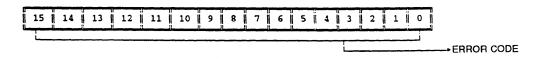

## Master Status Register (MSR)

The board uses this register to report board level status. From the host point of reference, this is a READ ONLY register. However, the contents of this register are not valid for 100 microseconds following a controller reset. Figure 3-2 shows the bit definition.

Figure 3-2 Master Status Register (MSR)

#### Bit 0 Controller Not Available (CNA):

The board sets this bit to 1 to indicate that it is *Not Available* to receive a command. This condition can be caused either by a controller reset or by the execution of controller diagnostics. CNA will also be set if a board initialization command fails to complete (see Chapter 5, *Initialize Controller Command*, page ?). The board will clear this bit when it is capable of accepting a command.

#### Bit 1 Board OK (BOK):

The board sets this bit to 1 when the power-up diagnostics are completed successfully. A 0 indicates that the board detected a failure during the power-up diagnostics. The host can start polling the Board OK bit 100 microseconds after the board has been powered up or reset, allowing approximately 200 milliseconds for normal power-up diagnostics to complete.

| BOK | CNA | Description                                                                                                                                                                                                              |

|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | The controller has failed to operate and is not capable of accepting a command.                                                                                                                                          |

| 0   | 1   | Controller is Not Available. If the controller is<br>not still executing power-up diagnostics, then<br>it has either failed to execute power-up<br>correctly or it has failed to complete a board<br>initialize command. |

| 1   | 1   | The controller has successfully completed<br>power-up diagnostics but it is not capable of<br>accepting a command, because it is executing<br>the diagnostics command.                                                   |

| 1   | 0   | The controller has completed diagnostics and is capable of receiving commands.                                                                                                                                           |

Table 3-2 Board OK/Controller Not Available Relationship

## Bits 2-15 Reserved (RSRV):

These bits are reserved and are cleared to 0 by the board.

.

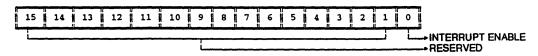

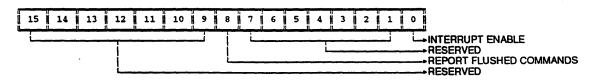

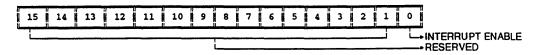

## Master Control Register (MCR)

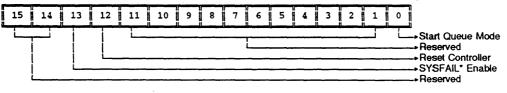

All bits in this register are both set and cleared by the host. From the board's point of reference, this is a **READ ONLY** register. The board does not ever set any of these bits. The bits are defined in Figure 3-3.

NOTE: Reserved bits must be cleared to 0 by the host.

#### Bit 0 Start Queue Mode (SQM):

Once the Command Queue and work queues are initialized, the SQM bit may be set to "1" by the host. The only operation performed by the 4220 board in response to the host setting this bit is to the *Queue Mode Started Bit* in the *Command Response Status Word* (see pages 3-18). The SQM bit is supported to provide backward compatibility with the V/SCSI 4210 Jaguar SCSI-1 controller.

#### Bits 1 - 11 Reserved (RSRV):

These bits are reserved and must be cleared to 0 by the host.

#### Bit 12 Reset Controller (RES):

The *RES* bit controls the microprocessor hardware reset line. It also causes a RESET on both of the SCSI buses, if the SCSI reset feature is enabled via jumper setting. The RES bit should be used only to recover from extreme error conditions. To ensure proper operation, the host must leave this bit set for at least 70 microseconds.

#### Bit 13 SYSFAIL\* Enable (SFEN):

The SFEN bit enables the board to drive the SYSFAIL\* signal on the VMEbus if it detects an internal failure during power-up diagnostics or if the firmware enters an unused exception vector. If this bit is 0, the board will not drive the SYSFAIL\* signal under any circumstances. The board initializes this bit to 0 after power-up.

The board does not read the SYSFAIL\* Enable bit until detecting an error in the power-up test. After detecting an error, the firmware simply loops on setting the SYSFAIL\* line to the level specified by the bit (provided that the board is sufficiently functional to have the bit cleared).

The host should wait until the BOK (Board OK) bit is set in the MSR before enabling this bit. The host may turn off SYSFAIL\* from the board by clearing this bit. The host may enable SYSFAIL\* after the board has been released from reset. This operation is performed by firmware, and it is possible the board may clear the bit if it is set too soon after power-up. The host should wait until the BOK (Board OK) bit is set in the MSR before modifying this bit.

**NOTE:** The board drives SYSFAIL\* at system reset and immediately clears SYSFAIL\* after reset if configured to do so via jumper setting.

## Bits 14-15 Reserved (RSRV):

These bits are reserved and must be cleared to 0 by the host.

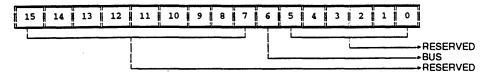

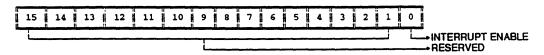

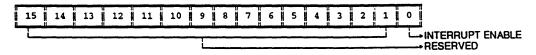

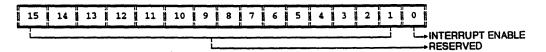

# Interrupt On Gueue Available Register (IGAR)

Each Command Queue entry only occupies a slot in the Command Queue until it is moved into a work queue. Thus, the host will almost always have slots available in the Command Queue for issuing commands. In the unlikely event that the Command Queue is full when the host attempts to enter a

command, the host must wait until the board transfers a command from the Command Queue to an internal work queue before it can enter the next command.

The host determines that the Command Queue is full by looking at the Go/Busy bit in the next available Command Queue entry. The Command Queue is full if the Go/Busy bit of the next available Command Queue entry is 1. If the Command Queue becomes full, the host can poll the Go/Busy bit, waiting until the next Command Queue entry becomes available. The Interrupt on Queue Available Register (IQAR) provides a mechanism to generate an optional interrupt to the host when a entry becomes available in the Command Queue.

The IQAR feature is enabled by setting the Interrupt on Queue Entry Available (IQEA) bit in the register. If the Interrupt on Queue Half Empty Enable bit is also set, the board will not interrupt until the Command Queue is half empty. Otherwise, the interrupt will occur as soon as the board detects one empty entry in the Command Queue. The host should wait until encountering the Queue Full condition before setting the IQEA bit. Once the IQEA bit is set, the board generates an interrupt when the necessary queue conditions are satisfied. The board then clears the IQEA bit.

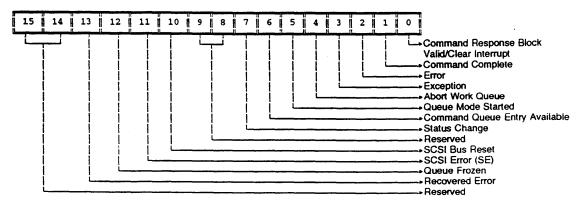

The level and vector for the IQEA interrupt are supplied by the host in the IQAR. When the necessary queue conditions are satisfied, the board clears the IQEA bit and sets the Queue Entry Available (CQA) bit, and the Command Response Block Valid (CRBV) bit, the Command Response Status Word (CRSW) of the CRB. Though the board provides this mechanism for interrupting the host when space becomes available in the Command Queue, it is preferable to set up a large enough Command Queue so that the full condition occurs infrequently. The number of entries in the Command Queue is set in the CIB (refer to Chapter 5, *Initialize Controller Command*, page ?).

Note that the generation of this interrupt is not real time. If the host fills in commands from completion interrupts, the queue may already have been filled in by the time the IQAR occurs. Therefore, the host must check the Go/Busy bit before issuing another command.

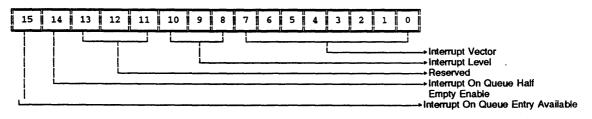

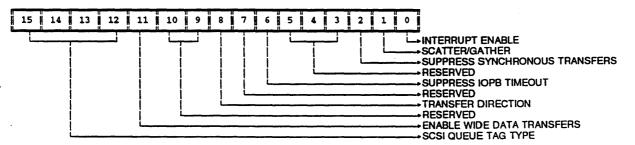

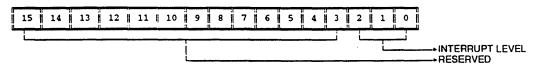

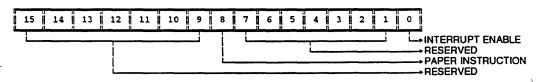

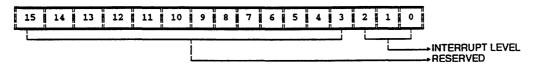

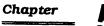

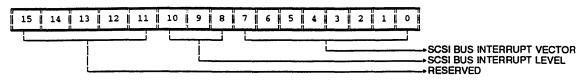

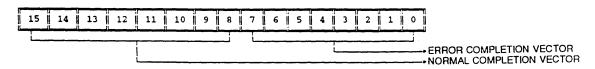

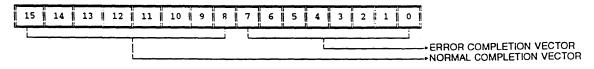

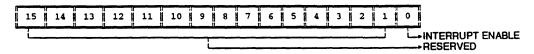

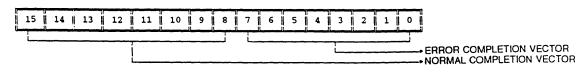

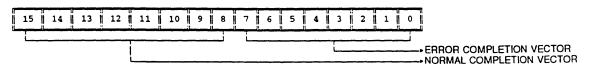

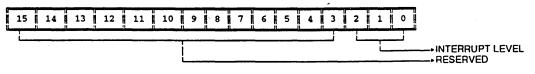

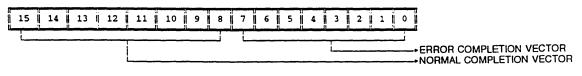

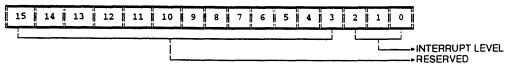

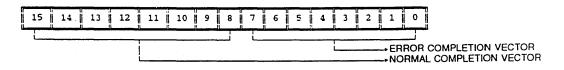

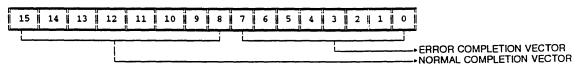

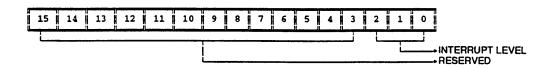

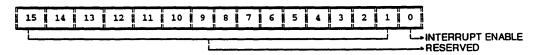

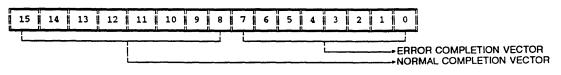

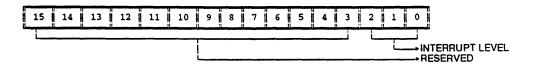

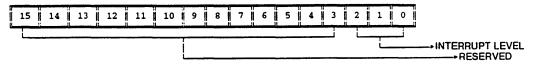

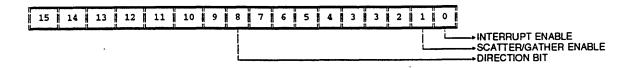

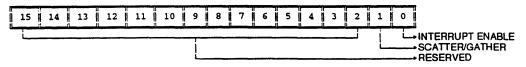

Figure 3-4 Interrupt On Queue Available Register (IQAR)

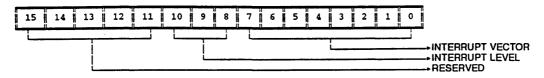

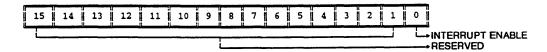

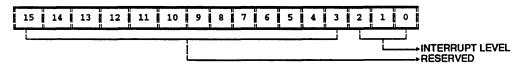

## Bits 0-7 Interrupt Vector for the Interrupt on Queue Available (IV):

The board uses this byte as the interrupt vector when issuing an Interrupt on Queue Available interrupt. This byte is set by the host and is not modified by the board. The host must not modify this byte after setting the IQEA bit.

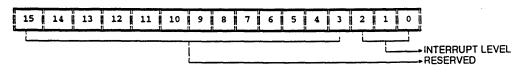

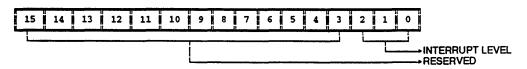

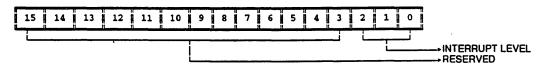

#### Bits 8-10 Interrupt Level for the Interrupt on Queue Available (IL):

These three bits determine the interrupt level that the board will use when issuing an Interrupt on Queue Available interrupt. These bits are set by the host and are not modified by the board. The host must not modify these bits after setting the IQEA bit.

Values of 1 through 7 are allowed. An interrupt level of 0 is allowed only when the IQEA bit is cleared.

#### Bits 11-13 Reserved (RSRV):

These bits must be cleared to 0 by the host.

#### Bit 14 Interrupt on Queue Half Empty Enable (IQHE):

This bit is a flag which causes the board to generate the IQEA interrupt when the Command Queue becomes half empty (rather than as soon as one entry becomes available). The Interrupt on Queue Half Empty Enable (IQHE) bit is valid only when the IQEA bit is set. The IQHE bit is set by the host and is not modified by the board. The host must not modify this bit after it has set the IQEA bit.

#### Bit 15 Interrupt on Queue Entry Available (IQEA):

This bit is set by the host to request an IQEA. The interrupt is generated either when the queue is half empty or as soon as one entry is available, depending upon the state of the IQHE bit. The board clears this bit prior to generating the IQEA interrupt. After the host sets this bit, requesting an interrupt, it cannot change any of the other bits in the IQAR.

#### **Gueue Head Pointer (GHP)**

The QHP provides a convenient place for the host to store the address of the next available entry in the Command Queue. The board will neither read nor write the QHP.

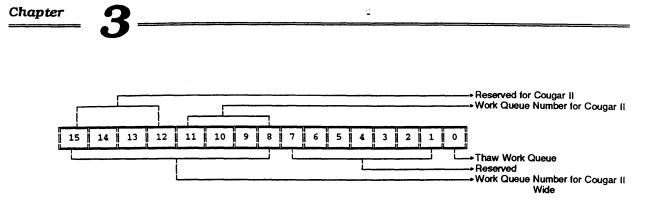

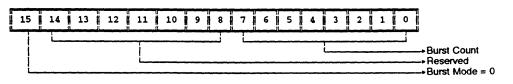

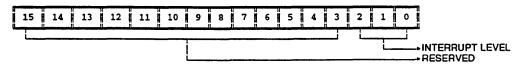

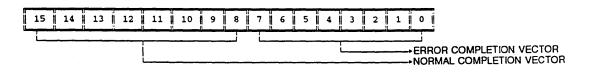

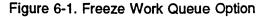

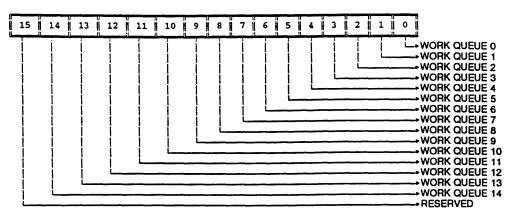

#### Thaw Work Queue Register (TWQR)

This field is used to restart a work queue that has been frozen due to a SCSI Pass-Through error or a SCSI bus reset when these options are enabled. A queue is thawed by writing the appropriate work queue number to the designated bits in the upper byte of the register and then setting the Thaw Work Queue bit (TWQ). An extension is defined to the Thaw Work Queue Register that allows work queues to be numbered from 1 to 255 for Cougar II Wide. Refer to Chapter 6, *Error Recovery Tools*, page 6-1, for additional information.

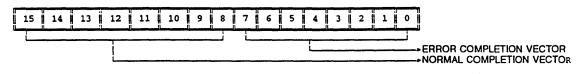

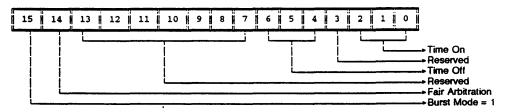

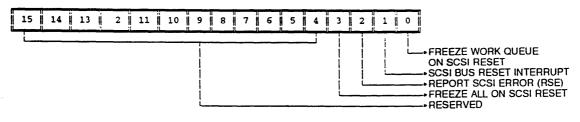

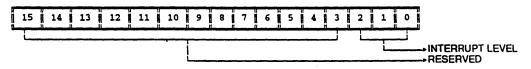

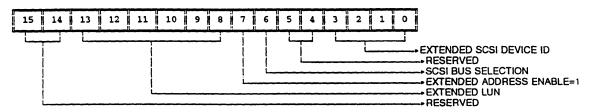

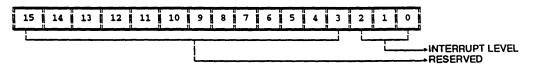

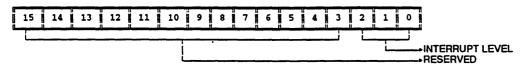

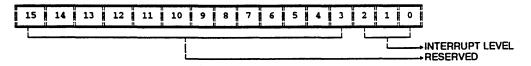

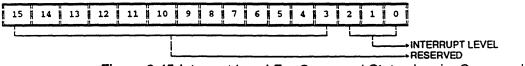

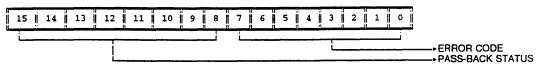

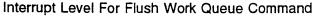

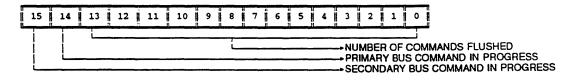

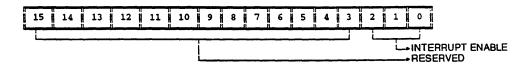

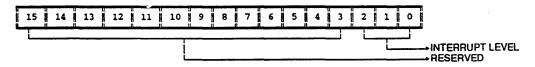

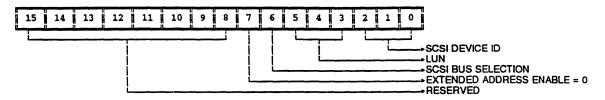

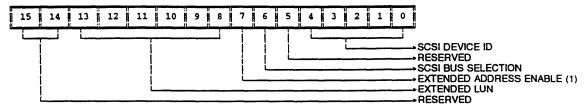

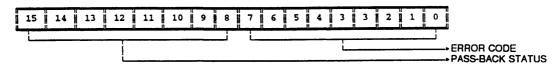

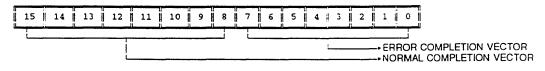

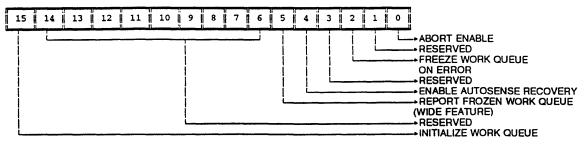

Figure 3-5 Thaw Work Queue Register

## Bit 0 Thaw Work Queue (TWQ):

Setting this bit causes the board to resume execution of commands in the work queue specified in the upper byte of this word. The board then clears the TWQ bit to acknowledge that the queue has been thawed.

## Bits 1-7 Reserved:

These bits are reserved and must be cleared to 0 by the host.

#### Bits 8-15 Work Queue Number for Cougar II Wide, Bits 8-11 Work Queue Number for Cougar II:

This field specifies the work queue number to be thawed. Values range from 1 to 14 for Cougar II, and 1 to 255 for Cougar II Wide. It is an error to thaw work queue 0.

## Bits 12-15 Reserved for Cougar II:

These bits are reserved for the Cougar II and must be cleared to 0 by the host.

# Master Command Entry (MCE)

The Master Command Entry (MCE) is an auto-initialized facility through which commands are issued to the board before the Command Queue and work queues have been initialized. The single slot of the MCE has the same 12-byte format as any on-board Command Queue entry. Space must be reserved in the Host Usable Space (HUS) portion for the I/O Parameter Block (IOPB) that is pointed to by the MCE. Typically, it will be used only when initializing the Command Queue. It does, however, provide a mechanism to issue a command to the board even if the Command Queue and all work queues are full. It provides a way to get one command into the board even when the Command Queue is *locked up*.

# **Command Gueue**

The *Command Queue* (CQ) consists of a user-programmed number of Command Queue entries. The host sets the size of the Command Queue when via the Initialize Controller command. Each Command Queue entry includes all of the information needed for the board to find, execute and respond to the commands

contained in the IOPB. The actual size of the Command Queue equals the number of entries times 12 bytes. The Command Queue must have at least one entry.

The Command Queue is circular, and it is up to the host to keep track of the next Command Queue entry that it can use. Because the queue is circular, the board infers chronological ordering of commands. Each Command Queue entry is *busy* only until the board can transfer the command to a work queue and then free its slot in the Command Queue.

## Command Gueue Entry (CGE)

A Command Queue entry is a 12-byte block containing all of the information needed for the host to find and execute a command. Each CQE is *busy* only until the board can transfer the command to a work queue and free the entry by clearing the Go/Busy bit. This mechanism allows a relatively small Command Queue to handle a large number of commands.

The purpose of the fields in a CQE will vary depending on whether onboard or offboard IOPBs are being used. Figure 3-6 shows the format of the two types of Command Queue entries.

## COMMAND QUEUE ENTRY FOR ONBOARD IOPBs:

| Word # | 15 | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |  |  |  | 0 |

|--------|----|---------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|---|

| 0x0    |    | QUEUE ENTRY CONTROL REGISTER          |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

| 0x1    |    | IOPB ADDRESS                          |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

| 0x2    |    | COMMAND TAG                           |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

| 0x3    |    | COMMAND TAG                           |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

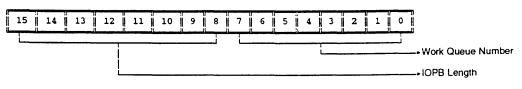

| 0x4    |    | IOPB LENGTH WORK QUEUE NUMBER         |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

| 0x5    |    | RESERVED                              |  |  |  |  |  |  |  |  |  |  |  |  |  |   |

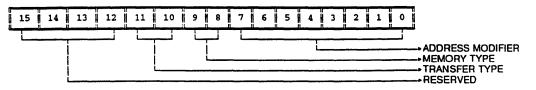

## COMMAND QUEUE ENTRY FOR OFFBOARD IOPBS:

| Word # | 15                          | 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  | 0 |  |

|--------|-----------------------------|---------------------------------------|--|--|--|--|--|--|--|--|--|---|--|

| 0x0    |                             | QUEUE ENTRY CONTROL REGISTER          |  |  |  |  |  |  |  |  |  |   |  |

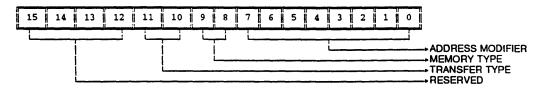

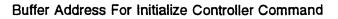

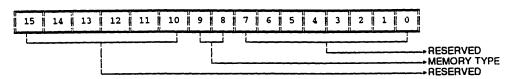

| 0X1    | RSRV TT MT ADDRESS MODIFIER |                                       |  |  |  |  |  |  |  |  |  |   |  |

| 0X2    |                             | HOST ADDRESS (MSW)                    |  |  |  |  |  |  |  |  |  |   |  |

| 0ХЗ    |                             | HOST ADDRESS (LSW)                    |  |  |  |  |  |  |  |  |  |   |  |

| 0X4    |                             | IOPB LENGTH WORK QUEUE NUMBER         |  |  |  |  |  |  |  |  |  |   |  |

| 0X5    |                             | RESERVED                              |  |  |  |  |  |  |  |  |  |   |  |

Figure 3-6 Command Queue Entry Format For Onboard And Offboard IOPBs and MCE

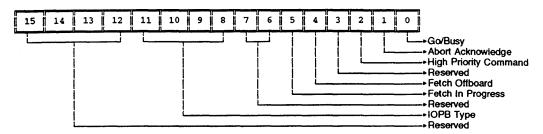

# CGE Word 0: Queue Entry Control Register

The Queue Entry Control Register (QECR):

- Kicks off command execution. Acknowledges a command abort sequence. Flags a high priority command. Signals whether a command is located Short I/O or system memory.

Figure 3-7 Queue Entry Control Register (QECR)

## Bit 0 Go/Busy (GO):

The GO bit is set by the host to initiate action on a CQE. The host must assemble the IOPB in the Host Usable Space (HUS) and the CQE in the Command Queue before it sets this bit. When the GO bit is set, the board moves the CQE and IOPB into internal memory and clears the GO bit, releasing the CQE.

#### Bit 1 Abort Acknowledge (AA):

When a command completes with a SCSI Pass-Through error, all commands in, and destined for, that work queue can optionally be aborted. This option is specified when the work queue is initialized (see Chapter 5, *Initialize Work Queue command*).

The AA bit is used to end the command abort sequence, allowing the host to reissue the command that completed with error, and allowing commands that were aborted due to the error. The host issues the command that completed with error, after appropriate error recovery, with the AA bit set. Subsequent commands should be submitted with the AA bit cleared, and normal queue operation will resume until another Pass-Through error occurs.

## Bit 2 High Priority Command (HPC):

The HPC bit flags a command so that the board places the command at the top of its work queue. If there are other commands in the work queue with the HPC bit set, the new command is queued up behind the other HPC.

#### Bit 3 Reserved (RSRV):

This bit is reserved and must be cleared to 0 by the host.

## Bit 4 Fetch Offboard (FOB):

This bit is only used in applications involving offboard IOPBs. If this bit is set, then the corresponding IOPB will be fetched from the host memory. The only other bit in the Queue Entry Control Register that is valid when the FOB bit is set is the Go/Busy bit (Bit 0). For a discussion of offboard IOPBs, refer to Chapter 6, *Offboard IOPBs*, page 6-17.

#### **Bits 5 Fetch In Progress:**

This bit is for internal board use only.

#### Bits 6-7 (RSRV) Reserved:

These bits are reserved and must be cleared to 0 by the host.

## Bits 8-11 IOPB Type:

These bits describe the IOPB type. The board supports only type zero IOPBs, so this field should be cleared to 0.

#### Bits 12-15 Reserved (RSRV):

These bits are reserved and must be cleared to 0 by the host.

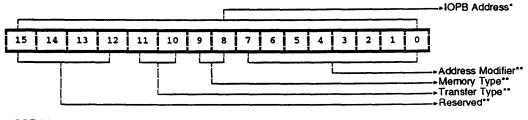

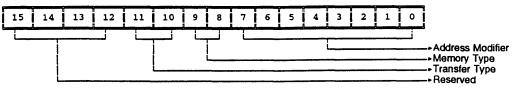

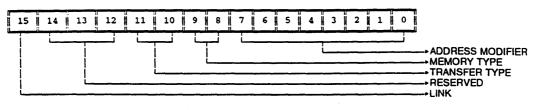

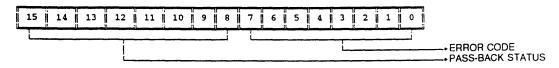

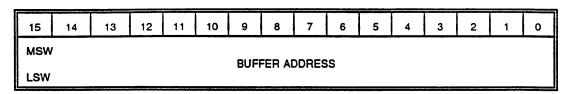

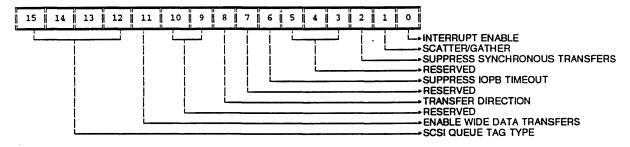

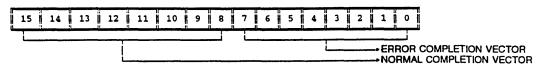

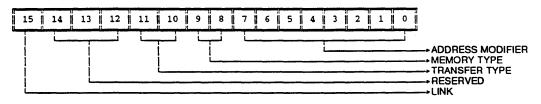

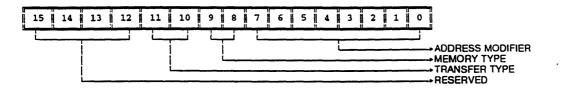

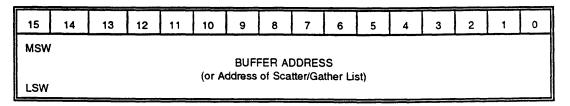

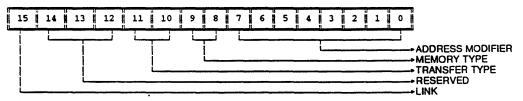

## CGE Word 1: