# V/ESDI 4201 Panther High-performance

VMEbus Enhanced Small Device Interface (ESDI) Disk Controller

**User's Guide**

# V/ESDI 4201 Panther

High-performance VMEbus Enhanced Small Device Interface (ESDI) Disk Controller

**User's Guide**

Document Number UG-0740-000-040

**Revision 040 Follows Revision X0F**

i

Release Date October, 1988

### CAUTION

Specific configurations of the V/ESDI 4201 use rows A & C of the connector on P2 for I/O signals. To avoid possible damage to this board, the backplane, or other system components, verify compatibility with the system before installing this board and applying power.

#### FOR ASSISTANCE IN USING THE V/ESDI 4201 OR ANY

#### OTHER INTERPHASE PRODUCT CALL:

#### INTERPHASE APPLICATIONS ENGINEERING DEPARTMENT

(214) 350-9000 919-9000

IN THE U.K., CALL:

(0296) 435661

#### **COPYRIGHT NOTICE**

No part of this publication may be stored in a retrieval system, transmitted, or reproduced in any way, including, but not limited to photocopy, photograph, electronic or mechanical, without prior written permission of INTERPHASE CORPORATION.

Information in this user document supersedes any preliminary specifications and/or data sheets that may have been made available. Every effort has been made to supply accurate and complete information. However, Interphase Corporation assumes no responsibility for its use. In addition, Interphase reserves the right to make product improvements without prior notice. Such improvements may include, but are not limited to, command codes and error codes.

#### NOTE

This document is confidential proprietary information of Interphase Corporation and shall not be disclosed or copied or used for any purpose other than for which it is specifically furnished without the prior written consent of Interphase Corporation.

### TABLE OF CONTENTS

| 1. | INTRODUCTION TO THE V/ESDI 4201        |

|----|----------------------------------------|

|    | Overview                               |

|    | BUSpacket Interface1-1                 |

|    | The FIFO Buffer 1-2                    |

|    | The Asynchronous State Machine         |

|    | Virtual Buffer Architecture 1-3        |

|    | Zero Latency 1-3                       |

|    | Prefetch Caching1-4                    |

|    | V/ESDI 4201 Optional SCSI Port 1-4     |

|    | V/ESDI 4201 Features and Functions 1-5 |

|    | Command Queing 1-6                     |

|    | Command Response 1-7                   |

|    | Command Parsing 1-7                    |

|    | Performance Advantages 1-8             |

|    | Command Grouping 1-8                   |

|    | Overlapped Seeks 1-8                   |

|    | Command Sorting 1-9                    |

|    | Search Cache on Reads 1-9              |

|    | Command Latency 1-9                    |

|    | Other Considerations 1-9               |

|    | Utilizations of VMEbus Facilities1-11  |

|    | VMEbus Structure1-11                   |

|    | Data Transfers 1-11                    |

|    | Bus Master                             |

|    | Bus Slave                              |

|    | Data Transfer Operations               |

|    | VMEbus Addressing1-12                  |

|    | Short I/O 1-13                         |

|    | Arbitration                            |

|    | Priority Interrupts1-15                |

|    | Interrupt Operation 1-15               |

### 2. INSTALLATION OF THE V/ESDI 4201

| Cabling Options        | 2-1 |

|------------------------|-----|

| Option Switch Settings | 2-4 |

| Jumper Settings        | 2-6 |

| Installation           | 2-7 |

### 3. INITIALIZING THE V/ESDI 4201

| Overview                                            |

|-----------------------------------------------------|

| Unit Initialization Block                           |

| Volume Specification: UIB Bytes 0-3 3-2             |

| Sectors/Track: UIB Byte 4                           |

| Spiral Skew: UIB Byte 5 3-3                         |

| Bytes Per Sector: UIB Bytes 6 and 7                 |

| Gap 1 Words: UIB Byte 8                             |

| Gap 2 Words: UIB Byte 9                             |

| Sector Interleave: UIB Byte A 3-3                   |

| Retry Count: UIB Byte B                             |

| Number of Cylinders: UIB Bytes C and D              |

| Attributes: UIB Byte E                              |

| Second Attributes Set: UIB Byte F                   |

| Status Change Interrupt Level, Register and Vector: |

| UIB Bytes 10 and 11                                 |

| Extended UIB                                        |

| Write Delay: UIB Byte 12 3-8                        |

| Number of Spares: UIB Byte 13 3-8                   |

| Command Complete Timout (MSB and LSB):              |

| UIB Byte 16 and 17                                  |

| Default UIB                                         |

| Initialization of Disk Media                        |

| Formatting Considerations                           |

| Spiral Skew                                         |

| How to Determine Skew                               |

| Interleave                                          |

| Physical and Logical Translation                    |

| Disk Surface Analysis                               |

| Faulty Media Mapping                                |

| Bad Track Mapping3-14                               |

| Bad sector Mapping                                  |

| Multiple Sector Slipping                            |

| Initializing the V/ESDI 4201 Controller             |

| Selecting the Drive Sector Sizes of the V/ESDI 4201 |

| Determine Minimum Bytes/Sector                      |

| Determine Sectors/Track                             |

| Provided Bytes/Sector and Sectors/Track             |

| Calculate Sectors/Track                             |

| Optional Drive Setups                               |

.

### 4. NON-MACSI OPERATION OF THE V/ESDI 4201

| Overview                        |

|---------------------------------|

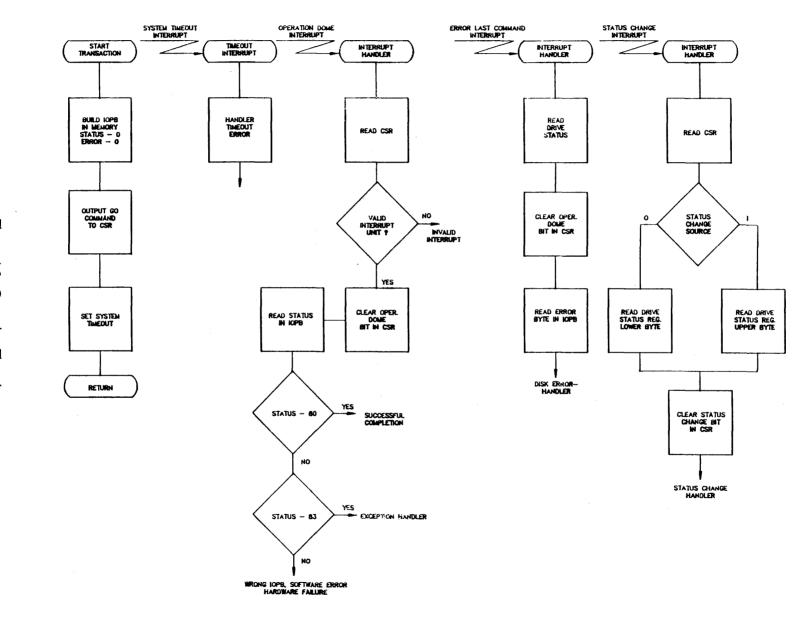

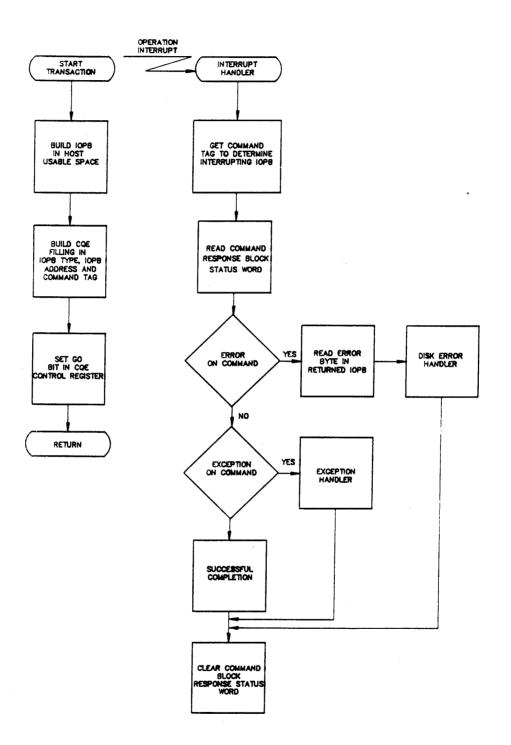

| How to Issue a Command 4-4      |

| Interrupts 4-4                  |

| IOPB and I/O Registers 4-6      |

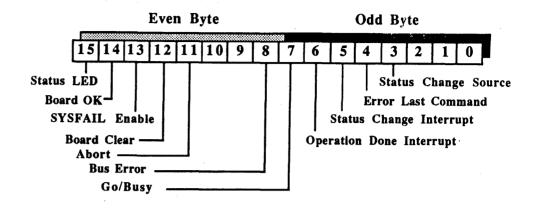

| Status Registers 4-6            |

| Command/Status Register 4-6     |

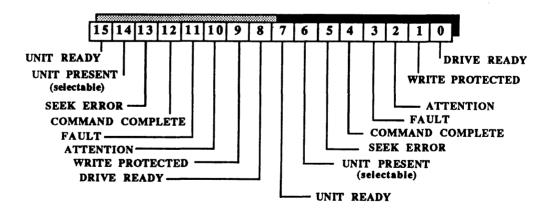

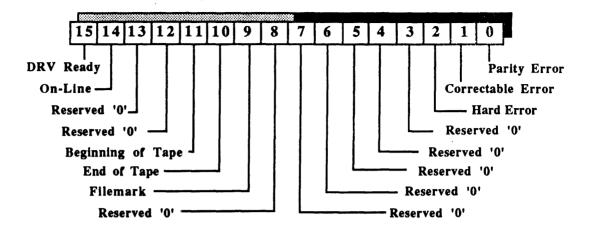

| Drive Status Register 4-10      |

| Enhancing ESDI Disk Performance |

| Linked IOPBs                    |

| Scatter/Gather Operation        |

| Scatter/Gather Lists            |

| Scatter/Gather Guidelines       |

| Scatter/Gather Completion       |

| Overlapped Seeks                |

| Status Change Interrupts        |

### 5. INPUT/OUTPUT PARAMETER BLOCK (IOPB)

| IOPB Format                                                  |

|--------------------------------------------------------------|

| Command Codes: IOPB Word Zero, Upper Byte 5-2                |

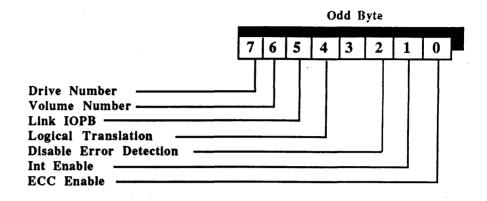

| Command Options: IOPB Word Zero, Lower Byte 5-2              |

| Command Status Codes: IOPB Word One, Upper Byte 5-4          |

| Error Codes: IOPB Word One, Lower Byte                       |

| Error Codes for Commands Completed with Exception 5-6        |

| Error Codes for Commands Completed with Error 5-7            |

| IOPB Words 2-13 5-8                                          |

| Cylinder Address (Word 2) 5-8                                |

| Head and Sector Numbers (Word 3) 5-9                         |

| Sector Count (Word 4) 5-9                                    |

| Buffer Address (Words 5 and 6) 5-9                           |

| Memory Type/Address Modifier Codes (Word 7) 5-9              |

| Optional Drive Number & Interrupt Level/Vector (Word 8) 5-10 |

| DMA Transfer Count and Error Interrupt (Word 9) 5-10         |

| Address Pointers (Words 10 and 11)                           |

| Memory Type and Address Modifier Codes (Word 12) 5-11        |

| Absolute Skew and Entry Count (Word 13) 5-12                 |

### 6. MULTIPLE ACTIVE COMMAND SOFTWARE INTERFACE (MACSI)

| MACSI Overview                               |

|----------------------------------------------|

| Command Queues                               |

| Work Queues                                  |

| Command Response Block                       |

| Performance Issues                           |

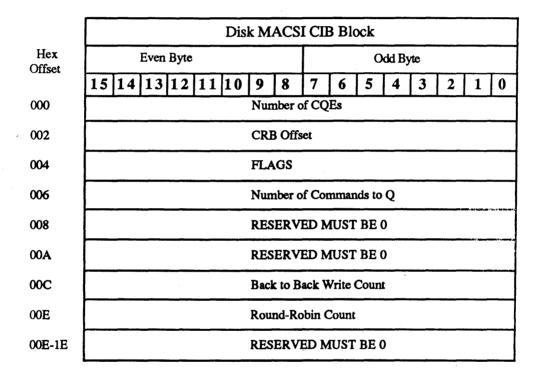

| Go to MACSI Mode Command                     |

| Number of Command Queue Entries              |

| Command Response Block Offset                |

| MACSI Flags                                  |

| Number of Command Queue Entries              |

| Back to Back Write Count                     |

| Round-Robin Count6-6                         |

| Go to MACSI Mode Error Conditions            |

| System Interface Detailed Description        |

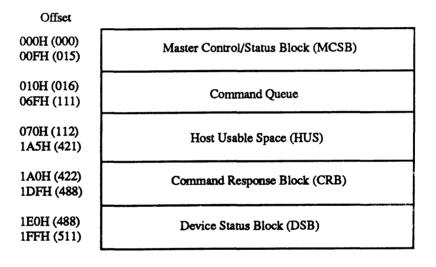

| Master Control/Status Block (MCSB)           |

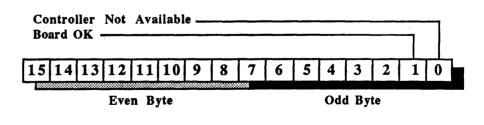

| Master Status Register (MSR)                 |

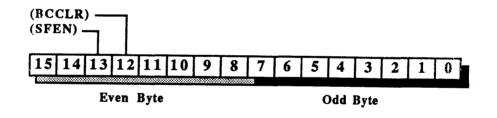

| Master Control Register (MCR)                |

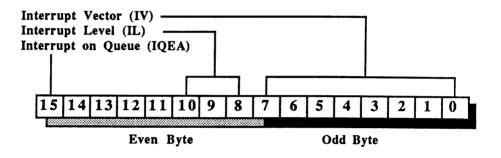

| Interrupt on Queue Available Register (IQAR) |

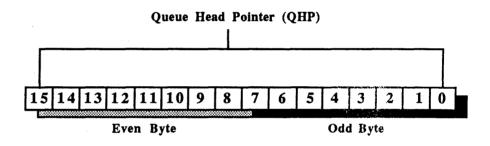

| Queue Head Pointer                           |

| Command Queue                                |

| Command Queue Entry (CQE)                    |

| Queue Entry Control Register (QECR)          |

| IOPB Address                                 |

| Command Tag                                  |

| IOPB Length                                  |

| Host Usable Space (HUS)6-18                  |

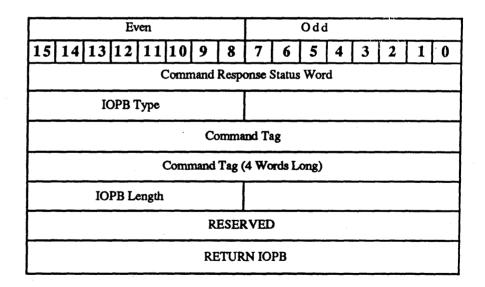

| Command Response Block (CRB)                 |

| Command Response Status Word (CRSW)          |

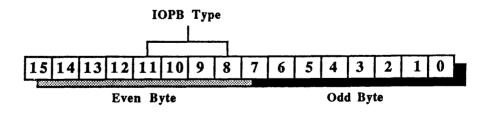

| IOPB Туре                                    |

| Command Tag                                  |

| IOPB Length                                  |

| Returned IOPB                                |

| Device Status Block (DSB)6-23                |

| Tape Status Register    6-23                 |

| Board Status Bits Register                   |

| VMEbus Interrupts                            |

| I/O Parameter Block and Commands             |

| Disk IOPBs6-26                               |

| SCSI IOPBs                                   |

| MACSI Mode Error Codes                       |

#### APPENDICES

- A. Specifications of the V/ESDI 4201

- B. Cable Interfaces

- C. Command Codes

- D. Error Codes

- E. "C" Language Data Structure

### **GLOSSARY OF TERMS**

INDEX

### FIGURES

| Figure 1-1  | Typical Computer System 1-7                    |

|-------------|------------------------------------------------|

| Figure 2-1  | Board Layout 2-2                               |

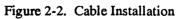

| Figure 2-2  | Cable Installation                             |

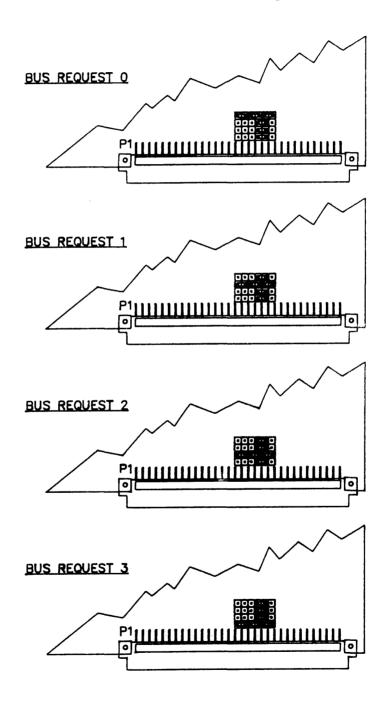

| Figure 2-3  | Jumper Configuration                           |

| Figure 3-1  | UIB Attribute Byte E 3-4                       |

| Figure 3-2  | UIB Second Attribute Byte F 3-6                |

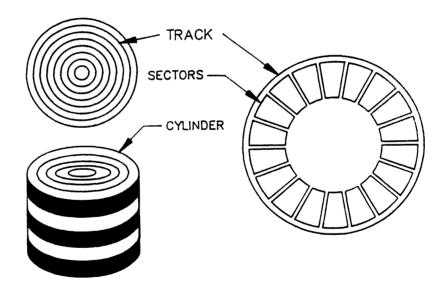

| Figure 3-3  | Typical Disk Unit                              |

| Figure 3-4  | Sample Formatted Sector                        |

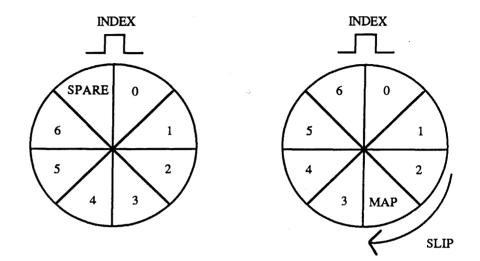

| Figure 3-5  | Sector Slip                                    |

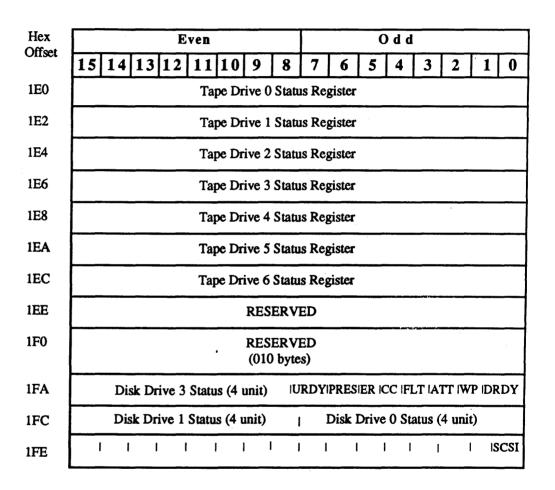

| Figure 4-1  | V/EDSI 4201 Standard Short I/O Format 4-2      |

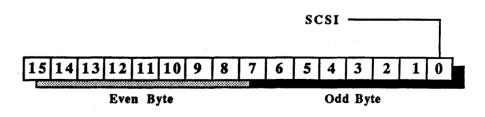

| Figure 4-2  | V/EDSI 4201 w/SCSI Port I/O Memory Format      |

| Figure 4-3  | Operations Flowchart 4-5                       |

| Figure 4-4  | Command Status Register Format 4-7             |

| Figure 4-5  | Drive Status Register 4-10                     |

| Figure 5-1  | Command Options Byte Format 5-3                |

| Figure 6-1  | MACSI Control Structures Block Diagram         |

| Figure 6-2  | MACSI CIB Block                                |

| Figure 6-3  | Example 4201 MACSI System Interface Memory Map |

| Figure 6-4  | Master Control/Status Block (MCSB) 6-11        |

| Figure 6-5  | Master Status Register (MSR)                   |

| Figure 6-6  | Master Control Register (MCR) 6-12             |

| Figure 6-7  | Interrupt on Queue Available Register (IQAR)   |

| Figure 6-8  | Queue Head Pointer/Queue Head Pointer in Use   |

| Figure 6-9  | Command Queue Entry (CQE) 6-16                 |

| Figure 6-10 | Queue Entry Control Register (QECR) 6-17       |

| Figure 6-11 Command Response Block (CRB) 6      | i-19 |

|-------------------------------------------------|------|

| Figure 6-12 Command Response Status Word (CRSW) | i-20 |

| Figure 6-13 IOPB Type 6                         | i-21 |

| Figure 6-14 Format of the Tape Status Register  | -24  |

| Figure 6-15 Board Status Bits Register          | -25  |

### **TABLES**

| Table 1-1 | Product Variations                           |

|-----------|----------------------------------------------|

| Table 2-1 | P2 Connector Scheme                          |

| Table 2-2 | Base Address Switch Settings 2-5             |

| Table 3-1 | UIB Format 3-2                               |

| Table 3-2 | Extended UIB 3-7                             |

| Table 3-3 | Default UIB 3-9                              |

| Table 4-1 | A1-A4 Command Codes 4-14                     |

| Table 4-2 | A5-A6 Command Codes 4-14                     |

| Table 5-1 | IOPB Format                                  |

| Table 5-2 | V/ESDI 4201 Disk Control Commands 5-2        |

| Table 5-3 | Command Status Codes 5-5                     |

| Table 5-4 | Error Codes                                  |

| Table 5-5 | IOPB Words 2-13 5-8                          |

| Table 5-6 | IOPB (Word 7) Memory Type Codes 5-9          |

| Table 5-7 | Linked IOPB (Word 12) Memory Type Codes 5-11 |

| Table 6-1 | Device Status Block                          |

## 1 INTRODUCTION

#### WARNING

Catastrophic DAMAGE can result if improper connections are made. Therefore, those planning to connect power sources to the VMEbus for the purpose of feeding the user defined pins of P2 (Rows A and C) should FIRST CHECK to ensure that all boards installed are compatible with those connections.

The Panther offers two modes of operation: Non-MACSI, which is explained in this user's guide primarily for backwards compatibility with previous versions of Interphase drivers and products; and MACSI, the command queing mode of operation, which offers the best possible performance from the board.

Non-MACSI operation is explained in Chapter 4. Input/Output Parameter Blocks are explained in Chapter 5 and MACSI operation is explained in Chapter 6.

#### Overview

The V/ESDI 4201 Panther is an extremely fast, intelligent, Enhanced Small Device Interface (ESDI) controller/formatter used to interface VMEbus-based systems to ESDI compatible disk drives. The V/ESDI 4201 can support any combination of four ESDI drives, hard or soft sectored.

Its intelligence is based on a M68000 16/32 bit microprocessor running with no wait states. The real key to the V/ESDI 4201, however, is the proprietary BUSpacket Interface<sup>SM</sup> and the Multiple Active Command Software Interface (MACSI).

The V/ESDI 4201 achieves a throughput far superior to that of any competitive controller by sending preformatted data packets across the VMEbus at rates up to 30 megabytes per second.

#### **BUSpacket Interface**

It is the BUSpacket Interface of the V/ESDI 4201 that enables it to operate at speeds of 30 megabytes/second on the VMEbus. Previous generations of disk controllers transferred data across the bus as fast as the internal buffer, the bus interface and the system memory would allow, but this generally resulted in data rates in the five to ten megabytes/second range. The BUSpacket Interface bursts preformatted data packets across the bus as fast as the system memory will allow.

With a bus data rate up to 30 megabytes/second the V/ESDI 4201 comes close to fully utilizing the 40 megabytes/second theoretical bandwidth of the VMEbus. This high bus data rate means that the V/ESDI 4201 spends less time on the bus than other controllers, conserving bus bandwidth for other processes.

There are two keys to the speed of the BUSpacket Interface: a deep FIFO buffer and a delay-line-based asynchronous state machine.

#### The FIFO Buffer

The deep FIFO buffer of the BUSpacket Interface is a very high speed 512-byte FIFO that can write a BUSpacket to (or read a BUSpacket from) the Panther's 128 Kbyte buffer with a fast block transfer. The FIFO itself is very fast so that once it is connected to the VMEbus, the DMA can proceed at 30 megabytes/second. Thus, the speed of the controller (on the VMEbus) is totally decoupled from the speed of the 128K RAM buffer and the peripheral device attached to the controller.

During a read from the disk, for example, the FIFO buffer is filled with a packet of data from the buffer memory prior to the controller acquiring the bus. Once on the bus, the packets are burst across the bus (in DMA mode). When the transfer is complete the bus is immediately released for other uses. This is continued until all of the information requested in the read or write command has been transferred to/from system memory. During a DMA operation to/from the BUS packet FIFO no other functions (such as caching) are impeded.

#### The Asynchronous State Machine

The V/ESDI 4201 uses an asynchronous state machine (in lieu of a traditional variety) in the BUSpacket Interface to control the DMA transfer of data to/from the VMEbus.

Synchronous state machines, which are typically used to control the entire DMA operation, must first synchronize the inherently asynchronous VMEbus control signals to avoid metastable states. This synchronization cycle will, on the average, delay the signal by one and a half periods of the synchronizing clock. This means that a synchronous state machine running at 20 MHz, for example, will delay any control signal off of the bus by an average of 75 nanoseconds before it uses it as an input to the state machine. Such a delay is an unacceptable portion of the 100 nanosecond cycle time required to achieve a 40 megabyte/second data rate on the VMEbus.

In contrast, the high-speed DMA transfer of the BUSpacket Interface on the V/ESDI 4201 is controlled by an asynchronous state machine that runs off of a tapped delay line. A tapped delay-line-based state machine avoids metastable states without incurring the delays caused by synchronizing the VMEbus signals. Since the VMEbus is an asynchronous bus, the tapped delay line state machine can essentially drive the bus as fast as system memory allows.

#### Virtual Buffer Architecturesm

The M68000, running under a proprietary, multitasking real time firmware operating system, is used to regulate controller activity, such as sequencing commands and setting up data transfer operations. Its most important function, however, is to manage the pool of virtual buffers that is composed from the V/ESDI 4201's 128 Kbytes of RAM.

At any given time individual buffers may be allocated to either the disk, the VMEbus, or the cache. The 68000 microprocessor will dynamically allocate and deallocate buffers as they are requested or released by the VMEbus or the disk. During a disk read, for example, the disk read task brings data into a free buffer. Simultaneously, as soon as any sector of interest has been captured, the bus write task begins moving data into system memory; thus, the sector buffer is freed. If the VMEbus cannot keep up with the drive, the buffers will hold the data until the bus is ready. The buffer thus prevents either overrun or underrun of data. The V/ESDI 4201 is able to apply many high-performance techniques which can reduce or eliminate disk rotational latencies. These methods include zero latency reads and writes, and intelligent caching.

#### Zero Latency

A traditional controller, upon receiving a multisector request from the operating system, will wait until it encounters the first required sector before beginning to read and transfer the data. Thus, it will incur an average rotational latency equivalent to one half of one track. If the request is for a full track of data, even with a 1:1 interleave factor, the traditional controller will take an average of one-and-half revolutions to complete the transfer.

The V/ESDI 4201 begins reading data as soon as the heads land on the track (i.e., zero rotational latency) and begins transferring data as soon as it encounters a sector of interest; it does not wait to rotate around to the beginning of the requested string. In this manner, the V/ESDI 4201 will never require more than a single revolution to transfer an entire track of data.

Zero latency writes are accomplished using the same principle. This technique is most effective for large disk transactions which may access many sectors of data per transaction.

### **Prefetch Caching**

To further reduce latency, the V/ESDI 4201 uses an intelligent caching scheme (prefetch caching) to anticipate which data sectors will be requested next. When the V/ESDI 4201 has completed a read operation and has transferred the requested data, it will continue to read sectors into the cache until all available buffers have been filled, or until it receives a command from the host requesting a head movement. And with the large 128 Kbyte RAM buffer, the V/ESDI 4201 can even cache across track boundaries. Thus, if subsequent requests from the operating system are for sectors logically contiguous with the previous sectors, these requests can be satisfied directly from the cache without having to access the disk. In disk intensive applications this can greatly improve overall system throughput.

This form of caching is particularly useful for UNIX and UNIX-like operating systems. Tests have shown improvements in disk operation averaging greater than 40 percent over operation with 1:1 interleave only. Caching shows the greatest improvement when disk activity is characterized by a large number of short transactions.

### V/ESDI 4201 Optional SCSI Port

The V/ESDI 4201 can be equipped with an optional SCSI port to provide convenient archiving and tape backup capabilities. This addition allows the V/ESDI 4201 to control not only four ESDI disk drives, but at the same time, to control up to seven SCSI devices.

When a V/ESDI 4201 is equipped with a SCSI port, the Short I/O memory format is modified to accomodate the additional command set, status registers, et cetera, that are required for SCSI device operations. In addition, 16 Kbytes of the 128 Kbytes of on-board RAM are used as a buffer between the tape devices and system memory. This buffer enables the V/ESDI 4201 to operate concurrent bus and tape operations. So while the tape is processing a transaction, the V/ESDI 4201 is reading/writing to/from the buffer to prepare for the next tape operation. This aids in providing tape streaming on a command basis.

SCSI operation is detailed in the V/ESDI 4201 Panther SCSI Port supplemental user's guide, UG-0780-000-XXX.

UNIX is a registered trademark of AT&TBell Laboratories.

### V/ESDI 4201 Features And Functions

The V/ESDI 4201 provides many options which are either under software control or are mechanically selectable by switch or jumper. For example, sector sizes are programmable varying from 128 bytes to 2048 bytes. The most important features and functions of the V/ESDI 4201 are outlined as follow:

- The BUSpacket Interface boosts DMA throughput in excess of 30 megabytes per second.

- The V/ESDI 4201 is controlled using a simple macro-level software interface.

- The on-board M68000 16/32 bit microprocessor relieves the system CPUs of disk handling tasks.

- Optional SCSI port to control up to seven SCSI devices.

- The V/ESDI 4201 can control up to four ESDI disk drives and seven SCSI devices concurrently.

- The V/ESDI 4201 supports 8-, 16-, or 32-bit wide data transfers, and provides 16-, 24-, or 32-bit addressing capability.

- 128 Kbytes of memory is provided; most of which is treated as a pool of virtual buffers.

- The V/ESDI 4201 supports disk data rates up to 24 Mb/s with a 1:1 interleave factor.

- Virtual Buffer Architecture reduces or eliminates data transfer delays caused by disk rotational latency and data overrun/underrun.

- A prefetch caching scheme with dynamic buffer allocation and deallocation is provided. Caching algorithms are optimized for UNIX, RMX/86 and similar operating systems.

- Automatic error correction is provided using a 32-bit or 48-bit error correction code (ECC).

- The V/ESDI 4201 can control four ESDI drives (hard or soft sectored).

- Self-diagnostics are performed after each hardware power-up and each software reset.

- Scatter/Gather comands allow the user to place contiguous disk data in noncontiguous areas of system memory or vice versa.

#### RMX/86 is a trademark of Intel Corporation.

- Overlapped and implied seeks are supported.

- Seven software programmable interrupt levels are provided.

- Bus priority is jumper selectable from zero to three.

- Defective media replacement on a sector or track basis is provided when formatting the disk.

- The disk can be addressed by either physical or logical sectors.

- Zero latency reads and writes insure maximum throughput.

- An interrupt on drive status change is a programmable option for such applications as overlapped seeks.

### **Command Queuing**

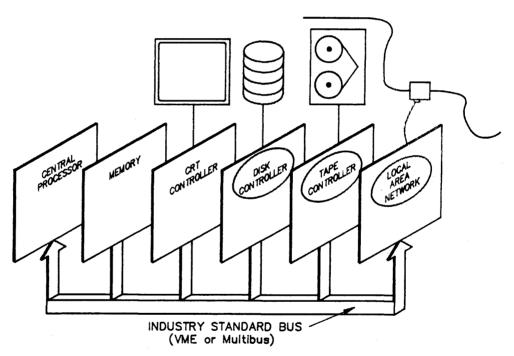

In a typical computer (Figure. 1-1) there is a host CPU, some system memory, and a peripheral controller. The host issues commands to the peripheral controller which in turn moves data from the peripheral into (or out of) system memory. The host begins an operation by issuing a command to the controller. If there is no command queue, the controller is idling until the "GO" bit is set in the command. Once the "GO" bit is set, the controller can "decode" the command and start the peripheral in operation. When the controller/peripheral pair finishes the operation (which will typically involve some data movement) the controller issues a command complete interrupt to the host. The host, after servicing the interrupt, starts the cycle over by issuing another command to the controller.

This scenario, with little modification, has been used by controller manufacturers for years. But as computer manufacturers begin pushing for better and better performance, the problems inherent in this scheme begin to seriously limit performance.

Specifically there are two "times" inherent in this serial "command - wait for response" scheme that limit performance: command response times and command parsing times. By overlapping command response and command parsing with peripheral operation, queuing schemes significantly improve system performance.

#### **Command Response**

In the typical system described above, it may be many microseconds before the "GO" bit in the next command can be set after the host receives the command complete interrupt from the previous command. The sequence is: the controller asserts the command complete interrupt, the host responds by doing a context switch, servicing the interrupt, loading the next command into the controller and setting the "GO" bit. While all of this is going on the controller and peripheral are idle. The controller cannot start processing a command until the "GO" bit of the command has been set.

With a command queue inside the controller the host can load a command into the controller and set the "GO" bit while the controller and peripheral are still processing the previous command. Thus all of the command response time is overlapped with actual peripheral activity. This not only improves performance of the controller/peripheral pair but it also removes time pressure from the operating system so that interrupt response times and context switch times are no longer in the "critical path" of controller operation. This may allow the system to operate the controller at a lower priority without noticeable degradation of peripheral performance.

Figure 1-1. Typical Computer System

#### **Command Parsing**

Once the host has set the "GO" bit in a command the controller must parse (decode) the command before it can be issued to the peripheral. It is not unusual for this command parsing to take hundreds of microseconds. And in a conventional system, command parsing cannot be done until after the "GO" bit has been set. A controller without a command queue cannot parse the command until the "GO" bit is set either. But with a command queue, the "GO" bit is set long before the command complete interrupt of the previous command is issued. Thus commands can be parsed while previous commands are being executed. This overlaps command parsing with peripheral operation.

### **Performance Advantages**

In addition to the performance advantages gained by overlapping certain controller and host activity with peripheral activity, as described above, an efficient command queuing scheme can improve system performance by optimizing the manner in which the peripherals themselves are controlled. This is true of disk operations in particular, because they are subject to mechanical rotational and head movement delays. Thus improved operation can often be achieved by modifying the "way" in which commands are passed from the controller to the disk.

There are five generalized techniques that can be applied:

- Command Grouping

- Overlapped Seeks

- Command Sorting

- Search Cache on Reads

- Command Latency

#### **Command Grouping**

Command Grouping is a scheme whereby the controller searches the command queue for commands that can be "grouped" into a single command before issuing the single, concatenated command to the disk. Thus only a single command is issued to the peripheral. Upon completion of this one "macro" command, the controller reports command completion of each of the individual, original commands.

#### **Overlapped Seeks**

Once a controller has issued a command to a disk, if there is a seek implied in the command, there will be some seek delay before the head is on cylinder and the disk is capable of transferring data. By issuing seek commands to all of the disks at once these seek times are overlapped so that only one of the seek delays is actually incurred, the others are overlapped with data movement and other activity.

Command queuing facilitates the overlapping of seeks because it makes it possible for the controller to search through the queue and find the next command for each disk.

#### **Command Sorting**

Disk seek times can also be minimized if the controller sorts the commands beforehand so that the disk is always seeking a nearby cylinder. To ensure that seeks to "outside" cylinders do get issued, the typical algorithm will not allow the head travel to "turn around" until it gets to an extreme. Because this is similar to the method used by elevators in deciding which floor to stop at next, this scheme is called an "elevator sort" algorithm.

Command queuing facilitates this type of command sorting because the controller can easily sort through all of the command in the queue and then issue them to the disk in a prescribed order.

#### Search Cache on Reads

Disk seek times and rotational delays can be eliminated entirely from read commands if the controller can use data that has already been read into the onboard cache. If the controller finds that the read command is requesting data that is already in the cache, then the command can be satisfied immediately without any waiting. This will work only in RAM-based caching controllers. FIFO based controllers have obvious problems implementing any type of useful cache search on reads.

#### **Command Latency**

Not all command queue schemes are the same, and even if the controller has a command queue, there may be differences. For example, another key parameter that affects overall system operation is command queue latency. This is a measure of the minimum time required (for the host to wait) between issuing commands to the queue. In general this time will be overlapped with peripheral operation, but it still slows the host down if it must wait a long time before it can issue the next command to the controller.

Ideally the controller can accept commands as fast as the host can normally write to memory. Anything less than this slows the host down.

#### **Other Considerations**

In addition to these performance advantages, there are other considerations that affect how useful a command queuing scheme is in a given situation.

In general there should be some mechanism to tailor the queue depth to the application. Longer queues require more manipulation by the controller and are thus slower but a queue that is too short for the application may not offer significant advantage over a simpler nonqueuing scheme.

Occasionally there is a need to be able to issue a command that does not pass through the queue at all, or at least to issue one that is placed at the top of the queue. In the final analysis there are good reasons for wanting a queuing mechanism that offers all of the performance advantages of short command queues and also provide the flexibility of multiple command queues. Interphase has developed Multiple Active Command Software Interface (MACSI) and has implemented it on several VMEbus controllers. It provides all of the performance advantages of simpler first generation command queuing schemes while still offering the power and flexibility that can only be provided by a multiple queue mechanism.

### Utilization Of VMEbus Facilities

The evolution of control applications from 8- and 16-bit buses has progressed up to the development of the VMEbus. The VMEbus is the first bus structure to support a true 32-bit processor. It is comprised of separate 32-bit data and address lines that not only support 32-bit transactions, but also the traditional 8- and 16-bit transactions as well. This makes the VMEbus particularly appropriate for stand-alone or remote process controller applications. In addition, the VMEbus provides the flexibility for expansion within the microcomputer environment. Given all of these advantages, the V/ESDI 4201 is able to exploit the potential of the VMEbus and provide performance necessary in today's systems.

#### **VMEbus Structure**

There are three basic signals which determine the operation of the VMEbus: the Bus Request signal (for getting on the bus), the Bus Grant signal (for allocating the bus for use), and 32 bits of addressing. The addressing is supplemented with six address modifier bits which are used to partition memory spaces. The address modifiers are used to expand memory space by breaking it up into functional blocks.

The VMEbus has seven prioritized interrupts for fully vectored operation. This means that during an interrupt cycle, an interrupt vector provides the CPU with a unique value that describes the interrupt. In nonvectored systems, the CPU must search registers for the cause of the interrupt. The advantage of the vectored interrupt, therefore, is to greatly decrease the amount of time the CPU must spend servicing interrupts.

### **Data Transfers**

All VMEbus data transfers are performed over the Data Transfer Bus (DTB). The DTB is 32 bits wide and is only used for data transfers. The VMEbus supports data transfers of eight, 16, or 32 bits. All data transfers take place between a bus master and a bus slave. The VMEbus supports multiple bus masters which provide the capability of moving large blocks of data without CPU intervention; thus, the CPU is not tied up for long periods of time during data transfers.

The V/ESDI 4201 uses the DTB to transfer commands, status and data between the host system, disk drive, and itself. The V/ESDI 4201 supports 8-, 16-, and 32-bit data transfers.

#### **Bus Master**

A DTB master can be any board that is capable of requesting the VMEbus. The V/ESDI 4201 performs all data transfers as a DTB master.

#### **Bus** Slave

A bus slave is a device that responds to the DTB master during data transfers. When commands are issued to the V/ESDI 4201, or status is read from the board, the V/ESDI 4201 is acting as a slave device.

#### **Data Transfer Operations**

During a data transfer cycle several things must happen. First, a bus master must request and be granted the bus. The master then puts the address of the slave to which the data will be transferred on the bus, and if it is a write operation, the data is also put on the bus. Since the VMEbus is completely asynchronous, the master must know when the address is valid and if the slave has either received the data or is ready for more data.

Once the address is valid, the master asserts an Address Strobe signal. Then, the master commands the data on the DTB bus with the Data Strobes. That tells the slave that the address is valid and the data is directed at that particular slave. Once the slave has received the data (write operation) or placed the data on the bus (read operation), the slave tells the master that the transfer is complete. To do this, the slave asserts a signal called Data Transfer Acknowledge (DTACK).

There are no restrictions on the VMEbus as to how long data transfers can be. The only real restriction is that the address strobe must precede the data strobe.

To start a command, a bus master (typically a CPU) will issue commands to the V/ESDI 4201 which is acting as a bus slave. After the V/ESDI 4201 has received the command and responded to it, it will then request the VMEDus, and when the bus is granted, the V/ESDI 4201 will transfer the data as a bus master.

#### VMEbus Addressing

The memory space accessible to the V/ESDI 4201 and the host CPU contains several subdivisions. Each subdivision requires a specific type of addressing. This partitioning of the memory space allows more efficient access and utilization of the memory. The addressing options include:

- ShortAddressing(16-bit)

- StandardAddressing(24-bit)

- ExtendedAddressing(32-bit)

The type of addressing is specified using a 6-bit address modifier code that also indicates the nature of the access. For example, address modifiers are commonly used to specify supervisory (restricted) memory access, and user (nonprivileged) memory access. The V/ESDI 4201 supports 16-, 24-, and 32-bit addressing as well as all address modifiers (as a bus master).

#### Short I/O

The V/ESDI 4201 requires that all data transfers of control information, command parameters, and status that occur with the host CPU acting as the bus master must be done through the short address space using either address modifiers 29 (user) or 2D (supervisor). This short address space is commonly referred to as Short I/O space. (A 512-byte block of this address space resides in the V/ESDI 4201 on-board RAM.)

The Short I/O is the window through which the host can send commands and parameters, and can review controller status and error codes. The reason that it is called Short I/O space is because any time a board sees a transaction with an address modifier of 29 or 2D in the address strobe, it only looks at the first (lower) 16 address lines even though the VMEbus supports the full 32 address lines. The upper 16 address lines in Short I/O are ignored.

By looking only at the lower 16 address lines, less hardware is needed and less time is spent decoding lines that are not necessary for functions such as reading command registers and status registers. The obvious result is improved performance and reduced cost.

The base address of this block of memory is set by the on-board DIP switches (see section 5).

The V/ESDI 4201 provides Short I/O space on-board as an added feature for improved performance. The 512 bytes of Short I/O provided can accommodate several commands at once. This proves advantageous to system performance by eliminating the need to DMA every command across the bus. So not only is system performance improved, but bus bandwidth is also conserved.

#### NOTE

Short I/O space limitations dictate that all accesses be either 8 or 16 bits. Therefore, if the CPU card generates a 32-bit data path and you are using the C programming language, then it is necessary to cast the 32-bit IOPB fields (i.e., buffer address and bytes/sector) as two 16-bit data types (unsigned shorts on MC68020). This is because the VMEbus short I/O space is 16 bits and will not respond properly to high-order data strobes.

### Arbitration

At some point, either on its own or when it receives a command, every bus master device needs to get on the VMEbus and must request access. This process of requesting and granting the bus is referred to as bus arbitration.

The VMEbus provides four levels of bus request (0-3) to provide prioritized requests. In addition, bus priority is provided by position of the board in the card cage. The closer the board is to slot one (system controller), the higher priority it is given.

The V/ESDI 4201 bus request priority is selectable via on-board jumpers. The factory setting is bus priority 3.

This system of prioritizing means that if two devices with the same priority simultaneously request the bus, the one closest to the system controller is granted bus access first. However, before any bus grant can be issued, the bus must first be cleared (i.e., the current bus master must release the Bus Busy signal).

A VMEbus system may utilize one of three different schemes of bus arbitration based on the two methods of prioritizing bus requests. The first method is called single level arbitration. In this scheme, every device on the bus is assigned the same priority level (e.g., level 3), and the bus requests are prioritized by slot only. This scheme is most useful in low-cost systems where the system controller is on the CPU board. In addition, it takes fewer gates to implement and is less expensive than the other two methods of arbitration. However, the remaining two options offer higher performance than single level arbitration.

The second type is called priority arbitration. Priority arbitration utilizes a signal called Bus Clear. When the system controller sees a request from a higher priority than the one already on the bus, the system controller drives the Bus Clear signal which is a recommendation to the bus master to get off of the bus. When the V/ESDI 4201 receives a bus clear, it will get off of the bus within two bus cycles. This provides better system performance by allowing the V/ESDI 4201 to be run at a low priority level and still not worry about it "hogging" the bus. Finally, the third type of arbitration is called round robin. With this type, there is no fixed priority based on level (i.e., three is not always the highest priority). Instead, priority is determined in a cyclical fashion. In other words, if a priority three is on the bus, the next bus grant will be given to priority two (even if another priority three is present), the next will be given to a priority one and the next to a zero and then back to three. It is useful in a system that is using many similar devices. For example, if four disk controllers are on the backplane and all need equal access to the bus, the need for "position" priority is eliminated. In this scheme, each board will have equal access regardless of board position.

The V/ESDI 4201 supports all three types of arbitration.

#### **Priority Interrupts**

Interrupts are a convenient way for a bus master to tell the CPU that it needs to communicate with another device across the bus. The VMEbus supports seven levels of interrupts with seven being the highest and one being the lowest. The interrupt operation is very similar to the bus grant operation, except the signals involved are the interrupt request from the board and the Interrupt Acknowledge

(IACK) signal from the system controller. Each V/ESDI 4201 command can be programmed with any one of the seven interrupt levels.

As in arbitration, interrupts are also prioritized by slot position. Therefore, if multiple boards request interrupts, the system controller drives the IACK signal and it is passed along serially by each board in the system until the interrupting board reads it.

#### **Interrupt Operation**

After reading a file, a disk controller may want to tell the CPU that it (the CPU) may now use that data. The disk controller gives up the bus and generates the interrupt request on the specified interrupt level. At some point, when the bus is clear, the system controller passes down the IACK signal. When the board that generated the interrupt reads the signal, it responds by issuing an interrupt vector (if enabled). An interrupt vector describes the interrupt to the system controller. When the interrupt vector is valid on the bus, the CPU is in master mode, and the interrupting device will respond with a data acknowledge signal. This tells the system controller it has the vector for the CPU. The V/ESDI 4201 supports unique error codes and vectors for several different types of operation. In addition, a different vector can be used to indicate normal completion or completion with error. This can significantly reduce system overhead by instantly identifying the status of each command as it is completed. The V/ESDI 4201 has a separate status change interrupt and vector to facilitate interrupt processing during overlapped seek operations. Because a unique vector can be used, the system can immediately identify the source of the interrupt with a minimum of processing.

By using unique vectors, the system driver does not need to access registers to take care of post-interrupt activity. Instead, the vector can tell the host exactly what happened, so the host can proceed without any futher delay. The following table summarizes specific functionality for each of the V/ESDI 4201 boards. For details, please contact Interphase Customer Service.

Table 1-1. Product Variations

| TABLE OF PRODUCT VARIATIONS |                                                                                                                                                      |  |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Dash # Description          |                                                                                                                                                      |  |  |

| - 0                         | No longer in production.<br>Standard product as per 4201 User's Guide.*                                                                              |  |  |

| - 1                         | No longer in production.<br>"B" Row only on P2 connector.*<br>Added 175ns delay line on the Bus Packet for<br>slower systems.                        |  |  |

| - 3                         | No longer in production.<br>Customer specific.<br>Berg Disk I/O connectors.                                                                          |  |  |

| - 4                         | No longer in production.<br>Customer specific.<br>Specific firmware required.                                                                        |  |  |

| - 5                         | Added 175ns delay line on the Bus Packet for<br>systems requiring slower VME accesses.<br>"B" Row only on P2 connector.<br>For Sun 3E and ISI users. |  |  |

| - 6                         | Full P2 connector.                                                                                                                                   |  |  |

| - 7                         | "B" Row only on P2 connector.                                                                                                                        |  |  |

| 4201 - DC/SE                | SCSI Port daughter card. Single-ended driver.<br>Cannot be converted to a differential.                                                              |  |  |

\* (Requires XOL or greater firmware)

## 2 INSTALLATION OF THE V/ESDI 4201

### **Cabling Options**

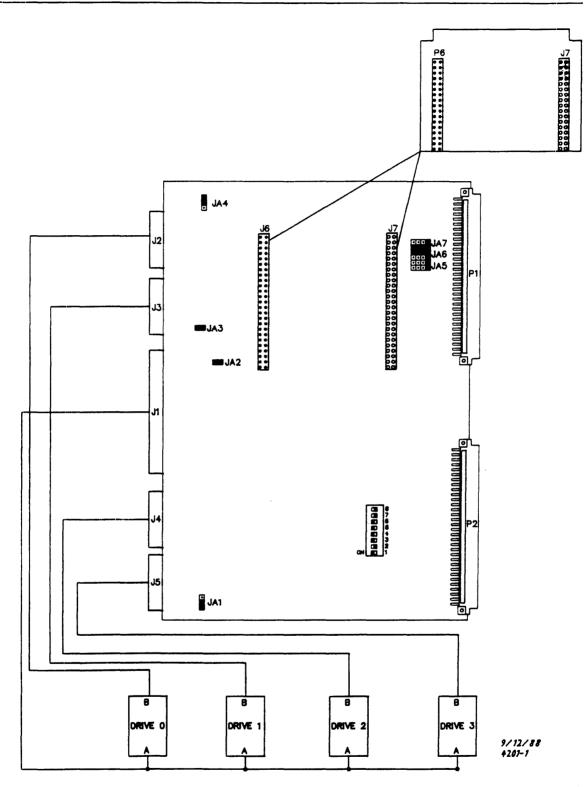

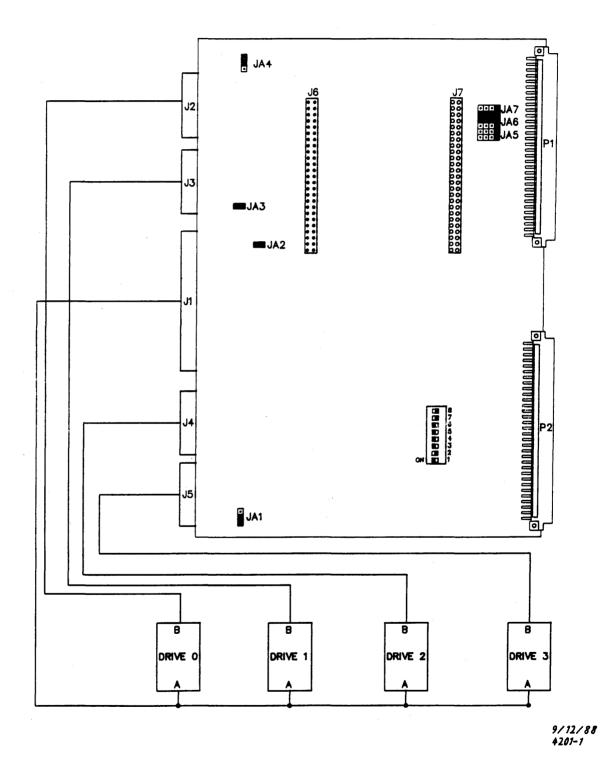

The ESDI drive cables connect to the V/ESDI 4201 through vertically mounted headers (J1-J5) on the V/ESDI 4201 card.

J1 is a 34-pin connector for the ESDI "A" cable. J2-J5 are 20-pin connectors for "B" cable connection of up to four ESDI drives. J2 is the header for drive zero and J3 is the header for drive one, J4 is the header for drive two, and J5 is the header for drive three. Connector pinouts for both the "A" cable and "B" cables are shown in Appendix B of the user's guide.

If connectors J2-J5 are used to connect the ESDI drives, the cables may be routed through the front of the VMEbus card cage.

For information concerning the installation of the optional V/ESDI 4201 SCSI port, refer to the supplemental user's guide: UG-0780-000-XXX. Details of SCSI connectors, installation procedures and other installation considerations are provided.

Figure 2-1 on the following page shows the position of the cable connections, the jumpers, and the location of the option switches on the V/ESDI 4201 printed circuit card. Please refer to the diagram for information as indicated in the remainder of this section of the user's guide.

Figure 2-1. Board Layout

|                       | VMEbus P2 Connector Scheme |          |          |

|-----------------------|----------------------------|----------|----------|

| Pin Row A Row B Row C |                            |          |          |

| 1                     | GND                        | + 5V     | HS3*     |

| 2                     | DIFFEN 0                   | GND      | HS2*     |

| 3                     | DIFFEN 1                   | RESERVED | HS0*     |

| 4                     | DIFFEN 2                   | A24      | HS1*     |

| 5                     | DIFFEN 3                   | A25      | XREQ*    |

| 6                     | DIFFEN 4                   | A26      | ESD1*    |

| 7                     | DIFFEN 5                   | A27      | ESD2*    |

| 8                     | DIFFEN 6                   | A28      | ESD3*    |

| 9                     | DIFFEN 7                   | A29      | UB2-6    |

| 10                    | DIFFEN 8                   | A30      | WATGATE* |

| 11                    | DIFFEN 9                   | A31      | ADGATE*  |

| 12                    | DIFFEN 10                  | GND      | GND      |

| 13                    | SCTL 0                     | + 5V     | + 12V    |

| 14                    | SCTL 1                     | D16      | CMDCPL1  |

| 15                    | SCTL 2                     | D17      | CMDCPL2  |

| 16                    | SCTL 3                     | D18      | CSDATA*  |

| 17                    | SCTL 4                     | D19      | INDEX*   |

| 18                    | SCTL 5                     | D20      | XACK*    |

| 19                    | SCTL 6                     | D21      | SECTOR*  |

| 20                    | SCTL 7                     | D22      | READY*   |

| 21                    | SCTL 8                     | D23      | ATTN*    |

| 22                    | SCSID* 0                   | GND      | UD1-2    |

| 23                    | SCSID* 1                   | D24      | UD1-1    |

| 24                    | SCSID* 2                   | D25      | UD1-6    |

| 25                    | SCSID* 3                   | D26      | UD1-7    |

| 26                    | SCSID* 4                   | D27      | UD1-10   |

| 27                    | SCSID* 5                   | D28      | UD1-9    |

| 28                    | SCSID* 6                   | D29      | UD1-14   |

| 29                    | SCSID* 7                   | D30      | UD1-15   |

| 30                    | SCSID* 8                   | D31      | UM9-2    |

| 31                    | + 12 <b>V</b>              | GND      | UB2-12   |

| 32                    | GND                        | + 5V     | GND      |

Table 2-1. P2 Connector Scheme

### **Option Switch Settings**

The V/ESDI 4201 has a switch block (S1) that contains eight switches (numbered 1-8). (see Figure 2-1).

Switches one through seven correspond to VMEbus address lines A9-A15 respectively. An OFF switch has a value of '1' and an ON switch has a value of '0', which are used to select the base address of the controller. Table 2-2 represents all possible base address and switch settings for the controller.

Switch 8 is used to select the address modifiers for the V/ESDI 4201 Short I/O space. If switch 8 is on, only supervisor accesses are permitted (address modifier 2D only). If switch 8 is off, then both 2D and 29 address modifiers are selected.

| BASE ADDRESS SWITCH SETTINGS     |                                 |              |                                 |

|----------------------------------|---------------------------------|--------------|---------------------------------|

| O = ON / CLOSE<br>F = OFF / OPEN |                                 |              |                                 |

| ADDRESS                          | SWITCH SETTING<br>7 6 5 4 3 2 1 | ADDRESS      | SWITCH SETTING<br>7 6 5 4 3 2 1 |

| 0000                             | 0000000                         | 8000         | F000000                         |

| 0200                             | 000000F                         | 8200         | FOOOOOF                         |

| 0400                             | 00000F0                         | 8400         | FOOOOFO                         |

| 0600                             | 00000FF                         | 8600<br>8800 | F0000FF<br>F000F00              |

| 0800<br>0A00                     | 0000F00<br>0000F0F              | 8A00         | FOOOFOF                         |

| 0000                             | 0000FF0                         | 8C00         | FOOOFFO                         |

| 0E00                             | OOOOF FF                        | 8E00         | FOOOFFF                         |

| 1000                             | 000F000                         | 9000         | FOOFOOO                         |

| 1200                             | OOOFOOF                         | 9200         | FOOFOOF                         |

| 1400                             | 000F0F0<br>000F0FF              | 9400<br>9600 | FOOFOFF                         |

| 1600<br>1800                     | OOOFFOO                         | 9800         | FOOFFOO                         |

| 1A00                             | OOOFFOF                         | 9A00         | FOOFFOF                         |

| 1C00                             | OOOFFFO                         | 9C00         | FOOFFFO                         |

| 1E00                             | OOOFFFF                         | 9E00         | FOOFFFF                         |

| 2000                             | 00F0000                         | A000         | FOFOOOO<br>FOFOOOF              |

| 2200                             | 00F000F<br>00F00F0              | A200<br>A400 | FOFOOFO                         |

| 2400<br>2600                     | OOFOOFF                         | A600         | FOFOOFF                         |

| 2800                             | 00F0F00                         | A800         | FOFOFOO                         |

| 2A00                             | OOFOFOF                         | AA00         | FOFOFOF                         |

| 2C00                             | OOFOFFO                         | AC00         | FOFOFFO                         |

| 2E00                             | OOFOFFF                         | AE00         | FOFOFFF<br>FOFFOOO              |

| 3000                             | OOFFOOO                         | B000<br>B200 | FOFFOOF                         |

| 3200<br>3400                     | OOFFOOF                         | B400         | FOFFOFO                         |

| 3600                             | OOFFOFF                         | B600         | FOFFOFF                         |

| 3800                             | OOFFFOO                         | B800         | FOFFFOO                         |

| 3A00                             | OOFFFOF                         | BA00         | FOFFFOF                         |

| 3C00                             | OOFFFFO                         | BC00         | FOFFFFO<br>FOFFFFF              |

| 3E00                             | OOFFFFF                         | BE00<br>C000 | FF00000                         |

| 4000<br>4200                     | 0F00000<br>0F0000F              | C200         | FFOOOOF                         |

| 4400                             | OFOOOFO                         | C400         | FFOOOFO                         |

| 4600                             | OFOOOFF                         | C600         | FFOOOFF                         |

| 4800                             | OFOOFOO                         | C800         | FFOOFOO                         |

| 4A00                             | OFOOFOF                         | CA00         | FFOOFOF<br>FFOOFFO              |

| 4000                             | OFOOFFO<br>OFOOFFF              | CC00<br>CE00 | FFOOFFF                         |

| 4E00<br>5000                     | OFOFOOO                         | D000         | FFOFOOO                         |

| 5200                             | OFOFOOF                         | D200         | FFOFOOF                         |

| 5400                             | OFOFOFO                         | D400         | FFOFOFO                         |

| 5600                             | OFOFOFF                         | D600         | FFOFOFF<br>FFOFFOO              |

| 5800                             | OFOFFOO                         | D800<br>DA00 | FFOFFOF                         |

| 5A00<br>5C00                     | OFOFFOF<br>OFOFFFO              | DC00         | FFOFFFO                         |

| 5E00                             | OFOFFF                          | DE00         | FFOFFFF                         |

| 6000                             | OFFOOOO                         | E000         | FFF0000                         |

| 6200                             | OFFOOOF                         | E200         | FFFOOOF                         |

| 6400                             | OFFOOFO                         | E400<br>E600 | FFFOOFO<br>FFFOOFF              |

| 6600                             | OFFOOFF<br>OFFOFOF              | EA00         | FFFOFOF                         |

| 6A00<br>6C00                     | OFFOFFO                         | EC00         | FFFOFFO                         |

| 6E00                             | OFFOFF                          | EE00         | FFFOFFF                         |

| 7000                             | OFFF000                         | F000         | FFFF000                         |

| 7200                             | OFFFOOF                         | F200         | FFFFOOF                         |

| 7400                             | OFFFOFO                         | F400<br>F600 | FFFFOFF                         |

| 7600                             | OFFFOFF                         | F800         | FFFFFOO                         |

| 7800<br>7A00                     | OFFFFOF                         | FA00         | FFFFFOF                         |

| 7C00                             | OFFFFFO                         | FC00         | FFFFFFO                         |

| 7E00                             | OFFFFFF                         | FE00         | FFFFFF                          |

| Table 2.2  | Bace Ad | dress Switch | Settings |

|------------|---------|--------------|----------|

| Table 2-2. | Base Ad | uress Switch | Settings |

2-5

### **Jumper Settings**

The user can select bus request priority from 0 (lowest) to 3 (highest) using the on-board jumpers JA5, JA6, and JA7. All of the possible jumper configurations for this jumper block are illustrated below. To locate the jumper block on the V/ESDI 4201, refer back to Figure 2-1.

In addition to the jumpers for selecting bus priority, there are several other on-board jumpers to configure the V/ESDI 4201 for specific hardware characteristics. Jumper E1 selects EPROM size (either 256K or 512K) and jumper E4 determines V/ESDI 4201 signal output (either to the on-board headers, or to VMEbus P2). For the physical location of these jumpers for this option, refer back to Figure 2-1.

The unmarked jumpers are for factory use only and should not be changed by the user. The board is shipped with the jumpers in the positions shown in Figure 2-1, at the beginning of this section.

### Installation

The V/ESDI 4201 is designed to ensure easy installation into the VME system.

Upon receipt of the board, check to make sure that no damage has occurred during shipping. Usually, a thorough visual inspection is sufficient since each board is thoroughly checked at Interphase just prior to shipment.

#### WARNING

The V/ESDI 4201 is extremely sensitive to electrostatic discharge (ESD), and the board could be damaged if it is handled improperly. Interphase ships the board enclosed in a special anti-static bag. Upon receipt of the board, take the proper measures to eliminate board damage due to ESD (i.e., wear a wrist ground strap or other grounding device).

#### WARNING

Do NOT install or apply power to a damaged board. Failure to observe this warning could result in extensive damage to the board and/or system.

If the board is undamaged and all parts are accounted for, proceed with the installation.

- 1. The first step is to set all on-board jumpers so that the V/ESDI 4201 is properly configured for operation within your system. Those options are discussed at the beginning of this section, and should be reviewed before continuing. The board is shipped from the factory set for Bus Request level 3 and with JA4 jumpered 1-2 (for drive cables connected directly to the controller rather than to the optional P2 Adapter Card).

- 2. Once the board is configured, ensure that both the system power and the disk drive power are OFF.

#### WARNING

System power and disk drive power must be OFF before the V/ESDI 4201 can be installed. Failure to do so may result in severe damage to the board and/or system board and/or system.

- 3. When the power is off, connect the "A" cable (see Appendix A for pin-out details) to the disk drive, making sure that the pins are properly oriented. If only one disk drive is used, it must be attached to the last connector on the cable.

- 4. Then, install terminators on the last drive on the cable. (If only one drive is connected, the terminators must be connected to that drive.)

- 5. After routing the "A" cable through the VME system to the proper card slot, connect a "B" cable (see Appendix A for pin-out details) to the disk drive. If more than one drive is being used, connect a "B" cable to each one, ensuring that the connectors are properly oriented.

- 6. Route the "B" cable to the proper VME card slot, and insert the V/ESDI 4201 about one-third of the way into the slot. Carefully connect the cables as follows:

- "A" Cable J1 "B" Cable - J2 (Drive 0) "B" Cable - J3 (Drive 1) "B" Cable - J4 (Drive 2) "B" Cable - J5 (Drive 3)

- 7. Carefully slide the board the rest of the way into the slot. It should slide all the way in without any difficulty. If it doesn't, pull it out and check to make sure that the cables are not in the way.

If there is not enough clearance for the board, the cable strain relief may be removed and installation continued.

- 8. Once the board is properly seated in the slot, tighten the captive mounting screws on each end of the board.

- 9. When the board is installed, run a complete test on the system to ensure system integrity.

# 3 INITIALIZING THE V/ESDI 4201

# Overview

The V/ESDI 4201 can control a wide variety of disk drives with differing formats, sizes, and speeds. To accommodate this diversity, the controller must be told which drive is attached to each of the ports, and which options are to be selected before using the drives. The Initialize command provides this information. Each port must be initialized upon power-up and again after every reset.

The V/ESDI 4201 also provides an Initialize Long command. It is used to load an extended UIB, which is required if multiple sector slipping is going to be used on the drive being initialized. The first nine words of both the standard UIB and the extended UIB are identical. However, the extended UIB has seven additional words appended to the end of a standard UIB.

When an Initialize command is issued, the buffer address in the IOPB points to a list of initialization parameters called a Unit Initialization Block (UIB). There are two different UIBs which may be read depending on whether a normal Initialize command (87 hex) or an Initialize Long command (7C hex) is issued. The standard UIB contains 18 bytes of information. Upon power-up, the V/ESDI 4201 installs default UIB parameters for each port. The default UIB contains the minimum information necessary to read data from a typical ESDI-type drive. This feature allows boot programs to be drive-independent.

# **Unit Initialization Block**

The UIB information for a specific drive can be stored in the first sector of data in that drive. The default UIB allows the host to read this information from the drive and to configure the V/ESDI 4201 to conform to the required drive specifications. The V/ESDI 4201 will not allow any type of Write or Format commands to be executed before an Initialize command has been issued and executed. Note that failure to initialize a drive before a Write or Format operation is attempted will result in an error code of 40 (HEX), unit not initialized. Since the end of the UIB does not fall on a long word boundary, the V/ESDI 4201 must access the UIB in word mode even if the "memory type" IOPB parameter is set to 03 (long word). The memory type will be changed to 02 by the V/ESDI 4201 if this occurs.

The following table shows the format of a standard UIB. This format is also used for the first nine words of the extended UIB. A description of the contents of each byte follows the table. When individual bits within each byte are not specifically noted, it may be assumed that they are "Don't Cares."

|        | Format of UIB                                   |

|--------|-------------------------------------------------|

| Byte # | DESCRIPTION                                     |

| 0      | V1SH - VOLUME 0 STARTING HEAD #                 |

| 1      | V1SH - VOLUME 0 NUMBER OF HEADS (2 drives only) |

| 2      | V1SH - VOLUME 1 STARTING HEAD # (2 drives only) |

| 3      | V1SH - VOLUME 1 NUMBER OF HEADS                 |

| 4      | SCT/TRK - SECTORS PER TRACK                     |

| 5      | SKEW - SPIRAL SKEWING FACTOR                    |

| 6      | BYTES/SCT (MSB) - BYTES PER SECTOR (UPPER BYTE) |

| 7      | BYTES/SCT (LSB) - BYTES PER SECTOR (LOWER BYTE) |

| 8      | GAP 1 - NUMBER OF WORDS IN GAP 1                |

| 9      | GAP 2 - NUMBER OF WORDS IN GAP 2                |

| Α      | SCT INT - SECTOR INTERLEAVE FACTOR              |

| В      | <b>RETRY - NUMBER OF RETRIES ON DATA ERROR</b>  |

| С      | CYL (MSB) - NUMBER OF CYLINDERS (UPPER BYTE)    |

| D      | CYL (LSB) - NUMBER OF CYLINDERS (LOWER BYTE)    |

| E      | ATTRIB - ATTRIBUTES                             |

| F      | ATTRIB - SECOND ATTRIBUTES SET                  |

| 10     | STATUS CHANGE INTERRUPT LEVEL                   |

| 11     | STATUS CHANGE INTERRUPT VECTOR                  |

|        |                                                 |

Table 3-1. UIB Format

## Volume Specification: UIB Bytes 0-3

Each drive can be separated into two volumes, and each volume can then be treated as an individual drive. This option is particularly useful when dealing with mixed media such as fixed and removable drives. It should be noted, however, that a drive need not have mixed media to use the volume selections. All fixed or removable drives can also be set up as if they contained two volume.

By specifying where the removable and fixed media starts, each medium can be treated as a separate drive. This prevents head increments from crossing medium boundaries. Bytes 0 and 1 specify the starting head and the number of heads for volume 0. Bytes 2 and 3 specify the starting head and the number of heads for volume 1. If volume 1 does not exist, bytes 2 and 3 must be 0.

## Sectors/Track: UIB Byte 4

UIB Byte four is the number of sectors with which each track will be formatted. The maximum allowable number of sectors is 160. This number indicates the usable sectors per track, and should not include the spare or runt sector, if either exists.

## Spiral Skew: UIB Byte 5

The spiral skew is used by the V/ESDI 4201 to determine the number of sectors that sector zero is offset from the index pulse. Setting the spiral skew factor allows head adjustments on each track without losing a revolution. This byte is used only during formatting and only when the spiral skew in the IOPB is set to zero. For a more detailed explanation of the use of spiral skew with the V/ESDI 4201, please refer to Appendix A.

## Bytes Per Sector: UIB Bytes 6 and 7

These two bytes are the number of data bytes per sector. Overhead bytes such as gaps are not included wen the bytes per sector is specified. The number entered in this field must be even (no half words). The minimum sector size is 256 bytes, and the maximum is 2408 bytes.

#### Gap 1 Words: UIB Byte 8

GAP 1 is all zeros gap before the header information on each sector. Byte 8 represents the number of words of zeros that are written in GAP 1 during a format only. Refer to Appendix A for suggested Gap 2 settings for specific drives.

## Gap 2 Words: UIB Byte 9

GAP 2 is the all zeros gap between the header and the data field on each sector. Byte 9 represents the number of words of zeros that is written in GAP 2 during a Format or Write operation. Refer to Appendix A for suggested Gap 2 settngs for specific drives.

## Sector Interleave: UIB Byte A

The sector interleave determines how the physical sectors are formatted on disk. With byte A set to '1', the sectors are formatted with the 1:1 interleave. With byte A set to '2', the sectors are formatted with 2:1. Other interleave factors are determined by setting this byte to the desired number (i.e., '3' = 3:1, '4' = 4:1, etc.). Interphase suggests that this byte be set to '1' for optimim performance.

## **Retry Count: UIB Byte B**

Byte B is the maximum number of rotational retries attempted when an error occurs in the data field. A maximum number of 15 retries is suggested, since a maximum number of 15 retry attempts can be posted.

# Number of Cylinders: UIB Bytes C and D

Bytes D and C represent the number of cylinders that the V/ESDI 4201 knows are on the drive. This number is used to determine if a Seek request is valid. Any Seek or implied Seek request for cylinders greater than the known number will result in an error.

## Attributes: UIB Byte E

Attributes such as reseek, move bad data, increment by head, etc. are defined by this byte. Each attribute is designated in the following figure which is then followed by a definition of each.

Figure 3-1. UIB Attribute Byte E

#### Bit 7 Reserved

This bit is reserved and must be set to '0'.

#### Bit 6 Spare Sector Enable

If this bit is set at '1', it allows the use of a spare sector on each track. The sector is allocated when the track is formatted. Refer to the Map Sector command in Appendix C for a discussion of sector mapping methods.

#### **Bit 5** Caching Enable

If '1', this bit enables sector caching. If '0', data is always transferred from the disk, and no extra data is moved into the on-board buffers. Zero latency operation is not affected.

#### Bit 4 Status Change

If '1', this bit enables an interupt and updating of the Status Change bit in the CSR (or optional status change register) when any unit's status changes (e.g., ready or not ready, explicit seek complete, etc.).

#### Bit 3 Reserved

This bit is reserved and must be set to '0'.

#### Bit 2 Increment by Head

If '1', this bit specifies the increment by head, then cylinder when a track boundary is crossed. If '0', increments are done by cylinder, then head at track boundaries. An increment by head scheme is usually preferred since head switch time is much less than cylinder-to-cylinder seek time.

#### Bit 1 Move Bad Data

If '1', this bit enables the transfer of possibly bad data into system memory. If the data is still in error after all retries and error correction attempts, and reseeks that are specified have been performed, the V/ESDI 4201 will normally post an error without transferring any data to system memory. if the Move Bad Data bit is set, the V/ESDI 4201 will move the bad data to system memory (set bit six of the error code byte in the IOPB) and return a Command Completed with Exception status in the IOPB.

#### **Bit 0 Reseek**

If '1', this bit enables a restore and reseek after the retry count has been exhausted on an erroneous data field. The restore and reseek operation is performed after the retry count has been exhausted and prior to applying ECC (if enabled).

## Second Attributes Set: UIB Byte F

This byte is used to select the type of ESDl drive that is being used (i.e., hard sectored, address mark, or embedded servo). In addition, this byte is used to select either 2 or 4 unit operation.

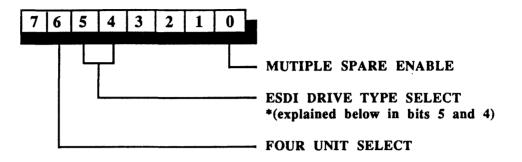

Figure 3-2. UIB Second Attribute Byte F

#### **Bit 6 Four-Unit Select**

This bit must be set to '1', if 4 unit operation is required. When this bit is set, the drive number must be selected by setting bits 12 and 13 of the upper byte of IOPB word 8 (or the IOPB interrupt level). If this bit is set, the normal drive number specification bit is no longer used.

For 4 unit operation, the Drive Status Registers reside at the base address plus 1FA (hex) and the base address plus 1FC (hex). The DSR at base address 1FA (hex) supports unit 3 (in the MSB) and unit 2 (in the LSB), and the DSR at base address +1FC (hex) supports unit 1 (in the MSB) and unit 0 (in the LSB). Also, if this bit is set, then bit 7 of UIB byte 10 (selects Optional Status Change Register) must also be set. The Optional Status Change Register resides at base address +1FE (hex).

## Bits 5, 4 ESDI Drive Type Select:

These two bits select the type of ESDI drive that is used. The specific types are selected as follows:

- 00 Hard Sector Drive

- 01 Embedded Servo Drive

- 10 Address Mark Drive

When selecting Embedded Servo-type drives (10), the "Sector Count Low" byte in the IOPB (Word 4, LSB) must contain the value calculated for the intersector gap (in bit times divided by 2). The intersector gap time can be found in the drive manual.

#### **Bit 0 - Multiple Spare Enable**

This bit must be set to '1' if more than one spare sector will be mapped but may only be set when INIT LONG (command 7C) is used. This bit may not be set if the Spare Sector Enable bit is set in UIB byte E (bit 6). This bit is usually set to '0'.

# Status Change Interrupt Level, Register and Vector: UIB Bytes 10 and 11

Bytes 10 and 11 of the UIB set the level and vector for the Status Change Interrupt for the drive being initialized. The level can be set to any number from one to seven. The vector is the data returned during the VME interrupt acknowledge cycle. Any value is acceptable. If bit 7 of UIB byte 10 is '1', this information is returned in the optional status change register at 1FE instead of the CSR. This bit is ignored if bit 4 in the UIB attributes byte is 0.

# **Extended UIB**

The following table shows the format and default settings of the extended UIB which is read when an Initialize Long command (7C) is issued.

| Byte#<br>(hex) | Contents<br>(hex) | Description                     | Default<br>Setung_(DEC)_ |  |

|----------------|-------------------|---------------------------------|--------------------------|--|

| 0              | 0                 | VOLUME 0 STARTING HEAD #        | 0                        |  |

| 1              | A                 | VOLUME 0 NUMBER OF HEADS        | 10                       |  |

| 2              | 0                 | VOLUME 1 STARTING HEAD #        | 0                        |  |

| 3              | 0                 | VOLUME 1 NUMBER OF HEADS        | 0                        |  |

| 4              | 40                | SECTORS PER TRACK               | 64                       |  |

| 5              | 0                 | SKEW                            | 0                        |  |

| 6              | 2                 | BYTES PER SECTOR (MSB)          | 512                      |  |

| 7              | 0                 | BYTES PER SECTOR (LSB)          |                          |  |

| 8              | 10                | NUMBER OF WORDS IN GAP 1        | 16                       |  |

| 9              | 20                | NUMBER OF WORDS IN GAP 2        | 32                       |  |

| A              | 1                 | INTERLEAVE FACTOR               | 1                        |  |