EAGLÉ ON 56] 837+5/20/44(512) 1/v=1 gap 1= 20 gap 2=30

# **SMD 2190**

High-performance Multibus<sup>®</sup> Storage Module Device (SMD) Disk Controller **User's Guide**

#### SMD 2190 DISK CONTROLLER USER'S GUIDE

| Document Number  | UG-0390-000-X0B |

|------------------|-----------------|

| Revision         | ХОВ             |

| Follows Revision | X0A             |

| Release Date     | May. 1987       |

#### FIRST PRINTING

#### COPYRIGHT NOTICE

No part of this publication may be stored in a retrieval system, transmitted, or reproduced in any way, including, but not limited to photocopy, photograph, electronic or mechanical, without prior written permission of INTERPHASE CORPORATION.

Information in this user document supersedes any preliminary specifications and/or data sheets that may have been made available. Every effort has been made to supply accurate and complete information. However, Interphase Corporation assumes no responsibility for its use. In addition, Interphase reserves the right to make product improvements without prior notice. Such improvements may include, but are not limited to, command codes and error codes.

#### FOR ASSISTANCE IN USING THE SMD 2190 OR ANY OTHER INTERPHASE PRODUCT CALL:

#### INTERPHASE APPLICATIONS ENGINEERING DEPARTMENT (214) 350-9000

# IN THE U.K., CALL: (0296) 435661

Virtual Buffer Architecture is a service mark of Interphase Corporation, UNIX is a registered trademark of AT&T Bell Laboratories, RMX/86 and Multibus are registered trademarks of INTEL Corporation.

. ..

# TABLE OF CONTENTS

# 1 INTRODUCTION TO THE SMD 2190

Overview / 1

# 2 SMD 2190 MODES OF OPERATION

Buffered Mode / 3 Direct Mode / 3 Buffered Mode/Direct Mode Interaction / 4 Cache Mode / 5 Fine Tuning Your System / 6 Example Cache Mode Configuration / 7

# 3 CONTROLLING THE SMD 2190

I/O Registers / 9 Input/Output Parameter Block / 11 Command Codes / 12 Command Options / 13 Status Codes / 13 Error Codes / 14 Unit Select / 14 Head Select / 14 Cylinder Select / 14 Starting Sector / 14 Sector Count / 15 DMA Count / 15 Buffer Address / 15 I/O Address / 15 Relative Address / 15

v

### TABLE OF CONTENTS (cont.)

# 3 CONTROLLING THE SMD 2190 (cont.)

Linked IOPB Address / 16 Command Options / 16 Addressing Modes / 17 Dual Porting / 18 Use of the Status and Error Bytes / 19

# 4 SOFT WARE INTERFACE CONSIDERATIONS

Introduction / 21 Status Driven Systems / 21 Interrupt Driven Systems / 23 Use of Linked IOPBs / 25

# 5 INITIALIZATION

Introduction / 27 Unit Initialization Block / 27 Number of Heads / 28 Sectors/Track / 28 Bytes/Sector / 29 Gap 1 / 29 Gap 2 / 30 Interleave/GRP/CE / 30 Retry Count / 31 ECC Enable / 31 Reseek Enable / 31 Move Bad Data Enable / 31 Increment By Head Enable / 31 Dual Port Drive / 31 Interrupt on Status Change / 32 Spiral Skew Factor / 32 Group Size / 32 UIB Parameters / 34

vi

# TABLE OF CONTENTS (cont.)

# 6 FORMATTING

Introduction / 39 Interleave Factor and Its Effects / 40 Buffered Mode / 40 Cache Mode / 40 General / 40 Spiral Formatting / 41 Formatting Faulty Media / 42

7 OPTION SWITCHES AND STRAPS

Introduction / 45 Switches / 45 Option Straps / 47 Other Straps / 49

# 8 SPECIFICATIONS

Electrical Specifications / 51 Physical Specifications / 51 Connectors / 51 Environmental Specifications / 51

#### **APPENDICES**

Appendix A - Commands / 55 Appendix B - Error Codes / 63 Appendix C - Auxiliary Port / 71

NOTES / 77

*INDEX* / 83

.

# ILLUSTRATIONS

| Figure | 1  |   | SMD 2190 I/O Registers                 | 10 |

|--------|----|---|----------------------------------------|----|

| Figure | 2  | - | R0 Command/Status Bytes                | 10 |

| Figure | 3  | - | IOPB Format                            | 12 |

| Figure | 4  | - | Error Codes For Successful Operations  | 14 |

|        |    |   | Addressing Modes                       | 18 |

| Figure | 6  | - | Typical Status Driven SMD Handler      | 22 |

| Figure | 7  | - | Unit Initialization Block              | 28 |

| Figure | 8  | - | SMD 2190 Alternate Track Format        | 43 |

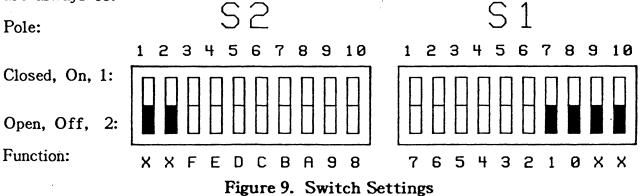

| Figure | 9  | - | Switch Settings                        | 45 |

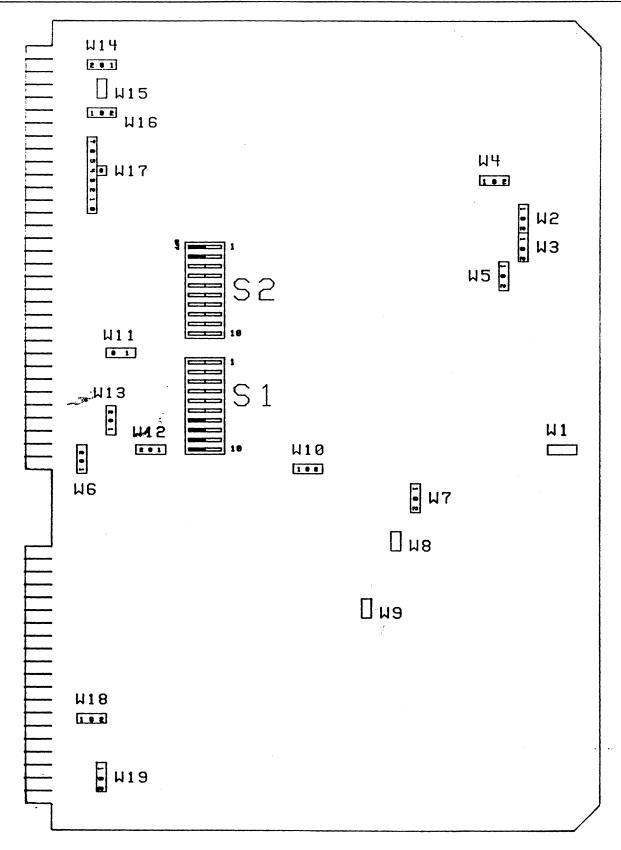

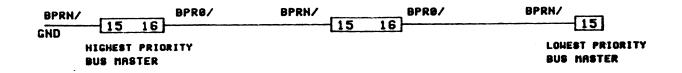

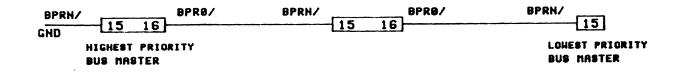

| Figure | 10 | - | Board Layout                           | 46 |

| Figure | 11 | - | Backplane Straps for Serial Connection | 48 |

# TABLES

13 33 35

| Table | 1 | - | Command Codes  |

|-------|---|---|----------------|

| Table | 2 | - | Example UIB    |

| Table | 3 | - | UIB Parameters |

#### PREFACE

This User's Guide is intended to be a reference document for users who already have a general understanding of the function of disk controllers, a general knowledge of Multibus system needs, and a familiarity with disk drives. It does not intend to provide information that should already be available to the user, instead it provides detailed descriptions of features over which the user has parametric control. The following information is provided:

- Section 1 Introduction to the SMD 2190

- Section 2 SMD 2190 Modes of Operation

- Section 3 Controlling the SMD 2190

- Section 4 Software Interface Considerations

- Section 5 Initialization

- Section 6 Formatting

- Section 7 Option Switches and Straps

- Section 8 Specifications

- Appendix A Commands

- Appendix B Error Codes

- Appendix C Auxiliary Port

- Notes Application Notes

- Index A Cross-reference of Terms and the Page Numbers on Which They Appear.

. .. х

•

# SECTION 1

#### INTRODUCTION TO THE SMD 2190

#### OVERVIEW

The SMD 2190 is an intelligent Controller/formatter for Storage Module Device (SMD) standard disk drives. Devices on the Multibus may command the SMD 2190 to perform a disk function, such as READ or WRITE a sector (or more) of data into or out of System Memory. All such functions have an extended list of the parameters to define the exact function to be performed. This list is called the IOPB (Input/Output Parameter Block) and is found in common memory, that is, memory accessible to both the requesting device, such as a CPU, and the SMD 2190. In order to cause a disk function to be performed, the IOPB is built in memory, a pointer to the IOPB is written into the Address Registers, and a "GO" is issued to the Command Register. The function is automatically completed by the SMD 2190. Both an "Operation Done" interrupt and "Done Status" are provided.

The SMD 2190 supports a wide variety of system configurations including 8- and 16-bit (or mixed) systems, single or multiple CPUs and other bus masters, serial and parallel bus priority, single user or multiuser/multitask environments, absolute or relative addressing modes, operation in Buffered Mode, Cached Mode or Direct Mode, as well as other features.

Multiple disk drives and types with varying speeds and capacities can be controlled simultaneously. The Interleave Factor, which is software programmable, can be optimized for optimum system-wide performance based on a wide number of factors. An optional on-board cache with an intelligent prefetch caching algorithm provides very high performance in systems that tend to make sequential disk sector accesses in separate sequential operating system transactions. A programmable Spiral Formatting skew factor allows multitrack transactions to not cost ar extra disk revolution due to head-to-head select times or track-to-track seek time: Finally, a number of initialization parameters control a wide number of operating parameters such as whether or not to correct errors with ECC, whether or not to move known bad (uncorrectable) data, the number of sectors per track, heads per unit, bytes per sector, and gap sizes in the disk formatting.

This document is a basic User's Guide for the most fundamental of operations, and makes no attempt to discuss File Management Systems, Disk Operating Systems and other such elaborate program structures.

If at any time you need assistance in using or configuring an SMD 2190, please call:

# INTERPHASE CORPORATION

### APPLICATIONS ENGINEERING DEPARTMENT

#### 214/350-9000

# IN THE U.K., CALL: (0296) 435661

### **SECTION 2**

### MODES OF OPERATION

#### BUFFERED MODE

The SMD 2190 has three basic modes of operation: the Buffered Mode, the Cache Mode, and the Direct Mode. In the Buffered Mode, all data to or from the disk is buffered on a sector basis in an on-board non-Multibus-accessible buffer memory. Sector sizes are programmable but are limited to a maximum of 3512 or 7608 bytes with normal or extended size buffers respectively. All recovery from data errors is done in the local buffer with no bus activity until data (on a READ) is ready to be DMAed in its final form into Multibus memory. The lowest Interleave Factor usable in the Buffered Mode is 2 (2 to 1) which will typically use about 30% of the bus bandwidth of a typically configured system during a large multisector transaction. This allows for a high throughput rate while still leaving enough of the bus for all of the other bus transactions typically needed for normal simultaneous operation. For comparison, the Cache Mode allows a 1 to 1 interleave but still only uses the same 30 percent of the bus bandwidth.

#### DIRECT MODE

The Direct Mode operates differently. Data does not go through the on-board sector buffer, but instead goes directly to and from Multibus-accessible memory. If error correction is necessary (on a READ), all bit manipulations must take place over the bus, which is, of course, slower than manipulation in the local buffer. If uncorrectable data errors exist, erroneous data will then exist in Multibus memory. Of course, the user is made aware of this fact with the Error and Status bytes of the IOPB. Operation in the Direct Mode allows sector sizes to be up to a full track long (one sector per track) with one stipulation. The error detection span of the ECC codes allows detection of errors in a full track sector, but the maximum span of the correction algorithm is 4096 bytes. This means that the limit of sector size in the Direct Mode is 4096 if you need error correction, and is a full track if you do not. Retries will still be done (unless disabled in the UIB) if an error is detected. Also, due to timing constraints, most drives must be run at sector sizes greater than 256 bytes if direct mode is to be used.

In the Direct Mode, the Interleave Factor can be 1, that is, contiguous physical and logical sectors. The primary disadvantage of using the Direct Mode is that while the sector of interest is under the Read/Write head of the disk, the SMD 2190 requires unrestricted access to the Multibus and its memory. The bus is released only between sectors of a multisector transaction, and the controller must be able to re-acquire the bus before the next sector comes around, otherwise it will have to wait a full disk revolution to pick up the next sector. This allows high priority events to interrupt the disk activity if necessary, but with a relatively high price in terms of data throughput. The bus is available for about 70 microseconds between sectors for uninterrupted operation in a Direct Mode multisector READ (READ DIRECT). If used in a system using Common Bus Request, the SMD 2190 will operate totally according to Multibus specifications, but the same high price can be incurred if another device locks out the disk from the bus during attempted disk transactions. One additional requirement is that the memory access time must be less than or equal to 480 nanoseconds for every transfer. This requirements.

These restrictions on bus usage during Direct Mode READS and WRITES are perfectly acceptable to a number of applications using a classic Multibus environment and cause no hardships in some specialized Multibus environments. Whether or not the bus latencies and overall bus bandwidth characteristics of Direct Mode operation are acceptable to your application must be considered carefully.

#### **BUFFERED MODE/DIRECT MODE INTERACTION**

Data written in either mode can be read in either mode. Multiple sectors of data written in Direct Mode with an Interleave of 1 will, however, be read back slowly (one sector per revolution) if read in the Buffered Mode. Also consider that it makes no sense to use the Direct Mode unless you are using an Interleave Factor of one and are using multisector transactions, or unless you need very large sectors. If you wish to mix Direct Mode transactions and Buffered Mode transactions on one disk unit, you should format part of the disk with an Interleave of one and part with an Interleave factor of two or more. The Interleave Factor that you use is specified while formatting the disk unit. The READ (81H) or READ DIRECT (91H) and WRITE (82H) or WRITE DIRECT (92H) commands specify whether Direct Mode or Buffered Mode is used. The VERIFY command can operate with any Interleave Factor format since there is no bus activity required.

# CACHE MODE

In addition to the Buffered Mode and Direct Mode, the SMD 2190 offers a mode of operation called the Cache Mode. This mode does two things: it allows physically contiguous sectors (Interleave of 1) to be accessed in one revolution of the disk without demanding excessive bus bandwidth, and it does a prefetch and caching of subsequent sectors on the same track in anticipation of a request for that data.

Many operating systems, particularly the UNIX and UNIX-like operating systems, commonly break file accesses into multiple accesses with atomic sizes from one to three sectors each. This is true even though the file may be many sectors long and may be written on the disk in logically consecutive sectors. Since there is necessarily an operating system interaction between these accesses, there is a delay between accesses that will always be long enough such that, if the disk is formatted 1 to 1 (Interleave = 1), the next sector of interest will have already traversed beneath the read head when the access is requested. The result is, naturally, that only one sector (or other atomic size) access can be made per revolution.

Many operating systems have lessened this problem by adding a "software interleave" to the disk hardware interleave, but this reduces the average throughput to something equivalent to a four or five to one interleave (or worse) for accesses of this type. Although the nature of disk activity in a real system is multifaceted and highly variable based on many factors, file activity of this type is almost always a majority of the activity. The only exception to this is in systems in which the files have become extremely scattered or where the memory available is much too small. The SMD 2190 Cache Mode operation is such that the average access to the first sector (or atomic unit) of a group of contiguous sectors accessed by separate disk transactions, is ruled primarily by the seek time and rotational latency of the drive as always. All subsequent accesses to the trailing sectors are made directly from the cache buffer without regard to the current location of the disk, other bus activity, or how much overhead exists between accesses. Since data is read on a 1 to 1 basis into the cache buffer, data is read at the maximum rate specified by the disk , and there is no possibility of data overrun or underruns. Since no "software interleave" is necessary, the final result is a significantly better throughput rate than with other approaches, for a majority of the disk transactions seen in most systems of this type.

Although Cache Mode operation can be used with the normal size SMD 2190 buffer which can cache up to six sectors of 512 bytes each, most users who wish to use Cache Mode will choose to use the optional extended size buffer. With the extended buffer, the cache size is up to 23 sectors of 512 bytes each. (With differing sector sizes, a different number of sectors can be cached.) The cache size is programmable and can be any nonzero number of sectors that will fit in the buffer. Most users are expected to set the cache size to be one half of a track of data. Therefore, if a track of data has 32 sectors, most users will opt for a cache size of 16 sectors.

#### FINE TUNING YOUR SYSTEM

One could ask why not always set the cache size to the maximum size of 23, which is perfectly acceptable. The decision is multifaceted and can be influenced by any natural tendency your operating system may have towards grouping of allocated sectors. The SMD 2190 will complete its caching function once it is started, and will incur some overhead before being able to start a new access. Therefore, there is a trade off between incurring too much overhead by bringing unnecessary sectors into the cache, and incurring the possibility of a wasted disk revolution by bringing in too few sectors.

Since many operating systems have a tendency to group sectors during the resources allocation function, the SMD 2190 caching algorithm allows a further refinement called "Grouping." This allows a track to be broken into groups of a size that makes sense for your application. If your system tends to group sectors into, for example, eight-sector units, you may choose to set your group size to either eight sectors, or, if there is some reasonable probability of two consecutive units of sectors being accessed sequentially, 16 sectors. If the cache size (or Group Size) is 16, then two sets of eight sectors will be brought into the cache if a READ is made to the first sector or group of sectors, in anticipation of subsequent READs.

If a track is broken into two groups of one-half track each, then the track is formatted 1 to 1 all the way around the disk. If the track is broken into more than two groups, it is further possible to interleave the groups. For example, a 32sector track could be broken into four groups of eight sectors each with groups interleaved 3 to 1. This would allow multiple, consecutive, eight-sector groups to be accessed in one revolution, without either group incurring extra overhead. The compromise however would be that it would take three revolutions of the disk to read all the data on the track. That would, however, be irrelevant if full track transfers are uncommon in the system.

### EXAMPLE CACHE MODE CONFIGURATION

All of the above may sound very complicated or confusing, but it merely demonstrates the extreme flexibility of the Cache Mode in allowing optimization for your system. Unless you have reason to do otherwise, use a one-half track cache/group size. Referring to the UIB format in Figure 5, and assuming your disk has 32 sectors per track, initialize the drive with the GRP (Group Enable) and CE (Cache Enable) bits and the LSB of the Interleave Factor byte (byte 6) set to 1, and the Group Size (Byte 15) set to 16 (decimal). When you Format the track, it will be formatted with a 1 to 1 sector interleave (contiguous sectors). Since the CE bit is ON, caching is enabled. When you read any sector or number of sectors, the SMD 2190 will automatically read the subsequent sectors up to the end of the caching group. Subsequent reads to data in cache will be completed with zero latency.

If you subsequently reinitialize with the CE bit OFF (GRP bit still ON), multisector reads are still done on a 1 to 1 basis into the buffer but no caching to the end of the caching group is done. If, for some reason, you want caching to be disabled on a selective basis, such as operating system accesses for which subsequent sequential sectors may never be relevant, leave the CE bit ON and use the READ NONCACHED (94H) command. It operates the same as the above but does not require re-initialization. If the GRP bit is 0, then the CE bit is ignored.

Although the intelligent caching algorithms are operating as long as the GRP and CE bits are ON, the user need never be aware of their actions. Operation is totally automatic and transparent to the user.

Multisector transfers of any size can be made disregarding starting sector, sector groupings, track changes, or other factors. Since the caching group size is programmable, it is possible that the number of caching groups is a noninteger. The SMD 2190 allows fragmented caching groups at the end of a track. No data is automatically cached across track boundaries.

### SECTION 3

#### CONTROLLING THE SMD 2190

#### I/O REGISTERS

The four input registers and one output register of the SMD 2190 allow the user to point the SMD 2190 to an IOPB in memory and initiate a command. They are shown in Figure 1 on the following page. The registers are referred to as R0, R1, R2, and R3 and are accessed via the IN and OUT (or equivalent) instructions. The 8- or 16-bit absolute I/O address can be selected via the SW1 and SW2 Dip Switches. The least significant two bits of the address select one of the four registers.

The IOPB address pointer registers, R1, R2, and R3, must be loaded with a 24-bit memory pointer to the first byte of the IOPB. They are write-only registers.

R0 is both Read and Write (Status and Command, respectively). The Command Register (R0) format is shown in Figure 2 on the following page. Four functions are performed: Hardware Reset, Select Bus Width, Clear Interrupt, and Go.

Bit 7 of the Command Register causes an actual hardware reset to the controlling microprocessor (8085), which forces the microcode to restart at 0. This does exactly the same thing as asserting the INIT/line on the bus. To use this function, set the bit to '1' and then set it to '0' at least two microseconds later. To verify completion of the hardware reset function after the above sequence, observe the hardware BUSY bit. It will go to a '1' and then go to a '0', at which time reset is complete.

Bit 5 of the Command Register (R0) selects an 8- or 16-bit data bus. Bit 1 is used to clear a pending interrupt and turn off the Operation Done status bit. This is accomplished by writing 02 (or 22) to R0.

Bit 0 is used to start a new function specified in the IOPB (pointed to by R1, R2, and R3). This is done by issuing a GO (01 or 21) to R0. The user may also write a CLEAR INT and GO (03 or 23) to R0, if desired. The SMD 2190 will first clear the interrupt (and status bit), then proceed to execute the command and finally, set the new interrupt (and status bit).

|    | WRITE         | READ   | ADDR1 | ADDR0 |

|----|---------------|--------|-------|-------|

| RO | COMMAND       | STATUS | 0     | 0     |

| R1 | XMB IOPB MEM. |        | 0     | 1     |

| R2 | MSB ADDRESS   |        | 1     | 0     |

| R3 | LSB REGISTERS |        | 1     | 1     |

|    |               |        |       |       |

$\rm I/O$  address bits ADR2-ADRF of RØ are defined by dip switches SW1 and SW2.

# Figure 1. SMD 2190 I/O Registers

COMMAND (R0)

| 7<br>RESET | 6<br>0 | 5<br>BUS | 4<br>DSBL<br>INTR | 3<br>0 | 2<br>0 | 1<br>CLR<br>INT | 0<br>GO |

|------------|--------|----------|-------------------|--------|--------|-----------------|---------|

|------------|--------|----------|-------------------|--------|--------|-----------------|---------|

STATUS (R0)

| 7<br>R3 | 6<br>R2 | 5<br>R1 | 4<br>R0 | 3<br>0 | 2<br>STAT<br>CHNG<br>INT | 1<br>OP<br>DONE<br>INT | 0<br>BUSY | •- |

|---------|---------|---------|---------|--------|--------------------------|------------------------|-----------|----|

|---------|---------|---------|---------|--------|--------------------------|------------------------|-----------|----|

### Figure 2. R0 Command/Status Bytes

The Status Register (R0) has three operation status bits and four drive status bits. The BUSY bit indicates when the SMD 2190 is busy performing an operation. The Operation Done Interrupt bit indicates when a disk operation has been completed. The Status Change Interrupt indicates a change in disk status (if enabled in the UIB as explained later). A visual indicator (LED 1) also indicates a pending interrupt. Further information is also found in the IOPB.

An interrupt-driven system will typically check the status bit to verify that the disk was the source of an interrupt. More information regarding interrupts is provided in the interrupt-driven systems section. For those applications not requiring the Operation Done Interrupt, bit 4 of the Command Register (R0) may be set. When this bit is '0', the SMD 2190 will generate interrupts on whatever level is selected by the straps on the board (one of eight levels).

A system that does not use interrupts (status-driven) will typically have no need for the Status Register and will use the Status Code byte in the IOPB. The clear interrupt command need not be issued under these conditions.

The four MSBs of the Status Register (RO) indicate the Ready Status of each of up to four separate SMD drives and can be observed at any time. If initialized to do so, an interrupt is generated when the Ready Status of any drive changes. This is most useful when overlapped seeks are used. In that case, a Normal Operation Complete Interrupt indicates acceptance of the SEEK command by the drive; then, a subsequent Status Change Interrupt is generated when the drive has completed the seek operation. This is described in more detail in later sections.

# INPUT/OUTPUT PARAMETER BLOCK

The Input/Output Parameter Block (IOPB) directs the operation of the SMD 2190. The format of the IOPB is shown in Figure 3. Although some commands do not need certain parameters, the format of the IOPB remains consistent.

Since the Status Code and Error Code bytes of the IOPB are updated by the controller, the IOPB must reside in RAM, although the operating program may reside in PROM.

| 0              | COMMAND             |                   |  |  |  |  |  |

|----------------|---------------------|-------------------|--|--|--|--|--|

| 1              | COMMAND OPTIONS     |                   |  |  |  |  |  |

| 2              | STATUS              |                   |  |  |  |  |  |

| 3              | ERROR               |                   |  |  |  |  |  |

| 4              | UNIT SELECT         |                   |  |  |  |  |  |

| 5              | HEAD SELECT         |                   |  |  |  |  |  |

| 6<br>7         | CYLINDER SELECT     | MSB<br>LSB        |  |  |  |  |  |

| 8<br>9         | STARTING            | MSB<br>LSB        |  |  |  |  |  |

| 10<br>11       | SECTOR COUNT        | MSB<br>LSB        |  |  |  |  |  |

| 12             | DMA COUNT           |                   |  |  |  |  |  |

| 13<br>14<br>15 | BUFFER ADDRESS      | XMB<br>MSB<br>LSB |  |  |  |  |  |

| 16<br>17       | I/O ADDRESS         | LSB<br>MSB        |  |  |  |  |  |

| 18<br>19       | RELATIVE ADDRESS    | MSB<br>LSB        |  |  |  |  |  |

| 20             | RESERVED            |                   |  |  |  |  |  |

| 21             |                     | XMB               |  |  |  |  |  |

| 55             | LINKED IOPB ADDRESS | MSB               |  |  |  |  |  |

| 23             |                     | LSB               |  |  |  |  |  |

A description of each IOPB element follows the figure.

Figure 3. IOPB Format

#### **COMMAND CODES**

This byte identifies the nature of the operation to be performed. A list of Command Codes is found in Table 1, and a detailed description of each code is provided in Appendix A.

Table 1: Command Codes

| 81<br>82<br>83<br>84<br>85<br>86<br>87<br>89 | READ<br>WRITE<br>VERIFY<br>FORMAT TRACK<br>MAP<br>REPORT CONFIGURATION<br>INITIALIZATION<br>RESTORE | 8A<br>8F<br>90<br>91<br>92<br>93<br>94 | SEEK<br>RESET<br>READ RAW DATA<br>DIRECT READ<br>DIRECT WRITE<br>READ ABSOLUTE<br>READ NONCACHED |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|

|                                              |                                                                                                     |                                        |                                                                                                  |

### **COMMAND OPTIONS**

This byte controls data bus width for the data buffer transfer and for independently controlling linked IOPBs. It also sets the addressing mode for these two functions independently. Although four addressing modes can be defined, only two are supported.

#### STATUS CODE

Once a disk command is accepted, operation status is provided. The three possible status indicators are listed below.

80H = Operation Successful, ready for next command 81H = Operation in progress, busy 82H = Error on last command

The user generally initializes the IOPB with a 00 in the Status Byte to indicate that the operation has not yet been acknowledged. It is not necessary to observe the BUSY (81H) indication before looking for successful (80H) or unsuccessful (82H) completion. In fact, operations that can show immediate (or very fast) completion may never report the BUSY condition.

#### ERROR CODES

If the Status Code = 82H after an operation, this byte provides an error code. A complete list of error codes can be found in Appendix B. If the Status = 80H, this byte provides the number of automatic error recovery procedures required before successful completion of the operation. The upper four bits indicate whether Error Correction has been applied, whether Bad Data has been transferred (only possible if enabled), and whether a RESTORE and RESEEK was done. The lower four bits represent the number of retries required.

| 7  | 6  | 5 | ч  | 3 | 2                    | 1 | 0    |

|----|----|---|----|---|----------------------|---|------|

| EC | BD | 0 | RS |   | NUMBER<br>ROTATIONAL |   | RIES |

# Figure 4. Error Codes for Sucessfully Completed Operations

# UNIT SELECT

This byte is used for the binary selection of a disk unit from zero to three.

#### **HEAD SELECT**

This byte is used to Select the head to be used. The head address is determined by the type of SMD drive being used.

#### CYLINDER SELECT

This 16-bit word selects the disk cylinder.

### STARTING SECTOR

This word is used for the 16-bit number (0-N) of the starting sector of the operation. The sector and cylinder numbers start from 00.

. ..

#### SECTOR COUNT

This word specifies the 16-bit number of sequentially numbered sectors to transfer. implied seeks are automatic when crossing a cylinder or head boundary.

#### DMA COUNT

This byte sets the maximum number of bus transactions (bytes or words) to allow in one burst (bus acquisition). The minimum DMA count is three. If the DMA COUNT byte is set to zero, then a full sector is transferred.

#### **BUFFER ADDRESS**

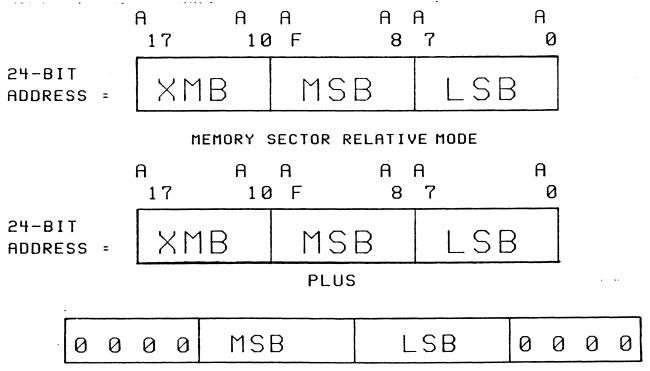

This three-byte (24-bit) value points to the beginning of the system memory data buffer. Its effective value is based on the addressing mode (either Absolute or Memory Sector Relative).

#### I/O ADDRESS

This 16-bit value specifies where the SMD 2190 Input/Output Registers are located within the Multibus I/O space. It must be set to the starting I/O Address of the I/O Write and Read Register (R0).

#### **RELATIVE ADDRESS**

This 16-bit value is the Addressing offset or Memory Sector address and is used only if Relative addressing is used. Future relative addressing modes (1,0 and 1,1) will use this value in different ways.

#### RESERVED

Byte 20 in the IOPB is not used at this time. In order to insure compatibility with future firmware versions install a '0' in this location.

#### LINKED IOPB ADDRESS

This three-byte (24-bit) value must point to the address of the linked IOPB if the Link Bit of the Command Options byte is set. All addressing modes apply to this value and the mode may be different from the data buffer addressing mode. In most cases, the Absolute Addressing mode will be used for all IOPBs.

#### COMMAND OPTIONS BYTE

The Command Options byte of the IOPB provides for several bit mapped options. Each bit of this byte is discussed below.

#### Bit 7 Link Bit

The Link bit, if set, says to automatically link to the next IOPB as a part of this transaction. Bytes 21, 22, 23 point to the next IOPB. No Done Interrupt is generated until the last linked IOPB in a sequence has been completed, however, the Status and Error bytes of the completed parts of the linked transactions are updated as the individual IOPBs are satisfied. The Linked IOPBs section more completely describes linked transactions.

#### Bit 6 REL1 IOPB & Bit 5 REL0 IOPB

If the Link bit is set, these bits identify the addressing mode of the pointer to the next IOPB (bytes 21, 22, 27). If the bits are 00, the Absolute Address in the pointer is used. If the bits are 01, the Memory Sector Relative Mode as described below, is used to calculate the effective address. If the Link bit is '0', these bits are ignored. Other bit combinations are reserved for future addressing modes.

. ..

#### Bit 4 Bus IOPB

If this bit is '0', the linked IOPB is addressed in Byte (8-bit) mode. If this bit is '1', the linked IOPB is addressed in Word (16-bit) mode. If the Link bit is '0', this bit is ignored.

#### Bit 3 RSRV

If this bit is a '1', the drive will remain Reserved after completion of this IOPB for dual ported drives that have been initialized as such by the UIB. If this bit is a '0', the drive is released after this operation. If the drive is not initialized for dual porting, this bit is ignored. (See also Dual Porting Section.)

### Bit 2 REL1 Buffer

#### Bit 1 RELO Buffer

These bits define the method of calculating the effective Buffer Address. If the bits are '00', the effective address is the absolute number found in bytes 13, 14, 15. If the bits are '01', the Memory Sector Relative Mode, is used to calculate the effective address. Other bit combinations are reserved for future addressing modes.

### Bit 0 Bus Buffer

If this bit is '0', the data DMA is done in Byte (8-bit) mode. If this bit is '1', the data DMA is done in Word (16-bit) mode. Commands that do not move any data over the Multibus ignore this bit.

#### ADDRESSING MODES

The SMD 2190 currently supports two addressing modes; Absolute and Memory Sector Relative. These two modes are used to calculate effective addresses for both Buffer pointers and Linked IOPB pointers and are shown in Figure 4.

In the Absolute Mode, the pointers are literals. In the Memory Sector Relative Mode, pointers are calculated by taking the Relative Address word (bytes 18, 19) of the IOPB shifted left four places into a 24-bit field of zeros and adding that to the 24-bit values in the Buffer Address or Linked IOPB Address as appropriate. This is primarily useful to support the Memory Sector Relative addressing scheme of the 8086. Future address modes may be added as customer inputs are received.

#### DUAL PORTING

If the SMD 2190 is to be used in conjunction with a drive implementing the Dual Port Option, then the Dual Port Drive bit in the UIB must be set to a '1' for the Initialize command. When the SMD 2190 attempts to select a drive that is reserved by the other channel, it will wait 500 milliseconds for the drive to go "not busy" before reporting the error back to the operating system. If the RSRV bit in the Command Option byte of the IOPB is set to '0', then the channel will be released on completion of that operation. If the RSRV bit is set to '1', then the channel will remain reserved at the completion of that operation (this feature should be used for overlapped seeks, read after writes, and other back-to-back operations).

Most dual ported drives have a protection timeout that will release a channel after a specified length of time (typically 500 milliseconds) if the drive has been deselected but not released on that channel. If so desired, this timeout can be disabled by a switch in the drive.

Figure 5. Addressing Modes

## USE OF THE STATUS AND ERROR BYTES

The Status and Error bytes of the IOPB are normally initialized by the user to 00 before the transaction is started. When the GO bit is set in R0 (hardware register), the SMD 2190 automatically fetches the IOPB starting at the address pointed to in R1, R2, and R3 as described earlier, and updates the Status byte to a 81H to indicate that the operation is in progress (BUSY). The SMD 2190 then does all the work necessary to complete the transaction. If the transaction has been successfully completed, the Status byte is then set to 80H to indicate it is a successful completion and is ready for the next transaction. An interrupt is also generated if enabled.

If an unrecoverable error condition is encountered, the Status byte is set to 82H and an Error Code is written into the Error byte. An interrupt is also generated, if enabled. The Error Codes are are described in Appendix B. A "most primitive error" reporting approach reports the lowest level causative factor which allows for a quick determination of the true source of the error. This avoids the common problem of higher level errors masking lower level problems, typical of the diagnostic reporting techniques of many competitive units.

If the Status byte indicates a successful completion, the Error byte takes on a new meaning which can be useful in predicting future problems in a slowly degrading system. The lowest four bits indicate the number of retries required to complete the transaction. Bit 7 indicates if Error Correction has been applied. Bit 4 indicates if a Restore and Reseek sequence was required. Bit 6 is set if known bad data (uncorrectable) has been moved into system memory. This is only possible if the SMD 2190 has been initialized in its UIB to move bad data.

It should be understood that with any error correction technique there is a minute possibility of miscorrected data. The ECC technique used by the SMD 2190 is the highest reliability technique used by any known competitive unit and is less susceptible to miscorrected errors than most competitive units.

The SMD 2190 first retries data reads found to be in error and only after an error is deemed to be a "hard error" is error correction attempted using ECC algorithms. The confidence in data received without error on a Retry should be considered just as high as that received without error on the first try, but a large number of retries over a period of time may indicate a gradual degradation of the system or the stored data on disk. This may be due to media contamination, degraded heads, or other factors. The intention is to allow preventive action before the disk degrades beyond its useful limits or before uncorrectable hard errors appear. System performance will, of course, degrade if a large number of retries or error corrections become necessary.

The Initialization section describes the large number of system operating options available with regard to error recovery.

# SECTION 4

#### SOFTWARE INTERFACE CONSIDERATIONS

#### INTRODUCTION

The SMD 2190 is exceptionally simple to use. It is essentially automatic in nature, including error recovery and executes macro-level (operation oriented) commands. The software operating environment may be characteristically one of two types, Interrupt driven or Status driven.

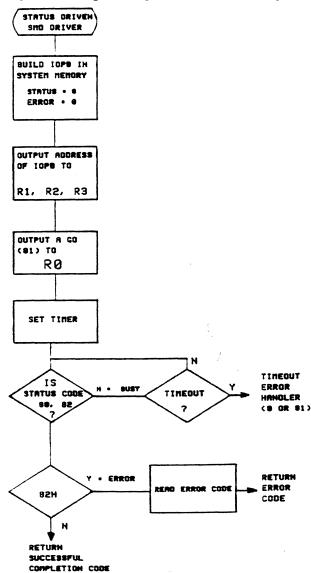

#### STATUS DRIVEN SYSTEMS

Single user/Single task systems are typically Status driven; that is, once a command is issued, the program waits for completion of the command, as indicated by observing Status, before proceeding to the next operation. This arrangement is perfectly suitable for many systems and is the easiest to implement. For such systems, all interrupts are disabled by removing W17 as described later in Section 7, Option Switches and Straps.

Status driven systems have no need for the Status hardware register (R0), unless Drive Ready Status is of interest, and operate by observing the Status Code byte of the IOPB. When the IOPB is originally written in system memory, the Status Code and Error Code bytes should be initialized to '0'. When the SMD 2190 recognizes the GO command (01 or 21 output to R0) it puts operation status in the Status Code byte. An 81H indicates Busy (operation in progress), 80H indicates Ready For Next Command (operation successfully completed), and a 82H indicates Error on Last Command. If an error is indicated, the Error Code byte indicates the nature of the error as defined in Appendix B. The only routine precaution that should normally be taken in a Status-driven system is a timeout to protect against system hang-ups. The SMD 2190 has internal timeouts to protect against disk drive oriented hang-ups and Multibus access timeouts, once the command is accepted (typically 30 microseconds after issuing the command).

The following flowchart indicates operation of the SMD 2190 in a status driven system. The timeout is optional and its implementation is determined by system hardware, which normally includes a realtime clock (which may run on an interrupt level even though the system is status driven) or a hardware interval timer. If used as shown in the flowchart, the timeout duration should take into consideration the normal time to complete the given operation, including retries.

Figure 6. Typical Status Driven SMD Handler

Many systems use a fixed location to hold the IOPB to be used by the SMD 2190. In such systems, it is not necessary to rewrite R1, R2 and R3 for each transaction. Except in systems that may routinely have one or more disk drives turned off, or where an operator is required to change a removable cartridge, the Drive Ready Status bits of R0 are seldom observed after initial power ON. Should a drive not be Ready at the time of an attempted operation, a specific error code is returned.

# INTERRUPT DRIVEN SYSTEMS

Multiuser/Multitask and some realtime systems are typically interrupt driven; that is, once the command is given, the other programs in the system proceed to run and the CPU is notified of completion (successful or not) of the disk function via an interrupt. There must obviously be an interrupt handler program, and the disk task is generally one of a number of tasks scheduled by a Realtime Operating System of some type. The interrupt can be verified (in a polled-interrupt environment) by reading the hardware Status Register (R0), and can be reset by outputting a Clear Interrupt (02 or 22) to R0, or, if more work is to be done immediately, by writing a Clear Interrupt and a Go (03 or 23) to R0. The interrupt level is selectable via Strap W17.

The hardware interrupt condition is cleared instantaneously upon receipt of any I/O write to the command register (R0), or to any of the address registers (R1, R2, or R3), but the Operation Done or Disk Status Change bits in the Status Register (R0) are cleared only upon receipt of the Clear Interrupt bit. It is also important to understand that the function of clearing the interrupt is controlled by firmware, includes several housekeeping tasks, and takes from 20 to 70 microseconds to complete based on the uncertainty of certain events. If it is necessary for the software to issue separate Clear Interrupt and GO commands, one must be aware that a GO command issued during the up to 70 microsecond uncertainty period can be missed, or can overwrite the Clear Interrupt command. In order to avoid this situation one can either:

1. Insure that at least 70 microseconds elapses after issuing the CLEAR INTERRUPT before the GO is issued. The Address Register can be written to during this period without any problems.

2. Observe that the hardware Operation Done (or Disk Status Change) bit (collectively referred to as the Interrupt Pending bit) is cleared before issuing the next GO command. The SMD 2190 clears the bit as the last item of the Clear Interrupt function, and is the true indicator of completion of the task.

If it is possible to issue a combined Clear Interrupt and Go, it is best to do so since there is no possibility of missing the command and no time is wasted waiting for availability of the hardware register. This is generally feasible if disk commands have been queued up by the operating system. Recall that the hardware interrupt condition can be cleared without issuing the Clear Interrupt command, as mentioned above.

The program must still check the Status Code of the IOPB to determine success of the operation. All Error Codes retain the same meanings as in a Status-driven system. If multiple tasks, or even multiple CPUs in a multiprocessor system, are to have access to the disk it is most common to have a single task, or the Operating System itself, handle intimate scheduling of disk activities.

In addition to the Operation Done and Disk Status Change interrupt-status bits of register R0, a Busy status bit of R0 is provided. It indicates that the SMD 2190 is currently busy doing some operation, and is not available for starting a new command. R0-R3 are, of course, available to any Bus Master (CPU or otherwise) on the BUS. If more than one CPU in a multiprocessor system is to have direct access to the SMD 2190, some contention resolution mechanism should be employed, other than simply observing the Busy bit. Recall that it takes about 30 microseconds from the time that the SMD 2190 recognizes a Go command until the Busy bit goes true.

Care should be taken to not re-enable interrupts in the interrupt handler until after clearing the interrupt. The interrupt handler must normally reset the source of interrupt while interrupts are still disabled. The user may either simply set or pulse the CLR INT bit. If pulsed, the bit must stay on for at least ten microseconds.

Status driven systems (interrupt disabled) do not require resetting of the interrupt. If the user wishes to observe the operation complete LED, which would otherwise stay permanently on, a combination of CLR INT and GO (03 or 23) may be issued. The interrupt bit (and LED 1) is cleared first. This combination command may also be used by an interrupt handler if it wishes to start the next command immediately.

On boards with firmware revisions of 4.10 and greater, if the status change interrupt is enabled in the UIB, the hardware status byte is updated in the following manner. When the board is not busy and no interrupts are pending the disk drives are checked approximately every 16 milliseconds for a change in status. If a change is detected bits R0 through R3 are updated and the Status Change Interrupt is set. The values in R0 through R3 are not updated until the status change interrupt has been cleared. These ready status values and the status change interrupt or interrupts are cleared, any and all ready status changes since the last update are reported. If the status change interrupt is not set in the UIB then the ready status values are updated without regard to interrupt pending conditions.

# USE OF LINKED IOPBS

Single or multisectored transactions may be automatically linked by setting the Link bit to a '1' and providing a pointer to the next IOPB as described earlier.

Set up and start the transaction as always. Only the pointer to the first IOPB is written into the address registers. As soon as the first IOPB is accepted, the Status Code byte in that IOPB is set to Busy (81H). At the end of the transaction of the first IOPB, its Status byte is set to 80H (or 82H, if in error) in the IOPB, but no interrupt is generated unless there is an error (R0 will continue to indicate Busy). If the Link is set, the next IOPB is fetched and its Status Code byte is set to Busy. At the completion of that transaction, the Status Code byte indicates 80H (or 82H, if in error), and so on until the Link bit is not set OR any unrecoverable error is seen in any transaction. In either case, the interrupt is generated to indicate completion, successful or not.

In the case of a successfully completed transaction, all Status Code bytes in all linked IOPBs will be set to 80H (ready for next command -- no error). Only the last IOPB need be checked because any unrecoverable condition in the chained transaction will abort the transaction.

In the case of any unrecoverable condition, the user may see where the transaction was aborted by observing the Status Code byte in the sequential IOPBs. If an 80H is seen, there was no error. If an 82H is seen, this is where the chain was broken. All subsequent IOPBs will still show '0' for Status to indicate they have not been acknowledged. If the user is interrupted and R0 shows Operation Complete, the last IOPB will indicate either success or abortion (or Error, if encountered in the last IOPB transaction). Typically, the user will remember only the first and last IOPBs. The last to indicate success, and the first to allow tracking down the problem, if an error occurs. A status driven system user may either set a long timeout and observe only the last IOPB, or choose to follow completion of each IOPB in succession.

If a linked transaction needs to be aborted before completion, write a '0' to R0. The current IOPB will be completed, but the link will be broken.

## SECTION 5

#### INITIALIZATION

### INTRODUCTION

The SMD 2190 can handle up to four SMD disk drives with differing capacities, data bit capacities, bit rates, number of heads or cylinders and even differing optimum intersegment gap sizes. Varying data rates can also affect the optimum Interleave Factor and there can even be a mixture of optimum Interleave Factors in a mixed system. For example, the SMD 2190 can simultaneously control a Lark (8 MBytes fixed/8 MBytes removable) operating with 256 byte sectors at 9.6 Mbits/sec and a Fujitsu Eagle (474 MBytes Fixed) with 512 byte sectors and running at 15 Mbits/sec.

The SMD 2190's vast flexibility is attribuatable to the Initialize command (87H) which allows all the variables of both the disk drive and the system environment to be set, and therefore optimized for the given application.

#### UNIT INITIALIZATION BLOCK

Upon power up, Multibus Reset, issuance of the RST bit, or after issue of the Reset (8FH) command at any time, each of the ports in use (from 1 to 4) must be initialized. A sequence of Initialize commands may be linked if desired. In order to Initialize a disk drive unit, simply issue an Initialize command with the proper unit selected and the Buffer Address pointing to the appropriate Unit Initialization Block (UIB) which may be any place in system accessible memory (either RAM or PROM). The format of the UIB is shown in Figure 5.

Interphase will help you configure your system and will send you a UIB Format to meet your needs. For assistance, please call: Applications Engineering Department, (214) 350-9000. In the U.K., please call: (0296) 435661

## Figure 7. Unit Initialization Block

## NUMBER OF HEADS

The number of heads is the number of addressable data heads of your disk unit. This does not include servo heads. In addition, some disk drives have tandem multiple heads on the same disk surface to decrease seek times. These tandem heads are actually accessed by cylinder selection, not head selection. In that case, those multiple heads count as one.

# SECTORS/TRACK

The number of sectors you can fit on a track is a function of the size of the track (physical bytes per track) and the size of the sector. Each sector has about 70 bytes of overhead in addition to the number of data bytes, regardless of the data field size. This is split between the header and the two gaps (Gap1 and Gap2).

28

Other factors include the end of the track gap, whether or not the drive has an embedded servo, and sometimes, the Interleave Factor and operating mode. A set of tables for common drives and configurations is found later in this section. If your drive is not mentioned in the tables, you may choose to call Interphase for advice. The table shows conservative gap sizes and sectors/track that will work for all operating modes: Buffered, Direct, and Cache. In some cases, Buffered mode operation will allow more sectors/track by varying other parameters. For more in-depth information, contact the Interphase Application Engineering Department.

In addition to the obvious function, this parameter is also used to determine that an entire track has been searched for a given sector. The SMD 2190 will allow two revolutions of the disk (2 x this parameter) before reporting "sector not found" if the sector of interest does not exist or has errors in its header.

Your disk drive has sets of switches or straps that must be set to select the number of sector pulses it is to generate per revolution. Consult your disk drive manuals for that information. Setting their switches is commonly an activity that causes problems since an incorrect setting can appear to work but cause the controller to appear to malfunction only on some sectors.

# BYTES/SECTOR (LOW BYTE) BYTES/SECTOR (HIGH BYTE)

The number of data bytes per sector. Normally determined by the software operating system being used. It can be any even number from 2 (4 with ECC) to 3512 (7608 if extended buffer) in the Buffered Mode and any even number up to 65536 in the Direct Mode (maximum of 4096 if Error Correction is required).

### BYTES IN GAP 1

The Gap between the Sector/Index and the Start of Header. Determined primarily by the drive being used. Table 2 in this section shows gap sizes for most drives.

## BYTES IN GAP 2

The Gap between the End of Header and the Start of Data Field. Determined primarily by the drive being used. Table 2 in this section shows Gap2 sizes for most drives.

#### INTERLEAVE FACTOR/GRP/CE

The sector interleave factor to be used during Formatting is fully programmable. When the GRP and CE bits (bit 7 and 6 respectively) are '0', a normal formatting mode is used and the lower 6 bits of the byte are a binary sector interleave factor to be used during formatting. The valid range is from 1 to 63, although a reasonable number when using the standard Buffered Mode is usually low (2, 3, 4, etc.) and should never be more than the number of sectors on a track. The optimum interleaving factor is largely determined by the numerous system loading and bus bandwidth variables. A track intended to be used in Direct Mode will generally use an interleave of 1, physically consecutive sector numbering. So long as GRP and CE are '0', this parameter has no operational effect except during the formatting function. A sector or group of sectors written with one interleave factor can be read with any other interleave factor set.

When GRP and CE bits are set to '1' and a track is formatted, group formatting as described in the Cache Mode section is used, with byte 15 setting the size of the group and the low six bits of byte 6 setting the Group Interleave. For use during formatting, both GRP and CE should be either '0' or '1'. During Operation if the GRP Bit is set to '0', then CE is ignored.

Anytime after formatting with GRP and CE set to '1', the CE (Cache Enable) bit may be left ON '1' to enable caching or OFF '0' to disable caching. Caching can also be enabled after normal Buffer Mode formatting, but that seldom makes any sense. Use of the GRP and CE bits are more completely explained in the Cache Mode section.

A table in this section shows minimum suggested interleave factors for normal buffer mode operation. You may always choose a larger interleave factor that may be found to be optimum if your system is heavily loaded and has a lot of interrupt activity that requires heavy bus bandwidth. If you are using Cache Mode operation refer to the Cache Mode section.

#### **RETRY COUNT**

The number of rotational retries (0-15) to perform (if a data error is detected) before error correction is attempted. Most users select a Retry Count of three.

## ECC ENABLE

If this byte is a '1', Error Correction is enabled. If it is a '0', Error Correction is disabled.

#### RESEEK ENABLE

If this byte is a '1', a Reseek operation is performed after rotational retries or Error Correction fail to yield positive results. If it is a '0', no Reseek is performed. Note that since this operation includes a seek to track zero (Recalibrate) then back, it can take a long time to complete.

## **MOVE BAD DATA ENABLE**

If this bit is a '1', uncorrectable data, if encountered, is moved into system memory on a Read operation. In this case the Error byte of the IOPB indicates an uncorrectable error as described earlier.

### **INCREMENT BY HEAD ENABLE**

When a multisector operation traverses a track boundary, the controller automatically addresses the next track. If this parameter is a '0', the next cylinder (same head) is accessed, forcing an implied seek. If this parameter is set to '1', the head number is incremented first, accessing the rest of the tracks in this cylinder before a seek to the next cylinder is performed.

# DUAL PORT DRIVE

If the byte is a '1', this UIB is for a dual ported drive. The Command Options byte of the IOPB controls reserving and releasing the device. If this byte is '0', this UIB is not for a dual ported drive.

# INTERRUPT ON STATUS CHANGE

When overlapped seeks are used, this option allows the system to be interrupted when the disk drive reaches its final destination in addition to the normal interrupt. (The SEEK (8AH) command is complete when the drive accepts the command and starts the head motion). If this byte is a '1' an interrupt is generated any time a disk drive changes its Ready to Read, Write, or Seek status (except as part of an implied seek). If a drive asynchronously changes status, such as with a drive failure or operator intervention, an interrupt is also generated. A bit in the hardware status register (R0), as described earlier, indicates that this is the source of interrupt. If this byte is a '0', no Status Change interrupts are generated.

#### SPIRAL SKEW FACTOR

This byte controls the track-to-track skewing during formatting to implement the Spiral Formatting feature. The SMD 2190 formats adjacent tracks on a disk such that a sector zero on one is slightly skewed from the next. This is done so that the head select times do not cause the waste of a disk revolution in multisector transactions that overlap track boundaries. The Skew Factor is, therefore, primarily a function of the head switch time, the sector size, and the spin rate. Spiral skew is only applicable when the increment by head option is selected (which is the recommended mode of operation).

For Buffered and Direct Mode operation, it is usually best to set the Skew Factor to the Interleave plus two. For Cache Mode operation, it is usually best to set it to the group size.

### **GROUP SIZE**

When the GRP bit in Byte 6 is a '1', this byte sets the size of the group, as defined in the Cache Mode section. When the sector size is 512 bytes per sector, the maximum is six sectors when used with a normal buffer size and 23 when used with a board with the extended buffer installed.

#### BYTES 16, 17, 18

Reserved for Future Use. Set them to a '0' to insure compatibility with future options.

# SUGGESTED (UIB) PARAMETERS

The following Table and Disk Drive Notes contain a summary of suggested UIB parameter values and relevant disk drive information for existing disk drives and common systems configurations. This set of guidelines will be updated as more disk drive models become available.

Many parameters, such as Interleave Factor, Retry Count, etc., will, of course, operate reliably over a wide range of values with greater or lesser system throughput. The optimum values may be determined heuristically or theoretically during the system development cycle if desired. If your disk drive is not listed in the Table or your system configuration is unusual, you may choose to contact Interphase Corporation for suggested UIB parameters.

The Interleave Factor and Spiral Skew Factor are used only by the FORMAT command. If you are experimenting with different Interleave Factors, you will, of course, have to Reformat your media to see any effect. The SMD 2190 will be able to Read and Write on to a unit reliably even if it has been initialized with a different Interleave Factor than the one it was formatted with. This means you can use older units even if you have later optimized your system for higher performance.

Also, the Gap1 and Gap2 bytes allow optimization for highest reliability based on the actual type of drive being used. The PLO lock time varies significantly from drive type to drive type while still being SMD compatible. Programmability in these parameters insures the ability to operate all current and future SMD drives. Gap1 programmability is particularly powerful in the embedded servo-type drives available from some manufacturers.

Finally, some users have cleverly allowed multiple types of drives to be installed in their systems and determine the system configuration by reading the first sector on one of the drives. They then initialize each drive based on this information. This is very simple to do with the SMD 2190. The only parameter that needs to be correct to read one, or a few, sectors is the number of bytes per sector which is generally consistent from drive to drive in real systems. Simply set the number of sectors/track to be very large during a dummy initialize, read the sector(s) of interest (not crossing a track boundary), and then reinitialize all the ports with correct parameters. Certain parameters, such as Heads/Unit, Interleave Factor, etc., are checked for valid ranges, but the dummy parameters need not be correct for the particular drive in use during this procedure.

#### Table 2 – Example UIB

UIB BYTE

# CONTENTS

## HEX VALUE

| 0                     | NUMBER OF HEADS<br>SECTORS/TRACK | 07<br>20 |

|-----------------------|----------------------------------|----------|

| 2                     | BYTES/SECTOR (LOW)               | 00       |

| 2<br>3<br>4<br>5<br>6 | BYTES/SECTOR (HIGH)              | 02       |

| 4                     | GAP1                             | 14       |

| 5                     | GAP2                             | 1Ė       |

| 6                     | GRP/CE/INTERLEAVE                | C1       |

|                       | RETRY COUNT                      | 03       |

| 7<br>8<br>9           | ECC ENABLE (0 OR 1)              | 01       |

| 9                     | RESEEK ENABLE (0 OR 1)           | 00       |

| 10                    | MOVE BAD DATA ENABLE (0 OR 1)    | 00       |

| 11                    | INCREMENT BY HEAD (0 OR 1)       | 01       |

| 12                    | DUAL PORT DRIVE (0 OR 1)         | 00       |

| 13                    | STATUS CHANGE INT. (0 OR 1)      | 00       |

| 14                    | SPIRAL SKEW FACTOR               | 10       |

| 15                    | GROUP SIZE (SECTORS)             | 10       |

| 16                    | RESERVED                         | 00       |

| 17                    | RESERVED                         | 00       |

| 18                    | RESERVED                         | 00       |

DRIVE MODEL:

FUJITSU 2312K 84 MByte

SET DRIVE SWITCHES S2=11111111 S3=00100000

CONFIGURATION: 512 Byte Sectors (32 Sectors/Track) Cache Mode On 16 Sector Cache Groups Error Correction On Increment By Head On

> As a free service Interphase will provide a UIB per your configuration Call the Applications Engineering Department: (214)350-9000

> > In the U.K., please call: (0296) 435661

. ..

# Table 3 - UIB PARAMETER TABLE (Values are in Decimal Notation)

|              | CEC                                    | mong      |       |                         | P SIZE   |     |                                                                                                                | D MODE                                                                                                           | DISK  |

|--------------|----------------------------------------|-----------|-------|-------------------------|----------|-----|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|

| DRIVE TYPE   |                                        |           | /TRAC | •                       | 512/1024 |     | TERLI                                                                                                          |                                                                                                                  | DRIVE |

| & MODEL      | 256                                    | 512       | 1024  | G1                      | G2       | 256 | 512                                                                                                            | 1024                                                                                                             | NOTES |

| AMPEX        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| DM940, DM980 | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| 9160, 9300   | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| DFR SERIES   | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| 9100, 9200   | 44                                     | 22        | 12    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| CAPRICORN    | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| CDC          |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| 9400, 9700   | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1,2   |

| LARK 9455    | 64                                     | 32        | XX    |                         | 20/30/30 | 3   | 2                                                                                                              | X                                                                                                                | 1,3   |

| LARK 9457    | XX                                     | 32        | XX    |                         | 20/30/30 | X   | 2                                                                                                              | X                                                                                                                | 1,3   |

| CDC FSD      | 64                                     | 32        | 16    |                         | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | -,-   |

| CDC 9771XMD  | 160                                    | 80        | 40    | • •                     | 20/30/30 | 4   | 3                                                                                                              | 3                                                                                                                | -     |

|              |                                        |           |       |                         |          | -   | -                                                                                                              | i de la composición de | *     |

| CENTURY DATA |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| T80, T3000   | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| T20, T25,T50 | 44                                     | 22        | 12    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| M20,M40,M80  | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| AMS190       | 75                                     | 40        | 20    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| M160, AMS380 | 80                                     | 50        | 25    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| C2075, C8048 | 64                                     | 32        | XX    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | X                                                                                                                | 1     |

| DISK TEK ONE |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| ALL MODELS   | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

|              |                                        |           |       | 648.55.5 <sup>214</sup> | •        |     |                                                                                                                |                                                                                                                  |       |

| FUJITSU      |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| 2311, 2312   | 64                                     | 32        | 16    |                         | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1,5   |

| M2284        | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| M2351/EAGLE  | 80                                     | <u>44</u> | 24    | 18/20/20                | 20/30/30 | 4   | 3_                                                                                                             | 3                                                                                                                | 4     |

| KENNEDY/BASF |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| 6170         | 32                                     | 22        | 11    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| MICROPOLIS   |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| 1400 SERIES  | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

| NEC CORP.    |                                        |           |       |                         |          |     |                                                                                                                |                                                                                                                  |       |

| D2200 SERIES | 64                                     | 32        | 16    | 18/20/20                | 20/30/30 | 3   | 2                                                                                                              | 2                                                                                                                | 1     |

|              |                                        |           |       |                         |          |     | an an the second se |                                                                                                                  |       |

•

| DRIVE TYPE<br>& MODEL |    | -  | /TRACI<br>1024 |          | P SIZE<br>512/1024<br>G2 | INT | ERLE | D MODE<br>CAVE<br>1024 | DISK<br>DRIVE<br>N <b>OTES</b> |

|-----------------------|----|----|----------------|----------|--------------------------|-----|------|------------------------|--------------------------------|

| PRIAM                 |    |    |                |          |                          |     |      |                        |                                |

| 3350, 6650            | 64 | 32 | 16             | 18/20/20 | 20/30/30                 | 3   | 2    | 2                      | 1                              |

| 3450, 7050            | 32 | 21 | 12             | 18/20/20 | 20/30/30                 | 3   | 2    | 2                      | 1                              |

| 15450, 803            | 64 | 32 | 16             | 18/20/20 | 20/30/30                 | 3   | 2    | 2                      | 1                              |

| SLI                   |    |    |                |          |                          |     |      |                        |                                |