# DRAFT

# MAX 2 COMPUTER SYSTEM

# REFERENCE MANUAL and MICROPROGRAMMING GUIDE

International Meta Systems, Inc. 3655 Torrance Blvd. Torrance, CA 90503

MCS - 02 September 1987 MCS - 01a February 1987 MCS - 01 January 1987 Copyright International Meta Systems Inc., 1987, 1988

# TABLE OF CONTENTS

| SUMMA | RY.    | • •   | •        |                   | •                      | •              | •            | •              | •         | •              | •          | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 1        |

|-------|--------|-------|----------|-------------------|------------------------|----------------|--------------|----------------|-----------|----------------|------------|------|---------------|-----|-----|-----|-----|-----|--------------|-------------|-----|----------|

|       | DUCTI  |       |          |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 2        |

| I SY  | STEM   | ARCI  | HITE     | CTU               | JRE                    | •              | •            | •              | •         | •              | •          | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 3        |

| II F  | PC/323 | 0 CI  | PU E     | XEC               | CUT:                   | IVE            | : S          | SYS            | TE        | M              | •          | •    | •             | •   | •   | •   |     | •   | •            |             | •   | 8        |

|       | FUNCT  | 'ION  | KEY      | DE                | CFI                    | $\Gamma$ I $N$ | II.          | ONS            | 5         | •              | •          | •    | •             | •   | • " | •   | •   | •   | •            | •           | •   | 13       |

|       | FUNCI  | 'ION  | KEY      | St                | JMMZ                   | ARY            | -            | •              | •         | •              | •          | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 22       |

| PROGE | RAM OF | ERA   | TION     | Ι.                |                        | •              | •            | •              | •         | •              | •          | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 23       |

| III   | MICRO  | PRO   | GRAM     | IIM               | 1G                     |                |              |                |           |                |            | •    |               |     |     |     |     |     |              |             |     | 24       |

|       | INSTE  | UCT:  | ION      | PI                | PEL:                   | INE            | 3            | •              | •         | •              | •          |      | •             | •   | •   | •   | •   |     | •            |             |     | 26       |

|       | LEFT   |       |          |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     |          |

|       | RIGHT  |       |          |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     |          |

|       | OFF-C  |       |          |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     |          |

| 1.0   | SPECI  | IAL-  | PURI     | POSI              | E R                    | EG:            | s:           | ref            | RS        |                |            |      |               |     |     |     |     |     |              |             |     | 30       |

|       | 1.1    | X R   | EGIS     | STEI              | ₹.                     | _              |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 30       |

|       | 1.2    | MEM   | ORY      | ADI               | ORE                    | SŠ             | RI           | īĞ1            | เรา       | ידידו<br>דידיו | ₹ /        | MZ   | ۱R            |     | _   |     |     |     |              |             |     | 30       |

|       | 1.3    | MEM   | ORY      | TNI               | ייווס                  | ~~<br>RI       | ₹ <b>(</b> - | רכי<br>רפיז    | יבי       | 2 /            | M          | rr ۱ | ·,            | _   | -   | •   | •   | •   |              | •           | •   | 30       |

|       | 1.4    | MEM   | ORV      | OU                | יוזסי                  | יים די         | 2 E.C        | 3T S           | ייי       | <br>7D         | /          | AOF  | ?<br>? \      | •   |     | •   | •   | ·   | •            | Ĭ           | ·   | 31       |

|       | 1 5    | K D   | ECT (    | ייט<br>ושידי      | - L C                  |                |              | J \            | ,,,       | J1(            | ( -        | 101  | ` /           | •   | •   | •   | •   | •   | •            | •           | •   | 31       |

|       | 1.5    | T T X | r cu     | נים עם<br>נית ד כ | . D                    | ыĊ-            | rer          | ים.<br>חישים   | •         | •<br>• T C     | י<br>סי    | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 21       |

|       | 1 7    | DYM.  | נס ת     |                   |                        | EG.            | LO.          | 2 /<br>T 177 E |           | ( Tir.         | or,        | ;    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 21       |

|       | 1.7    | DAT   | A KI     | TOUR<br>SGT:      | DIE.                   | K<br>CT        | נע )         | 7D             | •         | •<br>FD '      | •          | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 21       |

|       | 1.8    | INT   | ERKU     | J.P.T.            | KE                     | GT;            | 2.T.1        | 1K<br>101      | ( ]       | LK             | )          | •    |               | •   | •   | •   | •   | •   | •            | •           | •   | 34       |

|       | 1.9    | TN.T. | ERRU     | J.F.T.            | MA                     | SK             | _KI          | . حاث          | LS        | LEL            | <b>₹</b> ( | ( TI | 1K )          |     | •   | •   | •   | •   | •            | •           | •   | 32       |

|       | 1.10   | EX'   | TERI     | 1AV               | IN                     | PU'            | r i          | REC            | GIS       | STE            | ΞR         | ( E  | EIF           | ?)  | •   | •   | •   | •   | •            | •           | •   | 32       |

| 2.0   | INST   | RUCT  | ION      | FO                | RMA                    | Т              |              |                | •         | •              | •          | •    |               | •   |     |     | •   |     | •            |             |     | 34       |

|       | 2.1    | "T"   | (T)      | ARG               | $\mathbf{E}\mathbf{T}$ | OPI            | ER.          | INA            | ))        | F              | ΙΕΙ        | D    | •             | •   |     | •   | •   | •   | •            | •           | •   | 35       |

|       | 2.2    | "A"   | (PI      | RIM               | ARY                    | II             | JPI          | JT             | OI        | PE             | RAI        | VD)  | ) I           | ΊI  | ELD | )   |     | •   |              |             |     | 36       |

|       | 2.3    | OPE   | RAT      | OR I              | FIE                    | $_{ m LD}$     | •            | •              | •         | •              | •          | •    | •             | •   | •   | •   | •   | •   | •            | •           | •   | 37       |

|       | 2.4    | "B"   | (SI      | ECO               | NDA                    | RY             | II           | JPI.           | JΤ        | OI             | PE         | RAI  | ND)           | ]   | FIE | LI  | )   |     |              |             |     | 39       |

|       | 2.5    | OVE   | RFLO     | WC                | IN                     | AR:            | ITI          | IMF            | ${ m cm}$ | $IC_{\ell}$    | LC         | G    | $\mathbb{C}Z$ | L.  | /SF | TE  | T   |     |              |             |     |          |

|       |        | INS   | TRU      | CTI               | SNC                    | •              |              | •              |           |                |            |      | •             |     |     |     |     |     |              |             |     | 41<br>42 |

|       | 2.6    | "C"   | (R       | IGH'              | гн                     | ANI            | <b>S</b>     | SII            | DE '      | ) I            | FIE        | ELI  | )             |     |     |     |     |     |              |             |     | 42       |

|       |        | 2.6   | . i      | CO                | NDI                    | тт             | )N           | AL             | ТŦ        | RAI            | ISI        | PE.  | RS.           | ·   | rRA | . ( | , L | 11= | -8           |             | F)  | 43       |

|       |        |       | . 2      |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 45       |

|       |        | 2.6   |          | UN                |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 45       |

|       |        | 2.6   |          | LI                |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 46       |

|       |        |       | .5       |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 46       |

|       |        |       |          |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 47       |

|       |        |       | •6<br>•7 |                   |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             | •   | 4.       |

|       |        |       |          | [C]               |                        |                |              |                |           |                |            |      |               |     |     |     |     |     |              |             |     | 48       |

|       |        | 2.6   | .8       | EX                | TEŔ                    | NA.            | L :          | BUS            | S :       | INS            | STI        | RUC  | CT:           | [O] | NS. | . I | BUS | 3   | <i>(</i> [ ( | <b>C</b> 1: | =2. | 3)50     |

| 3.2<br>3.3<br>3.4 | PIPELII PIPELII PIPELII                                                                                             | NE PHASI<br>NE PHASI<br>NE PHASI<br>NE PHASI                                                    | E I .<br>E III<br>E IV                   | • •                                        | • •                     |                                                                                             | •         |      | •   | • | • | • | 54<br>55<br>56<br>57                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------|-----------|------|-----|---|---|---|----------------------------------------------------------------|

| 3.5               | CACHE 1 3.5.1                                                                                                       | MMING/T<br>MEMORY<br>WRITE (<br>READ C                                                          | CACHE                                    | SEQU                                       | <br>ENCE                |                                                                                             | •         |      | •   | • | • | • | 58<br>58                                                       |

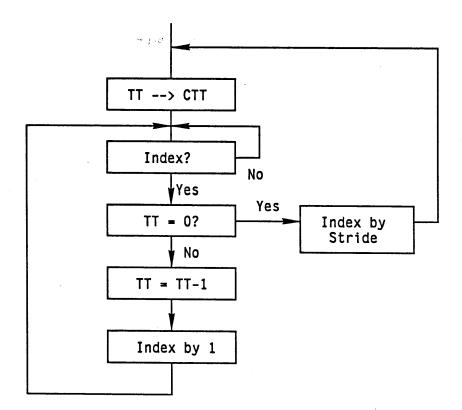

| 4.5               | LOOPS 4.1.1 4.1.2 4.1.3 OUT OF TRANSF REGIST ACCESS                                                                 | GRAMMING BOTTOM TOP TE ARRAYS SEQUEN ER VECT ER SHAR ING PRE                                    | TEST ST LOC MICE CE EXE OR BRA ING STORE | LOOP<br>DPS<br>ROCAC<br>ECUTI<br>ANCHI     | S .<br>HE L<br>ON<br>NG | COM                                                                                         | es<br>MIC | CROS | STO |   | • | • | 60<br>61<br>61<br>62<br>63<br>64<br>65                         |

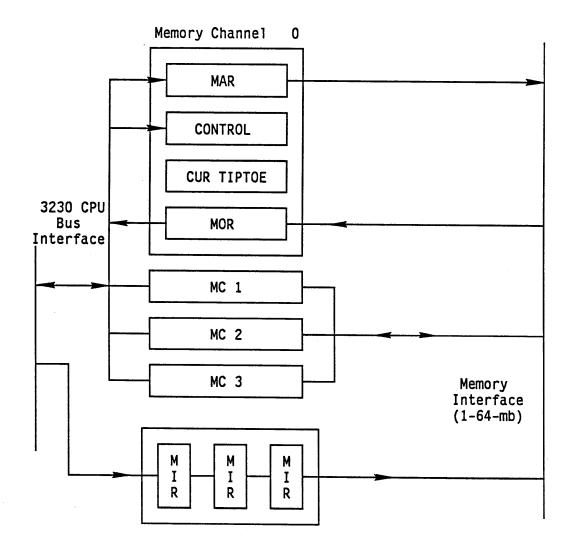

| 5.0 MEMO          | MEMORY<br>5.1.1                                                                                                     | RFACE CONTRO BUS EM BUS RE INDEXI TYPICA                                                        | LLER I                                   | INTER<br>ERATI<br>OPER                     | FACE<br>ONS             | e<br>ons                                                                                    |           |      | • • | • | • | • | 66<br>68<br>69                                                 |

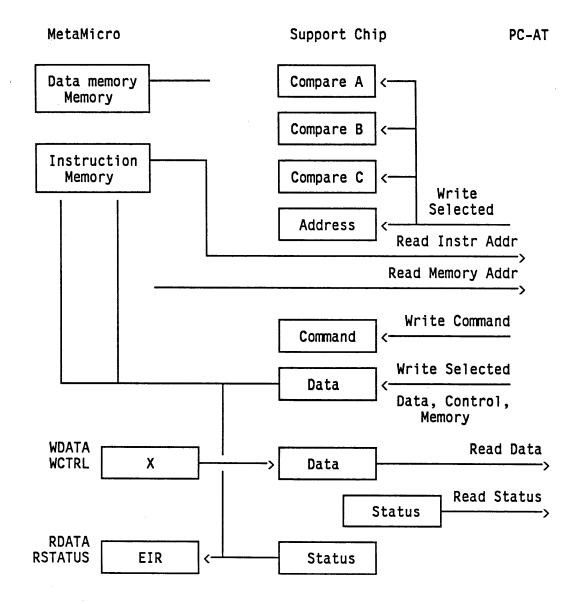

|                   | METAMI<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>INTERI<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7 | SUPPORT CRO TO ACCESS STATUS READ F WRITE FACE TO ACCESS READ S STATUS WRITE WRITE READ S OTHER | TO METAMETAMETATUS TO POMMA SELECT       | ETAMI ONS IONS ICRO FUNC C-AT ND RE TED RE | CTION<br>EGIST          | ·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>·<br>· |           |      |     | • |   |   | 76<br>77<br>78<br>78<br>78<br>79<br>80<br>80<br>81<br>82<br>82 |

|                   | BUS EN                                                                                                              | DINT COF<br>MIT AND<br>E PROGRA                                                                 | RECEI                                    | VE FU                                      | INCT:                   | ION                                                                                         | s.        | •    |     | • | • | • | 85<br>85<br>87                                                 |

| APPENDIX<br>Al    | LANGUAC                                                                                                             | EMBLER S<br>GE ELEME<br>COMMENT<br>IDENTIE                                                      | NTS .                                    | • •                                        |                         | •                                                                                           |           | •    |     |   |   |   | 89<br>90<br>90                                                 |

|         | A1.3 NUMBERS 90                             |

|---------|---------------------------------------------|

|         | A1.3.1 DECIMAL INTEGERS 90                  |

|         | A1.3.2 HEXADECIMAL INTEGERS 90              |

|         | Al.3.3 CHARACTERS 91                        |

|         | Al.3.4 REAL NUMBERS 91                      |

|         | A1.3.5 DOUBLE PRECISION NUMBERS 91          |

|         | A1.4 EXPRESSIONS 91                         |

|         | Al.4.1 LOGICAL OPERATORS 92                 |

|         | A1.4.2 SHIFT OPERATORS 92                   |

| A2      |                                             |

|         | A2.1 ASSEMBLER ACTION COMMANDS 94           |

|         | A2.1.1 LABEL (LONG LABEL DEFINITION) . 94   |

|         | A2.1.2 CHANGE, UNCHANGE (KEYWORD            |

|         | ALTERATION) 95                              |

|         | A2.1.3 INST, DATA (INSTRUCTION, DATA MODE   |

|         | INITIATION) 95                              |

|         | A2.1.4 ORG (SET ORIGIN OF ABSOLUTE CODE) 95 |

|         | A2.1.5 DC (DEFINE CONSTANT) 96              |

|         | A2.1.6 RS (RESERVE STORAGE) 96              |

|         | A2.1.7 EQU (EQUATE SYMBOLS) 96              |

|         | A2.2 ASSEMBLER LISTING COMMANDS 97          |

|         | A2.2.1 HEADER (PAGE HEADINGS) 97            |

|         | A2.2.2 EJECT (PAGE EJECTION) 97             |

|         | A2.2.3 LIST, NOLIST (ASSEMBLY LISTING ON,   |

|         | OFF)                                        |

|         | A2.2.4 LISTC, NOLISTC (LISTING COMMANDS     |

|         | ON, OFF 97                                  |

|         | A2.2.5 BLOCKS, NOBLOCKS (BLOCK STRUCTURE    |

|         | ANNOTATION CONTROL) 9                       |

|         | A2.2.6 FORMAT, NOFORMAT (FORMATTED LISTING  |

|         | CONTROL)                                    |

|         | A2.2.7 COMWIDTH (COMMENT WIDTH FOR          |

|         | JUSTIFICATION) 98                           |

|         | A2.2.8 ILIST, NOLIST (INCLUDE FILE          |

|         | PRINTING ON, OFF) 98                        |

|         | A2.2.9 WARN, NOWARN (WARNING MESSAGE        |

|         | PRINTING ON, OFF) 98                        |

|         | A2.2.10 END (END OF ASSEMBLY) 98            |

|         | A2.2.11 CODELEN 99                          |

|         | A2.2.12 IFON, IFOFF 99                      |

|         | A2.3 DEFAULT OPTIONS 99                     |

| A3      | PRE-PROCESSOR COMMANDS                      |

|         | A.3.1 #IF #ELSE #END 100                    |

|         | A.3.2 #INCLUDE 100                          |

|         | A.3.3 #DEFINE 100                           |

| A4      | STANDARD ASSEMBLER MNEMONICS 103            |

| INDEX . |                                             |

#### SUMMARY

This manual provides an architectural overview of the MAX 2 hardware for the PC-AT. Within that system it describes the instruction set and the symbolic assembly language used to create microprograms and explains the operating characteristics of the hardware. An Executive System, resident on the PC controls loading programs, debugging 3230 CPU programs, and the I/O between the MAX 2 and the PC. Appendix A describes assembler features and use. The descriptions of the assembly formats of the instructions are interleaved in the description of the hardware instruction set.

Italics are used in assembly-language descriptions, and tables of equivalence between assembly mnemonics and binary microcode are provided.

Assembly language descriptions employ BNF (Backus-Naur Form) to define language syntax. The BNF structure is as follows:

- a. All names appearing in angle brackets, <...>, are names of syntactic types.

- b. The symbol "::=" means "is defined as".

- c. The symbol " | " indicates a choice.

- d. Items appearing within square brackets, [...], are optional.

- e. Items appearing within set braces, {...}, may be repeated zero or more times.

## INTRODUCTION

The 3230 CPU is the processor element (VSLI microprocessor chip) of the MAX 2 expansion board for the IBM PC-AT and compatible personal computers. This document is a combination reference manual and microprogramming guide for the MAX 2/MetaMicro computer system. Throughout this document, micro-programming examples, used to describe the operation of the hardware, are presented in the assembly-language of the 3230 CPU.

### I SYSTEM ARCHITECTURE

In recent years, two fundamental categories of computer design have been widely discussed: the conventional microcoded complex-instruction-set computer (CISC) architecture and the non-microcoded reduced-instruction-set computer (RISC) architecture, both of which rely heavily on compilers to transform application software to run on the computer. The IMS "Meta" architecture is a third category, a minimalinstruction-set computer (MISC) that is substantially different in software architecture. Meta architecture supports the execution of application programming languages without the need for conventional compilers. 1

IMS Meta architecture resolves a bottom-up problem of VLSI performance and a top-down problem of software functionality. Both problems constrain future data processing technology, but are not resolved by either CISC or RISC approaches. Both problems can be resolved in the MISC architecture by concentration of the object program encoding, which relieves the off-chip/on-chip traffic in the so-called "von Neumann bottleneck."

Encoding concentration is facilitated by language interpretation: the direct execution of the most abstract form of a program -- a compressed image of its high-level language statements. Simple encoding algorithms compress the semantic information content of a high-level source program into a binary image that averages less than half its original size. reduces the object program size compared to a compiled program by an order of magnitude.

VLSI Performance - The bottom-up problem of VLSI performance relates to the increasing disparity between VLSI chip speeds and the speed of off-chip circuitry such as large dynamic memories and external busses. Reducing silicon circuit feature size allows enormous gains in clock speeds of processing that takes place on-chip, roughly proportional to the reduction in VLSI feature size. Going from two-micron to one-micron feature size results in a two to threefold gain in onchip clock speed. This magnifies the problem of the von-Neumann bottleneck, because of the large number of

<sup>1</sup> This eliminates a conventional compiler's primary function: transforming high-level language programs into expanded low-level machine code.

cycles that a processor may have to wait for information transmitted from large offchip memories. The on-chip/off-chip performance disparity can be relieved by reducing the size of the program code (instructions) and the frequency with which data must be transmitted between the very large and relatively slow dynamic memories and the faster on-chip processors and static memories. Executing a program in its most abstract (concentrated) form minimizes the instruction traffic. Using small, high-speed memory for data memorying of data structures minimizes the data traffic. The net effect is an order-of-magnitude gain in effective memory bandwidth as compared to the expanded machine-language image produced by a conventional compiler.

Software Functionality - The major top-down problem removed by the Meta approach is the complexity of high-order language implementation. Languages which have shown the highest level of programmer productivity have dynamic characteristics such as dynamic binding and data type redefinition that do not lend themselves to systems with compilers and static loaders. Application language interpretation eliminates the assembly language software interface and uses the 3230 CPU hardware instruction set to directly execute the high-level language, making the hardware into a microprogrammed igh-level language machine.

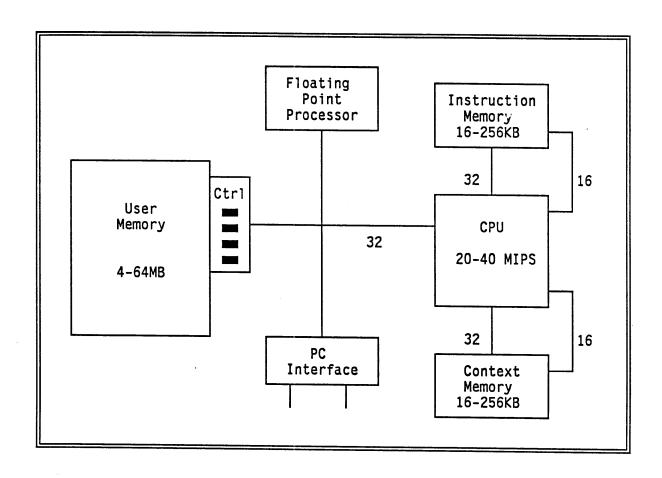

FIGURE 1 MAX 2/MetaMicro Architecture

The MAX 2/MetaMicro architecture executes compressedsource images of high-level languages via microprogramming. Functionally, it consists of the following subsystems:

#### Α. METASYSTEM:

- Microsystem: Minimal Instruction Set Computer (MISC)

- (a) 3230 CPU Processor: a usermicroprogrammable processor consisting of a single very-high-speed integrated circuit (VHSIC) chip,

- (b) Instruction memory: a register-speed static memory of up to 64K 32-bit words, used as a read-only instruction memory to the 3230 CPU processor, containing interpreter loaded from the supporting PC-AT,

- Data memory: a register-speed static (C) memory of up to 64K 32-bit words, used as a local read/write storage by microprograms,

- User memory: a large dynamic main memory 2. external to the microsystem, used to store high-level language code and data,

- PC-Channel: interface channel logic con-3. necting to the computer bus of the PC-AT,

- METACOMPUTER (Virtual Machine): a micro-program, В. resident in the instruction memory, that loads and encodes an application source language program into a compressed binary image in the user memory, then interprets the application language by executing the binary image. When boot-loaded from the PC, the metacomputer converts the general-purpose metasystem into a special-purpose application language machine, masking the features of the metasystem like a high-order language masks hardware features.3230 CPU's microprogramming features are optimized for the implementation of metacomputer code for any type of high-order language. Because each language has its own compressed source-executable image (instruction set architecture) that is

independent of the metasystem, the design of the metacomputer is not constrained by the design of the hardware. This offers complete freedom in the development of high-order-language machines. Since the metacomputer code resides in a separate high-speed memory (instruction memory) which is externally loadable, the hardware can change its language merely by loading a new metacomputer.

Application-language interpretation sharply reduces software complexity and leverages the performance of application languages. The computer is substantially more user-friendly because the language that it executes directly corresponds to the one in which the program was written, i.e., the program is executed as written, not as a highly transformed machine-language program generated by a compiler.

In addition to its use as a high-level language interpretation engine, the MetaMicro is designed to function as the control element of systems such as disk controllers, telemetry processors, parallel architecture building blocks, and in other digital processing environments that use general-purpose microprogrammed logic.

The 3230 CPU performs arithmetic and logical operations on 32-bit-wide parallel data and is controlled by a microprogram employing 32-bit-wide parallel instructions. The 3230 CPU employs eight 32-bit-wide general-purpose registers and ten special-purpose registers. The 32-bitwide data memory memory of up to 64K words is directly accessible by the 3230 CPU to use as a large register file or to implement software structures such as push-down stacks and hash-addressed heap-storage. The MetaMicro may be configured to communicate with other MetaMicros or peripheral hardware via a 32-bit-wide bidirectional asynchronous external bus.

#### PC/METAMICRO EXECUTIVE SYSTEM ΙΙ

This section describes the operation of the PC/MetaMicro development system. The system has two versions: one which runs a MetaMicro computer and a second which simulates MetaMicro execution.

The system is controlled by the user through the use of function keys. Functions are provided which:

- Load microprograms

- 2. Start programs and control execution

- 3. Display I/O

- 4. Display instruction execution

- 5. Breakpoint at instruction location or data ref.

- 6. Change interpreter instruction

- Display registers, stacks, and the external bus 7.

- Dump memory, data memory, registers, and stacks

Control the form and format of the display screen.

Information from the execution is displayed in two windows on the screen :

Upper screen window: Lines of terminal-directed input/output to and from the MetaMicro are displayed in the upper window of the PC screen. Lines of data received from the MetaMicro are scrolled upward in this window and up to 99 lines overflowing the screen are retained for subsequent browsing.

Lower screen window: A trace of the code being executed in the 3230 CPU under control of the PC is displayed in the lower window on the PC screen. Lines of data displayed are scrolled upward in this window and up to 99 lines overflowing the screen are retained for subsequent browsing.

There are two formats for the display. The normal form, shown in Figure 1, is organized into three fields: (1) The assembler -symbolic form of the executing instructions, (2) the contents of the Xregister in hexidecimal, and (3) the contents of the X register diplayed as characters (values <X'20' are displayed as ~).

In an alternate mode, controlled by SHIFT-F9, the lower window display is organized into three columns, from left to right:

- (a) The 3230 CPU location counter four hexadecimal characters.

- (b) The 32 bit instruction of the 3230 CPU, organized left to right as the T, A, OP, F, B, C and Address fields, displayed in hexadecimal format.

- (C) The X-register of the 3230 CPU organized high order (bit 31) to low order (bit 0) in binary format.

A sample of this screen display is shown in Figure 2.

## PC/MetaMicro Development System

X: MAR: KR: 000000AA9 0000 0AAA

STACK: TOP -> BOTTOM

| 1oc                                                                          | instruction                                                                                                                                                                           | x register    |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| C6D:<br>C6E:<br>C6F:<br>C70:<br>C71:<br>C72:<br>C95:<br>C96:<br>C97:<br>C98: | MAR := 0 = 0007F R7 := R6 SRL 2 LDK 000 R6 := R6 AND 3 MAR := 0 = 0007E R7 := MOR - R7 TRA C95 X := X = 0 TRA C73 ON NZ LSR := RC AND 3 KR := R6 SRL 2 R7 := 0 = 000FF NOP RETURN C9B | 0000007F      |

| C99:<br>C9B:                                                                 | X := MOR SRL 8 TRA C9A                                                                                                                                                                | 00000000 ~~~~ |

waiting:

#### FIGURE 2

The instructions shown in figure 2, above, are shown as they move through the instruction pipeline. At the bottom of the screen the location indicates the next instructions in phase 1 and phase 2 of the execution pipeline. Phased execution is covered in Section III and shown in figure 6.

# (C) Int'l Meta Systems Inc., 1986,1987

| 00000002 |      | R3:<br>00000004<br>KR: | R4:<br>00000005<br>IR: | R5:<br>00000000 | R6:<br>00000000 | R7:<br>00000000 |  |

|----------|------|------------------------|------------------------|-----------------|-----------------|-----------------|--|

| 0000006  | 0000 | 0000                   | 00                     |                 |                 | y.              |  |

| 1oc                                                | instruction                                                                                                                                                          | x register                                                                                                                                                                                                                                           |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:<br>1:<br>2:<br>3:<br>4:<br>5:<br>6:<br>7:<br>8: | 1 0 3 0 1 0 0 0 0<br>8 1 3 0 1 0 0 0 0<br>9 1 3 0 1 0 0 0 0<br>A 1 3 0 1 0 0 0 0<br>B 1 3 0 1 0 0 0 0<br>C 1 3 0 1 0 0 0 0<br>D 1 3 0 1 0 0 0 0<br>E 1 3 0 1 0 0 0 0 | 0000 0000 0000 0000 0000 0000 0000 0001<br>0000 0000 0000 0000 0000 0000 0000 0010<br>0000 0000 0000 0000 0000 0000 0000 0011<br>0000 0000 0000 0000 0000 0000 0000 0100<br>0000 0000 0000 0000 0000 0000 0101<br>0000 0000 0000 0000 0000 0000 0110 |

waiting:

FIGURE 3

| RO:<br>000000002<br>X:<br>00000006                                   | R1: R2<br>00000003 00<br>MAR: KR<br>0000 000                                                 | : IR:                                                             | X:<br>AR:<br>BR:<br>MAR:<br>KR:<br>EIR:<br>IR:<br>IMR: | 00000001<br>0000<br>0000<br>00000000<br>0000       | R0:<br>R1:<br>R2:<br>R3:<br>R4:<br>R5:<br>R6: | 00000002<br>00000003<br>00000004<br>00000005<br>00000000<br>00000000<br>00000000 | 0000<br>0000<br>0000<br>0000             | 0000<br>0000<br>0000<br>0000<br>0000<br>0000 |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------|

| 1oc                                                                  | instruction                                                                                  |                                                                   |                                                        | x reg                                              | jist                                          | er                                                                               |                                          | للصيد                                        |

| C99:<br>C9B:<br>C9A:<br>76B:<br>76C:<br>76D:<br>76E:<br>76F:<br>77F: | X := MOR + 0<br>R7 := X AND F<br>R6 := X - 000<br>R6 := X - 0<br>R0 := R0 + 2<br>R1 := X - 1 | L 8 TRA C9A<br>D RETURN 000<br>R7 LDK 000<br>D22<br>TRA 77F ON NZ |                                                        | 00000<br>00000<br>00000<br>FFFFF<br>FFFFF<br>FFFFF | 0000<br>0000<br>FDE<br>FDE                    | ~~~~<br>~~~~<br>~~~~<br>~~~~                                                     | RUN<br>1oc<br>001A<br>0000<br>0000<br>go | - 11                                         |

waiting:

FIGURE 4

The development system is invoked by a call for the program MMX and the interpreter by the program MMXS.

The functions supported are controlled by function keys F1 through F10 as well as the ctrl-, alt- and shift-versions of these keys. Many of the keys respond with queries for parameters. In these cases an escape or an empty line will back out of the query.

#### FUNCTION KEY DEFINITIONS

#### F1: Output Scroll Up

Fl scrolls up the MetaMicro input/output display (upper window). The last 99 lines of MetaMicro input/output are retained for display. Scrolling past the end of the saved lines yields a "no more data" message.

#### F2: Instruction Scroll Up

F2 scrolls up the 3230 CPU instruction display (lower window). The last 99 lines of 3230 CPU instruction execution are retained for display.

#### F3: Output Scroll Down

F3 scrolls down the MetaMicro input/output display (upper window).

## F4: Instruction Scroll Down

${

m F4}$  scrolls down the 3230 CPU instruction display (lower window).

# F5: Interpreter Run Mode Toggle

F5 toggles the "run" mode. The first F5 puts the 3230 CPU into the running state. The 3230 CPU executes instructions until the next F5 terminates the "run" mode. The "run" mode permits the 3230 CPU to execute instructions independent of the controlling PC.

#### F6: Instruction Step Execution

F6 steps the 3230 CPU (causes the 3230 CPU to execute one cycle) and displays the results in the lower window.

#### F7: Clear 3230 CPU

F7 initiates a clear cycle for the 3230 CPU. The 3230 CPU's location counted is set to zero, the interrupts are reset and the pipe-line is "flushed".

## F8: Set Instruction Location

Sets the location counter of the 3230 CPU. The user is prompted for a hexadecimal entry for the location counter value.

#### F9: Load Interpreter

F9 loads selected portions of the interpreter into the instruction memory of the 3230 CPU. The user is prompted for a starting and ending address (hexadecimal) for the portion of the memory to be loaded.

#### F10: Display/Edit Interpreter

F10 initiates the display and edit sequence for the interpreter of the 3230 CPU. The location of the first instruction to be displayed or edited is prompted for. The requested 3230 CPU instruction is displayed in either symbolic form or in hexadecimal format in the sequence T, A, OP, F, B, C and Address depending on the display format selected. [ENTER] moves to the next 3230 CPU instruction. Right arrow [->] moves to the first field for editing, re-displaying the fields in symbolic. Editing is accomplished by over-typing the field ([->] or [<-] leaveing it intact). An escape in any field discards any changes made to the instruction and moves to the next instruction. The cursor returns to the left of the instruction when an [ENTER] is pressed for any input field. Right arrow [->] selects a field for rediting; [ENTER] moves to the next instruction. The instruction is re-displayed in

symbolic form for correctness verification. Another F10 prompts for another location.

Modified instructions are both retained in a memory image in the PC and also written into the memory of the MetaMicro.

## LOGGING AND COPYING OUTPUT TO FILES OR PRINTER

I/O to the two display windows may be directed to files or the the printer using the function keys below. When one of the function keys is pressed the system prompts the user for the name of a file to be used. Any valid DOS file name may be used or 'PRN' outputs directly to the printer. The displayed file name can be accepted with CR. Space CR selects the printer. ESC turns off logging.

#### ALT-F1: PC I/O Print Log Toggle

ALT-F1 toggles logging to the printer of the PC input/output as it is displayed in the upper window. Normally, this is I/O directed to the terminal by the executing MetaMicro program, but may also include Debug output. (See Shift F1). The "L" indicator at the top of the window shows the on/off status of this switch.

## ALT-F2: Interpreter Print Log Toggle

ALT-F2 toggles logging to the printer of the MetaMicro output as it is displayed in the lower window. The "L" indicator at the top of the window shows the on/off status of this switch.

## ALT-F3: Print Input/Output Display Lines

ALT-F3 prints the last "n" lines of the MetaMicro input/output display (upper window). "n" is prompted for.

# ALT-F4: Print Interpreter Display Lines

ALT-F4: prints the last "n" lines of the 3230 CPU instruction display (lower window). "n" is prompted for.

#### ALT-F5: Run-Until Address Toggle

ALT-F5 toggles the "run-until" option for the 3230 CPU. This option allows the user to specify up to three values that will halt the 3230 CPU when they are encountered as a location counter value or a memory reference address value. A menu is displayed which allows setting of values and marking (with an asterisk) of their use as location value, memory reference, or both (See figure 2). Field-to-field movement is accomplished with the arrow keys. Placing the cursor on "go" in the menu initiates execution. ALT-F5 with the menu displayed exits the address setting mode without establishing any addresses and removes the menu. An ALT-F5 while running until a stop terminates the mode.

## ALT-F6: Step Until Address Toggle

ALT-F6 toggles the "step-until" option for the 3230 CPU. This option allows the user to specify up to three values that will halt the 3230 CPU when they are encountered as a location counter value or a memory reference address value. A menu is displayed which allows setting of values and marking (with an asterisk) of their use as location value, memory reference, or both (See figure 2). Field-to-field movement is accomplished with the arrow keys. Placing the cursor on "go" in the menu initiates execution. ALT-F6 with the menu displayed exits the address setting mode without establishing any addresses and removes the menu. An ALT-F6 while running until a stop terminates the mode.

## ALT-F7: Write Interpreter to Disk

ALT-F7 permits the user to write (edited) interpreter to disk. The user may specify a new file name or use the file name from which the original MetaMicro image was read. Files are written with the extension .PCH.

#### ALT-F8: Unused

Unused.

#### ALT-F9: Interpreter Load File

ALT-F9 makes it possible to specify a new interpreter file for the MetaMicro. The user is prompted for the file name and the MetaMicro memory image is read for subsequent loading into the MetaMicro. There follows a set of questions to complete interpreter loading. (See "Program Operation" for a full description.)

#### ALT F10 - DOS SHELL

Alt F10 invokes a second copy of the command interpreter (usually command.com) and allows you to run any program or batch job that can normally be run from the command line. To return to MMX you type EXIT (CR) at the prompt.

The command processor used is determined by the COMSPEC variable in the environment. When DOS is started it sets this variable to command.com.To use another command processor instead of command.com set COMSPEC correctly (see your DOS manual for directions for using the SET command).

The program on the metamicro will continue to run uninterrupted as long as neither screen nor disk I/O is requested. If I/O is needed the metamicro waits until control is returned to MMX to continue.

There are some precautions that should be taken while you are in a shell process. Never alter or delete any file that is being used by the metamicro, the results are unpredictable. Run only proven programs in the shell. If a program hangs the machine, work in progress in the MMX will probably be lost. Do not run another copy of MMX as it will not be initialized correctly.

#### SHIFT-F1: Debug Mode Toggle

SHIFT-F1 toggles the "debug mode". This mode causes the PC/MetaMicro I/O interface logic to display status information in the MetaMicro output portion (upper window) of the screen as they are executed. Status information about each transfer between the MetaMicro and the development system is displayed in the form shown in Figure 5 below. Debug mode output is distinguished by 'DEBUG:' at the beginning of each output

```

DEBUG: ctrlword = 31

DEBUG: DATA

DEBUG: 128 bytes read

DEBUG: 59 bytes returned

DEBUG: EOM

DEBUG: command = 9, unit = 10, flags = 0, ucb = 3

DEBUG: ctrlword = 31

DEBUG: DATA

DEBUG: STAT

DEBUG: error # 41

DEBUG: 0 bytes returned

DEBUG: EOM

DEBUG: command = 2, unit = 10, flags = 0, ucb = 3

DEBUG: ctrlword = 31

DEBUG: ACK

DEBUG: command = 4, unit = 6, flags = 0, ucb = -1

DEBUG: message # 41

DEBUG: crtlword = 31

41: "BEGIN TEST" PAUSE {}:

DEBUG: ACK

DEBUG: command = 18, unit = 0, flags = 0, ucb = 0

DEBUG: ctrlword = 31

DEBUG: ACK

DEBUG: command = 4, unit = 6, flags = 0, ucb = 3

DEBUG: message # 11

DEBUG: crtlword = 31

11: End of rule execution.

DEBUG: ACK

DEBUG: crtlword = 31

DEBUG: 2 bytes written

DEBUG: ACK

DEBUG: command = 2, unit = 6, flags = 0, ucb = 3

DEBUG: crtlword = 31

DEBUG: ACK

```

line. The "D" indicator at the top of the screen shows the on/off status of this switch.DEBUG: command = 9,

unit = 10, flags = 0, ucb = -1

FIGURE 5 - Sample Debug Mode Output

#### SHIFT-F2: Register Display Toggle

SHIFT-F2 toggles the register display in the upper window of the screen. Interpreter only. Note that AR and BR are not user accessible registers. The interpreter knows them as inputs to the ALU.

## SHIFT-F3: Stack Display Toggle

SHIFT-F3 toggles the stack display in the upper window of the screen. Interpreter only.

#### SHIFT-F4: External Bus Display Toggle

SHIFT-F4 toggles the external bus display in the upper window of the screen. Interpreter only.

# SHIFT-F6: DUMP Memory, Data memory, Registers, Stacks

SHIFT-F6 prompts for requests to display the memory, data memory, registers, or stack. They are displayed in the upper window. For memory dumps, prompts request the starting location and the number of words to dump. ESC interrupts a long dump.

## SHIFT-F8: Change Screen Display Mode

SHIFT-F8 cycles the screen display through three display modes: 1) full screen for the upper I/O window, 2) full screen for the lower instruction display window, and 3) half I/O window, half instruction window. The default is half-and-half.

## SHIFT-F9: Toggle Programming Rule Checker

SHIFT-F9 toggles the rule checker in the interpreter and when the executive is running the 3230 CPU in step mode. This mode, which is normally on, checks for violations of programming rules imposed by hardware timing, considerations. The user is told of programming constructs which do not allow sufficient time for register contents to be available before use and other rules discussed in section 3.

#### SHIFT-F10: SET

This function key allows the setting of several executive modes of operation. A prompt requests a single letter input:

- I Interrupt Register contents for interpreter

- R Rule checking mode

- D Disassembly mode

- B Bell mode

Interrrupt Register prompts for the value to be placed in the Interrupt Register and is only available in the interpreter.

Rule checking controls whether programming rule checking is done during stepping and stepping-until modes. In stepping mode errors are displayed in the lower screen window. In stepping-until mode the error is displayed in the upper window where it can be logged. Default is on.

Disassembly mode controls the instruction display: numeric or symbolic. The default is symbolic.

Bell mode lets you turn the error bell on or off. Default is on.

CTRL-F1: RUN - Start Interpreter

CTRL-F2: HALT - Stop Interpreter

## CTRL-F3: Attention - Interrupt Interpreter

The three keys CTRL-F1 through F3 send status signals to the interpreter via setting status values and rasing a flag. Meanings of these unsolicited signals are determined by the interpreter for a particular high-level language. The meanings above are used by FORTRAN and other IMS products.

#### CTRL-F9: Assign I/O Units

This function allows the assignment and display of the correspondence between I/O unit number and DOS filename. Existing assignments are displayed, changes or new assignments can be made. New and changed assignments are filed permanently on prompted request.

At the prompt for a unit assignment number entering 'tab' displays all the current files assigned to units. Entering a unit number shows the current assignment which may be replaced with any valid DOS file name or accepted as is. The assignment is not checked until the file is opened.

#### CTRL-F10: Exit Development System

CTRL-F10 terminates execution of the PC/MetaMicro Development System, returning control to DOS. The user is prompted for a final yes/no confirmation for exit.

#### FUNCTION KEY SUMMARY

| Output Display<br>Scroll-Up | 2<br>Mic. Instruc.<br>Scroll-Up |

|-----------------------------|---------------------------------|

| 3                           | 4                               |

| Output                      | Mic. Instruc.                   |

| Down                        | Down                            |

| 5                           | 6                               |

| Interpreter                 | Interpreter                     |

| Run/Stop                    | Single Step                     |

| 7<br>Clear                  | 8<br>Set<br>Location            |

| 9                           | 10                              |

| Load                        | Display/Edit                    |

| Interpreter                 | Interpreter                     |

| ALT                                  | ALT              |

|--------------------------------------|------------------|

| PC I/O 1                             | Interpreter 2    |

| Printer Log                          | Printer Log      |

| ON/OFF                               | ON/OFF           |

| 2                                    | Print 4          |

| Print PC I/O                         | Interpreter      |

| Last n Lines                         | Last n Lines     |

| Run Until 5                          | Step Until 6     |

| Data or                              | Data or          |

| Instruction                          | Instruction      |

| 7<br>Write<br>Interpreter            |                  |

| Supply 9<br>Interpreter<br>File Name | Second 10<br>DOS |

| SHIFT                   | SHIFT                          |

|-------------------------|--------------------------------|

| DEBUG<br>I/O            | * 2<br>Register<br>Display     |

| * 3<br>Stack<br>Display | * 4<br>External Bus<br>Display |

|                         | 6<br>DUMP                      |

| 7                       | 8<br>Screen<br>Toggle          |

| 9<br>Rule Check         | SET 10                         |

| CONTROL                 | CONTROL    |

|-------------------------|------------|

| RUN 1                   | 2<br>HALT  |

| Attention 3             | 4          |

|                         |            |

| 7                       | 8<br>      |

| 9<br>Assign<br>I/O Unit | 10<br>EXIT |

<sup>\*</sup> interpreter only

### PROGRAM OPERATION

To execute an already prepared MetaMicro program the following steps are required.

- Load MMX by typing MMX at the DOS prompt or if 1. already in MMX, use ALT-F9 to supply interpreter file name.

- At the request for interpreter file name supply 2. the full name of the file. A file extension of .MMC will bes assumed.

- 3. At the request for the file assignment file, the default, if any, will be displayed.

- a) CR will use the default

- b) a named file plus CR will use that file (.ASN will be assigned if no extension is given.)

- C) blank CR or ESC means no assign file

- The next prompt provides for selective 4. interpreter loading. There are three possibilities:

- CR to load the full interpreter. a) This is the normal case.

- P for partial loading. You will be prompted b) for beginning and ending addresses.

- N or ESC to not load interpreter. C)

- The next prompt asks if you are ready to run. 5. or Y begins execution, any other key takes you to the MMX "waiting" state for function key commands.

#### III MICROPROGRAMMING

The 3230 CPU processor includes twenty-four hardware operations that are combined into a two instruction per word format. There are eight op codes in the left hand side (LHS) and sixteen op codes in the right hand side (RHS). A typical composite instruction consists of:

LHS Portion: an arithmetic, logic, or shift operation between two operands with the result assigned to a third operand; and

RHS Portion: an external bus (unidirectional or bidirectional) operation, a conditional/unconditional transfer/skip operation, a subroutine link/return operation, an interrupt handling operation, or a memory indexing operation.

A typical composite instruction, including a shift and a bidirectional bus operation, is the following:

LHS RHS

R5 := R0 SLR 4

RHS

BUS EMIT MEMWORD REC MEMSTATUS

This composite instruction performs a left rotational shift of general register R0 by four bits, stores the result in general register R5 as well as the X (result) register, then emits the contents of the X register to the external bus address "MEMWORD" (an assembley-parameter) and initiates the receipt of the status information from bus address "MEMSTATUS". The bus operations are executed as the next instruction executions take place. The result of the bus REC operation ultimately appears in the external input register (EIR). See 2.6.8 for details.

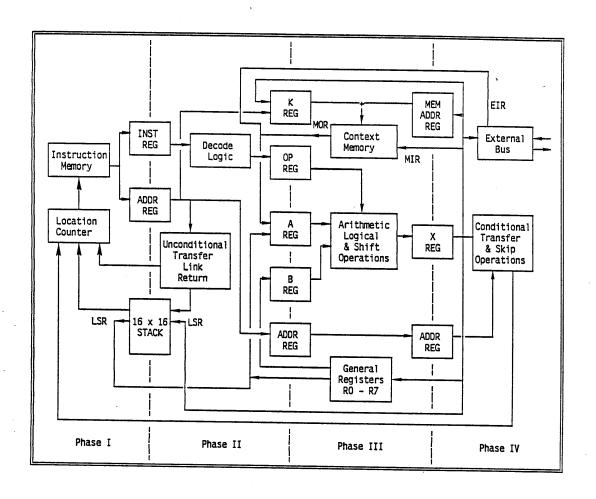

FIGURE 6 - Four-Phase Pipeline Operation

#### INSTRUCTION PIPELINE

To achieve the high instruction throughput rate of 30 to 50 million instructions per second, the 3230 CPU is implemented as a "pipelined" computer with the following four phases. (Phases are shown in Figure 6).

- 1. Composite instruction fetch

- Composite instruction decode and operand fetch, execution of RHS unconditional transfer, link, return, interrupt conditional link or memory indexing operations

- 3. Arithmetic/Logic/Shift execution

- Conditional transfer/skip or external bus I/O initiation

Complete execution of a composite instruction requires that it pass through the four phases listed above. Each phase requires that one clock cycle and four composite instruction words are in the process of execution (one in each phase) at any point in time. A composite instruction is completed each clock cycle. Most composite instruction words are the equivalent of two complete instructions of a typical CISC or RISC architecture.

In Figure 6 the register positioning on a phase boundary indicates that the information is provided for that register by the preceding phase and is available to the succeeding phrase.

#### LEFT HAND SIDE FORMAT

The LHS of the composite instruction usually has the form:

$$\langle T \rangle := \langle A \rangle$$

op  $\langle B \rangle$

where <T> is a register, := denotes "assign", <A> is a register or the literal zero, and <B> is a register or a literal. The op token is one of eight arithmetic, logic, or shift operators.

The LHS instructions in assembly format are described briefly below. Arithmetic and logical operation apply to either short or long operands.

| Operators - | <u>Function</u>                     |

|-------------|-------------------------------------|

| <b>+</b>    | Add                                 |

| -           | Subtract 🕏                          |

| - +         | Reverse Subtract                    |

| XOR         | Exclusive OR                        |

| OR          | Logical OR                          |

| AND         | Logical AND                         |

| SLR, SLL    | Left Shift: rotational and logical  |

| SRR. SRL    | Right Shift: rotational and logical |

## Examples: (leading period denotes start of comment)

```

R5 := R0 SLL 6

.shift R0 left-logical 6 bits,

.assign to R5 and X

R0 := X XOR R5

.XOR X with R5, assign to R0

X := R3 + KR

.add KR to R3, assign to X

MIR := R5 AND X'7FFFF'

.R5 and hex literal, store in data memory

```

The registers used in these instructions are described briefly below:

| Register(s) | Name                                    | Size (bits) |

|-------------|-----------------------------------------|-------------|

| RO R7       | General Registers                       | 32          |

| X           | Result Register                         | 32          |

| MAR         | Memory Address Register                 | 16          |

| MIR         | Memory Input Register                   | 32          |

| MOR         | Memory Output Register                  | 32          |

| KR          | K Register                              | 16          |

| LSR         | Link Stack Register File                | 16 x 16     |

| IR          | Interrupt Register                      | 8           |

| IMR         | Interrupt Mask Register                 | 8           |

| EIR         | External Input Register                 | 32          |

| DATA        | Next instruction used as 32-bit literal | 32          |

## RIGHT HAND SIDE FORMAT

The RHS of the composite instruction has the form:

<code> <phrase>

where <code> is one of sixteen operations, including external bus read/write/control, subroutine link/return, conditional interrupt handling, conditional and unconditional transfers and skips and memory indexing. The <phrase> is a structure of one or more operands and keywords.

The RHS instructions are summarized below:

| <u>Operator</u>  | <u>Function</u>                                                         |  |

|------------------|-------------------------------------------------------------------------|--|

| TRA              | Transfer unconditionally                                                |  |

| TRA ON           | Transfer conditionally on Overflow or not overflow X reg low bit 0 or 1 |  |

|                  | X reg high bit 0 or 1                                                   |  |

|                  | X reg zero or non-zero                                                  |  |

| SKIP             | Skip conditionally                                                      |  |

| LINK             | Subroutine link                                                         |  |

| LINK C           | Link conditional on interrupt                                           |  |

| RETURN           | Subroutine link                                                         |  |

| LDK              | Load K register                                                         |  |

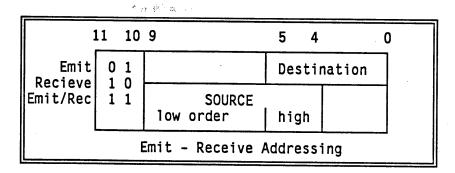

| BUS FROMTO       | Initiate bus source to des tination transfer                            |  |

| BUS EMIT Recieve | X register to bus destination and bus source to EIR                     |  |

#### Examples:

- ... LINK PROC1 .call microsubroutine PROC1, push return address on Link Stack Register (LSR) File

- ... SKIP 3 IF STATUS HAS NLB .skip 3 instructions on condition "not low bit"

- ... BUS EMIT MEMC .emit X register to bus .address MEMC

- ... TRA LOOP3 ON Z .transfer to LOOP3 if X register is zero

... RETURN DELTA

subroutine return to top LSR value plus DELTA value, pop LSRThe LHS and the RHS are combined into an instruction that executes in a single 3230 CPU clock cycle. A clock cycle delay can be introduced by the use of the no-operation, NOP. Also the NOP command is used for a null LHS where only an RHS is desired in a composite instruction. NOP is an assembler pseudo op that generates the LHS institution X:= 0 SLR 1.

#### Composite Examples:

X:=R5 SLR 6 TRA PROC3 ON HB .shift, assign, .transfer if negative

MIR:=X+2 SKIP 2 IF STATUS HAS NHB .add, assign, .skip conditional

X:=R2+R3 BUS EMIT DES1 REC DES4 .add, assign,

.bus emit

.bus receive

R3:=X-R4 TRA L30 ON Z .subtract, assign, .transfer on zero

NOP TRA LOC16 .unconditional transfer with LHS negated

R4:=X SRR 4 RETURN 6 .shift, assign, subroutine return plus 6

#### OFF-CHIP INTERFACES

Interfaces between the 3230 CPU processor and other subsystems are through the special registers and the external bus operations. The data memory is accessed using the MIR, MAR, MOR, and the K register in LHS operations. The user memory and the PC-channel are accessed via the RHS external bus operations. The BUS EMIT operation sends the contents of the X register to a specified bus destination. The BUS REC operation receives an input into the external input register (EIR) from a specified bus source.

# 1.0 SPECIAL-PURPOSE REGISTERS

In addition to the eight general-purpose 32-bit-wide registers provided for the temporary storage of intermediate results, a set of special-purpose registers provide program interfaces to special hardware logic. The term "source" is used to designate registers used as sources of input operands <A> and <B>; the term "result" is used to designate registers used as the object of the assign operation. Certain registers may be used both as source and result.

#### 1.1 X REGISTER

All instructions, including NOP, produce a 32-bit-wide result as a consequence of an Arithmetic/Logical/Shift operation. This result can be directed to one of the general-purpose registers, to one of the special-purpose registers, or neither. However, the result will always reside in the X register as well as in any general- or special-purpose register specified. In the symbolic assembly language, the X register is often specified as the result register and classed as a special-purpose register. When so specified, it has the meaning "the X register and no other register".

## 1.2 MEMORY ADDRESS REGISTER (MAR)

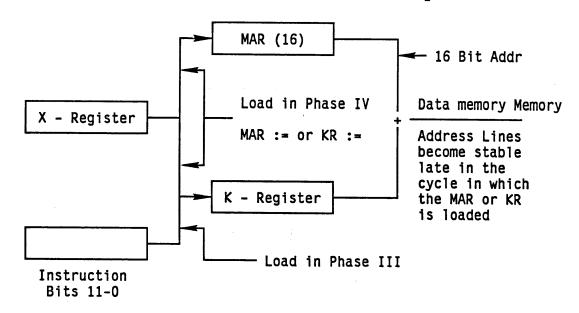

The MAR is 16 bits wide and is used to hold an address which, summed together with the contents of the "K Register" (see 1.5 below), selects a memory location in the Data memory memory.

# 1.3 MEMORY INPUT REGISTER (MIR)

The MIR can be used only as a result register, not as an operand source. A result directed to the MIR will be stored in the memory location within the data memory memory as specified by the sum of the MAR and the K Register.

#### 1.4 MEMORY OUTPUT REGISTER (MOR)

The MOR can be used only as an operand source, not as a result register. It specifies that the contents of the memory location of the Data memory memory as addressed by the sum of the K Register and the MAR is selected as an operand source.

#### 1.5 K REGISTER

The K register is a multi-function, 16-bit-wide register that exhibits many of the characteristics of an index register in a conventional single-address computer. As specified in 1.3 above, the K register, in summation with the MAR, forms the memory address used to reference the data memory memory. It can also be used like a general register. See 2.6.2 for more details.

#### 1.6 LINK STACK REGISTER (LSR)

The LSR is a 16-bit-wide, 16 element last-in-first-out-(LIFO) register stack whose primary function is to implement the subroutine "LINK" and "RETURN" instructions of the 3230 CPU. However, it can also be used as a source or result register. Its use as a source is equivalent to a POP, while its use as a result is equivalent to a PUSH. When conflicts arise (as when the LSR appears in the "T" field preceding a Link or Return instruction), the use of the LSR for "LINK" and "RETURN" takes precedence over the use as a source or result register. Another way to view LSR is as a window onto the 16 element stack. PUSH moves the window up and stores; POP fetches and moves the window down. The stack is circularly connected: 16 POPs leave the stack unchanged. There are no fill or empty stack conditions.

#### 1.7 DATA REGISTER (DR)

The DR can be used only as an operand source, not as a result register. The DR is not a specific hardware register; when specified it means that the next instruction is to be considered a 32-bit data value. The assembler directive DC is often used to define the value for the data registers.

## 1.8 INTERRUPT REGISTER (IR)

The IR can be specified both as a source and result register. It is 8 bits wide and represents 8 boolean flags that can be set (=1) by events and conditions external to the scope of the 3230 CPU. The bits can be reset (=0) by the 3230 CPU. When used as a source register, the IR represents an 8-bit-wide value, each bit of which is the state or condition of an independent variable in a set of boolean variables. When used as a result register, writing a value into the register will reset those boolean variables for which a corresponding "one" bit exists in the value. The IR and the IMR work in conjunction with the Link Conditional instruction (See 2.64 and 3.2)

Assignments of the bits in the interrupt register are :

| Bit                | Set Condition                                                                |  |  |

|--------------------|------------------------------------------------------------------------------|--|--|

| 0<br>1<br>2<br>3-7 | External bus parity error I/O Timeout, IOTMO Data memory parity error Unused |  |  |

## 1.9 INTERRUPT MASK REGISTER (IMR)

The IMR can be used only as a result register, not as an operand source. It is 8 bits wide and represents a mask for the 8 boolean flags of the Interrupt Register (IR). The IMR and the IR operate in conjunction with the Link Conditional instruction (see 2.6.4 and 3.2).

## 1.10 EXTERNAL INPUT REGISTER (EIR)

The EIR is the input termination of the MetaMicro External Bus (EB). This register can be used as a source operand only and is loaded by action on the EB. As the EB operates asynchronously from the operation of the 3230 CPU, special consideration must be given to its use. When an EB operation that results in data input to the 3230 CPU (the EIR) is initiated, the EIR contents are undefined until the bus operation is completed. If the EIR is referenced by the 3230 CPU before the bus operation is complete, the 3230 CPU will stop and wait for completion, thus synchronizing the 3230 CPU and the EB. However, if synchronization does not take place within 16 3230 CPU clock cycles,

operation will proceed unconditionally and a positive pulse will be generated on the external pin labeled IOTMO (input/output timeout). This signal sets bit 1 of the Interrupt Register, IR. The value of the EIR under forced continuation circumstances is the previous EIR value.

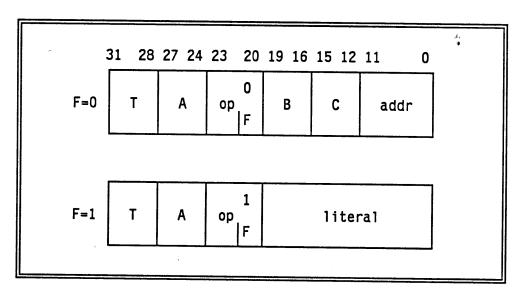

# 2.0 INSTRUCTION FORMAT

The 3230 CPU employs two forms of instruction encoding as shown below, designated  $\underline{\text{composite}}$  (F=0) and  $\underline{\text{LHS-only}}$  (F=1).

In assembler format, instructions consist of two statements:

RHS: optional statement, providing a second instruction of up to 16 alternative operations, including external bus instructions, subroutine link/return (both conditional and unconditional), conditional skips, secondary loading of the K register, and conditional/unconditional transfers.

<instruction> :: = <LHS\_stmt> [<RHS\_stmt>]

For LHS Arithmetic/Logical/Shift operations the 3230 CPU employs a three-address instruction format that can be represented symbolically as a simple assignment statement of the form:

<T>:=<A>op<B>

wherein a register specified by the "T" field takes on the value of some binary operation (op) performed on the contents of the register specified by the "A" field and the contents of the register specified by the "B" field. In the case of literal or immediate data representation of magnitude < 8, the "B" field may represent the data directly.

In assembler format, these statements have the following general form:

#### Examples:

X := X SLL 4 IMR := RO XOR R4 NOP

## 2.1 "T" (TARGET OPERAND) FIELD

The "T" field (bits 31-28) is four bits wide and references the registers as shown in the table below.

In assembler format, the "T" field is defined as follows:

where

<gen\_reg>::=RO | R1 | R2 | R3 | R4 | R5 | R6 | R7

The "T" field assembler mnemonics and equivalences are given in the following table:

| T FIELD          |                                                                                                              |                                                                                                         |                                                                                                                                                                                                              |  |

|------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HEX              | BINARY                                                                                                       | MNEMONIC                                                                                                | MEANING .                                                                                                                                                                                                    |  |

| 0123456789ABCDEF | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1011<br>1100<br>1101<br>1110 | (not used)<br>X<br>MAR<br>MIR<br>KR<br>LSR<br>IR<br>IMR<br>RO<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7 | X REGISTER MEMORY ADDRESS REGISTER MEMORY INPUT REGISTER K REGISTER LINK STACK REGISTER (push INTERRUPT REGISTER INTERRUPT MASK REGISTER GENERAL REGISTER 0  " " 1  " " 2  " " 3  " " 4  " " 5  " " 6  " " 7 |  |

# 2.2 "A" (PRIMARY INPUT OPERAND) FIELD

The "A" field (bits 27-24) is four bits wide and references the registers in the table below.

In assembler format, the "A" field is defined as follows:

<A\_field> ::=

<gen\_reg> | 0 | X | EIR | MOR | KR | LSR | IR | DATA

The "A" field assembler mnemonics and equivalences are given in the following table:

|                  | A FIELD                                                                                                      |                                                                                                 |                                                                                                                                                                                                                   |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HEX              | BINARY                                                                                                       | MNEMONIC                                                                                        | MEANING .                                                                                                                                                                                                         |  |  |

| 0123456789ABCDEF | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1011<br>1100<br>1101<br>1110 | O<br>X<br>EIR<br>MOR<br>KR<br>LSR<br>IR<br>DATA<br>RO<br>R1<br>R2<br>R3<br>R4<br>R5<br>R6<br>R7 | THE LITERAL ZERO X REGISTER EXTERNAL INPUT REGISTER MEMORY OUTPUT REGISTER K REGISTER LINK STACK REGISTER (POP) INTERRUPT REGISTER DATA REGISTER GENERAL REGISTER 0 " " 1 " 2 " " 2 " " 3 " " 4 " " 5 " " 6 " " 7 |  |  |

### 2.3 OPERATOR FIELD

The "op" field (bits 23-20) is four bits wide<sup>2</sup> and specifies the Arithmetic/Logical/Shift operation that is to be performed on the data sources specified by the "A" and "B" fields. The encoding of the "op" field is Shown in the table below.

In assembler format, the "op" field takes the form:

<sup>2</sup> Bit 20 (the "F" field) is used as a suboperation qualifier and format modifier to distinguish between rotational and logical shifts and to specify whether the "B" field is "short" (register operand or 3-bit literal) or "long" (a 20-bit literal in the "C" and address fields).

The arithmetic operators include addition, subtraction, and reverse subtraction (indicated by using  $a + with a - before the A_field)$ :

The logical operators are OR, AND, and XOR:

$$\langle L\_op \rangle : : = OR \mid AND \mid XOR$$

The shift operators are logical shift left or right and rotational shift left or right.

The <No\_op> (empty operation) statement,

will generate the code:

The "op" field assembler mnemonics and equivalences are given in the following table:

|                  | OP FIELD                                                                                                     |                                                                                   |                                                                                                                                                                                                                                                                                                |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| HEX              | BINARY                                                                                                       | MNEMONIC                                                                          | MEANING                                                                                                                                                                                                                                                                                        |  |  |

| 0123456789ABCDEF | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1011<br>1100<br>1101<br>1110 | SLR<br>SLL<br>- +<br>- +<br>-<br>+<br>XOR<br>XOR<br>OR<br>OR<br>AND<br>SRR<br>SRL | SHIFT LEFT ROTATIONAL SHIFT LEFT LOGICAL REVERSE SUBTRACT REVERSE SUB. 20-BIT LITERAL SUBTRACT SUBTRACT 20-BIT LITERAL ADD ADD 20-BIT LITERAL EXCLUSIVE OR EXCLUSIVE OR 20-BIT LITERAL LOGICAL OR LOGICAL OR 20-BIT LITERAL LOGICAL AND LOGICAL AND SHIFT RIGHT ROTATIONAL SHIFT RIGHT LOGICAL |  |  |

### Examples:

NOP

X := RO + R2

IMR := -X + RO

RO := O-1

R7 := R5 AND 1

X := R1 OR X'7FFF'

R5 := MOR AND 1

X := MOR XOR NAME\_T

X := RO SLL 6

SR := R5 SRL 6

X := R7 SRR 2

## 2.4 "B" (SECONDARY INPUT OPERAND) FIELD

The "B" field (bits 19-16) is four bits wide in its short form (F bit = 0). For short form operations involving arithmetic/logical manipulation (op=2,4,6,8,A,C), the "B" field references the registers and or literals as shown in the table below:

In assembler format, the short form "B" field may be either a general register or an expression representing the literals (0-7).

<B\_field>::=<gen\_reg> | <expr>

The assembler mnemonic equivalences for arithmetic and logical operations are given in the following table:

|                                 | B FIELD - Arithmetic & Logical                                                                               |                                         |                   |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|--|--|

| HEX                             | BINARY                                                                                                       | MNEMONIC                                | MEANING .         |  |  |

| 0 1 2 3 4 5 6 7 8 9 A B C D E F | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1011<br>1100<br>1101<br>1110<br>1111 | EXPRESSION  " " RO R1 R2 R3 R4 R5 R6 R7 | 3 BIT-LITERAL = 0 |  |  |

For operations involving shifting (op=0,2,E,F), the "B" field specifies the shift values as listed in the table below.

For shift operations, the "B" field must be an expression whose value is between 1 and 8, inclusive, which are converted by the assembler to the values 0-7.

The assembler mnemonic equivalences are given in the following table:

| ·                                    | B FIELD - Shifts                                     |                          |                                     |   |  |

|--------------------------------------|------------------------------------------------------|--------------------------|-------------------------------------|---|--|

| HEX                                  | BINARY                                               | MNEMONIC                 | MEANING                             |   |  |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110 | EXPRESSION " " " " " " " | SHIFT 1 " 2 " 3 " 4 " 5 " 6 " 7 " 8 | • |  |

#### 2.5 OVERFLOW IN ARITHMETIC/LOGICAL/SHIFT INSTRUCTIONS