# M83-SERIES MODEL 8/32 MAINTENANCE MANUAL

## CONSISTS OF:

| GENERAL DESCRIPTION<br>General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29-394A12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCESSOR<br>Maintenance Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01-078R01A21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WRITABLE CONTROL STORE<br>Installation Specification<br>Maintenance Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35-555F01A20<br>35-555F01A21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

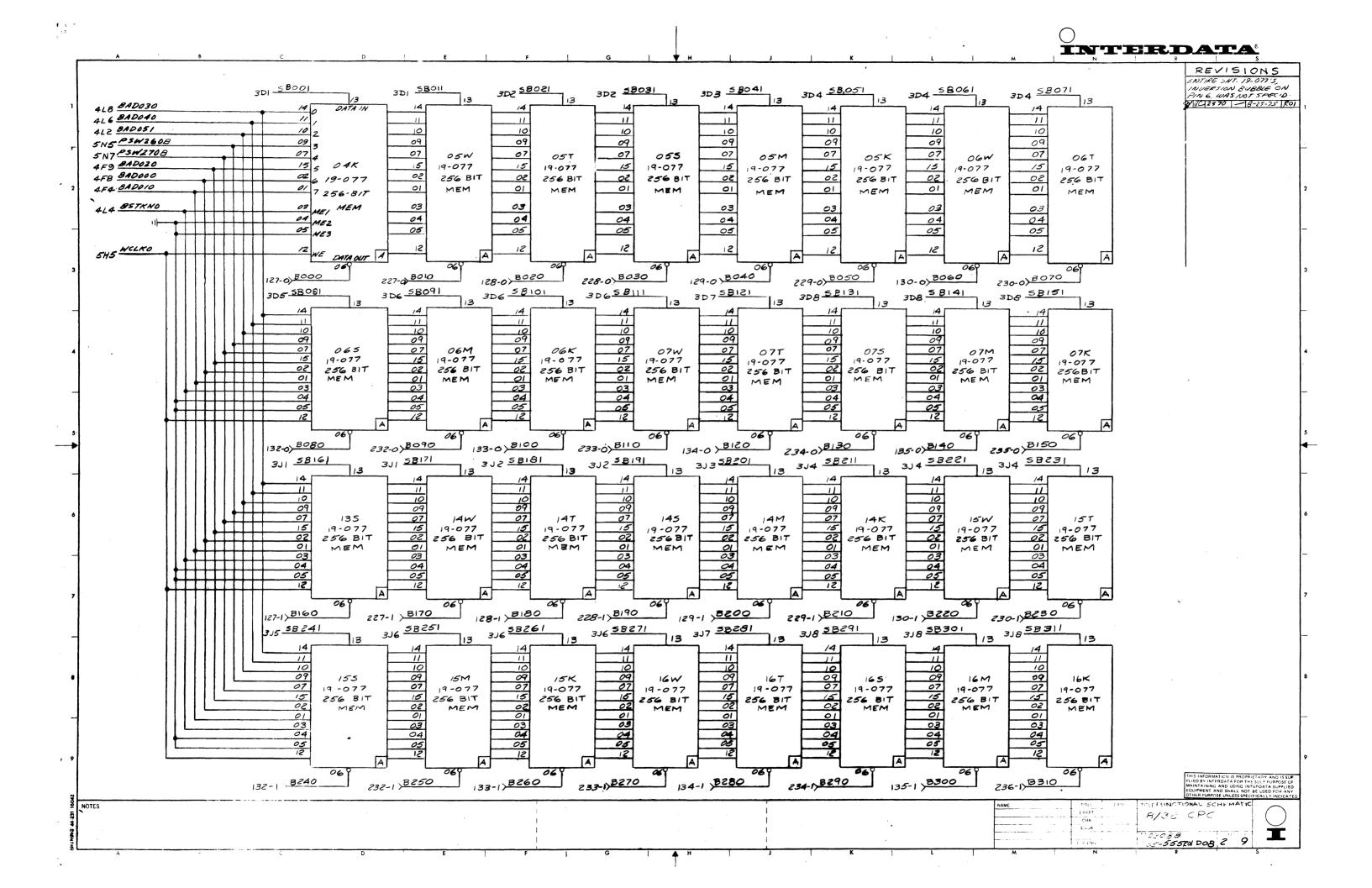

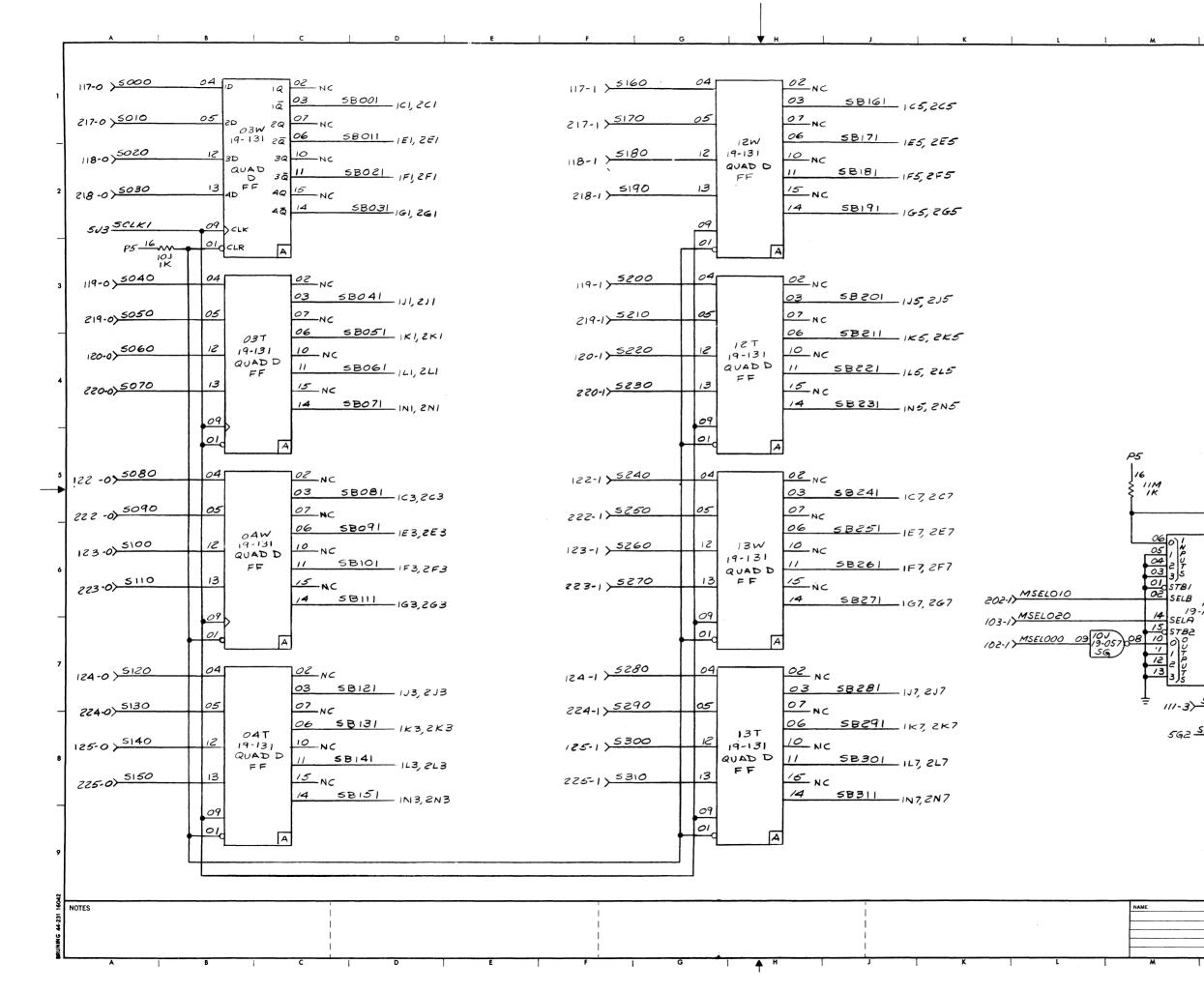

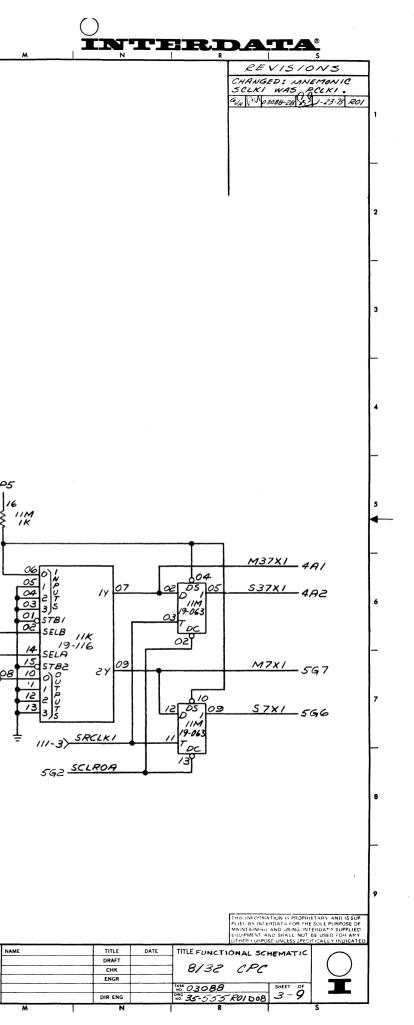

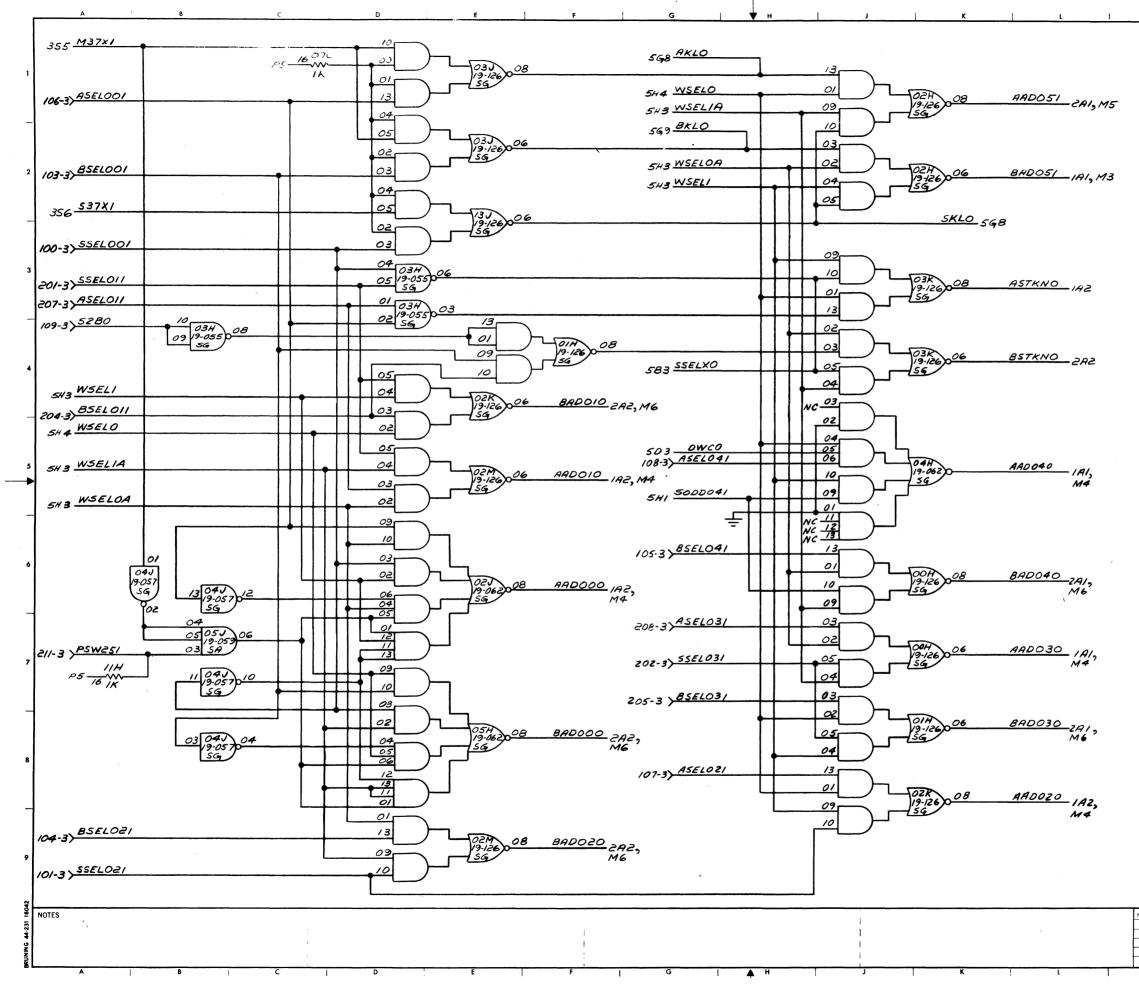

| MEMORY<br>Main Memory System Maintenance Specification<br>32KB Memory Maintenance Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35-535R01A21<br>29-370R03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EXTENDED SELECTOR CHANNEL<br>Installation Specification<br>Maintenance Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 02-328R01A20<br>02-328A21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DISPLAY PANEL<br>Hexadecimal Display Panel Information Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 09-065R01A12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

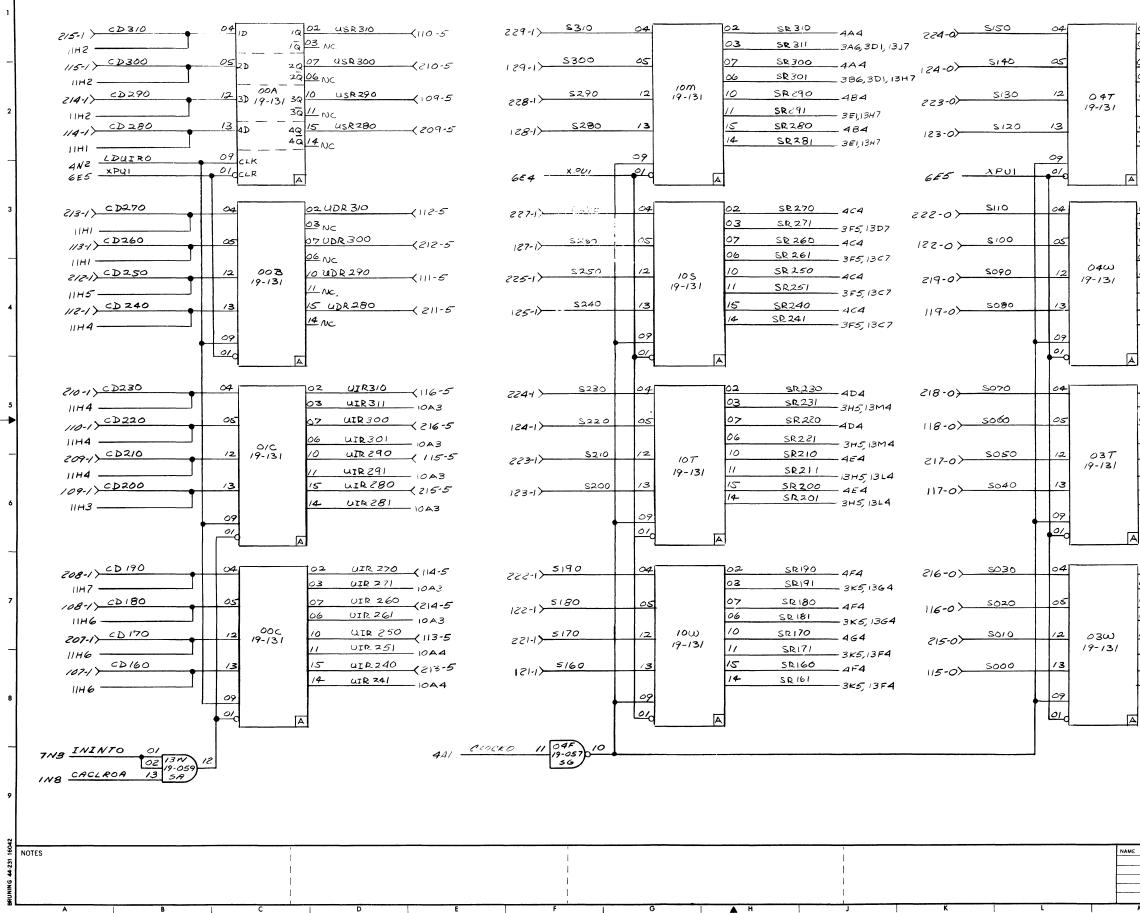

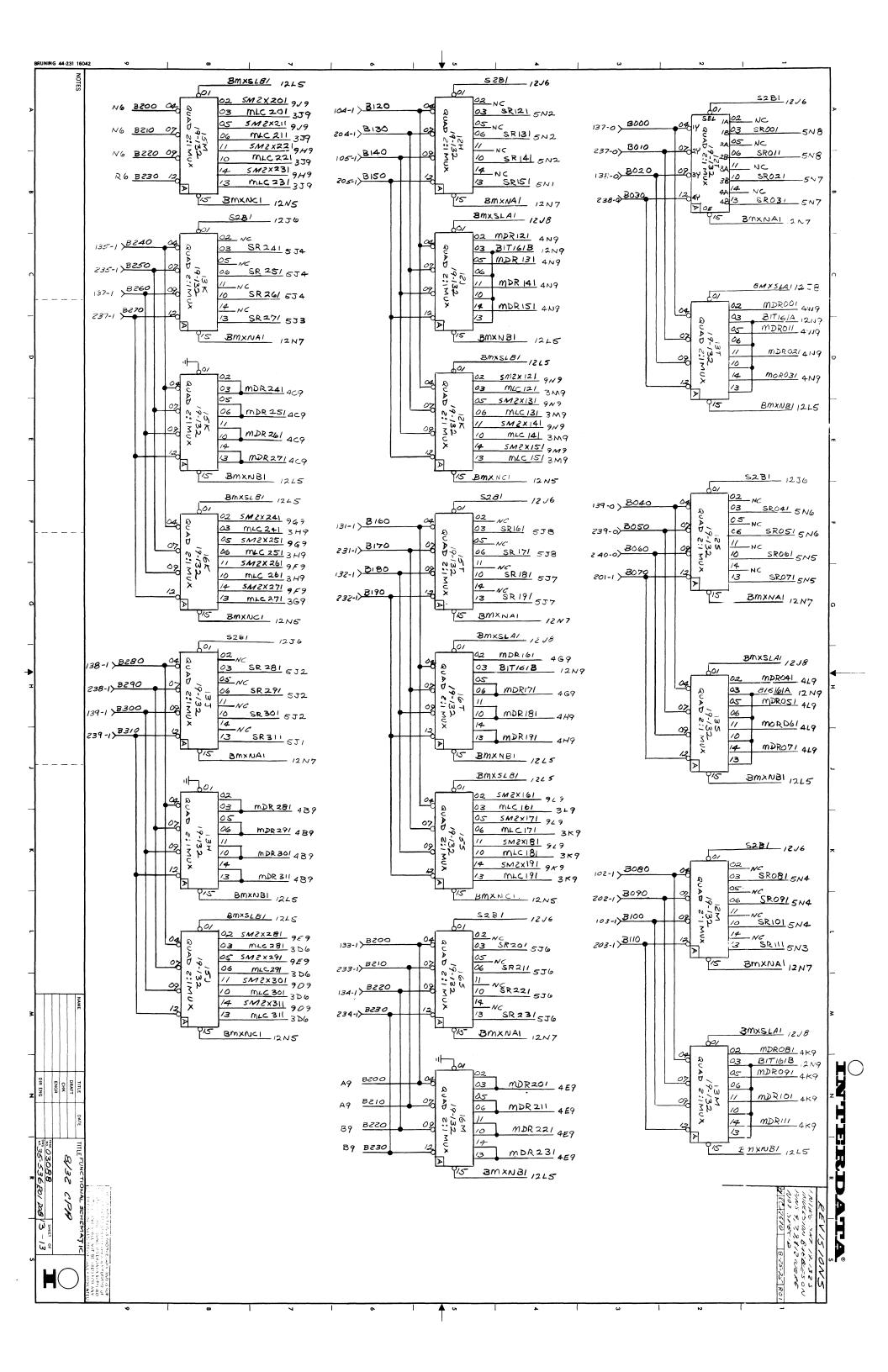

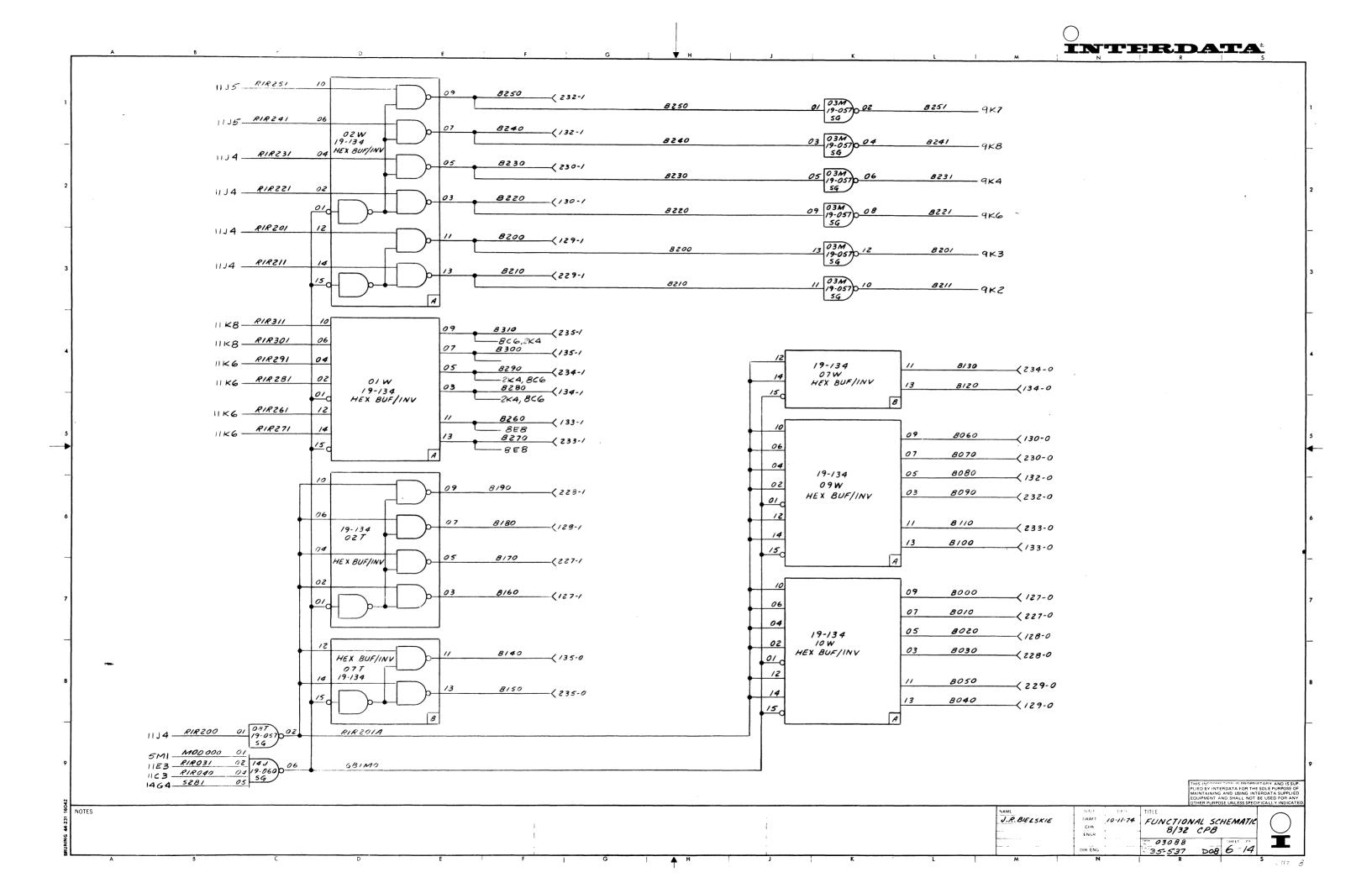

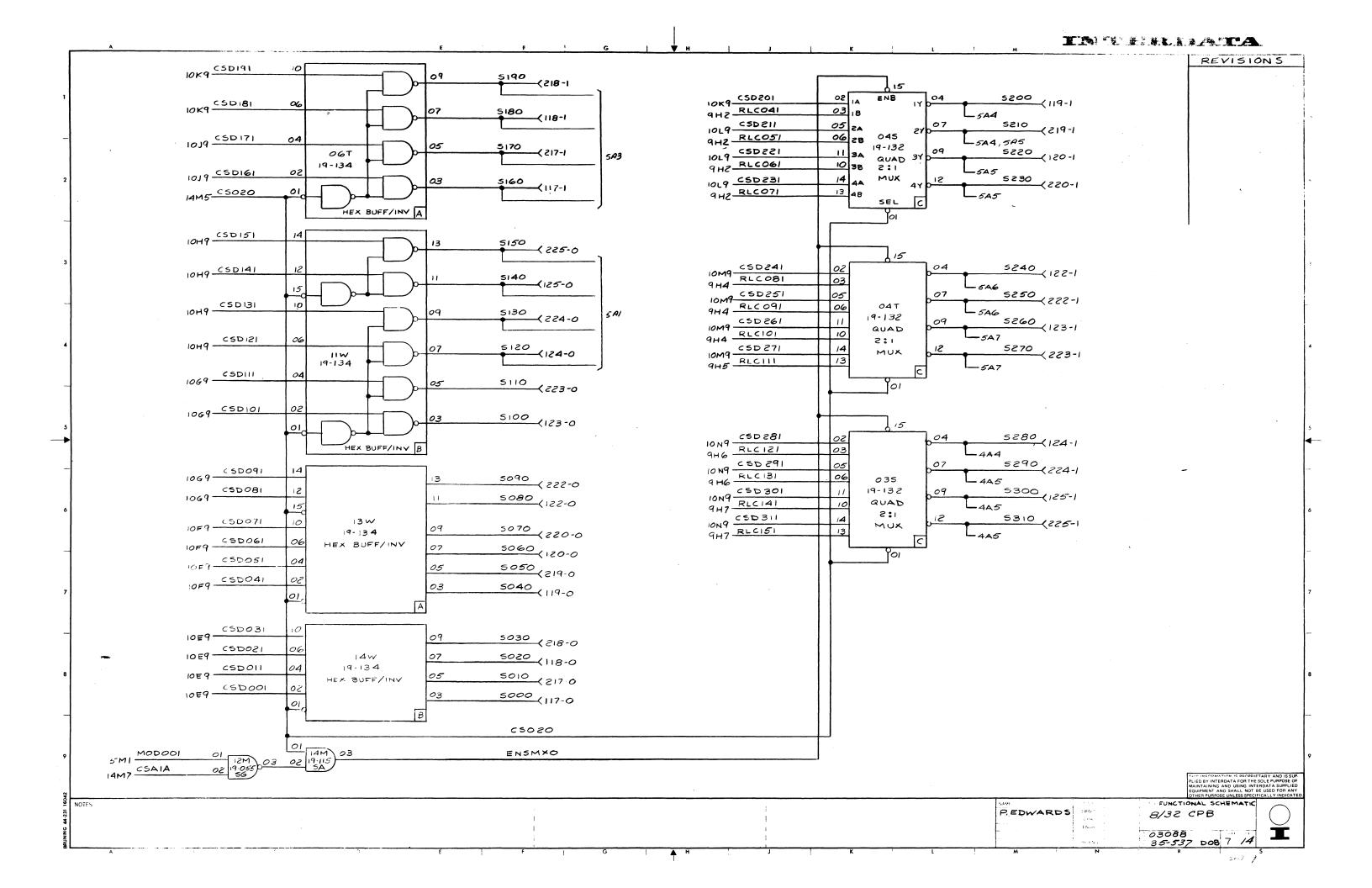

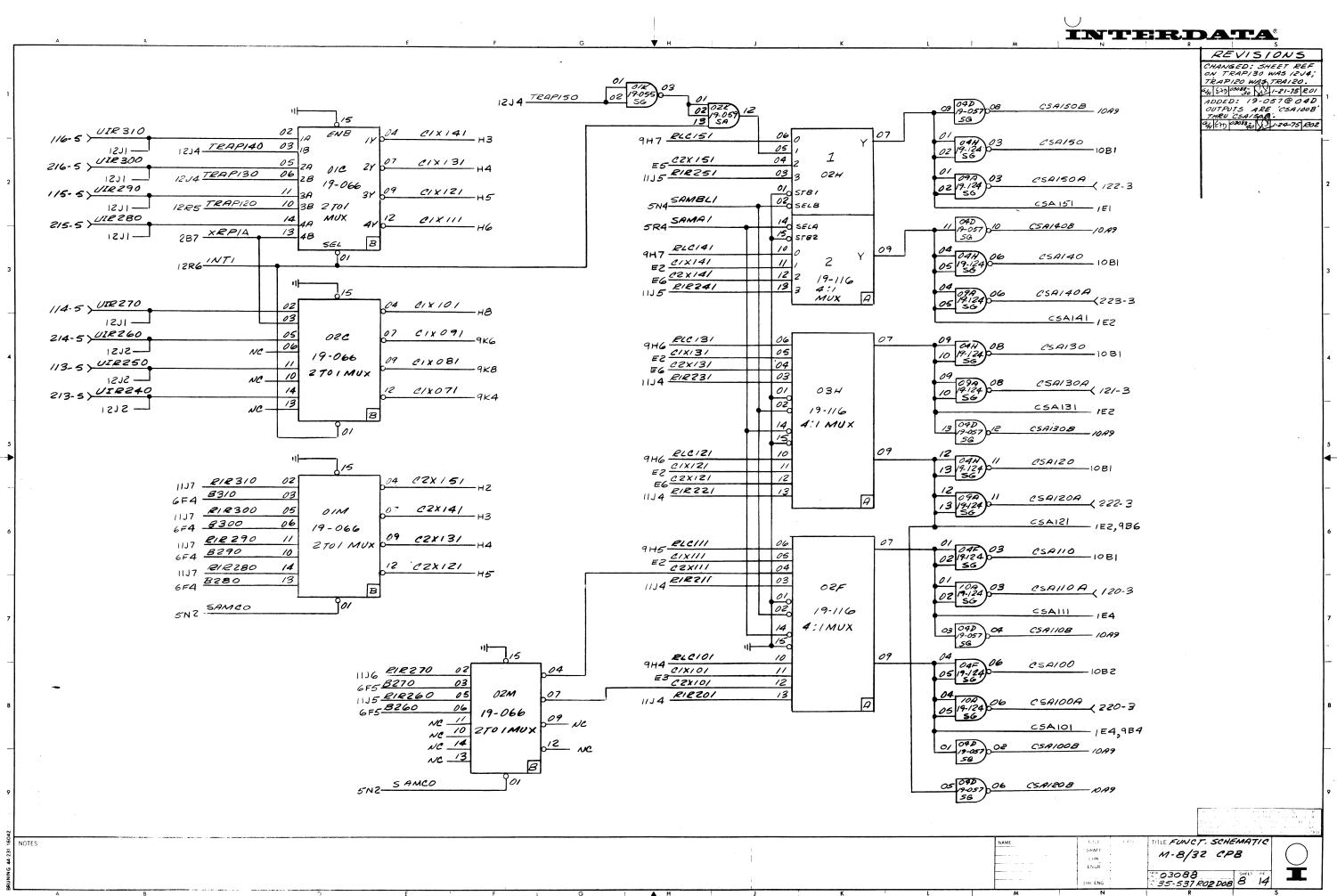

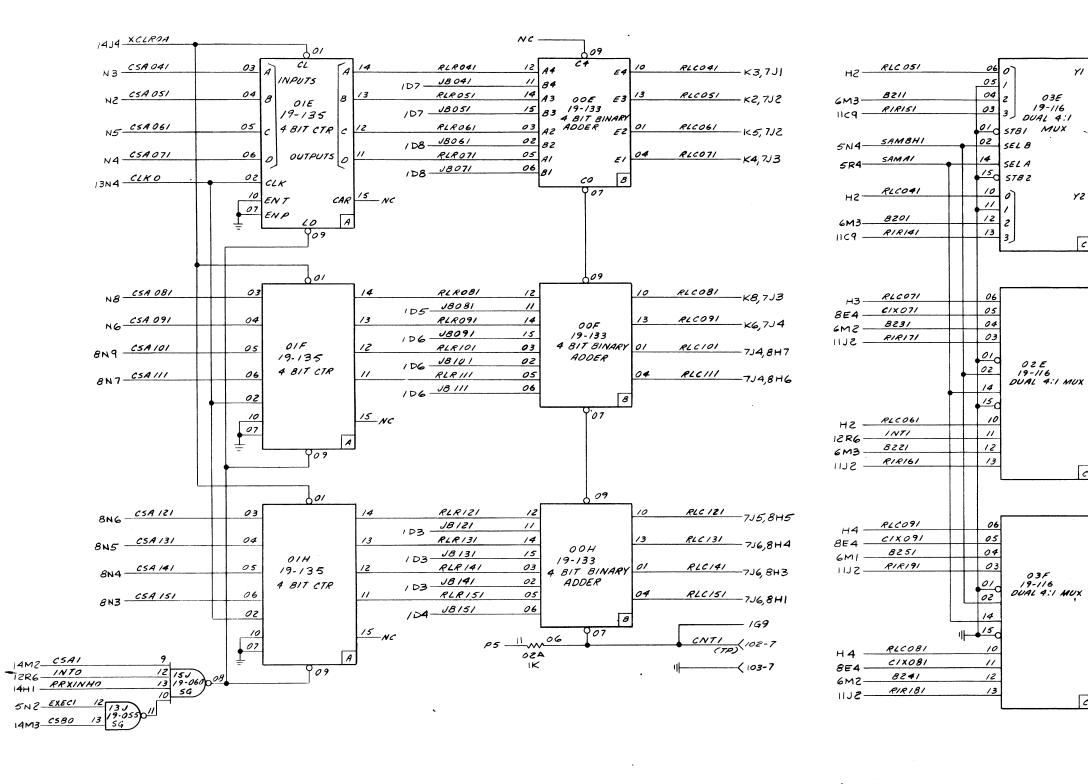

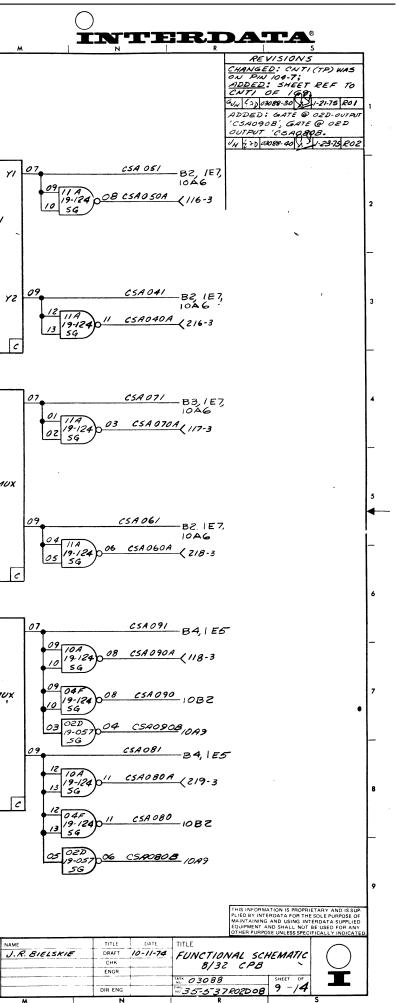

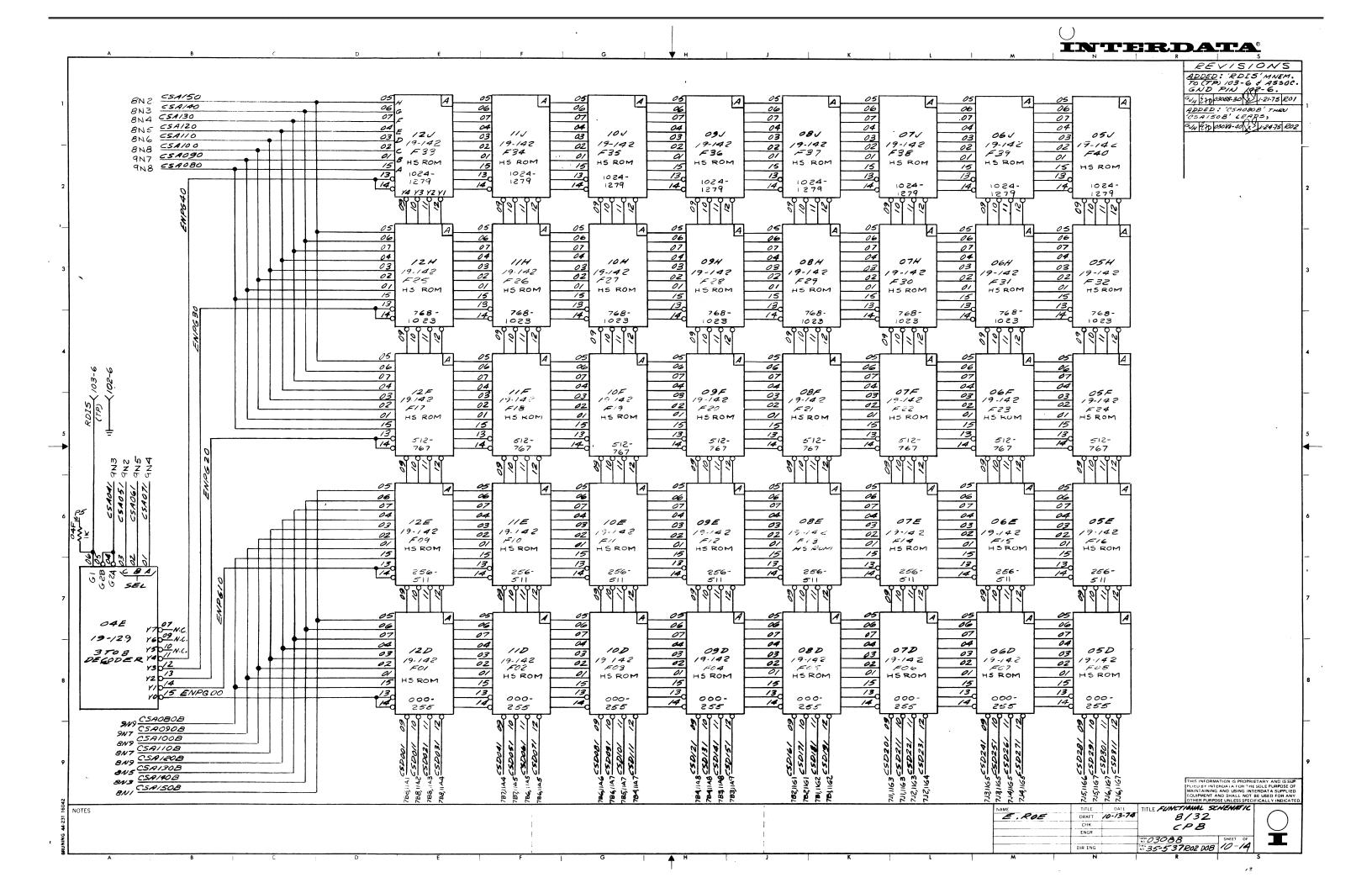

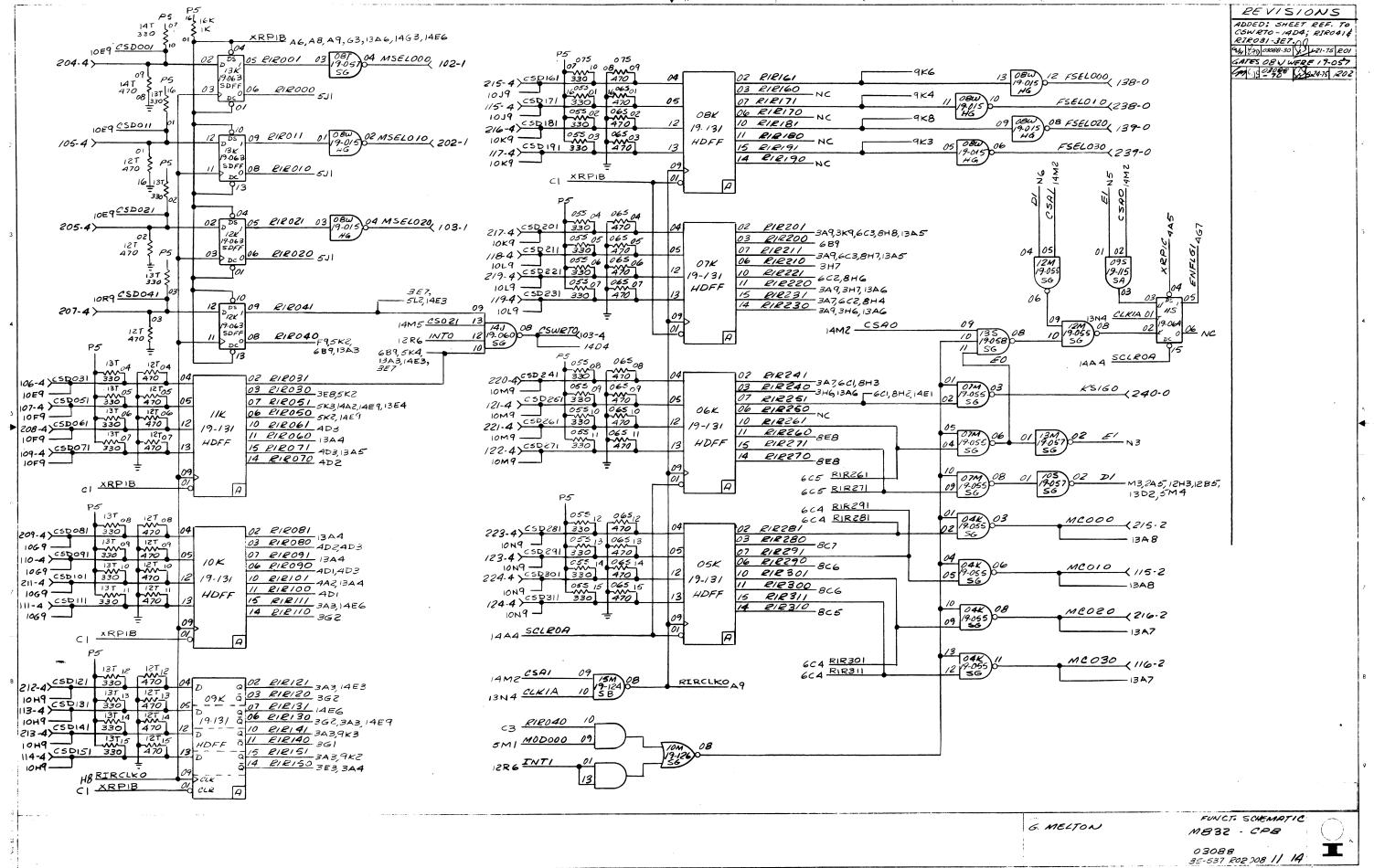

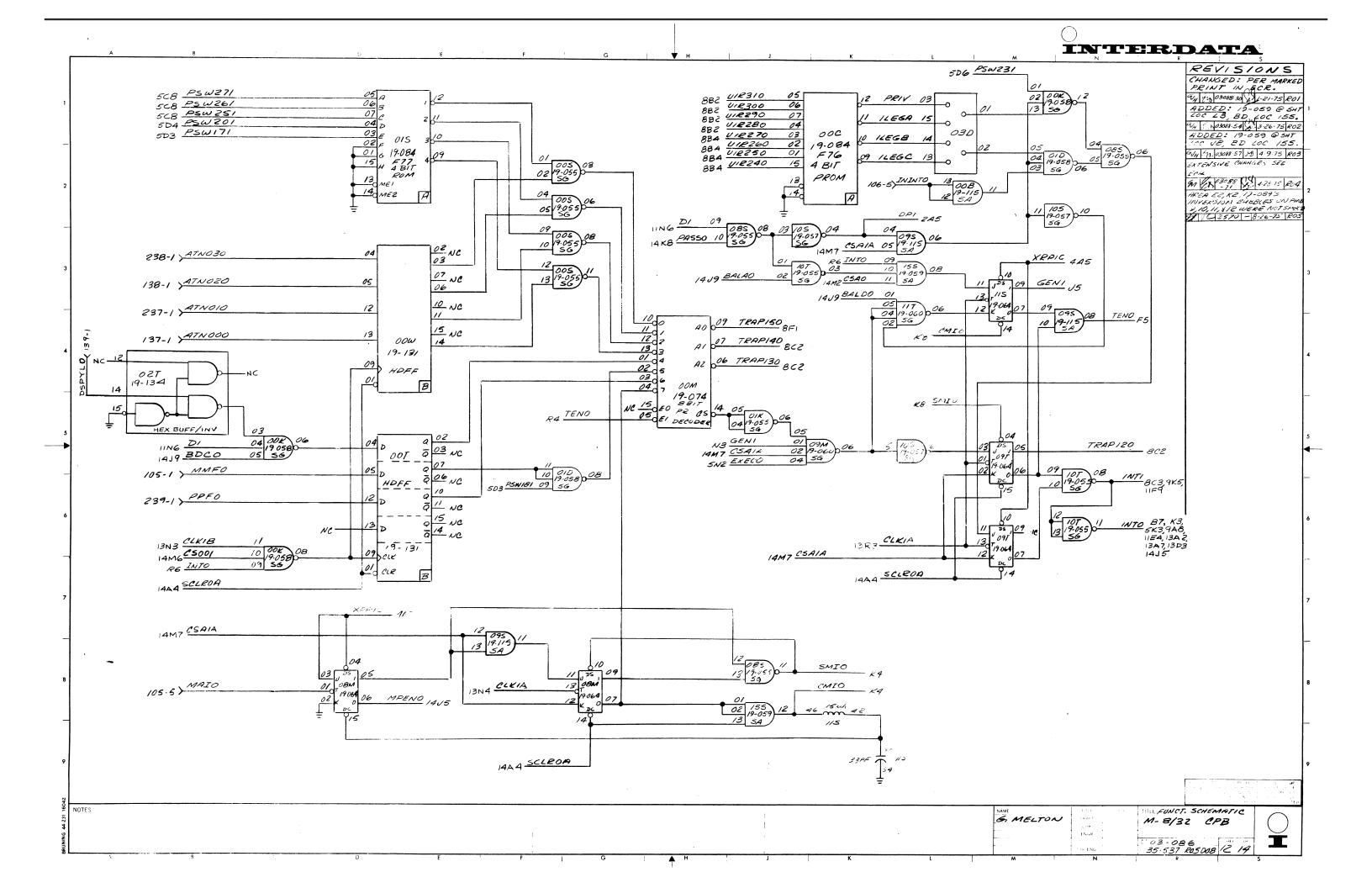

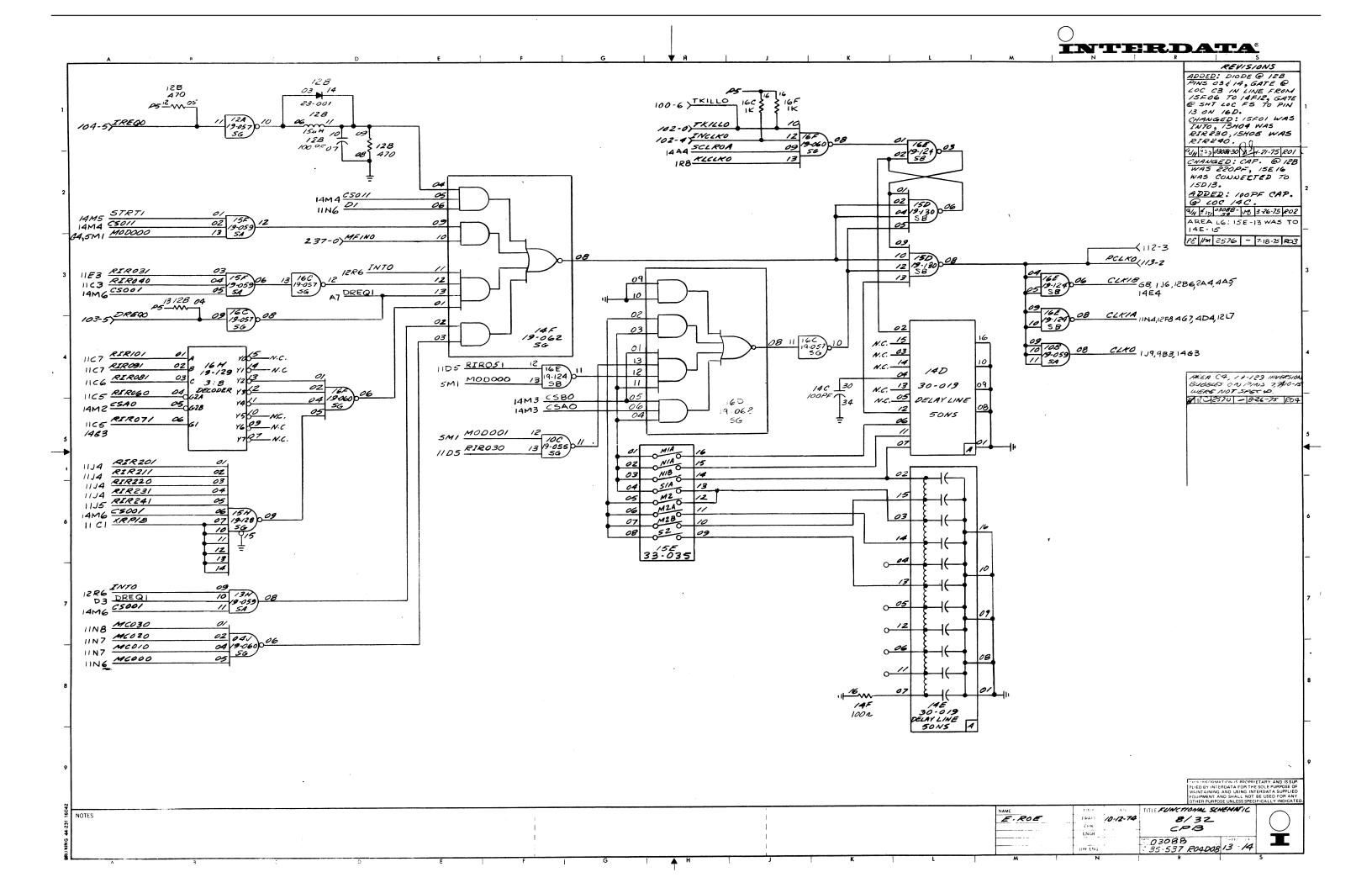

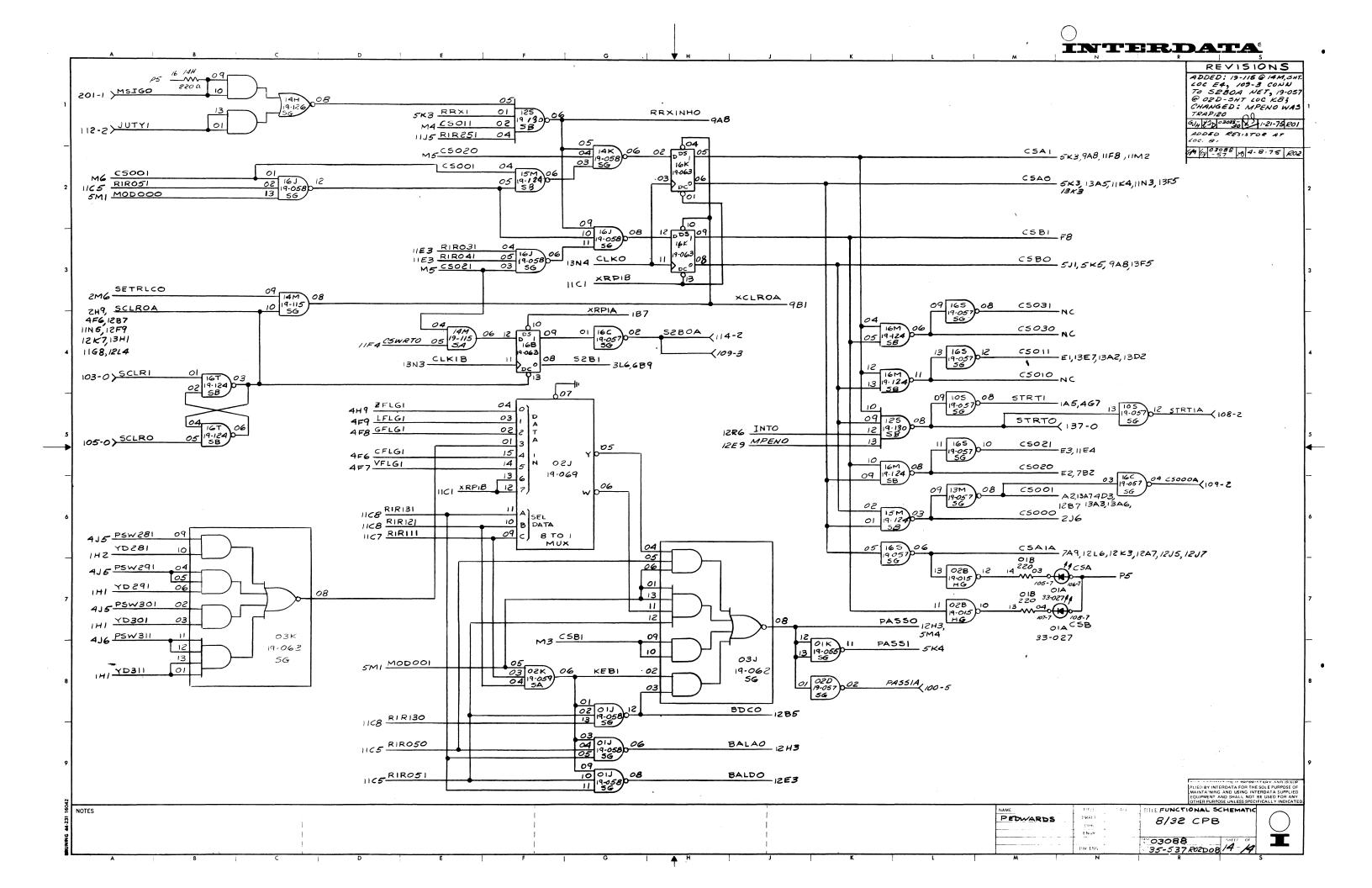

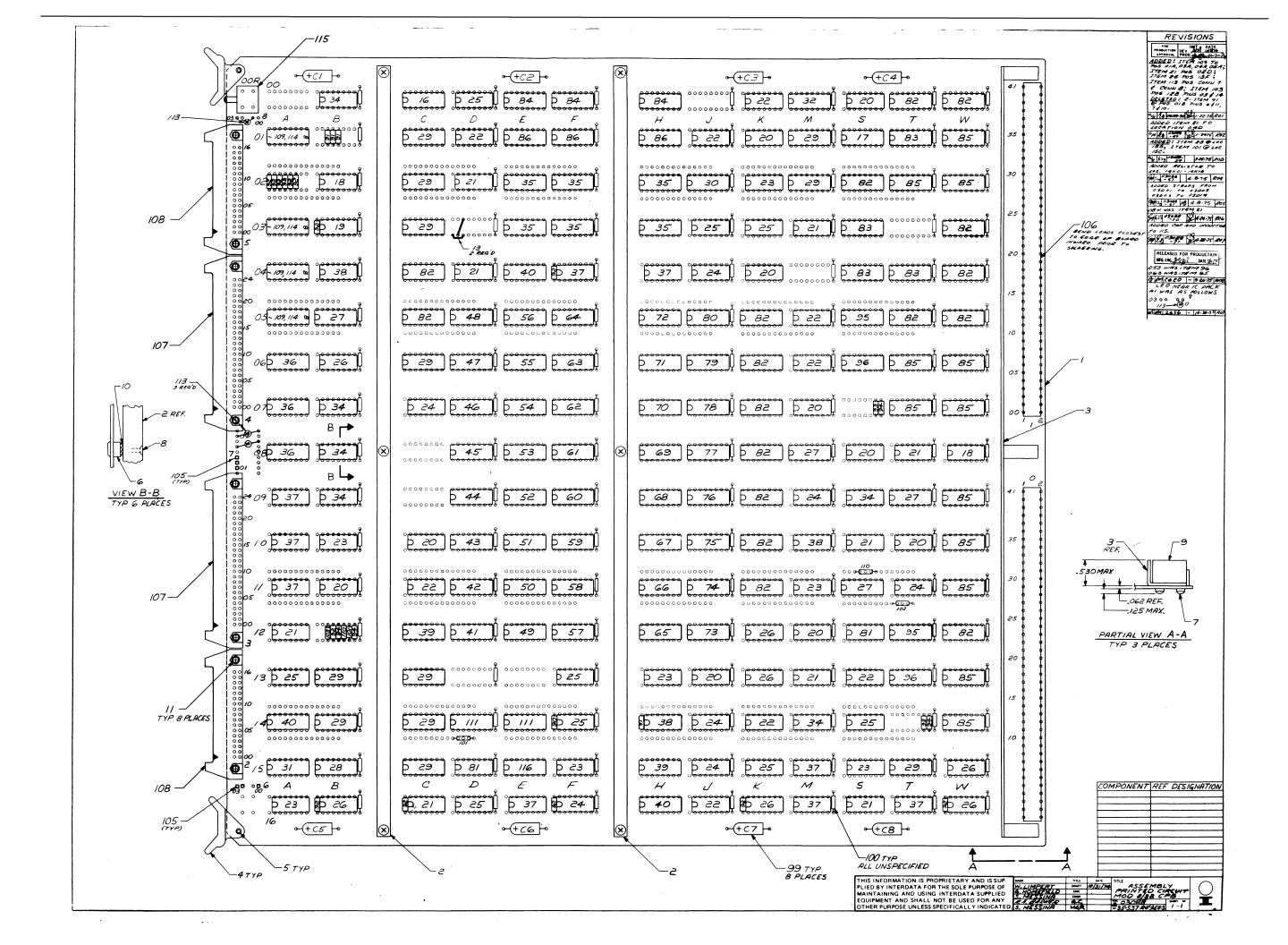

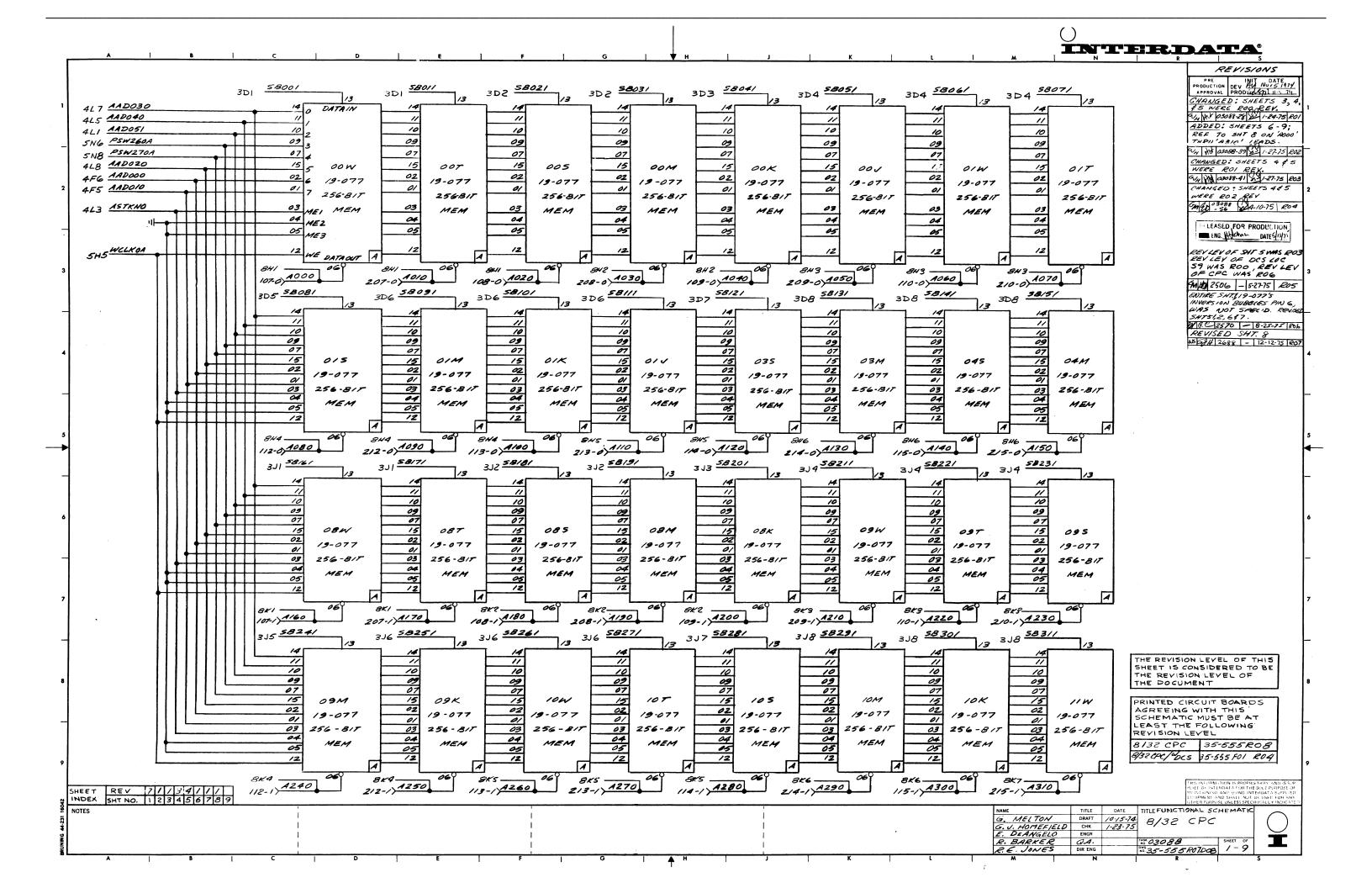

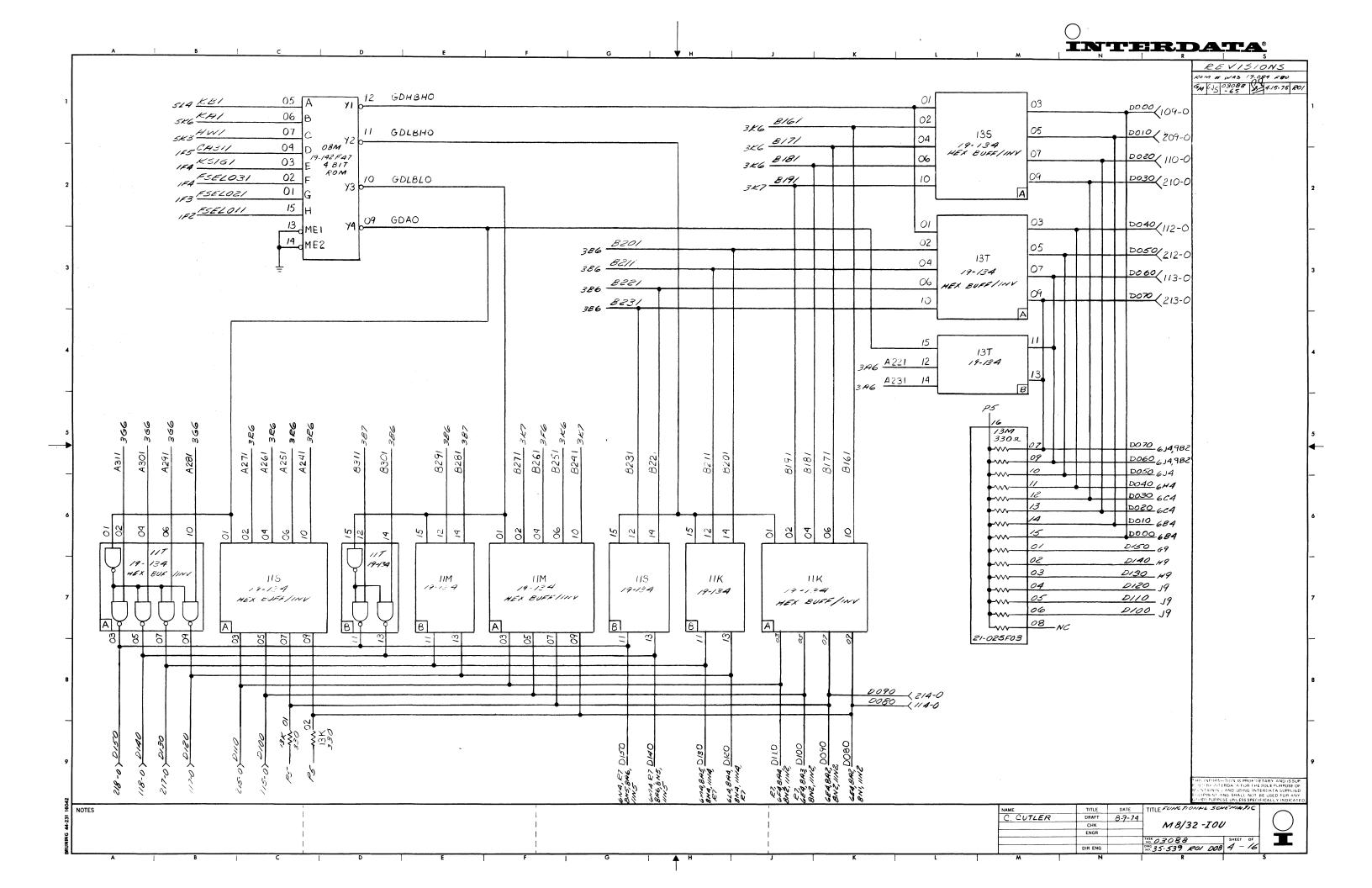

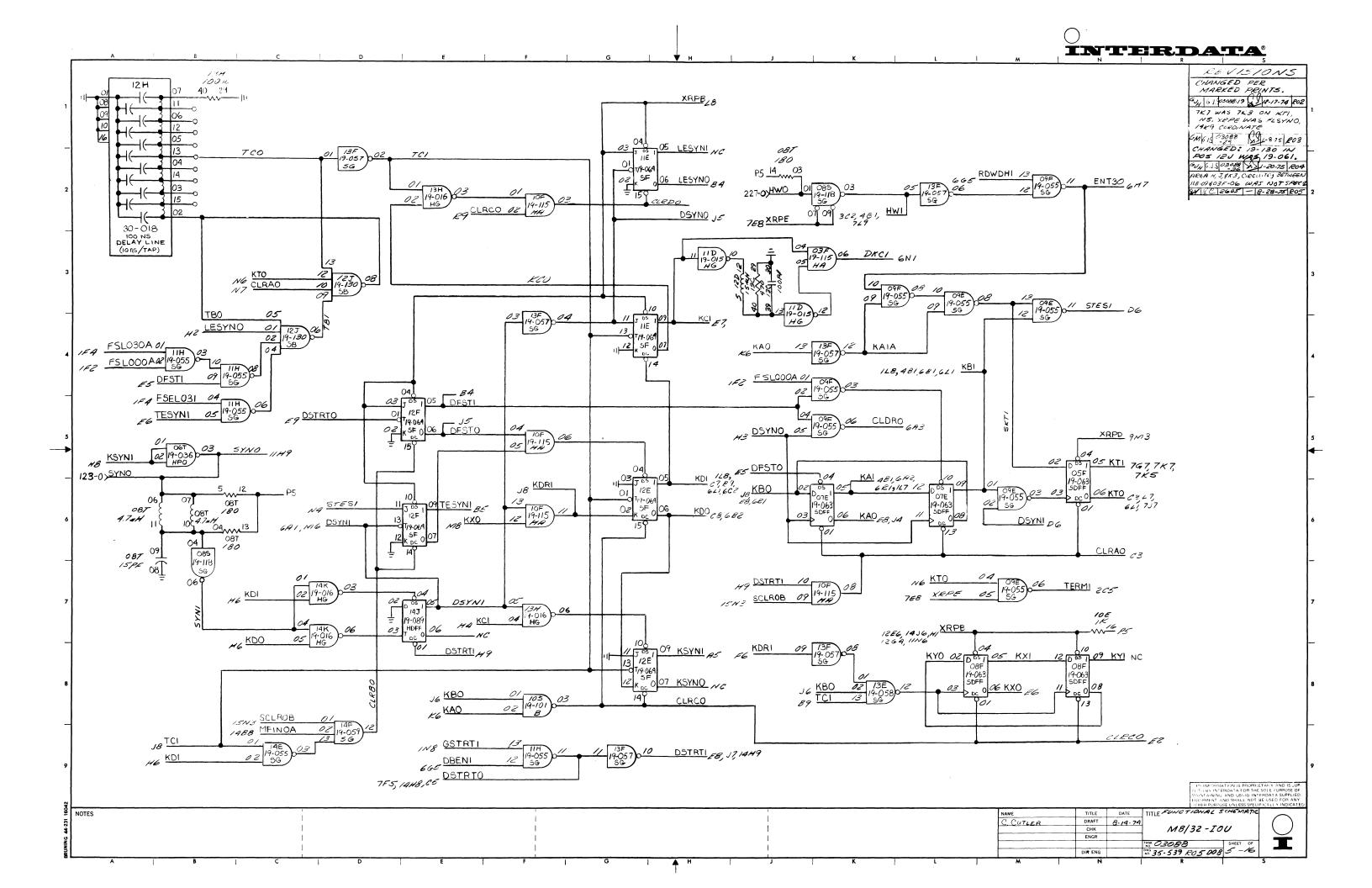

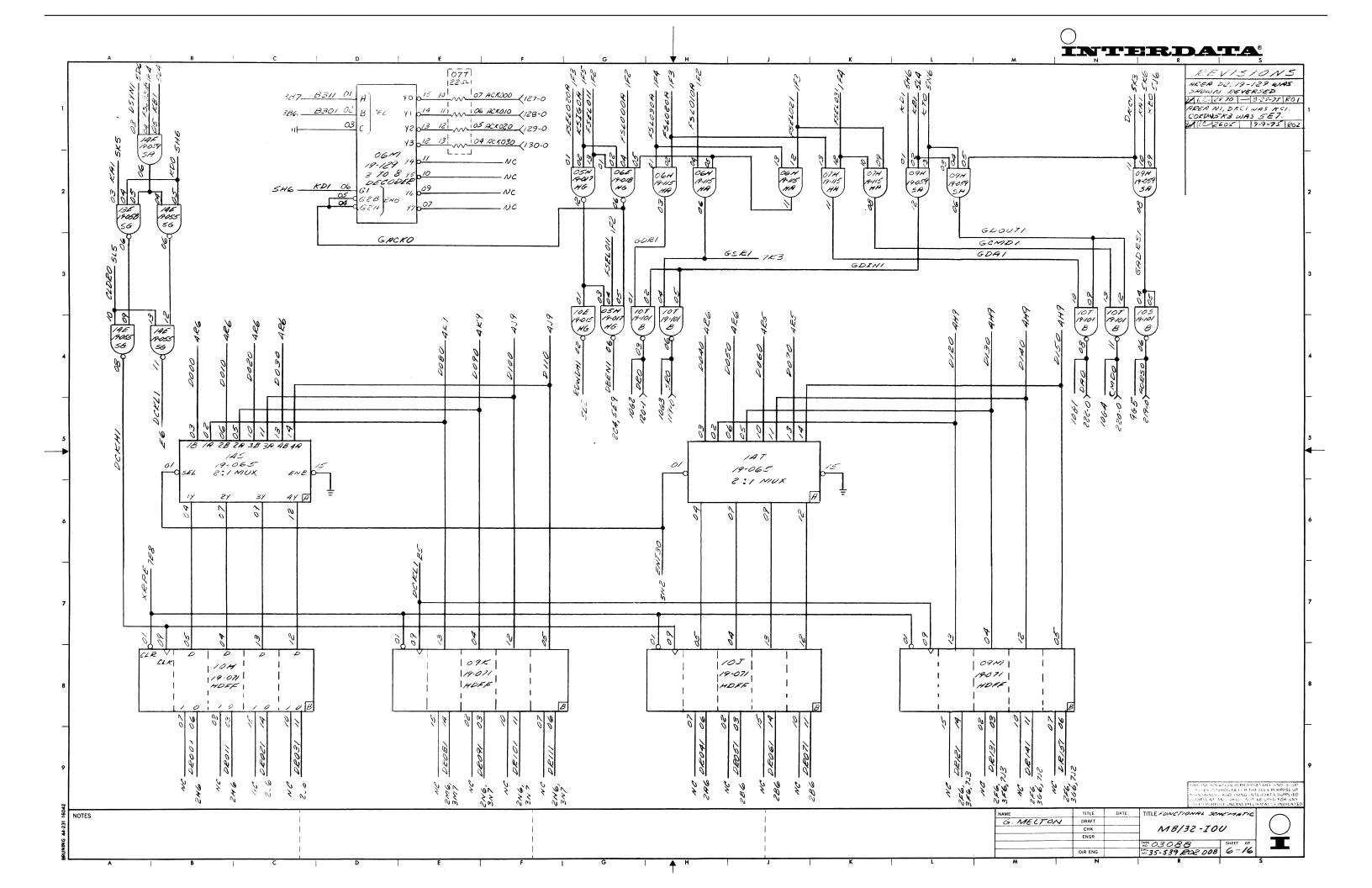

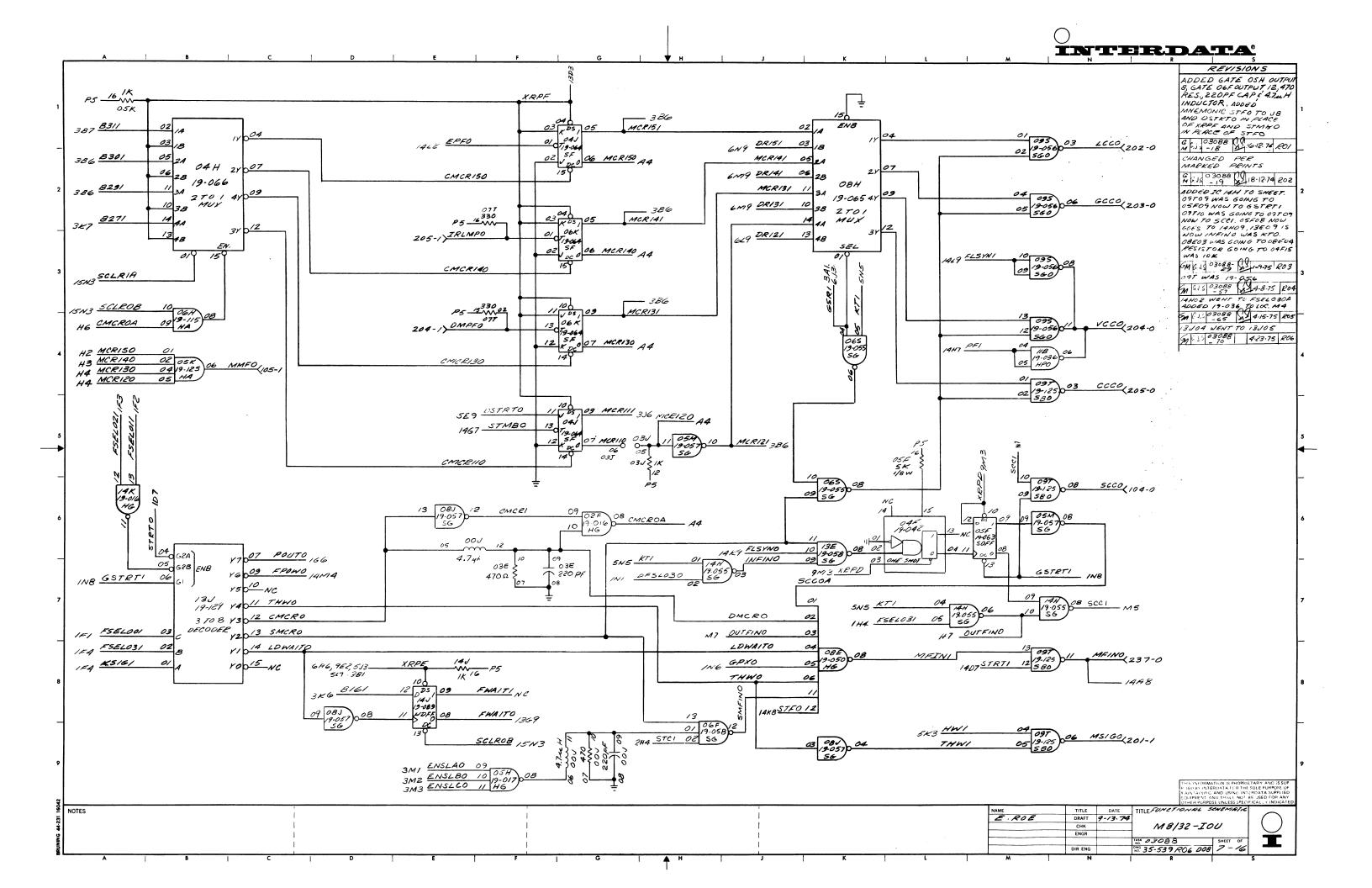

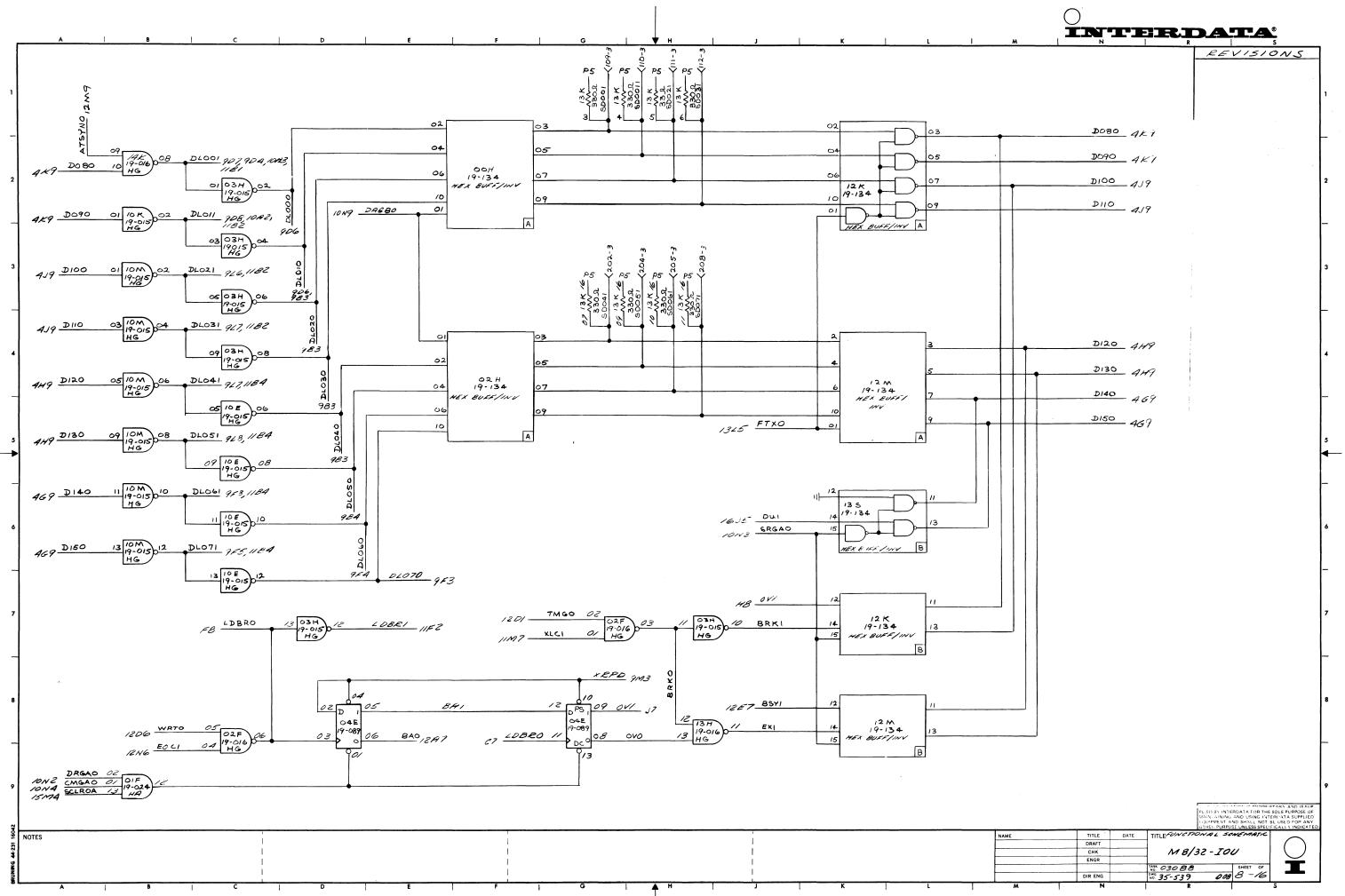

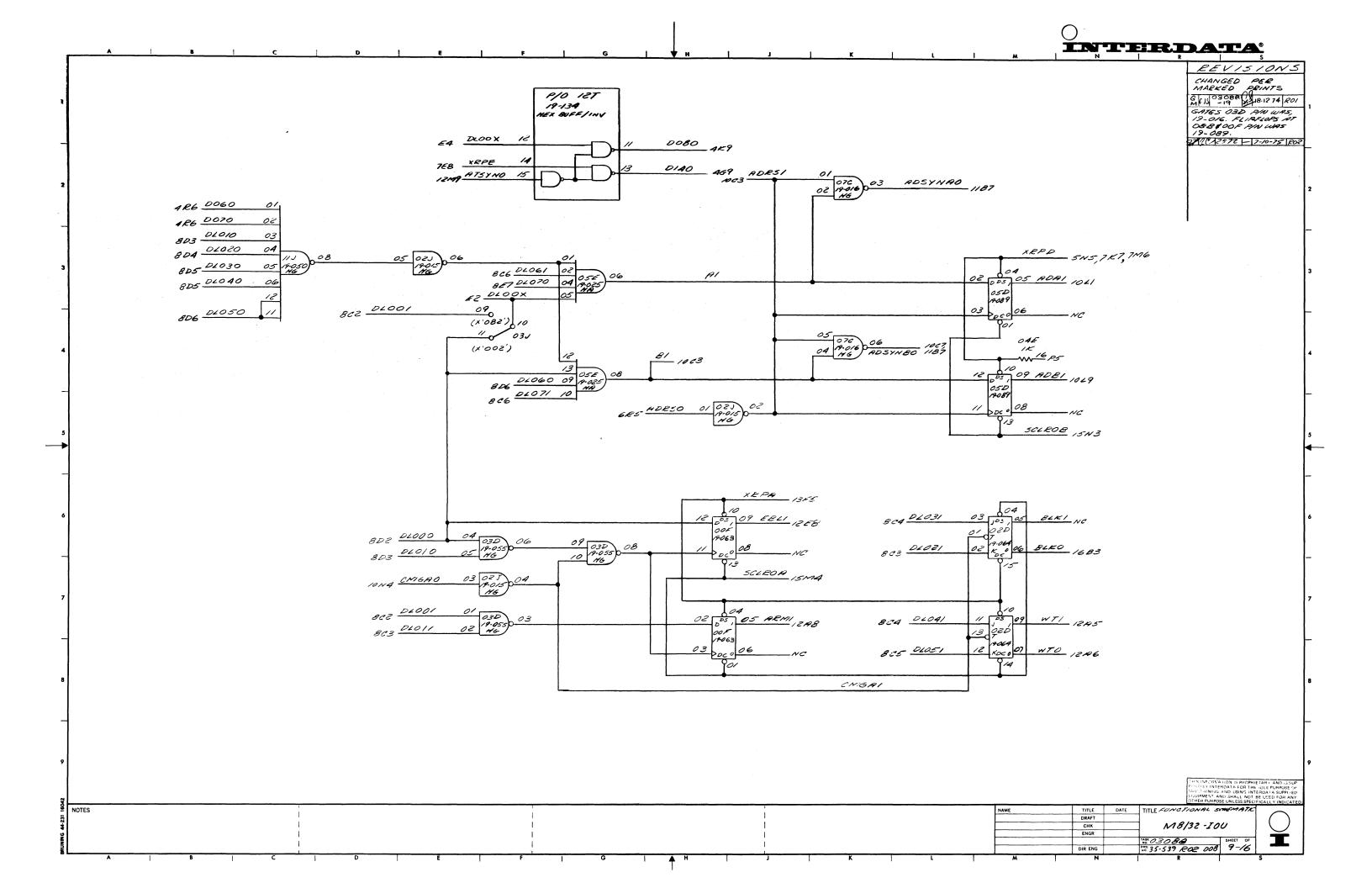

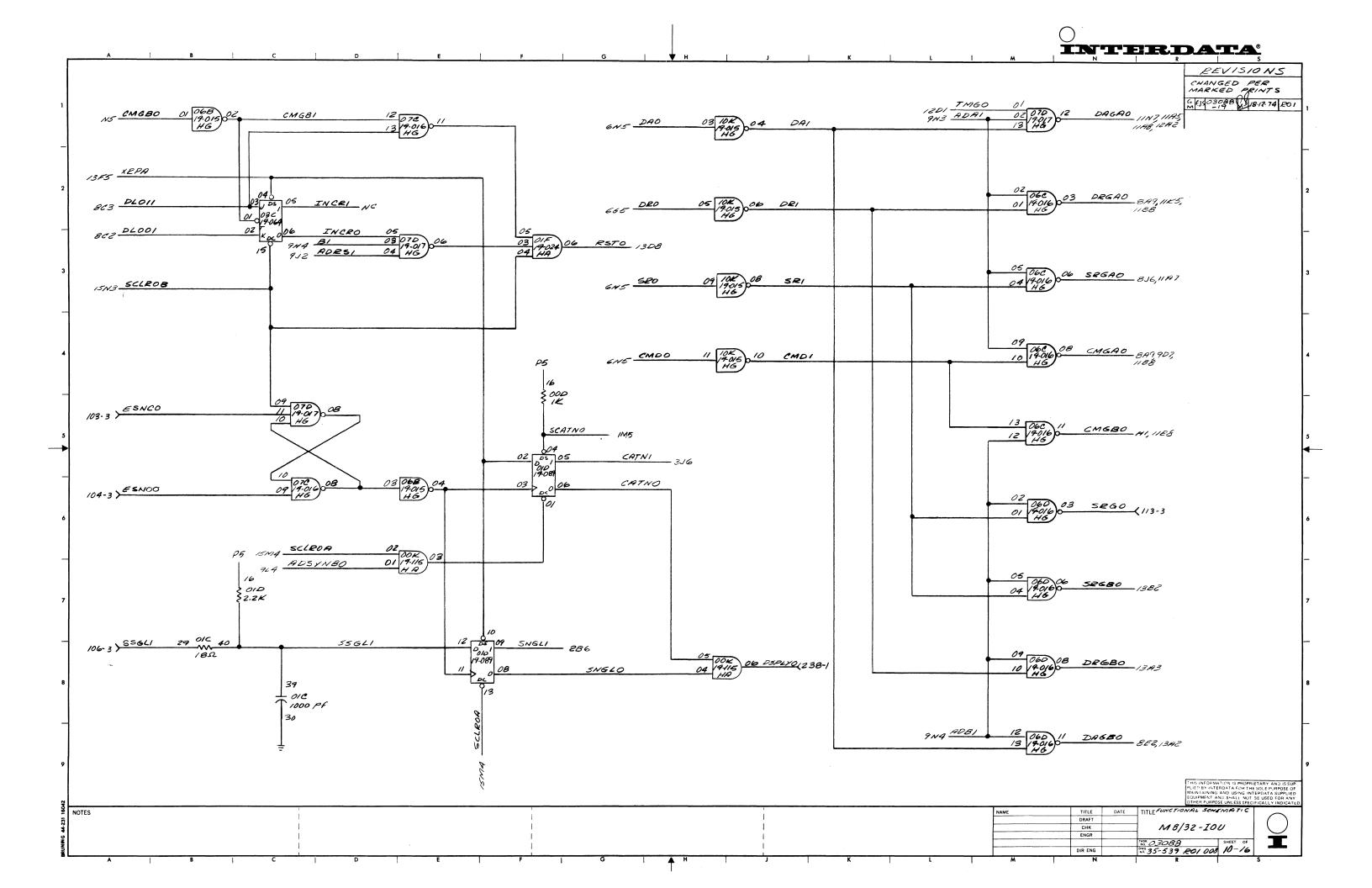

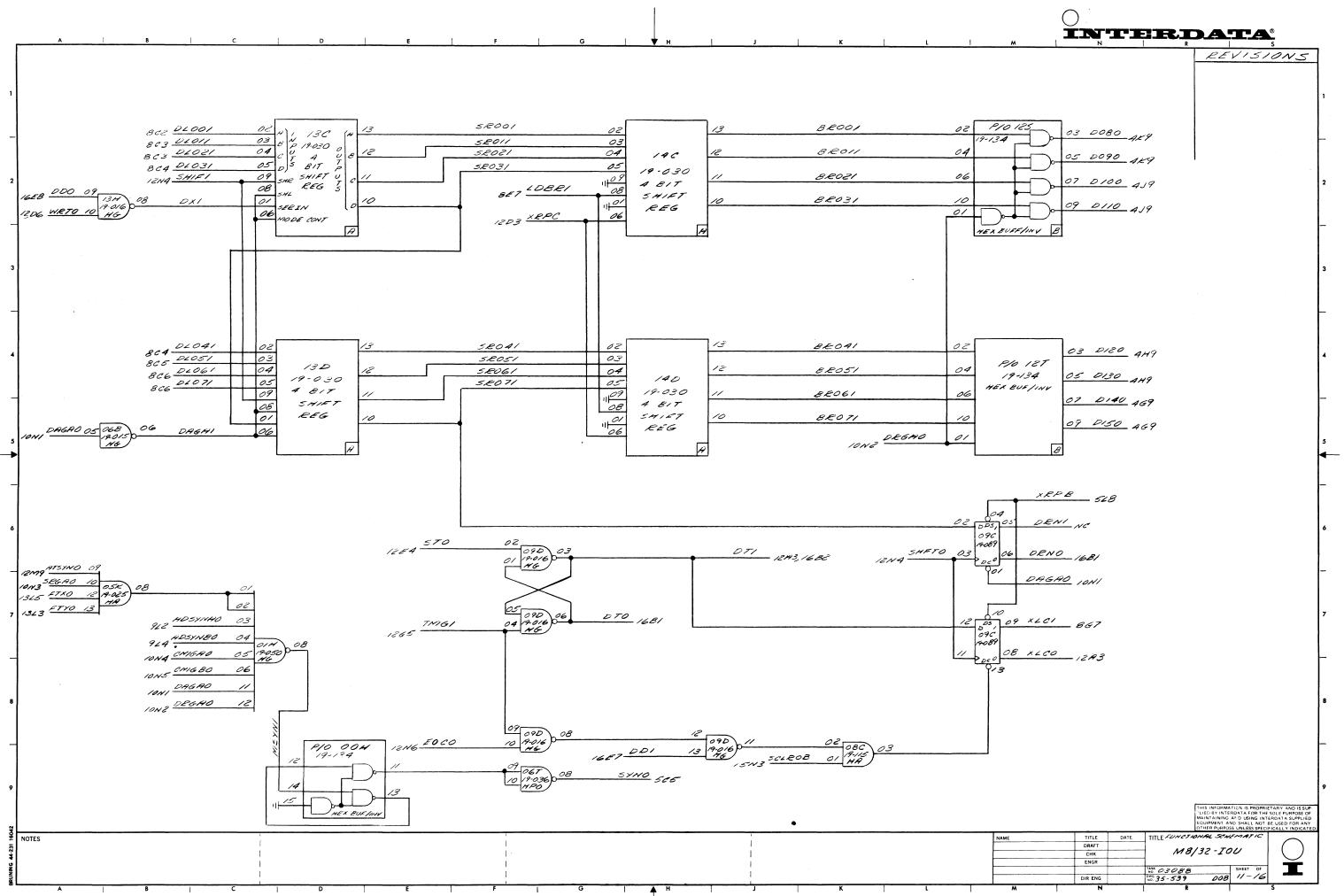

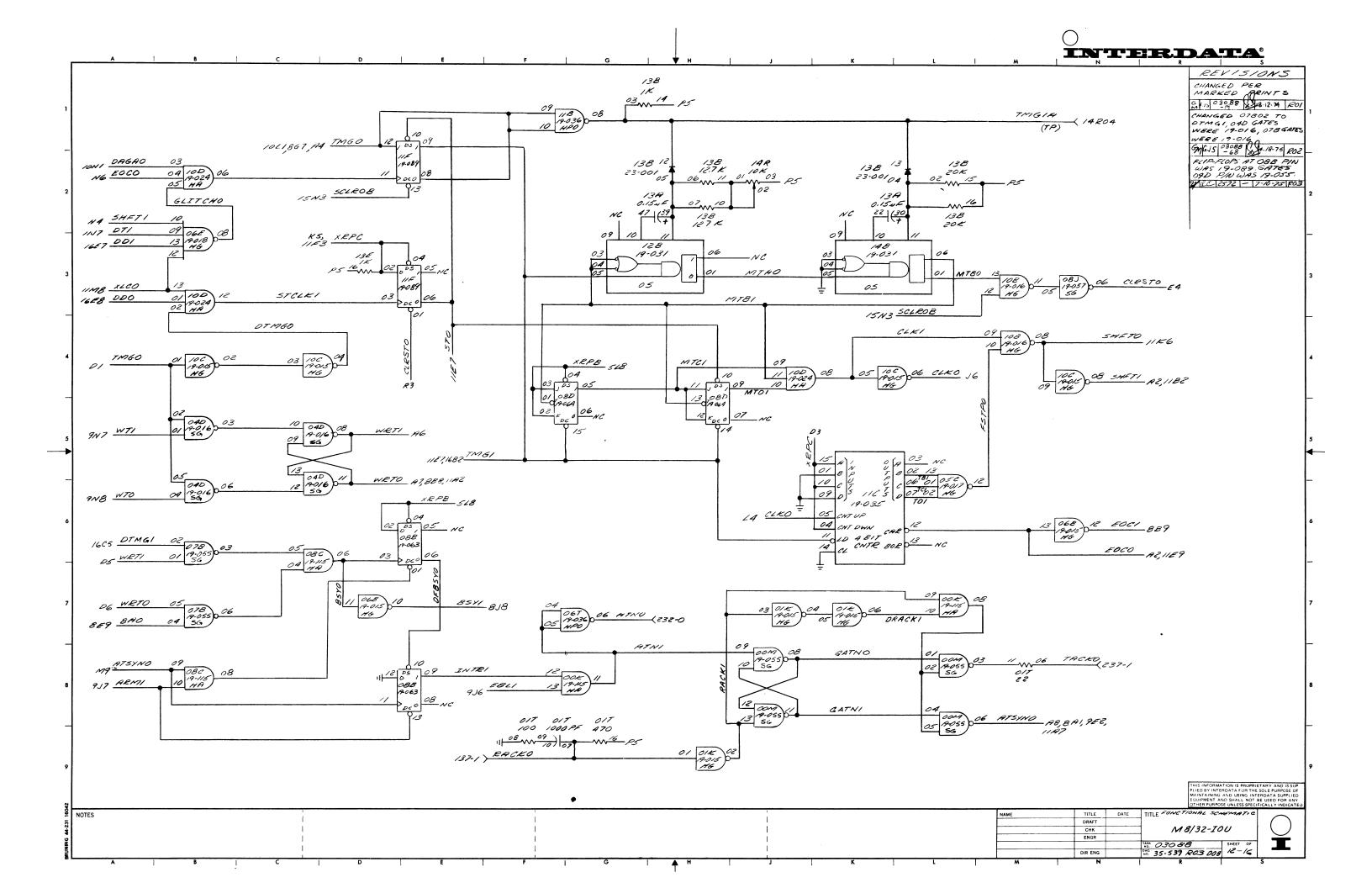

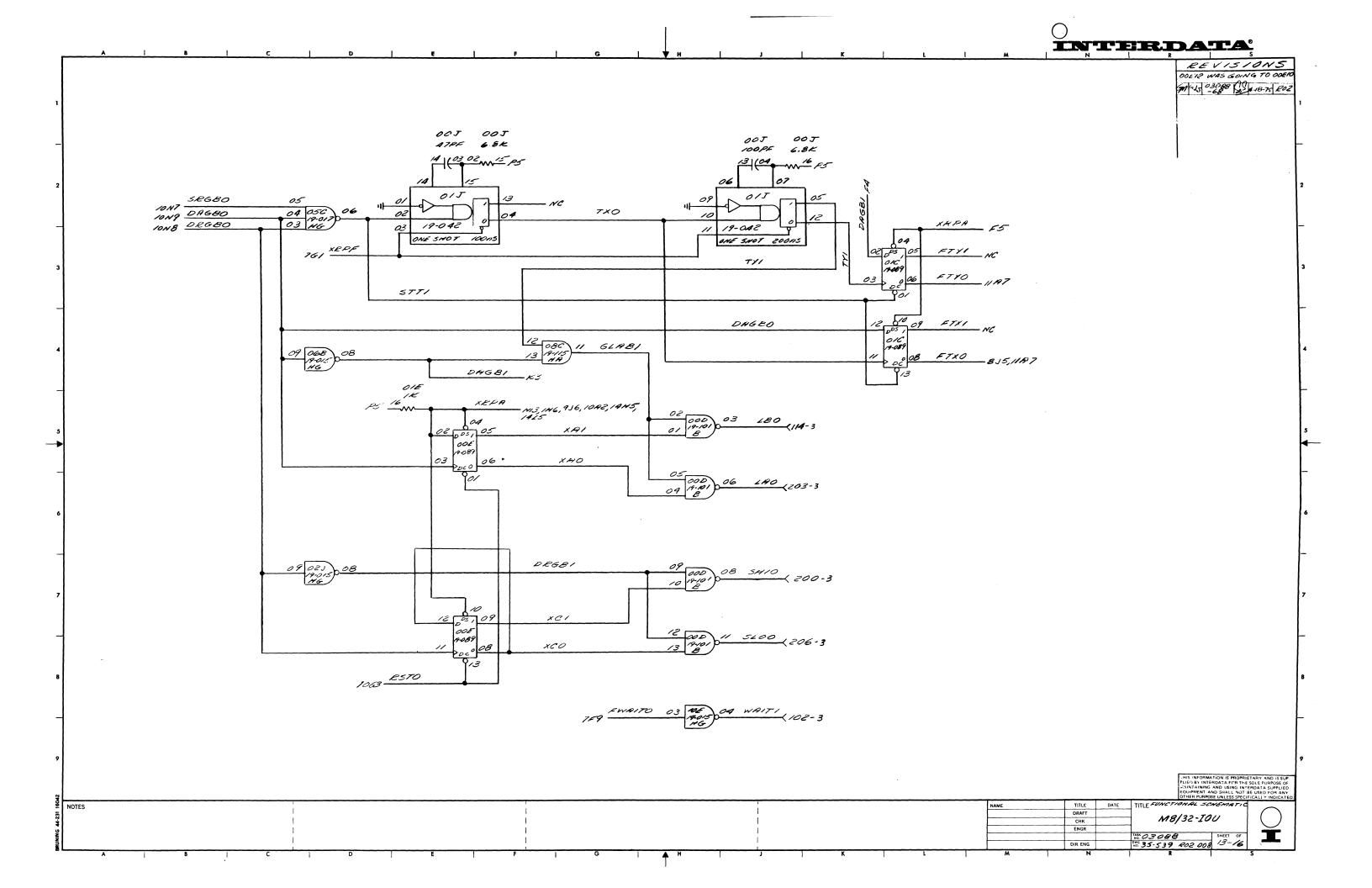

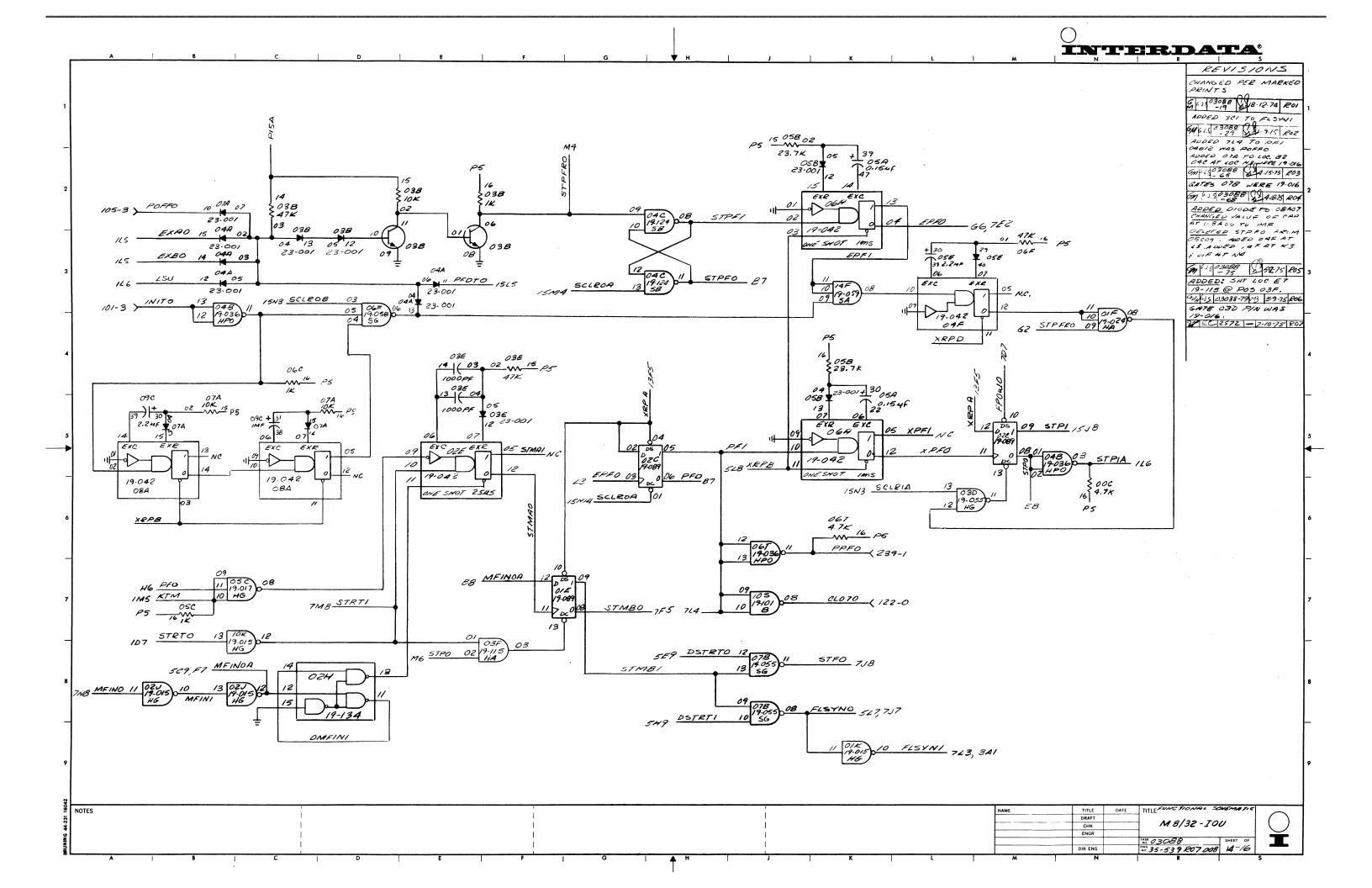

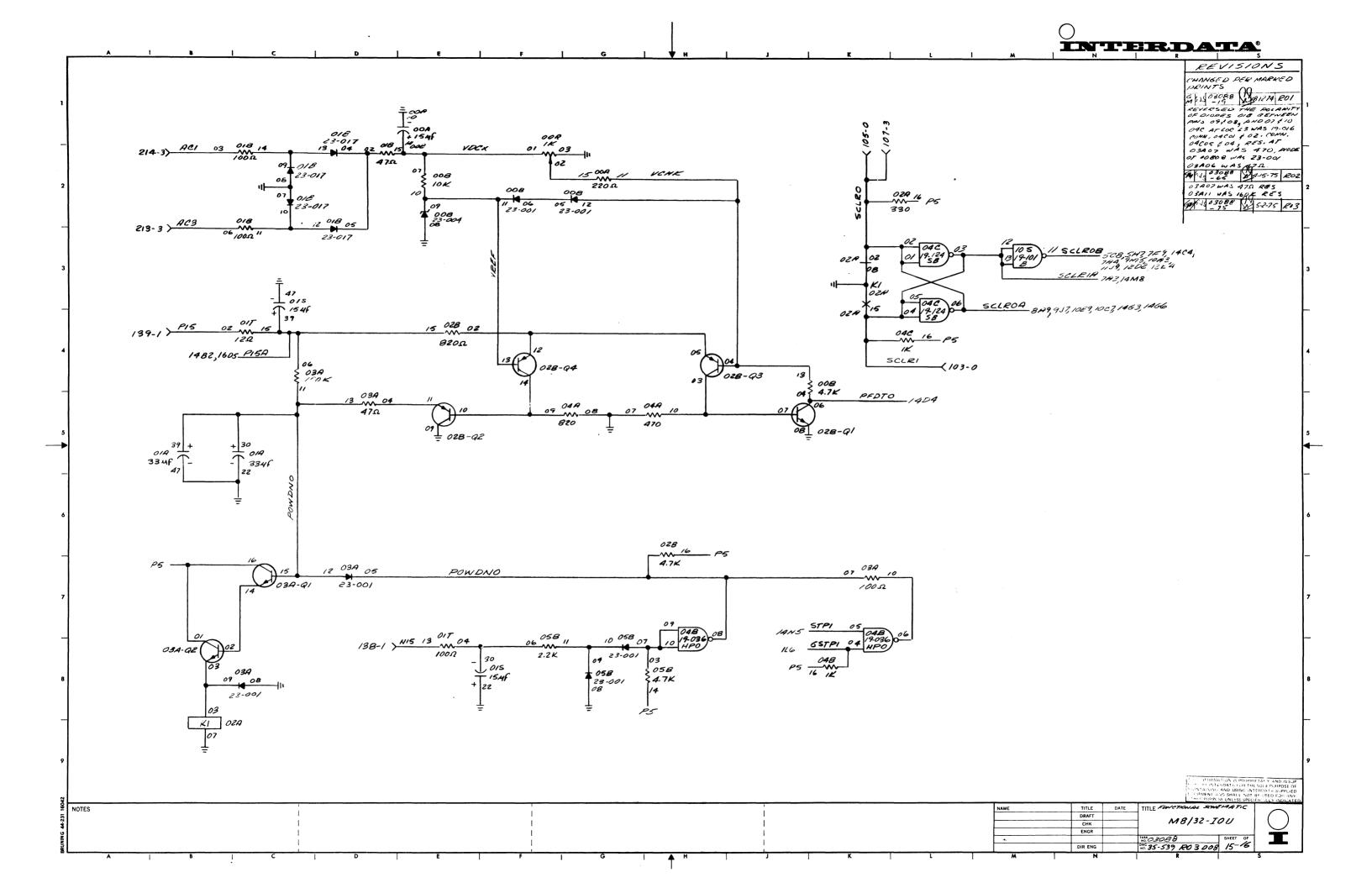

| DRAWINGS<br>Back Panel Map<br>Processor CPU-A Schematic<br>Processor CPU-B Assembly<br>Processor CPU-B Schematic<br>Processor CPU-B Assembly<br>Processor CPU-C Schematic<br>Processor CPU-C Assembly<br>Processor IOU Assembly<br>Processor IOU Assembly<br>Processor ALU Schematic<br>Processor ALU Schematic<br>Processor ALU Assembly<br>Memory Bus Controller (MBC) Schematic<br>Local Memory Interface (LMI) Schematic<br>Local Memory Interface (LMI) Assembly<br>Extended Selector Channel Schematic<br>Extended Selector Channel Assembly<br>Hexadecimal Display Panel Schematic<br>Hexadecimal Display Panel Assembly<br>DMA Terminator Assembly<br>DMA Terminator Assembly<br>DMA Terminator Assembly<br>DMA Terminator Assembly<br>I/O Bus Terminator Assembly<br>I/O Bus Terminator Assembly<br>I/O Bus Terminator Assembly<br>Power Supply Schematic<br>Power Supply Assembly | 01-078R03D08<br>35-536R17D08<br>35-536R12E03<br>35-537R09D08<br>35-537R09E03<br>35-555R06D08<br>35-555R04E03<br>35-558R04E03<br>35-538R05E03<br>35-538R05E03<br>35-538R05E03<br>35-535R04E03<br>35-535R04E03<br>35-534R06D08<br>35-534R06D08<br>35-534R06D08<br>35-534R04E03<br>02-328M02R01D08<br>35-519R03D03<br>35-519R03D03<br>35-548E08<br>35-569D08<br>35-569D08<br>35-569D08<br>35-569D08<br>35-569D08<br>35-569B01C03<br>35-578B03<br>35-433B08<br>35-433B08<br>35-433R02B03<br>34-024R02D08<br>34-024R01D03 |

THIS MANUAL CONTAINS PROPRIETARY INFORMATION AND IS SUPPLIED BY INTERDATA FOR THE SOLE PURPOSE OF USING AND MAINTAINING INTERDATA SUPPLIED EQUIPMENT AND SHALL NOT BE USED FOR ANY OTHER PURPOSE UNLESS SPECIFICALLY AUTHORIZED IN WRITING.

Subsidiary of PERKIN-ELMER Oceanport, New Jersey 07757, U.S.A.

> (c) INTERDATA INC., 1975 All Rights Reserved Printed in U.S.A. November 1975

## M83 SERIES MODEL 8/32 PROCESSOR GENERAL DESCRIPTION

#### 1. INTRODUCTION

The Model 8/32 Processor is a 32 bit micro-programmed minicomputer. By combining advanced circuits, packaging, and micro-programming, INTERDATA gives the user a price/performance optimized machine. The Model 8/32 was developed because of a need for a high-speed 32 bit minicomputer. Because of INTERDATAs experience with 16 bit minicomputers and a user instruction format that is readily suited for a 32 bit machine, INTERDATA is able to provide a 32 bit machine. The Model 8/32 is upward compatible with current INTERDATA Processors. Through micro-programming, the Model 8/32 Processor is able to provide present and future owners of INTERDATA's 16 bit minicomputers the ability to grow into a 32 bit Model 8/32 without having to regenerate all the programs that were created on their 16 bit Processors.

The Model 8/32 has 148 instructions defined which include arithmetic and logical, operational, list processing, floating point, cyclic redundancy checking, and bit and byte manipulation instructions. Double indexing is also allowed, along with a multitude of branch instructions. There are 40 extended branch instructions (Mnemonics) defined which brings the total instructions to 180. Through these instructions and direct addressing, coding and debugging time is reduced to a minimum.

The Model 8/32 offers 32 General Registers, each 32 bits wide in two sets of 16, (optionally expandable to 8 sets). Stack set selection is controlled by bits in the Program Status Word. The multi-stack organization offers fast and simple context, switching without the necessity of storing and restoring register stacks. See <u>32 Bit Series Reference Manual</u>, Publication Number 29-365.

The Model 8/32 provides a flexible input/output system in addition to the conventional means of programmed I/O. The Model 8/32 can have up to 1,024 auto driver channels. These provide fast automatic character input/output operations, including automatic conversion from one character to another. Each character is transferred into or out of memory without any effect on a running program except for a small amount of stolen time.

The Model 8/32 is capable of directly addressing up to 1,048,576 bytes of memory. Memory is constructed of 32KB memory modules. Memory is addressable to the eight-bit byte level. No paging or indirect addressing is required by the user instruction sets.

The Memory Access Controller (MAC) uses sixteen 32 bit hardware registers to allow segmentation, relocation, and memory protection of user programs. There are five different ways memory may be protected.

- 1. Address invalid-not accessible to user

- 2. Non-present address

- 3. Write-protected; read only

- 4. Write then interrupt

- 5. Instruction execution not allowed

The 8/32 Memory Bus Controller provides access to the extended Direct Memory Access Bus. The extended Direct Memory Access Bus is a high quality, high speed bus that may have up to seven extended Direct Memory Access (DMA) devices on the bus.

## 2. SCOPE

This specification is intended to enable the digital technician to understand the INTERDATA documentation system. Number Notation, the Part Numbering System, and the Drawing System are described. A cross reference between INTERDATA part numbers and standard industry part numbers for Integrated Circuits, Transistors, etc., is found in Appendix 1. A list of other publications which may be useful in the programming or trouble shooting of the Model 8/32 system is found in Table 1.

## **TABLE 1. RELATED PUBLICATIONS**

| Title                                      | Publication Number |

|--------------------------------------------|--------------------|

| 32KB Memory Maintenance Manual             | 29-370*            |

| Multiplexor Bus Buffer Instruction Manual  | 29-267             |

| Loader Storage Unit Users Manual           | 29-308             |

| Paper Tape Reader/Punch Instruction Manual | 29-291             |

| Universal Logic Module Instruction Manual  | 29-311             |

| 1600 BPI Magnetic Tape Instruction Manual  | 29-309             |

| Cassette Users Manual                      | 29-298             |

| 7 Inch Teletype Manual                     | 29-288             |

\*Will be included in this Manual.

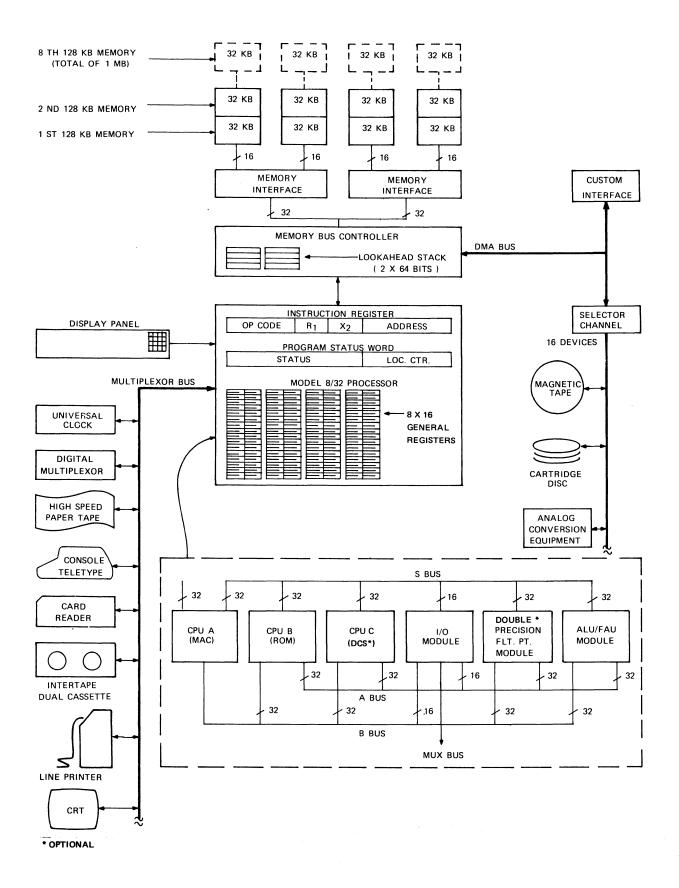

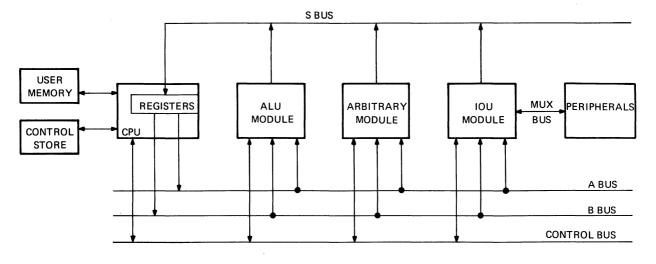

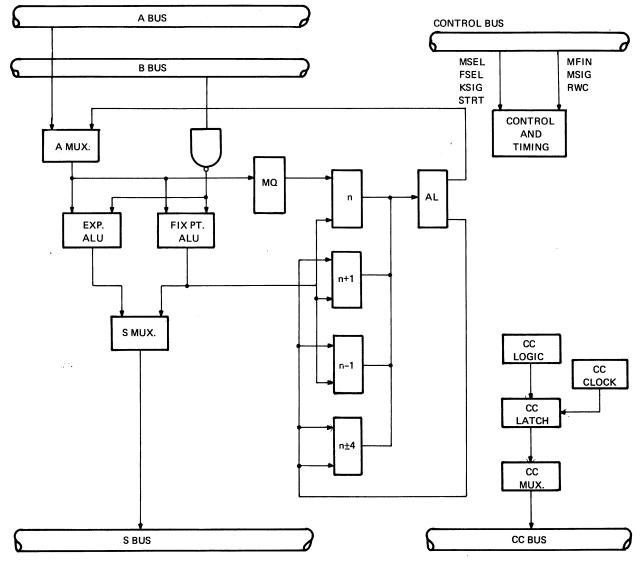

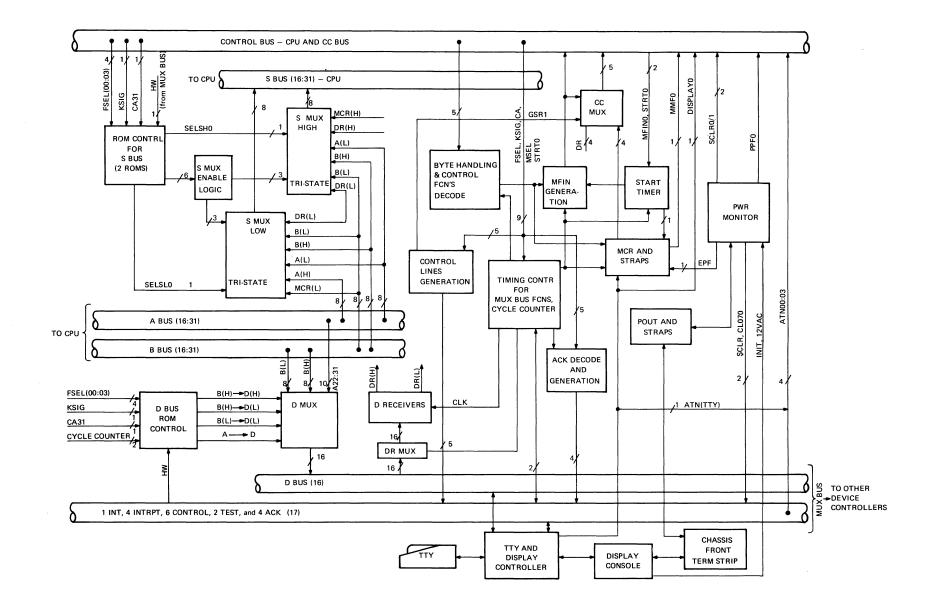

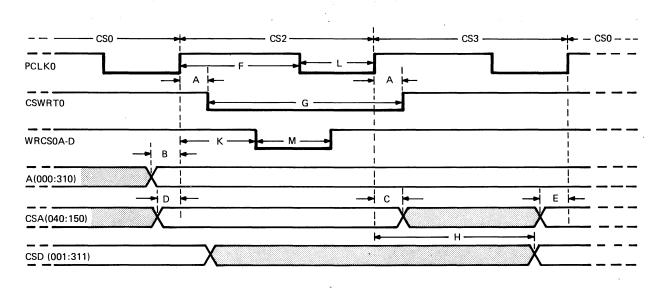

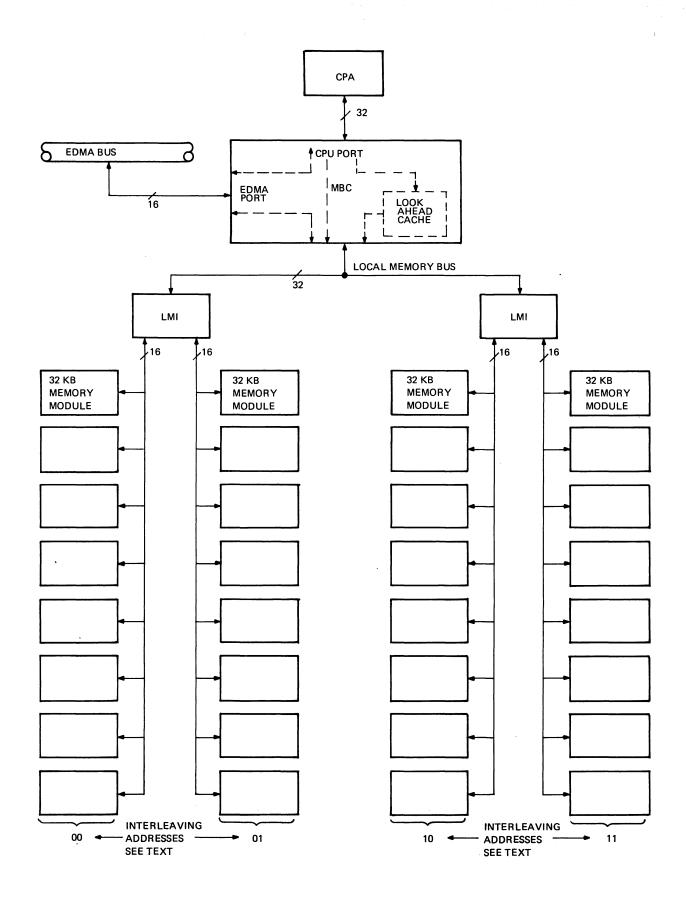

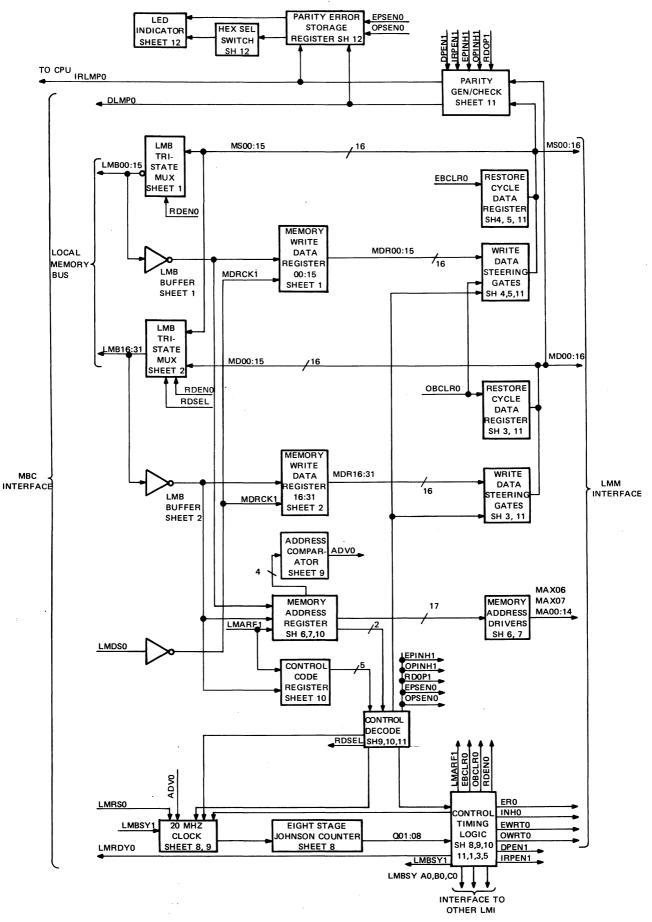

## 3. BLOCK DIAGRAM

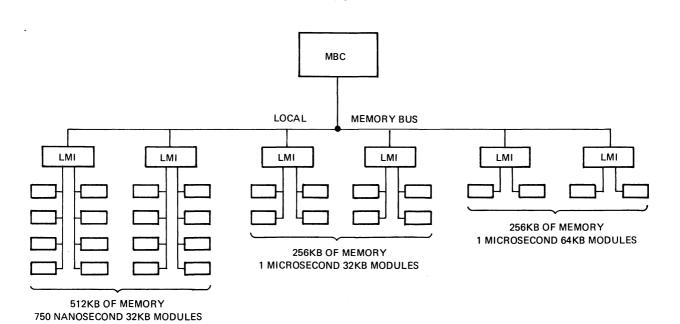

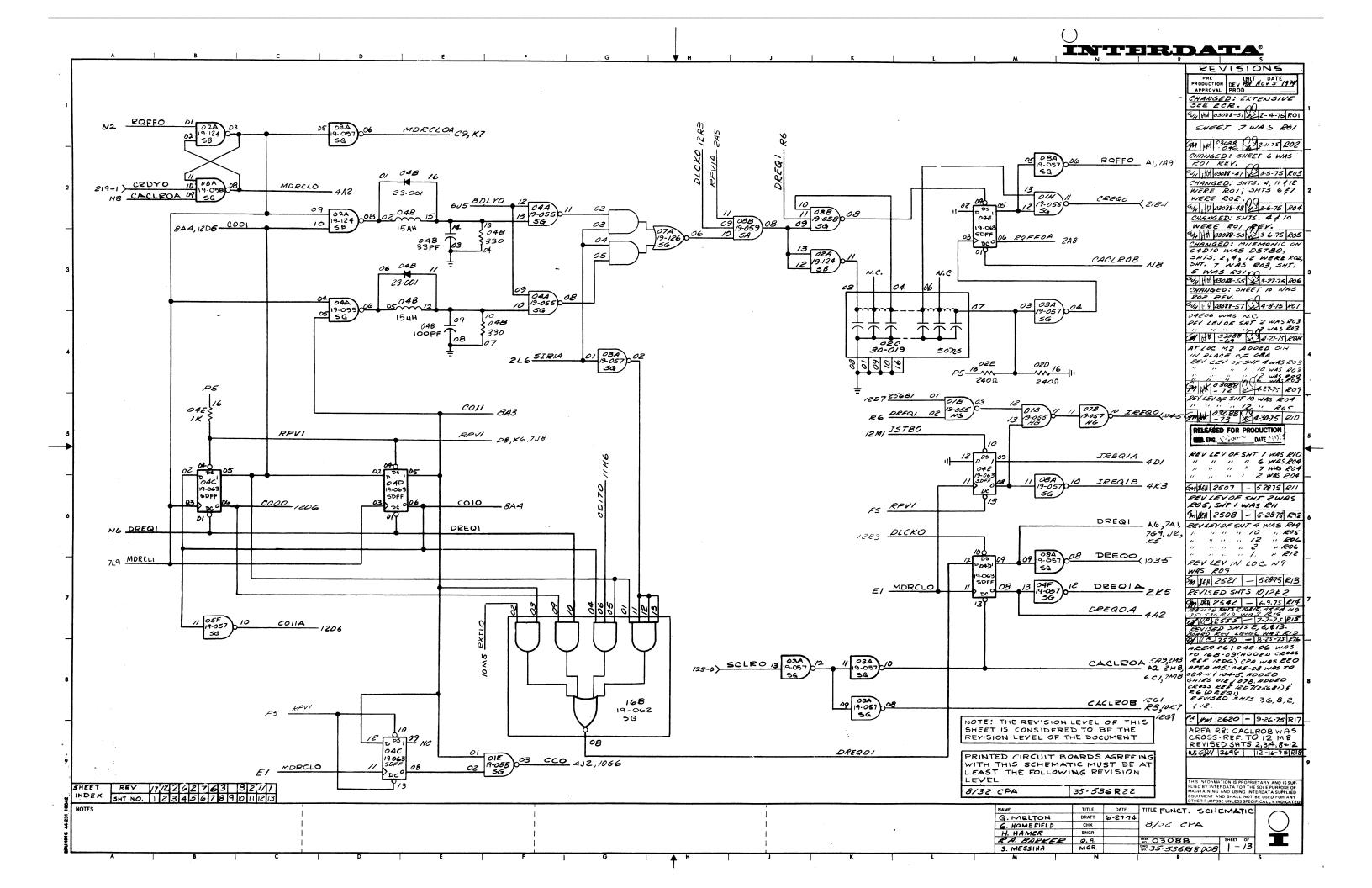

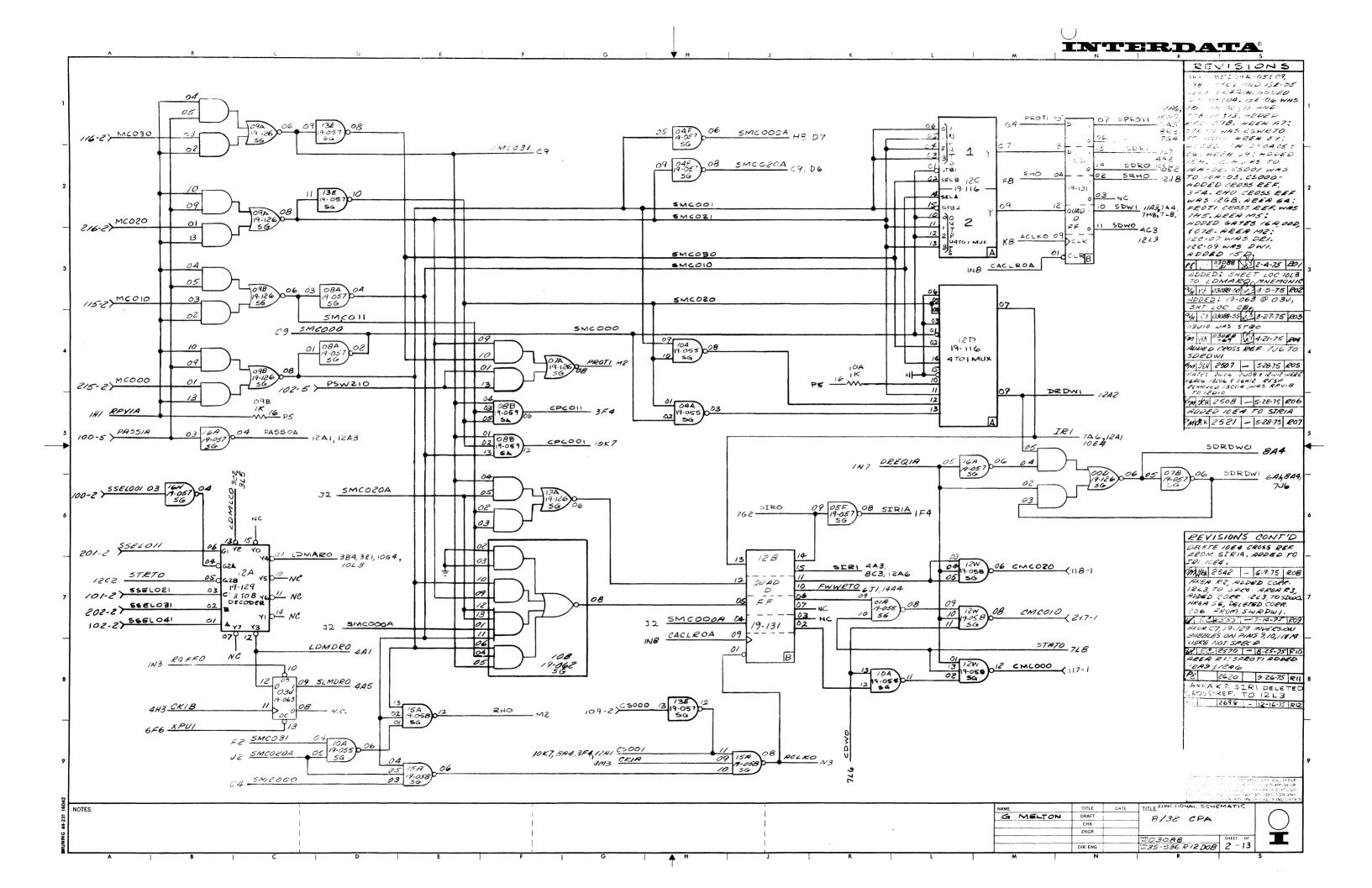

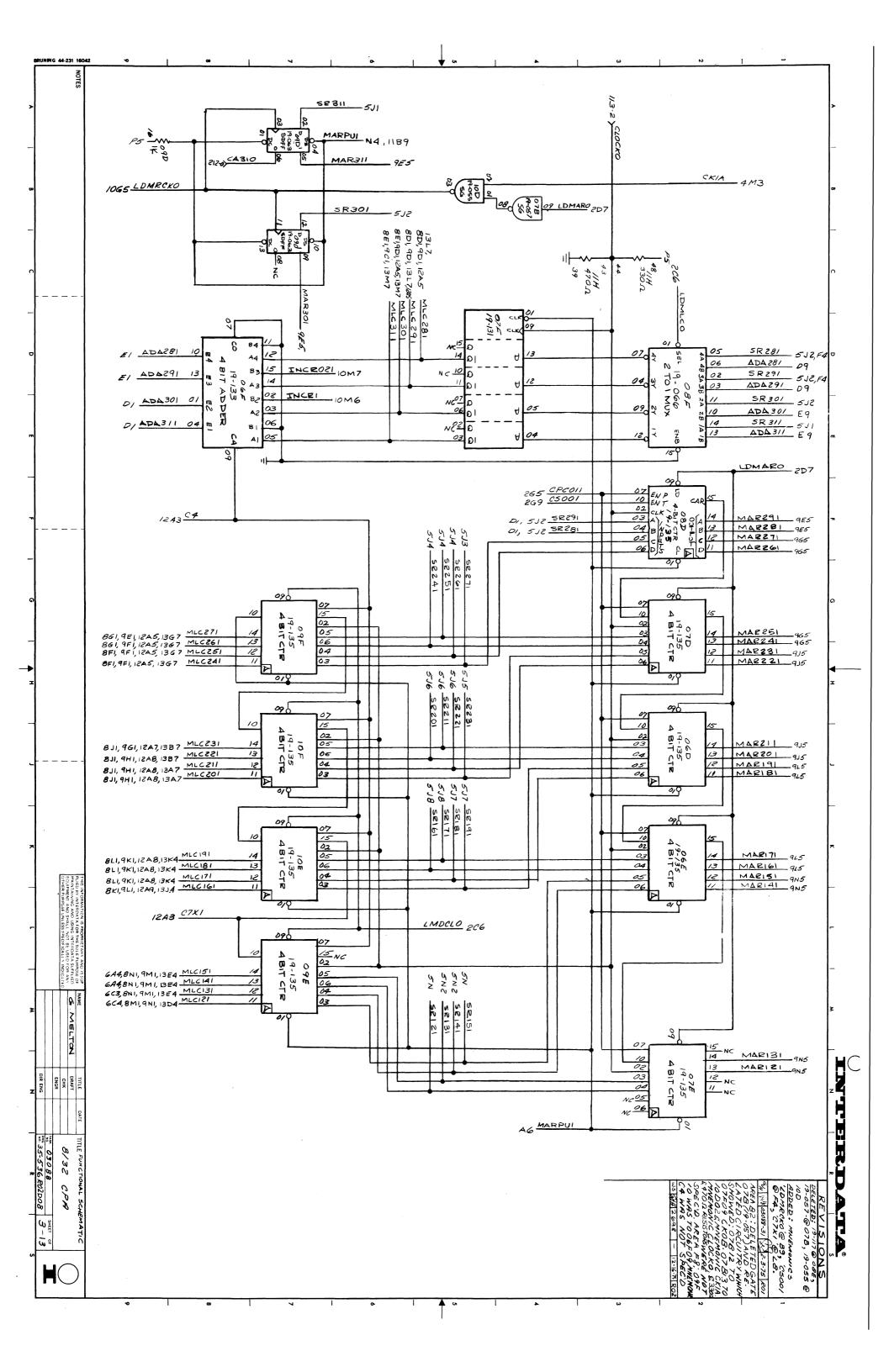

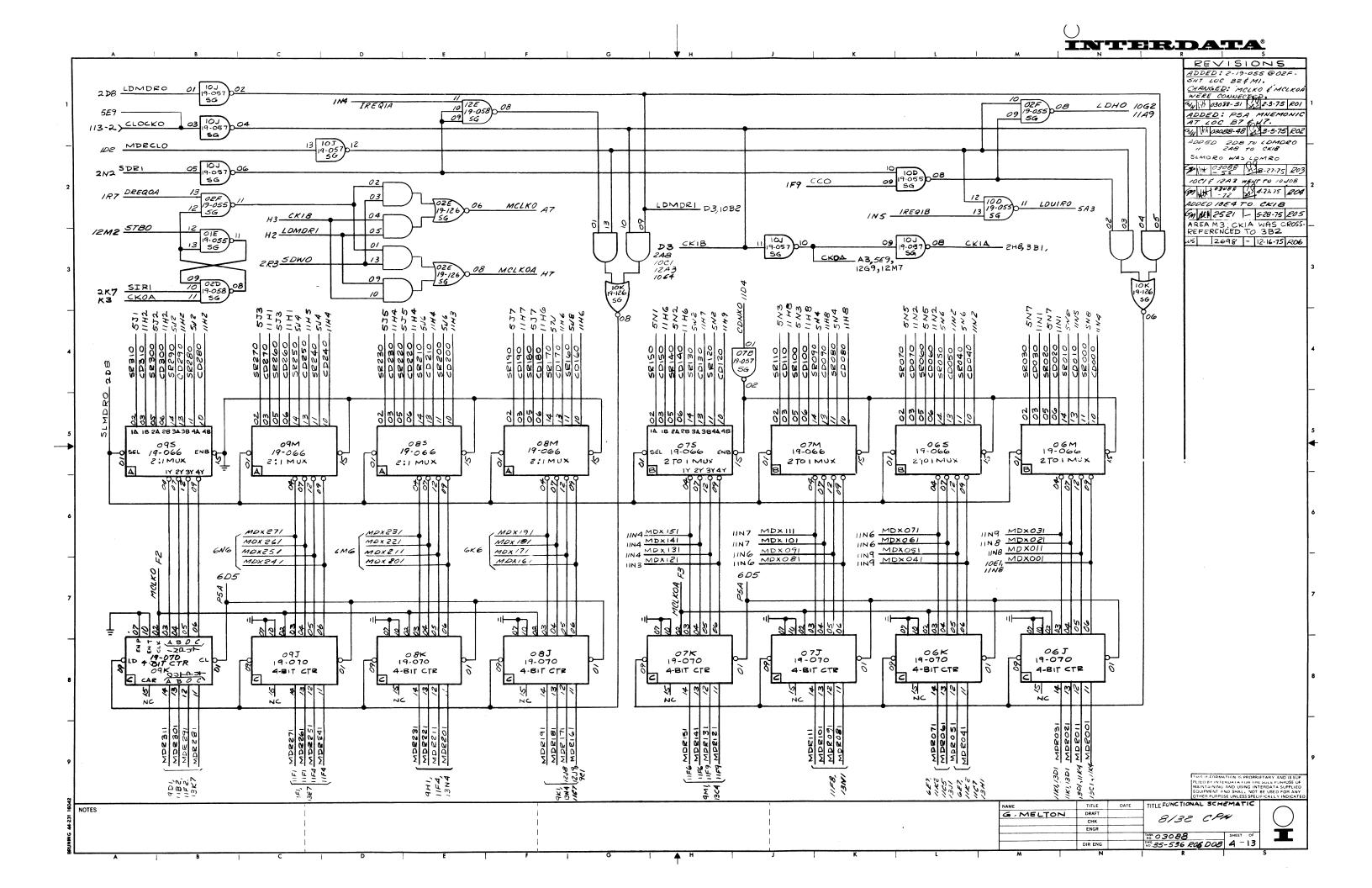

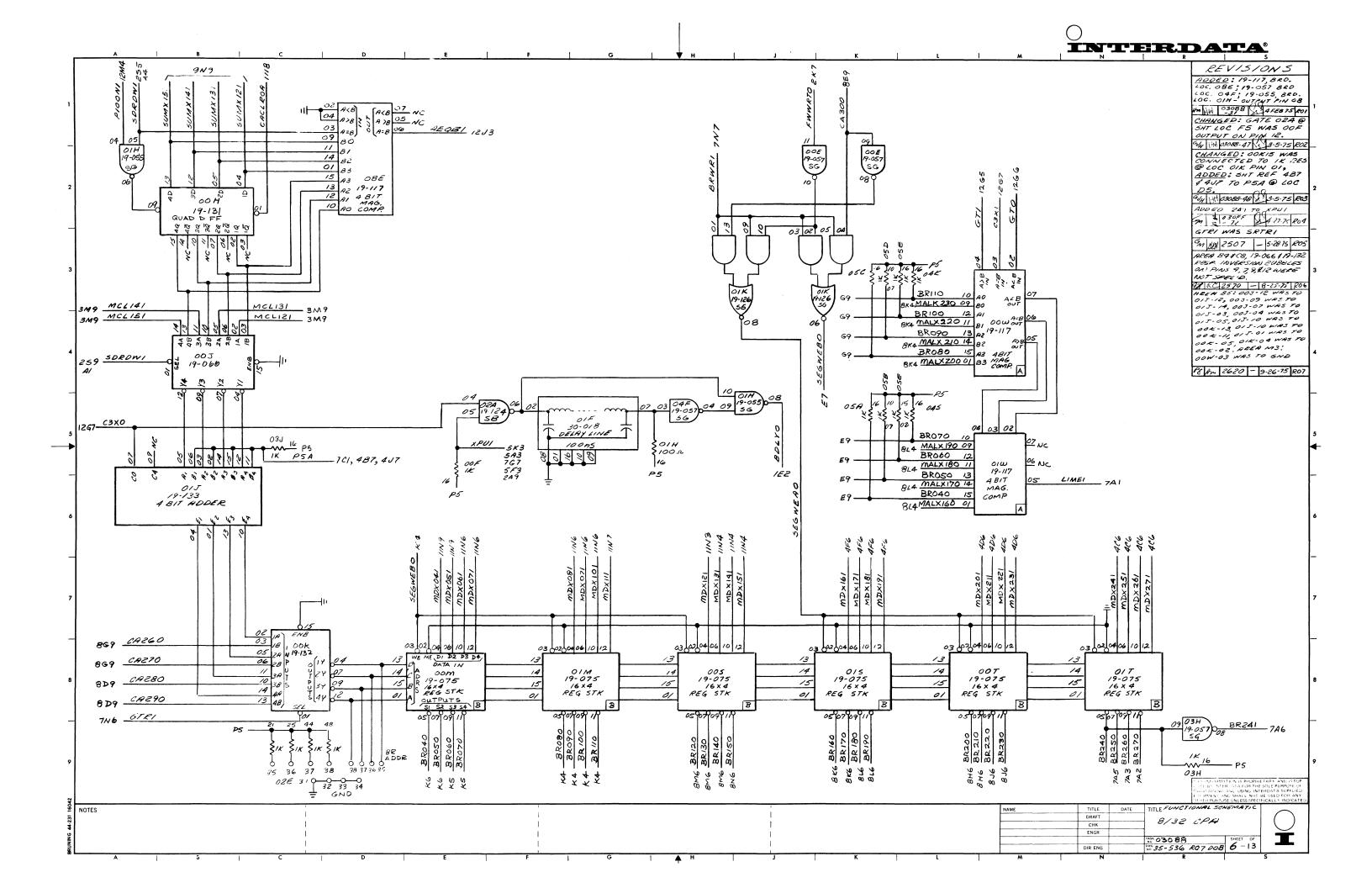

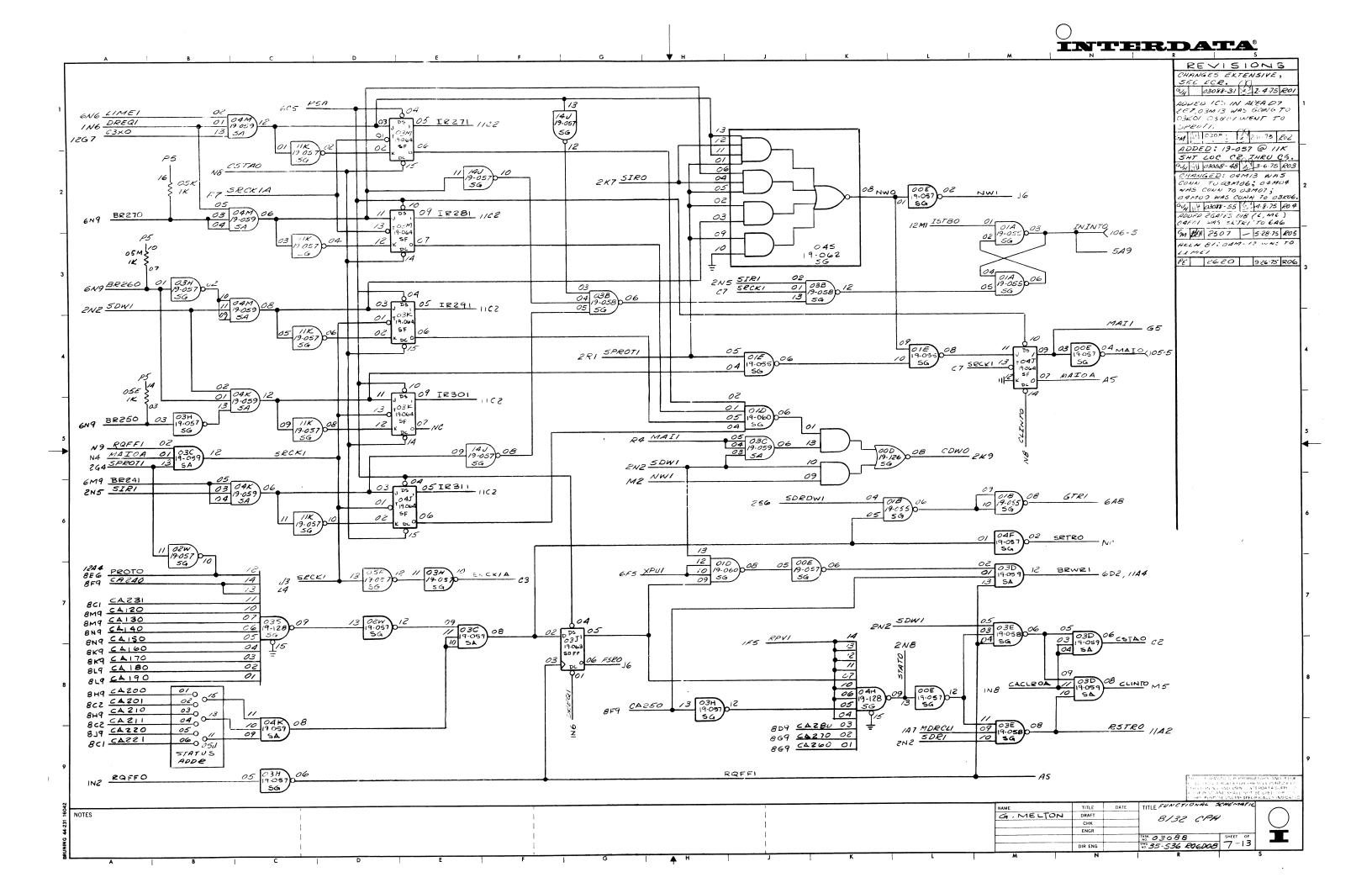

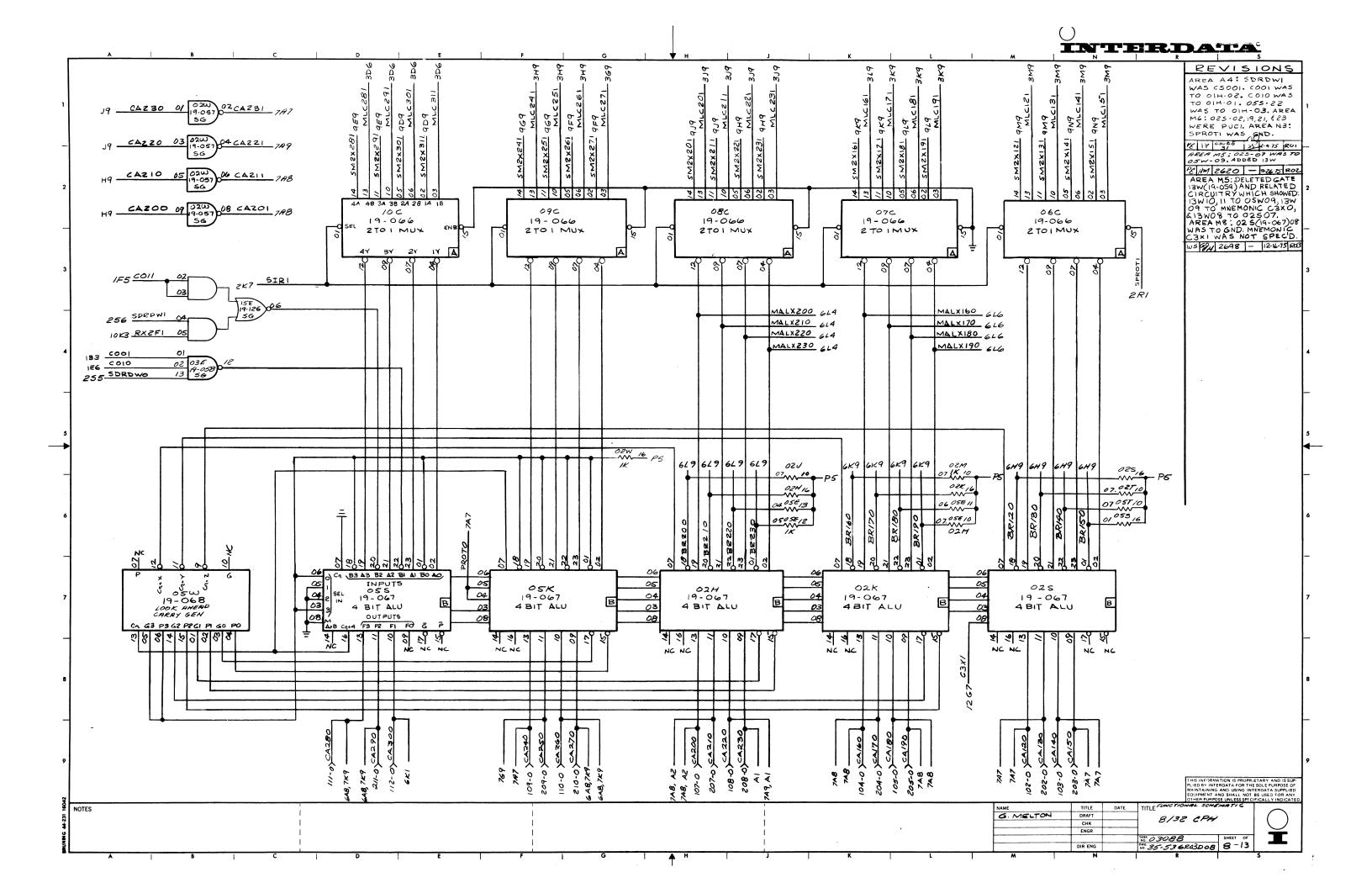

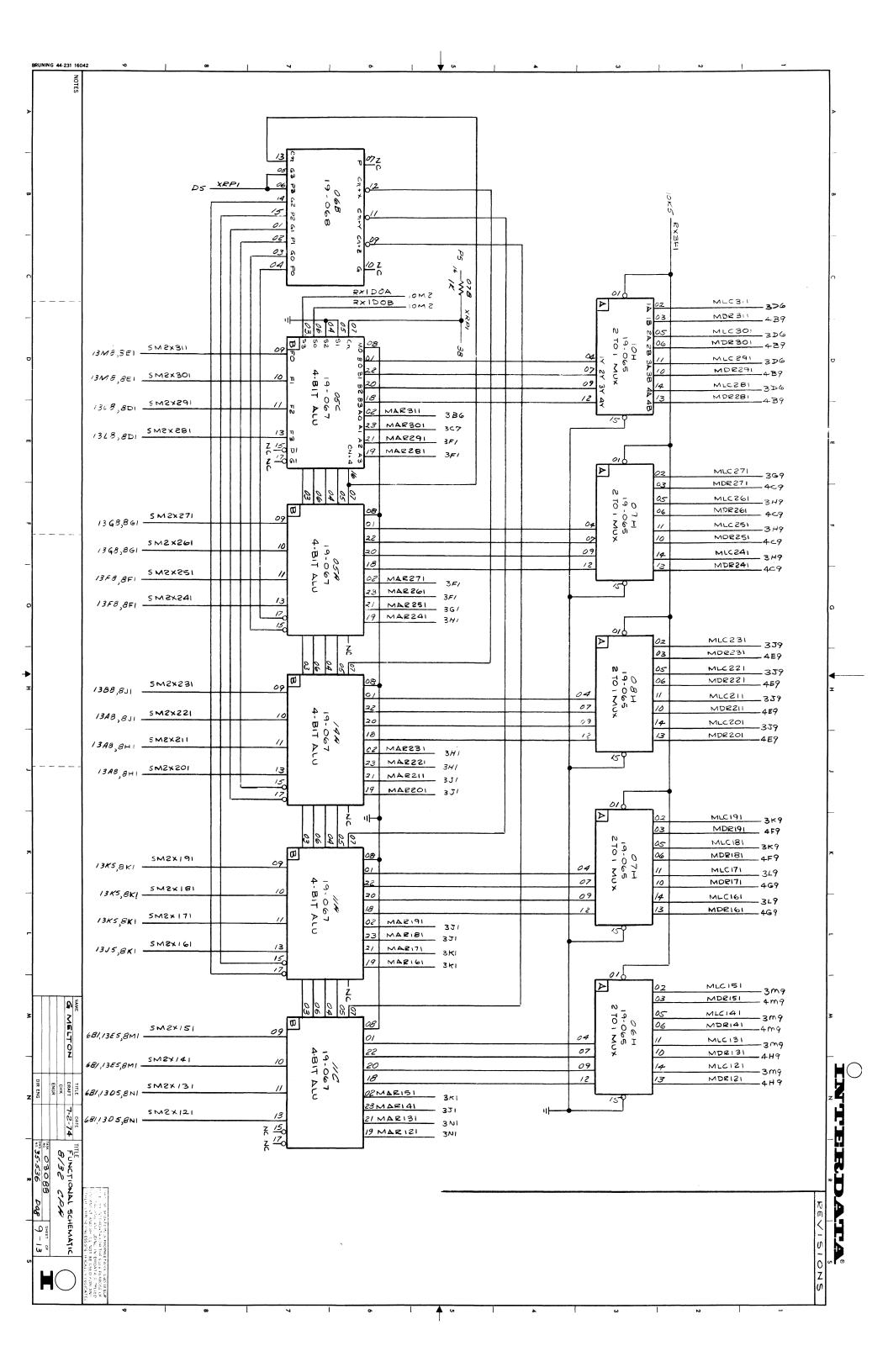

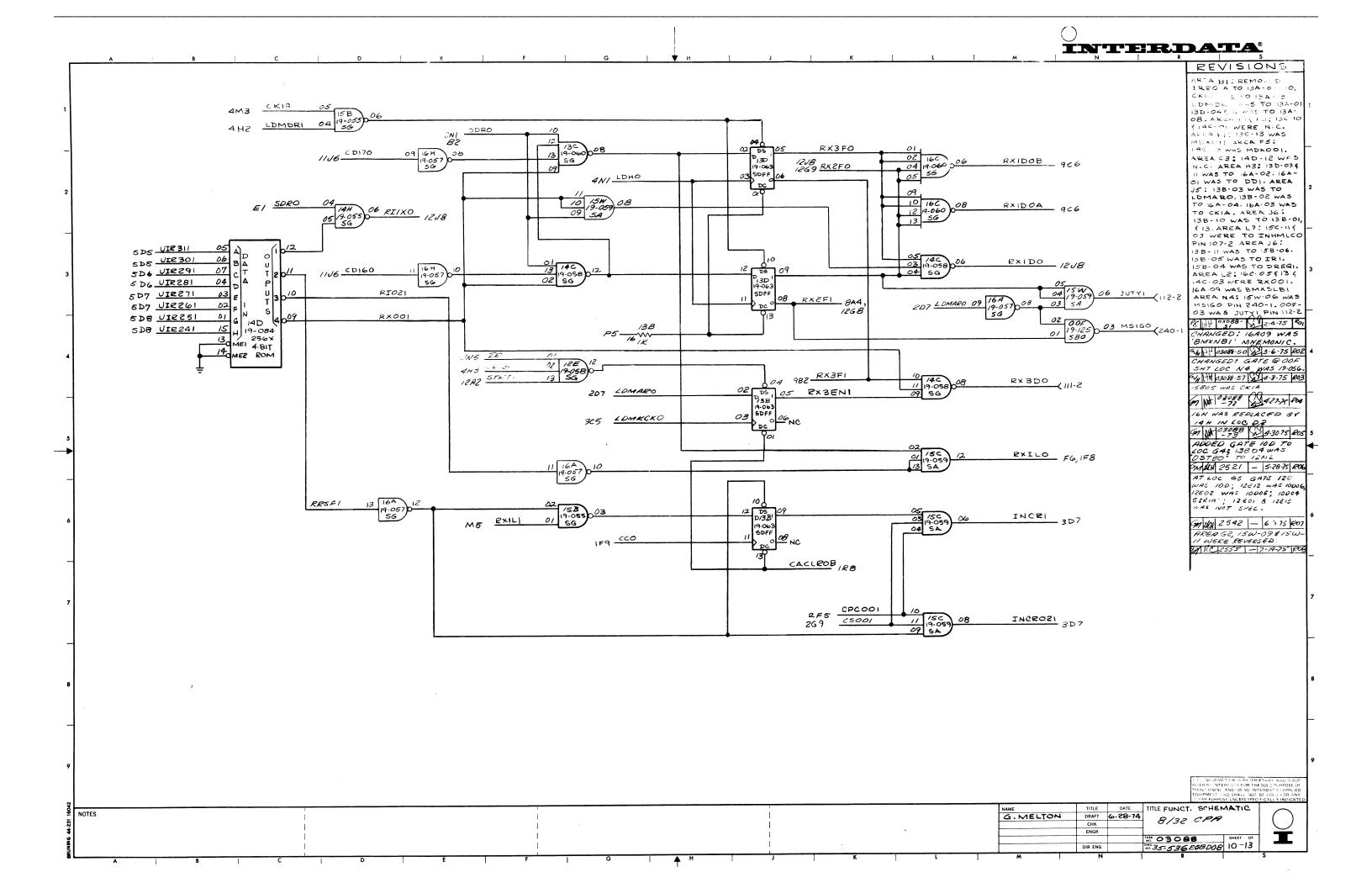

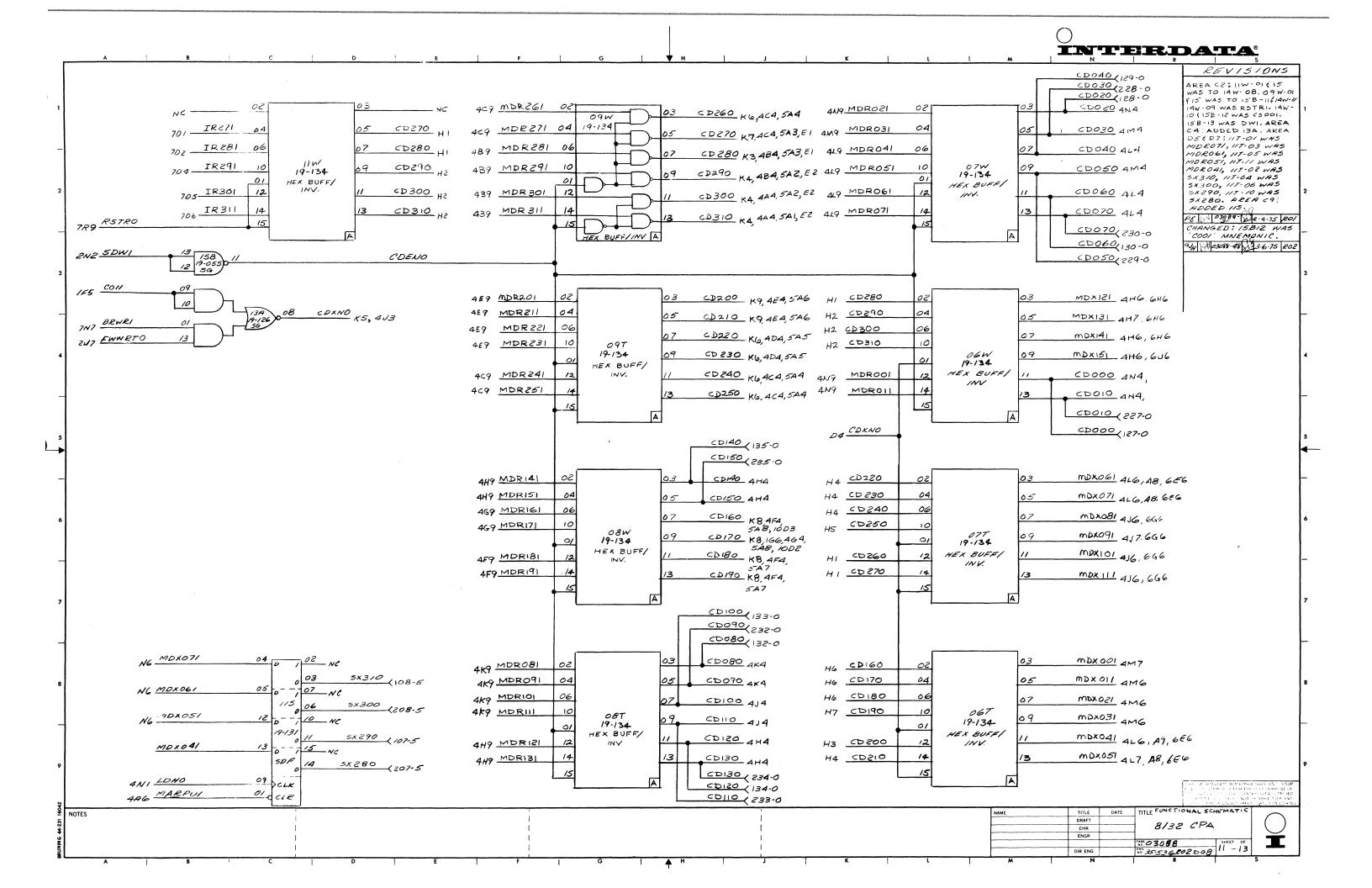

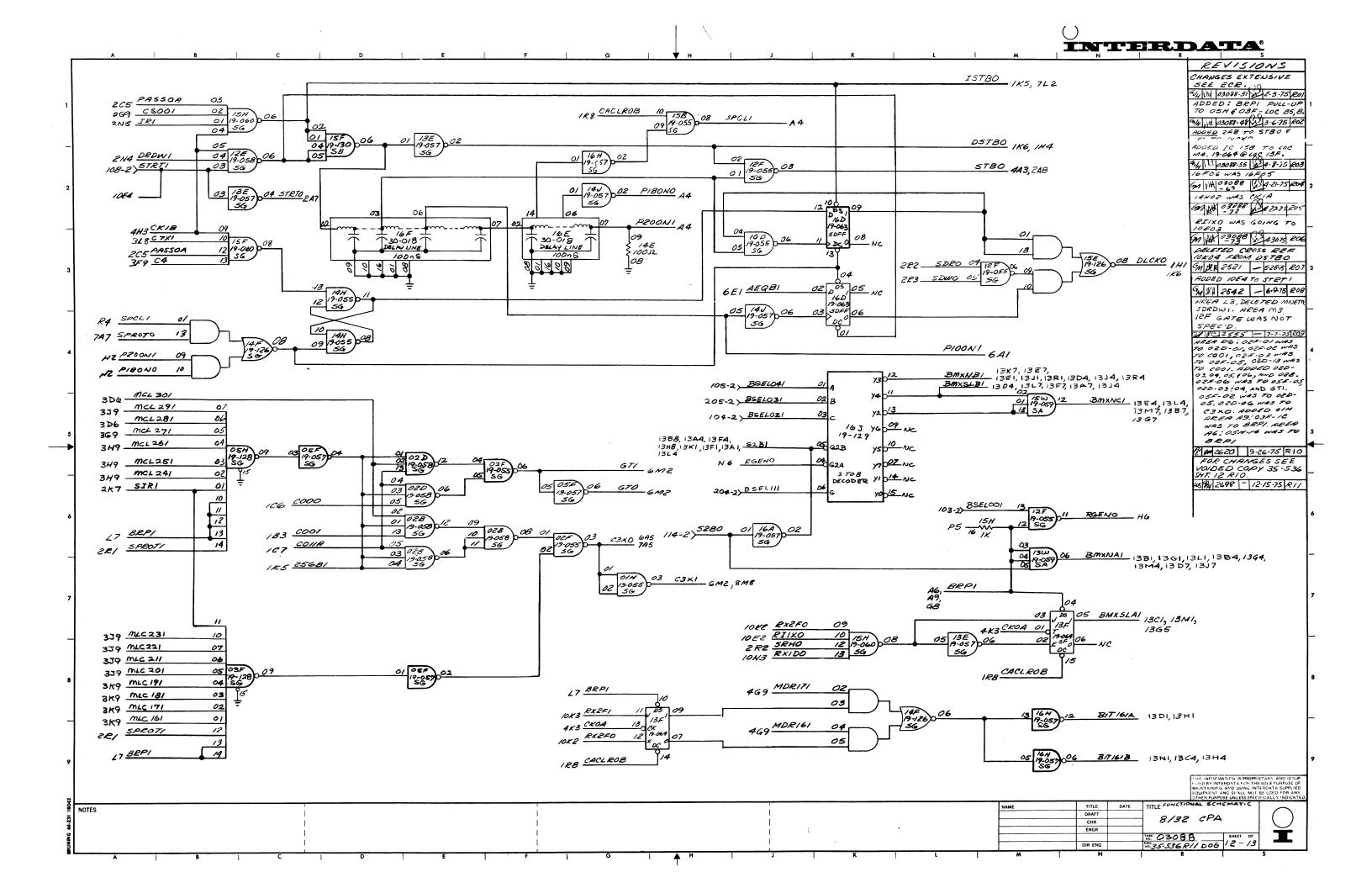

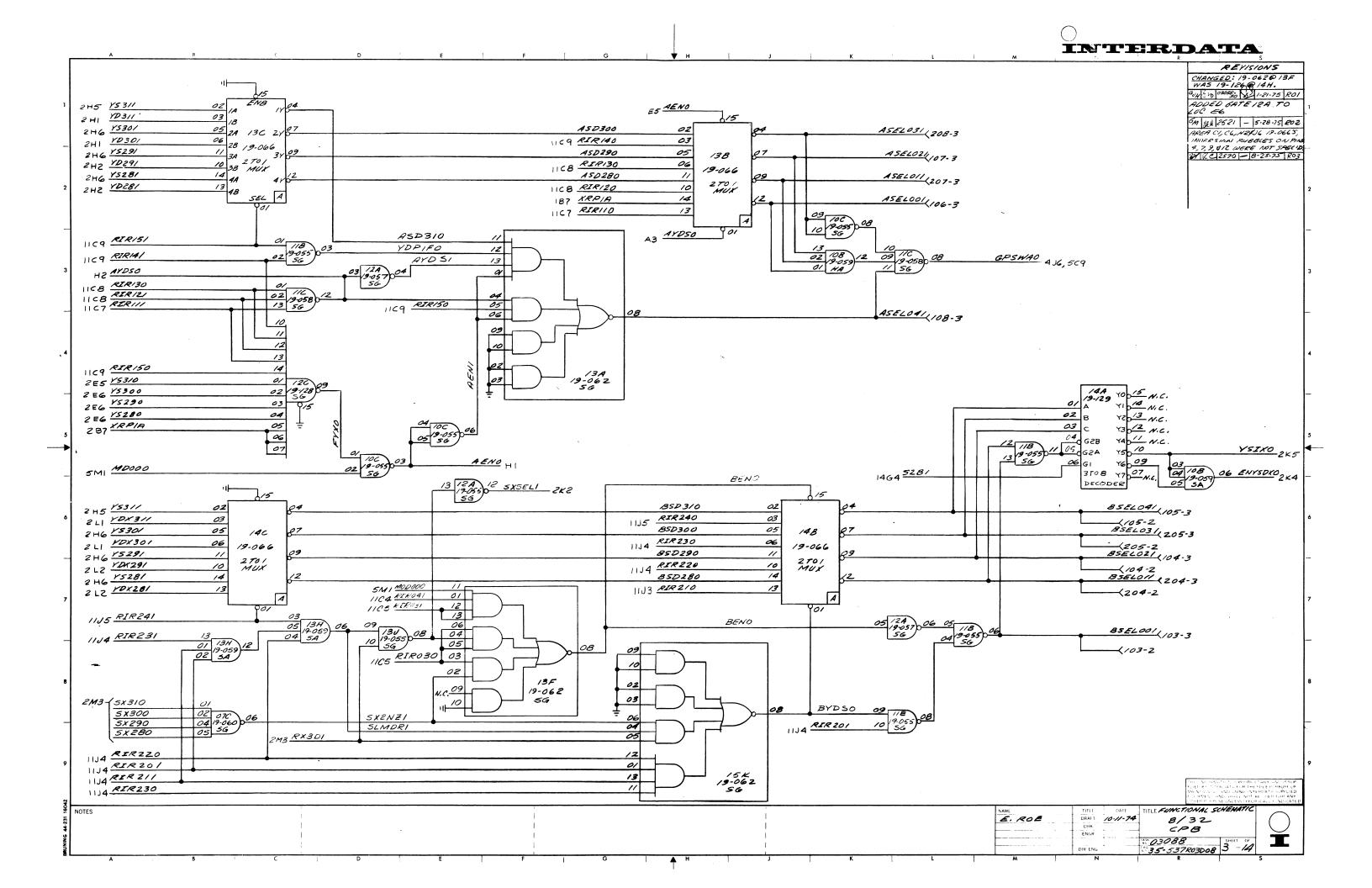

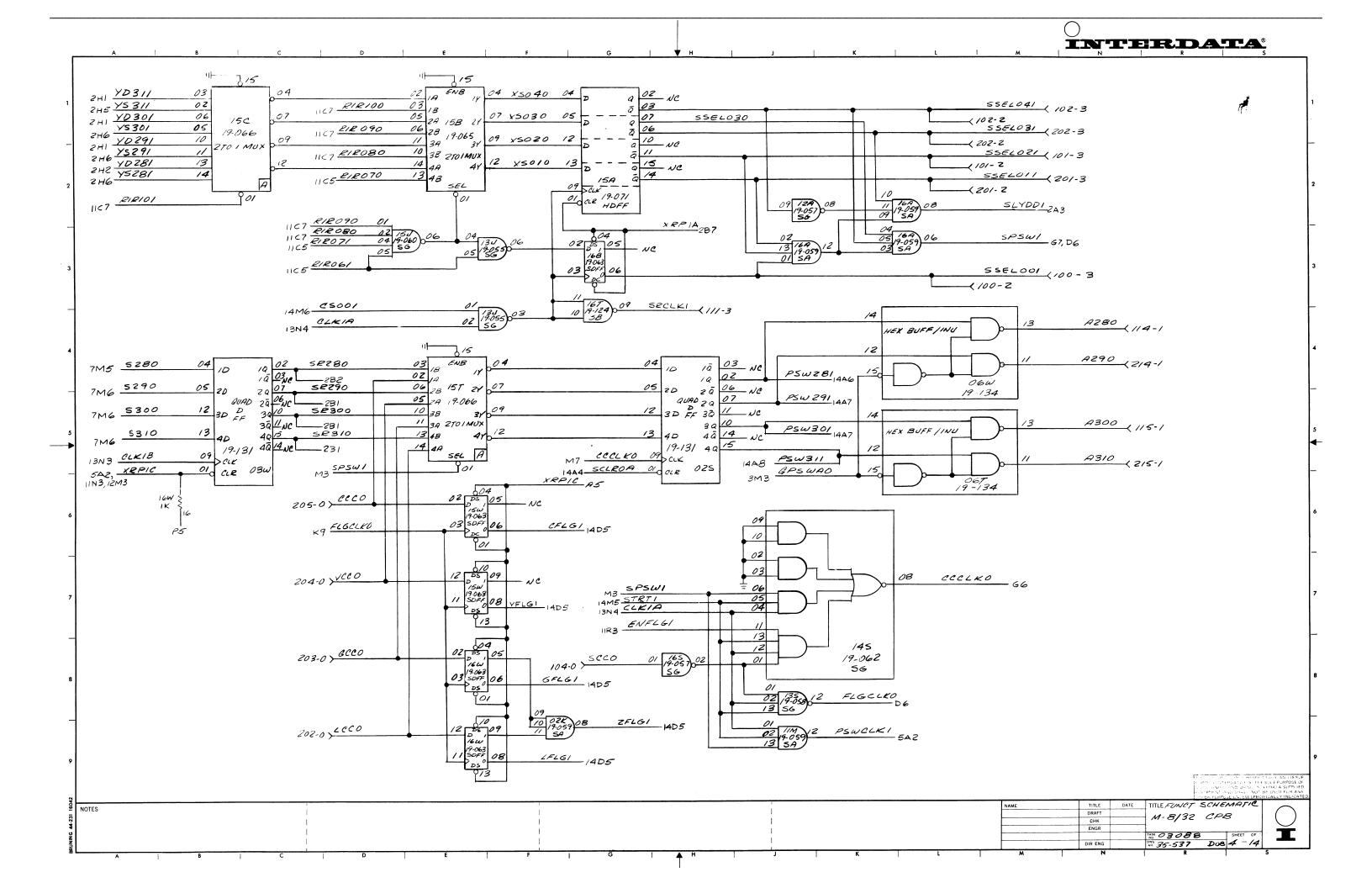

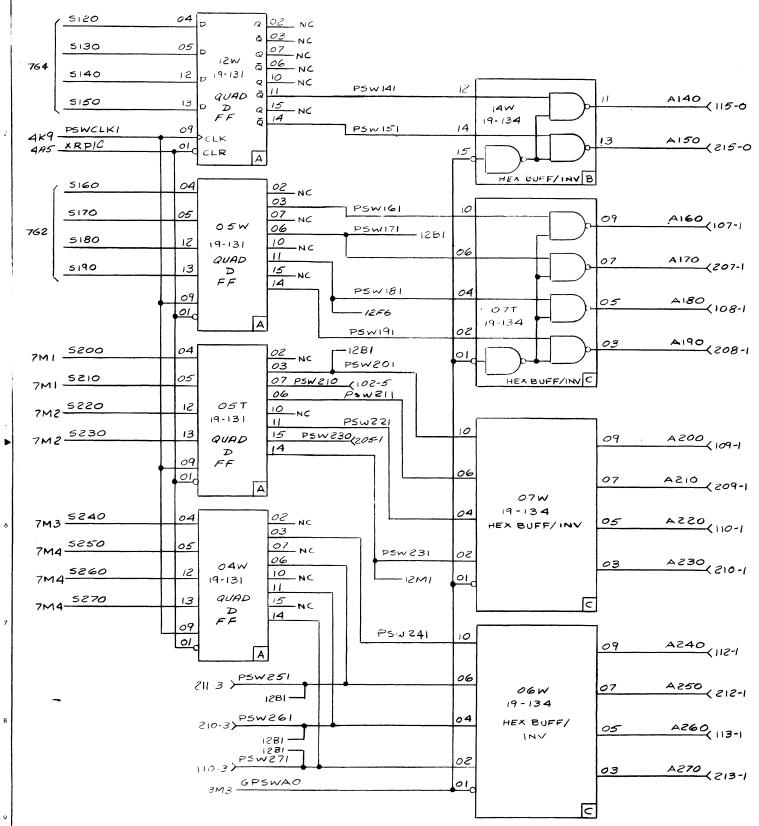

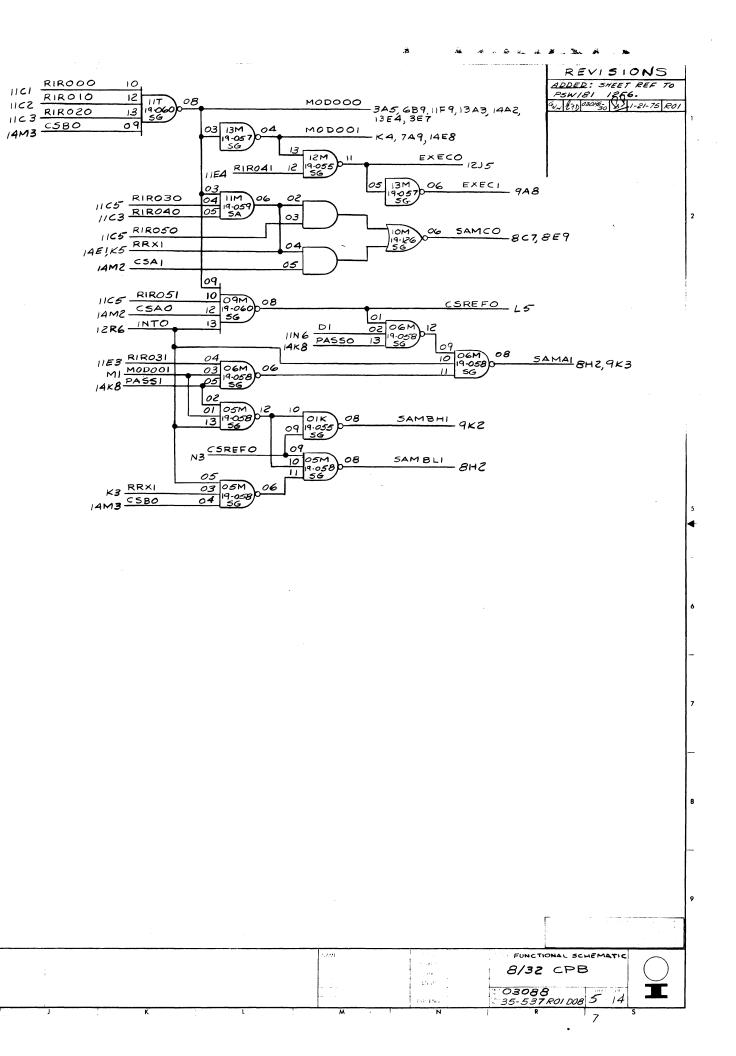

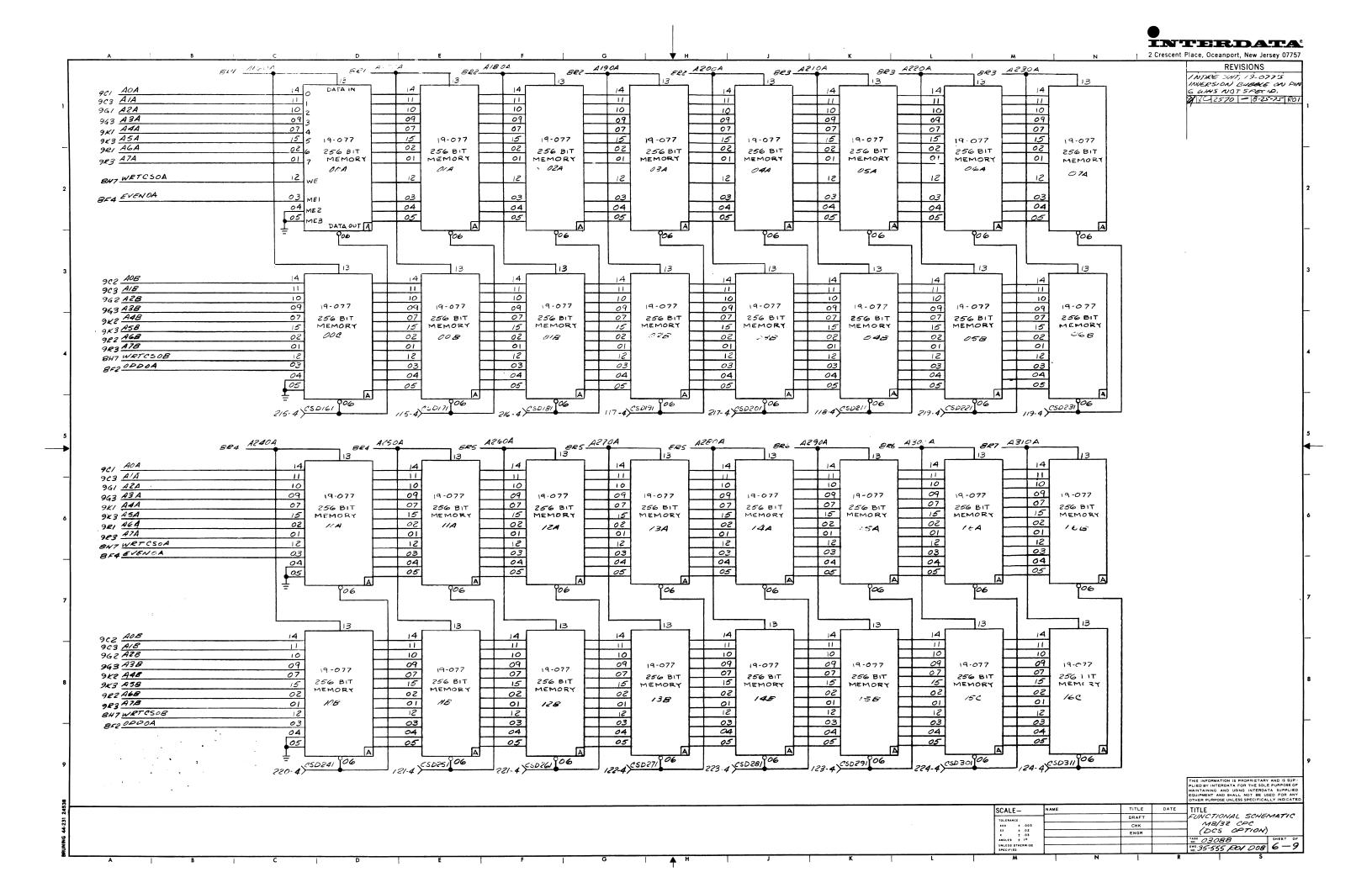

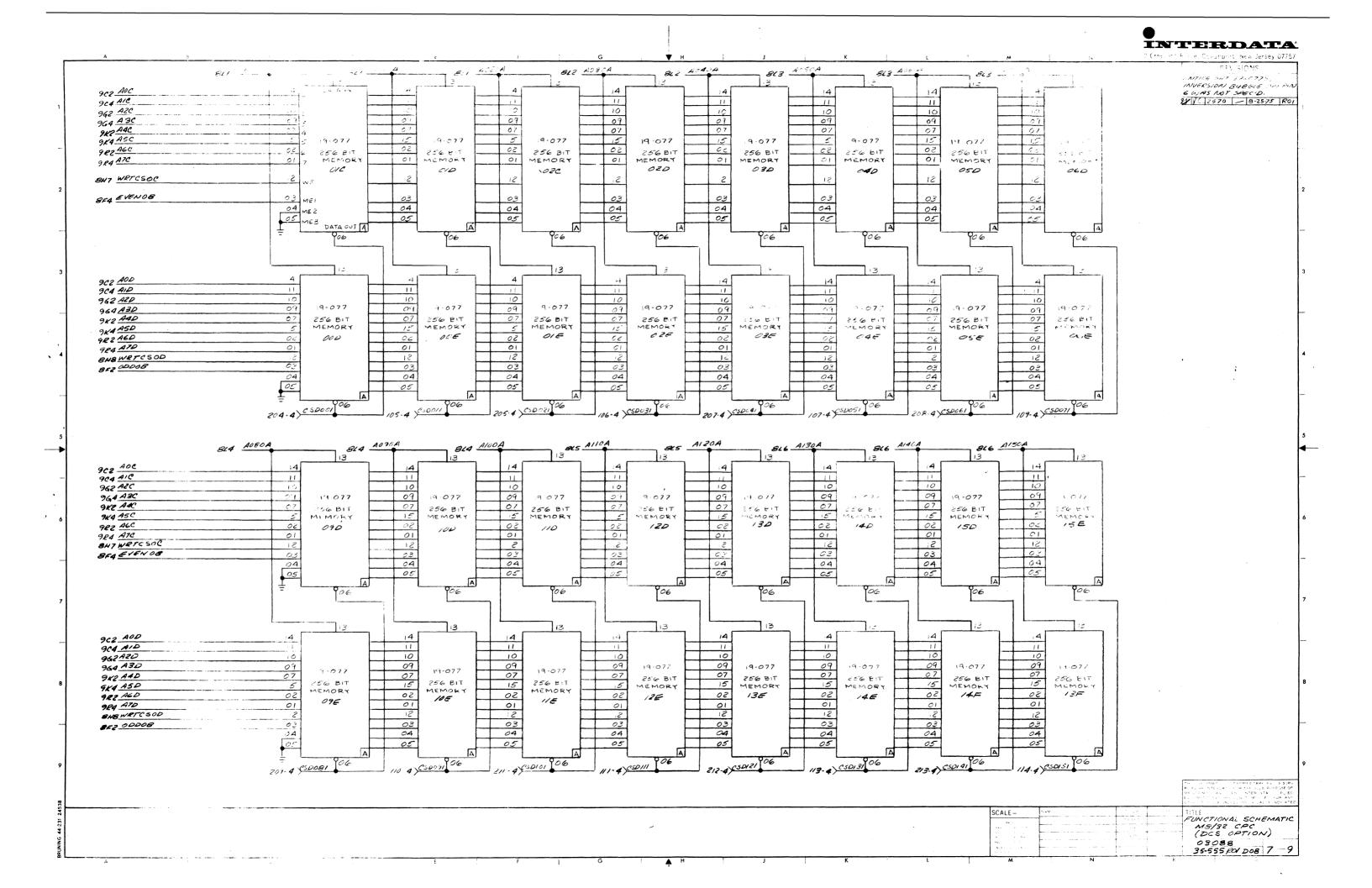

A simplified block diagram of the Model 8/32 system is shown in Figure 1. The Processor logic is contained on three circuit boards. The Memory Bus Controller (MBC), Local Memory Interface (LMI) and memory are contained on separate boards. The Arithmetic/Logic Unit (ALU) and Input/Output Unit (IOU) are also separate boards.

| Part Number | Description                     | Card File Position |

|-------------|---------------------------------|--------------------|

| 35-534      | Local Memory Interface<br>(LMI) | 3T, 6T             |

| 35-535      | Memory Bus Controller<br>(MBC)  | 1T                 |

| 35-536      | Control Processor A<br>(CPA)    | OT                 |

| 35-537      | Control Processor B<br>(CPB)    | 7B                 |

| 35-538      | Arithmetic Logic Unit<br>(ALU)  | 4B                 |

| 35-539      | Input/Output Unit<br>(IOU)      | 3B                 |

| 35-555      | Control Processor C<br>(CPC)    | 6 <b>B</b>         |

| ·           | Input/Output                    | 2B, 1B, 0B         |

|             | Memory                          | 7T, 5T, 4T, 2T     |

|             | Options                         | 5B                 |

This information is proprietary and is supplied by INTERDATA for the sole purpose of using and maintaining INTERDATA supplied equipment and shall not be used for any other purpose unless specifically authorized in writing.

## Figure 1. 8/32 Processor Block Diagram

This information is proprietary and is supplied by INTERDATA for the sole purpose of using and maintaining INTERDATA supplied equipment and shall not be used for any other purpose unless specifically authorized in writing.

,

## 4. DOCUMENTATION

This section describes the style and conventions used with INTERDATA documentation.

## 4.1 Number Notation

The most common form of number notation used in INTERDATA documentation is hexadecimal notation. In this system, groups of four binary digits are represented by a single hexadecimal digit. Table 2 lists the hexadecimal characters employed.

| Binary | Decimal | Hexadecimal | Binary | Decimal | Hexadecimal | Binary | Decimal | Hexadecimal |

|--------|---------|-------------|--------|---------|-------------|--------|---------|-------------|

| 0000   | 0       | 0.          | 0110   | 6       | 6           | 1100   | 12      | С           |

| 0001   | 1       | 1           | 0111   | 7       | 7           | 1101   | 13      | D           |

| 0010   | 2       | 2           | 1000   | 8       | 8           | 1110   | 14      | E           |

| 0011   | 3       | 3           | 1001   | 9       | 9           | 1111   | 15      | F           |

| 0100   | 4       | 4           | 1010   | 10      | Α           |        |         |             |

| 0101   | 5       | 5           | 1011   | 11      | В           |        |         |             |

| L      | I       | L           |        | l       | L           | L      | ļ       |             |

## TABLE 2. HEXADECIMAL NOTATION DATA

To differentiate between decimal and hexadecimal numbers, hexadecimal numbers are preceded by the letter "X", and the number is enclosed in single quotation marks. Examples of hexadecimal numbers are: X'1234', X'2EC6', X'A340', X'EEFA', and X'10B9'.

## 4.2 Part Numbering System

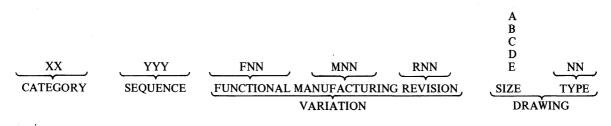

INTERDATA parts, drawings, and publications employ a common numbering system. The part number and drawing numbers for drawings which describe the part are related. The publication number is also often related to the part number of the device or program described. Figure 2 shows the format used for INTERDATA part numbers. The fields are described in the following paragraphs.

#### Figure 2. Part Number Format

4.2.1 <u>Category Field</u>. The two-digit Category number indicates the broad class or category to which a part belongs. Typical examples of category number assignments are:

01 - Basic Hardware Systems

- 02 Basic Hardware Expansions

- 03 Basic Software Systems

- 04 Software Packages

- 05 Micro-programs

- 06 Test Programs

- 07 Subroutines of General Utility

- 10 Spare Parts Packages

- 12 Card File Assemblies

- 13 Panels

- 17 Wire and Cables

- 19 Integrated Circuits

- 20 Transistors

- 27 Peripheral Equipment

- 29 Manuals

- 34 Power Supplies

- 35 Assembled Printed Circuit Boards

- 36 Electro-Mechanical Devices

4.2.2 <u>Sequence Field</u>. The Sequence number identifies a particular item within the category. Sequence numbers are assigned serially, and have no other significance.

## NOTE

The Sequence Field, like all other part number fields, may be lengthened as required. The field lengths shown on Figure 2 are minimum lengths (insignificant zeros must be added to maintain these minimums).

A part number must contain a Category number and a Sequence number. All other fields are optional.

4.2.3 <u>Functional Variation Field</u>. The optional Functional Variation Field consists of the letter "F" followed by two digits. The F field is used to distinguish between parts which are not necessarily electrically or mechanically equivalent, but which are described by the same set of drawings. For example, a power supply may be strapped internally to operate on either 110 VAC or 220 VAC. Except for this strap, all power supplies of this type are identical. The strapping option is easily described by a note on the assembly and test specification drawings. Therefore, this is a functional variation.

4.2.4 <u>Manufacturing Variation Field</u>. The optional Manufacturing Variation Field consists of the letter "M" followed by two digits.

The M Field is used to distinguish between parts which are electrically and mechanically equivalent (interchangeable), but which vary in method of manufacture. For example, if leads are welded instead of soldered on an assembly, the M Field changes.

An important exception to the meaning of the M Field exists for categories related to software. In software, the M Field number, when used, indicates the form in which a particular program is presented. For example, define a program as a set of machine instructions. These same identical instructions may be presented on punched cards, paper tape, or magnetic tape; and for any of these they could be in symbolic form or in relative or absolute binary form. Thus, there are many ways to present the same identical program.

The format for the M field and its meaning for software is:

#### Mxy

where x identifies the media selection (i.e., paper tape, mag tape, cassette, etc.) and y identifies object or source and the format.

| Meaning of x   |   | Meaning of y                                      |

|----------------|---|---------------------------------------------------|

| Paper tape     | 1 | 1 Object program standard format 32 bit Processor |

| Cassette       | 2 | 4 Memory Image                                    |

| Mag tape (800) | 3 | 6 Object program standard format 16 bit Processor |

| Cards          | 4 | 7 Object non-standard format                      |

| Disc (2.5)     | 5 | 8 Object established task                         |

|                |   |                                                   |

9 Source program

The above numbers refer to the physical program placed on an approved media for INTERDATA Software. A paper tape object program in standard format and for a 16 bit Processor has an M16 identifier. A magnetic tape object program in standard format and for a 32 bit Processor has an M31 identifier.

In addition to the above, there are three unique M numbers which have special meaning:

- M99 always refers to a documentation package.

- M00 always refers to a conceptual object program divorced from any media. This reference is used for all parts lists when object programs may be on any media.

- M09 always refers to a conceptual source program and is used on all parts lists where any media may be used.

#### NOTE

M00 and M09 may only be used on parts lists and never identify a physical program on any media.

4.2.5 <u>Revision Field</u>. The optional Revision Field consists of the letter "R" followed by two digits. The R Field is used to indicate minor electrical or mechanical changes to a part which do not change the part's original character. R Field changes often reflect improvements. A part with a revision level HIGHER than the one specified will work. A part with a revision level LOWER than specified should not be used.

**4.2.6** Drawing Field. The optional Drawing Field consists of a letter from "A" to "E" followed by two digits. The letter indicates the size of the original drawing. The sizes for each letter are:

A - 8½" X 11" B - 11" X 17" C - 17" X 22" D - 22" X 34" E - 34" X 44"

The two digits indicate the drawing type as follows:

| 13 - Program Listing               |

|------------------------------------|

| 14 - Abstracts                     |

| 15 - Program Description           |

| 16 - Operating Instructions        |

| 17 - Program Design Specifications |

| 18 - Flow Charts                   |

| 19 - Product Specification         |

| 20 - Installation Specification    |

| 21 - Maintenance Specification     |

| 22 - Programming Specification     |

|                                    |

4.2.7 Examples. The following list provides examples of the part numbering system. The numbers were arbitrarily selected, and in most cases are fictitious.

- 35-060 The 60th printed-circuit board assigned a part number under this system.

- 35-060M01 A printed circuit board electrically and mechanically interchangeable with the 35-060, but differing in method of manufacture.

- 35-060F01 A printed-circuit board not electrically and mechanically interchangeable with the 35-060, but described by the same set of drawings.

- 35-060R01 A revised 35-060 printed-circuit board. Probably supercedes the 35-060.

- 35-060A01 The 8<sup>1</sup>/<sub>2</sub> by 11 inch parts list for a 35-060.

- 35-060B08 The 11 by 17 inch schematic for a 35-060.

- 06-072 The 72nd utility program assigned a part number.

- 06-072A13 An 8<sup>1</sup>/<sub>2</sub> by 11 inch listing of the 06-072 program.

- 06-072M03 An absolute binary deck of punched cards for the 06-072 program.

- 06-072A12 An 8½ by 11 inch information drawing on the 06-072 program. Probably a part of the program.

29-060 The 60th manual assigned a number under this system. Note that this number is not referenced in any way to the part number of equipment described in the manual.

#### 4.3 Drawing System

This section describes the drawings provided with INTERDATA equipment. Note that drawings provided with peripheral devices and other purchased items may vary from the system described in this section.

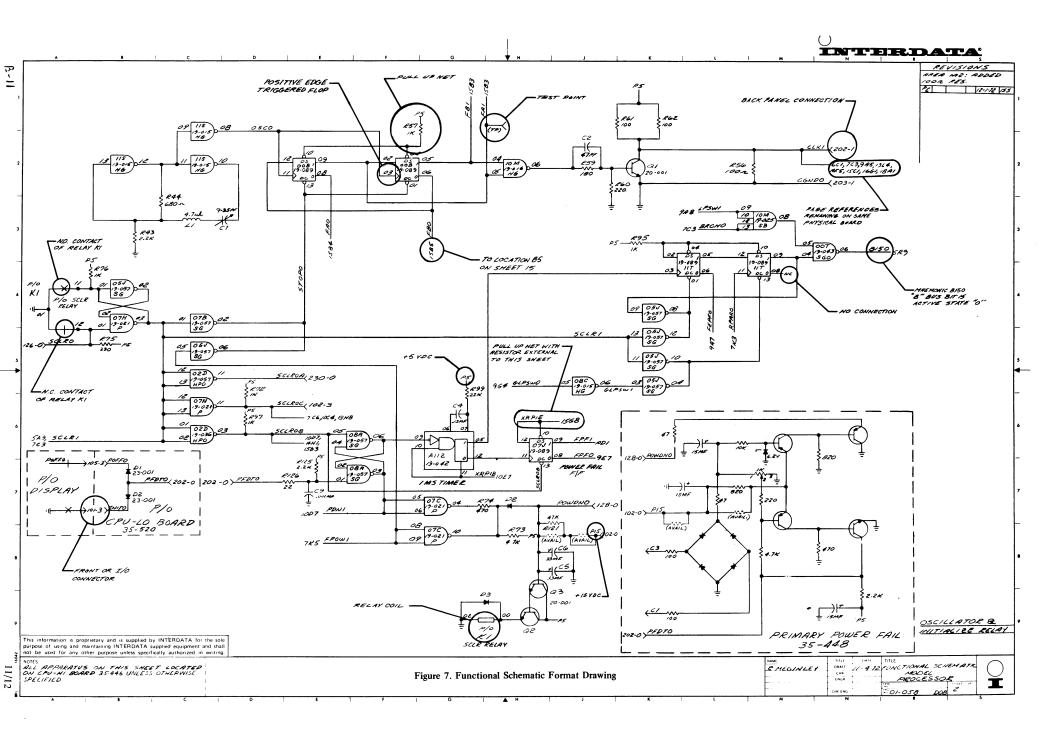

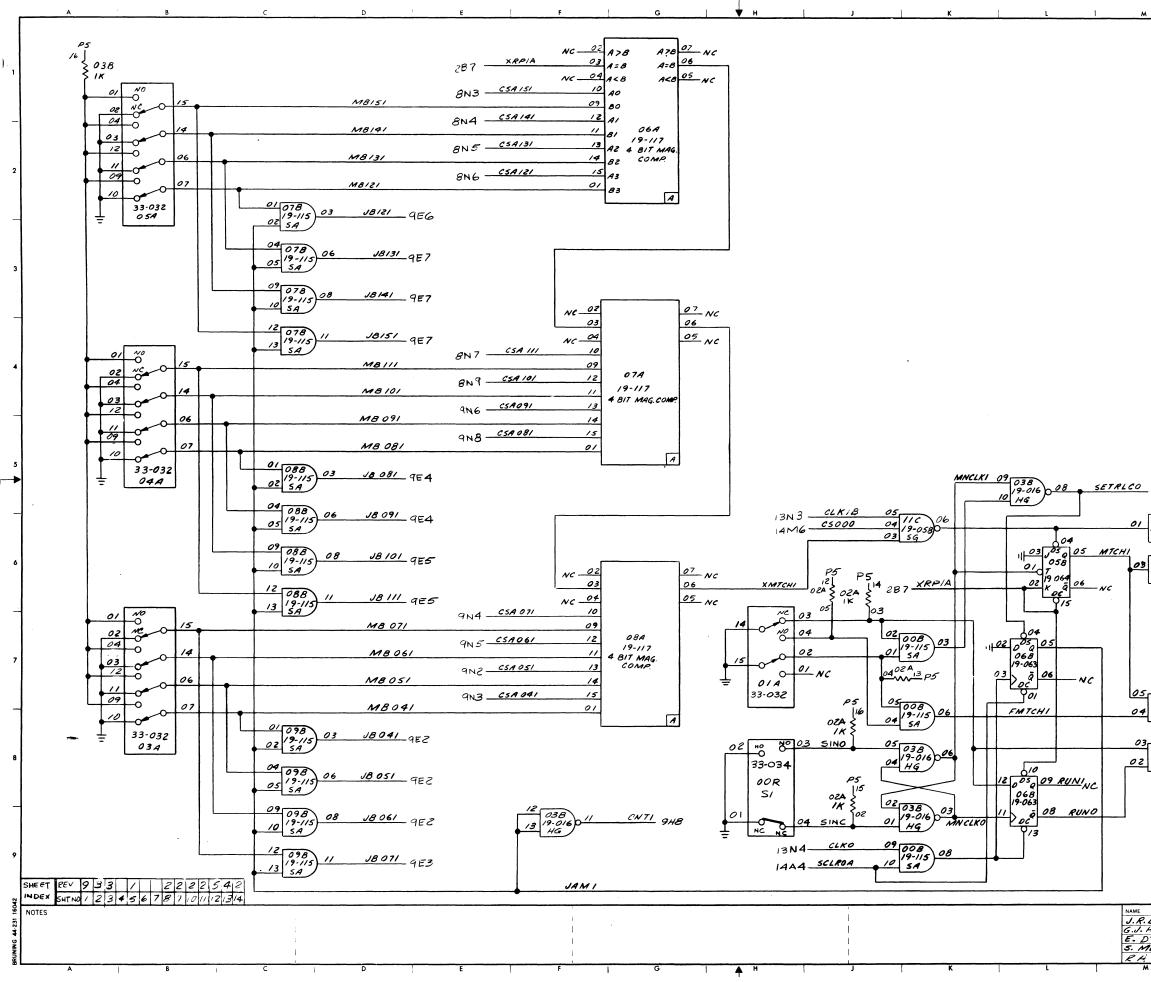

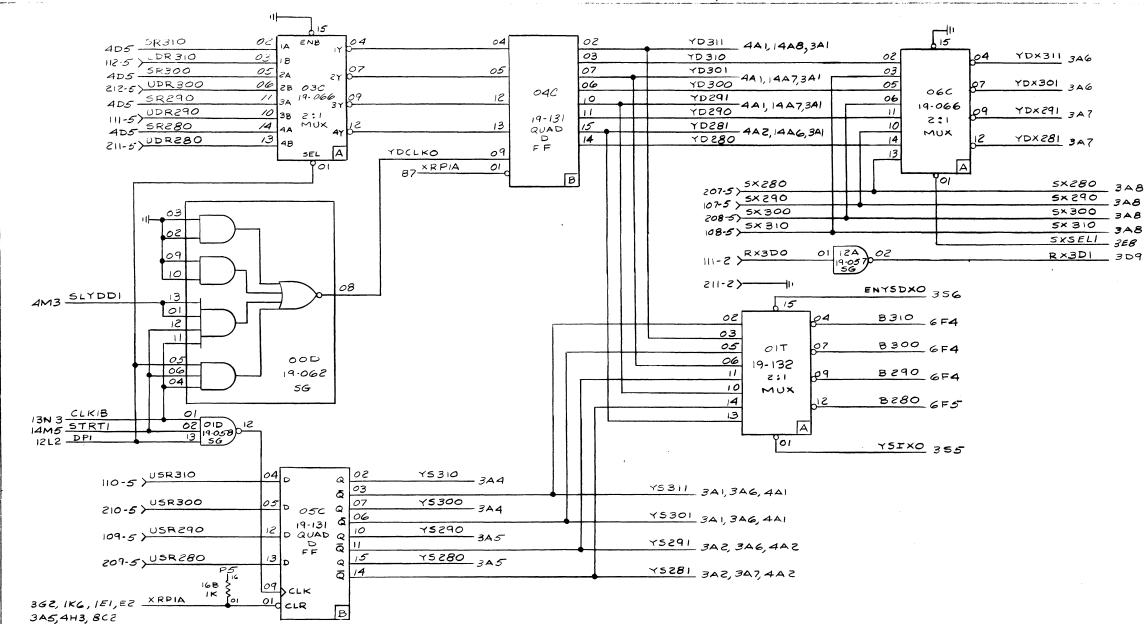

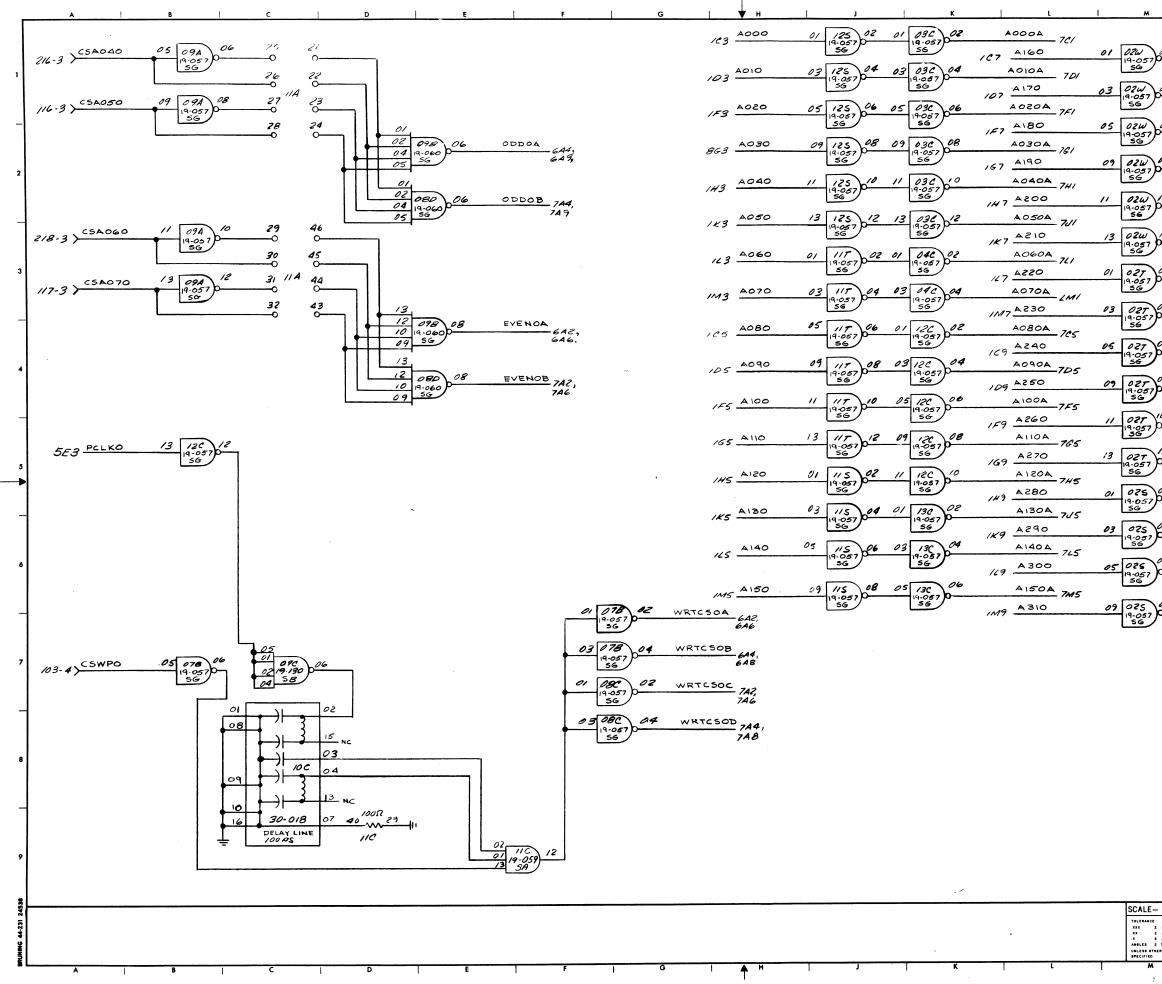

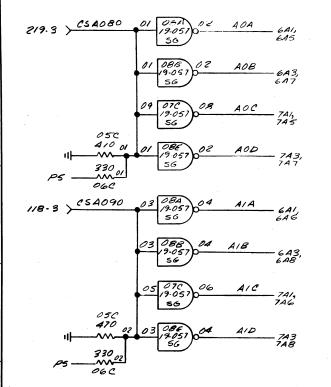

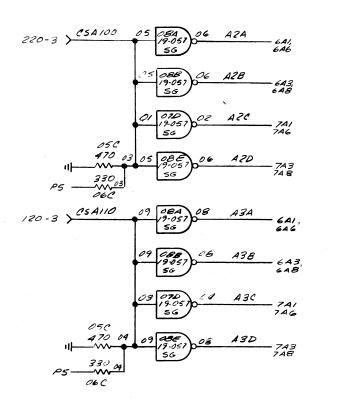

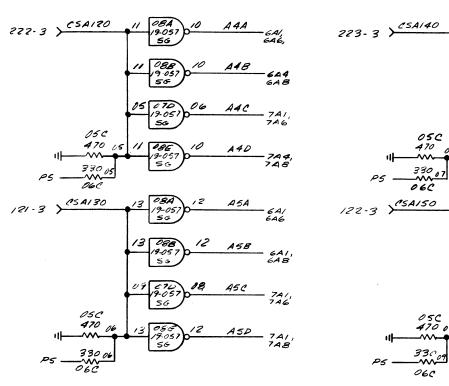

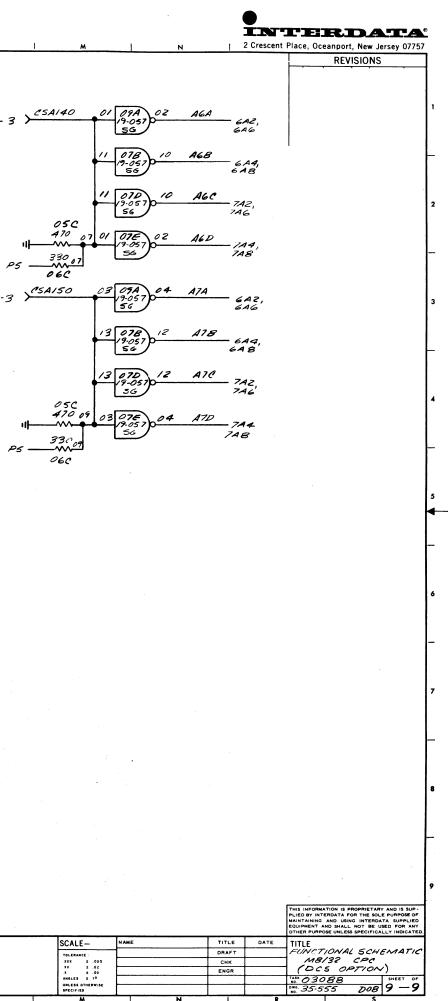

A digital system may be divided into a collection of functionally independent circuits such as memory, Processor, and I/O device controllers. These circuits may or may not be saleable units in their own right, but in the electrical sense they are essentially self contained and capable of performing their function with minimum dependence on other functional circuits in the system. Hence a functional circuit is treated as a building block. Each schematic contains a variety of information including type and location of discrete Integrated Circuits (IC's), pin connections, all interconnections within the schematic, connector pin numbers and connections to other schematics. Further, the schematics are drawn to reflect, in an orderly fashion, all logical operations performed by the circuits. Generally, symbols used on schematics conform to MIL-STD-806B.

Registers are named according to the following rules:

- 1. The register Mnemonic name has a maximum of three letters, excluding "I, O, Q, and Z".

- 2. Each bit in the register is numbered, usually starting at 00 on the left, or most significant positions, and continuing to N-1 on the right, where N is the number of bits in the register.

- 3. The 00 bit is the Most Significant Bit and the N-1 is the Least Significant Bit.

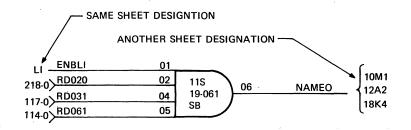

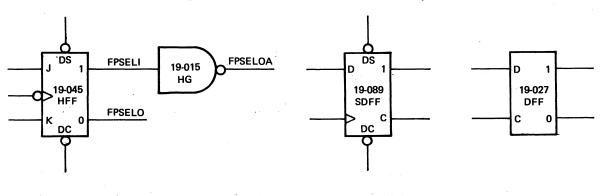

The IC's, mounted directly on the logic board, are represented on the schematic drawings by logic symbols. Each symbol contains the reference designation, device part number (category and sequence), and symbol Mnemonic designation. Refer to Figure 3.

Figure 3. Example of a Schottky Buffer

The designations, numbers, and references shown in Figure 3 are:

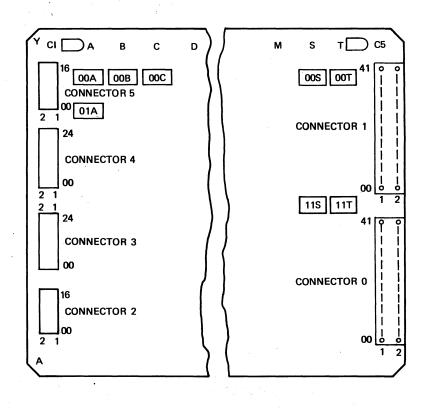

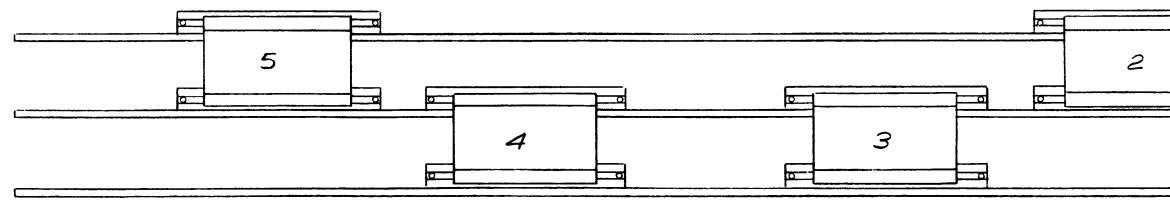

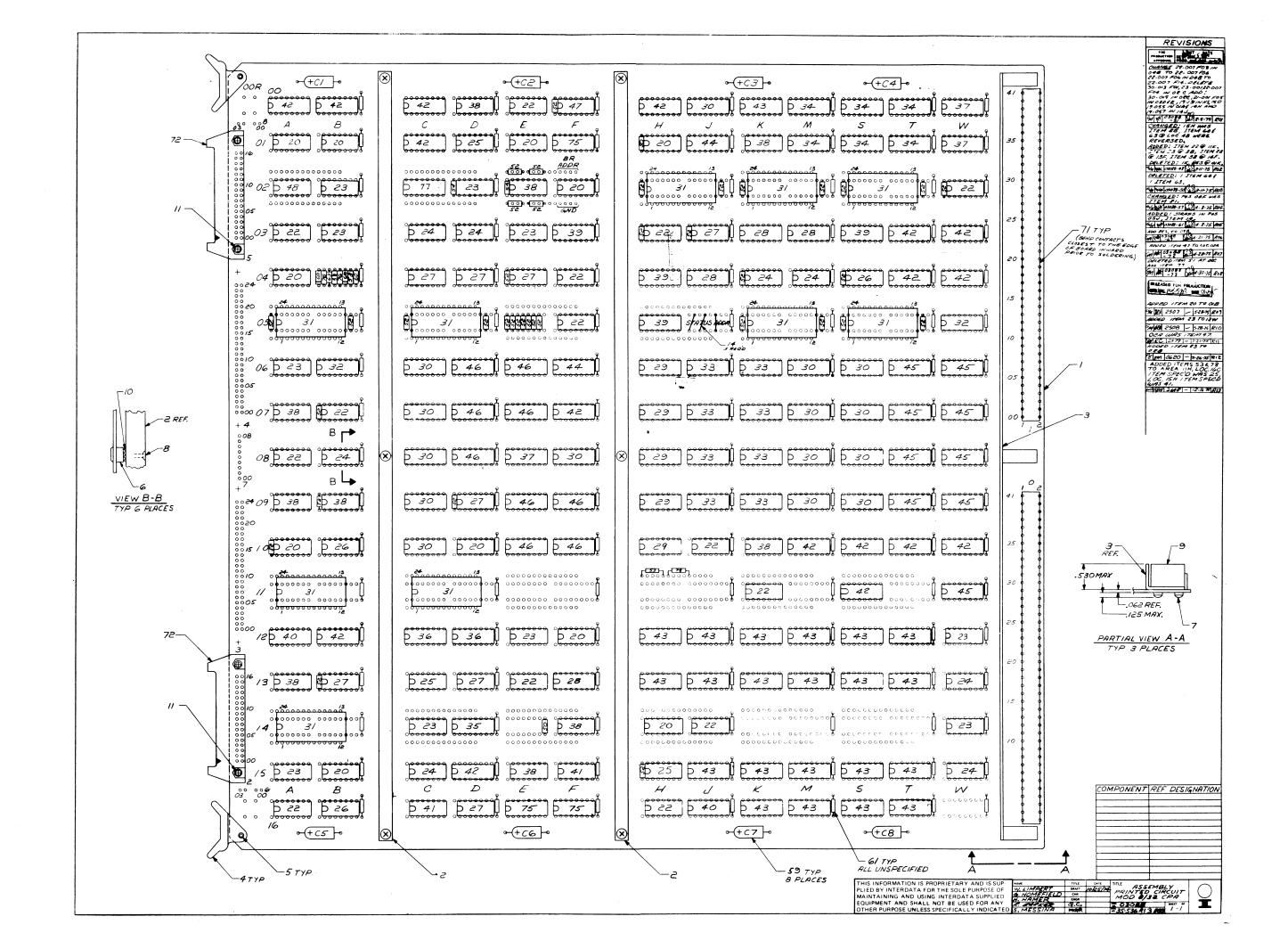

- 11S This indicates the component location on the logic board. Figure 4 illustrates the method generally used to determine component location on a logic board. With the logic board oriented so that the header connectors (Conn 0 and Conn 1) are on the right, the components are numbered from left to right starting in the upper left corner. That is, the first IC in the upper left corner is 00A and the first capacitor is C1. Test points are lettered right to left from A-Y (omitting I, O, L, E).

- 19-061 The number 19 is the category number of ICs, and the 061 is the sequence number of the component.

SB - Indicates this component is a Schottky Buffer. Some other common designations used are:

P - Power Gate SA - Schottky AND Gate SB - Schottky Buffer SG - Schottky Gate SGO - Schottky Gate, Open Collector HG - High Speed Gate HPO - High Speed Power Gate, Open Collector SFF - Schottky Flip-flop

L1 - This input lead is from area L1 on the same schematic sheet.

10M1, 12A2, 18K4 - Indicate outputs to another logic schematic sheet.

218-0, 117-0, 114-0, - Indicate inputs from Connector 0.

Note that the pin numbers (01, 02, 04, 05 and 06) correspond directly to the actual IC pin numbers.

Figure 4 also shows the locations of the header connectors (Conn 0 and Conn 1) and the cable connectors (Conn 2 and Conn 3). All logic boards always contain Header Connectors 0 and 1, however, any combination (either, both, or none) of cable connectors (Conn 2 and Conn 3) may be provided.

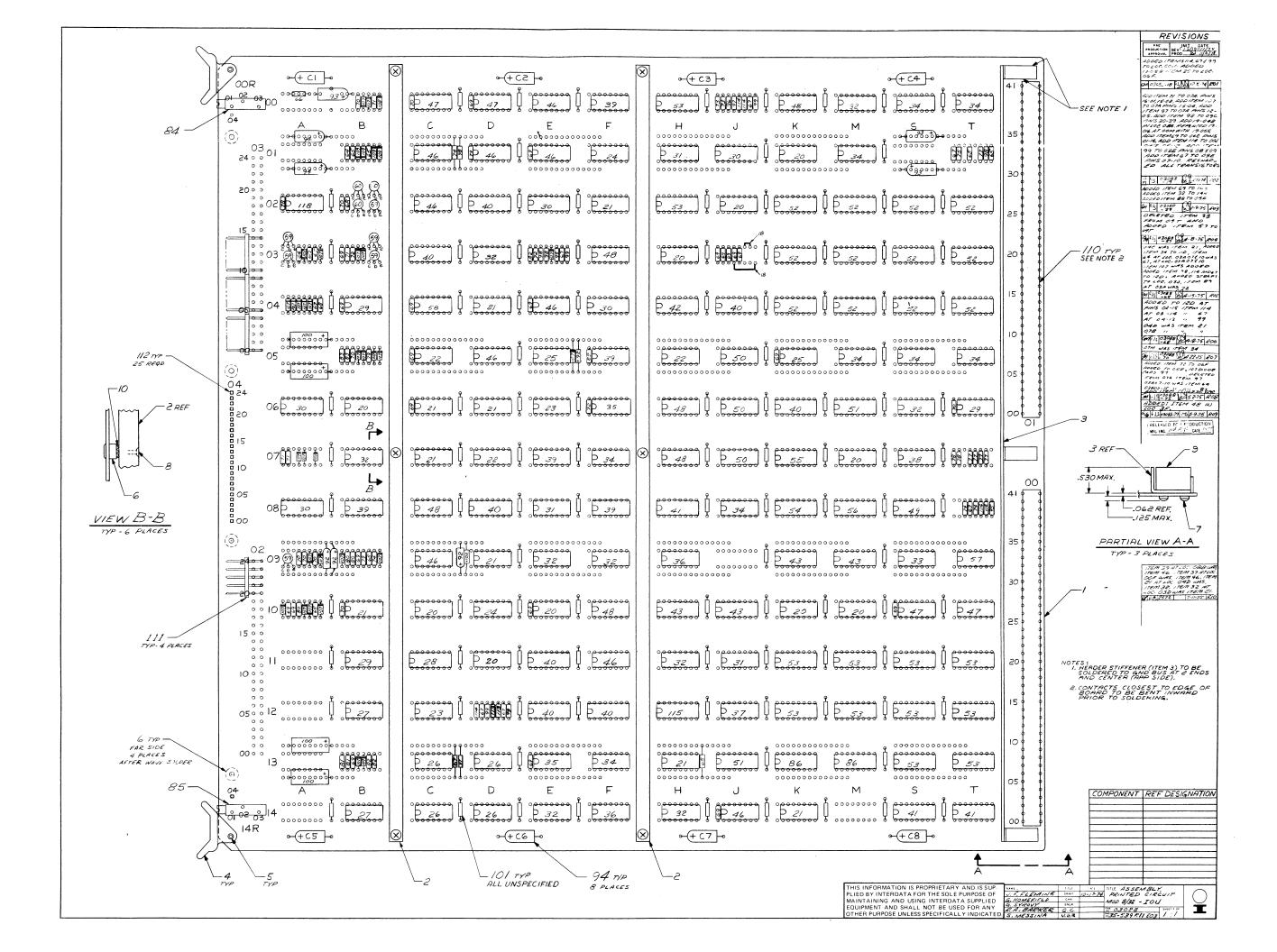

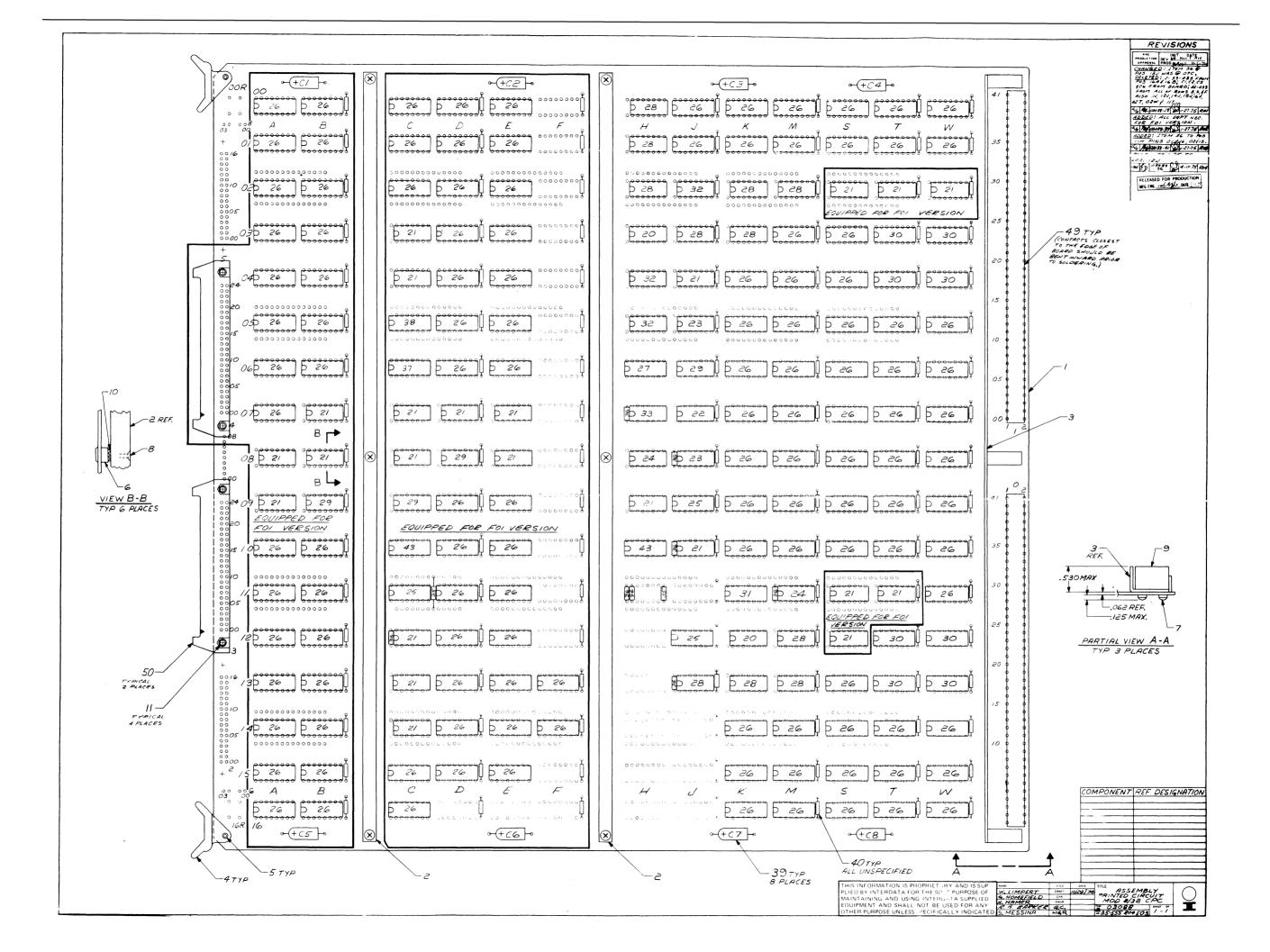

Figure 4. Example of a Logic Board Layout

Clocked devices, flip-flops and counters in particular, are drawn in a manner which indicates information concerning their inputs. An input which has a circle adjacent to the pin designation implies a low active signal is required to perform the specified operation. In addition, a fotated V at the clock input shows that the device changes state on an edge. Thus, if no circle is present the chip is positive edge triggered. Refer to Figure 5 for examples.

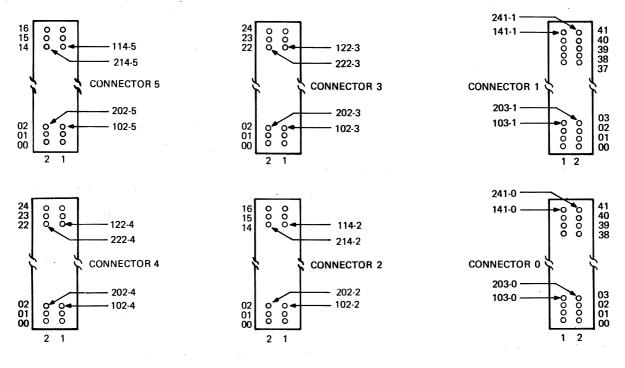

Figure 6 provides the pin numbering scheme for the header and cable connectors. Header connectors always have 2 rows of pins and 42 positions. Cable connectors always have 2 rows of pins but may vary in the number of positions.

A. NEGATIVE EDGE TRIGGERED

4

#### **B. POSITIVE EDGE TRIGGERED**

C. POSITIVE LEVEL TRIGGERED

## Figure 5. Examples of Clocked Devices

This information is proprietary and is supplied by INTERDATA for the sole purpose of using and maintaining INTERDATA supplied equipment and shall not be used for any other purpose unless specifically authorized in writing.

Figure 6. Connector Pin Numbering

A net is defined as an electrical connection between two or more points in a circuit. Ordinarily, a net has an originating end (usually an output where the signal is generated) and one or more terminating ends. Often it is convenient to assign descriptive mnemonic names to nets as a way of identifying them on schematics. Whether a net is named or not is sometimes arbitrary. However, a net is always assigned a name if:

- 1. The net is contained on one drawing sheet but is not shown as a complete solid line on that sheet.

- 2. Part of the net appears on more than one sheet.

- 3. Part of the net connects with a different schematic.

- 4. Part of the net leaves a logic board.

If a net is named, the following rules are observed.

- 1. All mnemonic names are a maximum of six characters.

- 2. All decimal digits and upper case letters are permitted.

- 3. No other characters permitted.

- 4. Where possible, Mnemonics are descriptive. However, it should be recognized that descriptive names are not always possible and a danger of misinterpreting a Mnemonic exists.

- 5. Mnemonic names are not repeated within a schematic.

- 6. Every Mnemonic is suffixed by a state indicator. This indicator consists of the digit "1" for the logically true state, or the digit "0" for the logically false state. For example, the set side of a flip-flop would have the "1" state indicator, while the reset side would have the "0" state indicator. The state indicator for a function changes each time that function is inverted. Thus, the state indicator permits assigning the same Mnemonic to functions that are identical except for an inversion.

- 7. When a logical function is inverted, an inversion indicator is added after the state indicator. This allows for functionally equivalent, but electrically different nets to have the same Mnemonic name. For example, assume a signal NAME1, NAME1 may be inverted to produce NAME0. If NAME0 is then inverted, NAME1A is produced. NAME1 and NAME1A are functionally equivalent, but physically different nets.

Sometimes a net fans-out to many sheets in a schematic. It is also possible for a net to fan-out to sheets in different schematics. In these situations, the net is assigned a mnemonic name. The net is also "zoned" from sheet to sheet to allow for properly identifying the originating and terminating ends of the net. The originating end of a net is defined as the collector at which a signal is generated. All other points to which the net connects are called terminating ends. When a lead leaves a sheet at the originating end, it is zoned to each and every sheet on which the net reappears, by indicating first the page number, followed by the schematic number that contains the page. For example, assume that the gate shown on Figure 3 is on a schematic, Sheet 20. The output NAMEO, appears on Sheets 10, 12 and 18 of the schematic. Note that the schematic number is implied. When a net enters a sheet from another sheet, it is labeled, with the same Mnemoric name, and is zoned back to the originating end of the only. Thus, on Figure 3, the ENBL1 may, however, have many other terminations in addition to the one shown. Generally, then, when a net leaves the sheet where it originates, it is zoned to every other sheet where the net terminates, while the terminating end is zoned only to the originating sheet. Note that in the Model 8/32 schematics, signals are co-ordinated between sheets only when the sheets are related to the same board. When a signal leaves a board, the Back Panel Map must be used.

When a lead leaves a logic board, it usually does so through a logic board back panel connector pin. These connector pins must be shown on the schematic even if the complete net is shown on one drawing sheet. Only the connector pin number need be indicated under the pin symbol, since the connector number itself is implied by the logic board location number in the logic symbol or in the footnote. Thus, on Figure 3, RD061 enters the logic board on Pin 114 of Header Connector 0.

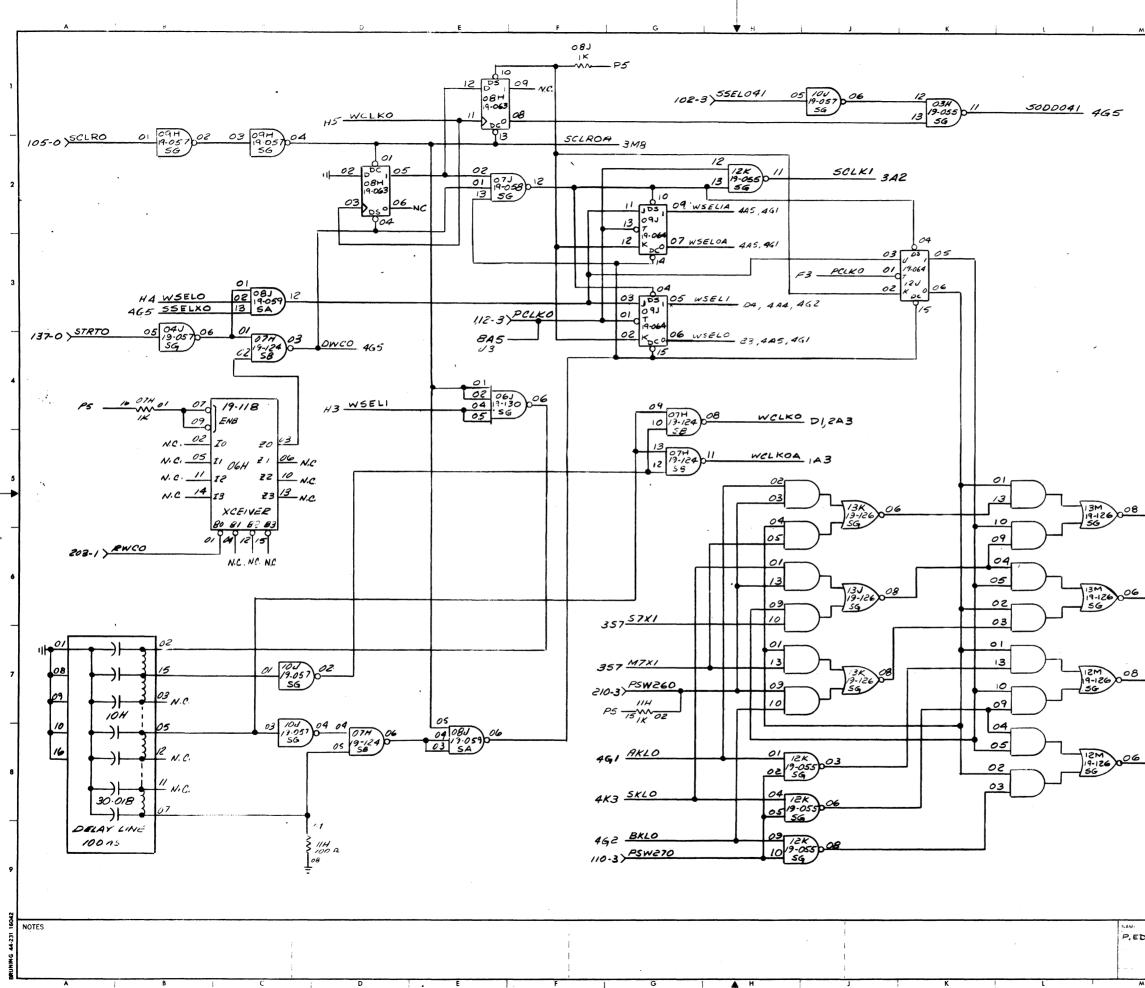

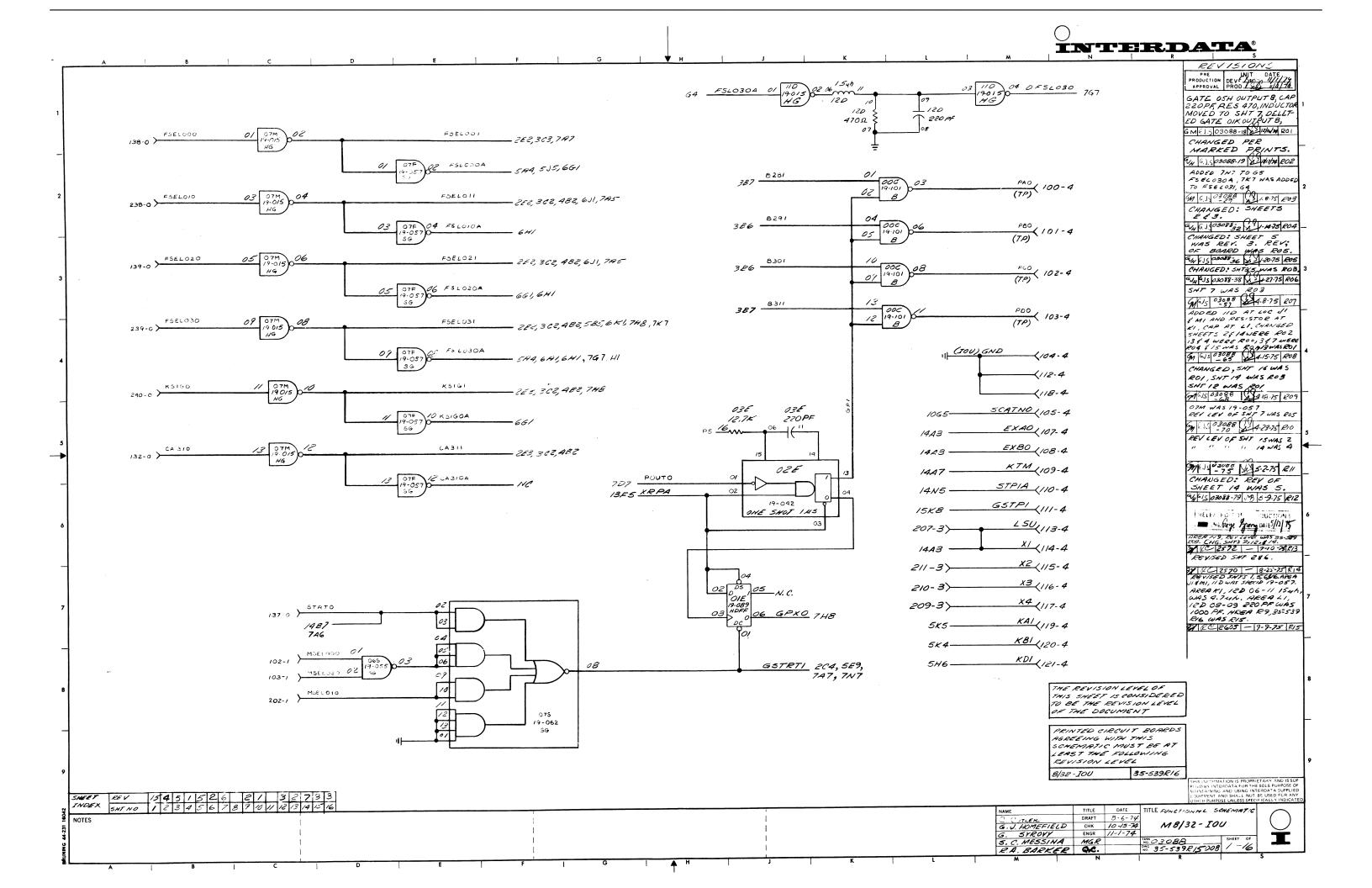

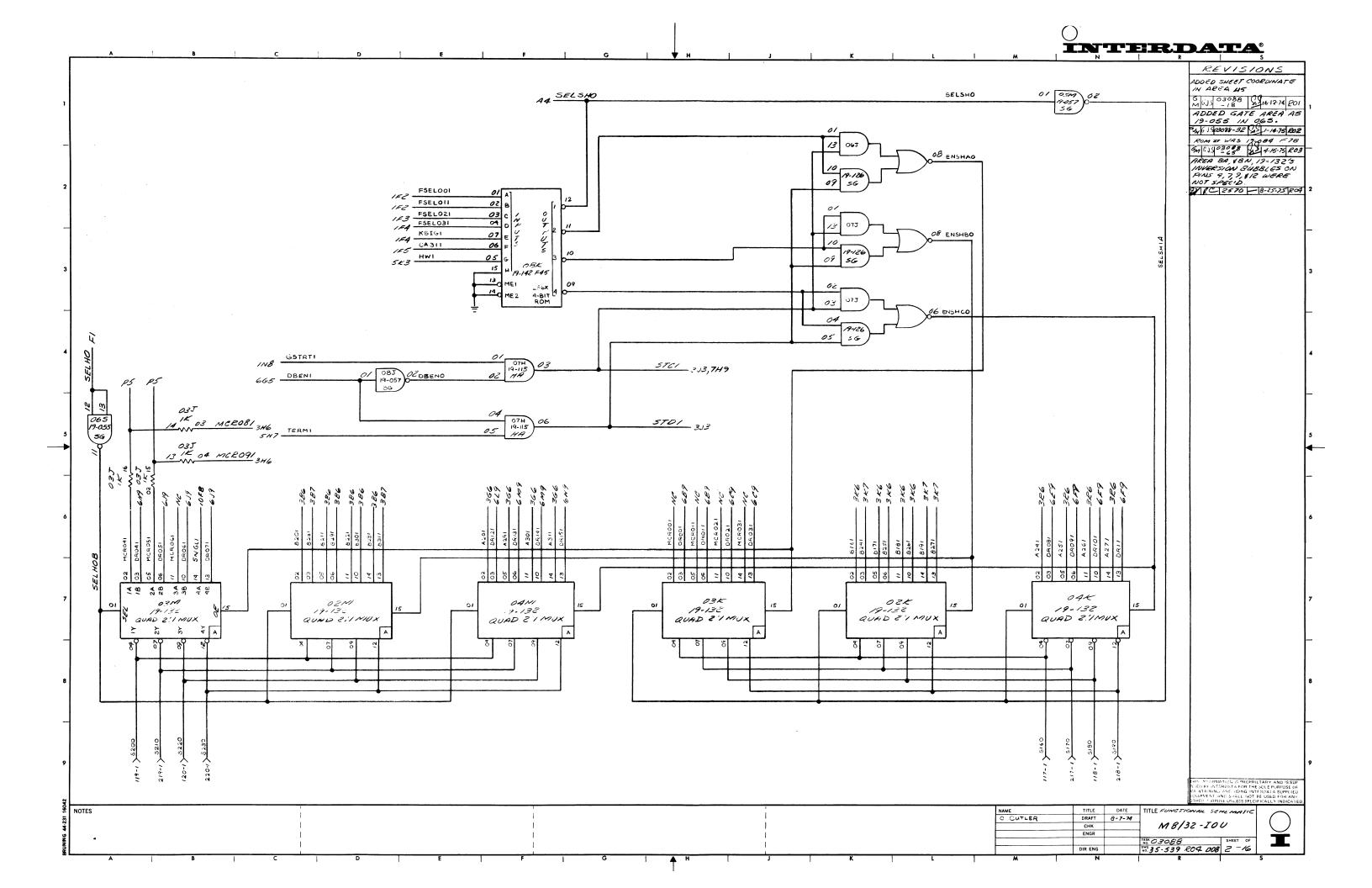

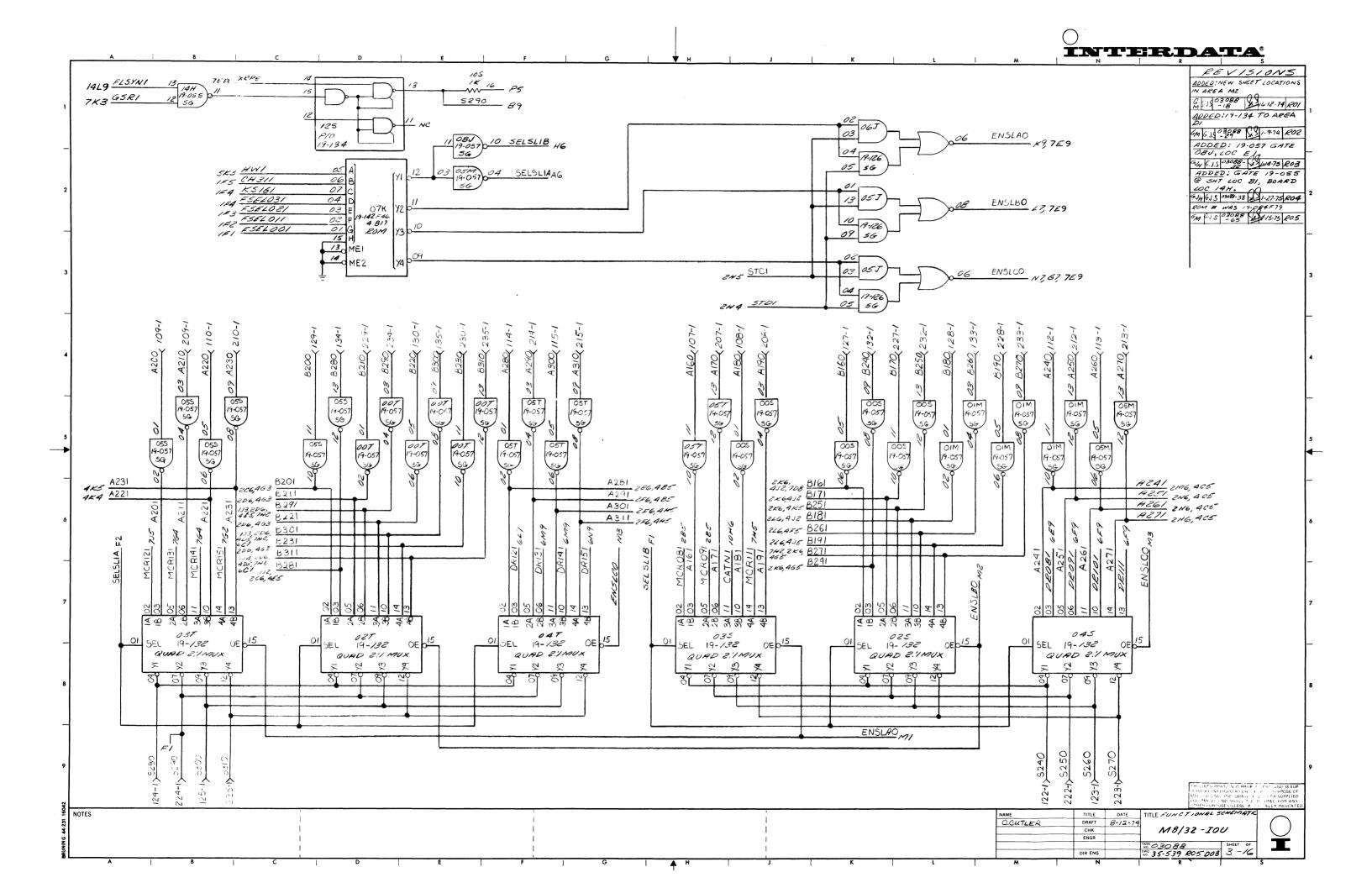

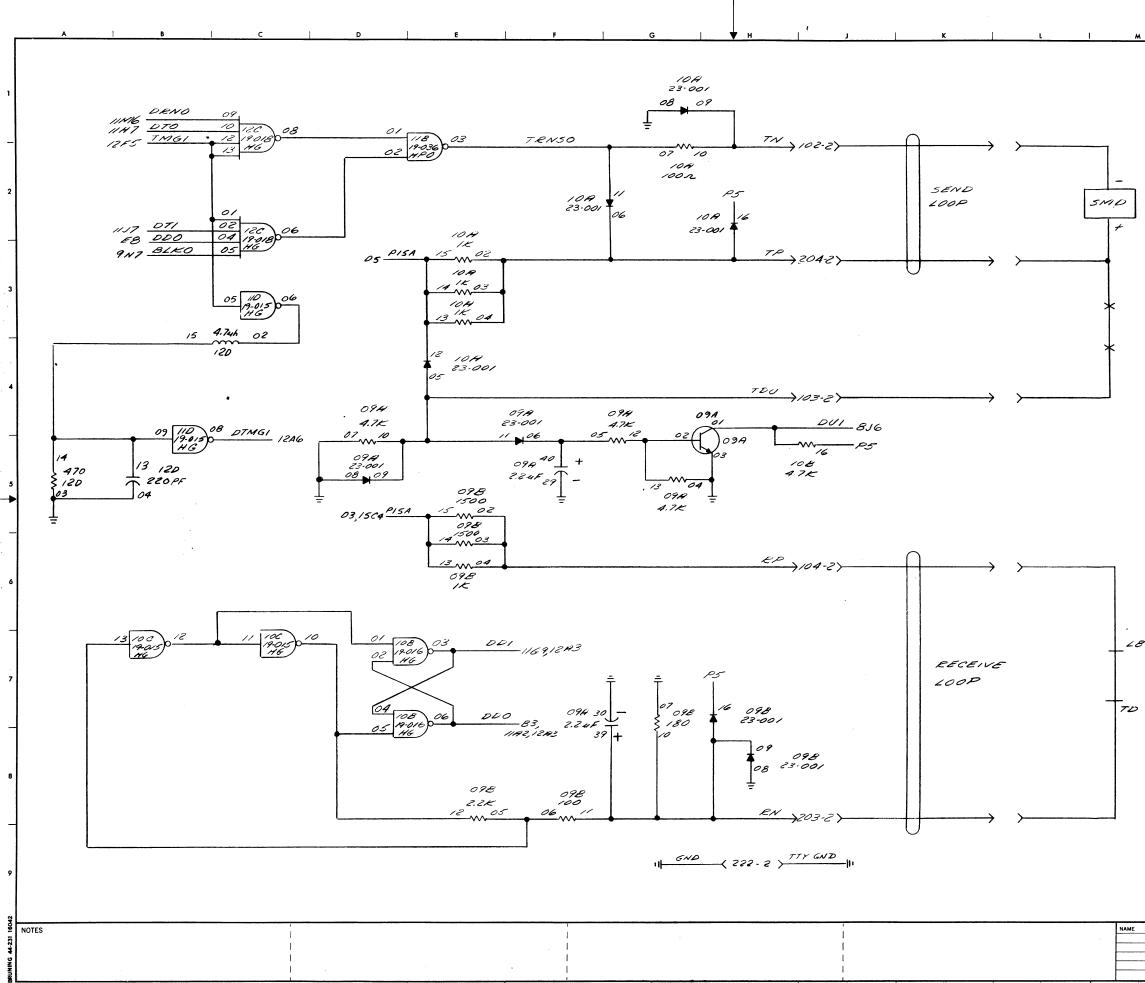

Figure 7 is a typical schematic sheet with call-outs illustrating many of the conventions described in this section.

The schematic drawings for the basic Digital System and some of the more common expansions are commonly included in the rear of the appropriate Digital System Maintenance Manual. Schematic drawings for other expansions are included with the expansion or with the publications that describe the expansion.

## APPENDIX 1

## PART NUMBER CROSS REFERENCE TABLE

| INTERDATA Part Number | Туре                                                   | JEDIC Number       |

|-----------------------|--------------------------------------------------------|--------------------|

| 19-001                | Dual 4 Input Nand DTL                                  | 15861              |

| 19-002                | Triple 3 Input Nand DTL                                | 15863              |

| 19-003                | Quad 2 Input Nand DTL                                  | 15849N             |

| 19-004                | Hex 1 Input Nand DTL                                   | 15837N             |

| 19-005                | Dual Power Gate DOC                                    | 863 <b>3</b> N     |

| 19-006                | Dual Buffer DTL                                        | 1582N              |

| 19-007                | Flip-Flop DTL                                          | 15848N             |

| 19-008                | Gate Expander Dual 4 Input DTL                         | 15833N             |

| 19-009                | 8 Bit Stack DTL                                        | 903059 (Fairchild) |

| 19-010                | Differential Compartor LIN                             | 72710L             |

| 19-012                | Dual 4 Input Buffer TTL                                | 74H40H             |

| 19-013                | Quad 2 Input Nand DTL                                  | 15846              |

| 19-014                | Dual J-K Flip-Flop DTL                                 | 158097N            |

| 19-015                | Hex Inverter 1 Input                                   | 74H04H             |

| 19-016                | Quad 2 Input TTL                                       | 74H00N             |

| 19-017                | Triple 3 Input TTL                                     | 74H10N             |

| 19-018                | Dual 4 Input TTL                                       | 74H20N             |

| 19-019                | Single 8 Input TTL                                     | MC3015 (Motorola)  |

| 19-020                | Operational Amplifier LIN                              | MC1709C (Motorola) |

| 19-021                | Quad 2 Input Power DOC                                 | 15858N             |

| 19-022                | Dual J-K Flip-Flop TTL                                 | MC3061P (Motorola) |

| 19-023                | Selected Dual Buffer 19-006 with 20-30 nsec. delay DTL | 15832N             |

| 19-024                | Triple 3 Input AND TTL                                 | 74H11N             |

| 19-025                | Dual 4 Input AND TTL                                   | 74H21N             |

| 19-026                | 2-2-2-3 Input AND-OR TTL                               | 74H52              |

|                       |                                                        |                    |

This information is proprietary and is supplied by INTERDATA for the sole purpose of using and maintaining INTERDATA supplied equipment and shall not be used for any other purpose unless specifically authorized in writing.

A1-1

| INTERDATA Part Number | Туре                                  | JEDIC Number           |

|-----------------------|---------------------------------------|------------------------|

| 19-027                | 4 Bit Latch TTL                       | 7475N                  |

| 19-028                | 4 Bit Adder TTL                       | 7483N                  |

| 19-029                | Quad Exclusive - OR TTL               | 7486N                  |

| 19-030                | 4 Bit Shift Register TTL              | 7495N                  |

| 19-031                | One Shot TTL                          | 74121N                 |

| 19-032                | 1 out of 10 Decoder TOC               | 74145N<br>5445<br>7445 |

| 19-033                | Sense Amplifier LIN                   | 7524N                  |

| 19-034                | Retriggerable One Shot TTL            | 74122N                 |

| 19-035                | 4 Bit Counter TTL                     | 74193N                 |

| 19-036                | Quad 2 Input Open Collector TTL       | 7438N                  |

| 19-037                | High Performance Operational Amp      | 7748393 (Fairchild)    |

| 19-038                | Dual 4 line to 1 line Mux TTL         | 74153                  |

| 19-039                | 4 Bit ALU TTL                         | 74181                  |

| 19-040                | Look Ahead Carry TTL                  | 74182                  |

| 19-041                | 4 x 4 Register Stack TTL              | 74170                  |

| 19-042                | Dual Retriggerable One Shot TTL       | 74123N                 |

| 19-043                | Quad 2 Input Open Collector TTI       | 74H01N                 |

| 19-044                | Hex Inverter Open Collector TTL       | 74H05N                 |

| <b>19-045</b>         | Dual J-K Flip-Flop TTL                | 74H106                 |

| 19-046                | Quad RS-232C Line Driver              | MC1488L (Motorola)     |

| 19-047                | Quad RS-232C Line Receiver            | MC1489AL (Motorola)    |

| 19-048                | 8 Bit Shifter                         | 74198N                 |

| 19-050                | 8 Input Nand TTL                      | 74H30                  |

| 19-051                | 1024 Bit PROM TTL                     | 74187 (Fairchild)      |

| 19-055                | Quad 2 Input Nand STTL                | 74S00                  |

| 19-056                | Quad 2 Input Nand Open Collector STTL | 74S03                  |

| 19-057                | Hex 1 Input Inverter STTL             | 74S04                  |

| 19-058                | Triple 3 Input Nand STTL              | 74S10                  |

| 19-059                | Triple 3 Input AND STTL               | 74S11                  |

| 19-060                | Dual 4 Input Nand STTL                | 74S20                  |

| INTERDATA Part Number | Type                                               | JEDIC Number                            |

|-----------------------|----------------------------------------------------|-----------------------------------------|

| 19-061                | Dual 4 Input Buffer STTL                           | 74S40                                   |

| 19-062                | 2-2-3-4 Input AND-OR Inverter STTL                 | 74S64                                   |

| 19-063                | Dual D Edge Triggered Flip-Flop STTL               | 74S74                                   |

| 19-064                | Dual J-K Flip-Flop STTL                            | 74S112                                  |

| 19-065                | Quad 2:1 Mux Non-inverting STTL                    | 74S157                                  |

| 19-066                | Quad 2:1 Mux Inverting STTL                        | 74S158                                  |

| 19-067                | 4 Bit ALU STTL                                     | 74S181                                  |

| 19-068                | Carry Look Ahead STTL                              | 74S182                                  |

| 19-069                | 8 line to 1 line Mux STTL                          | 74151                                   |

| 19-070                | 4 Bit Syncronous Counter TTL                       | 74161                                   |

| 19-071                | Quad D Edge Triggered Flip-Flop                    | 74175                                   |

| 19-072                | 4 Bit Left/Right Shift Register TTL                | 74194                                   |

| 19-073                | Dual 4:1 Mux Tri-State TTL                         | 8214 (National)                         |

| 19-074                | 8 Bit Priority Encoder TTL                         | 9318 (Fairchild)                        |

| 19-075                | 16 x 4 Register Stack TTL                          | 3101A (Intel)                           |

| 19-076                | 1024 Bit Memory MOS                                | TM54062                                 |

| 19-077                | 256 Bit Memory TTL                                 | 6531 (Monolithic Memories)              |

| <b>19-078</b>         | Dual 4 Input Nand-OC                               | 74822                                   |

| 19-080                | High-Speed PROM                                    | 82S29 (Signetics)                       |

| 19-081                | Univ. Asynchronous Receiver/Transmit-<br>ters      | TR1042A (Western Digital)               |

| 19-082                | 2-2-3-4 Input AND-OR Invert Open<br>Collector STTL | 74S65                                   |

| 19-083                | 9 Bit Parity Generator/Checker STTL                | 82S62 (Signetics)                       |

| 19-085                | Monolithic Timing Circuit                          | MC1555 (Motorola)<br>NE555V (Signetics) |

| 19-086                | 741 C DIP Operational Amplifier                    | U6A7741393 (Fairchild)                  |

| 19-087                | 747 DIP Operational Amplifier                      | U7A774 (Fairchild)                      |

| 19-088                | 737 C DIP Operational Amplifier                    | U6A773393 (Fairchild)                   |

| 19-089                | Dual D Edge Triggered Flip-Flop                    | 74H74                                   |

| 19-090                | High Speed (710) Differential Compara-<br>tor DIP  | U6A771093 (Fiarchild)                   |

| 19-091                | Retriggerable Single One Shot                      | 9600 (Fairchild)                        |

Туре

| 19-092         | Negative Voltages Regulator                       | MC1463R (Motorola)                            |

|----------------|---------------------------------------------------|-----------------------------------------------|

| 19-093         | Positive Voltages Regulator                       | MC1469R (Motorola)                            |

| 19-094         | Voltage Regulator                                 | U6A7723393 (Fairchild)<br>MC1723CL (Motorola) |

| 19-095         | Linear Positive Voltage Regulator                 | U9H7805393 (Fairchild)                        |

| 19-096         | First In-First Out Serial Memory<br>64 Word 4 Bit | 3341 (Fairchild)                              |

| 19-097         | Amplifier                                         | LH0002H (National)                            |

| 19-098         | Quad 2:1 Multiplexor Non-Inverting                | 74157                                         |

| 19-099         | Dual Sense Amplifier                              | 75234N                                        |

| 19-100         | Driver                                            | 75452N                                        |

| 19-101         | 4-2 Input Buffer                                  | 7437N                                         |

| 19-102         | 6-1 Input Buffer OC                               | 7407N                                         |

| 19-103         | 1 out of 10 Decoder                               | 7442N                                         |

| 19-104         | Current Switch                                    | 75325N                                        |

| 19-105         | Dual Diffential Driver                            | Fairchild 9614                                |

| 19-106         | Dual Diffential Receiver                          | Fairchild 9615                                |

| 19-107         | Sense Amplifier                                   | SN7520N                                       |

| <b>19-10</b> 8 | Quad 2 Input Nand                                 | SN7400N                                       |

| 19-109.        | Hex Inverter Open Collector                       | SN7406N                                       |

| 19-110         | Hex Inverter                                      | SN7404N                                       |

| 19-111         | Dual 4 Input Nand                                 | SN7440N                                       |

| 19-112         | Optically Coupled Isolator                        | TIL-111 4N25                                  |

| 19-113         | 360 Dual Transmitter                              | TI 75123                                      |

| 19-114         | 360 Triple Receiver                               | TI 75124                                      |

| 19-115         | Quad 2 Input AND                                  | 74H08                                         |

| 19-116         | Dual 4:2 Multiplexor STTL                         | 74S153                                        |

| 19-117         | 4 Bit Magnitude Comparator STTL                   | 74S85                                         |

| 19-118         | Quad Bus Transceiver TTL                          | 26S12A                                        |

| 19-119         | Expandable AND-OR <sup>I</sup> nvert TTL          | 74455                                         |

| 19-120         | Dual Timer                                        | Signetics NE556                               |

|                |                                                   |                                               |

| INTERDATA Part Number | Туре                                    | JEDIC Number                         |

|-----------------------|-----------------------------------------|--------------------------------------|

| 19-121                | Matched Pair 19-085 (P. S. Timing)      | See 19-085                           |

| 19-123                | Dual Voltage Controlled Oscillator      | 74S124                               |

| 19-124                | Quad 2 Input Nand Buffer, STTL          | 74\$37                               |

| 19 -125               | O.C. Quad 2 Input Nand Buffer, STTL     | 74S38                                |

| 19 - 126              | Dual 2 Wide-2 input AOI, STTL           | 74S51                                |

| 19 -127               | Quad Exclusive-OR, STTL                 | 74\$86                               |

| 19 -128               | 12 Input Nand-Tri State, STTL           | 74\$134                              |

| 19-129                | 3 to 8 Decoder, STTL                    | 74\$138                              |

| 19 - 130              | Dual 4 in. Nand 50 Ohm Driver, STTL     | 74S140                               |

| 19-131                | Quad D Flip Flop, STTL                  | 74S175                               |

| 19 - 132              | Quad 2/1 MuxTri State, STTL             | 74S258                               |

| 19 - 133              | 4 Bit Binary Adder, TTL                 | 74283                                |

| 19-134                | Hex Buffers/Inverts, TTL                | 8T98                                 |

| 19 - 135              | 4 Bit Binary Counter, STTL              | 93\$16                               |

| 20-001                | Transistor NPN High Speed Switch        | 2N3646                               |

| 20-002                | Transistor PNP 500 MA                   | MPS6534 (Motorola)                   |

| 20-003                | Transistor                              | 2N3902                               |

| 20-004                | Transistor NPN                          | 2N5189                               |

| 20-006                | Transistor NPN 15 Amps 100W T03<br>case | 2N3055 (RCA)                         |

| 20-007                | Transistor NPN 3 Amps                   | TIP31A                               |

| 20-008                | Transistor PNP 3 Amps                   | TIP32A                               |

| 20-009                | Transistor Triac 2 Amps 100V            | A03001 (Electronic Control<br>Corp). |

| 20-010                | Transistor NPN 500 MA Code Driver       | 2N5845                               |

| 20-011                | Transistor Photo                        | 2N5777                               |

| 20-012                | Transistor PNP High Current Switch      | 2N2907                               |

| 20-013                | Transistor NPN                          | 2N3303                               |

| 20-014                | Transistor NPN                          | 2N4238                               |

| 20-015                | Transistor PNP                          | 2N4235                               |

| 20-016                | Transistor PNP                          | 2N3740                               |

| INTERDATA Part Number | Type                               | JEDIC Number            |

|-----------------------|------------------------------------|-------------------------|

| 20-017                | Transistor NPN                     | 2N3766                  |

| 20-018                | Transistor, Power Silicon NPN      | 2N3054                  |

| 20-019                | Transistor NPN Fast PWR Switch     | 2N6308 (Motorola)       |

| 20-020                | Transistor Switching 1 Amp T05 can | 2N3725                  |

| 20-021                | Transistor NPN Silicon             | MPS3646 (Motorola)      |

| 20-022                | Transistor NPN                     | 1N1711                  |

| 20-023                | Transistor PNP                     | 2N2905A                 |

| 20-024                | Transistor Switch                  | 2N3776                  |

|                       |                                    |                         |

| 20-025                | PNP HI SPEED Switch                | 2N3467                  |

| 20-026                | Transistor Module, Quad            | MPQ3725                 |

| 20-027                | Transistor                         | 2N2369                  |

| 20-029                | Transistor                         |                         |

| 21-025F01             | 1K ohm-15 to Common DIP            | 898-1-1K ohm (Beckman)  |

| 21-025F02             | 470 ohm-15 to Common DIP           | 898-1-470 ohm (Beckman) |

| 21-025F03             | 330 ohm-15 to Common DIP           | 898-1-330 ohm (Beckman) |

| 23-001                | Diode High Speed-High Current      | 1N914                   |

| 23-002                | Diode 5.1 V Zener                  | 1M5.1ZS5 (Motorola)     |

| 23-003                | Diode 10V Zener                    | 1M10ZS5 (Motorola)      |

| 23-004                | Diode 6.2 V Zener                  | 1M6.2ZS5 (Motorola)     |

| 23-007                | Diode Mot Bridge                   | MDA962-2 (Motorola)     |

| 23-008                | Diode Int. Rectifier               | 40HF-5R                 |

| 23-009                | Diode                              | 1N4735                  |

| 23-010                | Diode Int. Rectifier               | S1Y1P                   |

| 23-011                | Diode Rectifier                    | 2N681                   |

| 23-012                | Diode Thermister                   | KA31J1 (Fenwall)        |

| 23-013                | Diode 9.4V                         | 1N216 <b>3</b>          |

| 23-014                | Diode                              | 1N3880                  |

| 23-015                | Diode                              | 1N3889                  |

| 23-016                | Diode Bridge Recitifer             | VS448 (Varo)            |

| 23-017                | Diode                              | 1N2070                  |

|                       |                                    |                         |

.

•

.

| INTERDATA Part Number                                                                                            | Type                                                       | JEDIC Number                     |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------|

| and a second s |                                                            |                                  |

| 23-018                                                                                                           | Diode 18 V Zener                                           | 1N4746A                          |

| 23-019                                                                                                           | Diode                                                      | 1N3615                           |

| 23-020                                                                                                           | Diode 8.2V Zener                                           | 1N756A                           |

| 23-021                                                                                                           | Diode 9.1 V Zener                                          | 1N757A                           |

| 23-022                                                                                                           | Diode 3.3V Zener                                           | 1N746A                           |

| 23-023                                                                                                           | Diode Bridge Rectifier                                     | KBH2506 (General Instrument)     |

| 23-024                                                                                                           | Diode, Power Fast Rec. 30 Amps.                            | 1N3909                           |

| 23-025                                                                                                           | Diode, Power Fast Rec. 3 Amps.                             | A115A (General Electric)         |

| 23-026                                                                                                           | Triac 600V 30 Amps                                         | 2N6162                           |

| 23-027                                                                                                           | Diac 32V                                                   | 1N5761                           |

| 23-028                                                                                                           | Power SCR Thyristor                                        | 2N4441                           |

| 23-029                                                                                                           | Diode                                                      | 1N4607                           |

| 23-030                                                                                                           | Diode                                                      | 1N4156                           |

| 23-031                                                                                                           | Diode 6.6 V Zener                                          | 1N4736                           |

| 23-032                                                                                                           | Diode 8.8 V Zener                                          | 1N4739                           |

| 23-033                                                                                                           | 16 Diode Array                                             | 45190 (Litton)                   |

| 30-018                                                                                                           | 100 nsec. Delay Line 10 taps                               | 30-018 (Princeton Advanced Eng.) |

| 30-019                                                                                                           | 50 nsec. Delay Line 10 taps                                | 30-018 (Princeton Advanced Eng.) |

| 33-034                                                                                                           | PR CKT Count Butt Contact<br>Push Button Switch ¼ AMP SPDT |                                  |

| 33-035                                                                                                           | 8 Pole Dip Switch AMP Part No. 4351665                     |                                  |

"

•

i

## MODEL 8/32 PROCESSOR MAINTENANCE SPECIFICATION

## TABLE OF CONTENTS

| 1. INTRODUCTION                                  |          |

|--------------------------------------------------|----------|

| 1.1 Packaging                                    | 1        |

|                                                  |          |

| 1.2 Processor                                    |          |

| 1.3 Control Store                                |          |

| 1.4 Peripherals                                  | <b>1</b> |

| 2. INTERNAL ARCHITECTURE                         |          |

|                                                  |          |

| 2.1 Modules                                      |          |

| 2.2 Micro-Instructions                           |          |

| 2.3 Interrupts                                   |          |

| 2.4 Registers                                    |          |

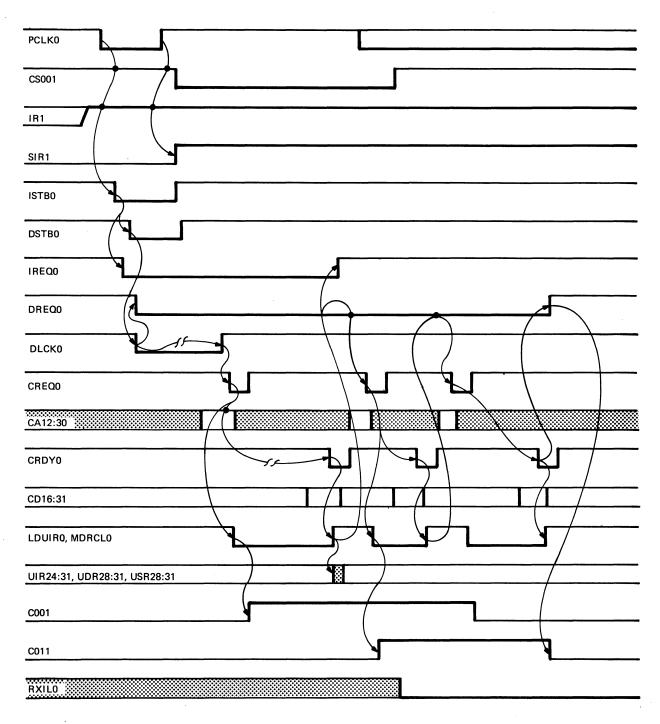

| 2.5 Processor Timing                             |          |

|                                                  |          |

| 3. FUNCTIONAL DESCRIPTION OF THE BASIC PROCESSOR |          |

| 3.1 Processor Busses                             |          |

| 3.2 Registers                                    |          |

| 3.3 Interrupts                                   |          |

|                                                  |          |

| 3.4 Control Store Memory                         |          |

| 3.5 Micro-Programming                            |          |

| 3.6 Processor Block Diagram Analysis             |          |

| 4. CPA GENERAL DESCRIPTION                       |          |

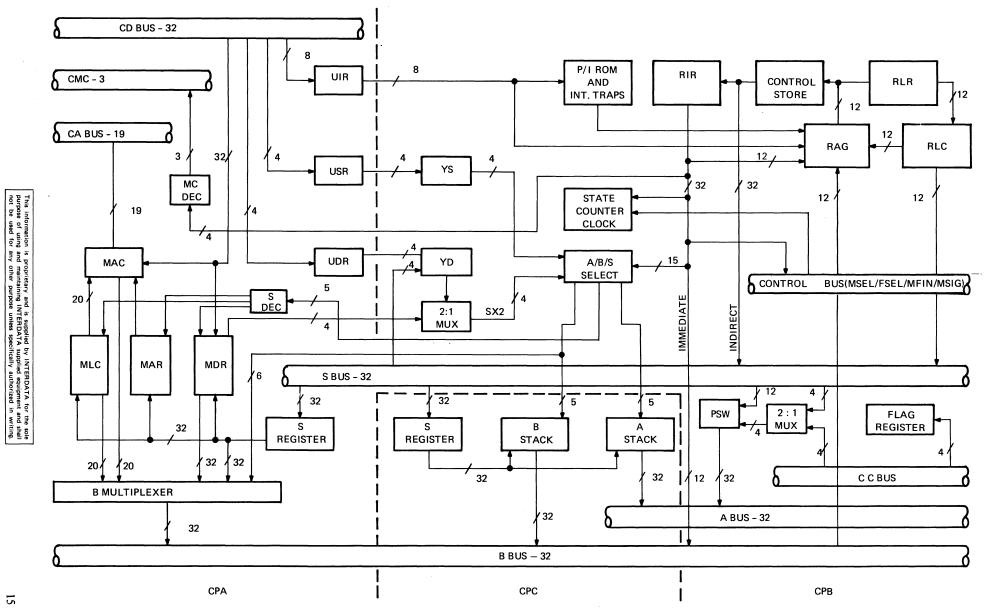

| 4.1 CPA Block Diagram Description                | 17       |

| 4.1 Cr A block Diagram Description               |          |

|                                                  |          |

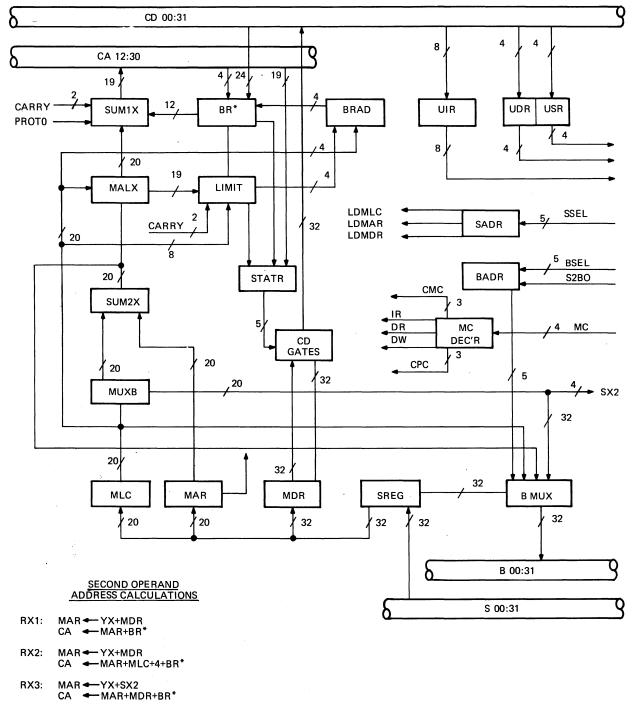

| 4.3 Memory Reference Operations                  |          |

| 4.4 S Bus Operations                             |          |

| 4.5 B Bus Operations                             |          |

| 5. CPB FUNCTIONAL DESCRIPTION                    |          |

| 5.1 State Counter and Control                    |          |

| 5.2 Clock and Control                            |          |

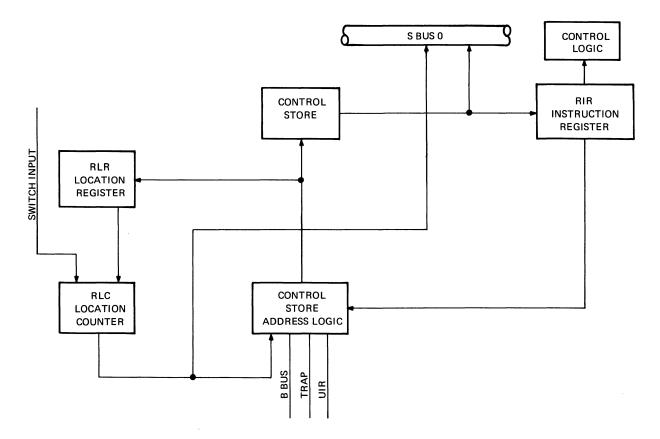

| 5.3 Control Store                                |          |

| 5.4 Bus Selection                                |          |

| 5.5 Interrupts                                   |          |

| 5.6 PSW Register                                 |          |

| 5.7 Branch Control                               |          |

| 5.8 A, B, and S Gating                           |          |

|                                                  |          |

| 5.9 Test Aids                                    | 41       |

## TABLE OF CONTENTS (Continued)

|     | CPC C                                                                                                                                                            | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |             | • •                                   | • • •                                 | • • •                                 | • •                                   | • •                                                                                                                                                                                                                  | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •••                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          | •••                                                                                                                                                                                                                                                                                                                   | • •                                   | •          | •                                                                                                        | • •                                                | ••• | 42                                                                                                                                                                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 6.1                                                                                                                                                              | A and B Stacks (ASTK and BSTK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |                                       |                                       |                                       |                                       |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                                                                                                                                                                                                                                                                                                       |                                       |            |                                                                                                          |                                                    |     | 43                                                                                                                                                                                                                                             |

|     |                                                                                                                                                                  | S Buffer (SBUFF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                                       |                                       |                                       |                                       |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                                                                                                                                                                                                                                                                                                       |                                       |            |                                                                                                          |                                                    |     |                                                                                                                                                                                                                                                |

|     |                                                                                                                                                                  | Stack Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |                                       |                                       |                                       |                                       |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |                                                                                                                                                                                                                                                                                                                       |                                       |            |                                                                                                          |                                                    |     |                                                                                                                                                                                                                                                |