# UNIVERSAL PROM PROGRAMMER REFERENCE MANUAL

Manual Order Number: 9800133F

Copyright © 1975, 1976, 1977 Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051 The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

| ICE-30          | MCS         |

|-----------------|-------------|

| ICE-80          | MEGACHASSIS |

| INSITE          | MICROMAP    |

| INTEL           | MULTIBUS    |

| INTELLEC        | PROMPT      |

| LIBRARY MANAGER | RMX         |

|                 | UPI         |

ii

## TABLE OF CONTENTS

1

| SECTION |                                                                                                                                                                                                                                                                                           | PAGE NO.                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1       | INTRODUCTION<br>1.1 SYSTEM OVERVIEW<br>1.2 CONTROL COMPUTER SOFTWARE REQUIREMENT                                                                                                                                                                                                          | 1-1<br>1-3<br>1-7                 |

| 2       | <pre>THE CONTROL BOARD 2.1 FUNCTIONAL DESCRIPTION: CONTROL BOARD 2.2 THEORY OF OPERATION: CONTROL BOARD 2.2.1 READ STATUS SEQUENCES 2.2.2 CONTROL/ADDRESS OUTPUT SEQUENCE 2.2.3 PROM READ DATA SEQUENCE 2.2.4 PROM PROGRAM DATA SEQUENCE 2.3 PIN LIST: CONTROL BOARD</pre>                | 2-9<br>2-9                        |

| 3       | SYSTEM UTILIZATION<br>3.1 INSTALLATION<br>3.1.1 CABLING<br>3.1.2 PERSONALITY CARD INSTALLATION<br>3.1.3 PROM DEVICE INSERTION<br>3.1.4 SOCKET BOARD REPLACEMENT<br>3.1.5 I/O PORT ASSIGNMENTS<br>3.2 INTERFACING<br>3.2.1 INTERFACE SIGNAL DESCRIPTION<br>3.2.2 OPERATING CHARACTERISTICS | 3-10<br>3-11<br>3-12<br>3-16      |

| 4       | <pre>THE UPP-878 PERSONALITY CARD 4.1 2708/2704 PROM 4.2 FUNCTIONAL DESCRIPTION: UPP-878         PERSONALITY CARD         4.2.1 SYSTEM SOFTWARE REQUIREMENTS 4.3 PIN LIST: UPP-878 PERSONALITY CARD</pre>                                                                                 | 4-1<br>4-3<br>4-5<br>4-13<br>4-13 |

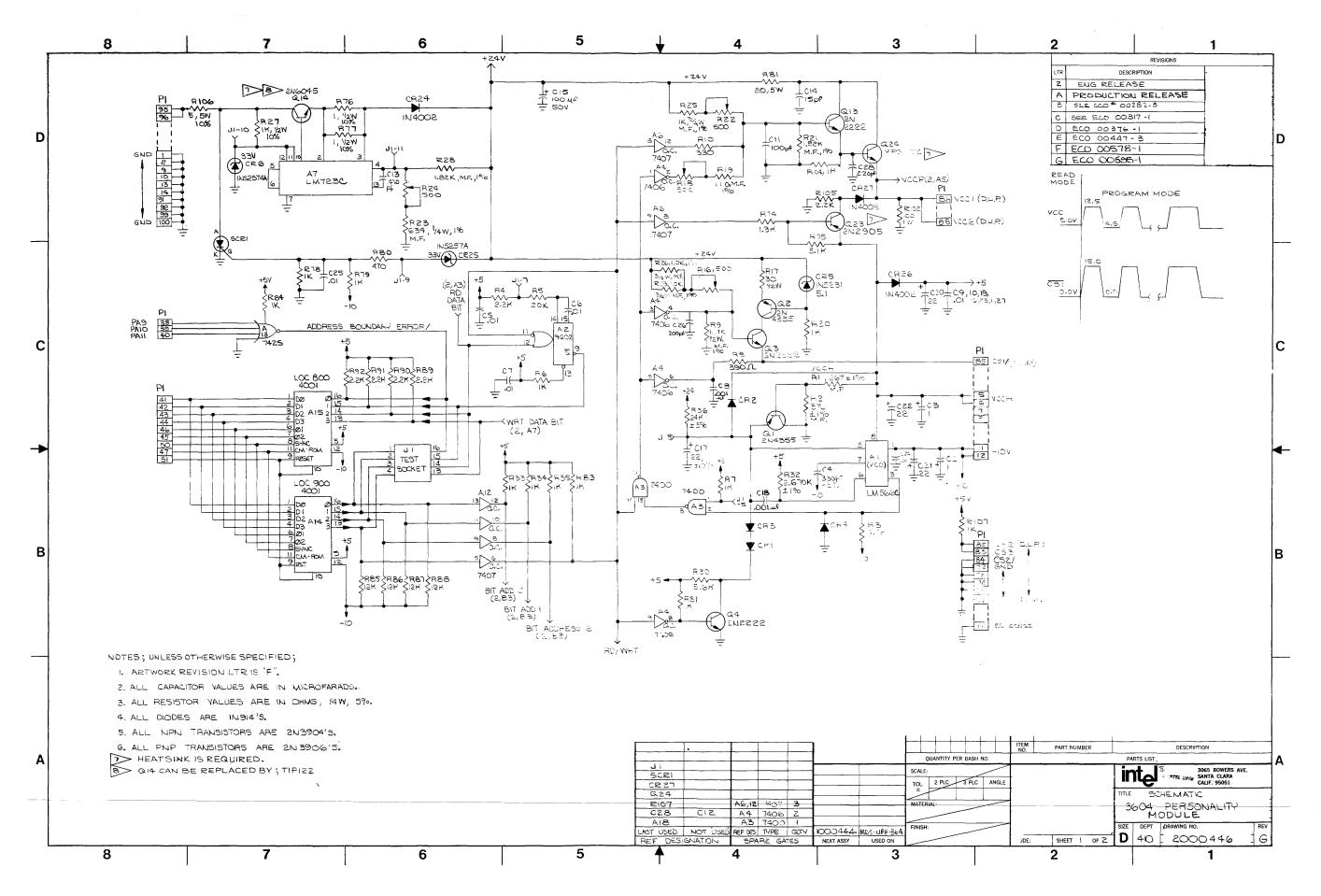

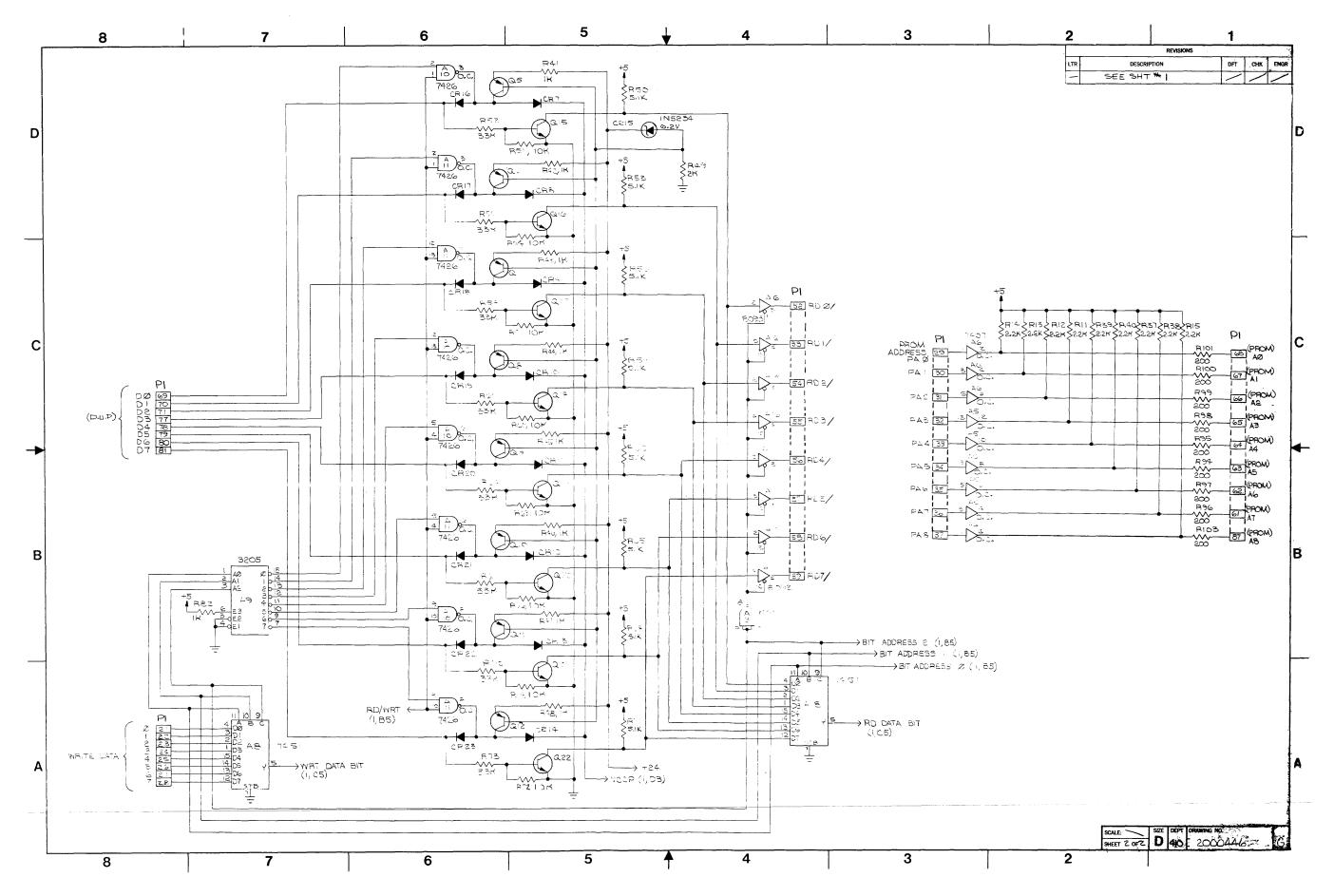

| 5       | <pre>THE UPP-864 PERSONALITY CARD 5.1 3604/3624/3602/3622/3621 PROM 5.2 FUNCTIONAL DESCRIPTION: UPP-864         PERSONALITY CARD 5.3 PROGRAMMING PROCEDURE 5.4 PIN LIST: UPP-864 PERSONALITY CARD</pre>                                                                                   | 5-1<br>5-3<br>5-4<br>5-13<br>5-15 |

| 6       | THE UPP-361 PERSONALITY CARD<br>6.1 3601 PROM<br>6.2 FUNCTIONAL DESCRIPTION: UPP-361<br>PERSONALITY CARD<br>6.3 PIN LIST: UPP-361 PERSONALITY CARD                                                                                                                                        | 6-1<br>6-3<br>6-4<br>6-12         |

| 7       | <pre>THE UPP-872 PERSONALITY CARD 7.1 1702A/1602A PROM 7.2 FUNCTIONAL DESCRIPTION: UPP-872         PERSONALITY CARD 7.3 PIN LIST: UPP-872 PERSONALITY CARD</pre>                                                                                                                          | 7-1<br>7-3<br>7-5<br>7-11         |

## SECTION

PAGE NO.

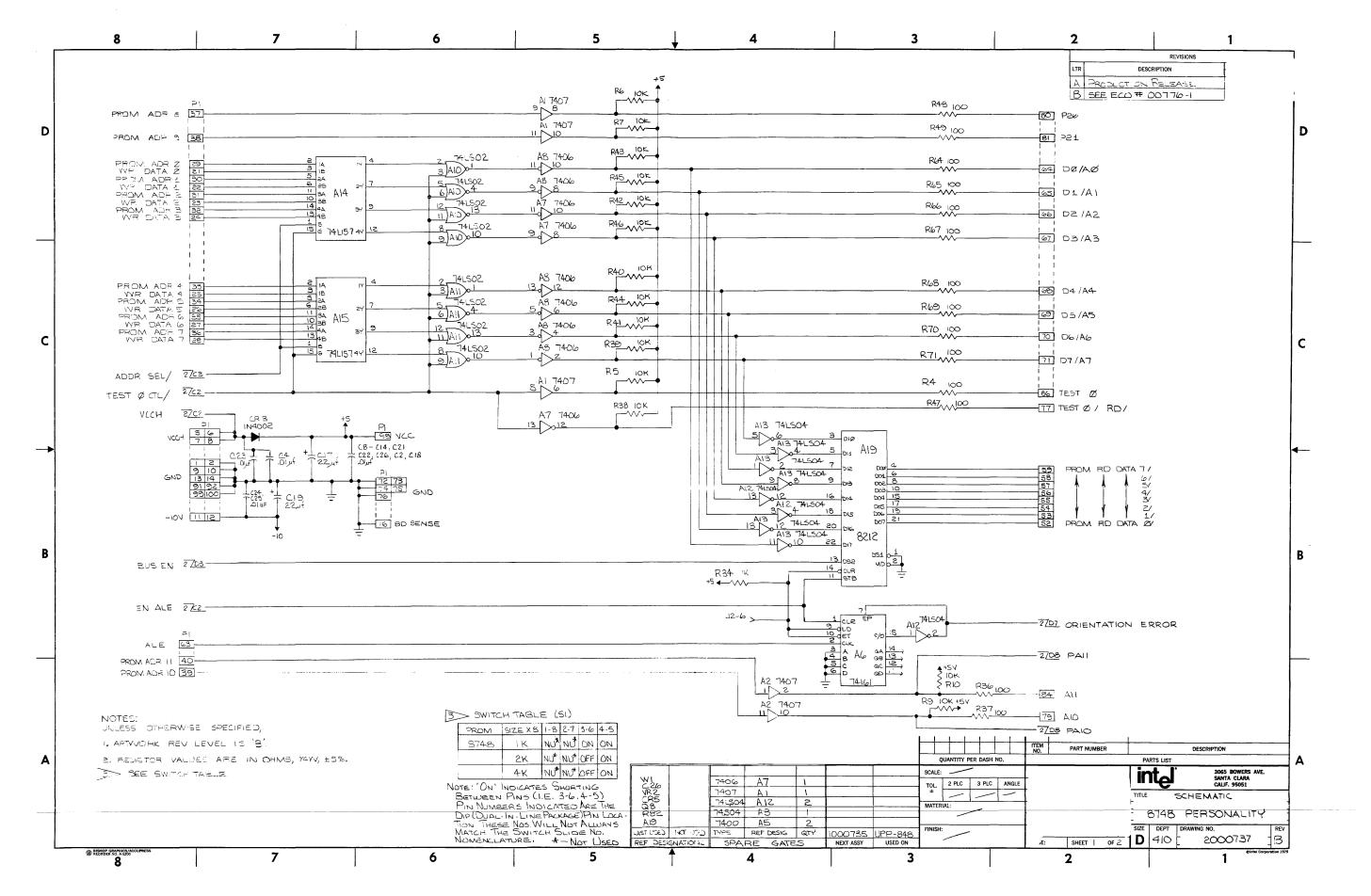

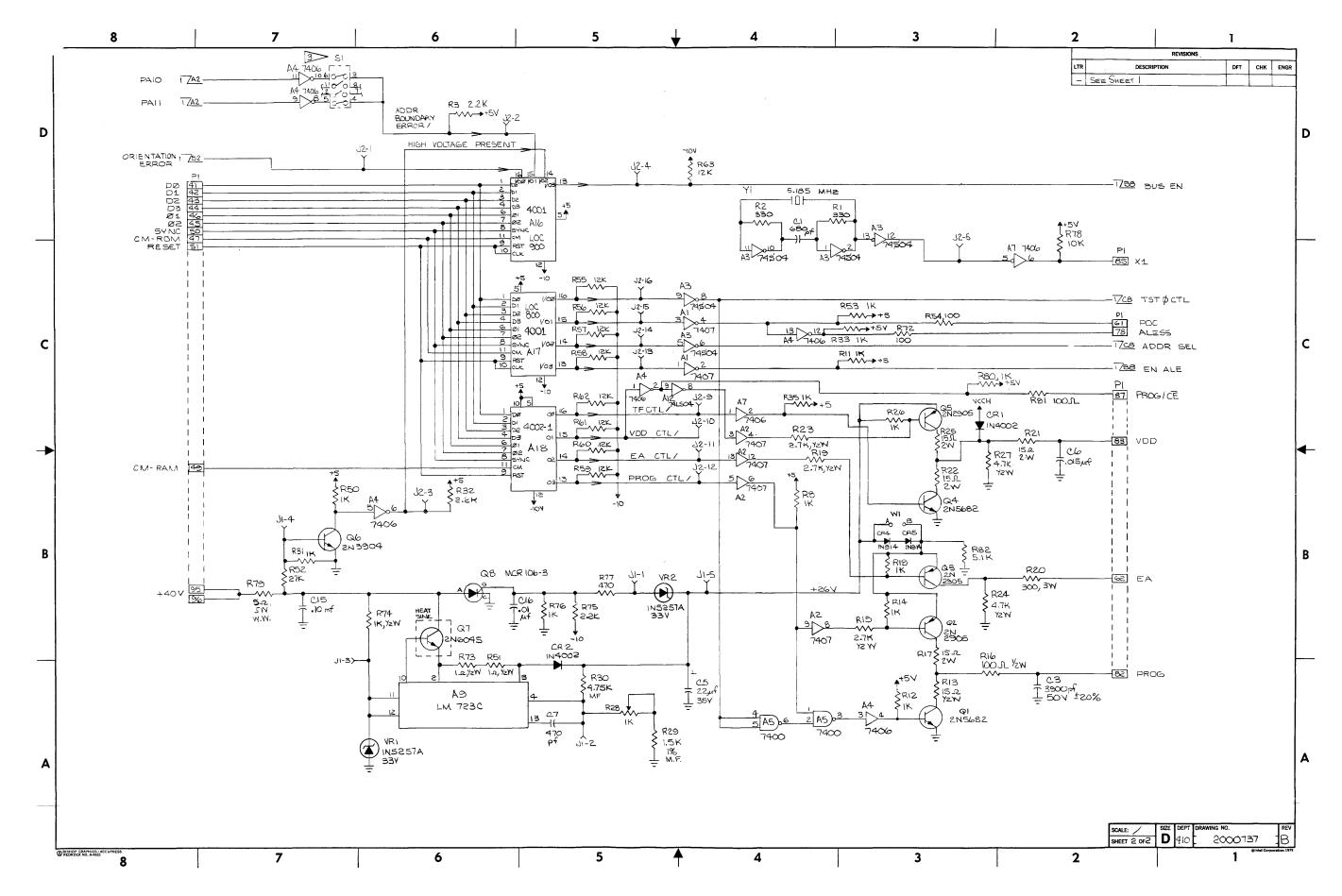

| 8  | THE UPP-848 PERSONALITY CARD<br>8.1 8748 PROM MICROCOMPUTER<br>8.2 8748 ADAPTER FOR 24-PIN SOCKETS<br>8.3 FUNCTIONAL DESCRIPTION: UPP-848<br>8.4 PIN LIST: UPP-848 PERSONALITY CARD                                                                                                                                              | 8-3                                                                   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

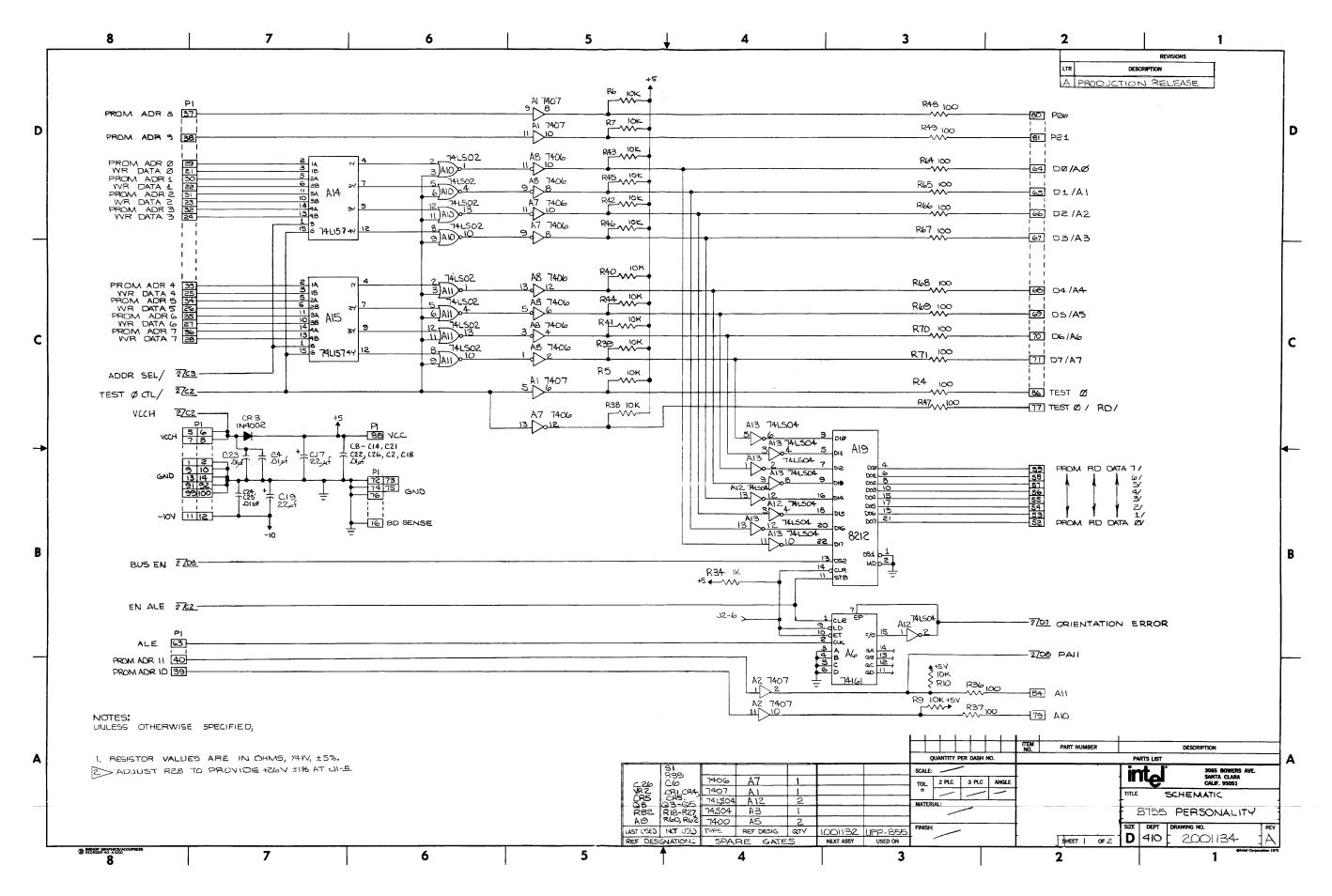

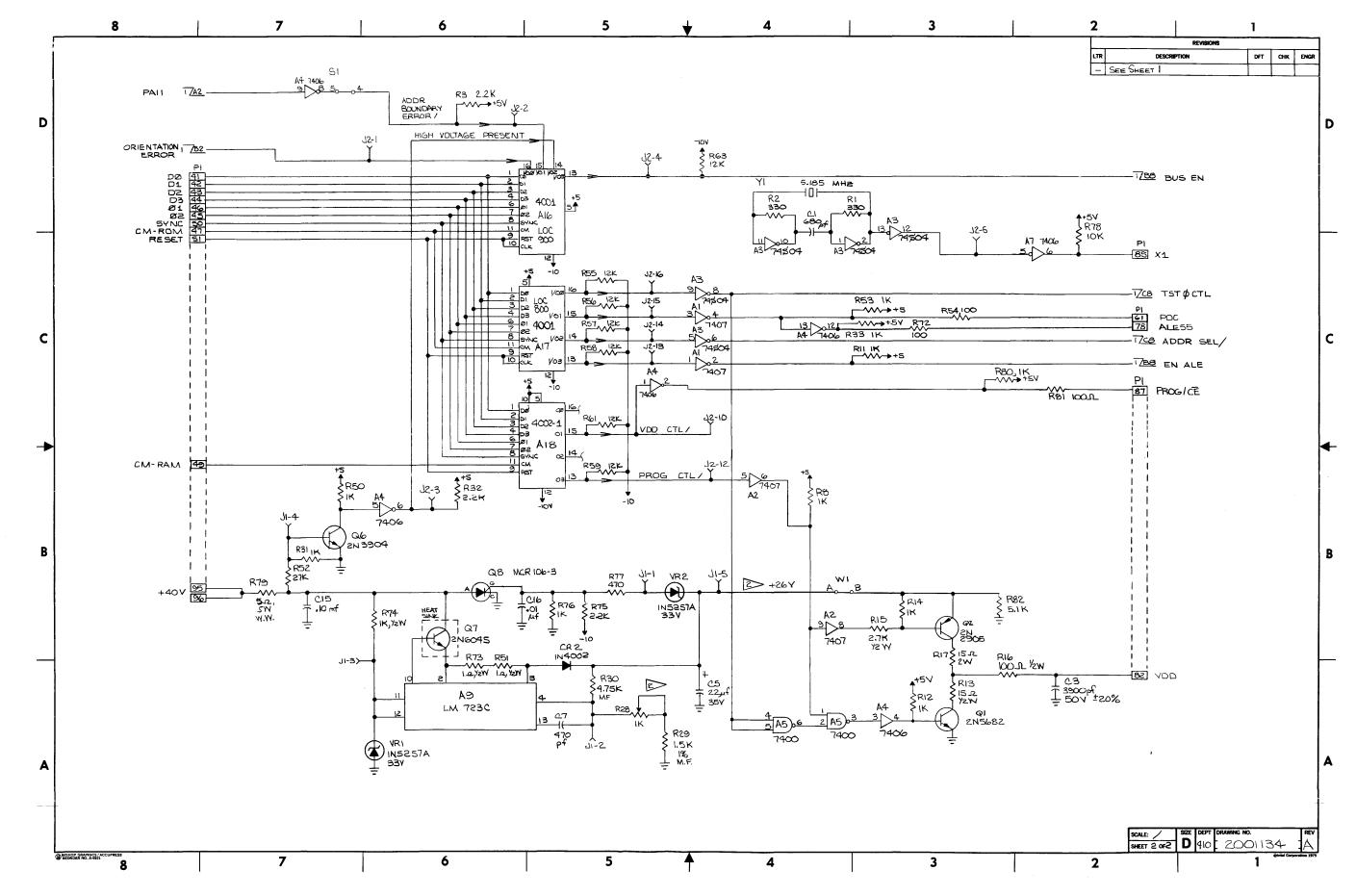

|    | <ul> <li>THE UPP-855 AND UPP-955 PERSONALITY CARDS</li> <li>9.1 8755 AND 8755A PROM-I/O DEVICES</li> <li>9.2 8755 AND 8755A ADAPTERS</li> <li>9.3 FUNCTIONAL DESCRIPTION: UPP-855 AND UPP-955 PERSONALITY CARDS</li> <li>9.4 SYSTEM SOFTWARE REQUIREMENTS</li> <li>9.5 PIN LIST: UPP-855 AND UPP-955 PERSONALITY CARD</li> </ul> |                                                                       |

| 10 | <pre>10.1 PROM CHARACTERISTICS<br/>10.1.1 2716 PROM<br/>10.1.2 2758 PROM<br/>10.1.3 2758 S-1865 PROM<br/>10.1.4 PROGRAMMING<br/>10.1.5 ADDRESS BOUNDARIES<br/>10.1.6 ERASING PROMS<br/>10.2 FUNCTIONAL DESCRIPTION: UPP-816<br/>PERSONALITY CARD</pre>                                                                           | 10-1<br>10-1<br>10-2<br>10-2<br>10-2<br>10-4<br>10-6<br>10-7<br>10-12 |

| 11 | <pre>11.1 APPLICABLE DOCUMENTATION 11.2 GENERAL 11.3 OPERATING INSTRUCTIONS</pre>                                                                                                                                                                                                                                                | 11-1<br>11-1<br>11-3<br>11-3<br>11-4                                  |

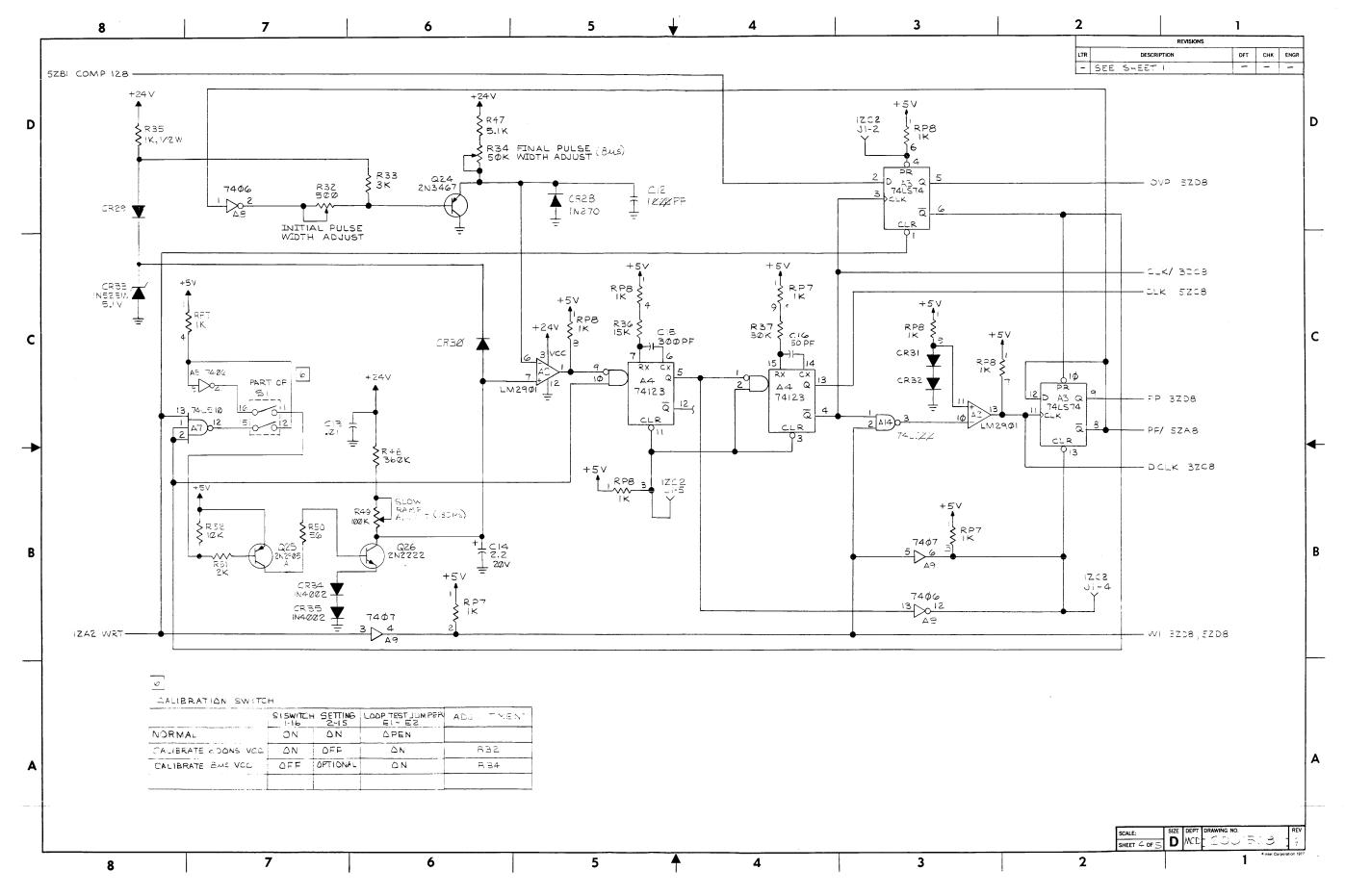

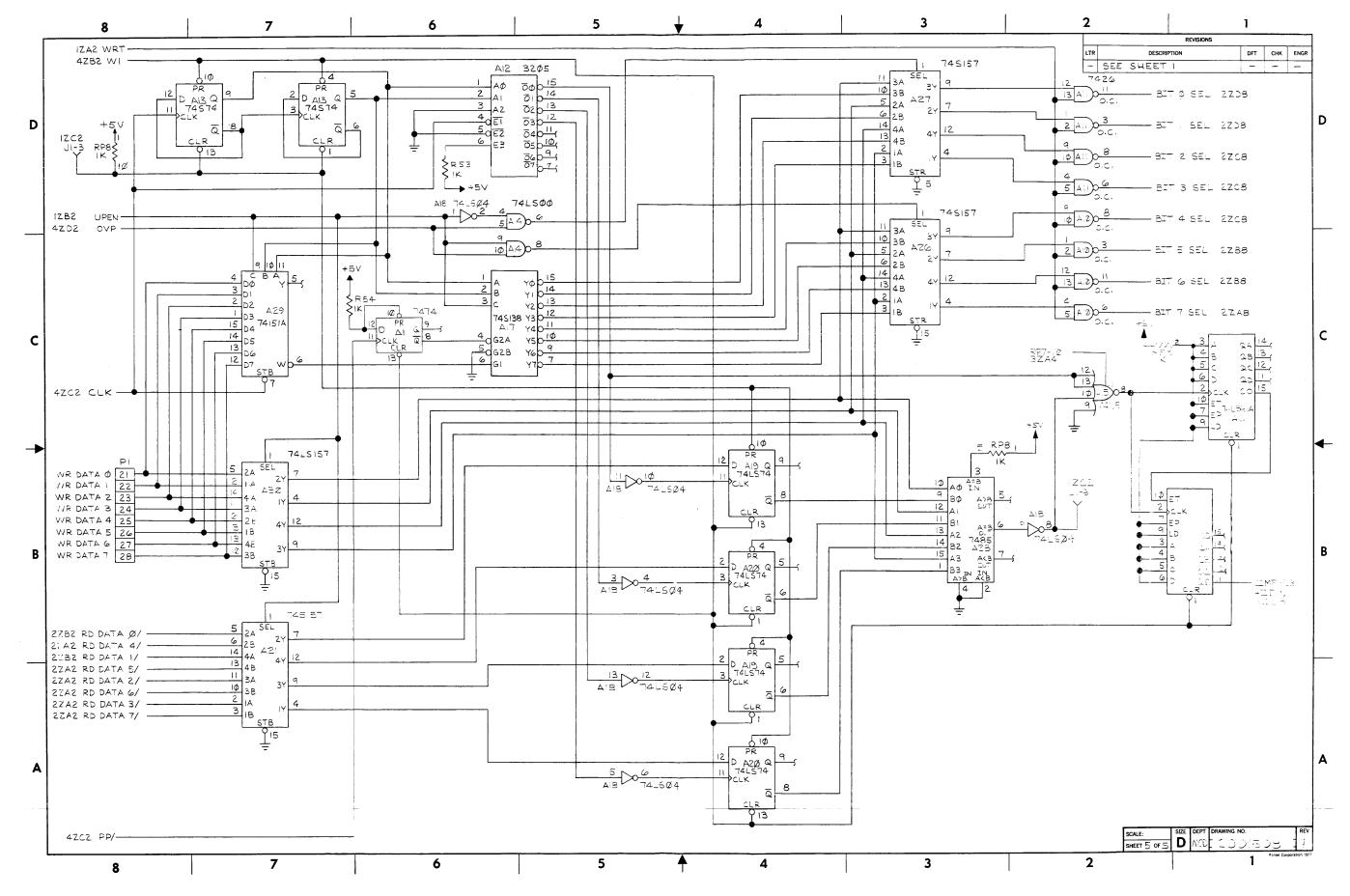

| 12 | <ul> <li>12.1 INTRODUCTION</li> <li>12.2 FUNCTIONAL DESCRIPTION: UPP-865<br/>PERSONALITY CARD</li> <li>12.2.1 PROM READ OPERATION</li> <li>12.2.2 PROM PROGRAM OPERATION</li> <li>12.3 PROGRAMMING PROCEDURE</li> <li>12.4 THE UPP-555, UPP-562, AND UPP-565<br/>ADAPTERS</li> <li>12.5 CALIBRATION PROCEDURES</li> </ul>        | 12-1<br>12-3<br>12-10<br>12-10<br>12-14<br>12-18<br>12-23<br>12-27    |

## TABLE OF CONTENTS (Continued)

| APPENDIX A | INTELLEC MDS MONITOR: PROM PROGRAMMER<br>COMMANDS | A-1 |

|------------|---------------------------------------------------|-----|

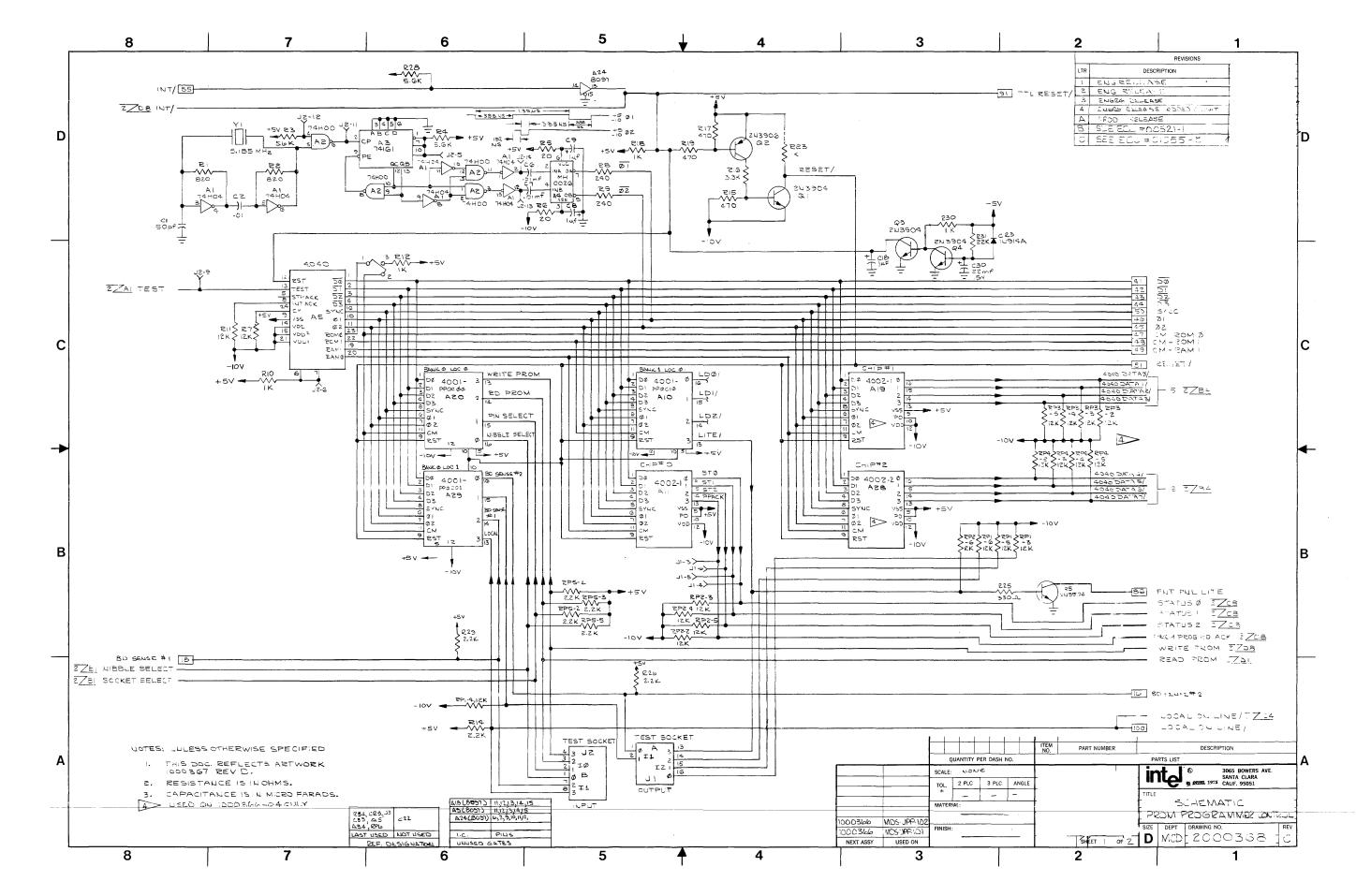

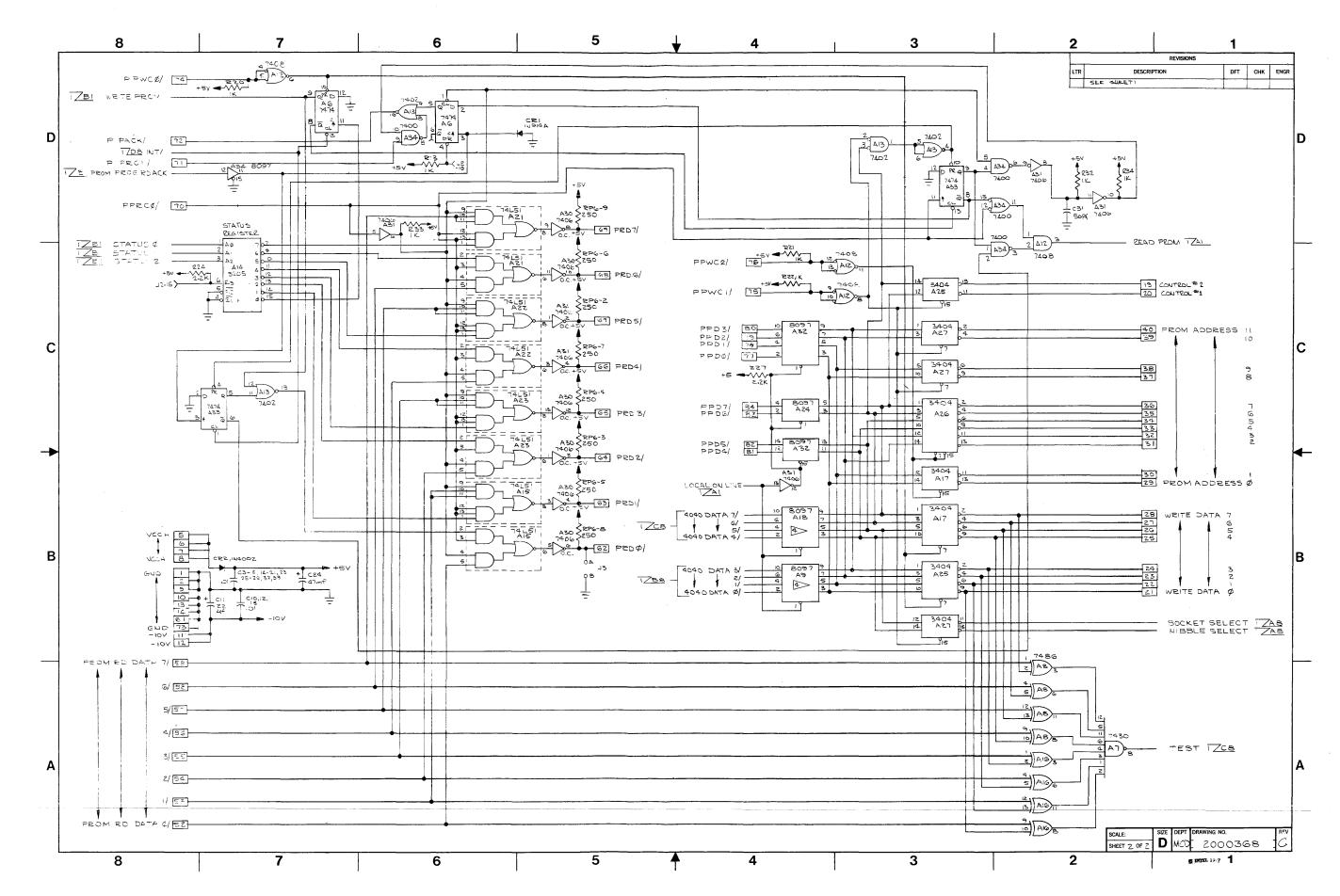

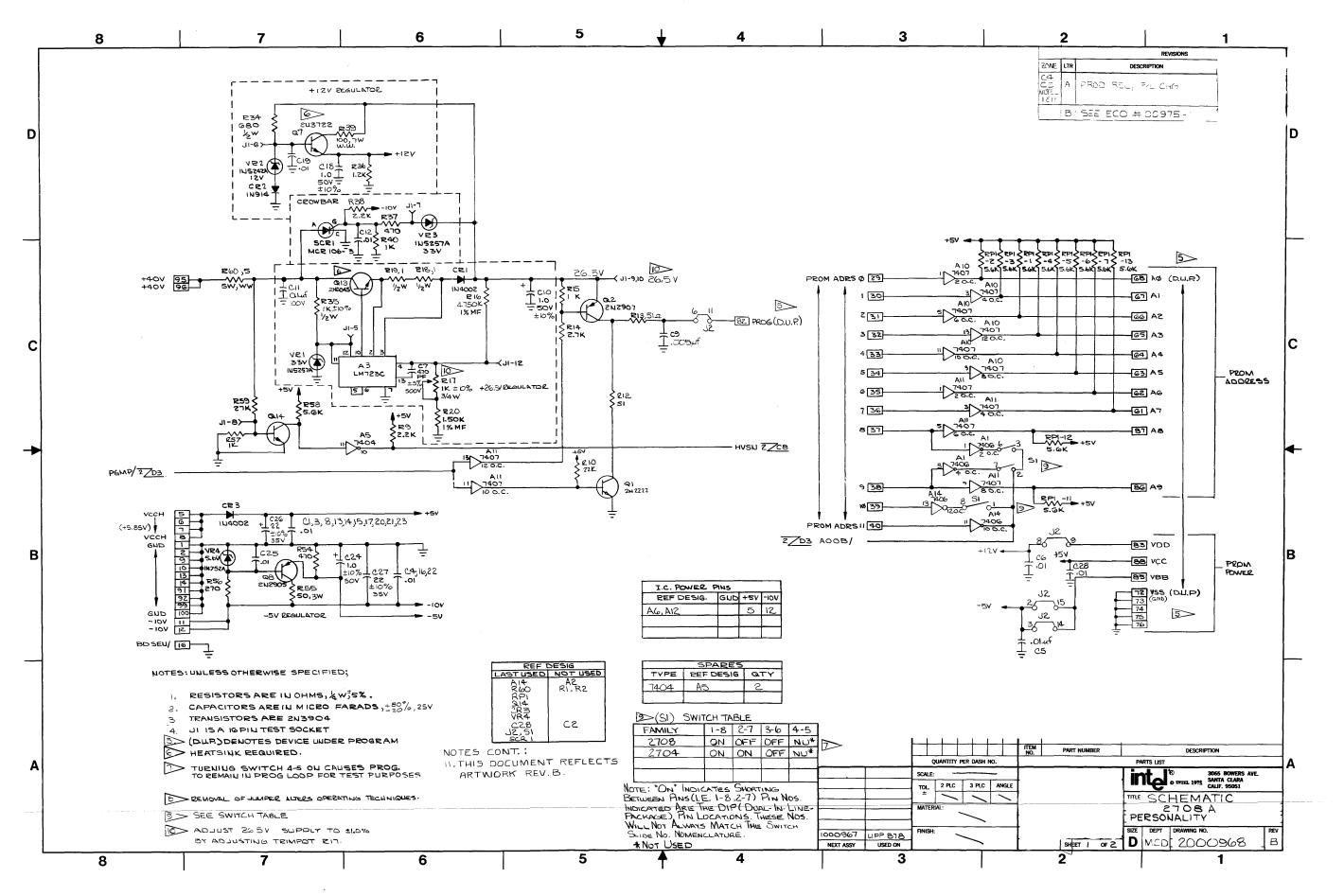

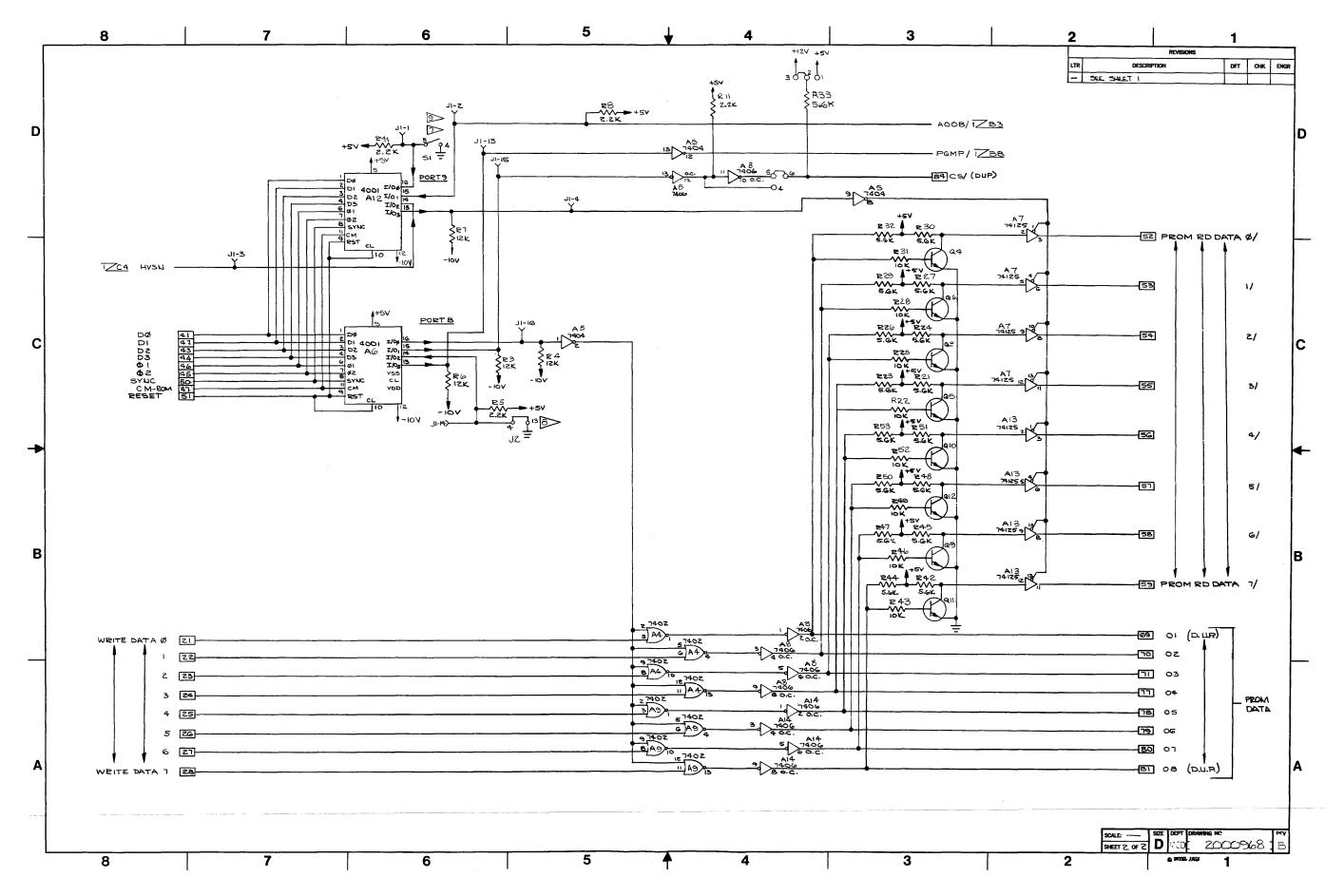

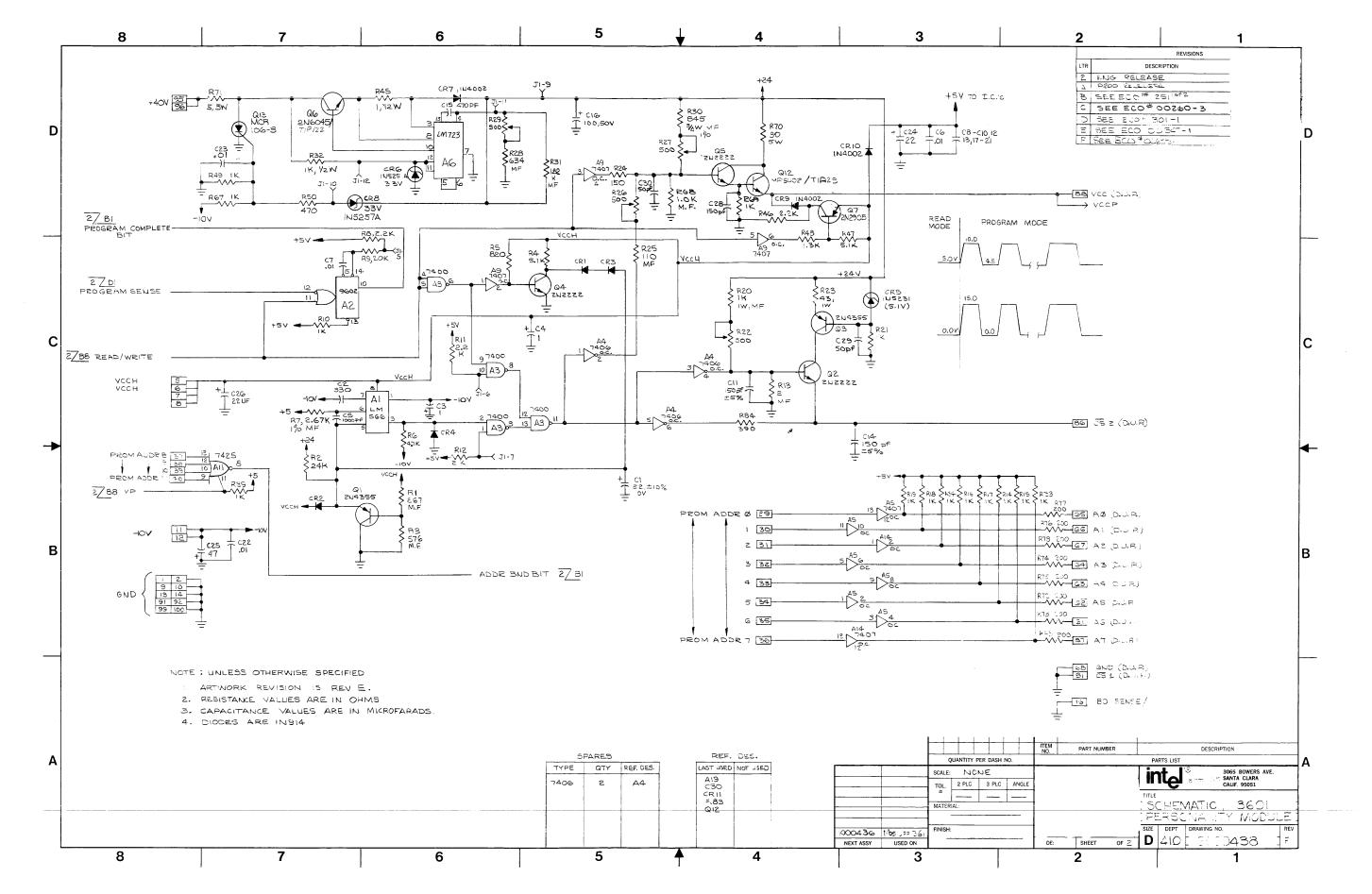

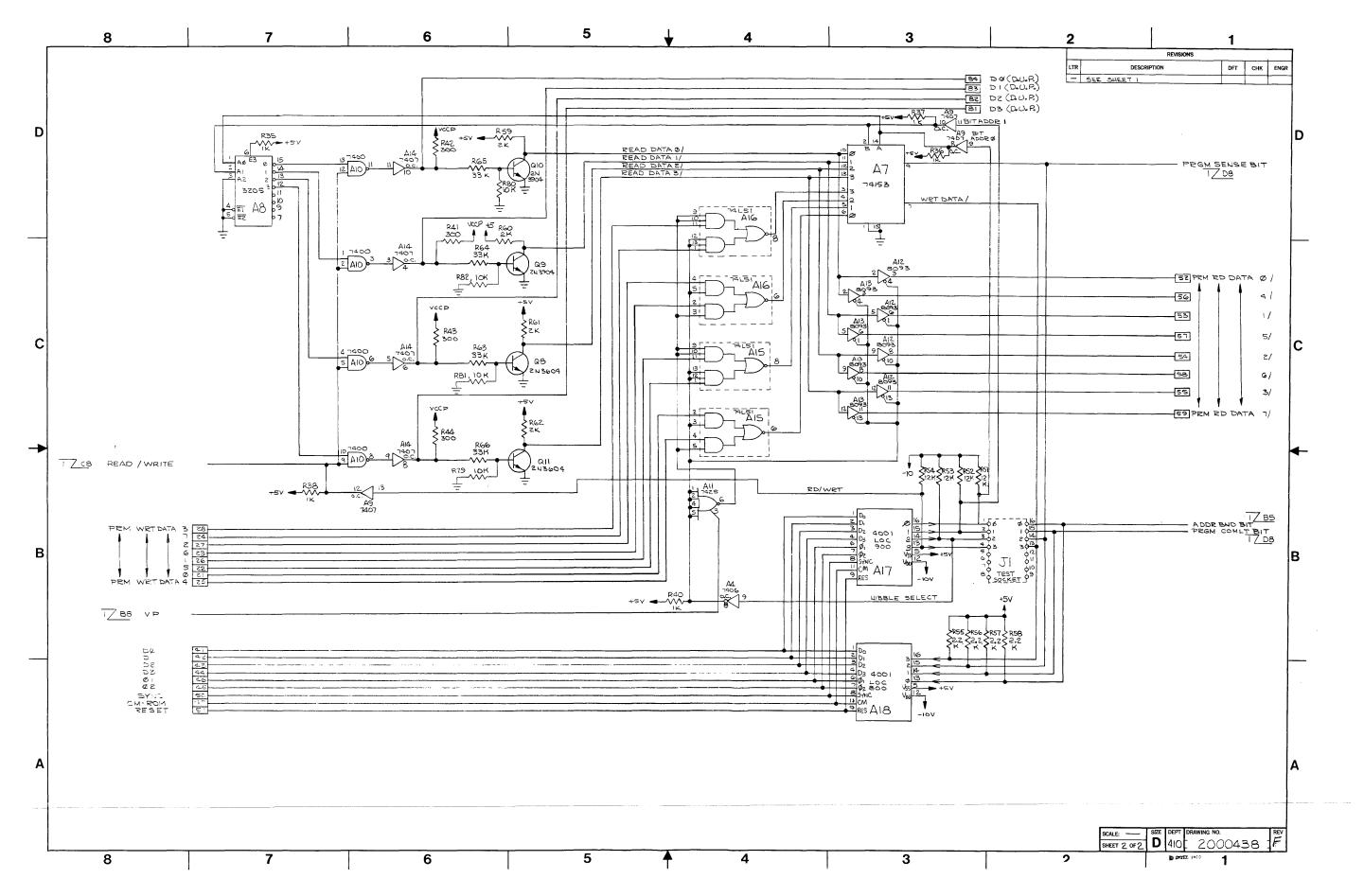

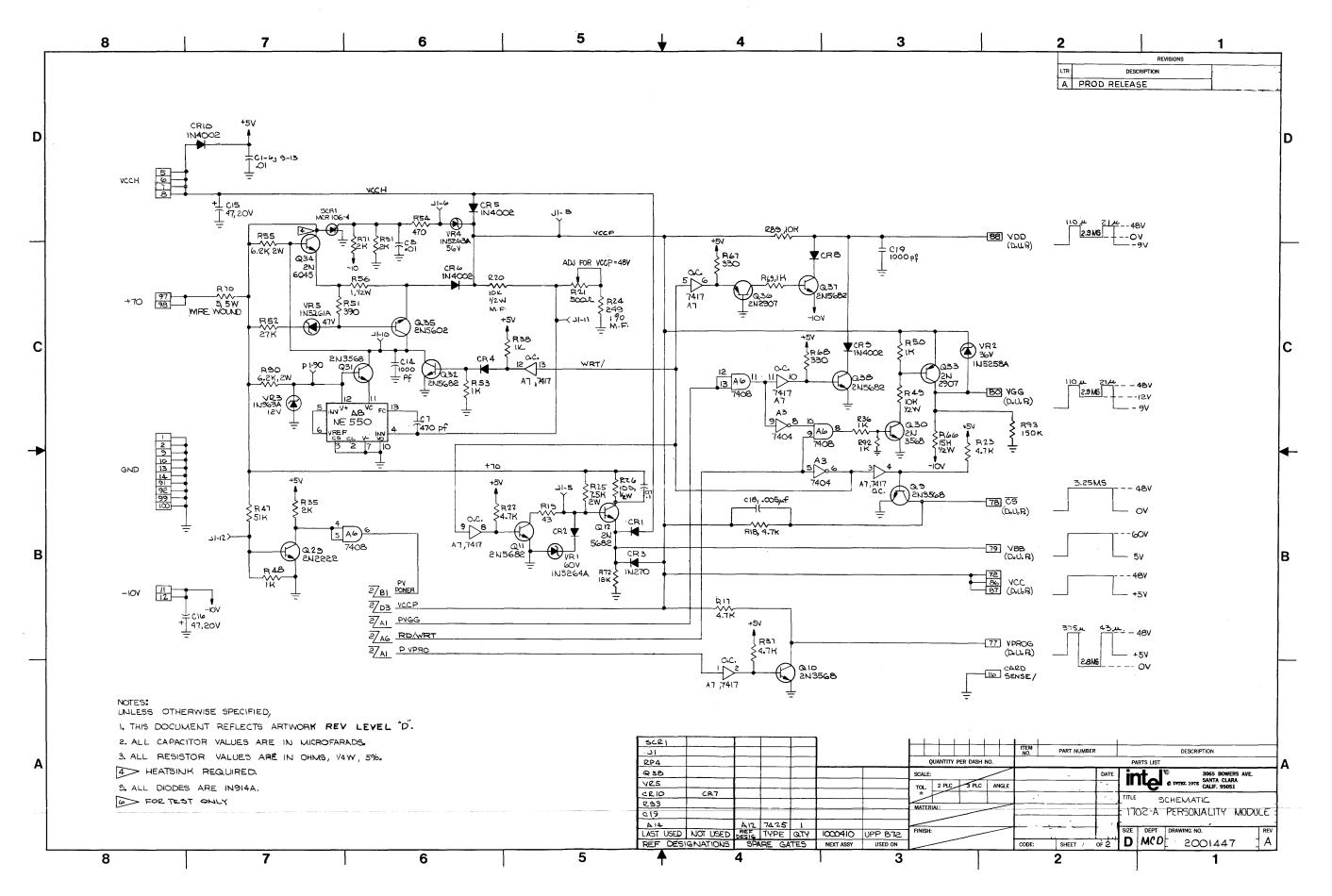

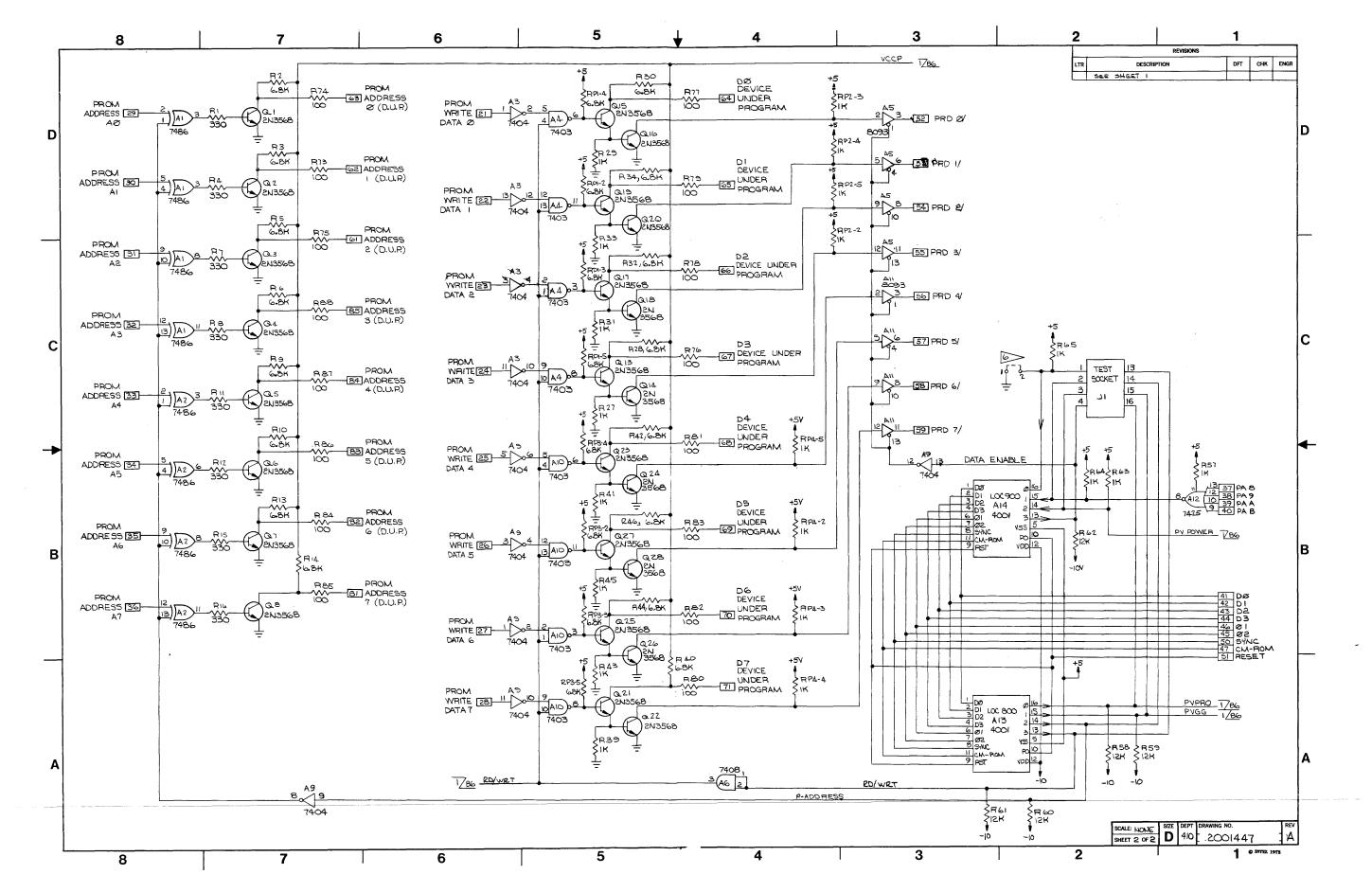

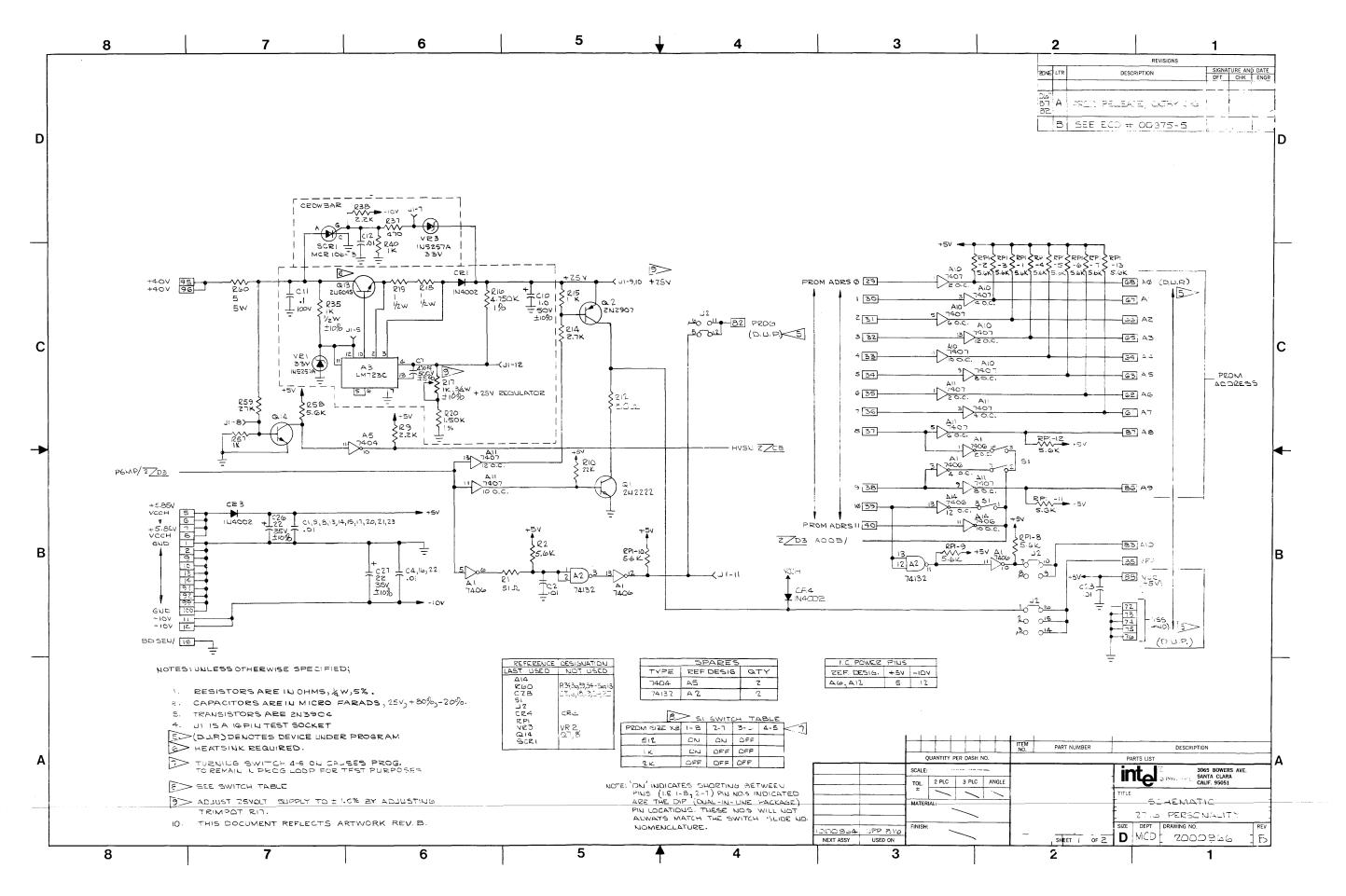

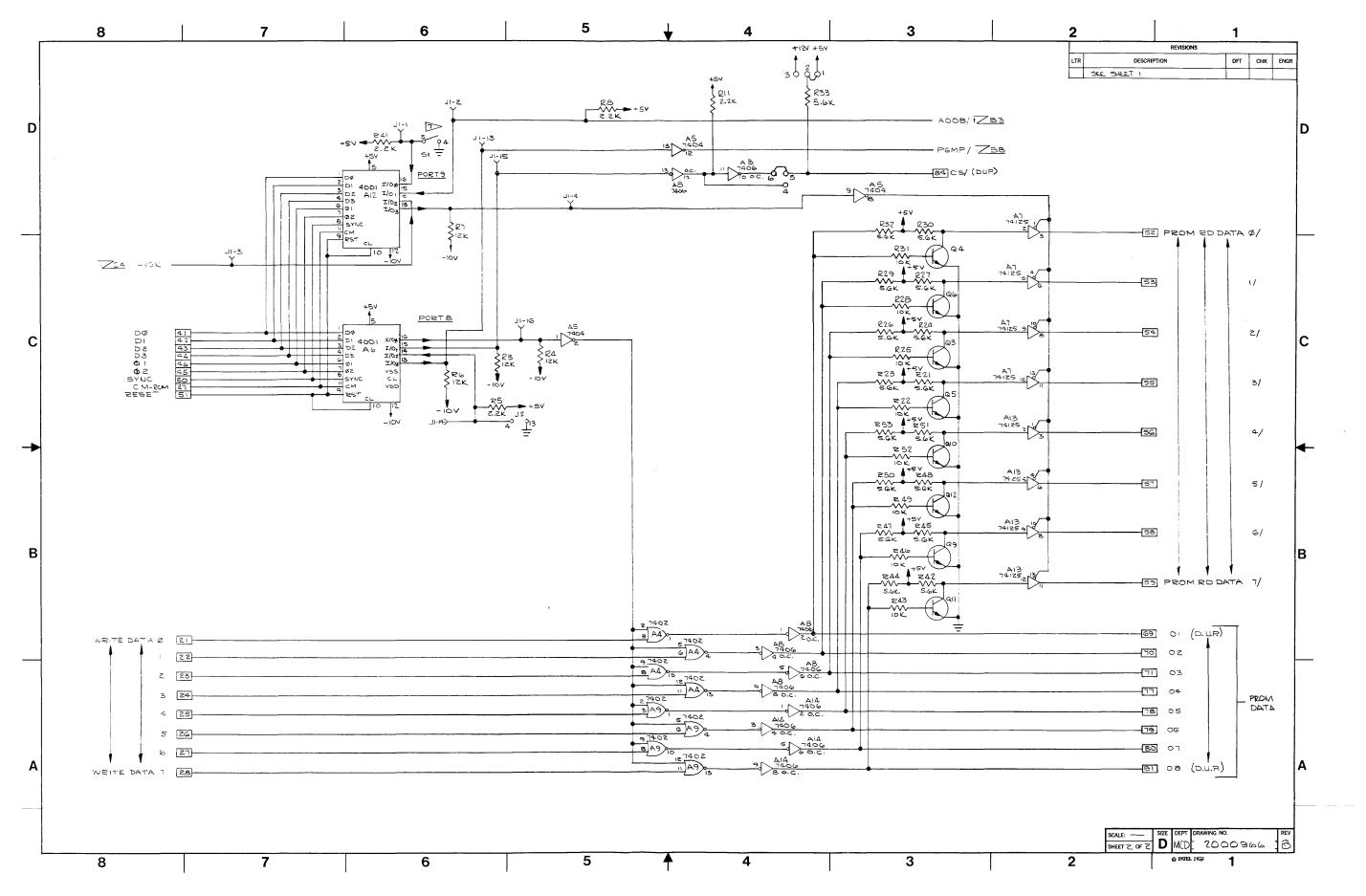

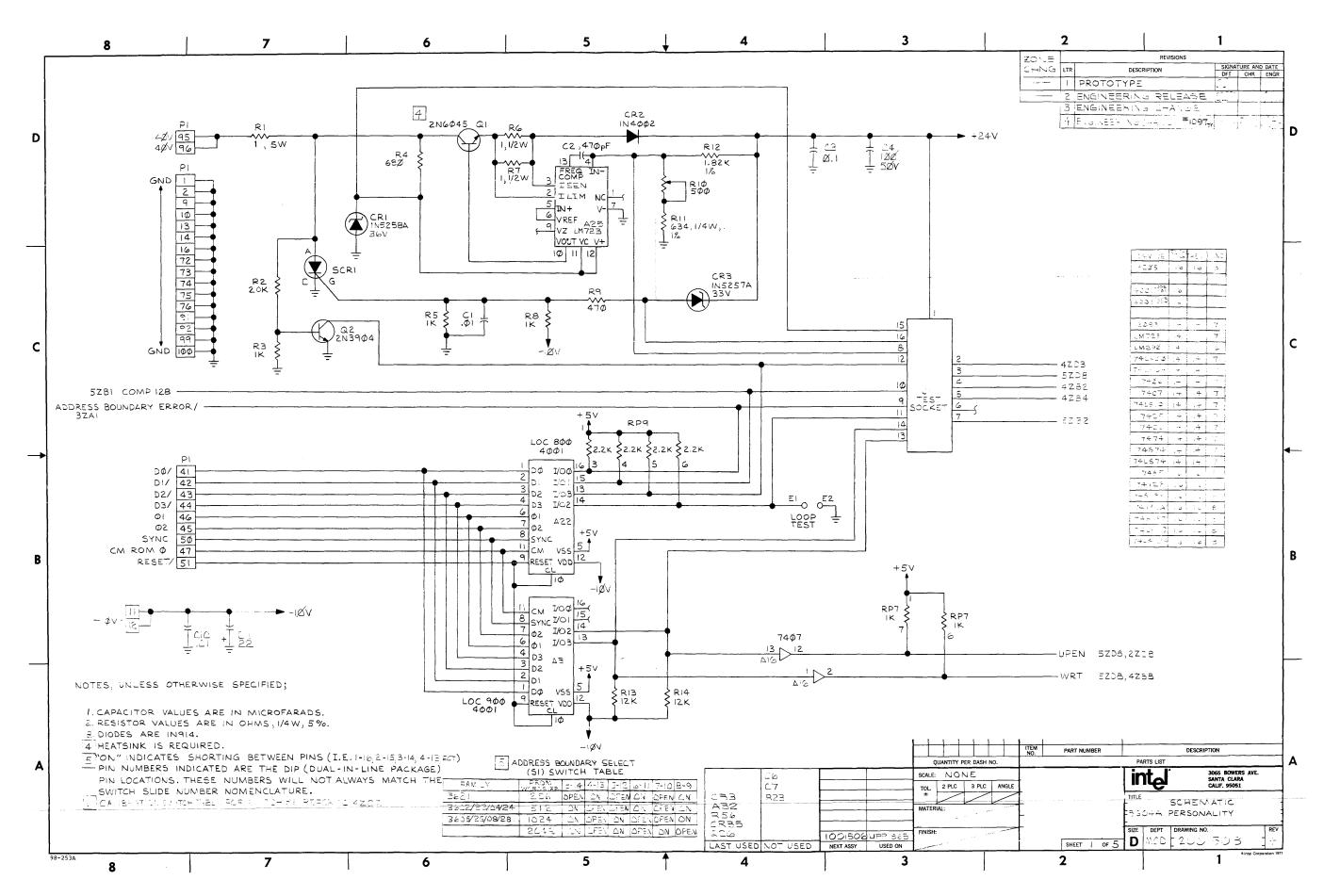

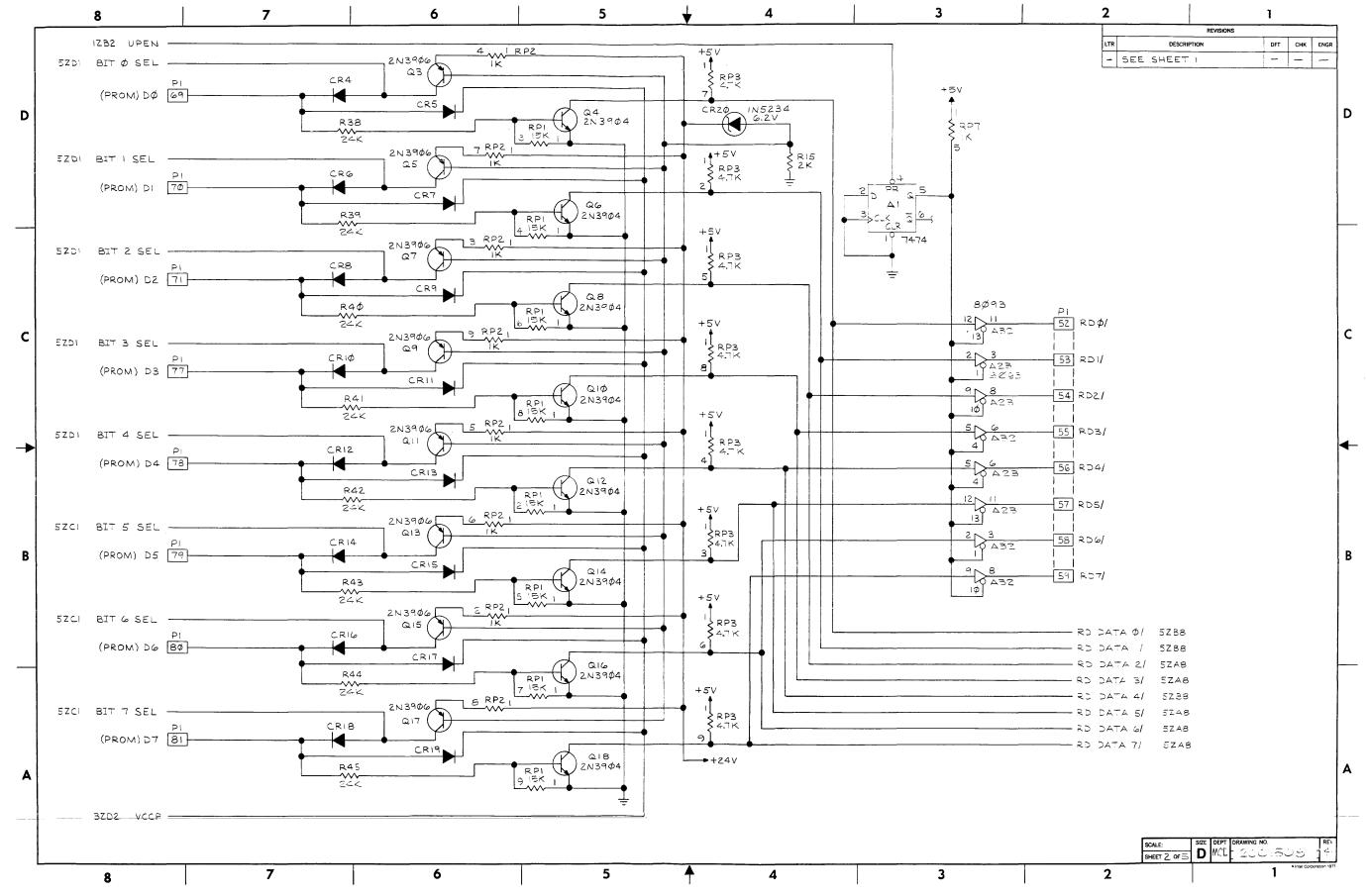

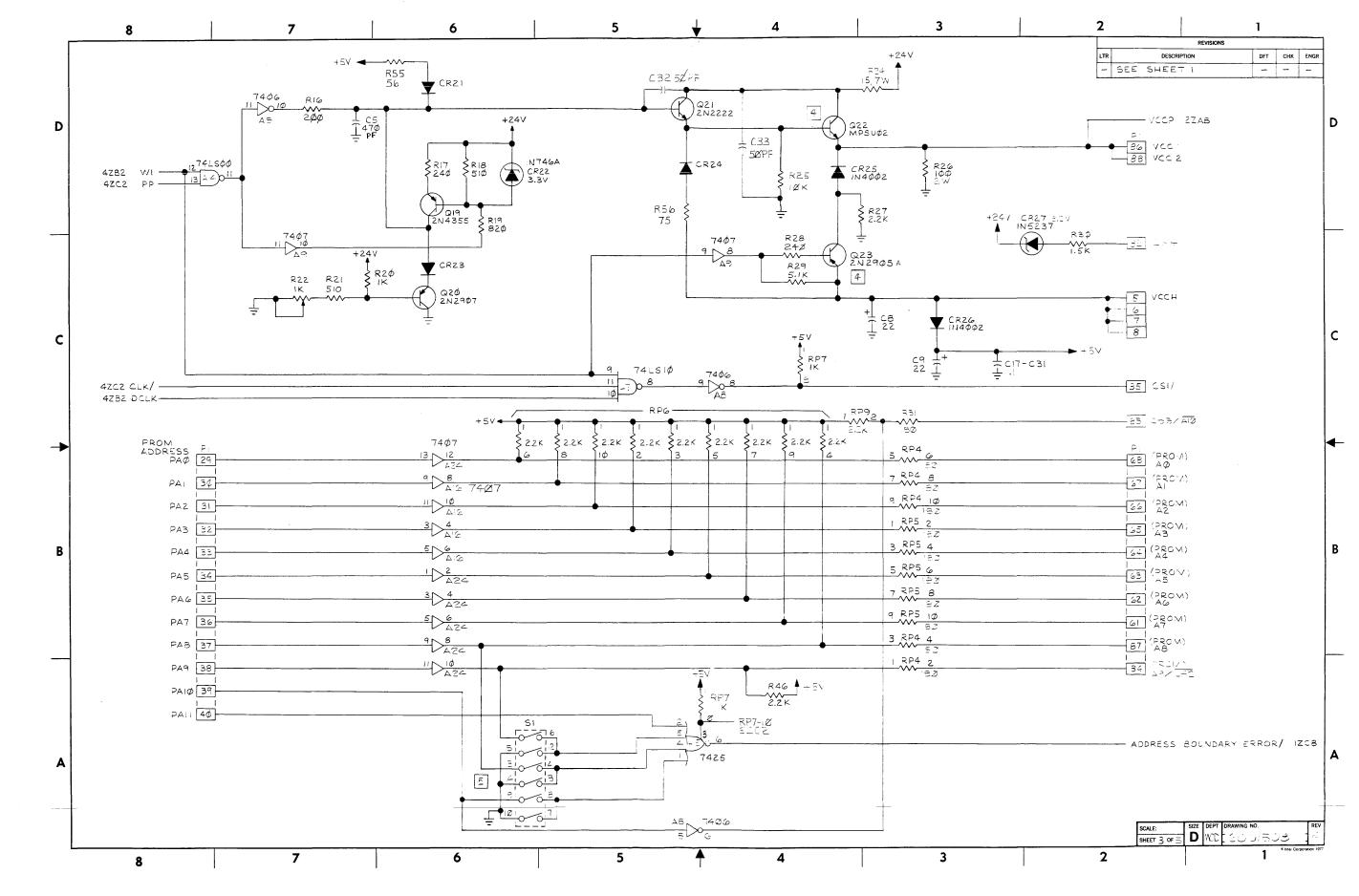

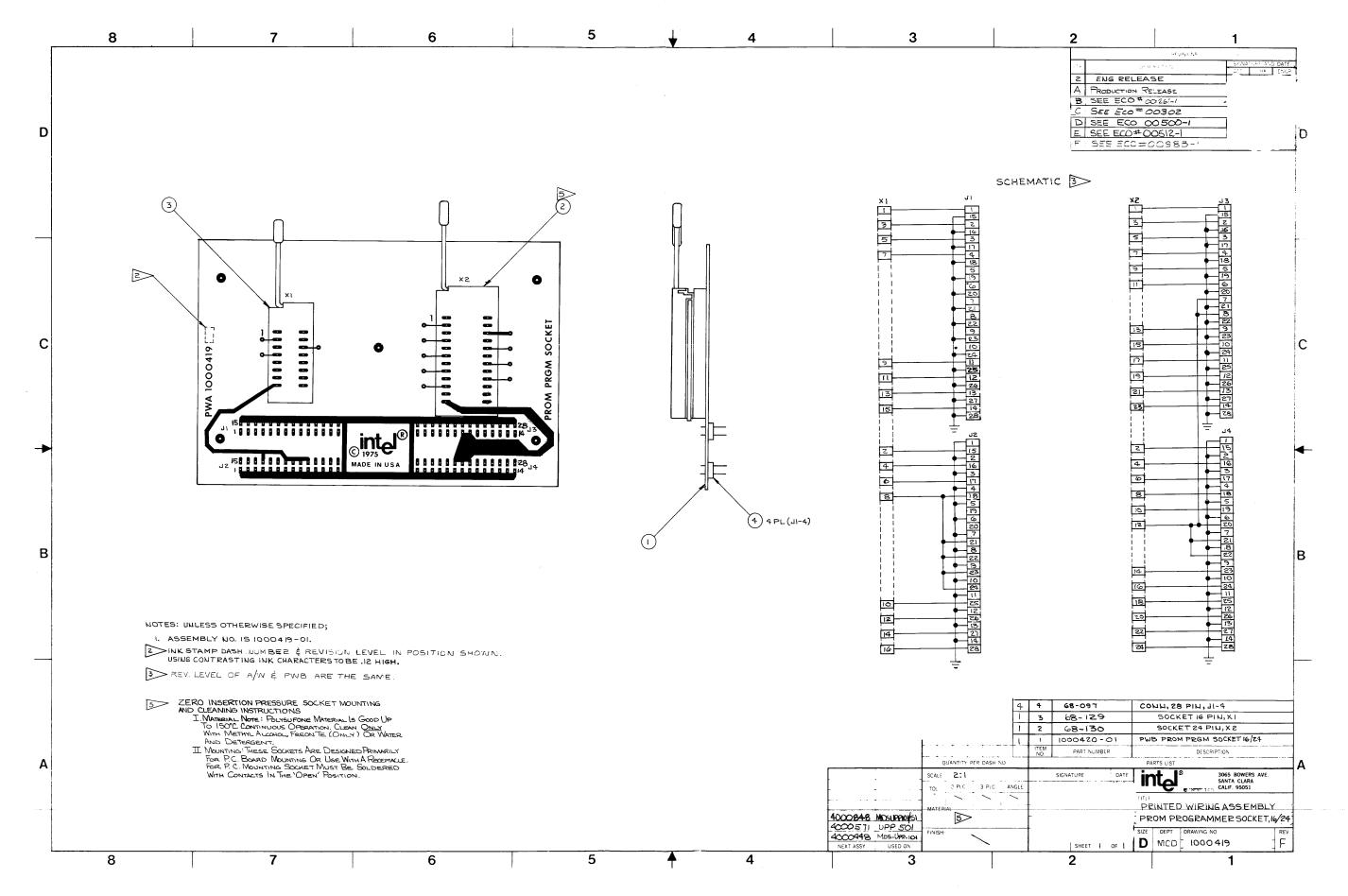

| APPENDIX B | UNIVERSAL PROM PROGRAMMER SCHEMATICS              | B-1 |

| APPENDIX C | 2708 FAMILY SOFTWARE FOR THE INTELLEC MDS         | C-1 |

## LIST OF ILLUSTRATIONS

## FIGURE

## PAGE NO.

|                                               | PROM PROGRAMMER: FRONT PANEL AND CABINET<br>PROM PROGRAMMER: DATA FLOW<br>READ STATUS (FLOW CHART)<br>STATUS WORD<br>CONTROL AND ADDRESS PARAMETERS<br>PROGRAMMING ONE BYTE (FLOW CHART)<br>READ DATA - METHOD 1 (FLOW CHART)<br>READ DATA - METHOD 2 (FLOW CHART) | 1-4<br>1-6<br>1-8<br>1-9<br>1-10<br>1-12<br>1-14<br>1-15 |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7 | CONTROL BOARD BLOCK DIAGRAM<br>01 and 02 TIMING<br>PROM PROGRAMMER STATUS WORD<br>READ STATUS TIMING<br>PROM READ DATA TIMING<br>USING START RD BIT OF CONTROL BYTE<br>PROM PROGRAM WRITE TIMING                                                                   | 2-3<br>2-5<br>2-10<br>2-11<br>2-14<br>2-16<br>2-19       |

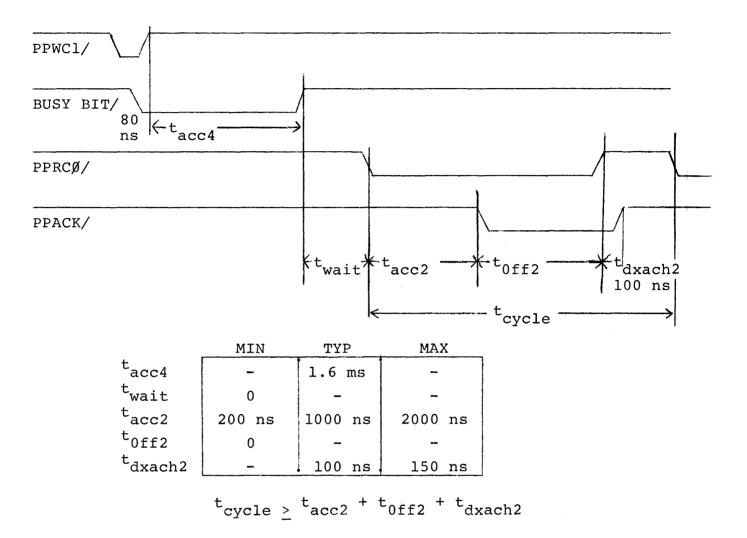

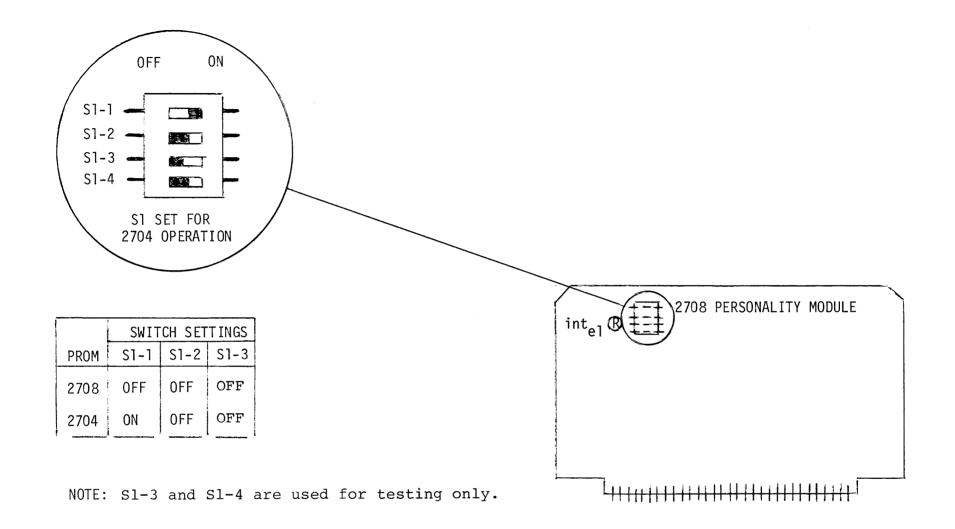

| 3-1<br>3-2<br>3-3<br>3-4                      | CABLING<br>TOP VIEW OF PROM PROGRAMMER (COVER REMOVED)<br>UNIVERSAL PROM PROGRAMMER (TOP VIEW)<br>AC CHARACTERISTICS                                                                                                                                               | 3-5<br>3-8<br>3-13<br>3-21                               |

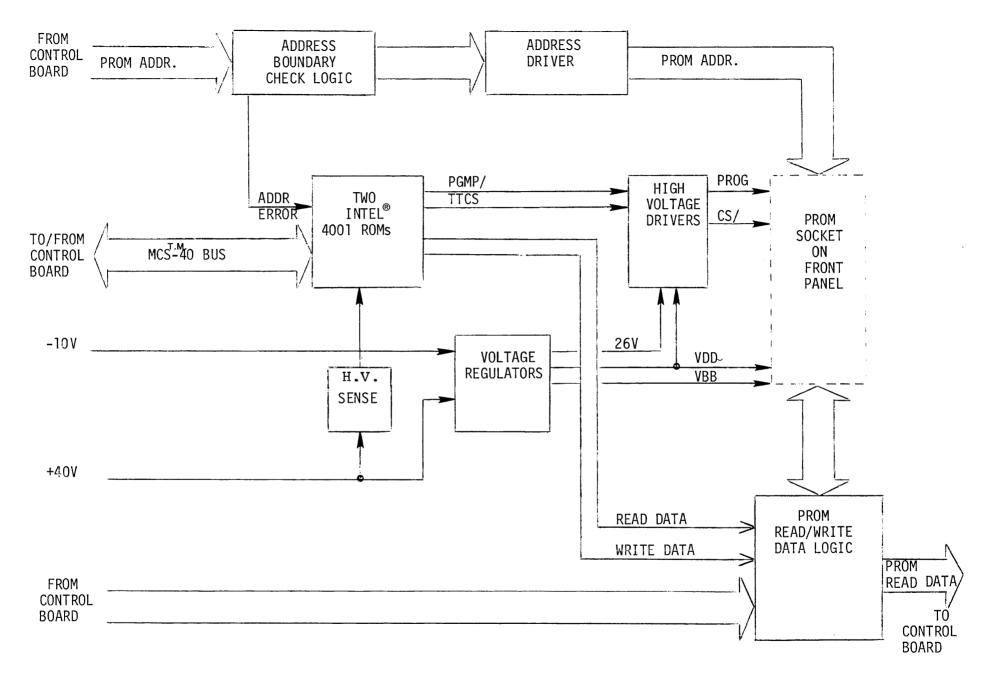

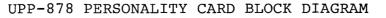

| 4-2                                           | UPP-878 PERSONALITY CARD BLOCK DIAGRAM<br>LOCATION AND OPERATION OF SW1<br>UPP-878 PERSONALITY CARD PROGRAM TIMING<br>UPP-878 SYSTEM SOFTWARE (FLOW CHART)                                                                                                         | 4-6<br>4-10<br>4-12<br>4-14                              |

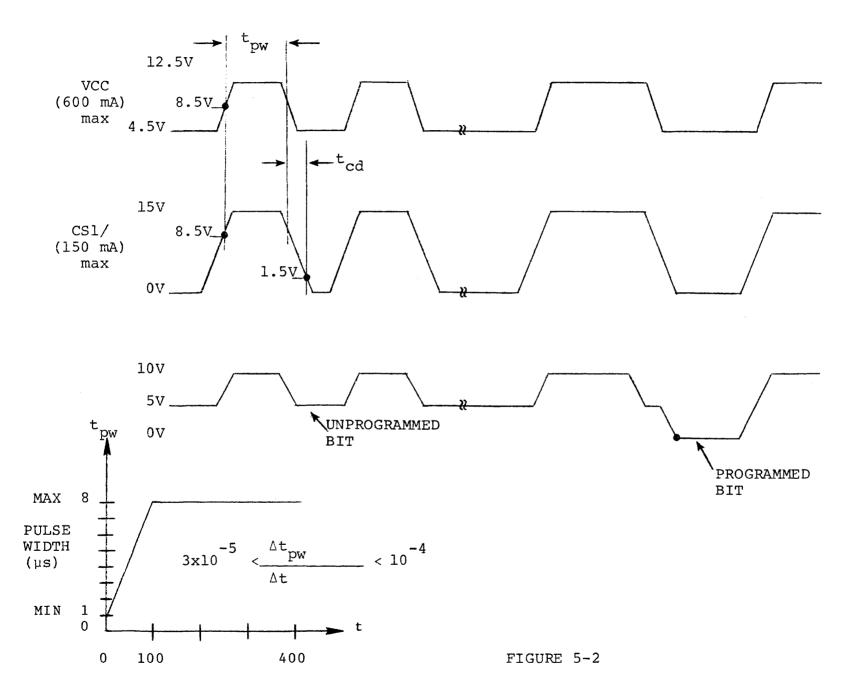

| 5-1<br>5-2<br>5-3                             | UPP-864 PERSONALITY CARD FUNCTIONAL BLOCK<br>DIAGRAM<br>PROGRAMMING PULSE TIMING DIAGRAM<br>FRONT VIEW OF UPP WITH ADAPTER                                                                                                                                         | 5-5<br>5-11<br>5-14                                      |

| 6-1<br>6-2                                    | UPP-361 PERSONALITY CARD FUNCTIONAL BLOCK<br>DIAGRAM<br>PROGRAMMING PULSE TIMING DIAGRAM                                                                                                                                                                           | 6-5<br>6-11                                              |

## LIST OF ILLUSTRATIONS (Continued)

| FIGURE                                       |                                                                                                                                                                                                                             | PAGE NO.                                                   |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

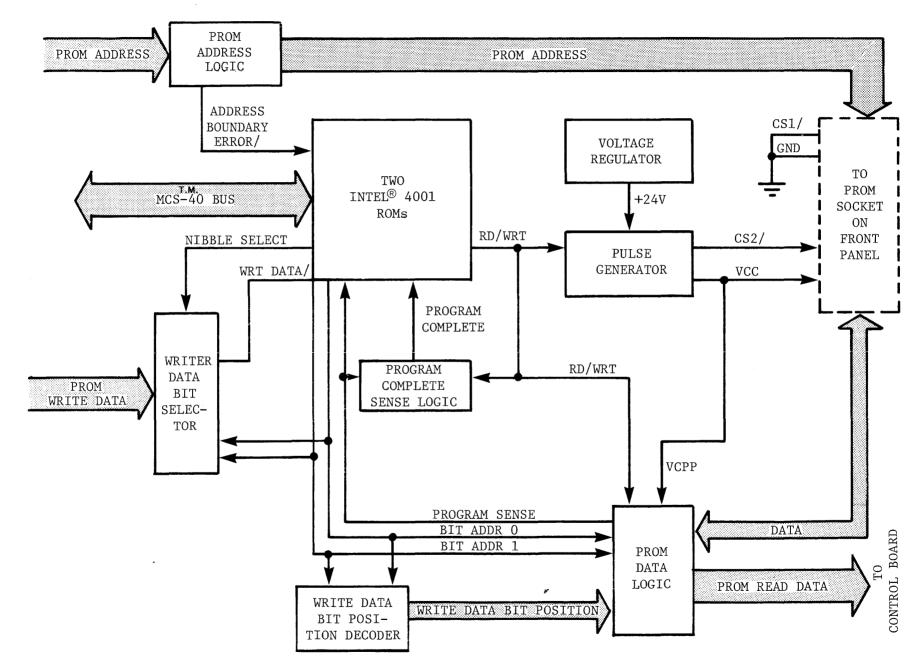

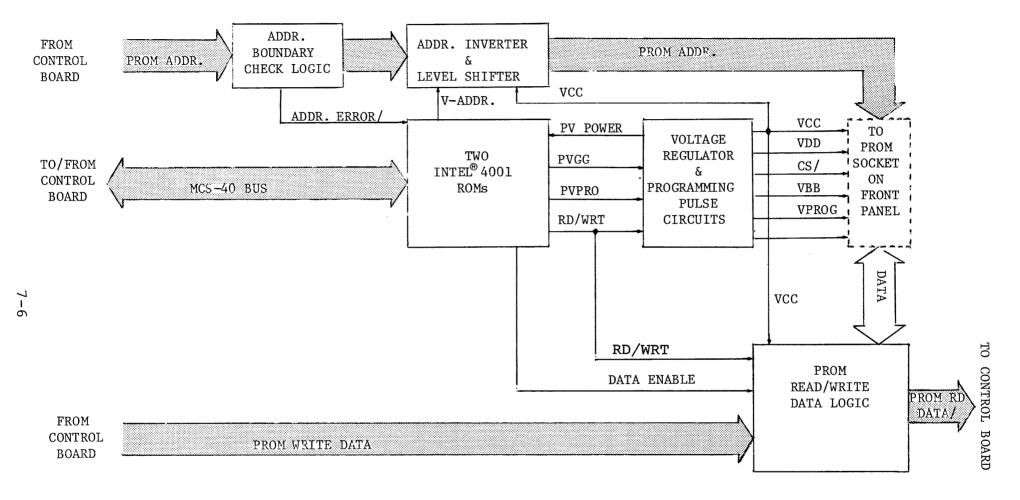

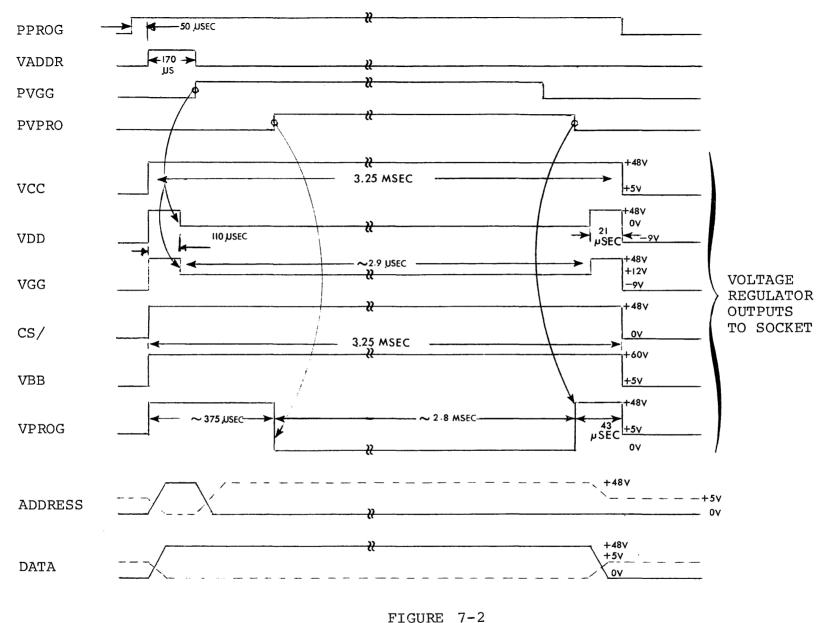

| 7-1<br>7-2                                   | UPP-872 PERSONALITY CARD BLOCK DIAGRAM<br>UPP-872 PERSONALITY CARD: PROGRAM TIMING                                                                                                                                          | 7-6<br>7-10                                                |

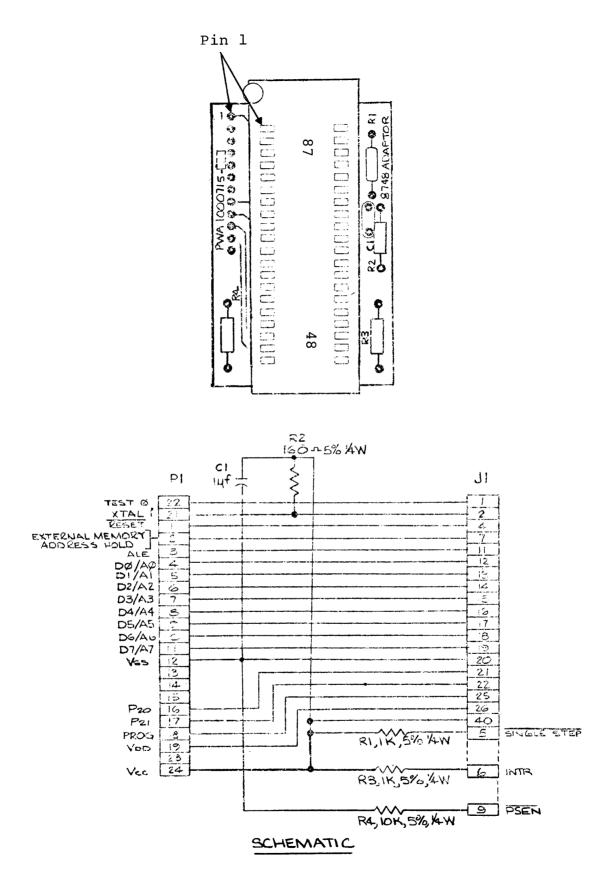

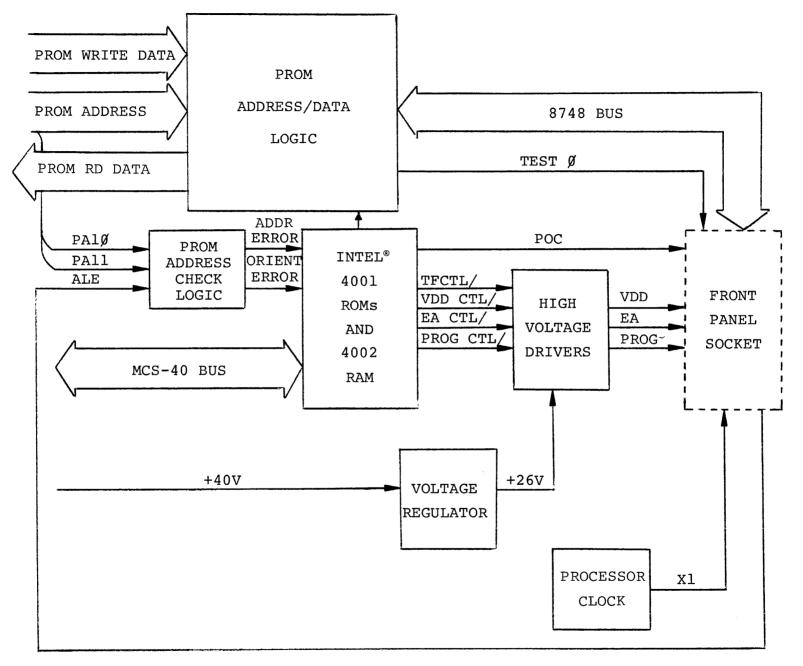

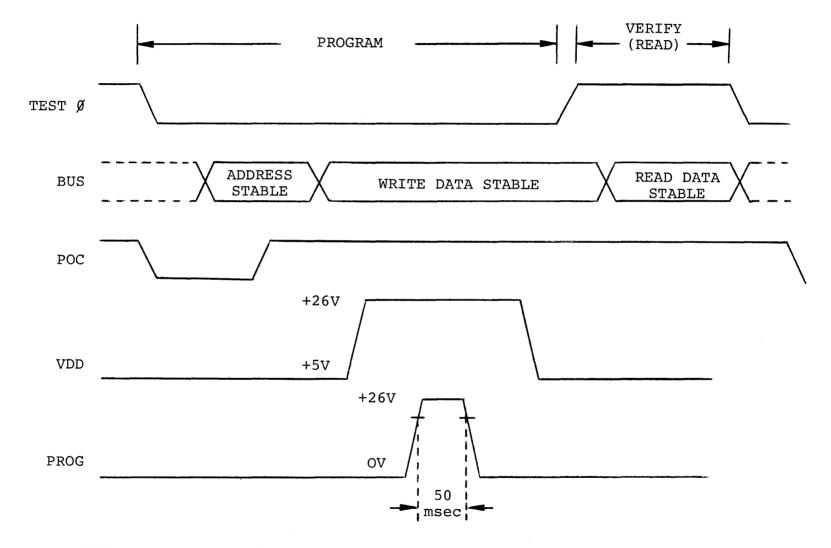

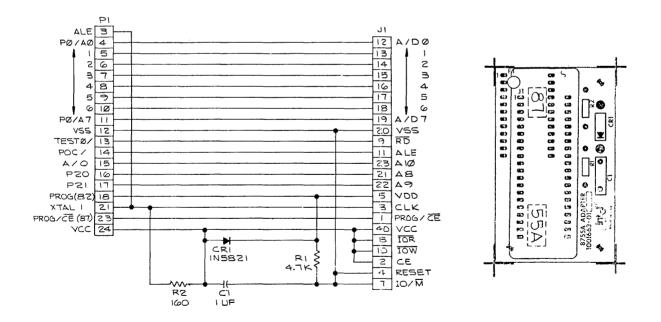

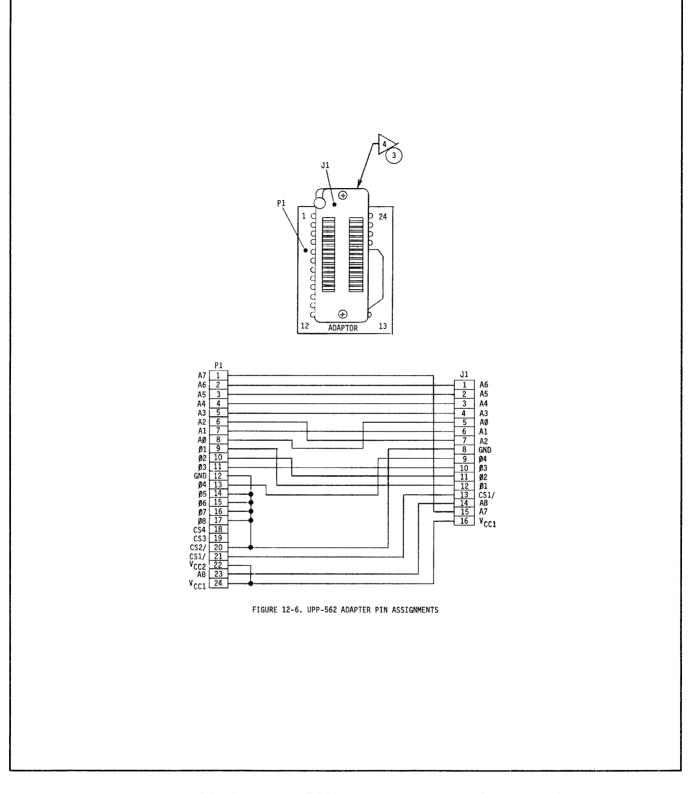

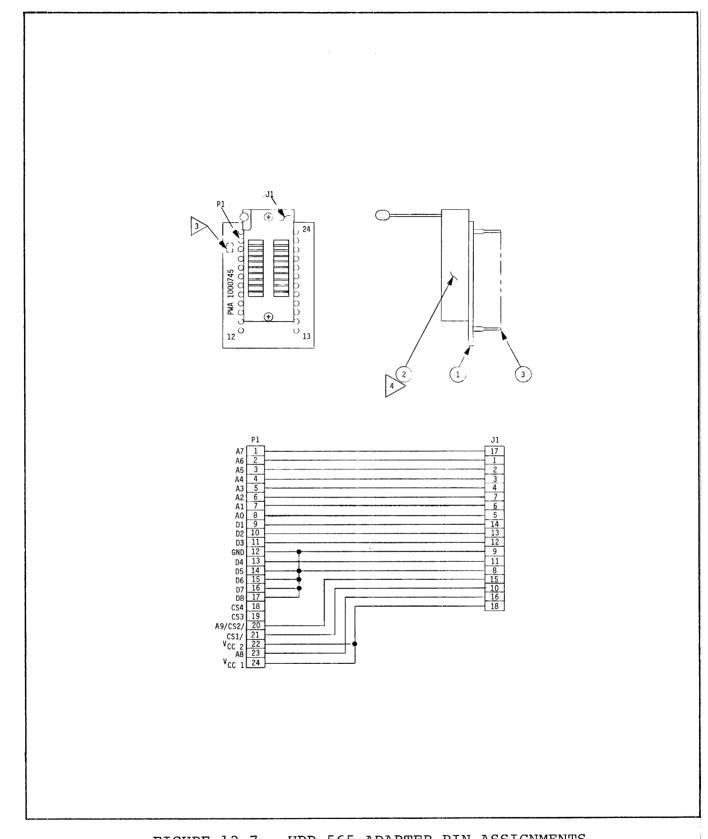

| 8-1<br>8-2                                   | 8748 ADAPTER PIN ASSIGNMENTS<br>UPP-848 PERSONALITY CARD FUNCTIONAL BLOCK                                                                                                                                                   | 8-4                                                        |

| 8-3                                          | DIAGRAM<br>UPP-848 PERSONALITY CARD (WITH 8748 ADAPTER)                                                                                                                                                                     | 8-6                                                        |

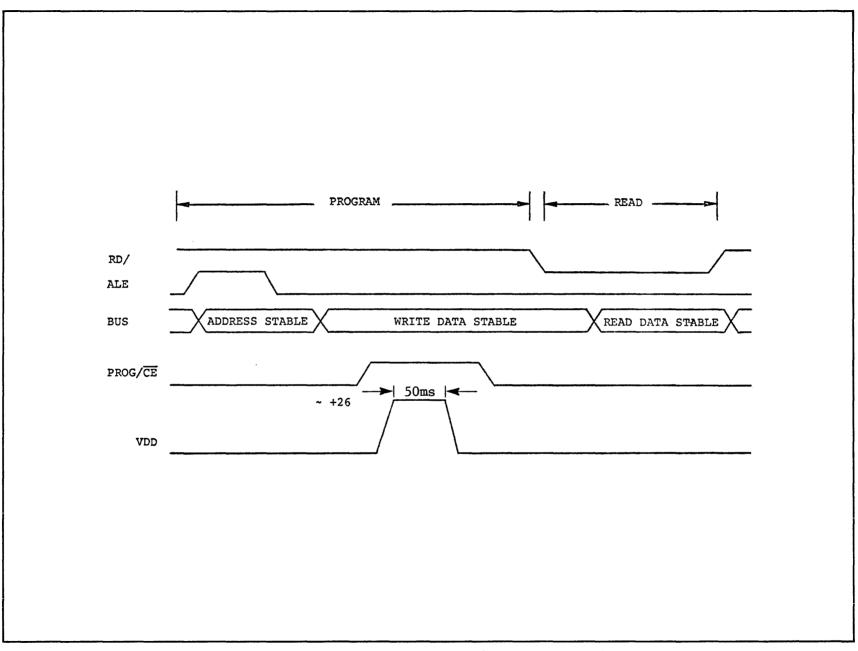

| 0                                            | TIMING FOR THE 8748                                                                                                                                                                                                         | 8-11                                                       |

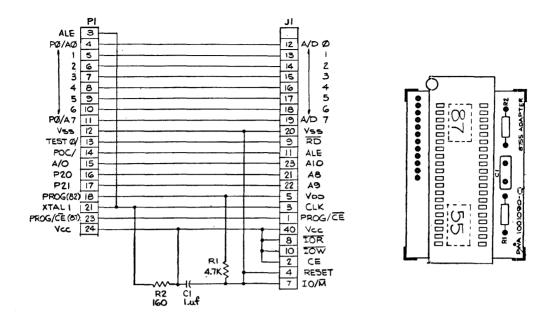

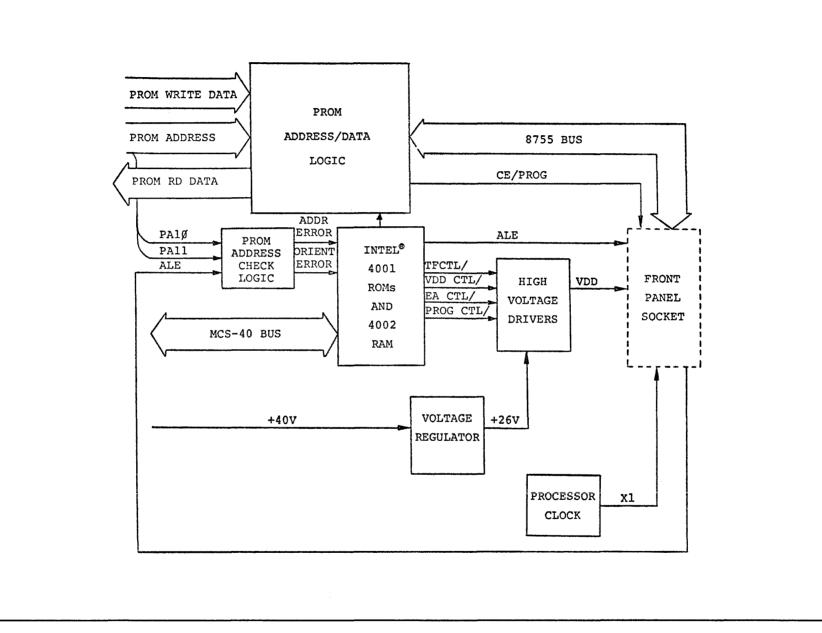

| 9-1<br>9-2<br>9-3<br>9-4                     | 8755 ADAPTER PIN ASSIGNMENTS<br>8755A ADAPTER PIN ASSIGNMENTS<br>PERSONALITY CARD FUNCTIONAL BLOCK DIAGRAM<br>PERSONALITY CARD (WITH ADAPTER) TIMING                                                                        | 9-2<br>9-2<br>9-6<br>9-8                                   |

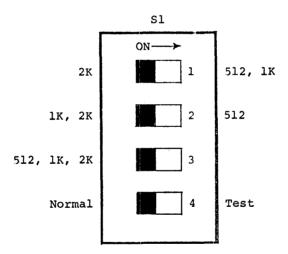

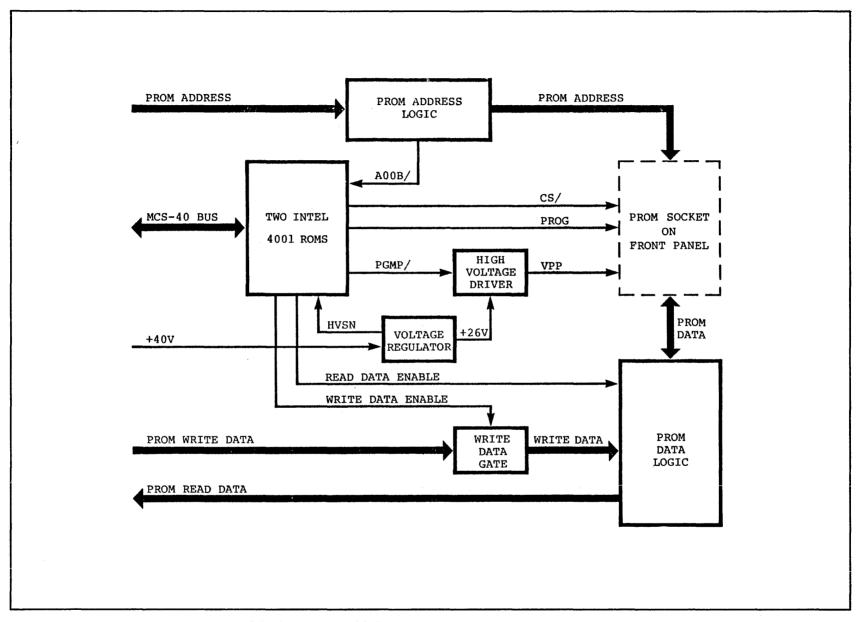

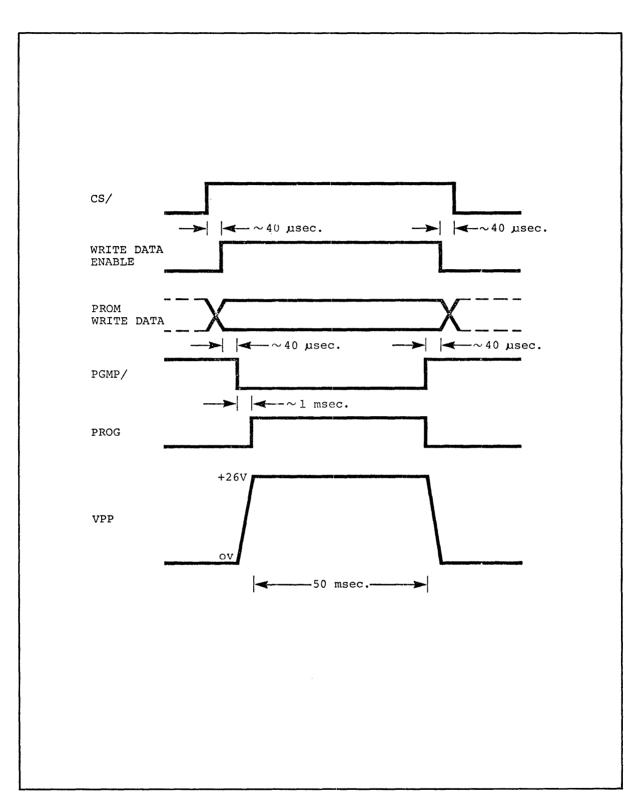

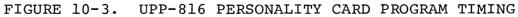

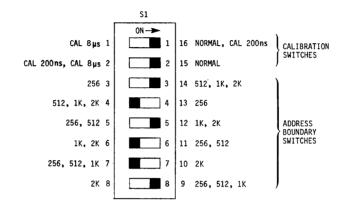

| 10-1<br>10-2<br>10-3                         | SWITCH FUNCTIONS FOR S1<br>UPP-816 PERSONALITY CARD BLOCK DIAGRAM<br>UPP-816 PERSONALITY CARD PROGRAM TIMING                                                                                                                | 10-5<br>10-8<br>10-13                                      |

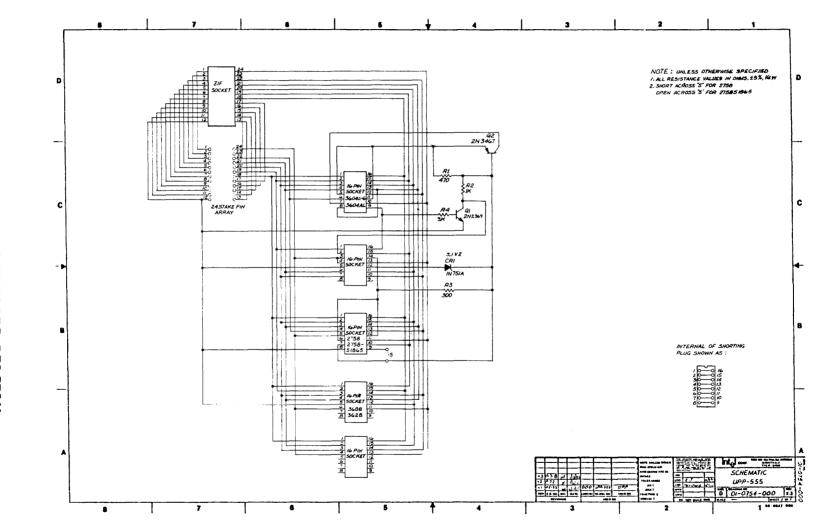

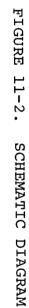

| 11-1<br>11-2                                 | PHYSICAL LAYOUT<br>SCHEMATIC DIAGRAM                                                                                                                                                                                        | 11-7<br>11-8                                               |

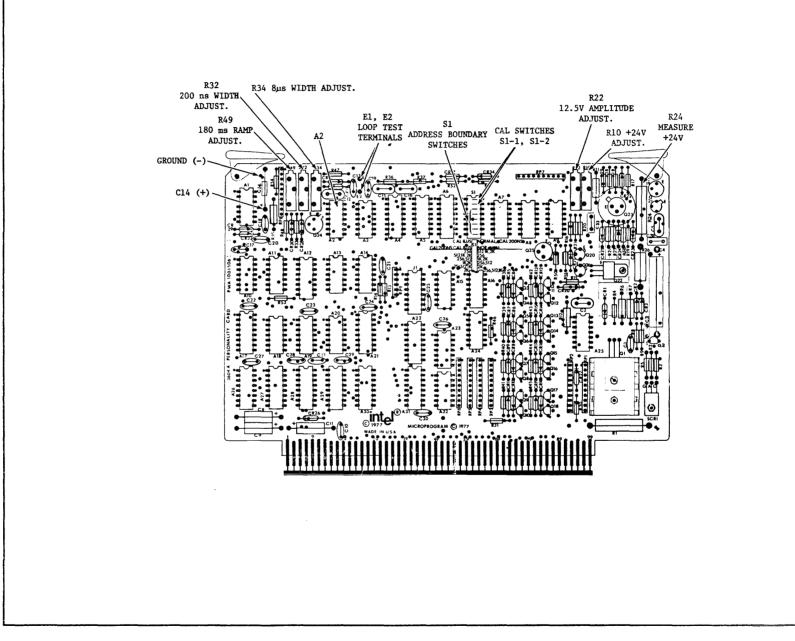

| 12-1                                         | UPP-865 PERSONALITY CARD FUNCTION BLOCK                                                                                                                                                                                     |                                                            |

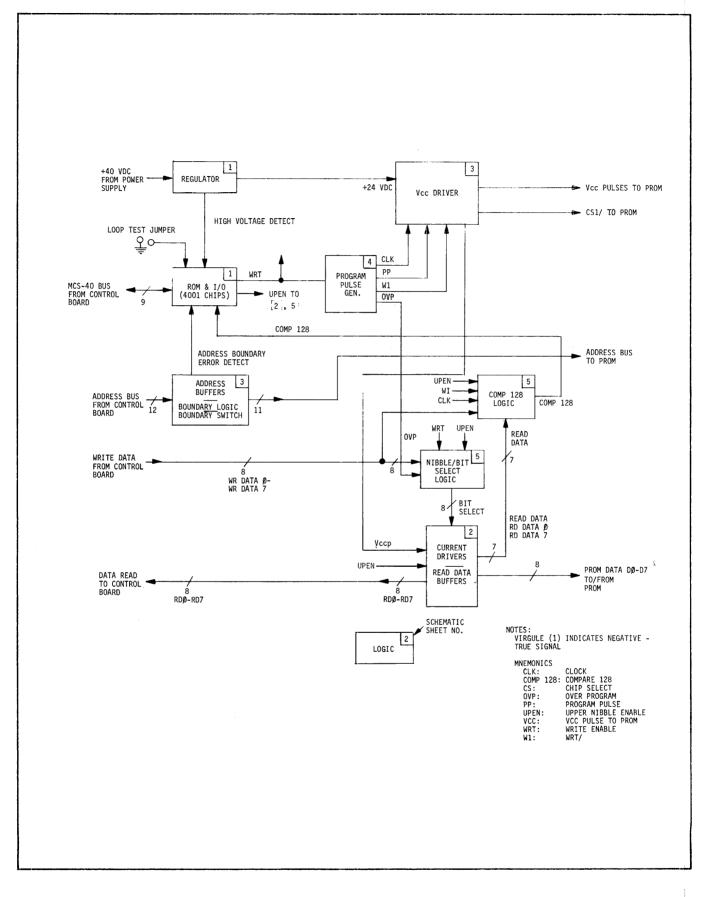

| 12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7 | DIAGRAM<br>UPP-865 PROGRAMMING PULSE TIMING DIAGRAM<br>PULSE WIDTH VS PROGRAMMING TIME<br>UPP-865 COMPONENT IDENTIFICATION<br>SWITCH FUNCTIONS FOR S1<br>UPP-562 ADAPTER PIN ASSIGNMENTS<br>UPP-565 ADAPTER PIN ASSIGNMENTS | 12-5<br>12-12<br>12-13<br>12-16<br>12-17<br>12-20<br>12-21 |

| 12-8<br>12-9                                 | FRONT VIEW OF UPP WITH ADAPTER<br>TIMING RAMP WAVEFORM                                                                                                                                                                      | 12-22<br>12-26                                             |

LIST OF TABLES

| TABLE             | · ·                                                                                                                     | PAGE NO.               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1-1               | PERSONALITY CARD SELECTION                                                                                              | 1-2                    |

| 2-1               | CONTROL BOARD PIN LIST                                                                                                  | 2-21                   |

| 3-1<br>3-2<br>3-3 | I/O PORT ADDRESSES: INTELLEC 8/8,                                                                                       | 3-4<br>3-14            |

| 3-4<br>3-5        | INTELLEC 8/80<br>BACK PANEL CONNECTOR PIN LIST<br>DC CHARACTERISTICS                                                    | 3-15<br>3-17<br>3-24   |

| 4-1<br>4-2        | UPP-878 PERSONALITY CARD DEVICE SELECTION<br>UPP-878 PERSONALITY CARD PIN LIST                                          | 4-2<br>4-15            |

| 5-1<br>5-2        | UPP-864 PERSONALITY CARD DEVICE SELECTION<br>UPP-864 PERSONALITY CARD PIN LIST                                          | 5-2<br>5-16            |

|                   | UPP-361 PERSONALITY CARD DEVICE SELECTION<br>UPP-361 PERSONALITY CARD PIN LIST                                          | 6-2<br>6-13            |

|                   | UPP-872 PERSONALITY CARD DEVICE SELECTION<br>UPP-872 PERSONALITY CARD PIN LIST                                          | 7-2<br>7-12            |

| 8-1               | UPP-848 PERSONALITY CARD PIN LIST                                                                                       | 8-14                   |

| 9-1               | PERSONALITY CARD PIN LIST                                                                                               | 9-13                   |

| 10-1<br>10-2      | PROM ADDRESS BOUNDARY SWITCH SETTINGS<br>UPP-816 PERSONALITY CARD PIN LIST                                              | 10-5<br>10-14          |

| 11-1<br>11-2      | UPP-555 ADAPTER PROM SET<br>SIGNAL SUMMARY                                                                              | 11-2<br>11-6           |

| 12-2              | UPP-865 PERSONALITY CARD DEVICE SELECTION<br>PROM ADDRESS BOUNDARY SWITCH SETTINGS<br>UPP-865 PERSONALITY CARD PIN LIST | 12-2<br>12-15<br>12-28 |

-.

#### CHAPTER 1

#### INTRODUCTION

The Universal PROM Programmer (UPP) is a peripheral device, designed to simplify the programming of Intel's family of electrically programmable read only memories (PROMs). Because it is a "peripheral" device, the PROM Programmer must be interfaced to a "control computer", such as one of Intel's INTELLEC microcomputer development systems. The control computer transfers commands, memory addresses, control information and data to the PROM Programmer, enabling it to program a particular PROM or to read the contents of a previously programmed PROM. The PROM Programmer also includes provisions that allow the control computer to read the internal status of the PROM Programmer peripheral.

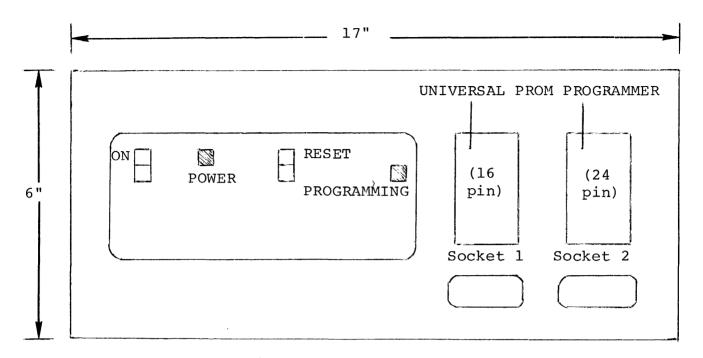

On the front panel of the Universal PROM Programmer are mounted two zero-insertion-force sockets; one 16-pin, the other 24-pin (UPP-101). As an option two 24-pin sockets can be mounted instead (UPP-102). Each socket is driven by a printed circuit board within the PROM Programmer that contains the electronic circuits required to program a particular class of PROMs. These printed circuit boards with the device-related circuitry are referred to as "personality cards". The Universal PROM Programmer can contain two different types of personality cards at any given time (one associated with each socket) The personality cards are easily exchanged to allow users to reconfigure their UPP, as required to program the PROM devices. There are several different personality cards and adaptors that are used for programming the various PROM devices listed in Table 1-1.

The Universal PROM Programmer comes in a 17"x6"x7" cabinet that houses all of the peripheral's printed circuit boards, as well as the power supply.

## Table 1-1

## Personality Card Selection<sup>1</sup>

| PROM                           | PERSONALITY<br>CARD     | ADAPTER                              | NO. OF<br>PINS | NO. OF<br>PINS         | ORGANIZATION                     | ACCESS<br>TIME    |

|--------------------------------|-------------------------|--------------------------------------|----------------|------------------------|----------------------------------|-------------------|

| 1602A<br>1702A                 | UPP-872<br>(Chapter 7)  | -                                    | 24             | 2048                   | 256 x 8                          | 1.0 µs            |

| 2704<br>2708                   | UPP-878<br>(Chapter 4)  | _                                    | 24             | 4096<br>8192           | 512 x 8<br>1024 x 8              | 500 ns            |

| 2716<br>2758<br>2758<br>S-1865 | UPP-816<br>(Chapter 10) | _<br>UPP-555 <sup>2</sup><br>UPP-555 | 24             | 16,384<br>8192<br>8192 | 2048 x 8<br>1024 x 8<br>1024 x 8 | 450 ns            |

| 3601<br>M3601                  | UPP-361<br>(Chapter 6)  | -                                    | 16             | 1024                   | 256 x 4                          | 70 ns<br>90 ns    |

| 3602<br>3602A                  |                         | } UPP-562                            | 16             | 2048                   | 512 x 4                          | 70 ns             |

| 3604<br>3604A                  |                         | } –                                  | 24             | 4096                   | 512 x 8                          | 70 ns             |

| 3604L-6<br>3604 AL             |                         | <b>UPP-555</b>                       | 24             | 4096                   | 512 x 8                          | 90 ns             |

| 3605                           | UPP-865                 | UPP-565                              | 18             | 4096                   | 1024 x 4                         | 70 ns             |

| 3608                           | (Chapter 12)            | UPP-555                              | 24             | 8192                   | 1024 x 8                         | 80 ns             |

| 3621                           |                         | UPP-562                              | 16             | 1024                   | 256 x 4                          | 70 ns             |

| 3622<br>3622A                  |                         | } UPP-562                            | 16             | 2048                   | 512 x 4                          | 70 ns             |

| 3624<br>3624A                  |                         | -                                    | 24             | 4096                   | 512 x 8                          | 70 ns             |

| 3625<br>3628                   | UPP-865<br>(Chapter 12) | UPP-565<br>UPP-555                   | 18<br>24       | 4096<br>8192           | 1024 x 4<br>1024 x 8             | 70 ns<br>80 ns    |

| 8748                           | UPP-848<br>(Chapter 8)  | supplied                             | 40             | 8192                   | 1024 x 8                         | not<br>applicable |

| 8755                           | UPP-855<br>(Chapter 9)  | supplied                             | 40             | 16 204                 | 2048 0                           | 400 ==            |

| 8755A                          | UPP-955<br>(Chapter 9)  | supplied                             | 40             | 16,384                 | 2048 x 8                         | 400 ns            |

NOTES:

1. Preliminary Notice: This is not a final specification and is subject to change.

2. optional

#### 1.1 SYSTEM OVERVIEW

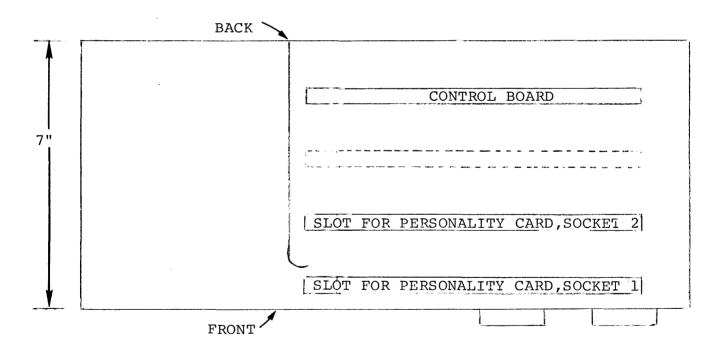

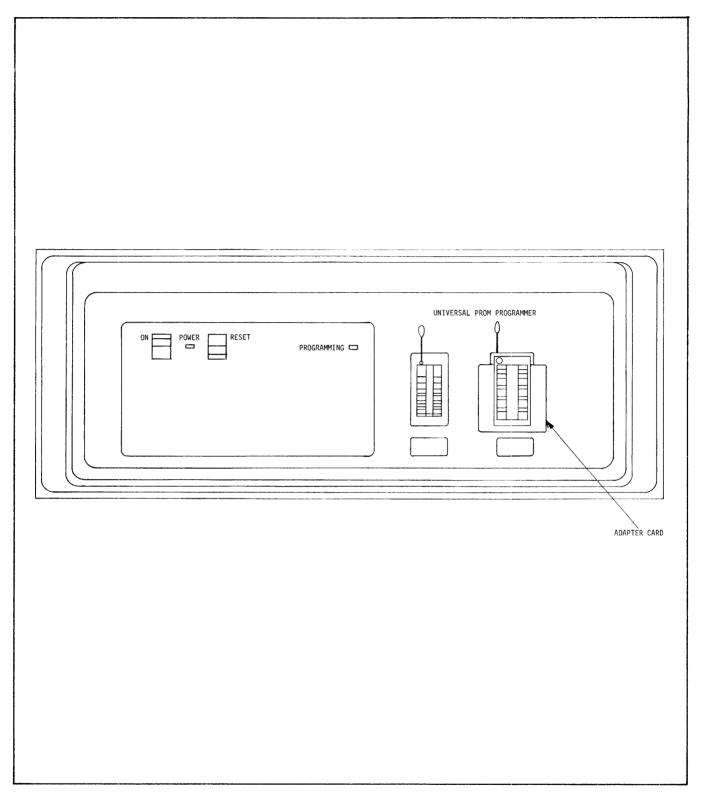

The Universal PROM Programmer consists of a Front Panel, a Control Board, two personality card slots and the power supply, as shown in Figure 1-1.

The <u>Front Panel</u> includes a POWER ON switch and indicator (5VDC power), a RESET switch which will initialize the peripheral when pressed (The RESET function should be used only if the control computer can't communicate with the U.P.P. because the 4040 did not initialize correctly. RESET should not be used when the control computer is reading or programming a PROM.), a PROGRAMMING indicator that lights when a PROM is being programmed, and two zero-insertionforce sockets. Each socket is connected to one of the two personality card slots in the card rack. There are two socket configurations available. One configuration provides a 16-pin socket on the left (socket #1) and a 24-pin socket on the right (socket #2)(UPP-101); the other configuration provides two 24-pin sockets (UPP-102).

#### --WARNING--

Caution must be taken to insert the PROM in the front panel socket correctly (pin 1 in the upper left side). Damage to the PROM and/or personality card is possible if a program attempt is made when the PROM is inserted upside down.

Each <u>personality card</u> contains ROM memory (that stores the program/ read routines), as well as all of the electronics (e.g., voltage regulators and level shifters), required to program a particular class of PROMs. There are two slots in the peripheral for personality cards, one associated with each Front Panel socket. The different types of personality cards (see Table 1-1) can be easily exchanged to reconfigure the peripheral's programming capability. A complete list of PROMs programmed by a personality card is found in the chapter describing that card.

FRONT VIEW (UPP-101)

TOP VIEW

FIGURE 1-1 PROM PROGRAMMER: FRONT PANEL AND CABINET

#### --CAUTION--

When inserting a personality card, make sure that the power is off and that the card is placed in the card slot associated with the socket that will hold the PROM being programmed.

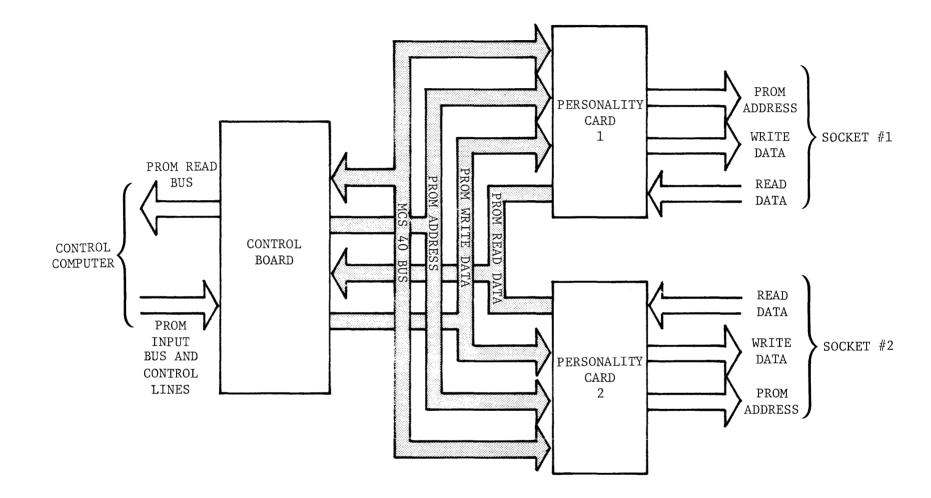

The Control Board, as its name implies, is the controlling module within the PROM Programmer. The Control Board accepts commands from the control computer, and, in turn, directs the appropriate personality card to perform the specified operation. The Control Board can cause a personality card to read or program a particular PROM location. The Control Board also maintains a status word that can be read by the control computer. In addition to supervising the execution of commands, the Control Board is responsible for receiving and storing the 12-bit PROM address, the 8-bit write data byte and four control bits from the control computer. The PROM address and write data are, in turn, passed onto the personality During read operations, the Control Board accepts the read cards. data byte from the personality card and transfers it to the control computer. Figure 1-2 illustrates the primary data paths between the control computer, the Control Board and the personality cards.

The <u>power supply</u> transforms standard 115/230 VAC power into the following DC levels for use by the Universal PROM Programmer:

| +5.85 | VDC, | regulated (N | /CCH)                      |

|-------|------|--------------|----------------------------|

| -10   | VDC, | regulated    |                            |

| +40   | VDC, | unregulated  | )                          |

| -40   | VDC, | unregulated  | (protected by 1 Amp fuses) |

| +70   | VDC, | unregulated  | 1                          |

NOTE: Do not use slow blow type fuses.

NOTE: In the remaining chapters of this manual we will be describing the circuitry on the Control Board and the various personality cards. Both active-high (positive true) and active-low (negative true) signals appear on these PCB's. The following convention should eliminate any confusion when reading subsequent chapters or when referring to the schematics in Appendix B: whenever a signal is active-low, its mnemonic is followed by a slash; for example, RESET/ means that the level on that line will be low when the peripheral is being cleared. When the slash is omitted from the signal mnemonic, it specifies that the signal is activehigh; that is, the level on the RESET line will be high when the peripheral is being cleared.

1.2 CONTROL COMPUTER SOFTWARE REQUIREMENT

All operations that are performed by the Universal PROM Programmer are initiated by commands from the control computer. The control computer should:

- Read the internal status of the PROM Programmer

- Cause the PROM Programmer to read data at a particular PROM location

- Cause the PROM Programmer to program data into a particular PROM location

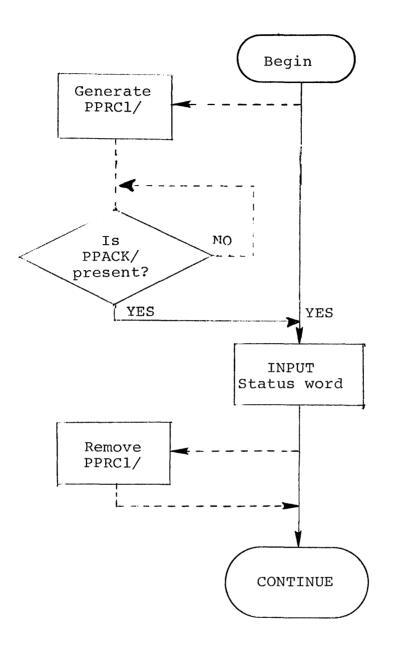

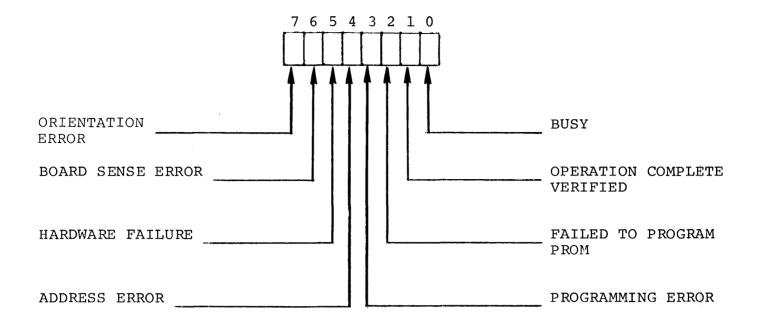

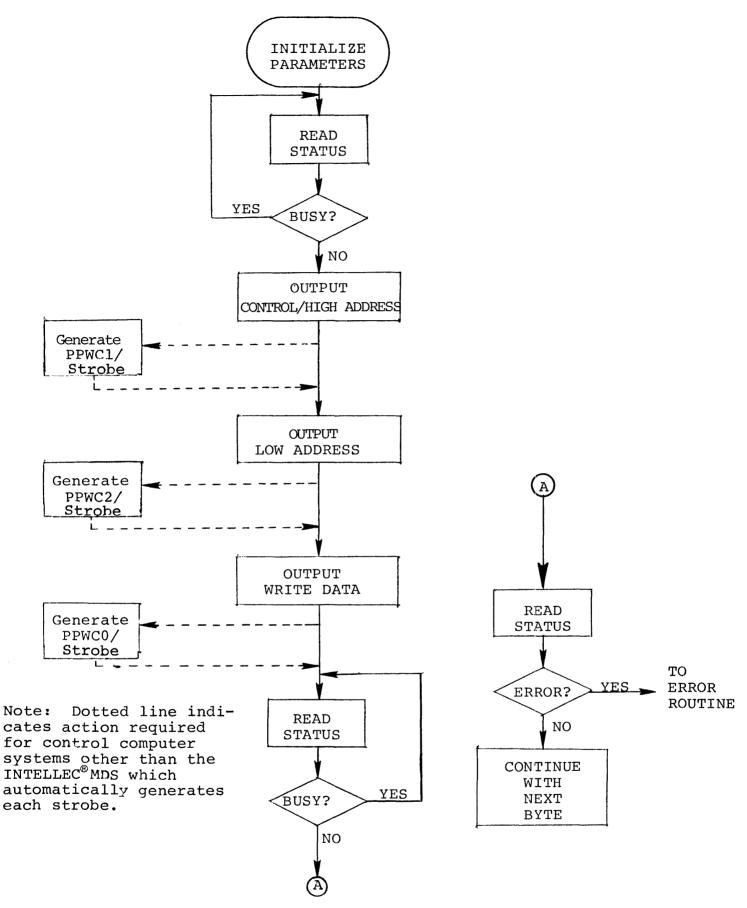

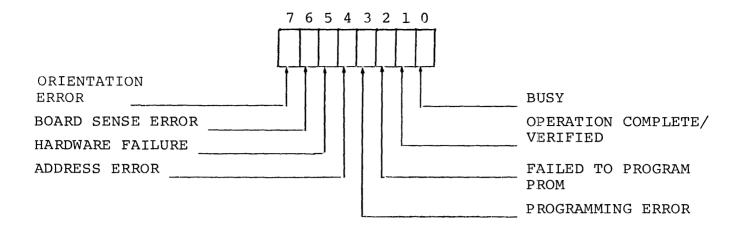

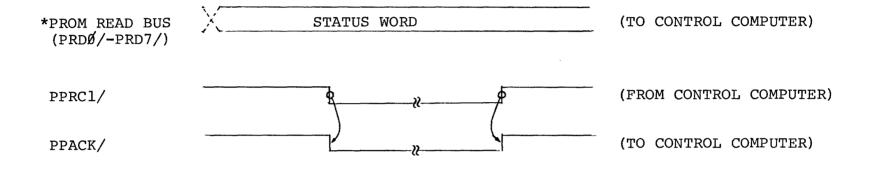

The control computer would normally read the PROM Programmer's 8-bit status word to determine if it is busy, before beginning a read or program sequence (see Figure 1-3). If bit 0 of the status word is true, the peripheral is busy. The status word is always available on the PROM read bus, except during read data cycles. If the control computer does not require that its read status cycles be acknowledged, it can merely examine the contents of the PROM read bus. If the control computer does require a read acknowledge (as does the INTELLEC<sup>®</sup>MDS system), the control computer should send a read status pulse (PPRC1/) to the peripheral. PPRC1/ will cause the PROM Programmer to generate an acknowledge signal (PPACK/) and return it to the control computer. Bit definitions for the status word are shown in Figure 1-4.

Note: Dotted line indicates action required by control computer systems other than the INTELLEC<sup>®</sup>MDS which automatically generates the necessary strobes.

Figure 1-3. Read Status (Flow chart)

Where:

- BIT 0 = BUSY indicates that a program data operation is in progress.

- BIT 1 = OPERATION COMPLETE/VERIFIED indicates that a data read or program operation has been successfully completed.

- BIT 2 = FAILED TO PROGRAM PROM indicates that the PROM Programmer was unable to successfully program the PROM.

- BIT 3 = PROGRAMMING ERROR indicates that a program data word called for a fused bit position to be reprogrammed which is impossible on Bipolar PROMs.

- BIT 4 = ADDRESS ERROR indicates that the PROM address was out of bounds.

- BIT 6 = BOARD SENSE ERROR indicates that a personality card was not present when the Control Board tried to access it.

- BIT 7 = Orientation error indicates that the PROM is in upside down.

- NOTE: All bits are mutually exclusive. Bits 1-7 are invalid, unless bit  $\emptyset$ , BUSY, is false.

FIGURE 1-4

STATUS WORD

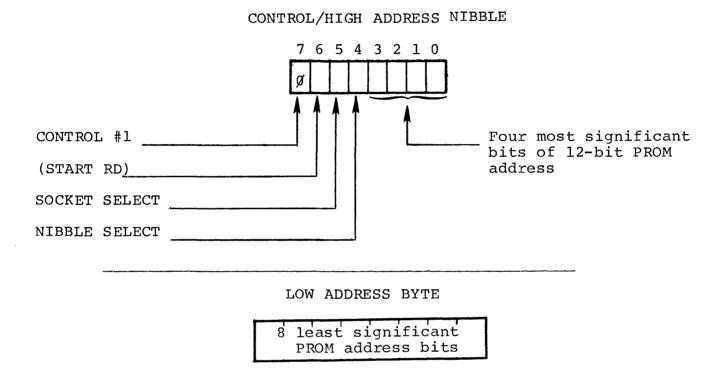

Having determined that the PROM Programmer is not busy, the control computer can then begin passing the PROM Programmer the parameters it will require to perform a data read or program operation. The control computer must output an 8-bit control/high address nibble and an 8-bit low address byte as shown in Figure 1-5.

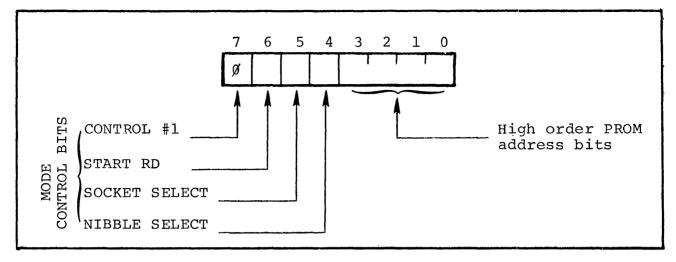

The control computer must output the control/high address byte with the PPWC1/ strobe. The most significant bit is an undefined control bit (CONTROL #1); it must be false (logical 0). (START RD) will, if set (logical 1), initiate a read data operation. SOCKET SELECT (bit 5) identifies one of the two sockets on the Front Panel (if SOCKET SELECT = logical 1, socket #1 is selected; if SOCKET SELECT = logical 0, socket #2 is selected). When programming a PROM that is organized into 4-bit words, NIBBLE SELECT (bit 4) specifies whether the upper or lower four bits of the 8-bit write data byte are to be used (if NIBBLE SELECT = logical 1, the most significant 4 bits of the write data byte are programmed into the addressed PROM location; if NIBBLE SELECT = logical 0, the least significant 4 bits are used). When programming an

#### 8-bit word, NIBBLE SELECT is ignored.

The control computer must output the low address byte with the PPWC2/ strobe. The contents of the low address byte, together with the four least significant bits (0-3) of the control/high address nibble, form the l2-bit PROM address that uniquely identifies the particular location to be accessed within the selected PROM.

After the control/high address and low address parameter bytes have been output to the PROM Programmer, the control computer can initiate the actual data read or program operation.

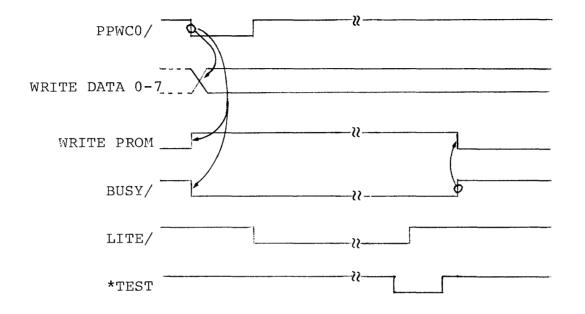

#### DATA PROGRAM OPERATION:

A data program operation is initiated when the control computer outputs an eight-bit write data word with the program strobe signal (PPWC0/). The write data word is the data that will be written into the addressed location within the selected PROM. As we mentioned above, the NIBBLE SELECT control bit can select either half of the write data byte when programming a PROM with 4-bit words (e.g., the 3601 PROM). The PPWCO/ strobe latches the write data byte and sets the WRITE PROM-BUSY/ command latch in the PROM Programmer. Because WRITE PROM is latched, it is not necessary for the control computer to maintain PPWC0/ throughout the data The PROGRAMMING indicator on the Front Panel is program cycle. lit while the data is being written into the addressed PROM location. After the PROM location is successfully programmed or when an error is detected, the internal status word is updated and the WRITE PROM-BUSY/ latch is reset.

To determine when a data program cycle has been completed, the control computer should periodically read the status word from the Universal PROM Programmer, checking for <u>not</u> busy. When the status word does indicate not busy, the control computer should read the status word again to determine if an error occurred or if the operation was completed successfully.

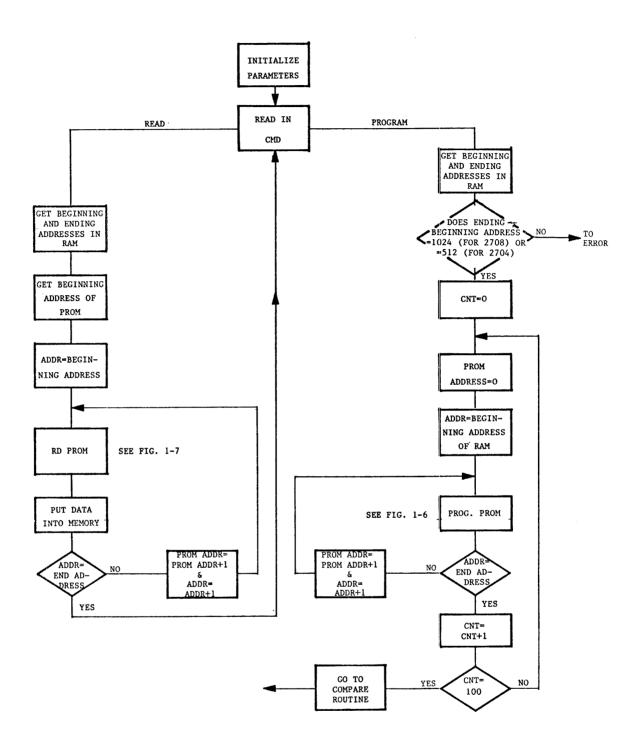

Figure 1-6 provides a flow chart for the data program operation.

Figure 1-6. Programming One Byte (Flow chart)

#### DATA READ OPERATIONS:

There are two methods for reading data from the Universal PROM Programmer.

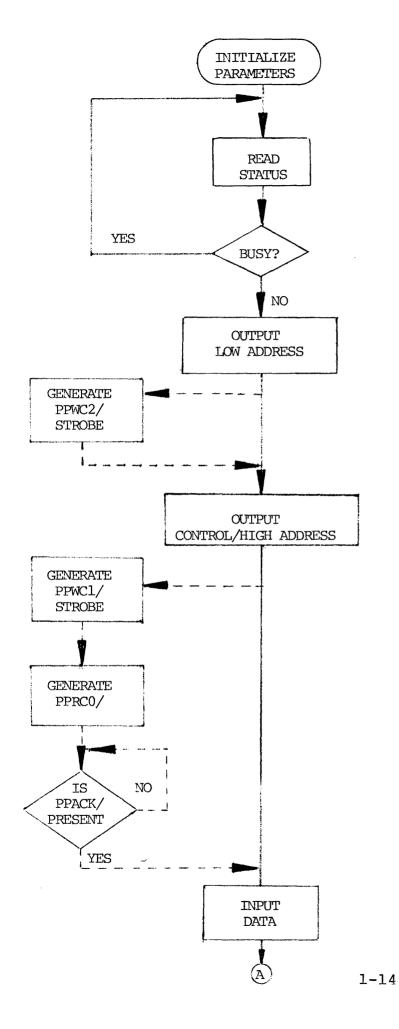

A data read operation can be initiated when the control computer sends the read data command (PPRCO/) to the PROM Programmer. The PROM Programmer will read the contents of the PROM location specified by the 12-bit PROM address (previously output by the control computer), and return the data to the control computer, with a read acknowledge signal, PPACK/. PPACK/ informs the control computer that valid data is on the input bus. It is the responsibility of the control computer to remove its PPRCO/ signal when it receives PPACK/. After removing PPRCO/, the control computer must read the status word from the Universal PROM Programmer to determine whether the data is valid, or invalid due to an address out of bounds error or a board sense error. Refer to Figure 1-7.

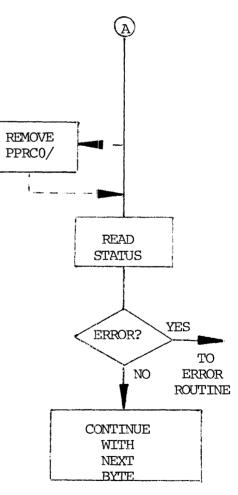

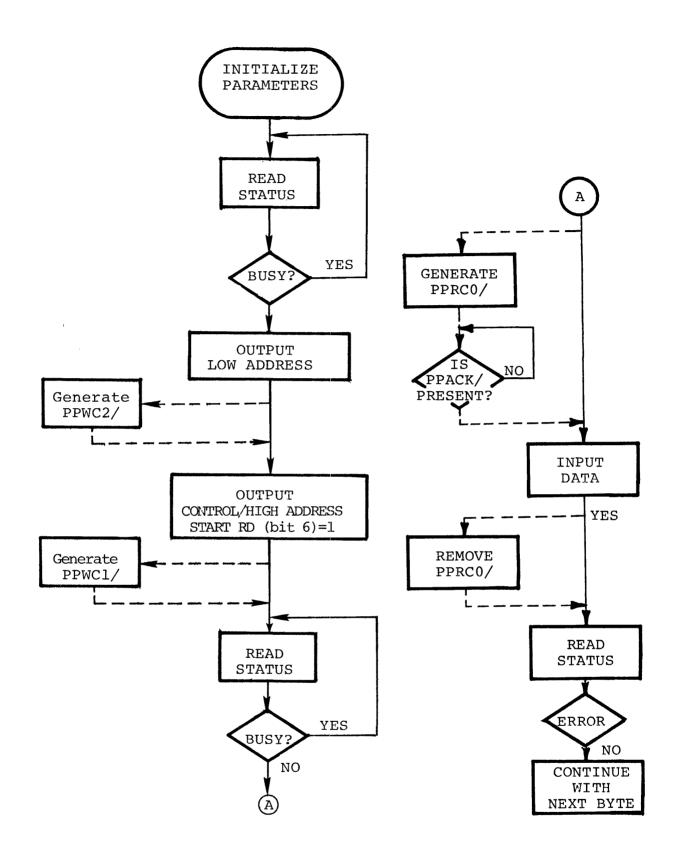

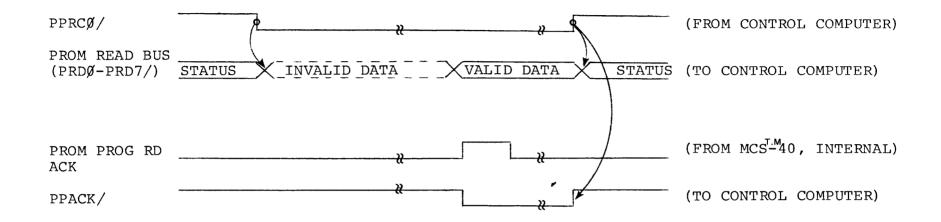

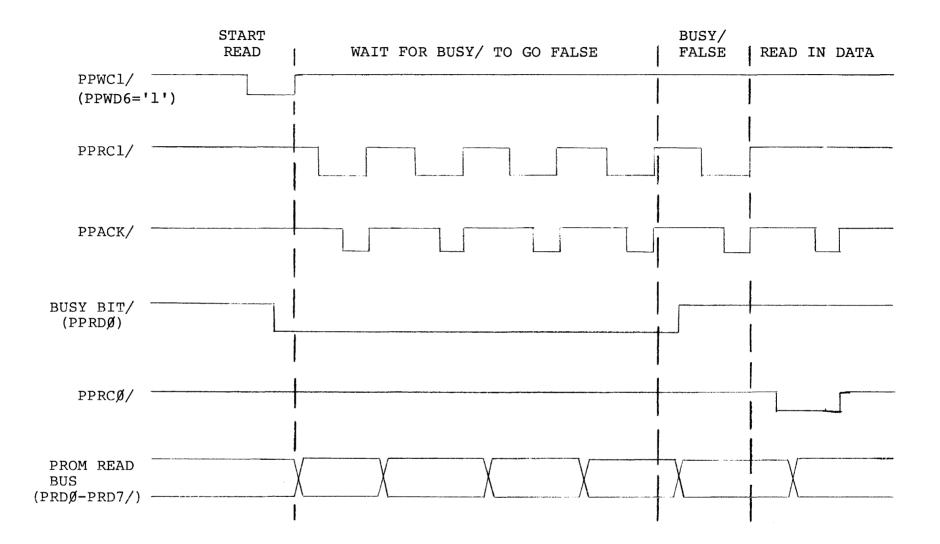

The other method for reading data which avoids the acknowledge delay mentioned above is a status check approach. The control computer outputs (with PPWC1/) the control/high address byte to the Universal PROM Programmer with bit 6 (START RD) true. The control computer then reads the status word, waiting for busy (bit  $\beta$ ) to go false. When busy does go false, the control computer should input the data byte by issuing the read data command (PPRC0/). The data and the read acknowledge (PPACK/) will be returned in less than 1 µsec. Then the control computer should read the status word again to determine if the read data is valid. The control computer need not be occupied for an extended period of time when reading data with this method. Refer to Figure 1-8.

NOTE: When reading a 4-bit PROM, the 4-bit data is in lower four bits of the 8-bit word sent to the control computer.

In Appendix A we have summarized the PROM Programmer commands which have been coded in the INTELLEC<sup>®</sup>MDS Monitor program and which are available to users when the Universal PROM Programmer is being controlled by an INTELLEC<sup>®</sup>MDS system.

Figure 1-7. Read Data -Method 1 (Flow Chart)

> Note: Dotted line indicates action required by control computer systems other than the IN-TELLEC<sup>®</sup>MDS which automatically generates the necessary strobes.

Note: Dotted line indicates action required by control computer systems other than the INTELLEC<sup>®</sup>MDS which automatically generates the necessary strobes.

Figure 1-8. Read Data-Method 2 (Flow chart)

## CHAPTER 2 THE CONTROL BOARD

The Control Board coordinates all operations performed by the Universal PROM Programmer. The Control Board receives commands from the control computer, and, in turn, directs the appropriate personality card in the performance of the particular operation specified by the control computer's command. The Control Board can cause a personality card to <u>read</u> a particular location in a PROM, or the Control Board can cause a personality card to <u>program</u> a particular location in PROM. The Control Board also maintains a status word that can be read by the control computer.

In addition to supervising the execution of commands from the control computer, the Control Board is responsible for receiving and storing:

- the 12-bit address that identifies the PROM location to be accessed during read or program operations,

- the 8-bit data word that is to be written into the addressed PROM location during program operations, and

- the four control bits that specify the socket and nibble to be used during read or program operations.

Section 2.1 identifies the various functional blocks within the Control Board. The next section, 2.2, explains how these functional blocks interact to execute each of the PROM Programmer operations. The final section in this chapter provides a pin list for the Control Board.

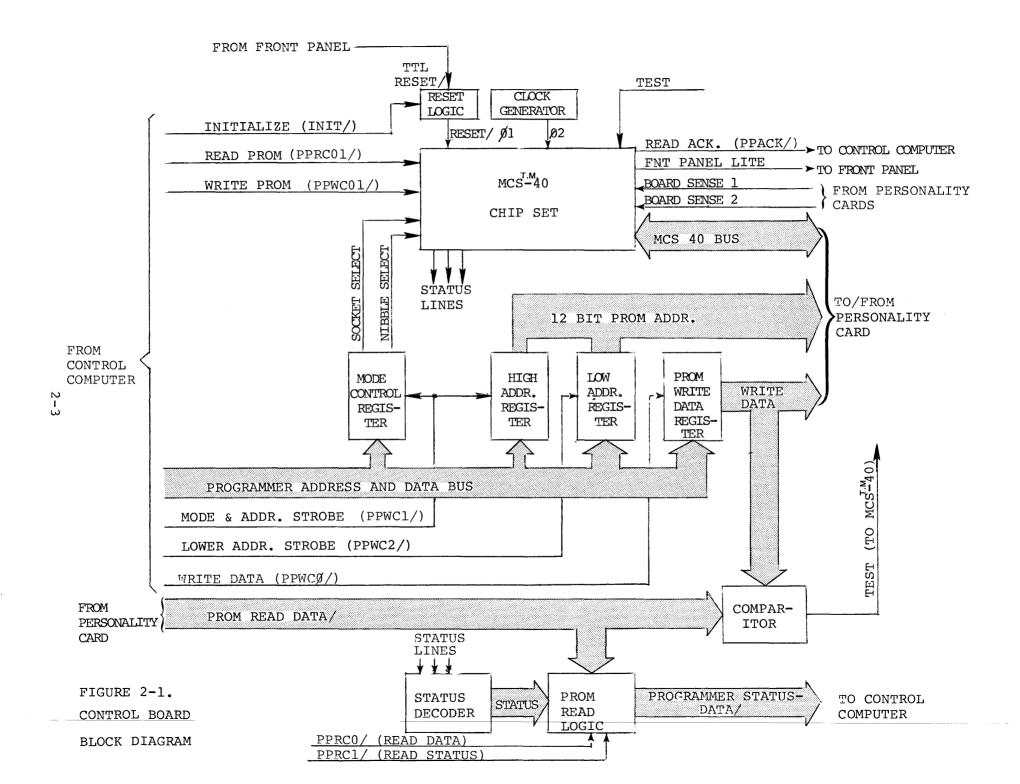

#### 2.1 FUNCTIONAL DESCRIPTION: CONTROL BOARD

For descriptive purposes, the Control Board can be viewed as consisting of ten functional blocks:

- 1)  $MCS^{T.M}_{-40}$  chip set

- 2) Reset logic

- 3) Clock generator

- 4) Mode control register (4 bits)

- 5) High address register (4 bits)

- 6) Low address register (8 bits)

- 7) PROM write data register (8 bits)

- 8) Status decoder

- 9) PROM read logic

- 10) Comparator

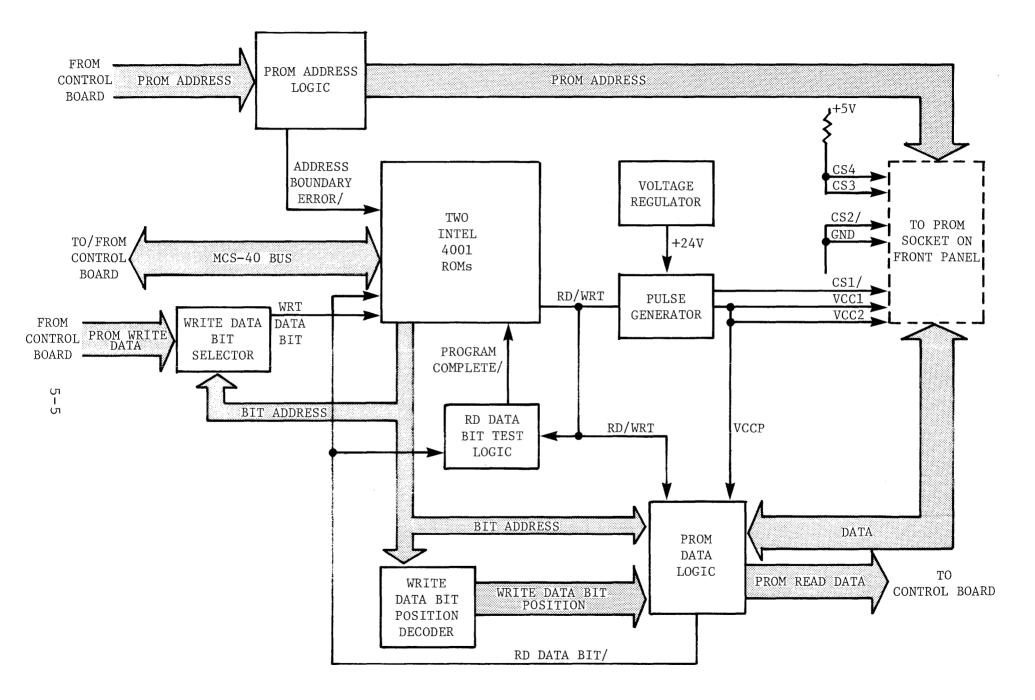

as shown in Figure 2-1.

At the heart of the Control Board is the Intel® 4040 microprocessor. Instructions for the microprocessor are stored in ROM chips (Intel<sup>®</sup> 4001). Three chips are located on the Control Board with the 4040 itself; they contain instructions for operations which are independent of the characteristics of a particular PROM. Two additional ROM chips are located on each personality card; they contain instructions which are dependent on the characteristics of the PROM for which the personality card is designed. There is also one chip of RAM (Intel® 4002) for the microprocessor; it is located on the Control Board. The 4001 ROM chips each provide four input or output lines, while the 4002 RAM chip provides four output lines that allow the 4040 microprocessor to communicate with circuitry outside of the MCS-40 chip set. The 4040 communicates with the 4002 RAM and 4001 ROM chips via the  $MCS^{T.M}_{-40}$  bus that consists of:

- 4 data lines (D0-D3),

- a SYNC line,

- the two clock signals ( $\emptyset$ l and  $\emptyset$ 2), and

- four memory control lines (CM-ROM0, CM-ROM1, CM-RAM0, and CM-RAM1).

In the following paragraphs, we will use the term " $\underline{MCS}^{\underline{T}\underline{M}}_{\underline{T}\underline{M}}$ " to refer to the chip set that includes the 4040 microprocessor the 4001 ROM's and the 4002 RAM.

There are two circuit blocks included on the Control Board that are necessary for the operation of the  $MCS^{T.M}_{-40}$ , the reset logic and the clock generator.

The <u>reset logic</u> supplies a reset signal (RESET/) to the MCS<sup>T.M</sup>40. When this signal is true (active low) all of the MCS<sup>T.M</sup>40's internal registers are cleared and the program counter is set to location zero. The effect of this is that the PROM Programmer will be properly initialized to accept a command from the control computer. The reset signal will be supplied whenever one of the following occurs:

- 1) the power switch on the front panel is switched from OFF to ON,

- 2) the reset switch on the front panel is pressed,

- 3) the initialize line (INT/) is pulsed by the control computer.

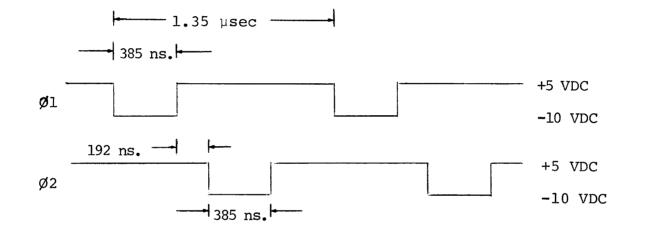

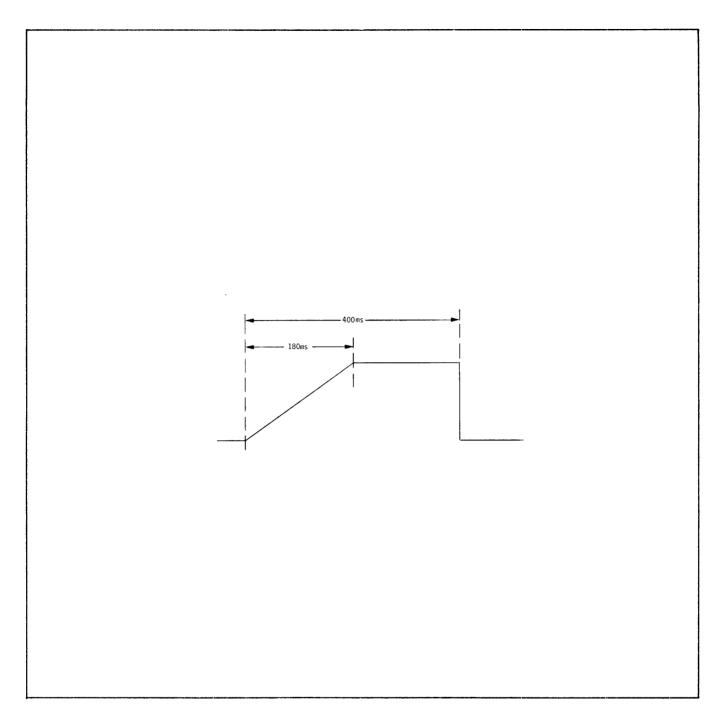

The <u>clock generator</u> supplies the two clock inputs,  $\emptyset$ l and  $\emptyset$ 2, that provide a timing reference for the MCS<sup>T.M</sup>40. The clock generator is driven by a 5.185 MHz crystal oscillator. Timing for  $\emptyset$ l and  $\emptyset$ 2 is illustrated in Figure 2-2.

The <u>mode control register</u> stores the four control bits that are output by the control computer with the four high order PROM address bits:

FIGURE 2-2. Øl and Ø2 TIMING

CONTROL/HIGH ADDRESS BYTE, OUTPUT BY CONTROL COMPUTER

The most significant mode control bit, CONTROL #1, is not used on the Control Board but must be false (logical  $\emptyset$ ) because it is latched and made available at the board's edge connector. Bit 6 (START RD) will, when set (logical 1), initiate a read data operation in the Universal PROM Programmer. The other two mode control bits, SOCKET SELECT and NIBBLE SELECT, are latched then made available to the MCS<sup>T\_M</sup>40 through input port 0, bits 0 and 1 of the 4001 ROM at A20. SOCKET SELECT specifies which of the two sockets on the front panel is to be read or programmed. NIBBLE SELECT specifies which nibble is to be programmed when programming a 4-bit device. NIBBLE SELECT is ignored when programming or reading PROMs that are organized into 8-bit words.

The control computer generates the PPWC1/ strobe when the Control/ High Address nibble is on the data lines (PPD0/-PPD7). PPWC1/ latches the four control bits into the mode control register, and, at the same time, latches the four address bits into the high address register. The contents of the <u>high address register</u> constitute the four most significant bits of the 12-bit PROM address, and are made available to the personality cards via lines, PROM ADDRESS 8 through PROM ADDRESS 11.

The <u>low address register</u> stores the eight low order PROM address bits that are output (via lines PPD0/-PPD7/) by the control computer along with the PPWC2/ strobe. PPWC2/ latches the address bits into the low address register. The address bits are made available to the personality cards via lines, PROM ADDRESS 0 through PROM ADDRESS 7. The twelve PROM ADDRESS bits uniquely identify the PROM location to be accessed (bit 0 is the least significant bit).

When the control computer issues a program command, it places the data to be written into the PROM on data lines, PPD0/-PPD7/, and issues the PPWC0/ strobe. PPWC0/ latches the data byte into the PROM write data register, and starts the program data operation. The contents of this register are made available to the personality cards via lines WRITE DATA 0 through WRITE DATA 7 (bit 0 is the least significant bit).

The Control Board provides a status word that can be read by the control computer. The MCS<sup>T.M</sup>40 maintains this status word by periodically updating the contents of the three status lines (STATUS 0, STATUS 1 and STATUS 2) through an output port on the 4002 RAM chip (All). These three status lines specify one of eight possible conditions. STATUS 0, STATUS 1 and STATUS 2 are applied to the status decoder which activates one of eight outputs. The eight outputs of the status decoder constitute the PROM Programmer status word.

The status word is fed to the <u>PROM read logic</u>. The PROM read logic enables the status word onto the PROM read bus (PRD0/-PRD7/) at all times, except during PROM read data operations. When the control computer issues the read status command, PPRC1/, the PROM read logic merely acknowledges the command by generating PPACK/; the status word is already available on the bus.

When the control computer issues a PROM read data command, PPRC0/, the PROM read logic disables the status word and gates the data word read from the PROM (via the appropriate personality card) onto the PROM read bus lines. After the  $MCS^{T.M}_{-4}0$  determines that the

data word has been read and placed on the bus, it causes the PROM read logic to acknowledge the command by generating PPACK/. When the control computer removes its read data command (i.e., when PPRC0/ goes false), the status word is again enabled through the read status logic.

The <u>comparator</u> provides a means of comparing the 8-bit PROM write data from the control computer and the PROM data read from a personality card. The TEST line from the comparator is applied directly to the 4040 microprocessor, indicating the outcome of the comparison.

#### 2.2 THEORY OF OPERATION: CONTROL BOARD

In this section we will describe how the functional blocks on the Control Board interact to execute each of the possible operations. We will begin by describing the read status operation, because it is the operation that would normally be executed first, to determine whether or not the PROM Programmer was busy. We will then discuss the sequences in which the control computer outputs control and address information. This would usually be done immediately prior to actually executing a PROM read data or PROM program data operation. Finally, we will describe the read data and program data operations.

#### 2.2.1 READ STATUS SEQUENCES

As we mentioned in Section 2.1, the MCS<sup>-M</sup>40 maintains an eight-bit status word by updating three status lines (STATUS 0-STATUS 2) whenever internal status changes. These three status lines are output from three bits on the 4002 RAM (All) Port, and applied to the status decoder logic which activates one of its eight outputs as determined by the levels on the three status lines. The eight-bit status word is gated through the PROM read logic and driven over the PROM read bus (pins 62-69) by eight 7406 open-collector inverting driver circuits.

The control computer can read the status word by issuing the read status command, PPRC1/ (pin 71). PPRC1/ directly enables the acknowledge signal PPACK/ (pin 72) which can be used to strobe the status word into the control computer and/or reset the read status command.

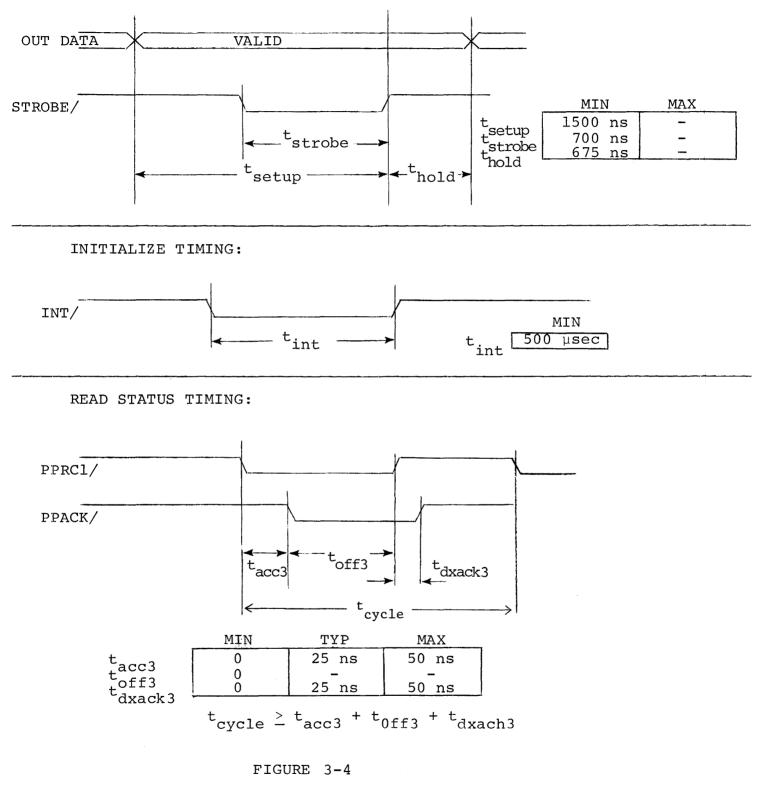

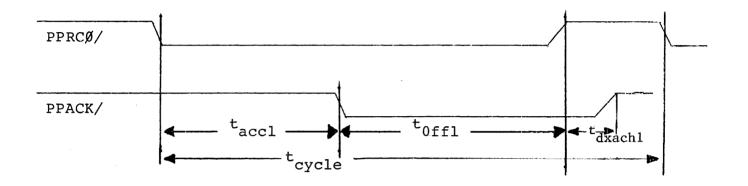

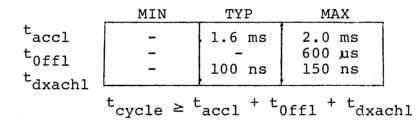

The PROM status word is illustrated in Figure 2-3. Read status timing is shown in Figure 2-4.

NOTE: Bits 1-7 in the status word are only valid if bit 0 is false (i.e., if the PROM Programmer is not busy). All of the status bits are mutually exclusive (i.e., only one can be true at any given time).

#### FIGURE 2-3

#### PROM PROGRAMMER STATUS WORD

### 2.2.2 CONTROL/ADDRESS OUTPUT SEQUENCES

Before actually beginning a read data or program data operation, the control computer must provide the PROM Programmer with certain control information, as well as a 12-bit address that specifies the PROM location to be accessed. This information is output in two sequences.

The first byte consists of four control bits and the four most significant bits of the 12-bit address. As we mentioned earlier, the control bit portion includes one bit (CONTROL #1) which is buffered and passed to the Control Board's edge connector. The control bit is reserved for future use and must be maintained in a  $\beta$  state. The START RD bit can be used to initiate a read data operation. Another control bit, SOCKET SELECT, specifies which of the two sockets on the front panel are to be accessed (SOCKET SELECT - logical 1 for socket #1 and SOCKET SELECT - logical 0 for socket #2). The other control bit is referred to as NIBBLE SELECT. Because some PROM's are organized in 4-bit words (e.g., 3601), there must be a means of specifying which 4 bits of the 8-bit write data byte are to be written into the PROM during program sequences. When NIBBLE SELECT = logical 1

\*The status word is on the PROM read bus at all times except during the execution of PROM read data commands (see Section 2.2.3).

FIGURE 2-4. READ STATUS TIMING

the four most significant bits of the write data register are used; when NIBBLE SELECT = logical 0, the least significant bits are used. When 4-bit PROM words are read, the 4 bits are duplicated on bits 0-3 and 4-7 at the PROM read bus. NIBBLE SELECT is ignored when programming or reading PROMs organized into 8-bit words.

The control/high address strobe, PPWCl/ (received at pin 75) latches the four control bits into the mode control register and the four address bits into the high address register.

The other byte that must be output by the control computer prior to a read or program data operation is the low order address byte. This byte is strobed into the eight-bit low address register by the low address signal, PPWC2/ (pin 76). These bits constitute the eight least significant bits of the 12-bit PROM address. All twelve address lines (PROM ADDRESS 0-11) are made available to the personality cards (via pins 29-40).

#### 2.2.3 PROM READ DATA SEQUENCE

There are two methods of reading data from the PROM Programmer. The first method is when the control computer can initiate a PROM data operation by issuing the read data command, PPRCO/ (received at pin 70). PPRCO/ disables the read logic gates that had allowed the PROM status word onto the PROM read bus, and enables the PROM RD DATA lines from the personality cards (pins 52-59) through the read logic and onto the PROM read bus (PRD0/-PRD7).

PPRCO/ is inverted and applied to input port 0, bit 2 of the 4001 ROM at A20, under the mnemonic, RD PROM. When not busy, the MCS-40 stays in a program loop that alternately examines the RD PROM and WRITE PROM input ports on the 4001 ROM. If the MCS-40 finds a true level on RD PROM, it will then examine the SOCKET SELECT input at port 0, bit 1 on the same 4001 ROM. Having determined which socket,

and consequently which PROM and personality card, are to be accessed, the  $MCS^{T.M}_{-}40$  then examines the board sense input for the personality card associated with the selected socket, BD SENSE #1 (input port 1, bit 2 on the 4001 ROM at A29) or BD SENSE #2 (input port 1, bit 0 on the 4001 ROM at A29). If the appropriate board is not present, an error condition is indicated in the status word, an acknowledge (PPACK/) is generated and the operation is terminated.

Having determined the socket to be accessed, the  $MCS^{T-M}_{-40}$  transfers program control to the proper read routine stored in the 4001 ROM's on the appropriate personality card. Using the I/O ports on the personality card ROM's, the  $MCS^{T-M}_{-40}$  can, by executing the read routine stored in these ROM's, cause the personality card to read the addressed PROM location (refer to Chapters 3-6), and send the data to the Control Board on the PROM RD DATA 0-7 lines (pins 52-59). Recall that these lines are enabled through the PROM read logic and out onto the PROM read bus, PRDO/-PRD7/ (pins 62-69).

When the addressed PROM location has been successfully read and the data is on the PROM read bus, the MCS<sup>T.M</sup>40 sets the COMPLETE/VERIFIED bit in the status word and issues the PROM PROG RD ACK signal from the output port, bit 3, on the 4002 RAM (All). PROM PROG RD ACK, in turn, generates PPACK/ which is made available to the control computer via pin 72. PPACK/ indicates that data is on the PROM read bus (PRD0/-PRD7/). The control computer can strobe the data in with PPACK/. The control computer must reset the PPRC0/ command <u>after</u> it has accepted the data from the PROM read bus. When PPRC0/ goes false, PPACK/ also goes false. The eight-bit PROM status word is again enabled through the PROM read logic and out onto the PROM read bus. The control computer should read the status word to verify that the data is valid and that no error occurred.

Figure 2-5 illustrates PROM read data timing for this method.

FIGURE 2-5 PROM READ DATA TIMING

The other method for reading is a status check approach. The control computer outputs a Control/high address byte with bit 6 (START RD) set (logical 1). The accompanying strobe (PPWC1/), in conjunction with the START RD bit, sets BUSY (bit 0) in the status register and generates the READ PROM signal which is applied to input port 0, bit 2 of the 4001 ROM at A20. The MCS-40 will interrogate the input port and cause the appropriate personality card to read the addressed PROM location and make it available to the Control Board, as described above for the first method.

When the data is read (or an error occurs), the  $MCS^{T.M}_{-40}$  outputs PROM PROG RD ACK from the output port, bit 3, on the 4002 RAM at All. PROM PROG RD ACK, in turn, clears the READ PROM Signal to the  $MCS^{T.M}_{-40}$  and the BUSY bit in the status word. When the control computer reads the status word and determines that BUSY is false, the control computer should then issue the PROM read data command (PPRC0/). PPRC0/ will cause the read acknowledge signal (PPACK/) to be generated with 1 µsec. PPRC0/ also enables the data byte through the PROM read logic and onto the PROM read bus, PRD0/-PRD7/ (pins 62-69). The control computer should read the status word again to verify that valid data is available and that no errors occurred. This method of reading data from the Universal PROM Programmer prevents the control computer from being occupied for an extended period of time.

USING START RD BIT OF CONTROL BYTE

#### 2.2.4 PROM PROGRAM DATA SEQUENCE

The control computer initiates a PROM program data operation by outputting eight-bits of write data to the PROM Programmer, and by issuing the program data strobe, PPWCO/ (received at pin 74).

The eight write data bits are received on lines PPD0/-PPD7/ (pins 77-84), and latched into the write data register by PPWCO/. The contents of the write data register are available to the personality cards on lines WRITE DATA 0-7 (pins 21-28). If the particular PROM to be programmed is organized into 4-bit words, the NIBBLE SELECT bit of the mode control register (see Section 2.2.2) will dictate which 4-bits of the 8-bit write data byte are actually to be written into the addressed PROM location.

PPWCO/ also sets the busy latch (A6-10) in the status logic. The low  $\overline{Q}$  output of this latch (BUSY/) is gated through the PROM read logic onto line FRDO/, and constitutes bit 0 of the PROM status word. Thus, the busy status is indicated immediately instead of waiting to be software set by the MCS<sup>T.M</sup>40. The high Q output of the busy latch is labeled WRITE PROM, and is applied to input port 0, bit 3, on the 4001 ROM at A20.

As we mentioned in the previous section, the  $MCS^{T.M}_{-4}0$  stays in a program loop that alternately examines the RD PROM and WRITE PROM inputs on the 4001 ROM. If the  $MCS^{T.M}_{-4}0$  finds a true level on WRITE PROM, it will then examine the SOCKET SELECT input at port 1 on the same 4001 ROM. Having determined which socket, and consequently which PROM and personality card, are to be accessed, the  $MCS^{T.M}_{-4}0$  then examines the board sense input for the personality card associated with the selected socket, BD SENSE #2 (input port 1, bit 0, on the 4001 ROM at A29). If the appropriate board is not present, an error condition is indicated in the status word and the operation is terminated.

2-17

If the PROM to be programmed is organized into 4-bit words, the NIBBLE SELECT input (port 0, bit 0, on the 4001 ROM at A20) is examined to determine which 4-bits from the PROM write data register are to be used.

Having determined the socket and nibble to be accessed, the MCS<sup>-T.M.</sup> 40 updates the three status lines, (STATUS 0-2) to indicate an internal busy state, and outputs an active-low pulse on the LITE/ line (bank 1, port 0, bit 3, on the 4001 ROM at Al0) to illuminate the PROGRAMMING indicator on the front panel of the Universal PROM Programmer (FNT PNL LITE signal at pin 86). The  $MCS^{T.M}_{-}40$ , then, transfers program control to the proper program routine stored in the 4001 ROM's on the appropriate personality card. Using the I/O ports on the personality card ROM's, the  $MCS^{T.M}_{-}40$  can, by executing the program routine stored in these ROM's, cause the personality card to write the proper data bits into the addressed PROM location (refer to Chapters 3-6 for specific descriptions of the personality cards).

When the addressed PROM location has been successfully programmed, the  $MCS^{T.M}_{-40}$  turns off the PROGRAMMING indicator on the front panel, sets the COMPLETE/VERIFIED bit in the status word, and clears the busy latch (BUSY/ and WRITE PROM both go false).

Note that the PROM Programmer does not return an acknowledgement signal to the control computer during Write command sequences (PPWC0/, PPWC1/, and PPWC2/).

Figure 2-7 illustrates timing for a program data sequence.

2-18

\* When low, TEST indicates that the PROM location was successfully programmed. (8-bit operation only)

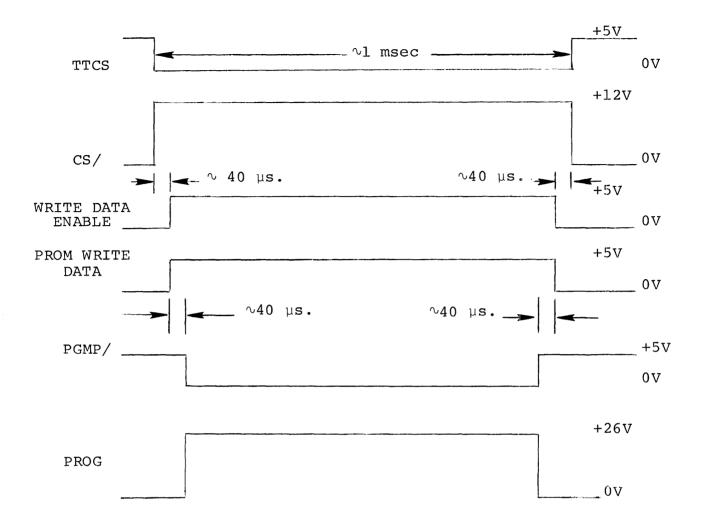

> FIGURE 2-7 PROM PROGRAM WRITE TIMING

### 2.3 PIN LIST: CONTROL BOARD

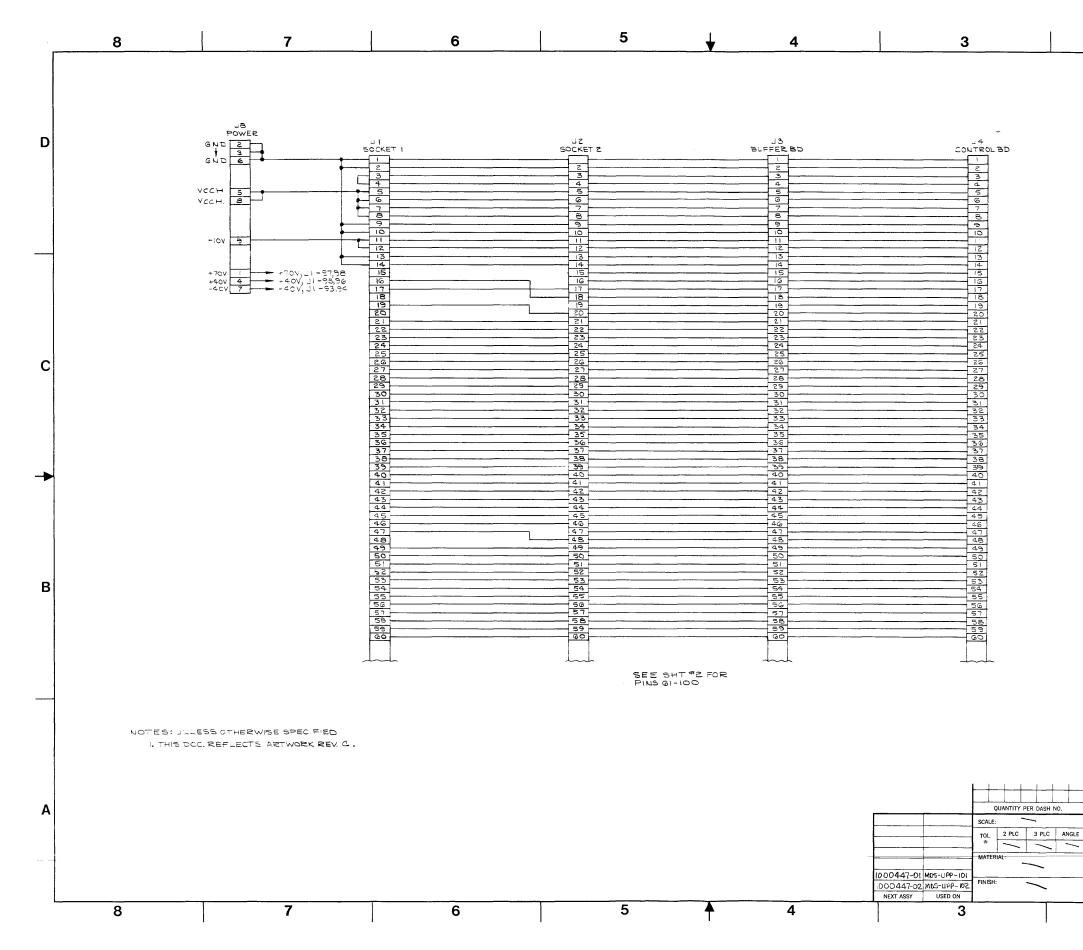

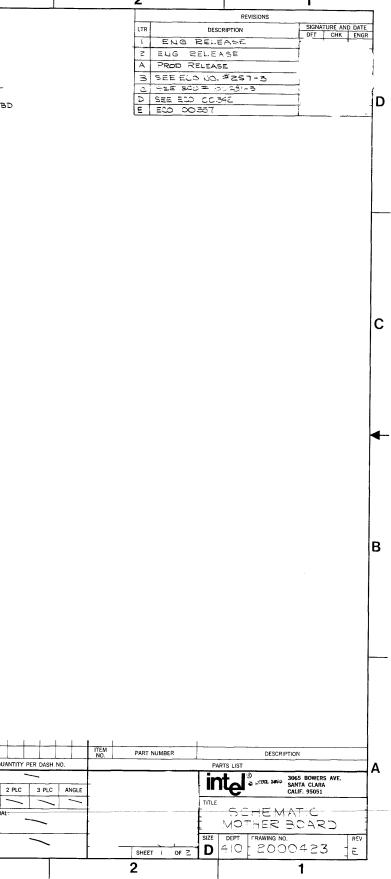

The Control Board communicates with control computer, the personality cards and the PROM Programmer front panel through a 100-pin double-sided PC edge connector. Pin allocations and designated signal function for the 100-pin connector are listed in Table 2-1.

# TABLE 2-1. CONTROL BOARD PIN LIST

| PIN                                                      | MNEMONIC                                                                                                                                                               | FUNCTION                                                                                                                                       | *SOURCE                         | *DESTINATION(S)                       |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------|

| 1<br>2<br>3                                              | G N D<br>G N D                                                                                                                                                         | Ground                                                                                                                                         |                                 | · · · · · · · · · · · · · · · · · · · |

| 3<br>4<br>5<br>7<br>8<br>9<br>10                         | VCCH<br>VCCH<br>VCCH<br>VCCH<br>GND<br>GND                                                                                                                             | Power inputs<br>(5.85 VDC)<br>Ground                                                                                                           | PS<br>PS<br>PS<br>PS            |                                       |

| 11<br>12<br>13<br>14<br>15                               | - 1 0 V<br>- 1 0 V<br>G N D<br>G N D                                                                                                                                   | Power inputs<br>Ground                                                                                                                         | PS<br>PS                        |                                       |

| 16<br>17                                                 | BD SENSE #2                                                                                                                                                            | Board Sense #2                                                                                                                                 | PC#2                            | СВ                                    |

| 18<br>19<br>20<br>21<br>22                               | BD SENSE #1<br>CONTROL #2<br>CONTROL #1<br>WRITE DATA O<br>WRITE DATA 1                                                                                                | Board Sense #1<br>Control bits                                                                                                                 | P C # 1<br>C B                  | СВ                                    |

| 23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32 | WRITE DATA 2<br>WRITE DATA 3<br>WRITE DATA 4<br>WRITE DATA 5<br>WRITE DATA 6<br>WRITE DATA 7<br>PROM ADDRESS 0<br>PROM ADDRESS 1<br>PROM ADDRESS 2<br>PROM ADDRESS 3   | Write data bus to<br>personality cards                                                                                                         | СВ                              | PC's                                  |

| 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41       | PROM ADDRESS 4<br>PROM ADDRESS 5<br>PROM ADDRESS 6<br>PROM ADDRESS 7<br>PROM ADDRESS 8<br>PROM ADDRESS 9<br>PROM ADDRESS 9<br>PROM ADDRESS 10<br>PROM ADDRESS 11<br>DO | PROM address bus to<br>personality cards                                                                                                       | СВ                              | PC's                                  |

| 42<br>43<br>44<br>45                                     | D1<br>D2<br>D3<br>Ф2                                                                                                                                                   | MCS <sup>T.M</sup> 40 data bus<br>(bi-directional)                                                                                             | CB <del>∢→</del> PC's           | PC's ←→ CB                            |

| 46<br>47<br>48<br>49<br>50                               |                                                                                                                                                                        | MCS <sup>T_4</sup> 0 clock signals<br>Enable ROM bank 0<br>Enable ROM bank 1<br>Enable RAM bank 1<br>MCS <sup>T_4</sup> 0 Syn-<br>chronization | C B<br>C B<br>C B<br>C B<br>© B | PC'S<br>PC<br>PC<br>PC<br>PC's        |

# TABLE 2-1. (CONTINUED)

| N MNEMONIC                                                                                                     | FUNCTION                                                                  | *SOURCE        | *DESTINATION(S |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------|----------------|

| 1 RESET/<br>2 PROM RD DATA 0/<br>3 PROM RD DATA 1/<br>4 PROM RD DATA 2/                                        |                                                                           | СВ             | PC's           |

| PROM RD DATA 2/<br>PROM RD DATA 3/<br>PROM RD DATA 4/<br>PROM RD DATA 5/<br>PROM RD DATA 6/<br>PROM RD DATA 7/ | ZData read from PROM                                                      | PC             | СВ             |

| GND<br>PRDO/<br>PRD1/                                                                                          | ground .                                                                  |                |                |

| PRD2/<br>PRD3/<br>PRD4/<br>PRD5/<br>PRD6/<br>PRD7/                                                             | Data read bus to<br>contról computer                                      | CB             | CC             |

| PPRCO/<br>PPRC1/<br>PPACK/<br>GND                                                                              | Read data command<br>Read status command<br>Acknowledgement<br>ground     | CC<br>CC<br>CB | CB<br>CB<br>CC |

| PPWCO/<br>PPWC1/<br>PPWC2/<br>PPDO/<br>PPD1/<br>PPD2/                                                          | Program data command<br>Control/high address strobe<br>Low-address strobe | сс<br>сс<br>сс | CB<br>CB<br>CB |

| PPD3/<br>PPD4/<br>PPD5/<br>PPD6/<br>PPD7/                                                                      | Data output bus<br>from control computer                                  | cc             | СВ             |

| INT/<br>FNT PNL LITE                                                                                           | Initialization signal<br>PROGRAMMING light driver                         | CC<br>CB       | CB<br>FP       |

| TTL RESET/                                                                                                     | RESET switch                                                              | FP             | СВ             |

| LOCAL ON LINE/                                                                                                 | Not used at present                                                       |                |                |

#### CHAPTER 3

#### SYSTEM UTILIZATION

The Universal PROM Programmer was designed to simplify the task of programming Intel's family of PROMs. The operation is basically one of just inserting the PROM in a socket on the front panel and then directing the control computer to issue the appropriate commands to the PROM Programmer.

In the typical case where the control computer is one of Intel's INTELLEC<sup>®</sup> microcomputer development systems, the use of the PROM Programmer is particularly easy. Section 3.1 provides the information necessary for the physical installation of the PROM Programmer and for PROM devices. Refer to Appendix A for the details of the keyboard operator commands accepted by the INTELLEC<sup>®</sup>MDS Monitor for use with the PROM Programmer.

Section 3.2 contains the detailed interfacing requirements of the PROM Programmer. This information is provided for those applications where the PROM Programmer is controlled by a computer other than the INTELLEC<sup>®</sup>MDS system.

#### 3.1 INSTALLATION

Installation procedures for the PROM Programmer are quick and easy to perform. However, to prevent possible electrical shock or damage to the components of the PROM Programmer, it is important that the instructions provided in this section be carefully followed.

Section 3.1.1 specifies the cabling requirements of the PROM Programmer. Section 3.1.2 contains step-by-step instructions for the removal and installation of personality cards. Section 3.1.4 contains the procedure for replacing the socket board assembly. Section 3.1.5 lists I/O port assignments when using the Universal PROM Programmer with an INTELLEC<sup>®</sup>MDS, INTELLEC<sup>®</sup>8/MOD 8 or INTELLEC<sup>®</sup>8/MOD 80 system.

#### 3.1.1 CABLING

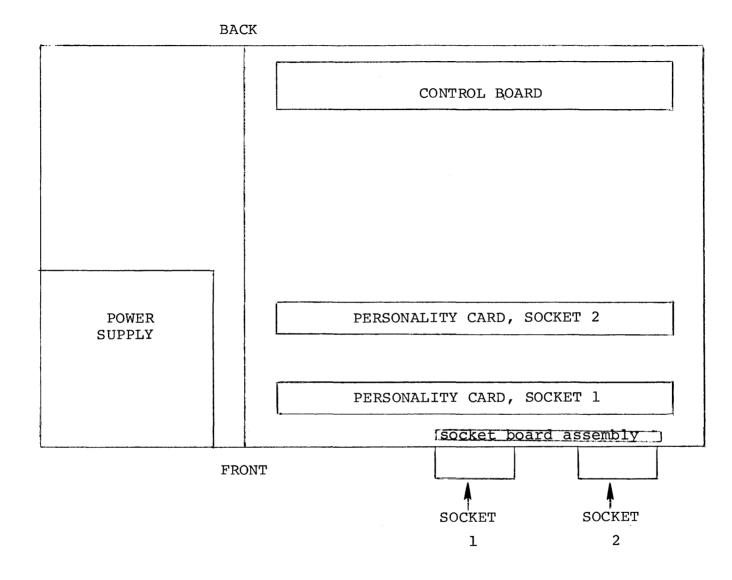

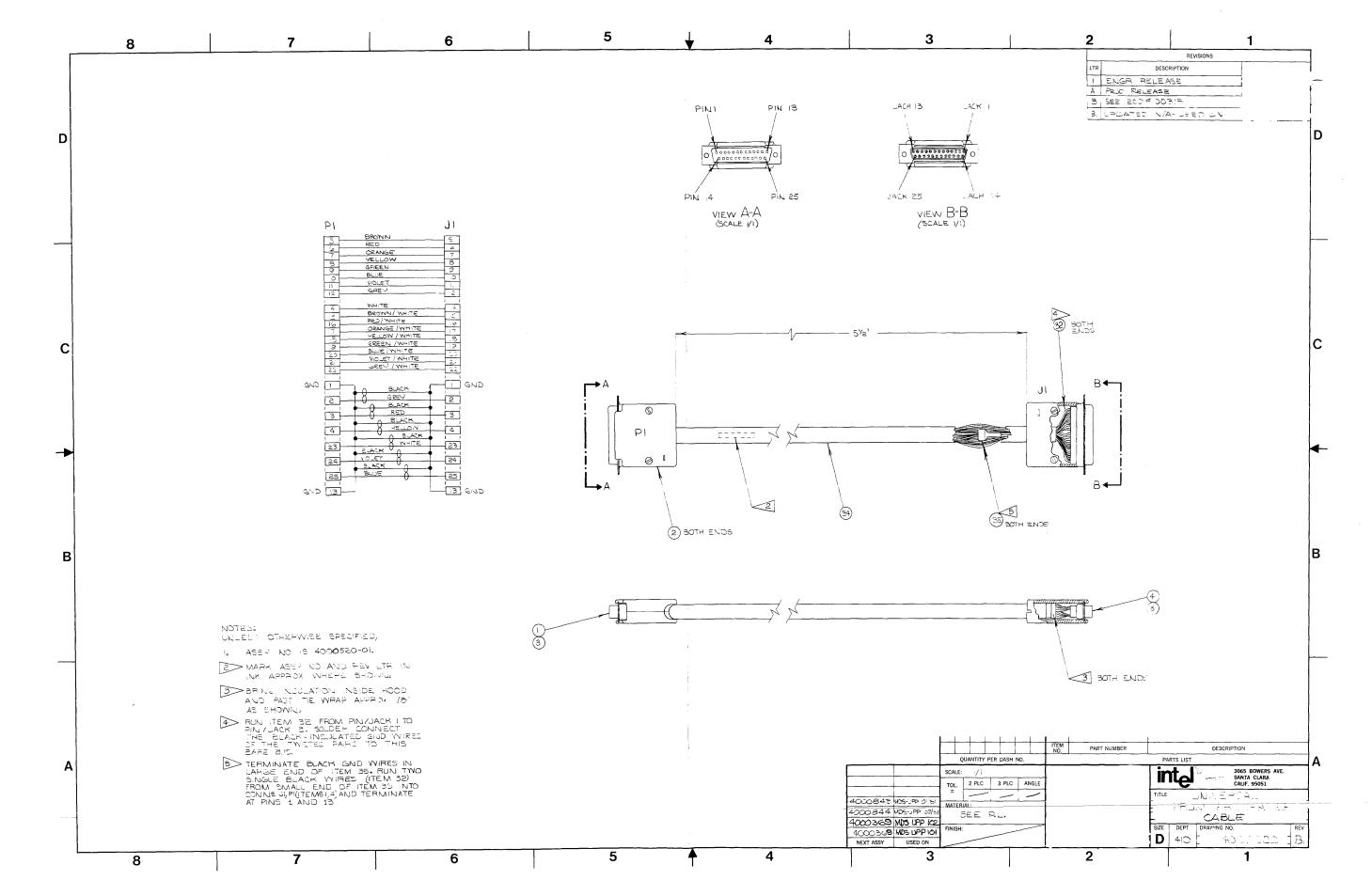

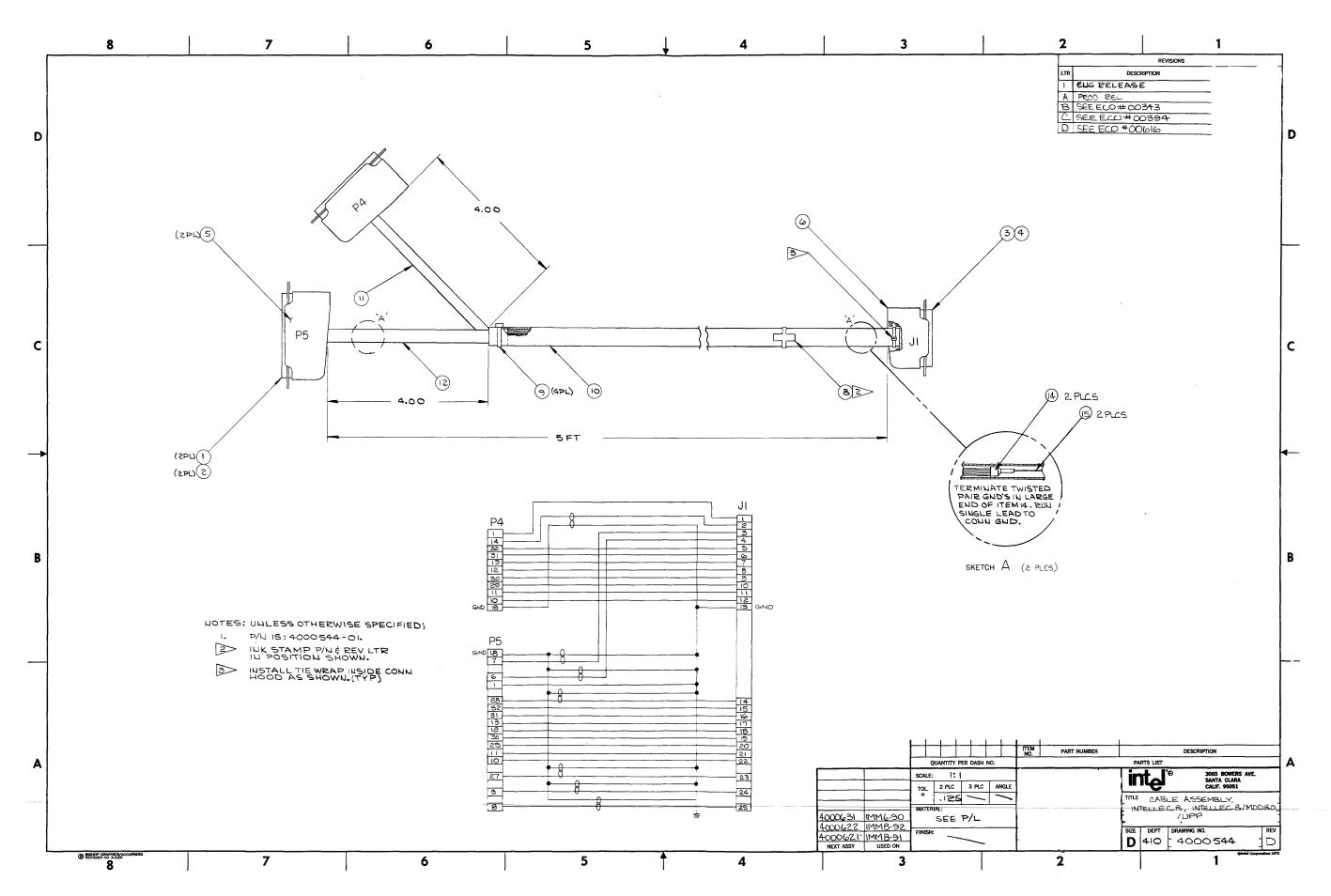

The Universal PROM Programmer connects to the control computer via a 22 gauge, multi-strand wire cable. Seven lines on the cable require twisted pair wire; one wire is grounded (see Table 3-1). Standard cables provided by Intel are 5 feet, the maximum length of the cable is 10 feet.

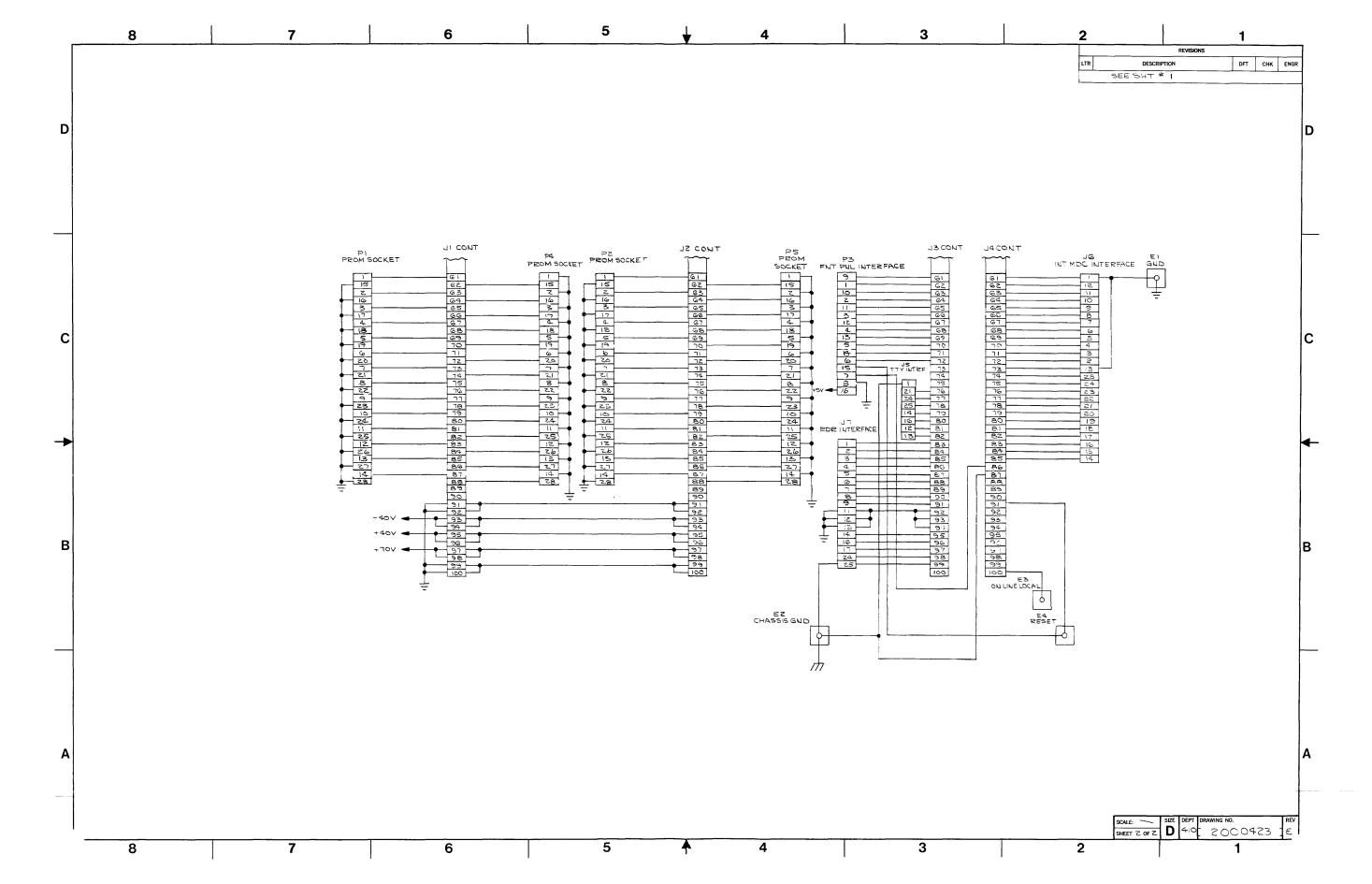

One end of the cable, with a 25-pin connector (AMP 205261-6 or 205201-7) plugs into a 25-pin socket connector ITT cannon DBC-25P-AA, in the Universal PROM Programmer. All lines are terminated in this 25-pin socket connector.

The other end of the cable is attached to the control computer:

## INTELLEC<sup>®</sup> MDS

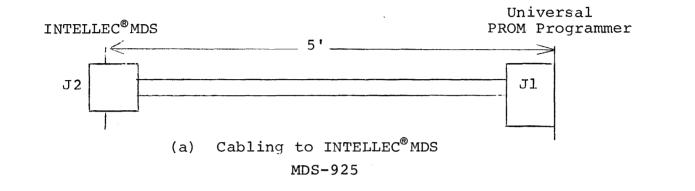

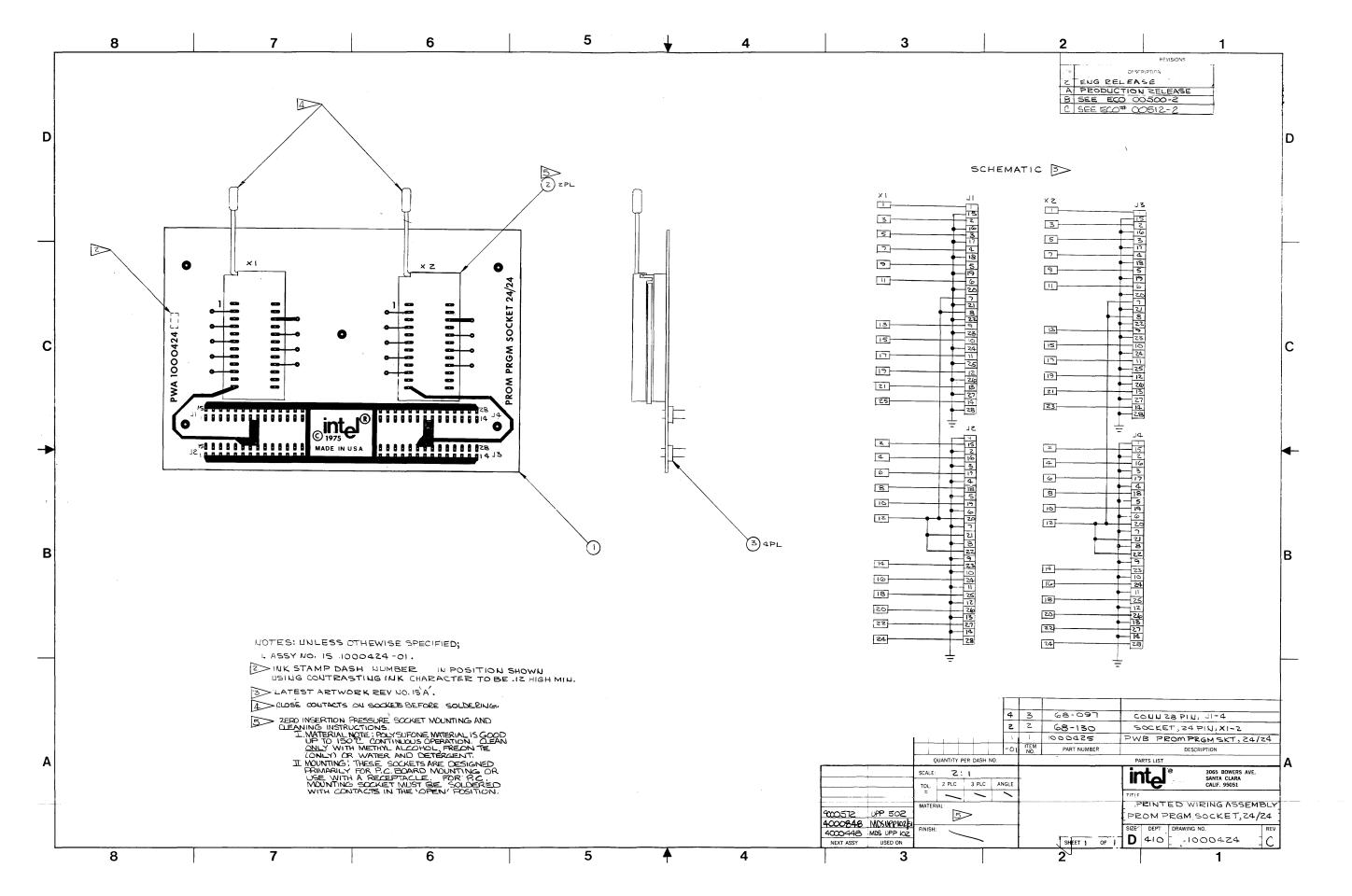

When the Universal PROM Programmer is used with an INTELLEC<sup>®</sup> MDS system, the cable (MDS-UPP-900) is attached to the back panel of the INTELLEC<sup>®</sup> MDS system via a 25-pin connector plug (AMP 205208-1) and pin assembly (AMP 205202-6 or AMP 205202-7) as shown in Figures 3-1 (a) and Appendix B-27.

## TABLE 3-1

| CONNECTOR PIN | ASSIGNMENTS |

|---------------|-------------|

|---------------|-------------|

| **SIGNAL                                                                                                                                                                                                                                        | Universal PROM<br>Programmer<br>Connector Pin                                                                                                                                                                        | INTELLEC <sup>®</sup> MDS<br>Connector Pin                                                                                                                                                                          | INTELLEC <sup>®</sup> 8/MOD 80<br>INTELLEC 8/MOD 8                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND<br>PPACK/<br>PPRC1/<br>PRC0/<br>PRD7/<br>PRD6/<br>PRD5/<br>PRD4/<br>PRD3/<br>PRD2/<br>PRD1/<br>PRD0/<br>GND<br>INT/<br>PPWD7/<br>PPWD6/<br>PPWD6/<br>PPWD5/<br>PPWD4/<br>PPWD3/<br>PPWD2/<br>PPWD1/<br>PPWD0/<br>PPWC2/<br>PPWC1/<br>PPWC0/ | J1-l $J1-2*$ $J1-3*$ $J1-4$ $J1-5$ $J1-6$ $J1-7$ $J1-8$ $J1-9$ $J1-10$ $J1-11$ $J1-12$ $J1-13$ $J1-14*$ $J1-15$ $J1-14*$ $J1-15$ $J1-16$ $J1-17$ $J1-18$ $J1-19$ $J1-20$ $J1-21*$ $J1-22*$ $J1-23*$ $J1-24*$ $J1-25$ | J2-1 $J2-2*$ $J2-3*$ $J2-4$ $J2-5$ $J2-6$ $J2-7$ $J2-8$ $J2-9$ $J2-10$ $J2-11$ $J2-12$ $J2-13$ $J2-14*$ $J2-15$ $J2-16$ $J2-17$ $J2-16$ $J2-17$ $J2-18$ $J2-19$ $J2-20$ $J2-21*$ $J2-22*$ $J2-23*$ $J2-24*$ $J2-25$ | $\begin{array}{c} P4-1 \\ P4-14 \\ P5-7 \\ P5-6 \\ P4-32 \\ P4-31 \\ P4-13 \\ P4-12 \\ P4-29 \\ P4-11 \\ P4-29 \\ P4-11 \\ P4-10 \\ P5-1 \\ P5-28 \\ P5-32 \\ P5-31 \\ P5-31 \\ P5-13 \\ P5-12 \\ P5-30 \\ P5-29 \\ P5-11 \\ P5-10 \\ P5-27 \\ P5-9 \\ P5-8 \end{array}$ |

\* Twisted pair wiring \*\* Refer to Section 3.2 for signal summary

(c) Cabling to INTELLEC<sup>®</sup> 8/MOD 80, INTELLEC<sup>®</sup> 8/MOD 8

IMM 6-90

FIGURE 3-1 CABLING

## INTELLEC<sup>®</sup>8/MOD 80, INTELLEC<sup>®</sup>8/MOD 8

When the Universal PROM Programmer is used with an INTELLEC<sup>®</sup> 8/MOD 80, or INTELLEC<sup>®</sup>8/MOD 8 system, the cable is attached to the back panel of the INTELLEC<sup>®</sup>8/MOD 80 or INTELLEC<sup>®</sup> 8/MOD 8 system via two 37-pin connector plugs (AMP 205310-0) and pin assemblies (AMP 205310-0) as shown in Figures 3-1 (c) and Appendix B-28.

Table 3-1 correlates pin assignments on the Universal PROM Programmer connector with pin assignments on the connectors used with INTELLEC<sup>®</sup>MDS and INTELLEC<sup>®</sup>8/MOD 80 INTELLEC<sup>®</sup>8/MOD 8 systems.

#### 3.1.2 PERSONALITY CARD INSTALLATION

Since some applications require the ability to program a variety of PROM devices, the personality cards of the Universal PROM Programmer have been designed so that they may be easily exchanged by the operator. This feature gives the PROM Programmer the capability to program any Intel<sup>®</sup> PROM.

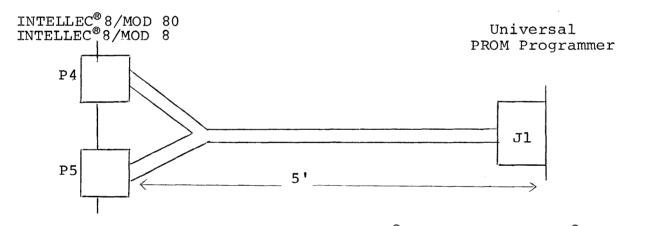

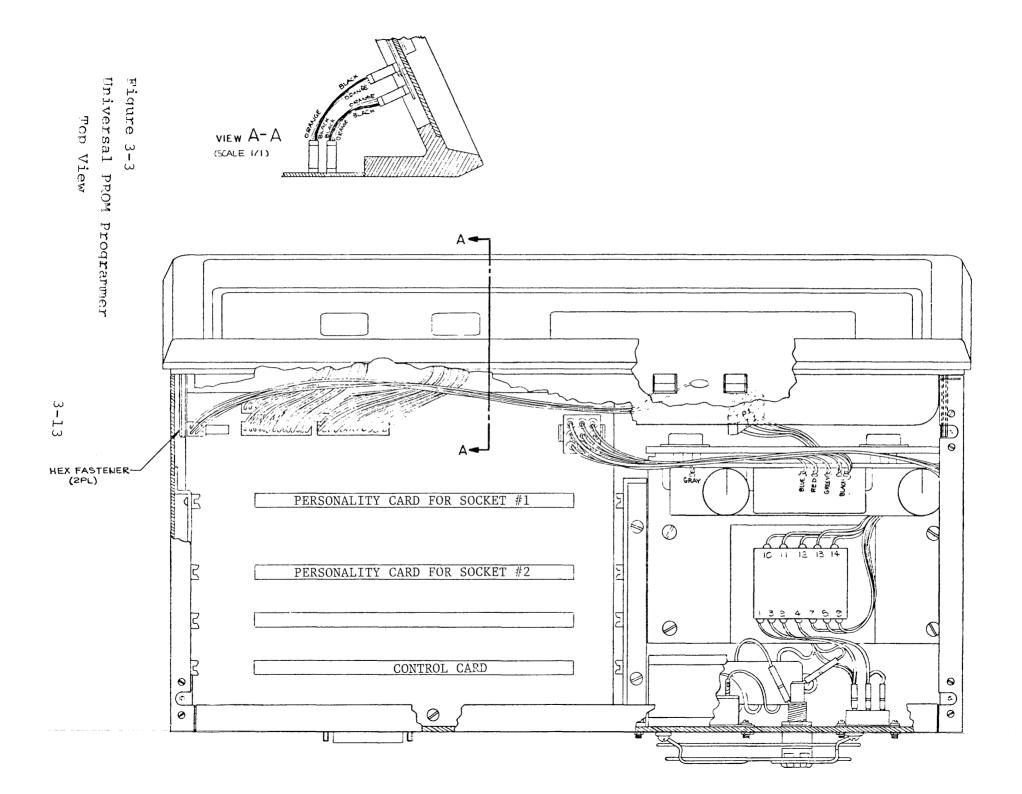

Figure 3-2 shows the PROM Programmer as viewed from the top, with the cover removed. Notice there are slots for three printed circuit cards. The Control Board is located near the rear of the PROM Programmer; it is not normally removed. The two slots near the front are for the personality cards. The slot nearest the front holds the personality card that controls Socket 1 (16-pin socket on MDS-UPP-501; 24-pin socket on MDS-UPP-502). The other slot holds the personality card that controls Socket 2 (the 24-pin socket). The step-by-step procedure for exchanging personality cards is given below.

ω -8

#### --WARNING--

Turn the ON/OFF switch on the front panel OFF and remove the AC power cord from the power source before removing the cover of the PROM Programmer. This will prevent electrical shock as well as protect the components of the PROM Programmer.

Remove the cover of the PROM Programmer by twisting each of the four screws on the cover approximately 1/4 turn counterclockwise to unlock them, and lift the cover off.

#### --WARNING--

The system power must be off for at least 60 seconds before the personality card is removed or inserted. This time is needed so the power supply can discharge. If this is not done, damage may occur to the personality cards.

- 2) If necessary, remove the previously installed personality card by first lifting up the two plastic locking tabs (one at each corner). Then grasp the edge of the personality card and pull it straight up and out of the cabinent.

- 3) Select the personality card to be installed. Note the card number designation (e.g., "UPP-878 Personality Module") printed on one side of the card. This side must face toward the front of the PROM Programmer when it is installed. The 100-pin edge connector on the personality card mates with the slot in the PROM Programmer.

- Carefully slide the selected personality card into the card slot. Press down on the two plastic locking tabs to secure the card in place.

- 5) Double check to be sure you placed the right card in the correct socket (see Figure 3-2). Mark the identification panel located under the socket on the front panel with the designation of the personality card you have just installed.

- 6) Place the cover back on top of the PROM Programmer and fasten it by turning the four screws clockwise.

#### CAUTION

Never operate the Universal PROM Programmer with the cover off, as it will impede required air flow.

#### 3.1.3 PROM DEVICE INSERTION

The correct insertion of the PROM in the socket on the front panel is very important. There are two things you must avoid doing:

- <u>DON'T</u> insert the PROM in the socket unless it is compatible with the personality card indicated below the socket on the identification panel.

<u>DON'T</u> insert the PROM upside down.

- Check the markings on the top of the PROM and on the identification panel to be sure they match. Using a mismatched personality card

and PROM could possibly destroy the PROM, cause damage to the personality card, or both. When inserting the PROM be sure the semi-circular notch on one end of the PROM is at the top of the socket. An upside down PROM could harm the PROM and perhaps the personality card too.

#### CAUTION

A PROM should not be in one of the sockets when power is turned on or when the Universal PROM Programmer or control computer is RESET, as it may result in the accidental programming of a PROM location.

#### 3.1.4 SOCKET BOARD REPLACEMENT

#### --WARNING--

Turn the ON/OFF switch on the front panel OFF <u>and</u> <u>remove the AC power cord</u> from the power source before removing the cover of the PROM Programmer. This will prevent electrical shock as well as protect the components of the PROM Programmer.

- 1) Remove the cover of the PROM Programmer by twisting each of the four screws on the cover approximately 1/4 turn counterclockwise to unlock them, and lift the cover off.

- 2) If necessary, remove the installed personality cards by first lifting up the two plastic locking tabs (one at each corner). Then grasp the edge of the personality card and pull it straight up and out of the cabinet.

- 3) Carefully remove the front Bezel by removing 2 Hex nuts at the top corner of the UPP. Then pull the Bezel forward from the bottom to release 2 quick disconnect fasteners located at the lower left and right sides of the Bezel. Internal cables will restrict travel to approximately 4". Lay the Bezel in front of the UPP.

- 4) Remove the 4 cable assemblies from the front panel socket board.

- 5) Remove the 5 screws and lift out the socket board.

- 6) Place the dress cover on the front of the new socket board. (This cover provides electrical isolation between the chassis and the socket board.)

- 7) Install the new socket board and replace the 5 screws.

- 8) Replace the 4 cable assemblies as shown in Figure 3-3.

- 9) Replace the Bezel by fastening the quick disconnect fasteners and Hex nuts.

- 10) Replace the personality cards. Double check to be sure you placed the right card in the correct socket (see Figure 3-2).

- 11) Place the cover on top of the PROM Programmer and fasten it by turning the four screws clockwise.

#### CAUTION

A PROM should not be in one of the sockets when power is turned on or when the Universal PROM Programmer or Control Computer is RESET, as it may result in the accidental programming of a PROM location.

#### 3.1.5 I/O PORT ASSIGNMENTS

Table 3-2 lists those INTELLEC<sup>®</sup>MDS I/O port addresses that are dedicated for use with Universal PROM Programmer. Table 3-3 provides the dedicated port addresses on the INTELLEC<sup>®</sup>8/MOD 8 and INTELLEC<sup>®</sup>8/MOD 80 systems.

| DIRECTION | I/O PORT ADDRESS | FUNCTION                                                                                                                                                                    |

|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT     | ØØFØ             | Read PROM data<br>(LSB=DØ)                                                                                                                                                  |

|           | ØØFl             | Read PROM status<br>DØ=BUSY<br>D1=COMPLETE/VERIFIED<br>D2=FAILED TO PROGRAM<br>D3-D7=OTHER ERRORS*                                                                          |

| OUTPUT    | øøfø             | Write PROM data<br>(LSB=DØ)                                                                                                                                                 |

|           | ØØFl             | Output Control/High Address byte<br>DØ-D3=most significant four bits of<br>PROM address<br>D4=NIBBLE SELECT<br>D5=SOCKET SELECT<br>D6=START RD<br>D7=CONTROL #1 (must be Ø) |

|           | øøf2             | Output eight least significant bits of<br>12-bit PROM address<br>(LSB=DØ)                                                                                                   |

TABLE 3-2 I/O PORT ADDRESSES: INTELLEC<sup>®</sup> MDS

\*See Section 1.2 for complete list of errors.

## TABLE 3-3

I/O PORT ADDRESSES: INTELLEC<sup>®</sup> 8/8, INTELLEC<sup>®</sup> 8/80

DESCRIPTION I/O INTELLEC<sup>®</sup> 8/8 INTELLEC<sup>®</sup> 8/80

|        |        | PORT |   | BIT | PORT | -   | BIT |

|--------|--------|------|---|-----|------|-----|-----|

| PPACK/ | INPUT  | 7    |   | ø   | 7    | -   | 0   |

| PPRC1/ | OUTPUT | D    |   | 1   | 5    | -   | 1   |

| PPRCØ/ | OUTPUT | D    |   | Ø   | 5    | -   | ø   |

| PPRD7/ | INPUT  | 6    | - | 7   | 6    |     | 7   |

| PPRD6/ | INPUT  | 6    | - | 6   | 6    | -   | 6   |

| PPRD5/ | INPUT  | 6    | - | 5   | 6    | -   | 5   |

| PPRD4/ | INPUT  | 6    |   | 4   | 6    |     | 4   |

| PPRD3/ | INPUT  | 6    | - | 3   | 6    | -   | 3   |

| PPRD2/ | INPUT  | 6    | - | 2   | 6    |     | 2   |

| PPRD1/ | INPUT  | 6    | - | 1   | 6    |     | 1   |

| PPRDØ/ | INPUT  | 6    | - | ø   | 6    | -   | 0   |

| INT/   | OUTPUT | D    | - | 7   | 5    | -   | 7   |

| PPWD7/ | OUTPUT | Е    | - | 7   | 6    | -   | 7   |

| PPWD6/ | OUTPUT | Е    | - | 6   | 6    | -   | 6   |

| PPWD5/ | OUTPUT | Е    | - | 5   | 6    |     | 5   |

| PPWD4/ | OUTPUT | Е    | - | 4   | 6    | -   | 4   |

| PPWD3/ | OUTPUT | Е    | - | 3   | 6    | -   | 3   |

| PPWD2/ | OUTPUT | Е    |   | 2   | 6    | -   | 2   |

| PPWD1/ | OUTPUT | Е    | - | 1   | 6    | ••• | 1   |

| PPWDØ/ | OUTPUT | E    | - | ø   | 6    | -   | ø   |

| PPWC2/ | OUTPUT | D    |   | 6   | 5    | -   | 6   |

| PPWC1/ | OUTPUT | D    |   | 5   | 5    | -   | 5   |

| PPWCØ/ | OUTPUT | D    | - | 4   | 5    | -   | 4   |

#### 3.2 INTERFACING