intel®

## Pentium<sup>®</sup> Processor Specification Update

Release Date: March, 1995

Order Number: 242480-002

Information is this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive, and iCOMP trademarks has been issued to Intel Corporation.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

**®INTEL CORPORATION 1995**

â

÷

## int<sub>el</sub>.

4

## CONTENTS

| REVISION HISTORY                                                            | v  |

|-----------------------------------------------------------------------------|----|

| PREFACE                                                                     | vi |

| Part I: Specification Updates for 60- and 66-MHz Pentium® Processors        |    |

| GENERAL INFORMATION                                                         | 3  |

| SPECIFICATION CHANGES                                                       | 8  |

| ERRATA                                                                      | 13 |

| SPECIFICATION CLARIFICATIONS                                                | 27 |

| DOCUMENTATION CHANGES                                                       |    |

| Part II: Specification Updates for 75-, 90- and 100-MHz Pentium® Processors |    |

| GENERAL INFORMATION                                                         |    |

| SPECIFICATION CHANGES                                                       |    |

| ERRATA                                                                      | 49 |

| SPECIFICATION CLARIFICATIONS                                                | 86 |

| DOCUMENTATION CHANGES                                                       | 91 |

|                                                                             |    |

.

.

## **REVISION HISTORY**

| Date of Revision | Version | Description                                                                                                                                                                                                                                                                             |

|------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 1995    | -001    | This document consolidates information previously contained in various versions of stepping information, notably the B, C and D stepping of Pentium® Processor at iCOMP® Index (510\60, 567\66) and the B and C stepping of Pentium Processor at iCOMP Index (610\75, 735\90, 815\100). |

| March 1995       | -002    | Added Errata 22–25 and Spec Clarification 15 to Part I. Added Spec Change 12, Errata 24–27, 8DP–12DP and 11AP, Spec Clarification 3, and Doc Change 6 to Part II.                                                                                                                       |

## PREFACE

This document is an update to the specifications contained in the *Pentium*<sup>™</sup> *Family User's Manual*. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools. It contains Specification Changes, Errata, Specification Clarifications, and Documentation Changes, and is divided into the following two parts:

- Part I: Specification Update for 60- and 66-MHz Pentium processors

- Part II: Specification Update for 75-, 90-, and 100-MHz Pentium processors

## **Contact Information**

For questions or comments, please call one of the following numbers:

#### DIRECT NUMBERS

| US and Canada                                                       | 1-800-628-8686                                                                                  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| US (from overseas)                                                  | 1-916-356-3551                                                                                  |

| Australia                                                           | 61-2-975-3300                                                                                   |

| England                                                             | +44 (0) 1793 431144                                                                             |

| France                                                              | +44 (0) 1793 421777                                                                             |

| Germany                                                             | +44 (0) 1793 421333                                                                             |

| Hong Kong                                                           | 852-844-4555                                                                                    |

| India                                                               | 91-80-2215065                                                                                   |

| Japan<br>Korea<br>People's Republic of China<br>Singapore<br>Taiwan | 91-80-2215065<br>0120-868686<br>82-2-767-2500<br>86-1-505-0386<br>65-735-3811<br>886-2-514-4200 |

## Nomenclature

**Specification Changes** are modifications to the generally available specification of the Pentium processor. These modifications will be reflected in the *Pentium*<sup>™</sup> *Family User's Manual*.

**Errata** describe any problems associated with the current stepping of the Pentium processor and workarounds that allow the system designer to use this stepping.

**Specification Clarifications** describe a specification in greater detail or highlight complex design situations that may require implementation changes.

**Documentation Changes** include typos, errors, or omissions from the published specification of the Pentium processor. The changes will be incorporated in the next revision of the document in error.

### Identification Information

The Pentium processor can be identified by the following register contents:

| Family <sup>1</sup> | 60- and 66-MHz Model 1 <sup>2</sup> | 75-, 90-, and 100-MHz Model 2 <sup>2</sup> |

|---------------------|-------------------------------------|--------------------------------------------|

| 05h                 | 01h (described in Part I)           | 02h (described in Part II)                 |

NOTES:

1 The Family corresponds to bits [11:8] of the EDX register after RESET, bits [11:8] of the EAX register after the CPUID instruction is executed, and the generation field of the Device ID register accessible through Boundary Scan.

2 The Model corresponds to bits [7:4] of the EDX register after RESET, bits [7:4] of the EAX register after the CPUID instruction is executed, and the model field of the Device ID register accessible through Boundary Scan.

## Part I:

Specification Update for 60- and 66-MHz Pentium<sup>®</sup> Processors

.

٠

•

## intel.

## **GENERAL INFORMATION**

## Marking

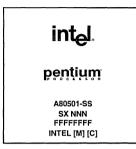

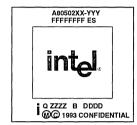

B-1 Production Units - Top:

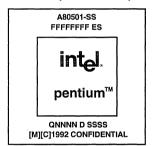

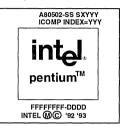

D-1 Sample Units – Top:

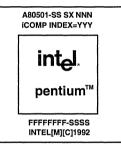

D-1 Production Units – Top:

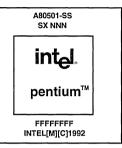

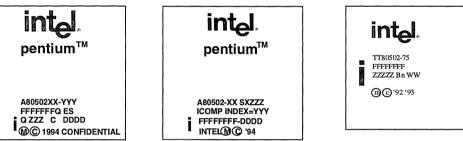

#### C-1 Production Units – Top:

**D-1 Production Units – Bottom:**

#### NOTES:

- SS = Speed (MHz).

- SX NNN = S-Spec number.

- FFFFFFF = FPO # (Test Lot Traceability #).

- For packages with heat spreaders, the inner line box defines the spreader edge.

- Ink Mark = All logo information on the heat spreader.

- Laser Mark = The two lines of information above and below the heat spreader. All bottomside information is laser mark.

- ES = Engineering Sample.

- QNNNN = Sample Specification number.

- SSSS = Serialization code.

- YYY = iCOMP® index (510 for 60-MHz and 567 for 66-MHz product).

- On the bottomside, the inner line box defines the edge of the metallic package lid.

- Bottomside, first two lines = Reserved for Intel internal use.

- Bottomside, third line = Copyright info; the last four digits of this line are reserved for Intel internal use.

| CPUID |        |       |          |                  |                            |        |                 |                   |       |

|-------|--------|-------|----------|------------------|----------------------------|--------|-----------------|-------------------|-------|

| Туре  | Family | Model | Stepping | Mfg.<br>Stepping | Speed<br>(MHz)<br>Core/Bus | S-Spec | V <sub>cc</sub> | T <sub>CASE</sub> | Notes |

| 0     | 5      | 1     | 3        | B1'              | 50/50                      | Q0399  | 4.75V-5.25V     | 0°C-85°C          | 1, 2  |

| 0     | 5      | 1     | 3        | B1'              | 60/60                      | Q0352  | 4.75V-5.25V     | 0°C-85°C          | 1     |

| 0     | 5      | 1     | 3        | B1'              | 60/60                      | Q0400  | 4.75V-5.25V     | 0°C-75°C          | 1, 2  |

| 0     | 5      | 1     | 3        | B1'              | 60/60                      | Q0394  | 4.75V-5.25V     | 0°C-80°C          | 2, 3  |

| 0     | 5      | 1     | 3        | B1'              | 66/66                      | Q0353  | 4.90V-5.25V     | 0°C-75°C          | 1     |

| 0     | 5      | 1     | 3        | B1'              | 66/66                      | Q0395  | 4.90V-5.25V     | 0°C-70°C          | 2, 3  |

| 0     | 5      | 1     | 3        | B1"              | 60/60                      | Q0412  | 4.75V-5.25V     | 0°C-85°C          | . 1   |

| 0     | 5      | 1     | 3        | B1"              | 60/60                      | SX753  | 4.75V-5.25V     | 0°C-85°C          | 1     |

| 0     | 5      | 1     | 3        | B1"              | 66/66                      | Q0413  | 4.90V-5.40V     | 0°C-75°C          | 1     |

| 0     | 5      | 1     | 3        | B1"              | 66/66                      | SX754  | 4.90V-5.40V     | 0°C-75°C          | 1, 4  |

| 0     | 5      | 1     | 5        | C1               | 60/60                      | Q0466  | 4.75V-5.25V     | 0°C-80°C          | 3     |

| 0     | 5      | 1     | 5        | C1               | 60/60                      | SX835  | 4.75V-5.25V     | 0°C-80°C          | 3     |

| 0     | 5      | 1     | 5        | C1               | 66/66                      | Q0467  | 4.90V-5.40V     | 0°C-70°C          | 3     |

| 0     | 5      | 1     | 5        | C1               | 66/66                      | SX837  | 4.90V-5.40V     | 0°C-70°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 60/60                      | Q0625  | 4.75V-5.25V     | 0°C-80°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 60/60                      | SX948  | 4.75V-5.25V     | 0°C-80°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 60/60                      | SX974  | 5.15V-5.40V     | 0°C-70°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 66/66                      | Q0626  | 4.90V-5.40V     | 0°C-70°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 66/66                      | SX950  | 4.90V-5.40V     | 0°C-70°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 66/66                      | Q0627  | 5.15V-5.40V     | 0°C-70°C          | 3     |

| 0     | 5      | 1     | 7        | D1               | 66/66                      | SX949  | 5.15V-5.40V     | 0°C-70°C          | 3     |

## Basic 60- and 66-MHz Pentium® Processor Identification Information

NOTES:

1. Non-heat spreader package.

3. Heat spreader package (see Specification Change #2).

4. 66 MHz B1" shipped after work week 34 of 1993 were tested to  $V_{CC} = 4.90V - 5.40V$

## Summary Table of Changes

The following table indicates the Specification Changes, Errata, Specification Clarifications, or Documentation Changes which apply to the 60- and 66-MHz Pentium processor. Intel intends to fix some of the errata in a future stepping of the component, and to account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

#### CODES USED IN SUMMARY TABLE

| X:                        | Specification Change or Clarification that applies to this stepping.                                   |

|---------------------------|--------------------------------------------------------------------------------------------------------|

| Doc:                      | Document change or update that will be implemented.                                                    |

| Fix:                      | This erratum is intended to be fixed in a future step of the component.                                |

| Fixed:                    | This erratum has been previously fixed.                                                                |

| Shaded:                   | This erratum is either new or modified from the previous version of the document.                      |

| (No mark) or (Blank Box): | This erratum is fixed in listed stepping or specification change does not apply to<br>listed stepping. |

| NO. | B1 | C1 | D1 | Plans | SPECIFICATION CHANGES                                                                              |  |  |  |

|-----|----|----|----|-------|----------------------------------------------------------------------------------------------------|--|--|--|

| 1   | X  | х  | х  | Doc   | V <sub>CC</sub> Specification Change at 66 MHz                                                     |  |  |  |

| 2   | x  | x  | x  | Doc   | Mechanical/Thermal/Case Temperature Specifications for Pentium®<br>Processor Heat Spreader Package |  |  |  |

| 3   | х  | х  | х  | Doc   | DP0-7 Read Data Setup Time Specification Change                                                    |  |  |  |

| 4   | Х  | Х  | х  | Doc   | CLK Toggle during V <sub>CC</sub> Ramp                                                             |  |  |  |

| NO. | B1 | C1 | D1 | Plans | ERRATA                                                                                             |  |  |  |

| 1   | X  |    |    | Fixed | BOFF# hold timing                                                                                  |  |  |  |

| 2   | X  |    |    | Fixed | Incomplete initialization may flush the internal pipeline                                          |  |  |  |

| 3   | X  |    |    | Fixed | IV pin may not be asserted under certain conditions                                                |  |  |  |

| 4   | х  |    |    | Fixed | Testability writes to data TLB may store wrong parity                                              |  |  |  |

| 5   | х  |    |    | Fixed | LRU bits in the data cache TLBs are updated incorrectly                                            |  |  |  |

| 6   | х  |    |    | Fixed | A replacement writeback cycle may invade a locked sequence                                         |  |  |  |

| 7   | х  |    |    | Fixed | RUNBIST instruction generates incorrect BIST signature                                             |  |  |  |

| 8   | х  | Х  |    | Fixed | Data breakpoint mistakenly remembered on a faulty instruction                                      |  |  |  |

| 9   | х  | Х  | х  | Doc   | RESET affects RUNBIST instruction execution in Boundary Scan                                       |  |  |  |

| 10  | х  | х  |    | Fixed | Locked operation during instruction execution tracing may hang the processor                       |  |  |  |

## int<sub>el</sub>.

.

.

| NO.                                             | B1                                                            | C1                                                            | D1                                                       | Plans                                                       | ERRATA (Cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 11                                              | Х                                                             | х                                                             |                                                          | Fixed                                                       | Breakpoint or single-step may be missed for one instruction following STI                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 12                                              | х                                                             | х                                                             |                                                          | Fixed                                                       | Internal snoop problem due to reflection on address bus                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 13                                              | Х                                                             | х                                                             |                                                          | Fixed                                                       | Internal parity error on uninitialized data cache entry                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 14                                              | Х                                                             | х                                                             |                                                          | Fixed                                                       | Missing shutdown after an IERR#                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 15                                              | Х                                                             | Х                                                             |                                                          | Fixed                                                       | Processor core may not serialize on bus idle                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 16                                              | х                                                             | х                                                             |                                                          | Fixed                                                       | SMIACT# assertion during replacement writeback cycle                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

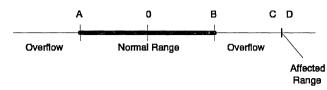

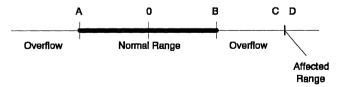

| 17                                              | Х                                                             | х                                                             | х                                                        | Doc                                                         | Overflow undetected on some numbers on FIST                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 18                                              | Х                                                             | х                                                             | х                                                        | Doc                                                         | Six operands result in unexpected FIST operation                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 19                                              | Х                                                             | х                                                             |                                                          | Fixed                                                       | Snoop with table-walk violation may not invalidate snooped line                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 20                                              | х                                                             | х                                                             |                                                          | Fixed                                                       | Slight precision loss for floating point divides on specific operand pairs                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 21                                              | Х                                                             | х                                                             | Х                                                        | Doc                                                         | Power-up BIST failure                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 22                                              | X                                                             | Х                                                             | Х                                                        | Doc                                                         | FLUSH#, INIT or Machine Check dropped due to floating point exception                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 23                                              | X                                                             | X                                                             | Х                                                        | Doc                                                         | Floating point operations may clear Alignment Check bit                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 24                                              | Х                                                             | Х                                                             | Х                                                        | Doc                                                         | CMPXCHG8B across page boundary may cause invalid opcode exception                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 25                                              | X                                                             | Х                                                             | Х                                                        | Doc                                                         | Single step debug exception breaks out of HALT                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| NO.                                             |                                                               |                                                               |                                                          |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| NO.                                             | B1                                                            | C1                                                            | D1                                                       | Plans                                                       | SPECIFICATION CLARIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1                                               | B1<br>X                                                       | C1<br>X                                                       | D1<br>X                                                  | <b>Plans</b><br>Doc                                         | SPECIFICATION CLARIFICATIONS BREQ Assertion                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                                                 |                                                               |                                                               |                                                          |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 1                                               | X                                                             | Х                                                             | Х                                                        | Doc                                                         | BREQ Assertion                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1<br>2                                          | X<br>X                                                        | X<br>X                                                        | X<br>X                                                   | Doc<br>Doc                                                  | BREQ Assertion<br>STR, SLDT, SMSW and MOV r/m16,SREG instructions                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1<br>2<br>3                                     | X<br>X<br>X                                                   | X<br>X<br>X                                                   | X<br>X<br>X                                              | Doc<br>Doc<br>Doc                                           | BREQ Assertion<br>STR, SLDT, SMSW and MOV r/m16,SREG instructions<br>Parity error during BIST                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1<br>2<br>3<br>4                                | X<br>X<br>X<br>X                                              | X<br>X<br>X<br>X                                              | X<br>X<br>X<br>X                                         | Doc<br>Doc<br>Doc<br>Doc                                    | BREQ Assertion<br>STR, SLDT, SMSW and MOV r/m16,SREG instructions<br>Parity error during BIST<br>BOFF# with internal snoop hit                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 1<br>2<br>3<br>4<br>5                           | X<br>X<br>X<br>X<br>X<br>X                                    | X<br>X<br>X<br>X<br>X                                         | X<br>X<br>X<br>X<br>X                                    | Doc<br>Doc<br>Doc<br>Doc<br>Doc                             | BREQ Assertion         STR, SLDT, SMSW and MOV r/m16,SREG instructions         Parity error during BIST         BOFF# with internal snoop hit         Frequent toggling of the R/S# pin                                                                                                                                                                                                                                                                               |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6                      | X<br>X<br>X<br>X<br>X<br>X<br>X                               | X<br>X<br>X<br>X<br>X<br>X<br>X                               | X<br>X<br>X<br>X<br>X<br>X                               | Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc                      | BREQ Assertion         STR, SLDT, SMSW and MOV r/m16,SREG instructions         Parity error during BIST         BOFF# with internal snoop hit         Frequent toggling of the R/S# pin         BT3-BT0 pins are floated as a result of AHOLD assertion                                                                                                                                                                                                               |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                 | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                          | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                          | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                     | Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc                      | BREQ Assertion         STR, SLDT, SMSW and MOV r/m16,SREG instructions         Parity error during BIST         BOFF# with internal snoop hit         Frequent toggling of the R/S# pin         BT3-BT0 pins are floated as a result of AHOLD assertion         TSS's I/O map base address vs. TSS limit                                                                                                                                                              |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8            | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                     | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X                | Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc               | BREQ Assertion         STR, SLDT, SMSW and MOV r/m16,SREG instructions         Parity error during BIST         BOFF# with internal snoop hit         Frequent toggling of the R/S# pin         BT3-BT0 pins are floated as a result of AHOLD assertion         TSS's I/O map base address vs. TSS limit         I/O trap restart in System Management mode                                                                                                           |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9       | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X      | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X           | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X      | Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc        | BREQ Assertion         STR, SLDT, SMSW and MOV r/m16,SREG instructions         Parity error during BIST         BOFF# with internal snoop hit         Frequent toggling of the R/S# pin         BT3-BT0 pins are floated as a result of AHOLD assertion         TSS's I/O map base address vs. TSS limit         I/O trap restart in System Management mode         The IBT pin is asserted on some selector loads                                                    |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10 | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc<br>Doc | BREQ Assertion         STR, SLDT, SMSW and MOV r/m16,SREG instructions         Parity error during BIST         BOFF# with internal snoop hit         Frequent toggling of the R/S# pin         BT3-BT0 pins are floated as a result of AHOLD assertion         TSS's I/O map base address vs. TSS limit         I/O trap restart in System Management mode         The IBT pin is asserted on some selector loads         Data bus floats in T1, TD or Ti bus states |  |  |  |

# int<sub>el</sub>.

4

ø

## PENTIUM® PROCESSOR SPECIFICATION UPDATE

| NO. | B1 | C1 | D1 | Plans | SPECIFICATION CLARIFICATIONS (Cont'd)                       |  |  |  |  |  |

|-----|----|----|----|-------|-------------------------------------------------------------|--|--|--|--|--|

| 14  | X  | х  | X  | Doc   | Inexpected parity check to page 0 during TLB miss reads     |  |  |  |  |  |

| 15  | X  | Х  | Х  | Doc   | Jsing POP SS to switch between different stack sizes        |  |  |  |  |  |

| 16  | х  | х  | х  | Doc   | SMI# during CPU shutdown                                    |  |  |  |  |  |

| NO. | B1 | C1 | D1 | Plans | DOCUMENTATION CHANGES                                       |  |  |  |  |  |

| 1   | Х  | х  | Х  | Doc   | Dead clock timing diagram description, Volume 1, page 6-52  |  |  |  |  |  |

| 2   | х  | х  | х  | Doc   | State of the PWT pin during bus cycles, Volume 3, page 10-6 |  |  |  |  |  |

## **SPECIFICATION CHANGES**

Specification Changes will be incorporated into the *Pentium*<sup>™</sup> *Family User's Manual*, Volume 1 and/or Volume 3, (Order Numbers: 241428 and 241430, respectively).

## 1. V<sub>CC</sub> Specification Change at 66 MHz

The V<sub>CC</sub> specification for the Pentium processor operating at 66 MHz is V<sub>CC</sub> = 4.90V to 5.40V. The new V<sub>CC</sub> range extends the operating V<sub>CC</sub> limit at the high end by 150mV over the previous V<sub>CC</sub> range as shown in the table below.

|                                    | Old            | New            |

|------------------------------------|----------------|----------------|

| Operating $V_{CC}$ Range at 66 MHz | 4.90V to 5.25V | 4.90V to 5.40V |

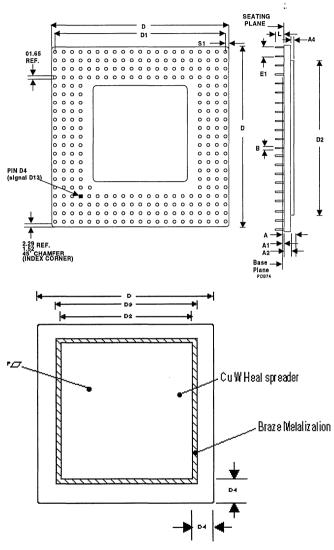

### 2. Mechanical/Thermal/Case Temperature Specifications for Pentium<sup>®</sup> Processor Heat Spreader Package

Following are the changes to the Pentium processor mechanical, thermal, and case temperature specifications necessitated by the addition of a heat spreader to the package for improved thermal performance of the die.

#### **MECHANICAL SPECIFICATIONS**

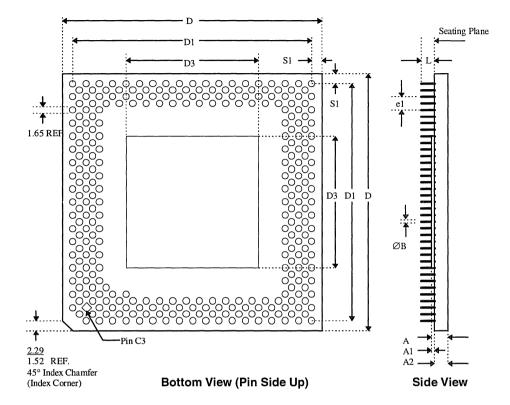

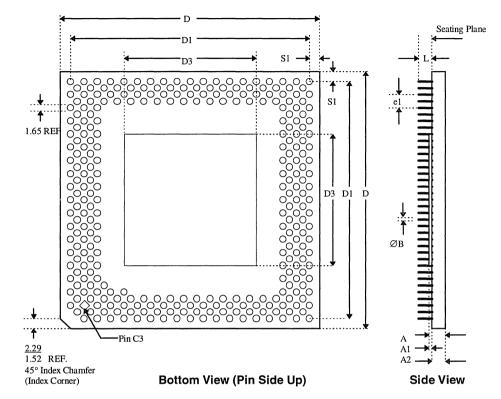

The changes to the Pentium processor, 273-pin PGA package, mechanical specification (Chapter 9 of the *Pentium™ Family User's Manual*, Volume 1, Order Number 241428) are summarized as follows:

- 1. Figure 9-1 is changed to reflect the addition of the heat spreader.

- 2. Figure 9-2 added to show the top view of the package.

- 3. Table 9-2 updated.

- 4. The weight of the heat spreader package increases to approximately 2X the weight of the standard PGA package (70.7 grams vs. 33.2 grams).

The following two figures show the new package dimensions for the Pentium processor. The mechanical specifications are provided in the table following these figures.

## intel

#### PENTIUM® PROCESSOR SPECIFICATION UPDATE

**Top View of Package**

## int<sub>el</sub>.

| Family: Ceramic Pin Grid Array Package |        |        |                                          |        |       |                                          |  |

|----------------------------------------|--------|--------|------------------------------------------|--------|-------|------------------------------------------|--|

|                                        |        |        | Millimeters                              | Inches |       |                                          |  |

| Symbol                                 | Min    | Max    | Notes                                    | Min    | Max   | Notes                                    |  |

| А                                      | 3.91   | 4.70   | Solid Lid                                | 0.154  | 0.185 | Solid Lid                                |  |

| A1                                     | 0.38   | 0.43   | Solid Lid                                | 0.015  | 0.017 | Solid Lid                                |  |

| A2                                     | 2.62   | 2.97   |                                          | 0.103  | 0.117 |                                          |  |

| A4                                     | 0.97   | 1.22   |                                          | 0.038  | 0.048 |                                          |  |

| В                                      | 0.43   | 0.51   |                                          | 0.017  | 0.020 |                                          |  |

| D                                      | 54.66  | 55.07  |                                          | 2.152  | 2.168 |                                          |  |

| D1                                     | 50.67  | 50.93  |                                          | 1.995  | 2.005 |                                          |  |

| D2                                     | 37.85  | 38.35  | Spreader Size                            | 1.490  | 1.510 | Spreader Size                            |  |

| D3                                     | 40.335 | 40.945 | Braze                                    | 1.588  | 1.612 | Braze                                    |  |

| D4                                     | 8.3    | 382    |                                          | 0.3    | 330   |                                          |  |

| E1                                     | 2.29   | 2.79   |                                          | 0.090  | 0.110 |                                          |  |

| F                                      |        | 0.127  | Flatness of spreader measured diagonally |        | 0.005 | Flatness of spreader measured diagonally |  |

| L                                      | 2.54   | 3.30   |                                          | 0.120  | 0.130 |                                          |  |

| N                                      | 2      | 73     | Total Pins                               | 2      | 73    | Total Pins                               |  |

| S1                                     | 1.651  | 2.16   |                                          | 0.065  | 0.085 |                                          |  |

#### Pentium® Processor Mechanical Specifications

#### THERMAL SPECIFICATIONS

The following table provides the new thermal parameter specifications for the Pentium processor heat spreader package:

|                      |                 | Θ <sub>CA<sup>2</sup></sub> vs. Airflow (ft/min) |     |     |     |     |      |

|----------------------|-----------------|--------------------------------------------------|-----|-----|-----|-----|------|

|                      | Θ <sub>JC</sub> | 0                                                | 200 | 400 | 600 | 800 | 1000 |

| With 0.25" Heat Sink | 0.6             | 8.3                                              | 5.4 | 3.5 | 2.6 | 2.1 | 1.8  |

| With 0.35" Heat Sink | 0.6             | 7.4                                              | 4.5 | 3.0 | 2.2 | 1.8 | 1.6  |

| With 0.65" Heat Sink | 0.6             | 5.9                                              | 3.0 | 1.9 | 1.5 | 1.2 | 1.1  |

| Without Heat Sink    | 1.2             | 10.5                                             | 7.9 | 5.5 | 3.8 | 2.8 | 2.4  |

#### Junction-to-Case and Case-to-Ambient Thermal Resistances for the Pentium® Processor (With and Without a Heat Sink<sup>1</sup>)

#### NOTES:

1. Heat Sink: 2.1 sq. in. base, omni-directional pin AI heat sink with 0.050 in. pin width, 0.143 in pin-to-pin center spacing and 0.150 in. base thickness. Heat sinks are attached to the package with a 2 to 4 mil thick layer of typical thermal grease. The thermal conductivity of this grease is about 1.2 w/m °C.

O<sub>CA</sub> values are typical values. The actual O<sub>CA</sub> values depend on the air flow in the system (which is typically unsteady, non-uniform and turbulent) and thermal interactions between Pentium processor and surrounding components through PCB and the ambient.

The following is a description of how the heat spreader improves the package thermal performance:

Since the Pentium processor requires an external heat sink in order to maintain the junction and case temperatures below the acceptable levels, the main contributors to the total junction to ambient thermal resistance are junction to case ( $\Theta_{JC}$ ), case to heat sink ( $\Theta_{CS}$ ), and heat sink to ambient ( $\Theta_{SA}$ ) thermal resistances.

$\Theta_{JC}$  is mainly a function of internal construction of the package and packaging material, thermal properties such as the die size and die attach, and ceramic thermal conductivity.  $\Theta_{CS}$  is a function of the thickness and thermal properties of the interface material between the package and heat sink, package and heat sink flatness, and surface finish and effective heat transfer area between the package and the heat sink.  $\Theta_{SA}$  is a function of both the heat sink design and the airflow type and rate.

Using a heat spreader in the package lowers the overall thermal resistance in two ways:

- 1. It increases the effective heat transfer area between the package and the heat sink and as a result lowers  $\Theta_{CS}$ . The actual reduction in  $\Theta_{CS}$  depends on the magnitude of  $\Theta_{CS}$  without a heat spreader. The larger the value of  $\Theta_{CS}$  without using a heat spreader, the larger will be the reduction in the value of  $\Theta_{JA}$  if a heat spreader is used.

- 2. A heat spreader may also improve the heat sink thermal performance by increasing the effective heat transfer area in the heat sink and making the fins away from the die more effective.

Using a heat spreader with a thermal grease interface will result in about .4 c/w lower  $\Theta_{CA}$  than that for the package without the heat spreader. Thermal grease is considered one of the more thermally efficient materials for use as an interface between heat sink and package. Thermally conductive adhesives and conductive tapes or films typically have poorer thermal performance when compared to a thin layer of thermal grease, because grease facilitates a larger reduction in thermal resistance.

#### CASE TEMPERATURE SPECIFICATIONS

Following are the case temperature specifications for the Pentium processor with and without the heat spreader on the package:

#### Pentium® Processor Package Without Heat Spreader

The case temperature specifications for the Pentium processor package without heat spreader at 60 and 66 MHz are as follows (Note: This applies to B1" and previous steppings):

- 1. T<sub>C</sub> (case temperature) 0°C to 85°C @60 MHz.

- 2. T<sub>C</sub> (case temperature) 0°C to 75°C @66 MHz.

#### Pentium® Processor With Heat Spreader Package

The case temperature specifications for the Pentium processor heat spreader package at 60 and 66 MHz are as follows (Note: This applies to C1 and later steppings):

- 1. T<sub>C</sub> (case temperature) 0°C to 80°C @60 MHz.

- 2.  $T_C$  (case temperature) 0°C to 70°C @66 MHz.

In the case of the Pentium processor with heat spreader package, the case temperature is measured at the center of the package top surface on the heat spreader. The procedure to measure the case temperature, is outlined in Chapter 10 of the *Pentium™ Family User's Manual*, Volume 1 (Order Number 241428).

The thermal specification of the heat spreader package calls for 5 degrees Celsius lower case temperature than the non-spreader package for both 60- and 66-MHz versions. The lower case temperature requirement of the heat spreader package is due to its lower junction to ambient thermal resistance compared to a non-heat

spreader package with the same heat sink. For example, at 66-MHz, the heat spreader package will have 0.4\*16=6.4 degrees Celsius lower case temperature than a non-heat spreader package with the same heat sink design and grease interface. This implies that in a system designed for a non-spreader package, if the non-spreader package is replaced with a heat spreader package, the measured case temperature will be lower by 6.4 degrees Celsius for the 66-MHz and 5.8 degrees Celsius for the 60-MHz versions. The actual reduction in the case temperature will be slightly higher or lower depending on the efficiency of the thermal interface. Therefore, a more conservative value of 5 degrees Celsius is used as the difference between the case temperature specifications of the two package types for both frequency versions. The expectation is that the ambient temperature in the system will be maintained while gaining the benefits of lower junction and case temperatures when the heat spreader package is added to an existing system with the same airflow and unmodified heat sink.

## 3. DP[7:0] Read Data Setup Time Specification Change

The following tables show the new A.C. Specification for the Data Parity (DP0-7) Read Data Setup Time for the Pentium processor at 66 and 60 MHz:

| Symbol           | Symbol Parameter                            |  | Max | Unit |

|------------------|---------------------------------------------|--|-----|------|

| t <sub>34a</sub> | t <sub>34a</sub> DP0-7 Read Data Setup Time |  |     | ns   |

#### 66-MHz Pentium® Processor A.C. Specification

#### 60-MHz Pentium® Processor A.C. Specification

| Symbol           | Parameter                  | Min | Max | Unit |

|------------------|----------------------------|-----|-----|------|

| t <sub>34a</sub> | DP0-7 Read Data Setup Time | 4.3 |     | ns   |

## 4. CLK Toggle during V<sub>CC</sub> Ramp

The following note has been added to the **clock** pin description: 'It is recommended that CLK begin toggling within 150 ms after  $V_{CC}$  reaches its proper operating level. This recommendation is only to ensure long-term reliability of the device.'

## ERRATA

## 1. BOFF# Hold Timing

**PROBLEM:** Silicon characterization indicates that the processor does not meet the specified hold time, 1.5ns, for the BOFF# signal. Data indicates that a minimum hold time of 2.0ns is required.

**IMPLICATION:** If a minimum hold time of 2.0ns is not met for the BOFF# input, the processor may drive undefined or incorrect cycles on to the external bus.

**WORKAROUND:** System must guarantee a minimum hold time of 2.0ns at the BOFF# input to the Pentium processor.

STATUS: This erratum is fixed to meet the minimum specified hold time of 1.5ns on the C-stepping.

## 2. Incomplete Initialization May Flush the Internal Pipeline

**PROBLEM:** If a memory write occurs before the first branch instruction immediately after RESET, then the internal pipeline may get flushed unexpectedly. Assuming normal distribution of code space, this unexpected flush has the probability of 1 in 2<sup>26</sup> of occurring.

**IMPLICATION:** The probability of this unexpected flush occurring is very low. When it happens, its only effect is to flush the internal pipeline and re-fetch the correct opcodes again. The instructions will still be executed correctly.

In the FRC (Functional Redundancy Checking) environment, where the clock-by-clock behavior of the processor needs to be checked deterministically, it may cause the system to report an error.

WORKAROUND: After RESET, ensure that the first write to memory occurs after a branch instruction.

**STATUS:** This erratum is fixed on the C-stepping.

## 3. IV Pin May Not Be Asserted under Certain Conditions

**PROBLEM:** The IV pin is driven active by the Pentium processor to indicate that an instruction in the v-pipe has completed execution. In the following case, the IV pin may not get asserted:

When a mispredicted instruction (pair) reaches the execution stage, it will cause a pipeline flush. If in this clock, a fault is detected on the instruction in the u-pipe, the IV pin will not be asserted for a v-pipe instruction of the next instruction pair which is executed next.

**IMPLICATION:** The fact that the IV pin is not asserted under certain conditions will affect the reliability of the execution tracing data. It will also affect the performance monitoring event count for instructions executed in the v-pipe.

**WORKAROUND:** Disabling the v-pipe will allow execution tracing to work properly.

**STATUS:** This erratum is fixed on the C-stepping.

## 4. Testability Writes to Data TLB May Store Wrong Parity

**PROBLEM:** During testability writes to the data TLB, an incorrect tag parity may be computed and stored with the tag address. Subsequently, when this entry is read during a normal (non-testability) cycle, an internal parity error (IERR#) may be generated.

**IMPLICATION:** The internal parity error may occur only if a non-testability access is made to the same data TLB entry which had been previously written on a testability write. This problem will not show up if the data TLB is flushed after having been used for testability purposes using the TLB test registers.

**WORKAROUND:** Ensure that the data TLB is flushed after having been used for testability writes and before being used for normal operation.

STATUS: This erratum is fixed on the C-stepping.

## 5. LRU Bits in the Data Cache TLBs Are Updated Incorrectly

**PROBLEM:** Due to a circuit problem, the LRU bits for the data cache TLBs are updated incorrectly when both the u and v pipes access the same set. As the TLBs are organized as 4-Way set associative, more specifically this problem occurs when a u-pipe match is found on Way 0 and a v-pipe match is found on Way 1, or the u-pipe match is found on Way 2 and the v-pipe match is found on Way 3 of the same set.

**IMPLICATION:** The LRU bits are used to handle replacements in the TLB. In this specific case, the pseudo LRU mechanism is not strictly adhered to. Any performance degradation resulting from this is expected to be negligible.

#### WORKAROUND: None

STATUS: This erratum is fixed on the C-stepping.

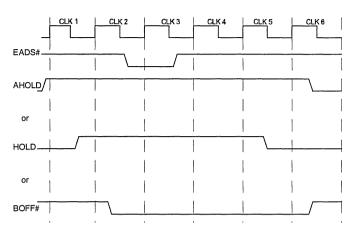

## 6. A Replacement Writeback Cycle May Invade a Locked Sequence

**PROBLEM:** During a locked read-modify-write (RMW) sequence, if BOFF# or AHOLD is asserted before the write portion of the RMW sequence is completed, then the write cycle will be held off in the internal write buffer until the BOFF# or AHOLD signal is deasserted. During the time that the bus is backed off, if another locked instruction (i.e., with a LOCK prefix) enters the instruction pipeline and initiates a replacement writeback in the data cache, then as soon as the bus is freed, the writeback cycle due to the replacement writeback may be issued in front of the locked write cycle pending in the write buffer. After completion of the writeback cycle, the processor will issue the write cycle to complete the RMW sequence.

**IMPLICATION:** This problem will only affect those systems which do not expect a replacement writeback cycle in the middle of a locked RMW sequence. Furthermore, the timing of events needed for the above problem to manifest itself has a low probability of occurrence. Note that even though the bus cycles are reordered in this case, the correct bus cycles are run and should not cause any data coherency problems.

**WORKAROUND:** Do not assert BOFF# or AHOLD in between the read and the write portion of a locked readmodify-write sequence.

STATUS: This erratum is fixed on the C-stepping.

## 7. RUNBIST Instruction Generates Incorrect BIST Signature

**PROBLEM:** The Pentium processor TAP instruction, RUNBIST, generates incorrect BIST signature if issued while the processor is in Probe mode. The BIST result is also incorrect if the RUNBIST instruction is issued during a repeated MOVS (move data from string to string) instruction.

**IMPLICATION:** The BIST may report an incorrect signature indicating self-test failure even though the processor may not be faulty.

**WORKAROUND:** Do not issue the (TAP) RUNBIST instruction when the processor is in Probe mode, or during a repeated MOVS instruction .

STATUS: This erratum is fixed on the C-stepping.

## 8. Data Breakpoint Mistakenly Remembered on a Faulty Instruction

**PROBLEM:** In the following two cases, an instruction that has data breakpoints enabled and also generates a fault before completing execution may cause an unexpected data breakpoint to occur later in the code or may cause the software to hang:

#### CASE 1:

For the first failing case to occur, the data breakpoint must be set on an instruction that is **not** a simple instructions are those that are entirely hardwired and do not require any microcode control) and includes multiple memory references (e.g., a read operation followed by a write operation). In addition, this instruction also generates a fault before completing execution. The data breakpoint must be set on one memory operation (e.g., a data read portion), and the fault occurs on a subsequent memory operation (e.g., a data write portion). If later in the code, a fault during a repeated string operation is encountered, then a spurious debug exception will be reported first, followed by the fault for the string operation. This unexpected debug exception during the string operation may only occur if no other debug exception is taken before the string operation is executed.

#### CASE 2:

For the second failing case, the data breakpoint must be set on the data read of iteration X of a repeated string instruction, and a fault must occur on the data write of the same iteration X. In this case, the Pentium processor takes the debug exception first, before handling the fault. When the faulting iteration is restarted after the debug exception is handled, the data breakpoint is again detected when the fault is encountered, and the processor returns to the debug exception handler. This will cause repeated entries into the debug exception handler for the same iteration. This loop may occur forever, unless the debug exception handler modifies the data breakpoints or the return instruction pointer.

**IMPLICATION:** In the first case, a data breakpoint may occur when it is not expected. In the second case, a repeated string instruction has a data breakpoint set on the read portion and a fault occurs on the corresponding write. This may cause the software to hang.

**WORKAROUND:** When setting data breakpoints, be aware of the above failure cases. Note that code and I/O breakpoints can be set properly and are not affected by this erratum.

**STATUS:** This erratum is fixed in the D-stepping.

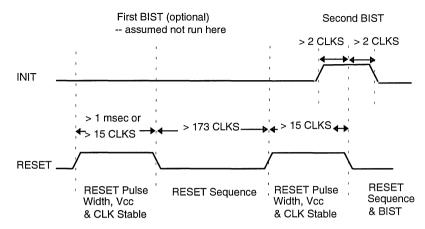

## 9. RESET Affects RUNBIST Instruction Execution in Boundary Scan

**PROBLEM:** The Boundary Scan TAP instruction, RUNBIST, is affected by the assertion of the RESET pin. If the RESET pin is asserted while the processor is executing the TAP instruction, RUNBIST (TAP command field = 0111, and the TAP controller is in the Run-Test-Idle state), then the processor indicates a BIST failure.

**IMPLICATION:** The IEEE 1149.1-1990 specification states "the design of the component shall ensure that results of the self-tests executed in response to the RUNBIST instruction are not affected by signals received at the non-clock system input pins". The Pentium processor does not meet this requirement.

WORKAROUND: Ensure that the RESET pin is deasserted while the RUNBIST (TAP) instruction is executing.

STATUS: This erratum affects all steppings of the 60- and 66-MHz Pentium processor.

### 10. Locked Operation during Instruction Execution Tracing May Hang the Processor

**PROBLEM:** During instruction execution tracing (TR12.TR bit set to '1') the processor can internally buffer up to two Branch Trace messages. If there is a possibility of a third Branch Trace message being delivered from the instruction being executed, the machine will stall in order to avoid overwriting either of the two messages that are already buffered. If this instruction is performing a "locked read-modify-write" operation, the processor can hang up due to internal service contention for the bus controller logic.

**IMPLICATION:** This problem does not affect normal operation (TR12.TR bit is not set). It only affects operation while the instruction execution tracing feature is enabled. A hardware RESET will be required to get the processor out of the deadlock condition if it occurs.

**WORKAROUND:** Do not enable instruction execution tracing.

**STATUS:** This erratum is fixed in the D-stepping.

### 11. Breakpoint or Single-Step May Be Missed for One Instruction Following STI

**PROBLEM:** If the next instruction following STI is the target of a mispredicted branch, the processor may shut off the interrupt window for one instruction following STI. This will prevent breakpoints, single-step or other external interrupts from being recognized during this time.

**IMPLICATION:** The processor may not recognize NMI, SMI#, INIT, FLUSH#, BUSCHK#, R/S#, code/data breakpoint and single-step for one instruction after executing STI. This is not a problem unless breakpoints or single stepping is used. The only possible effect is that they may be missed.

**WORKAROUND:** Do not set a breakpoint on the next sequential instruction after STI. Alternatively, disabling branch prediction will prevent this problem from occurring.

**STATUS:** This erratum is fixed in the D-stepping.

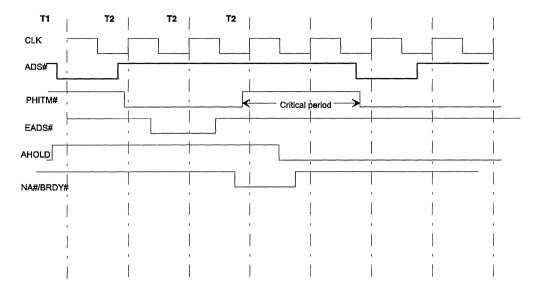

## 12. Internal Snoop Problem Due to Reflection on Address Bus

**PROBLEM:** An internal snoop occurs in the following three cases:

- 1. An access is made to the code cache, and that access is a miss.

- 2. An access is made to the data cache, and that access is a miss or a write-through.

## intel

3. There is an access to the page table/directory entries.

In all of these cases, the address used for the internal snoop is obtained from the input buffer of the address I/O buffers inside the chip. If there is signal reflection on the address lines A[31:5] which causes the setup/hold time inside the chip to be violated, then the internal snoop may fail.

When the reflection on the address I/O buffer is above (or below) the trip point of an input buffer (i.e., 1.5V for a TTL input) for a high to low (or low to high) transition, then the internal snoop address will not be valid until after the address reflection falls below (or transitions above) the trip point in the clock ADS# and address is driven. If the reflection causes the wrong snoop address A[31:5] to be latched inside the chip due to setup/hold time violation, then an incorrect internal snoop may occur.

**IMPLICATION:** When the failure occurs, a wrong cache line may be snooped causing either a line to remain valid when it should not, a valid line to become invalid when it should not, or an invalid line to be snooped.

In the first case, when a valid line should be invalidated and is not, a cache coherency problem between the code and data cache is possible (e.g., self-modifying code). In the second case, when a valid cache line is incorrectly made invalid, an unexpected writeback cycle may occur if the line was in the modified state, and an unexpected bus cycle may occur to re-allocate the cache line. The third case, where an invalid line is snooped, will not cause any detectable failure.

An additional failure mechanism can be seen if address lines A[11:5] are transitioning while being sampled. In this case, the internal snoop may fail, causing a tag parity error during the snoop resulting in an IERR# assertion.

The magnitude of the reflection is dependent upon the I/O buffer vs. transmission line impedance mismatch and the length/layout of trace (transmission line). There is sufficient margin built into the external timing specification for the address bus and I/O buffer models, and it is not expected that any failures will be seen on existing systems. In a lab environment, a failure was forced by adding a 12 inch coaxial cable (with no termination) along with a 330 ohm pull-up resistor on the address line to induce excessive reflection. Removing either the pull-up resistor or adding termination to the coaxial cable eliminated the failure.

**WORKAROUND:** To avoid any internal snoop failures, ensure that the address A[31:5] setup and hold times are not violated at the processor's input due to reflection in the clock in which the processor drives the address bus and ADS# is asserted. Note: Meeting the setup and hold times at the processor's input is not necessary in the clocks where ADS# is not asserted.

STATUS: This erratum is fixed in the D-stepping.

## 13. Internal Parity Error on Uninitialized Data Cache Entry

**PROBLEM:** In the following case, an incorrect internal parity error (IERR#) may be reported due to an uninitialized entry in the data cache during a special qword (64-bit) read. This may occur if the qword read issued to the u-pipe is also followed by a v-pipe read, and the v-pipe read is to a different odd bank and different way than the u-pipe qword read. In addition, the u-pipe address corresponding to this different way must have invalid and uninitialized data. Under these conditions, the processor may check the invalid data for parity errors and incorrectly assert the IERR# pin.

**IMPLICATION:** After power-on reset, before the data cache is completely initialized, the processor may incorrectly report an IERR# and shutdown.

**WORKAROUND:** After power-on reset, initialize all entries in the data cache before the cache is enabled. The easiest way to do this is to invoke BIST (built-in self test) after reset. Alternatively, software can initialize the data cache by reading data from memory appropriately, or writing into all its locations through the cache test registers.

STATUS: This erratum is fixed in the D-stepping.

#### Missing Shutdown after an IERR# 14.

PROBLEM: If an internal parity error is reported to the IERR# pin and a mispredicted branch or a trap/fault/interrupt with a higher priority than shutdown occurs, then the processor may not shutdown.

**IMPLICATIONS:** During the reporting of an internal parity error, the IERR# pin may go active without a processor shutdown. Note that IERR# due to an internal parity error will not occur unless the parity error is induced through parity reversal testing or if the chip is defective.

WORKAROUND: The system can latch an IERR# assertion at the processor clock edge and force a shutdown by asserting NMI or initializing the processor through RESET or INIT. Note: IERR# is a glitch free signal, so no spurious assertions of IERR# will occur.

STATUS: This erratum is fixed in the D-stepping.

#### 15. Processor Core May Not Serialize on Bus Idle

PROBLEM: Under rare circumstances, the processor may not serialize with the bus when the processor core is waiting for the bus to finish pending cycles and BOFF# is asserted. The processor will not reorder bus cycles; it may only start with the next event (fetching and executing subsequent instructions) before waiting for all pending bus cycles to complete. The following cases have been identified that may be affected by this:

| SMI# pending                                                            | If BOFF# is used to back off a bus cycle while an SMI# is pending, the<br>processor may assert SMIACT# before re-starting the aborted bus cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serializing instruction                                                 | If BOFF# is used to back off a bus cycle due to a serializing instruction, the processor may start executing the next instruction before restarting or completing the previous bus cycle. The processor, however, will not reorder any bus cycles for the new instruction in front of bus cycles for the previous instruction.                                                                                                                                                                                                                                                                                                                      |

| Invalidation during cache line fill                                     | If BOFF# is used to back off a cache line fill and BOFF# occurs after the data<br>has been returned to the processor but before the end of the line fill, an<br>invalidation request during this time may result in the cache invalidation to<br>occur before the line fill has completed, This may cause the cache line to<br>remain in a valid state after the invalidation has completed. Note that if the<br>invalidation request comes in via WBINVD or FLUSH#, the line fill would have<br>to be backed off at least twice (or once for INVD) in order for the cache line to<br>remain in a valid state after the invalidation has completed. |

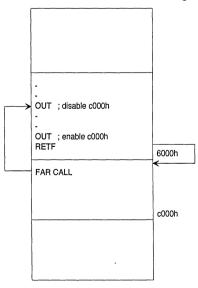

| OUT instruction                                                         | If BOFF# is used to back off a bus cycle due to an OUT instruction, the processor may start executing the next instruction before the bus cycle due to OUT has completed (note: the OUT instruction is similar to the serializing instructions except that it does not stop the prefetch of the subsequent instruction). The processor, however, will not reorder any bus cycles for the new instruction in front of the OUT bus cycle.                                                                                                                                                                                                             |

| <b>IMPLICATION:</b> This problem has different possible implications as | only been observed in internal test vehicles. The events described above have follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

different possible implications as follows:

| SMI# pending            | The processor may enter SMM before restarting the aborted bus cycle. The SMIACT# assertion may cause the restarted bus cycle to run to SMRAM space.                                                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serializing Instruction | Since the cycles are not reordered, a system should not encounter any<br>problems unless it depends on the serializing instruction to cause an external<br>event prior to execution of the next instruction. |

Invalidation during cache line fillIn a rare instance, a cache line may remain in the valid state (E or S state)<br/>after the cache invalidation has completed.OUT instructionSince the cycles are not reordered, a system should not encounter any<br/>problems unless it depends on the OUT instruction to cause an external<br/>event prior to execution of the next instruction. For example, an OUT<br/>instruction may be used to assert the A20M# signal prior to the next<br/>instruction. In this case, observed code has followed the OUT with an I/O<br/>read (IN) to ensure the signal is properly asserted. A second case, could be<br/>using an OUT instruction to configure/initialize and interrupt controller and<br/>follow it with STI to enable interrupts. Once again no failure would be<br/>observed. The controller would respond with the spurious interrupt vector.

**WORKAROUND:** Restrict the use of BOFF# for the described events. In addition, the SMI# pending event can be eliminated by locating SMRAM so that it does not shadow standard memory and does not require SMIACT# for memory decode. The OUT or serializing instruction events are eliminated if the next instruction does not depend on the result of the event before executing the instruction.

**STATUS:** This erratum is fixed in the D-stepping.

## 16. SMIACT# Assertion during Replacement Writeback Cycle

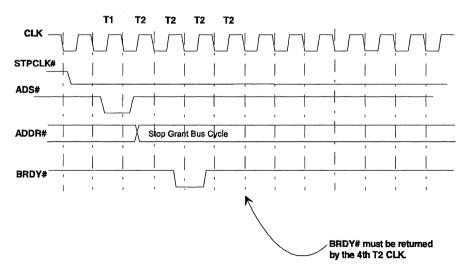

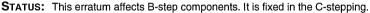

**PROBLEM:** If a data read cycle triggers a replacement writeback cycle and the SMI# signal is asserted prior to the first BRDY# of the read cycle, the processor may assert the SMIACT# signal prematurely.

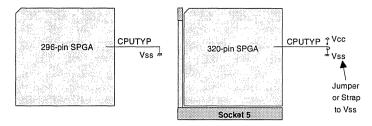

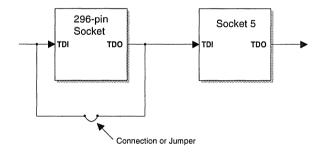

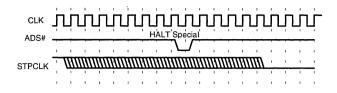

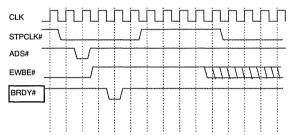

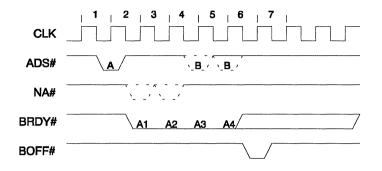

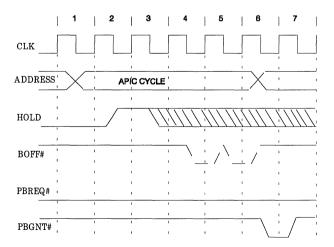

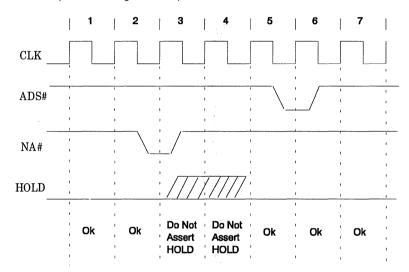

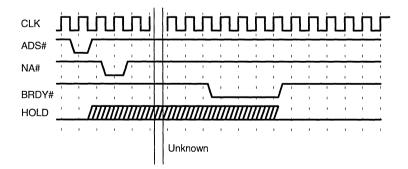

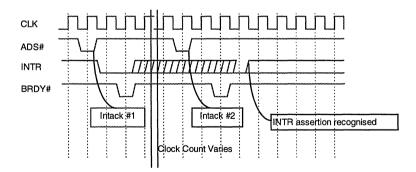

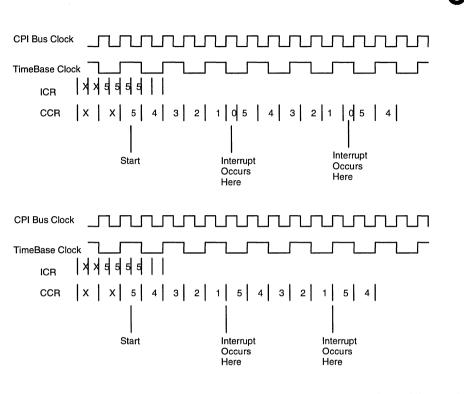

Before the processor asserts SMIACT# in response to an SMI# request, it should complete all pending write cycles (including emptying the write buffers). However, if the appropriate conditions occur, the SMIACT# signal may get asserted during the replacement writeback cycle a few clocks after the last BRDY# of the read cycle.