ISBC 108A/116A™ COMBINATION MEMORY AND I/O EXPANSION BOARDS HARDWARE REFERENCE MANUAL

Manual Order Number: 9800862-01

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

| 1            |  |

|--------------|--|

| ICE          |  |

| iCS          |  |

| Insite       |  |

| Intel        |  |

| Intelevision |  |

| Intellec     |  |

iSBC Library Manager MCS Megachassis Micromap Multibus Multimodule PROMPT Promware RMX UPI µScope

and the combination of ICE, iCS, iSBC, MCS, or RMX and a numerical suffix.

# PREFACE

This manual provides general information, installation, principles of operation, and service information for the iSBC 108A/116A Combination Memory and I/O Expansion Boards. Additional information is available in the following document: *Intel MULTIBUS Interfacing*, Application Note AP-28.

This manual is divided into the following chapters and appendixes:

- "Introduction", which describes the iSBC 108A/116A Combination Memory and I/) Expansion Boards and their features.

- "Preparation For Use", which describes unpacking, installation, and how to configure the boards.

- "Programming Information", which describes the programming for the USART and PPI.

- "Principles of Operation", which describes how the circuits operate.

- "Service Information", which lists the replaceable parts and contains the circuit schematics.

- "Appendix A", which contains the mnemonics list.

- "Appendix B", which describes the differences in the jumper configurations for the old style boards and the new A versions.

# CONTENTS

#### CHAPTER 1 GENERAL INFORMATION

| Introduction       | 1-1   |

|--------------------|-------|

| Description        | 1-1   |

| Serial I/O Port    | 1-1   |

| Parallel I/O Ports | 1 - 2 |

| Interrupts         | 1-2   |

| Equipment Supplied | 1-2   |

| Specifications     | 1-2   |

#### CHAPTER 2 PREPARATION FOR USE

| Introduction                        | 2-1    |

|-------------------------------------|--------|

| Unpacking and Inspection            | 2-1    |

| Installation Considerations         | 2-1    |

| Power Requirement                   | 2-1    |

| Cooling Requirement                 | 2-1    |

| Physical Dimensions                 | 2 - 1  |

| Bus Interfacing Requirements        | 2-1    |

| Jumper Configurations               | 2-3    |

| RAM, ROM/PROM Page Select           | 2-8    |

| RAM Base Address                    | 2-11   |

| ROM/PROM Base Address               | 2-11   |

| ROM/PROM Type Selection             | 2-13   |

| I/O Base Address                    | 2-15   |

| Advanced Acknowledge                | 2 - 16 |

| Serial I/O Port                     | 2 - 16 |

| Parallel I/O Ports                  | 2-18   |

| Interrupts                          | 2-20   |

| Auxiliary Power                     | 2-21   |

| Teletype Adaptor Power              | 2-21   |

| Additional Power Connection Options | 2-21   |

| Component Installation              | 2-26   |

| ROM/PROM                            | 2-27   |

| Line Drivers/Terminators            | 2-27   |

| Rise Time/Noise Capacitors          | 2-27   |

| Serial I/O Port Cabling             | 2-27   |

| Parallel I/O Port Cabling           | 2-27   |

| Board Installation                  | 2-27   |

## CHAPTER 3 PROGRAMMING INFORMATION

| I/O Base Address3-1I/O Address Assignment3-18251A USART Programming3-1Mode Instruction Format3-1Synchronization Characters3-2Command Instruction Format3-3Reset3-3Addressing3-3 | Introduction               | 3-1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|

| 8251A USART Programming3-1Mode Instruction Format3-1Synchronization Characters3-2Command Instruction Format3-3Reset3-3                                                          | I/O Base Address           | 3-1 |

| Mode Instruction Format3-1Synchronization Characters3-2Command Instruction Format3-3Reset3-3                                                                                    | I/O Address Assignment     | 3-1 |

| Synchronization Characters3-2Command Instruction Format3-3Reset3-3                                                                                                              | 8251A USART Programming    | 3-1 |

| Command Instruction Format3-3Reset3-3                                                                                                                                           | Mode Instruction Format    | 3-1 |

| Reset 3-3                                                                                                                                                                       | Synchronization Characters | 3-2 |

|                                                                                                                                                                                 | Command Instruction Format | 3-3 |

| Addressing 3-3                                                                                                                                                                  | Reset                      | 3-3 |

|                                                                                                                                                                                 | Addressing                 | 3-3 |

# Initialization3-3Operation3-48255A PPI Programming3-4Rest of the selection3-5Mode Selection3-5Addressing3-5Initialization3-6Operation3-6Port X+6 and X+A Bit Set/Reset3-8Interrupt Status Mask3-8

# **CHAPTER 4**

PAGE

| PRINCIPLES OF OPERATION                 | PAC     | ЪЕ  |

|-----------------------------------------|---------|-----|

| Introduction                            |         | 4-1 |

| Functional Description                  |         | 4-1 |

| ROM/PROM Memory                         |         | 4-1 |

| RAM Memory                              | • • • • | 4-1 |

| Programmable Peripheral Interface       |         | 4-1 |

| Driver/Terminator Interface             |         | 4-2 |

| Programmable Communications Interface . | ••••    | 4-2 |

| Baud Rate Generator                     |         | 4-2 |

| Interrupt Status/Mask Registers         |         | 4-2 |

| Circuit Analysis                        |         | 4-2 |

| Multibus Interface Circuits             |         | 4-2 |

| I/O Address Code                        | •••     | 4-2 |

| I/O Function Decoder                    | · · · · | 4-3 |

| RAM Address Decode                      | •••     | 4-3 |

| PROM Address Decode                     | •••     | 4-3 |

| ROM/PROM Logic                          |         | 4-3 |

| Clock Logic                             | •••     | 4-3 |

| RAM Controller                          | ••••    | 4-3 |

| Baud Rate Generator                     |         | 4-4 |

| Acknowledge Generator                   |         | 4-4 |

| Serial I/O Port                         | •••     | 4-4 |

| Parallel I/O Ports                      |         | 4-5 |

| Interrupt Logic                         |         | 4-5 |

#### CHAPTER 5 SERVICE INFORMATION

| Introduction                  | 5-1   |

|-------------------------------|-------|

| Service Diagrams              | 5 - 1 |

| Replaceable Parts             | 5-1   |

| Service and Repair Assistance | 5-1   |

APPENDIX A MNEMONICS

APPENDIX B JUMPER CONFIGURATION

#### PAGE

| TABLE  | TITLE                                | PAGE   |

|--------|--------------------------------------|--------|

| 1-1    | Specifications                       | . 1-2  |

| 2-1    | Connector P1 Pin Assignments         | . 2-2  |

| 2-2    | Multibus Signal Functions            | . 2-3  |

| 2-3    | Connector P2 Pin Assignments         | . 2-3  |

| 2-4    | Connector J1 Pin Assignments         | . 2-4  |

| 2-5    | Connector J2 Pin Assignments         | . 2-5  |

| 2-6    | Connector J3 RS232C Signal Interface | . 2-6  |

| 2-7    | iSBC 108A/116A™ Board                |        |

|        | AC Characteristics                   | . 2-8  |

| 2-8    | iSBC 108A/116A™ Board                |        |

|        | DC Characteristics                   | . 2-9  |

| 2-9    | Page Select Jumper Connections       | 2-12   |

| 2-10   | RAM Base Address Selection           | 2-12   |

| 2-11   | ROM/PROM Base Address Selection .    | . 2-12 |

| 2 - 12 | ROM/PROM Configuration vs.           |        |

|        | Address Space                        | . 2-13 |

| 2-13   | I/O Base Address Selection           | . 2-15 |

|        |                                      |        |

| TABLE  | TITLE                                                                          | PAGE        |

|--------|--------------------------------------------------------------------------------|-------------|

| 2-14   | I/O Page Selection                                                             | . 2-15      |

| 2-15   | AACK/ and XACK/ Jumper Selection                                               | 2 - 16      |

| 2-16   | Baud Rate Select Jumpers                                                       | . 2-17      |

| 2-17   | Clock Path Options                                                             | 2-18        |

| 2-18   | Parallel I/O Configuration Key                                                 | 2-21        |

| 2-19   | Parallel I/O Configuration List                                                | 2-22        |

| 2 - 20 | Parallel I/O Line Drivers                                                      | 2-27        |

| 3-1    | I/O Address Assignment                                                         | 3-1         |

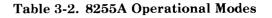

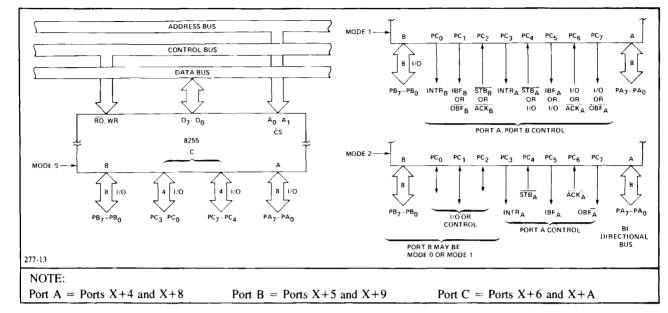

| 3-2    | 8255A Operational Modes                                                        | 3-6         |

| 3-3    | Mode Definition Summary Table                                                  | 3-7         |

| 3-4    | Basic 8255A Operation                                                          | 3-8         |

| 4-1    | Interrupt Logic Operations                                                     | ·· 4-6      |

| 5 - 1  | User-Replaceable Parts List                                                    | ·· 5-2      |

| 5-2    | List of Manufacturer's Codes                                                   | ·· 5-3      |

| B-1    | Jumper Configuration Changes from<br>iSBC 108/116 <sup>TM</sup> Boards to iSBC |             |

|        | 108A/116A™ Boards                                                              | <b>B-</b> 1 |

| FIGUR | E TITLE                             | PAGE |

|-------|-------------------------------------|------|

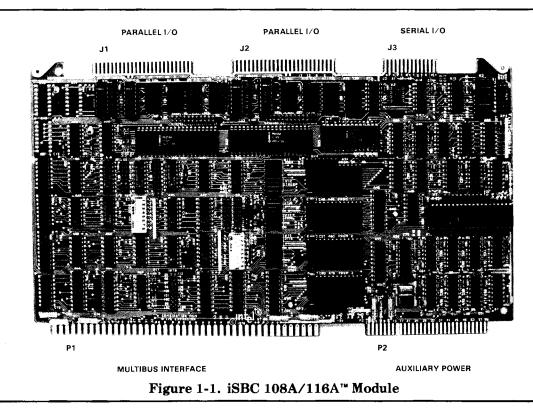

| 1-1   | iSBC 108A/116A <sup>™</sup> Module  | 1.1  |

| 2-1   | iSBC 108A/116A™ Board               |      |

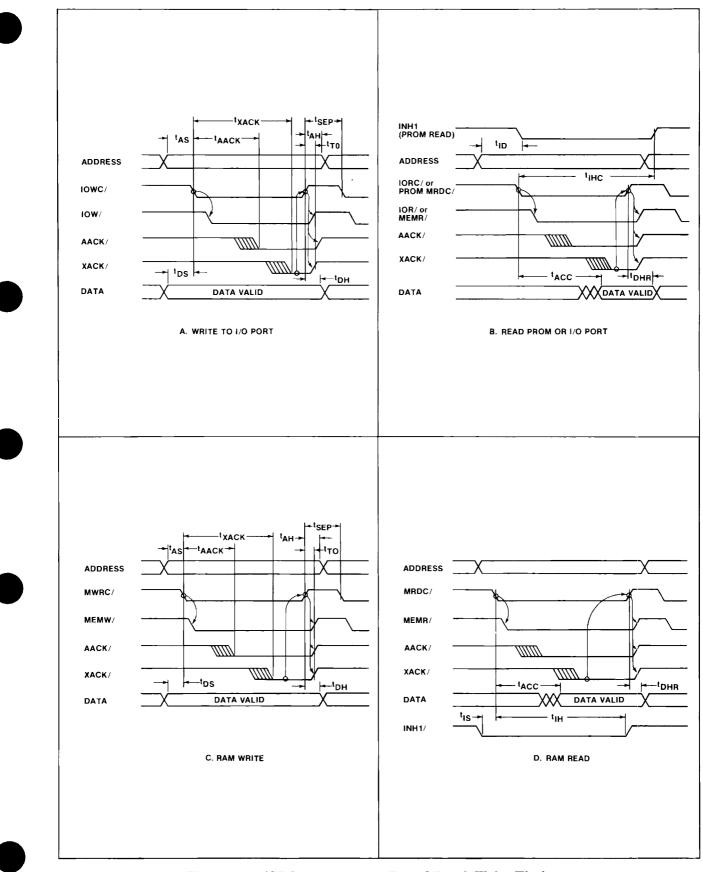

|       | Read/Write Timing                   | 2-7  |

| 2-2   | RAM and ROM/PROM Page and I         | Base |

|       | Address Jumper and Switch           |      |

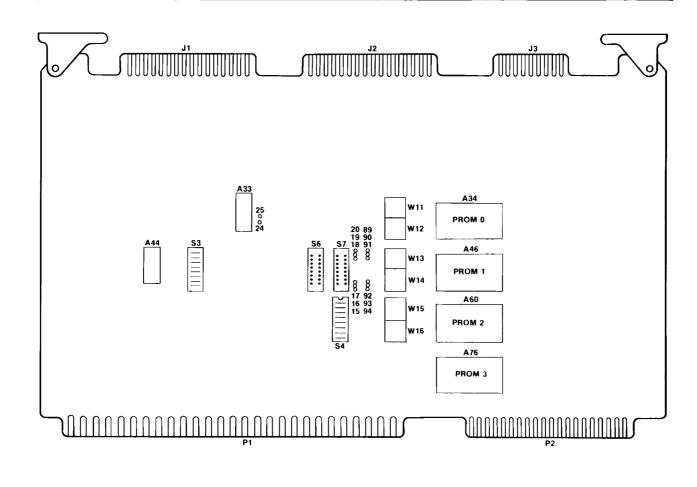

|       | Locations                           | 2-11 |

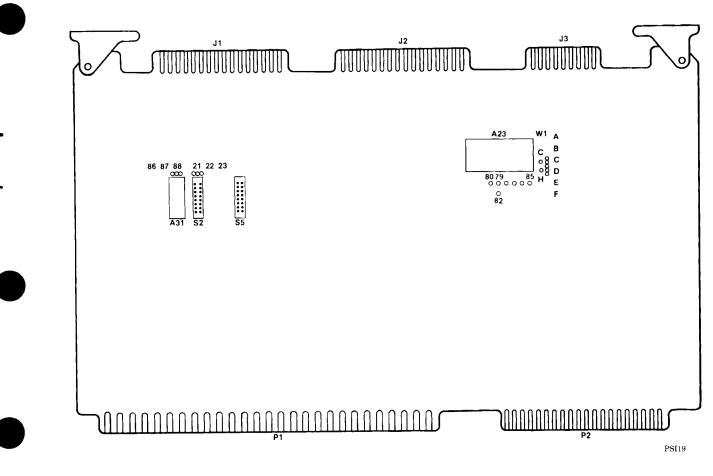

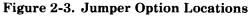

| 2-3   | Jumper Option Locations             | 2-17 |

| 2-4   | Jumper Locations for Clock Source,  |      |

|       | Baud Rate, Interrupts, Parallel I/O |      |

|       | Ports, and Power Options            | 2-18 |

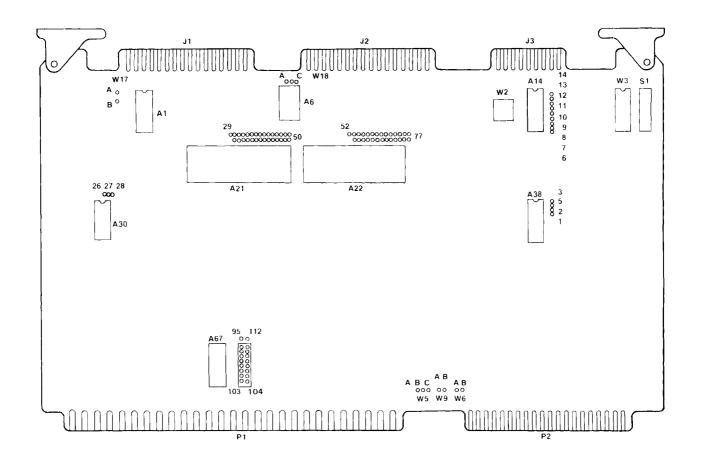

| 2-5   | DIP Header Jumper W3                |      |

|       | Configurations                      | 2-19 |

| 2-6   | iSBC 108A/116A <sup>™</sup> Board   |      |

|       | Interrupt Signals                   | 2-20 |

| 3-1   | Mode Instruction Format,            |      |

|       | Asynchronous Mode                   | 3-2  |

| 3-2   | Asynchronous Mode Protocol          | 3-2  |

| 3-3   | Mode Instruction Format,            |      |

|       | Synchronous Mode                    | 3-2  |

# ILLUSTRATIONS

| FIGURI | E TITLE                                   | PAGE        |

|--------|-------------------------------------------|-------------|

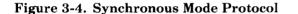

| 3-4    | Synchronous Mode Protocol                 | 3-3         |

| 3-5    | USART Command Instruction                 | 3-3         |

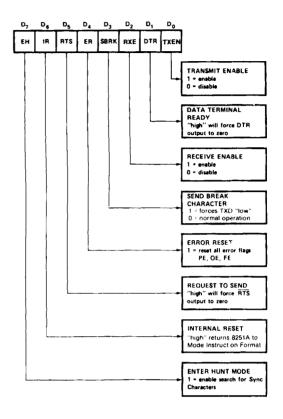

| 3-6    | Typical USART Initialization and D        | ata         |

|        | I/O Sequence                              | 3-4         |

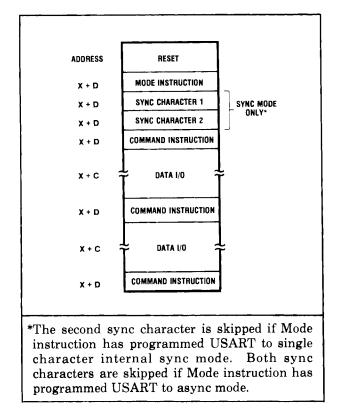

| 3-7    | USART Status Read Format                  | 3-5         |

| 3-8    | 8255A Control Word Format                 | 3 <b>-6</b> |

| 3-9    | Mode/Register Format                      | 3-7         |

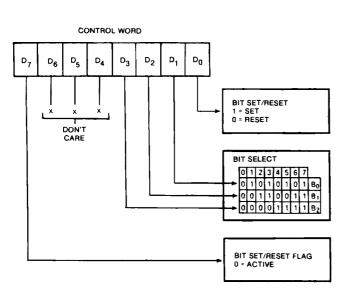

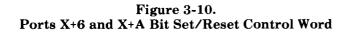

| 3-10   | Ports X+6 and X+A Bit Set/Reset           |             |

|        | Control Word                              |             |

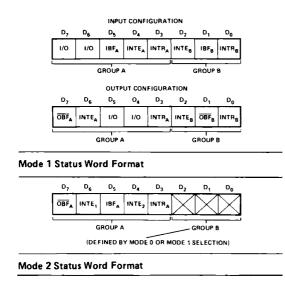

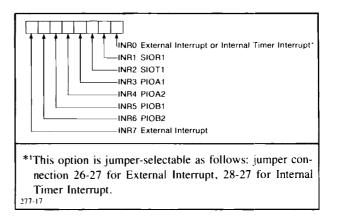

| 3-11   | 8255A Status Read Format                  | 3-9         |

| 3-12   | Interrupt Mask Word Format                | 3-9         |

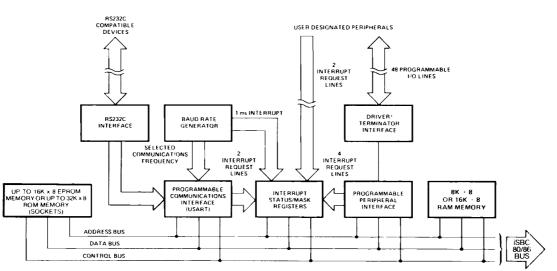

| 4-1    | iSBC 108A/116A™ Board                     |             |

|        | Functional Block Diagram                  | 4-1         |

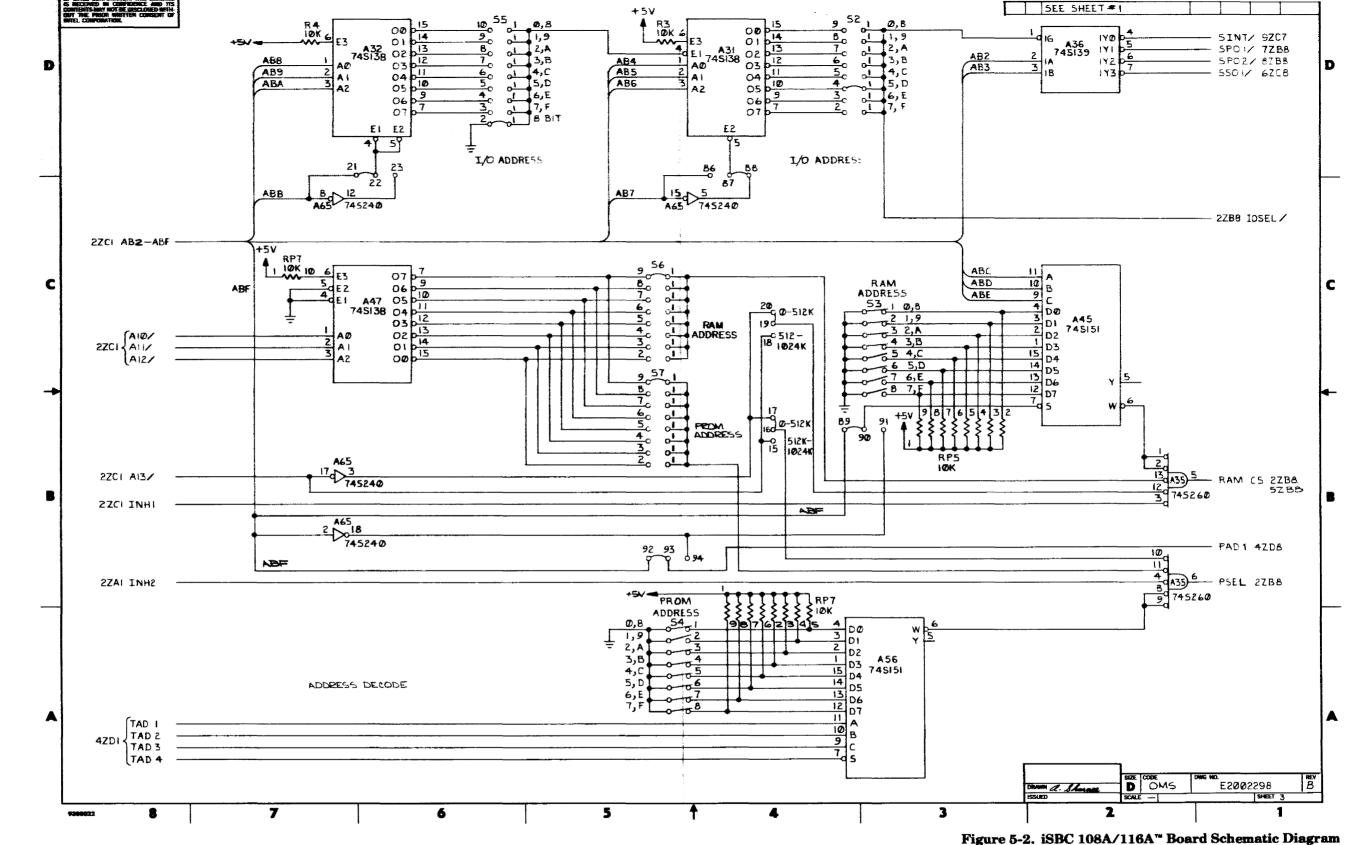

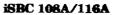

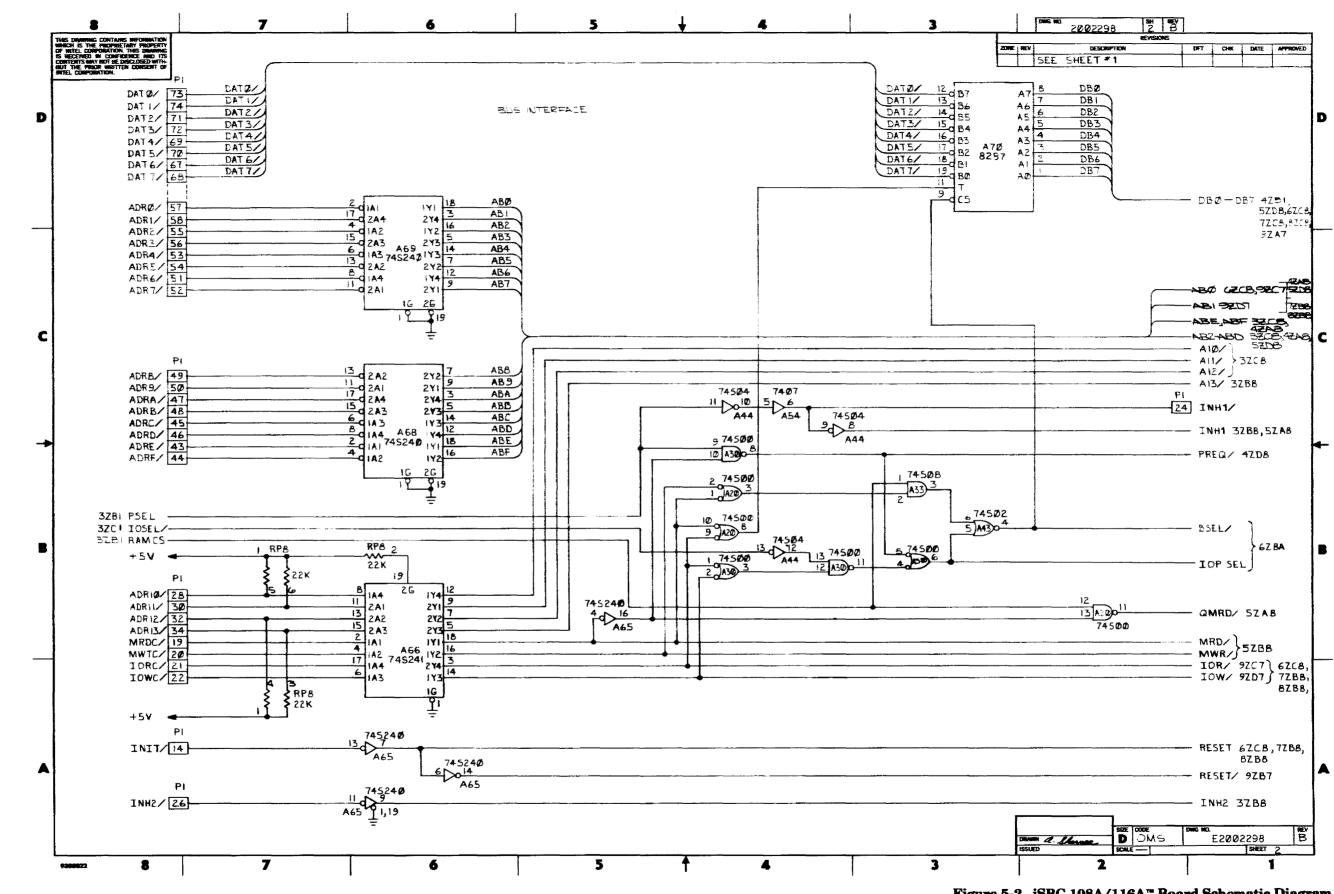

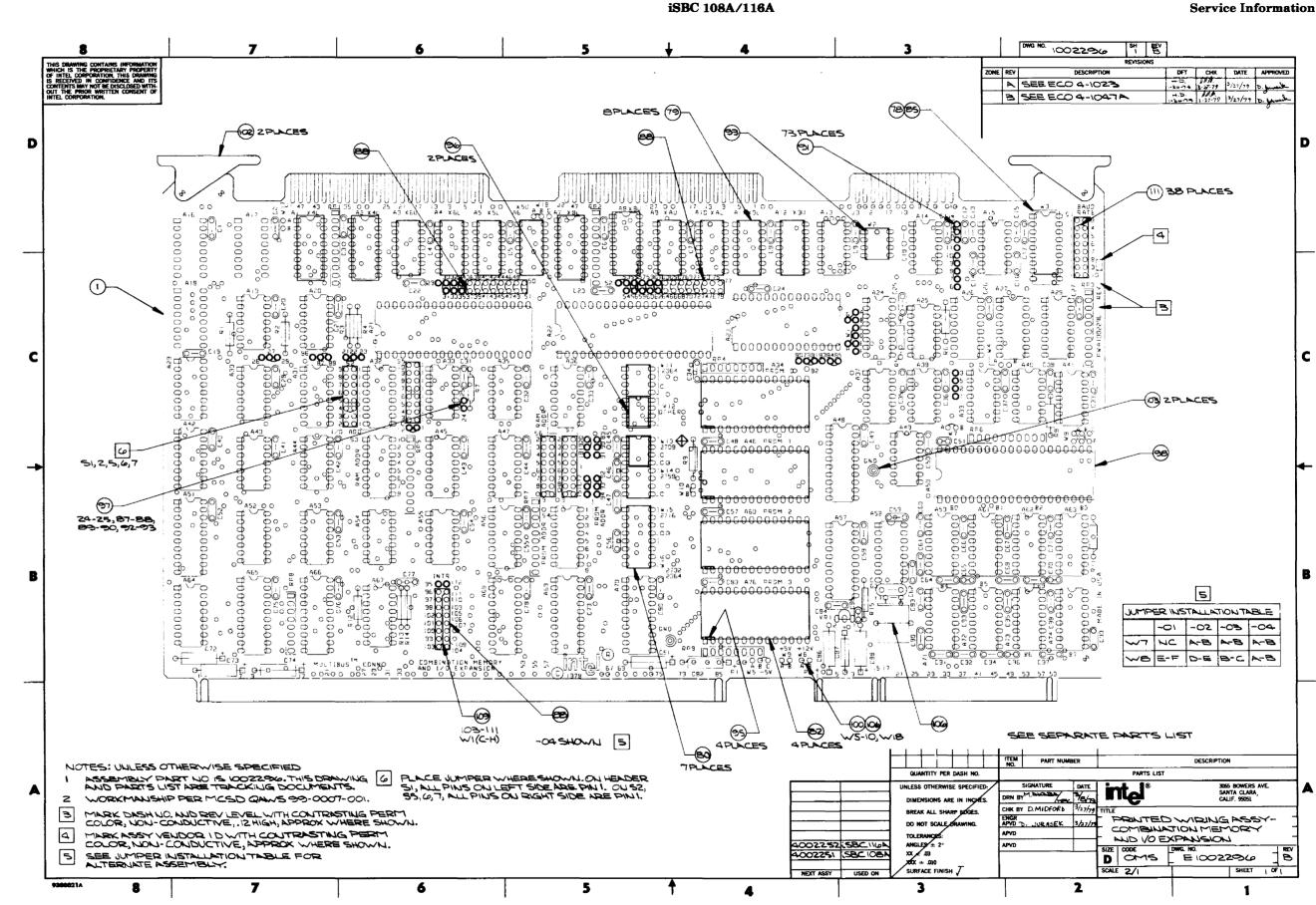

| 5-1    | iSBC 108A/116A™ Board                     |             |

|        | Parts Location                            | 5-5         |

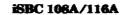

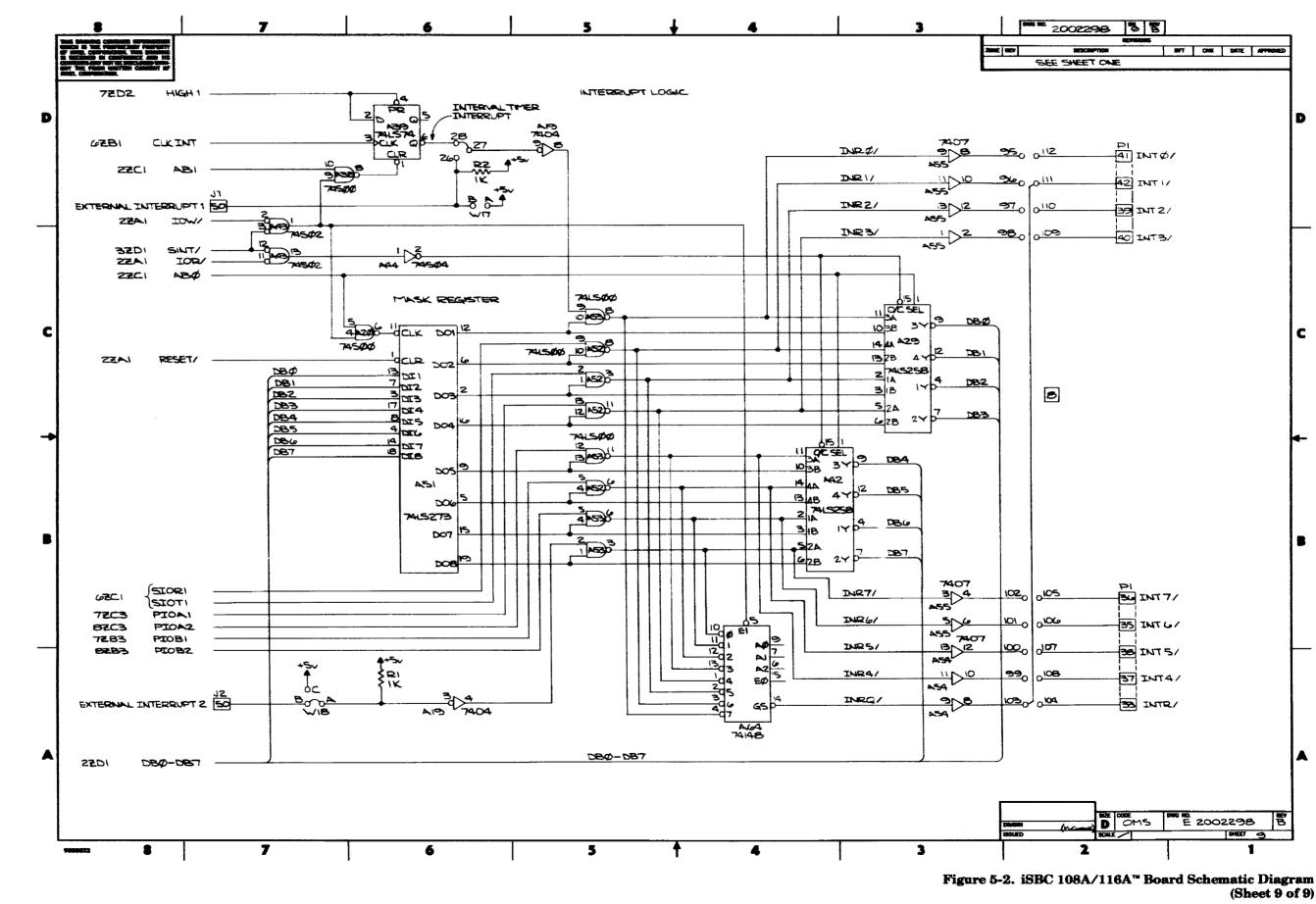

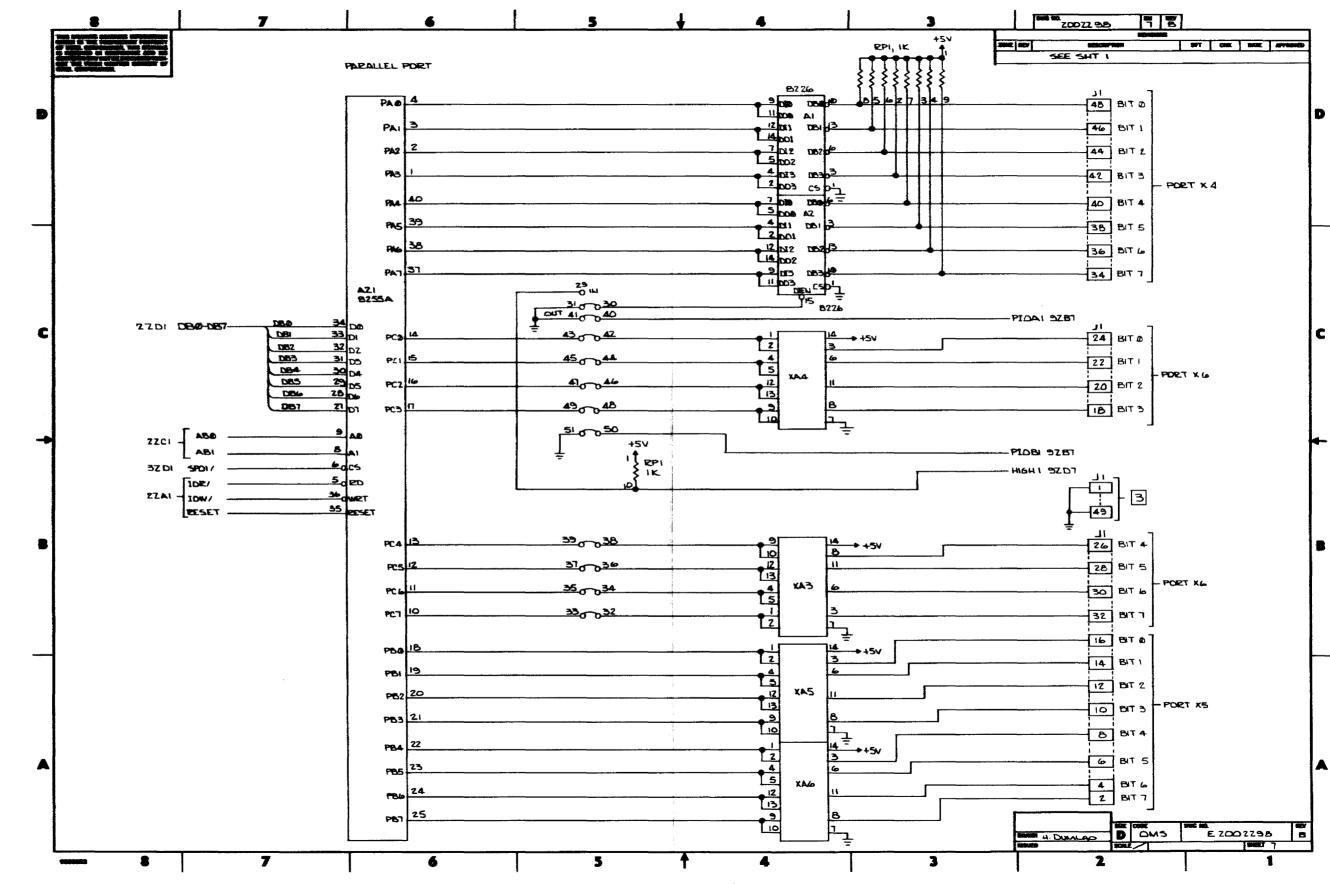

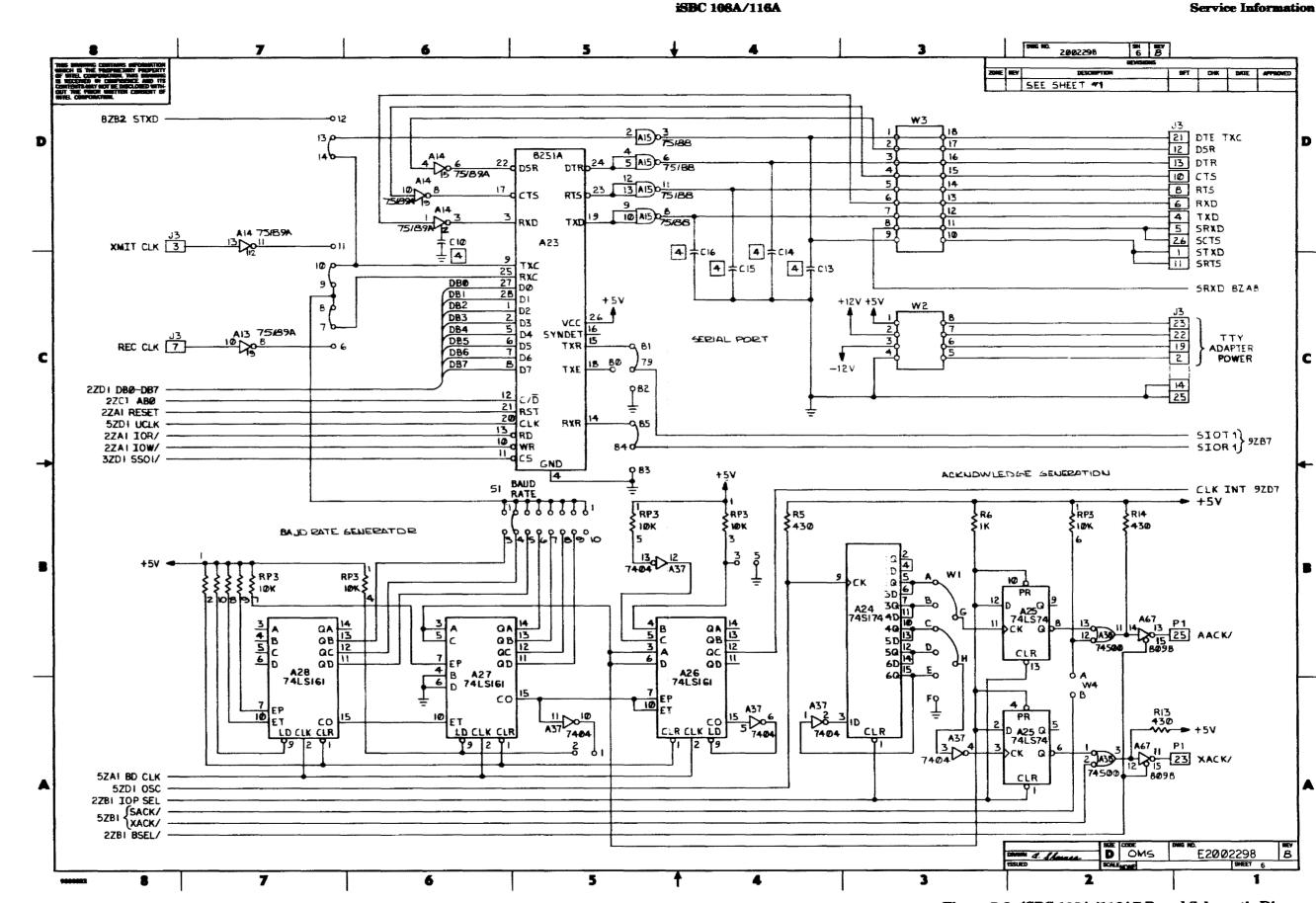

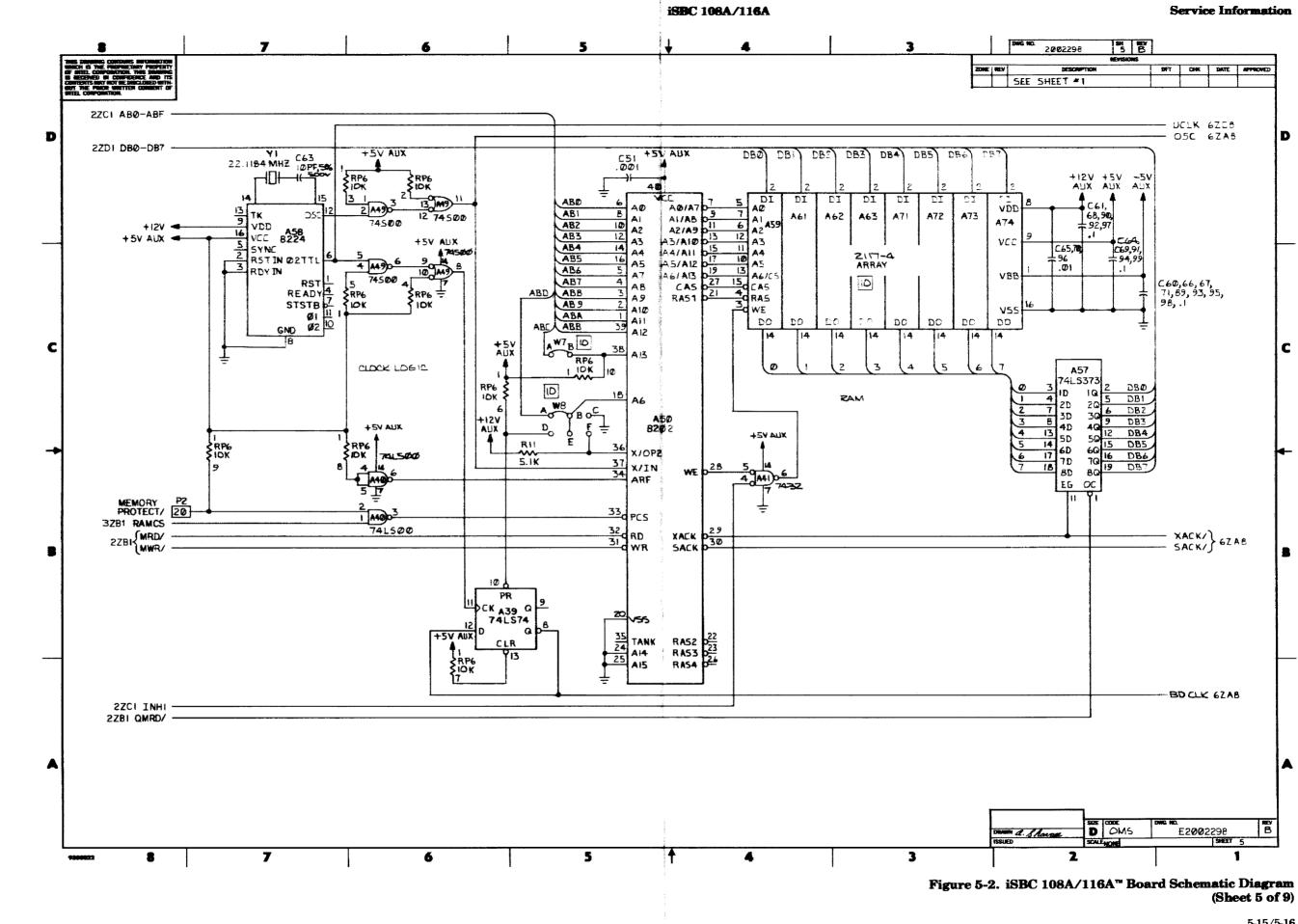

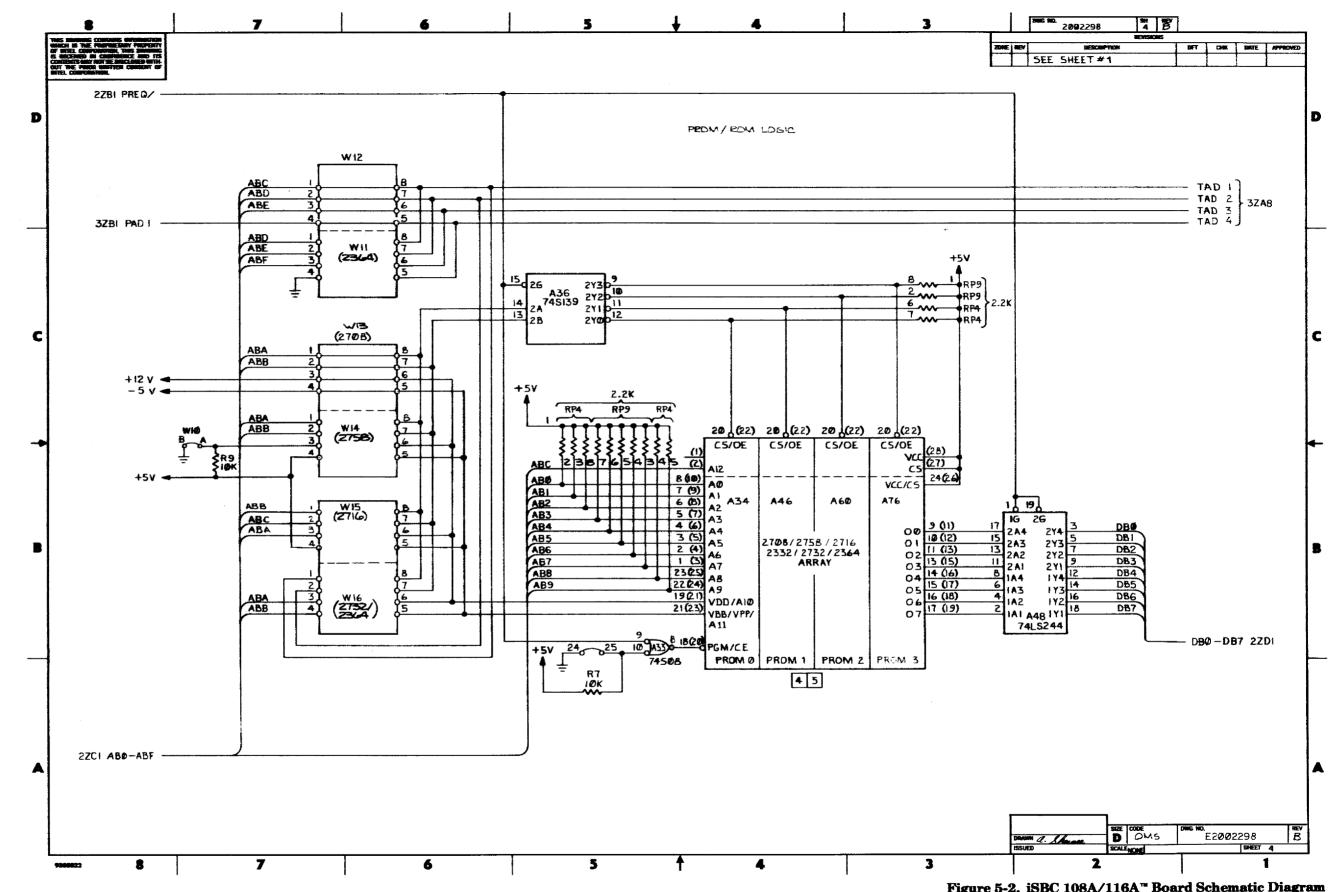

| 5-2    | iSBC 108A/116A™ Board                     |             |

|        | Schematic Diagram                         | 5-7         |

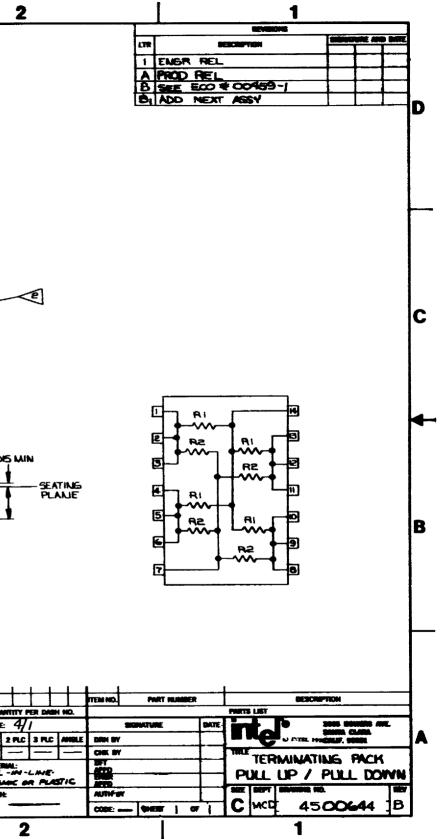

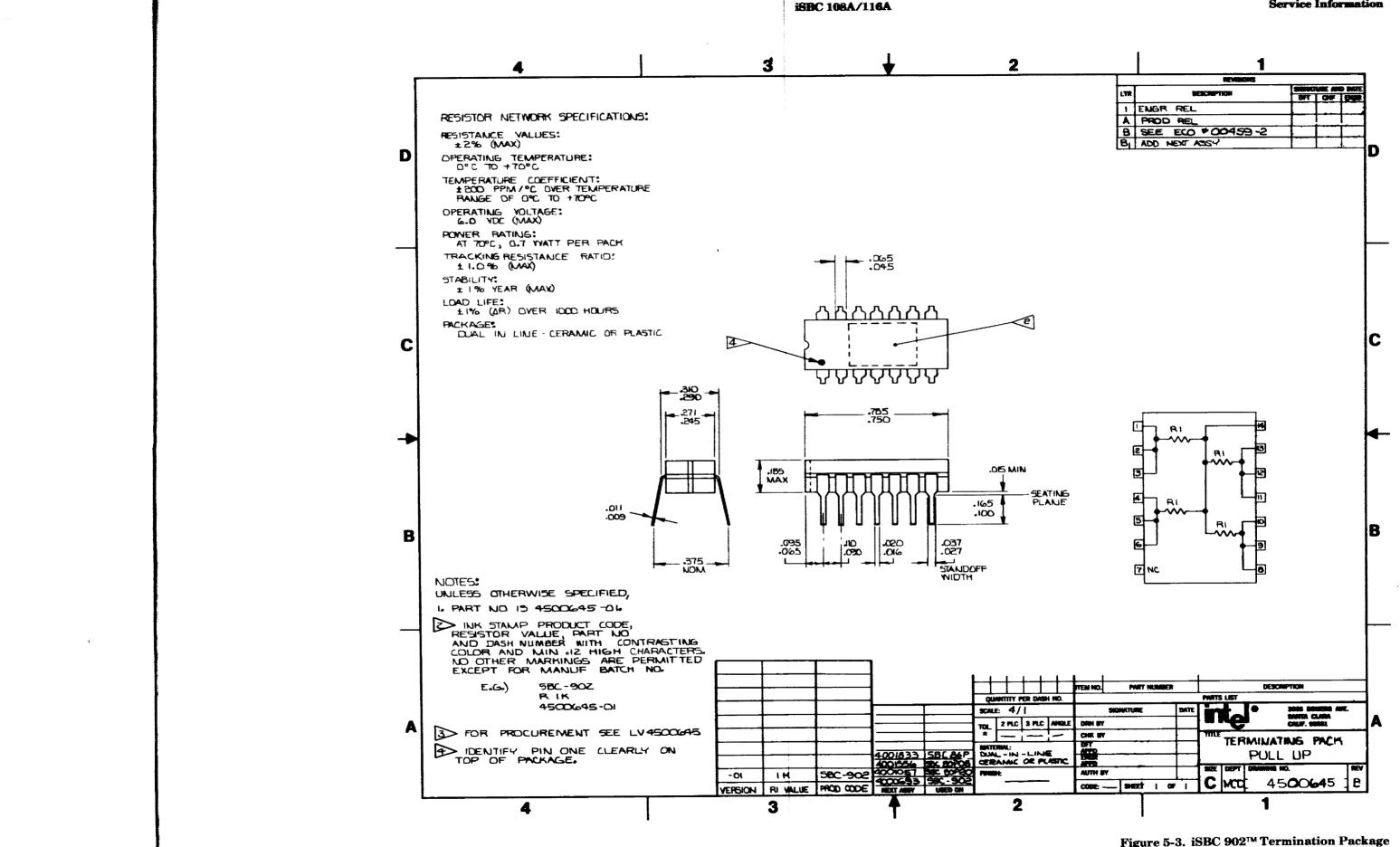

| 5-3    | iSBC 902 <sup>™</sup> Termination Package | . 5-25      |

| 5-4    | iSBC 901 <sup>™</sup> Termination Package |             |

# CHAPTER 1 GENERAL INFORMATION

#### **1-1. INTRODUCTION**

The iSBC 108A/116A Combination Memory and I/O Expansion Boards (figure 1-1) are members of a complete line of iSBC 80/86 Memory and I/O expansion boards designed to interface directly with any iSBC 80/86 Single Board Computer via the system bus. The iSBC 108A/116A board provides up to 16K bytes of RAM and up to 32K bytes of ROM or up to 16K bytes of PROM capacity, as well as parallel and serial I/O ports.

#### **1-2. DESCRIPTION**

The iSBC 108A board and iSBC 116A board contain 8K and 16K bytes, respectively. Both boards provide up to 32K of ROM or up to 16K bytes of PROM, and also include 48 parallel I/O lines controlled by two Intel 8255A Programmable Peripheral Interface (PPI) devices, and a single serial I/O port implemented with an Intel 8251A Universal Synchronous/ Asychronous Receiver/Transmitter (USART). Eight user-configurable interrupt lines are also provided.

The iSBC 108A/116A modules are designed for installation in a standard iSBC 604/614 Modular

Backplane and Cardcage with an iSBC 80/86 Single Board Computer, or for use with an Intellec System.

#### 1-3. SERIAL I/O PORT

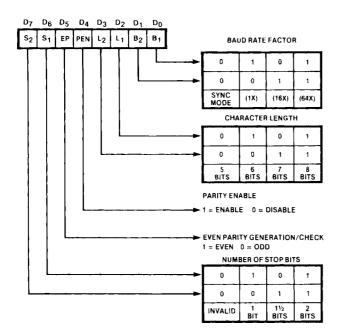

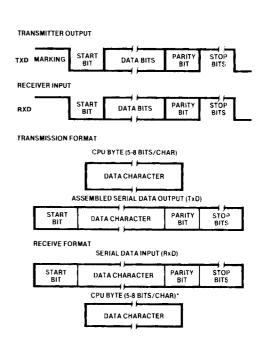

A serial I/O interface, programmable for most synchronous or asynchronous serial data transmission protocols, is provided onboard by an Intel 8251A Universal Synchronous/Asynchronous Receiver/Transmitter. In the synchronous mode, the following functions are programmable.

- a. Character length

- b. Sync character (or characters)

- c. Parity

In the asynchronous mode, the following functions are programmable:

- a. Character length

- b. Baud rate factor (clock divide ratios of 1, 16, or 64)

- c. Stop bits

- d. Parity

#### **General Information**

In both synchronous and asynchronous modes, the serial I/O port features half- or full-duplex doublebuffered transmit or receive capability. In addition, USART error detection circuits can check for parity, overrun, and framing errors. The USART may be jumpered to use external clock signals or the onboard baud rate generator. The USART communicates with peripheral devices through a 26-pin edge connector.

#### 1-4. PARALLEL I/O PORTS

The iSBC 108A/116A modules each include two Intel 8255A Programmable Peripheral Interfaces that control three 8-bit I/O ports each, giving six programmable parallel I/O ports on board. System software can configure the ports in combinations of bidirectional and unidirectional input/output and can configure two ports as status registers or I/O registers. Sockets are provided for user-installed driver or terminator devices to suit a particular user application. The six I/O ports communicate with peripheral devices through two 50-pin edge connectors.

#### **1-5. INTERRUPTS**

Six jumper-programmable interrupts are available from the I/O ports, two from each 8255A PPI device,

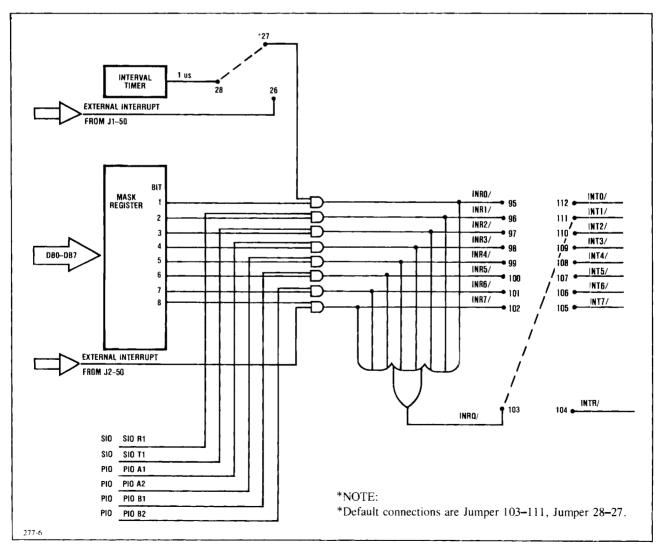

and two from the 8251A USART. The parallel I/O interrupts may be configured to generate interrupts when certain flag bits are set in the status register, and the serial I/O interrupts may be configured to generate interrupts when the transmit or receive buffers are ready for new data, or when the transmitter is empty. Two other interrupts are available, both of which accept signals from user-designated peripheral devices via edge connectors J1 and J2. One of these interrupts may be jumpered to an interval timer, which supplies 1 ms interrupt signals.

#### **1-6. EQUIPMENT SUPPLIED**

The following are supplied with the iSBC 108A/116A Combination Memory and I/O Expansion Boards:

- a. Schematic Diagram, dwg. no. 2002298

- b. Assembly Drawing, dwg. no. 1002296.

#### **1-7. SPECIFICATIONS**

Specifications for the iSBC 108A/116A modules are listed in table 1-1.

| ROM/PROM:             | 8K or 16K bytes of ROM/PROM or 32K bytes of ROM starting at any jumper-<br>selectable base address on a 4K byte boundary. Refer to paragraph 2-8 for further<br>details. |                                                             |                     |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------|--|--|--|

|                       |                                                                                                                                                                          | ddresses must reside in one<br>ress range of X0000H to X7F  |                     |  |  |  |

| RAM:                  | 8K or 16K segments starting at any jumper-selectable base address on a 4K boundry. Refer to paragraph 2-8 for further details.                                           |                                                             |                     |  |  |  |

|                       |                                                                                                                                                                          | s must reside in one of thirty<br>of X0000H to X7FFFH or X8 |                     |  |  |  |

| Memory Response Time: | Memory                                                                                                                                                                   | Access (ns)                                                 | Cycle (ns)          |  |  |  |

|                       | RAM<br>PROM/ROM                                                                                                                                                          | 450 max⁺<br>450 max                                         | 580 max*<br>635 max |  |  |  |

Table 1-1. Specifications.

| Port                                 | PPI<br>1A | PPI<br>1B   | PPI<br>1C | PPI<br>2A                                                     | PPI<br>2B                          | PPI<br>2C                                  | 8255A<br>No. 1<br>Control                     | 8255A<br>No. 2<br>Control                          | USART<br>Data                                          | USART<br>Contro             |

|--------------------------------------|-----------|-------------|-----------|---------------------------------------------------------------|------------------------------------|--------------------------------------------|-----------------------------------------------|----------------------------------------------------|--------------------------------------------------------|-----------------------------|

| Address                              | XX4       | XX5         | XX6       | XX8                                                           | ххэ                                | ХХА                                        | XX7                                           | ххв                                                | ххс                                                    | XXD                         |

| NOTE: XX                             | is two he | k digits as | signed by | / jumper s                                                    | selection.                         | • <u> </u>                                 | · · · · · · · · · · · · · · · · · · ·         |                                                    |                                                        | ·                           |

| /O TRANSFE                           | R RATE    |             |           |                                                               |                                    |                                            |                                               |                                                    |                                                        |                             |

| Parallel:                            |           |             |           | Read or V                                                     | Vrite ack                          | nowledge                                   | e time 575 n                                  | s max                                              |                                                        |                             |

| Serial:                              |           |             |           | (USART)                                                       |                                    |                                            |                                               |                                                    |                                                        |                             |

|                                      |           |             |           |                                                               |                                    |                                            |                                               | Baud R                                             | ate (Hz)                                               |                             |

|                                      |           |             |           |                                                               | equency (                          |                                            | Synchron                                      | ous (                                              | Asynchro<br>Program Sel                                |                             |

|                                      |           |             |           |                                                               |                                    |                                            |                                               | -                                                  | ÷ 16                                                   | ÷ 64                        |

|                                      |           |             |           | 307.2<br>153.6<br>76.8<br>38.4<br>19.2<br>9.6<br>4.8<br>6.98  | i.                                 | <br>38400<br>19200<br>9600<br>4800<br>6980 |                                               | 9200<br>9600<br>4800<br>2400<br>1200<br>600<br>300 | 4800<br>2400<br>1200<br>600<br>300<br>150<br>75<br>110 |                             |

| SERIAL COM<br>CHARACTER<br>Synchrone | ISTICS    | TIONS       |           | 5-8 bit ch                                                    |                                    |                                            |                                               |                                                    |                                                        |                             |

| Asynchroi                            | nous:     |             |           | Automatio<br>5-8 bit ch<br>Break ch<br>1, 1-1/2,<br>False sta | naracters<br>aracters<br>or 2 stop | generatio<br>bits                          | on and detec                                  | tion                                               |                                                        |                             |

| INTERRUPTS                           | 3         |             |           | Eight inte<br>Interface<br>connecto                           | (4 lines),                         | the USAR                                   | s may origina<br>IT (2 lines) or<br>al Timer. | ate from the<br>user specifi                       | Programma<br>ed devices vi                             | ble Periphe<br>a the I/O ec |

| INTERRUPT<br>ADDRESSES               |           | R           |           | Interr                                                        | upt Mask                           | Register                                   |                                               | XX1                                                |                                                        |                             |

|                                      |           |             |           |                                                               |                                    | is Registe                                 |                                               | XX0                                                |                                                        |                             |

|                                      |           |             |           | L                                                             |                                    |                                            | I                                             | d by jumper                                        |                                                        |                             |

## Table 1-1. Specifications (Continued)

| INTERFACES                       |                            |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

|----------------------------------|----------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------|---------------------------|--|--|

| Bus:                             |                            | All signals T                 | TL compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                            |                               |                           |  |  |

| Parallel I/O:                    |                            | All signals TTL compatible    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

| Serial I/O:                      |                            | RS232C                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

| Interrupt Reques                 | sts:                       | All TTL compatible            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

| CONNECTORS                       |                            |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

|                                  |                            | Interface                     | No. of<br>Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Centers<br>(in.)                                           |                               |                           |  |  |

|                                  |                            | Bus (P1)                      | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0.156                                                      | CDC VPB01E43A                 | 00A1                      |  |  |

|                                  |                            | Parallel I/C                  | ) 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                            | 3M 3415-000 or<br>TI H312125  |                           |  |  |

|                                  |                            | Serial I/O                    | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                            | 3M 3462-000 or<br>TI H312113  |                           |  |  |

|                                  |                            | Aux Power                     | (P2) 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                            | AMP PE5-14559 o<br>TI H311130 | or                        |  |  |

|                                  |                            | NOTE: Conr<br>conform to I    | nector heights an<br>htel OEM packag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | id wire-wrap pin<br>ing.                                   | lengths are not               | guaranteed to             |  |  |

| PHYSICAL CHAR                    | ACTERISTICS                |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

| Width:                           |                            | 12.00 in. (30.                | 48 cm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            |                               |                           |  |  |

| Height:                          |                            | 6.75 in. (17.                 | 15 cm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            |                               |                           |  |  |

| Depth:                           |                            | 0.50 in. ( 1.2                | 27 cm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                            |                               |                           |  |  |

| Weight:                          |                            | 14 oz. (397.3                 | gm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            |                               |                           |  |  |

| ELECTRICAL CHA                   | RACTERISTICS               |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

| Average DC Cur                   | rent:                      |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            |                               |                           |  |  |

|                                  | No EPROM or<br>Terminators | 4 2708's and<br>8 Terminators | 4 2716's and<br>No Terminators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 2732's and<br>No Terminators                             | Aux Power<br>RAM Accessed     | Aux Power<br>No RAM Acces |  |  |

| $V_{DD} = +12 \pm 5\%$           | 250 mA                     | 520 mA                        | 250 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250 mA                                                     | 175 mA                        | 20 mA                     |  |  |

| V <sub>CC</sub> = +5 ±5%         | 2.9 A                      | 3.6 A                         | 3.3 A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.5 A                                                      | 0.45 A                        | 0.45 A                    |  |  |

| V <sub>BB</sub> = -5 <u>+</u> 5% |                            | 180 mA                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                                                          | 3 mA                          | 3 mA                      |  |  |

| V <sub>AA</sub> = -12 ±5%        | 70 mA                      | 70 mA                         | 70 mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70 mA                                                      |                               |                           |  |  |

| AUXILIARY POWI                   | ĒR                         | requiring bat                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | vided to allow sep<br>ad/write memory,<br>rs on the board. |                               |                           |  |  |

| MEMORY PROTECT                   |                            | Auxiliary cor<br>memory on t  | nnector which, whether which is the second | MEMORY PROT<br>nen asserted, disa<br>put is provided for   | bles Read/Write               | access to RAM             |  |  |

## Table 1-1. Specifications (Continued)

.

-

÷

| I/O Drivers:                  | TORS                                                                | ina lina deivara ar     | d torminata             | e aro all as                 | mpatible with the        | 1/0 4-6                |  |  |

|-------------------------------|---------------------------------------------------------------------|-------------------------|-------------------------|------------------------------|--------------------------|------------------------|--|--|

| I/O Drivers.                  |                                                                     | the iSBC 108A/1         |                         | s are an CL                  | mpatible with the        |                        |  |  |

|                               | Driver                                                              | Characteristic          | Sink<br>Current<br>(mA) | Driver                       | Characteristic           | Sink<br>Currer<br>(mA) |  |  |

|                               |                                                                     | 1,0C<br>1<br>NI<br>1,0C | 48<br>48<br>16<br>16    | 7409<br>7408<br>7403<br>7400 | NI,OC<br>NI<br>I,OC<br>I | 16<br>16<br>16<br>16   |  |  |

|                               | NOTE: I =                                                           | inverting; NI = no      | n-inverting; (          | DC = open                    | collector.               | .I                     |  |  |

|                               | Ports 1 and                                                         | d 4 have 25 mA tot      | tem-pole driv           | ers and 1 k                  | Ω terminators.           |                        |  |  |

| I/O Terminators:              | Terminators: $220\Omega/330\Omega$ divider or 1 k $\Omega$ pull-up. |                         |                         |                              |                          |                        |  |  |

|                               | +5                                                                  |                         |                         |                              |                          |                        |  |  |

|                               | 220 Ω                                                               |                         |                         |                              |                          |                        |  |  |

|                               | 220 Ω /330 Ω                                                        |                         |                         |                              |                          |                        |  |  |

|                               |                                                                     | <u> </u>                | Ω                       |                              |                          |                        |  |  |

|                               |                                                                     |                         |                         |                              |                          |                        |  |  |

|                               |                                                                     |                         |                         |                              |                          |                        |  |  |

|                               |                                                                     |                         | Ω                       |                              |                          |                        |  |  |

| Bus Drivers:                  | <br>1 kΩ +:                                                         |                         | Ω                       |                              | <b>o</b> se              | IC 902 OPT             |  |  |

| Bus Drivers:                  | 1 kΩ +<br>Funct                                                     | 5 <b>/</b>              | Ω<br>Characte           | ristic                       | o se<br>Sink Curren      |                        |  |  |

| Bus Drivers:                  |                                                                     | ion                     | <u> </u>                | te                           |                          |                        |  |  |

| Bus Drivers:<br>ENVIRONMENTAL | Funct                                                               | ion                     | Characte<br>Tri-Sta     | te                           | Sink Curren<br>32        |                        |  |  |

|                               | Funct                                                               | ion<br>/ledge           | Characte<br>Tri-Sta     | te                           | Sink Curren<br>32        |                        |  |  |

## Table 1-1. Specifications (Continued)

# CHAPTER 2 PREPARATION FOR USE

#### 2-1. INTRODUCTION

This chapter provides instructions for installing the iSBC 108A/116A Combination Memory and I/O Expansion Boards. These instructions include unpacking and inspection; installation considerations such as power and cooling requirements, physical dimensions, and bus interface requirements; jumper configurations; optional battery backup power and memory protect connections; board installation; and programming considerations.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and packing materials for the agent's inspection.

For repairs to a product damaged in shipment, contact the Intel MCD Technical Support Center (see paragraph 5-4) to obtain a Repair Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that the salvageable shipping cartons and packing material be saved for future use if the product must be shipped.

#### 2-3. INSTALLATION CONSIDERATIONS

The iSBC 108A/116A boards are designed to interface with an Intel iSBC 80/86 Single Board Computer based system or an Intel Intellec System. Important installation and interfacing criteria are presented in the following paragraphs.

#### **2-4. POWER REQUIREMENT**

Power requirements for the iSBC 108A/116A boards are specified in table 1-1. For installation in an iSBC 80/86 Single Board Computer based system, ensure that the system power supply has sufficient +5V, -5V, -12V, and +12V current capacity to accommodate the additional requirement. For installation in an Intellec system, calculate the total +5V, +12V, and -12V current requirements for the standard modules and all installed optional modules. Ensure that the additional current requirement will not exceed the capacity of the Intellec System power supplies.

# NOTE

If Intel 2708 PROMs are installed, the iSBC 108A/116A boards cannot be used in the Intellec System.

2-5. COOLING REQUIREMENT

The iSBC 108A/116A boards dissipate 370 gram/ calories per minute (1.5 BTU/minute) and adequate circulation of air must be provided to prevent a temperature rise above  $55^{\circ}$ C (131°F). The Intel System 80/86 enclosures and the Intellec System include fans to provide adequate intake and exhaust of ventilating air.

#### 2-6. PHYSICAL DIMENSIONS

Physical dimensions of the iSBC 108A/116A boards are as follows:

- a. Width: 30.48 cm (12.00 inches)

- b. Depth: 17.15 cm ( 6.75 inches)

- c. Thickness: 1.27 cm (0.50 inch)

#### 2-7. BUS INTERFACING REQUIREMENTS

The iSBC 108A/116A boards are designed for installation in a standard Intel iSBC 604/614 Modular Backplane and Cardcage or in the Intellec System motherboard. As shown in figure 1-1, edge connector P1 provides interface to the Multibus system bus. Connector P1 pin assignments are listed in table 2-1 and descriptions of the signal functions are given in table 2-2. Edge connector P2 is an auxiliary power input described in paragraph 2-29. Connector P2 pin assignments are listed in table 2-3. As shown in figure 1-1, edge connectors J1 and J2 provide connections for the Parallel I/O Ports. Connector J1 and J2 pin assignments are listed in table 2-4 and 2-5 respectively. As shown in figure 1-1, edge connector J3 provides a connection for the serial I/O port. Connector J3 pin assignments are listed in table 2-6.

# NOTE

When the iSBC 108A/116A board is installed in an Intellec System, it is necessary to configure the Intellec CPU module for qualified memory write command.

# iSBC108A/116A

## **Preparation For Use**

| PIN*     | SIGNAL  | FUNCTION                     | PIN*     | SIGNAL         | FUNCTION      |

|----------|---------|------------------------------|----------|----------------|---------------|

| 1        | GND     |                              | 44       | ADRF/          | l             |

| 2        | GND     | Ground                       | 45       | ADRC/          |               |

| 3        | +5 VDC  |                              | 46       | ADRD/          |               |

| 4        | +5 VDC  |                              | 47       | ADRA/          |               |

| 5        | +5 VDC  |                              | 48       | ADRB/          |               |

| 6        | +5 VDC  |                              | * 49     | ADR8/          |               |

| 7        | +12 VDC | Power input                  | 50       | ADR9/          | Address Bus   |

| 8        | +12 VDC | i ower input                 | 50       | ADR6/          | Y Hudiess Dus |

| 9        | -5 VDC  |                              | 52       | ADR7           |               |

| 10       | -5 VDC  | )                            | 52       | ADR4/          |               |

| 11       | GND     |                              | 55       | ADR5/          |               |

| 12       | GND     | Ground                       | 55       | ADR3/          |               |

| 13       | BCLK/   | Bus Clock                    | 56       | ADR2/<br>ADR3/ |               |

| 13       | INIT/   | System Initialize            | 57       | ADR3/<br>ADR0/ |               |

| 15       | 11111/  | System minanze               | 58       | ADR0/<br>ADR1/ | J             |

| 16       |         |                              | 58<br>59 |                | /             |

| 17       | BUSY/   | Bus Busy                     | 60       |                |               |

| 18       | 0031/   | Dus Dusy                     | 61       |                |               |

| 19       | MRDC/   | Manage David Carrier         |          |                |               |

| 19<br>20 |         | Memory Read Command          | 62       |                |               |

| 20<br>21 | MWTC/   | Memory Write Command         | 63       |                |               |

| 21       | IORC/   | I/O Read Command             | 64       |                |               |

|          | IOWC/   | I/O Write Command            | 65       |                |               |

| 23       | XACK/   | Transfer Acknowledge         | 66       |                | <b>\</b>      |

| 24       | INH1/   | RAM Inhibit                  | 67       | DAT6/          |               |

| 25       | AACK/   | Advanced Acknowledge         | 68       | DAT7/          |               |

| 26       | INH2/   | ROM/PROM Inhibit             | 69       | DAT4/          |               |

| 27       |         |                              | 70       | DAT5/          | Data bus      |

| 28       | ADR10/  |                              | 71       | DAT2/          |               |

| 29       |         |                              | 72       | DAT3/          |               |

| 30       | ADR11/  | Address Bus                  | 73       | DAT0/          |               |

| 31       |         |                              | 74       | DAT1/          | /             |

| 32       | ADR12/  |                              | 75       | GND            | } Ground      |

| 33       | INTR/   | Direct Interrupt Request     | 76       | GND            | J             |

| 34       | ADR13/  | Address Bus                  | 77       |                |               |

| 35       | INT6/   | Interrupt request on level 6 | 78       |                |               |

| 36       | INT7/   | Interrupt request on level 7 | 79       | -12 VDC        |               |

| 37       | INT4/   | Interrupt request on level 4 | 80       | -12 VDC        |               |

| 38       | INT5/   | Interrupt request on level 5 | 81       | +5 VDC         | Power input   |

| 39       | INT2/   | Interrupt request on level 2 | 82       | +5 VDC         | r ower input  |

| 40       | INT3/   | Interrupt request on level 3 | 83       | +5 VDC         |               |

| 41       | INT0/   | Interrupt request on level 1 | 84       | +5 VDC         | 1             |

| 42       | INT1/   | Interrupt request on level 0 | 85       | GND            | } Ground      |

| 43       | ADRE/   | Address Bus                  | 86       | GND            | f Ground      |

# Table 2-1. Connector P1 Pin Assignments

\*All unassigned pins are reserved.

iSBC108A/116A

#### Table 2-2. Multibus Signal Functions

| Signal                       | Functional Description                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AACK/                        | Advance Acknowledge: This signal is issued by the iSBC 108A/116A board in response to a read or write command. The AACK/ signal allows the system controller to proceed with the current instruction cycle.                                                                                                                                           |  |  |  |  |  |  |

| ADRO/-ADRF/<br>ADR10/-ADR13/ | Address: These 20 lines transmit the address of the memory location or I/O port to be accessed.<br>ADRF/ is the most significant bit except where ADR10/ through ADR13/ are used. ADR10/<br>through ADR13/ are transmitted only by those bus masters capable of addressing beyond 64K of<br>memory. In this case, ADR13/ is the most significant bit. |  |  |  |  |  |  |

| DAT0/-DAT7/                  | Data: These eight bidirectional data lines transmit and receive information to and from the addressed memory location or I/O port. DAT7/ is the most significant bit.                                                                                                                                                                                 |  |  |  |  |  |  |

| INH1/                        | Inhibit RAM: Prevents RAM from responding to a bus access. Allows a PROM module to overlay RAM.                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| INH2/                        | Inhibit PROM: Prevents ROM/PROM from responding to a bus access. Allows auxiliary ROM to overlay normal ROM.                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| INIT/                        | Initialization: Resets the entire system to a known internal state.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| INT0/-INT7/                  | Interrupt: These eight lines are used for system interrupt requests.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| INTR/                        | Interrupt Request: Supports coded interrupt requests in special applications of interrupt structure.                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| IORC/                        | I/O Read Command: Indicates that the address of an I/O port is on the system address lines and<br>that the output of that port is to be read (placed) onto the system data lines.                                                                                                                                                                     |  |  |  |  |  |  |

| IOWC/                        | I/O Write Command: Indicates that the address of an I/O port is on the system address lines and that the contents on the system data lines are to be accepted by the addressed port.                                                                                                                                                                  |  |  |  |  |  |  |

| MRDC/                        | Memory Read Command: Indicates that the address of a memory location is on the system address lines and that the contents of that location are to be read (placed) onto the system data lines.                                                                                                                                                        |  |  |  |  |  |  |

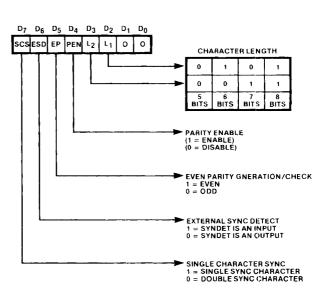

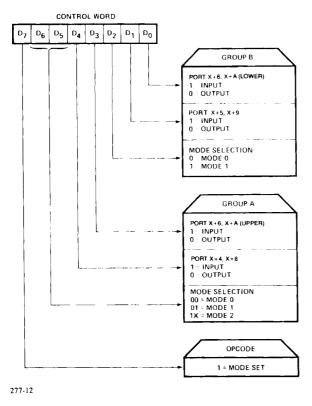

| MWRC/                        | Memory Write Command: Indicates that the address of a memory location is on the system address lines and that the contents on the system data lines are to be written into that location.                                                                                                                                                             |  |  |  |  |  |  |