# iSBC 86/12 SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Manual Order Number: 9800645A

®

# iSBC 86/12 SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Manual Order Number: 9800645A

Copyright © 1978 Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

The information in this manual is subject to change without notice. Intel Corporation makes no warranty of any kind with regard to this manual, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this manual. Intel Corporation makes no commitment to update nor to keep current the information contained in this manual.

No part of this manual may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation. The following are trademarks of Intel Corporation and may be used only to describe Intel products:

| ICE- 30           | iSBC                    | MULTIBUS |

|-------------------|-------------------------|----------|

| ICE-80            | LIBRARY MANAGER         | PROMPT   |

| INSITE            | MCS                     | UPI      |

| INTEL<br>INTELLEC | MEGACHASSIS<br>MICROMAP | RMX      |

This manual provides general information, installation, programming information, principles of operation, and service information for the Intel iSBC 86/12 Single Board Computer. Additional information is available in the following documents:

- 8086 Assembly Language Reference Manual, Order No. 9800640

- Intel MCS-85 User's Manual, Order No. 98-366

- Intel 8255A Programmable Peripheral Interface, Application Note AP-15

- Intel 8251 Universal Synchronous/Asynchronous Receiver/Transmitter, Application Note AP-16

- Intel MULTIBUS Interfacing, Application Note AP-28

- Intel 8259 Programmable Interrupt Controller, Application Note AP-31

# CONTENTS

## CHAPTER 1 GENERAL INFORMATION

| Introduction                | 1-1 |

|-----------------------------|-----|

| Description                 | 1-1 |

| System Software Development | 1-3 |

| Equipment Supplied          | 1-3 |

| Equipment Required          | 1-3 |

| Specifications              | 1-3 |

PAGE

#### CHAPTER 2 PREPARATION FOR USE

| Introduction                                 |

|----------------------------------------------|

| Unpacking and Inspection 2-1                 |

| Installation Considerations 2-1              |

| User-Furnished Components 2-1                |

| Power Requirement 2-1                        |

| Cooling Requirement 2-1                      |

| Physical Dimensions 2-1                      |

| Component Installation 2-1                   |

| ROM/EPROM Chips 2-1                          |

| Line Drivers and I/O Terminators 2-4         |

| Jumper/Switch Configuration 2-4              |

| RAM Addresses (Multibus Access) 2-4          |

| Priority Interrupts 2-6                      |

| Serial I/O Port Configuration 2-9            |

| Parallel I/O Port Configuration 2-9          |

| Multibus Configuration 2-9                   |

| Signal Characteristics 2-13                  |

| Serial Priority Resolution 2-13              |

| Parallel Priority Resolution 2-13            |

| Power Fail/Memory Protect Configuration 2-13 |

| Parallel I/O Cabling 2-23                    |

| Serial I/O Cabling 2-23                      |

| Board Installation 2-23                      |

## CHAPTER 3 PROGRAMMING INFORMATION

| Introduction                |

|-----------------------------|

| Failsafe Timer 3-1          |

| Memory Addressing 3-1       |

| CPU Access                  |

| Multibus Access 3-2         |

| I/O Addressing 3-3          |

| System Initialization       |

| 8251A USART Programming 3-4 |

| Mode Instruction Format 3-4 |

| Sync Characters             |

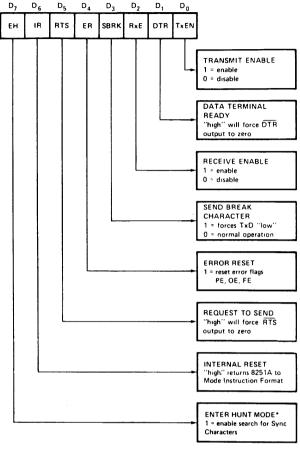

| Command Instruction Format  |

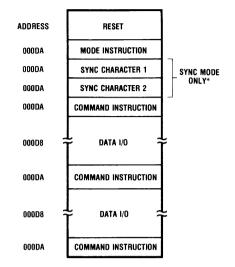

| Reset                       |

| Addressing 3-5              |

| Initialization              |

| Operation                   |

| Data Input/Output 3-7       |

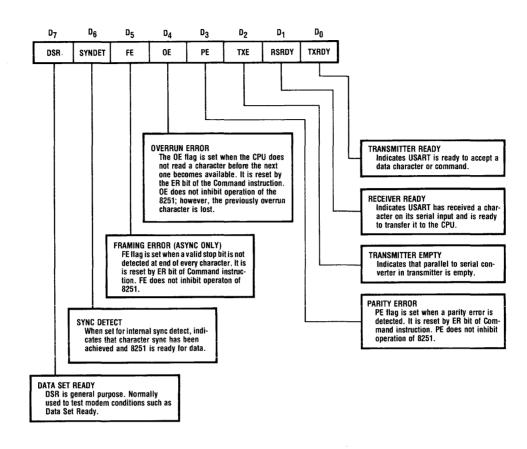

| Status Read 3-7             |

| PAGE                                        |

|---------------------------------------------|

| 8253 PIT Programming 3-8                    |

| Mode Control Word and Count 3-8             |

| Addressing                                  |

| Initialization                              |

| Operation                                   |

| Counter Read 3-13                           |

| Clock Frequency/Divide Ratio Selection 3-13 |

| Rate Generator/Interval Timer 3-14          |

| Interrupt Timer 3-14                        |

| 8255A PPI Programming 3-14                  |

| Control Word Format 3-15                    |

| Addressing 3-15                             |

| Initialization                              |

| Operation                                   |

| Read Operation 3-16                         |

| Write Operation                             |

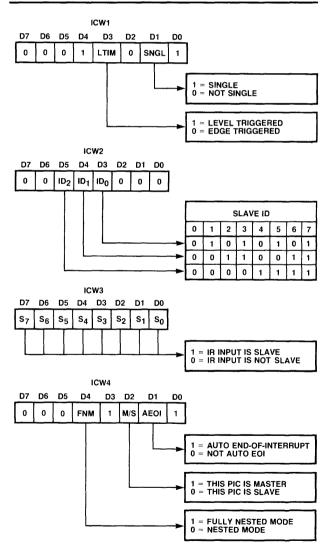

| 8259A PIC Programming 3-17                  |

| Interrupt Priority Modes 3-17               |

| Nested Mode 3-17                            |

| Fully Nested Mode 3-17                      |

| Automatic Rotating Mode 3-17                |

| Specific Rotating Mode 3-17                 |

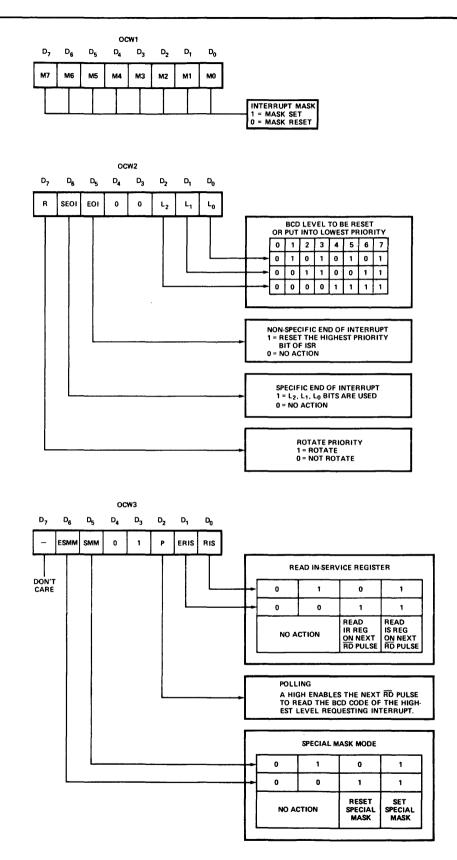

| Special Mask Mode 3-18                      |

| Poll Mode 3-18                              |

| Status Read 3-18                            |

| Initialization Command Words 3-18           |

| Operation Command Words 3-19                |

| Addressing 3-19                             |

| Initialization 3-19                         |

| Operation                                   |

| Hardware Interrupts 3-25                    |

| Non-Maskable Interrupt (NMI) 3-25           |

| Maskable Interrupt (INTR) 3-25              |

| Master PIC Byte Identifier 3-25             |

| Slave PIC Byte Identifier 3-25              |

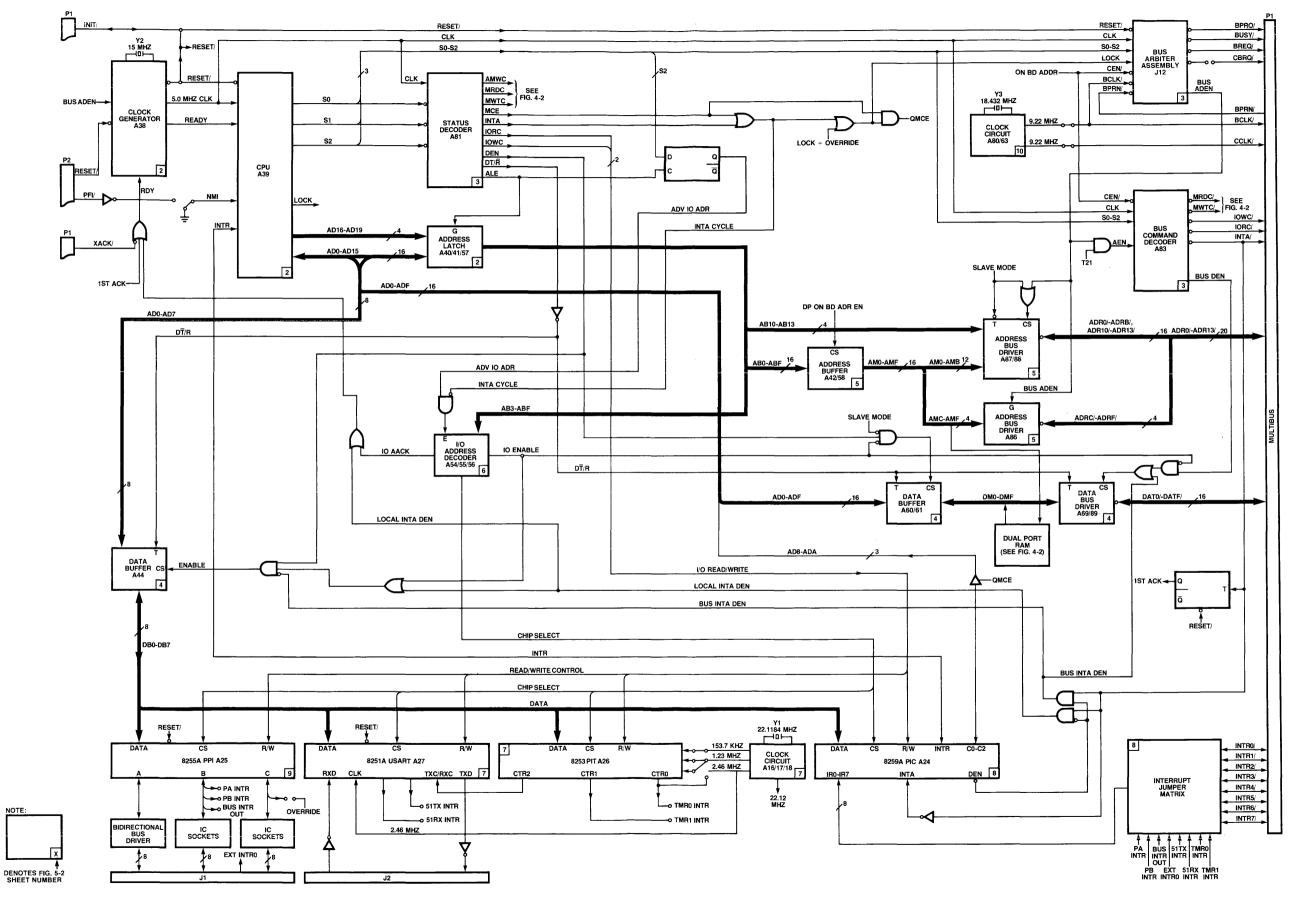

# CHAPTER 4 PRINCIPLES OF OPERATION

| Introduction               | 1  |

|----------------------------|----|

| Functional Description 4-  | 1  |

| Clock Circuits 4-          | -1 |

| Central Processor Unit 4-  | -1 |

| Interval Timer 4-          | -1 |

| Serial I/O 4-              | -1 |

| Parallel I/O 4-            | -1 |

| Interrupt Controller 4-    | -2 |

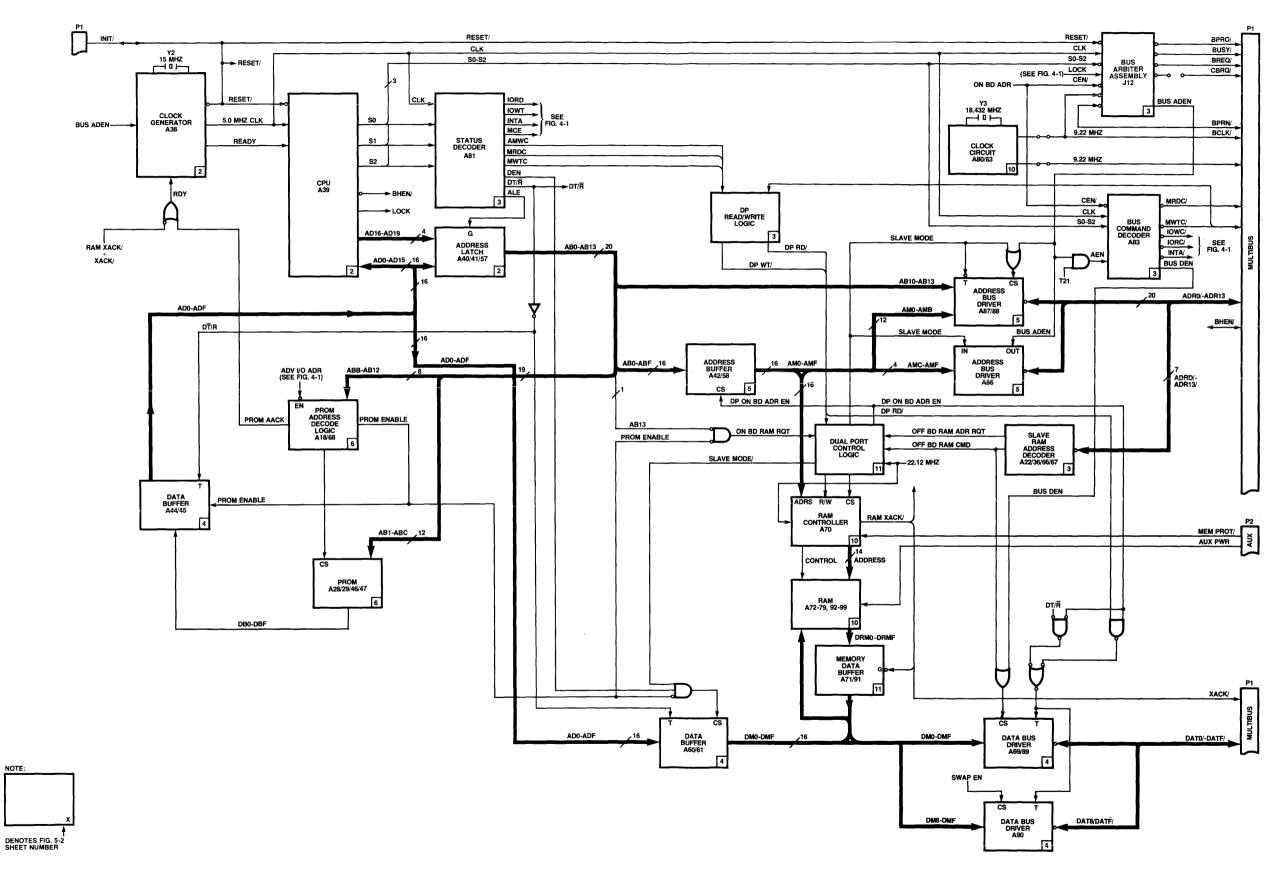

| ROM/EPROM Configuration 4- |    |

| RAM Configuration 4-       | -2 |

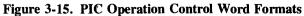

| Bus Structure 4-           | -2 |

| Multibus Interface 4-      | -3 |

# **CONTENTS (Continued)**

| Circuit Analysis 4-3         |

|------------------------------|

| Initialization               |

| Clock Circuits 4-4           |

| Central Processor Unit 4-4   |

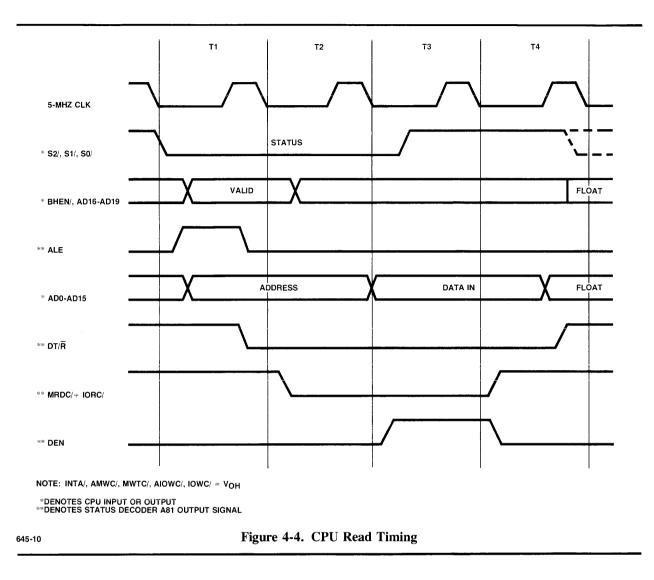

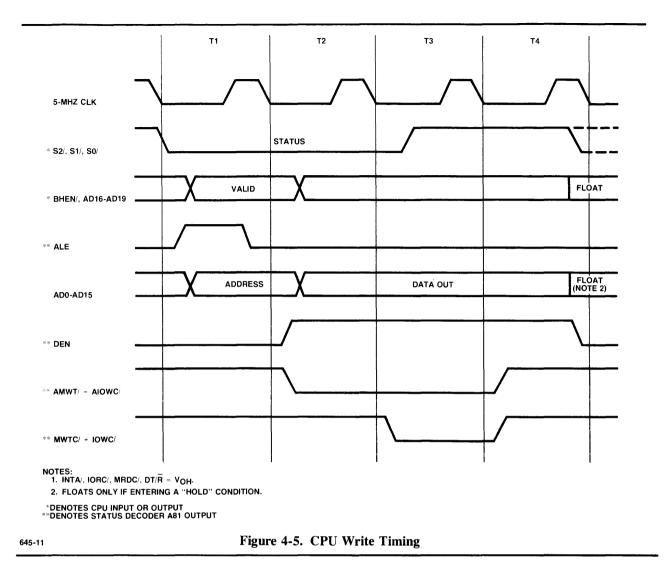

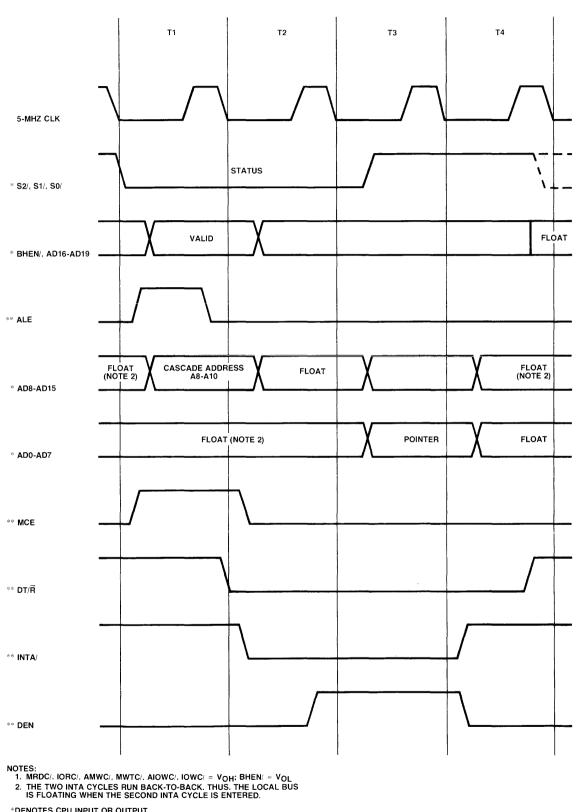

| Basic Timing 4-4             |

| Bus Timing 4-4               |

| Address Bus 4-6              |

| Data Bus 4-6                 |

| Bus Time Out 4-6             |

| Internal Control Signals 4-8 |

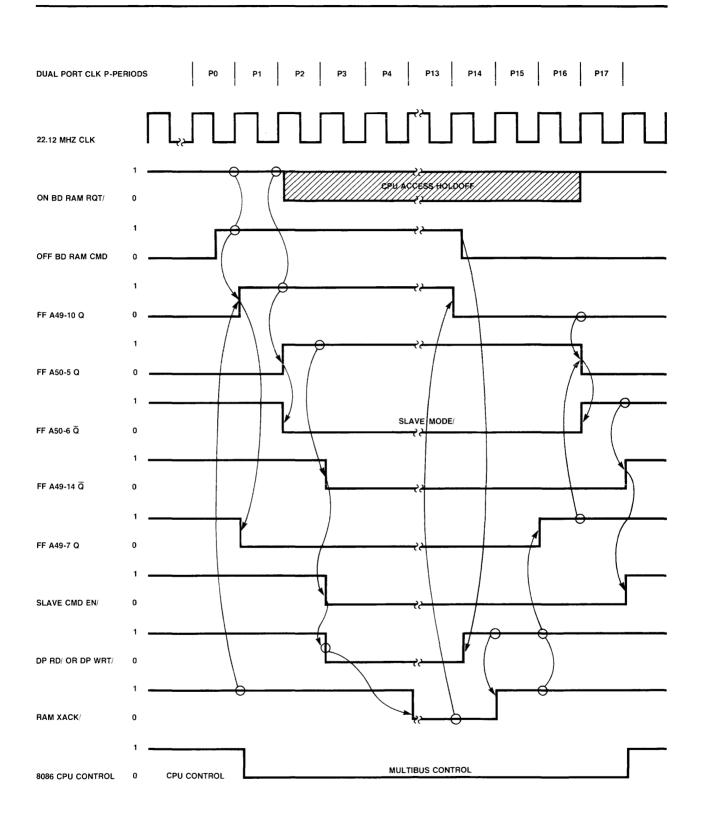

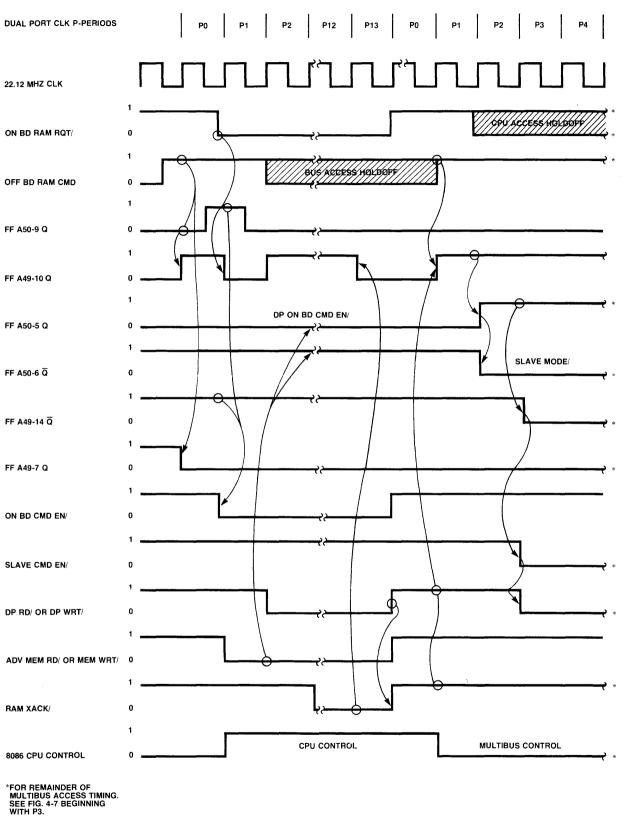

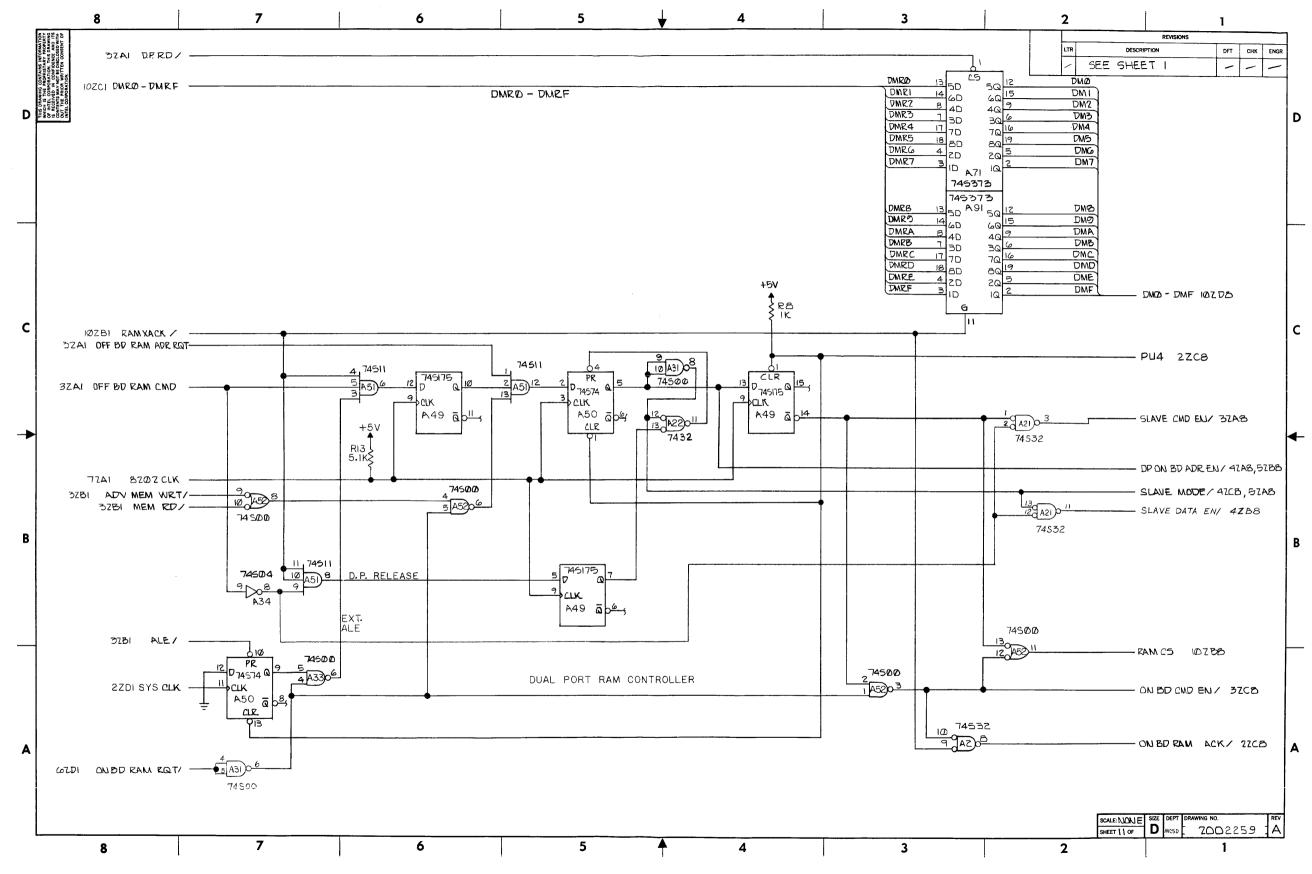

| Dual Port Control Logic 4-8  |

| Multibus Access Timing 4-8   |

| CPU Access Timing 4-8        |

| Multibus Interface           |

| I/O Operation 4-11           |

| On-Board I/O Operation 4-11  |

| System I/O Operation 4-12    |

| ROM/EPROM Operation          |

## PAGE

| I                             | PAGE   |

|-------------------------------|--------|

| RAM Operation                 | 4-12   |

| RAM Controller                | . 4-12 |

| RAM Chips                     | . 4-13 |

| On-Board Read/Write Operation | . 4-13 |

| Bus Read/Write Operation      | . 4-13 |

| Byte Operation                | . 4-13 |

| Interrupt Operation           | . 4-14 |

| NBV Interrupt                 | . 4-14 |

| BV Interrupt                  | . 4-14 |

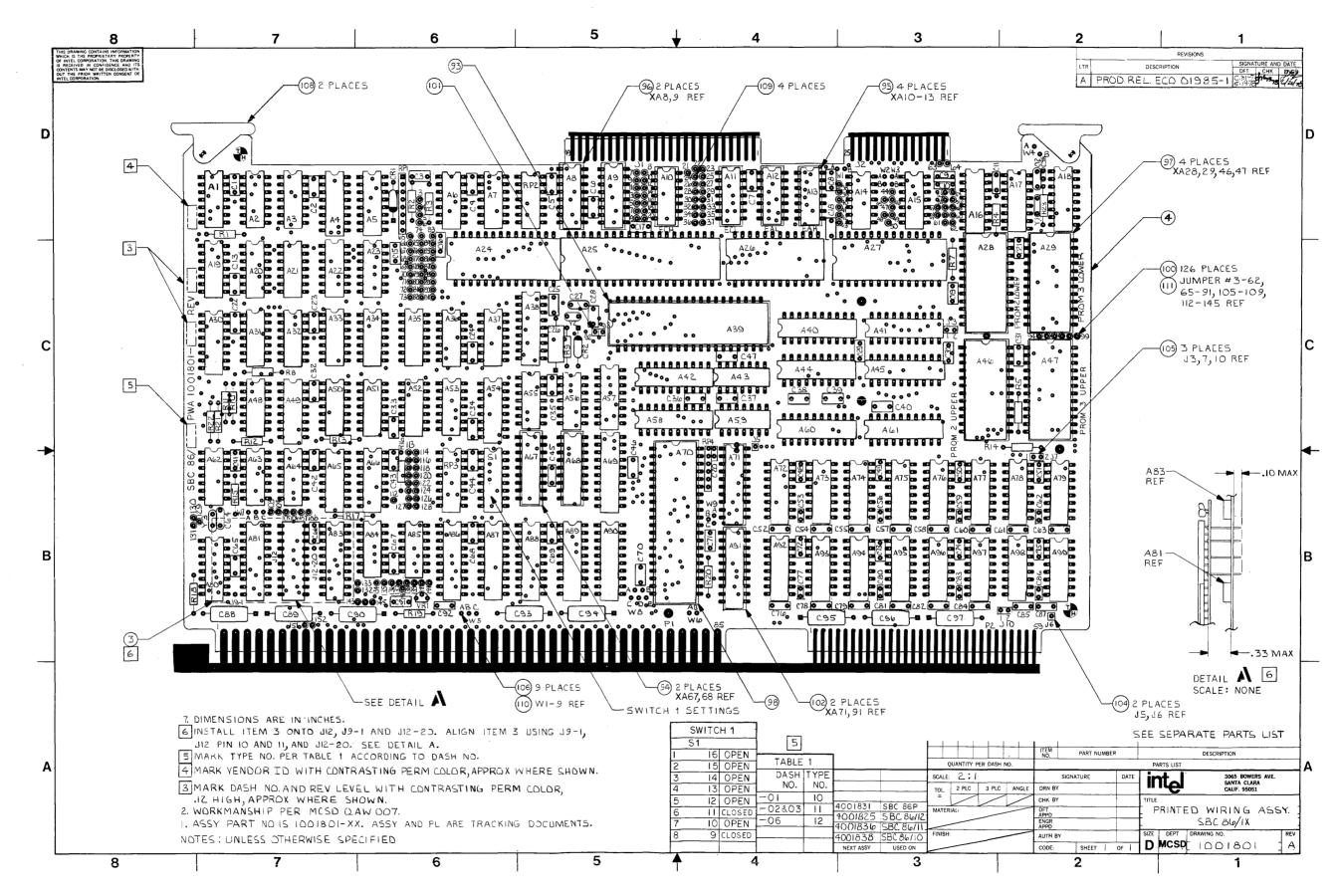

#### CHAPTER 5 SERVICE INFORMATION

| SERVICE INFORMATION           |     |

|-------------------------------|-----|

| ntroduction                   | 5-1 |

| Replaceable Parts             | 5-1 |

| Service Diagrams              | 5-1 |

| Service and Repair Assistance | 5-1 |

|                               |     |

v

# APPENDIX A

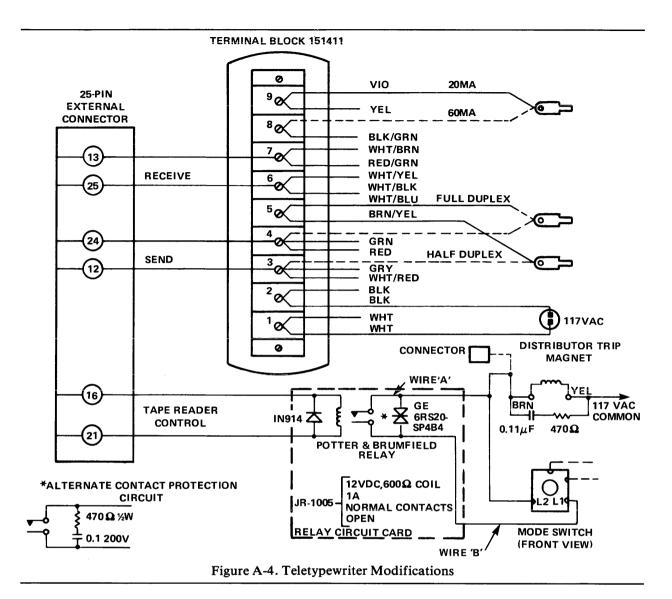

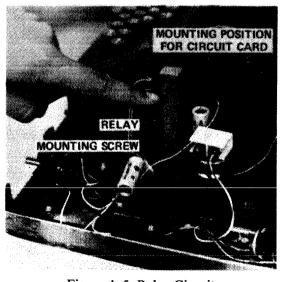

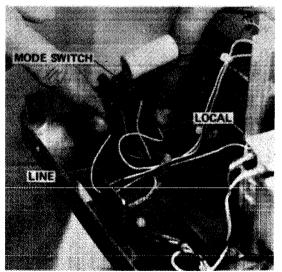

| TELETYPEWRITER MODIFICATI | ONS |

|---------------------------|-----|

|---------------------------|-----|

\_intel\_

# TABLES

| TA | BL | Æ |

|----|----|---|

|    |    |   |

PAGE TABLE

TITLE

PAGE

| 1-1  | Specifications 1-4                           |

|------|----------------------------------------------|

| 2-1  | User-Furnished and Installed Components 2-2  |

| 2-2  | User-Furnished Connector Details 2-3         |

| 2-3  | Line Driver and I/O Terminator Locations 2-4 |

| 2-4  | Jumper and Switch Selectable Options 2-5     |

| 2-5  | Priority Interrupt Jumper Matrix 2-8         |

| 2-6  | Serial I/O Connector J2 Pin Assignments Vs   |

|      | Configuration Jumpers 2-9                    |

| 2-7  | Parallel I/O Port Configuration Jumpers 2-10 |

| 2-8  | Multibus Connector PI Pin Assignments 2-14   |

| 2-9  | Multibus Signal Functions                    |

| 2-10 | iSBC 86/12 DC Characteristics                |

| 2-11 | iSBC 86/12 AC Characteristics                |

| ~ 11 | (Master Mode) 2-18                           |

| 2-12 | iSBC 86/12 AC Characteristics                |

| 2-12 | (Slave Mode)                                 |

| 2-13 | Auxiliary Connector P2 Pin Assignments 2-22  |

| 2-13 | Auxiliary Signal (Connector P2)              |

| 2-1- | DC Characteristics                           |

| 2-15 | Parallel I/O Connector J1                    |

| 2-15 | Pin Assignments                              |

| 2-16 | Parallel I/O Signal (Connector J1)           |

| 2-10 | DC Characteristics                           |

| 2-17 | Connector J2 Vs RS232C Pin                   |

| 2-17 |                                              |

| 2.1  | Correspondence                               |

| 3-1  | On-Board Memory Addresses                    |

|      | (CPU Access) 3-2                             |

| 3-2  | I/O Address Assignments 3-3                  |

| 3-3  | Typical USART Mode or Command                |

|      | Instruction Subroutine 3-7                   |

| 3-4  | Typical USART Data Character Read            |

|      | Subroutine                                   |

| 3-5  | Typical USART Data Character Write           |

|      | Subroutine                                   |

|      |                                              |

| 3-6  | Typical USART Status Read Subroutine 3-9      |

|------|-----------------------------------------------|

| 3-7  | PIT Counter Operation Vs Gate Inputs 3-12     |

| 3-8  | Typical PIT Control Word Subroutine 3-12      |

| 3-9  | Typical PIT Count Value Load                  |

|      | Subroutine                                    |

| 3-10 | Typical PIT Counter Read Subroutine 3-13      |

| 3-11 | PIT Count Value Vs Rate Multiplier for        |

|      | Each Baud Rate                                |

| 3-12 | PIT Rate Generator Frequencies and            |

|      | Timer Intervals                               |

| 3-13 | PIT Time Intervals Vs Timer Counts 3-15       |

| 3-14 | Typical PPI Initialization Subroutine 3-16    |

| 3-15 | Typical PPI Port Read Subroutine 3-16         |

| 3-16 | Typical PPI Port Write Subroutine 3-16        |

| 3-17 | Typical PIC Initialization Subroutine         |

|      | (NBV Mode) 3-21                               |

| 3-18 | Typical Master PIC Initialization Subroutine  |

|      | (BV Mode) 3-21                                |

| 3-19 | Typical Slave PIC Initialization Subroutine   |

|      | (BV Mode) 3-22                                |

| 3-20 | PIC Operation Procedures 3-22                 |

| 3-21 | Typical PIC Interrupt Request                 |

|      | Register Read Subroutine 3-24                 |

| 3-22 | Typical PIC In-Service Register               |

|      | Read Subroutine                               |

| 3-23 | Typical PIC Set Mask Register Subroutine 3-24 |

| 3-24 | Typical PIC Mask Register Read                |

|      | Subroutine                                    |

| 3-25 | Typical PIC End-of-Interrupt Command          |

|      | Subroutine 3-25                               |

| 5-1  | Replaceable Parts 5-1                         |

| 5-2  | List of Manufacturers' Codes 5-3              |

|      |                                               |

# ILLUSTRATIONS

| 1-1       iSBC 86/12 Single Board Computer       1-1         2-1       Dual Port RAM Address Configuration<br>(Multibus Access)       2-7         2-2       Simplified Master/Slave PIC<br>Interconnect Example       2-8         2-3       Bus Exchange Timing (Master Mode)       2-19         2-4       Bus Exchange Timing (Slave Mode)       2-20         2-5       Surger Developer Schemer Schemer       2-10 | FIGURI     | E TITLE PAGE                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------|

| <ul> <li>2-1 Dual Port RAM Address Configuration<br/>(Multibus Access)</li></ul>                                                                                                                                                                                                                                                                                                                                     | 1-1        | iSBC 86/12 Single Board Computer 1-1                                       |

| <ul> <li>2-2 Simplified Master/Slave PIC<br/>Interconnect Example</li></ul>                                                                                                                                                                                                                                                                                                                                          | 2-1        |                                                                            |

| Interconnect Example                                                                                                                                                                                                                                                                                                                                                                                                 |            |                                                                            |

| 2-3Bus Exchange Timing (Master Mode)2-192-4Bus Exchange Timing (Slave Mode)2-20                                                                                                                                                                                                                                                                                                                                      | 2-2        |                                                                            |

| 2-4 Bus Exchange Timing (Slave Mode) 2-20                                                                                                                                                                                                                                                                                                                                                                            | 2.2        | Interconnect Example                                                       |

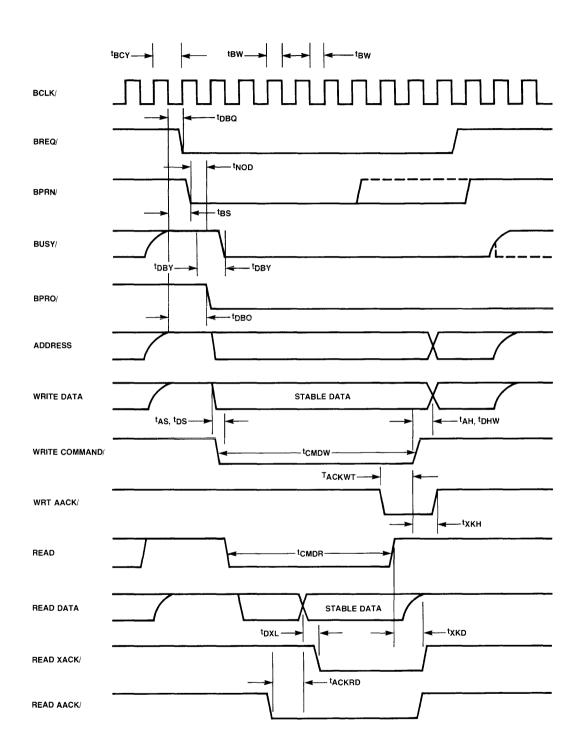

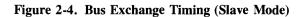

| 2-4 Bus Exchange Timing (Slave Wode)                                                                                                                                                                                                                                                                                                                                                                                 |            | Bus Exchange Timing (Master Mode) 2-19<br>Bus Exchange Timing (Slave Mode) |

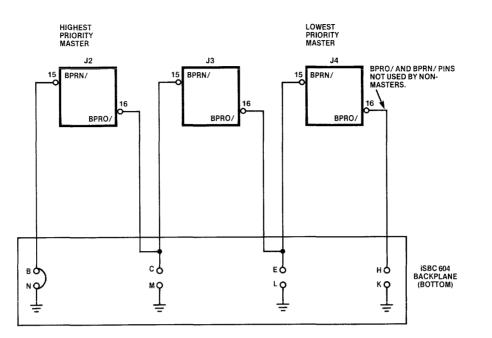

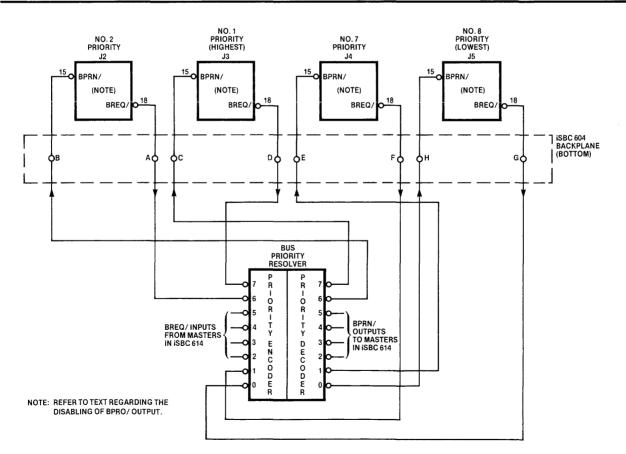

| 7.5 NATION PROPERTY PACOLUTION NONAMA 777                                                                                                                                                                                                                                                                                                                                                                            | 2-4<br>2-5 | Serial Priority Resolution Scheme                                          |

| 2-5       Serial Fhore Resolution Scheme                                                                                                                                                                                                                                                                                                                                                                             |            |                                                                            |

| 3-1 Dual Port RAM Addressing                                                                                                                                                                                                                                                                                                                                                                                         |            | Dual Port RAM Addressing                                                   |

| (Multibus Access)                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                                            |

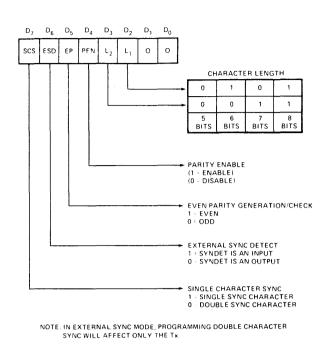

| 3-2 USART Synchronous Mode Instruction                                                                                                                                                                                                                                                                                                                                                                               | 3-2        |                                                                            |

| Word Format 3-4                                                                                                                                                                                                                                                                                                                                                                                                      |            |                                                                            |

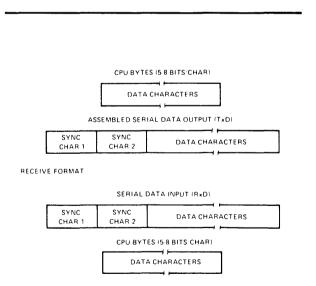

| 3-3 USART Synchronous Mode Transmission                                                                                                                                                                                                                                                                                                                                                                              | 3-3        | USART Synchronous Mode Transmission                                        |

| Format 3-4                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                                            |

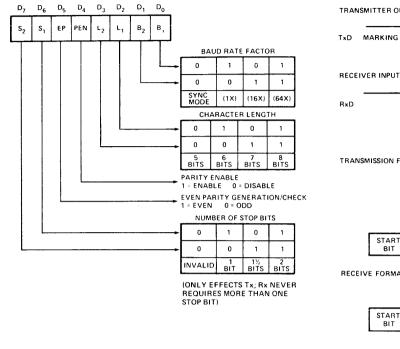

| 3-4 USART Asynchronous Mode Instruction                                                                                                                                                                                                                                                                                                                                                                              | 3-4        |                                                                            |

| Word Format                                                                                                                                                                                                                                                                                                                                                                                                          | 2.5        |                                                                            |

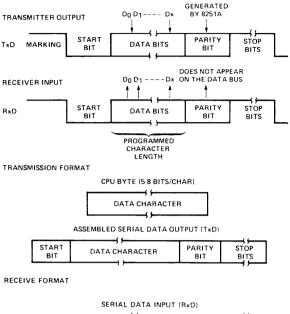

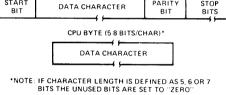

| 3-5 USART Asynchronous Mode Transmission                                                                                                                                                                                                                                                                                                                                                                             | 3-3        |                                                                            |

| Format                                                                                                                                                                                                                                                                                                                                                                                                               | 3-6        |                                                                            |

| Word Format                                                                                                                                                                                                                                                                                                                                                                                                          | 5-0        |                                                                            |

| 3-7 Typical USART Initialization and                                                                                                                                                                                                                                                                                                                                                                                 | 3-7        |                                                                            |

| I/O Data Sequence                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                                            |

| 3-8 USART Status Read Format 3-9                                                                                                                                                                                                                                                                                                                                                                                     | 3-8        | USART Status Read Format 3-9                                               |

| 3-9 PIT Mode Control Word Format 3-10                                                                                                                                                                                                                                                                                                                                                                                | 3-9        | PIT Mode Control Word Format 3-10                                          |

| 3-10 PIT Programming Sequence Examples 3-11                                                                                                                                                                                                                                                                                                                                                                          | 3-10       | PIT Programming Sequence Examples 3-11                                     |

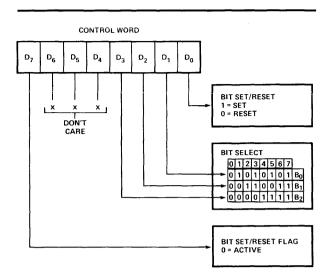

| FIGUR | E TITLE                               | PAGE   |

|-------|---------------------------------------|--------|

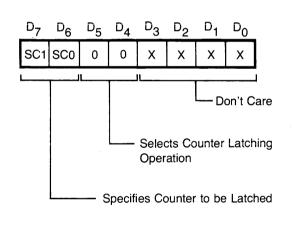

| 3-11  | PIT Counter Register Latch Control    |        |

|       | Word Format                           |        |

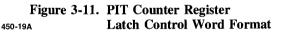

| 3-12  | PPI Control Word Format               | . 3-15 |

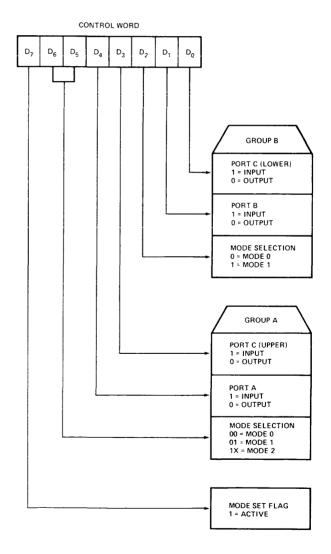

| 3-13  | PPI Port C Bit Set/Reset Control      |        |

|       | Word Format                           | . 3-17 |

| 3-14  | PIC Initialization Command            |        |

|       | Word Formats                          | . 3-18 |

| 3-15  | PIC Operation Control Word Formats    | . 3-20 |

| 4-1   | iSBC 86/12 Input/Output and Interrupt |        |

|       | Simplified Logic Diagram              |        |

| 4-2   | iSBC 86/12 ROM/EPROM and Dual Port RA | AM     |

|       | Simplified Logic Diagram              | . 4-17 |

| 4-3   | Internal Bus Structure                | 4-3    |

| 4-4   | CPU Read Timing                       | 4-5    |

| 4-5   | CPU Write Timing                      | 4-6    |

| 4-6   | CPU Interrupt Acknowledge             |        |

|       | Cycle Timing                          | 4-7    |

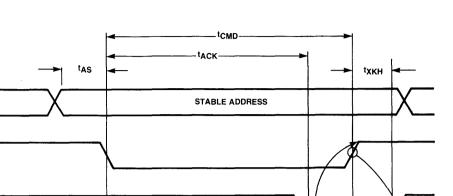

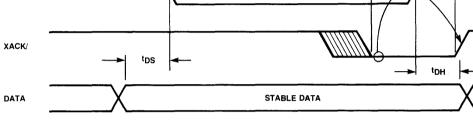

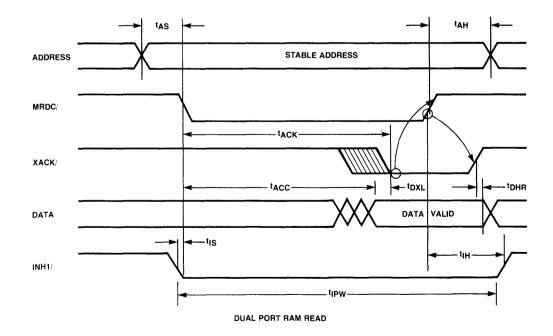

| 4-7   | Dual Port Control Multibus Access     |        |

|       | Timing With CPU Lockout               | 4-9    |

| 4-8   | Dual Port Control CPU Access Timing   |        |

|       | With Multibus Lockout                 | . 4-10 |

| 5-1   | iSBC 86/12 Parts Location Diagram     | 5-6    |

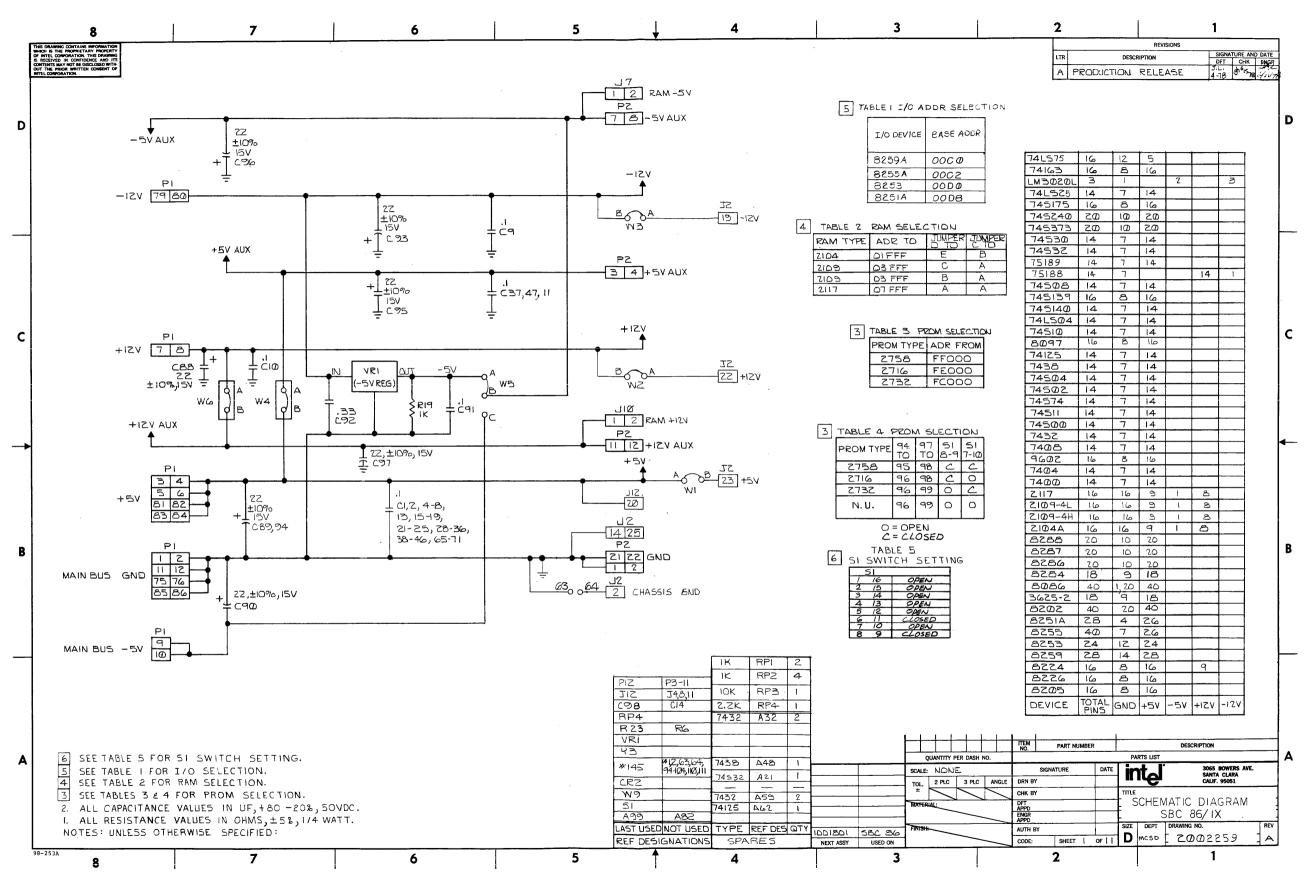

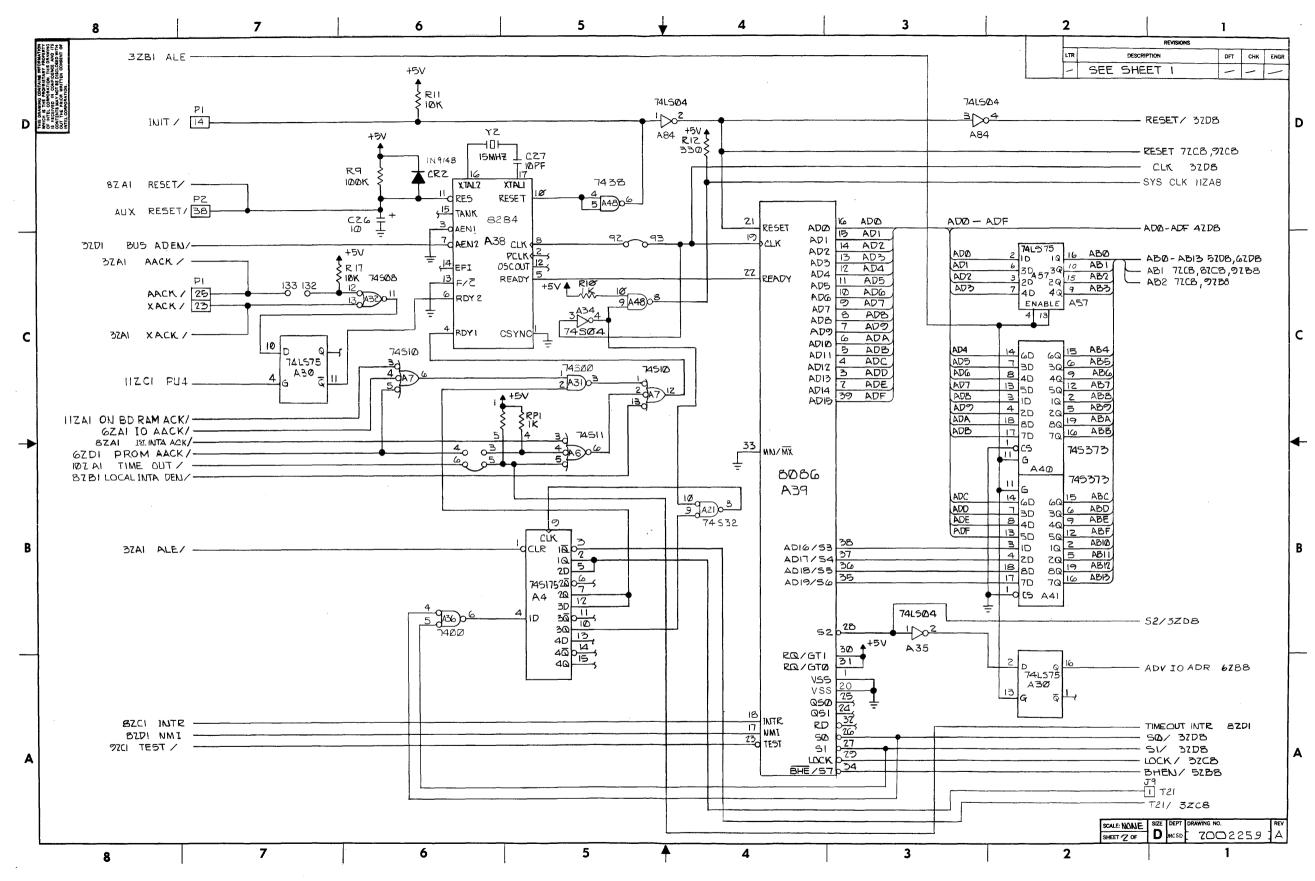

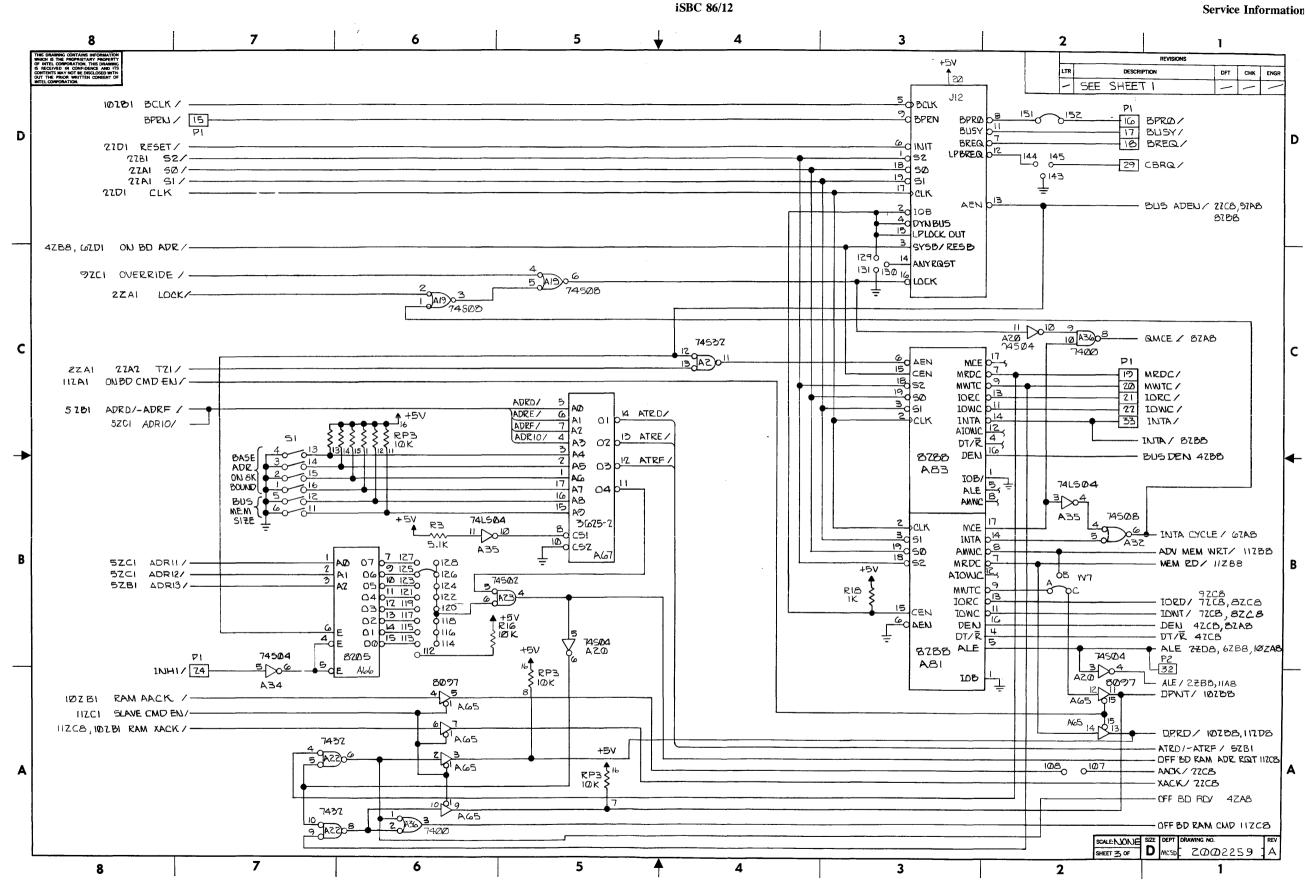

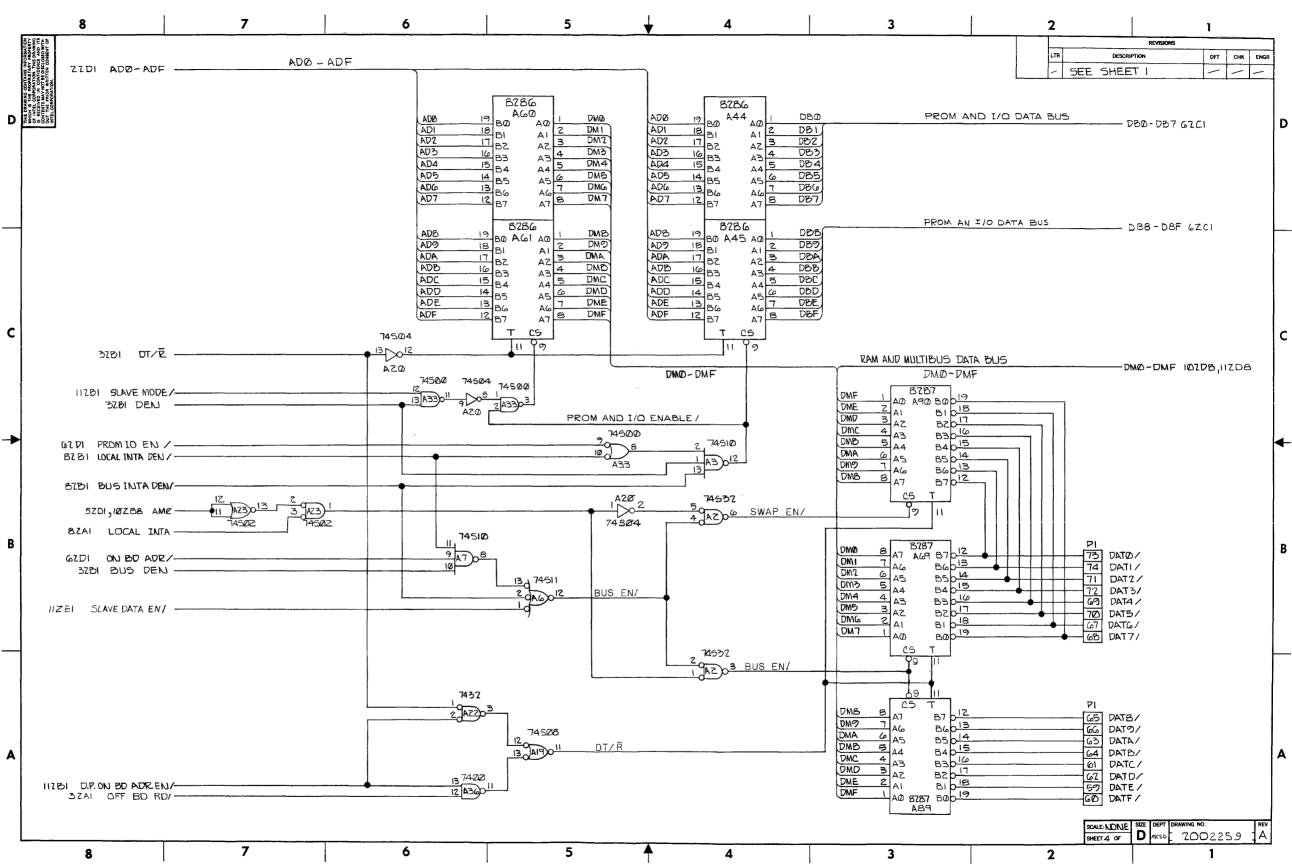

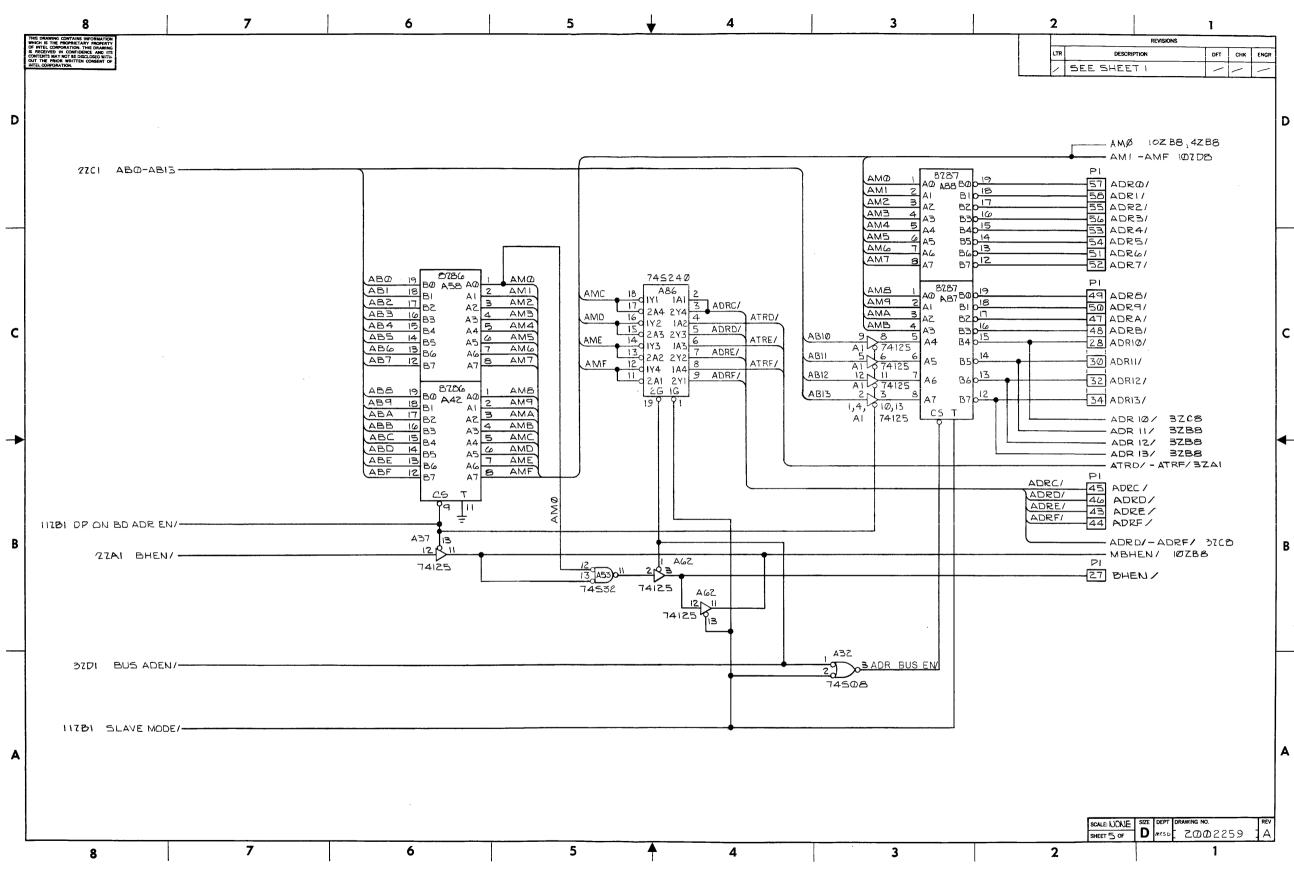

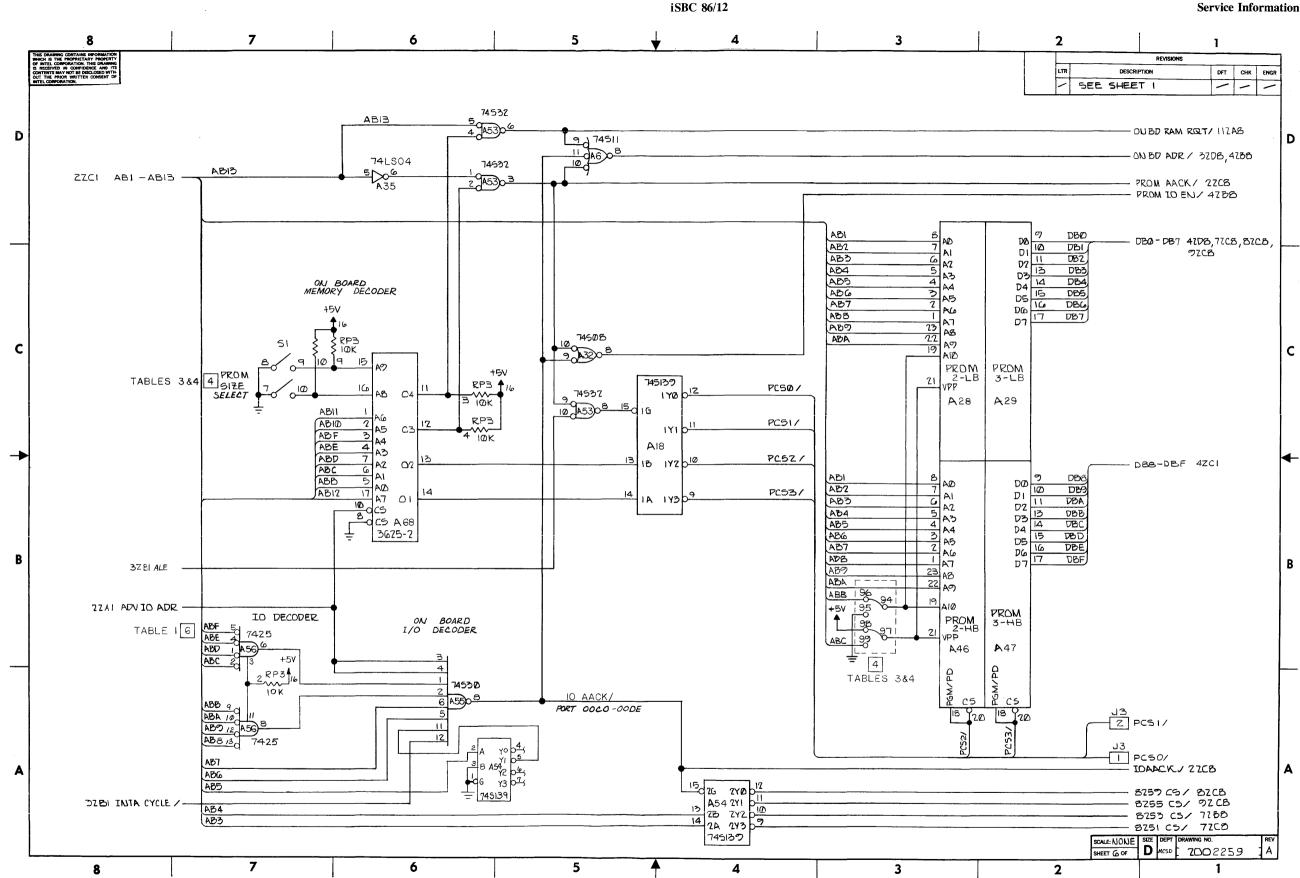

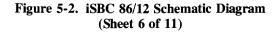

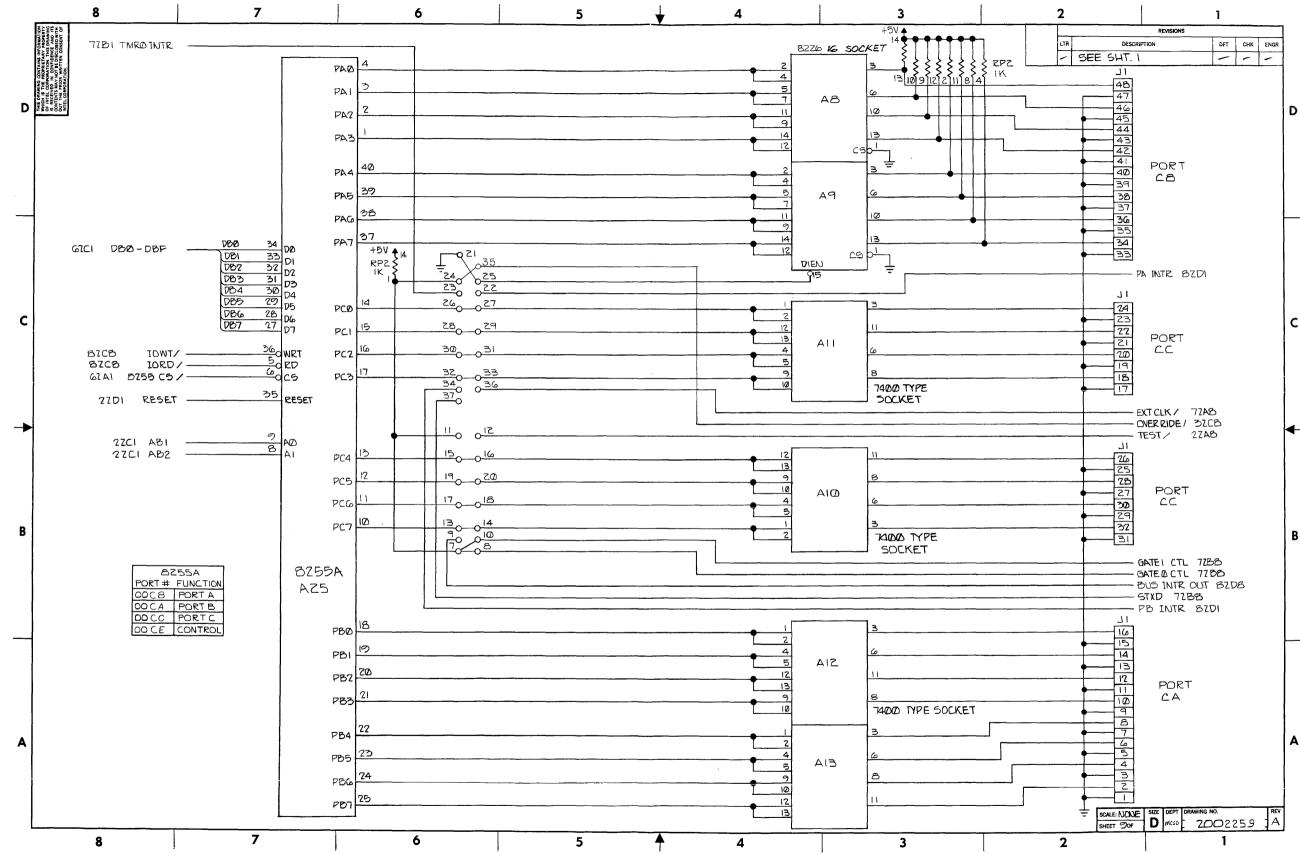

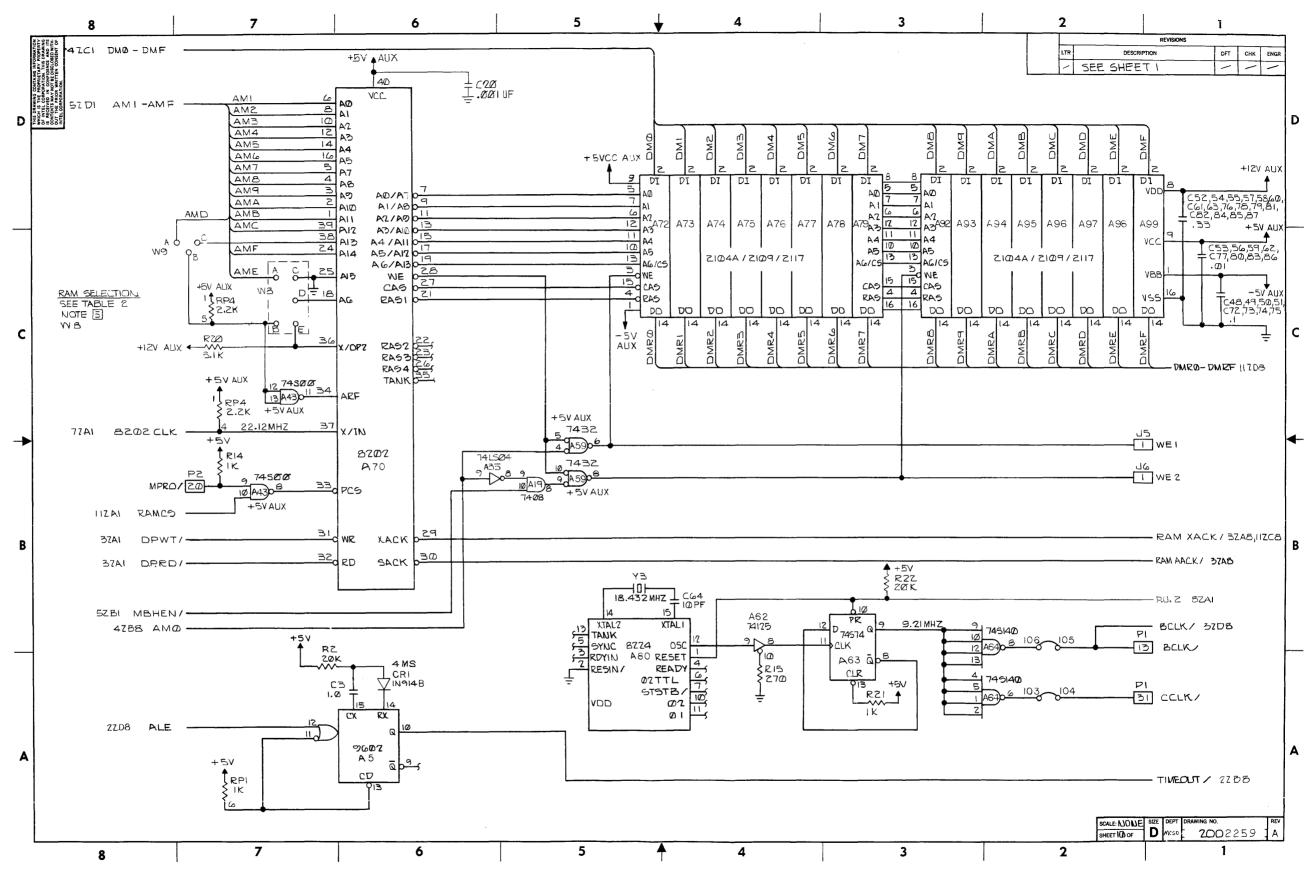

| 5-2   | iSBC 86/12 Schematic Diagram          |        |

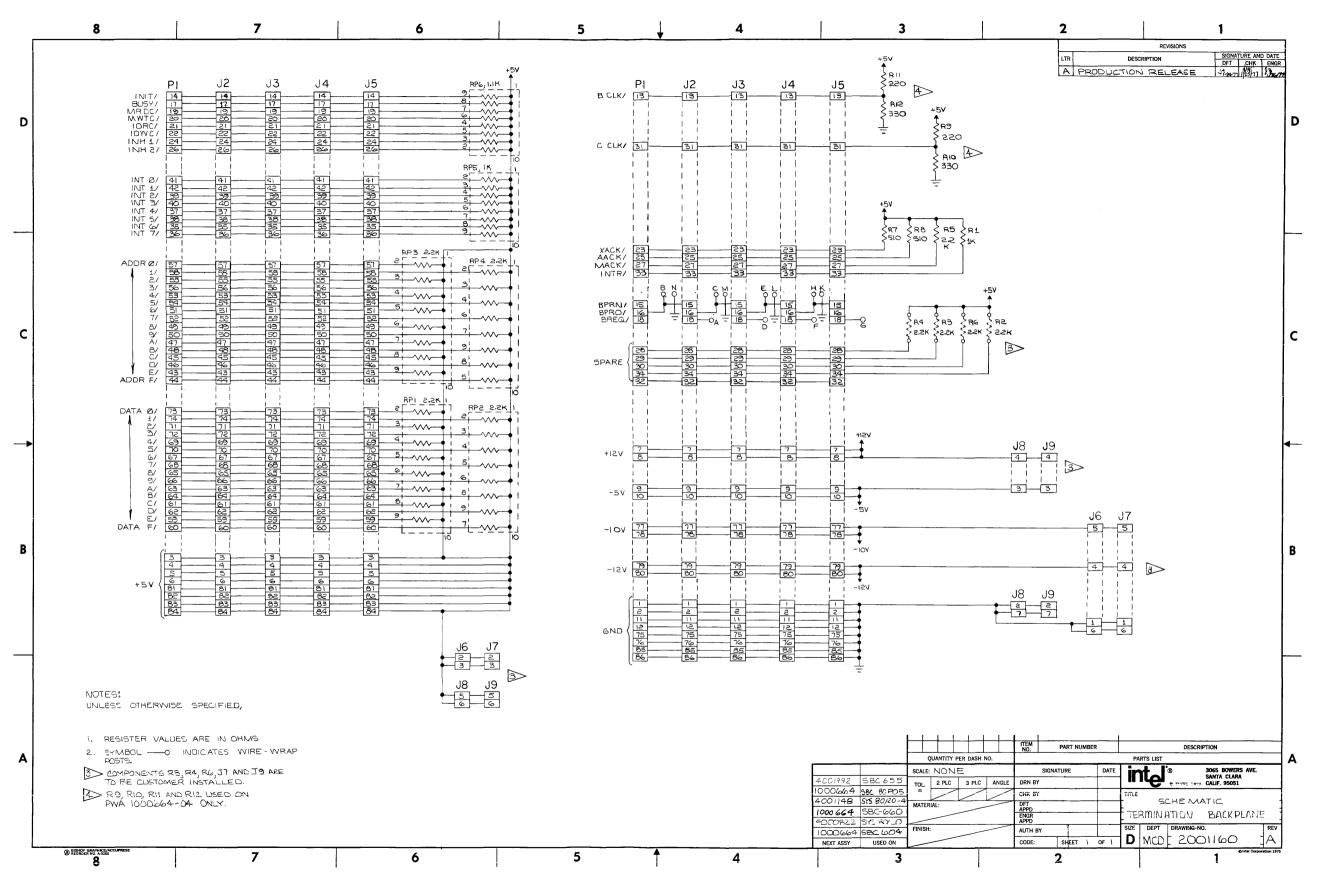

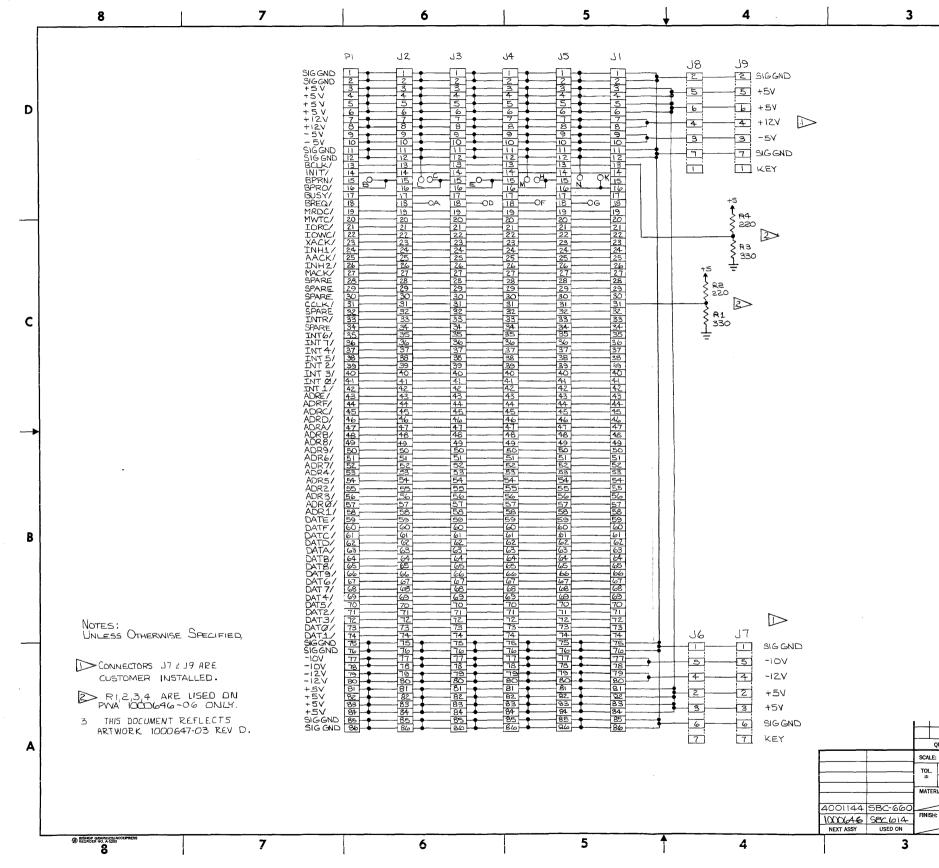

| 5-3   | iSBC 604 Schematic Diagram            | . 5-29 |

| 5-4   | iSBC 614 Schematic Diagram            | . 5-31 |

# CHAPTER 1 GENERAL INFORMATION

# **1-1. INTRODUCTION**

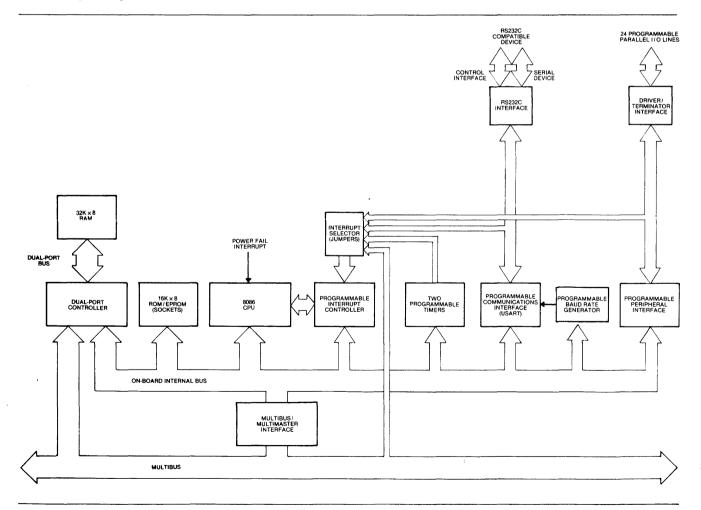

The iSBC 86/12 Single Board Computer, which is a member of Intel's complete line of iSBC 80/86 computer products, is a complete computer system on a single printed-circuit assembly. The iSBC 86/12 includes a 16-bit central processing unit (CPU), 32K bytes of dynamic RAM, a serial communications interface, three programmable parallel I/O ports, programmable timers, priority interrupt control, Multibus control logic, and bus expansion drivers for interface with other Multibus-compatible expansion boards. Also included is dual port control logic to allow the iSBC 86/12 to act as a slave RAM device to other Multibus masters in the system. Provision is made for user installation of up to 16K bytes of read only memory.

# **1-2. DESCRIPTION**

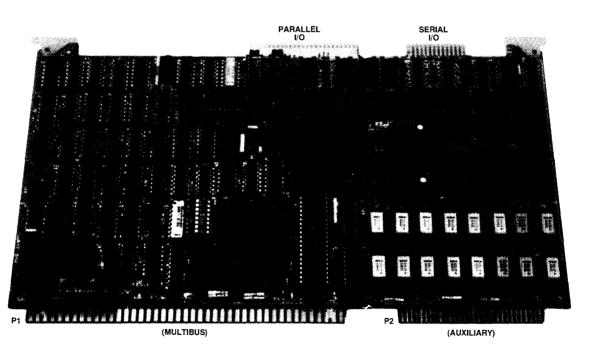

645-1

The iSBC 86/12 Single Board Computer (figure 1-1) is controlled by an Intel 8086 16-Bit Microprocessor (CPU). The 8086 CPU includes four 16-bit general purpose registers that may also be addressed as eight 8-bit registers. In addition, the CPU contains two 16-bit pointer registers and two 16-bit index registers. Four 16-bit segment registers allow extended addressing to a full megabyte of memory. The CPU instruction set supports a wide range of addressing modes and data transfer operations, signed and unsigned 8-bit and 16-bit arithmetic including hardware multiply and divide, and logical and string operations. The CPU architecture features dynamic code relocation, reentrant code, and instruction lookahead.

The iSBC 86/12 has an internal bus for all on-board memory and I/O operations and accesses the system bus (Multibus) for all external memory and I/O operations. Hence, local (on-board) operations do not involve the Multibus, making the Multibus available for true parallel processing when several bus masters (e.g., DMA devices and other single board computers) are used in a multimaster scheme.

Dual port control logic is included to interface the dynamic RAM with the Multibus so that the iSBC 86/12 can function as a slave RAM device when not in control of the Multibus. The CPU has priority when accessing onboard RAM. After the CPU completes its read or write

operation, the controlling bus master is allowed to access RAM and complete its operation. Where both the CPU and the controlling bus master have the need to write or read several bytes or words to or from on-board RAM, their operations are interleaved. For CPU access, the on-board RAM addresses are assigned from the bottom up of the 1-megabyte address space; i.e., 00000-07FFF<sub>H</sub>. The slave RAM address decode logic includes jumpers and switchers to allow partitioning the on-based RAM into any 128K segment of the 1-megabyte system address space.

The slave RAM can be configured to allow either 8K, 16K 24K, or 32K access by another bus master. Thus, the RAM can be configured to allow other bus masters to access a segment of the on-board RAM and still reserve another segment strictly for on-board use. The addressing scheme accommodates both 16-bit and 20-bit addressing.

Four IC sockets are included to accommodate up to 16K bytes of user-installed read only memory. Configuration jumpers allow read only memory to be installed in 2K, 4K, or 8K increments.

The iSBC 86/12 includes 24 programmable parallel I/O lines implemented by means of an Intel 8255A Programmable Peripheral Interface (PPI). The system software is used to configure the I/O lines in any combination of unidirectional input/output and bidirectional ports. The I/O interface may be customized to meet specific peripheral requirements and, in order to take full advantage of the large number of possible I/O configurations, IC sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the parallel I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 24-programmable I/O lines and signal ground lines are brought out to a 50-pin edge connector (JI) that mates with flat, woven, or round cable.

The RS232C compatible serial I/O port is controlled and interfaced by an Intel 8251A USART (Universal Syncronous/Asynchronous Receiver/Transmitter) chip. The USART is individually programmable for operation in most synchronous or asynchronous serial data transmission formats (including IBM Bi-Sync).

In the synchronous mode the following are programmable:

- a. Character length,

- b. Sync character (or characters), and

- c. Parity.

In the asynchronous mode the following are programmable:

- a. Character length,

- b. Baud rate factor (clock divide ratios of 1, 16, or 64),

- c. Stop bits, and

- d. Parity.

In both the synchronous and asychronous modes, the serial I/O port features half- or full-duplex, double buffered transmit and receive capability. In addition, USART error detection circuits can check for parity, overrun, and framing errors. The USART transmit and receive clock rates are supplied by a programmable baud rate/time generator. These clocks may optionally be supplied from an external source. The RS232C command lines, serial data lines, and signal ground lines are brought out to a 50-pin edge connector (J2) that mates with flat or round cable.

Three independent, fully programmable 16-bit interval timer/event counters are provided by an Intel 8253 Programmable Interval Timer (PIT). Each counter is capable of operating in either BCD or binary modes; two of these counters are available to the systems designer to generate accurate time intervals under software control. Routing for the outputs and gate /trigger inputs of two of these counters may be independently routed to the 8259A Programmable Interrupt Controller (PIC). The gate/trigger inputs of the two counters may be routed to I/O terminators associated with the 8255A PPI or as input connections from the 8255A PPI. The third counter is used as a programmable baud rate generator for the serial I/O port. In utilizing the iSBC 86/12, the systems designer simply configures, via software, each counter independently to meet system requirements. Whenever a given time delay or count is needed, software commands to the 8253 PIT select the desired function. The contents of each counter may be read at any time during system operation with simple operations for event counting applications, and special commands are included so that the contents of each counter can be read "on the fly".

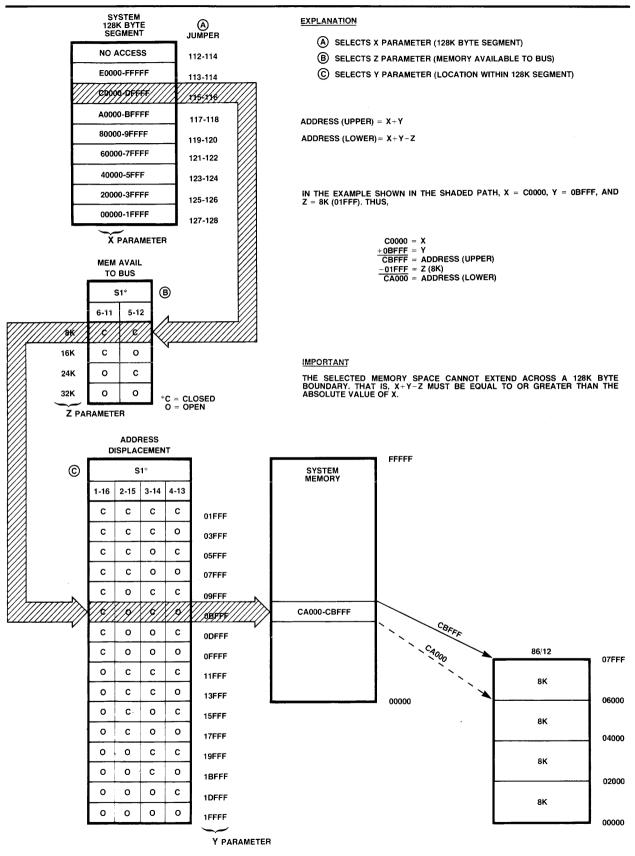

The iSBC 86/12 provides vectoring for bus vectored (BV) and non-bus vectored (NBV) interrupts. An on-board Intel 8259A Programmable Interrupt Controller (PIC) handles up to eight NBV interrupts. By using external PIC's slaved to the on-board PIC (master), the interrupt structure can be expanded to handle and resolve the priority of up to 64 BV sources.

The PIC, which can be programmed to respond to edgesensitive or level-sensitive inputs, treats each true input signal condition as an interrupt request. After resolving the interrupt priority, the PIC issues a single interrupt request to the CPU. Interrupt priorities are independently programmable under software control. The programmable interrupt priority modes are:

- a. Fully Nested Priority. Each interrupt request has a fixed priority: input 0 is highest, input 7 is lowest.

- b. Auto-Rotating Priority. Each interrupt request has equal priority. Each level, after receiving service, becomes the lowest priority level until the next interrupt occurs.

- c. Specific priority. Software assigns lowest priority. Priority of all other levels is in numerical sequence based on lowest priority.

The CPU includes a non-maskable interrupt (NMI) and a maskable interrupt (INTR). The NMI interrupt is intended to be used for catastrophic events such as power outages that require immediate action of the CPU. The INTR interrupt is driven by the 8259A PIC which, on demand, provides an 8-bit identifier of the interrupting source. The CPU multiplies the 8-bit identifier by four to derive a pointer to the service routine for the interrupting device.

Interrupt requests may originate from 18 sources without the necessity of external hardware. Two jumperselectable interrupt requests can be automatically generated by the Programmable Peripheral Interface (PPI) when a byte of information is ready to be transferred to the 8086 CPU (i.e., input buffer is full) or a byte of information has been transferred to a peripheral device (i.e., output buffer is empty). Two jumper-selectable interrupt requests can be automatically generated by the USART when a character is ready to be transferred to the 8086 CPU (i.e., receive channel buffer is full) or when a character is ready to be transmitted (i.e., transmit channel data buffer is empty.) A jumper-selectable interrupt request can be generated by two of the programmable counters and eight additional interrupt request lines are available to the user for direct interfaces to user-designated peripheral devices via the Multibus. One interrupt request line may be jumper routed directly from a peripheral via the parallel I/O driver/terminator section and one power fail interrupt may be input via auxiliary connector P2.

The iSBC 86/12 includes the resources for supporting a variety of OEM system requirements. For those applications requiring additional processing capacity and the benefits of multiprocessing (i.e., several CPU's and/or controllers logically sharing systems tasks with communication over the Multibus), the iSBC 86/12 provides full bus arbitration control logic. This control logic allows up to three bus masters (e.g., combination of iSBC 86/12 DMA controller, diskette controller, etc.) to share the Multibus in serial (daisy-chain) fashion or up to 16 bus masters to share the Multibus using an external parallel priority resolving network.

The Multibus arbitration logic operates synchronously with the bus clock, which is derived either from the iSBC 86/12 or can be optionally generated by some other bus master. Data, however, is transferred via a handshake between the controlling master and the addressed slave module. This arrangement allows different speed controllers to share resources on the same bus, and transfers via the bus proceed asynchronously. Thus, the transfer speed is dependent on transmitting and receiving devices only. This design prevents slower master modules from being handicapped in their attempts to gain control of the bus, but does not restrict the speed at which faster modules can transfer data via the same bus. The most obvious applications for the master-slave capabilities of the bus are multiprocessor configurations, high-speed direct memory access (DMA) operations, and high-speed peripheral control, but are by no means limited to these three.

## 1-3. SYSTEM SOFTWARE DEVELOPMENT

The development cycle of iSBC 86/12 based products may be significantly reduced using an Intel Intellec Microcomputer Development System. The resident text editor and system monitor greatly simplify the design, development, and debug of iSBC system software. An optional diskette operating system provides a relocating loader and linkage editor, and a library manager.

Intel's high level programming language, PL/M 86, is also available as a resident Intellec Microcomputer Development System option. PL/M 86 provides the capability to program in a natural, algorithmic language and eliminates the need to manage register usage or allocate memory. PL/M 86 programs can be written in a much shorter time than assembly language programs for a given application.

# **1-4. EQUIPMENT SUPPLIED**

The following are supplied with the iSBC 86/12 Single Board Computer:

- a. Schematic diagram, dwg no. 2002259

- b. Assembly drawing, dwg no. 1001801

# **1-5. EQUIPMENT REQUIRED**

Because the iSBC 86/12 is designed to satisfy a variety of applications, the user must purchase and install only those components required to satisfy his particular needs. A list of components required to configure all the intended applications of the iSBC 86/12 is provided in table 2-1.

# **1-6. SPECIFICATIONS**

Specifications of the iSBC 86/12 Single Board Computer are listed in table 1-1.

| WORD SIZE                                |                                                                                                                                                                                                                                                            |                                                    |                                                          |                                              |  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|----------------------------------------------|--|

| Instruction:<br>Data                     | 8, 16, 24, or 32 bits.<br>8/16 bits.                                                                                                                                                                                                                       |                                                    |                                                          |                                              |  |

| CYCLE TIME:                              | 800 nanosecond for fastest executable instruction (assumes instruction is in the queue).<br>1.2 microseconds for fastest executable instruction (assumes instruction is not in the queue).<br>queue).                                                      |                                                    |                                                          |                                              |  |

| MEMORY CAPACITY<br>On-Board ROM/EPROM:   | Up to 16K bytes; user installed in                                                                                                                                                                                                                         | 1K, 2K, or 4K byte inc                             | rements.                                                 |                                              |  |

| On-Board Dynamic RAM:                    | 32K bytes. Integrity maintained du                                                                                                                                                                                                                         | ring power failure with                            | user-furnish                                             | ed batteries.                                |  |

| Off-Board Expansion:                     | Up to 1 megabyte of user-specified                                                                                                                                                                                                                         | d combination of RAM                               | , ROM, and I                                             | EPROM.                                       |  |

| MEMORY ADDRESSING<br>On-Board ROM/EPROM: | FF000-FFFFF <sub>H</sub> (using 2758 EPRC<br>FE000-FFFFF <sub>H</sub> (using 2316E ROM<br>FC000-FFFFF <sub>H</sub> (using 2332 ROM)                                                                                                                        | I's or 2716 EPROM's                                | s), and                                                  |                                              |  |

| On-Board RAM:<br>(CPU Access)            | 00000-07FFF <sub>H</sub> .                                                                                                                                                                                                                                 |                                                    |                                                          |                                              |  |

| On-Board RAM:<br>(Multibus Access)       | Jumpers and switches allow board to act as slave RAM device for access by another bus master. Addresses may be set within any 8K boundary of any 128K segment of the 1-megabyte system address space. Access is selectable for 8K, 16K, 24K, or 32K bytes. |                                                    |                                                          |                                              |  |

| SERIAL COMMUNICATIONS<br>Synchronous:    | 5-, 6-, 7-, or 8-bit characters.<br>Intemal; 1 or 2 sync characters.<br>Automatic sync insertion.                                                                                                                                                          |                                                    |                                                          |                                              |  |

| Asynchronous:                            | 5-, 6-, 7-, or 8-bit characters.<br>Break character generation.<br>1, $1\frac{1}{2}$ , or 2 stop bits.<br>False start bit detection.                                                                                                                       |                                                    |                                                          |                                              |  |

| Sample Baud Rate:                        |                                                                                                                                                                                                                                                            | Baud F                                             | Rate (Hz) <sup>2</sup>                                   |                                              |  |

|                                          | Frequency <sup>1</sup><br>(kHz, Software Selectable)                                                                                                                                                                                                       | Synchronous                                        | Asynch                                                   | ironous                                      |  |

|                                          |                                                                                                                                                                                                                                                            |                                                    | ÷16                                                      | ÷64                                          |  |

|                                          | 153.6<br>76.8<br>38.4<br>19.2<br>9.6<br>4.8<br>2.4<br>1.76                                                                                                                                                                                                 |                                                    | 9600<br>4800<br>2400<br>1200<br>600<br>300<br>150<br>110 | 2400<br>1200<br>600<br>300<br>150<br>75<br>— |  |

|                                          | Notes: 1. Frequency selected by I/0<br>Baud Rate Register.                                                                                                                                                                                                 | C writes of appropriate                            | 16-bit freque                                            | ncy factor to                                |  |

|                                          | <ol> <li>Baud rates shown here a<br/>programmable rates avai<br/>may be generated utilizin<br/>mable Interval Timer (us)</li> </ol>                                                                                                                        | lable. Any frequency fr<br>g on-board crystal osci | om 18.75 Hz 1<br>Ilator and 16-                          | to 613.5 kHz                                 |  |

| INTERVAL TIMER AND BAUD RATE<br>GENERATOR<br>Input Frequency (selectable): | 2.46 MHz ±0.1%<br>1.23 MHz ±0.1%<br>153.6 kHz ±0.1%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (0.82 µsec pe   | eriod nominal), ar | nd                                      |                                         |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|-----------------------------------------|-----------------------------------------|

| Output Frequencies:                                                        | Function Single Timer Dual Timers (Two Timers Cascaded)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                    |                                         |                                         |

|                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Min.            | Max.               | Min.                                    | Max.                                    |

|                                                                            | Real-Time<br>Interrupt<br>Interval                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.63 μsec       | 427.1 msec         | 3.26 µsec                               | 466.5<br>minutes                        |

|                                                                            | Rate<br>Generator<br>(Frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.342 Hz        | 613.5 kHz          | 0.000036 Hz                             | 306.8 kHz                               |

| SYSTEM CLOCK (8086 CPU):                                                   | 5.0 MHz ±0.1%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                    |                                         |                                         |

| I/O ADDRESSING:                                                            | All communication is via read and w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                    |                                         | nterrupt Controller<br>r to table 3-2.  |

| INTERFACE COMPATIBILITY<br>Serial I/O:                                     | EIA Standard RS232C signals provided and supported:<br>Clear to Send Receive Data<br>Data Set Ready Secondary Receive Data*<br>Data Terminal Ready Secondary CTS*<br>Request to Send Transmit Clock*<br>Receive Clock Transmit Data<br>*Can support only one.                                                                                                                                                                                                                                                                                    |                 |                    |                                         |                                         |

| Parallel I/O:                                                              | 24 programmable<br>IC sockets includ<br>required for interf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | led for user in | stallation of line | rt includes bidire<br>drivers and/or l, | ctional bus driver.<br>O terminators as |

| INTERRUPTS:                                                                | 8086 CPU includes non-maskable interrupt (NMI) and maskable interrupt (INTR).<br>NMI interrupt is provided for catastrophic event such as power failure; NMI vector<br>address is 00008. INTR interrupt is driven by on-board 8259A PIC, which provides<br>8-bit identifier of interrupting device to CPU. CPU multiplies identifier by four to derive<br>vector address. Jumpers select interrupts from 18 sources without necessity of<br>external hardware. PIC may be programmed to accommodate edge-sensitive or<br>level-sensitive inputs. |                 |                    |                                         |                                         |

| COMPATIBLE CONNECTORS/CABLES:                                              | S: Refer to table 2-2 for compatible connector details. Refer to paragraphs 2-21 and 2-22 for recommended types and lengths of I/O cables.                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                    |                                         |                                         |

| ENVIRONMENTAL REQUIREMENTS<br>Operating Temperature:                       | 0° to 55°C (32° to 131°F).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                    |                                         |                                         |

| Relative Humidity:                                                         | To 90% without o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ondensation.    |                    |                                         |                                         |

| PHYSICAL CHARACTERISTICS<br>Width:<br>Height:<br>Thickness:<br>Weight:     | 30.48 cm (12.00<br>17.15 cm (6.75 ir<br>1.78 cm (0.7 inch<br>539 gm (19 ounc                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iches).<br>i).  |                    |                                         |                                         |

| Table 1-1. Specifications (Contin | nued) |

|-----------------------------------|-------|

|-----------------------------------|-------|

| CONFIGURATION                  | $V_{CC} = +5V \pm 5\%$ | $V_{DD} = +12V \pm 5\%$ | $V_{BB} = -5V \pm 5\%$ | $V_{AA} = -12V \pm 5\%$ |

|--------------------------------|------------------------|-------------------------|------------------------|-------------------------|

| Without EPROM <sup>1</sup>     | 5.2A                   | 350 mA                  |                        | 40 mA                   |

| RAM Only <sup>3</sup>          | 390 mA                 | 40 mA                   | 1.0 mA                 | —                       |

| With iSBC 5304                 | 5.2A                   | 450 mA                  | _                      | 140 mA                  |

| With 4K EPROM⁵<br>(Using 2758) | 5.5A                   | 450 mA                  | _                      | 140 mA                  |

| With 8K ROM⁵<br>(Using 2316E)  | 6.1A                   | 450 mA                  |                        | 140 mA                  |

| With 8K EPROM⁵<br>(Using 2716) | 5.5A                   | 450 mA                  |                        | 140 mA                  |

| With 16K ROM⁵<br>(Ųsing 2332)  | 5.4A                   | 450 mA                  | ·                      | 140 mA                  |

#### Table 1-1. Specifications (Continued)

Notes: 1. Does not include power for optional ROM/EPROM, I/O drivers, and I/O terminators.

2. Does not include power required for optional ROM/EPROM, I/O drivers, and I/O terminators.

3. RAM chips powered via auxiliary power bus.

4. Does not include power for optional ROM/EPROM, I/O drivers, and I/O terminators. Power for iSBC 530 is supplied via serial port connector.

5. Includes power required for four ROM/EPROM chips, and I/O terminators installed for16 I/O lines; all terminator inputs low.

# CHAPTER 2 PREPARATION FOR USE

# **2-1. INTRODUCTION**

This chapter provides instructions for the iSBC 86/12 Single Board Computer in the user-defined environment. It is advisable that the contents of Chapters 1 and 3 be fully understood before beginning the configuration and installation procedures provided in this chapter.

# 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, contact the Intel Technical Support Center (see paragraph 5-3) to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be reshipped.

# 2-3. INSTALLATION CONSIDERATIONS

The iSBC 86/12 is designed for use in one of the following configurations:

- a. Standalone (single-board) system.

- b. Bus master in a single bus master system.

- c. Bus master in a multiple bus master system.

Important criteria for installing and interfacing the iSBC 86/12 in these configurations are presented in following paragraphs.

## 2-4. USER-FURNISHED COMPONENTS

The user-furnished components required to configure the iSBC 86/12 for a particular application are listed in table 2-1. Various types and vendors of the connectors specified in table 2-1 are listed in table 2-2.

#### **2-5. POWER REQUIREMENT**

The iSBC 86/12 requires +5V, -5V, +12V, and -12V power. The -5V power, which is required only for the dual port RAM, can be supplied by the system -5V supply, an auxiliary battery, or by the on-board -5V regulator. (The -5V regulator operates from the system -12V supply.)

## 2-6. COOLING REQUIREMENT

The iSBC 86/12 dissipates 451 gram-calories/minute (1.83 Btu/minute) and adequate circulation of air must be provided to prevent a temperature rise above  $55^{\circ}$ C (131°F). The System 80 enclosures and the Intellec System include fans to provide adequate intake and exhaust of ventilating air.

## **2-7. PHYSICAL DIMENSIONS**

Physical dimensions of the iSBC 86/12 are as follows:

- a. Width: 30.48 cm (12.00 inches).

- b. Height: 17.15 cm (6.75 inches).

- c. Thickness: 1.78 cm (0.70 inch).

# 2-8. COMPONENT INSTALLATION

Instructions for installing optional ROM/EPROM and parallel I/O port line drivers and/or line terminators are given in following paragraphs. When installing these chip components, be sure to orient pin 1 of the chip adjacent to the white dot located near pin 1 of the associated IC socket. The grid zone location on figure 5-1 (parts location diagram) is specified for each component chip to be installed.

## 2-9. ROM/EPROM CHIPS

IC sockets A28, A29, A46, and A47 (figure 5-1 zone C3) accommodate 24-pin ROM/EPROM chips. Because the CPU jumps to location FFFF0 on a power up or reset, the ROM/EPROM address space resides in the topmost portion of the 1-megabyte address space and must be loaded from the top down. IC sockets A29 and A47 accommodate the top of the ROM/EPROM address space and must always be loaded; IC sockets A28 and A46 accommodate the ROM/EPROM space directly below that installed in A29 and A47.

| ltem<br>No. | ltem                         | Descri                                                                                                                                                         | otion                                   | Use                                                                                                                                    |  |  |

|-------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

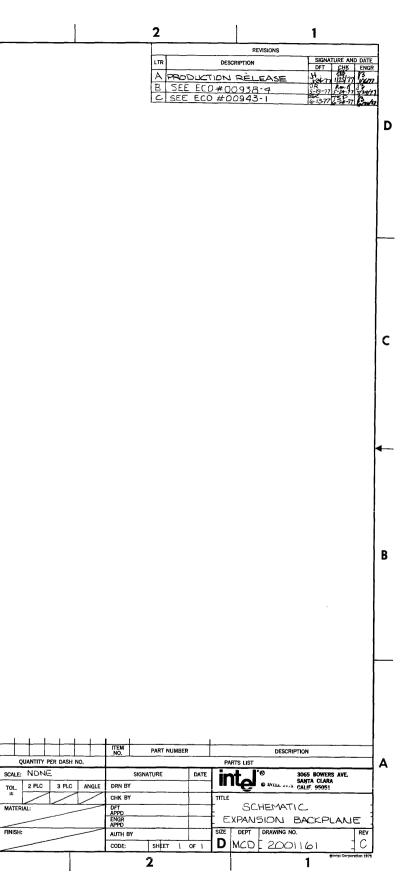

| 1           | iSBC 604                     | Modular Backplane<br>cludes four slots wit<br>(See figure 5-3.)                                                                                                | and Cardcage. In-<br>h bus terminators. | Provides power input pins and Multibus signal interface between iSBC 86/12 and three additional boards in a multiple board system.     |  |  |

| 2           | iSBC 614                     | Modular Backplane<br>cludes four slots witho<br>(See figure 5-4.)                                                                                              |                                         | Provides four-slot extension of iSBC 604.                                                                                              |  |  |

| 3           | Connector<br>(mates with P1) | See Multibus Con<br>table 2-2.                                                                                                                                 | nector details in                       | Power inputs and Multibus signal inter-<br>face. Not required if iSBC 86/12 is in-<br>stalled in an iSBC 604/614.                      |  |  |

| 4           | Connector<br>(mates with P2) | See Auxiliary Con<br>table 2-2.                                                                                                                                | nector details in                       | Auxiliary backup battery and asso-<br>ciated memory protect functions.                                                                 |  |  |

| 5           | Connector<br>(mates with J1) | See Parallel I/O Co<br>table 2-2.                                                                                                                              | nnector details in                      | Interfaces parallel I/O port with Intel 8255A<br>PPI.                                                                                  |  |  |

| 6           | Connector<br>(mates with J2) | See Serial I/O connector details in table 2-2.                                                                                                                 |                                         | Interfaces serial I/O port with Intel 8251A<br>USART.                                                                                  |  |  |

| 7           | ROM/EPROM Chips              | Two or four each of the following types:<br><u>ROM</u> or <u>EPROM</u><br><u>-</u> 2758<br>2316E 2716<br>2332 <u>-</u>                                         |                                         | Ultraviolet Erasable PROM (EPROM) for development. Masked ROM for dedi-<br>cated program.                                              |  |  |

| 8           | Line Drivers                 | TypeCurrentSN7403 I, OC16 mASN7400 I16 mASN7408 NI16 mASN7409 NI, OC16 mATypes selected as typical; I = inverting, NI = noninverting, and OC = open collector. |                                         | Interface parallel I/O ports CA and CC with<br>Intel 8255A PPI. Requires two line driver<br>IC's for each 8-bit parallel output port.  |  |  |

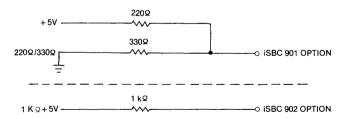

| 9           | Line Terminators             | Intel iSBC 901 Divider or iSBC 902<br>Pull-Up:<br>iSBC 901<br>330<br>iSBC 902<br>iSBC 902<br>iSBC 902<br>iSBC 902<br>iSBC 902                                  |                                         | Interface parallel I/O ports CA and CC with<br>Intel 8255A PPI. Requires two 901's or two<br>902's for each 8-bit parallel input port. |  |  |

| Table 2-1. | <b>User-Furnished</b> | and Installed | Components |

|------------|-----------------------|---------------|------------|

|------------|-----------------------|---------------|------------|

| Function                     | No. Of<br>Pairs/<br>Pins | Centers<br>(inches) | Connector<br>Type       | Vendor                                               | Vendor Part No.                                                                   | Intel<br>Part No.        |

|------------------------------|--------------------------|---------------------|-------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------|

| Parallel<br>I/O<br>Connector | 25/50                    | 0.1                 | Flat Crimp              | 3M<br>3M<br>AMP<br>ANSLEY<br>SAE                     | 3415-0000 WITH EARS<br>3415-0001 W/O EARS<br>88083-1<br>609-5015<br>SD6750 SERIES | iSBC 956<br>Cable<br>Set |

| Parallel<br>I/O<br>Connector | 25/50                    | 0.1                 | Soldered                | AMP<br>VIKING<br>TI                                  | 2-583485-6<br>3VH25/1JV5<br>H312125                                               | N/A                      |

| Parallel<br>I/O<br>Connector | 24/50                    | 0.1                 | Wirewrap <sup>1</sup>   | TI<br>VIKING<br>CDC <sup>3</sup><br>ITT CANNON       | H311125<br>3VH25/1JND5<br>VPB01B25D00A1<br>EC4A050A1A                             | N/A                      |

| Serial<br>i/O<br>Connector   | 13/26                    | 0.1                 | Flat Crimp              | 3M<br>AMP<br>ANSLEY<br>SAE                           | 3462-0001<br>88106-1<br>609-2615<br>SD6726 SERIES                                 | iSBC 955<br>Cable<br>Set |

| Serial<br>I/O<br>Connector   | 13/26                    | 0.1                 | Soldered                | TI<br>AMP                                            | H312113<br>1-583485-5                                                             | N/A                      |

| Serial<br>I/O<br>Connector   | 13/26                    | 0.1                 | Wirewrap <sup>1</sup>   | ТІ                                                   | H311113                                                                           | N/A                      |

| Multibus<br>Connector        | 43/86                    | 0.156               | Soldered <sup>1</sup>   | CDC <sup>3</sup><br>MICRO PLASTICS<br>ARCO<br>VIKING | VPB01E43D00A1<br>MP-0156-43-BW-4<br>AE443WP1 LESS EARS<br>2VH43/1AV5              | N/A                      |

| Multibus<br>Connector        | 43/86                    | 0.156               | Wirewrap <sup>1,2</sup> | CDC <sup>3</sup><br>CDC <sup>3</sup><br>VIKING       | VFB01E43D00A1 or<br>VPB01E43A00A1<br>2VH43/1AV5                                   | MDS 985                  |

| Auxiliary<br>Connector       | 30/60                    | 0.1 .               | Soldered <sup>1</sup>   | ti<br>Viking                                         | H312130<br>3VH30/1JN5                                                             | N/A                      |

| Auxiliary<br>Connector       | 30/60                    | 0.1                 | Wirewrap <sup>1,2</sup> | CDC <sup>3</sup><br>TI                               | VPB01B30A00A2<br>H311130                                                          | N/A                      |

| Table 2-2. | <b>User-Furnished</b> | Connector | Details |

|------------|-----------------------|-----------|---------|

|            |                       |           |         |

NOTES:

Connector heights are not guaranteed to conform to OEM packaging equipment. 1.

2.

Wirewrap pin lengths are not guaranteed to conform to OEM packaging equipment. CDC VPB01 ..., VPB02 ..., VPB04 ..., etc. are identical connectors with different electroplating thicknesses or З. metal surfaces.

The low-order byte (bits 0-7) of ROM/EPROM must be installed in sockets A29 and A28; the high-order byte (bits 8-15) must be installed in sockets A47 and A46. Assuming that 2K bytes of EPROM are to be installed using two Intel 2758 chips, the chip containing the low-order byte must be installed in IC socket A29 and the chip containing the high-order byte must be installed in IC socket A47. In this configuration, the usable ROM/EPROM address space is FF800-FFFFF. Two additional Intel 2758 chips may be installed later in IC sockets A28 and A46 and occupy the address space FF000-FF7FF. (Even addresses read the low-order bytes and odd addresses read the high-order bytes.)

The default (factory connected) jumpers and switch S1 are configured for 2K by 8-bit ROM/EPROM chips (e.g., two or four Intel 2716's). If different type chips are installed, reconfigure the jumpers and switch S1 as listed in table 2-4.

#### 2-10. LINE DRIVERS AND I/O TERMINATORS

Table 2-3 lists the I/O ports and the location of associated 14-pin IC sockets for installing either line drivers or I/O terminators. (Refer to table 2-1 items 8 and 9.) Port C8 is factory equipped with Intel 8226 Bidirectional Bus Drivers and requires no additional components.

# 2-11. JUMPER/SWITCH CONFIGURATION

The iSBC 86/12 includes a variety of jumper- and switchselectable options to allow the user to configure the board for his particular application. Table 2-4 summarizes these options and lists the grid reference locations of the jumpers and switches as shown in figure 5-1 (parts location diagram) and figure 5-2 (schematic diagram). Because the schematic diagram consists of 11 sheets, grid references to figure 5-2 may be either four or five alphanumeric characters. For example, grid reference 3ZB7 signifies sheet 3 Zone B7.

Study table 2-4 carefully while making reference to figures 5-1 and 5-2. If the default (factory configured) jumpers and switch settings are appropriate for a particular function, no further action is required for that function. If, however, a different configuration is required, reconfigure the switch settings and/or remove the default jumper(s) and install an optional jumper(s) as specified. For most options, the information in table 2-4 is sufficient for proper configuration. Additional information, where necessary for clarity, is described in subsequent paragraphs.

# 2-12. RAM ADDRESSES (MULTIBUS ACCESS)

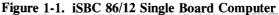

The dual port RAM can be shared with other bus masters via the Multibus. One jumper wire connected between a selected pair of jumper posts (113 through 128) places the dual port RAM in one of eight 128K byte segments of the 1-megabyte address space. Switch S1 is a dual-inline package (DIP) composed of eight individual single-pole, single-throw switches. (Two of these individual switches are used for ROM/EPROM configuration.) Two switches (6-11 and 5-12) are configured to allow 8K, 16K, 24K, or 32K bytes of dual port RAM to be accessed. Four switches (1-16, 2-15, 3-14, and 4-13) are configured to displace the addresses from the top of the selected 128K byte segment of memory.

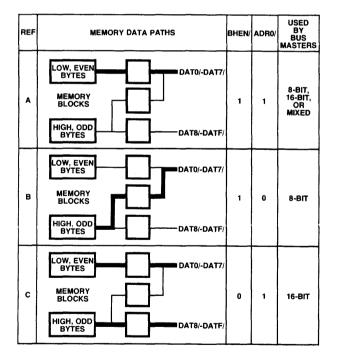

Figure 2-1 provides an example of 8K bytes of dual port RAM being made accessible from the Multibus and how the addresses are established. Note in figure 2-1 that the Multibus accesses the dual port RAM from the top down. Thus, as shown for 8K byte access via the Multibus, the bottom 24K bytes of the iSBC 86/12 on-board RAM is reserved strictly for on-board CPU access.

|              | I/O Port | Bits       | Driver/Terminator | Fig. 5-1 Grid Ref. | Fig. 5-2* Grid Ref |

|--------------|----------|------------|-------------------|--------------------|--------------------|

|              | C8       | 0-7        | None Required     | —                  |                    |

| 8255A<br>PPI | СА       | 0-3<br>4-7 | A12<br>A13        | ZD4<br>ZD4         | 9ZA3<br>9ZA3       |

| Interface    | сс       | 0-3<br>4-7 | A11<br>A10        | ZD5<br>ZD5         | 9ZC3<br>9ZB3       |

Table 2-3. Line Driver and I/O Terminator Locations

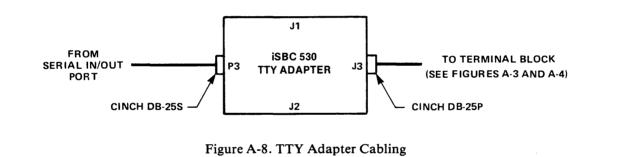

| Function                           | Fig. 5-1<br>Grid Ref. | Fig. 5-2<br>Grid Ref. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |  |  |  |  |