# SBC 519 PROGRAMMABLE I/O EXPANSION BOARD HARDWARE REFERENCE MANUAL

Manual Order Number: 9800385B

Revision B includes technical corrections (Figure 2-3, Table 4-1, and Table 7-2) and new schematics.

Copyright © 1977, 1979 Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

| ICE      | iSBC            | MULTIBUS              |

|----------|-----------------|-----------------------|

| INSITE   | LIBRARY MANAGER | PROMPT                |

| INTEL    | MCS             | RMX                   |

| INTELLEC | MEGACHASSIS     | UPI                   |

| iCS      | MICROMAP        | <b><i>u</i></b> scope |

TABLE OF CONTENTS

| CHAPTER |                                         | PAGE |  |  |  |  |  |

|---------|-----------------------------------------|------|--|--|--|--|--|

| 1       | INTRODUCTION                            | 1-1  |  |  |  |  |  |

| 2       | FUNCTIONAL/PROGRAMMING CHARACTERISTICS  | 2-1  |  |  |  |  |  |

| 2.1     | FUNCTIONAL DESCRIPTION                  | 2-1  |  |  |  |  |  |

| 2.2     | PROGRAMMING CHARACTERISTICS             | 2-4  |  |  |  |  |  |

| 2.2.1   | PARALLEL I/O INTERFACE ADDRESSES        | 2-4  |  |  |  |  |  |

| 2.2.2   | PROGRAMMABLE INTERRUPT CONTROLLER       | 2-4  |  |  |  |  |  |

| 2.2.3   | INTERVAL TIMER                          | 2-6  |  |  |  |  |  |

| 3       | THEORY OF OPERATION                     | 3-1  |  |  |  |  |  |

| 3.1     | BUS INTERFACE                           | 3-1  |  |  |  |  |  |

| 3.1.1   | BUS ADDRESS, CONTROL, DATA BUFFERS      | 3-2  |  |  |  |  |  |

| 3.1.2   | SYSTEM ADDRESS DECODE LOGIC             |      |  |  |  |  |  |

| 3.1.3   | COMMAND DECODE                          | 3-3  |  |  |  |  |  |

| 3.1.4   | ADVANCE/TRANSFER ACKNOWLEDGE GENERATION | 3-4  |  |  |  |  |  |

| 3.2     | PARALLEL I/O INTERFACE                  | 3-5  |  |  |  |  |  |

| 3.2.1   | 8255A OPERATIONAL SUMMARY               | 3-6  |  |  |  |  |  |

| 3.2.2   | PARALLEL I/O CONFIGURATIONS             | 3-16 |  |  |  |  |  |

| 3.3     | INTERRUPT CONTROLLER                    | 3-24 |  |  |  |  |  |

| 3.3.1   | 8259 BASIC FUNCTIONAL DESCRIPTION       | 3-25 |  |  |  |  |  |

| 3.3.2   | 8259 DETAILED OPERATIONAL SUMMARY       | 3-29 |  |  |  |  |  |

| 3.4     | INTERVAL TIMER                          | 3-38 |  |  |  |  |  |

| . 4     | USER SELECTABLE OPTIONS                 | 4-1  |  |  |  |  |  |

| 4.1     | BASE I/O ADDRESS SELECTION              | 4-2  |  |  |  |  |  |

| 4.2     | ADVANCE/TRANSFER ACKNOWLEDGE TIMING     | 4-2  |  |  |  |  |  |

•

ii

| 4.3      | INTERVAL TIMER PERIOD SELECTION                       |              |  |  |  |  |  |  |  |

|----------|-------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| 4.4      | PARALLEL I/O OPTIONS                                  |              |  |  |  |  |  |  |  |

| 4.4.1    | PORTS 1,4 AND 7 (8255A PORT A)                        |              |  |  |  |  |  |  |  |

| 4.4.2    | PORTS 2,5 AND 8 (8255A PORT B)                        |              |  |  |  |  |  |  |  |

| 4.4.3    | PORTS 3,6 AND 9 (8255A PORT C)                        |              |  |  |  |  |  |  |  |

| 4.5      | INTERRUPT PRIORITY OPTIONS                            |              |  |  |  |  |  |  |  |

| 5        | SYSTEM INTERFACING                                    |              |  |  |  |  |  |  |  |

|          |                                                       |              |  |  |  |  |  |  |  |

| 5.1      | ELECTRICAL CONNECTIONS                                |              |  |  |  |  |  |  |  |

| 5.2      | SYSTEM BUS SIGNAL DEFINITIONS                         | 5 <b>-</b> 8 |  |  |  |  |  |  |  |

| 6        | COMPATIBLE EQUIPMENT                                  |              |  |  |  |  |  |  |  |

| 6.1      | SBC-80/10 AND SBC-80/20 6-                            |              |  |  |  |  |  |  |  |

| 6.2      | MASTER MODULES 6-                                     |              |  |  |  |  |  |  |  |

| 6.3      | MODULAR BACKPLANE CARDCAGE                            |              |  |  |  |  |  |  |  |

| 6.4      | INTELLEC MICROCOMPUTER DEVELOPMENT SYSTEM<br>CARDCAGE |              |  |  |  |  |  |  |  |

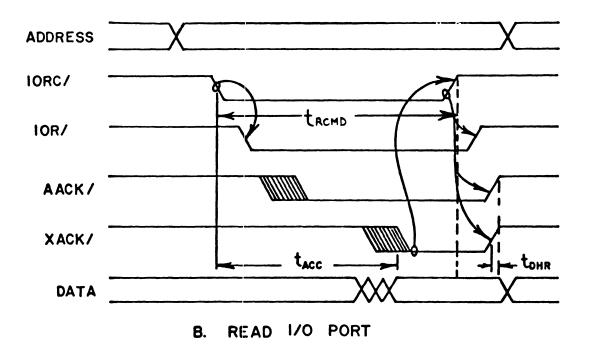

| 7        | SBC-519 SPECIFICATIONS                                | 7-1          |  |  |  |  |  |  |  |

| 7.1      | DC POWER REQUIREMENTS                                 |              |  |  |  |  |  |  |  |

| 7.2      | AC CHARACTERISTICS                                    |              |  |  |  |  |  |  |  |

| 7.3      | DC CHARACTERISTICS                                    |              |  |  |  |  |  |  |  |

| 7.4      | ENVIRONMENT                                           |              |  |  |  |  |  |  |  |

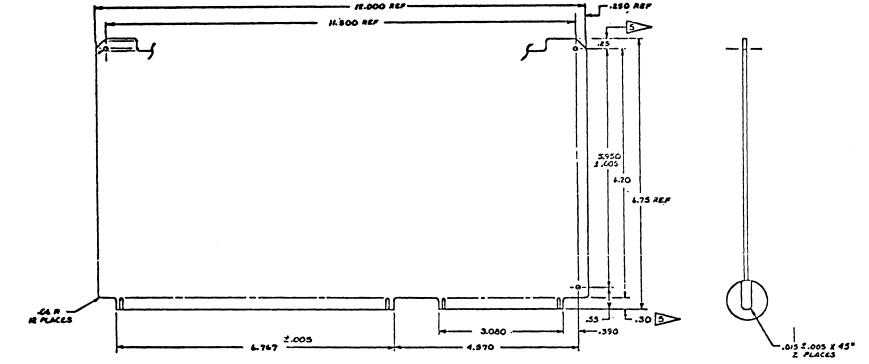

| 7.5      | SBC-519 BOARD OUTLINE                                 | 7-1          |  |  |  |  |  |  |  |

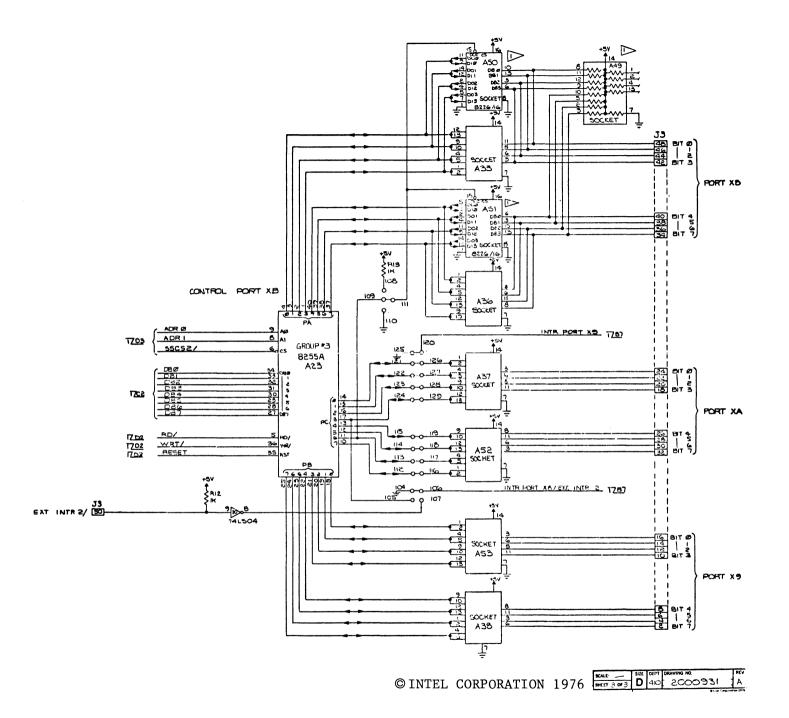

| APPENDIX | A. SBC-519 SCHEMATICS                                 | A-1          |  |  |  |  |  |  |  |

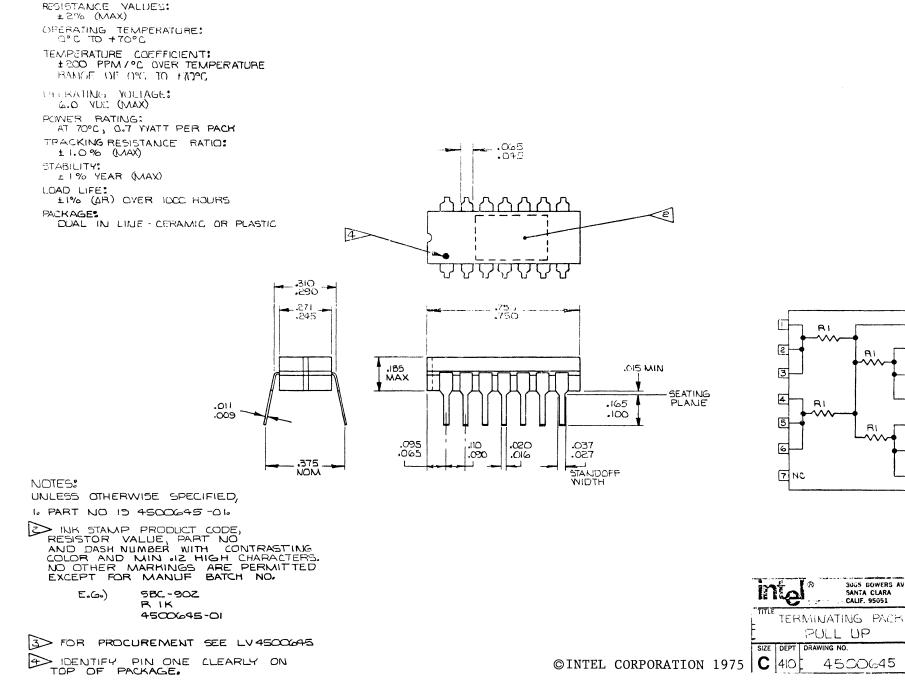

| APPENDIX | B. SBC-901, SEC-902 SCHEMATICS                        | B-1          |  |  |  |  |  |  |  |

| APPENDIX | C. INTERRUPT SERVICE ROUTINE PROGRAMMING<br>NOTES     | C-1          |  |  |  |  |  |  |  |

|          |                                                       |              |  |  |  |  |  |  |  |

PAGE

# LIST OF ILLUSTRATIONS

| FIGURE |                                     | PAGE |

|--------|-------------------------------------|------|

| 2-1    | SBC-519 Functional Block Diagram    | 2-2  |

| 2-2    | 8259 Initialization Sequence        | 2-7  |

| 2-3    | Interval Timer Ports                | 2-7  |

| 3-1    | 8255A Pin Assignments               | 3-7  |

| 3-2    | Mode Definition Control Word Format | 3-7  |

| 3-3    | Bit Set/Reset Control Word Format   | 3-9  |

| 3-4    | 8255A Mode O Timing                 | 3-11 |

| 3-5    | Examples of Mode 0 Configuration    | 3-11 |

| 3-6    | Mode 1 Input Configuration          | 3-13 |

| 3-7    | 8255A Mode 1 Input Timing           | 3-13 |

| 3-8    | Mode 1 Output Configuration         | 3-15 |

| 3-9    | Mode 1 Basic Output timing          | 3-15 |

| 3-10   | Mode 2 Port Configuration           | 3-17 |

| 3-11   | Mode 2 Timing                       | 3-17 |

| 3-12   | 8259 Interrupt Controller           | 3-26 |

| 3-13   | Priority Level BCD Code             | 3-30 |

| 3-14   | Operation Command Word Formats      | 3-33 |

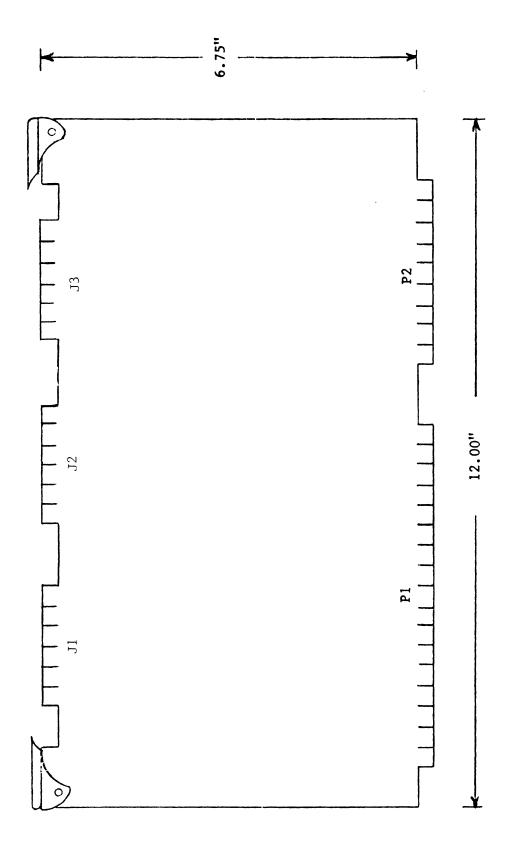

| 5-1    | SBC-519 Edge Connectors             | 5-5  |

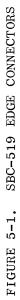

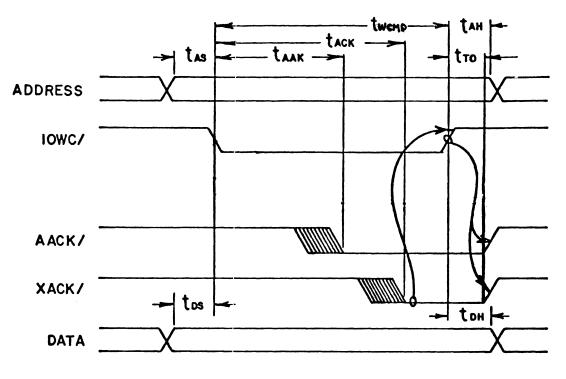

| 7-1    | Write and Read I/C Port Timing      | 7-5  |

| 7-2    | Board Outline Drawing               | 7-6  |

| TABLE |                                               | PAGE |

|-------|-----------------------------------------------|------|

| 2-1   | Parallel I/O Port Addresses                   | 2-5  |

| 2-2   | Interrupt Controller Port Addresses           | 2-5  |

| 2-3   | 8259 Instruction Set                          | 2-8  |

| 3-1   | Chip Select Decode Combinations               | 3-3  |

| 3-2   | 8255A Mode Definition Summary                 | 3-18 |

| 3-3   | Basic 8255A Operation for Group 1, 2 or 3     | 3-20 |

| 3-4   | Parallel I/O Port Addresses                   | 3-20 |

| 3-5   | Summary of Operation Command Word Programming | 3-34 |

| 4-1   | Base I/O Address Selection                    | 4-2  |

| 4-2   | Advance/Transfer Acknowledge Timing           | 4-3  |

| 4-3   | Interval Timer Period Selection               | 4-3  |

| 4-4   | Parallel I/O Interface Configurations         | 4-6  |

| 4-5   | Port 1, Mode 0 Input Configuration            | 4-8  |

| 4-6   | Port 4, Mode 0 Input Configuration            | 4-9  |

| 4-7   | Port 7, Mode 0 Input Configuration            | 4-10 |

| 4-8   | Port 1, Mode 0 Latched Output Configuration   | 4-11 |

| 4-9   | Port 4, Mode 0 Latched Output Configuration   | 4-12 |

| 4-10  | Port 7, Mode 0 Latched Output Configuration   | 4-13 |

| 4-11  | Port 1, Mode 1 Input Strobed                  | 4-14 |

| 4-12  | Port 4, Mode 1 Input Strobed                  | 4-15 |

| 4-13  | Port 7, Mode 1 Input Strobed                  | 4-16 |

| 4-14  | Port 1, Mode 1 Latched Output Configuration   | 4-17 |

| 4-15  | Port 4, Mode 1 Latched Output Configuration   | 4-18 |

| 4-16  | Port 7, Mode 1 Latched Output Configuration   | 4-19 |

| TABLE |                                                    | PAGE |

|-------|----------------------------------------------------|------|

| 4-17  | Port 1, Mode 2 Bidirectional Configuration         | 4-20 |

| 4-18  | Port 4, Mode 2 Bidirectional Configuration         | 4-21 |

| 4-19  | Port 7, Mode 2 Bidirectional Configuration         | 4-22 |

| 4-20  | Port 2, Mode 0 Input Configuration                 | 4-24 |

| 4-21  | Port 5, Mode 0 Input Configuration                 | 4-25 |

| 4-22  | Port 8, Mode 0 Input Configuration                 | 4-26 |

| 4-23  | Port 2, Mode 0 Latched Output Configuration        | 4-27 |

| 4-24  | Port 5, Mode 0 Latched Output Configuration        | 4-28 |

| 4-25  | Port 8, Mode 0 Latched Output Configuration        | 4-29 |

| 4-26  | Port 2, Mode 1 Strobed Input Configuration         | 4-30 |

| 4-27  | Port 5, Mode 1 Strobed Input Configuration         | 4-31 |

| 4-28  | Port 8, Mode 1 Strobed Input Configuration         | 4-32 |

| 4-29  | Port 2, Mode 1 Latched Output Configuration        | 4-33 |

| 4-30  | Port 5, Mode 1 Latched Output Configuration        | 4-34 |

| 4-31  | Port 8, Mode 1 Latched Output Configuration        | 4-35 |

| 4-32  | Port 3 (Lower) Mode 0 Input Configuration          | 4-37 |

| 4-33  | Port 6 (Lower) Mode 0 Input Configuration          | 4-38 |

| 4-34  | Port 9 (Lower) Mode 0 Input Configuration          | 4-39 |

| 4-35  | Port 3 (Upper) Mode 0 Input Configuration          | 4-40 |

| 4-36  | Port 6 (Upper) Mode 0 Input Configuration          | 4-41 |

| 4-37  | Port 9 (Upper) Mode 0 Input Configuration          | 4-42 |

| 4-38  | Port 3 (Lower) Mode 0 Latched Output Configuration | 4-43 |

| 4-39  | Port 6 (Lower) Mode 0 Latched Output Configuration | 4-44 |

| 4-40  | Port 9 (Lower) Mode 0 Latched Output Configuration | 4-45 |

| 4-41  | Port 3 (Upper) Mode 0 Latched Output Configuration | 4-46 |

| 4-42  | Port 6 (Upper) Mode 0 Latched Output Configuration | 4-47 |

vi

| TABLE |                                                             | PAGE |

|-------|-------------------------------------------------------------|------|

| 4-43  | Port 9 (Upper) Mode 0 Latched Output Configuration          | 4-48 |

| 4-44  | Port 3 Restriction Summary                                  | 4-49 |

| 4-45  | Port 6 Restriction Summary                                  | 4-51 |

| 4-46  | Port 9 Restriction Summary                                  | 4-53 |

| 4-47  | Interrupt Source Selection                                  | 4-55 |

| 5-1   | SBC Boards Compatible Connector Hardware                    | 5-2  |

| 5-2   | Pin Assignments for Connector J1                            | 5-6  |

| 5-3   | Pin Assignments for Connector J2                            | 5-7  |

| 5-4   | Pin Assignments for Connector $J3$                          | 5-8  |

| 5-5   | Pin Assignments for Connector P1                            | 5-11 |

| 6-1   | SBC-519 Access Characteristics When Used With the SBC-80/10 | 6-2  |

| 7-1   | SBC-519 DC Power Requirements                               | 7-2  |

| 7-2   | SBC-519 AC Characteristics                                  | 7-2  |

| 7-3   | SBC-519 DC Characteristics                                  | 7-3  |

### CHAPTER 1

# INTRODUCTION

The SBC-519 TTL Programmable General Purpose I/O (TTL PGPI/O) board is a member of Intel<sup>9</sup>s complete line of SBC 80 I/O expansion boards. The SBC-519 provides expanded parallel I/O capacity to any SBC 80 Single Board Computer via the system bus. It also provides a vectored polled interrupt scheme that is capable of resolving up to eight interrupts according to a program-controlled priority structure. An interval timer is included on the SBC-519 board to provide a time-based interrupt source for real-time processing applications.

The parallel I/O expansion feature uses three Intel 8255A Programmable Peripheral Interfaces. Together, these devices provide 72 I/O lines, which can be configured by the system software to meet a wide variety of peripheral interface requirements. These 72 lines can be implemented in various combinations of unidirectional input/output and bi-directional ports, which the user can program to operate in any of three modes.

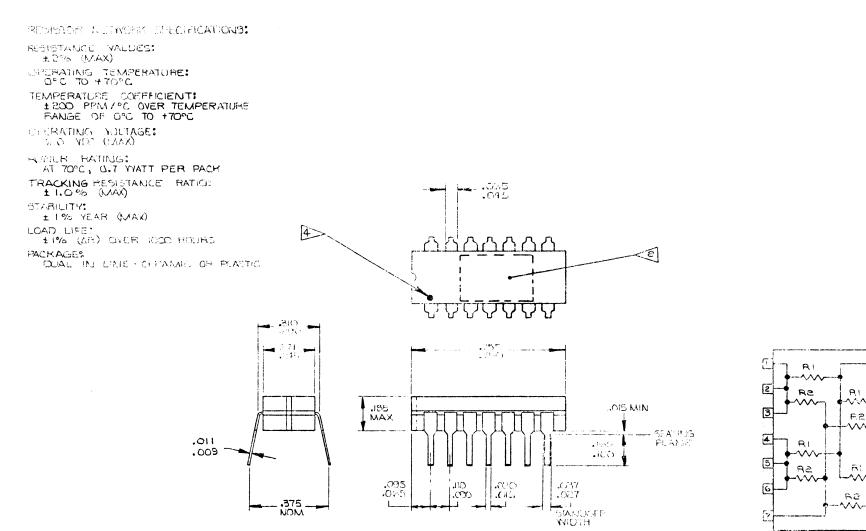

So that full advantage can be taken of the large number of possible I/O configurations, sockets are provided for interchangeable quad I/O line drivers and terminators. This provision allows the user to select sink currents, polarities and other characteristics appropriate to the application.

The SBC-519 includes an Intel 8259 Programmable Interrupt Controller, which gathers up to eight interrupt sources and generates

a single priority interrupt. The 8259 supplies the CPU with a three-bit vector (highest priority) for each interrupt request.

1

There are 10 potential interrupt sources available to the 8259 device: six from the 8255A's, three from external sources and one from the interval timer. Jumper pads on the SBC-519 allows any combination of up to eight interrupt sources to be selected from this set of 10.

The 8259 resolves priority among the eight interrupt inputs according to a program-selected algorithm. A variety of priority algorithms is available to the programmer so that the manner in which the 8259 handles interrupt requests can be adapted to different system characteristics. Because they are program-controlled, these algorithms can be changed dynamically to accommodate changing system requirements. The 8259 can be programmed to operate in the following non-exclusive modes.

- . Rotating Priority Mode

- Special Mask Mode

- Polled Mode (Note: This mode is always used for submitting interrupt requests to CPU.)

The user also has the option of by-passing the 8259 and driving the SBC bus interrupt lines directly.

The 8255A and 8259 port registers are addressed as I/O ports. Address assignments are made by on-board jumper selection. The selected base I/O address must be on a 16-byte boundary. No other address assignment constraint is imposed by the SBC-519.

The user can also jumper-select the Interval Timer period from four possibilities, whose values are determined by the CCLK frequency in the following relationships:  $4608 \times 1/\text{CCLK}$ ;  $9216 \times 1/\text{CCLK}$ ;  $18,432 \times 1/\text{CLCK}$  and  $36,864 \times 1/\text{CCLK}$ . If CCLK is supplied by an SBC 80/10 or 80/20, the four possible Interval Timer periods are 0.5 ms, 1 ms, 2 ms and 4 ms.

All SBC-519 circuit elements reside on a single  $6.75 \times 12$  inch printed circuit card and are physically and electrically compatible with the SBC 80 system bus. The SBC-519 is also compatible with the Intellec Microcomputer Development System bus, as defined in Chapter 6.0.

## CHAPTER 2

# FUNCTIONAL/PROGRAMMING CHARACTERISTICS

This chapter briefly describes the organization of the SBC-519 from two points of view. The principal functions performed by the hardware are identified and the general data flow is illustrated in Section 2.1. This section is intended as an introduction to the detailed information provided in Chapter 3, Theory of Operations. Section 2.2 summarizes the information needed by the programmer to initialize and access the L/O and interrupt facilities on the SBC-519.

## 2.1 FUNCTIONAL DESCRIPTION

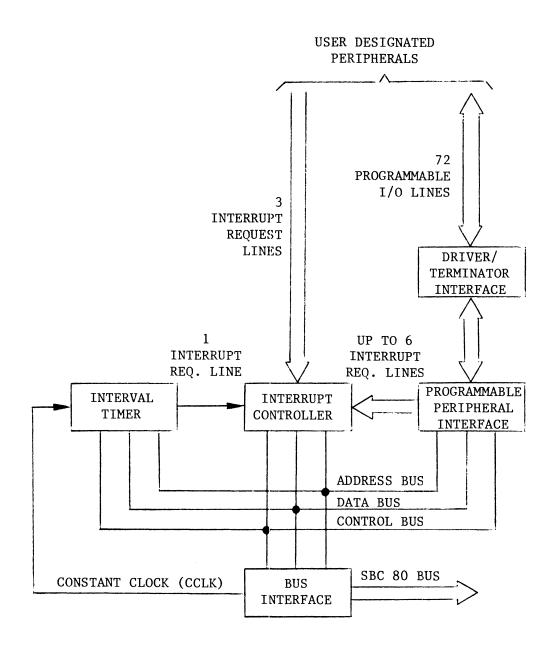

To facilitate the following description, the SBC-519 is divided into functional blocks, as shown in Figure 2-1.

- 1) Bus Interface

- 2) Parallel I/O Interface

- 3) Interrupt Controller

- 4) Interval Timer

The <u>Bus Interface</u> logic consists of those circuit elements most directly involved with communication between the bus master and the SBC-519. These include bus address/control line receiver, bidirectional data buffer, I/O port select decode logic and transfer acknowledge generation and line driver circuits.

The <u>Parallel I/O Inter: ace</u> consists of three Intel 8255A Programmable Peripheral Interface devices, and twenty-four 14-pin sockets

FIGURE 2-1. SBC-519 FUNCTIONAL BLOCK DIAGRAM

for installing quad line driver and/or terminator packages as required to satisfy the particular I/O interface requirements. The input/output configuration of each 8255A device is programmed independently, with the three ports (A, B and C) of each device treated as a separate group. Wire wrap jumper pins allow the user to implement up to six I/O lines (two per group) to be implemented as interrupt request lines.

The Intel 8259 <u>Interrupt Controller</u> resolves interrupt requests from up to eight different sources according to a program-selected priority scheme. Interrupt request (IR) inputs to the 8259 are determined by on-board jumper selection. Priority assignments for the eight IR inputs can be changed under program control using the rotating priority mode. Individual IR inputs can also be masked or unmasked under program control. When polled by the CPU, the 8259 issues a three-bit vector that identifies the current interrupt request having the highest priority.

The <u>Interval Timer</u> is formed by a cascaded set of four binary counters; a D-type flip-flop latches the timer output. This timer circuit is driven by the system's CCLK (9.216 MHz for SBC 80/10 or 80/20). A jumper pad in the circuit provides the means for selecting one of four possible interrupt periods. If CCLK is provided by an SBC 80/10 or 80/20, the available periods are: 0.5 ms, 1 ms, 2 ms or 4 ms. A second jumper pad allows the Interval Timer output to be applied to IR input 0 (normally highest priority) or to disable that input. The Interval Timer output can also be read directly by the CPU whether the IRO input to the 8259 is enabled or disabled.

# 2.2 PROGRAMMING CHARACTERISTICS

This section summarizes the SBC-519 addressing characteristics. The module's base I/O address is assigned through the use of wire wrap jumper pins on the board. These two jumpers are part of the board's address decode circuit for system address bits 4-7. They allow the selection of a base address for the SBC-519 on a 16-bit boundary. Address bits 0-3 are decoded by other logic to select 1 of 16 data, status or control ports on the board.

Program access to SBC-519 module's 16 ports is discussed in the following subsections.

## 2.2.1 PARALLEL I/O INTERFACE ADDRESSES

The parallel I/O interface consists of three identical groups of parallel I/O ports, with three eight-bit ports in each group. Each port is separately addressable. In addition, each group includes a control register, which has its own address. These control registers are written into in order to specify certain operating characteristics for their respective ports.

These various ports and registers are accessed at the addresses shown in Table 2-1.

## 2.2.2 PROGRAMMABLE INTERRUPT CONTROLLER

There are two port addresses associated with the 8259. These are used for outputting command words to the 8259 and for reading various 8259 registers. The 8259 port addresses are shown in Table 2-2.

| Group<br>Port       | 1 (A19)<br>Address | -                   | 2 (A22)<br>Address | Group 3<br>Port     |    |

|---------------------|--------------------|---------------------|--------------------|---------------------|----|

| 1                   | XO                 | 4                   | X4                 | 7                   | X8 |

| 2                   | X1                 | 5                   | X5                 | 8                   | X9 |

| 3                   | X2                 | 6                   | X6                 | 9                   | XA |

| Control<br>Register | X3                 | Control<br>Registe: | X7                 | Control<br>Register | XB |

TABLE 2-1. PARALLEL I/O PORT ADDRESSES

| TIDEE 2 2. INTERRET CONTROLLER FORT ADDRESSES | TABLE 2-2. | INTERRUPT | CONTROLLER | PORT | ADDRESSES |

|-----------------------------------------------|------------|-----------|------------|------|-----------|

|-----------------------------------------------|------------|-----------|------------|------|-----------|

| Port<br>Addr | Read | Write | Function                                                                                     |

|--------------|------|-------|----------------------------------------------------------------------------------------------|

| XC           | 1    | 0     | Read interrupt vector, interrupt<br>request register (IRR) or in-<br>service register (ISR). |

| XC           | 0    | 1     | Write initialization command word (ICW) or operation command word (OCW).                     |

| XD           | 1    | 0     | Read interrupt mask register (IMW).                                                          |

| XD           | 0    | 1     | Write ICW or OCW.                                                                            |

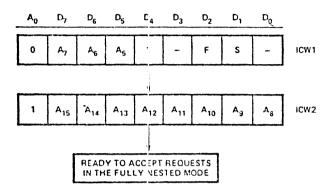

ICW's (Input Command Word) are used to prepare the 8259 for normal operation. A two-byte ICW sequence (ICWl and ICW2) is output to the 8259 in order to reset the edge sense circuit, special mask mode flip-flop and status read flip-flop. This sequence also clears the interrupt mask register (IMR) and assigns priority 7 (lowest priority) to the Interrupt Request 7 (IR7) input.

Figure 2-2 shows the 8259 initialization sequence.

The OCW's (Output Command Word) are used to command the 8259 to operate in various interrupt modes: rotating priority mode, special mask mode or polled mode.

Table 2-3 lists the instruction set used for programming the 8259. Those instructions that are not available to the SBC-519's Interrupt Controller are shaded in the table.

Further details regarding 8259 operation are provided in Chapter 3.

# 2.2.3 INTERVAL TIMER

The same port addresses are used to sample the Interval Timer output as to reset the Interval Timer output latch. The output is sampled by executing an input (read) to port address XE or XF. The state of the Interval Timer is represented on data line 0. The Interval Timer is reset by executing a write to port XE or XF with a  $\emptyset\emptyset$  in the accumulator. The timer interval is set by hardware jumper. The timer will cause the timer flag to interrupt the bus master once a cycle (one time interval). The bus master must service the interrupt by resetting the timer flag. If the bus master does not reset the timer flag before the next time interval was expired, the timer flag will not generate a new interrupt.

FIGURE 2-2. 8259 INITIALIZATION SEQUENCE

| PORT     | WRITE | READ | FUNCTION                                                                                  |

|----------|-------|------|-------------------------------------------------------------------------------------------|

| XE or XF | 1     |      | RESET INTERRUPT FLAG<br>ACC = 00                                                          |

| XE or XF |       | 1    | READ INTERRUPT FLAG<br>DØ = 0 INTERRUPT OCCURRED<br>= 1 NO INTERRUPT<br>D1-D7 = UNDEFINED |

FIGURE 2-3. INTERVAL TIMER PORTS

TABLE 2-3. 8259 INSTRUCTION SET

| INST. |             |    | 77         |     | D <b>7</b> |     |     |     | D1 | D0            |                                                                                                      |

|-------|-------------|----|------------|-----|------------|-----|-----|-----|----|---------------|------------------------------------------------------------------------------------------------------|

| No.   | MN EMON I C | AO | D7         | D6  | D5         | D4  | D3  | D2  | D1 | DO            | OPERATION DESCRIPTION                                                                                |

| 1     | ICW1 A      | 0  | A7         | A6  | A5         | 1   | -   | 1   | 1  | -             | Byte 1 initialization, format = $4$ , single.                                                        |

| 2     | ICW1 B      | 0  | A <b>7</b> | A6  | A5         | 1   | -   | 1   | 0  | -             | Byte 1 initialization, format = 4, not single.                                                       |

| 3     | ICW1 C      | 0  | A7         | A6  | A5         | 1   | -   | 0   | 1  | -             | Byte 1 initialization, format = 8, single.                                                           |

| 4     | ICW1 D      | 0  | A7         | A6  | A5         | 1   | -   | 0   | 0  | -             | Byte 1 initialization, format = 8, not single                                                        |

| 5     | ICW2        | 1  | A15        | A14 | A13        | A12 | A11 | A10 | A9 | A8            | Byte 2 initialization (Address No. 2)                                                                |

| 6     | ICW3 M      | 1  | S7         | S6  | S5         | S4  | S3  | S2  | S1 | S0            | Byte 3 initialization - master.                                                                      |

| 7     | ICW3 S      | 1  | -          | -   | -          | -   | -   | S2  | S1 | S0            | Byte 3 initialization – slave.                                                                       |

| 8     | OCW1        | 1  | M7         | M6  | M5         | M4  | M3  | M2  | M1 | MO            | Load mask reg. read mask reg.                                                                        |

| 9     | OCW2 E      | 0  | 0          | 0   | 1          | 0   | 0   | 0   | 0  | 0             | Non specific EO1.                                                                                    |

| 10    | OCW2 SE     | 0  | 0          | 1   | 1          | 0   | 0   | L2  | L1 | LO            | Specific EO1, L2, L1, L0 code of ISFF to be reset.                                                   |

| 11    | OCW2 RE     | 0  | 1          | 0   | 1          | 0   | 0   | 0   | 0  | 0             | Rotate at EO1 (Auto Mode).                                                                           |

| 12    | OCW2 RSE    | 0  | 1          | 1   | 1          | 0   | 0   | L2  | L1 | L0            | Rotate at EO1 (Specific Mode). L2, L1, L0, code of line to be reset and selected as bottom priority. |

| 13    | OCW2 RS     | 0  | 1          | 1   | 0          | 0   | 0   | L2  | L1 | $\mathbf{LO}$ | L2, L1, L0 code of bottom priority line.                                                             |

| 14    | OCW3 P      | 0  | -          | 0   | 0          | 0   | 1   | 1   | 0  | 0             | Poll mode.                                                                                           |

| 15    | OCW3 RIS    | 0  | -          | 0   | 0          | 0   | 1   | 0   | 1  | 1             | Read IS register.                                                                                    |

| 16    | OCW3 RR     | 0  | -          | 0   | 0          | 0   | 1   | 0   | 1  | 0             | Read requests register.                                                                              |

| 17    | OCW3 SM     | 0  | -          | 1   | 1          | 0   | 1   | 0   | 0  | 0             | Set special mask mode.                                                                               |

| 18    | OCW3 RSM    | 0  | -          | 1   | 0          | 0   | 1   | 0   | 0  | 0             | Reset special mask mode.                                                                             |

Notes:

1. In the master mode  $\overline{SP}$  pin = 1, in slave mode  $\overline{SP}$  = 0.

2. (-) = do not care.

NOTE: All mnemonics copyright 1976 Intel Corporation.

#### CHAPTER 3

# THEORY OF OPERATION

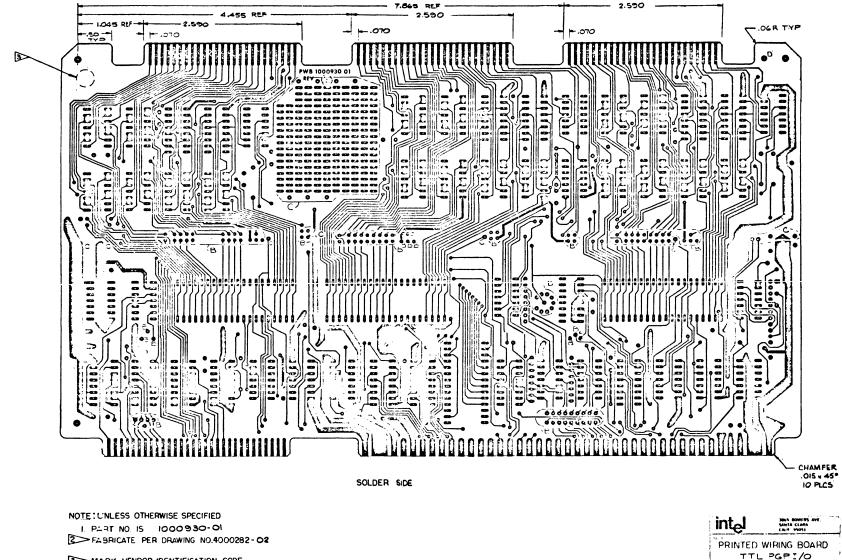

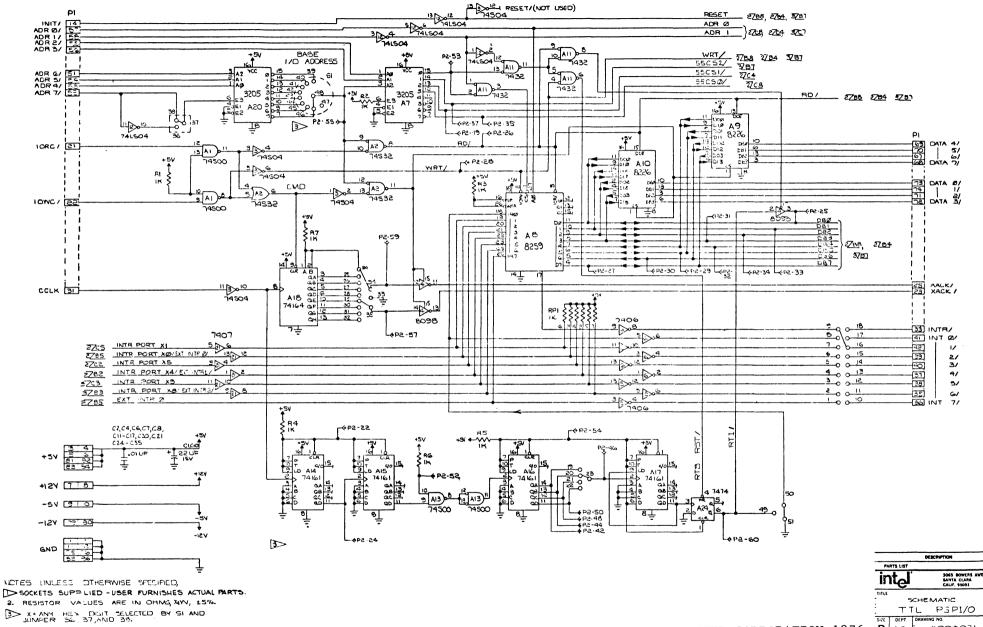

In the preceding chapter, each of the SBC-519 functional blocks was identified and briefly defined. This chapter explains how these functions are implemented. For detailed circuit information, refer to the SBC-519 schematics, which are provided in Appendix A.

Note: Both active-high (positive true) and active-low (negative true) signals appear in the SBC-519 schematics. To avoid confusion when referring to these signals in this chapter, the following convention is used. The mnemonic (signal label) for each active-low signal is terminated by a slash; e.g., IOW/ means that the signal level on that line will be low when the I/O write command is true (active). A mnemonic without the slash refers to an active-high signal; e.g., the line labeled EXT INTRO is at the high logic level when the external interrupt 0 signal is true.

#### 3.1 BUS INTERFACE

The Bus Interface refers to those logic elements that participate directly in the following types of system bus activity.

- 1) System address, control and data buffering

- 2) System address decoding

- 3) System control signal propagation

- 4) Transfer acknowledge generation.

The four groups of Bus Interface logic responsible for these

tasks are described in the following paragraphs.

## 3.1.1 BUS ADDRESS, CONTROL, DATA BUFFERS

The bus address and control signal buffer circuit consists of inverting line receivers of the 74LSO4 (address) and 74SOO (control) types. These circuits restore the signals on the system bus lines to their proper logic levels with very high switching speed.

The data buffers are formed by two Intel 8226 inverting bidirectional driver/receiver chips (A9 and A10). The system data bus is connected to the devices<sup>†</sup> DB pins. The D0 and DI pins of each chip are connected, via printed wires, to the 8259 outputs and to the data/control pins of the three 8255A devices.

Directional control (RD/) for A9 and A10 is exercised by the I/O read command (IORC/). If the read command is asserted by the bus master, and the matching base I/O address is present, the data buffer's driver mode is selected. At all other times, the data buffer's receiver circuits are enabled.

The chip select (CS/) for the data buffer is enabled when a command is gated into the board.

# 3.1.2 SYSTEM ADDRESS DECODE LOGIC

This logic decodes the appropriate system bus address bits into a chip select for one of the 8255A devices, the 8259 device, or for the Interval Timer. It also produces an enable for the read/write command decode logic.

The base I/O address is decoded by an Intel 3205 one out of eight binary decoder, A2O. This device is enabled by either ADR7/ or ADR7, as determined by the jumper selection at jumper pins 36, 37, 38. When enabled, A2O decodes address bits ADR4/, ADR5/ and ADR6/ into one of eight outputs.

Jumper pad S1 allows the base I/O address enable to be taken

from any one of the eight A20 outputs.

When the ADR4/ through ADR7/ bits correspond to the selected base I/O address, an enable is provided to a chip select generator and to the read/write command gates.

The chip select generator consists of an Intel 3205 device (A7) that is enabled by the decoded base I/O address. When enabled, A7 decodes address bits ADR2/ and ADR3/ into one of four chip select outputs. One of the four outputs is further decoded with ADR1 and ADR1/ to provide an enable for the Interval Timer read/write logic.

Table 3-1 identifies the address bit combinations required to produce these chip selects and enables.

| Address Bits |     |       | Select                                                                   |

|--------------|-----|-------|--------------------------------------------------------------------------|

| 3            | 2   | 1     |                                                                          |

| 0            | 0   | x     | 55CSO/; selects 8255A at A19                                             |

| 0            | 1   | x     | 55CS1/; selects 8255A at A22                                             |

| 1            | 0   | x     | 55CS2/; selects 8255A at A23                                             |

| 1            | 1   | 0     | Selects 8259                                                             |

| 1            | 1   | 1     | Enables Interval Timer read/write gates                                  |

|              | = A | ADR b | to decode port select in 8255A<br>it is high (false)<br>it is low (true) |

TABLE 3-1. CHIP SELECT DECODE COMBINATIONS

# 3.1.3 COMMAND DECODE

A pair of 74S00 NAND gates buffer the IORC/ (I/O Read Command) and IOWC/ (I/O Write Command) inputs from the system bus.

These gates are permanently enabled so that any I/O read or I/O

write command appearing on the system bus is passed on to the Advance/ Transfer Acknowledge Generator via OR gate A2. The output of A2 is designated CMD.

CMD is inverted and then enabled by the decoded base I/O address at gate A2 to produce the board enable. This signal, BD ENABLE/ controls the 3-state gates that drive AACK/ and XACK/ on the system bus.

The output of the IOWC/ receiver (Al-8) is inverted and forwarded to the Interrupt Controller (A8), the Interval Timer write gate (All-4) and the three Peripheral I/O Interface chips (A19, A22, A23). This internal write enable, designated WRT/, is qualified at each of these destinations by the appropriate chip select.

The output of the IORC/ receiver (A1-11) is enabled by the decoded base I/O address at A2-8. The resulting internal read enable, RD/, is applied to the Interrupt Controller (A8), the Interval Timer read gate (A11-9) and to the bidirectional bus driver chips (A9, A10).

# 3.1.4 ADVANCE/TRANSFER ACKNOWLEDGE GENERATION

This logic provides a transfer acknowledge response, XACK, to notify the bus master that data has either been accepted from the system bus (during a WRITE operation) or placed on the system bus (during a READ operation). An advance acknowledge response, AACK, is also provided for use in certain 8080-based systems, where it can decrease by one the number of wait states needed to complete a READ or WRITE operation.

AACK is used in certain I/O applications where an early acknowledgment to the 8080 is needed to allow it to proceed to the T3 state following the current T2 or wait state. Such applications have the following

characteristics--XACK is generated too late for the 8080 to detect it in

the current state, but

- 1) valid read data will be placed on the system bus by the time the 8080 needs it in the current state, or

- 2) write data will be accepted from the system bus by the time the 8080 has completed its WRITE operation.

In either case, AACK is sent to the 8080 early enough in the current state (T2 or wait) to prevent the bus master from entering a subsequent wait state. The I/O transaction is completed during the current T2 or wait state and the bus master moves on to T3.

# NOTE: All SBC boards connected to the system bus must have AACK compatibility for any one of them to use the feature unless the uncompatible board can jumper off AACK.

Both acknowledge responses are generated by Al8, an eight-bit serial in, parallel out shift register. When enabled by CMD, Al8 shifts CCLK/ pulses. These produce a sequence of high-true pulses at Al8's Q outputs. The outputs occur at approximately 100 ns intervals.

The appropriate Q outputs are selected by hardwire connections to the inputs of a pair of 3-state gates (A4-12, A4-14). These gates allow the AACK/ and XACK/ outputs onto the system bus when enabled by BD ENABLE/.

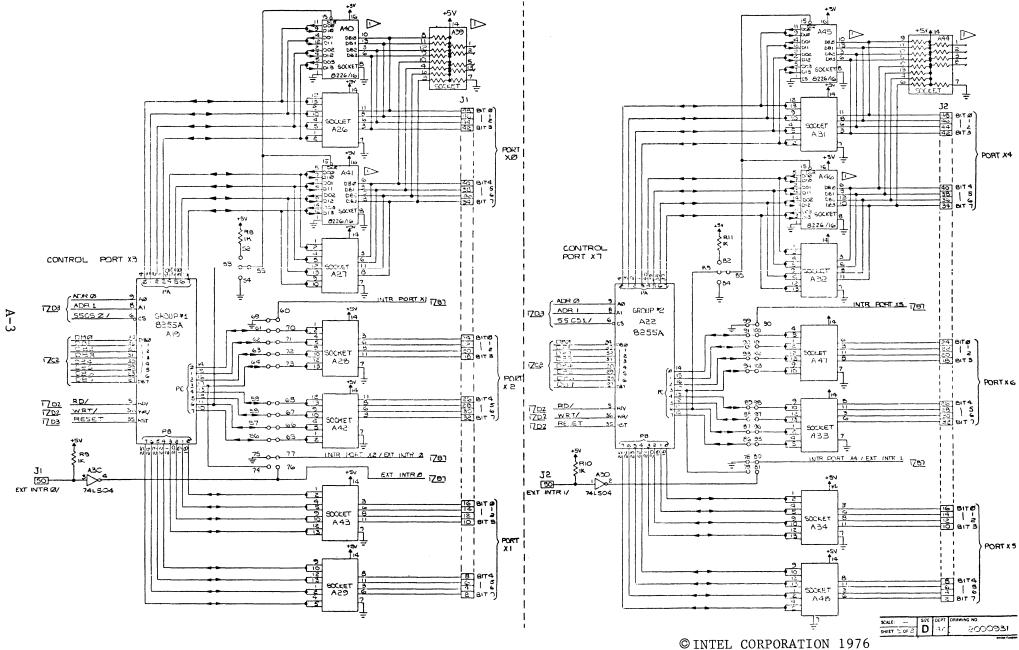

3.2 PARALLEL I/O INTERFACE

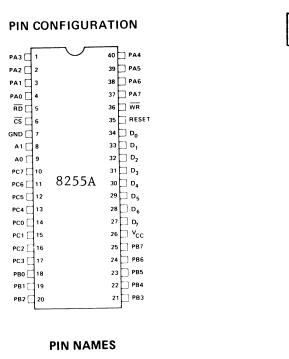

The Parallel I/O Interface logic on the SBC-519 provides 72 signal lines for the transfer and control of data to or from peripheral devices. Sockets are provided for the installation of appropriate line driver and/or termination networks for all 72 lines. The optional drivers and terminators are installed in groups of four lines by insertion into the 14-pin sockets or 16-pin sockets for Intel's 8216 or 8226 bidirectional drivers. Bidirectional bus driver chips (e.g., 8216 or 8226) can be used in certain socket positions. These are identified in Chapter 4.

All 72 signal lines emanate from the I/O ports on three Intel 8255A Pro grammable Peripheral Interface devices, as shown on sheets 2 and 3 of the SBC-519 schematic. These 8255A devices, Al9, A22 and A23, allow for a wide

variety of I/O configurations. Before describing the possible configurations, however, we will summarize the general operational characteristics of the 8255A device.

#### 3.2.1 8255A OPERATIONAL SUMMARY

The 8255A contains three 8-bit ports (A,B, and C). All can be configured in a wide variety of functional characteristics by the system software but each has its own special features or "personality" to further enhance the power and flexibility of the 8255A.

- <u>Port A</u>: One 8-bit data output latch/buffer and one 8-bit data input latch.

- <u>Port B</u>: One 8-bit data input/output latch/buffer and one 8-bit data input buffer.

- <u>Port C</u>: One 8-bit data output latch/buffer and one 8-bit data input buffer (no latch for input). This port can be divided into two 4-bit ports under the mode control. Each 4-bit port contains a 4-bit latch and it can be used for the control signal outputs and status signal inputs in conjunction with Ports A and B.

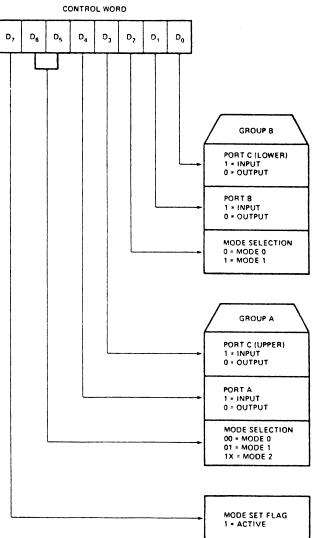

The bus master dictates the operating characteristics of the ports by outputting two different types of control words to the 8255A:

- 1) mode definition control word (bit 7 = 1)

- 2) port C bit set/reset control word (bit 7 = 0)

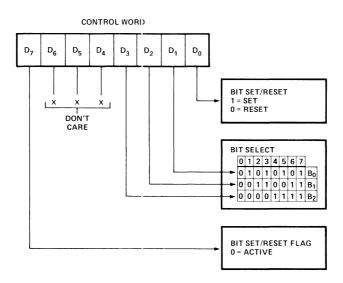

Bit 7 of each control word specifies its format, as shown in Figures 3-2 and 3-3, respectively.

## Mode Selection

There are three basic modes of operation that can be selected by the system software:

Mode 0 - Basic Input/Output Mode 1 - Strobed Input/Output Mode 2 - Bidirectional Bus

When the RESET input goes "high" all ports will be set to the Input Mode O (i.e., all 24 lines will be in the high impedance state). After the RESET is removed the 8255A can remain in the Input mode with no additional initialization required. During the execution of the

| D7-D0   | DATA BUS (BI-DIRECTIONAL |

|---------|--------------------------|

| RESET   | RESET INPUT              |

| CS      | CHIP SELECT              |

| RD      | READ INPUT               |

| WR      | WRITE INPUT              |

| A0, A1  | PORT ADDRESS             |

| PA7-PA0 | PORT A (BIT)             |

| PB7-PB0 | PORT B (BIT)             |

| PC7-PC0 | PORT C (BIT)             |

| Vcc     | +5 VOLTS                 |

| GND     | Ø VOLTS                  |

FIGURE 3-1. 8255A PIN ASSIGNMENTS FIGURE 3-2. MODE DEFINITION CONTROL WORD FORMAT system program, the other modes may be selected using a single OUT instruction. This allows a single 8255A to service a variety of peripheral devices with a simple software maintenance routine.

The modes for Port A and Port B can be separately defined, while Port C is divided into two portions as required by the Port A and Port B definitions. All of the output registers, including the status flipflops, will be reset whenever the mode is changed except for  $\overline{OBF}$  in modes 1 and 2. Modes may be combined so that their functional definition can be tailored to almost any I/O structure. For instance, Group B can be programmed in Mode 0 to monitor simple switch closings or display computational results, Group A could be programmed in Mode 1 to monitor a keyboard or tape reader on an interrupt-driven basis.

Single Bit Set/Reset Feature

Any of the eight bits of Port C can be Set or Reset using a single OUT instruction (see Figure 3-3). This feature reduces software requirements in Control-based applications.

When Port C is being used as status/control for Port A or B, these bits can be set or reset by using a Bit Set/Reset operation just as if they were data output ports.

#### Interrupt Control Functions

When the 8255A is programmed to operate in Mode 1 or Mode 2, control signals are provided that can be used as interrupt request inputs to the bus master. The interrupt request signals, generated from Port C can be inhibited or enabled by setting or resetting the associated INTE flip-flop, using the Bit set/reset function of Port C.

FIGURE 3-3. BIT SET/RESET CONTROL WORD FORMAT

This function allows the Programmer to disallow or allow specific I/O devices to interrupt the bus master without affecting any other device in the interrupt structure.

INTE flip-flop definition:

(BIT-SET) - INTE is SET - Interrupt enable (BIT-RESET) - INTE is RESET - Interrupt disable

NOTE: All mask flip-flops are automatically reset during mode selection and device Reset.

## Operating Modes

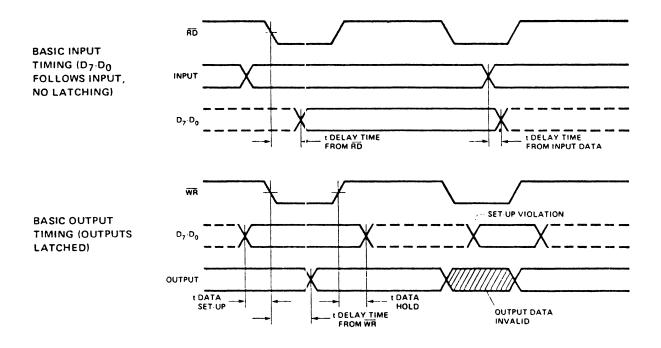

Mode 0 (Basic Input/Output):

This functional configuration provides simple Input and Output operations for each of the three ports. No "hand-shaking" is required, data is simply written to or read from a specified port. Mode 0 timing is illustrated in Figure 3-4. Mode 0 Basic Functional Definitions:

- . Two 8-bit ports and two 4-bit ports.

- . Any port can be input or output.

- . Outputs are latched.

- Inputs are not latched.

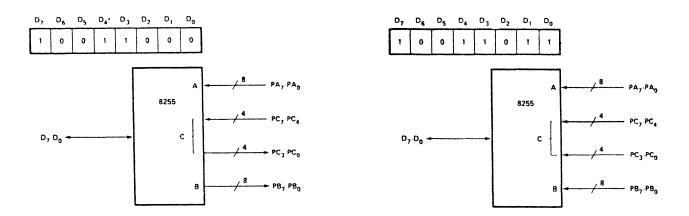

Sixteen different Input/Output configurations are possible in this Mode. Figure 3-5 shows two possible configurations.

Mode 1 (Strobed Input/Output):

This functional configuration provides a means for transferring I/O data to or from a specified port in conjunction with strobes or "handshaking" signals. In Mode 1, Port A and Port B use the lines on Port C to generate or accept these "handshaking" signals.

Mode 1 Basic Functional Definitions:

- Two transfer ports (A and B).

- Each transfer port contains one 8-bit data port and 4 bits from one half of the control/data port (Port C).

- The 8-bit data port can be either input or output. Both inputs and outputs are latched.

Input Control Signal Definition for Mode 1

STB (Strobe Input)

A "low" on this input loads data into the input latch.

## IBF (Input Buffer Full F/F)

A "high" on this output indicates that the data has been loaded into the input latch; in essence, an acknowledgement. IBF is set by the falling edge of the STB input and is reset by the rising edge of the  $\overline{\text{RD}}$  input.

FIGURE 3-4. 8255A MODE 0 TIMING

FIGURE 3-5. EXAMPLES OF MODE 0 CONFIGURATION

INTR (Interrupt Request)

A "high" on this output can be used to interrupt the bus master when an input device is requesting service. INTR is set by the rising edge of  $\overline{\text{STB}}$  if IBF is a 1 and INTE is a 1. It is reset by the falling edge of  $\overline{\text{RD}}$ . This procedure allows an input device to request service from the bus master by simply strobing its data into the port.

INTE A Controlled by bit set/reset of PC4. INTE B Controlled by bit set/reset of PC2.

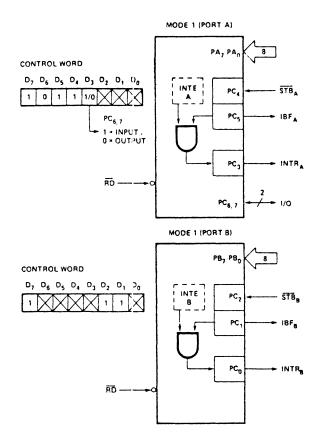

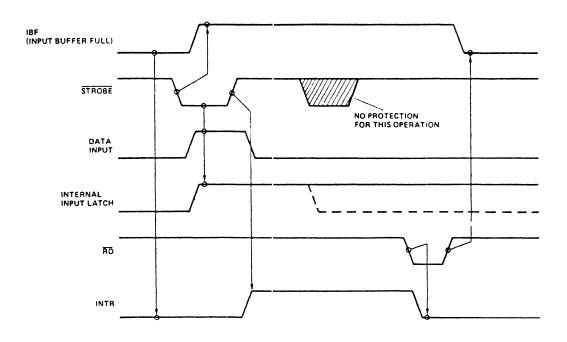

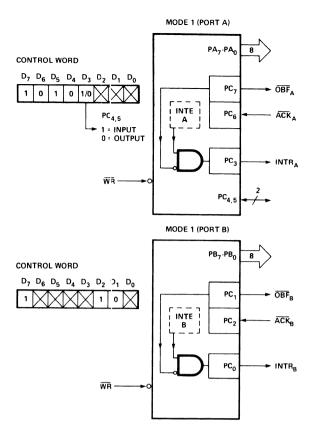

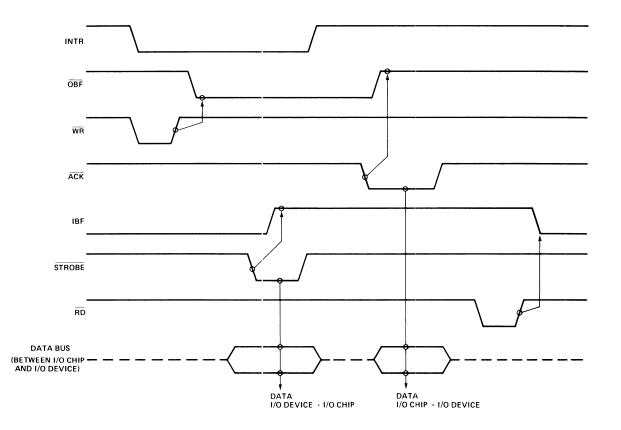

Figure 3-6 illustrates the Mode 1 input configuration, while Figure 3-7 shows the basic timing for Mode 1 input.

Output Control Signal Definition for Mode 1 OBF (Output Buffer Full F/F)

The OBF output will go low to indicate that the bus master has written data out to the specified port. The OBF F/F will be set by the rising edge of the  $\overline{WR}$  input and reset by the falling edge of the  $\overline{ACK}$  input signal.

ACK (Acknowledge Input)

A low on this input informs the 8255A that the data from Port A or Port B has been accepted. In essence, a response from the peripheral device indicating that it has received the data output by the bus master.

INTR (Interrupt Request)

A high on this output can be used to interrupt the bus master

FIGURE 3-6. MODE 1 INPUT CONFIGURATION

MODE 1 (STROBED INPUT) BASIC TIMING

•

FIGURE 3-7. 8255A MODE 1 INPUT TIMING

when an output device has accepted data transmitted by the bus master. INTR is set by the rising edge of  $\overline{ACK}$  if  $\overline{OBF}$  is a 1 and INTE is a 1. It is reset by the falling edge of  $\overline{WR}$ .

INTE A

Controlled by bit set/reset of PC6.

INTE B

Controlled by bit set/reset of PC2.

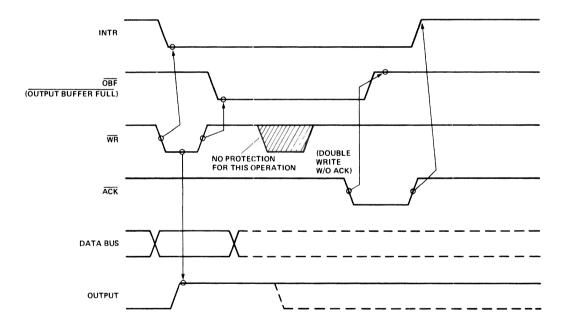

Figure 3-8 illustrates the Mode 1 output configuration, while Figure 3-9 shows basic Mode 1 output timing.

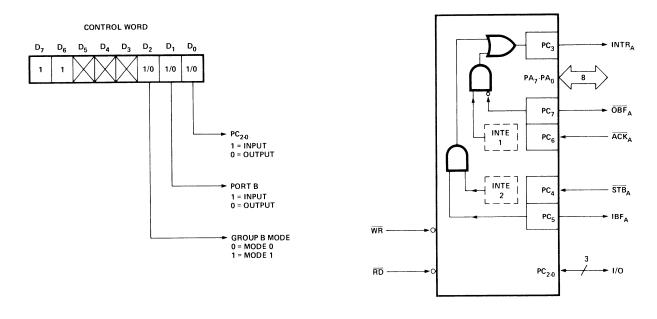

Mode 2 (Strobed Bidirectional Bus I/O):

This functional configuration provides a means for communicating with a peripheral device or structure on a single 8-bit bus for both transmitting and receiving data (bidirectional bus I/O). "Handshaking" signals are provided to maintain proper bus flow discipline in a similar manner to Mode 1. Interrupt generation and enable/disable functions are also available.

Mode 2 Basic Functional Definitions:

- Used in Port A only.

- . One 8-bit, bidirectional data Port (Port A) and a 5-bit control Port (Port C).

- · Both inputs and outputs are latched.

- The 5-bit control Port (Port C) is used for control and status for the 8-bit, bidirectional data Port (Port A).

Bidirectional Bus I/O Control Signal Definition

INTR (Interrupt Request)

A high on this output can be used to interrupt the bus master for both input or output operations.

ţ

FIGURE 3-8. MODE 1 OUTPUT CONFIGURATION

FIGURE 3-9. MODE 1 BASIC OUTPUT TIMING

Output Operation Control Signals

OBF (Output Buffer Full)

The  $\overrightarrow{OBF}$  output will go low to indicate that the bus master has written data out to Port A.

ACK (Acknowledge)

A low on this input enables the 3-state output buffer of Port A to send out the data. Otherwise, the output buffer will be in the high-impedance state.

INTR A and B (The INTE flip-flop associated with  $\overline{OBF}$ )

Controlled by bit set/reset of PC6 (INTE 1)

Input Operation Control Signals

STB (Strobed Input)

A low on this input indicates that data has been loaded into the input latch.

IBF (Input Buffer Full F/F)

A high on this output indicates that data has been loaded into the input latch.

INTE 2 (The INTE flip-flop associated with IBF)

Controlled by bit set/reset PC4 (INTE 2)

$INTR_A = PC6 \cdot OBF_A + PC4 \cdot IBF_A$

Figure 3-10 illustrates the port configuration for Mode 2, Figure 3-11 shows Mode 2 timing, and Table 3-2 summarizes 8255A Mode definition.

# 3.2.2 PARALLEL I/O CONFIGURATIONS

As shown on sheets 2 and 3 of the schematic, there are three 8255A devices, one located at A19, A22 and A23. For convenience the following device designations will be used: The device at A19 is called the "group 1" device, the device at A22 is referred to as the "group 2" device and

FIGURE 3-10. MODE 2 PORT CONFIGURATION

FIGURE 3-11. MODE 2 TIMING

## MODE DEFINITION SUMMARY TABLE

|                 | MO | DE 0 | 1 | MODE 1           |       | MODE 2       |           |

|-----------------|----|------|---|------------------|-------|--------------|-----------|

|                 | IN | OUT  |   | IN               | OUT   | GROUP A ONLY |           |

| PA <sub>0</sub> | IN | OUT  | 1 | IN               | OUT   | <b></b>      | 6         |

| PA1             | IN | OUT  |   | IN               | ουτ   | <>           |           |

| PA2             | IN | OUT  |   | IN               | ουτ   | ←→           |           |

| PA3             | IN | OUT  |   | IN               | ουτ   | ←→           |           |

| PA4             | IN | OUT  | 1 | IN               | Ουτ   | <b></b>      |           |

| PA5             | IN | OUT  |   | IN               | OUT   | ←→           |           |

| PA6             | IN | OUT  |   | IN               | ουτ   | <>           |           |

| PA7             | IN | OUT  |   | IN               | ουτ   | <>           |           |

| PBO             | IN | OUT  |   | IN               | Ουτ   |              |           |

| PB1             | IN | OUT  |   | IN               | OUT   |              |           |

| PB <sub>2</sub> | IN | OUT  |   | IN               | OUT   |              |           |

| PB3             | IN | OUT  |   | IN               | OUT   |              | MODE 0    |

| PB4             | IN | OUT  |   | IN               | OUT   |              | OR MODE 1 |

| PB5             | IN | OUT  |   | IN               | OUT   |              | ONLY      |

| PB6             | IN | OUT  |   | IN               | Ουτ   |              |           |

| PB7             | IN | OUT  |   | IN               | OUT   |              |           |

| PC0             | IN | оυт  |   | INTRB            | INTRB | I/O          |           |

| PC1             | IN | OUT  |   | 1BF <sub>B</sub> | OBFB  | I/O          |           |

| PC2             | IN | OUT  |   | STBB             | ACKB  | I/O          |           |

| PC3             | IN | Ουτ  |   | INTRA            | INTRA | INTRA        |           |

| PC4             | IN | OUT  |   | STBA             | 1/0   | STBA         |           |

| PC5             | IN | OUT  |   | IBFA             | 1/0   | IBFA         |           |

| PC6             | IN | OUT  |   | 1/0              | ACKA  | ACKA         |           |

| PC7             | IN | OUT  |   | 1/0              | OBFA  | OBFA         |           |

TABLE 3-2. 8255A MODE DEFINITION SUMMARY

the device at A23 is referred to as the "group 3" device. Each device has three eight-bit ports. The "group 1" ports are designated Ports 1, 2 and 3; the "group 2" ports are designated Ports 4, 5 and 6 and the "group 3" ports are designated Ports 7, 8 and 9.

All three groups communicate with the bus master via the bidirectional bus drivers A9 and A10. Except for their separate chip select lines, they all use the same signal lines: the 8-bit data bus (DBO-DB7) and five control/address lines (IOR/, IOW/, RESET, ADRO and ADR1). The three select lines are labeled 55 CS0/ (A19), 55 CS1/ (A22) and 55 CS2/ (A23). The data lines bring control bytes or data bytes to an 8255A or deliver data from an 8255A to the bidirectional data buffer at the interface. The chip select control signals, 55 CSO/, 55 CS1/ and 55 CS2/, select the group 1, 2 and 3 devices, respectively, when the proper I/O address appears on the system address bus. 55 CSO/, 55CS1/ or 55 CS2/ results from decoding address bits 2 through 7 (ADR2-7), as shown on sheet 1 of the schematic. The two least significant address bits (ADR0 and ADR1) select the control register (when programming an 8255A) or one of the three I/O ports (when reading or writing data). IOR/ (8255A  $\rightarrow$  bus master) and IOW/ (bus master  $\rightarrow$  8255A) indicate the direction of data flow, as summarized in Table 3-3. Specific I/O addresses for the nine ports and three 8255A control registers on the SBC-519 are listed in Table 3-4.

A high on the RESET line clears all internal 8255A registers including the control register; all ports (A, B and C) are set for input.

All three groups have the same interface characteristics with respect to the system bus. They are also both capable of the same range of configurations with respect to their peripheral interfaces.

| _ <u>A1</u>      | <u>A0</u>        | IOR/        | _10W/            | <u></u>          | Input Operation (Read)                                                                                                            |

|------------------|------------------|-------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0<br>0<br>1      | 0<br>1<br>0      | 0<br>0<br>0 | 1<br>1<br>1      | 0<br>0<br>0      | Port A $\rightarrow$ Data Bus<br>Port B $\rightarrow$ Data Bus<br>Port C $\rightarrow$ Data Bus                                   |

|                  |                  |             |                  |                  | Output Operation (Write)                                                                                                          |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>1<br>1 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | Data Bus $\rightarrow$ Port A<br>Data Bus $\rightarrow$ Port B<br>Data Bus $\rightarrow$ Port C<br>Data Bus $\rightarrow$ Control |

|                  |                  |             |                  |                  | Disable Function                                                                                                                  |

| x<br>1           | x<br>1           | x<br>0      | x<br>1           | 1<br>0           | Data Bus $\rightarrow$ High-Impedance Illegal                                                                                     |

TABLE 3-4. PARALLEL I/O PORT ADDRESSES

| Port                        | 8255 Device Location                                        | *Eight-Bit Address (Hexadecimal)         |

|-----------------------------|-------------------------------------------------------------|------------------------------------------|

| Group 1<br>1<br>2<br>3<br>- | A19 Port (A)<br>A19 Port (B)<br>A19 Port (C)<br>A19 Control | XO<br>X1<br>X2<br>X3 For I/O write only. |

| Group 2<br>4<br>5<br>6<br>- | A22 Port (A)<br>A22 Port (B)<br>A22 Port (C)<br>A22 Control | X4<br>X5<br>X6<br>X7 For I/O write only. |

| Group 3<br>7<br>8<br>9<br>- | A23 Port (A)<br>A23 Port (B)<br>A23 Port (C)<br>A23 Control | X8<br>X9<br>XA<br>XB For I/O write only. |

\*Notes: X is any hex digit assigned by jumper selection

The operating characteristics of each port are determined by the mode and direction control information supplied by the bus master in its control word. In addition, certain mode/port relationships impose restrictions on the use of other ports in the group. These mode-related characteristics and restrictions are discussed briefly below. Details regarding mode implementation and the associated interport restrictions are presented in Chapter 4, User Selectable Options.

Since the three groups are functionally identical, only one group (group 1) will be referred to in the following discussion. Statements made about group 1 ports apply equally to group 2 and 3 ports. The reader should keep in mind, however, that the peripheral interface consists of three sets of equally versatile ports, which are independently programmed.

The allowable port configurations for each group are summarized below:

Port 1 (Group 1 Port A)

Mode 0 Input Mode 0 Output (Latched) Mode 1 Input (Strobed) Mode 1 Output (Latched) Mode 2 Bidirectional

Port 2 (Group 1 Port B)

Mode 0 Input Mode 0 Output (Latched) Mode 1 Input (Strobed) Mode 1 Output (Latched)

Port 3 (Group 1 Port C)

Mode 0 8 Bit Input Mode 0 8 Bit Output (Latched) Mode 0 Split 4 bit input and 4 bit output NOTE: Control mode dependent upon Port A and B mode. Port 1 is the most versatile of the three group 1 ports. It can be programmed to function in any one of the three 8255A operating modes. The first port is the only port in the group that can communicate with its peripheral devices via bidirectional bus driver circuits (two 8226/16 bus driver devices at A40 and A41).

Before Port 1 is programmed for input or output in any one of three operating modes (as described in Section 3.2.1), certain jumper connections must be made to allow the port to function properly in the chosen mode. The 52-53-54-55 jumper pad specifies the direction of data flow for the two 8226/16 bidirectional bus drivers. If input in mode 0 or mode 1 is to be programmed for Port 1, jumper pair 52-55 should be connected. If output in mode 0 or mode 1 is to be used jumper pair 54-55 should be connected. If Port 1 is to be programmed for bidirectional mode 2, then a wire must be run from jumper pin 53 to pin 55. This connection allows the Port 3 acknowledge output ACK/, which is available at bit 6 of Port 3, to dynamically dictate direction for the two 8226/16 devices.

NOTE: \*Indicates a default connection, which is the factoryselected connection. If some path other than the one provided by a default connection is selected (e.g., pins 52-55), the default wire must be removed (e.g., delete 53-55\*)

When Port 1 is programmed for mode 1 or mode 2, an interrupt can be added to the Port 1 bit array by connecting jumper pins 74 and 77 (delete  $75-77^{*}$ ). This allows the INTR output from bit 3 of Port 3 to activate the peripheral I/O interrupt request INTR PORT XØ. Refer back to Section 3.2.1 for details regarding INTR.

INTR PORT  $X\emptyset$  is forwarded to the interrupt logic shown on sheet 1 of the schematic.

When Port 1 is in mode 0, which has no provision for interrupts, the default connections  $64-73 \times 75-77$  must remain to allow the use of bit 3 of Port 3 and to inhibit Port 1 interrupts.

Because the 8226 bus drivers are inverting devices, all data input to or output from Port I is considered to be negative true with respect to the levels at the Jl edge connector. If 8216 bus drivers are used all data is positive true with respect to levels at the Jl edge connector.

Port 2 can be programmed for input or output in either mode 0 or mode 1 (see Section 3.2.1). If Port 2 is to be used for input (in either mode), terminator networks must be installed in the sockets at A43 and A29. Because of the passive nature of termination networks, data that is input to Port 2 must be positive true. If Port 2 is to be used for output (in either mode), driver networks must be installed in the sockets at A43 and A29. Assuming that the drivers are inverting devices, then the data being output will be negative true at the J1 edge connector.

When Port 2 is programmed for mode 1, a Port 2 interrupt can be implemented by connecting jumper pins 61-60 (delete  $69-60^*$ ). This allows the INTR output from bit 0 of Port 3 to activate the peripheral I/O interrupt request INTR PORT X1. This interrupt is forwarded to the interrupt logic shown on sheet 1 of the schematic.

When Port 2 is in mode 0, the default connections  $61-70^*$  and  $69-60^*$  must remain to allow the use of bit 0 of Port 3 and to inhibit Port 2 interrupts.

As was described in Section 3.2.1, the use of Port 3 depends on

the modes programmed for Ports 1 and 2. If Port 1 is in mode 1 or mode 2, bits 3, 4, 5, 6 and 7 of Port 3 can have the following dedicated control functions.

Port 3 bit  $3 \rightarrow INTR$  (interrupt request) - input or outputPort 3 bit 4  $\leftarrow$  STB/ (input strobe)Port 3 bit 5  $\rightarrow$  IBF (input buffer full flag)Port 3 bit 6  $\leftarrow$  ACK/ (output acknowledge)Port 3 bit 7  $\rightarrow$  OBF/ (output buffer full flag)

If Port 2 is in mode 1, bits 0, 1 and 2 of Port 3 have these dedicated control functions:

While certain Port 3 bits are available if Port 1 is in mode 1 or if Port 2 is in mode 0, the use of Port 3 as an eight-bit data path is restricted to those configurations that have both Port 1 and Port 2 programmed for mode 0. In this case all 8 bits of Port 3 can be programmed for mode 0 input (termination networks must be installed in the sockets at A28 and A42) or output (driver networks must be installed at A28 and A42) or split 4 bits input and 4 bits output.

NOTE: If Port 1 and 2 are not both in mode 0, then a driver network must be installed in the sockets at A42 and a termination network must be installed at A28, so that the Port 3 control lines can function properly.

#### 3.3 INTERRUPT CONTROLLER

The Interrupt Controller logic consists of Intel's powerful 8259 Interrupt Controller device and various sets of jumper pins that allow the user to select up to eight interrupt sources out of 10 possible sources for connection to the 8259's eight interrupt request inputs.

The 8259 resolves priority among the eight levels according to an algorithm that is program-selected by the user. The Interrupt Controller is shown on sheet 1 of the SBC-519 schematic (Appendix A).

Section 3.3.1 provides a basic functional description of the 8259 and Section 3.3.2 summarizes the operational characteristics of the 8259.

#### 3.3.1 8259 BASIC FUNCTIONAL DESCRIPTION

The 8259 is a device specifically designed for use in real time interrupt driven, microcomputer systems. It manages eight levels of requests. It is programmed by the system's software as an I/O peripheral. A selection of priority algorithms is available to the programmer so that the manner in which the requests are processed by the 8259 can be configured to match the user's system requirements. The priority assignments and algorithms can be changed or reconfigured dynamically at any time during the main program. This means that the complete interrupt structure can be defined as required, based on the total system environment.

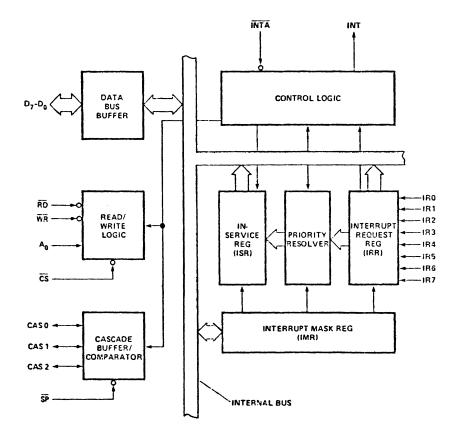

A functional block diagram of the 8259 is shown in Figure 3-12. The various functional blocks are described below:

Interrupt Request Register (IRR) and In-Service Register (ISR)

The interrupts at the IR input lines are handled by two registers in cascade, the Interrupt Request Register (IRR) and the In-Service Register (ISR). The IRR is used to store all the interrupt levels that

FIGURE 3-12. 8259 INTERRUPT CONTROLLER

are requesting service; and the ISR is used to store all the interrupt levels that are being serviced.

Whenever there is a positive transition at an IR input, the corresponding IRR bit is set and the INT line is raised high. Since IRR bits are set independently of one another, more than one IRR bit can be set at the same time so long as they are not masked. Masked IRR bits are held reset regardless of any transitions at their IR inputs.

The bus master responds to the interrupt request (INT) by placing the 8259 in the polled mode and then reading the 8259 port. The resulting RD/ pulse sets the ISR bit that corresponds to the highest priority active (set) IRR bit and then resets that IRR bit. The ISR bit remains set during the service routine until an EOI (End of Interrupt) or SEOI (Specific End of Interrupt) command is received by the 8259.

Priority Resolver

This logic block determines the priorities of the bits set in the IRR. The highest priority is selected and strobed into the corresponding bit of the ISR during RD/ pulse.

INT (Interrupt)

This output goes to the bus master.

INTA/(Interrupt Acknowledge)

This input is not used in the SBC-519's 8259.

Interrupt Mask Register (IMR)

The IMR stores the bits of the interrupt lines to be masked. The IMR operates on both the IRR and the ISR. Masking of a higher priority

bit will not affect the interrupt request lines of lower priority.

## Data Bus Buffer

This 3-state, bidirectional, 8-bit buffer is used to interface the 8259 to the SBC-519's internal data bus. Control words and status information are transferred through the Data Bus Buffer.

## Read/Write Control Logic

The function of this block is to accept commands from the bus master. It contains the Initialization Command Word (ICW) registers and Operation Command Word (OCW) registers, which store the various control formats for device operation. This function block also allows the status of the 8259 to be transferred onto the SBC-519 internal data bus.

#### CS/(Chip Select)

A "low" on this input enables the 8259. No reading or writing of the chip will occur unless the device is selected.

#### WR/(Write)

A "low" on this input enables the bus master to write control words (ICWs and OCWs) to the 8259.

## RD/(Read)

A "low" on this input enables the 8259 to send the status of the interrupt Request Register (IRR). In Service Register (ISR), the Interrupt Mask Register (IMR) or the BCD of the interrupt level on to the data bus. This input signal is used in conjunction with WR/ and RD/ signals to write commands into the various command registers as well as reading the various status registers of the chip. In the SBC-519, this line is tied directly to system address bit 0.

SP/(Slave Program)

Not used in SBC-519.

#### 3.3.2 8259 DETAILED OPERATIONAL SUMMARY

The powerful features of the 8259, as implemented in the SBC-519, are its programmability and its utilization of an interrupt vector response to a poll from the bus master. The normal sequence of events that the 8259 interacts with the Bus Master is as follows:

- 1. One or more of the INTERRUPT REQUEST lines (IR7-0) are raised high signaling the 8259 that the corresponding peripheral equipment(s) is demanding service.

- 2. The 8259 accepts these requests, resolves the priorities and sends an INT to the bus master.

- 3. The Bus Master acknowledges the INT by outputting an OCW3 word to the 8259 with the P bit set. This places the 8259 in the polled mode.

- 4. Following this OCW3, the bus master issues a RD/pulse to the 8259.

- 5. The RD/pulse causes the 8259 to set the appropriate IS flip-flop and gates the BCD code of the highest priority level requesting service out to the Bidirectional Data Buffer (A9, A10). The BCD code occupies bits 0-2 of the 8259 output byte. Bit 7 is an interrupt flag and is set. See Figure 3-13.

- 6. The same RD/pulse enables the bus driver elements of the Bidirectional Data Buffer, which drive the BCD code and interrupt flag onto the system data bus.

A0

- 7. The bus master shifts the BCD code two places to the left and adds it to the base address of the jump table. The resulting vector points to the location in the jump table that contains the base address of the appropriate interrupt service routine. The bus master jumps to that location and begins servicing the interrupt,

- 8. At the conclusion of the service routine, the bus master outputs an OCW2 with the EOI or SEOI bit set. If the EOI bit is set, the highest level active ISR bit is reset. If the SEOI bit is set, the BCD code of the appropriate priority level is also supplied in the OCW2 to specify the ISR bit that is to be reset. In either case, the EOI or SEOI bit resets the IS flip-flop that corresponds to the interrupt service routine just completed.

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|----|----|----|----|----|----|----|

| 1  |    |    |    |    | W2 | W1 | WO |

- WO-2: BCD code of the highest priority level requesting service.

- I: Interrupt flag = 1

- (): Undefined

FIGURE 3-13. PRIORITY LEVEL BCD CODE

#### Programming the 8259

The 8259 accepts two types of command words generated by the bus master.

- 1. Initialization Command Words (ICWs): Before normal operation can begin, the 8259 must be brought to a starting point--by a two-byte ICW sequence, timed by WR/pulses. This sequence is shown in Figure 2.2.

- NOTE: Bit D0 through D3 and A5 through A15 are ignored by the SBC-519's 8259. They can assume any value without affecting operation of this 8259. However, they do have significance in other 8259 applications.

- 2. Operation Command Words (OCWs): These are the command words that command the 8259 to operate in various modes, including:

- Rotating priority mode

- . Special mask mode

• Polled mode (This mode is always in effect during interrupt servicing.)

The OCWs can be written into the 8259 at anytime during operation.

Initialization Command Words 1 and 2: (ICW1 and ICW2)

Whenever a command is issued with A0 = 0 and D4 = 1 this is interpreted as Initialization Command Word 1 (ICW1), and initiates the initialization sequence. During this sequence, the following occur automatically:

- a. The edge sense circuit is reset, which means that following initialization, an interrupt request (IR) input must make a low to high transition to generate an interrupt.

- b. The interrupt Mask Register is cleared.

- c. IR 7 input is assigned priority 7.

- d. Special Mask Mode Flip-flop and status Read Flip-flop are reset.

Initialization Command Word 2 (ICW2) is received by the 8259 right after ICW1. ICW1 provides two psuedo control bits and 2 or 3 psuedo interrupt CALL address bits. ICW2 provides 8 additional psuedo CALL address bits. These are referred to here as <u>psuedo</u> control and CALL address bits because the <u>SBC-519 8259 does not use them</u>. While they have no significance in the SBC-519, the Initialization Command Words are <u>required</u> by the 8259 and, so, are a necessary part of the 8259 programming architecture.

#### Operation Command Words (OCWs)

After the ICWs are programmed into the 8259, the chip is ready to accept interrupt requests at its input lines. At any time following initialization sequence, a selection of algorithms can command the 8259 to operate in various modes through the Operation Command Words (OCWs).

One of these modes, the polled mode, is invoked each time the 8259 issues an INTR/ to the bus master. The other modes are optional and can be implemented as needed to change priority relationships (rotating priority mode) or disable selected interrupt levels (mask mode).

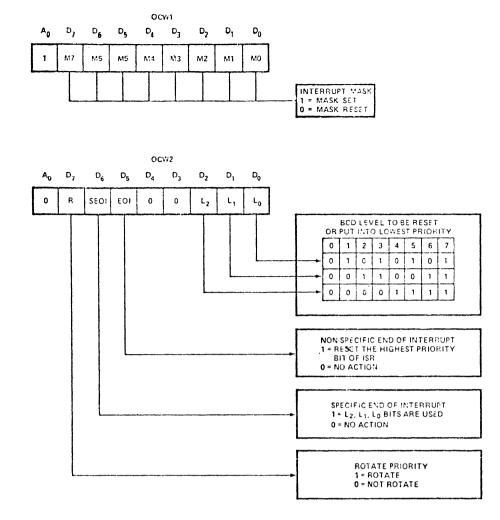

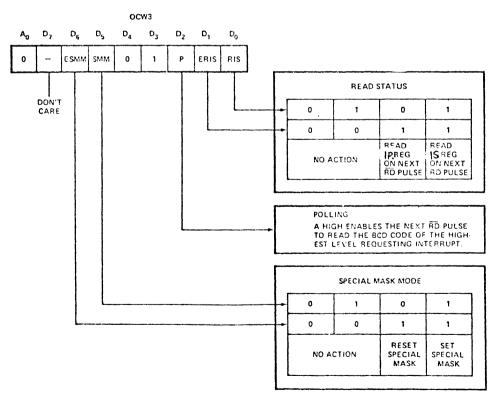

These modes and their associated OCWs are summarized in Table 3-5 and Figure 3-14 and are described below.

#### Polled Mode

The 8259 enters the polled mode when it receives an OCW3 command with the P bit set. This occurs in response to the INTR/ signal that the 8259 issues to the bus master. The 8259 issues INTR/ whenever its highest priority interrupt request is not currently being serviced. INTR/ may occur during the service routine for a lower priority interrupt. How such events are managed is entirely a function of program structure. For example, the current service routine can be allowed to run to completion before servicing the new, higher priority request. In this case, the bus master INT input would remain disabled until completion of the service routine. Or, a routine næsting procedure can be used to process the higher priority request immediately. This technique requires that the bus master's INT input be enabled (via the EI instruction) while each service routine is being executed.

When in the polled mode, the 8259 treats the subsequent RD/ pulse as an interrupt acknowledge. It resets the appropriate IR flip-flop, sets the corresponding IS flip-flop and enables the BCD code representing the interrupting level onto the data bus. This BCD code is used by the CPU as a pointer to a jump table. The designated jump table location contains the base address of the appropriate interrupt service routine. When the service routine is completed, it removes the 8259 from the polled mode. See Appendix C for additional service routine design information.

FIGURE 3-14. OPERATION COMMAND WORD FORMATS

## TABLE 3-5. SUMMARY OF OPERATION COMMAND WORD PROGRAMMING

|      | A0 | D4 | D3 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OCW1 | 1  |    |    | M7-M0                                                                                                                                                                                                        | IMR (Interrupt Mask Register). WR will load it while status can be read with RD.                                                                                                                                                                                                                                                                                                                      |

| OCW2 | 0  | 0  | 0  | R       SEOI       EOI         0       0       0         0       1       0         0       1       1         1       0       0         1       1       0         1       1       0         1       1       1 | No Action.<br>Non-specific End of Interrupt.<br>No Action.<br>Specific End of Interrupt: L2, L1, L0 is the BCD level to be reset.<br>No Action.<br>Rotate priority at ECI. (Auto Mode)<br>Rotate priority, L2, L1, L0 becomes bottom priority without<br>Ending of Interrupt.<br>Rotate priority at EOI (Specific Mode), L2, L1, L0 becomes<br>bottom priority, and its corresponding IS FF is reset. |

| OCW3 | 0  | 1  | 0  | ESMM SMM<br>0 0<br>1 1<br>1 0<br>1 1<br>ERIS RIS<br>0 0<br>0 1<br>1 0<br>1 1                                                                                                                                 | <ul> <li>Special Mask not Affected.</li> <li>Reset Special Mask.</li> <li>Set Special Mask.</li> <li>No Action.</li> <li>Read IR Register Status.</li> <li>Read IS Register Status.</li> </ul>                                                                                                                                                                                                        |

\* Note: The 8080 INT input must be disabled during:

1. Initialization sequence for all the 8259 in the system.

2. Any control command execution.

Interrupt Masks

Each Interrupt Request input can be masked individually by the Interrupt Mask Register (IMR) programmed through OCW1. The IMR will operate on both the Interrupt Request Register and the In-Service Register.

#### CAUTION

When interrupt sources are asynchronous with respect to the main program, it is possible for an ISR bit to be set between the time the program reads the IR status and the time it masks that IR level with an OCW1. If this happens, the IR level, although masked, will still inhibit the lower priorities. If desired, the lower priority interrupts can be enabled in either of two ways: (1) Write an End of Interrupt (EOI) command (OCW2) to reset the masked ISR bit or (2) Set the Special Mask Mode (SMM) using OCW3; the SMM technique is discussed later in the Special Mask Mode description.

Rotating Priority Mode

The Rotating Priority Mode of the 8259 serves an application of interrupting devices of equal priority such as communication channels. There are two variations of the rotating priority mode:

1. Auto Mode -- In this mode, a device after being serviced receives the lowest priority, so a device requesting an interrupt will have to wait, in the worst case, until 7 other devices are serviced at most once each, i.e., if the priority and "in service" status is:

| BEFORE ROTATE   | <u>157</u> | <u>1 S6</u> | 1S5     | $\underline{IS4}$ | 153        | $\underline{1S2}$ | <u>IS1</u> | ISO        |

|-----------------|------------|-------------|---------|-------------------|------------|-------------------|------------|------------|

| "IS" STATUS     | 0          | 1           | 0       | 1                 | 0          | 0                 | 0          | 0          |

|                 |            |             | OWEST 1 | PRIORI            | <u>ry</u>  | HIG               | IEST PI    | RIORITY    |

| PRIORITY STATUS | 7          | 6           | 5       | 4                 | 3          | 2                 | 1          | 0          |

| AFTER ROTATE    | <u>157</u> | <u>1S6</u>  | 185     | <u>IS4</u>        | <u>IS3</u> | <u>IS2</u>        | <u>IS1</u> | <u>IS0</u> |

| "IS" STATUS     | 0          | 1           | 0       | 0                 | 0          | 0                 | 0          | 0          |

|                 |            |             |         |                   |            |                   |            |            |

|                 |            | L(          | OWEST 1 | PRIORI            | ry         | HIG               | IEST P     | RIORITY    |

| PRIORITY STATUS | 4          | 3           | 2       | 1                 | 0          | 7                 | 6          | 5          |

In this example, the In-Service FF corresponding to line 4 (the highest priority FF set) was reset and line 4 became the lowest priority, while all the other priorities rotated correspondingly. The Rotate command is issued in OCW2, where: R = 1, EOI = 1, SEOI = 0.