### iSBC® 80/24A SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Order Number: 148437-001

THE GREEN PAGES AT THE END OF THIS MANUAL CONTAIN ERRATA. IF NO GREEN PAGES ARE PRESENT, THIS MANUAL HAD NO ERRATA AT PRESS TIME.

Copyright 1985, Intel Corporation, All Rights Reserved Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

| <b>REVISION HISTORY</b> | DATE  |

|-------------------------|-------|

| Original Issue.         | 11/85 |

|                         |       |

|                         |       |

|                         |       |

|                         |       |

|                         |       |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| Above             | iLBX                   | iPDS            | ONCE          |

|-------------------|------------------------|-----------------|---------------|

| BITBUS            | im                     | iPSC            | OpenNET       |

| COMMputer         | iMDDX                  | iRMX            | Plug-A-Bubble |

| CREDIT            | iMMX                   | iSBC            | PROMPT        |

| Data Pipeline     | Insite                 | iSBX            | Promware      |

| GENIUS            | Intel                  | iSDM            | QueX          |

| Δ                 | intel                  | iSXM            | QUEST         |

| i                 | intelBOS               | Library Manager | Ripplemode    |

| <sup>1</sup> 2ICE | Intelevision           | MCS             | <b>RMX/80</b> |

| ICE               | inteligent Identifier  | Megachassis     | RUPI          |

| iCEL              | inteligent Programming | MICROMAINFRAME  | Seamless      |

| iCS               | Intellec               | MULTIBUS        | SLD           |

| iDBP              | Intellink              | MULTICHANNEL    | UPI           |

| iDIS              | iOSP                   | MULTIMODULE     | VLSiCEL       |

|                   |                        |                 |               |

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Copyright 1985, Intel Corporation, All Rights Reserved

### PREFACE

This manual provides general information, installation and setup instructions, programming guidelines for the on-board devices, board level principles of operation, and repair and replacement assistance information for the iSBC 80/24A Single Board Computer. Related information is provided in the following documents:

- Intel MULTIBUS Specification, Order Number 9800683.

- Intel MULTIBUS Interfacing, Application Note AP-28A.

- Intel Microsystems Component Handbook, Order Number 230843.

- Using the 8259A Programmable Interrupt Controller, Application Note AP-59.

- Intel Memory Components Handbook, Order Number 210830.

- Intel's 5V EPROM/ROM Family, Application Note AP-30.

- Intel MCS-80/85 Family User's Manual, Order Number 205775.

- Intel RMX/80 User's Guide, Order Number 9800522.

- Intel iSBC 604/614 Cardcage Hardware Reference Manual, Order Number 9800708.

- Intel iSBC 655 System Chassis Hardware Reference Manual, Order Number 9800709.

- Intel iSBC 660 System Chassis Hardware Reference Manual, Order Number 9800505.

- Intel iSBX 331 Fixed/Floating Point Math MULTIMODULE Board Hardware Reference Manual, Order Number 142668.

- Intel iSBX 344 Intelligent BITBUS<sup>™</sup> Interface Board User's Guide, Order Number 148009.

- Intel iSBX 350 Parallel I/O MULTIMODULE Board Hardware Reference Manual, Order Number 9803191.

- Intel iSBX 351 Serial I/O MULTIMODULE Board Hardware Reference Manual, Order Number 9803190.

·

### NOTE TO READERS:

This hardware reference manual utilizes a *visual* scheme to denote section levels, rather than a *numerical* scheme used in many technical documents. This visual scheme allows you to more readily identify which section headings are subsections. Therefore, each section will have the same numbering convention throughout the manual (i.e., section 1-3, section 2-20, section 4-32). The visual distinction among the different sizes and the different fonts used for section headings indicate what level or order a particular section occupies. The following example illustrates how this system is used in this manual:

| 3-27. 8259A PIC PROGRAMMING      | 1st Order Heading |

|----------------------------------|-------------------|

| 3-28. INTERRUPT PRIORITY MODES   | 2nd Order Heading |

| 3-29. FULLY NESTED MODE. In this | 3rd Order Heading |

By glancing through this manual before you start reading, the visual method of section ordering will become apparent. You may also refer to the Table of Contents on page vii, to see how the sections compare to each other.

### CONTENTS

#### CHAPTER 1 GENERAL INFORMATION Introduction

| Introduction                  | 1-1   |

|-------------------------------|-------|

| Description                   | 1-1   |

| Documentation Supplied        | 1-2   |

| Additional Equipment Required | 1-2   |

| Specifications                | 1 - 2 |

### CHAPTER 2

| PREPARATION FOR USE                                     |       |

|---------------------------------------------------------|-------|

| Introduction                                            |       |

| Unpacking & Inspection                                  | . 2-1 |

| Installation Considerations                             | . 2-1 |

| Minimal Operating Requirements                          | . 2-1 |

| Power Requirements                                      | . 2-1 |

| Cooling Requirements                                    | . 2-1 |

| Component Installation                                  |       |

| ROM/PROM/EPROM Installation                             |       |

| EPROM Device Type Configuration                         | . 2-2 |

| Line Drivers & I/O Terminators                          |       |

| Jumper Configurations                                   |       |

| RAM Capacity & Addressing                               |       |

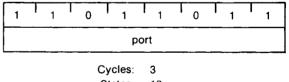

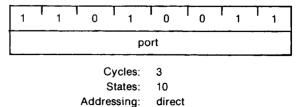

| Serial Port                                             |       |

| Parallel Ports                                          |       |

| Interrupt Matrix                                        |       |

| Connector Information                                   |       |

| Multibus <sup>®</sup> Signal Characteristics            | 2-14  |

| Parallel I/O DC Characteristics                         |       |

| Board Priority Resolution                               | 2-26  |

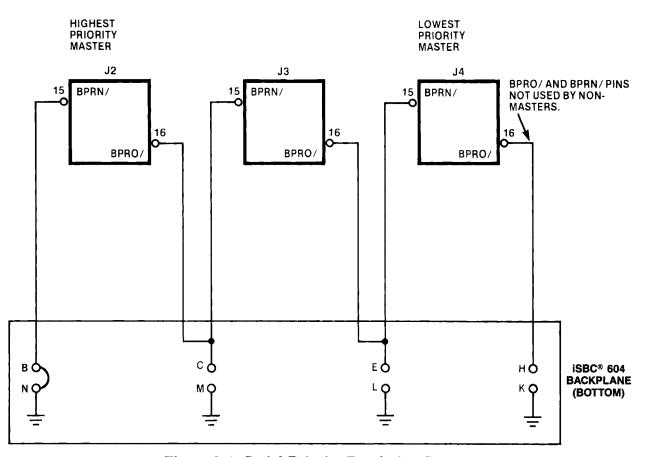

| Serial Priority                                         | 2-26  |

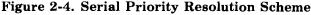

| Parallel Priority Resolution                            | 2-27  |

| Power-Fail/Battery Backup Provisions                    | 2-27  |

| Parallel I/O Cabling                                    | 2-28  |

| Serial I/O Cabling                                      | 2-29  |

| Current Loop (TTY) Interface                            | 2-30  |

| Multimodule <sup>™</sup> Boards & iSBX <sup>™</sup> Bus |       |

| Final Installation                                      |       |

#### CHAPTER 3 PROGRAMMING INFORMATION

| Introduction                               |

|--------------------------------------------|

| Memory Addressing 3-1                      |

| I/O Addressing 3-1                         |

| System Initialization 3-1                  |

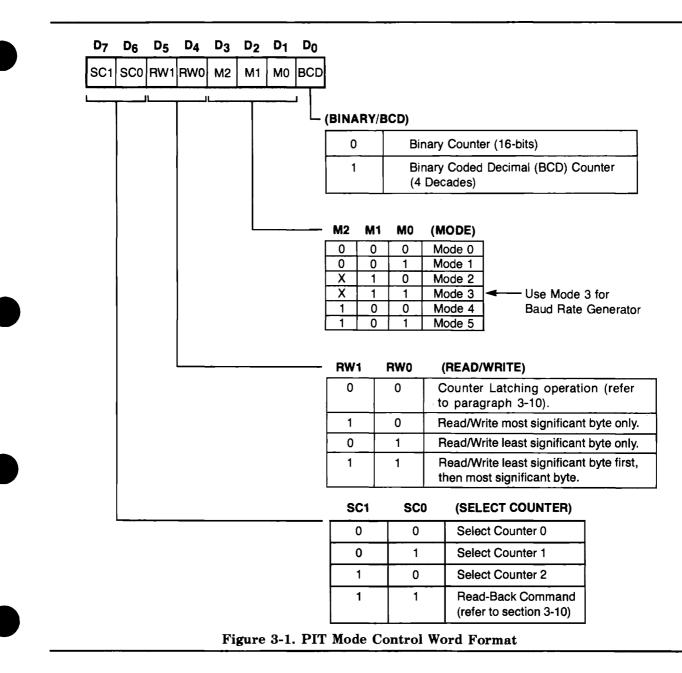

| 8254 Programmable Interval Timer           |

| (PIT) Programming                          |

| Mode Control Word & Count                  |

| Addressing                                 |

| Initialization                             |

| Operation                                  |

| Counter Read                               |

| Clock Frequency/Divide Ratio Selection 3-8 |

| Rate Generator/Interval Timer              |

| Interrupt Timer                            |

| 8251A Programmable Communications          |

| Interface (PCI) Programming                |

| Mode Instruction Format                    |

#### PAGE

#### PAGE

| Sync Characters                         |        |

|-----------------------------------------|--------|

| Command Instruction Format              | 3-11   |

| Reset                                   | 3-12   |

| Addressing                              | 3-12   |

| Initialization                          | 3-12   |

| Operation                               | 3-13   |

| 8255A Programmable Peripheral Interface |        |

| (PPI) Programming                       | 3-15   |

| Control Word Format                     |        |

| Addressing                              |        |

| Initialization                          |        |

| Operation                               |        |

| 8259A Programmable Interrupt Controller |        |

| (PIC) Programming                       | 3-17   |

| Interrupt Priority Modes                |        |

| Fully Nested Mode                       |        |

| Auto-Rotating Mode                      | 3-17   |

| Specific Rotating Mode                  | 3-18   |

| Polled Mode                             | 3-18   |

| Interrupt Mask                          | 3-18   |

| Special Mask Mode                       | 3-18   |

| Status Read                             | 3-18   |

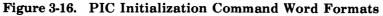

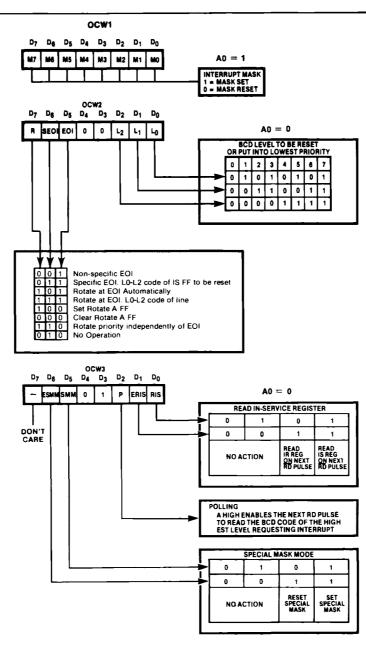

| Initialization Command Words            | 3-18   |

| Operation Command Words                 | 3-20   |

| Addressing                              | 3-20   |

| Initialization                          | 3-20   |

| Operation                               | 3-20   |

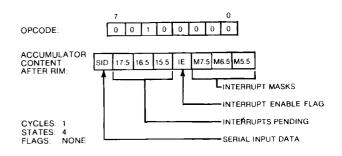

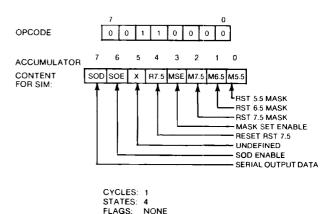

| 8085A Interrupt Handling                | 3-25   |

| Trap Interrupt                          | 3-25   |

| RST 7.5, 6.5, and 5.5 Inputs            | 3-25   |

| INTR Interrupt                          | 3-25   |

| RMX/80 <sup>™</sup> Software            | 3-26   |

| System Program Development              | . 3-26 |

|                                         |        |

#### **CHAPTER 4**

#### PRINCIPLES OF OPERATION

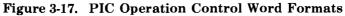

| Introduction                            | 4-1 |

|-----------------------------------------|-----|

| Functional Description 4                | 4-1 |

| Timing 4                                | 4-1 |

| Central Processing Unit (CPU) 4         | 4-1 |

| Interval Timer 4                        | 4-2 |

| Serial I/O 4                            | 4-2 |

| Parallel I/O 4                          | 4-2 |

| Interrupt Control                       | 4-2 |

| ROM/EPROM Configuration 4               | 4-2 |

| RAM Configuration                       | 4-3 |

| Multimodule <sup>™</sup> Boards         | 4-3 |

| Multibus <sup>®</sup> Interface Control | 4-3 |

| Circuit Analysis                        | 4-3 |

| Initialization                          | 4-4 |

| Clock Circuits                          | 4-4 |

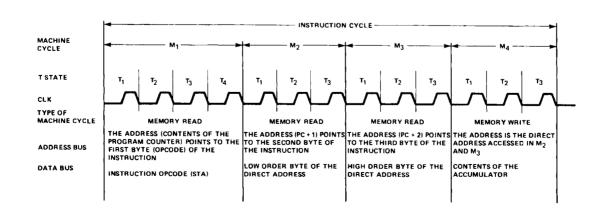

| 8085A-2 CPU Timing                      | 4-4 |

| Instruction Timing                      | 4-4 |

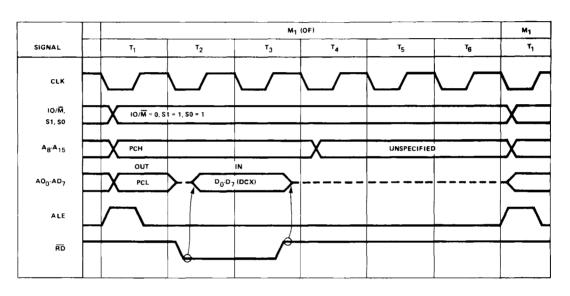

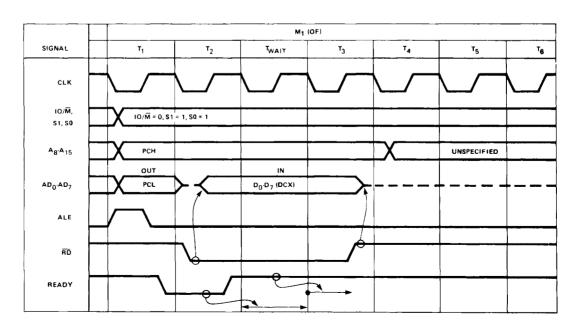

| Opcode Fetch Timing                     | 4-5 |

| Memory Read Timing                      |     |

|                                         |     |

### **CONTENTS** (Continued)

#### PAGE

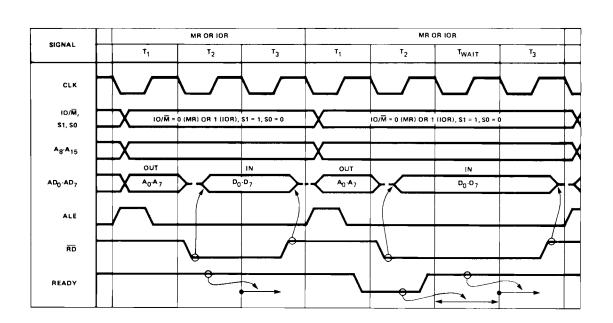

| I/O Read Timing              |     |     | 4-7  |

|------------------------------|-----|-----|------|

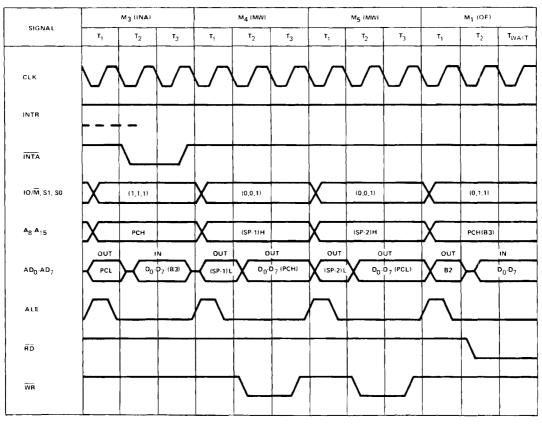

| Memory Write Timing          |     |     | 4-7  |

| I/O Write Timing             |     |     | 4-8  |

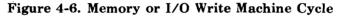

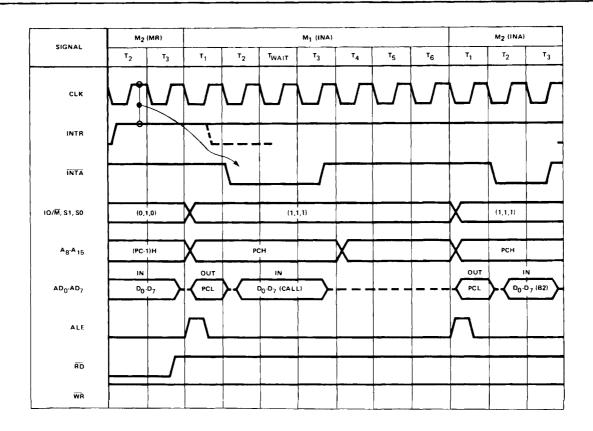

| Interrupt Acknowledge Timing |     |     | 4-8  |

| Address Bus                  |     | ••• | 4-10 |

| Bus Time-Out                 |     | ••• | 4-10 |

| Data Bus                     |     | ••• | 4-10 |

| Read/Write Signal Generation |     |     |      |

| I/O Control Signals          |     | ••• | 4-10 |

| Memory Control Signals       | • • | ••• | 4-10 |

| I/O Operation                |     |     | 4-11 |

| On-Board I/O Operation       |     |     | 4-11 |

| Off-Board I/O Operation      |     |     | 4-11 |

| Multibus® Interface          |     |     | 4-11 |

| Multibus® Override Feature   | ••• | •   | 4-12 |

| Failsafe Timer               |     |     | 4-12 |

| Interrupt Operation          | • • |     | 4-12 |

| Conclusion                   | ••  |     | 4-13 |

|                              |     |     |      |

#### PAGE

**TABLES**

Page

#### CHAPTER 5 SERVICE AND REPAIR INFORMATION

| Introduction                |  |

|-----------------------------|--|

| Service & Repair Assistance |  |

| Service Diagrams 5-1        |  |

| Internal Signals 5-3        |  |

#### APPENDIX A 8085A INSTRUCTION SET

APPENDIX B DECODE PROM (U32)

Table

APPENDIX C iSBC 80/20-4 BOARD; iSBC 80/24 BOARD; iSBC 80/24A BOARD FUNCTIONAL DIFFERENCES

| Table   | Title                                     | Page |

|---------|-------------------------------------------|------|

|         |                                           |      |

| 1-1.    | Specifications                            | 1-2  |

| 2-1.    | EPROM/ROM Configurations                  | 2-2  |

| 2-2.    | Wait State Jumpers                        | 2-3  |

| 2-3.    | Recommended I/O Terminators               |      |

| 2-4.    | Jumper Connections                        |      |

| 2-4A.   | Numerical Listing of Jumpers              |      |

| 2-5.    | Serial Port Jumper Options                | 2-9  |

| 2-6.    | <b>Configuration Jumpers for Parallel</b> |      |

|         | Ports E4 – EA                             | 2-10 |

| 2-7.    | Interrupt Matrix Jumper                   |      |

|         | Connections                               |      |

| 2-8.    | User Furnished Connector Details          | 2-16 |

| 2-9.    | Connector P1 Pin Assignments              |      |

| 2-10.   | Connector P1 Signal Definitions           |      |

| 2 - 11. | Connector P2 Pin Assignments              |      |

| 2-12.   | Connector P2 Signal Definitions           |      |

| 2-13.   | AC Characteristics at 4.84 MHz            | 2-20 |

| 2-14.   | AC Characteristics at 2.42 MHz            |      |

| 2-15.   | DC Characteristics (P1 Signals)           |      |

| 2-16.   | DC Characteristics (P2 Signals)           | 2-24 |

| 2-17.  | DC Characteristics (J1 & J2                    |

|--------|------------------------------------------------|

|        | Parallel I/O Ports) 2-24                       |

| 2-18.  | Connector J1 Pin Assignments 2-29              |

| 2-19.  | Connector J2 Pin Assignments 2-29              |

| 2-20.  | Connector J3 Pin Assignments 2-30              |

| 2-21.  | Connector Pin Correspondence                   |

|        | (25-Pin to 26-Pin) 2-30                        |

| 2-22.  | iSBX™ Bus Connector Pin                        |

|        | <b>Assignments</b> 2-31                        |

| 2-22A. | iSBX <sup>™</sup> Bus Signal Descriptions 2-31 |

| 3-1.   | EPROM/ROM Memory Size 3-1                      |

| 3-2.   | On-Board RAM Address                           |

|        | Space (Hexadecimal) 3-1                        |

| 3-3.   | I/O Port Addressing 3-2                        |

| 3-4.   | PIT Counter Operation Vs. Gate Inputs . 3-5    |

| 3-5.   | PIT Register Addresses 3-5                     |

| 3-6.   | Typical PIT Control Word 3-6                   |

| 3-7.   | PIT Control Word & Count Loading 3-6           |

| 3-8.   | Typical PIT Counter Read Subroutine 3-7        |

| 3-9.   | PIT Count Values & Rate Multipliers 3-9        |

Title

# \_intel

## **TABLES (Continued)**

| Table | Title                                   | Page   |   |

|-------|-----------------------------------------|--------|---|

| 3-10. | PIT Baud Rate Factors                   | 3-9    |   |

| 3-11. | PIT Rate Generator Frequencies          |        | ; |

|       | & Timer Intervals                       | . 3-10 |   |

| 3-12. | PIT Timer Intervals & Timer Counts      | 3-10   |   |

| 3-13. | PCI Address Assignments                 | 3 - 12 |   |

| 3-14. | Typical PCI Mode or Command             |        |   |

|       | Instruction Subroutine                  | 3-13   |   |

| 3-15. | Typical PCI Data Character              |        | ; |

|       | Read Subroutine                         | 3-13   |   |

| 3-16. | Typical PCI Data Character              |        | ; |

|       | Write Subroutine                        | 3-14   |   |

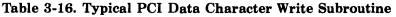

| 3-17. | Typical PCI Status Read Subroutine      | 3-14   |   |

| 3-18. | Parallel Port Configurations            | 3-15   | ł |

| 3-19. | Parallel Port I/O Addresses             | 3-15   | 4 |

| 3-20. | Typical PPI Initialization Subroutine . | 3-16   | 1 |

| 3-21. | Parallel I/O Interface Configurations . | 3-17   |   |

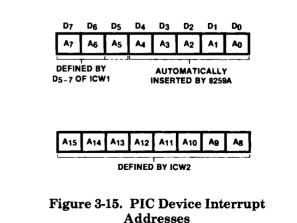

| 3-22. | PIC Device Address Insertion            | 3-20   | ] |

| 3-23. | PIC Addressing                          | . 3-20 | ( |

| 3-24. | Typical PIC Initialization Subroutine . | . 3-21 | ( |

| 3-25. | PIC Equates                             |        | ( |

| Table          | Title                                  | Page   |

|----------------|----------------------------------------|--------|

| 3-26.          | PIC Operation Procedures               | 3-22   |

| 3-27.          | Typical PIC Interrupt Request Register | 0.00   |

| 0.00           | Read Subroutine                        | 3-23   |

| 3-28.          | Typical PIC In-Service Register        |        |

|                | Read Subroutine                        | 3-24   |

| 3-29.          | Typical PIC Set Mask Register          |        |

|                | Subroutine                             | 3-24   |

| 3-30.          | Typical PIC Mask Register Read         |        |

|                | Subroutine                             | 3-24   |

| 3-31.          | Typical PIC End Of Interrupt           |        |

|                | Command Subroutine                     | 3-24   |

| 3- <b>3</b> 2. | Interrupt Vector Locations & Priority  | 3 - 25 |

| 3-33.          | Typical RST 5.5 Interrupt Routine      | 3-26   |

| 4-1.           | CPU Status & Control Lines             | 4-5    |

| 5-1.           | Glossary of Internal Signal            |        |

|                | Mnemonics                              | 5-3    |

| <b>B-1</b> .   | Decode PROM Map                        | . B-2  |

| C-1.           | Summary of 8085A Instructions          | . C-1  |

| C-2.           | Pin Assignments                        |        |

| C-3.           | Jumper Pairs                           |        |

|                |                                        |        |

### FIGURES

| Figure       | Title                               | Page   | Fi |

|--------------|-------------------------------------|--------|----|

| 1-1.         | iSBC® 80/24A Single Board           |        | 3- |

|              | Computer                            | 1-1    | 3- |

| <b>2-1</b> . | EPROM/ROM Device Positioning        |        |    |

|              | Guide                               | 2-2    | 3- |

| 2-2.         | EPROM Device Type Configurations    |        | 3- |

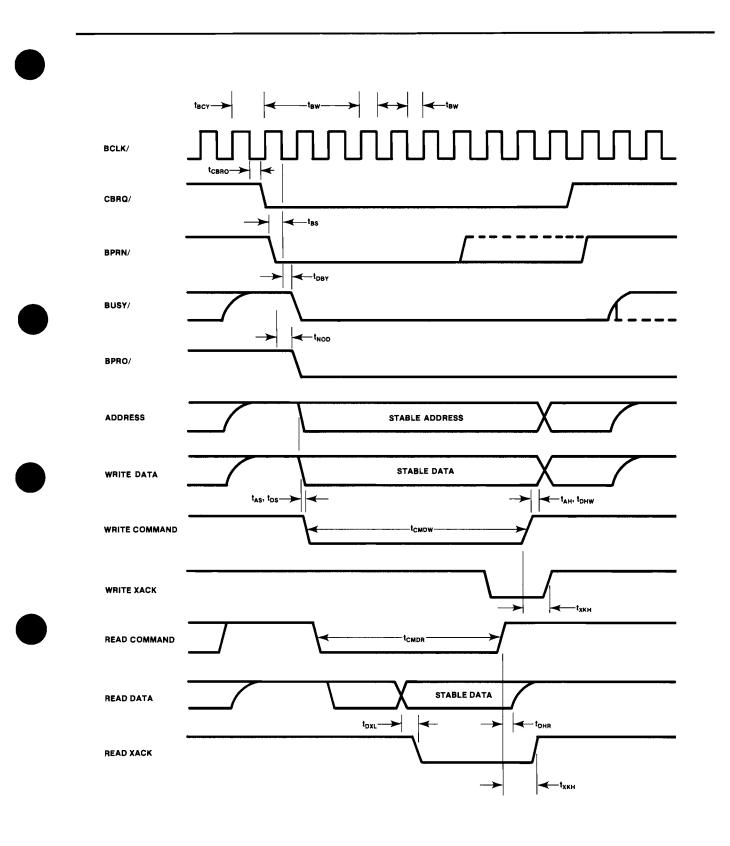

| 2-3.         | System Timing Diagram               |        |    |

| 2-4.         | Serial Priority Resolution Scheme   |        | 3- |

| 2-5.         | Parallel Priority Resolution Scheme |        |    |

| 3-1.         | PIT Mode Control Word Format        |        | 4- |

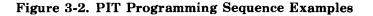

| 3-2.         | PIT Programming Sequence Example    |        |    |

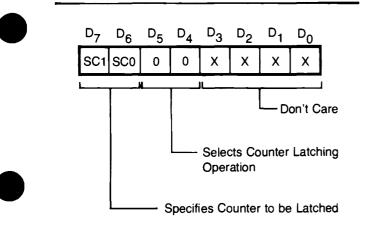

| 3-3.         | PIT Counter Register Latch Control  |        | 4- |

|              | Word Format                         | 3-7    | 4- |

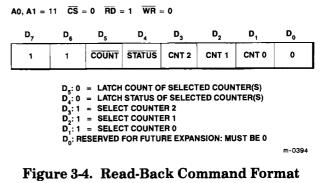

| 3-4.         | Read-Back Command Format            |        | 4- |

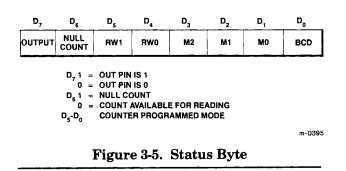

| 3-5.         | Status Byte                         |        | _  |

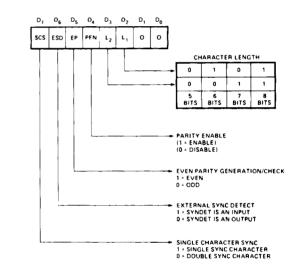

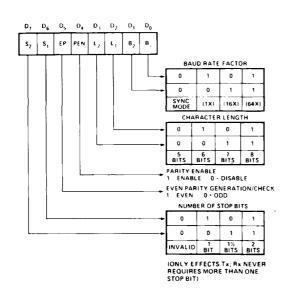

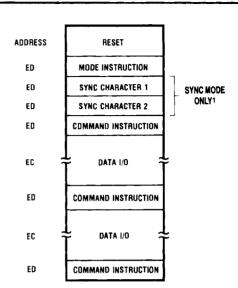

| 3-6.         | PCI Synchronous Mode Instruction    |        | 4- |

| •••          | Word Format                         | 3-10   | 4- |

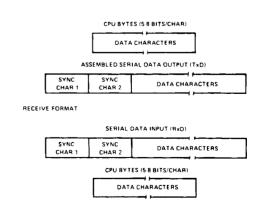

| 3-7.         | PCI Synchronous Mode Transmission   |        | 4- |

| • • • •      | Format                              |        | -  |

| 3-8.         | PCI Asynchronous Mode Instruction   |        | 5- |

| 0 0.         | Word Format                         | 3-11   | Ŭ  |

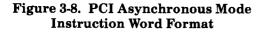

| 3-9.         | PCI Asynchronous Mode Transmissio   |        | 5- |

| 00.          | Format                              |        | Ŭ  |

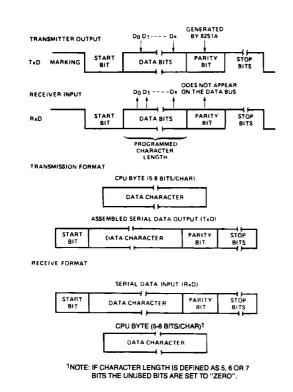

| 3-10.        | PCI Command Instruction Word        |        | 5- |

| 0 10.        | Format                              | 3.11   | Ŭ  |

| 3-11.        | Typical PCI Initialization & Data   |        | 5- |

| U 11.        | I/O Sequence                        | 3.12   | 0- |

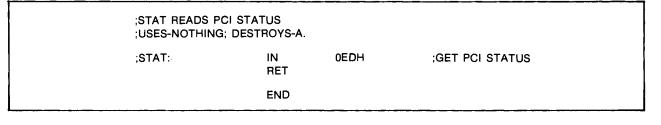

| 3-12.        | PCI Status Read Format              |        |    |

| 0-14.        | 1 Of Status Reau Pormat             | . 0-14 |    |

|              |                                     |        |    |

| Figure     | Title                                         | Page   |

|------------|-----------------------------------------------|--------|

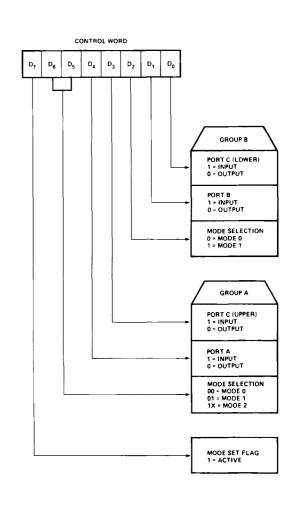

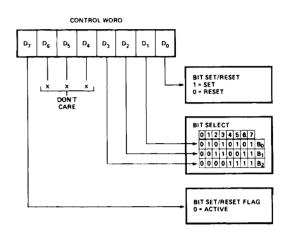

| 3-13.      | PPI Control Word Format                       | . 3-15 |

| 3-14.      | PPI Port C Bit Set/Reset Control              |        |

|            | Word Format                                   |        |

| 3-15.      | PIC Device Interrupt Address                  | . 3-18 |

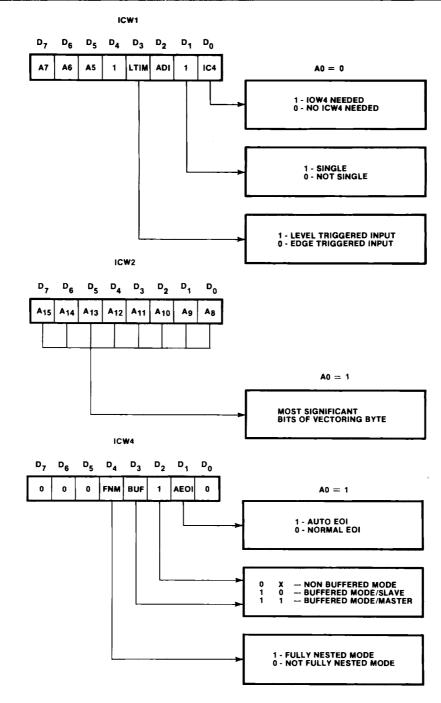

| 3-16.      | PIC Initialization Command                    |        |

|            | Word Formats                                  | . 3-19 |

| 3-17.      | PIC Operation Control Word                    |        |

|            | Formats                                       | 3-21   |

| 4-1.       | iSBC® 80/24A Board Simplified                 |        |

|            | Block Diagram                                 |        |

| 4-2.       | Typical CPU Instruction Cycle                 |        |

| 4-3.       | Opcode Fetch Machine Cycle                    | 4-6    |

| 4-4.       | Opcode Fetch Machine Cycle With<br>Wait State | 4-6    |

| 4-5.       | Memory or I/O Read Machine Cycle              | 4-7    |

| 4-6.       | Memory or I/O Write Machine Cycle             | 4-8    |

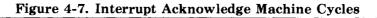

| 4-7.       | Interrupt Acknowledge Machine                 |        |

|            | Cycle                                         | 4-9    |

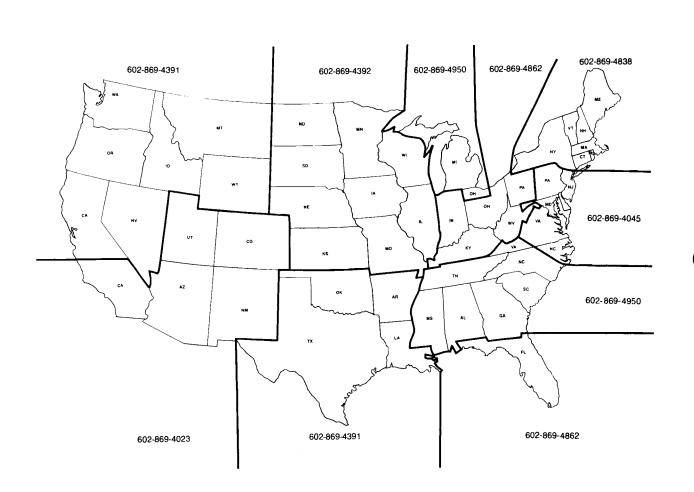

| 5-1.       | Territorial Service Telephone                 |        |

|            | Numbers                                       | 5-2    |

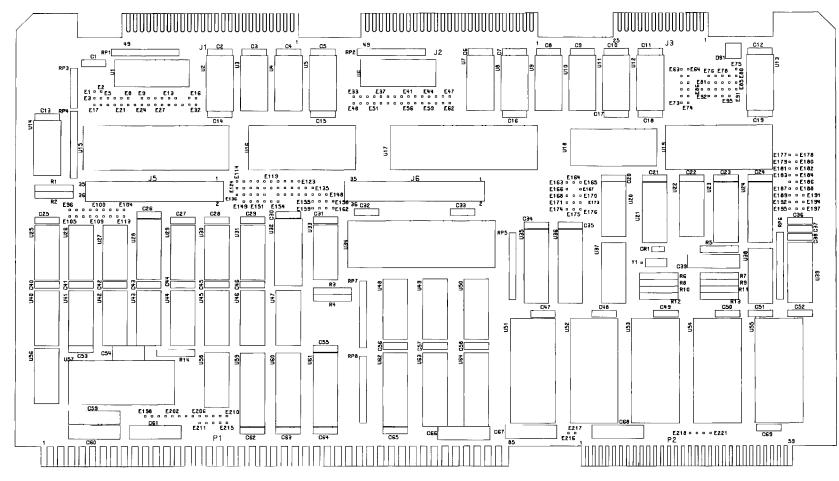

| 5-2.       | iSBC® 80/24A Board Component                  |        |

|            | Location Diagram                              |        |

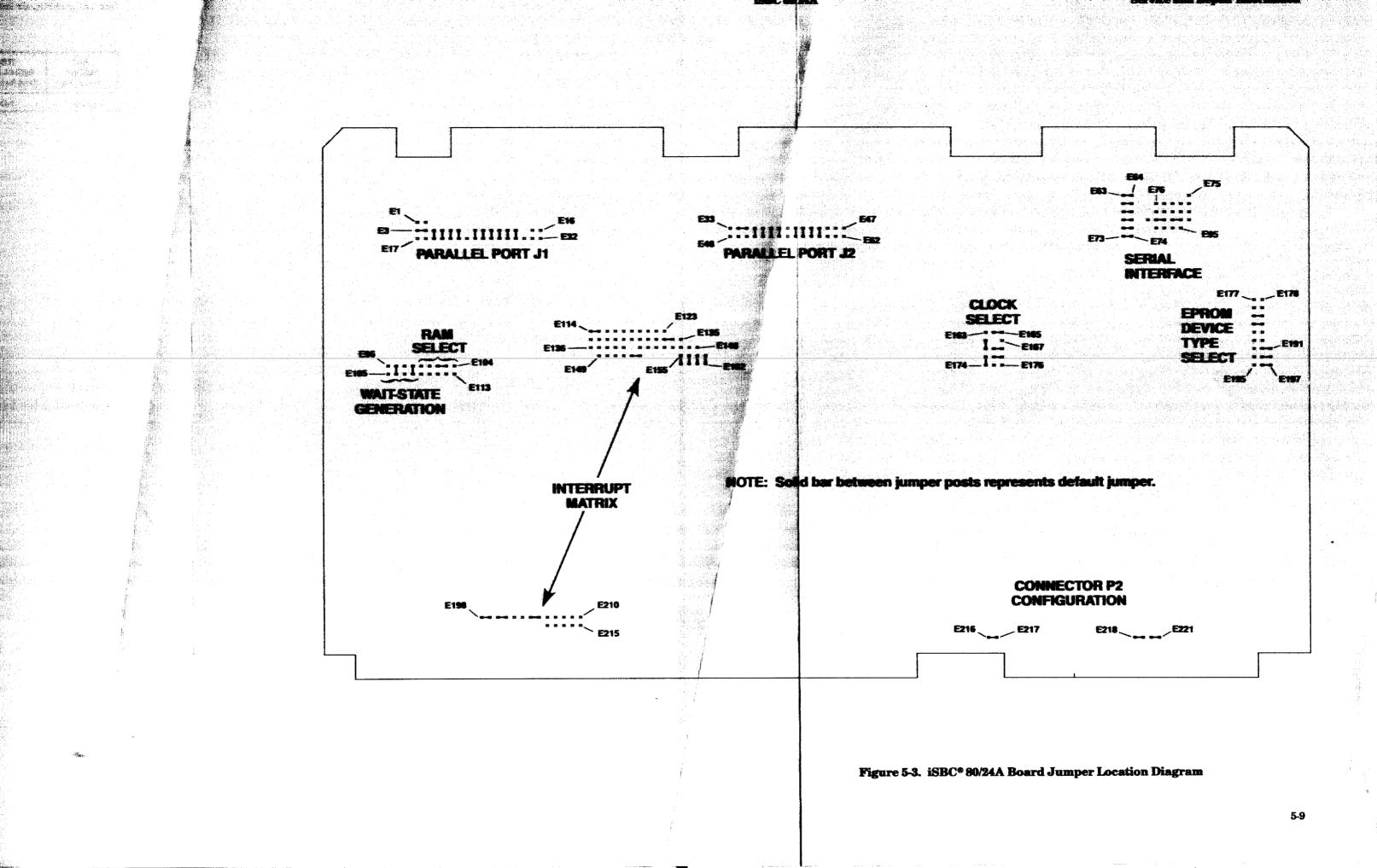

| 5-3.       | iSBC® 80/24A Board Jumper Locatio             |        |

| <b>F</b> 4 | Diagram                                       |        |

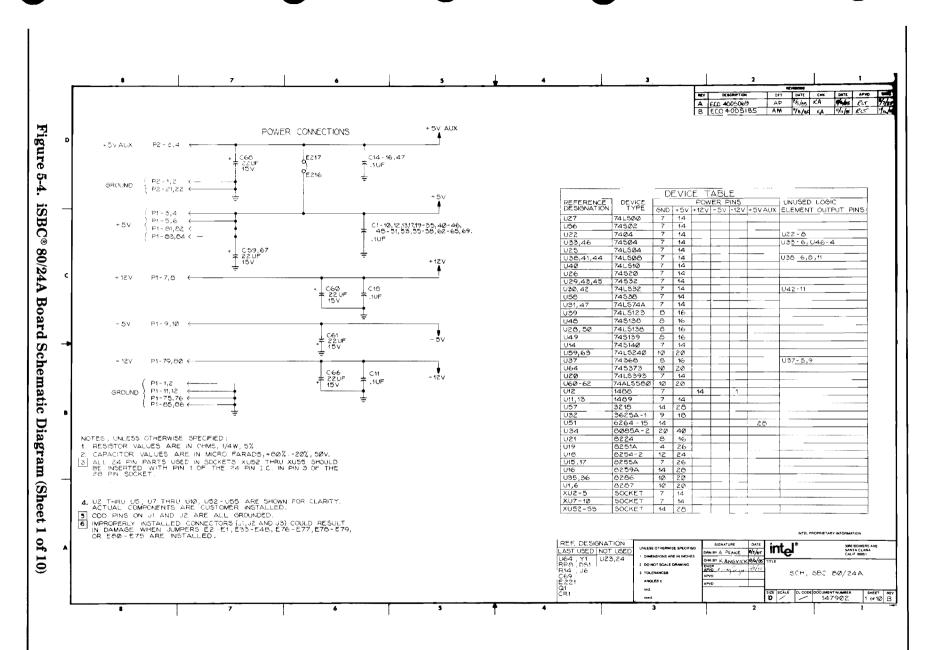

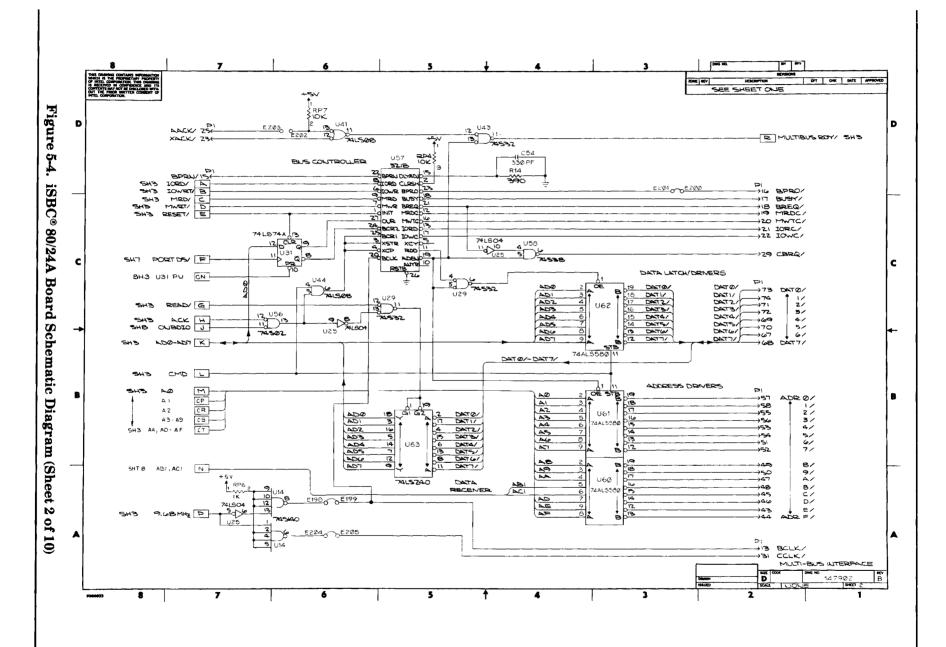

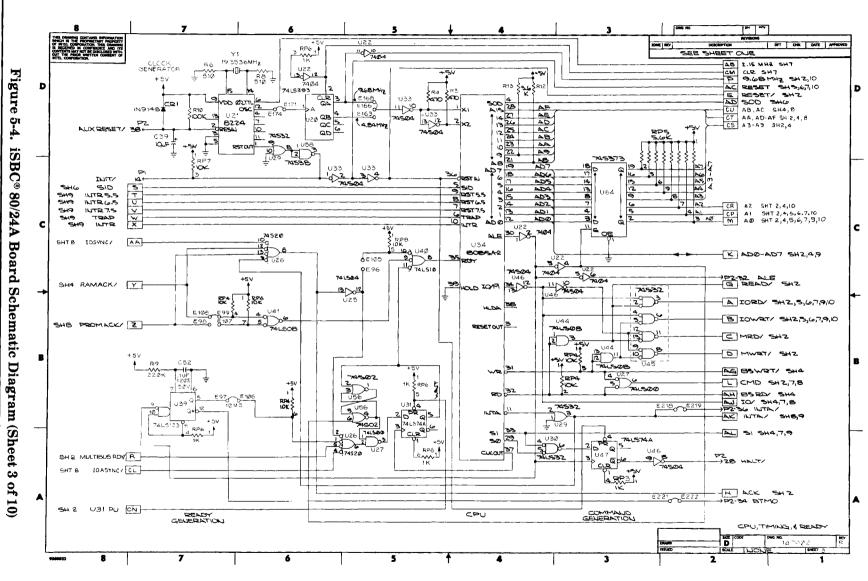

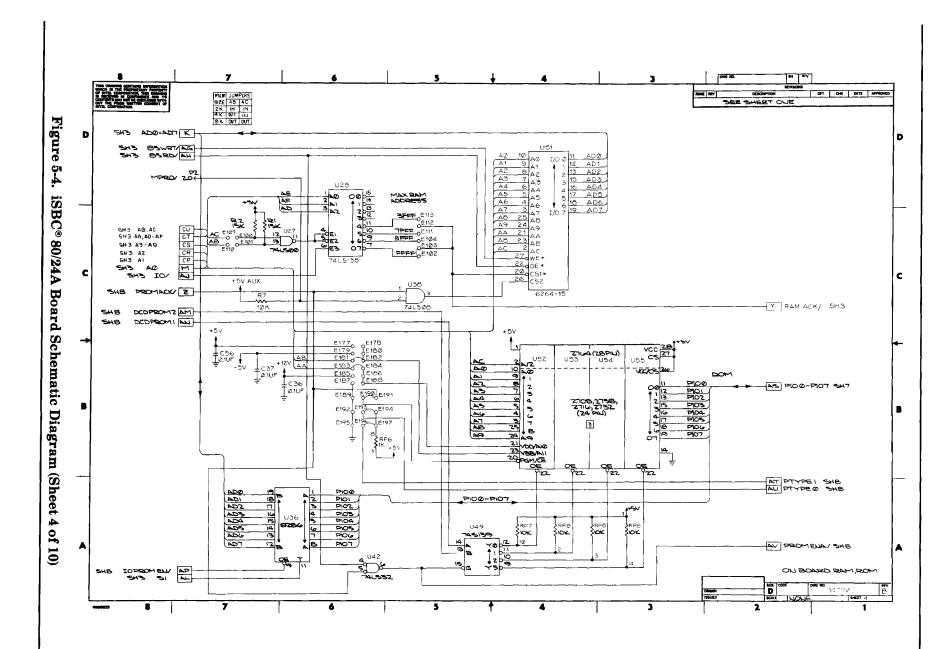

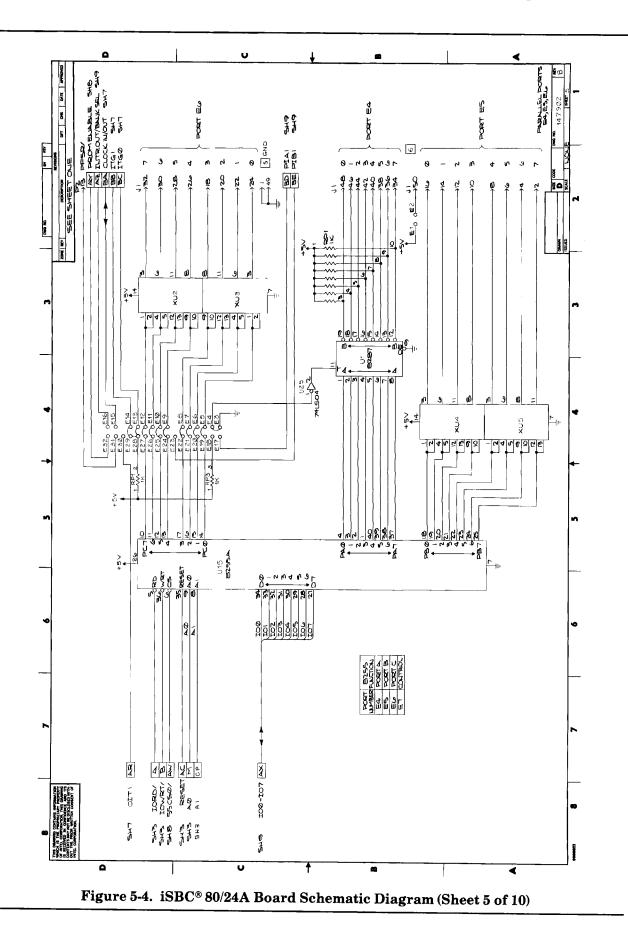

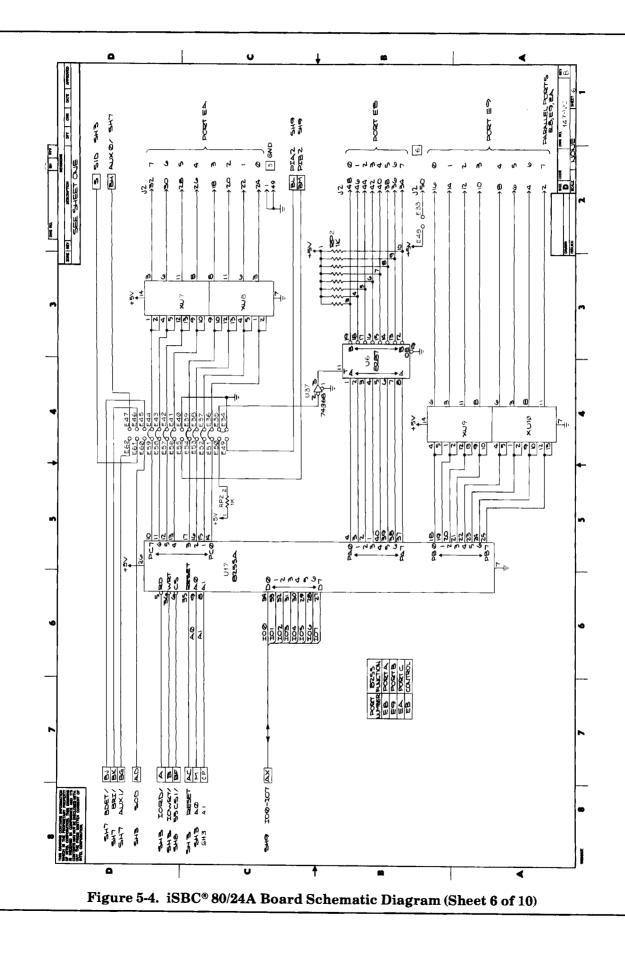

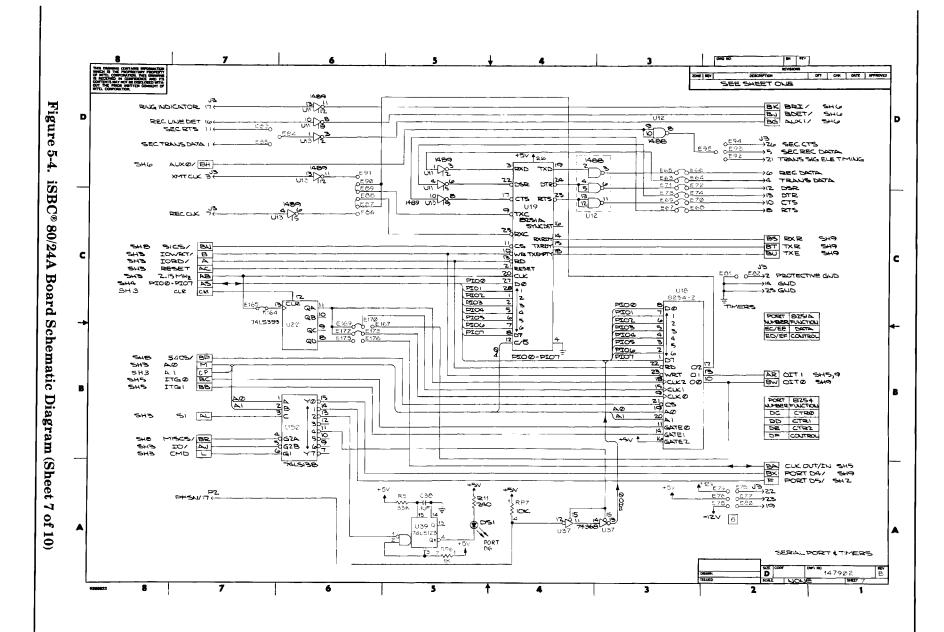

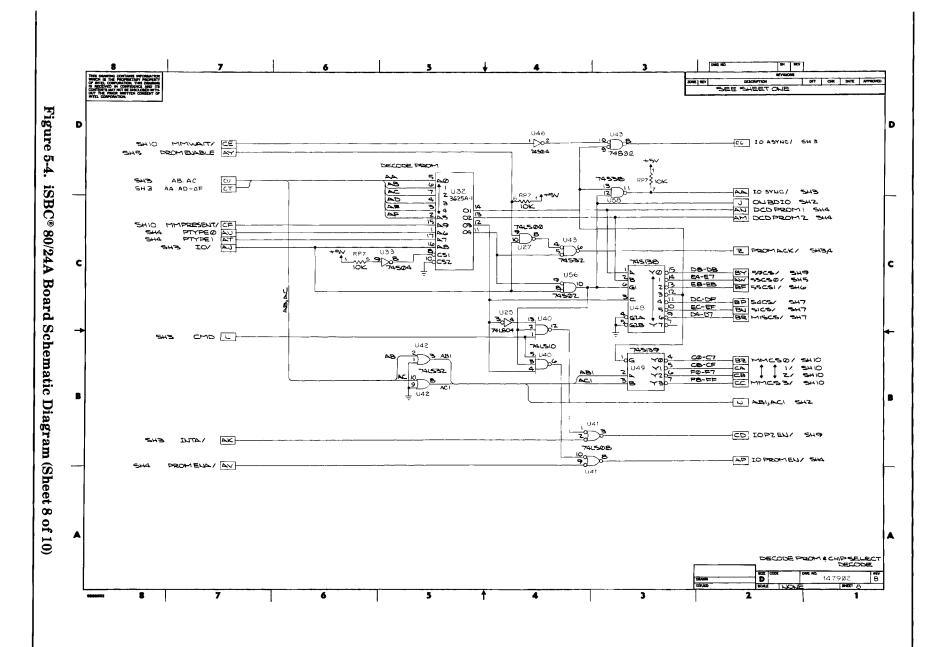

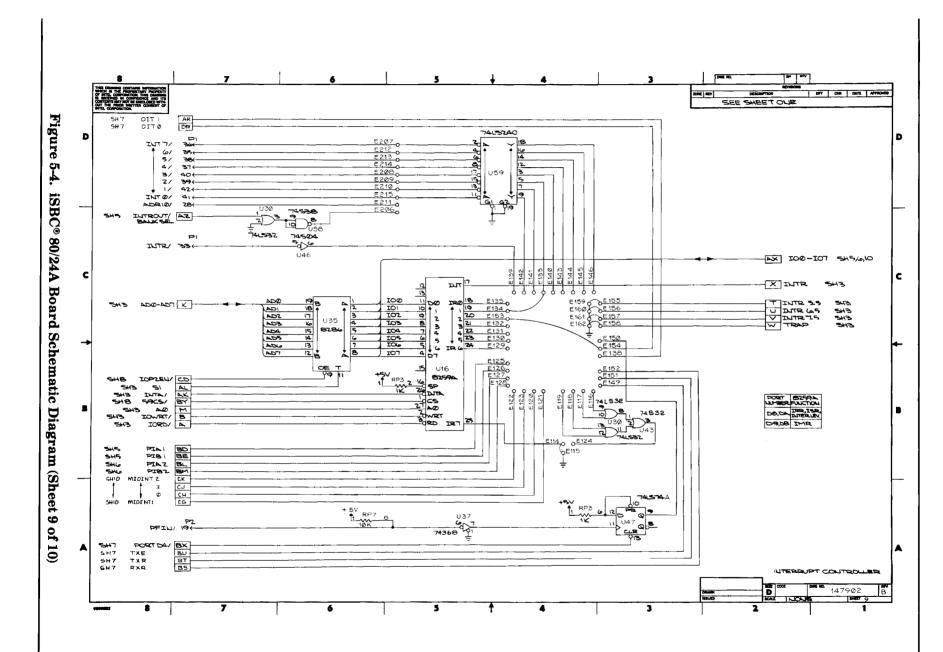

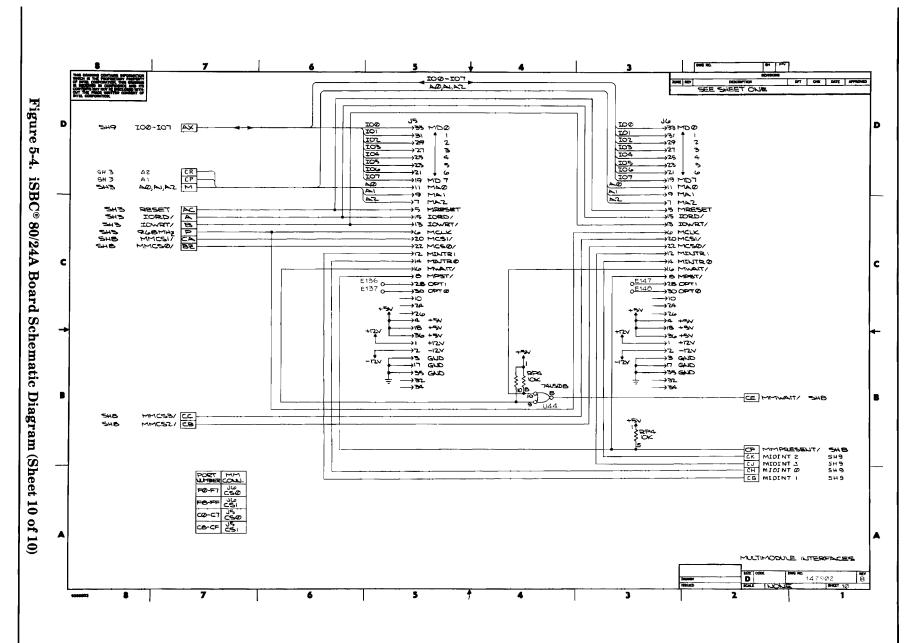

| 5-4.       | iSBC® 80/24A Board Schematic Diag             |        |

|            | (Sheets 1 – 10)                               | 5-11   |

### CHAPTER 1 GENERAL INFORMATION

#### **1-1. INTRODUCTION**

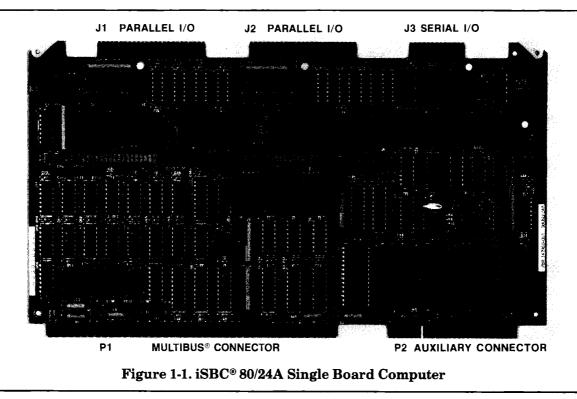

The iSBC 80/24A Single Board Computer is a Multibus and Multimodule compatible computer system on a single printed circuit assembly (figure 1-1). The iSBC 80/24A board includes an Intel 8085A-2 microprocessor, 8K bytes of on-board random access memory (RAM), sockets for up to 32K bytes of on-board read-only memory (ROM), six programmable 8-bit I/O ports, one programmable serial communications channel, a programmable interval timer, a programmable interrupt controller, and advanced bus controller circuitry.

This manual provides the information you will need to promptly install and operate the iSBC 80/24A board. To optimize your application of this flexible board, we suggest reading the entire manual before attempting installation and operation.

#### **1-2. DESCRIPTION**

The iSBC 80/24A board is controlled by an Intel 8085A-2 microprocessor operating at 4.84 MHz. System access is provided by the Multibus connector and an auxiliary connector. Off-board peripheral I/O operations are handled through 48 parallel lines, a serial communications channel connector and two iSBX Multimodule connectors.

The iSBC 80/24A board can directly access up to 64K bytes of memory. A single SRAM device supplies 8K bytes of on-board RAM. Also, the board can accept up to 32K bytes of user-installed ROM, PROM, or EPROM devices (either 24- or 28-pin devices as defined in Chapter 2).

The on-board 8254 Programmable Interval Timer (PIT) provides three independent counter outputs which may be configured to a variety of applications, including frequency output, rate generator, interval timer and real-time interrupts. One of these counters serves as the baud rate clock for the on-board 8251A Programmable Communications Interface (PCI) device.

Serial I/O operation is handled by an Intel 8251A Programmable Communications Interface (PCI) device. The board is configured to the RS232C structure; however, it may be adapted to a TTY interface using optional equipment. Baud rates are software programmable via the on-board timer.

ports may be configured to a variety of dedicated or general purpose applications. Two Intel 8287 Bus Transceiver devices are supplied for two of the ports and sockets for line driver or terminator devices are provided for the other four ports.

Up to eight interrupts are controlled by the 8259A Programmable Interrupt Controller (PIC), while four additional interrupts are handled directly by the 8085A-2 CPU. An interrupt jumper matrix allows the interrupt structure to be easily configured to your application.

Two iSBX bus connectors are provided on the iSBC 80/24A board. These connectors are designed to expand the board's I/O functions, using special purpose add-on Multimodule boards, such as the iSBX 344 Intelligent BITBUS<sup>™</sup> Interface Board. One or two iSBX Multimodule boards may be added, as required by your application.

The iSBC 80/24A board is designed to operate as a full master in any Intel Multibus compatible chassis. The board may also reside in your own custom

designed chassis, using Multibus compatible connectors (refer to Chapter 2).

#### **1-3. DOCUMENTATION SUPPLIED**

Each iSBC 80/24A board is shipped with a current set of schematic diagrams. Refer to Chapter 5 for related information.

#### 1-4. ADDITIONAL EQUIPMENT REQUIRED

The iSBC 80/24A board requires few optional components for operation. Depending on your application, you may need to purchase up to three I/O connectors and cables. Any on-board ROM/PROM must also be purchased separately. Chapter 2 provides information for selecting these items, based on your specific needs.

#### **1-5. SPECIFICATIONS**

Specifications of the iSBC 80/24A board are provided in table 1-1.

| CPU                                          | Intel 8085A-2                                    |

|----------------------------------------------|--------------------------------------------------|

| Operating Rate:                              | 4.84 MHz (default)<br>2.42 MHz (optional)        |

| Single Clock Cycle:                          | 206 ns (at 4.84 MHz)                             |

| Basic Instruction Cycle (four clock cycles): | 824 ns                                           |

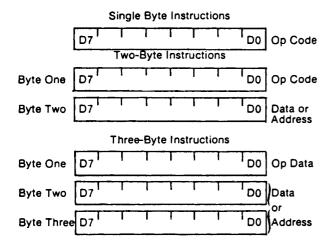

| WORD SIZE                                    |                                                  |

| Instruction:                                 | 8, 16, or 24 bits                                |

| Data:                                        | 8 bits                                           |

| Address:                                     | 16 bits                                          |

| SYSTEM CLOCK:                                | 9.68 MHz                                         |

| RAM ACCESS TIME:                             | 70 ns maximum (Valid data out from READ command) |

| MEMORY ADDRESSING<br>(factory configuration) |                                                  |

| On-Board ROM/EPROM:                          | 0-7FFFH                                          |

| On-Board RAM: E                              | E000-FFFFH                                       |

#### Table 1-1. Specifications

| MEMORY CAPACITY                 |                                                                       |                            |                   |        |            |                  |                  |                    |         |

|---------------------------------|-----------------------------------------------------------------------|----------------------------|-------------------|--------|------------|------------------|------------------|--------------------|---------|

| On-Board ROM/EPROM:             | Up to 32K byte                                                        | s (user-in                 | staller           | -1)    |            |                  |                  |                    |         |

| On-Board RAM:                   | 8K bytes                                                              | 3 (0361-11)                | Stanot            | .,     |            |                  |                  |                    |         |

|                                 | •                                                                     |                            |                   |        |            |                  |                  |                    |         |

| Off-Board Expansion:            | Up to 64K byt                                                         |                            |                   |        |            |                  |                  |                    |         |

|                                 | Note: ROM/EI                                                          | PROM ma                    | ay be             | adde   | d in 1     | IK, 2K, 4        | K, or 8K         | byte in            | crer    |

| I/O ADDRESSING                  |                                                                       |                            | _                 | _      |            |                  |                  |                    |         |

| On-Board Programmable I/O:      | 82                                                                    | 55 No. 1                   | 825               | 55 No  | . 2        | 8255             | 8255             | 8251               |         |

|                                 | Port 1                                                                | 2 3                        | 4                 | 5      | 6          | No. 1<br>Control | No. 2<br>Control | Data               | 8<br>Co |

|                                 |                                                                       |                            |                   |        | -+-        |                  | Control          | <u> </u>           |         |

|                                 | Address E4                                                            | E5 E6                      | E8                | E9     | EA         | E7               | EB               | EC                 |         |

| Optional:                       | J5 Multimo                                                            | odule                      | J6                | Multi  | modu       | le               |                  |                    |         |

|                                 | CO-CF                                                                 |                            |                   | F0-    | FF         |                  |                  |                    |         |

| ON-BOARD I/O CAPACITY           |                                                                       |                            |                   |        |            |                  |                  |                    |         |

| Parallel:                       | 48 programma                                                          | able lines                 | S.                |        |            |                  |                  |                    |         |

| Serial:                         | 1 Transmit; 1                                                         | Receive;                   | ; 1 SI            | D; 1 ; | SOD        |                  |                  |                    |         |

|                                 | Note: Expand                                                          | able with                  | n Opti            | ional  | Multi      | module           | boards           |                    |         |

| CHARACTERISTICS<br>Synchronous: | 5-8 bit charac<br>Internal or ex<br>Automatic Syr                     | ernal ch                   |                   | er syn | ichroi     | nization         |                  |                    |         |

| Asynchronous:                   | 5-8 bit charac<br>Break charact<br>1, 1½, or 2 sto<br>False start bit | ters<br>er gener<br>p bits | ation             |        |            |                  |                  |                    |         |

| SERIAL BAUD RATES:              | Output                                                                |                            | Bau               | id Ra  | te (H      | z)               |                  | 8254               | PIT     |

|                                 | Frequency<br>in kHz                                                   | Synch                      | ironoi            | JS     | Asyı       | nchrono          |                  | ud Rate<br>iex Not |         |

|                                 |                                                                       |                            |                   |        | ÷16        | s ÷e             | 54 M             | SB                 | L       |

|                                 | 153.6                                                                 | ļ ·                        |                   |        | 9600       |                  |                  | 00                 | C       |

|                                 | 76.8                                                                  | · ·                        |                   |        | 4800       |                  |                  | 00                 | 0       |

|                                 | 38.4                                                                  |                            | 400               |        | 2400       |                  |                  | 00                 | 1       |

|                                 |                                                                       | 19                         | 200               |        | 1200       |                  |                  | 00                 | 3       |

|                                 | 19.2                                                                  | <u>ہ</u>                   | 600               |        | 600        |                  | 1                | 00                 | Ē       |

|                                 | 19.2<br>9.6                                                           |                            | 900               |        | 300<br>150 |                  |                  | 00<br>01           | (       |

|                                 | 19.2<br>9.6<br>4.8                                                    | 4                          | 800               | 1      |            |                  |                  |                    |         |

|                                 | 19.2<br>9.6                                                           | 4                          | 800<br>400<br>760 |        | 11(        |                  |                  | )2                 |         |

|                                 | 19.2<br>9.6<br>4.8<br>2.4                                             | 4                          | 400               |        |            |                  |                  |                    |         |

#### 1-3

| INTERRUPTS                                             |                                   |                   |                |                   |                           |

|--------------------------------------------------------|-----------------------------------|-------------------|----------------|-------------------|---------------------------|

| Register Address<br>(Hex notation, I/O address space): | Interrupt Reque                   | st Begister       | DA or D8       | 1                 |                           |

| (nex notation, no address space).                      | In-Service Regis                  |                   | DA or D8       |                   |                           |

|                                                        | Mask Register                     |                   | DB or D9       |                   |                           |

|                                                        | Command Register                  |                   | DA or D8       | 1                 |                           |

|                                                        | Block Address I                   |                   | DB or D9       | 1                 |                           |

|                                                        | Status (Polling                   |                   | DA or D8       | 1                 |                           |

|                                                        |                                   |                   |                | 1                 |                           |

| TIMERS                                                 |                                   |                   |                |                   |                           |

| Register Address<br>(Hex notation, I/O address space): | Control Register DF<br>Timer 0 DC |                   |                |                   |                           |

|                                                        | Timer 1                           | DD                |                |                   |                           |

|                                                        | Timer 2                           | DE                |                |                   |                           |

|                                                        |                                   |                   | Į              |                   |                           |

| Input Frequencies:                                     |                                   |                   |                |                   |                           |

| Reference:                                             | 1.0752 MHz ±0.1%                  | (0.930 µsec       | period, nomina | 1)                |                           |

| Event Rate:                                            | 1.1 MHz max                       |                   |                |                   |                           |

| Output Frequencies/                                    | r                                 |                   |                |                   |                           |

| Timing Intervals:                                      | Function                          |                   | mer/Counter    |                   | er/Counter<br>s Cascaded) |

|                                                        |                                   | Min.              | Max.           | Min.              | Max.                      |

|                                                        | Real-Time<br>Interrupt            | 1.86 <i>µ</i> sec | 60.948 msec    | 3.72 <i>µ</i> sec | 1.109 hrs                 |

|                                                        | Programmable<br>One-Shot          | 1.86 <i>µ</i> sec | 60.948 msec    | 3.72 <i>µ</i> sec | 1.109 hrs                 |

|                                                        | Rate Generator                    | 16.407 Hz         | 537.61 kHz     | 0.00025 Hz        | 268.81 kHz                |

|                                                        | Square-Wave<br>Rate Generator     | 16.407 Hz         | 537.61 kHz     | 0.00025 Hz        | 268.81 kHz                |

|                                                        | Software<br>Triggered Strobe      | 1.86 <i>µ</i> sec | 60.948 msec    | 3.72 <i>µ</i> sec | 1.109 hrs                 |

|                                                        | Hardware<br>Triggered Strobe      | 1.86 <i>µ</i> sec | 60.948 msec    | 3.72 <i>µ</i> sec | 1.109 hrs                 |

| INTERFACES                                             | L <u></u>                         |                   | <u> </u>       | L                 |                           |

| Multibus:                                              | All signals TTL cor               | nnatible          |                |                   |                           |

| Parallel I/O:                                          | All signals TTL cor               | •                 |                |                   |                           |

| Interrupt Requests:                                    | All signals TTL cor               | •                 |                |                   |                           |

|                                                        |                                   |                   |                |                   |                           |

| Timer:                                                 | All signals TTL cor               | •                 |                |                   |                           |

| Serial I/O:                                            | RS232C compatibl                  | e, data set o     | configuration  |                   |                           |

| iSBX Bus:                                              | All signals TTL cor               | npatible          |                |                   |                           |

| PHYSICAL CHARACTERISTICS                               |                                   |                   |                |                   |                           |

| Width:                                                 | 12 in (30.48 cm)                  |                   |                |                   |                           |

| Length:                                                | 6.75 in (17.15 cm)                |                   |                |                   |                           |

| Height:                                                | 0.5 in (1.27 cm)                  |                   |                |                   |                           |

| Weight:                                                | 13.50 oz (383 g)                  |                   |                |                   |                           |

|                                                        | 10.00 02 (000 g)                  |                   |                |                   |                           |

#### Table 1-1. Specifications (Continued)

#### Table 1-1. Specifications (Continued)

#### ENVIRONMENTAL REQUIREMENTS

| Operating Temperature: | 0°C to 55°C (32°F to 130°F)                                                               |

|------------------------|-------------------------------------------------------------------------------------------|

| Storage Temperature:   | −40°C to 70°C (−40°F to 158°F)                                                            |

| Operating Humidity:    | Up to 90% relative humidity without condensation at 55 °C                                 |

| Storage Humidity:      | Up to 95% relative humidity without condensation at 55°C                                  |

| Airflow Requirements:  | Minimum of 200 linear feet per minute of airflow at an ambient temperature of 0°C to 55°C |

#### ELECTRICAL CHARACTERISTICS

Input Power:

| Configuration Description |                                                                                                                                                         |                  | Current Required  |                  |                   |  |  |  |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|------------------|-------------------|--|--|--|

|                           | Configuration Description                                                                                                                               | Icc              | [DD               | BB               | ]AA               |  |  |  |

| 1                         | Assumes the following items are installed: four 2708 EPROM devices, eight 220/330 ohm I/O termination packs in the parallel I/O interface (driven low). | 3.28 A           | 300 ma            | 180 ma           | 20 ma             |  |  |  |

| 2                         | Assumes the 2708 EPROM devices and the iSBC 901 termination networks are <i>not</i> installed.                                                          | 2.66 A           | 40 ma             | 0 ma             | 20 ma             |  |  |  |

| 3                         | Same as note 1, except four 2758 EPROM devices are installed instead of 2708 devices.                                                                   | 3.44 A           | 40 ma             | 0 ma             | 20 ma             |  |  |  |

| 4                         | Same as note 1, except four 2716 EPROM devices are installed instead of 2708 devices.                                                                   | 3.44 A           | 40 ma             | 0 ma             | 20 ma             |  |  |  |

| 5                         | Same as note 1, except four 2732A EPROM devices are<br>installed instead of 2708 devices.                                                               | 3.46 A           | 40 ma             | 0 ma             | 20 ma             |  |  |  |

| 6                         | Same as note 1, except four 2764A EPROM devices are installed instead of 2708 devices.                                                                  | 3.42 A           | 40 ma             | 0 ma             | 20 ma             |  |  |  |

| 7                         | Same as note 1, with the addition of an iSBC 530 TTY adaptor module connected.                                                                          | 3.28 A           | 400 ma            | 180 ma           | 120 ma            |  |  |  |

| 8                         | Battery backup current requirements for 8K RAM (board not operating).                                                                                   | 10 ma            |                   | _                | _                 |  |  |  |

| 9                         | Current requirements for 8K RAM (board operating).                                                                                                      | 88 ma            | _                 | -                | -                 |  |  |  |

|                           | Voltage:                                                                                                                                                | Vcc =<br>+5v ±5% | VDD =<br>+12v ±5% | Vвв =<br>−5v ±5% | VAA =<br>-12v ±5% |  |  |  |

#### Table 1-1. Specifications (Continued)

#### LINE DRIVERS AND TERMINATORS

I/O Drivers:

The following line drivers are all compatible with the I/O driver sockets.

| Driver | Characteristic | Sink Current (mA) |  |

|--------|----------------|-------------------|--|

| 7438   | I, OC          | 48                |  |

| 7437   | 1              | 48                |  |

| 7432   | NI             | 16                |  |

| 7426   | I, OC          | 16                |  |

| 7409   | NI, OC         | 16                |  |

| 7408   | NI             | 16                |  |

| 7403   | I, OC          | 16                |  |

| 7400   | 1              | 16                |  |

Note: I = inverting; NI = non-inverting; OC = open collector.

Ports E4 and E8 have 25 mA totem-pole dividers and 1  $k\Omega$  terminators.

I/O Terminators:

220/330 ohm Divider Pull Up/Pull Down Terminator Pack

1k ohm Pull Up Terminator Pack

1kΩ +5-----

### CHAPTER 2 PREPARATION FOR USE

#### **2-1. INTRODUCTION**

This chapter provides specific information enabling you to install the iSBC 80/24A board into your own system, with minimal effort. The board's default, or factory configuration for RAM addressing, ROM type, and other variables is described, followed by procedures for altering the default configuration. In this manner, the board will accommodate a variety of applications. To completely familiarize yourself with the flexibility of the iSBC 80/24A board, we recommend reading the entire chapter before installation and use.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment contact Intel Customer Support Service (see section 5-2) to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

#### 2-3. INSTALLATION CONSIDERATIONS

There are several environmental requirements which should be considered, prior to board installation. These requirements are discussed in sections 2-4 through 2-6.

#### 2-4. MINIMAL OPERATING REQUIREMENTS

The iSBC 80/24A board default configuration is described in Chapter 1. In order to operate the board you may need additional equipment. For most applications this will typically be the following:

- a. CPU software, residing in on-board ROM (section 2-8).

- b. I/O connectors and cables (section 2-16).

- c. Line drivers or terminators for parallel I/O ports (section 2-10).

Instructions for installing these components are given in this chapter.

#### 2-5. POWER REQUIREMENTS

Four voltages are required for operating the iSBC 80/24A board in most configurations: +5 Vdc, -5 Vdc, +12 Vdc, and -12 Vdc. All must be within  $\pm 5.0\%$  of absolute. However, some configurations do not require all voltages (e.g., if 2708 EPROM devices are not used, the -5 Vdc requirement is eliminated). Power requirements for the various board configurations are listed in table 1-1. The table does not include power required by any optional Multimodule boards which may be installed on the iSBC 80/24A board. Refer to the specific Multimodule board hardware reference manual for its power requirements.

#### 2-6. COOLING REQUIREMENTS

Operating temperature range for the iSBC 80/24A board is 0° to 55° Celsius. If the board is installed into an iSBC 655 or iSBC 660 System Chassis, or an iCS Industrial Chassis, adequate cooling is provided by the supplied fans. However, if the board is used in another chassis, ensure adequate cooling by providing a minimum of 200 linear feet per minute of airflow at a ambient temperature of 0° to 55°C.

#### 2-7. COMPONENT INSTALLATION

Instructions for installing optional ROM/EPROM, and line drivers or terminators are given in the following sections. Multimodule boards are discussed in section 2-26.

MOS-type devices are extremely sensitive to transient voltages, especially static electricity discharges. Caution should be exercised in low humidity environments during device installation, to prevent static discharge. Always ground yourself before handling MOS devices to ensure any static charge which may have accumulated is discharged. After picking up the device, do not walk on carpeted floors; install the device immediately following the grounding.

#### 2-8. ROM/PROM/EPROM INSTALLATION

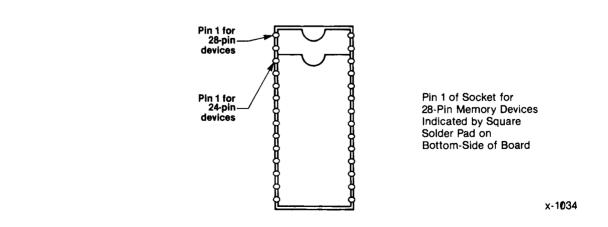

Sockets U52 through U55 are reserved for optional ROM/PROM/EPROM devices. A maximum of 32K bytes may be installed. A summary of compatible device types, capacity, and addressing is provided in table 2-1. Device types may not be mixed; however, empty sockets are allowed (provided they are not addressed).

After selecting the ROM type which best suits your application, carefully insert each device into its socket.

Never install any device into a board when power is applied. Damage to the board, device, and power supply could result.

LITIO

ROM sockets U52-55 are 28-pin sockets. If you are inserting 24-pin devices, ensure they are positioned as shown in figure 2-1 to avoid damage to the devices or to the iSBC 80/24A board.

When using EPROMs with access times less than 300ns, no EPROM wait states are necessary at either operating speed. Insert jumper E98-107 for the EPROM acknowledge to by-pass the wait state generating circuit. Note that inserting E96-105 causes both the EPROM and on-board I/O to by-pass the wait state generation circuit. This should only be done when operating the iSBC 80/24A in its slower mode (2.43 MHz). Refer to table 2-2 for the wait state jumper options.

EPROMs with access times greater than 500ns cannot be used with the iSBC 80/24A board in the 4.84 MHz operating mode.

| Device                                                              | Socket | and Ad        | Total ROM     |               |                    |  |  |

|---------------------------------------------------------------------|--------|---------------|---------------|---------------|--------------------|--|--|

| Type/Size                                                           | U52    | U53           | U54           | U55           | Range (Hex)        |  |  |

| 2708/2758<br>2608<br>(1K × 8)                                       | 0-03FF | 0400-<br>07FF | 0800-<br>0BFF | 0C00-<br>0FFF | 0000-0FFF<br>(4K)  |  |  |

| 2716<br>2316 E<br>(2K × 8)                                          | 0-07FF | 0800-<br>0FFF | 1000-<br>17FF | 1800-<br>1FFF | 0000-1FFF<br>(8K)  |  |  |

| 2732, 2732A<br>(4K × 8)                                             | 0-0FFF | 1000-<br>1FFF | 2000-<br>2FFF | 3000-<br>3FFF | 0000-3FFF<br>(16K) |  |  |

| 2764, 2764A <sup>*</sup><br>(8K × 8)                                | 0-1FFF | 2000-<br>3FFF | 4000-<br>5FFF | 6000-<br>7FFF | 0000-7FFF<br>(32K) |  |  |

| NOTE: EPROM/ROM types cannot be mixed.<br>* = Default configuration |        |               |               |               |                    |  |  |

#### Table 2-1. EPROM/ROM Configurations

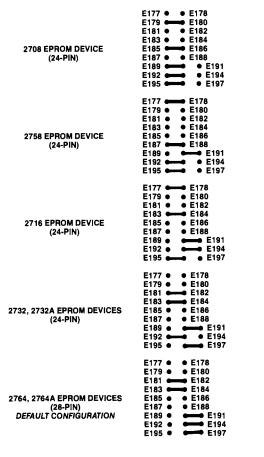

#### 2-9. EPROM DEVICE TYPE CONFIGURATION

Once your optional EPROM devices are installed, you must configure the EPROM device type jumper post array for your device type (see figure 2-2 for possible configurations). The default configuration is for 2764 devices ( $8K \ge 8$ ).

| EPROM MAXIMUM ACCESS<br>TIME (tacc, in ns) | 4.84 MHz Oper        | rating Speed      | 2.42 MHz Oper        | ating Speed       |

|--------------------------------------------|----------------------|-------------------|----------------------|-------------------|

|                                            | Wait State<br>Needed | Jumpers<br>Needed | Wait State<br>Needed | Jumpers<br>Needed |

| tac > 300ns                                | 0                    | E98-107           | 0                    | E96-105           |

| 300 > tacc > 500                           | 1*                   | none              | 0                    | E96-105           |

| 500 > tacc > 775                           | _                    | _                 | 0                    | E96-105           |

NOTE: SOLID BAR BETWEEN TWO JUMPER POSTS (E.G., E196–197) REPRESENTS A PUSH-ON JUMPER.

m-0393

Figure 2-2. EPROM Device Type Jumper Configuration

Incorrectly configuring the EPROM device type jumpers can result in damage to the EPROM devices and to the iSBC 80/24A board itself.

#### 2-10. LINE DRIVERS AND I/O TERMINATORS

Either line driver and/or I/O terminator devices can be installed (as required) in sockets U2-U5 and U7-U10. These sockets correspond to the 32 parallel I/O lines (without drivers or terminators). Ports E4 and E8 have Intel 8287 transceiver devices installed at the factory. Refer to table 2-3 for recommended I/O terminators and to table 1-1 (Chapter 1) for recommended line drivers for the iSBC 80/24A board.

| Table 2-3. Reco | mmended I/O | Terminators |

|-----------------|-------------|-------------|

|-----------------|-------------|-------------|

| I/O Terminator Pack               | Vendors/Part Number                      |

|-----------------------------------|------------------------------------------|

| 220/330 ohm Pull Up/Pull          | iSBC 901                                 |

| Down Terminator Pack              | Beckman Instrument<br>(Part #1899-746-1) |

| 1k ohm Pull Up<br>Terminator Pack | iSBC 902                                 |

|                                   | Beckman Instrument<br>(Part #1899-747-1) |

|                                   | Dale Electronics<br>(Part #MDP14-00-593) |

#### 2-11. JUMPER CONFIGURATIONS

Much of the flexibility of your iSBC 80/24A board is due to the use of jumper connections which may easily be altered from their default configurations to suit your particular application. Table 2-4 summarizes the jumper connections and their uses. Table 2-4A lists the jumper connections in numerical order, and indicates the factory default configurations. Physical locations of jumper posts on the board are shown in figure 5-3. Jumper connections are also shown schematically in figure 5-4.

### NOTE

Jumper posts are shown on the schematic diagrams with an E prefix (e.g., E86).

#### 2-12. RAM CAPACITY AND ADDRESSING

The on-board RAM capacity and addressing is jumper configurable. The default configuration is 8K bytes of RAM from E000-FFFFH. To alter these configurations, refer to table 2-4 and section 4-10.

#### Table 2-4. Jumper Connections

| Function           | Fig. 5-3<br>Ref. | Jumper<br>Pair       | Description                                                                                        |  |

|--------------------|------------------|----------------------|----------------------------------------------------------------------------------------------------|--|

| MULTIBUS SIGNALS   |                  |                      |                                                                                                    |  |

| AACK/              | Sh. 2-D6         | E202-203             | Connects AACK/ signal from P1-25.                                                                  |  |

| BPRO/              | Sh. 2-D3         | E200-201*            | Connects BPRO/ to P1-16.                                                                           |  |

| BCLK/              | Sh. 2-A6         | E198-199*            | Connects BCLK/ to P1-13.                                                                           |  |

| CCLK/              | Sh. 2-A6         | E204-205*            | Connects CCLK/ to P1-31.                                                                           |  |

| втмо               | Sh. 3-A2         | E220-221*            | Connects BTMO to P2-34.                                                                            |  |

| INTA/              | Sh. 3-B2         | E218-219*            | Connects INTA/ to P2-36.                                                                           |  |

| PFSR/              | Sh. 5-D4         | E31-XX               | Connects 8224 OSC output to U20 Counter.                                                           |  |

| TIMING & CPU       |                  |                      |                                                                                                    |  |

| 4.84 MHz Operation | Sh. 3-D5         | E166-168*            | * Uses 9.68 MHz clock input                                                                        |  |

| 2.42 MHz Operation | Sh. 3-D5         | E163-166             | Uses 4.84 MHz clock input                                                                          |  |

|                    | Sh. 3-C5         | E96-105              |                                                                                                    |  |

| 8224 OSC Output    | Sh. 3-D6         | E171-174*            | Connects 8224 OSC output to U20 Counter.                                                           |  |

| RAM:               | Sh. 4-C7         | E109-100             | Indicates 4K RAM on-board.                                                                         |  |

| AMOUNT ON-BOARD    | Sh. 4-C7         | E109-100<br>E101-110 | Both jumpers in indicates 2K RAM; or<br>Both jumpers out indicates 8K RAM. (default configuration) |  |

| Function                                 | Fig. 5-3<br>Ref.     | Jumper<br>Pair                                     | Description                                                 |                                    |                  |                                                                  |

|------------------------------------------|----------------------|----------------------------------------------------|-------------------------------------------------------------|------------------------------------|------------------|------------------------------------------------------------------|

| RAM ADDRESSING                           | Sh. 4-C5             |                                                    | Note: To dis                                                | able all on-board                  | d RAM, remove    | all jumpers from                                                 |

| Selects maximum<br>(hexadecimal)         |                      |                                                    | 2K                                                          | 4K                                 | 8K               | posts E102, 103,<br>104, 111, 112                                |

| •                                        |                      | E112-113                                           | 3800-3FFF                                                   | 3000-3FFF                          | 2000-3FFF        | and 113.                                                         |

|                                          |                      | E111-112                                           | 7800-7FFF                                                   | 7000-7FFF                          | 6000-7FFF        |                                                                  |

|                                          |                      | E103-104                                           | B800-BFFF                                                   | B000-BFFF                          | A000-BFFF        |                                                                  |

|                                          |                      | E102-103*                                          | F800-FFFF                                                   | F000-FFFF                          | E000-FFFF        |                                                                  |

|                                          |                      |                                                    | NOTE: Install                                               | one jumper or                      | ıly.             |                                                                  |

| 8254 PIT                                 |                      |                                                    |                                                             |                                    |                  | ······································                           |

| inputs/Outputs                           | Sh. 7-C6             | E167-170 }                                         | Connects Time                                               | er 0 output to Tim                 | er 1 input.      |                                                                  |

|                                          |                      | E167-176                                           |                                                             | er 0 output to Par                 |                  | per matrix.                                                      |

|                                          |                      | E169-170 <sup>*</sup> )<br>E172-173 <sup>*</sup> ) | Provides 1.075                                              | MHz to CLK0 a                      | nd CLK1 inputs.  |                                                                  |

|                                          |                      | E170-175<br>E173-175                               | Provides 134.4                                              | KHz to CLK0 ar                     | nd CLK1 inputs.  |                                                                  |

|                                          |                      | E170-176 }<br>E173-176 }                           | Connects para                                               | llel port E6 jump                  | er matrix to one | or more timer inputs.                                            |

|                                          |                      | E172-176                                           | Connects 1.07                                               | 5 MHz to paralle                   | l port E6 jumper | matrix.                                                          |

|                                          |                      | E175-176                                           | Connects 134.                                               | 4 KHz to parallel                  | port E6 jumper   | matrix.                                                          |

| Gate Inputs                              | Sh. 5-D4             | E13-28 *<br>E14-29 *                               | Provides + 5 volts to gate 0 and gate 1 inputs of 8254 PIT. |                                    |                  |                                                                  |

| SERIAL PORT                              |                      |                                                    | Refer to sect                                               | ion 2-13.                          |                  |                                                                  |

| Internal Clocks                          |                      |                                                    |                                                             |                                    |                  |                                                                  |

| RxC<br>TxC                               | Sh. 7-C6<br>Sh. 7-C6 | E87-88 <sup>*</sup><br>E89-90 <sup>*</sup> }       | Connects PC                                                 | I device to PIT                    | Timer 2 outpu    | it. (Baud rate clock)                                            |

| External Clocks                          |                      |                                                    |                                                             |                                    |                  |                                                                  |

| RxC<br>TxC                               | Sh. 7-C6<br>Sh. 7-C6 | E86-88<br>E89-91                                   |                                                             | C input to J3-7<br>C input to J3-3 |                  |                                                                  |

| Secondary RTS                            | Sh. 7-D7             | E83-84                                             | Connects J3-                                                | 11 input to AU                     | X1/ parallel po  | rt EA matrix.                                                    |

| Secondary TxD                            | Sh. 7-D7             | E84-85                                             | Connects J3-                                                | 1 input to AUX                     | (1/ parallel por | t EA matrix.                                                     |

| Secondary CTS                            | Sh. 7-D2             | E94-95                                             | Connects J3-                                                | -26 output to A                    | UX0/ parallel p  | ort EA matrix.                                                   |

| Secondary RxD                            | Sh. 7-D2             | E93-95                                             |                                                             | -5 output to AL                    |                  |                                                                  |

| Secondary TxC                            | Sh. 7-D2             | E92-95                                             |                                                             | -21 output to A                    |                  |                                                                  |

| Auxiliary Output 0<br>(AUX0/)            | Sh. 6-D4             | E47-XX                                             |                                                             | ctory jumper for                   |                  | nnect to selected port EA<br>Serial Channel protocol             |

| Auxiliary Input 1<br>(AUX1/)             | Sh. 6-D4             | E62-XX                                             | E83-84-85. So<br>factory jumpe                              | r for that bit. Sel                | nect to selected | jumper matrix<br>I port EA bit; remove<br>as required for Serial |

| Ring Indicator<br>(input)                | Sh. 6-D4             | E46-XX                                             |                                                             |                                    |                  | bit. Connect to selecte<br>t bit.                                |

| Received Line Signal<br>Detector (input) | Sh. 6-D4             | E45-XX                                             |                                                             | -16 input to sel<br>remove factory |                  | bit. Connect to selecte<br>t bit.                                |

| PARALLEL PORTS                           |                      |                                                    |                                                             |                                    |                  |                                                                  |

| Operating Modes                          | Sh. 5-D4<br>Sh. 6-D4 | See table<br>2-7                                   |                                                             | igurations depe<br>to section 2-14 |                  | A mode and bit restric                                           |

| Table 2-4. Jumper Con | nections (Continued) |

|-----------------------|----------------------|

|-----------------------|----------------------|

| Function                         | Fig. 5-3<br>Ref.            | Jumper<br>Pair            | Description                                                                                                                                                                                           |  |

|----------------------------------|-----------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Interrupt Out/<br>Bank Select    | Sh. 5-D4<br>and<br>Sh. 9-D5 | E16-XX<br>and<br>E206-211 | Output only. Allows the selected E6 bit (posts E24-27 or E19-22) to be used as output flag on P1-28. Port C must be in output mode.                                                                   |  |

| Serial Input Data<br>(SID) line  | Sh. 6-D4                    | E61-XX                    | Data will be routed directly from J2 pin to 8085A-2 SID input. Connect to selected port EA bit (posts E41-44 or E36-39); remove factory jumper for that bit.                                          |  |

| Serial Output Data<br>(SOD) line | Sh. 6-D4                    | E60-XX                    | Data from 8085A-2 SOD output will be routed directly to J2 pin.<br>Connect to selected port EA bit (posts E41-44 or E36-39); remove<br>factory jumper.                                                |  |

| PROM Enable                      | Sh. 5-D4                    | E32-XX                    | Allows software selection of PROM ACK/ signal. Connect to<br>selected port E6 bit; remove factory jumper for that bit. This signal is<br>usually generated by address decode PROM. Refer to Sh. 8-C5. |  |

| PFSR/ Signal                     | Sh. 5-D4                    | E31-XX                    | Connects Power Fail Sense Reset signal to P2-13. Refer to section<br>2-22. Connect to selected port E6 bit; remove factory jumper for<br>that bit.                                                    |  |

| INTERRUPTS                       |                             |                           | Refer to section 2-15.                                                                                                                                                                                |  |

| Priority                         | Sh. 9-B5                    | Matrix                    | Various configurations allowed. Refer to section 2-15 and table 2-7                                                                                                                                   |  |

| FAILSAFE TIMER                   | Sh. 3-B7                    | E97-106*                  | Provides READY signal to CPU after 10 ms if response is not provide<br>by addressed I/O or memory. CPU will be in wait state until READ<br>signal is true.                                            |  |

| POWER CONNECTION                 |                             |                           |                                                                                                                                                                                                       |  |