# iSBC® 286/10A SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Order Number: 147532-001

THE GREEN PAGES AT THE END OF THIS MANUAL CONTAIN ERRATA. IF NO GREEN PAGES ARE PRESENT, THIS MANUAL HAD NO ERRATA AT PRESS TIME.

Additional copies of this manual or other Intel literature may by obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update or to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BITBUS        | <sup>i</sup> m         | iRMX            | OpenNET       |

|---------------|------------------------|-----------------|---------------|

| COMMputer     | iMDDX                  | iSBC            | Plug-A-Bubble |

| CREDIT        | iMMX                   | iSBX            | PROMPT        |

| Data Pipeline | Insite                 | iSDM            | Promware      |

| Genius        | $int_el$               | iSXM            | QUEST         |

| i             | $int_elBOS$            | KEPROM          | QueX          |

| i             | Intelevision           | Library Manager | Ripplemode    |

| $1^2$ ICE     | inteligent Identifier  | MCS             | RMX/80        |

| ICE           | inteligent Programming | Megachassis     | RUPI          |

| iCS           | Intellec               | MICROMAINFRAME  | Seamless      |

| iDBP          | Intellink              | MULTIBUS        | SLD           |

| iDIS          | iOSP                   | MULTICHANNEL    | UPI           |

| iLBX          | iPDS                   | MULTIMODULE     |               |

$Centronics\ is\ a\ trademark\ of\ Centronics\ Data\ Computer\ Corporation.$

$Copyright\,1985, Intel\,Corporation$

| REV. | REVISION HISTORY | DATE  |

|------|------------------|-------|

| -001 | Original Issue.  | 05/85 |

|      |                  |       |

|      |                  | i     |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

#### INTENDED AUDIENCE AND PURPOSE

This manual provides sufficient information for a user to successfully

- Configure the jumpers and interfaces on the board for a specific application.

- Install the board into a standard MULTIBUS system environment.

- Program the board for operation in its system environment.

This manual is written for software and hardware engineers and requires a medium to high level of technical expertise in both the software and hardware operation of the iAPX 286 CPU chip and its family of peripheral support chips.

#### **RELATED PUBLICATIONS**

To avoid redundancy, this manual references technical information contained in these technical publications:

- iAPX 286 Hardware Reference Manual, Order Number: 21Ø76Ø.

- iAPX 286 Programmer's Reference Manual, Order Number: 210498.

- Intel Microsystem Components Handbook, Order Number: 23Ø843.

- Intel Memory Components Handbook, Order Number: 210830.

- Intel MULTIBUS® Specification, Order Number: 98ØØ683.

- Intel iLBX™ Bus Specification, Order Number: 145695.

- Intel iSBX™ Bus Specification, Order Number: 142686.

- EIA Standard for RS232C Interfacing, EIA-RS-232C.

- EIA Standard for RS422A Interfacing, EIA-RS-422A.

- EIA Standard for RS449 Interfacing, EIA-RS-499.

Other Intel publications you may find helpful are

- Introduction to the iAPX 286, Order Number: 21Ø3Ø8.

- Intel iAPX 286 Data Sheet, Order Number: 21\( \pi 253. \)

- Intel Application Note AP-134, Asynchronous Communications with the 8274 Multiple Protocol Serial Controller.

- Intel Application Note AP-145, Synchronous Communications with the 8274 Multiple Protocol Serial Controller.

- iSBC® Ø12EX/Ø1ØEX/Ø2ØEX/Ø4ØEX RAM Boards Hardware Reference Manual, Order Number: 147783.

The previous and other Intel publications are listed in Intel's Literature Guide, Order Number: 210621. See page ii for the ordering address.

#### PREFACE (continued)

#### NOTATIONAL CONVENTIONS

This manual uses two special characters, the asterisk (\*) and the section symbol (§):

- \* Used after a signal mnemonic to indicate that the signal is active-low. Signal mnemonics without a trailing asterisk are active-high. The asterisk replaces the slash (/) previously used to indicate the active state of a signal; the slash is still used on the schematic diagrams.

- § Used after a jumper connection to indicate a factory-installed jumper (default configuration).

You will encounter NOTES, CAUTIONS, and WARNINGS throughout this manual. Notes emphasize information for special consideration. Cautions indicate possible errors that could result in software or hardware damage. Most importantly, warnings indicate there is a possibility of personal injury.

#### **ORGANIZATION OF THIS MANUAL**

This section provides a short abstract of each chapter.

#### CHAPTER 1. GENERAL INFORMATION

This chapter provides a brief overview of the features of the iAPX 286 CPU and the iSBC 286/10A Single Board Computer. The chapter also contains the specifications that the user needs to use the board in a system.

#### CHAPTER 2. BOARD OPERATION

This chapter provides a functional description based on the board's block diagram. The chapter also supplies the default configuration of each block.

#### PREFACE (continued)

#### **CHAPTER 3. INSTALLATION**

This chapter supplies information to help you prepare for board installation and provides a preview of user-supplied components/equipment that may be needed. The board's operating requirements are also supplied.

#### **CHAPTER 4. CONFIGURATION**

This chapter contains jumper, addressing, interface, and programming information for configuring each function on the board.

#### **CHAPTER 5. SERVICE INFORMATION**

This chapter provides service and repair assistance instructions and schematic diagrams for the board.

#### APPENDIX A. JUMPER INFORMATION

This appendix consolidates all the jumper information and can be used as a quick reference. The appendix shows the jumper locations, explains jumper functions, and provides a jumper index for the schematic.

#### APPENDIX B. MULTIDROP CONSIDERATIONS

This appendix provides a functional multidrop example, which includes calculations for determining bias and terminator resistor values.

#### APPENDIX C. PAL EQUATIONS

This appendix supplies the pin-out description and equations for PAL U74 and a summary of the primary decode memory maps that define local and iLBX memory.

#### PREFACE (continued)

#### APPENDIX D. WAIT-STATE REQUIREMENTS

This appendix provides information on wait-state requirements for local and dual-port memory.

#### APPENDIX E. MEMORY SOCKET MATRIX CONFIGURATIONS

This appendix provides information for configuring the local and dual-port memory socket's matrices for different device sizes and types.

#### APPENDIX F. iSBC® 341 MEMORY BOARD INSTALLATION

This appendix provides information for installing the iSBC 341 memory board for four more local or dual-port sockets.

#### APPENDIX G. I/O PORT ADDRESS LIST

This appendix consolidates all the I/O addresses and can be used as a quick reference.

## CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PAGE                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| CHAPTER 1 GENERAL INFORMATION 1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-1<br>1-2<br>1-3<br>1-3                                                                 |

| CHAPTER 2 BOARD OPERATION 2.1 Introduction. 2.2 Functional Description. 2.2.1 Clock Generation Circuits. 2.2.2 Central Processor. 2.2.3 Serial I/O Interfaces. 2.2.4 Parallel I/O Interface. 2.2.5 On-Board Memory. 2.2.5 Ucal Memory. 2.2.5.1 Local Memory. 2.2.5.2 Dual-Port Memory. 2.2.6 iSBXTM Interfaces. 2.2.7 iLBXTM, Synchronous, and Auxiliary Interfaces. 2.2.8 MULTIBUS® Interface. 2.2.9 Programmable Interval Timers. 2.2.10 Programmable Interval Controllers. 2.2.11 Numeric Processor Extension. | 2-1<br>2-1<br>2-3<br>2-5<br>2-6<br>2-6<br>2-7<br>2-7<br>2-8<br>2-8<br>2-9<br>2-9<br>2-10 |

| CHAPTER 3 INSTALLATION 3.1 Introduction. 3.2 Unpacking and Inspecting the Board. 3.3 Preparing the Board Environment. 3.3.1 Power Requirements. 3.3.2 Cooling Requirements. 3.3.3 Physical Dimensions. 3.4 Compatible Equipment. 3.5 Components Required. 3.6 Component Installation. 3.6.1 Memory Components. 3.6.2 Line Driver Devices. 3.6.3 Resistor Packs. 3.6.3.1 Bias Resistors. 3.6.3.2 Termination Resistors.                                                                                            | 3-1<br>3-1<br>3-2<br>3-2<br>3-3<br>3-3<br>3-4<br>3-6<br>3-6<br>3-8<br>3-10<br>3-10       |

| 3.7 Connector and Cable Parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-1Ø<br>3-13                                                                             |

#### CONTENTS (continued)

|                                                              | PAGE         |

|--------------------------------------------------------------|--------------|

|                                                              |              |

|                                                              |              |

| CHAPTER 4                                                    |              |

| CONFIGURATION 4.1 Introduction                               | 4-1          |

| 4.2 CPU and CPU Support Circuitry Configurations             | 4-1          |

| 4.2.1 CPU Mode Selection                                     | 4-2          |

| 4.2.2 CPU Wait-State Selection                               | 4-3          |

| 4.2.3 CPU Clock Selection                                    | 4-3          |

| 4.3 8Ø287 Math Processor Extension Configuration             | 4-3          |

| 4.3.1 8Ø287 Installation                                     | 4-3          |

| 4.3.2 8Ø287 Jumper Configurations                            | 4-3          |

| 4.3.3 8Ø287 Programming                                      | 4-5          |

| 4.4 Interrupt Handling (with the PIC devices)                | 4-5          |

| 4.4.1 Interrupt Modes                                        | 4-6          |

| 4.4.2 Mode Selection                                         | 4-7          |

| 4.4.3 Interrupt Jumper Matrix Configuration                  | 4-8<br>4-11  |

| 4.4.4 Interrupt Support Logic                                | 4-11<br>4-11 |

| 4.4.4.2 Changing Signals from Edge-Triggered to Level-Active | 4-11<br>4-12 |

| 4.4.5 PIC Programming                                        | 4-12         |

| 4.4.5.1 PIC Port Addressing                                  | 4-12         |

| 4.4.5.2 PIC Initialization Sequence                          | 4-12         |

| 4.5 Programmable Interval Timers (with the PIT device)       | 4-15         |

| 4.5.1 PIT Jumper Configurations                              | 4-15         |

| 4.5.2 PIT Programming                                        | 4-17         |

| 4.5.3 PIT Programming Example                                | 4-19         |

| 4.6 iSBX™ Interfaces - J5 & J6                               | 4-2Ø         |

| 4.6.1 iSBX™ Bus Description                                  | 4-2Ø         |

| 4.6.2 iSBX™ Interface Configurations                         | 4-2Ø         |

| 4.6.2.1 Interface Addressing                                 | 4-2Ø         |

| 4.6.2.2 Jumper Configurations                                | 4-22         |

| 4.7 MULTIBUS® Interface - P1                                 | 4-22         |

| 4.7.1 MULTIBUS® Interface Description                        | 4-22<br>4-23 |

| 4.7.2 MULTIBUS® Interface Configurations                     | 4-25<br>4-25 |

| 4.8.1 Parallel Interface Description                         | 4-25         |

| 4.8.1.1 Interface Pin Assignments                            | 4-26         |

| 4.8.1.2 Interface Drive Characteristics                      | 4-26         |

| 4.8.1.3 Interface Cabling                                    | 4-27         |

| 4.8.2 PPI Jumper Configurations                              | 4-27         |

| 4.8.3 PPI Device Programming                                 | 4-27         |

| 4.8.3.1 PPI Port Addresses                                   | 4-27         |

| 4.8.3.2 PPI Initialization                                   | 4-3Ø         |

| 4.8.4 Bit Assignments for PPI Signals                        | 4-31         |

| 4.9 Serial I/O Interfaces (with the MPSC device) - J2 & J3   | 4-33         |

| 4.9.1 Serial Jumper Information                              | 4-33         |

| 4.9.2 8274 MPSC Channel A - Connector J2                     | 4-34         |

| 4.9.2.1 Connector J2 Description                             | 4-34         |

| 4.9.2.2 Connector J2 Configurations                          | 4-34         |

#### CONTENTS (continued)

|                                                                      | PAGE |

|----------------------------------------------------------------------|------|

| GWADED ( (cont.) tour 4)                                             |      |

| CHAPTER 4 (continued)                                                | 4 42 |

| 4.9.3 8274 MPSC Channel B - RS232C Interface - Connector J3          | 4-42 |

| 4.9.3.1 Connector J3 Description                                     | 4-42 |

| 4.9.3.2 Connector J3 Configuration                                   | 4-42 |

| 4.9.4 Serial Interface Programming Information                       | 4-42 |

| 4.9.4.1 8274 MPSC Addressing                                         | 4-43 |

| 4.9.4.2 8274 MPSC Initialization                                     | 4-44 |

| 4.1Ø Front Panel Interface - J4                                      | 4-44 |

| 4.10.1 Front Panel Interface Description                             | 4-46 |

| 4.10.2 Front Panel Configurations                                    | 4-46 |

| 4.11 iLBX <sup>rm</sup> , Synchronous, and Auxiliary Interfaces - P2 | 4-47 |

| 4.11.1 iLBX Interface Description                                    | 4-49 |

| 4.11.1.1 iLBX™ Interface Configurations                              | 4-49 |

| 4.11.1.2 iLBX Bus Connector Installation Instructions                | 4-49 |

| 4.11.1.3 iLBX™ Bus Timing Specifications                             | 4-5Ø |

| 4.11.2 Synchronous Interface Description                             | 4-51 |

| 4.11.3 Auxiliary Interface Description                               | 4-52 |

| 4.12 Memory Configuration                                            | 4-53 |

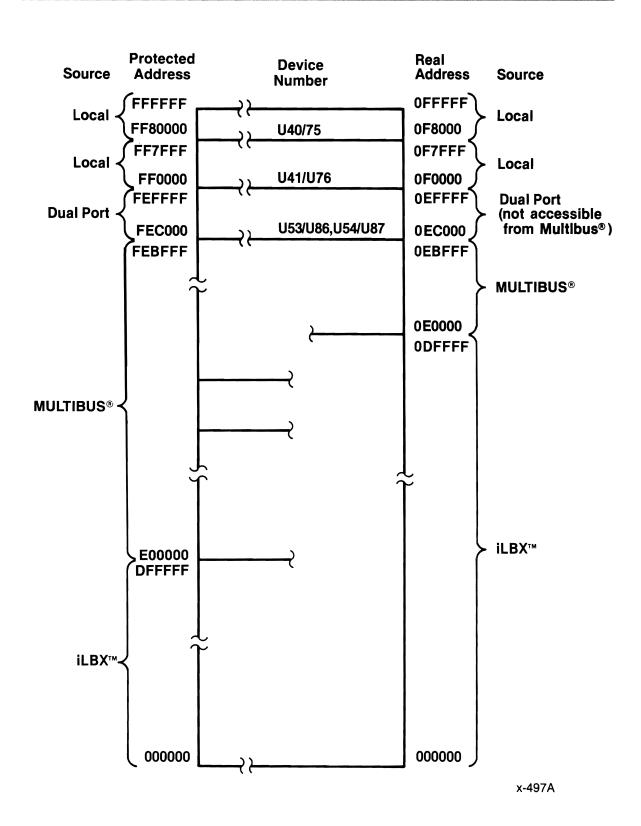

| 4.12.1 Memory Map (Default Configuration)                            | 4-53 |

| 4.12.2 Overview of the Memory Configuration Options                  | 4-56 |

| 4.12.3 Local Memory Configuration                                    | 4-57 |

| 4.12.3.1 Local Memory Socket Pair Descriptions                       | 4-57 |

| 4.12.3.2 Local Memory Configuration Sequence Overview                | 4-59 |

| 4.12.4 Dual-Port Memory Configuration                                | 4-69 |

| 4.12.4.1 Dual-Port Memory Socket Pair Description                    | 4-69 |

| 4.12.4.2 Dual-Port Memory Configuration Sequence Overview            | 4-7Ø |

| 4.12.5 iSBC® 341 Memory Expansion MULTIMODULE™ Board                 | 4-81 |

| 4.12.6 iLBX <sup>™</sup> Memory Configuration                        | 4-81 |

| 4.12.7 Synchronous Interface Memory Configuration                    | 4-82 |

| 4.12.8 MULTIBUS® Memory Configuration                                | 4-83 |

| 4.13 Memory Configuration Examples                                   | 4-83 |

|                                                                      |      |

| CHAPTER 5                                                            |      |

| SERVICE INFORMATION                                                  |      |

| 5.1 Introduction                                                     | 5-1  |

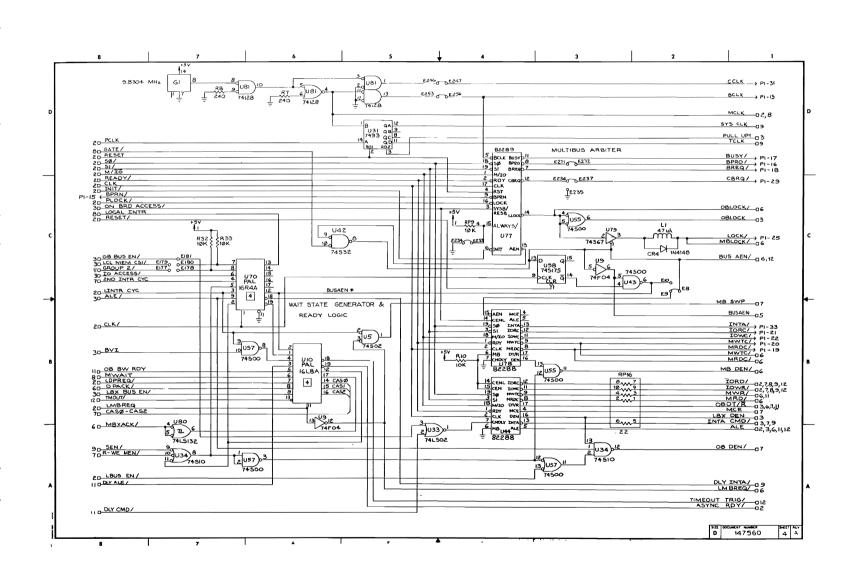

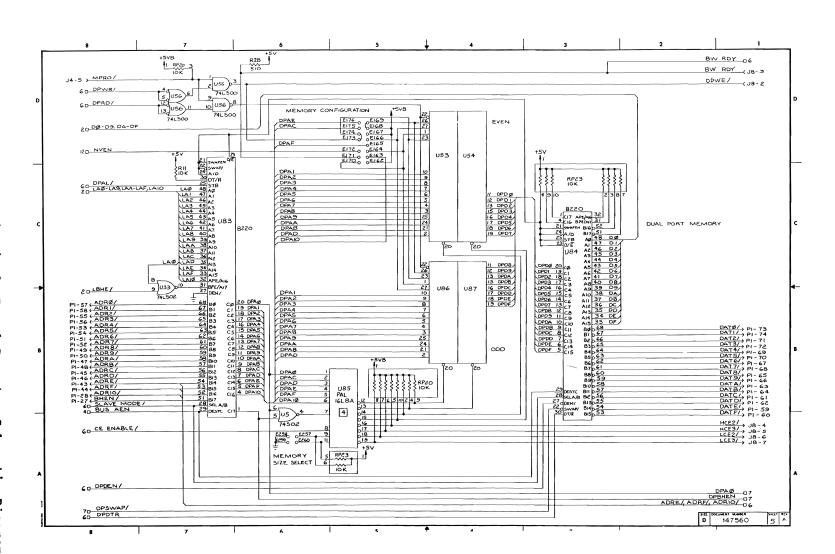

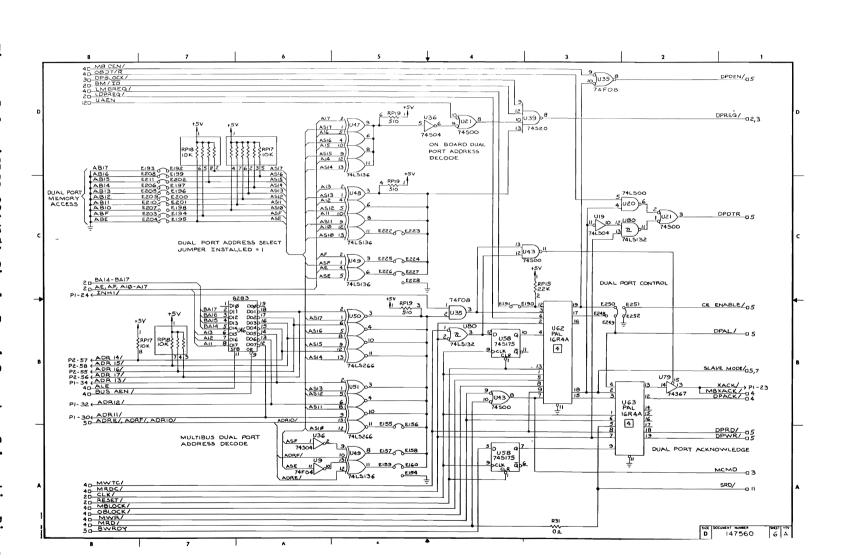

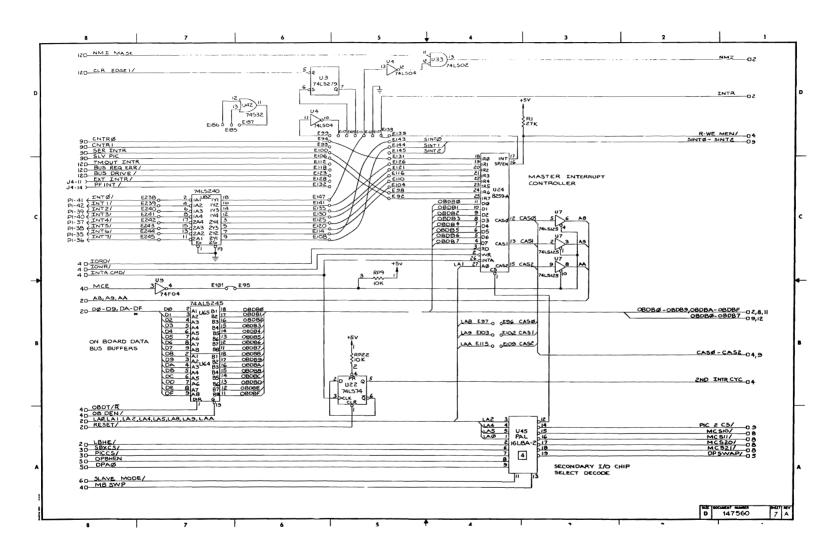

| 5.2 Service Diagrams                                                 | 5–1  |

| 5.3 Service and Repair Assistance                                    | 5–1  |

| APPENDIX A                                                           |      |

| JUMPER INFORMATION                                                   |      |

| A.1 Introduction                                                     | A-1  |

#### CONTENTS (continued)

|                                                   | PAGE                                   |

|---------------------------------------------------|----------------------------------------|

| APPENDIX B                                        |                                        |

| MULTIDROP CONSIDERATIONS  B.1 Introduction        | B-1<br>B-2<br>B-3<br>B-4<br>B-6<br>B-8 |

| APPENDIX C                                        |                                        |

| PAL EQUATIONS C.1 Introduction                    | C-1                                    |

| APPENDIX D WAIT-STATE REQUIREMENTS                |                                        |

| D.1 Introduction                                  | D-1                                    |

| APPENDIX E MEMORY SOCKET MATRIX CONFIGURATIONS    |                                        |

| E.1 Introduction                                  | E-1<br>E-1<br>E-2                      |

| APPENDIX F iSBC@ 341 MEMORY BOARD INSTALLATION    |                                        |

| F.1 Introduction                                  | F-1<br>F-1<br>F-3<br>F-4               |

| APPENDIX G I/O PORT ADDRESS LIST G.1 Introduction | G-1                                    |

| INDEX Ind                                         | iex-1                                  |

| ERRATA Last Page(s) of Ma                         | anual                                  |

## TABLES

|                      |                                                         | PAGE |

|----------------------|---------------------------------------------------------|------|

| 1-1.                 | Specifications                                          | 1-4  |

| 3-1.                 | User-Supplied Components                                | 3-4  |

| 3-2.                 | Compatible Memory Devices                               | 3-7  |

| 3-3.                 | User-Supplied Connector Information                     | 3-11 |

| 3-4.                 | Cable Information                                       | 3-13 |

| 4-1.                 | CPU and Numeric Processor Clock Options                 | 4-4  |

| 4-2.                 | Interrupt Source Jumper Matrix Options                  | 4-9  |

| 4-3.                 | Interrupt Destination Jumper Matrix Options             | 4-1Ø |

| 4-4.                 | Default 8259A Interrupt Level Configuration             | 4-1Ø |

| 4-5.                 | Port Addresses for the 8259A PIC Devices                | 4-13 |

| 4-6.                 | Parameter Sequence for PIC Initialization               | 4-14 |

| 4-7.                 | PIT Jumper Connections                                  | 4-16 |

| 4-8.                 | Port Addresses for the 8254 PIT Device                  | 4-18 |

| 4-9.                 | PIT Programming Sequence                                | 4-19 |

| 4-1Ø.                | I/O Port Addresses for iSBX™ Connectors                 | 4-21 |

| 4-11.                | iSBX <sup>™</sup> Jumper Options                        | 4-22 |

| 4-12.                | MULTIBUS® Interface Jumpers                             | 4-23 |

| 4-13.                | MULTIBUS® Release Modes                                 | 4-24 |

| 4-14.                | Connector J1 Pin Assignments                            | 4-26 |

| 4-15.                | Connector J1 Interface DC Characteristics               | 4-26 |

| 4-16.                | Parallel I/O Jumper Options                             | 4-28 |

| 4-17.                | PPI Port Addresses                                      | 4-3Ø |

| 4-18.                | Parameter Sequence for PPI Device Initialization        | 4-31 |

| 4-19.                | PPI Bit Assignments (Default Configuration)             | 4-32 |

| 4-2Ø.                | Serial I/O Jumper Options                               | 4-33 |

| 4-21.                | Pin Assignments for Connector J2 - RS422A/449 Interface | 4-36 |

| 4-22.                | Serial I/O Interface Configuration Comparison           | 4-37 |

| 4-23.                | RS232C Pin Assignment                                   | 4-43 |

| 4-24.                | Serial I/O Port Addresses                               | 4-44 |

| 4-25.                | 8274 Parameter Sequence for Initialization              | 4-45 |

| 4-26.                | Connector J4 Pin Assignments                            | 4-46 |

| 4-27.                | Connector J4 Interface DC Characteristics               | 4-47 |

| 4-28.                | Connector P2 Interface Options                          | 4-48 |

| 4-29.                | Timing for the iLBX' Interface                          | 4-5Ø |

| 4-29.<br>4-3Ø.       | Memory Map (Primary Decode) Options                     | 4-62 |

| 4-3 <b>v</b> . 4-31. | Local Memory Map - Primary Decode Option Ø              | 4-63 |

| 4-31.                |                                                         | 4-63 |

| 4-32.                | Local Memory Map - Primary Decode Option 1 (Default)    | 4-63 |

|                      | Local Memory Map - Primary Decode Option 2              |      |

| 4-34.                | Local Memory Map - Primary Decode Option 3              | 4-64 |

| 4-35.                | Jumper Configurations for Secondary Decode Options      | 4-66 |

| 4-36.                | Local Memory Configurations Allowed By                  | ,    |

|                      | Each Secondary Option                                   | 4-67 |

| 4-37.                | Local Memory Wait-State Jumpers                         | 4-68 |

| 4-38.                | Memory Device Size Selection - Dual-Port                | 4-72 |

| 4-39.                | Megabyte Starting Page Configuration                    | 4-75 |

#### TABLES (continued)

|                                                             |                                                                                                                                                                                                                                    | PAGE                                                 |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 4-4Ø.<br>4-41.<br>4-42.<br>4-43.<br>4-44.<br>4-45.<br>4-46. | 64K Starting Page Configuration                                                                                                                                                                                                    | 4-76<br>4-76<br>4-78<br>4-79<br>4-84<br>4-87<br>4-9Ø |

| 5-1.                                                        | Schematic Index                                                                                                                                                                                                                    | 5-4                                                  |

| A-1.<br>A-2.<br>A-3.                                        | Numerical List of Jumpers and Their Functions  Stake-Pin Schematic Index  Default Jumper Listing and Schematic Index  Primary Decode PAL U74 Device Description                                                                    | A-2<br>A-7<br>A-7                                    |

| C-2.<br>C-3.<br>C-4.                                        | PAL Equations for U74  PAL U74 Memory Map (Compatibility Mode - UAEN Low)  PAL U74 Memory Map (PVAM - UAEN High)                                                                                                                   | C-3<br>C-4<br>C-4                                    |

| D-1.<br>D-2.<br>D-3.<br>D-4.                                | Local Memory Requirements for 1 Wait-State at 8.0 MHz  Local Memory Requirements for 2 Wait-States at 8.0 MHz  Local Memory Requirements for 3 Wait-States at 8.0 MHz  Dual-Port Memory Requirements for 2 Wait-States at 8.0 MHz. | D-2<br>D-2<br>D-3<br>D-3                             |

| E-1.                                                        | Byte-Wide Socket AC and DC Specifications                                                                                                                                                                                          | E-1                                                  |

| F-1.                                                        | Jumper Configurations for Types of Memory Devices                                                                                                                                                                                  | F-4                                                  |

| G-1.<br>G-2.                                                | I/O Port Addresses for iSBX™ Bus Connectors                                                                                                                                                                                        | G-1<br>G-2                                           |

|                                                             | FIGURES                                                                                                                                                                                                                            |                                                      |

| 1-1.                                                        | iSBC® 286/1ØA Single Board Computer                                                                                                                                                                                                | 1-1                                                  |

| 2-1.                                                        | Block Diagram                                                                                                                                                                                                                      | 2-2                                                  |

| 3-1.<br>3-2.<br>3-3.                                        | User-Supplied Components Location Diagram                                                                                                                                                                                          | 3-5<br>3-6<br>3-8                                    |

## FIGURES (continued)

|              |                                                             | PAGE |

|--------------|-------------------------------------------------------------|------|

| 4-1.         | Interrupt Jumper Matrix                                     | 4-8  |

| 4-2.         | PIT Default Jumper Configuration                            | 4-17 |

| 4-2.         | PPI Default Jumper Configuration                            | 4-17 |

| 4-3.<br>4-4. |                                                             | 4-25 |

|              | Serial I/O Interface Options                                | 4-33 |

| 4-5.         | DCE and DTE Interface Block Diagram                         |      |

| 4-6.         | DIP Header for DCE and DTE Operation                        | 4-39 |

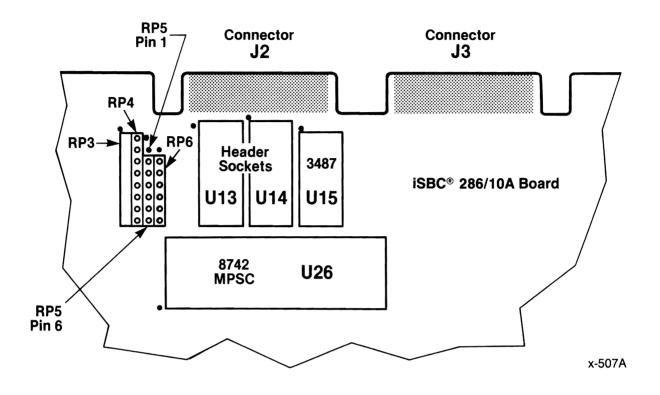

| 4-7.         | RP5 Location                                                | 4-40 |

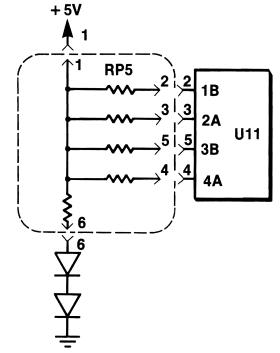

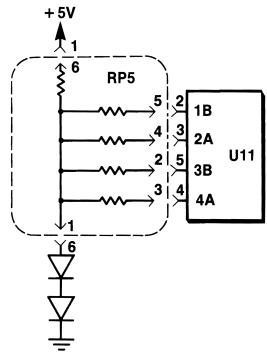

| 4-8.         | RP5 Configurations                                          | 4-41 |

| 4-9.         | Default Memory Map                                          | 4-54 |

| 4-1Ø.        | Local Memory Socket Pairs and Jumper Matrices               | 4-58 |

| 4-11.        | Stake Pin Format in the Jumper Matrix                       | 4-6Ø |

| 4-12.        | Local Memory Jumper Location                                | 4-62 |

| 4-13.        | Size/Justification Jumper Locations on the Board            | 4-65 |

| 4-14.        | Dual-Port Memory Socket Pairs and Jumper Matrix             | 4-69 |

| 4-15.        | Dual-Port Jumper Locations                                  | 4-73 |

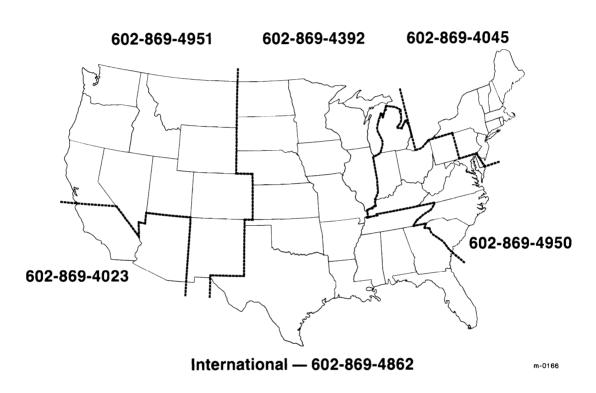

| 5-1.         | Territorial Service Telephone Numbers                       | 5-3  |

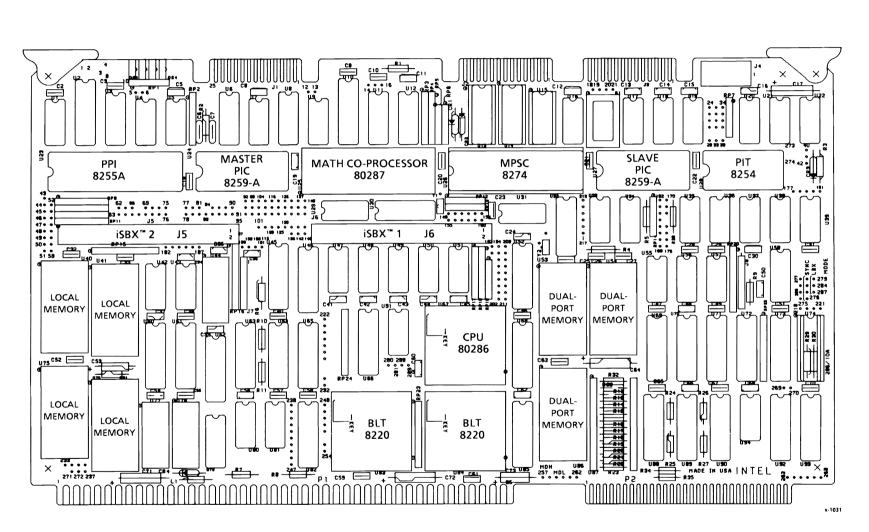

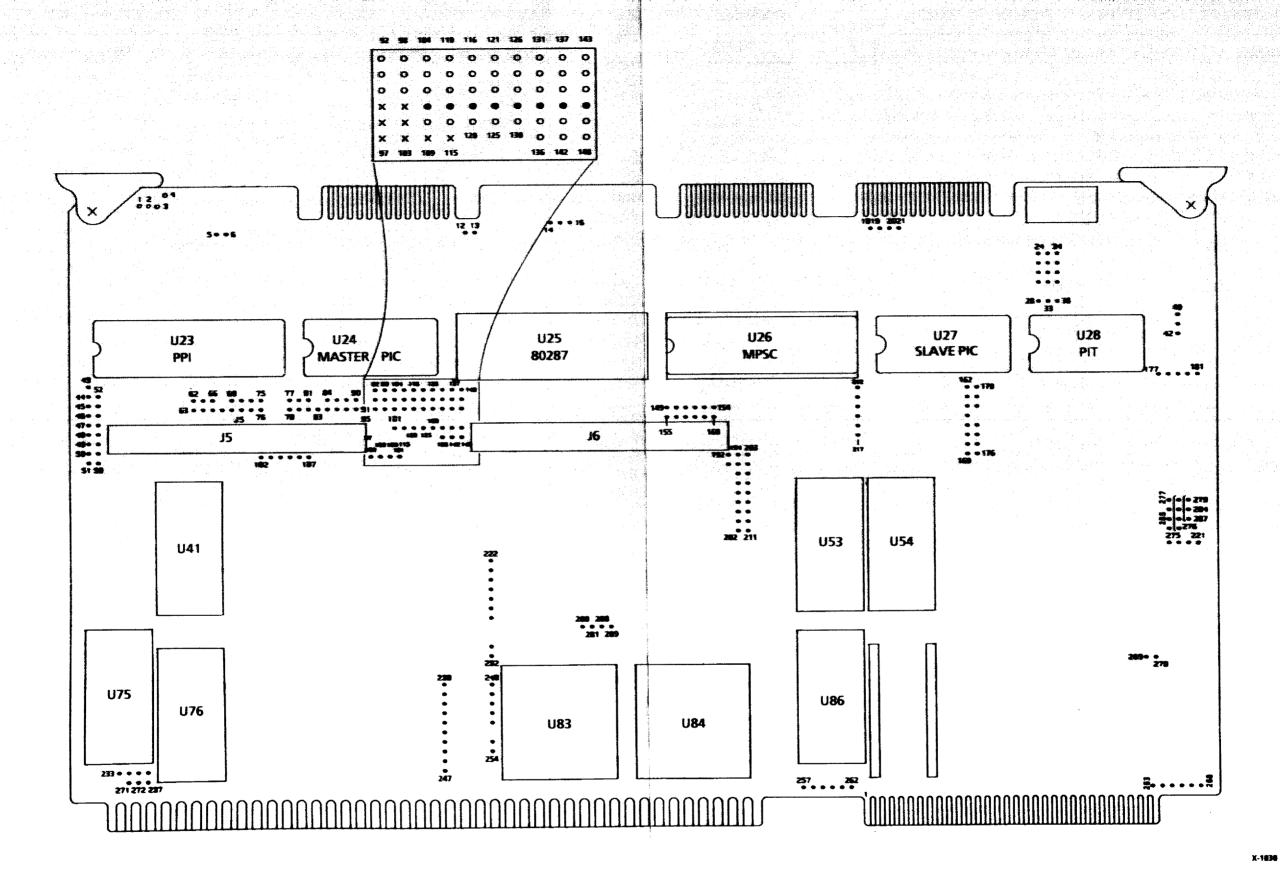

| 5-2.         | iSBC@ 286/1ØA Single Board Computer Parts Location Diagram. | 5–5  |

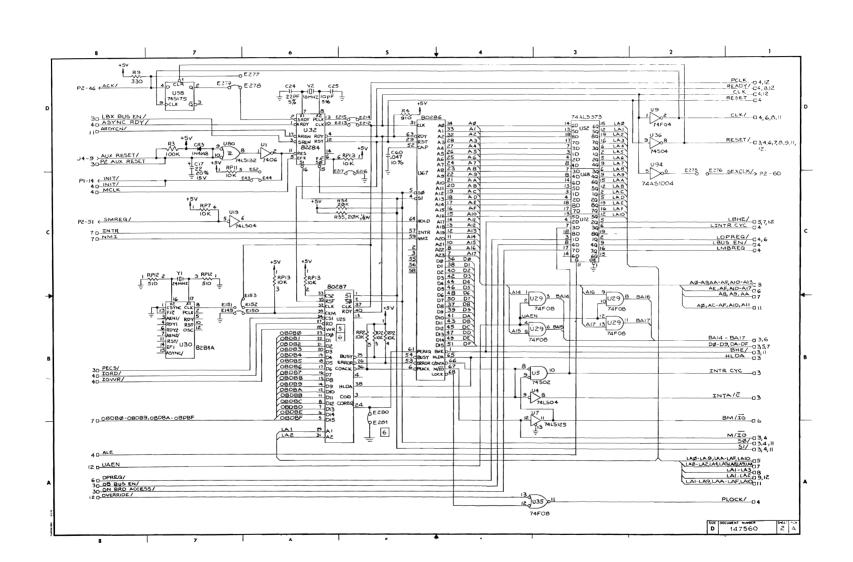

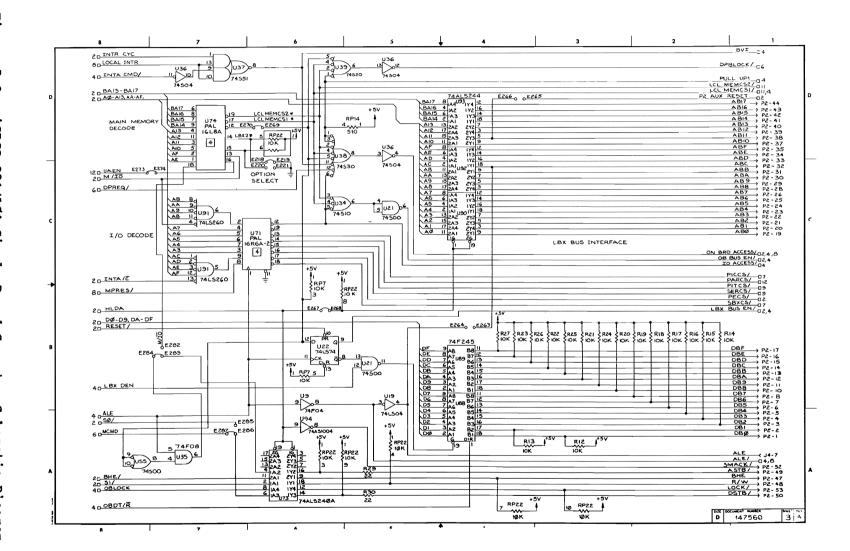

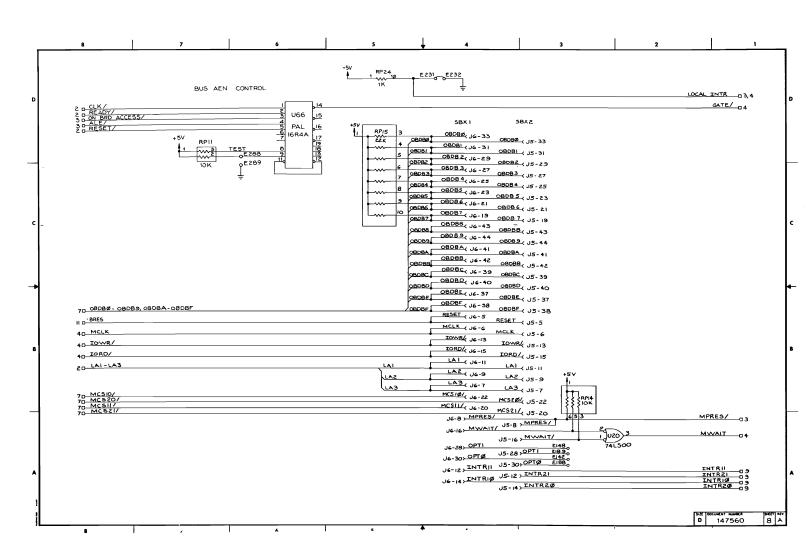

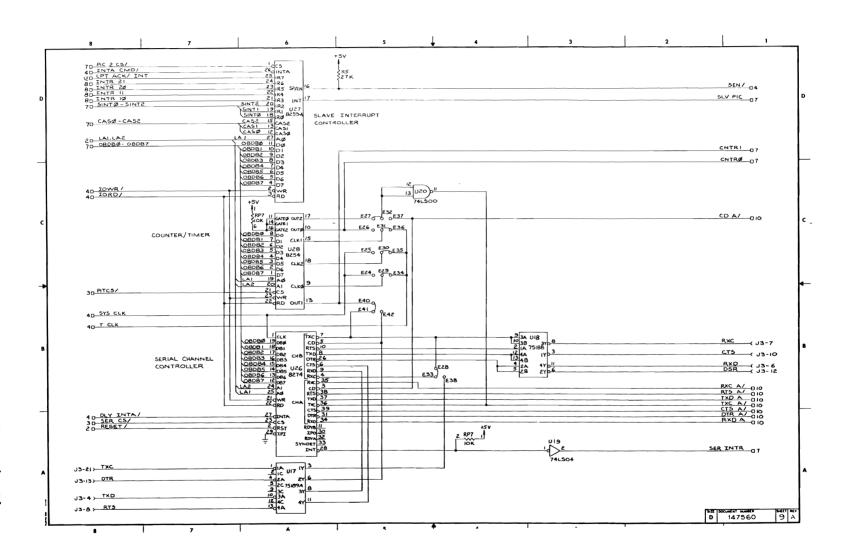

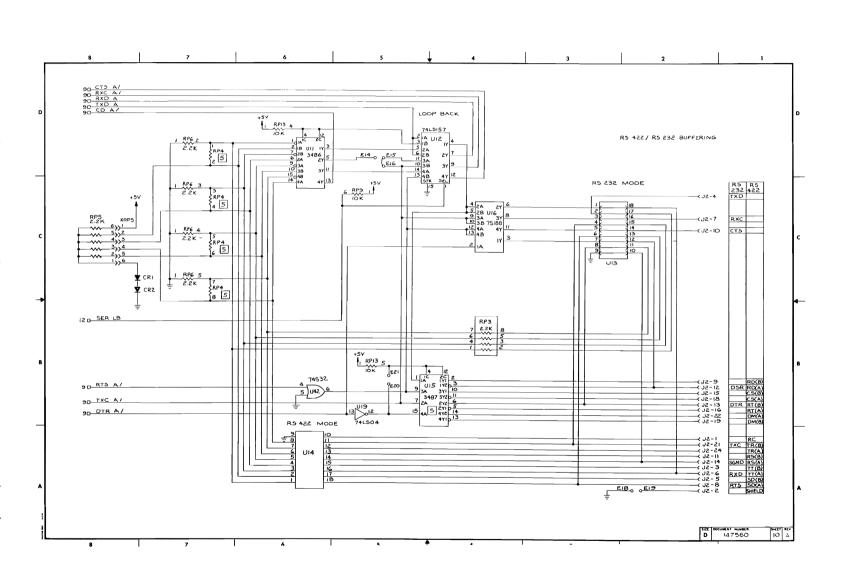

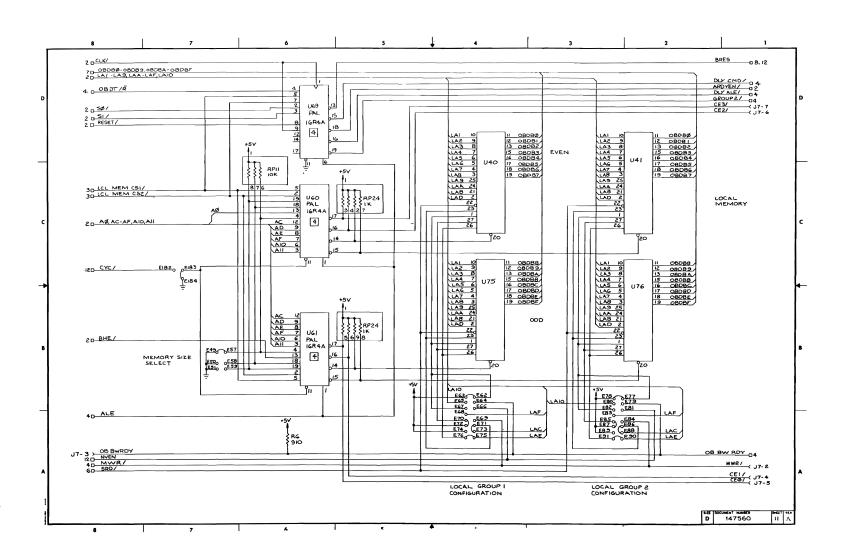

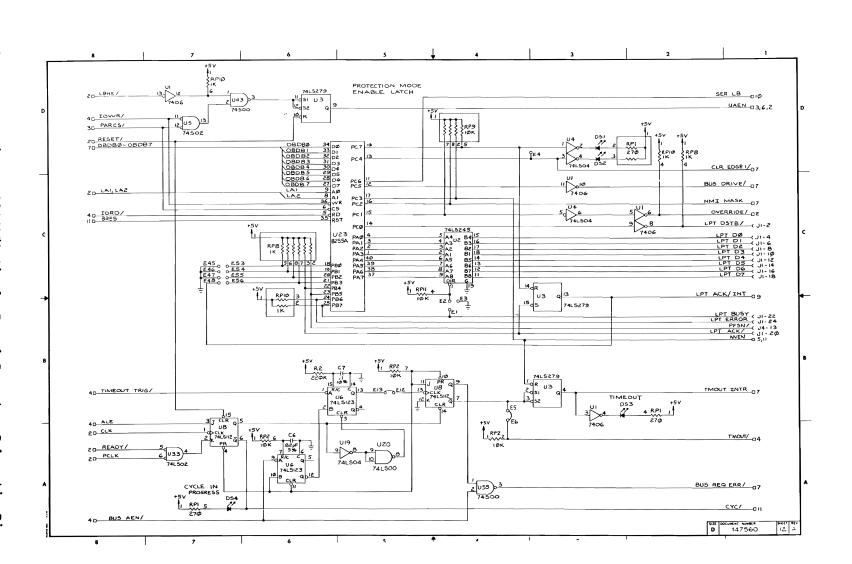

| 5-3.         | iSBC@ 286/1ØA Single Board Computer Schematic Diagram       | 5–6  |

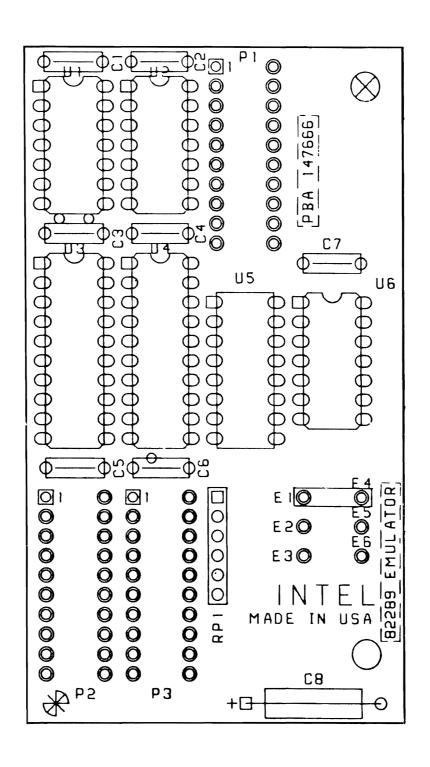

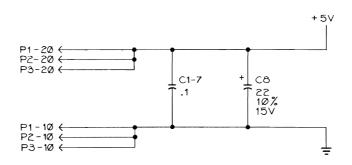

| 5-4.         | 82289 Emulator Parts Location Diagram                       | 5-18 |

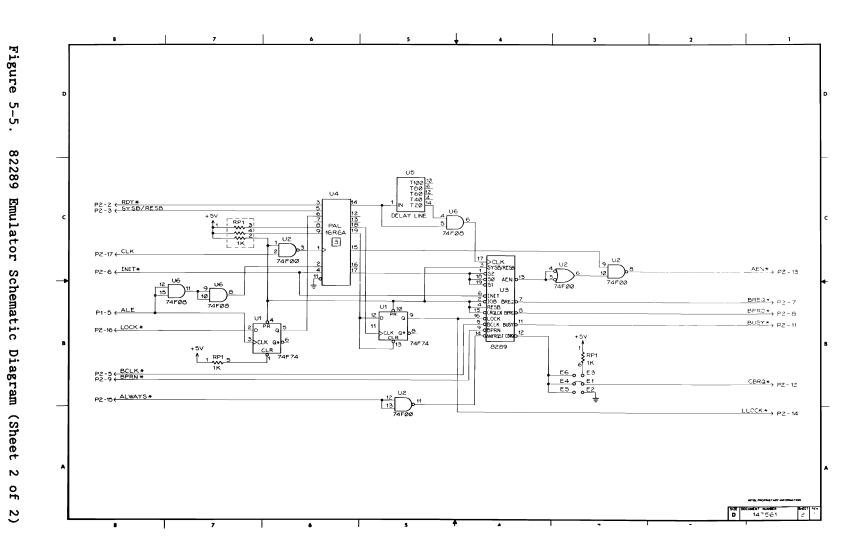

| 5-5.         | 82289 Emulator Schematic Diagram                            | 5–19 |

| A-1.         | iSBC® 286/1ØA Board Jumper Post Location Diagram            | A-7  |

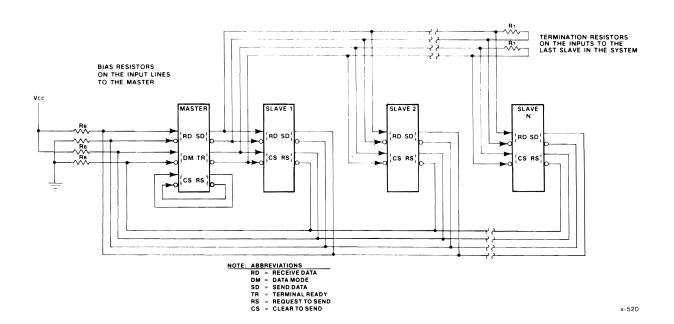

| B-1.         | Full-Duplex RS422A/449 Multidrop Configuration Example      | B-2  |

| B-2.         | System Example - Bias and Terminator Resistor Placement     | B-4  |

| B-3.         | Case 1 Example (Lines Floating)                             | B-5  |

| B-4.         | Case 2 Example (Lines Driven)                               | B-7  |

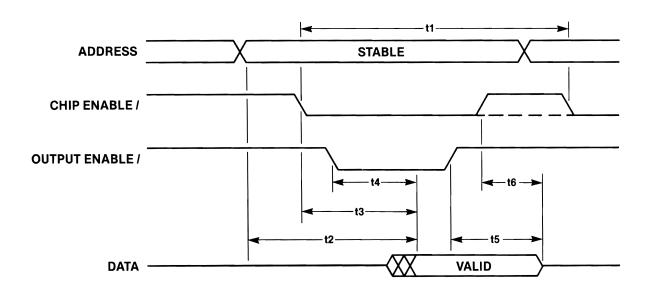

| D-1.         | Read Cycle                                                  | D-4  |

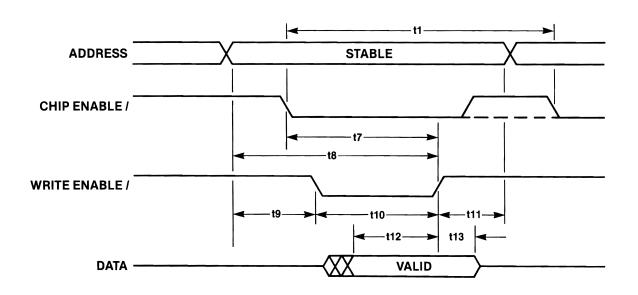

| D-2.         | Write Cycle                                                 | D-4  |

|              | •                                                           |      |

| E-1.         | Memory Sockets' Pin-Out                                     | E-3  |

| E-2.         | Jumper Matrix Configurations for Static RAM Devices         | E-4  |

| E-3.         | Jumper Matrix Configurations for iRAM Devices               | E-5  |

| E-4.         | Jumper Matrix Configurations for EPROM Devices              | E-6  |

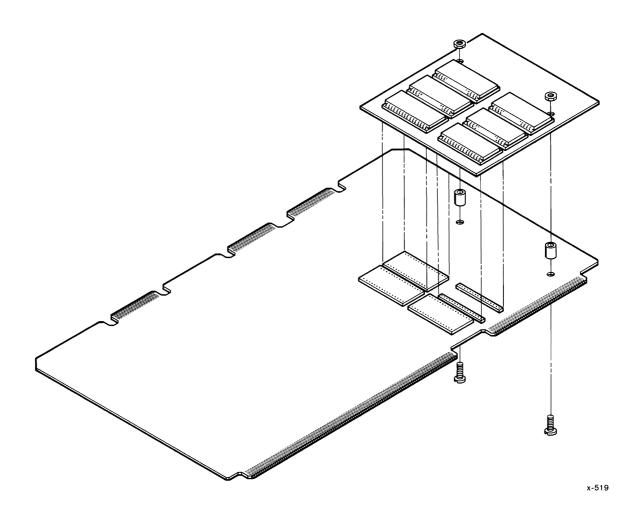

| F-1.         | iSBC® 341 Board Orientation (for dual-port memory)          | F-3  |

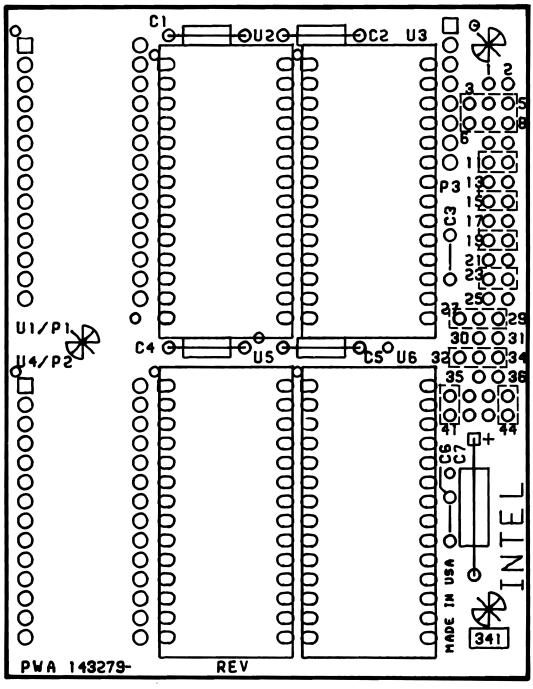

| F-2.         | iSBC@ 341 Board Parts Location Diagram                      | F-5  |

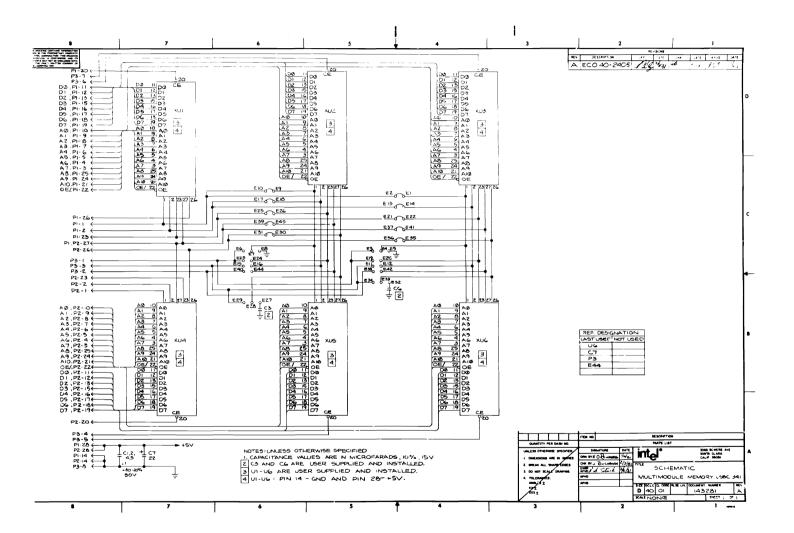

| F-3.         | iSBC@ 341 Board Schematic Diagram                           | F-6  |

#### 1.1 INTRODUCTION

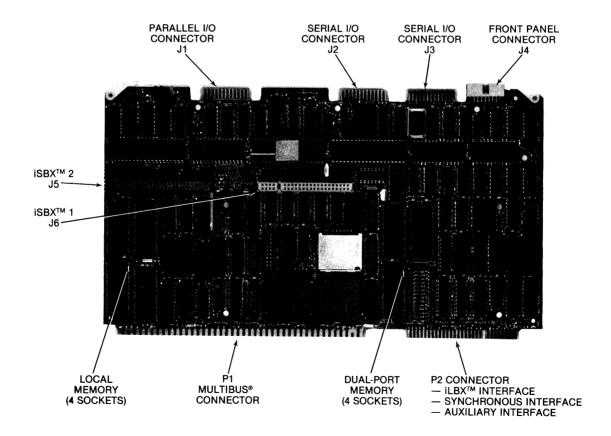

The iSBC® 286/1ØA Single Board Computer (Figure 1-1) is a board-level solution for high-speed, multiuser, multitasking, real-time, multiprocessor system applications.

This manual provides all information necessary to use the iSBC 286/1ØA board. This chapter provides a brief overview of the features and the specifications of the iSBC 286/1ØA processor board.

Figure 1-1. iSBC@ 286/1ØA Single Board Computer

iSBC® 286/1ØA 1-1

#### GENERAL INFORMATION

The board contains the standard MULTIBUS® connector (P1), an iLBX™ Bus connector (P2), and three I/O edge connectors (J1, J2, and J3). Connector J4 provides the signals for operating a system front panel, and connectors J5 and J6 provide two iSBX™ bus interfaces.

#### 1.2 iAPX 286 CPU FEATURES

The design of the iAPX 286 CPU provides the iSBC 286/10A board with several features:

- Two modes of operation: Protected Virtual Address Mode (PVAM) and Real Address Mode

- Concurrent instruction decoding within the CPU

- Bus cycle pipelining on the local bus

- Extended iAPX 86, 88 instruction set

- Large address space PVAM Real Mode

16 megabytes physical 1 megabyte

1 gigabyte virtual

- Four levels of process protection (PVAM)

- Automatic memory access verification (PVAM)

For detailed information, refer to Intel's iAPX 286 PROGRAMMER'S REFERENCE MANUAL.

#### 1.3 BOARD FEATURES

In addition to the iAPX 286 features, the iSBC 286/10A board contains several other features:

- An iLBX (Local Bus Extension) interface for high-speed memory expansion

- A synchronous interface for high-speed memory expansion

- A front panel interface

- 8 JEDEC sockets for optional memory components

4 sockets for local memory (expandable to 8)

4 sockets for dual-port memory (expandable to 8)

- Configurable memory capacity up to 128K bytes of dual-port

up to 256K bytes of local

- Two programmable serial I/O interfaces

- Accepts the 80287 Numeric Processor Extension

- Two 8- or 16-bit iSBX bus interface connectors for I/O expansion

- Centronics-compatible parallel I/O printer interface

- 15 levels of vectored interrupt control

Refer to Chapter 2 for a general description of these features and Chapter 4 for configuring and programming information.

#### 1.4 BOARD SPECIFICATIONS

Table 1-1 contains the specifications for the iSBC 286/10A board.

iSBC@ 286/1ØA 1-3

#### GENERAL INFORMATION

Table 1-1. Specifications

CPU

Intel iAPX 286 CPU

WORD SIZE

Instruction:

8, 16, 24, 32, 40, or 48 bits

Data:

8 to 80 bits

Physical Addressing:

2Ø bits (1 Mbyte) - Real Address mode

24 bits (16 Mbyte) - PVAM

Virtual Addressing:

1 gigabyte

PVAM

SYSTEM CLOCK SPEED:

or 4.9 MHz

8.Ø MHz (default)

INSTRUCTION

EXECUTION TIME

375 nsec

25Ø nsec, instruction in queue

**MEMORY**

On-board Memory:

Eight 28-pin JEDEC-compatible chip sockets hold user-provided memory devices in 2Kx8, 8Kx8, 16Kx8, 32Kx8, or 64Kx8 capacity. Four sockets are dedicated to dual-port memory; four sockets are dedicated to local memory. The iSBC 341 memory expansion board adds four sockets to both local and dual-port

${\tt memory.}$

MAXIMUM LOCAL MEMORY

256K bytes (maximum in 4 or 8 sockets)

MAXIMUM DUAL-PORT

MEMORY

128K bytes (maximum in 4 or 8 sockets)

PHYSICAL CHARACTERISTICS

Width: Height: 3Ø.48 cm (12.ØØ in) 17.15 cm (6.75 in)

Depth:

1.42 cm (Ø.56 in) with no MULTIMODULE boards

1.82 cm (Ø.718 in) with iSBC 341

MULTIMODULE board

2.95 cm (1.16 inches) with an iSBX MULTIMODULE

board

Weight:

534 gm (19 oz)

-----(continued)------

1-4 iSBC® 286/1ØA

Table 1-1. Specifications (continued)

ENVIRONMENTAL REQUIREMENTS

Operating Temperature: ذC to 55°C

Relative Humidity: to 90%, noncondensing

Air Velocity:

200 linear feet/minute minimum

INTERFACE COMPLIANCE LEVELS:

MULTIBUS® Compliance: Master D16 M24 I16 VØ2 E L

iSBX™ Bus Compliance: D16/16 I iLBX<sup>TM</sup> Bus Compliance: PM D16 A24

I/O CAPABILITY

Parallel: 24 programmable I/O lines using one 8255A PPI

> device; 18 of the lines are configurable. Default configured for on-board functions and direct operation with a printer using the

Centronics interface standard.

Serial: 2 serial interfaces using the 8274 MPSC

device. Connector J2 is configurable for either RS232C or RS422A/449 operation; Connector J3 is configured for only RS232C

(DCE) operation.

I/O Expansion: 2 iSBX bus connectors providing expansion via

addition of 8-bit or 16-bit iSBX MUlTIMODULE

boards, in increments as follows:

one single-wide MULTIMODULE board, or

two single-wide MULTIMODULE boards, or

one double-wide MULTIMODULE board, or

one single- and one double-wide

MULTIMODULE board

SERIAL COMMUNICATIONS

CHARACTERISTICS

Protocols:

Supports the following modes of the 8274 MPSC:

Bit-synchronous

Byte-synchronous Asynchronous

Synchronous:

5- to 8-bit characters; internal character or

HDLC/SDLC synchronization; automatic sync bit

insertion, even or odd parity.

Asynchronous: 5- to 8-bit characters; break character

generation; 1, 1-1/2, or 2 stop bits; false

start-bit detection, even or odd parity.

-----(continued)------

iSBC@ 286/1ØA 1-5

Table 1-1. Specifications (continued)

#### 8274 Baud Rates:

| Frequency (kHz)       |             | Baud         | Rate (Hz) |        |       |  |

|-----------------------|-------------|--------------|-----------|--------|-------|--|

| (Software Selectable) | Synchronous | Asynchronous |           |        |       |  |

| Reference: 1.23 MHz   | ÷1          | ÷ 1          | ÷16       | ÷ 32   | ÷ 64  |  |

| 615.                  | 615,000     | 615,000      | 38,400    | 19,200 | 9,600 |  |

| 307.                  | 307,000     | 307,000      | 19,200    | 9,600  | 4,800 |  |

| 154.                  | 154,000     | 154,000      | 9,600     | 4,800  | 2,400 |  |

| 76.8                  | 76,800      | 76,800       | 4,800     | 2,400  | 1,200 |  |

| 38.4                  | 38,400      | 38,400       | 2,400     | 1,200  | 600   |  |

| 19.2                  | 19,200      | 19,200       | 1,200     | 600    | 300   |  |

| 9.6                   | 9,600       | 9,600        | 600       | 300    | 150   |  |

| 4.8                   | 4,800       | 4,800        | 300       | 150    | 75    |  |

| 2.4                   | 2,400       | 2,400        | 150       | 75     | -     |  |

| 1.2                   | 1,200       | 1,200        | 75        | _      | -     |  |

| 0.6                   | 600         | 600          | -         | _      | -     |  |

2175

#### ELECTRICAL CHARACTERISTICS

#### DC Power Requirements:

| Supply Voltage            | Current Required (typical) (max.) |       |

|---------------------------|-----------------------------------|-------|

| +5V <u>+</u> 5%           | 5.6 A                             | 7.1 A |

| +12V <u>+</u> 5% (note 1) | 5Ø mA                             | 5Ø mA |

| -12V <u>+</u> 5% (note 1) | 5Ø mA                             | 5Ø mA |

#### Notes:

- 1. ±12 volts is required for RS232C interface.

- Values do not include power for memory devices or iSBX MULTIMODULE boards. If you add either, add their power requirements to the data in this table.

-----(continued)------

1-6 iSBC® 286/1ØA

Table 1-1. Specifications (continued)

| VISUAL INDICATORS |                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 Red LEDs        | User-programmable after the 8255 PPI is initialized. On after a reset.                                                                                       |

| 1 Yellow LED      | Time-out indicator. On when no acknowledge signal is found after an iLBX, synchronous, or MULTIBUS access has been requested. Turned off by program control. |

| 1 Green LED       | On when a cycle is in progress (between ALE and READY).                                                                                                      |

#### 2.1 INTRODUCTION

This chapter provides an overview of the operation of the board and of the functional devices. Each functional area of the board is shown in the block diagram and its default configuration will be explained. Refer to Chapter 4 for more detailed information.

#### 2.2 FUNCTIONAL DESCRIPTION

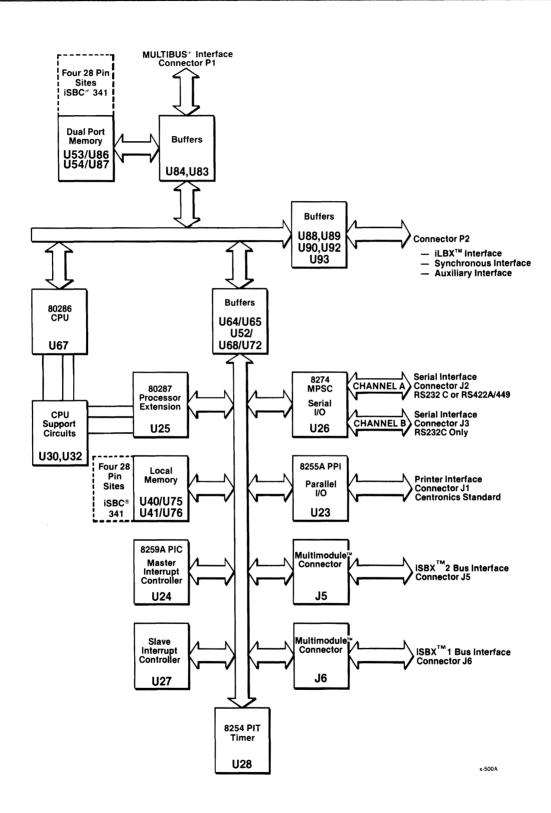

A functional block diagram of the iSBC 286/1 $\emptyset$ A board is shown in Figure 2-1. The following sections describe each of the functional units of the block diagram.

#### 2.2.1 CLOCK GENERATION CIRCUITS

The iSBC 286/10A board contains three clock generator devices, the 82284, 8284A, and G1. These devices operate independently and provide these jumper-selectable clock rate options:

- Operate the 8Ø286 CPU at 4.9 MHz or 8 MHz (default).

- 2. Operate the 8Ø287 synchronously with the 8Ø286 CPU:

- 8Ø287 at 3.28 MHz with 8Ø286 CPU at 4.9 MHz.

- 80287 at 5.33 MHz with 80286 CPU at 8.0 MHz (default).

Operate the 8Ø287 asynchronously with the 8Ø286 CPU:

8Ø287 at 8.Ø MHz independent of 8Ø286 clock.

iSBC® 286/1ØA 2-1

181-

Figure 2-1. Block Diagram

#### 2.2.2 CENTRAL PROCESSOR

The 80286 CPU operates in one of two modes: Real Address mode or Protected Virtual Address Mode (PVAM). The CPU automatically operates in Real Address mode after power-up or reset. Issuing one software command, which changes the contents of the Machine Status Word Register, switches the 80286 CPU from Real Address mode to PVAM. A word-write to the parallel port switches the iSBC 286/10A board from 20-bit to 24-bit addressing.

#### NOTE

After switching the 80286 CPU from Real Address mode to PVAM, you cannot switch back to Real Address mode without a hardware RESET.

The differences between the two modes are quite significant and are listed in the following sections. For more information, refer to Intel's iAPX 286 PROGRAMMER'S REFERENCE MANUAL.

#### REAL ADDRESS MODE

- The 80286 executes a superset of the 8086 instruction set.

- The 8Ø286 can access up to one megabyte of address space.

- The 8Ø286 can access up to 64K 8-bit I/O addresses or up to 32K 16-bit I/O addresses.

- The memory protection hardware features of the 80286 are disabled.

- The 8Ø286 begins program execution at memory location FFFFØH in the Real Address mode.

iSBC® 286/1ØA 2-3

#### **BOARD OPERATION**

#### PROTECTED VIRTUAL ADDRESS MODE

- The 8Ø286 executes a superset of the Real Address mode instruction set with additional instructions specifically for use with PVAM.

- The 80286 can access up to 16 megabytes of physical address space and up to one gigabyte of virtual address space.

- The 8Ø286 can access the same number of I/O ports as in Real Address mode.

- The 8Ø286 performs automatic memory access verification. Each memory segment is assigned a Read only, Read/Write, Execute/Read, or Execute access right. On every memory access, the iAPX 286 CPU automatically verifies that the access rights are not being violated.

- The 8Ø286 provides four privilege levels. An error flag indicates when any privilege level restriction is violated. The hardware enforces a strict protection algorithm that

- -- allows tasks to access data in only those segments with an equal or lower privilege level

- -- allows tasks to call only those segments with an equal or higher privilege level

- -- allows only those tasks executing at the highest privilege level to execute instructions that alter the CPU state (for example, the HALT instruction)

In both modes of operation, the 8Ø286 allows space for up to 256 interrupt vectors. Interrupt vectors Ø through 31 are used by internally generated interrupts and are reserved. Vectors 32 through 256 share the hardware interrupt request pin (INTR) and are identified by their interrupt vector during an interrupt acknowledge cycle. All are available through software interrupts.

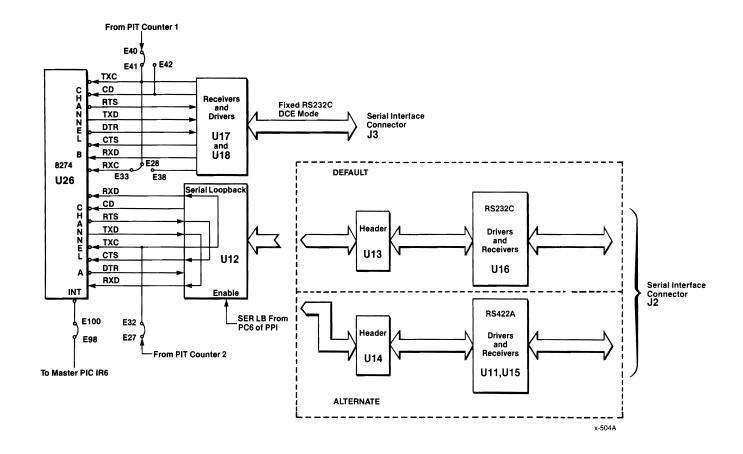

#### 2.2.3 SERIAL I/O INTERFACES

The serial I/O on the iSBC 286/1ØA board consists of an 8274 Multiple Protocol Serial Controller (MPSC) device controlling two 26-pin connectors, J2 and J3. Channel A of the 8274 MPSC operates the serial interface at Connector J2; Channel B operates Connector J3. Because the two channels are independent, they can operate simultaneously.

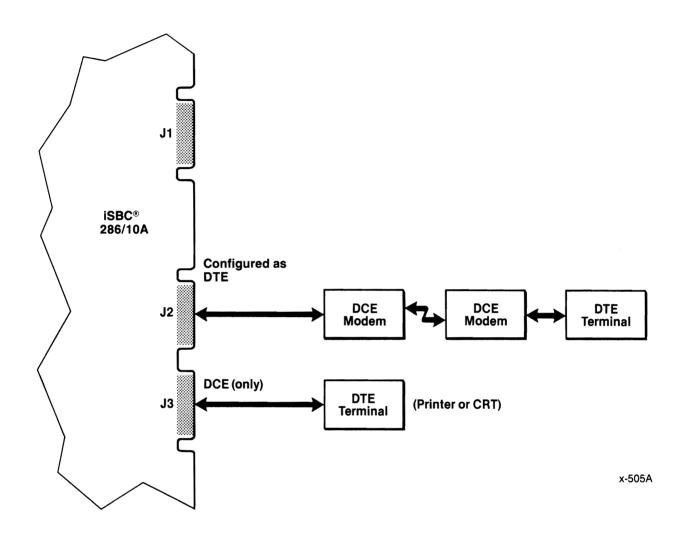

In the default configuration, the iSBC 286/10A board provides a specific interface standard on each of the serial I/O connectors:

- Connector J2 is configured as an RS232C DCE (Data Communications Equipment) interface via Channel A. Connector J2 may also be altered for RS232C DTE (Data Terminal Equipment) mode or as an RS422/449 (DTE or DCE mode) interface.

- Connector J3 is configured as an RS232C DCE interface via Channel B and cannot be altered.

Depending on how the 8274 MPSC is programmed, the interfaces are in either an interrupt-driven mode or a polled-interrupt mode.

In the default configuration, the 8274 MPSC operates in an interrupt-driven mode; that is, an interrupt request signal (SER INTR) is activated whenever either channel needs service. By activating the SER INTR signal, the 8274 MPSC provides an interrupt acknowledge signal at interrupt level 6 to the master 8259A PIC. With the interrupt request, the 8274 MPSC also provides an 8-bit interrupt vector address on the local data bus.

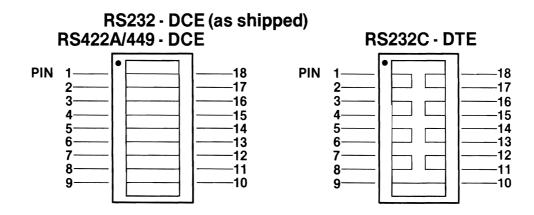

#### Connector J2

The iSBC 286/1ØA board provides configuration control on Channel A (Connector J2). In the default configuration, the iSBC 286/1ØA board operates Channel A as an RS232C DCE interface. By altering the DIP header configuration, Channel A is reconfigured as an RS232C DTE interface. By changing the orientation of a socketed resistor pack, adding a socketed IC, and moving a DIP header, Channel A can be reconfigured as an RS422A/449 interface. The interface is also compatible with CCITT X.25, a European serial interfacing standard, when configured as an RS422A/449 interface.

#### Connector J3

Channel B (Connector J3) is not reconfigurable. Channel B must operate as an RS232C interface in DCE mode.

iSBC® 286/1ØA 2-5

#### **BOARD OPERATION**

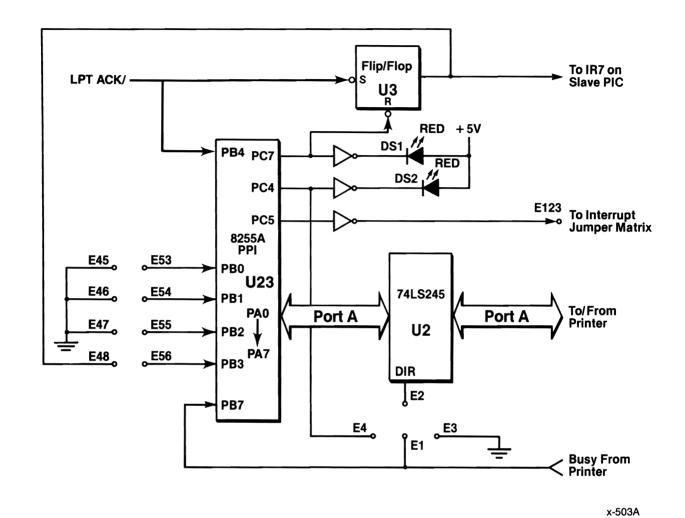

#### 2.2.4 PARALLEL I/O INTERFACE

The parallel I/O on the iSBC 286/1ØA board consists of an 8255A PPI device controlling J1, the 26-pin parallel I/O port. Chapter 4 supplies detailed information for the interface.

The iSBC 286/10A board provides jumpers for configuring the printer interface as interrupt-driven. The interface logic can generate an interrupt request to the on-board 8259A PIC via the LPT ACK/INT signal.

In the default configuration, the iSBC 286/1ØA board provides signals at Connector J1 that are plug-compatible with the Centronics standard interface. The iSBC 286/1ØA board also provides interface drivers and receivers for the printer interface. To use the Centronics printer interface, an initialization routine must initialize the 8255A PPI device for operation in Mode Ø with Port B as input, Port A as output, and Port C as output. The printer interface is complete and ready to use when the iSBC 286/1ØA board is received.

The direction of operation of Port A can be reconfigured. However, undefined board operation may result if Ports B and C are also reconfigured.

#### 2.2.5 ON-BOARD MEMORY

The on-board memory space on the iSBC 286/1ØA board consists of three separate memory areas: local memory one, local memory two, and dual-port memory space. Each area is configurable and independent of the others. The local memory is accessible only to the on-board CPU, while the dual-port memory is accessible by both the on-board CPU and another MULTIBUS board.

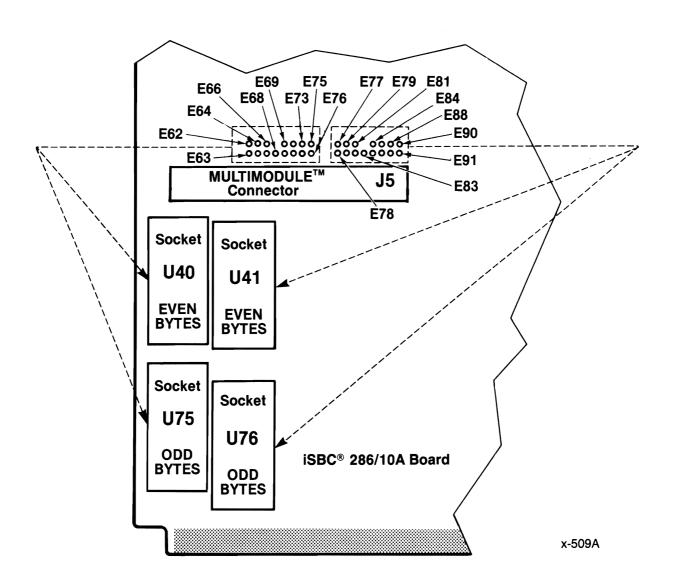

Local memory consists of chip sockets U4Ø/U75 (local memory one) and U41/U76 (local memory two). In the default configuration, each local memory socket pair is prepared for immediate installation of 27128 (16Kx8) EPROM devices. You can reconfigure the board to accept a maximum of 256K bytes of memory at the local memory chip sockets. Local memory supports only EPROM devices.

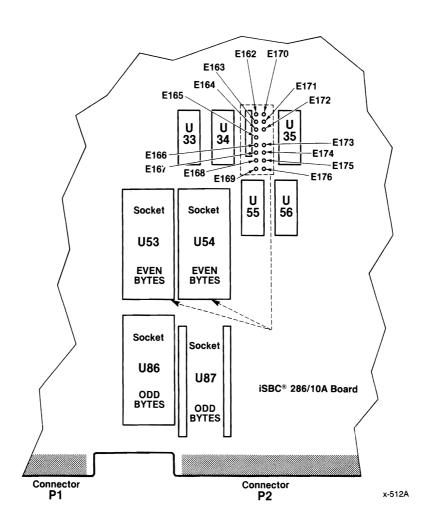

Dual-port memory consists of chip sockets U53/U86 and U54/U87 and will accept immediate installation of four 2Kx8 Static RAM devices. You can reconfigure the dual-port memory to accept a different device type, consuming up to 128K of memory space. The dual-port locations support EPROM, EEPROM (only those with 5V programming signals), Static RAM, and iRAM.

In addition to the socketed memory, both local and dual-port memory can be expanded by installing an iSBC 341 Memory Expansion MULTIMODULE board. The iSBC 341 board connects (piggyback) onto the iSBC 286/1ØA board and allows installation of four more memory devices into the address space. The iSBC 341 board does not increase the maximum capacity, which is 256K bytes for local memory and 128K bytes for dual-port memory.

2-6 iSBC® 286/1ØA

When choosing which memory space to use (dual-port or local), consider these issues:

- 1) Memory device access time

- 2) Whether other MULTIBUS boards in the system require access to the data

Typically, the access time for the dual-port memory is higher than the access time for local memory, because of the added time for the MULTIBUS arbitration logic.

In the default configuration, the CPU circuitry inserts two wait-states when accessing the dual-port memory sockets and one wait-state when accessing the local memory sockets. The number of wait-states is reconfigurable for local memory.

#### 2.2.5.1 Local Memory

The local memory array is subdivided into two independent parts of memory address space: socket pair U4Ø/U75 and socket pair U41/U76. Socket pair U4Ø/U75 is intended to hold EPROM containing the bootstrap routine for the board and, as such, must <u>ALWAYS</u> be top-justified (contain the highest addresses) in the local memory address space. Socket pair U41/U76 is for user-configuration. One iSBC 341 board can be installed into chip sockets U41/U76 on the iSBC 286/1ØA board, but the total memory cannot exceed 256K bytes.

#### 2.2.5.2 Dual-Port Memory

Other bus masters and the on-board CPU may access the dual-port memory on the iSBC 286/10A board. The dual-port memory on the iSBC 286/10A board appears to the on-board CPU and other bus masters to be an independent byte-wide memory resource on the MULTIBUS interface. The on-board CPU, however, has priority in a simultaneous access to the dual-port memory. Other MULTIBUS masters must arbitrate for control before accessing the dual-port memory. One iSBC 341 Memory Expansion MULTIMODULE Board can be installed into chip sockets U54/U87 on the iSBC 286/10A board, but the total memory cannot exceed 128K bytes.

iSBC® 286/1ØA 2-7

#### **BOARD OPERATION**

#### 2.2.6 iSBX™ INTERFACES

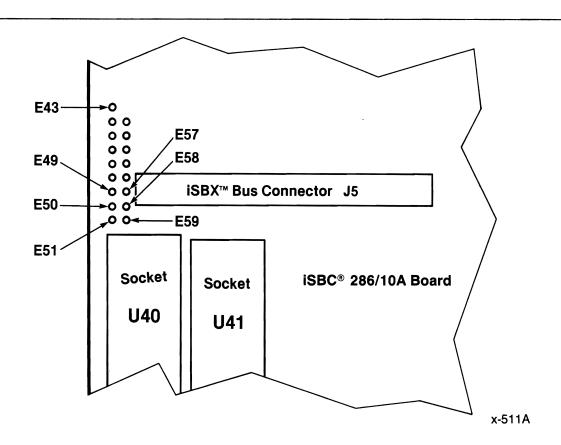

The iSBC 286/10A board provides two iSBX bus interfaces at connectors J5 and J6. Each interface can perform either 8-bit or 16-bit operations, depending on the capabilities of the iSBX MULTIMODULE board installed.

All I/O operations with the iSBX bus interface require a minimum 2 wait-state delay. Each iSBX bus interface has the option of inserting additional wait-states at the 80286 CPU, by controlling its MWAIT\* signal.

The iSBC 286/1ØA board assigns I/O port addresses ØØ8ØH through ØØBFH to the iSBX bus connectors if at least one iSBX MULTIMODULE board is installed. If no iSBX MULTIMODULE board is installed, the iSBC 286/1ØA board performs MULTIBUS I/O operations rather than iSBX bus interface operations for port addresses ØØ8ØH through ØØBFH.

#### 2.2.7 iLBX™, Synchronous, and Auxiliary Interfaces

The iSBC 286/1ØA board has Connector P2 default configured as an iLBX interface. By connecting a memory board to the iSBC 286/1ØA board via the iLBX bus interface, the local memory space can be expanded to a full 14 megabytes physically located off-board.

You can also configure Connector P2 for use as a synchronous interface. The synchronous interface is also an off-board local memory extension that performs at 8.0 MHz with 0 wait-states, using Intel's EX line of RAM boards.

Although the iSBC 286/10A board contains a special connector (J4) for front panel signals, some applications may require signals on the iLBX (P2) connector that operate compatibly with the auxiliary connector on other Intel single board computers. You can disable the iLBX bus interface and reconfigure the P2 connector for bussing these auxiliary signals.

#### 2.2.8 MULTIBUS® INTERFACE

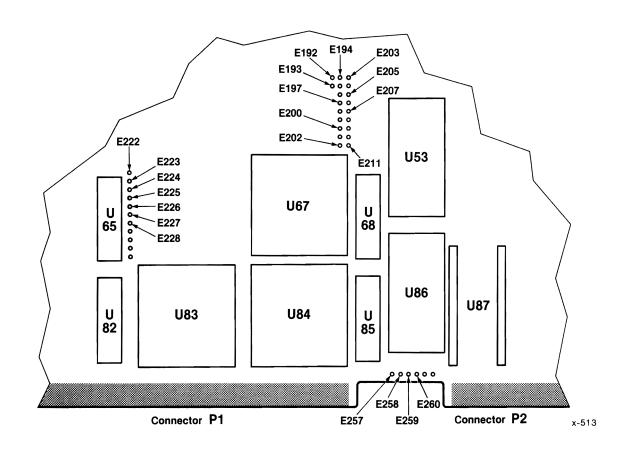

The iSBC 286/10A board provides some control over the MULTIBUS interface signals, including the bus lock (LOCK\*), bus priority output (BPRO\*), common bus request (CBRQ\*), bus clock (BCLK\* and CCLK\*), and interrupt (INTRx\*) signals.

The iSBC 286/10A board provides for either a serial or parallel bus priority resolution scheme. Each scheme has advantages and disadvantages. The serial scheme requires no additional backplane hardware but limits the system to three or less masters. The parallel scheme allows up to 16 masters in the system but requires additional hardware on the backplane. Refer to the INTEL MULTIBUS SPECIFICATION for more details.

The 82289 MULTIBUS Arbiter provides all the needed signals for controlling MULTIBUS arbitration.

2-8

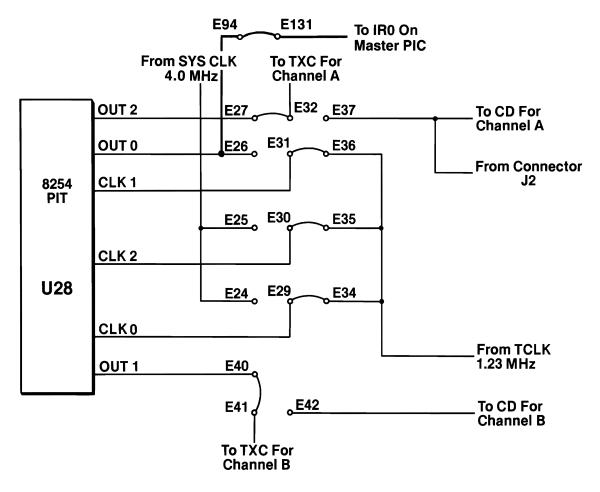

#### 2.2.9 PROGRAMMABLE INTERVAL TIMERS

The iSBC 286/1 $\emptyset$ A board contains an 8254 Programmable Interval Timer (PIT). The 8254 PIT contains three independent, 16-bit programmable counters (Counters  $\emptyset$ , 1, and 2).

In the default configuration, all of the counters provide dedicated functions on-board:

- Counter Ø provides a programmable real-time interrupt.

- Counter 1 provides the clock for Channel B of the 8274 MPSC.

- Counter 2 provides a transmit clock for Channel A of the 8274 MPSC.

Because the counters are dedicated, the iSBC 286/1ØA board expects a specific power-on initialization for the PIT. The initialization firmware should initialize all three counters for operation, as specified in Chapter 4.

The default jumper configuration of the iSBC 286/10A board routes the TCLK clock signal (1.23 MHz clock) into the CLK input for all three counters within the 8254 PIT. The iSBC 286/10A board also provides a jumper-selectable 4 MHz clock signal (SYS CLK).

#### 2.2.10 PROGRAMMABLE INTERRUPT CONTROLLERS

The iSBC 286/10A board contains two 8259A Programmable Interrupt Controller (PIC) devices. Each 8259A PIC provides eight independent levels of interrupt priority.

The iSBC 286/10A board can monitor or generate the MULTIBUS interrupt signals (INT0\* through INT7\*). In the default configuration, the board monitors all interrupt signals from the MULTIBUS interface.

The iSBC 286/10A board expects the initialization routine to configure the master PIC and the slave PIC, cascaded through interrupt level IR7 on the master PIC. This configuration provides 15 levels of on-board interrupt priority plus Non-Maskable Interrupt (NMI).

As shipped, the iSBC 286/10A board contains jumpers connecting two interrupt levels (IR6 and IR7) on the master PIC to the on-board direct-vectored interrupt devices. A direct-vectored interrupt device can generate an interrupt signal to the master PIC and an interrupt vector to the CPU. The devices on the iSBC 286/10A board that can operate as direct-vectored devices are the slave PIC (on IR7) and the 8274 MPSC (on IR6), if programmed for operation in direct-vectored mode.

iSBC@ 286/1ØA 2-9

#### **BOARD OPERATION**

The iSBC 286/1ØA board can form a non-direct-vectored interrupt scheme; however, both PIC devices and the 8274 MPSC device must be programmed for non-direct-vectored mode operation. In this type of operation, the slave device gives an interrupt to the master PIC, which passes it on to the CPU. The CPU polls the slave device to determine the interrupt requirements. Neither the slave PIC nor the master PIC provides a vector.

You can define specific interrupt levels on the master PIC as bus-vectored interrupts. The master PIC receives an interrupt indication from a slave device on one of the MULTIBUS interrupt lines and passes it on to the CPU, then the MULTIBUS device provides the vector on the bus.

The iSBC 286/1 $\emptyset$ A board provides jumpers for configuring interrupt levels  $\emptyset$  through 7 of the master PIC. Levels  $\emptyset$  through 2 are configurable on the slave PIC, but interrupt levels 3 through 7 are fixed.

#### NOTE

Interrupt IR6 on the master PIC is used as an on-board interrupt. The hardware does not allow the use of IR6 to service a bus-vectored interrupt.

#### 2.2.11 NUMERIC PROCESSOR EXTENSION

The iSBC 286/10A board reserves a 40-pin socket at chip location U25 for installing an 80287 Numeric Processor Extension. The 80287 Numeric Processor Extension provides a high-speed math processing device that supports the specifications in the IEEE Microcomputer Floating Point Standard P754.

Programming the 80287 is done exactly as for the 8087, with escape sequences into the instruction execution sequence. When the 80286 executes an escape sequence, it starts program execution in the 80287. At that point, the 80286 and 80287 devices execute instructions in parallel until the 80286 executes a WAIT instruction to wait for completion of the 80287 operation.

Before installing the 80287 chip, remove jumper E280 – E281. Failure to do so will damage the 80287 device.

#### 3.1 INTRODUCTION

This chapter provides a preview of equipment and components that you may need for your application. This chapter includes information on preparing the board's environmental conditions and also lists the equipment and components that are user-supplied. Programming and configuration information is located in Chapter 4.

#### 3.2 UNPACKING AND INSPECTING THE BOARD

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents are damaged, keep the carton and packing material for the agent's inspection. Refer to Chapter 5 for repair and servicing information.

#### 3.3 PREPARING THE BOARD ENVIRONMENT

The iSBC 286/10A board has several specific power, cooling, and physical space requirements. These requirements are explained in the following sections and are summarized in Table 1-1.

iSBC@ 286/1ØA 3-1

#### 3.3.1 POWER REQUIREMENTS

Power is provided for the iSBC 286/10A board through the MULTIBUS interface. At most, the board will require three voltage levels and ground:

- +5 volt power source for all configurations

- <u>+</u>12 volt power source for configurations requiring an RS232C interface or possibly a MULTIMODULE board

- Ground for all configurations

The iSBC 286/10A board requires a specific minimum amount of current at each power source, depending on four factors:

- 1) The type of user-supplied memory devices on the board

- 2) The quantity of user-supplied memory devices on the board

- 3) The types of user-supplied memory expansion MULTIMODULE boards on the board

- 4) The type of serial interface at Connector J2 on the board (either RS422A/449 or RS232C)

Table 1-1 lists the current requirements for each supply voltage required to operate the board in its default configuration (with an RS232C interface, but no memory chips). To calculate the total current, add the extra currents for your application to the currents in the table.

#### 3.3.2 COOLING REQUIREMENTS

The iSBC 286/10A board dissipates a maximum of 527.0 gram-calories of heat per minute (2.0 BTU per minute). To dissipate this heat and prevent possible heat damage to the board, provide adequate air circulation to prevent the ambient air around the board from rising above 55°C (131°F). Typically, a minimum air flow of 200 linear feet per minute across the board provides enough air circulation.

#### 3.3.3 PHYSICAL DIMENSIONS

The physical dimensions of the iSBC 286/1ØA board are

Width: 3Ø.48 cm (12.ØØ inches) Length: 17.15 cm (6.75 inches)

Depth: 1.42 cm (Ø.56 inches) with no MULTIMODULE boards

1.82 cm (Ø.718 inches) with an iSBC 341 MULTIMODULE board

2.95 cm (1.16 inches) with an iSBX MULTIMODULE board

Weight: 534 gm (19 ounces)

## 3.4 COMPATIBLE EQUIPMENT

The iSBC 286/10A board is designed to operate as either a master or an intelligent slave with other single board computers on the MULTIBUS interface. For more information on the MULTIBUS architecture, refer to the MULTIBUS HANDBOOK.

The memory configuration on the iSBC 286/10A board allows an iSBC 341 Memory Expansion MULTIMODULE Board to be added at these chip sockets:

- U41/U76 for local memory

- U54/U87 for dual-port memory

The iSBX bus interfaces are electrically and mechanically compatible with either 8-bit or 16-bit iSBX MULTIMODULE boards.

If a MULTIMODULE board is installed onto iSBX bus connector J5, ensure that the LEDs are not damaged during the connection.

The iSBC 286/10A board does not accept an iSBC 337A Numeric Data Processor MULTIMODULE board. Instead, use the 40-pin chip socket provided for the 80287 Numeric Processor Extension.

Before installing the 80287 chip, remove jumper E280-E281. Failure to do so may damage the 80287 device.

The iLBX bus interface on the iSBC 286/10A board operates compatibly with the iLBX specification. The synchronous interface on Connector P2 supports Intel's line of high-speed, high-density EX memory boards.

iSBC@ 286/1ØA 3-3

## 3.5 COMPONENTS REQUIRED

Figure 3-1 shows the location for the user-supplied parts. Table 3-1 lists all of the components that could be required for the iSBC 286/1 $\rlap/$ A board. Install only those components required to satisfy your application.

Table 3-1. User-Supplied Components

| Item<br>No. | Part                                      | Description                                                                                                                                                                                                                     |

|-------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | Memory                                    | The local memory sockets will accept only EPROM memory devices. The dual-port sockets will accept EPROM, iRAM, or Static RAM devices. The dual-port sockets will only accept those EEPROM devices using 5V programming signals. |

| 2           | Termination<br>Resistor Pack<br>(RP4)     | Provide a termination resistor pack at RP4 whenever the iSBC 286/10A board is used in a point-to-piont RS422A/449 application. Refer to Appendix B for more information.                                                        |

| 3           | Bias Resistor<br>Pack (RP5,RP6)           | Remove or change bias resistor packs at RP5 and RP6 whenever the iSBC 286/10A board is used in a Multidrop RS422A/449 application. Refer to Appendix B for more information.                                                    |

| 4           | 3487 (U15)                                | Provide an IC (3487) device at socket U15 when using the J2 connector as an RS422A/449 interface.                                                                                                                               |

| 5           | Programmable<br>Array Logic<br>Chip (U74) | Change the PAL whenever a memory configuration is required beyond those provided by PAL U74. The PAL is a 16L8A device by Monolithic Memories, Inc., or an equivalent.                                                          |

| 6           | 8ø287                                     | Insert an 80287 in socket U25 to achieve high performance floating-point instruction. To prevent possible damage, remove jumper E280-E281 before 80287 insertion.                                                               |

## 3.6 COMPONENT INSTALLATION

The following sections provide instructions for installing the user-supplied memory devices and bias/termination resistors. Figure 3-1 shows an approximate location for each component. Table 3-1 gives a description of each type of component. Any electrically and mechanically equivalent components may be substituted.

When installing the integrated circuit packages into the sockets on the iSBC 286/10A board, ensure that pin 1 of the chip is inserted into pin 1 of the chip socket. This orientation places pin 1 of the chip closest to the silk-screened dot (which indicates pin 1 of the socket).

#### 3.6.1 MEMORY COMPONENTS

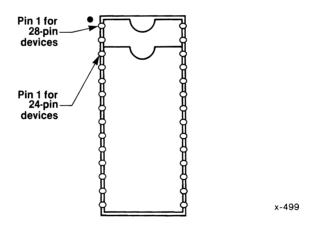

The iSBC 286/1ØA board contains no memory components when shipped from the factory. One of several different types of memory components can be installed into the memory sockets, including EPROM, iRAM, and Static RAM devices. Figure 3-2 shows how to install either 24-pin or 28-pin memory chips into the JEDEC-compatible sockets. Refer to Chapter 4 for instructions on configuring the memory addresses at each socket.

Figure 3-2. Memory Chip Installation

CAUTION

Never insert components into a board when power is applied. Doing so could damage the components.

All MOS components such as ROM, EPROM, and RAM devices are highly susceptible to damage from static electricity. Use extreme caution when installing MOS components in a low-humidity environment. Always ground yourself before handling MOS components; this ensures that a static charge build-up is not dissipated through the MOS devices.

User-supplied memory devices can be installed into the eight 28-pin JEDEC-compatible chip sockets on the iSBC 286/10A board. Table 3-2 lists these types of memory devices. In selecting memory components, you can substitute any electrically and mechanically equivalent devices.

| Table 3-2. | Compatible | Memory | Devices |

|------------|------------|--------|---------|

|------------|------------|--------|---------|

| Memory | Memory   | Chip    | Chip Location |              |  |

|--------|----------|---------|---------------|--------------|--|

| Туре   | Capacity | Example | Local         | Dual-Port    |  |

|        |          |         |               |              |  |

| Static | 2Kx8     |         | no            | yes          |  |

| RAM    | 8Kx8     |         | no            | yes          |  |

|        | 16Kx8    |         | no            | yes          |  |

| iRAM   | 8Kx8     | 2186    | no            | yes          |  |

|        | 16Kx8    |         | no            | yes          |  |

| EPROM  | 4Kx8     | 2732    | yes           | yes          |  |

| EFROM  | 8Kx8     | 2764    | - 1           | <del>-</del> |  |

|        | 16Kx8    | 27128   | yes           | yes          |  |

|        |          |         | yes           | yes          |  |

|        | 32Kx8    | 27256   | yes           | yes          |  |

|        | 64Kx8    | 27512   | yes           | yes          |  |

# NOTE

The iSBC 286/10A board is designed to accept most byte-wide components in the memory sockets. Typically, system operation requires EPROM devices in sockets U40/U75 to hold the bootstrap program.

# NOTE

The iSBC 286/10A board can accommodate both 24and 28-pin memory chips in the same socket. The 24-pin integrated circuits must be installed, as shown in Figure 3-2, with pin 1 of the integrated circuit in pin 3 of the socket.

#### 3.6.2 LINE DRIVER DEVICES

When shipped from the factory, the iSBC 286/10A board contains the line driver and line receiver chips required for RS232C interfaces at Connectors J2 and J3. Connector J2 can be modified for RS422A/449 operation, while Connector J3 cannot be modified.

#### 3.6.3 RESISTOR PACKS

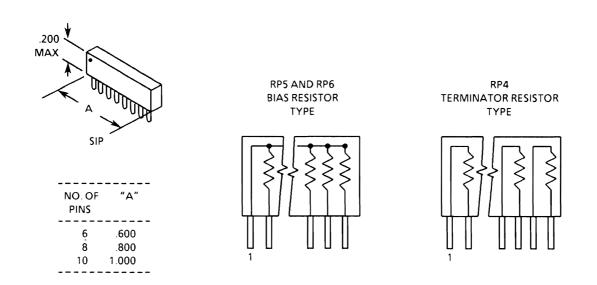

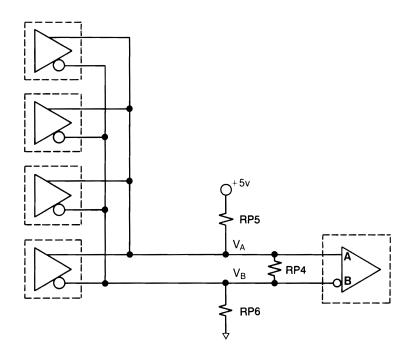

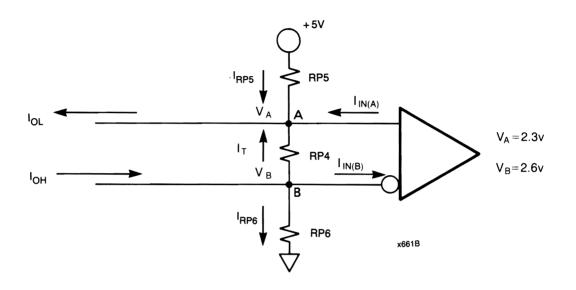

The iSBC 286/1ØA board contains two resistor packs (RP5 and RP6) that perform biasing and one empty socket for a termination resistor pack (RP4). Figure 3-3 shows the bias and terminator resistor types.

F-0037

Figure 3-3. Bias and Terminator Resistor Types

The functions of each resistor pack depend on the operating mode of the interface at Connector J2, as follows:

RP4 TERMINATION - For an RS422A/449 multidrop network, if the board is the farthest slave from the master in the network, install a resistor pack at RP4 to properly terminate the signal lines. Refer to Appendix B for instructions on calculating the value for RP4.

For an RS232C interface application, do not install a resistor pack at RP4.

RP5 BIAS - For an RS422A/449 master interface (either a multidrop or point-to-point network), install the resistor pack at RP5 with pin 1 closest to connector J2 (18Ø-degree rotation from the default configuration). RP5 maintains voltage levels on the signal lines.

For an RS422A/449 slave interface in a multidrop network, remove the resistor pack at RP5.

For an RS232C interface, install the resistor pack at RP5 with pin-1 closest to the MULTIBUS connector (the default configuration).

RP6 BIAS - For an RS422A/449 master interface in a multidrop network, install the resistor pack at RP6 (the default configuration). RP6 maintains voltage levels on the signal lines.

For an RS422A/449 slave interface in a multidrop network, remove the resistor pack at RP6.

For an RS232C application, install the resistor pack at RP6 (the default configuration) to maintain voltage levels on the signal lines.

The following sections provide more information on the default configuration of each R-pack.

#### **INSTALLATION**

#### 3.6.3.1 Bias Resistors

When shipped from the factory, the iSBC 286/10A board contains two six-pin sockets with 2.2K ohm bias resistor packs (RP5 and RP6). These resistor packs provide bias for a four-drop RS422A/449 interface at Connector J2. At shipment, the SIP devices are installed so that pin 1 of RP5 is in pin 6 of its socket, and pin 1 of RP6 is in pin 1 of its socket.

By removing RP5, rotating it 180 degrees, and reinstalling it so that pin 1 is farthest from the MULTIBUS connector (so that pin 1 of the pack is in pin 1 of the socket), the board is configured to hold the four noninverting inputs to Ull at an inactive voltage level. This is required because the RS232C interface does not implement those lines.

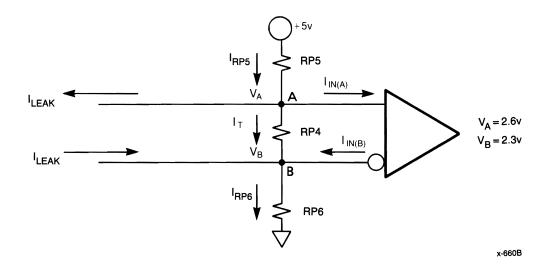

By changing the value of the resistor pack, the bias at the serial interface receivers can be changed. Appendix B shows how to calculate the bias resistor values for an application.

#### 3.6.3.2 Termination Resistors

When shipped from the factory, the iSBC 286/10A board provides an empty socket at RP4 for a single in-line resistor pack (SIP) RP4.

Termination resistors are required only for RS422A/449 interface applications on Connector J2. They provide a means of reducing the amount of signal noise between the lines of a differential pair. If the iSBC 286/1ØA board is the unit farthest from the primary master in a multidrop network, install an eight-pin termination SIP into socket RP4.

Determine the resistor value to terminate a multidrop or point-to-point network by performing a series of calculations as listed in Appendix B.

#### 3.7 CONNECTOR AND CABLE PARTS

Some connector parts are required for the iSBC 286/10A board when it is used in certain applications. Figure 3-1 shows the approximate location of the five connector types:

- Three 26-pin edge connectors (J1, J2, and J3)

- A 14-pin front panel interface connector (J4)

- Two 36- or 44-pin iSBX bus connectors (J5 and J6)

- An 86-pin MULTIBUS interface connector (P1)

- A 6Ø-pin iLBX bus interface connector (P2)

3-1Ø iSBC@ 286/1ØA

Table 3-3 provides a list of connector parts that are ready-made to interface to the board connectors. The table also provides the manufacturers' names and part numbers to order the connectors. Any electrically and mechanically equivalent parts may be substituted.

Table 3-4 provides information on cables compatible with the connector parts in Table 3-3 for the serial I/O interfaces at Connectors J2 and J3.

Table 3-3. User-Supplied Connector Information

| Function                                                      | # of<br>Pins | Centers<br>(inches) | Connector<br>Type                                                                              | Vendor                                                            | Vendor Part<br>Number                                                                                                                                        |

|---------------------------------------------------------------|--------------|---------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MULTIBUS<br>connector<br>(P1)                                 | 86           | Ø.156               | Soldered <sup>1</sup> PC board mount Wirewrap Without ears Wirewrap (.128 dia.) Mounting holes | VIKING<br>ELFAB<br>EDAC<br>ELFAB<br>EDAC<br>ELFAB                 | 2KH43/9AMK12<br>BS1562D43PBB<br>337Ø8654Ø2Ø1<br>BW1562D43PBB<br>337Ø8654Ø2Ø2<br>BW1562A43PBB                                                                 |

| iLBX bus<br>connector<br>(P2)                                 | 6Ø           | Ø.1<br>Ø.1          | Solder Solder Soldered  Wirewrap No ears  Wirewrap Wirewrap (.128 dia.)                        | KELAM KELAM T&B Ansley ELFAB EDAC ELFAB EDAC ELFAB EDAC TI Viking | RF3Ø-28Ø3-5<br>11Ø-1Ø-ØØ1-37<br>A3Ø2Ø<br>97169ØØ1<br>34Ø6Ø5243ØØ<br>BW1Ø2ØD3ØPBB<br>345Ø6Ø54Ø2Ø1<br>BS1Ø2ØA3ØPBB<br>345Ø6Ø5248Ø2<br>H421121-3Ø<br>3KH3Ø/9JNK |

| iSBX bus<br>connector<br>male<br>16-bit<br>female<br>(J5, J6) | 36           | Ø.1                 | Soldered                                                                                       | Viking<br>Viking                                                  | ØØØ292-ØØØ1<br>ØØØ291-ØØØ1                                                                                                                                   |

-----(continued)-----

iSBC@ 286/1ØA 3-11

## **INSTALLATION**

Table 3-3. User-Supplied Connector Information (continued)

| Function                                    | # of<br>Pins | Centers<br>(inches) | Connector<br>Type                                | Vendor                    | Vendor Part<br>Number                                |