Copyright© 1984 Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051 Order Number: 146414-001

# iSBC® 186/03 SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Order Number: 146414-001

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a) (9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BITBUS<br>COMMputer<br>CREDIT<br>Data Pipeline<br>GENIUS<br>A<br>i<br>i<br>1 <sup>2</sup> ICE<br>ICE<br>iCS<br>iDBP<br>iDIS | iLBX<br>im<br>iMMX<br>Insite<br>Intel<br>intel<br>intelBOS<br>Intelevision<br>inteligent Identifier<br>inteligent Programming<br>Intellec<br>Intellick | iPDS<br>iRMX<br>iSBC<br>iSBX<br>iSDM<br>iSXM<br>Library Manager<br>MCS<br>Megachassis<br>MICROMAINFRAME<br>MULTIBUS<br>MULTIBUS<br>MULTICHANNEL | Plug-A-Bubble<br>PROMPT<br>Promware<br>QUEX<br>QUEST<br>Ripplemode<br>RMX/80<br>RUPI<br>Seamless<br>SOLO<br>SYSTEM 2000<br>UPI |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                             | iOSP                                                                                                                                                   | MULTIMODULE                                                                                                                                     |                                                                                                                                |

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Copyright © 1983, Intel Corporation

| REV. | REVISION HISTORY | DATE |

|------|------------------|------|

| -001 | Original Issue.  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

|      |                  |      |

iv

#### PREFACE

This manual describes the use of the iSBC 186/03 Single Board Computer. By reading this manual you will acquire sufficient knowledge of the board to enable you to successfully:

- Configure the jumpers and interfaces on the board to suit your application.

- Begin programming the board for operation in your system environment.

This manual references the information contained in other Intel technical publications, including:

- Introduction to the 80186 Microprocessor (AP-186), Order Number: 210973.

- Intel iAPX 186 Data Sheet, Order Number: 210451.

- Intel Microprocessor and Peripheral Handbook, Order Number: 210844.

- Intel Memory Components Handbook, Order Number: 210830.

- Intel iLBX<sup>™</sup> Bus Specification, Order Number: 145695.

- Intel MULTIBUS® Specification, Order Number: 9800683.

- Intel iSBX<sup>™</sup> Bus Specification, Order Number: 142686.

- EIA Standard for RS232C Interfacing, EIA-RS-232C.

- EIA Standard for RS422A Interfacing, EIA-RS-422A.

- EIA Standard for RS449 Interfacing, EIA-RS-449.

- Intel Application Note AP-134, Asynchronous Communications With The 8274 Multiple Protocol Serial Controller.

- Intel Application Note AP-145, Synchronous Communications With The 8274 Multiple Protocol Serial Controller.

This text uses two special characters, the asterisk (\*) and the § symbol. Their interpretation is as follows:

- \* Used after a signal mnemonic to indicate that the signal is an active-low signal. A signal mnemonic without a trailing asterisk as an active-high signal. This notation replaces the use of the slash (/) that was previously used to indicate the active state of a signal.

- § Used after a jumper connection to indicate that the jumper is installed when the board is shipped from the factory.

vi

# CONTENTS

|                                                             | PAGE       |

|-------------------------------------------------------------|------------|

| CHAPTER 1                                                   |            |

| GENERAL INFORMATION                                         |            |

| 1.1 Introduction                                            | 1-1        |

| 1.2 Key Features                                            | 1-1        |

| 1.3 Description                                             | 1-2        |

| 1.4 Documentation Supplied                                  | 1-4        |

| 1.5 Additional Equipment Required                           | 1-5        |

| 1.6 Compliance Level: 796 Bus Specification (IEEE Standard) | 1-5        |

| 1.7 Compliance Level: Intel iSBX™ Bus Specification         | 1-5        |

| 1.8 Compliance Level: Intel iLBX™ Bus Specification         | 1-6        |

| 1.9 Specifications                                          | 1-6        |

|                                                             |            |

| CHAPTER 2<br>BOARD OPERATION AND CONFIGURATION              |            |

| 2.1 Introduction                                            | 2-1        |

| 2.2 CPU and Support Circuitry Configurations                | 2-1        |

| 2.2.1 Wait-States for On-Board Resources                    | 2-1<br>2-3 |

| 2.3 Memory Configuration                                    | 2-3        |

| 2.3.1 Memory Map (Default Configuration)                    | 2-3<br>2-4 |

| ,                                                           | 2-4<br>2-6 |

|                                                             | 2-6<br>2-6 |

|                                                             | 2-0<br>2-6 |

|                                                             | 2-0<br>2-7 |

| · · · · · · · · · · · · · · · · · · ·                       |            |

|                                                             | 2-7        |

|                                                             | 2-9        |

|                                                             | 2-15       |

| 2.3.4.5 Using NVRAMs                                        | 2-15       |

| 2.3.4.6 Using EEPROMS                                       | 2-16       |

| 2.4 Direct Memory Access (DMA) Controller                   | 2-17       |

| 2.5 iLBX <sup>m</sup> Bus Interface Description             | 2-19       |

| 2.5.1 iLBX <sup>m</sup> Bus Interface Jumper Configurations | 2-20       |

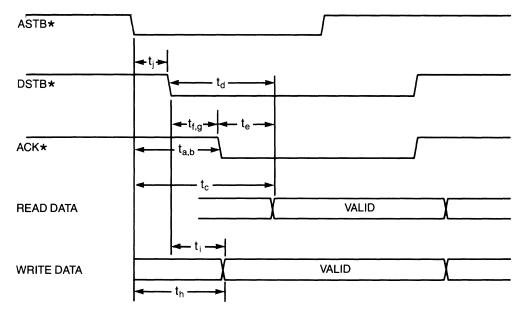

| 2.5.1.1 iLBX <sup>™</sup> Bus Timing Specifications         | 2-21       |

| 2.6 Interrupt Configuration                                 | 2-24       |

| 2.6.1 Interrupt Jumper Matrix Configuration                 | 2-26       |

| 2.6.1.1 On-Board Interrupt Sources                          | 2-27       |

| 2.7 Timers                                                  | 2-30       |

| 2.7.1 Timer Jumper Configurations                           | 2-30       |

| 2.7.1.1 80186 Timers                                        | 2-31       |

| 2.7.1.2 80130 Timers                                        | 2-31       |

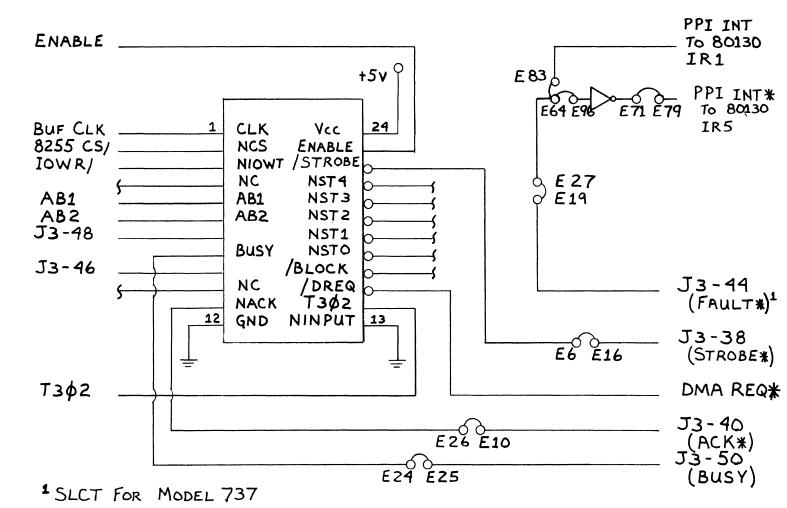

| 2.8 Parallel I/O Interface - Connector J3                   | 2-32       |

| 2.8.1 Parallel Interface Pin Assignments                    | 2-33       |

| 2.8.2 Parallel Interface Drive Characteristics              | 2-34       |

| 2.8.3 Parallel Interface Cabling                            | 2-35       |

| 2.8.4 Parallel Interface Jumper Configurations              | 2-35       |

| 2.9 Serial I/O Interfaces                                   | 2-37       |

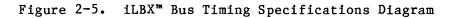

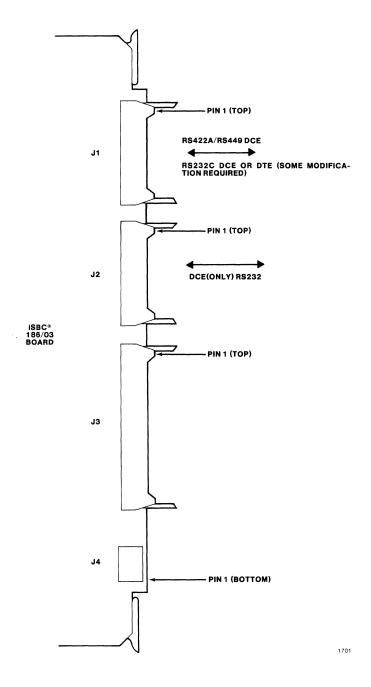

| 2.9.1 Connector J1 Description                              | 2-38       |

| 2.9.1.1 Connector J1 Configurations                         | 2-41       |

| 2.9.1.2 RS232C DCE Configuration Sequence                   | 2-42       |

| 2.9.1.3 RS232C DTE Configuration Sequence                   | 2-42       |

1

| CHAPTER 2 (continued)                                           |    |

|-----------------------------------------------------------------|----|

| 2.9.1.4 Multidrop Configuration (RS422A/449 Interface Only) 2-4 | 3  |

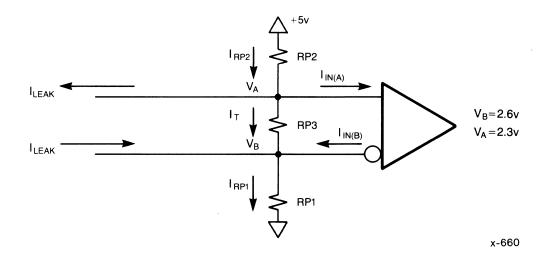

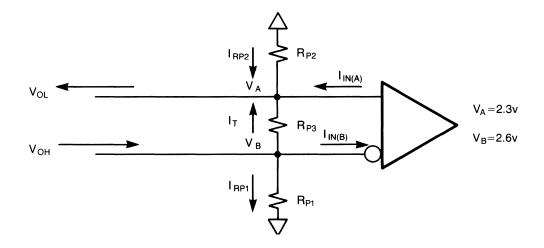

| 2.9.1.5 Bias and Termination Resistor Requirements 2-4          | .4 |

| 2.9.2 Connector J2 - RS232C Interface - Channel B 2-4           | 6  |

| 2.9.2.1 Connector J2 Description 2-4                            | 6  |

| 2.9.2.2 Connector J2 Configurations 2-4                         | 7  |

| 2.10 iSBX <sup>™</sup> Bus Interface                            | 7  |

| 2.10.1 iSBX <sup>™</sup> Bus Descriptions 2-4                   | 7  |

| 2.10.2 iSBX <sup>™</sup> Bus Interface Configurations 2-4       | 7  |

| 2.10.2.1 iSBX <sup>™</sup> Bus I/O Addresses 2-4                | 8  |

| 2.10.2.2 iSBX <sup>™</sup> Bus Jumper Configurations 2-4        | 8  |

| 2.10.2.3 iSBX <sup>™</sup> Bus Clock Configurations 2-4         | 9  |

| 2.11 MULTIBUS® Interface 2-5                                    | 0  |

| 2.11.1 MULTIBUS® Interface Description 2-5                      | 0  |

| 2.11.2 MULTIBUS® Interface Configurations 2-5                   | 0  |

| 2.11.2.1 Jumper Configurations                                  | 1  |

| 2.12 Front Panel Interface - Connector J4 2-5                   | ;4 |

| 2.12.1 Front Panel Interface Description 2-5                    | 4  |

| 2.12.2 Front Panel Configurations 2-5                           | 6  |

| 2.12.3 Battery Backup Configurations 2-5                        | 57 |

| 2.13 Connector P2 Interface 2-5                                 | 7  |

| 2.13.1 Auxiliary Interface Description 2-5                      | 57 |

# CHAPTER 3

| INSTALLATION                                       |      |

|----------------------------------------------------|------|

| 3.1 Introduction                                   | 3-1  |

| 3.2 Unpacking and Inspection Your Board            | 3-1  |

| 3.3 Preparing Your Board Environment               | 3-1  |

| 3.3.1 Power Requirements                           | 3-1  |

| 3.3.2 Cooling Requirements                         | 3-2  |

| 3.3.3 Connector and Cable Parts                    | 3-2  |

| 3.3.4 Components Required                          | 3-5  |

| 3.4 Compatible Equipment                           | 3-8  |

| 3.5 Component Installation                         | 3-8  |

| 3.5.1 Memory Components                            | 3-8  |

| 3.5.2 Line Driver Devices                          | 3-11 |

| 3.5.3 Resistor Packs                               | 3-11 |

| 3.5.3.1 Bias Resistors                             | 3-12 |

| 3.5.3.2 Termination Resistors                      | 3-12 |

| 3.6 P2 Connector Installation                      | 3-13 |

| 3.6.1 iLBX <sup>™</sup> Bus Connector Installation | 3-13 |

| 3.6.2 Auxiliary Connector Installation             | 3-14 |

| 3.7 MULTIBUS® Address Termination Resistors        | 3-14 |

| 3.8 Optional 10MHz Oscillator                      | 3-14 |

| 3.9 PAL Devices                                    | 3-15 |

|                                                    |      |

| CHAPTER 4                                                   | PAGE |

|-------------------------------------------------------------|------|

| PROGRAMMING INFORMATION                                     |      |

| 4.1 Introduction                                            | 4-1  |

| 4.2 iAPX 186 Processor Initialization                       | 4-1  |

| 4.2.1 iRMX <sup>™</sup> 86 Compatibility Mode               | 4-2  |

| 4.2.2 Internal Peripheral Interface                         | 4-2  |

| 4.3 Memory Addressing                                       | 4-2  |

| 4.3.1 iLBX <sup>™</sup> Bus Memory                          | 4-5  |

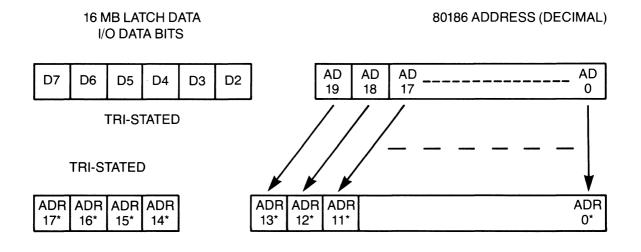

| 4.3.2 16M-Byte MULTIBUS® Memory Addressing                  | 4-6  |

| 4.4 I/O Addressing                                          | 4-6  |

| 4.4.1 iSBX <sup>™</sup> Bus I/O Addressing                  | 4-6  |

| 4.5 DMA Controller                                          | 4-10 |

| 4.6 DMA Programming                                         | 4-10 |

| 4.7 Interrupt Controller Programming                        | 4-13 |

| 4.7.1 80130 Master Interrupt Controller                     | 4-16 |

| 4.7.2 80186 Interrupt Controller                            | 4-17 |

| 4.7.3 Programming the 80130 Interrupt Controller            | 4-17 |

| 4.7.3.1 80130 Interrupt Initialization (ICWs)               | 4-18 |

| 4.7.3.2 Operation Command Words (OCWs)                      | 4-20 |

| 4.7.3.3 Interrupt Masks                                     | 4-21 |

| 4.7.3.4 End Of Interrupt (EOI)                              | 4-21 |

| 4.7.3.5 Fully Nested Mode                                   | 4-22 |

| 4.7.3.6 Special Fully Nested Mode                           | 4-22 |

| 4.7.3.7 Edge/Level Triggered Modes                          | 4-22 |

| 4.7.3.8 Local/Non-local Interrupts                          | 4-23 |

| 4.7.3.9 Reading the 80130 Interrupt Control Status          | 4-23 |

| 4.7.4 8259A Interrupt Controller                            | 4-24 |

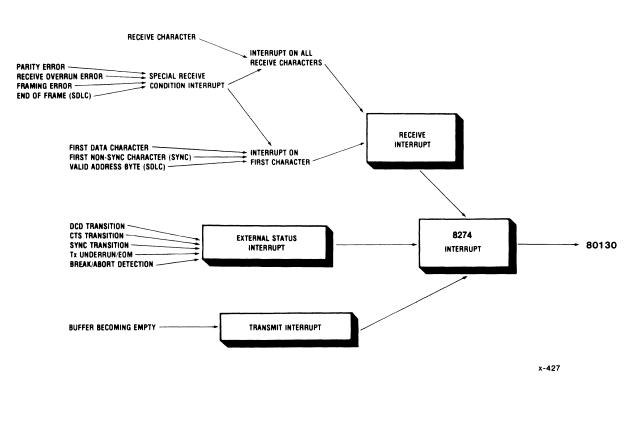

| 4.7.5 8274 Interrupt Controller                             | 4-24 |

| 4.8 Timers                                                  | 4-25 |

| 4.8.1 80186 Timers                                          | 4-25 |

| 4.8.2 80130 Timers                                          | 4-26 |

| 4.8.2.1 Description of 80130 Timer Modes                    | 4-26 |

| 4.8.2.1.1 80130 Timer 0 Operation                           | 4-27 |

| 4.8.2.1.2 80130 Timer 1 Operation                           | 4-27 |

| 4.8.2.1.3 80130 Timer 2 Operation                           | 4-28 |

| 4.8.2.2 80130 Timer Programming                             | 4-28 |

| 4.8.2.2.1 Control Word Register                             | 4-29 |

| 4.8.2.2.2 80130 Timer Read Operations                       | 4-30 |

| 4.8.3 80130 PIT Programming Example                         | 4-30 |

| 4.8.4 Count Values for Common Baud Rates                    | 4-31 |

| 4.9 Parallel Port Programming                               | 4-31 |

| 4.9.1 PPI Initialization                                    | 4-32 |

| 4.10 Serial Interface Programming Information               | 4-32 |

| 4.10.1 8274 MPSC Addresses                                  | 4-32 |

| 4.10.2 8274 MPSC Programming Information                    | 4-32 |

| 4.10.2.1 8274 MPSC Register Descriptions                    | 4-34 |

| 4.10.3 8274 MPSC Operating Modes                            | 4-39 |

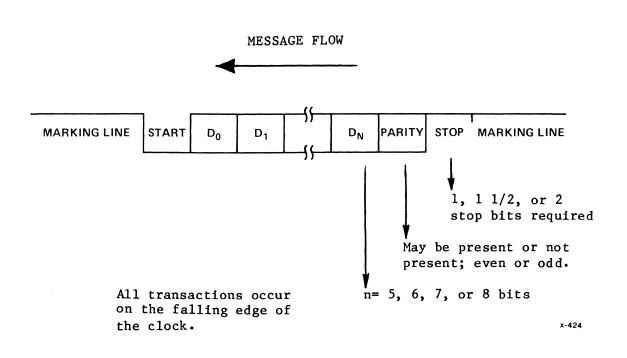

| 4.10.3.1 Asynchronous Mode Operation                        | 4-39 |

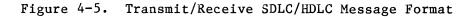

| 4.10.3.2 Synchronous 8274 MPSC Operation (Monosync, Bisync) | 4-44 |

|                                                                                                                                                                                                         | PAGE                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| CHAPTER 4 (continued)<br>4.10.4 8274 MPSC Interrupts<br>4.10.5 8274 MPSC DMA Operation<br>4.10.6 8274 MPSC Initialization                                                                               | 4-58<br>4-60<br>4-60      |

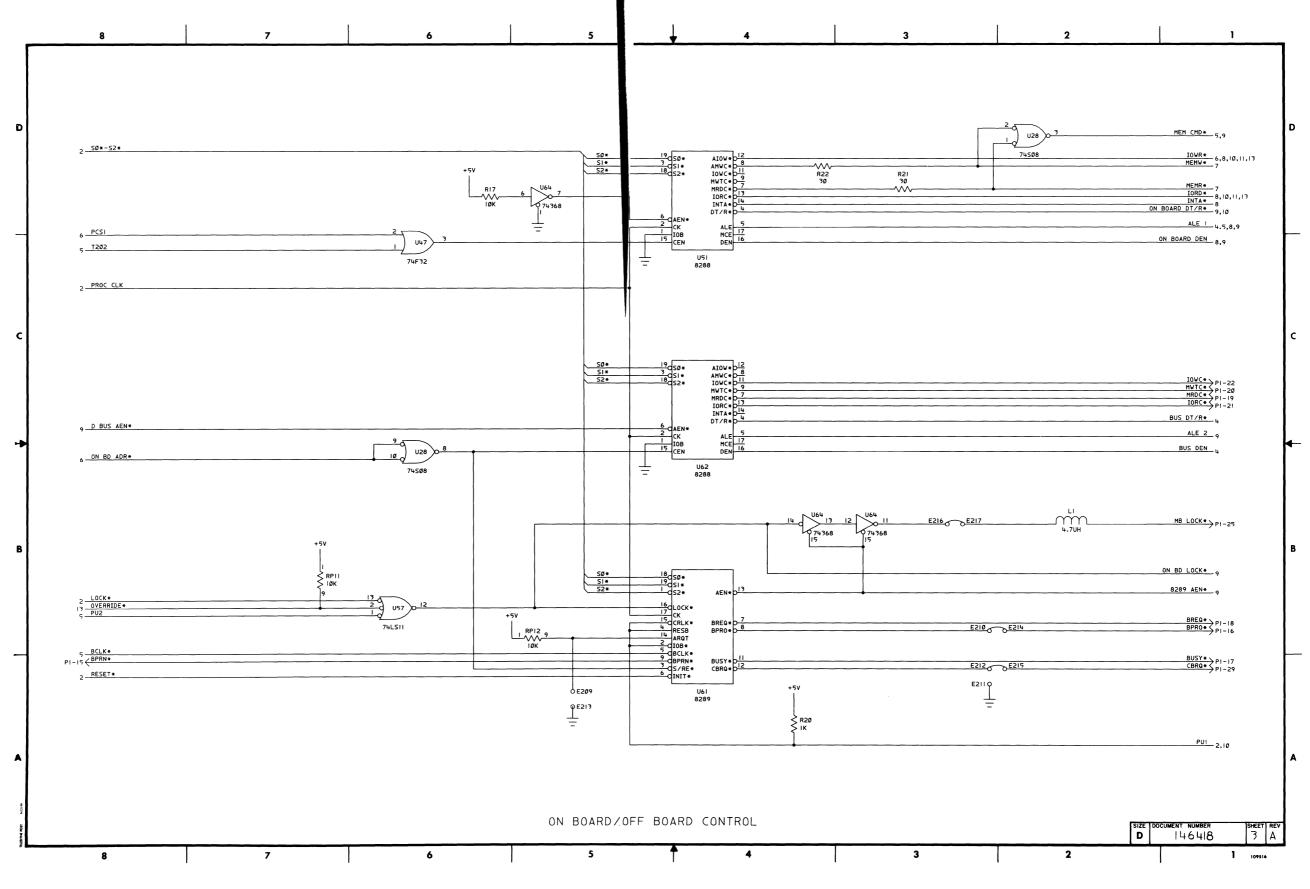

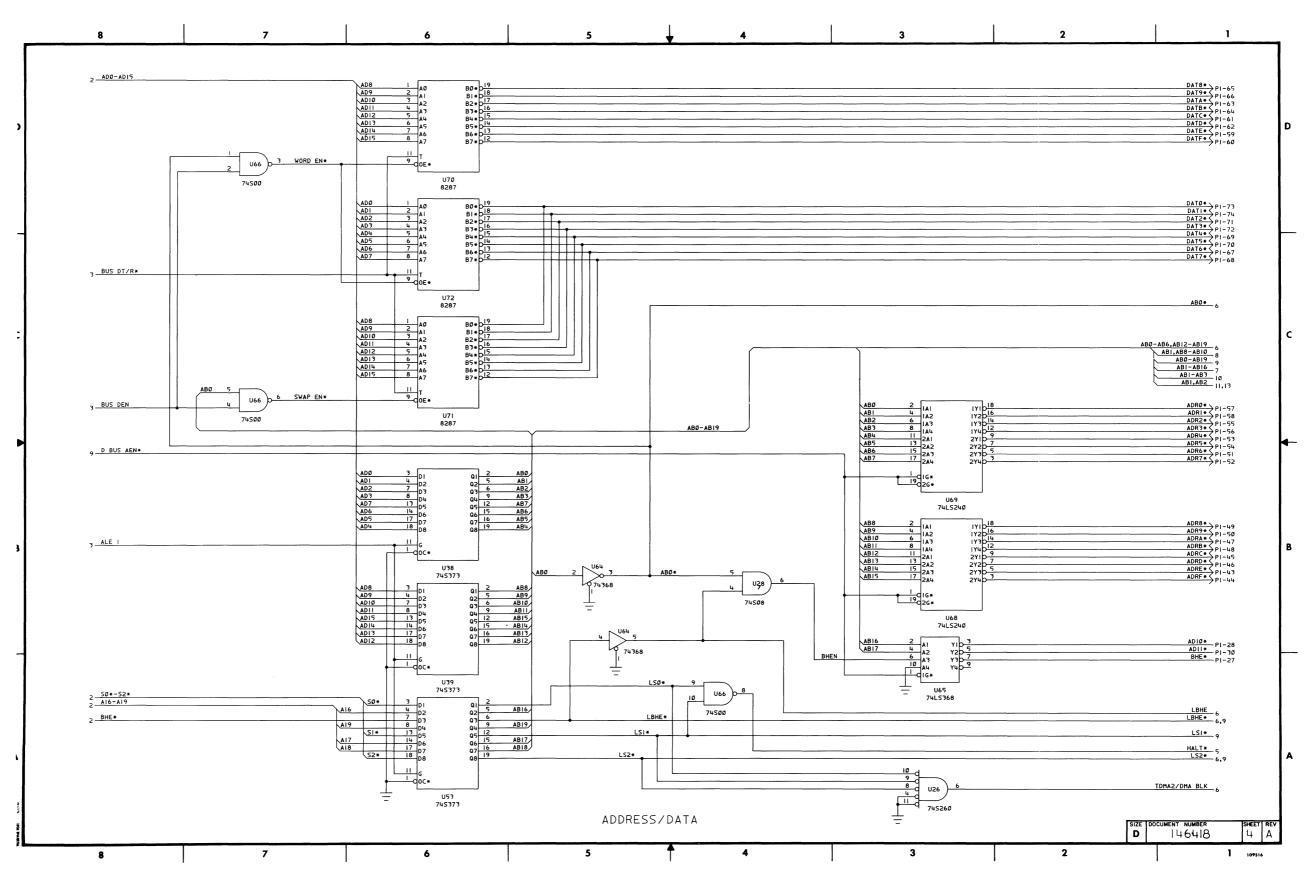

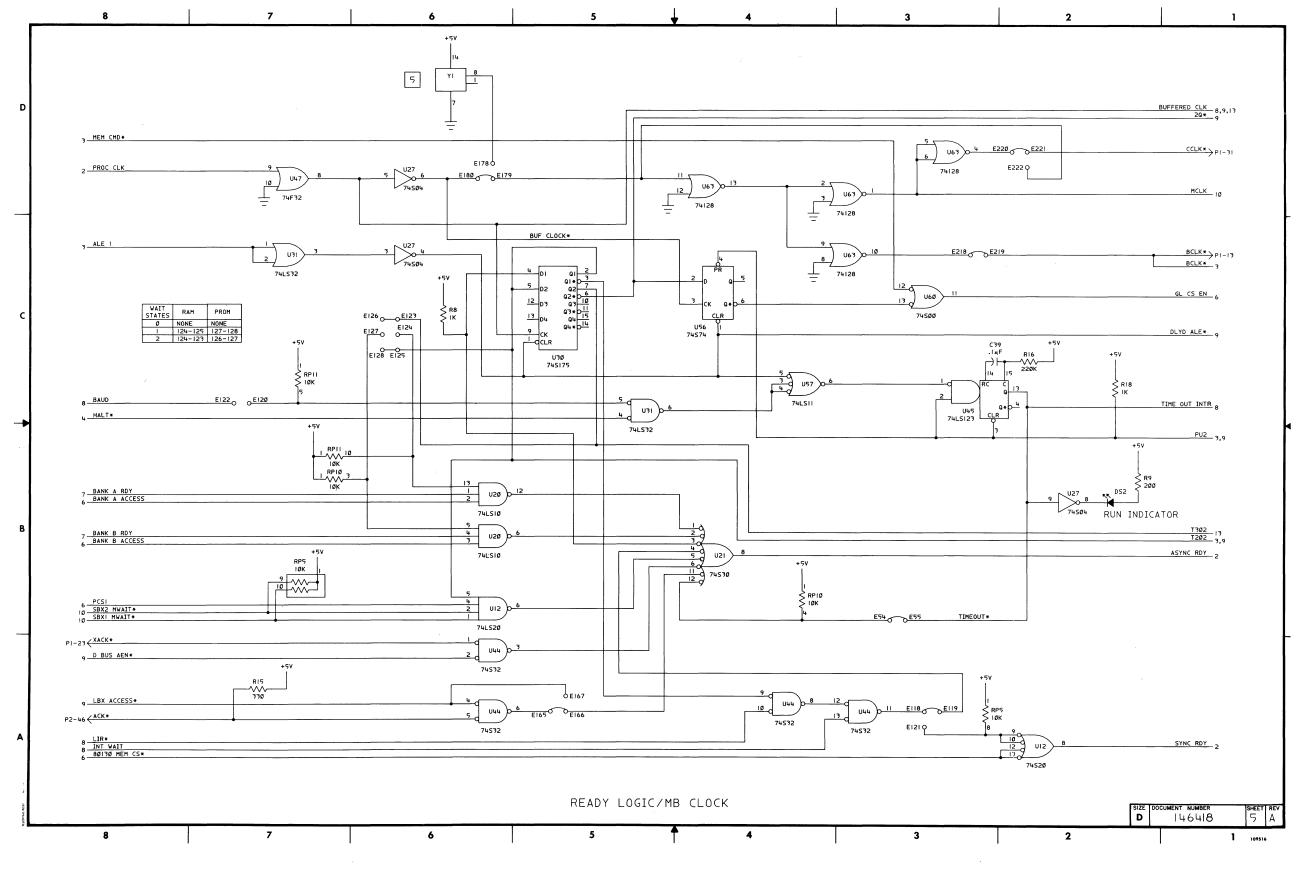

| CHAPTER 5<br>SERVICE INFORMATION<br>5.1 Introduction<br>5.2 Service Diagrams<br>5.3 Service and Repair Assistance                                                                                       | 5-1<br>5-1<br>5-1         |

| APPENDIX A<br>JUMPER LISTS FOR THE 1SBC <sup>®</sup> 186/03 BOARD                                                                                                                                       | A-1                       |

| APPENDIX B<br>MULTIDROP CONSIDERATIONS<br>B.1 Introduction<br>B.2 Multidrop Description<br>B.3 Case 1: Lines Floating<br>B.4 Case 2: Lines Driven                                                       | B-1<br>B-1<br>B-3<br>B-5  |

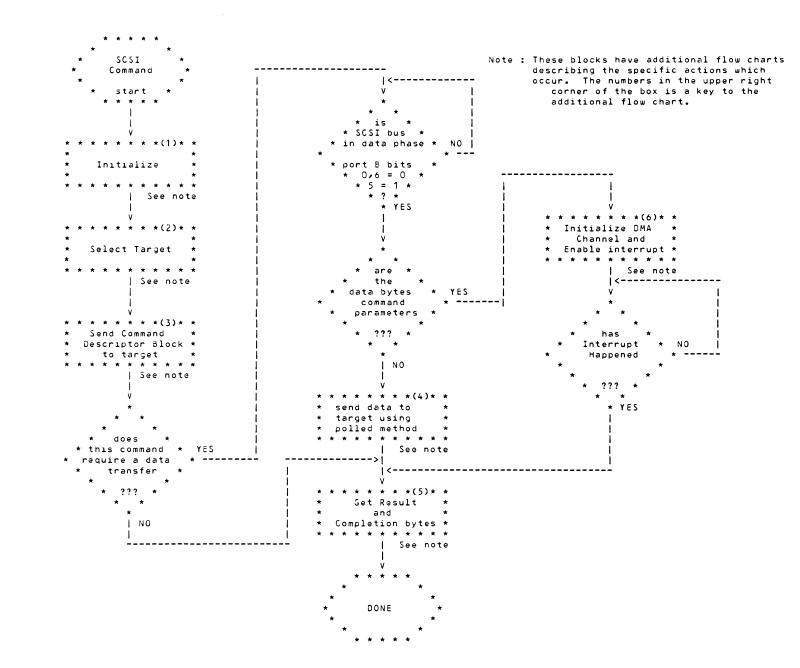

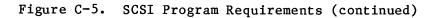

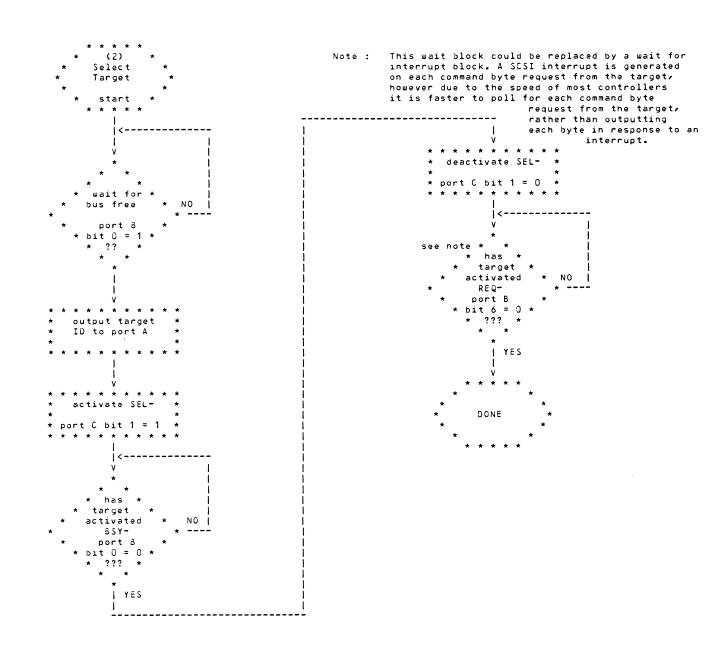

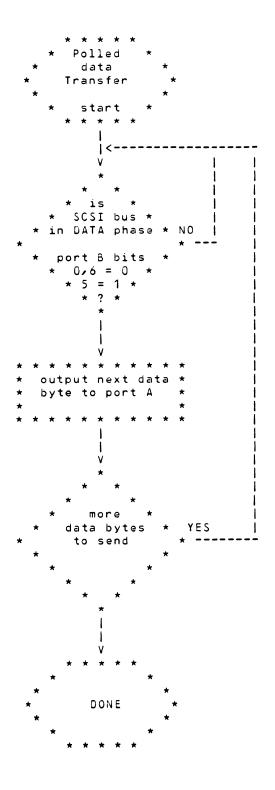

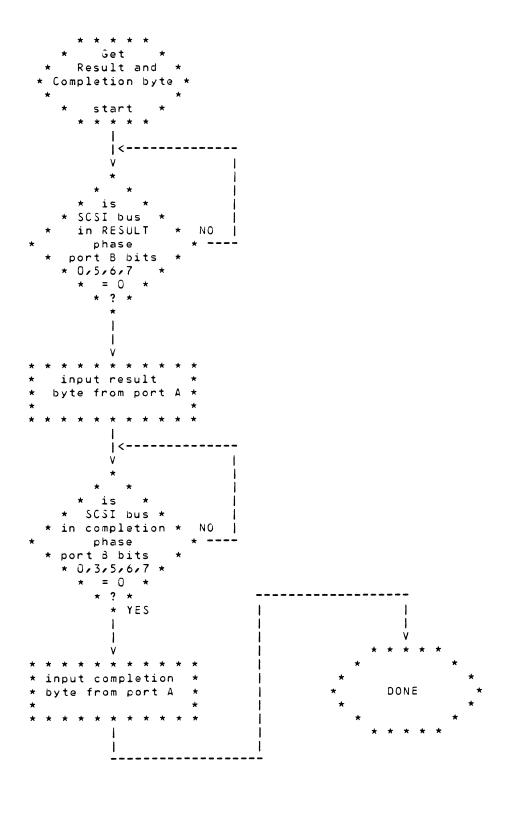

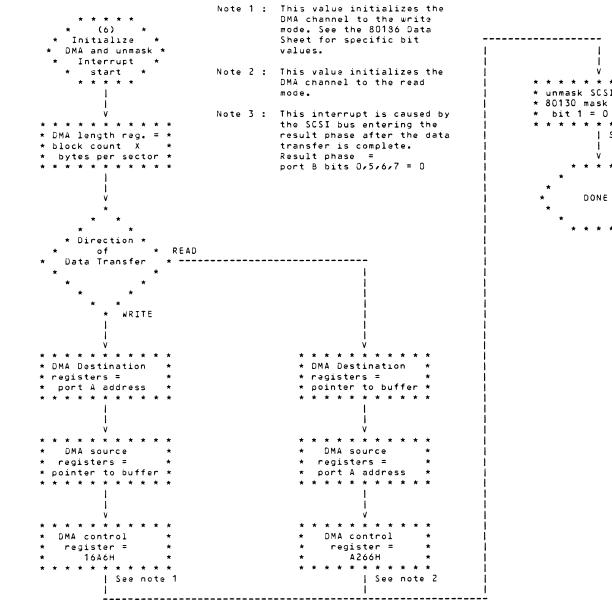

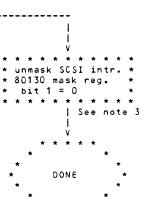

| APPENDIX C<br>PARALLEL PORT CONFIGURATIONS<br>C.1 Introduction<br>C.2 SCSI Interface Configuration<br>C.3 SCSI Operation with the iSBC <sup>®</sup> 186/03 Board<br>C.4 Centronics Printer Interface    | C-1<br>C-3<br>C-7<br>C-22 |

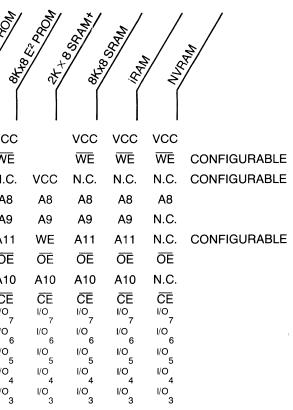

| APPENDIX D<br>UNIVERSAL MEMORY SITE REQUIREMENTS<br>AND JUMPER CONFIGURATIONS<br>D.1 Introduction<br>D.2 DC Characteristics<br>D.3 Jumper Matrix Configuration                                          | D-1<br>D-1<br>D-1         |

| APPENDIX E<br>iSBC <sup>®</sup> 341 MEMORY EXPANSION BOARD INSTALLATION<br>E.1 Introduction<br>E.2 iSBC <sup>®</sup> 341 Installation<br>E.3 Jumper Configuration Information<br>E.4 Reference Diagrams | E-1<br>E-1<br>E-2<br>E-5  |

| APPEN | IDIX F  |        |                         |                                         |     |

|-------|---------|--------|-------------------------|-----------------------------------------|-----|

| iSBC  | 186/03  | BOARD  | PROGRAMMING             | EXAMPLES                                |     |

| F.1   | Introdu | uction | • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | F-1 |

|       |         |        |                         |                                         |     |

| גיזממ |         |        |                         |                                         |     |

| APPENDIX G                  |     |

|-----------------------------|-----|

| MEMORY DECODE PAL EQUATIONS |     |

| G.1 Introduction            | G-1 |

## TABLES

| 1-1.  | iSBC® 186/03 Board Specifications                         | 1-7  |

|-------|-----------------------------------------------------------|------|

| 2-1.  | Allowable Mixtures In Bank A (RAM Bank)                   | 2-8  |

| 2-2.  | PROM Site Addresses and Jumpers (U40, 41, 73, 74)         | 2-12 |

| 2-3.  | Bank A (RAM) Site Addresses and Jumpers (U42, 43, 75, 76) | 2-14 |

| 2-4.  | Wait-State Jumper Options                                 | 2-15 |

| 2-5.  | DMA Request Multiplexer Addressing                        | 2-18 |

| 2-6.  | DRQO Source Selection                                     | 2-18 |

| 2-7.  | DRQ1 Source Selection                                     | 2-19 |

| 2-8.  | iLBX™ Bus Address Ranges                                  | 2-20 |

| 2-9.  | iLBX™ Bus Timing Specifications                           | 2-22 |

| 2-10. | Interrupt Source Jumper Matrix Options                    | 2-24 |

| 2-11. | Interrupt Destination Jumper Matrix Options               | 2-25 |

| 2-12. | Default Interrupt Level Assignments                       | 2-26 |

| 2-13. | Parallel Interface Default Pin Assignments                | 2-33 |

| 2-14. | Parallel Interface Drive Characteristics                  | 2-34 |

| 2-15. | Parallel Port Jumper Options                              | 2-37 |

| 2-16. | Pin Assignment For Connector J1 - RS422A/449 Interface    | 2-40 |

| 2-17. | Serial I/O Interface Configuration Comparison             | 2-41 |

| 2-18. | RS232C Pin Assignment                                     | 2-46 |

| 2-19. | iSBX <sup>™</sup> Bus Size Selection                      | 2-48 |

| 2-20. | iSBX™ Bus Interface Options                               | 2-49 |

| 2-21. | iSBX <sup>™</sup> System Clock Options                    | 2-50 |

| 2-22. | MULTIBUS® Interface Jumpers                               | 2-51 |

| 2-23. | MULTIBUS® Interface Arbitration Jumpers                   | 2-52 |

| 2-24. | Connector J4 Pin Assignments                              | 2-54 |

| 2-25. | Connector J4 Interface DC Characteristics                 | 2-55 |

| 3-1.  | iSBC® 186/03 Board Connector List                         | 3-3  |

| 3-2.  | iSBC® 186/03 Board Connector Cable Information            | 3-5  |

| 3-3.  | User-Furnished Components                                 | 3-7  |

| 3-4.  | Compatible Memory Devices                                 | 3-10 |

| 4-1.  | Socket Pair Address Ranges                                | 4-3  |

| 4-2.  | iLBX™ Bus Address Ranges                                  | 4-5  |

| 4-3.  | Local I/O Port Addresses                                  | 4-8  |

| 4-4.  | iSBX™ Bus Chip Select Signals                             | 4-9  |

| 4-5.  | DRQO Source Selection                                     | 4-11 |

| 4-6.  | DRQ1 Source Selection                                     | 4-11 |

| 4-7.  | Port Addresses for 80186 Internal I/O Registers           | 4-12 |

|       |                                                           |      |

# TABLES (continued)

1

| 4-8.  | DMA Request MUX Addressing                                |

|-------|-----------------------------------------------------------|

| 4-9.  | Port Addresses for 80130, 8259A, and 8274                 |

|       | Interrupt Functions                                       |

| 4-10. | Parameter Sequence for 80130, 825A, & 8274 Initialization |

| 4-11. | 80186 Timer Information                                   |

| 4-12. | Port Addresses for the 80130 PIT                          |

| 4-13. | PIT Programming Example                                   |

| 4-14. | Timer Count Values for Common Baud Rates                  |

| 4-15. | Asynchronous Mode Programming Sequence                    |

| 4-16. | Bisync Mode Transmit Programming Sequence                 |

| 4-17. | Bisync Mode Receive Programming Sequence                  |

| 4-18. | SDLC Mode Transmit Sequence                               |

| 4-19. | 8274 Parameter Sequence for Initialization                |

| A-1.  | Installed Jumpers (As-Shipped Configuration)              |

| A-2.  | Numerical List of Jumpers and their Functions             |

| C-1.  | Parallel Port Bit Assignments (Default Configuration)     |

| C-2.  | XU18 (Handshake Circuitry) PAL Equations                  |

| C-3.  | XU16 (Parity Circuitry) PAL Equations                     |

| C-4.  | Transfer Phase Signals                                    |

| C-5.  | Centronics Interface PAL Equations for U18                |

| C-6.  | Centronics Interface Jumpers                              |

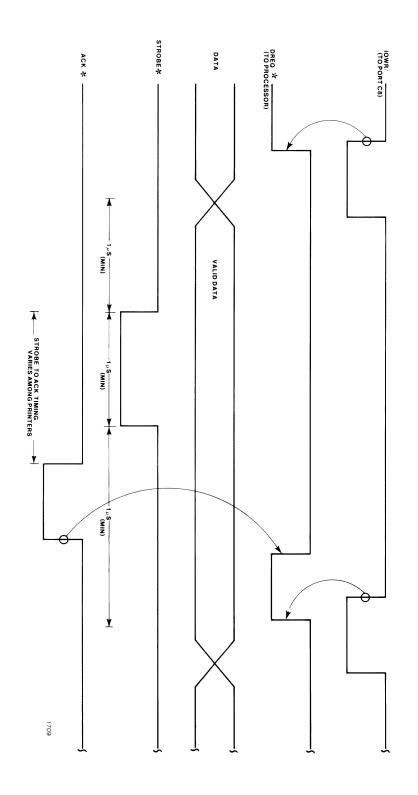

| C-7.  | Centronics Interface Cable Pin Assignments                |

| D-1.  | Universal Memory Site DC Specifications                   |

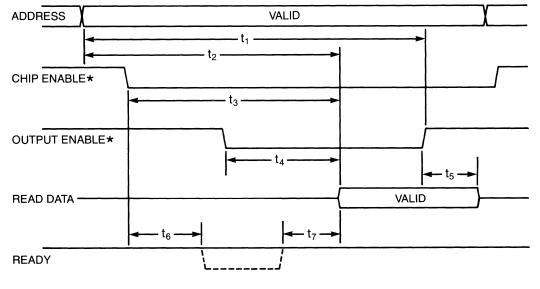

| D-2.  | Normal READ Cycle at 6MHz                                 |

| D-3.  | Normal WRITE Cycle at 6MHz                                |

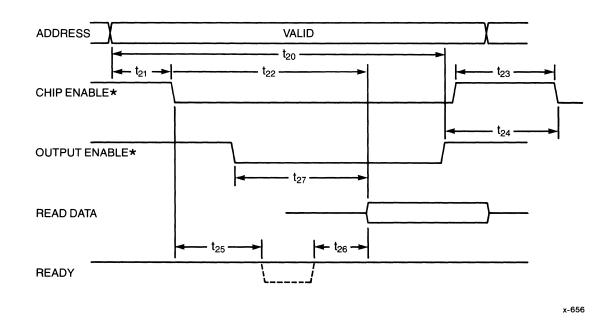

| D-4.  | iRAM READ Cycle at 6MHz (Bank A Only)                     |

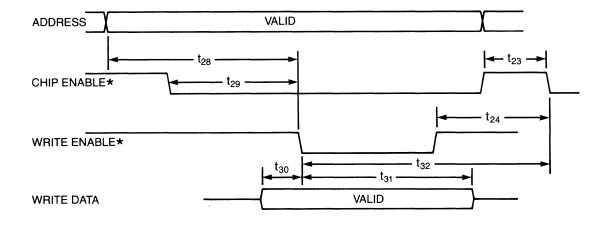

| D-5.  | iRA, WRITE Cycle at 6MHz (Bank A Only)                    |

| E-1.  | Jumper Configurations for Types of Memory Devices         |

| G-1.  | Memory Decode PAL (U59) Equations                         |

|       |                                                           |

# FIGURES

| 2-1.  | Block Diagram                                          | 2-2  |

|-------|--------------------------------------------------------|------|

| 2-2.  | Default Memory Map                                     | 2-5  |

| 2-3.  | Local Memory Socket Pairs and Jumper Matrices          | 2-9  |

| 2-4.  | Memory Size Configuration Matrix                       | 2-11 |

| 2-5.  | iLBX <sup>™</sup> Bus Timing Specifications Diagram    | 2-23 |

| 2-6.  | Default Configuration of Interrupt Jumper Matrix       | 2-27 |

| 2-7.  | Physical Locations of Connectors and Pin 1 Assignments | 2-36 |

| 2-8.  | RS232C Cable Diagram for Connector Jl                  | 2-39 |

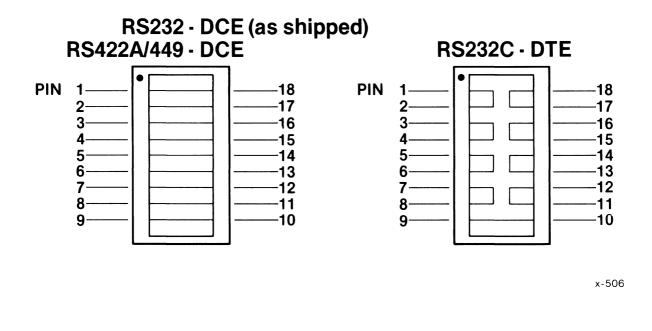

| 2-9.  | DIP Header for DCE and DTE Operation                   | 2-43 |

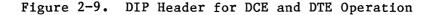

| 2-10. | RP2 Configurations for RS442A.449 and RS232C           | 2-45 |

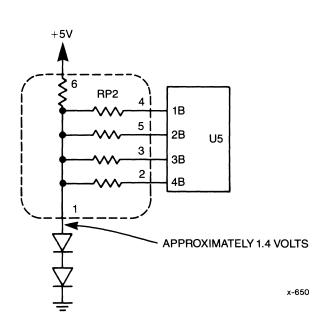

| 2-11. | Connector J4 Pinout Map.                               | 2-55 |

| 3-1.  | User-Furnished Components on the iSBC® 186/03 Board    | 3-6  |

| 3-2.  | Memory Installation                                    | 3-9  |

| 4-1.  | iSBC® 186/03 Memory Map.                               | 4-4  |

| 4-2.  | 16M-Byte and 1M-Byte MULTIBUS® Addressing              | 4-7  |

| 4-3.  | Asynchronous Message Format                            | 4-40 |

# FIGURES (continued)

| 4-4   | Synchronous Message Formats-8274 MPSC                     | 4-44        |

|-------|-----------------------------------------------------------|-------------|

| 4-5.  | Transmit/Receive SDLC/HDLC Message Format                 | 4-51        |

| 4-6.  | Interrupt Structure                                       | 4-59        |

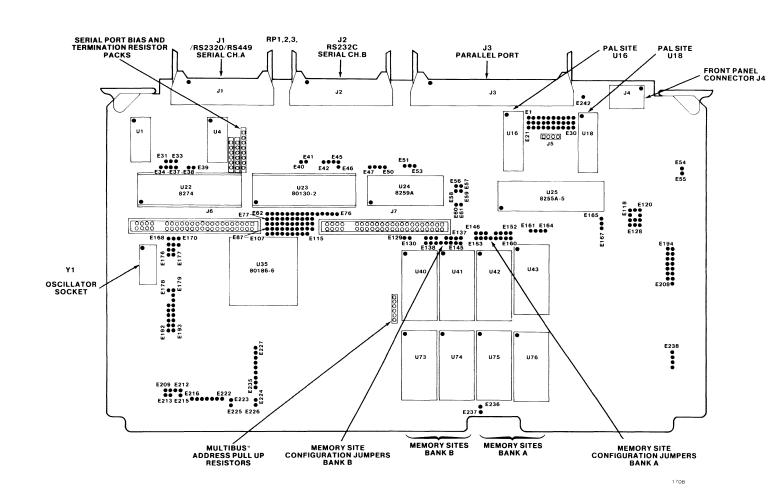

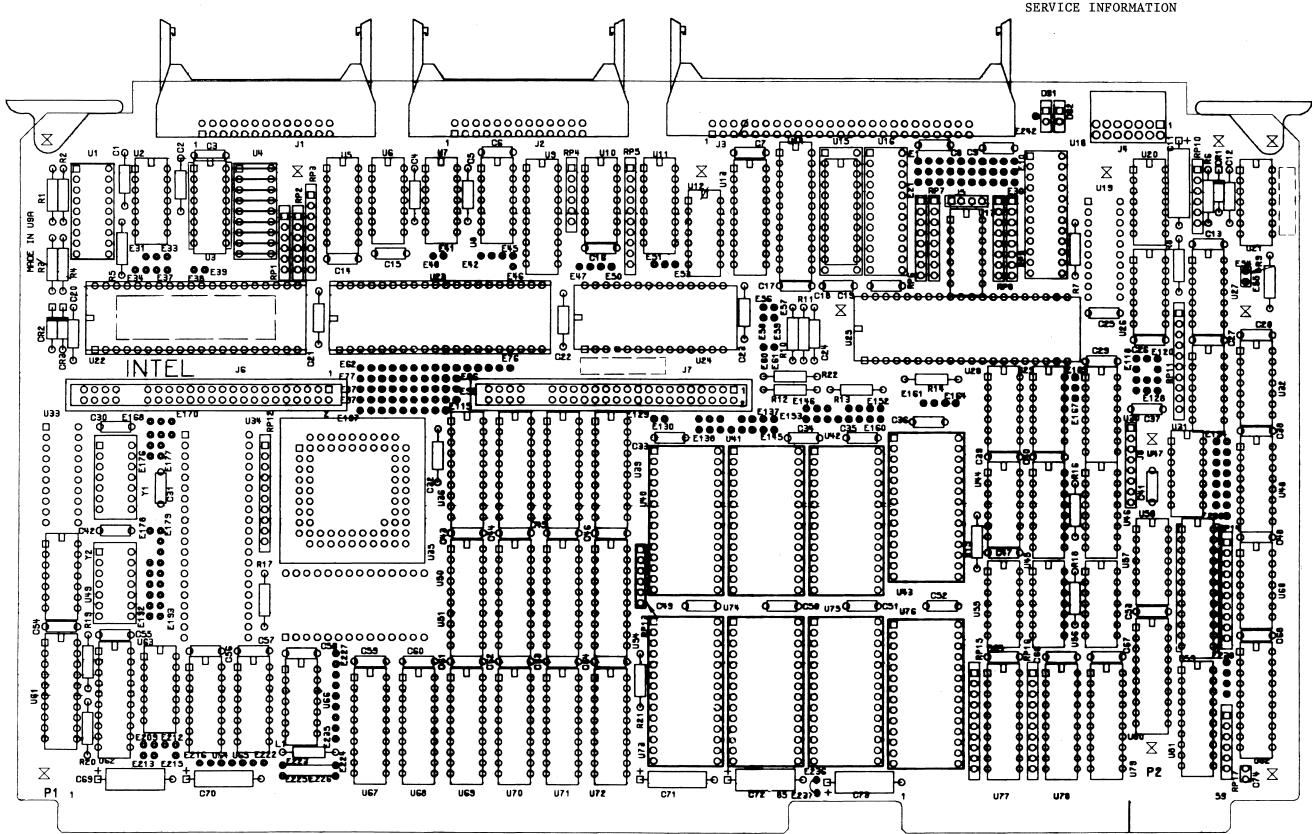

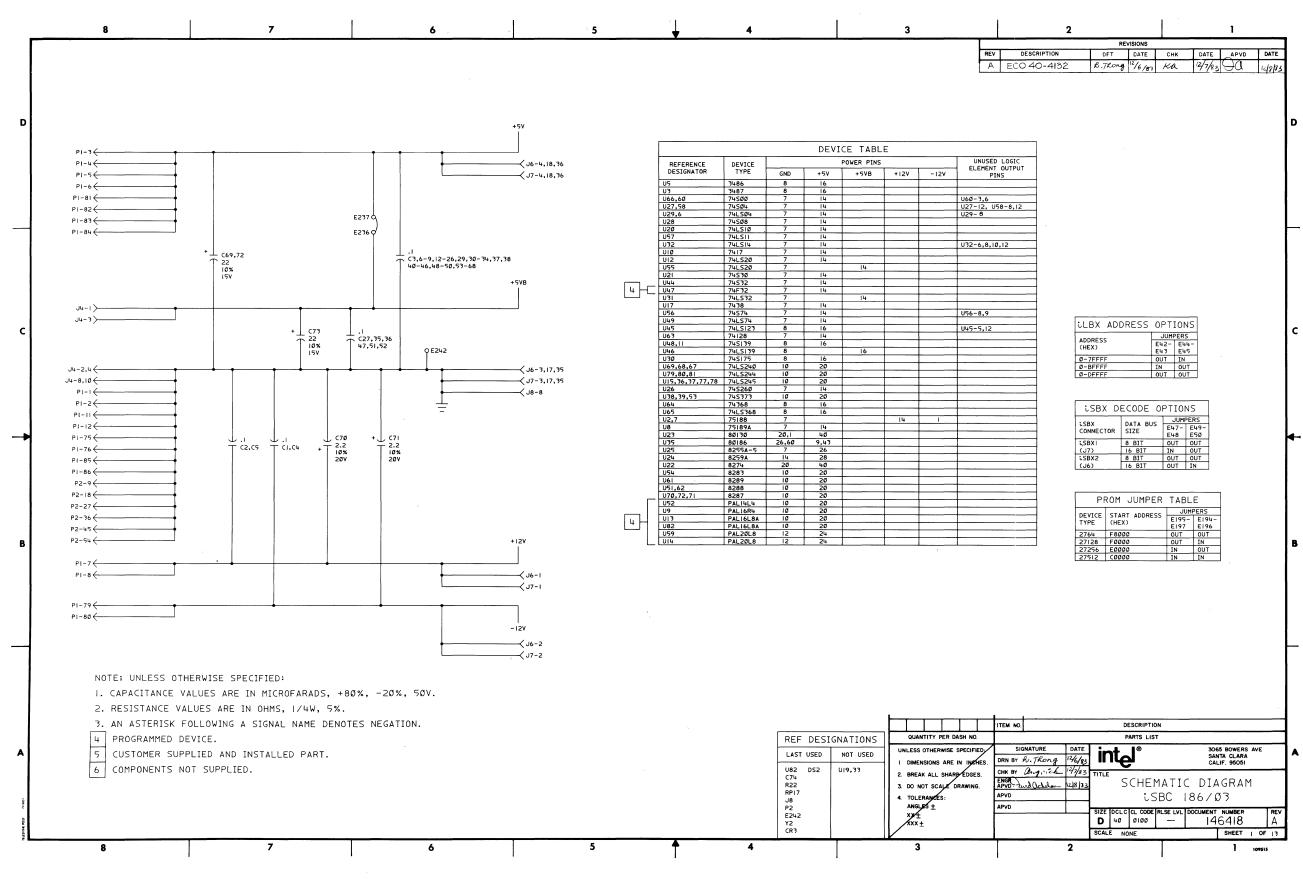

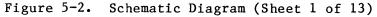

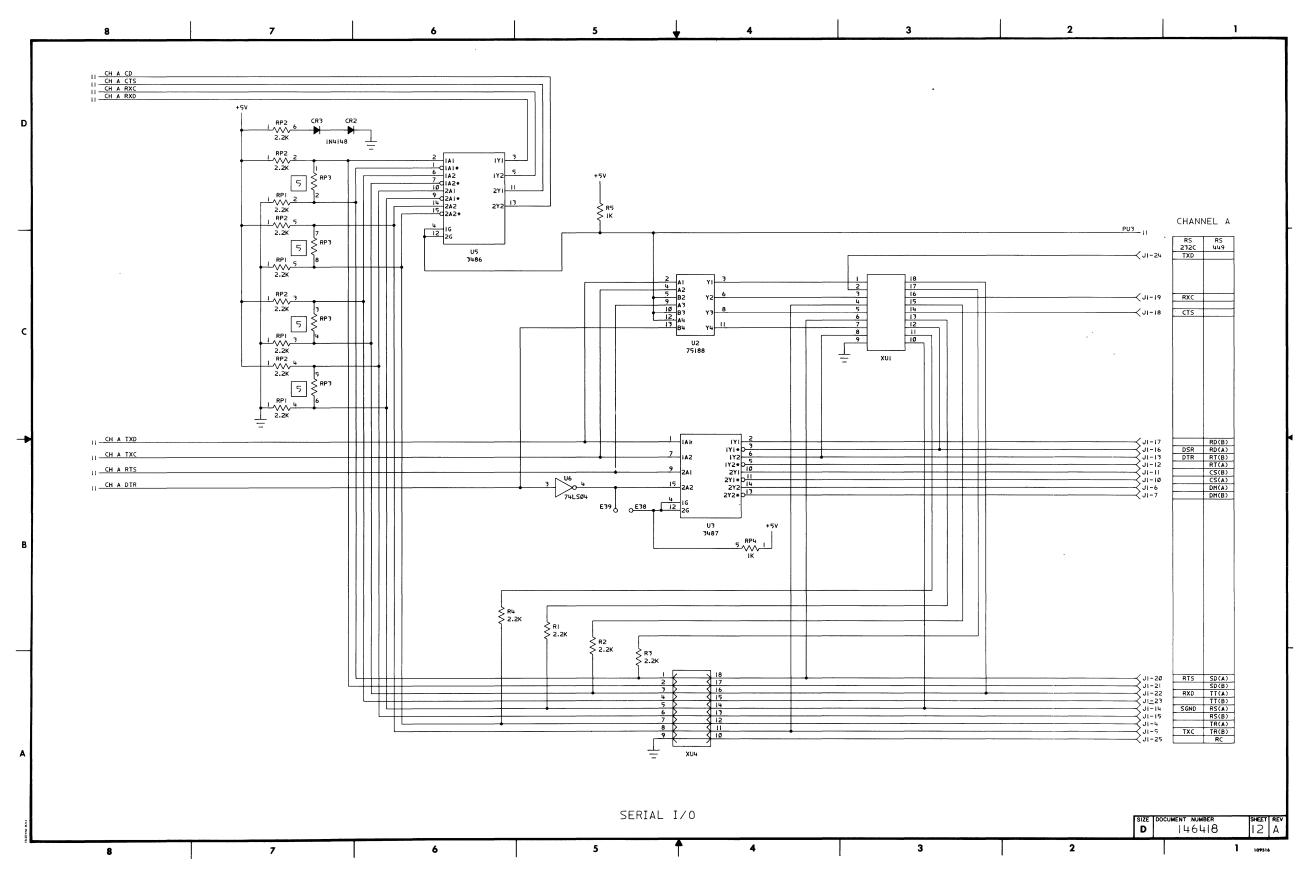

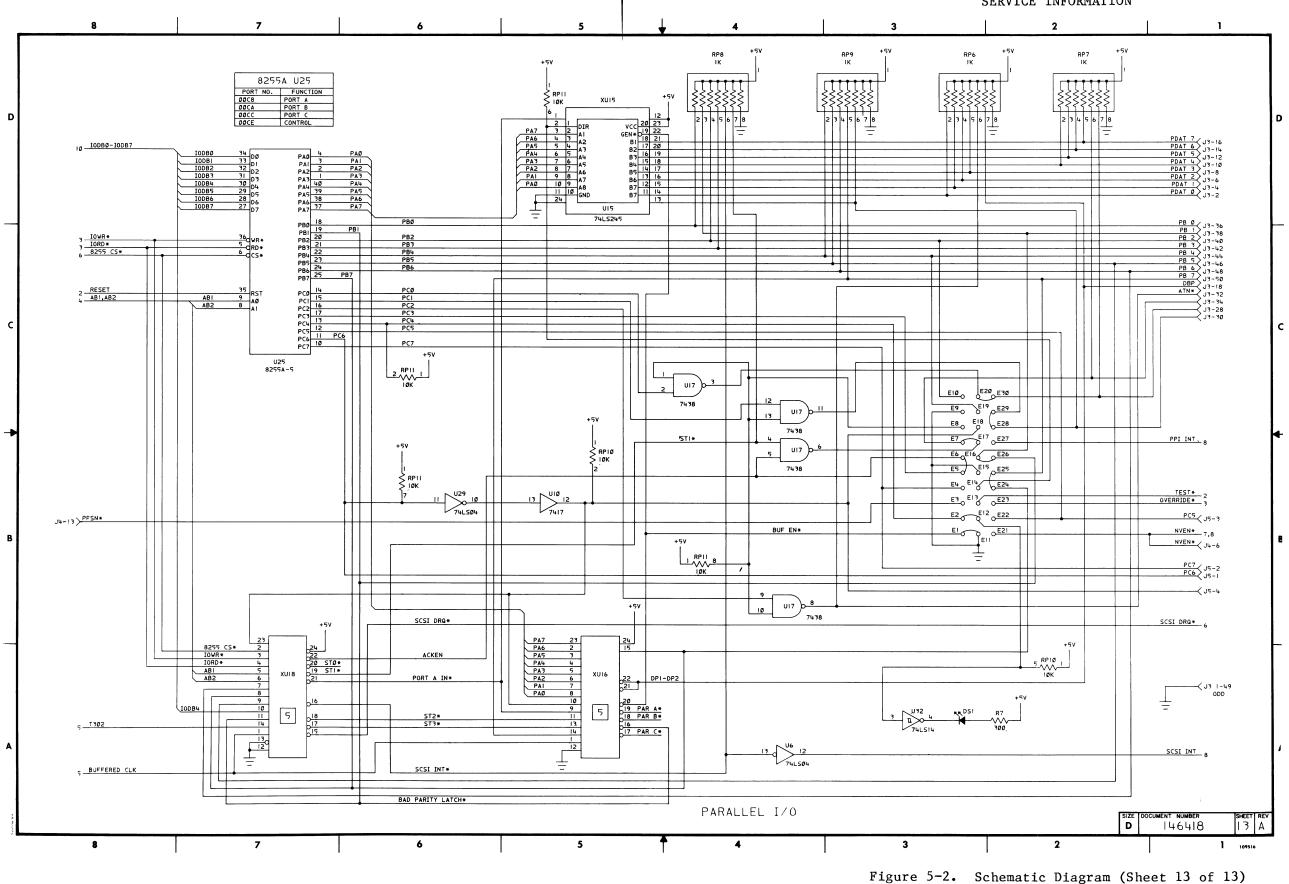

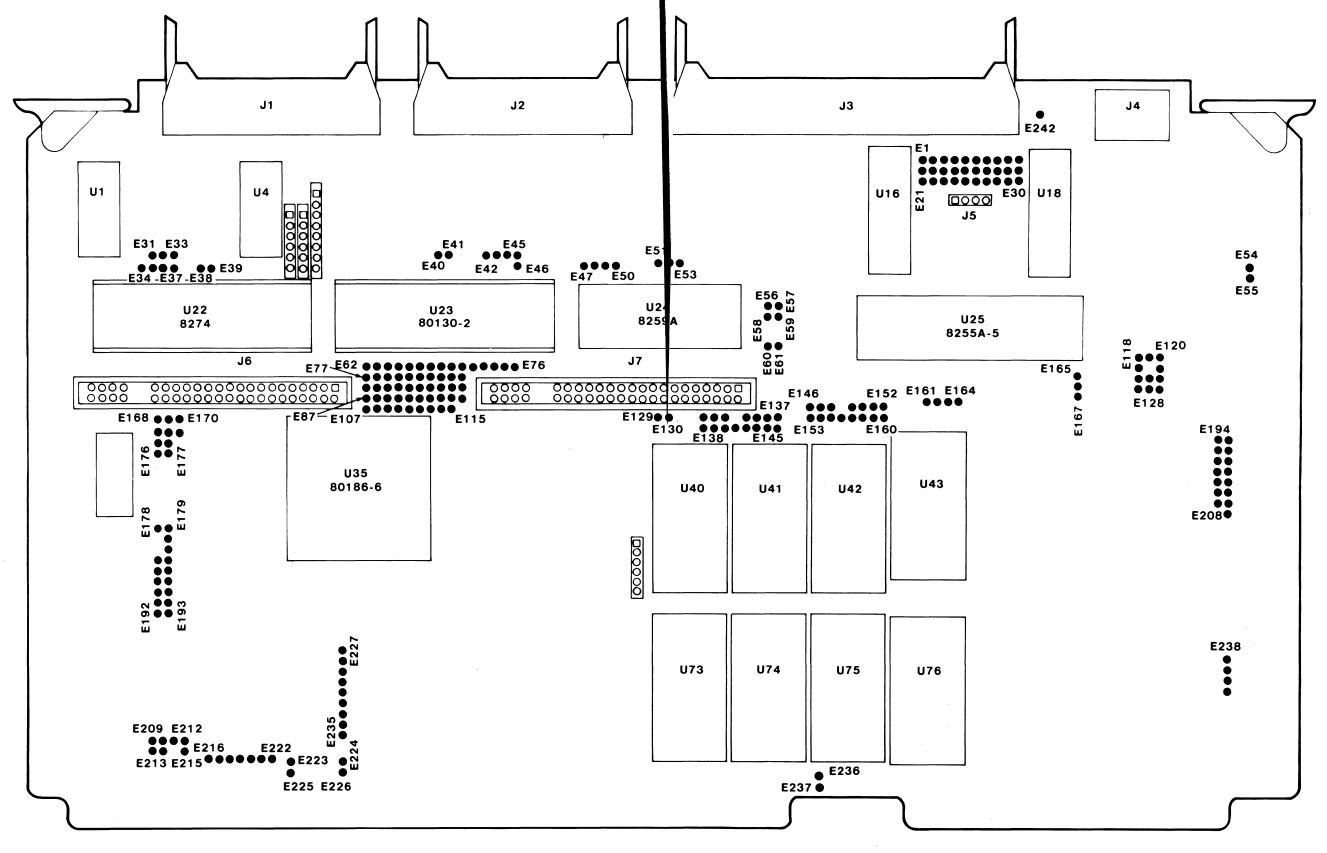

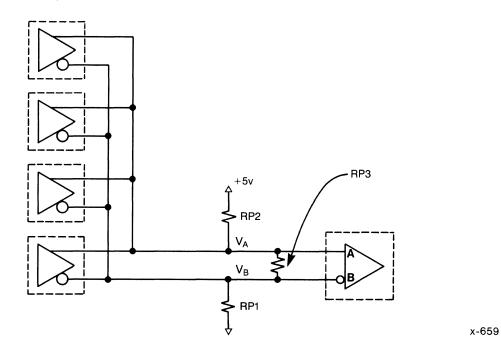

| 5-1.  | Parts Location Diagram                                    | 5-3         |

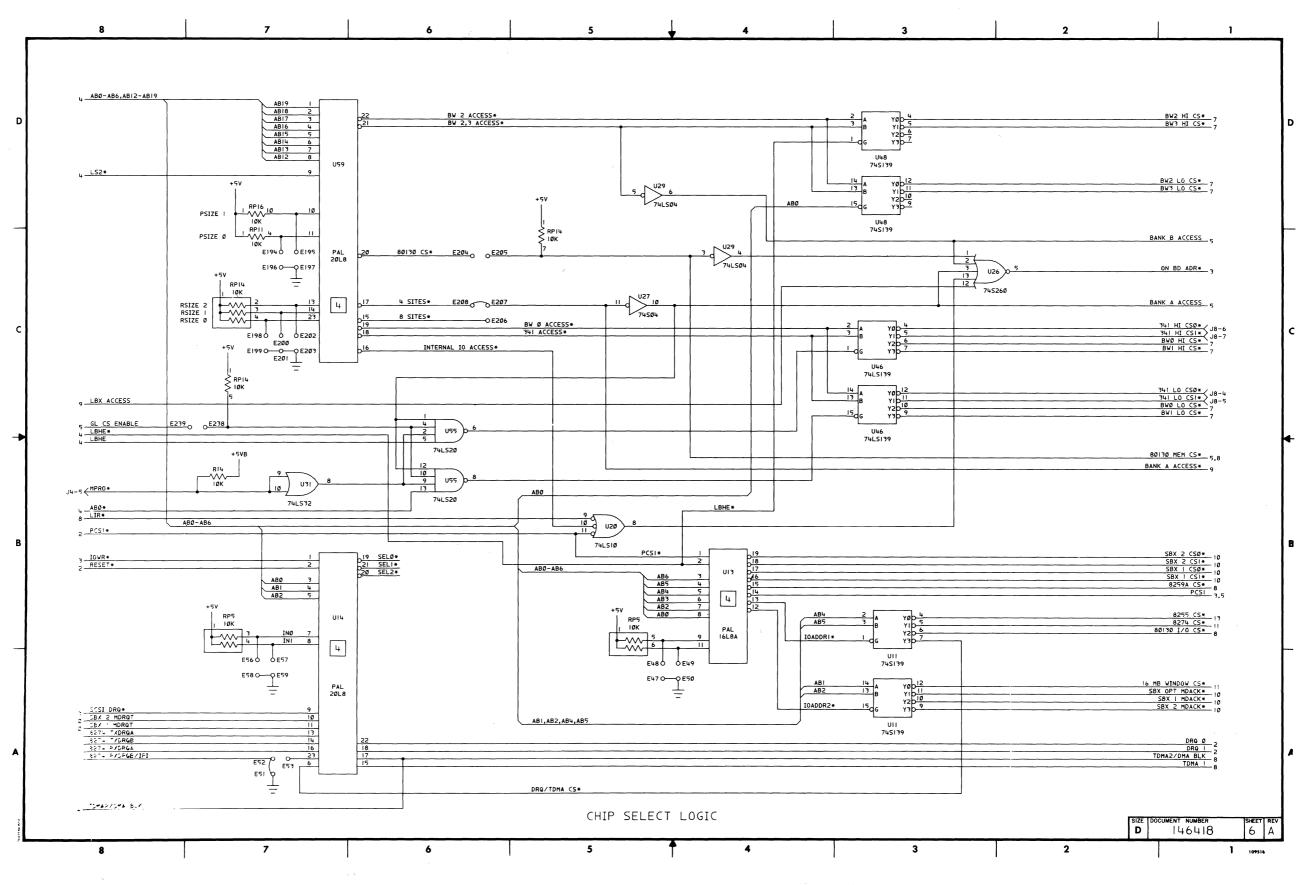

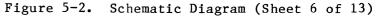

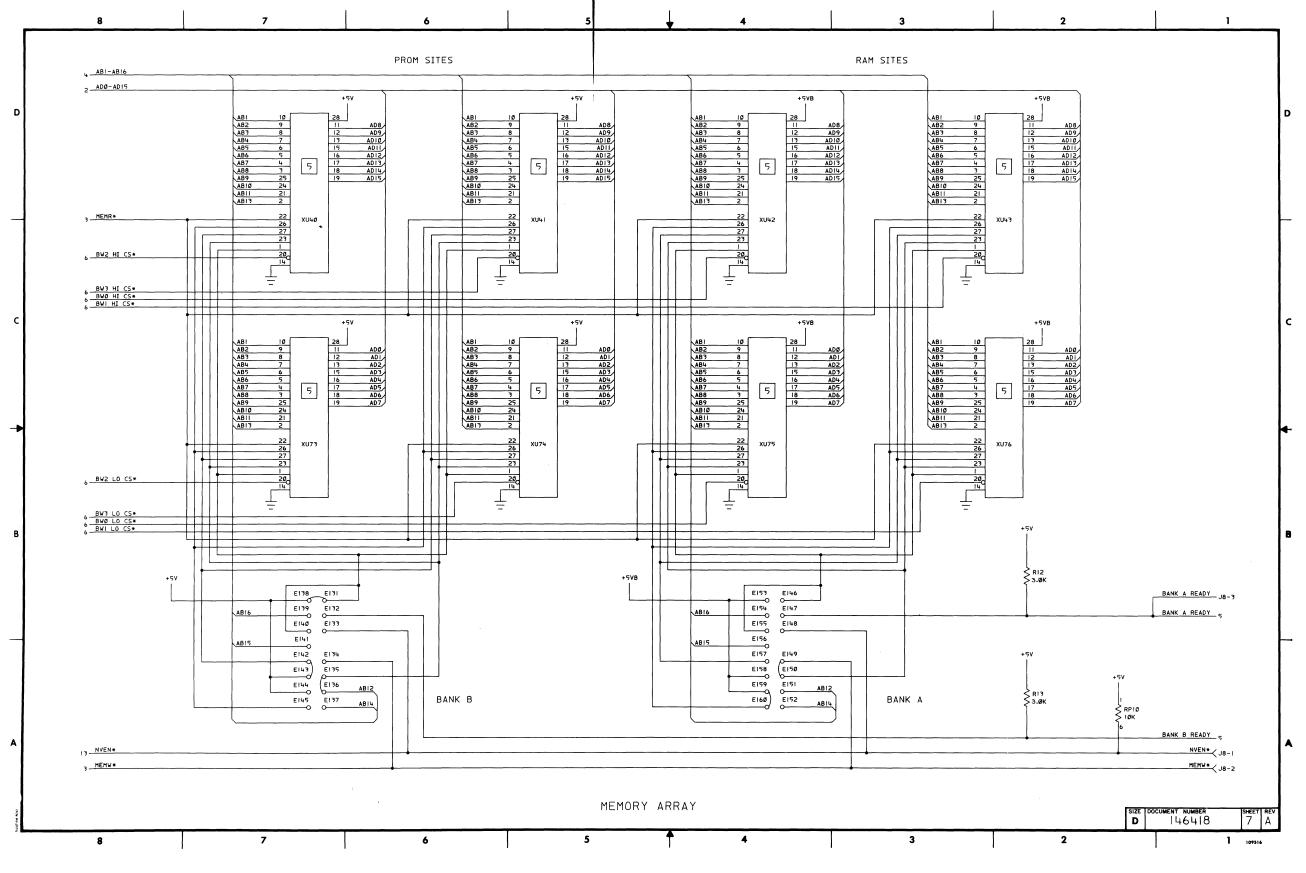

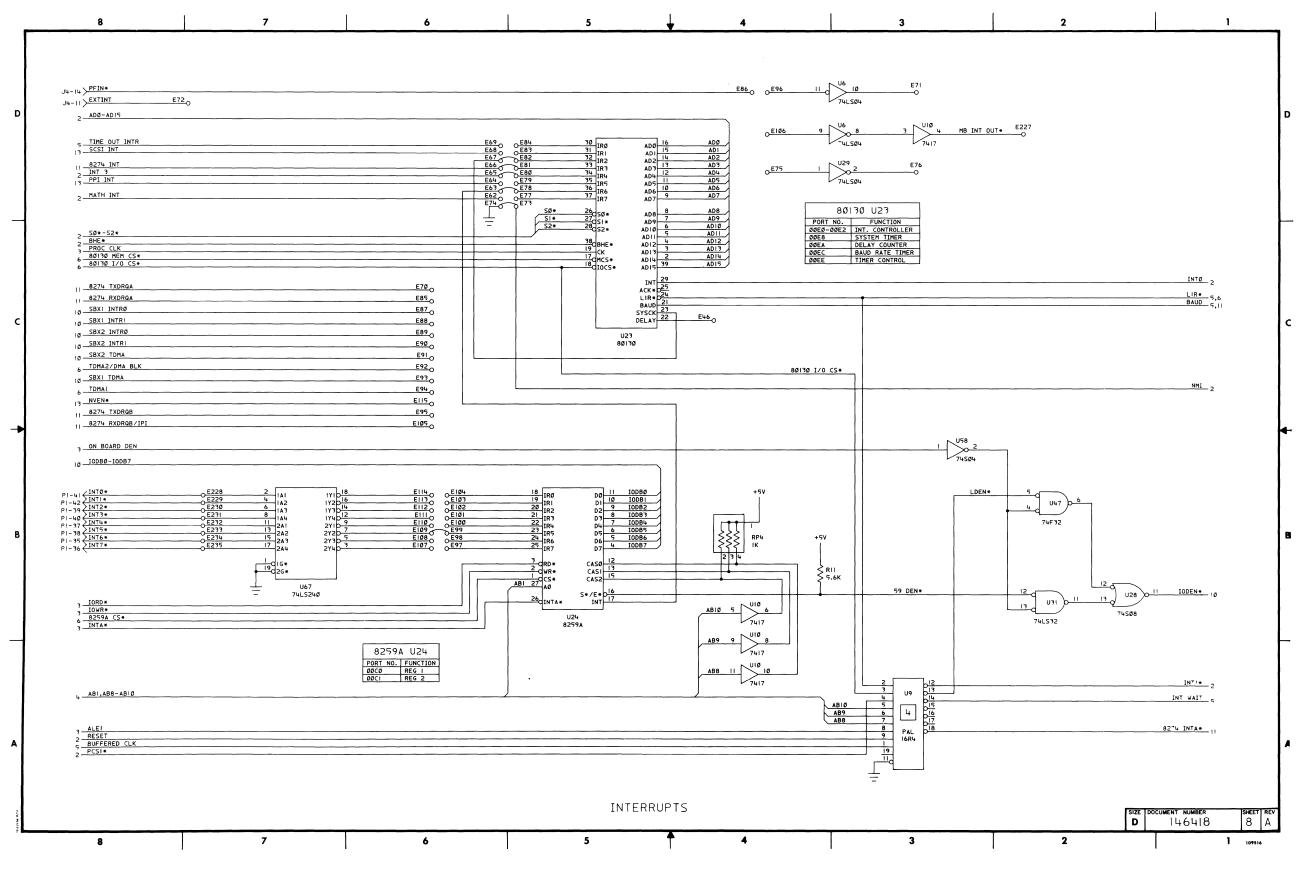

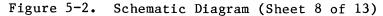

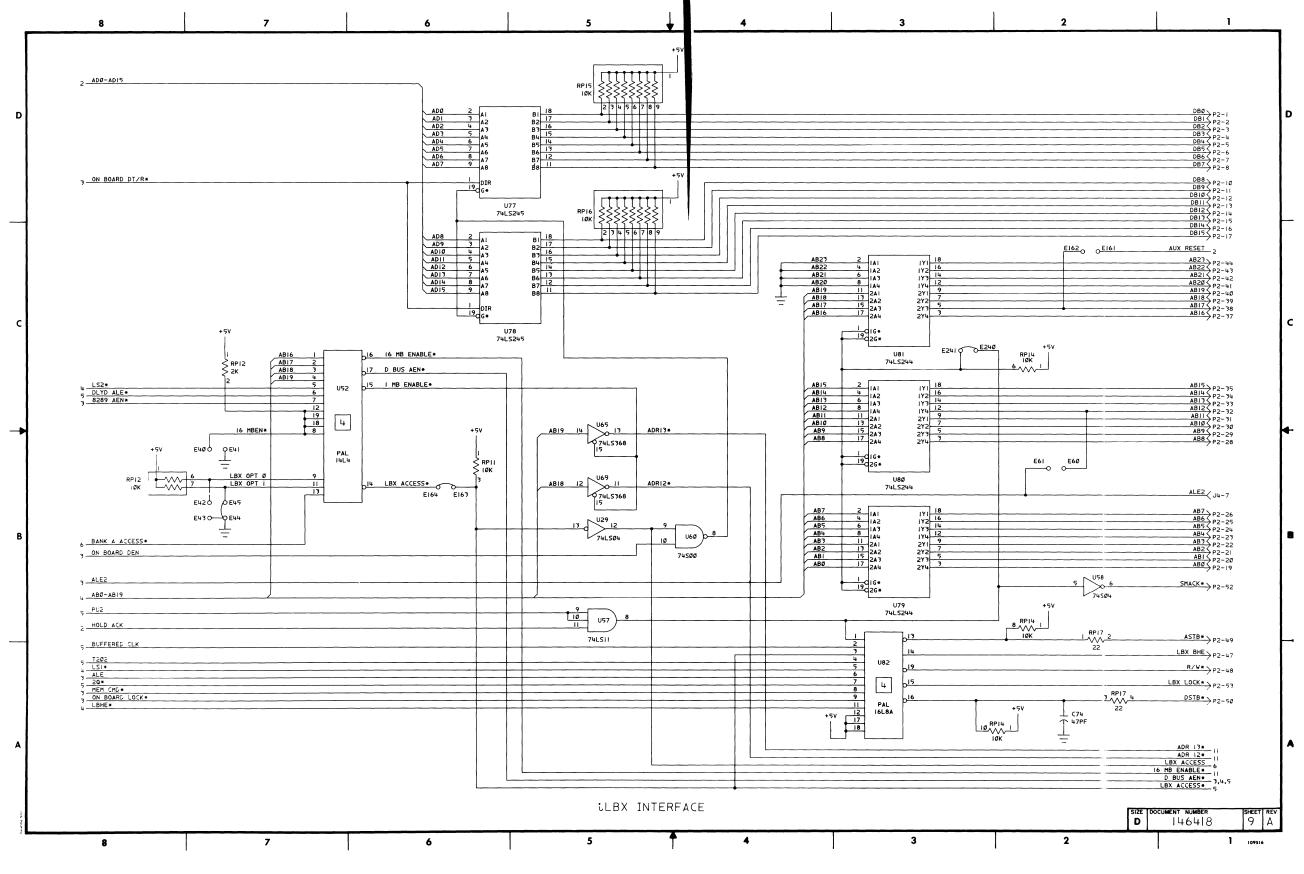

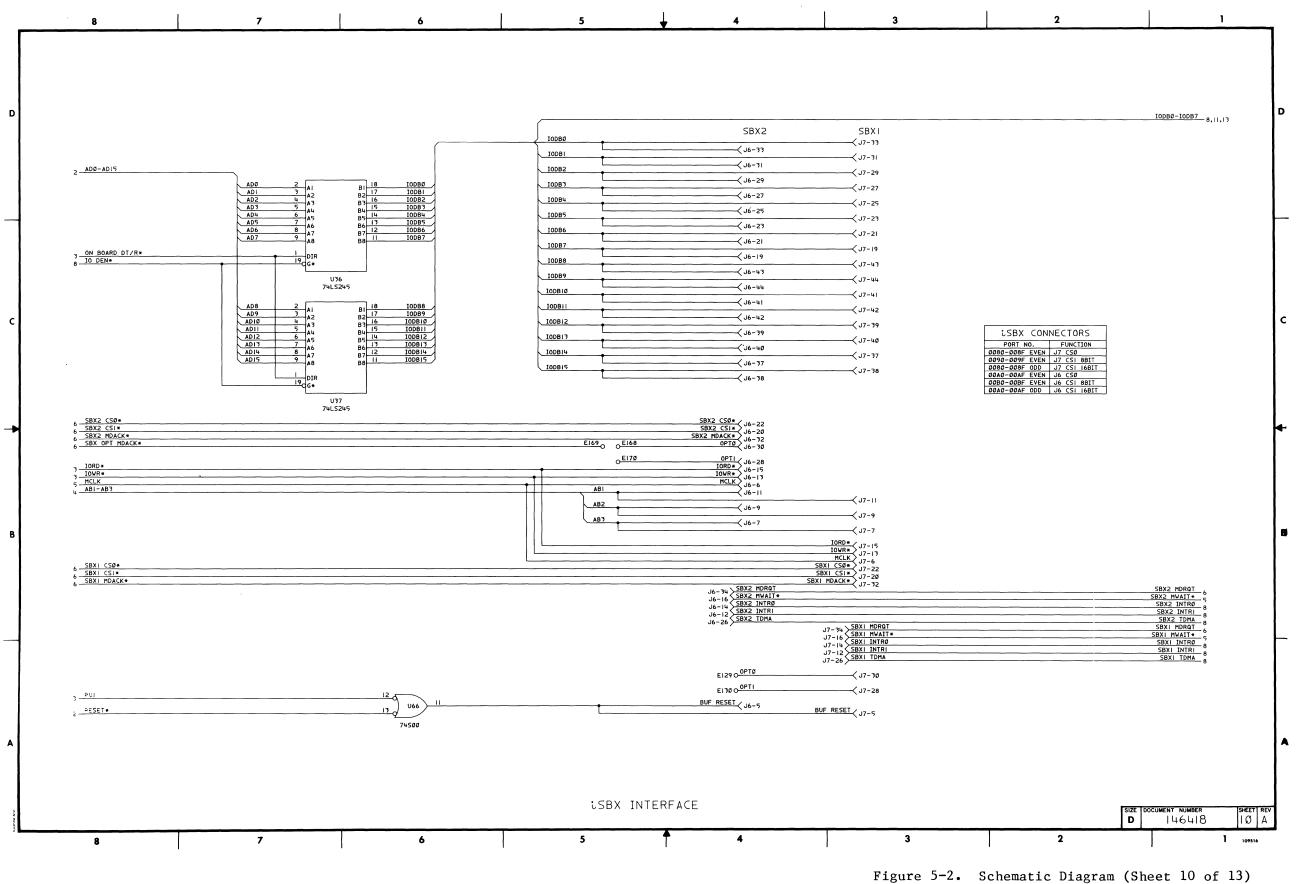

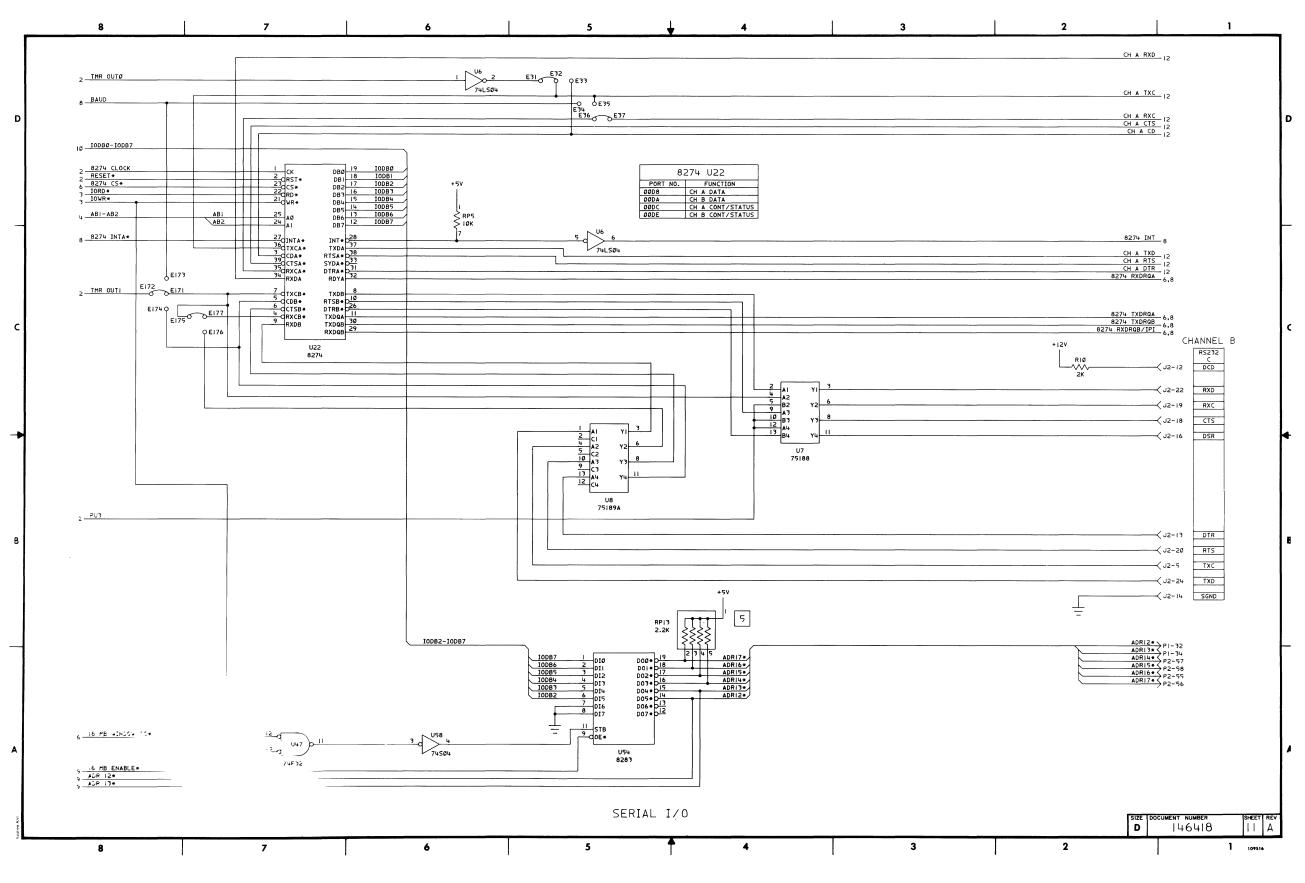

| 5-2.  | Schematic Diagram                                         | 5-5         |

| A-1.  | Jumper Post Location Diagram                              | A-11        |

| B-1.  | Example Configuration                                     | B-2         |

| B-2.  | Case 1 Example Configuration                              | 8-4         |

| B-3.  | Case 2 Configuration Example                              | B-6         |

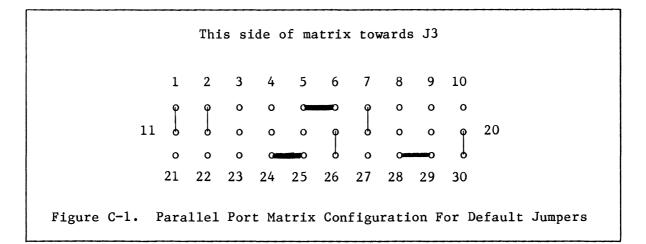

| C-1.  | Parallel Port Matrix Configuration for Default Jumpers    | C-2         |

| C-2.  | Parallel Port Matrix Configuration for SCSI Jumpers       | C-4         |

| C-3.  | Cable Assembly Data for SCSI Interface                    | C-7         |

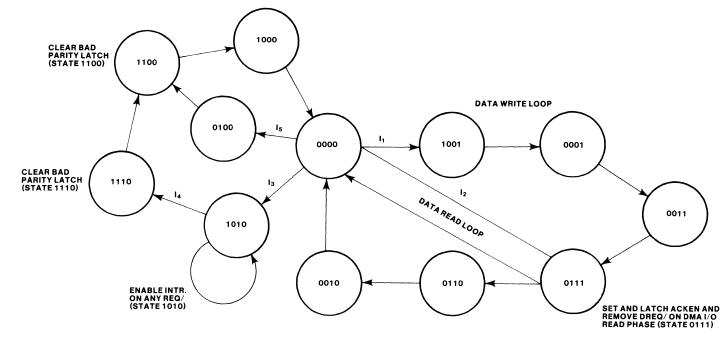

| C-4.  | SCSI State Machine Diagram                                | C-9         |

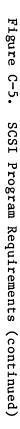

| C-5.  | SCSI Program Requirements                                 | C-15        |

| C-6.  | Parallel port Matrix Configuration for                    |             |

|       | Centronics Jumper                                         | C-25        |

| C-8.  | Cable Fabrication Diagram                                 | C-27        |

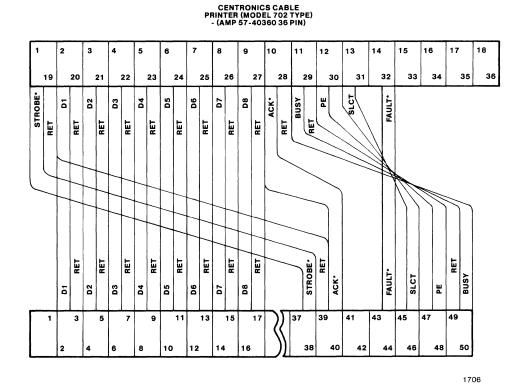

| C-9.  | FAULT* Timing Specification                               | C-28        |

| C-10. | Centronics PAL with Jumper Connections                    | C-29        |

| D-1.  | Compatible Device Types                                   | D-3         |

| D-2.  | Jumper Matrix Configurations for Static RAM Devices       | D-5         |

| D-3.  | Jumper Matrix Configurations for iRAM Devices             | D-6         |

| D-4.  | Jumper Matrix Configurations for EPROM Devices            | D <b>-7</b> |

| D-5.  | Jumper Matrix Configurations for NVRAM Devices            | D-9         |

| D-6.  | Jumper Matrix Configurations for EEPROM Devices           | D-10        |

| D-7.  | Normal READ Cycle                                         | D-13        |

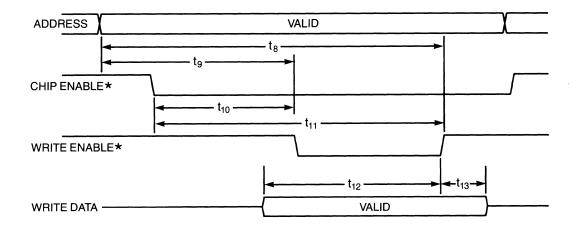

| D-8.  | Normal WRITE Cycle                                        | D-14        |

| D-9.  | iRAM READ Cycle                                           | D-14        |

| D-10. | iRAM WRITE Cycle                                          | D-15        |

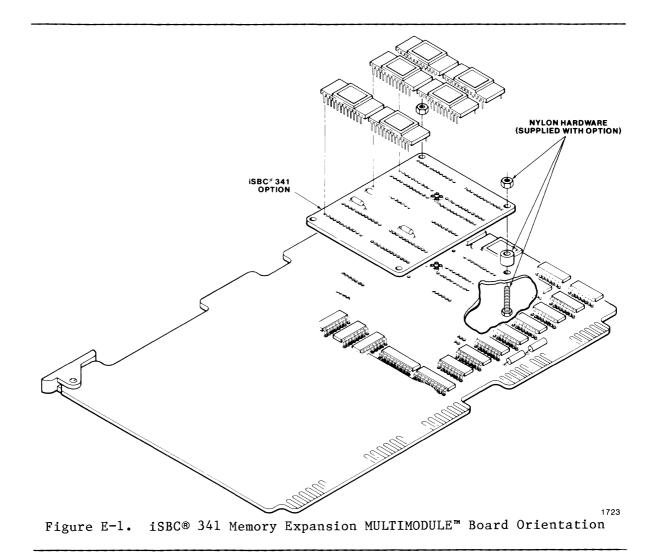

| E-1.  | iSBC® 341 Memory Expansion MULTIMODULE" Board Orientation | E-3         |

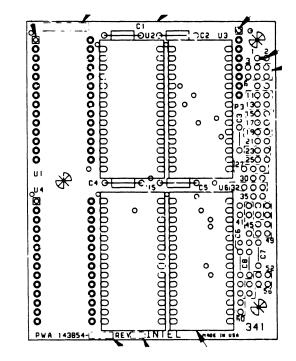

| E-2.  | Parts Location Diagram                                    | E-6         |

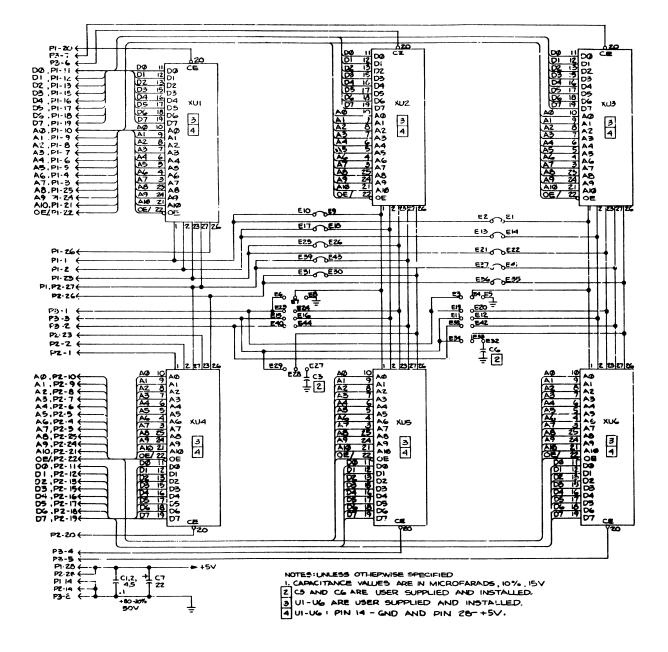

| E-3.  | Schematic Diagram                                         | E-7         |

| F-1.  | iSBC <sup>®</sup> 186/03 Programming Example              | F-2         |

#### CHAPTER 1. GENERAL INFORMATION

# 1.1 INTRODUCTION

The iSBC 186/03 Single Board Computer is a general purpose, 16-bit computer system on a MULTIBUS-compatible printed circuit board. The board supports the high-speed memory execution bus (iLBX bus) for local memory expansion, and the iSBX MULTIMODULE Bus for low-cost I/O expansion. The board is designed to interface to the Small Computer System Interface (SCSI) with some reconfiguration and optional components.

The purpose of this chapter is to introduce you to this state-of-the-art product in a quick and concise manner. This chapter gives a list of key features of the board, provides a brief description of the board, and lists the product specifications.

#### 1.2 KEY FEATURES

This section provides a brief list of key features on the iSBC 186/03 board. More detailed descriptions of the features are located in the "Description" section of this chapter.

- iAPX 186 (80186) high-integration microprocessor.

- iAPX 86/30 (80130) operating system processor.

- Eight byte-wide memory sites for EPROM, EEPROM, SRAM, iRAM, or NVRAM. Configurable memory capacity: up to 32k bytes of RAM and up to 256k bytes of ROM memory on the board; or up to 512k bytes of ROM if on-board RAM is not used.

- iSBC 341 Memory Expansion MULTIMODULE board-compatible, expanding RAM to 64K-bytes.

- iLBX local memory expansion bus for high-speed transfers to/from iLBX memory expansion boards.

- 27 interrupt sources on-board using the 80186, 80130, and 8259A interrupt controllers, and the 8274 serial controller.

- Two serial I/O channels controlled by an 8274 multi-protocol serial controller (MPSC).

- General purpose parallel interface; can easily be reconfigured to the SCSI or Centronics interface by adding custom PALs (programmable array logic devices) as defined in Appendix C of this manual.

- Two iSBX bus interface connectors for low-cost I/O expansion.

- Master capability on the MULTIBUS interface.

- Dedicated front panel interface connector.

#### **1.3 DESCRIPTION**

This section provides more detail on each of the board features previously mentioned.

#### iAPX 186 (80186) Microprocessor

The iSBC 186/03 board is controlled by an Intel 80186 microprocessor operating at 6 MHz. The processor integrates two DMA channels, three timers and an interrupt controller on a single chip. The 80186 is object code compatible with existing 8086 and 8088 software; however, the 80186 instruction set has been expanded to include 10 new instructions. The built-in, on-chip functions are controlled by register programming, similar to other Intel peripheral components.

#### 80130 Operating System Processor

The on-board 80130 component adds several functions to the iSBC 186/03 board: a subset of the iRMX 86 Operating System Nucleus in on-chip memory, three additional programmable timers, and an additional programmable interrupt controller. This subset of the iRMX 86 Nucleus provides operating system primitives for those applications performing functions such as real-time control. If the application requires more of the iRMX 86 Nucleus primitives than are provided in the 80130, they can be added by using the iRMX 86 Interactive Configuration Utility (ICU).

Intel offers run-time foundation software to support applications which range from general purpose to high-performance solutions. The iRMX 86 Nucleus provides an event-driven multitasking structure which includes task scheduling, task management, intertask communications and interrupt servicing for high-performance applications.

The entire iRMX 86 Operating System consists of the Nucleus and other pieces or "sub-systems". If the application tasks require features such as asychronous I/O control, priority-based resource allocation, file support for peripheral controllers, or a human interface/command line interpreter, such functions can be provided by one or more of the iRMX 86 Operating System subsystems. For execution, the iRMX 86 Operating System can be loaded into RAM or programmed into EPROM.

The iRMX 86 Operating System provides a rich set of features and options to support sophisticated applications solutions. In addition to supporting real-time requirements, the iRMX 86 Operating System has a powerful but easy-to-use human interface.

#### GENERAL INFORMATION

Services provided by the iRMX 86 Operating System include facilities for executing programs concurrently, sharing resources and information, servicing asynchronous events and interactively controlling system resources and utilities. The iRMX 86 Operating System can be readily extended to support assembler, PL/M, PASCAL, and FORTRAN software development environments. The modular building block software lends itself well to customized application solutions.

#### Local Memory

Up to 16 Megabytes of total system memory may be addressed by the iSBC 186/03 board, using a paging technique. Of this amount, a maximum of 256K-bytes of EPROM type local memory (using four 64K x 8 EPROM devices), and a maximum of 32K-bytes of RAM type local memory (using four 8K x 8 RAM devices) may reside on-board. If the RAM required for your application resides off-board, up to 512K-bytes of EPROM may reside on board (using eight 64K x 8 EPROM devices).

The on-board RAM can be increased to 64K-bytes by adding the optional iSBC 341 expansion board and four additional 8k x 8 devices. Local memory can operate at zero, one, or two wait-states depending on memory type.

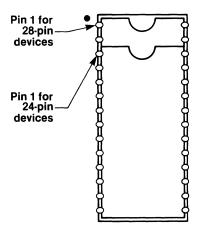

The board will accept a wide variety of memory devices, including PROM, EPROM, EEPROM, SRAM, iRAM, and NVRAM devices. Either 24 or 28-pin devices may be used. Device types are specified by configuring two universal site jumper matrices.

#### iLBX<sup>™</sup> Bus Local Memory Expansion

Local memory resource may be expanded via the Local Bus Extension (iLBX) interface which appears to the 80186 as local memory. The iSBC 186/03 board implements the iLBX bus as a Primary Master, using the optimized mode. Up to 896K-bytes of iLBX bus memory (RAM or PROM) can be added, with zero wait states (using an iSBC 428 board) or one wait-state (using an iSBC 012CX board) performance.

#### Interrupts

Interrupts may originate from numerous on-board or off-board sources. All interrupts, except the 80186 non-maskable interrupt (NMI), are handled by the 80130, configured as the master interrupt controller, and three other slave interrupt controllers. External system interrupts can be connected via the MULTIBUS lines to the 80130 or the 8259A. The 8259A, 8274, and the interrupt controller portion of the 80186 are configured as slaves to the 80130 device. An interrupt jumper matrix allows interrupt configuration flexibility and provides priority selection. Many internal system interrupts are handled by the 80186.

#### Serial I/O

Serial I/O operation is handled by an Intel 8274 Multi-Protocol Serial Communications (MPSC) device. This device supports two serial I/O channels. One channel may be configured for either RS232C or RS422/449 applications. The other channel handles only the RS232C application. The MPSC interface device transmits data at a rate that is programmable at 1, 1/16, 1/32, or 1/64 of the clock rate using the output from one of the on-board counters.

### Parallel I/O

The iSBC 186/03 board uses one Intel 8255A-5 Programmable Peripheral Interface device to control three, 8-bit, parallel I/O ports. The parallel interface may be configured for a variety of dedicated or general purpose applications. By purchasing and programming Programmable Array Logic (PAL) devices as described later in this manual, you can implement a high-performance SCSI (Small Computer System Interface, ANSIx379.2/82-2) Disk interface or a Centronics Type line printer interface, each using one DMA channel from the 80186 processor. The parallel port may also be used to implement many custom parallel interfaces by designing custom PALs to implement the unique handshake requirements of that interface.

# iSBX<sup>™</sup> Bus I/O Expansion

Two iSBX bus connectors (J6 & J7) are provided on the iSBC 186/03 board. These connectors are designed to expand the board's I/O functions, using iSBX MULTIMODULE boards, such as the iSBX 350 Parallel I/O MULTIMODULE Board. The MULTIMODULE boards reside directly on the iSBC 186/03 board. The iSBC 186/03 board supports either 8-bit or 16-bit iSBX boards. The iSBC 186/03 board accommodates two single-wide iSBX MULTIMODULE boards or one single-wide and one double-wide iSBX MULTIMODULE boards.

#### MULTIBUS® Interface

Off-board system access is provided by the MULTIBUS connector (P1) and a portion of the iLBX bus connector (P2). The iSBC 186/03 board is designed to operate as a full master in any Intel MULTIBUS compatible chassis or backplane. The board can also reside in a custom chassis.

# 1.4 DOCUMENTATION SUPPLIED

Each iSBC 186/03 board is shipped with a schematic diagram. Because the schematic diagram in this manual may not be the latest version, the drawings shipped with the board should be saved for future reference.

#### 1.5 ADDITIONAL EQUIPMENT REQUIRED

The iSBC 186/03 board requires a few optional components for basic operation. Depending on your application, you may need to purchase mating connectors for the parallel I/O connector, serial I/O connectors, iLBX bus connector, and an auxiliary connector. Any on-board memory devices must also be purchased separately. Additional devices may be required for the parallel port interface as described in Appendix C and an optional oscillator may be required when using certain iSBX boards. Chapter 3 provides information for selecting these items.

### 1.6 COMPLIANCE LEVEL: 796 BUS SPECIFICATION (IEEE STANDARD)

All Intel MULTIBUS-compatible boards are designed around guidelines set forth in the 796 BUS SPECIFICATION (IEEE STANDARD - formerly the "Intel MULTIBUS Specification"). The standard requires that certain board operating characteristics, such as data bus width and memory addressing paths, be clearly stated in the board's printed specifications (i.e., reference manual). Used properly, this information quickly summarizes the level of compliance the board bears to the published 796 BUS SPECIFICATION. It clearly states the board's level of compatibility to the MULTIBUS structure. Refer to the 796 BUS SPECIFICATION or the INTEL MULTIBUS SPECIFICATION for additional information.

The following notation states the iSBC 186/03 board's level of compliance to the 796 BUS SPECIFICATION:

D16 M24 I16 VO EL

This notation is decoded as follows:

D16 = Data path is 8 and/or 16 bits M24 = Memory address path is up to 24 bits I16 = I/O address path is 8 bits or 16 bits V0 = Non-Bus-Vectored interrupts are supported; and EL = Level-triggered and edge-triggered interrupts are supported.

As shipped, the BCLK\* and CCLK\* frequency on the iSBC 186/03 board is 6 MHz whereas the CCLK\* specification is 10 MHz. A socket is provided so that you can purchase and install a 10 MHz oscillator, if desired. See Chapter 3 for additional information.

# 1.7 COMPLIANCE LEVEL: INTEL iSBX<sup>™</sup> BUS SPECIFICATION

All Intel iSBX bus-compatible boards are designed around guidelines set forth in the Intel iSBX BUS SPECIFICATION. The standard requires that certain board operating characteristics, such as data bus width and employment of interlocked operation, be clearly stated in the board's printed specifications. Used properly, this information quickly summarizes the level of compliance the board bears to the published iSBX BUS SPECIFICATION. It clearly states the board's level of compatibility to the iSBX bus structure. Refer to the iSBX BUS SPECIFICATION for additional information.

The following notation states the iSBC 186/03 board's level of compliance to the iSBX BUS SPECIFICATION:

#### D16/16 DMA

This notation is decoded as follows:

- The DMA indicates that the board supports DMA operations to an iSBX bus connector.

- The D16/16 means that the 16-bit CPU board can interface to either an 8-bit or a 16-bit expansion module.

#### 1.8 COMPLIANCE LEVEL: INTEL iLBX™ BUS SPECIFICATION

All Intel iLBX bus-compatible boards are designed around guidelines set forth in the Intel iLBX BUS SPECIFICATION. The standard requires that certain board operating characteristics, such as data bus width, address path width, and other characteristics, be clearly stated in the board's printed specifications (i.e., reference manual). Used properly, this information quickly summarizes the level of compliance the board bears to the published iLBX BUS SPECIFICATION. It clearly states the board's level of compatibility to the iLBX bus structure. Refer to the iLBX BUS SPECIFICATION for additional information.

The following notation states the iSBC 186/03 board's level of compliance to the iLBX BUS SPECIFICATION:

PM D16

This notation is decoded as follows:

PM Primary Master device D16 A 16-bit data path

For additional iLBX bus timing requirements and specifications, refer to the iLBX bus section in Chapter 2.

### **1.9** SPECIFICATIONS

Specifications of the iSBC 186/03 board are provided in Table 1-1.

| CPU                             | Intel iAPX 186 CPU (referred to as the 80186)                                                                                                                                                                                                                                      |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | inter this 100 ord (referred to as the 60100)                                                                                                                                                                                                                                      |

| WORD SIZE                       |                                                                                                                                                                                                                                                                                    |

| Instruction:                    | 8, 16, 24, or 32 bits                                                                                                                                                                                                                                                              |

| Data:                           | 8 to 16 bits                                                                                                                                                                                                                                                                       |

| Address:                        | 20 bits - 1M byte address mode<br>24 bits - 16M byte Address mode                                                                                                                                                                                                                  |

| SYSTEM CLOCK SPEED              | 6.0 MHz, 167 nanoseconds period                                                                                                                                                                                                                                                    |

| BASIC INSTRUCTION<br>CYCLE TIME | <pre>l microsecond 333 nanoseconds (assumes instruction in the queue). Note: Basic instruction cycle is defined as the fastest instruction time (i.e., two clock cycles plus instruction fetch). Zero wait-state memory is assumed.</pre>                                          |

| LOCAL MEMORY ARRAY              |                                                                                                                                                                                                                                                                                    |

| On-board Memory:                | Eight 28-pin JEDEC-compatible, byte-wide<br>sockets hold user-provided memory devices in<br>2k x 8, 8k x 8, 16k x 8, 32k x 8, or 64k x 8<br>capacity. Four sockets are dedicated to<br>EPROM or EEPROM memory; four sockets may be<br>used for EPROM, EEPROM, NVRAM or RAM memory. |

| Maximum EPROM Memory:           | 256K-bytes (maximum in four sockets); or<br>512K-bytes in eight sockets if on-board RAM<br>is not required.                                                                                                                                                                        |

| Maximum RAM Memory:             | 32k bytes (maximum in 4 sockets). Optional<br>iSBC 341 Memory Expansion MULTIMODULE board<br>increases RAM capacity to 64K-bytes.                                                                                                                                                  |

| Maximum System Memory:          | 16 Megabytes                                                                                                                                                                                                                                                                       |

| MEMORY ACCESS TIMES             | Refer to Appendix D                                                                                                                                                                                                                                                                |

| DEFAULT MEMORY ADDRESSING       | Hexidecimal notation                                                                                                                                                                                                                                                               |

| On-Board RAM<br>On-Board ROM    | 00000 - 01FFF (four 2K x 8 RAMS)<br>F8000 - FFFFF (four 8K x 8 PROMS)                                                                                                                                                                                                              |

Table 1-1. iSBC® 186/03 Board Specifications

Table 1-1. iSBC<sup>®</sup> 186/03 Board Specifications (continued)

```

ON-BOARD I/O ADDRESSING

Hexidecimal notation

iAPX 186 Internal Register Base

FF00

Address

iSBX Connector J7 ( 8-bit board)

80 - 9E Even Bytes or Word

iSBX Connector J7 (16-bit board)

80 - \delta E Even Bytes or Word

81 - 8F Odd Bytes Only

iSBX Connector J6 ( 8-bit board)

A0 - BE Even Bytes or Word

iSBX Connector J6 (16-bit board)

AO - AE Even Bytes or Word

Al - AF Odd Bytes Only

SBX Opt MDACK

D2 (Byte or word)

SBX 1 MDACK

D4 (Byte or word)

SBX 2 MDACK

D6 (Byte or word)

CO ICW1, OCW2, OCW3,

Slave Interrupt Controller (8259)

Status, & Poll (Bytes only)

C2 ICW2, ICW3, ICW4, OCW1 &

Masks (Bytes only)

Parallel Interface (8255)

C8 PPI Port A (Bytes)

CA PPI Port B (Bytes)

CC PPI Port C (Bytes)

CE PPI Control (Bytes)

16MB Window Latch

DO (Byte, write only)

Serial Interface (8274)

CH A Data

D8 (Bytes)

DA (Bytes)

CH B Data

CH A Control/Status

DC (Bytes)

CH B Control/Status

DE (Bytes)

80130 I/O Addresses

Master Interrupt Controller

EO - E2 (Byte access only)

E8 (Byte access only)

System Timer

Delay Timer

EA (Byte access only)

Baud Rate Timer

EC (Byte access only)

Timer Control

EE (Byte access only)

```

Table 1-1. iSBC® 186/03 Board Specifications (continued)

Special DMA Registers

DRQ MUX PAL Sel 0F0 - F1 (Byte access only)DRQ MUX PAL Sel 1F2 - F3 (Byte access only)DRQ MUX PAL Sel 2F4 - F5 (Byte access only)DRQ MUX PAL TDMAF6 (Byte access only)ReservedF7 - FF (Byte access only)

INTERFACES

| MULTIBUS           | All signals TTL compatible |

|--------------------|----------------------------|

| Parallel I/O       | All signals TTL compatible |

| Interrupt Requests | All signals TTL compatible |

| iSBX bus           | All signals TTL compatible |

| Serial I/O         | RS 232C compatible, DCE    |

|                    | RS422A/449 DCE, DTE        |

I/O CAPABILITY

Parallel:

Serial:

Two serial interfaces using the 8274 MPSC device. Connector Jl is configurable for either RS232C or RS422A/449 operation, Connector J2 is configured for only RS232C operation.

24 programmable I/O lines using one 8255A PPI device; reconfigurable to the new SCSI interface or the Centronics type line

Expansion: Two 16-bit iSBX bus connectors (J6 and J7) providing expansion via addition of 8-bit or 16-bit iSBX MULTIMODULE boards, in increments as follows:

printer interface.

• one single-wide MULTIMODULE board, or

- two single-wide MULTIMODULE boards, or

- one double-wide MULTIMODULE board, or

• one single- and one double-wide MULTIMODULE board

SERIAL COMMUNICATIONS CHARACTERISTICS

Protocols:

Bit-synchronous Byte-synchronous Asynchronous Table 1-1. iSBC® 186/03 Board Specifications (continued)

٦

| Synchronous:                                                                                 | 5 to 8 bit ch<br>synchronizati                            | -                                    |                                |         |          |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------|--------------------------------|---------|----------|

| Asynchronous:                                                                                | 5 to 8 bit ch<br>bits; false s                            |                                      | •                              | •       | top      |

| 8274 Baud Rates:                                                                             |                                                           |                                      |                                |         |          |

| (Reference 6MHz)                                                                             | Synchro-                                                  |                                      | Asynci                         | nronous |          |

| (80130 Clock )                                                                               | nous<br>X1                                                | X1                                   | X16                            | X32     | X64      |

| 750K                                                                                         | 750к                                                      | 750K                                 |                                |         |          |

| 600K                                                                                         | 600K                                                      | 600K                                 |                                | 19.2K   | 9600     |

| 300K                                                                                         | 300K                                                      | 300K                                 | 19 <b>.</b> 2K                 | 9600    | 4800     |

| 153 <b>.</b> 8K                                                                              | 153.8K                                                    | 153 <b>.</b> 8K                      | 9600                           | 4800    | 2400     |

| 76 <b>.</b> 9K                                                                               | 76.9K                                                     | 76 <b>.</b> 9K                       | 4800                           | 2400    | 1200     |

| 38.4K                                                                                        | 38.4K                                                     | 38.4K                                | 2400                           | 1200    | 600      |

| 19 <b>.</b> 2K                                                                               | 19.2K                                                     | 19.2K                                | 1200                           | 600     | 300      |

|                                                                                              | 9600                                                      | 9600                                 | 600                            | 300     | 150      |

|                                                                                              | 4800                                                      | 4800                                 | 300                            | 150     |          |

|                                                                                              | 2400                                                      | 2400                                 | 150                            | 75      |          |

|                                                                                              | 1200<br>600                                               | 1200<br>600                          | 75<br>                         |         |          |

| PHYSICAL CHARACTERIS                                                                         | STICS                                                     |                                      |                                |         |          |

| Width                                                                                        | 12.00 in                                                  | . (30.48 d                           | ( m .                          |         |          |

| Length                                                                                       |                                                           | . (17.91 d                           |                                |         |          |

| Thickness                                                                                    |                                                           | (1.27)                               |                                |         |          |

|                                                                                              |                                                           | •                                    | •                              |         |          |

| Weight                                                                                       | 13.0 oz.                                                  | (369 gram                            | ns)                            |         |          |

| Weight                                                                                       |                                                           | (369 gra                             | ns)                            |         |          |

| -                                                                                            | CTERISTICS                                                |                                      |                                |         |          |

| ENVIRONMENTAL CHARA                                                                          | CTERISTICS<br>32°F to                                     | 131°F (0°0                           | C to 55°                       | •       |          |

| ENVIRONMENTAL CHARA                                                                          | CTERISTICS<br>32°F to                                     |                                      | C to 55°                       | •       | (INIMUM) |

| ENVIRONMENTAL CHARAG                                                                         | CTERISTICS<br>32°F to<br>200 line                         | 131°F (0°0                           | C to 55°<br>• air ve           | •       | 1INIMUM) |

| ENVIRONMENTAL CHARAG<br>Operating:<br>Temperature<br>Air Flow<br>Humidity:<br>Non-Operating: | CTERISTICS<br>32°F to<br>200 line<br>0 to 95%             | 131°F (O°c<br>ar ft/min<br>non-condo | C to 55°<br>• air ve           | •       | IINIMUM) |

| ENVIRONMENTAL CHARAG<br>Operating:<br>Temperature<br>Air Flow<br>Humidity:                   | CTERISTICS<br>32°F to<br>200 line<br>0 to 95%<br>-40° C t | 131°F (0°¢<br>ar ft/min              | C to 55°<br>• air ve<br>ensing | •       | (INIMUM) |

Table 1-1. iSBC® 186/03 Board Specifications (continued)

Power Requirements Maximum Heat Dissipation 57.5 Watts 818.5 gcal/minute (3.31 Btu/minute)

ELECTRICAL CHARACTERISTICS

DC Power Requirements:

| Supply Volt                              | e Curre                                                                |

|------------------------------------------|------------------------------------------------------------------------|

| +5V +5% (r<br>+12V +5% (r<br>-12V +5% (r |                                                                        |

| Notes: 1.<br>2.                          | 2 volts is r<br>terface.<br>lues are for<br>thout memory<br>LTIMODULE. |

\*\*\*

.

#### CHAPTER 2. BOARD OPERATION AND CONFIGURATION

### 2.1 INTRODUCTION

In order for you to successfully use the iSBC 186/03 Single Board Computer, you must understand how to configure each of the functions on your board. This chapter describes the jumper configuration of each function and any relevant interfacing information.

The functional topics covered in this chapter are presented in this order:

- CPU and Support Circuitry Configuration

- Memory Configuration

- Direct Memory Access (DMA)

- iLBX Bus Interface P2

- Interrupts

- Timers

- Parallel I/O Interface J3

- Serial I/O Interfaces J1 and J2

- iSBX Bus Interfaces J6 and J7

- MULTIBUS Interface P1

- Front Panel Interface J4

Appendix A of this manual provides a jumper location diagram and two jumper lists: a numerical listing of all jumpers on the iSBC 186/03 board, and a list of the default jumper configuration of the board.

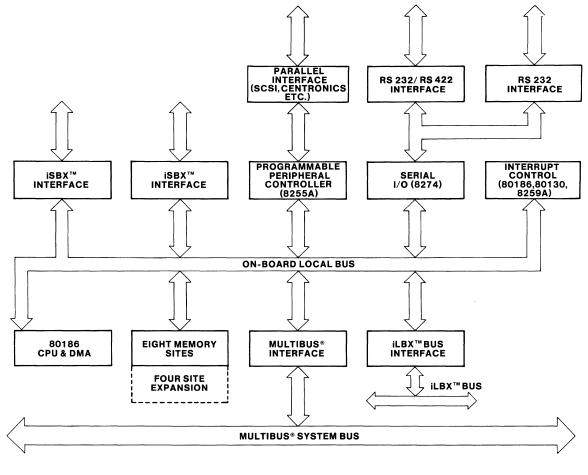

Figure 2-1 shows a block diagram of the various functions on the board. The following paragraphs describe the configurations available for each functional area.

### 2.2 CPU AND SUPPORT CIRCUITRY CONFIGURATIONS

The iSBC 186/03 board provides several configuration options used to configure the operation of the CPU and its support circuits. Those options are as follows:

- Wait-state selection

- CPU timer selection

- CPU DMA operation

- CPU Slave Interrupt Controller

- CPU Clock Speed

1729

Figure 2-1. Block Diagram

### 2.2.1 WAIT-STATES FOR ON-BOARD RESOURCES

The iSBC 186/03 board generates wait states to extend CPU operation until the current on-board access (either memory or I/O) is complete. The iSBC 186/03 board allows you to individually configure the number of wait-states (zero, one, or two) for each memory bank (A and B). Refer to Appendix D for timing requirements for wait states of various memory types.

You cannot configure the wait-states for on-board I/O accesses on the iSBC 186/03 board; an on-board I/O operation requires a minimum of one wait-state. However, iSBX bus I/O wait-states can be extended with the iSBX bus MWAIT\* signal.

Normally, an iLBX bus access requires a minimum of one wait state, provided the iLBX bus timing response meets the specification outlined in Table 2-9. A special mode allows the iLBX bus interface to run at zero wait-states if an iSBC 428 memory board is used with static RAM.

### 2.3 MEMORY CONFIGURATION

This section provides the information needed to partition the memory resources addressable by the iSBC 186/03 board. One of the first tasks is to determine the memory requirements needed for your particular application. You need to consider the amount, speed, type, and size of the memory devices required.

The iSBC 186/03 board provides eight 28-pin, byte-wide sockets into which various memory devices can be installed. These eight sockets on the iSBC 186/03 board are partitioned into two banks: Bank A and Bank B. A jumper configurator block (one for each bank) defines the type and size of the memory device installed. Each bank (four sockets) may be configured for the device type and size required by installing the configurator block push-on jumpers. These configuration blocks allow all sockets to be compatible with ROM, PROM, EPROM, SRAM, EEPROM, or NVRAM devices (see the "Allowable Memory Device Types" section, following), and the four Bank A sites are also compatible with iRAMs. However, there are restrictions on which devices can be mixed in a bank and which devices are supported by the decode logic.

The following paragraphs provide configuration information for the memory space on the iSBC 186/03 board. The information is presented in the following sequence:

- MEMORY MAP (DEFAULT CONFIGURATION)

- CONFIGURATION OVERVIEW

- 16M BYTE MODE

- BANK A MEMORY CONFIGURATION

- BANK B MEMORY CONFIGURATION

- 80130 MEMORY CONFIGURATION

- Battery Backup

- Using NVRAMs

#### 2.3.1 MEMORY MAP (DEFAULT CONFIGURATION)

As shipped, the iSBC 186/03 board allows installation of four 2K x 8 SRAM devices in sockets U42/U75 and U43/U76 and installation of four 8K x 8 EPROM devices in sockets U40/U73 and U41/U74. AC and DC memory requirements are listed in Appendix D. The default address range assigned to the 8K-bytes of static random access memory (SRAM) devices is from 00000H to 01FFFH. The default address range assigned to the 32K-bytes of Read Only Memory (ROM) devices is from F8000H up to FFFFFH. (Note that when only two EPROMS are used, they must are installed in sockets U41/U74).

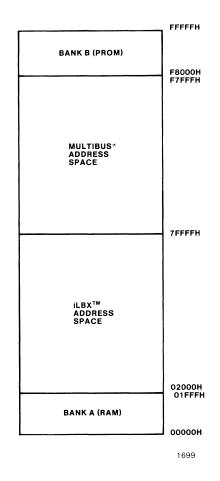

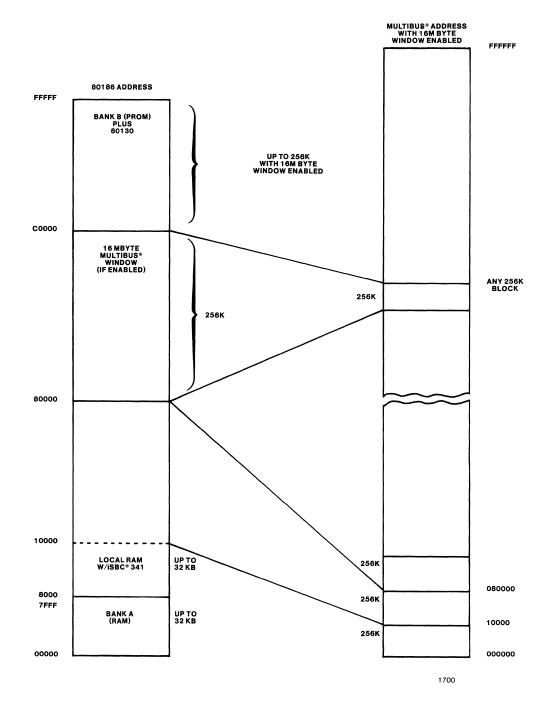

In the default configuration the iSBC 186/03 board assigns the iLBX address range immediately above the Bank A address space from 02000H to 7FFFFH and the MULTIBUS System Bus address resource beginning at 80000H and going up to the bottom of PROM memory. Figure 2-2 shows the default iSBC 186/03 memory map.

Bank A is an on-board memory resource and is typically assigned to the lower portion of memory for RAM devices. Bank B is an on-board memory resource and is assigned to the upper portion of memory for program storage. The 16k bytes of 80130 memory is another on-board resource and is located just below Bank B (PROM) memory, but is disabled in the as-shipped configuration. The MULTIBUS memory is an off-board resource and involves bus arbitration before access is permitted. The iLBX bus memory is an off-board resource but appears to the CPU as local on-board memory.

#### Default Address Range

| Bank A (RAM) Address Space (U42/U75)           | 000000H-000FFFH   |

|------------------------------------------------|-------------------|

| Bank A (RAM) Address Space (U43/U76)           | 001000H-001FFFH   |

| Bank B (PROM) Memory Address Space At U40/U73: | OF8000H-OFBFFFH   |

| Bank B (PROM) Memory Address Space At U41/U74: | OFCOOOH-OFFFFFH   |

| iLBX Bus Interface Address Space:              | 002000H-07FFFFH** |

\*\* Bank A RAM address space overlays the iLBX bus address space so that iLBX bus memory starts immediately above the Bank A address space.

Figure 2-2. Default Memory Map

#### 2.3.2 OVERVIEW OF THE MEMORY CONFIGURATION OPTIONS

The iSBC 186/03 board provides you with configuration control features for the memory space on the board. You can configure the Banks (Bank A and Bank B) as two independent memory address spaces depending on how you configure the jumper matrices for the sockets. Your configuration of the iLBX memory depends on the operation of the iLBX bus memory boards.

The similarities between the Bank A and Bank B memory configuration options are:

- 1. A standard jumper matrix format for selecting a device type.

- 2. 28-pin JEDEC sockets for the 24 or 28-pin memory devices.

- 3. Wait-state selection.

The major differences between the Bank A and Bank B memory configuration options are:

- 1. Bank A supports iRAM, SRAM, EPROM, EEPROM, or NVRAM devices.

- 2. One iSBC 341 expansion board for Bank A; none for Bank B.

- 3. Bank B supports ROM, PROM, EPROM, or EEPROM devices only.

- 4. Bank B must be assigned to upper memory.

- 5. Bank A could be assigned to either lower (typical) or upper memory residing below the assigned memory space for Bank B.

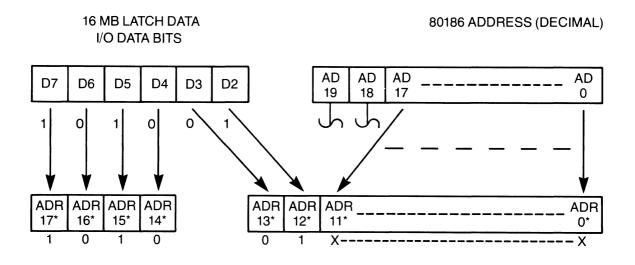

#### 2.3.3 16M-BYTE MODE

The iSBC 186/03 board can be configured for either 1 Mbyte or 16 Mbyte address space. The 80186 device on the iSBC 186/03 board is only capable of addressing 1 Mbyte. However, a paging technique is used to access up to 16 Mbytes (using a latch at I/O address 00D0H). To enable the 16 Mbyte addressing, you must install a jumper between E40 and E41. The 16 Mbyte addressing is then accomplished by writing the upper six bits of the 16 Mbyte address to the latch at I/O address 00D0H. The 16 Mbyte address space is then accessed by issuing the corresponding address (excluding the upper two bits in the 1 Mbyte address) within the third 256 Kbyte page of the 80186 address space (80000H through BFFFFH). The iSBC 186/03 board automatically places 24 bits of the address onto the P1 and the P2 connectors. If no other board provides termination for the upper four address lines, then a 2.2K ohm resistor must be installed in socket RP13 on the iSBC 186/03 board. Refer to Chapter 4 for more details on programming the 16M byte address mode.

#### 2.3.4 LOCAL MEMORY CONFIGURATION

This section of the manual describes options that are available to you in configuring the local and iLBX bus memory resources on the iSBC 186/03 board. You need an understanding of this information if you do not wish to use the memory on the board in the as-shipped configuration.

The following paragraphs present information on the local memory configuration in this order:

- Description of the sockets

- Allowable device type mixtures

- Overview of the configuration sequence

- Details of the configuration sequence

## 2.3.4.1 Local Memory Socket Pair Descriptions

The design of the iSBC 186/03 board is such that it allows you to partition the local memory into two pieces and configure each piece independently.

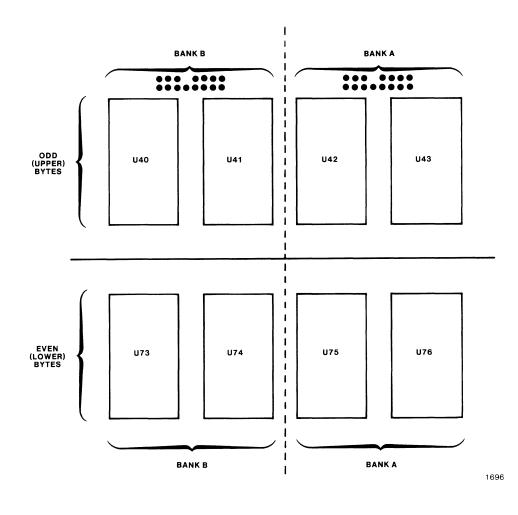

Figure 2-3 shows the partitioning of the Bank B memory sockets and their relative positions as they appear on the iSBC 186/03 board. Sockets U40 and U73 are a socket set, referred to as pair U40/U73; sockets U41 and U74 are a set, referred to as pair U41/U72.

Bank B memory socket pairs U40/U73 and U41/U74 are always located at upper memory. These sockets are intended for EPROM or EEPROM that contains the program for a power-up sequence, such as the Intel iSDM 86 Monitor.

Bank A memory socket pairs U42/U75 and U43/U76, on the other hand, are moveable within the memory map; you can either assign the memory to the lower portion of memory starting at address OH, or you can locate it immediately below socket pairs U40/U73 and U41/U74 to provide more EPROM space.

### 2.3.4.2 Allowable Memory Device Types (Bank A and Bank B)

An array of stake pins is provided for each bank of four sockets to configure the banks for different device types. In the PROM bank (Bank B), all sockets must be populated with the PROM/EPROM/EEPROM devices for program storage. In the RAM bank (Bank A), each pair of sockets must be populated with the same devices, and devices may be mixed between pairs of iRAM, SRAM, EEPROM, and NVRAM devices as represented by an "X" in Table 2-1 (See note below when using EEPROM or NVRAM devices). All address ranges for each socket pair in the PROM bank are the same size, and all address ranges for each socket pair in the RAM bank are the same size.

|                                                                                                                                                                                                                | SRAM<br>4K, 8K, 16K | SRAM<br>32K | iRAM<br>3K, 16K | EEPROM+<br>2K, 4K<br>8K, 16K | NVRAM<br>1/2K, 1K, 2K<br>4K, 8K |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|-----------------|------------------------------|---------------------------------|--|

| SRAM 4K, 8K,<br>16K                                                                                                                                                                                            |                     | Х           | X               | Х                            | Х                               |  |

| SRAM 32K                                                                                                                                                                                                       | х                   |             | None            | None                         | None                            |  |

| iRAM 8K, 16K                                                                                                                                                                                                   | Х                   | None        |                 | None++                       | None                            |  |

| EEPROM+ 2K,<br>4K, 8K, 16K                                                                                                                                                                                     | Х                   | None        | None++          |                              | None                            |  |

| NVRAM 1/2K,<br>1K, 2K, 4K,<br>8K                                                                                                                                                                               | х                   | None        | None            | None                         |                                 |  |

| Notes: All device sizes are X 8 (byte-wide).<br>+ = "SMART" 2817A type devices only.<br>++ = Timing constraint does not allow EEPROM to be mixed with iRAM.<br>Mixtures are not allowed in Bank B (PROM Bank). |                     |             |                 |                              |                                 |  |

Table 2-1. Allowable Mixtures In Bank A (RAM Bank)

Figure 2-3. Local Memory Socket Pairs and Jumper Matrices

### 2.3.4.3 Memory Configuration Sequence Overview

You can logically step through the entire local memory configuration sequence by performing a series of 4 operations, as follows:

1. Select a memory device type for each Bank. You configure the board for operation with a specific type of memory device by installing or removing jumpers at jumper matrix E131 through E145 for Bank B socket pairs U40/U73 and U41/U74, and E146 through E160 for Bank A socket pairs U42/U75 and U43/U76. Jumper E238-E239 must be installed when using iRAMs in Bank A. The iRAM devices are not allowed in Bank B.

- 2. Select the memory address and memory size for Bank B memory. This is a combination selection that is coordinated by PAL U59, the memory decode PAL. Make the selection by configuring jumper inputs E194 through E197 for the PAL. This selects one of four memory map configurations (see Step 2 below, and Table 2-2) for all of the Bank B memory. If one of these four options does not provide a suitable solution, custom-program a replacement PAL for socket U59 to create your own solution. The source equation for the factory installed PAL is provided in Appendix G.

- 3. Select a memory size and either top or bottom justify Bank A <u>memory</u>. This is another combination selection coordinated by PAL U59. Make the selection by configuring jumper inputs E198 through E203 for the PAL devices (see Step 3 below and Table 2-3). This changes the size of the memory space and determines whether Bank A is bottom-justified (starting at OH) or top-justified (starting immediately below Bank B). The decode options support 2K x 8, 8K x 8, and 32K x 8 RAMs. If one of these options does not provide a suitable application, a custom PAL may be programmed for socket U59.

- 4. Select the number of wait-states required for each socket pair. You select the number of CPU wait-states by configuring jumper E123 through E128. The jumpers provide options from zero to two wait-states at each Bank, depending on the requirements of your memory devices. Refer to Step 4 below.

- 5. Enable or Disable the 80130 memory. To enable the 16K-bytes of memory contained in the 80130, install jumper E204-E205. Refer to table 2-2 and table 2-3 for address ranges. To disable the 80130 memory, remove the jumper.

Subsequent sections provide the details required for each step of the configuration sequence.

STEP 1 - Selecting a Memory Device Type For Each Bank

The jumper matrix for each bank allows all the sockets to be compatible with ROM, PROM, EPROM, EEPROM, static RAM (SRAM), non-volatile RAM (NVRAM), or Intel iRAM devices. However, because the address decoding logic requires Bank B to be used for program storage only, Bank B can only be used for ROM, PROM, EPROM, or EEPROM, unless the decode PROM is actually removed and modified or replaced.

The jumper matrix consists of 15 stake pins arranged in two rows. The pin arrangement is a standard format, as shown in Figure 2-4; the missing pin serves as a key to the orientation of the matrix. Figure 2-4 also lists the signals that are assigned to each pin of the matrix.

There are two of these jumper matrices on the iSBC 186/03 board; one for the Bank A memory socket pairs and one for the Bank B memory socket pairs. Configure each matrix independently for the type of memory device installed. You can mix types within Bank A, providing you use the guidelines set forth in Table 2-1. Mixtures are not allowed in Bank B.

| Address Bit A13           | • • | To pin 26 of 28 pin site |

|---------------------------|-----|--------------------------|

| Address Bit All           | • • | Vcc                      |

| To pin 23 of 28 pin site  | • • | Vcc                      |

| Write Enable Signal WE*   | • • | To pin 27 of 28 pin site |

| Missing pin (key)         | •   | Al4 Address Bit          |