| REV. | <b>REVISION HISTORY</b> | PRINT<br>DATE |

|------|-------------------------|---------------|

| -01  | Original Issue          | 1/82          |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The Information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined as ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP            | Insite             | iSBC            | Multibus      |

|----------------|--------------------|-----------------|---------------|

| CREDIT         | Intel              | iSBX            | Multimodule   |

| i              | int <sub>e</sub> l | Library Manager | Plug-A-Bubble |

| ICE            | Intelevision       | MCS             | PROMPT        |

| iCS            | Intellec           | Megachassis     | RMX/80        |

| <sup>i</sup> m | iOSP               | Micromainframe  | System 2000   |

| iMMX           | iRMX               | Micromap        | UPI           |

PREFACE

This manual provides general information, installation and setup instructions, programming guidelines for the on-board, programmable devices, board level principles of operation, and service information for the iSBC 86/14 and iSBC 86/30 Single Board Computers. Related information is provided in the following publications:

| Manual                                                                        | Number  |

|-------------------------------------------------------------------------------|---------|

| The 8086 Family User's Manual                                                 | 9800722 |

| iSBC <sup>m</sup> Applications Manual                                         | 142687  |

| Intel Multibus" Specification                                                 | 9800683 |

| Intel Multibus <sup>™</sup> Interfacing, Application Note                     | AP-28A  |

| MCS-86 Assembly Language Programming Manual                                   | 9800640 |

| PL/M 86 Programming Manual                                                    | 9800466 |

| Intel iSBX <sup>m</sup> Bus Specification                                     | 142686  |

| Designing iSBX <sup>m</sup> Multimodule <sup>m</sup> Boards, Application Note | AP-96   |

| Using the iRMX <sup>m</sup> 86 Operating System, Application Note             | AP-86   |

| Intel Component Data Catalog                                                  |         |

| The 8086 Primer, by Stephen P. Morse. Hayden Book Company, Inc.,              |         |

| Rochelle Park, N.J., 1980. ISBN: 0-8104-5165-4                                |         |

#### NOTE TO READERS

This hardware reference manual utilizes a visual scheme to denote section levels, rather than a numerical scheme used in many technical documents. This visual scheme allows you to more readily identify which section headings are sub-sections. The visual distinction among the different sizes used in the paragraph headings indicates what level or order a particular paragraph occupies. The following example illustrates how this system is used in this manual:

| 3-27. | 8259A PIC PROGRAMMING    | lst | Order | Heading |

|-------|--------------------------|-----|-------|---------|

| 3-28. | INTERRUPT PRIORITY MODES | 2nd | 0rder | Heading |

| 3-29. | Fully Nested Mode        | 3rd | 0rder | Heading |

By glancing through this manual before you start reading, the visual method of paragraph ordering should be apparent. You may also refer to the Contents on page iv, to see how the paragraph levels compare to each other.

This manual documents both the iSBC 86/14 Single Board Computer and the iSBC 86/30 Single Board Computer. The design and operation of the two boards is similar enough to allow doing so. Throughout the manual, the title of the two boards has been condensed to be, simply, the iSBC 86/14/30 board. Where this type of name occurs, you may assume that the boards are operating identically. Where the two boards do not operate identically, their names are separated and the descriptions of their operation are also separated.

## CONTENTS

iv

| CHAPTER 1<br>GENERAL INFORMATION          | 8   |

|-------------------------------------------|-----|

| 1-1. Introduction                         | 1-1 |

| 1-2. Description                          | 1-2 |

| 1-3. Optional RAM and ROM/EPROM Expansion | 1-7 |

| 1-4. System Software Development          | 1-7 |

| 1-5. Equipment Supplied                   |     |

| 1-6. Equipment Required                   | 1-8 |

| 1-7. Specifications                       | 1-8 |

## CHAPTER 2

| PREPARATION FOR USE                                        |     |

|------------------------------------------------------------|-----|

| 2-1. Introduction                                          | 2-1 |

| 2-2. Unpacking And Inspection                              | 2-1 |

| 2-3. Installation Considerations                           | 2-1 |

| 2-4. Power Requirements                                    | 2-2 |

| 2-5. Cooling Requirements                                  | 2-2 |

| 2-6. Physical Dimensions                                   | 2-2 |

| 2-7. User-Furnished Components                             | 2-2 |

| 2-8. User-Furnished Component Installation                 | 2-7 |

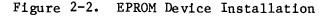

| 2-9. EPROM Device Installation                             | 2-8 |

| 2-10. Line Driver Installation                             | 2-1 |

| 2-11. Jumper/Switch Configuration                          | 2-1 |

| 2-12. RAM Address Configuration Jumpers                    | 2-2 |

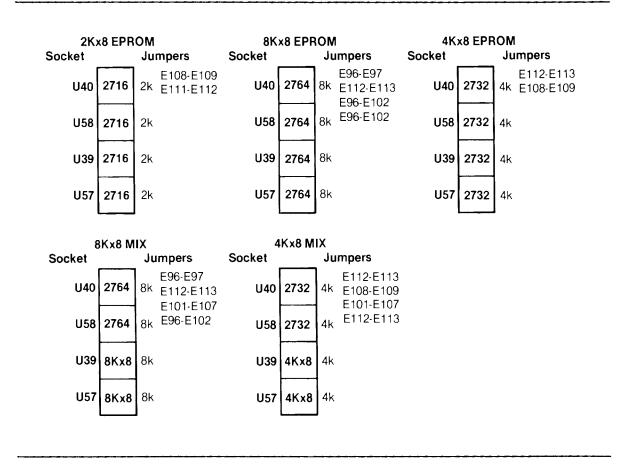

| 2-13. iSBC 86/14 Board RAM Address Configuration           | 2-2 |

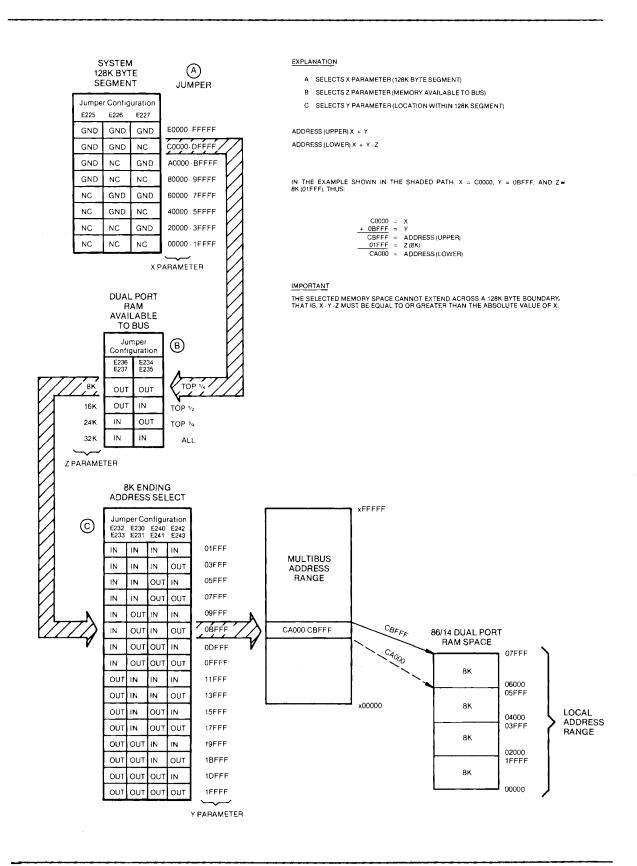

| 2-14. iSBC 86/30 Board RAM Address Configuration           | 2-2 |

| 2-15. Dual Port RAM Size Selection                         | 2-3 |

| 2-16. Size Select For iSBC 86/14 Board                     | 2-3 |

| 2-17. Size Select For iSBC 86/30 Board                     | 2-3 |

| 2-18. Ready Circuitry Jumper Configuration                 | 2-3 |

| 2-19. 8253-5 PIT Jumper Configuration                      | 2-3 |

| 2-20. 8255A PPI Jumper Configuration                       | 2-3 |

| 2-21. 8259A PIC and Interrupt Jumper Configuration         | 2-4 |

| 2-22. Multibus Vectored Interrupts                         | 2-4 |

| 2-23. 8251A PCI and Serial Interface Jumper Configurations | 2-4 |

| 2-24. Failsafe Timer Jumper Configuration                  | 2-4 |

| 2-25. Status Register Jumper Configurations                | 2-4 |

| 2-26. iSBX Bus Interface Jumper Configuration              | 2-4 |

| 2-27. Multibus Interface Jumper Configuration              | 2-4 |

| 2-28. Bus Arbitration Jumper Configurations                | 2-4 |

| 2-29. Multibus Interface Specifications                    | 2-5 |

| 2-30. Signal Characteristics                               | 2-5 |

| 2-31. Multibus Priority Resolution                         | 2-6 |

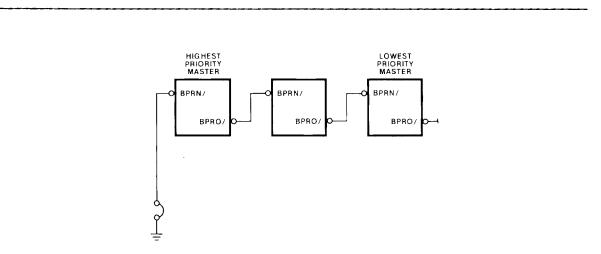

| 2-32. Serial Priority Resolution                           | 2-6 |

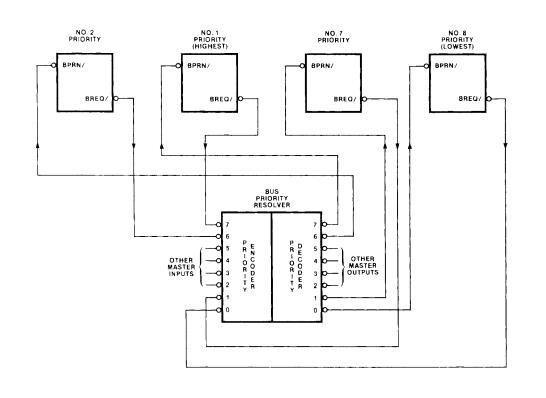

| 2-33. Parallel Priority Resolution                         | 2-6 |

| 2-34. Auxiliary (P2) Interface Specifications              | 2-6 |

# Page

|                                                           | Page |

|-----------------------------------------------------------|------|

| CHAPTER 2 (continued)                                     |      |

| 2-35. Parallel I/O Interface                              | 2-68 |

| 2-36. Parallel I/O Cabling Requirements                   | 2-69 |

| 2-37. Serial I/O Interface                                | 2-70 |

| 2-38. Serial I/O Cabling Requirements                     | 2-70 |

| 2-39. Current Loop (TTY) Interface                        | 2-72 |

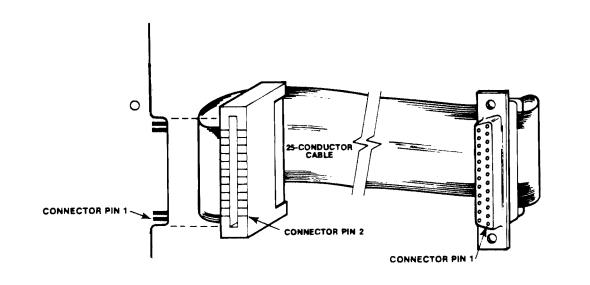

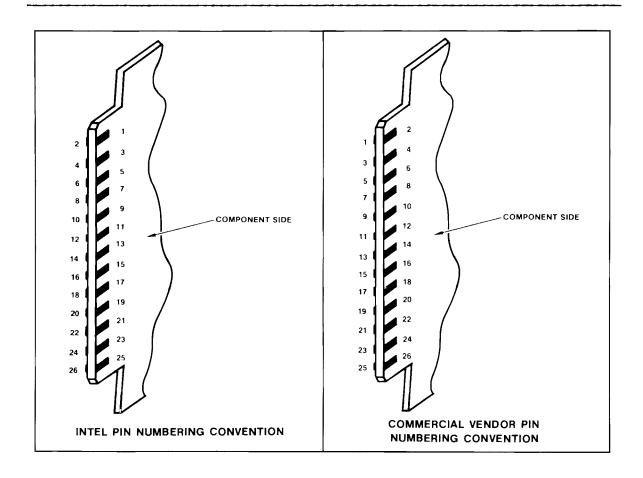

| 2-40. Connector Pin Numbering Information                 | 2-73 |

| 2-41. iSBX Bus Interface                                  | 2-73 |

| 2-42. Power Fail Battery Backup Provisions                | 2-76 |

| 2-43. iSBC Multimodule Board Installation                 | 2-77 |

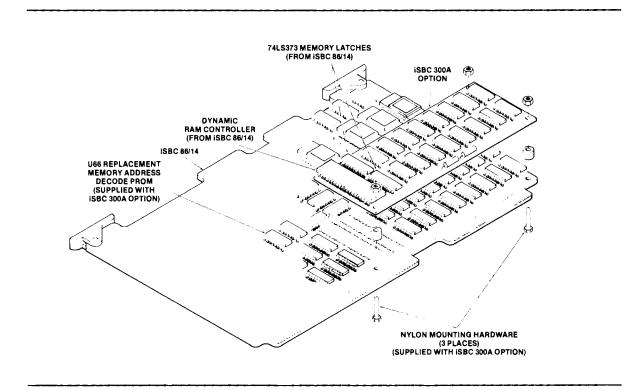

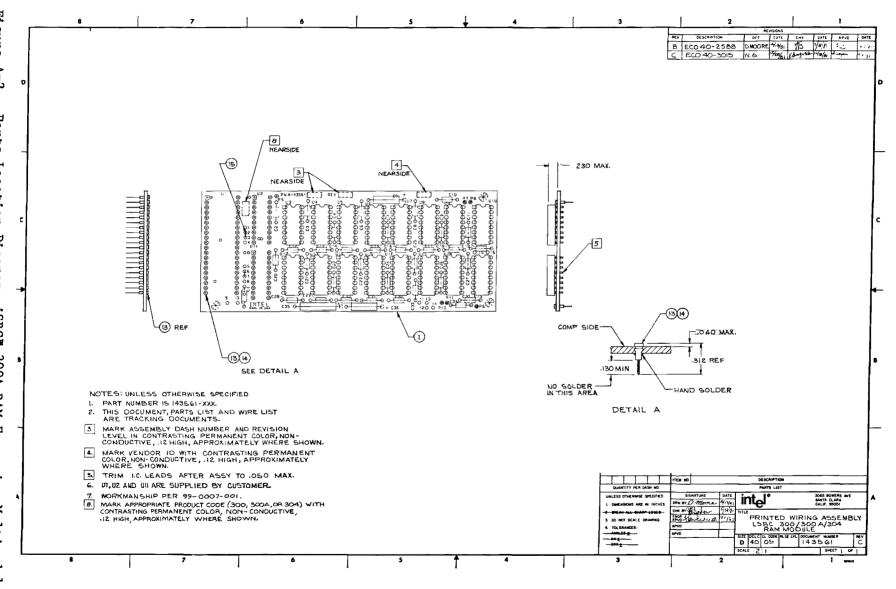

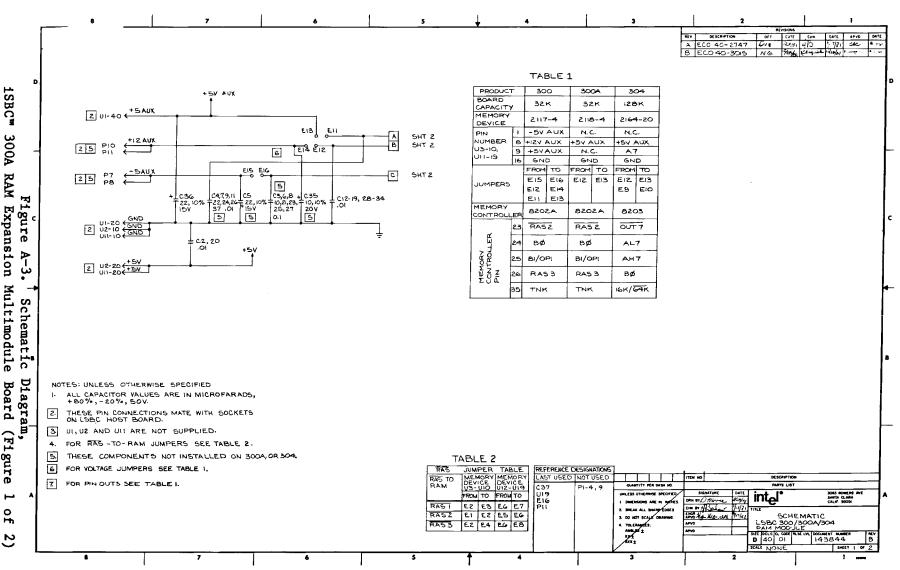

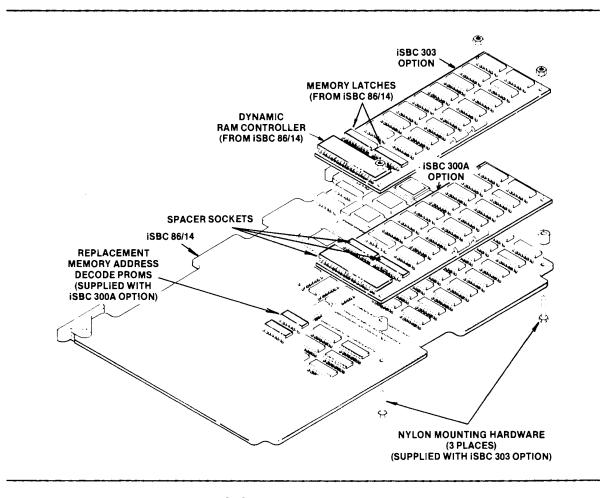

| 2-44. iSBC 300A RAM Expansion Multimodule Board           | 2-77 |

| 2-45. iSBC 304 RAM Expansion Multimodule Board            | 2-77 |

| 2-46. iSBC 337 Numeric Data Processor                     | 2-78 |

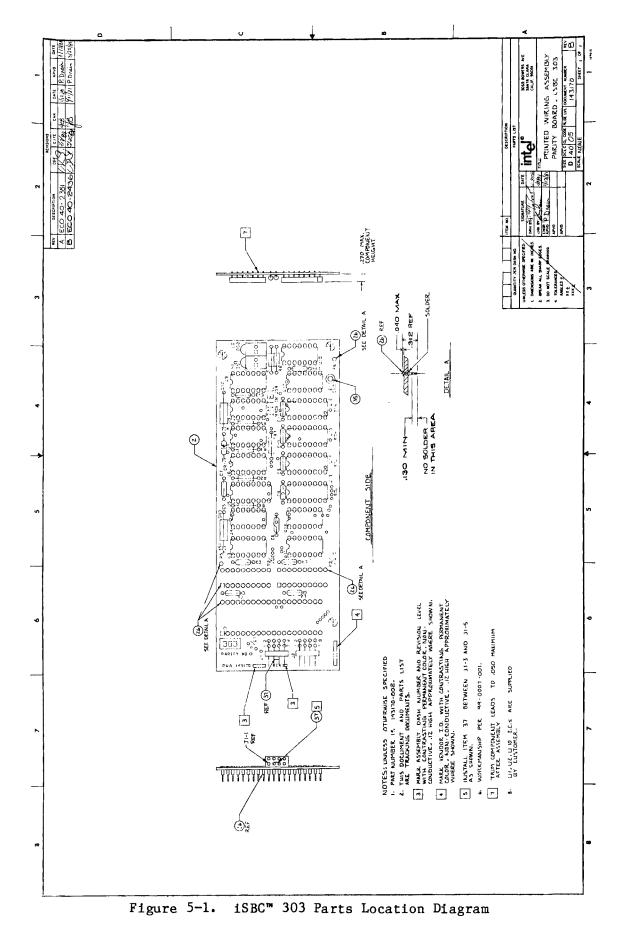

| 2-47. iSBC 303 Parity Generator/Checker Multimodule Board |      |

| Installation                                              | 2-78 |

| 2-48. iSBX Multimodule Board Installation                 | 2-78 |

| 2-49. iRMX 86 System Software                             | 2-80 |

| 2-50. Final Installation                                  | 2-81 |

## CHAPTER 3

| PROGRAMMING INFORMATION                              |       |

|------------------------------------------------------|-------|

| 3-1. Introduction                                    | 3-1   |

| 3-2. Memory Addressing                               | 3-1   |

| 3-3. iSBC 86/14 Board Memory Addressing              | 3-1   |

| 3-4. iSBC 86/30 Board Memory Addressing              | 3-3   |

| 3-4. I/O Addressing                                  | 3-3   |

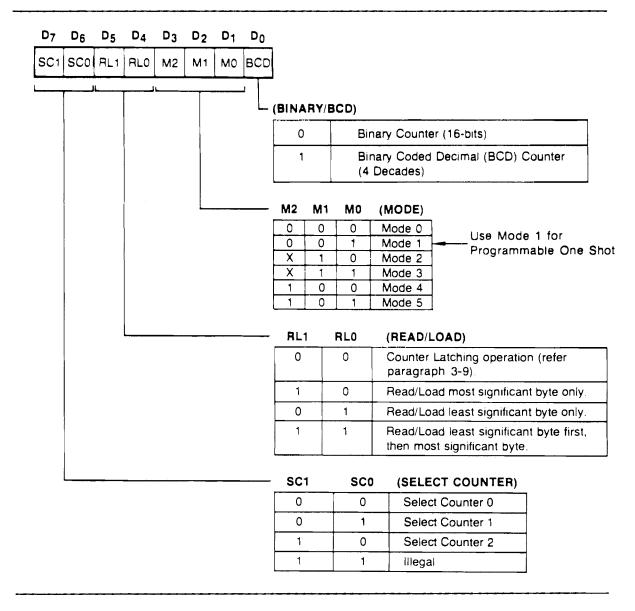

| 3-5. 8253-5 Pit Programming                          | 3-8   |

| 3-6. Mode Control Word and Count                     | 3-8   |

| 3-7. Addressing                                      | 3-12  |

| 3-8. Initialization                                  | 3-12  |

| 3-9. Operation                                       | 3-13  |

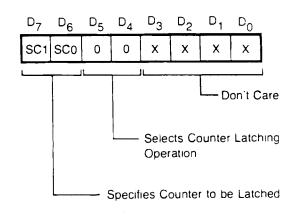

| 3-10. Counter Read                                   | 3-13  |

| 3-11. Clock Frequency/Divide Ratio Selection         | 3-16  |

| 3-12. Rate Generator/Interval Timer                  | 3-16  |

| 3-13. Interrupt Timer                                | 3-17  |

| 3-14. 8251A PCI Programming                          | 3-18  |

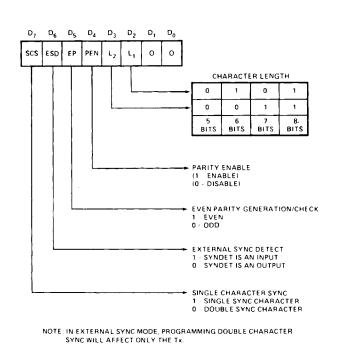

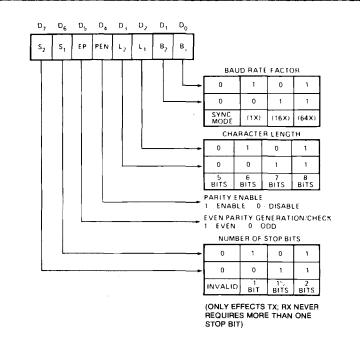

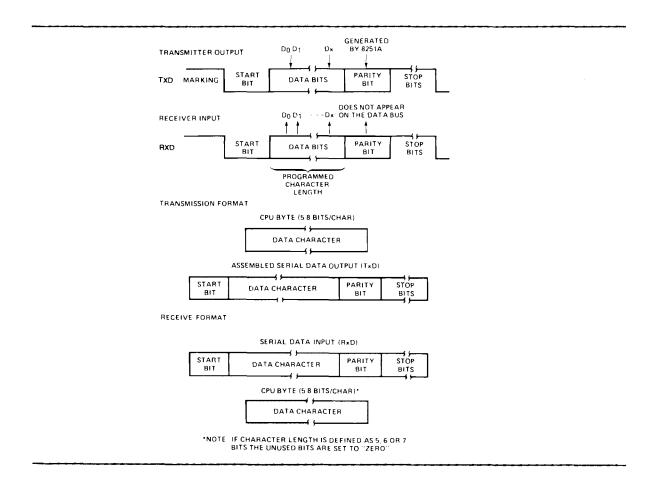

| 3-15. Mode Instruction Format                        | 3-18  |

| 3-16. Sync Characters                                | 3-21  |

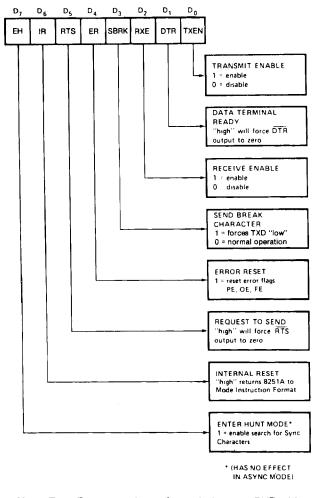

| 3-17. Command Instruction Format                     | 3-21  |

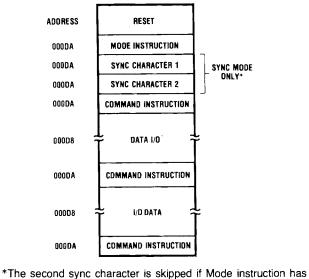

| 3-18. Reset                                          | 3-22  |

| 3-19. Addressing                                     | 3-22  |

| 3-20. Initialization                                 | 3-22  |

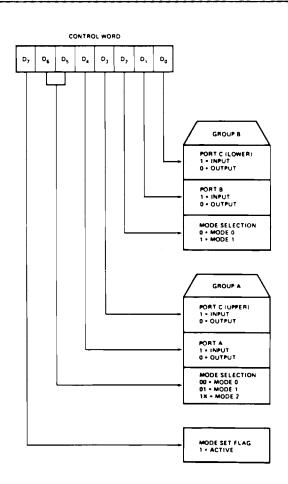

| 3-21. 8255A PPI Programming                          | 3-28  |

| 3-22. Control Word Format                            | 3-29  |

| 3-23. Addressing                                     | 3-29  |

| 3-24. Initialization                                 | 3-30  |

| 3-25. Operation                                      | 3-30  |

| 5 251 operacionititititititititititititititititititi | • • • |

|                                                        | Page |

|--------------------------------------------------------|------|

| CHAPTER 3 (continued)                                  | _    |

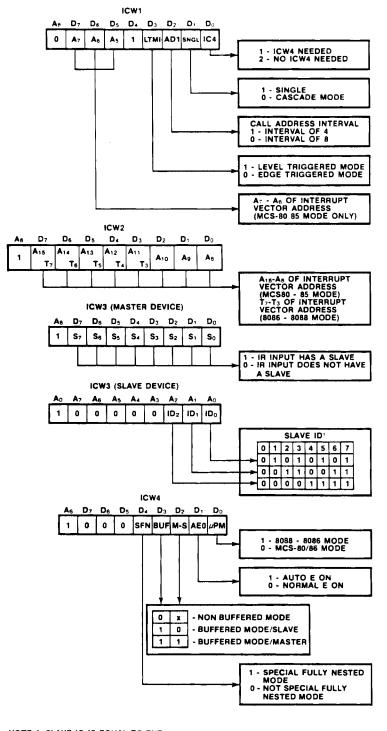

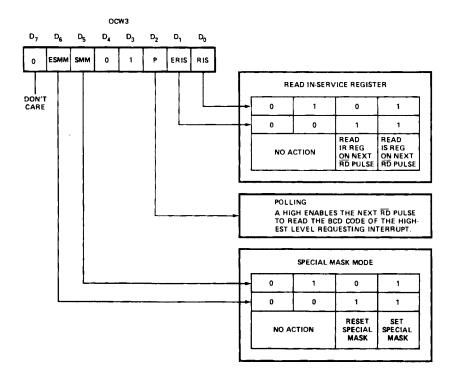

| 3-26. 8259A PIC Programming                            | 3-33 |

| 3-27. Interrupt Priority Modes                         | 3-34 |

| 3-28. Fully Nested Mode                                | 3-34 |

| 3-29. Special Fully Nested Mode                        | 3-34 |

| 3-30. Automatic Rotating Mode                          | 3-35 |

| 3-31. Specific Rotating Mode                           | 3-35 |

| 3-32. Special Mask Mode                                | 3-35 |

| 3-33. Poll Mode                                        | 3-36 |

| 3-34. Status Read                                      | 3-36 |

| 3-35. Initialization Command Words                     | 3-36 |

| 3-36. Operation Command Words                          | 3-41 |

| 3-37. Addressing                                       | 3-41 |

| 3-38. Initialization                                   | 3-41 |

| 3-39. Operation                                        | 3-43 |

| 3-40. 8086-2 Interrupt Handling                        | 3-48 |

| 3-41. Non-Maskable Interrupt (NMI)                     | 3-48 |

| 3-42. Maskable Interrupt (INTR)                        | 3-48 |

| • · · · ·                                              | 3-48 |

| 3-43. Master PIC Byte Identifier                       | 3-49 |

|                                                        | 3-49 |

| 3-45. Status Register Programming                      | 3-50 |

| 3-46. Edge-Triggered Interrupt Sense Latch Programming | 3-30 |

|                                                        |      |

| CHAPTER 4                                              |      |

| PRINCIPLES OF OPERATION                                |      |

| <ul> <li>4-1. Introduction.</li> <li>4-2. Functional Description.</li> <li>4-3. 8086-2 Microprocessor.</li> <li>4-4. On-Board Timing.</li> <li>4-5. Random Access Memory (RAM) Array.</li> <li>4-6. Eraseable Programmable Read Only Memory (EPROM) Array.</li> <li>4-7. Address Decoding.</li> <li>4-8. Memory Address Decoding.</li> <li>4-9. I/O Address Decoding.</li> <li>4-10. Interval Timer.</li> <li>4-11. Serial I/O Control Circuitry.</li> <li>4-12. Parallel I/O control Circuitry.</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>4-3. 8086-2 Microprocessor.</li> <li>4-4. On-Board Timing.</li> <li>4-5. Random Access Memory (RAM) Array.</li> <li>4-6. Eraseable Programmable Read Only Memory (EPROM) Array.</li> <li>4-7. Address Decoding.</li> <li>4-8. Memory Address Decoding.</li> <li>4-9. I/O Address Decoding.</li> <li>4-10. Interval Timer.</li> <li>4-11. Serial I/O Control Circuitry.</li> <li>4-12. Parallel I/O Control Circuitry.</li> </ul>                                                                   |

| <ul> <li>4-4. On-Board Timing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>4-4. On-Board Timing</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>4-5. Random Access Memory (RAM) Array</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>4-6. Eraseable Programmable Read Only Memory (EPROM) Array</li> <li>4-7. Address Decoding</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>4-7. Address Decoding.</li> <li>4-8. Memory Address Decoding.</li> <li>4-9. I/O Address Decoding.</li> <li>4-10. Interval Timer.</li> <li>4-11. Serial I/O Control Circuitry.</li> <li>4-12. Parallel I/O Control Circuitry.</li> </ul>                                                                                                                                                                                                                                                            |

| <ul> <li>4-8. Memory Address Decoding.</li> <li>4-9. I/O Address Decoding.</li> <li>4-10. Interval Timer.</li> <li>4-11. Serial I/O Control Circuitry.</li> <li>4-12. Parallel I/O Control Circuitry.</li> </ul>                                                                                                                                                                                                                                                                                            |

| <ul> <li>4-9. I/O Address Decoding.</li> <li>4-10. Interval Timer.</li> <li>4-11. Serial I/O Control Circuitry.</li> <li>4-12. Parallel I/O Control Circuitry.</li> </ul>                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>4-10. Interval Timer</li> <li>4-11. Serial I/O Control Circuitry</li> <li>4-12. Parallel I/O Control Circuitry</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

| 4-11. Serial I/O Control Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4-12. Parallel I/O Control Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4-13. Interrupt Control and Timing Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4-14. 8203 Dynamic Ram Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4-15. Dual Port Size/Address Decode PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-16. Bus Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4-17. Multibus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-18. iSBX Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-19. Detailed Circuit Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4-20. Power-On Initialization Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4-21. CPU Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

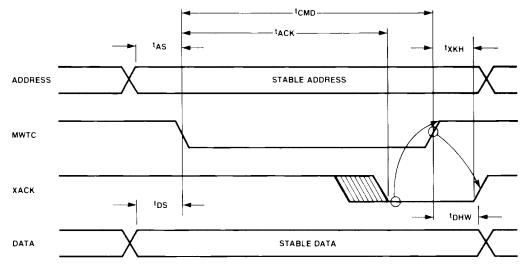

| 4-22. Multibus Data Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4-23. Even Byte Transfer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4-24. Odd Byte (Swap) Transfer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-25. 16-bit Transfer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTER 4 (continued)                                           |

|-----------------------------------------------------------------|

| 4-26. Dual Port RAM Access Control Logic                        |

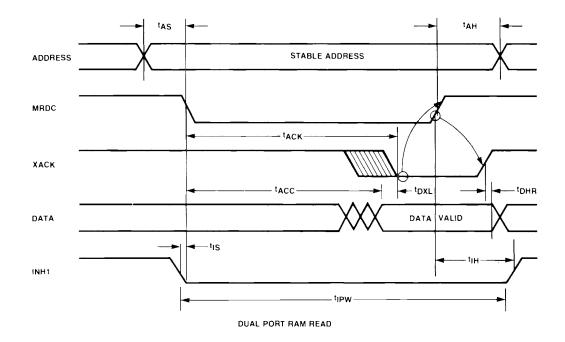

| 4-27. Dual Port RAM Access Operation                            |

| 4-28. Dual Port RAM Access Cycle Without Contention (Not Busy). |

| 4-29. Dual Port RAM Access Cycle With Contention                |

| 4-30. RAM Controller Operation Timing                           |

| 4-31. On-Board EPROM Access Sequence                            |

| 4-32. EPROM READ Operation                                      |

| 4-33. Static RAM WRITE Operation                                |

| 4-34. On-Board I/O Access Operation                             |

| 4-35. iSBX Bus Access Operation                                 |

| 4-36. Typical Local Access to Multibus Resource                 |

| 4-37. Interrupt Operation                                       |

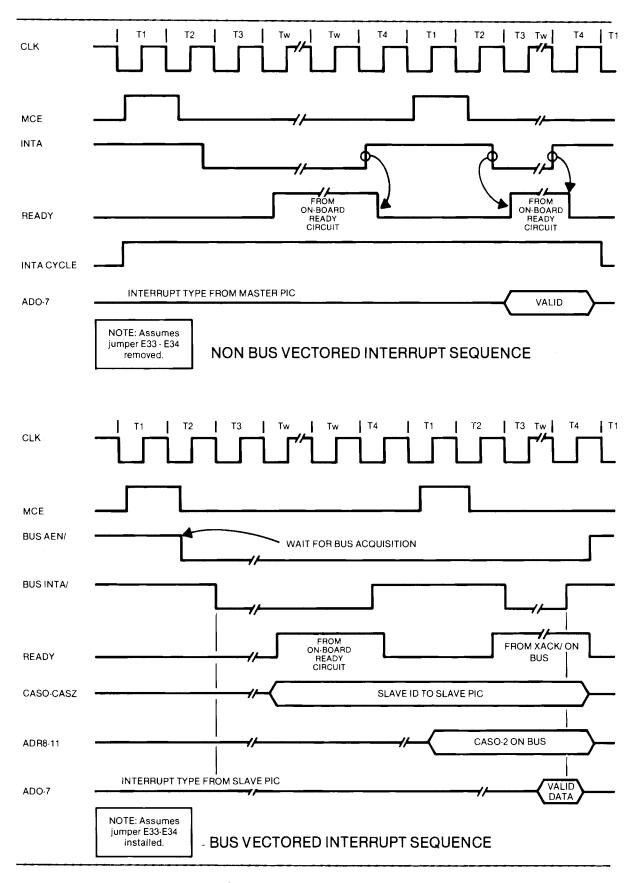

| 4-38. NBV Interrupt Sequence                                    |

| 4-39. BV Interrupt Sequence                                     |

| 4-40. Failsafe Timer Operation                                  |

| 4-41. Chip Select Circuit Operation                             |

| 4-42. I/O Chip Select Operation                                 |

| 4-43. EPROM Chip Select Operation                               |

| 4-44. RAM Chip Select Operation                                 |

| 4-45. Bus Control Operation                                     |

# CHAPTER 5

| SERV | ICE INFORMATION               |     |

|------|-------------------------------|-----|

| 5-1. | Introduction                  | 5-1 |

| 5-2. | Replaceable Parts             | 5-1 |

| 5-3. | Service Diagrams              | 5-1 |

| 5-4. | Service and Repair Assistance | 5-4 |

## APPENDIX A

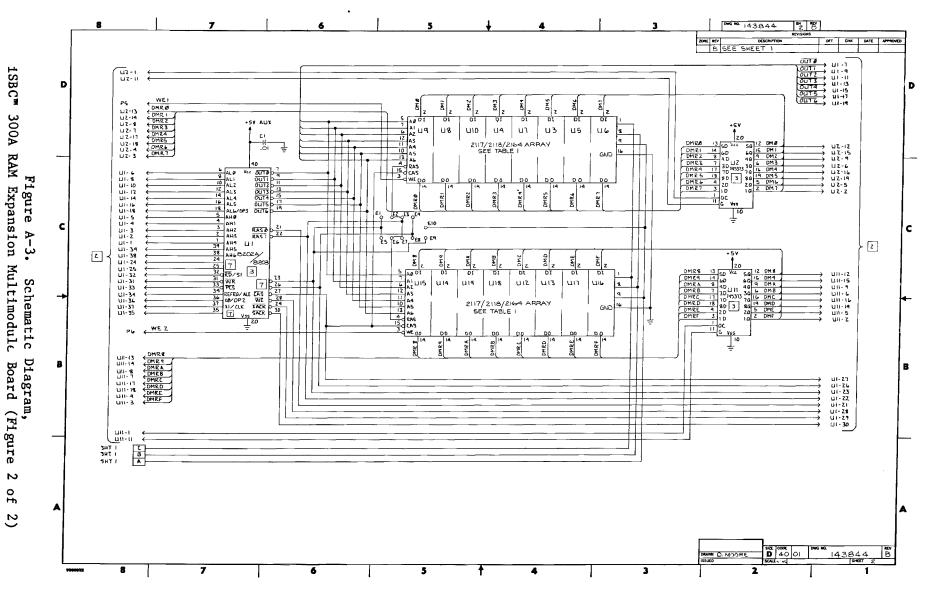

| 300A RAM EXPANSION MULTIMODULE BOARD INSTALLATION |                                                                                        |

|---------------------------------------------------|----------------------------------------------------------------------------------------|

| Introduction                                      | A-1                                                                                    |

| iSBC 300A Installation                            | A-1                                                                                    |

| Service Information                               | A−2                                                                                    |

| Replaceable Parts                                 | A-2                                                                                    |

| Service Diagrams                                  | A−2                                                                                    |

|                                                   | Introduction.<br>iSBC 300A Installation.<br>Service Information.<br>Replaceable Parts. |

## APPENDIX B

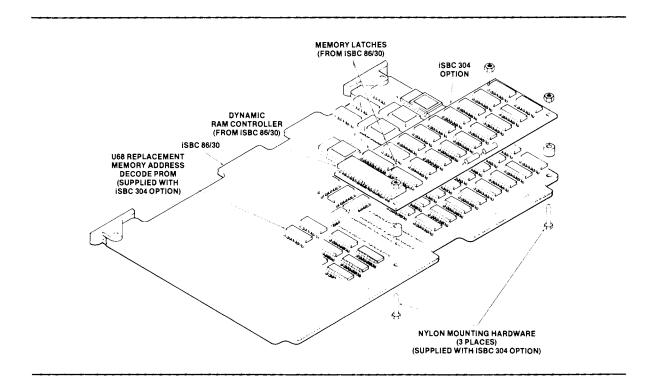

| 1SBC | 304 RAM EXPANSION MULTIMODULE BOARD INSTALLATION |     |

|------|--------------------------------------------------|-----|

| B-1. | Introduction                                     | B-1 |

| B-2. | iSBC 304 Installation                            | B-1 |

| B-3. | Service Information                              | B-2 |

| B-4. | Replaceable Parts                                | B-2 |

| B-5. | Service Diagrams                                 | B-2 |

|                                             | rage       |

|---------------------------------------------|------------|

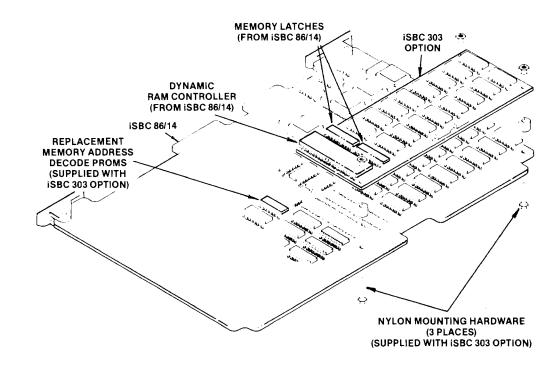

| APPENDIX C                                  |            |

| 1SBC 303 PARITY GENERATOR MULTIMODULE BOARD | C-1        |

| Contents                                    | C-2        |

| C-1. Chapter 1. General Information         | C-2<br>C-2 |

| 1-1. Introduction                           |            |

| 1-2. Description                            | C-2        |

| 1-3. Equipment Supplied                     | C-3        |

| 1-4. Specifications                         | C-3        |

| C-2. Chapter 2. Preparation For Use         | C~5        |

| 2-1. Introduction                           | C-5        |

| 2-2. Unpacking & Inspection                 | C5         |

| 2-3. Installation Considerations            | C-5        |

| 2-4. Power Requirements                     | C-5        |

| 2-5. Cooling Requirements                   | C-5        |

| 2-6. Physical Dimensions                    | C-6        |

| 2-7. Connector Configuration                | C-6        |

| 2-8. Jumper Configuration                   | C-6        |

| 2-9. Installation Procedure                 | C-8        |

| 2-10. Installation Onto Base Board          | C-8        |

| 2-11. Installation Onto iSBC 303 Board      | C-11       |

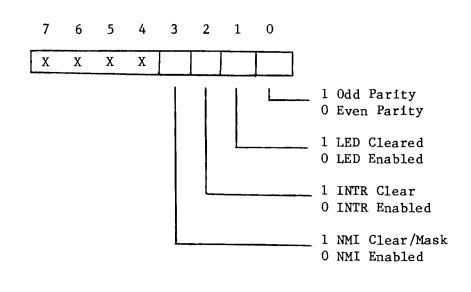

| C-3. Chapter 3. Programming Information     | C-14       |

| 3-1. Introduction                           | C-14       |

| 3-2. Programming Considerations             | C-14       |

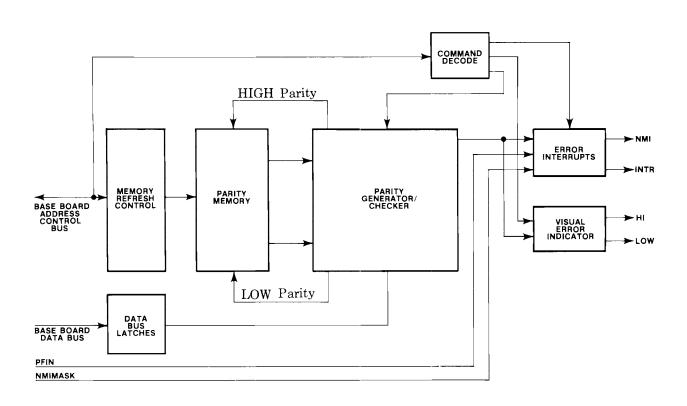

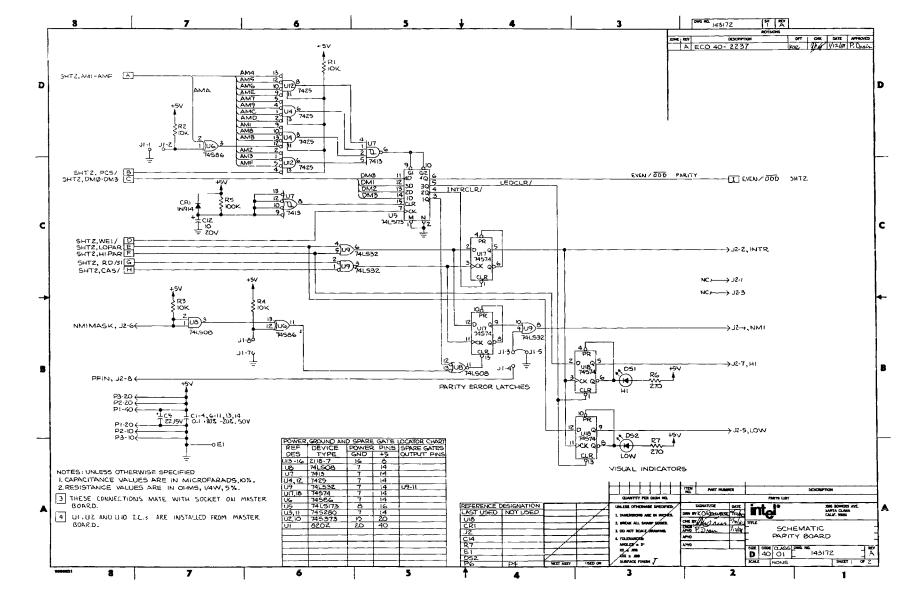

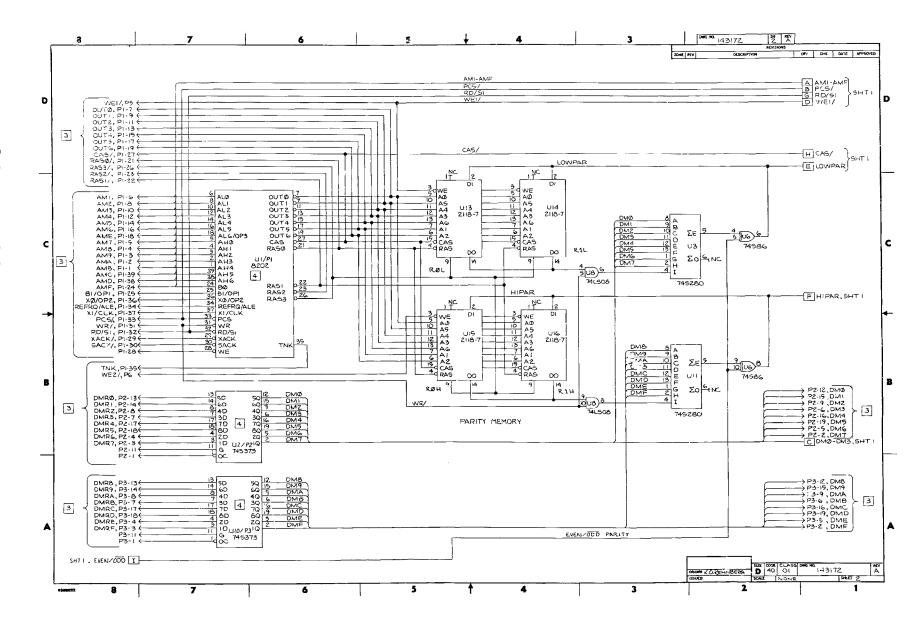

| C-4. Chapter 4. Principles of Operation     | C-15       |

| 4-1. Introduction                           | C-15       |

| 4-2. Functional Description                 | C-15       |

| 4-3. Parity Generator/Checker               | C-16       |

| 4-4. Parity Memory                          | C-16       |

| 4-5. Parity Generation                      | C-16       |

| 4-6. Parity Checker                         | C-16       |

| 4-7. Memory Refresh Control                 | C-16       |

| 4-8. Data Bus Latches                       | C-16       |

| 4-9. Command Decode                         | C-17       |

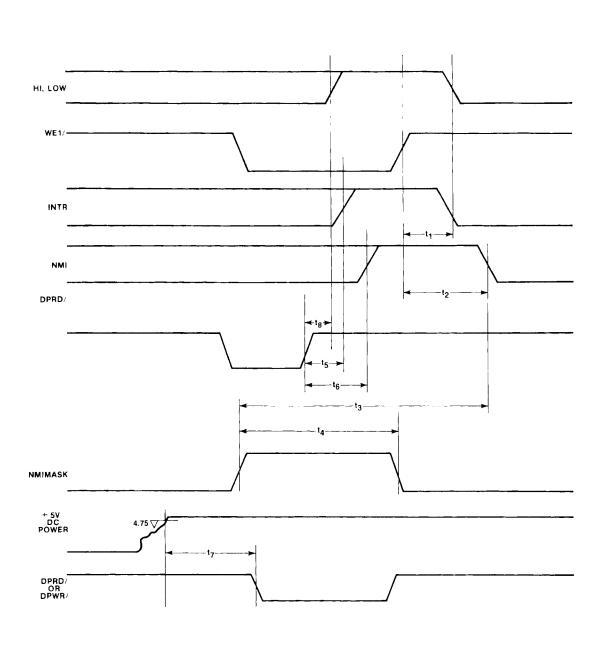

| 4-10. Error Interrupts                      | C-17       |

| 4-11. INTR                                  | C-17       |

| 4-12. NMI                                   | C-17       |

| 4-13. Visual Error Indicators               | C-17       |

| 4-14. Error Indicator Signals               | C-18       |

| 4-15. Circuit Analysis                      | C-18       |

| 4-16. Parity Memory                         | C-18       |

| 4-17. Parity Generation                     | C-18       |

| 4-18. Parity Checker                        | C-19       |

| 4-19. Data Bus Latches                      | C-19       |

| 4-20. INTR Interrupt                        | C-19       |

| 4-21. NMI Interrupt                         | C-19       |

| 4-22. HI/LO Indicators                      | C-19       |

| 4-23. Address and Command Decode            | C-20       |

,

| APPENDIX C (continued)              | -    |

|-------------------------------------|------|

| C-5. Chapter 5. Service Information | C-21 |

| 5-1. Introduction                   | C-21 |

| 5-2. Diagnostic Test                | C-21 |

| 5-3. Replaceable Parts              | C-21 |

| 5-4. Service Diagrams               |      |

| 5-5. Service and Repair Assistance  | C-22 |

| 5-6. Internal Signals               | C-23 |

| APPENDIX | D. |

|----------|----|

|----------|----|

| 1SBC 86/12A DIFFERENCES                           |      |

|---------------------------------------------------|------|

| D-1. Introduction                                 | D-1  |

| D-2. Functional Differences                       | D-1  |

| D-3. Software Compatibility                       | D-1  |

| D-4. Power Requirements                           | D-2  |

| D-5. Timing                                       | D-3  |

| D-6. Memory                                       | D-4  |

| D-7. I/O Port Addressing                          | D-4  |

| D-8. Pin Assignment/Signal Definition Differences | D-6  |

| D-9. Jumper Post Numbering                        | D-7  |

| D-10. Interrupt Differences                       | D-11 |

| D-11. Physical Differences                        | D-12 |

# FIGURES

| 1-1.  | iSBC 86/14/30 Single Board Computer                     | 1-2  |

|-------|---------------------------------------------------------|------|

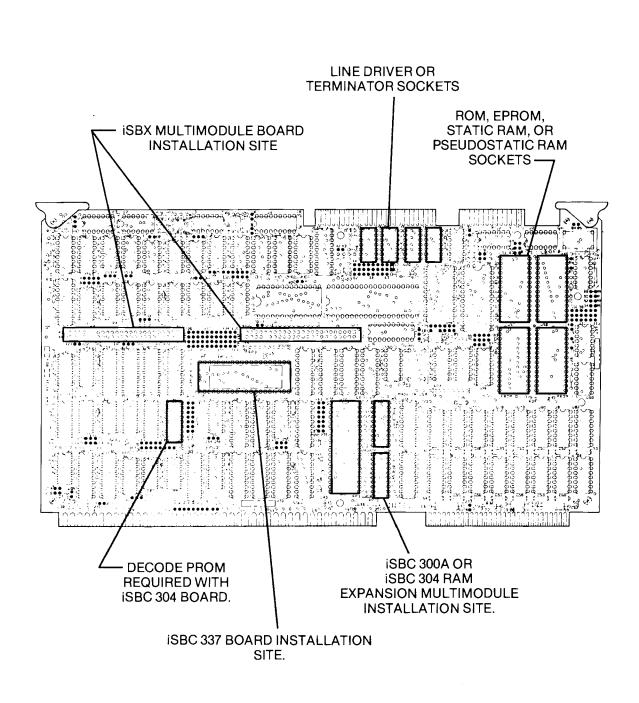

| 2-1.  | iSBC 86/14/30 Board User-Furnished Component Locations  | 2-3  |

| 2-2.  | EPROM Device Installation                               | 2-9  |

| 2-3.  | Typical Memory Configuration                            | 2-10 |

| 2-4.  | iSBC 86/14 Board Multibus Address Configuration Example | 2-28 |

| 2-5.  | iSBC 86/30 Board Multibus Address Configuration Example | 2-29 |

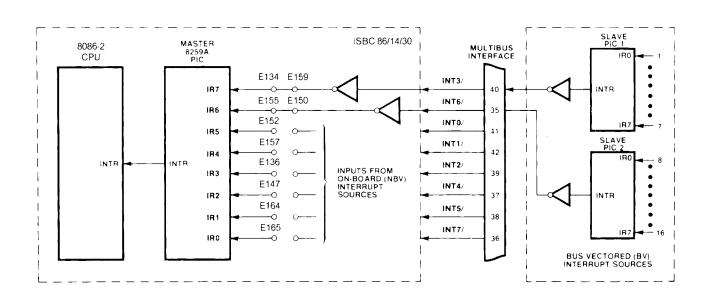

| 2-6.  | Typical Mater/Salve PIC Interconnect Example            | 2-45 |

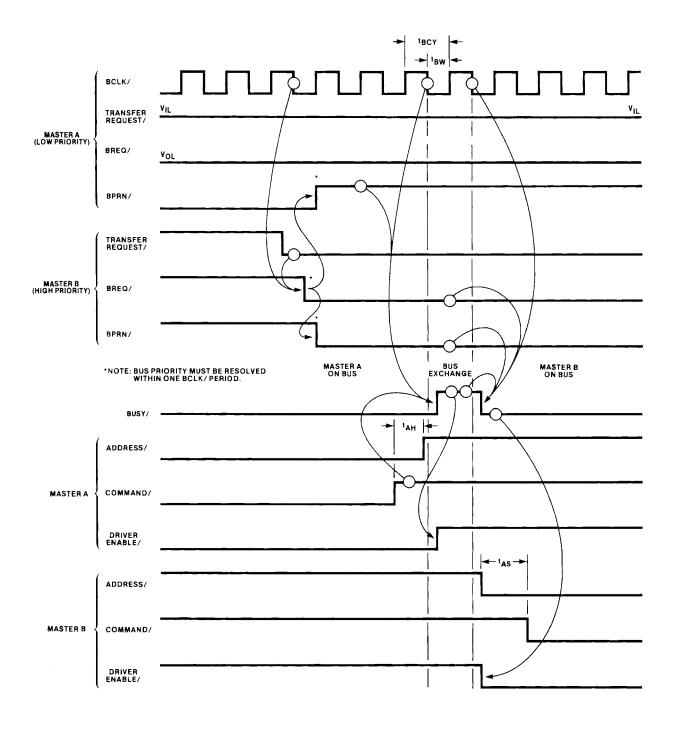

| 2-7.  | Bus Exchange Timing (Master Mode)                       | 2-60 |

| 2-8.  | Bus Exchange Timing (Slave Mode)                        | 2-61 |

| 2-9.  | Serial Priority Resolution Scheme                       | 2-63 |

| 2-10. | Parallel Priority Resolution Scheme                     | 2-64 |

|       | Serial Cabling Diagram                                  | 2-70 |

|       | Pin Numbering Conventions                               | 2-73 |

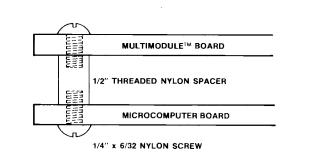

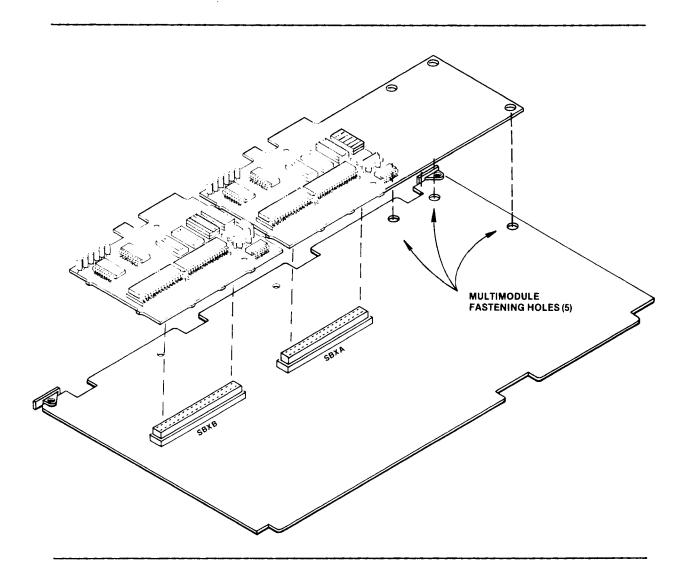

|       | Spacer Installation Technique                           | 2-79 |

|       | iSBX Multimodule Board Orientation                      | 2-80 |

| 3-1.  | PIT Control Word Format                                 | 3-9  |

| 3-2.  | PIT Programming Sequence Examples                       | 3-10 |

| 3-3.  | PIT Counter Register Latch Control Word Format          | 3-16 |

| 3-4.  | PCI Synchronous Mode Instruction Word Format            | 3-19 |

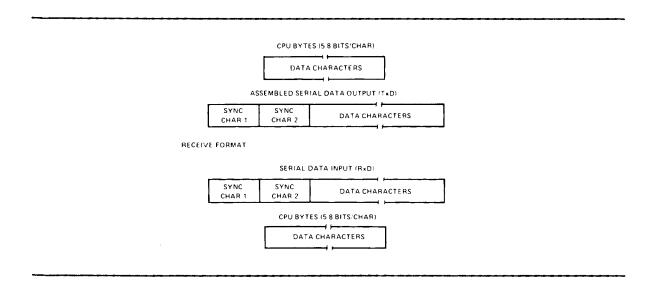

| 3-5.  | PCI Synchronous Mode Transmission Format                | 3-19 |

| 3-6.  | PCI Asynchronous Mode Instruction Word Format           | 3-20 |

## CONTENTS

# FIGURES (continued)

|       |                                                            | Pag |

|-------|------------------------------------------------------------|-----|

| 3-7.  | PCI Asynchronous Mode Transmission Format                  | 3-2 |

| 3-8.  | PCI Command Instruction Word Format                        | 3-2 |

| 3-9.  | Typical PCI Initialization and Data I/O Sequence           | 3-2 |

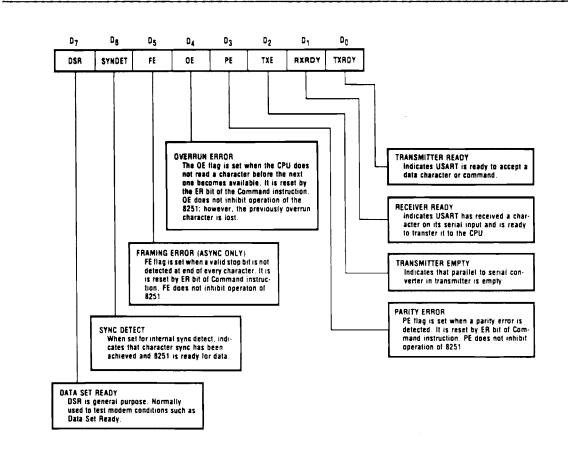

| 3-10. | PCI Status Byte Format                                     | 3-2 |

| 3-11. | PPI Control Word Format                                    | 3-2 |

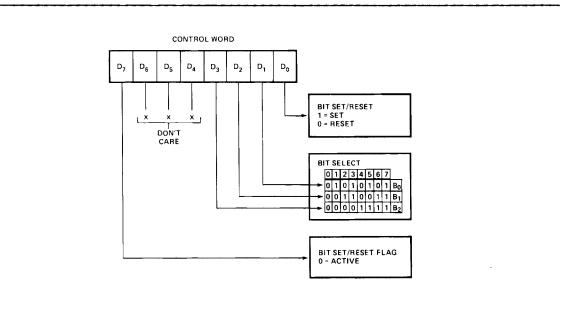

| 3-12. | PPI Port C Bit Set/Reset Control Word Format               | 3-3 |

| 3-13. | Initialization Command Word (ICW) Formats                  | 3-3 |

| 3-14. | Operation Command Word (OCW) Formats                       | 3-4 |

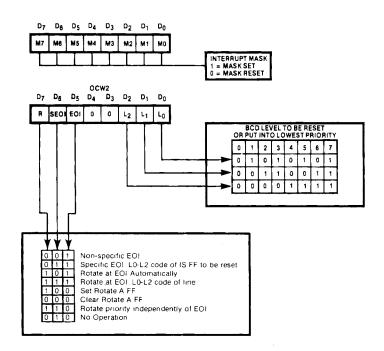

| 3-15. | Data Byte Format For Status Register                       | 3-5 |

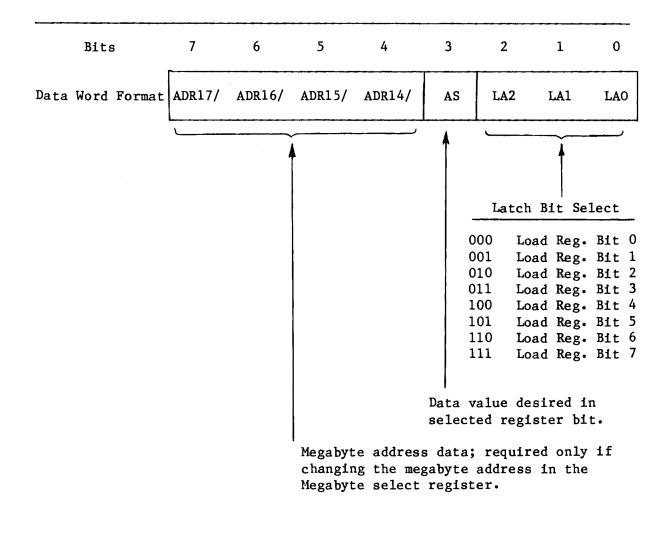

| 4-1.  | iSBC 86/14/30 Board Block Diagram                          | 4-2 |

| 4-2.  | Internal Bus Structure                                     | 4-1 |

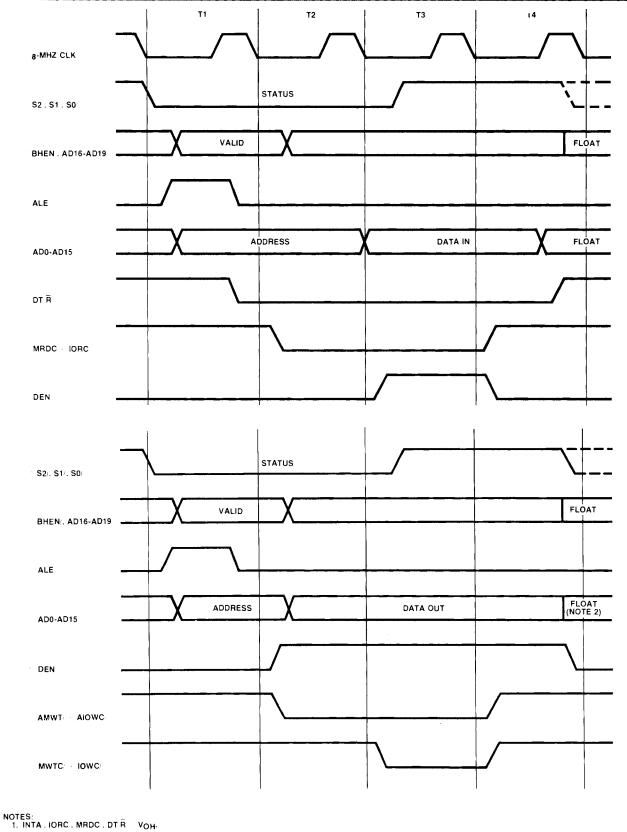

| 4-3.  | READ and WRITE Operation Timing                            | 4-1 |

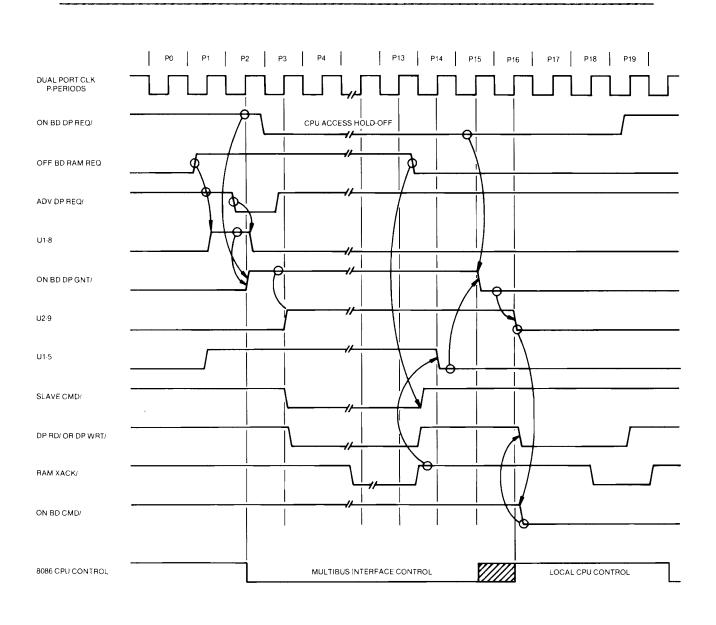

| 4-4.  | Slave Mode Dual Port Access (CPU Lockout)                  | 4-2 |

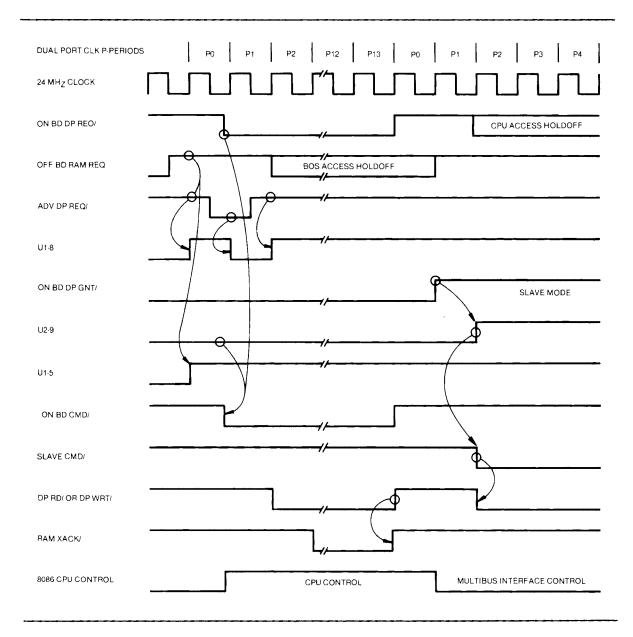

| 4-5.  | Master Mode Dual Port Access (Multibus Lockout)            | 4-2 |

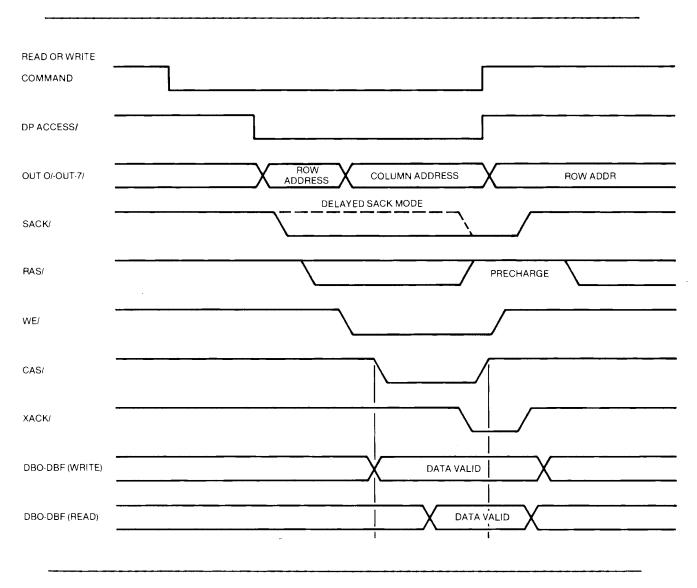

| 4-6.  | Typical Dynamic RAM Operation Sequence                     | 4-2 |

| 4-7.  | Multibus access Timing                                     | 4-3 |

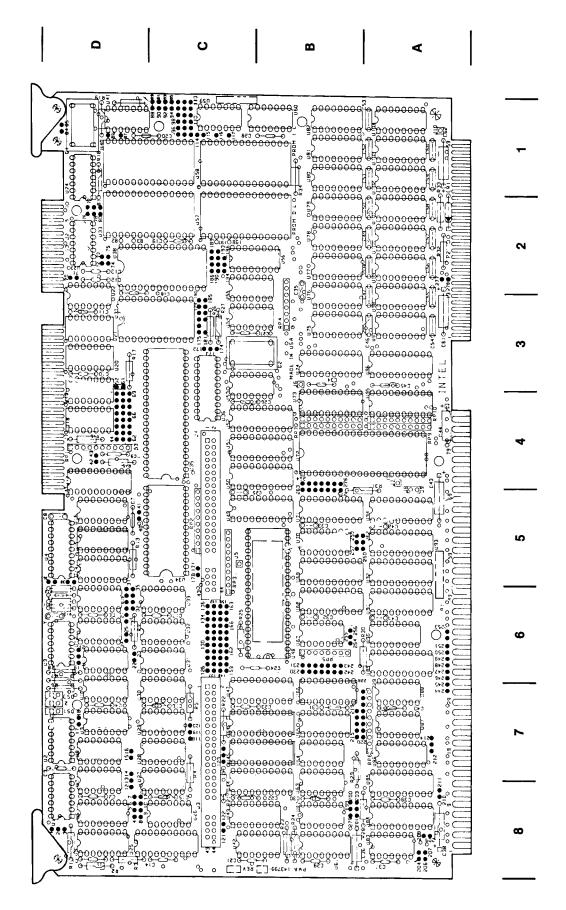

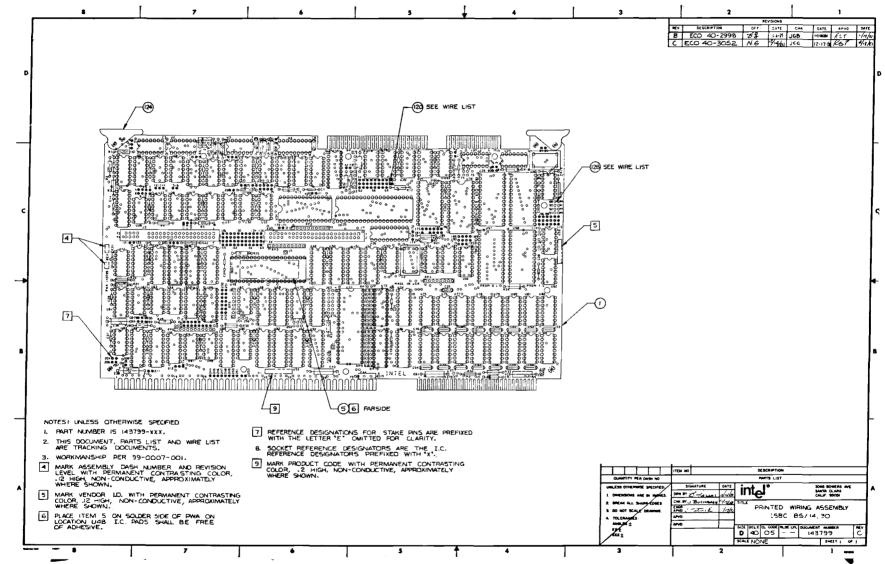

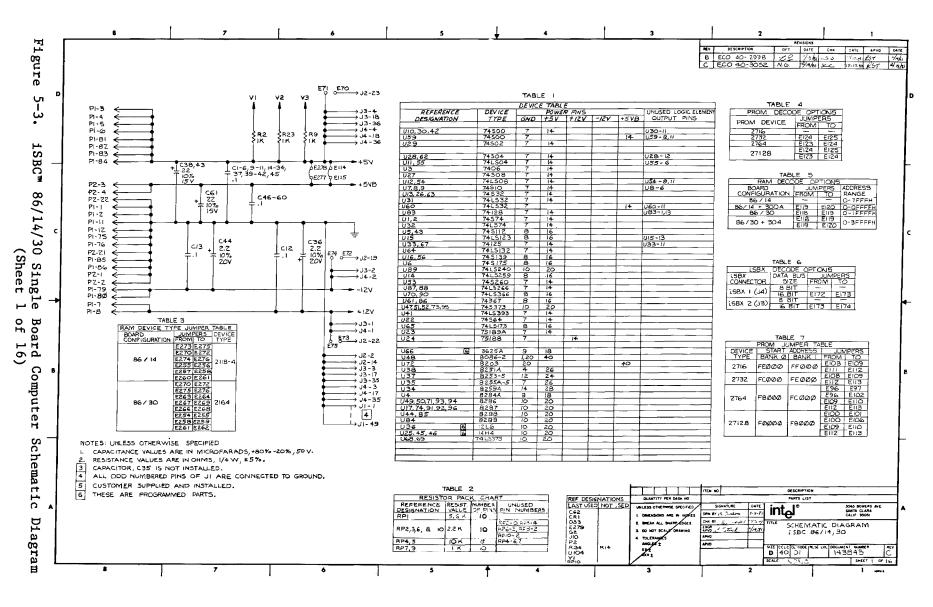

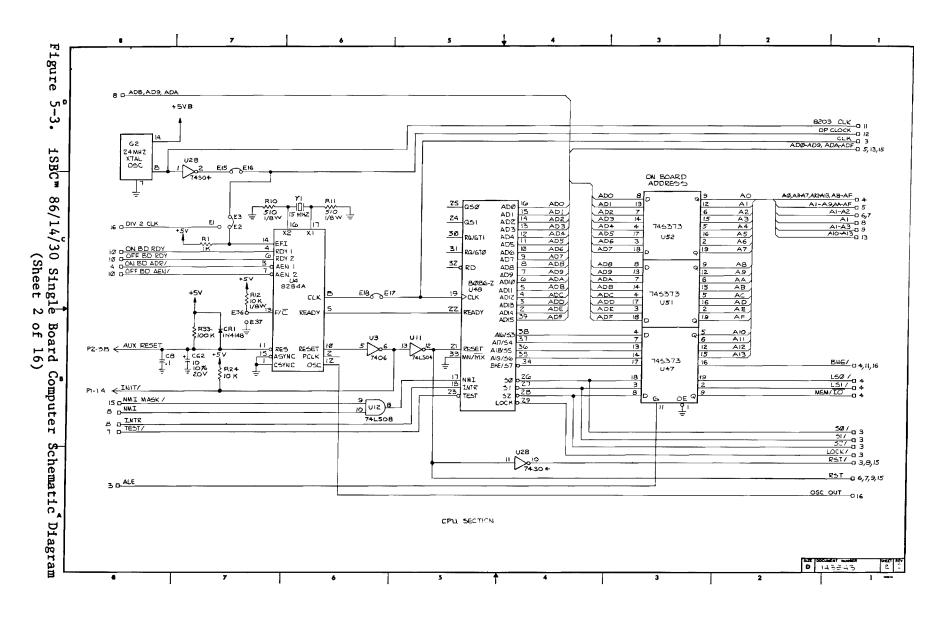

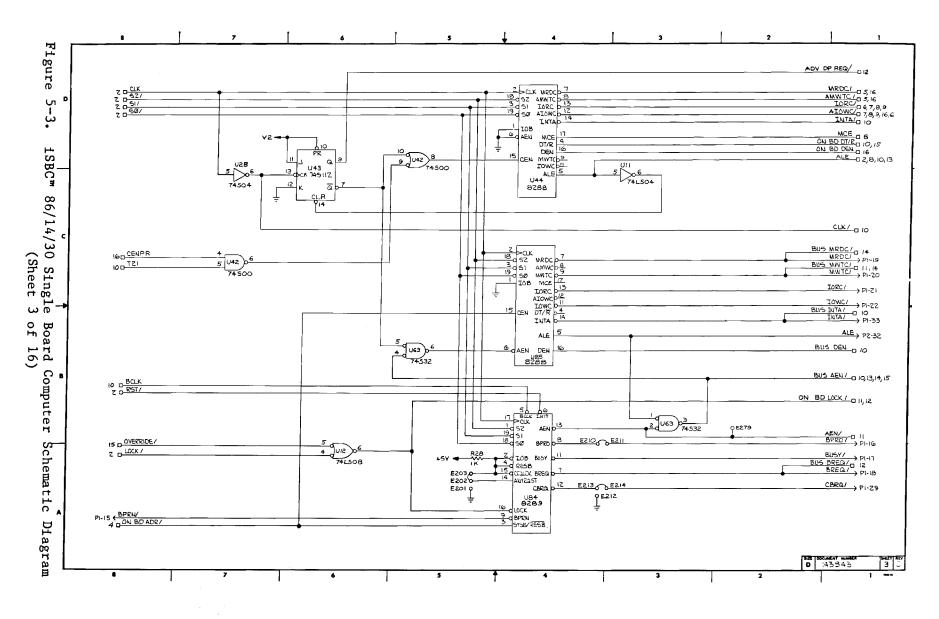

| 5-1.  | iSBC 86/14/30 Board Jumper Location Diagram                | 5-7 |

| 5-2.  | iSBC 86/14/30 Single Board Computer Parts Location Diagram | 5-9 |

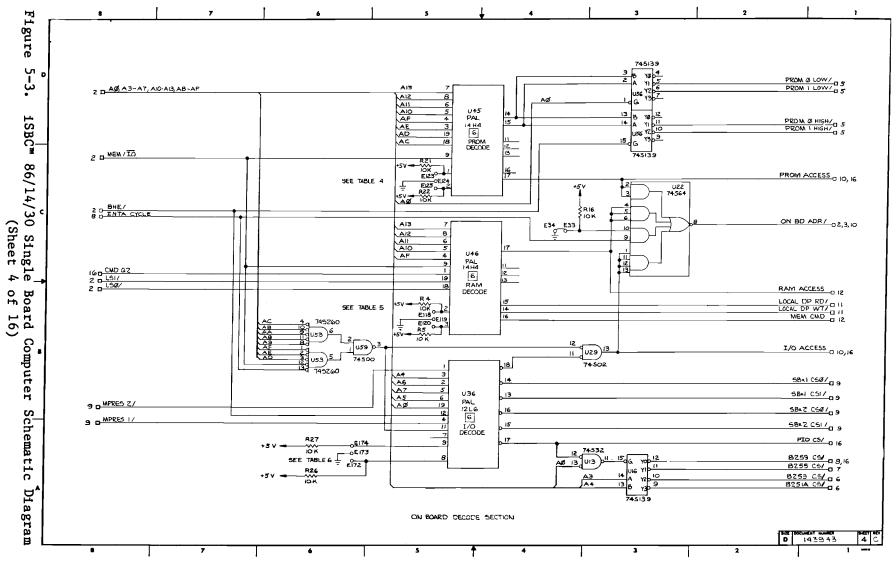

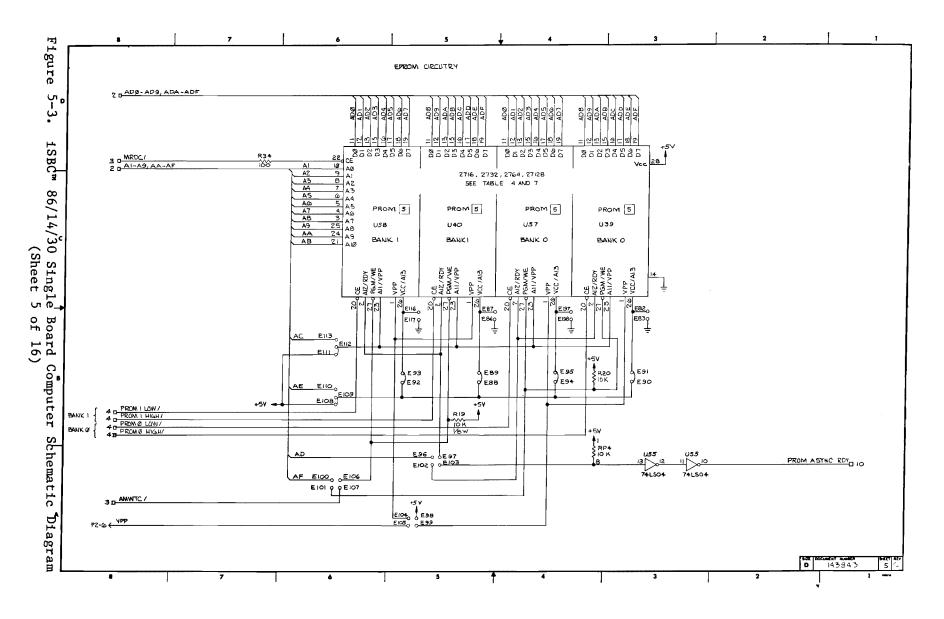

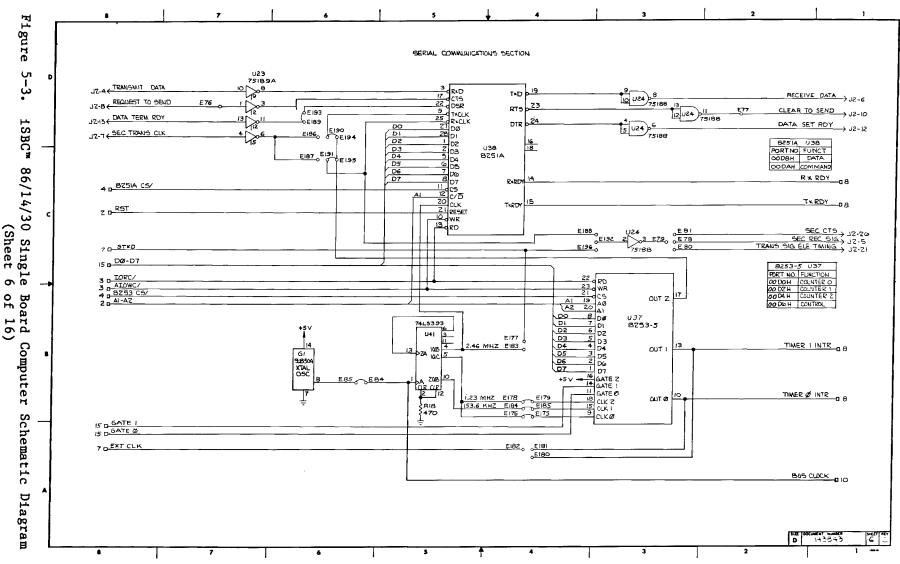

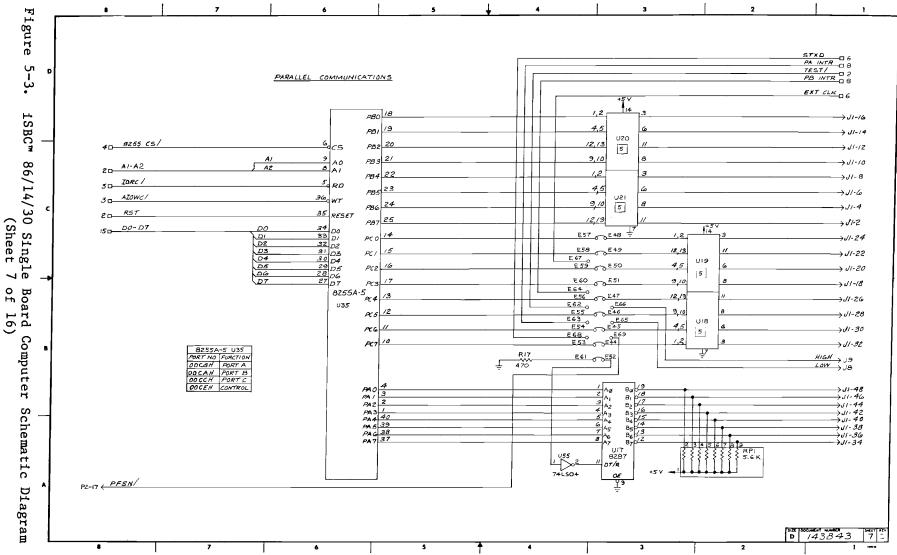

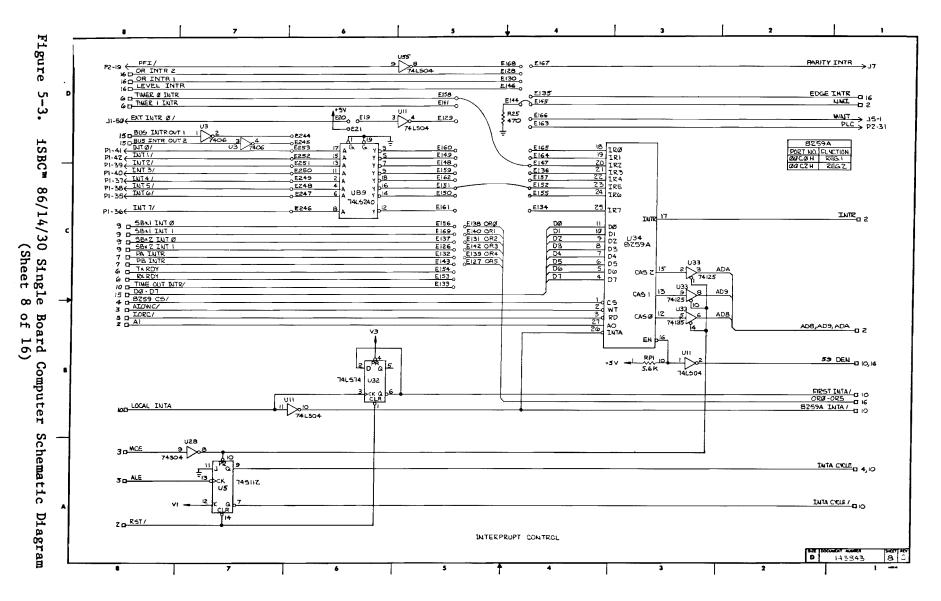

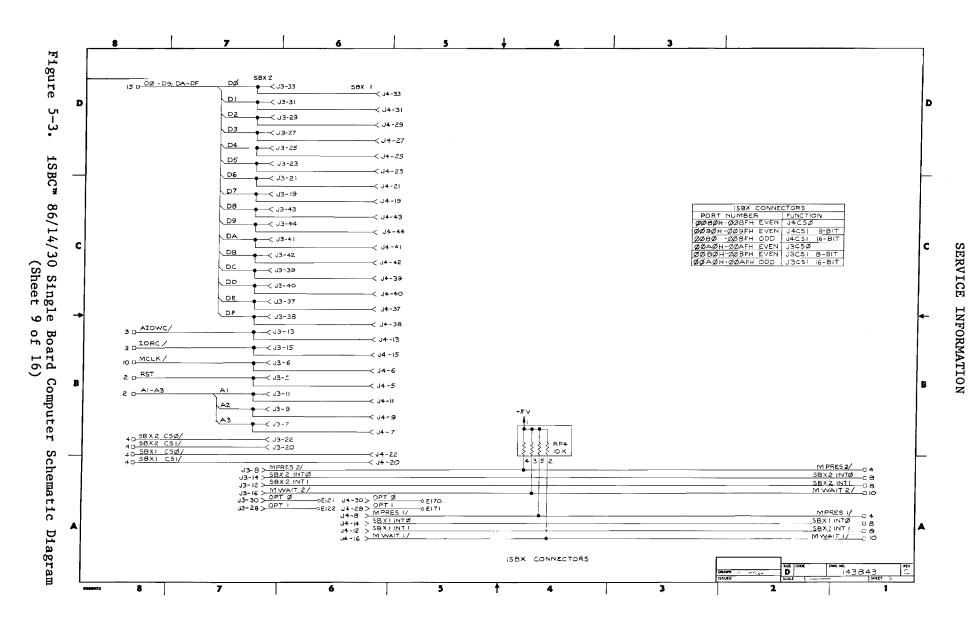

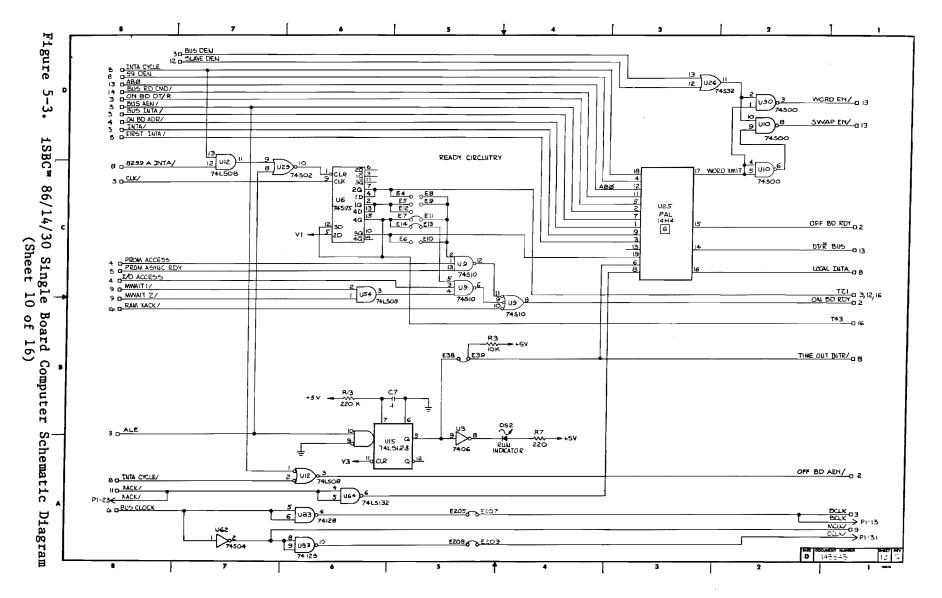

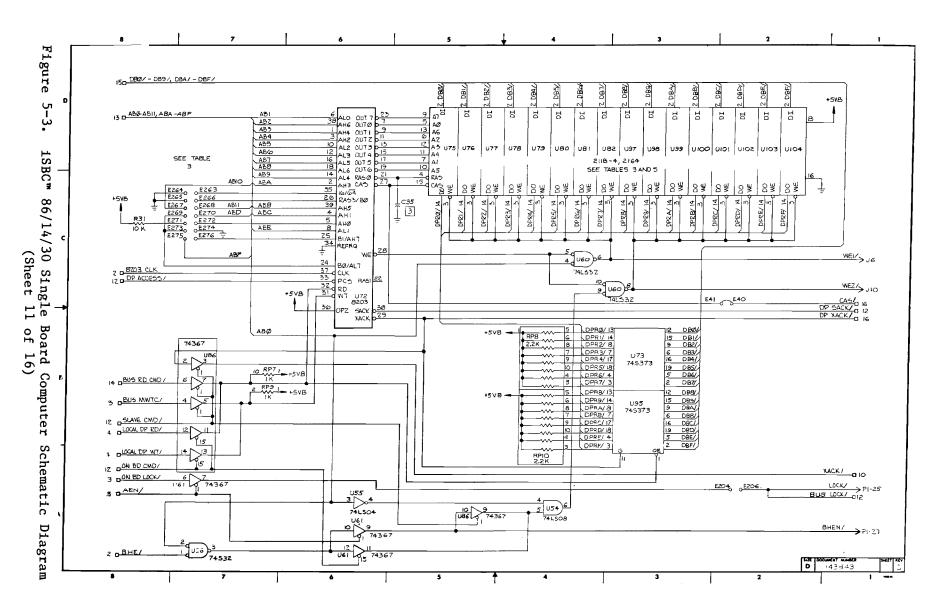

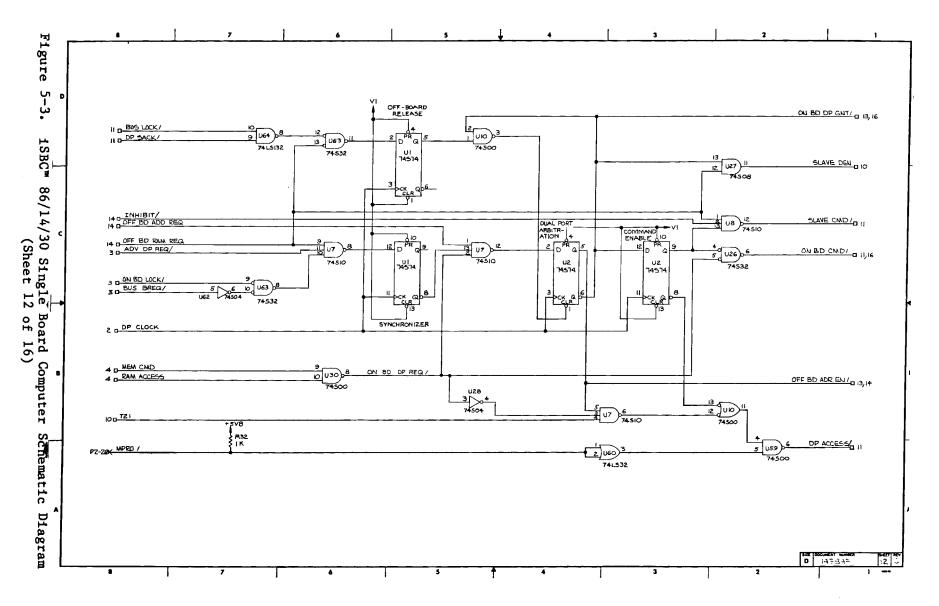

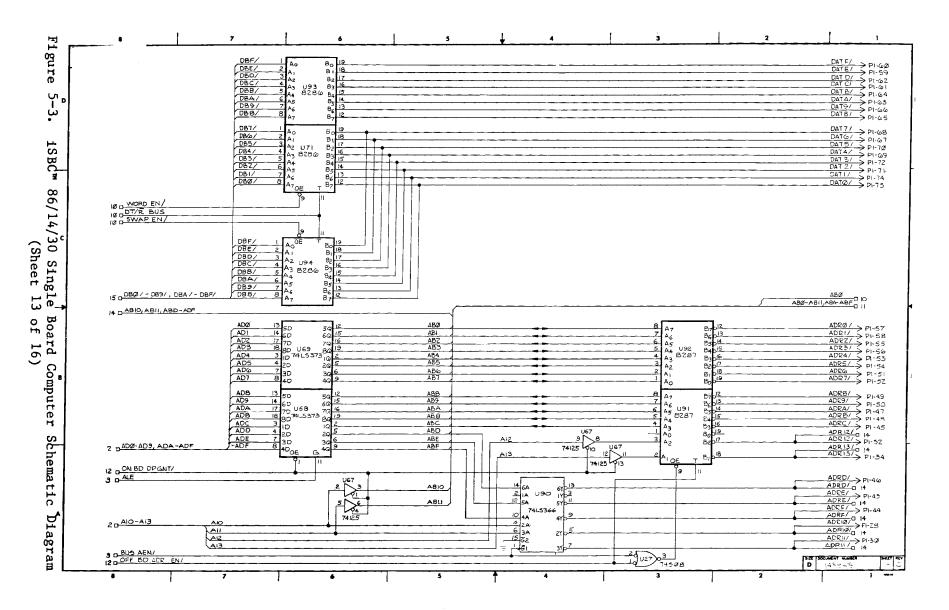

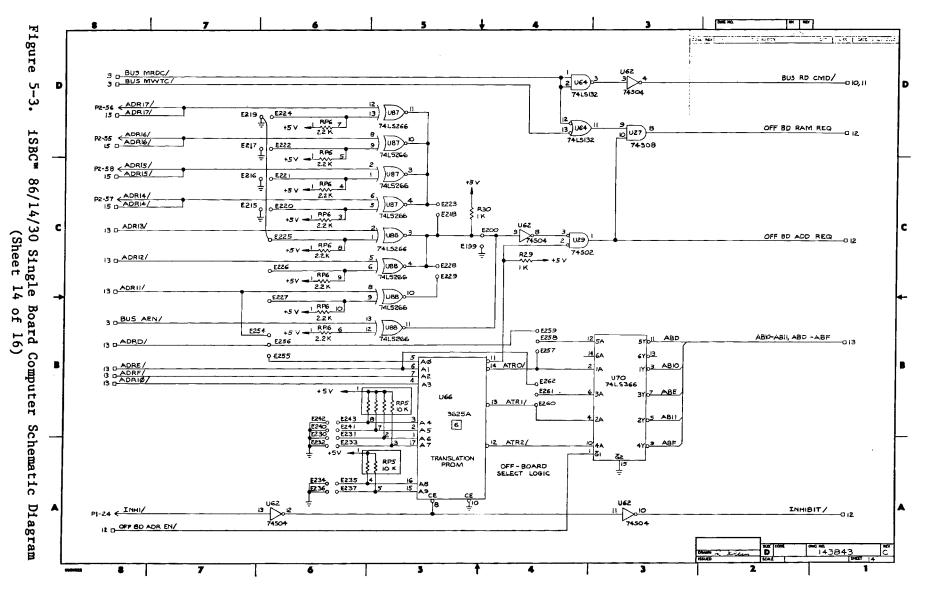

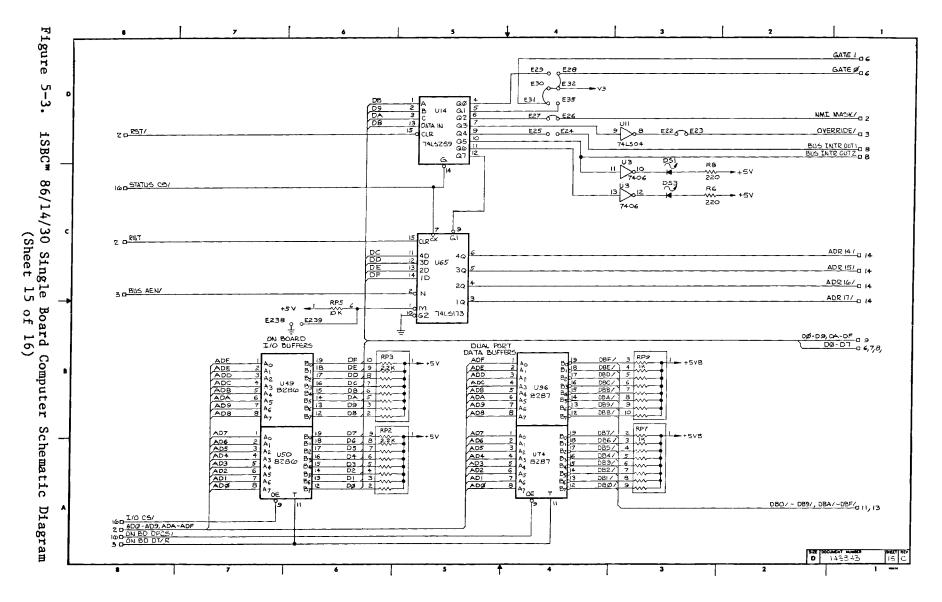

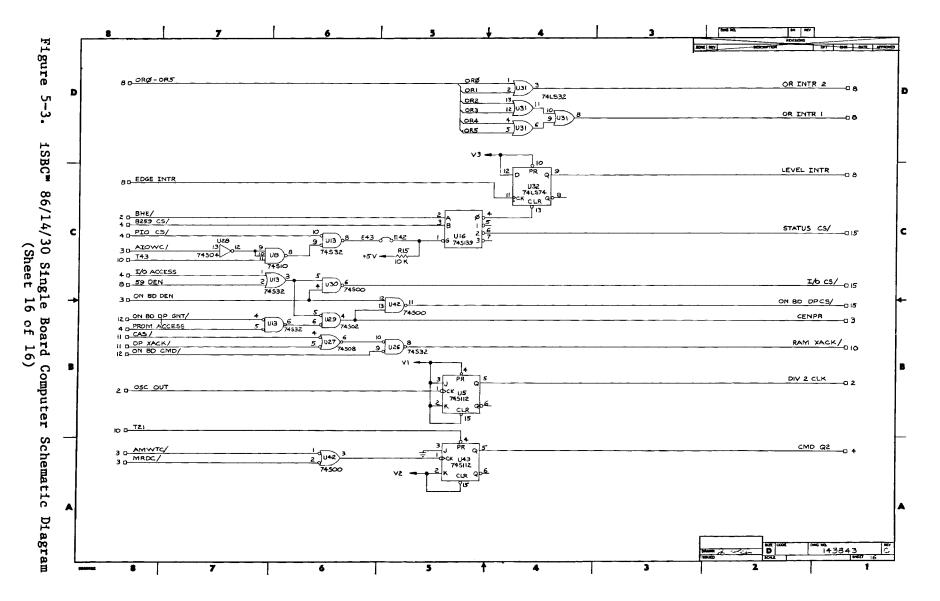

| 5-3.  | iSBC 86/14/30 Single Board Computer Schematic Diagram      |     |

|       | (16 Sheets)                                                | 5-1 |

|       |                                                            | -   |

## TABLES

| 1-1.  | Specifications                                         | 1-8  |

|-------|--------------------------------------------------------|------|

| 2-1.  | User-Furnished Components                              | 2-4  |

| 2-2.  | User-Furnished Connector Information                   | 2-6  |

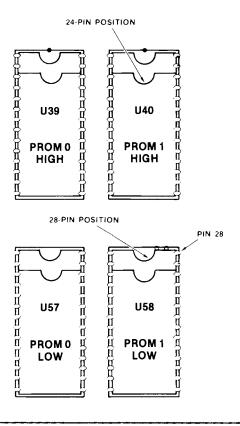

| 2-3.  | EPROM Socket Address Assignments                       | 2-9  |

| 2-4.  | User-Configurable Jumper Functions                     | 2-11 |

| 2-5.  | Jumper Listing By Numerical Order                      | 2-18 |

| 2-6.  | Megabyte Address Select                                | 2-25 |

| 2-7.  | 128k Page Selection for iSBC 86/14 Board               | 2-25 |

| 2-8.  | 8k Ending Address Boundary Select for iSBC 86/14 Board | 2-26 |

| 2-9.  | 256k Page Selection for iSBC 86/30 Board               | 2-27 |

| 2-10. | 32k Ending boundary Select for iSBC 86/30 Board        | 2-27 |

| 2-11. | iSBC 86/14 board Dual Port RAM Size Select             | 2-30 |

| 2-12. | iSBC 86/30 Board Dual Port RAM Size Select             | 2-32 |

| 2-13. | Wait-state Jumper Configuration                        | 2-33 |

| 2-14. | PIT Output Signal Jumper                               | 2-34 |

| 2-15. | Parallel Port Jumper Configuration                     | 2-35 |

| 2-16. | Interrupt Source and Level Selecting Options           | 2-42 |

| 2-17. | Multibus Interface Jumper Options                      | 2-48 |

| 2-18. | Multibus Interface Arbitration Options                 | 2-50 |

| 2-19. | Connector P1 Pin Assignments                           | 2-51 |

| 2-20. | Connector Pl Signal Descriptions                       | 2-53 |

| 2-21. | P1 Connector DC Characteristics                        | 2-55 |

| 2-22. | P1 Connector AC Characteristics                        | 2-58 |

# CONTENTS

# TABLES (continued)

|       |                                                        | Page |

|-------|--------------------------------------------------------|------|

| 2-23. | P1 Connector AC Characteristics                        | 2-59 |

| 2-24. | Auxiliary Connector P2 Pin Assignments                 | 2-66 |

| 2-25. | Auxiliary Connector P2 DC Characteristics              | 2-67 |

| 2-26. | Parallel I/O Connector J1 Pin Assignments              | 2-68 |

| 2-27. | Parallel I/O Connector J1 DC Characteristics           | 2-69 |

| 2-28. | Parallel I/O Cabling Information                       | 2-69 |

| 2-29. | Serial I/O Connector J2 Pin Assignments                | 2-71 |

| 2-30. | RS232C Types                                           | 2-72 |

| 2-31. | iSBX Bus Connector J3 and J4 Pin Assignments           | 2-74 |

| 2-32. | iSBX Bus Signal Descriptions                           | 2-75 |

| 3-1A. | iSBC 86/14 Board Memory Map                            | 3-2  |

| 3-1B. | iSBC 86/30 Board Memory Map                            | 3-4  |

| 3-2.  | RAM Address Range Configuration                        | 3-5  |

| 3-3.  | I/O Port Address List                                  | 3-6  |

| 3-4.  | PIT counter Operation Vs. Gate Inputs                  | 3-12 |

| 3-5.  | Typical PIT Control Word Subroutine                    | 3-14 |

| 3-6.  | Typical PIT Counter Value Load Subroutine              | 3-15 |

| 3-7.  | Typical PIT Counter Read Subroutine                    | 3-15 |

| 3-8.  | PIT Rate Generator Frequencies and Timer Intervals     | 3-17 |

| 3-9.  | PIT Time Intervals Vs. Timer Counts                    | 3-18 |

| 3-10. | PCI Address Assignments                                | 3-22 |

| 3-11. | Typical PCI Mode or Command Instruction Subroutine     | 3-25 |

| 3-12. | Typical PCI Data Character Read Subroutine             | 3-25 |

| 3-13. | Typical PCI Data Character Write Subroutine            | 3-26 |

| 3-14. | Typical PCI Status Read Subroutine                     | 3-27 |

| 3-15. | Parallel Port Configurations                           | 3-28 |

| 3-16. | Parallel Port I/O Address                              | 3-30 |

| 3-17. | Typical PPI Initialization Subroutine                  | 3-31 |

| 3-18. | Typical PPI Port Read Subroutine                       | 3-31 |

| 3-19. | Typical PPI Port Write Subroutine                      | 3-31 |

| 3-20. | Parallel I/O Interface Configurations                  | 3-33 |

| 3-21. | Interrupt Type Pointers                                | 3-38 |

| 3-22. | Typical PIC Initialization Subroutine (NBV Mode)       | 3-42 |

| 3-23. | Typical Master PIC Initialization Subroutine (BV Mode) | 3-42 |

| 3-24. | Typical Slave PIC Initialization Subroutine (BV Mode)  | 3-43 |

| 3-25. | PIC Operation Procedures                               | 3-44 |

| 3-26. | Typical PIC Interrupt Request Register Read Subroutine | 3-46 |

| 3-27. | Typical PIC In-Service Register Read Subroutine        | 3-46 |

| 3-28. | Typical PIC Set Mask Register Subroutine               | 3-47 |

| 3-29. | Typical PIC Set Mask Register Read Subroutine          | 3-47 |

| 3-30. | Typical PIC End-Of-Interrupt Command Subroutine        | 3-47 |

## CONTENTS TABLES (continued)

Page

| 4-1.  | 8086-2 Status Bid Decodes                         |

|-------|---------------------------------------------------|

| 4-2.  | Data Transfer Modes                               |

| 4-3.  | EPROM Static Access Time Vs. Wait-state Selection |

| 4-4.  | I/O Access Time Vs. Wait-state Selection          |

| 4-5.  | iSBX Bus Width Select                             |

| 4-6.  | PAL U36 Operation                                 |

| 4-7.  | EPROM Chip Capacity Select                        |

| 4-8.  | PAL U45 Operation                                 |

| 4-9.  | RAM Array Capacity Select                         |

| 4-10. | PAL U46 Operation                                 |

| 4-11. | PAL U25 Operation                                 |

| 5-1.  |                                                   |

|       | Replaceable Parts                                 |

| 5-2.  | Manufacturer's Codes                              |

### 1-1. INTRODUCTION

The iSBC 86/14 and the iSBC 86/30 Single Board Computers, members of Intel's complete line of 8-bit and 16-bit single board computer products, are an enhanced version of the iSBC 86/12A board that is contained on a single printed circuit board. The iSBC 86/14 and iSBC 86/30 boards provide a maximum of 64k bytes and 256k bytes of dynamic dual port RAM, respectively, and feature 8 MHz CPU operation with Multimodule board expansion via two iSBX Bus connectors.

The iSBC 86/14 board and iSBC 86/30 board (hereafter referred to jointly as the iSBC 86/14/30 board) provide a complete computer system that is designed around the 16-bit iAPX 86/10 HMOS microprocessor (8086-2 CPU), the main processing device on the boards. The iAPX 86/10 microprocessor may be operated at either a 5 MHz clock rate or an 8 MHz clock rate on the iSBC 86/14/30 board in performing both 8-bit and 16-bit data transfers to/from the single board computer.

The iSBC 86/14/30 board provides a direct iSBC 86/12A board replacement that is shipped with 32k bytes (maximum on the iSBC 86/14 board) or 128k bytes (maximum on the iSBC 86/30 board) of dynamic RAM, 4 sockets for installation of up to 64k bytes of user-provided EPROM devices, a serial communications port providing an RS232C interface, three parallel I/O ports providing 24 individual I/O lines, two iSBX Bus connectors providing interface to either 8-bit or 16-bit Multimodule board expansion, two independently programmable interval timers, and nine levels of interrupt priority supporting bus-vectored interrupts.

The iSBC 86/14/30 board is fully Multibus interface compatible and is configurable for operation in a multi-master system environment. The on-board RAM is expandable via addition of the plug-in memory expansion boards available from Intel: the iSBC 300A RAM Expansion Multimodule Board (86/14) and the iSBC 304 RAM Expansion Multimodule Board (86/30). As shipped, the each version of the board configures the RAM totally as a dual port resource. The RAM may be removed from the dual port configuration in increments of one-fourth of the total RAM size.

Compatibility of the iSBC 86/14/30 board with the iSBC 86/12A board includes compatibility with the processing expansion features available in the iSBC 337 Numberic Data Processor, and the iSBC 303 Parity Generator/Checker Multimodule Board (86/14 only). Appendix D at the end of this manual contains a brief description of the major functional and operational differences between the iSBC 86/14/30 board and the iSBC 86/12A board.

## 1-2. DESCRIPTION

The iSBC 86/14/30 Single Board Computer, shown in Figure 1-1, is a memory intensive processor board designed around the 16-bit Intel iAPX 86-10 Microprocessor (8086-2 CPU). The iSBC 86/14/30 board can be configured for full compatibility with the software and hardware functions provided by the iSBC 86/12A board; this includes compatibility with time dependent code execution when the iSBC 86/14/30 board operates at a 5 MHz clock rate.

### Figure 1-1. iSBC<sup>™</sup> 86/14/30 Single Board Computer

The iSBC 86/14/30 board uses an internal bus during all on-board memory and I/O operations, and uses the Multibus interface during all off-board memory and I/O operations. Hence, local (on-board) operations do not involve the Multibus interface and allow true parallel processing in a multi-master system. The features of the iSBC 86/14/30 board are listed and described in the following text.

- \* 8086-2 CPU (iAPX 86/10) providing operation at either 5 or 8 MHz clock frequency.

- \* Fully software compatible with the iSBC 86/12A Single Board Computer.

- \* 32k bytes of dual port RAM available on the iSBC 86/14 board; expandable to 64k bytes maximum with on-board refresh.

- \* 128k bytes of dual port RAM available on the iSBC 86/30 board; expandable to 256k bytes maximum with on-board refresh.

- \* Four JEDEC compatible 24/28 pin sockets for installation of up to 64k bytes of EPROM onto either version of the board.

- \* Two iSBX Bus connectors providing either 8-bit or 16-bit interfaces to Multimodule boards.

- \* +5 volt only power requirement, unless using an RS232C interface or certain Multimodule boards.

- \* 24 programmable parallel I/O lines via the 8255A PPI.

- 9 levels of interrupt priority via the 8259A PIC, expandable to 65 levels.

- \* 1 serial I/O port provided via the 8251A PCI.

- \* two user-programmable 16-bit BCD or binary event timers/counters via the 8253-5 PIT.

- \* Full Multibus interface compatibility.

- \* 8203 Dynamic RAM Controller.

- 20-bit addressing with bank-select, allowing for access of up to 16-megabytes of System memory.

The iAPX 86/10 CPU is a 40-pin LSI device providing an interface with either 8-bit or 16-bit systems. The iAPX 86/10 CPU is configured on the iSBC 86/14/30 board for MAXIMUM mode operation which allows the iSBC 86/14/30 board the ability to control the 8288 Bus Controller and the 8289 Bus Arbiter devices.

The 8086-2 CPU contains four 16-bit general purpose registers that may be addressed as eight 8-bit registers. Additionally, the CPU contains two 16-bit pointer registers and two 16-bit index registers. The four 16-bit segment registers in the 8086-2 allow extended access to a full megabyte-page of memory addresses. The 8086-2 CPU supports a wide range of addressing modes and data transfer operations, signed and unsigned 8and 16-bit arithmetic operations including multiply and divide functions, and logical and string operations. The architecture of the 8086-2 CPU provides several data transfer features including instruction look-ahead, dynamic code relocation, and reentrant code execution. Two iSBX Bus interfaces are available on the iSBC 86/14/30 board via the J3 and J4 connectors. Each is capable of accepting either an 8-bit or a 16-bit iSBX Multimodule board. The iSBX Bus connectors allow expansion of the functionality of the iSBC 86/14/30 board in small increments by installing Multimodule boards such as the iSBX 311 Analog Input Multimodule Board, the iSBX 328 Analog Output Multimodule Board, the iSBX 350 Parallel I/O Multimodule Board, the iSBX 351 Serial I/O Multimodule Board, the iSBX 331 Fixed/Floating Point Math Multimodule Board, the iSBX 332 Floating Point Math Multimodule Board, and others.

Dual port control logic is included to interface the dynamic RAM with the Multibus interface so that the iSBC 86/14/30 board can function as a slave RAM device when not in control of the Multibus interface. The 8086-2 CPU has priority when accessing on-board RAM. After the CPU completes its read or write operation, the controlling bus master is allowed to access RAM and complete its operation. Where both the CPU and the controlling bus master have the need to write or read several bytes or words to or from on board RAM, their operations are interleaved (unless restricted via Multibus interface control signals).

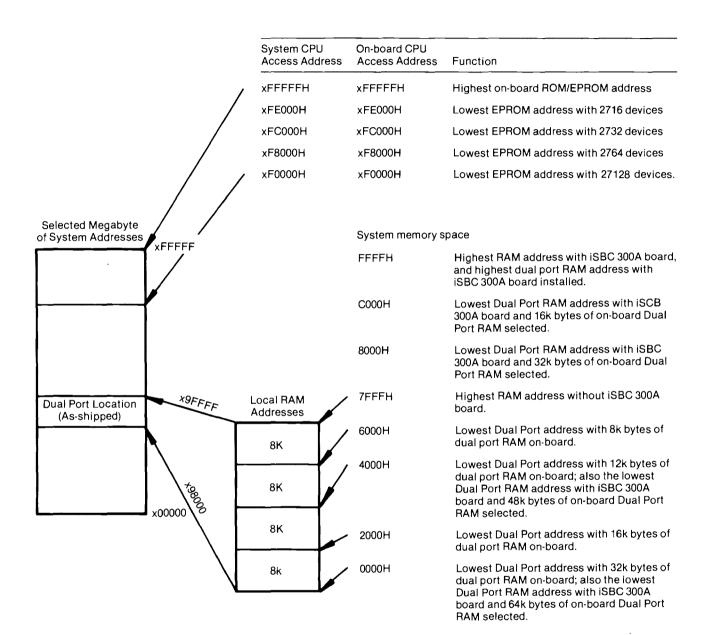

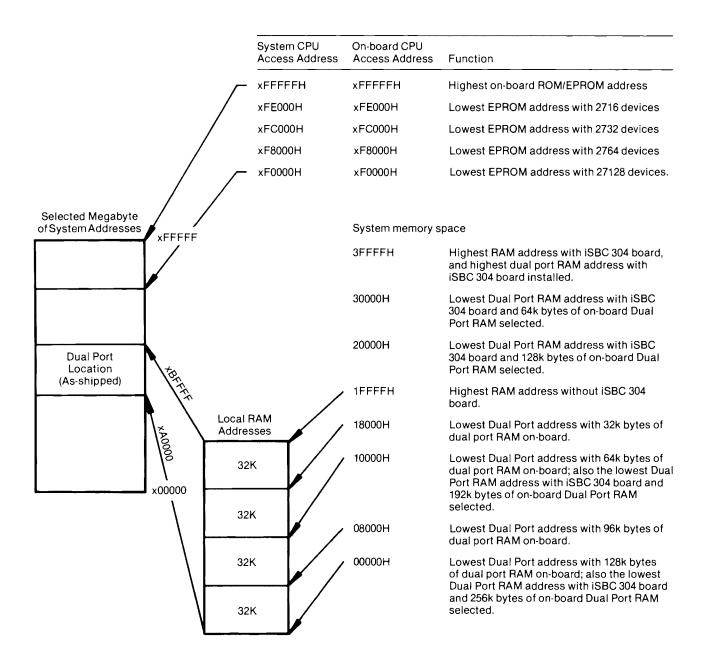

The slave RAM feature on the iSBC 86/14 board can be configured to allow either 8k, 16k, 24k, or 32k byte access by another bus master. If the iSBC 300A RAM Expansion Multimodule Board is installed the dual port memory increments are 16k, 32k, 48k, or 64k. The slave RAM feature on the iSBC 86/30 board can be configured to allow either 32k, 64k, 96k or 128k byte access by another bus master. If the iSBC 304 RAM Expansion Multimodule Board is installed the dual port memory increments are 64k, 128k, 192k, or 256k. Thus, the iSBC 86/14/30 board can be configured to allow other bus masters to access a segment of the on-board RAM and still reserve another segment strictly for on-board use. The addressing scheme accommodates 16-bit, 20-bit, and 24-bit addressing.

Four 28-pin IC sockets are included to accommodate user-installed read only memory. Configuration jumpers allow read memory to be installed in 2k, 4k, 8k, or 16k byte increments. The memory address decoding scheme on the iSBC 86/14/30 board assumes that the two ROM/EPROM sockets, providing the low byte and high byte of any word access, contain the same memory capacity.

The iSBC 86/14/30 board includes 24 programmable parallel I/O lines implemented by means of an Intel 8255A-5 Programmable Peripheral Interface (PPI). Software configures the I/O lines in any combination of unidirectional input/output and bidirectional ports. The I/O interface may be customized to meet specific peripheral requirements and, in order to take full advantage of the large number of possible I/O configurations, IC sockets are provided for interchangeable I/O line drivers and terminators. Hence, the flexibility of the parallel I/O interface is further enhanced by the capability of selecting the appropriate combination of optional line drivers and terminators to provide the required sink current, polarity, and drive/termination characteristics for each application. The 24-programmable I/O lines and signal ground lines are brought out to a 50-pin edge connector (J1). The RS232C-compatible serial I/O port at connector J2 is controlled and interfaced by an Intel 8251A PCI (Programmable Communications Interface) chip. The PCI is individually programmable for operation in most synchronous or asynchronous serial data transmission formats (including IBM Bi-Sync). In the synchronous mode the following features are programmable:

- a. Character length,

- b. Sync character (or characters), and

- c. Parity.

In the asynchronous mode the following features are programmable:

- a. Character length,

- b. Baud rate factor (clock divide ratios of 1, 16, or 64),

- c. Stop bits, and

- d. Parity.

In both the synchronous and asynchronous modes, the serial I/O port features half- or full-duplex, double buffered transmit and receive capability on an RS232C compatible interface. In addition, PCI error detection circuits can check for parity, overrun, and framing errors. The PCI transmit and receive clock rates are supplied by a programmable baud rate/time generator. These clocks may optionally be supplied from an external source. The RS232C command lines, serial data lines, and signal ground lines are brought out to a 26-pin edge connector (J2).

Three independent, fully programmable 16-bit interval timer event counters are provided by an Intel 8253-5 Programmable Interval Timer (PIT). Each counter is capable of operating in either BCD or binary modes; two of these counters are available to the systems designer to generate accurate time intervals under software control. Routing for the outputs and trigger inputs of two of these counters may be independently configured in the interrupt jumper matrix. The gate/trigger inputs of the two counters may be routed to I/O terminators associated with the 8255A PPI or as input connections from the 8255A PPI. The third counter is used as a programmable baud rate generator for the serial I/O port.

In using the PIT counters on the iSBC 86/14/30 board, the systems designer simply configures, via software, each counter independently to meet system requirements. Whenever a given time delay or count is needed, software commands to the 8253-5 PIT select the desired function. The contents of each counter may be read at any time during system operation with simple operations for event counting applications, and special commands are included so that the contents of each counter can be read "on the fly".

The iSBC 86/14/30 board provides vectoring for bus vectored (BV) and non-bus vectored (NBV) interrupts. An on-board Intel 8259A Programmable Interrupt Controller (PIC) handles up to eight BV or NBV interrupts. By using external PIC's slaved to the on-board PIC (master), the interrupt structure can be expanded to handle and resolve the priority of up to 64 BV sources. The PIC, which can be programmed to respond to edge-sensitive or level-sensitive inputs, treats each true input signal condition as an interrupt request. After resolving the interrupt priority, the PIC issues a signle interrupt request to the CPU. Interrupt priorities are independently programmable under software control. The programmable interrupt priority modes are:

- Fully Nested Mode. Each interrupt request has a fixed priority: input 0 is highest, input 7 is lowest.

- b. Special Fully Nested Mode. This mode is the same as nested mode, except that when a slave PIC is being serviced, it is not locked out from the master PIC priority logic and when exiting from the interrupt service routine, the software must check for pending interrupts from the slave PIC just serviced.

- c. Auto-Rotating Priority Mode. Each interrupt request has equal priority. Each level, after receiving service, becomes the lowest priority level until the next interrupt occurs.

- Specific Priority Mode. Software assigns lowest priority.

Priority of all other levels is in numerical sequence based on lowest priority.

- e. Special Mask Mode. Interrupts at the level being serviced are inhibited, but all other levels of interrupts (higher and lower) are enabled.

- f. Poll. The CPU internal interrupt enable is disabled. Interrupt service is acheived by programmer initiative using a Poll command.

The CPU includes a non-maskable interrupt (NMI) and a maskable interrupt (INTR). The NMI is intended to be used for catastrophic events such as power failures that require immediate action of the CPU. The INTR interrupt is driven by the 8259A PIC which, on demand, provides an 8-bit identifier of the interrupting source. The CPU multiplies the 8-bit identifier by four to derive a pointer to the service routine for the interrupting device.

Interrupt requests may originate from 28 sources without the necessity of external hardware. Two jumper-selectable interrupt requests can be automatically generated by the Programmable Peripheral Interface (PPI) when a byte of information is ready to be transferred to the 8086-2 CPU (e.g., input buffer is full) or a byte of information has been transferred to a peripheral device (e.g., output buffer is empty). Two jumper-selectable interrupt requests can be automatically generated by the PCI when a character is ready to be transferred to the 8086-2 CPU (e.g., receive channel buffer is full) or when a character is ready to be transmitted (e.g., transmit channel data buffer is empty). A jumper-selectable interrupt request can be generated by two of the programmable counters and eight additional interrupt request lines are available to the user for direct interfaces to user-designated peripheral devices via the Multibus interface. One interrupt request line may be jumper routed directly from a peripheral via the parallel I/Odriver/terminator section and one power fail interrupt may be input via auxiliary connector P2.

The iSBC 86/14/30 board includes the resources for supporting a variety of OEM system requirements. For those applications requiring additional processing capacity and the benefits of multiprocessing (e.g., several CPU's and/or controllers logically sharing systems tasks with communication over the Multibus interface), the iSBC 86/14/30 board provides full bus arbitration control logic. This control logic allows up to three bus masters (e.g., combination of iSBC 86/14 board, DMA controller, diskette controller) to share the Multibus interface in serial (daisy-chain) priority fashion or up to 16 bus masters to share the Multibus interface using an external parallel priority resolving network.

The Multibus interface arbitration logic operates synchronously with the bus clock, which is derived either from the iSBC 86/14/30 board or can be optionally generated by some other bus master. Data, however, is transferred via a handshake between the controlling master and the addressed slave module. This arrangement allows different speed controllers to share resources on the same bus, and transfers via the bus proceed asynchronously. Thus, the transfer speed is dependent on transmitting and receiving devices only. This design prevents slower master modules from being handicapped in their attempts to gain control of the bus, but does not restrict the speed at which faster modules can transfer data via the same bus. The most obvious applications for the master-slave capabilities of the bus are multiprocessor configurations, high-speed direct memory access (DMA) operations, and high-speed peripheral control, but are by no means limited to these three.

The iSBC 86/14/30 board contains programmable resources for sending and receiving a 4-bit bank select address with any 20-bit Multibus address. This feature allows access to one of 16 megabytes of Multibus address space and mapping of on-board dual Port RAM into any one of 16 megabytes of Multibus address space.

#### 1-3. OPTIONAL RAM AND ROM/EPROM EXPANSION

Adding the optional iSBC 300A RAM Expansion Multimodule Board onto the iSBC 86/14 board allows the on-board RAM to be expanded by 32k bytes (for an on-board total of 64k bytes). If the optional iSBC 304 RAM Expansion Multimodule is installed onto the iSBC 86/30 board, the amount of on-board RAM can be expanded by 128k bytes (for an on-board total of 256k bytes).

#### 1-4. SYSTEM SOFTWARE DEVELOPMENT

The development cycle of iSBC 86/14/30 Single Board Computer based products may be significantly reduced using an Intel Intellec Microcomputer Development System with the optional MDS-311 8086 Software Development package. The MDS-311 8086 Software Development package includes Intel's high level programming language, PL/M 86. PL/M 86 provides the capability to program in a natural, algorithmic language and eliminates the need to manage register usage or allocate memory. PL/M 86 programs can be written in a much shorter time than assembly language programs for a given application.

#### 1-5. EQUIPMENT SUPPLIED

Each iSBC 86/14/30 board is shipped with a current revision of the schematic diagram. Insert the drawing into this manual if it is a later revision level than the contained drawing. No other equipment is provided with the iSBC 86/14/30 board.

### 1-6. EQUIPMENT REQUIRED

Because the iSBC 86/14/30 board is designed to satisfy a variety of applications, the user must purchase and install only those components required to satisfy his particular needs. A list of components required to configure the iSBC 86/14/30 board is provided in Chapter 2.

#### 1-7. SPECIFICATIONS

Specifications of the iSBC 86/14/30 Single Board Computer are listed in Table 1-1.

Table 1-1. Specifications

| WORD SIZE<br>Instruction:        | 8, 16, 24, 32, 40, or 48 bits.                                                 |

|----------------------------------|--------------------------------------------------------------------------------|

| Data:                            | 8/16 bits.                                                                     |

| SYSTEM CLOCK SPEED:              | 5.00 MHz or 8.00 MHz, jumper selectable.                                       |

| INSTRUCTION CYCLE TIME<br>8 MHz: | 750 nanoseconds.<br>250 nanoseconds (assumes instruction is in the<br>queue).  |

| 5 MHz:                           | 1.2 microseconds.<br>400 nanoseconds (assumes instruction is in the<br>queue). |

| MEMORY CYCLE TIME<br>RAM:        | 750 nanoseconds.                                                               |

l

Table 1-1. Specifications (continued)

| EPROM:                                       | 500 to 875 nanoseconds, jumper selectable.                                                                                                                                                                                            |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMORY ARRAY<br>On-board EPROM:              | 4 chip sockets; user-provided EPROM device in<br>2k by 8-bit, 4k by 8-bit, 8k by 8-bit, or 16k<br>by 8-bit capacity.                                                                                                                  |

| On-board Dynamic RAM:                        |                                                                                                                                                                                                                                       |

| iSBC 86/14 Board                             | 32k bytes of dynamic RAM (64k bytes if iSBC<br>300A RAM Expansion Multimodule Board is<br>installed); data integrity maintained during<br>power failure with user-furnished batteries.                                                |

| iSBC 86/30 Board                             | 128k bytes of dynamic RAM (256k bytes if iSBC<br>304 RAM Expansion Multimodule Board is<br>installed); data integrity maintained during<br>power failure with user-furnished batteries.                                               |

| Off-board Expansion:                         | Up to 16 megabytes of user-specified combination of RAM, ROM, and EPROM.                                                                                                                                                              |

| MEMORY ADDRESS RANGES                        |                                                                                                                                                                                                                                       |

| On-board EPROM:                              | FE000-FFFFFH (using 2k by 8 bit Statics or<br>EPROMs),<br>FC000-FFFFFH (using 4k by 8-bit Statics or<br>EPROMs),<br>F8000-FFFFFH (using 8k by 8-bit Statics or<br>EPROMs),<br>F0000-FFFFFH (using 16k by 8-bit Statics or<br>EPROMs). |

| On-board Dual<br>Port RAM (local             |                                                                                                                                                                                                                                       |

| CPU Access):<br>1SBC 86/14 Board             | 00000-07FFFH, as-shipped configuration.<br>00000-0FFFFH (if iSBC 300A RAM Expansion<br>Multimodule Board is installed).                                                                                                               |

| 1SBC 86/30 Board                             | 00000-lFFFFH, as-shipped configuration.<br>00000-3FFFFH (if iSBC 304 RAM Expansion<br>Multimodule Board is installed).                                                                                                                |

| On-board RAM (Multibus<br>Interface Access): | Jumpers allow the board to act as slave RAM device for access by another bus master.                                                                                                                                                  |

Table 1-1. Specifications (continued)

| iSBC 86/14 Board                         | Default Multibus address of the dual port RAM<br>is set at 9FFFFH through 98000H; all on-board<br>RAM is dual ported.                                                                                                                                                                                                                                  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Multibus addresses (for dual port RAM) may<br>begin at any 8k boundary of any 1-megabyte<br>segment of 16 megabytes of system address<br>space. RAM is removed from the dual port in<br>increments of 8k (e.g., either a 0k, 8k, 16k,<br>24k, or 32k). The dual port addresses must not<br>overlap a 128k byte boundary.                               |

| iSBC 86/30 Board                         | Default Multibus address of the dual port RAM<br>is set at BFFFFH down through A0000H; all<br>on-board RAM is dual ported.                                                                                                                                                                                                                             |

|                                          | Multibus addresses (for dual port RAM) may<br>begin at any 32k boundary within any 1-megabyte<br>segment of 16 megabytes of system address<br>space. RAM is removed from the dual port in<br>increments of 32k (e.g., either a Ok, 32k, 64k,<br>96k, or 128k). The Multibus address for the<br>dual port RAM must not overlap a 256k byte<br>boundary. |

| I/O CAPABILITY                           |                                                                                                                                                                                                                                                                                                                                                        |

| Parallel:                                | 24 programmable I/O lines using the 8255A PPI.                                                                                                                                                                                                                                                                                                         |

| Serial:                                  | 1 programmable RS232C interface using the 8251A PCI.                                                                                                                                                                                                                                                                                                   |

| Expansion:                               | 2 iSBX Bus Connectors providing expansion via<br>either single-wide or double-wide, 8-bit or<br>16-bit, Multimodule boards.                                                                                                                                                                                                                            |

| SERIAL COMMUNICATIONS<br>CHARACTERISTICS |                                                                                                                                                                                                                                                                                                                                                        |

| Synchronous:                             | 5 to 8 bit characters; internal or external character synchronization; automatic sync bit insertion.                                                                                                                                                                                                                                                   |

| Asynchronous:                            | 5 to 8 bit characters; break character<br>generation; 1, 1 1/2, or 2 stop bits; false<br>start—up detection.                                                                                                                                                                                                                                           |

| Baud Rates:                                        |                         |                                        |                              |         |

|----------------------------------------------------|-------------------------|----------------------------------------|------------------------------|---------|

|                                                    | Frequency               |                                        | Baud Rate (Hz                | )       |

|                                                    | (kHz)                   | Synchrone                              |                              | hronous |

|                                                    |                         |                                        | divide by 16                 |         |

|                                                    | 153.6                   | ***                                    | 9600                         | 2400    |

|                                                    | 76.8                    |                                        | 4800                         | 1200    |

|                                                    | 38.4                    | 38400                                  |                              | 600     |

|                                                    | 19.2                    | 19200                                  | 1200                         | 300     |

|                                                    | 9.6                     | 9600                                   | 600                          | 150     |

|                                                    | 4.8                     | 4800                                   |                              | 75      |

|                                                    |                         | 2400                                   | 150                          |         |

|                                                    | 1.76                    | 1760                                   | 110                          |         |

| TIMER OPERATIONS                                   | 2.46 MHz +              | 0 19 Pofe                              |                              |         |

| Input Frequencies:                                 | 1.23 MHz +<br>153.6 kHZ | 0.1%                                   | erence                       |         |

| PHYSICAL CHARACTERISTICS<br>Width:                 | 12.00 in.               | (30.48 cm.                             | )                            |         |

| Height:                                            | 6.75 in. (              | •                                      |                              |         |

| Depth:                                             | 0.70 in. (              |                                        |                              |         |

| Weight:                                            | 14 oz. (38              | 8 gm.)                                 |                              |         |

|                                                    |                         |                                        |                              |         |

| ENVIRONMENTAL REQUIREMEN                           | TS                      |                                        |                              |         |

| Operating Temp:                                    | 0 to 55°C               |                                        |                              |         |

| Relative Humidity:                                 | to 90%, no              | n-condensi                             | ng                           |         |