# iSBC 88/25™ SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Order Number: 143825-001

Copyright © 1981 Intel Corporation

| REV. | <b>REVISION HISTORY</b> | PRINT<br>DATE |

|------|-------------------------|---------------|

| -001 | Original Issue          | 10/81         |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

,

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP    | Intelevision    | Micromap       |

|--------|-----------------|----------------|

| CREDIT | Intellec        | Multibus       |

| i      | iRMX            | Multimodule    |

| ICE    | iSBC            | Plug-A-Bubble  |

| iCS    | iSBX            | PRÖMPT         |

| im     | Library Manager | Promware       |

| INSITE | MCS             | RMX/80         |

| Intel  | Megachassis     | System 2000    |

| Intel  | Micromainframe  | UPI            |

| -      |                 | <i>µ</i> Scope |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or RMX and a numerical suffix.

# PREFACE

This manual provides general information, installation and setup instructions, programming guidelines for the on-board, programmable devices, board level principles of operation, and service information for the iSBC 88/25 Single Board Computer. Related information is provided in the following publications:

- The iAPX 88 Book, Order Number 210200.

- iSBC Applications Manual, Order Number 142687.

- Intel Multibus Specification, Order No. 9800683.

- Intel Multibus Interfacing, Application Note AP-28A.

- Intel iSBX Bus Specification, Order No. 142686.

- Designing iSBX Multimodule Boards, Application Note AP-96.

- *iSBC 337 Numeric Data Processor Hardware Reference Manual,* Order No. 142887.

- *iRMX 88 Reference Manual*, Order No. 143232.

- Introduction to the iRMX 80/88 Real-Time Multitasking Executives, Order No. 143238.

- *iRMX 88 Installation Instructions*, Order No. 143231.

- *iRMX 80/88 Interactive Configuration Utilities*, Order No. 142603.

- Guide to Writing Device Drivers for the iRMX 86 and iRMX 88 I/O Systems, Order No. 142926.

- The Intel Peripheral Design Handbook.

- The Intel Component Data Catalog.

- The Intel Systems Data Catalog.

# Jinta

# **CONTENTS**

# CHAPTER 1 GENERAL INFORMATION

| Introduction                  | 1-1 |

|-------------------------------|-----|

| Description                   | 1-2 |

| Documentation Supplied        | 1-2 |

| Additional Equipment Required | 1-3 |

| Specifications                | 1-3 |

PAGE

#### **CHAPTER 2 PREPARATION FOR USE**

| Introduction                           | $2 \cdot 1$ |

|----------------------------------------|-------------|

| Unpacking and Inspection               | 2-1         |

| Installation Considerations            | 2-1         |

| Minimal Operating Requirements         | 2-1         |

| Power Requirements                     | 2-1         |

| Cooling Requirements                   | $2 \cdot 1$ |

| ROM/PROM Installation                  |             |

| iSBC 341 Module Installation           | 2-3         |

| Page Select Jumper Configuration       | 2-3         |

| On Board RAM Expansion and             |             |

| iSBC 302 RAM Module                    |             |

| Installation                           | 2-4         |

| Byte-Wide RAMS                         | 2-6         |

| Line Drivers and I/O Terminators       | 2-6         |

| Jumper Configurations                  | 2-6         |

| Interval Timer Jumper Configurations   | 2-6         |

| Serial Port Jumper Connections         | 2-6         |

| Parallel Port Jumper Configurations    | 2-8         |

| Port C8 Transceiver Conversion         | 2-9         |

| Interrupt Matrix Jumper Configurations | 2-9         |

| Multibus Vectored Interrupts           | 2-14        |

| System Clock Jumper Selection          |             |

| Bus Clock and Constant Clock Selection | 2-15        |

| Wait State Generator Selection         | 2-15        |

| Failsafe Timer Selection               | 2-15        |

| Multibus Interface Arbitration         | 2-16        |

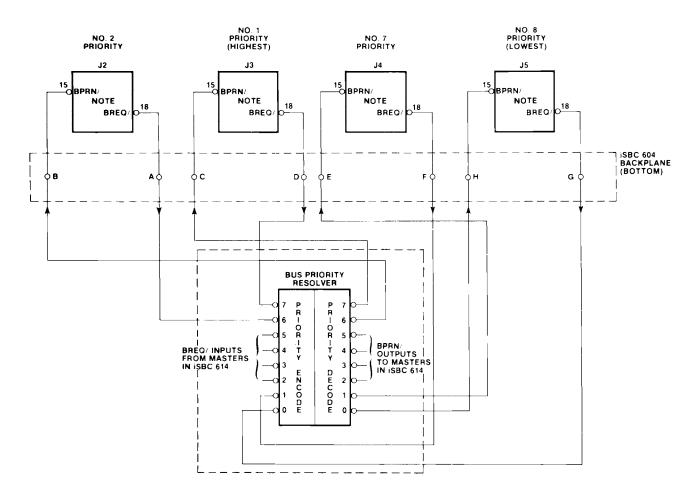

| Board Priority Resolution              | 2-16        |

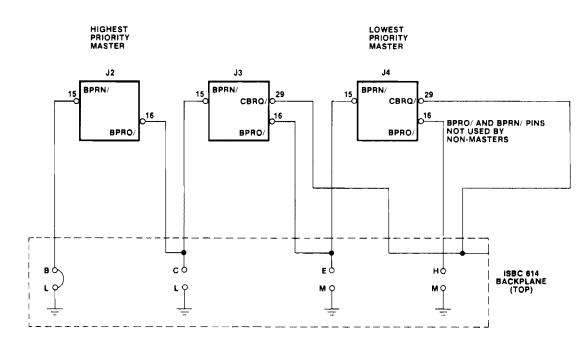

| Serial Priority Resolution             | 2-17        |

| Parallel Priority Resolution           | 2-18        |

| Connector Information                  | 2-18        |

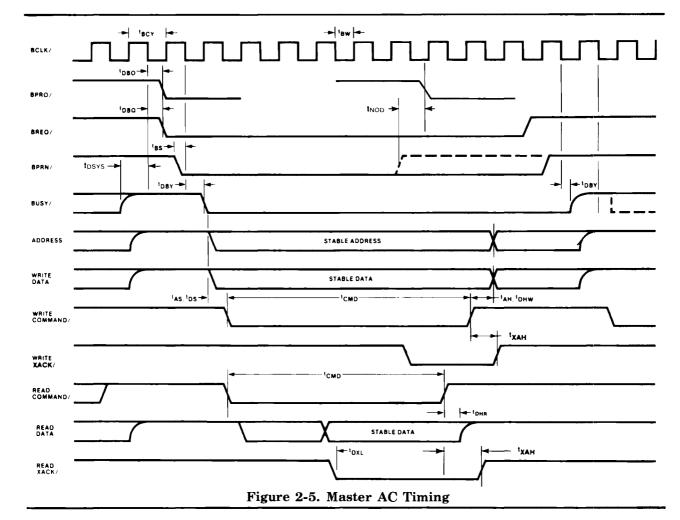

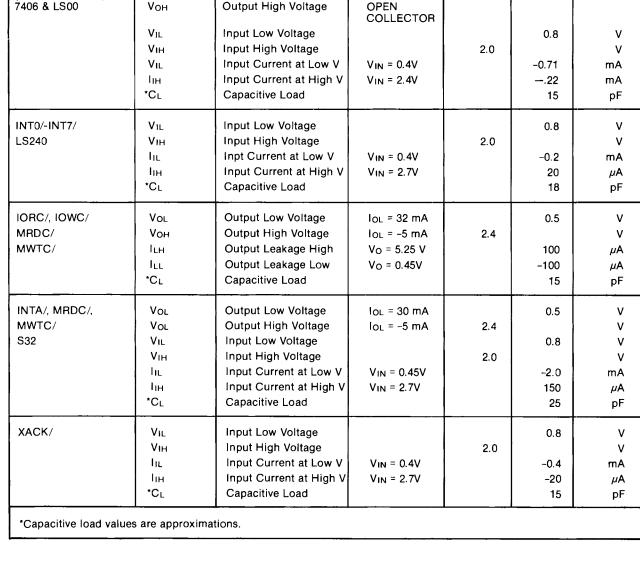

| Multibus Signal Characteristics        | 2-18        |

| Parallel I/O DC Characteristics        | 2-27        |

| Power Fail Battery Backup Provisions   |             |

| Parallel I/O Cabling                   | 2-28        |

| Serial I/O Cabling                     | 2-29        |

| Multimodule Boards and the iSBX Bus    | 2-29        |

| Final Installation                     | 2-30        |

# CHAPTER 3 PROGRAMMING INFORMATION

| Introduction              | 3-1 |

|---------------------------|-----|

| Memory Addressing         | 3-1 |

| I/O Addressing            | 3-1 |

| System Initialization     |     |

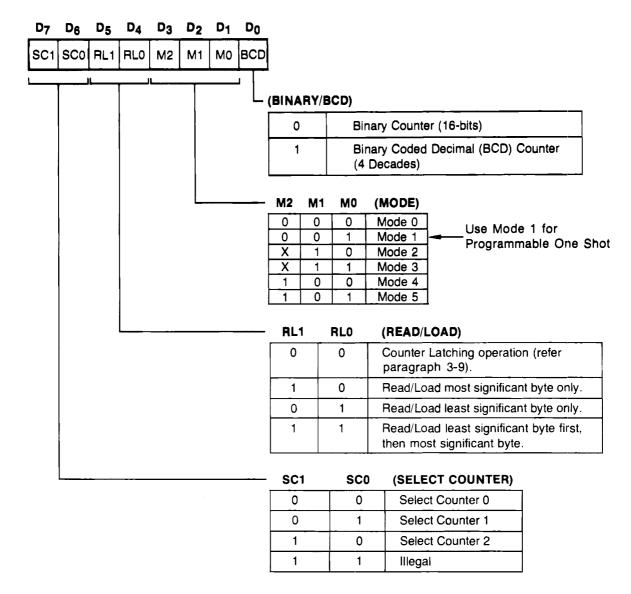

| 8253 PIT Programming      | 3-2 |

| Mode Control Word & Count | 3-2 |

| Addressing                | 3-5 |

## PAGE

|                                        | IU | OL   |

|----------------------------------------|----|------|

| Initialization                         |    | 3-5  |

| Operation                              |    | 3-5  |

| Counter Read                           |    | 3-5  |

| Clock Frequency/Divide Ratio Selection |    | 3-7  |

| Rate Generator/Interval Timer          |    | 3-7  |

| Interrupt Timer                        |    |      |

| 8251A PCI Programming                  |    | 3-8  |

| Mode Instruction Format                |    | 3-8  |

| Sync Characters                        |    | 3-8  |

| Command Instruction Format             |    | 3-9  |

| Reset                                  |    |      |

| Addressing                             |    |      |

| Initialization                         |    |      |

| 8255A PPI Programming                  |    |      |

| Control Word Format                    |    |      |

| Addressing                             |    |      |

| Initialization                         |    |      |

| Operation                              |    |      |

| 8259A PIC Programming                  |    |      |

| Interrupt Priority Modes               |    |      |

| Fully Nested Mode                      |    |      |

| Special Fully Nested Mode              |    |      |

| Automatic Rotating Mode                |    |      |

| Specific Rotating Mode                 |    |      |

| Special Mask Mode                      |    | 3-16 |

| Poll Mode                              |    |      |

| Status Read                            |    | 3-17 |

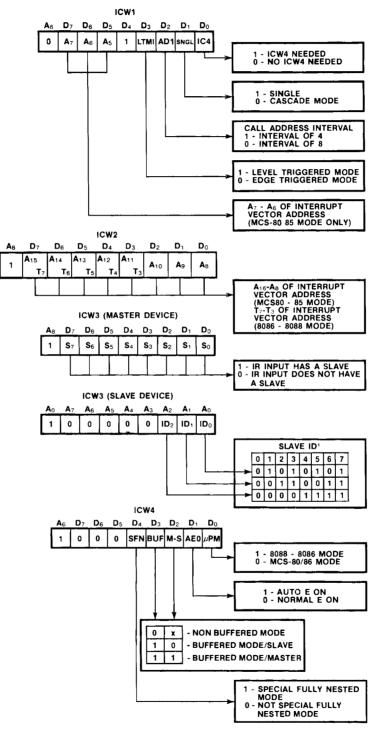

| Initialization Command Words           |    | 3-17 |

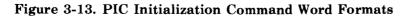

| Operation Command Words                |    |      |

| Addressing                             |    |      |

| Initialization                         |    |      |

| Operation                              |    |      |

| 8088 Interrupt Handling                |    | 3-24 |

| Non-Maskable Interrupt (NMI)           |    |      |

| Maskable Interrupt (INTR)              |    | 3-25 |

| Master PIC Byte Identifier             |    | 3-25 |

| Slave PIC Byte Identifier              |    | 3-25 |

|                                        |    |      |

# CHAPTER 4 PRINCIPLES OF OPERATION

| Introduction                 | 4-1 |

|------------------------------|-----|

| Major Functional Blocks      | 4-1 |

| 8088 Processor               |     |

| On-Board Timing              |     |

| Random Access Memory (RAM)   | 4-1 |

| Read-Only Memory (ROM)       |     |

| Address Decoding             |     |

| Memory Address Decoding      | 4-3 |

| I/O Address Decoding         |     |

| 8253-5 Interval Timer        |     |

| Serial Port Circuitry        | 4-4 |

| Parallel Port Interface      | 4-4 |

| Interrupt Control and Timing | 4-4 |

| Multibus Interface           |     |

| iSBX Multimodule Interface   |     |

# **CONTENTS** (Continued)

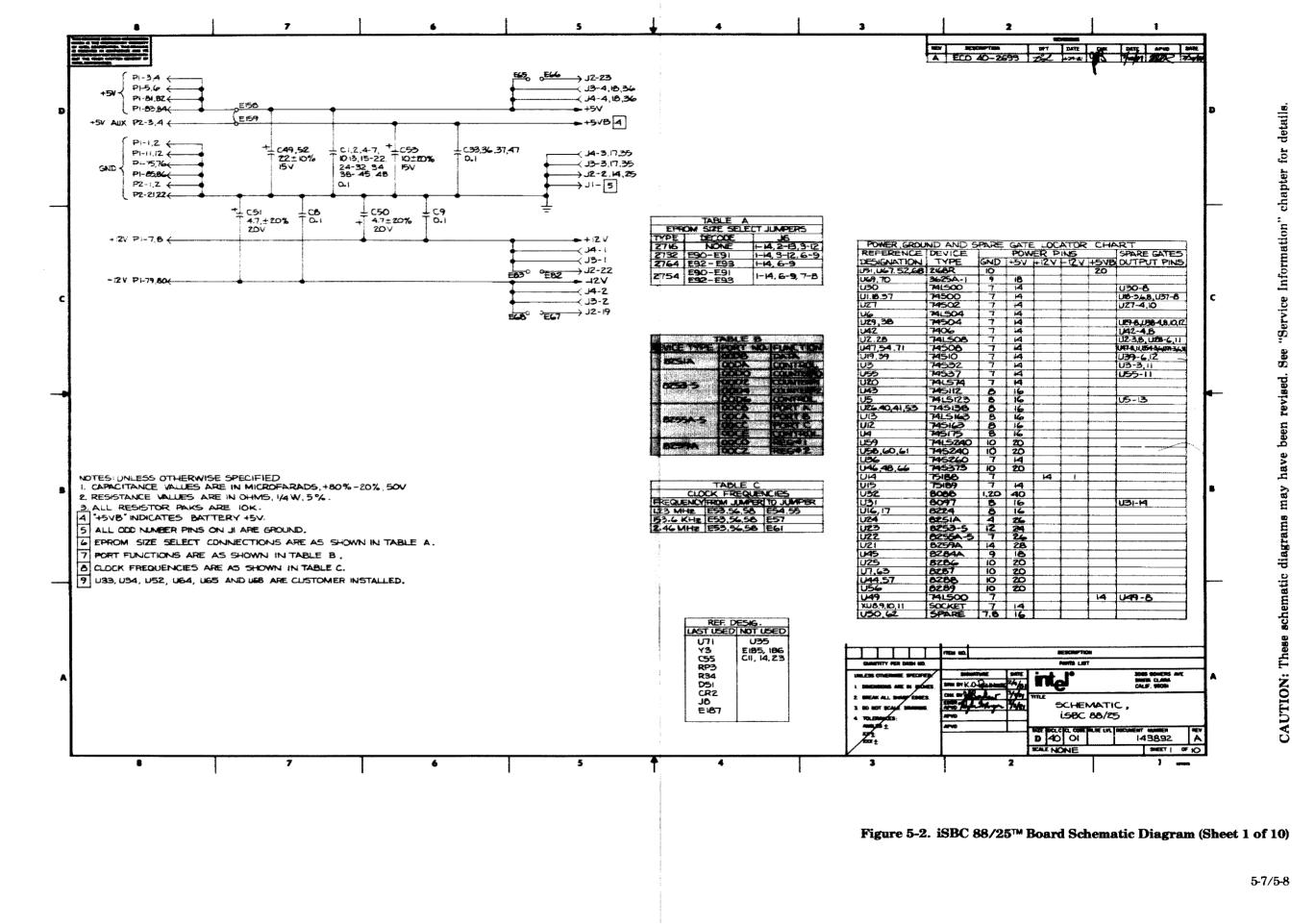

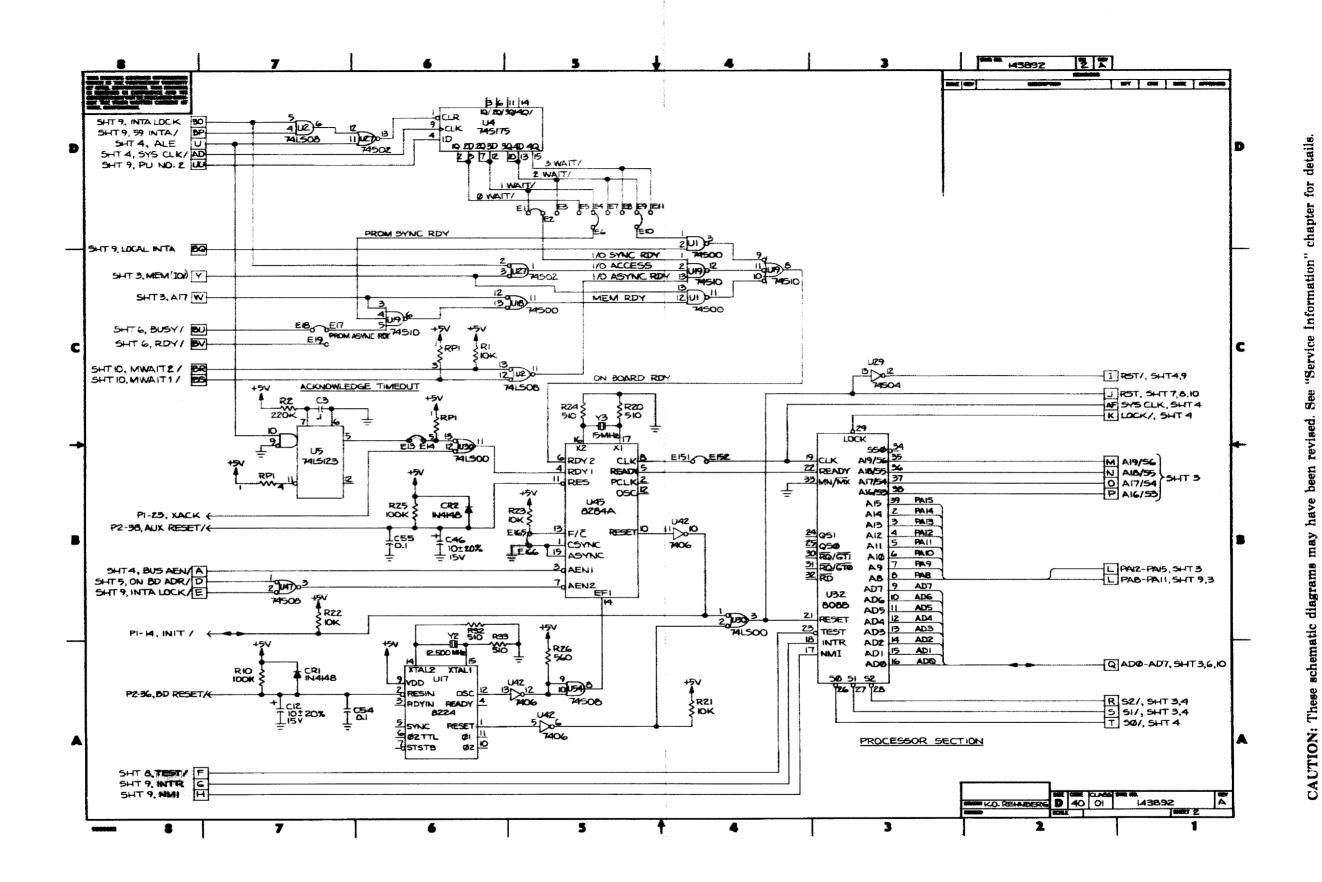

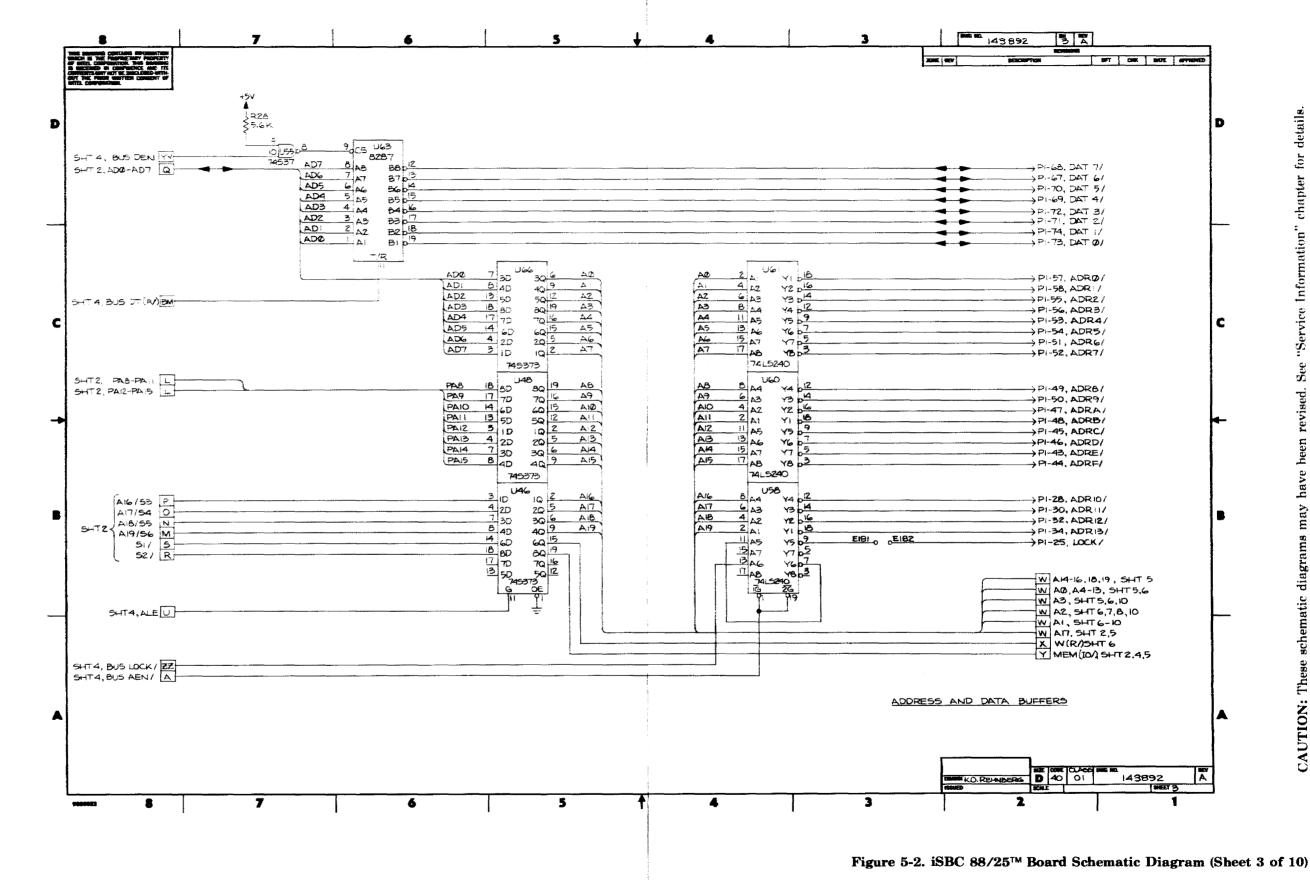

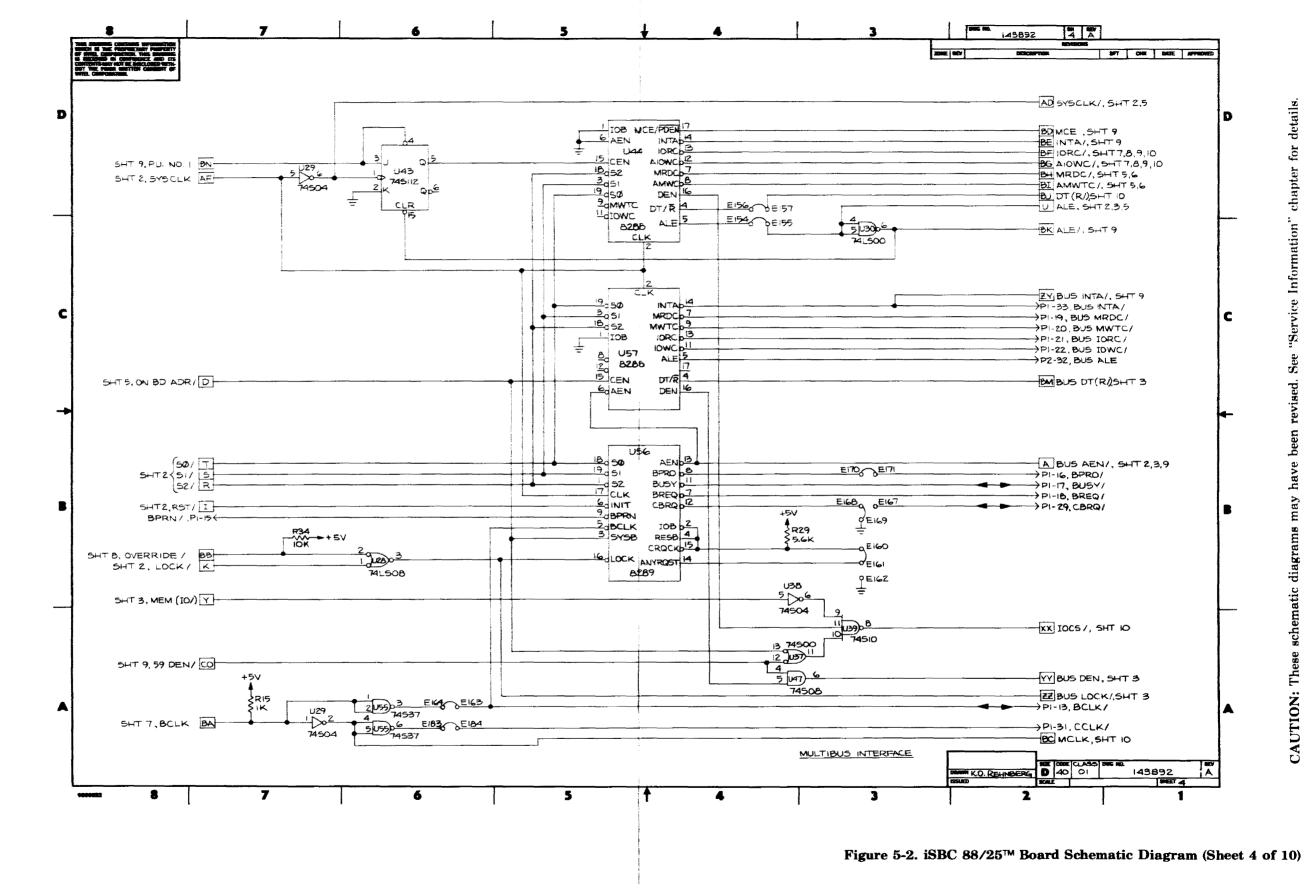

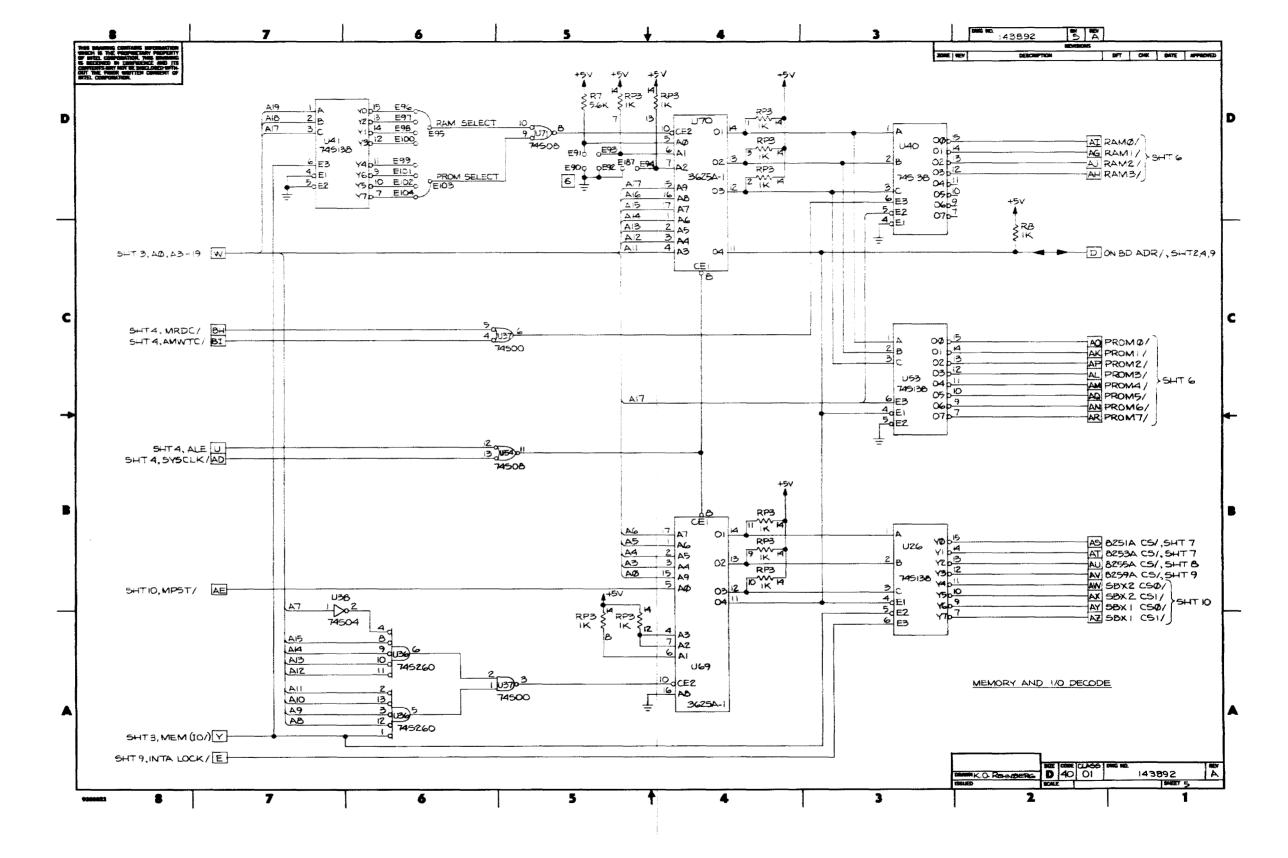

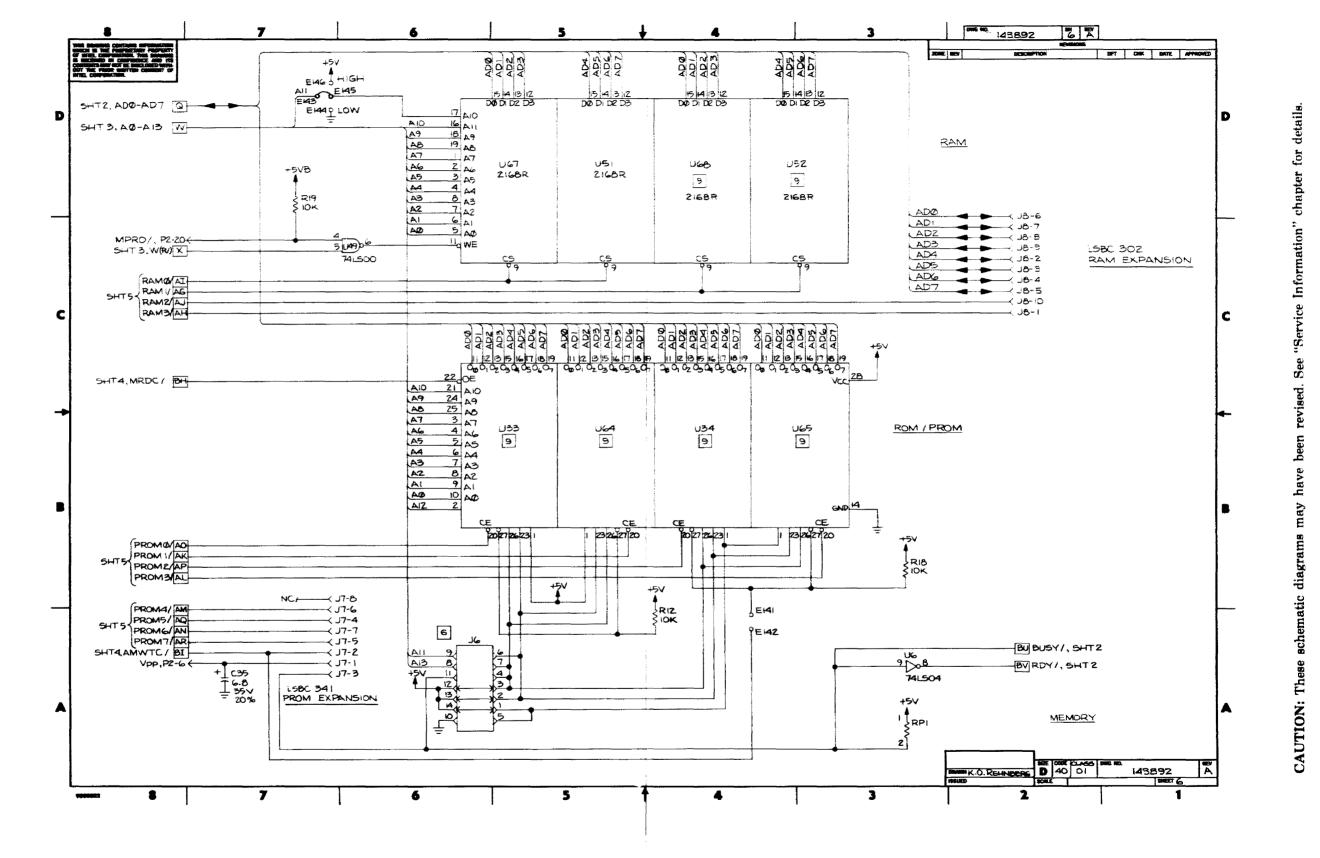

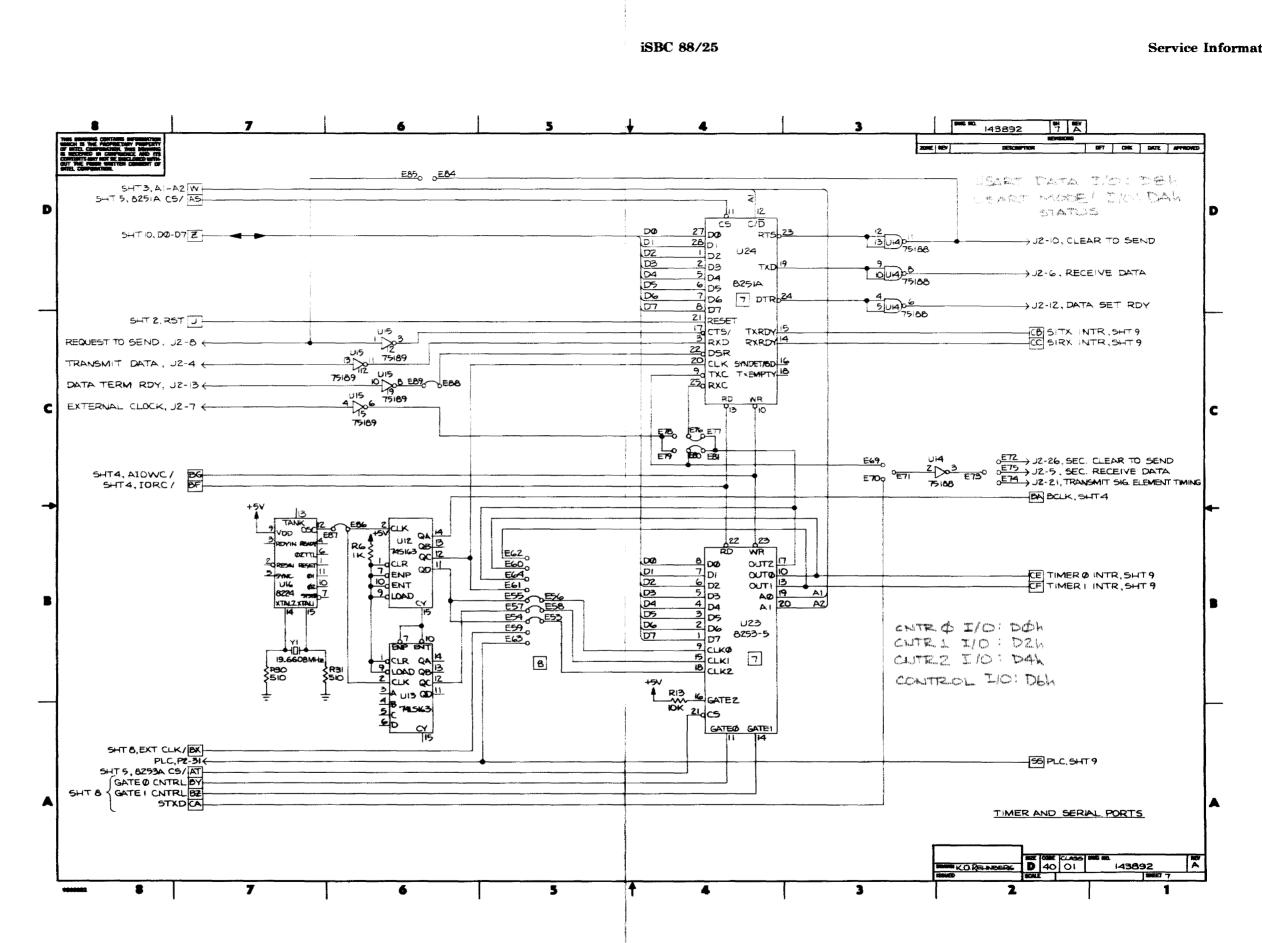

#### CHAPTER 5 SERVICE INFORMATION

|                               | 0-1 |

|-------------------------------|-----|

| Service and Repair Assistance | 5-1 |

| Replacement Parts             | 5-1 |

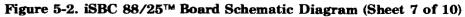

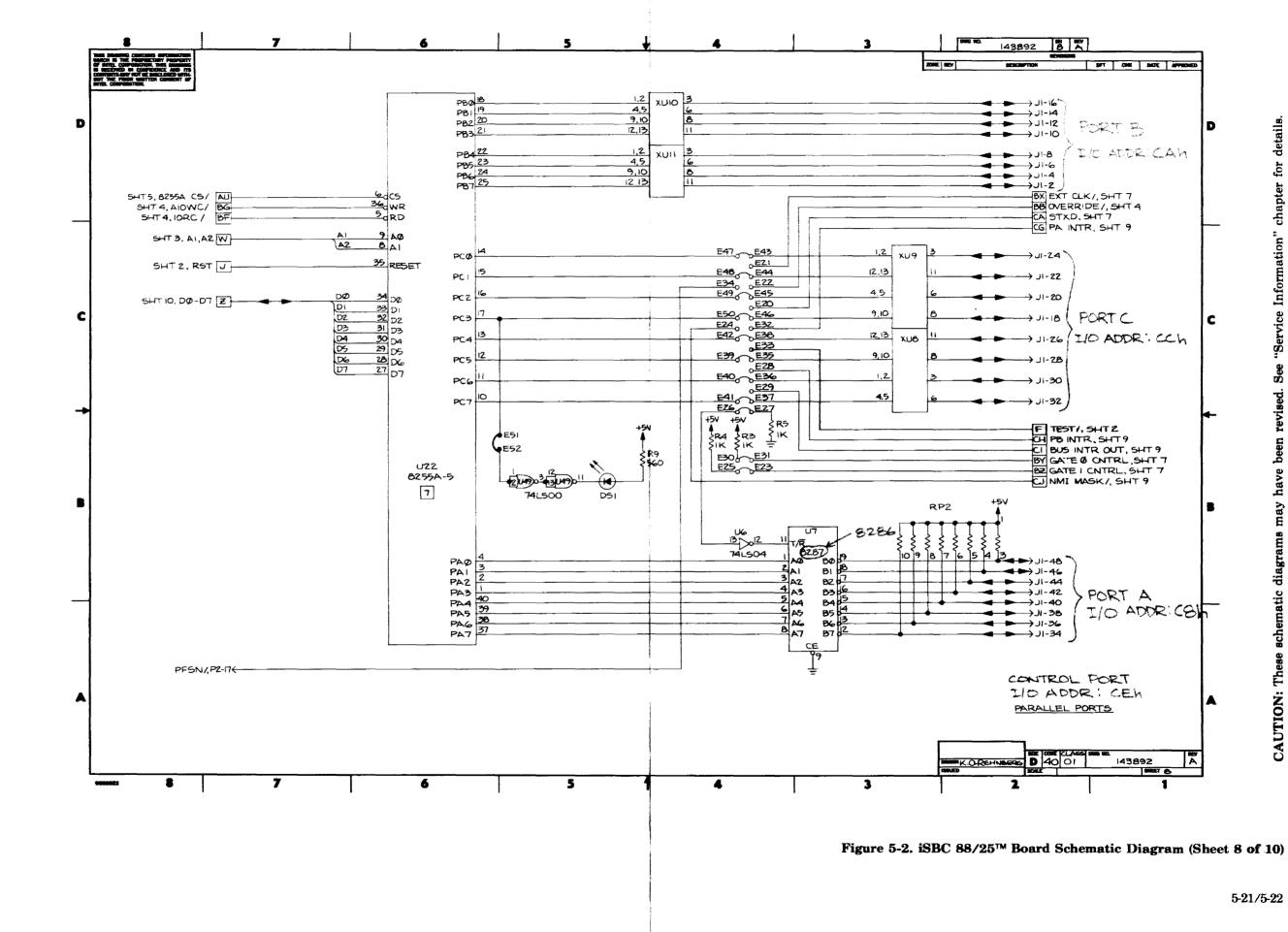

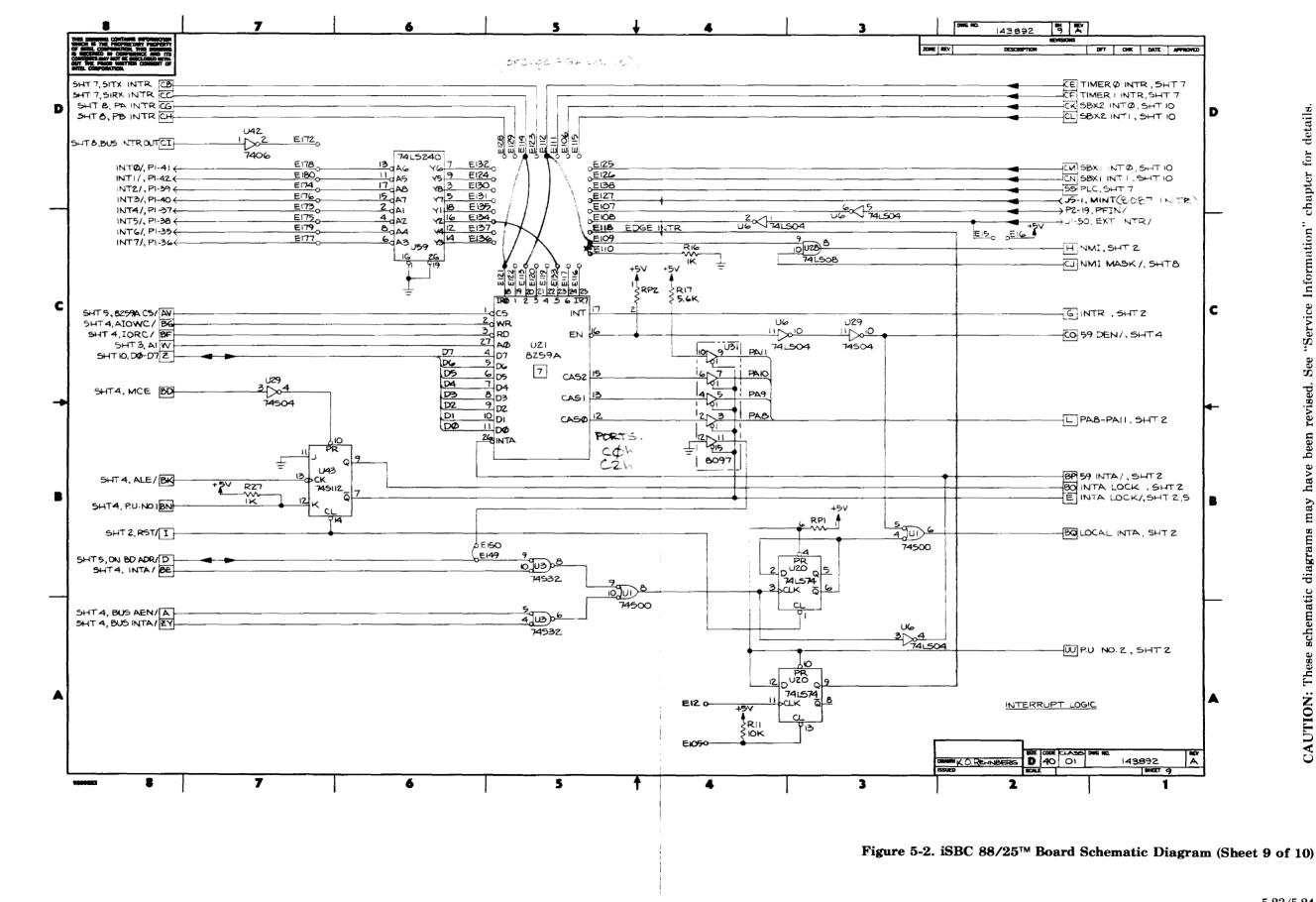

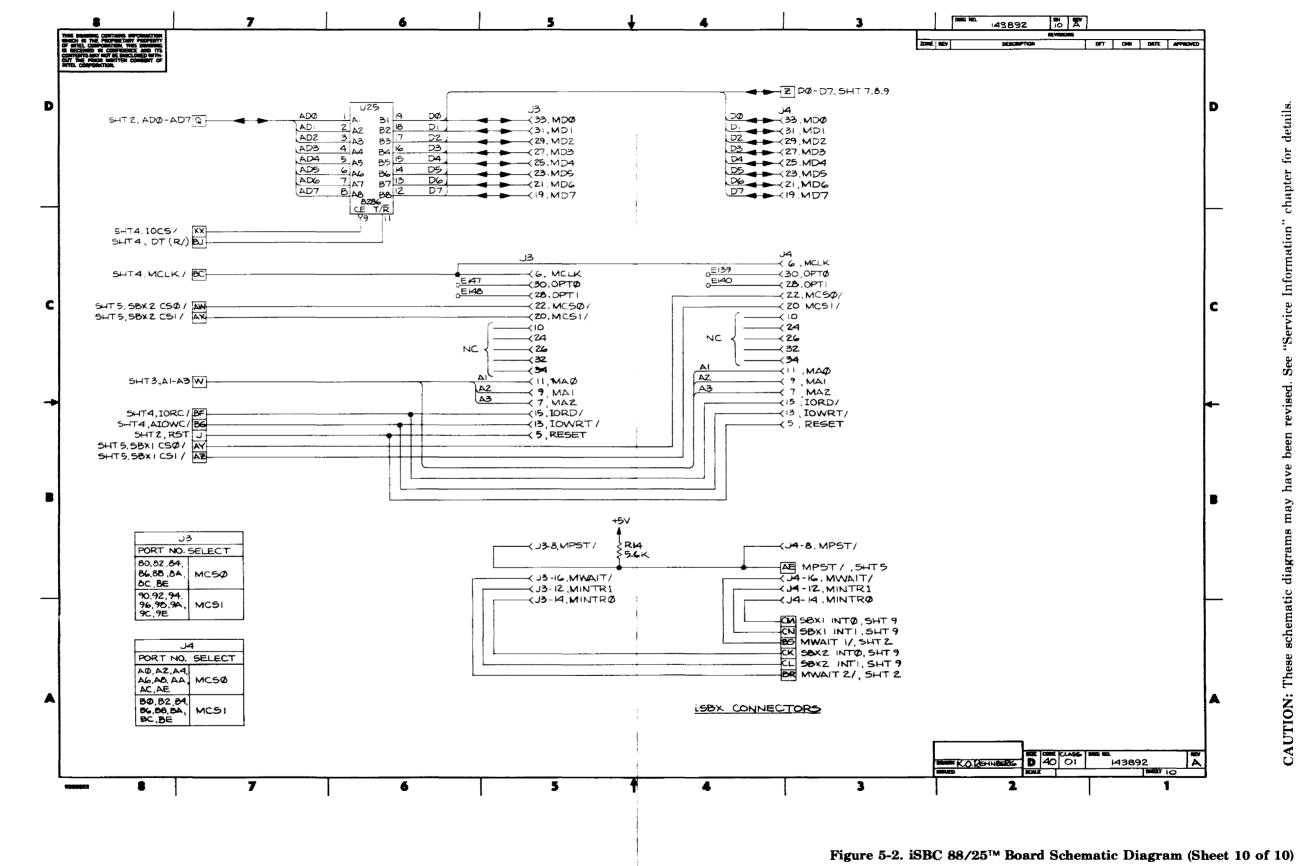

| Service Diagrams              | 5-1 |

PAGE

5 1

#### APPENDIX A DECODE PROM MEMORY MAPS

APPENDIX B iSBX 341 JUMPER CONNECTIONS

TABLES

| Table        | Title                                        | Page         |

|--------------|----------------------------------------------|--------------|

| 1-1          | Board Specifications                         | 1-3          |

| 2-1          | ROM/PROM Configurations                      |              |

| 2-2          | RAM Configurations                           |              |

| 2-3          | <b>ROM/PROM</b> Jumper Configurations        |              |

| 2-4          | Page Select Jumpers                          |              |

| 2-5          | iSBC 88/25 Factory Default                   |              |

|              | Jumper Summary                               | 2-4          |

| 2-5A         | iSBC 88/25 Numerical Jumper List .           | 2-5          |

| 2.6          | Line Driver and Terminator Circuits          |              |

| 2-7          | Interval Timer Input Jumper                  |              |

|              | Configurations                               | 2-6          |

| 2-8          | Serial Port Jumper Configurations            |              |

| 2-9          | Connector J2 Pin Assignments                 |              |

| 2-10         | Parallel Port Default Jumper                 |              |

|              | Connections                                  | 2-8          |

| $2 \cdot 11$ | Parallel Port CC Jumper Configuration        |              |

| 2 - 12       | Parallel Port Jumpers and Restriction        | ns 2-10      |

| 2 - 13       | Interrupt Matrix Jumper                      |              |

|              | Configurations                               | 2-14         |

| 2-14         | Multibus Interrupt Output Jumper             |              |

|              | Configurations                               | 2-14         |

| 2-15         | Wait State Generator Jumpers                 |              |

| 0.1.0        | and Times                                    | $\dots 2-16$ |

| 2-16         | 8289 Bus Arbiter Jumper                      | 0.4 <b>-</b> |

|              | Configurations                               | 2-17         |

| 2-17         | User Furnished Connector Details .           | 2-20         |

| 2 - 18       | Multibus Interface Connector                 | 0.04         |

|              | P1 Pin Assignments                           |              |

| 2-19         | Connector P2 Pin Assignments                 | 2-22         |

| 2-20         | Multibus Interface Signal Functions          |              |

| 2-21         | P2 Signal Definitions                        |              |

| 2-22         | iSBC 88/25 Board DC Characteristic           | s. 2-24      |

| 2 - 23       | Auxiliary Signal (Connector P2)              |              |

| 2.24         | DC Characteristics                           |              |

| 2-24         | AC Characteristics                           |              |

| 2-25         | Parallel I/O DC Characteristics              | 2-27         |

| 2-26         | Parallel I/O Connector                       | 0.00         |

| 0.07         | J1 Pin Assignments                           |              |

| 2-27<br>2-28 | Bulk Cable TypesConnector J2 Pin Assignments |              |

| 2-28<br>2-29 | RS232 Signals Pin Correspondence .           |              |

| 2-29<br>2-30 | iSBX Bus Connector Pin Assignment            |              |

| 2-30<br>2-31 | iSBX Bus Signal Descriptions                 |              |

| 2-01         | iobri Das orginal Descriptions               | 2-00         |

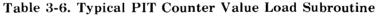

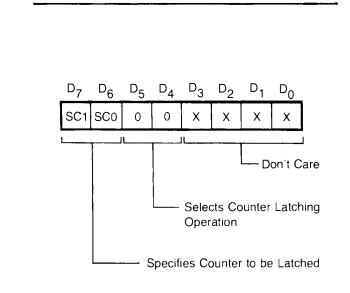

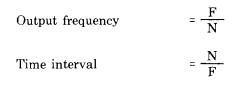

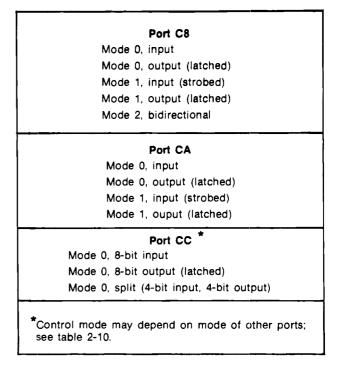

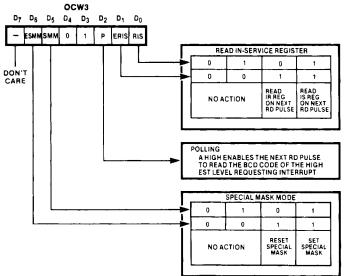

#### Table Title Page On-Board ROM Addresses ..... 3-1 3-1 On-Board RAM Addresses ..... 3-1 3-23-3 I/O Port Addresses ..... 3-2 PIT Counter Operations Vs. Gate Inputs 3-5 3-4 Typical PIT Control Word Subroutine ... 3-6 3-5 Typical PIT Counter Value 3-6 3-7 Typical PIT Counter Read Subroutine .. 3-6 PIT Rate Generator Frequencies 3-8and Timér Intervals ..... 3-7 3-9 PIT Time Intervals Vs. Timer Counts ... 3-8 PCI Address Assignments ..... 3-10 3-103-11Typical PCI Mode or Command Instruction Subroutine ...... 3-11 3-12Typical PCI Data Character Read 3-13 Typical PCI Data Character Write 3-14 Typical PCI Status Read Subroutine ... 3-12 Parallel Port Configurations ...... 3-13 3-153-16 Parallel Port I/O Address ..... 3-13 3-17Typical PPI Initialization Subroutine . 3-14 Typical PPI Port Read Subroutine .... 3-14 3-183-19Typical PPI Port Write Subroutine .... 3-14 Parallel I/O Interface Configurations . 3-15 3-20Interrupt Type Pointers ...... 3-17 3-21Typical PIC Initialization Subroutine 3-22(NBV Mode) ..... 3-21 3-23Typical Master PIC Initialization Subroutine (BV Mode) ..... 3-21 3-24Typical Slave PIC Initialization Subroutine (BV Mode) ..... 3-21 PIC Operation Procedures ...... 3-22 3-25Typical PIC Interrupt Request Register 3-26Read Subroutine ...... 3-23 3-27Typical PIC In-Service Register Read Subroutine ...... 3-24 3-28Typical PIC Set Mask Register 3-29Typical PIC Mask Register Read 3-30 Typical PIC End-Of-Interrupt Command

5-1 iSBC 88/25 Replacement Parts List .... 5-2

# \_int<sub>e</sub>L\_

# ILLUSTRATIONS

| Figure | e Title Page                             |

|--------|------------------------------------------|

| 1-1    | iSBC 88/25 Single Board Computer 1-1     |

| 2-1    | ROM/PROM Device Insertion 2-3            |

| 2-2    | Simplified Master/Slave PIC              |

|        | Interconnect Example 2-15                |

| 2-3    | Serial Priority Resolution Scheme 2-18   |

| 2-4    | Parallel Priority Resolution Scheme 2-19 |

| 2-5    | Master AC Timing 2-23                    |

| 3-1    | PIT Control Word Format 3-3              |

| 3-2    | PIT Programming Sequence Examples . 3-4  |

| 3-3    | PIT Counter Register Latch Control       |

|        | Word Format 3-7                          |

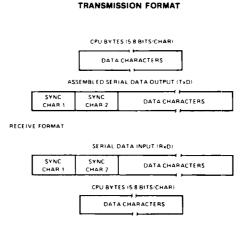

| 3-4    | PCI Synchronous Mode Instruction         |

|        | Word Format 3-8                          |

| 3-5    | PCI Synchronous Mode Transmission        |

|        | Format 3-8                               |

|        |                                          |

| Figur       | e Title                                    | Page            |

|-------------|--------------------------------------------|-----------------|

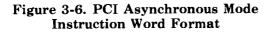

| 3-6         | PCI Asynchronous Mode Instruction          |                 |

|             | Word Format                                |                 |

| 3-7         | PCI Asynchronous Mode Transmissi<br>Format |                 |

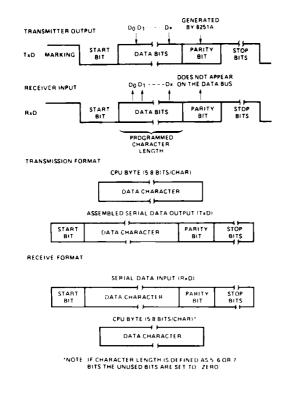

| 3-8         | PCI Command Instruction Word Form          |                 |

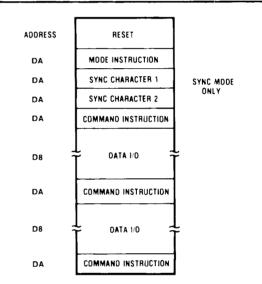

| 3- <b>9</b> | Typical PCI Initialization and Data        | I/O             |

|             | Sequence                                   | 3-10            |

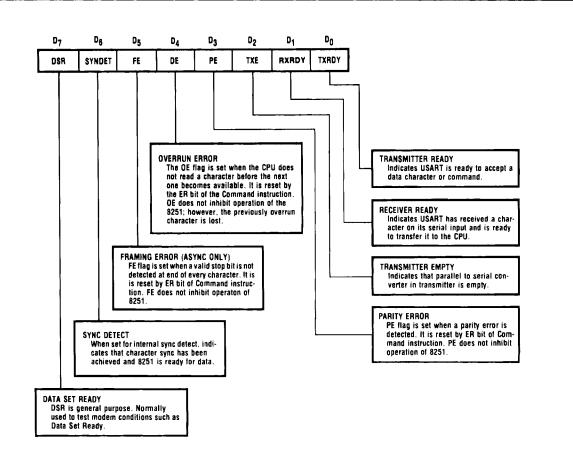

| 3-10        | PCI Status Read Format                     | 3-12            |

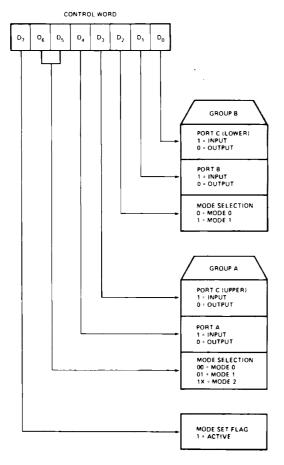

| 3-11        | PPI Control Word Format                    | 3-13            |

| 3-12        | PPI Port C Bit Set/Reset Control We        | ord             |

|             | Format                                     | 3-15            |

| 3-13        | PIC Initialization Command Word            |                 |

|             | Format                                     | 3-18            |

| 3-14        | PIC Operation Control Word Format          | <b>s</b> . 3-20 |

# CHAPTER 1 GENERAL INFORMATION

#### **1-1. INTRODUCTION**

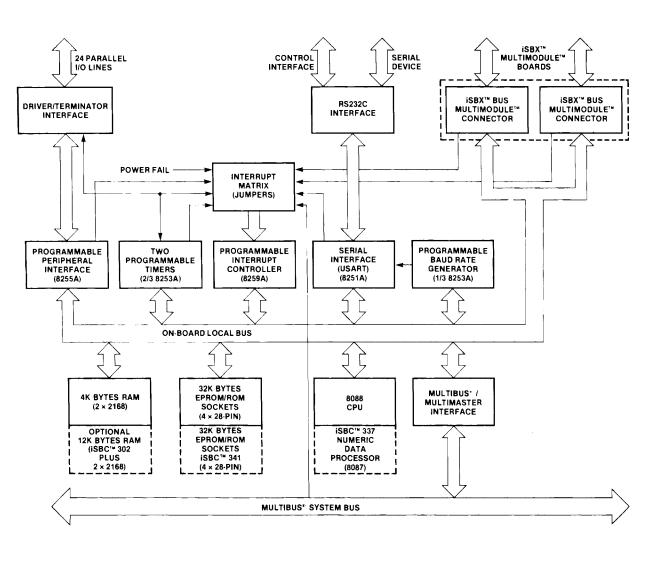

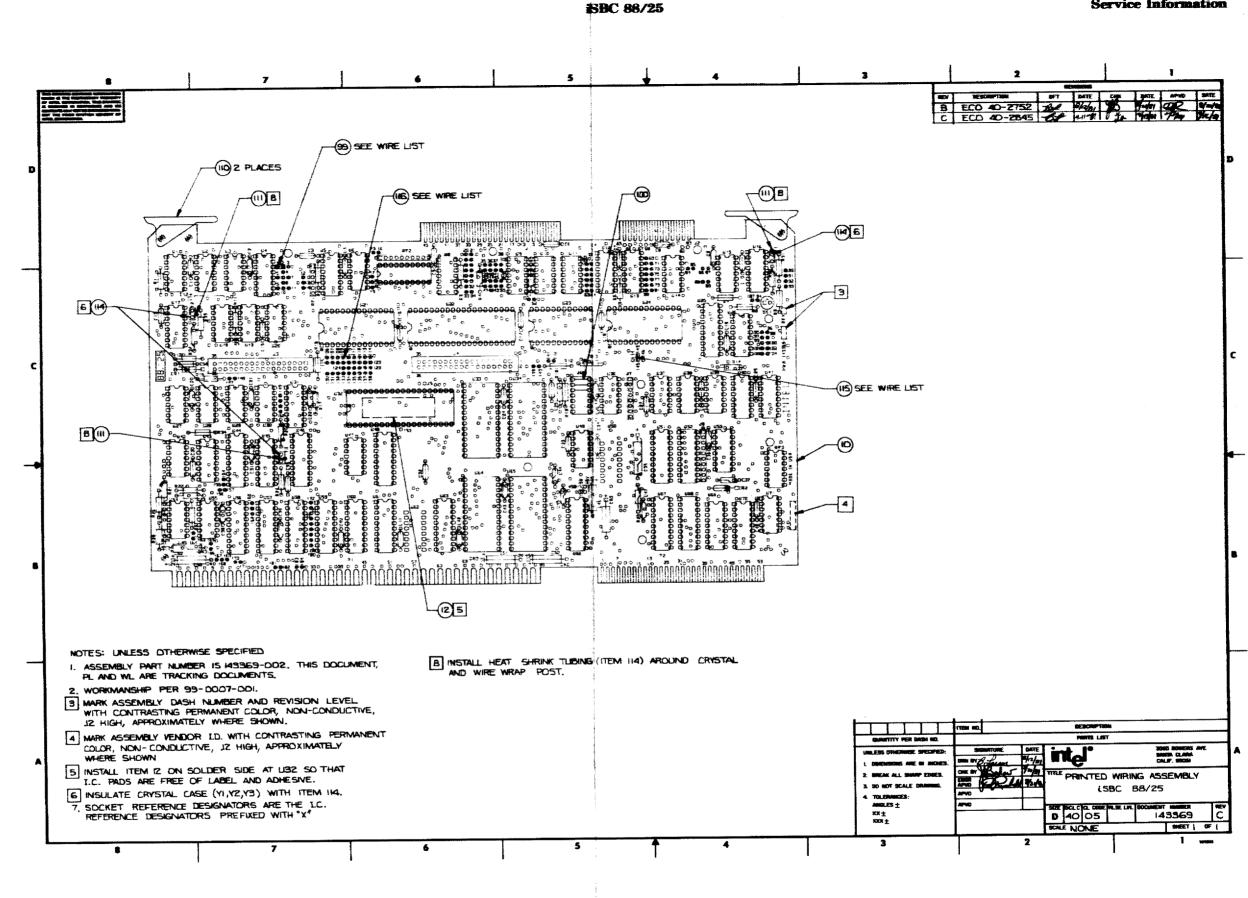

The iSBC 88/25 Single Board Computer is an Intel Multibus and iSBX Multimodule compatible, 8-bit computer system on a single printed circuit assembly (Figure 1-1). The iSBC 98/00 board includes on Intel 2008 microprocessor parallel 1/O lines, one seriek I/O and three programmable interval timera and a procommunitie interval controller. Sockets are provided for a maximum of 64K bytes of read-only memory (ROM). The iSBC 88/25 board will also accept the iSBC 337 Numeric Data Processor Multimodule board.

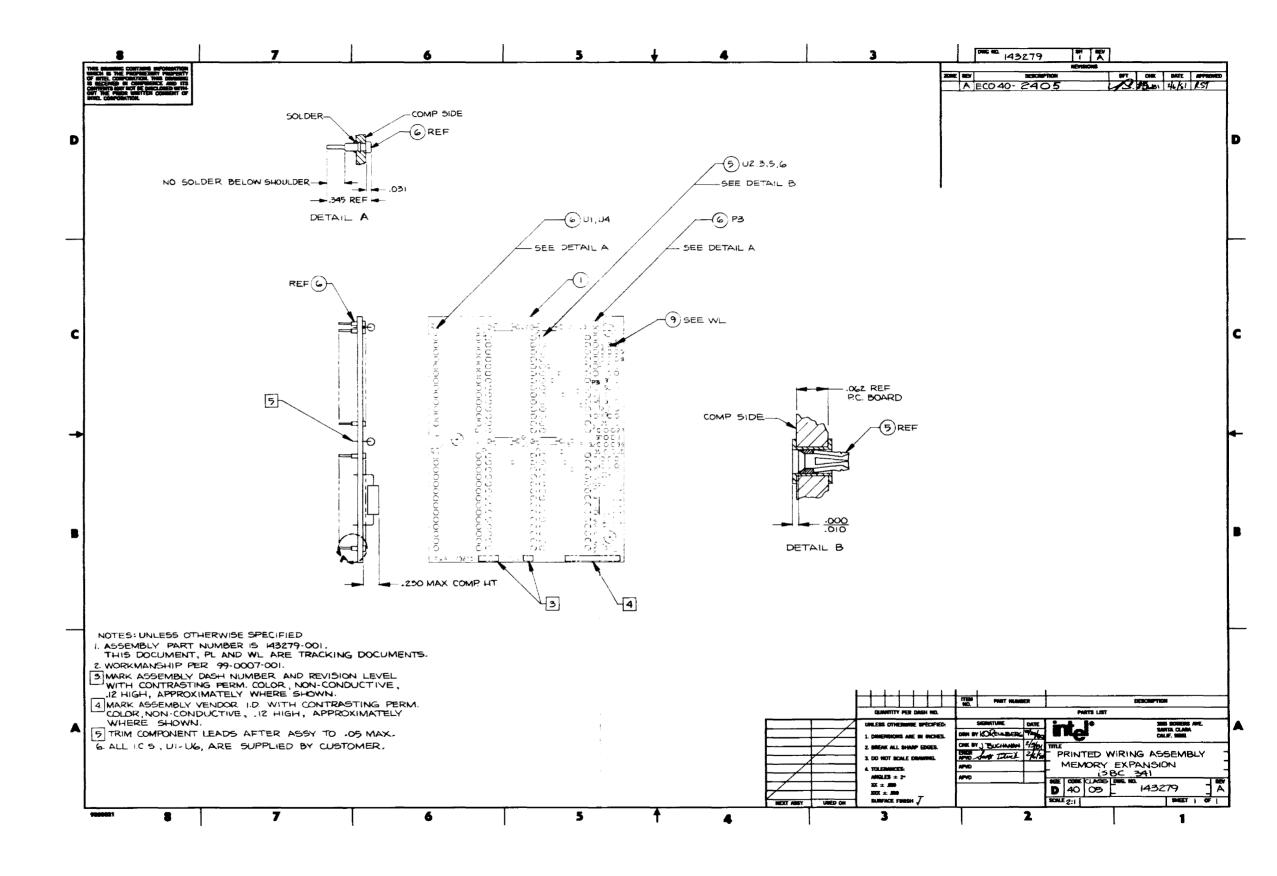

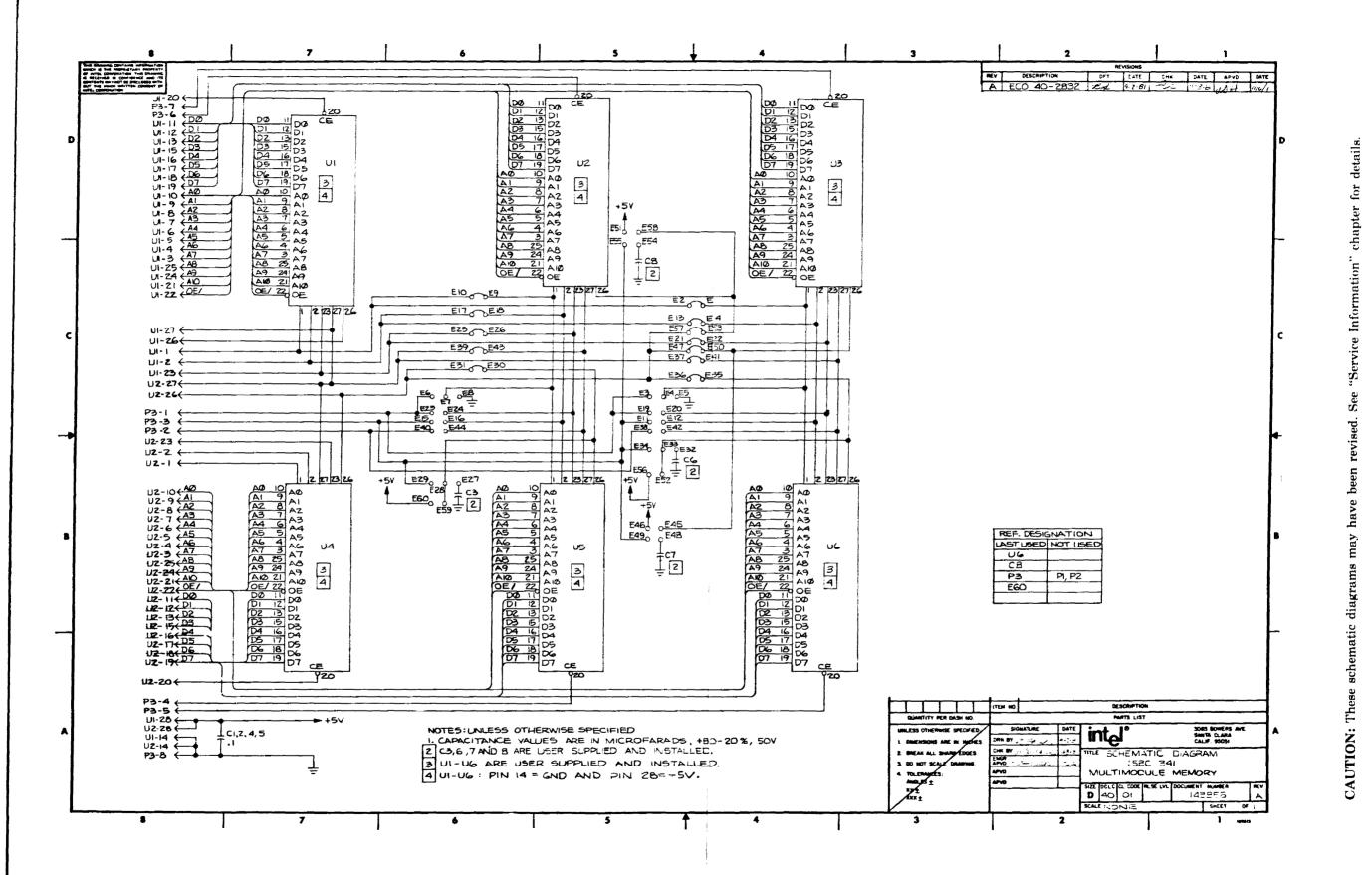

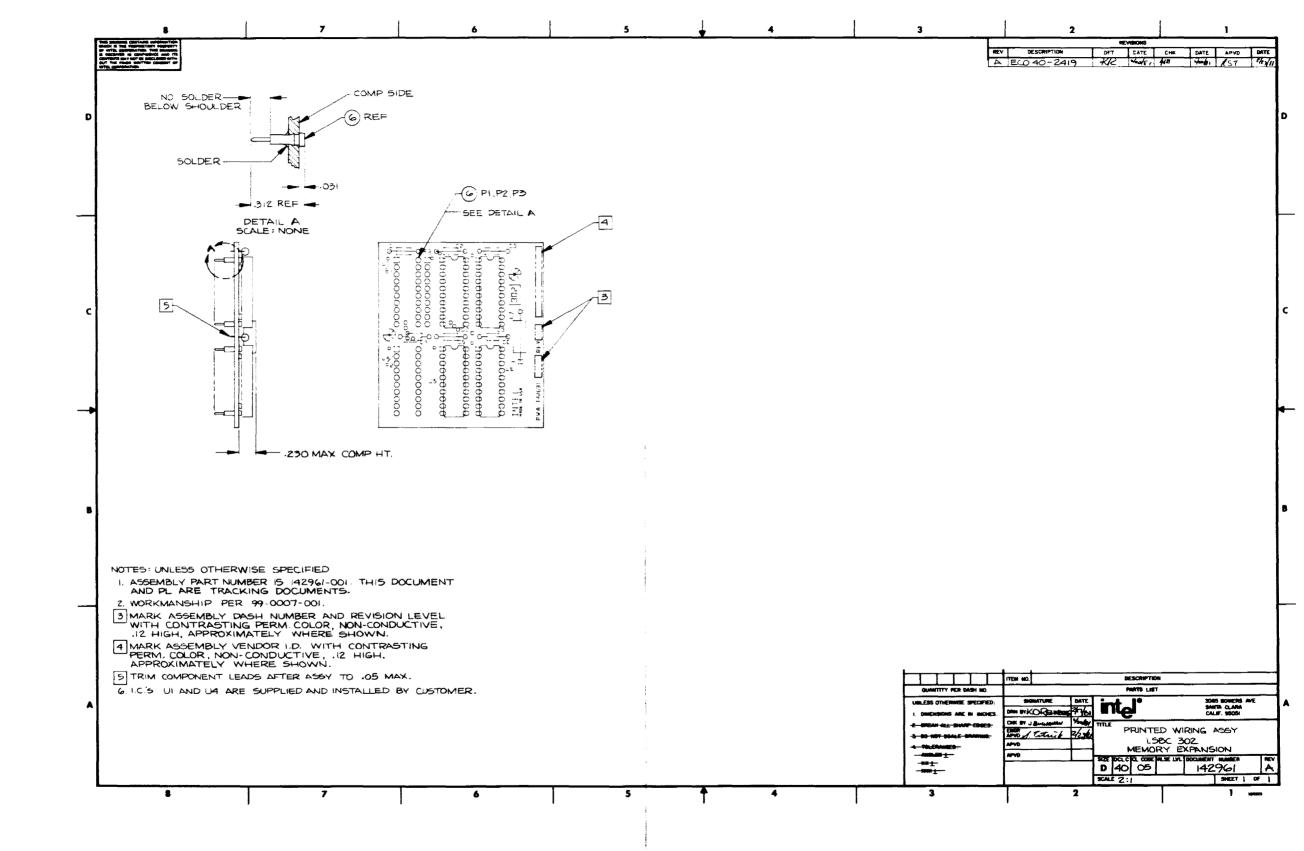

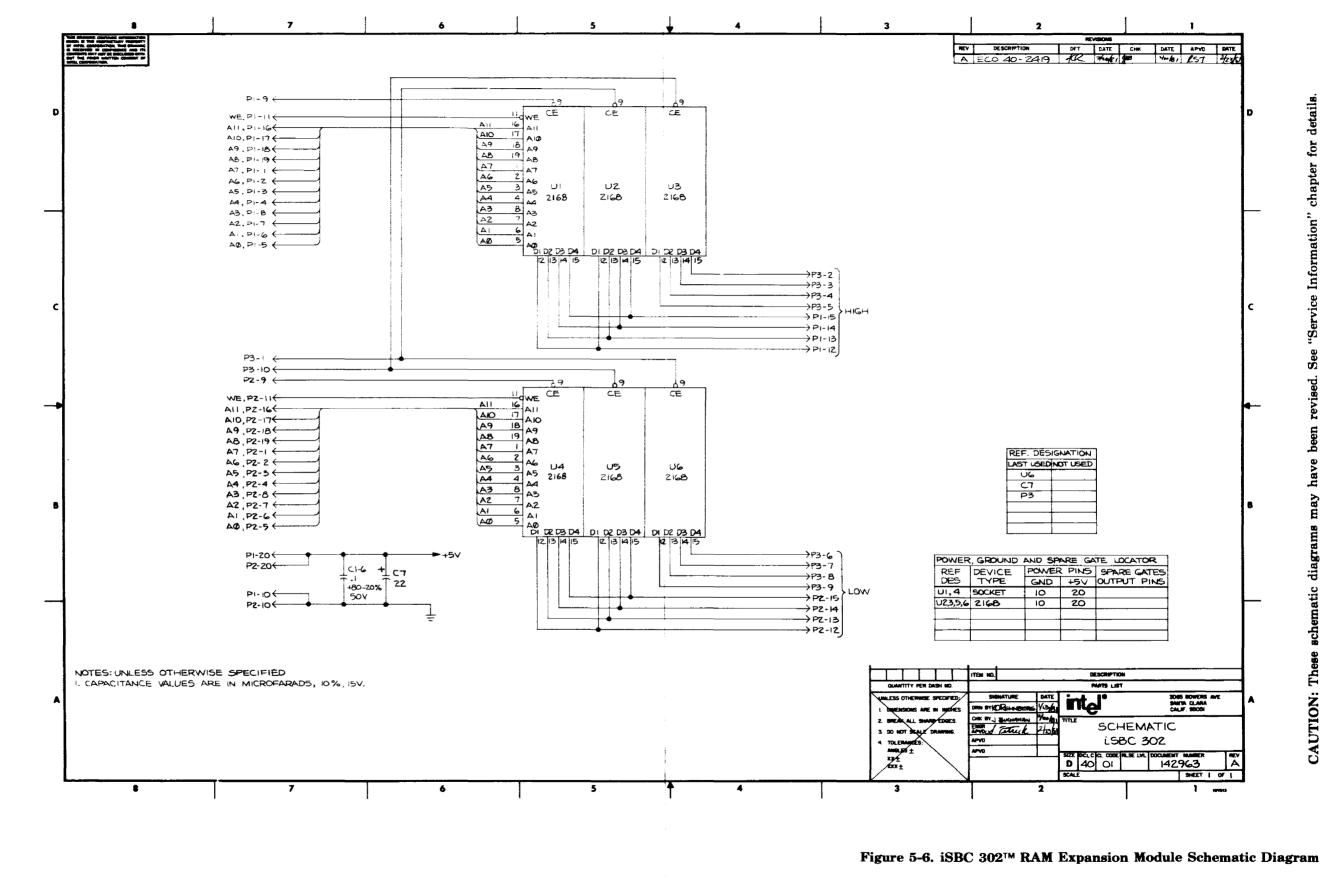

On board RAM expansion may be accomplished in two increments, by first adding the iSBC 302 RAM Expansion Module, adding 8K bytes, for a total of 12K bytes. Then two additional 2168 RAM devices may be added to the iSBC 302 board for a total of 16K bytes.

The iSBC 88/25 board will also accept the JEDEC compatible so called "byte wide" RAM devices such as the Intel 2188 (8K x 8) dynamic RAMs. These "byte wide" RAMs reside in sockets normally used for ROM/EPROM devices and do not require any special refresh circuitry. Two of these devices may reside on-board, and four additional devices may be used with the iSBC 341 ROM Expansion Module.

On-board ROM size may be increased by adding the ROM/EPROM device which suits your application. The four on-board sockets will accept either 24-pin or 28-pin ROM/EPROM devices such as Intel 2716 (2K x 8), 2732 (4K x 8), 2764 (8K x 8) and 27840 (16K x 8) devices to a maximum of 64K bytes of ROM/EPROM on-board. In addition, on-board ROM/EPROM size may be increased to a maximum of 128K bytes, using the iSBC 341 ROM Expansion Module.

Alternatively, the iSBC 88/25 board and the iSBC 341 ROM Expansion board may be equipped with Intel 2854 Electrically Erasable Programmable Read-Only Memory (EEPROM) devices. These devices allow on-board reprogramming using iSBC 88/25 board circuitry and an external power source.

Additional on-board I/O capabilities are provided via the two iSBX Multimodule connectors on the iSBC 88/25 board. These connectors allow any of the optional 8-bit iSBX Multimodule boards to be used on the iSBC 88/25 board.

The Intel 8088 microprocessor is software compatible with the Intel 8086 microprocessor. The iSBC 88/25 board will operate with the Intel iRMX 88 or the iRMX 86 Realtime Multitasking Executive operating system.

This hardware reference manual provides the information you will need to promptly install and operate

Figure 1-1. iSBC 88/25Single Board Computer

the iSBC 88/25 Single Board Computer. To optimize your application of this board, we suggest reading the entire manual before attempting installation and operation.

#### **1-2. DESCRIPTION**

The iSBC 88/25 board is controlled by an Intel 8088 microprocessor operating at 5 MHz. Processor support is provided by an Intel 8284A Clock Generator-Driver and an Intel 8288 Bus Controller.

Up to 1 Megabyte of total system memory can be directly addressed by the iSBC 88/25 board. Of this amount, a maximum of T44K bytes may reside onboard (16K RAM + 128K ROM). However if using the so called "byte wide" 28-pin RAM devices in ROM/ EPROM sockets, RAM size will increase, and ROM/ EPROM size will decrease accordingly.

**The iSBC** 88/25 hoard is shipped from the factory with the two Intel 2168 RAM devices in sockets U54 and U67. These two devices provide 4K bytes of onboard RAM. To increase the amount of on-board RAM beyond 4K bytes, the optional iSBC 302 RAM expansion module must be installed. The RAM expansion module is equipped with four Intel 2168 devices, thereby adding 8K bytes of on-board RAM. This results in a total of 12K bytes of on on-board RAM.

The iSBC 302 RAM Expansion Module plugs directly into socket U52 and U68. Two additional 2168 RAM devices may be installed on the iSBC 302 RAM Expansion Module, for a maximum of 16K bytes. The last two devices occupy the highest RAM address space (see Table 2-2 for RAM addressing). Installing any additional RAM requires a jumper installation.

In addition, the so called "byte wide" 28-pin RAM devices may be used on the iSBC 88/25 board, residing in two on-board ROM/EPROM sockets and up to four iSBC 341 sockets.

The board will accept a wide variety of Intel programmable read-only memory devices. Either 24 or 28-pin devices may be used. Four on-board sockets are provided, with expansion provided by the optional iSBC 341 ROM Expansion Module. Refer to Chapter 2 for complete information.

The on-board 8253-5 Programmable Interval Timer provides three independent counter outputs which may be configured to a variety of applications, including frequency output, rate generator, interval timer and real-time interrupts. One of the counters serves as the ball rate has been applied to the counters programmable Communications Interface device.

Serial I/O operation is handled by an Intel 8251A Programmable Communications Interface device. The board is configured to the RS 232C standard. However, this may be converted to a current loop TTY serial interface using optional equipment. Baud rates are software programmable using the on-board interval timer.

The iSBC 88/25 board utilizes one Intel 8255A-5 Programmable Peripheral Interface device to control the three, 8-bit, parallel I/O ports. All 24 lines may be configured to a variety of dedicated or general purpose applications. One particle equipped with an Intel 8287 Rue Transceiven. The other two ports are equipped with sockets for line drivers or terminators.

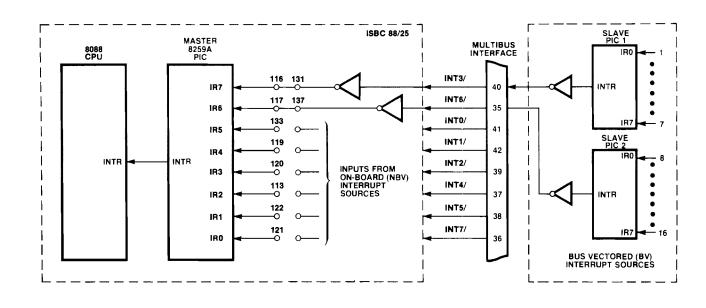

All interrupts, except the Intel 8088 non-maskable interrupt (NMI), are handled by the on-board Intel 8259A Programmable Interrupt Controller device. System interrupts can be connected to the interrupt controller via the Multibus lines, and additional interrupts may originate from one or two iSBX Multimodule boards. An on-board interrupt jumper matrix allows interrupt configuration flexibility and provides priority selection.

Two iSBX bus connectors (J3 and J4) are provided on the iSBC 88/25 board. These connectors are designed to expand the board's I/O functions and add peripherals, using special purpose optional iSBX Multimodule boards, such as the iSBX 350 Parallel I/O Multimodule Board. The Multimodule boards reside directly on the iSBC 88/25 board. One or two iSBX Multimodules may be added, as required by your application.

Off-board system access is provided by the Multibus connector (P1) and an auxiliary connector (P2). Offboard peripheral operations are handled through 24 parallel I/O lines (connector J1), a serial communications channel (connector J2), and two iSBX Multimodule connectors.

The iSBC 88/25 board is designed to operate as a full bus master in any Intel Multibus compatible chassis or backplane. The board may also reside in your own custom chassis, using Multibus compatible connectors (refer to Chapter 2).

For enhanced numerics processing capability, the iSBC 337 Numeric Data Processor Multimodule extends the 8088 architecture and data set. Over 60 numeric instructions offer arithmetic, trigonometric, transcendental, and exponential high-speed operations. Supported data types with the iSBC 337 option include 16, 32, and 64-bit integer, and 32 and 64-bit floating point, 18-digit packed BCD and 80-bit temporary.

#### **1-3. DOCUMENTATION SUPPLIED**

Each iSBC 88/25 board is shipped with a corresponding set of schematic diagrams. These drawings

should be inserted into the back of this manual for future reference. Refer to Chapter 5 for related information.

#### **1-4. ADDITIONAL EQUIPMENT REQUIRED**

The iSBC 88/25 board requires few optional components for basic operation. Depending on your application, you may need to purchase a parallel I/O connector, a serial I/O connector, and additional RAM if more than 4K bytes are required. Any onboard ROM must also be purchased separately. Chapter 2 provides information for selecting these items.

#### **1-5. SPECIFICATIONS**

Specifications of the iSBC 88/25 board are provided in Table 1-1.

| Granting, Bete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Intel 8088                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                           |

| Single Processor Cycle<br>Minimum Processor Bus Cycle<br>(four single cycles)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 200 nanoseconds<br>800 nanoseconds                                                                                                                                                                                                                                                                                        |

| NULTIBUS CLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9.830 MHz (BCLK/ & CCLK/)                                                                                                                                                                                                                                                                                                 |

| יכו Clock Input<br>רוד Input 0 & 2<br>רוד Input 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.458 MHz<br>1.229 MHz<br>153.6 KHz                                                                                                                                                                                                                                                                                       |

| AM ACCESS TIME<br>ROM/PROM/EPROM ACCESS TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100 nsecs max, Address to Data<br>520 - 1120 nsecs (0 - 3 Waits)                                                                                                                                                                                                                                                          |

| IEMORY CAPACITY<br>Maximum On-Board ROM/EPROM<br>Maximum On-Board RAM<br>Remaining Off-Board Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1M Byte<br>128K Bytes<br>16K Bytes<br>856K Bytes                                                                                                                                                                                                                                                                          |

| MENIOT MERCENNES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Aliseticianian dunca cloci sogia                                                                                                                                                                                                                                                                                          |

| On-Board RAM, w/two 2168 + iSBC 302, partial<br>On-Board RAM, w/two 2168 + iSBC 302, full<br>On-Board ROM<br>With iSBC 341 Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 - 02FFF<br>0 - 03FFF<br>FE000 - FFFFF using 2716 devices<br>FC000 - FFFFF using 2732 devices<br>F8000 - FFFFF using 2764 devices<br>FC000 - FFFFF using 27840 devices<br>F8000 - FFFFF using 2716 devices<br>F8000 - FFFFF using 2716 devices<br>F0000 - FFFFF using 27840 devices<br>E0000 - FFFFF using 27840 devices |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All notation in hexadecimal<br>80 — 9F*<br>A0 - BF*                                                                                                                                                                                                                                                                       |

| ICHID: IC | C0<br>C2                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CB-read/write                                                                                                                                                                                                                                                                                                             |

| Relincontrol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CA-<br>CC-<br>CE- write command                                                                                                                                                                                                                                                                                           |

| Counter D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D0                                                                                                                                                                                                                                                                                                                        |

| Genelocation<br>Genelocation<br>Genelocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D2<br>D4<br>D6                                                                                                                                                                                                                                                                                                            |

| Seriel*Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D8                                                                                                                                                                                                                                                                                                                        |

| Modesen-Slatus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Da                                                                                                                                                                                                                                                                                                                        |

Table 1-1. Board Specifications

## **General Information**

.

-

| Table 1-1. Board Specifications (Con | ontinued) |

|--------------------------------------|-----------|

|--------------------------------------|-----------|

| INTERFACES<br>Multibus<br>Parallel I/O<br>Interrupt Reqeusts<br>Interval Timer<br>iSBX Bus<br>Serial I/O                                                                                                     |                  | All signals TTL c<br>All signals TTL c<br>RS 232C compat<br>terminal. | ompatible<br>ompatible<br>ompatible<br>ompatible | e as a data set o | r data        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------|---------------|

| ELECTRICAL REQUIREMENTS<br>Configuration                                                                                                                                                                     | +5Vdc            | +12Vdc*                                                                                                                                                   | -12Vdc*                                          | +5 Batt**         | ]             |

| Standard Board, no ROM/EPROM                                                                                                                                                                                 | 3.8A             | 25mA                                                                                                                                                      | 23mA                                             | 400mA             | 1             |

| Maximum Operating Requirements<br>(with all options)                                                                                                                                                         | 11.2A            | 2A                                                                                                                                                        | 2A                                               | 700mA             |               |

| *+12Vdc & -12Vdc are required for RS232 a<br>**For battery backup option only.<br>PHYSICAL CHARACTERISTICS<br>Width<br>Length<br>Thickness<br>Weight                                                         | pplication only. | 12.00 in. (30.48 c<br>6.75 in. (17.15 c<br>0.50 in. ( 1.27 c<br>14 oz. (388 gram                                                                          | ;m)<br>;m)                                       |                   | ، <b>ب</b> ور |

| ENVIRONMENTAL CHARACTERISTICS<br>Minimum Power Requirements<br>Maximum Power Requirements<br>Minimum Heat Dissipation<br>Maximum Heat Dissipation<br>Operating Temperature Range<br>Operating Humidity Range |                  | 20 Watts<br>115 Watts<br>344 gcal/minute<br>1640 gcal/minute<br>0°C — 55°C<br>90% max non-co                                                              |                                                  |                   |               |

c

# CHAPTER 2 PREPARATION FOR USE

#### **2-1. INTRODUCTION**

This chapter provides specific information enabling you to install the iSBC 88/25 Single Board Computer into your system, with minimal effort. The board's default or factory configuration for RAM addressing, ROM/PROM size, and other variables are described, followed by procedures for altering the default configuration. In this manner the board will accommodate a variety of applications. To completely familiarize yourself with the flexibility of the iSBC 88/25 board, we recommend reading Chapters 2 and 3 before installation and use.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment contact the Intel Product Service HOTLINE to obtain a return authorization number and further instructions (see Section 5-2). A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

#### 2-3. INSTALLATION CONSIDERATIONS

There are several general requirements which should be considered prior to board installation and use. These requirements are discussed in Sections 2-4 through 2-6.

#### 2-4. MINIMAL OPERATING REQUIREMENTS

The iSBC 88/25 board factory default configuration is described in Chapter 1. In order to operate the board you may need additional equipment. For most applications this will typically be the following:

- a. CPU software, residing in on-board ROM/ PROM (Section 2-7).

- b. I/O connectors and cables (Sections 2-28; 2-32; 2-33).

- c. Additional on-board RAM, if more than 4 bytes are required (Section 2-10).

d. Line drivers or terminators for parallel I/O lines (Section 2-12).

Instructions for installing these items are provided in the sections listed above.

#### 2-5. POWER REQUIREMENTS

Three voltages are required for operating the iSBC 88/25 board in most configurations: +5Vdc, +12Vdc, and -12 Vdc. All must be within  $\pm 5\%$  of absolute. However, some configurations do not require all voltages. Power requirements for the various board configurations are listed in Table 1-1. The table includes power required by an optional iSBC Multimodule board which may be installed.

#### 2-6. COOLING REQUIREMENTS

Operating temperature range for the iSBC 88/25board is 0° to 55°C. If the board is installed into an Intel system chassis, adequate cooling is provided by the fans supplied. However, if the board is used in another chassis, ensure adequate cooling is provided by taking temperature readings inside the chassis at the site environment.

#### 2-7. ROM/PROM INSTALLATION

Sockets U33, U34 and U64, U65 are reserved for optional ROM/PROM devices. A maximum of 64K bytes may be installed in these four sockets, using four 16K byte 28-pin devices. A summary of compatible device types, capacity, and addressing is provided in Table 2-1. Device types may not be mixed, however empty sockets are allowed (provided they are not addressed).

Before installing the devices on the board several jumper connections may be required to specify device size and power scheme. Table 2-3 specifies the board's factory default jumper configuration (set for 2716 devices) and summarizes the other possible ROM/PROM jumper connections.

.

Never install any device onto a board when power is applied. Damaged to the board, device and power supply could result.

The ROM/PROM sockets are 28-pin sockets which are used for both 24-pin and 28-pin devices. When inserting devices, ensure that pin 1 of the ROM/PROM device corresponds with pin 1 of the socket. Use the upper white dot for 28-pin devices and the lower white dot for 24-pin devices (Figure 2-1).

Table 2-1 provides address ranges when the optional iSBC 341 ROM/PROM Expansion Module is installed on the iSBC 88/25 board. This operation will double the existing ROM space. The addressed listed include ROM/PROM space already on the iSBC 88/25 board. Refer to Section 2-9 for iSBC 341 board installation information. Refer to Section 2-22 for PROM Wait State information. The board is configured at the factory for 2716 type devices, requiring 2 wait states.

|                  |                 | iSBC            | 88/25           |                 |                         | iSBC            | 341             |                          |

|------------------|-----------------|-----------------|-----------------|-----------------|-------------------------|-----------------|-----------------|--------------------------|

| _                | U33             | U64             | U34             | U65             | U2*                     | U5*             | U3*             | U6*                      |

| 2716's           | FF800-<br>FFFFF | FF000-<br>FF7FF | FE800-<br>FEFFF | FE000-<br>FE7FF | FD800-<br>FDFFF         | FD000-<br>FD7FF | FC800-<br>FCFFF | FC000-<br>FC7FF          |

| 27 <b>32's</b> ; | FF000-          | FEOOO-          | FD000-<br>FDFFF | FC000<br>FCFFF  | FB000-<br>FBFFF         | FA000-<br>FAFFF | F9000-<br>F9FFF | F8000-<br>F8FFF          |

| <del>27640</del> | FE000<br>EFFFF  | FORF            | FA000-<br>FBFFF | F8000-<br>F9FFF | <b>F</b> 6000-<br>F7FFF | F4000-<br>F5FFF | F2000-<br>F3FFF | F0000-<br>F1F <b>F</b> F |

| 27840's          | FC000-<br>FFFFF | F8000-<br>FBFFF | F4000-<br>F7FFF | F0000-<br>F3FFF | EC000-<br>EFFFF         | E8000-<br>EBFFF | E4000-<br>E7FFF | E:0000-<br>E3FFF         |

#### Table 9.1 DOM/DDOM C

#### Table 2-2. RAM Configurations

|              | iSBC 88/25   |        |         |       | iSBC    | 302*  |         |       |

|--------------|--------------|--------|---------|-------|---------|-------|---------|-------|

|              | U67          | U51    | U3      | U5    | U2      | U6    | U1      | U4    |

| Nibble       | Low          | High   | High    | Low   | High    | Low   | Low     | High  |

| Address      | 8990 -       | :00PF# | 01000 - | 01FFF | 02000 - | 02FFF | 03000 - | 03FFF |

| *Install jun | nper 94-187. |        | •       |       | •       |       |         |       |

#### Table 2-3. ROM/PROM Jumper Configurations

|                           | 2716*<br>2K x 8            | 2732<br>4K x 8               | 2764<br>8K x 8              | 27840<br>16K x 8         |

|---------------------------|----------------------------|------------------------------|-----------------------------|--------------------------|

| J6<br>Jumpers             | 1 - 14<br>2 - 13<br>3 - 12 | 1 - 14#<br>9 - 12*<br>6 - 9* | <b>988001,4</b> 0<br>6 - √9 | 1 - 14<br>5 - 9<br>7 - 8 |

| Decode<br>PROM<br>Jumpers | None                       | <b>#</b> 90 - 91 <b>#</b>    | 9 <b>2 -</b> 93             |                          |

28-PIN DEVICE PIN 1  $\Box$  $\Box$ 24-PIN DEVICE PIN 1 Π  $\Box$  $\Box$  $\Box$ П ROM PROM SOCKET  $\Box$  $\Box$  $\Box$  $\Box$  $\Box$  $\Box$

Figure 2-1. ROM/PROM Device Insertion

#### 2-8. iSBC 341 MODULE INSTALLATION

The optional iSBC 341 ROM/PROM Expansion Module is designed to increase the amount of iSBC 88/25 on-board ROM/PROM. The size of the devices used on the module must match the size of the devices used on the board. For example, if the iSBC 88/25 board is equipped with 4K X 8 EPROM devices, the iSBC 341 module must also use 4K X 8 EPROM devices. The following procedure is recommended for iSBC 341 module installation:

a. Turn off power and remove iSBC 88/25 board from system.

- b. Carefully remove ROM/PROM device from board socket U34 and install it into socket U1 on the iSBC 341 module. Similarly, remove the ROM/PROM device from board socket U65 and install it into socket U4 on the iSBC 341 module. Be sure to install these two devices in the sockets indicated.

- c. Carefully insert all remaining ROM/PROM devices into the iSBC 341 module. Refer to CAUTION notice in Section 2-7 for related socket information.

- d. Using the hardware supplied with the iSBC 341 module install it onto the iSBC 88/25 board. The module connector fits directly into ROM/PROM sockets U34 and U65 and board connector J7.

- e. Install jumper connection 94-187 on the iSBC 88/25 board.

## NOTE

When jumper 94-187 is installed both RAM and ROM / PROM memory areas are expanded.

f. Installation is complete. The iSBC 88/25 board is now ready to be installed into your system cardcage.

#### 2-9. PAGE SELECT JUMPER CONFIGURATION