# iSBC® 86/05 SINGLE BOARD COMPUTER HARDWARE REFERENCE MANUAL

Order Number: 143153-002

| REV. | REVISION HISTORY          | PRINT<br>DATE |

|------|---------------------------|---------------|

| -001 | Original Issue            | 2/81          |

| -002 | Corrects technical errors | 2/83          |

|      |                           |               |

|      |                           |               |

| Ē    |                           |               |

|      |                           |               |

|      |                           |               |

|      |                           |               |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| AEDIT              | iLBX                   | iOSP            | MULTIBUS      |

|--------------------|------------------------|-----------------|---------------|

| BITBUS             | im                     | iPDS            | MULTICHANNEL  |

| BXP                | iMMX                   | iRMX            | MULTIMODULE   |

| COMMputer          | Insite                 | iSBC .          | Plug-A-Bubble |

| CREDIT             | Intel                  | iSBX            | PROMPT        |

| i                  | IntelBOS               | iSDM            | Promware      |

| iATC               | Intelevision           | iSXM            | Ripplemode    |

| 1 <sup>2</sup> ICE | inteligent Identifier  | Library Manager | RMX/80        |

| ICE                | inteligent Programming | MCS             | RUPI          |

| iCS                | Inteilec               | Megachassis     | System 2000   |

| iDBP               | Intellink              | MICROMAINFRAME  | UPI           |

| iDIS               |                        |                 |               |

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

<sup>\*</sup>MULTIBUS is a patented Intel bus.

#### **PREFACE**

This manual pertains to both versions of the iSBC 86/05 Single Board Computer. It was written specifically to reflect the newer version (145895) of the iSBC 86/05 Single Board Computer. If you have the old version (143240) refer to Appendix C for the differences between these versions. The manual provides general information, installation, and setup instructions, programming guidelines for the on-board, programmable devices, and service information for the iSBC 86/05 Single Board Computer. Related information is provided in the following publications:

- The 8086 Family User's Manual, Order Number: 9800722.

- iSBC® Applications Manual, Order Number: 142687.

- Intel Multibus® Specification, Order Number: 9800683.

- Intel Multibus<sup>®</sup> Interfacing, Application Note AP-28A.

- MCS-86 Assembly Language Programming Manual, Order Number: 9800640.

- PL/M 86 Programming Manual, Order Number: 9800466.

- Intel iSBX<sup>™</sup> Bus Specification, Order Number: 142686.

- Designing iSBX<sup>™</sup> Multimodule<sup>™</sup> Boards, Application Note AP-96.

- Using the iRMX<sup>™</sup> 86 Operating System, Application Note AP-86.

- iSBC® 337 Numeric Data Processor Hardware Reference Manual, Order Number: 142887.

- The 8086 Primer, by Stephen P. Morse. Hayden Book Company, Inc., Rochelle Park, N.J., 1980. ISBN: 08104-5165-4.

# CONTENTS

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PAGE                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| CHAPTER 1 GENERAL INFORMATION 1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-1<br>1-2<br>1-3<br>1-4<br>1-4<br>1-4                                                               |

| CHAPTER 2 PREPARATION FOR USE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |

| PREPARATION FOR USE 2.1 Introduction. 2.2 Unpacking and Inspection. 2.3 Installation Considerations. 2.3.1 Minimal Operating Requirements. 2.3.1.1 Power Requirements. 2.3.1.2 Cooling Requirements. 2.4 System Considerations. 2.4.1 Memory Allocation Considerations. 2.4.2 Triming Considerations. 2.4.2.2 Fail-Safe Timer Selection. 2.4.2.3 Clock Generator. 2.4.2.4 Interval Timers. 2.4.3 Interface Arbitration. 2.4.3.1 Common Bus Request. 2.4.3.2 Any Request. 2.4.4 Priority Resolution Considerations. 2.4.4.5 Interrupt Considerations. 2.4.5.1 Non-Bus Vectored Interrupts. 2.4.5.2 Bus Vectored Interrupts. 2.4.6.1 Multibus® Interface. 2.4.6.2 Serial I/O Considerations. 2.4.6.3 Parallel I/O Considerations. 2.4.6.4 iSBX™ Interface Considerations. 2.4.6.4 iSBX™ Interface Considerations. 2.4.6.4 iSBX™ Interface Considerations. 2.4.6.3 Jumper Configurations. | 2-1 2-1 2-1 2-1 2-2 2-2 2-2 2-3 2-3 2-3 2-3 2-3 2-4 2-4 2-5 2-5 2-6 2-8 2-9 2-10 2-10 2-11 2-11 2-11 |

| 2.5.1 Memory Jumper Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2-20<br>2-20<br>2-22                                                                                 |

# CONTENTS (continued)

|                                                                 | PAGE         |

|-----------------------------------------------------------------|--------------|

| CHAPTER 2 (continued)                                           |              |

| ·                                                               | 2-24         |

| 2.5.3 Serial Port Jumper Connections                            | 2-24         |

|                                                                 | 2-23         |

| 2.5.5 Interrupt Matrix Jumper Configurations                    | 2-34         |

|                                                                 |              |

|                                                                 | 2-36         |

| 2.5.5.3 Parallel Port Interrupts A, B (PA INTR & PB INTR)       | 2-36         |

| 2.5.5.4 Transmit and Receive Interrupts (51TxINTR & 51RxINTR)   | 2-36         |

| 2.5.5.5 Power Line Clock (PLC)                                  | 2-37         |

| 2.5.5.6 Math Interrupt (MINT)                                   | 2-37         |

| 2.5.5.7 Power Fail Interrupt (PFIN/)                            | 2-37         |

| 2.5.5.8 External Interrupt 0 (EXT INTRO)                        | 2-37         |

| 2.5.5.9 Non-Maskable Interrupt Input Mask                       | 2-37         |

| 2.5.5.10 Multibus® Interrupt Output Option (BUS INTR OUT)       | 2-38         |

| 2.5.6 Multibus® Vectored Interrupts                             | 2-38         |

| 2.5.7 On-Board Timing Jumper Selection                          | 2-39         |

| 2.5.7.1 Bus Clock & Constant Clock Selection                    | 2-39         |

| 2.5.7.2 Wait State Generator Selection                          | 2-39         |

| 2.5.8 iSBX <sup>™</sup> Multimodule Board Mode Jumper Selection | 2-40         |

| 2.5.9 Bus Arbiter Jumper Configuration                          | 2-40         |

| 2.5.10 Power Fail Battery Backup Provisions                     | 2-42         |

| 2.6 Installation                                                | 2-43         |

| 2.6.1 ROM/PROM Installation                                     | 2-43         |

| 2.6.2 Line Drivers & I/O Terminators                            | 2-44         |

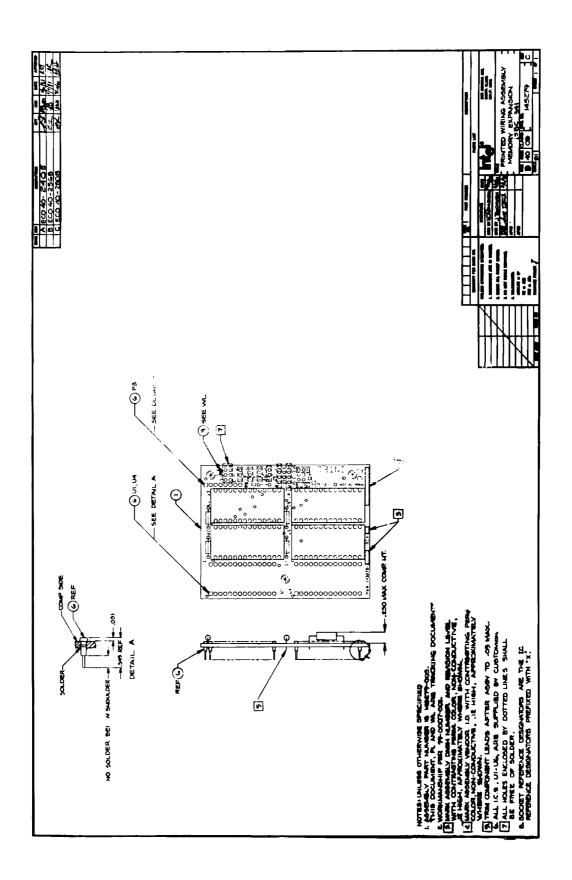

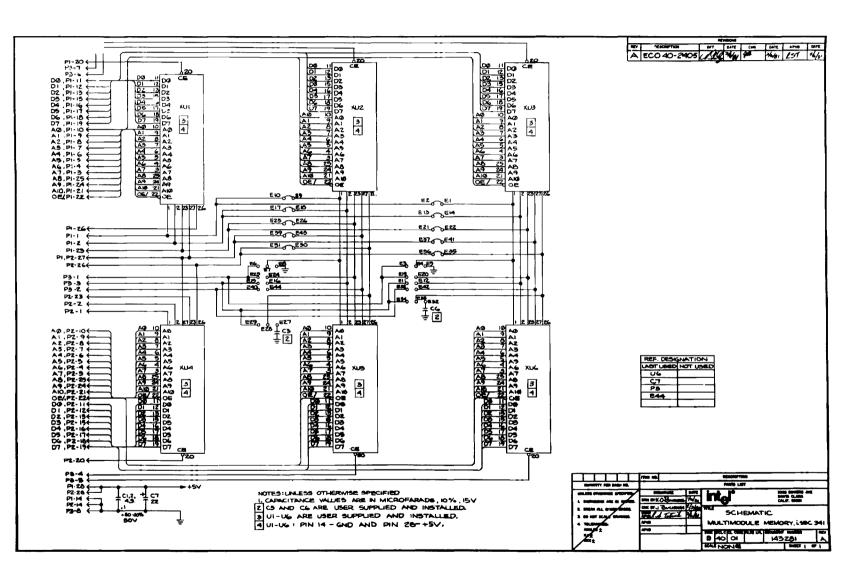

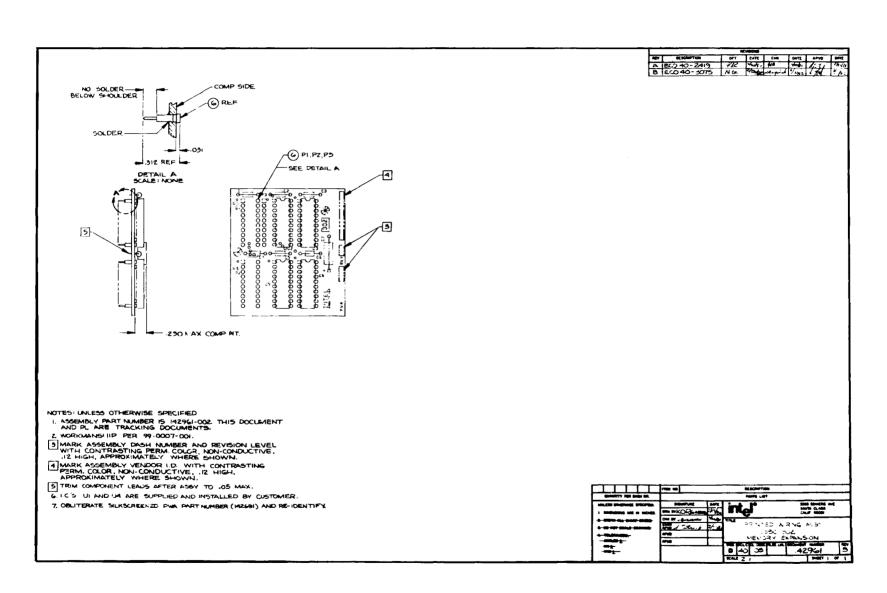

| 2.6.3 iSBC® 341 PROM/ROM Expansion Module Installation          | 2-45         |

| 2.6.4 iSBC® 302 RAM Module Installation                         | 2-46         |

| 2.6.5 iSBX <sup>™</sup> Multimodule Board Installation          | 2-47         |

| 2.6.6 Final Installation                                        | 2-48         |

| 2.7 Connector Information                                       | 2-48         |

| 2.7.1 Parallel I/O Cabling                                      | 2-48         |

| 2.7.2 Serial I/O Cabling                                        | 2-49         |

| ·                                                               |              |

| CHAPTER 3                                                       |              |

| PROGRAMMING INFORMATION                                         |              |

| 3.1 Introduction                                                | 3-1          |

| 3.2 Memory Addressing                                           | 3-1<br>3-1   |

|                                                                 | 3-1<br>3-2   |

| , , , , , , , , , , , , , , , , , , , ,                         | 3-2<br>3-2   |

|                                                                 | -            |

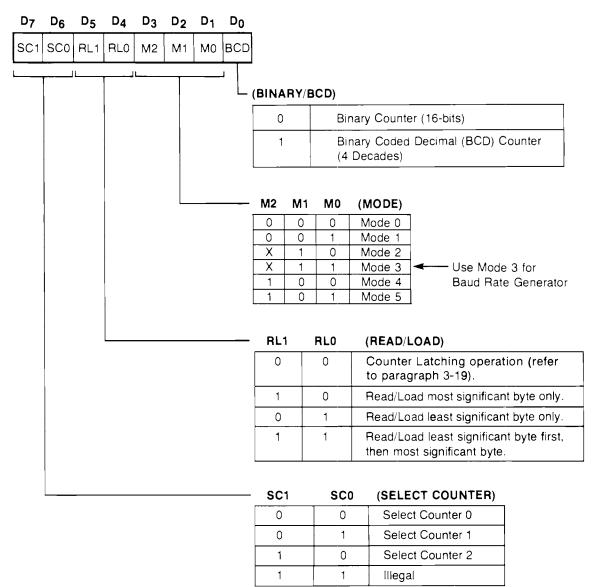

| 3.5 8253 Interval Timer Programming                             | 3-4          |

| 3.5.1 Addressing                                                | 3 <b>-</b> 5 |

| 3.5.2 Mode Control Word & Count                                 | 3-5          |

| 3.5.3 Initialization                                            | 3-6          |

| 3.5.4 Operation                                                 | 3-12         |

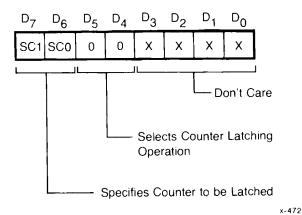

| 3.5.4.1 Counter Read                                            | 3-13         |

| 3.5.4.2 Clock Frequency/Divide Ratio Selection                  | 3-13         |

| 3.5.4.3 Rate Generator/Interval Timer                           | 3-16         |

| 3.5.4.4 Interrupt Timer                                         | 3-17         |

| 3.6 8251A PCI Programming                                       | 3-17         |

# CONTENTS (continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PAGE |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CHAPTER 3 (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

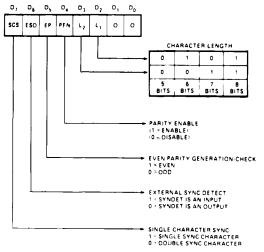

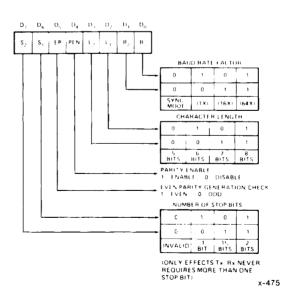

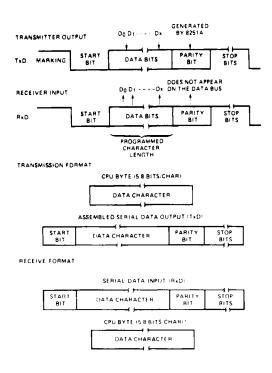

| 3.6.1 Mode Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-18 |

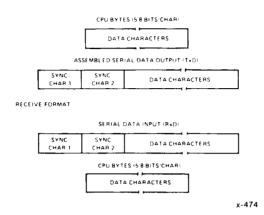

| 3.6.2 Sync Characters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-18 |

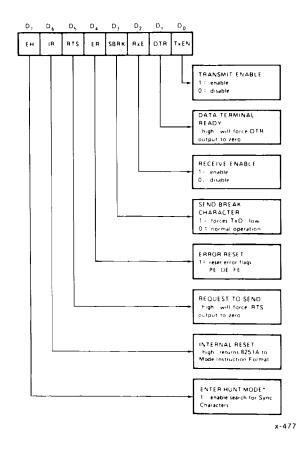

| 3.6.3 Command Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-21 |

| 3.6.4 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-22 |

| 3.6.5 Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-22 |

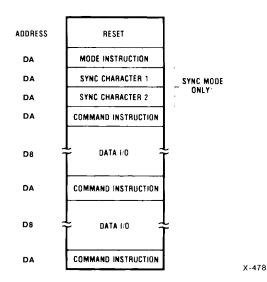

| 3.6.6 Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-23 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-26 |

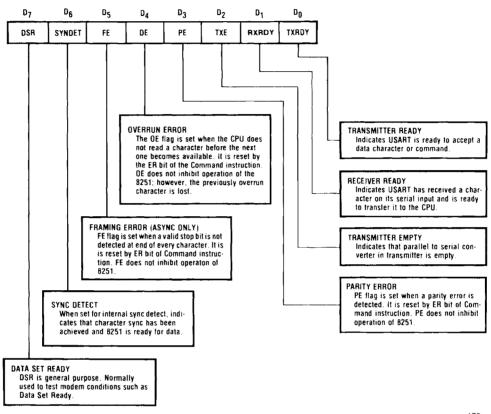

| 3.6.7 Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

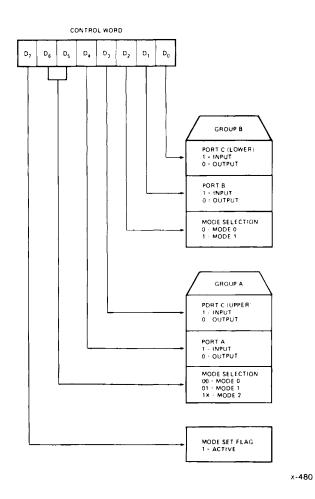

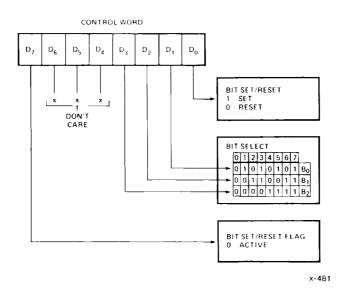

| 3.7 8255A PPI Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-29 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-30 |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-32 |

| 3.7.3 Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-32 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-32 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-33 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-35 |

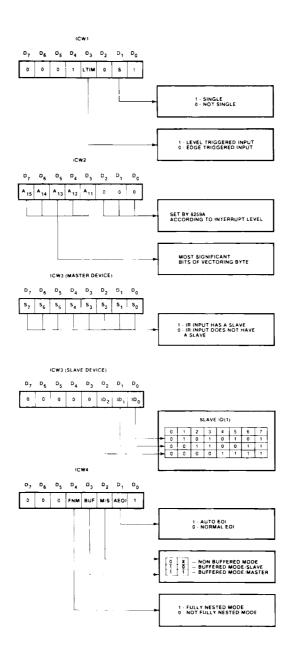

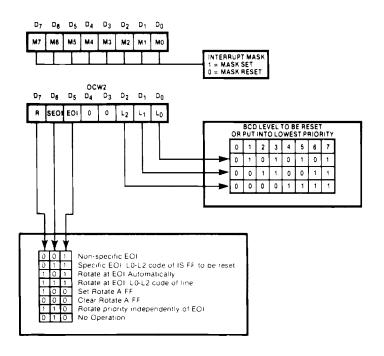

| 3.8.1 Interrupt Priority Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-37 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-37 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-37 |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-38 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-38 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-38 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-42 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-42 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |