## i960<sup>®</sup> Processors and Related Products

High-Performance 32-Bit RISC Processors for Embedded Applications

### LITERATURE

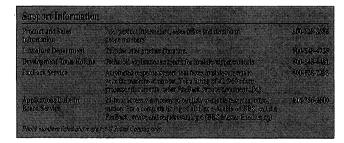

For additional information on Intel products in the U.S. or Canada, call Intel's Literature Center at (800) 548-4725 or write to:

#### Intel Literature P.O. Box 7641 Mt. Prospect, II 60056-7641

To order literature outside of the U.S. and Canada contact your local international sales office.

### **CURRENT DATABOOKS**

Product line databooks contain datasheets, application notes, article reprints, and other design information. Databooks can be ordered in the U.S. and Canada by calling TAB/McGraw-Hill at 1-800-822-8158; outside of the U.S. and Canada contact your local international sales office.

| Title                                                | Intel Order Number | ISBN          |

|------------------------------------------------------|--------------------|---------------|

| Automotive Products                                  | 231792             | N/A           |

| Embedded Applications (2 vol. set)                   | 270648             | 1-55512-242-6 |

| Embedded Microcontrollers                            | 270646             | 1-55512-230-2 |

| Embedded Microprocessors                             | 272396             | 1-55512-231-0 |

| Flash Memory (2 vol. set)                            | 210830             | 1-55512-232-9 |

| Intel486™ Microprocessors and Related Products       | 241731             | 1-55512-235-3 |

| i960® Processors and Related Products                | 272084             | 1-55512-234-5 |

| Military and Special Products                        | 210461             | N/A           |

| Networking                                           | 297360             | 1-55512-236-1 |

| OEM Boards, Systems and Software                     | 280407             | 1-55512-237-X |

| Packaging                                            | 240800             | 1-55512-238-8 |

| Pentium <sup>™</sup> Processors and Related Products | 241732             | 1-55512-239-6 |

| Peripheral Components                                | 296467             | 1-55512-240-X |

A complete set of this information is available on CD-ROM through Intel's Data on Demand program, order number 240897. For information about Intel's Data on Demand ask for item number 240952.

Ξ.

### 24-HOUR AUTOMATED TECHNICAL SUPPORT\*

Intel's Application Bulletin Board System (BBS) and FaxBack System are at your service, 24-hours a day, at no charge, and the information is updated frequently.

#### FaxBack SYSTEM

Technical and product information are available 24-hours a day! Order documents containing:

- Product Announcements

- Product Literature

- Intel Device Characteristics

- Design/Application Recommendations

- Stepping/Change Notifications

- Quality and Reliability Information

Information on the following subjects is also available:

- Microcontroller and Flash

- OEM Branded Systems

- Multibus/BBS Listing

- Multimedia

- Development Tools

- Quality and Reliability/Change Notification

- Microprocessor/PCI/Peripheral

- Intel Architecture Lab

To use FaxBack for Intel components and systems, dial (800) 628-2283 or (916) 356-3105 (U.S. and Canada)  $or +44\{0\}$  1793-496646 (Europe) and follow the automated voice-prompt menu. Document orders will be faxed to the fax number you specify. Catalogs are updated twice a month, so call for the latest information!

#### **BULLETIN BOARD SYSTEM**

Intel's Application Bulletin Board System (BBS) enables file retrieval 24-hours a day. The following can be located on the BBS:

- Software Drivers

- Tool Information

- Software/Application Utilities

- Product/Technical Documentation

- Firmware Upgrades

- Quality and Reliability Data

To use the Intel Application BBS (components and systems), dial (916) 356-3600 for download access (U.S. and Canada) or +44{0} 1793-496340 (Europe). The BBS will support 1200–19200 baud rate modem. *Typical modem configuration: 9600 baud rate, No Parity, 8 Data Bits, 1 Stop Bit.* A directory listing of BBS files is also available through FaxBack or our 800 BBS (800-897-2536).

#### **Retail Products**

Information on Intel's retail products (Coprocessors and wireless, video, personal conferencing and network products) is available through the following services:

Internet :ftp.intel.com (143.185.65.2)CompuServe :GO INTELFORUM (modem settings: E-7-1, up to 14.4 Kbps)

| Country       | BBS (N-8-1, up to 14.4 Kbps) | FaxBack                             |  |  |  |

|---------------|------------------------------|-------------------------------------|--|--|--|

| North America | (503) 264-7999               | (800) 525-3019 or<br>(503) 264-6835 |  |  |  |

| Europe        | +44 1 793-432955             | +44 1 793-432509                    |  |  |  |

| Australia     | +61 2 975-3066               | +61 2 975-3922                      |  |  |  |

| Taiwan        | +886 2 718-6422              | +886 2 514-0815                     |  |  |  |

| Singapore     | +65 256-4776                 | +65 256-5350                        |  |  |  |

| Hong Kong     | +852 530-4116                | +852 844-4448                       |  |  |  |

| Korea         | +822 784-3430                | +822 767-2594                       |  |  |  |

\*Support services provided courtesy of Intel Application Support

### i960<sup>®</sup> Processors and Related Products

High-Performance 32-Bit RISC Processors for Embedded Applications

1995

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

©INTEL CORPORATION, 1995

### DATASHEET DESIGNATIONS

Intel uses various datasheet markings to designate each phase of the document as it relates to the product. The markings appear in the lower inside corner of each datasheet page. Following are the definitions of each marking:

Datasheet Marking

#### Description

Product Preview

Advanced Information

Contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product becomes available.

Contains information on products being sampled or in the initial production phase of development.\*

Contains preliminary information on new products in production.\*

No Marking

Preliminary

Contains information on products in full production.\*

\* Specifications within these datasheets are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

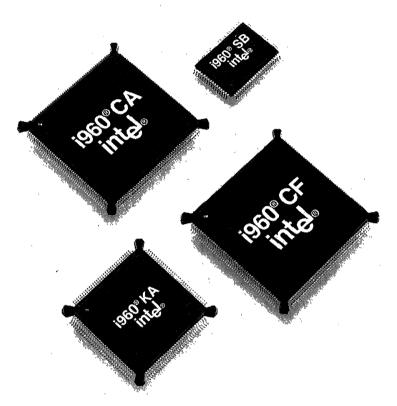

### i960<sup>®</sup> Microprocessor Family

**Memories and Peripherals**

**Development Support Tools**

3

1

2

### **Table of Contents**

| Alphanumeric Index                                                          | x              |

|-----------------------------------------------------------------------------|----------------|

| CHAPTER 1                                                                   | ·              |

| i960® Microprocessor Family                                                 |                |

| PRODUCT OVERVIEWS AND DATA SHEETS                                           |                |

| 80960SA Embedded 32-Bit Microprocessor with 16-Bit Burst Data Bus           | 1-1            |

| 80960SB Embedded 32-Bit Microprocessor with 16-Bit Burst Data Bus           | 1-39           |

| i960 KA/KB Processor Product Overview                                       | 1-76           |

| 80960KA Embedded 32-Bit Microprocessor                                      | 1-81           |

| 80960KB Embedded 32-Bit Microprocessor with Integrated Floating-Point Unit  | 1-118          |

| 80960CA Product Overview                                                    | 1-158          |

| 80960CA-33, -25, -16 32-Bit High Performance Embedded Processor             | 1-196          |

| 80960CF-33, -25, -16 32-Bit High Performance Superscalar Processor          | 1-264          |

| 80960CF-40 32-Bit High-Performance Superscalar Processor                    | 1-331          |

| 80960JA/JF Embedded 32-Bit Microprocessor                                   | 1-390<br>1-442 |

| 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor                 | 1-442          |

| 82961KD Printer Coprocessor                                                 | 1-499          |

|                                                                             | 1-500          |

| CHAPTER 2                                                                   |                |

| Memories and Peripherals                                                    |                |

| DATA SHEETS                                                                 |                |

| 82596CA High-Performance 32-Bit Local Area Network Coprocessor              | 2-1            |

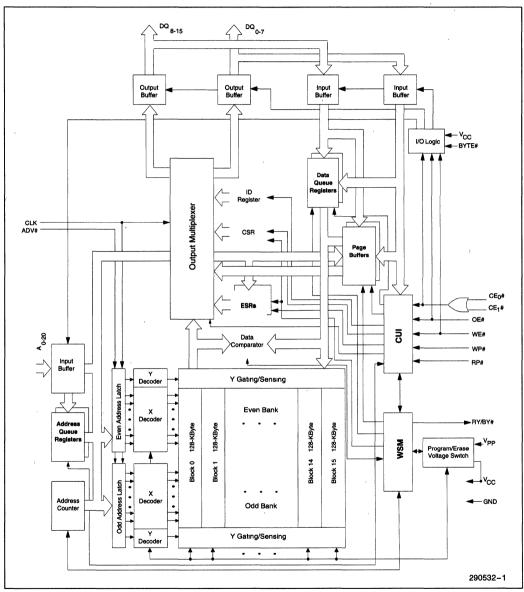

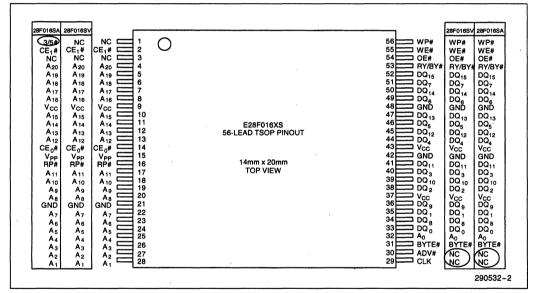

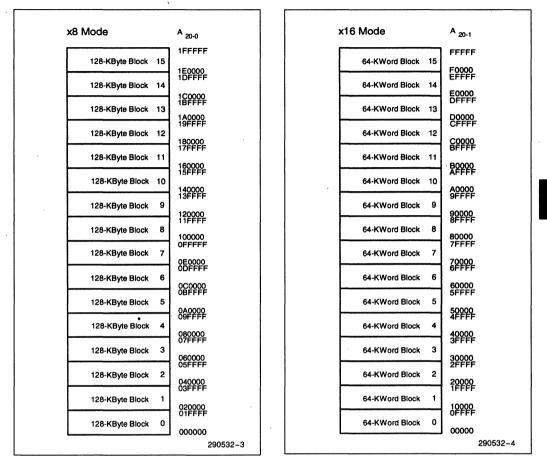

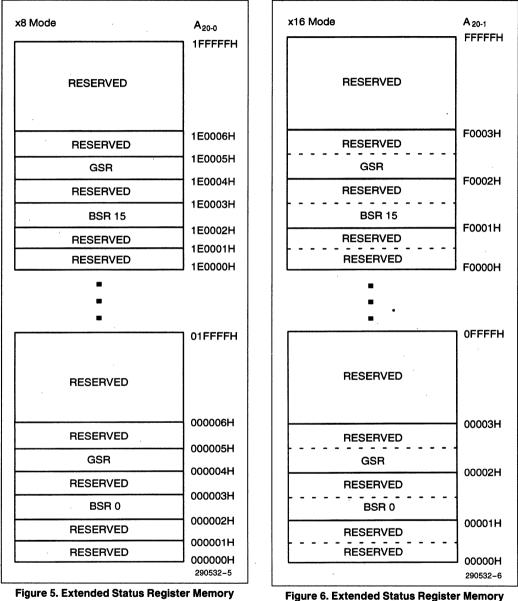

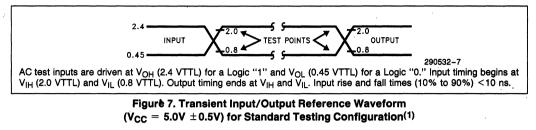

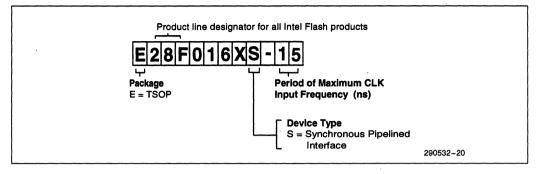

| 28F016XS 16-Mbit (1 Mbit x 16, 2 Mbit x 8) Synchronous Flash Memory         | 2-77           |

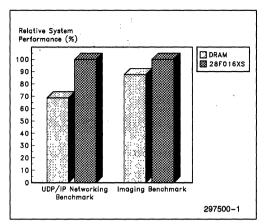

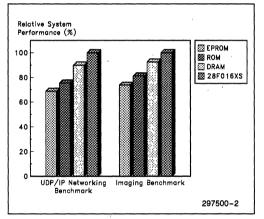

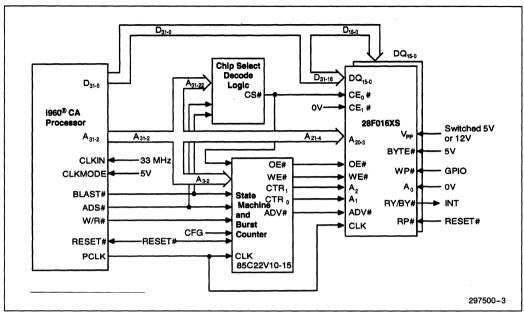

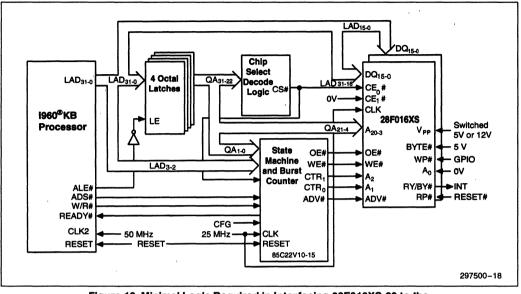

| Technical Paper, Interfacing the 28F016XS to the i960 Microprocessor Family | 2-124          |

| CHAPTER 3                                                                   |                |

| Development Support Tools                                                   |                |

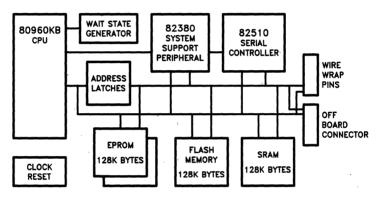

| QT960 Evaluation and Prototyping Board                                      | 3-1            |

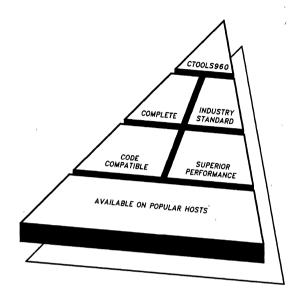

| C Programming Tools for the i960 Microprocessor Family                      | 3-4            |

| GNU/960 Software Toolset                                                    | 3-8            |

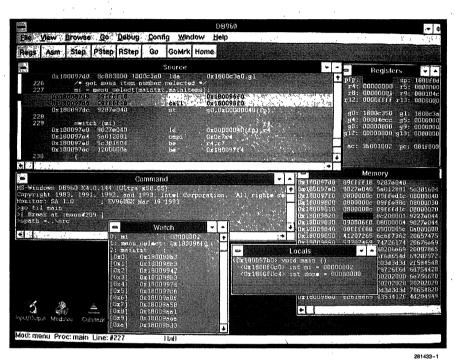

| DB960 Source-Level Retargetable Debugger                                    | 3-10           |

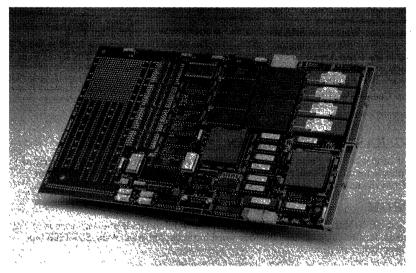

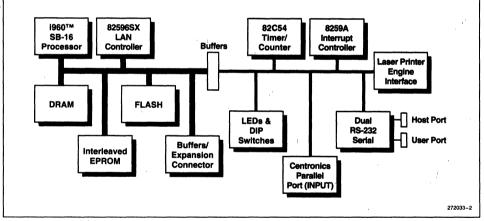

| EP80960Cx Evaluation Platform                                               | 3-13           |

| i960 SA/SB Evaluation Board                                                 | 3-15           |

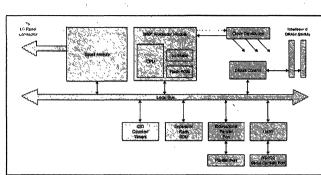

| i960 Microprocessor Evaluation Platform (Cyclone EP)                        | 3-17           |

х

### Alphanumeric Index

| 28F016XS 16-Mbit (1 Mbit x 16, 2 Mbit x 8) Synchronous Flash Memory         | 2-77  |

|-----------------------------------------------------------------------------|-------|

| 80960CA Product Overview                                                    | 1-158 |

| 80960CA-33, -25, -16 32-Bit High Performance Embedded Processor             | 1-196 |

| 80960CF-33, -25, -16 32-Bit High Performance Superscalar Processor          | 1-264 |

| 80960CF-40 32-Bit High-Performance Superscalar Processor                    | 1-331 |

| 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor                 | 1-442 |

| 80960JA/JF Embedded 32-Bit Microprocessor                                   | 1-390 |

| 80960KA Embedded 32-Bit Microprocessor                                      | 1-81  |

| 80960KB Embedded 32-Bit Microprocessor with Integrated Floating-Point Unit  | 1-118 |

| 80960SA Embedded 32-Bit Microprocessor with 16-Bit Burst Data Bus           | 1-1   |

| 80960SB Embedded 32-Bit Microprocessor with 16-Bit Burst Data Bus           | 1-39  |

| 82596CA High-Performance 32-Bit Local Area Network Coprocessor              | 2-1   |

| 82961KD Printer Coprocessor                                                 | 1-499 |

| AP-506 Designing for 80960Cx and 80960Hx Compatibility                      | 1-500 |

| C Programming Tools for the i960 Microprocessor Family                      | 3-4   |

| DB960 Source-Level Retargetable Debugger                                    | 3-10  |

| EP80960Cx Evaluation Platform                                               | 3-13  |

| GNU/960 Software Toolset                                                    | 3-8   |

| i960 KA/KB Processor Product Overview                                       | 1-76  |

| i960 Microprocessor Evaluation Platform (Cyclone EP)                        | 3-17  |

| i960 SA/SB Evaluation Board                                                 | 3-15  |

| QT960 Evaluation and Prototyping Board                                      | 3-1   |

| Technical Paper, Interfacing the 28F016XS to the i960 Microprocessor Family | 2-124 |

### i960<sup>®</sup> Microprocessor Family

. .

,

### 80960SA EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS

- High-Performance Embedded Architecture

- 20 MIPS\* Burst Execution at 20 MHz

- 7.5 MIPS Sustained Execution at 20 MHz

- 512-Byte On-Chip Instruction Cache — Direct Mapped

- Parallel Load/Decode for Uncached Instructions

- Multiple Register Sets

- Sixteen Global 32-Bit Registers

- Sixteen Local 32-Bit Registers

- Four Local Register Sets Stored On-Chip

- Register Scoreboarding

- Pin Compatible with 80960SB

- Built-in Interrupt Controller

4 Direct Interrupt Pins

31 Priority Levels, 256 Vectors

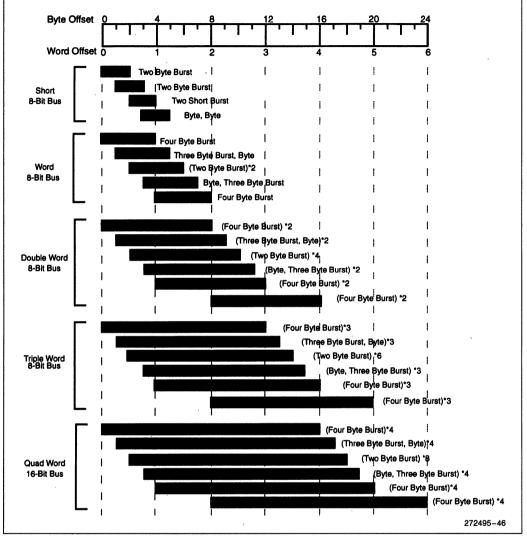

- Easy to Use, High Bandwidth 16-Bit Bus — 32 Mbytes/s Burst

- Up to 16 Bytes Transferred per Burst

- 32-Bit Address Space, 4 Gigabytes

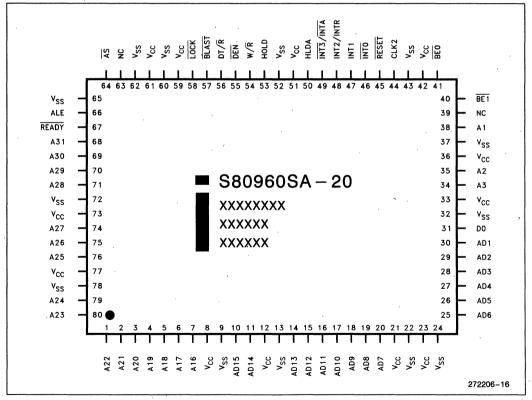

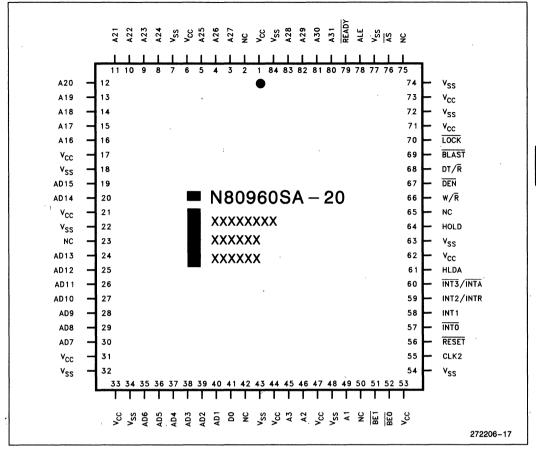

- 80-Lead Quad Flat Pack (EIAJ QFP)

- 84-Lead Plastic Leaded Chip Carrier (PLCC)

- Software Compatible with 80960KA/KB/CA/CF Processors

The 80960SA is a member of Intel's i960<sup>®</sup> 32-bit processor family, which is designed especially for low cost embedded applications. It includes a 512-byte instruction cache and a built-in interrupt controller. The 80960SA has a large register set, multiple parallel execution units and a 16-bit burst bus. Using advanced RISC technology, this high performance processor is capable of execution rates in excess of 7.5 million instructions per second\*. The 80960SA is well-suited for a wide range of cost sensitive embedded applications including non-impact printers, network adapters and I/O controllers.

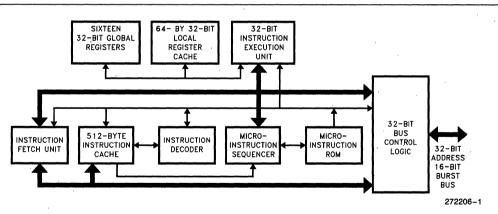

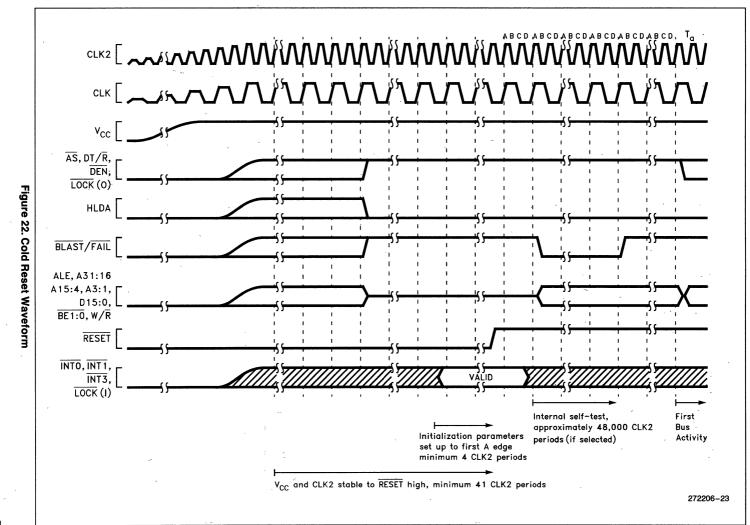

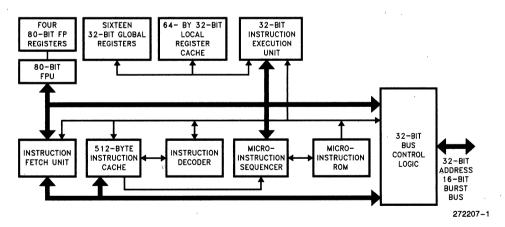

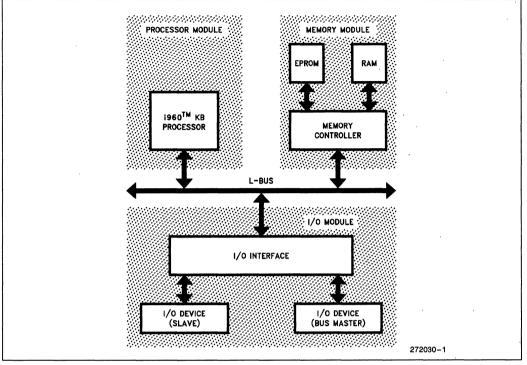

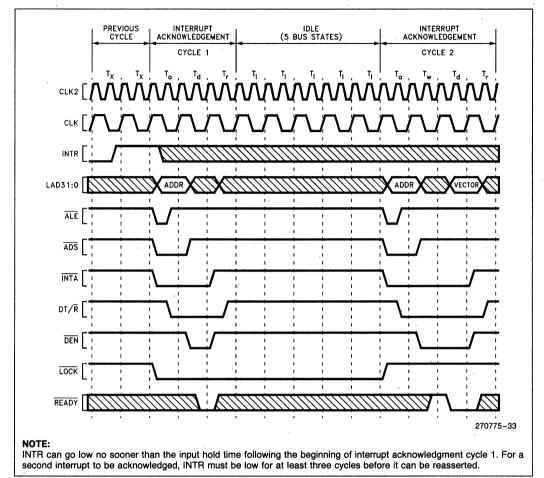

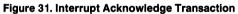

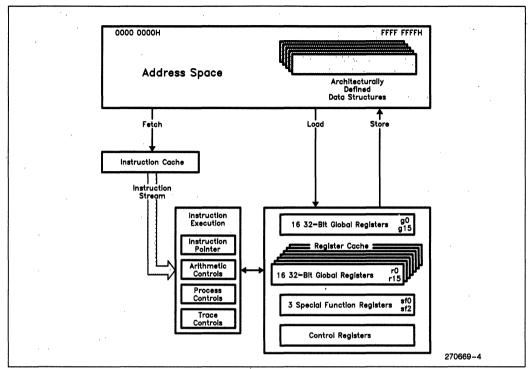

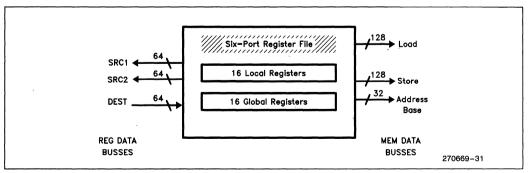

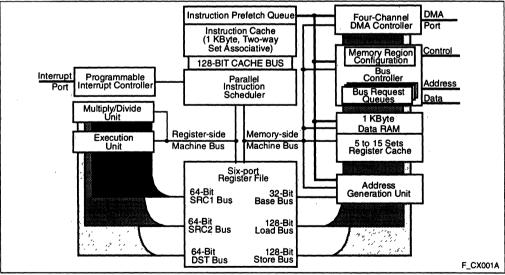

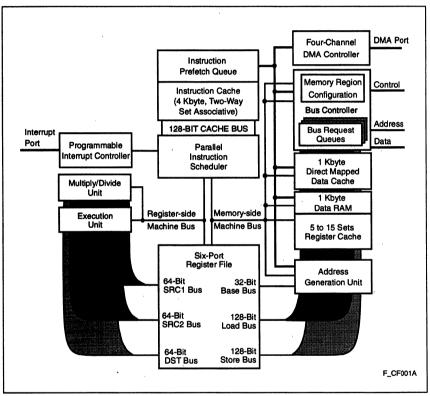

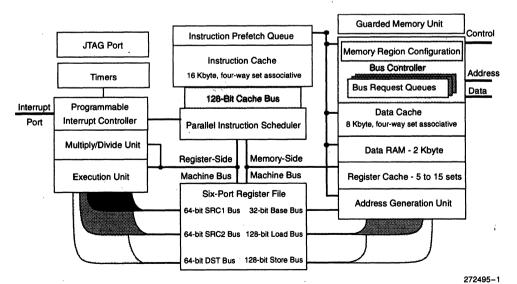

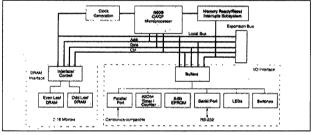

Figure 1. The 80960SA Processor's Highly Parallel Architecture

\*Relative to Digital Equipment Corporation's VAX-11/780 at 1 MIPS (VAX-11 is a trademark of Digital Equipment Corporation).

### 80960SA

### EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS

| CONTENTS                                          | PAGE |

|---------------------------------------------------|------|

| 1.0 THE 1960® PROCESSOR                           | 1-4  |

| 1.1 Key Performance Features                      | 1-5  |

| 1.1.1 Memory Space and<br>Addressing Modes        |      |

|                                                   |      |

| 1.1.2 Data Types         1.1.3 Large Register Set |      |

| 1.1.4 Multiple Register Sets                      |      |

| 1.1.5 Instruction Cache                           |      |

| 1.1.6 Register Scoreboarding                      |      |

| 1.1.7 High Bandwidth Bus                          |      |

| 1.1.8 Interrupt Handling                          |      |

| 1.1.9 Debug Features                              |      |

| 1.1.10 Fault Detection                            |      |

| 1.1.11 Built-in Testability                       | 1-10 |

| 1.1.12 CHMOS                                      | 1-10 |

| 2.0 ELECTRICAL SPECIFICATIONS                     | 1-14 |

| 2.1 Power and Grounding                           | 1-14 |

| 2.2 Power Descupling                              |      |

| Recommendations                                   |      |

| 2.3 Connection Recommendations                    |      |

| 2.4 Characteristic Curves                         |      |

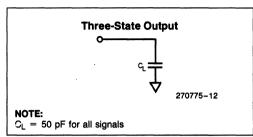

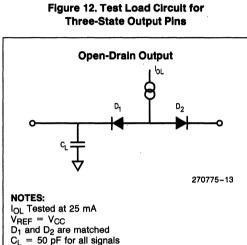

| 2.5 Test Load Circuit                             |      |

| 2.7 DC Characteristics                            |      |

| 2.8 AC Specifications                             |      |

| 2.8.1 AC Specification Tables                     |      |

| ·                                                 |      |

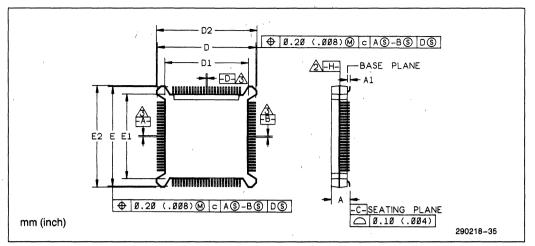

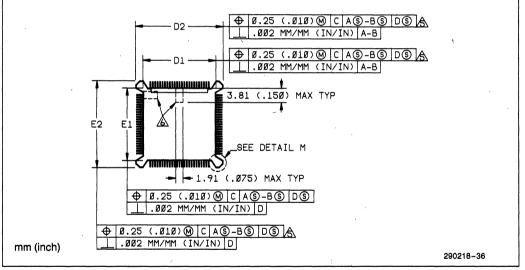

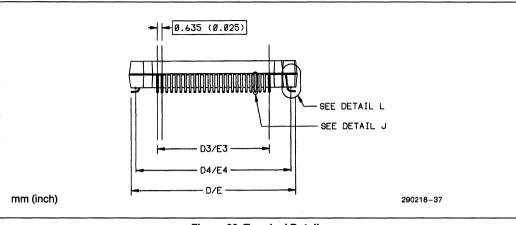

| 3.0 MECHANICAL DATA                               |      |

| 3.1 Packaging                                     |      |

| 3.3 Pinout                                        |      |

| 3.4 Package Thermal Specification                 |      |

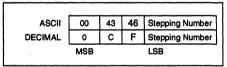

| 3.5 Stepping Register Information                 |      |

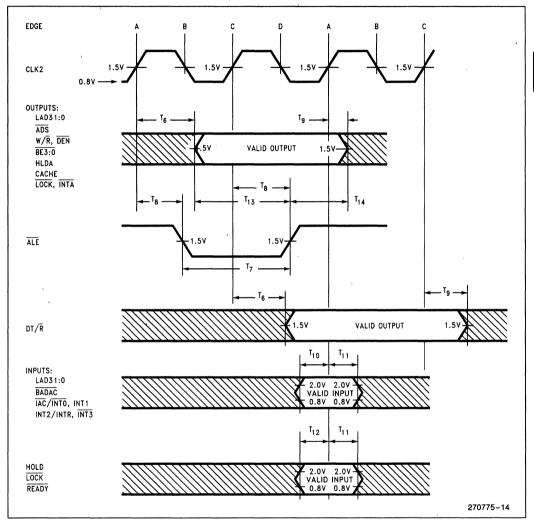

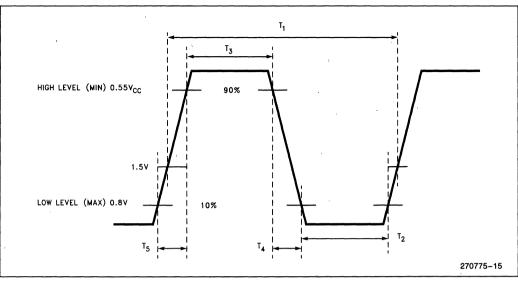

| 4.0 WAVEFORMS                                     | 1-31 |

| 5.0 REVISION HISTORY                              |      |

### CONTENTS

#### PAGE

| FIGURES    |                                                                     |

|------------|---------------------------------------------------------------------|

| Figure 1.  | The 80960SA Processor's<br>Highly Parallel Architecture 1-1         |

| Figure 2.  | 80960SA Programming<br>Environment                                  |

| Figure 3.  | Instruction Formats 1-7                                             |

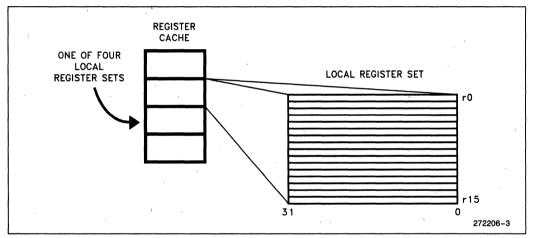

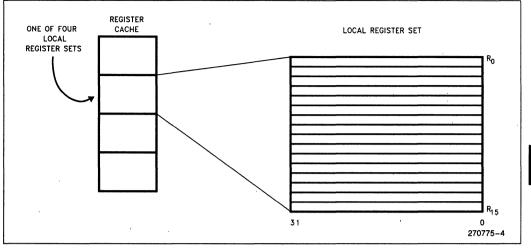

| Figure 4.  | Multiple Register Sets Are<br>Stored On-Chip 1-8                    |

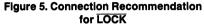

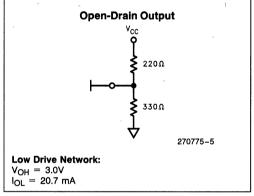

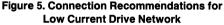

| Figure 5.  | Connection<br>Recommendations for Low<br>Current Drive Network 1-14 |

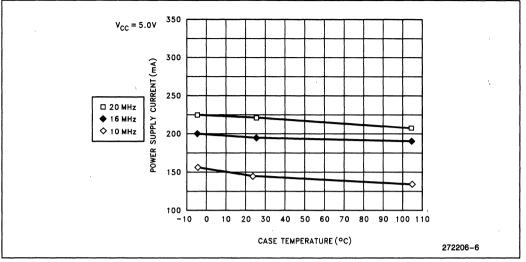

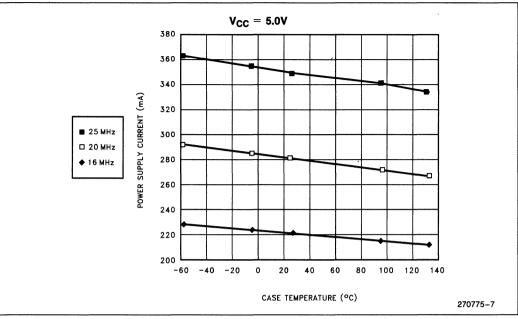

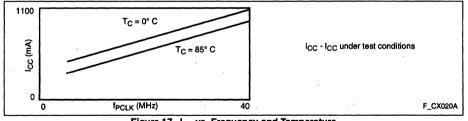

| Figure 6.  | Typical Supply Current vs.<br>Case Temperature 1-15                 |

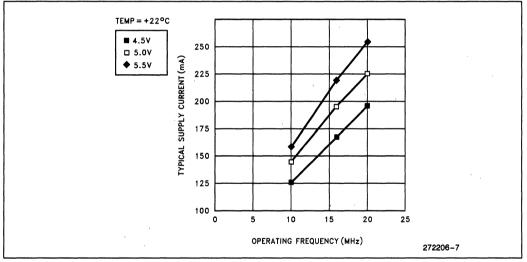

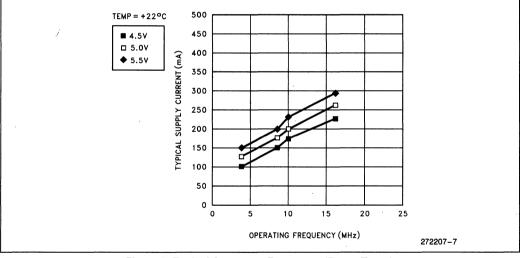

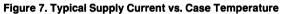

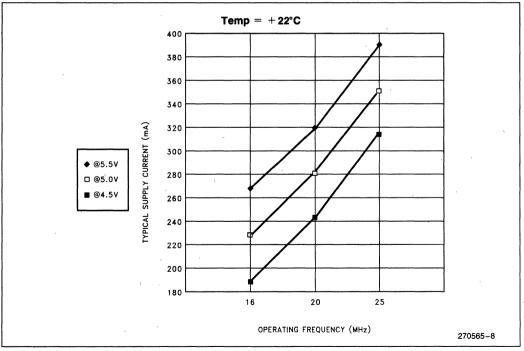

| Figure 7.  | Typical Current vs. Frequency<br>(Room Temp) 1-15                   |

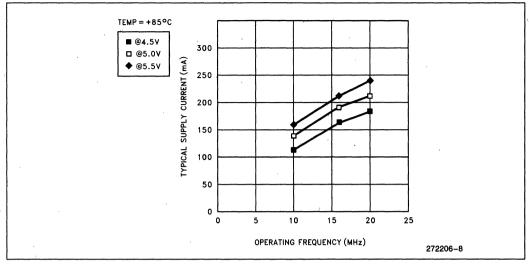

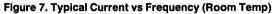

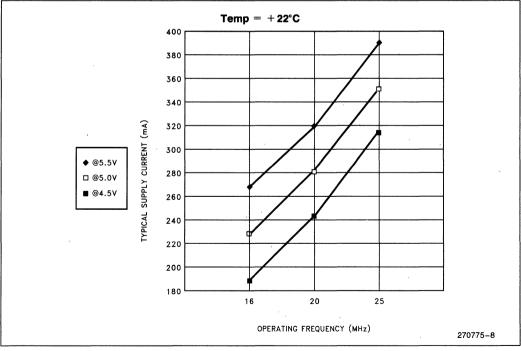

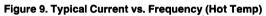

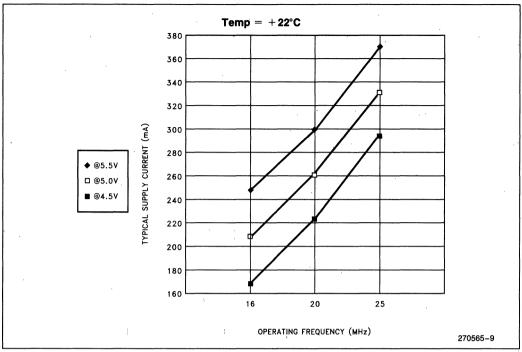

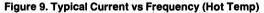

| Figure 8.  | Typical Current vs. Frequency<br>(Hot Temp) 1-16                    |

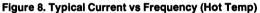

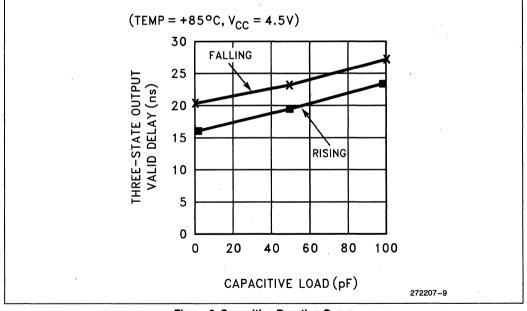

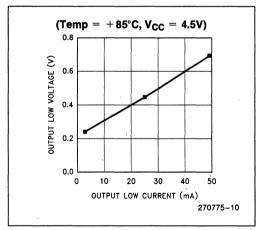

| Figure 9.  | Capacitive Derating Curve 1-16                                      |

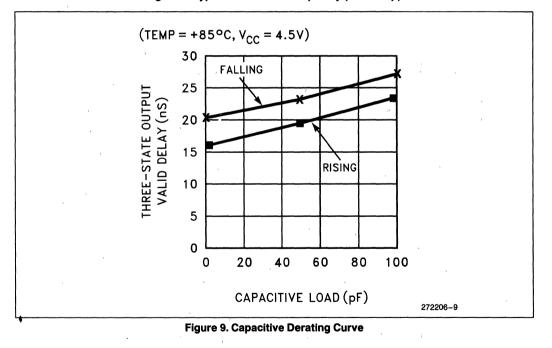

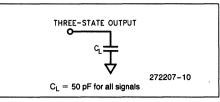

| Figure 10. | Test Load Circuit for Three-<br>State Output Pins 1-17              |

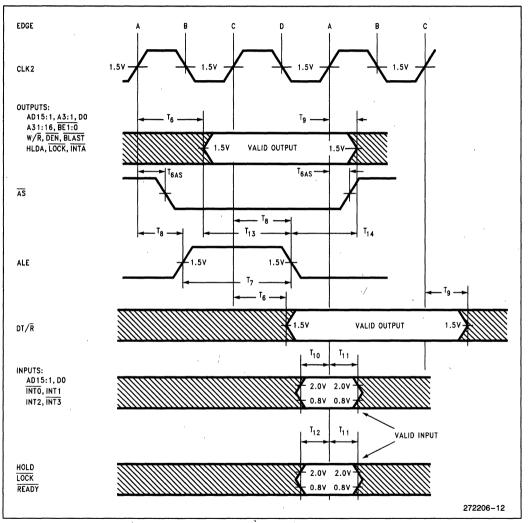

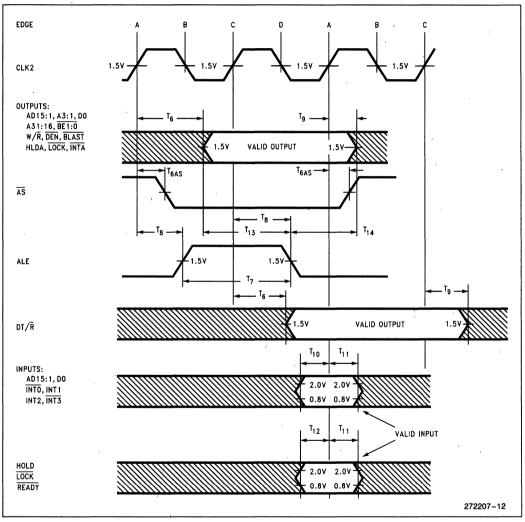

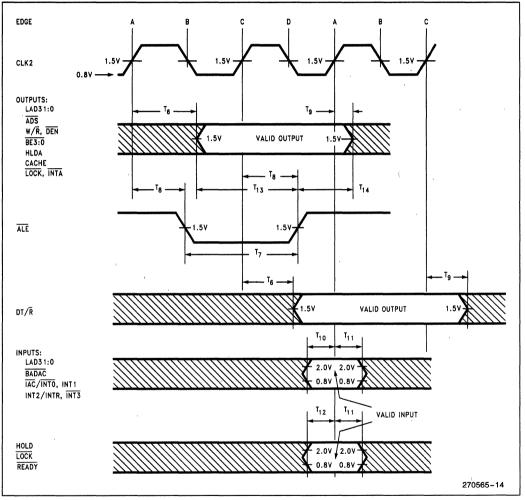

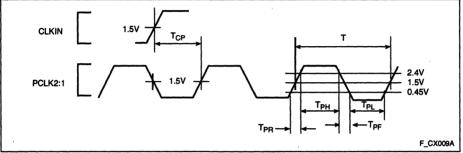

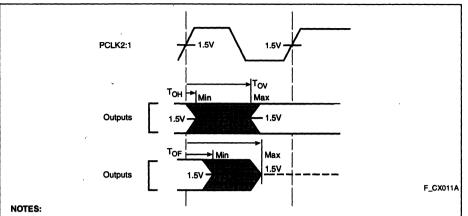

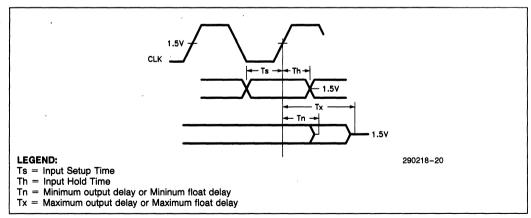

| Figure 11. | Drive Levels and Timing<br>Relationships for 80960SA<br>Signals     |

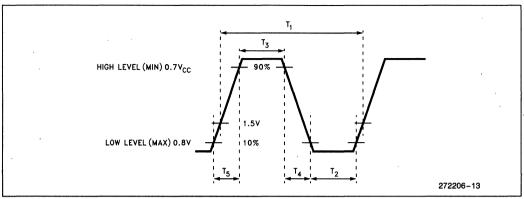

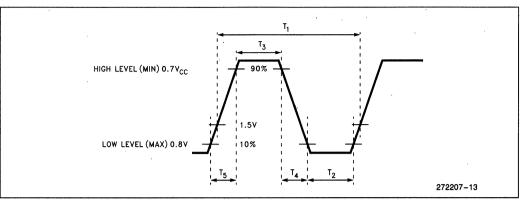

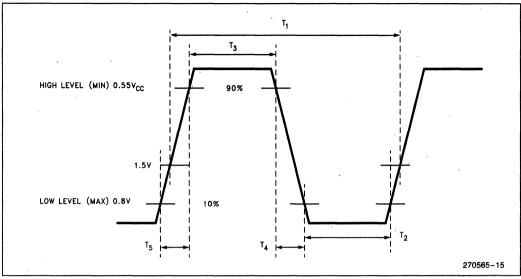

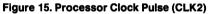

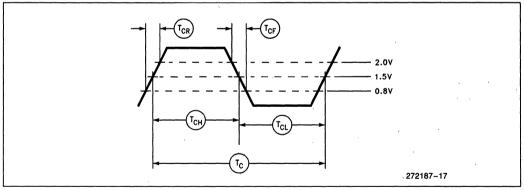

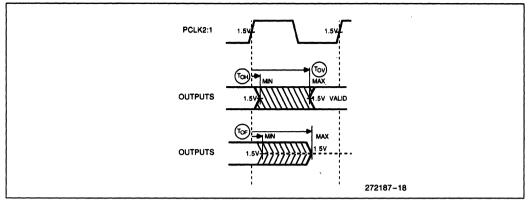

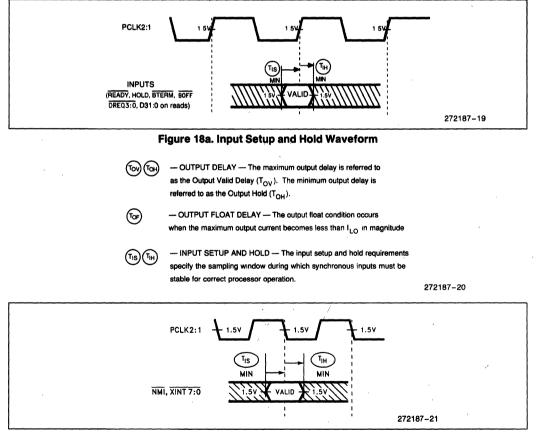

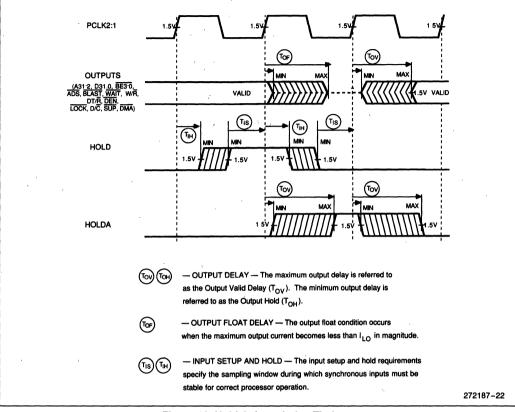

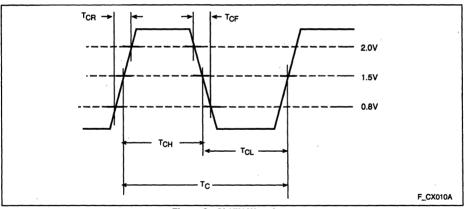

| Figure 12. | Processor Clock Pulse<br>(CLK2) 1-23                                |

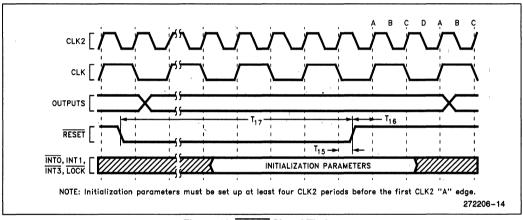

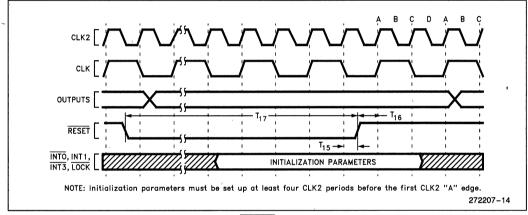

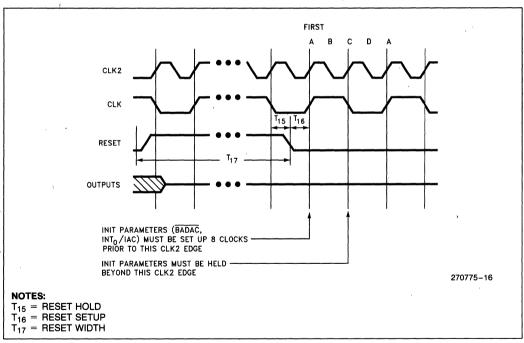

| Figure 13. | RESET Signal Timing 1-23                                            |

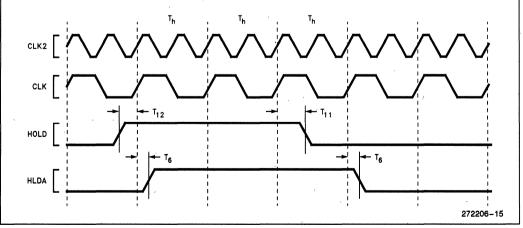

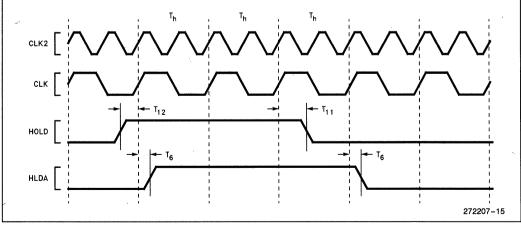

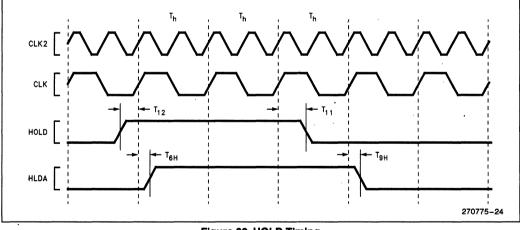

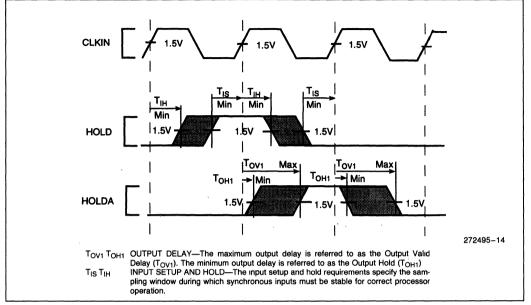

| Figure 14. | HOLD Timing 1-23                                                    |

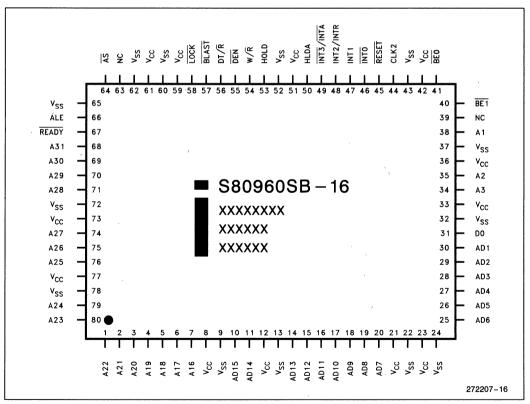

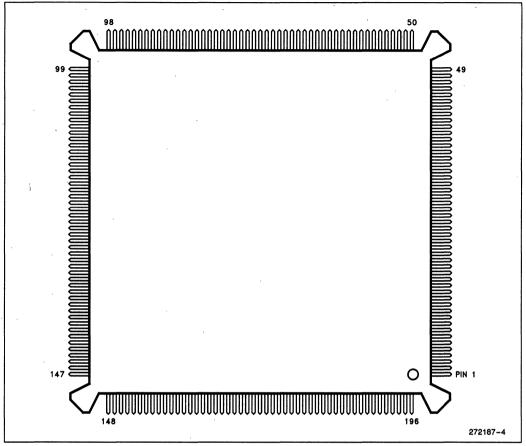

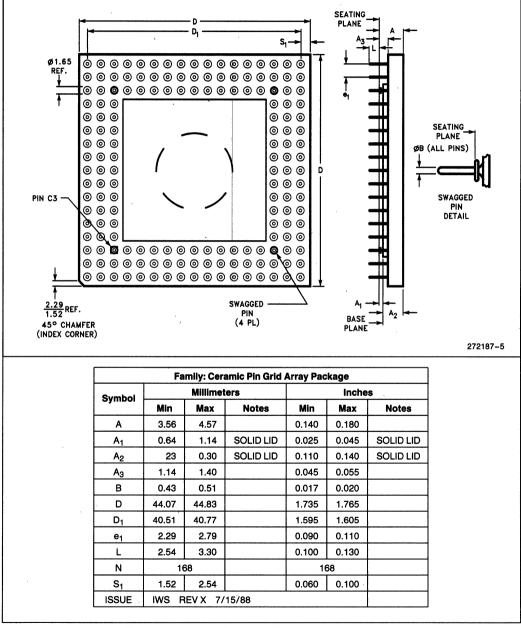

| Figure 15. | 80-Lead EIAJ Quad Flat Pack<br>(QFP) Package 1-24                   |

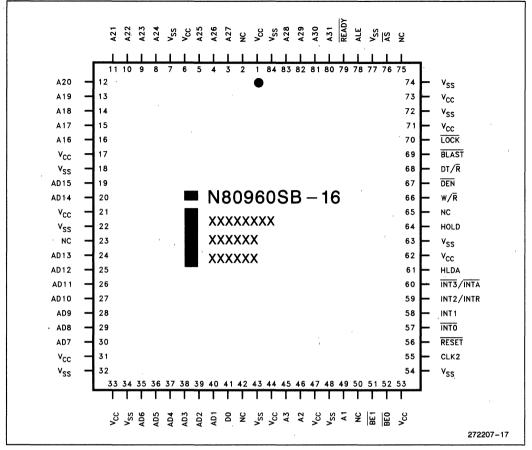

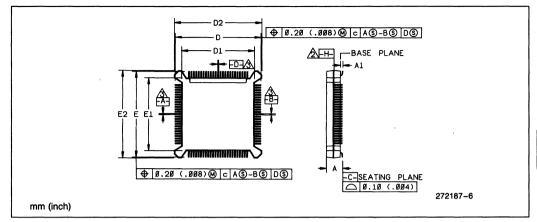

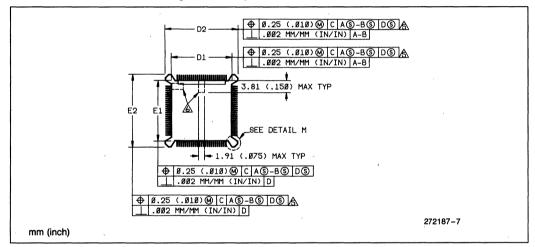

| Figure 16. | 84-Lead Plastic Leaded Chip<br>Carrier (PLCC) Package 1-25          |

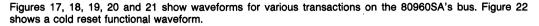

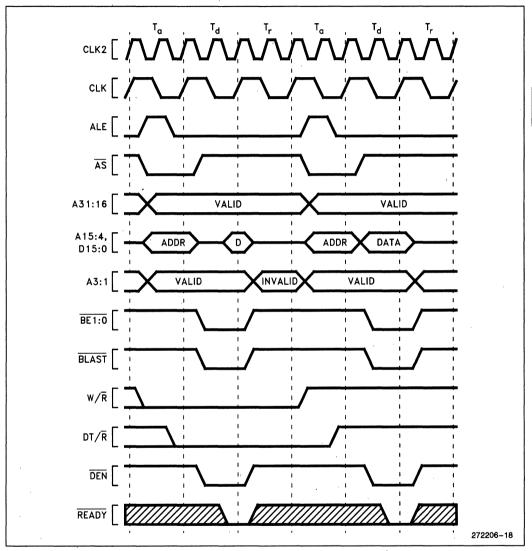

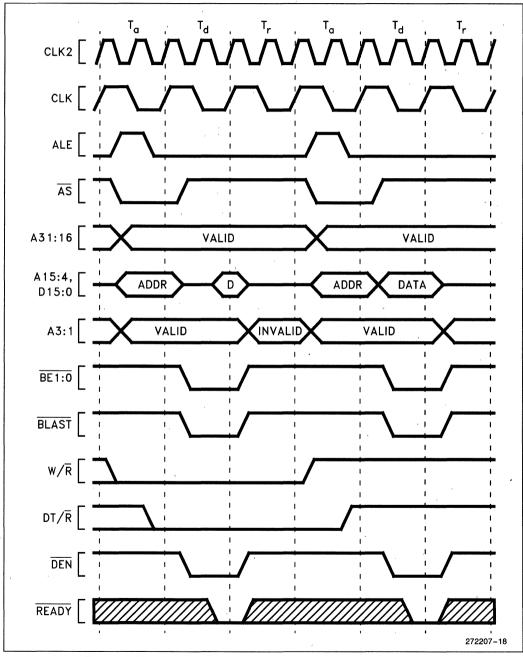

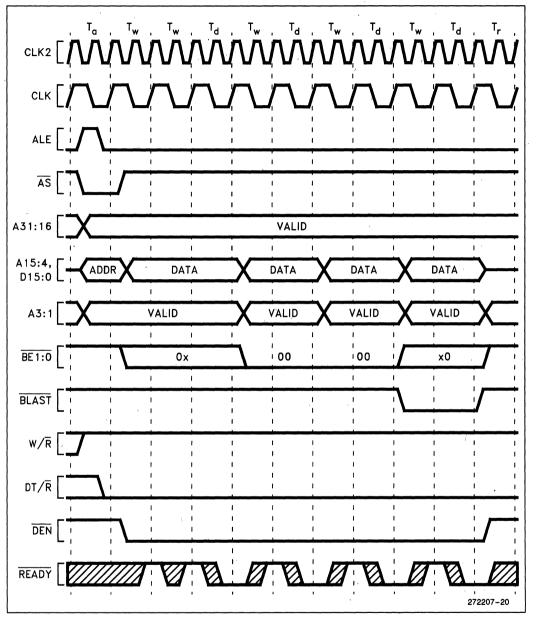

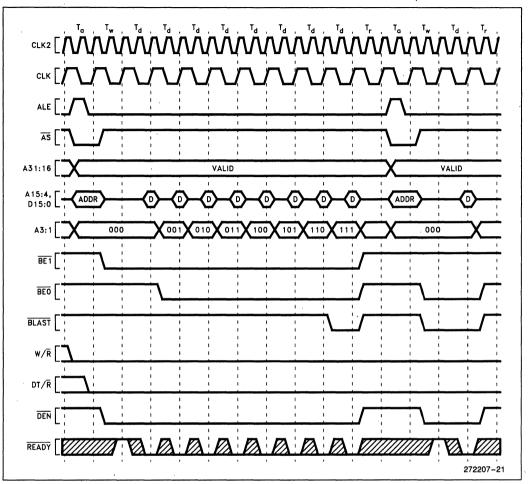

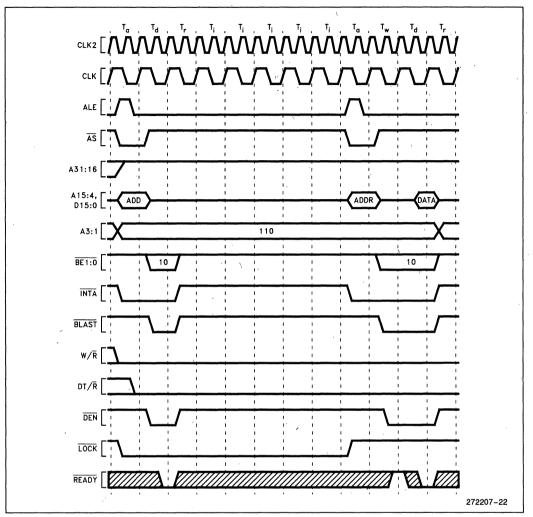

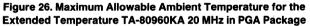

| Figure 17. | Non-Burst Read and Write<br>Transactions Without Wait<br>States1-31 |

### CONTENTS

#### PAGE

1

### FIGURES

| 2 |

|---|

| ; |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

### CONTENTS

#### PAGE

### TABLES

| Table 5.  | DC Characteristics 1-18                              |

|-----------|------------------------------------------------------|

| Table 6.  | 80960SA AC Characteristics<br>(10 MHz)1-20           |

| Table 7.  | 80960SA AC Characteristics<br>(16 MHz)1-21           |

| Table 8.  | 80960SA AC Characteristics<br>(20 MHz)1-22           |

| Table 9.  | 80960SA QFP Pinout—In Pin<br>Order1-26               |

| Table 10. | 80960SA QFP Pinout—In<br>Signal Order 1-27           |

| Table 11. | 80960SA PLCC Pinout—In Pin<br>Order1-28              |

| Table 12. | 80960SA PLCC Pinout—In<br>Signal Order 1-29          |

| Table 13. | 80960SA QFP Package<br>Thermal Characteristics 1-30  |

| Table 14. | 80960SA PLCC Package<br>Thermal Characteristics 1-30 |

| Table 15. | Die Stepping Cross<br>Reference 1-30                 |

### 1

#### 1.0 THE i960® PROCESSOR

The 80960SA is a member of the 32-bit architecture from Intel known as the i960 processor family. These microprocessors were especially designed to serve the needs of embedded applications. The embedded market includes applications as diverse as industrial automation, avionics, image processing, graphics and networking. These types of applications require high integration, low power consumption, quick interrupt response times and high performance. Since time to market is critical, embedded microprocessors need to be easy to use in both hardware and software designs. All members of the i960 processor family share a common core architecture which utilizes RISC technology so that, except for special functions, the family members are object-code compatible. Each new processor in the family adds its own special set of functions to the core to satisfy the needs of a specific application or range of applications in the embedded market.

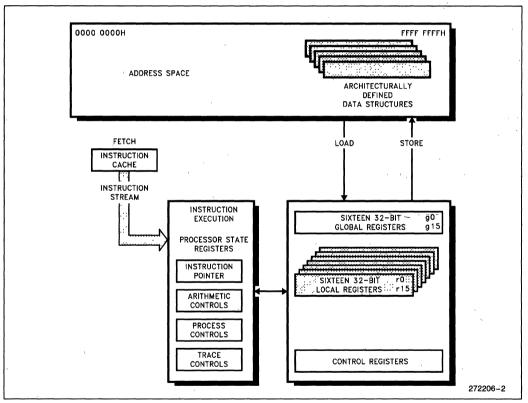

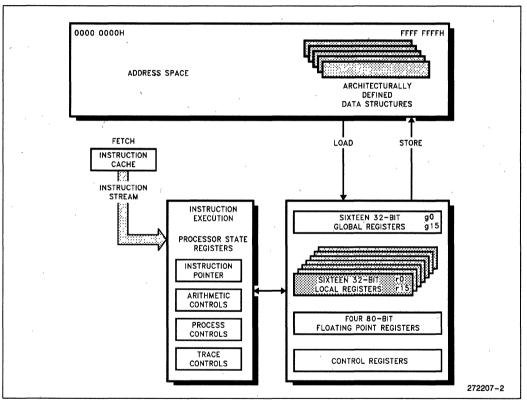

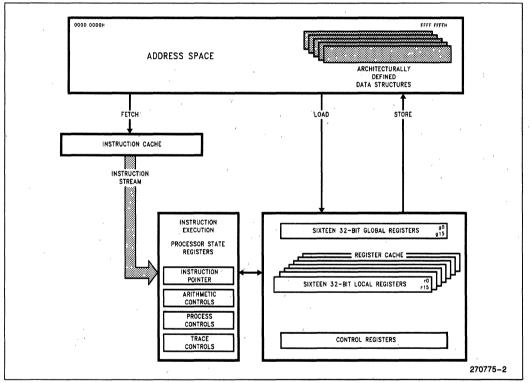

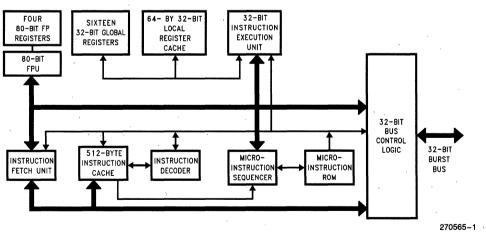

Figure 2. 80960SA Programming Environment

#### 1.1 Key Performance Features

The 80960SA architecture is based on the most recent advances in microprocessor technology and is grounded in Intel's long experience in the design and manufacture of embedded microprocessors. Many features contribute to the 80960SA's exceptional performance:

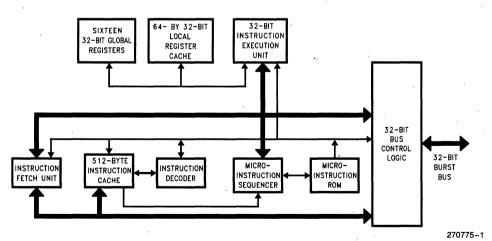

- Large Register Set. Having a large number of registers reduces the number of times that a processor needs to access memory. Modem compilers can take advantage of this feature to optimize execution speed. For maximum flexibility, the 80960SA provides thirty-two 32-bit registers. (See Figure 2.)

- Fast Instruction Execution. Simple functions make up the bulk of instructions in most programs so that execution speed can be improved by ensuring that these core instructions are executed as quickly as possible. The most frequently executed instructions—such as register-register moves, add/subtract, logical operations and shifts—execute in one to two cycles. (Table 1 contains a list of instructions.)

- 3. Load/Store Architecture. One way to improve execution speed is to reduce the number of times that the processor must access memory to perform an operation. As with other processors based on RISC technology, the 80960SA has a Load/Store architecture. As such, only the LOAD and STORE instructions reference memory; all other instructions operate on registers. This type of architecture simplifies instruction decoding and is used in combination with other techniques to increase parallelism.

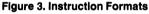

- 4. Simple Instruction Formats. All instructions in the 80960SA are 32 bits long and must be aligned on word boundaries. This alignment makes it possible to eliminate the instruction alignment stage in the pipeline. To simplify the instruction decoder, there are only five instruction formats; each instruction uses only one format. (See Figure 3.)

- 5. Overlapped Instruction Execution. Load operations allow execution of subsequent instructions to continue before the data has been returned from memory, so that these instructions can overlap the load. The 80960SA manages this process transparently to software through the use of a register scoreboard. Conditional instructions also make use of a scoreboard so that subsequent unrelated instructions may be executed while the conditional instruction is pending.

- 6. Integer Execution Optimization. When the result of an arithmetic execution is used as an operand in a subsequent calculation, the value is sent immediately to its destination register. At the same time, the value is put on a bypass path to the ALU, thereby saving the time that otherwise would be required to retrieve the value for the next operation.

- 7. Bandwidth Optimizations. The 80960SA gets optimal use of its memory bus bandwidth because the bus is tuned for use with the on-chip instruction cache: instruction cache line size matches the maximum burst size for instruction fetches. The 80960SA automatically fetches four words in a burst and stores them directly in the cache. Due to the size of the cache and the fact that it is continually filled in anticipation of needed instructions in the program flow, the 80960SA is relatively insensitive to memory wait states. The benefit is that the 80960SA delivers outstanding performance even with a low cost memory system.

- Cache Bypass. If a cache miss occurs, the processor fetches the needed instruction then sends it on to the instruction decoder at the same time it updates the cache. Thus, no extra time is spent to load and read the cache.

| Data Movement         | Arithmetic                 | Logical             | <b>Bit and Bit Field</b> |  |  |  |  |

|-----------------------|----------------------------|---------------------|--------------------------|--|--|--|--|

| Load                  | Add                        | And                 | Set Bit                  |  |  |  |  |

| Store                 | Subtract                   | Not And             | Clear Bit                |  |  |  |  |

| Move                  | Multiply                   | And Not             | Not Bit                  |  |  |  |  |

| Load Address          | Divide                     | Or                  | Check Bit                |  |  |  |  |

|                       | Remainder                  | Exclusive Or        | Alter Bit                |  |  |  |  |

|                       | Modulo                     | Not Or              | Scan For Bit             |  |  |  |  |

|                       | Shift                      | Or Not              | Scan Over Bit            |  |  |  |  |

|                       | Extended Multiply          | Nor                 | Extract                  |  |  |  |  |

|                       | Extended Divide            | Exclusive Nor       | Modify                   |  |  |  |  |

|                       |                            | Not                 |                          |  |  |  |  |

|                       |                            | Nand                |                          |  |  |  |  |

|                       | ·                          | Rotate              | 5 A                      |  |  |  |  |

| Comparison            | Branch                     | Call/Return         | Fault                    |  |  |  |  |

| Compare               | Unconditional Branch       | Call                | Conditional Fault        |  |  |  |  |

| Conditional Compare   | Conditional Branch         | Call Extended       | Synchronize Faults       |  |  |  |  |

| Compare and Increment | Compare and Branch         | Call System         |                          |  |  |  |  |

| Compare and Decrement |                            | Return              |                          |  |  |  |  |

|                       |                            | Branch and Link     |                          |  |  |  |  |

| Debug                 | Miscellaneous              | Decimal             |                          |  |  |  |  |

| Modify Trace Controls | Atomic Add                 | Move                |                          |  |  |  |  |

| Mark                  | Atomic Modify              | Add and Carry       |                          |  |  |  |  |

| Force Mark            | Flush Local Registers      | Subtract with Carry |                          |  |  |  |  |

|                       | Modify Arithmetic Controls | ,                   |                          |  |  |  |  |

|                       | Scan Byte for Equal        |                     |                          |  |  |  |  |

|                       | Test Condition Code        |                     |                          |  |  |  |  |

| Synchronous           | 1 r                        | •                   |                          |  |  |  |  |

| Synchronous Load      |                            |                     |                          |  |  |  |  |

| Synchronous Move      | 1                          |                     |                          |  |  |  |  |

Table 1. 80960SA Instruction Set

| Control                 | Opcode |         | Displacement |          |    |         |     |         |

|-------------------------|--------|---------|--------------|----------|----|---------|-----|---------|

| Compare and<br>Branch   | Opcode | Reg/Lit | Reg          | М        |    | Displac | eme | ent     |

| Register to<br>Register | Opcode | Reg     | Reg/Lit      | Modes    |    | Ext'd   | Ор  | Reg/Lit |

| Memory Access—<br>Short | Opcode | Reg     | Base         | М        | X  | 1       |     | Offset  |

| Memory Access—<br>Long  | Opcode | Reg     | Base         | Mode     |    | Scale   | XX  | Offset  |

|                         |        |         | Di           | splaceme | nt |         |     |         |

**Figure 3. Instruction Formats**

#### 1.1.1 MEMORY SPACE AND ADDRESSING MODES

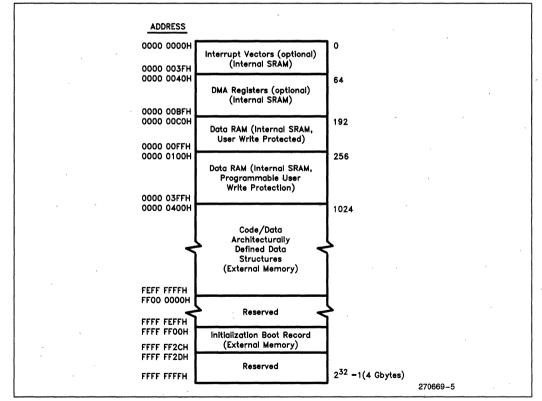

The 80960SA offers a linear programming environment so that all programs running on the processor are contained in a single address space. Maximum address space size is 4 Gigabytes (2<sup>32</sup> bytes).

For ease of use the 80960SA has a small number of addressing modes, but includes all those necessary to ensure efficient execution of high-level languages such as C. Table 2 lists the memory addressing modes.

#### Table 2. Memory Addressing Modes

- 12-Bit Offset

- 32-Bit Offset

- Register-Indirect

- Register + 12-Bit Offset

- Register + 32-Bit Offset

- Register + (Index-Register x Scale-Factor)

- Register x Scale Factor + 32-Bit Displacement

- Register + (Index-Register x Scale-Factor) + 32-Bit Displacement

Scale-Factor is 1, 2, 4, 8 or 16

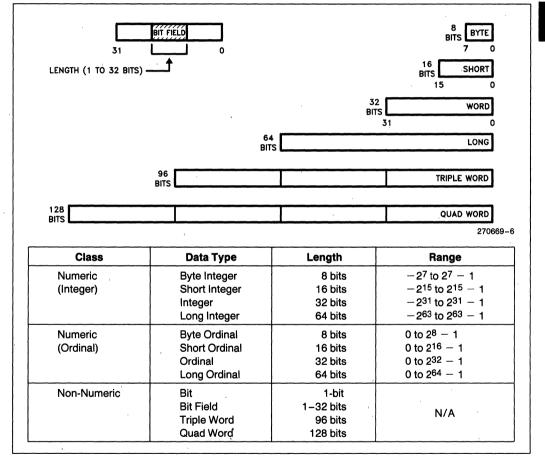

#### 1.1.2 DATA TYPES

The 80960SA recognizes the following data types:

Numeric:

- 8-, 16-, 32- and 64-bit ordinals

- 8-, 16-, 32- and 64-bit integers

Non-Numeric:

- Bit

- Bit Field

- Triple Word (96 bits)

- Quad-Word (128 bits)

#### 1.1.3 LARGE REGISTER SET

The 80960SA programming environment includes a large number of registers. In fact, 32 registers are available at any time. The availability of this many registers greatly reduces the number of memory accesses required to perform algorithms, which leads to greater instruction processing speed.

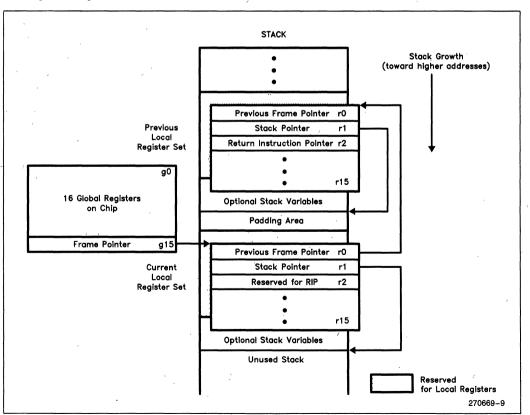

There are two types of general-purpose register: local and global. The global registers consist of sixteen 32-bit registers (g0 though g15). These registers perform the same function as the general-

purpose registers provided in other popular microprocessors. The term global refers to the fact that these registers retain their contents across procedure calls.

The local registers, on the other hand, are procedure specific. For each procedure call, the 80960SA allocates 16 local registers (r0 through r15). Each local register is 32 bits wide.

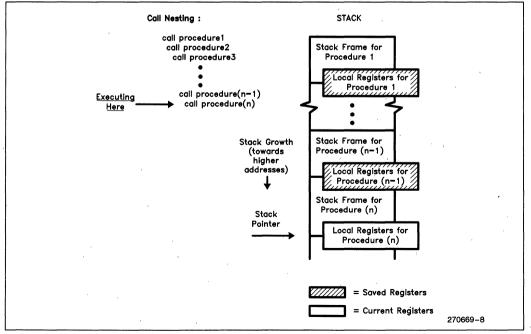

#### 1.1.4 MULTIPLE REGISTER SETS

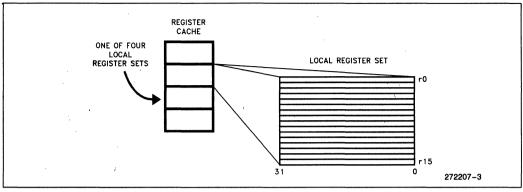

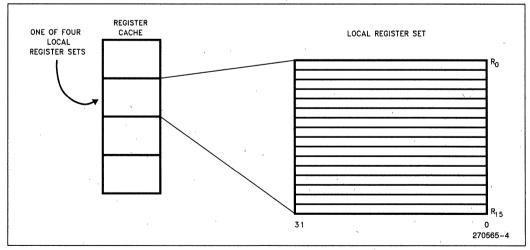

To further increase the efficiency of the register set, multiple sets of local registers are stored on-chip (See Figure 4). This cache holds up to four local register frames, which means that up to three procedure calls can be made without having to access the procedure stack resident in memory. Although programs may have procedure calls nested many calls deep, a program typically oscillates back and forth between only two to three levels. As a result, with four stack frames in the cache, the probability of having a free frame available on the cache when a call is made is very high. In fact, runs of representative C-language programs show that 80% of the calls are handled without needing to access memory.

If four or more procedures are active and a new procedure is called, the 80960SA moves the oldest local register set in the stack-frame cache to a procedure stack in memory to make room for a new set of registers. Global register g15 is the frame pointer (FP) to the procedure stack.

Global registers are not exchanged on a procedure call, but retain their contents, making them available to all procedures for fast parameter passing.

Figure 4. Multiple Register Sets Are Stored On-Chip

#### 1.1.5 INSTRUCTION CACHE

To further reduce memory accesses, the 80960SA includes a 512-byte on-chip instruction cache. The instruction cache is based on the concept of locality of reference; most programs are not usually executed in a steady stream but consist of many branches, loops and procedure calls that lead to jumping back and forth in the same small section of code. Thus, by maintaining a block of instructions in cache, the number of memory references required to read instructions into the processor is greatly reduced.

To load the instruction cache, instructions are fetched in 16-byte blocks; up to four instructions can be fetched at one time. An efficient prefetch algorithm increases the probability that an instruction will already be in the cache when it is needed.

Code for small loops often fits entirely within the cache, leading to a great increase in processing speed since further memory references might not be necessary until the program exits the loop. Similarly, when calling short procedures, the code for the calling procedure is likely to remain in the cache so it will be there on the procedure's return.

#### 1.1.6 REGISTER SCOREBOARDING

The instruction decoder is optimized in several ways. One optimization method is the ability to overlap instructions by using register scoreboarding.

Register scoreboarding occurs when a LOAD moves a variable from memory into a register. When the instruction initiates, a scoreboard bit on the target register is set. Once the register is loaded, the bit is reset. In between, any reference to the register contents is accompanied by a test of the scoreboard bit to ensure that the load has completed before processing continues. Since the processor does not need to wait for the LOAD to complete, it can execute additional instructions placed between the LOAD and the instruction that uses the register contents, as shown in the following example:

ld data\_2, r4 ld data\_2, r5 Unrelated instruction Unrelated instruction add r4, r5, r6 In essence, the two unrelated instructions between LOAD and ADD are executed "for free" (i.e., take no apparent time to execute) because they are executed while the register is being loaded. Up to three load instructions can be pending at one time with three corresponding scoreboard bits set. By exploiting this feature, system programmers and compiler writers have a useful tool for optimizing execution speed.

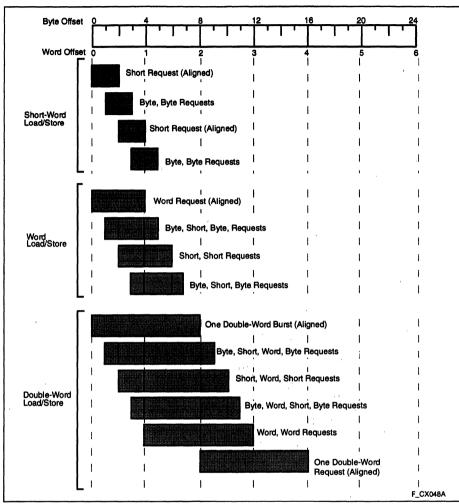

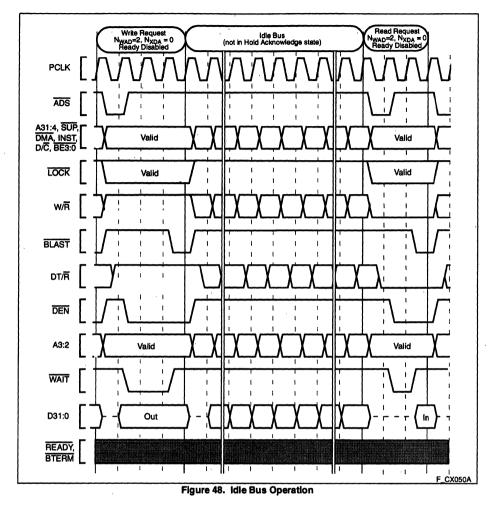

#### 1.1.7 HIGH BANDWIDTH BUS

The 80960SA CPU resides on a high-bandwidth address/data bus. The bus provides a direct communication path between the processor and the memory and I/O subsystem interfaces. The processor uses the bus to fetch instructions, manipulate memory and respond to interrupts. Bus features include:

- 16-bit data path multiplexed onto the lower bits of the 32-bit address path

- Eight 16-bit half-word burst capability which allows transfers from 1 to 16 bytes at a time

- High bandwidth reads and writes with 32 Mbytes/s burst (at 20 MHz)

Table 3 defines bus signal names and functions; Table 4 defines other component-support signals such as interrupt lines.

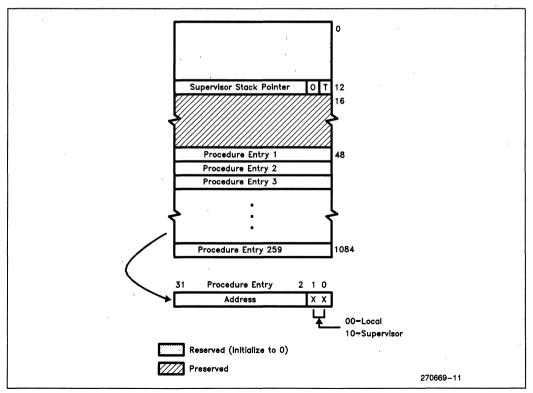

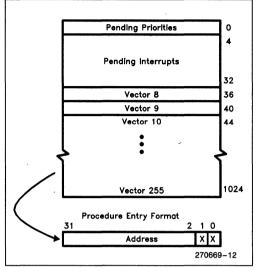

#### 1.1.8 INTERRUPT HANDLING

The 80960SA can be interrupted in one of two ways: by the activation of one of four interrupt pins or by sending a message on the processor's data bus.

The 80960SA is unusual in that it automatically handles interrupts on a priority basis and can keep track of pending interrupts through its on-chip interrupt controller. Two of the interrupt pins can be configured to provide 8259A-style handshaking for expansion beyond four interrupt lines.

#### 1.1.9 DEBUG FEATURES

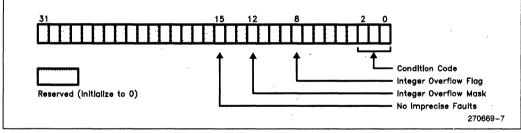

The 80960SA has built-in debug capabilities. There are two types of breakpoints and six trace modes. Debug features are controlled by two internal 32-bit registers, the Process-Controls Word and the Trace-Controls Word. By setting bits in these control words, a software debug monitor can closely control how the processor responds during program execution.

#### 80960SA

The 80960SA provides two hardware breakpoint registers on-chip which, by using a special command, can be set to any value. When the instruction pointer matches either breakpoint register value, the breakpoint handling routine is automatically called.

The 80960SA also provides software breakpoints through the use of two instructions: MARK and FMARK. These can be placed at any point in a program and cause the processor to halt execution at that point and call the breakpoint handling routine. The breakpoint mechanism is easy to use and provides a powerful debugging tool.

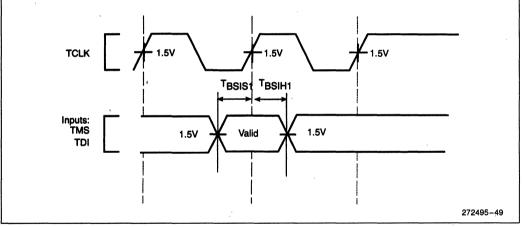

Tracing is available for instructions (single step execution), calls and returns and branching. Each trace type may be enabled separately by a special debug instruction. In each case, the 80960SA executes the instruction first and then calls a trace handling routine (usually part of a software debug monitor). Further program execution is halted until the routine completes, at which time execution resumes at the next instruction. The 80960SA's tracing mechanisms, implemented completely in hardware, greatly simplify the task of software test and debug.

#### 1.1.10 FAULT DETECTION

The 80960SA has an automatic mechanism to handle faults. Fault types include trace and arithmetic faults. When the processor detects a fault, it automatically calls the appropriate fault handling routine and saves the current instruction pointer and necessary state information to make efficient recovery possible. Like interrupt handling routines, fault handling routines are usually written to meet the needs of specific applications and are often included as part of the operating system or kernel. For each of the fault types, there are numerous subtypes that provide specific information about a fault. The fault handler can use this specific information to respond correctly to the fault.

#### 1.1.11 BUILT-IN TESTABILITY

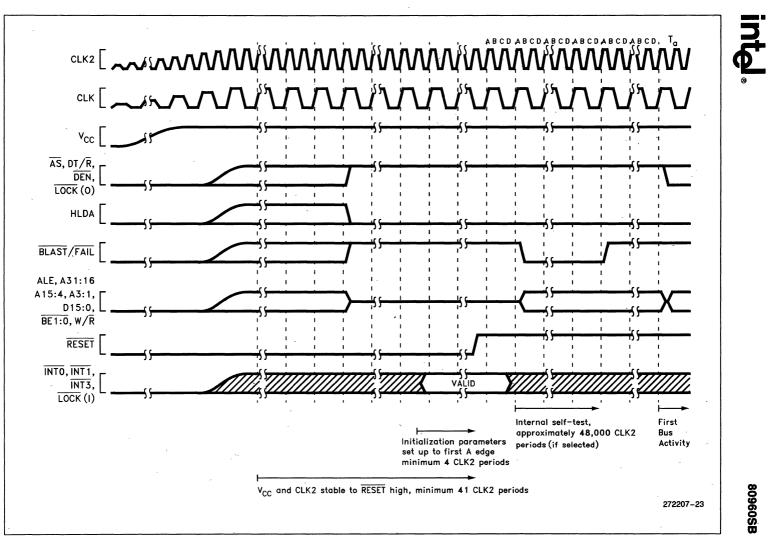

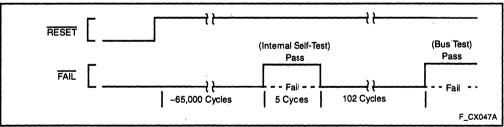

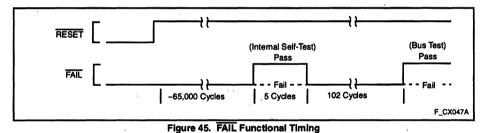

Upon reset, the 80960SA automatically conducts an exhaustive internal test of its major blocks of logic. Then, before executing its first instruction, it does a zero check sum on the first eight words in memory to ensure that the memory image was programmed correctly. If a problem is discovered at any point during the self-test, the 80960SA asserts its FAIL pin and will not begin program execution. Self test takes approximately 24,000 cycles to complete.

System manufacturers can use the 80960SA's selftest feature during incoming parts inspection. No special diagnostic programs need to be written. The test is both thorough and fast. The self-test capability helps ensure that defective parts are discovered before systems are shipped and, once in the field, the self-test makes it easier to distinguish between problems caused by processor failure and problems resulting from other causes.

#### 1.1.12 CHMOS

The 80960SA is fabricated using Intel's CHMOS IV (Complementary High Speed Metal Oxide Semiconductor) process. The 80960SA is available at 10 and 16 MHz in the QFP package and at 10, 16 and 20 MHz in the PLCC package.

| Name       | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK2       | I           | <b>SYSTEM CLOCK</b> provides the fundamental timing for 80960SA systems. It is divided by two inside the 80960SA to generate the internal processor clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A31:16     | 0<br>T.S.   | <b>ADDRESS BUS</b> carries the upper 16 bits of the 32-bit physical address to memory. It is valid throughout the burst cycle; no latch is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AD15:1, D0 | 1/O<br>T.S. | <b>ADDRESS/DATA BUS</b> carries the low order 32-bit addresses and 16-bit data to and from memory. AD15:4 must be latched since the cycle following the address cycle carries data on the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A3:1       | O<br>T.S.   | <b>ADDRESS BUS</b> carries the word addresses of the 32-bit address to memory. These three bits are incremented during a burst access indicating the next word address of the burst access. Note that A3:1 are duplicated with AD3:1 during the address cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

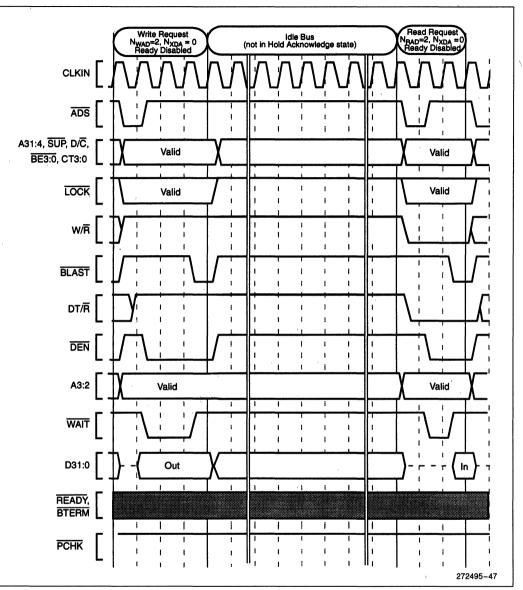

| ALE        | O<br>T.S.   | <b>ADDRESS LATCH ENABLE</b> indicates the transfer of a physical address. ALE is asserted during a $T_a$ cycle and deasserted before the beginning of the $T_d$ state. It is active high and floats to a high impedance state during a hold cycle ( $T_h$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ĀS         | O<br>T.S.   | <b>ADDRESS STATUS</b> indicates an address state. $\overline{AS}$ is asserted every T <sub>a</sub> state and deasserted during the following T <sub>d</sub> state. $\overline{AS}$ is driven HIGH during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| W/R        | 0<br>T.S.   | <b>WRITE/READ</b> specifies, during a $T_a$ cycle, whether the operation is a write or read. It is latched on-chip and remains valid during $T_d$ cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

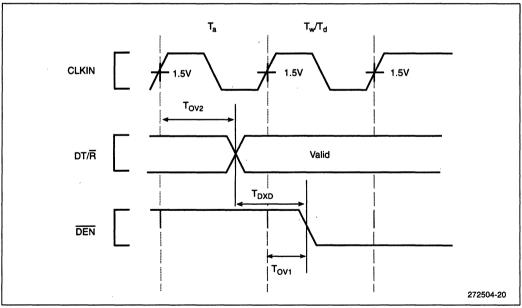

| DEN        | O<br>T.S.   | <b>DATA ENABLE</b> is asserted during $T_d$ cycles and indicates transfer of data on the AD lines. The AD lines should not be driven by an external source unless $\overline{DEN}$ is asserted. When $\overline{DEN}$ is asserted, outputs from the previous cycle are guaranteed to be three-stated. In addition, $\overline{DEN}$ deasserted indicates inputs have been captured and therefore input hold times can be disregarded. $\overline{DEN}$ is driven HIGH during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DT/R       | 0<br>T.S.   | <b>DATA TRANSMIT/RECEIVE</b> indicates the direction of data transfer to and from the bus. It is low during $T_a$ and $T_d$ cycles for a read or interrupt acknowledgment; it is high during $T_a$ and $T_d$ cycles for a write. DT/ $\overline{R}$ never changes state when $\overline{DEN}$ is asserted. DT/ $\overline{R}$ is driven HIGH during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| READY      | 1           | <b>READY</b> indicates that data on AD lines can be sampled or removed. If $\overrightarrow{READY}$ is not asserted during a T <sub>d</sub> cycle, the T <sub>d</sub> cycle is extended to the next cycle by inserting a wait state (T <sub>w</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LOCK       | 1/O<br>O.D. | <b>BUS LOCK</b> prevents bus masters from gaining control of the bus during Read/<br>Modify/Write (RMW) cycles. The processor or any bus agent may assert $LOCK$ .<br>At the start of a RMW operation, the processor examines the $LOCK$ pin. If the pin is<br>already asserted, the processor waits until it is not asserted. If the pin is not asserted,<br>the processor asserts $LOCK$ during the $T_a$ cycle of the read transaction.<br>The processor deasserts $LOCK$ in the $T_a$ cycle of the write transaction. During the<br>time $LOCK$ is asserted, a bus agent can perform a normal read or write but not a RMW<br>operation. The processor also asserts $LOCK$ during interrupt-acknowledge<br>transactions.<br>Do not leave $LOCK$ unconnected. It must be pulled HIGH for the processor to function<br>properly.<br><b>ONCE MODE:</b> The LOCK pin is sampled during reset. If it is asserted LOW at the end<br>of reset, all outputs will be three-stated until the part is reset again. ONCE mode is |

#### Table 3. 80960SA Pin Description: Bus Signals

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

used in conjunction with an in-circuit emulator.

| Name       | Туре      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE1:0      | 0<br>T.S. | <b>BYTE ENABLE LINES</b> specify which data bytes (up to two) on the bus take part in the current bus cycle. <b>BE1</b> corresponds to AD15:8; <b>BE0</b> corresponds to AD7:1, D0. The byte enable lines are asserted appropriately during each data cycle. <b>INITIALIZATION FAILURE</b> indicates that the processor has failed to initialize correctly. The failure state is indicated by a combination of <b>BLAST</b> asserted and <b>BE1:0</b> not asserted. This condition occurs after <b>RESET</b> is deasserted and before the first bus transaction begins. FAIL is asserted while the processor performs a self-test. If the self-test completes successfully, FAIL is deasserted. The processor then performs a zero checksum on the first eight words of memory. If it fails, FAIL is asserted for a second time and remains asserted; if it passes, system initialization continues and FAIL remains deasserted. |

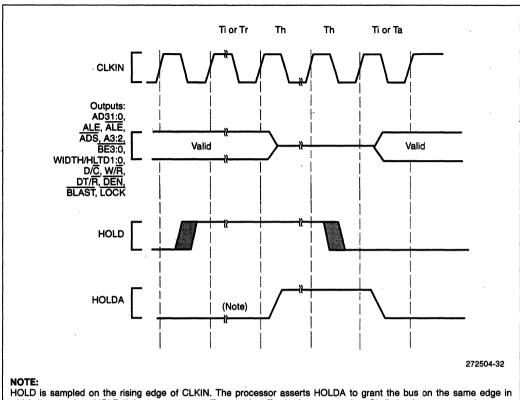

| HOLD       | l         | <b>HOLD:</b> A request from an external bus master to acquire the bus. When the processor receives HOLD and grants bus control to another master, it floats its three-state bus lines, then asserts HLDA and enters the $T_h$ state. When HOLD is deasserted, the processor deasserts HLDA and enters the $T_i$ or $T_a$ state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HLDA       | 0<br>T.S. | HOLD ACKNOWLEDGE: Notifies an external bus master that the processor has relinquished control of the bus. This signal is always driven. At reset it is driven LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BLAST/FAIL | 0<br>T.S. | <b>BURST LAST</b> indicates the last data cycle ( $T_d$ ) of a burst access. It is asserted low during the last $T_d$ and associated with $T_w$ cycles in a burst access.<br><b>INITIALIZATION FAILURE</b> indicates that the processor has failed to initialize correctly. The failure state is indicated by a combination of BLAST asserted and BE1:0 not asserted. This condition occurs after RESET is deasserted and before the first bus transaction begins. FAIL is asserted while the processor performs a self-test. If the self-test completes successfully, FAIL is deasserted. The processor then performs a zero checksum on the first eight words of memory. If it fails, FAIL is asserted for a second time and remains asserted; if it passes, system initialization continues and FAIL remains deasserted.                                                                                                      |

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

| Name      | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      |      |                                     |  |  |

|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------------------------|--|--|

| RESET     | 1           | <b>RESET</b> clears the processor's internal logic and causes it to reinitialize.<br>During RESET assertion, the input pins are ignored (except for INT0, INT1, INT3, LOCK), the three-state output pins are placed in a HIGH impedance state (except for DT/R, DEN, and $\overline{AS}$ ) and other output pins are placed in their non-asserted states.<br>RESET must be asserted for at least 41 CLK2 cycles for a predictable reset.<br>Optionally, for a synchronous reset, the LOW and HIGH transition of RESET should occur after the rising edge of both CLK2 and the external bus CLK and before the next rising edge of CLK2.<br>The interrupt pins indicate the initialization sequence executed. Typical initialization requires driving only INT0 and INT3 to a HIGH state. The reset conditions follow: |      |      |      |                                     |  |  |

|           |             | INTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | INT1 | INT3 | LOCK | Action Taken                        |  |  |

|           |             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x    | 1    | 1    | Run-self-test (core initialization) |  |  |

|           |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0    | 1    | 1    | Disable self-test                   |  |  |

|           |             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1    | ×    | x    | Reserved                            |  |  |

|           |             | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ×    | 0    | x    | Reserved                            |  |  |

|           |             | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x    | x    | 0    | ONCE mode (see LOCK pin)            |  |  |

| INTO      |             | <b>INTERRUPT 0</b> indicates a pending interrupt. To signal an interrupt in a synchronous system, this pin—as well as the other interrupt pins—must be enabled by being deasserted for at least one bus cycle and then asserted for at least one additional bus cycle. In an asynchronous system the pin must remain deasserted for at least two system clock cycles and then asserted for at least two more system clock cycles. The interrupt control register must be programmed with an interrupt vector before using this pin.<br>INTO is sampled during reset to determine if the self-test sequence is to be executed.                                                                                                                                                                                         |      |      |      |                                     |  |  |

| INT1      | I,          | <b>INTERRUPT 1,</b> like INT0, provides direct interrupt signaling. INT1 is sampled during reset to determine if the self-test sequence is to be executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |      |      |                                     |  |  |

| INT2/INTR | 1           | <b>INTERRUPT2/INTERRUPT REQUEST:</b> The interrupt control register determines how this pin is interpreted. If INT2, it has the same interpretation as the INT0 and INT1 pins. If INTR, it is used to receive an interrupt request from an external interrupt controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      |      |                                     |  |  |

| INT3/INTA | I/O<br>T.S. | <b>INTERRUPT3/INTERRUPT ACKNOWLEDGE:</b> The interrupt control register determines how this pin is interpreted. If INT3, it has the same interpretation as the INT0 and INT1 pins. If INTA, it is used as an output to control interrupt-acknowledge transactions. The INTA output is latched on-chip and remains valid during T <sub>d</sub> cycles; as an output, it is open-drain. INT3 must be pulled HIGH during reset.                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |                                     |  |  |

| NC        | N/A         | <b>NOT CONNECTED</b> indicates pins should not be connected. Never connect any pin marked NC; these pins may be reserved for factory use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      |      |                                     |  |  |

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

#### 80960SA

## intel

#### 2.0 ELECTRICAL SPECIFICATIONS

#### 2.1 Power and Grounding

The 80960SA is implemented in CHMOS IV technology and therefore has modest power requirements. Its high clock frequency and numerous output buffers (address/data, control, error and arbitration signals) can cause power surges as multiple output buffers simultaneously drive new signal levels. For clean on-chip power distribution,  $V_{CC}$  and  $V_{SS}$  pins separately feed the device's functional units. Power and ground connections must be made to all 80960SA power and ground pins. On the circuit board, all  $V_{CC}$  pins must be strapped closely together, preferably on a power plane; all  $V_{SS}$  pins should be strapped together, preferably on a ground plane.

#### 2.2 Power Decoupling Recommendations

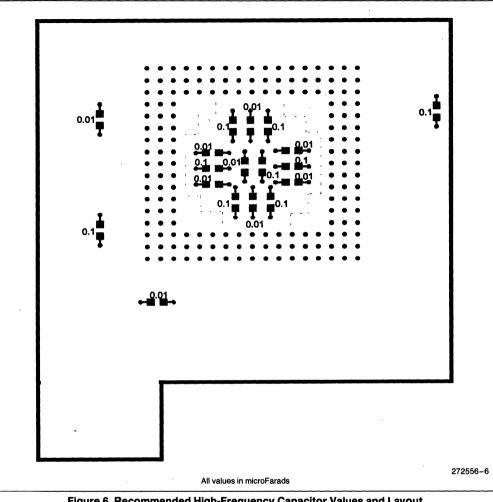

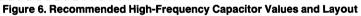

Place a liberal amount of decoupling capacitance near the 80960SA. When driving the bus the processor can cause transient power surges, particularly when connected to a large capacitive load.

Low inductance capacitors and interconnects are recommended for best high frequency electrical performance. Inductance is reduced by shortening board traces between the processor and decoupling capacitors as much as possible.

#### 2.3 Connection Recommendations

For reliable operation, always connect unused inputs to an appropriate signal level. In particular, if one or more interrupt lines are not used, they should be pulled up. No inputs should ever be left floating.

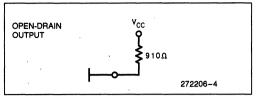

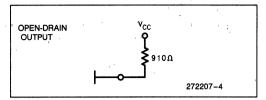

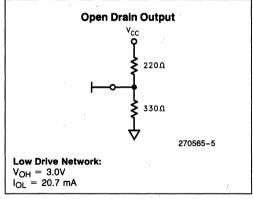

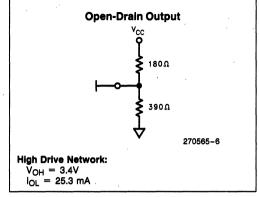

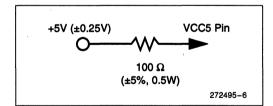

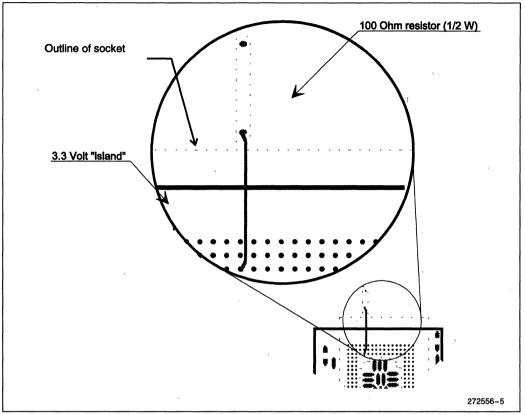

The LOCK open drain pin requires a pullup resistor whether or not the pin is used as an output. Figure 5 shows the recommended resistor value. Do not connect external logic to pins marked NC.

#### 2.4 Characteristic Curves

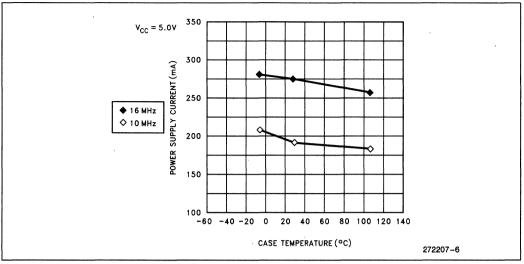

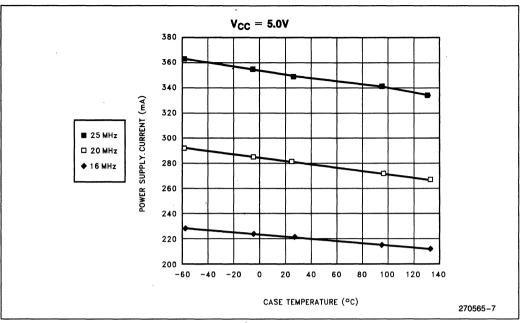

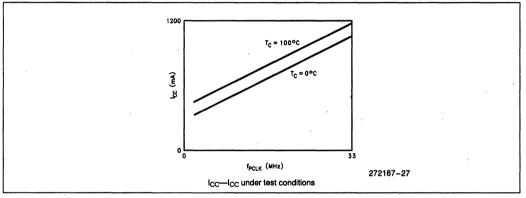

Figure 6 shows typical supply current requirements over the operating temperature range of the processor at supply voltage ( $V_{CC}$ ) of 5V. Figure 7 shows the typical power supply current ( $I_{CC}$ ) that the 80960SA requires at various operating frequencies when measured at three input voltage ( $V_{CC}$ ) levels.

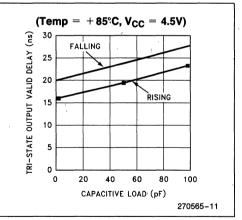

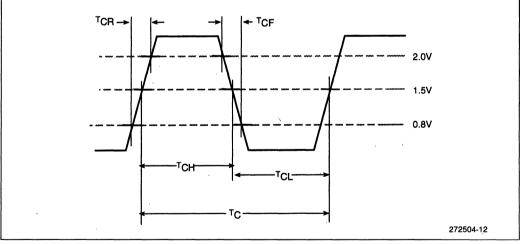

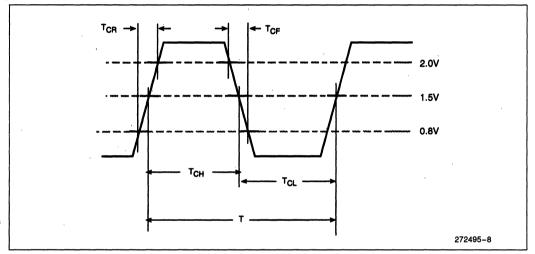

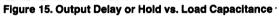

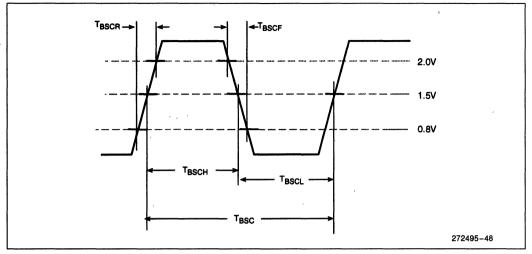

For a given output current  $(I_{OL})$  the curve in Figure 8 shows the worst case output low voltage  $(V_{OL})$ . Figure 9 shows the typical capacitive derating curve for the 80960SA measured from 1.5V on the system clock (CLK) to 0.8V on the falling edge and 2.0V on the rising edge of the bus address/data (AD) signals.

#### 80960SA

## intel

1-16

## int<sub>el</sub>.

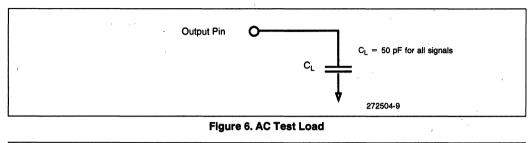

### 2.5 Test Load Circuit

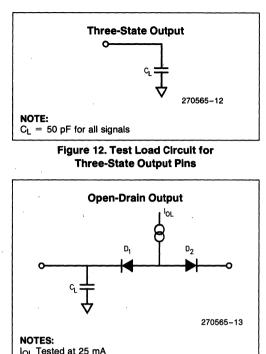

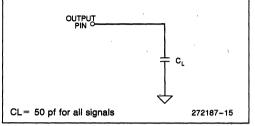

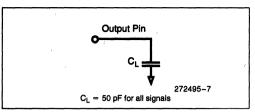

Figure 10 illustrates the load circuit used to test the 80960SA's output pins.

Figure 10. Test Load Circuit for Three-State Output Pins

#### 2.6 Absolute Maximum Ratings\*

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### 2.7 DC Characteristics

80960SA (10 and 16 MHz QFP) 80960SA (10 and 16 MHz PLCC) 80960SA (20 MHz PLCC)

|                     |        |        |            | = 5V ±5% |

|---------------------|--------|--------|------------|----------|

| $T_{CASE} =$        | 0°C to | +85°C, | $V_{CC} =$ | 5V ±10%  |

| T <sub>CASE</sub> = | °C to  | +85°C, | $V_{CC} =$ | 5V ±5%   |

| Symbol           | Parameter                                                                        | Min                 | Max                      | Units                | Notes                                                                                                              |

|------------------|----------------------------------------------------------------------------------|---------------------|--------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|

| VIL              | Input Low Voltage                                                                | -0.3                | + 0.8                    | V                    |                                                                                                                    |

| VIH              | Input High Voltage                                                               | 2.0                 | V <sub>CC</sub> + 0.3    | v                    |                                                                                                                    |

| V <sub>CL</sub>  | CLK2 Input Low Voltage                                                           | -0.3                | + 0.8                    | V                    |                                                                                                                    |

| V <sub>CH</sub>  | CLK2 Input High Voltage                                                          | 0.7 V <sub>CC</sub> | V <sub>CC</sub> + 0.3    | v                    | -                                                                                                                  |

| V <sub>OL</sub>  | Output Low Voltage                                                               |                     | 0.45<br>0.45<br>0.60     |                      | $I_{OL} = 4.0 \text{ mA}$<br>$I_{OL} = 6 \text{ mA}, \text{LOCK Pin}$<br>$I_{OL} = 20 \text{ mA}, \text{LOCK Pin}$ |

| VOH              | Output High Voltage                                                              | 2.4                 |                          | v                    | All TS, -2.5 mA (1)                                                                                                |

| lcc              | Power Supply Current:<br>10 MHz-QFP<br>10 MHz-PLCC<br>16 MHz-PLCC<br>20 MHz-PLCC | ,                   | 240<br>240<br>300<br>340 | mA<br>mA<br>mA<br>mA | $T_{CASE} = 0^{\circ}C$ $T_{CASE} = 0^{\circ}C$ $T_{CASE} = 0^{\circ}C$ $T_{CASE} = 0^{\circ}C$                    |

| ILI1             | Input Leakage Current,<br>Except INT0, LOCK                                      |                     | ± 15                     | μΑ                   | $0 \le V_{IN} \le V_{CC}$                                                                                          |

| I <sub>LI2</sub> | Input Leakage Current,<br>INTO, LOCK                                             |                     | - 300                    | μΑ                   | $V_{IN} = 0.45V^{(2)}$                                                                                             |

| IOL              | Output Leakage Current                                                           |                     | ±15                      | μΑ                   |                                                                                                                    |

| CIN              | Input Capacitance                                                                |                     | 10                       | pF                   | $f_{\rm C} = 1  \rm MHz^{(3)}$                                                                                     |