# Flash Memory Volume 2

PCMCIA Flash Memory Cards

PCMCIA-ATA Flash Memory Drives

Flash Automotive Components

> WYLE Were Customer Specific

SANTA CLARA DIVISION 3000 Bowers Avenue Santa Clara, CA 95051-0919 (408) 727-2500 • (800) 866-9953

intel Flash Memory

Vol. 2 1995

intel

INTA

## LITERATURE

For additional information on Intel products in the U.S. or Canada, call Intel's Literature Center at (800) 548-4725 or write to:

Intel Literature P.O. Box 7641 Mt. Prospect, II 60056-7641

To order literature outside of the U.S. and Canada contact your local international sales office.

## **CURRENT DATABOOKS**

Product line databooks contain datasheets, application notes, article reprints, and other design information. Databooks can be ordered in the U.S. and Canada by calling TAB/McGraw-Hill at 1-800-822-8158; outside of the U.S. and Canada contact your local international sales office.

| Title                                                | Intel Order Number | ISBN          |

|------------------------------------------------------|--------------------|---------------|

| Automotive Products                                  | 231792             | N/A           |

| Embedded Applications (2 vol. set)                   | 270648             | 1-55512-242-6 |

| Embedded Microcontrollers                            | 270646             | 1-55512-230-2 |

| Embedded Microprocessors                             | 272396             | 1-55512-231-0 |

| Flash Memory (2 vol. set)                            | 210830             | 1-55512-232-9 |

| Intel486™ Microprocessors and Related Products       | 241731             | 1-55512-235-3 |

| i960® Processors and Related Products                | 272084             | 1-55512-234-5 |

| Military and Special Products                        | 210461             | N/A           |

| Networking                                           | 297360             | 1-55512-236-1 |

| OEM Boards, Systems and Software                     | 280407             | 1-55512-237-X |

| Packaging                                            | 240800             | 1-55512-238-8 |

| Pentium <sup>™</sup> Processors and Related Products | 241732             | 1-55512-239-6 |

| Peripheral Components                                | 296467             | 1-55512-240-X |

A complete set of this information is available on CD-ROM through Intel's Data on Demand program, order number 240897. For information about Intel's Data on Demand ask for item number 240952.

# intel

## 24-HOUR AUTOMATED TECHNICAL SUPPORT\*

Intel's Application Bulletin Board System (BBS) and FaxBack System are at your service, 24-hours a day, at no charge, and the information is updated frequently.

## FaxBack SYSTEM

Technical and product information are available 24-hours a day! Order documents containing:

- Product Announcements

- Product Literature

- Intel Device Characteristics

- Design/Application Recommendations

- Stepping/Change Notifications

- Quality and Reliability Information

Information on the following subjects is also available:

- Microcontroller and Flash

- OEM Branded Systems

- Multibus/BBS Listing

- Multimedia

- Development Tools

- Quality and Reliability/Change Notification

- Microprocessor/PCI/Peripheral

- Intel Architecture Lab

To use FaxBack for Intel components and systems, dial (800) 628-2283 or (916) 356-3105 (U.S. and Canada)  $or +44\{0\}$  1793-496646 (*Europe*) and follow the automated voice-prompt menu. Document orders will be faxed to the fax number you specify. Catalogs are updated twice a month, so call for the latest information!

## **BULLETIN BOARD SYSTEM**

Intel's Application Bulletin Board System (BBS) enables file retrieval 24-hours a day. The following can be located on the BBS:

- Software Drivers

- Tool Information

- Software/Application Utilities

- Product/Technical Documentation

- Firmware Upgrades

- Quality and Reliability Data

To use the Intel Application BBS (components and systems), dial **(916) 356-3600** for download access (U.S. and Canada) *or* +44{0} *1793-496340* (*Europe*). The BBS will support 1200–19200 baud rate modem. *Typical modem configuration: 9600 baud rate, No Parity, 8 Data Bits, 1 Stop Bit.* A directory listing of BBS files is also available through FaxBack or our 800 BBS (800-897-2536).

## **Retail Products**

Information on Intel's retail products (Coprocessors and wireless, video, personal conferencing and network products) is available through the following services:

| Internet :<br>CompuServe : | GO INTELFORUM (modem settings: E-7-1, up to 14.4 Ki | ops)                                |

|----------------------------|-----------------------------------------------------|-------------------------------------|

| Country                    | BBS (N-8-1, up to 14.4 Kbps)                        | FaxBack                             |

| North America              | (503) 264-7999                                      | (800) 525-3019 or<br>(503) 264-6835 |

| Europe                     | +44 1 793-432955                                    | +44 1 793-432509                    |

| Australia                  | +61 2 975-3066                                      | +61 2 975-3922                      |

| Taiwan                     | +886 2 718-6422                                     | +886 2 514-0815                     |

| Singapore                  | +65 256-4776                                        | +65 256-5350                        |

| Hong Kong                  | +852 530-4116                                       | +852 844-4448                       |

| Korea                      | +822 784-3430                                       | +822 767-2594                       |

|                            |                                                     |                                     |

\*Support services provided courtesy of Intel Application Support

An intel and (140 405 05 0)

# inte

## Flash Memory Volume 2

PCMCIA Flash Memory Cards, PCMCIA-ATA Flash Memory Drives, Flash Automotive Components Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

© INTEL CORPORATION, 1995

## DATASHEET DESIGNATIONS

Intel uses various datasheet markings to designate each phase of the document as it relates to the product. The markings appear in the lower inside corner of each datasheet page. Following are the definitions of each marking:

| Datasheet Marking    | Description                                                                                                                                                                                             |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview      | Contains information on products in the design phase of<br>development. Do not finalize a design with this<br>information. Revised information will be published<br>when the product becomes available. |

| Advanced Information | Contains information on products being sampled or in the initial production phase of development.*                                                                                                      |

| Preliminary          | Contains preliminary information on new products in production.*                                                                                                                                        |

| No Marking           | Contains information on products in full production.*                                                                                                                                                   |

\* Specifications within these datasheets are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

# intal

8

g

Drives

**Flash Automotive Components**

**Process Engineering Reports**

. r

# intel

Flash Memory SmartDie<sup>TM</sup> Products

## **Article Reprints**

11

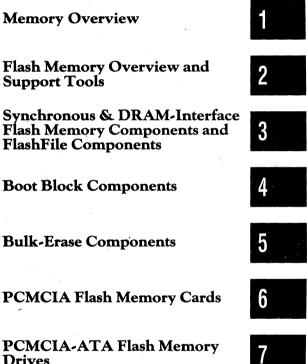

## **Table of Contents**

| Alphanumeric Index                                                                             | xv    |

|------------------------------------------------------------------------------------------------|-------|

| CHAPTER 1                                                                                      |       |

| Memory Overview                                                                                |       |

| Intel Memory Technologies                                                                      | 1-1   |

| CHAPTER 2                                                                                      |       |

| Flash Memory Overview and Support Tools                                                        |       |

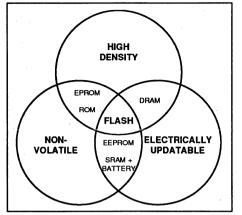

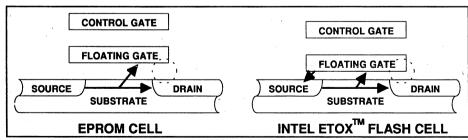

| Flash Memory Overview                                                                          | 2-1   |

| SUPPORT TOOLS                                                                                  |       |

| Flash Memory Customer Support                                                                  | 2-7   |

| Sprint PLUS48/Intel Support Version                                                            | 2-9   |

| Multi-APRO Programmer/Intel Support Version                                                    | 2-13  |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                                 | 2-16  |

| Small Outline Package Guide Overview                                                           | 2-18  |

|                                                                                                | 2-20  |

| APPLICATION NOTES                                                                              | 2-22  |

| AP-357 Power Supply Solutions for Flash Memory AP-374 Flash Memory Write Protection Techniques | 2-22  |

| AB-29 Flash Memory Applications in Laser Printers                                              | 2-04  |

| TECHNICAL PAPER                                                                                | 2-71  |

| Small and Low Cost Power Supply Solution for Intel's Flash Memory Products                     | 2-78  |

| CHAPTER 3                                                                                      |       |

| Synchronous and DRAM-Interface Flash Memory Components                                         |       |

| PRODUCT BRIEFS                                                                                 |       |

| Intel 28F016XS Embedded Flash RAM Product Brief                                                | 3-1   |

| Intel 28F016XD Embedded Flash RAM Product Brief                                                | 3-2   |

| DATA SHEETS                                                                                    | • -   |

| 28F016XS 16-Mbit (1-Mbit x 16, 2-Mbit x 8) Synchronous Flash Memory                            | 3-3   |

| 28F016XD 16-Mbit (1-Mbit x 16) DRAM - Interface Flash Memory                                   | 3-50  |

| APPLICATION NOTES                                                                              |       |

| AB-58 28F016XD - Based SIMM Designs                                                            |       |

| AP-398 Designing with the 28F016XS                                                             | 3-112 |

| AP-384 Designing with the 28F016XD                                                             | 3-142 |

| AP-600 Performance Benefits and Power/Energy Savings of 28F016XS-Based                         | 0 170 |

|                                                                                                | 3-172 |

| TECHNICAL PAPERS<br>Interfacing the 28F016XS to the i960 <sup>®</sup> Microprocessor Family    | 3-196 |

| Interfacing the 28F016XS to the Intel486 <sup>TM</sup> Microprocessor Family                   | 3-190 |

| FlashFile <sup>TM</sup> Components                                                             | 0 200 |

| DATA SHEETS                                                                                    |       |

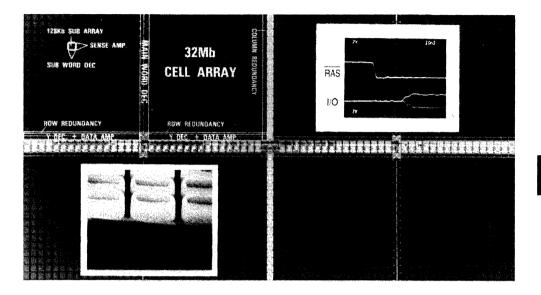

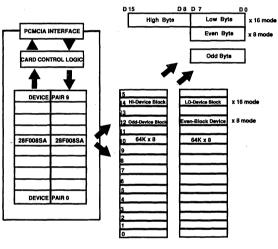

| DD28F032SA 32-Mbit (2-Mbit x 16, 4-Mbit x 8) FlashFile Memory                                  | 3-257 |

| 28F016SV 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile Memory                                    | 3-303 |

| 28F016SA 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile Memory                                    | 3-359 |

| Extended Temperature 28F016SA 16-Mbit (1-Mbit x 16, 2-Mbit x 8) FlashFile                      |       |

| Memory                                                                                         | 3-403 |

| 28F008SA 8-Mbit (1-Mbit x 8) FlashFile Memory (Extended Temperature                            |       |

| Specifications Included)                                                                       | 3-443 |

| 28F008SA-L 8 Mbit (1Mbit x 8) Flash Memory                                                     | 3-476 |

| APPLICATION NOTES                                                                              |       |

| AP-607 Multi-Site Layout Planning with Intel's FlashFile Components, Including                 | 2 504 |

| ROM Compatibility                                                                              | 3-504 |

## CONTENTS

## Table of Contents (Continued)

| AP-393 28F016SV Compatibility with 28F016SA<br>AP-359 28F008SA Hardware Interfacing<br>AP-360 28F008SA Software Drivers<br>AP-362 Implementing Mobile PC Designs Using High Density FlashFile | 3-533<br>3-551<br>3-562 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Components                                                                                                                                                                                    | 3-585<br>3-640<br>3-654 |

| 28F016XS, 28F016XD<br>AP-378 System Optimization Using the Enhanced Features of the 28F016SA<br>AP-399 Implementing Mobile Intel486 SX Microprocessor PC Designs Using                        | 3-667<br>3-722          |

| FlashFile™ Components<br>ENGINEERING REPORT                                                                                                                                                   | 3-74 <u>3</u><br>3-783  |

|                                                                                                                                                                                               | 3-783                   |

| CHAPTER 4                                                                                                                                                                                     |                         |

| Boot Block Components                                                                                                                                                                         |                         |

| DATA SHEETS                                                                                                                                                                                   |                         |

| 8-Mbit (512K x 16, 1-Mbit x 8) SmartVoltage Boot Block Flash Memory Family<br>4-Mbit (256K x 16, 512K x 8) SmartVoltage Boot Block Flash Memory Family                                        | 4-1                     |

| (Extended Temperature Specifications Included)                                                                                                                                                | 4-13                    |

| 2-Mbit (128K x 16, 256K x 8) SmartVoltage Boot Block Flash Memory Family                                                                                                                      | 4-13                    |

| (Extended Temperature Specifications Included)                                                                                                                                                | 4-68                    |

| 28F400BX-T/B, 28F004BX-T/B 4 Mbit (256K x 16, 512K x 8) Boot Block Flash                                                                                                                      | + 00                    |

| Memory Family                                                                                                                                                                                 | 4-124                   |

| 28F400BL-T/B, 28F004BL-T/B 4-Mbit (256K x 16, 512K x 8) Low Power Boot                                                                                                                        |                         |

| Block Flash Memory Family                                                                                                                                                                     | 4-174                   |

| 28F200BX-T/B, 28F002BX-T/B 2 Mbit (128K x 16, 256K x 8) Boot Block Flash                                                                                                                      |                         |

| Memory Family                                                                                                                                                                                 | 4-218                   |

| 28F200BL-T/B, 28F002BL-T/B 2-Mbit (128K x 16, 256K x 8) Low Power Boot                                                                                                                        |                         |

| Block Flash Memory Family                                                                                                                                                                     | 4-265                   |

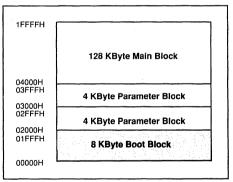

| 28F001BX-T/28F001BX-B 1M (128K x 8) CMOS Flash Memory                                                                                                                                         | 4-307                   |

| APPLICATION NOTES                                                                                                                                                                             |                         |

| AP-604 Using Intel's Boot Block Flash Memory Parameter Blocks to Replace                                                                                                                      |                         |

| EEPROM                                                                                                                                                                                        | 4-341                   |

| AB-60 2/4/8-Mbit SmartVoltage Boot Block Flash Memory Family Overview                                                                                                                         | 4-349                   |

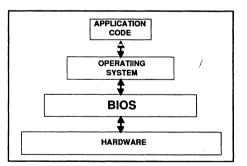

| AP-341 Designing an Updatable BIOS Using Flash Memory                                                                                                                                         | 4-357                   |

| AP-363 Extended Flash Bios Concepts for Portable Computers                                                                                                                                    | 4-400                   |

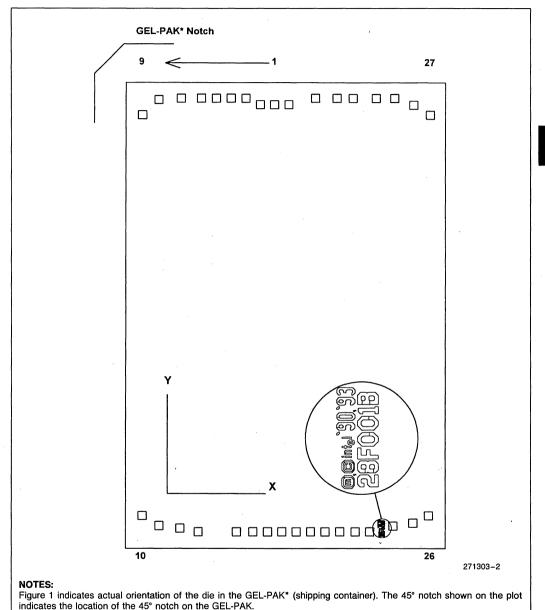

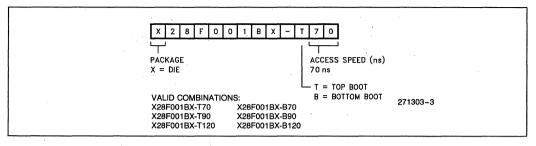

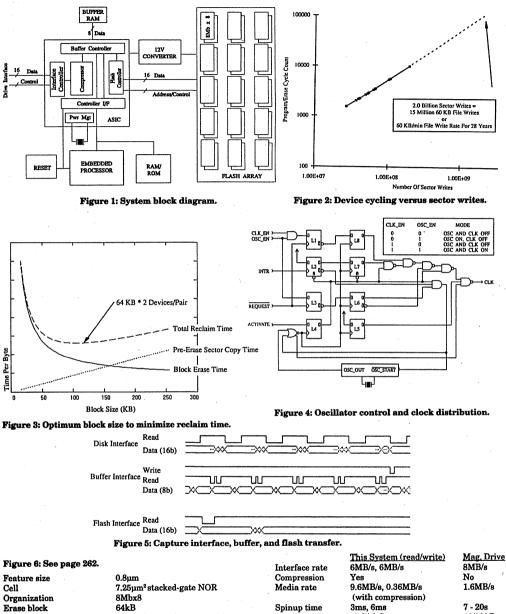

| ENGINEERING REPORTS<br>ER-26 The Intel 28F001BX-T and 28F001BX-B Flash Memories                                                                                                               | 4 400                   |

| ER-29 The Intel 2/4-Mbit Boot Block Flash Memory Family                                                                                                                                       | 4-422                   |

| TECHNICAL PAPER                                                                                                                                                                               | 4-40/                   |

| Boot Block Flash: The Next Generation White Paper                                                                                                                                             | 4-466                   |

| CHAPTER 5                                                                                                                                                                                     |                         |

|                                                                                                                                                                                               |                         |

## **Bulk-Erase Components**

| DA | TΑ | SH | Е | ΕT | S |

|----|----|----|---|----|---|

|----|----|----|---|----|---|

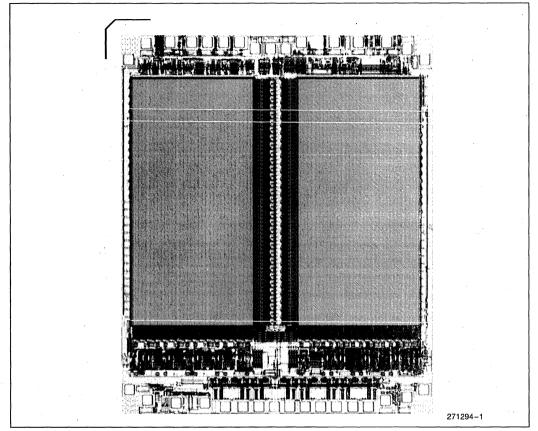

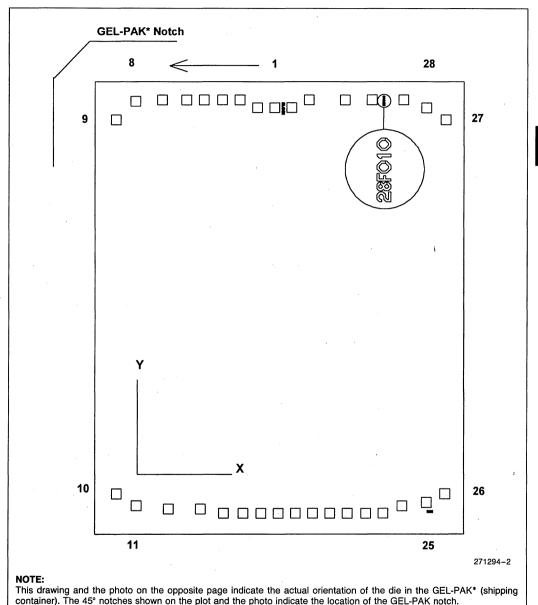

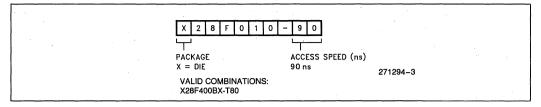

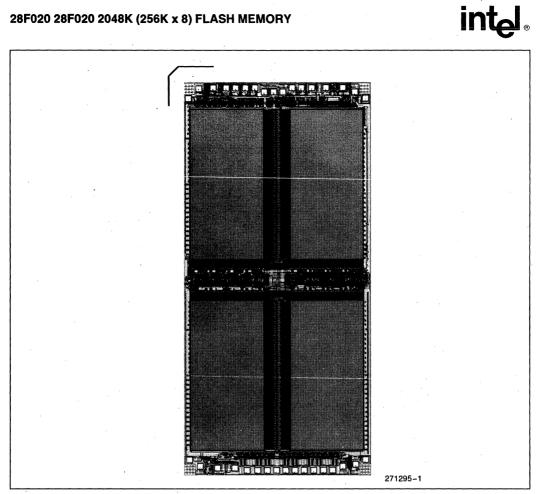

| 28F020 2048K (256K x 8) CMOS Flash Memory | 5-1  |

|-------------------------------------------|------|

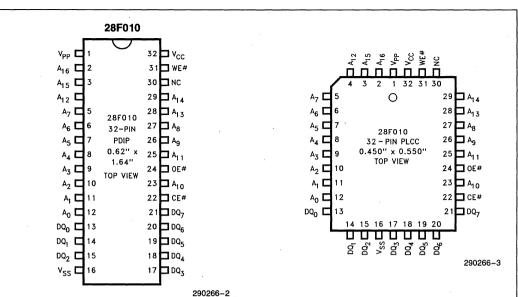

| 28F010 1024K (128K x 8) CMOS Flash Memory | 5-33 |

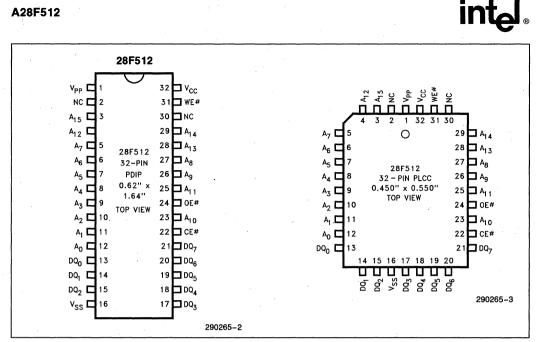

| 28F512 512K (64K x 8) CMOS Flash Memory   | 5-64 |

## Table of Contents (Continued)

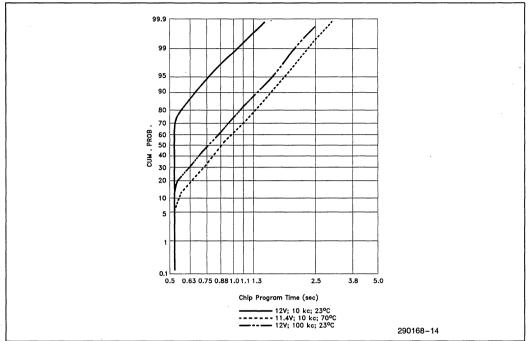

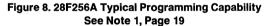

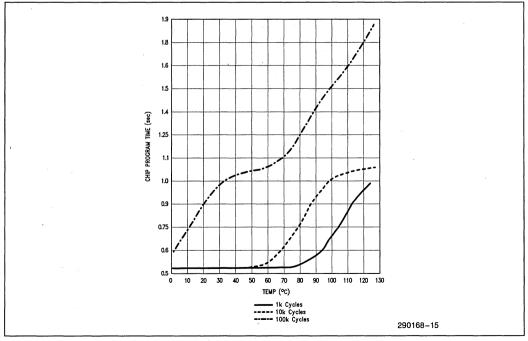

| 28F256A 256K (32K x 8) CMOS Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-92                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| AP-316 Using Flash Memory for In-System Reprogrammable Nonvolatile Storage .<br>AP-325 Guide to First Generation Flash Memory Programming<br>ENGINEERING REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-117<br>5-162                                                           |

| ER-24 Intel Flash Memory 28F256A, 28F512, 28F010, 28F020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-184                                                                    |

| CHAPTER 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                          |

| PCMCIA Flash Memory Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                          |

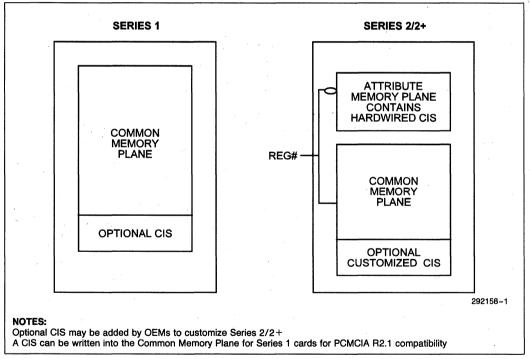

| Series 2+ Flash Memory Card User's Manual OverviewDATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-1                                                                      |

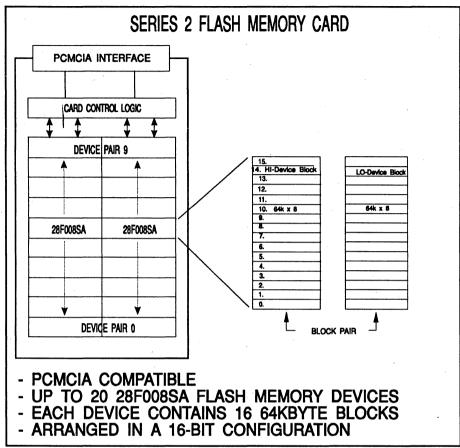

| Series 2+ Flash Memory Cards 4-, 8-, 20- and 40-Megabyte<br>Series 2 Flash Memory Cards iMC002FLSA/iMC004FLSA/iMC010FLSA/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-2                                                                      |

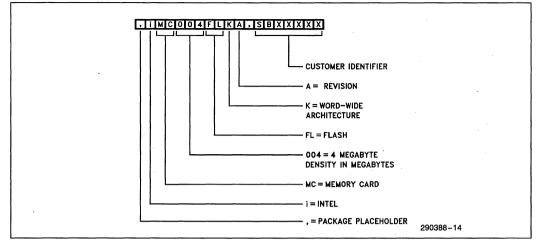

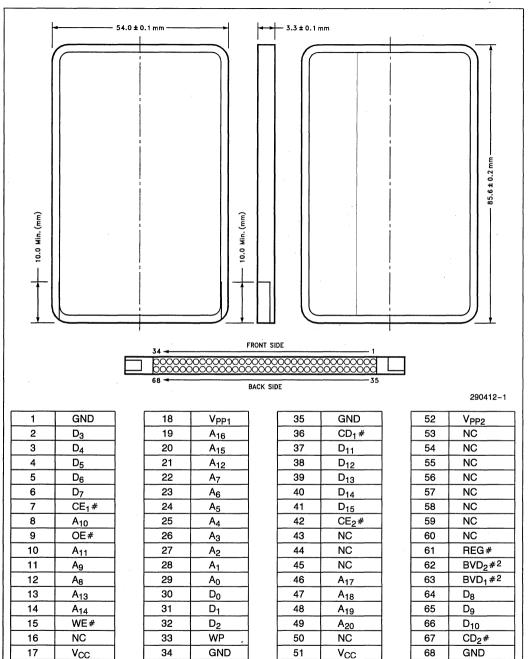

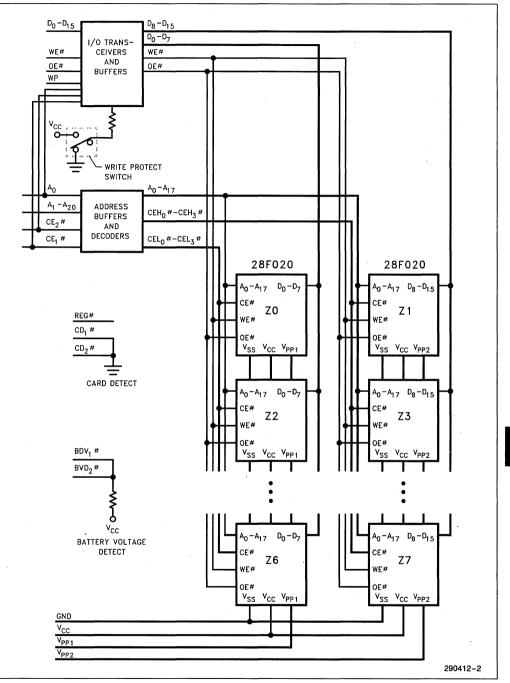

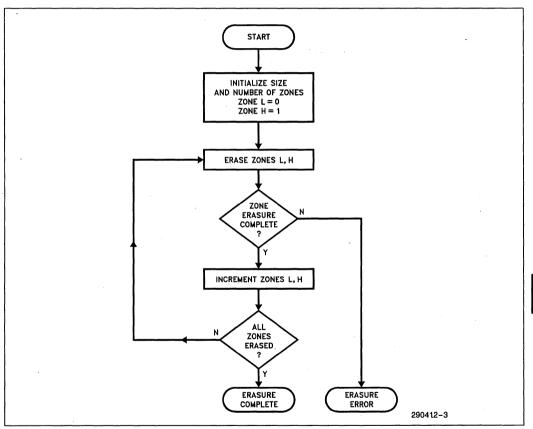

| iMC020FLSA ( <i>Extended Temperature Specifications Included</i> )iMC004FLKA 4-Megabyte Flash Memory Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6-42<br>6-80                                                             |

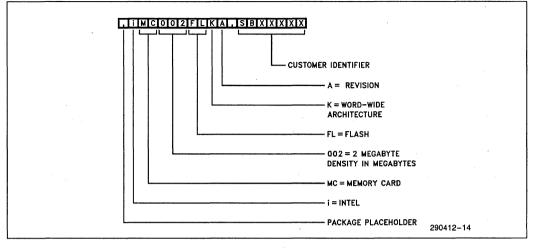

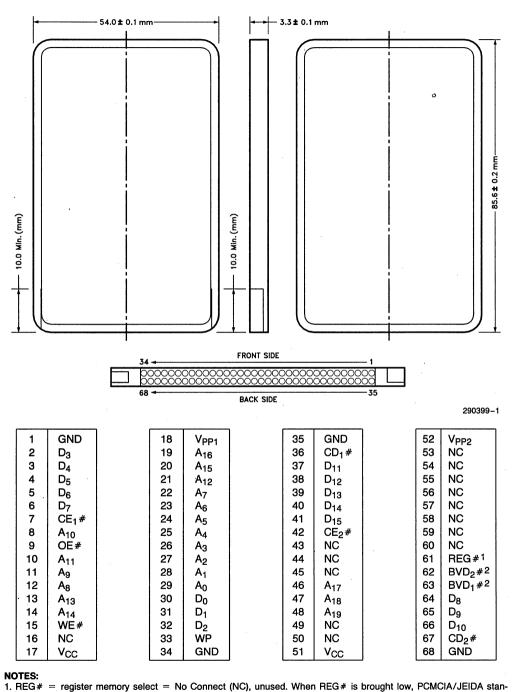

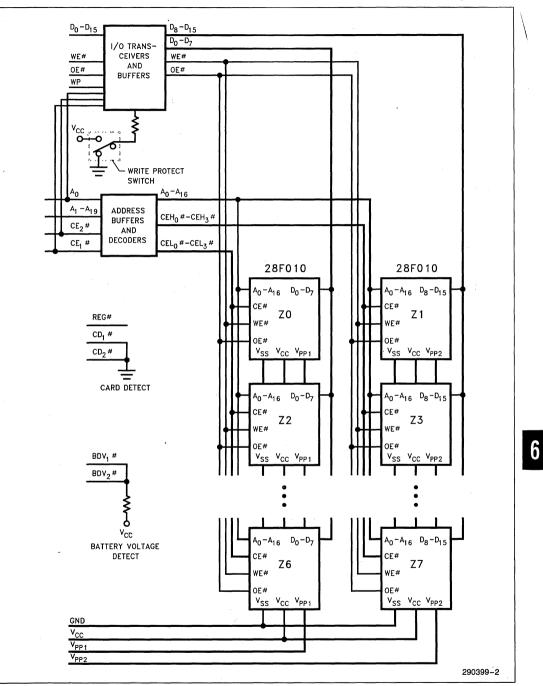

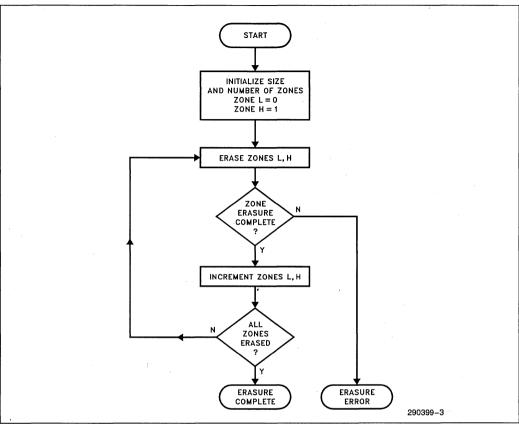

| iMC002FLKA 2-Mbyte Flash Memory Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                          |

| iMC001FLKA 1-Megabyte Flash Memory Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-140                                                                    |

| AP-606 Interchangeability of Series 1, Series 2 and Series 2+ Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                          |

| Cards AP-343 Solutions for High Density Applications Using Intel Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-170<br>6-185                                                           |

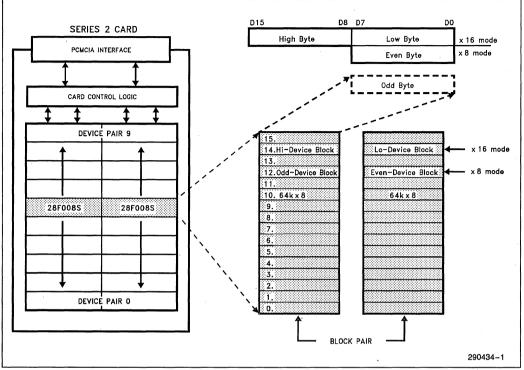

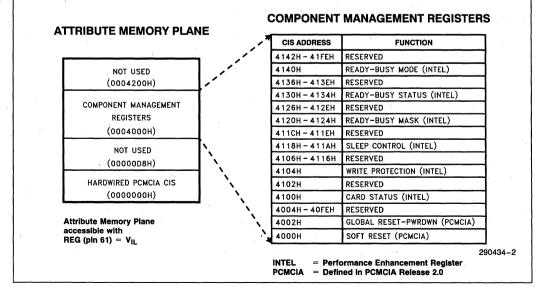

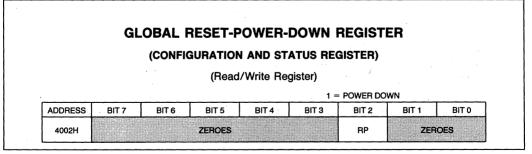

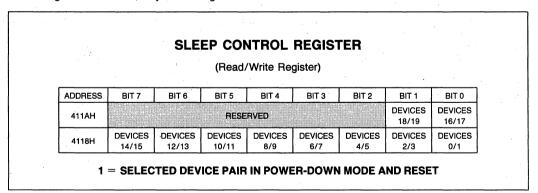

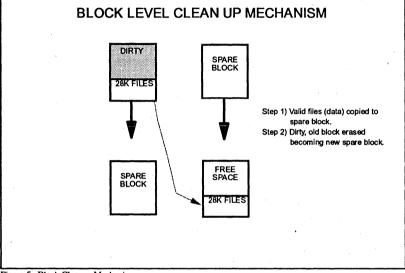

| AP-343 Solutions for Figh Density Applications Using Inter Flash Memory Card.<br>AP-361 Implementing the Integrated Registers of the Series 2 Flash Memory Card.<br>SUPPORT TOOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6-215                                                                    |

| Flash Memory Card and Flash Drive Evaluation Kit Product Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-232                                                                    |

| TECHNICAL PAPER Intel FlashFile Memory-The Key to Diskless Mobile PCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6-234                                                                    |

| CHAPTER 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                          |

| PCMCIA-ATA Flash Memory Drives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                          |

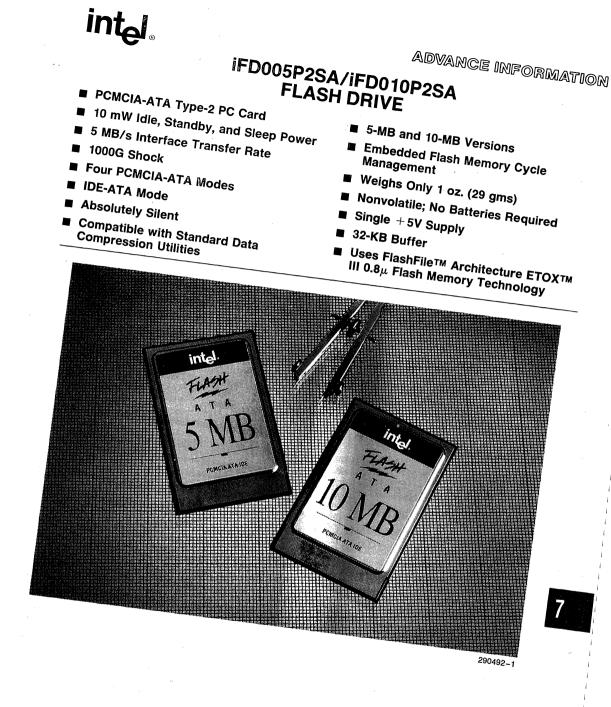

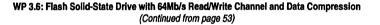

| PCMCIA-ATA Flash Memory Drives<br>DATA SHEET<br>iFD005P2SA/iFD010P2SA Flash Drive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-1                                                                      |

| PCMCIA-ATA Flash Memory Drives<br>DATA SHEET<br>iFD005P2SA/iFD010P2SA Flash Drive<br>DESIGN GUIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-1<br>7-46                                                              |

| PCMCIA-ATA Flash Memory Drives<br>DATA SHEET<br>iFD005P2SA/iFD010P2SA Flash Drive<br>DESIGN GUIDE<br>Flash Drive Design Guide (for iFD005P2SA/iFD010P2SA)<br>SUPPORT TOOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-46                                                                     |

| PCMCIA-ATA Flash Memory Drives<br>DATA SHEET<br>iFD005P2SA/iFD010P2SA Flash Drive<br>DESIGN GUIDE<br>Flash Drive Design Guide (for iFD005P2SA/iFD010P2SA)<br>SUPPORT TOOLS<br>Flash Memory Card and Flash Drive Evaluation Kit Product Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-46                                                                     |

| PCMCIA-ATA Flash Memory Drives<br>DATA SHEET<br>iFD005P2SA/iFD010P2SA Flash Drive<br>DESIGN GUIDE<br>Flash Drive Design Guide (for iFD005P2SA/iFD010P2SA)<br>SUPPORT TOOLS<br>Flash Memory Card and Flash Drive Evaluation Kit Product Brief<br>CHAPTER 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7-46                                                                     |

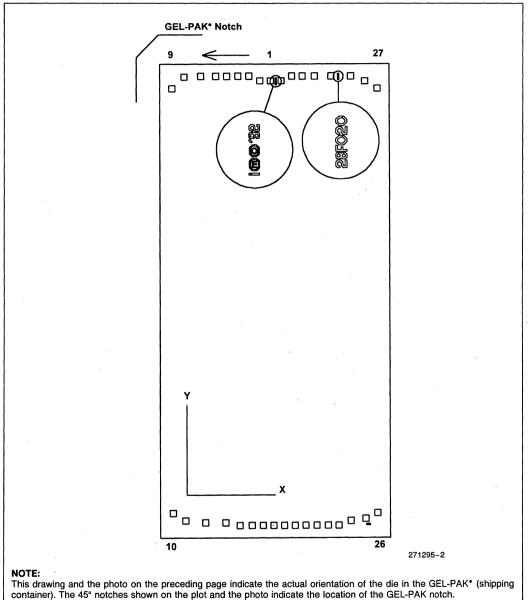

| PCMCIA-ATA Flash Memory Drives<br>DATA SHEET<br>iFD005P2SA/iFD010P2SA Flash Drive<br>DESIGN GUIDE<br>Flash Drive Design Guide (for iFD005P2SA/iFD010P2SA)<br>SUPPORT TOOLS<br>Flash Memory Card and Flash Drive Evaluation Kit Product Brief<br>CHAPTER 8<br>Flash Automotive Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7-46                                                                     |