intel®

Microcomputer Boards and Systems

1990

# Microcomputer Boards and Systems

Order Number 280407

# LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your local sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 7641 Mt. Prospect, IL 60056-7641 In the U.S. and Canada call toll free (800) 548-4725

# **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| TITLE                                                                                       | LITERATURE<br>ORDER NUMBER |

|---------------------------------------------------------------------------------------------|----------------------------|

| SET OF 11 HANDBOOKS<br>(Available in U S and Canada only)                                   | 231003                     |

| EMBEDDED APPLICATIONS                                                                       | 270648                     |

| 8-BIT EMBEDDED CONTROLLERS                                                                  | 270645                     |

| 16-BIT EMBEDDED CONTROLLERS                                                                 | 270646                     |

| 16/32-BIT EMBEDDED PROCESSORS                                                               | 270647                     |

| MEMORY                                                                                      | 210830                     |

| MICROCOMMUNICATIONS<br>(2 volume set)                                                       | 231658                     |

| MICROCOMPUTER SYSTEMS                                                                       | 280407                     |

| MICROPROCESSORS                                                                             | 230843                     |

| PERIPHERALS                                                                                 | 296467                     |

| PRODUCT GUIDE<br>(Overview of Intel's complete product lines)                               | 210846                     |

| PROGRAMMABLE LOGIC                                                                          | 296083                     |

| ADDITIONAL LITERATURE<br>(Not included in handbook set)                                     |                            |

| AUTOMOTIVE SUPPLEMENT                                                                       | 231792                     |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK                                                     | 210997                     |

| INTEL PACKAGING OUTLINES AND DIMENSIONS<br>(Packaging types, number of leads, etc.)         | 231369                     |

| INTERNATIONAL LITERATURE GUIDE                                                              | E00029                     |

| LITERATURE PRICE LIST (U.S. and Canada)<br>(Comprehensive list of current Intel Literature) | 210620                     |

| MILITARY<br>(2 volume set)                                                                  | 210461                     |

| SYSTEMS QUALITY/RELIABILITY                                                                 | 231762                     |

Intel the Microcomputer Company:

When Intel invented the microprocessor in 1971, it created the era of microcomputers. Whether used in embedded applications such as automobiles or microwave ovens, or as the CPU in personal computers or supercomputers, Intel's microcomputers have always offered leading-edge technology. Intel continues to strive for the highest standards in memory, microcomputer components, modules and systems to give its customers the best possible competitive advantages.

# MICROCOMPUTER BOARDS AND SYSTEMS HANDBOOK

1990

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

376, 386, 387, 486, 4-SITE, Above, ACE51, ACE96, ACE186, ACE196, ACE960, BITBUS, COMMputer, CREDIT, Data Pipeline, DVI, ETOX, FaxBACK, Genius, i, <sup>1</sup>/<sub>7</sub>, i486, 1750, i860, ICE, ICEL, ICEVIEW, ICS, IDBP, IDIS, I<sup>2</sup>ICE, ILBX, IMDDX, IMMX, Inboard, Insite, Intel, Intel, Intel386, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, IOSP, IPAT, IPDS, IPSC, IRMK, IRMX, ISBC, ISBX, ISDM, ISXM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, MultiSERVER, ONCE, OpenNET, OTP, PRO750, PROMPT, Promware, QUEST, QueX, Quick-Erase, Quick-Pulse Programming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, TooITALK, UPI, Visual Edge, VLSICEL, and ZapCode, and the combination of ICE, ICS, IRMX, ISBC, ISBX, ISXM, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

# **CUSTOMER SUPPORT**

#### **INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE**

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, consulting services and network management services. For detailed information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It can start with assistance during your development effort to network management. 100 Intel sales and service offices are located worldwide—in the U.S., Canada, Europe and the Far East. So wherever you're using Intel technology, our professional staff is within close reach.

### HARDWARE SUPPORT SERVICES

Intel's hardware maintenance service, starting with complete on-site installation will boost your productivity from the start and keep you running at maximum efficiency. Support for system or board level products can be tailored to match your needs, from complete on-site repair and maintenance support to economical carry-in or mail-in factory service.

Intel can provide support service for not only Intel systems and emulators, but also support for equipment in your development lab or provide service on your product to your end-user/customer.

#### SOFTWARE SUPPORT SERVICES

Software products are supported by our Technical Information Service (TIPS) that has a special toll free number to provide you with direct, ready information on known, documented problems and deficiencies, as well as work-arounds, patches and other solutions.

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and; *COMMENTS Magazine*). Basic support consists of updates and the subscription service. Contracts are sold in environments which represent product groupings (e.g., iRMX<sup>®</sup> environment).

#### **CONSULTING SERVICES**

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

### **CUSTOMER TRAINING**

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>TM</sup> and LAN applications.

#### NETWORK MANAGEMENT SERVICES

Today's networking products are powerful and extremely flexible. The return they can provide on your investment via increased productivity and reduced costs can be very substantial.

Intel offers complete network support, from definition of your network's physical and functional design, to implementation, installation and maintenance. Whether installing your first network or adding to an existing one, Intel's Networking Specialists can optimize network performance for you.

.

·

# **Table of Contents**

| Alphanumeric Index                                                                                              | xii            |

|-----------------------------------------------------------------------------------------------------------------|----------------|

| MULTIBUS® II PRODUCTS                                                                                           |                |

| CHAPTER 1                                                                                                       |                |

| MULTIBUS® II Single Board Computers                                                                             |                |

| iSBC 486/125DU and 386/133 Single Board Computers                                                               | 1-1            |

| iSBC 386/116 and 386/120 MULTIBUS II Single Board Computers                                                     | 1-5            |

| iSBC 286/100A MULTIBUS II Single Board Computer                                                                 | 1-13<br>1-22   |

| iSBC 186/100 MULTIBUS II Single Board Computer                                                                  | 1-22           |

| CHAPTER 2                                                                                                       | 1-01           |

|                                                                                                                 |                |

| MULTIBUS <sup>®</sup> II Memory Expansion Boards<br>iSBC MM01, MM02, MM04, MM08 High Performance Memory Modules | 2-1            |

| iSBC MM01FP, MM02FP, MM04FP, MM08FP High Performance Memory                                                     | 2-1            |

| Modules                                                                                                         | 2-5            |

| iSBC MEM/320, 340 Cache-Based MULTIBUS II RAM Boards                                                            | 2-9            |

| iSBC MEM/601 MULTIBUS II Universal Site Memory Expansion Board                                                  | 2-13           |

| CHAPTER 3                                                                                                       |                |

| MULTIBUS® II I/O PRODUCTS                                                                                       |                |

| MULTIBUS II I/O Product Family                                                                                  | 3-1            |

| CHAPTER 4                                                                                                       |                |

| MULTIBUS <sup>®</sup> II System Packaging and Development Accessories                                           |                |

| SYSTEM PACKAGING                                                                                                |                |

| iSBC PKG/606, iSBC PKG/609 MULTIBUS II Cardcage Assemblies                                                      | 4-1            |

| iSBC PKG/902, iSBC PKG/903 MULTIBUS II iLBX II Backplanes                                                       | 4-5<br>4-8     |

| DEVELOPMENT ACCESSORIES                                                                                         | 4-0            |

| iSBC CSM/001 Central Services Module                                                                            | 4-10           |

| iSBC Central Services Module/002                                                                                | 4-15           |

| iSBC LNK/001 Board MULTIBUS II to MULTIBUS I Link Board                                                         | 4-17           |

| MULTIBUS II High Performance SBC General Purpose Test Fixture (GPTF)                                            | 4-22           |

| CHAPTER 5                                                                                                       |                |

| MULTIBUS® II Architecture                                                                                       |                |

| MULTIBUS II Bus Structure                                                                                       | 5-1            |

| Designing a Central Services Module for MULTIBUS II                                                             | 5-15           |

| MULTIBUS II Interconnect Design Guide                                                                           | 5-45           |

| MULTIBUS II Simplifies Partitioning of a Complex Design                                                         | 5-128          |

| MIX Architecture Design Guide                                                                                   | 5-174          |

| MULTIBUS® II TECHNICAL PAPERS                                                                                   | 5 004          |

| Enhancing System Performance with the MULTIBUS II Architecture                                                  | 5-221<br>5-225 |

|                                                                                                                 | 0-220          |

| ISBX™ BUS PRODUCTS                                                                                              |                |

|                                                                                                                 |                |

| ISBXTM Expansion Modules<br>ISBX GRAPHICS MODULES                                                               |                |

| ISBX GRAPHICS MODULES<br>ISBX 279 Display Subsystem                                                             | 6-1            |

| iSBX PERIPHERAL CONTROLLERS                                                                                     | 0-1            |

| iSBX 217C 1/4-Inch Tape Drive Interface MULTIMODULE Board                                                       | 6-4            |

| iSBX 218A Flexible Disk Controller                                                                              | 6-6            |

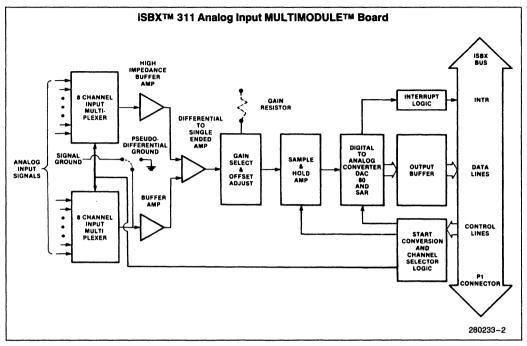

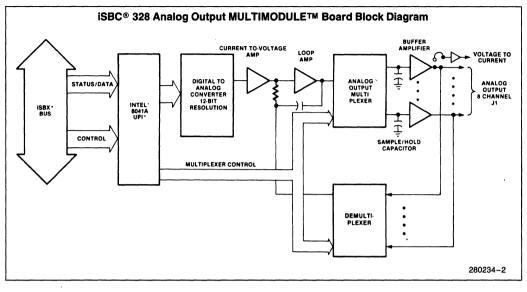

| iSBX DIGITAL AND ANALOG I/O BOARDS<br>iSBX 311 Analog Input MULTIMODULE Board<br>iSBX 328 Analog Output MULTIMODULE Board<br>iSBX 350 Parallel I/O MULTIMODULE Board<br>iSBX 488 GPIB MULTIMODULE Board<br>iSBX SERIAL COMMUNICATION BOARDS | 6-10<br>6-13<br>6-16<br>6-19 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| iSBX 351 Serial I/O MULTIMODULE Board<br>iSBX 354 Dual Channel Serial I/O MULTIMODULE Board<br>iSBX ARCHITECTURE                                                                                                                            | 6-22<br>6-26                 |

| iSBX I/O Expansion Bus                                                                                                                                                                                                                      | 6-29                         |

| CHAPTER 7                                                                                                                                                                                                                                   |                              |

| Real-Time Systems and Software                                                                                                                                                                                                              |                              |

| REAL-TIME SYSTEMS                                                                                                                                                                                                                           |                              |

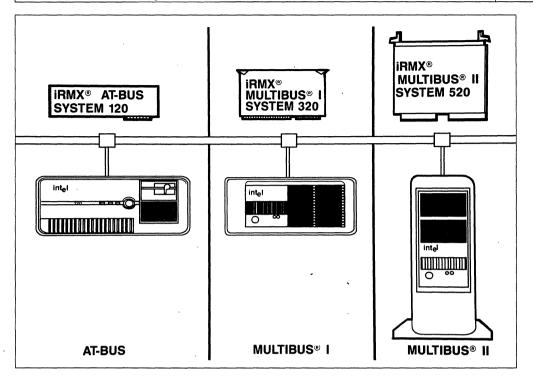

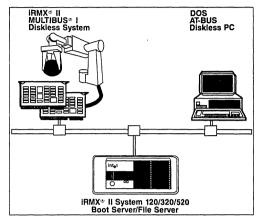

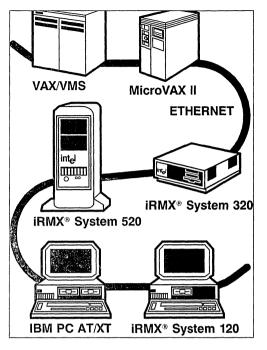

| System 120                                                                                                                                                                                                                                  | 7-1                          |

| System 310 AP                                                                                                                                                                                                                               | 7-5                          |

| System 310 AP 386 Upgrade                                                                                                                                                                                                                   | 7-7                          |

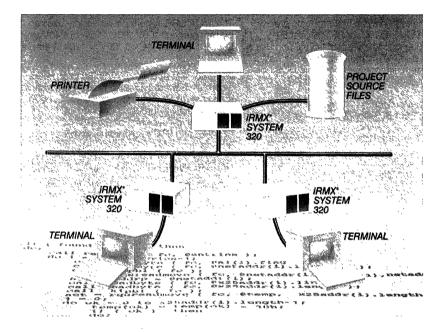

| System 320                                                                                                                                                                                                                                  | 7-9                          |

|                                                                                                                                                                                                                                             | 7-11                         |

| OPÉRATING SYSTEM SOFTWARE IRMK Real-Time Kernel                                                                                                                                                                                             | 7 1 4                        |

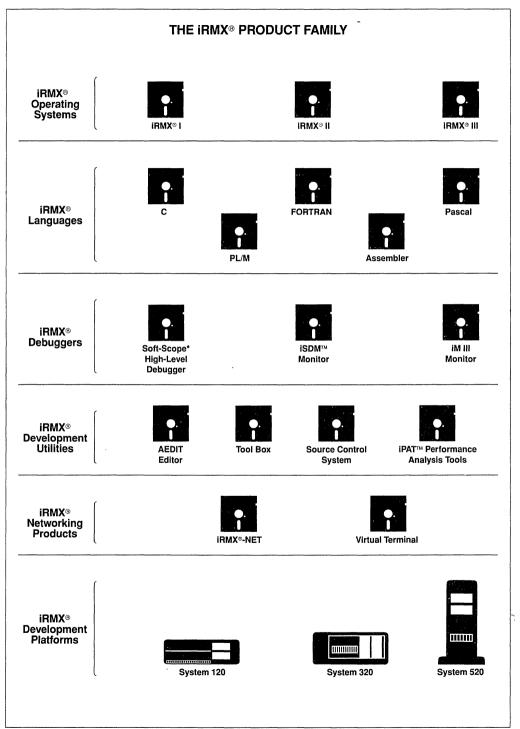

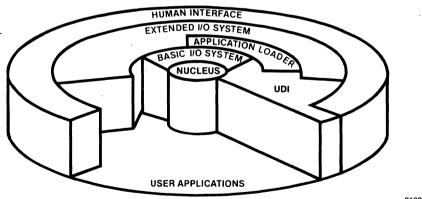

| iRMX Operating System Family                                                                                                                                                                                                                | 7-14<br>7-21                 |

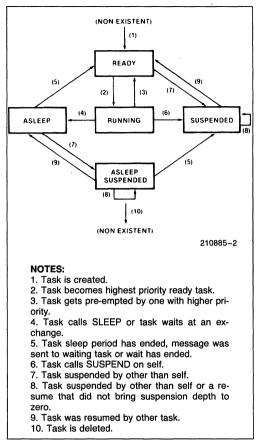

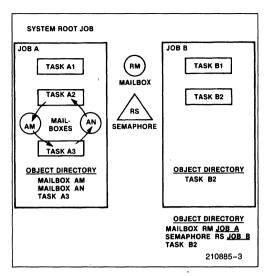

| iRMX Operating System                                                                                                                                                                                                                       | 7-21                         |

| Intel System V/386 Product Family                                                                                                                                                                                                           | 7-40                         |

| Software Migration from iRMX 86 to iRMX 286                                                                                                                                                                                                 | 7-61                         |

| SOFTWARE DEVELOPMENT TOOLS                                                                                                                                                                                                                  | 7-01                         |

| AEDIT Source Code and Text Editor                                                                                                                                                                                                           | 7-92                         |

| iPAT Performance Analysis Tool                                                                                                                                                                                                              | 7-94                         |

| iRMX Source Control System                                                                                                                                                                                                                  | 7-98                         |

| iRMX Toolbox                                                                                                                                                                                                                                | 7-100                        |

| iRMX Virtual Terminal                                                                                                                                                                                                                       | 7-102                        |

| iRMX X.25 Communications Software                                                                                                                                                                                                           | 7-104                        |

| iSDM System Debug Monitor                                                                                                                                                                                                                   | 7-106                        |

| Soft-Scope II Source-Level Debugger                                                                                                                                                                                                         | 7-110                        |

| MULTIBUS® I PRODUCTS                                                                                                                                                                                                                        |                              |

| CHAPTER 8                                                                                                                                                                                                                                   |                              |

| MULTIBUS® I Single Board Computers                                                                                                                                                                                                          |                              |

| iSBC 386/12 and iSBC 386/12S Single Board Computers                                                                                                                                                                                         | 8-1                          |

| iSBC 386/21/22/24/28 and 386/31/32/34/38 Single Board Computers                                                                                                                                                                             | 8-9                          |

| iSBC 286/12, 286/14, 286/16 Single Board Computers                                                                                                                                                                                          | 8-18                         |

| iSBC 286/10A Single Board Computer                                                                                                                                                                                                          | 8-25                         |

| iSBC 186/03A Single Board Computer                                                                                                                                                                                                          | 8-30                         |

| iSBC 86C/38 Single Board Computer                                                                                                                                                                                                           | 8-39                         |

| iSBC 86/35 Single Board Computer                                                                                                                                                                                                            | 8-43                         |

| iSBC 86/14 and iSBC 86/30 Single Board Computers                                                                                                                                                                                            | 8-48                         |

| iSBC 86/05A Single Board Computer                                                                                                                                                                                                           | 8-53                         |

| iSBC 88/25 Single Board Computer                                                                                                                                                                                                            | 8-59                         |

| iSBC 80/30 Single Board Computer                                                                                                                                                                                                            | 8-65                         |

| iSBC 80/24A Single Board Computer                                                                                                                                                                                                           | 8-71<br>8-77                 |

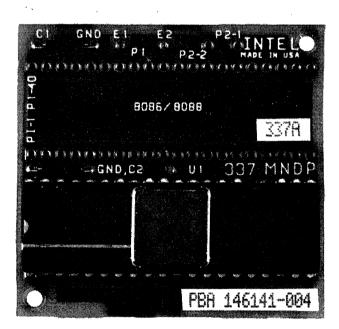

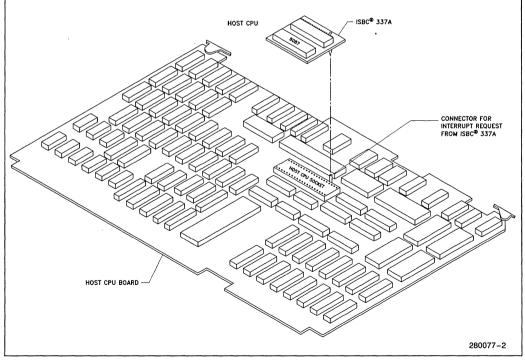

| iSBC 80/10B Single Board ComputeriSBC 337A MULTIMODULE Numeric Data Processor                                                                                                                                                               |                              |

|                                                                                                                                                                                                                                             | 0-02                         |

# **CHAPTER 9**

# MULTIBUS® I Memory Expansion Boards

| DI | RAM EXPANSION BOARDS                                            |      |

|----|-----------------------------------------------------------------|------|

|    | iSBC MM01, MM02, MM04, MM08 High Performance Memory Modules     | 9-1  |

|    | iSBC MM01FP, MM02FP, MM04FP, MM08FP High Performance Memory     |      |

|    | Modules                                                         | 9-5  |

|    | iSBC 012EX, 010EX, 020EX, and 040EX High Performance RAM Boards | 9-9  |

|    | iSBC 012CX, 010CX, 020CX iLBX RAM Boards                        | 9-13 |

|    | iSBC 314 512K Byte RAM MULTIMODULE Board                        | 9-17 |

|    | iSBC 304 128K Byte RAM MULTIMODULE Board                        | 9-21 |

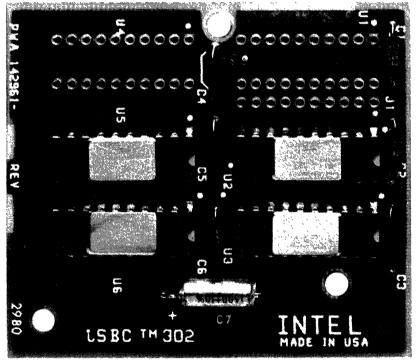

|    | iSBC 302 8K Byte RAM MULTIMODULE Board                          | 9-24 |

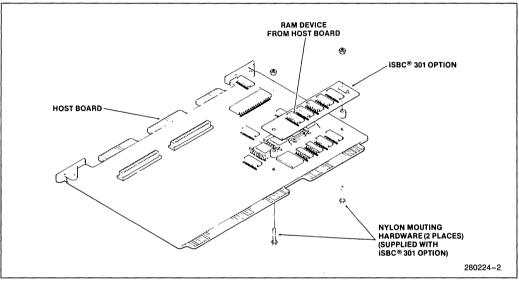

|    | ISBC 301 4K Byte RAM MULTIMODULE Board                          | 9-26 |

| Eł | PROM EXPANSION BOARDS                                           |      |

|    | iSBC 429 Universal Site Memory Expansion Board                  | 9-29 |

|    | iSBC 428 Universal Site Memory Expansion Board                  | 9-32 |

|    | iSBC 341 28-Pin MULTIMODULE EPROM                               | 9-36 |

|    |                                                                 |      |

# **CHAPTER 10**

# MULTIBUS® I Peripheral Controllers

| iSBC 221 Peripheral Controller                | 10-1  |

|-----------------------------------------------|-------|

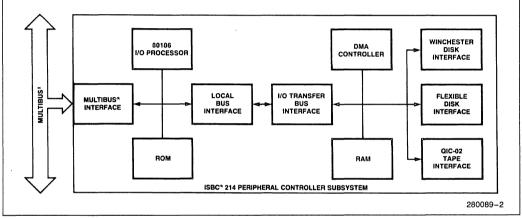

| iSBC 214 Peripheral Controller Subsystem      | 10-4  |

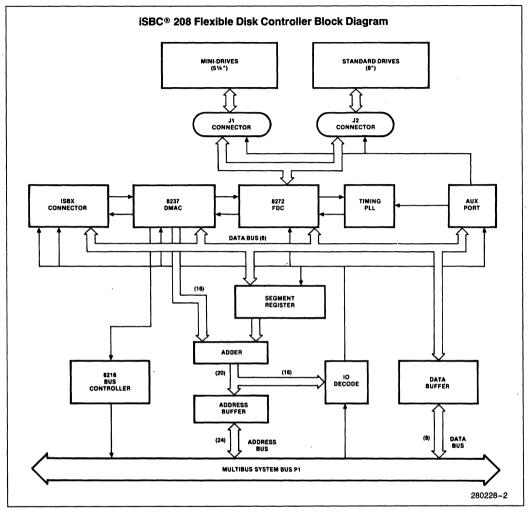

| iSBC 208 Flexible Diskette Controller         | 10-7  |

| iSBC 215 Generic Winchester Controller        | 10-11 |

| iSBC 220 SMD Disk Controller                  | 10-16 |

| See Chapter 6 for iSBX Peripheral Controllers |       |

|                                               |       |

### CHAPTER 11

### **MULTIBUS® I Serial Communication Boards**

| iSBC 548/549 Terminal Controllers                       | 11-1  |

|---------------------------------------------------------|-------|

| iSBC 188/56 Advanced Communicating Computer             | 11-5  |

| iSBC 544A Intelligent Communications Controller         | 11-14 |

| iSBC 534 Four Channel Communication Expansion Board     | 11-20 |

| iSBC 88/45 Advanced Data Communications Processor Board | 11-24 |

| See Chapter 6 for iSBX Serial Communication Boards      |       |

# **CHAPTER 12**

# MULTIBUS® I Digital and Analog I/O Boards

| iSBC 519A Programmable I/O Expansion Board                 | 12-1  |

|------------------------------------------------------------|-------|

| iSBC 517 Combination I/O Expansion Board                   | 12-3  |

| iSBC 556 Optically Isolated I/O Board                      | 12-7  |

| iSBC 569 Intelligent Digital Controller                    | 12-10 |

| iSBC 589 Intelligent DMA Controller                        |       |

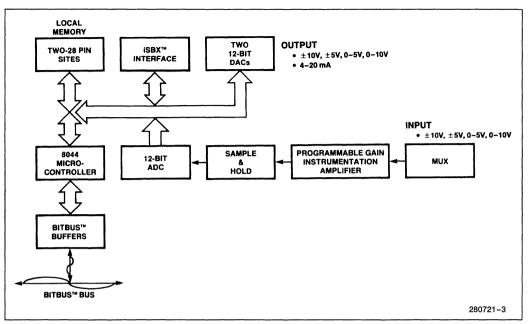

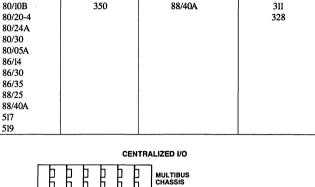

| iSBC 88/40A Measurement and Control Computer               |       |

| iSBC 108A/116A Combination Memory and I/O Expansion Boards |       |

| See Chapter 6 for iSBX Digital and Analog I/O Boards       |       |

### **CHAPTER 13**

# MULTIBUS® I System Packaging and Power Supplies

| SYP 341 Cardcage Module                    | . 13-1  |

|--------------------------------------------|---------|

| SYP 342 Peripheral Module                  | . 13-3  |

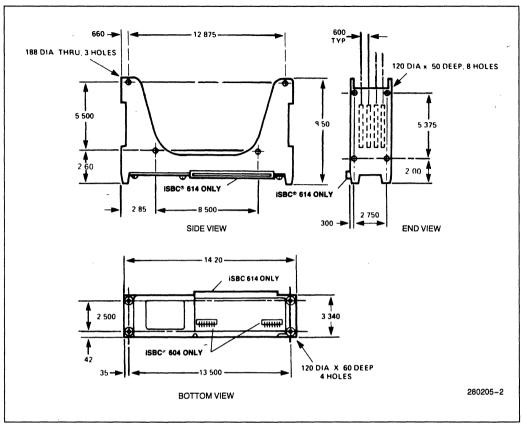

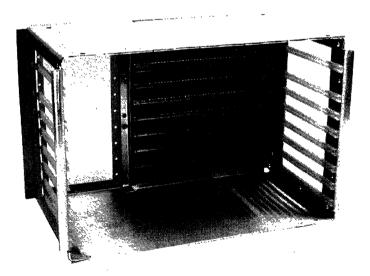

| iSBC 604/614 Modular Cardcage Assemblies   | . 13-5  |

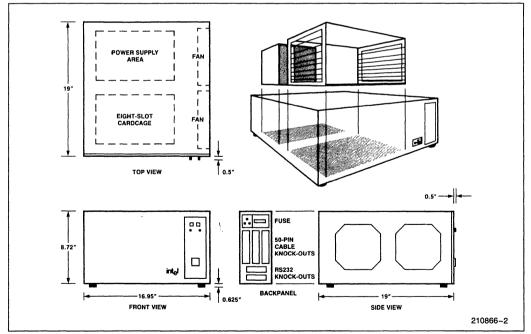

| iSBC 608/618 Cardcages                     | . 13-8  |

| iSBC 661 System Chassis                    | . 13-12 |

| iSBC 640 Power Supply                      | . 13-15 |

| iCS 80 Industrial Chassis Kit 635, Kit 640 |         |

| CHAPTER 14                                                                |       |

|---------------------------------------------------------------------------|-------|

| MULTIBUS® I Architecture                                                  |       |

| MULTIBUS System Bus                                                       | 14-1  |

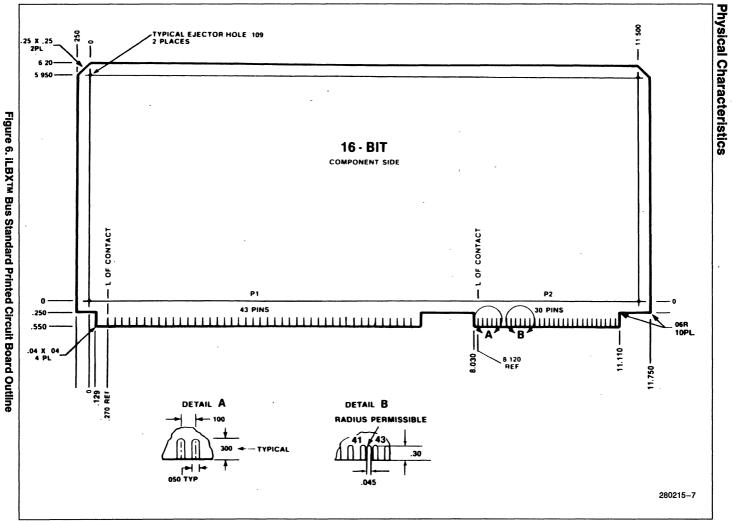

| iLBX Execution Bus                                                        | 14-13 |

| See Chapter 6 for iSBX I/O Expansion Bus                                  |       |

| SYSTEMS PRODUCTS                                                          |       |

| CHAPTER 15                                                                |       |

| ISA Boards and Systems                                                    |       |

| ISA BOARDS AND SYSTEMS                                                    |       |

| Intel386 MicroComputer Model 302                                          | 15-1  |

| Intel386 MicroComputer Model 302-20                                       | 15-3  |

| Intel386 MicroComputer Model 303                                          | 15-5  |

| Intel486 MicroComputer Model 401                                          | 15-8  |

| Intel386 MicroComputer Model 300SX                                        | 15-11 |

| Intel386 MicroComputer Model 301Z                                         | 15-14 |

| SOFTWARE PRODUCTS                                                         |       |

| Intel Software Products                                                   | 15-16 |

| ISA BOARDS AND SYSTEMS SUPPORT                                            |       |

| Intel OEM Support                                                         |       |

| Value-Added Distribution                                                  | 15-22 |

| LOCAL AREA NETWORK PRODUCTS                                               |       |

| CHAPTER 16                                                                |       |

| Local Area Network Boards and Software                                    |       |

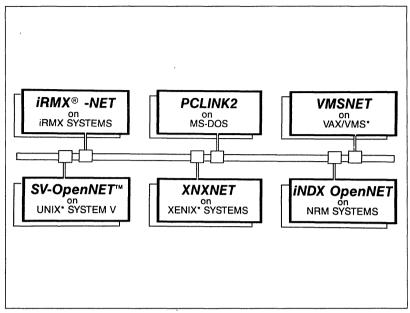

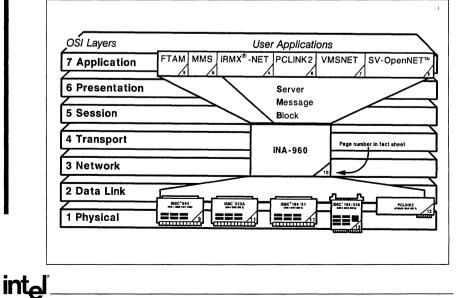

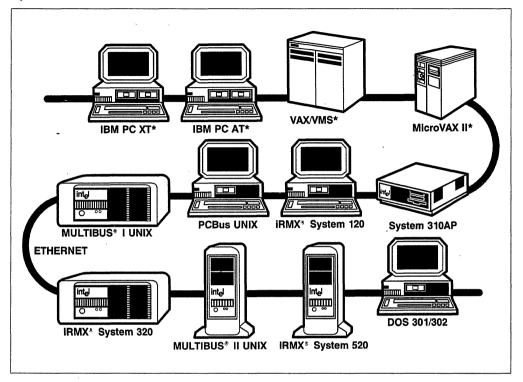

| OpenNET Local Area Network Family                                         | 16-1  |

| iSBX 586 Ethernet Data Link Engine                                        | 16-16 |

| iSBC552A and iSXM552A IEEE 802.3 Compatible Network Interface Adaptor     | 16-18 |

| iSBC 186/51 Communicating Computer                                        | 16-21 |

| See Chapter 3 for MULTIBUS II Networking Board Products                   |       |

| BITBUSTM PRODUCTS                                                         | 1     |

| CHAPTER 17                                                                |       |

|                                                                           |       |

| Distributed Control Modules<br>BITBUS STARTER KIT                         |       |

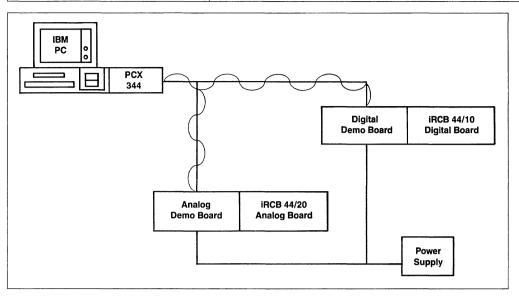

| BITBUS Starter Kit                                                        | 17-1  |

| BITBUS OPERATING SYSTEM SOFTWARE                                          | 17-1  |

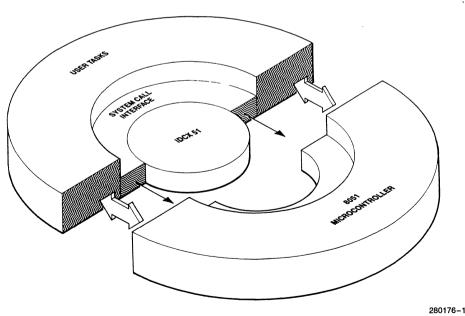

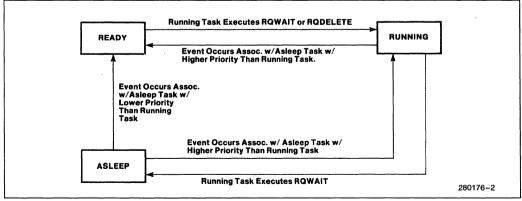

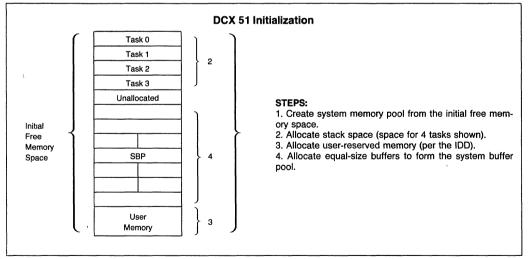

| iDCX 51 Distributed Control Executive                                     | 17-5  |

| BITBUS LANGUAGES AND TOOLS                                                | 17-5  |

| DCS100 BITBUS Toolbox Host Software Utilities                             | 17-13 |

| DCS110 Bitware DCS120 Programmers Support Package                         | 17-20 |

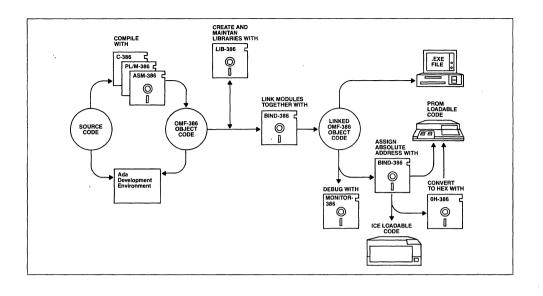

| 8051 Software Development Packages                                        | 17-25 |

| ICE-5100/044 In-Circuit Emulator                                          | 17-28 |

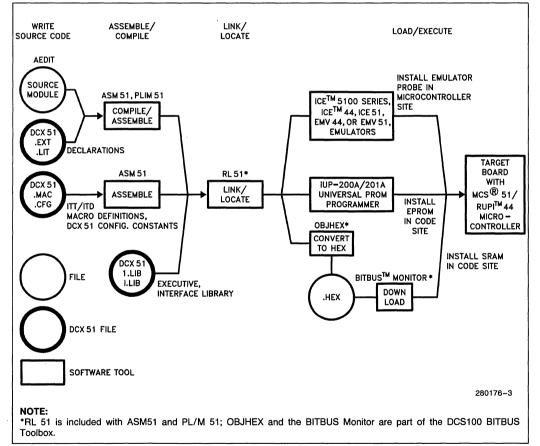

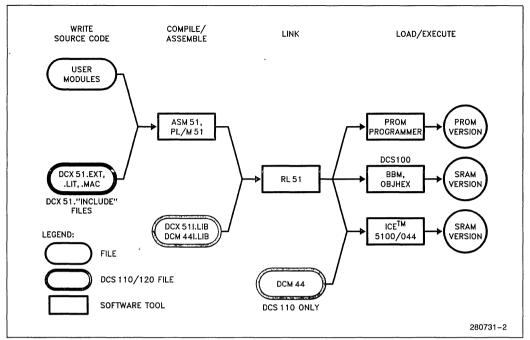

| BITBUS Software Development Environment                                   | 17-32 |

| BITBUS BOARDS                                                             |       |

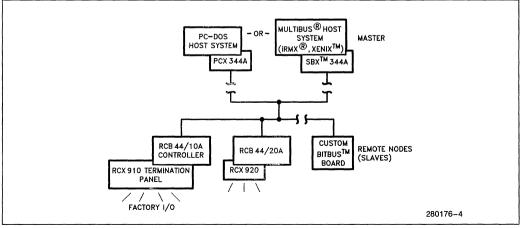

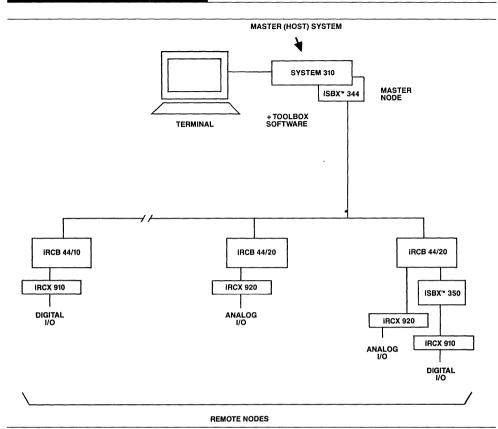

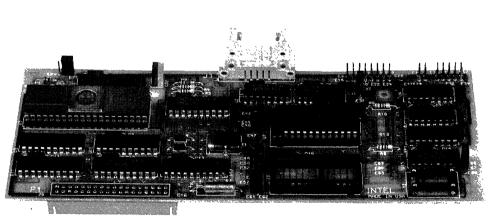

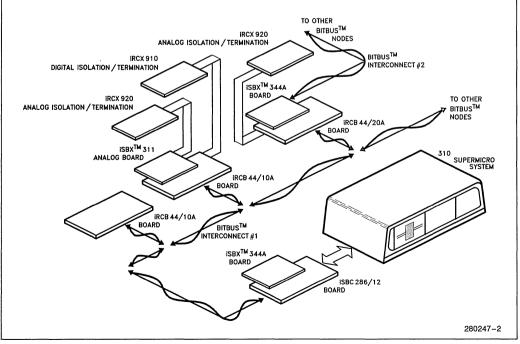

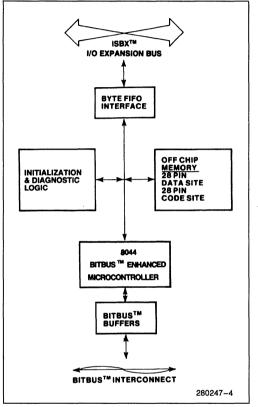

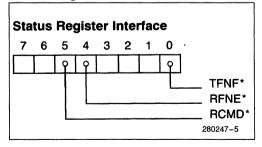

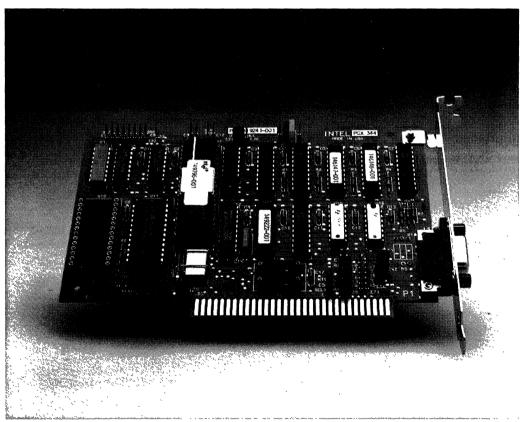

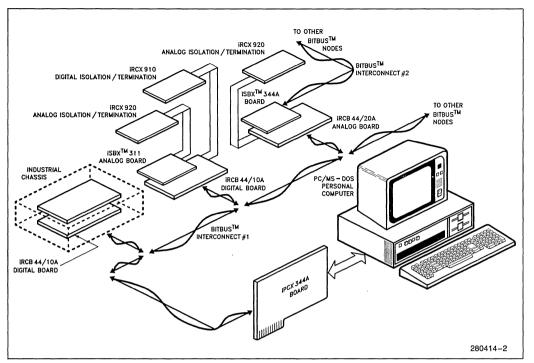

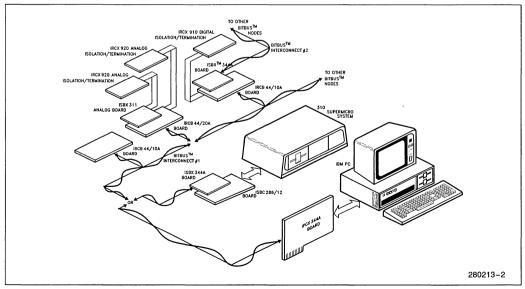

| iSBX 344A BITBUS Intelligent MULTIMODULE Board                            | 17-36 |

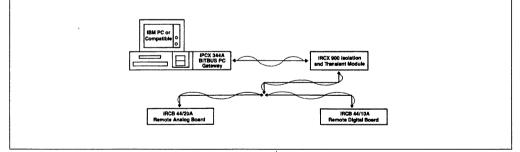

| iPCX 344A BITBUS IBM PC Interface Board                                   | 17-44 |

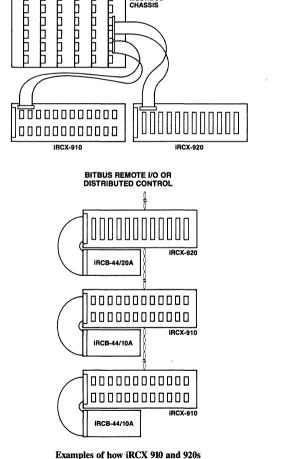

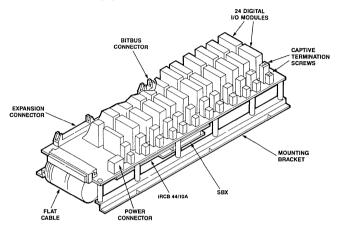

| iRCB 44/10A BITBUS Digital I/O Remote Controller Board                    | 17-50 |

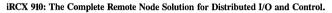

| iRCB 44/20A Analog I/O Controller                                         | 17-59 |

| iRCX 910/920 Digital/Analog Signal Conditioning Isolation and Termination |       |

| Panels                                                                    | 17-67 |

| iRCX 900 Isolation Module                                                 | 17-71 |

| BITBUS COMPONENTS                                                         |       |

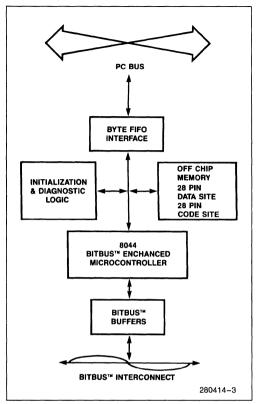

| 8044 BITBUS Enhanced Microcontroller                                      | 17-73 |

\_

| 8044AH/8344AH/8744AH High Performance 8-Bit Microcontroller with On-Chip<br>Serial Communication Controller | 17-94 |

|-------------------------------------------------------------------------------------------------------------|-------|

| SERVICE AND SUPPORT                                                                                         |       |

| CHAPTER 18                                                                                                  |       |

| Service and Support                                                                                         | 40.4  |

| iRUG Description                                                                                            |       |

| Intel Systems Customer Service                                                                              | 18-2  |

# Alphanumeric Index

| 8044 BITBUS Enhanced Microcontroller                                             | 17-73 |

|----------------------------------------------------------------------------------|-------|

| Communication Controller                                                         | 17-94 |

| 8051 Software Development Packages                                               | 17-25 |

| AEDIT Source Code and Text Editor                                                | 7-92  |

| BITBUS Software Development Environment                                          | 17-32 |

| BITBUS Starter Kit                                                               | 17-1  |

| DCS100 BITBUS Toolbox Host Software Utilities                                    | 17-13 |

| DCS110 Bitware DCS120 Programmers Support Package                                | 17-20 |

| Designing a Central Services Module for MULTIBUS II                              | 5-15  |

| Enhancing System Performance with the MULTIBUS II Architecture                   | 5-221 |

| ICE-5100/044 In-Circuit Emulator                                                 | 17-28 |

| iCS 80 Industrial Chassis Kit 635, Kit 640                                       | 13-18 |

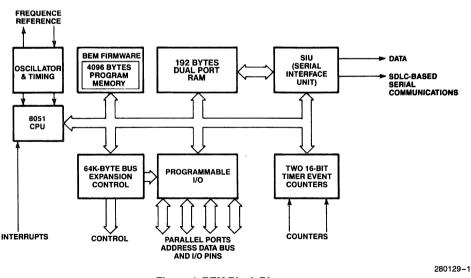

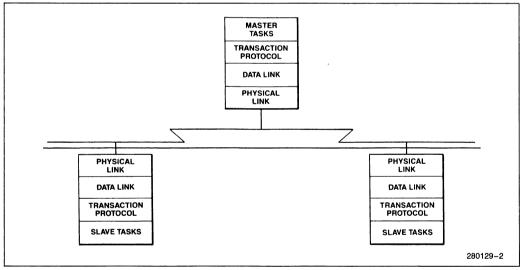

| iDCX 51 Distributed Control Executive                                            | 17-5  |

| iLBX Execution Bus                                                               | 14-13 |

| Increasing System Reliability with MULTIBUS II Architecture                      | 5-225 |

| Intel OEM Support                                                                | 15-20 |

| Intel Software Products                                                          | 15-16 |

| Intel System V/386 Product Family                                                | 7-57  |

| Intel Systems Customer Service                                                   | 18-2  |

| Intel386 MicroComputer Model 300SX                                               | 15-11 |

| Intel386 MicroComputer Model 301Z                                                | 15-14 |

| Intel386 MicroComputer Model 302                                                 | 15-1  |

| Intel386 MicroComputer Model 302-20                                              | 15-3  |

| Intel386 MicroComputer Model 303                                                 | 15-5  |

| Intel486 MicroComputer Model 401                                                 | 15-8  |

| iPAT Performance Analysis Tool                                                   | 7-94  |

| iPCX 344A BITBUS IBM PC Interface Board                                          | 17-44 |

| iRCB 44/10A BITBUS Digital I/O Remote Controller Board                           | 17-50 |

| iRCB 44/20A Analog I/O Controller                                                | 17-59 |

| iRCX 900 Isolation Module                                                        | 17-71 |

| iRCX 910/920 Digital/Analog Signal Conditioning Isolation and Termination Panels | 17-67 |

| iRMK Real-Time Kernel                                                            | 7-14  |

| iRMX I Operating System                                                          | 7-40  |

| iRMX Operating System Family                                                     | 7-21  |

| iRMX Source Control System                                                       | 7-98  |

| iRMX Toolbox                                                                     | 7-100 |

| iRMX Virtual Terminal                                                            | 7-102 |

| iRMX X.25 Communications Software                                                | 7-104 |

| iRUG Description                                                                 | 18-1  |

| iSBC 012CX, 010CX, 020CX iLBX RAM Boards                                         | 9-13  |

| iSBC 012EX, 010EX, 020EX, and 040EX High Performance RAM Boards                  | 9-9   |

| iSBC 108A/116A Combination Memory and I/O Expansion Boards                       | 12-22 |

| iSBC 186/03A Single Board Computer                                               | 8-30  |

| iSBC 186/100 MULTIBUS II Single Board Computer                                   | 1-22  |

| iSBC 186/51 Communicating Computer                                               | 16-21 |

| iSBC 188/56 Advanced Communicating Computer                                      | 11-5  |

| iSBC 208 Flexible Diskette Controller                                            | 10-7  |

| iSBC 214 Peripheral Controller Subsystem                                         | 10-4  |

| iSBC 215 Generic Winchester Controller                                           | 10-11 |

| iSBC 220 SMD Disk Controller                                                     | 10-16 |

| iSBC 221 Peripheral Controller                                                   | 10-1  |

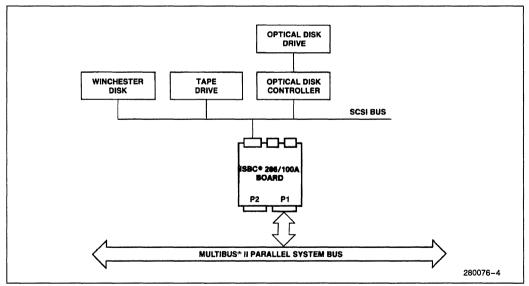

| iSBC 286/100A MULTIBUS II Single Board Computer                                  | 1-13  |

| iSBC 286/10A Single Board Computer                                               | 8-25  |

|                                                                                  |       |

# Alphanumeric Index (Continued)

| iSBC 286/12, 286/14, 286/16 Single Board Computers                    | 8-18  |

|-----------------------------------------------------------------------|-------|

| iSBC 301 4K Byte RAM MULTIMODULE Board                                | 9-26  |

| iSBC 302 8K Byte RAM MULTIMODULE Board                                | 9-24  |

| iSBC 304 128K Byte RAM MULTIMODULE Board                              | 9-21  |

| iSBC 314 512K Byte RAM MULTIMODULE Board                              | 9-17  |

| iSBC 337A MULTIMODULE Numeric Data Processor                          | 8-82  |

| iSBC 341 28-Pin MULTIMODULE EPROM                                     | 9-36  |

| iSBC 386/116 and 386/120 MULTIBUS II Single Board Computers           | 1-5   |

| iSBC 386/12 and iSBC 386/12S Single Board Computers                   | 8-1   |

| iSBC 386/21/22/24/28 and 386/31/32/34/38 Single Board Computers       | 8-9   |

| iSBC 428 Universal Site Memory Expansion Board                        | 9-32  |

| iSBC 429 Universal Site Memory Expansion Board                        | 9-29  |

| iSBC 486/125DU and 386/133 Single Board Computers                     | 1-1   |

| iSBC 517 Combination I/O Expansion Board                              | 12-3  |

| iSBC 519A Programmable I/O Expansion Board                            | 12-1  |

| iSBC 534 Four Channel Communication Expansion Board                   | 11-20 |

| iSBC 544A Intelligent Communications Controller                       | 11-14 |

| iSBC 548/549 Terminal Controllers                                     | 11-1  |

| iSBC 556 Optically Isolated I/O Board                                 | 12-7  |

| iSBC 569 Intelligent Digital Controller                               | 12-10 |

| iSBC 589 Intelligent DMA Controller                                   | 12-13 |

| iSBC 604/614 Modular Cardcage Assemblies                              | 13-5  |

| iSBC 608/618 Cardcages                                                | 13-8  |

| iSBC 640 Power Supply                                                 | 13-15 |

| iSBC 661 System Chassis                                               | 13-12 |

| iSBC 80/10B Single Board Computer                                     | 8-77  |

| iSBC 80/24A Single Board Computer                                     | 8-71  |

| iSBC 80/30 Single Board Computer                                      | 8-65  |

| iSBC 86/05A Single Board Computer                                     | 8-53  |

| iSBC 86/14 and iSBC 86/30 Single Board Computers                      | 8-48  |

| iSBC 86/35 Single Board Computer                                      | 8-43  |

| iSBC 86C/38 Single Board Computer                                     | 8-39  |

| iSBC 88/25 Single Board Computer                                      | 8-59  |

| iSBC 88/40A Measurement and Control Computer                          | 12-17 |

| iSBC 88/45 Advanced Data Communications Processor Board               | 11-24 |

| iSBC Central Services Module/002                                      | 4-15  |

| iSBC CSM/001 Central Services Module                                  | 4-10  |

| iSBC LNK/001 Board MULTIBUS II to MULTIBUS I Link Board               | 4-17  |

| iSBC MEM/320, 340 Cache-Based MULTIBUS II RAM Boards                  | 2-9   |

| iSBC MEM/601 MULTIBUS II Universal Site Memory Expansion Board        | 2-13  |

| iSBC MM01, MM02, MM04, MM08 High Performance Memory Modules           | 2-1   |

| iSBC MM01, MM02, MM04, MM08 High Performance Memory Modules           | 9-1   |

| iSBC MM01FP, MM02FP, MM04FP, MM08FP High Performance Memory Modules   | 2-5   |

| iSBC MM01FP, MM02FP, MM04FP, MM08FP High Performance Memory Modules   | 9-5   |

| iSBC PKG/606, iSBC PKG/609 MULTIBUS II Cardcage Assemblies            | 4-1   |

| iSBC PKG/902, iSBC PKG/903 MULTIBUS II iLBX II Backplanes             | 4-5   |

| iSBC552A and iSXM552A IEEE 802.3 Compatible Network Interface Adaptor | 16-18 |

| iSBX 217C 1/4-Inch Tape Drive Interface MULTIMODULE Board             | 6-4   |

| iSBX 218A Flexible Disk Controller                                    | 6-6   |

| iSBX 279 Display Subsystem                                            | 6-1   |

| iSBX 311 Analog Input MULTIMODULE Board                               | 6-10  |

| iSBX 328 Analog Output MULTIMODULE Board                              | 6-13  |

| iSBX 344A BITBUS Intelligent MULTIMODULE Board                        | 17-36 |

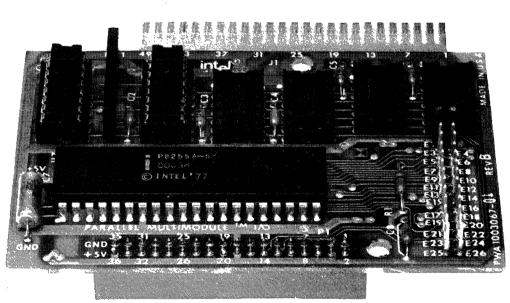

| iSBX 350 Parallel I/O MULTIMODULE Board                               | 6-16  |

# Alphanumeric Index (Continued)

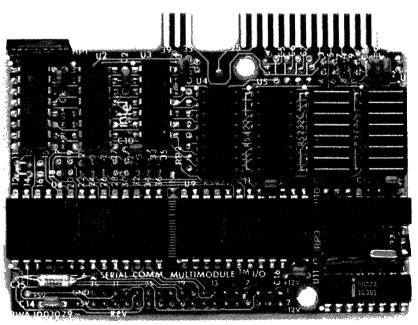

| iSBX 351 Serial I/O MULTIMODULE Board                                | 6-22  |

|----------------------------------------------------------------------|-------|

| iSBX 354 Dual Channel Serial I/O MULTIMODULE Board                   | 6-26  |

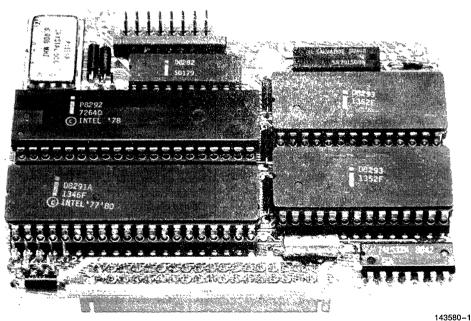

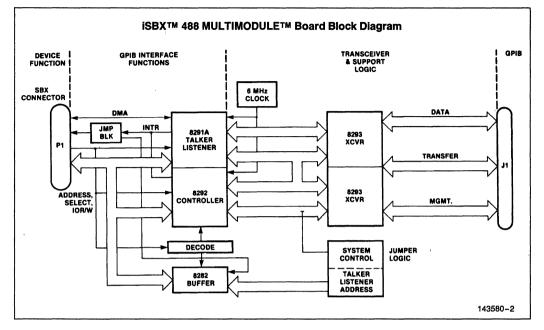

| iSBX 488 GPIB MULTIMODULE Board                                      | 6-19  |

| iSBX 586 Ethernet Data Link Engine                                   | 16-16 |

| iSBX I/O Expansion Bus                                               | 6-29  |

| iSDM System Debug Monitor                                            | 7-106 |

| MIX Architecture Design Guide                                        | 5-174 |

| MULTIBUS II Bus Structure                                            | 5-1   |

| MULTIBUS II High Performance SBC General Purpose Test Fixture (GPTF) | 4-22  |

| MULTIBUS II I/O Product Family                                       | 3-1   |

| MULTIBUS II Interconnect Design Guide                                | 5-45  |

| MULTIBUS II PC Subsystem                                             | 1-31  |

| MULTIBUS II Simplifies Partitioning of a Complex Design              | 5-128 |

| MULTIBUS System Bus                                                  | 14-1  |

| OpenNET Local Area Network Family                                    | 16-1  |

| Soft-Scope II Source-Level Debugger                                  | 7-110 |

| Software Migration from iRMX 86 to iRMX 286                          | 7-61  |

| SYP 341 Cardcage Module                                              | 13-1  |

| SYP 342 Peripheral Module                                            | 13-3  |

| SYP 500 MULTIBUS II System Chassis                                   | 4-8   |

| System 120                                                           | 7-1   |

| System 310 AP                                                        | 7-5   |

| System 310 AP 386 Upgrade                                            | 7-7   |

| System 320                                                           | 7-9   |

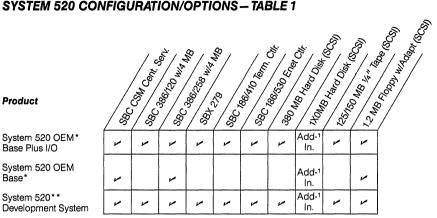

| System 520                                                           | 7-11  |

| Value-Added Distribution                                             | 15-22 |

# MULTIBUS® II Single Board Computers

1

. · · . . .

# iSBC®486/125DU AND 386/133\* SINGLE BOARD COMPUTERS

# ADDING i486<sup>™</sup> AND 386<sup>™</sup> CPU POWER TO MULTIBUS<sup>®</sup> II

The iSBC® 486/125DU (Development Unit) and iSBC 386/133\* Single Board Computers provide immediate access to the i486™ and 386™ 32-bit microprocessors on MULTIBUS II, the industry standard multiprocessing system bus. The iSBC 486/125DU board enables the system architect to prototype and validate an i486 processor based system today. Boasting the 33MHz 386 processor and a feature set compatible with its predecessors, the iSBC 386/133 board offers an immediate performance boost for current MULTIBUS II designs. The iSBC 486/125DU and iSBC 386/133 boards are also fully compatible. Design and ship systems in volume today using iSBC 386/133 boards, and easily upgrade them to i486 CPU performance later.

# FEATURES

#### iSBC® 486/125DU

- i486<sup>™</sup> CPU operating at 25MHz with onchip FPU and cache

- 8MB on-board DRAM with parity

#### iSBC® 486/125DU AND iSBC® 386/133

- 82258 ADMA with 16-byte "blast" mode Two 32-pin JEDEC EPROM Sites with

- Built-in-self-test (BIST) iLBX<sup>™</sup> II interface

- Two RS-232 asynchronous serial ports

- One iSBX<sup>™</sup> connector

- 3 programmable interval timers, 15 levels of interrupt

#### iSBC® 386/133

- 386<sup>™</sup> CPU operating at 33MHz

- 387<sup>™</sup> Numeric Coprocessor

- 64KB SRAM zero wait-state cache

- 1-16MB on-board DRAM with parity

- Full 32-bit MULTIBUS II (IEEE/ANSI 1296) Parallel System Bus interface

- Connector for on-board CSM option

- Full Operating Systems Support: iRMX<sup>®</sup> II and UNIX\*\* System V/386 operating systems, and iRMK™ I real-time kernel

386/133 board is also manufactured under product code pSBC386/133 by Intel Puerto Rico, Inc.

© Intel Corporation 1989

September, 1989 Order Number 281007-001

#### 386™ MICROPROCESSOR SPEED AND PERFORMANCE

The iSBC 386/133 Single Board Computer features the highest speed 386<sup>™</sup> microprocessor available today – 33MHz. It also includes a 387<sup>™</sup> floating-point coprocessor running at 33MHz. The 121-pin, extended math coprocessor socket could also house a WEITEK 3167 floating-point unit (FPU) instead of the 387 FPU.

# HIGH-SPEED ON-BOARD MEMORY

For optimum CPU performance, the iSBC 386/133 board includes a 64K Byte cache memory resulting in zero wait-state read accesses on cache hits. The iSBC 386/133 board provides 1-16MB of parity protected, fast-page DRAM memory. The memory interface is designed to support up to 64M bytes, allowing for further memory expansion when 4 Mbit DRAM modules become available.

This board also includes two 32-pin JEDEC sites for up to 512KB of EPROM using 27020, 2 Mbit EPROM devices. These sites, as shipped, contain BIST (Built-In-Self-Test) and IDX (Initialization and Diagnostics eXecutive) power-up diagnostics residing in two preprogrammed 27010 EPROMs.

#### 82258 ADMA COPROCESSOR WITH 16-BYTE "BLAST" MODE

The 82258 Advanced DMA coprocessor provides 4 DMA channels. Two channels are allocated to data transfers to/from the iSBX<sup>™</sup> bus interface. The remaining two channels handle data transfers between the MPC and on-board memory. Special logic on the board allows the 82258 to transfer data to and from the MPC 4-bytes ("fly-by") or 16-bytes ("blast" mode) at a time; or at a sustained rate of 13.3M bytes/sec or 20.0M bytes/sec.

#### BALANCED SET OF ON-BOARD I/O: TWO SERIAL PORTS, ISBX™ CONNECTOR

Through extensive use of surface mount technology, the iSBC 386/133 board has increased the on-board I/O features over previous MULTIBUS II CPU boards. It provides two serial ports based on Intel's 82530 Serial Communications Controller and one iSBX connector, capable of supporting a single- or doublewide, 8- or 16-bit iSBX MULTIMODULE™ board.

#### *iLBX™ II INTERFACE FOR MEMORY MAPPED I/O EXPANSION*

The iLBX<sup>™</sup> II interface on P2 provides expansion for 64M Bytes of off-board memory or memory mapped I/O. It operates at 8MHz and is completely compatible with the iLBX II interface on the iSBC 286/100A and the iSBC MEM 3xx memory modules.

#### ON-BOARD CSM (CENTRAL SERVICES MODULE) CAPABILITY

An iSBC CSM/002 connector on the iSBC 386/133 provides an on-board CSM option. The iSBC CSM/002 module performs all CSM functions required by the IEEE/ANSI 1296 Specification. It also provides a battery-backed time-of-day clock, periodic alarm function, and 28 bytes of non-volatile RAM. The iSBC 386/133 with CSM module is installed in slot zero of a MULTIBUS II chassis and requires only one slot.

### FULLY COMPATIBLE WITH iSBC® 386/116,120 AND iSBC® 486/125DU

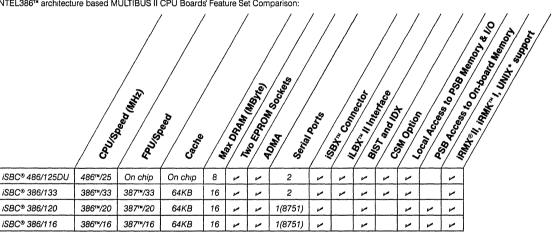

The iSBC 386/133 board is fully compatible with the INTEL386 family of MULTIBUS II boards, namely the iSBC 386/116, 386/120 and 486/125DU. Table 1 shows that the iSBC 386/133 feature set, with the exception of PSB access to on-board memory, is a super set of the iSBC 386/116, 120 feature set and matches that of the iSBC 486/125DU. Your 16MHz and 20MHz designs may be upgraded to 33MHz for an immediate system performance boost with a simple board swap.

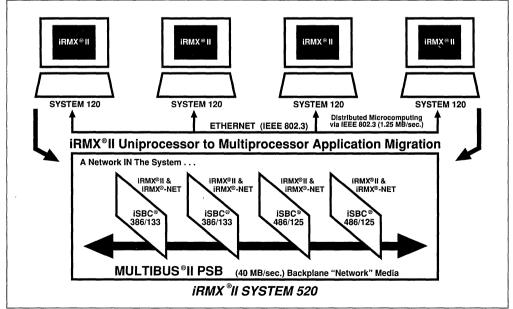

# PLUG-AND-PLAY WITH SYSTEM 520

Conforming to the MULTIBUS II Systems Architecture (MSA), this board integrates cleanly into the System 520. All you need is the "System Integration Toolkit" (SIT kit) that contains all the firmware necessary to operate in the System 520 enviroment. Install the firmware, plug the iSBC 386/133 into an empty slot, and start the system. It's that simple.

#### COMPREHENSIVE DEVELOPMENT AND OPERATING SYSTEM SUPPORT

Operating system support includes the iRMX<sup>®</sup> II Real-Time operating system and UNIX System V/386 operating system. The iRMK<sup>™</sup> I real-time kernel is available for 32-bit embedded applications. All three include MULTIBUS II transport for full message passing support. To ease MULTIBUS II modules development, Intel offers both the iRMX and UNIX operating system versions of the System 520 Development System which can support on-target and/or cross-hosted software development in one chassis.

#### DEVELOPMENT VEHICLE FOR FAST TIME TO MARKET WITH i486™ CPU

The iSBC 486/125DU Development Unit provides the system architect the opportunity to start designing today an i486™ processor-based system using an industry standard, off-the-shelf board. These units are currently available in limited sample quantities.

#### i486™ MICROPROCESSOR: THE HIGHEST PERFORMANCE COMPATIBILITY PROCESSOR

The heart of the iSBC 486/125DU board is the i486™ microprocessor, the newest and fastest member of the popular INTEL386™ 32-bit processor family. It is binary compatible with 386 microprocessors and offers two to three times the performance. The i486 microprocessor provides the highest level of performance through a state-of-the-art design containing a pipelined architecture, 8KB cache, and a high-performance local bus interface. Frequent instructions execute in one cycle. The performance is further enhanced by an on-chip floating-point unit (FPU) that is binary compatible with the 387 numerics coprocessor.

# HIGH-SPEED MEMORY INTERFACE **OPTIMIZES i486™ CPU PERFORMANCE**

The iSBC 486/125DU board comes with 8 MBytes of byte-parity protected DRAM. On-board memory access is optimized via a two way interleaved memory design using fast page DRAMs. The iSBC 486/125DU board fits in a single MULTIBUS II slot.

#### COMPLETELY COMPATIBLE WITH THE iSBC® 386/133

As shown in Table 1, all the I/O and MULTIBUS II architecture support features of the iSBC 386/133 are also provided on the iSBC 486/125DU for full compatibility with the iSBC 386/133. Both boards are supported by the iRMX, iRMK and UNIX operating systems.

# TABLE 1

INTEL386\*\* architecture based MULTIBUS II CPU Boards' Feature Set Comparison:

#### WORLD WIDE SERVICE AND SUPPORT

Should these or any Intel board ever need service. Intel maintains a world wide network of service and repair facilities to keep you and your customers up and running. For unique applications requiring customization of our products, the Intel Custom Board and Systems Group is available to modify, integrate and test Intel boards and system components to your requirements.

# **INTEL QUALITY – YOUR GUARANTEE**

The iSBC 386/133 and iSBC 486/125DU boards. are designed and manufactured to meet Intel's strict standards, assuring their reliability and high quality.

# SPECIFICATIONS

### **CPU CLOCK RATE**

iSBC 386/133:

iSBC 486/125DU:

#### **CACHE MEMORY**

iSBC 386/133: iSBC 486/125DU: 64K bytes 0 wait state on read hit 8K bytes on-chip 0 wait state on read hit

386™ CPU @ 33.3MHz 387™ FPU @ 33.3MHz

i486™ CPU @ 25MHz

#### DMA CLOCK RATES/MAXIMUM BANDWIDTH\*

82258 ADMA 10MHz/20 MB per second \*assumes transfer between local DRAM and MPC.

### **ON-BOARD DRAM MEMORY**

| Model            | Supplied |

|------------------|----------|

| iSBC 486/125 DU  | 8MB      |

| iSBC 386/133 F01 | 1MB      |

| iSBC 386/133 F02 | 2MB      |

| iSBC 386/133 F04 | 4MB      |

| iSBC 386/133 F08 | 8MB      |

- Single-bit parity error detection per byte

- iSBC 386/133 only: Memory expansion possible with one additional iSBC MM0xFP module. Maximum on-board memory capacity = 16MB (64MB w/ 4Mbit DRAMs)

NOTE: Model suffixes F02 and F08 require two MULTIBUS II card slots. iSBC 486/125DU with 8MB fits in one MULTIBUS II slot.

#### **EPROM MEMORY**

| Two JEDEC sites | provide following capacity: |

|-----------------|-----------------------------|

| Devices         | Capacity                    |

| 27010           | 256K byte (supplied)        |

| 27020           | 512K byte                   |

### INTERFACES

| <ul> <li>MULTIBUS II PSB:</li> </ul> | 32-bit Parallel System Bus |

|--------------------------------------|----------------------------|

|                                      | (ANSI/IEEE 1296) interface |

|                                      | with full message passing  |

|                                      | capability                 |

| <ul> <li>iSBX Bus:</li> </ul>        | Compliance Level:          |

|                                      | D16/16 DMA                 |

| <ul> <li>iLBX II Bus:</li> </ul>     | Compliance Level: PRQA     |

Serial I/O: RS232C DTE ASYNC

# SERIAL I/O PORT

- Channel A & B: RS232C compatible DTE Asynchronous interface

- 9-pin D-shell shielded connector

- Configurable baud rates: 300,600,1200,2400,4800,9600,19200, and 38400

#### PHYSICAL DIMENSIONS

| Height:            | 233 mm (9.18 inches)  |

|--------------------|-----------------------|

| Depth:             | 220 mm (8.65 inches)  |

| Front Panel Width: | 19.2 mm (0.76 inches) |

# **ELECTRICAL CHARACTERISTICS**

DC Power Requirements (Typical): +5V, 13A ±12V, 200mA

NOTE: Does not include power for iSBX module, or added iSBC MM0x modules.

For the second iSBC MM0x module, add: iSBC MM01-FP or iSBC MM04-FP +5V, 0.71A iSBC MM02-FP or iSBC MM08-FP +5V, 0.96A

#### **REFERENCE MANUAL**

iSBC 386/133 Single Board Computer User's Guide (order number 457629-001)

iSBC 486/125DU Single Board Computer User's Guide (order number 459600-001)

#### **ORDERING INFORMATION**

| Order Code<br>SBC486125DU | Description<br>25MHz 486 CPU-based<br>Development Unit w/ 8MB DRAM |

|---------------------------|--------------------------------------------------------------------|

| SBC386133F01              | 33MHz 386 CPU board w/ 1MB<br>DRAM                                 |

| SBC386133F02              | 33MHz 386 CPU board w/ 2MB<br>DRAM                                 |

| SBC386133F04              | 33MHz 386 CPU board w/ 4MB<br>DRAM                                 |

| SBC386133F08              | 33MHz 386 CPU board w/ 8MB<br>DRAM                                 |

| SBCMM01FP                 | 1MB, 85ns memory expansion module                                  |

| SBCMM02FP                 | 2MB, 85ns memory expansion module                                  |

| SBCMM04FP                 | 4MB, 85ns memory expansion module                                  |

| SBCMM08FP                 | 8MB, 85ns memory expansion module                                  |

| SBCCSM002                 | CSM Option Module                                                  |

| SIT133KIT                 | System 520 firmware for iSBC 386/133                               |

For more information or the number of your nearest Intel sales office, call 800-548-4725 (good in the U.S. and Canada).

# isBC® 386/116 AND 386/120\* MULTIBUS® II SINGLE BOARD COMPUTERS

- High Performance 32-bit 386<sup>TM</sup>

Processor Operating at 16 MHz or 20 MHz

- 80387 Numerics Co-Processor Providing IEEE 754 Floating Point Instruction Set, Operating at 16 MHz or 20 MHz

- 64K byte Static RAM Cache Providing Zero Wait State Reads

- 1, 2, 4 or 8M Bytes of On-Board Dual-Ported Dynamic RAM Memory with Parity Error Detection, Expandable to 16M Bytes

- 82258 DMA Controller Providing 4 High Performance DMA Channels

- 32-Bit MULTIBUS®II Parallel System Bus (IEEE 1296) Interface with Full Message Passing Capability

- 8-, 16-Bit iSBX™ Bus (IEEE P959) Interface with DMA for I/O Expansion

- Resident Firmware to Support Built-In-Self-Test (BIST) Power-Up Diagnostics

- MULTIBUS II Interconnect Space for Software Configurability and Diagnostics

- One RS 232C Serial I/O Port

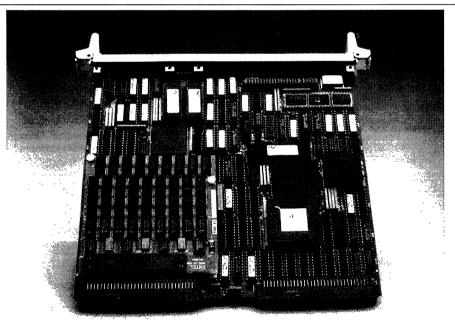

The iSBC 386/116 and 120 MULTIBUS II Single Board Computers are based on Intel's 386 high performance 32-bit microprocessor. The 386 CPU maintains software compatibility with the entire 8086 microprocessor family and delivers new performance standards for microcomputer-based systems. Four versions of the iSBC 386/116 and 120 boards are offered: the M01, which contains 1M byte of DRAM; the M02, which contains 2M bytes of DRAM; the M04, which includes 4M bytes of DRAM; and the M08 which contains 8M bytes of DRAM. An optional memory expansion module can be added to expand the iSBC 386/116 or 120 board's resident memory to a maximum of 16M bytes.

The 64K byte static RAM cache enables the 386 CPU to execute at its full potential performance, while the MULTIBUS II bus provides an interface for reliable, high performance multiprocessing.

280631-1

The iSBC® 386/116 and iSBC® 386/120 are also manufactured under product code piSBC® 386/116 and iSBC® 386/120 by Intel Puerto Rico, Inc.

# FUNCTIONAL DESCRIPTION

#### Overview

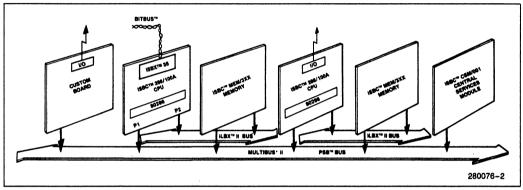

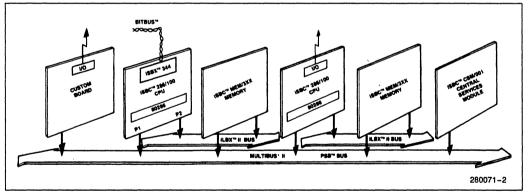

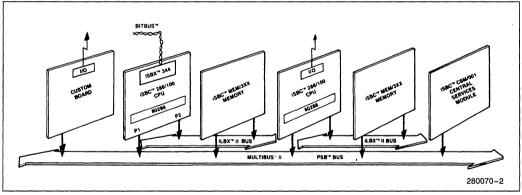

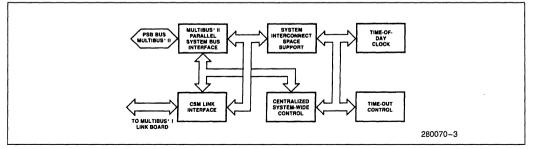

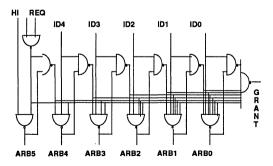

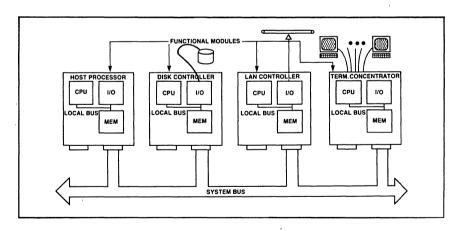

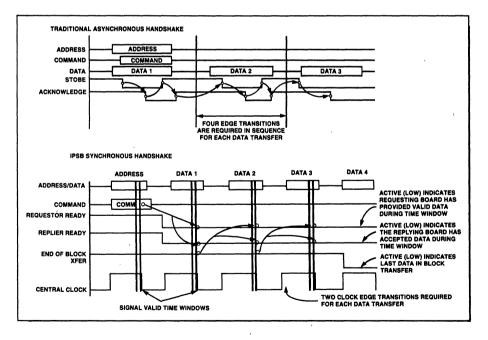

The iSBC 386/116 and 120 boards utilize Intel's 386 32-bit microprocessor. The advanced capabilities of the MULTIBUS II architecture coupled with the high performance and compatibility features of the 386 CPU, provide the designer with a superior 32-bit solution for multiprocessing applications. By using the MULTIBUS II architecture, multiprocessing systems are enhanced through advanced bus features including: 21-board distributed arbitration, virtual interrupts, hardware-assisted message passing, bus parity for high reliability, and software configurability using interconnect address space. The MULTIBUS II parallel system bus (iPSB) interface on the iSBC 386/116 and 120 boards support full message passing and dual-port architectures and is fully compatible with other SBCs based on the MULTIBUS II (IEEE 1296) bus specification.

The iSBC 386/116 and 120 boards are offered in four versions: M01, M02, M04 and M08 which contain 1, 2, 4 and 8M bytes of resident DRAM memory respectively. This memory is physically located on an expansion board, and can be accessed directly from the iSBC 386/116 or 120 board's local bus or by another CPU over the iPSB bus. This dual-port memory can be expanded to a maximum of 16M bytes though the addition of a second Intel iSBC MM01, MM02, MM04 or MM08 (1, 2, 4 or 8M byte) memory expansion module. Parity error detection is included on all resident DRAM memory.

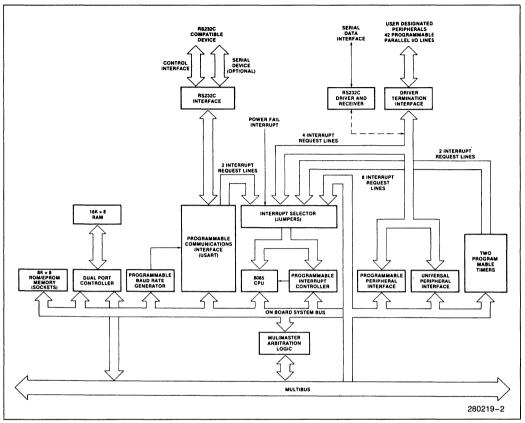

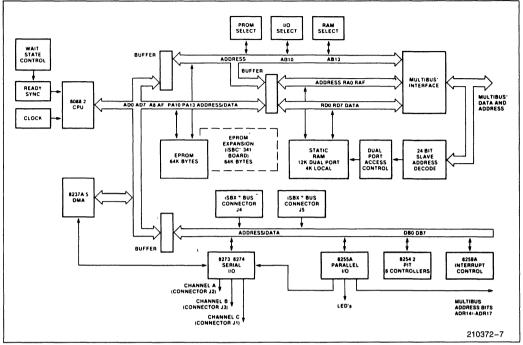

# Architecture

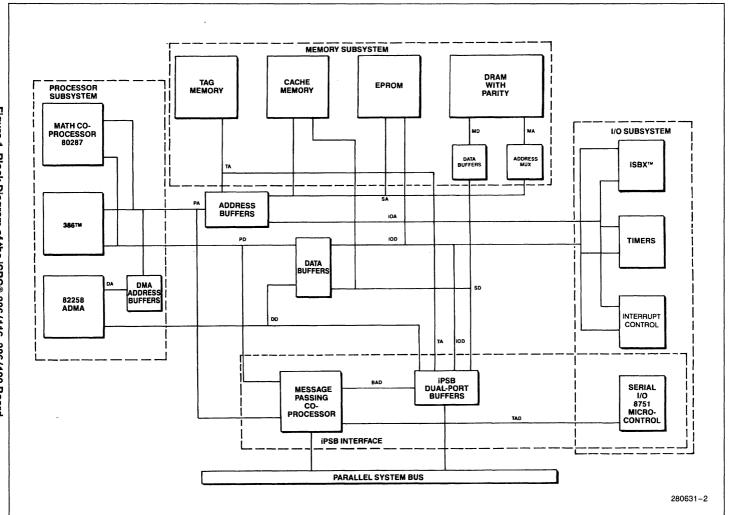

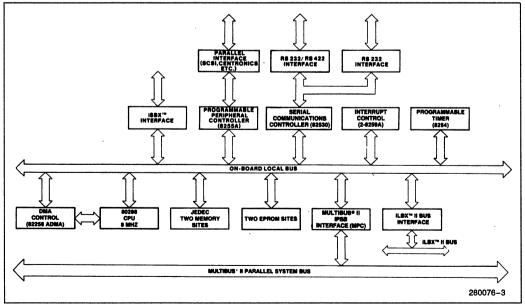

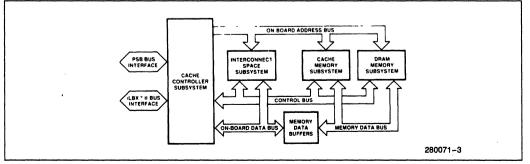

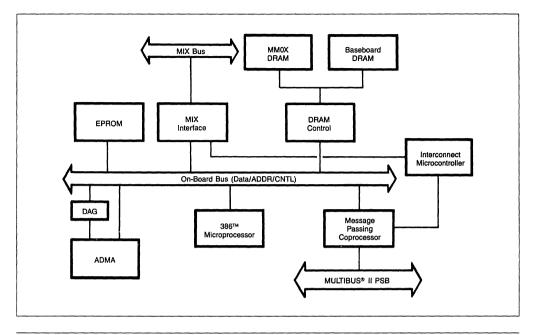

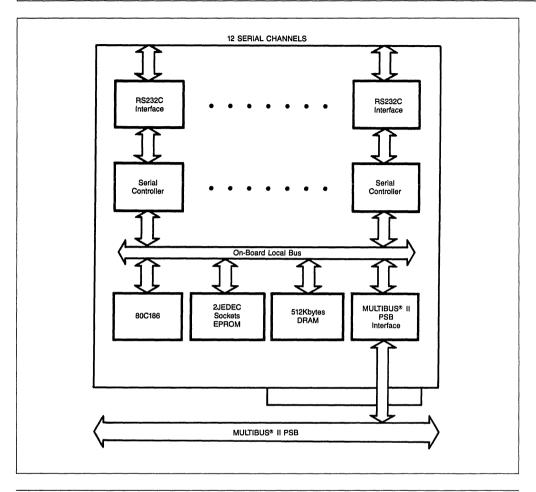

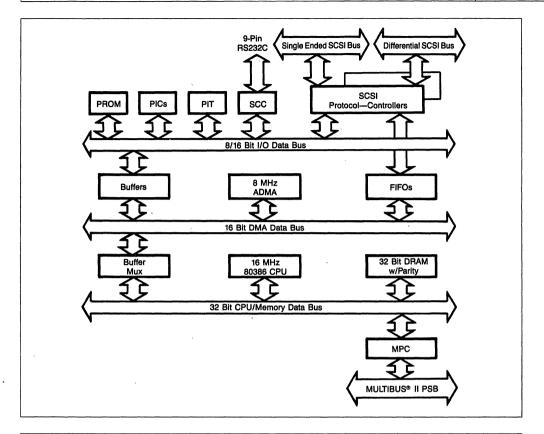

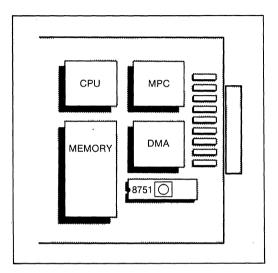

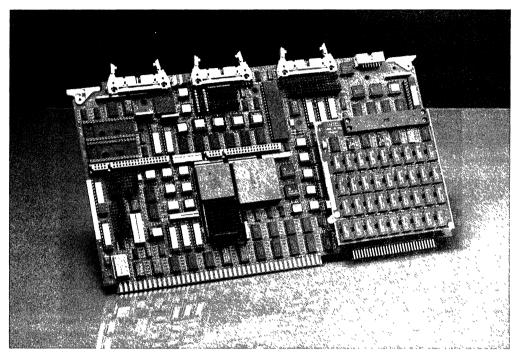

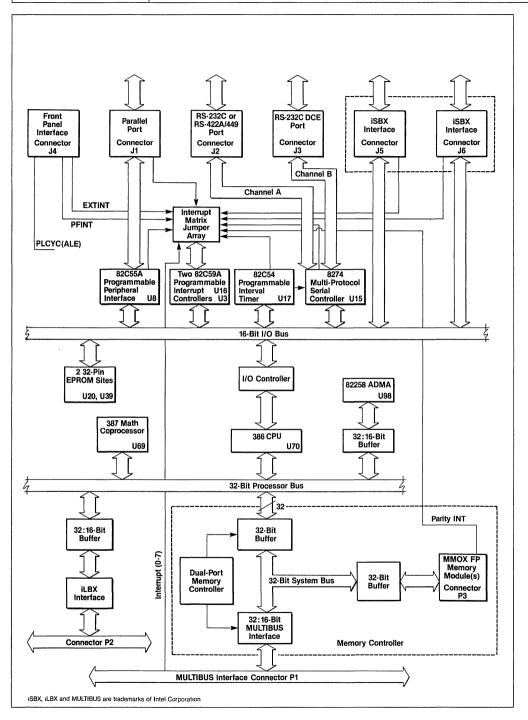

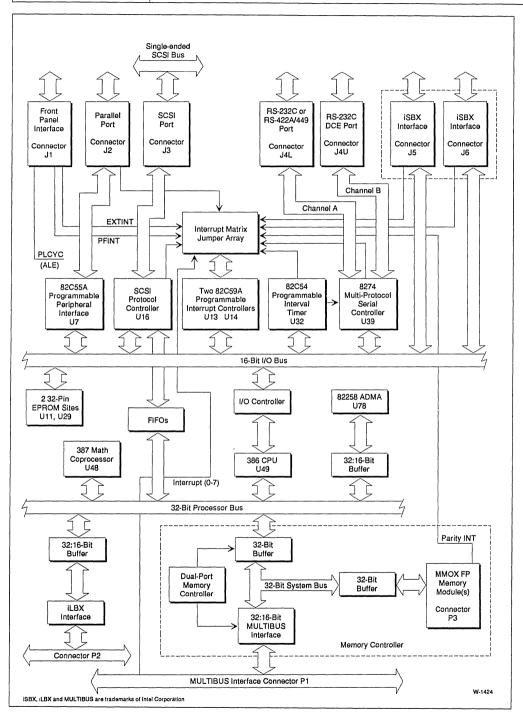

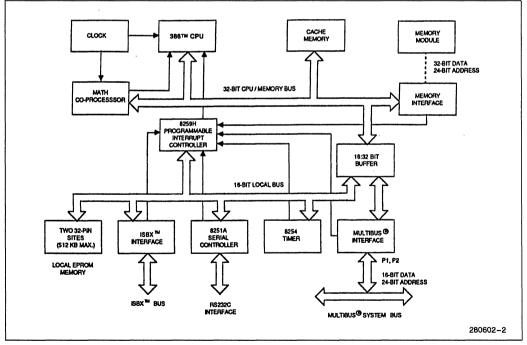

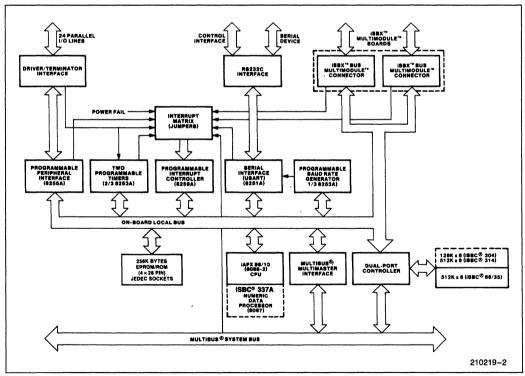

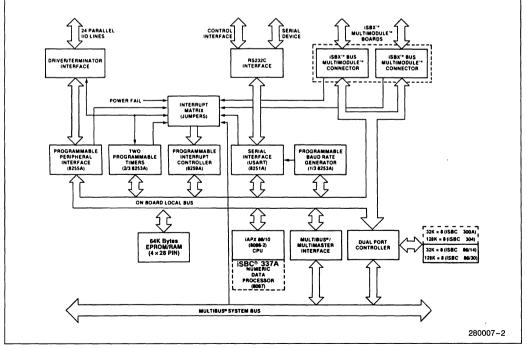

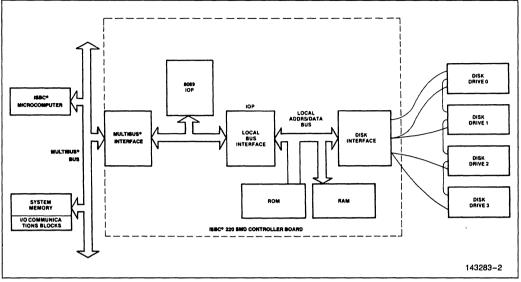

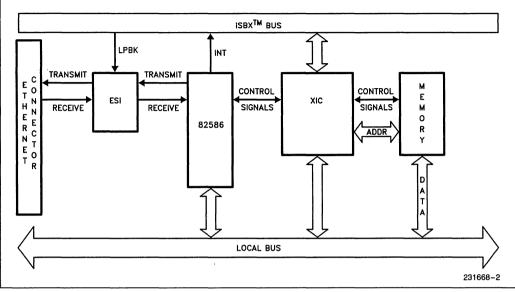

The iSBC 386/116 and 120 logic consists of eight resource modules and three interfaces connected together over an on-board local bus. The resources include the 386 CPU, the 80387 numeric co-processor, the 82258 DMA controller, the dual-port DRAM memory, the SRAM cache memory, the EPROM memory with BIST software, the programmable timers and the interrupt controllers. Interfaces included are the iPSB parallel system bus, the iSBX I/O bus and the RS 232C serial I/O interface. A block diagram of the iSBC 386/116, 120 board is shown in Figure 1. The following text describes each of the resources and interfaces.

#### 386™ PROCESSOR

Intel's 386 CPU is the central processor for the iSBC 386/116 and 120 boards. This is the first 32-bit member of Intel's 8086 family of microprocessors. At 16 MHz and 20 MHz, the 386 is capable of

executing at sustained rates of 4 and 5 million 32-bit instructions per second, respectively. This performance is made possible through a state-of-the-art design combining advanced VLSI semiconductor technology, a pipelined architecture, address translation caches and a high performance local bus interface.

The 386 processor provides a rich, generalized register and instruction set for manipulating 32-bit data and addresses. Features such as scaled indexing and a 64-bit barrel shifter ensure the efficient addressing and fast instruction processing. Special emphasis has been placed on providing optimized instructions for high-level languages and operating system functions. Advanced functions, such as hardware-supported multitasking and virtual memory support, provide the foundation necessary to build the most sophisticated multitasking and multiuser systems. Many operating system functions have been placed in hardware to enhance execution speed. The integrated memory management and protection mechanism translates virtual addresses to physical addresses and enforces the protection rules necessary for maintaining task integrity in a multiprocessing environment.

The 386 CPU provides access to the large base of software developed for the 8086 family of microprocessors. Binary code compatibility allows execution of existing 16-bit applications without recompilation or reassembly, directly in a virtual 8086 environment. Programs and even entire operating systems written for 8086 family processors can be run as tasks under 32-bit operating systems written for the 386 CPU.

#### 80287 NUMERIC CO-PROCESSOR

The 80387 is a high-performance floating-point coprocessor that takes numerics functions which would normally be performed in software by the 386 microprocessor and instead executes them in hardware. The instruction set executed by the 80387 is compatible with the IEEE 754 floating point standard, with high-precision 80-bit architectures and full support for single, double and extended precision operations. The 80387 executes floating point operations at a rate of 1.5M Whetstones per second at 16 MHz, and 1.86M Whetstones per second at 20 MHz.

#### 82258 ADVANCED DMA CO-PROCESSOR

The 82258 is a high performance 4 channel DMA co-processor. Unlike other DMA devices, the 82258 has processing capabilities. Its command chaining feature and data manipulation capabilities (compare, verify, translate), allow the 82258 to execute simple

Figure 1. Block Diagram of the iSBC® 386/116, 386/120 Board

1-7

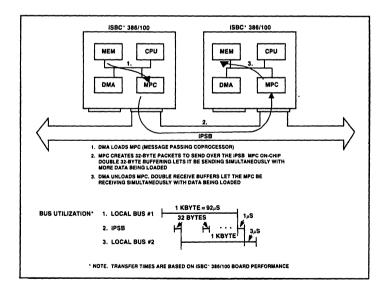

input/output programs without processor intervention. This allows the 386 CPU more time for general purpose processing, thus improving total system performance. The 82258 shares ownership of the on-board local bus via the 386 processor's HOLD, HOLD ACKNOWLEDGE co-processor protocol. The maximum percentage of on-board local bus utilization by the 82258 is user programmable.

The four 82258 channels are allocated to iSBC 386/ 116 or 120 on-board resources as shown in Table 1. Special logic on the boards allows the 82258 to transfer data to and from the message passing coprocessor (MPC) 32-bits at a time using single cycle mode. Using this mode, the 82258 (which operates at 8 MHz on 386/116 and 10 MHz on 386/120) can load or unload an MPC solicited message (from or to resident DRAM) at a sustained rate of 10.7M bytes and 13.3 Mbytes per second, respectively.

**Table 1. DMA Channel Allocation**

| Channel | Function                       |

|---------|--------------------------------|

| 0       | iSBX DMA support               |

| 1       | iSBX DMA support               |

| 2       | MPC Solicited Message Receive  |

| 3       | MPC Solicited Message Transmit |

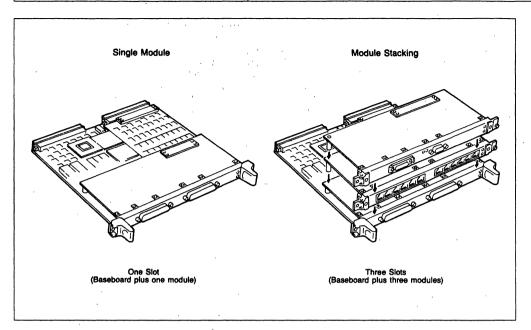

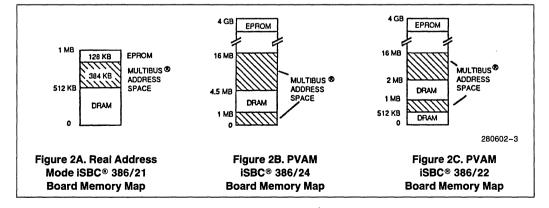

#### DUAL-PORTED DYNAMIC RAM

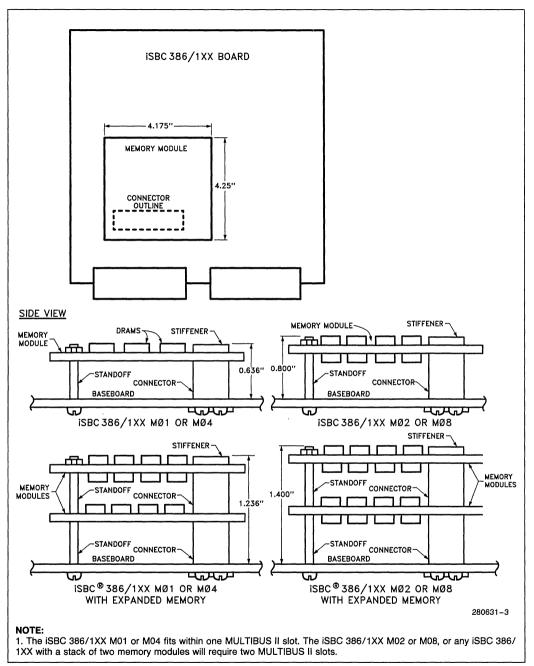

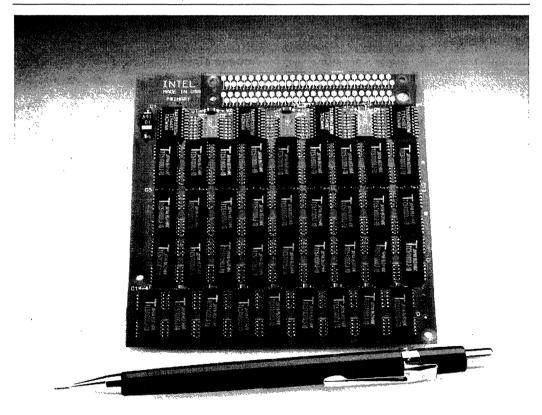

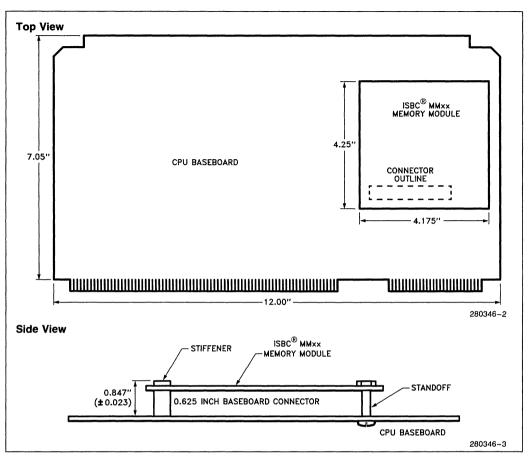

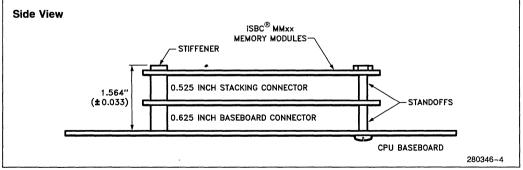

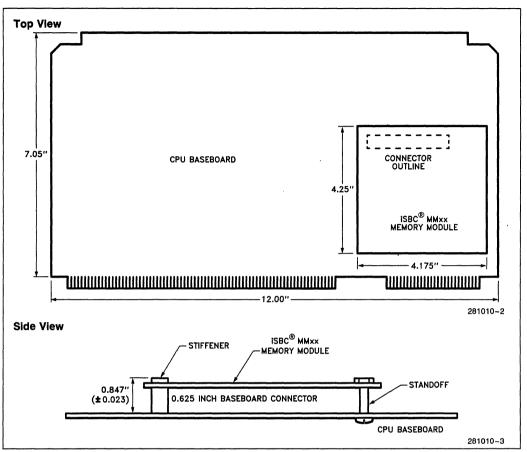

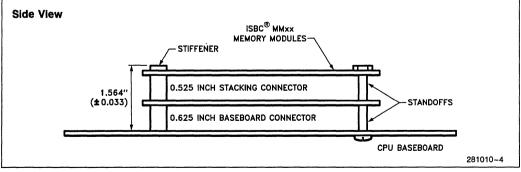

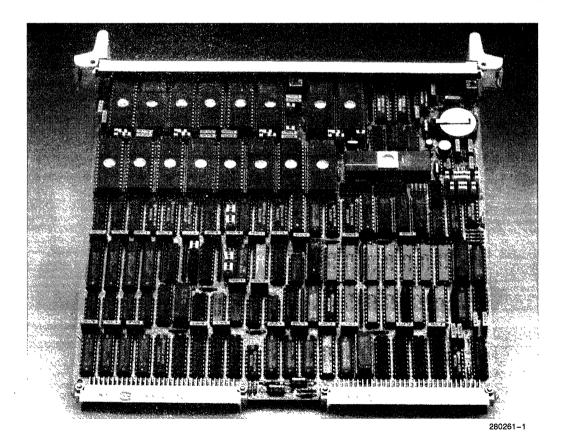

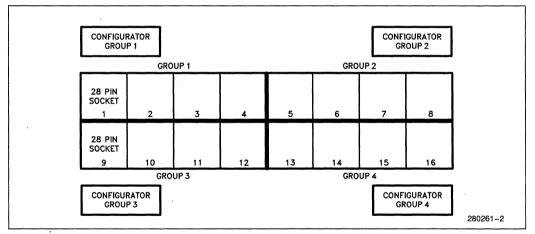

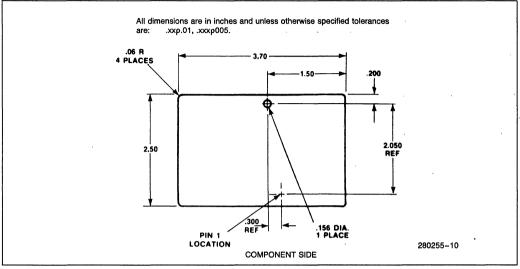

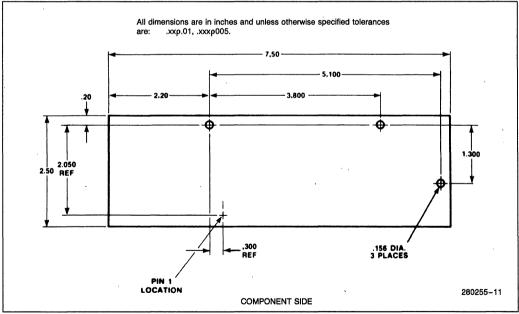

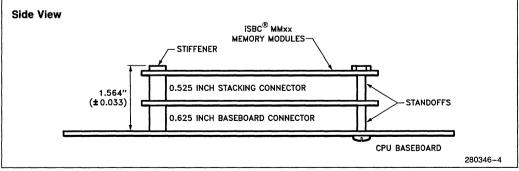

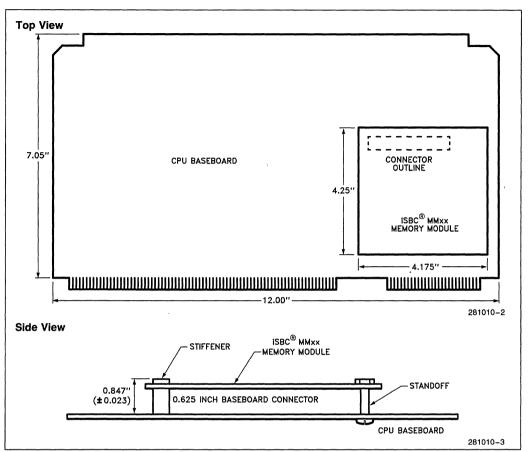

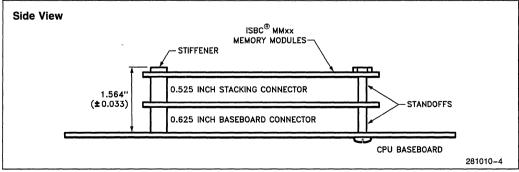

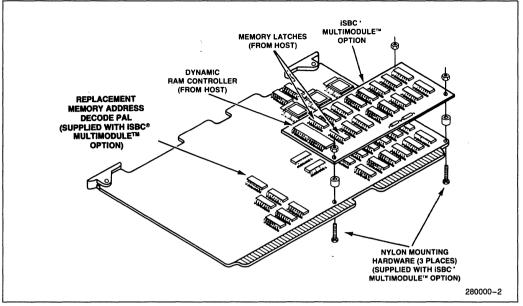

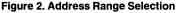

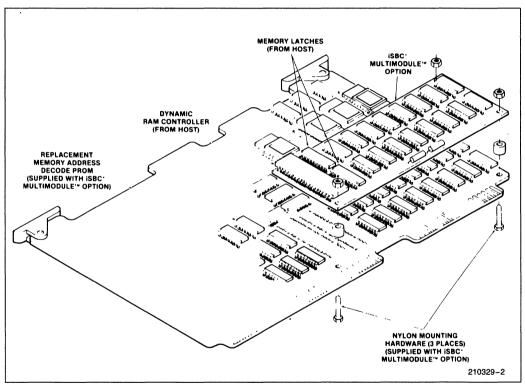

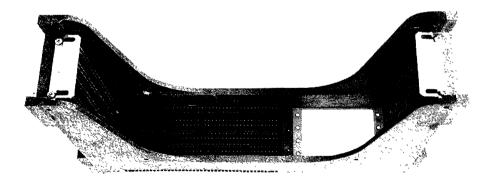

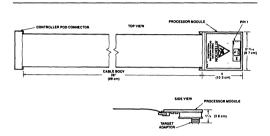

The iSBC 386/116 and 120 boards include 1, 2, 4 or 8M bytes of DRAM depending upon the version. This memory can be extended to a maximum of 16M bytes through the addition of an Intel iSBC MM01, MM02, MM04 or MM08: 1, 2, 4 or 8M byte memory expansion module. The DRAM refresh control, dualport control and parity generation/checking logic is physically located on the baseboard, while the actual DRAM components are located on low-profile surface mount expansion boards. Each iSBC 386/116 or 120 board is shipped with one expansion memory module installed and may be expanded to contain two total memory expansion modules. The memory expansion module mechanics are shown in Figure 2.\*

#### \*NOTE:

Only one single-sided memory module (MM01 or MM04) installed onto the iSBC 386/116 or 120 board will fit within one MULTIBUS II slot. A double-sided module (MM02 or MM08) or any stack of two modules will require two MULTIBUS II slots.

Parity error detection is provided on a byte-by-byte basis. The parity logic normally generates and checks for odd parity with detected errors signaled via an on-board LED and a CPU interrupt. Even parity can be forced to generate a parity error for diagnostic purposes. The DRAM is accessible from both the on-board local bus and the iPSB bus. The amount of memory accessible from the iPSB bus and the iPSB address aliasing values are dynamically configurable via interconnect space registers.

#### CACHE MEMORY

The cache memory on the iSBC 386/116 and 120 boards allow zero wait-state accesses to memory when the data requested is resident in the cache memory. The static RAM cache has 16,384 32-bit data entries with 8-bit "tag" fields. Each 32-bit DRAM memory location maps to one (and only one) cache data entry. The "tag" fields are used to determine which 32-bits of DRAM memory currently resides in each cache data entry. The combination of a direct mapped cache data array and a tag field ensures data integrity and accurate, high performance identification of cache "hits".

Data integrity is maintained for cache "misses" (DRAM memory READs not in the cache) and DRAM memory WRITEs through a simple, yet effective replacement algorithm. 386 CPU generated cache READ "misses" cause the data field of the cache entry corresponding to the addressed memory to be filled from the DRAM array and the tag field to be updated. All iPSB or ADMA READs are treated as cache "misses", except that the cache is not updated. All WRITE "hits", local and iPSB generated, cause the cache data field to be updated. WRITE "misses" do not update the cache. The cache memory size and replacement algorithm are designed to optimize both the probability of cache "hits" and local bus utilization.

#### **EPROM MEMORY**

Two 32-pin JEDEC EPROM sites capable of supporting up to 512K bytes of EPROM (using 27020 EPROMs) are supplied on the iSBC 386/116 and 120 boards. These sites, as shipped, contain built-inself-test power-up diagnostics residing in two preprogrammed 27512 EPROMs. These EPROMs may be replaced by the user. Jumper configurations allow the use of 2764, 27128, 27256, 27512, 27010, and 27020 EPROMs.

#### 8254 PROGRAMMABLE TIMERS

The iSBC 386/116 and 120 boards contain an Intel 8254 component which provides three independent programmable 16-bit interval timers. These may be used for real-time interrupts or time keeping operations. Outputs from these timers are routed to one of the two 8259A interrupt controllers to provide software programmable real-time interrupts.

# isBC® 386/116 AND 386/120 MULTIBUS® II SINGLE BOARD COMPUTERS

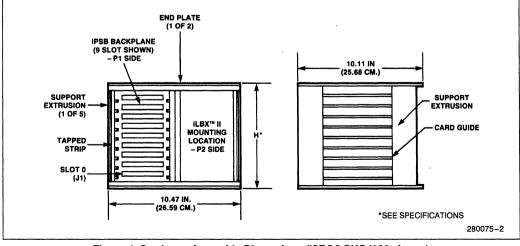

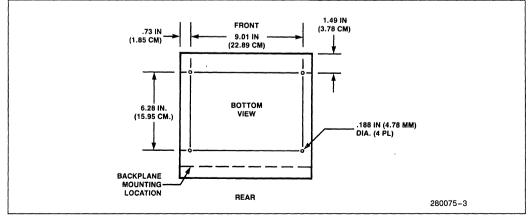

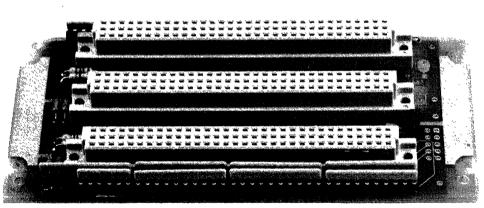

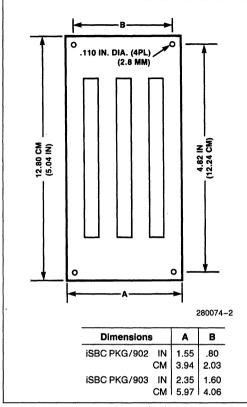

Figure 2. iSBC® 386/116 and 120 Boards Memory Module Mechanics

#### INTERRUPT CONTROL

Two Intel 8259A programmable interrupt controllers on the iSBC 386/116 and 120 boards are used in a master-slave configuration for prioritizing up to 15 separate on-board interrupt sources. The devices and functions are listed in Table 2.

The MULTIBUS II iPSB bus utilizes virtual interrupts (called unsolicited messages) for board-to-board signaling. The bus interface component (MPC) queues-up incoming virtual interrupts from the iPSB bus and generates a single message interrupt (MINT) signal. This signal is connected into one of the 8259A interrupt controllers for prioritization and interruption of the host 386 CPU. Error conditions occurring on the iPSB bus will cause the MPC to generate an error interrupt (EINT) signal. This signal is connected to another 8259A interrupt input.

Other interrupt sources come from the 82258 DMA controller, the 8254 timers, the iSBX interface, the 8751 serial port, and the DRAM parity checker.

#### SERIAL I/O INTERFACE

One RS 232C compatible serial I/O port is provided via the Intel 8751 microcontroller. This port is configured as a data terminal equipment (DTE) asynchronous serial port. Mechanically, the serial port exits through the iSBC 386/116 or 120 board's front panel via a 9-pin D-shell connector.

#### **IPSB BUS INTERFACE**

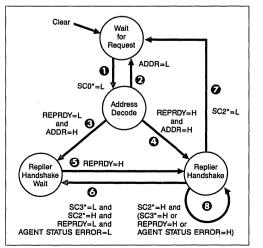

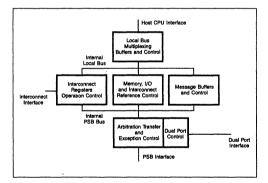

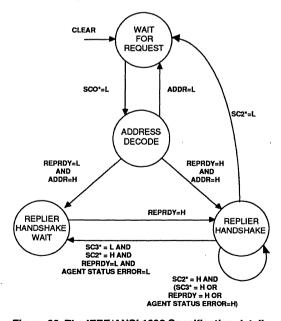

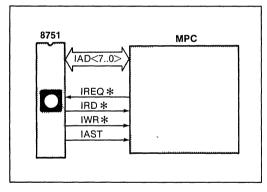

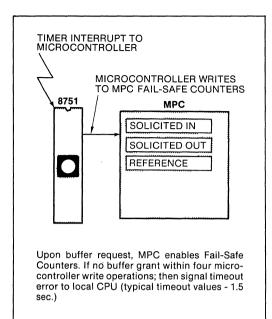

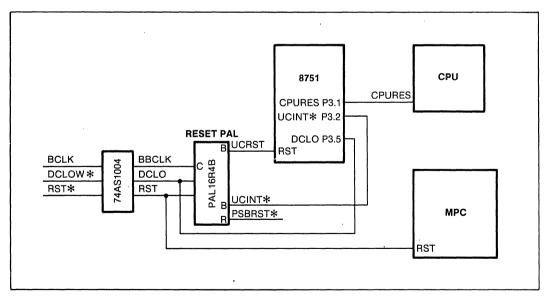

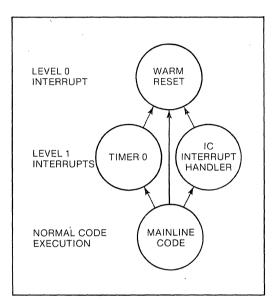

The MULTIBUS II parallel system bus interface is implemented by Intel's MPC (message passing coprocessor) and a pre-programmed 8751 microcontroller. This interface supports full arbitration, transfer and error checking features as defined in the iPSB specifications. In addition, the interface supports advanced features of the iPSB bus including hardware message passing and autoconfiguration through geographic addressing.

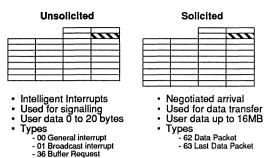

The MPC component contains nine 32-byte buffers which are used to decouple iPSB bus traffic from iSBC 386/116 or 120 local bus traffic through the concept known as message passing. These nine buffers are utilized as follows: four buffers queue-up incoming unsolicited messages, one buffer stores an out-going unsolicited message, two buffers are used to double-buffer an out-going solicited message, and two buffers are used to double-buffer an incoming solicited message. These buffers are capable of transferring data packets over the iPSB bus at its maximum transfer rate. Unsolicited messages include address and type fields and 28 bytes of userdefined data, and are transferred over the iPSB bus in 900 ns. Solicited messages are automatically divided into small packets, with each packet containing address and type fields and 32 bytes of user-defined data. Each solicited message packet is transferred over the iPSB bus in 1000 ns.

| Device              | Function                                                                                                                     | Number of<br>Interrupts |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| MPC-MINT            | Signals arrival of virtual interrupt over<br>iPSB bus, solicited input complete,<br>transmit FIFO not full or transmit error | 1                       |

| MPC-EINT            | Signals error condition on the iPSB bus                                                                                      | 1 .                     |

| 82258 DMA           | Transfer complete                                                                                                            | 1                       |

| 8254 Timers         | Timers 0, 1, 2 outputs, function<br>determined by timer mode                                                                 | 3                       |

| 8751 Serial Port    | Serial diagnostic port requests                                                                                              | 1                       |