# intel

## Microcontroller Handbook

#### **LITERATURE**

In addition to the product line Handbooks listed below, the INTEL PRODUCT GUIDE (no charge, Order No. 210846) provides an overview of Intel's complete product line and customer services.

Consult the INTEL LITERATURE GUIDE for a complete listing of Intel literature. TO ORDER literature in the United States, write or call the Intel Literature Department, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only). TO ORDER literature from international locations, contact the nearest Intel sales office or distributor (see listings in the back of most any Intel literature).

| 1984 HANDBOOKS                                                                                                                                                                                                                                                                                            | U.S. PRICE                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Memory Components Handbook (Order No. 210830) Contains all application notes, article reprints, data sheets, and other design info on RAMs, DRAMs, EPROMs, E <sup>2</sup> PROMs, Bubble Memories.                                                                                                         | <b>\$15.00</b> ormation   |

| Telecommunication Products Handbook (Order No. 230730) Contains all application notes, article reprints, and data sheets for telecommunication.                                                                                                                                                           | 7.50 unication            |

| Microcontroller Handbook (Order No. 210918) Contains all application notes, article reprints, data sheets, and design information MCS-48, MCS-51 and MCS-96 families.                                                                                                                                     | 15.00 on for the          |

| Microsystem Components Handbook (Order No. 230843) Contains application notes, article reprints, data sheets, technical papers for m cessors and peripherals. (2 Volumes) (Individual User Manuals are also availab 8085, 8086, 8088, 186, 286, etc. Consult the Literature Guide for prices ar numbers.) | ole on the                |

| Military Handbook (Order No. 210461) Contains complete data sheets for all military products. Information on Leadl Carriers and on Quality Assurance is also included.                                                                                                                                    | 10.00 less Chip           |

| Development Systems Handbook (Order No. 210940) Contains data sheets on development systems and software, support options, arkits.                                                                                                                                                                        | <b>10.00</b><br>nd design |

| OEM Systems Handbook (Order No. 210941) Contains all data sheets, application notes, and article reprints for OEM box systems.                                                                                                                                                                            | 15.00<br>ards and         |

| Software Handbook (Order No. 230786)  Contains all data sheets, applications notes, and article reprints available from Intel, as well as 3rd Party software.                                                                                                                                             | 10.00 directly            |

<sup>\*</sup> Prices are for the U.S. only.

# APPLICATION FOR FREE SUBSCRIPTION TO SOLUTIONS MAGAZINE

Intel SC6-714 3065 Bowers Avenue

Solutions is a bimonthly customer magazine covering all of Intel's new product announcements and offering useful application information. If you wish to receive SOLUTIONS regularly, please fill in the requested information and mail it back to:

See reverse side for European return addresses.

|    | San                                                                    | ta C | Clara, CA 95051                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                                     |                                                                         |

|----|------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------|-------------------------------------|-------------------------------------------------------------------------|

| TI | here                                                                   | is r | no charge—just your continued                                                                                                                                                                                                                                                                                                                                                       | inte                 | res                | t in I                              | ntel products.                                                          |

| 1. | Your<br>AA<br>BB<br>AC<br>AD<br>AE<br>AF                               |      | Hardware Design Engineer Software Design Engineer Technician A                                                                                                                                                                                                                                                                                                                      |                      |                    | Mark<br>Purc<br>Educ<br>Com<br>Data | reting or Sales hasing/Buyer eator puter Hobbyist Processing r          |

| 2. | Your<br>AN<br>AP<br>AQ<br>AR<br>AS<br>AT<br>AU<br>AV<br>AW<br>AX<br>AZ |      | Manufacturer of computers or peripher Manufacturer of computers or peripher Manufacturer of control equipment Manufacturer of test/measurement equipment Manufacturer of communication/telect Manufacturer of office/business equipment System integration User of computer equipment Research lab/consultant Software house Government/military agency Sales office or distributor | ral e<br>uipm<br>omm | qui<br>ent<br>unic | oment                               | struments                                                               |

| 3. | Your<br>BB                                                             |      | pany's/division's products fall primaril<br>Industrial BC □ Military BD                                                                                                                                                                                                                                                                                                             |                      |                    | nsum                                | ner                                                                     |

| 4. | Do vo<br>BE                                                            |      | wn or use an Intel microcomputer deve<br>Yes BF □ No                                                                                                                                                                                                                                                                                                                                | elop                 | men                | t syst                              | tem or design aid?                                                      |

| 5. |                                                                        | in-h | ucts that are purchased to your specific<br>louse?<br>Incorporated into products to be sold<br>Used in-house                                                                                                                                                                                                                                                                        | atio                 | ns ii<br>BJ        |                                     | orated into products to be sold or are they  Both                       |

| 6. | Who<br>BK                                                              | -    | <b>/ou usually buy from?</b><br>Distributor <b>BL</b> □ Manufacture                                                                                                                                                                                                                                                                                                                 | r                    |                    |                                     |                                                                         |

| 7. | I am<br>70<br>71<br>72                                                 |      | rested in the following product areas: Microcomputer Components Microcomputer Boards and Systems Memory Components                                                                                                                                                                                                                                                                  |                      | 73<br>74<br>75     |                                     | Memory Boards and Systems Military Products Telecommunications Products |

|    |                                                                        |      |                                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                                     |                                                                         |

|    |                                                                        |      |                                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                                     | ,                                                                       |

|    | -                                                                      | -    |                                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                                     |                                                                         |

| Pł | none                                                                   |      |                                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                                     | · · · · · · · · · · · · · · · · · · ·                                   |

|    |                                                                        |      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                            |                      |                    |                                     |                                                                         |

|    | -                                                                      |      | State                                                                                                                                                                                                                                                                                                                                                                               | Zip                  |                    |                                     | Country                                                                 |

| CO | RP 16                                                                  | 64C  |                                                                                                                                                                                                                                                                                                                                                                                     |                      |                    |                                     |                                                                         |

For a free subscription to the European edition of *SOLUTIONS* please mail this card to one of the regional offices listed below:

#### Intel Corporation (UK) Ltd

Piper's Way Swindon, SN3 1RJ Wiltshire, England

#### Intel Corporation S.A.R.L.

5 Place de la Balance Silic 223 94528 Rungis Cedex France

#### Intel Corporation Italia Spa Milanofiori, Palazzo E 20094 Assago (Milano)

Italy

#### Intel Semiconductor GmbH

Seidlstrasse 27 D-8000 Munchen 2 West Germany

#### Intel Sweden AB

Box 20092 Archimedesvagen 5 S-16120 Bromma Sweden

## **MICROCONTROLLER HANDBOOK**

1984

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i,  $\hat{\uparrow}$ , ICE, iCS, iDBP, iDIS, I $^2$ ICE, iLBX, i<sub>m</sub>, iMMX, Insite, Intel, int<sub>e</sub>l, int<sub>e</sub>lBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iSBC, iSBX, iSDM, iSXM, Library Manager, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, Plug-A-Bubble, PROMPT, Promware, QUEST, QUEX, Ripplemode, RMX/80, RUPI, Seamless; SOLO, SYSTEM 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

#### **Table of Contents**

| MCS®-96 FAMILY                          |       |

|-----------------------------------------|-------|

| CHAPTER 1                               |       |

| Introduction to MCS®-96                 | 1-1   |

| CHAPTER 2                               |       |

| Architectural Overview                  | 2-1   |

| CHAPTER 3                               |       |

| MCS®-96 Software Design Information     | 3-1   |

| CHAPTER 4                               |       |

| Hardware Design Information             | 4-1   |

| CHAPTER 5                               |       |

| MCS®-96 Data Sheet                      | 5-1   |

| MCS®-51 FAMILY                          |       |

| CHAPTER 6                               |       |

| MCS®-51 Architecture                    | 6-1   |

| CHAPTER 7                               | 0-1   |

| NOOR 54 Management Operation Address in |       |

| Modes and Boolean Processor             | 7 1   |

| CHAPTER 8                               | /=1   |

| MCS®-51 Instruction Set                 | 0 1   |

| CHAPTER 9                               | 0-1   |

| MCS®-51 Application Examples            | 0.1   |

| CHAPTER 10                              | 9-1   |

| Article Reprints                        | 10.1  |

| CHAPTER 11                              | 10-1  |

| MCS®-51 Data Sheets                     |       |

| 8031AH/8051AH                           |       |

|                                         |       |

| 8032AH/8052AH                           |       |

| 8751H                                   | 11-25 |

| 01100                                   |       |

| CMOS                                    |       |

| CHAPTER 12                              |       |

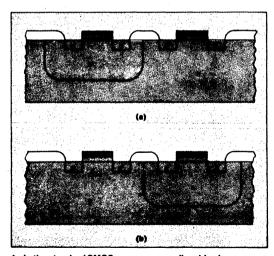

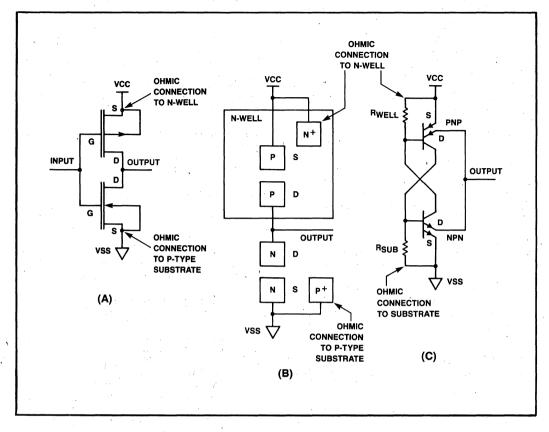

| Design Considerations When Using CHMOS  |       |

| Inside CMOS Technology                  | 12-6  |

| MOOR 40 FAMILY                          |       |

| MCS®-48 FAMILY                          |       |

| CHAPTER 13                              |       |

| The Single Component MCS®-48 System     | 13-1  |

| CHAPTER 14                              |       |

| Expanded MCS®-48 System                 | 14-1  |

| CHAPTER 15                              |       |

| MCS®-48 Instruction Set                 | 15-1  |

| CHAPTER 16                              |       |

| MCS®-48 Data Sheets                     |       |

| MCS®-48 Data Sheets 8243                | 16-1  |

| 8048AH/8748H/8035AHL/8049AH             |       |

| 8749H/8039AHL/8050AH/8040AHL            | 16-7  |

| MCS®-48 Express                         | 16-20 |

| 90030 7/90040-7                         | 16 0/ |

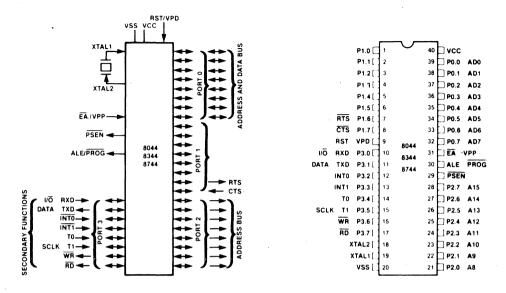

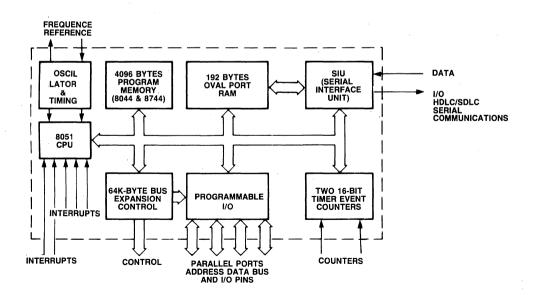

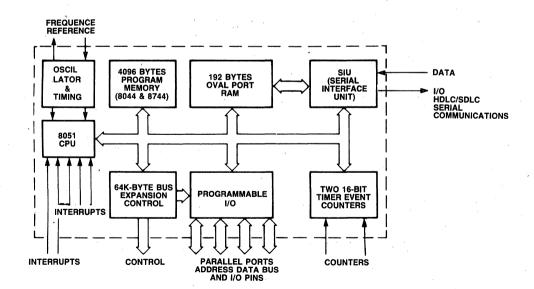

| WITH ON-CHIP COMMUNICATION CONTROLLER CHAPTER 17 |           |

|--------------------------------------------------|-----------|

| The RUPI™-44 Family                              | <br>17-1  |

| CHAPTER 18 8044 Architecture                     |           |

|                                                  |           |

| CHAPTER 19<br>8044 Serial Interface              | 19-1      |

| CHAPTER 20                                       |           |

| 8044 Applications Examples                       | <br>20-1  |

| CHAPTER 21                                       |           |

| RUPI™ Data Sheets<br>8044AH/8344AH8744           |           |

| 8044AH/8344AH                                    | <br>21-1  |

| 8744                                             | <br>21-20 |

| CHAPTER 22 RUPI™ Article Reprint                 |           |

| PACKAGING INFORMATION                            |           |

| CHADTED 23                                       | 23-1      |

## Introduction to MCS®-96

## CHAPTER 1 INTRODUCTION TO MCS®-96

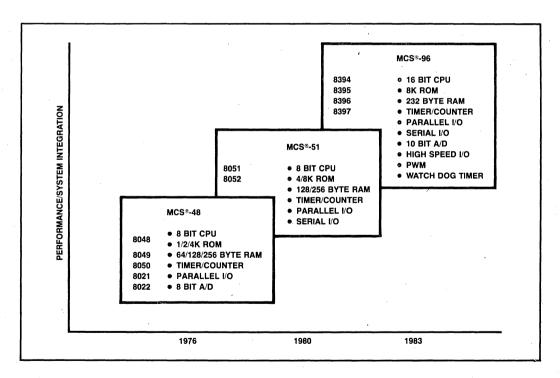

### 1.0 CONTINUING MICROCONTROLLER EVOLUTION

Beginning with the introduction of the world standard 8048 (MCS®-48) Microcontroller in 1976, Intel has continued to drive the evolution of single chip microcontrollers. In 1980, Intel introduced the 8051 (MCS-51) offering performance levels significantly higher than the 8048. With the advent of the 8051, the microcontroller applications base took a marked vertical leap. These versatile chips are used in applications from keyboards and terminals to controlling automobile engines. The 8051 quickly gained the position of the second generation world standard microcontroller.

Now that the semiconductor process technologies are

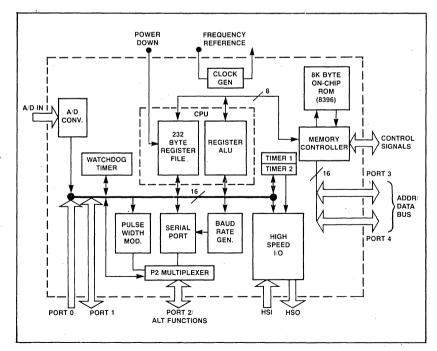

being pushed to new limits, it has become possible to integrate more than 100,000 transistors onto a single silicon chip. Microcontroller designers at Intel have taken today's process technology achievements and forged a new generation of single chip microcontrollers called the MCS-96. The 8096 (generic part number for MCS-96) offers the highest level of system integration ever achieved on a single chip microcontroller. It uses over 120,000 transistors to implement a high performance 16-bit CPU, 8K bytes of program memory, 232 bytes of data memory and both analog and digital types of I/O features. Figure 1-1 shows the evolution of single chip microcontroller at Intel.

Figure 1-1. Evolution of Microcontrollers at Intel

#### 1.1 INTRODUCTION TO THE MCS®-96

The 8096 consists of a 16-bit powerful CPU tightly coupled with program and data memory along with several I/O features all integrated onto a single piece of silicon. The CPU supports bit, byte, and word operations. 32-bit double words are also supported for a subset of the instruction set. With a 12 MHz input frequency, the 8096 can perform a 16-bit addition in 1.0  $\mu$ s and 16  $\times$  16 multiply or 32/16 divide in 6.5  $\mu$ s.

Four high-speed trigger inputs are provided to record the times at which external events occur with a resolution of 2  $\mu$ s (at 12 MHz crystal frequency). Up to six high-speed pulse generator outputs are provided to trigger external events at preset times. The high speed output unit can simultaneously perform timer functions, up to four such

16-bit software timers can be in operation at once in addition to the two 16-bit hardware timers.

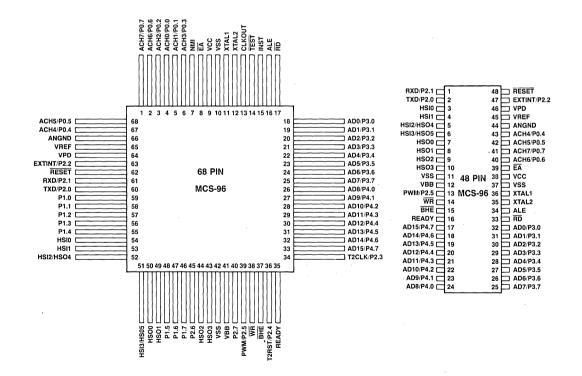

An optional on-chip A/D converter converts up to four (in the 48-pin version) or 8 (in the 68-pin version) analog input channels into 10-bit digital values. Also provided on-chip, is a serial port, a watchdog timer, and a pulse-width modulated output signal. Table 1.1 shows the features and benefits summary for the MCS-96.

The 8096 with its 16-bit CPU and all the I/O features and interface resources on a single piece of silicon represents the highest level of system integration in the world of microcontrollers. It will open up new applications which had to use multiple chip solutions in the past.

Table 1-1 MCS®-96 Features and Benefits Summary

| FEATURES                                                           | BENEFITS                                                                                                                         |  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| 16-Bit CPU                                                         | Efficient machine with higher throughput.                                                                                        |  |

| 8K Bytes ROM                                                       | Large program space for more complex, larger programs.                                                                           |  |

| 232 Bytes RAM                                                      | Large on-board register file.                                                                                                    |  |

| Hardware MUL/DIV                                                   | Provides good math capability 16 by 16 multiply or 32 by 16 divide in 6.5 µs @ 12 MHz.                                           |  |

| 6 Addressing Modes                                                 | Provides greater flexibility of programming and data manipulation.                                                               |  |

| High Speed I/O Unit 4 dedicated I/O lines 4 programmable I/O lines | Can measure and generate pulses with high resolution (2 $\mu$ s @ 12 MHz).                                                       |  |

| 10-Bit A/D Converter                                               | Reads the external analog inputs.                                                                                                |  |

| Full Duplex Serial Port                                            | Provides asynchronous serial link to other processors or systems.                                                                |  |

| Up to 40 I/O Ports                                                 | Provides TTL compatible digital data I/O including system expansion with standard 8 or 16-bit peripherals.                       |  |

| Programmable 8 Source Priority<br>Interrupt System                 | Respond to asynchronous events.                                                                                                  |  |

| Pulse Width Modulated Output                                       | Provides a programmable pulse train with variable duty cycle. Also used to generate analog output.                               |  |

| Watchdog Timer                                                     | Provides ability to recover from software malfunction or hardware upset.                                                         |  |

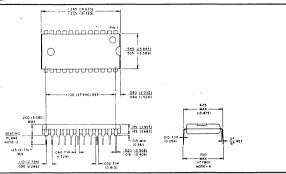

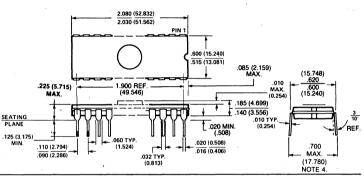

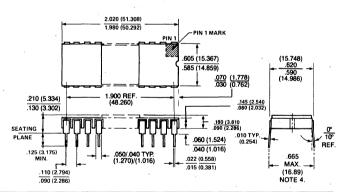

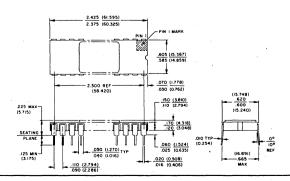

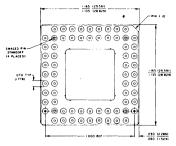

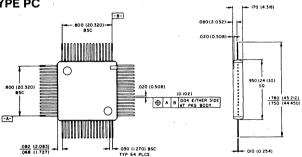

| 48 Pin (DIP) & 68 Pin (Flatpack, Pin<br>Grid Array) Versions       | Offers a variety of package types to choose from to better fit a specific application need for number of I/O's and package size. |  |

#### 1.2. MCS®-96 APPLICATIONS

The MCS-96 products are stand-alone high performance single chip microcontrollers designed for use in sophisticated real-time demanding applications such as industrial control, instrumentation and intelligent computer peripherals. The wide base of applications cut across all industry segments (see table 1.2). With the 16-bit CPU horse-power, high-speed math processing and high-speed I/O, the 8096 is ideal for complex motor control and axis control systems. Examples include three phase, large horse-power AC motors and robotics.

With its 10-bit A/D converter option, the device finds usage in data acquisition systems and closed-loop analog controllers. It permits considerable system integration by

#### Table 1-2 MCS®-96 Broad Base of Applications

#### INDUSTRIAL

Motor Control

Robotics

Discrete and Continuous Process Control

Numerical Control

Intelligent Transducers

#### INSTRUMENTATION

Medical Instrumentation

Liquid and Gas Chromatographs

Oscillioscopes

#### CONSUMER

Video Recorder

Laser Disk Drive

High-end Video Games

#### **GUIDANCE & CONTROL**

Missile Control

Torpedo Guidance Control

Intelligent Ammunition

Aerospace Guidance Systems

#### DATA PROCESSING

**Plotters**

Color and B&W Copiers

Winchester Disk Drive

Tape Drives

Impact and Non-Impact Printers

#### **TELECOMMUNICATIONS**

Modems

Intelligent Line Card Control

#### AUTOMOTIVE .

Ignition Control

Transmission Control

Anti Skid Braking

Emission Control

combining analog and digital I/O processing in the single chip.

This chip is ideally suited in the area of instrumentation products such as gas chromatographs, which combine analog processing with high speed number crunching. The same features make it a desirable component for aerospace applications like missile guidance and control.

### 1.3. MCS®-96 FAMILY DEVELOPMENT SUPPORT TOOLS

The product family is supported by a range of Intel software and hardware development tools. These tools shorten the product development cycle, thus bringing the product to the market sooner.

### 1.3.1. MCS®-96 Software Development Package

The 8096 software development package provides development system support specifically designed for the MCS-96 family of single chip microcontrollers. The package consists of a symbolic macro assembler ASM-96, Linker/Relocator RL-96 and the librarian LIB-96. Among the high level languages, PLM-96 is offered along with a floating point math package. Additional high level languages are being developed for the MCS-96 product family.

#### 1.3.2. ASM-96 MACRO Assembler

The 8096 macro assembler translates the symbolic assembly language instructions into the machine executable object code. ASM-96 enables the programmer to write the program in a modular fashion. The modular programs divide a rather complex program into smaller functional units, that are easier to code, to debug, and to change. The separate modules can then be linked and located into one program module using the RL-96 utility. This utility combines the selected input object modules into a single output object module. It also allocates memory to input segments and binds the relocatable addresses to absolute addresses. It then produces a print file that consists of a link summary, a symbol table listing and an intermediate cross-reference listing. LIB-96, another utility helps to create, modify, and examine library files. The ASM-96 runs on Intellec Series III or IV.

#### 1.3.3. PL/M-96

The PL/M-96 compiler translates the PL/M-96 language into 8096 relocatable object modules. This allows improved programmer productivity and application reliability. This high level language has been efficiently designed to map into the machine architecture, so as not to trade off higher programmer productivity with inefficient code. Since the language and the compiler are optimized for the 8096 and its application environment, developing software with PL/M-96 is a 'low-risk' project.

### 1.3.4. Hardware Development Support: iSBE-96

The iSBE-96 is a hardware execution and debug tool for the MCS-96 products. It consists of a monitor/debugger resident in an 8096 system. This development system interfaces with the user's 8096 system via two ribbon cables, one for the 8096 I/O ports, and the other for the memory bus. The iSBE-96 is controlled by an Intellec Series III or other computer system over a serial link. Power for the iSBE-96 can be supplied by plugging it into the MULTIBUS® card slot, or by an external power supply. The iSBE-96 is contained on one standard MULTIBUS board.

The iSBE-96 provides the most often used features for real-time hardware emulation. The user can display and modify memory, set up break points, execute with or without breakpoints and change the memory map. In addition, the user can single step through the system program.

#### 1.3.5. MCS®-96 Workshop

The workshop provides the design engineer or system designer hands-on experience with the MCS-96 family of products. The course includes an explanation of the Intel 8096 architecture, system timing, input/output design. The lab sessions allow the attendees to gain in-depth knowledge of the MCS-96 product family and support tools

#### 1.3.6. Insite™ Library

The Intel Insite Library contains several application programs. A very useful program contained in the Insite is SIM-96, the software simulator for 8096. It allows software simulations of user's system. The simulator provides the ability to set breakpoints, examine and modify memory, disassemble the object code and single step through the code.

#### 1.4. MCS®-96 FAMILY OF PRODUCTS

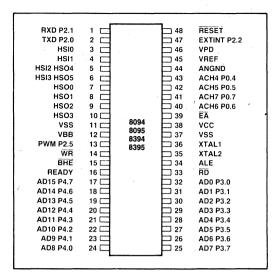

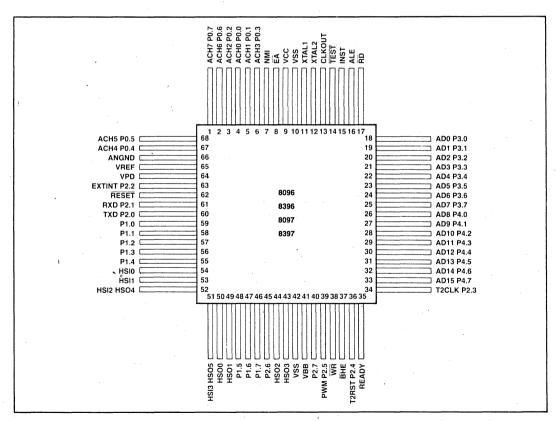

Although 8096 is the generic part number often used for the MCS-96 products throughout this manual, the product family consists of eight configurations with eight part numbers including the 8096. This wide variety of products is offered to best meet user's application requirements in terms of number of I/O's and package size. The options include on-board 8K bytes of mask programmed memory, 10-bit A/D converter, and 48 or 68 pin package type.

Table 1-3 summarizes all the current products in the MCS®-96 product family.

Table 1-3 MCS®-96 Family of Products

| OP1            | 68 PIN  | 48 PIN |      |

|----------------|---------|--------|------|

| DIGITAL        | ROMLESS | 8096   | 8094 |

| I/O            | ROM     | 8396   | 8394 |

| ANALOG<br>AND  | ROMLESS | 8097   | 8095 |

| DIGITAL<br>I/O | ROM     | 8397   | 8395 |

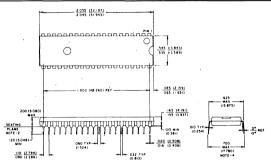

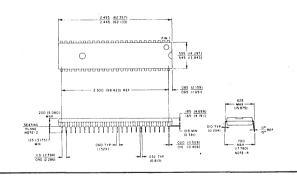

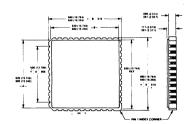

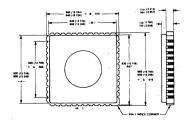

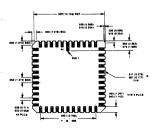

The 48 pin version is available in a DIP (dual inline) package.

The 68 pin version comes in two packages, the Plastic Flatpack and the Pin Grid Array.

# **Architectural Overview**

## CHAPTER 2 ARCHITECTURAL OVERVIEW

#### 2.0. INTRODUCTION

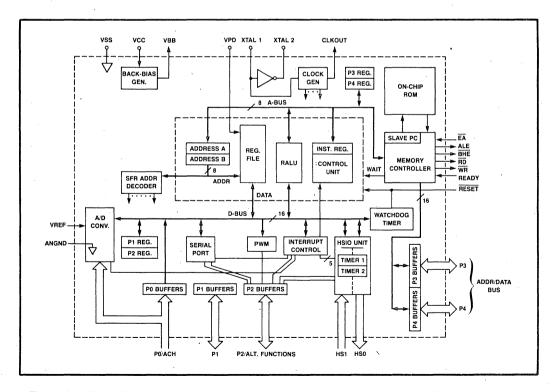

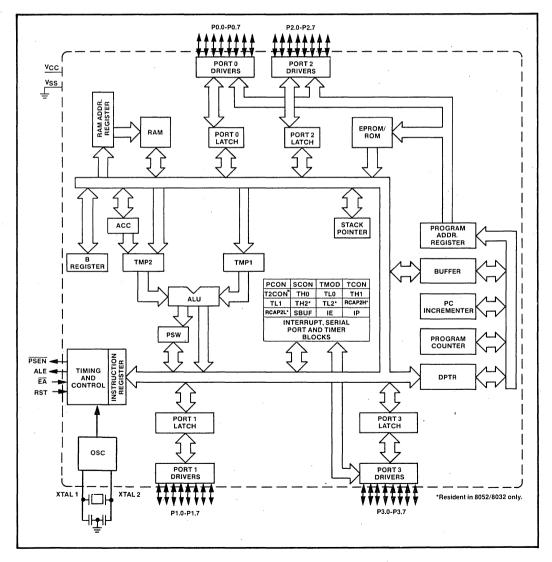

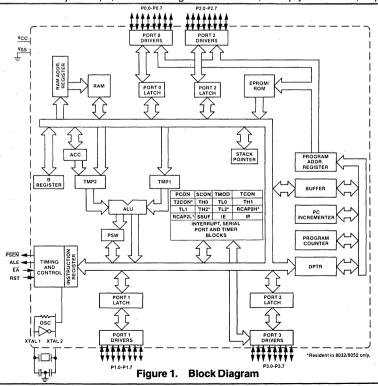

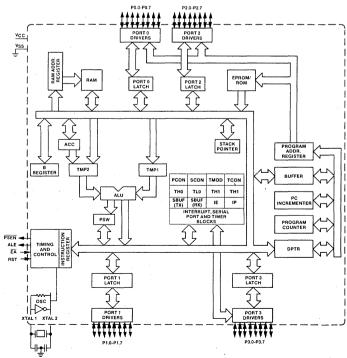

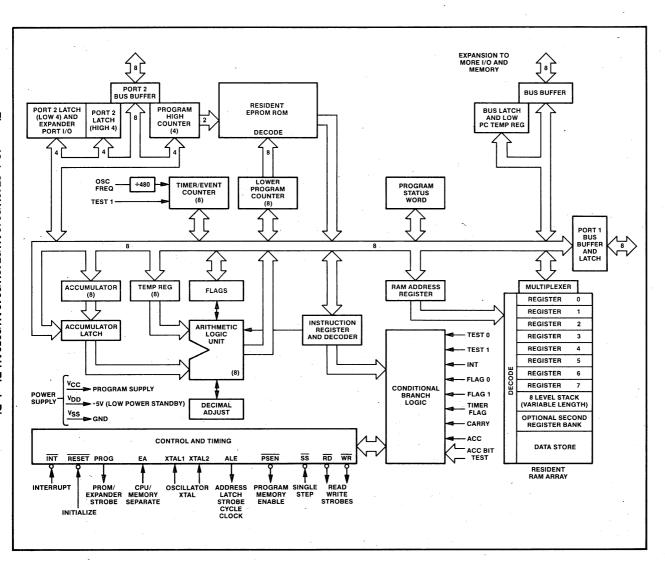

The 8096 can be separated into several sections for the purpose of describing its operation. There is a CPU, a programmable High Speed I/O Unit, an analog to digital converter, a serial port, and a Pulse Width Modulated (PWM) output for digital to analog conversion. In addition to these functional units, there are some sections which support overall operation of the chip such as the clock generator and the back-bias generator. The CPU and the programmable I/O make the 8096 very different from any other microcontroller, let us first examine the CPU.

#### 2.1. CPU OPERATION

The major components of the CPU on the 8096 are the Register File and the RALU. Communication with the outside world is done through either the Special Function Registers (SFRs) or the Memory Controller. The RALU (Register/Arithmetic Logic Unit) does not use an accumulator, it operates directly on the 256-byte register space made up of the Register File and the SFRs. Efficient I/O

operations are possible by directly controlling the I/O through the SFRs. The main benefits of this structure are the ability to quickly change context, the absence of accumulator bottleneck, and fast throughput and I/O times.

#### 2.1.1. CPU Buses

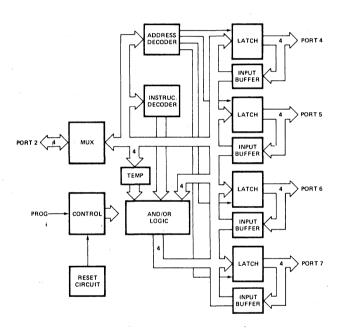

A "Control Unit" and two buses connect the Register File and RALU. Figure 2-1 shows the CPU with its major bus connections. The two buses are the "A-Bus" which is 8-bits wide, and the "D-Bus" which is 16-bits wide. The D-Bus transfers data only between the RALU and the Register File or Special Function Registers (SFRs). The A-Bus is used as the address bus for the above transfers or as a multiplexed address/data bus connecting to the "Memory Controller". Any accesses of either the internal ROM or external memory are done through the Memory Controller.

Within the memory controller is a slave program counter (Slave PC) which keeps track of the PC in the CPU. By having most program fetches from memory referenced to

Figure 2-1. Block Diagram (For simplicity, lines connecting port registers to port buffers are not shown.)

the slave PC, the processor saves time as addresses seldom have to be sent to the memory controller. If the address jumps sequence then the slave PC is loaded with a new value and processing continues. Data fetches from memory are also done through the memory controller, but the slave PC is bypassed for this operation.

#### 2.1.2. CPU Register File

The Register File contains 232 bytes of RAM which can be accessed as bytes, words, or double-words. Since each of these locations can be used by the RALU, there are essentially 232 "accumulators". The first word in the Register File is reserved for use as the stack pointer so it can not be used for data when stack manipulations are taking place. Addresses for accessing the Register File and SFRs are temporarily stored in two 8-bit address registers by the CPU hardware.

#### 2.1.3. RALU Control

Instructions to the RALU are taken from the A-Bus and stored temporarily in the instruction register. The Control

Unit decodes the instructions and generates the correct sequence of signals to have the RALU perform the desired function. Figure 2-1 shows the instruction register and the control unit.

#### 2.1.4. RALU

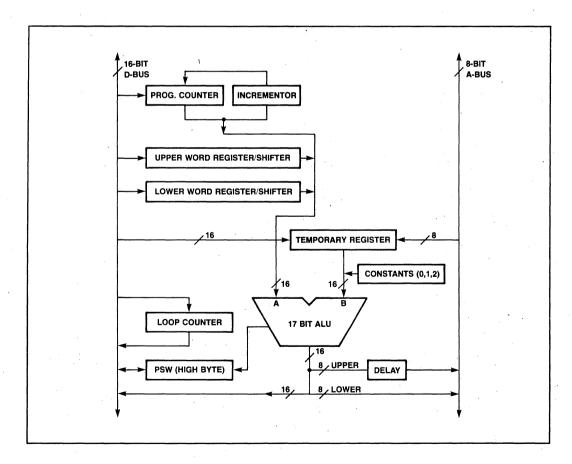

Most calculations performed by the 8096 take place in the RALU. The RALU, shown in Figure 2-2, contains a 17-bit ALU, the Program Status Word (PSW), the Program Counter (PC), a loop counter, and three temporary registers. All of the registers are 16-bits or 17-bits (16 + sign extension) wide. Some of the registers have the ability to perform simple operations to off-load the ALU.

A separate incrementer is used for the PC; however, jumps must be handled through the ALU. Two of the temporary registers have their own shift logic. These registers are used for the operations which require logical shifts, including Normalize, Multiply, and Divide. The "Lower Word" register is used only when double-word quantities are being shifted, the "Upper Word" register is used

Figure 2-2. RALU Block Diagram

#### ARCHITECTURAL OVERVIEW

whenever a shift is performed or as a temporary register for many instructions. Repetitive shifts are counted by the 5-bit "Loop Counter".

A temporary register is used to store the second operand of two operand instructions. This includes the multiplier during multiplications and the divisor during divisions. To perform subtractions, the output of this register can be complemented before being placed into the "B" input of the ALU.

The DELAY shown in Figure 2-2 is used to convert the 16-bit bus into an 8-bit bus. This is required as all addresses and instructions are carried on the 8-bit A bus. Several constants, such as 0, 1 and 2 are stored in the RALU for use in speeding up certain calculations. These come in handy when the RALU needs to make a 2's complement number or perform an increment or decrement instruction.

#### 2.2. BASIC TIMING

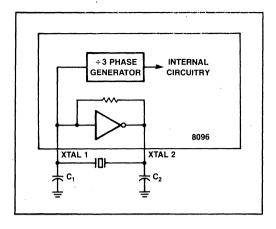

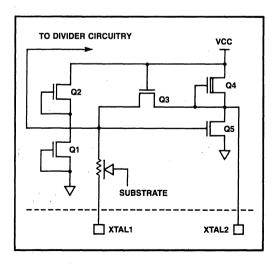

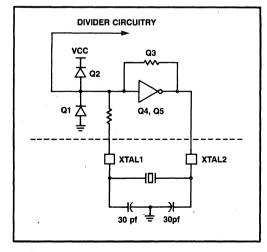

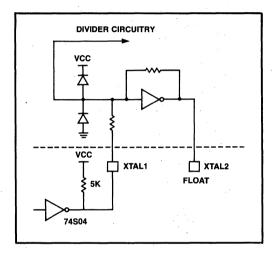

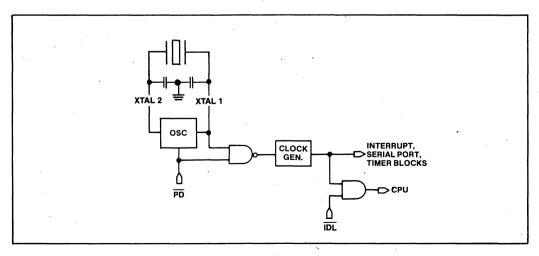

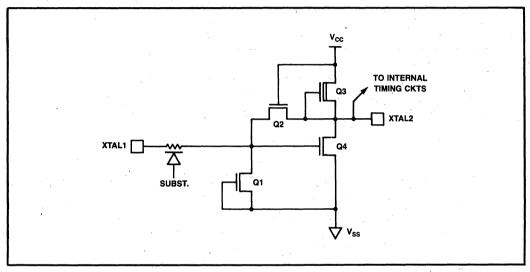

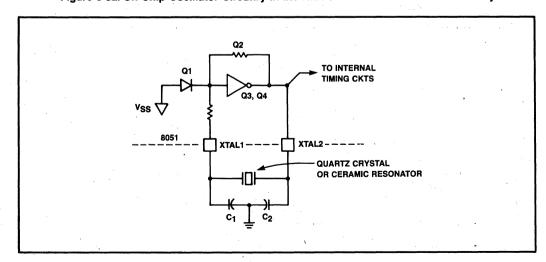

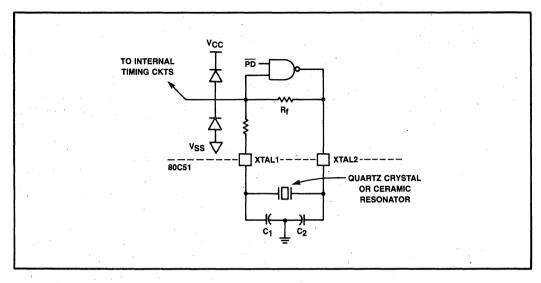

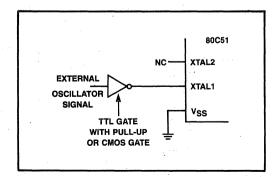

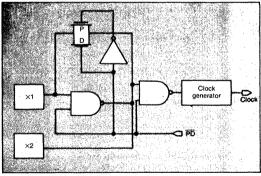

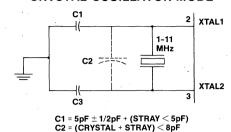

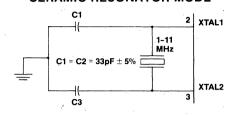

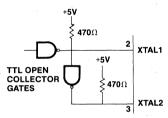

The 8096 requires an input clock frequency of between 6.0 MHz and 12 MHz to function. This frequency can be applied directly to XTAL1. Alternatively, since XTAL1 and XTAL2 are inputs and outputs of an inverter, it is also possible to use a crystal to generate the clock. A block diagram of the oscillator section is shown in Figure 2-3. Details of the circuit and suggestions for its use can be found in section 4.1.

#### 2.2.1. Internal Timings

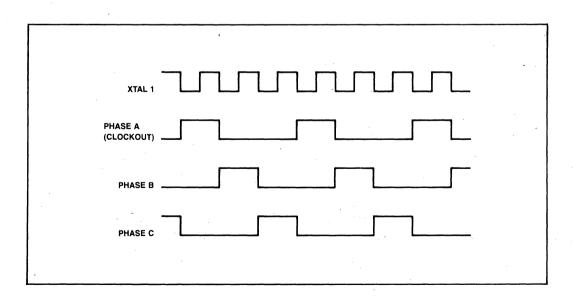

The crystal or external oscillator frequency is divided by

Figure 2-3. Block Diagram of Oscillator

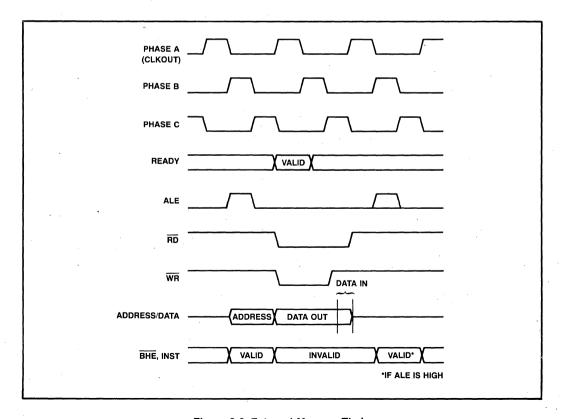

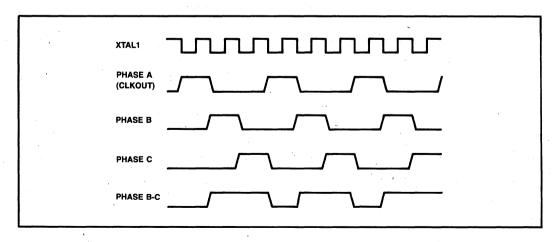

3 to generate the three internal timing phases as shown in Figure 2-4. Each of the internal phases repeat every 3 oscillator periods: 3 oscillator periods are referred to as one "state time", the basic time measurement for 8096 operations. Most internal operations are synchronized to either Phase A, B or C, each of which have a 33% duty cycle. Phase A is represented externally by CLKOUT, a signal available on the 68-pin part. Phases B and C are not available externally. The relationships of XTAL1, CLKOUT, and Phases A, B, and C are shown in Figure 2-4. It should be noted that propagation delays have not

Figure 2-4. Internal Timings Relative to XTAL 1

been taken into account in this diagram. Details on these and other timing relationships can be found in sections 4.1, 4.4 and 4.6.

The RESET line can be used to start the 8096 at an exact time to provide for synchronization of test equipment and multiple chip systems. Use of this feature is fully explained under RESET, sections 2.15 and 4.1.

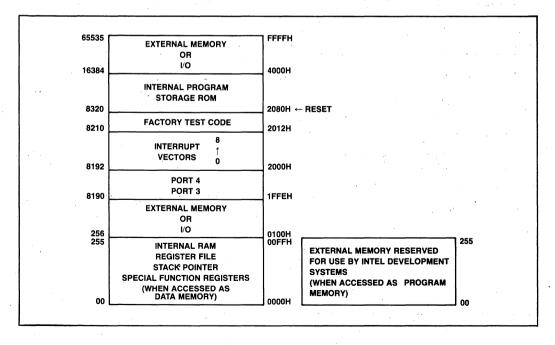

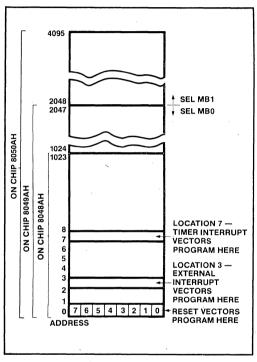

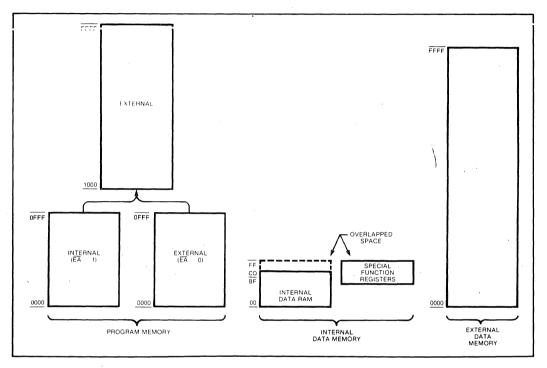

#### 2.3. MEMORY SPACE

The addressable memory space on the 8096 consists of 64K bytes, most of which is available to the user for program or data memory. Locations which have special purposes are 0000H through 00FFH and 1FFEH through 2010H. All other locations can be used for either program or data storage or for memory mapped peripherals. A memory map is shown in figure 2-5.

#### 2.3.1. Register File

Locations 00H through 0FFH contain the Register File and SFRs. Complete information on this section of memory space can be found in section "RAM SPACE". No code can be executed from this internal RAM section. If an attempt to execute instructions from locations 000H through 0FFH is made, the instructions will be fetched from *external* memory. This section of external memory is reserved for use by Intel development tools. Execution of a nonmaskable interrupt (NMI) will force a call to

external location 0000H, therefore, the NMI instruction is also reserved for Intel development tools.

#### 2.3.2. Reserved Memory Spaces

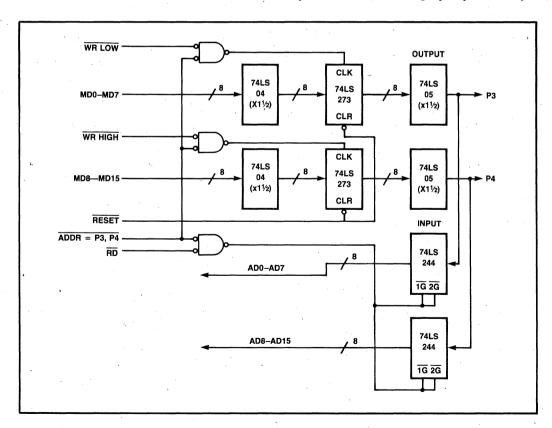

Locations 1FFEH and 1FFFH are reserved for Ports 3 and 4 respectively. This is to allow easy reconstruction of these ports if external memory is used in the system. An example of reconstructing the I/O ports is given in section 4.6.7. If ports 3 and 4 are not going to be reconstructed then these locations can be treated as any other external memory location.

The 9 interrupt vectors are stored in locations 2000H through 2011H. The 9th vector is used by Intel development systems, as explained in section 2.5. Internal locations 2012H through 2077H are reserved for Intel's factory test code. These locations may be used in external memory.

Resetting the 8096 causes instructions to be fetched starting from location 2080H. This location was chosen to allow a system to have up to 8K of RAM continuous with the register file. Further information on reset can be found in section 2.15.

#### 2.3.3. Internal ROM

When a ROM part is ordered, the internal memory locations 2080H through 3FFFH are user specified as are the interrupt vectors in locations 2000H through 2011H.

Figure 2-5. Memory Map

Instruction and data fetches from the internal ROM occur only if the part has a ROM,  $\overline{EA}$  is tied high, and the address is between 2000H and 3FFFH. At all other times data is accessed from either the internal RAM space or external memory and instructions are fetched from external memory.

#### 2.3.4. Memory Controller

The RALU talks to the memory (except for the locations in the register file and SFR space) through the memory controller which is connected to the RALU by the A-bus and several control lines. Since the A-bus is eight bits wide, the memory controller uses a Slave Program Counter to avoid having to always get the instruction location from the RALU. This slave PC is incremented after each fetch. When a jump or call occurs, the slave PC must be loaded from the A-bus before instruction fetches can continue.

In addition to holding a slave PC, the memory controller contains a 3 byte queue to help speed execution. This queue is transparent to the RALU and to the user unless wait states are forced during external bus cycles. The instruction execution times shown in Tables 3-3 and 3-4 show the normal execution times with no wait states

added. Reloading the slave PC and fetching the first byte of the new instruction stream takes 4 state times. This is reflected in the jump taken/not-taken times shown in Table 3-4.

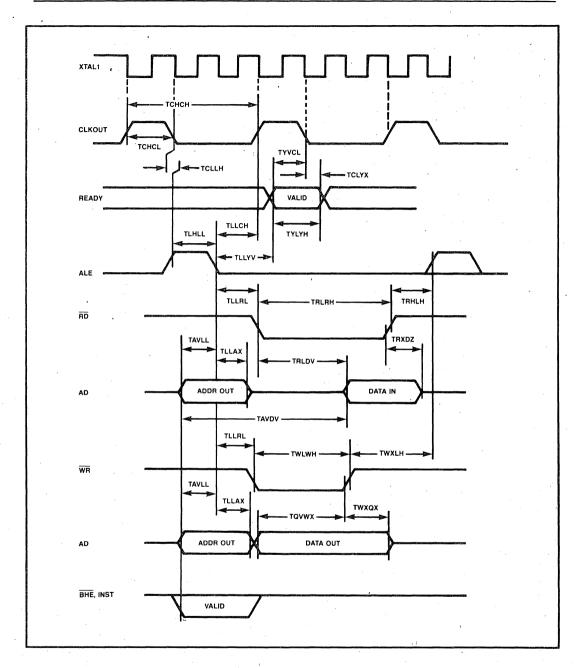

#### 2.3.5. System Bus

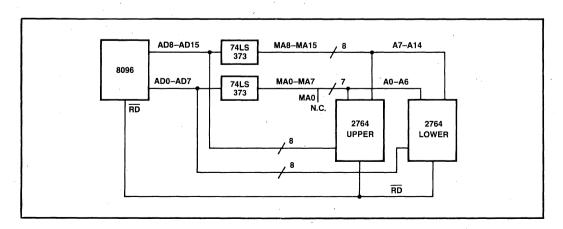

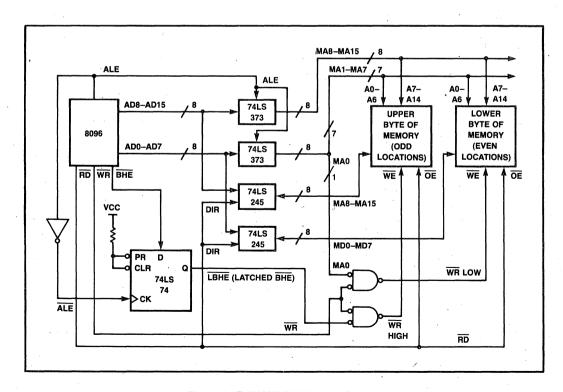

External memory is addressed through lines AD0 through AD15 which form a 16-bit multiplexed (address/data) data bus. These lines share pins with I/O ports 3 and 4. The falling edge of the Address Latch Enable (ALE) line is used to provide a clock to a transparent latch (74LS373) in order to demultiplex the bus. A typical circuit and the required timings are shown in section 4.6. Since the 8096's external memory can be addressed as either bytes or words, the decoding is controlled with two lines, Bus High Enable ( $\overline{BHE}$ ) and Addresss/Data Line 0 (AD0). The  $\overline{BHE}$  line must be transparently latched, just as the addresses are.

To avoid confusion during the explanation of the memory system it is reasonable to give names to the demultiplexed address/data signals. The address signals will be called MA0 through MA15 (Memory Address), and the data signals will be called MD0 through MD15 (Memory Data).

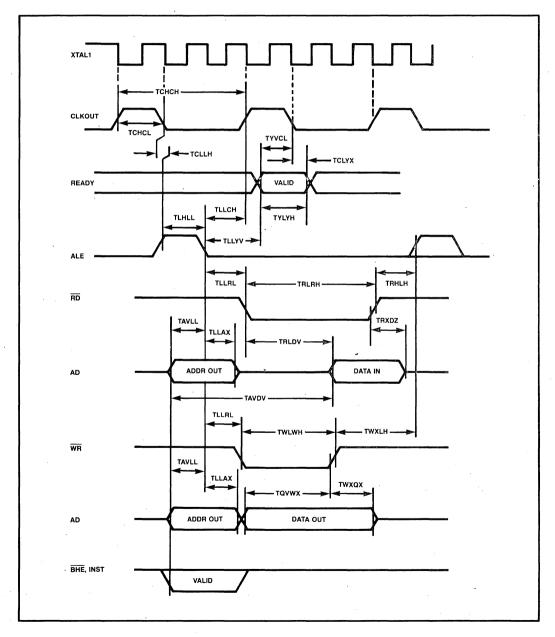

Figure 2-6. External Memory Timings

When  $\overline{BHE}$  is active (low), the memory connected to the high byte of the data bus should be selected. When MAO is low the memory connected to the low byte of the data bus should be selected. In this way accesses to a 16-bit wide memory can be to the low (even) byte only (MAO=0,  $\overline{BHE}$ =1), to the high (odd) byte only (MAO=1,  $\overline{BHE}$ =0), or to both bytes (MAO=0,  $\overline{BHE}$ =0). When a memory block is being used only for reads,  $\overline{BHE}$  and MAO need not be decoded.

Figure 2-6 shows the idealized waveforms related to the following description of external memory manipulations. For exact timing specifications please refer to the latest data sheet. When an external memory fetch begins, the address latch enable (ALE) line rises, the address is put on AD0-AD15 and BHE is set to the required state. ALE then falls, the address is taken off the pins, and the RD (Read) signal goes low. The READY line can be pulled low to hold the processor in this condition for a few extra state times.

#### 2.3.6. Ready

The READY line can be used to hold the processor in the above condition in order to allow access to slow memories or for DMA purposes. Sampling of the READY line occurs internally during Phase 2, which is the signal that generates CLKOUT. There is a minimum time in which READY must be stable before CLKOUT goes low. If this set-up time is violated while the part is going to the not-ready state, the part may fail to operate predictably.

Since READY is synchronized with CLKOUT, the 8096 will be in a not-ready condition for a period equal to some multiple of CLKOUT, although the READY line can be brought high at any time. There is a maximum time for holding the 8096 in the not-ready condition, typically on the order of 1  $\mu$ S. The exact time is specified in the data sheet for the particular part and temperature range desired.

The data from the external memory must be on the bus and stable for a minimum of the specified set-up time before the rising edge of  $\overline{RD}$ . The rising edge of  $\overline{RD}$  latches the information into the 8096. If the read is for data, the INST pin will be low when the address is valid, if it is for an instruction the INST pin will be high during this time. The 48-lead part does not have the INST pin.

Writing to external memory requires timings that are similar to those required when reading from it. The main difference is that the write  $(\overline{WR})$  signal is used instead of the  $\overline{RD}$  signal. The timings are the same until the falling edge of the  $\overline{WR}$  line. At this point the 8096 removes the address and places the data on the bus. The READY line must be held in the desired state at that time as described above. When the  $\overline{WR}$  line goes high the data should be latched to the external memory. INST is always low during a write, as instructions cannot be written. The exact timing specifications for memory accesses can be found in the data sheet.

Figure 2-7. Register File Memory Map

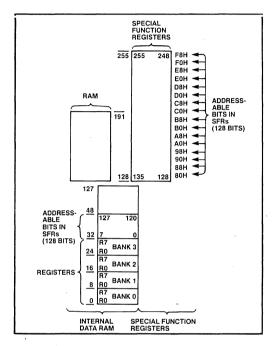

#### 2.4. RAM SPACE

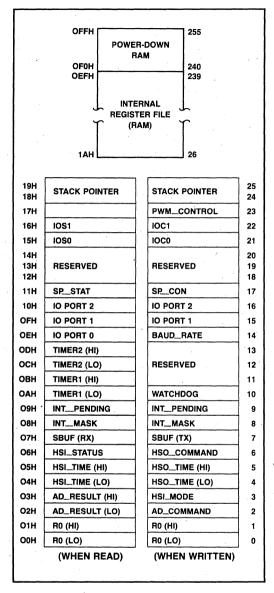

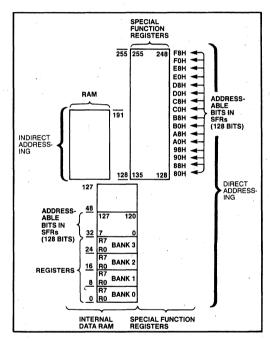

The internal register locations on the 8096 are divided into two groups, a register file and a set of Special Function Registers (SFRs). The RALU can operate on any of these 256 internal register locations. Locations 00H through 17H are used to access the SFRs. Locations 18H and 19H contain the stack pointer. There are no restrictions on the use of the remaining 230 locations except that code cannot be executed from them.

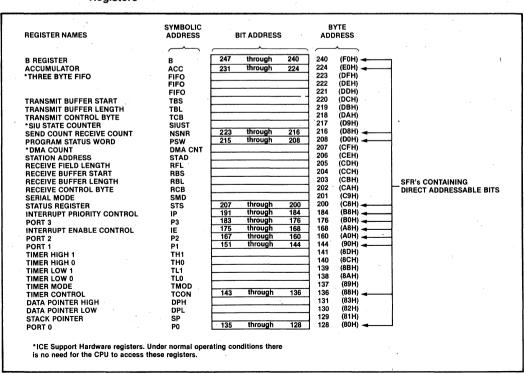

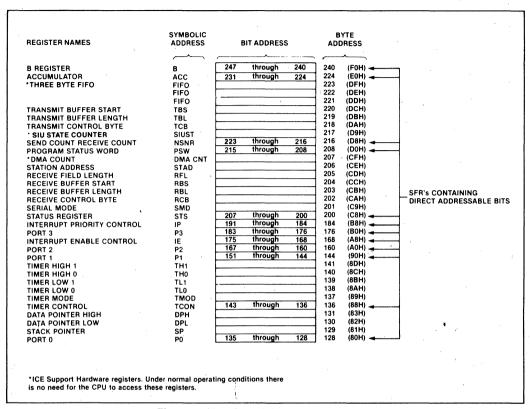

#### 2.4.1. Special Function Registers

All of the I/O on the 8096 is controlled through the SFRs. Many of these registers serve two functions; one if they are read from, the other if they are written to. Figure 2-

7 shows the locations and names of these registers. A summary of the capabilities of each of these registers is shown in Figure 2-8, with complete descriptions reserved for later chapters.

| Register    | Description                                                                                                              | Chapter         |

|-------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| R0          | Zero Register — Always reads as a zero, useful for a base when indexing and as a constant for calculations and compares. | 3.2.7           |

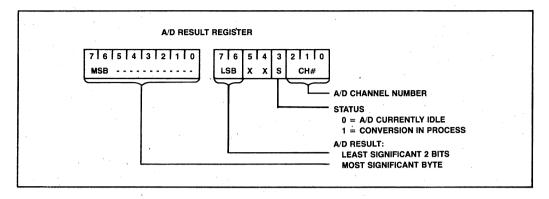

| AD_RESULT   | A/D Result Hi/Low — Low and high order Results of the A/D 2.9.3 converter                                                |                 |

| AD_COMMAND  | A/D Command Register — Controls the A/D                                                                                  | 2.9.2           |

| HSL_MODE    | HSI Mode Register — Sets the mode of the High Speed Input unit.                                                          | 2.7.1           |

| HSL_TIME    | HSI Time Hi/Lo — Contains the time at which the High Speed Input unit was triggered.                                     | 2.7.4           |

| HSQ_TIME    | HSO Time Hi/Lo — Sets the time for the High Speed Output to execute the command in the Command Register.                 | 2.8.3           |

| HSQ_COMMAND | HSO Command Register — Determines what will happen at the time loaded into the HSO Time registers.                       | 2.8.2           |

| HSL_STATUS  | HSI Status Registers — Indicates which HSI pins were detected at the time in the HSI Time registers.                     | 2.7.4           |

| SBUF (RX)   | Receive buffer for the serial port, holds contents to be outputed.                                                       | 2.11            |

| SBUF (TX)   | Transmit buffer for the serial port, holds the byte just received by the serial port.                                    | 2.11            |

| INT_MASK    | Interrupt Mask Register — Enables or disables the individual interrupts.                                                 | 2.5.2<br>3.6.2  |

| INT_PENDING | Interrupt Pending Register — Indicates when an interrupt signal has occurred on one of the sources.                      | 2.5.2<br>3.6.2  |

| WATCHDOG    | Watchdog Timer Register — Written to periodically to hold off automatic reset every 64K state times.                     | 2.14            |

| TIMER1      | Timer 1 Hi/Lo — Timer 1 high and low bytes.                                                                              | 2.6.1<br>2.7-8  |

| TIMER2      | Timer 2 Hi/Lo — Timer 2 high and low bytes.                                                                              | 2.6.2<br>2.7-8  |

| IOPORT0     | Port 0 Register — Levels on pins of port 0.                                                                              | 2.12.1          |

| BAUD_RATE   | Register which contains the baud rate, this register is loaded sequentially.                                             | 2.11.4          |

| IOPORT1     | Port 1 Register — Used to read or write to Port 1.                                                                       | 2.12.2          |

| IOPORT2     | Port 2 Register — Used to read or write to Port 2.                                                                       | 2.12.3          |

| SP_STAT     | Serial Port Status — Indicates the status of the serial port.                                                            | 2.11.3          |

| SP_CON      | Serial port control — Used to set the mode of the serial port.                                                           | 2.11.1          |

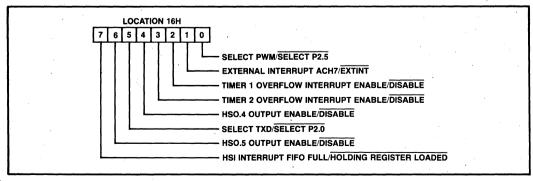

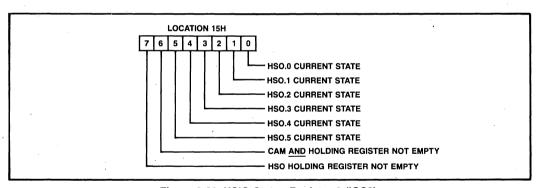

| IOS0        | I/O Status Register 0 — Contains information on the HSO status.                                                          | 2.13.4          |

| IOS1        | I/O Status Register 1 — Contains information on the status of the timers and of the HSI.                                 | 2.13.5<br>3.7.2 |

| IOC0        | I/O Control Register 0 — Controls alternate functions of HSI pins, Timer 2 reset sources and Timer 2 clock sources.      | 2.13.2          |

| IOC1        | I/O Control Register 1 — Controls alternate functions of Port 2 pins, timer interrupts and HSI interrupts.               | 2.13.3          |

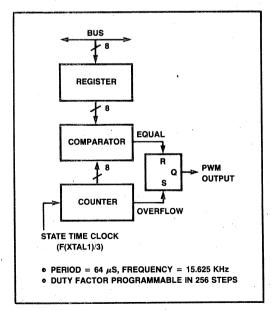

| PWM_CONTROL | Pulse Width Modulation Control Register — Sets the duration of the PWM pulse.                                            | 2.10<br>4.3.2   |

Figure 2-8. SFR Summary

Within the SFR space are several registers labeled as "RESERVED". These registers are reserved for future expansion or test purposes. Reads or writes of these registers may produce unexpected results. For example, writing to location 000CH will set both timers to 0FFFXH, this feature is for use in testing the part and should not be used in programs.

#### 2.4.2. Power Down

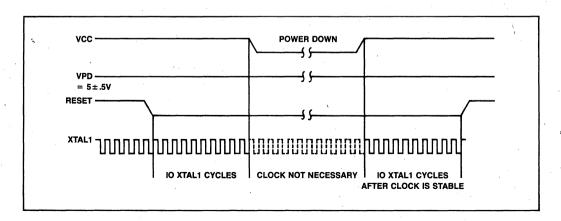

The upper 16 RAM locations (0F0H through 0FFH) receive their power from both the VCC pin and the VPD pin. If it is desired to keep the memory in these locations alive during a power down situation, one need only keep voltage on the VPD pin. The current required to keep the RAM alive is approximately 1 milliamp (refer to the data sheet for the exact specification).

To place the 8096 into a power down mode, the  $\overline{RESET}$  pin is pulled low. Two state times later the part will be in reset. This is necessary to prevent the part from writing into RAM as the power goes down. The power may now be removed from the VCC pin, the VPD pin must remain within specifications. The 8096 can remain in this state for any amount of time and the 16 RAM bytes will retain their values.

To bring the 8096 out of power down, RESET is held low while VCC is applied. Two state times after the oscillator and the back bias generator have stabilized (~1 millisecond), the RESET pin can be pulled high. The 8096 will begin to execute code at location 02080H 10 state times after RESET is pulled high. Figure 2-9 shows a timing diagram of the power down sequence. To ensure that the 2 state time minimum reset time (synchronous with CLKOUT) is met, it is recommended that 10 XTAL1 cycles be used. Suggestions for actual hardware connections are given in section 4.1. Reset is discussed in section 2.15.

#### 2.5. INTERRUPT STRUCTURE

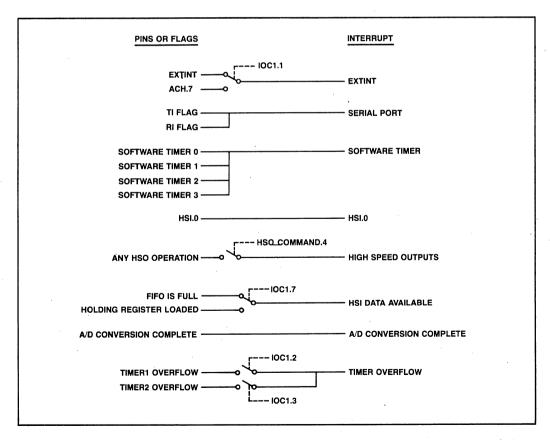

#### 2.5.1. Interrupt Sources

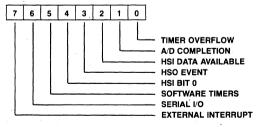

Eight interrupt sources are available on the 8096. When enabled, an interrupt occurring on any of these sources will force a call to the location stored in the vector location for that source. The interrupt sources and their respective véctor locations are listed in Figure 2-10. In addition to the 8 standard interrupts, there is a TRAP instruction which acts as a software generated interrupt. This instruction is not currently supported by the MCS-96 Assembler and is reserved for use by Intel development systems. Many of the interrupt sources can be activated by several methods, Figure 2-11 shows all of the possible sources for interrupts.

| Source          | Vector I       | _ocation      | Priority       |  |

|-----------------|----------------|---------------|----------------|--|

|                 | (High<br>Byte) | (Low<br>Byte) |                |  |

| Software        | 2011H          | 2010H         | Not Applicable |  |

| Extint          | 200FH          | 200EH         | 7 (Highest)    |  |

| Serial Port     | 200DH          | 200CH         | 6              |  |

| Software Timers | 200BH          | 200AH         | 5              |  |

| HSI.0           | 2009H          | 2008H         | 4              |  |

| High Speed      | 2007H          | 2006H         | 3              |  |

| Outputs         |                |               |                |  |

| HSI Data        | 2005H          | 2004H         | 2              |  |

| Available       | ٠.             |               |                |  |

| A/D Conversion  | 2003H          | 2002H         | 1              |  |

| Complete        |                |               |                |  |

| Timer Overflow  | 2001H          | 2000H         | 0 (Lowest)     |  |

Figure 2-10. Interrupt Vector Locations

Figure 2-9. Power Down Timing

#### 2.5.2. Interrupt Control

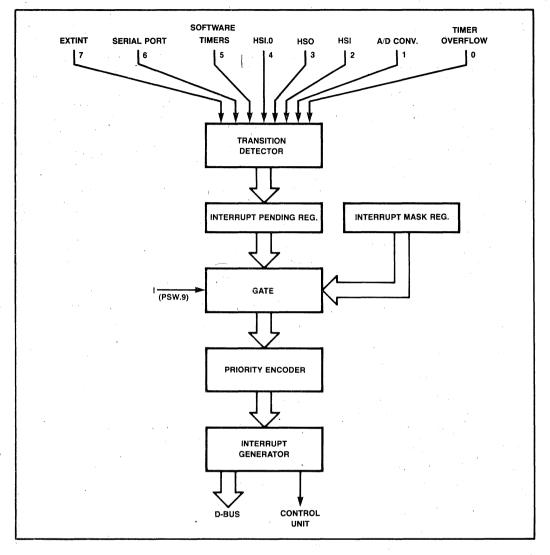

A block diagram of the interrupt system is shown in Figure 2-12. Each of the interrupt sources is tested for a 0 to 1 transition. If this transition occurs, the corresponding bit in the Interrupt Pending Register, located at 0009H, is set. Since this register can be written to, it is possible to generate software interrupts by setting bits within the register, or remove pending interrupts by clearing the bits in this register. The pending register can be set even if the interrupt is disabled.

Caution must be used when writing to the pending register to clear interrupts. If the interrupt has already been acknowledged when the bit is cleared, a 4 state time "partial" interrupt cycle will occur. This is because the 8096 will have to fetch the next instruction of the normal instruction flow, instead of proceeding with the interrupt processing as it was going to. The effect on the program will be essentially that of an extra NOP. This can be prevented by clearing the bits using a 2 operand immediate logical, as the 8096 holds off acknowledging interrupts during these "read/modify/write" instructions.

Enabling and disabling of individual interrupts is done through the Interrupt Mask Register, located at 0008H. If the bit in the mask register is a 1 then the interrupt is enabled, otherwise it is disabled. Even if an interrupt is masked it may still become pending. It may, therefore, be desirable to clear the pending bit before unmasking an interrupt.

The Interrupt Mask Register is also the low byte of the PSW. All of the interrupts may be enabled and disabled simultaneously by using the "EI" (Enable Interrupt) and "DI" (Disable Interrupt) instructions. EI and DI set and clear PSW.9, the interrupt enable bit, they do not effect the contents of the mask register.

#### 2.5.3. Interrupt Priority Programming

The priority encoder looks at all of the interrupts which are both pending and enabled, and selects the one with the highest priority. The priorities are shown in Figure 2-10 (7 is highest, 0 is lowest.) The interrupt generator then forces a call to the location in the indicated vector location. This location would be the starting location of the Interrupt Service Routine (ISR).

Figure 2-11. All Possible Interrupt Sources

Figure 2-12. Block Diagram of Interrupt System

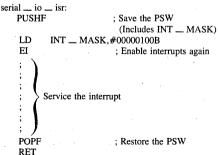

At least one instruction in the ISR will always be executed before another interrupt can be acknowledged. Usually this instruction is "DI" or "PUSHF" (push flags). The PUSHF instruction pushes the PSW onto the stack and then clears it.

Clearing the PSW disables all interrupts in two ways; by clearing PSW.9, the interrupt enable bit and because the Interrupt Mask Register is located in bits 0 through 7 of the PSW. The interrupts which should be permitted to interrupt this ISR can then be set in the mask register and an "EI" instruction executed.

By selectively determining which interrupts are enabled or disabled within which interrupt service routines, it is possible to configure the interrupt system in any way one would desire. More information on programming the interrupts can be found under software programming of interrupts, section 3.6.

The last two instructions in an ISR are normally a "POPF" (pop flags), which restores the PSW and, therefore, the interrupt mask register, followed by a "RET", which restores the Program Counter. Execution will then continue from the point at which the call was forced.

#### 2.5.4. Interrupt Timing

Interrupts are not always acknowledged immediately. If the interrupt signal does not occur prior to 4 state-times before the end of an instruction, the interrupt will not be acknowledged until after the next instruction has been executed. This is because an instruction is fetched and prepared for execution a few state times before it is actually executed.

There are 6 instructions which always inhibit interrupts from being acknowledged until after the next instruction has been executed. These instructions are:

EI, DI — Enable and Disable Interrupts

POPF, PUSHF — Pop and Push Flags

SIGND — Prefix to perform signed multiply

and divide

TRAP — Software interrupt

When an interrupt is acknowledged, a call is forced to the location indicated by the specified interrupt vector. This call occurs after the completion of the instruction in process, except as noted above. The procedure of getting the vector and forcing the call requires 21 state times. If the stack is in external RAM an additional 3 state times are required.

The maximum number of state times required from the time an interrupt is generated (not acknowledged) until the 8096 begins executing code at the desired location is the time of the longest instruction, NORML (Normalize -43 state times), plus the 4 state times prior to the end of the previous instruction, plus the response time (21 to 24 state times). Therefore, the maximum response time is 71 (43+4+24) state times. This does not include the 12 state times required for PUSHF if it is used as the first instruction in the interrupt routine or additional latency caused by having the interrupt masked or disabled.

Interrupt latency time can be reduced by careful selection of instructions in areas of code where interrupts are expected. Using 'EI' followed immediately by a long instruction (e.g. MUL, NORML, etc.) will increase the maximum latency by 4 state times, as an interrupt cannot occur between EI and the instruction following EI. The 'DI', 'PUSHF', 'POPF' and 'TRAP' instructions will also cause the same situation. Typically the PUSHF, POPF and TRAP instructions would only effect latency when one interrupt routine is already in process, as these instructions are seldom used at other times.

#### 2.6. TIMERS

Two 16-bit timers are available for use on the 8096. The first is designated "Timer 1", the second, "Timer 2". Timer 1 is used to synchronize events to real time, while Timer 2 can be clocked externally and synchronizes events to external occurences.

#### 2.6.1. Timer 1

Timer 1 is clocked once every eight state times and can be cleared only by executing a reset. The only other way to change its value is by writing to 000CH but this is a test mode which sets both timers to 0FFFXH and should not be used in programs.

#### 2.6.2. Timer 2

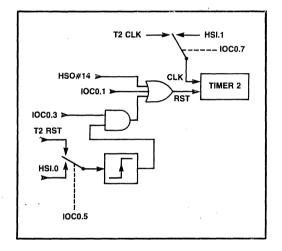

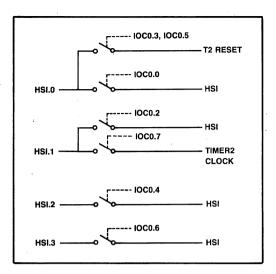

Timer 2 can be incremented by transitions (one count each transition, rising and falling) on either T2CLK or HSI.1. The multiple functionality of the timer is determined by the state of I/O Control Register 0, bit 7 (IOC0.7). To ensure that all CAM entries are checked each count of Timer 2, the maximum transition speed is limited to once per eight state times. Timer 2 can be cleared by: executing a reset, by setting IOC0.1, by triggering HSO channel 0EH, or by pulling T2RST or HSI.0 high. The HSO and CAM are described in section 2.8. IOC0.3 and IOC0.5 control the resetting of Timer 2. Figure 2-13 shows the different ways of manipulating Timer 2.

Figure 2-13. Timer 2 Clock and Reset Options

#### 2.6.3. Timer Interrupts

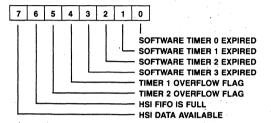

Both Timer 1 and Timer 2 can be used to trigger a timer overflow interrupt and set a flag in the I/O Status Register 1 (IOS1). The interrupts are controlled by IOC1.2 and IOC1.3 respectively. The flags are set in IOS1.6 and IOS1.7, respectively.

Caution must be used when examining the flags, as any access (including Compare and Jump on Bit) of IOS1 clears the whole byte, including the software timer flags. It is, therefore, recommended to write the byte to a temporary register before testing bits. The general enabling and disabling of the timer interrupts are controlled by the Interrupt Mask Register bit 0. In all cases, setting a bit enables a function, while clearing a bit disables it.

#### 2.6.4. Timer Related Sections

The High Speed I/O unit is coupled to the timers in that the HSI records the value on Timer 1 when transitions

Figure 2-14. High Speed Input Unit

occur and the HSO causes transitions to occur based on values of either Timer 1 or Timer 2. The Baud rate generator can use the T2CLK pin as input to its counter. A complete listing of the functions of IOS1, IOC0, and IOC1 are in section 2.13.

#### 2.7. HIGH SPEED INPUTS

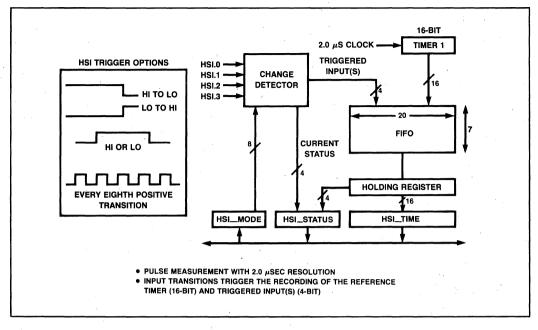

The High Speed Input Unit (HSI), can be used to record the time at which an event occurs with respect to Timer 1. There are 4 lines (HSI.0 through HSI.3) which can be used in this mode and up to a total of 8 events can be recorded. HSI.2 and HSI.3 share pins with HSO.4 and HSO.5. The I/O Control Registers (IOC0 and IOC1) are used to determine the functions of these pins. A block diagram of the HSI unit is shown in Figure 2-14.

#### 2.7.1. HSI Modes

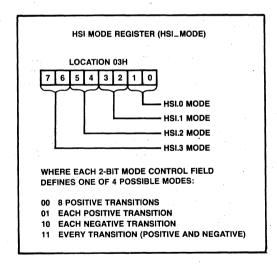

There are 4 possible modes of operation for each of the HSI. The HSI mode register is used to control which pins will look for what type of events. The 8-bit register is set up as shown in Figure 2-15.

High and low levels each need to be held for at least 1 state time to ensure proper operation. The maximum input speed is 1 event every 8 state times except when the 8 transition mode is used, in which case it is 1 transition per state time.

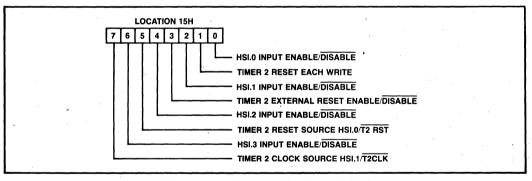

The HSI lines can be individually enabled and disabled using bits in IOC0, at location 0015H. Figure 2-16 shows

Figure 2-15. HSI Mode Register Diagram

the bit locations which control the HSI pins. If the pin is disabled, transitions will not be entered in the FIFO.

#### 2.7.2. HSI FIFO

When an HSI event occurs, a 7x20 FIFO stores the 16 bits of Timer 1 and the 4 bits indicating the state of the

Figure 2-16. IOC0 Control of HSI Pin Functions

4 HSI lines at the recorded timer value. It can take up to 8 state times for this information to reach the holding register. When the FIFO is full, one additional event can be stored by considering the holding register part of the FIFO. If the FIFO and holding register are full any additional events will not be recorded.

#### 2.7.3. HSI Interrupts

Interrupts can be generated from the HSI unit in one of

two ways, determined by IOC1.7. If the bit is a 0, then an interrupt will be generated every time a value is loaded into the holding register. If it is a 1, an interrupt will only be generated when the FIFO, (independent of the holding register), has six or seven entries in it. Since all interrupts are rising edge triggered, if IOC1.7 = 1, the processor will not be re-interrupted until the FIFO first contains 5 or less records, then contains six or more.

#### 2.7.4. HSI Status

Bits 6 and 7 of the I/O Status register 1 (IOS1) indicate the status of the HSI FIFO. If bit 6 is a 1, the FIFO contains at least seven entries. If bit 7 is a 1, the FIFO contains at least 1 entry. The FIFO may be read after verifying that it contains valid data. Caution must be used when reading or testing bits in IOS1, as this action clears the entire byte, including the software and hardware timer overflow flags. It is best to store the byte and then test the stored value.

Reading the HSI is done in two steps. First, the HSI Status register is read to obtain the current state of the HSI pins and their state at the recorded time. Second, the HSI Time register is read. Reading the Time register unloads one word of the FIFO, so if the Time register is read before the Status register, the information in the Status register will be lost. The HSI Status register is at location 06H and the HSI Time registers are in locations 04H and 05H.

It should be noted that many of the Status register conditions are changed by a reset, see section 2.15.2. A complete listing of the functions of IOS0, IOS1, and IOC1 can be found in section 2.13.

Figure 2-17. High Speed Output Unit

#### 2.8. HIGH SPEED OUTPUTS

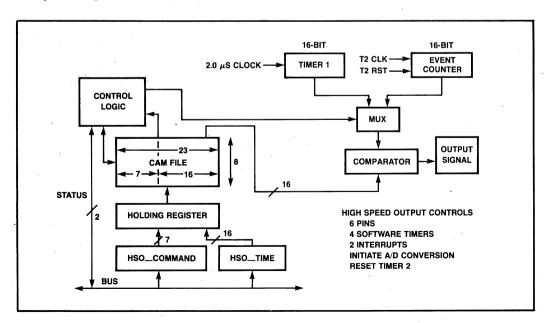

The High Speed Output unit (HSO) is used to trigger events at specific times with minimal CPU overhead. These events include: starting an A to D conversion, resetting Timer 2, setting 4 software flags, generating interrupts, and switching up to 6 output lines. Up to 8 events can be pending at any one time.

#### 2.8.1. HSIO Shared Pins

Two of the 6 output lines (HSO.0 through HSO.5) are shared with the High Speed Input (HSI) lines. HSO.4 and HSO.5 are shared with HSI.2 and HSI.3, respectively. Bits 4 and 6 of the I/O Control Register 1 (IOC1) are used to enable HSO.4 and HSO.5 as outputs.

#### 2.8.2. HSIO CAM

A block diagram of the HSO unit is shown in Figure 2-17. The Content Addressable Memory (CAM) file is the center of control. One CAM register is compared with a time value every state time. Therefore, it takes 8 state times to compare all CAM registers with a timer.

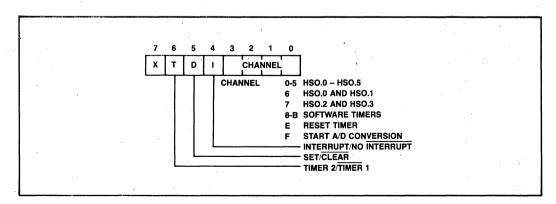

Each CAM register is 23 bits wide. Sixteen bits specify the time at which the action is to be carried out and 7 bits specify both the nature of the action and whether Timer 1 or Timer 2 is the reference. The format of the command to the HSO unit shown in Figure 2-18.

To enter a command into the CAM file, write the 7-bit "Command Tag" into location 0006H followed by the time at which the action is to be carried out into word address 0004H. Writing the time value loads the HSO Holding Register with both the time and the last written command tag. The command does not actually enter the CAM file until an empty CAM register becomes available.

Care must be taken when writing the command tag for the HSO. If an interrupt occurs during the time between writing the command tag and loading the time value, and the interrupt service routine writes to the HSO time register, the command tag will be loaded into the CAM with the time value from the interrupt routine. One way of avoiding this problem would be to disable interrupts when writing commands and times to the HSO unit.

#### 2.8.3. HSO Status

Before writing to the HSO, it is desirable to ensure that the Holding Register is empty. If it is not, writing to the HSO will overwrite the value in the Holding Register. I/O Status Register 0 (IOS0) bits 6 and 7 indicate the status of the HSO unit. This register is described in section 2.13.4. If IOS0.6 equals 0, the holding register is empty and at least one CAM register is empty. If IOS0.7 equals 0, the holding register is empty.

One location in the CAM file is checked each state-time. Thus, it takes 8 state-times for the Holding Register to have had access to all 8 CAM registers. Similarly, it takes 8 state-times for the comparator to have had access to all 8 CAM registers. This defines the time-resolution of the HSO unit to be 8 state-times (2.0  $\mu$ sec, if the oscillator frequency is 12 MHz). Note that the comparator does not look at the holding register, so instructions in the holding register do not execute.

#### 2.8.4. Clearing The HSO

All 8 CAM locations of the HSO are compared before any action is taken. This allows a pending event to be cancelled by simply writing the opposite event to the CAM. However, once an entry is placed in the CAM, it cannot be removed until either the specified timer matches the written value or the chip is reset.

Timer 1 is incremented only once every 8 state-times. When it is being used as the reference timer for an HSO action, the comparator has a chance to look at all 8 CAM registers before Timer 1 changes its value. Following the same reasoning, Timer 2 has been synchronized to allow it to change at a maximum rate of once per 8 state-times. Timer 2 increments on both edges of the input signal.

Figure 2-18. HSO Command Tag Format

If Timer 2 is being used as the reference timer, the user must ensure that it is not cleared before all references to it in the CAM have been recognized. If this occurs, the unrecognized references will remain in the CAM, blocking further entries to those CAM registers until the part is reset or the references are recognized.

#### 2.8.5. Software Timers

The HSO can be programmed to generate interrupts at preset times. Up to four such "Software Timers" can be in operation at a time. As each preprogrammed time is reached, the HSO unit generates a Software Timer interrupt. The interrupt service routine can then examine I/O Status register 1 (IOS1) to determine which software timer expired and caused the interrupt. When the HSO resets Timer 2 or starts an A to D conversion, it can also be programmed to generate a software timer interrupt but there is no flag to indicate that this has occurred.

Each read or test of any bit in IOS1 will clear the whole byte. Be certain to save the byte before testing it unless you are only concerned with 1 bit.

A complete listing of the functions of IOS0, IOS1, and IOC1 can be found in section 2.13. The Timers are described in section 2.6 and the HSI is described in section 2.7.

#### 2.9. ANALOG INPUTS

The A to D converter on the 8096 provides a 10-bit result on one of 8 input channels. Conversion is done using successive approximation with a result equal to the ratio of the input voltage divided by the analog supply voltage. If the ratio is 1.00, then the result will be all ones. The A/D converter is available on the 8097, 8397, 8095 and 8395 members of the MCS<sup>®</sup>-96 family.

#### 2.9.1. A/D Accuracy

Each conversion requires 168 state-times ( $42\mu S$  at 12 MHz) independent of the accuracy desired or value of input voltage. The input voltage must be in the range of 0 to VREF, the analog reference and supply voltage. For proper operation, VREF (the reference voltage and analog power supply) must be held at VCC  $\pm$  0.3V with VREF =  $5.0 \pm 0.5$ V. The A/D result is calculated from the formula:

1023 × (input voltage-AVGND) / (VREF-AVGND)

It can be seen from this formula that changes in VREF or AVGND effect the output of the converter. This can be advantageous if a ratiometric sensor is used since these sensors have an output that can be measured as a proportion of VREF.

If high absolute accuracy is needed it may be desirable to use a separate power supply, or power traces, to operate the A/D converter. There is no sample and hold circuit internal to the chip, so the input voltage must be held constant for the entire 168 state times. Examples of conecting the A/D converter to various devices are given in section 4.3.

#### 2.9.2. A/D Commands

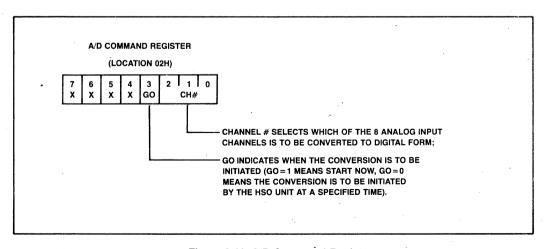

Analog signals can be sampled by any one of the 8 analog input pins (ACH0 through ACH7) which are shared with Port 0. ACH7 can also be used as an external interrupt if IOC1.1 is set (see section 2.5). The A/D Command Register, at location 02H, selects which channel is to be converted and whether the conversion should start immediately or when the HSO (Channel #14) triggers it. A to D commands are formatted as shown in Figure 2-19.

The command register is double buffered so it is possible

Figure 2-19. A/D Command Register

Figure 2-20. A/D Result Register

to write a command to start a conversion triggered by the HSO while one is still in progress. Care must be taken when this is done since if a new conversion is started while one is already in progress, the conversion in progress is cancelled and the new one is started. When a conversion is started, the result register is cleared. For this reason the result register must be read before a new conversion is started or data will be lost.

#### 2.9.3. A/D Results

Results of the analog conversions are read from the A/D Result Register at locations 02H and 03H. Although these addresses are on a word boundary, they must be read as

Figure 2-21. Pulse Width Modulated (D/A) Output

individual bytes. Information in the A/D Result register is formatted as shown in Figure 2-20. Note that the status bit may not be set until 8 state times after the go command. Information on using the HSO is in section 2.8.

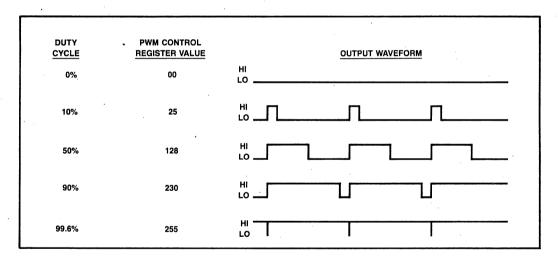

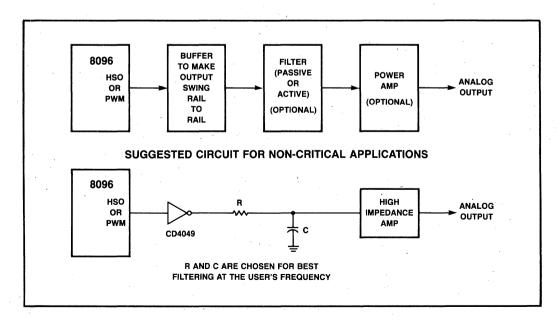

### 2.10. PULSE WIDTH MODULATION OUTPUT (D/A)

Digital to analog conversion can be done with the pulse width modulation output; a block diagram of the circuit is shown in Figure 2-21. The 8-bit counter is incremented every state time. When it equals 0, the PWM output is set to a one. When the counter matches the value in the PWM register, the output is switched low. When the counter overflows, the output is once again switched high. A typical output waveform is shown in Figure 2-22. Note that when the PWM register equals 00, the output is always low.

The output waveform is a variable duty cycle pulse which repeats every 256 state times (64  $\mu$ S at 12MHz). Changes in the duty cycle are made by writing to the PWM register at location 17H. There are several types of motors which require a PWM waveform for most efficient operation. Additionally, if this waveform is integrated it will produce a DC level which can be changed in 256 steps by varying the duty cycle.

Details about the hardware required for smooth, accurate D/A conversion can be found in section 4.3.2. Typically, some form of buffer and integrator are needed to obtain the most usefulness from this feature.

The PWM output shares a pin with Port 2, pin 5 so that these two features cannot be used at the same time. IOC1.0 equal to 1 selects the PWM function instead of the standard port function. More information on IOC1 is in section 2.13.3.

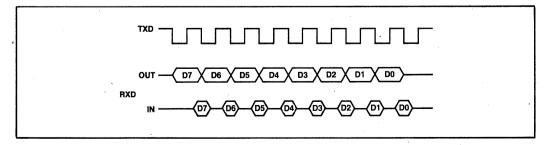

#### 2.11. SERIAL PORT

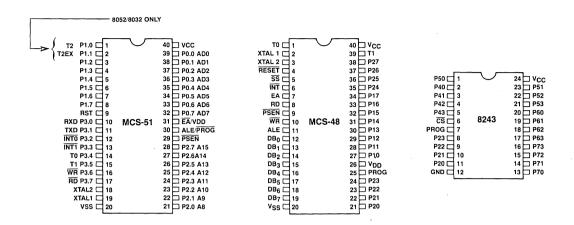

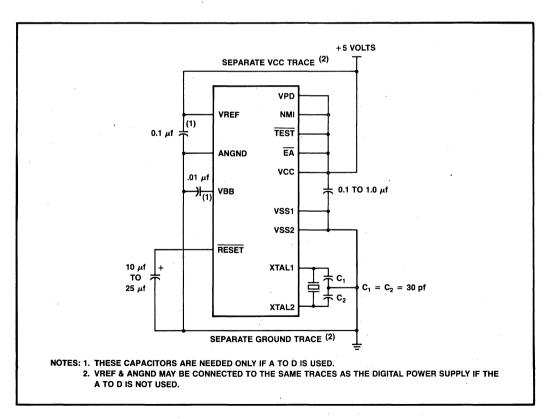

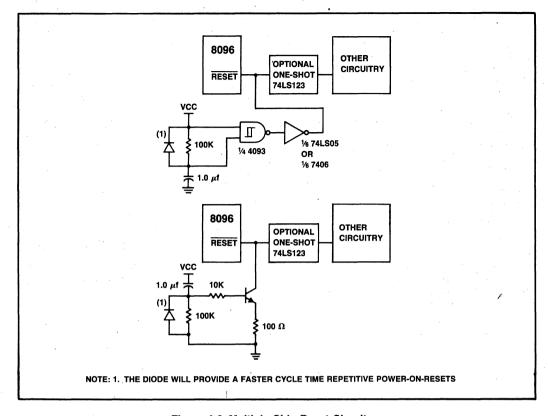

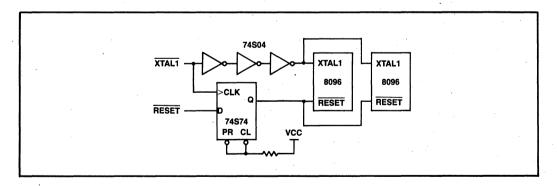

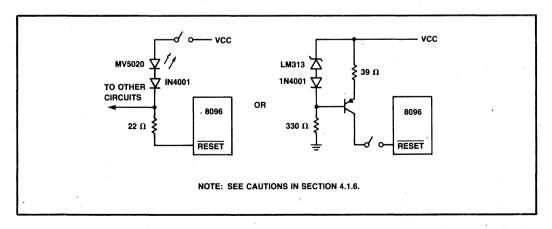

The serial port is compatible with the MCS-51 serial port. It is full duplex, meaning it can transmit and receive si-