intellec 8

intellec 8

Reference

Manual

Rev. 1

intellec8 Reference Manual Rev. 1

CAUTION

CAUTION

Do not operate the INTELLEC 8 with the cover removed.

The resulting diversion of cooling air may cause overheating the internal power supplies.

The resulting to the internal power supplies and damage to the internal power supplies.

# TABLE OF CONTENTS

| INTRODUCTION                             |    | Instruction Fetch (PCI)                   | 22 |

|------------------------------------------|----|-------------------------------------------|----|

| GENERAL DESCRIPTION                      | v  | Memory Reference Operations (PCR and PCW) | 22 |

| SPECIFICATIONS                           | v  | I/O Operations                            | 22 |

| THE SCOPE OF THIS MANUAL                 | vi | Interrupt Cycle                           | 23 |

|                                          |    | Hold Operation                            | 23 |

| CHAPTER 1                                |    | UTILIZATION                               | 24 |

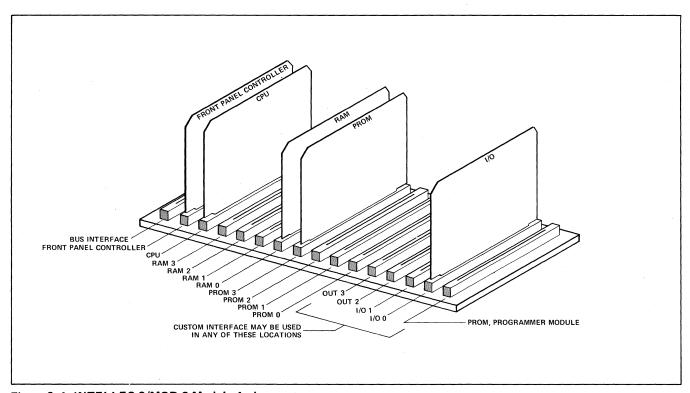

| INTELLEC 8/MOD 8 SYSTEM OVERVIEW         | 1  | Installation Requirements                 | 24 |

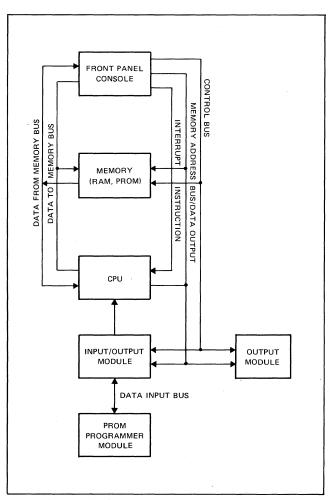

| FUNCTIONAL DESCRIPTION OF MODULES        | 1  | Signal Requirements                       | 24 |

| FRONT PANEL CONSOLE OPERATIONS           | 2  | Pin List                                  | 24 |

| MEMORY REFERENCE OPERATIONS              | 2  |                                           |    |

| Memory Read Operations                   | 2  | CHAPTER 3                                 |    |

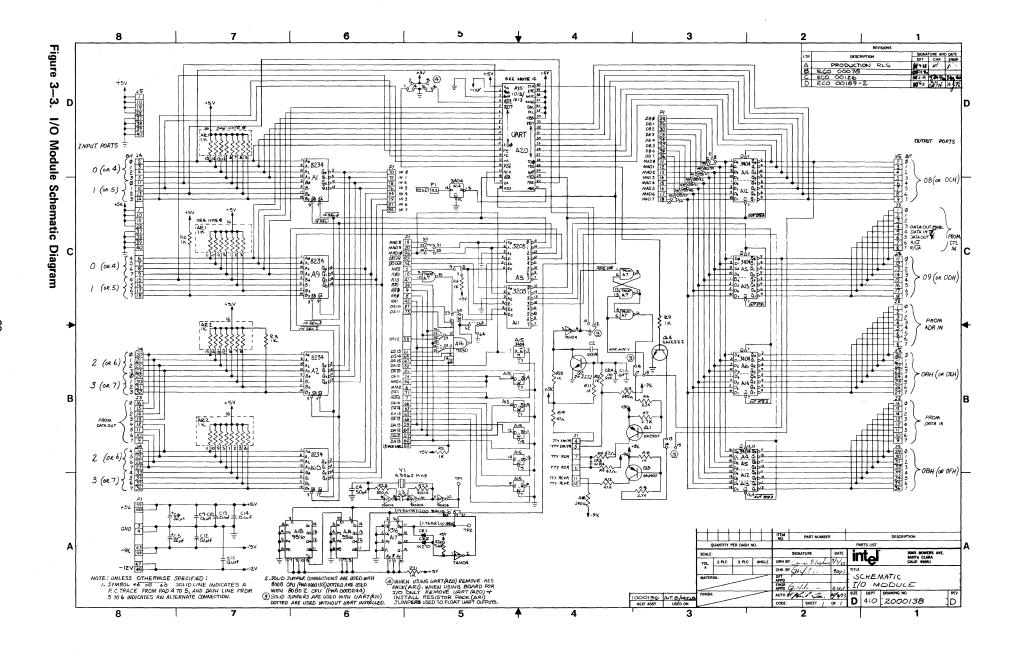

| Memory Write Operations                  | 2  | THE imm8-60 INPUT/OUTPUT CARD             | 29 |

| INPUT/OUTPUT OPERATIONS                  | 2  | THE imm8-60 INPUT/OUTPUT CARD—            |    |

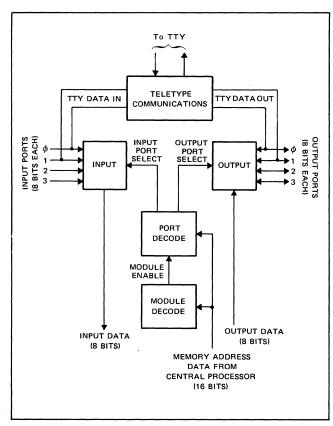

| Input Operations                         | 3  | GENERAL FUNCTIONAL DESCRIPTION            | 29 |

| Output Operations                        | 3  | The Functional Units                      | 29 |

| Teletype Operations                      | 3  | Module and Port Select Operations         | 30 |

| INTERRUPT OPERATIONS                     | 3  | Input Operation                           | 30 |

| PROM PROGRAMMING OPERATIONS              | 3  | Output Operation                          | 30 |

|                                          |    | Teletype Input Operation                  | 30 |

| CHAPTER 2                                |    | Teletype Output Operation                 | 30 |

| THE imm8-82 CENTRAL PROCESSOR MODULE     | 5  | THE imm8-60 INPUT/OUTPUT CARD—            |    |

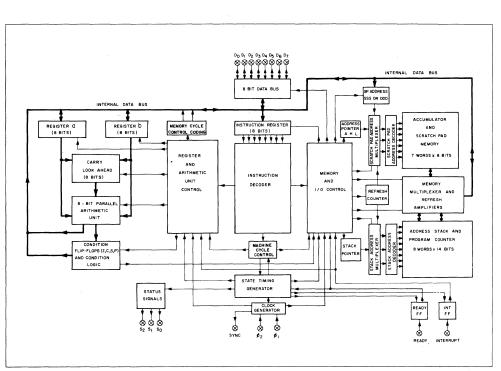

| THE FUNCTION OF A CPU                    | 6  | THEORY OF OPERATION                       | 31 |

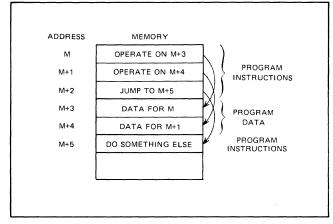

| The Computer System                      | 6  | Module Selection                          | 31 |

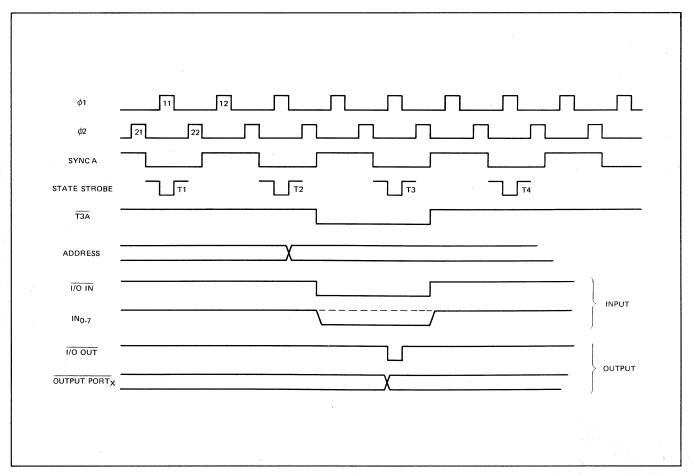

| The Architecture of a CPU                | 7  | Input Operations                          | 32 |

| FUNCTIONAL ORGANIZATION OF THE           |    | Output Operations                         | 32 |

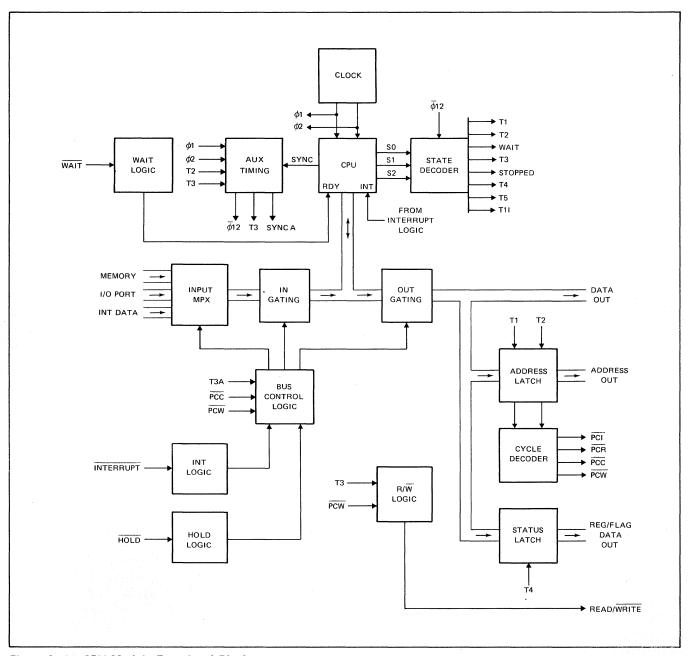

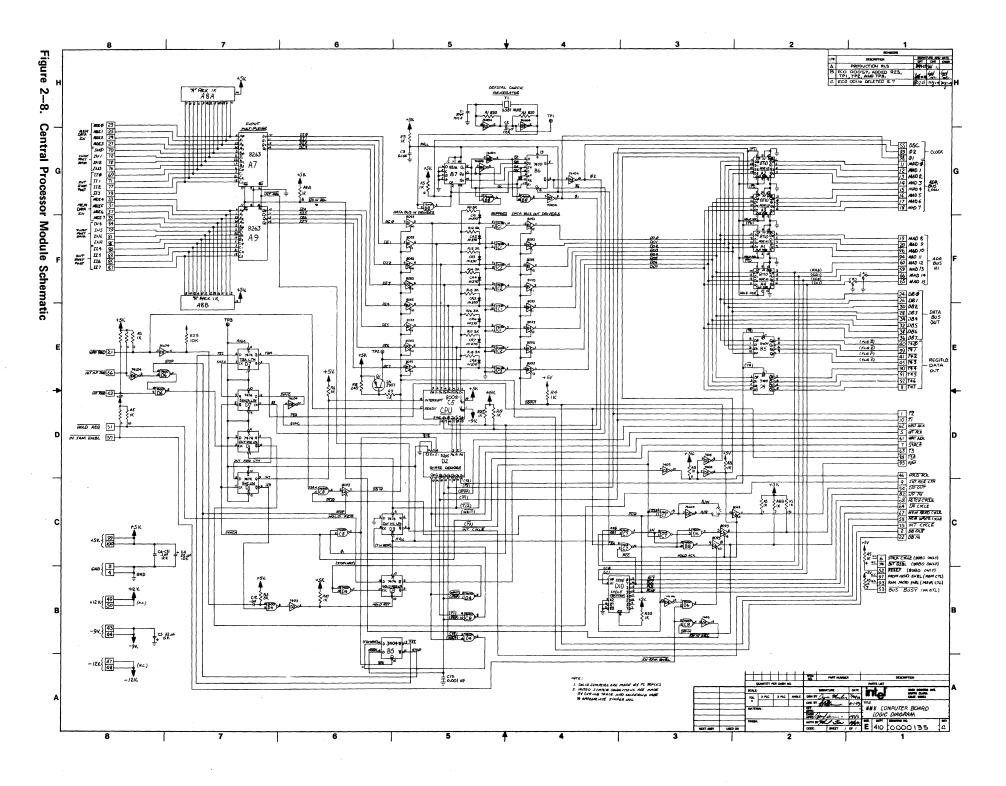

| CENTRAL PROCESSOR MODULE                 | 10 | Teletype Communications                   | 32 |

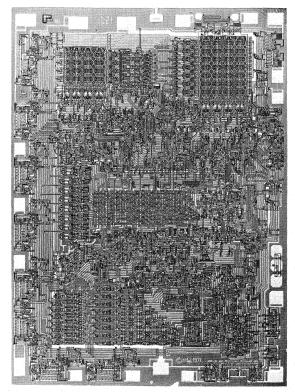

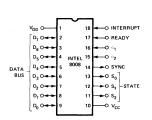

| 8008-1 EIGHT-BIT PARALLEL                |    | THE imm8-60 INPUT/OUTPUT CARD—            |    |

| CENTRAL PROCESSOR UNIT                   | 12 | UTILIZATION                               | 34 |

| Capabilities of the 8008-1               | 12 | User-Available Options                    | 35 |

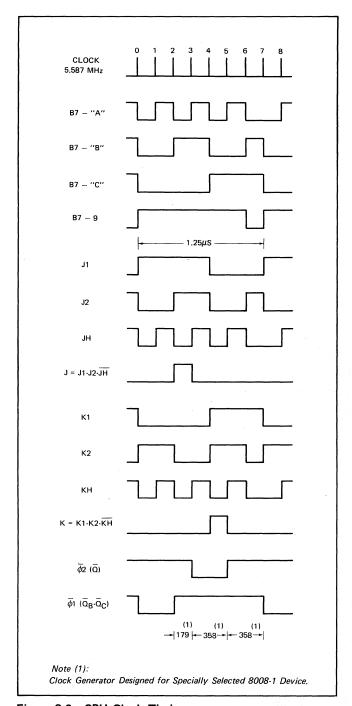

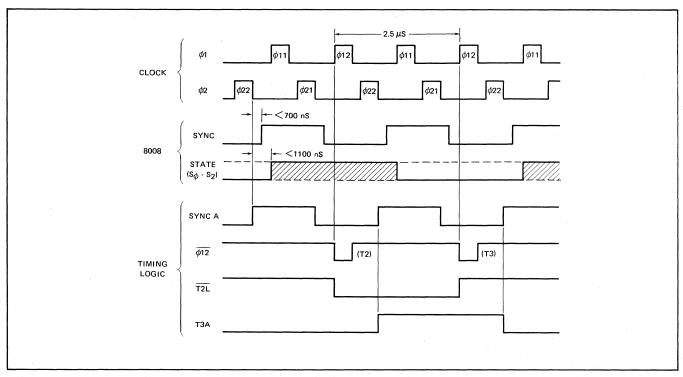

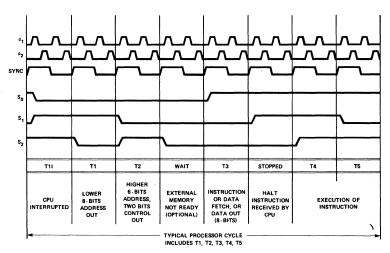

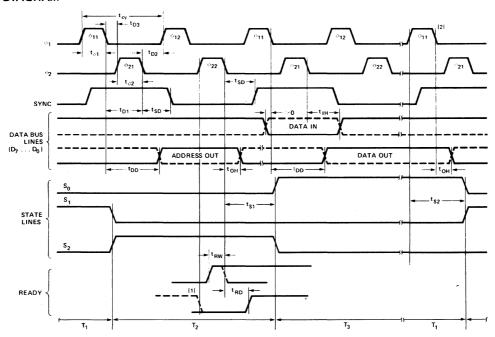

| Clock Timing                             | 13 | Installation Data                         | 36 |

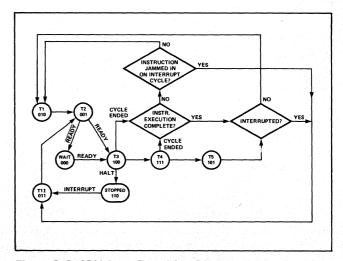

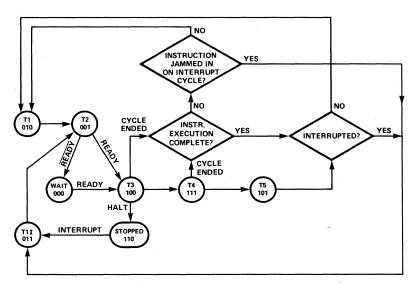

| The Processor Cycle                      | 13 | Teletype Modifications                    | 36 |

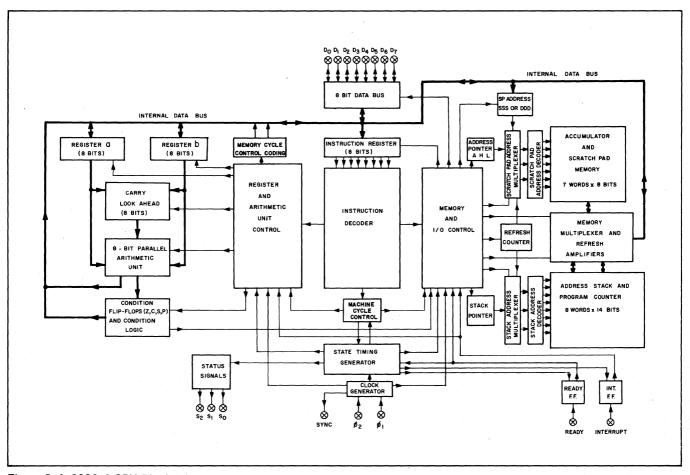

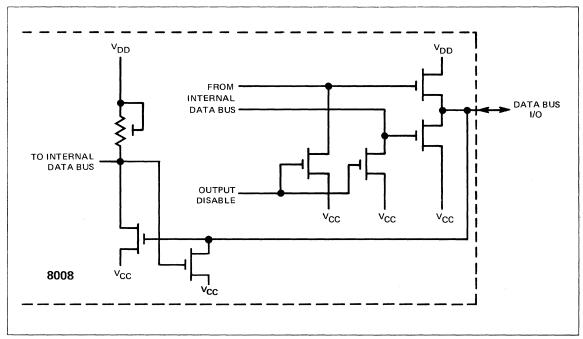

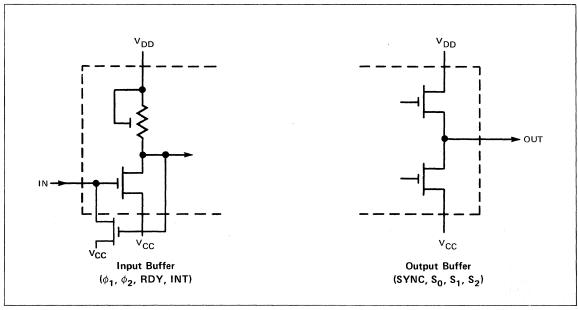

| Architecture of the 8008-1               | 15 |                                           |    |

| 8008-1 Instruction Set                   | 18 | CHAPTER 4                                 |    |

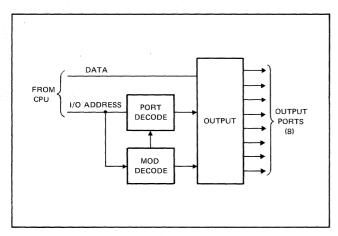

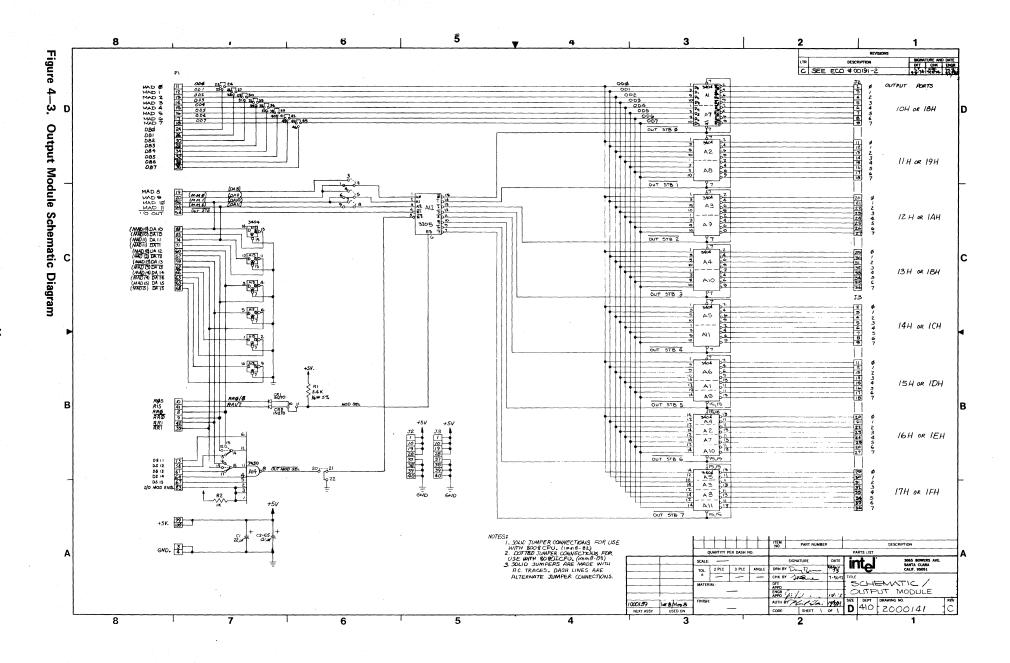

| Interrupt                                | 18 | THE imm8-62 OUTPUT CARD                   | 39 |

| Start-Up of the 8008-1                   | 19 | GENERAL FUNCTIONAL DESCRIPTION            | 39 |

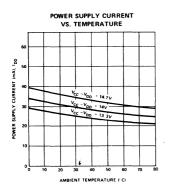

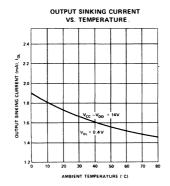

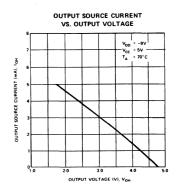

| Electrical Characteristics and Timing of |    | DETAILED FUNCTIONAL THEORY                | 39 |

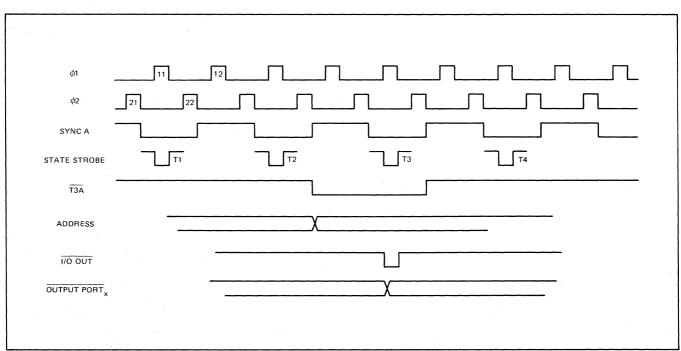

| The 8008-1                               | 19 | Module Decoding                           | 39 |

| PERIPHERAL LOGIC                         | 19 | Port Decoding                             | 40 |

| Timing Logic                             | 19 | Output Operations                         | 40 |

ĺ

| CARD UTILIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42 | Search/Wait Operations              | 61      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------|---------|

| User Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 | Processor Control Operations        | 61      |

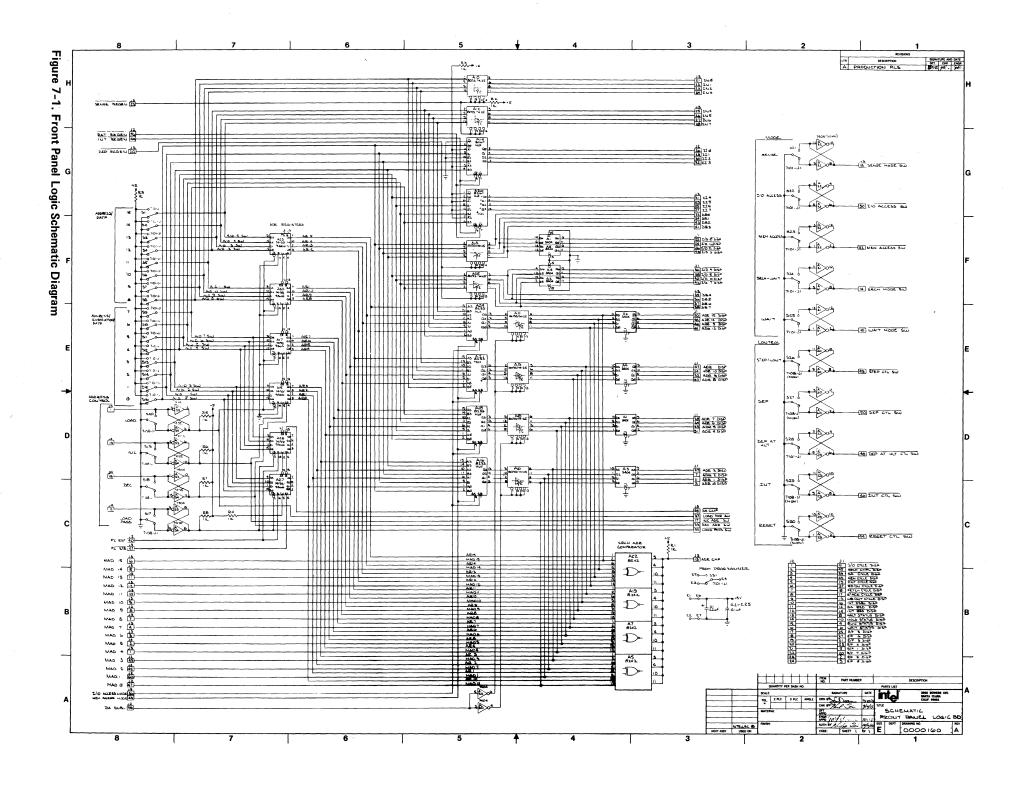

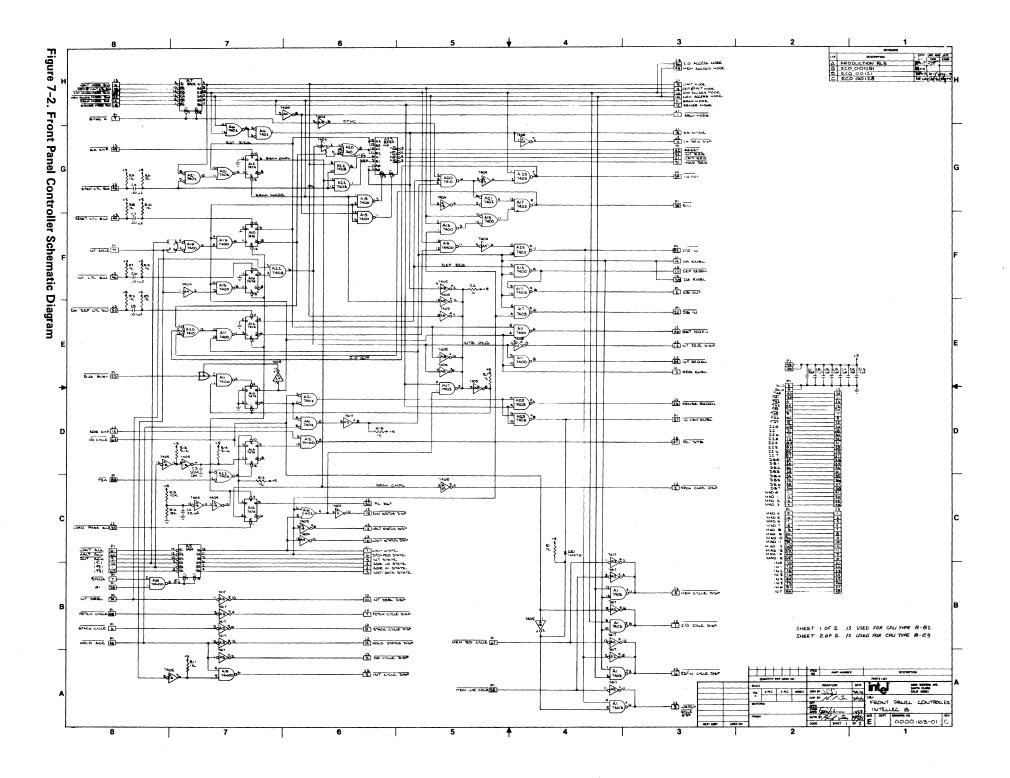

| CHAPTER 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | CHAPTER 8                           |         |

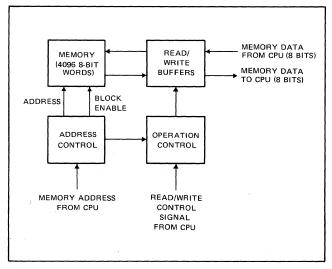

| THE imm6-28 RANDOM ACCESS MEMORY CARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43 | THE CHASSIS, MOTHER BOARD, AND      |         |

| GENERAL FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 43 | POWER SUPPLIES                      | 65      |

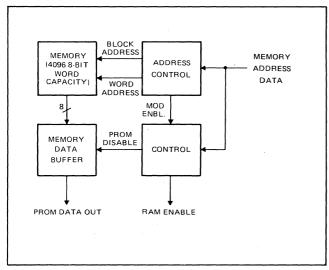

| The Four Functional Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43 |                                     |         |

| Memory Addressing Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 | CHAPTER 9                           |         |

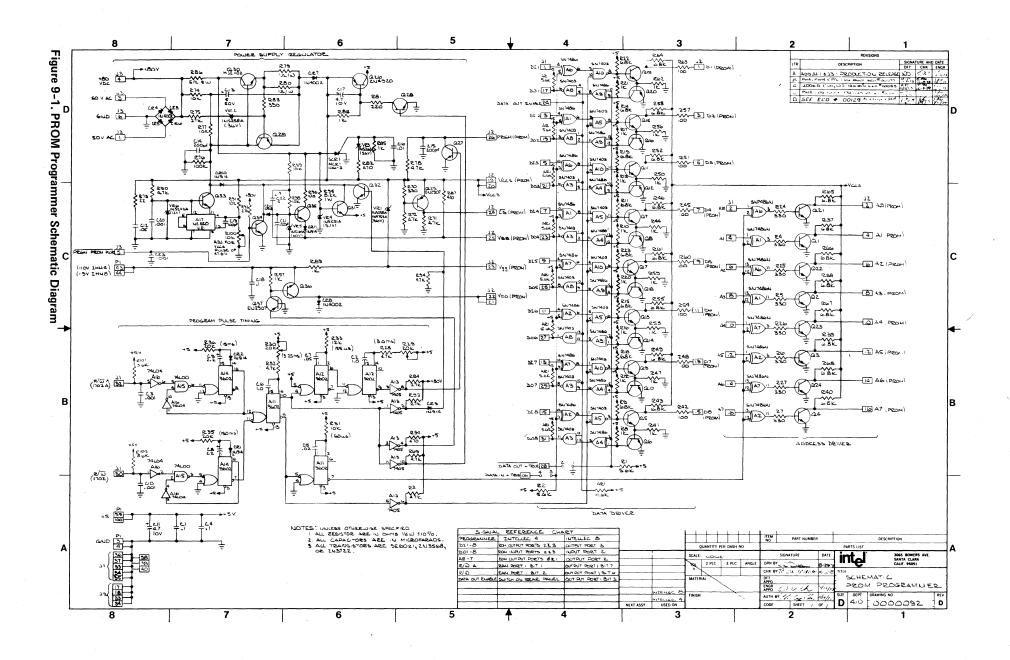

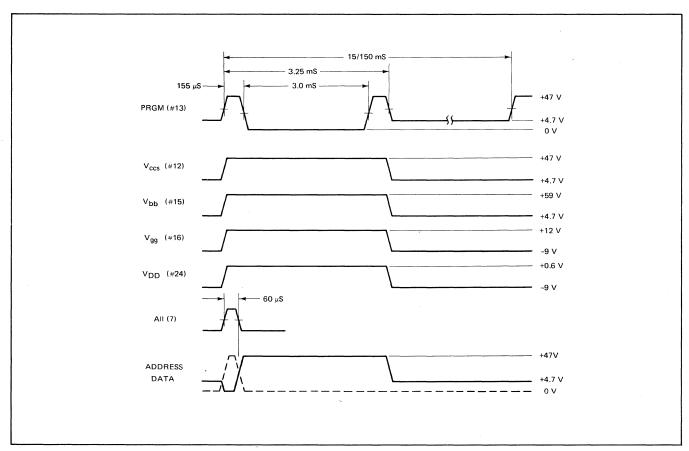

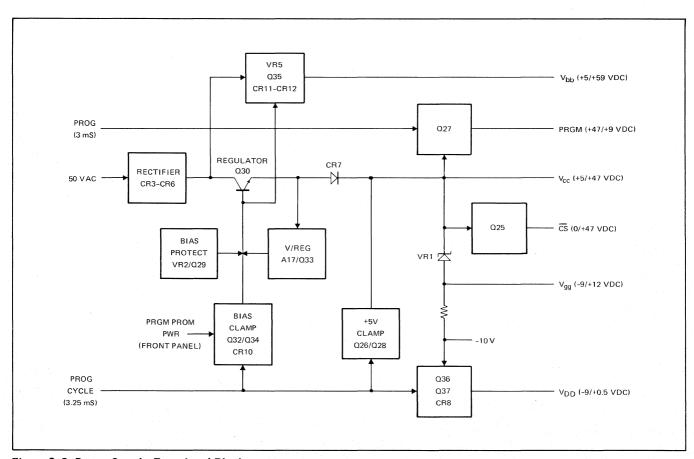

| Memory Write Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44 | THE imm8-76 PROM PROGRAMMER MODULE  | 67      |

| Memory Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44 | THE 1602A AND 1702A PROGRAMMABLE    |         |

| THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44 | READ ONLY MEMORY                    | 67      |

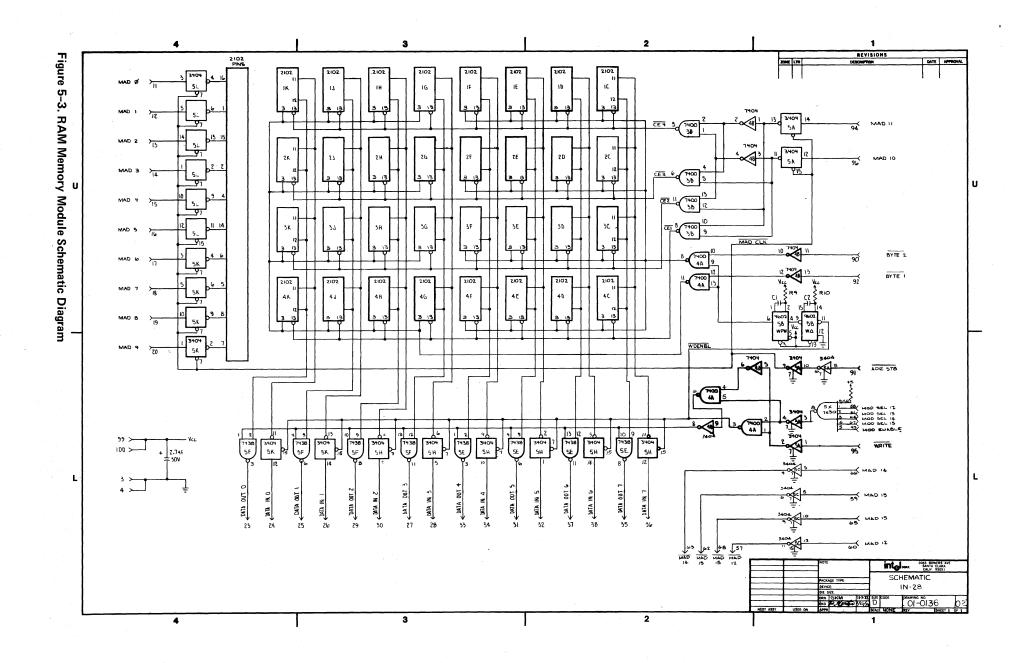

| Physical Memory Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44 | FUNCTIONAL DESCRIPTION              | 68      |

| Memory Address Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44 | Interface to the Intellec 8/MOD 8   | 68      |

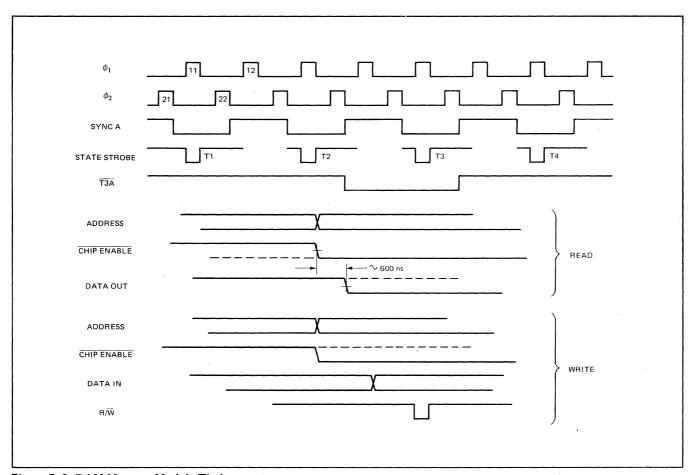

| Memory Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45 | THEORY OF OPERATION                 | 69      |

| Memory Write Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45 | Data Distribution                   | 69      |

| UTILIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47 | Control and Timing                  | 69      |

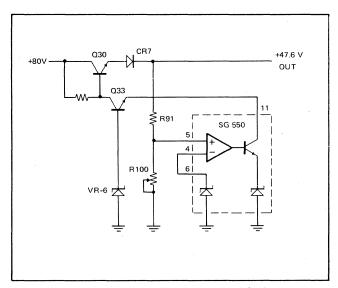

| Memory Address Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47 | Power Supply                        | 69      |

| Installation Data and Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 47 | UTILIZATION                         | 73      |

| The tand to the date of the da |    | Installation                        | 73      |

| CHAPTER 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | Pin List                            | 73      |

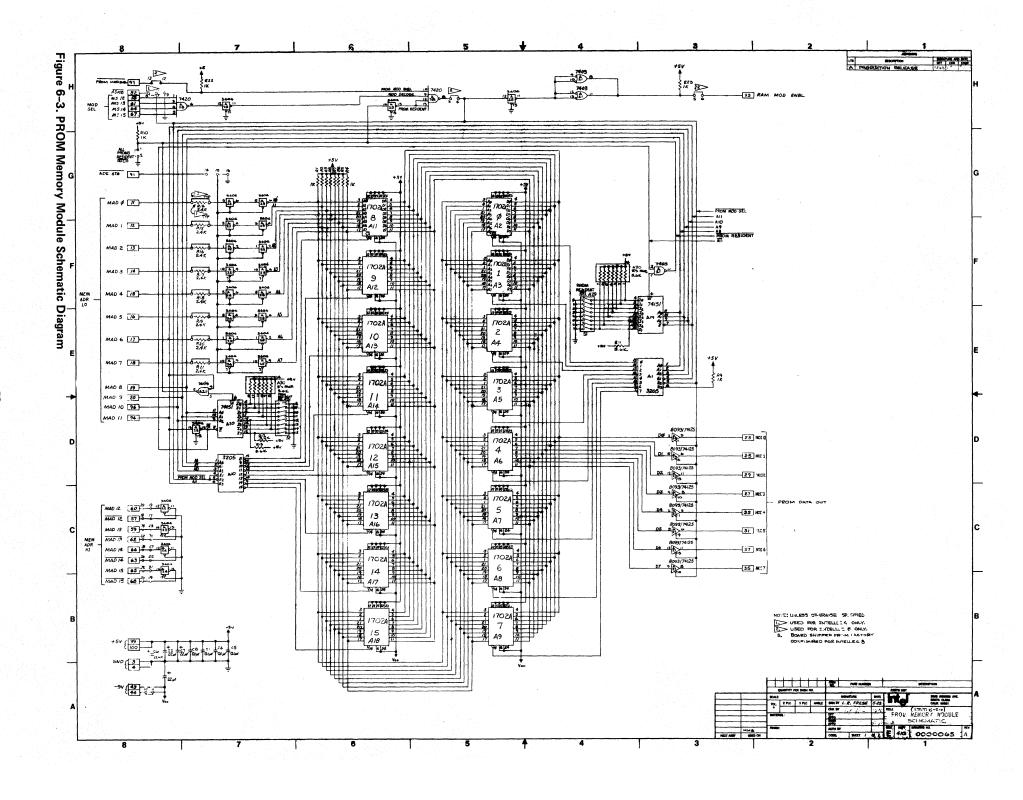

| THE imm6-26 PROGRAMMABLE READ-ONLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                                     |         |

| MEMORY CARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49 | CHAPTER 10                          |         |

| GENERAL FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 | INTELLEC 8/MOD 8 SYSTEM UTILIZATION | 77      |

| The Four Functional Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49 | INTELLEC 8/MOD 8 INSTALLATION       | 77      |

| Memory Read Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50 | SYSTEM I/O INTERFACING              | 77.     |

| THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50 | INTELLEC 8/MOD 8 SYSTEM             | -       |

| Physical Memory Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 | OPERATING REQUIREMENTS              | 77      |

| Memory Address Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 | EXTERNAL DEVICE CONTROLLER          |         |

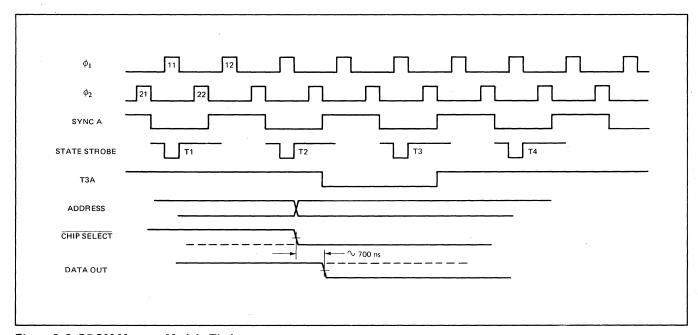

| Memory Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51 | INTERFACING                         | 82      |

| Random Access Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51 |                                     |         |

| UTILIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |                                     |         |

| Memory Address Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53 |                                     |         |

| PROM Installation, Removal, Programming,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | APPENDIX A                          |         |

| and Erasure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53 | 8008 INSTRUCTION SET                | vii     |

| Installation Data and Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53 |                                     |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | APPENDIX B                          |         |