## UPI-41A User's Manual

9800504-02 Rev.B

# inte

### UPI 41A<sup>™</sup> USER'S MANUAL

APRIL 1980

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9 (a) (9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of the Intel Corporation.

The following are trademarks of Intel Corporation and may only be used to describe Intel products:

| i            | Intellec        | Multimodule |

|--------------|-----------------|-------------|

| ICE          | iSBC            | PROMPT      |

| ICS          | Library Manager | Promware    |

| im           | MCS             | RMX         |

| Insite       | Megachassis     | UPI         |

| Intel        | Micromap        | μScope      |

| Intelevision |                 |             |

and the combinations of ICE, iCS, MCS or RMX and a numerical suffix.

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

#### **Table of Contents**

####

#### **CHAPTER 2**

| Functional Description         | . 2-1 |

|--------------------------------|-------|

| Basic Features                 | . 2-1 |

| Pin Description                | . 2-1 |

| CPU Section                    | . 2-4 |

| Program Memory                 | . 2-4 |

| Data Memory                    | . 2-5 |

| Program Counter                | . 2-6 |

| Program Status Word            | . 2-6 |

| Conditional Branch Logic       |       |

| Dscillator and Timing Circuits | . 2-7 |

| nternal Timer / Event Counter  | . 2-9 |

| Fest Inputs                    | 2-11  |

| nterrupts and DMA              | 2-11  |

| Reset                          |       |

| Data Bus Buffer                | 2-13  |

| System Interface               | 2-14  |

| nput/Output Interface          | 2-15  |

| I/O Ports                      | 2-15  |

| I/O Port Expansion             | 2-16  |

#### **CHAPTER 3**

| nstruction Set              | 3-1 |

|-----------------------------|-----|

| ntroduction                 | 3-1 |

| Instruction Set Description | 3-3 |

| Instruction Set Summary     | 3-3 |

| Alphabetic Listing          |     |

#### **CHAPTER 4**

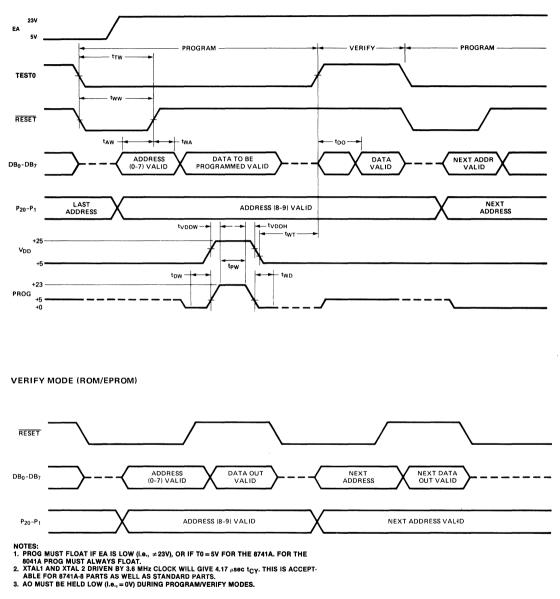

| 4-Single-step, Programming and Power-down Modes | 1 |

|-------------------------------------------------|---|

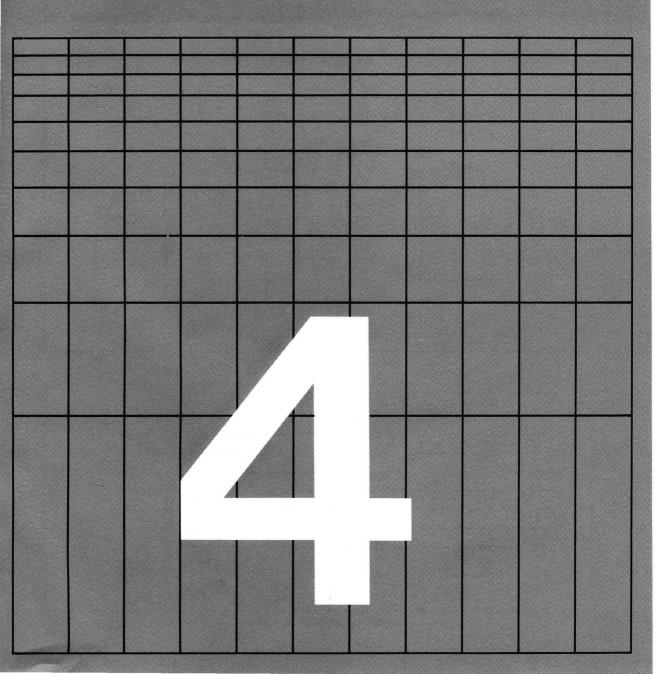

| 8741A Single-Step                               | 1 |

| Programming and Verification                    | 3 |

| External Access                                 | 4 |

| 8041A Power Down Mode                           | 4 |

#### **CHAPTER 5**

| System Operation             | j-1 |

|------------------------------|-----|

| Bus Interface                | j-1 |

| Design Examples              | j-2 |

| General Handshaking Protocol | j-4 |

#### **CHAPTER 6**

| Application Notes                        | <br> | <br>     |

|------------------------------------------|------|----------|

| Abstracts                                | <br> | <br>     |

| Application Notes                        | <br> | <br>     |

| Introduction to the UPI 41A <sup>™</sup> | <br> | <br>6-5  |

| Keyboard Scanning Application            | <br> | <br>6-47 |

#### CHAPTER 7

| Data Sheets                                                           |                |

|-----------------------------------------------------------------------|----------------|

| 8041A/8641A/8741A, Universal Peripheral Interface 8-bit Microcomputer |                |

| 8243 MCS-48™ Input / Output Expander                                  | <b>. 7-1</b> 1 |

| 8292 GPIB Controller                                                  |                |

| 8294 Data Encryption Unit                                             |                |

| 8295 Dot Matrix Printer Controller                                    |                |

#### **CHAPTER 8**

| System Support                                                 | . 8-1 |

|----------------------------------------------------------------|-------|

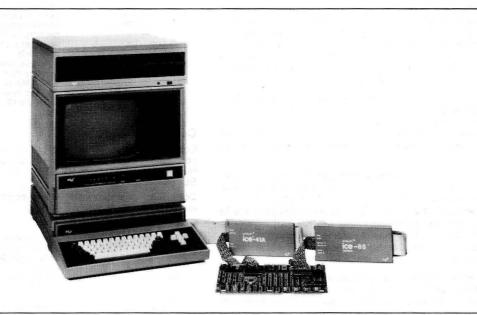

| ICE 41A™ UPI 41A™ In-Circuit Emulator                          |       |

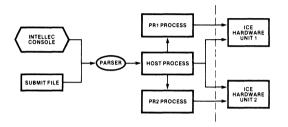

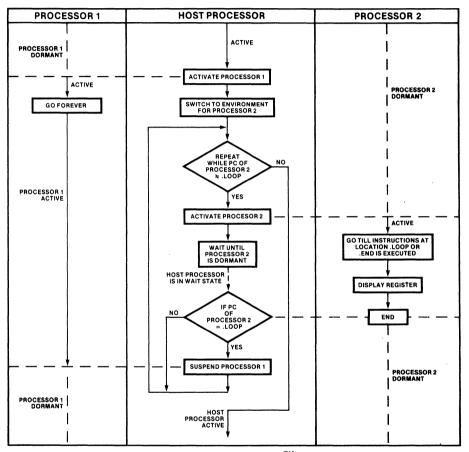

| Multi ICE Software, Multiple-In-Circuit-Emulator               | . 8-5 |

| MCS-48™ Diskette-Based Software Support Package                |       |

| Model 230 Intellec® Series II Microcomputer Development System | 8-11  |

| UPP-103 Universal PROM Programmer                              | 8-15  |

## CHAPTER 1 INTRODUCTION

#### CHAPTER 1 INTRODUCTION

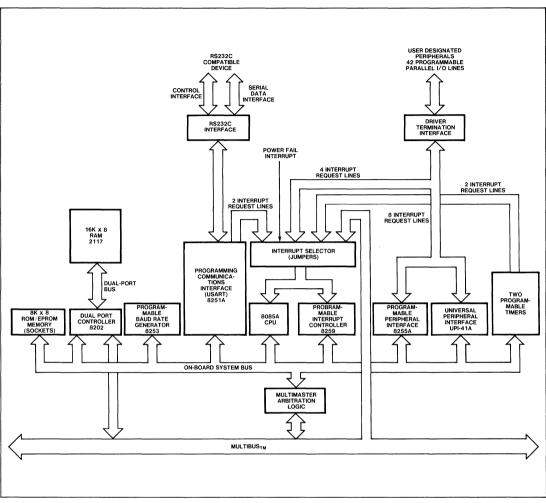

Accompanying the introduction of microprocessors such as the 8080, 8085, and 8086 there has been a rapid proliferation of intelligent peripheral devices. These special purpose peripherals extend CPU performance and flexibility in a number of important ways.

**Table 1-1. Intelligent Peripheral Devices**

| 8255 (GPIO)      | Programmable Peripheral<br>Interface                     |

|------------------|----------------------------------------------------------|

| 8251 (USART)     | Programmable<br>Communication Interface                  |

| 8253 (TIMER)     | Programmable Interval Timer                              |

| 8257 (DMA)       | Programmable DMA Controller                              |

| 8259             | Programmable Interrupt<br>Controller                     |

| 8272 (DDFDC)     | Programmable Floppy Disk<br>Controller                   |

| 8273 (SDLC)      | Programmable Synchronous<br>Data Link Controller         |

| 8275 (CRT)       | Programmable CRT<br>Controller                           |

| 8279 (PKD)       | Programmable<br>Keyboard/Display Controller              |

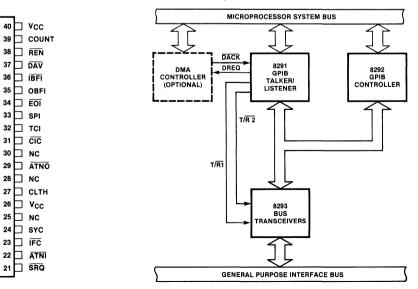

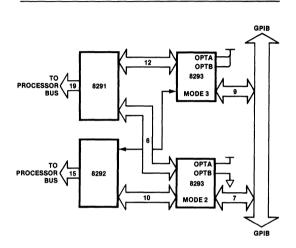

| 8291, 8292, 8293 | Programmable GPIB System<br>Talker, Listener, Controller |

Intelligent devices like the 8272 floppy disk controller and 8273 synchronous data link controller (see Table 1-1) can preprocess serial data and perform control tasks which off-load the main system processor. Higher overall system throughout is achieved and software complexity is greatly reduced. The intelligent peripheral chips simplify master processor control tasks by performing many functions externally in peripheral hardware rather than internally in main processor software.

Intelligent peripherals also provide system flexibility. They contain on-chip mode registers which are programmed by the master processor during system initialization. These control registers allow the peripheral to be configured into many different operation modes. The user-defined program for the peripheral is stored in main system memory and is transferred to the peripheral's registers whenever a mode change is required. Of course, this type of flexibility requires software overhead in the master system which tends to limit the benefit derived form the peripheral chip.

In the past, intelligent peripherals were designed to handle very specialized tasks. Separate chips were designed for communication disciplines, parallel I/O, keyboard encoding, interval timing, CRT control, etc. Yet, in spite of the large number of devices available and the increased flexibility built into these chips, there is still a large number of microcomputer peripheral control tasks which are not satisfied.

With the introduction of the Universal Peripheral Interface (UPI) microcomputer. Intel has taken the intelligent peripheral concept a step further by providing an intelligent controller that is fully user programmable. It is a complete single-chip microcomputer which can connect directly to a master processor data bus. It has the same advantages of intelligence and flexibility which previous peripheral chips offered. In addition, the UPI is user-programmable: it has 1K bytes of ROM or EPROM memory for program storage plus 64 bytes of RAM memory for data storage or initialization from the master processor. The UPI device allows a designer to fully specify his control algorithm in the peripheral chip without relying on the master processor. Devices like printer controllers and keyboard scanners can be completely self-contained, relying on the master processor only for data transfer.

The UPI family consists of three components:

- 8741A microcomputer with EPROM memory

- 8041A microcomputer with ROM memory

- 8243 I/O expander device

The 8741A and 8041A single chip microcomputers are functionally equivalent except for the type of program memory available with each. These devices have the following main features:

- 8-bit CPU

- 8-bit data bus interface registers

- 1K by 8 bit ROM or EPROM memory

- 64 by 8 bit RAM memory

- Interval timer/event counter

- Two 8-bit TTL compatible I/O ports

- Resident clock oscillator

The 8243 device is an I/O multiplexer which allows expansion of I/O to over 100 lines (if seven devices are used). All three parts are fabricated with Nchannel MOS technology and require a single, 5Vsupply for operation.

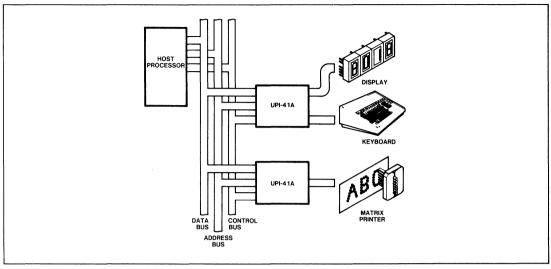

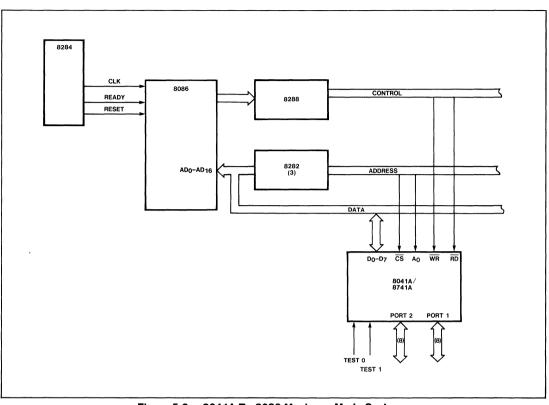

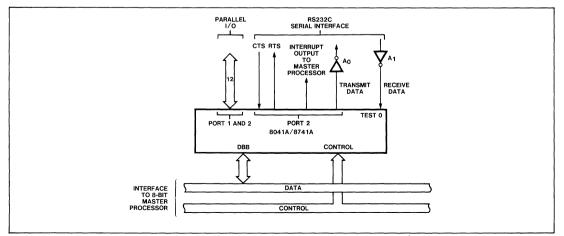

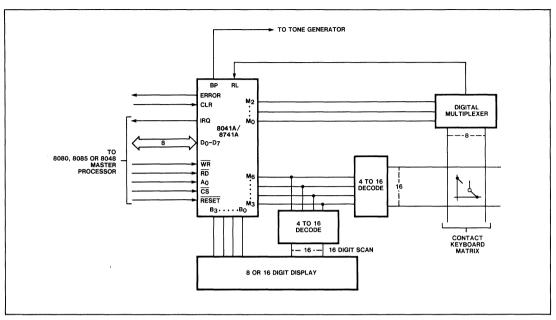

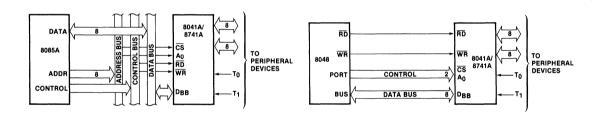

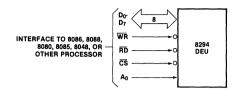

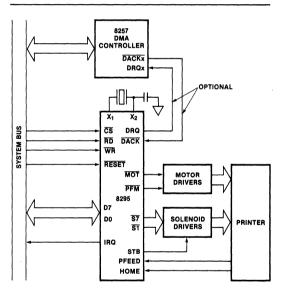

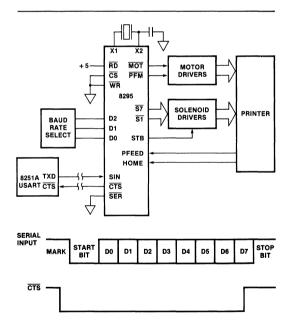

Figure 1-1. Interfacing Peripherals To Microcomputer Systems

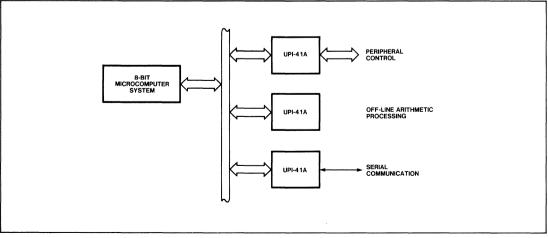

#### INTERFACE REGISTERS FOR MULTI-PROCESSOR CONFIGURATIONS

In the normal configuration, the 8041A/8741A interfaces to the system bus, just like any intelligent peripheral device (see Figure 1-1). The host processor and the 8041A/8741A form a loosely coupled multiprocessor system, that is, communications between the two processors are direct. Common resources are three addressable registers located physically on the 8041A/8741A. These registers are the Data Bus Buffer Input (DBBIN), Data Bus Buffer Output (DBBOUT), and Status (STATUS) registers. The host processor may read data from DBBOUT or write commands and data into DBBIN. The status of DBBOUT and DBBIN plus user-defined status is supplied in STATUS. The host may read STATUS at any time. An interrupt to the UPI processor is automatically generated (if enabled) when DBBIN is loaded.

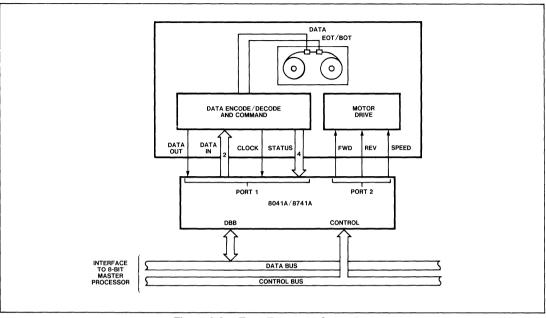

Because the UPI contains a complete microcomputer with program memory, data memory, and CPU it can function as a "Universal" controller. A designer can program the UPI to control printers, tape transports, or multiple serial communication channels. The UPI can also handle off-line arithmetic processing, or any number of other low speed control tasks.

#### **POWERFUL 8-BIT PROCESSOR**

The UPI contains a powerful, 8-bit CPU with 2.5  $\mu$ sec cycle time and two single-level interrupts. Its

instruction set includes over 90 instructions for easy software development. Most instructions are single byte and single cycle and none are more than two bytes long. The instruction set is optimized for bit manipulation and I/O operations. Special instructions are included to allow binary or BCD arithmetic operations, table lookup routines, loop counters, and N-way branch routines.

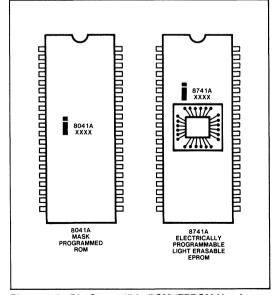

Figure 1-2. Pin Compatible ROM/EPROM Versions

### SPECIAL INSTRUCTION SET FEATURES

- For Loop Counters: Decrement Register and Jump if not zero.

- For Bit Manipulation: AND to A (immediate data or Register) OR to A (immediate data or Register) XOR to A (immediate data or Register) AND to Output Ports (Accumulator) OR to Output Ports (Accumulator) Jump Conditionally on any bit in A

- For BDC Arithmetic: Decimal Adjust A Swap 4-bit Nibbles of A Exchange lower nibbles of A and Register Rotate A left or right with or without Carry

- For Lookup Tables: Load A from Page of ROM (Address in A) Load A from Current Page of ROM (Address in A)

#### **Features for Peripheral Control**

The UPI 8-bit interval timer/event counter can be used to generate complex timing sequences for control applications or it can count external events such as switch closures and position encoder pulses. Software timing loops can be simplified or eliminated by the interval timer. If enabled, an interrupt to the CPU will occur when the timer overflows.

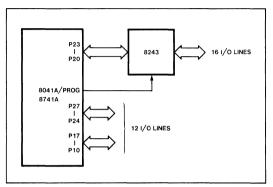

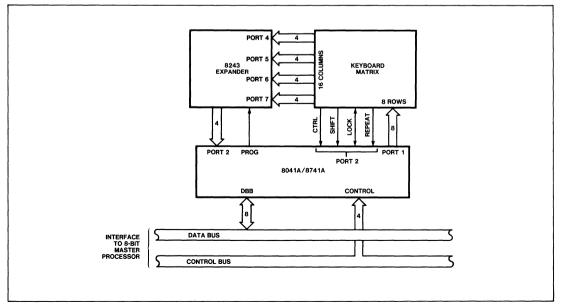

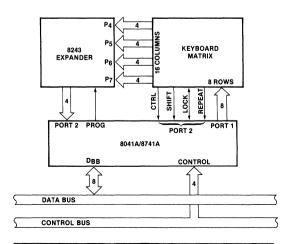

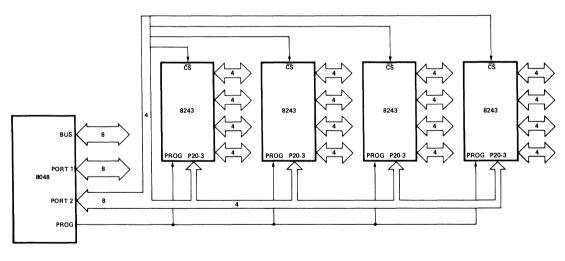

The UPI I/O complement contains two TTL-compatible 8-bit bidirectional I/O ports and two generalpurpose test inputs. Each of the 16 port lines can individually function as either input or output under software control. Four of the port lines can also function as an interface for the 8243 I/O expander which provides four additional 4-bit ports that are directly addressable by UPI software. The 8243 expander allows low cost I/O expansion for large control applications while maintaining easy and efficient software port addressing.

Figure 1-4. 8243 I/O Expander Interface

#### **On-Chip Memory**

The UPI's 64 bytes of data memory include dual working register banks and an 8-level program counter stack. Switching between the register banks allows fast response to interrupts. The stack is used to store return addresses and processor status upon entering a subroutine.

The UPI program memory is available in two types to allow flexibility in moving from design to prototype to production with the same PC layout. The 8741A device with EPROM memory is very economical for initial system design and development.

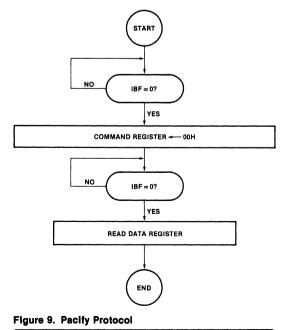

Figure 1-3. Interfaces And Protocols For Multiprocessor Systems

Its program memory can be electrically programmed using the Intel Universal PROM Programmer. When changes are needed, the entire program can be erased using UV lamp and reprogrammed in about 20 minutes. This means the 8741A can be used as a single chip "breadboard" for very complex interface and control problems. After the 8741A is programmed it can be tested in the actual production level PC board and the actual functional environment. Changes required during system debugging can be made in the 8741A program much more easily than they could be made in a random logic design. The system configuration and PC layout can remain fixed during the development process and the turn around time between changes can be reduced to a minimum.

At any point during the development cycle, the 8741A EPROM part can be replaced with the low cost 8041A part with factory mask programmed memory. The transition from system development to mass production is made smoothly because the 8741A and 8041A parts are completely pin compatible. This feature allows extensive testing with the EPROM part, even into initial shipments to customers. Yet, the transition to low-cost ROM is simplified to the point of being merely a package substitution.

#### **PREPROGRAMMED UPI's**

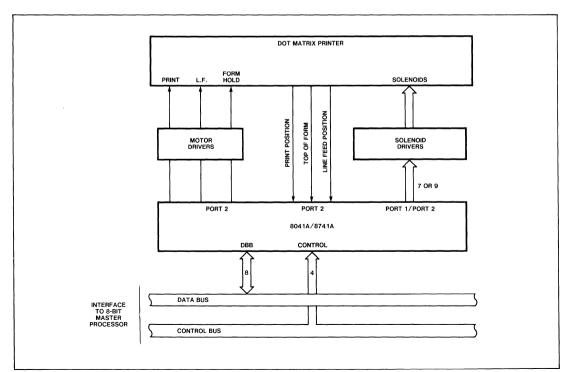

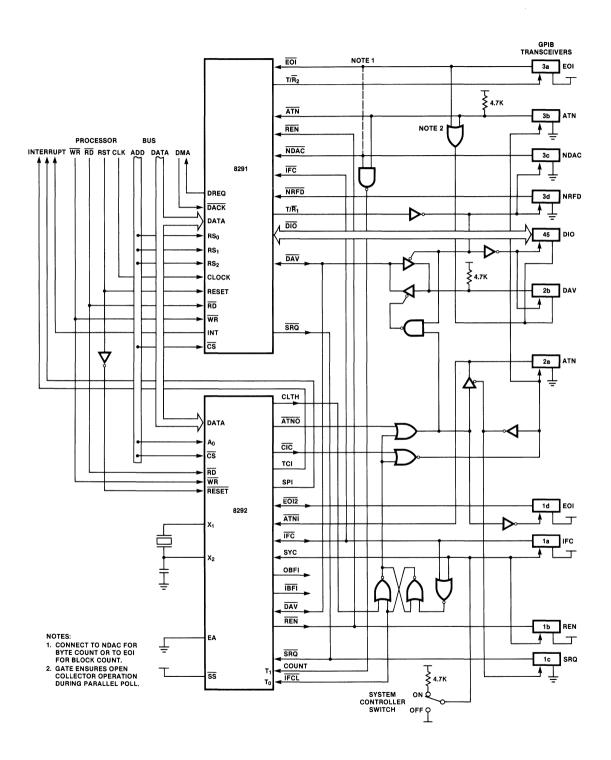

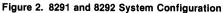

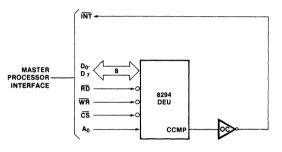

The 8292, 8294, and 8295 are 8041A's that are programmed by Intel and sold as standard peripherals.

The 8292 is a GPIB controller, part of a three chip GPIB system. The 8294 is a Data Encryption Unit that implements the National Bureau of Standards data encryption algorithm. The 8295 is a dot matrix printer controller designed especially for the LRC 7040 series dot matrix impact printers. These parts illustrate the great flexibility offered by the UPI family.

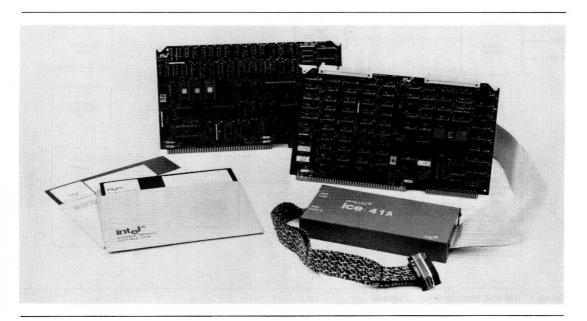

#### DEVELOPMENT SUPPORT

The UPI microcomputer is fully supported by Intel with development tools like the UPP PROM programmer already mentioned. An ICE-41A in-circuit emulator is also available to allow UPI software and hardware to be developed easily and quickly. The combination of device features and Intel development support make the UPI an ideal component for low-speed peripheral control applications.

#### **UPI DEVELOPMENT SUPPORT**

- 8048/8041A Assembler

- Universal PROM Programmer UPP Series

- ICE-41A Module

- MULTI-ICE

- Insite User's Library

- Application Engineers

- Training Courses

### CHAPTER 2 FUNCTIONAL DESCRIPTION

#### CHAPTER 2 FUNCTIONAL DESCRIPTION

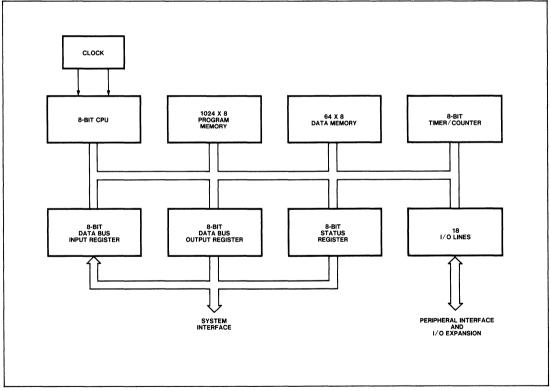

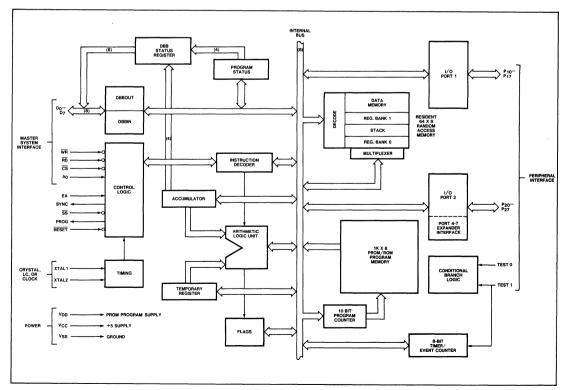

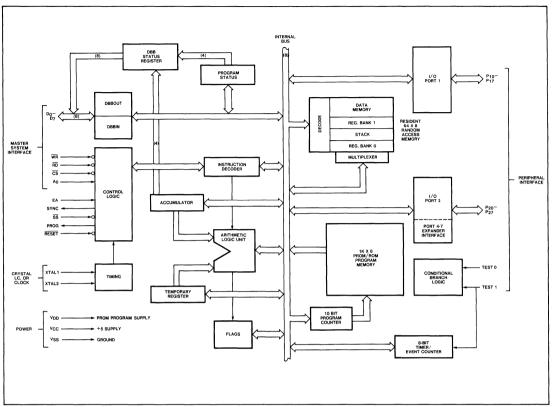

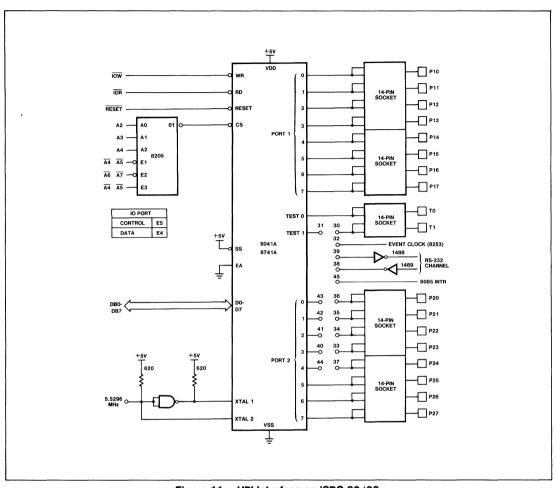

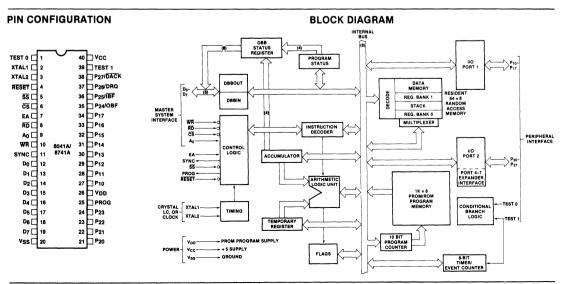

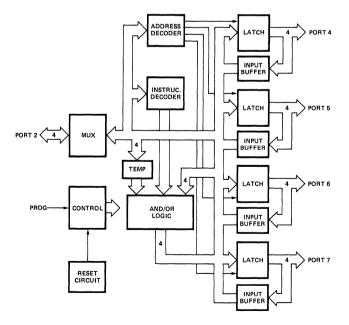

The UPI-41A microcomputer is an intelligent peripheral controller designed to operate in MCS-86, MCS-85, MCS-80, and MCS-48 systems. The UPI'S architecture, illustrated in Figure 2-1, is based on a low cost, single-chip microcomputer with program memory, data memory, CPU, I/O, event timer and clock oscillator in a single 40-pin package. Special interface registers are included which enable the UPI to function as a peripheral to an 8-bit master processor.

This chapter provides a basic description of the UPI microcomputer and its system interface registers. Unless otherwise noted the descriptions in this section apply to both the 8741A (with UV erasable program memory) and the 8041A (with factory mask programmed memory). These two devices are so similar that they can be considered identical under most circumstances. All functions described in this chapter apply to both the 8041A and 8741A.

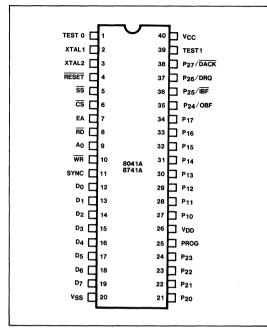

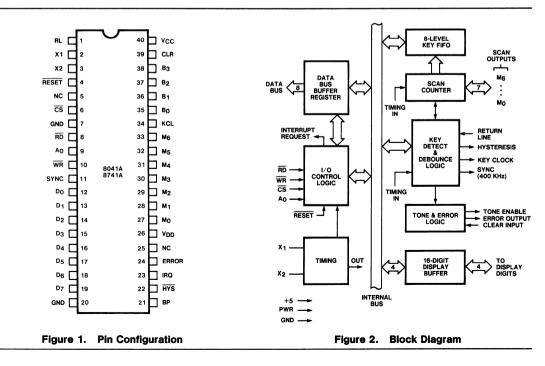

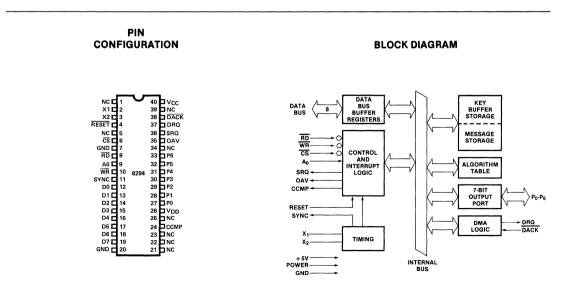

#### **PIN DESCRIPTION**

The 8741A and 8041A are packaged in 40-pin Dual In-Line (DIP) packages. The pin configuration for both devices is shown in Figure 2-2. Figure 2-3 illustrates the UPI Logic Symbol.

Figure 2-1. UPI-41A Single Chip Microcomputer

Figure 2-2. Pin Configuration

PROGRAM PROM +5V GND -XTAL -PORT #1 8 RESET SINGLE STEP PORT #2 DATA BUS BUFFER INTERFACE 8041A 8741A Ā TEST READ WRITE SYNC CONTROL CONTROL/ TEST MODE CHIP SELECT

Figure 2-3. Logic Symbol

The following section summarizes the functions of each UPI-41A pin. NOTE that several pins have two or more functions which are described in separate paragraphs.

| Symbol                                  | Pin No.        | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-----------------------------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D <sub>0</sub> -D <sub>7</sub><br>(BUS) | 12-19          | I/O  | <b>Data Bus:</b> Three-state, bidirectional DATA BUS BUFFER lines used to interface the UPI-41A microcomputer to an 8-bit master system data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| P <sub>10</sub> -P <sub>17</sub>        | 27-34          | I/O  | Port 1: 8-bit, PORT 1 quasi-bidirectional I/O lines.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| P <sub>20</sub> -P <sub>27</sub>        | 21-24<br>35-38 | I/O  | <b>Port 2:</b> 8-bit, PORT 2 quasi-bidirectional I/O lines. The lower 4 bits $(P_{20}-P_{23})$ inter<br>face directly to the 8243 I/O expander device and contain address and data information<br>during PORT 4-7 access. The upper 4 bits $(P_{24}-P_{27})$ can be programmed to provid-<br>interrupt Request and DMA Handshake capability. Software control can configure P <sub>2</sub> ,<br>as Output Buffer Full (OBF) interrupt, P <sub>25</sub> as Input Buffer Full (IBF) interrupt, P <sub>27</sub><br>as DMA Request (DRQ), and P <sub>27</sub> as DMA ACKnowledge (DACK). |  |

| WR                                      | 10             | I    | Write: I/O write input which enables the master CPU to write data and command words to the UPI-41A INPUT DATA BUS BUFFER.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| RD                                      | 8              | I    | <b>Read:</b> I/O read input which enables the master CPU to read data and status words from the OUTPUT DATA BUS BUFFER or status register.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| <u>CS</u>                               | 6              | I    | Chip Select: Chip select input used to select one UPI-41A microcomputer out of sev-<br>eral connected to a common data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| A <sub>0</sub>                          | 9              | I    | <b>Command/Data Select:</b> Address input used by the master processor to indicate whether byte transfer is data $(A_0=0)$ or command $(A_0=1)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| TEST 0,<br>TEST 1                       | 1<br>39        | Ι    | <b>Test Inputs:</b> Input pins which can be directly tested using conditional branch instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                                         |                |      | <b>Frequency Reference:</b> TEST 1 (T <sub>1</sub> ) also functions as the event timer input (under software control). TEST 0 (T <sub>0</sub> ) is used during PROM programming and verification in the 8741A.                                                                                                                                                                                                                                                                                                                                                                       |  |

| Т | able | 2-1. | Pin | Description |

|---|------|------|-----|-------------|

|---|------|------|-----|-------------|

#### FUNCTIONAL DESCRIPTION

| Symbol            | Pin No. | Туре | Name and Function                                                                                                                                                                              |  |

|-------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XTAL 1,<br>XTAL 2 | 2<br>3  | I    | <b>inputs:</b> Inputs for a crystal, LC or an external timing signal to determine the internal oscillator frequency.                                                                           |  |

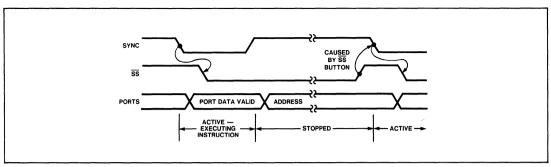

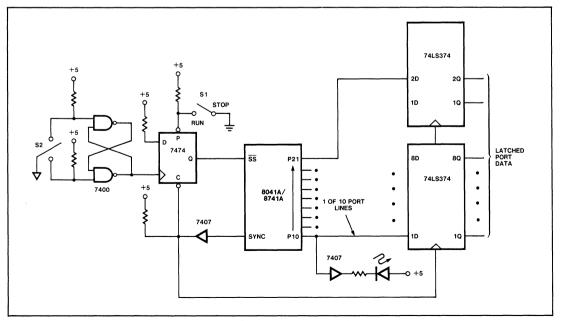

| SYNC              | 11      | 0    | <b>Dutput Clock:</b> Output signal which occurs once per UPI-41A instruction cycle. SYNC can be used as a strobe for external circuitry; it is also used to synchronize single step operation. |  |

| EA                | 7       | I    | External Access: External access input which allows emulation, testing and PROM/ ROM verification.                                                                                             |  |

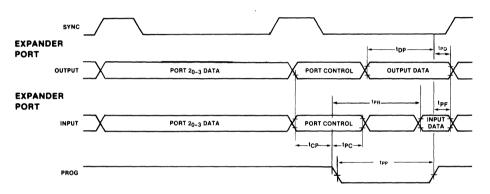

| PROG              | 25      | I/O  | <b>Program:</b> Multifunction pin used as the program pulse input during PROM program-<br>ming.                                                                                                |  |

|                   |         |      | During I/O expander access the PROG pin acts as an address/data strobe to the 8243.                                                                                                            |  |

| RESET             | 4       | Ι    | Reset: Input used to reset status flip-flops and to set the program counter to zero.                                                                                                           |  |

|                   |         |      | <b>RESET</b> is also used during PROM programming and verification.                                                                                                                            |  |

| SS                | 5       | I    | <b>Single Step:</b> Single step input used in the 8741A in conjunction with the SYNC output to step the program through each instruction.                                                      |  |

| V <sub>CC</sub>   | 40      |      | Power: +5V main power supply pin.                                                                                                                                                              |  |

| V <sub>DD</sub>   | 26      |      | <b>Power:</b> +5V during normal operation. +25V during programming operation. Low power standby pin in ROM version.                                                                            |  |

| VSS               | 20      |      | Ground: Circuit ground potential.                                                                                                                                                              |  |

#### Table 2-1. Pin Description (Continued)

The following sections provide a detailed functional description of the UPI microcomputer. Figure 2-4 il-

lustrates the functional blocks within the UPI device.

Figure 2-4. UPI-41A™ Block Diagram

#### **CPU SECTION**

The CPU section of the UPI-41A microcomputer performs basic data manipulations and controls data flow throughout the single chip computer via the internal 8-bit data bus. The CPU section includes the following functional blocks shown in Figure 2-4:

- Arithmetic Logic Unit (ALU)

- Instruction Decoder

- Accumulator

- Flags

#### Arithmetic Logic Unit (ALU)

The ALU is capable of performing the following operations:

- ADD with or without carry

- AND, OR, and EXCLUSIVE OR

- Increment, Decrement

- Bit complement

- Rotate left or right

- Swap

- BCD decimal adjust

In a typical operation data from the accumulator is combined in the ALU with data from some other source on the UPI-41A internal bus (such as a register or an I/O port). The result of an ALU operation can be transferred to the internal bus or back to the accumulator.

If an operation such as an ADD or ROTATE requires more than 8 bits, the CARRY flag is used as an indicator. Likewise, during decimal adjust and other BCD operations the AUXILIARY CARRY flag can be set and acted upon. These flags are part of the Program Status Word (PSW).

#### **Instruction Decoder**

During an instruction fetch, the operation code (opcode) portion of each program instruction is stored and decoded by the instruction decoder. The decoder generates outputs used along with various timing signals to control the functions performed in the ALU. Also, the instruction decoder controls the source and destination of ALU data.

#### Accumulator

The accumulator is the single most important register in the processor. It is the primary source of data to the ALU and is often the destination for results as well. Data to and from the I/O ports and memory normally passes through the accumulator.

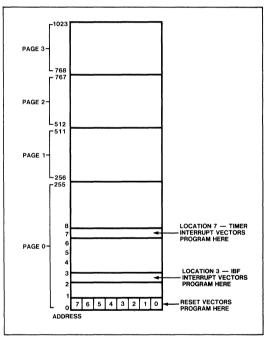

#### **PROGRAM MEMORY**

The UPI-41A microcomputer has 1024 8-bit words of resident, read-only memory for program storage. Each of these memory locations is directly addressable by a 10-bit program counter. Depending on the type of application and the number of program changes anticipated, two types of program memory are available:

- 8041A with mask programmed ROM Memory

- 8741A with electrically programmable EPROM Memory

The 8041A and 8741A are functionally identical parts and are completely pin compatible. The 8041A has ROM memory which is mask programmed to user specification during fabrication. The 8741A is electrically programmed by the user using the Universal PROM Programmer (UPP series) with a UPP-848 Personality Card. It can be erased using ultraviolt light and reprogrammed at any time.

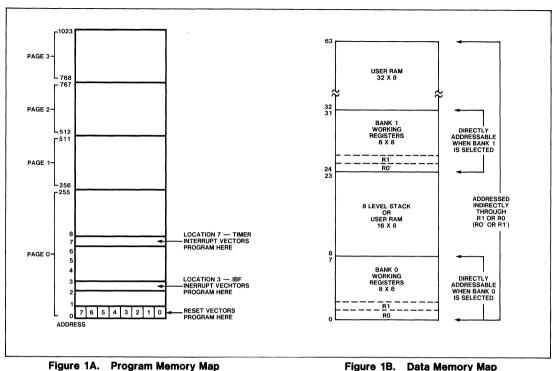

A program memory map is illustrated in Figure 2-5. Memory is divided into 256 location 'pages' and three locations are reserved for special use:

Figure 2-5. Program Memory Map

#### **INTERRUPT VECTORS**

#### 1) Location 0

Following a **RESET** input to the processor, the next instruction is automatically fetched from location 0.

#### 2) Location 3

An interrupt generated by an Input Buffer Full (IBF) condition (when the IBF interrupt is enabled) causes the next instruction to be fetched from location 3.

#### 3) Location 7

A timer overflow interrupt (when enabled) will cause the next instruction to be fetched from location 7.

Following a system  $\overline{\text{RESET}}$ , program execution begins at location 0. Instructions in program memory are normally executed sequentially. Program control can be transferred out of the main line of code by an input buffer full (IBF) interrupt or a timer interrupt, or when a jump or call instruction is encountered. An IBF interrupt (if enabled) will automatically transfer control to location 3 while a timer interrupt will transfer control to location 7.

All conditional JUMP instructions and the indirect JUMP instruction are limited in range to the current 256-location page (that is, they alter PC bits 0-7 only). If a conditional JUMP or indirect JUMP begins in location 255 of a page, it must reference a destination on the following page.

Program memory can be used to store constants as well as program instructions. the UPI-41A instruction set contains an instruction (MOVP3) designed specifically for efficient transfer of look-up table information from page 3 of memory.

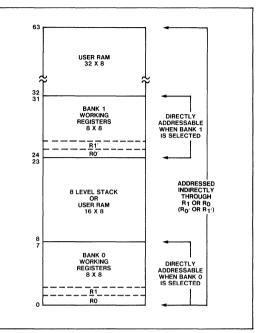

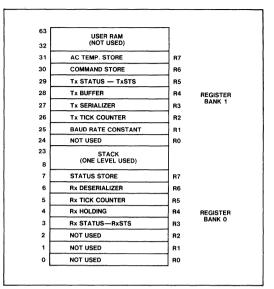

#### DATA MEMORY

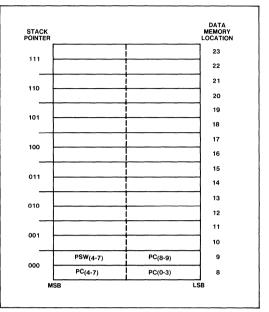

The UPI-41A universal peripheral interface has 64 8-bit words of random access data memory. This memory contains two working register banks, an 8level program counter stack and a scratch pad memory, as shown in Figure 2-6. The amount of scratch pad memory available is variable depending on the number of addresses nested in the stack and the number of working registers being used.

#### **Addressing Data Memory**

The first eight locations in RAM are designated as working registers  $R_0$ - $R_7$ . These locations (or registers) can be addressed directly by specifying a register number in the instruction. Since these locations are easily addressed, they are generally used to store frequently accessed intermediate results. Other locations in data memory are addressed indirectly by using  $R_0$  or  $R_1$  to specify the desired address. Since all RAM locations (including the eight working registers) can be addressed by 6 bits, the two most significant bits (6 and 7) of the addressing registers are ignored.

#### **Working Registers**

Dual banks of eight working registers are included in the UPI-41A data memory. Locations 0-7 make up register bank 0 and locations 24-31 form register bank 1. A RESET signal automatically selects regis-

Figure 2-6. Data Memory Map

ter bank 0. When bank 0 is selected, references to  $R_0-R_7$  in UPI-41A instructions operate on locations 0–7 in data memory. A "select register bank" instruction is used to select between the banks during program execution. If the instruction SEL RB1 (Select Register Bank 1) is executed, then program references to  $R_0-R_7$  will operate on locations 24–31. As stated previously, registers 0 and 1 in the active register bank are used as indirect address registers for all locations in data memory.

Register bank 1 is normally reserved for handling interrupt service routines, thereby preserving the contents of the main program registers. The SEL RB1 instruction can be issued at the beginning of an interrupt service routine. Then, upon return to the main program, an RETR (return & restore status) instruction will automatically restore the previously selected bank. During interrupt processing, registers in bank 0 can be accessed indirectly using  $R_0'$  and  $R_1'$ .

If register bank 1 is not used, registers 24–31 can still serve as additional scratch pad memory.

#### **Program Counter Stack**

RAM locations 8–23 are used as an 8-level program counter stack. When program control is temporarily passed from the main program to a subroutine or interrupt service routine, the 10-bit program counter and bits 4-7 of the program status word (PSW) are stored in two stack locations. When control is returned to the main program via an RETR instruction, the program counter and PSW bits 4-7 are restored. Returning via an RET instruction does not restore the PSW bits, however. The program counter stack is addressed by three stack pointer bits in the PSW (bits 0-2). Operation of the program counter stack and the program status word is explained in detail in the following sections.

The stack allows up to eight levels of subroutine 'nesting'; that is, a subroutine may call a second subroutine, which may call a third, etc., up to eight levels. Unused stack locations can be used as scratch pad memory. Each unused level of subroutine nesting provides two additional RAM locations for general use.

The following sections provide a detailed description of the Program Counter Stack and the Program Status Word.

#### **PROGRAM COUNTER**

The UPI-41A microcomputer has a 10-bit program counter (PC) which can directly address any of the 1024 locations in program memory. The program counter always contains the address of the next instruction to be executed and is normally incremented sequentially for each instruction to be executed when each instruction fetches occurs.

When control is temporarily passed from the main program to a subroutine or an interrupt routine, however, the PC contents must be altered to point to the address of the desired routine. The stack is used to save the current PC contents so that, at the end of the routine, main program execution can continue. The program counter is initialized to zero by a RESET signal.

#### **PROGRAM COUNTER STACK**

The Program Counter Stack is composed of 16 locations in Data Memory as illustrated in Figure 2-7. These RAM locations (8 through 23) are used to store the 10-bit program counter and 4 bits of the program status word.

An interrupt or CALL to a subroutine causes the contents of the program counter to be stored in one of the 8 register pairs of the program counter stack.

A 3-bit Stack Pointer which is part of the Program Status Word (PSW) determines the stack pair to be used at a given time. The stack pointer is initialized by a RESET signal to 00H which corresponds to RAM locations 8 and 9.

Figure 2-7. Program Counter Stack

The first call or interrupt results in the program counter and PSW contents being transferred to RAM locations 8 and 9 in the format shown in Figure 2-7. The stack pointer is automatically incremented by 1 to point to locations 10 and 11 in anticipation of another CALL.

Nesting of subroutines within subroutines can continue up to 8 levels without overflowing the stack. If overflow does occur the deepest address stored (locations 8 and 9) will be overwritten and lost since the stack pointer overflows from 07H to 00H. Likewise, the stack pointer will underflow from 00H to 07H.

The end of a subroutine is signaled by a return instruction, either RET or RETR. Each instruction will automatically decrement the Stack Pointer and transfer the contents of the proper RAM register pair to the Program Counter.

#### **PROGRAM STATUS WORD**

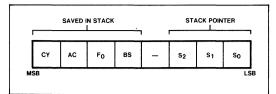

The 8-bit program status word illustrated in Figure 2-8 is used to store general information about program execution. In addition to the 3-bit Stack Pointer discussed previously, the PSW includes the following flags:

- CY Carry

- AC Auxiliary Carry

- $F_0 Flag 0$

- BS Register Bank Select

Figure 2-8. Program Status Word

The Program Status Word (PSW) is actually a collection of flip-flops located throughout the machine which are read or written as a whole. The PSW can be loaded to or from the accumulator by the MOV A, PSW or MOV PSW,A instructions. The ability to write directly to the PSW allows easy restoration of machine status after a power-down sequence.

The upper 4 bits of the PSW (bits 4, 5, 6, and 7) are stored in the PC Stack with every subroutine CALL or interrupt vector. Restoring the bits on a return is optional. The bits are restored if an RETR instruction is executed, but not if an RET is executed.

PSW bit definitions are as follows:

- Bits 0-2 Stack Pointer Bits S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>

- Bit 3 Not Used

- Bit 4 Working Register Bank

- 0 = Bank 0

- 1 = Bank 1

- Bit 5 Flag 0 bit (F<sub>0</sub>) This is a general purpose flag which can be cleared or complemented and tested with conditional jump instructions. It may be used during data transfer to an external processor.

- Bit 6 Auxiliary Carry (AC) The flag status is determined by an ADD instruction and is used

by the Decimal Adjustment instruction DAA.

• Bit 7 Carry (CY) The flag indicates that a previous operation resulted in overflow of the accumulator.

#### **CONDITIONAL BRANCH LOGIC**

Conditional Branch Logic in the UPI-41A allows the status of various processor flags, inputs, and other hardware functions to directly affect program execution. The status is sampled in state 3 of the first cycle.

Table 2-2 lists the internal conditions which are testable and indicates the condition which will cause a jump. In all cases, the destination address must be within the page of program memory (256 locations) in which the jump instruction occurs.

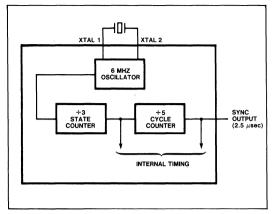

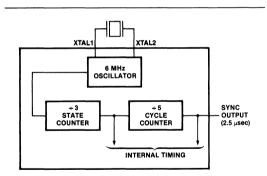

#### **OSCILLATOR AND TIMING CIRCUITS**

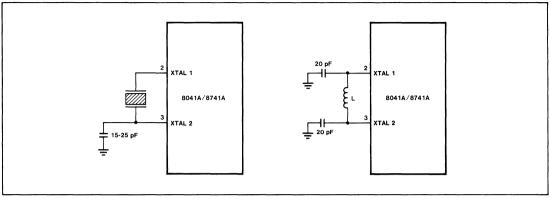

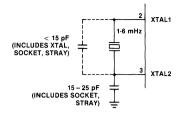

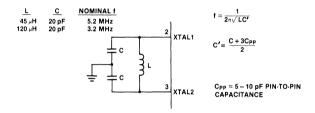

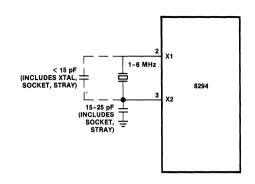

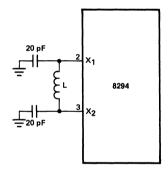

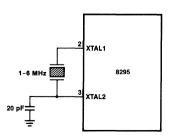

The 8041A's internal timing generation is controlled by a self-contained oscillator and timing circuit. A choice of crystal, L-C or external clock can be used to derive the basic oscillator frequency.

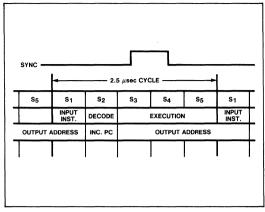

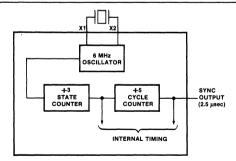

The resident timing circuit consists of an oscillator, a state counter and a cycle counter as illustrated in Figure 2-9. Figure 2-10 shows instruction cycle timing.

#### Oscillator

The on-board oscillator is a series resonant circuit with a frequency range of 1 to 6 MHz. Pins XTAL 1 and XTAL 2 are input and output (respectively) of a high gain amplifier stage. A crystal or inductor and capacitor connected between XTAL 1 and XTAL 2 provide the feedback and proper phase shift for os-

| Table 2-2. Conditional Branch Instructions | Table 2-2 | . Conditional | Branch | Instructions |

|--------------------------------------------|-----------|---------------|--------|--------------|

|--------------------------------------------|-----------|---------------|--------|--------------|

| Device             | Instruction I | Inemonic     | Jump Condition<br>Jump if:        |  |

|--------------------|---------------|--------------|-----------------------------------|--|

| Accumulator        | JZ<br>JNZ     | addr<br>addr | All bits zero<br>Any bit not zero |  |

| Accumulator bit    | JBb           | addr         | Bit "b" = $1$                     |  |

| Carry flag         | JC<br>JNC     | addr<br>addr | Carry flag = 1<br>Carry flag = 0  |  |

| User flag          | JFO           | addr         | $F_0$ flag = 1                    |  |

| Timer flag         | JF1<br>JTF    | addr<br>addr | $F_1$ flag = 1<br>Timer flag = 1  |  |

| Test Input 0       | JT0<br>JNT0   | addr<br>addr | $T_0 = 1$<br>$T_0 = 0$            |  |

| Test Input 1       | JT1           | addr         | $T_1 = 1$                         |  |

| Input Buffer flag  | JNT1<br>JNIBF | addr<br>addr | $T_1 = 0$<br>IBF flag = 0         |  |

| Output Buffer flag | JOBF          | addr         | OBF flag = 1                      |  |

Figure 2-9. Oscillator Configuration

cillation. Recommended connections for crystal or L-C are shown in Figure 2-11.

#### **State Counter**

The output of the oscillator is divided by 3 in the state counter to generate a signal which defines the state times of the machine.

Each instruction cycle consists of five states as illustrated in Figure 2-10 and Table 2-3. The overlap of

Figure 2-10. Instruction Cycle Timing

address and execution operations illustrated in Figure 2-10 allows fast instruction execution.

#### **Cycle Counter**

The output of the state counter is divided by 5 in the cycle counter to generate a signal which defines a machine cycle. This signal is call SYNC and is available continously on the SYNC output pin. It can be used to synchronize external circuitry or as a general purpose clock output. It is also used for synchronizing single-step in the 8741A.

| INSTRUCTION            | CYCLE 1              |                              |                          |                            |                            | CYCLE 2                 |                  |                              |                   |    |

|------------------------|----------------------|------------------------------|--------------------------|----------------------------|----------------------------|-------------------------|------------------|------------------------------|-------------------|----|

| MOTION                 | S1                   | S2                           | \$3                      | S4                         | S5                         | S1                      | S2               | S3                           | S4                | S5 |

| IN A,Pp                | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Increment<br>Timer         | _                          | -                       | Read Port        | -                            | _                 |    |

| OUTL P <sub>P</sub> ,A | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Increment<br>Timer         | Output<br>To Port          | -                       | -                | -                            | -                 | -  |

| ANL Pp, DATA           | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Increment<br>Timer         | Read Port                  | Fetch<br>Immediate Data | -                | Increment<br>Program Counter | Output<br>To Port | -  |

| ORL Pp, DATA           | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Increment<br>Timer         | Read Port                  | Fetch<br>Immediate Data | -                | Increment<br>Program Counter | Output<br>To Port | -  |

| MOVD A,Pp              | Fetch<br>Instruction | Increment<br>Program Counter | Output<br>Opcode/Address | Increment<br>Timer         | -                          | -                       | Read<br>P2 Lower | -                            | -                 | -  |

| MOVD Pp,A              | Fetch<br>Instruction | Increment<br>Program Counter | Output<br>Opcode/Address | Increment<br>Timer         | Output Data<br>To P2 Lower | -                       | -                | -                            | -                 | -  |

| ANLD Pp,A              | Fetch<br>Instruction | Increment<br>Program Counter | Output<br>Opcode/Address | Increment<br>Timer         | Output<br>Data             | -                       | -                | _                            | -                 | -  |

| ORLD Pp,A              | Fetch<br>Instruction | Increment<br>Program Counter | Output<br>Opcode/Address | Increment<br>Timer         | Output<br>Data             | _                       | -                | -                            | -                 | -  |

| J (Conditional)        | Fetch<br>Instruction | Increment<br>Program Counter | Sample<br>Condition      | Increment<br>Timer         | -                          | Fetch<br>Immediate Data | -                | Update<br>Program Counter    | -                 | -  |

| IN A,DBB               | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Increment<br>Timer         | -                          |                         |                  |                              |                   |    |

| OUT DBB,A              | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Increment<br>Timer         | Output<br>To Port          |                         |                  |                              |                   |    |

| STRT T<br>STRT CNT     | Fetch<br>Instruction | Increment<br>Program Counter | -                        | -                          | Start<br>Counter           |                         |                  |                              |                   |    |

| STOP TONT              | Fetch<br>Instruction | increment<br>Program Counter | -                        | -                          | Stop<br>Counter            | ]                       |                  |                              |                   |    |

| EN I                   | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Enable<br>Interrupt        | -                          | ]                       |                  |                              |                   |    |

| DIS I                  | Fetch<br>Instruction | Increment<br>Program Counter | -                        | Disable<br>Interrupt       | -                          | ]                       |                  |                              |                   |    |

| EN DMA                 | Fetch<br>Instruction | Increment<br>Program Counter | -                        | DMA Enabled<br>DRQ Cleared | -                          | ]                       |                  |                              |                   |    |

| EN FLAGS               | Fetch<br>Instruction | Increment<br>Program Counter | -                        | OBF, IBF<br>Output Enabled | -                          | ]                       |                  |                              |                   |    |

Table 2-3. Instruction Timing Diagram

Figure 2-11. Recommended Crystal and L-C Connections

#### **Frequency Reference**

The external crystal provides high speed and accurate timing generation. A crystal frequency of 5.9904 MHz is useful for generation of standard communication frequencies by the 8741A and 8041A. However, if an accurate frequency reference and maximum processor speed are not required, an inductor and capacitor may be used in place of the crystal as shown in Figure 2-11.

A recommended range of inductance and capacitance combinations is given below:

- $L = 130 \ \mu H$  corresponds to 3 MHz

- $L = 45 \,\mu H$  corresponds to 5 MHz

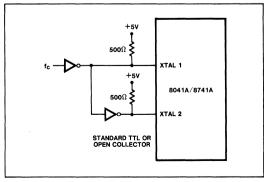

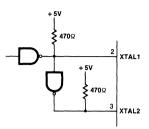

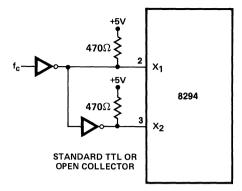

An external clock signal can also be used as a frequency reference to the 8741A or 8041A; however, the levels are *not* TTL compatible. The signal must be in the 1-6 MHz frequency range and must be connected to pins XTAL 1 and XTAL 2 by buffers with a suitable pull-up resistor to guarantee that a logic "1" is above 3.8 volts. The recommended connection is shown in Figure 2-12.

Figure 2-12. Recommended Connection For External Clock Signal

#### INTERVAL TIMER/EVENT COUNTER

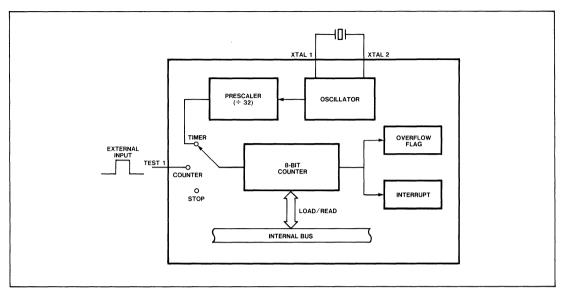

The 8041A has a resident 8-bit timer/counter which has several software selectable modes of operation. As an interval timer, it can generate accurate delays from 80 microseconds to 20.48 milliseconds without placing undue burden on the processor. In the counter mode, external events such as switch closures or tachometer pulses can be counted and used to direct program flow.

#### **Timer Configuration**

Figure 2-13 illustrates the basic timer/counter configuration. An 8-bit register is used to count pulses from either the internal clock and prescaler or from an external source. The counter is presettable and readable with two MOV instructions which transfer the contents of the accumulator to the counter and vice-versa. The counter is initialized solely by the MOV T.A instruction: it is not cleared by a RESET signal. The counter is stopped by a **RESET** or STOP TCNT instruction and remains stopped until restarted either as a timer (START T instruction) or as a counter (START CNT instruction). Once started, the counter will increment to its maximum count (FFH) and overflow to zero continuing its count until stopped by a STOP TCNT instruction or RESET.

The increment from maximum count to zero (overflow) results in setting the Timer Flag (TF) and generating an interrupt request. The state of the overflow flag is testable with the conditional jump instruction, JTF. The flag is reset by executing a JTF or by a RESET signal.

The timer interrupt request is stored in a latch and ORed with the input buffer full interrupt request. The timer interrupt can be enabled or disabled independent of the IBF interrupt by the EN TCNTI and

Figure 2-13. Timer Counter

DIS TCTNI instructions. If enabled, the counter overflow will cause a subroutine call to location 7 where the timer service routine is stored. If the timer and Input Buffer Full interrupts occur simultaneously, the IBF source will be recognized and the call will be to location 3. Since the timer interrupt is latched, it will remain pending until the DBBIN register has been serviced and will immediately be recognized upon return from the service routine. A pending timer interrupt is reset by the initiation of a timer interrupt service routine.

#### **Event Counter Mode**

The START CNT instruction connects the TEST 1 input pin to the counter input and enables the counter. Note that this instruction does not clear the counter. The counter is incremented on high to low transition of TEST 1. The maximum count rate is one count per three instruction cycles (every 7.5 microseconds when using a 6 MHz crystal). There is no minimum frequency limit. The TEST 1 input must remain high for a minimum of 500 ns (at 6 MHz) during a count cycle.

#### **Timer Mode**

The START T instruction connects an internal clock to the counter input and enables the counter. The input frequency is derived from a divide by 32 prescaler connected to the 400 kHz machine cycle clock. The configuration is illustrated in Figure 2-13. The resulting 12.5 kHz clock provides a counter increment every 80  $\mu$ sec. Various delays and timing sequences between 80  $\mu$ sec and 20.48 msec can easily be generated with a miniumum of software timing

loops. Times longer than 20 msec can be accurately measured by accumulating multiple overflows in a register under software control. For time resolution less than 80  $\mu$ sec an external clock can be applied to the TEST 1 input and the counter can be operated in the event counter mode. The 2.5  $\mu$ sec SYNC output divided by 3 or more can serve as the external clock. Software loops can also be used to "fine tune" long delays generated by the timer.

#### **TEST 1 Event Counter Input**

The TEST 1 pin is multifunctional. It is automatically initialized as a test input by a  $\overrightarrow{\text{RESET}}$  signal and can be tested using UPI-41A conditional branch instructions.

In the second mode of operation, illustrated in Figure 2-13, the TEST 1 pin is used as an input to the internal 8-bit event counter. The Start Counter (STRT CNT) instruction controls an internal switch which connects TEST 1 through an edge detector to the 8-bit internal counter. Note that this instruction does not inhibit the testing of TEST 1 via conditional Jump instructions.

In the counter mode the TEST 1 input is sampled once per instruction cycle. After a high level is detected, the next occurence of a low level at TEST 1 will cause the counter to increment by one.

The event counter functions can be stopped by the Stop Timer/Counter (STOP TCNT) instruction. When this instruction is executed the TEST 1 pin becomes a test input and functions as previously described.

#### **TEST INPUTS**

There are two multifunction pins designated as Test Inputs, TEST 0 and TEST 1. In the normal mode of operation, status of each of these lines can be directly tested using the following conditional Jump instructions:

- JT0 Jump if TEST 0 = 1

- JNT0 Jump if TEST 0 = 0

- JT1 Jump if TEST 1 = 1

- JNT1 Jump if TEST 1 = 0

The test inputs are TTL compatible. An external logic signal connnected to one of the test inputs will be sampled at the time the appropriate conditional jump instruction is executed. The path of program execution will be altered depending on the state of the external signal when sampled.

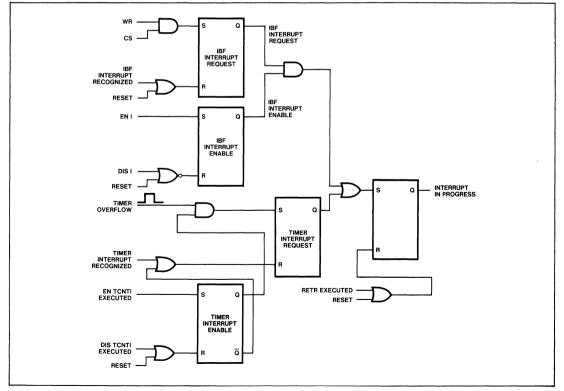

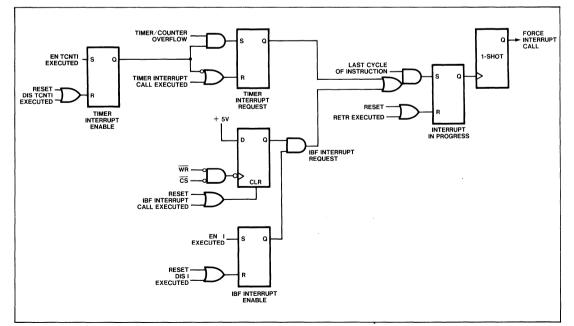

#### INTERRUPTS

The 8041A/8741A has the following internal interrupts:

- Input Buffer Full (IBF) interrupt

- Timer Overflow interrupt

The IBF interrupt forces a CALL to location 3 in program memory; a timer-overflow interrupt forces a CALL to location 7. The IBF interrupt is enabled by the EN I instruction and disabled by the DIS I instruction. The timer-overflow interrupt is enabled and disabled by the EN TNCTI and DIS TCNTI instructions, respectively.

Figure 2-14 illustrates the internal interrupt logic. An IBF interrupt request is generated whenever  $\overline{WR}$  and  $\overline{CS}$  are both low, regardless of whether interrupts are enabled. The interrupt request is cleared upon entering the IBF service routine only. That is, the DIS I instruction does not clear a pending IBF interrupt.

#### Interrupt Timing Latency

When the IBF interrupt is enabled and an IBF interrupt request occurs, an interrupt sequence is initiated as soon as the currently executing instruction is completed. The following sequence occurs:

- A CALL to location 3 is forced.

- The program counter and bits 4–7 of the Program Status Word are stored in the stack.

- The stack pointer is incremented.

Location 3 in program memory should contain an

Figure 2-14. Interrupt Logic

unconditional jump to the beginning of the IBF interrupt service routine elsewhere in program memory. At the end of the service routine, an RETR (Return and Restore Status) instruction is used to return control to the main program. This instruction will restore the program counter and PSW bits 4-7, providing automatic restoration of the previously active register bank as well. RETR also re-enables interrupts.

A timer-overflow interrupt is enabled by the EN TCNTI instruction and disabled by the DIS TCNTI instruction. If enabled, this interrupt occurs when the timer/counter register overflows. A CALL to location 7 is forced and the interrupt routine proceeds as described above.

The interrupt service latency is the sum of current instruction time, interrupt recognition time, and the internal call to the interrupt vector address. The worst case latency time for servicing an interrupt is 7 clock cycles. Best case latency is 4 clock cycles.

#### **Interrupt Timing**

Interrupt inputs may be enabled or disabled under program control using EN I, DIS I, EN TCNTI and DIS TCNTI instructions. Also, a RESET input will disable interrupts. An interrupt request must be removed before the RETR instruction is executed to return from the service routine, otherwise the processor will re-enter the service routine immediately. Thus, the WR and  $\overline{CS}$  inputs should not be held low longer than the duration of the interrupt service routine.

The interrupt system is single level. Once an interrupt is detected, all further interrupt requests are latched but are not acted upon until execution of an RETR instruction re-enables the interrupt input logic. This occurs at the beginning of the second cycle of the RETR instruction. If an IBF interrupt and a timer-overflow interrupt occur simultaneously, the IBF interrupt will be recognized first and the timeroverflow interrupt will remain pending until the end of the interrupt service routine.

#### **External Interrupts**

An external interrupt can be created using the UPI-41A timer/counter in the event counter mode. The counter is first preset to FFH and the EN TCNTI instruction is executed. A timer-overflow interrupt is generated by the first high to low transition of the TEST 1 input pin. Also, if an IBF interrupt occurs during servicing of the timer/counter interrupt, it will remain pending until the end of the service routine.

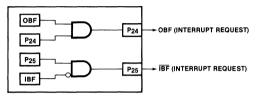

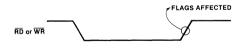

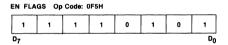

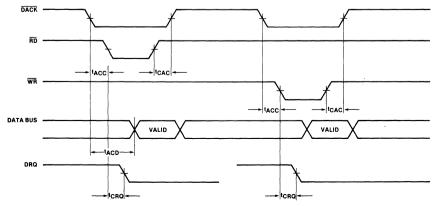

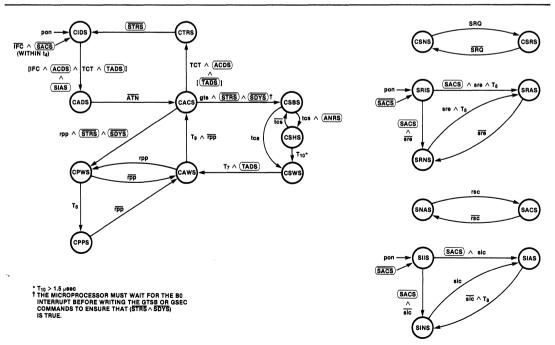

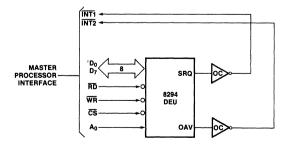

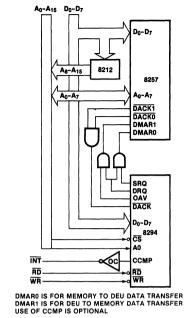

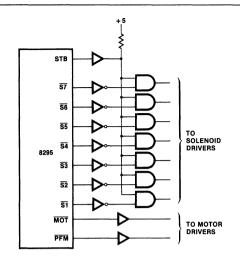

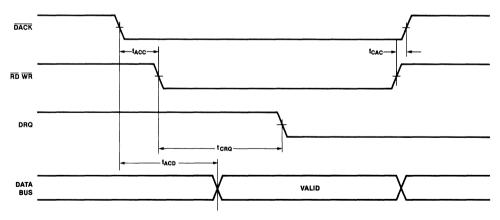

#### Host Interrupts And DMA

If needed, two external interrupts to the host system can be created using the EN FLAGS instruction. This instruction allocates two I/O lines on PORT 2 (P24 and P25). P24 is the Output Buffer Full interrupt request line to the host system; P25 is the Input Buffer empty interrupt request line. These interrupt outputs reflect the internal status of the OBF flag and the IBF inverted flag. Note, these outputs may be inhibited by writing a "0" to these pins. Reenabling interrupts are typically enabled after power on since the I/O ports are set in a "1" condition. The EN FLAG's effect is only cancelled by a device RESET.

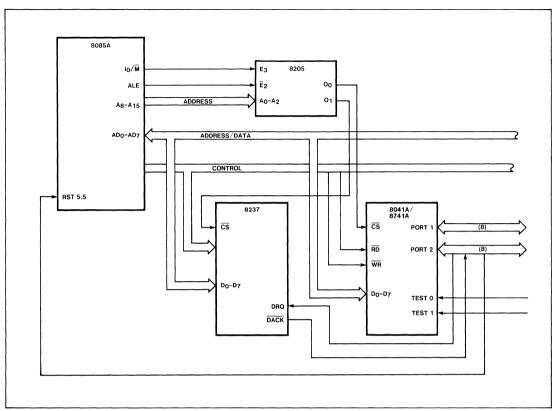

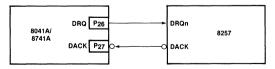

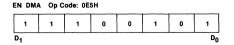

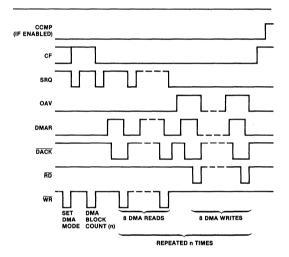

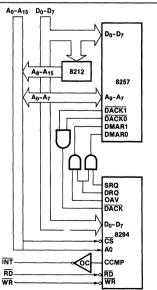

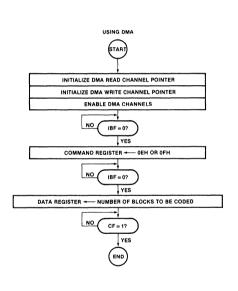

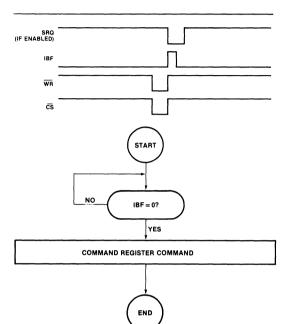

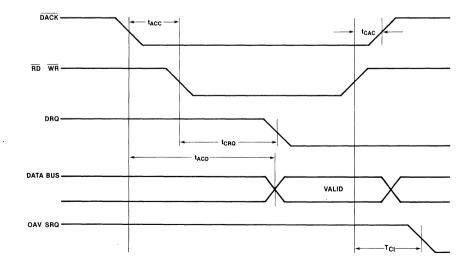

DMA handshaking controls are available from two pins on PORT 2 of the UPI-41A microcomputer. These lines (P<sub>26</sub> and P<sub>27</sub>) are enabled by the EN DMA instruction. P<sub>26</sub> becomes DMA request (<u>DRQ</u>) and P<sub>27</sub> becomes DMA acknowledge (DACK). The UPI program initiates a DMA request by writing a "1" to P<sub>26</sub>. The DMA controller transfers the data into the DBBIN data register using DACK which acts as a chip select. The EN DMA instruction can only be cancelled by a chip RESET.

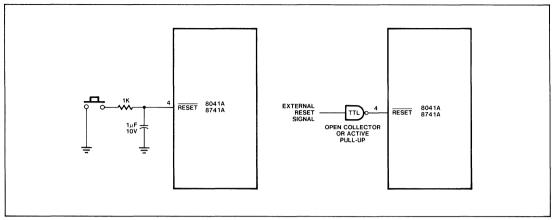

#### RESET

The RESET input on the 8041A/8741A provides a means for internal initialization of the processor. An automatic initialization pulse can be generated at power turn-on simply by connecting a 1  $\mu$ fd capacitor between the RESET input and ground as shown in Figure 2-15. It has an internal pull-up resistor to charge the capacitor and a Schmitt-trigger circuit to generate a clean transition.

If an external RESET pulse is used it must hold the RESET input low for at least 10 milliseconds after the power supply is within tolerance. Figure 2-15 illustrates a configuration using an external TTL gate to generate the RESET input. This configuration can be used to derive the RESET signal from the 8224 clock generator in an 8080 system.

The  $\overline{\text{RESET}}$  input performs the following functions:

- Sets Program Counter to zero.

- Sets the Stack Pointer to zero

- Selects Register Bank 0

- Sets PORTS 1 and 2 to the Input Mode

- Disables interrupts.

- Stops the timer.

- Clears the timer flag.

- Clears F<sub>0</sub> and F<sub>1</sub> flip-flops.

Figure 2-15. External Reset Configuration

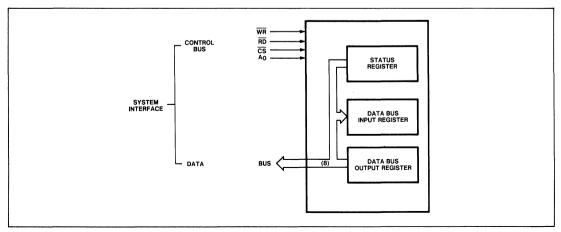

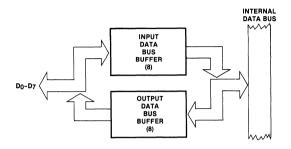

#### DATA BUS BUFFER

Two 8-bit data bus buffer registers, DBBIN and DBBOUT, serve as temporary buffers for commands and data flowing between it and the master processor. Externally, data is transmitted or received by the DBB registers upon execution of an INput or OUTput instruction by the master processor. Four control signals are used:

- A<sub>0</sub> Address input signifying control or data

- $\overline{CS}$  Chip Select

- $\overline{\text{RD}}$  Read strobe

- WR Write strobe

Transfer can be implemented with or without UPI program interference by enabling or disabling an internal UPI interrupt. Internally, data transfer between the DBB and the UPI accumulator is under software control and is completely asynchronous to the external processor timing. This allows the UPI software to handle peripheral control tasks independent of the main processor while still maintaining a data interface with the master system.

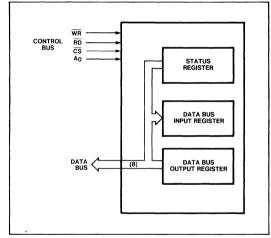

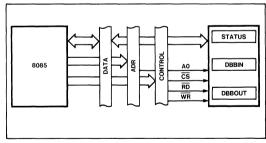

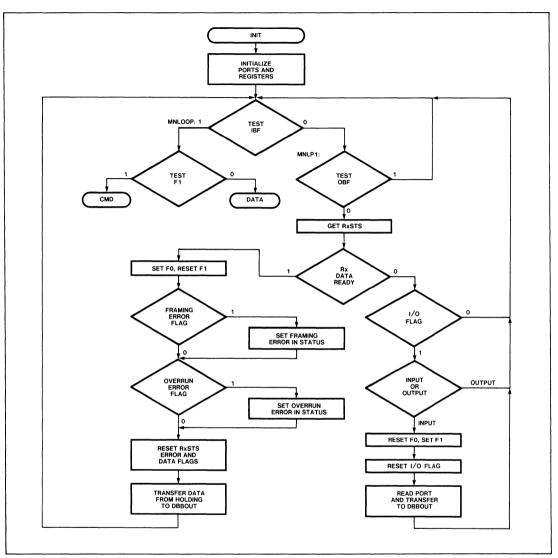

#### Configuration

Figure 2-16 illustrates the internal configuration of the DBB registers. Data is stored in two 8-bit buffer registers, DBBIN and DBBOUT. DBBIN and DBBOUT may be accessed by the external processor using the WR line and the RD line, respectively. The data bus is a bidirectional, three-state bus which can be connected directly to an 8-bit microprocessor system. Four control lines (WR, RD, CS, A0) are used by the external processor to transfer data to and from the DBBIN and DBBOUT registers.

2-16. Data Bus Buffer Configuration

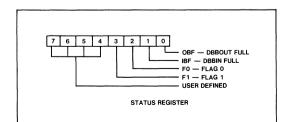

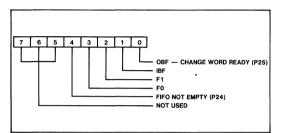

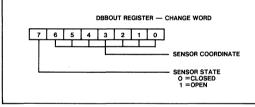

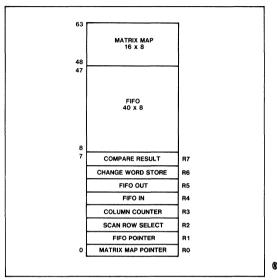

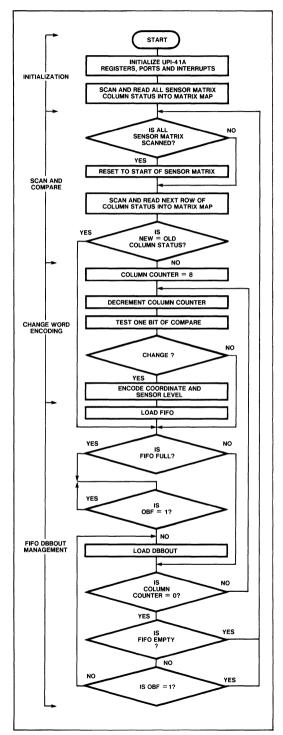

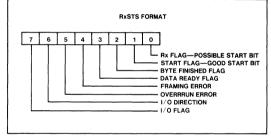

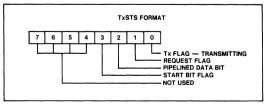

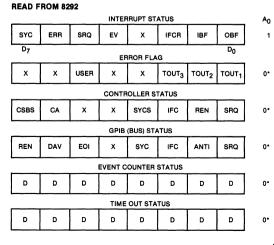

An 8-bit register containing status flags is used to indicate the status of the DBB registers. The eight status flags are defined as follows:

- **OBF Output Buffer Full** This flag is automatically set when the 8041A loads the DBBOUT register and is cleared when the master processor reads the data register.

- **IBF Input Buffer Full** This flag is set when the master processor writes a character to the DBBIN register and is cleared when the 8041A INputs the data register contents to its accumulator.

- F0 This is a general purpose flag which can be cleared or toggled under 8041A software control. The flag is used to transfer 8041A status information to the master processor.

- F1 Command/Data This flag is set to the condition of the A0 input line when the master processor writes a character to the data register. The F1 flag can also be cleared or toggled under 8041A program control.

- ST4 Through ST7 These bits are user defined status bits. They are defined by the MOV STS,A instruction.

All flags in the status register are automatically cleared by a **RESET** input.

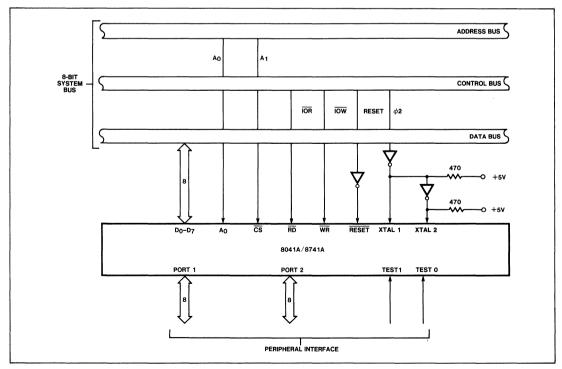

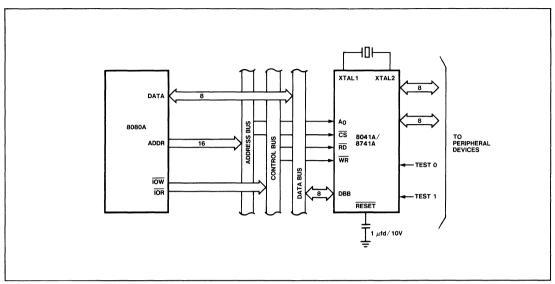

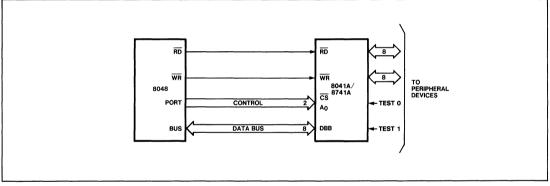

#### SYSTEM INTERFACE

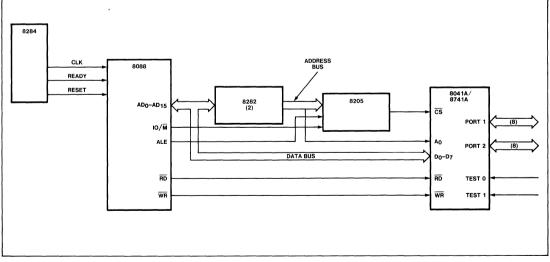

Figure 2-17 illustrates how an 8041A can be connected to a standard 8080-type bus system. Data lines D<sub>0</sub>-D<sub>7</sub> form a three-state, bidirectional port which can be connected directly to the system data bus. The UPI bus interface has sufficient drive capability (400  $\mu$ A) for small systems, however, a larger system may require buffers.

Four control signals are required to handle the data and status information transfer:

- $\overline{WR}$  I/O WRITE signal used to transfer data from the system bus to the UPI DBBIN register and set the F1 flag in the status register.

- RD I/O READ signal used to transfer data from the DBBOUT register or status register to the system data bus.

- CS CHIP SELECT signal used to enable one 8041A out of several connected to a common bus.

- A0 Address input used to select either the 8-bit status register or DBBOUT register during an I/O READ. Also, the signal is used to set the F1 flag in the status register during an I/O WRITE.

Figure 2-17. Interface to 8080 System Bus

The  $\overline{WR}$  and  $\overline{RD}$  signals are active low and are standard MCS-80 peripheral control signals used to synchronize data transfer between the system bus and peripheral devices.

The  $\overline{CS}$  and  $A_0$  signals are decoded from the address bus of the master system. In a system with few I/O devices a linear addressing configuration can be used where  $A_0$  and  $A_1$  lines are connected directly to  $A_0$ and  $\overline{CS}$  inputs (see Figure 2-17).

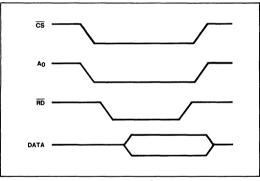

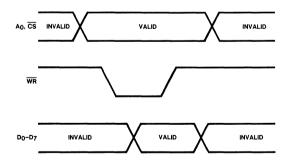

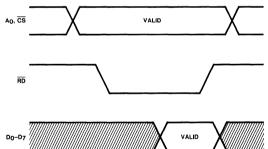

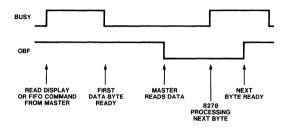

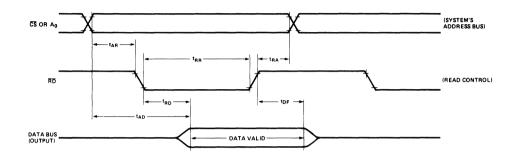

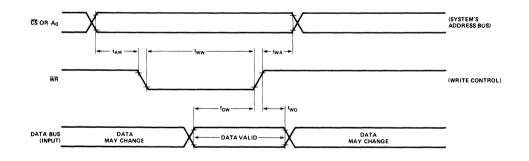

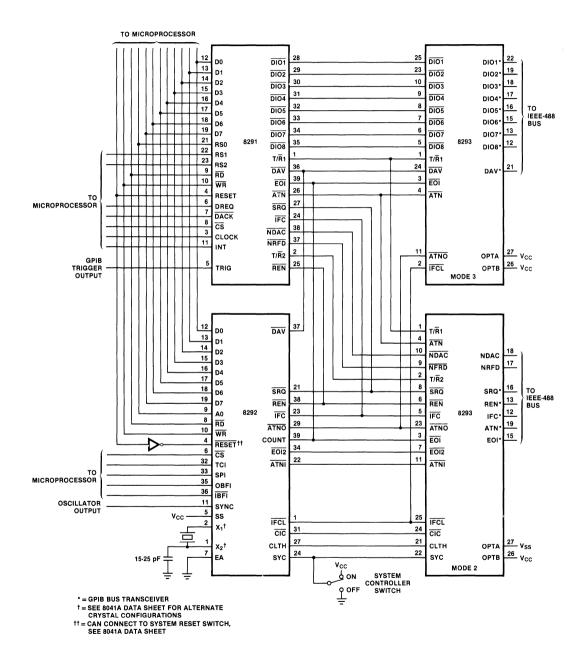

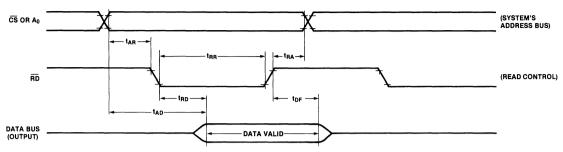

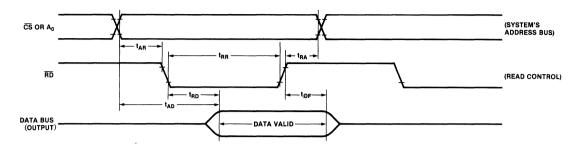

#### Data Read

Table 2-4 illustrates the relative timing of a DBBOUT Read. When  $\overline{CS}$ ,  $A_0$ , and  $\overline{RD}$  are low, the contents of the DBBOUT register is placed on the three-state Data lines  $D_0$ - $D_7$  and the OBF flag is cleared.

The master processor uses  $\overline{CS}$ , A<sub>0</sub>,  $\overline{WR}$ , and  $\overline{RD}$  to control data transfer between the DBBOUT register and the master system. The following operations are under master processor control:

Table 2-4. Data Transfer Controls

| CS | RD | WR | Ao  |                              |

|----|----|----|-----|------------------------------|

| 0  | 0  | 1  | 0 Ŭ | Read DBBOUT register         |

| 0  | 0  | 1  | 1   | Read STATUS register         |

| 0  | 1  | 0  | 0   | Write DBBIN data register    |

| 0  | 1  | 0  | 1   | Write DBBIN command register |

| 1  | x  | х  | х   | Disable DBB                  |

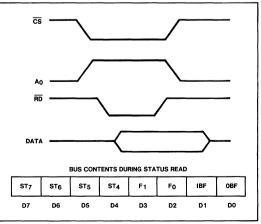

#### **Status Read**

Table 2-4 shows the logic sequence required for a STATUS register read. When  $\overline{CS}$  and  $\overline{RD}$  are low with A<sub>0</sub> high, the contents of the 8-bit status register appears on Data lines D<sub>0</sub>-D<sub>7</sub>.

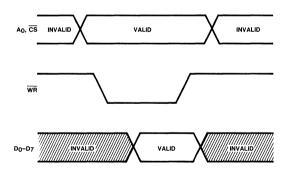

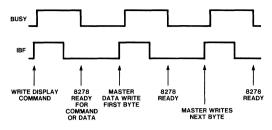

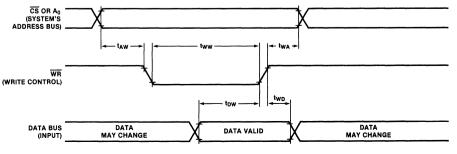

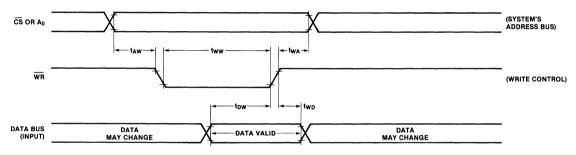

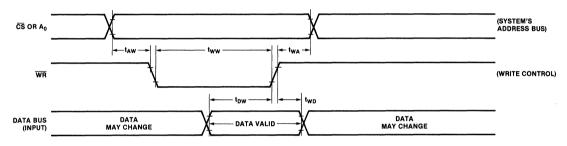

#### **Data Write**

Table 2-4 shows the sequence for writing information to the DBBIN register. When  $\overline{CS}$  and  $\overline{WR}$  are low, the contents of the system data bus is latched into DBBIN. Also, the IBF flag is set and an interrupt is generated, if enabled.

#### **Command Write**

During any write (Table 2-4), the state of the A<sub>0</sub> input is latched into the status register in the  $F_1$  (command/data) flag location. This additional bit is used to signal whether DBBIN contents are command (A<sub>0</sub> = 1) or data (A<sub>0</sub> = 0) information.

#### INPUT/OUTPUT INTERFACE

The UPI-41A has 16 lines for input and output functions. These I/O lines are grouped as two 8-bit TTL compatible ports: PORTS 1 and 2. The port lines can individually function as either inputs or outputs under software control. In addition, the lower 4 lines of PORT 2 can be used to interface to an 8243 I/O expander device to increase I/O capacity to 28 or more lines. The additional lines are grouped as 4-bit ports: PORTS 4, 5, 6, and 7.

#### PORTS 1 and 2

PORTS 1 and 2 are each 8 bits wide and have the same I/O characteristics. Data written to these ports by an OUTL Pp,A instruction is latched and remains unchanged until it is rewritten. Input data is sampled at the time the IN, A,Pp instruction is executed. Therefore, input data must be present at the PORT until read by an INput instruction. PORT 1 and 2 inputs are fully TTL compatible and outputs will drive one standard TTL load.

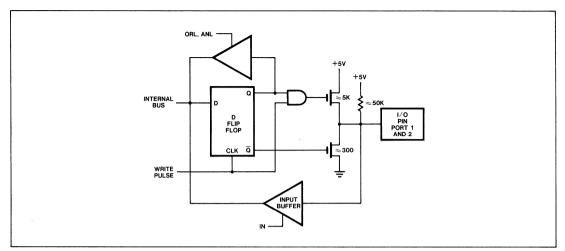

#### **Circuit Configuration**

The PORT 1 and 2 lines have a special output structure (shown in Figure 2-18) that allows each line to serve as an input, an output, or both, even though outputs are statically latched.

Each line has a permanent high impedance pull-up  $(50K\Omega)$  which is sufficient to provide source current for a TTL high level, yet can be pulled low by a standard TTL gate drive. Whenever a "1" is written to a line, a low impedance pull-up (5K) is switched in momentarily (500 ns) to provide a fast transition from 0 to 1. When a "0" is written to the line, a low impedance pull-down  $(300\Omega)$  is active to provide TTL current sinking capability.

To use a particular PORT pin as an input, a logic "1" must first be written to that pin.

**NOTE:** A  $\overline{\text{RESET}}$  initializes all PORT pins to the high impedance logic "1" state.

An external TTL device connected to the pin has sufficient current sinking capability to pull-down the pin to the low state. An IN A,Pp instruction will sample the status of PORT pin and will input the proper logic level. With no external input connected, the IN A,Pp instruction inputs the previous output status.

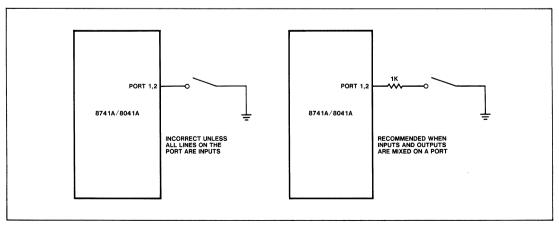

This structure allows input and output information on the same pin and also allows any mix of input and output lines on the same port. However, when inputs and outputs are mixed on one PORT, a PORT write will cause the strong internal pull-ups to turn on at all inputs. If a switch or other low impedance device is connected to an input, a PORT write ("1" to an input) could cause current limits on internal lines to

Figure 2-18. Quasi-Bidirectional Port Structure

be exceeded. Figure 2-19 illustrates the recommended connection when inputs and outputs are mixed on one PORT.

The bidirectional port structure in combination with the UPI-41A logical AND and OR instructions provides an efficient means for handling single line inputs and outputs within an 8-bit processor.

#### PORTS 4, 5, 6, and 7

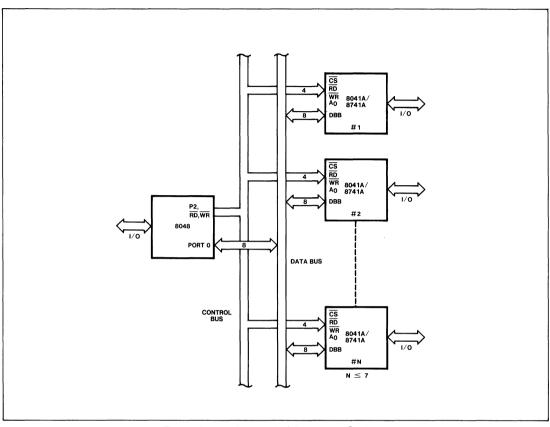

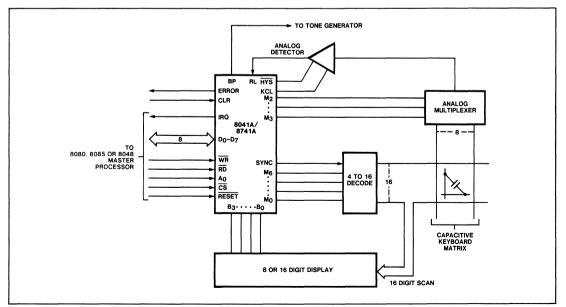

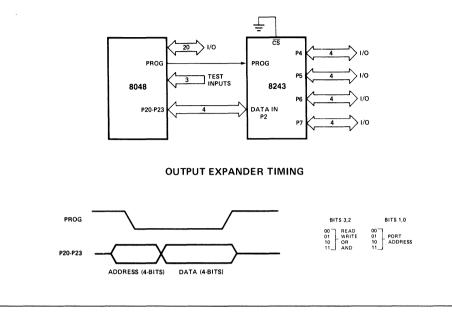

By using an 8243 I/O expander, 16 additional I/O lines can be connected to the UPI-41A and directly addressed as 4-bit I/O ports using UPI-41A instructions. This feature saves program space and design time, and improves the bit handling capability of the UPI-41A.

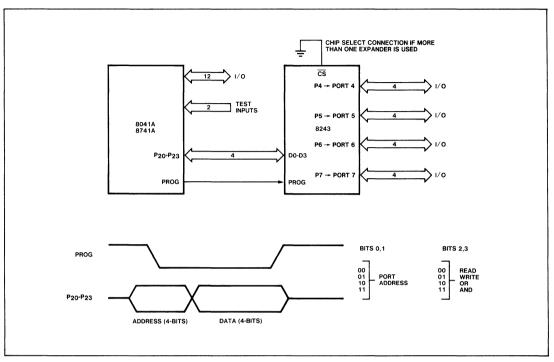

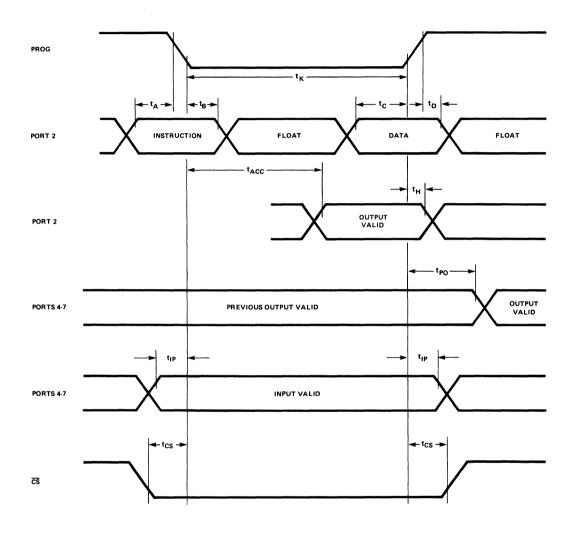

The lower half of PORT 2 provides an interface to the 8243 as illustrated in Figure 2-20. The PROG pin is used as a strobe to clock address and data information via the PORT 2 interface. The extra 16 I/O lines are referred to in UPI software as PORTS 4, 5, 6, and 7. Each PORT can be directly addressed and can be ANDed and ORed with an immediate data mask. Data can be moved directly to the accumulator from the expander PORTS (or vice-versa).

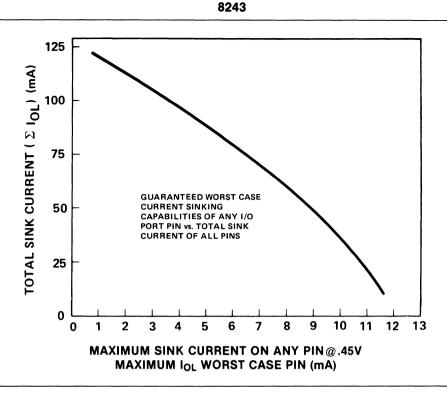

The 8243 I/O ports, PORTS 4, 5, 6, and 7, provide more drive capability than the UPI-41A bidirectional ports. The 8243 output is capable of driving about 5 standard TTL loads.

Figure 2-19. Recommended PORT Input Connections

Figure 2-20. 8243 Expander Interface

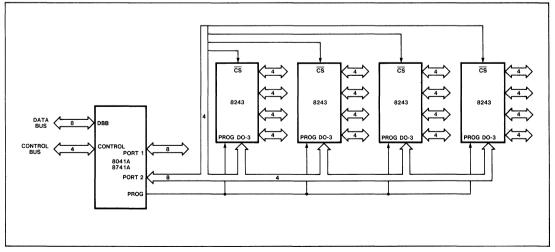

Multiple 8243's can be connected to the PORT 2 interface. In normal operation, only one of the 8243's would be active at the time an Input or Output command is executed. The upper half of PORT 2 is used to provide chip select signals to the 8243's. Figure 2-21 shows how four 8243's could be connected. Software is needed to select and set the proper PORT 2 pin before an INPUT or OUTPUT command to PORTS 4-7 is executed. In general, the software overhead required is very minor compared to the added flexibility of having a large number of I/O pins available.

Figure 2-21. Multiple 8243 Expansion

## CHAPTER 3 INSTRUCTION SET

#### CHAPTER 3 INSTRUCTION SET

The UPI-41A Instruction Set is opcode-compatible with the MCS-48 set except for the elimination of external program and data memory instructions and the addition of the data bus buffer instructions. It is very straightforward and efficient in its use of program memory. All instructions are either 1 or 2 bytes in length (over 70% are only 1 byte long) and over half of the instructions execute in one machine cycle. The remainder require only two cycles and include Branch, Immediate, and I/O operations.

The UPI-41A Instruction Set efficiently handles the single-bit operations required in control applications. Special instructions allow port bits to be set or cleared individually. Also, any accumulator bit can be directly tested via conditional branch instructions. Additional instructions are included to simplify loop counters, table look-up routines and N-way branch routines.

The UPI-41A Microcomputer handles arithmetic operations in both binary and BCD for efficient interface to peripherals such as keyboards and displays.

The instruction set can be divided into the following groups:

- Data Moves

- Accumulator Operations

- Flags

- Register Operations

- Branch Instructions

- Control

- Timer Operations

- Subroutines

- Input/Output Instructions

#### Data Moves (See Instruction Summary)

The 8-bit accumulator is the control point for all data transfers within the UPI-41A. Data can be transferred between the 8 registers of each working register bank and the accumulator directly (i.e., with a source or destination register specified by 3 bits in the instruction). The remaining locations in the RAM array are addressed either by  $R_0$  or  $R_1$  of the active register bank. Transfers to and from RAM require one cycle.

Constants stored in Program Memory can be loaded directly into the accumulator or the eight working registers. Data can also be transferred directly between the accumulator and the on-board timer/ counter, the Status Register (STS), or the Program Status Word (PSW). Transfers to the STS register alter bits 4-7 only. Transfers to the PSW alter machine status accordingly and provide a means of restoring status after an interrupt or of altering the stack pointer if necessary.

#### **Accumulator Operations**

Immediate data, data memory, or the working registers can be added (with or without carry) to the accumulator. These sources can also be ANDed, ORed, or exclusive ORed to the accumulator. Data may be moved to or from the accumulator and working registers or data memory. The two values can also be exchanged in a single operation.

The lower 4 bits of the accumulator can be exchanged with the lower 4 bits of any of the internal RAM locations. This operation, along with an instruction which swaps the upper and lower 4-bit halves of the accumulator, provides easy handling of BCD numbers and other 4-bit quantities. To facilitate BCD arithmetic a Decimal Adjust instruction is also included. This instruction is used to correct the result of the binary addition of two 2-digit BCD numbers. Performing a decimal adjust on the result in the accumulator produces the desired BCD result.

The accumulator can be incremented, decremented, cleared, or complemented and can be rotated left or right 1 bit at a time with or without carry.

A subtract operation can be easily implemented in UPI-41A software using three single-byte, singlecycle instructions. A value can be subtracted from the accumulator by using the following instructions:

- Complement the accumulator

- Add the value to the accumulator

- Complement the accumulator

#### Flags

There are four user accessible flags:

- Carry

- Auxiliary Carry

- F<sub>0</sub>

- F<sub>1</sub>

The Carry flag indicates overflow of the accumulator, while the Auxiliary Carry flag indicates overflow between BCD digits and is used during decimal adjust operations. Both Carry and Auxiliary Carry are part of the Program Status Word (PSW) and are stored in the stack during subroutine calls. The  $F_0$ and  $F_1$  flags are general-purpose flags which can be cleared or complemented by UPI instructions.  $F_0$  is accessible via the Program Status Word and is stored in the stack with the Carry flags.  $F_1$  reflects the condition of the  $A_0$  line, and caution must be used when setting or clearing it.

#### **Register Operations**

The working registers can be accessed via the accumulator as explained above, or they can be loaded with immediate data constants from program memory. In addition, they can be incremented or decremented directly, or they can be used as loop counters as explained in the section on branch instructions.

Additional Data Memory locations can be accessed with indirect instructions via  $R_0$  and  $R_1$ .

#### **Branch Instructions**

The UPI-41A Instruction Set includes 17 jump instructions. The unconditional jump instruction allows jumps anywhere in the 1K words of program memory. All other jump instructions are limited to the current page (256 words) of program memory.

Conditional jump instructions can test the following inputs and machine flags:

- TEST 0 input pin

- TEST 1 input pin

- Input Buffer Full flag

- Output Buffer Full flag

- Timer flag

- Accumulator zero

- Accumulator bit

- Carry flag

- F<sub>0</sub> flag

- F<sub>1</sub> flag

The conditions tested by these instructions are the instantaneous values at the time the conditional jump instruction is executed. For instance, the jump on accumulator zero instruction tests the accumulator itself, not an intermediate flag.

The decrement register and jump if not zero (DJNZ) instruction combines decrement and branch operations in a single instruction which is useful in implementing a loop counter. This instruction can designate any of the 8 working registers as a counter and can effect a branch to any address within the current page of execution.

A special indirect jump instruction (JMPP @A) allows the program to be vectored to any one of several different locations based on the contents of the accumulator. The contents of the accumulator point to a location in program memory which contains the jump address. As an example, this instruction could be used to vector to any one of several routines based on an ASCII character which has been loaded into the accumulator. In this way, ASCII inputs can be used to initiate various routines.

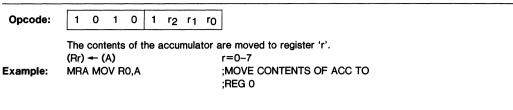

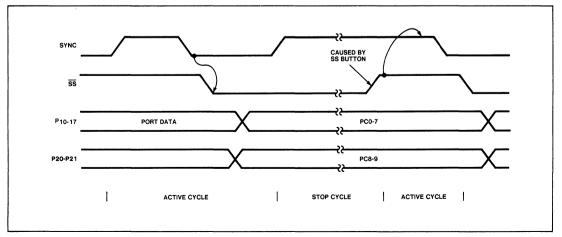

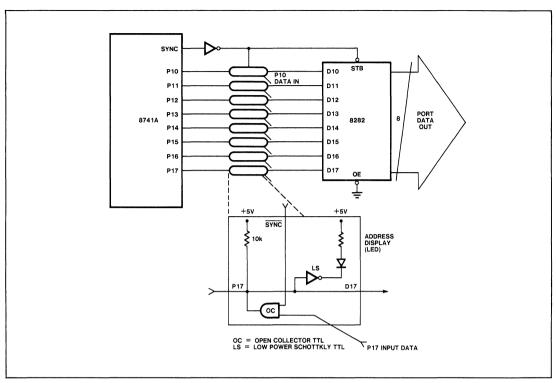

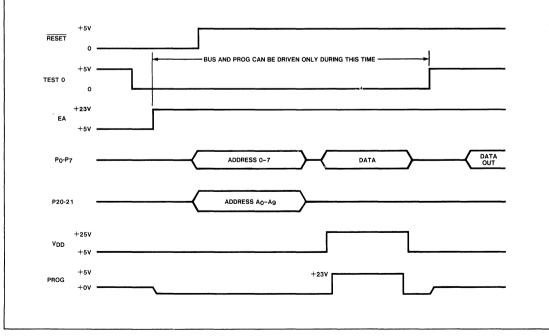

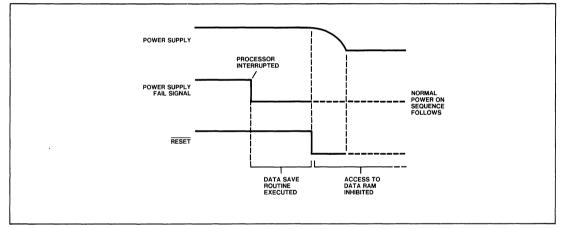

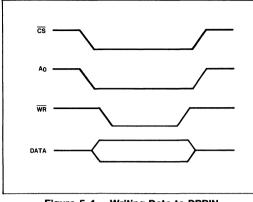

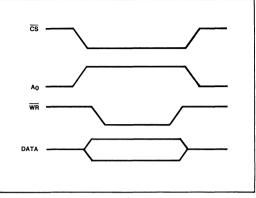

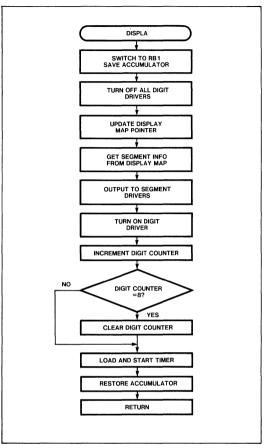

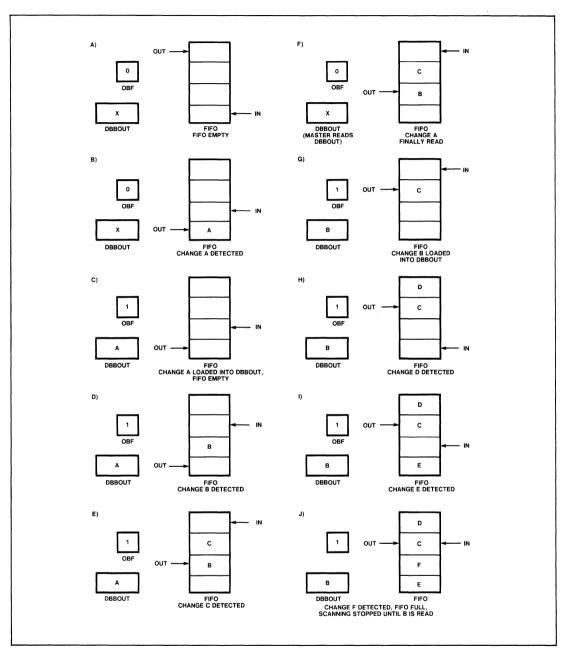

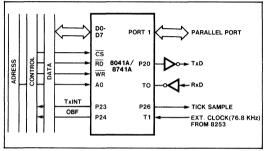

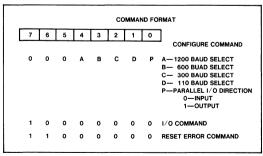

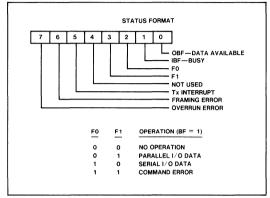

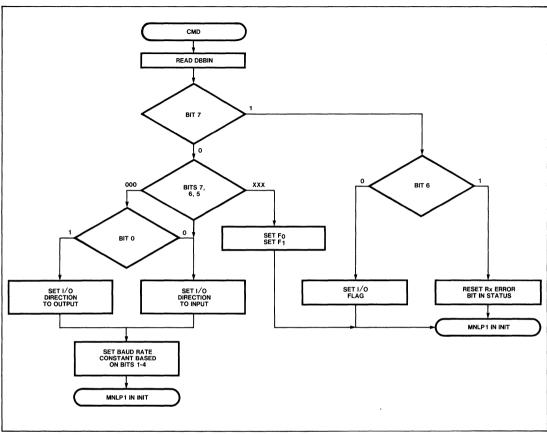

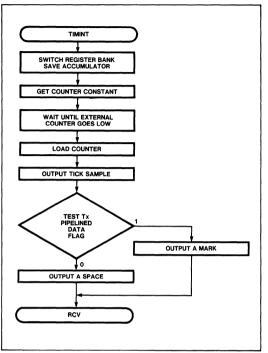

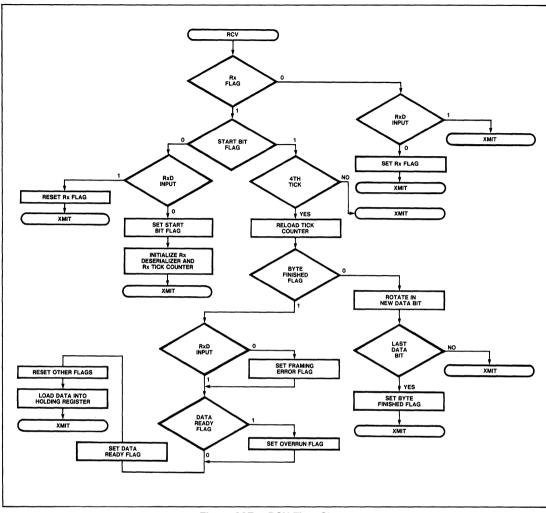

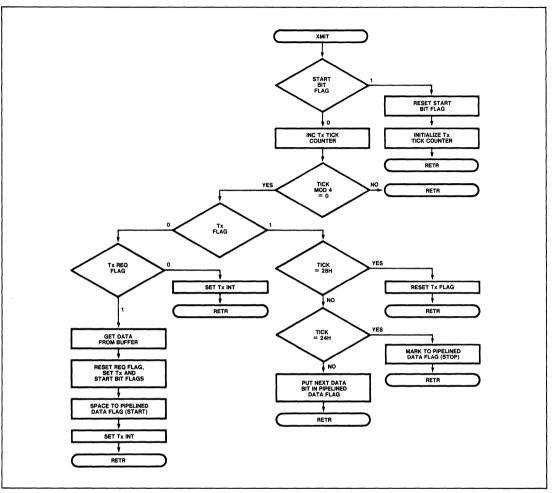

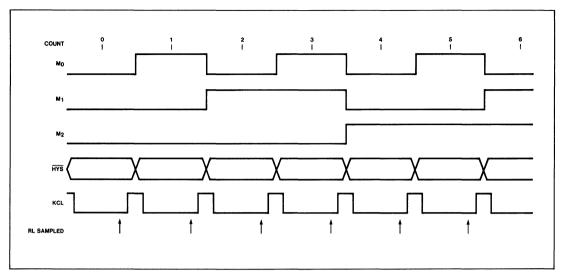

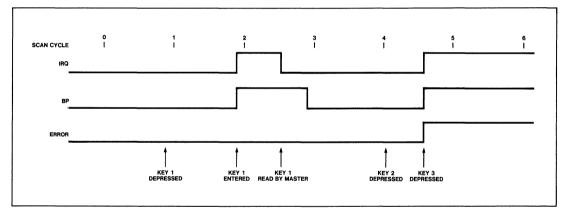

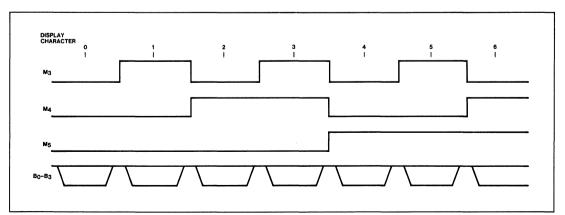

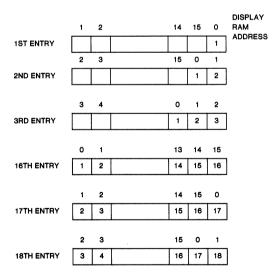

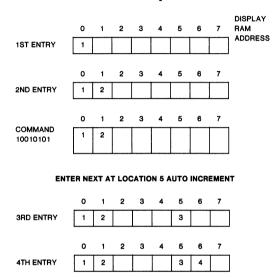

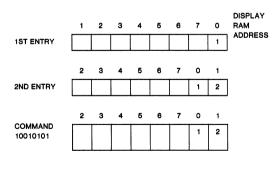

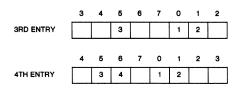

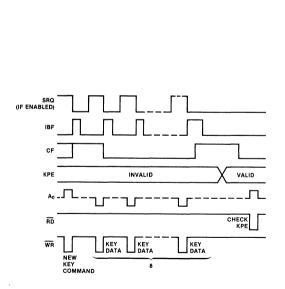

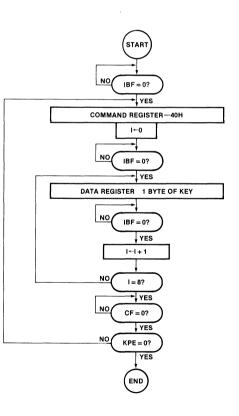

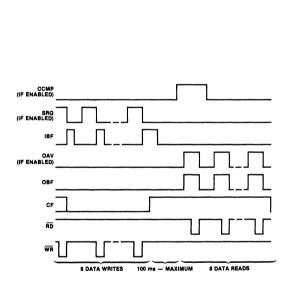

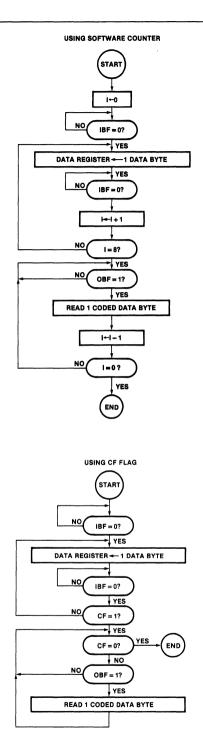

#### Control