Original Equipment Manufacturers' Information

IBM 7631 File Control

IBM

Original Equipment Manufacturers' Information IBM 7631 File Control

. .

# PREFACE

The information in this manual will assist designers of accessory equipment for IBM 7631 File Control Models 1, 2, 3, 4, and 5 and IBM 1301 Disk Storage Models 1 and 2. Additional details about the operation and use of these units in integrated data processing systems may be obtained from the local IBM Sales Office. If additional technical information is needed, customer engineering manuals are available from the local IBM Sales Office.

Descriptions and data in this manual are subject to engineering development modification.

Address comments regarding the contents of this publication to: IBM Corporation, Customer Manuals, Dept. 298, PO Box 390, Poughkeepsie, N.Y.

# CONTENTS

| IBM 7631 FILE CONTROL      | •   | • | • | • | • | • | • | • | • |   | • | • | 5  |

|----------------------------|-----|---|---|---|---|---|---|---|---|---|---|---|----|

| Magnetic Disk Recording    | •   | • | • | • | • | • | • |   | • | • | • |   | 5  |

| Access Mechanism           | •   | • | • | • | • | • | • | • | • | ٠ | • | • | 5  |

| Access Motion Time         | •   | • | • | • | • | • | • | • | • | ٠ | • | • | 6  |

| Cylinder Recording         | •   | • | • | • | • | • | • | • | • | • | • | • | 7  |

| Data Track                 | •   | • | • | • | • | • | • | • | • | • | • | • | 7  |

| Track Capacity (7000 Syste | ems | ) | • | • | • | • | • | • | • | • | • | • | 9  |

| Track Capacity (1410 Syste | ems | ) | • | • | • | • | • | • | • | • | • | • | 9  |

| Format Track               | •   | • | • | • | • |   | • | • | • | • | • | • | 9  |

| Planning the Format Track  | •   | • | • | • | • |   | • | • | • | • | • | • | 10 |

| Timing Considerations .    | •   | • | • | • | • | • | • | • | • | • | • | • | 11 |

|                            |     |   |   |   |   |   |   |   |   |   |   |   |    |

| FUNCTIONS    | AND   | OPER   | ATIC | ONS  | •  | •    | •    | •   | •  | • | • | • | • | • | 13 |

|--------------|-------|--------|------|------|----|------|------|-----|----|---|---|---|---|---|----|

| File Control | Opera | ations | with | 7000 | Se | ries | : Sy | ste | ms |   | • | • |   | • | 13 |

# IBM 7631 MODELS 2, 3, 4 FILE CONTROL WITH IBM 7000

| SERIES SYSTEMS                                    | •   | •   | •  | • | 16 |

|---------------------------------------------------|-----|-----|----|---|----|

| Functional Description of Lines 7000 Series Syste | ms, | /76 | 31 | • | 16 |

| Organization of Information                       | •   | •   | •  | • | 16 |

| Description of Signal Lines from Computer to 7631 | •   | •   | •  | • | 17 |

| Read Command                                      |     | •   | •  |   | 17 |

| Description of Signal Lines from 7631 to Computer |     | •   | •  | • | 18 |

| Timing of Lines 7631 in 7000 Series Operation     |     | •   | •  |   | 19 |

| IBM 7631 N  | NOI  | DEL  | S 2 | A    | ND  | 4 C | )PE | RA' | ГΙС | DN | ۰. | ٠ | ٠ | • | • | ٠ | • | 21 |

|-------------|------|------|-----|------|-----|-----|-----|-----|-----|----|----|---|---|---|---|---|---|----|

| Operationa  | 1 CI | har  | act | eris | tic | s.  | •   |     | •   | •  | •  |   | • | • |   | • | • | 21 |

| Control Co  | mm   | ane  | ds  |      | •   | •   |     | •   | •   | •  | •  |   | • |   | • | • | • | 21 |

| Sense       |      | •    |     | •    | •   |     | •   | •   | •   | •  | •  |   | ٠ |   |   | • | • | 22 |

| Attention   |      | •    | •   | ٠    | •   | •   | •   | •   | •   | •  | •  | • | • | • | • | • | • | 23 |

| Write       | •    | •    | •   | •    | •   | •   | •   | ٠   | •   | •  | •  | • | • |   |   | • | • | 23 |

| Read        | •    | •    | •   | •    | •   | ٠   | •   | •   |     | •  | •  | • | • | • | ٠ | • | • | 26 |

| Address Co  | mp   | arir | ŋ   | •    | •   | •   | •   | •   | •   | •  | •  | • | • | • | • | • | • | 28 |

| Instruction | Tir  | nes  |     | •    |     |     |     |     |     |    |    |   |   |   |   |   |   | 28 |

| IBM 7631 MODELS 1, 3, AND 5 WITH IBM 1410 SYSTEM                | ••• | 29 |

|-----------------------------------------------------------------|-----|----|

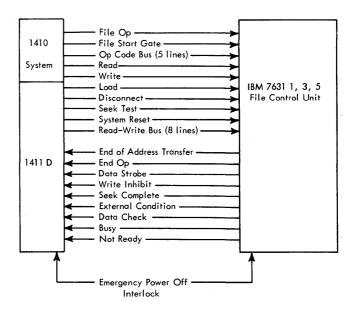

| Functional Description of Lines 1410 System to         IBM 7631 |     | 29 |

| 7621 /1 /10 T: :                                                | ••• | 31 |

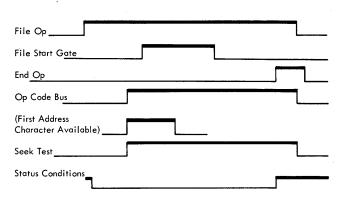

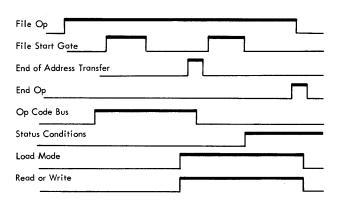

| Functions, 1410 System/7631 File Control                        | ••• | 32 |

| IBM 7631 MODELS 1, 3, AND 5 OPERATION                           |     | 35 |

| Instruction Handling, 1410/7631                                 |     | 35 |

| Head Select Under An Address Transfer Cycle                     |     | 35 |

|                                                                 |     | 35 |

| Operations Requiring Address Transfer and Read or               |     |    |

| Write Cycles                                                    |     | 36 |

|                                                                 |     | 40 |

|                                                                 |     | 40 |

|                                                                 |     | 41 |

| Busy                                                            |     | 41 |

| A                                                               |     | 41 |

|                                                                 | •   | 41 |

|                                                                 |     | 42 |

| Instruction Times                                               |     | 42 |

|                                                                 |     |    |

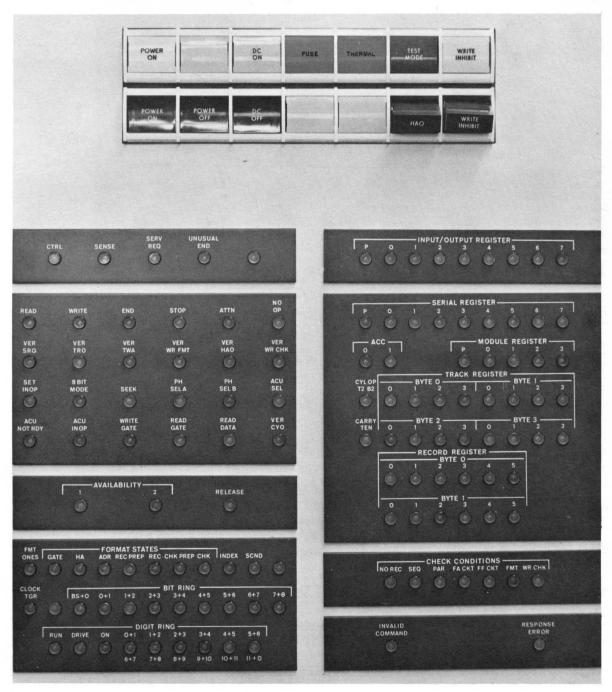

| CONTROL PANEL                                                   | • • | 43 |

| Operator's Switch and Light Panel                               |     | 44 |

| Customer Engineering Test Panel and Machine Indicating          |     |    |

| Lamps                                                           | •   | 45 |

| Communication Channel Jacks                                     | • • | 46 |

| APPENDIX                                                        | •   | 48 |

| Physical Specifications                                         |     | 48 |

| Cabling and Terminations                                        |     | 49 |

|                                                                 |     | 50 |

| File Control Status Word                                        |     | 56 |

| Format Track                                                    | •   | 57 |

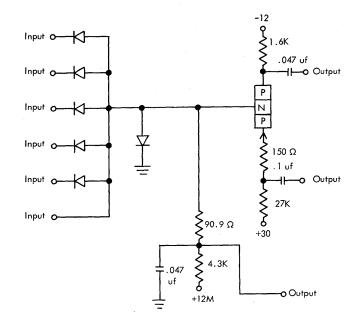

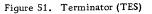

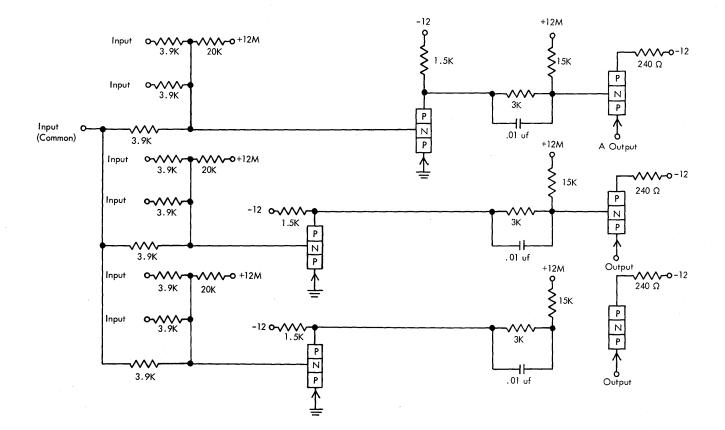

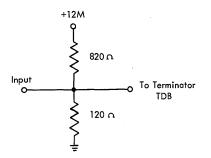

| Design Considerations for Cable Drivers and Terminators         | •   | 57 |

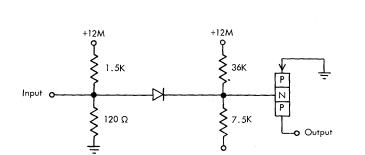

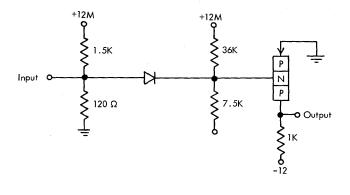

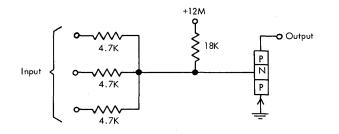

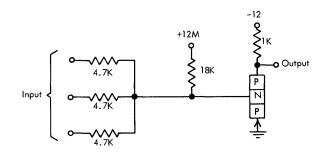

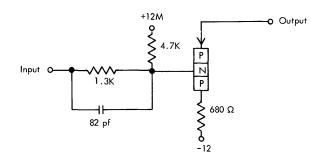

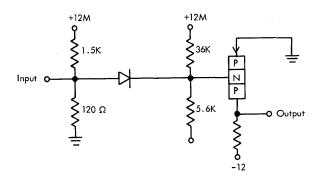

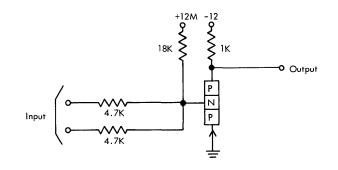

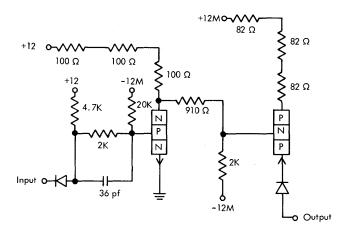

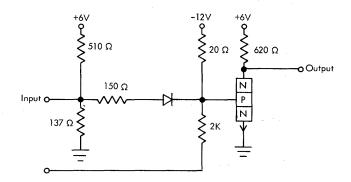

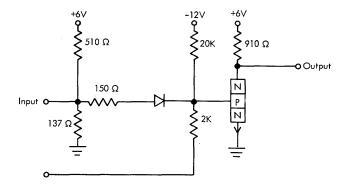

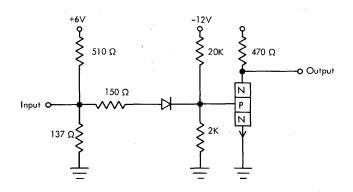

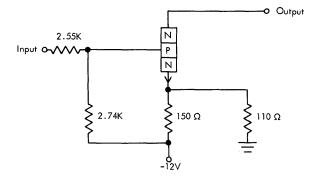

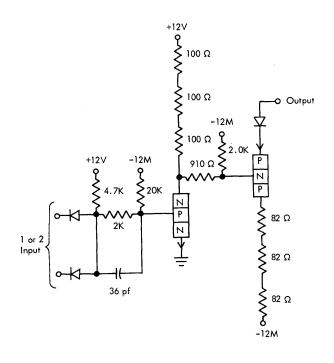

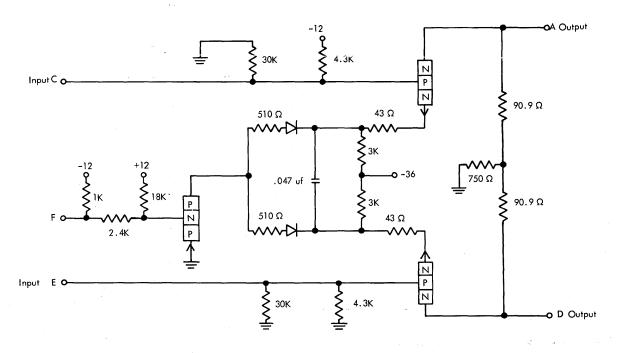

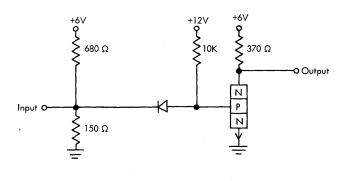

| Circuits Drivers and Terminators                                |     | 58 |

#### IBM 7631 FILE CONTROL

High-speed magnetic disk storage provides large external storage capacity to supplement internal core storage of a computer system. The IBM 1301 Disk Storage and its associated IBM 7631 File Control provide large storage capacity, fast access time to data recorded on the disks, and the ability to handle fixed or variable length records.

# MAGNETIC DISK RECORDING

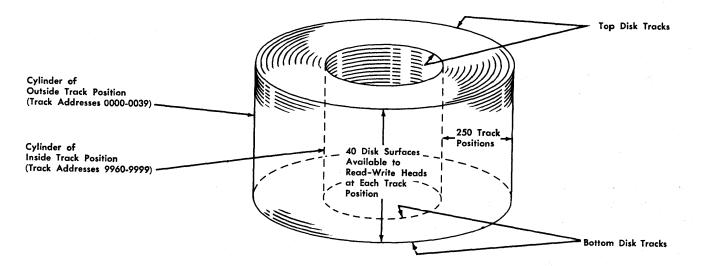

The magnetic disk is a thin metal disk coated on both sides with magnetic recording material. Twentyfive disks are mounted on a vertical shaft, with a small separation between the disks to provide space for the movement of read-write assemblies. The shaft revolves, spinning the disks at a maximum of 1790 revolutions per minute.

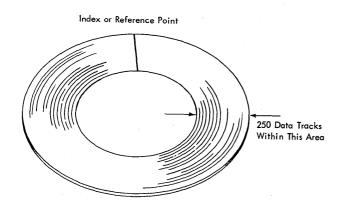

Data are stored as magnetized spots in concentric tracks on each surface of the disk (Figure 1). There are 250 tracks for the storing of data on each surface. The tracks are accessible for reading and writing by positioning the read-write heads between the spinning disks.

#### ACCESS MECHANISM

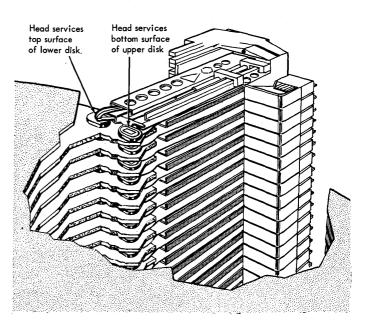

The read-write heads are mounted on an access mechanism which has 24 arms arranged like teeth on a comb (Figure 2). The arms move horizontally between the disks. (No vertical motion is involved.) Two read-write heads are mounted on each arm. One of the heads services the bottom surface of the upper disk while the other head services the top surface of the lower disk. Thus, it is possible to read or write on either side of a disk.

Figure 1. Magnetically Coated Disk

Figure 2. Head Arrangement

The magnetic disk data surface can be used repetitively. Each time new information is stored on a track, old information on the track is erased as the new information is recorded. The recorded data may be read as often as desired and will remain recorded in the tracks of a disk until it is written over.

Disk storage, like trays of cards or magnetic tape, provides external storage capacity to supplement internal core storage of a computer. Disk storage has a major advantage, however, in that all records contained in the 1301 are program-addressable, providing random access to any record or group of records, that is, faster access to any record.

Although the total number of character positions of the track is fixed, the number of records and the number of characters per record can be arranged to suit the needs of the using system. Thus, data can be stored on the track in any convenient arrangement within track limitations. Addresses must be provided to identify the track and the individual records to the computer. Also, space must be provided in the form of gaps to separate address and record areas, as well as to separate records in the record areas.

A format track is used to provide a means of defining and monitoring the address, record, and gap areas for the data tracks. In the 1301, one format track monitors 40 associated data tracks. The format track can be written and rewritten to describe the desired data track format as often as required to suit the needs of the user.

A disk storage module is comprised of the stack of 25 magnetic disks and its associated access mechanism.

Of the 25 disks, 20 disks (40 surfaces) are used to store data; of the other ten surfaces, six are used as alternate surfaces, one is a format surface, and one is a clock surface (Figure 3). The other two are not used. Each of the data storage surfaces and the format surface contains 250 concentric tracks that are accessible for reading and writing.

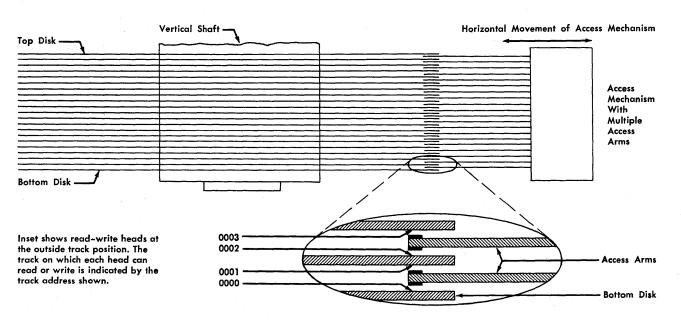

Read-write heads are mounted on the 24 arms of the access mechanism that moves the arms horizontally between the disks (Figure 4). No vertical motion is involved. Two read-write heads are mounted on each arm. One of the heads services the bottom

| DISK | SURFACE | MODULE 0                    | MODULE 1          |

|------|---------|-----------------------------|-------------------|

| 24   | 40      | Not Used                    | Not Used          |

| **   | 39      |                             |                   |

| 23   | 38      |                             |                   |

| 20   | 37      |                             |                   |

| 22   | 36      | Sector Sector Sector Sector |                   |

| ~~   | 35      |                             | 167               |

| 21   | 34      |                             | lar -             |

| 21   | 33      |                             | Ser - Contraction |

| 20   | 32      | 1                           | 1                 |

| 20   | 31      | 140                         |                   |

| 10   | 30      |                             | -                 |

6-19 2-29

| 5   | / |           |                   |  |  |

|-----|---|-----------|-------------------|--|--|

| 4   | 0 |           |                   |  |  |

| •   | 1 | Alternate | Alternate         |  |  |

| 2   | 2 |           |                   |  |  |

|     | 3 |           |                   |  |  |

| 2   | 4 |           |                   |  |  |

|     | 5 |           |                   |  |  |

| , 1 | 6 | Alternate | Alternate         |  |  |

|     | - | Format    | Format            |  |  |

| 0   | - | Spare     | Spare             |  |  |

|     | - | Clock     | Spare<br>Not Used |  |  |

.

Figure 3. Disk Surface Orientation

face of the disk above the arm and the other head services the upper face of the disk below the arm.

The read-write heads on the 24 access arms are aligned one above the other and are mechanically moved in parallel to one of the 250 cylinder positions of the module. When the access mechanism is positioned at a specific cylinder, 40 data tracks of information are available without any further motion of the access mechanism. Only electronic head switching is necessary to select a particular track in the cylinder. With the cylinder mode optional feature, it is possible to read or write a cylinder or part of a cylinder of tracks in one operation.

# ACCESS MOTION TIME

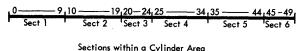

The time required for the access mechanism to move from one cylinder to another is related to the distance the arm moves, within certain machine defined limits. To calculate the time required, consider the 250 cylinders of a module organized into five areas of 50 cylinders per area (Figure 5). Also consider each area of cylinders further divided into six sections. Access motion time for any one access is as follows:

1. To move the access arm within a section of any one area requires 50 milliseconds.

2. To move the access arm from one section to another section of an area requires 120 milliseconds.

3. To move the access arm from one area to another area (crossing an area boundary) requires 180 milliseconds.

For example, to move the access arm from track 0000 to 1960 requires 120 milliseconds of access

Figure 4. Module and Access Mechanism

motion time. To move the access arm from track 1960 to 2000 requires 180 milliseconds.

# CYLINDER RECORDING

Since the heads and disk tracks are mechanically aligned one above the other, the vertical alignment of the tracks can be considered as a cylinder of tracks (Figure 6). Thus, with the access mechanism placed in any one of the 250 cylinders, 40 tracks of data are available without further access motion; only electronic head switching is necessary.

The tracks are numbered sequentially, from the bottom to the top of the cylinder (corresponding to the 40 heads, 00 to 39), starting at the outermost cylinder (000) to the innermost cylinder (249). Thus with large storage areas for reference tables, the data can be conveniently stored in a cylinder of tracks

| Area | Cylinder  |

|------|-----------|

| А    | 0 - 49    |

| В    | 50 - 99   |

| с    | 100 - 149 |

| D    | 150 - 199 |

| E    | 200 - 249 |

Cylinder Areas

Sections within a Cynnder Are

Figure 5. Access Motion Areas and Sections

or in a number of adjacent cylinders. This technique reduces access time to a minimum.

The cylinder arrangement of tracks also permits the optional feature -- the cylinder mode of operation -- to read or write a cylinder of tracks, or part of a cylinder, in one operation.

# DATA TRACK

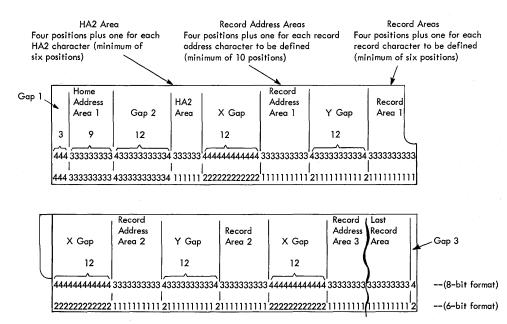

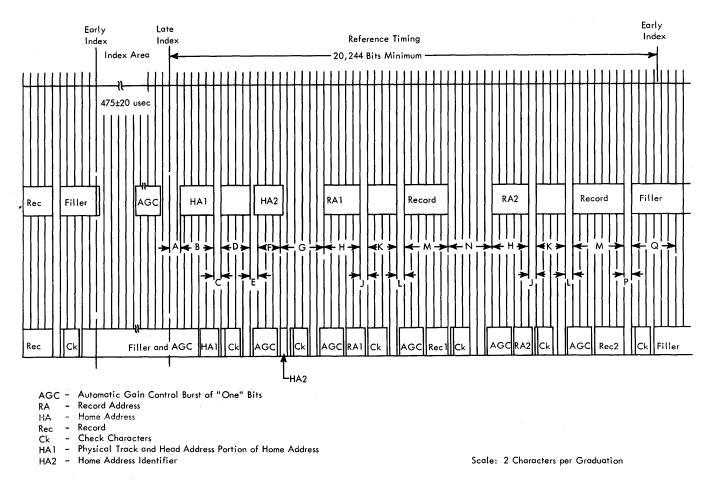

The basic fixed recording area of the 1301 is the data track. The physical make-up of the track limits it to a specific overall recording capacity. The overall storage capacity of all data tracks are equal. The entire recording area cannot be used to store data, however, as a number of character positions must be set aside to provide a means of identifying the track to the using system, or a home address (HA). To provide random access to any record on the track, additional character positions must be used for each record on the track, or a record address (RA). Additional character positions are required for gaps (G) to separate addresses and records. Since the tracks are circular, an index point (I) must be used to indicate the beginning or the end of the track. Therefore, each of the 10,000 data tracks must have an index point, one home address, a record address for each record stored on the track, and the necessary gaps to separate the address and the records (Figure 7).

#### Index Point

The index point of the track is the reference point of the track; that is, it indicates both the beginning and the end of the track. The index point is used by the file control in conjunction with its various modes of operation.

Figure 6. Track Cylinders

# Index G HA G RA G Record G RA G Record G G Index

Figure 7. Track Layout

#### Home Address (HA)

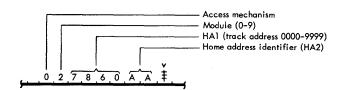

There is one home address for each of the 10,000 tracks. The home address follows the index point and consists of two parts called home address one (HA1) and home address two (HA2).

HA1

The HA1 portion of the home address is the track number. HA1 is prerecorded; it cannot be written by the customer. The track number is a four-digit number (0000-9999), that indicates the physical location of the track within the module. The tracks are numbered sequentially beginning at the lowest track of the outermost cylinder (track number 0000). Continuing up through the cylinder, 0000-0039 represents the 40 data tracks of the outermost cylinder. The numbers continue with the lowest track of the adjacent cylinder, track number 0040, up the cylinder to track number 0079. Continuing through each of the cylinders in a like manner, the last track number (9999) is the top track of the innermost cylinder. With this method of numbering, adjacent tracks on the same disk always differ by 40. This provides a means of determining the track number for any track within any cylinder by the simple formula: Given the head number and the cylinder number, the track number is the product of the cylinder number and 40, plus the head number. For example, for cylinder number 241 and head number 20 the track number is:  $241 \times 40 = 9640; 9640 + 20 = 9660.$

Also, with the track number known, the cylinder number and head number can be determined by dividing the track number by 40. The quotient is the cylinder number and the remainder is the head number. For example, given the track number 0590,  $0590 \div 40 = 014$  with a remainder of 30. Thus, the cylinder number is 014 and the head number is 30.

#### HA2

The second portion of the home address (HA2) is called the home address identifier. This portion of the address further identifies the track to the using system. HA2 is written by the user and consists of two or more characters that can be numeric, alphabetic, or special characters, depending on the requirements of the using system. Two characters are required for HA2. Even though only two characters are compared during address verification operations, additional characters can be used as a convenience for fixed word length systems.

HA2 can be written to serve any convenient purpose. For example, it can be used as a coded file protect device or it can be used to identify or tag a category of records, such as receipts, withdrawals, payments, inventory, etc.

#### Record Address (RA)

The record address consists of six or more characters that can be numeric, alphabetic, or special characters. It is used to identify the individual record on the track to the using system. A record address is assigned and written by the user to fit any convenient addressing system. It requires no relationship to the home address of the track where it is written, since an address is transmitted to the file control for each functional order. The home address used for seek orders, and the record address used in the prepare-to-verify (single record) order, need not be related in any way.

The record address normally consists of six characters and, even though the first four (high-order positions) can be alphabetic or special characters, depending on the system, only the numeric bit positions of these characters are compared during address verification operations. All bits of the fifth and sixth characters are compared during address verification.

#### Gap (G)

To distinguish between addresses and records, gaps are written between address and record areas. The gaps contain check characters and internal synchronization information required for proper machine operation.

Data are read and written on a track in six-bit or eight-bit characters or "bytes" serially by bit and serially by character. The eight-bit mode permits the use of packed format feature (packing two fourbit digits into one eight-bit character) on the 1301 by any system using that feature.

Since there are 250 tracks on each of the 40 disk storage surfaces in a module, 10,000 addressable data tracks are available in each module.

# TRACK CAPACITY (7000 SYSTEMS)

Each track on a disk has 2840 six-bit or 2205 eightbit character positions available for recording information. However, this will vary depending upon the system involved and is exclusive of HA1 and all associated gaps. Character positions necessary for home address 2, the record addresses, and gaps must be considered, however, in determining the number of character positions available for the records. In general, the track area available for record storage is the total track capacity less the character positions necessary for addresses and gaps.

#### TRACK CAPACITY (1410 SYSTEMS)

Each data track of the disk has a capacity of 2,840 six-bit or 2,205 eight-bit character positions for recording information and is exclusive of HA1 and all associated gaps. These figures have been adjusted to compensate for the character positions used in the prerecorded home address 1 and the gaps for the home address. To determine the number of character positions available for record storage, the character positions required for HA2, the record addresses, and the gaps must be considered. With HA2 representing the number of characters in the home address identifier, N representing the number of records on the track, L representing the number of characters per record, RA representing the number of record address characters (assumed to be the same for each record address), and 32 representing the number of character positions required for record address gaps, track capacity used can be determined by the following formulas:

For the six-bit mode:

HA2 + N (L + RA + 32) = 2,840 or less.

For the eight-bit mode:

HA2+N (L+RA+32) = 2,205 or less.

With HA2 equal to two character positions, RA equal to six characters positions, and L of constant length, the formulas can be reduced to:

For the six-bit mode:

N = 2838/(L+38) records per track.

For the eight-bit mode:

N = 2203/(L+38) records per track.

For a number of variable length records within the same track, the calculations require the summation of a series of quantities representing the number of records and their length or

$N_1(L_1+38) + N_2(L_2+38) + \dots N_n(L_n+38) = 2838$  (six-bit mode)

$N_1(L_1+38) + N_2(L_2+38) + \dots$  $N_n(L_n+38) = 2203$  (eight-bit mode)

$N_1$  is the number of records of  $L_1$  length in the track,  $N_2$  is the number of records of  $L_2$  length, etc.

The number of records per track for different record lengths (80 to 2800) and the number of character positions remaining that can be used as desired by the program are shown in Figure 8. To calculate the size of record that can be placed in the remainder of a track, assuming that the same size record address is to be used, subtract 38 from the remainder.

# FORMAT TRACK

The advanced characteristics of the 1301 permit flexibility in establishing how the disk storage space is to be allocated, organized, and addressed. This concept of disk storage use makes possible a wide variety of storage formats to meet the needs of many varied applications. The concept also requires that the user organize the disk storage in some particular format prior to its use as a data storage device. These activities can be likened to the wiring of a control panel for unit record machines, to the housekeeping preparations for a program, or to masking a storage area for future use. For clarity of understanding disk storage, it is important that the operations required for establishing disk storage format should not be confused with the operations related to the use of disk storage.

Before any data can be written on or read from a data track within a cylinder, a format track for that cylinder must be written. The 250 format tracks, one for each cylinder, are located on one of the additional disk surfaces not used for data.

The function of the format track is to control the use of the data tracks of a cylinder. Once a format track has been written, it establishes the location, character size, and mode of reading or writing which can take place in the home address area, the record address areas, the record areas, and certain gap areas. Data to be written on or read from each data track of a cylinder must conform to the format established by the format track for that cylinder.

The layout and writing of the format track is under the complete control of the user. Once written, however, the format for a cylinder of tracks remains fixed until the format track is rewritten.

| Characters<br>per Record |    | it Mode<br>5) Remainder |    | 3it Mode<br>5) Remainder |

|--------------------------|----|-------------------------|----|--------------------------|

| 80                       | 24 | 6                       | 18 | 79                       |

| 100                      | 20 | 78                      | 15 | 133                      |

| 200                      | 11 | 220                     | 9  | 61                       |

| 300                      | 8  | 134                     | 6  | 175                      |

| 400                      | 6  | 210                     | 5  | 113                      |

| 500                      | 5  | 148                     | 4  | 51                       |

| 1000                     | 2  | 762                     | 2  | 127                      |

| 2165                     | 1  | 635                     | 1  | 0                        |

| 2800                     | 1  | 0                       |    |                          |

Figure 8. Records per Track for Various Record Sizes

# PLANNING THE FORMAT TRACK

The control characters used to write a format track must first be organized in core storage as a record (format control record). The write format track instruction transfers the core storage format control record to the 7631 File Control. It is converted to a special bit configuration for machine control purposes and is written on the addressed format track. Since the format track defines, in machine form, the control action previously defined in the core storage format control record, explanation of how the data tracks of a cylinder are defined will be made in terms of the core storage format control record.

Four different characters, BCD 1, 2, 3, and 4 are used to compose a format control record in core storage. The BCD characters 1 and 2 are used to define areas of the data track which will be handling data in a six-bit mode. The BCD characters 3 and 4 are used to define areas of the data track which will be handling data in an eight-bit mode. It should be noted that certain areas of the format track are used for machine control and data checking purposes. These areas must be unconditionally provided for in the core storage format control record.

A typical core storage layout of a format control record in both the six-bit and eight-bit mode is shown in Figure 9.

# Track Identification Area

The track identification area consists of Gap 1, HA1, and Gap 2. It is always written to indicate the eightbit mode and is the same for all format control records. Gap 1 consists of three 4's; HA1 is nine 3's; Gap 2 is a 4 followed by ten 3's and a 4. From this point, the remaining area of the format control record must indicate either a six-bit or eight-bit mode of operation. It cannot be a combination of the two modes.

### Home Address 2 Area (HA2)

The format of the home address 2 (HA2) area must provide for four more character positions than the number of characters to be used for HA2. For example, if HA2 is to be a two-character home address identifier (minimum size), six BCD characters (1 or 3) must be used.

# X Gap Area

An X gap area must precede every record address area of the format control record. This gap is indicated by 12 BCD characters (either 2's or 4's depending on the mode of operation).

NOTE:

X Gap will always precede a record address area.

Y Gap will always follow a record address area.

Last record area to be defined must be followed by a 4 or 2, depending on the mode of operation. Eleven character positions must be reserved on disk after the Gap 3. This area of the format track is automatically written by the 7631 File Control.

Figure 9. Organization of Core Storage Control Record

# **Record Address Area**

This area must provide for four more character positions than the number of characters to be used for the record address. For example, if a record address is to be six digits in length, then ten BCD 1's or 3's must be used in the format control record to define the record address area. Because a record address must have a minimum of six character positions, the record address area of the format control record must provide for a minimum of ten character positions.

# Y Gap Area

A Y gap area must follow every record address area of the format track record. This gap is made up of one BCD 2 or 4, followed by ten BCD 1's or 3's and a BCD 2 or 4.

#### Record Area

This area must provide for four more BCD character positions than the characters required in the disk record. For example, for an 80-character record, 84 BCD 1's or 3's must be provided in the format control record. Data records can be a minimum of two characters in length. Therefore, the format control record must contain a minimum of six BCD characters. From this point the sequence of the areas to be established in the format data record is an X gap, record address area, Y gap, record area, etc., until the last record area.

#### Gap 3 Area

Gap 3 is a one-character gap that follows the last record area of the format track. Gap 3 is indicated in the format control record by a BCD 2 or 4, depending upon the mode of operation to be used.

NOTE: Although the format track does not need to be completely formatted for use, it does require that at least 11 character positions be reserved (not used) following the Gap 3 area of the format track. This area will be written automatically by the 7631.

# TIMING CONSIDERATIONS

The disk rotation speed of 1790 revolutions per minute, combined with the data recording method, makes possible a maximum rate of 70,000 or 90,000 characters per second. An entire cylinder (112,000 characters) can be read in approximately 1360 milliseconds. A whole module (28,000,000 characters) can be read in less than seven minutes. These rates include access motion time and rotational delay time, and are significant to timing estimates for such operations as file maintenance, audit trail preparation, and disk scheduling searching, where large volumes of data can be used in the same sequence in which the data are arranged in disk storage.

When reading or writing a series of tracks, system time of 350 microseconds is provided at the end of the track to permit verification of the home address (HA) of the next track to be processed. This allotted time permits the verification of the HA immediately following the end of the previously processed track instead of waiting for a disk revolution (33 milliseconds) to reposition the HA for verification.

In establishing job times for programs that make reference to individual records or groups of records in disk storage, the disk storage reference cycle is considered. A disk storage reference cycle includes the time required to complete all the disk storage operations for a particular processing operation. A typical disk storage reference cycle (move mode), assuming a random distribution of records within the disk storage module, is shown in Figure 10.

If the records in disk storage are arranged in such a way that no access motion time is required (all records for the job stored in the same cylinder), the total disk storage reference cycle time is reduced to 88 milliseconds (Figure 10). Thus, the distribution of records within disk storage affects total job time.

Access motion time within specific groups of ten adjacent cylinders is 50 milliseconds. Access motion time within specific groups of 50 adjacent cylinders is 120 milliseconds. To compute average data access time (the time required to seek a particular data record or track in disk storage), add 17 milliseconds average rotational delay time to access motion time.

Access motion time between cylinders in a disk storage module is shown in Figure 11.

NOTE: Numbers shown in the above chart are track numbers of the lowest numbered track in each cylinder and are the "cylinder addresses." Examples:

| 160 ms                | Average access motion time                                                        | 0    |

|-----------------------|-----------------------------------------------------------------------------------|------|

| 17 ms                 | Average rotational delay time                                                     | 1 17 |

| 3 ms                  | Read (using a 270 character record)                                               | 3    |

| 31 ms                 | Available processing time before<br>the record can be written back                | 31   |

| 3 ms                  | Write                                                                             | 3    |

| 31 ms                 | Elapsed rotation time before a<br>WRITE DISK CHECK instruction<br>can be executed | 31   |

| <u>3 ms</u><br>248 ms | can be executed<br>WRITE DISK CHECK<br>Total Disk Storage Reference Cycle Time    | 88   |

Figure 10. Disk Storage Reference Cycle Comparison

Group 1, Block 1, contains ten cylinders (0000-0360) and 400 tracks (0000-0399); Group 3, Block 1, contains five cylinders (0800-0960) and 200 tracks (0900-0999).

Access motion time is calculated as follows: Movement between cylinders in the same group in a block is 50 milliseconds. Movement between cylinders not in the same group in a block requires: 120 milliseconds when within any one of the five blocks (examples, between cylinders 0000 and 0400, 0000 and 1960), 180 milliseconds when between any of the five blocks (examples, between cylinders 1960 and 2000, 0000 and 9960).

To approximate average access motion time for a job (assuming a random distribution of records):

1. Determine the numbers of the cylinders to be used.

2. Select a used cylinder in the block that contains the most cylinders used.

3. From that cylinder:

a. Count the number of cylinders used in the same group and multiply this count by 50 ms.

b. Count the remaining number of cylinders used in the same block and multiply this count by 120 ms.

c. Count the remaining number of other cylinders used in the disk storage unit and multiply this count by 180 ms.

d. Divide the sum of a, b, and c, above, by the total number of cylinders used.

| Group 1 | 0000-0360 | 2000-2360 | 4000-4360 | 6000-6360 | 8000-8360 |

|---------|-----------|-----------|-----------|-----------|-----------|

| Group 2 | 0400-0760 | 2400-2760 | 4400-4760 | 6400-6760 | 8400-8760 |

| Group 3 | 0800-0960 | 2800-2960 | 4800-4960 | 6800-6960 | 8800-8960 |

| Group 4 | 1000-1360 | 3000-3360 | 5000-5360 | 7000-7360 | 9000-9360 |

| Group 5 | 1400-1760 | 3400-3760 | 5400-5760 | 7400-7760 | 9400-9760 |

| Group 6 | 1800-1960 | 3800-3960 | 5800-5960 | 7800-7960 | 9800-9960 |

|         | BLOCK 1   | BLOCK 2   | BLOCK 3   | BLOCK 4   | BLOCK 5   |

|         | 0000-1960 | 2000-3960 | 4000-5960 | 6000-7960 | 8000-9960 |

NOTE: Numbers shown in the above chart are track numbers of the lowest numbered track in each cylinder and are the "cylinder addresses."

Examples: Group 1, Block 1 contains 10 cylinders (0000-0360) and 400 tracks (0000-0399); Group 3, Block 1 contains 5 cylinders (0800-0960) and 200 tracks (0800-0999).

Access Motion Time is calculated as follows:

Movement between cylinders in the same group in a block is 50 milliseconds;

Movement between cylinders not in the same group in a block requires:

120 Milliseconds when within any one of the 5 blocks.

Examples, between cylinders 0000 and 0400; 0000 and 1960;

180 Milliseconds when between any of the 5 blocks.

Examples, between cylinders 1960 and 2000; 0000 and 9960.

To approximate average access motion time for a specific job (assuming a random distribution of records):

- 1. Determine the numbers of the cylinders to be used.

- 2. Select a used cylinder in the block that contains the most cylinders used.

- 3. From that cylinder:

- A. Count the number of cylinders used in the same group and multiply this count by 50 ms,

- B. Count the remaining number of cylinders used in the same block and multiply this count by 120 ms,

C. Count the remaining number of other cylinders used in the disk storage unit and multiply this count by 180 ms,

D. Divide the sum of A, B, and C by the total number of cylinders used.

Figure 11. Access Motion Time

The IBM 7631 File Control is used to control the operation of up to five IBM 1301 Disk Storage units. It contains electronic circuitry for performing the following functions:

1. Transferring of addresses from the computer to the 1301.

2. Notifying the computer when a 1301 file seek has been completed.

3. Searching the file tracks for the particular record addressed by the computer.

4. Obtaining assembled data from the computer system and sending it to the IBM 1301 in a serial by bit manner during a write operation.

5. Accepting serial data from the IBM 1301 Disk Storage during a read operation and assembling it into characters for transmission to the computer systems.

6. Providing status information to the computer system, on command.

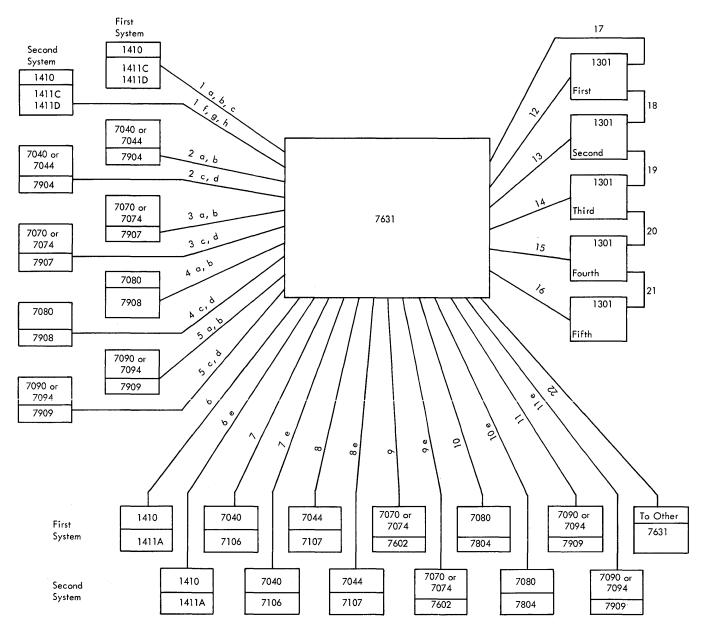

The IBM 7631 File Control may be used with any IBM Data Processing System that uses the IBM 1301 Disk Storage; however, different models of the 7631 are required depending on the computer system involved. The different models and their system or systems assignments are:

Model 1 - For disk storage use with a single IBM 1410 system

Model 2 - For disk storage use with a single IBM 7040, 7044, 7070, 7074, 7080, 7090 or 7094 system

Model 3 - For shared disk storage use by an IBM 7000 system (as listed above) and an IBM 1410 system

Model 4 - For shared disk storage use by two IBM 7000 systems (as listed above).

Model 5 - For shared disk storage use by two IBM 1410 systems.

A maximum of five IBM 1301 Disk Storage units may be used per system or combination of systems with a maximum of two IBM 7631 File Controls connected to the five disk storage units.

Because of basic operational and design differences between the IBM 7000 and IBM 1410 systems, two types of programming and systems connecting lines are used. The operational information and line functions for computer to 7631-1301 operations are separately provided in this manual. Additionally, 7631-1301 operations in specific IBM Data Processing Systems are available in the following IBM references. System Reference Form No.

| 1410    | A22-6670 |

|---------|----------|

| 7040/44 | A22-6649 |

| 7070/74 | G22-6594 |

| 7080    | G22-6604 |

| 7090    | A22-6528 |

| 7094    | A22-6703 |

|         |          |

The functions performed by the 7631 and 1301 and the using 7000 systems data channels are based on the execution of commands, orders and instructions.

# FILE CONTROL OPERATIONS WITH 7000 SERIES SYSTEMS

#### Commands

The 7631 uses four commands relating to disk storage operation: read, write, sense, and control. (A command is defined as system-coded information, decoded by a system data channel and executed by the file control, to perform a specific function.) The four commands executed by the 7631 are:

<u>Read Command</u>: A command that sets up the necessary control circuitry in the connecting data channel to permit information stored in the disk storage to be read and transmitted to the computer system, through the file control.

Write Command: A command that sets up the control circuitry in the connecting data channel to permit information to be transmitted from the computer system, through the file control, to the disk storage, and to write upon a designated disk track.

<u>Sense Command</u>: A command which causes transmission of status information from the file control to the computer system to indicate the status of the disk storage unit or units and the file control. Status conditions such as error and unusual conditions as well as attention conditions are affected by the sense command.

<u>Control Command</u>: A command which is used to transmit orders to the file control. (An order is defined as control coded information that is decoded and executed by the file control to perform a specific function.) Orders are transmitted to the file control in the same manner as data are normally transmitted. The file control recognizes the information as an order and sets up the necessary decoding and execution circuitry to process the order. Transmission of orders to the file control as a result of the command is the same for all computer systems using the 7631 File Control, although they may be initiated by a different method.

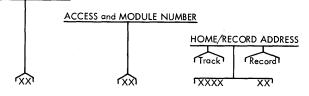

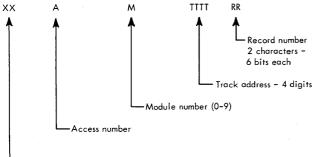

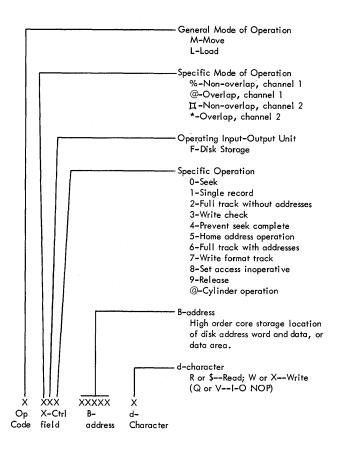

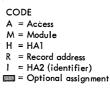

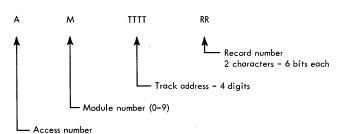

#### Orders

Orders normally consist of a two-digit operation code and eight characters to define addresses. When address information is not required, the order consists of the operation code only. The make-up of the order is shown in Figure 12.

Orders are transmitted from the computer's data channel as BCD characters over the write bus. The 7631 File Control accepts the digit portion of the first eight characters of the order (operation code, access and module number, and the first four positions of the address) and all bits in the ninth and tenth characters of the order.

Operation Code: A two-digit code that specifies the operation to be performed. This portion of the order is always numeric. The operation code is all that is required for the following orders: no operation, six-bit mode, eight-bit mode, and release.

Access and Module Number: These two positions of the order, which are always numeric, specify the module in which the operation will take place.

Record or Home Address: This portion of the order gives the home or record address, depending on the type of operation that is to take place.

The 7631 File Control will decode and execute any of 13 orders transmitted from the computer by the control command. The 7631 decodes the transmitted order, accepts address information, performs the designated function, and then transmits an end signal or unusual end signal to the computer. In the case of a seek order, the file control sends the end signal after decoding the order. It then performs the seek

#### OPERATION CODE

Figure 12. Order Format

| Order                                      | Mnemonic<br>Code | Numeric<br>Code |

|--------------------------------------------|------------------|-----------------|

| No Operation                               | DNOP             | 00              |

| Release                                    | DREL             | 04              |

| Eight-Bit Mode                             | DEBM             | 08              |

| Six-Bit Mode                               | DSBM             | 09              |

| Seek                                       | DSEK             | 80              |

| Prepare to Verify, Single Record           | D∨SR             | 82              |

| Prepare to Write, Format                   | DWRF             | 83              |

| Prepare to Verify, Track with No Addresses | DVTN             | 84              |

| Prepare to Verify, Cylinder Operation      |                  |                 |

| (Optional Feature)                         | DVCY             | 85              |

| Prepare to Write Check                     | DWRC             | 86              |

| Set Access Inoperative                     | DSAI             | 87              |

| Prepare to Verify, Track with Addresses    | DVTA             | 88              |

| Prepare to Verify, Home Address            | DVHA             | 89              |

Figure 13. Table of Orders

and, at the completion of the seek operation, sends an attention signal to the computer.

Orders requiring the two-digit operation code only are: no operation, release, six-bit mode, and eightbit mode. The orders, with their mnemonic code and their numeric operation code, are shown in Figure 13.

#### **Operation Signals**

Signals are generated to provide a communication link between the file control and the computer. The signals generated to indicate that a specific condition exists, are:

Attention: Indicates that a previously given seek operation has successfully positioned the access mechanism at the specified location and selected the desired head.

End: Indicates the successful completion of an operation. This signal can indicate the successful transmission of an order to the file control or it can indicate the successful completion of a read or write operation.

Unusual End: Always indicates an unsuccessful operation. This signal can indicate that an error has been sensed during a read or write operation, or when any other check condition has occurred, or it might indicate that an unsuccessful attempt to transmit data has occurred.

Stop: Indicates that the computer has sensed the end of a read or write field.

#### Status Data

Status data are set in bit form for each read, write, and control operation performed by the file control and are available to the computer by means of the sense command. The status data should be called for by the computer before the initiation of the next read, write, or control command. (The initiation of the next command resets all error indications of the status data.) The attention bit for the addressed module is also reset.

The make-up of the status data transmitted to the data channel of the using system is shown in Figure 14.

Status character 0 summarizes the type of check or condition. Characters 1 and 2 give the type of check encountered during the operation and the mode of operation; character 3 gives the different unusual conditions; and characters 4, 5, and 6 give the attention indications. Characters 7,8, and 9 are reserved.

| Status<br>Char | Bit<br>No.       | BCD<br>Bit       | Assignment                                                                                         | Comment                  |

|----------------|------------------|------------------|----------------------------------------------------------------------------------------------------|--------------------------|

| 0              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Reserved<br>Program Check<br>Data Check<br>Exceptional Condition                                   | Summary<br>Byte          |

| ١              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Invalid Sequence<br>Invalid Code<br>Format Check<br>No Record Found                                | Program<br>Check         |

| 2              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Invalid Address<br>Response Check<br>Data Compare Check<br>Parity or Check Char Code Check         | Data Check               |

| 3              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Access Inoperative<br>Access Not Ready<br>Disk Storage Circuit Check<br>File Control Circuit Check | Exceptional<br>Condition |

| 4              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Reserved<br>Six-Bit Mode<br>Reserved<br>Reserved                                                   | Data Mode                |

| 5              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Module 0<br>Module 1 (Disk Only)<br>Module 2<br>Module 3 (Disk Only)                               | Attention                |

| 6              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Module 4<br>Module 5 (Disk Only)<br>Module 6<br>Module 7 (Disk Only)                               | Attention                |

| 7              | 3<br>5<br>6<br>7 | A<br>4<br>2<br>1 | Module 8<br>Module 9 (Disk Only)<br>Reserved<br>Reserved                                           | Attention                |

| 8,9            |                  |                  | Reserved                                                                                           |                          |

Figure 14. Status Data Bit Assignment

File Control Checks

The 7631 File Control checks for twelve individual error conditions that are possible in the operation of disk storage. The sensing of any one of these conditions causes an unusual end signal to be sent to the computer. Their position in the status word is shown in the Appendix.

Parity or Character Check: The 7631 is an oddparity machine. As characters are transferred from the computer, the bit count of each is checked. If an even number is detected, this check bit, as well as the summary data check bit, will be set into the status data. The character code check is made by generating three check characters for each address and record as bits are read from the disk surface during a read operation. These newly generated characters are then compared bit by bit with those previously generated and recorded in the gap following each address and each record during the write operation. Failure to compare will indicate the occurrence of an error. Response Check: The response check indicates that a character was not received by the 7631 within the allotted time. Response check can only occur as a result of a read or write operation.

Data Compare Check: Data compare check can occur only during a write check operation. The condition indicates that a compare error was detected somewhere during write check. During a write check operation data are read from the disk surface and compared bit by bit with those transferred from the computer.

Format Check: The format check occurs during either format write or a write check of a format track. The cause may be either an illegal code (any but a BCD 1, 2, 3, or 4) or because a stop signal was not sent to the file control prior to sensing the index point.

<u>No Record Found</u>: The no-record-found indication occurs if the file control fails to locate the track address that was issued to it on a prepare-to-verify order.

Invalid Sequence: The invalid sequence condition can occur during write operations in two ways, namely, when a write command is received by the file control without a preceding and properly executed prepare-to-verify or prepare-to-write format order. In the second case, invalid sequence occurs when a write check order is preceded by other than a prepare-to-verify order, prepare-to-write format order, and properly executed write command. When reading, a prepare-to-verify is the only legal order than can precede a read command.

Invalid Code: The invalid-code indication occurs when the file control is given an order that cannot be performed.

Access Inoperative: This indication occurs when the access mechanism fails to respond to a seek order. The access may be mechanically out of order or may not exist.

Access Not Ready: The access-not-ready indication shows that the addressed access is in motion from some prior seek order.

Disk Storage Circuit Check: This check indicates a circuit failure in the 1301 Disk Storage.

File Control Circuit Check: This check occurs due to malfunctioning of the gap detection circuit, address comparison circuit, or the check character code generator in the file control, the format skew detector circuit, or the basic timing rings of the 7631.

<u>Invalid Address</u>: Invalid address is set by an invalid configuration of bits sent to the 1301.

# FUNCTIONAL DESCRIPTION OF LINES -- 7000 SERIES SYSTEM/7631

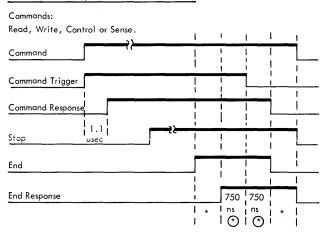

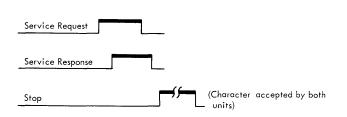

The lines are divided functionally into five groups. Generally speaking, any signal must be maintained until its response is provided by the receiving unit. See Figure 15.

#### Initiation of Operation (Five Lines)

The operation is initiated by one of the four commands, namely read, write, control, and sense and their common response (command response). Both read and sense commands establish transfer of information from the 7631 to the computer. Read is associated with the transfer of data while sense is associated with the transfer of status of the 7631. Both write and control commands establish transfer of information from the computer to the 7631. Write is associated with the transfer of data while control is associated with the transfer of housekeeping orders to the 7631. Commands are sequentially executed over the interface. An operation associated with any of the four commands must be properly terminated prior to issuance of the next command.

# Information Transfer (20 Lines)

Information is transmitted over the read bus and the write bus on the demand and response basis. Demand is indicated by service request and response by service response. Information is transferred parallel by byte. The byte may be up to eight data bits in size.

# Termination of Operation (Four Lines)

An operation may be terminated by either the computer or the 7631. The computer accomplishes this by the stop signal. The 7631 indicates successful completion with end signal and abnormal completion by unusual end signal. In either case the computer responds with end response. The cause of unusual end may be determined by analysis of the status information obtained by means of a subsequent sense command.

#### Asynchronous Signaling (Two Lines)

The 7631 can present an asynchronous signal to the computer by means of an attention signal. An attention signal indicates to the computer that a change in status in the 7631 has occurred which requires atten-

|                                       | - Operational Out            |           |

|---------------------------------------|------------------------------|-----------|

| 7000 System                           | - Read Command               |           |

| Data                                  | Write Command                |           |

| Channel Unit                          | - Control Command            |           |

| Channel Onli                          | Sense Command                |           |

|                                       | Write Data Bit 0             |           |

|                                       | Write Data Bit 1             |           |

|                                       | Write Data Bit 2             |           |

|                                       | Write Data Bit 3             | 7631 2, 4 |

| 7004 7007                             | Write Data Bit 3             | File      |

| 7904, 7907                            |                              | Control   |

| 7908 or 7909                          | Write Data Bit 5             |           |

|                                       | Write Data Bit 6             | Unit      |

|                                       | Write Data Bit 7             |           |

|                                       | Write Data Bit (Parity)      |           |

|                                       | • Service Response One>      |           |

|                                       | Stop>                        |           |

| • • • • • • • • • • • • • • • • • • • | End Response One 🗕 🗡         |           |

|                                       | - Attention Response         |           |

| -                                     | - Operational In             |           |

| <b>4</b>                              | Command Response             |           |

|                                       | - Read Data Bit 0            |           |

|                                       | Read Data Bit 1              |           |

| <b></b>                               | Read Data Bit 2              |           |

|                                       | - Read Data Bit 3            |           |

|                                       | - Read Data Bit 4            |           |

|                                       | - Read Data Bit 5.           |           |

|                                       | Read Data Bit 6              |           |

|                                       | Read Data Bit 7              |           |

|                                       | - Read Data Bit /            |           |

|                                       | - Service Request            |           |

|                                       |                              |           |

|                                       | - Unusual End                |           |

|                                       | - Attention                  |           |

|                                       | Attention                    |           |

| <b>€</b> En                           | nergency Power Off Interlock | <u>•</u>  |

Figure 15. Operating Lines - IBM 7000 Series Data Processing Systems to/from IBM 7631-2 and 4

tion. This signal may come at any time whether or not one of the command operations is in process. The computer signals to the 7631 the recognition of attention by sending attention response.

#### Interlocks (Two Lines) -- Non Power

In addition to the logical interlocks (signal and response) mentioned above, the computer and 7631 are interlocked by means of operational-in and operational-out. Each line reflects the operational state of the unit at its driver end.

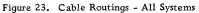

# ORGANIZATION OF INFORMATION

Information on the read bus and the write bus is arranged so that bit position 0 of a bus always carries the highest order bit, with bits in descending order being assigned to bit positions of the bus string in the computer or 7631, the bit-from-bit position 0 of a byte always adjoins the bit-from bit position 7 of the preceding byte. As a result, a message consisting of several bytes always appears as bus bit positions 0, 1, 2, 3, 4, 5, 6, 7, 0, 1, 2, etc.

When a byte is transmitted over the connecting lines that consists of less than eight bits, the bits must be placed in the highest-numbered continuous bit positions of the bus. Thus, when a computer or 7631 transmits only the six bits of the BCD code over the lines, bit B is placed in bit position 2 of the bus, bit A in bit position 3, etc., and bit 1 is placed in position 7. When the computer or 7631 places information on or receives information from only four lines of a bus, it must use bit positions 4, 5, 6, and 7. Any unused lines of the read or write bus must include the low-numbered bit positions of the bus, i.e., bit position 0 and bit positions adjacent to it. The parity bit of any byte must always appear in the parity bit position. Unused lines must always present logical zeros to the receiving end.

# DESCRIPTION OF SIGNAL LINES FROM COMPUTER TO 7631

#### Operational Out

The operational out line is used for interlocking purposes. The lines from the computer are significant only when the operational out line is up.

The down-state of the operational out signal is used to reset the 7631. Any down-state of sufficient duration to cause a response from the terminator circuit provides the reset. The meaning of the reset is defined by the 7631. To insure a proper reset, the operational out line must remain down for at least 6 usec.

# READ COMMAND

The read command line is used to signal the 7631 to cause the next block to be read into the computer. The read command signal, as well as all other command signals, is loop checked by the command response line.

The read command signal must not be initiated unless command response is down, and unless stop and end response are either down or are dropped at the time read command is raised. The read command signal must remain up until the rise of command response. It must fall before the rise of end response.

#### Write Command

The write command line is used to signal the 7631 to proceed with writing a block of data. Loop checking and signal timing specifications are the same as for read command.

#### Control Command

The control command line is used to signal the 7631 that it must accept information from the computer over the write bus and must perform the operation encoded in this information. Examples are: seek, prepare to write format, etc. Loop checking and signal timing specifications are the same as the read command.

#### Sense Command

The sense command line is used to signal the 1301 to send status information to the computer over the read bus. The information sent depends on the definition of the sense data word. Loop checking and signal timing specifications are the same as for read command.

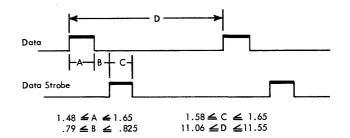

#### <u>Write</u> Bus

The write bus is used for sending both data and control information to the 7631. It consists of nine lines -- eight data lines plus one line for odd parity. Not all of these lines need be used.

Data must be valid on the write bus from the rise of service response until the fall of service request.

The assignment of bit positions on the nine lines on the write bus is as follows:

| Line Name                                                                                                                                      | Assignment A                                                                                         | Assignment B                                                                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| Parity Bit<br>Bus Bit Position 0<br>Bus Bit Position 1<br>Bus Bit Position 2<br>Bus Bit Position 3<br>Bus Bit Position 4<br>Bus Bit Position 5 | Bit C - BCD<br>Unused - BCD<br>Word Mark<br>Bit B - BCD<br>Bit A - BCD<br>Bit 8 - BCD<br>Bit 4 - BCD | Parity<br>Bit 8<br>Bit 4<br>Bit 2<br>Bit 1<br>Bit 1<br>Bit 8<br>Bit 4<br>Second |  |  |

| Bus Bit Position 6<br>Bus Bit Position 7                                                                                                       | Bit 2 - BCD<br>Bit 1 - BCD                                                                           | Bit 2<br>Bit 1 Numeric<br>Character                                             |  |  |

#### Service Response

The service response line is used to signal the 7631 in recognition of a signal on the service request line. Service response indicates to the 7631 that the computer is transmitting or has received information on the data busses.

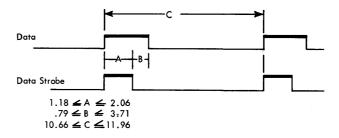

During write and control operations, the rise of service response indicates that data is available on the write bus. The rise of service response is delayed sufficiently to insure that it does not precede data when measured at the cable connectors at the computer under worst-case skew conditions. Skew that is caused within cables and 7631 circuitry is accommodated by the 7631. Within the above skew limitations, data must be valid from the rise of service response until the fall of service request. During read and sense operations, service response must rise when the computer has accepted the information on the read bus.

The service response signal must rise before the fall of service request. In the case of cyclic devices, service response must rise before the fall of service request by a time period specified by the 7631. If service response rises too late, the 7631 recognizes the overrun condition.

The service response signal must remain up until the fall of service request. It falls after the fall of service request.

#### Stop

The stop line is used to signal the 7631 that the computer has recognized the end of a record or operation. If the 7631 recognizes the end of operation first and generates an end or unusual end signal, no stop signal occurs.

Upon receipt of the stop signal, the 7631 proceeds to its normal ending point. No further service request is sent and no further service response is expected. To complete the ending procedure, the 7631 sends an end or unusual end signal at the proper time and receives in return an end response from the computer.

The stop signal may rise any time when the command response line is up except when both service request and service response lines are also up. If stop is issued when service request is up, it replaces service response, in which case read and sense operations data on the read bus is not accepted.

The stop signal must remain up until the fall of command response. It must fall when or before a new command signal is sent to the 7631.

#### End Response

The end response line is used to signal the 7631 in recognition of a signal on the end or unusual end lines. The end response signal restores the 7631 to the conditions necessary for accepting a new command.

The end response signal must remain up until the fall of both command response and end or unusual end. It must fall when or before a new command signal is sent to the 7631.

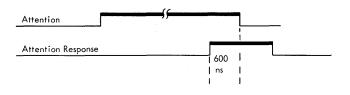

#### Attention Response

The attention response line is used to signal the 7631 in recognition of a signal on the attention line. The attention response signal causes the fall of the attention line. The attention response signal must remain up until the fall of attention and must fall after the fall of attention.

DESCRIPTION OF SIGNAL LINES FROM 7631 TO COMPUTER

#### Operational In

The operational in line is used for interlocking purposes. During operation the lines from the 7631 are significant only when the operational in line is up. When the operational in line is down, the 7631 normally will not respond to any signal from the computer.

#### Read Bus

The read bus is used for sending both data and sense information to the computer. It consists of nine lines -- eight data lines plus one line for odd parity. All of these lines need not be used.

Data must be valid on the read bus from the rise of service request until the rise of service response.

The assignment of bit positions on the nine lines of the read bus is the same as on the write bus.

# Command Response

The command response line is used to signal the computer in recognition of a signal on any of the four command lines. It indicates the ability of the 7631 to initiate the command.

The command response signal will rise within 6 usec of the rise of any of the four commands. If, because of skew, stop or end response from the preceding operation overlap the command, command response cannot rise until stop and end response are down and it will not fall during the execution of the command. It will fall within 6 usec of the rise of end response.

#### Service Request

The service request line is used to signal the computer when the 7631 wants to transmit or receive a byte of information.

During read and sense operations, service request rises when information is available on the read bus and service response is down. The rise of service request must be delayed to guarantee that it does not precede data when measured at the cable connectors at the computer under worst-case skew conditions. Skew that is caused within computer circuitry must be accommodated by the computer. Within the above skew limitations, data must be valid until the rise of service response. During write and control operations, service request rises when or before information is required on the write bus and service response is down.

The service request signal must fall after the rise of service response. During read and sense operations, service request must fall within 6 usec of the rise of service response.

When the next cycle time is reached, in the case of cyclic devices, and service response has not occurred, the 7631 must drop service request and must recognize an overrun condition. The minimum interval between the rise of service response and the fall of service request is part of the 7631 specifications.

# End

The end line is used to signal the computer that the 7631 has recognized the normal ending of an operation. If any abnormality such as data check, program check, end of file, or cancel condition has occurred, the end signal is not used and an unusual end signal is given instead.

The end signal cannot rise until service response for the last service request has been received. The end line must stay up until end response is received from the computer. It must fall within 6 usec of the rise of end response.

The 7631 gives an end signal after every normal operation. The computer may or may not have previously given a stop signal. In any case, the computer gives an end response signal after receiving an end signal from the 7631.

#### Unusual End

The unusual end line is used to signal the computer that the operation being executed has resulted in an unusual condition and has been terminated. This signal is a summary of all unusual conditions such as data check, program check, end of file, out of material, or cancel. If an unusual end signal occurs, the end signal is not given. The computer therefore sees end or unusual end, but not both.

The unusual end signal must stay up until end response is received from the computer. It must fall within 6 usec of the rise of end response. No further service request may be sent after unusual end rises.

The computer may or may not have given a stop signal before the 7631 signals unusual end. In any case, the computer gives an end response after receiving an unusual end signal from the 7631.

#### Attention

The attention line is used to signal the computer that an access mechanism has come to rest.

The attention signal can rise at any time except when attention response is up. It must stay up until the 7631 receives an attention response from the computer. Attention must fall within 6 usec of the rise of attention response.

Turning off the attention signal generally does not reset the conditions which caused the indication. The conditions are available for transmission to the computer on a sense command.

TIMING OF LINES -- 7631 IN 7000 SERIES OPERA-TION

# Commands

Read, Write, Control or Sense:

Timings shown are maximum. They are measured from the time a signal rises on the interface cable until the 7631 brings up its responding signal on the interface cable.

\* Timings are a Computer function. The length of these timings has no effect on 7631 operation.

1. Get command from computer.

2. Command will not be initiated unless command response, end, and stop are down.

3. Command response will rise no later than 1.1 microseconds after the command is initiated.

4. If stop is issued, the 7631 will proceed to its normal ending point.

5. The rise of end causes the 7631 to detach itself from the I-O device and signals end to the computer.

6. The rise of end response causes the command to be reset.

7. Command going down causes command response and end to be reset.

8. The fall of end should cause end response and stop to fall.

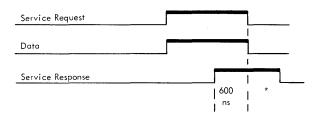

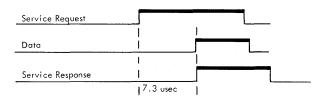

Service request and response:

1. Service response must be down for service request to rise.

2. Service response is the system acknowledgment of service request.

3. Service request falling causes service response to fall.

4. A service response must rise within 7.3 microseconds after the rise of service request or an overrun condition will be indicated.

5. Timings shown are maximum.

Read or Sense:

\* Timing is a computer function.

1. Service request rises when data is available on the bus.

2. Rise of service response indicates that data has been accepted by the computer.

3. Service response rising causes service request to fall.

Write or Control:

1. Service request rises when data is requested in the 7631.

2. Rise of service response indicates data is available on the bus.

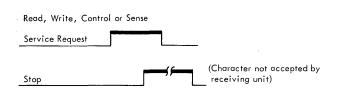

# Stop

Read, Write, Control or Sense:

1. Stop is issued when service request is up.

1. Stop is issued when both service request and service response are down.

Attention

Timings shown are maximum.

1. Attention may rise any time except when attention response is up.

2. Attention holds up until attention response rises.

#### OPERATIONAL CHARACTERISTICS

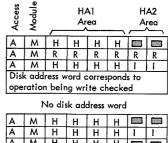

Data handling (reading and writing) can be handled in five different modes:

Home Address Operation: Comparing the physical home address (HA1) followed by transfer of the home address identifier (HA2) plus all addresses and records on a given track.

Single Record Operation: Comparing a record address followed by transfer of the associated single record only.

Track Operation: Comparing the entire home address (HA1 and HA2) followed by transfer of all record addresses and records on a single track.

<u>Track Without Addresses</u>: Comparing the entire home address requested, followed by transfer of all records contained in the remainder of the track.

Cylinder Operation: Optional feature -- comparing the entire home address of a particular track in a cylinder followed by transfer of all records contained in that track and all succeeding tracks of higher address within that cylinder.

# CONTROL COMMANDS

The 7631 File Control executes thirteen particular orders under the control command. The orders, standardized at a common length of either ten or two digits, are transmitted to the file control over the write bus in response to service requests by the file control. The first two command digits comprise the operation code and the remaining digits provide the necessary address information. Six-bit mode, eightbit mode, no-op and release are orders which require no address information and consequently are of two digits in length. The remaining orders demand ten digits. The file control decodes the command, accepts the address information, performs the designated function, and transmits an end signal to the processing system upon completion.

During execution of the control function, the file control performs various checking operations. It performs a parity check on op codes and address information, confirms that a valid op code has been accepted, and verifies disk storage ready and operative lines. If any check conditions are present, the control operation is immediately terminated and an unusual end signal is sent to the using system.

#### Seek (DSEK)

The seek order transmitted to the file control includes the address of the access unit and cylinderhead location to which the access is to be moved. The file control selects the particular access mechanism, encodes the cylinder-head digits into the file's track and head code and sends the address to the 1301. An end signal is then issued and the file control is available for further operations while the access moves to the requested address.

The end of the seek order does not signify that the access has reached its proper position nor that it necessarily will, as there is a possibility of the file going to memory address. It means only that the file control has sent an address to the selected access and that no error conditions were encountered.

#### Set Access Inoperative (DSAI)

This order is sent to the file control accompanied by the address of a particular access mechanism. The file control sets the inoperative relay in the access and issues a normal end signal to the system. The set access inoperative signal from the adapter to the 1301 Disk Storage will be issued regardless of the level of the ready line.

# Prepare to Verify Orders

The PV order specifies the manner in which a subsequent read or write command is to be performed, provides an address for subsequent verification, selects the desired module and access and, with the exception of DVSR, selects the addressed head. An end signal indicates that the PV order and associated address have been accepted by the file control and that no check conditions have been encountered. The read or write which follows a PV order initiates a search for the particular record address.

Prepare to Verify -- Single Record Operation: The DVSR order prepares the file control to read or write one particular record in a track. The record address is supplied for subsequent verification. The head that is selected for the DVSR was determined during a previous seek or PV order.

Prepare to Verify Track Operation (DVTA): The DVTA order prepares the file control to read or write record addresses and records on a particular track. The home address of the track is supplied for subsequent verification. Prepare to Verify Track Without Addresses (DVTN): The DVTN order prepares the file control to read or write only records on a particular track. The home address of the track is supplied for subsequent verification.

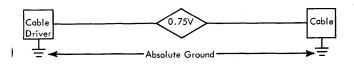

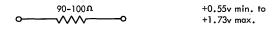

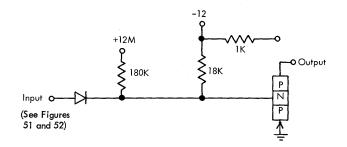

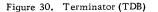

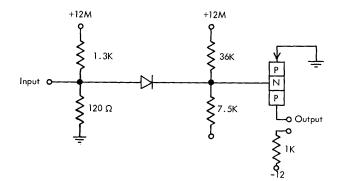

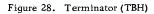

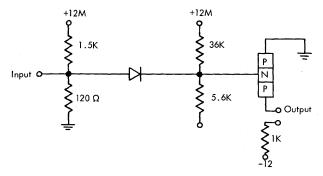

Prepare to Verify -- Cylinder (DVCY): The DVCY order prepares the file control to read or write only records in a particular cylinder. The home address of the track within the cylinder at which it is desired to start the operation is supplied for subsequent verification.