# Maintenance Library

| PSG                                                                                            | MIM                                                                | PCM*                                           | MDM                                                                                                                            | ECM*          | MSM*                                   |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------|

| INTRO<br>MLX<br>START<br>ISOLATE<br>REPAIR<br>MD<br>LOG<br>PROG<br>SC-FRU<br>INDEX<br>(MASTER) | TRANS<br>LGND/GLOS<br>LOC<br>PWR<br>CARR<br>MAP<br>SAFETY<br>INDEX | VISUAL<br>INDEX<br>CATALOG<br>NUMERIC<br>INDEX | MICROFICHE<br>CARD/CABLE/<br>VOLTAGE<br>CHARTS<br>A-BOARD LRM<br>B-BOARD LRM<br>C-BOARD LRM<br>POWER<br>DIAGRAMS<br>RD<br>INST | ECDs<br>INDEX | HELP<br>SENSE<br>OPER<br>DIAG<br>INDEX |

| VOL. R05                                                                                       | VOL. R10                                                           | VOL. R20                                       | VOL. R30                                                                                                                       | VOL. R40      | VOL R60                                |

\* These volumes are shipped in microfiche and are located in volume R30.

Direct Access Storage Models J and K Maintenance Information

P/N 4519943 2 Sides EC 475248 25Apr88 © Copyright IBM Corporation 1987

FRONT-1

The drawings and specifications contained in this manual shall not be reproduced in whole or in part without written permission from the IBM Corporation.

IBM has prepared this maintenance manual for the use of IBM service representatives in the installation, maintenance. and repair of the specific machines indicated. IBM makes no representation that it is suitable for any other purpose.

Information contained in this manual is subject to change. Any such change will be included in following revisions.

This material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information does not necessarily mean that IBM intends to announce such IBM products, programming, or services in your country.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office servicing your locality.

A form for reader's comments is supplied at the back of this manual. If the form has been removed, send comments to:

International Business Machines Corporation Department G26/098 5600 Cottle Road San Jose, California 95193

You can use this form to communicate your comments about this manual, its organization, or its subject matter with the understanding that IBM can use and distribute the information you supply in any way it believes correct without any obligation to you.

FRONT-2

ų

#### Preface

The Maintenance Support Manual (MSM), Volume R60 of the maintenance library, is designed to help the IBM service representative maintain the IBM 3380 Direct Access Storage, Models AJ4, BJ4, AK4, and BK4.

When maintaining any of these models, use the IBM Maintenance Device diskette and the maintenance library manuals shipped with the machine, and/or the manuals shipped with the AJ4 or AK4 unit to which the machine and the IBM Maintenance Device connect.

Always start any maintenance action on a 3380 Model AJ4, BJ4, AK4, or BK4 by following the instructions in the PSG, Volume R05.

When a 3380 Model AJ4 or AK4 is connected to the same storage director as a 3380 Model AA4, AD4, or AE4, instructions in the MD or notes in this manual indicate when to use the information in the other 3380 maintenance library manuals.

In this manual, the following terms are used to simplify the distinction among the various 3380 models.

| 3380    | = all 3380 models     |

|---------|-----------------------|

| 3380-J  | = 3380 AJ4, BJ4       |

| 3380-K  | = 3380 AK4, BK4       |

| 3380-JK | = 3380 AJ4, BJ4, AK4, |

|         | BK4                   |

| A unit  | = 3380 AJ4, AK4       |

| B unit  | = 3380 BJ4, BK4       |

The complete model name will be used to specify a single model. (For example, 3380 Model AJ4.)

#### Maintenance Manual Ordering Procedure

#### For USA

Parts of this manual can be ordered from the IBM San Jose plant by using the Wiring Diagram/Logic Page Request, Order No. Z150-0130 (U/M 015). In the logic-page columns, enter the part number [1], and engineering change number [2] shown at the bottom of each page.

P/N 1234567 [1] SAFETY-3 [3] EC 123456 [2]

Whole volumes can be ordered by including the volume number and the machine serial number.

Hard copy versions of microfiche manuals can be ordered from the IBM San Jose plant by sending in the Documentation Request card (Form No. 927-8390) that is included in the microfiche packet.

It is recommended that one hard copy set of all microfiche manuals be ordered for each account. Because a machine serial number is not required for ordering, ECs affecting the contents of these manuals will update the microfiche copies only, and the customer engineer will be instructed by the EC to reorder new hard copy support documentation. The Documentation Request card can also be used to order any other manual in the 3380-JK maintenance library. Only the most current version of any manual will be sent. No automatic updates to any manual ordered by this card will be sent.

#### For Europe, Middle East, and Africa (EMEA)

Wiring diagram and logic page requests are handled through the MLC plant in Mainz, Germany.

Hard copy manuals can be ordered from the MLC plant in Mainz, Germany by sending in the Documentation-Request card that is included in the microfiche packet.

#### How to Update this Manual

This manual is under engineering change control. Put pages in by part number [1] and page number [3]. The EC level and date are given in the EC history block on the first page of the part-numbered group of pages.

#### **Related Publications**

The following is a list of documents that may help to understand and/or repair the 3380-JK:

- IBM 3380-JK Direct Access Storage Introduction, GC26-4491

- Using the IBM 3380-JK Direct Access Storage in an MVS Environment, GC26-4492

- Using the IBM 3380-JK Direct Access Storage in a VM Environment, GC26-4493

- Using the IBM 3380-JK Direct Access Storage in a VSE Environment. GC26-4494

- Maintaining IBM Disk Storage Media, GC26-4495

- Master Index, GC26-4496

- IBM 3880 Storage Control, Models 1, 2, 3, and 4 Reference Manual, GA26-1661

- Device Support Facilities: Primer for the User of IBM 3380 Direct Access Storage, GC26-4498

- IBM 3990 Storage Control Introduction, GC32-0098

- IBM 3990 Storage Control Planning, Installation, and Storage Administration Guide, GA32-0100

- IBM 3990 Storage Control Reference, GA32-0099

- Cache Device Administration, GC35-0101

Œ

1

### About This Manual

The Maintenance Support Manual (MSM) is used with the Product Service Guide (PSG) when servicing a 3380.

The MSM is divided into four sections, each with specific purposes. The sections are:

- HELP

- SENSE

- OPER

- DIAG

A brief description of each section follows.

#### HELP

This section supplies the customer engineer with DASD maintenance information that is not supplied in the guided maintenance package.

#### SENSE

This section contains the 3380-JK sense data descriptions that identify the contents of each format by messages, bytes, and bits. It supplies page references to additional information on each error symptom, along with the priority of service actions and the primary symptom code.

#### OPER

This section contains the theory of operation for the 3380-JK.

#### DIAG

This section contains the run procedures for each diagnostic routine, along with its associated isolation codes.

# EC History of Front Matter

| EC HISTORY OF P/N 4519969 |            |           |            |

|---------------------------|------------|-----------|------------|

| EC Number                 | Date Of EC | EC Number | Date Of EC |

| 475245                    | 14Nov86    | 475248    | 25Apr88    |

| 475246                    | 21Ju187    |           |            |

| 475247                    | 11Sep87    |           |            |

Notes:

á

. .

Ą

# Contents

| Ordering This Manual                    | HELP-1  |

|-----------------------------------------|---------|

| Introduction                            | HELP-1  |

| Contents                                | HELP-1  |

| Guided Maintenance Procedures Failure . | HELP-1  |

| General                                 | HELP-1  |

| Using the ECM with symptom codes        | HELP-2  |

| Solid and Intermittent Checklists       | HELP-2  |

| Swapped Cards                           | HELP-2  |

| Block FRU Replacement                   | HELP-2  |

| Single Symptom                          | HELP-2  |

| EREP Release Level                      | HELP-2  |

| EREP in a Multisystem Environment       | HELP-3  |

| Definitions                             | HELP-3  |

| Failure boundary                        | HELP-3  |

| Unguided Maintenance Documentation      | HELP-4  |

| The SENSE Section                       | HELP-4  |

| The DIAG Section                        | HELP-4  |

| The OPER Section                        | HELP-4  |

| Error Condition Descriptions            | HELP-4  |

| Reference Diagrams                      | HELP-4  |

| Intermittent Failures                   | HELP-5  |

| Intermittent Failure Checklist          | HELP-5  |

| Solid Failure Checklist                 | HELP-6  |

| Error and Check Handling                | HELP-8  |

| Propagation and Priority of Errors      | HELP-8  |

| Failure Indications and Symptom         |         |

| Gathering                               |         |

| DASD Error Log                          | HELP-8  |

| Error Thresholds and Storage Control    |         |

| Retry                                   |         |

| Error Recovery                          | HELP-10 |

| Analyze Format of Sense Data            | HELP-11 |

| To Analyze Format 1 (SC=9xxx)           | HELP-13 |

| To Analyze Format 9 (SC= 9xxx)          | HELP-14 |

| To Analyze Format 4 (SC=4xxx)           | HELP-14 |

| To Analyze Format 7 (SC=Dxxx)           | HELP-16 |

| To Analyze Format 8 (SC=Exxx)           | HELP-17 |

| Analysis with multiple ECDs             | HELP-18 |

| Service Aids                            | HELP-18 |

| The 0F0X Symptom (Format 0)             | HELP-18 |

| Motor Control Errors                    | HELP-19 |

| Failures in error and status reporting  |         |

|                                         | HELP-20 |

| Voltage and Ripple Checking             | HELP-20 |

| No Sense Data Failures                  | HELP-20 |

| Diagnostic looping                      | HELP-22 |

| Scoping                                 | HELP-22 |

| EC History of Help Section              | HELP-23 |

| 3380-JK and 3380-DE Differences         | SENSE-1 |

| Sense Data Introduction                 | SENSE-1 |

| Symptom Code Assignments by Sense         |           |

|-------------------------------------------|-----------|

| Format                                    | SENSE-2   |

| Format, Byte, and Bit Table Headings      |           |

| Format 1                                  |           |

| Format 4                                  | SENSE-14  |

| Format 5                                  | SENSE-22  |

| Format 6                                  | SENSE-29  |

| Format 7                                  | SENSE-31  |

| Format 8                                  | SENSE-40  |

| Format 9                                  | SENSE-50  |

| Byte Text Headings                        | SENSE-59  |

| Unit Check Description, Bytes 0,1,2       | SENSE-59  |

| String ID                                 | SENSE-61  |

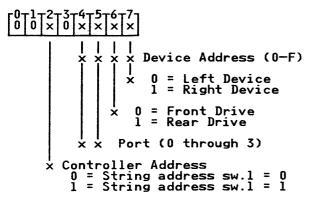

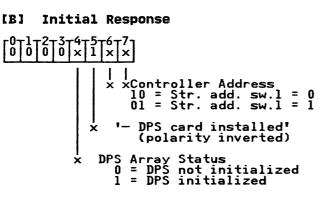

| Path and Device Physical Identifier, Byte | 021102 01 |

| 4                                         | SENSE-61  |

| Seek Head and Cylinder Address, Byte 5    | CENCE OF  |

| and 6                                     | SENSE-62  |

| Format and Message, Byte 7                | SENSE-62  |

| String Features, Byte 8                   | SENSE-62  |

| Device Power Status, Byte 10              | SENSE-62  |

| Device Check-2 Status, Byte 10            | SENSE-63  |

| •                                         | SENSE-63  |

| Servo Status - 0, Bytes 12 and 13         |           |

| Servo Status-1, Bytes 14 and 16           | SENSE-66  |

| Checkpoint Log Byte 15                    | SENSE-66  |

| Checkpoint Log Value Meanings             | SENSE-66  |

| Device Status 1, Byte 19                  | SENSE-74  |

| Device Status 2, Byte 20                  | SENSE-75  |

| Record ID. Bytes 8 through 12             | SENSE-76  |

| Sector Number, Byte 13                    | SENSE-76  |

| Head Offset Value, Byte 15                | SENSE-76  |

| ECC Status, Bytes 16 and 17, Format 4     | SENSE-77  |

| Storage Control Data Transfer Error       |           |

| Bits, Byte 10                             | SENSE-77  |

| Connection Check Alert and Power          |           |

| Status, Byte 11                           | SENSE-78  |

| Controller 0 or 1 Check-1 Status, Byte 12 |           |

| or 14                                     | SENSE-79  |

| Controller 0 or 1 Check-1 Status 2, Byte  |           |

| 13 or 15                                  | SENSE-79  |

| Controller Sequencer Microcode            |           |

| Detected Check 1 Errors, Bytes 16 and     |           |

| 18                                        | SENSE-80  |

| Controller 0 or 1 RCC Transfer Status,    |           |

| Bytes 17 and 19                           | SENSE-81  |

| Controller Fault Log A, Byte 11           | SENSE-82  |

| Controller Fault Log B, Byte 12           | SENSE-83  |

| Controller Fault Log C, Byte 13           | SENSE-83  |

| Controller Fault Log D, Byte 14           | SENSE-84  |

| Controller Fault Log E, Byte 15           | SENSE-85  |

| Controller Fault Log F, Byte 16           | SENSE-85  |

| Controller Fault Log G, Byte 17           | SENSE-86  |

| Controller Sequencer Microcode            |           |

| Detected Check 2 Errors, Byte 18          | SENSE-87  |

|                                           |           |

•

**CONTENTS-1**

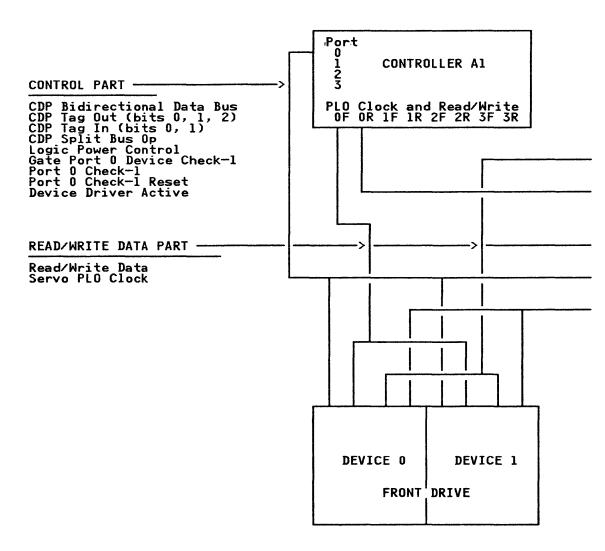

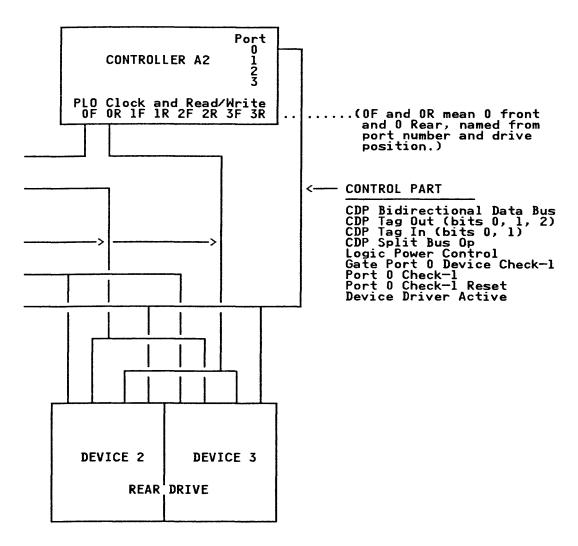

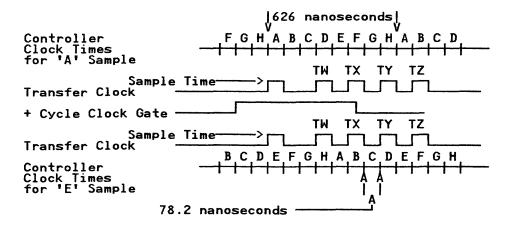

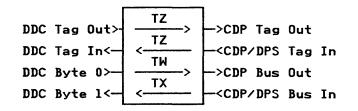

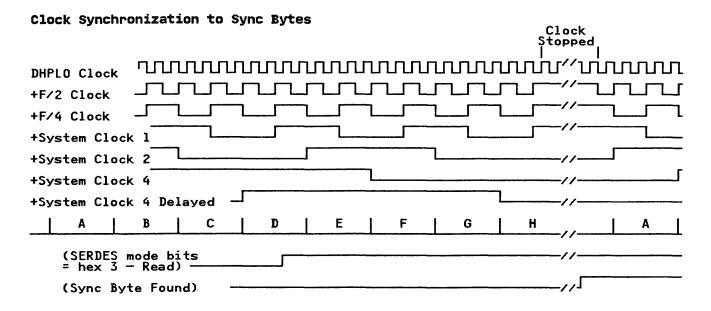

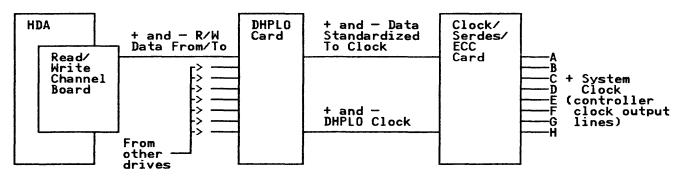

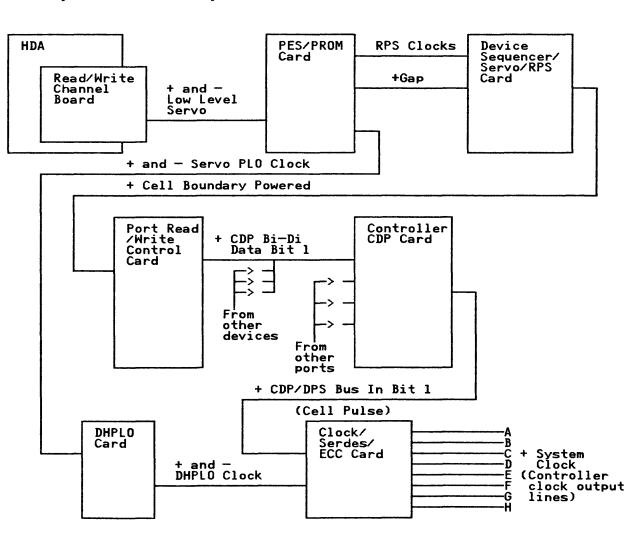

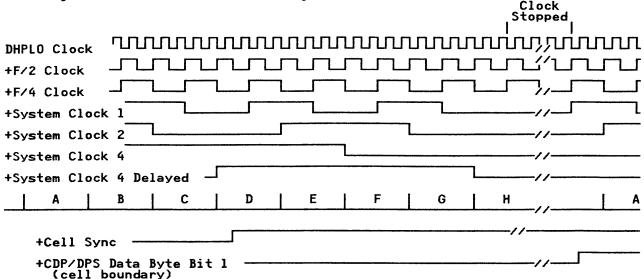

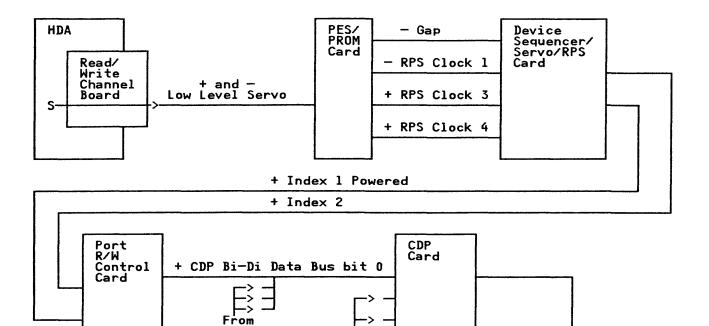

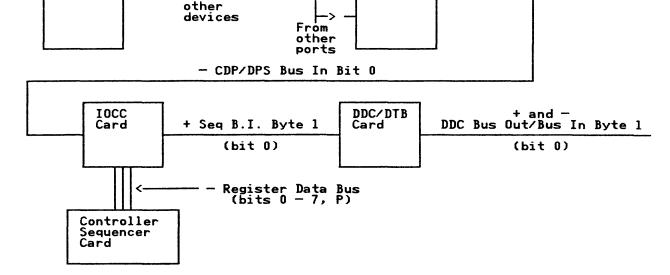

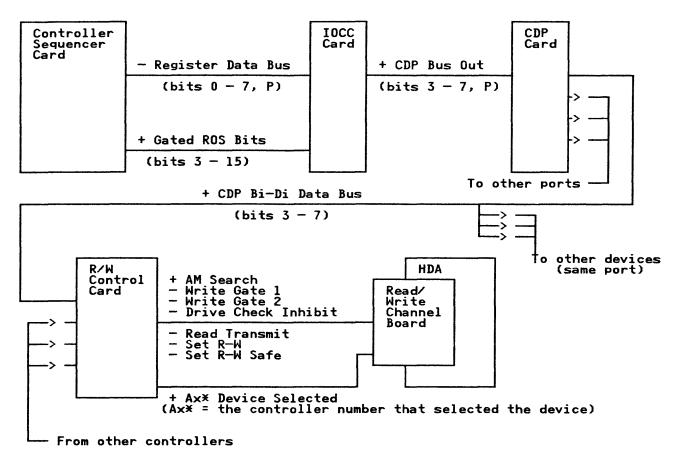

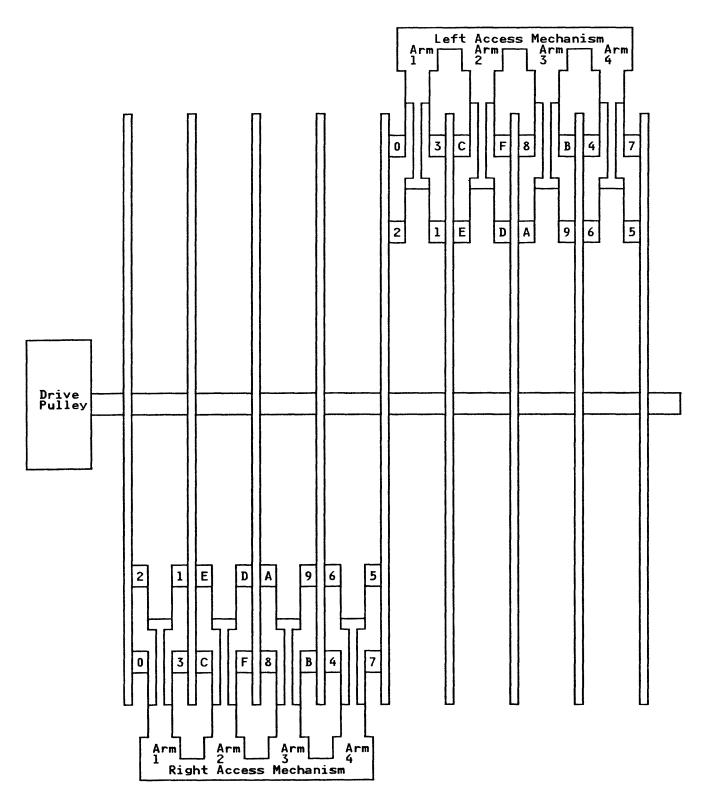

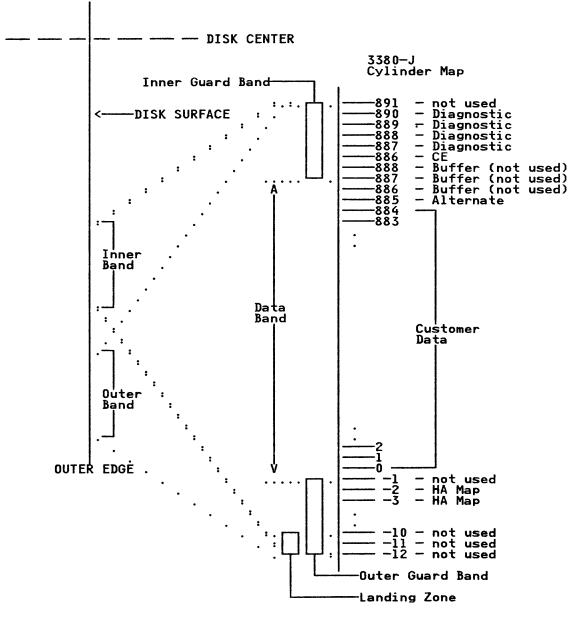

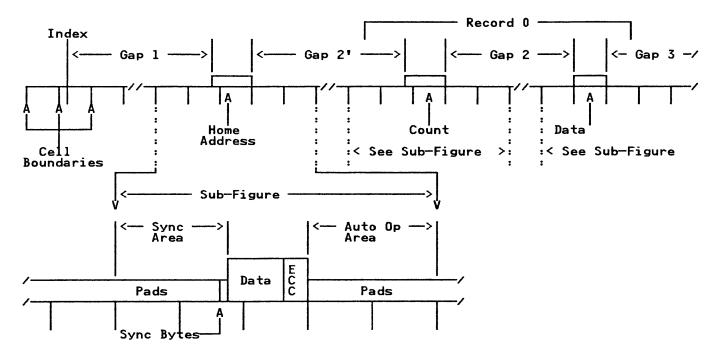

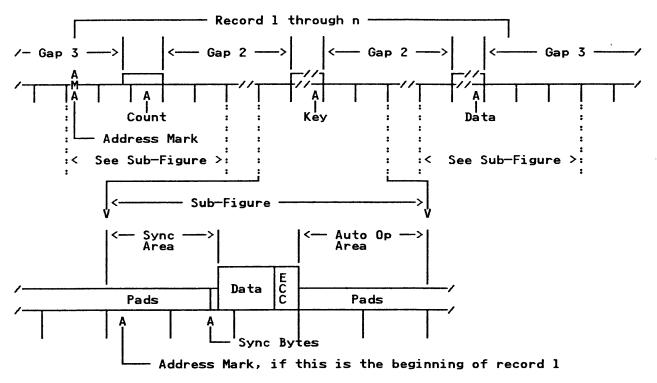

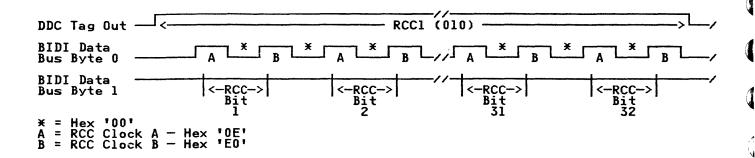

Read/Write Status-2, Byte 13 ..... SENSE-89 Read/Write Status-3, Byte 14 ..... SENSE-90 Read/Write Status 4, Byte 18 ..... SENSE-90 Format 8, Message A ..... SENSE-91 EC History of Sense Section ..... SENSE-92 About This Section ..... OPER-1 Introduction ..... OPER-5 Physical Parts ..... OPER-6 Controller Functions ..... OPER-7 Device Functions ..... OPER-9 DPS Functions (Optional) ..... OPER-11 Control Interface ..... OPER-13 DDC Tag Out (Bits 0, 1, and 2) ..... OPER-13 DDC Tag In (Bits 0 and 1) .... OPER-14 Device Interface ..... OPER-15 Controller Port Signals ..... OPER-16 CDP Bidirectional Data Bus ..... OPER-17 CDP Tag Out (Bits 0, 1, and 2) ..... OPER-17 CDP Split Bus Op ..... OPER-18 Logic Power Control ..... OPER-18 Gate Port x Device Check-1 ..... OPER-18 Port x Check-1 Reset ..... OPER-19 CDP Tag In (Bits 0 and 1) .... OPER-19 Port Check 1 ..... OPER-19 Device Driver Active ..... OPER-19 Read/Write Data and Servo Clock Signals OPER-20 Controller - to - Controller Connection . . OPER-20 Line Descriptions ..... OPER-20 Controller Path Control ..... OPER-22 Transfer Clock and Feedthrough Path Control ..... OPER-22 Controller Clock ..... OPER-25 Clock Sync to Sync Byte ..... OPER-25 Clock Sync to Cell Boundary ..... OPER-26 The Device ..... OPER-28 Device Logic ..... OPER-28 Device Sequencer Microcode ..... OPER-38 Head Disk Assembly ..... OPER-44 Access Mechanism Positioning - Servo Operations ..... OPER-48 Servo Control ..... OPER-48 Track Format and Processing ..... OPER-50 Track Format ..... OPER-50 Track Format Processing ..... OPER-53 **Command Transfers During Track** Processing ..... OPER-54 Write Paths ..... OPER-57 Drive Padding ..... OPER-57 pads ..... OPER-57 Address Marks ..... OPER-57 Sync Bytes ..... OPER-57 Data and Fill ..... OPER-57

Read/Write Status-1, Byte 12 ..... SENSE-88

| ECC Bytes                           | OPER-   |

|-------------------------------------|---------|

| Write Data Transfer (first half)    | OPER/   |

| Write Data Transfer (second half)   | OPER    |

| Read Paths                          | •       |

| Recognizing Address Marks           |         |

| Recognizing Sync Bytes              |         |

| Reading Data and Fill               |         |

| Reading ECC Bytes From The Disk     |         |

| Transferring ECC Correction Bytes   |         |

| Read Data Transfer (First Half)     |         |

| Read Data Transfer (Second Half)    |         |

| Serdes Mode and ECC Mode Bits       |         |

| Serdes Mode Bits                    |         |

| ECC Functions                       |         |

| ECC Mode Bits                       |         |

| Selection – De-Selection – Polls    | OPER-I  |

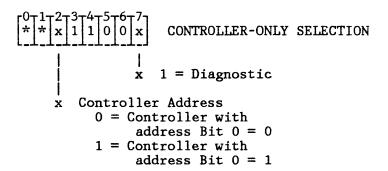

| Controller-Only Selection           | OPER-I  |

| Device Selection With DPS           | OPER-   |

| Device Selection With DPS           |         |

|                                     | OPER-   |

| Device De-Selection                 | OPER-   |

| Polls                               | OPER    |

| 3380-JK Commands                    | OPER-I  |

| Immediate Commands                  | OPER-I  |

| Extended Commands                   | OPER    |

| Immediate Controller Commands       | OPER-   |

| Device Commands                     | OPER-   |

| Device Command Types                | OPER    |

| Command Descriptions                |         |

| DPS Commands                        | OPER-1( |

| The Controller                      | OPER-1  |

| Controller Logic                    | OPER-1( |

| Controller Sequencer Microcode      | OPER-1( |

| Failure Detection and Reporting     | OPER-'  |

| Controller Check 1 Errors           | OPER-1  |

| Controller Check 2 and Device Check |         |

| 1 Errors                            | OPER-'  |

| Device Check 2 Errors               | OPER-11 |

| Data Checks Errors                  | OPER-11 |

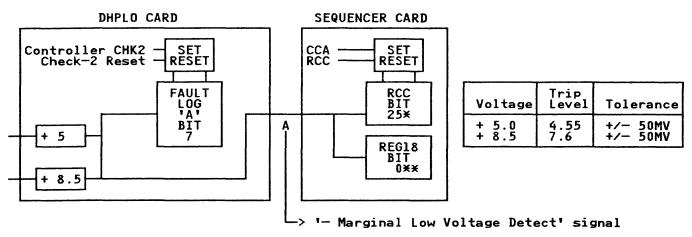

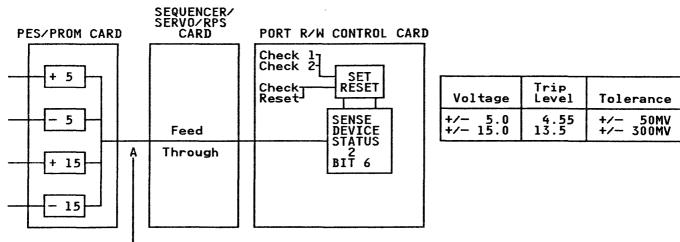

| Under-Voltage Detection             | OPER-1  |

| Storage Control Detected Failures   | OPER-12 |

| Miscellaneous                       | OPER-12 |

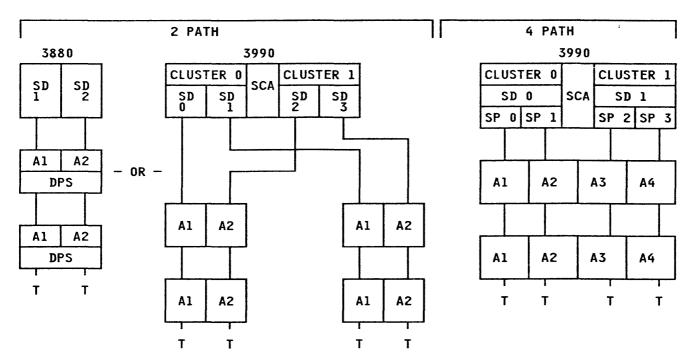

| Subsystem Paths                     | OPER-1  |

| Quiesce and Resume Commands         | OPER-12 |

| Unconditional Reserve Release and   |         |

| Reset Allegiance                    | OPER-1  |

| System Write Inhibit and Storage    |         |

| Control Fencing                     | OPER-12 |

| EC History of Operation Section     |         |

| Introduction                        |         |

| Diagnostic Routine Operating        |         |

| Procedures                          | . DIAC  |

| MD Connection Test                  |         |

| Parameters                          |         |

|                                     | i       |

|                                     |         |

# CONTENTS-

*.*

| Test Description                        | DIAG-7             |

|-----------------------------------------|--------------------|

|                                         |                    |

| CTL-I Tests                             |                    |

| IC Descriptions                         | DIAG-10            |

| CTL-I Test IC Descriptions              | DIAG-35            |

| Routine 80 - Controller Tests           | DIAG-40            |

| Parameters                              | DIAG-40            |

| Tests                                   | DIAG-40            |

| Routine 81 - Device Logic Tests         | DIAG-42            |

| Parameters                              | DIAG-42            |

| Test Descriptions                       | DIAG-43            |

| Routine 82 - Servo Tests                | DIAG-44            |

| Parameters                              | DIAG-44            |

| Test Descriptions                       | DIAG-44            |

| Routine 83 - Read/Write Data Transfer   |                    |

| Tests                                   | DIAG-45            |

| Parameters                              | DIAG-45            |

| Routine 84 - Read/Write Function Tests  | DIAG-46            |

| Parameters                              | DIAG-46            |

| Test Descriptions                       | DIAG-40<br>DIAG-46 |

| Routine 85 - Seek Exerciser             | DIAG-40<br>DIAG-47 |

|                                         |                    |

| Parameters                              | DIAG-48            |

| Routine 8A - Incremental Seek Exerciser | DIAG-48            |

| Parameters                              | DIAG-49            |

| Routine 90 - DPS Test                   | DIAG-50            |

| Parameters                              | DIAG-51            |

| Test Descriptions                       | DIAG-51            |

| Routine 91 - Home Address Scan          | DIAG-52            |

| Parameters                              | DIAG-52            |

| Routine 93 - DDC Tests                  | DIAG-53            |

| Parameters                              | DIAG-53            |

| Routine 96 - Device Status Test         | DIAG-53            |

| Parameters                              | DIAG-53            |

| Routine 97 - Sense Utility              | DIAG-54            |

| Parameters                              | DIAG-54            |

| Routine 98 - Error Log Search           | DIAG-54            |

| Parameters                              | DIAG-55            |

| Routine 99 - Motor Start Test           | DIAG-57            |

| Parameters                              | DIAG-58            |

| Test Descriptions                       | DIAG-59            |

| Routine 9C - CE Track Repair            | DIAG-60            |

| Parameters                              | DIAG-60            |

| Routine 9D - DPS Array Display/Dump     | 50.0000            |

| Utility                                 | DIAG-62            |

| Parameters                              | DIAG-63            |

| Routine 9E - Patch Diagnostic Microcode | DIAG-65            |

| Routine 9F - Set/Reset/Sense CE Mode    | DIAG-66            |

| Parameters                              | DIAG-66            |

|                                         |                    |

| Routine C0 - Controller Test            | DIAG-67            |

| Parameters                              | DIAG-67            |

| Routine D3 - DDC Tests                  | DIAG-67            |

| Parameters                              | DIAG-67            |

| References                              | DIAG-68            |

| Test Number                             | DIAG-68            |

| Command Code                            | DIAG-68 |

|-----------------------------------------|---------|

| Modifier Count                          | DIAG-68 |

|                                         |         |

| Bus Out (DBO)                           | DIAG-68 |

| Bus in (DBI)                            | DIAG-68 |

| Tag Out and Tag In Decoded              | DIAG-69 |

| Selection Address for Controller/Device |         |

| Tested                                  | DIAG-69 |

| Request Connection Check Bits 0         |         |

| through 7                               | DIAG-70 |

| Request Connection Check Bits 8         |         |

| through 15                              | DIAG-71 |

| Request Connection Check Bits 17        |         |

| through 24                              | DIAG-71 |

| Request Connection Check Bits 25        |         |

| through 32                              | DIAG-71 |

| Storage Control Check Indicators        | DIAG-72 |

| Incorrect Bus In Bits                   | DIAG-72 |

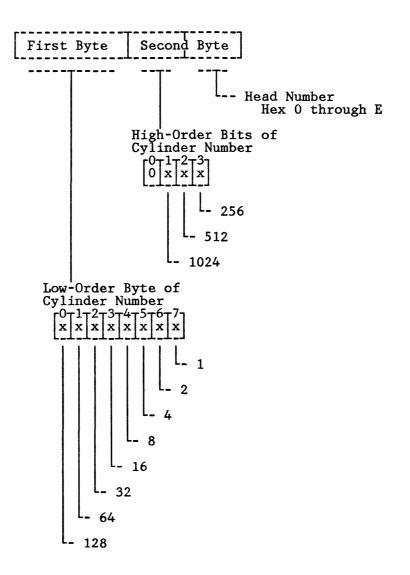

| Track Physical Address                  | DIAG-72 |

| EC History of Diagnostic Section        | DIAG-75 |

|                                         |         |

# EC History of Table of Contents

| EC HISTORY OF P/N 4519944 |            |           |            |

|---------------------------|------------|-----------|------------|

| EC Number                 | Date Of EC | EC Number | Date Of EC |

| 475245                    | 14Nov86    | 475248    | 25Apr88    |

| 475246                    | 21Ju187    |           |            |

| 475247                    | 11Sep87    |           |            |

Notes:

P/N 4519944 4 Sides EC 475248 25Apr88 © Copyright IBM Corp 1987, 1988

.

# **CONTENTS-**4

ł

/ ...

### **Ordering This Manual**

At least one hard copy of this manual should be in each account. To order a hard copy of this manual. complete and return the Documentation Request card No. 927-8390 included with the microfiche located in Volume R30 of each machine. A hard copy will be sent to the address indicated on the card, either home, office, or account. This manual is not shipped in hard copy form with each machine because of the expected low usage and storage space requirements. No EC updates will be made to the hard copy, they must be ordered. The machine will continue to receive microfiche updates for ECs.

#### Introduction

This manual should not be used for servicing 3380-DE, it should solely be used to maintain 3380-JK.

The purpose of the HELP section is to provide the CE with DASD maintenance information that is not provided in the guided maintenance package. This material is most beneficial if it has been read and understood prior to the more difficult repair action.

**Note:** The term storage control is used as an overall term in this section to mean the functions within the 3880-3 storage director or the functions within the 3990 storage path.

#### Contents

The contents of this section are as follows:

- "Guided Maintenance Procedures Failure" "General"

- "Unguided Maintenance Documentation" on page HELP-4

"Intermittent Failure Checklist" on page HELP-5

- "Solid Failure Checklist" on page HELP-6

- "Error and Check Handling" on page HELP-8

- "Analyze Format of Sense Data" on page HELP-11

- "Service Aids" on page HELP-18

#### **Guided Maintenance Procedures Failure**

The guided maintenance procedures could fail for one of the following reasons:

- The MD symptom analysis procedure might have omitted this FRU (card, board, cable, top-card connector, and so on) because of the low probability of failure or an incorrect symptom priority assignment.

- The fault is not in the circuits being monitored or the detection circuitry, but in the error collection circuitry.

The following failures can occur, primarily during installation:

- The MD diskette is not compatible with the storage control functional diskette or, the use of a down level MD or storage control functional diskette.

- Incorrect cable lengths or loose cables. The maximum CTL-I cable length is 61 meters (200 feet).

- Incorrect subsystem physical configuration.

- String address incorrectly set.

- Improperly defined system parameters, such as, SYSGEN, IOCP, and UCWs.

These failures can occur at any time:

- Bent pins in a board or in a cable socket.

- Environment (temperature, humidity) out of spec.

- Wall power, voltage change, loss of phase, and so on.

- Open grounds, ground loops, and so on.

- A misinterpretation of MAP instructions by the CE.

٧.

## General

The material under this heading provides overall guidance in servicing the 3380-JK.

#### Using the ECM with symptom codes

It is presumed that you will come to this manual to resolve a problem that the MD did not resolve.

The ECM Index lists primary symptom codes only. A primary symptom code is a symptom code that is generated if one and only one symptom (check, error, message, etc.) was created by a failure. Therefore, **not** all symptom codes that you receive in 3380-JK sense data will be listed or explained.

If you need to determine which symptom code the system was identifying, and the exact code is not listed, look for similar codes with the letter 'X' replacing some of the characters. The entries with 'X' follow all normal entries. For example, 9XXX would indicate all codes beginning with '9'. 9XXX would be the last symptom code listing with the first character of 9.

The symptom code does not always provide all the available information about a fault. With many faults, you must analyze the first 24 bytes of the sense before you can be fully aware of all the symptoms. The symptom code generator only uses the highest priority symptoms to develop a code and discards the remaining symptoms. Those remaining symptoms may be needed to point to the fault. See "To Analyze Format 1 (SC=9xxx)" on page HELP-13

#### Solid and Intermittent Checklists

Use the solid and intermittent checklists located in this section to help resolve problems.

- Intermittent failure checklist page HELP-5

- Solid failure checklist page HELP-6

Before using the checklists, an understanding of the following material is suggested.

### **Swapped Cards**

Cards should not be swapped between devices or machines for the following reasons:

- The probability of creating an additional problem on another machine is too great. The impact of this type of problem is unacceptable to both the customer and IBM.

- 2. Problems affecting the data integrity of a device can be propagated to another device or the system.

If any card swapping occurs, it must only be done in instances where you absolutely cannot impact the customer's system or the customer's data. For example, card swapping is allowed between devices during an installation.

#### **Block FRU Replacement**

Install card FRUs singly with a solid failure. If the replacement FRU does not fix the problem, remove it and try the next FRU in the FRU list.

The CE is expected to perform block FRU replacement for an intermittent failure. On the subsequent service call, if the first set of FRUs listed by the MD fails to correct the problem, the second set of suggested FRUs are to be installed. **Do not remove the first set of FRUs at that time!**

Block FRU replacement on an intermittent failure will reduce the number of calls required to resolve a failure. An intermittent failure is a failure that the MD can not repeatedly detect.

#### Single Symptom

If multiple symptoms are available, do not use a single symptom, like a console message, to resolve a problem. A single symptom might mislead you. Collect all the available symptoms and take action only after understanding all of them.

Attack the permanent error symptoms first, then the temporary error symptoms.

The priority of Sense Formats is 7, 8, 1, 9, 4. The priority of each error symptom is assigned in the SENSE section.

#### **EREP Release Level**

The maintenance package for the 3380-JK requires the use of the Environmental Recording, Editing, and Printing (EREP) Program at Release 3.3.2 or later to be fully effective. EREP is an important tool that must be in place and running when it is needed for the analysis of the more complex DASD problem. If your customer has not installed EREP at Release Level 3.3.2 or later, provide the assistance necessary to help get it installed. Data Check problems are virtually impossible to resolve without the use of the system exception report, due to the way the 3380-JK and storage controls handle data errors.

In addition, the CE should be trained in the proper use of EREP reports. If you are not trained in the use of EREP at Release 2.1 or later, request training from your manager.

### EREP in a Multisystem Environment

If your installation has more than one operating system, each system has a separate error reporting data set (ERDS). Merge the records from all ERDS onto a history data set and run EREP against the combined data. Only EREP reports, that contain all DASD error records, can provide you with a complete picture of the performance of the DASD. See the EREP manual, GC28-1378-1 for details.

#### Definitions

An intermittent failure is an error that cannot repeatedly be detected by the 3380-JK microdiagnostics. An intermittent failure service call can be initiated with either a permanent or temporary error indication.

A Permanent failure is an error that can be detected by the microdiagnostic. It will probably be a customer reported error and a console message or EREP should be available. A permanent error is an error that an error recovery procedure did not successfully recover from. A temporary equipment check can only be discovered from an EREP report. A temporary equipment check never generates a console message. A temporary data or seek check has a console message and Log Rec entries only on threshold counter overflow. A temporary error is an error that an error recovery procedure did successfully recover from.

**A permanent equipment check or data check** generates both a console message and a Log Rec entry that can be examined with EREP.

**A Primary Symptom Code** is the symptom code that is generated if one and only one symptom (check, error, message, etc.) were created by a fault.

#### Track, Record, Area, Field

Track, a track has records written on it.

**Record**, a record can contain the following areas, a count area, a key area, and a data area.

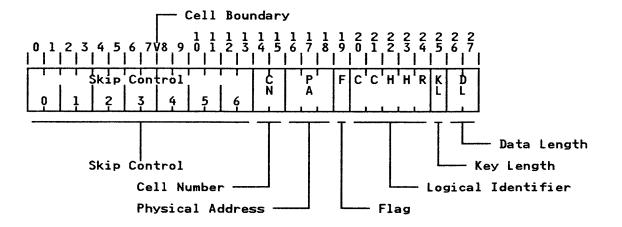

**Area**, for example, a count area contains the following fields, a skip displacement field, CCHHR field, data length field, etc.

**Field**, for example, a CCHHR field contains the cylinder number, head number and the record number.

#### Failure boundary

Failure boundary definitions for this maintenance package are as follows:

**Device** - A failure pertaining to an actuator and its associated logic and/or media, regardless of which controllers are failing. Sense byte 4, bits 3 through 7 identify the device.

**Drive** - A failure pertaining to both devices associated with a single head-disk-assembly (HDA), regardless of which controllers are failing. Sense byte 4, bits 3 through 6 identify the drive.

**Port** - A failure pertaining to multiple devices on both HDA's and limited to a single port number (0, 1, 2, etc.) regardless of which controllers are failing (see note). Sense byte 4, bits 3 through 5 identify the port. **Controller** - A failure of two or more devices on different ports and limited to a single controller (see note). Sense byte 4, bits 0 and 1 identify the path.

**Note:** If only one port is in use, the determination between port and controllers cannot be made. For this situation, the failure boundary in EREP is 'Unknown'.

**Unknown** - The failure boundary cannot be determined.

### **Unguided Maintenance Documentation**

The material under this heading describes the 3380-JK maintenance package sections that help resolve the problems that the guided maintenance package failed to resolve.

#### The SENSE Section

The SENSE section lays out the sense bytes by format providing bit definition and a reference to additional information about each symptom. It also provides priority to each error.

## The DIAG Section

The DIAG section contains the following:

- Descriptions of diagnostics

- Isolation code (IC) descriptions

- IC error byte descriptions with cross references

- Description of diagnostic commands

The diagnostic descriptions contain information about the routines and about the parameters and run options. The descriptions include references to the commands used to test the machine functions and to the isolation codes that identify specific kinds of errors.

Each IC description lists the associated error bytes. With the English names for the bytes (not the byte and number), you can easily locate the IC error byte bit descriptions for additional information in the SENSE section. Where applicable, the names used are the same as those used in the SENSE section. This section also provides cross references to the Isolation Code E-bytes. The commands that are described in the DIAG section are those special commands that are not used during usual customer operations. See "Diagnostic looping" on page HELP-22.

#### The OPER Section

The commands that are used in customer operations are described in the OPER section. The OPER section does not contain procedures to perform, it contains the theory of operation for the 3380-JK.

### **Error** Condition Descriptions

The error condition descriptions (ECDs) are located in the Error Conditions Manual (ECM).

The ECDs are formatted in most cases as follows:

- Title or the name of the check

- What the check means

- How the check is indicated: Primary Symptom Code Sense Data Checkpoint Code

- Where in the hardware or software the checker is located

- How the checker works

- When the checker works

- How the checker is reset

- Diagnostics that will force the checker on, and that exercise the function that the checker is checking

- References to data in other manuals

- Service aids (may be provided)

- Nets known to set the checker (may be provided)

#### **Reference Diagrams**

The reference diagrams (RDs), located in the Maintenance Diagrams Manual (MDM) can be used to help define the following:

- 1. The source of the always active check indication.

- 2. Identify how errors of each of the formats are collected.

- 3. Identify associated errors and their collection paths.

4. The potential fault boundary of a failure when a forced diagnostic error is not being detected.

#### **Intermittent Failures**

The number of repeat calls can be reduced with action on an intermittent failure. This is the failure that usually takes a little extra effort and time, to prevent future problems.

#### Finding an Intermittent Failure

The FRU list usually finds an intermittent logic failure. The items that are often missed are loose or poor connections, and power. Once the error has been analyzed, a list of possible failing connections should be compiled. Next, select a diagnostic that exercises the failing portion of the machine. While looping the diagnostic, stress the connections in whatever way possible. Scope the connections while stressing them and watch for a change in amplitude or the presence of noise. Scope the nets involved with this failure and compare them with the same nets on a working device. Often a difference can be detected and yet the failure is intermittent. The scope can be used to find an intermittent voltage problem also. Check the scope for a ripple or voltage fluctuation that does not show up on the meter.

Additional test equipment is available for an intermittent problem and should be considered. A logic analyzer can be hooked up to trigger on the error and capture the condition of the nets involved or in question before and after the failure. A voltage analyzer can monitor ac or dc voltages for spikes or fluctuations. The time stamps can be used to compare with other failure indication times.

Have all of the available resources been used? Do not overlook the RETAIN system, the branch office specialist, and the support center.

# **Intermittent Failure Checklist**

The following checklist provides the recommended corrective actions to take if the MD maintenance package fails to isolate an intermittent failure. An intermittent failure is one where the microdiagnostics do not detect a fault, yet EREP or system console messages indicate a problem. The actions are in a suggested sequence. However, you may perform them out of sequence if you have identified a suspect area.

- \_\_\_\_ Verify the MD MAP instructions. If necessary, review the initial isolation steps to confirm that no errors occurred.

- Review as much symptom information about the problem as possible from the following sources:

Console messages Customer problem report Customer run program output, for example, ICKDSF and EREP

- \_\_\_\_ From the collected data, determine if the correct symptom code and failure boundary was chosen for the initial and following repair actions.

- Verify that the DASD subsystem is correctly configured. Determine if the cables to the device under test have been swapped (Logic exchanged bit active in device status-2 byte Byte 20, bit 4 of Format 1, 8, or 9).

- Verify compatibility of the storage control functional diskette with the 3380-JK MD diskette.

- If this is a newly installed machine, verify the following:

- The total lengths of the CTL-I interface cables do not exceed 61 meters (200 feet).

- The base plate ground check has been performed.

- \_ Verify the ground connection on cables that use ground connectors (both ends).

- \_\_\_\_ If the fault is confined or located within an identifiable area, replace all the FRUs within that area.

- \_\_\_\_ Verify that the fault is not in the error and status reporting logic.

- Order a logic board to have on hand in case you need it later. Continue isolating the failure.

- Run the diagnostics against associated devices (if not already done) to verify or possibly redefine the failure boundary.

- \_\_\_\_\_ If the failure is in a single device, perform the B-board cable swap procedure to aid in the isolation between the HDA and its associated logic (see CARR-1 Entry Q).

- Analyze the EREP data for the initial error. Define each error bit using the SENSE and ECD sections. Read the ECD references to understand the meaning of functions being checked and to be able to identify potential contributing nets by net names.

If additional symptoms exist, analyze each of these additional symptoms carefully. Try to identify the commonality of FRUs or nets. Determine if there are additional FRUs that should be replaced.

- Examine each net and replace any FRUs on the net not previously replaced.

- Remove each of the replaced FRUs and carefully examine the sockets for bent or broken pins or foreign material on the pins or in the sockets. Check the associated top-card connectors for bent or broken pins or open land patterns. Check the sockets of associated cables for bent or broken pins.

- \_\_\_\_ Inspect the board back panels for a visible problem such as a loose wire, wires too tight, foreign material, and so on.

- Use a digital meter to measure the correct value of each of the board voltage pins in the replaced FRUs. Do not use a scope. See PWR-1 Entry A for the voltage values of the pins.

- \_\_\_\_ Scope all of the power supplies for ripple or noise. Do not use a meter. See "Voltage and Ripple Checking" on page HELP-20.

- \_\_\_\_ Run the diagnostic suggested by the ECD. Select the loop and stop on the error option. Stress the cables associated with the symptom while looking for an error stop.

- Scope nets identified in the ECD as contributors to the symptom. Look for an unusual condition. Run the diagnostic on a good device or controller in the same machine and compare signals.

- Consider the use of a logic analyzer or a voltage analyzer to gather more information to isolate the intermittent failure.

## **Solid Failure Checklist**

The following checklist provides the recommended corrective actions to take to repair a solid failure. The actions are in a suggested sequence. However, you may perform them out of sequence if you have identified a suspect area.

If additional symptom information is gained during any of the steps, return to any previous step that may have required that information, and repeat the step using the additional information.

- Verify the MD MAP instructions. If necessary, review the initial isolation to confirm that no errors were made.

- Verify the DASD subsystem configuration (2-path? 4-path? 1 string? 2 strings? 1-unit string? 4-unit string? and so on.) Determine if the cables to the device under test have been swapped (Logic Exchanged bit active in device status-2 byte: Byte 20, bit 4 of Format 1, 8, or 9).

- If the MD maintenance procedure required definition of the failure boundary, ensure that it was correctly defined. Review the initial isolation if necessary.

- If system sense data, from EREP or the console is available, compare the symptoms identified by the IC error bytes. If they are different, examine each bit of both the IC and the sense data to get a fuller understanding of the fault.

- Verify compatibility of the storage control functional diskette with the 3380-JK MD diskette.

- \_\_\_\_ Identify all the symptoms indicated by the diagnostic error stop. Analyze each of the bits of the error stop to identify both the symptom and the boundary of the fault. Use the ECD section of the ECM.

- If necessary, run the diagnostics on other devices and paths to positively identify the fault boundary.

- \_\_\_\_ If this is a newly installed machine, verify the following:

- The total cable lengths of the CTL-I interface cables does not exceed 61 meters (200 feet)

- The subsystem configuration

- The string addressing

- The base plate ground check has been performed

- Inspect for loose cables, cards, or top-card connectors

- The top-card connectors are not located correctly

- The cable plugging on controller board

- Verify the ground connection on cables that ground connectors (both ends).

- If the fault is confined or located within an identifiable area, replace all the FRUs within that area.

- Verify that the fault is not in the error and status reporting logic.

- Order a logic board to have on hand in case you need it later. Continue isolating the error.

- Run the diagnostics against associated devices (if not already done) to verify or possibly redefine the fault boundary.

- \_\_\_\_ If the failure is in a single device, perform the B-board cable swap procedure to aid in the isolation between the HDA and its associated logic (see CARR-1 Entry Q).

Analyze the initial and following IC stops using the ECDs. Become familiar with the functions being checked to be able to identify potential contributing nets by net names. This means that the ECDs must be understood and that ECD references are read if required.

**Note:** If, in the following steps, additional symptoms are developed, it is expected that the new symptoms will be just as carefully analyzed to determine what is failing.

Remove each of the replaced FRUs and carefully examine the sockets for bent or broken pins or foreign material on the pins or in the sockets. Check the associated top-card connectors for bent or broken pins or open land patterns. Check the sockets of associated cables for bent or broken pins.

**Note:** Remember that there are cables on the pin side of the A-Board.

Be especially careful when checking sockets that have three rows of pins, because pushed-in pins are very hard to see.

- \_\_\_\_ Inspect the board back panels for a visible problem such as a loose wire, wires too tight, foreign material, and so on.

- Use a digital meter to measure the correct value of each of the board voltage pins in the replaced FRUS. See the voltage charts in the Maintenance Diagrams Manual (MDM), Volume R30 to identify the voltage pins associated with each FRU Do not use a scope. See PWR-1 Entry A for the voltage values of the pins.

- \_\_\_\_ Scope all of the power supplies for ripple or noise. Do not use a meter. See "Voltage and Ripple Checking" on page HELP-20.

- With a diagnostic suggested by the ECD, loop the diagnostic without stopping on the error. Scope nets identified in the ECD as contributors to the symptom. Look for an unusual condition. Run the diagnostic on a

good device or controller in the same machine and compare signals.

### **Error and Check Handling**

#### Propagation and Priority of Errors

Check circuits cannot always prevent further processing. Therefore, some errors may cause other errors to be reported to the system. The problem of determining which error is the real error and which error is the result of the real error can only be resolved by understanding the errors.

The MD uses a priority process to resolve this problem, but it is not always successful. The reason it is not always successful is that not all of the bits of the sense data are examined. Only the bits with the highest priority are used to develop a symptom code or an IC stop. Other bits that can indicate the true error may not be examined. It is up to you to determine if the unexamined sense bits are relevant to your problem.

Only the examination of all the sense bits and your understanding of their meaning will make it possible for you to distinguish real errors from the propagated errors.

# Failure Indications and Symptom Gathering

There are many different methods used by customers to provide problem data to the CE. Verify that the MD symptom code you used matches the problem reported by the customer. It may provide some needed information such as a better understanding of failure boundaries.

#### **Console Messages**

If you initiated the call with only console messages, request that an EREP report be run for the failing string or strings. It is strongly recommended that you ask your customer to provide a current EREP for the failing machine with each 3380-JK trouble call. This starts a practice which ensures an available EREP report with each call and a quicker intermittent failure resolution. Also, EREP shows both temporary and permanent errors. You may get a significantly different view of the problem. An equipment check or data check console message is only provided by the system for permanent errors. While this may be the only system indication, the use of the console message should be reserved as the primary source of error information for only those failures where it is impossible to collect EREP. You should primarily rely on the expanded detail of EREP reports for error data to make repairs.

#### EREP

If you started your call with EREP, a more careful look at EREP may be required.

- 1. Do you have both System Exception and the Event History Reports?

- 2. Have you searched and marked all the entries and collected all of the symptoms provided by the failing device?

- 3. Are other devices on the string failing?

- 4. If there is another string on the CTL-I interface, are there failures on that string also?

- 5. Do all of the devices on the string show usage?

- 6. What is the failure symptom? If there is more than one failure symptom, did you choose the one with the most PERMs?

- 7. Determine the time window. What time did the first error occur? The last error occur? On all failing devices?

- 8. Have you chosen the right error?

The priority of symptom codes on 3380-JK are D, E, 9, 4 (or Format 7, 8, 1, 9, 4).

At the completion of your analysis of EREP reports, you should be ready to answer the following questions:

- What symptom has the most permanent or temporary indications? Be able to list the other symptoms.

- Are all or some of the devices failing? Be able to identify the failing devices. Identify those devices that are probably not failing.

- Was the correct symptom used on the initial MD call.

For more details on EREP, see the Environmental Recording, Editing, and Printing Program User's Guide and Reference manual, Order No. GC28-1378.

# **DASD Error Log**

When EREP is not available, it may be advisable to examine each of the error logs. Details on how to run the error log function can be found in the LOG section of the Product Support Guide.

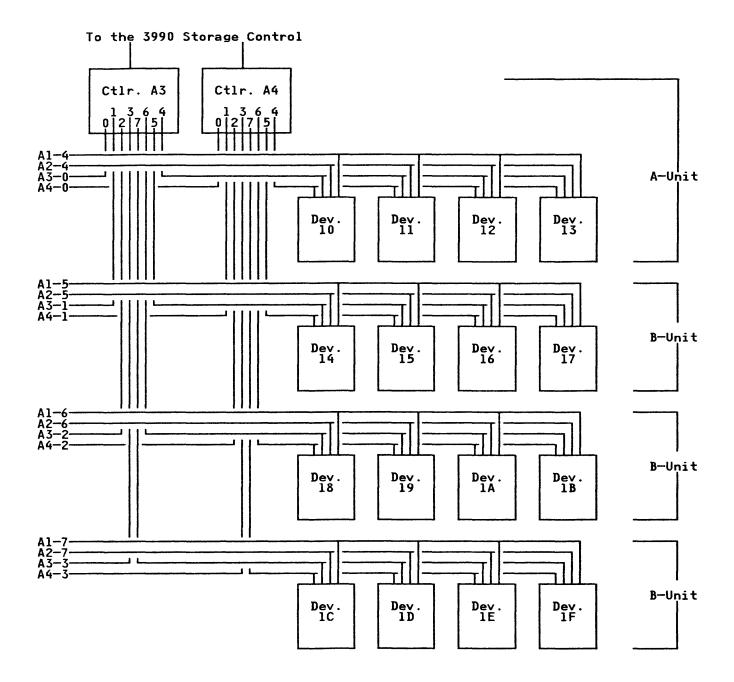

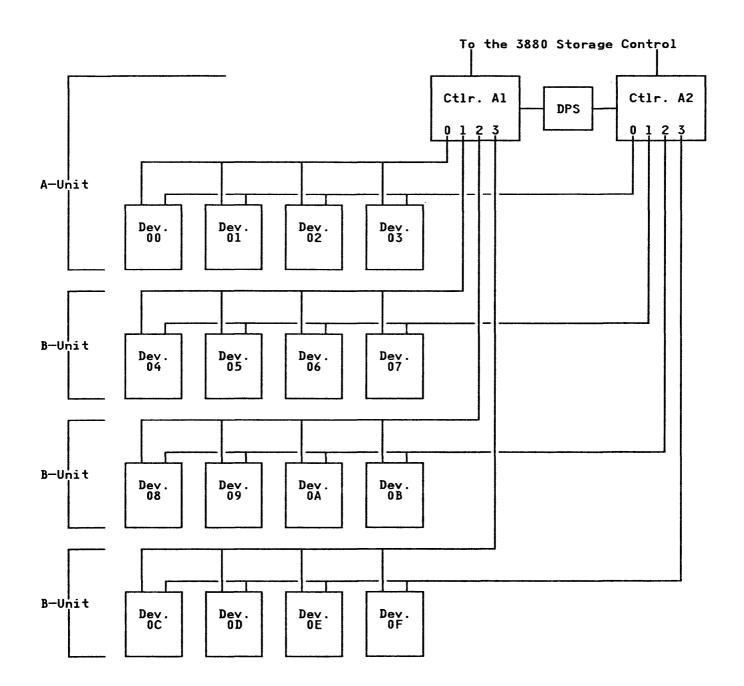

Each error log can store sixteen 32 byte entries for errors that occur on the associated storage director/storage path. On a 3990-3380-JK 4-path subsystem of two strings, there are eight error logs. All of the first 24 bytes of sense data are included in the 32 bytes.

The 3990 error logs have a time stamp indicating the difference in hours from the time the error log was retrieved and the time the error actually took place. The 3880 does not have a time stamp capability. Searching in the error logs with the MD minimally impacts customer operations.

If you use the DASD Error Logs, be aware that all errors are logged, including all retry attempts. Careful examination of the time stamp is required, because the logs may be old and not pertinent to this failure. A single log only provides the information from one path, and unless all paths are examined, incorrect fault boundary assumptions will be made, confusing rather that aiding in the isolation of the problem. In that no usage data is available, the absence of errors is no indication that the path if exercised would not also fail. Therefore, use EREP, if it is at all available, to overcome the shortcomings of the DASD Error Log.

# Error Thresholds and Storage Control Retry

The 3380-JK machine design expects a very small number of temporary data and seek checks. These temporary checks are thresholded so that they essentially become transparent to the customer normal operations and thruput. Thresholding is set low enough to ensure no data loss, yet high enough to ensure good performance without unnecessary maintenance activity.

The storage control maintains a Data Check and a Seek Check counter for each device. The storage control performs the error recovery for data checks and seek checks without significant operating system Error Recovery Procedure assistance. Permanent Data Checks and Seek Checks detected by the storage control error recovery procedure are reported to the operating system for ending the job, developing a console message, and developing an entry to the system error logs.

#### **Data Checks**

With each successful 3380-JK data check recovery, the storage control examines the device's data check and bytes read counters. If the bytes read counter reaches its maximum value before the data check counter reaches its threshold then both counters will be reset. However, if the check counter exceeds the threshold, the 3990 storage path logs the temporary data check and the next 23 data checks occurring on that device on any path of the storage control. The 3880-3 storage director logs the temporary data check and the next 23 data checks occurring on that device only through that storage director. The first record will have the First Error Logged bit active, byte 2 bit 2. The EREP Data Transfer Summary will use that bit to indicate which device tripped the threshold. The last check will have the Message to the Operator Bit active. That will signal the system ERP to develop a console message indicating logging is complete.

Threshold logging mode cannot be reset by the MD. Only an IML of the storage control can prematurely terminate the logging of the 24 temporary data checks.

#### **Seek Checks**

Seek check logging is similar to data check logging. The storage control counts the number of temporary seek errors and compares it to a predetermined number of motion seeks. If the motion seek counter reaches its maximum value before the seek check threshold is reached, both counters will be reset. The first seek check that causes the storage control to enter logging mode will be a Format 1 sense record. The information in byte 2, bit 2 will indicate First Log Error in addition to the seek check sense data. The storage control will log the next seven seek checks reported by the device in logging mode. With the eighth seek check, the storage control will set a bit in the sense to indicate to the system ERP to generate a console message indicating that threshold logging is complete.

#### Summary

Temporary Data Checks and Temporary Seek Checks that the storage control error recovery procedure has successfully recovered from are counted in the independent device counters. When the check count exceeds a predetermined threshold, the storage control reports the next 24 (temporary or permanent) Data Checks of the device, or the next 8 (temporary or permanent) Seek Checks on the failing device to the operating system.

The checks are reported as Environmental Data Present sense data on the next Start I/O command to the device. The error reporting does not occur in the current CCW.

### **Error Recovery**

There are times when it is necessary to know how checks and errors are usually recovered. An additional source for that information is in the IBM 3880 Storage Control Description, Order No. GA26-1661. IBM 3990 Storage Control Reference, Order No. GA32-0099-0. The information is in the Error Recovery Procedures chapter under the following headings:

- Error Correction Function Count, Key, and Data Devices

- Internal Retry

- Command Retry

- Error Condition Table 3380

#### Data Check Error Recovery

**Data Check Detection and Correction:** The storage control buffers all data transferred during a read operation. The buffer is large enough to contain an entire track. Previous storage controls were only capable of buffering the HA, Count and Key areas. Correction for the data area occurred in the host processor main memory. With the 3880-3 and 3990 storage controls the correction of the data area will occur in the storage control.

**Data Check Detection:** On recognition of a data check from the End Op code of the controller, the storage control issues commands to the controller ECC logic to generate and send to the storage control the data correction syndromes. The storage control analyzes the syndromes to determine if the syndrome data provides sufficient information to correct the data read or if the data read is uncorrectable.

#### First

The storage control on recognition of a data check responds to the channel with retry status (unit check, channel end, and status modifier).

The channel on recognition of the retry status, decrements its CCW pointer to return the pointer to the failing command. It does not generate an I/O interrupt to the system.

#### Second

The storage control collects and analyzes the syndromes to determine if the data check is correctable or uncorrectable.

- If the Data Check is correctable, the storage control applies the correction to the HA, Count, Key or Data area that is still in its buffer. It reorients itself to the failing record and raises Request In to the channel. The channel then reissues the last command. While the storage control transfers the buffered corrected data to the channel, it clocks over the area on the disk. The storage control and the channel then, without interruption, continue processing the remainder of the CCW string.

- If the Data Check is uncorrectable, the storage control holds up Request In until it receives a Locate Interrupt from the device indicating that the failing record is in position to be reread.' The channel then reissues the command and the storage control rereads the record. The channel overlays the previously read data in main memory with the reread data.

The reread results in one of three conditions.

a. The record is reread without error.

If the data area is correctly reread, the storage control continues with the CCW string and reacts as if no error occurred.

The data check will only be reported to the system if logging mode is active because of threshold overflow. The data check will be reported, with the environmental data bit on. At the next Start I/O to the storage control a unit check causes the ERP to collect sense from the storage control and develop a Format 4 sense record, which the ERP will then log.

b. A record is reread with a correctable data check.

If the data area is reread with a data check and the storage control determines that the error was correctable, it corrects it within its buffer. Also, if logging mode is in effect because of threshold logging, it reports the data check for logging on the next Start I/O to the storage control.

c. A record is reread with an uncorrectable data error again.

If the record reread is again uncorrectable, the storage control again responds to the channel with Retry Status. While the storage control is waiting for the start of the record for another retry, it steps its retry counter, examines the retry counter to determine if offset should be invoked for this retry and performs other housekeeping chores. With the Locate Interrupt from the device and the subsequent Request In from the storage control, the channel reissues the command.

If the record is never successfully read, the storage control posts Unit Check to the system. The ERP performs a sense command and receives, from the storage control, a Format 4 sense record with the Data Check and Permanent bits set.

#### Offset

During the uncorrectable data check retries, the storage control instructs the device to apply offset to the read head. Offset moves the head first to one side of the center of the track for a retry effort, then to the other. Each sequence moves the head further and further from the center of the track. Every data check that is recovered with offset is logged, so, that with EREP, a correct analysis can be performed.

It is possible for an intermittent read data error, which is occurring often, to be reported as a servo track following problem.

# **Analyze Format of Sense Data**

This is the procedure to analyze any format of sense data. Use this procedure to analyze console messages that contain sense data, the sense bytes of an EREP summary, and the EREP Event History report sense data.

**Note:** Keep in mind that valid error and status bits are dependent on proper reporting and correct operation of the error reporting path. Power faults anywhere on the path may cause invalid reporting of errors.

The following steps show how to examine a single sense record type. A later section covers the analysis of multiple symptom sense records.

It is assumed that you are familiar with DASD EREP reports. It is also assumed that you are aware of the importance of determining usage before determining failure boundaries, since unselected devices cannot log errors.

- First Locate the SENSE section of this manual.

- Second Determine the subsystem path in use at the time of failure by examining the first 24 bytes of the sense record.

**Format** of the sense data is defined in byte 7 bits 0 through 3.

Subsystem ID or Storage Director Physical ID for Formats 1, 4, 7, 8, and 9, is in byte 21.

**String ID** is in byte 3 except for Format 4, where it is in byte 14.

**Device ID** is the low-order 5 bits of byte 4.

Path Used is in byte 4 bits 0 and 1.

If multiple sense records are available, attempt to define the boundary of the failure. Determine the following:

- If one or more than one device is failing. Byte 4. bits 3 through 7, remain the same if only one device is failing.

- If one or more than one drive is failing. Byte 4, bits 3 through 6, remain the same if only one drive is failing.

- If one or more than one port is failing. Byte 4, bits 3 through 5, remain the same if only one port is failing.

- If one or more controllers in the string are failing. Byte 4, bits 0 and 1, remain the same if only one controller in the string is failing.

- If one or both controllers on a CTL-I interface is failing. Byte 21 and Byte 3 remain the same if only one controller on the CTL-I is failing.

With the above in mind, you can see that if only a single sense data record is available, the important initial boundary definition cannot be made.

To determine if only one device is failing. decide if the failing devices have similar symptoms. Do not make that decision based only on one symptom code; base it on the same or similar symptoms. The problem of similar symptoms may require bit analysis of the sense data. Some bits are status indicators and some bits are error indicators. It is beneficial to know the difference. Be aware that some of the status indicators, when off, indicate an error condition.

Third With the format of the sense data, locate the correct format chart to define the bits.

The charts, in addition to the names of the error bytes and bits, indicate the usual condition of the bit. Pointers are provided to byte and bit descriptions in the SENSE section. Bit description text gives pointers to ECD text that provide additional details about the symptom.

- Fourth Determine what type of error recovery action the storage control requested of the operating system by examining bytes 0 through 2. For example, an equipment check causes the operating system to save the first sense data, retry the operation ten additional times, and log in Log Rec the first error data and whether the recovery was successful (temporary error) or unsuccessful (permanent error).

- Fifth Determine the priority of the sense data records. In general, Format 7 identifies errors that require the highest service priority. The format service priority sequence for 3380-JK is Format 7, 8, 1, 9, and 4. Therefore, take action on the highest priority format, yet be familiar with the lower priority errors.

Before performing further analysis, review "Error Thresholds and Storage Control Retry" on page HELP-9 if you are not completely familiar with 3380 error thresholds.

- Sixth Carefully examine the combined EREP data and determine the following:

- The permanent and temporary errors

- The time the error or check was logged

- The host processor unit that collected the error data

If the initial symptom code chosen to repair the machine with the MD did not resolve the problem, re-examine the EREP data closely. If at anytime you determine that the initial symptom code was not the best choice and you have determined what the correct symptom code is, use the MD to provide you with the new FRU list.

Examine byte 7, bit 0 - 3. If the format of the data you wish to analyze is:

Format 1 go to "To Analyze Format 1 (SC=9xxx)" on page HELP-13.

Format 4 go to "To Analyze Format 4 (SC=4xxx)" on page HELP-14.

Format 7 go to "To Analyze Format 7 (SC=Dxxx)" on page HELP-16.

Format 8 go to "To Analyze Format 8 (SC=Exxx)" on page HELP-17.

Format 9 go to "To Analyze Format 9 (SC=9xxx)" on page HELP-14.

# To Analyze Format 1 (SC=9xxx)

The following procedure examines the Format 1 errors in a priority manner. While the highest priority bits are examined first, ensure that all the bits are examined to get a complete view of the symptoms being reported. Do not stop at the first symptom. Review all of the symptoms in the sense record.

#### Byte 20, bit 6 (Device Logic Undervoltage Status)

When active, this bit indicates a device undervoltage condition. This bit is a status bit and will not create an equipment check but will create a unique symptom code. This bit can only be reported concurrently with an equipment check. It will not indicate missing voltages.

#### Byte 7 (Format and Message)

Examine byte 7 for format and message. Bits 0 through 3 should have only bit 3 active, indicating Format 1. If bits 4 through 7 are other than zero, the storage control microcode detected the error and the message code description can be found in the SENSE section.

If the message code is other than zero, the remaining sense data will not, in most instances, contain significant symptom information. If the device itself has detected an error condition, that condition normally results in message code zero.

#### Byte 19, bit 3 (Device Error).

If this bit is on because of a check-2 error, there should be a bit on in sense byte 11 (Device Check-2 Status) and that error should be pursued.

#### 1. If byte 19, bit 3 is not active:

- Examine byte 20, bit 1 (Servo Inhibit) and bit 7 (Seek Incomplete). If these bits are on, it can mean servo inhibit or seek incomplete are active by themselves. Examine byte 15 for a checkpoint log value that is an indication of the reason for either or both of these errors.

- Examine byte 10, bit 3 (Device Sequence Complete). This status bit should be on to indicate that the device has completed a normal power on, including a rezero, a clean cycle and a warm up cycle. The servo mechanism should also be track following.

If bit 3 is not active and the contents of byte 10 (Device Power Status) is equal to hexcode '0E', the device is in the 3-minute clean cycle.

- Examine byte 20, bit 5 (Operator Panel Disable Switch). This status bit, when active, indicates that the Enable/Disable switch on the A unit operator panel is in the Disable position.

- Examine byte 19, bit 4 (Online). This bit should be on to indicate that the device is ready for customer use.

- If bit 4 is off:

- Examine byte 10, bit 6 (Motor Brake Latch). This bit should be on indicating that the device sequencer has picked the brake relay which releases the drive motor brake.

- Examine byte 10, bit 4 (Motor Run Latch). This bit should be on which indicates that the device sequencer started the motor.

- Examine byte 10, bit 5 (Spindle Control Bit 0). This bit should be on, to indicate that the drive motor and brake relays are picked.

- Examine byte 10, bit 7 (Spindle Control Bit 1). This bit should be off, to indicate that the MSA relay is not picked. This relay is picked to start the drive motor and then dropped.

#### 2. If byte 19, bit 3 is active:

- Examine byte 11, bit 3 (Checkpoint Check). If this bit is on, examine the contents of byte 15. See the SENSE section, Format 1, Byte 15 for checkpoint descriptions on page SENSE-66.

- Examine byte 11, bit 6 (Power Card Check). When this bit is active, it indicates that there is a failure within the card.

- Examine byte 11, bit 1 (Servo Control Check). When this bit is active, it indicates that there is an internal failure in the servo control function.

- Examine byte 11, bit 2 (RPS Check). A failure in this area would prevent the correct detection of index, guard bands, and sector compare.

- Examine byte 11, bit 0 (Device Sequencer Check). If this bit is active, the device

sequencer is failing and the sequencer cannot execute the power-on sequence.

• Examine byte 11, bit 7 (Funnel Parity Check). The Funnel is in the data path from the device to the CDP Bus.

# To Analyze Format 9 (SC=9xxx)

The following procedure examines the Format 9 errors in a priority manner. While the highest priority bits are examined first, ensure that all the bits are examined to get a complete view of the symptoms being reported. Do not stop at the first symptom. Review all of the symptoms in the sense record.

#### Byte 20, bit 6 (Device Logic Voltage Status)

When active, this bit indicates a device undervoltage condition. This bit is a status bit and will not create an equipment check, but will create a unique symptom code. It can only be reported concurrently with an equipment check. This bit will not indicate missing voltages.

#### Byte 7 (Format and Message)

Examine the contents of byte 7 for a message code. Bits 0 and 3 active indicate Format 9. If bits 4 through 7 are other than zero, the storage control microcode detected the error and the message code description can be found in the SENSE section.

For message codes 7, A, or E examine bytes 16 and 17, Track Physical Address Read, and compare with bytes 5 and 6, Seek Address.

#### Byte 11, bit 5 (Read/Write Check)

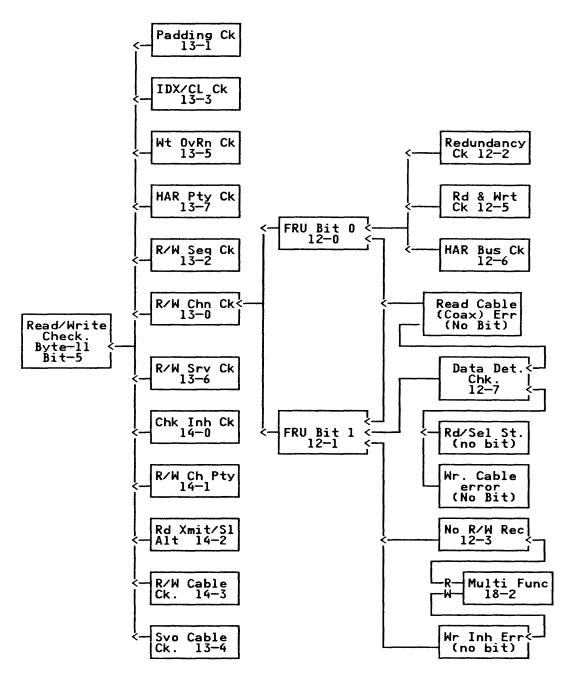

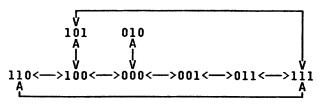

This bit indicates that some other sense bit is on in byte 12, 13, 14 or 18. See Figure 1 to determine the source of the error. As an example, if the error was byte 18, bit 2 (Multi-Function), byte 12, bit 1 would be set along with byte 13, bit 0 and byte 11, bit 5.

#### Byte 13, bit 4 (Servo Cable Check)

The servo cable brings servo signals from the disk read/write channel board to the controller.

#### To Analyze Format 4 (SC=4xxx)

To fully understand the contents of this format, an understanding of Data Check error recovery is required. If you have not already done so, see the IBM 3880 Storage Control Description, Order No. GA26-1661, Error Recovery Procedures, Error Correction Function - Count, Key, and Data Devices.

#### Byte 7 (Format and Message Code)

Examine byte 7 for a format and message code. Bits 0 through 3 indicate the format, bits 4 through 7 identify areas where the data check occurred. See SENSE-16.

#### Bytes 22 and 23 (Symptom Code)

Examine bytes 22 and 23 for symptom codes. These bytes will indicate the area in which the data check occurred. It will also indicate whether the error was recoverable and if recovery required the use of offset. Byte 23 will also show whether an undervoltage condition existed at the time the data check was detected, whether track following was lost, and whether a No Read Data condition occurred.

#### **Byte 1 (Unit Check Description)**

Examine byte 1. If bit 0, the permanent error bit, is not active, it indicates that the storage control error recovery procedure was able to successfully recover the data. In this case, byte 2 bit 3, Environmental Data Present, will also be active in most instances. It is active to indicate that the storage control and the Operating System Error Recovery Procedure did not log the Format 4 data check during the data check recovery. The storage control waits until the next Start I/O command to the device to have the data check logged with the Environmental Data Present indication by the operating system. This logging occurs only if the temporary data check threshold for the device has been exceeded.

#### Byte 15 (Head Offset Value)

Examine Byte 15. If any of bits 0 through 3 are active, it indicates that head offset was required to successfully recover the record.

#### Bytes 5 and 6 (Head and Cylinder Address)

Bytes 5 and 6 indicate which head and cylinder address the storage control sent the device actuator for the last seek command.

#### Bytes 8 through 12 (Record ID)

Bytes 8 through 12 provide the last cylinder, head, and record address read from the disk before, or during, the read with the data check. This data may be unreliable on HA or Count area errors.

#### Single Error Records

The analysis of a single Format 4 record does not. provide very much significant hardware fault information. The EREP System Exception Report Summaries provide a better analysis tool.

#### **Multiple Error Records**

For multiple error records, it is suggested that the EREP DASD Data Transfer Summaries be used to identify failing data paths and failing data tracks.

# To Analyze Format 7 (SC=Dxxx)

The following procedure examines the Format 7 errors in a priority manner. While the highest priority bits are examined first, ensure that all the bits are examined to get a complete view of the symptoms being reported. Do not stop at the first symptom. Review all of the symptoms in the sense record.

#### **Controller RCC Transfer Status**

Examine byte 17 bit 0 for the controller addressed as 0 and byte 19 bit 0 for the controller addressed as 1 for a Controller Undervoltage condition. Zero is the active failing state and 1 is the normal state. This is a status bit and can only report concurrently with a Format 7 symptom code, not by itself. It also cannot report a missing voltage.

#### Byte 7 (Format and Message)

Examine byte 7 for a message code. If the message code is not zero, the storage control microcode detected an error condition.

#### Byte 10 (DTI/XES Register)

Examine byte 10, bits 0 through 3. If any of these bits are active, it indicates an error condition detected by the storage control. The low-order bits indicate the status of Tag In before sense collection.

#### Byte 3 (String ID)

Byte 3 is the string ID of the controller that initiated a connection check alert (CCA) or the ID of the controller the storage control suspects is having the problem indicated in the byte 7 message code.

**Note:** If the String ID in byte 3 is hexcode '00' or 'FF', it is invalid.

#### Byte 11 (Connection Check Alert and Power Status)

Examine Byte 11. Bits 0 and 1 identify the controller on the CTL-I that had a controller check-1 condition. Byte 11, bit 0 and byte 17, bit 6 active together certify the error bits in bytes 12, 13, 16, and 17 for the controller addressed as 0. Byte 11, bit 1 and byte 19, bit 6 active together certify the error bits in byte 14, 15, 18, and 19 for the controller addressed as 1.

#### **Controller Check-1 Status**

Bytes 12 and 13 (Controller 0 Check-1 Status) Sense bytes 12 and 13 have the Check-1 error information for the Controller addressed as 0.