|   | - |   | and some of the local division of the local |   |  |

|---|---|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

|   |   |   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |  |

|   | - | _ | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _ |  |

|   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

| _ |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _ |  |

|   | - | _ | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |  |

|   |   |   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |  |

|   | - |   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - |  |

|   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

|   |   | _ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

|   | - | _ | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | - |  |

|   | - |   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |  |

|   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

|   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - |  |

|   | - |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

|   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

|   |   |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |  |

Geneele contente cont

••5

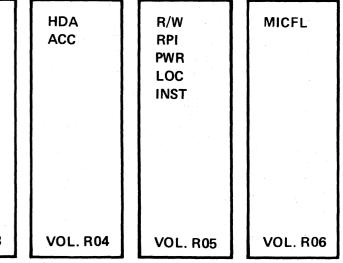

| INDEX<br>MLX<br>LGND<br>START<br>FSI<br>MSG<br>SENSE<br>MICRO | OLT<br>OPER<br>PANEL<br>CTL-I | DEV-I<br>DATA |

|---------------------------------------------------------------|-------------------------------|---------------|

| VOL. R01                                                      | VOL. R02                      | VOL. R03      |

Volumes R01 through R06 accompany each Control Module and support all 3350s attached.

BA0000 2358629 441300 31 Mar 76 3350 Seq. 1 of 2 Part No.

Copyright IBM Corporation 1976

# PREFACE

#### MAINTENANCE INFORMATION MANUAL ORDERING PROCEDURE (IBM Internal)

Individual pages of the 3350 Maintenance Information Manual can be ordered from the San Jose plant by using the Wiring Diagram/Logic Page Request (Order No. 120-1679). In the columns headed "Logic Page" enter the page identifier information: sequence number, sheet number, part number, and EC number. Groups of pages can be ordered by including a description (section, volume, etc.) and the machine serial number.

This manual was prepared by the IBM General Products Division, Technical Publishing, Department G26, San Jose, California 95193.

© Copyright International Business Machines Corporation 1976

|      |                       |                     |                     | <br> |  |

|------|-----------------------|---------------------|---------------------|------|--|

| 3350 | BA0000<br>Seq. 2 of 2 | 2358629<br>Part No. | 441300<br>31 Mar 76 |      |  |

Copyright IBM Corporation 1976

# SAFETY

# **CE SAFETY PRACTICES**

All Customer Engineers are expected to take every safety precaution possible and observe the following safety practices while maintaining IBM equipment:

- You should not work alone under hazardcus conditions or around equipment with dangerous voltage. Always advise your manager if you MUST work alone.

- Remove all power, ac and dc, when removing or assembling major components, working in immediate areas of power supplies, performing mechanical inspection of power supplies, or installing changes in machine circuitry.

- After turning off wall box power switch, lock it in the Off position or tag it with a "Do Not Operate" tag, Form 229-1266. Pull power supply cord whenever possible.

- 4. When it is absolutely necessary to work on equipment having exposed operating mechanical parts or exposed live electrical circuitry anywhere in the machine, observe the following precautions:

- a. Another person familiar with power off controls must be in immediate vicinity.

- b. Do not wear rings, wrist watches, chains, bracelets, or metal cuff links.

- c. Use only insulated pliers and screwdrivers.

- d. Keep one hand in pocket.

- When using test instruments, be certain that controls are set correctly and that insulated probes of proper capacity are used.

- f. Avoid contacting ground potential (metal floor strips, machine frames, etc.). Use suitable rubber mats, purchased locally if necessary.

- 5. Wear safety glasses when

- a. Using a hammer to drive pins, riveting, staking, etc.

- b. Power or hand drilling, reaming, grinding, etc.

- c. Using spring hooks, attaching springs.

- d. Soldering, wire cutting, removing steel bands.

- e. Cleaning parts with solvents, sprays, cleaners, chemicals, etc.

- Performing any other work that may be hazardous to your eyes. REMEMBER – THEY ARE YOUR EYES.

- 6. Follow special safety instructions when performing specialized tasks, such as handling cathode ray tubes and extremely high voltages. These instructions are outlined in CEMs and the safety portion of the maintenance manuals.

- 7. Do not use solvents, chemicals, greases, or oils that have not been approved by IBM.

- Avoid using tools or test equipment that have not been approved by IBM.

- 9. Replace worn or proken tools and test equipment.

- Lift by standing or pushing up with stronger leg muscles this takes strain off back muscles. Do not lift any equipment or parts weighing over 60 pounds.

- 11. After maintenance, restore all safety devices, such as guards, shields, signs, and grounding wires.

- 12. Each Customer Engineer is responsible to be certain that no action on his part renders products unsafe or exposes customer personnel to hazards.

- 13. Place removed machine covers in a safe out-of-the-way place where no one can trip over them.

- 14. Ensure that all machine covers are in place before returning machine to customer.

$\frac{\partial \mathcal{L}}{\partial t} = \frac{\partial \mathcal{L}}{\partial t} + \frac{\partial$

15. Always place CE tool kit away from walk areas where no one can trip over it; for example, under desk or table.

- 11

- 16. Avoid touching moving mechanical parts when lubricating, checking for play, etc.

- 17. When using stroboscope, do not touch  $\ensuremath{\mathsf{ANYTHING}}\xspace$  it may be moving.

- Avoid wearing loose clothing that may be caught in machinery. Shirt sleeves must be left buttoned or rolled above the elbow.

- 19. Ties must be tucked in shirt or have a tie clasp (preferably nonconductive) approximately 3 inches from end. Tie chains are not recommended.

- 20. Before starting equipment, make certain fellow CEs and customer personnel are not in a hazardous position.

- 21. Maintain good housekeeping in area of machine while performing and after completing maintenance.

Knowing safety rules is not enough. An unsafe act will inevitably lead to an accident. Use good judgment - eliminate unsafe acts.

#### ARTIFICIAL RESPIRATION

#### **General Considerations**

- Start Immediately Seconds Count Do not move victim unless absolutely necessary to remove from danger. Do not wait or look for help or stop to loosen clothing, warm the victim, or apply stimulants.

- 2. Check Mouth for Obstructions Remove foreign objects.

- 3. After victim is breathing by himself or when help is available:

- a. Loosen clothing.

- b. Place victim on his side.

- c. Keep victim warm.

- Remain in Position After victim revives, be ready to resume respiration if necessary.

- 5. Call a Doctor

- Have someone summon medical aid. 6. Don't Give Up

Continue without interruption until victim is breathing without help or is certainly dead.

#### **Rescue Breathing for Adults**

Place victim on back; lift neck and tilt head way back. (Quickly remove any noticeable food or objects from mouth.)

Pinch nose closed; make airtight seal around victim's mouth with your mouth; and forcefully breathe into victim until chest rises (expands).

- 3. Continue breathing for the victim 12 times per minute WITHOUT STOPPING.

- 4. If chest does not rise (expand), roll victim onto side and pound firmly between shoulder blades to remove blocking material. Also, try lifting jaw higher with your fingers. Resume rescue breathing.

PREFACE/SAFETY

11

# **OLT CONTENTS**

#### **RUNNING REFRESHER**

| OLTSEP      |   |   | • |   |   | • |   |   |   | OLT 5 |

|-------------|---|---|---|---|---|---|---|---|---|-------|

| OS/VS-OLTEP |   |   |   |   | • |   |   | • |   | OLT 6 |

| DOS-OLTEP . | • | • | • | • | • | • | • | • | • | OLT 7 |

**REQUIREMENTS** . . . . . . . . . . OLT 10

# **TEST DESCRIPTIONS**

| T3350 PSA |   | • |  | • | • | • | • | • | OLT 20        |

|-----------|---|---|--|---|---|---|---|---|---------------|

| T3350 PSB |   |   |  |   |   |   |   |   | OLT 24        |

| T3350 PSC |   |   |  |   |   |   |   |   | <b>OLT 25</b> |

| T3350 WT  | • |   |  |   |   |   |   |   | <b>OLT 26</b> |

|           |   |   |  |   |   |   |   |   |               |

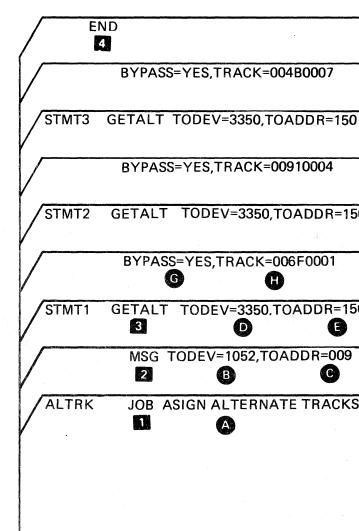

#### ALTERNATE TRACK ASSIGNMENT . OLT 30

**ERROR MESSAGES** . . . OLT 48 through 280

For additional information on OLTS and a bibliography, see the System/370 Diagnostic Reference Summary (Order No. SY25-0512) and the OLT Users Guide (Order No. D99-3350).

| 3350         BB0001         2358071         441300         441303         441308           Seq. 1 of 2         Part No. ( )         31 Mar 76         30 Jul 76         18 Aug 78 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# OLT CONTENTS OLT 1

OLT CONTENTS OLT 1

# **RUNNING REFRESHER – OLTSEP**

For additional information, see System/370 Diagnostic Reference Summary (Order No. SY25-0512).

#### Preparation

Mount OLTSEP disk or tape and IPL.

#### Starting OLTSEP

#### **OLTSEP** prints:

04 SEP188D ENTER DATE AND TIME IN THE FOLLOWING FORMAT 'MM/DD/YY, HH/MM/SS'

Reply:

r 04, 'MM/DD/YY' or r 04, 'MM/DD/YY, HH/MM/SS' or PSW RESTART

**OLTSEP** prints:

SEP102I OLTS RUNNING

SEP107I OPTIONS ARE NTL, NEL, EP, CP, NPP, PR, FE, NMI, SI

SEP105D ENTER DEV/TEST/OPT 01

If it is desired to run OLTs from card decks, the RDR device must be varied from its default of the IPL device to card. To do this, reply:

r 01, 'VARY RDR=00C'

00C is the address of the card reader. Modify the address to conform to your system.

#### **OLTSEP** prints:

SEP219I VARY COMPLETE

01 SEP105D ENTER DEV/TEST/OPT

If the RDR device is to remain the IPL device, do not reply with the VARY command.

#### Make a Run Request

© Copyright IBM Corporation 1976

Make a run request to select the test you want to run. Reply:

r 01, '160/3350PSA//' (See OLT descriptions, OLT 20 through 26.)

This reply begins testing on device 160, runs OLTS section PSA, and uses the default options. To select another sequence of testing, enter a reply of:

r 01, '160/3350PSA, 2/NFE/'

This runs only routine 2 of the OLT section PSA, and causes all the default options to be selected except the option FE (first error communications), which will be altered to NFE.

See OS/VS-OLTEP Make a Run Request on OLT 6 for additional examples.

#### **Options**

| OPTION              | YES        | NO  | DEFA |

|---------------------|------------|-----|------|

| TEST LOOP           | TL (VALUE) | NTL | NTI  |

| ERROR LOOP          | EL         |     |      |

|                     | EL(I)      |     |      |

|                     | EL (VALUE) | NEL | NEI  |

| ERROR PRINT         | EP         | NEP | EP   |

| CONTROL PRINT       | CP         | NCP | CP   |

| PARALLEL PRINT      | PP (VALUE) | NPP | NPI  |

| PRINT               | PR         | NPR | PR   |

| FIRST ERROR COMM.   | FE         | NFE | FE   |

| MANUAL INTERVENTION | *MI        | NMI | NM   |

| SPURIOUS INTERRUPT  | SI         | NSI | SI   |

| DATA ENTRY FIELD    | EXT=(DATA) |     |      |

| REMOTE ENTRY        | *RE        | NRE | RE   |

|                     |            |     |      |

\*RE and MI are mutually exclusive (only one can be on).

#### Halt OLTSEP

To halt OLTSEP at any time, press the Request key on the console. **OLTSEP** prints:

SEP1071 OPTIONS ARE -----SEP105D ENTER DEV/TEST/OPT 01

Reply:

r 01, '(newDEVice/(newTEST)/(newOPTions)' New instructions to OLTSEP

or to continue: (EOB)

or to continue or restart the section under test:

r 01,'///'

or to terminate the section under test: r 01, 'CANCEL'

| 3380 | BB0001      | 2358071  | 441390    | 441303    | 441308    | <br> |

|------|-------------|----------|-----------|-----------|-----------|------|

| 3350 | Seq. 2 of 2 | Part No. | 31 Mar 76 | 30 Jul 76 | 18 Aug 78 |      |

#### **RUNNING REFRESHER – OLTSEP**

OLT 5

AULT

Ľ

L

P

1I

RUNNING REFRESHER - OLTSEP OLT 5

$\bigcirc$

# **RUNNING REFRESHER – OS/VS-OLTEP**

For additional information, see System/370 Diagnostic Reference Summary (Order No. SY25-0512).

#### Preparation

Units to be tested may be varied offline. This is accomplished through the console by using the Vary command. Examples:

V 160, OFFLINE (Varies unit 160 offline.) V(160, 161, 162), OFFLINE (Varies units 160, 161, and 162 offline.)

(The System replies: 160, 161, 162 OFFLINE when the vary is completed.)

SYSRES cannot be varied offline.

3350 OLTS PSA and PSB can be run online and they will not destroy data on any disk. However, to perform maintenance on the drive, you must vary the drive offline before starting OLTEP. If FRIEND (OLT T0200A) is used to write, the drive must be varied offline.

#### Starting OS/VS-OLTEP

1. S – causes a job to be started if a reader procedure is incorporated in the system. Examples:

S OLTEP (For an MVT or VS2 system.)

S OLTEP. PX (For an MFT or VS1 system, where X is the partition number OLTEP is to run in. If in doubt, ask an operator which partition to use.)

/

or

Use JCL on cards to execute program IFDOLT.

2. Once OLTEP is running, it generates various messages. Examples:

IFD10210LTS RUNNING (To inform you that OLTEP is running.)

00 IFD104D REPLY ANY CHARACTER TO REQUEST COMMUNICATION. (A reply of any character to the above request causes a communication interval.)

#### Make A Run Request

# OLTEP waits for a reply after issuing the message.

01 IFD005D ENTER-DEVICE/TEST/OPTION (See OLT descriptions, OLT 20 through 28.) Examples of DEVICE/TEST/OPTION replies: (The commands are given in this sequence.)

- 1. r 01, '160/3350PSA/EP/'

- 2. r 01,'/3350PSA//'

- 3. r 01, '161///'

- 4. r 01, '160, 163, 165/3350PSA, PSB/PP/'

- 5. r 01,'160-163/3350PSA//'

- 6. r 01, '260/3350PSA, 2/NEP, MI/NRE/'

The commands carry forward until they are changed.

| Examples | Devices<br>(nine maximum) | Tests                  | Options           |

|----------|---------------------------|------------------------|-------------------|

| 1.       | 160                       | 3350PSA                | EP,CP,PR,FE,SI    |

| 2.       | 160                       | 3350PSA                | EP,CP,PR,FE,SI    |

| 3.       | 161                       | 3350PSA                | EP,CP,PR,FE,SI    |

| 4.       | 160,163,165               | 3350PSA and PSB        | PP,EP,CP,PR,FE,SI |

| 5.       | 160,161,162,163           | 3350PSA                | EL,EP,CP,PR,FE,SI |

| 6.       | 260                       | 3350PSA routine 2 only | PR,FE,MI,SI       |

#### Options

Use the OPTIONS list from OLTSEP, OLT 5.

#### Halt OS/VS-OLTEP

Reply to the outstanding request with any character to force communication. OLTEP prints:

01 IFD005DENTER--DEVICE/TEST/OPTION/

Reply:

r 01, 'CANCEL' (This cancels OLTEP.)

| 3350 | <b>BB0006</b><br>Seq. 1 of 2 | <b>2358072</b><br>Part No. | 441300<br>31 Mar 76 | 441 303<br>30 Jul 76 | 441308<br>18 Aug 78 |  | - |

|------|------------------------------|----------------------------|---------------------|----------------------|---------------------|--|---|

|      |                              |                            |                     |                      |                     |  |   |

#### RUNNING REFRESHER – OS/VS-OLTEP OLT 6

RUNNING REFRESHER – OS/VS-OLTEP OLT 6

# **RUNNING REFRESHER – DOS-OLTEP**

For additional information, see System/370 Diagnostic Reference Summary (Order No. SY25-0512).

#### Preparation

Units to be tested must not be assigned to either of the Foreground Programs. The Background Program must be available for CE use.

#### **Starting DOS-OLTEP**

Job Control Cards may be put in the reader or JCL commands may be entered from the system console. The example shown is for the console.

- AR START BG

- // JOB OLTEP BG

- BG //ASSGN SYS014, X'160'

- //EXEC IJZADOLT, REAL, SIZE=28K BG

- BG E0021 OLTS RUNNING

- BG E005D ENTER -- DEV/TEST/OPT/

This is printed after the first error, after operating the Interrupt switch, or at job completion.

#### Make a Run Request

Make a run request to select the test you want to run. Reply:

r 01, '160/3350PSA//' (Test 160 with 3350PSA.) BG E158I ST3350A UNIT 0160 (Testing has begun.)

#### **Option Field Entries**

/ (Run with default options on initial request only.) NTL, NEL, EP, CP, NAP/ (Run with default options.) AP/ (Run with default options but print on SYSLST.)

#### Halt DOS-OLTEP

To halt DOS-OLTEP at any time, operate the CP/Interrupt switch. **DOS-OLTEP** prints:

BG 01E105D ENTER - DEV/TEST/OPT

#### Reply:

BG R 01, 'Cancel'

| 3350 | <b>BB0006</b><br>Seq. 2 of 2 | 2358072<br>Part No. | 441300<br>31 Mar 76 | 441303<br>30 Jul 76 | 441308<br>18 Aug 78 | n an |  |

|------|------------------------------|---------------------|---------------------|---------------------|---------------------|------------------------------------------|--|

|      |                              |                     |                     |                     |                     |                                          |  |

© Copyright IBM Corporation 1976

# RUNNING REFRESHER – DOS-OLTEP OLT 7

#### RUNNING REFRESHER – DOS-OLTEP OLT 7

# **3350 OLT REQUIREMENTS**

#### 3350 OLT Tests

PSA – HA and R0 Format and Readability on 3350 HDA.

PSB – Data Readability (burst check) on 3350 HDA.

PSC – SD Directory and HA Recovery

WT – Write test on any selected track.

T0200A – OLT(S)EP Friend

These tests are described on OLT 20 through 26.

#### **Program Requirements**

3350 OLTs run under DOS OLTEP REL 32, VS1

OLTEP release 5, VS2 OLTEP release 3 (with ICR), or

OLTSEP release 8.0 or higher.

3350 OLTs test 3330 Compatibility Mode volumes under operating systems that support the 3330.

OLTEP requires a system or private library containing:

- Standalone Online Test Support Processor (SOSP)

- Configuration Data Set (CDS), see 3350 CDS description.

- 3350 OLT Sections.

OLTSEP requires a load tape or disk load file containing:

- IPL Loader.

- OLTSEP Nucleus.

- OLTSEP Transient Modules.

- Standalone Online Test Support Processor (SOSP).

- Configuration Data Set (CDS), see 3350 CDS description.

- 3350 OLT Sections.

For additional information, see OLT Users Guide (D99-3350) and System/370 Diagnostic Reference Summary (SY25-0512).

#### **Equipment Requirements**

3350 OLTs may be run on any 3350 string. There are no special equipment requirements.

#### **3350** Configuration Data Set (CDS)

Configuration data must be correctly supplied in the OLTEP or OLTSEP libraries. CDS for the 3350 should appear as follows (one card per drive):

| CC 01    | Blank                                                       |

|----------|-------------------------------------------------------------|

| CC 02–04 | CDS                                                         |

| CC 10–17 | Device Address (Example –<br>0000 0160)                     |

| CC 18–19 | Blank                                                       |

| CC 20-21 | Feature Code $(02 = 3830-2 \text{ or ISC})$                 |

|          | storage control)                                            |

|          | (10 = 3830-3  staging)                                      |

|          | adapter storage                                             |

|          | control)                                                    |

|          | (Blank = other)                                             |

|          | attachment)                                                 |

| CC 22–23 | Device class (20)                                           |

| CC 24–25 | Device Type (Mode, see Note.)                               |

|          | 3350 = 0B                                                   |

|          | 3330-1 = 09                                                 |

|          | 3330-11 = 0D                                                |

| CC 26–29 | Blank                                                       |

| CC 30–31 | Flags (04 = 2-channel switch or string<br>switch installed) |

|          | (40 = device shared)                                        |

|          | (44 = both of the above)                                    |

| CC 32–35 | Blank                                                       |

| CC 36–37 | CUCDS suffix (see 3830 CDS                                  |

|          | requirements)                                               |

| CC 38    | /                                                           |

|          |                                                             |

These cards for other devices on the system must be included in CDS.

#### SOSP

The Standalone Online Test Support Processor (SOSP) may be used to create a master load tape or disk load file for OLTSEP. SOSP does not support the 3350 as a resident device.

SOSP also has facilities for the following:

- Add, replace, or delete OLTs from the master file.

- Duplicate master files (DUP).

- Print the contents of a master file (LIST).

- Generate and modify the Configuration Data Set (CONFIG).

The SOSP Operators Guide (D99-SOSPB) has details for selecting the options.

#### **Error Messages**

To locate the error message referenced by the error printout, use the section number and REFNUM from the first printout line as an index to OLT pages starting on OLT 40. Messages with REFNUMs ending in 91 through 99 are common to all sections and are found at the start of the error message listing under Common Error Messages (see OLT 40, 50, and 60).

Note: At least one CDS card must be included with Device Type 0B(3350) for correct 'Autoedit' function. If there are no drives in 3350 Mode, add a dummy CDS with Class 20, Device Type 0B.

| 3350 | <b>BB0010</b><br>Seq. 1 of 2 | <b>2358073</b><br>Part No. | 441300<br>31 Mar 76 | 441303<br>30 Jul 76 | 441308<br>18 Aug 78 | 441310<br>27 Jun 80 |   |

|------|------------------------------|----------------------------|---------------------|---------------------|---------------------|---------------------|---|

|      |                              |                            |                     |                     |                     |                     | - |

# 3350 OLT REQUIREMENTS OLT 10

# 3350 OLT REQUIREMENTS OLT 10

# **TEST DESCRIPTIONS**

#### **USE OF OLTs**

The Online Tests for the 3350 are designed to test the following:

- The readability and accuracy of the Home Address and Record Zero fields.

- The data integrity of data records.

- The ability of the 3350 to write and read different bit patterns on selected tracks.

#### **SECTIONS**

T3350PSA – HDA HA/R0 Scan (requires 8K)\* T3350PSB - HDA Burst Test (requires 8K)\* T3350PSC - SD Directory and HA Recovery (requires 16K)\* T3350WT – Write Test (requires 8K, attempts to get 8K more storage)\*

\*CPU storage

#### T3350PSA HDA HA/R0 SCAN

This section tests the readability and accuracy of HA and R0 fields on the HDA.

#### **Running Considerations**

1. This section requires that a completely operational file subsystem be used. Hardware errors invalidate results and the internal retry capability of the storage control must present hard errors to the OLT.

OLT recalibrate/retry is performed once, then the error is printed and processing continues.

Thirty hardware errors occurring on any one cylinder cause premature termination of the OLT (see OLT 210, REFNUM 0000A). Appropriate diagnostics should be run against the failing drive and/or corrective action completed before continuing to scan the HDA.

- 2. This OLT does not scan data on the CE cylinder. The CE cylinder is 1024, heads 0 through 29.

- 3. If the 3830 Model 2, ISC, or 3880 is placed in Forced Error Logging mode while running this section, errors normally transparent to the system program (retried at the storage control level) are displayed on the test printout. This is most effective for intermittent/soft errors.

Do not use the Forced Error Logging mode if the string is shared.

#### **Routine Descriptions**

Routine 1: This routine is run by default. It scans the entire HDA except the CE cylinder. Home Addresses and Record Zeros are scanned for readability and data accuracy. Invalid HA and/or R0 fields are printed in expected-received form. HA and up to 16 bytes of R0 (8-byte Count field, 8-byte Data field) are displayed when an error is found. Alternate and defective tracks are verified to point to a valid mate. If none is found, an appropriate error message is printed.

Routine 2: This routine must be selected. It allows specific tracks to be tested.

User options:

- 1. Select track or tracks to be scanned.

- 2. R0 data length to be tested (8 or any).

#### **Running Details**

This OLT requires 4 to 6 minutes to run, or longer when run under VS-OLTEP.

1. In most cases, the default mode of operation (routine 1 only) successfully tests an HDA.

Enter:

/3350PSA//

2. If some specific area of the HDA is suspected, the test time can be shortened by selecting the track(s) to be tested (routine 2).

Enter:

/3350PSA,2//

Message:

ENTER TRACKS(S), 'ALL'OR'END' AS 'CCCHH-CCCHH 'OR 'CCCHH'

#### Reply:

or

'ALL',EOB

or 'END',EOB

or

'CCCHH-CCCHH', EOB

'CCCHH', EOB

or

EOB ( DEFAULT = 'ALL' TRACKS )

Valid limits for CCCHH are:

3350 volume = '00000' through '22F1D'3330-1 volume = '00000' through '19412' 3330-11 volume = '00000' through '32812'

#### 3. If the R0 data is not 8 bytes long:

Enter:

/3350PSA,2//

#### Message:

ENTER TRACKS(S), 'ALL' OR 'END' AS 'CCCHH-CCCHH' OR 'CCCHH'

#### If specific tracks are required:

#### Reply:

'CCCHH' or 'CCCHH-CCCHH' (the identity of the suspect track(s)) or

EOB ( DEFAULT = 'ALL' TRACKS

| 3350        | <b>BB0010</b>   | <b>2358073</b> | 441300    | 441303    | 441308    | 441309    | 441310    |

|-------------|-----------------|----------------|-----------|-----------|-----------|-----------|-----------|

|             | Seq. 2 of 2     | Part No.       | 31 Mar 76 | 30 Jul 76 | 18 Aug 78 | 15 Jul 79 | 27 Jun 80 |

| © Copyright | IBM Corporation | 1976           |           |           |           |           |           |

#### TEST DESCRIPTIONS

**OLT 20**

Message: ENTER RO DATA LENGTH

Reply: 'ANY',EOB or '8',EOB

See OLT 200 for example.

# **TEST DESCRIPTIONS**

#### **T3350PSB HDA BURST TEST**

This section tests the readability of data records on the HDA.

#### **Running Considerations**

- 1. This section requires that the Home Addresses and Record 0s are valid and readable, therefore T3350PSA should be run before T3350PSB.

- 2. This section also requires that a completely operational file subsystem be used. Hardware errors invalidate results and the internal retry capability of the storage control must present hard errors to the OLT.

OLT recalibrate/retry is performed once, then the error is printed and processing continues.

Thirty hardware errors occurring on any one cylinder cause premature termination of the OLT (see OLT 250, REFNUM 0000A). Appropriate diagnostics should be run against the failing drive and/or corrective action completed before continuing to scan the HDA.

- 3. This OLT does not scan data on the CE cylinder. The CE cylinder is 1024, heads 0 through 29.

- 4. If the 3830 Model 2, ISC, or 3880 is placed in Forced Error Logging mode while running this section, errors normally transparent to the system program (retried at the storage control level) are displayed on the test printout. This is most effective for intermittent/soft errors. Do not use Forced Error Logging mode if the string is shared.

#### **Routine Descriptions**

Routine 1: This routine is run by default. It scans the entire HDA for readability (burst check), all records, and all tracks (except CE tracks). A statistical summary is printed at the end of the OLT. All data records are read with the SILI and SKIP bits on. No data is transferred or printed.

Routine 2: This routine must be selected. It allows specific tracks to be tested.

Routine 3: This routine must be selected. It allows a track to be selected for a burst check on that part of the track containing valid data, then forms a tight scope loop.

#### **Running Details**

This OLT requires 5 to 30 minutes to run. Running time depends on storage control and HDA usage and density (for special cases, see routine 2 and 3 description).

1. In most cases, the default mode of operation (routine 1 only) successfully tests an HDA.

Enter:

/3350PSB//

2. If a specific area of the HDA is suspected, the test time can be shortened by selecting the track(s) to be tested (routine 2).

Enter:

/3350PSB,2//

Message:

ENTER TRACK(s), 'ALL'OR'END' AS'CCCHH-CCCHH'OR'CCCHH'

Reply:

'ALL',EOB or

- 'END',EOB

- or

'СССНН-СССНН', ЕОВ

- or 'CCCHH', EOB

- or

EOB ( DEFAULT= 'ALL ' TRACKS )

Valid limits for CCCHH are:

3350 volume = '00000' through '22F1D' 3330-1 volume = '00000' through '19412' 3330-11 volume = '00000' through '32812'

3. If a hardware failure is causing a Data Check:

Enter:

/3350PSB,3//

Message:

ENTER TRACK FOR SCOPING

#### Reply:

CCCHH of the track to be looped.

The OLT starts a tight loop of the track and continues until terminated by a normal console request or OLT(S)EP intervention.

Command Chain may terminate when an abnormal condition occurs or the last data record has been read. Use OLT T0200A (FRIEND) or 3350 microdiagnostic routine B1 if a full track read of all gaps and fields is desired.

# TEST DESCRIPTIONS OLT 24

# **TEST DESCRIPTIONS**

#### **T3350PSC SKIP DISPLACEMENT OLT**

This OLT is designed to create a track-by-track directory (SDMAP) of nonzero SDs (Skip Displacements) and, if necessary, restore the SD information from the directory to one or more tracks, or analyze a track and generate the necessary skip displacement.

The directory of nonzero SDs must be created on each installed HDA and upon installation of a new 3350 or replacement HDA.

#### **ROUTINE DESCRIPTIONS**

#### Default Mode, Build SD Directory Routine M4

The Build SD Directory routine will:

- Build a directory of nonzero SDs on cylinder 561 using the Card Input option.

- Scan all HA/ROs on an HDA, storing a directory of nonzero SDs on cylinder 561.

The Build SD Directory routine will write only on cylinder 561. Customer data will not be destroyed during this step. On newer HDAs the SD Directory may have been written at the plant. (This can be determined by running T3350PSC in default mode.)

#### **OPTIONAL ROUTINES**

Any SD loss can be recovered after the SD Directory has been created by using the optional routines of this OLT. Routine M5 will analyze a track and assign a new skip displacement to allow a defect to be skipped thereby eliminating the need to assign an alternate track.

Caution: The Write HA with SD Bytes function is a Format Write. Any existing data on a track that undergoes HA/SD restoration (routines M1, M2, M3, or M5) will be lost.

#### Routine M1

Routine M1 will restore the SDs to the selected tracks from the directory, or from input provided by the user through CECOMS.

#### Routine M2

Routine M2 will scan all HA/ROs on an HDA and rewrite those which produce data checks, obtaining SD data from the SD Directory or from the user through CECOMS.

#### **Routine M3**

Routine M3 will rewrite all HA/ROs on an HDA, obtaining SD data from the SD Directory or from card input.

#### Routine M5

Routine M5 will analyze a selected track or range of adjacent tracks on a single surface. If an unusable surface area is found, Routine M5 will develop the necessary skip displacement data to allow use of the track using the skip defect function. This is preferable to alternate track assignment. Routine M5 can be used with both fixed and movable heads. This routine is available in OLT at version level 2.0 or later.

#### **RUNNING CONSIDERATIONS**

Invoke the OLT as follows:

- 1. Install OLT T3350PSC in OLT(S) EP OLTLIB.

- Ensure that the 3830 Functional microcode disk (P/N 2. 4168811 at EC 437465 with REA 13-57853 or later) is installed.

- Select OLT xxx-yyy/3350PSC/NFE where xxx-yyy is 3. the address range of 3350s having the SD Directory created.

The T3350PSC will only run against drives that are in native mode. This is necessary so that all tracks on a volume are available to be scanned. After T3350PSC has completed the Build SD Directory run, the CE may return the drive to compatibility mode. (For information on native/compatible plugging, see INST 4.)

Note: After the reconstructions (routines M1, M2, M3, or M5) have been made in native mode, it will be necessary to reinitialize in compatibility mode to restore the format.

#### **RUNNING DETAILS**

The OLT PSC routines M2 and Build SD Directory run in about 10 minutes under OLTSEP. Routine M3 runs in about 25 minutes. Expected run times for routine M5 are between 3 to 35 minutes per track, depending on system environment. The run is about twice as long under VS1 or DOS OLTEP and up to three times as long under VS2 OLTEP. This OLT is 16,000 bytes long for routines M1 through M4, and 44,000 bytes long for M5. The drive to be run must be offline and in native mode.

#### When to run OLT T3350PSC

BUILDING AN SD DIRECTORY

Run T3350PSC in default mode:

- On all installed HDA.

- At installation of any 3350 or replacement HDA.

# **RUNNING DETAILS (Continued)**

**RESTORING SD DATA**

Run T3350PSC using optional routines:

• If AP1 or OLT T3350PSA detects unreadable home addresses.

FSC = 4940, 4944, or 4949.

Single Track Failure: use routine M1.

Multiple Track Failure: use routine M2.

Unknown extent of damage (HA Read Failure and/or unknown accuracy of SD data in HA fields): use routine M3.

#### **GENERATING SD DATA**

Run T3350PSC routine M5:

- If a track has been flagged defective and the user wishes to attempt to recover use of the track.

- If a track has recurring data checks and factory SD is known to be correct (restore routine M1, M2, or M3 has been run).

#### **EQUIPMENT REQUIREMENTS**

The following equipment is required:

Storage Control Unit or ISC and 3350 Disk Drive and Controller.

T3350PSC must be used with 3830 functional microdisk, P/N 4168811 at EC 437465 with REA 13-57853 or later.

See OLT Users Guide (Order No. D99-3350) for additional information.

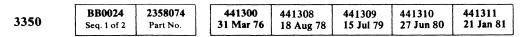

441308 **BB0024** 2358074 441300 441309 441310 441311 3350 31 Mar 76 18 Aug 78 15 Jul 79 21 Jan 81 Seq. 2 of 2 Part No. 27 Jun 80

©Copyright IBM Corporation 1976, 1980, 1981

#### TEST DESCRIPTIONS OLT 25

$\mathbf{O} = \mathbf{O} =$

# **TEST DESCRIPTIONS**

#### **T3350WT WRITE TEST**

This section tests the write and read capability of any selected HDA track. It also tests Index if 3330 Compatability Mode is used. T3350 WT writes a pattern on the CE track that is required for the scoping procedure used with microdiagnostic routine B1, Read test.

#### **Running Considerations**

#### Caution: The following steps must be followed to avoid loss of data.

- 1. Before running this test, OLT T3350PSA must be run and errors acted upon.

- 2. This OLT writes on any selected track. To test write and read capability, use only the CE track. The CE track is cylinder 1024 ('X400HH', where HH is head 0 through 29).

- 3. Always select a CE track first and test write/read. Resolve any errors detected on the CE track before selecting a non-CE track.

- 4. Always make sure that there is backup for data on a non-CE track or that it has been dumped.

- 5. If you are unsure about the status of data on the track to be tested, use the options to CHANGE the track selected or TERMINATE the test.

- 6. Once the data can be considered scratch data, reply GO to begin testing.

#### **Routine Descriptions**

Routine 1: This routine writes and reads records that are alternately all zeros and all ones.

Data = 0000......and FFFF.....

Running time is 20 seconds.

Routine 2: This routine writes and reads records with only one bit set per byte. The bit is then shifted right within the byte.

Data = 80808.....through 010101..... Running time is 90 seconds.

Routine 3: This routine writes and reads records with the worst case pattern. On each of two successive passes, the pattern is shifted right once to make sure bit shift errors are detected.

Data = DB6DB6D......,6DB6DB6.....,B6DB6DB...

Running time is 35 seconds.

Routine 4: This is a dummy routine.

Routine 5: This routine only runs if selected.

Enter:

'/3350WT,5//'

It writes a single 2048 byte record on the track selected, then reads it 1024 times. This write/read routine is repeated ten times.

Data = worst case (DB6DB6D.....)

Running time is 3 minutes.

Routine 6: This routine only runs if selected.

Enter:

'/3350WT,6//'

A CE track must be selected. This routine writes a 256 byte R1 on the CE track selected and then terminates.

Data = AAAAAAAAFFFFFFFFF.....

Running time is 5 seconds.

#### **Running Details**

This OLT runs for 2 minutes on each track selected for testing, or longer when run under VS-OLTEP. Each tested track is restored with a standard R0 before another track can be selected. This OLT must be allowed to terminate or be cancelled. Routines 1 through 3 run by default for a thorough write/read test.

Enter:

'/T3350WT//'

However, any routine or combination of routines can be selected to reduce the run time or to extend the test to include 10,000 reads (see Routine 5 description).

| 3350         BB0026         2358075         441300         441308           3350         Seq. 1 of 2         Part No.         31 Mar 76         18 Aug 78 | 3350 | <b>BB0026</b><br>Seq. 1 of 2 | 2358075<br>Part No. | 441300<br>31 Mar 76 | 441308<br>18 Aug 78 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|---------------------|---------------------|---------------------|--|--|--|

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|---------------------|---------------------|---------------------|--|--|--|

© Copyright IBM Corporation 1976

# TEST DESCRIPTIONS OLT 26

# FRIEND

#### **T0200A FRIEND**

The FRIEND OLT is a special diagnostic tool to support diagnosis of unique problems. Complete operation instructions are found in the Maintenance Diagnostic Program Users Guide For Friend (D99-0200).

#### **Running Considerations**

FRIEND truncates sense data to the rightmost non-zero byte.

FRIEND runs online under VS/OS/DOS OLTEP or OLTSEP. The Online Test Executive Program (OLTEP) or Online Test Standalone Execute Program (OLTSEP) schedules and controls the activity of FRIEND and provides communication with the operator. An I/O unit may be tested using FRIEND under OLTEP with minimum interference to the operation of other programs running in the system. This provides a method of testing I/O devices while customer programs are being processed by the system. Operation of FRIEND under OLTSEP eliminates the requirement for an operating system (OS) where an OS is not present.

FRIEND allows the user to construct man-readable S/360/370 channel programs.

FRIEND provides no data protection other than that of the OLT(S)EP.

#### **Running Details**

SELECTING FRIEND

Enter;

#### T0200A//

OLTSEP options (MI, TL, etc.) have no effect when running FRIEND.

If the controller being tested is shared and FRIEND is running standalone under OLTSEP, use Block Multiplex mode (Control Reg 0, bit 0).

After FRIEND is loaded and in control, the following messages are printed:

| 04 SEP1001   | FRIEND running V/L=XX   |

|--------------|-------------------------|

| 04 SEP 100 1 | Dataarea in bytes=XXXXX |

| 04 SEP101D   | Enter FRIEND command    |

#### COMMAND ENTRY

The program is now ready to receive user input in the form of CCW commands or interpreter commands. These may be entered singly or as a command string. String data must always end with a slash, for example:

| 3350 | <b>BB0026</b><br>Seq. 2 of 2 | 2358075<br>Part No. | 441300<br>31 Mar 76 | 441308<br>18 Aug 78 |  |  |

|------|------------------------------|---------------------|---------------------|---------------------|--|--|

|      |                              |                     |                     |                     |  |  |

© Copyright IBM Corporation 1976

#### SK/CYL=0/HD=0/SIDEQ/RCDNO.=3/TIC/ RDDATAINTO\$A/NOP/GO/

This reads the volume label into a location known to FRIEND as \$A. As each successive command or command string is entered, FRIEND processes each one and then prints 'ENTER CMND' when that command or string has been processed and it is ready to accept additional input. If more information is required, FRIEND asks for it. The FRIEND OLTSEP does not insert any CCW commands (such as SFM, TIC, or SET MODE).

**TERMINATING FRIEND**

Enter:

r04,END

#### **FRIEND** Examples

To verify a possible bad track, enter:

SK/CYL=XXX/HD=XXX/RDHAINTO\$A /RDROINTO\$B/KL=0/DL=8/GO/

To rewrite a bad track (standard R0), enter:

SFM/MASK=C0/SK/CYL=XX/HD=XX/ SRCHEQHA/TIC/WRR0/KEY=0/DATA=8X00/GO/

MASK=C4 must be entered to SK/WRITE on a CE track (cylinder 1024, heads 0 through 29).

#### **Command Summary**

| Primary               | Alternate | (hex) | Explanation                          |  |  |

|-----------------------|-----------|-------|--------------------------------------|--|--|

| No Operation          | NOP       | 03    | No Operation                         |  |  |

| Seek                  | SK        | 07    | Control Seek                         |  |  |

| Recalibrate           | RECAL     | 13    | Recalibrate                          |  |  |

| Restore               | RESTR     | 17    | Restore                              |  |  |

| Set File Mask         | SFM       | 1F    | Set File Mask                        |  |  |

| Seek Cyl              | SKCYL     | OB    | Seek Cylinder                        |  |  |

| Seek Hd               | SKHD      | 1B    | Seek Head                            |  |  |

| Release (see<br>Note) | REL       | 94    | Release                              |  |  |

| Reserve (see<br>Note) | RSV       | B4    | Reserve                              |  |  |