GC20-1877-0 File No. S/370-01

# **Systems**

# A Guide to the IBM 4341 Processor

This guide presents hardware I/O device, programming systems, and other pertinent information about the IBM 4341 Processor that describes its significant new features and advantages. Knowledge of System/360 hardware and I/O devices is assumed. The contents of the guide are intended to aquaint the reader with the 4341 Processor and to be of benefit in planning for its installation.

#### First Edition (April 1979)

This guide is intended for planning purposes only. It will be updated from time to time; however, the reader should remember that the authoritative sources of system information are the system library publications for the 4341 Processor, its associated components and its programming support. These publications will first reflect any changes.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form has been provided at the back of this publication for readers' comments. If this form has been removed, address comments to: IBM Corporation, Technical Publications, Dept. 824, 1133 Westchester Avenue, White Plains, New York 10604. IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

1

© Copyright International Business Machines Corporation 1979

PREFACE

This publication assumes the reader is familiar with a System/360 Model 22 or higher. The reader should have a general knowledge of System/360 architecture, channels, I/O devices, and programming systems support. This publication highlights and discusses the significance of only those hardware, I/O, and programming systems features of the 4341 Processor that are different from those of System/360 Models 22 and up.

This publication is also designed for readers who are knowledgeable about System/370 architecture, channels, I/O devices, and programming | systems. Features of the 4341 Processor that are like the same features | in System/370 processors are identified. Compatibility between the architectures implemented in 4300 Processors and System/370 Processors and their programming systems support are also discussed.

| Section | 01: Highlights                                        | 1  |

|---------|-------------------------------------------------------|----|

| Section | 05: Technology, Architecture, and Physical Components | 15 |

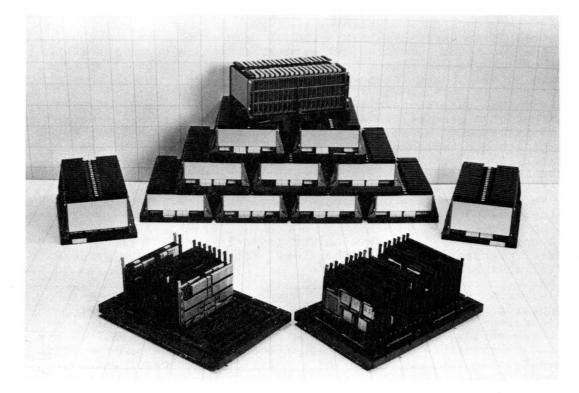

| 05:05   | Technology                                            | 15 |

|         | Introduction                                          | 15 |

|         | System/360 Technology                                 | 16 |

|         | System/370 Technology.                                | 17 |

|         | 4341 Processor Technology                             | 18 |

| 05:10   | 4341 Processor Technology                             | 32 |

| 05.10   | Design Objectives and Architecetures.                 |    |

|         | Design Objectives                                     | 32 |

|         | Architectures impremented.                            | 52 |

|         | System/360 Program Compatibility with the             | 25 |

|         | 4341 Processor                                        | 35 |

|         | System/370 Program Compatibility with the             | ~  |

|         | 4341 Processor                                        | 36 |

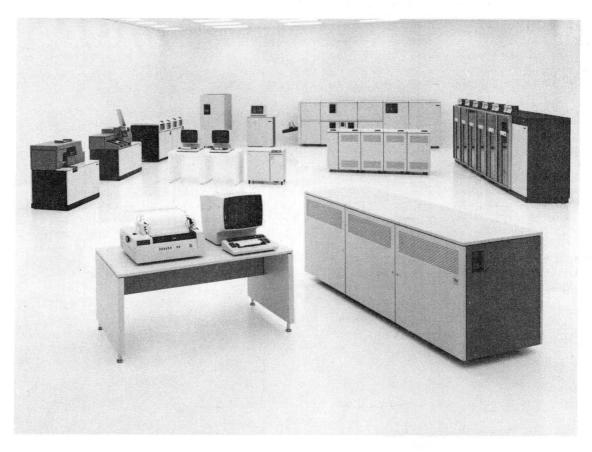

| 05:15   | 4341 Processor                                        | 37 |

|         | 10. The #2#1 Dresser                                  | 39 |

|         | 10: The 4341 Processor                                |    |

| 10:05   |                                                       | 39 |

|         | General Description                                   |    |

|         | Control Registers                                     | 41 |

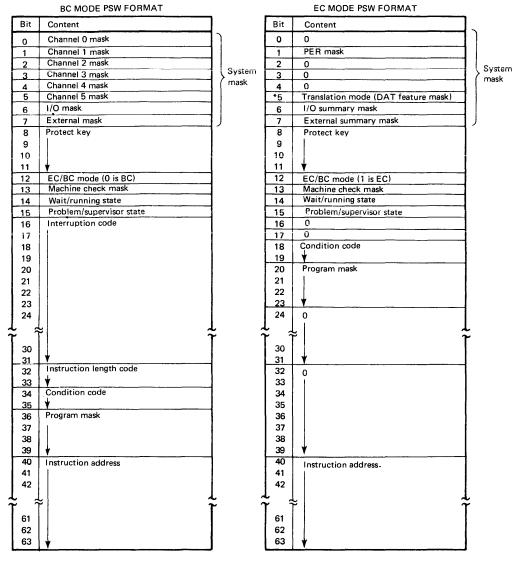

|         | Basic Control Mode                                    | 41 |

|         | Extended Control Mode                                 |    |

|         | Expanded Instruction Set                              | 47 |

|         | Byte-Oriented Operands                                | 49 |

|         | Monitoring Feature                                    | 49 |

|         | Architecture Implementation Alterations               | 50 |

|         | Interval Timer                                        |    |

|         | Interval Timer                                        | 51 |

|         | Clock Comparator and CPU Timer                        |    |

| 10:10   |                                                       |    |

| 10:10   | Processor Storage.                                    |    |

|         |                                                       | 52 |

|         | Auxiliary Storage.                                    | 53 |

|         | The Storage Control Function                          | 55 |

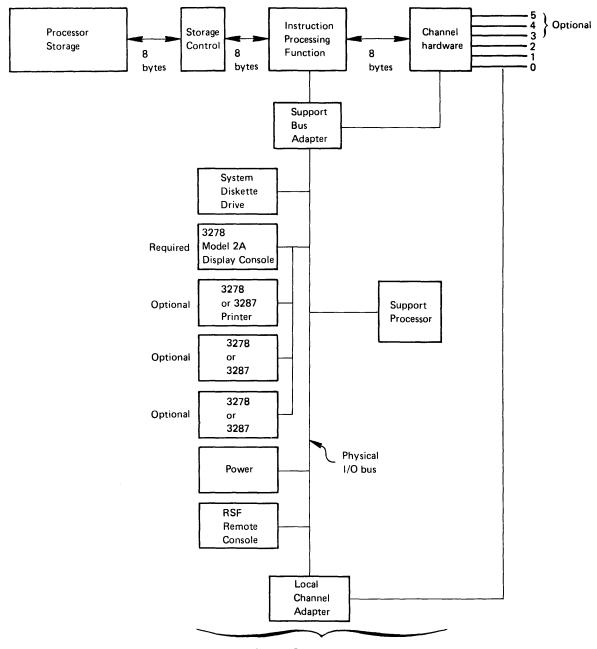

| 10:15   | The Support Processor Subsystem                       | 59 |

|         | Components and Functions                              | 59 |

|         | System Initialization                                 | 60 |

|         | System Diskette Drive                                 | 61 |

|         | Natively Attached Devices                             | 62 |

|         | Support Bus Adapter                                   | 62 |

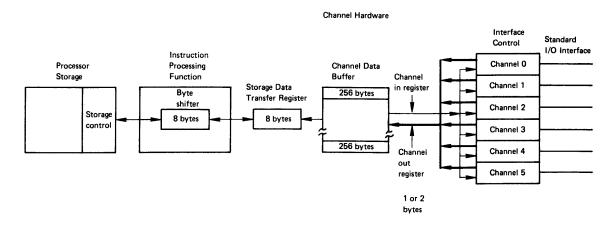

| 10:20   | Channels                                              | 62 |

|         | General Description                                   | 62 |

|         | Device Addresses and Unit Control Words               | 64 |

|         | General Operation of the Channels                     |    |

|         | Byte Multiplexer Channel                              | 66 |

|         | Block Multiplexer Channels                            | 67 |

| 10:25   | Block Multiplexing Operations with Count, Key, Data   | 07 |

| 10.23   |                                                       | 71 |

| 10.20   | Rotational Position Sensing Devices                   | 11 |

| 10:30   | Block Multiplexing Operations with Fixed Block        | 70 |

|         | Architecture Devices                                  | 75 |

|         | Fixed Block Architecture Design                       | 75 |

|         | Track Formatting                                      | 75 |

|         | Command Set                                           | 75 |

|         | Read and Write Command Execution                      | 79 |

|         | Differences Between FBA and CKD Channel Programs      | 80 |

|         | Advantages                                            | 81 |

| 10:35   | Standard and Optional Features                        | 81 |

|         | Standard Features.                                    | 81 |

|         | Optional Features.                                    | 83 |

|         |                                                       |    |

|                                                                          | 12: Operator Console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •              | •                                     | 84                                                                                                                                                                                                      |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12:05                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •              | •                                     | 84                                                                                                                                                                                                      |

|                                                                          | Operator/Operating System Communication Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •              | •                                     | 84                                                                                                                                                                                                      |

|                                                                          | Operator Control Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | •                                     | 87                                                                                                                                                                                                      |

|                                                                          | Keyboard $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                                       | 88                                                                                                                                                                                                      |

|                                                                          | Display Controls and Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                                       | 89                                                                                                                                                                                                      |

|                                                                          | Configuration Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |                                       | 90                                                                                                                                                                                                      |

| 12:10                                                                    | Operator Displays.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                       | 91                                                                                                                                                                                                      |

|                                                                          | General Selection Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |                                       | 91                                                                                                                                                                                                      |

|                                                                          | Program Load Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                                       | 93                                                                                                                                                                                                      |

|                                                                          | Display/Alter Display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •              | •                                     | 95                                                                                                                                                                                                      |

|                                                                          | Check Control Display.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •              | •                                     | 96                                                                                                                                                                                                      |

|                                                                          | Operation Rate Control Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •              | •                                     | 96                                                                                                                                                                                                      |

|                                                                          | Compare (Mrage Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •              | •                                     | 97                                                                                                                                                                                                      |

| 40.45                                                                    | Compare/Trace Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •              | •                                     |                                                                                                                                                                                                         |

| 12:15                                                                    | Maintenance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •              | •                                     | 97                                                                                                                                                                                                      |

| ~                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                                       |                                                                                                                                                                                                         |

|                                                                          | 15: Virtual Storage and Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ٠              | •                                     | 98                                                                                                                                                                                                      |

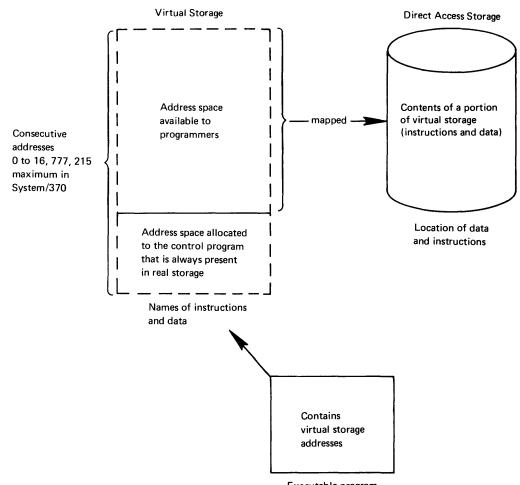

| 15:05                                                                    | Virtual Storage Concepts, Advantages, and Terminology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ٠              | ٠                                     | 98                                                                                                                                                                                                      |

|                                                                          | The Need for Larger Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                                       |                                                                                                                                                                                                         |

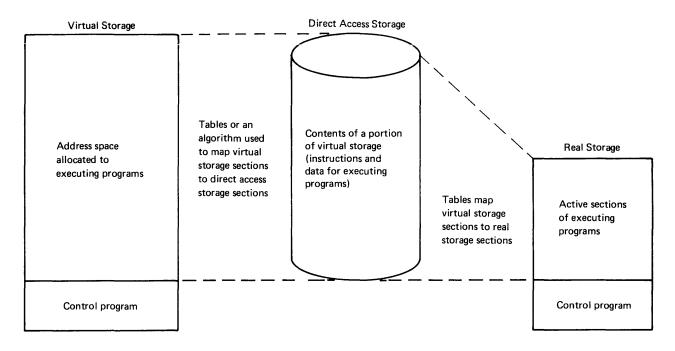

|                                                                          | Virtual Storage and Address Translation Concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                                       | 102                                                                                                                                                                                                     |

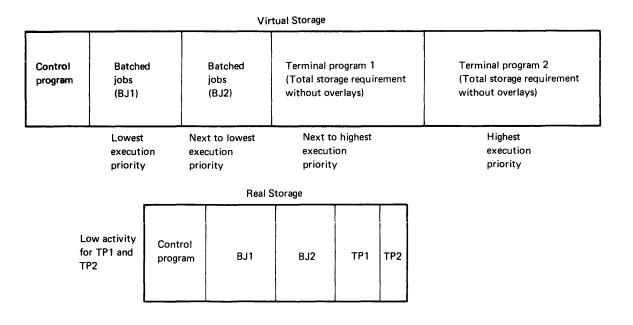

|                                                                          | General Advantages Offered by IBM Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                       |                                                                                                                                                                                                         |

|                                                                          | that Support a Virtual Storage Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | •                                     | 108                                                                                                                                                                                                     |

|                                                                          | Virtual Storage and Address Translation Terminology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |                                       | 116                                                                                                                                                                                                     |

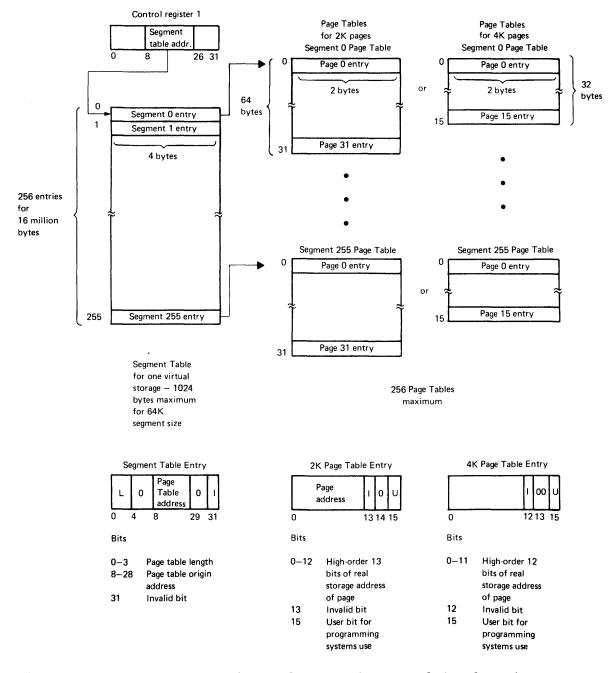

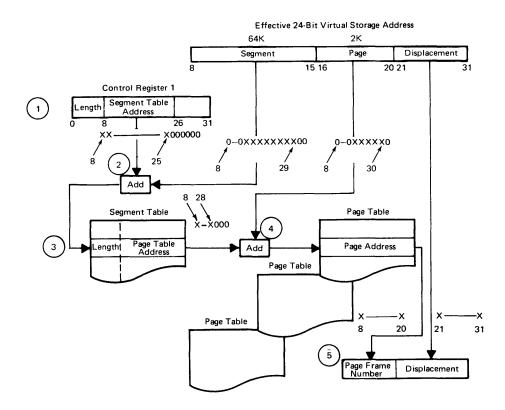

| 15:10                                                                    | Address Translation Facility for the 4341 Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                       |                                                                                                                                                                                                         |

| 2012-                                                                    | Operating in System/370 Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _              |                                       | 121                                                                                                                                                                                                     |

|                                                                          | Virtual Storage Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |                                       |                                                                                                                                                                                                         |

|                                                                          | Operation of Dynamic Address Translation Hardware.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •              | •                                     | 122                                                                                                                                                                                                     |

|                                                                          | Features To Support Demand Paging.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |                                       |                                                                                                                                                                                                         |

|                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |                                       |                                                                                                                                                                                                         |

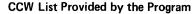

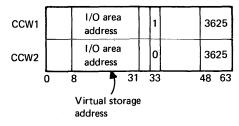

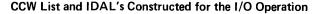

| 45.45                                                                    | Channel Indirect Data Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •              | •                                     | 132                                                                                                                                                                                                     |

| 15 <b>:</b> 15                                                           | Address Translation Facility for the 4341 Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |                                       | 1.24                                                                                                                                                                                                    |

|                                                                          | Operating in ECPS:VSE Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •              | ٠                                     | 134                                                                                                                                                                                                     |

|                                                                          | Virtual Storage Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •              | ٠                                     | 135                                                                                                                                                                                                     |

|                                                                          | Operation of Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                | •                                     | 140                                                                                                                                                                                                     |