IBM System/370

.

Vector Operations

Publication Number SA22-7125-1 File Number S370-01

#### Second Edition (August 1986)

This edition obsoletes the previous edition, SA22-7125-0. It contains a number of detailed changes, which are indicated by a vertical line in the margin to the left of the change.

Changes are made periodically to the information herein; before using this publication in connection with the operation of IBM equipment, refer to the latest *IBM System/370*, *30xx*, and *4300 Processors Bibliography*, GC20-0001, for the editions that are applicable and current.

This publication is provided for use in conjunction with other relevant IBM publications, and IBM makes no warranty, express or implied, relative to its completeness or accuracy.

IBM may have patents or pending patent applications covering subject matter described herein. Furnishing this publication does not constitute or imply a grant of any license under any patents, patent applications, trademarks, copyrights, or other rights of IBM or of any third party, or any right to refer to IBM in any advertising or other promotional or marketing activities. IBM assumes no responsibility for any infringement of patents or other rights that may result from the use of this publication or from the manufacture, use, lease, or sale of apparatus described herein.

Licenses under IBM's utility patents are available on reasonable and nondiscriminatory terms and conditions. Inquiries relative to licensing should be directed, in writing, to: Director of Contracts and Licensing, International Business Machines Corporation, Armonk, New York 10504.

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product is not intended to state or imply that only IBM's product may be used. Any functionally equivalent product may be used instead.

Publications are not stocked at the address given below. Requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Product Publications, Department B98, PO Box 390, Poughkeepsie, NY, U.S.A. 12602. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

© Copyright International Business Machines Corporation 1986

This publication contains, for reference purposes, a detailed definition of the machine functions provided by the IBM System/370 vector facility. The vector facility operates as a compatible extension of the functions of System/370 as described in one of the Principles of Operation publications, either the facilities of the System/370 extended architecture (370-XA) in *IBM 370-XA Principles of Operation*, SA22-7085, or those of the System/370 architecture in *IBM System/370 Principles of Operation*, GA22-7000.

The publication should not be considered an introduction or a textbook. It is written as a reference for use principally by assembler-language programmers, although anyone concerned with the functional details of vector operations may find it useful. It describes each function at the level of detail needed to prepare an assembler-language program which relies on that function.

This publication does not describe all the instructions or other functions needed to write a complete program using vectors. It includes a description only functions which are added of to System/370 as part of the vector facility. The reader is assumed to be familiar with either the IBM 370-XA of *Operation* IBM Principles or System/370 Principles of Operation, as appropriate. Terms and concepts referred to in this publication but explained in those Principles of Operation publications are not explained again in this publication.

Writing a program in assembler language requires a familiarity with the notations and conventions of that language, as well as with the facilities of the operating system under which the program is to be run. The reader should refer to the appropriate programming publications for such information.

## Terminology

As used in this publication, a *scalar* is a single data item, which may be a floating-point number, a binary integer, or a set of logical data. A *vector* is a linearly ordered collection of such scalars, where each scalar is an *element* of the vector. All elements of a single vector are of the same type: floatingpoint numbers (floating-point vector), binary integers (binary vector), or logical data (logical vector).

Scalar instructions are instructions which perform load, store, arithmetic, or logical operations on scalars that may reside in storage, floating-point registers, or general registers. Vector instructions perform similar operations on vectors that may reside in storage or in registers of the vector facility. Only vector instructions and related operations are described in this publication. Scalar instructions are described in the IBM 370-XA Principles of Operation or IBM System/370 Principles of Operation.

| Chapter 1. Introduction<br>Compatibility Considerations<br>Vector and Scalar Operations . | <b>1-1</b><br>1-1<br>1-1 |

|-------------------------------------------------------------------------------------------|--------------------------|

| Model-Dependent Vector Functions                                                          | 1-2                      |

| Chapter 2. Vector Facility                                                                | 2-1                      |

| Vector-Facility Structure                                                                 | 2-1                      |

| Vector-Data Registers                                                                     | 2-1                      |

| Vector Registers                                                                          | 2-1                      |

| Vector Registers                                                                          | 2-1                      |

| Vector Parameters                                                                         | 2-1                      |

| Section Size                                                                              | 2-1                      |

| Partial-Sum Number<br>Vector-Status Register<br>Vector-Mask-Mode Bit                      | 2-2                      |

| Vector-Status Register                                                                    | 2-2                      |

| Vector-Mask-Mode Bit                                                                      | 2-3                      |

| Vector Count                                                                              | 2-3                      |

| Vector Interruption Index .                                                               | 2-3                      |

| Vector In-Use Bits                                                                        | 2-4                      |

| Vector In-Use Bits<br>Vector Change Bits<br>Vector-Activity Count<br>Modes of Operation   | 2-4                      |

| Vector-Activity Count                                                                     | 2-4                      |

| Medea of Operation                                                                        |                          |

| Nodes of Operation                                                                        | 2-6                      |

| Vector-Operation Control                                                                  | 2-6                      |

| Vector-Instruction Operands and                                                           | o <b>-</b>               |

| Results                                                                                   | 2-7                      |

| Arithmetic Vectors in Storage                                                             | 2-8                      |

| Access by Sequential                                                                      |                          |

| Addressing                                                                                | 2-8                      |

| Addressing                                                                                |                          |

| Selection                                                                                 | 2-9                      |

| Arithmetic Vectors in Registers                                                           | 2-10                     |

| Operands in Vector Registers                                                              | 2-10                     |

| Operands in Scalar Registers                                                              | 2-10                     |

| Bit Vectors                                                                               | 2-10                     |

| Vector Sectioning                                                                         | 2-11                     |

| Conditional Arithmetic                                                                    | 2-12                     |

| Vector-Mask Mode                                                                          | 2-12                     |

| Vector-Mask Mode                                                                          |                          |

| Vector-Mask Mode                                                                          | 2-12                     |

| Common Instruction Descriptions                                                           | 2-12                     |

| Instruction Classes                                                                       | 2-13                     |

| Instruction Formats                                                                       | 2-13                     |

| Field Designations                                                                        | 2-13                     |

|                                                                                           | 2-15                     |

| Three-Operand Instruction<br>Formats                                                      | 0 15                     |

|                                                                                           | 2-15                     |

| Summary of Instructions by Class and Format                                               | 0 15                     |

| Class and Format                                                                          | 2-15                     |

| Class-IM and Class-IC                                                                     | <u> </u>                 |

| Instructions                                                                              | 2-15                     |

| Class-IM Instructions                                                                     | 2-17                     |

| Class-IC Instructions                                                                     | 2-17                     |

| Storage Operands for QST and                                                              |                          |

| VST Formats                                                                               | 2 <b>-</b> 18            |

| Class-NC Instructions                                                                     | 2-19                     |

| VS-Format Instructions                                                                    | 2 <b>-</b> 19            |

| Instructions In Other Classes                                                             | 2-19                     |

| Vector Interruptions                                                                      | 2-20                     |

| Interruptible Vector             |               |

|----------------------------------|---------------|

| Instructions                     | 2-20          |

| Units of Operation               | 2-20          |

| Operand Parameters               | 2-21          |

| Arithmetic Exceptions            | 2-21          |

| Exception-Extension Code .       | 2-21          |

|                                  | 2-21          |

| Types of Ending for Units of     | 0 00          |

| Operation                        | 2-22          |

| Effect of Interruptions During   |               |

| Execution                        | 2-23          |

| Setting of Instruction           |               |

| Address                          | 2-23          |

| Address                          |               |

| Code                             | 2-23          |

| Setting of Storage Address       | 2-24          |

| Setting of Vector                |               |

| Interruption Index               | 2-25          |

| Program-Interruption Conditions  | 2-25          |

| Access Exceptions for Vector     | 2 25          |

|                                  | 2-25          |

| Operands                         |               |

|                                  | 2-26          |

| Exponent-Underflow Exception     | 2-26          |

| Floating-Point-Divide            | 0.04          |

| Exception                        | 2-26          |

| Specification Exception .        | 2-26          |

| Unnormalized-Operand             |               |

| Exception                        | 2-27          |

| Vector-Operation Exception       | 2 <b>-</b> 27 |

| Priority of Vector               |               |

| Interruptions                    | 2-27          |

| Program Switching                | 2-28          |

| Program Switching                |               |

| Save Instructions                | 2-28          |

| Restore Operations               | 2-28          |

| Save Operations                  | 2-29          |

| Clear Operations                 | 2-29          |

| Sava-Area Requirements           | 2-29          |

| Save-Area Requirements           |               |

| Relationship to Other Facilities | 2-30          |

| Program-Event Recording (PER)    | 2-30          |

| Vector-Store Operations          | 2-30          |

| Storage-Operand Consistency      | 2-30          |

| Storing into Instruction         |               |

| Stream                           | 2-30          |

| Resets                           | 2-31          |

| Machine-Check Handling           | 2-31          |

| Vector-Facility Failure .        | 2-31          |

| Vector-Facility Source           | 2-31          |

| Validation of Vector-Facility    | £ 31          |

|                                  | 2-31          |

| Registers                        | 2-31          |

| Chapter 3. Vector-Facility       |               |

| Instructions                     | 3-1           |

|                                  | 3-1           |

| ACCUMULATE                       |               |

| ADD                              | 3-3           |

| AND                              | 3-4           |

| AND TO VMR                       | 3-5           |

| CLEAR VR                     | 5 SAVE VMR                                    |

|------------------------------|-----------------------------------------------|

| COMPARE                      |                                               |

| COMPLEMENT VMR               | 7 SAVE VSR                                    |

| COUNT LEFT ZEROS IN VMR 3-   |                                               |

| COUNT ONES IN VMR            |                                               |

| DIVIDE                       |                                               |

| EXCLUSIVE OR                 |                                               |

| EXCLUSIVE OR TO VMR 3-1      |                                               |

| EXTRACT ELEMENT              | 0 STORE HALFWORD                              |

| EXTRACT VCT                  |                                               |

| EXTRACT VECTOR MASK MODE 3-1 |                                               |

| LOAD                         | 1 STORE VECTOR PARAMETERS 3-38                |

| LOAD BIT INDEX               | 2 STORE VMR                                   |

| LOAD COMPLEMENT              | 5 SUBTRACT                                    |

| LOAD ELEMENT                 |                                               |

| LOAD EXPANDED                |                                               |

| LOAD HALFWORD                | 6 ZERO PARTIAL SUMS 3-41                      |

| LOAD INDIRECT                |                                               |

| LOAD INTEGER VECTOR 3-1      | 8 Appendix A. Instruction-Use                 |

| LOAD MATCHED                 | 8 Éxamples A-1                                |

| LOAD NEGATIVE                | 9 Operations on Full Vectors A-1              |

| LOAD POSITIVE                |                                               |

| LOAD VCT AND UPDATE 3-2      | 0 Vectors with Stride A-2                     |

| LOAD VCT FROM ADDRESS 3-2    |                                               |

| LOAD VMR                     |                                               |

| LOAD VMR COMPLEMENT          | - compute and energy record additional in the |

| LOAD ZERO                    |                                               |

| MAXIMUM ABSOLUTE             |                                               |

| MAXIMUM SIGNED               | 0                                             |

| MINIMUM SIGNED               |                                               |

| MULTIPLY                     | L                                             |

| MULTIPLY AND ACCUMULATE 3-2  |                                               |

| MULTIPLY AND ADD 3-2         | 6 Sparse Added to Sparse to Give              |

| MULTIPLY AND SUBTRACT 3-2    |                                               |

| OR                           | 0                                             |

| OR TO VMR                    |                                               |

| RESTORE VAC                  | 0                                             |

| RESTORE VMR                  |                                               |

| RESTORE VR                   |                                               |

| RESTORE VSR                  |                                               |

| SAVE CHANGED VR              |                                               |

| SAVE VAC                     | 3 Index X-1                                   |

|                              |                                               |

.

The vector facility is a compatible addition to the IBM System/370 architecture. Use of the facility may benefit applications in which a great deal of the time of the central processing unit (CPU) is spent executing arithmetic or logical instructions on data which can be treated as vectors. By replacing loops of scalar instructions with the vector instructions provided by the vector facility, such applications may take advantage of the order inherent in vector data to improve performance.

When the vector facility is provided on a CPU, it functions as an integral part of that CPU:

- 1. Standard System/370 instructions can be used for all scalar operations.

- 2. Data formats which are provided for vectors are the same as the corresponding System/370 scalar formats.

- 3. Long-running vector instructions are interruptible in the same manner as long-running scalar instructions; their execution can be resumed from the point of interruption after appropriate action has been taken.

- 4. Program interruptions due to arithmetic exceptions are handled in the same way as for scalar-arithmetic instructions, and the same fixup routines can be used with at most some minor extensions.

- 5. Vector data may reside in virtual storage, with access exceptions being handled in the customary manner.

# COMPATIBILITY CONSIDERATIONS

Compatibility with System/370 scalar operations has been one of the major objectives of the vector architecture, so as to provide the same result data when equivalent functions are programmed on machines without the vector facility. Some departures from strict compatibility are introduced, however, for the sake of performance and to provide implementers of the vector facility more flexibility in making design choices.

## Vector and Scalar Operations

Although operations on vector operands are generally compatible, element by element, with the corresponding scalar operations, there are certain differences between the vector and scalar architectures:

- Operands of vector-facility instructions must be aligned on integral boundaries; scalar-instruction operands need not be so aligned. (See the section "Vector-Instruction Operands and Results" on page 2-7.)

- Vector divide and multiply operations do not permit unnormalized floating-point operands; the corresponding scalar instructions do. Vector programs may encounter the unnormalized operand exception. (See the instruction descriptions and the section "Unnormalized-Operand Exception" on page 2-27.)

- Because the result of a series of floating-point additions may depend their sequence, the results on produced by the vector instructions ACCUMULATE or MULTIPLY AND ACCUMU-LATE, followed by SUM PARTIAL SUMS, are not necessarily identical with those produced by scalar summation loops, unless the scalar loops are written to perform the additions in exactly the same sequence as defined for the vector instructions. (See the instruction descriptions and the section "Partial-Sum Number" on page 2-2.)

- If, during execution of MULTIPLY AND ACCUMULATE, MULTIPLY AND ADD, or MULTIPLY AND SUBTRACT, the multiplication of an element pair results in an exponent underflow, a true zero is used in place of the product even when the exponent-underflow mask in the PSW is one. The vector and scalar results are the same, however, when the mask bit is zero

or when an exponent underflow occurs during the addition or subtraction. (See the instruction descriptions and the section "Exponent-Underflow Exception" on page 2-26.)

• Vector-facility instructions cannot safely be used to store into the current instruction stream, whereas all other instructions are interlocked to permit this. (See the section "Vector-Store Operations" on page 2-30.)

## Model-Dependent Vector Functions

Programmers should keep the following restrictions in mind to ensure that programs will run successfully regardless of which implementation techniques have been chosen on a particular model.

The program should not depend on specific values of the model-dependent vector parameters (section size and partial-sum number). Likewise, the program should not depend on the contents of fields that are described as "reserved" or "undefined." Specifically:

- The section size should not be treated as a numeric constant. Thus, save-area sizes should be computed from the section-size value obtained at execution time. (See the section "Save-Area Requirements" on page 2-29.) The section size may be obtained by executing the instruction STORE VECTOR PARAMETERS.

- The program should not rely on reserved bits 0-14 of the vectorstatus register being zeros when placed in a general register by the instruction EXTRACT VECTOR MASK MODE, or on the bits being stored as zeros by SAVE VSR. (See the instruction descriptions "EXTRACT VECTOR MASK MODE" on page 3-11 and "SAVE VSR" on page 3-34.)

- The program should not depend on any particular values being stored by the instruction SAVE VMR in the undefined part of the save area for the vector-mask register; nor should

the program depend on the presence or absence of access exceptions for that portion of the VMR save area when executing RESTORE VMR or SAVE VMR. (See the instruction descriptions "SAVE VMR" on page 3-33 and "RESTORE VMR" on page 3-29.)

- When a program using vector-facility instructions is interrupted, it cannot be safely resumed on another machine with a different section size or partial-sum number, unless the interruption occurred at a point that is known to be independent of the section size or partial-sum number, respectively.

- The exact result produced by the vector instructions ACCUMULATE or MULTIPLY AND ACCUMULATE, followed by SUM PARTIAL SUMS, may depend on the partial-sum number of the model because that number affects the sequence of performing the floating-point additions.

The program should not rely on receiving a specific program interruption, either operation exception or vector-operation exception, to indicate whether the vector facility is installed in any CPU of the configuration, since it depends on the model which of the two exceptions occurs. (See the section "Vector-Operation Control" on page 2-6.)

Problem-state programs should not depend on the setting of the vector change bits, which may be altered by actions of the control program that are unrelated to the actions of a problem-state program. Supervisor-state programs can depend on the accuracy of vector change bits that are zeros; vector change bits may sometimes be set to one, however, even when the corresponding vectorregister pair has not been changed. Note also that the effect on the vector change bits of executing the instructions RESTORE VR and RESTORE VSR depends on whether the CPU is in the problem or supervisor state. (See the section "Vector Change Bits" on page 2-4.)

PER events for general-register alteration may or may not be recognized for vector-facility instructions.

# CHAPTER 2. VECTOR FACILITY

## VECTOR-FACILITY STRUCTURE

The vector facility provides:

- 1. The vector-facility registers:

- 16 vector registers

- A vector-mask register

- A vector-status register

- A vector-activity count

- 2. 171 instructions

- 3. The following exceptions and exception indications:

- An unnormalized-operand exception

- A vector-operation exception

- An exception-extension code for arithmetic exceptions

- 4. A vector-control bit, bit 14 of control register 0

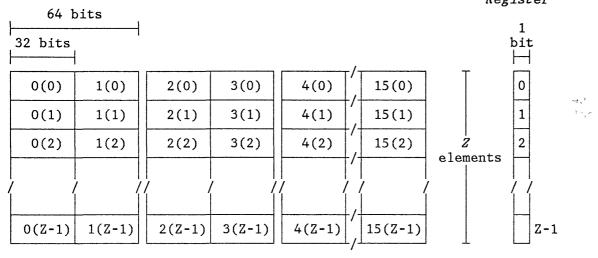

Figure 2-1 on page 2-2 shows the registers provided by the vector facility.

#### Vector-Data Registers

#### Vector Registers

There are 16 vector registers, numbered 0-15. They are used to hold one or more of the vector operands in most arithmetic, comparison, logical, load, and store operations. Unlike the general and floating-point registers, the vector registers are multipurpose in that vectors of floating-point, binaryinteger, and logical data can all be accommodated.

Each vector register contains a number of element locations of 32 bits each. Depending on the operation, a vector operand may occupy a single vector register or an even-odd pair of registers. The element locations of a vector register are identified by consecutive element numbers, starting with 0.

#### Vector-Mask Register

There is one vector-mask register (VMR), which is used as:

- The target of the result of vectorcompare operations,

- The source and target of logical operations on bit vectors, and

- The source of the mask for maskcontrolled operations.

## **Vector Parameters**

The section size and the partial-sum number are model-dependent parameters which control certain operations of the vector facility.

#### Section Size

The number of element locations in a vector register, which is also the number of bit positions in the vector-mask register, is called the section size. The section size is a power of 2; depending on the model, the section size may be 8, 16, 32, 64, 128, 256, or 512.

The element locations of a vector register, as well as the bit positions in the vector-mask register, are numbered from 0 to one less than the section size.

In a multiprocessing configuration, the section size is the same for each CPU which has the vector facility installed.

The section size of a model may be obtained by executing the instruction STORE VECTOR PARAMETERS, which places the value as a 16-bit binary integer in the left half of a word in storage. Vector Registers

Vector-Mask Register

Vector-Status Register

Vector-Activity Count

*Note:* Z is the section size (model-dependent).

Figure 2-1. Registers of the Vector Facility

## Partial-Sum Number

The partial-sum number is the number of partial sums produced when executing the instruction ACCUMULATE or MULTIPLY AND ACCUMULATE. It is also the number of vector-register elements set to zero by the instruction ZERO PARTIAL SUMS, as well as the number of vector-register elements summed by the instruction SUM PARTIAL SUMS.

Depending on the model, the partial-sum number may range from 1 up to and including the section size.

In a multiprocessing configuration, the partial-sum number is the same for each CPU which has the vector facility installed.

The partial-sum number of a model may be obtained by executing the instruction STORE VECTOR PARAMETERS, which places the value as a 16-bit binary integer in the right half of a word in storage.

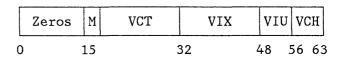

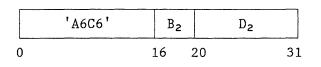

## Vector-Status Register

The vector-status register (VSR) is 64 bits long and contains five fields of information, which describe the current status of the vector and vector-mask registers and of a mode of operation. The fields are arranged as follows:

The contents of the vector-status register as a whole may be examined by the instruction SAVE VSR and altered by the instruction RESTORE VSR. Bits 0-14 of the VSR are reserved for possible future use and are stored as zeros by SAVE VSR; if the instruction RESTORE VSR specifies other than all zeros for these bit positions, a specification exception is recognized.

## Vector-Mask-Mode Bit

When the vector-mask-mode bit (M), bit 15 of the vector-status register, is one, the vector-mask mode is on, and arithmetic and logical instructions are executed under the control of bits in the vector-mask register. When the bit is zero, the mode is off. For details, see the section "Conditional Arithmetic" on page 2-12.

## Vector Count

The vector count (VCT), bits 16-31 of the vector-status register, is a 16-bit unsigned binary integer. Together with the vector interruption index, it determines for most vector operations the number of element locations to be processed in vector registers or the number of bit positions to be processed in the vector-mask register.

Elements in register positions with element numbers less than the vector count are called the active elements of the vector register. Likewise, bits in bit positions of the vector-mask register with bit numbers less than the vector count are called the active bits of the vector-mask register. Only the active elements or bits take part in operations where the number of elements or bits processed is determined by the vector count.

The vector count may range in value from zero up to and including the section size. A specification exception is recognized if the instruction RESTORE VSR attempts to place a value in the vector-count field which exceeds the section size. The instruction EXTRACT VCT may be used to examine the vector count.

The following instructions may be used to set the vector count. If they specify a number greater than the section size, they set the vector count equal to the section size.

LOAD BIT INDEX LOAD VCT AND UPDATE LOAD VCT FROM ADDRESS

For information on using the vector count with vectors of any length, see the section "Vector Sectioning" on page 2-11.

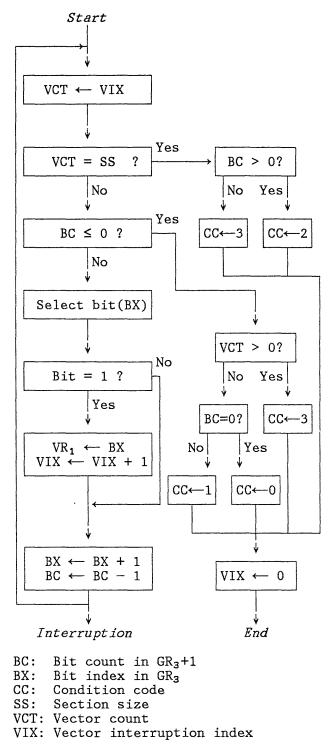

## Vector Interruption Index

The vector interruption index (VIX), bits 32-47 of the vector-status register, is a 16-bit unsigned binary integer. It specifies the number of the first element location in any vector register, or of the first bit position in the vector-mask register, to be procby an interruptible essed vector instruction which depends on the vector The vector interinterruption index. used to control ruption index is resumption of the operation after such an instruction has been interrupted. It is normally zero at the start of exe-cution, and it is set to zero at completion.

For details concerning the operation of the vector interruption index and the effect of an interruption, see the section "Vector Interruptions" on page 2-20.

The vector interruption index may range from zero to the section size. It may be examined by using the instruction SAVE VSR, and it may be set explicitly by RESTORE VSR. The instruction CLEAR VR sets the vector interruption index to zero. A specification exception is recognized if the instruction RESTORE VSR attempts to place a value in the vector-interruption-index field which exceeds the section size.

#### Programming Notes

- 1. Since the vector interruption index is always set to zero upon completion of any instruction which depends on it, the program normally need not be concerned with setting its value.

- 2. The vector interruption index may be set to zero explicitly by use of the instruction CLEAR VR with a zero operand.

- 3. If it is desired to operate on a vector in a vector register starting at other than element location 0, this may be done by first setting the vector interruption index (VIX) to the initial element number. The VIX may be set by using the instruction SAVE VSR to place the current

contents of the vector-status register (VSR) in storage, placing the initial element number in the field which corresponds to the VIX, and then returning the result to the VSR by means of RESTORE VSR. Such modification of the VSR can be performed safely when the CPU is in the problem state. If a program modifying the VSR is to be executed in the supervisor state, however, additional precautions may have to be taken; see the section "Vector Change Bits," programming note 3 on page 2-5.

#### Vector In-Use Bits

The eight vector in-use bits (VIU), bits 48-55 of the vector-status register, correspond to the eight vector-register pairs 0, 2, 4, 6, 8, 10, 12, and 14.

The vector in-use bits indicate which vector-register pairs are to be saved and restored by SAVE VR and RESTORE VR. These instructions ignore vectorregister pairs for which the vector in-use bit is zero.

During execution of instructions which use the vector registers, the vector in-use bit associated with a vectorregister pair is set to one whenever any element in either or both of the registers is loaded or modified. When a register is used as the source of an operand, its vector in-use bit remains unchanged.

The vector in-use bits are set by the instruction RESTORE VSR. If that instruction changes a vector in-use bit from one to zero, it causes the corresponding vector-register pair to be cleared to zeros. A vector in-use bit is set to zero when the instruction CLEAR VR clears the corresponding vector-register pair to zeros.

See the section "Program Switching" on page 2-28 for a discussion of the vector in-use bits.

Vector Change Bits

The eight vector change bits (VCH), bits 56-63 of the vector-status register, correspond to the eight vector-register pairs 0, 2, 4, 6, 8, 10, 12, and 14.

The vector change bits indicate which vector-register pairs are to be saved by the privileged instruction SAVE CHANGED VR. That instruction saves a vectorregister pair if the corresponding vector change bit is one; it then sets the vector change bit to zero.

If the vector in-use bit associated with a vector-register pair is set to zero by the instruction CLEAR VR or RESTORE VSR, the corresponding vector change bit is also set to zero.

During execution of an instruction which uses the vector registers, the vector change bit associated with a vectorregister pair is set to one whenever any element in either or both of the registers is loaded or modified. An exception is the instruction RESTORE VR; when the CPU is in the supervisor state, execution of RESTORE VR leaves the vector change bits unchanged.

When a vector register is used as the source of an operand, its vector change bit remains unchanged.

See the section "Program Switching" on page 2-28 for further discussion of the vector change bits.

. 1 13 -

#### Programming Notes

- 1. The vector change bit is always zero when the vector in-use bit is zero. When the vector change bit is set to one, the vector in-use bit is also set to one.

- 2. As pointed out in the section "Program Switching" on page 2-28, vector change bits are intended for use by control programs operating in the supervisor state. When the CPU is in the problem state, the value of the vector change bits "stored by SAVE VSR is undefined; problem-state programs should, therefore, not depend on the value of these bits.

A program operating in the problem state cannot set a vector change bit

to zero, except by also setting the corresponding in-use bit to zero (clearing the vector-register pair). In the problem state, the instruction RESTORE VSR sets the vector change bit to one for every pair of vector registers whose in-use bit is set to one.

- If a program uses the instruction 3. RESTORE VSR to modify the contents of the vector-status register while the CPU is in the supervisor state, and the program is subject to interruptions for which the interruption handler may cause a SAVE CHANGED VR instruction to be executed, care must be taken to ensure that the vector change bits reflect all modifications of the active vector reg-A safe procedure is to isters. supply ones in all bit positions of the operand of RESTORE VSR which correspond to the vector change bits. This precaution is unnecessary in the problem state, because RESTORE VSR then sets the vector change bits to ones regardless of the operand.

- 4. A program operating in the supervisor state can depend on the accuracy of vector change bits that are zeros. When the program is a guest in a virtual-machine environment, however, vector change bits may be overindicated, so that a bit may be set to one even when the corresponding vector-register pair has not been changed.

## Vector-Activity Count

The vector-activity count (VAC) provides a means for measuring and scheduling the machine resources used in executing instructions of the vector facility.

The vector-activity count has this format:

|   | 00000000 |   |   |    |

|---|----------|---|---|----|

| ( | )        | 8 | ( | 63 |

Bits 8-63 are a 56-bit unsigned binary integer. In the basic form, this integer is incremented by adding a one in bit position 51 every microsecond while a vector-facility instruction is being executed. In models having a higher or lower resolution, a different bit position is incremented at such a frequency that the rate of incrementing the vector-activity count is the same as if a one were added in bit position 51 every microsecond during those periods. Bits 0-7 are zeros.

The contents of the vector-activity count may be obtained by executing the privileged instruction SAVE VAC, and they may be set by means of the privileged instruction RESTORE VAC. Bits 0-7, and any rightmost bit positions which are not incremented, are stored as zeros by SAVE VAC and are ignored by RESTORE VAC.

When incrementing the vector-activity count causes a carry to be propagated out of bit position 8, the carry is ignored, and counting continues from zero. The program is not alerted, and no interruption occurs as a result of the overflow. Except for such wraparound, or an explicit restore or reset operation, the value of the count never decreases.

The vector-activity count is not incremented during execution of the instructions RESTORE VAC and SAVE VAC. In addition, depending on the model, the count may not be incremented during execution of some other short, uninterruptible instructions of the vector facility.

The vector-activity count is incremented only when the CPU is in the operating state.

## Programming Notes

- 1. The vector-activity count is not intended to be a precise measure of vector execution time. The count may or may not advance during the execution of a particular vectorfacility instruction. In the aggregate, however, the count reflects the execution time of the vector portion of normal application programs.

- 2. The format of the vector-activity count has been chosen to permit the use of unnormalized scalar floating-

point instructions to perform fast addition and subtraction of VAC values.

## Modes of Operation

The operation of the vector facility is independent of the architectural mode, except for the range of storage addresses which can be specified. The 370-XA architectural mode provides the choice of operating in either a 31-bit addressing or 24-bit mode; the System/370 architectural mode does not. On a CPU which provides both the 370-XA and System/370 modes, vector operations in the System/370 mode are the same as in the 370-XA mode when in the 24-bit addressing mode. Thus, an address size of 24 bits is available in either the 370-XA or System/370 mode, but vector operations with an address size of 31 bits can be performed only in the 370-XA In the System/370 mode, instrucmode. tions of the vector facility may be executed in both the EC and BC modes.

In both the 370-XA and System/370 modes, vector operations are governed by the vector-control bit.

## Vector-Operation Control

When the vector facility is installed and available on a CPU, execution of vector-facility instructions can be completed only if bit 14 of control register 0, the vector-control bit, is one. Executing a vector-facility instruction when the vector-control bit is zero causes a vector-operation exception to be recognized and a program interruption to occur. The initial value of the vector-control bit is zero.

When the vector facility is not installed or not available on this CPU but is installed on any other CPU which is or can be placed in the configuration, executing a vector-facility instruction causes a vector-operation exception to be recognized regardless of the state of the vector-control bit.

If the vector facility is not installed on any CPU which is or can be placed in the configuration, it depends on the model whether executing a vectorfacility instruction causes a vectoroperation exception or an operation exception to be recognized.

A vector facility, though installed, is considered not available when it is not in the configuration, when it is in certain maintenance modes, or when its power is off.

Figure 2-2 summarizes the effect of the vector-control bit according to whether the vector facility is installed and whether vector instructions can be executed by the program.

|                                                  | Vector Facility on This CPU |                    |                                                 |                            |  |  |  |

|--------------------------------------------------|-----------------------------|--------------------|-------------------------------------------------|----------------------------|--|--|--|

| Vector<br>Facility<br>Installed<br>on<br>Another | T                           | A                  | Effect of<br>Vector-<br>Facility<br>Instruction |                            |  |  |  |

| CPU                                              | In-<br>stalled              | Avail-<br>able     | VC = 0                                          | VC = 1                     |  |  |  |

| Yes or No                                        | Yes                         | Yes                | VOP                                             | Exe-<br>cute               |  |  |  |

| Yes or No<br>Yes<br>No                           | Yes<br>No<br>No             | No<br>(NA)<br>(NA) | VOP<br>VOP<br>VOP or<br>OP                      | VOP<br>VOP<br>VOP or<br>OP |  |  |  |

Explanation:

OP Operation exception

- VC Vector-control bit (control

- register 0, bit 14)

- VOP Vector-operation exception

Figure 2-2. Vector Control

#### Programming Notes

- 1. The control program may use the vector-control bit to defer enabling of the CPU for vector operations and to delay allocation of a vector-save area until a program attempts to use the facility by executing its first vector instruction. Because the resulting vector-operation exception nullifies the operation, the instruction address does not need to be adjusted in order to resume the program.

- 2. The control program may also keep the vector-control bit set to zero

to prevent a program from examining or changing the contents of the vector-facility registers. This may be useful when a program that does not use the vector facility is to be run after a program that does use the facility has been interrupted. If the next program to use the vector registers is the original program, then running the intervening program with the vectorcontrol bit set to zero may eliminate the need for information held in the vector facility to be saved and later restored.

A possible exception is the vectoractivity count (VAC). When the vector-control bit is zero, the VAC may or may not be incremented during the brief period of detecting that an instruction requires the vectoroperation exception to be recognized. The number of times that the VAC might be stepped in this way is small, however, compared to the counts accumulated during execution of a vector-application program.

3. When a machine check indicating vector-facility failure occurs, the machine has made a previously available vector facility unavailable. Until the cause of the failure is removed and the facility is made available again, attempting to execute a vector instruction causes a vector-operation exception to be recognized even though the vectorcontrol bit is one. (See the section "Vector-Facility Failure" on page 2-31.)

# VECTOR-INSTRUCTION OPERANDS AND RESULTS

The vector facility provides for operations on vectors of short (32-bit) and long (64-bit) floating-point numbers, 32-bit signed binary integers, and 32-bit logical data. A few operations deal with vectors of 16- and 64-bit signed binary integers. There are also operations on vectors of individual bits, which are generally used as mask bits.

All binary-arithmetic vector operations treat elements of 32-bit binary integers

as signed; any fixed-point-overflow exceptions are recognized. Binarycomparison operations also deal with 32-bit signed binary integers. Logical vector operations, including shifts, treat elements as 32-bit logical data.

Most instructions which operate on floating-point, binary-integer, or logical vectors use a format that explicitly designates three operands: two source operands and one target operand. The operands may be:

- In storage,

- In a vector register, or a pair of vector registers, or

- In a scalar (general or floatingpoint) register.

Instructions which use mask bits generally designate an implicit operand in the vector-mask register, and they also may explicitly designate storage, vector-register, and scalar-register operands.

All vector operands in storage must be aligned on integral boundaries. When an instruction requires boundary alignment and the storage operand is not designated on the appropriate boundary, a specification exception is recognized.

An instruction which processes operands in vector or scalar registers must designate a valid register number for each such operand. If an invalid register number is designated, a specification exception is recognized.

Figure 2-3 on page 2-8 summarizes the vector-data formats, the associated operations, and the boundary-alignment and register-number requirements.

Vectors of 16-, 32-, and 64-bit elements containing arithmetic or logical data are collectively referred to as arithmetic vectors. Arithmetic vectors in storage must be on integral boundaries. The elements of arithmetic vectors have the same formats as scalar data of the same data type.

Vectors of individual bits are referred to as bit vectors (see the section "Bit Vectors" on page 2-10).

| V                                                 | 10 |    | n in Bits  |          | A1 /                                | Valid Register Numbers |                    |  |

|---------------------------------------------------|----|----|------------|----------|-------------------------------------|------------------------|--------------------|--|

| Data Type                                         |    | 16 | ы Б.<br>32 | 64       | Alignment<br>Required In<br>Storage | Scalar<br>Register     | Vector<br>Register |  |

|                                                   |    |    |            | <u> </u> | 5772480                             |                        |                    |  |

| Floating point<br>Short<br>Long<br>Binary integer |    |    | A          | A        | Word<br>Doubleword                  | Even FR<br>Even FR     | Any VR<br>Even VR  |  |

| 16-bit signed<br>32-bit signed                    |    | S  | В          |          | Halfword<br>Word                    | Any GR                 | Any VR<br>Any VR   |  |

| 64-bit signed<br>Logical                          |    |    | L          | Р        | <br>Word                            | <br>Any GR             | Even VR<br>Any VR  |  |

| Bit                                               | 1  | Ì  |            |          | Byte                                |                        |                    |  |

Explanation:

- -Does not apply А All arithmetic, load, and store operations В Some arithmetic and all load and store operations FR Floating-point register GR General register Logical and shift operations L Logical operations on bits in storage and in vector-mask Μ register; comparison results 64-bit binary integers, which occur only as the result of Ρ a binary multiply operation Only load and store operations, which convert between 16 bits S in storage and 32 bits in a vector register VR Vector register

Figure 2-3. Types of Vector Data

#### Programming Note

Logical-data elements may also be considered as 32-bit unsigned binary integers, but no arithmetic or comparison operations are provided to process such vectors.

#### Arithmetic Vectors in Storage

Arithmetic vectors in storage may be loaded and stored in one of two ways:

- By sequential addressing (contiguously or with stride)

- By indirect element selection

Most arithmetic, comparison, and logical instructions may also access one of the vector operands directly from storage by sequential addressing. Indirect element selection is available only for load and store operations.

## Access by Sequential Addressing

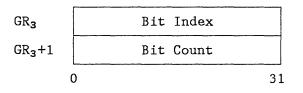

Vector elements are most often accessed in storage in a regular sequence of addresses. The instruction specifies a general register containing the starting address and, optionally, another general register containing the stride. The stride, which is a 32-bit signed binary integer, is the number of element locations by which the operation advances when proceeding from one element to the next. The maximum number of elements to be accessed is specified by the vector count.

A stride of one specifies a contiguous vector, for which successive elements are in adjacent storage locations; this stride is the default when no general register is specified for the stride. A stride of zero causes the same element to be used repeatedly as the storage operand. A negative stride causes elements to be accessed in a descending sequence of addresses.

During the execution of instructions which access an arithmetic vector in sequentially, the storage starting address contained in the general register is updated as successive elements in storage are accessed. At the end of instruction execution, or at the time of any interruption, the contents of the general register have been updated to the storage address of the next vector element due to be processed if instruction execution had not ended or been Likewise, when instrucinterrupted. tions process a bit vector in storage, the starting address in the general register is updated by the number of bytes accessed during execution.

Such automatic updating of vector addresses is used to process a vector in sections when the vector has more elements than will fit into a vector register. It also assists in resuming instruction execution after an interruption.

For more details on sequential addressing, see the section "Class-IM and Class-IC Instructions" on page 2-15. For more information on sectioning, see the section "Vector Sectioning" on page 2-11.

#### Programming Note

A contiguous vector is implied when zero is specified in the instruction field that designates the general register containing the stride. This differs from a zero stride, which is specified by placing a value of zero in the general register containing the stride, and which causes reuse of the same element in storage. A zero stride is generally not desired because the scalar form of an instruction is usually faster than repeated use of the same storage location. (See the section "Operands in Scalar Registers" on page 2-10.)

## Access by Indirect Element Selection

Indirect element selection permits vector elements to be loaded or stored in an arbitrary sequence. With the instructions used for indirect element selection, LOAD INDIRECT and STORE INDI-RECT, the locations of the individual operand elements to be loaded or stored are designated by a vector of element numbers in a vector register. Each such element number indicates the position of the corresponding operand element relative to the start of the operand vector. The number of operand elements accessed, which is also the number of element numbers used for indirect element selection, is equal to or less than the vector count.

The element numbers used for indirect element selection are 32-bit signed binary integers. They may be positive, negative, repeated, and in any order. Successive operand elements are located in storage at addresses  $A + w \star E(0)$ , A + $w \star E(1)$ ,  $A + w \star E(2)$ , ..., where A is the origin of the operand vector in storage, w is the width in bytes (4 or 8) of each element, and E(0), E(1), E(2), ... are the successive element numbers in a vector register.

General-register address updating does not apply to the instructions LOAD INDI-RECT and STORE INDIRECT.

#### Programming Notes

- 1. For a discussion of address updating, see the programming notes under "Vector Sectioning" on page 2-11.

- 2. Vectors of element numbers may be stored as 16-bit signed binary integers when the element numbers remain within the range of such integers. The vector instructions LOAD HALFWORD and STORE HALFWORD perform the conversion between the 16-bit and 32-bit formats.

- 3. Accessing vectors in storage in the arbitrary sequence permitted by indirect element selection may be significantly slower than accessing contiguous vector elements.

# Arithmetic Vectors in Registers

## Operands in Vector Registers

Any vector register can be designated for a vector of short floating-point numbers, 32-bit signed binary integers, or 32-bit logical data. Even-odd vector-register pairs are coupled to hold long floating-point numbers or the 64-bit signed binary integers which result from binary multiplication.

When a vector register is modified, those elements in the vector register beyond the last element to be modified are left unchanged.

Most operations on floating-point, binary, or logical vectors which may be performed with one vector operand in storage and one operand in a vector register may also be performed with both operands in vector registers. When both operands are in vector registers, the corresponding pairs of elements from each vector-register operand generally have the same element number (but see the descriptions of ACCUMULATE and MUL-TIPLY AND ACCUMULATE for an exception to this rule).

## Operands in Scalar Registers

Operations on floating-point, binary, or logical vectors may specify as one source operand the contents of a scalar register, that is, of a floating-point or general register, the other operand being a vector. This scalar operand is used repeatedly and treated as a vector of identical elements of the same length as the vector operand.

Some vector instructions which obtain one of the source operands from a scalar register also produce a scalar result, which replaces the contents of the same scalar register.

## **Bit Vectors**

A group of bits in contiguous bit positions is called a bit vector. Bit vectors are the operands of logical operations where one of the operands is in the vector-mask register. They are used in operations on arithmetic vectors under mask control. A bit vector in storage must begin on a byte boundary, but it may end at any bit position, the remaining bits of the rightmost byte being ignored. When the instruction STORE VMR stores a bit vector with the vector count specifying a number of bits that is not a multiple of 8, the final byte stored is padded on the right with zeros.

When used for the control of load and store operations or for arithmetic and logical operations in the vector-mask mode, the appropriate bit vector must first be placed in the vector-mask register. Each bit in the vector-mask register corresponds sequentially, one for one, to an element of one or both of the vector-register operands.

Bit vectors in the vector-mask register are generated or altered by the following vector instructions:

AND TO VMR COMPARE COMPLEMENT VMR EXCLUSIVE OR TO VMR LOAD VMR LOAD VMR COMPLEMENT OR TO VMR

#### Programming Notes

- 1. Examples of the use of bit vectors for mask control are shown in Appendix A.

- 2. Since the section size is a multiple of 8 and bit vectors start on a byte boundary, every section of a bit vector also starts on a byte boundary. Thus, after an instruction has completed processing a full section of bits, the next bit is always the leftmost bit of the byte specified by the updated address.

- When a bit vector is used as a mask 3. to identify selected elements of an arithmetic vector with one bits and the remaining elements with zero bits, the bit vector is logically equivalent to a vector containing a set of element numbers in ascending sequence, which may be used for indirect selection of the arithmetic-vector elements. The vector of element numbers consists merely of the bit indexes (bit

numbers) of the one bits in the bit vector.

A bit vector may be converted to a vector of element numbers by the instruction LOAD BIT INDEX. This instruction operates directly on a bit vector in storage and produces a vector of element numbers in a vector register; the vector-mask register is not used.

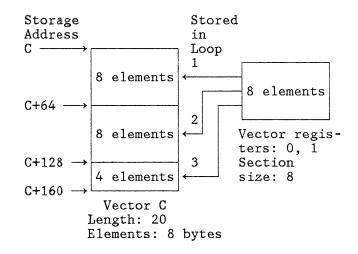

# Vector Sectioning

Vector sectioning is a programming technique for processing vectors the length of which may exceed the section size. Such vectors are processed by dividing them into smaller sections and using a loop of instructions, referred to as a sectioning loop, which repeats the appropriate sequence of instructions for all consecutive sections of the specified vectors. To assist with such sectioning, addresses of vector operands in storage and bit-vector parameters are automatically updated, and the instruction LOAD VCT AND UPDATE is provided.

The LOAD VCT AND UPDATE instruction specifies a general register that has initially been loaded with the total number of vector elements to be processed. The instruction sets the vector count to the lesser of the section size and the general-register contents. It also subtracts this value from the current contents of the general register, which then contains the number of elements remaining to be processed during subsequent passes through the sectioning loop.

LOAD VCT AND UPDATE sets the condition code to provide the program with an indication of whether a complete vector has been processed. The program may use the instruction BRANCH ON CONDITION for loop control to repeat the sequence of instructions for each section. A sectioning loop may also be closed by testing the residual count in the general register for zero and branching back to the start of the loop if not zero.

For most vector operations, the program can be written such that sectioning is independent of the section size. There are occasions, however, when knowledge of the actual section size is desirable; this value is available to the program by executing the instruction STORE VECTOR PARAMETERS.

## Programming Notes

- 1. Examples of sectioning are shown in Appendix A.

- 2. One method of controlling the vector count for sectioning is to place the instruction LOAD VCT AND UPDATE at the beginning of the loop and an appropriate BRANCH ON CONDITION instruction at the end of the loop. This is usually sufficient because most vector-facility instructions do not set the condition code. If the sectioning loop does contain an instruction that modifies the condition code, the final BRANCH ON CON-DITION instruction could be preceded by a LOAD AND TEST instruction to test the general register containing the residual vector count.

Appendix A also illustrates other techniques.

- 3. If a sectioning loop contains more than one reference to the same vector in storage, such as a load followed later by a store, the program must ensure, by retaining a copy of the current address, that all addresses within the loop which specify the same vector refer to the same section.

- The instructions which provide indi-4. rect element selection, LOAD INDI-RECT and STORE INDIRECT, progress one section of element numbers at a time. But sectioning of the vector of element numbers used for addressing is performed by a preceding instruction which loaded or generated the element numbers by means of sequential addressing. The indirect-selection instructions themselves do not provide for Each element address updating. address is computed separately from an element number and from the specified starting address, which remains unchanged.

# **Conditional Arithmetic**

## Vector-Mask Mode

The vector-mask mode allows for conditional execution of arithmetic and logical instructions, depending on the mask bits in the vector-mask register.

When the vector-mask mode is in effect, operand elements are processed if they are in positions which correspond to mask bits that are ones. In positions which correspond to zero mask bits, the target locations remain unchanged, no arithmetic or operand-access exceptions are recognized for those positions, the corresponding change bits in storage remain unchanged, and no PER event for storage alteration is indicated. When the vector-mask mode is not in effect, the mask bits are ignored, and all active elements are processed.

The arithmetic and logical vector instructions which are under the control of the vector-mask mode are:

ACCUMULATE ADD AND DIVIDE EXCLUSIVE OR LOAD COMPLEMENT LOAD NEGATIVE LOAD POSITIVE MAXIMUM ABSOLUTE MAXIMUM SIGNED MINIMUM SIGNED MULTIPLY MULTIPLY AND ACCUMULATE MULTIPLY AND ADD MULTIPLY AND SUBTRACT OR SHIFT LEFT SINGLE LOGICAL SHIFT RIGHT SINGLE LOGICAL SUBTRACT

Except for LOAD COMPLEMENT, LOAD NEGA-TIVE, and LOAD POSITIVE, which are considered arithmetic instructions for this purpose, load and store instructions are not controlled by the vector-mask mode; neither are instructions which modify the vector-mask register, such as COMPARE. LOAD EXPANDED, LOAD MATCHED, STORE COMPRESSED, and STORE MATCHED do depend on the vector-mask register for their execution, but this is independent of the mode setting.

For more details, see the section "Class-IM and Class-IC Instructions" on page 2-15.

# Instructions Controlling the Vector-Mask Mode

The instruction SET VECTOR MASK MODE (VSVMM) turns the vector-mask mode on or off. EXTRACT VECTOR MASK MODE (VXVMM) places the current value of the mode in a general register.

#### Programming Notes

- 1. The vector-mask mode is useful when arithmetic vector operations depend on the result of a vector comparison. Only elements which are to be processed are subject to arithmetic and access exceptions.

- 2. Since loading, comparing, and storing are operations which are not subject to the vector-mask mode, it is frequently possible to leave the vector-mask mode in effect while performing the arithmetic for an entire sectioning loop.

#### COMMON INSTRUCTION DESCRIPTIONS

Many vector-facility instructions have common characteristics and obey common rules for accessing the elements of their vector operands. This section describes the common aspects, which are not repeated in individual instruction descriptions.

Some instructions contain fields that vary slightly from the basic format, and in some instructions, the operation performed does not follow the general rules stated in this section. Any exceptions to these rules are noted in the individual instruction descriptions, as are the rules for instruction formats and types not covered in this section.

The rules are grouped according to instruction classes and formats.

### Programming Note

Many load and all store operations on vectors are the same for binary and short floating-point operands, so that only a single set of operation codes is provided for them. However, for programming convenience, both binary and short floating-point mnemonics are assigned to these operation codes.

Separate operation codes are provided for short floating-point and binary operands when the operation must distinguish between floating-point and general registers, as in loading or extracting an element, or when the operation depends on the data type, such as LOAD COMPLEMENT.

## | Instruction Classes

Vector-facility instructions are classified into one of nine classes: IM, IC, IG, IP, IZ, NC, NZ, N1, and N0. The properties of these nine instruction classes are summarized in Figure 2-4.

| Instruc-<br>tion<br>Class | Number of<br>Elements<br>or Bits | Execution<br>Inter-<br>ruptible? | Mask Mode |

|---------------------------|----------------------------------|----------------------------------|-----------|

| IM                        | VCT - VIX                        | Yes                              | Yes       |

| IC                        | VCT - VIX                        | Yes                              | No        |

| IG                        | GR and<br>VIX                    | Yes                              | No        |

| IP                        | PSN - VIX                        | Yes                              | No        |

| IZ                        | SS                               | Yes                              | No        |

| NC                        | VCT                              | No                               | No        |

| NZ                        | SS                               | No                               | No        |

| N1                        | One                              | No                               | No        |

| NO                        | None                             | No                               | No        |

|                           | L                                | L                                | I         |

Explanation:

| GR  | Number of bits determined by     |

|-----|----------------------------------|

|     | contents of a general register   |

| PSN | Number of elements determined by |

|     | partial-sum number               |

| SS  | Section size                     |

| VCT | Vector count                     |

| VIX | Vector interruption index        |

|     | -                                |

Figure 2-4. Vector-Facility Instruction Classes The instruction classes distinguish:

- Whether the instruction is interruptible (I\_) or not interruptible (N\_),

- Whether instruction execution depends on the vector interruption index (IM, IC, IG, IP),

- Whether instruction execution depends on the setting of the vector-mask mode (IM),

- Whether the number of vector elements or bits processed is variable and is controlled by the vector count (IM, IC, NC) or by a general register (IG),

- Whether the number of vector elements or bits processed is the partial-sum number (IP) or the section size (IZ, NZ),

- Whether just one vector element is processed (N1) or none (N0).

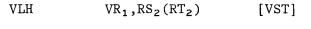

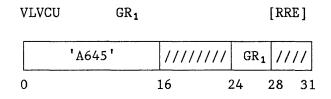

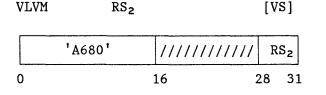

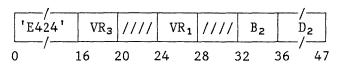

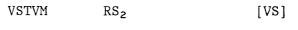

## | Instruction Formats

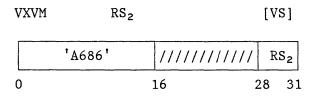

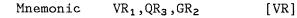

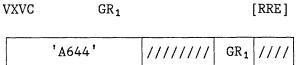

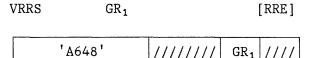

The instruction formats used by vectorfacility instructions are shown in Figure 2-5 on page 2-14. The first four are the base formats - QST, QV, VST, and VV, where Q indicates that the format provides for a scalar-register operand, ST indicates a storage operand (with stride), and V indicates a vectorregister operand. Most of the arithmetic instructions are available in all For the four of these base formats. vector-comparison instructions, the VR1 field of the base formats is interpreted as a modifier  $(M_1)$ .

Bit positions which are shown in instruction formats as shaded (///) are unassigned.

## Field Designations

The field designations in the instruction formats indicate the use of the field and the type of operation in which the field participates.

$B_2$  and  $D_2$  Fields:  $B_2$  designates a base register, and  $D_2$  is a displacement. They are used for addressing in the same way as with scalar instructions.

| First    | Second   | Third    |

|----------|----------|----------|

| Halfword | Halfword | Halfword |

|          |          |          |

## Base Formats

| QST Format  | Op Code | QR <sub>3</sub> RT <sub>2</sub> VR <sub>1</sub> RS <sub>2</sub>        |

|-------------|---------|------------------------------------------------------------------------|

|             | 0       | 16 20 24 28 31                                                         |

| QV Format   | Op Code | $QR_3 //// VR_1 VR_2$                                                  |

|             | 0       | 16 20 24 28 31                                                         |

| VST Format  | Op Code | VR <sub>3</sub> RT <sub>2</sub> VR <sub>1</sub> RS <sub>2</sub>        |

|             | 0       | 16 20 24 28 31                                                         |

| VV Format   | Op Code | VR <sub>3</sub> //// VR <sub>1</sub> VR <sub>2</sub>                   |

|             | 0       | 16 20 24 28 31                                                         |

| Other Forma | ts      |                                                                        |

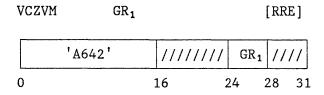

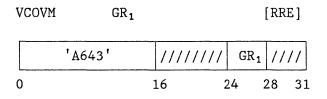

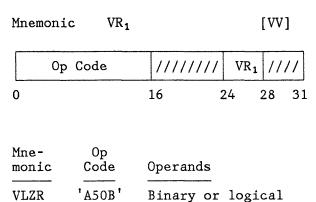

| RRE Format  | Op Code | /////// GR <sub>1</sub> ////                                           |

|             | 0       | 16 24 28 31                                                            |

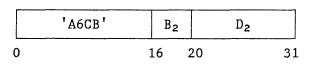

| RSE Format  | Op Code | R <sub>3</sub> //// VR <sub>1</sub> //// B <sub>2</sub> D <sub>2</sub> |

|             | 0       | 16 20 24 28 <u>3</u> 2 36 47                                           |

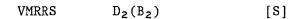

| S Format    | Op Code | B <sub>2</sub> D <sub>2</sub>                                          |

|             | 0       | 16 20 31                                                               |

| VR Format   | Op Code | QR <sub>3</sub> //// VR <sub>1</sub> GR <sub>2</sub>                   |

|             | 0       | 16 20 24 28 31                                                         |

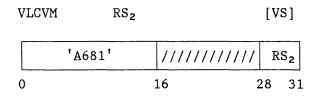

| VS Format   | Op Code | //////// RS <sub>2</sub>                                               |

|             | 0       | 16 _ 28 31                                                             |

Figure 2-5. Vector-Facility Instruction Formats

$FR_3$  Field:  $FR_3$  designates a (scalar) floating-point register. It is a more specific description of the QR<sub>3</sub> field used in some instruction descriptions, and the same rules and restrictions apply as for QR<sub>3</sub>.

*GR Field*: GR designates a (scalar) general register or a pair of general registers. Unless otherwise indicated in the individual instruction definitions, the contents of the general registers designated by the  $GR_1$  and  $GR_2$ fields are called the first operand and second operand, respectively. When designating the third operand ( $GR_3$ ), it is a more specific indication of the  $QR_3$ field used in some instruction descriptions, and the same rules and restrictions apply as for  $QR_3$ .  $QR_3$  Field:  $QR_3$  designates a scalar register, with the operation code determining whether it is a floating-point or general register. In the QST format, the  $QR_3$  field must not designate a general register which is the same as that designated by the  $RS_2$  field; otherwise, a specification exception is recognized. For instructions in the QV or VR formats with only two operands, one a vector and one a scalar, the scalar operand is called the second operand and is designated by a  $QR_2$ field.

$R_3$  Field:  $R_3$  is shown in individual instruction descriptions as either VR<sub>3</sub>, to designate a vector register, or GR<sub>3</sub>, to designate a general register.

$RS_2$  Field:  $RS_2$  designates a general register containing a storage-operand address. The address is updated during execution. The  $RS_2$  field cannot designate the same general register as the  $RT_2$  field or, in the QST format, as the  $GR_3$  or  $QR_3$  field. (Note that the field can designate general register 0.)

$RT_2$  Field:  $RT_2$  designates a general register containing a stride. The field cannot designate general register 0; if the  $RT_2$  field is zero, a stride of 1 is specified. It also cannot designate the same general register as the  $RS_2$  field.

VR Field: VR designates a vector register or a pair of vector registers. The VR<sub>1</sub>, VR<sub>2</sub>, and VR<sub>3</sub> fields designate the first, second, and third operands, respectively, in vector registers or pairs of vector registers, as required for the data type specified by the operation code.

#### Three-Operand Instruction Formats

All nonstore vector instructions which explicitly specify three operands in the QST, QV, RSE, VST, and VV formats use the first-operand location as the target for the result and the second- and third-operand locations for the source operands. These three-operand operations may be shown symbolically as:

Operand 1 =Operand  $3 \cdot$ Operand 2

where • represents an arithmetic or logical operation. Operand 1 is always in vector registers. Operand 2 is in storage or in vector registers. Operand 3 is either in vector registers or in a scalar register. An instruction may specify the same or different vector registers for the target and source operands.

Vector-comparison instructions are similar to these three-operand instructions, except that they designate a modifier  $(M_1)$  instead of a first operand  $(VR_1)$ , and they place the result in the vector-mask register.

### | Summary of Instructions by Class and | Format

Figure 2-6 on page 2-16 briefly lists all instructions of the vector facility according to class and format within the class.

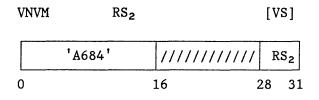

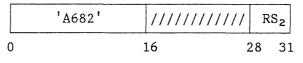

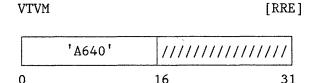

## Class-IM and Class-IC Instructions

Most vector instructions are in either class IM or IC. Instructions in both classes are interruptible, the number of elements processed is determined by the vector count, and they depend on the vector interruption index. Class-IM instructions are also under the control of the vector-mask mode; class-IC instructions are independent of the vector-mask mode.

For both classes, the elements of each operand are processed in sequence from element X, where X is the initial value of the vector interruption index (normally zero), to C-1, where C is the vector count.

The number of elements that are processed for each operand is called the net count. If C is greater than X, then the net count is C-X; otherwise the net count is zero. For vector instructions which combine vector operands with a scalar operand, the scalar operand is considered to be replicated as many times as indicated by the net count.

If the net count is zero at the start of instruction execution, the vector interruption index is set to zero, and execution is completed immediately. No elements are processed, no operandaccess exceptions occur, the change bits for any storage operand remain unchanged, and no PER event for storage

|                                                                                                                                                                                                |                                              | Instruction                                                      | Instruction Formats When Operands Are                                                                                                    |                                        |                      |                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|-----------------------------------|