GY27-7237-1

# IBM System/360 Operating System Machine Check Handler for The IBM System/370 Models 135 and 145

Program Number 360S-DN-539

**OS Release 21**

**Systems**

,

## PREFACE

This publication describes the design of the Machine-Check Handler (MCH) program and what it does to prevent or minimize downtime for System/370 Models 135 and 145.

#### ORGANIZATION OF THIS MANUAL

The "Introduction" summarizes the operation of MCH. This section contains definitions and descriptions needed to understand the second section "Method of Operation."

The "Method of Operation" describes the functions of the program and shows how the major data areas are used by MCH.

The "Program Organization" section describes the modules that constitute MCH and the operation of each of these modules. Flowcharts of each module are provided at the end of this section.

"MCH Data Areas" describes the fields of information used by MCH in its principal data area, the MCH Common Area. The "Diagnostic Aids" section describes several techniques that can be used to determine the source of problems that arise in MCH.

The "MCH Module Directory" section is a guide to the named areas of code in the program listing.

The appendixes contain a table showing where MCH messages originate, a detailed description of the machine-check interruption code, and the MCH wait state codes.

## PREREQUISITE PUBLICATIONS

To use this manual effectively, the reader should be familiar with the System/ 360 Operating System and have available the following publication:

IBM System/370 Principles of Operation, GA22-7000.

Second Edition (March 1972)

This is a major revision of, and obsoletes, GY27-7237-0. This edition applies to Release 21 of the IBM System/360 Operating System and to all subsequent versions of the operating system unless otherwise indicated in new editions or Technical Newsletters. Changes are periodically made to the information contained here; any such changes will be reported in subsequent revisions or Technical Newsletters.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be addressed to IBM Corporation, Programming Publications, Department 636, Neighborhood Road, Kingston, New York 12401.

This publication was prepared for production using an IBM computer to update the text and to control the page and line format. Page impressions for photo-offset printing were obtained from an IBM 1403 Printer using a special print chain.

# CONTENTS

| SECTION 1: INTRODUCTION                                |     | • | • | • |   | • | 1              |

|--------------------------------------------------------|-----|---|---|---|---|---|----------------|

| Recovery Design of the Models 135 and 145              |     |   |   |   |   |   | 1              |

| Hardware Recovery Features of the Models 135 and 145 . |     |   |   |   | • |   | 1              |

| Automatic Recovery Features                            |     |   |   |   |   |   | 1              |

| CPU Retry                                              |     |   | • |   |   |   | 1              |

| ECC Validity Checking                                  |     |   |   |   |   |   | 3              |

| Fixed Storage Locations                                |     | - |   |   |   |   | 3              |

| Fixed Logout Area                                      |     | - |   |   |   |   | 3              |

| Extended Logout Area                                   |     | - | • |   |   | • | 3              |

| Control Registers                                      | •   | • | • | • | • | • | 3              |

| Modes of Becovery Operation                            | ••  | • | • | • | • | • |                |

| Modes of Recovery Operation                            | •   | • | • | • | • | • |                |

| Modes of Recovery Operation of the Model 145           |     | • | • | • | • | • | 5              |

| Modes of the Mode Commanda                             | • • | • | • | ٠ | • | • | 5              |

| Use of the Mode Commands                               | • • | • | • | • | • | • | 5              |

| Mode Command for the Model 135                         | • • | • | • | ٠ | ٠ | • | 2              |

| Mode Command for the Model 145                         |     |   |   |   |   |   |                |

| MCH Error Recovery                                     | • • | • | ٠ | • | • | ٠ | 6              |

| System Recovery                                        | • • | • | ٠ | ٠ | • | ٠ | 6              |

| System-Supported Restart                               | • • | • | ٠ | • | • | • | 6              |

| System Repair                                          | • • | • | ٠ | ٠ | ٠ | ٠ | 7              |

| Physical Characteristics                               | • • | • | ٠ | ٠ | • | ٠ | 7              |

| Main Storage Requirements                              |     | • | ٠ | • | • | • | 7              |

| Auxiliary Storage Requirements                         |     |   |   |   |   |   |                |

| Overlay Structure of MCH                               |     | • | • | • | • | • | 8              |

|                                                        |     |   |   |   |   |   |                |

| SECTION 2: METHOD OF OPERATION                         |     | • | • | • | • | • | 10             |

| The Logic of MCH                                       |     | • | • | • | • | • | 10             |

| Communications                                         |     |   |   |   |   |   |                |

| Initialization                                         |     | • | • | • | • | • | 10             |

| Saving the Environment                                 |     | • | • | • | • | • | 14             |

| Module Loading                                         |     |   |   |   |   |   |                |

| Hardware Error Analysis                                |     | • | • | • | • |   | 17             |

| Types of Hardware Malfunctions                         |     |   |   |   |   |   | 17             |

| System Damage                                          |     |   |   |   |   |   | 17             |

| System Damage                                          |     |   |   |   |   |   | 17             |

| Program Damage Recovery                                |     | - | - |   | - |   | 19             |

| Recording and Termination                              |     |   |   |   | - |   | 19             |

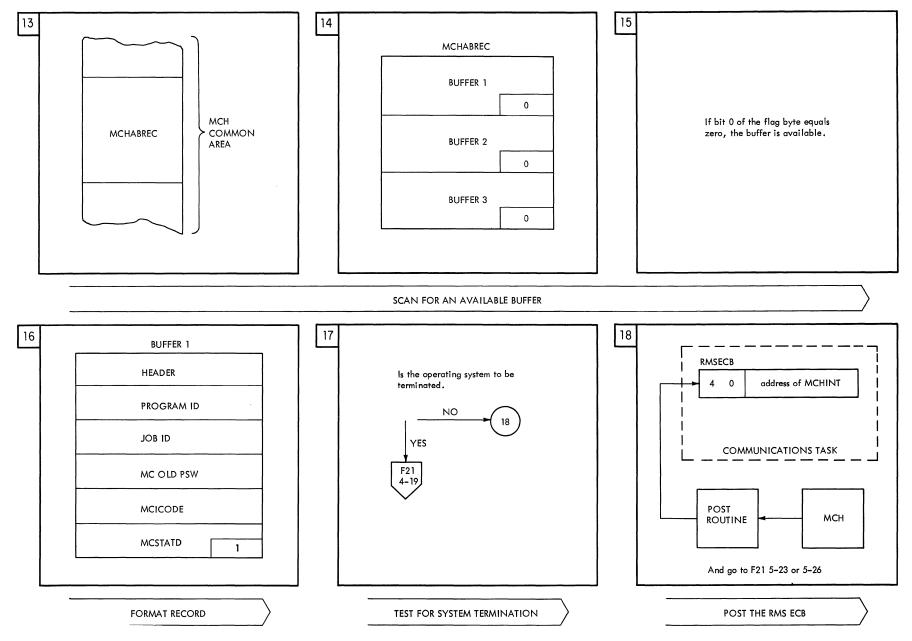

| Error Recording                                        |     |   |   |   | - | - | 20             |

| Emergency Recording                                    |     | - |   | _ |   |   | 20             |

| Emergency Recording                                    |     |   |   |   |   | • | 23             |

|                                                        |     | • | • | • | • | - |                |

| OPERATION DIAGRAMS                                     |     | • | • |   | • |   | 25             |

|                                                        |     |   |   |   |   |   |                |

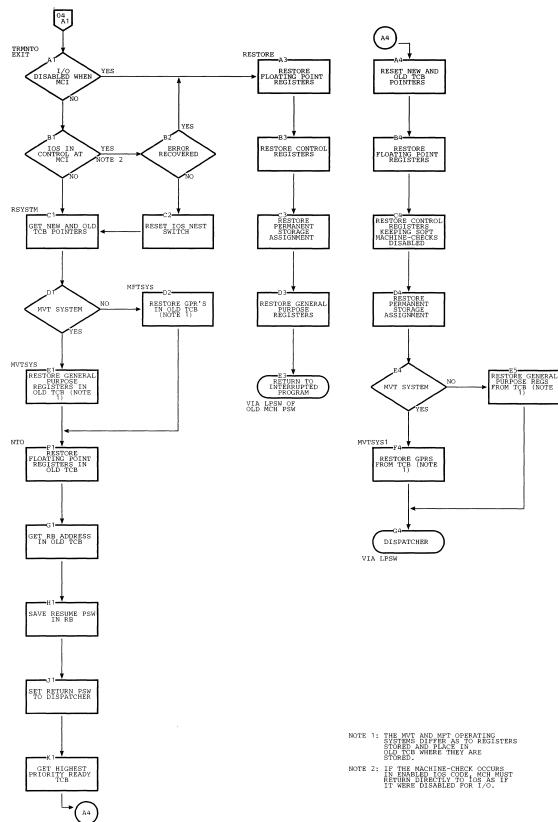

| SECTION 3: PROGRAM ORGANIZATION                        |     | • |   |   | • | • | 47             |

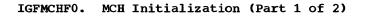

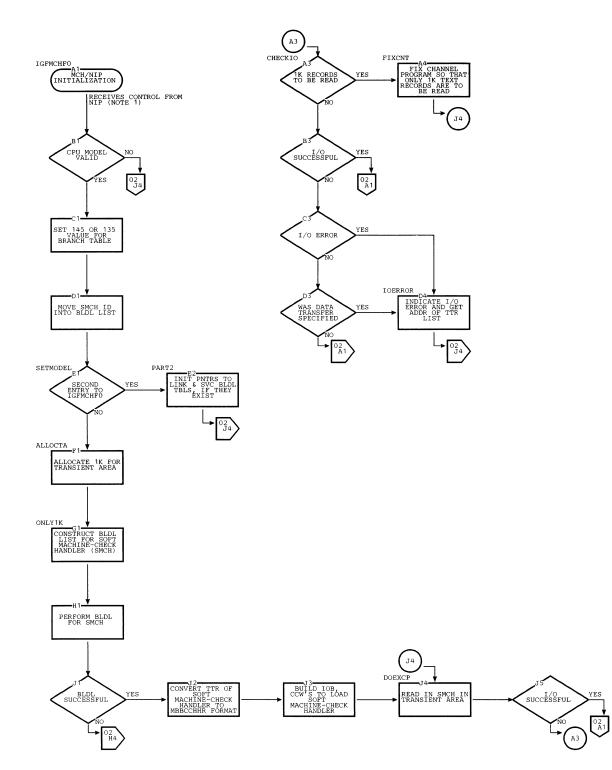

| MCH Initialization                                     |     |   |   |   |   |   | 47             |

| MCH Initialization                                     |     |   |   |   |   | - | 48             |

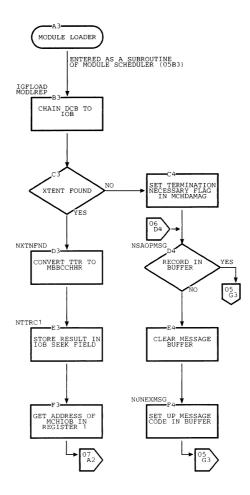

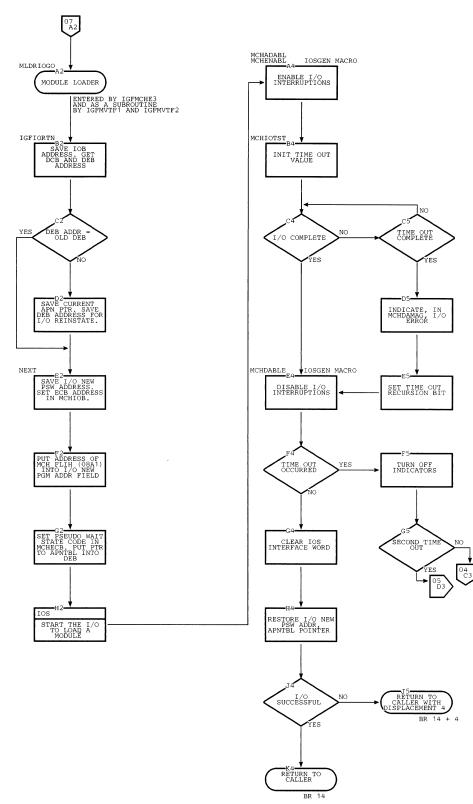

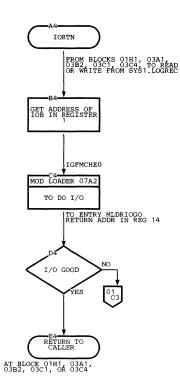

| MCH Module Loader                                      |     |   |   |   |   |   | 48             |

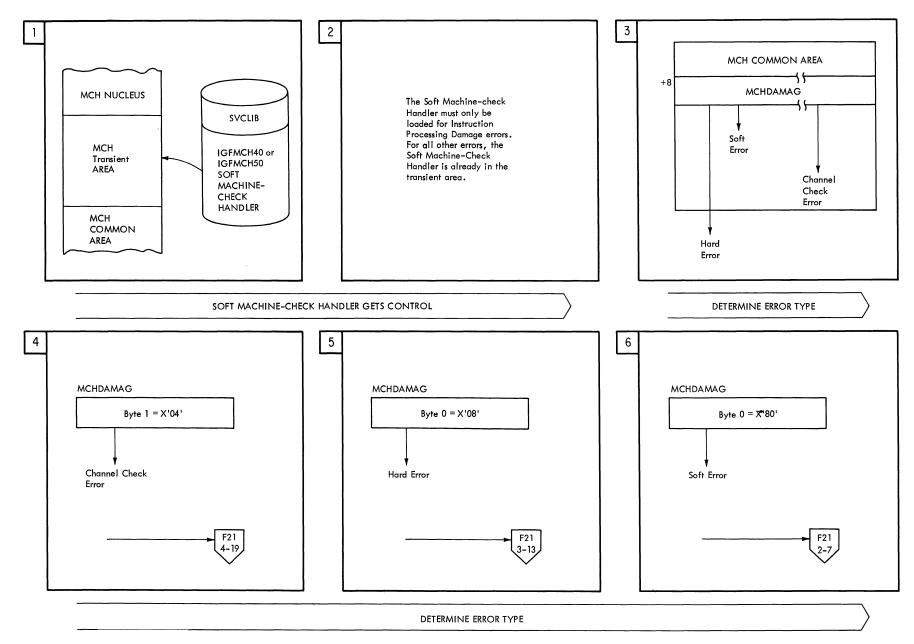

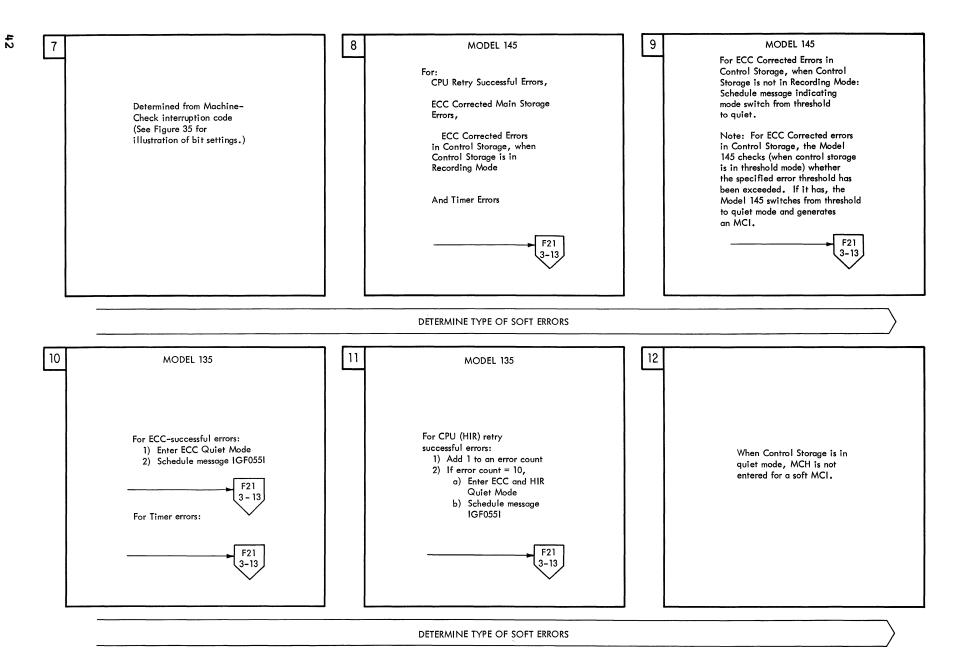

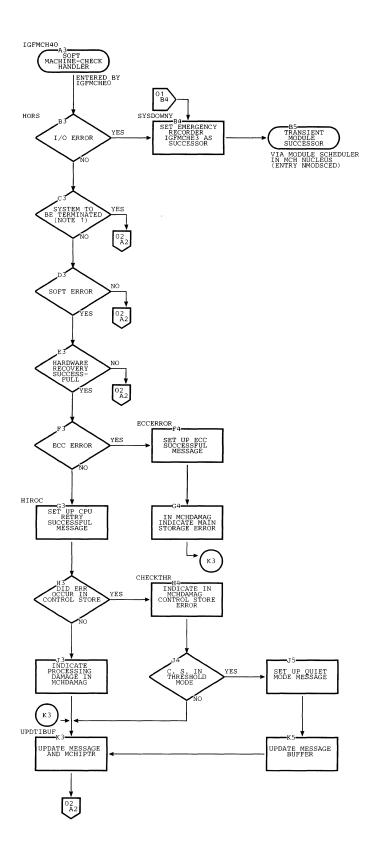

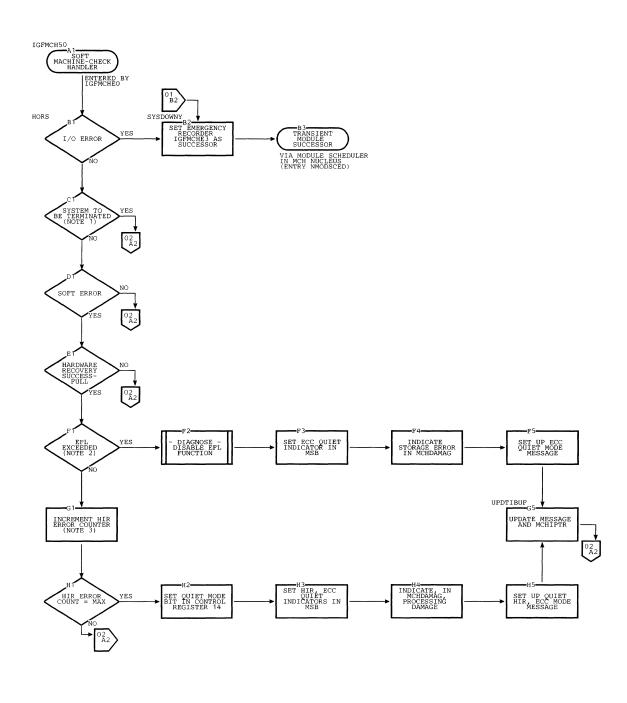

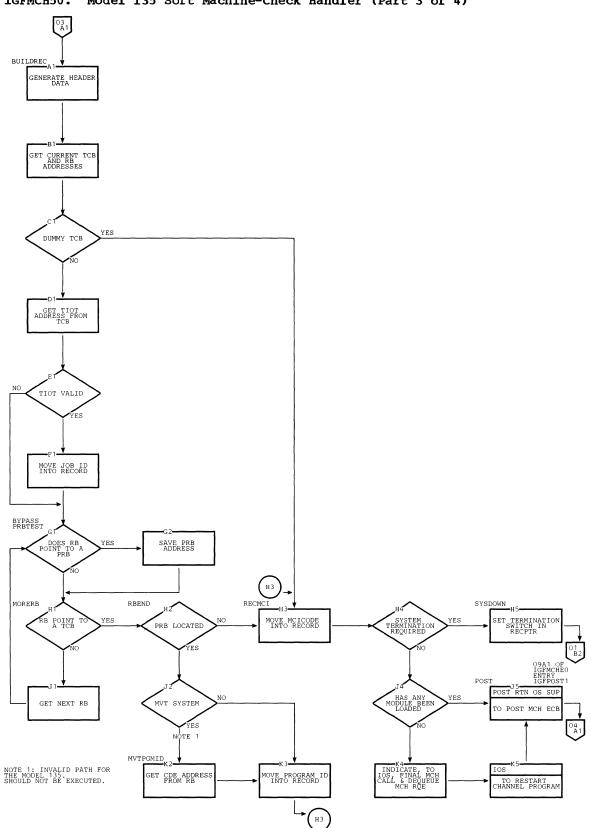

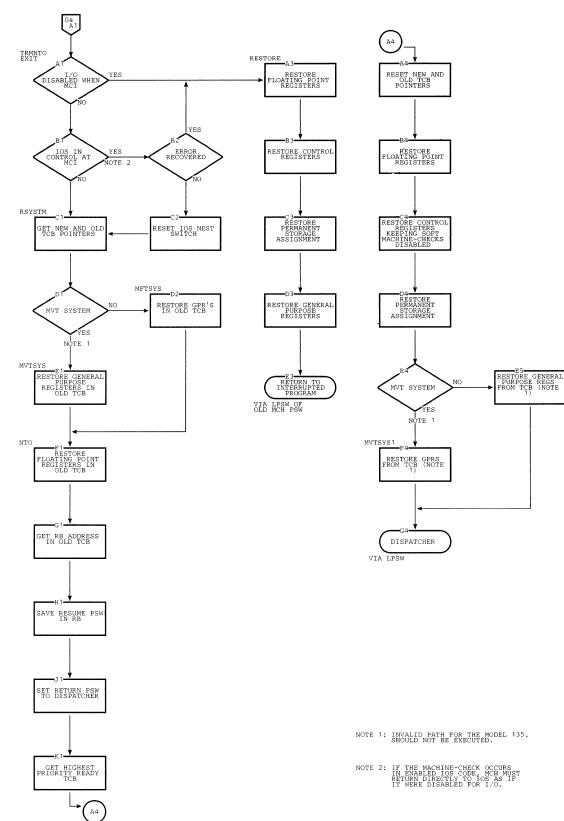

| Soft Machine-Check Handler (Model 135 Only)            |     | - |   | - | - | - | 50             |

| Soft Machine-Check Handler (Model 145 Only)            |     |   |   |   |   |   | 51             |

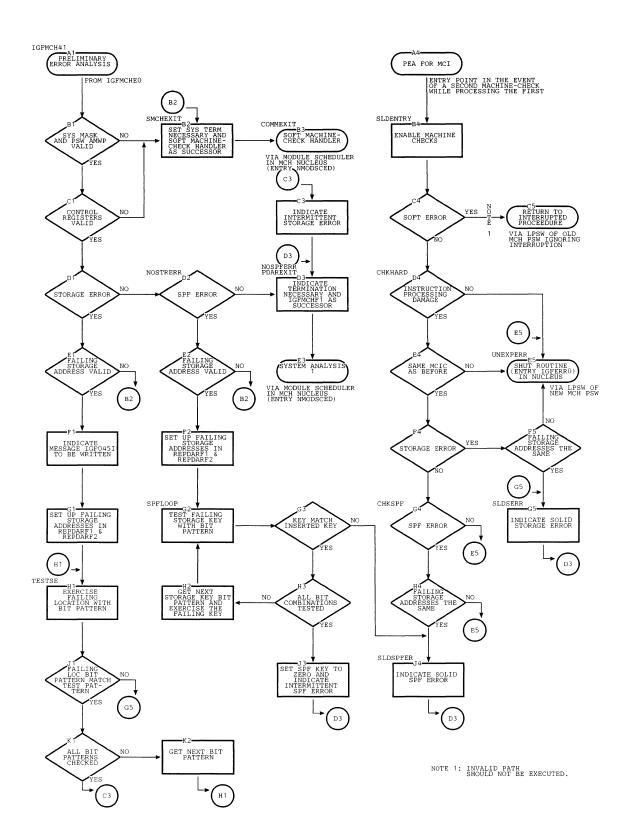

| Preliminary Error Analysis                             |     |   |   |   |   |   | 53             |

| System Analysis                                        | ••  | • | • | • | • | • | 50             |

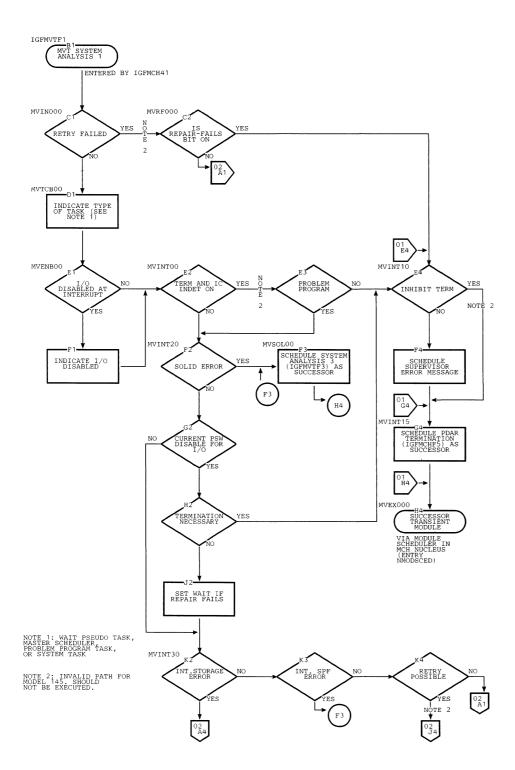

| MVT System Analysis 1 (Model 145 Only)                 | • • | • | • | • |   |   | 54             |

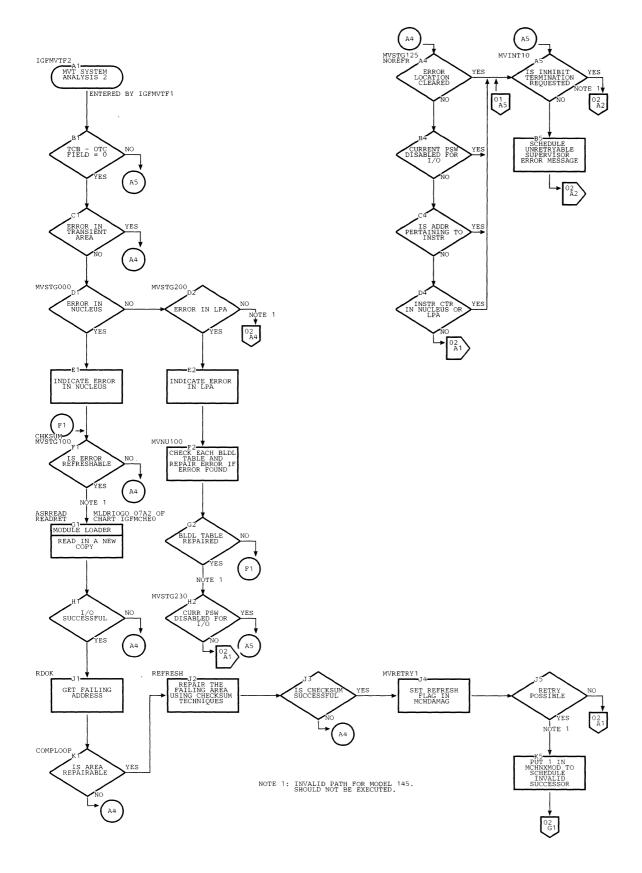

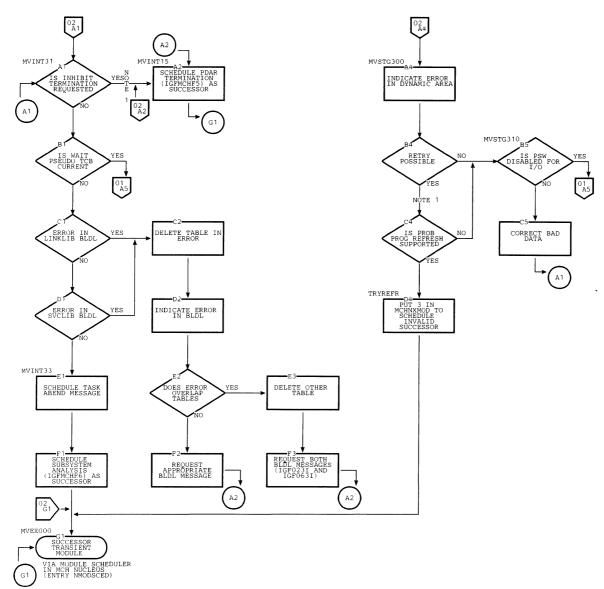

| MVT System Analysis 2 (Model 145 Only)                 | •   | • | • | • |   |   | 54             |

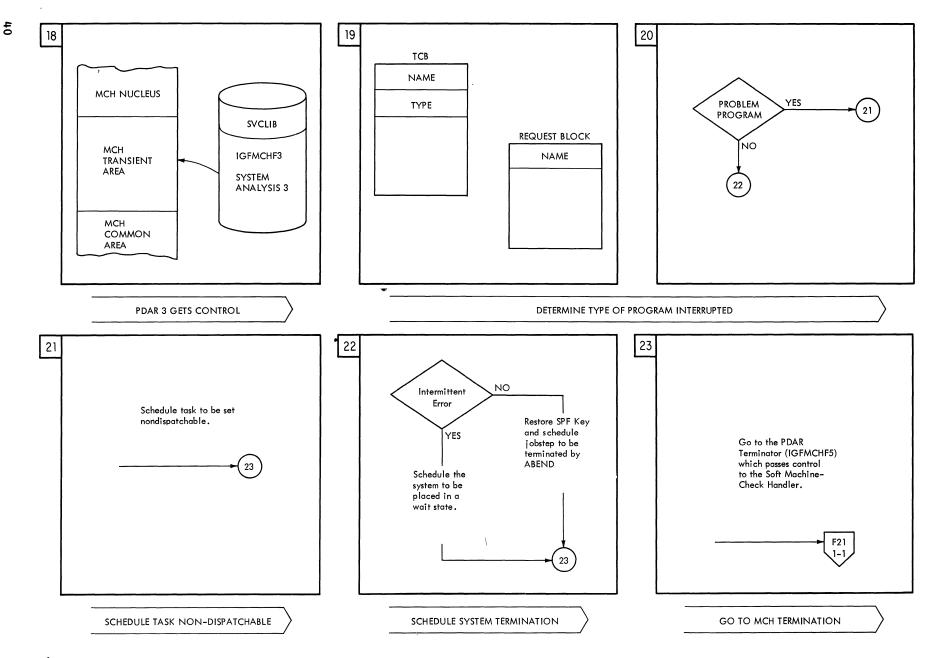

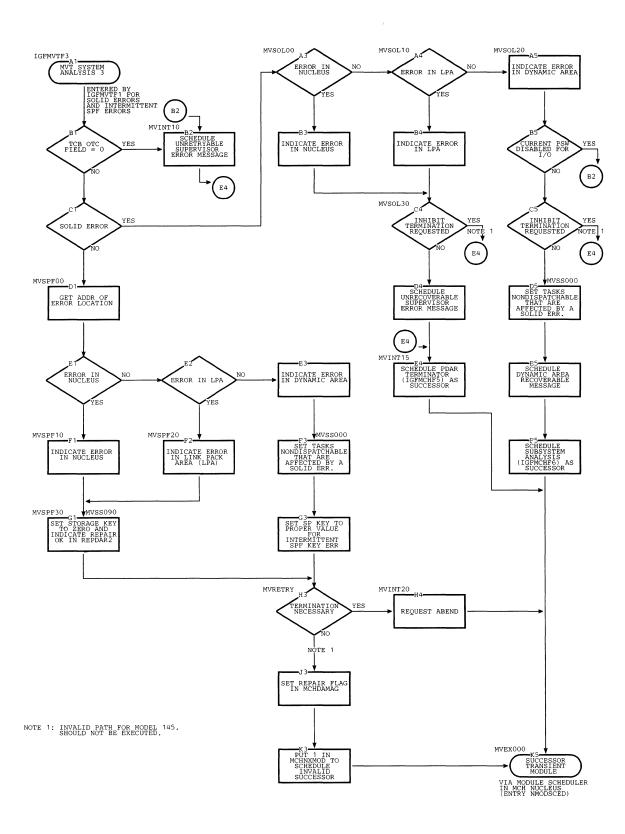

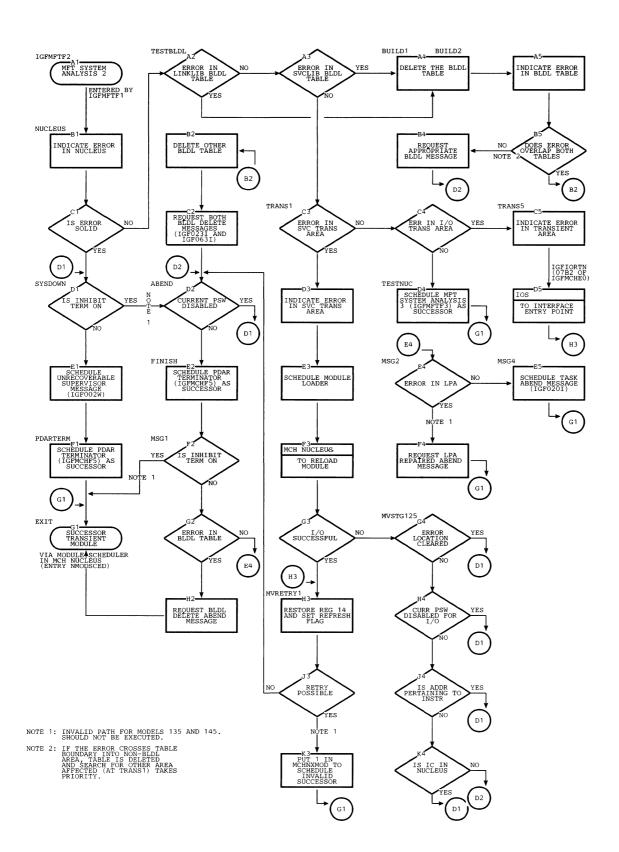

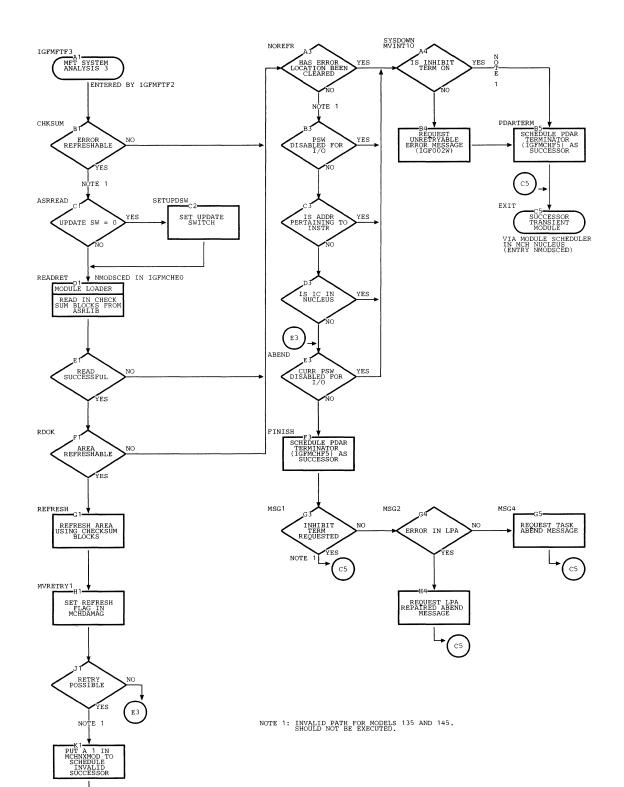

| MVT System Analysis 3 (Model 145 Only)                 |     | • | • | • |   |   | 55             |

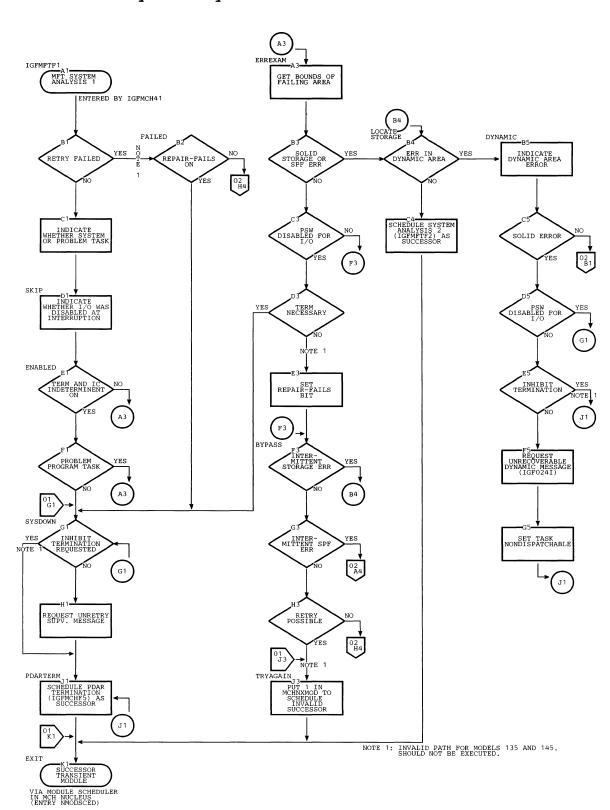

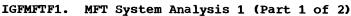

| MFT System Analysis 1                                  | ••  | • | • | • | • | • | 56             |

| MFT System Analysis 1                                  | •   | • | • | • | • | • | - J 0<br>- E 4 |

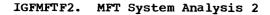

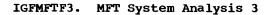

| MFT System Analysis 2                                  | • • | • | • | • | • | • | 20             |

| PDAR Terminator                                        |     |   |   |   |   |   | 57             |

| FUAR ICHMINATOL                                        | • • | • | ٠ | • | • | • | 5/             |

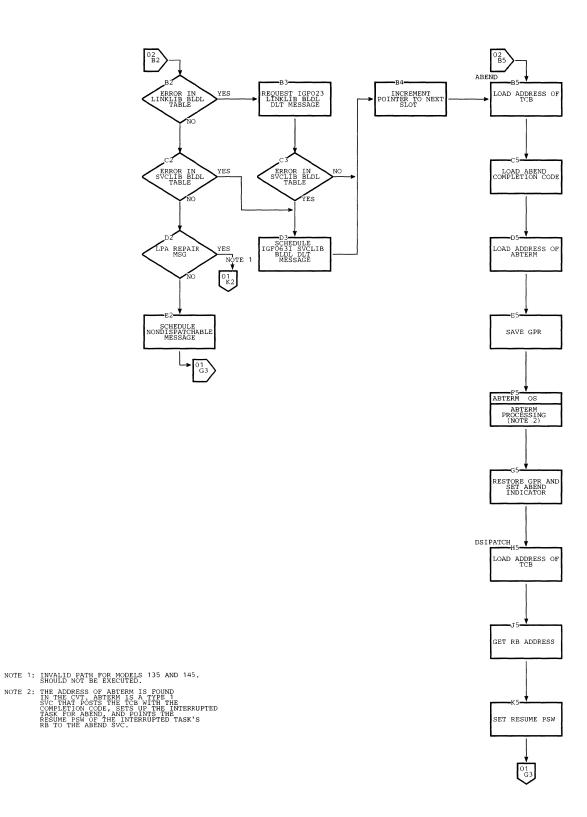

| TSO Subsystem Analysis (Model 145 only)                | • • | • | • | • | • | ٠ | 20             |

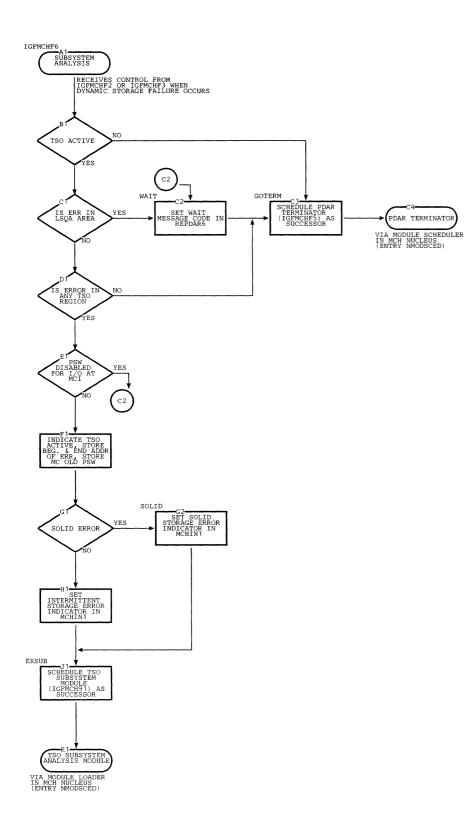

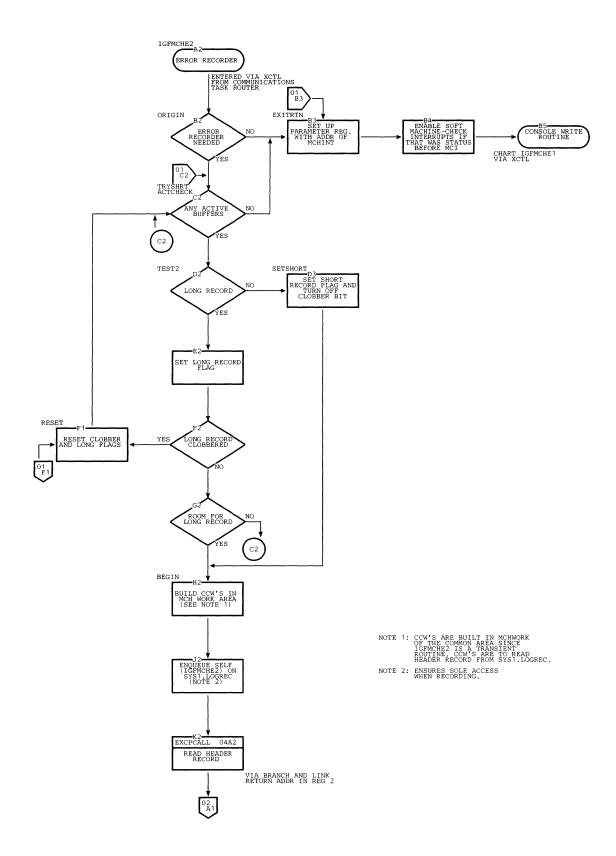

| Error Recorder                                         | • • | • | • | • | • | • | 20             |

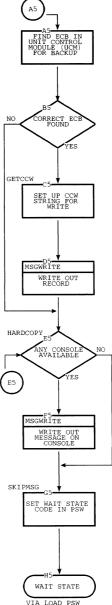

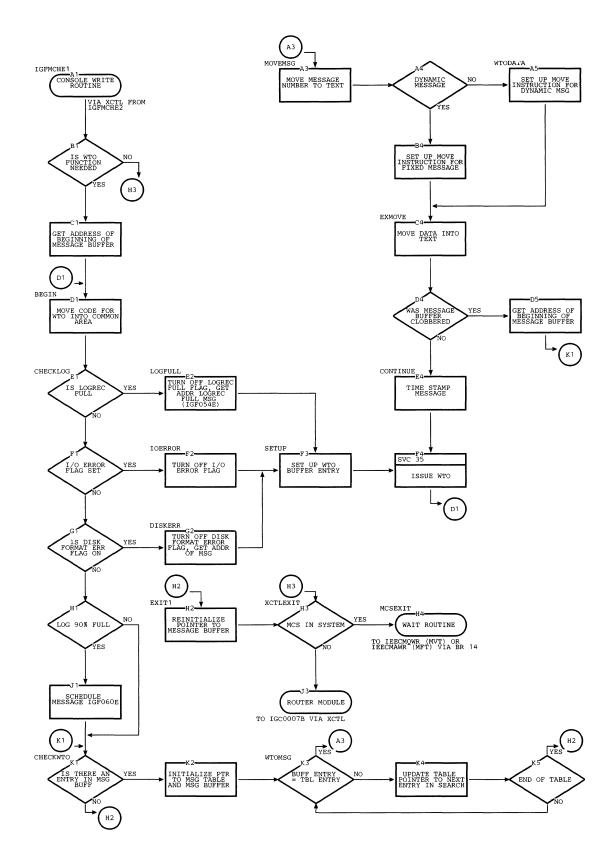

| Console Write Routine                                  | • • | ٠ | ٠ | • | • | • | 27             |

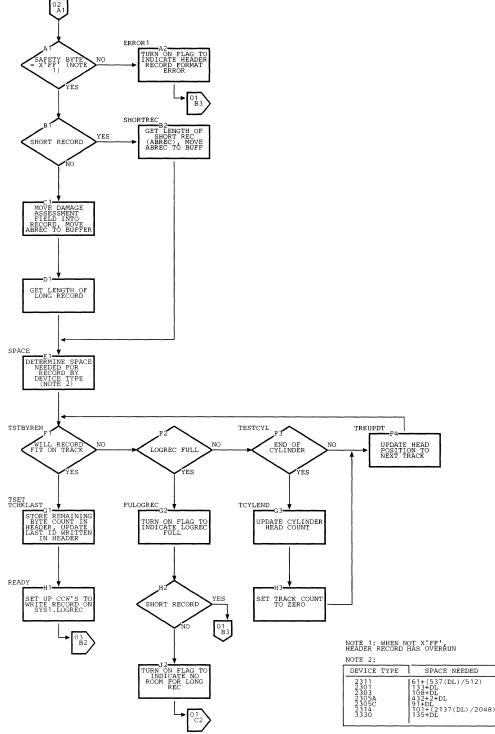

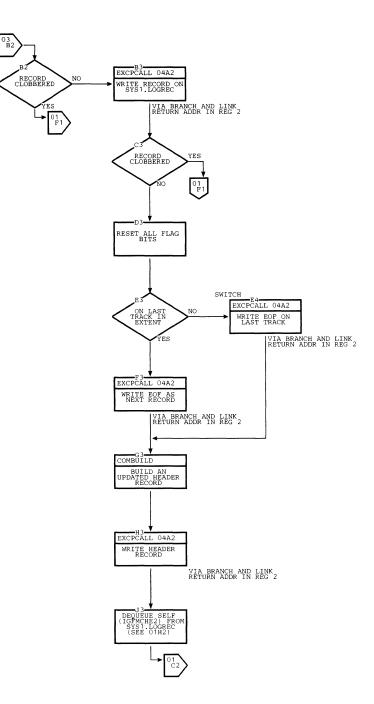

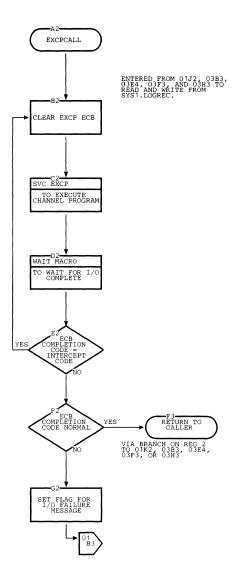

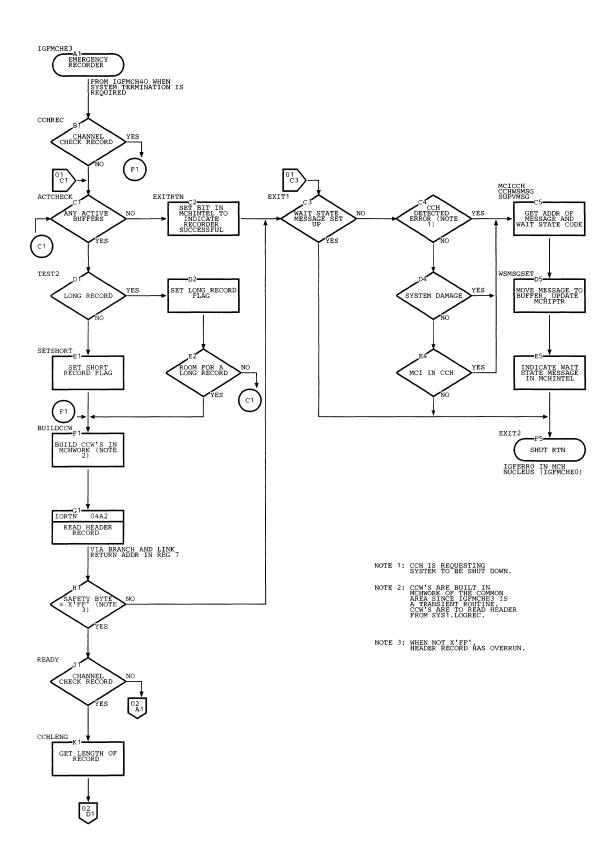

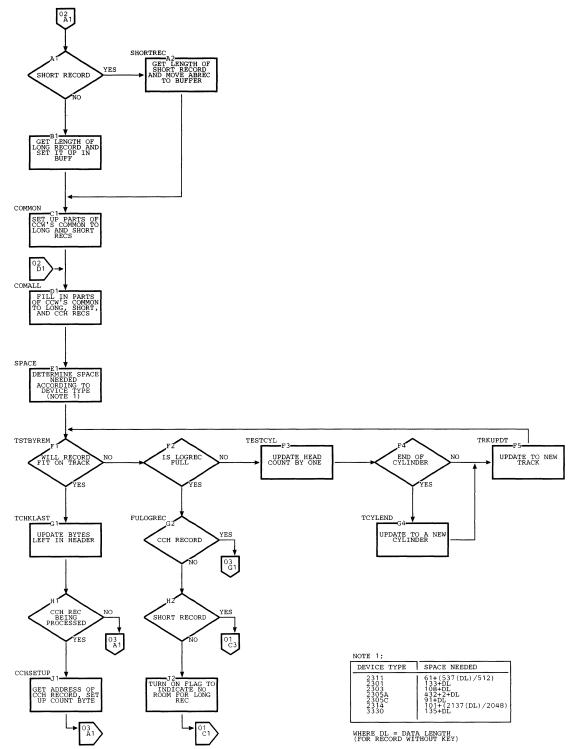

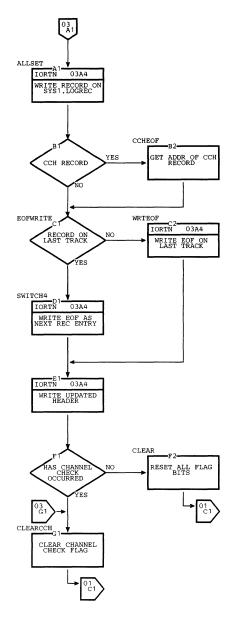

| Emergency Recorder                                     | • • | • | • | • | ٠ | ٠ | 27             |

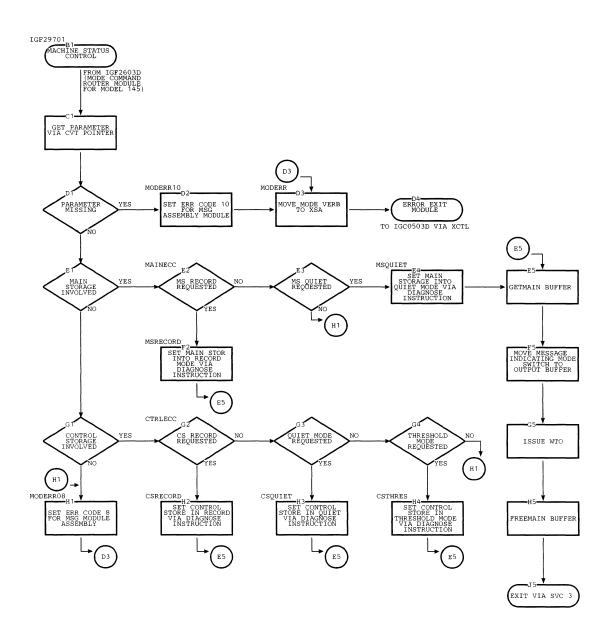

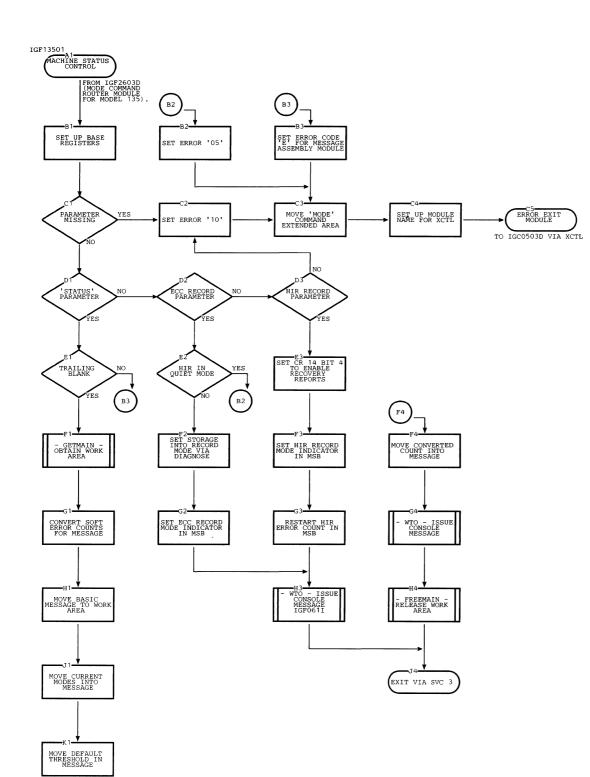

| Machine Status Control (Model 145 only) Machine Status Control (Model 135 Only)                                                                                                                                                                                                                                                                                                     |                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| FLOWCHARTS                                                                                                                                                                                                                                                                                                                                                                          | 61                |

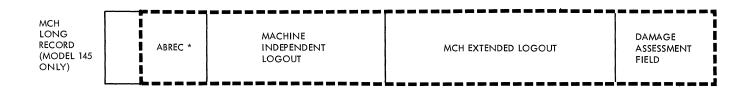

| SECTION 4: MCH DATA AREAS         Model Dependent Common Area         MCH Independent Common Area         Record Buffer Build Area         Fixed Logout         Extended Logout         Damage Assessment Field Buffer Area         Subsystem Data Area (Model 145 Only)         Machine Status Block         Model 135 Machine Status Block         Model 145 Machine Status Block |                   |

| SECTION 5: DIAGNOSTIC AIDS                                                                                                                                                                                                                                                                                                                                                          | 118<br>118<br>118 |

| SECTION 6: MCH MODULE DIRECTORY                                                                                                                                                                                                                                                                                                                                                     | ••••••121         |

| APPENDIX A: MCH MESSAGE TABLE AND WAIT STATE CODES                                                                                                                                                                                                                                                                                                                                  | 123               |

| APPENDIX B: MACHINE-CHECK INTERRUPTION CODE                                                                                                                                                                                                                                                                                                                                         | •••••125          |

| INDEX                                                                                                                                                                                                                                                                                                                                                                               | 127               |

| Figure 1.   | Machine-check handler overview                               |

|-------------|--------------------------------------------------------------|

| Figure 2.   | Modes of recovery operation                                  |

| Figure 3.   | MCH resident area                                            |

| Figure 4.   | Main storage and auxiliary storage relationships 8           |

| Figure 5.   | MCH overlay structure                                        |

| Figure 6.   | MCH overlay structure                                        |

| Figure 7.   | General processing of Model 145 soft errors 12               |

| Figure 8.   | General processing of Model 135 soft errors 13               |

| Figure 9.   | MCH responses to error-on-error conditions 14                |

| Figure 10.  | MCH and environment before initialization 15                 |

| Figure 11.  | MCH and environment after initialization 16                  |

| Figure 12.  | Finding and loading MCH modules (Model 145 modules           |

| illustrated | 1)                                                           |

| Figure 13.  | MCH error record                                             |

| Figure 14.  | CCH error record                                             |

| Figure 15.  | Main storage error, soft error, system damage, and CCH       |

| error       |                                                              |

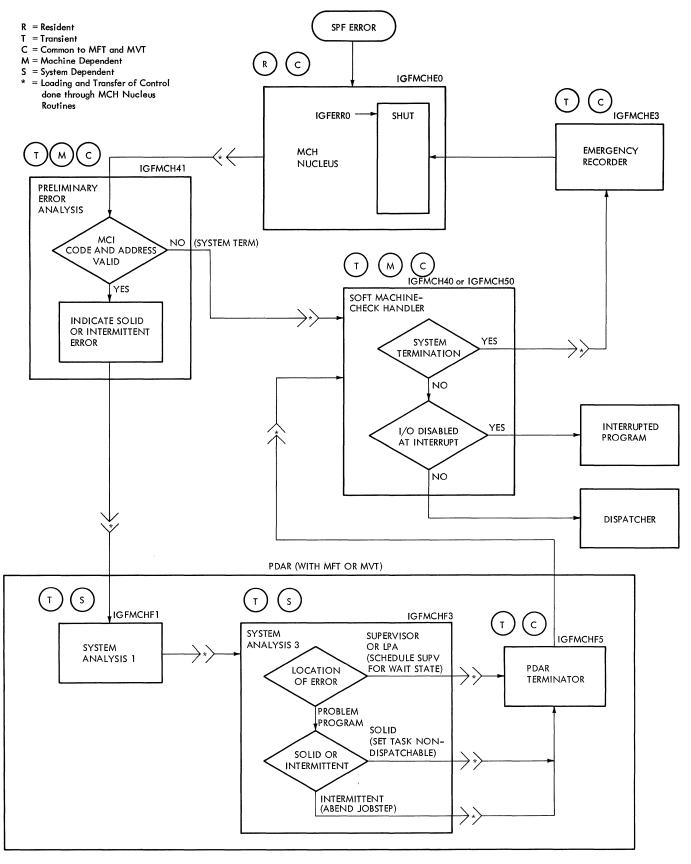

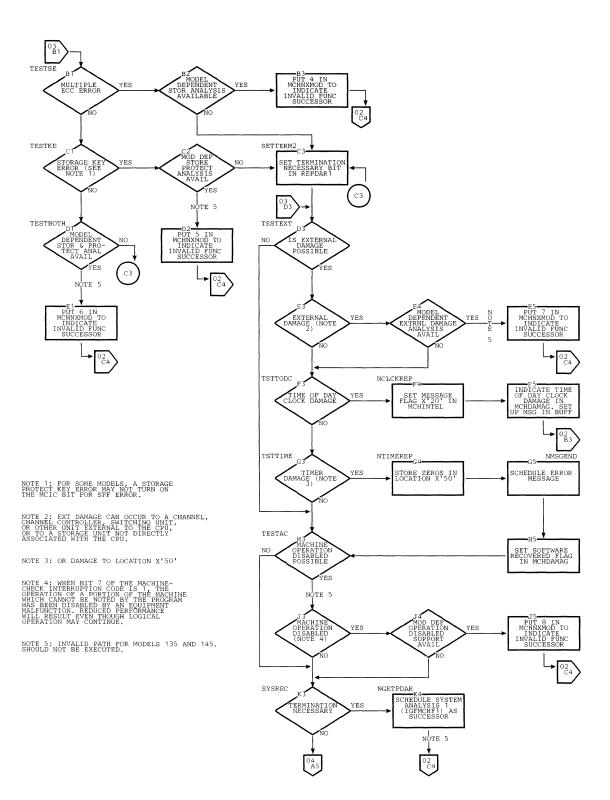

| Figure 16.  | Flow of control for SPF key error                            |

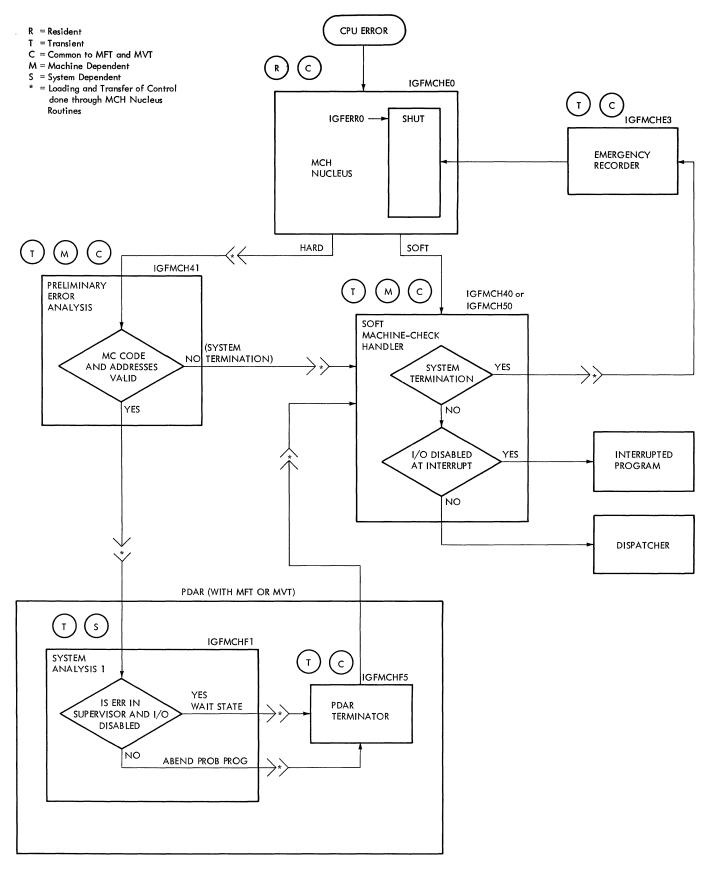

| Figure 17.  | Flow of control for CPU error                                |

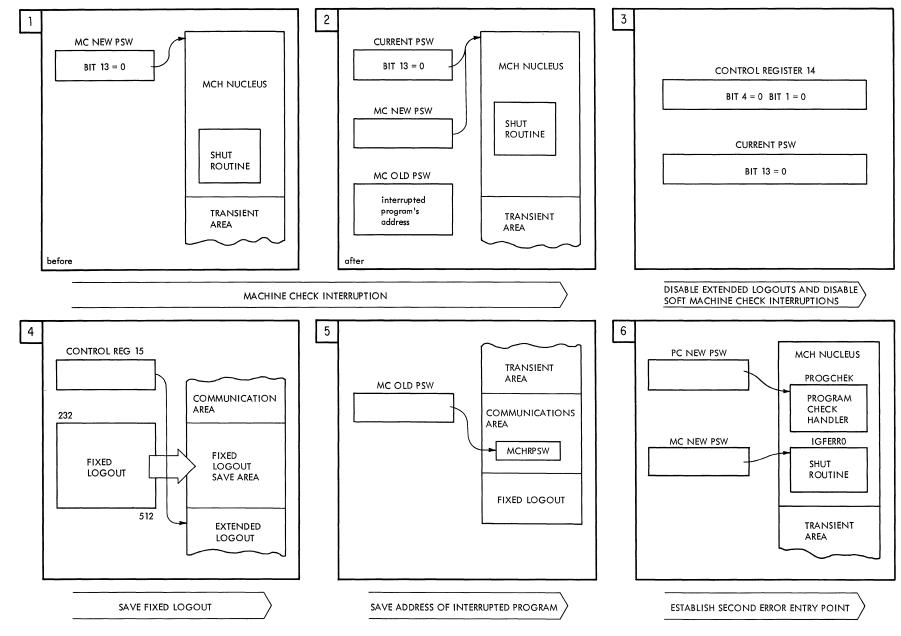

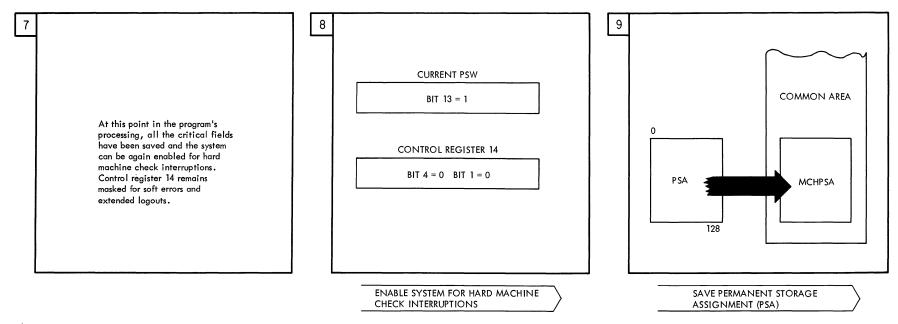

| Figure 18.  | Initialization                                               |

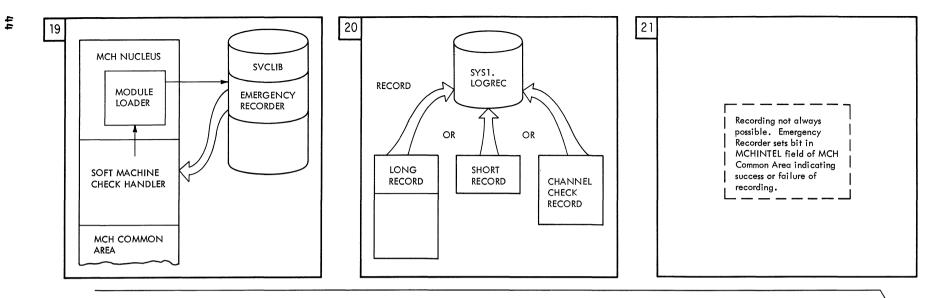

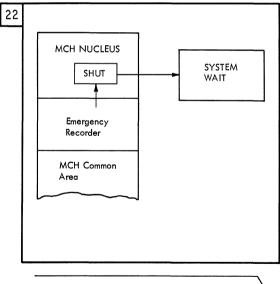

| Figure 19.  | Hardware error analysis                                      |

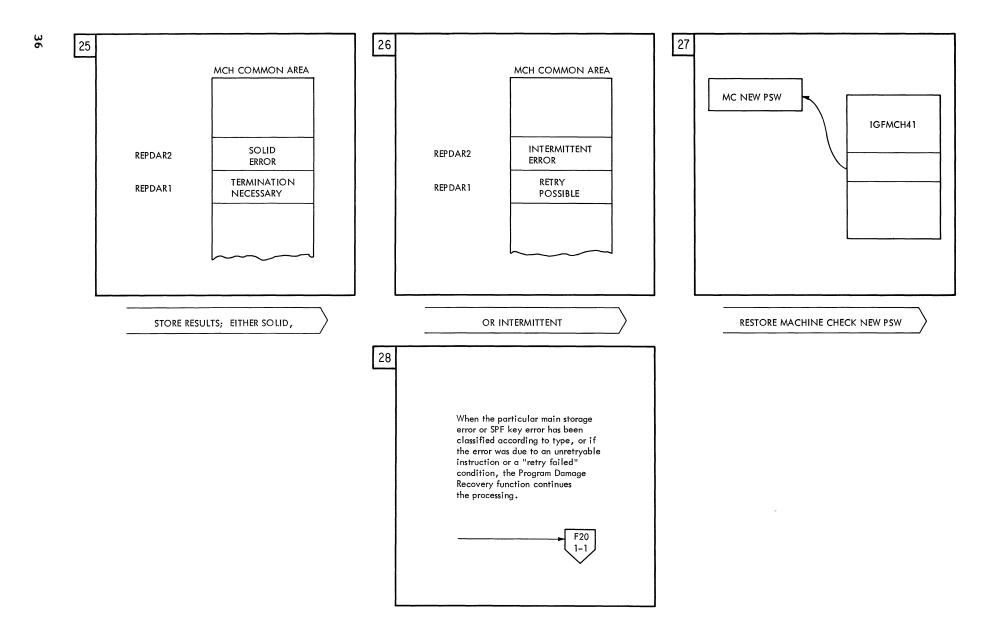

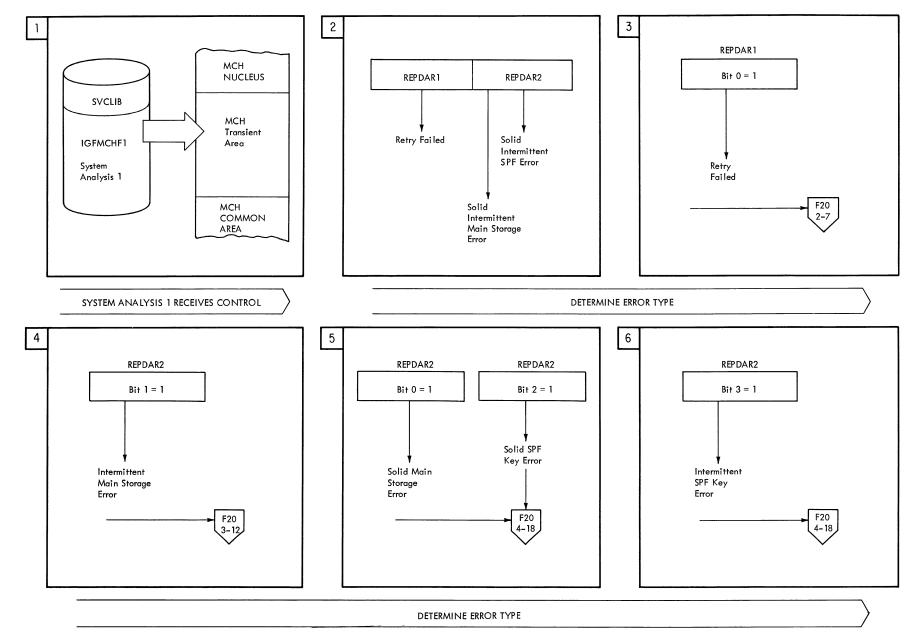

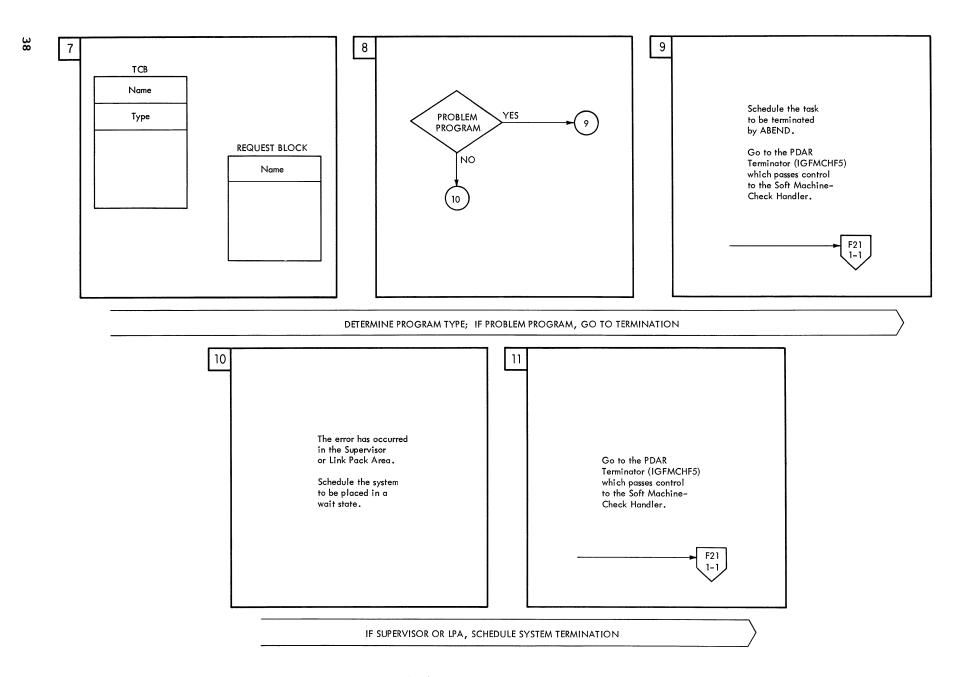

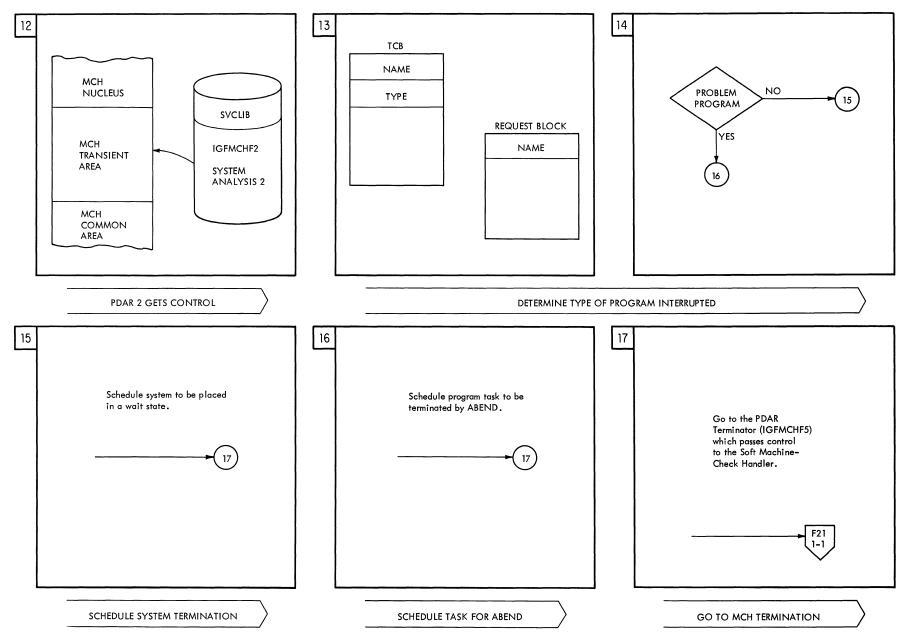

| Figure 20.  | Program damage recovery                                      |

| Figure 21.  | Recording and termination                                    |

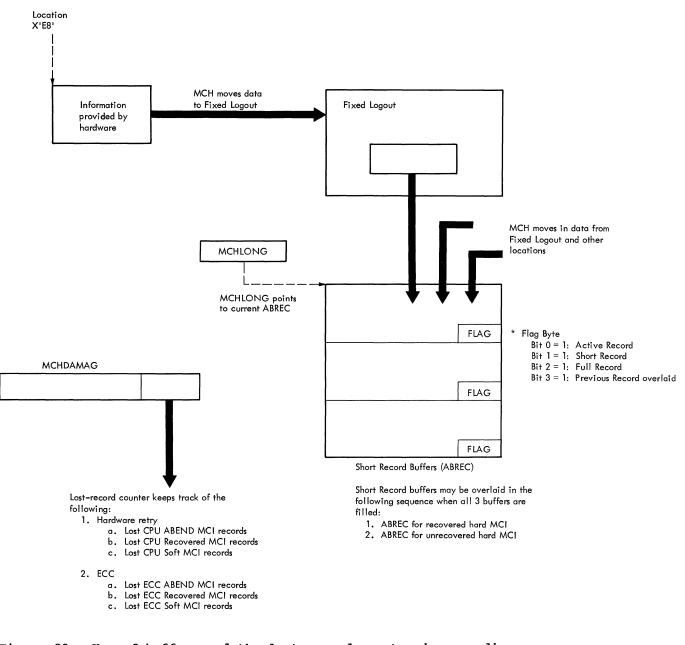

| Figure 22.  | Use of buffers and the lost-record counter in recording . 52 |

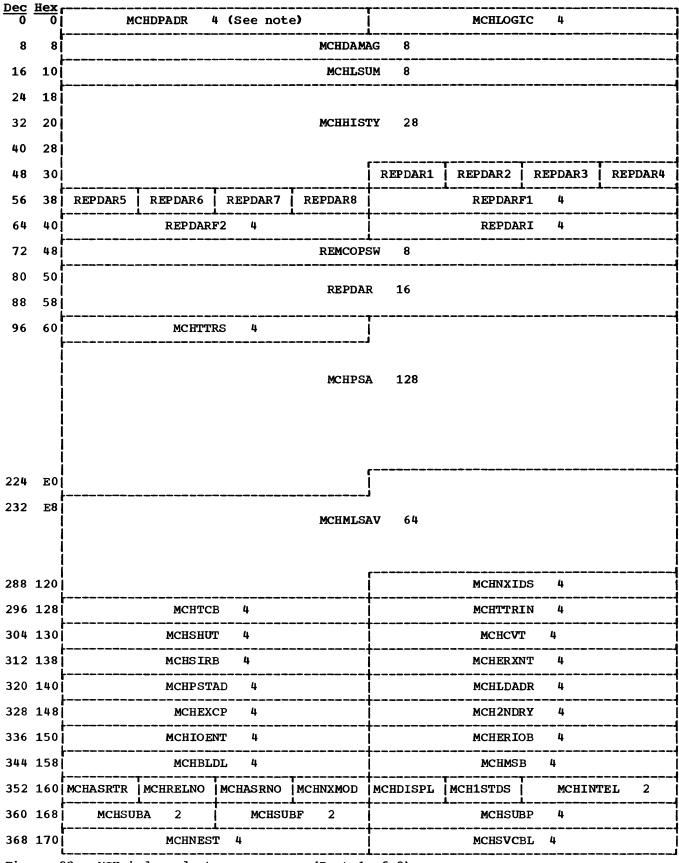

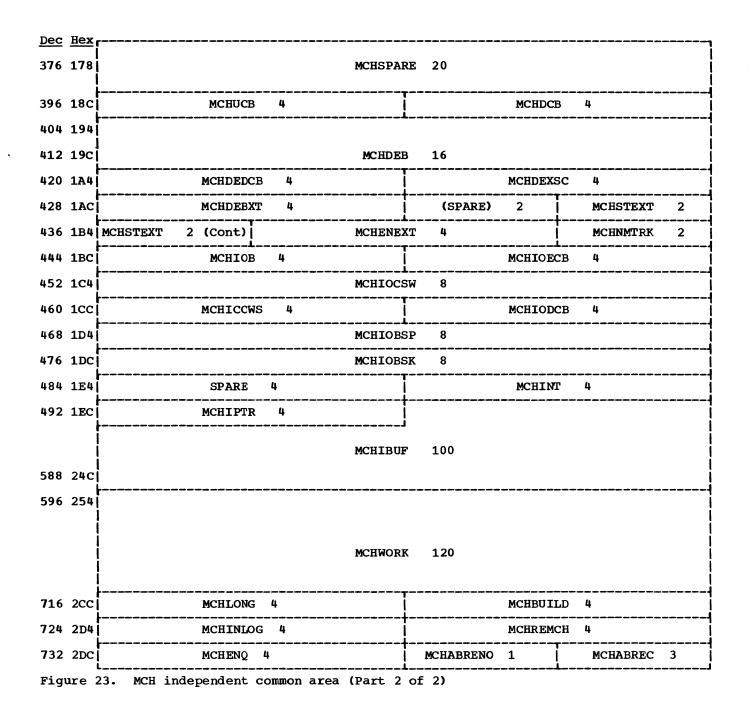

| Figure 23.  | MCH independent common area                                  |

| Figure 24.  | Fields of MCHDEB                                             |

| Figure 25.  | Fields of MCHINTEL                                           |

| Figure 26.  | Fields of MCHIOB                                             |

| Figure 27.  | Fields of MCHLSUM                                            |

| Figure 28.  | PDAR control and action bytes                                |

| Figure 29.  | Fields of ABREC                                              |

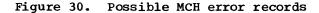

| Figure 30.  | Possible MCH error records                                   |

| Figure 31.  | Fields of the Fixed Logout                                   |

| Figure 32.  | Fields of the Extended Logout for the Model 145 116          |

| Figure 33.  | Fields of the Extended Logout for the Model 135 117          |

| Figure 34.  | Register conventions                                         |

| Figure 35.  | Sample machine-check interruption codes for the Model        |

| 145         |                                                              |

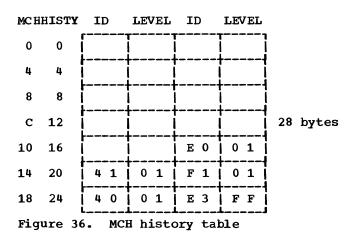

| Figure 36.  | MCH history table                                            |

| Figure 37.  | MCH message table                                            |

| -           | -                                                            |

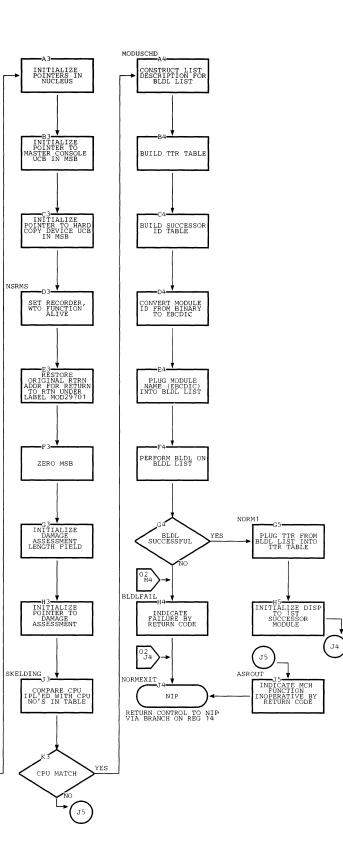

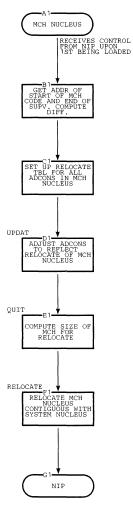

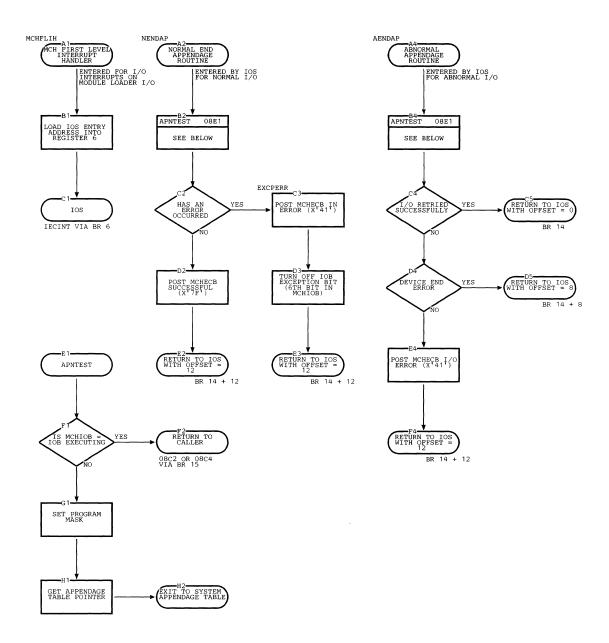

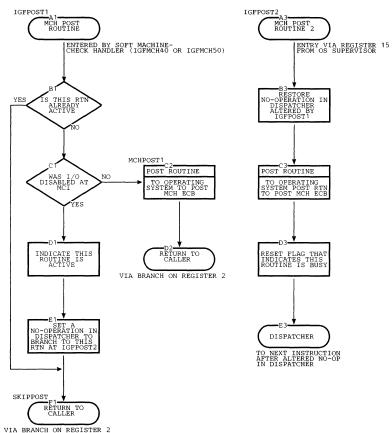

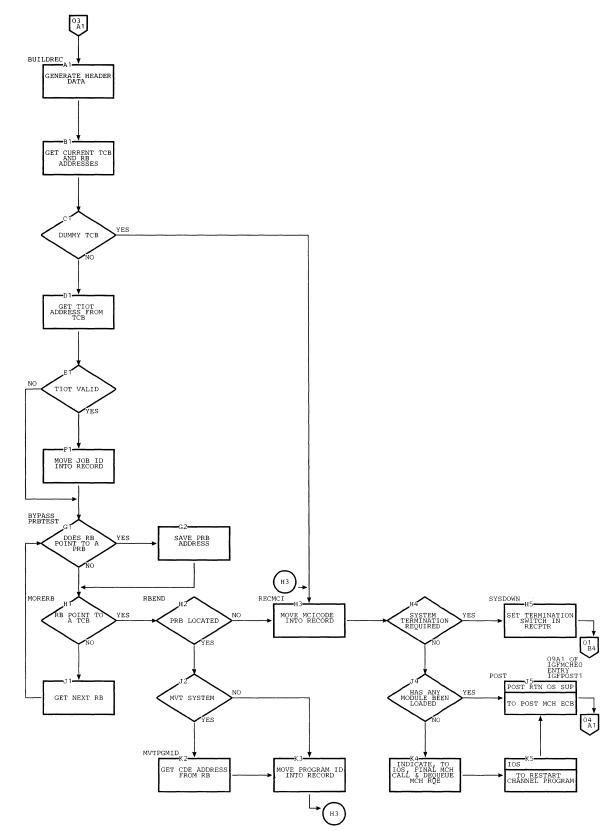

| IGFMCHF0. | MCH Initialization                   |

|-----------|--------------------------------------|

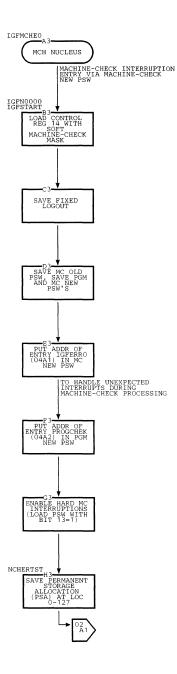

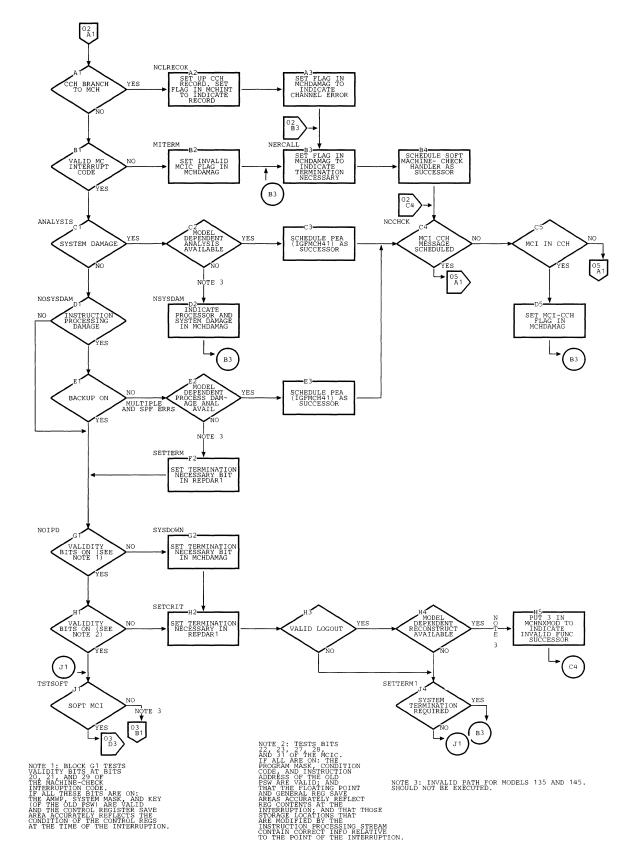

| IGFMCHE0. | MCH Nucleus                          |

| IGFMCH40. | Model 145 Soft Machine-Check Handler |

| IGFMCH50. | Model 135 Soft Machine-Check Handler |

| IGFMCH41. | Preliminary Error Analysis           |

| IGFMVTF1. | MVT System Analysis 1                |

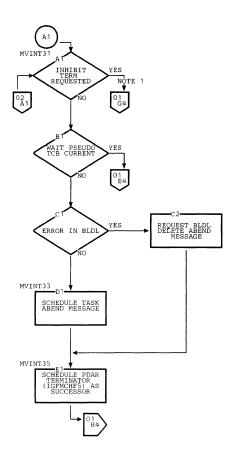

| IGFMVTF2. | MVT System Analysis 2                |

| IGFMVTF3. | MVT System Analysis 3                |

| IGFMFTF1. | MFT System Analysis 1                |

| IGFMFTF2. | MFT System Analysis 2                |

| IGFMFTF3. | MFT System Analysis 3                |

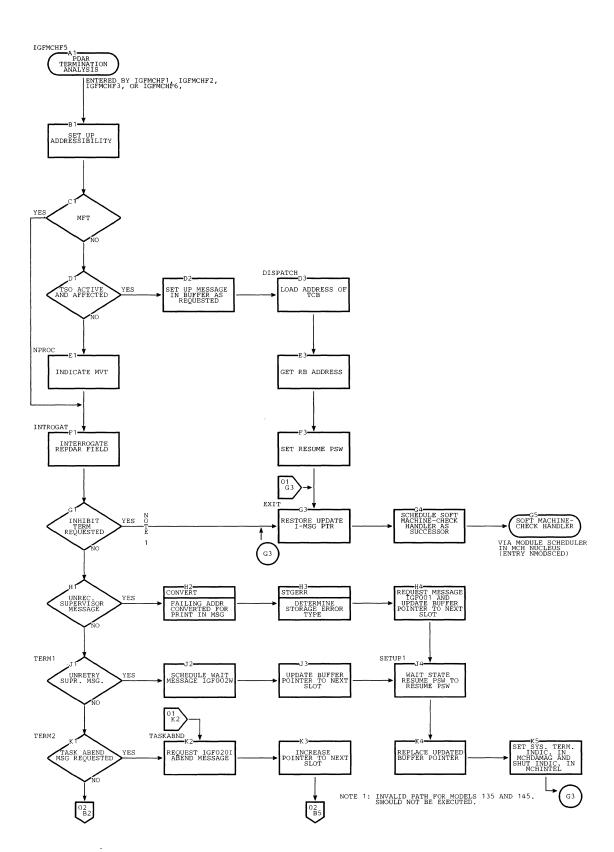

| IGFMCHF5. | PDAR Terminator                      |

| IGFMCHF6. | TSO Subsystem Analysis               |

| IGFMCHE2. | Error Recorder                       |

| IGFMCHE1. | Console Write Routine                |

| IGFMCHE3. | Emergency Recorder                   |

| IGF29701. | Model 145 Machine Status Control     |

| IGF13501. | Model 135 Machine Status Control     |

|           |                                      |

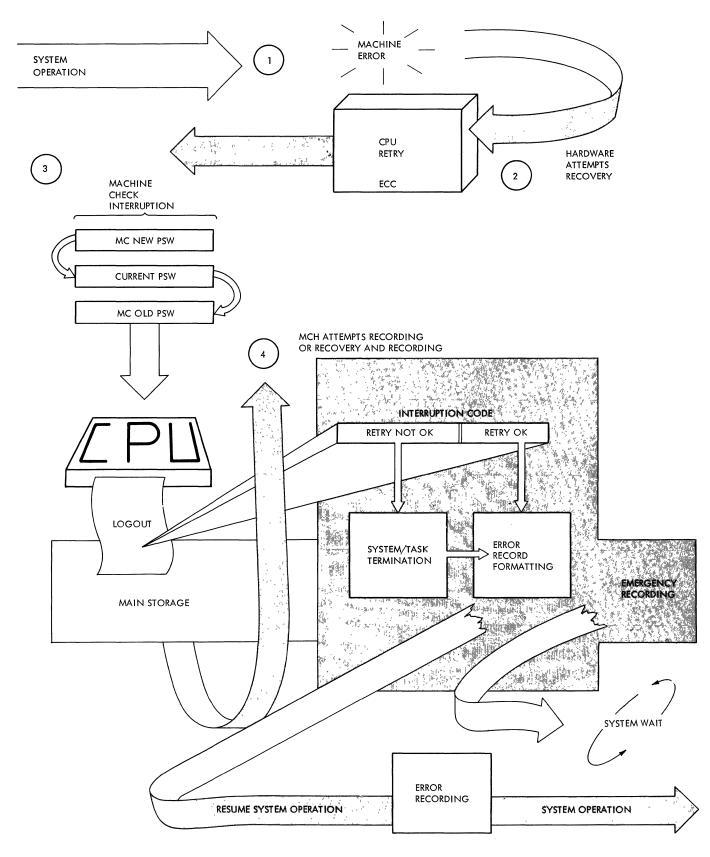

This publication describes the operations of the Machine-Check Handler (MCH) program for the IBM System/370 Models 135 and 145. The Machine-Check Handler for the Model 135 is a standard component of the MFT version of the System/360 Operating System. The Machine-Check Handler for the Model 145 is a standard component of both the MFT and MVT versions of the System/360 Operating System. The purpose of the Machine-Check Handler is to minimize the effects of machine malfunctions on jobs in process. MCH does this, on the occurrence of a machine-check interruption, by attempting to correct the malfunction and by producing diagnostic records and messages to help system maintenance personnel find the cause of the problem. See Figure 1 for an overview of the Machine-Check Handler.

## RECOVERY DESIGN OF THE MODELS 135 AND 145

Machine malfunctions originate in the CPU, main storage, and control storage. When one of these fails, hardware facilities attempt to correct the malfunction. CPU malfunctions are corrected through microprogram routines which retry the failing operation. This is called CPU retry. Malfunctions in main and control storage are corrected by Error Checking and Correction (ECC). These two recovery features are described in more detail later in this section.

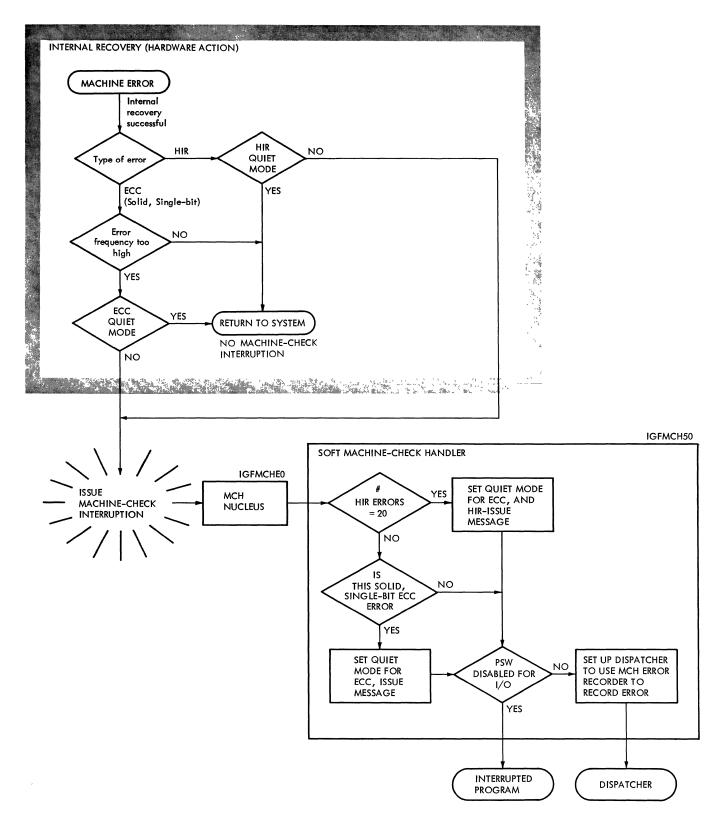

CPU retry and ECC are not always successful in their attempts to correct a malfunction. For this reason there are two types of machine-check interruptions. A "soft" machine-check interruption (sometimes called a recovery report) is generated when:

- CPU retry has corrected the malfunction,

- ECC has corrected the malfunction (Model 145 only), or

- ECC has encountered a solid, single-bit error that has reached an Error Frequency Limit such that ECC is correcting the error 256 times within 416 micro-seconds (Model 135 only).

A "hard" machine-check interruption (sometimes called a damage report) is generated when the malfunction has not been corrected. When a machine-check interruption occurs, MCH immediately gets control. If a soft machine-check interruption occurs, MCH records information about the malfunction. If a hard machine-check interruption occurs, in addition to recording information about the malfunction, MCH attempts to shield the operating system from the adverse effects of the malfunction.

The machine logs out information describing the cause of the malfunction and the status of the system at the time of the interruption. This information is used by the Machine-Check Handler to carry out its recovery and recording operations.

## HARDWARE RECOVERY FEATURES OF THE MODELS 135 AND 145

The operation of the Machine-Check Handler depends on certain recovery actions taken by the hardware. It also depends on information given to it by the hardware. Some of the features of the hardware are described here.

#### AUTOMATIC RECOVERY FEATURES

The Models 135 and 145 have two "builtin" methods of recovering from machine malfunctions: CPU retry and ECC. Whenever circumstances permit, these two hardware features recover from machine malfunctions without assistance from the software.

## CPU Retry

CPU errors are automatically retried by microprogram routines. These routines save source data before it is altered by the operation. When an error is detected, a microprogram routine returns the CPU to the beginning of the operation, or to a point where the operation was executing correctly, and the operation is repeated. After eight unsuccessful retries, the error is considered permanent.

The CPU retry feature allows the machine to recover from temporary CPU failures that would otherwise make it necessary to reload the operating system or terminate the executing program.

After each successful use of CPU retry, there is a soft machine-check interruption unless CPU retry is in quiet mode. After eight unsuccessful retries, there is a hard machine-check interruption.

Figure 1. Machine-check handler overview

## ECC Validity Checking

ECC checks the validity of data from main and control storage, automatically correcting single-bit errors. It also detects multiple-bit errors but does not correct them.

Data enters and leaves storage through a storage adapter unit. This unit makes the ECC validity check on each doubleword by insuring that the doubleword contains the appropriate parity bit for each byte. If a single-bit error is detected, the erroneous bit is corrected. The corrected doubleword is then sent back into main or control storage and on to the CPU. MCH is notified by a machine-check interruption and retrieves the failing storage address from the fixed logout. Note that with MCH for the Model 135, the threshold of such soft machine checks must be exceeded before a machine-check interruption occurs.

When a multiple-bit storage error is detected, a machine-check interruption is generated, and the error location is placed in the fixed logout. MCH gains control and attempts to recover from the error.

### FIXED STORAGE LOCATIONS

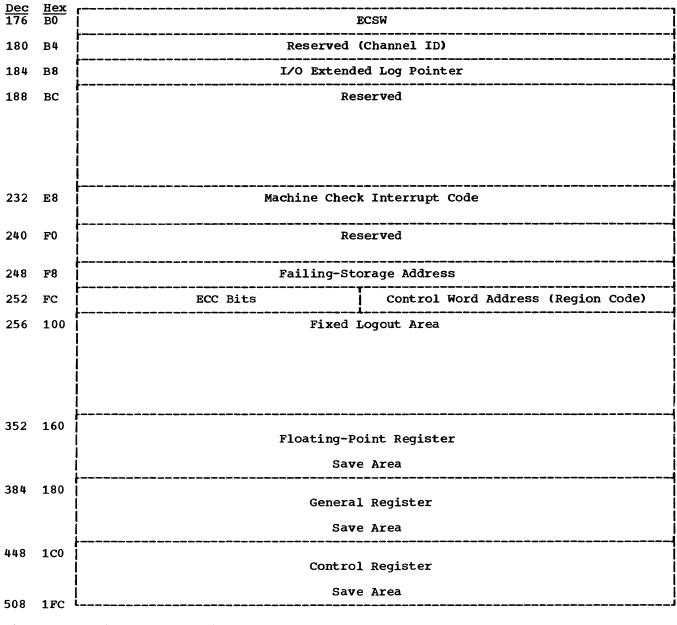

There are four fixed storage locations in the Models 135 and 145: the fixed area in decimal locations 0-127, the I/O communications area in locations 160-191, the fixed logout area in locations 232-511, and the extended logout area. On the Model 135, the extended logout is a 14 byte field contained within the fixed logout area at location 256. On the Model 145, the extended logout is in locations 512-703, unless the pointer to the Model 145 logout area (control register 15) specifies otherwise.

## Fixed Logout Area

Data is put into the fixed logout area (232-511) when any type of machine-check interruption occurs. The data stored is processed by the Machine-Check Handler. The layout of this area is model independent among the System/370 models; however, all models do not use every field in the fixed logout. The fixed logout area contains the machine-check interruption code which indicates the reason for the interruption. Other fields in the area preserve the status of the system at the time of the machine-check interruption and the contents of the general purpose, floating point, and control registers.

## Extended Logout Area

The extended logout area contains data that is model-dependent. On the Model 145, the extended logout begins at the address specified in control register 15 and is a maximum length of 192 bytes long. Control register 15 is set to point to decimal location 512 by the hardware during IPL or system reset.

On the Model 135, the extended logout is contained in decimal locations 256 through 269 (an area within the fixed logout). If the extended logout mask bit in control register 14 is enabled for logouts, data is logged into the extended logout area for all types of machine-check interruptions. This data is recorded by MCH in the SYS1. LOGREC data set.

#### CONTROL REGISTERS

Two control registers are used by MCH for loading and storing control information.

Control register 14 contains mask bits which specify whether certain conditions can cause machine-check interruptions and mask bits which control conditions under which an extended logout may occur.

Control register 15, used only on the Model 145, contains the address of the extended logout area.

The control registers are referred to by MCH through the use of two privileged instructions: LOAD CONTROL and STORE CON-TROL. LOAD CONTROL furnishes a means of loading control information from main storage to control registers; STORE CONTROL permits information to be transferred from control registers to main storage.

The publication <u>IBM System/370 Prin-</u> ciples of Operation, GA22-7000, contains a detailed description of the use of control registers.

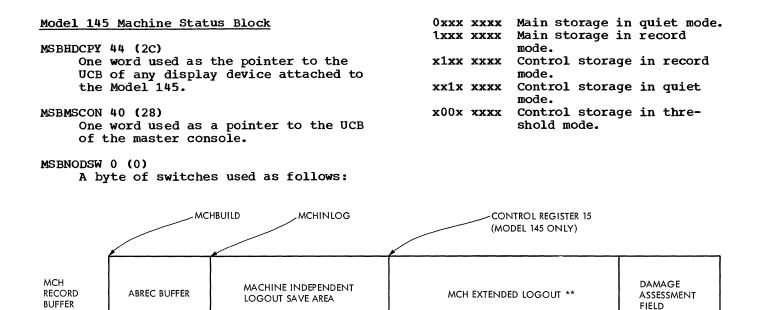

#### MODES OF RECOVERY OPERATION

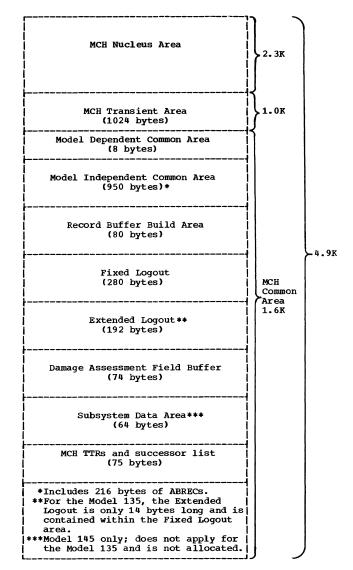

The type of recording done by MCH depends upon the current "mode" of the CPU, main storage, and control storage. There are three possible modes: quiet mode, recording mode, and threshold mode.

In quiet mode, machine checks corrected by CPU retry or ECC do not cause machinecheck interruptions.

In recording mode, machine failures corrected by these features do cause interruptions for recording purposes. In threshold mode, a preset frequency of such errors must occur before a soft machine-check interruption occurs. Note that hard (uncorrected) machine failures always result in a machine-check interruption regardless of mode.

There is a MODE command that can be used to vary the current mode (see "Use of the MODE Commands" in this section).

MODES OF RECOVERY OPERATION OF THE MODEL 135

The Model 135 can operate in either recording mode or quiet mode (see Figure 2).

CPU Malfunctions

When the CPU is in recording mode, a

soft machine-check interruption occurs each time a machine malfunction is repaired by CPU retry. When 20 such soft machine checks have occurred, the Soft Machine-Check Handler will automatically switch the CPU from recording mode to quiet mode.

<u>Note</u>: Main and control storage are switched automatically to quiet mode along with the CPU. See "Use of the Mode Commands" in this section.

When the CPU is in quiet mode, no machine-check interruption is issued for a soft error. Switching from quiet mode to recording mode can be accomplished by issuing the MODE command.

|                                                                                                                                |                 |                        |                    | MCH Er<br>(Interru |             |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------|--------------------|--------------------|-------------|

| Mode                                                                                                                           | Error Location  | Error Type             | Solid/Intermittent | 135                | 145         |

| Quiet                                                                                                                          | Main Storage    | Multiple-bit<br>(hard) | NA                 | Yes                | Yes         |

|                                                                                                                                |                 | Single-bit<br>(soft)   | NA                 | No                 | No          |

|                                                                                                                                | Control Storage | Multiple-bit           | NA                 | Yes                | Yes         |

|                                                                                                                                |                 | Single-bit             | NA                 | No                 | No          |

|                                                                                                                                | СРИ             | NA                     | NA                 | NA                 | NA          |

| Recording                                                                                                                      | Main Storage    | Multiple-bit           | NA                 | Yes                | Yes         |

|                                                                                                                                |                 | Single-bit             | Solid              | No                 | No          |

|                                                                                                                                |                 | Single-bit             | Intermittent       | Yes                | Yes         |

|                                                                                                                                | Control Storage | Multiple-bit           | NA                 | Yes                | Yes         |

|                                                                                                                                |                 | Single-bit             | Solid              | No <b>*</b>        | No <b>*</b> |

|                                                                                                                                |                 | Single-bit             | Intermittent       | Yes                | Yes         |

|                                                                                                                                | СРИ             | Multiple-bit           | NA                 | Yes                | Yes         |

|                                                                                                                                |                 | Single-bit             | NA                 | Yes                | Yes         |

| Threshold                                                                                                                      | Main Storage    | NA                     | NA                 | NA                 | NA          |

|                                                                                                                                | Control Storage | Multiple-bit           | NA                 | NA                 | Yes         |

|                                                                                                                                |                 | Single-bit             | NA                 | NA                 | No <b>*</b> |

|                                                                                                                                | СРИ             | NA                     | NA                 | NA                 | NA          |

| *Single-bit errors in control storage will generate an interruption only if the hard-<br>ware specified threshold is exceeded. |                 |                        |                    |                    |             |

Figure 2. Modes of recovery operation

## Main and Control Storage

In recording mode, a machine-check interruption occurs for each malfunction except solid, single-bit errors that occur below a certain rate. If the rate (or frequency) of single-bit errors becomes too high, a soft machine-check interruption occurs and main and control storage are automatically switched to quiet mode by the Soft Machine-Check Handler.

<u>Note</u>: The CPU is not automatically switched to quiet mode along with main and control storage. See "Use of the Mode Commands" in this section.

In quiet mode, no soft machine-check interruptions occur. A switch from quiet to recording mode can be made by issuing the MODE command.

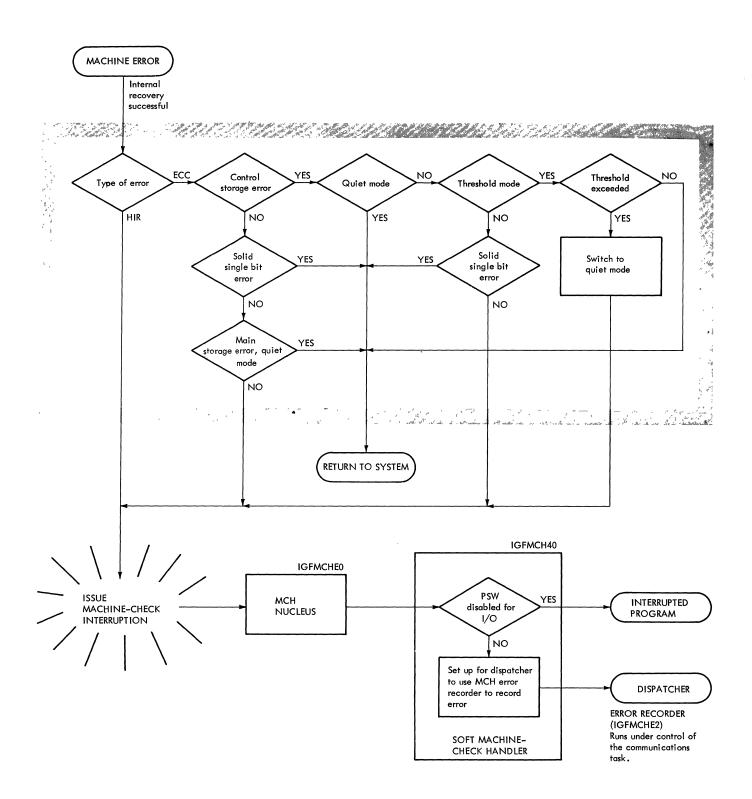

MODES OF RECOVERY OPERATION OF THE MODEL 145

Three modes of operation for the Model 145 are used; recording mode, quiet mode, and threshold mode. Depending on the source of the malfunction, one, two, or all three modes may apply (see Figure 2):

CPU Malfunctions

Only the recording mode applies to CPU operations. In this mode, a machine-check interruption occurs for each malfunction.

## Main Storage Malfunctions

In recording mode, a machine-check interruption occurs for each malfunction except solid, single bit errors. In quiet mode, only hard errors cause machine-check interruptions. Soft ECC errors do not cause interruptions when main storage is in quiet mode.

Control Storage Malfunctions

In recording mode, a machine-check interruption occurs for each malfunction. In quiet mode, only hard errors generate machine-check interruptions; soft errors do not cause interruptions. In threshold mode, no interruptions are generated for soft ECC errors unless a specified number of soft errors occur within a specified time. The frequency of errors that will be tolerated is preset by the hardware. When that frequency is exceeded, a machine-check interruption occurs, control storage is automatically switched into quiet mode and a message is sent to the operator.

## USE OF THE MODE COMMANDS

The MODE command is an operator command used to switch between recording, quiet, and (145 only) threshold modes. The 135 MODE command can also be used to display the current mode status.

## Mode Command for the Model 135

The format of the Model 135 MODE command is:

| Operation | Operand                              |  |  |

|-----------|--------------------------------------|--|--|

| MODE      | (STATUS<br>HIR RECORD<br>ECC RECORD) |  |  |

STATUS

causes the current status of both CPU retry (HIR) and ECC to be displayed in a message (IGF053I). The message also contains the CPU retry current error count and error count threshold for soft machine checks. The response to the command MODE STATUS is:

IGF053I MODE STATUS-ECC ( QUIET ) RECORD ( HIR ) QUIET ( RECORD ) COUNT-NN THRESHOLD-NN

When the current error count equals the error count threshold (20), the Soft Machine-Check Handler switches both CPU retry and ECC to quiet mode. ECC is automatically switched to quiet mode along with CPU retry because the bit used to mask off CPU retry recording mode (bit 4 in control register 14) also masks off ECC recording mode.

When an Error Frequency Limit (EFL) of 256 single-bit error corrections within 416 micro-seconds has been reached, a soft ECC interruption occurs and the Soft Machine-Check Handler switches ECC (main and control storage) to quiet mode. CPU retry is not automatically switched to quiet mode along with ECC because ECC can be masked off independently with a DIAG-NOSE instruction. Notice that solid, single-bit error corrections do not cause machine-check interruptions unless they occur with a greater frequency than the Error Frequency Limit. Also note that only Control Storage is referenced frequently enough for the EFL to be exceeded.

HIR RECORD

causes the CPU retry feature to enter recording mode. When the command to

enter recording mode is issued, the CPU current error count is reset to zero. If the CPU retry feature is already in recording mode when this form of the command is issued, the current error count is still reset to zero.

#### ECC RECORD

causes the ECC feature to enter recording mode. If this form of the MODE command is issued when CPU retry is in quiet mode, it is rejected as a command error. One bit in control register 14, which is used to mask off CPU retry recording mode, also masks off ECC recording mode. Therefore, CPU retry must be in recording mode before ECC can be switched to recording mode.

## Mode Command for the Model 145

The format of the Model 145 MODE command is:

| Operation | Operand          |                                |  |  |

|-----------|------------------|--------------------------------|--|--|

| MODE      | (MAIN)<br>(CNTR) | , RECORD<br>, QUIET<br>, THRES |  |  |

#### MAIN

causes main storage to be placed in the specified mode.

#### CNTR

causes control storage to be placed in the specified mode. Note that control storage is physically identical to main storage and that both are contained within the same unit. Main storage contains problem programs and control (supervisor) programs. Control storage contains the basic instruction set.

#### RECORD

causes the specified storage to be set to recording mode. In recording mode, a machine-check interruption occurs for all machine errors (except solid, single-bit errors)<sup>1</sup> whether they have been corrected or not.

## QUIET

causes the specified storage to be set to quiet mode. In quiet mode, machine

<sup>1</sup>Solid, single-bit errors in Control Storage can sometimes reach such a frequency as to exceed a preset Error Frequency Limit. In such cases, a solid, single-bit error causes a machine-check interruption. checks corrected by CPU Retry or ECC do not cause machine-check interruptions.

#### THRES

causes control storage to be set to threshold mode. This operand can <u>only</u> be used for control storage. When in threshold mode, a pre-specified number of soft errors must occur before a soft machine-check is issued and control storage is automatically switched to quiet mode. Notice that solid, single-bit error corrections do not cause soft machine-check interruptions unless it is a solid, single-bit error in control storage that exceeds the preset threshold.

<u>WARNING</u>: The Model 145 MODE command is intended for use <u>only</u> by IBM personnel. Issuing the RECORD form of this command at the wrong time can cause significant degradation in performance.

## MCH ERROR RECOVERY

Recovery from a machine malfunction is handled by both hardware recovery facilities and the MCH program. MCH recovery can be classified into three categories: system recovery, system-supported restart, and system repair. These levels of error recovery are discussed in the order in which they are attempted.

#### SYSTEM RECOVERY

When the hardware cannot recover the system from the machine check, system recovery takes place. MCH attempts to keep the system working at the expense of the task in which the error appeared. The processing of the task containing the error is terminated either by normal methods of job termination (ABEND) or by marking the task nondispatchable. System recovery only takes place if the task in question is not critical to continued system operation. An error in a critical task would require a system-supported restart.

#### SYSTEM-SUPPORTED RESTART

System-supported restart (warm start) requires the operator to re-IPL the system. The operator is notified that a critical error has occurred and that system continuation is impossible. This type of recovery is used when system recovery has failed or has been judged impossible.

## SYSTEM REPAIR

System repair takes place at the discretion of the operator. Usually, the operator will have tried to recover by systemsupported restart one or more times with no success. An example of this type of error is when a hard error occurs so frequently that system-supported restart would not be successful. System repair always requires the services of maintenance personnel.

#### PHYSICAL CHARACTERISTICS

## MAIN STORAGE REQUIREMENTS

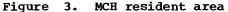

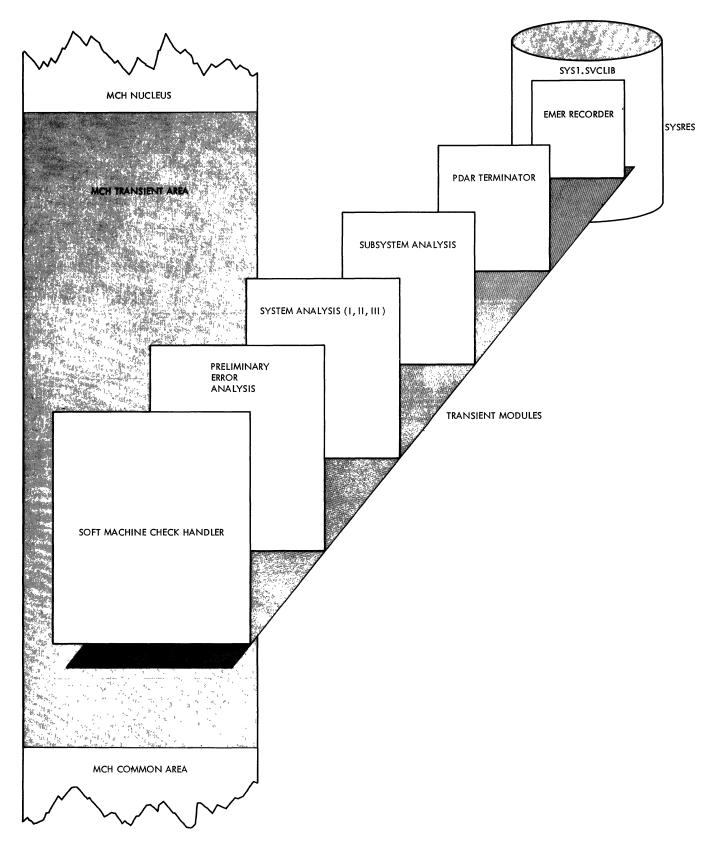

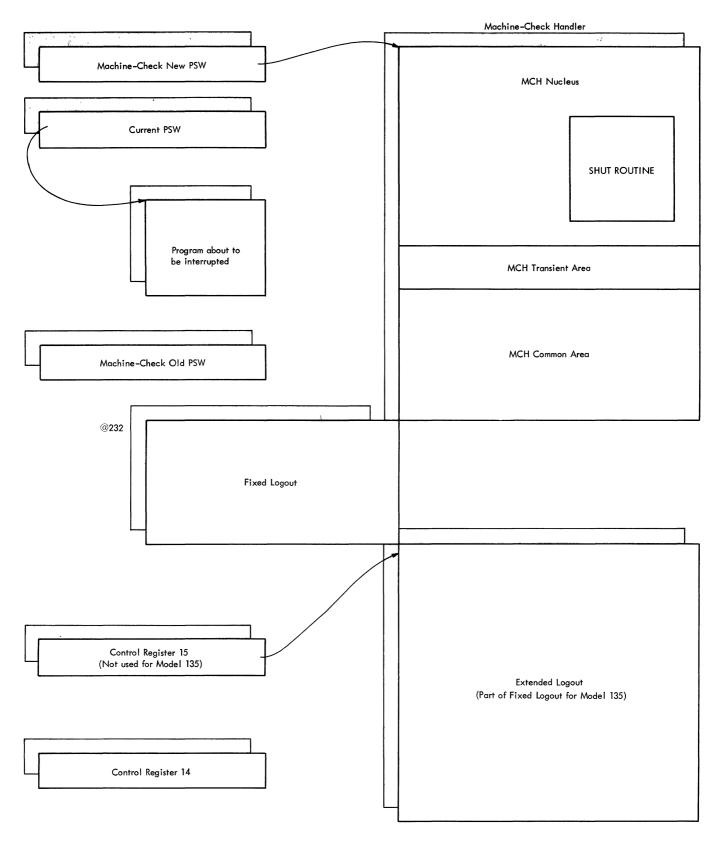

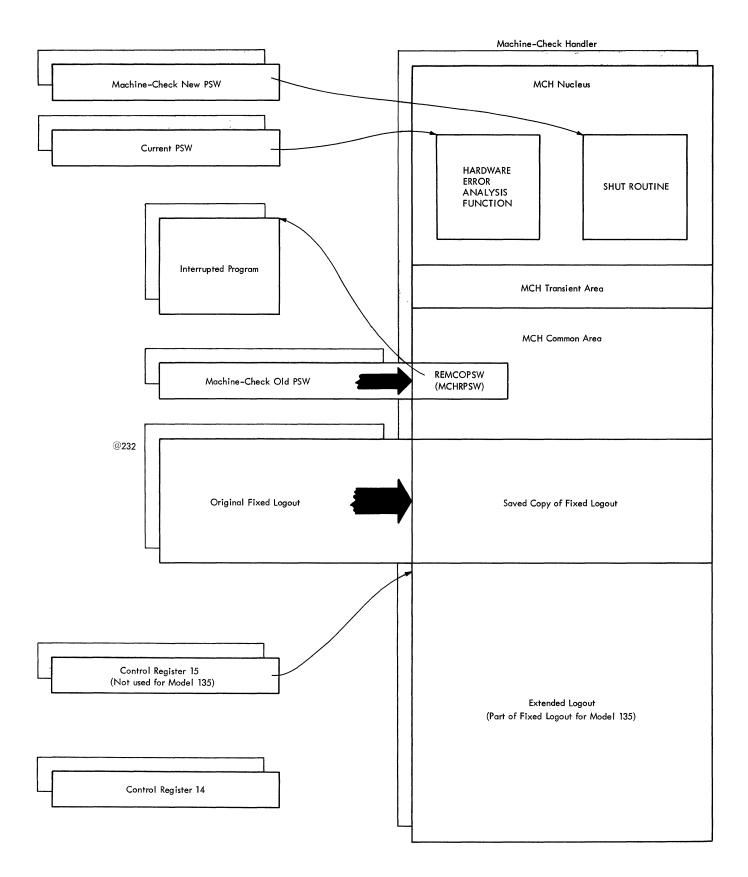

The Machine-Check Handler operates within the MCH Resident Area. The MCH Resident Area, as shown in Figure 3, occupies 4.9K bytes in the fixed area of main storage. The MCH Resident Area is divided into three sections: the MCH Nucleus Area, the MCH Transient Area, and the MCH Common Area.

<u>MCH Nucleus Area</u>: The MCH Nucleus Area contains the control module of the program. It is 2.3K bytes long and its contents remain in storage unchanged.

<u>MCH Transient Area</u>: The MCH Transient Area occupies 1K bytes of main storage adjacent to the MCH Nucleus Area. It is used by the MCH transient (or overlay) routines, which reside on SYS1.SVCLIB.

<u>MCH Common Area</u>: The MCH Common Area is used for intermodule communication and construction of the MCH error record. A portion of the MCH Common Area, called the Subsystem Data Area, is used for communication between MCH and any subsystems which may be running under the operating system. The MCH Common Area is partitioned into several smaller data areas. The contents of these partitions are described in Section 4.

The fixed and extended logout areas are reserved to log the data about the machine malfunction. The fixed logout area primarily contains information that is model independent. It extends from location 176 to location 511 (decimal). MCH only uses that portion from 232 through 511. The extended logout area contains only modeldependent data and is 192 bytes long for the Model 145 and 14 bytes long for the Model 135.

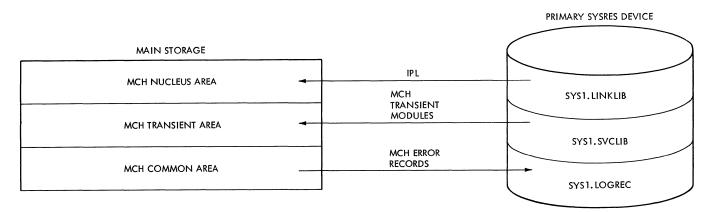

#### AUXILIARY STORAGE REQUIREMENTS

The MCH transient modules occupy 13K bytes (Model 145) or 10K bytes (Model 135) in SYS1.SVCLIB on the primary SYSRES device. The MCH Nucleus and the MCH Initialization module (used to initialize MCH during NIP operations) are allocated 8.7K bytes on SYS1.LINKLIB.

The configuration of the system in use determines the amount of space required in SYS1.LOGREC for MCH to write its error records. (See <u>IBM System/360 Operating</u> <u>System Storage Estimates</u>, GC28-6551, for details.) Figure 4 shows the Machine-Check Handler in main storage and auxiliary storage.

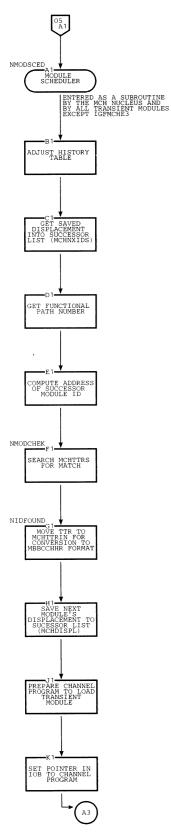

## OVERLAY STRUCTURE OF MCH

While the MCH Nucleus remains in main storage at all times, most other MCH modules are in main storage only when they are being used and are called <u>transient</u> <u>modules</u>. These nonresident modules are stored in the SYS1.SVCLIB data set. Figure 5 illustrates the overlay structure of MCH.

When the Machine-Check Handler is not being used, the Soft Machine-Check Handler occupies the transient area. The Soft Machine-Check Handler is an MCH module that prepares the recovery report for soft machine-check interruptions. Having the Soft Machine-Check Handler reside in the transient area eliminates the need to bring in modules from auxiliary storage when a soft machine-check interruption occurs.

The MCH Nucleus, which can be thought of as the control program for the Machine-Check Handler, resides permanently in the MCH Nucleus Area. The Module Loader is included in the MCH Nucleus. When a machine-check interruption occurs, and the Nucleus determines that transient modules are needed to continue processing the machine-check interruption, control is given to the Module Loader to load a transient module from SYS1.SVCLIB. The first module brought into the transient area then overlays the Soft Machine-Check Handler. Each transient module can determine which transient module will succeed it. When the current transient module finishes its processing, it specifies the logical path number of the successor module to the Module Loader. The Module Loader then transfers control to the I/O Supervisor, which reads the next module into the transient area. After all processing has been completed, the Soft Machine-Check Handler is read back into the transient area. Except for system termination, the Soft Machine-Check Handler is always the final successor module, since it must be resident when MCH is again given control. When the system must be terminated, the Emergency Recorder is the last module in the Transient Area.

## Figure 4. Main storage and auxiliary storage relationships

Figure 5. MCH overlay structure

This section describes the functions of the Machine-Check Handler. For the reader who is unfamiliar with the operation of the program, this section will serve as an introduction to the logic described in the "Program Organization" section of the manual. For the reader familiar with MCH, this section, especially the illustrations, can be used for review.

This section is divided into two parts: the first tells why MCH operates as it does, and the second shows the operations that take place.

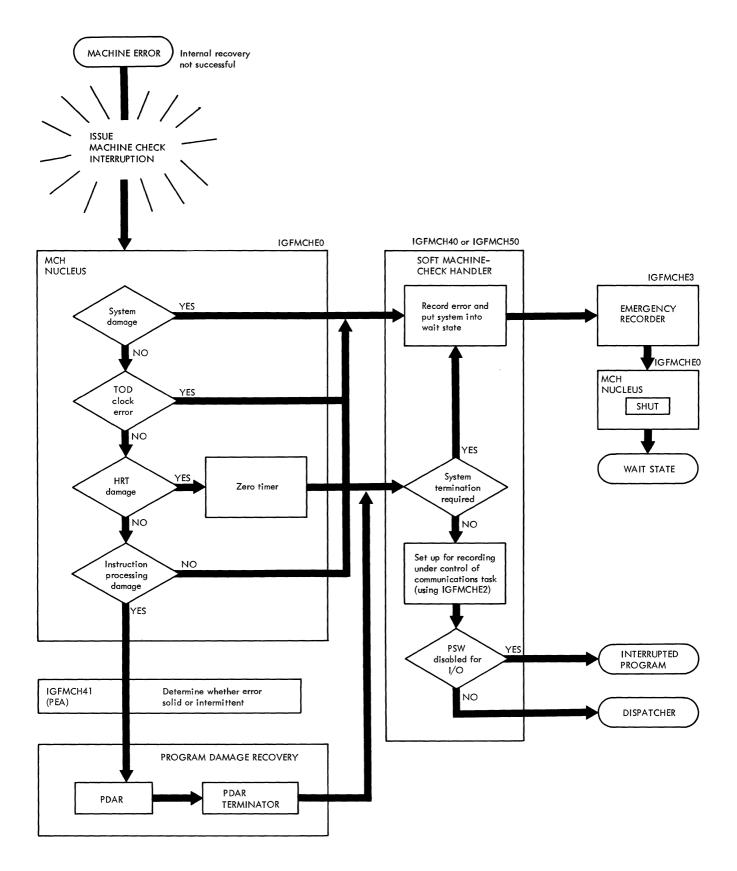

#### THE LOGIC OF MCH

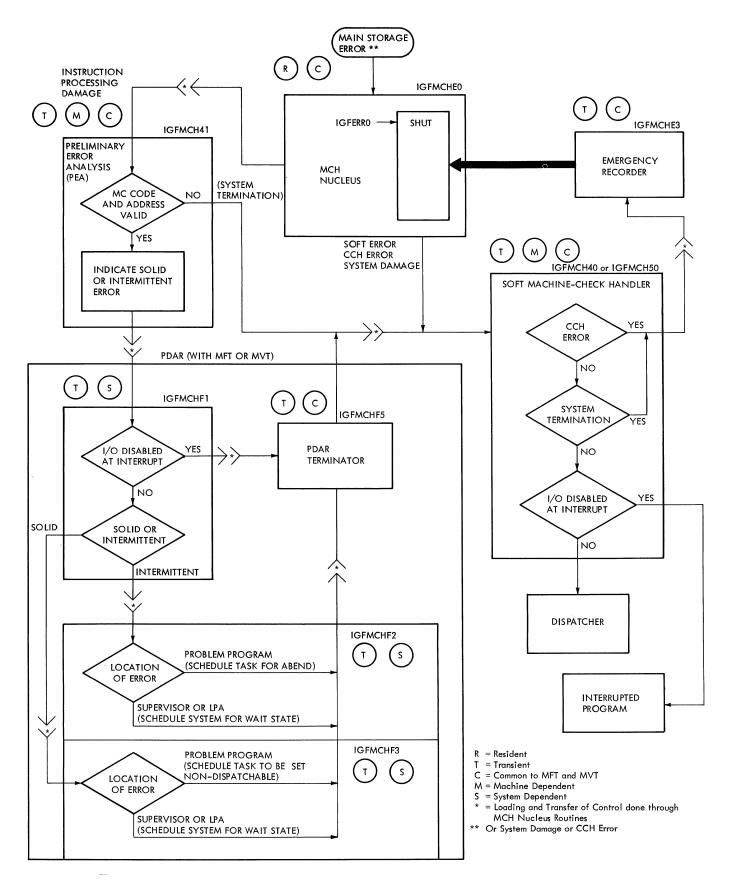

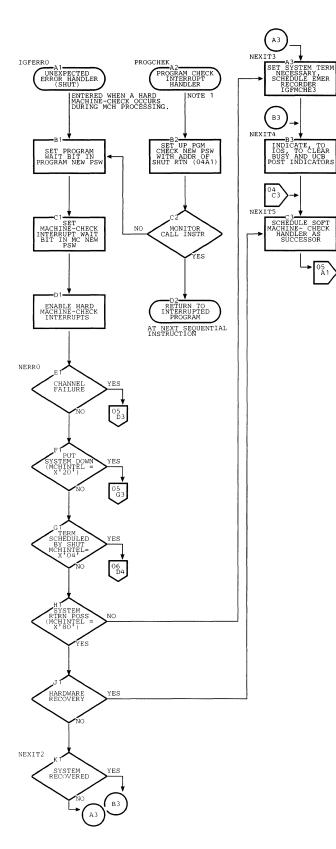

MCH has two basic methods of operation: one for hard machine-check interruptions and one for soft (see Figures 6, 7, and 8). In processing a hard machine-check interruption, the Machine-Check Handler goes through four stages of operation:

- 1. Initialization

- 2. Hardware error analysis

- 3. Program damage recovery

- 4. Recording and termination

For a soft machine-check interruption, step 3, program damage recovery, is omitted. Since, by definition, a soft machine-check interruption signifies that the error has already been corrected by the circuitry (CPU retry and ECC), program damage recovery is not necessary. Figures 6, 7, and 8 illustrate the general processing involved in handling each type of machine-check interruption.

In addition to the four steps mentioned above, the Machine-Check Handler controls whether the machine will operate in recording mode or quiet mode. This function is logically independent from normal MCH processing.

The machine must communicate with the Machine-Check Handler and the components of the Machine-Check Handler must communicate with each other. In addition, MCH externally communicates with the operator and system maintenance personnel.

#### COMMUNICATIONS

To deal effectively with each machinecheck interruption, MCH must have certain data concerning the nature of the malfunction. The hardware produces a logout that gives the Machine-Check Handler the information it needs to properly analyze the error. The Machine-Check Handler moves this information into the MCH Common Area. The transient modules use the Common Area to communicate with each other. The MCH Nucleus also uses the Common Area; it stores and retrieves data about the attempted recovery. Section 4 of this manual describes the Common Area fully.

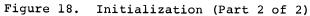

## INITIALIZATION

MCH normally receives control through a machine-check interruption. Should another machine-check interruption occur while MCH has control, processing would stop and control would go back to the beginning of MCH. As a result, the first machine-check interruption would never be processed since the information about it in the logout area would be lost. To minimize this possibility, MCH receives control with the system disabled for further interruptions. Disabling, however, is only a temporary measure to give the MCH Nucleus time to make some emergency provisions. The following initializing steps are taken by the MCH Nucleus:

- It disables soft machine-check interruptions. Since soft errors have already been corrected, priority to interrupt MCH processing is given to hard errors. If the error being handled is hard and MCH is attempting to recover, there is no need to interrupt processing to report a soft error. If the present error is soft, there is no reason for one soft error to have priority over another.

- 2. It saves the contents of the fixed logout area in the MCH Common Area. If a hard machine-check interruption occurs now, the original data will not be overlaid by data from the second error. Also, extended logouts are prevented via a mask setting in control register 14 so that the extended logout area will not be overlaid.

Figure 6. General processing of hard errors

Figure 7. General processing of Model 145 soft errors

Figure 8. General processing of Model 135 soft errors

- 3. It saves the machine check old PSW. Then if a second error should occur, causing the current PSW to replace the old, control can be given back (through an LPSW instruction) to the program that was interrupted first (provided the error was corrected with the original system status intact).

- 4. It alters the address in the machine check new PSW to point to the SHUT (Special Handler for Unusual Termination) routine. A second machine-check interruption now sends control to the SHUT routine, rather than to the beginning of MCH. Note that a second machine-check interruption implies an error within MCH or IOS. If the machine-check new PSW were never altered and the error recurred, the Machine-Check Handler would go into a loop. Also, since the second error is within MCH, it is recognized that MCH is operating in a degraded state and might not be able to recover from the original error.

- 5. It alters the address in the program check new PSW to point to a special program check handler that intercepts and recognizes all program-check interruptions. If the interruption is caused by a Monitor Call, it is ignored. If the interruption is not caused by a Monitor Call, control is passed to the SHUT routine.

- 6. It enables hard machine-check interruptions. Soft machine-check interruptions remain disabled until error recording is completed.

There is always the danger that a machine malfunction may occur immediately after MCH is entered and the system is disabled for interruptions. If this happens, the machine comes to a hard stop, no instructions are executed and no interruptions occur. The machine can only be removed from the hard stop by a system reset or IPL.

Figure 9 shows MCH responses to various error-on-error conditions.

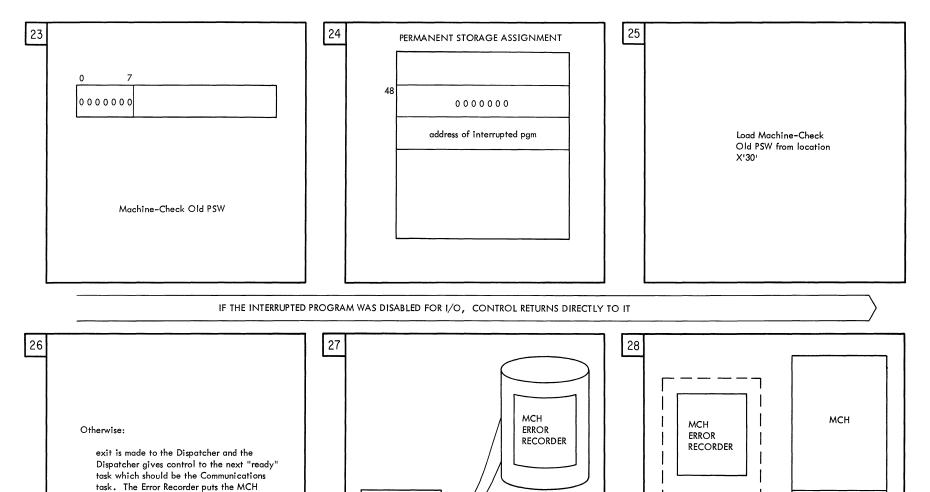

## Saving the Environment

The Machine-Check Handler saves the fixed logout and the machine check old PSW to protect them from a second machine-check interruption. The address where the fixed logout is saved is contained in MCHINLOG in the Common Area. Once the system has been reenabled for interruptions, MCH saves the permanent storage assignment (PSA). The PSA extends from location 0 through location 128 (decimal). The four data areas are saved in the following locations:

- Fixed Logout address contained in MCHINLOG in the MCH Common Area

- Extended Logout of Model 135 a fixed save area (decimal location 256) within the Fixed Logout

- Extended Logout of Model 145 address contained in control register 15

- Machine-Check Old PSW MCHRPSW (REMCOPSW) in the Common Area

- Permanent Storage Assignment MCHPSA in the MCH Common Area

Figures 10 and 11 illustrate the MCH environment before and after initialization.

## Module Loading

The Machine-Check Handler uses the facilities of the I/O Supervisor to bring the

| Error<br>Condition                                     | Special<br>Circumstances                    | MCH Response                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hard<br>on<br>Soft                                     | Error within<br>MCH                         | An analysis is made to determine the severity of the<br>error. For any error other than system damage, an attempt<br>is made to record the original error and return control<br>to the point of interruption. The occurrence of another<br>hard error during this attempt will result in a wait<br>state, with a message if possible. |

| Recovery made  <br>  from original  <br>  Hard   error |                                             | An attempt is made to record the original error and control is returned to the system.                                                                                                                                                                                                                                                |

| on<br>Hard                                             | Recovery not<br>made from<br>original error | The system is placed in a disabled wait state with a corresponding message written to the operator.                                                                                                                                                                                                                                   |

Figure 9. MCH responses to error-on-error conditions

Figure 10. MCH and environment before initialization

Figure 11. MCH and environment after initialization

MCH transient modules into main storage. Since an I/O interruption takes place after the new module has been read into the MCH transient area, MCH saves the address portion of the I/O new PSW and replaces it with the address of a section of its own code. This permits the Machine-Check Handler to service the I/O interruption. The original address contained in the I/O new PSW is replaced prior to returning to the system.

Figure 12 shows the module loading operation and explains the logic of scheduling a successor module.

#### HARDWARE ERROR ANALYSIS

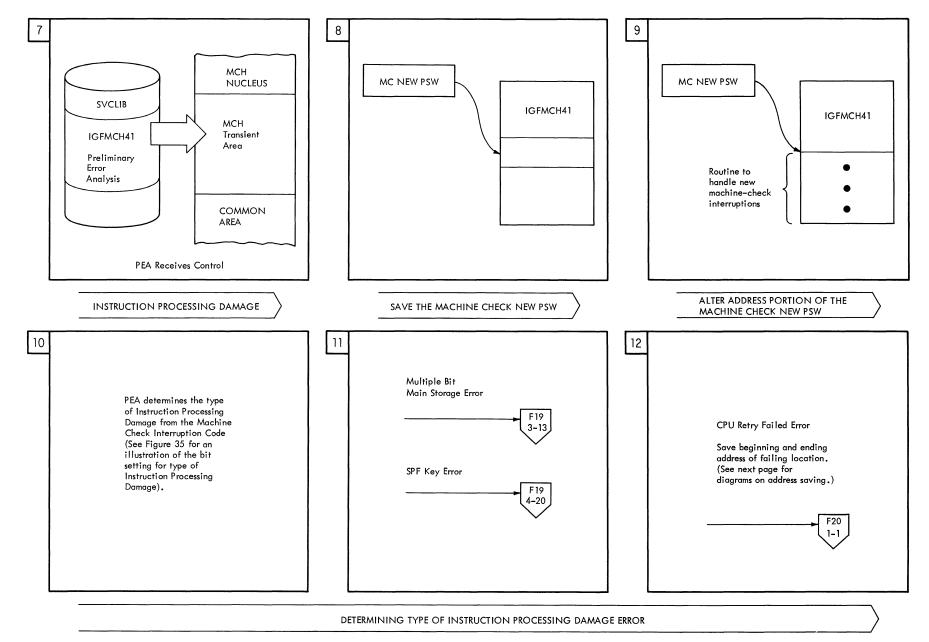

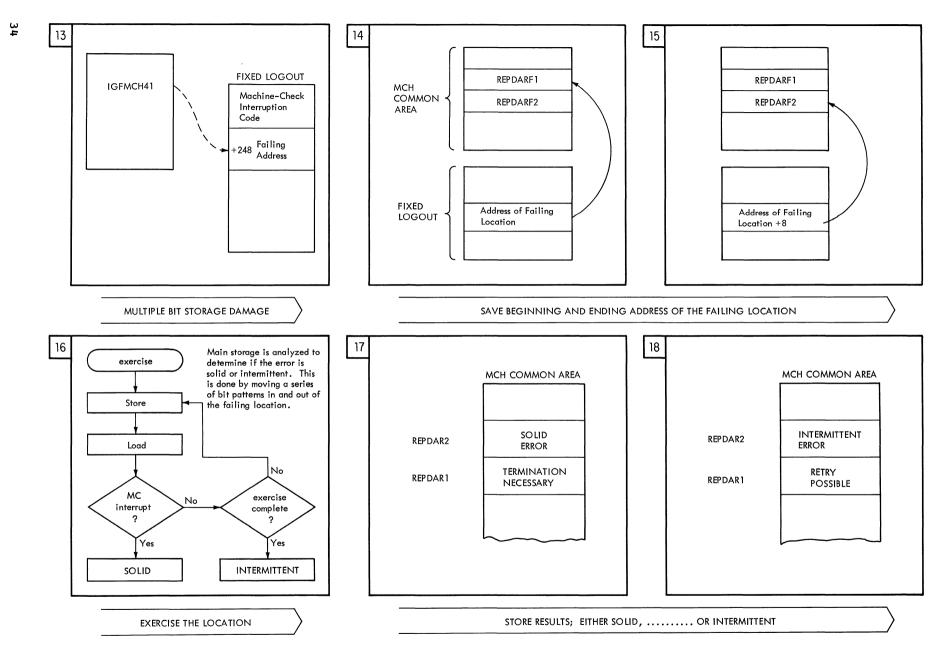

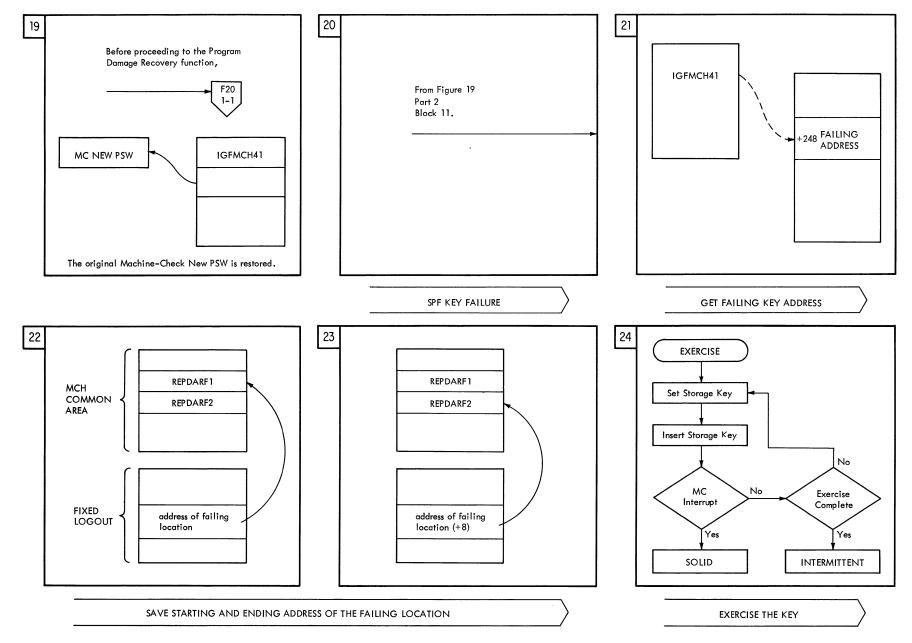

To accurately assess the extent of the damage at the time of the machine-check interruption, the MCH Nucleus and the Preliminary Error Analysis (PEA) modules analyze the hardware error. MCH must identify the type of error, where it occurred, and under what special circumstances, if any.

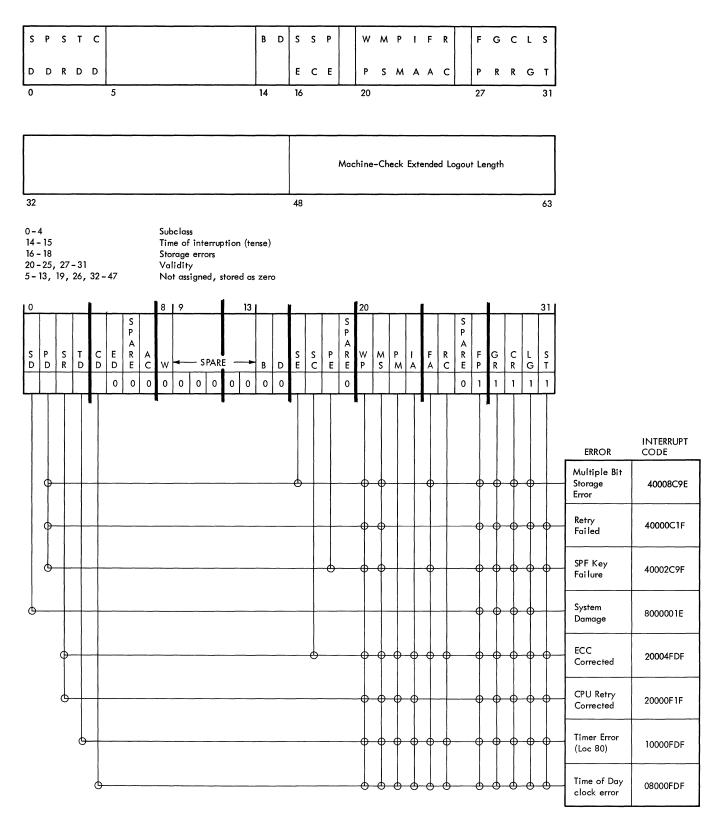

To understand the hardware analysis function, some of the major fields of the machine-check interruption code are discussed first. Appendix B describes the interruption code fully.

MACHINE CHECK SUBCLASSES: Bits 0 through 4, the subclasses, indicate the machine check condition causing the interruption. On each interruption, at least one of these bits must be set. If multiple errors have occurred, several bits may be on.

TENSE: This field indicates the timeliness of the interruption status. For example, bit 14, when one, indicates that the instruction address in the machine check old PSW points to the instruction in which the error occurred. If the bit were set to zero, the instruction address would be pointing to an instruction beyond the point of error.

STORAGE ERRORS: This field informs MCH that the error was in main storage.

VALIDITY: The validity bits represent the various fields stored during the machinecheck interruption. Any bit that is zero indicates that the associated data (general registers, condition code, etc.) has been affected by the error.

EXTENDED LOGOUT LENGTH: (Model 145 only) This field indicates the length in bytes of the extended logout area pointed to by control register 15.

## Types of Hardware Malfunctions

The following types of hardware failures can be identified by the MCH Nucleus from the machine-check interruption code:

- System Damage An error occurred that could not be attributed to the instruction referred to by the machine-check old PSW.

- Instruction Processing Damage An error occurred during the processing of the instruction indicated by the machine-check old PSW. The instruction was either unretryable or unsuccessfully retried, or the damage resulted from a multiple bit failure in main storage or a Storage Protect Feature (SPF) error.

- CPU Retry Successful (Soft error) The CPU instruction was successfully retried.

- ECC Successful (Soft error) A single bit storage error was corrected by the ECC facility.

- Time of Day Clock Damage An error occurred in the time of day clock making it invalid for time stamping.

- Timer Damage The high-resolution timer at location 80 contains a parity error.

## System Damage

System damage occurs when the machine circuitry or the microcode in the CPU has failed. Multiple-bit errors in control storage are included in this category. By presenting the malfunction as system damage in the machine-check interruption code, the machine informs MCH that system operation must stop. In this case the MCH Nucleus places the system in the wait state.

## Instruction Processing Damage

Any type of instruction processing damage has some program damage or potential program damage associated with it. MCH must therefore ultimately associate the error with a system or user task and then take whatever action is necessary to keep the system operating. The first step is to determine from the bit settings in the interruption code the type of error that occurred. The common bit settings for various types of machine malfunctions are shown in Appendix B.

There are three types of malfunctions that are classified as instruction processing damage. Bit one, the instructionprocessing-damage bit, is on (set to 1) in

## FINDING SUCCESSOR MODULE

#### LOADING SUCCESSOR MODULE

## Procedure

- 1. Module Loader saves displacement to successor list for module just loaded.

- 2. Transient module places a code into MCHNXMOD to designate its successor.

- 3. Module Loader adds saved displacement to MCHNXMOD and subtracts 1 to determine successor.

#### Example

- If PEA (IGFMCH41) is loaded, the Module Loader saves X'1B' from its Displacement Table.

- 2. If PEA wants control passed to the Soft Machine-Check Handler (IGFMCH40), it places a X'02' in MCHNXMOD.

| з. | Module Loader adds: |         |

|----|---------------------|---------|

|    | MCHNXMOD            | X'02'   |

|    | Saved Displacement  | X'1B'   |

|    |                     | X'1D'   |

|    | and subtracts 1     | - X'01' |

|    |                     | X'1C'   |

The result of which points to 40 (IGFMCH40) in the successor list.

| MCH RESIDENT AREA                                      |                                                    |

|--------------------------------------------------------|----------------------------------------------------|

|                                                        | Module TTR and<br>address of MCH<br>Transient Area |

| MODULE<br>LOADER<br>MCHNXMOD                           | INPUT/<br>OUTPUT<br>SUPERVISOR                     |

|                                                        |                                                    |

| TRANSIENT                                              |                                                    |

| MODULE<br>"A"<br>•<br>•<br>SET SUCCESSOR<br>MODEL'S ID | SYS1.SVCLIB                                        |

|                                                        | Loading a module<br>into Transient<br>Area         |

|                                                        | SYSRES                                             |

Module Loader Displacement Table

**Displacement**

00

00

05

0A

0D

0E

10

1B

1D

TTR

005D02

005D06

005D0A

005D0E

005C04

005C08

005C10

005C0C

000000

Caller

E3

F1

F2

F3

F5

F6

40

41

91 \*\*

| Module Loader Successor List * |    |              |    |  |

|--------------------------------|----|--------------|----|--|

| Displacement                   | ID | Displacement | ID |  |

| 00                             | 00 | OF           | 91 |  |

| 01                             | F5 | 10           | 00 |  |

| 02                             | F2 | 11           | 41 |  |

| 03                             | F3 | 12           | 00 |  |

| 04                             | 00 | 13           | 00 |  |

| 05                             | 00 | 14           | 00 |  |

| 06                             | F5 | 15           | 00 |  |

| 07                             | 00 | 16           | 00 |  |

| 08                             | F3 | 17           | 00 |  |

| 09                             | F6 | 18           | F1 |  |

| 0A                             | 00 | 19           | 40 |  |

| OB                             | F5 | 1A           | E3 |  |

| 0C                             | F6 | 1B           | F1 |  |

| 0D                             | 40 | 1C           | 40 |  |

| OE                             | F5 | 1D           | F5 |  |

\* An ID of 00 indicates that a module has specified an invalid successor.

\*\* IGFMCH91 is the TSO Analysis module. Its original name is IKJEAM00 but it is linked into the SVCLIB at System Generation time as IGFMCH91.

# Figure 12. Finding and loading MCH modules (Model 145 modules illustrated)

all cases. The remaining related bit settings indicate the type of instruction processing damage that occurred. (Appendix B describes the use of each bit in the interruption code.)

- Retry failed This condition is indicated when the instruction processing damage bit is on and the error is neither a multiple-bit error nor an SPF key error. Since the PSW is pointing to the failing instruction and the instruction address is valid, MCH assumes that the CPU has retried the instruction but has not been successful.

- Multiple-bit error in main storage -MCH, through the Preliminary Error Analysis routine, determines whether this type of error is solid or intermittent by finding the location of the error and doing a series of stores and fetches using that area. This is termed exercising a location.

If data changes during a store or fetch, or if another machine-check interruption occurs during the exercise, MCH labels the error solid. Otherwise, MCH labels the error intermittent.

Since a valid machine-check interruption must be anticipated each time data is fetched from or stored into the location, the address in the machine-check new PSW is altered to point to code that services the expected interruption. The result of this test is placed in the Common Area. MCH eventually uses this information to assess the damage to the task occupying that particular section of main storage.

3. SPF key error - The severity of an SPF key error is determined in a way similar to that used for the multiple-bit storage error. The machine-check new PSW is made to point to a section of code that will service the expected machine-check interruption. A succession of fetches using all 16 possible key patterns is made to determine whether the error is solid or intermittent. The result of this analysis is placed in the MCH Common Area.

## PROGRAM DAMAGE RECOVERY

Having identified the hardware characteristics of the malfunction, MCH investigates the extent of the damage to the program executing at the time of the machinecheck interruption. After assessing the damage to the program, MCH attempts to recover the system by associating the damage with a particular task and terminating that task. This keeps the system in operation at the expense of only one job. If the supervisor is damaged, the system must be reloaded.

The modules responsible for system recovery are collectively known as the program damage assessment and repair modules or PDAR. To accurately assess the extent of the damage to the system, the PDAR modules use information placed in the MCH Common Area by the MCH Nucleus and Preliminary Error Analysis. In turn, each PDAR module uses the Common Area to convey the results of its operation to its successor.

In general, program damage recovery assists in the following:

- Damage assessment associating what is known about the hardware characteristics of the failure with the task occupying the location that was affected.

- Task Termination terminating any task that is in the problem program area.

- System Termination putting the system in the Wait state when the error occurs in the supervisor or Link Pack Area, making further system operation impossible.

Program damage recovery procedures are necessary for:

- Intermittent or solid SPF key error

- Intermittent or solid main storage errors

- Retry failed error

To recover from an intermittent main storage or SPF key error in a problem program, the task is terminated by ABEND.

To recover from a solid main storage error or SPF key error in a problem program, the task is terminated by setting its TCB nondispatchable.

For an uncorrectable error caused by a failing instruction in a problem program, the task is terminated by ABEND.

For all errors (SPF key, main storage, or failing retry) occurring in the supervisor or Link Pack Area, MCH places the system in the Wait state.

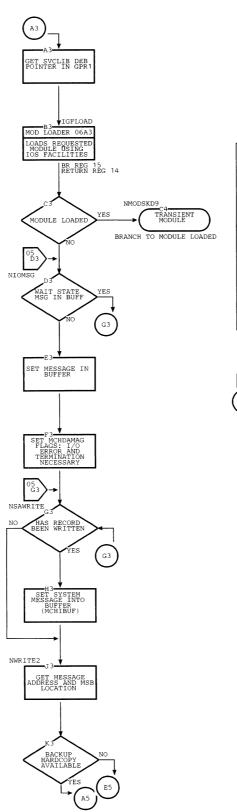

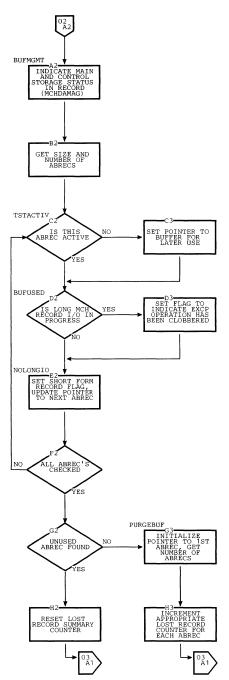

## RECORDING AND TERMINATION

The recording function of the Machine-Check Handler has two parts. The first is the normal error recording procedure of formatting an error record and eventually writing it on the SYS1.LOGREC data set. The second is emergency recording; that is, the recording attempted when MCH has determined that system continuation is impossible.

## Error Recording

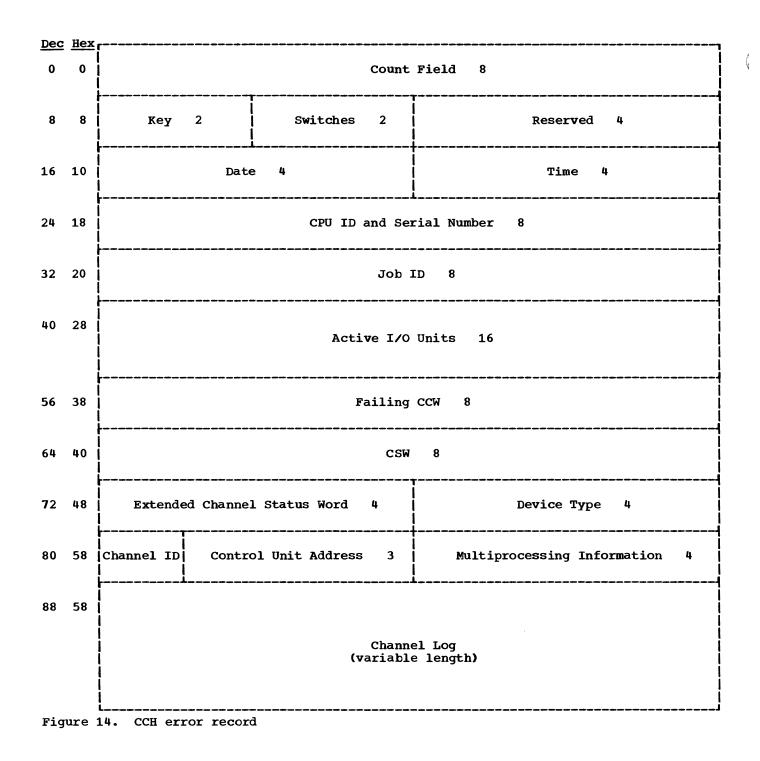

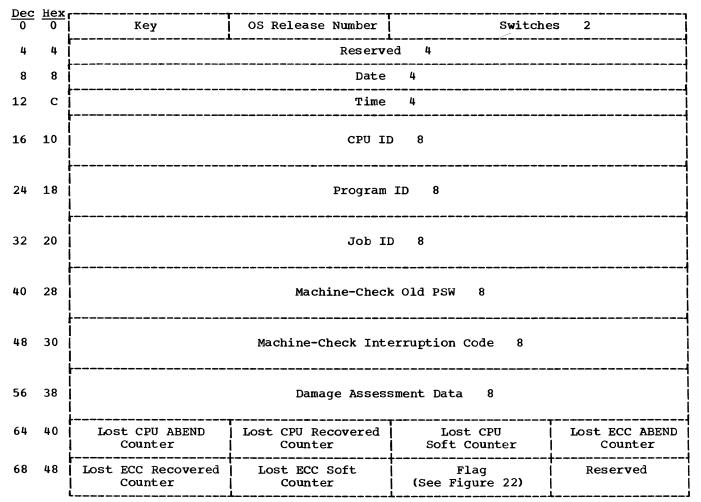

The typical MCH error record is illustrated in Figure 13. It consists of the MCH abbreviated record (ABREC), the fixed logout, the extended logout, and the damage-assessment field of the MCH Common Area. This record is produced for all machine-check interruptions.

Error recording involves formatting a record and writing it into the SYS1.LOGREC data set. Before MCH terminates its operation it formats the error MCH record. The actual writing of the record on the data set takes place after MCH terminates. MCH terminates before writing to decrease the chances of a second machine-check interruption's occurring while MCH is executing. In other words, if an interruption takes place during the I/O operation and MCH has not yet terminated, the interruption would have to be handled as an error-on-error condition. If MCH has terminated and a machine-check interruption occurs, MCH can handle the interruption in the normal manner.

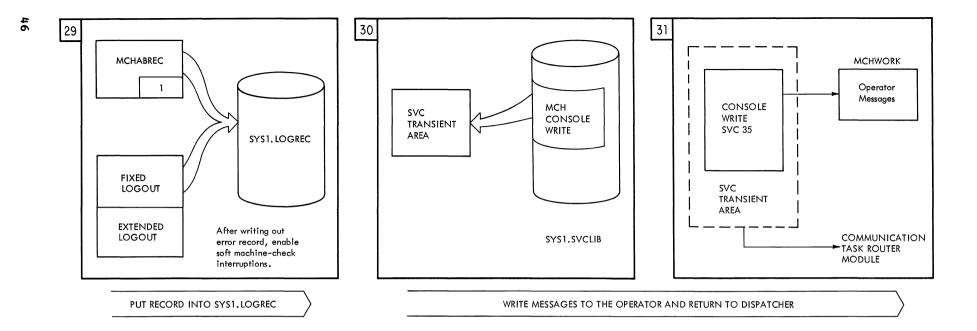

MCH does the following to put an error record in SYS1.LOGREC:

- 1. It formats the complete error record.

- It establishes the communications task (MCH Error Recorder) as an active task.

- It terminates itself by giving control to the Dispatcher or to the interrupted program.

If the dispatcher gets control it will dispatch the next ready task. This should be the communications task. The MCH Error Recorder then writes the MCH records into the SYS1.LOGREC data set.

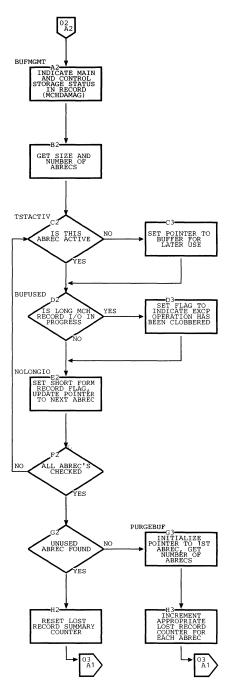

Should another machine-check interruption occur before the error record is written, the Error Recorder writes the short record of the first interruption and the complete error record of the second interruption. If a third interruption occurs after the record is formatted but before it is written, the short record of the first and second interruptions and the complete record of the third interruption are recorded.

The maximum number of error records that can be formatted for each recording operation is three. Therefore, if more than three interruptions occur before any recording is done, the record for the current interruption replaces the most recent soft error record. If no soft error records have been formatted, the most recent hard error record is replaced. Consequently, when the Error Recorder finally puts the error records into SYS1.LOGREC, they represent the three most recent machine checks with the hard machine checks taking priority. Also, the number of lost records and their characteristics are included in the error record.

The system remains in quiet mode until formatted error records have been written. Therefore, soft errors cannot cause formatted error records to be overlaid.

Note: The MCHDAMAG field of the MCH error record reflects the error analysis and action taken by MCH in its processing. The field is designed to be model independent in content. Thus, for a specific model all bits in the damage area or error type bytes of the field may not be implemented. Specifically, the buffer, control storage, extended main storage, address and mark bits are not set for all machines.

In addition, some RMS action data bits in this field are not set for all machines. The retry bit is set only if some type of software retry is attempted by MCH. Repair indicates that MCH has attempted to repair an SPF key failure. The Reconfigure bit indicates that MCH has performed some type of main storage reconfiguration. The refresh bit is set only if MCH has refreshed a portion of main storage. The setting of any of these bits indicates that MCH has performed the indicated action but does not imply that MCH was able to resume the task that was in control at the time of the error. For instance, task or system termination may be necessary if the retry was unsuccessful, a valid return point to the interrupted program is not available or an instruction is non-retryable.

Finally, for certain machine-check interruptions MCH makes an early determination that system termination is necessary and thus does not perform any further analysis as to type of error or area of damage. In these cases only the termination bit is set and possibly a system down code in the RMS action data area of the field.

## Emergency Recording

Emergency recording is necessary when the system cannot continue to operate. Instead of giving control to the operating

| Offs | et DECI | IMAL ( | HEX)  |                                                                                                                                                                     |  |  |

|------|---------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Mode | 1 135   | Mode   | 1 145 | Field<br>Name Description                                                                                                                                           |  |  |

|      |         |        |       | Header<br>24 bytes from MCHABREC in the MCH Common Area.                                                                                                            |  |  |

| 0    | (0)     | 0      | (0)   | Byte 1 Record ID.                                                                                                                                                   |  |  |

| 1    | (1)     | 1      | (1)   | Byte 2<br>xx System ID. OS=00.<br>x Not used.<br>x xxxx Release level.                                                                                              |  |  |

| 2    | (2)     | 2      | (2)   | Byte 3<br>1 Operator action message.<br>.1 System/370 machine.<br>xx xxxx Not used.                                                                                 |  |  |

| 3    | (3)     | 3      | (3)   | Byte 4Record type information:1Short form of record1.Record incomplete1.MCH terminated the systemx xxxxNot used.                                                    |  |  |

| 4    | (4)     | 4      | (4)   | Bytes 5-8 Not used.                                                                                                                                                 |  |  |

| 8    | (8)     | 8      | (8)   | Bytes 9-16 Date and time.                                                                                                                                           |  |  |

| 16   | (10)    | 16     | (10)  | Bytes 17-24 CPU Serial number.                                                                                                                                      |  |  |

| 24   | (18)    | 24     | (18)  | Program ID<br>8 bytes from MCHABREC in the MCH Common Area.                                                                                                         |  |  |

| 32   | (20)    | 32     | (20)  | Job ID<br>8 bytes from MCHABREC in the MCH Common area.                                                                                                             |  |  |

| 40   | (28)    | 40     | (28)  | <u>MC Old PSW</u><br>8 bytes from MCHABREC in the MCH Common Area.                                                                                                  |  |  |

| 48   | (30)    | 48     | (30)  | <u>MC Independent Loqout</u><br>280 bytes from the Fixed Logout Save Area.                                                                                          |  |  |

| 256  | (100)   | *      | *     | Extended Logout of Model 135<br>14 bytes contained within a scratch area of the Fixed Logout.                                                                       |  |  |

| *    | *       | 328    | (148) | Extended Logout of Model 145<br>192 bytes from the Extended Logout field (pointed to by con-<br>trol register 15).                                                  |  |  |

|      |         |        |       | *Note: Because of the difference in Extended Logouts for the<br>Models 135 and 145, MCH error record displacements differ<br>for the two models from this point on. |  |  |

|      |         |        |       | Damage Assessment Data<br>74 bytes.                                                                                                                                 |  |  |

|      |         |        | l     | Bytes 1-6 from MCHPDAR in the MCH Common Area.                                                                                                                      |  |  |

| 328  | (148)   | 520    | (208) | Bytes 1-2 Length of this field.                                                                                                                                     |  |  |

| 330  | (14A)   | 522    | (20A) | Bytes 3-6 Address of the Machine Dependent Common Area.                                                                                                             |  |  |

|      |         |        |       | Bytes 7-10 from MCHLOGIC in the MCH Common Area.                                                                                                                    |  |  |

| 334  | (14E)   | 526    | (20E) | Bytes 7-10 First level interrupt control field.                                                                                                                     |  |  |

|      |         |        |       | Bytes 11-18 from MCHDAMAG in the MCH Common Area.                                                                                                                   |  |  |

Figure 13. MCH error record (part 1 of 2)

| Offset DECIMAL (HEX) |           |     | IEX)    | Di al d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |