File No. S360-01 Order No. GA22-6943-1

# IBM Systems Reference Library

# IBM System/360 Model 195

# **Functional Characteristics**

This publication describes the organization and functional characteristics of the IBM System/360 Model 195, an information-processing system designed for ultrahigh-speed, large-scale scientific applications.

System components are described, and detailed consideration is given to the functions of processor storage, central processing unit, input/output channels, and operator-control and operator-intervention portions of the system control panel. Coding and timing considerations are discussed.

The reader is assumed to have a knowledge of information-processing systems and to have read the *IBM System/360 Principles of Operation*, GA22-6821.

#### Second Edition (August 1970)

This is a major revision of, and obsoletes, GA22-6943-0 and Technical Newsletter GN22-0345. The section headed "Operator Intervention" has been revised and rearranged. Other changes to the text, and small changes to illustrations, are indicated by a vertical line to the left of the change; changed or added illustrations are denoted by the symbol  $\bullet$  to the left of the caption.

Changes are periodically made to the specifications herein; before using this publication in connection with the operation of IBM systems, refer to the latest System/ 360 SRL Newsletter, GN20-0360, for the editions that are applicable and current.

Requests for copies of IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

This manual has been prepared by the IBM Systems Development Division, Product Publications, Dept. B98, PO Box 390, Poughkeepsie, N.Y. 12602. A form for readers' comments is provided at the back of this publication. If the form has been removed, comments may be sent to the above address.

©Copyright International Business Machines Corporation 1969, 1970

# Contents

| 5<br>6       |

|--------------|

| 6            |

| v            |

| 9            |

| 9            |

| 10           |

| 10           |

| 10           |

| 11           |

| 11           |

| 13           |

| 13           |

| 16           |

| 16           |

| 16           |

|              |

| 17           |

| 18           |

| 19           |

| 19           |

| 19           |

| 20           |

| - <i>4</i> ∪ |

| 20<br>20     |

|              |

.

| 2880 Block Multiplexer Chann | nel |     |     |    |   |   |   |   |   |   | 21 |

|------------------------------|-----|-----|-----|----|---|---|---|---|---|---|----|

| Extended Channel Feature     |     |     |     |    |   |   |   |   |   |   | 21 |

| Channel-to-Channel Adapter F |     |     |     |    |   |   |   |   |   |   | 22 |

| -                            |     |     |     |    |   |   |   |   |   |   |    |

| System Control Panel .       |     |     |     |    |   |   |   |   |   |   | 23 |

| System Control Functions.    |     |     |     |    |   |   |   |   |   | • | 23 |

| System Reset                 |     |     |     |    |   |   |   |   |   |   | 23 |

| Store or Display             |     |     |     |    |   |   |   |   |   |   | 23 |

| Initial Program Loading .    |     |     |     |    |   |   |   |   |   |   | 23 |

| Controls                     |     |     |     |    |   |   |   |   |   |   | 24 |

| Operator Control             |     |     |     |    |   |   |   |   |   |   | 24 |

| Operator Intervention Contr  |     |     |     |    |   |   |   |   |   |   | 26 |

| Operator Intervention Contr  |     |     |     |    |   |   |   |   |   |   | 31 |

| Key Switch and Meters .      |     |     |     |    |   |   |   |   |   |   | 34 |

| -                            |     |     |     |    |   |   |   |   |   |   |    |

| Appendix A: Coding Con       | sid | era | tio | ns |   |   |   |   |   |   | 35 |

|                              |     |     |     |    |   |   |   |   |   |   | 20 |

| Appendix B: Timing Cons      | sid | era | tio | ns |   |   |   |   |   |   | 36 |

| Instruction Processor Delays | s   |     |     |    |   |   |   |   |   |   | 36 |

| Transmission Time            |     |     |     |    |   |   |   |   |   |   | 36 |

| Branches                     |     |     |     |    |   |   |   |   |   |   |    |

| Fixed-Point Execution .      |     |     |     |    |   |   |   |   |   |   |    |

| Floating-Point Execution     |     |     |     |    |   |   |   |   |   |   | 37 |

| Selected Execution Times     |     |     |     |    |   |   |   |   |   |   | 38 |

|                              |     |     |     |    |   |   |   |   |   |   | 20 |

| Index                        |     | _   | _   |    | _ | _ | _ |   |   |   | 39 |

|                              | -   |     |     |    |   |   | • | • | • |   |    |

The IBM System/360 Model 195 is an information-processing system designed for ultrahigh-speed, large-scale computer applications. Its speed and power result primarily from advanced circuit technology, a high performance buffer for processor storage accesses, buffering within the processor, very fast execution times, a high degree of concurrency in operations, and employment of exceptionally efficient algorithms, particularly in floating-point operations.

Speed in accessing storage and in executing instructions is achieved with a high-speed buffer storage and multiple, interleaved processor storage elements, by functional buffering within the processor, and by an assembly-line approach to instruction processing. All of these factors are controlled to maintain a high degree of concurrent, continuous operation in the instruction unit and in several execution units. A unique internal bus system also plays a major role.

In the Model 195, five separate units – each to a large degree autonomous – may be operating concurrently: processor storage, storage control unit and buffer storage, instruction processor, fixed-point/VFL/decimal processor, and floating-point processor. Furthermore, each of these units may be performing several functions at one time. In the floating-point processor, for example, as many as three floating-point operations may be taking place concurrently.

Because of the concurrency achieved in the Model 195, the effective time required by a given instruction is not directly related to the rate at which that instruction can be processed. For example, one normalized floating-point-add operation requires two cycles and one normalized floating-point-multiply operation requires three cycles; if the operations are logically independent, it is possible in the Model 195 to process up to two add and one multiply instructions concurrently for a total of three cycles, rather than sequentially for a total of seven.

Although central processing unit (CPU) operations are to a high degree performed in parallel, no special optimization is required in preparing programs for CPU processing. In general, System/360 coding is processed in the CPU with a high degree of efficiency. Using the interrupt mechanism as a part of the problem program logic should be avoided. Although this use of interrupts applies reasonably well to slower, serial CPU's, such use degrades higher performance CPU's. In particular, certain program interrupts that occur at the end of a particular "assembly line" are too late to act as modifiers to the beginning of that line. This situation restricts the user from taking unique, in-line action based on exceptions like floating-point overflow.

Another consequence of the high-performance design is a recommendation (not a functional requirement) that FORTRAN users arrange arrays in COMMON so that long precision data precedes short-precision data, etc. This ensures

# that the data does not need to be aligned at execution time. (See *IBM System/360 FORTRAN IV Language*, GC28-6515.)

Model 195 machine cycle time is 54 nanoseconds; data flow is eight bytes (one doubleword) in parallel. The processor storage cycle time is 756 nanoseconds, and the buffer storage cycle time for successive read or successive write cycles is 54 nanoseconds. (Depending on the addressing pattern, an occasional Write followed by a Read may encounter a blank cycle.)

Monolithic circuitry is used in the Model 195. The advanced circuits have a basic delay time of less than 5 nanoseconds, compared to SLT delay times ranging from 5 to 30 nanoseconds. In packaging, densities many times that of SLT have been achieved. Boards approximately 8 by 12 inches can hold pluggable cards containing up to 4,000 circuits. Two of these boards can contain a floating-point-add execution unit for 64 bits in which both preshifting and postshifting are accomplished.

The buffer storage, also in monolithic technology, has a 54-nanosecond read cycle with an eight-byte data path. The buffer storage capacity of 32,768 bytes is packaged, using pluggable cards. on two 10- by 12-inch boards. Storage circuits lend themselves to much denser packaging techniques, with one board containing as many as 150,000 circuits.

#### **Relationship to Other Models of IBM System/360**

Because of the emphasis on high performance, the operation of the Model 195 in the following cases differs from that specified in the *IBM System/360 Principles of Operation*, GA22-6821.

- 1. The quotient of a floating-point-divide operation may differ in the Model 195 from that of other models by an amount equal to one bit in the low-order fraction position. For zero remainders, the results are indentical.

- 2. Several program interruptions that should, according to the *IBM System/360 Principles of Operation*, store a nonzero instruction-length code are imprecise in the Model 195. An imprecise interruption is one that causes an instruction-length code of zero to be stored; this code indicates that the address of the instruction causing the interruption has not been retained. When imprecise program interruptions occur, the interruption-code portion of the current PSW is used in a special way. (See the discussion of imprecise interruptions in "Instruction Processor.")

- 3. Because floating-point overflow and underflow cause imprecise interruptions on the Model 195, it is possible that subsequent instructions will be executed using the overflow or underflow results. For this reason, the results are made to differ from the standard System/360 results, which produce the correct fraction and a

wraparound exponent. In the Model 195, overflow produces the correct sign and the maximum fraction and exponent; underflow produces a true zero result. For those instructions that change the condition code, the code is 1 or 2 for overflow and 0 for underflow.

4. The Model 195 is capable of executing CPU stores out of sequence. Logical consistency is maintained within CPU programs, including the beginning and ending of I/O operations. However, if a CPU program is to modify a string of CCW's while they are being used by the channel, steps must be taken to arrange the CPU program so that the stores are made in sequence.

To provide a synchronization when other means are not practical, a branch instruction may be used. This particular branch instruction is a no-operation instruction for other models of System/360, but is implemented in the Model 195 in such a way that its execution is delayed until all previously decoded instructions have been completed. (See the handling of interrupts discussion in "Instruction Processor.")

#### System Components

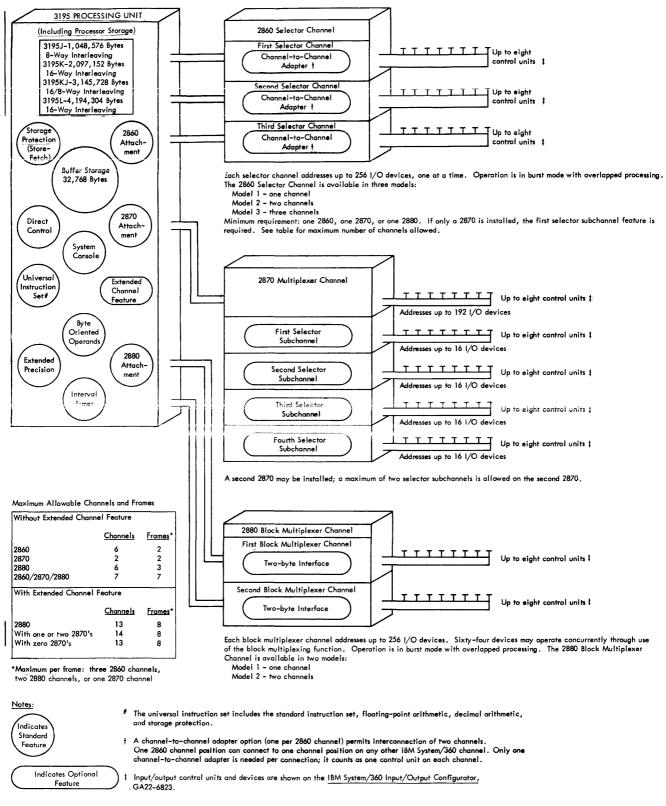

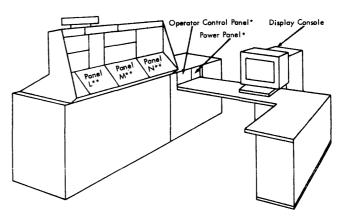

Major components of the Model 195 include an IBM 3195 Processing Unit (which includes the Processor Storage), an IBM 2860 Selector Channel, and/or an IBM 2870 Multiplexer Channel, and/or an IBM 2880 Block Multiplexer Channel. Input/output (I/O) devices are attached to the channels through control units (Figure 1). The four processor models are termed J, K, KJ, and L, depending upon the amount of processor storage available. (In this publication, main storage and processor storage are used interchangeably.)

| Processing<br>Unit Model | Processor Storage | Interleave<br>Factor |

|--------------------------|-------------------|----------------------|

| J                        | 1,048,576 bytes   | 8                    |

| К                        | 2,097,152 bytes   | 16                   |

| KJ                       | 3,145,728 bytes   | 16/8                 |

| L                        | 4,194,304 bytes   | 16                   |

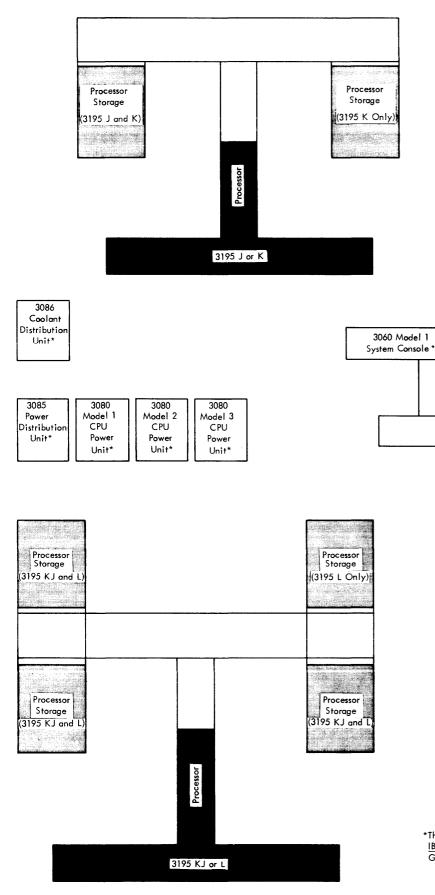

Figure 2 is an outline configuration of the 3195 J, K, KJ, and L Processing Units, including processor storage.

The standard features for any IBM 3195 Processing Unit (CPU) include:

Universal Instruction Set (including the Standard Instruction Set, Floating-Point Arithmetic, Decimal Arithmetic, and storage protection)

Extended Precision Floating-Point Arithmetic

Byte-Oriented Operands

Direct Control

Protection Features (Store and Fetch Protection)

Buffer Storage

Interval Timer (9.6-kilohertz – about 104-microsecond interval) 2860 Selector Channel Attachment 2870 Multiplexer Channel Attachment 2880 Block Multiplexer Channel Attachment Display Console Remote Operator Control Panel Attachment

Emergency Power-Off Control

Resolution of the interval timer is 104 microseconds. The timer is updated by decrementing bit position 28 every 104 microseconds (more precisely, at a frequency of 9.6 kilohertz). The updating takes place with minimal interference, and no backup storage for the timer is used.

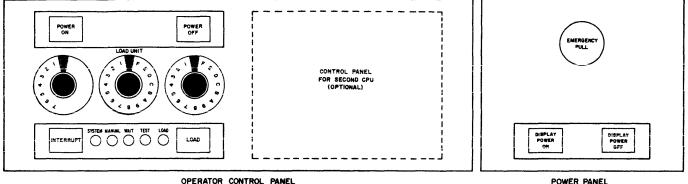

The display console, similar to an IBM 2250 Display Unit Model 1, is integrated with the system console, which is a stand-alone unit. Positioning a switch connects the display console with either an I/O channel or the system console. (When connected to a channel, the display console may be used for two-way communication with the system. When the display console is connected to the system console, the communication path is from the system console to the display console.) For connection to an I/O channel, the display console requires one control unit position on a 2860 Selector Channel, a 2880 Block Multiplexer Channel, or on a selector subchannel of a 2870 Multiplexer Channel.

Standard on the display console are an alphameric keyboard, character generator, light pen, 8,192-byte buffer (4,096 bytes of which are reserved for maintenance purposes and contain format control data), and operator control panel with one set of controls and indicator lights.

To control another System/360 processor, a second set of controls and indicator lights may be added as an optional feature to the operator control panel.

One set of the operator control panel controls and indicators may be duplicated as a remote panel on a stand-alone operator's console (IBM 2150 Console or IBM 2250 Display Unit Model 1). Provision for this attachment is a standard feature.

A channel-to-channel adapter, an optional feature, may be installed on an IBM 2860 Selector Channel (maximum of one per selector channel), permitting program-controlled, storage-to-storage operations to take place directly between I/O channels.

A variety of control units and input/output devices is available for use with the Model 195. Descriptions of these devices appear in separate publications. Configurators for I/O devices and for system components are also available. (See *IBM System/360 Bibliography*, GA22-6822.)

I

• Figure 1. System/360 Model 195 Configurator

\*These items may be positioned elsewhere as required. See <u>IBM System/360</u> Installation Manual-Physical Planning, GC22-6820.

• Figure 2. IBM 3195 J, K, KJ, L Processing Unit and Processor Storage Configurations

The central processing complex of the System/360 Model 195 is made up of seven stand-alone units: a CPU, three CPU power supply units, a power distribution unit, a coolant distribution unit, and a system console (Figure 2). (A motorgenerator set must be ordered separately and may be located in a remote area.)

# **CENTRAL PROCESSING UNIT**

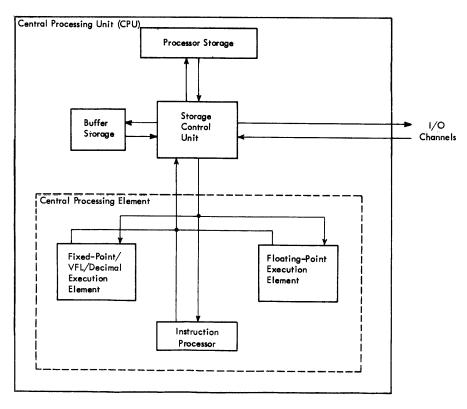

Functionally, the central processing unit consists of these major logical elements: instruction processor, fixed-point/ variable-field-length (VFL)/decimal execution element, floating-point execution element, high-speed buffer storage, storage control unit, and processor storage (Figure 3). The instruction processor and the two execution elements make up the central processing element (CPE), also called the processor.

The instruction processor is the major coordinating element in the Model 195. For each instruction, it determines what must be done and issues the operation to the proper execution unit. Branching, status switching, and I/O instructions are handled by the instruction processor; other instructions are issued by the instruction processor to other processor elements for completion.

The fixed-point/VFL/decimal execution element contains the general registers, which are used also by the instruction processor. Functionally, this element operates as an independent stored-program computer; it has its own instruction stream, its own execution circuitry, and a set of operand buffers.

The floating-point execution element also operates as an independent computer. Although most of the floating-point instructions require more than one cycle of execution time, this element is capable of sustaining an execution rate of up to one instruction per cycle.

The storage control unit handles all fetching and storing of data for the CPE. It is designed to minimize conflicting requests for storage and to make the most efficient use of storage.

The high-speed buffer storage provides the principal means of reducing average access time to main storage. The most current blocks (a block is eight doublewords) of storage are maintained in the buffer storage, the operation of which is not obvious to the programmer. The first processor fetch to a block, for a storage address within that block, accesses the addressed location and initiates a transfer of the block into the buffer storage.

Subsequent accesses to that block can then be made directly from'the buffer storage. Processor stores are made to both the buffer (if appropriate) and to processor storage. I/O fetches and stores are made to processor storage only.

Figure 3. Model 195 Logical Elements

An I/O store to a location also currently held in the buffer storage invalidates the appropriate block in the buffer storage.

# PROCESSOR STORAGE

Up to 4,194,304 bytes of processor storage are available with an individual access of eight bytes (a doubleword). Interleaving of processor storage is provided so that the addresses of successive doublewords are in successive, functionally independent units. Processor access to storage is performed in combination with the high-performance buffer storage. The effect is that average access time approaches the access time of the buffer storage. Transfers between the buffer storage and processor storage are made in blocks of eight doublewords. I/O accesses (eight bytes) to processor storage do not involve buffer storage except where necessary for control.

| Function Performed                                        | Time<br>(Nanoseconds) |

|-----------------------------------------------------------|-----------------------|

| Access time to buffer storage                             | 162                   |

| Access time to processor storage if not in buffer storage | 810                   |

| Access time to processor storage for I/O channels         | 648                   |

| Cycle time for buffer storage, successive                 |                       |

| read or successive write cycles                           | 54                    |

| Cycle time for processor storage                          | 756                   |

# INSTRUCTION PROCESSOR

The primary functions of the instruction processor are fetching and buffering instructions from storage, fetching required operands, issuing instructions to the appropriate

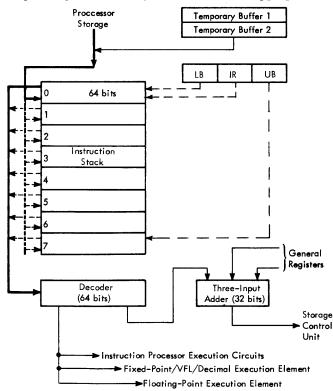

Figure 4. Instruction Processor

execution elements, handling interrupts, and executing all branching, status-switching, and I/O instructions.

The instruction processor has an instruction stack of eight doublewords, a set of three instruction-control registers, a set of temporary instruction buffer registers totaling two doublewords, a decoder, and a three-input adder for the generation of effective addresses (Figure 4). The instruction processor uses the general registers in the fixed-point/VFL/ decimal execution element.

## Instruction Fetching

Instructions fetched from storage are stored in the instruction stack of the instruction processor. An instruction stack is used for two principal reasons:

- 1. To minimize storage access time for instruction fetching.

- 2. To reduce the number of instruction fetches required while the program is executing a tight loop.

The instruction stack normally contains the current instruction doubleword, and seven doublewords of either history (instructions already decoded) or instructions to be executed. Keeping a number of doublewords ahead enables the fetching mechanism to fit instruction fetches into slack periods between data fetches and stores. The doublewords of history in the stack minimize refetching of instructions when a loop backward that can be contained in the instruction stack is detected.

The fetching mechanism operates differently under each of three conditions: initialization, normal operation, and recognition of a discontinuity. It is governed by three control registers: the instruction register (IR), the upper-bound (UB) register, and the lower-bound (LB) register. The IR points to the instruction being decoded, the UB register to the most recent doubleword brought into the stack, and the LB register to the earliest doubleword in the stack.

# Initialization

Initially, the instruction stack is empty. When instruction fetching is initiated, the main-storage address of the first doubleword of instructions is set into the UB and LB registers, and part of the address of the first instruction is set into the IR. The UB register, which controls the actual fetching of doublewords of instructions, brings the first doubleword into the appropriate position of the instruction stack. At the same time, the first doubleword is brought into the decoder.

As each instruction doubleword is fetched during initialization, the UB register is incremented (a doubleword being brought into the stack for each increment) until any of three conditions occurs:

- 1. The address in the UB register is seven doublewords higher than that of the IR (Figure 4). Doubleword instruction fetches are made whenever it does not delay data fetching or storing.

- 2. A branch instruction is decoded that sets conditional mode (see "Execution of Branching Instructions").

- 3. A discontinuity is recognized (see "Discontinuities").

#### Normal Operation

During normal operation, the instruction fetching mechanism continually attempts to fetch a doubleword (Figure 4). Fetching will not take place if any of the three conditions just described is present.

When incrementing the UB register would cause the three low-order bits of that register to match the three low-order bits of the LB register, both the UB and LB registers are incremented. This incrementing of both registers causes the earliest (oldest) doubleword in the stack to be replaced with the latest doubleword just fetched. The LB and UB registers then point to a doubleword positioned one doubleword higher in the stack. This relative positioning of the LB and UB pointers (instruction stack addressing) remains constant during normal operation.

#### Discontinuities

A branch operation, interrupt, or store into the instruction stream may cause a disruption in fetching. (Branching operations and interrupts are discussed separately. See "Execution of Branching Instructions" and "Handling Interrupts.")

If the store instruction results in the alteration of the contents of a doubleword in the stack, the instruction fetching mechanism treats that doubleword slot as empty and fetches the altered doubleword from storage.

Because the Model 195 can execute several instructions at one time, the instruction STORE \* + 4 presents a special problem. This problem is solved by making a check of the effective address of each store operation to determine whether the operation affects the instruction following the store; if the next instruction might be affected, measures are taken to preserve the logical consistency of the program.

#### Instruction Issuing

In addition to fetching and buffering instructions, the instruction processor fetches the required operands and issues instructions to the appropriate execution elements.

During each machine cycle, the instruction processor checks for interlocks. If there are none, the instruction selected by the instruction register is decoded. After an instruction has been decoded, the IR is incremented by the number of halfwords of the instruction just decoded, and the next instruction is then decoded. Decoding is the first of three possible stages in the issuing of the instruction.

# Stage 1

During decoding, the following are determined: 1. The type of operation to be performed.

- 2. Whether the operation stack for the appropriate execution element can accept the operation.

- 3. If a storage operand is required, whether a buffer register in the appropriate execution element is available to receive the operand; or, if a store operation is specified, whether a store address register is available in the storage control unit.

- 4. If an effective address is required, whether the threeinput adder and general registers used in generating the effective address are available.

When the results of these checks indicate that the instruction can be processed, the decoding control determines whether the instruction processor is operating in conditional mode (see "Execution of Branching Instructions"); if it is, the operation is tagged as conditional, indicating to the execution element that it is not to decode or execute the operation until signaled to do so. The operation is then issued for processing to the appropriate execution element (usually during stage 2), along with information about which buffer registers in the execution element, if any are needed, have been assigned by the instruction processor for use in the operation.

### Stage 2

If address generation is required, the pertinent operand addresses are routed to the three-input adder. (Another instruction can now be processed at stage 1) If the instruction is a store, a quick check is made of the effective address and, if this check indicates a possible store into the already fetched instruction stream, processing of the instruction at stage 1 is stopped until the processor determines whether the store is actually into the instruction stream. If it is, the processing at stage 1 remains stopped until the processor has issued a fetch to storage for the updated value of the instruction doubleword affected.

Fetches and stores can be made to operands that are not on proper boundaries; however, performance is degraded. Operands should be located on proper boundaries.

#### Stage 3

At this stage, the effective address of the storage operand is passed to the storage control unit. If a fetch operation is specified, the address of the buffer register to which the operand is to be issued is also specified. (During stage 3, another instruction can be processed at stage 1 and another at stage 2.)

#### **Execution of Branching Instructions**

The instruction processor executes all branching instructions. The actions taken by the instruction processor as a result of decoding a branch instruction are determined by the type of branch instruction to be processed, the availability of circuitry for processing, and the following:

- 1. Whether the instruction processor is in conditional mode (see "Conditional Mode").

- 2. Whether the instruction processor is in loop mode (see "Loop Mode").

- 3. If loop mode is established, whether the current instruction is that which defined the current loop.

- 4. Whether the current instruction is the target of an 'execute' instruction currently being processed.

When a branch is taken, the target address of the branch normally is set into the instruction register, and the UB and LB registers and instruction stack are adjusted as required.

When a conditional branch is encountered and loop mode is not set, the instruction processor operates as though either direction could be taken. It continues to process the instructions in the instruction stack as long as conditions permit, while issuing operations to the fixed-point and floatingpoint execution elements on a conditional basis. These conditional operations will not be executed until after the condition code is set.

The instruction processor also makes use of two temporary buffers. Into these buffers it fetches the branch-target doubleword and the succeeding doubleword. Therefore, regardless of the outcome of the branch operation, the instruction processor will have a lead in the correct direction.

#### Conditional Mode

Conditional mode is established when the instruction processor executes a 'branch on condition' instruction for which the condition code is not yet determined.

When conditional mode is set, no additional instruction fetches are made beyond the first two doublewords at the target address of the branch. The instruction processor continues to decode instructions, generate addresses, and issue operations to the fixed-point and floating-point execution elements. The operations issued, however, are tagged as conditional and cannot be decoded or executed until the condition code is set and the instruction processor sends a signal to the execution element.

The instruction processor continues to decode instructions conditionally until any of the following occurs:

- 1. The condition code is set.

- 2. No instructions are available in the instruction stack.

- 3. The operation stack of the fixed-point or floating-point execution element is full, and the currently decoded instruction needs the filled execution element.

- 4. An instruction to be executed within the instruction processor is decoded, or a variable-field-length instruction is decoded. (However, a no-operation instruction or an unconditional branch may be executed during conditional mode.)

#### Loop Mode

Whenever a branch backward is taken to a target fewer than eight doublewords back from the current address in the instruction register, loop mode is entered and the instruction stack is reinitialized to contain the pertinent eight doublewords. The loop is then locked into the instruction stack and, as a result, can be executed repetitively without refetching the instructions. Thus, conflicts between instruction fetching and data fetching are eliminated, and branches can be executed faster.

During loop mode reinitialization, when no data fetches or stores are to be made, an instruction doubleword is fetched every cycle until the instruction stack is full. If data fetches or stores are to be made, instruction doubleword fetches take second priority.

When loop mode is entered, the branch target address is placed in one special register, and the address of the branch instruction is placed in a second special register. Subsequently, when a branch instruction is decoded during loop mode, that instruction address is compared with the address (in the second special register) of the branch instruction that initiated loop mode; if they are the same, the branch is made to the target address in the first special register. Because no time is taken to re-form the address specified in the branch instruction, one cycle is saved.

If a conditional branch instruction is processed when loop mode is already set, it is assumed that the branch will be taken; therefore, during loop mode no temporary fetches (down the no-branch path) are made for conditional branches.

Loop mode is turned off when any of the following occurs:

- 1. A branch out of the instruction stack is taken.

- 2. The instruction processor starts to decode the 32nd halfword in the instruction stack.

- 3. The target of the quick loop is the same as the target of the outermost loop, and the branch closing the quick loop is not taken. (If two nested loops fit in the instruction stack, the innermost loop is called the quick loop.)

- 4. The base register or index register of the quick-loop branch is altered.

**Programming Notes:** Because of item 2, a loop with 29-31 halfwords should be aligned on a doubleword boundary. If the loop has fewer than 29 halfwords, the loop is executed in loop mode regardless of boundary alignment; if it has more than 31 halfwords, it is not executed in loop mode.

Because of item 3, if the nested loops both have the same target address, loop mode will be destroyed every time an exit is made from the quick loop. To prevent loop mode from being destroyed, a no-operation instruction may be used as a dummy branch target for the outer loop.

#### **Execution of Other Instructions**

The instruction processor executes all status-switching and I/O instructions and plays a large part in the execution of multiple-operation instructions. When one of these instructions is processed, the instruction processor usually does not issue any succeeding instruction until its part in processing the first instruction is completed.

None of these instructions is executed while conditional mode is set. Some require that all instructions being executed when that instruction is decoded, be completed prior to its execution. The instructions requiring this completion of other instructions are the four I/O instructions and 'load PSW', 'supervisor call,' 'set storage key,' and 'set program mask' (except when the old and new mask bits are the same). Also, one type of 'branch on condition' instruction (a no-operation instruction) is implemented in the Model 195 in such a way that all other instructions being executed when it is decoded must be completed before its execution. See the programming note in "Handling Interrupts."

The following instructions are classed as multiple-operation instructions:

| Load Multiple (LM)       | Move With Offset (MVO) |

|--------------------------|------------------------|

| Store Multiple (STM)     | Pack (PACK)            |

| Translate (TR)           | Unpack (UNPK)          |

| Translate and Test (TRT) | Edit (ED)              |

| And (NC)                 | Edit and Mark (EDMK)   |

| Or (OC)                  | Add Decimal (AP)       |

| Exclusive Or (XC)        | Subtract Decimal (SP)  |

| Compare Logical (CLC)    | Compare Decimal (CP)   |

| Move Zones (MVZ)         | Multiply Decimal (MP)  |

| Move Numerics (MVN)      | Divide Decimal (DP)    |

| Move (MVC)               | Zero and Add (ZAP)     |

|                          |                        |

These multiple-operation instructions have variable length data fields and require the issuing of more than one operation from the instruction processor to the fixed-point execution element, which shares responsibility for execution with the instruction processor. Also, each operation of a multiple-operation instruction issued to the fixed-point area contains information concerning at least one storage request.

The multiple-operation instructions are the only instructions, except 'convert to binary,' that cause operands to be fetched into the floating-point operand buffers for use in the fixed-point area. Four of the six fixed-point operand buffers are unavailable for reassignment while a multiple-operation instruction is being executed.

Usually, the instruction processor is available to issue the succeeding instruction after it has issued the last required operation to the fixed-point area. If the next instruction is in the SI format, it is not issued until the variable-field-length execution for the multiple-operation instruction is a 'translate and test' (TRT) or an 'edit and mark' (EDMK) instruction, the instruction processor will be available to issue subsequent instructions only after the entire TRT or EDMK instruction has been executed.

#### **Handling Interrupts**

The Model 195 performs all interrupt functions defined for the IBM System/360. (See *IBM System/360 Principles of Operation*, GA22-6821.) The supervisor call, external, machine check, and I/O interrupts are logically handled as defined.

The performance objectives of the Model 195, however, require some deviations in handling program exceptions. The program-exception deviations are basically those resulting from an operation that has been sent by the instruction processor to another element for execution, so that the current PSW no longer references the operation. Consequently, the interrupt-causing instruction cannot be directly identified. Such a program interrupt is called imprecise. An imprecise interrupt is identified by the storing of zero as the instruction-length code in the PSW current at the time of interrupt.

Logical accuracy is preserved in all situations where a basic machine status change is involved. For example, all instructions issued under a program mask are completed before the mask is changed to ensure that the mask stored is that which allowed the interrupt.

The instruction-length codes (ILC) for program interrupts on the Model 195 follow. The codes in this listing replace those listed for ILC on program interrupts in the *IBM System/360 Principles of Operation.*

| Program Exception     | ILC     |

|-----------------------|---------|

| Operation             | 1,2,3   |

| Privileged Operation  | 1,2     |

| Execute               | 2       |

| Protection            | 0       |

| Addressing            | 0,1,2,3 |

| Specification         | 1,2,3   |

| Data                  | 0       |

| Fixed-Point Overflow  | 0       |

| Fixed-Point Divide    | 0       |

| Decimal Divide        | 0       |

| Decimal Overflow      | 0       |

| Exponent Overflow     | 0       |

| Exponent Underflow    | 0       |

| Significance          | 0       |

| Floating-Point Divide | 0       |

|                       |         |

# Imprecise Interrupts

The following program exceptions always cause *imprecise* interrupts:

- 1. Data, fixed-point-overflow, fixed-point-divide, decimal overflow, and decimal divide exceptions signaled from the fixed-point/VFL/decimal execution element.

- 2. Exponent-overflow, exponent-underflow, significance, and floating-point-divide exceptions signaled from the floating-point execution element.

- 3. A protection exception when a protection violation is detected.

An addressing exception can produce either a precise or an imprecise program interrupt, as determined by the problem.

When an imprecise interrupt is signaled, the instruction processor ensures that all instructions that were decoded before the signal was recognized are completed before the interrupt is honored. When the interrupt is taken, the instruction address stored in the program old PSW points to the next instruction that would have been decoded, and for which an attempt would have been made to issue it, had the interrupt not occurred.

Imprecise interrupts that arise from conditional instructions (that is, instructions issued subsequent to a 'branch on condition' instruction for which the condition code is not yet determined) are noted and either activated or canceled, as appropriate, when the conditional instructions themselves are activated or canceled.

When an imprecise interrupt takes place, not just one but several exceptions may have occurred, because all decoded instructions are completed before the interrupt is taken. Also, because instructions can be executed out of sequence, the interrupt condition recognized first may not be the condition that logically should be recognized first. To account for both possibilities (an out-of-sequence detection and the occurrence of more than one type of exception, either within one or different instructions), the action taken when an imprecise interruption occurs is that each type of exception that took place is identified in bits 16-27 of the program old PSW, and bits 28-31 are set to zero. Also, the instruction-length code (bits 32-33) is set to zero.

| U (             | · · · · · · · · · · · · · · · · · · · |

|-----------------|---------------------------------------|

| Bit Position in | Program                               |

| Program Old PSW | Exception                             |

| 16              | Protection                            |

| 17              | Addressing                            |

| 18              | Not Used                              |

| 19              | Data                                  |

| 20              | Fixed-Point Overflow                  |

| 21              | Fixed-Point Divide                    |

| 22              | Exponent Overflow                     |

| 23              | Exponent Underflow                    |

| 24              | Significance                          |

| 25              | Floating-Point Divide                 |

| 26              | Decimal Overflow                      |

| 27              | Decimal Divide                        |

|                 |                                       |

*Note:* For an imprecise interrupt, the types of exceptions that occurred, but not the number of exceptions of any one type that occurred, are identified in the program old PSW.

#### Precise Interrupts

When the program interrupt is precise, bits 28-31 of the program old PSW identify the exception causing the interrupt; the remainder of the interrupt code (bits 16-27) is all zeros; and the instruction-length code (bits 32-33) is 1, 2, or 3, as appropriate.

A logical consistency is maintained when a precise program interrupt precedes an imprecise program interrupt that logically should have taken place first. If an imprecise interrupt occurs during execution of outstanding instructions before a precisely identifiable interrupt is honored, the instruction causing the precise interrupt is not executed, the precise interrupt condition associated with this instruction is not indicated, and the address of the instruction causing the precise interrupt is placed in the instruction-address portion of the program old PSW. In effect, the instruction causing the precise interrupt is treated as never having occurred, and a return to the program causes the original interrupting instruction to be reinitiated. (The same operation takes place when a supervisor-call interrupt is followed by an imprecise program interrupt that logically should have occurred first.)

# Addressing Exceptions

An addressing exception resulting in a precise program interrupt is produced if any of the following conditions is detected:

- 1. Any portion of the current instruction to be decoded lies outside available storage.

- The address generated for any of the following instructions lies outside available storage: 'read direct,' 'write direct,' 'load PSW,' 'set system mask,' 'set storage key', 'insert storage key,' and 'diagnose.'

- 3. Any portion of the target instruction for 'execute' lies outside available storage.

All other addressing exceptions, which are signaled after the completion of address generation leading to the fetching or storing outside of available storage, result in imprecise program interrupts.

# Specification Exceptions

A specification exception resulting in a precise program interrupt is produced if any of the following conditions is detected:

- 1. An attempt is made to execute an instruction specified at an odd-numbered location in storage.

- 2. The R1 field of an instruction specifies an odd-numbered register for the pair of general registers that contains a 64-bit operand.

- 3. A number other than 0, 2, 4, or 6 is specified for a floating-point register (0, 4 – Extended Precision).

- 4. The block address specified in 'set storage key' or 'insert storage key' has the four low-order bits not all zero.

- 5. The three low-order bits are not all zero in the address generated for 'load PSW' or 'diagnose.'

- 6. The multiplier or divisor in decimal arithmetic exceeds 15 digits and sign.

- 7. The first operand field is shorter than or equal to the second operand field in decimal multiplication or division.

#### **Programming Notes**

A program may not operate correctly on the Model 195 if identification of the instruction that caused an imprecise interrupt is required. When an imprecise interrupt occurs, the program old PSW does not reference the operation that caused it. Also, a program may not operate correctly on the Model 195 if it requires the honoring of an imprecise interrupt before some instruction later in the program is executed. When an imprecise interrupt is detected, all instructions decoded by that time are executed before the interrupt is taken. Therefore, several instructions following the instruction that caused the imprecise interrupt may be executed before the interrupt is taken. (How many of these subsequent instructions will be executed will vary, principally because the Model 195 can execute instructions concurrently and out of sequence.) It is possible, at the programmer's option, to return to the problem program but, because all decoded instructions are completed before the interrupt is taken, the instructions executed after the interrupt may have been adversely affected by the program exception.

If preciseness is a principal concern, the unwanted effects of imprecise program interrupts can usually be eliminated by testing and masking, as appropriate, and by using this 'branch on condition' instruction:

| Mnemonic | Туре | M <sub>1</sub> Field | R <sub>2</sub> Field |

|----------|------|----------------------|----------------------|

| BCR      | RR   | Not zero             | Zero                 |

This branch instruction is a no-operation instruction for System/360 generally, but is implemented in the Model 195 in such a way that its execution is delayed until all previously decoded instructions have been completed.

*Note:* The address in the instruction counter is that of the BCR instruction, and the instruction length code is as listed at the beginning of this section. The use of this no-operation instruction degrades the performance of the Model 195. It should be used only to eliminate a problem for which there is no other reasonable solution.

Note that a program may have been naturally arranged so that the adverse effects of certain imprecise program interrupts are eliminated in advance. For example, in addition to the branch (no-operation) instruction just mentioned, execution of the following instructions is delayed until all previously decoded instructions have been completed: the four I/O instructions, 'load PSW', 'supervisor call', 'set storage key', 'diagnose', and 'set program mask' (except when the old and new mask bits are the same).

The execution of instructions out of sequence may present a problem in a situation other than the one concerning imprecise interrupts. Although the CPU maintains a logical consistency with respect to its own operations, including the starting and ending of I/O operations, it cannot ensure logical consistency between the CPU and asynchronous units during their operations. For example, if an I/O channel program relies on proper sequencing of stores by the CPU to ensure proper channel operation, steps must be taken in the CPU program to guarantee that the stores actually are made in that sequence. The no-operation instruction can be used to accomplish this.

# Interrupt Example

The following example taken from the program controlled interrupt (PCI) appendage for dynamic buffer allocation in the basic telecommunications access method (BTAM) illustrates the dependence of an asynchronous channel program upon serial execution. The example also demonstrates use of the BCR instruction to effect serial execution.

The purpose of the PCI appendage is to maintain an uninterrupted transmission of data into main storage. The controlling factors in this transmission are the availability of buffers and the ability (of the appendage routine) to modify and chain two channel programs. Each channel program consists of the following two channel command word (CCW) chains:

| Chain 1 | CCW1 | READ | into a buffer with data chaining (CD) and PCI flags                   |

|---------|------|------|-----------------------------------------------------------------------|

|         | CCW2 | READ | into CCW3 with skip (SKIP) and suppress length indication (SLI) flags |

| Chain 2 | CCW3 | READ | into a buffer with CD and PCI flags                                   |

|         | CCW4 | READ | into CCW1 with SKIP and SLI flags                                     |

- 1. In Chain 1, CCW1 is initialized with the first available buffer address.

- 2. The address fields for CCW2 and CCW4 initially contain the storage addresses of CCW3 and CCW1, respectively.

- 3. When the PCI interrupt in CCW1 occurs, the PCI appendage routine determines the address of the next available buffer and stores it into the address field of CCW3.

- 4. The command code in CCW2 is changed from a READ to a transfer-in-channel (TIC), and the command code in CCW4 is reset to READ as shown in Chain 2. (The first time through the channel program, CCW4 is already set to READ.)

- 5. When the PCI interruption in CCW3 occurs, the PCI appendage routine determines the address of the next available buffer (after the one indicated in step 3) and stores it into the address field of CCW1.

- 6. The command code in CCW4 is changed from a READ to a TIC, and the command code in CCW2 is reset to READ as shown in Chain 1.

Steps 3 through 6 of the preceding sequence of events continue until the input data transmission is completed. The PCI appendage instructions that accomplish the alteration of the CCWs are:

- ST available buffer address into CCW3 (or CCW1)

- BCR 15,0

- MVI into CCW2 (or CCW4), the code for a TIC command

- MVI into CCW4 (or CCW2), the code for a READ command

On the Model 195, use of the BCR instruction effects a pipeline drain to ensure that the proper buffer address is stored before the READ command is changed to a TIC command. If, as could happen when the BCR instruction is omitted, the MVI instructions were completed out of sequence (i.e., before the ST instruction), the channel could fetch a READ (into buffer) command with an old buffer address. In such a situation, the new input would overlay the old data.

*Note:* In this example, it is assumed that the PCI appendage instructions necessary to alter the format of the CCWs were executed before the channel fetched the "READ xx (SKIP, SLI)" command. If, in a given situation, this is not the case, then the fetching of the "READ xx (SKIP,SLI)" command is executed without transfer of data and causes a normal termination. Then, the appropriate channel program must be restarted at the expense of additional input/output time.

## STORAGE CONTROL UNIT

The storage control unit (SCU) is the intermediary between main storage and the other system units. As such, it controls central processing element (CPE) access to the high-speed buffer storage backed up by the full capacity of main storage. The SCU:

- 1. Provides and controls data and address paths to and from main storage and the buffer storage for the central processing element, the channels, and the system console.

- 2. Controls the transfer of doubleword blocks of information from main storage to the high-speed buffer storage.

- 3. Buffers store operations pending the availability of store data.

- 4. Properly sequences CPE stores and fetches to the same address.

- 5. Provides the storage protection function.

#### **Buffer Storage**

Because of the sequential nature of most programs, a CPE fetch is likely to be followed by succeeding fetches to the same storage block. Access time for subsequent fetches is considerably reduced by placing the addressed block of main storage in the high-speed buffer storage. Block transfer is controlled by the storage control unit so that use of the buffer storage is not obvious to the programmer.

The Model 195's increased performance is due in part to the faster access to instructions and operands provided by the high-speed buffer storage. Whereas normal instruction or operand fetches from main storage require 810 nanoseconds, fetches from the buffer storage require only 162 nanoseconds.

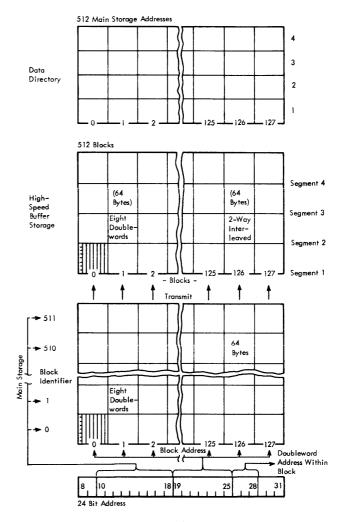

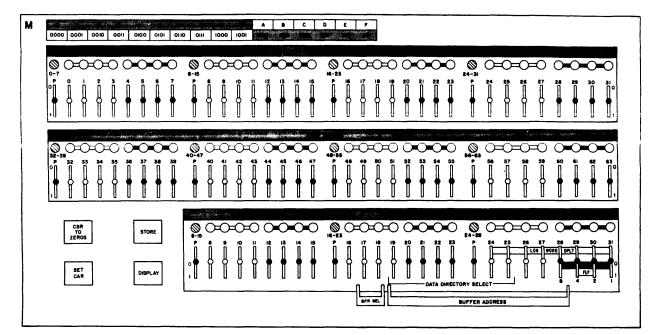

Main storage and the high-speed buffer storage (Figure 5) are similarly arranged. In main storage, eight doublewords (64 bytes) occupy each of the 128 blocks that form a segment. The largest processor storage, in the Model 195 L, has 512 segments. The buffer storage is arranged in a like manner but with four segments. Also provided are four data directories, one for each buffer segment, with 128 locations per directory. Each location in the directory contains the main storage address of the block of data in the corresponding block of the high-speed buffer storage.

Figure 5. High Speed Buffer Storage

#### **Buffer Storage Operation**

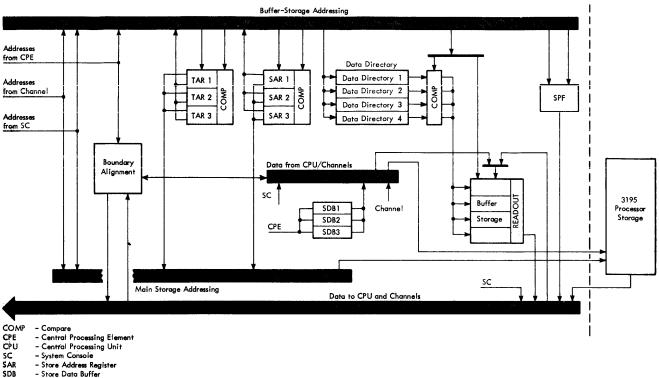

When the central processing element performs a store operation to main storage, the main storage address is placed in a store address register to await arrival of data in a store data buffer. See Figure 6. Comparing the address of the block addressed by the store operation with the block addresses in the data directory indicates whether the location also resides in the buffer storage. If so, the store is directed to both main storage and the buffer storage; if not, only main storage is modified by the store operation.

A channel or system console store to main storage must also determine when the addressed block resides in both main storage and the buffer storage, but for a different reason. Input from the channel or system console is directed only to main storage. Therefore, when the store address is also in the buffer storage, the addressed block is invalidated in the data directory. Consequently, it must be retransmitted from main storage before a subsequent fetch to that block is allowed.

SPF - Storage Protection Feature

TAR - Transfer Address Register

• Figure 6. Storage Control Unit Data Paths

CPE fetches from main storage are usually fetches from the high-speed buffer storage. The CPE fetch address is placed in a transfer address register (Figure 6), and a comparison is made with the store address register and the directory. An equal compare with the store address register causes the fetch to be delayed until the indicated store to that address is completed.

An equal comparison of the CPE fetch address and the data directory indicates that the data to be fetched resides in the high-speed buffer storage. The fetch is then made from the buffer storage and the data placed on the bus to the CPE.

When the fetch address does not reside in the buffer storage, a block transfer to the buffer storage is called for. The addressed doubleword is fetched from main storage and placed on the bus to the CPE. This doubleword is also transmitted to the buffer storage to become the first of eight doublewords in the block transfer. Subsequent fetches to this block can then be made from the high-speed buffer storage.

The block of doublewords transmitted to the buffer storage is placed in a block location corresponding to its main storage location as determined by the block address (Figure 5), and the block's main storage address is placed in the corresponding data directory location. The block may be placed, however, in any one of four possible buffer storage segments. Because all doublewords having the same block address are assigned to the same buffer storage location, four identical buffer segments are used to avoid conflicts. Which of the four buffer segments is used or replaced is determined by the replacement code. The replacement code is maintained to indicate the order of buffer storage segment usage. It indicates the most recently, second most recently, third most recently, and least recently accessed segment for each of the four possible blocks to be accessed.

The block transmitted from main storage replaces the least recently accessed segment block. Thus, the buffer always contains 512 blocks of main storage that have been used most recently.

Channel fetches are made only from main storage. Addresses from channels are held until the requested storage is free. Channel requests are then given highest priority to ensure against channel overrun.

# FIXED-POINT/VARIABLE-FIELD-LENGTH/DECIMAL EXECUTION ELEMENT

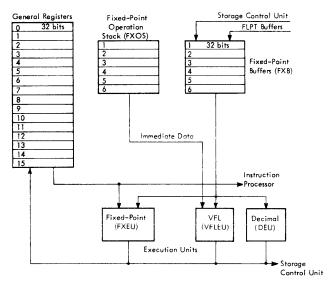

The fixed-point/variable-field-length (VFL)/decimal execution element executes all fixed-point arithmetic, logical, and variable-field-length and decimal arithmetic operations. It consists of six major logical elements (Figure 7):

- 1. An operation stack (FXOS) of six positions

- 2. Sixteen general registers

- 3. Six 32-bit operand buffers (FXB)

Figure 7. Fixed-Point/VFL/Decimal Execution Element

- 4. A fixed-point execution unit (FXEU)

- 5. A VFL execution unit (VFLEU)

- 6. A decimal execution unit (DEU)

Fetches from storage of data fields necessary for processing a fixed-point operation are initiated by the instruction processor, which also reserves in the fixed-point area the buffers that are to receive the requested operands.

The instruction processor also maintains for its own use counters that indicate whether: (1) the fixed-point operation stack has an available position, (2) which fixed-point buffers are available, and (3) which general registers are available to the instruction processor and which are being used by the fixed-point/VFL/decimal execution element.

During normal processing, operations in the FXOS are decoded serially and issued to either the fixed-point execution unit or the VFL or decimal execution unit. An operation can be executed if it has been decoded, if the data is available, and if the execution circuitry is free. When decoding is completed, the instruction processor is notified that the stack position and operand buffers assigned to that operation are free.

The execution of one operation is overlapped when possible with the decoding of the next. When a multiple-operation instruction is processed (see the discussion of multipleoperation instructions under "Instruction Processor"), decoding of the next instruction in the FXOS does not begin until the execution of the last of the multiple operations is begun.

Operations tagged as conditional are not decoded or executed until they are activated or canceled by the instruction processor. A canceled operation is decoded in one cycle, and execution of the operation consists of freeing any operand buffers previously assigned to the canceled operation without actual execution of the operation.

At any time during a fixed-point/VFL/decimal operation, the instruction processor can request a direct store into the general registers, which, because the instruction processor has priority, may delay fixed-point/VFL/decimal processing.

Fetches made during the execution of a multiple-operation instruction may require the use of operand buffers in the floating-point execution element; also, four of the six fixed-point operand buffers are unavailable for reassignment while such an instruction is being processed.

# FLOATING-POINT EXECUTION ELEMENT

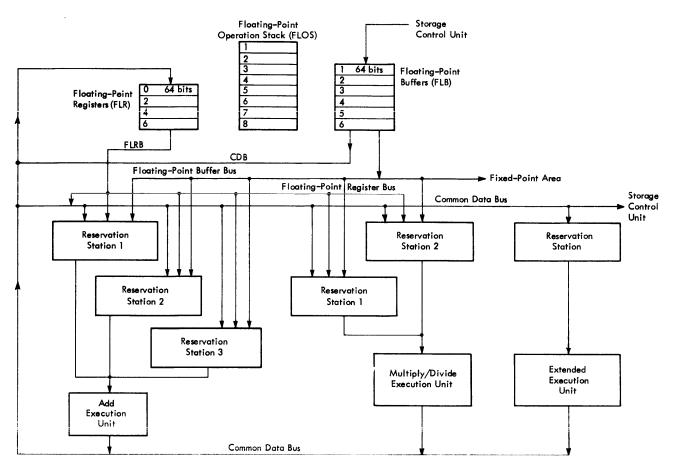

The floating-point execution element handles execution of the floating-point arithmetic operations, including the extended precision operations. (See "Extended Execution Unit.") Several operations can be executed at one time (maximum: two adds and one multiply or divide) if the operations are logically independent. This performance capability results largely from three significant features: (1) operand and instruction buffering, (2) multiple execution units employing extremely efficient algorithms, and (3) a common data bus, which links the several sets of execution circuitry so that the full power of the multiple execution units is realized without a reliance on programming for the special arrangement of instructions.

The floating-point area contains the following major logical elements (Figure 8):

- 1. An operation stack (FLOS) of eight positions.

- 2. Four floating-point registers (FLR).

- 3. Six operand buffers (FLB), which are also used by the fixed-point area when any multiple-operation instruction or the 'convert to binary' instruction is processed.

- 4. Three execution units: an add unit (preceded by three reservation stations) capable of performing two add operations concurrently, a multiply/divide (M/D) unit (preceded by two reservation stations), and an extended execution unit (preceded by one reservation station).

Decoding of operations in the FLOS proceeds serially. As an execution unit is selected for an operation (on the second cycle), the decoding of the next operation (on the first cycle) can begin. The FLOS issues operations subject to only one principal constraint: a reservation station of the appropriate type must be available.

The FLOS need not wait for all the operands to be available (as in the fixed-point area) before issuing the operation. Instead, the selected reservation station and controls hold the issued operation until the required operands have been collected and then engage the execution circuitry.

Because several operations may be in various stages of execution at one time, provision must be made for properly sequencing dependent operations. A system of tagging for usage of the common bus ensures proper sequencing and also facilitates fastest execution of independent operations.

The FLB and the common data bus execute all RX load operations. RR load and RR load and test operations are executed by the common data bus and special testing circuitry. Store operations are executed by the three store data buffers. Multiply and divide operations are executed

Figure 8. Floating-Point Execution Element

by an M/D unit, and the extended unit, if required. Add operations are executed in either the add unit or the extended unit.

Fetches for data fields needed to process a floating-point operation are initiated by the instruction processor, which also reserves the buffers in the floating-point area that are to receive the requested operands. The instruction processor also maintains for its own use counters that indicate whether the FLOS has an available position and which floating-point buffers are available.

When the FLOS completes decoding, it signals the instruction processor that the stack position is empty. If an operation has been decoded, the related operand buffer is set free at the time it is filled; if the operand buffer is filled before the related operation is decoded, however, the buffer is set free one cycle after decoding is completed.

Operations tagged as conditional are not decoded or executed until they are activated or canceled by the instruction processor. A canceled operation is decoded in one cycle, and execution of the operation consists of freeing all operand buffers previously assigned to the canceled operation without actual execution of the operation.

# **Add Execution Unit**

The add execution unit can begin execution if the operation has been decoded, the data is available, and another add operation of higher priority is not beginning on the same cycle. Two add operations can be executed concurrently by offsetting the start of the second operation one cycle from the start of the first. While two operations are being performed, the third reservation station may be acquiring data.

# **Multiply/Divide Execution Unit**

The multiply or divide execution unit can begin execution if the operation has been decoded, the data is available, another multiply or divide operation of higher priority is not beginning on the same cycle, and the execution circuitry is free. The two M/D reservation stations share a single execution section; therefore, only one M/D operation may be executed at a time.

# Extended Execution Unit

The extended execution unit (Figure 8) is a standard feature that provides additional logic for handling extended precision (28-digit fraction) floating-point operands. The feature includes seven instructions and additional controls for using the multiply unit. (Details of the extended-precision floating-point instructions are in *IBM System/360 Principles* of Operation, GA22-6821.)

Instruction execution begins when the operands are in the reservation station. For an extended-precision multiply operation, priority for the use of the multiply unit is required.

# Channels

The IBM 2870 Multiplexer Channel, the IBM 2860 Selector Channel, and the IBM 2880 Block Multiplexer Channel provide for attachment of I/O devices to the Model 195 system. The channel relieves the CPU of communicating directly with I/O devices and permits data processing to proceed concurrently with I/O operations.

Channel priority is independent of the channel address and is selected at time of installation. Priority is determined by pluggable circuit jumpers in the CPU. (*Note:* Only qualified maintenance personnel may insert or remove these circuit jumpers.) Guidelines for assigning priority are:

- 1. Channels with the 2301 Drum Storage or 2305 Fixed Head Storage attached should be assigned highest priorities.

- 2. The 2870 Multiplexer Channels with overrunable devices attached should follow in priority channels with a 2301 or 2305 attached.

- 3. Continue assigning priority in decreasing data rate order to channels with overrunable devices, that is, lower priority to lower data rate device.

- 4. Channels with non-overrunable devices should have lowest priority.

A standard channel-to-control-unit interface provides a uniform method of attaching control units to channels. Data is transferred a byte at a time between the I/O device and the channel. An optional two-byte-wide interface on the 2880 channel provides for attachment of devices with very high data rates. Data transfers between the channel and the SCU are eight bytes (one doubleword) in parallel for both selector and multiplexer channels.

The following descriptions include the maximum data rates attainable by the different channels. During system operation, the actual rates may be less than the maximums, depending on (1) channel priority, (2) the number of channels operating concurrently, (3) the speed of the devices operating on each channel, and (4) the type of channel programming used; for example, single record versus chained records.

#### **2860 SELECTOR CHANNEL**

The 2860 Selector Channel provides for attachment and control of I/O control units and associated devices. At least one 2860 (any model) is required if no 2870 Multiplexer or 2880 Block Multiplexer Channel is attached. The 2860 is available in three models:

- Model 1 provides one selector channel

- Model 2 provides two selector channels

- Model 3 provides three selector channels

The 2860 Selector Channel permits data rates of up to 1.3 million bytes a second. I/O operations are overlapped with processing and, depending on the data rates and channel programming considerations, all selector channels can operate concurrently. A set of channel control and buffer registers permits each channel to operate with a minimum of interference.

Eight control units can be attached to each selector channel. Each control unit may have more than one I/O device connected to it, but only one device per channel may transfer data at any given time. A selector channel operates only in burst mode, and may be assigned addresses one through six only.

## **2870 MULTIPLEXER CHANNEL**

The 2870 Multiplexer Channel provides for attachment of a wide range of low- to medium-speed I/O control units and associated devices. The basic 2870 Multiplexer Channel with 192 subchannels can attach eight control units and can address 192 I/O devices. The basic multiplexer channel can operate several multiplex-mode I/O devices concurrently or a single burst-mode device.

Two 2870's can be attached to the Model 195: the first one provides 196 subchannels including four optional selector subchannels; the second one provides 194 subchannels including two optional selector subchannels. The address of the first 2870 must be zero; the second 2870 may be assigned any address from one through six. The address priority assigned to the second 2870 should be as high as possible, but not higher than a selector channel with a 2301 drum attached

Selector subchannels are optional. Each selector subchannel can operate one I/O device concurrently with the basic multiplexer channel.

Each selector subchannel permits attachment of eight control units for certain devices having a data rate not exceeding 180 kilobytes (kb) a second. Regardless of the number of control units attached, a maximum of 16 I/O devices can be attached to a selector subchannel.

The maximum aggregate data rate for the multiplexer channel ranges from 110 kb to 670 kb, depending on the number of selector subchannels in operation. The first three selector subchannels may operate concurrently at up to 180 kb for each subchannel. When all four selector subchannels operate concurrently, the fourth has a maximum data rate of 100 kb.

Each selector subchannel in operation diminishes the basic multiplexer channel's maximum data rate of 110 kb; the

maximum data rates for concurrent selector subchannel operations are:

| Basic       | Data Rates for Selector Subchannel |         |          |        |

|-------------|------------------------------------|---------|----------|--------|

| Multiplexer | 1st or 2r                          | nd 2870 | 1st 2870 | Only   |

| Channel     | lst                                | 2nd     | 3rd      | 4th    |

| 110 kb      |                                    |         |          |        |

| 88 kb       | 180 kb                             |         |          |        |

| 66 kb       | 180 kb                             | 180 kb  |          |        |

| 44 kb       | 180 kb                             | 180 kb  | 180 kb   |        |

| 30 kb       | 180 kb                             | 180 kb  | 180 kb   | 100 kb |

*Note:* The 180-kb maximum data rate for 2870 selector subchannels pertains to attachment of magnetic tape devices; timing factors other than data rates may preclude attachment of direct-access storage devices that have lesser data rates. Also, note that when other channels in addition to the 2870 are in operation, the total system I/O data rate must be analyzed.

#### 2880 BLOCK MULTIPLEXER CHANNEL

The functional use of the 2880 Block Multiplexer Channel closely parallels that of the 2860 Selector Channel; devices that attach to the Model 195 through a 2860 may also attach through a 2880 assigned one of the addresses one through six. The 2880 is capable of higher data rates than the 2860, however, and also offers a block multiplexing capability. A two-byte I/O interface used with the high-speed data transfer mode permits data rates of up to three million bytes per second.

Unlike the 2860 and 2870 channels, the 2880 performs a channel logout on occurrence of a channel data check condition. The logout occurs at the completion of the current command and into locations 272 through 399. Data check logouts may be eliminated during selector mode operation by inserting the bypass-logout circuit jumper. (*Note:* Only qualified maintenance personnel may insert or remove the bypass-logout circuit jumper.)

At least one 2880 Block Multiplexer channel is required if no 2860 Selector or 2870 Multiplexer channels are attached. The 2880 always transfers data in burst mode, and may be assigned any address from one through thirteen.

Two models of the 2880 Block Multiplexer Channel are available:

Model 1 -provides one channel

Model 2 – provides two channels

The standard features of the 2880 are the high-speed data transfer mode (up to 1.5 million bytes per second) and the block-multiplexing capability (concurrent operation of up to 64 devices).

An optional feature is the two-byte interface which provides for a data transfer rate of up to 3.0 million bytes per second.

The basic 2880 Block Multiplexer Channel attaches to the standard one-byte I/O interface. The 2880 utilizes a high-speed data transfer mode that incorporates two additional interface tag lines, Data-In and Data-Out, to allow I/O data

rates up to 1.5 million bytes per second. Data rates of 1.5 to 3.0 million bps are achieved through additional buffering and use of an optional two-byte I/O interface. All data transfers over the two-byte interface are in the high-speed data transfer mode.

The block multiplexing function provides 64 subchannels to be block multiplexed over the standard I/O interface. Block multiplexing is similar to the byte multiplexing capability of the 2870 Multiplexer Channel; the principal difference is the quantity of data transferred per transmission. The 2880 multiplexes blocks (bursts) of data; that is, burst mode devices share the channel facilities and transmit data in burst mode. When the channel is multiplexing (interleaving) blocks of data on the single data path it may also control the nondata transfer activities of multiple devices.

Eight control units can be attached to each 2880 Block Multiplexer Channel. Each control unit may have more than one I/O device connected to it, but only one device per channel may transfer data at any given time. However, as many as 64 channel programs may be in concurrent execution in each 2880 channel through use of the block multiplexing function.

To facilitate conversion, the 2880 also operates in selector channel mode, thus permitting operation under the current operating system. A switch is provided on the system console for selection of either the selector or block multiplex mode.

#### EXTENDED CHANNEL FEATURE

This feature permits attachment of as many as 14 channels to the Model 195, in which case bit 6 in the system mask of the PSW masks channels 6-13 as a group rather than channel 6 alone.

Without the extended channel feature, one or two 2870's and up to six 2860's and/or 2880's may be attached to the CPU as follows:

| 2860's and/or 2880's |

|----------------------|

| 1 to 6               |

| 0 to 6               |

| 0 to 5               |

|                      |

With the extended channel feature the number of channels and frames allowed is as follows:

|                | Maximum Number Allowed |         |  |  |

|----------------|------------------------|---------|--|--|

| Channels       | Channels               | Frames* |  |  |

| 2860           | 6                      | 2       |  |  |

| 2870           | 2                      | 2       |  |  |

| 2860/2870      | 7                      | 4       |  |  |

| 2880           | 13                     | 8       |  |  |

| 2860/2880      | 13                     | 8       |  |  |

| 2870/2880      | 14                     | 8       |  |  |

| 2860/2870/2880 | 14                     | 8       |  |  |

\* Maximum channels per frame:

| 3 - 2 | 860 |

|-------|-----|

|-------|-----|

2 - 2880

1 - 2870

# CHANNEL-TO-CHANNEL ADAPTER FEATURE

A channel-to-channel adapter is available as an optional feature on the 2860. The adapter provides a path for operations to take place between two channels and synchronizes those operations. It may be used in multiple-processor or singleprocessor systems: in a multisystem, to achieve rapid communications between the channels of two System/360 models; in a single system, to move blocks of data from one main storage area to another.

The adapter uses one control-unit position on each of the two channels, but only one of the two connected channels requires the feature. In the Model 195, one adapter may be installed per 2860 selector channel.

When the 2870 or 2880 channel is connected to a 2860 channel, the channel-to-channel adapter is installed on the 2860 channel, not on the 2870 or 2880.

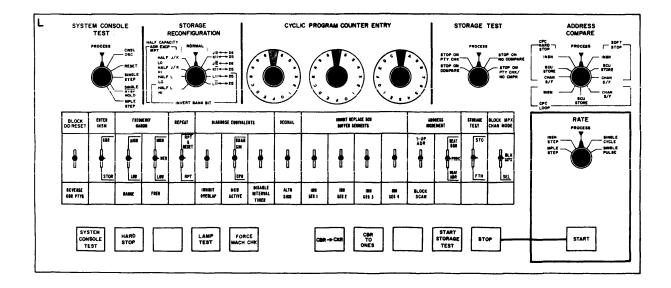

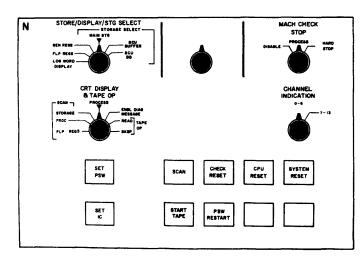

For restrictions on channel attachments for another IBM System/360 model used with the Model 195, refer to the Systems Reference Library (SRL) functional characteristics publication for that model. The system control panel on the system console contains the switches, keys, and indicator lights to operate and control the system (CPU, storage, channels, on-line control units, and input/output devices). Off-line control units and I/O devices, though part of the system environment, are not considered part of the system.

System controls are divided into three classes: operator control, operator intervention, and customer engineering control. This section of the manual discusses operator control and operator intervention.

Using the control panel, the operator can perform the following system control functions:

- 1. Reset the system.

- 2. Store and display information in storage, registers, and program status word (PSW).

- 3. Load initial program information.

# SYSTEM CONTROL FUNCTIONS

#### System Reset

The system-reset function resets the CPU, channels, and online nonshared control units and I/O devices.

The CPU is placed in the stopped state, and all pending interrupts are eliminated. All error-status indicators are reset to zero.

In general, the system is placed in such a state that processing can be initiated without machine checks occurring, except those caused by subsequent machine malfunction.