# oneywell

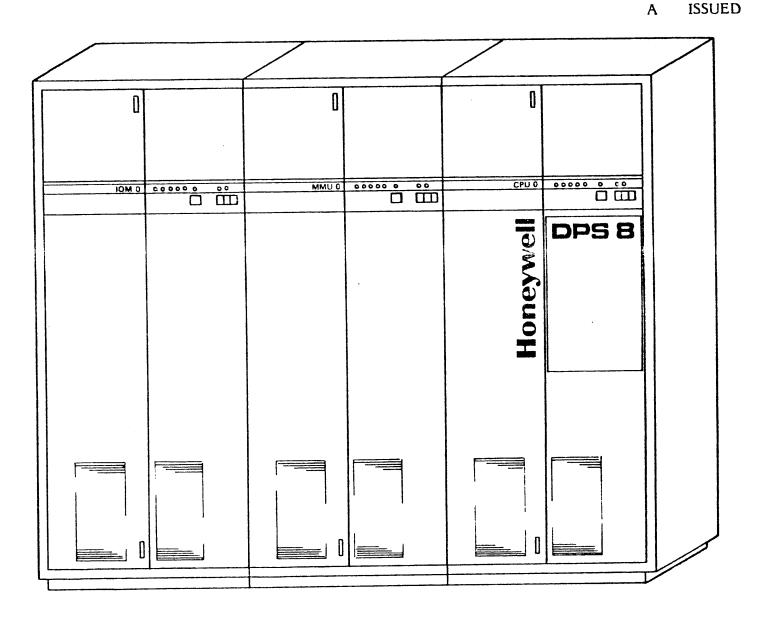

# FREESTANDING DPS 8

WCPU68LA/WIOU66LA/WMMU66LA

SYSTEM MANUAL

58009906

DPS 8 FREESTANDING MULTICS

The following notice is provided in accordance with the United States Federal Communications Commission's (FCC) regulations.

Warning This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

FREESTANDING MULTICS DPS-8 SINGLE SYSTEM MODULE

| A 11/81 PHAFPD902 58009906-040 58009906-030. 1F 58009906-014. 1F 58009906-017. 1, 2. 3F 58009906-015. 1-1 THRU 1-7F 58009906-051. 2-1 THRU 2-7, 2-7.1 2-8 THRU 2-40F 58009906-200. 4-1 THRU 4-5F  B 8/82 PHAFMJ228 58009906-040 58009906-015.1-4 58009906-015.1-4 58009906-015.1-4 58009906-015.1-4 58009906-015.1-4 58009906-015.2-8,2-10,2-11,2-12. 2-35,2-36 58009906-100.3-1,3-2,3-5,3-6 |          | RECORD OF REVISION |                                                                                                                                                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B 8/82 PHAFMJ228 58009906-040<br>58009906-041, 1F<br>58009906-001, 1F<br>58009906-015, 1-1 THRU 1-7F<br>58009906-051, 2-1 THRU 2-7, 2-7, 1<br>2-8 THRU 2-40F<br>58009906-100, 3-1 THRU 3-21F<br>58009906-200, 4-1 THRU 4-5F                                                                                                                                                                  | REV DATE | AUTHORIZATION      | PAGES AFFECTED                                                                                                                                                                                                               |  |

| B 8/82 PHAFMJ228 58009906-040 58009906-014,1F 58009906-015,1-4 58009906-051,2-8,2-10,2-11,2-12, 2-35,2-36                                                                                                                                                                                                                                                                                    | A 11/81  | PHAFPD902          | 58009906-030. 1F<br>58009906-041. 1F<br>58009906-014. 1F<br>58009906-001. 1F<br>58009906-017. 1. 2. 3F<br>58009906-015. 1-1 THRU 1-7F<br>58009906-051. 2-1 THRU 2-7. 2-7.1<br>2-8 THRU 2-40F<br>58009906-100. 3-1 THRU 3-21F |  |

|                                                                                                                                                                                                                                                                                                                                                                                              | 8/82     | PHAFMJ228          | 58009906-040<br>58009906-014,1F<br>58009906-015,1-4<br>58009906-051,2-8,2-10,2-11,2-12,<br>2-35,2-36                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                              |          |                    |                                                                                                                                                                                                                              |  |

|     | RECORD OF REVISION |               |                |  |

|-----|--------------------|---------------|----------------|--|

| REV | DATE               | AUTHORIZATION | PAGES AFFECTED |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               | •              |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               | _              |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

|     |                    |               |                |  |

#### TABLE OF CONTENTS

#### VOLUME 1F

| Binder, Red, B-Size 4-ring, 2-inch spine Standard System Separator Tabs, B Size Spine, Freestanding Multics DPS 8 System Manual Title Page: Vol 1F Frontispiece Record of Revisions Table of Contents Manual Contents | 58009884-008<br>58009885-018<br>58009906-030<br>58009906-040<br>58009906-041<br>58009906-014<br>58009906-001<br>58009906-017 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| General Tab                                                                                                                                                                                                           | 58009906-015                                                                                                                 |

| Physical Outline Tab                                                                                                                                                                                                  | 58009906-051                                                                                                                 |

| System Theory Tab                                                                                                                                                                                                     | 58009906-100                                                                                                                 |

| System Maintenance Tab                                                                                                                                                                                                | 58009906-200                                                                                                                 |

#### MANUAL CONTENTS

#### VOLUME 1F

| SECTION |                                                          | PAGE | SECTION   |                                            | PAGE |

|---------|----------------------------------------------------------|------|-----------|--------------------------------------------|------|

| 1.0     | GENERAL                                                  | 1-1  | 2.7.3     | IOM Cabinet Panels                         | 2-26 |

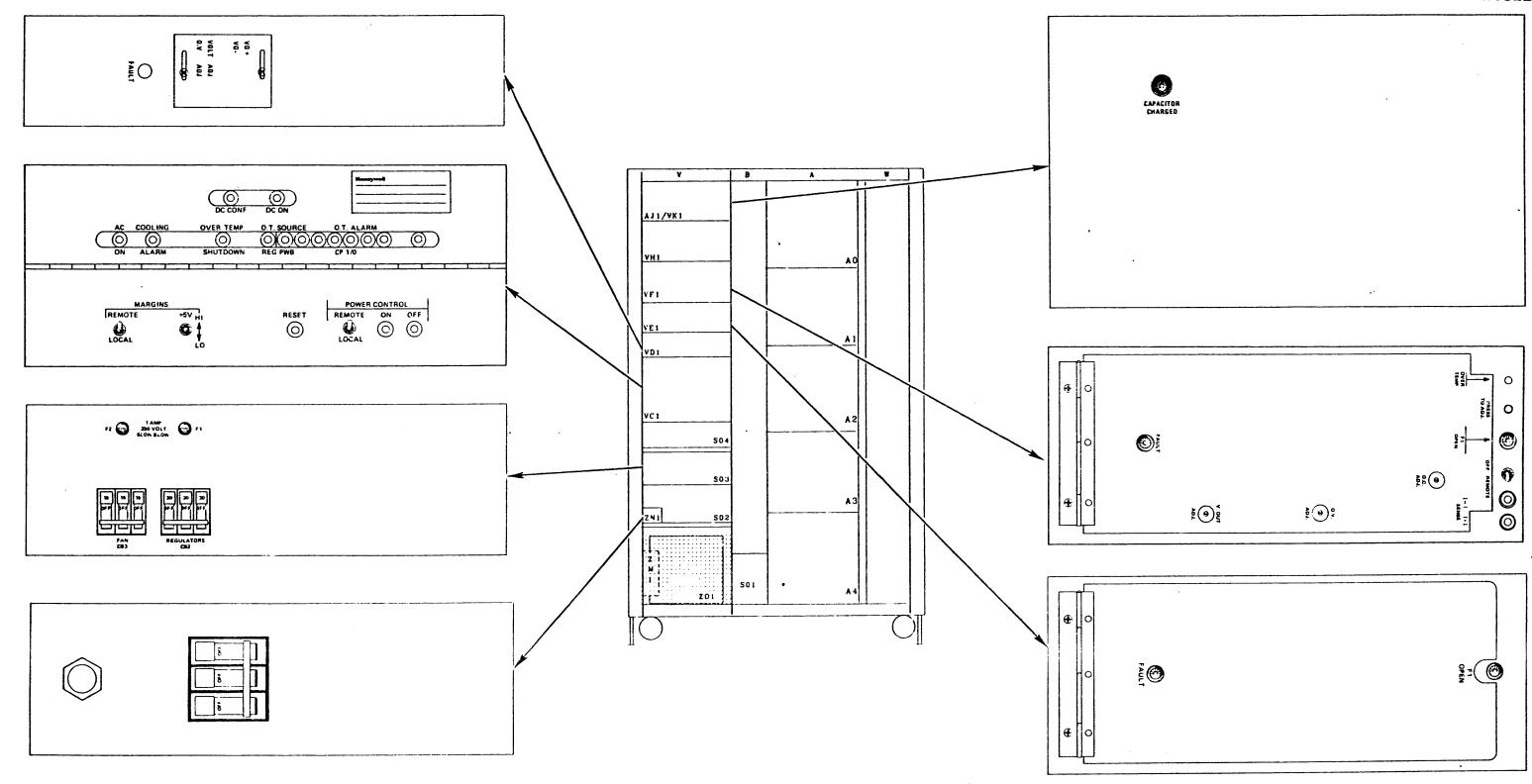

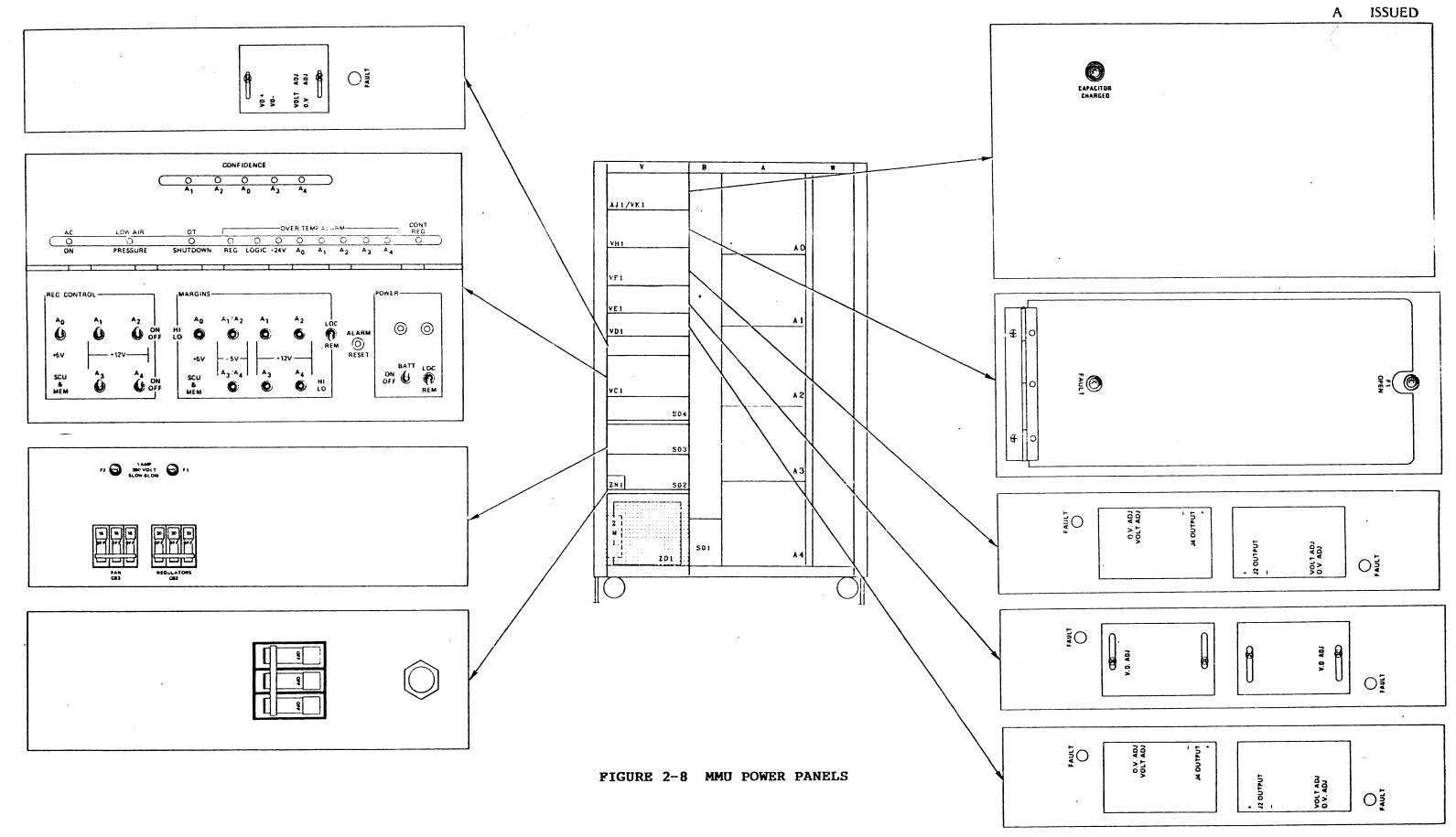

| 1.1     | INTRODUCTION                                             | 1-1  | 2.7.4     | MMU Cabinet Panels                         | 2-27 |

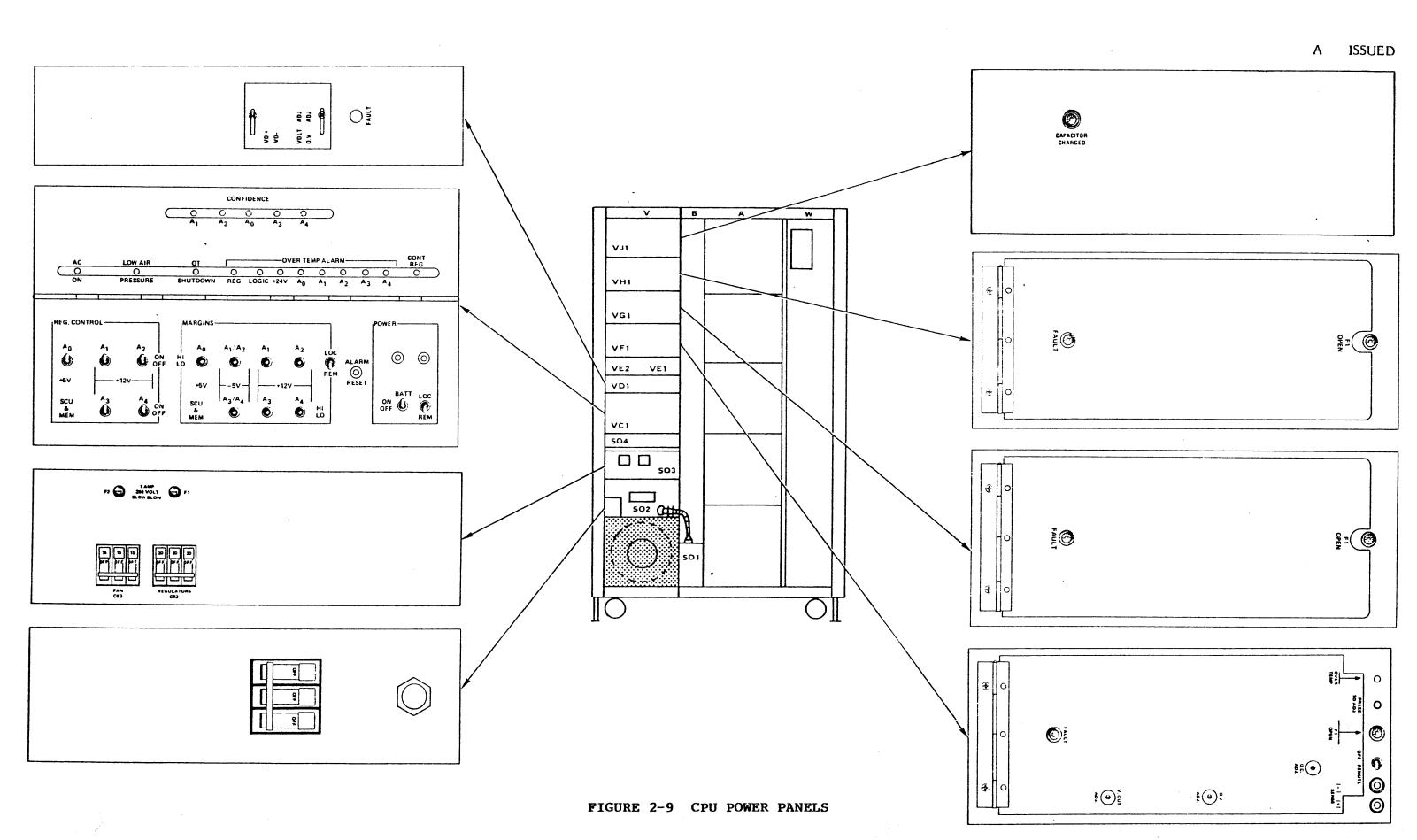

| 1.1.1   | Purpose                                                  | 1-1  | 2.7.5     | CPU Cabinet Panels                         | 2-28 |

| 1.1.2   | Scope                                                    | 1-1  | 2.7.6     | MPC Cabinet Panels                         | 2-29 |

| 1.1.3   | Objective                                                | 1-1  | 2.8       | SYSTEM OPTIONS                             | 2-30 |

| 1.1.4   | Documentation                                            | 1-1  | 2.8.1     | Introduction                               | 2-30 |

| 1.1.5   | Reference Support Documentation                          | 1-1  | 2.8.2     | IOM Options                                | 2-31 |

| 1.1.6   | Feedback                                                 | 1-2  | 2.8.3     | MMU Opcions                                | 2-34 |

| 1.2     | SYSTEM OVERVIEW                                          | 1-4  | 2.8.4     | CPU Options                                | 2-37 |

| 1.3     | SIGNAL FLOW                                              | 1-5  | 2.8.5     | MPC Options                                | 2-39 |

| 1.3.1   | Read Data                                                | 1-6  |           | -                                          |      |

| 1.3.2   | Write Data                                               | 1-6  | 3.0       | SYSTEM THEORY                              | 3-1  |

| 1.3.3   | Initialize (INZ)                                         | 1-6  | 3.1       | GENERAL INFORMATION                        | 3-1  |

| 1.3.4   | Refresh                                                  | 1-7F | 3.1.1     | Features of the Multics System             | 3-3  |

| 1.3.5   | ZAC                                                      | 1-7F | 3.1.1.1   | Associative Memories                       | 3-3  |

| 1.3.6   | System Console Signals                                   | 1-7F | 3.1.1.2   | Hardware-Controlled Cache                  | 3-3  |

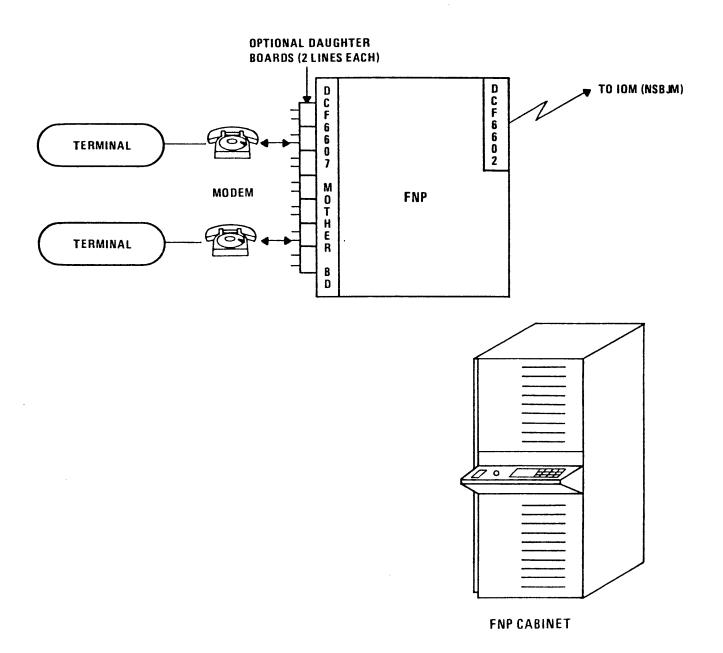

| 1.3.7   | FNP Signals                                              | 1-7F | 3.1.1.3   | Detailed Description                       | 3-4  |

| 1.3.8   | MPC Signals                                              | 1-7F | 3.2       | MMU CABINET                                | 3-5  |

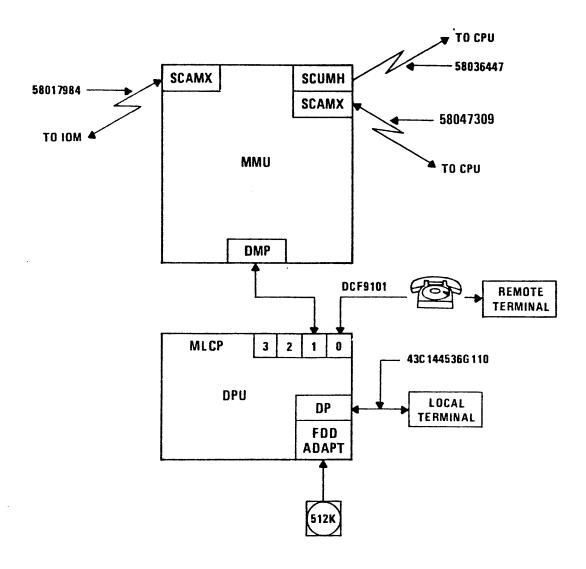

| 1.3.9   | DPU Signals                                              | 1-7F | 3.2.1     | MMU Introduction                           | 3-5  |

| 1.4     | TECHNICAL INSTRUCTIONS                                   | 1-7F | 3.2.2     | MMU Description                            | 3-5  |

| T • 4   | Indiki Cili Indika I I I I I I I I I I I I I I I I I I I |      | 3.2.3     | MMU Functions                              | 3-6  |

| 2.0     | PHYSICAL OUTLINE                                         | 2-1  | 3.3       | IOM CABINET                                | 3-7  |

| 2.1     | GENERAL INTRODUCTION                                     | 2-1  | 3.3.1     | IOM Introduction                           | 3-7  |

| 2.2     | PHYSICAL CABINET CONFIGURATION                           | 2-2  | 3.3.2     | IOM Description                            | 3-7  |

| 2.2.1   | Basic Cabinet Outline                                    | 2-2  | 3.3.2.1   | SCU Interface Port                         | 3-7  |

| 2.2.2   | Common Cabinet Components                                | 2-3  | 3.3.2.2   | I/O Interface Port                         | 3-8  |

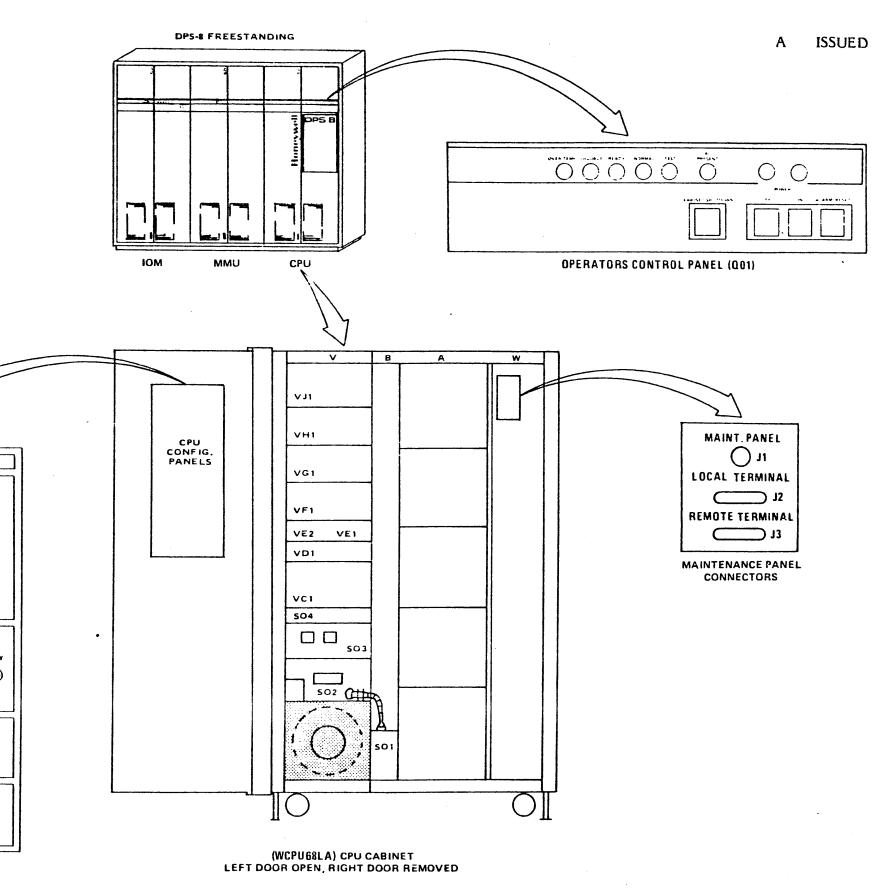

| 2.3     | CPU CABINET CONFIGURATION                                | 2-4  | 3.3.3     | IOM Functions                              | 3-9  |

| 2.3.1   | CPU Cabinet Components                                   | 2-5  | 3.4       | CPU CABINET                                | 3-10 |

| 2.3.2   | CPU Circuit Boards by Location                           | 2-6  | 3.4.1     | CPU Introduction                           | 3-10 |

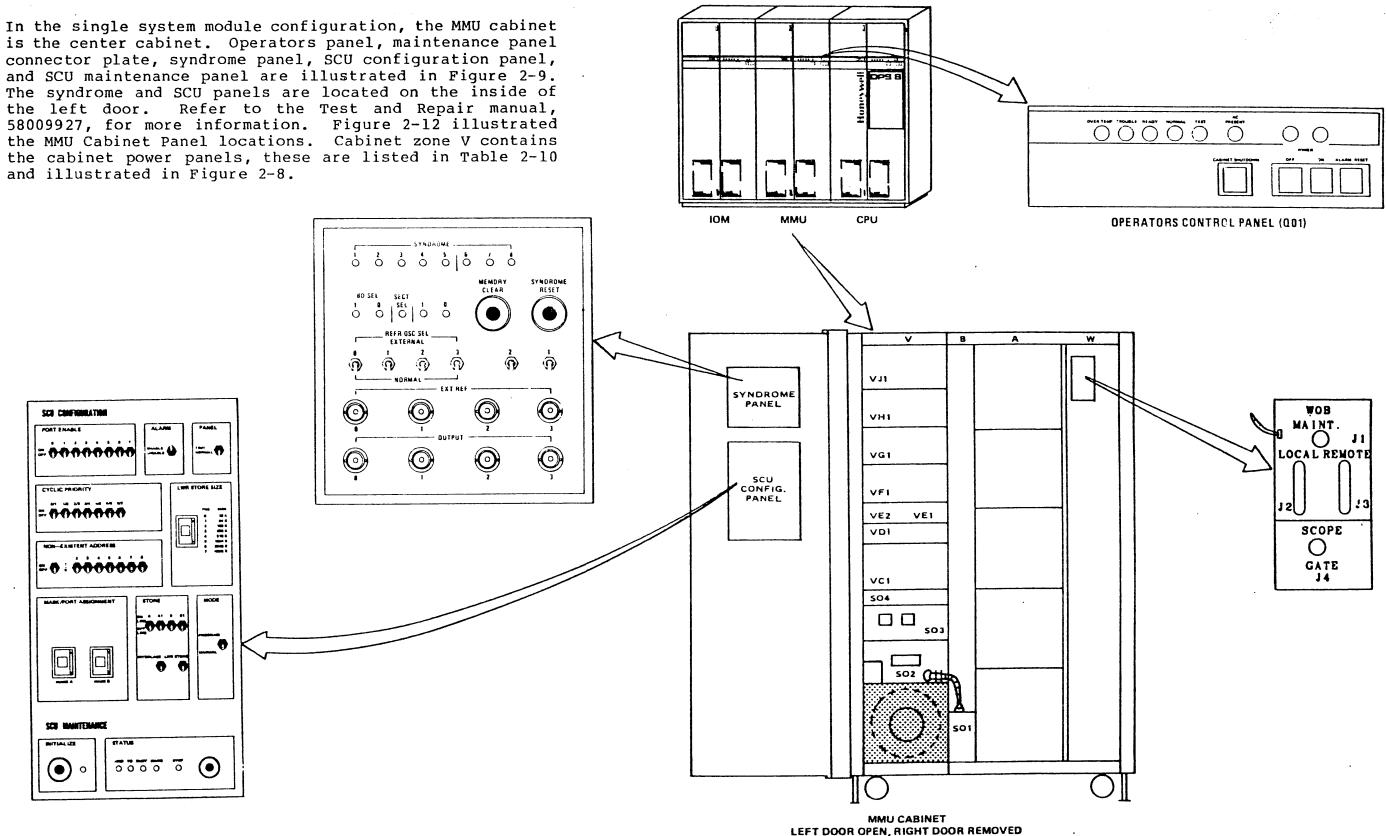

| 2.4     | MMU CABINET CONFIGURATION                                | 2-8  | 3.4.2     | CPU Description                            | 3-10 |

| 2.4.1   | MMU Cabinet Components                                   | 2-9  | 3.4.2.1   | Features of the Multics CPU                | 3-10 |

| 2.4.2   | MMU Circuit Boards by Location                           | 2-10 | 3.4.2.2   | CPU Functional Units                       | 3-11 |

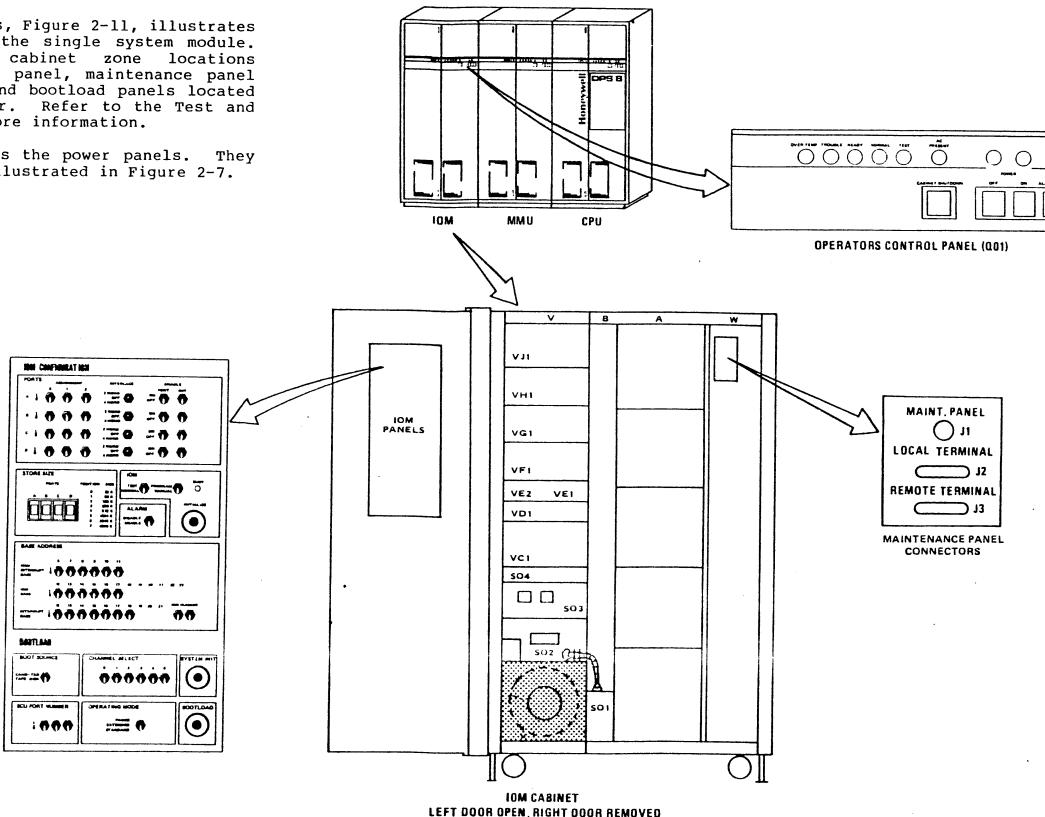

| 2.5     | IOM CABINET CONFIGURATION                                | 2-13 | 3.4.2.2.1 | Control Unit                               | 3-11 |

| 2.5.1   | IOM Cabinet Components                                   | 2-14 | 3.4.2.2.2 | Operations Unit                            | 3-12 |

| 2.5.2   | IOM Circuit Boards by Location                           | 2-15 | 3.4.2.2.3 | Decimal Unit                               | 3-12 |

| 2.6     | MPC CABINET CONFIGURATION                                | 2-17 | 3.2.2.2.4 | Appending Unit                             | 3-12 |

| 2.6.1   | MPC Cabinet Components                                   | 2-18 | 3.4.2.2.5 | Associative Memory Assembly                | 3-12 |

| 2.6.2   | MPC Circuit Boards by Location                           | 2-19 | 3.4.3     | CPU Functions                              | 3-12 |

| 2.7     | SYSTEM MAINTENANCE & CONTROL PANELS                      | 2-20 | 3.4.3.1   | Address Modification and Address Appending | 3-13 |

| 2.7.1   | Introduction                                             | 2-20 | 3.4.3.2   | Faults and Interrupts                      | 3-13 |

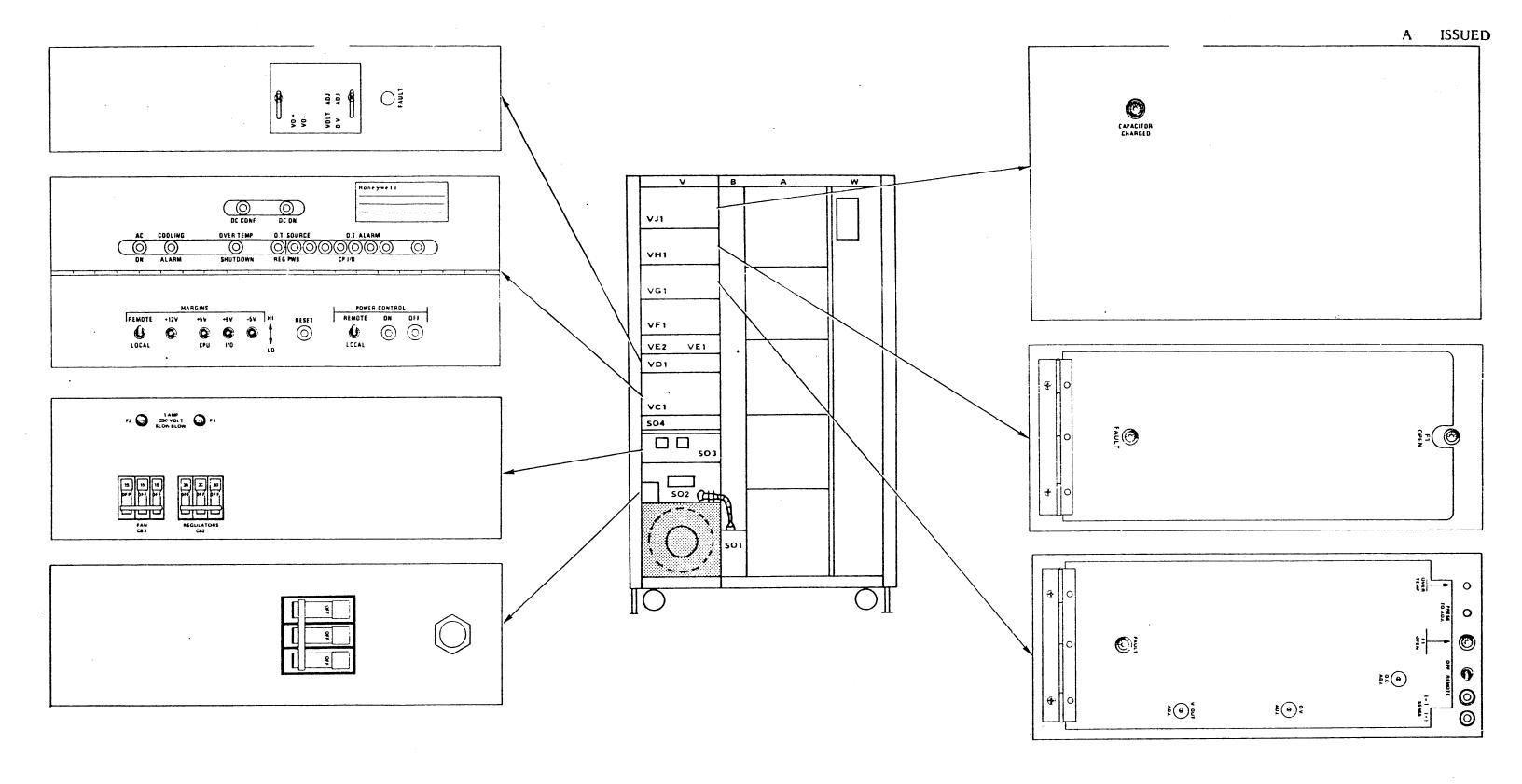

| 2.7.2   | Power Control Panels                                     | 2-21 | 3.4.3.3   | CPU Modes of Operation                     | 3-14 |

| SECTION                                                                                              |                                                                                                                                                                                                                                                                                                 | PAGE                                                                 |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 3.4.3.3.1<br>3.4.3.3.2<br>3.5<br>3.5.1<br>3.5.2<br>3.5.2.1<br>3.5.2.2<br>3.5.2.3<br>3.5.2.4<br>3.5.3 | Instruction Execution Modes Addressing Modes MPC CABINET MPC Introduction MPC Description Controller/Processor Link Adapter Controller Adapter Basic MPC MPC Functions DPU CABINET                                                                                                              | 3-14<br>3-15<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-16<br>3-16 |

| 3.6.1<br>3.6.2<br>3.6.3<br>3.7<br>3.7.1<br>3.7.2<br>3.7.3                                            | DPU Introduction DPU Description DPU Functions FNP CABINET FNP Introduction FNP Description FNP Functions                                                                                                                                                                                       | 3-18<br>3-18<br>3-19<br>3-20<br>3-20<br>3-21F                        |

| 4.0<br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3.1<br>4.3.2                     | SYSTEM MAINTENANCE MAINTENANCE INTRODUCTION GENERAL MAINTENANCE Care and Handling of Diskette Media Care and Handling of Disk Packs Care and Handling of Magnetic Tapes Cleaning Equipment Air Filters Care and Handling of Punch Cards TECHNICAL MAINTENANCE Total On-Line Test System (TOLTS) | 4-1<br>4-1<br>4-1<br>4-2<br>4-2<br>4-3<br>4-3<br>4-4                 |

| 4.3.3                                                                                                | Honeywell Error Analysis and Logging Sub-<br>system (HEALS)<br>Visual Information Display for Efficient<br>Operation (VIDEO)                                                                                                                                                                    | <b>4 – 4</b><br>4 – 4                                                |

| 4.3.4<br>4.3.5<br>4.3.6<br>4.3.7                                                                     | Statistical Collection File (SCF) and Summary Edit Program (GSEP) Auto II Field Subset Off-Line Test and Diagnostics Integrated Firmware and Diagnostics (IFAD)                                                                                                                                 | 4-5F<br>4-5F<br>4-5F<br>4-5F                                         |

58009906-017

#### MANUAL CONTENTS (Continued)

#### VOLUME 1F

3-18

3-20

#### LIST OF ILLUSTRATIONS

| FIGURE | DESCRIPTION                                           | PAGE |

|--------|-------------------------------------------------------|------|

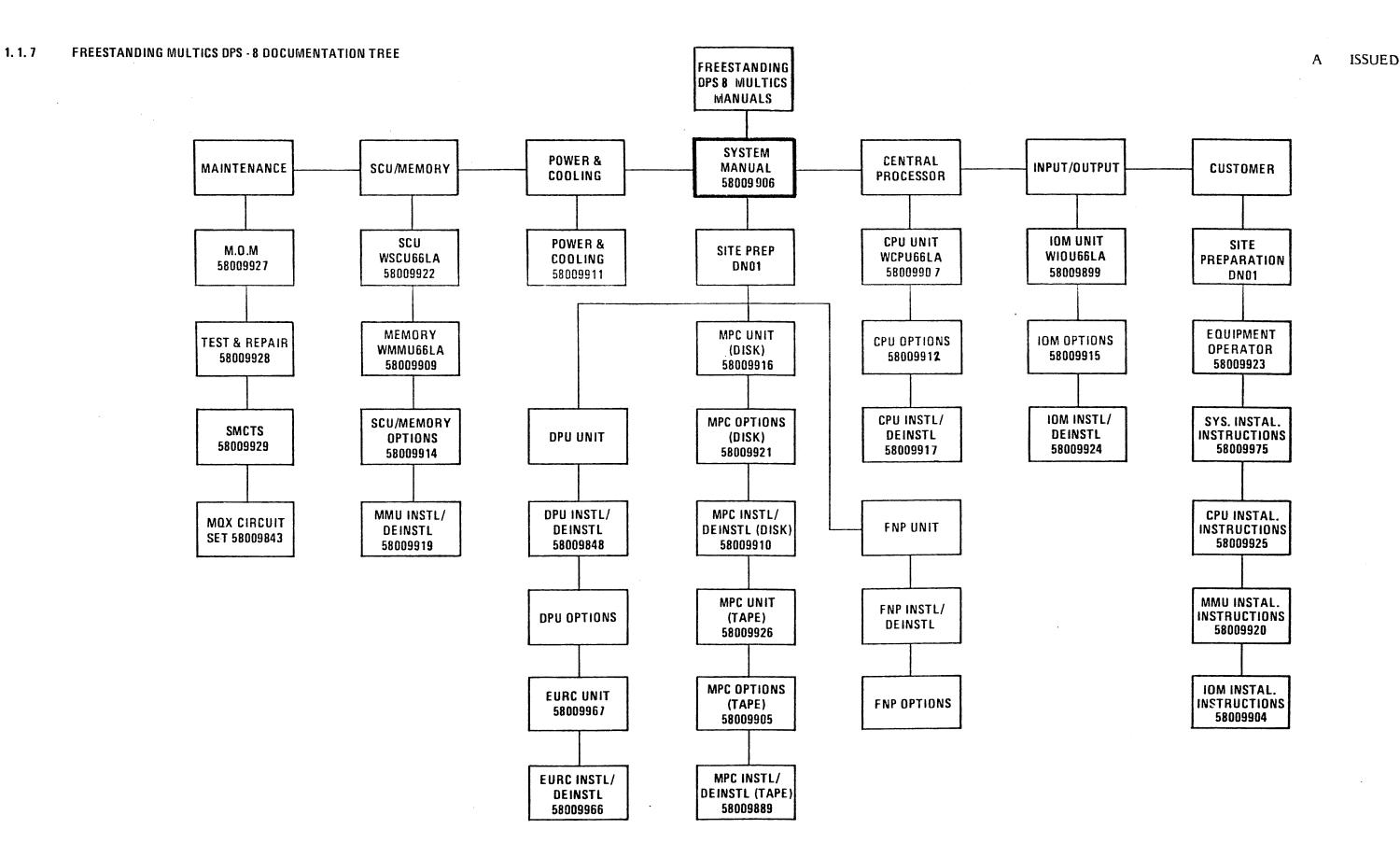

| 1-1    | FREESTANDING MULTICS DPS 8 SUPPORT DOCUMENTATION TREE | 1-3  |

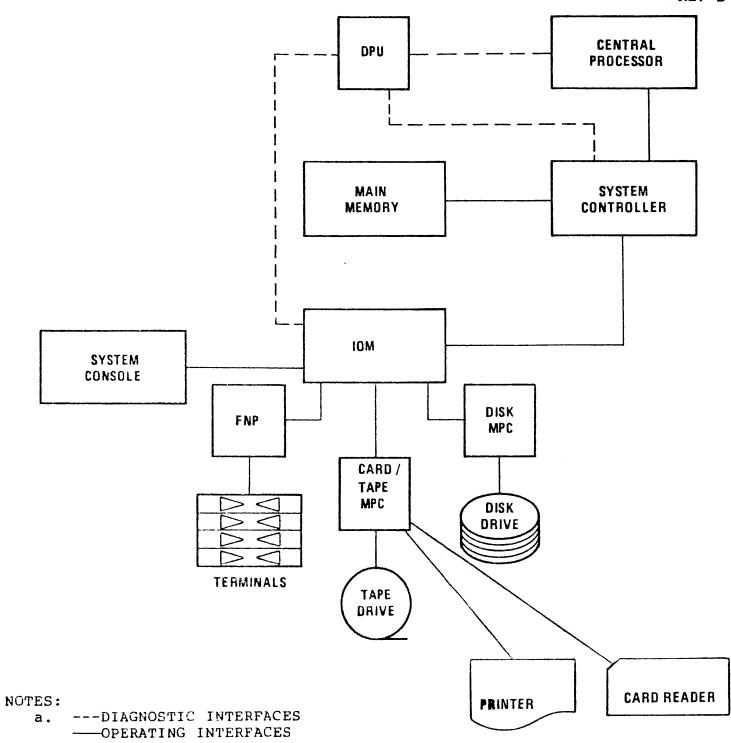

| 1-2    | FREESTANDING MULTICS DPS-8 SYSTEM COMPONENTS          | 1-4  |

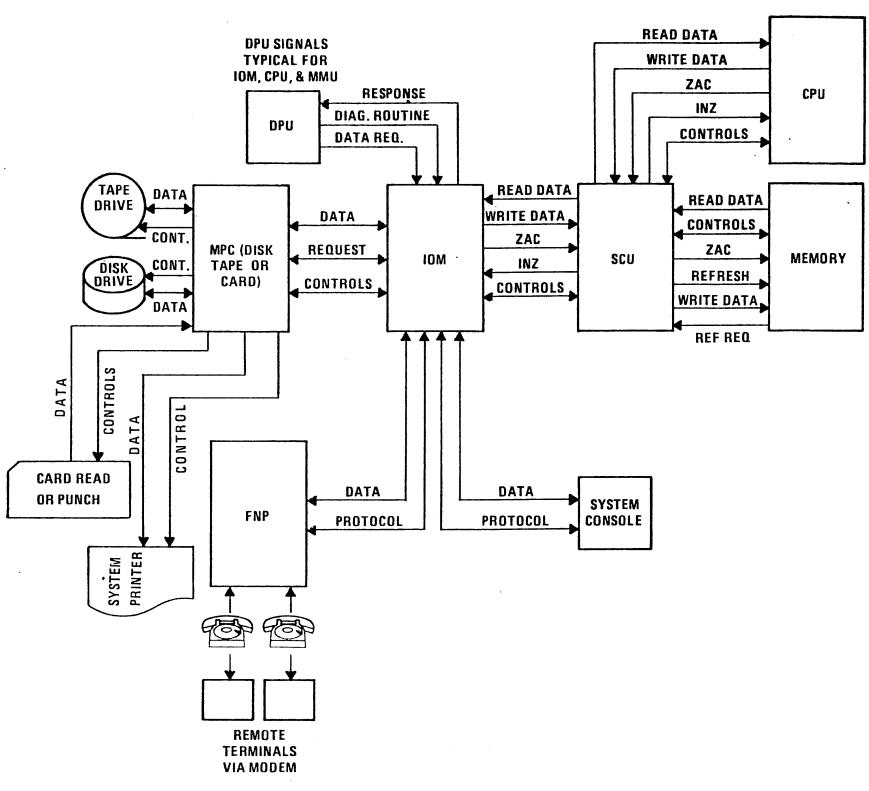

| 1-3    | FREESTANDING MULTICS SIGNAL FLOW                      | 1-6  |

| 2-1    | FREESTANDING MULTICS DPS 8 SINGLE SYSTEM MODULE       | 2-1  |

| 2-2    | PHYSICAL CABINET CONFIGURATION                        | 2-2  |

| 2-3    | CPU CABINET                                           | 2-4  |

| 2-4    | MMU CABINET                                           | 2-8  |

| 2-5    | IOM CABINET                                           | 2-13 |

| 2-6    | MPC CABINET                                           | 2-17 |

| 2-7    | IOM POWER PANELS                                      | 2-22 |

| 2-8    | MMU POWER PANELS                                      | 2-23 |

| 2-9    | CPU POWER PANELS                                      | 2-24 |

| 2-10   | MPC POWER PANELS                                      | 2-25 |

| 2-11   | IOM CABINET PANEL LOCATIONS                           | 2-26 |

| 2-12   | MMU CABINET PANEL LOCATIONS                           | 2-27 |

| 2-13   | CPU CABINET PANEL LOCATIONS                           | 2-28 |

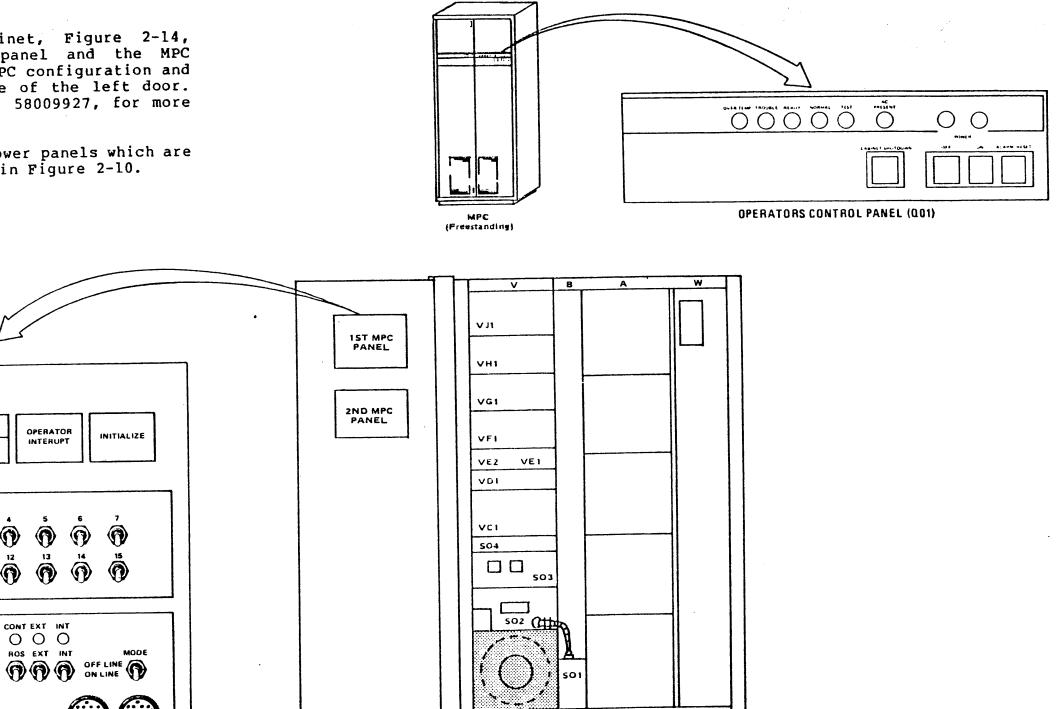

| 2-14   | MPC CABINET PANEL LOCATIONS                           | 2-29 |

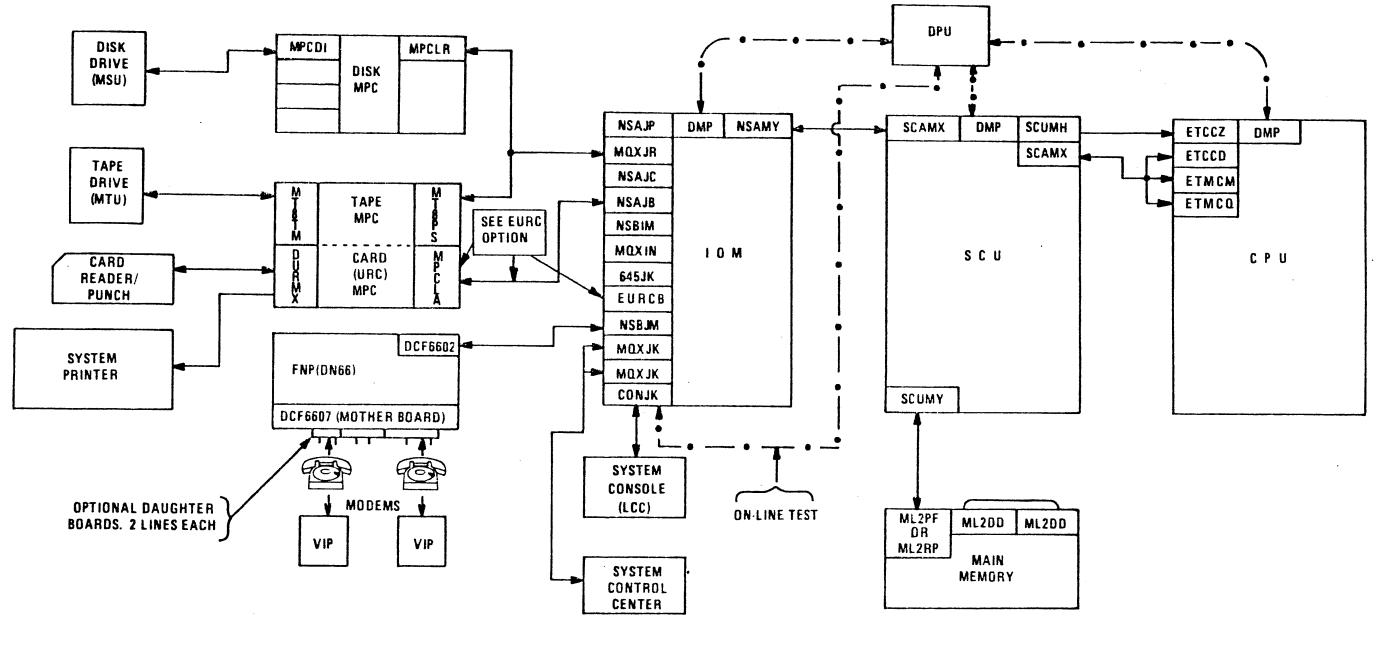

| 3-1    | FREESTANDING MULTICS DPS 8 SYSTEM FUNCTIONAL MAP      | 3-2  |

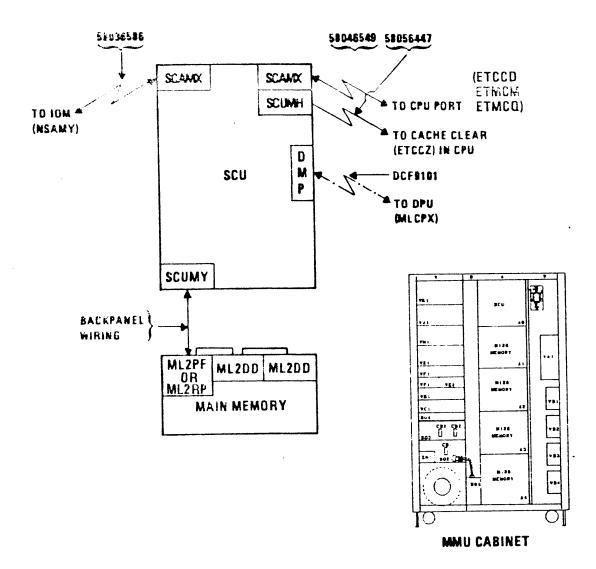

| 3-2    | MMU CABINET INTERFACES                                | 3-5  |

| 3-3    | IOM CABINET INTERFACES                                | 3-5  |

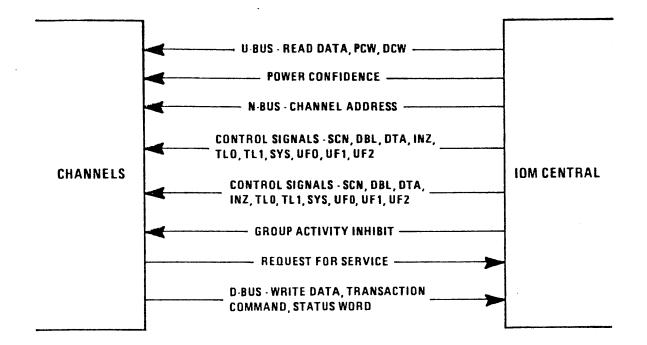

| 3-4    | I/O BUS INTERFACE                                     | 3-8  |

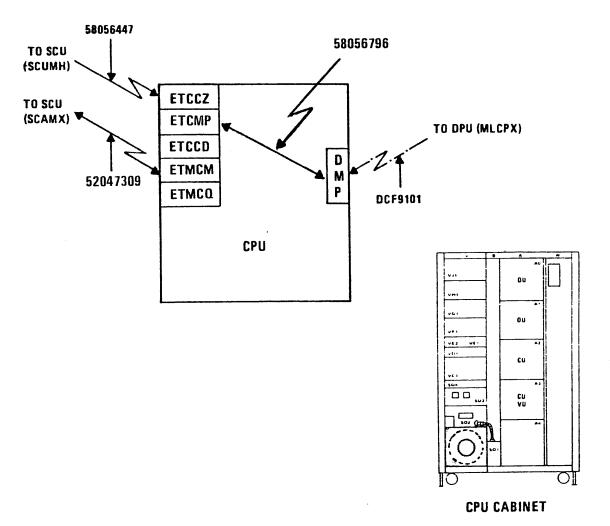

| 3-5    | CPU CABINET INTERFACES                                | 3-10 |

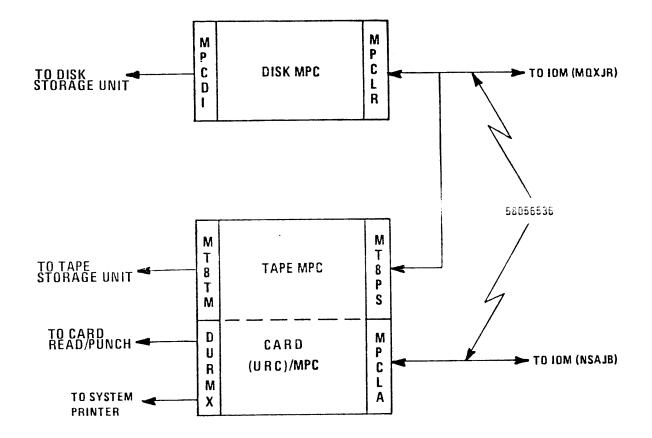

| 3-6    | MPC CABINET INTERFACES                                | 3-15 |

DPU CABINET INTERFACES

FNP CABINET INTERFACES

#### LIST OF TABLES

|   | TABLE | DESCRIPTION                       | PAGE  |

|---|-------|-----------------------------------|-------|

|   | 2-1   | COMMON COMPONENTS TO ALL CABINETS | 2-3   |

|   | 2-2   | CPU CABINET COMPONENTS            | 2-5   |

|   | 2-3   | CPU CIRCUIT BOARDS                | 2-6   |

|   | 2-4   | MMU CABINET COMPONENTS            | 2-9   |

|   | 2-5   | MMU CIRCUIT BOARDS                | 2-10  |

| • | 2-6   | IOM CABINET COMPONENTS            | 2-14  |

|   | 2-7   | IOM CIRCUIT BOARDS                | 2-15  |

|   | 2-8   | MPC CABINET COMPONENTS            | 2-18  |

|   | 2-9   | MPC CIRCUIT BOARDS                | 2-19  |

|   | 2-10  | POWER CONTROL PANELS              | 2-21  |

|   | 2-11  | IOM OPTIONS                       | 2-32  |

|   | 2-12  | MMU OPTIONS                       | 2-35  |

|   | 2-13  | CPU OPTIONS                       | 2-38  |

|   | 2-14  | MPC OPTIONS (DISK)                | 2-40F |

|   |       | ·                                 |       |

3-7

3-8

#### 1.1.1 Purpose

This manual is intended as a general system review and maintenance aid for TAC personnel in analyzing and diagnosing system problems beyond Level 1 procedure. This manual may also be used by FED system level students as a reference text.

#### 1.1.2 Scope

This manual presents a general outline of the overall system, a general description and function of each major unit, and interfaces and theory of operation of each unit.

#### 1.1.3 Objective

The intent of this manual is to integrate the system's independent major units and illustrate their interface functions (i.e., interface protocol instructions, data exchange and status signals) under GCOS program management control. Also included are the maintenance aids available to support maintenance and troubleshooting.

#### 1.1.4 Documentation

The documentation of this manual is divided into two parts (A) Support Documentation, (B) Reference Documentation.

- A. Support Documentation consists of those documents supplied with the system. Basically, these documents fall into two major categories: 1) Site Preparation and Installation/Deinstallation Manuals, and 2) Maintenance and Specialist Level System/Unit Manuals. Refer to Figure 1-1.

- 1. The Site Preparation and Installation/Deinstallation Manuals provide the information required to prepare the customers site for the systems installation and the deinstallation instructions.

A ISSUED

- 2. The Freestanding Multics DPS 8 Maintenance and Specialist Level System/Unit Manuals are divided into six major divisions of support documents, as shown in Figure 1-1.

- 1) System Manual provides a general description of the overall system.

- Power and Cooling Manuals provide a full description and theory of operation of the power supply, control, and distribution. In addition, the cooling system is described.

- 3) Central Processor Manuals provide a full description and theory of operation of the independent CPU's. Also, included is a list of options available to improve or expand the system or individual units.

- 4) Input/Output Manuals provide a full description and theory of operation of the independent I/O units and a list of options available to improve or expand the systems or its individual units.

- 5) The Memory/SCU Manuals provide a full description and theory of operation of the Memory/SCU cabinet units. Also provided are the available options.

- 6) Maintenance Manuals provide the operator and maintenance personnel with individual manuals for various maintenance procedures (software, hardware) necessary to test the different functions of the system.

- B. Reference Documentation consists of those documents not listed in the Support Documentation Tree from which additional information was extracted in the preparation of this manual. The appropriate reference documents will be listed within each theory section.

#### 1.1.5 Reference Support Documentation

Reference documentation used in this manual, in addition to those listed in Figure 1-1 Documentation Tree, will be listed on theory diagrams or at the end of each theory section.

#### 1.1.6 Feedback

To provide the user with a technically correct and current system manual, it is respectfully requested the reader submit any comments or corrections of errors, omissions or the format presentation of the material in this manual.

Comments submitted will be used in update revisions of this and future system manuals.

Address all comments to:

Honeywell Large System Product Support Mail Station P.O. Box 6000 Phoenix, AZ 85005 ATT: PMD (System Manuals)

FIGURE 1-1. FREESTANDING MULTICS DPS 8 SUPPORT DOCUMENTATION TREE

#### 1.2 SYSTEM OVERVIEW

The DPS 8 Freestanding Multics System is basically the Low Profile Freestanding DPS-E with the Central Processor Unit (CPU) redesigned to accept the Multics Operating System Software. Those features that make the Multics System unique from other operating systems are discussed in detail in Paragraphs 3.1.1 and 3.4.2. For more detailed information on the Multics CPU, refer to 58009907 Multics CPU Unit Manual.

The complete system consists of three or more single bay cabinets, plus options and the necessary peripheral equipment. Figure 1-2 shows the system components in their relationship to each other.

The Main Memory Unit (MMU) cabinet contains the System Controller Unit (SCU) in the AO card cage with the lower four card cages reserved for up to 16MW of memory for each MMU cabinet.

The Central Processor Unit (CPU) and Input/Output Multiplexer (IOM) cabinets house the logic in four card cages. In the IOM cabinet, the IOM Central is located in card cage AO.

Power control and distributing equipment for each cabinet is in locations VCl thru VKl. Refer to Table 2-1 for locations of discrete components. The Power Entry Module is located in SO3. The circuit breaker panel is located in SO2.

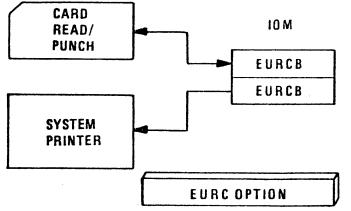

b. With EURC Option, Card MPC will not be present.

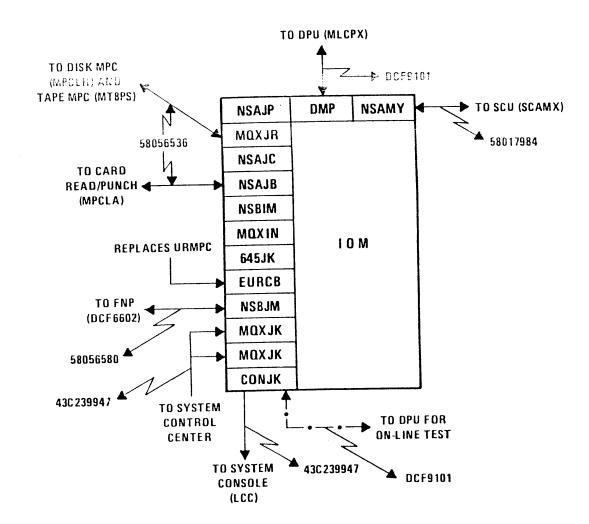

FIGURE 1-2. SYSTEM COMPONENTS

Cooling in each cabinet is provided by a blower in location 201 and a plenum located between the logic bays and the power components. Cool air intakes are located on the lower portion of the cabinet. Baffles in the plenum force the intake air out into the card cages. After circulation between the logic boards, the heated air is exhausted through louvers in the top of the cabinet.

#### 1.3 SIGNAL FLOW

Generally, an operating signal originates as a command from an operator of either the system console or a remote terminal, via the Front-end Network Processor (FNP), (see Figure 1-2). If bulk data is required to execute the command, the peripheral device (disk drive, tape drive, etc.) containing the bulk data will input through the Microprogrammed Peripheral Controller (MPC) to the input logic of the IOM. The CPU, via the SCU, allocates a block of main memory for use in processing the bulk data to fulfill the command. The bulk data is then transmitted to the block of main memory via the write data bus through the SCU.

When data is ready to be outputted, it is transmitted from main memory on the read data bus, via the SCU, to the

output logic of the IOM. From there, it is transmitted to the output device(s) (CRT, printer, etc.). Details concerning the type of command to be executed and the address in main memory to which the data is destined are carried on the Zone, Address, & Command (ZAC) bus.

When fault isolation of the system becomes necessary, the (optional) Diagnostic Processor Unit (DPU) is connected to the Dynamic Maintenance Panel (DMP) on any cabinet (CPU, IOM, MMU). The diagnostic routines and data requests follow the same paths as operating commands and data.

The following paragraphs provide an overview of the main system signals and their overall functions. Refer to Figure 1-3 for the system signal flow.

#### 1.3.1 Read Data

The CPU or IOM obtains data from the main memory by sending a \$INT to the SCU (control line), requesting to be serviced. At that time, ZAC information is placed in the port register, giving the details of the request and the address of the data. When the SCU forwards the ZAC information to memory, the data is placed on the read data bus (72 lines plus parity) and transmitted to the SCU port register for the active module.

#### 1.3.2 Write Data

When the CPU or IOM writes data into the main memory, a \$INT is sent to the SCU control line requesting service. At that time, ZAC information is placed in the port register defining the request and giving the address for the data word to be written into memory. When the SCU forwards the ZAC information to memory, the write data is placed on the write data bus and sent to the SCU memory port register.

#### 1.3.3 <u>Initialize (INZ)</u>

An INZ signal from any source is routed directly to the SCU for distribution to all units in the system. This clears the system for bootloading.

FIGURE 1-3. SIGNAL FLOW

The MOS memory chips must be refreshed every two milliseconds. Thus, the memory sends a refresh request for cyclic portions of memory every 16 microseconds. The SCU fills this request by addressing the cells to be refreshed.

#### 1.3.5 ZAC

The ZAC word defines the type of cycle requested by the \$INT, whether a single or double precision operation, and the portion of memory to be addressed. Like the data words, the ZAC word also contains parity bits for error detection.

#### 1.3.6 System Console Signals

Signals to and from the System Console consist of the necessary protocol format to access the portions of the system required by the duties of the console operator plus the information passing between operator and system.

#### 1.3.7 FNP Signals

FNP signals consist of the same information to and from the system console except that the signals originate from remote terminals in a network system.

**ISSUED**

#### 1.3.8 MPC Signals

Signals between the MPC and IOM consist of the bulk data stored on the accessed disk or magnetic tape, address information sufficient to specify/store the data being moved and the necessary information to control operation of the disk drive or tape drive connected to the MPC.

#### 1.3.9 DPU Signals

Signals between the DPU and IOM consist of the diagnostic routine inputted by the Field Engineer or other Computer Engineer troubleshooting the system, the data requests, and the responses from various registers, memory, and other parts of the system units. Requests may originate at the DPU console itself or via modem to the DPU from a remote location (such as the TAC Center).

#### 1.4 TECHNICAL INSTRUCTIONS

Each system, unit, option, and component is covered in detail by an instruction manual. For details of description, installation, deinstallation, theory of operation, maintenance, troubleshooting, site preparation, and a description of each chip used in the system, consult the appropriate instruction manual(s) listed in Figure 1-1. The manual drawing number is listed, along with the functional title, in each block.

#### 2.0 PHYSICAL OUTLINE

#### 2.1 GENERAL INTRODUCTION

The DPS 8 Freestanding Multics System is a composition of three cabinets; the Central Processor Unit (CPU); the Main Memory Unit (MMU); and the Input/Output Multiplexer (IOM). These three cabinets may be physically connected to form a single-system module. Any additional (optional) cabinet may be freestanding or connected to the existing module depending on the customer's requirements.

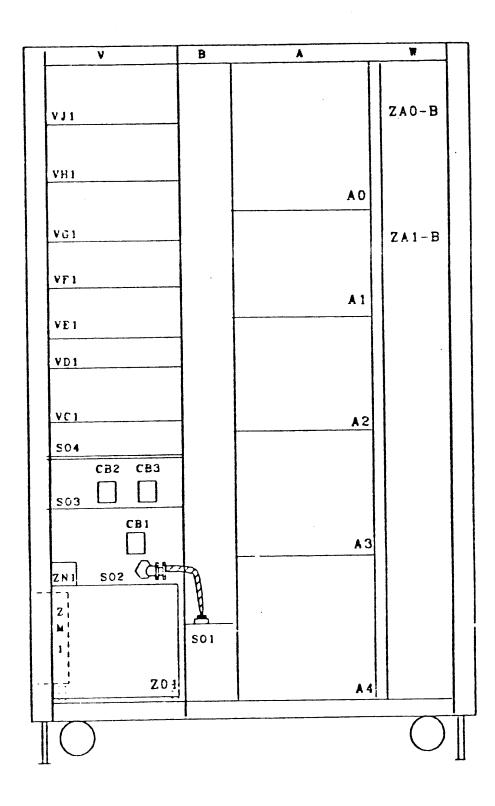

Figure 2-1 shows the Single System module configuration.

For additional information on these and other units within the system, refer to DN01 Site Preparation manual.

FIGURE 2-1 FREESTANDING MULTICS DPS-8 SINGLE SYSTEM

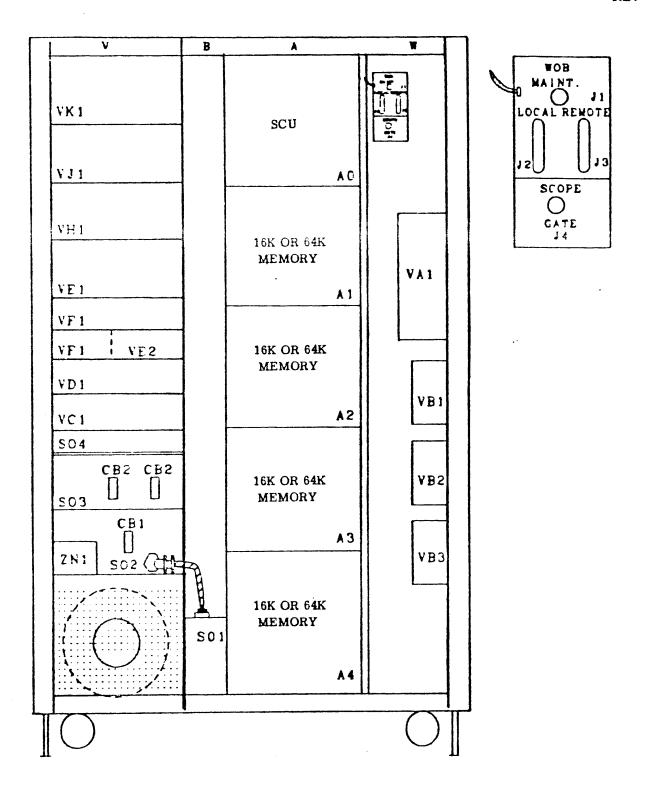

#### 2.2 PHYSICAL CABINET CONFIGURATION

All system units are hardware constructed in a common configuration. Every physical cabinet contains a power supply and cooling on the left, the logic boards in the center, and an options area on the right. Each cabinet is divided into four vertical zones. Figure 2-2 illustrates this physical cabinet configuration.

#### 2.2.1 Basic Cabinet Outline

Zone V houses the cabinet power supply, blower assembly with controls, and air flow sensor switch.

Zone B is the air flow plenum for air circulation over the power equipment and to the logic boards in Zone A.

Zone A contains the logic boards and back panel.

Zone W is a common option area. Its components and function depends on the cabinet and options.

#### A ISSUED

FIGURE 2-2 PHYSICAL CABINET CONFIGURATION

#### 2.2.2 Common Cabinet Components

In addition to having common zones within each cabinet, each zone contains common components. Table 2-1 lists the common components to all cabinets.

The components unique to a specific cabinet, (i.e. CPU unit) will be listed in its respective section.

Table 2-1 COMMON COMPONENTS TO ALL CABINETS

| Component<br>Designator           | Zone                                 | Description                                                                                           |

|-----------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|

| ZMI/ZO1                           | Bottom portion<br>Zone V             | Blower controls assembly and blowers                                                                  |

| ZNl                               | Left from lower position zone V      | Airflow sensor and switch assembly                                                                    |

| S01                               | Lower portion<br>of Plenum<br>Zone B | Site power connector<br>terminal board (S01 TB1)                                                      |

| S02                               | V                                    | Circuit Breaker Module,<br>contains circuit breaker<br>(SO2 CB1) that applies power<br>to the cabinet |

| 503                               | V                                    | Power Entry Module with circuit breakers (S03-CB2/CB3) for FAN and REG. power on/off control          |

| VC1                               | V                                    | Power Control Module with<br>Power Control & Configuration<br>switches and indicators                 |

| VD1                               | v                                    | 100 Watt Voltage Regulator                                                                            |

| Plenum                            | В                                    | Force air column to circulate air over and around power supplies and logic boards.                    |

| Logic Buckets<br>A0-A4            | A                                    | Logic card and back panel area.                                                                       |

| Depends on type cabinet & options | W                                    | Heat sensors, batteries, and special area depending on cabinet type CPU, MMU, or IOM requirements.    |

#### 2.3 CPU CABINET CONFIGURATION

The CPU cabinet contains a power and cooling component in Zones V and B, a cable bulkhead area in Zone W, and CPU circuit boards in Zone A.

Figure 2-3 illustrates the major components of the CPU cabinet, their physical location, and their zone designators.

Table 2-2 lists the component designator, zone, and description for each component.

Table 2-3 lists each circuit board in the CPU by module/slot, board mnemonic, and function.

FIGURE 2-3 CPU CABINET FRONT VIEW WITH DOORS REMOVED

# 2.5.1 IOM Cabinet Components

Table 2-6 IOM CABINET COMPONENTS

| Component<br>Designator | Zone                                 | Description                                                                                           |

|-------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|

| VJl                     | V                                    |                                                                                                       |

| VHl                     | v                                    | Dual +5V Power Regulator                                                                              |

| VG1                     | Λ                                    |                                                                                                       |

| VF1                     | v                                    | Dual +12V Regulator                                                                                   |

| VE1/VE2                 | v                                    | -5V Power Converter Regulator                                                                         |

| VD1                     | v                                    | Dual +24 Volt Regulator<br>100 Watt                                                                   |

| VCl                     | v                                    | Power Control Module with Power Control & Configuration switches and indicators                       |

| s03                     | v                                    | Power Entry Module with circuit breakers (S03-CB2/CB3) for FAN and REG. power on/off control          |

| S02                     | V                                    | Circuit Breaker Module,<br>contains circuit breaker<br>(S02 CB1) that applies power<br>to the cabinet |

| 501                     | Lower portion<br>of Plenum<br>Zone B | Site power connector terminal board (S01 TB1)                                                         |

| ZNl                     | Left from lower position zone        | Airflow sensor and switch assembly                                                                    |

| 201                     | v                                    | Blowers                                                                                               |

| ZM1                     | Bottom portion<br>Zone               | Blower controls assembly                                                                              |

Table 2-2 CPU CABINET COMPONENTS (continued)

| Component<br>Designator | Zone  | Description                                                                 |

|-------------------------|-------|-----------------------------------------------------------------------------|

| A0-A3                   | A*    | Card cages A0-A4. *See Table 2-3 for modules, card nomenclature, and slot.  |

| WOA-AON                 | W     | Seven cable connectors ports for external cables.                           |

| WOA                     | W     | Maintenance panel connection: Jl = Maintenance panel J2 = Local J3 = Remote |

| ZAO                     | W/AlQ | Temp sensors positioned at AlQ                                              |

| ZAl                     | W/A2P | Temp sensors positioned at A2P                                              |

### 2.3.2 CPU Circuit Boards By Location

Table 2.3 CPU CIRCUIT BOARDS BY LOCATION

| CPU CABINET |        |                            |  |

|-------------|--------|----------------------------|--|

| MODULE/SLOT | BOARD  | FUNCTION                   |  |

| AO A        | ETCMP  | DMP interface              |  |

| В           | 210    | 2.12 2.1362 2.436          |  |

| С           | EISDN  | Alignment Control          |  |

| D           | ETCDP  | Alpha-Numeric Control      |  |

| E           | ETCDG  | Timing & Control, #2, 3, 5 |  |

| F           | EISDE  | Exponent                   |  |

| G           | EISDF  | Exponent                   |  |

| н           | EISDC  | Timing & Control, #2, 3, 5 |  |

| J           | EISDQ  | Timing & Control, #2, 3, 5 |  |

| K           | EISDR  | Control, #1, 5             |  |

| L           | EISDB  | Control, #1, 5             |  |

| М           | EISDM  | Alignment Control          |  |

| N           | 645DL  |                            |  |

| Р ,         | EISDK  | Character Manipulation     |  |

| Q           | EISDD  | Timing & Control, #2, 3, 5 |  |

| R           | EISDAl | Adder Register             |  |

| S           | EISDA2 | Adder Register             |  |

| Т           | EISDA3 | Adder Register             |  |

| Ü           | EISDA4 | Adder Register             |  |

Table 2-3 CPU CIRCUIT BOARDS BY LOCATION (continued)

|             | CPU CABINET |                                |  |  |

|-------------|-------------|--------------------------------|--|--|

| MODULE/SLOT | BOARD       | FUNCTION                       |  |  |

| A1 A        | EISDA5      | Adder Register                 |  |  |

| В           | EISDAS      | Adder Register Adder Register  |  |  |

| C           | EISDA7      | 1                              |  |  |

| מ           | EISDA8      | Adder Register                 |  |  |

| E           | EISDJ       | Alignment                      |  |  |

| F           | ETCDH       | IPR Decode & Control           |  |  |

| G           | ETCAK       | OU Timing & Control            |  |  |

| H           |             |                                |  |  |

| J           | ETCAM       | Exponent Control               |  |  |

| K           | ETCAD       | OU Adder Control               |  |  |

| L           | ETCAJ       | OU I/O Data Control            |  |  |

| М           | ETCAB       | Indicators                     |  |  |

| N           | ETCAE       | Exp. Adder & Reg., Norm, Shift |  |  |

| P           | ETCAF       | OU I/O Data Align              |  |  |

| Q           | ETCAN       | OU Adder                       |  |  |

| R           | ETCAP       | Reg. Store & OU Output         |  |  |

| S           | ETMBA       | Address Prep                   |  |  |

| Т           |             |                                |  |  |

| U           | ETCBG       | Instruction Adder & Track      |  |  |

#### 2.3.2 CPU Circuit Boards By Location (Continued)

Table 2.3 CPU CIRCUIT BOARDS BY LOCATION (continued)

|             | CPU CABINET |                        |  |

|-------------|-------------|------------------------|--|

| MODULE/SLOT | BOARD       | FUNCTION               |  |

| A2<br>A     | ETMBL       |                        |  |

| В           | 21122       |                        |  |

| С           | ETMBB       | Address Registers      |  |

| D           |             |                        |  |

| E           | ЕТМВН       | Address Control        |  |

| F           |             |                        |  |

| G           | ETMBD       | Tag Cont & Decimal OPS |  |

|             |             | Sequencing             |  |

| Н           |             |                        |  |

| J           | ETMCX       |                        |  |

| K           | nmunu       | i                      |  |

| L           | ETMPX       |                        |  |

| M<br>N      | ЕТМСН       | IPR Decode & Control   |  |

| P           | ETHON       | Trk becode a control   |  |

| Q           | ETMCP       | INZ & Fault Control    |  |

| R           |             |                        |  |

| s           | ETMCG       | Fault & Mode Registers |  |

| T           |             |                        |  |

| ט           | ETCCU1      | History Board          |  |

Table 2.3 CPU CIRCUIT BOARDS BY LOCATION (continued)

|             | CPU CABINET |                           |  |

|-------------|-------------|---------------------------|--|

| MODULE/SLOT | BOARD       | FUNCTION                  |  |

| A 3         | ETCCU2      | History Board             |  |

| В           | ETCCC       | Cache Directory           |  |

| С           | ETMCM       | Port Control              |  |

| D           | '           |                           |  |

| E           | ETMCQ       | Port Sel, Addr Latch &    |  |

|             |             | Drive, Config. Registers  |  |

| F           |             |                           |  |

| G           | ETCCD1      | Cache Memory, Data Hub    |  |

| н           | ETCCD2      | Cache Memory, Data Hub    |  |

| J           | ETCCD3      | Cache Memory, Data Hub    |  |

| K           | ETCCD4      | Cache Memory, Data Hub    |  |

| L           | ETCCD5      | Cache Memory, Data Hub    |  |

| М           | ETCCD6      | Cache Memory, Data Hub    |  |

| N           | ETCCZ       | Cache Clear               |  |

| P           | ETCCY       | Cache Duplicate Directory |  |

| Q           | ЕТМРН       |                           |  |

| R           |             |                           |  |

| S           | ETMPA       |                           |  |

| Т           |             |                           |  |

| υ           | ЕТМРВ       |                           |  |

# 2.3.2 CPU Circuit Boards By Location (Continued)

Table 2.3 CPU CIRCUIT BOARDS BY LOCATION (continued)

|       |        | CPU   | CABINET  |

|-------|--------|-------|----------|

| MODUL | E/SLOT | BOARD | FUNCTION |

| A 4   | A      | ETMPC |          |

|       | В      |       |          |

|       | С      | ETMPE |          |

|       | D      |       |          |

|       | E      | ETMPF |          |

|       | F      |       |          |

|       | G      | ETMPD |          |

|       | Н      |       |          |

|       | J      |       |          |

|       | K      |       |          |

|       | L      |       |          |

|       | M      |       |          |

|       | N      |       |          |

|       | P      |       |          |

|       | Q<br>R |       |          |

|       | S      |       |          |

|       | T      |       |          |

|       | บ      |       |          |

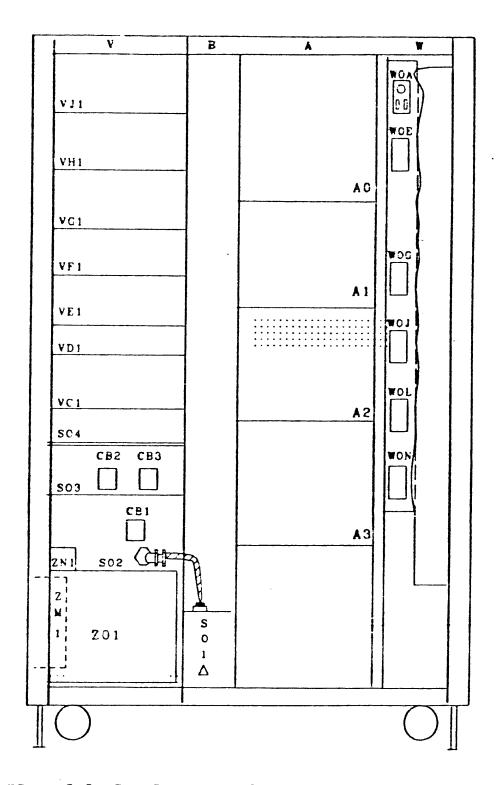

#### 2.4 MMU CABINET CONFIGURATION

The MMU cabinet contains a power and cooling component in Zones V and B, a cable bulkhead area in Zone W, SCU and memory circuit boards in Zone A. Zone W would also contain the battery power option if ordered.

Figure 2-4 illustrates the major components of the MMU cabinet, their physical location, and their zone designators.

Table 2-4 lists the component designator, zone, and description of each component.

Table 2-5 lists each circuit board in the MMU by module/slot, board mnemonic, and function.

FIGURE 2-4 MMU CABINET FRONT VIEW WITH DOORS REMOVED

#### 2.4.1 MMU Cabinet Components

Table 2-4 MMU CABINET COMPONENTS

| Component<br>Designator | Zone                                 | Description                                                                                           |

|-------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|

| ZMl                     | Bottom portion<br>Zone               | Blower controls assembly                                                                              |

| Z01                     | V                                    | Blowers                                                                                               |

| ZN1                     | Left from lower position zone V      | Airflow sensor and switch assembly                                                                    |

| S01                     | Lower portion<br>of Plenum<br>Zone B | Site power connector<br>terminal board (S01 TB1)                                                      |

| S02                     | v                                    | Circuit Breaker Module,<br>contains circuit breaker<br>(S02 CB1) that applies power<br>to the cabinet |

| S03                     | V                                    | Power Entry Module with circuit breakers (S03-CB2/CB3) for FAN and REG. power on/off control)         |

| vc1                     | v                                    | Power Control Module with Power Control & Configuration switches and indicators                       |

| VD1                     | v                                    | 124 Volt Regulator 100 Watt                                                                           |

| VE1/VE2                 | v                                    | 2 Dual -5V Regulator                                                                                  |

| VF1                     | v                                    | Dual +12V Regulator                                                                                   |

| VG1                     | v                                    | Dual +12V Regulator                                                                                   |

| VH 2                    | v                                    | +5V Power Regulator (Slave)                                                                           |

| VJ1                     | v                                    | +5V Power Regulator (Master)                                                                          |

| VK1                     | v                                    |                                                                                                       |

Table 2-4 MMU CABINET COMPONENTS

| Component<br>Designator | Zone          | Description                      |

|-------------------------|---------------|----------------------------------|

| A 0                     | A             | SCU logic module                 |

| A1-A4                   | A             | Four memory modules              |

| WOB                     | ₩ .           | Scope and maintenance connectors |

| ZAO                     | W/QA0E        | Temperature sensor               |

| ZAl                     | W/QAlJ        | Temperature sensor               |

| VAl                     | WO right side | Battery control                  |

| VB1                     | WO right side | Battery                          |

| VB2                     | WO right side | Battery                          |

| VB3                     | WO right side | Battery                          |

# 2.4.2 MMU Circuit Boards By Location

Table 2-5 MMU CIRCUIT BOARDS BY LOCATION

| MMU CABINET (SCU Module)                                                                       |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MODULE/SLOT                                                                                    | BOARD                                                                                                             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| A0 A A0 B A0 C A0 D A0 E A0 F A0 G A0 H A0 J A0 K A0 L A0 M A0 N A0 P A0 Q A0 R A0 S A0 T A0 U | SCAMM SCAME SCAMJ SCUMK SCAMC SCAMF SCUMY SCUMY SCUMY SCUMY SCAMX SCAMX SCAMX SCAMX SCAMX SCAMX SCAMX SCAMX SCAMX | Early Cycle Timing Look Ahead Mode Register Mask Register Config. Register Early Cycle Flags Memory Interface Port Memory Interface Port Memory Interface Port Memory Interface Port CPU/IOM Interface Port |  |  |  |

Table 2-5 MMU CIRCUIT BOARDS BY LOCATION (continued)

| MMU CABINET (Main Memory)                                                                      |                                                                                                       |                                                                                                                                                                                          |                                                                    |                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODULE/SLOT                                                                                    | BOARD                                                                                                 | FUNCTION                                                                                                                                                                                 | BOARD                                                              | FUNCTION                                                                                                                                                                                                                                                                                                                   |

|                                                                                                | 16K MEMORY                                                                                            |                                                                                                                                                                                          | 64K N                                                              | MEMORY                                                                                                                                                                                                                                                                                                                     |

| A1 A A1 B A1 C A1 D A1 E A1 F A1 G A1 H A1 J A1 K A1 L A1 N A1 N A1 P A1 Q A1 R A1 S A1 T A1 U | M128<br>M128<br>M128<br>M128<br>ML2DD<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128 | Memory Memory Memory EDAC Memory EDAC Memory Memory Memory Memory Memory Memory Memory Memory | M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64 | Memory |

# 2.4.2 MMU Circuit Boards By Location (continued)

Table 2-5 MMU CIRCUIT BOARDS BY LOCATION (continued)

|                                                                                                          | MMU CA                                                       | BINET (Main Me                                                                                                                                          | emory)                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODULE/SLOT                                                                                              | BOARD                                                        | FUNCTION                                                                                                                                                | BOARD                                                              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                          | 16K                                                          | 16K MEMORY                                                                                                                                              |                                                                    | MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A2 A A2 B A2 C A2 D A2 E A2 F A2 G A2 H A2 J A2 K A2 L A2 M A2 N A2 N A2 P A2 N A2 P A2 Q A2 R A2 C A2 C | M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128 | Memory Memory Memory EDAC Memory EDAC Memory Memory Memory SCU Port | M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64 | Memory |

Table 2-5 MMU CIRCUIT BOARDS BY LOCATION (continued)

|                                          |                                   | · · · · · · · · · · · · · · · · · · ·                        |                                                                                                                                    |                                                                    |                                                                                                                 |

|------------------------------------------|-----------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

|                                          | MMU CABINET (Main Memory)         |                                                              |                                                                                                                                    |                                                                    |                                                                                                                 |

| MODULE                                   | /SLOT                             | BOARD                                                        | FUNCTION                                                                                                                           | BOARD                                                              | FUNCTION                                                                                                        |

|                                          |                                   | 16K M                                                        | IEMORY                                                                                                                             | 64K M                                                              | EMORY                                                                                                           |

| A3 A | A B C D E F G H J K L M N P Q R S | M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128 | Memory Memory Memory EDAC Memory | M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64 | Memory |

| A3<br>A3                                 | T<br>U                            | M128<br>ML2PF                                                | Memory<br>SCU Port                                                                                                                 | ML2DD<br>ML2RP                                                     | EDAC<br>SCU Port                                                                                                |

Table 2-5 MMU CIRCUIT BOARDS BY LOCATION (continued)

| MMU CABINET (Main Memory)                                                                      |                                                                                                       |                                                                                                                                                         |                                                                    |                                                                                                                                    |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| MODULE/SLOT                                                                                    | BOARD                                                                                                 | FUNCTION                                                                                                                                                | BOARD                                                              | FUNCTION                                                                                                                           |

|                                                                                                | 16K                                                                                                   | MEMORY                                                                                                                                                  | 64K M                                                              | IEMORY                                                                                                                             |

| A4 A A4 B A4 C A4 D A4 E A4 F A4 G A4 H A4 J A4 K A4 L A4 M A4 N A4 P A4 Q A4 R A4 S A4 T A4 U | M128<br>M128<br>M128<br>M128<br>ML2DD<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128<br>M128 | Memory Memory Memory Memory EDAC Memory EDAC Memory Memory Memory SCU Port | M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64<br>M64 | Memory EDAC EDAC SCU Port |

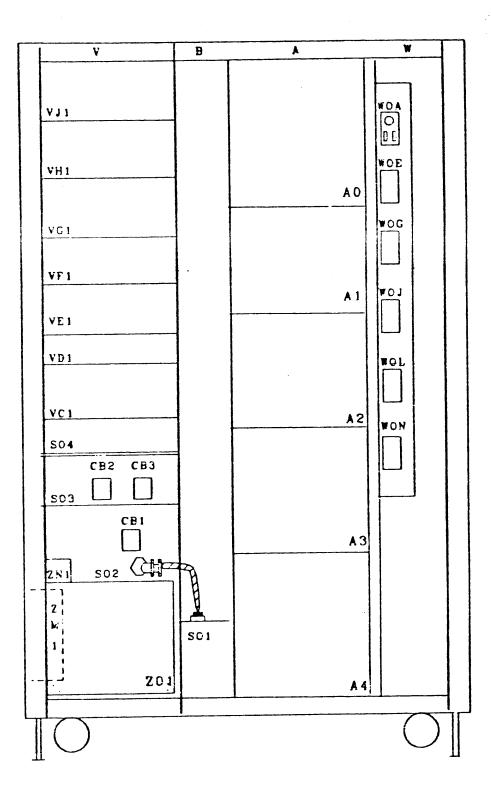

#### 2.5 IOM CABINET CONFIGURATION

The IOM cabinet contains a power and cooling component in Zones V and B, a cable bulkhead area in Zone W, and IOM circuit boards in Zone A.

Figure 2-5 illustrates the major components of the IOM cabinet, their physical location, and their zone designators.

Table 2-6 lists the component designator, zone, and description of each component.

Table 2-7 lists each circuit board in the IOM by module/slot, board name, and function.

#### A ISSUED

FIGURE 2-5 IOM CABINET FRONT DOORS REMOVED

# 2.5.1 IOM Cabinet Components

Table 2-6 IOM CABINET COMPONENTS

|                         | 1 1011 0                             | ABINET COMPONENTS                                                                                     |

|-------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------|

| Component<br>Designator | Zone                                 | Description                                                                                           |

| ZMl                     | Bottom portion<br>Zone               | Blower controls assembly                                                                              |

| Z01                     | v                                    | Blowers                                                                                               |

| ZN1                     | Left from lower position zone        | Airflow sensor and switch assembly                                                                    |

| S01                     | Lower portion<br>of Plenum<br>Zone B | Site power connector<br>terminal board (S01 TB1)                                                      |

| S02                     | V                                    | Circuit Breaker Module,<br>contains circuit breaker<br>(S02 CB1) that applies power<br>to the cabinet |

| S03                     | V                                    | Power Entry Module with circuit breakers (S03-CB2/CB3) for FAN and REG. power on/off control          |

| VC1                     | v                                    | Power Control Module with<br>Power Control & Configuration<br>switches and indicators                 |

| VD1                     | v                                    | Dual +24 Volt Regulator<br>100 Watt                                                                   |

| VE1/VE2                 | v                                    | -5V Power Converter Regulator                                                                         |

| VF1                     | v                                    | Dual +12V Regulator                                                                                   |

| VG1                     | v                                    |                                                                                                       |

| VHl                     | V                                    | Dual +5V Power Regulator                                                                              |

| VJ1                     | v                                    |                                                                                                       |

| A0-A4                   | A                                    | Logic modules                                                                                         |

| WOA                     | W                                    | Maintenance and scope cable connector                                                                 |

| WOA                     | W                                    | Adapter plate                                                                                         |

| ZA0                     | w .                                  | Temperature sensor AOB                                                                                |

| ZAl                     | W                                    | Temperature sensor AlB                                                                                |

A ISSUED

#### 2.5.2 IOM Circuit Boards By Location

Table 2-7 IOM CIRCUIT BOARDS BY LOCATION

|             | IOM CABINET (IOM) |                               |  |  |  |

|-------------|-------------------|-------------------------------|--|--|--|

| MODULE/SLOT | BOARD             | FUNCTION                      |  |  |  |

| A0<br>A     | NSBIM1            | Scratch Pad                   |  |  |  |

|             | NSBIM1            | Scratch Pad                   |  |  |  |

| В           |                   |                               |  |  |  |

| C           | NSAMYl            | SCU Interface                 |  |  |  |

| D           | NSAMY2            | SCU Interface                 |  |  |  |

| E           | NSAMY3            | SCU Interface                 |  |  |  |

| F           | NSAMY4            | SCU Interface                 |  |  |  |

| G           | NSAIC             | IOM Central                   |  |  |  |

| Н           | NSAIE             | IOM Central                   |  |  |  |

| J           | NSAIG             | IOM Central                   |  |  |  |

| K           | 645ID             | Extended Address              |  |  |  |

| L           | DMPIF             | Configuration Panel Interface |  |  |  |

| М           | DMPIH             | Configuration Panel Interface |  |  |  |

| N           | DMPIJ             | Configuration Panel Interface |  |  |  |

| P           | NSAIK             | IOM Central                   |  |  |  |

| Q           | NSAIB             | Control Board                 |  |  |  |

| R           |                   |                               |  |  |  |

| S           | NSDIA             | Control "A"                   |  |  |  |

| Т           |                   |                               |  |  |  |

| ט           | NSAIP             | Wraparound                    |  |  |  |

Table 2-7 IOM CIRCUIT BOARDS BY LOCATION (continued)

| IOM CABINET (IOM)          |         |                         |  |  |

|----------------------------|---------|-------------------------|--|--|

| MODULE/SLOT BOARD FUNCTION |         |                         |  |  |

| Al<br>A                    | MQXIU   | Bus Driver              |  |  |

| В                          | NSAJP   | PSIA                    |  |  |

| С                          | MQXJR - | Tape MPC Interface Port |  |  |

| D                          | NSAJC   | PSIA                    |  |  |

| E                          | MQXJR   | Disk MPC Interface Port |  |  |

| F                          | NSAJP   | PSIA                    |  |  |

| G                          | NSAJC   | PSIA                    |  |  |

| Н                          | NSAJB   | Card MPC Interface Port |  |  |

| J                          |         |                         |  |  |

| K                          |         |                         |  |  |

| L                          |         |                         |  |  |

| М                          |         |                         |  |  |

| N                          |         |                         |  |  |

| P                          |         |                         |  |  |

| Q                          |         |                         |  |  |

| R                          |         |                         |  |  |

| S                          |         |                         |  |  |

| Т                          |         |                         |  |  |

| U                          |         |                         |  |  |

#### 2.5.2 IOM Circuit Boards By Location (continued)