## GENERAL ELECTRIC

# DATANET-30 Systems Manual

613.pc

## DATANET-30 SYSTEMS MANUAL

.

July 1963 Rev. February 1966

COMPUTER DEPARTMENT

### PREFACE

DATANET is a General Electric registered trademark and is applied to GE products or systems using public or privately-owned transmission facilities to permit the processing of information at a point remote from its orgin. The DATANET-30 is a 128 channel data communications processor which enables remote terminal facilities to communicate with other remote terminal facilities, or a central information processing system.

This manual provides general information on DATANET-30 system configurations and on DATANET-30 hardware, but will not include information on transmission lines, digital subsets, remote terminal devices or other products included within a total communications complex.

Comments on this publication may be addressed to Technical Publications, Computer Department, General Electric Company, P. O. Box 2961, Phoenix, Arizona, 85002.

(c) 1963, 1965 by General Electric Company

DATANET-30.

## CONTENTS

Page

| INTR | ODUCTION                                                                       |

|------|--------------------------------------------------------------------------------|

| 1.   | GENERAL SYSTEMS DESCRIPTION                                                    |

|      | Teletype Message Switching System    5                                         |

|      | Functions                                                                      |

|      | Operation                                                                      |

|      | Switching Center Size                                                          |

|      | Small Switching Center       7         Medium Switching Center       8         |

|      | Large Switching Center                                                         |

|      | DATANET-30 as a Remote Concentrator                                            |

|      | Functions                                                                      |

|      | Operation                                                                      |

|      | The Network                                                                    |

|      | Functions         12           Operation         12                            |

|      |                                                                                |

|      | Communication/Data Processing Systems       12         Remote Inquiry       12 |

|      | Remote File Updating                                                           |

|      | Data Collection                                                                |

|      | Remote Data Processing 14                                                      |

|      | Time Sharing                                                                   |

|      | Equipment Configurations 14                                                    |

#### 2. DATANET-30 COMPONENTS

| General Description                        | 17        |

|--------------------------------------------|-----------|

|                                            | 17        |

|                                            | 18        |

| Channel Address 1                          | 18        |

| DATANET-30 Buffer Modules 1                | 18        |

|                                            | 18        |

| DATANET-30 to DATANET-30 1                 | 19        |

| DATANET-30 Peripheral Equipment            | 19        |

| EDP Center                                 | 19        |

| Communication Line Buffer                  | 20        |

| The Bit Buffer Unit Module 2               | 20        |

| The Character/Word Unit Module (CWU 930) 2 | 23        |

| Character/Word Unit Module (CWU 931)       | <b>26</b> |

|                                            | 26        |

| Dialing Adapter Channel (DAC 930)          | 27        |

|                                            | <b>27</b> |

| Controls and Indicators. 2                 | <b>27</b> |

|                                            | 27        |

#### Page

| Automatic Calling Unit (ACU)                                 |   |

|--------------------------------------------------------------|---|

| Interconnecting Computer Buffers 29                          |   |

| Processor Interrupt Unit (PIU 930) 29                        |   |

| Data Transfer                                                | ) |

| Controls and Indicators                                      | ļ |

| Computer Interface Unit (CIU 931) 30                         | ) |

| Data Transfer                                                |   |

| DATANET-30 to the Computer Interface Unit                    |   |

| External Computer to the Computer Interface Unit             |   |

| Data Flow Through the Computer Interface Unit                |   |

| Data i low initiagh the Computer interactor charge           |   |

|                                                              |   |

|                                                              |   |

|                                                              |   |

| Transmit Sequence                                            |   |

| Peripheral Equipment Buffers 34                              |   |

| Controller Selector Unit 34                                  |   |

| Common Peripheral Channel                                    |   |

| Data Transfer                                                |   |

| Peripheral Equipment Information                             | ) |

| RDC 930 Removable Disc Storage Subsystem                     | j |

| Removable Disc Unit Module (RDU 930) 36                      | j |

| Controls and Indicators                                      | ; |

| Memory Interrupt Cycle Assignment                            |   |

| Additional Storage Unit (ASU 930)                            |   |

| Extra Removable Disc Cartridge                               |   |

|                                                              |   |

|                                                              |   |

|                                                              |   |

|                                                              |   |

| The GE-200 Series Peripheral Switch                          |   |

| Console Unit                                                 |   |

| Switch Units                                                 |   |

| Programmed Peripheral Switch                                 |   |

| The GE-400/600 Series Peripheral Switch 44                   |   |

| Parallel Channel Adapt 4                                     |   |

| The DATANET-30 with a GE-115 System 4                        |   |

| DATANET-760 Keyboard/Display Terminal System                 | Ĺ |

| System Configuration 4                                       | L |

| Summary of DATANET-30 Components 42                          | 2 |

| Summary of Buffer Modules 4                                  | 2 |

| Summary of Transmission Speeds, Code Levels, Input/Output 44 |   |

|                                                              |   |

|                                                              |   |

| DATANET-30 PROCESSOR-DETAILED DESCRIPTION                    |   |

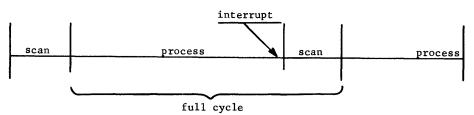

| Functional Sequence                                          | 5 |

| Block Diagram                                                | - |

| Representation of Information in Memory.                     |   |

| Alphanumeric Data Words                                      |   |

|                                                              |   |

|                                                              |   |

|                                                              |   |

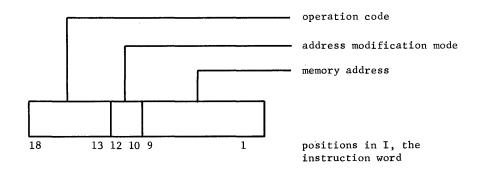

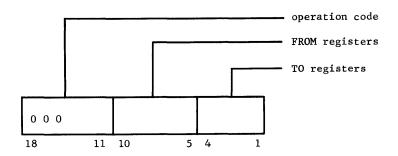

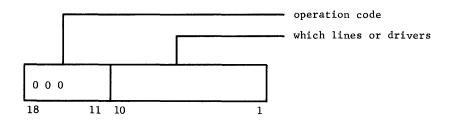

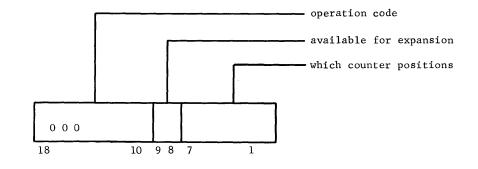

| Instruction Words Format                                     | J |

3.

| Detailed Block Diagram                    |

|-------------------------------------------|

| Description of Blocks                     |

| The Memory Unit                           |

| The Buffer Selector                       |

| The Controller Selector                   |

| Parity Network (21 no abb., N) $57$       |

| Hardware Load and Paper Tape Reader       |

| hardware Load and raper rape reader,      |

|                                           |

| Mapbed Time Olock                         |

|                                           |

| Dasie Hogram Oyele                        |

| Addressing memory,,,,,,,, .               |

| Direct Access to a Program Bank           |

| Direct Access to the Common Data Bank     |

| Direct Access to a Channel Table 60       |

| Indirect Addressing                       |

| Indirect Access from a Program Bank       |

| Indirect Access from the Common Data Bank |

| Indirect Access from a Channel Table      |

| Interrupt Interface                       |

| Allocation of Cycles                      |

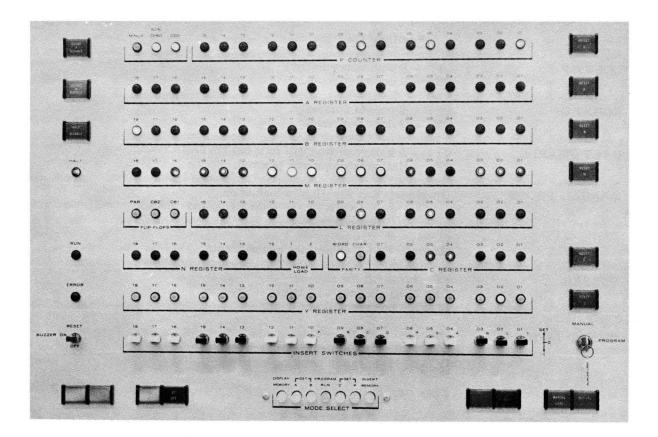

| Control Console                           |

#### 4. PROGRAMMING

| Program Preparation                    |

|----------------------------------------|

| Assembly Programs                      |

| Programming Aids                       |

| Utility Routines                       |

| Diagnostic                             |

| System Programming Considerations      |

| Message Switching Center               |

| Intergrated Data Processing            |

| Instruction Repertoire                 |

| Load Instructions                      |

| Store Instructions                     |

| Arithmetic Instructions                |

|                                        |

| Logical Instructions.                  |

| Register Transfer Instructions         |

| Branch Instructions                    |

| Special Instructions                   |

| Buffer Selector Instructions           |

| Controller Selector                    |

| Installation Information               |

| Components Sizes                       |

| Electrical Requirements                |

| Environmental Bequirements             |

| Environmental Requirements             |

| Ventilation                            |

| Cables to Communication Line Interface |

| Controller Selector Cables             |

| INDEX                                  |

Page

| DATANE | T - 30 |

|--------|--------|

|--------|--------|

.

## ILLUSTRATIONS

| Figure                                 |                                                                                                                                                                                                                                                                                                                                                                                                             | Page                 |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.<br>2.<br>3.<br>4.<br>5.<br>6.       | DATANET-30 Processor<br>System with RDC 930 Units<br>Medium Switching Center.<br>Large Switching Center.<br>Communication Lines with a Remote Concentrator<br>Nationwide Network                                                                                                                                                                                                                            | 7<br>8<br>9<br>10    |

| 7.<br>8.<br>9.<br>10.<br>11.<br>12.    | Remote File Updating         Data Collection         Remote Data Processing         DATANET-30 System ComponentsNot a Typical System         Bit Buffer Module         Receive Mode                                                                                                                                                                                                                         | 14<br>15<br>20       |

| 13.<br>14.<br>15.<br>16.<br>17.<br>18. | Transmit Mode<br>Echoplex Mode<br>Character/Word Buffer Channel<br>Character Buffer Transmit and Receive<br>Word Buffer Channel Transmit and Receive<br>Character Buffer Channel Block Diagram                                                                                                                                                                                                              | 25<br>25             |

| 19.<br>20.<br>21.<br>22.<br>23.<br>24. | <ul> <li>Dialing Adapter Units with Telephone Equipment and Bit Buffer</li> <li>Dialing Adapter Units with Telephone Equipment and Character</li> <li>or Word Buffers</li> <li>PIU Connecting Two DATANET-30's</li> <li>CIU 931 Connecting a DATANET-30 with an External Computer</li> <li>Data Transfer Through a CIU 931</li> <li>CIU 930 Connecting a DATANET-30 and a GE-200 Series Computer</li> </ul> | 28<br>29<br>30<br>31 |

| 25.<br>26.<br>27.<br>28.<br>29.<br>30. | DATANET-30 with Controller Selector Unit and Peripheral<br>Equipment<br>CPC Peripheral Equipment<br>DATANET-30/RDC 930 Block Diagram<br>DATANET-30 with a Card Reader<br>DATANET-30 with Card Punch and Reader Units<br>Typical PS-6010 Switch Application                                                                                                                                                  | 36<br>37             |

| 31.<br>32.<br>33.<br>34.<br>35.<br>36. | Parallel Channel Adapter Block Diagram                                                                                                                                                                                                                                                                                                                                                                      | 46                   |

DATANET-30-

### INTRODUCTION

With the trend toward more decentralization of company operations over a wider geographic area, with more products to sell to more customers, there is also the trend to centralize management of company operations. In order to make the right decision at the right time--of what to build, what materials to buy, how much of an item to ship to an area warehouse, what type of an inventory to maintain and the many other involved problems of a far flung modern business--the managers who make these decisions must have accurate data that represents the situation at the moment--today--not last week.

For effective control, management requires timely and accurate information which reflects the decisions on the total business environment. For example, better customer service, with shorter lead time on orders received and faster answers to inquiries is often the determining factor in where an order is placed.

The requirements for this unified systems approach to management and customer service take on added significance when one considers the size of the communications problem in business operations. The continued growth of business, increased specialization, and decentralization have created many barriers to the flow of information. Undoubtedly the most formidable communications problem is the sheer volume of information to be handled.

Concurrent with the need for timely and reliable information, another requirement developed. The trend toward decentralization created the need for data processing at district locations which, in many cases, is not economically justified. Hence, management must rely on a centrally located computer to handle the processing load for each district--a practice which again poses a problem in communications.

The development of computer-based data communications networks has progressed to the point where it is economically feasible to transmit data over public carrier facilities. New services and reduced rates are offered for transmission of digital data. In order to take advantage of these developments, and at the same time satisfy many needs in business communications, General Electric developed the DATANET-30.

DATANET-30.

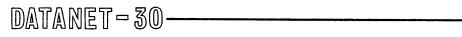

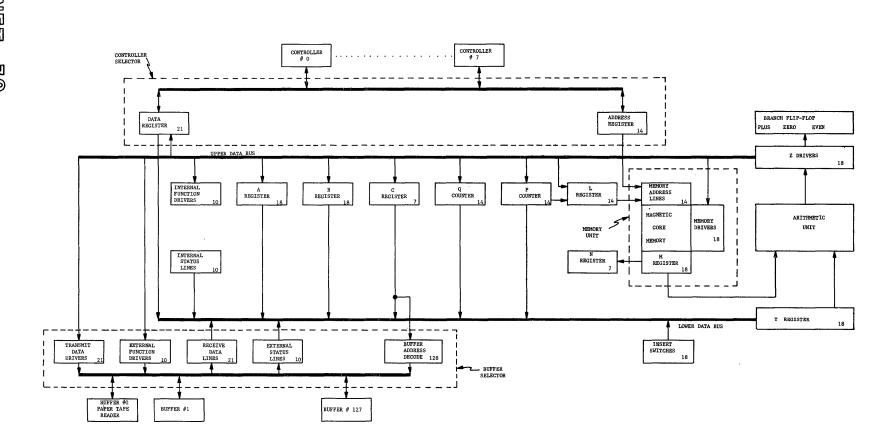

Figure 1. DATANET-30 Processor

## 1. GENERAL SYSTEMS DESCRIPTION

\*

The DATANET-30 is a real-time computer-designed primarily to automatically receive and process information originated at locations remote from the central computer (remote terminals)-- and to automatically transmit information to the remote terminals over normal common carrier communication facilities.

The DATANET-30 is:

- High speed

- Solid state

- Single address

- Special purpose

- Communications oriented

- Digital computer

has:

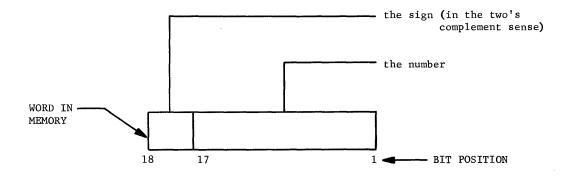

- A binary mode of operation

- A 7 microsecond word time

- A stored program

- A magnetic core memory

- Over 78 basic instructions

- 18-bit word in memory

- Up to 128 input/output channels

- Memory interrupt

- Indirect addressing and multiple indexing

- An elapsed time counter

- Patch plug adaptability to character and word length

- Patch plug adaptability to transmission and receiving speeds

#### performs:

- As central control for a DATANET-30 communication system

- As a communications controller for a GE-200, 400 or 600 Series General Purpose Computer

- Arithmetic and data manipulation operations

- On a real time basis

#### capable of:

- Controlled transmission of data over common carrier facilities

- Serving as a communications control between remote terminals and a computer

- Unattended operation

- Using a variety of remote terminal devices including Teletype keyboard printers, a computeral DATANET-760 Terminal

- Simultaneous transmission to remote terminals

- Simultaneous receiving from remote terminals

- Receiving and transmitting digital data over Teletype or telephone grade transmission lines--private or leased--or public dial-up services, manual and automatic

- Operating with 5, 6, 7, 8, level codes, and other codes up to 20 bits

- Operating at standard transmission/receive speeds (in bits per second) of 45; 50; 56.25; 66.2; 72.6; 75; 110; 150; 300; 600; 800; 1050; 1200; 1800; 2000 and 2400

- Storing and retrieving data on a disc storage unit

- Storing and retrieving data on magnetic tape compatible with a computer

- Printing reports on a high speed printer or Teletype machine

performs the functions of:

- Message assembly

- Message formatting

- Message disassembly

- Message scheduling

- Multiple message broadcast

- Store and forward communication

- Communications network control

- Control of switched network lines

- Message accounting and traffic analysis

- Producing traffic statistics

- Basic message routing and switching

- Handling priority messages

- Handling variable message lengths

- Maintaining a high line loading

- Journal keeping

- Alternate routing on a station or center basis

- Inserting time and date

- Message acknowledgment

- Control of multipoint private lines

- Code conversion

- Speed conversion

- Format control and conversion

- Providing cost allocation on message or station basis

- Error control--operator and code

- Character and word parity checking

- Automatic program reload

- "End of Transmission" and "End of Text" code detection under program control

The capability to receive the transmission of data from remote terminals allows a DATANET-30 system to perform as a:

- Message switching center where messages and data are going from one remote terminal to another

- Remote data processing where data from remote stations is processed at a central computer, and as needed, reports are sent to remote stations. The DATANET-30 can be programmed to handle data traffic for a data processing center with equal facility that it handles the administrative traffic normally associated with telegraph switching centers

- Remote inquiry where an answer is generated by the computer and transmitted to the station requesting

- Automatic data accumulation and distribution to/from a variety of points for batch processing by a computer

- File updating where reports from remote stations are processed by a central computer on a batch process basis

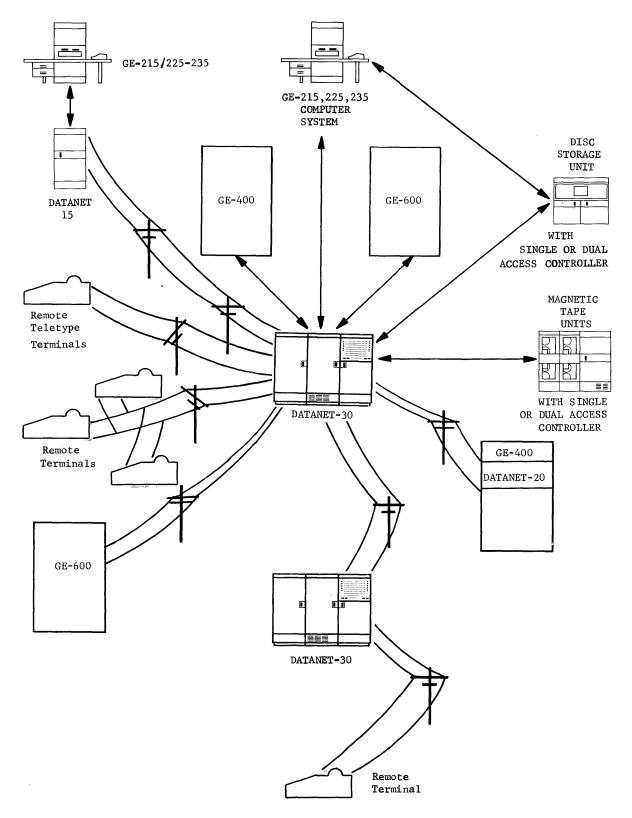

A DATANET-30 system consists of a variety of equipment, the choice of which depends upon system design and requirements. The following illustrations cover some of the combinations possible with a DATANET-30 to fill the communication requirements of modern business activities.

#### TELETYPE MESSAGE SWITCHING SYSTEM

The General Electric DATANET-30 switching center is a fully-automatic system designed to perform, store and forward message switching. The DATANET-30 switching center can be used to communicate with any of the following:

- 1. Direct-connected communication stations,

- 2. Multipoint private line connected stations,

- 3. Dial-up stations on public message networks,

- 4. Direct input/output with computer systems (core to core),

- 5. Indirect input/output with computer systems (via magnetic tape or a disc storage unit),

- 6. Communication with other networks or portions of a network.

#### **Functions**

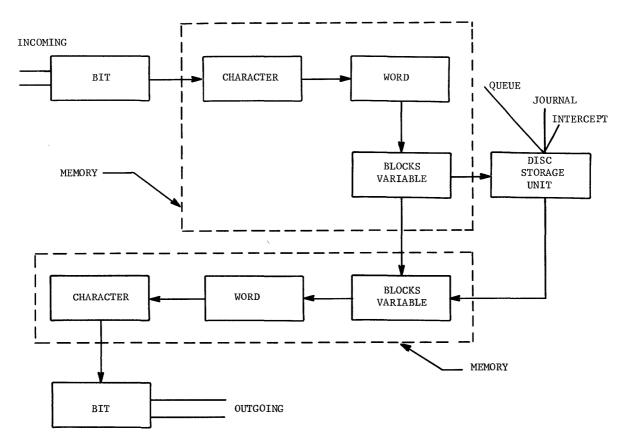

All the functions of transmitting to or receiving messages (data) from a remote terminal, and handling the messages enroute from origin to destination must be coordinated within the message switching system. This coordination is accomplished by providing means for the functions of:

- 1. Message Accumulation--Messages are assembled and routed under program control.

- 2. Message Distribution--Messages are distributed under program control.

- 3. Automatic Multipoint Private Line Control (Party Line)--Polling and selection of stations on the line is accomplished under program control.

- 4. In-Transit Storage--Storage is provided for message queueing.

- 5. Journal Storage -- Storage is provided for recording message journals.

- 6. Intercept Storage--Storage is provided for messages for stations closed due to limited time of operation, station malfunction, etc.

- 7. Message Accounting--Journal storage can be processed during off hours or low activity periods to provide daily status reports, and data for network study.

- 8. Traffic Analysis--The number of messages per line per station per day can be counted. The reports generated can then by typed out at the supervisory position. Such items as average message length, number of multiple message broadcasts, and operator errors in formatting may be included in the reports.

- 9. Multiple Message Broadcast--Individual messages can be routed to more than one outstation as designated by the routing indicators.

- 10. Automatic Restart--System is capable of automatically restarting itself in case of program malfunction.

- 11. Supervisory System Monitoring--One Automatic Send-Receive (ASR) and a Receive Only (RO) Teletype device are used for system monitoring. Headers of misrouted messages

can be printed out and corrected. The supervisor can send service messages to open or close out stations and/or to send data to intercept storage.

- 12. Format Conversion--Changing the order of spacing of data from the incoming order to the desired outgoing order.

- 13. Error Control--A variety of error detection and correction schemes can be used. Operator error codes can be recognized and a recovery or re-start procedure set up for that message. The DATANET-30 can be programmed to control the format of a message and notify the operator of any format errors. Also, transmission errors can be recognized through echoplex retransmission. Parity check of codes and block parity checks can be used.

- 14. Alternate Routing of Messages--Supervisory changes in routing on a temporary basis in case of line or terminal outage. Programmed automatic alternate routing is also possible.

- 15. Priority Messages--Messages may contain a "Priority Level Code" that can be recognized by the DATANET-30 program. Thus hot messages or data can be handled before routine administrative messages.

#### Operation

The operation of the switching center is fully automatic--under control of the program. The sequence of transmission of terminals on a multipoint private line is also controlled by the program. Each message contains a <u>destination code</u>--the name or number of the remote station or stations where the message is going. After a message is received from a remote station, the program interrogates the destination code of the message in memory, then transmits it to the proper remote terminals. The DATANET-30 is programmed to handle all normal messages in accordance with a standard format and standard routing codes for the system. A standard incoming message format would be used for all incoming traffic, including rush messages, normal messages, and service or control messages. The distinction between messages is made by the mnemonic address code.

The system is capable of operation with only occasional manual intervention and control. The control is accomplished through the supervisory terminal to open and close stations by time of day and enter other control messages. When a station is closed, the program forwards all messages for the closed station to intercept storage.

The supervisory terminal normally consists of a keyboard/printer Teletype unit. This terminal is used as a message intercept position for incorrectly routed or formatted messages. The supervisor looks at the messages and decides what action is necessary, such as, correct the heading and re-enter the message, ask for retransmission, etc. The terminal is also used to notify the supervisor of line malfunctions and for printing out periodic status reports on the switching center operation.

The detailed operation of each system will be developed according to individual system requirements, such as; routing, service and control codes, format, number of lines and remote terminals, and the many other overall system operational requirements.

#### SWITCHING CENTER SIZE

The number of communication lines to be connected to the DATANET-30 permits a broad definition for the size of a switching center and associated equipment. A switching center can be defined as small, medium or large.

#### Small Switching Center

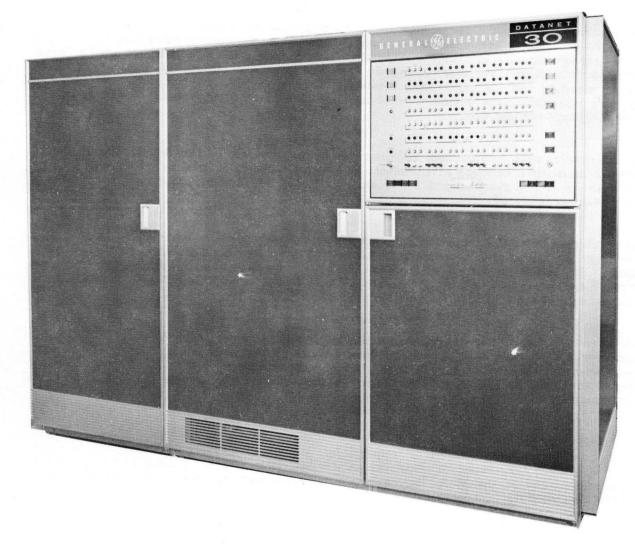

A small switching center would have an RDC 930 Removable Disc Unit and up to 10 communication lines of half duplex or full duplex operation. The amount of traffic is assumed to be in the range of 1 million characters per day throughput. The RDC 930 Removable Disc Unit is especially adaptable to this size system.

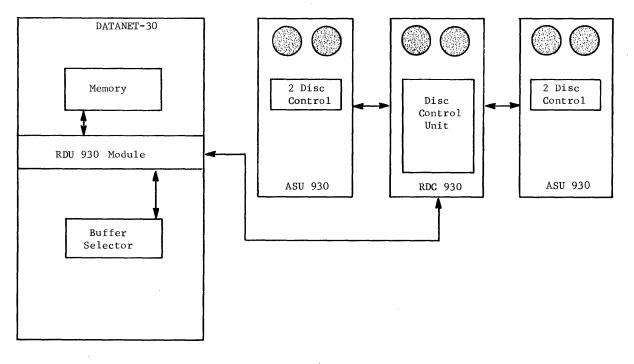

Figure 2. System with RDC 930 Units

#### Medium Switching Center

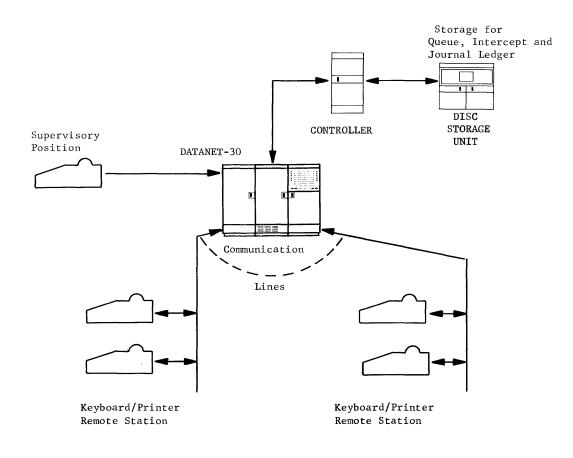

The medium switching center would have an M225B Disc Storage Unit and up to 30 communication lines of half duplex or full duplex operation. The amount of traffic is assumed to be in the range of 4 million characters per day throughput. The M225B Disc Storage Unit provides the capacity to operate this size system efficiently.

Figure 3. Medium Switching Center

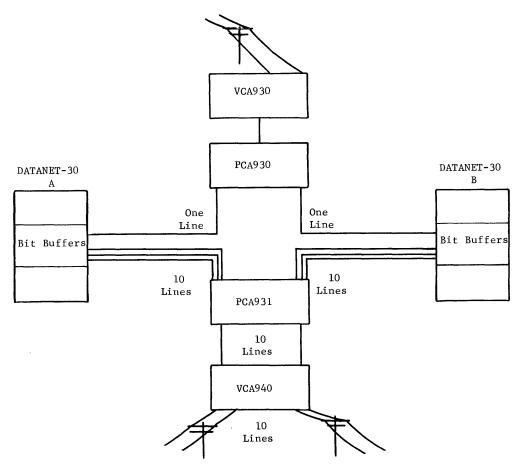

#### Large Switching Center

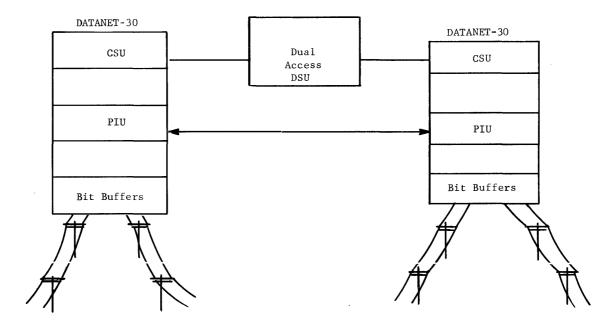

The large switching center would have more than one DATANET-30, one or more M225BX Disc Storage Units with Dual Access Controllers, and more than 30 communication lines. The communication lines would be of half duplex or full duplex operation with up to ten stations per line, or private line. The amount of traffic is assumed to exceed 10 million characters per day throughput.

Figure 4. Large Switching Center

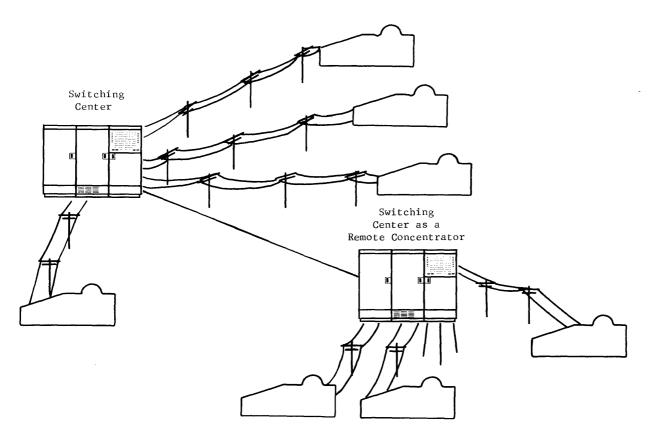

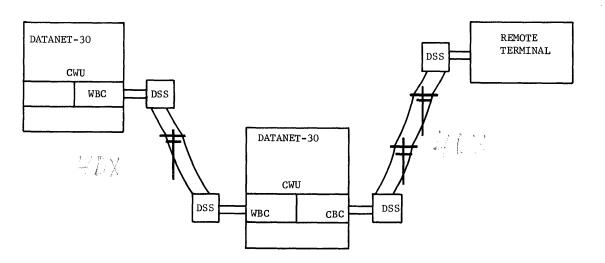

#### DATANET-30 AS A REMOTE CONCENTRATOR

When many remote stations are located many miles from the DATANET-30 switching center, it may be desirable to include one or more DATANET-30's to act as a concentrator for the more distant remote terminals. This will reduce the number of long distant lines coming into the switching center.

The remote concentrator is connected to the switching center via a "high speed" voice-quality trunk line. The DATANET-30 can "pack" many messages received at slow speed (75-110 bps) and transmit them. There are two main advantages:

- 1. Where the switching center would be overloaded if all remote terminals were directly connected, the use of the remote concentrator will reduce the time delay in a message from its origin to its destination. This is especially so if the remote stations were connected by multipoint private lines since it would then be possible to connect them via single lines on the remote concentrator.

- 2. Reduction in transmission line costs. If all remote stations were directly connected, there would be many "parallel" telegraph lines; whereas with the remote concentrator, there is one voice line.

Figure 5. Communication Lines with a Remote Concentrator

#### Functions

As a remote concentrator, the DATANET-30 takes traffic from low volume areas with low speed terminal devices and depending upon the program, performs the following functions:

- 1. Message accumulation and distribution

- 2. Code conversion

- 3. Speed conversion

- 4. Multiprivate line control

- 5. Error control

- 6. In-transit storage

- 7. Unattended operation

#### Operation

The messages are accumulated from many remote terminals and held in the in-transit storage until they can be transmitted at higher speed over a trunk line to a DATANET-30 switching center. When messages are received by a DATANET-30 remote concentrator from another DATANET-30, speed and code conversion are accomplished and the messages are transmitted out to the lower speed terminal devices. Hence, an increase in line utilization is obtained between two DATA-NET-30 centers and the low speed remote terminals. Traffic can be handled two ways:

The concentrator can act as a store and forward switching center between those remote terminals connected into the concentrator.

The concentrator can be operating in the capacity of a relay station with the message switching being done by a DATANET-30 functioning as a switching center. All messages would go one way to the switching center and then back to the concentrator for transmission to one of the remote stations.

#### THE NETWORK

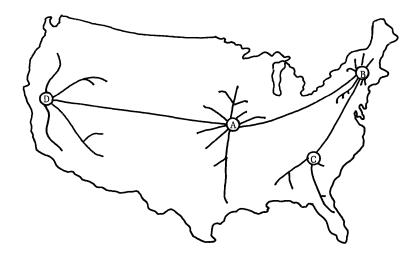

The DATANET-30 can be built up to a network configuration by interconnecting several DATA-NET-30 switching centers with high speed lines.

Figure 6. Nationwide Network

#### Functions

Each DATANET-30 would perform as a local switching center as well as a forwarding center for messages routed to a destination via one of the other DATANET-30 centers. Automatic alternate routing is also accomplished in the event that the line between any two centers should become inoperable or busy for long periods of time. Data processing could be associated with one of the DATANET-30 centers. Networks of this configuration require a comprehensive traffic analysis to insure that the capacity of the network is not exceeded.

#### Operation

An operator at a remote station on one DATANET-30 wishes to send a message to a remote station on another DATANET-30 of the network. The first DATANET-30 receives the message from the remote station, examines the destination code and determines that the message must be forwarded to another DATANET-30. When the trunk line is free, the message is forwarded to the other DATANET-30 where the destination code is examined and the message forwarded to the intended remote terminal. With proper coding of destination codes, messages may be simultaneously routed to several remote stations (multiple message broadcast).

#### COMMUNICATION/DATA PROCESSING SYSTEMS

In a direct access computer system, where remote terminals are capable of exchanging information with a central computer (EDP center) via data communication channels, the definition of the system depends on the job to be done. An individual system would be tailored to the requirement of the operating environment. The equipment variations are discussed later.

The list here is a generalized approach to system concepts:

Remote inquiry in real time Remote file updating in real time Remote file updating by batch processing Remote data collection by batch processing Remote data processing in real time Computer-to-computer communication Time sharing in real time

#### **Remote Inquiry**

Remote inquiry in real time can be defined as providing a reply to a remote terminal while the remote terminal is still on the line.

#### Remote File Updating

Remote file updating in real time is similar to remote inquiry except that the input is data to be used immediately to update existing records. The reply to the remote terminal supplying the data would be an acknowledgment or report of action taken.

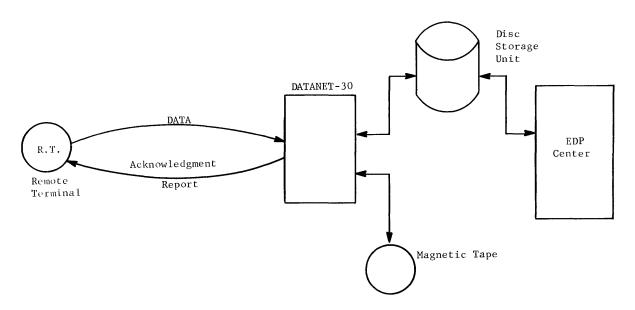

Figure 7. Remote File Updating

Remote file updating on a batch processing basis varies in the procedures used to update existing records. In this case, it may be more desirable to store the data on magnetic tape to process the data on a regular basis.

#### Data Collection

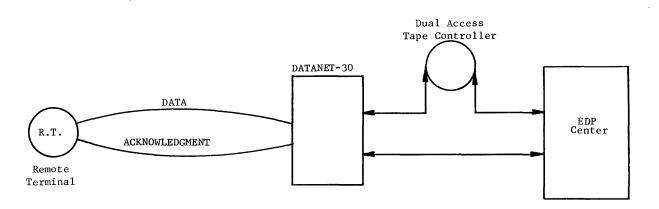

Data collection can be similar to remote file updating on both a real time and batch process basis. The data is collected on a real time basis and stored for later batch processing.

Figure 8. Data Collection

#### Remote Data Processing

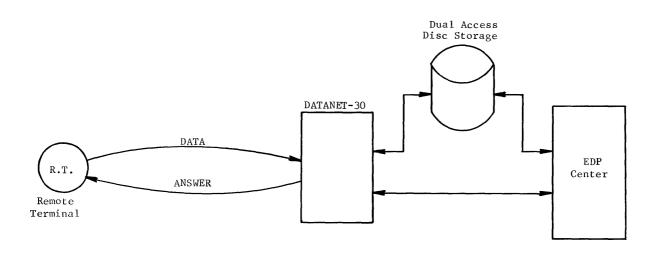

Remote data processing in real time places additional requirements on system design and programming. The remote terminal requires direct access to the EDP center and waits for an answer.

Figure 9. Remote Data Processing

#### **Time Sharing**

A GE-265 Time-Sharing System is a combination of a DATANET-30 communications processor, a GE-235 computer for high-speed scientific/data processing, and a proven software package with an easy-to-use language. A GE-265 System provides desk-side computations on an immediate and simultaneous basis. Remote terminals, such as Teletypes, access the system and provide computer access from any office where telephone service is available.

More information on the General Electric Time-Sharing System is available in various manuals covering operation and programming.

#### EQUIPMENT CONFIGURATIONS

Many factors are involved in deciding upon a system equipment configuration. The scope of this manual does not allow a full discussion of the various combinations. Therefore, equipment available for the design of a real time, direct access communication/data processing system is described from a functional viewpoint. Incorporation of the individual pieces into an operating system must necessarily be done on an individual basis.

Figure 10. DATANET-30 System Components-Not a Typical System

DATANET-30-

## 2. DATANET-30 COMPONENTS

#### GENERAL DESCRIPTION

The DATANET-30 consists of:

The data communications processor, to control the input/output flow of data, and manipulate the data as necessary.

Buffers to connect the communication facilities to the communications processor.

Buffers to interconnect computers.

Buffers to connect computer peripheral equipment to the communications processor.

#### Data Communications Processor

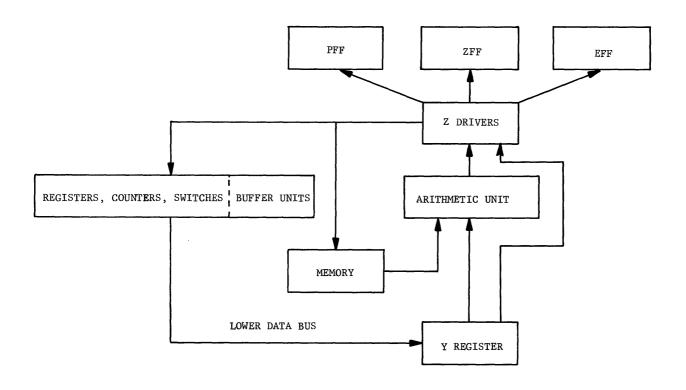

The communications processor contains a core memory, power supply, control and working registers, and the buffer selector.

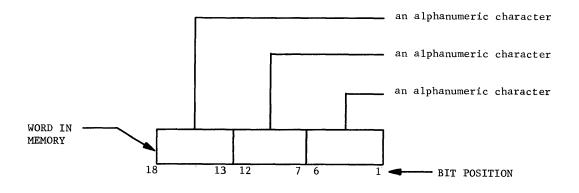

The magnetic core memory stores program instructions, alphanumeric information, and binary data. Standard memory units are available in sizes of 4,096, 8,192 and 16,384 words. Each word consists of 18 bits. The memory cycle time is 6.94 microseconds for a read-restore cycle, a clear-write cycle, or a read-compute-write cycle.

During a read-restore cycle, 18 bits of information are read from the memory and transferred to the working registers.

During a clear-write cycle, 18 bits of information are transferred from the working registers and written into memory.

During a read-compute-write cycle, 18 bits of information are read from memory, modified, and the new information is written back into memory.

The control and working registers include: An arithmetic unit capable of an 18-bit binary add; and logic for data manipulation.

#### Buffer Selector

The buffer selector is an important functional element of the DATANET-30. Low speed information flow between the communications processor and external equipment is through buffers connected to the buffer selector. All units directly connected to the buffer selector will be referred to as "buffers." The buffer selector contains one hundred twenty eight (128) channels numbered 0 to 127.

#### Channel Address

Each buffer occupies one channel address of the buffer selector whether it is for a simplex, half duplex, full duplex, or any other type of transmission facility. The desired buffer selector address of a channel is easily established by wiring a channel address plug. The address can be changed or new addresses (buffers) added by changing the plug wiring or inserting a different plug. The channel addresses in any given group of buffers need not be sequential. Channel 0 is always reserved for the paper tape reader.

#### DATANET-30 BUFFER MODULES

The DATANET-30 has physical space for 12 buffer modules. The buffer modules vary according to size of buffer storage and purpose. Depending upon the system, the twelve modules will contain the desired configuration of:

- A. Communication Line Buffers Bit Buffer Unit (BBU) Module Character/Word Unit (CWU) Module Dialing Adapter Unit (DAU) Module Telpak A Buffer Module

- B. Interconnecting Computer Buffers Computer Interface Unit (CIU) Modules Processor Interrupt Unit (PIU) Modules

- C. Peripheral Equipment Buffers Controller Selector Unit (CSU) Modules Common Peripheral Channel (CPC) Modules Removable Disc Unit (RDU) Module Card Read Unit (CRU) Module Punch Reader Unit (PRU) Modules

#### **Other System Components**

These components do not occupy space in the DATANET-30. They are connected externally to peripheral equipment and communication lines.

- 1. Parallel Channel Adapter

- 2. Manual Peripheral Switch

- 3. Programmed Peripheral Switch

- 4. Voltage Current Adapters

- 5. Digital Subsets

- 6. Communication Lines

#### DATANET-30 to DATANET-30

When one DATANET-30 is used as backup for another DATANET-30, or when it is otherwise necessary for one DATANET-30 to communicate with another, the following equipment is available:

Local

Processor Interrupt Unit Dual Access DSU Controller Dual Access Tape Controller

Remote

Word Buffer Unit Telpak A Buffer

#### **DATANET-30** Peripheral Equipment

Once the real time data is captured from the communication line by the DATANET-30, the data must be stored or otherwise processed depending upon the system design. In order for the DATANET-30 to handle the additional optional requirements of a real time, direct access/data communications system, the following equipment is available:

Controlled Selector Unit (CSU 931) Computer Interface Unit (CIU 930/931) Common Peripheral Channel (CPC 930) Card Read Unit (CRF 930) Punch Reader Unit (PRF 930) RDC 930 Removable Disc Unit

#### **EDP** Center

The EDP center can be any one of the three General Electric computer families. In order for the DATANET-30 to communicate with the EDP center, the following equipment is available:

Computer Interface Unit CIU 930/931 Common Peripheral Channel CPC 930 Dual Access DSU Controller (GE-200 Series Computer) Dual Access Tape Controller (GE-200 Series Computer)

DATANET-30-

#### COMMUNICATION LINE BUFFERS

#### The Bit Buffer Unit Module

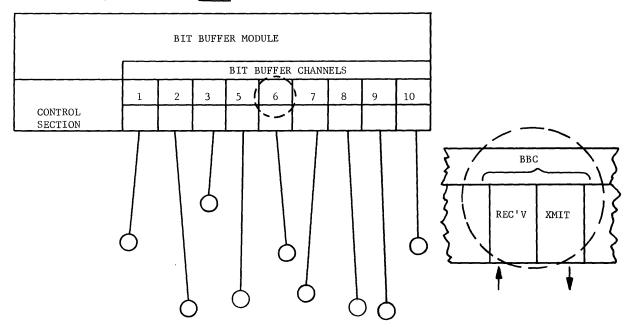

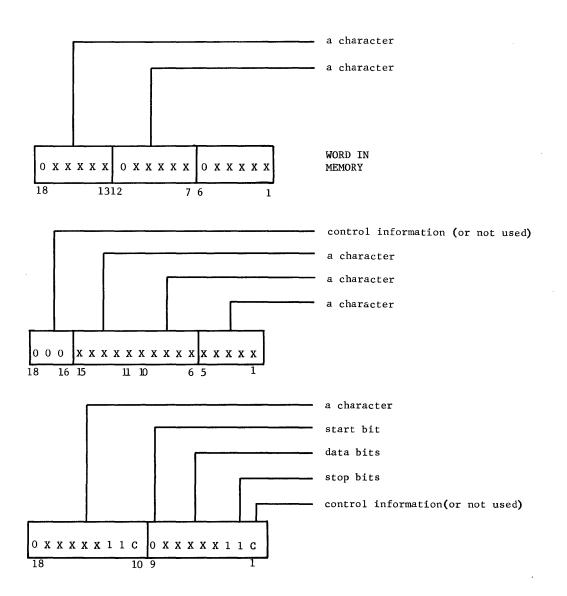

The bit buffer unit contains from one to ten buffer channels and one control section for that module. The control section contains a basic timing unit and common circuitry. The buffer control section contains hardware that is common to all the bit buffer channels in the unit module. Each bit buffer channel is capable of receiving and transmitting digital data. A bit buffer unit module may terminate from one to ten full duplex, half duplex, or simplex transmission lines which are all operating at the same bit rate.

Figure 11. Bit Buffer Module

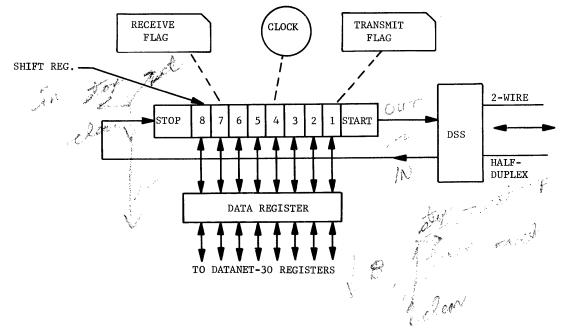

<u>THE BIT BUFFER CHANNEL</u> The Bit Buffer Channel (BBC) buffers one bit of information at a time between the DATANET-30 and the communication line. It is used on communication lines operating with stop-start asynchronous format (e.g., normal Teletype) and either 5, 6, 7 or 8 level codes.

Each bit buffer channel in a module is assigned a buffer selector address by the address plug for that module. The address applies to both the receive and the transmit section. The address for the bit buffers in a module can be whatever is desired for the system and they need not be sequential. Thus a bit buffer channel may be added to a module and given an address without disturbing the existing address arrangement.

System considerations limit operating speed of the bit buffer lines to the standard Teletype rates of 45, 50, 56.25, 66.2, 72.6, 75, 110, and 150 bits per second. The rate is established per module with a timing connector plug. The selected bit rate will apply to all the bit buffer channels physically located in a module. If more than one bit rate is used in a system, the different bit rate lines would be terminated in separate bit buffer unit modules using a timing connector plug set for the bit rate of that module.

The maximum number of lines which can operate simultaneously is dependent on the bit rate in use in the system, the volume of traffic and other factors. The slower the transmission rate, the higher is the number of remote stations that can be handled <u>simultaneously</u>.

More than one code level may be used within a bit buffer unit module. The program recognizes different code levels in use in the same system.

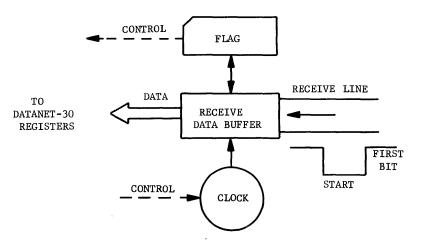

Receive Operation. The following is a brief description of the operation of the receive section of a bit buffer channel. Assume that the terminal device is sending marks, i.e., it is idle. Now the terminal device starts to send a bit stream (e.g., a character). When the start bit (a space) is received, a clock is started. The clock is used to time the future sampling of the line. The start bit is transferred into the receive data buffer and a receive flag is set. When the clock reaches the proper time, the line is sampled again, the bit on the line is transferred to the receive data buffer, and the receive flag is set. This process of sampling the line at regular intervals, transferring the data on the line to the receive data buffer, and setting the receive flag continues until the clock is stopped by the program. Since the bit buffer channel will transfer the information from the line into the receive data buffer every bit time, the program must test the receive flag and take away the bit in the receive data buffer before the line is sampled again. Whenever the bit is taken, the receive flag and the receive data buffer are automatically reset. At some point, the program decides that the appropriate number of bits have been received and sends a signal to the bit buffer channel which stops the clock. The receive flag will remain reset until another start bit is received. As a protection against noise on the transmission line causing the clock to start running, the bit buffer circuitry requires the space condition to exist on the line for at least one-half of a bit time to start the clock. Thus, noise of less duration than one-half of a bit time will have no effect.

Figure 12. Receive Mode

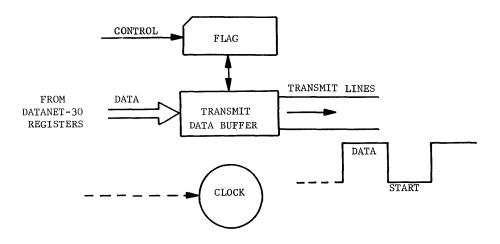

<u>Transmit Operation</u>. The following is a brief description of the operation of the transmit section. Assume that the program is not sending anything and that the transmit flag is set. This means that the bit buffer is ready to take a new bit. The program sends a bit to the transmit data buffer. This automatically resets the transmit flag. At regular intervals, the bit buffer transfers the bit in the transmit data buffer to the transmission line. When this happens, the transmit flag is automatically set by the bit buffer unit.

Figure 13. Transmit Mode

Since the bit buffer will transfer the bit in the transmit data buffer onto the line whether or not a new bit has been supplied, the program must test the transmit flag and provide a new bit before this transfer occurs. This process will repeat for each bit in the character. At the end of the bit stream which the program sends, the last bit will remain in the transmit data buffer and will be transferred to the line regularly. Therefore, the last bit in a bit stream will normally be a mark so that the line remains in the mark condition when no information is being transmitted. Note that with a bit buffer channel, the length of a character is completely under control of the program.

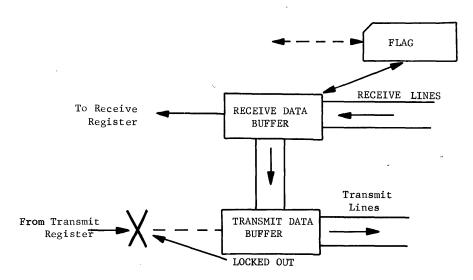

Echoplex

Figure 14. Echoplex Mode

Transmission errors may be detected by using a bit buffer with full duplex line in the following manner.

A bit buffer has the capability of echoing what is received. This is controlled by activating the appropriate instruction and, therefore, is under program control. When echoing, the bit received by the receive section is retransmitted over the transmit portion of the full-duplex line. In this way, a terminal device with error control capability can verify what was received by the DATANET-30 (actually, what is received back by the terminal device). Whenever a bit buffer channel is set up for echoing, the transmit section is locked out so that the bit ordinarily in the transmit data buffer cannot interfere with what is being sent back to the terminal device.

The usual equipment at the transmitting end is a keyboard printer send/receive unit. The information is transmitted in the normal manner but the printer does not print a hard copy as a direct result of the transmission. The transmitted signals are received by the receive section of a bit buffer and immediately transmitted back to the page printer of the transmitting terminal. Thus, the printed information indicates the number of possible errors involved in the transmission of the message.

This technique quickly shows whether or not the lines are working properly and in the case of an administrative message, whether or not it is possible to "read thru" the errors. If the errors are too high, the transmitting terminal can take appropriate action. If the transmission contains important numerical data where the numbers must be correct, the transmitting station again can immediately verify that the transmission was satisfactory.

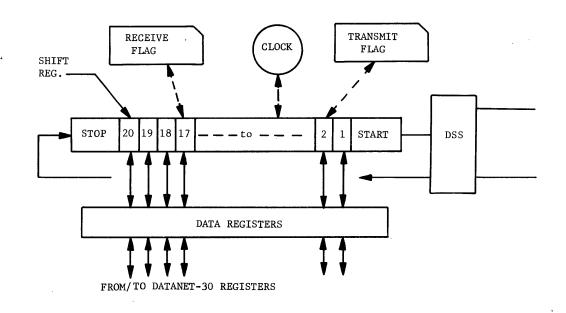

#### The Character/Word Unit Module (CWU 930)

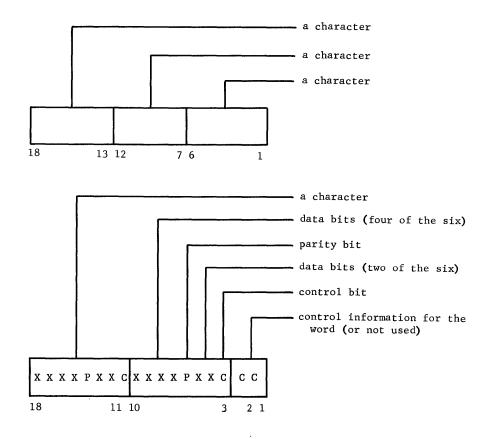

The character/word unit module occupies one module space and can contain either two Character Buffer Channels (CBC), two Word Buffer Channels (WBC), or one of each. The buffer selector address of each CBC or WBC is specified by the wiring of the address plug for the module, and each may be addressed independently of the other.

Figure 15. Character/Word Buffer Channel

The Character/Word Unit (CWU) provides buffering for one character (5, 6, 7 or 8 bits) of information between the DATANET-30 and the communications lines; or provides buffering for one word (20 bits) of information between two DATANET-30 data communications processors. As a character buffer, it is used on lines with transmission rates from 300 to 2400 bits per second with stop-start asynchronous format (e.g., normal Teletype).

THE CHARACTER BUFFER CHANNEL (CBC 930). The character buffer channel provides the interface between the DATANET-30 and a high speed remote terminal device over a half-duplex transmission line. Two character buffer channels are needed for full duplex operation.

A character buffer channel buffers a character length bit stream where the length is determined by the code of the remote terminal. Each CBC has a code level plug and a timing connector plug. The code level plug is specially wired for the character length of each CBC. The standard character lengths are 5, 6, 7 and 8 level code characters. System considerations require that a CBC be used on lines operating at 300 or more bits per second. The timing connector plug for a CBC would be wired for transmission speeds of 300, 600, 800, 1050, 1200, or 2400 bits per second. The transmission rate for each CBC may be independently selected.

Receive Sequence of the Character Buffer. The following is a brief description of the operation of an 8-bit character buffer channel in the receive mode. A word buffer channel will operate in exactly the same way except for the number of data bits. Assume that the CBC has been put in the receive mode by the program, that the receive flag is reset, and that the sending unit is transmitting marks, (i.e., it is idle). Now the sending unit starts to transmit an 8-bit word. The word is preceded by a start bit (a space) and followed by a stop bit (a mark). When the start bit is received, a clock is started. The clock is used to time the future sampling of the line. The start bit is shifted into the shift register. At regular intervals, the line is sampled and the bit which is there is shifted into the shift register. When the shift register is full, the 8-data bits are automatically transferred into the data register, the receive flag is set, and the clock is stopped. The clock will start again and the above process will repeat when the next start bit is received on the transmission line. As a protection against noise on the transmission line causing the clock to start running, the CBC circuitry requires the space condition to exist on the line for at least one-half of a bit time to start the clock; thus noise of less duration than one-half of a bit time will Since the CBC will transfer a character from the shift register into the data have no effect. register whether or not the data register and receive flag are reset, the program must test the receive flag and take the character before another one is transferred into the data register. When the program takes the character from the data register, the data register and the receive flag are automatically reset.

<u>Transmit Sequence of the CBC.</u> The following is a brief description of the operation of an 8-bit CBC in the transmit mode. Assume that the program has put the CBC in the transmit mode, the CBC is in the process of sending a word out on the line, and a word is waiting in the data register. When the current character has been shifted onto the line, the CBC will transfer the character in the data register to the shift register. At this time, the transmit flag will automatically be set. The 8 bits transferred into the shift register will automatically be preceded by a start bit and followed by 2 stop bits for transmission on the line, i.e., a total of 11 bits. When the shift register and repeat the process if the transmit flag is reset. However, if the transmit flag is still set, indicating that the program has not put a new character into the data register, the CBC will continue to put stop bits (marks) on the line until the transmit flag will be automatically reset and the above process will be repeated. For maximum line utilization, the program must test the transmit flag and supply a new character before the current one has been completely shifted onto the line.

Figure 16. Character Buffer Transmit and Receive

WORD BUFFER CHANNEL (WBC). The word buffer channel provides the interface with another DATANET-30 via a half-duplex transmission line. The WBC buffers a 20-bit word (plus start/ stop bits) at transmission speeds of 300, 600, 1200, 1800, 2000, or 2400 bits per second, depending on system considerations. The code level plug and the timing connector plug would be wired in

Figure 17. Word Buffer Channel Transmit and Receive

DATANET - 30 -----

accordance with system requirements. The 20 bit word transmitted (received) consists of an 18 bit word from the DATANET-30 memory plus one parity bit and one control bit generated by the transmitting DATANET-30.

The sequence of transmit and receive for the WBC is the same as for the character buffer channel except for the automatic addition of the parity and control bits to the transmitted word.

#### Character/Word Unit Module (CWU 931)

The Character/Word Unit module CWU 931 occupies one module space and is similar to CWU 930 except that characters are transmitted and received on a character synchronous basis. The character/word unit module (CWU 930) can contain two character buffer channels (CBC 931). A code level plug is required for each CBC 931.

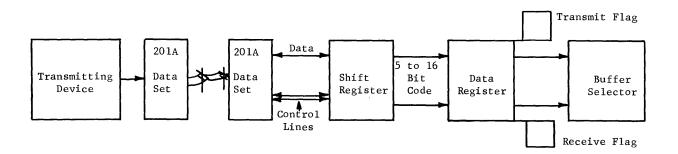

<u>CHARACTER BUFFER CHANNEL (CBC 931)</u>. One buffer channel provides the interface between the DATANET-30 and a half-duplex transmission line. The CBC is synchronized by the digital subset connected to the transmission line and therefore does not require a timing connector plug.

The buffer control unit contains hardware to control the character length as defined by the code level plug. Buffers in a module may be operating at different character lengths. The buffer channel operates with a character oriented device at speeds determined by the subset and remote terminal. A synchronous digital subset must be on each end of the transmission line. The standard bit rates are 2000 and 2400 bits per second.

The code level may be from 5- to 16-bit codes with character synchronization (no start/stop bits). The code level (character length) is selected or changed by a code level plug for each CBC. By changing code level plugs, the code level may be varied to meet different remote terminal operations or programming techniques.

The code level plug also defines the bit configuration of the synchronizing character, the number of bits per character, and where the receive lines will enter the data bits into the "working" register (A or B register); that is, the high- or low-order position of the A or B register. The code level plug can be arranged to accept two characters (8 level) before setting the receive flag. Also, the code level plug can be arranged to mask off a bit. The line interface is Bell System Dataphone Model 201A or 201B Data Set or equivalent.

Figure 18. Character Buffer Channel Block Diagram

#### Dialing Adapter Unit Module (DAU 930)

The Dialing Adapter Unit module may contain from one to ten Dialing Adapter Channels, DAC 930. The module is mounted in one of the spaces provided for buffer modules that interface with the buffer selector. Each DAC is an independent unit operating through the buffer selector and is associated with one transmit/receive buffer, such as a bit buffer, or character buffer, etc. Two buffer selector addresses are required, one for the DAC and one for the associated buffer.

DIALING ADAPTER CHANNEL (DAC 930). The General Electric Dialing Adapter Channel (DAC 930) provides the means for dialing telephone numbers of remote locations to transmit or receive data. The DAC 930, with its associated telephone equipment, enables the DATANET-30 to dial virtually any telephone number connected with the Bell System.

The associated telephone equipment consists of an Automatic Calling Unit (ACU) and a Data Set. The DAC 930 is used only to place the telephone call. The ACU actually dials the number and makes the connection.

The transmission or reception of data takes place through the associated Data Set and buffer on the buffer selector. Only one transmission line is associated with each DAC, ACU, and Data Set. If it is desired to dial out on more than one line, a separate DAC, ACU, and Data Set are used for each line (or call). Incoming calls are handled by the Data Set.

The DAC provides one four-bit digit buffer. One four-bit binary-coded decimal digit  $(0_{10}-9_{10})$  at a time is presented to the DAC by the DATANET-30 program. This digit occupies the four least-significant positions of a DATANET-30 word. The DAC then presents this digit to the telephone company ACU for dialing.

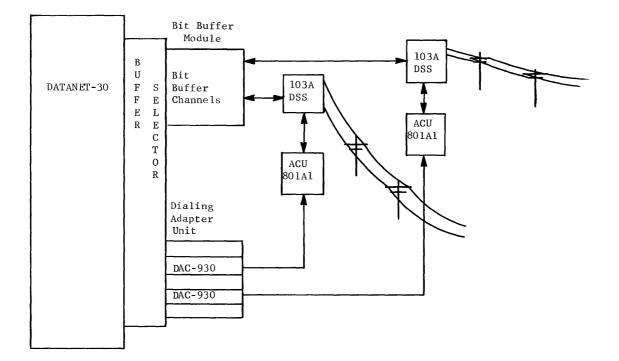

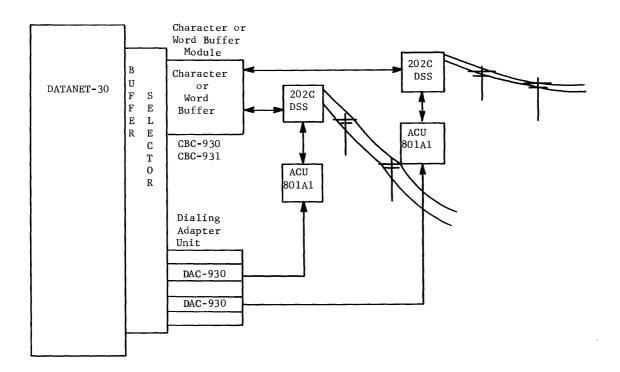

#### Configurations

A DAU may be set up in the configurations shown in Figures 19 and 20.

#### Controls and Indicators

There are no controls or indicators in the usual sense except for the MANUAL CLEAR button on the DATANET-30 control panel. All other controls and indicators are by program only.

#### Buffer Operations

The Dialing Adapter Channel and the Automatic Calling Unit may be used with several different digital subsets and transmit/receive buffers. The buffers in turn can connect to a variety of terminal equipment. The DEF and NES instructions for the transmit/receive buffers vary in accordance with the buffer used, the digital subset used, and the terminal equipment.

## DATANET-30-

Figure 19. Dialing Adapter Units with Telephone Equipment and Bit Buffers

Figure 20. Dialing Adapter Units with Telephone Equipment and Character or Word Buffers.

# Automatic Calling Unit (ACU)

The Telephone Company Data Auxiliary Set 801A for automatic calling is not covered in great detail. Anyone interested in more information than contained here may obtain a copy of the Data Auxiliary Set 801A-Interface Specification (March 1964) from:

Data and Teletypewriter Planning Engineer American Telephone and Telegraph Company 195 Broadway New York, New York 10007

The operating features of the ACU pertinent to the operation of the DAC are:

- 1. The ACU obtains the dial tone in response to a Call Request from the DAC.

- 2. The ACU dials the digit received from the DAC.

- 3. When the last digit has been dialed, the ACU waits for the called location to answer.

- 4. The ACU detects the answer signal.

- 5. The ACU then transfers control of the call (telephone line) to the Data Set connected to the ACU and the transmit/receive buffer.

- 6. If the call cannot be successfully completed, the Abandon Call and Retry timer of the ACU notifies the program.

# INTERCONNECTING COMPUTER BUFFERS

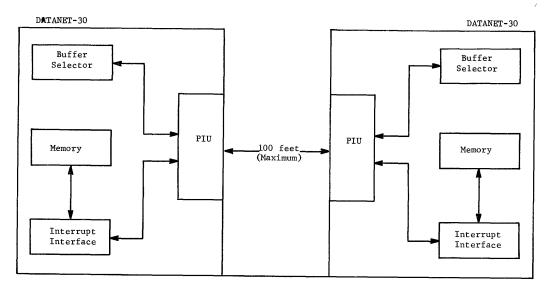

# Processor Interrupt Unit (PIU 930)

The DATANET-30 Processor Interrupt Unit (PIU 930) allows transfer of data from the memory of one DATANET-30 to the memory of another. One processor interrupt unit (PIU) for each DATANET-30 is required. Each PIU occupies one option module space and is assigned an address on the buffer selector. The address is specified by the address plug for the PIU.

DATANET - 30 -----

# Data Transfer

DATANET-30-

The PIU connects to the memory interrupt interface and is normally assigned interrupt cycle two. Only one interrupt cycle may be assigned to the PIU. This allows a transfer rate of 28,000 DATANET-30 words per second.

Data is transferred in both directions, but only in one direction at a time. Control of the direction of data transfer is established by either DATANET-30 on a receive only basis.

The PIU does not allow a program to initiate transmission. The DATANET-30 which is to receive data must initiate the data transfer. This method of operation protects the memory in one DATANET-30 from being destroyed by mistake by the other DATANET-30 program.

<u>CONTROLS AND INDICATORS.</u> All controls and indicators are by program only, except for manual reset on the control panel.

# COMPUTER INTERFACE UNIT (CIU 931)

The CIU 931 Computer Interface Unit provides the means for connecting the DATANET-30 and a GE-400 or -600 Series computer (Figure 22).

The computer interface unit (CIU) connects into the buffer selector of the DATANET-30 and into one standard input/output channel of the other computer. The buffer selector address of the CIU is specified by the buffer selector address channel for the CIU. Since the CIU connects the DATANET-30 with either a GE-400 or -600 Series computer, for the purposes here, both of these computers will be referred to as the "external computer." More than one CIU can be installed in a DATANET-30. Each CIU occupies two modules. There is no restriction on the number used, other than the physical space occupied.

Figure 22. CIU 931 Connecting a DATANET-30 with an External Computer

# Data Transfer

Data is transferred in both directions but only in one direction at a time. Control of the direction of data flow is established and maintained by either the external computer or the DATANET-30, Should both the DATANET-30 and the external computer desire control at exactly the same time, the external computer is given priority.

The CIU has an 18-bit buffer. Data is transferred one character at a time to or from the external computer and one DATANET-30 word at a time to or from the DATANET-30. The CIU contains the necessary shift circuitry to accumulate characters into words and separate sequential characters, depending on the direction of data transfer. Data transfer is illustrated in Figure 23.

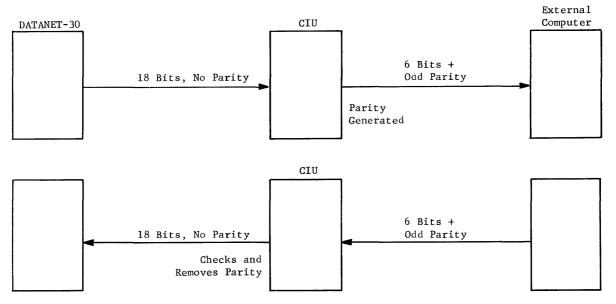

Figure 23. Data Transfer Through a CIU 931

<u>DATANET-30 TO THE COMPUTER INTERFACE UNIT.</u> When the CIU has received a word from the DATANET-30, a signal for the external computer to read is generated. The external computer initiates the transfer of one character at a time from the CIU. When the three characters have been transferred, the CIU notifies the DATANET-30 that another word can be transferred. The DATANET-30 program then transfers another word to the CIU. This process continues until the DATANET-30 or external computer sends an End Data Transfer signal to the CIU.

EXTERNAL COMPUTER TO THE COMPUTER INTERFACE UNIT. When the CIU has received three characters from the external computer, a signal for the DATANET-30 to transfer the three characters is sent to the DATANET-30. The DATANET-30 program must detect this signal and transfer the data from the CIU. When the data has been transferred from the CIU, the external computer can transfer three more characters to the CIU. This process continues until the external computer or DATANET-30 sends an End Data Transfer signal to the CIU.

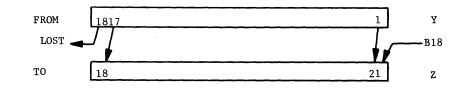

<u>DATA FLOW THROUGH THE COMPUTER INTERFACE UNIT</u>. When data is transferred from the CIU to the external computer, the most significant character of the DATANET-30 word is transferred first and the least significant last.

Characters received by the CIU from the external computer are assembled into a three-character word. The first character is transferred to the most significant part of the DATANET-30 word and the third character is transferred as the least significant.

If an End Data Transfer signal is received from the external computer before a full threecharacter word is shifted into the CIU, the characters in the data register are shifted to the most significant positions. Zeros are inserted by the CIU into the unfilled character positions before the word is transferred to the DATANET-30.

# COMPUTER INTERFACE UNIT (CIU 930)

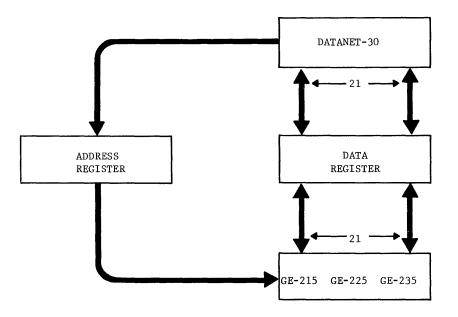

The Computer Interface Unit (CIU 930) provides the means for connecting a DATANET-30 and a General Electric 215/225/235 Computer. The Computer Interface Unit occupies one module of the DATANET-30. DATANET-30 must be within the standard distance of 50 feet from the computer. The DATANET-30 would be considered the same as another controller to the GE-200 Series computer as far as memory interrupt of the computer is concerned. However, the GE-200 Series computer cannot interrupt or access the DATANET-30 as is done with other controllers.

Figure 24. CIU 930 Connecting a DATANET-30 And a GE-200 Series Computer

### Data Transfer

DATANET-30

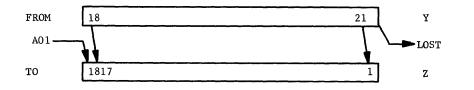

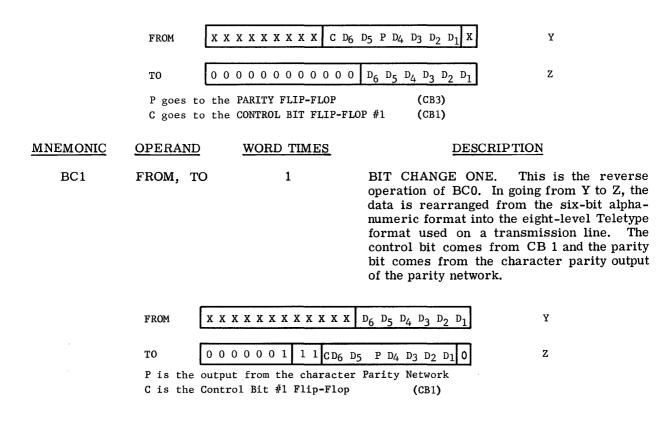

The CIU transfer 21-bit words between the DATANET-30 and the computer. The word is transferred in parallel. The memory address is also transferred in parallel from the address register to the GE-200 Series computer prior to data transfer. At the DATANET-30, the 21-bit word consists of an 18-bit word from memory, plus 1 parity bit and two control bits generated by the DATANET-30 circuitry. At the GE-215, 225, or 235 computer, this 21-bit word represents a 20-bit word plus memory parity. The CIU allows addressing any location in the GE-200 Series computer memory. The CIU connects into any channel of the DATANET-30 buffer selector in the same manner as any other DATANET-30 buffer. The buffer selector address of CIU is specified by the wiring of the buffer selector address plug for the CIU module. There is no DATANET-30 hardware restriction on the number of CIU's which may be used, other than the physical space occupied. On the computer side, the CIU can connect into any plug of the GE-200 Series computer controller selector.

The computer interface unit can be tested for a Busy-Not Busy condition, by the DATANET-30. This Busy-Not Busy test tells the DATANET-30 whether or not it can put data into the data register and address register, and whether or not it can take data from the data and address registers.

When the computer has traffic for the DATANET-30, the computer will set a flag in the computer memory, which is interrogated by the DATANET-30. When the DATANET-30 is ready to accept the traffic, a control instruction is sent to the computer, the computer program is interrupted, and the traffic is transmitted under control of the DATANET-30. The DATANET-30 then processes the traffic and sends it on to the remote station for which the traffic is intended. Thus the computer and the DATANET-30 exchange control words, instructions and traffic under the control of the DATANET-30.

<u>RECEIVE SEQUENCE</u>. The following is a brief description of the operation of a CIU in the receive mode; that is, taking words out of the GE-225 memory. Assume that nothing is happening as far as the CIU is concerned. At some point, the program in the DATANET-30 decides to take a block of words. The program puts a number equal to one less than the initial address of the block--the GE-225 address--in the address register of the CIU. Then the program sends a control signal to the CIU which increases the address register by one, puts the CIU in the receive mode, resets the data register, interrupts the GE-225 program for 1 word time, and initiates the transfer of the word from the specified GE-225 memory location to the data register in the CIU. After the word is in the data register, the CIU is no longer busy--this condition can be tested by the program. The program now executes an instruction to take the word out of the data register of the CIU and into the DATANET-30. This instruction also increases the address in the CIU address register by one, puts the CIU in the receive mode, resets the data register, and initiates the transfer of another word from the GE-225 memory. This process repeats until the DATANET-30 program decides that sufficient words have been received.

TRANSMIT SEQUENCE. The following is a brief description of the operation of a CIU in the transmit mode; that is, transferring words into the GE-225 memory. Assume that nothing is happening as far as the CIU is concerned. At some point, the program in the DATANET-30 decides to put a block of words into the GE-225. The program puts a number equal to one less than the initial address--the GE-225 address--in the address register of the CIU. Then the program transfers a word into the CIU data register with an instruction. This instruction also puts the CIU in the transmit mode, increases the address in the address register by one, interrupts the 225 program for 1 word time, and initiates the transfer of the word from the data register into the GE-225 memory. After the word has been written in the GE-225 memory, the CIU is no longer busy. The DATANET-30 program can now put another word in the data register and send it to the GE-225. This process repeats until the DATANET-30 program decides that sufficient words have been transferred.

DATANET-30.

# PERIPHERAL EQUIPMENT BUFFERS

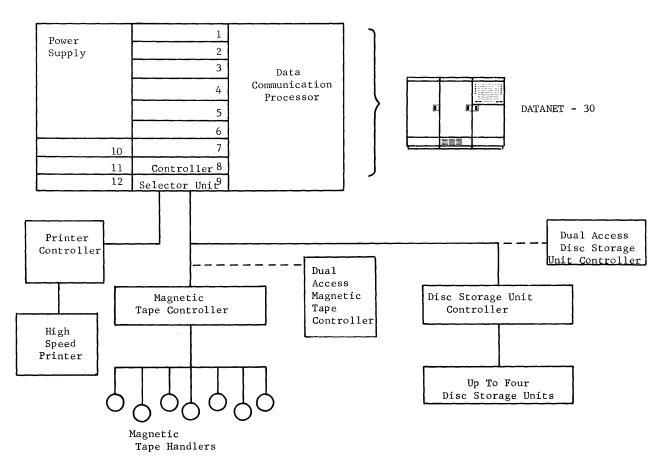

# The Controller Selector Unit

The controller selector unit permits attaching GE-200 Series computer peripherals to the DATANET-30 and enables simultaneous transfer of data to and from the DATANET-30 on a memory interrupt basis. The eight high speed channels, numbered 0 through 7, operate on a priority basis, with channel 0 having the highest priority and channel 7 the lowest.

Figure 25. DATANET-30 with Controller Selector Unit and Peripheral Equipment

<u>Peripheral Equipment Information</u>. Information for each peripheral device is contained in the manual for the particular peripheral equipment and in the appropriate appendix of CPB 1019A, the <u>DATANET-30</u> Programming Reference Manual.

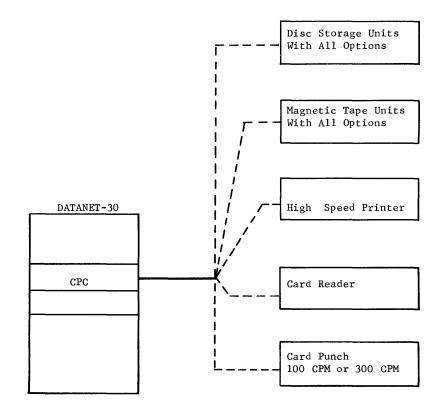

# Common Peripheral Channel

The Common Peripheral Channel (CPC) module permits connecting GE-400 or 600 Series peripheral equipment to the DATANET-30, and enables data transfer to and from the DATANET-30 on a memory interrupt basis. Each CPC occupies two option module spaces, and is assigned an address on the buffer selector. The address is specified by the address plug for the CPC. One peripheral device at a time connects to one CPC.

From one to four CPC's can be installed in a DATANET-30. The maximum is determined by the space available or by the number of memory interrupt cycles used.

Figure 26. CPC Peripheral Equipment

<u>DATA TRANSFER</u>. Data is transferred via the CPC one character at a time to or from the peripheral and one DATANET-30 word at a time to or from the DATANET-30. The CPC contains the necessary shift circuitry to accumulate characters into words and to separate sequential characters, depending on the direction of transfer.

The CPC can transfer any number of characters from 0 to 49,152 (16,384 word memory at three characters/word) between a peripheral and the DATANET-30 memory. Any starting address within a 16k memory may be specified. The CPC accesses memory sequentially under memory interrupt control.

<u>PERIPHERAL EQUIPMENT INFORMATION.</u> Information for each peripheral device is contained in the manual for the particular peripheral equipment and in Appendix G of CPB 1019A, the DATANET-30 Programming Reference Manual.

# RDC 930 REMOVABLE DISC STORAGE SUBSYSTEM

The RDC 930 Removable Disc Subsystem provides the DATANET-30 with a low-cost, removable media, random access storage unit packaged in modular free-standing cabinets. The disc control unit contains two disc mechanisms. Additional storage units may be added for a maximum of six disc mechanisms per system.

Communication with the DATANET-30 is provided by the Removable Disc Unit Module RDU 930 mounted in the DATANET-30 option module rack. One module space is required for the RDU 930. The RDU 930 interfaces with the buffer selector and interrupt interface of the DATANET-30. The buffer selector address is specified by the buffer selector address plug for the RDU 930. The block diagram, Figure 27 illustrates a complete DSU-100 Subsystem.

Figure 27. DATANET-30/RDC 930 Block Diagram

# Removable Disc Unit Module (RDU 930)

The RDU 930 provides the necessary control functions to transfer data to or from memory, and to issue commands to the disc control unit. The interrupt interface allows the transfer of an 18-bit DATANET-30 word to or from memory on a memory interrupt basis.

The memory address counter directs the flow of data. Up to 16,384 consecutive memory locations may be addressed. The address counter is counted up one, each time a word is transferred to or from memory. Command word sequencing control directs the RDU and the disc control unit.

# Controls and Indicators

Except for manual reset on the DATANET-30 control panel, all controls and indicators for the RDU 930 are by program only. The controls and indicators for the RDC 930 are located on the disc control unit.

# Memory Interrupt Cycle Assignment

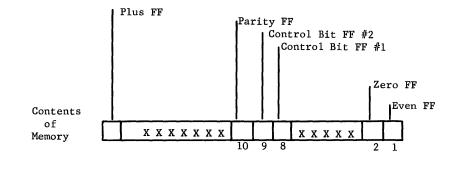

The RDC 930 is assigned two out of five nonadjacent memory cycles. Selection of the memory cycles is determined by what other equipment in the system also uses interrupt cycles. When determined, switches on the RDU 930 are set to assign cycles to the removable disc system.

Two disc control units (RDC 930) can be connected to a DATANET-30 if different memory cycles are assigned. The number of disc control units that can be connected to the DATANET-30 is limited by the memory cycles available. A different buffer selector address would be used to address each RDC 930.

The disc control unit contains the necessary logic and circuits to control the read/write head positioning, data transfer, and associated functions of the removable discs located in the control unit, as well as provide some control functions for each additional storage unit (ASU 930).

# Additional Storage Unit (ASU 930)

The additional storage unit (ASU 930) provides two additional disc handlers for added storage capacity. This unit is an additional cabinet with electronics and two disc drivers. It is connected to and is under control of the RDC 930. Two ASU 930 units may be connected to each RDC 930 providing a maximum of six disc drive mechanisms per disc control unit.

# Extra Removable Disc Cartridge (ASD 930)

Extra removable discs may be kept available in the same manner as magnetic tape reels, thus providing a removable storage media.

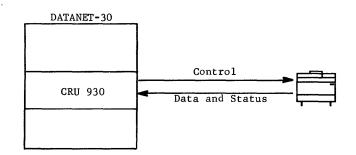

# CARD READER UNIT

One card reader unit (CRU 930) connects the CRF 930 card reader to the DATANET-30. The card reader unit occupies one option module space and is assigned an address on the buffer selector. The buffer selector address is specified by the address plug for the CRU.

Figure 28. DATANET-30 with a Card Reader

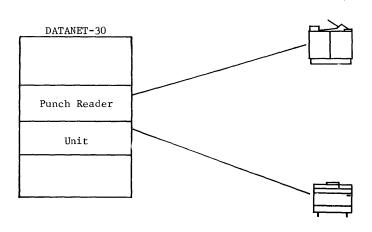

# Punch Reader Unit

The Punch Reader Unit (PRU 930) connects the CPF 930 card punch and the CRF 930 card reader to the DATANET-30. The card punch used is the GE-200 Series 100 card-per-minute punch. The card reader is optional with this module. When used, it operates the same as when the CRF 930 is installed with a CRU 930 module described above.

The card punch operates via the buffer selector and requires eight buffer selector addresses. The PRU 930 consists of two modules. Functional control of the punch is by the DATANET-30 program via the buffer selector.

Figure 29. DATANET-30 with Card Punch and Reader Units

# OTHER SYSTEM COMPONENTS

# The GE-200 Series Peripheral Switch

The Peripheral Switch (PSC 201) is an optional feature for the GE-200 Series computers and the DATANET-30. The number of peripheral controllers which may be switched between the G-E systems is as follows:

| GE-215 | 3 Peripheral Controllers |

|--------|--------------------------|

|--------|--------------------------|

- GE-225 8 Peripheral Controllers

- GE-235 7 Peripheral Controllers

- DATANET-30 8 Peripheral Controllers

This switching capability permits optimum utilization of all peripheral equipment for multiple systems operation. The peripheral switch control subsystem does not affect the independent and unrelated operation of the two central processors.

The peripheral switch consists of two types of units, the switch control console connected to two central processors, and the peripheral switch units each connected to one of the peripheral

controllers to be switched. A complete peripheral switch control subsystem consists of one switch control console and eight peripheral switch units. A minimum subsystem consists of a control console and one switch unit.

<u>CONSOLE UNIT</u>. The switch control console performs two functions: (1) assigns each controller selector to the desired central processor and (2) assigns the selected priority channel to each I/O device. The console is the control center of the peripheral switching subsystem. All controls necessary for the switching operation, and the interconnections for each of the peripheral switch units and the two central processors, are contained within the switch control console.

<u>SWITCH UNITS.</u> The switch unit contains switching relays. The unit is mounted inside the peripheral controller. Two standard priority control connectors on the switch unit connect to each of the central processors. Other connectors connect to the switch control console. Any combination of one or more peripheral controllers may be connected to the peripheral switch control console, limited only by any specific assignment characteristic of input/output devices on the controller selector.

Additional information is contained in the manual for the Compatibles 200 Peripheral Switch Control Subsystem.

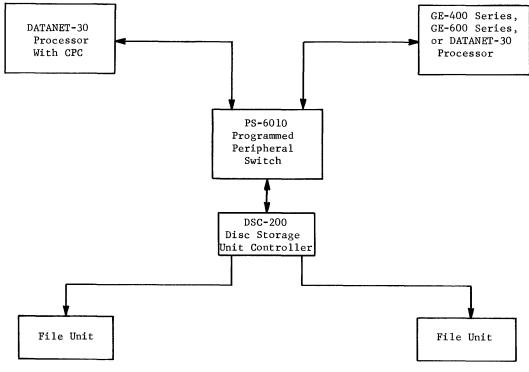

# PROGRAMMED PERIPHERAL SWITCH

The Programmed Peripheral Switch (PS-6010) is a modular, free-standing, program-controlled switch. It is used to connect either of two processors to a single peripheral controller. Each processor may be a GE-400 Series central processor, a GE-600 Series Processor, or a DATANET-30. A typical application of the PS-6010 switch is shown in Figure 30. For additional information, refer to the manual on this equipment.

Figure 30. Typical PS-6010 Switch Application

<u>THE GE-400/600 SERIES PERIPHERAL SWITCH</u>. The peripheral switch subsystem (PSC 200) can be used with a GE-400/600 Series and DATANET-30 computer system.

One peripheral at a time would be switched to the CPC 930 of the DATANET-30. For additional information refer to the manual on this equipment.

### Parallel Channel Adapter

DATANET-30

The Parallel Channel Adapter is a manual switch used to switch communication lines from one DATANET-30 to another or to connect two DATANET-30's in parallel to the same line at the same time.

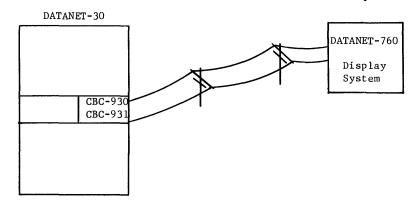

Figure 31. Parallel Channel Adapter Block Diagram