## GenRad Corp. futuredata PROGRAMMING THE AMDS

GenRad FUTUREDATA COMPUTER CORPORATION 5730 BUCKINGHAM PARK WAY CULVER CITY, CA 90230

### PREFACE

This manual provides information on the AMDS memory structure, utility subroutines, and direct I/O programming, and is organized in three sections as follows:

- "Debugger Memory Usage" describes memory configuration and the essentials of Debugger operation.

- "I/O Service Subroutines" explains the calling conventions and operation of the system I/O routines contained on the AMDS Utility Source Package diskette. The I/O subroutine calls provide access to system resources.

- 3) "Direct I/O Programming" provides a detailed discussion of the AMDS I/O structure. This information is helpful for the user who wishes to write custom utility programs for interfacing with specialized devices.

i

TABLE OF CONTENTS

| Section  | Pa                                 |

|----------|------------------------------------|

| <b>1</b> | Programming the AMDS               |

|          | MEMORY CONFIGURATION               |

|          | DEBUGGER INTERRUPT VECTOR USAGE    |

|          | DEBUGGER USE OF THE CPU STACK      |

| 2        | I/O Service Subroutines            |

|          | KEYBOARD INPUT/CRT OUTPUT          |

|          | Keyboard and CRT Display Functions |

|          | MSGIN                              |

|          | MSGOUT                             |

|          | KEYIN                              |

|          | ΤVΟUΤ                              |

|          | DISPCUR                            |

|          | OUTCUR                             |

|          | BLNKCUR                            |

|          | KBDIN                              |

|          | KBDTST                             |

|          | DISK INPUT/OUTPUT                  |

|          | File Control Block                 |

|          | Diskette Directory                 |

|          | Error Return Codes                 |

|          | Function Definitions               |

|          | Open                               |

|          | Read                               |

|          | Write                              |

|          | Close                              |

|          | Create                             |

|          | Delete                             |

|          | Rename                             |

|          | Change Attributes                  |

|          | Free Space                         |

|          | Overlapped I/O                     |

|          | Examples                           |

|          | Reading From a File                |

|          | Writing Into a File                |

ii

# TABLE OF CONTENTS (Concluded)

| Section |                            | Page |

|---------|----------------------------|------|

|         | EIA INPUT/OUTPUT           | . 31 |

|         | Definitions                | . 31 |

|         | EIASET                     | . 31 |

|         | EIAIN                      | . 31 |

|         | EIAOUT                     | . 31 |

|         | ECBRATE                    | . 32 |

|         | ECBLEN                     | . 32 |

|         | ECBUNIT                    | . 32 |

|         | Examples                   | . 33 |

|         | ASCII Data Configuration   | . 33 |

|         | ECB Communication          | . 33 |

|         | CASSETTE TAPE INPUT/OUTPUT | . 35 |

|         | Error Recovery             | . 35 |

|         | WRITE                      | . 35 |

|         | READ                       | . 37 |

|         | READR                      | . 39 |

|         | Cassette Rewind Routine    | . 39 |

| 3       | Direct I/O Programming     | . 40 |

|         | KEYBOARD INPUT             | 41   |

|         | BREAK KEY                  | 42   |

|         | CRT DISPLAY SELECT         | 43   |

|         | CRT DISPLAY OUTPUT         | . 44 |

|         | MEMORY PROTECTION          | 46   |

|         | REAL-TIME CLOCK            | . 48 |

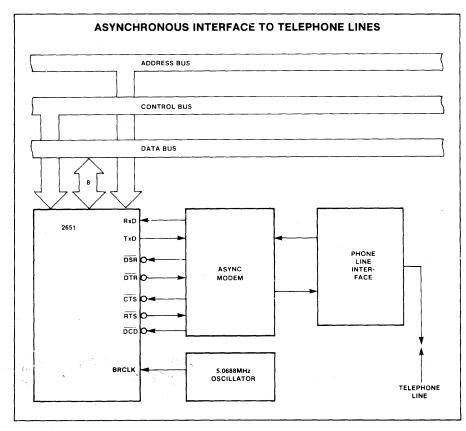

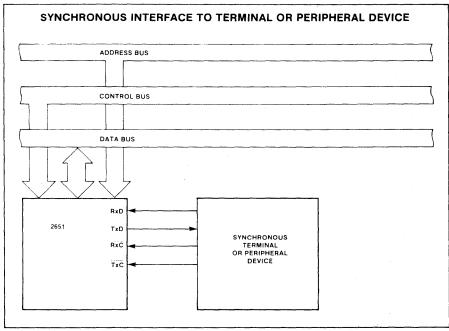

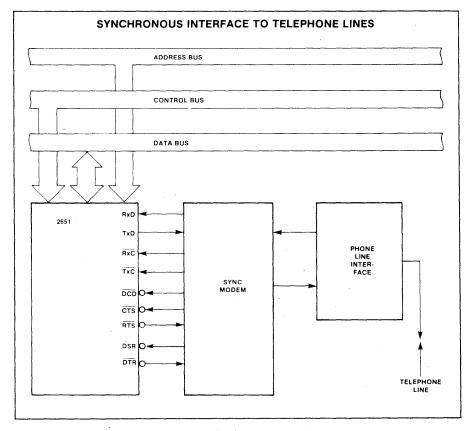

|         | SERIAL I/O PORTS           | . 49 |

|         | DISK I/O PORT              | . 55 |

|         | PRINTER PORT               | . 56 |

|         | BOARD STATUS PORT          | . 57 |

|         | BOARD COMMAND PORT         | . 58 |

|         | JUMPER SELECTION           | . 59 |

|         | AMDS I/O PORT ADDRESSES    | . 61 |

.

## LIST OF TABLES

| <u>Table</u> | Page                                          |

|--------------|-----------------------------------------------|

| 1-1.         | Debugger Address and Vector Allocation        |

| 2-1.         | I/O Service Subroutine Functions              |

| 2-2.         | CRT Display Control Command Functions 6       |

| 2-3.         | Disk File Control Block Fields                |

| 2-4.         | Disk File Management Functions and FCB Fields |

| 2-5.         | Disk File Management Error Return Codes       |

| 2-6.         | EIA Send-Control Block                        |

| 2-7.         | EIA Baud Rate Select Codes                    |

| 2-8.         | Tape Write Control Block                      |

| 2-9.         | Tape Read-Control Block                       |

| 2-10.        | Tape Read Routine Error Codes                 |

| 3-1.         | Keyboard Input Commands                       |

| 3-2.         | BREAK Key Commands                            |

| 3-3.         | CRT Display Select                            |

| 3-4.         | CRT Field Attributes                          |

| 3-5.         | CRT Display Line Offsets                      |

| 3-6.         | Protect Command Bit Assignments               |

| 3-7.         | Memory Protect Commands                       |

| 3-8.         | Real-Time Clock Commands                      |

| 3-9.         | Serial Port 1 Read Commands                   |

| 3-10.        | Serial Port 1 Write Commands                  |

| 3-11.        | Serial Port 2 Read Commands                   |

| 3-12.        | Serial Port 2 Write Commands                  |

| 3-13.        | Disk I/O Port Commands                        |

| 3-14.        | Printer I/O Commands                          |

| 3-15.        | Board Status Port Commands                    |

| 3-16.        | Board Command Port Commands                   |

| 3-17.        | Jumper Functions                              |

| 3-18.        | Summary of I/O Port Addresses                 |

|              |                                               |

DEBUGGER USE OF THE CPU STACK

Upon entry to the Debugger, the stack pointer is set to a valid (nonprotected RAM) address. When program execution is interrupted by the BREAK key or a breakpoint instruction, control is transferred to the Debugger which stores the machine status and registers on the stack and saves the stack pointer address. The user may or may not reset the stack pointer after the interrupt; Debugger execution will continue automatically in either case. Note, however, that if the user resets the stack pointer to an invalid address, the machine status display may show incorrect data.

The Debugger Execute command (E) stores the starting address on the stack, reloads the registers, and executes a return instruction. The return instruction transfers control to the execute address which is stored on the stack. If the stack pointer is not valid, the execute command will fail and the message "SP NOT IN RAM" will be displayed.

The "Z S=n" command is used to reset the stack pointer. Since the Debugger generates the machine status display from the data on the stack, the display changes each time the "Z S=n" command is entered.

Upon Debugger entry or upon re-entry (after hitting the RESET key), the stack pointer is set to the first byte in memory below the Debugger. When a program is executed using the "E" command, this value is loaded into the stack pointer register. The user may use this value or may load a new one.

## Section 2 I/O Service Subroutines

Relocatable subroutines, including a number of I/O service subroutines, are available to the user. Service subroutines greatly simplify input/ output operations to standard peripheral devices. These subroutines may be actuated by execution of a CALL instruction (for 8080/85A/Z8O) or JSR instruction (6800/02) to the appropriate entry point, as shown in Table 2-1.

I/O subroutines are provided for keyboard input/CRT display output, disk input/output, EIA send/receive, and cassette tape read/write functions. The routines have convenient calling conventions for use with the I/O devices. The routines interpret user requests and perform the detailed low-level I/O operations required to accomplish the requested operations.

The I/O service subroutines are listed in Table 2-1 and are described in detail on the following pages.

I/O Service Subroutines

| I/O Type 🛛 🛛 | Global Label | File    | Service Function                   |

|--------------|--------------|---------|------------------------------------|

| Keyboard/    | KEYIN        | KEYIN.R | Read a character from the key-     |

| CRT Display  |              |         | board or command file              |

|              | MSGOUT       | KIO.R   | Write a message a line at a time   |

|              |              |         | to the CRT display                 |

|              | MSGIN        |         | Read and echo a line from the      |

|              |              |         | keyboard                           |

|              | TVOUT        |         | Write a character to the CRT       |

|              |              |         | display                            |

|              | DISPCUR      |         | Display the cursor                 |

|              | OUTCUR       |         | Display the cursor                 |

|              | BLNKCUR      |         | Blank the cursor                   |

|              | KBDIN        |         | Read a character from the keyboard |

|              | KBDTST       |         | Test for keyboard input            |

| Disk         | DISK         | DIO.R   | Entry to the disk routines         |

|              | DISKW        |         | Wait for completion of disk I/O    |

| EIA          | EIASET       | EIA.R   | Set EIA parameters                 |

|              | EIAIN        |         | Input a character from the EIA     |

|              |              |         | port                               |

|              | EIAOUT       |         | Send a character to the EIA port   |

| Tape         | READ         | TIO.R   | Read a record from tape            |

| :            | READR        |         | Re-entry read from tape            |

|              | WRITE        |         | Write a record to tape             |

|              | REWIND       | :       | Rewind tape Unit(s)                |

#### KEYBOARD INPUT/CRT DISPLAY OUTPUT

The keyboard and CRT display terminal may be addressed directly (see Section 3). However, a much easier method of accessing them is obtained by use of MSGIN and MSGOUT which access a line at a time; KEYIN and TVOUT which access a character at a time; the cursor display routines (DISPCUR, OUTCUR, and BLNKCUR); and the bypass command file routines (KBDTST and KBDIN).

The TVOUT routine operates the CRT display in the following manner. The cursor is first initialized to the top left display location by outputting a clear (DLE=X'10') character. The ASCII representation of the character to be displayed is then loaded into the accumulator\* prior to calling the TVOUT routine. A cursor is displayed at the next character position. When that character is stored, the cursor is advanced, moving from the last character of the line to the first character of the following line. When the last character of the bottom line is reached, it moves to the first character of the top line.

A horizontal dividing line below the cursor (consisting of underline (\_\_) characters) separates the data most recently displayed (above the line) from older data (below the line). As new data are received and entered onto the display, the dividing line moves down. At the bottom of the screen it wraps around to the top so that the data remain on the screen until they are written over on the next cycle. All registers and flags are saved.

The most commonly used control commands are interpreted as shown in Table 2-2.

| Table 2-2.      | CRT Display Control Command Functions       |

|-----------------|---------------------------------------------|

| Character       | Function                                    |

| Carriage Return | Moves the cursor to the left of the current |

|                 | line.                                       |

| Line-Feed       | Moves the cursor down one line.             |

| Backspace       | Moves the cursor back one space.            |

| DLE(X'10')      | Clears the screen and leaves the cursor at  |

|                 | the top left corner.                        |

|                 |                                             |

\* In this document the word "accumulator" refers to the "A" register in 8080/85A/Z80 systems and to accumulator "A" in 6800/02 systems.

#### Keyboard Input/CRT Display Output

Keyboard and CRT Display Functions. The nine keyboard CRT I/O functions are defined below.

-----

MSGIN

MSGIN reads a line at a time from the keyboard or command file and echoes the data on the display. MSGIN uses routines in the KEYIN.R, LINEIN.R and KIO.R files.

\_\_\_\_\_\_

#### MSGOUT

\_\_\_\_\_

Displays a line at a time. When MSGOUT is called, a message is written to the CRT display refresh page. The address of the message is passed in the HL register pair (or Index register for 6800/02 systems). The message is terminated by X'00'.

-----

#### KEYIN

KEYIN reads a character at a time from the keyboard or command file and returns it in the accumulator. If the accumulator is zero when the routine is called, the character is converted to upper case; if non-zero, lower case characters can be read. The Command File Processor and KEYIN use memory from X'D600' to X'D7FF' for the command file workspace. The user should not alter this region if KEYIN is used. KEYIN uses the LINEIN routine (in file LINEIN.R) and routines in file DIO.R.

\_\_\_\_\_

#### TVOUT

Displays a character at a time. The accumulator must contain the character to be displayed; no other parameters are used.

DISPCUR

When called, this routine displays the cursor. If the content of the HL register pair/Index register is zero, the cursor is displayed at the next location to be used by TVOUT. If the HL register pair/Index register has a non-zero value, this value is assumed to be a display refresh page address at which the cursor will be displayed. This entry point assumes there are no field attribute characters in the display refresh page.

#### OUTCUR

OUTCUR is used to display the cursor when field attribute characters are present in the display refresh page (see Section 3) or when the cursor location is in row-column form. At the time of invocation, the accumulator should contain the column number and the B register/accumulator B should contain the row number.

#### BLNKCUR

This routine blanks the cursor. No parameters are used.

\_\_\_\_\_\_

\_\_\_\_\_

#### KBDIN

KBDIN reads a character from the keyboard and returns the result in the accumulator. This routine can be used to read from the keyboard even if command file processing is active.

\_\_\_\_\_

#### KBDTST

This routine tests the keyboard status register. If new data are available, the accumulator will be non-zero on return. If a keystroke has not been detected, the accumulator will be zero.

I/O Service Subroutines

### Disk Input/Output

#### DISK INPUT/OUTPUT

FUTUREDATA RDOS allows user programs to implement all of the disk file management functions. These functions (Create, Delete, Open, Close, Read, Write, Rename, Change Attributes, and Free Space) are made available through a single entry point in the relocatable disk I/O package DIO (residing in file NDIO.R).

<u>File Control Block</u>. The Disk I/O service routines are invoked by executing a call to the entry point, DISK. The instruction, CALL DISK (or JSR DISK for 6800/02 systems), invokes the disk I/O package. The address of a 26-byte parameter list (see Table 2-3) which is passed in the HL register pair/Index register, completely specifies the operation to be performed. This list is called a File Control Block (FCB), and should be built in any convenient area in read/write memory. The FCB is used to determine the required function, file name, location of the I/O buffers, etc.

The Disk I/O routines return a completion code in the accumulator to indicate whether the operation was performed successfully, or if an abnormal condition was detected. When errors are detected, the HL register pair/ Index register points to the address of an ASCII message giving the nature of the error. This message is terminated by a byte of zero and may be displayed by calling the MSGOUT I/O service subroutines.

The 13 fields contained within the FCB are listed in Table 2-3. Table 2-4 shows the file management functions and how they relate to the FCB fields.

|       | Table 2-3. | File Control Block Fields                  |

|-------|------------|--------------------------------------------|

| Field | Bytes      | Function                                   |

| CBFLO | 1          | X'00' - perform function defined by FCBFL1 |

|       |            | X'02' - create file                        |

|       |            | X'04' - open file                          |

|       |            | X'08' - close file                         |

|       |            | X'10' - delete file                        |

|       |            | X'20' - rename file                        |

|       |            | X'40' - change file attributes             |

|       |            |                                            |

X'80' - free unused space

| Table      | 2-3. Fi      | le Control | Block Fields    | (Continued)                   |

|------------|--------------|------------|-----------------|-------------------------------|

| <br>Field  | <u>Bytes</u> |            |                 | Function                      |

| FCBFL1     | 1            |            | Read-Write Fund | ctions                        |

|            |              |            | <u>Bit</u> *    | Function                      |

|            |              |            | 0               | Read Sector                   |

|            |              |            | 1               | Write Sector                  |

|            |              |            | 2               | Perform Write Check           |

|            |              |            | 3               | Unused                        |

|            |              |            | 4               | Automatically increment       |

|            |              |            |                 | sector number                 |

|            |              |            | 5               | Read or Write Object Data     |

|            |              |            | 6               | Unused                        |

|            |              |            | 7               | Do not wait for completion    |

| FCBADR     | 2            |            | Address of dat  | a block in main memory to     |

|            |              |            | be transferred  | to (from) diskette. For Č     |

|            |              |            | the 8080/85A/Z  | 80, the address is in low-    |

|            |              |            | high format; f  | or the 6800/02 the address    |

|            |              |            | is in high-low  | format.                       |

| FCBLEN     | 2            |            | Length of data  | block in main memory to be    |

|            |              |            | transferred to  | (from) diskette. For          |

|            |              |            | 8080/85A/Z80,   | the length is in low-high     |

|            |              |            | format; high-l  | ow format for 6800/02. The    |

|            |              |            | maximum allowa  | ble length is the sector      |

|            |              |            |                 | skette, 128 bytes.            |

| FCBSEC     | 2            |            |                 | sector to be read or written. |

|            |              |            |                 | or is designated as l. The    |

|            |              |            |                 | ative to the beginning of the |

|            |              |            |                 | ated as "n". For 8080/85A/Z80 |

|            |              |            | ·               | is stored in low-high format; |

|            |              |            | high-low forma  |                               |

| FCBUN      | 1            |            | Selects drive   | 0 (X'00') or drive 1 (X'01'). |

| *Low-order | (rightmo     | st) bit is | zero.           |                               |

-----

|                          | Tab    | le 2-3. Fi | le Contr | ol Block Fields (Concluded)                  |

|--------------------------|--------|------------|----------|----------------------------------------------|

|                          | Field  | Bytes      |          | Function                                     |

|                          | FCBDIR | ]          |          | Directory entry location. This field         |

|                          |        |            | :        | is set and used by the Disk I/O routines.    |

|                          | FCBNAM | 10         |          | Alphanumeric file name, left-justified       |

|                          |        |            |          | in the field, i.e., if the file name is      |

|                          |        |            |          | less than 10 characters long, it must be     |

|                          |        |            |          | followed by a sufficient number of space     |

|                          |        |            |          | characters (X'20') to fill the field.        |

|                          | FCBREF | 1          |          | First track of file. This field is set       |

|                          |        |            |          | and used by the Disk I/O routines.           |

|                          | CBATR  | ]          |          | File attributes.                             |

|                          |        |            |          | Bit Function                                 |

|                          |        |            |          | 0 Write Protect                              |

|                          |        |            |          | 1 Permanent File                             |

|                          |        |            |          | 2 Source File                                |

|                          |        |            |          | 3 Object File                                |

|                          |        |            |          | 4 Relocatable File                           |

|                          |        |            |          | 5 Command File                               |

|                          |        |            |          | 6 Blind File                                 |

|                          |        |            |          | 7 System File                                |

|                          | FCBEOF | 2          |          | Specifies end of file (one greater than      |

|                          |        |            |          | the number of sectors within a file).        |

|                          |        |            |          | An empty file is shown as X'0001'. This      |

| -12 <sup>14</sup><br>- 1 |        |            |          | field is stored in a normal high-low format. |

|                          |        |            |          | When a file is opened for output, the high   |

|                          |        |            |          | order bit is set; the bit is reset when the  |

|                          |        |            |          | file is closed.                              |

|                          | FCBINT | 1          |          | Initial file size, specified in tracks.      |

|                          |        |            |          | This field is required only for Create.      |

|                          |        |            |          | The minimum size is 1 (X'Ol'), and the       |

|                          |        |            |          | maximum size is 76 (X'4C').                  |

|                          | FCBEXT | 1          |          | Extension size in tracks. Used when file     |

|                          |        |            |          | must expand. Allowable values are the same   |

|                          |        |            |          | as the initial allocation.                   |

|                          |        |            |          | 11                                           |

|            |                                                     | Table 2-4. File Management Functions | and FCB Fields                            |

|------------|-----------------------------------------------------|--------------------------------------|-------------------------------------------|

|            |                                                     | FCBFLO - 1 byte                      | FCBFL1 - 1 byte                           |

| Function   | Value                                               | Function Description                 | Function Description                      |

| Open       | X'04'                                               | Selects the Open function.           | Bits 0* and 1 are examined to determine   |

|            |                                                     |                                      | whether file is to be opened for reading  |

|            |                                                     |                                      | or writing, respectively.                 |

| Read       | X'00'                                               | Causes function specified by         | Bit O is set to designate a Read opera-   |

|            |                                                     | FCBFL1 to be performed.              | tion. Bit 4 is optionally set to indicate |

|            | анан сайтаан ал |                                      | sequential reading of the file.           |

| Write      | X'00'                                               | Causes function specified by         | Bit 1 is set to perform a Write. Bit 2    |

|            |                                                     | FCBFL1 to be performed.              | is set to perform a Write Check. Bit 4    |

|            |                                                     |                                      | specifies that FCBSEC is automatically    |

|            |                                                     |                                      | incremented before each Write for writing |

|            |                                                     |                                      | sequentially.                             |

| Close      | X'08'                                               | Selects Close function.              | Bits O and 1 are set to indicate that     |

|            |                                                     |                                      | the file was opened for reading or writ-  |

|            | · · ·                                               |                                      | ing, respectively.                        |

| Create     | X'02'                                               | Selects Create function.             | Bits 0 and 1 are set to indicate that     |

|            |                                                     |                                      | the file was opened for reading or writ-  |

|            |                                                     |                                      | ing, respectively.                        |

| Delete     | X'10'                                               | Selects Delete function.             |                                           |

| Rename     | X'20'                                               | Selects Rename function.             |                                           |

| Change     | X'40'                                               | Selects Change Attributes            |                                           |

| Attributes |                                                     | function.                            |                                           |

| Free Space | X'80'                                               | Selects Free Space function.         |                                           |

\*Bit zero is the rightmost bit.

12

Disk Input/Output

Table 2-4. File Management Functions and FCB Fields (Continued) FCBADR - 2 bytes FCBLEN - 2 bytes

### Function Description

Gives address of buffer to which data is to be transferred. Stored in low-high (8080/85A/Z80) or high-low (6800/02).

Specifies the address from which data for

Stored in low-high (8080/85A/Z80); high-

Write operations are to be obtained.

low (6800/02).

Write

Function

0pen

Read

Close Create Delete Rename Change Attributes Free Space

3

Specifies number of bytes in buffer to be transferred, maximum of 128 bytes.

Function Description

Stored in low-high format (8080/85A/Z80); high-low (6800/02).

Indicates size of data area to be transferred. Low-high format (8080/85A/Z80); high-low (6800/02).

Service Subroutines

I/0

|                     | FCBSEC - 2 bytes                                                                                           | FCBUN - 1 bvte                        |

|---------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------|

| unction             | Function Description                                                                                       | Function Description                  |

| Open                |                                                                                                            | Specifies disk drive to be accessed.  |

| Read                | Specifies number of sector to be read.<br>Stored in low-high format (8080/85A/Z80);<br>high-low (6800/02). | Drive number; field set prior to Open |

| lrite               | Designates number of sector to be written.<br>Low-high (8080/85A/Z80); high-low (6800/02).                 | Field set prior to Open.              |

| Close               |                                                                                                            | Field set prior to Open.              |

| reate               |                                                                                                            | Selects disk drive to be accessed.    |

| elete               |                                                                                                            | Field set prior to Open.              |

| lename              |                                                                                                            | Field set prior to Open.              |

| hange<br>Ittributes |                                                                                                            | Field set prior to Open.              |

| ree Space           |                                                                                                            | Field set prior to Open.              |

|                 | Table 2-4. File Management<br>FCBDIR - 1 byte | t Functions and FCB Fields (Continued)                                       |  |

|-----------------|-----------------------------------------------|------------------------------------------------------------------------------|--|

| Function        | Function Description                          | · · · · · · · · · · · · · · · · · · ·                                        |  |

| Open            |                                               | Function Description<br>Specifies 10-character name of file to<br>be opened. |  |

| open            | i<br>i                                        | Spectries to-character halle of the to 2                                     |  |

| en a secondar a | 1                                             | be opened.                                                                   |  |

| Read            |                                               | ut ut                                                                        |  |

| Write           | Field set by Open.                            |                                                                              |  |

| Close           | Field set by Open.                            | Field set prior to Open.                                                     |  |

| Create          |                                               | Specifies name of file to be created.                                        |  |

| Delete          | Field set by Open.                            |                                                                              |  |

| Rename          | Field set by Open.                            | Contains new file name.                                                      |  |

| Change          | Field set by Open.                            | Field set by Open.                                                           |  |

| Attributes      |                                               |                                                                              |  |

| Free Space      | Field set by Open.                            | Field set by Open.                                                           |  |

|            | FCBREF - 1 byte      | FCBATR - 1 byte                           |

|------------|----------------------|-------------------------------------------|

| Function   | Function Description | Function Description                      |

| 0pen       |                      |                                           |

| Read       | Field set by Open.   |                                           |

| Write      | Field set by Open.   | Field set by Open.                        |

| Close      | Field set by Open.   | Field set by Open. May be reset prior     |

|            |                      | to Close if attributes are to be changed. |

| Create     |                      | Indicates which attributes are to be      |

|            |                      | initially assigned to the new file.       |

| Delete     | Field set by Open.   | Field set by Open.                        |

| Rename     | Field set by Open.   | Field set by Open.                        |

| Change     | Field set by Open.   | Field set by Open. May be updated prior   |

| Attributes |                      | to execution of Change Attributes functio |

| Free Space | Field set by Open.   | Field set by Open.                        |

Disk Input/Output

|            | Table 2-4. File Management Functions        | and FCB Fields (Continued)                |

|------------|---------------------------------------------|-------------------------------------------|

|            | FCBEOF - 2 bytes                            | FCBINT - 1 byte                           |

| Function   | Function Description                        | Function Description                      |

| Open       |                                             |                                           |

| Read       | Field set by Open.                          |                                           |

| Write      | Field set by Open.                          |                                           |

| Close      | Field set by Open and updated during Write. |                                           |

| Create     |                                             | Number of tracks to be allocated to file. |

| Delete     |                                             |                                           |

| Rename     | Field set by Open.                          |                                           |

| Change     | Field set by Open. May be updated prior to  |                                           |

| Attributes | execution of Change Attributes function.    |                                           |

| Free Space | Field set by Open.                          |                                           |

| Table 2-4. File Management Functions and FCB Fields (Concluded) |

|-----------------------------------------------------------------|

| FCBEXT - 1 byte                                                 |

| Function Description                                            |

|                                                                 |

|                                                                 |

| Field set by Open.                                              |

| Field set by Open.                                              |

| Number of tracks to be taken during a Write                     |

| when additional space is required.                              |

|                                                                 |

| Field set by Open.                                              |

| Field set by Open.                                              |

|                                                                 |

| Field set by Open. Used to determine amount                     |

| of space used in file.                                          |

|                                                                 |

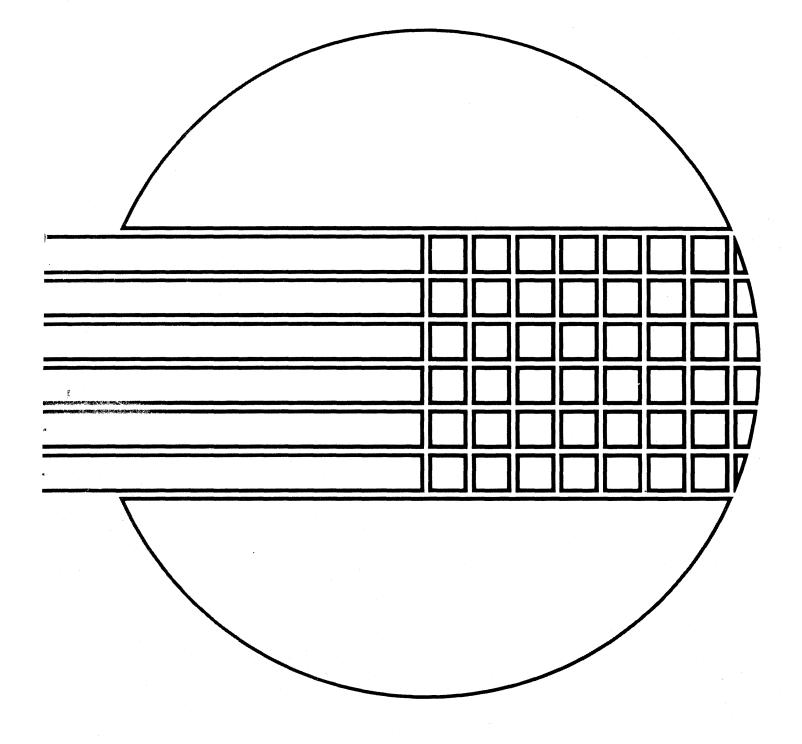

<u>Diskette Directory</u>. All diskettes used with FUTUREDATA RDOS must have a directory located on physical track zero. The directory is created when the diskette is initialized with the "I" command in the File Manager. The file name "DIR" is entered for the directory. DIR is given the "permanent" and "write protect" attributes. The purpose of the directory is to store the name of each file, its location on the diskette, its attributes, its current end-of-file location, and size of expansion when additional space is required.

The directory is made up of one sector containing a track map and ten sectors containing file name information. The track map maintains a list of both unallocated tracks and those allocated to existing files. The file name sectors contain one entry for each file allocated on the diskette. Each name entry is 16 bytes long. Eight entries fit into each 128-byte sector; thus, ten sectors can accommodate a maximum of 80 entries, with a maximum of 76 usable sectors.

The following FCB fields are contained in each file name entry: FCBNAM (10 bytes), FCBREF (1 byte), FCBATR (1 byte), FCBEOF (2 bytes), FCBINT (1 byte), and FCBEXT (1 byte).

The file name entries are initialized with the Create function, removed with the Delete function, and changed with the Rename function. The file attributes, end-of-file, and expansion size can be modified with the Change Attributes function.

Error Return Codes. A completion code is loaded into the accumulator upon return from the Disk I/O routines. This code indicates whether the requested function executed successfully, or whether an error condition was encountered. The accumulator is set to zero if no errors have been found. If an error has been detected, an error code is placed in the accumulator, and the HL register pair/Index register is set to point to an ASCII message describing the error. The error message is stored in memory as a sequence of ASCII characters followed by a zero byte indicating the end of the message. The error message may be displayed by the calling program.

The I/O error messages and the data file management functions that generate them are shown in Table 2-5.

|                       |                                                                              |      | 1        | 1     | 1           |        | nent Func | 1                |                      |              |

|-----------------------|------------------------------------------------------------------------------|------|----------|-------|-------------|--------|-----------|------------------|----------------------|--------------|

| I/O Routine<br>Messag |                                                                              | 0pen | Read     | Write | Close       | Create | Delete    | Rename           | Change<br>Attributes | Free<br>Spac |

| eturn Code            | Definition                                                                   |      |          |       |             |        | <br>-     |                  |                      | 1            |

|                       | Function completed successfully.                                             | X    | X        | X     | Х           | X      | X         | X                | X                    | X            |

| - PERM I/O ERR        | Unrecoverable error.                                                         | Х    | X        | Х     | Х           | Х      | Х         | X                | X                    | X            |

| - END FILE            | Reading of a sector<br>beyond the end-of-file<br>was requested.              |      | <b>X</b> |       | `           |        |           | ·<br>·<br>·<br>· |                      |              |

| - DISK FULL           | No space is available<br>to expand the size of<br>the file.                  |      |          | Х     | •• <b>v</b> | X      |           | · · · ·          |                      |              |

| - FILE NOT FOUND      | Specified file was not<br>found in diskette<br>directory.                    | X    | •        |       |             |        |           | •                |                      |              |

| - DUPLICATE<br>NAME   | File name specified is<br>already used on the<br>diskette.                   |      |          |       |             | X      |           | X                |                      |              |

| – PARM ERR            | Invalid field in FCB.                                                        | Х    | X        | Х     | X           | Х      | Х         | X                | X                    | X            |

| - DRIVE NOT UP        | Selected disk drive not ready.                                               | Х    | X        | Х     | X           | Х      | X         | Х                | X                    | Х            |

| - PERM FILE           | File requested for<br>deletion has the<br>permanent attribute.               |      |          |       |             |        | Х         |                  | · · · · ·            |              |

| - WRITE PROTECT       | Attempt was made to<br>open a file with the<br>Write Protect attri-<br>bute. | X    |          | Х     | •           |        |           |                  |                      |              |

| O - FILE NOT OPEN     | File has not been opened.                                                    |      | Х        | Х     | Х           |        | Х         | X                | Х                    | Х            |

2]

Table 2-5. Disk File Management Error Return Codes

<u>Function Definitions</u>. The file management functions are described in the paragraphs below.

<u>Open Function</u>. Before a file can be accessed on diskette, it must be "opened". The Open function uses the ASCII file name given in the FCB to locate the file name entry in the diskette directory. This entry provides the information necessary for file access such as location on the diskette, end-of-file, etc.

<u>Read Function</u>. The Read function causes the disk unit to seek the requested file sector. Data from the sector are then transferred into the memory buffer specified by the FCBADR field of the FCB. The diskette sectors contain 128 bytes; the length to be transferred to memory (up to 128 bytes) can be explicitly specified in the FCB.

File sectors are numbered sequentially, starting with the number 1. The sector to be read is contained in the FCBSEC field of the FCB. Even though a file may be composed of a number of non-contiguous tracks, the Disk I/O routines automatically compute the location of the requested sector.

When a file is first opened, the FCBSEC field is set to zero. If direct access to file sectors is required, the program must enter the sector numbers in the FCBSEC field prior to each read request. If sequential accessing to file sectors is desired, bit 4 of the FCBFL1 field may be set so that FCBSEC will be incremented by the Disk I/O routines. The first Read request reads the first sector of the file, the second request reads the second sector, etc. Bit 4 specifies that the current value of the FCBSEC field will be automatically incremented by one, prior to each Read request.

Prior to each Read operation, the Disk I/O routines compare the requested sector number with the end-of-file sector number in the FCBEOF field. If a sector beyond the end-of-file is requested, the Read function returns with code in the accumulator specifying an "end-file" condition.

<u>Write Function</u>. Writing to a diskette sector consists of two physical operations. First, the data from memory are written to the diskette. That sector is then read to insure that the data have been successfully written. This secondary Read is known as a "Write Check" operation.

The RDOS Disk I/O routines allow the Write and the Write Check to be performed either by one call, or by separate calls. Bits 1 and 2 of the

### Disk Input/Output

FCBFL1 field specify which operations are to be performed. Normally, both bits 1 and 2 should be set so that the Write and Write Check operations will be performed. However, if both operations are performed by one call, there is a delay of one diskette revolution (167 ms) between the Write and the Write Check, since the same sector must be accessed twice.

In some circumstances, it is possible to design a program so that a large amount of data can be written sequentially from memory. In this case, a significant amount of write time can be saved if all of the Write operations are performed first. FCBSEC must then be reset to the first written sector to perform the Write Checks.

When the Write and Write Check operations are performed separately, it is possible to write five sectors per revolution (30 sectors per second) and to Write Check five sectors per revolution.

As with the Read function, the file must be opened before a Write operation can occur. The Write function requires the FCBADR field (specifying the address) and the FCBLEN field (specifying the file size) to define the memory buffer to be written to diskette.

FCBSEC designates the number of the sector to be written into. FCBSEC is initialized to zero when the file is first opened. For direct writing, FCBSEC is set by the program prior to initiating the Write operation. For sequential writing, bit 4 of FCBFL1 must be set; the Disk I/O routines will then automatically increment FCBSEC prior to each Write operation.

Before writing to the diskette, the Disk I/O routines check that the sector number specified by FCBSEC is less than the end-of-file reference in FCBEOF. Before a sector is sequentially written, FCBSEC is incremented by one. If FCBSEC becomes greater than FCBEOF, the Disk I/O routines attempt to allocate more space for the file. The number of tracks obtained when an allocation extension is made is given by the value in FCBEXT. Sector allocation may continue until free space on the diskette is unavailable.

When the user wishes to shorten an existing file, the FCBEOF field must be reset to a value one sector greater than the number of the last used sector. When a previously written file is to be rewritten sequentially, the FCBEOF field should be reset to X'0001' immediately after the file is opened. The field will then be automatically incremented to keep track of the new end-of-file.

<u>Close Function</u>. The Close function updates the diskette directory with new or modified information, such as file attributes and end-of-file location. If a file has been opened for reading only and no changes were made to its directory entry (this is the usual case), the Close function is not manditory. However, if the file has been opened for writing, it is recommended that the file be closed since there is a possibility that information about the file or file length has changed.

The Close function can be used to set or change file attributes. This is accomplished by changing the FCBATR field prior to execution of the function.

<u>Create Function</u>. The Create function is used to set up new files on a diskette. Create automatically opens the file so that other functions can be performed directly after creation.

The size of the new file is specified by the FCBINT field. When the file is created, the attributes specified in FCBATR and the extension size specified in FCBEXT are stored in the file's diskette directory entry for later use.

<u>Delete Function</u>. The Delete function is used to erase an existing file, return the previously allocated space to the free track pool, and remove the file's directory entry.

<u>Rename Function</u>. The Rename function is used to change the name of an existing file.

Change Attributes Function. The Change Attributes function allows the attributes of an existing file to be modified. The following FCB fields may be affected by this function: the attribute field (FCBATR), the end-offile field (FCBEOF), and the expansion size field (FCBEXT).

<u>Free Space Function</u>. The Free Space function can be used to return unused tracks to the free track pool. When an existing file is rewritten, the new data may occupy less space than the data originally stored in the file. The Free Space function uses the current end-of-file, as specified by the FCBEOF field, and returns all tracks not needed by the new file to the free track pool. If all of the tracks are used, the Free Space function makes no changes.

<u>Overlapped I/O</u>. The Disk I/O routines provide for processor execution overlapped with disk reading or writing. Overlapped I/O is selected by setting the high-order bit of the FCBFL1 field. When overlapped I/O is specified, the Disk I/O routines return to the calling program upon execution of the disk Read or Write commands. To check for completion of the requested operation, the user program must call the Disk routines a second time.

When a Read operation is desired, the first call to the Disk I O routines checks the parameters, starts the read function, and returns control to the calling program. The read operation transfers data from diskette into a sector-sized buffer contained in the disk control unit. The second call to the Disk routines checks for completion of the Read. If the Read operation has not been completed, the program waits. If the operation has been completed, the data are transferred from the control unit buffer into the buffer specified in the FCB.

The Write operation is begun by the Disk routines' transfer of data from the buffer specified in the FCB to the disk control unit sector buffer. The Disk routines return to the calling program, and a second call is made to the Disk routines. If the Write operation has not been completed, the program waits. If the Write has been completed, the Disk routines return to the calling program.

The Write Check process is similar to that of the Write operation. When overlapped I/O is selected, only one operation can be performed by a single call to the Disk I/O routines. If both the Write and Write Check functions are selected, only the Write operation will be performed.

The first call to the Disk routines, which initiates overlapped I/O, is performed in the same fashion as calls for non-overlapped functions. For the 8080/85A/Z80, the HL register pair contains the address of the FCB, and the Call instruction references the Disk I/O entry point (DISK). For the 6800/02, the Index Register contains the address of the FCB, and the JSR instruction references the Disk I/O entry point (DISK).

The second call to the Disk routines, which completes the function, references a secondary entry point (DISKW). The wait entry does not require that the FCB address be loaded into the HL register pair/Index register, since the FCB referenced when the operation was initiated is used. However, the

accumulator must be set to indicate one of the following actions: 1) if the accumulator is set to zero, normal processing will occur as described above; 2) if the accumulator is set to non-zero (e.g., X'Ol'), the I/O operation in progress will be terminated immediately.

Since both disk drives are accessed through the same control unit, it is not possible to perform concurrent operations to both disk drives. Thus, if the second disk drive must be accessed while operation is in progress on the first, one of two actions must be taken: 1) the operation on the first drive must be completed by a call with the accumulator set to zero, or 2) the operation must be aborted by a call with the accumulator set to non-zero. In the latter case, the operation must be restarted if the data are needed.

Return codes are generated by both the first and second calls to the Disk routines. An error check must be made following both the initial call and the call completing the operation. If an I/O error is detected during the second call to the Disk routines, automatic error recovery is attempted. The operation is re-tried ten times without returning to the calling program. During error recovery, overlapped execution is temporarily suspended. If the error is recoverable, the return code indicates successful completion; if not, the I/O error return code is generated.

#### Disk Input/Output

### I/O Service Subroutines

Examples. The following paragraphs contain example sequences for creating, opening, reading, writing, and closing files using the 8080/85A/ Z80. When using the 6800/02, two-byte fields in the File Control Block (B-type addresses) must be in high-low format (A-type addresses).

<u>Reading From a File</u>. In order to read from an existing file, the file must be opened. This is accomplished by calling the Disk routines with the Open function selected by an X'O4' in the first byte of the FCB. In the example below, the FCB has the symbolic name "RFCB". RFCB is set up in memory using Define Constant (DC) Assembler directives. The fields required by Open and Read are initialized in RFCB.

The instruction sequence for opening the file is as follows. Note: the GLBL Disk directive must occur once (and only once) in an assembly that calls the Disk I/O routines.

|      | (GLBI | DISK     |        |       |      |     | EXTERNAL ENTRY POINT)               |

|------|-------|----------|--------|-------|------|-----|-------------------------------------|

|      | LXI H | I,RFCB   |        |       |      |     | LOAD H,L WITH FCB ADDR              |

|      | MVI N | 1,X'04'  |        |       |      |     | SELECT OPEN FUNCTION                |

|      | CALL  | DISK     |        |       |      |     | CALL DISK ROUTINE                   |

|      | ORA A | Ę        |        |       |      |     | CHECK RETURN CODE                   |

|      | JNZ B | ERROR    |        |       |      |     | HANDLE ERROR RETURN                 |

|      | MVIN  | 1,0      |        |       |      |     | SELECT READ FUNCTION FOR LATER      |

| Sect | ors t | from the | open f | ile c | an b | e s | sequentially read by the following: |

|      | (GLBI | _ DISK   |        |       |      |     | EXTERNAL ENTRY POINT)               |

|      | XI H  | , RFCB   |        |       |      |     | LOAD H,L WITH ADDR OF RFCB          |

|      | CALL  | DISK     |        |       |      |     | CALL DISK ROUTINE                   |

|      | ORA A | A T      |        |       |      |     | CHECK RETURN CODE                   |

|      | JNZ E | ERROR    |        |       |      |     | HANDLE ERROR CONDITION              |

| The  | File  | Contro1  | Block  | for t | he a | bo  | ve operations is as follows:        |

| RFCE | B DC  | 0        |        |       |      |     | FUNCTION IS SET LATER               |

|      | DC    | X'11'    |        |       |      |     | SELECT READ & INCREMENT             |

|      | DC    | B(IBUF)  |        |       |      |     | ADDR OF READ BUFFER                 |

|      | DC    | B(128)   |        |       |      |     | LENGTH OF READ BUFFER               |

|      | DC    | B(0)     |        |       |      |     | SECTOR # INIT BY OPEN               |

|      |       |          |        |       |      |     |                                     |

SHLD FCBEOF

•

.

| DC       | 0                           | SELECT UNIT ZERO                         |

|----------|-----------------------------|------------------------------------------|

| DC       | 0                           | FIELD SET BY OPEN                        |

| DC       | 'FILENAME '                 | FILE NAME                                |

| DC       | 0                           | FIELD SET BY OPEN                        |

| DC       | 0                           | ATTRIBUTE SET BY OPEN                    |

| DC       | A(0)                        | EOF SET BY OPEN                          |

| DC       | 0                           | ALLOCATE SET BY OPEN                     |

| DC       | 0                           | EXTENSION SIZE SET BY OPEN               |

| IBUF DS  | 128                         | READ BUFFER                              |

|          | Writing Into a File. The    | example below shows the procedure for    |

| creating | and writing into a file.    | First, the file is created with the      |

| followin | g sequence:                 |                                          |

| (GLB     | L DISK                      | EXTERNAL ENTRY POINT)                    |

| LXI      | H,WFCB                      | LOAD FCBADDR                             |

| MVI      | M,X'02'                     | SELECT CREATE                            |

| CALL     | DISK                        | CALL DISK ROUTINE                        |

| ORA      | А                           | CHECK RETURN CODE                        |

| JNZ      | ERROR                       | HANDLE ERROR CONDITION                   |

| MVI      | Μ,Ο                         | SELECT WRITE FUNCTION                    |

| If the u | user wishes to write into a | n existing file, the file can be opened  |

| by selec | tion of the Open function   | (X'04') rather than the Create function. |

| When the | file is being rewritten,    | the end-of-file field must be reset as   |

| follows: |                             |                                          |

| • •      |                             |                                          |

|          |                             |                                          |

| LXI      | H,X'0100'                   | X'0001' REVERSED                         |

In order to sequentially write the next sector each time, the following calling routine can be used:

SET TO X'0001'

I/O Service Subroutines

(GLBL DISK EXTERNAL ENTRY POINT) • LXI H,WFCB LOAD FCBADDR CALL DISK CALL DISK ROUTINE ORA A CHECK RETURN CODE JNZ ERROR HANDLE ERROR CONDITION . • After writing is completed, the file must be closed, as shown below. (GLBL DISK EXTERNAL ENTRY POINT) . • LXI H,WFCB ADDR OF FCB MVI M,X'08' SELECT CLOSE CALL DISK CALL DISK ORA A CHECK RETURN CODE JNZ ERROR HANDLE ERROR CONDITION . The FCB for writing is initialized by the following: WFCB DC 0 FILLED IN DURING EXECUTION DC X'16' SELECT WRITE AND CHECK DC B(OBUF) ADDR OF WRITE BUFFER DC B(128) LENGTH OF WRITE BUFFER DC B(0)SECTOR # SET BY OPEN DC 1 WRITE TO UNIT 1 DC 0 SET BY OPEN DC 'WRITEFILE ' FILE NAME DC 0 SET BY OPEN DC O ATTRIBUTES

ECBRATE. The ECBRATE field of the ECB contains a code which selects the transmission and reception (Baud) rate. Sixteen rate codes are allowed as shown in Table 2-7. Note: Using rate codes not listed in the table produces unpredictable effects.

ECBLEN. The ECBLEN field specifies the number of bits in the data to be transmitted and received. Usual values are 5, 6, 7, or 8; other character lengths cause unpredictable results. Transmission of the byte passed in the accumulator begins with the low-order bit; e.g., when 7 is specified as the length, the low-order 7 bits are transmitted.

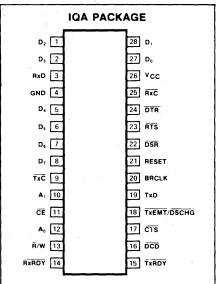

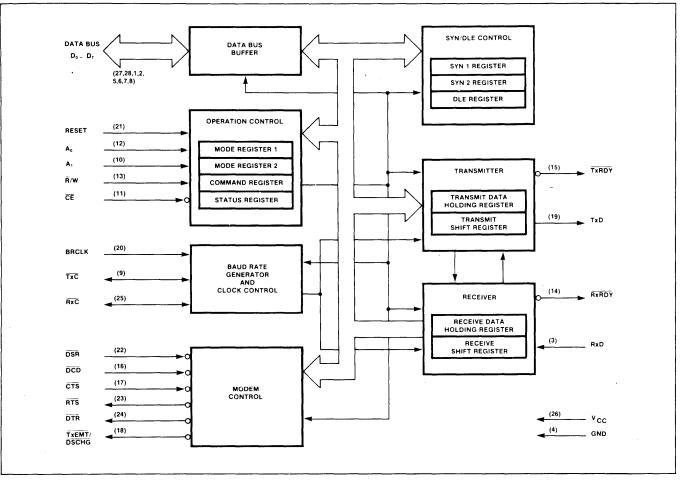

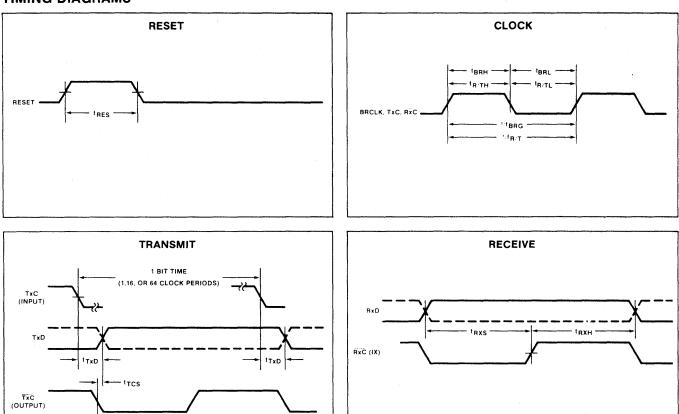

ECBUNIT. The ECBUNIT field selects which EIA port is to be initialized. A value of one selects EIA port 1; a value of two selects EIA port 2. The EIA routines assume that port 1 is configured to simulate a terminal and port 2, a modem. After initialization by EIASET. port 1 holds its Request to Send and Data Terminal Ready lines high (see Section 3 for more information).

|         | Table 2-6. | . EIA | Send-Contr |       | lock                            |

|---------|------------|-------|------------|-------|---------------------------------|

| Field   | = of Bytes |       |            |       | Functions                       |

| ECBFLAG | 1          |       | Contains   | flag  | bits having the following       |

|         | :          |       | meaning:   |       |                                 |

|         |            |       | Bit        |       | Function                        |

|         |            |       | 0          |       | Send break. Used by EIAOUT.     |

|         |            |       | 1          |       | Selects two stop bits for TTY.  |

|         |            |       | 2          |       | Disables parity bit generation/ |

|         |            |       |            |       | checking.                       |

|         |            |       | 3          |       | Selects odd parity.             |

|         |            |       | 4-7        |       | Unused:                         |

| ECBRATE | 1          |       | Transmiss  | ion/w | reception rate select code      |

|         |            |       | (see Tabl  | e 2-7 | 7).                             |

| ECBLEN  | 1          |       | Length (i  | n bit | ts) of characters to be         |

|         |            |       | transmitt  | ed/re | eceived.                        |

| ECBUNIT | 1          |       | EIA line   | Seleo | ct (1 or 2).                    |

|         |            |       |            |       |                                 |

## EIA Input/Output

### I/O Service Subroutines

|                                                                                                                | Table 2-7. | EIA Baud Rate Select Codes |  |

|----------------------------------------------------------------------------------------------------------------|------------|----------------------------|--|

| a the second | Code       | Rate (Bits/Second)         |  |

|                                                                                                                | 0          | 50                         |  |

|                                                                                                                | ]          | 75                         |  |

|                                                                                                                | 2          | 110                        |  |

|                                                                                                                | 3          | 134.5                      |  |

|                                                                                                                | 4          | 150                        |  |

|                                                                                                                | 5          | 300                        |  |

|                                                                                                                | 6          | 600                        |  |

|                                                                                                                | 7          | 600                        |  |

|                                                                                                                | 8          | 1200                       |  |

|                                                                                                                | 9          | 1800                       |  |

|                                                                                                                | A A        | 2400                       |  |

|                                                                                                                | В          | 3600                       |  |

|                                                                                                                | С          | 4800                       |  |

|                                                                                                                | D          | 7200                       |  |

|                                                                                                                | E          | 9600                       |  |

|                                                                                                                | · F        | 19200                      |  |

#### Examples.

<u>ASCII Data Configuration</u>. The most common application for the EIA send/receive routines is ASCII character data exchange. ASCII data have the following specifications:

| Parity    | Yes/Even                   |  |  |  |  |  |  |  |

|-----------|----------------------------|--|--|--|--|--|--|--|

| Stop Bits | Two for TTY, one otherwise |  |  |  |  |  |  |  |

| Length    | 7 bits                     |  |  |  |  |  |  |  |

ECB Communication. The EIA control block (ECB) configuration for communication with a Teletype on EIA line 2 is as follows:

SCBFLAG = X'02' SCBRATE = 2 SCBLEN = 7 SCBUNIT = 2

The EIA control block configuration for communication with a modem at 300 Baud on EIA line 1 is as follows:

- SCBFLAG = X'00' SCBRATE = 5 SCBLEN = 7

- SCBUNIT = 1

If it is necessary to control the Request to Send or Data Terminal Ready bits or to read the Clear to Send or Data Carrier Detect status on port 1, direct I/O programming is used. For further information, refer to Section 3.

## Cassette Tape Input/Output

CASSETTE TAPE INPUT/OUTPUT

The cassette I/O service routines provide for reading, writing, and rewinding of cassette tapes. Data on cassette are formatted as fixed-length records separated by inter-record gaps. The gaps are sufficiently long to allow the tape to be stopped at the end of a record and restarted to read the next record. The tape I/O routines read or write a record at a time and automatically turn the tape units on and off.

The cassette tapes begin with a short length of plastic leader which must be bypassed before reading or writing begins. A flag bit indicating the first Read or Write causes the I/O routines to automatically space past the leader.

Parameters are passed to the I/O routines in the form of a 7-byte writecontrol block (WCB) and a 6-byte read-control block (RCB). The control block address must be loaded into the HL register pair/Index register prior to calling the Read or Write subroutines.

<u>Error Recovery</u>. For increased reliability, the I/O routines provide for redundant recording of data records. Any number of copies of each record can be specified and will automatically be written by the cassette Write routine. During reading, if an error is detected, the Read routine tries to read the record again. If another copy is available, it is possible to recover from the error. If the Read routine cannot find another copy, it returns with an error code.

The error recovery scheme uses sequence numbers which are recorded with the data of each record. Thus, when an error occurs, subsequent data can be automatically identified as another copy of the desired record. If the tape is manually backed up for re-try, the sequence numbers are again used to identify the desired record.

<u>WRITE</u>. The WCB contains the fields shown in Table 2-8. These fields represent seven sequential bytes in memory and provide the cassette Write routine with the information necessary to process the request. For the first Write, bit 0 (low-order) of WCBFLAG is set to one so that a leader is written, and automatically reset to zero afterward. Bits 1 and 2 of WCBFLAG are used in those cases where sequences of records are to be written without inter-record gaps. When bit 1 is set to one, the Write routine leaves the cassette unit on. (Normally, the unit is turned on before writing a record and off afterwards). In conjunction with Bit 2, which suppresses the writing of an inter-record gap, multiple records can be formatted without gaps. The gap in front of the data is usually necessary to allow the tape unit sufficient time to come up to speed.

The WCBADR field of the WCB specifies that the beginning data block address be written to tape. The length of this block is specified by WCBLEN. Both WCBADR and WCBLEN are 2-byte (16-bit) fields with the low-order byte stored before the high-order (8080/85A/Z80) or high-low (6800/02) byte. The WCBUNIT field specifies the tape unit to be addressed, either 1 or 2. Finally, the WCBCOPY field specifies the number of record copies to be written. For maximum data density without automatic error recovery, one copy may be specified. For most other applications, two copies (providing a hard error rate of about one in 1xE12 bits) are adequate. All registers and flags in 8080/85A/Z80 systems are saved and restored by the cassette write routine. The 6800/02 version does not save the flags.

|         |       | Table 2-8. | Write Co | ontrol B | lock                             |

|---------|-------|------------|----------|----------|----------------------------------|

| Field   | Bytes |            |          |          | Function                         |

| WCBFLAG | 1     |            | Bits     | in this  | field request special functions  |

|         |       |            | as fo    | ollows:  |                                  |

|         |       |            |          | Bit      | Function                         |

|         |       |            |          | 0        | Flags Write of first record.     |

|         |       |            |          | ]        | Leaves tape unit on after Write. |

|         |       |            |          | 2        | Suppresses writing an inter-     |

|         |       |            |          |          | record gap ahead of data.        |

|         |       |            |          | 3-7      | Unused; should be zero.          |

|         |       |            |          |          |                                  |

I/O Service Subroutines

Cassette Tape Input/Output

|         | Table 2-8. | Write Control Block (Concluded)              |

|---------|------------|----------------------------------------------|

| Field   | Bytes      | Function                                     |

| WCBADR  | 2          | Address of data block to be written.         |

|         |            | Address is stored in low-order byte format   |

| 9<br>19 |            | followed by high-order byte (8080/85A/Z80),  |

|         |            | or high-low format (6800/02).                |

| WCBLEN  | 2          | Length of data block to be written.          |

|         |            | Length is stored as low-order byte, followed |

|         |            | by high-order byte (8080/85A/Z80), or high-  |

|         |            | low (6800/02).                               |

| WCBUNIT | 1          | Write unit (1 or 2).                         |

| WCBCOPY | ,1         | Number of copies of data to be written.      |

|         |            |                                              |

<u>READ</u>. The read-control block contains the fields shown in Table 2-9. These fields represent six sequential bytes in memory and provide the Read routine with the information necessary to process the request. As with the Write routine, the control block address must be loaded into the HL register/ Index register prior to calling. For the first tape read, bit 0 of RCBFLAG is set to one. This causes the Read routine to reset the record sequence number counter to zero in order to begin reading a new tape. The bit is automatically reset to zero after the first read. Bit 1 of RCBFLAG specifies that the cassette unit is to remain on after the Read, allowing Reads where inter-record gaps are not written.

Normally, the Read routine expects the records to have sequential record numbers beginning with zero. However, under some conditions, it is useful to suppress sequential number checking and to reset the sequence number counter to the number of the next record read. Bit 2 of RCBFLAG performs this function. Once a record is read and the sequence counter is reset, zeroing bit 2 allows normal reading of sequential records.

## Cassette Tape Input/Output

|         |       | Table 2-9. Read-Control Block             |

|---------|-------|-------------------------------------------|

| Field   | Bytes | Function                                  |

| RCBFLAG | 1     | Bits of this field request special func-  |

|         |       | tions as follows:                         |

|         |       | Bit Function                              |

|         |       | 0 Flags Read of first record.             |

|         |       | 1 Leaves tape unit on after               |

|         |       | Read.                                     |

|         |       | 2 Accepts record with any                 |

|         |       | sequence number.                          |

|         |       | 3-7 Unused; should be 0.                  |

| RCBADR  | 2     | Address of data block into which data fro |

|         |       | tape is to be placed. Address is stored   |

|         |       | as low-order byte, followed by high-order |

|         |       | byte (8080/85A/Z80) or high-low (6800/02) |

| RCBLEN  | 2     | Length of data block. Length is stored a  |

|         |       | low-order byte followed by high-order byt |

|         |       | (8080/85A/Z80) or high-low (6800/02).     |

| RCBUNIT | 1     | Read unit (1 or 2).                       |

The RCBADR and RCBLEN fields specify the address and length of the read memory area. Both fields are two bytes (16 bits) long, and values are stored with the low-order byte first. RCBUNIT specifies the read unit; either 1 or 2.

Upon return from the Read routine, the accumulator contains a completion code: zero for success, non-zero for error. Several types of errors are classified by the value of the return code as follows:

|                          | Table 2 | -10. Tape Read Routine Error Codes                     |

|--------------------------|---------|--------------------------------------------------------|

| <i>272</i> <b>-</b> 2000 | Code    | Definition                                             |

|                          | 1       | Checksum error, normal re-try should be attempted.     |

| • • • • • •              | 2       | Data on tape are not recognizable, and re-try probably |

|                          |         | will not be successful. This code results when the     |

|                          |         | tape data have a different record size than specified  |

|                          |         | by the RCB.                                            |

| Table 2-10. | Tape Read Routine Error Codes (Concluded)             |

|-------------|-------------------------------------------------------|

| Code        | Definition                                            |

| 3           | No data have been read from the tape for an unusual   |

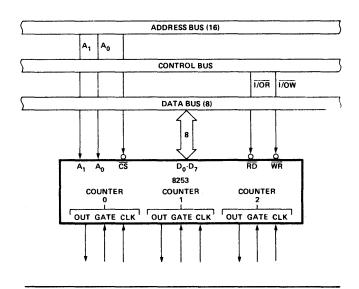

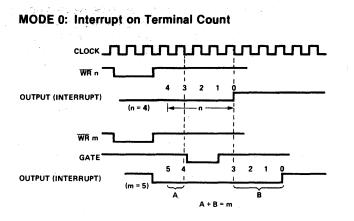

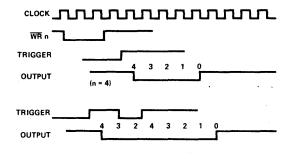

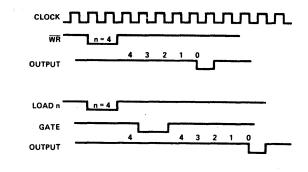

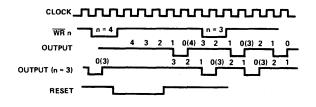

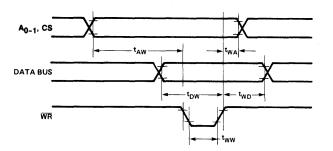

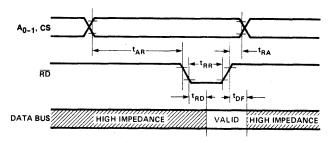

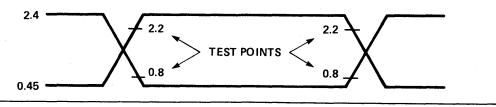

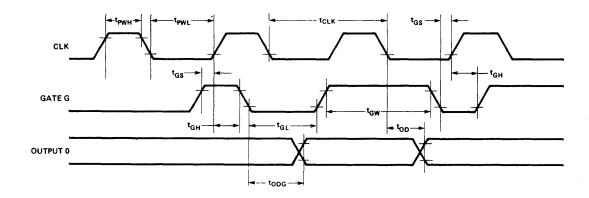

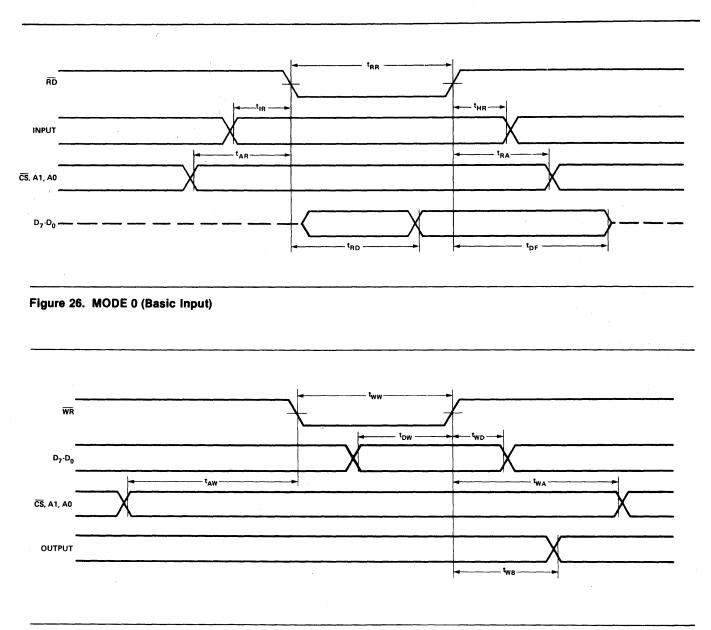

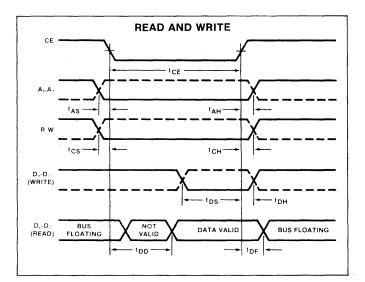

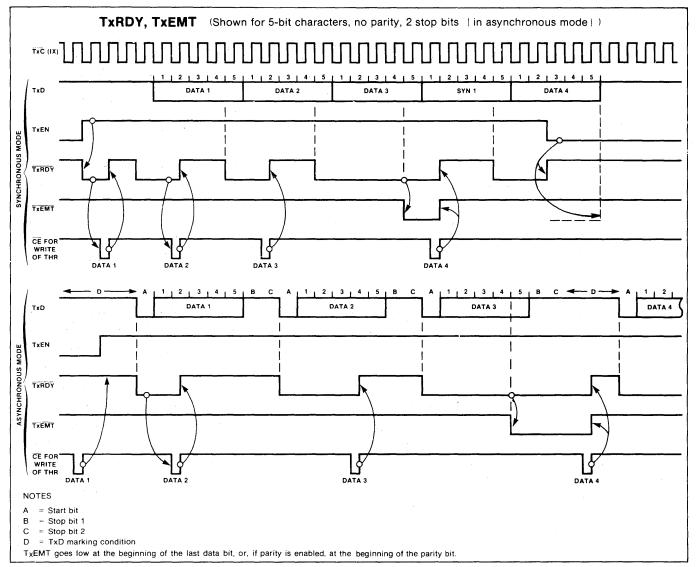

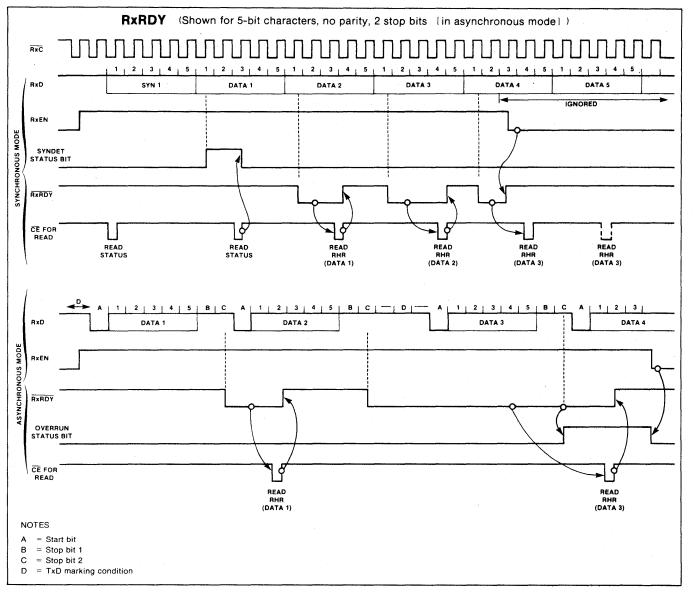

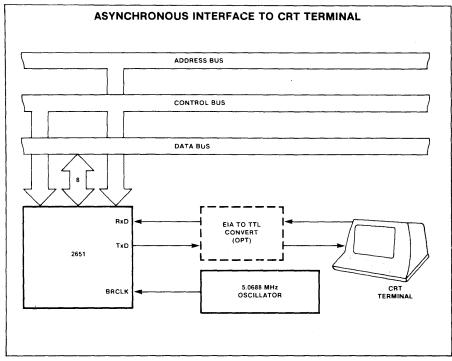

|             | length of time. Possibly, a blank tape is being read. |