|         | REVISION RECORD |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Edition | Date published  | Revised contents                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| А       | Mar. 1, 1981    | First Edition                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| В       | Aug. 10, 1982   | Second Edition                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| С       | Jan., 1983      | Third Edition                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| D       | Apr., 1983      | Fourth Edition                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

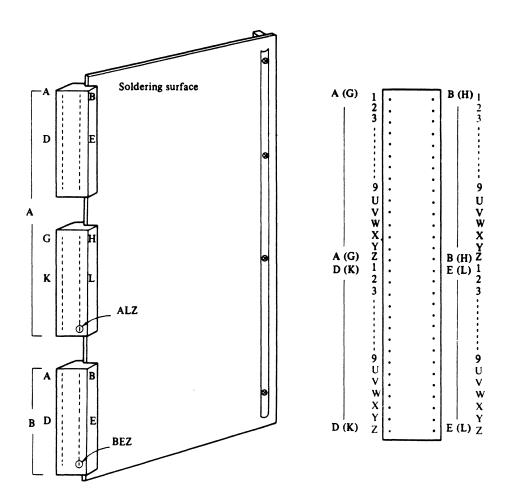

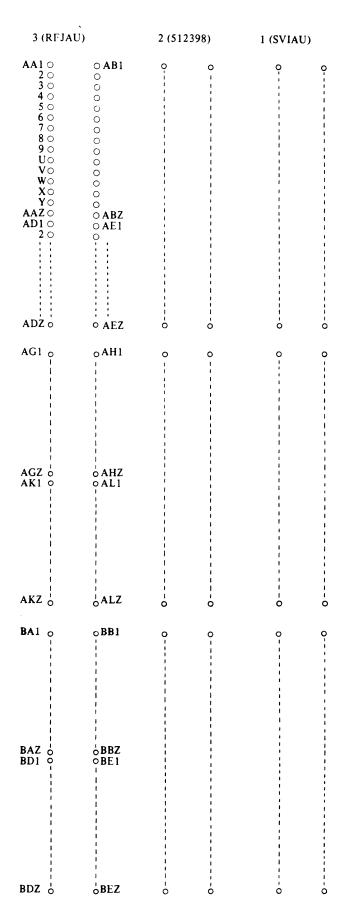

| E       | Sept., 1984     | i, 1-1, 1-17, 2-8, 3-8, 3-19, 7-15, 8-6 ~ 8-16, 9-18, 10-2, 10-8, 10-10, 11-3, 11-4, 11-6, 13-6, 13-7, 13-11, 14-10, 14-11, 15-3, 15-9 ~ 15-16, 17-12, 17-21, 17-27, 17-30, 17-33, 17-36, 17-38, 17-39, 17-43 ~ 17-49, 17-68, 17-75 ~ 17-81, 17-83, 17-88, 17-90, 17-91 |  |  |  |  |  |  |

| F       | Mar., 1985      | ı, ıı. vi, 1-1, 1-3, 1-5, 1-6, 1-8, 1-11, 2-1 <b>~</b> 2-3, 2-5, 2-7, 3-1, 3-2, 5-18 <b>~</b> 5-19B, 5-30, 5-32, 7-23, 7-24, 7-27, 7-29, 7-30, 9-18, 13-13, 14-10, 14-11, 14-20, 15-3, 15-6, 15-7                                                                       |  |  |  |  |  |  |

|         |                 |                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|         |                 | Specification No.: B03P-4655-0001A                                                                                                                                                                                                                                      |  |  |  |  |  |  |

The contents of this manual is subject to change without prior notice.

All Rights Reserved, Copyright © 1981 – 1985 FUJITSU LIMITED

### omments concerning this manual to one of the following addresses:

### **:UJITSU LIMITED**

nternational Marketing

Marunouchi 1-6-1, Chiyoda-ku, Tokyo 100 JAPAN

TEL:

03-216-3211

FAX:

03-213-7174, 03-216-9353

TLX:

J22833

Cable:

"FUJITSULIMITED TOKYO"

### FUJITSU AMERICA INC.

3055 Orchard Drive, San Jose, California 95134-2017, U.S.A.

TFL.

408-946-8777

FAX

408-945-1318

TLX:

230-176207

TWX:

910-338-2193

### FUJITSU EUROPE LIMITED

54 Jermyn Street, London SW1Y 6NQ, ENGLAND

TEL: 1-408-0043 FAX: 1-629-9826 TLX: 263871 FT ERP G

### FUJITSU ELECTRONIK GmbH

Sonnen Straße 29, D-8000 Munchen 2, F.R. GERMANY

TEL: 89-592891 ~ 4 FAX: 89-592895 TLX: 41-5213994

### **FUJITSU NORDIC AB**

Kungsgaton 44, 111 35 Stockholm, SWEDEN

TEL: 8-231125 FAX: 8-106865 TLX: 54-13411

## FUJITSU ITALIA S.p.A.

Via Lazzaroni, 4, 20124 Milano, ITALIA

TEL: 2-607-3601 FAX: 2-688-6637 TLX: 350142 FJITLY I

### FUJITSU AUSTRALIA LIMITED

41 McLaren Street, North Sydney, N.S.W. 2060, AUSTRALIA

TEL: 2-922-1822 FAX: 2-922-2653 TLX: 71-25233

## LIST OF EFFECTIVE PAGES

| PAGE  | REV |

|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|-------|-----|

| Cover | F   | 3-14  | E1  | 6-1   | E1  | 8-8   | E   | 10-11 | В   | 13-24 | В   |

| Blank |     | 3-15  | E1  | 6-2   | E1  | 8-9   | E   | 10-12 | С   | 13-25 | В   |

| 1     | F   | 3-16  | в   | 6-3   | E1  | 8-10  | E   | 10-13 | С   | 13-26 | D1  |

| Blank |     | 3-17  | B1  | 6-4   | E1  | 8-11  | E   | 10-14 | В   | 14-1  | E1  |

| 111   | F   | 3-18  | В   | 6-5   | С   | 8-12  | E   | 10-15 | в   | 14-2  | E1  |

| ıv    | F   | 3-19  | E   | 6-6   | С   | 8-13  | E   | 10-16 | в   | 14-3  | в   |

| v     | D   | 3-20  | E1  | 6-7   | E1  | 8-14  | E   | 10-17 | c   | 14-4  | в   |

| Blank |     | 3-21  | c   | Blank | l   | 8-15  | E   | 10-18 | c   | 14-5  | В   |

| VI    | F   | 3-22  | B1  | 7-1   | В   | 8-16  | E   | 11-1  | E1  | 14-6  | В   |

| VII   | D   | 4-1   | E1  | 7-2   | В   | 8-17  | В   | 11-2  | E1  | 14-7  | В   |

| VIII  | F   | 4-2   | В   | 7-3   | E1  | 8-18  | В   | 11-3  | E   | 14-8  | E1  |

| Blank |     | 4-3   | E1  | 7-4   | B1  | 8-19  | B1  | 11-4  | E   | 14-9  | c   |

| 1-1   | F   | 4-4   | В   | 7-5   | В   | 8-20  | B1  | 11-5  | В   | 14-10 | F   |

| 1-2   | E1  | 4-5   | E1  | 7-6   | В   | 9-1   | В   | 11-6  | В   | 14-11 | F   |

| 1-3   | F   | 4-6   | E1  | 7-7   | В   | 9-2   | В   | 11-7  | c   | 14-12 | В   |

| 1-4   | D1  | 5-1   | E1  | 7-8   | В   | 9-3   | В   | 11-8  | С   | 14-13 | c   |

| 1-5   | F   | 5-2   | E1  | 7-9   | E1  | 9-4   | В   | 11-9  | В   | 14-14 | В   |

| 1-6   | F   | 5-3   | E1  | 7-10  | В   | 9-5   | В   | 11-10 | В   | 14-15 | В   |

| 1-7   | C   | 5-4   | В   | 7-11  | E1  | 9-6   | E1  | 11-11 | В   | 14-16 | В   |

| 1-8   | F   | 5-5   | В   | 7-12  | В   | 9-7   | E1  | Blank |     | 14-17 | В   |

| 1-9   | E1  | 5-6   | E1  | 7-13  | E1  | 9-8   | В   | 12-1  | E1  | 14-18 | В   |

| 1-10  | C   | 5-7   | В   | 7-14  | E1  | 9-9   | В   | 12-2  | E1  | 14-19 | В   |

| 1-10  | F   | 5-8   | В   | 7-15  | E.  | 9-10  | В   | 12-3  | E1  | 14-20 | F   |

| 1-12  | В   | 5-9   | В   | 7-16  | В   | 9-11  | В   | 12-4  | E1  | 15-1  | В   |

| 1-13  | E1  | 5-10  | E1  | 7-17  | В   | 9-12  | E1  | 12-5  | В   | 15-2  | B1  |

| 1-13  | B1  | 5-10  | В   | 7-18  | В   | 9-13  | В   | 12-6  | В   | 15-3  | F.  |

| 1-15  | E1  | 5-12  | В   | 7-19  | В   | 9-14  | В   | 12-7  | В   | 15-4  | В   |

| 1-15  | E1  | 5-13  | В   | 7-20  | В   | 9-15  | E1  | Blank |     | 15-5  | В   |

| 1-17  | E   | 5-14  | В   | 7-21  | E1  | 9-16  | В   | 13-1  | D   | 15-6  | F   |

| Blank |     | 5-15  | В   | 7-22  | В   | 9-17  | В   | 13-2  | E1  | 15-7  | F   |

| 2-1   | F   | 5-16  | В   | 7-23  | F   | 9-18  | F   | 13-3  | E1  | 15-8  | E1  |

| 2-2   | F   | 5-17  | E1  | 7-24  | F   | 9-19  | В   | 13-4  | E1  | 15-9  | E   |

| 2-3   | F   | 5-18  | F   | 7-25  | В   | 9-20  | В   | 13-5  | E1  | 15-10 | E   |

| 2-4   | E1  | 5-19  | F   | 7-26  | В   | 9-21  | В   | 13-6  | E1  | 15-11 | E   |

| 2-5   | F   | 5-19A | F   | 7-27  | F   | 9-22  | В   | 13-7  | E1  | 15-12 | E1  |

| 2-6   | E1  | 5-19B | F   | 7-28  | В   | 9-23  | В   | 13-8  | D   | 15-13 | E1  |

| 2-7   | F   | 5-20  | В   | 7-29  | F   | 9-24  | E1  | 13-9  | E1  | 15-14 | E   |

| 2-8   | E   | 5-21  | E1  | 7-30  | F   | 9-25  | В   | 13-10 | E1  | 15-15 | E1  |

| 3-1   | F   | 5-22  | D   | 7-31  | В   | 9-26  | E1  | 13-11 | E   | 15-16 | E   |

| 3-2   | F   | 5-23  | D   | 7-32  | В   | 9-27  | В   | 13-12 | E1  | 15-17 | В   |

| 3-3   | E1  | 5-24  | В   | 7-33  | В   | Blank |     | 13-13 | F   | 15-18 | В   |

| 3-4   | E1  | 5-25  | E1  | 7-34  | В   | 10-1  | В   | 13-14 | E1  | 15-19 | В   |

| 3-5   | E1  | 5-26  | C   | 7-35  | В   | 10-2  | E   | 13-15 | D   | 15-20 | В   |

| 3-6   | E1  | 5-27  | D1  | 7-36  | В   | 10-3  | В   | 13-16 | D   | 15-21 | В   |

| 3-7   | E1  | 5-28  | E1  | 8-1   | B1  | 10-4  | В   | 13-17 | В   | 15-22 | В   |

| 3-8   | E   | 5-29  | D1  | 8-2   | В   | 10-5  | В   | 13-18 | E1  | 15-23 | В   |

| 3-9   | E1  | 5-30  | F   | 8-3   | В   | 10-6  | С   | 13-19 | E1  | 15-24 | В   |

| 3-10  | E1  | 5-31  | E1  | 8-4   | В   | 10-7  | С   | 13-20 | E1  | 15-25 | В   |

| 3-11  | E1  | 5-32  | F   | 8-5   | В   | 10-8  | E   | 13-21 | D   | Blank |     |

| 3-12  | E1  | 5-33  | D   | 8-6   | E   | 10-9  | В   | 13-22 | В   | 16-1  | В   |

| 3-13  | E1  | 5-34  | D1  | 8-7   | E   | 10-10 | E1  | 13-23 | В   | 16-2  | В   |

| PAGE  | REV | PAGE  | REV | PAGE  | REV |   | PAGE  | REV | PAGE   | REV |   | PAGE   | REV |

|-------|-----|-------|-----|-------|-----|---|-------|-----|--------|-----|---|--------|-----|

| 16-3  | С   | 16-35 | С   | 17-23 | В   |   | 17-55 | F   | 17-87  | F   | 1 | 17-119 | F   |

| 16-4  | С   | 16-36 | С   | 17-24 | В   |   | 17-56 | F   | 17-88  | F   |   | 17-120 | F   |

| 16-5  | В   | 16-37 | С   | 17-25 | В   |   | 17-57 | F   | 17-89  | F   |   | 17-121 | F   |

| 16-6  | В   | 16-38 | С   | 17-26 | В   | l | 17-58 | F   | 17-90  | F   |   | 17-122 | F   |

| 16-7  | В   | 16-39 | С   | 17-27 | E   |   | 17-59 | F   | 17-91  | F   |   | 17-123 | F   |

| 16-8  | В   | 16-40 | С   | 17-28 | В   |   | 17-60 | F   | 17-92  | F   |   | 17-124 | F   |

| 16-9  | В   | 16-41 | С   | 17-29 | В   |   | 17-61 | F   | 17-93  | F   |   |        |     |

| 16-10 | В   | 16-42 | С   | 17-30 | E   |   | 17-62 | F   | 17-94  | F   |   |        |     |

| 16-11 | В   | 16-43 | С   | 17-31 | С   | l | 17-63 | F   | 17-95  | F   |   |        |     |

| 16-12 | В   | 16-44 | С   | 17-32 | В   |   | 17-64 | F   | 17-96  | F   |   |        |     |

| 16-13 | В   | 17-1  | B1  | 17-33 | E   | l | 17-65 | F   | 17-97  | F   |   |        |     |

| 16-14 | В   | 17-2  | В   | 17-34 | С   |   | 17-66 | F   | 17-98  | F   |   |        |     |

| 16-15 | В   | 17-3  | В   | 17-35 | В   |   | 17-67 | F   | 17-99  | F   |   |        |     |

| 16-16 | В   | 17-4  | В   | 17-36 | E   |   | 17-68 | F   | 17-100 | F   |   |        |     |

| 16-17 | В   | 17-5  | С   | 17-37 | В   |   | 17-69 | F   | 17-101 | F   |   |        |     |

| 16-18 | В   | 17-6  | В   | 17-38 | E   |   | 17-70 | F   | 17-102 | F   |   | İ      |     |

| 16-19 | В   | 17-7  | В   | 17-39 | E   |   | 17-71 | F   | 17-103 | F   |   |        |     |

| 16-20 | В   | 17-8  | В   | 17-40 | В   |   | 17-72 | F   | 17-104 | F   |   |        |     |

| 16-21 | В   | 17-9  | С   | 17-41 | В   |   | 17-73 | F   | 17-105 | F   |   |        |     |

| 16-22 | В   | 17-10 | В   | 17-42 | В   |   | 17-74 | F   | 17-106 | F   |   |        |     |

| 16-23 | В   | 17-11 | D   | 17-43 | E1  |   | 17-75 | F   | 17-107 | F   |   |        |     |

| 16-24 | В   | 17-12 | E   | 17-44 | E1  |   | 17-76 | F   | 17-108 | F   |   |        |     |

| 16-25 | В   | 17-13 | В   | 17-45 | E   |   | 17-77 | F   | 17-109 | F   |   |        |     |

| 16-26 | В   | 17-14 | В   | 17-46 | E1  |   | 17-78 | F   | 17-110 | F   |   |        |     |

| 16-27 | С   | 17-15 | В   | 17-47 | E1  |   | 17-79 | F   | 17-111 | F   |   |        |     |

| 16-28 | E1  | 17-16 | В   | 17-48 | Ε   | 1 | 17-80 | F   | 17-112 | F   |   |        |     |

| 16-29 | С   | 17-17 | В   | 17-49 | E   |   | 17-81 | F   | 17-113 | F   |   |        |     |

| 16-30 | С   | 17-18 | В   | 17-50 | В   |   | 17-82 | F   | 17-114 | F   |   |        |     |

| 16-31 | С   | 17-19 | В   | 17-51 | В   |   | 17-83 | F   | 17-115 | F   |   |        |     |

| 16-32 | С   | 17-20 | В   | 17-52 | В   |   | 17-84 | F   | 17-116 | F   |   |        |     |

| 16-33 | С   | 17-21 | E   | 17-53 | F   |   | 17-85 | F   | 17-117 | F   |   |        |     |

| 16-34 | С   | 17-22 | В   | 17-54 | F   |   | 17-86 | F   | 17-118 | F   |   |        |     |

Note 1: A revision of each page except "A" is indicated by the Revision Letter with the specification number of this manual in the bottom of the page.

Note 2: A bar by the page number in this page indicates pagination rather than content has changed.

$<sup>^{\</sup>star}$  17-75 thru 17-105 have page number changes and/or revision changes.

### INTRODUCTION

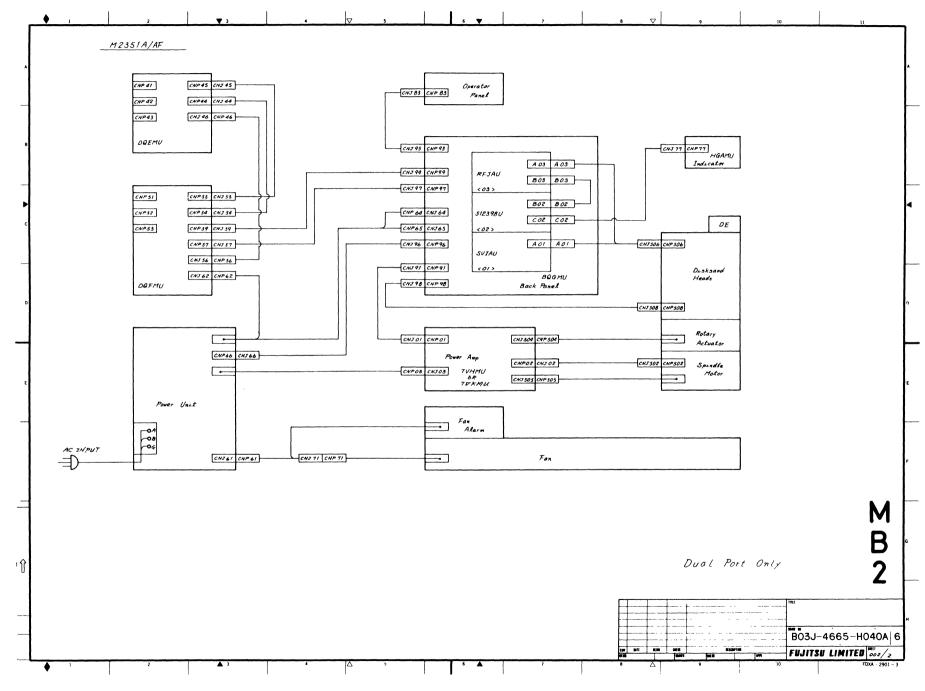

This manual is for customer engineers who handle the new Mini-Disk Drive M2351A/AF. It describes how to operate, handle and maintain the drive.

This manual consists of the following seventeen chapters.

- Chapter 1 GENERAL INFORMATION

- Chapter 2 INSTALLATION

- Chapter 3 OPERATION AND CHECKOUT

- Chapter 4 SYSTEM INSTALLATION

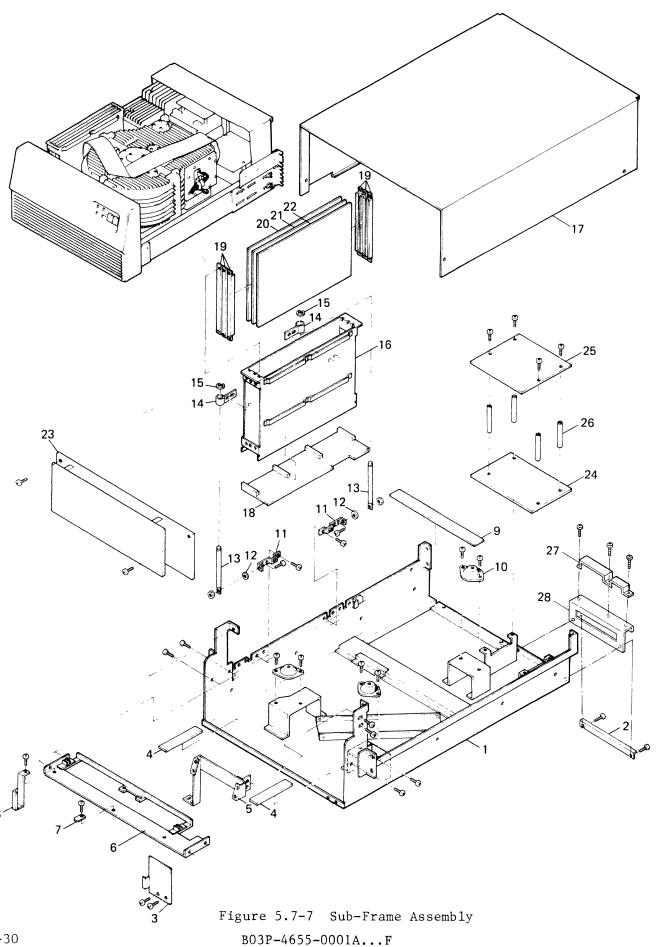

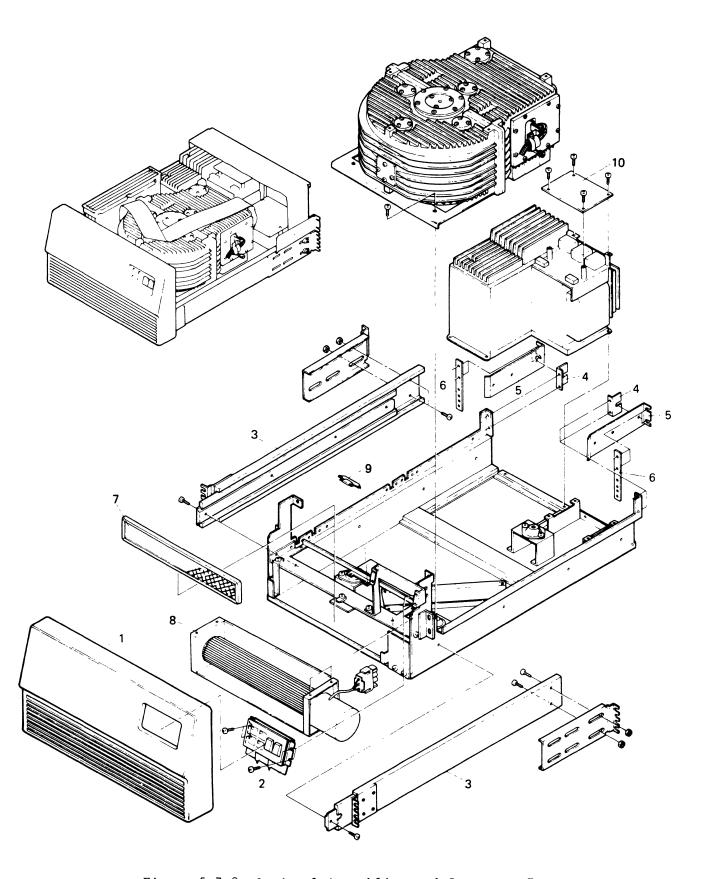

- Chapter 5 MECHANICAL ASSEMBLIES

- Chapter 6 DATA FORMAT

- Chapter 7 INTERFACE

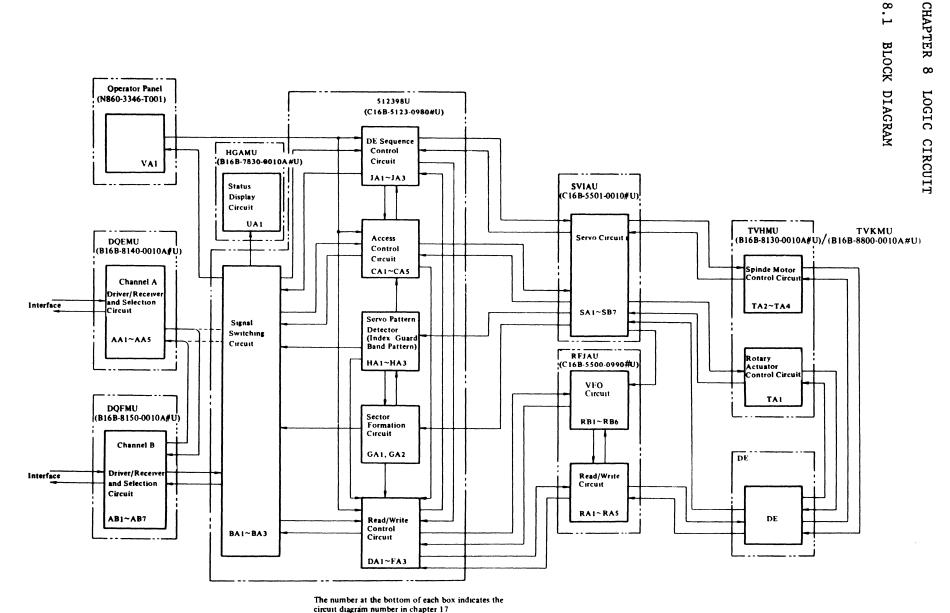

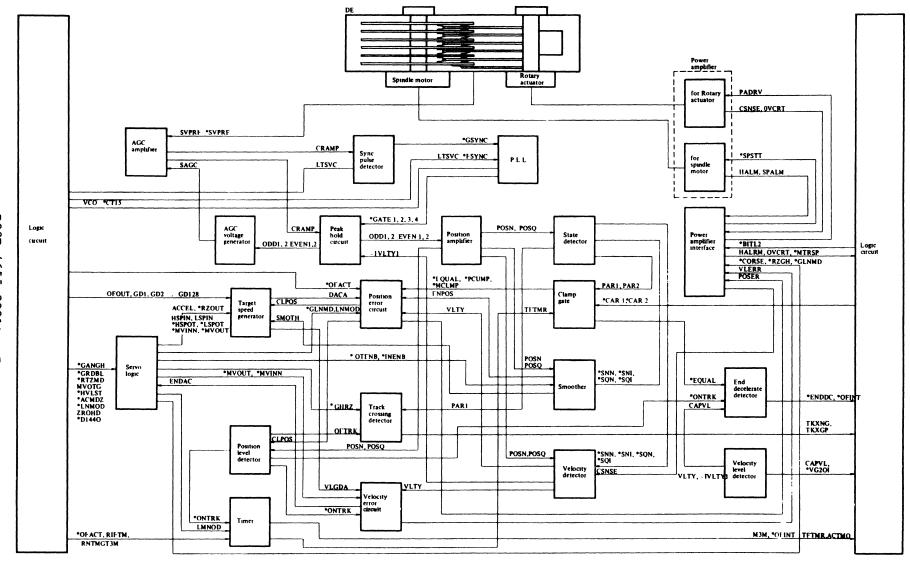

- Chapter 8 LOGIC CIRCUIT

- Chapter 9 SERVO CIRCUIT

- Chapter 10 READ/WRITE CIRCUIT

- Chapter 11 VFO CIRCUIT

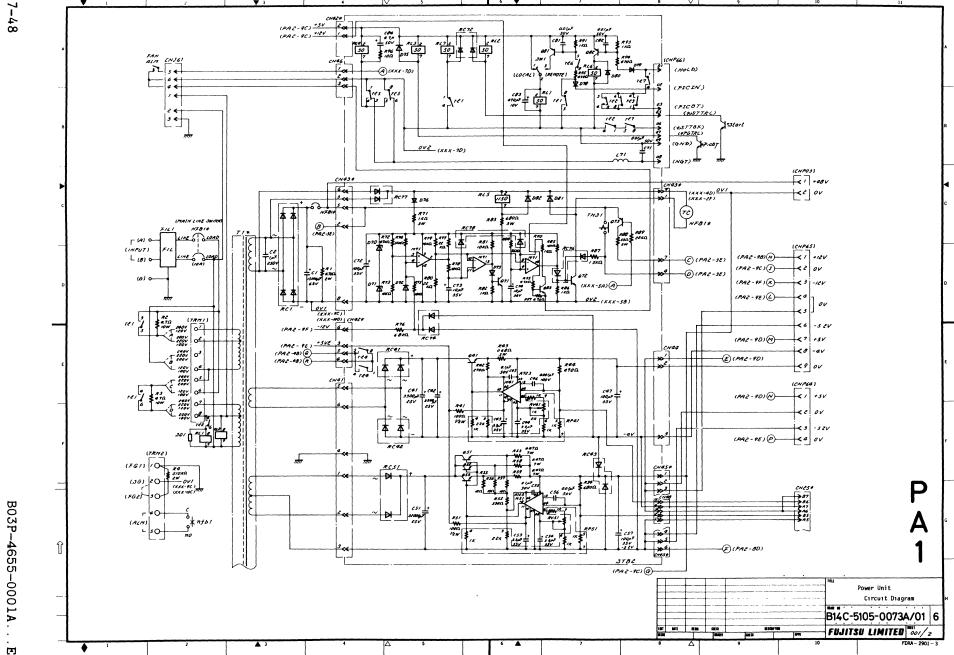

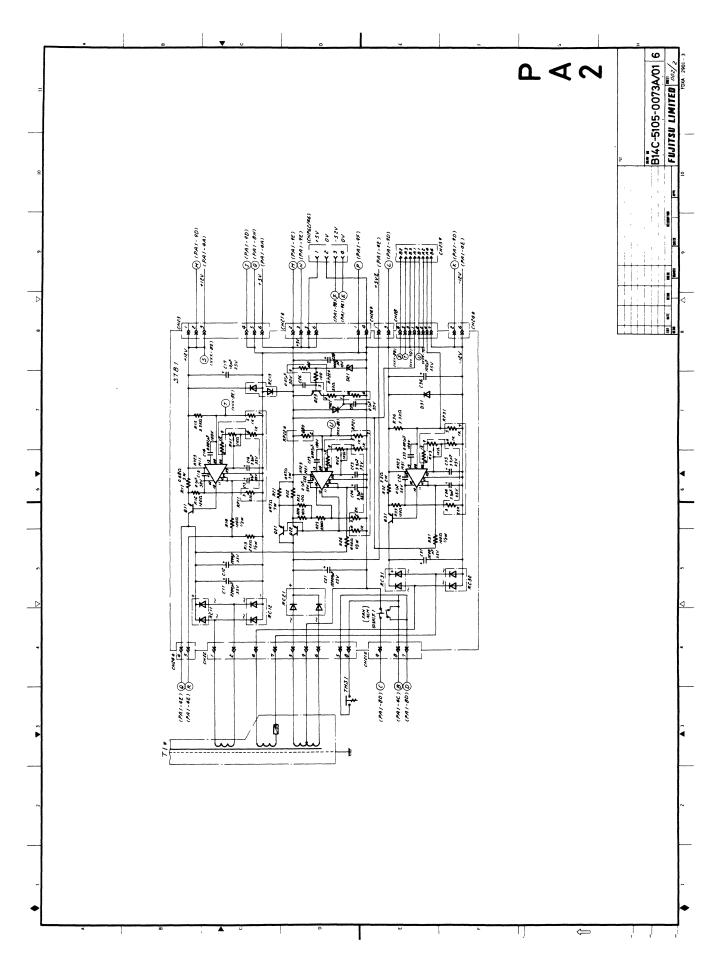

- Chapter 12 DC POWER SUPPLY UNIT

- Chapter 13 MAINTENANCE

- Chapter 14 ELECTRICAL TEST AND ADJUSTMENT

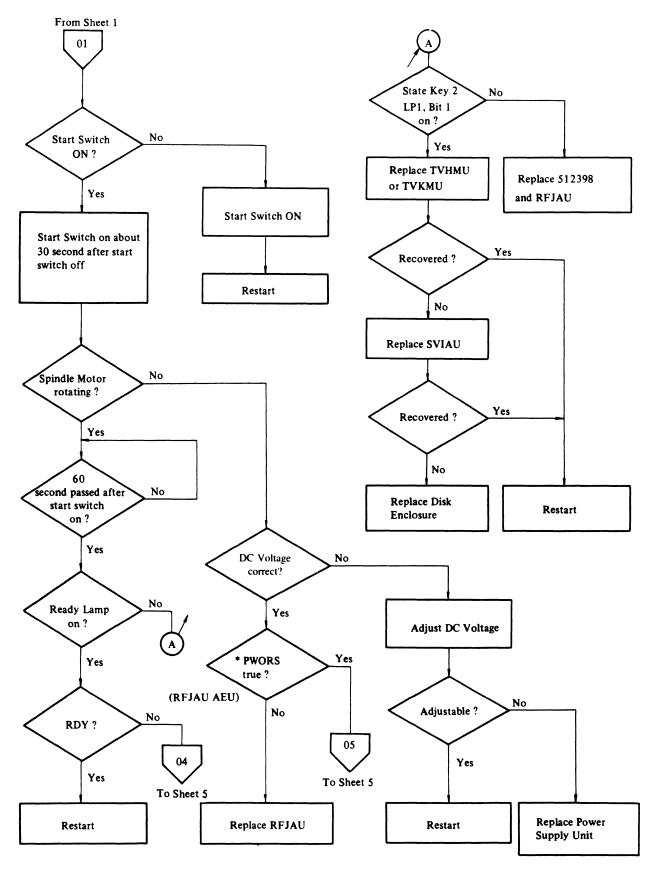

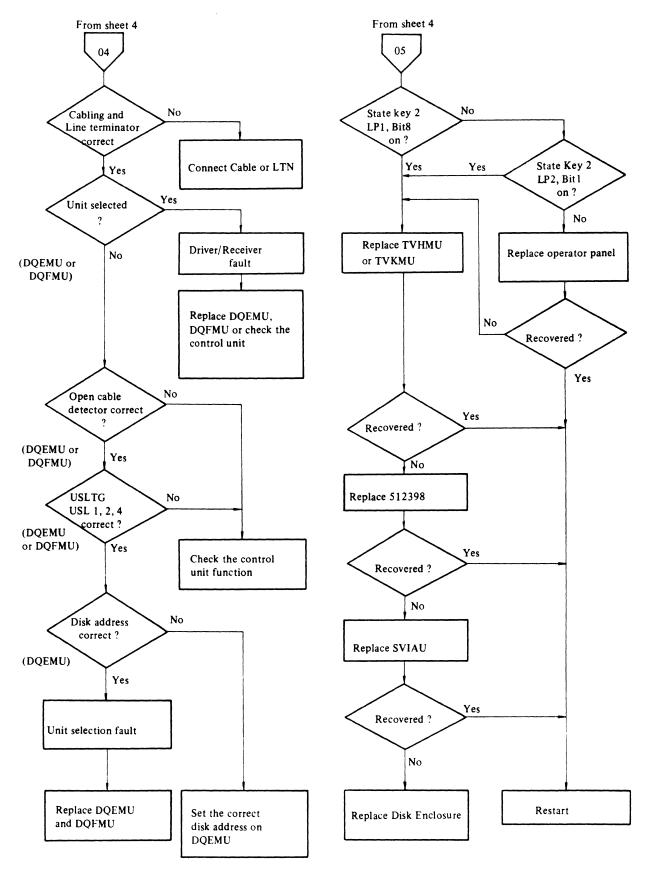

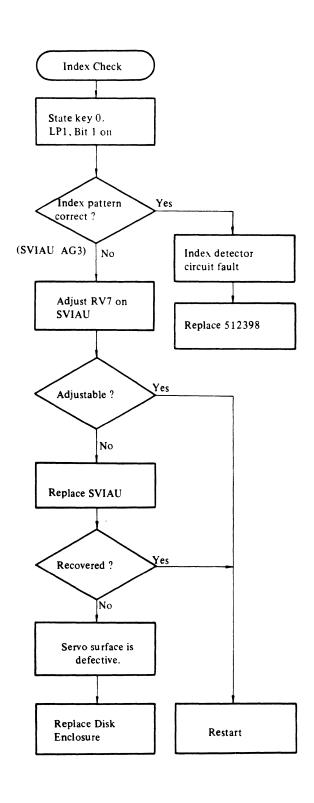

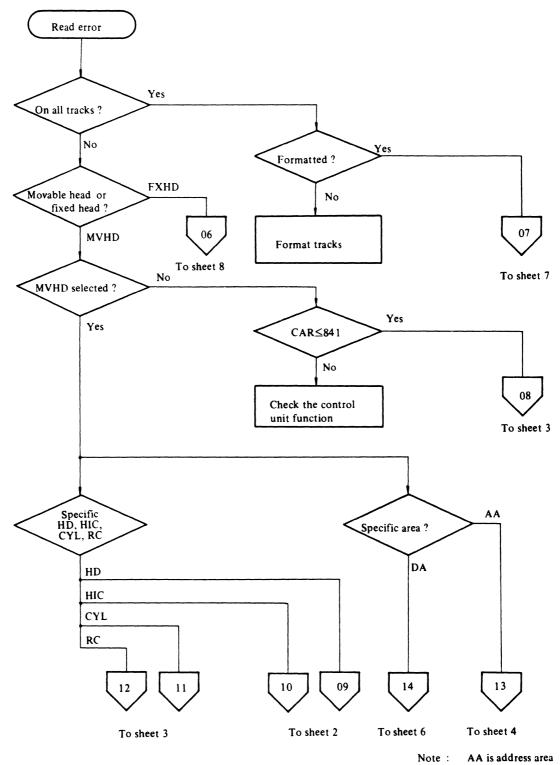

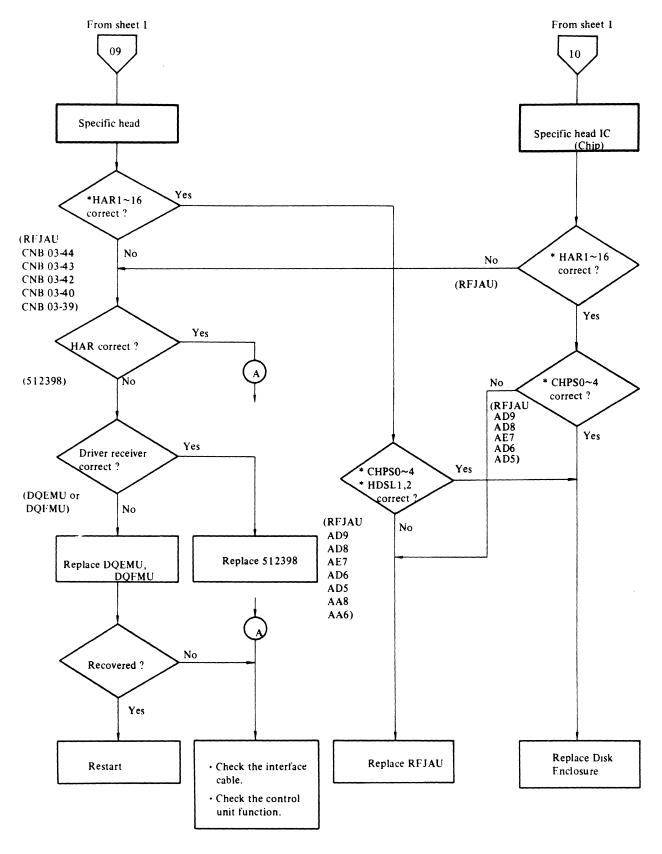

- Chapter 15 TROUBLE SHOOTING

- Chapter 16 DESCRIPTION OF ICs

- Chapter 17 SCHEMATICS

## Table of Contents

| CHAPTER | 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9 | GENERAL INFORMATION  GENERAL DESCRIPTION  FEATURES  PERFORMANCE SPECIFICATIONS  ENVIRONMENTAL SPECIFICATIONS  CABLE AND CONNECTOR SPECIFICATIONS  OPTIONS  SPARE PARTS  MAINTENANCE TOOLS AND EQUIPMENT  RELIABILITY AND SERVICE GOALS | 1-1<br>1-2<br>1-5<br>1-7<br>1-8<br>1-9<br>1-11            |

|---------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| CHAPTER | 2<br>2.1<br>2.2                                                  | INSTALLATION                                                                                                                                                                                                                           | 2-1                                                       |

| CHAPTER | 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7               | OPERATION AND CHECKOUT  DC POWER SUPPLY UNIT  INTERFACE PCBs  LOGIC PCB (C168-5123-0980#U)  SECTOR COUNT  OPERATOR PANEL  INDICATOR UNIT HGAMU (B16B-7830-0010A#U)  STANDALONE CHECK                                                   | 3-1<br>3-3<br>3-6<br>3-8<br>3-17<br>3-19                  |

| CHAPTER | 4.1<br>4.2<br>4.3                                                | SYSTEM INSTALLATION                                                                                                                                                                                                                    | 4-1<br>4-2                                                |

| CHAPTER | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6                           |                                                                                                                                                                                                                                        | 5-1<br>5-4<br>5-7<br>5-16<br>5-18<br>5-18<br>5-19<br>5-20 |

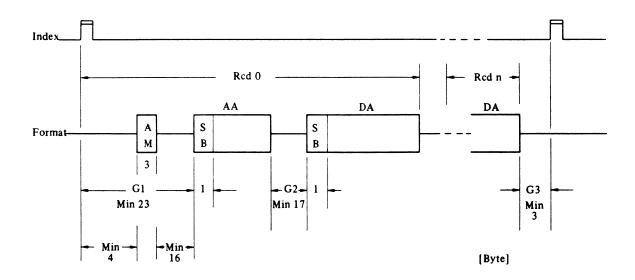

| CHAPTER | 6.1<br>6.2                                                       | DATA FORMAT  FORMAT  TRACK EFFICIENCY  MEDIA SPECIFICATIONS                                                                                                                                                                            | 6-1<br>6-3                                                |

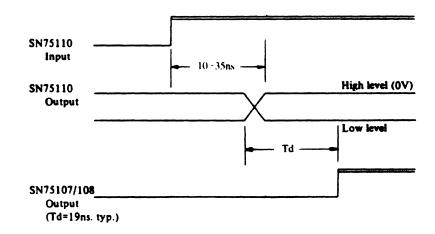

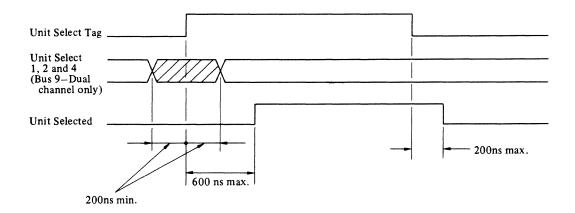

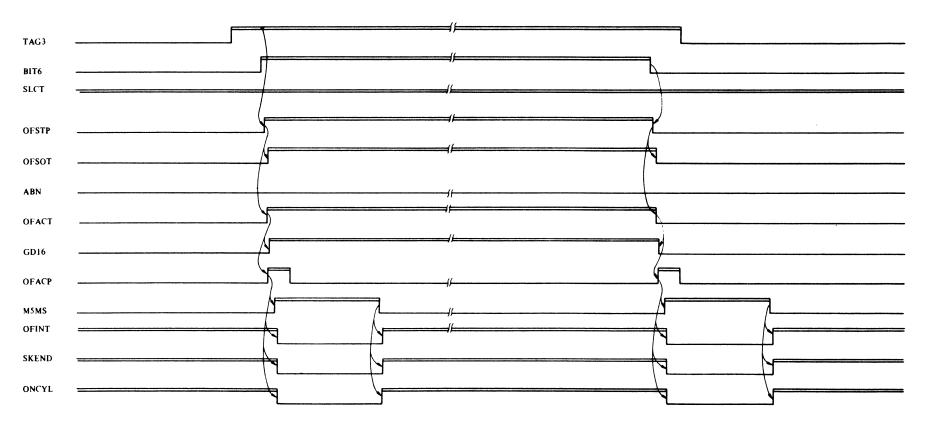

| CHAPTER | 7 7.1 7.2 7.3 7.4 7.5 7.6 7.7                             | INTERFACE SIGNAL TRANSMISSION DRIVER/RECEIVER PIN ASSIGNMENT OF INTERFACE CONNECTORS A-CABLE INPUT SIGNALS A-CABLE OUTPUT SIGNALS B-CABLE INPUT SIGNALS B-CABLE OUTPUT SIGNALS TIME SPECIFICATIONS | 7-1<br>7-4<br>7-5<br>7-12<br>7-20<br>7-21               |

|---------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

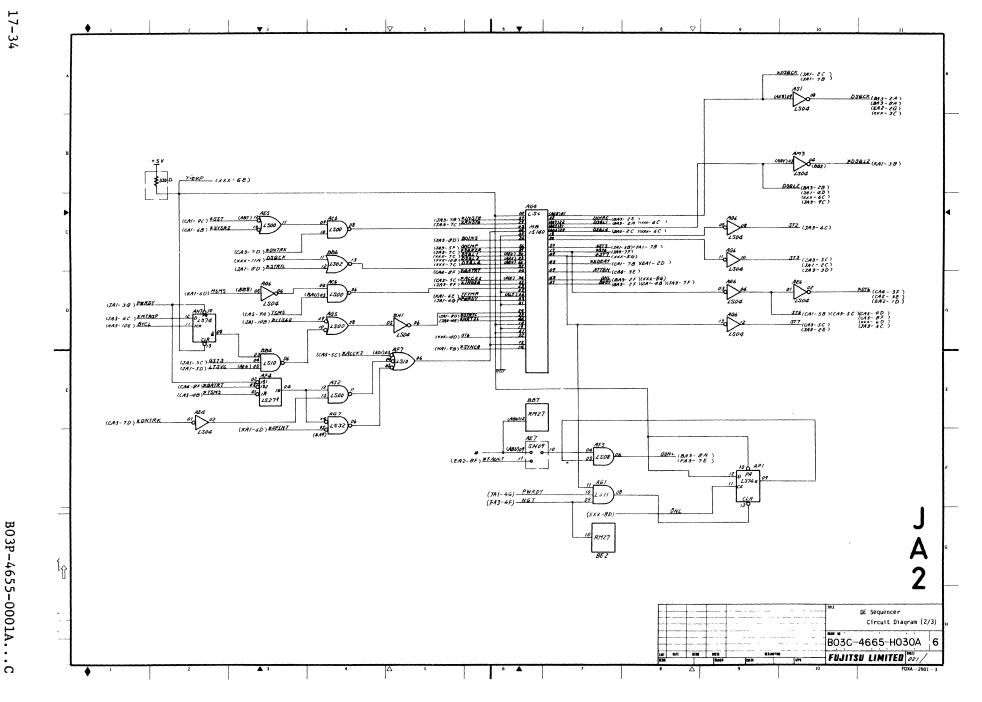

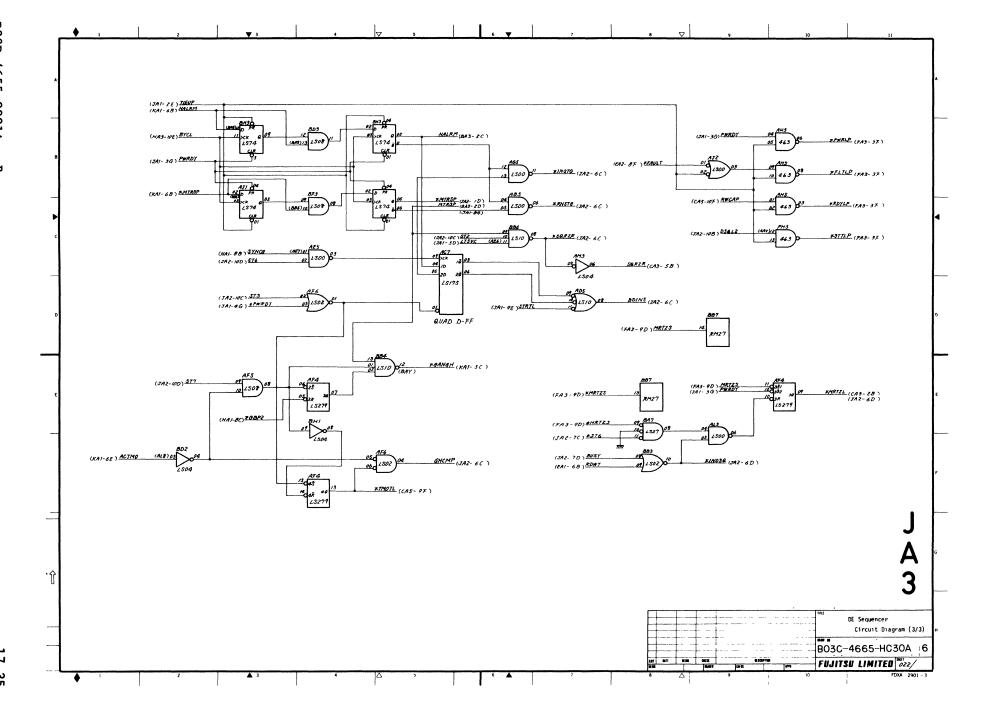

| CHAPTER | 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8 | LOGIC CIRCUIT BLOCK DIAGRAM  DE SEQUENCE SELECTION OUTLINE OF ACCESS CONTROL SEQUENCE RTZ SYSTEM RTZ/MANUAL RTZ SEEK OFFSET FAULT AND ERROR DETECTION                                              | 8-1<br>8-2<br>8-5<br>8-6<br>8-7<br>8-10<br>8-14<br>8-17 |

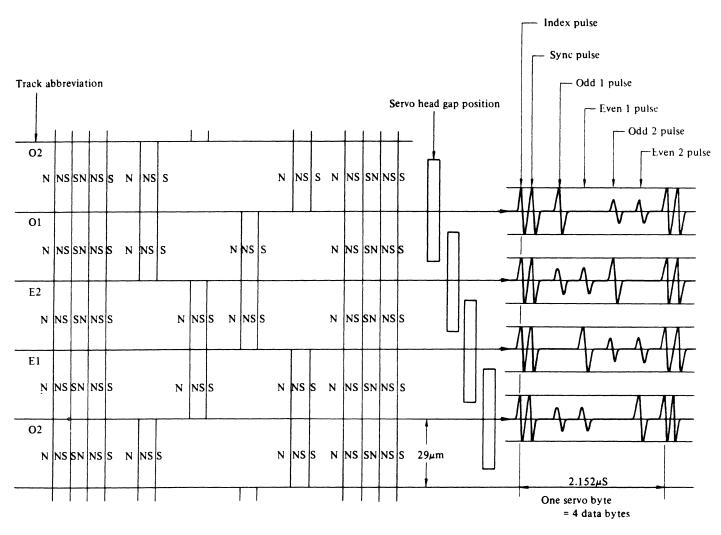

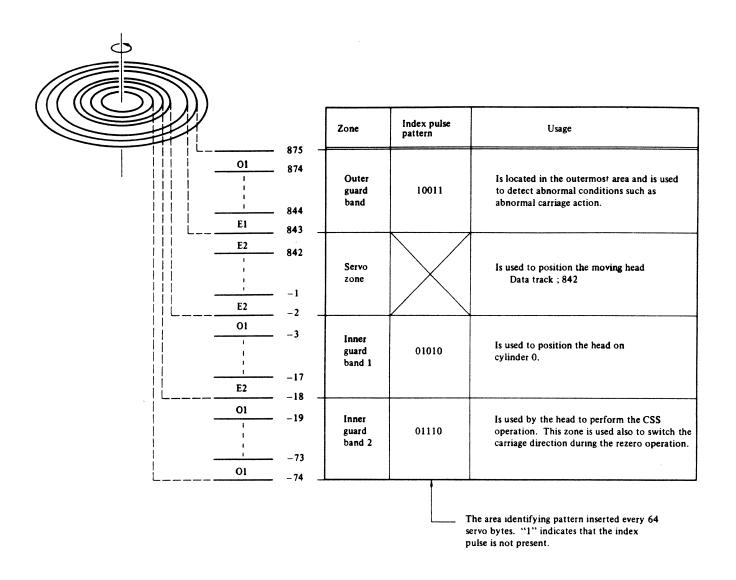

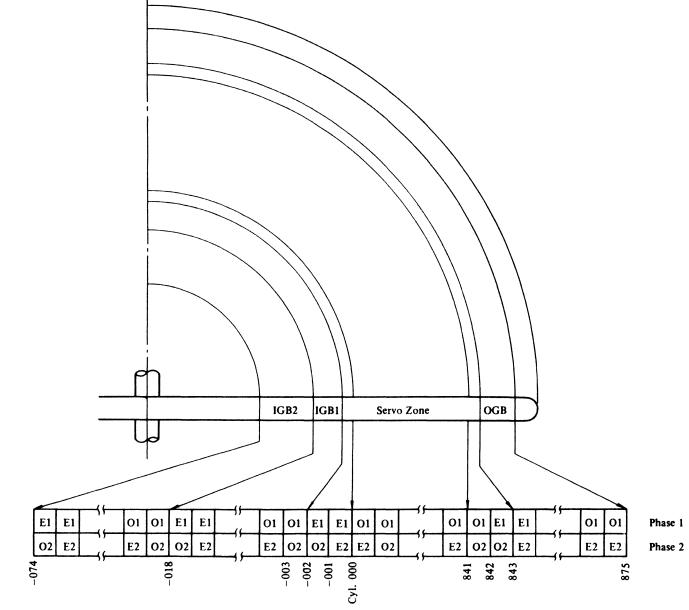

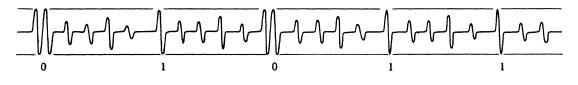

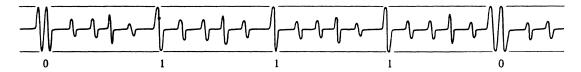

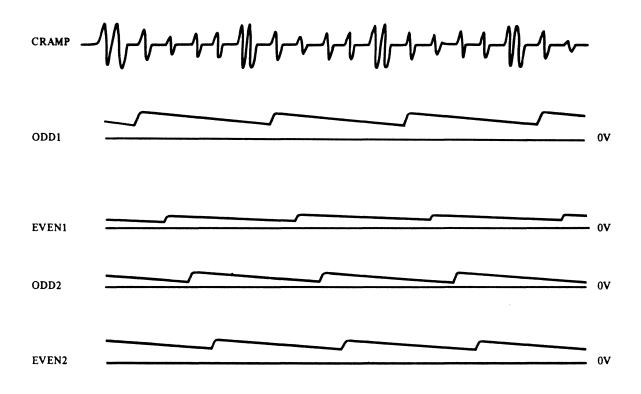

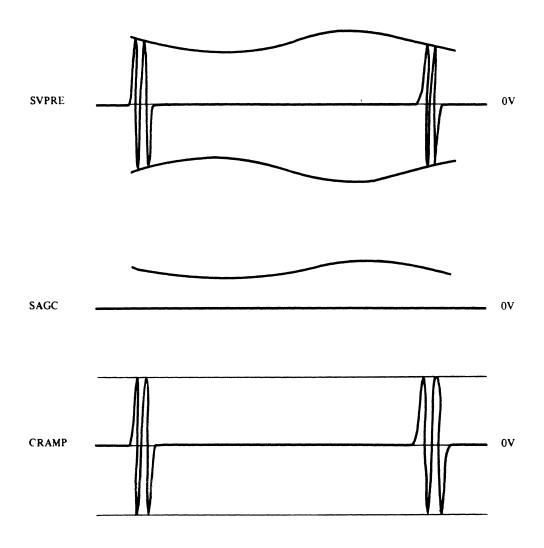

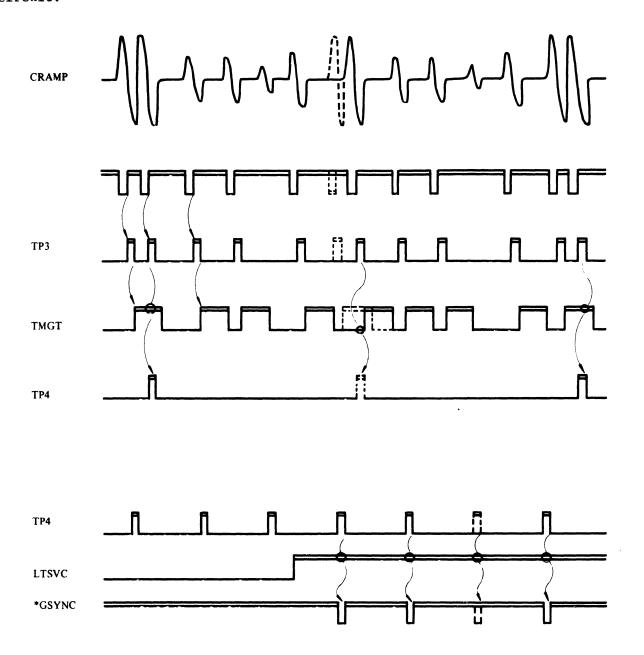

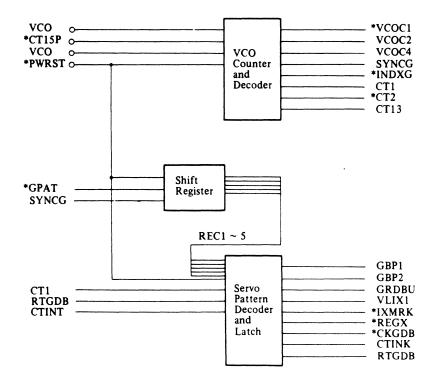

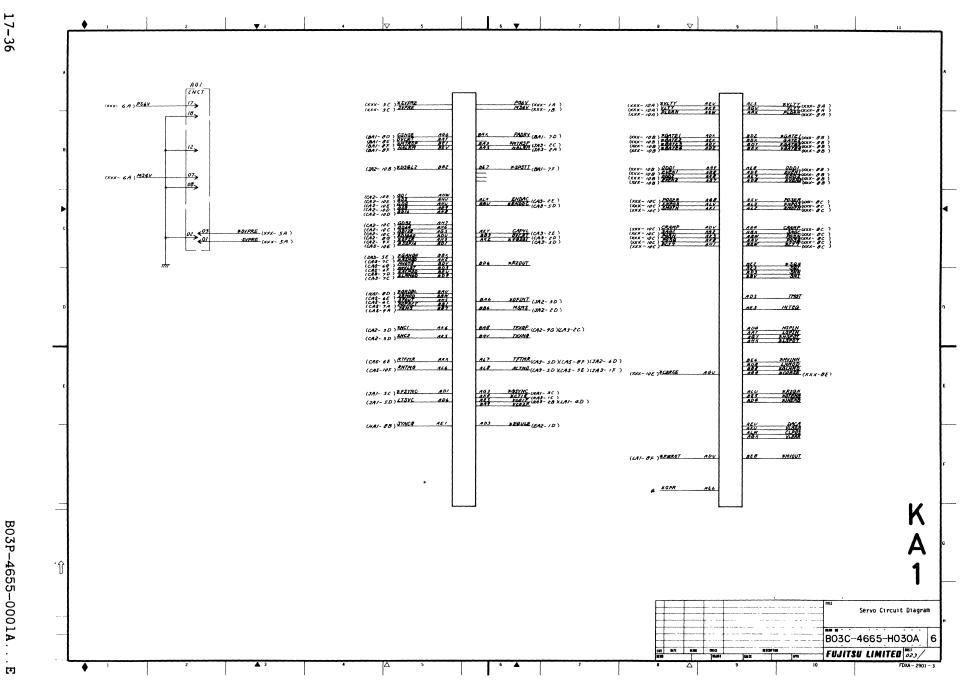

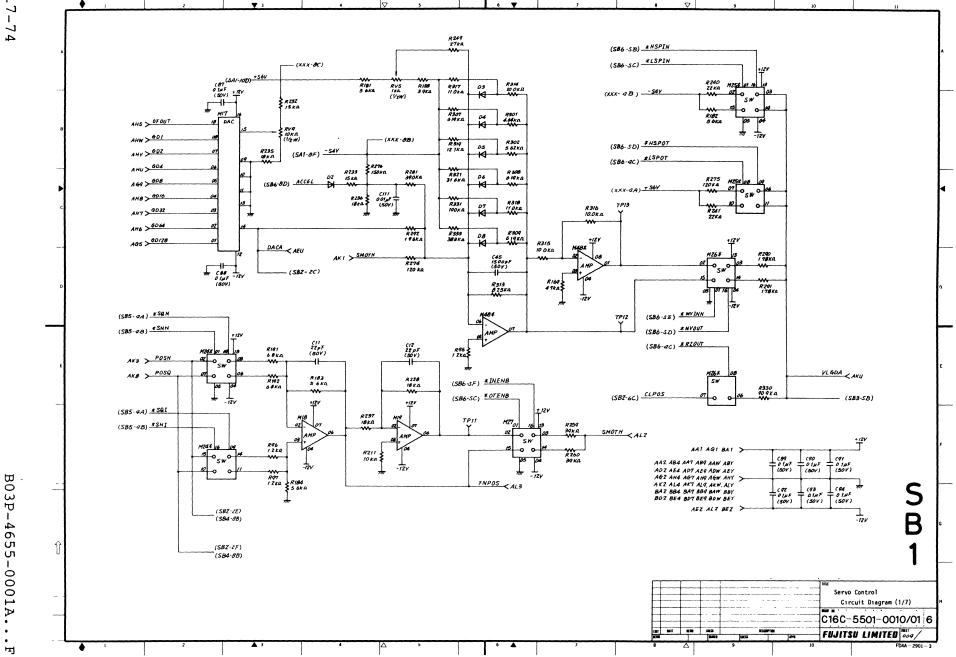

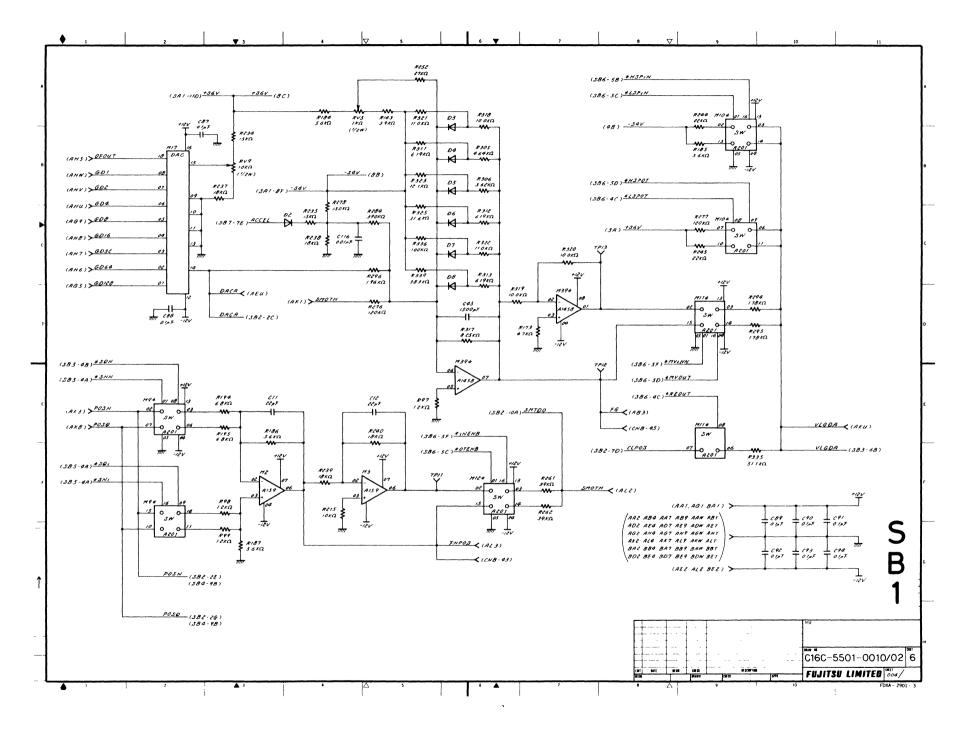

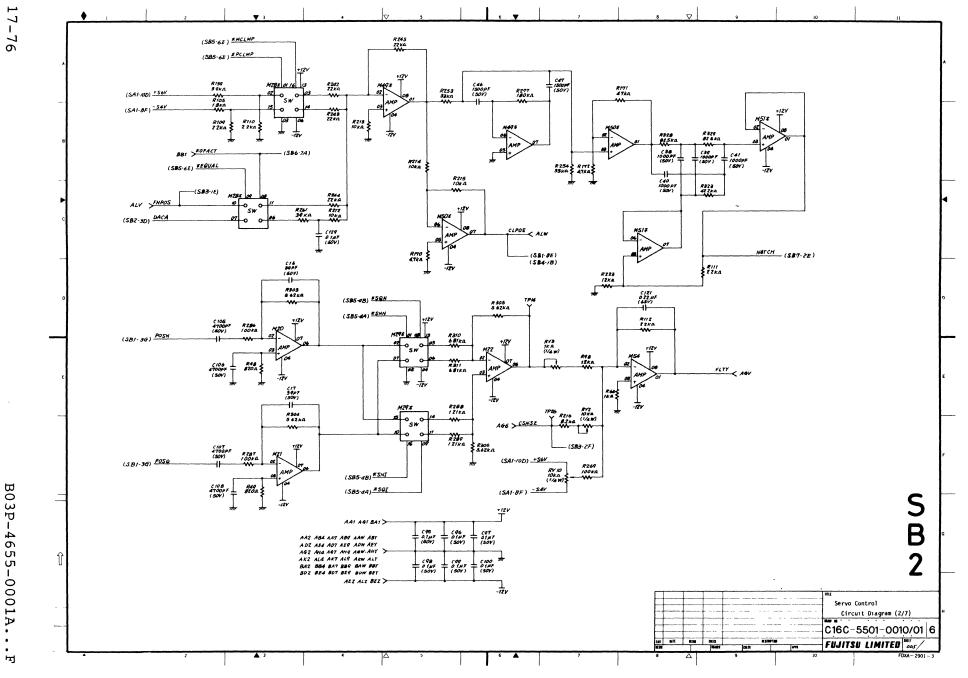

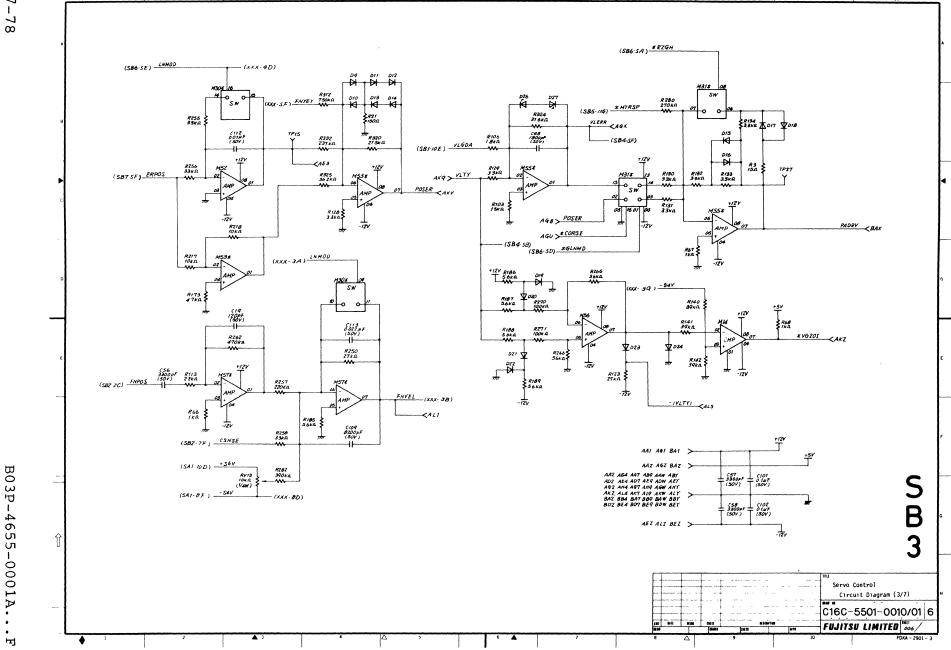

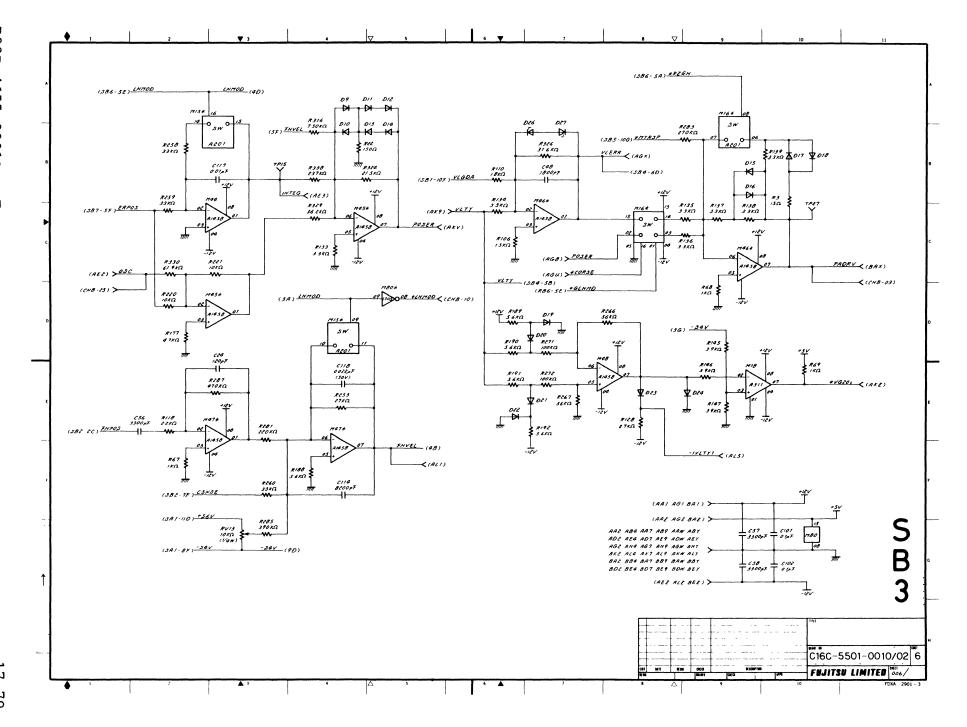

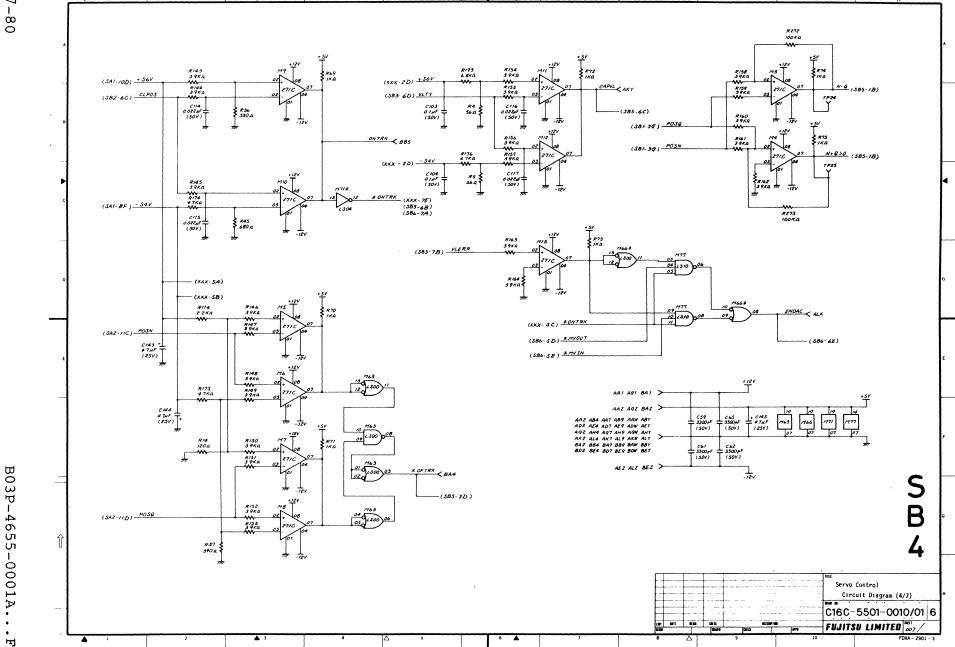

| CHAPTER | 9<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5                      | SERVO CIRCUIT DATA AND SERVO ZONE SERVO FORMAT SEEK CONTROL OPERATION REZERO CONTROL OPERATION SERVO BLOCK DIAGRAM                                                                                 | 9-1<br>9-3<br>9-7<br>9-9                                |

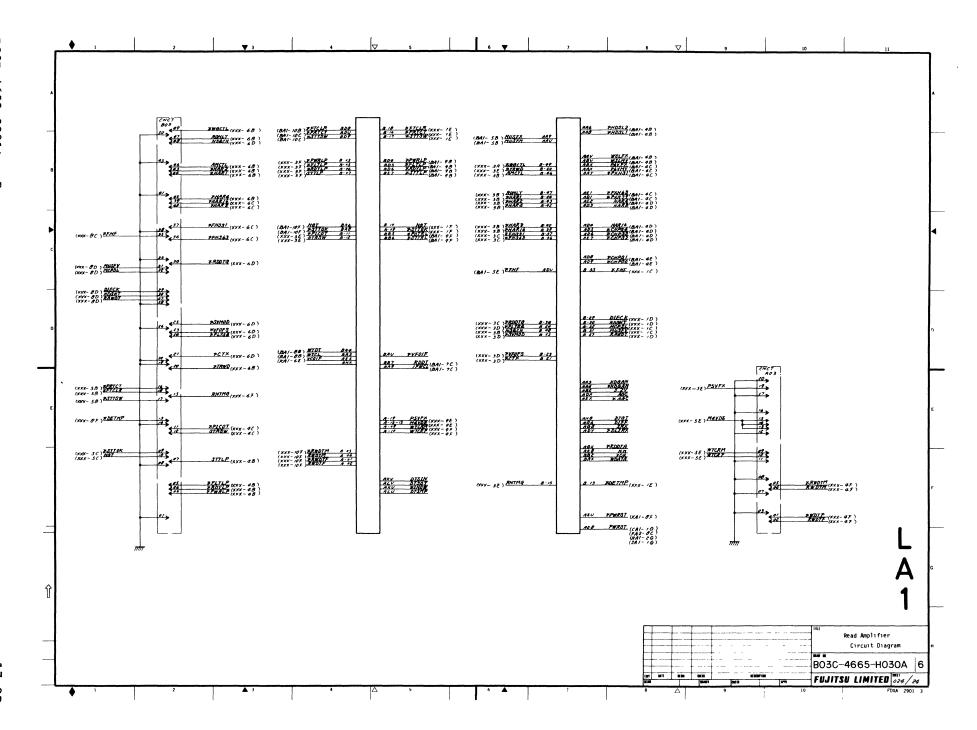

| CHAPTER | 10<br>10.1<br>10.2<br>10.3<br>10.4                        | READ WRITE CIRCUIT WRITE CIRCUIT READ CIRCUIT ERROR DETECTING CIRCUIT DE INTERFACE                                                                                                                 | 10-1<br>10-6<br>10-1                                    |

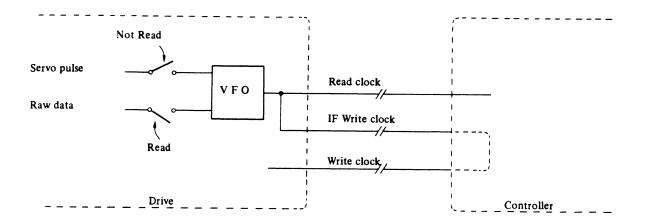

| CHAPTER | 11.1<br>11.2<br>11.3                                      | VFO CIRCUIT                                                                                                                                                                                        | 11-1<br>11-5<br>11-7                                    |

| CHAPTER | 12<br>12.1<br>12.2<br>12.3<br>12.4                        | DC POWER SUPPLY UNIT INPUT REQUIREMENT OUTPUT CONDITIONS ALARM DETECTIONS CONTROL OF SPINDLE MOTOR                                                                                                 | 12-2<br>12-2<br>12-4                                    |

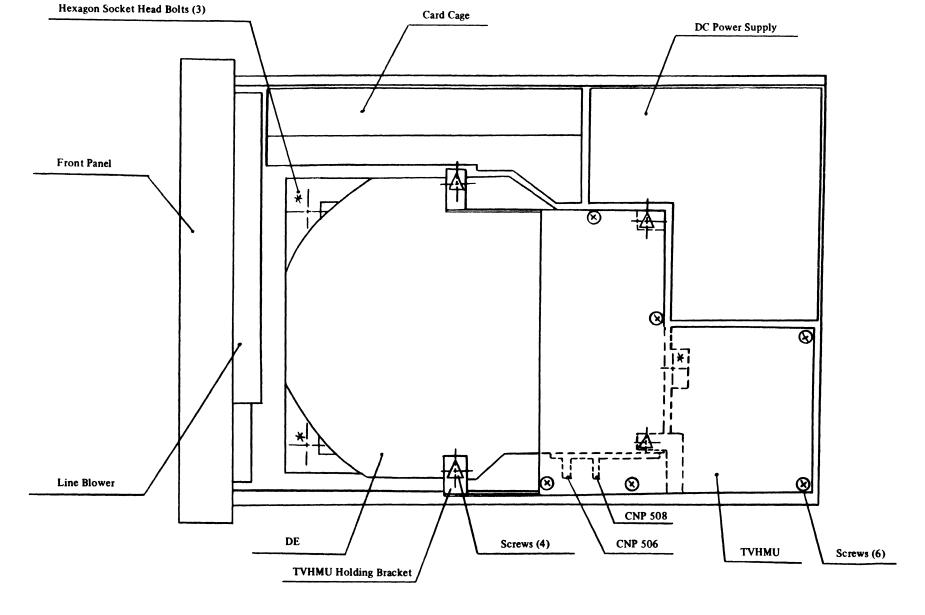

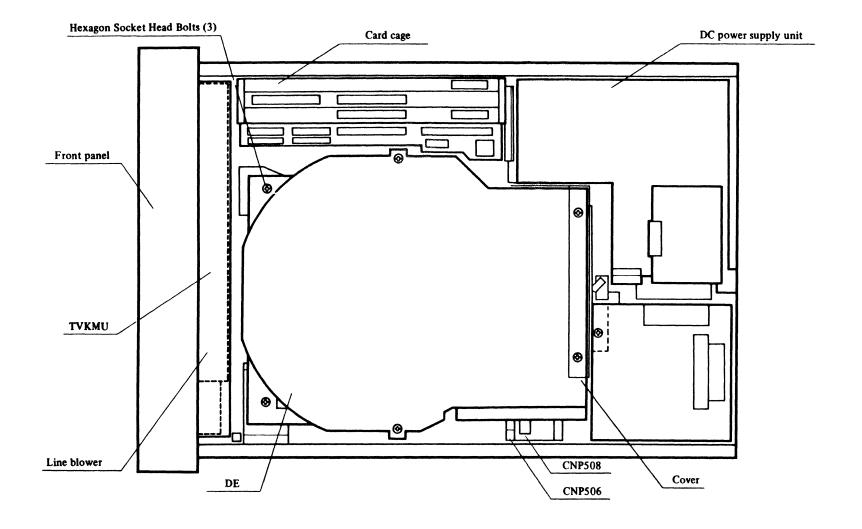

| CHAPTER | 13    | MAINTENANCE AND PARTS REPLACEMENT                 | 13-1          |

|---------|-------|---------------------------------------------------|---------------|

|         | 13.1  | GENERAL PRECAUTIONS                               | 13-1          |

|         |       | DE REPLACEMENT                                    |               |

|         | 13.2  | 2.1 DE replacement of old version                 | 13-4          |

|         | 13.3  | 2.2 DE replacement of New version                 | 13-6          |

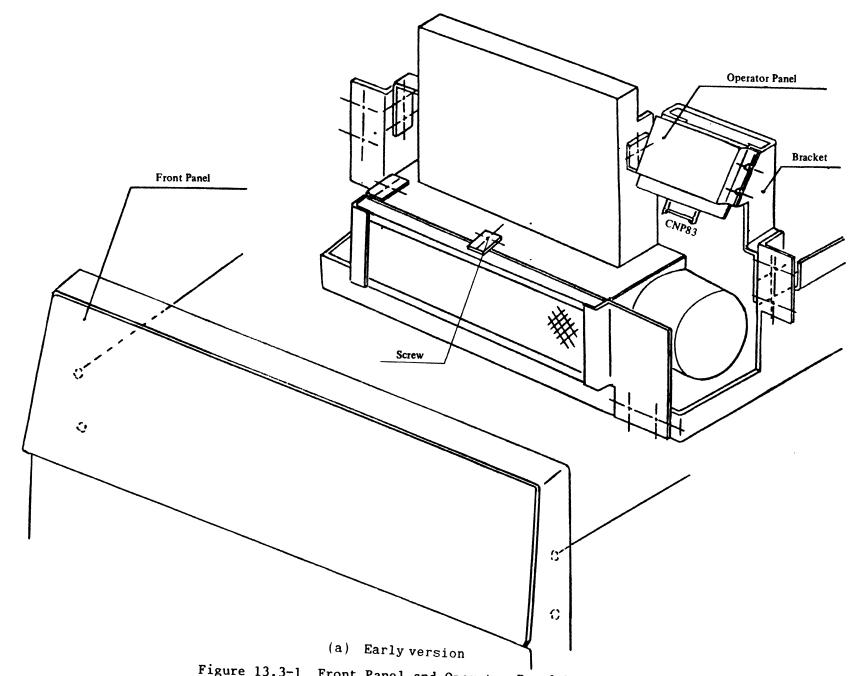

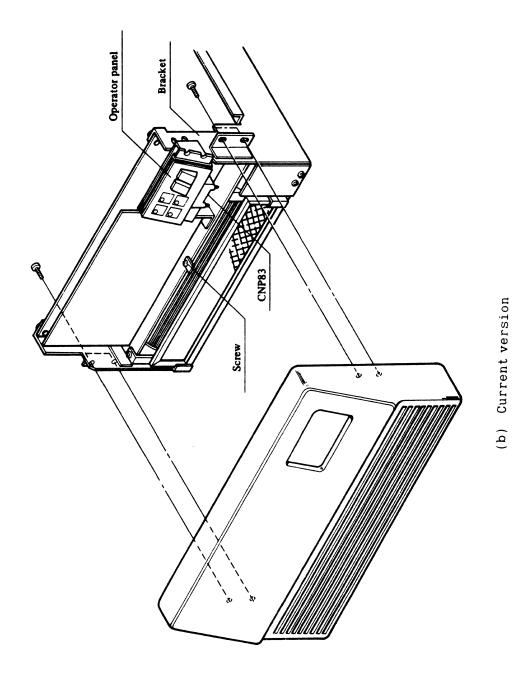

|         | 13.3  | FRONT PANEL AND OPERATOR PANEL                    | 13-8          |

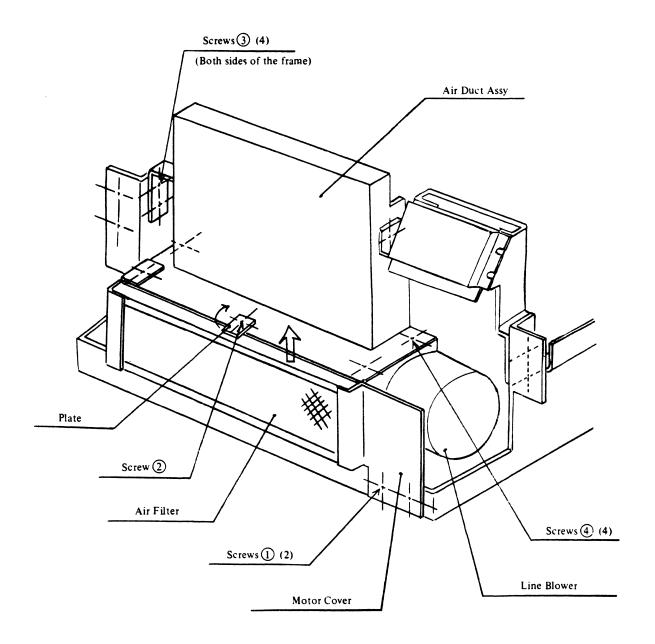

|         | 13.4  | AIR FILTER                                        | 13-11         |

|         | 13.5  | LINE BLOWER (Refer to Figure 13.4-1)              | 13-14         |

|         | 13.   | 5.1 Old version (Refer to Figure 13.4-1 (a))      | 13-14         |

|         | 13.   | 5.2 New version (Refer to Figure 13.4-1 (b))      | 13-14         |

|         | 13.6  | BACK PANEL (BQGMU)                                | 13-15         |

|         | 13.7  | HOUR METER                                        | 13-17         |

|         | 13.8  | DUAL CHANNEL OPTION                               | 13-20         |

|         | 13.9  | DC POWER SUPPLY UNIT                              |               |

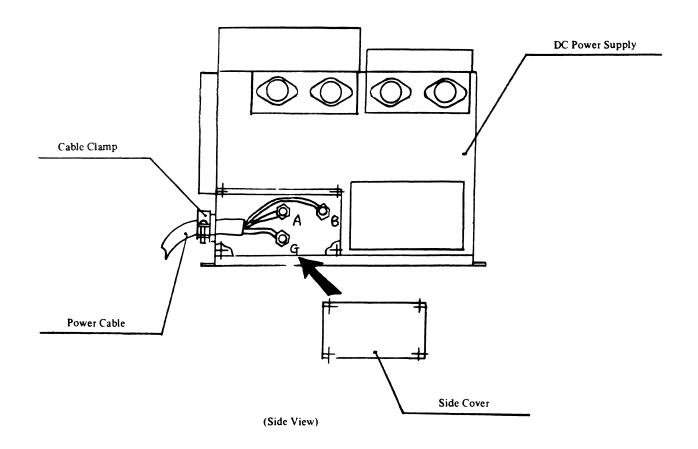

|         | 13.10 | POWER CABLE                                       |               |

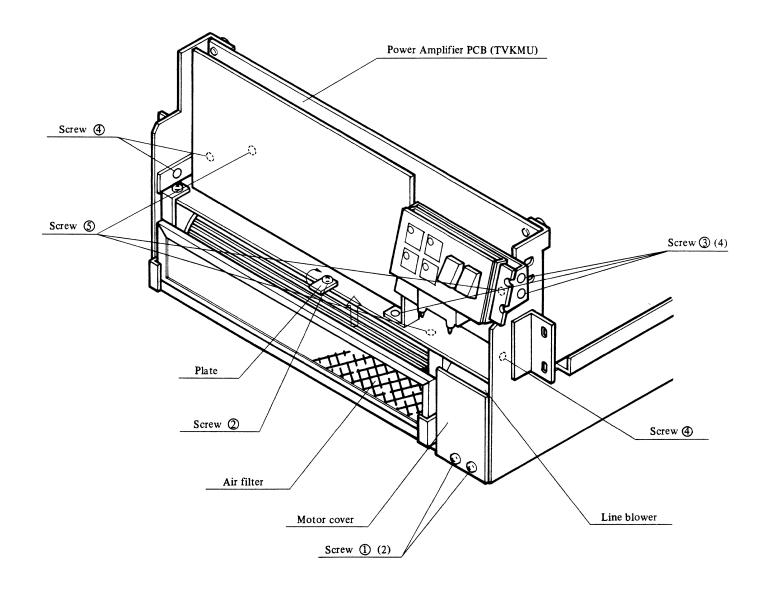

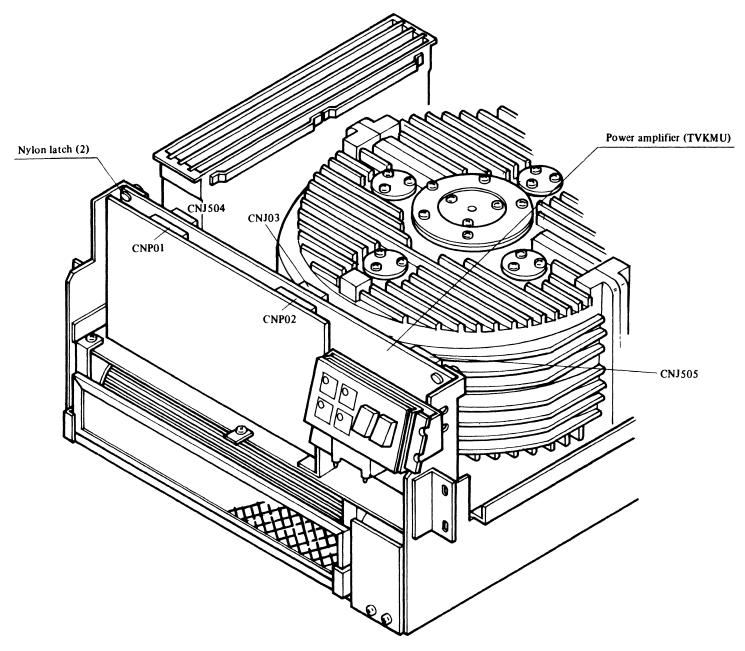

|         |       | POWER AMPLIFIER (TVKMU) (Refer to Figure 13.11-1) |               |

|         |       |                                                   |               |

| CHAPTER | 14    | ELECTRICAL TEST AND ADJUSTMENT                    | 14-1          |

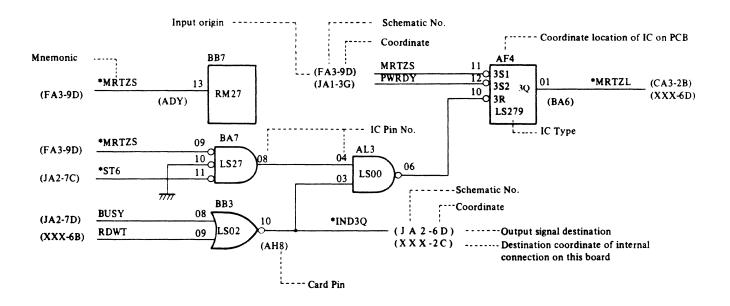

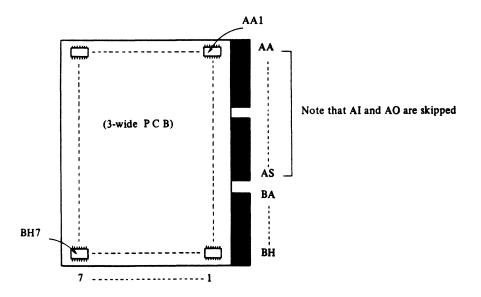

|         | 14.1  | GUIDE TO PCBs AND LOGIC DIAGRAMS (SCHEMATICS)     | 14-1          |

|         | 14.2  | ADJUSTMENT OF SERVO CIRCUIT                       | 14-4          |

|         | 14.3  | ADJUSTMENT OF READ/WRITE CIRCUIT                  | 14-15         |

|         | 14.4  | ADJUSTMENT OF VFO CIRCUIT                         | 14-19         |

|         |       |                                                   |               |

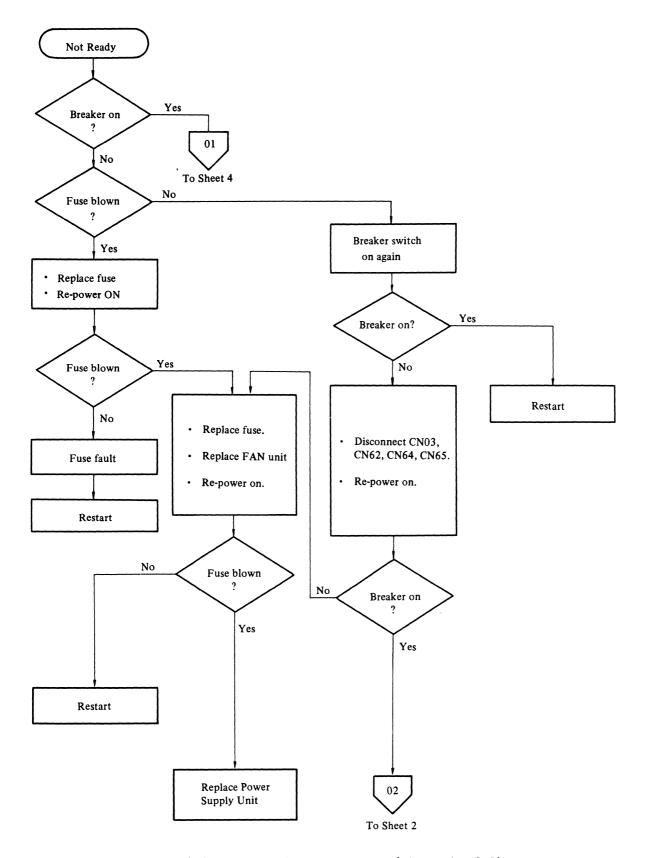

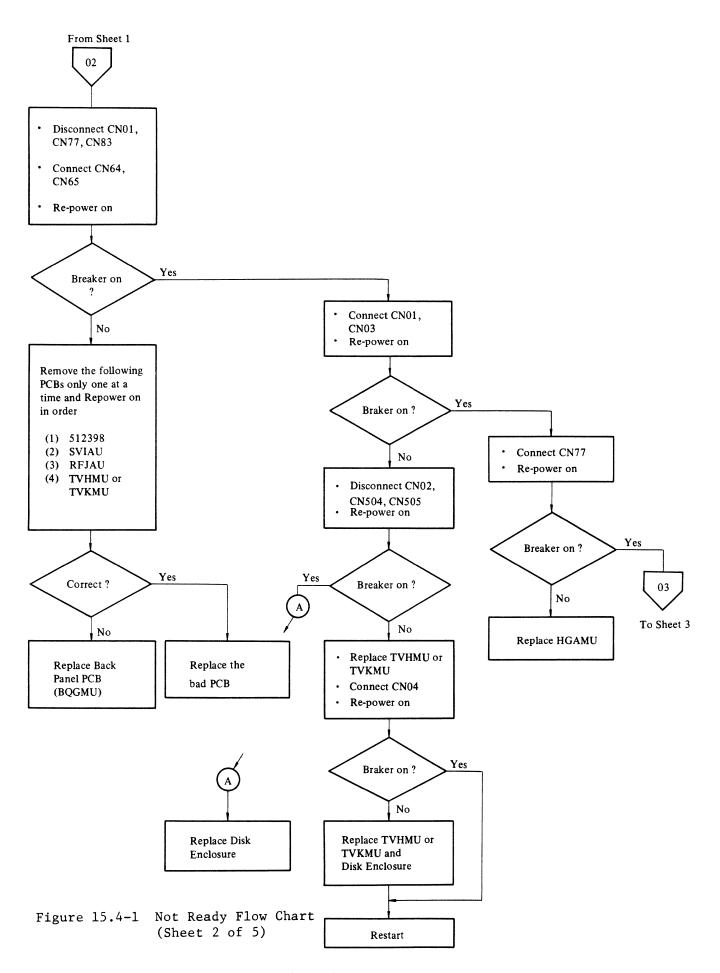

| CHAPTER | 15    | TROUBLE SHOOTING                                  | 15 <b>-</b> 1 |

|         | 15.1  | INTRODUCTION                                      | 15-1          |

|         | 15.2  | ERROR STATE                                       | 15-2          |

|         | 15.3  | TROUBLE SHOOTING SYMBOL                           | 15-4          |

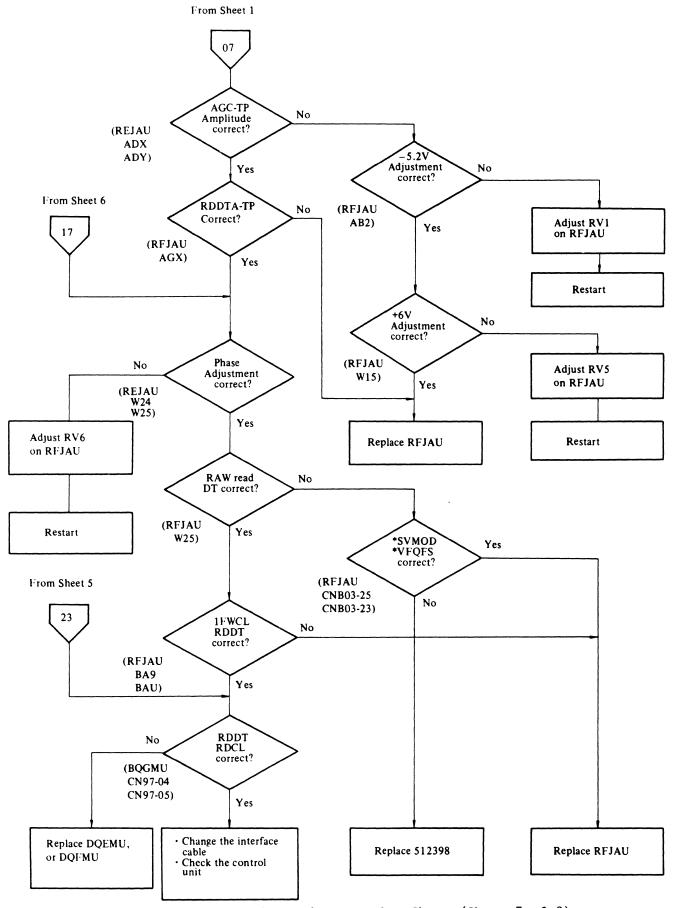

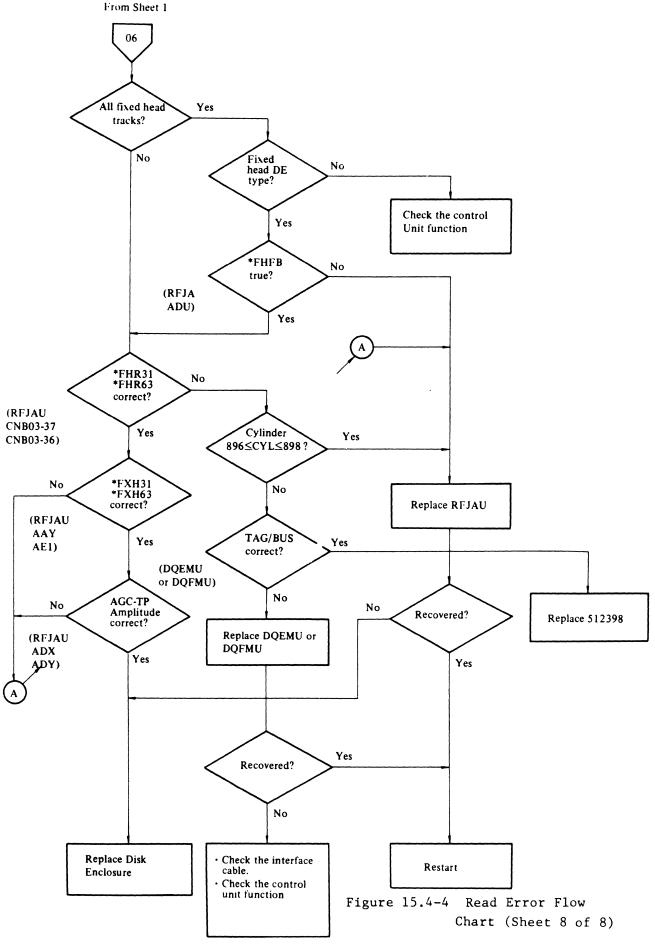

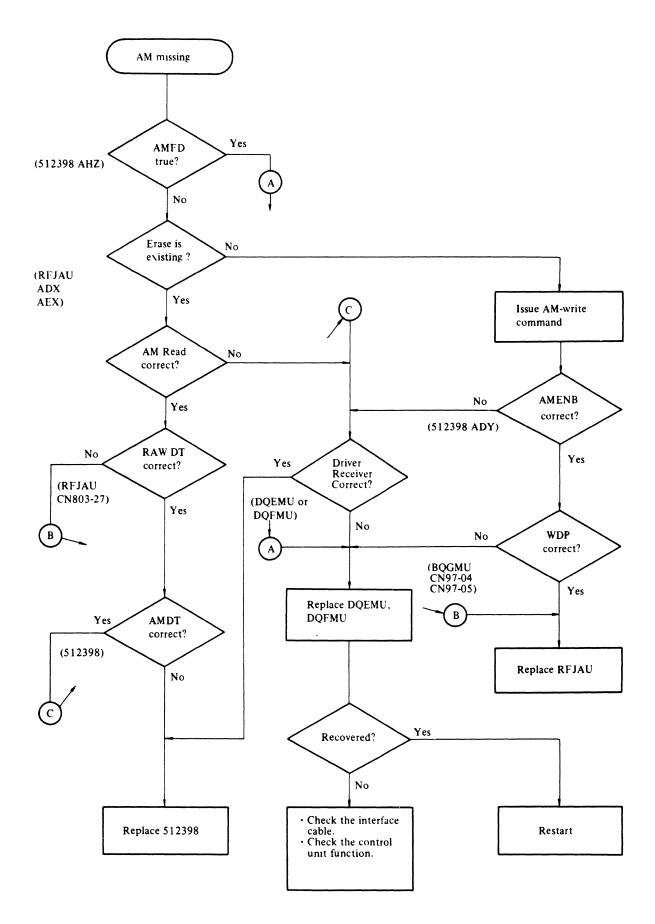

|         | 15.4  | TROUBLE SHOOTING FLOW CHART                       | 15-5          |

|         |       |                                                   |               |

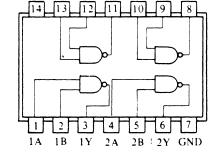

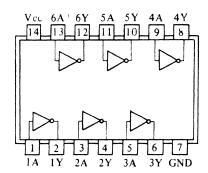

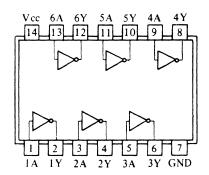

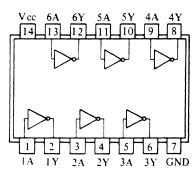

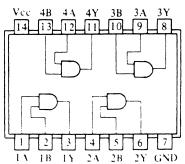

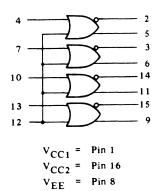

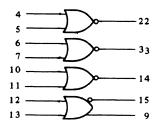

| CHAPTER | 16    | DESCRIPTION OF ICs                                | 16-1          |

|         | 16.1  | INTRODUCTION                                      | 16-1          |

|         | 16.2  | INTERCHANGEABILITY                                | 16-2          |

|         | 16.3  | DETAIL OF ICs                                     | 16-5          |

|         |       |                                                   |               |

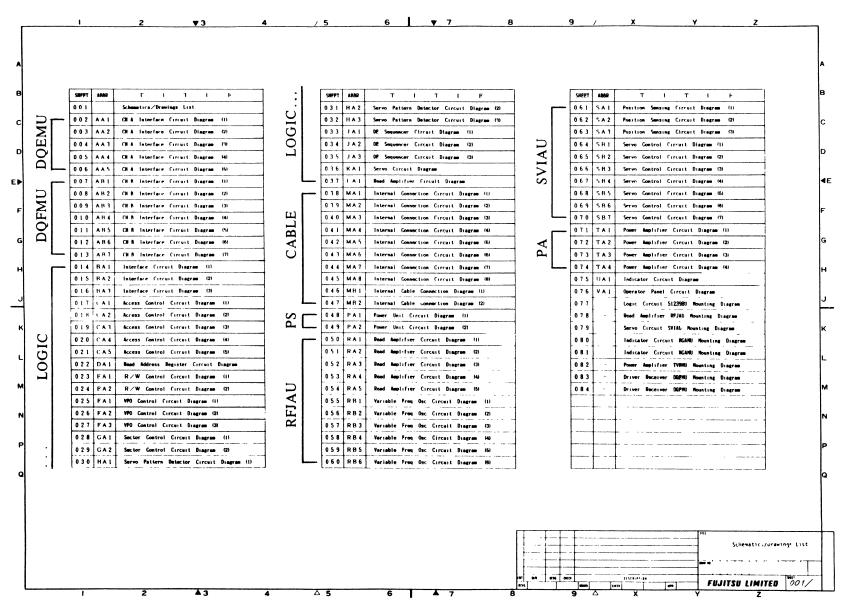

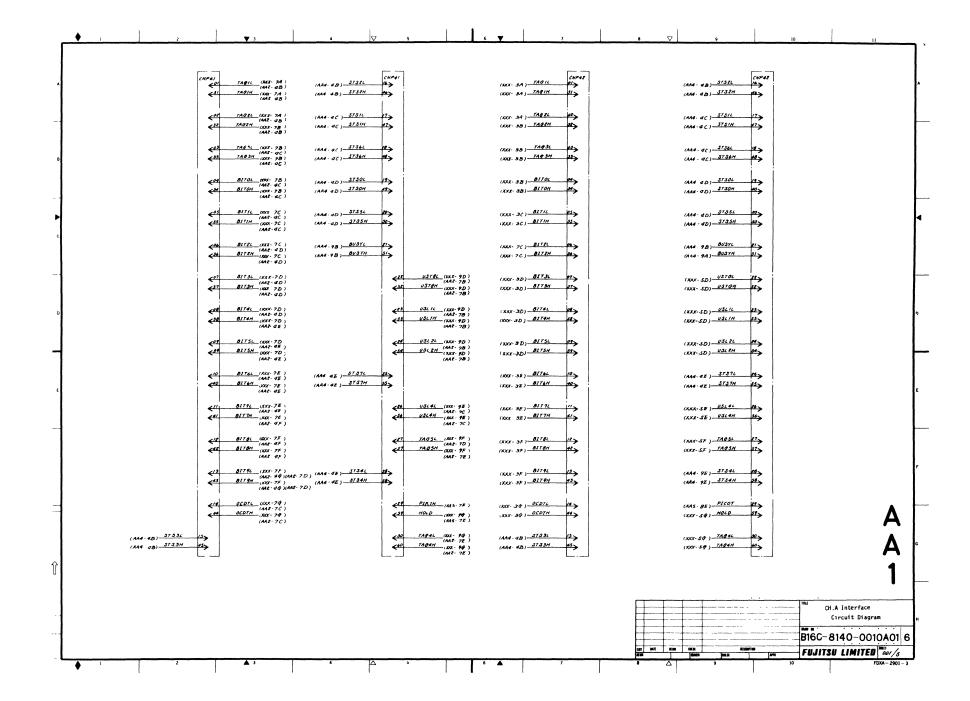

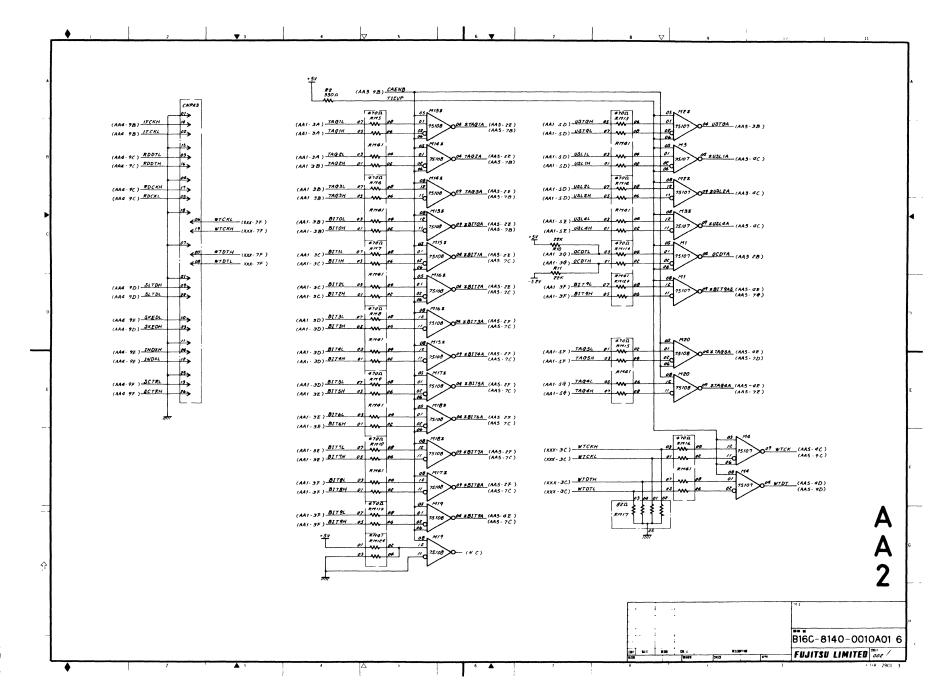

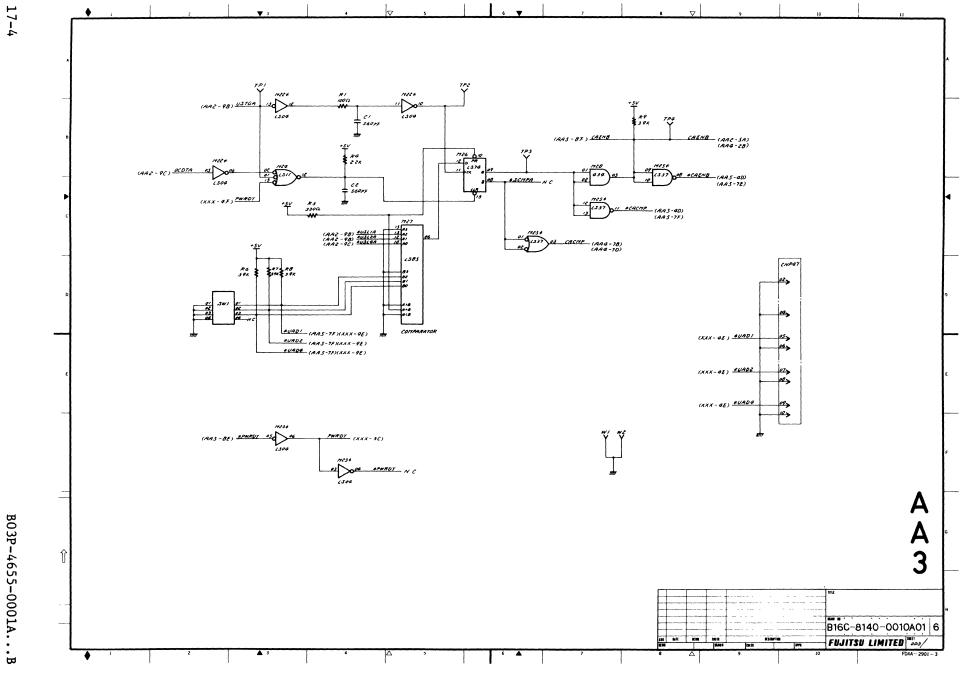

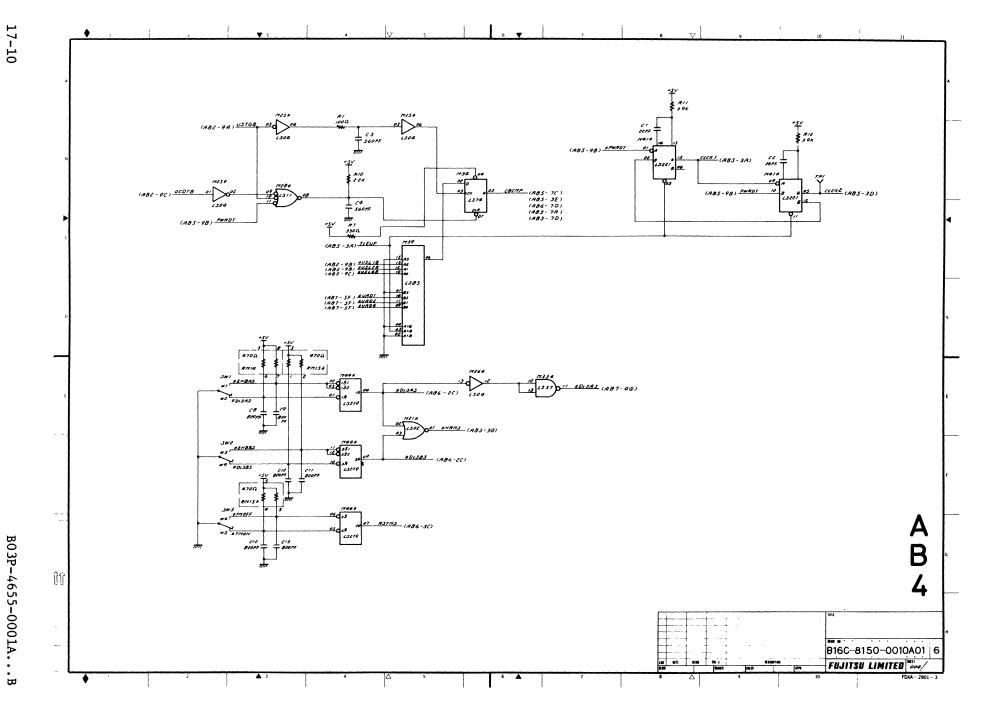

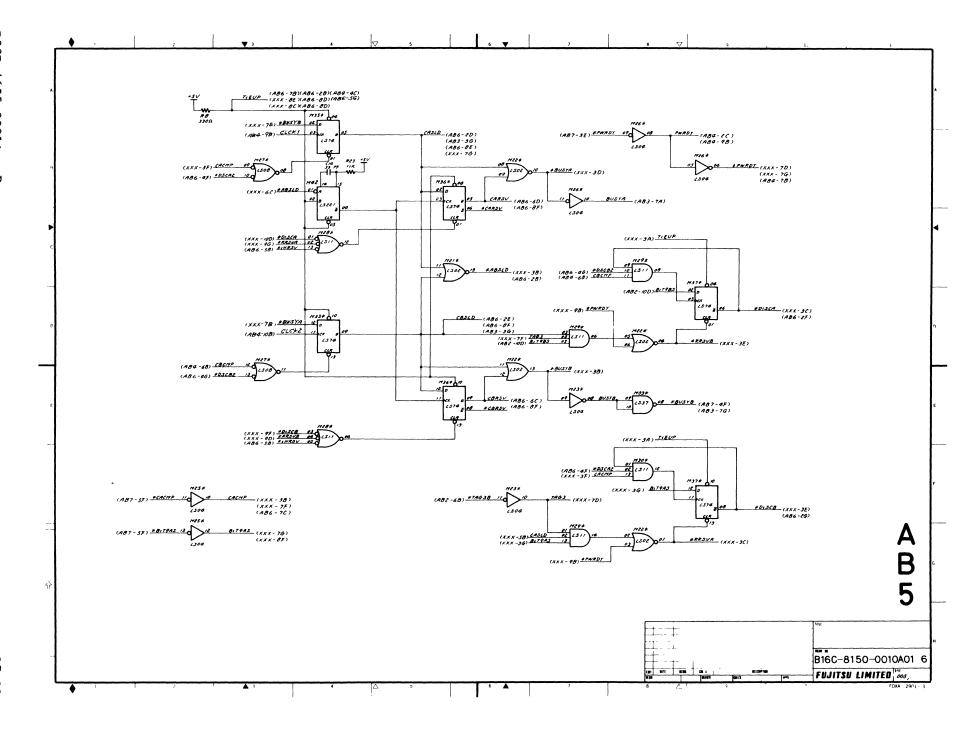

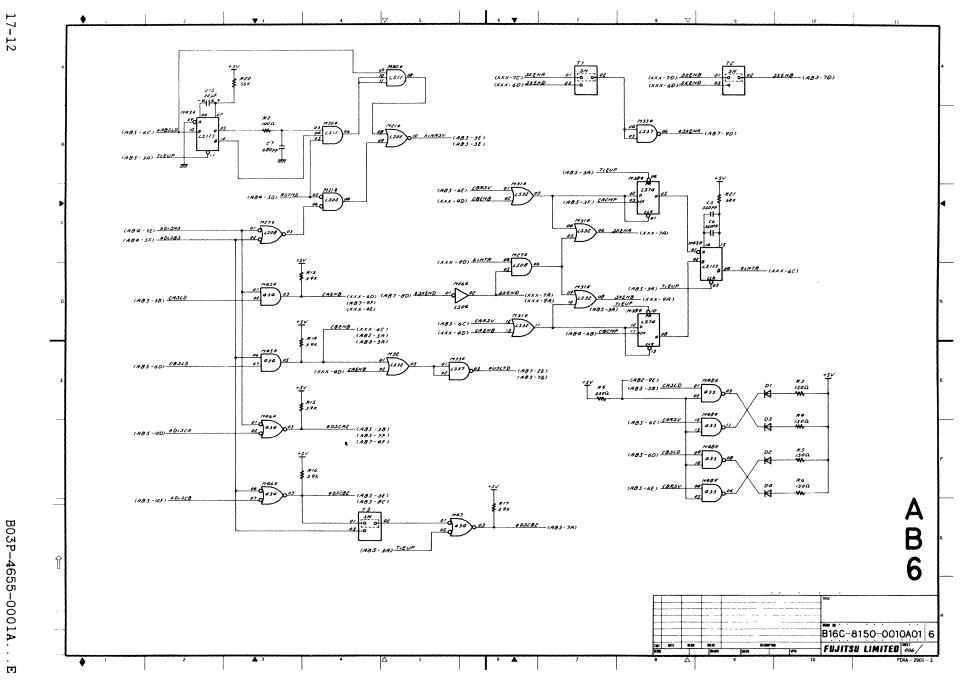

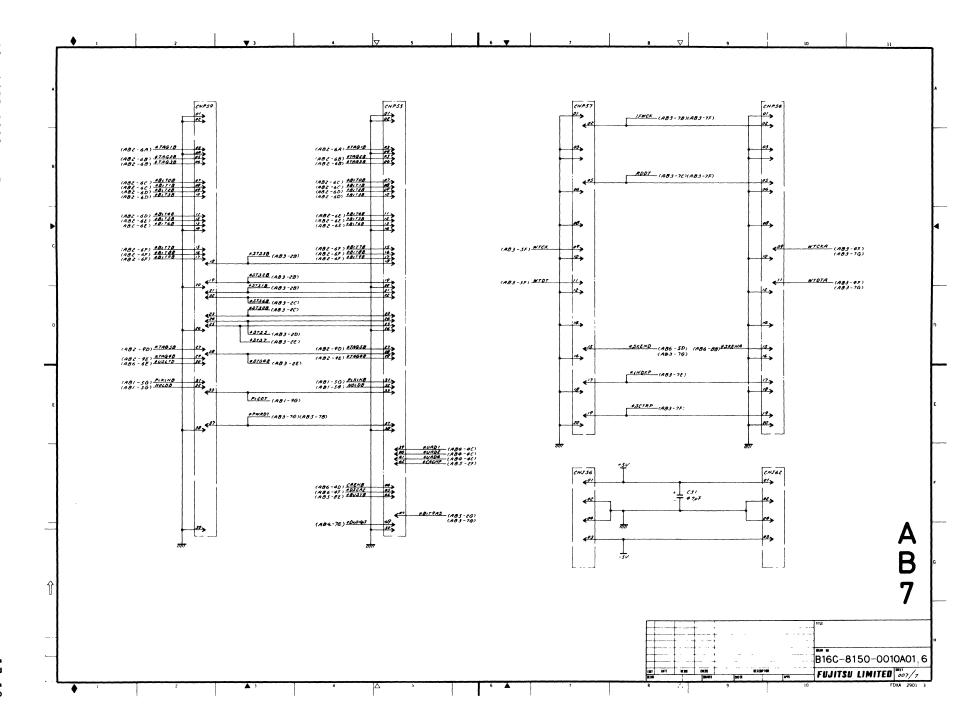

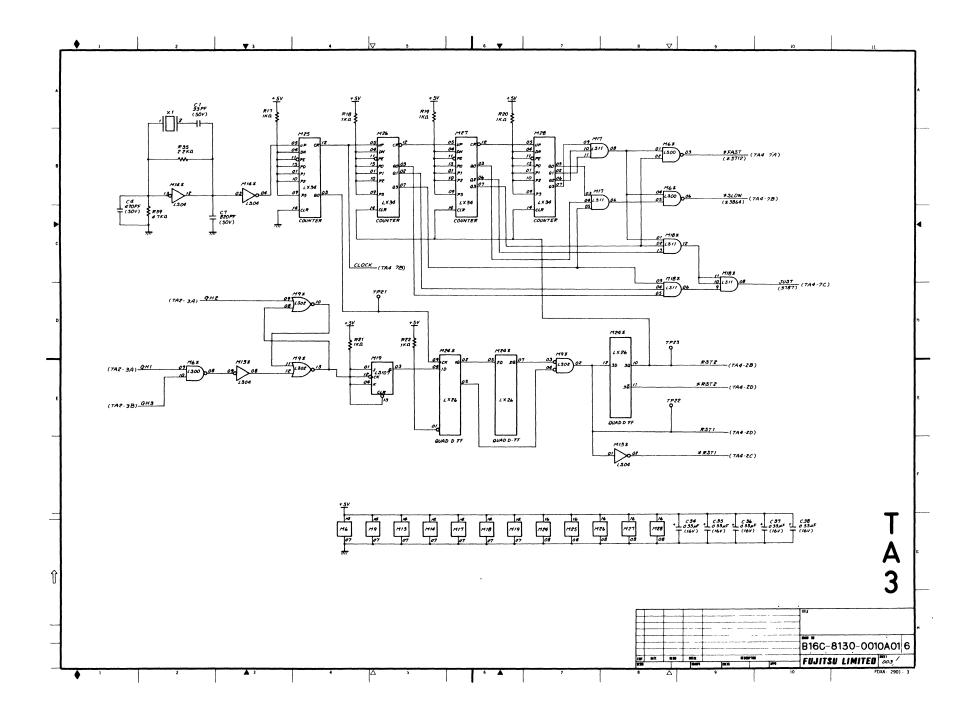

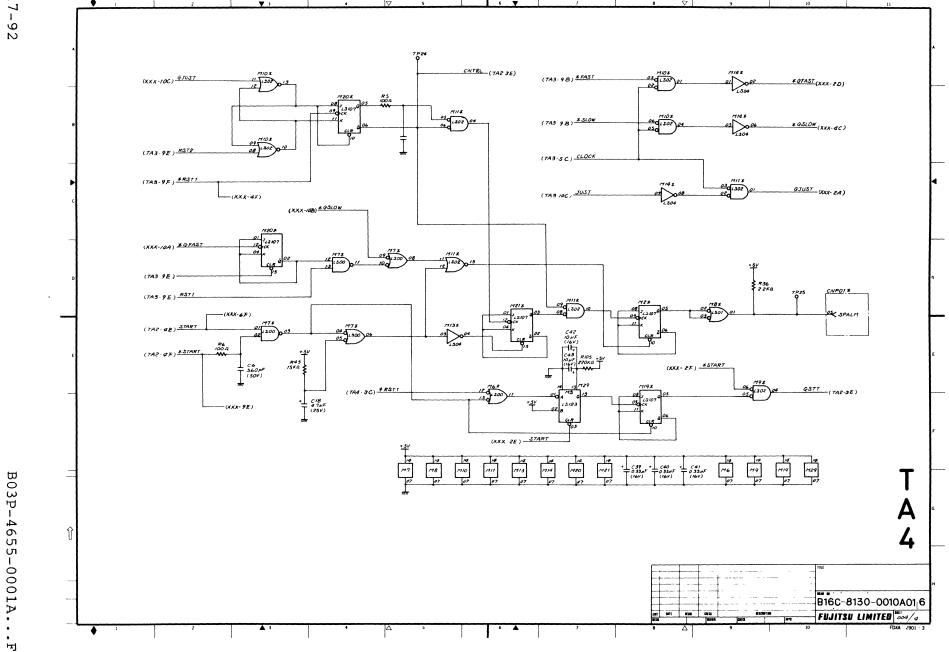

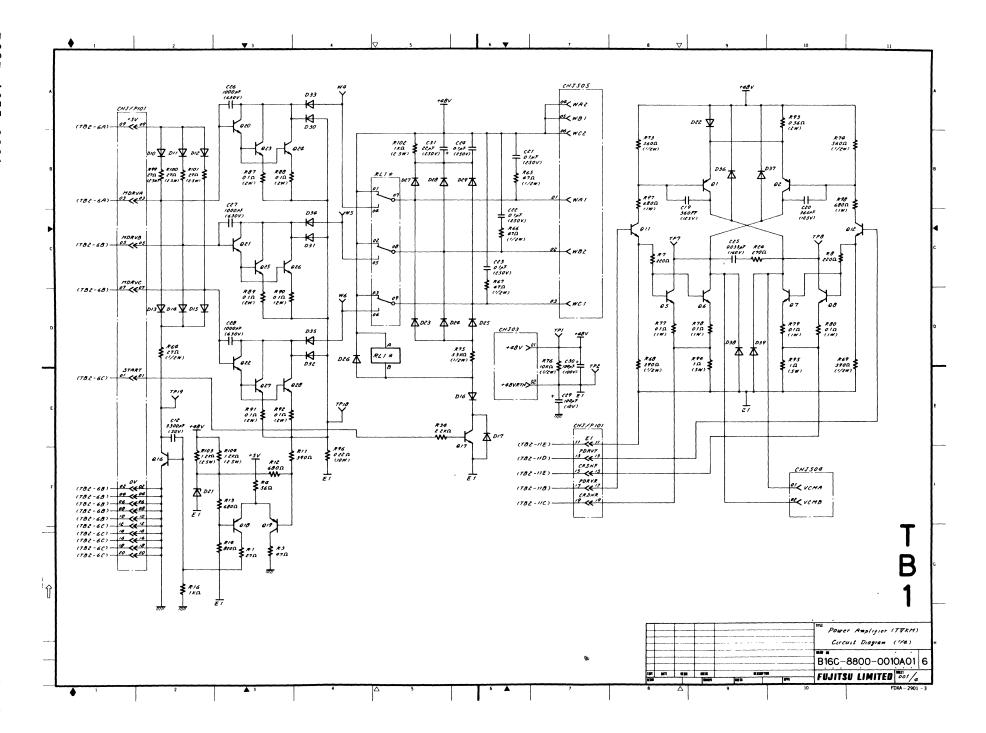

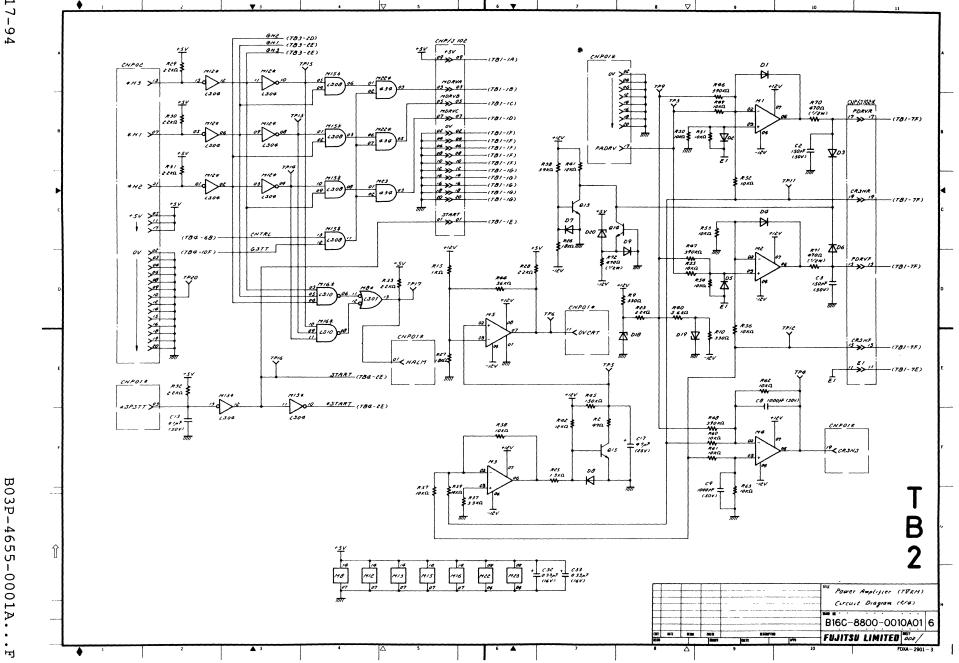

| CHAPTER | 17    | SCHEMATICS                                        | 17-1          |

|         | 17.1  | SCHEMATICS/DRAWINGS                               | 17-1          |

|         | 17.2  | ABBREVIATIONS                                     | 17-112        |

### 1.1 GENERAL DESCRIPTION

The M2351 Disk Drive is a compact state-of-the-art moving head disk drive with a storage capacity of up to 474 megabytes (unformatted) in a very compact package. It uses Winchester type heads and platters, allowing higher recording density, data transfer rate, and greater reliability, while offering a faster access time. The media is non-removable. This drive is appropriate for large capacity, high speed data storage in an online and/or batch system.

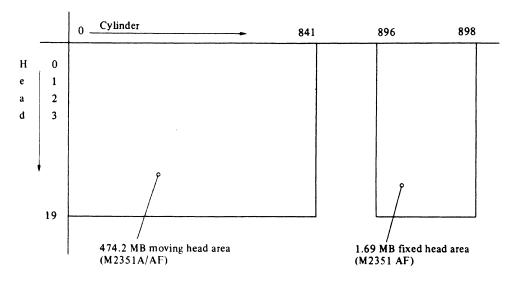

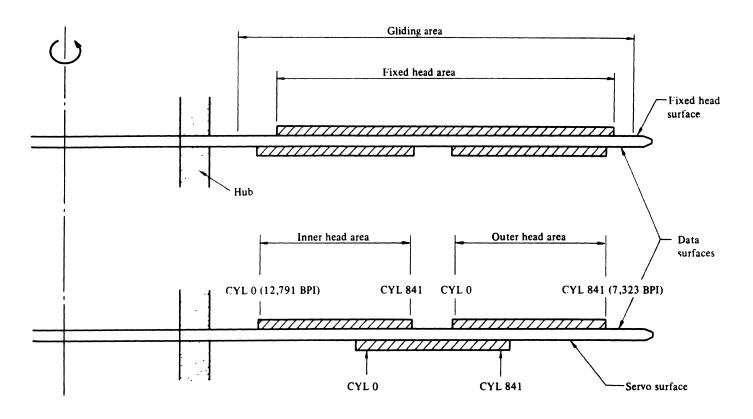

Model M2351A is of the Non-Fixed-Head type, and model M2351AF is of the Fixed-Head type with an unformatted fixed-head capacity of 1.69 megabytes to further improve the system throughput.

Higher cost/performance and improved reliability can be achieved in computer systems that utilize M2351 disk drives.

The drive is designed to meet the following standards:

- 1. UL478 Electronic Data Processing Unit and Systems.

- 2. CSA C22.2 No. 154-1975 Data Processing Equipment.

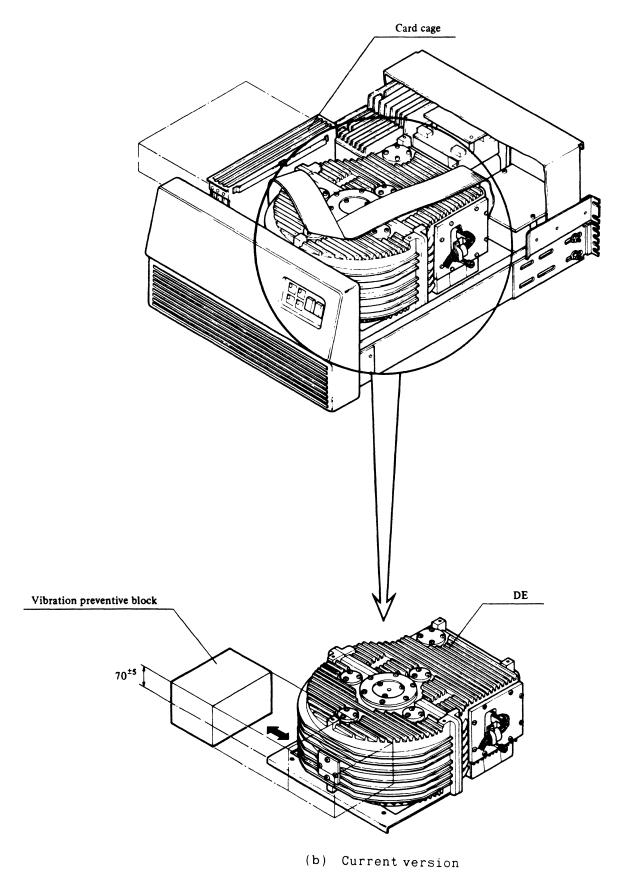

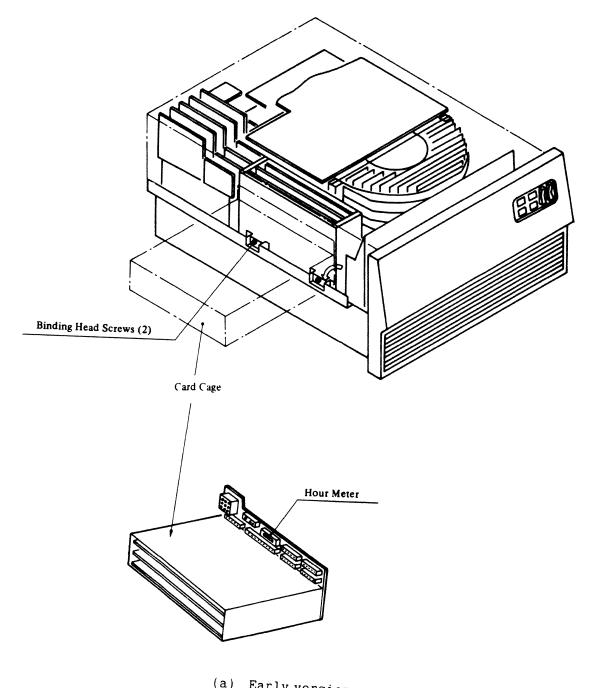

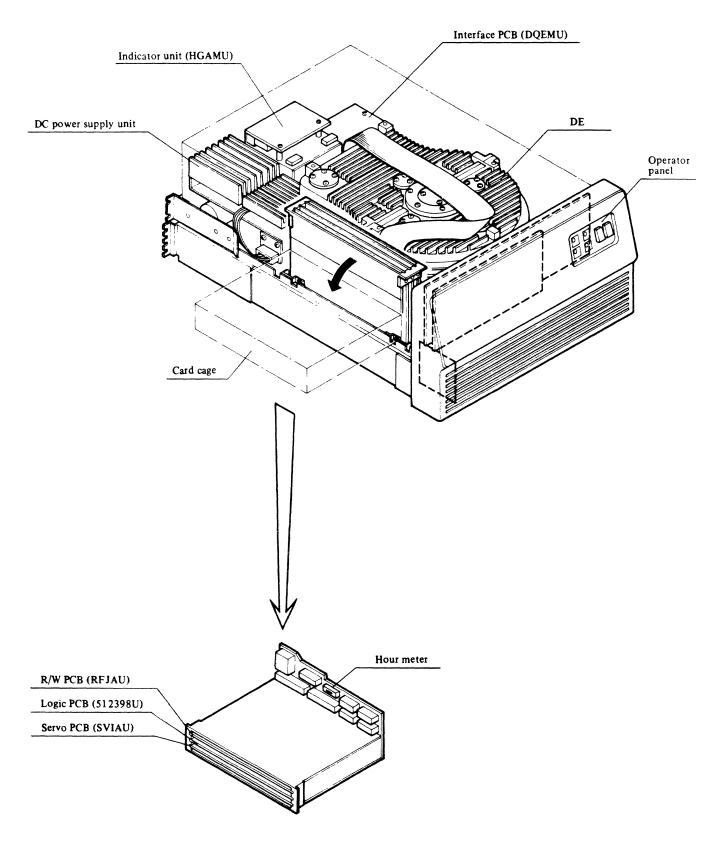

Note: ''Early version'' denotes M2351A (- #1898) and ''Current version'' denotes M2351A (#1899-). Regarding the M2351AF, all drives are ''Current version''.

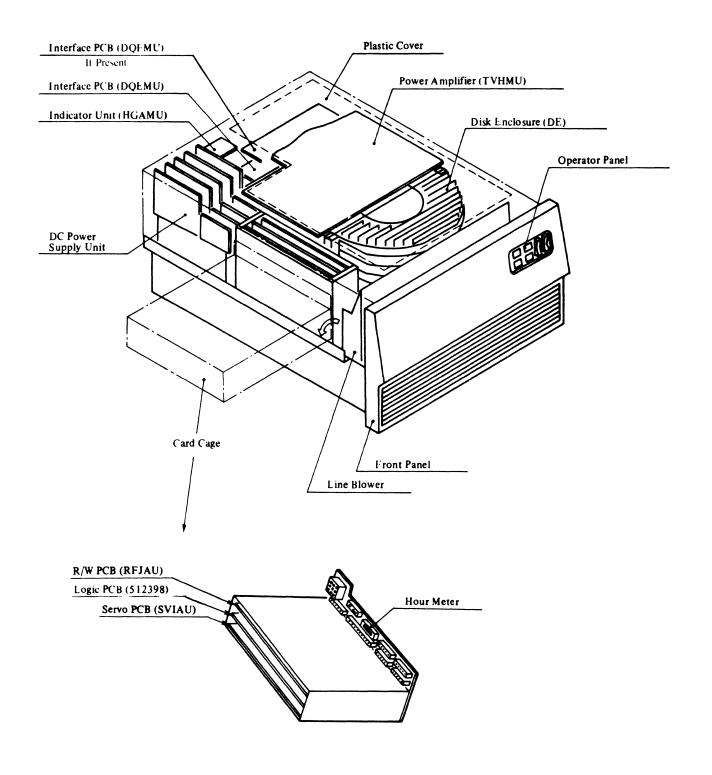

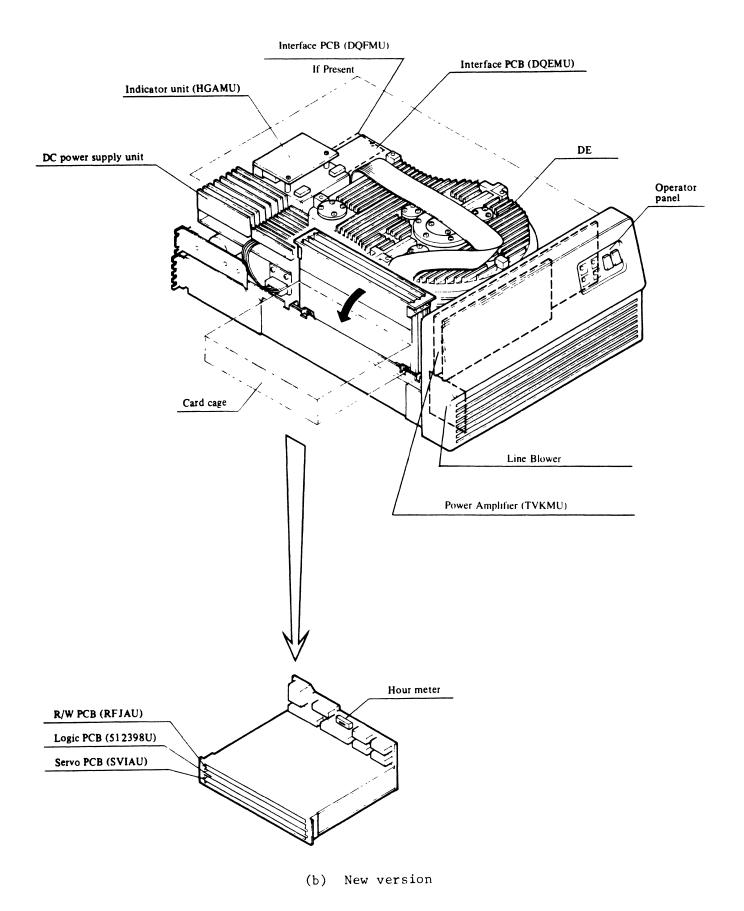

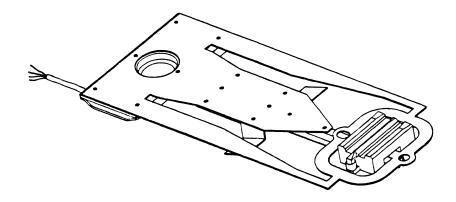

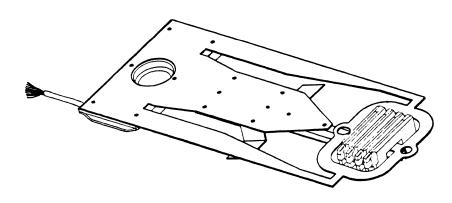

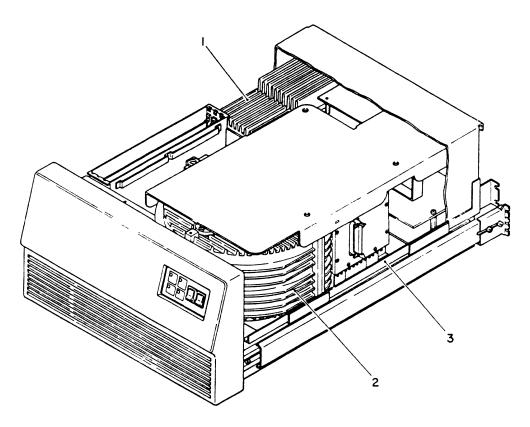

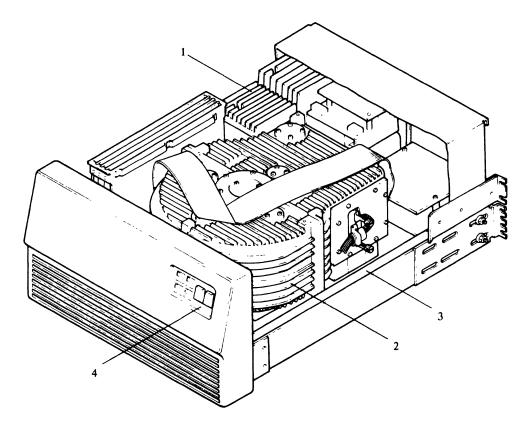

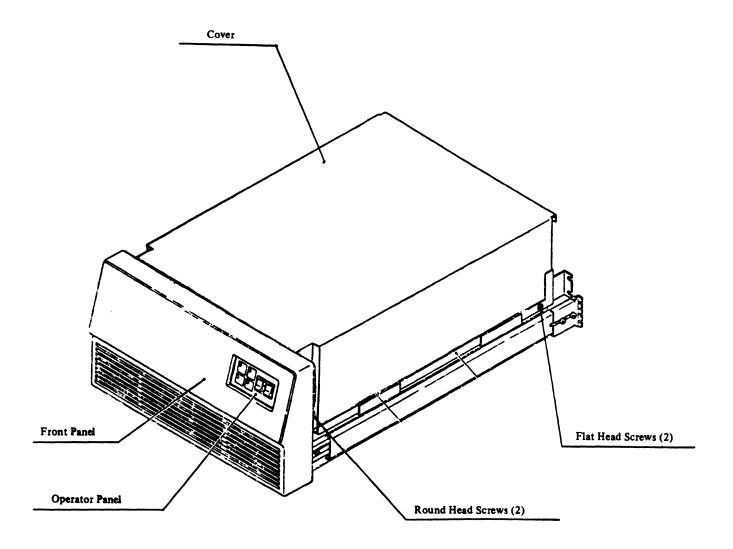

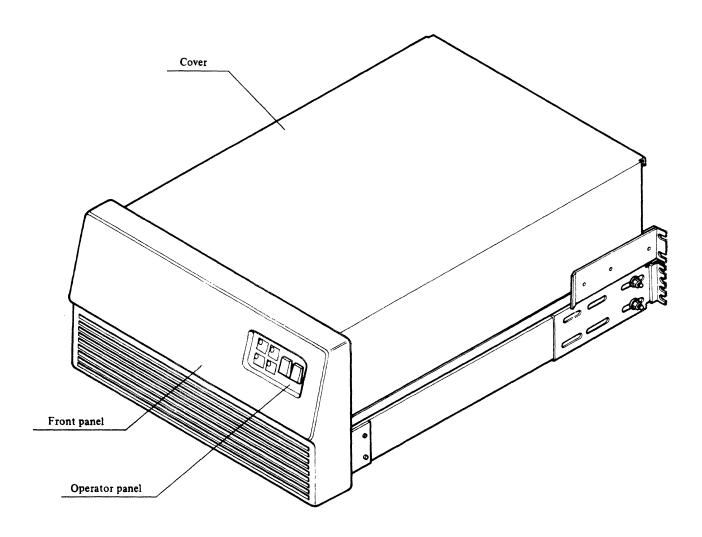

Fig. 1.1-1 External View of M2351A/AF B03P-4655-0001A...E1

### 1.2 FEATURES

## (1) Large Capacity and High Performance

- 474 megabytes of unformatted data can be stored on six disks.

- The M2351 disk drive provides exceedingly high performance characteristics such as 1.859 megabytes per second data transfer, 18 milliseconds average access time, and 7.58 milliseconds average latency time.

### (2) Compact Size

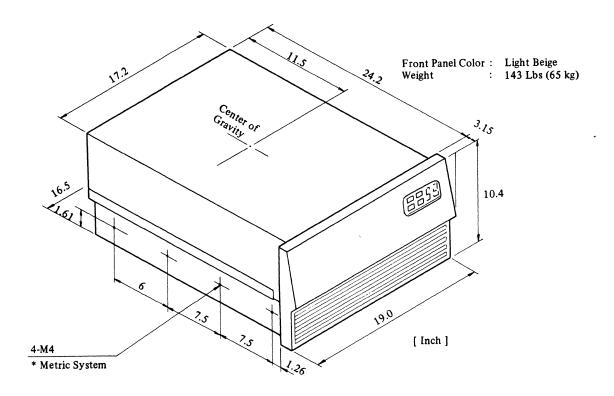

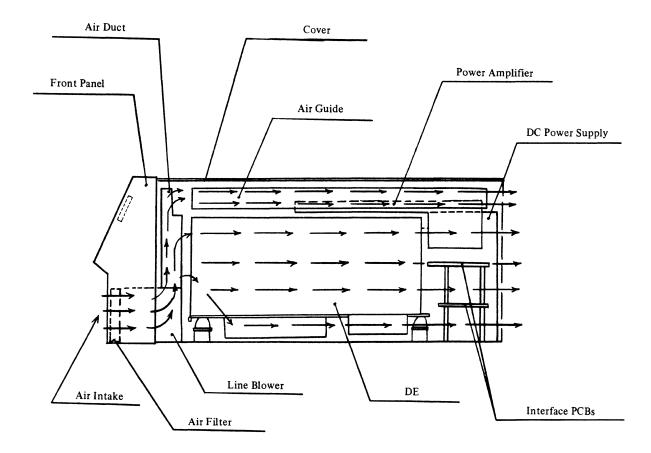

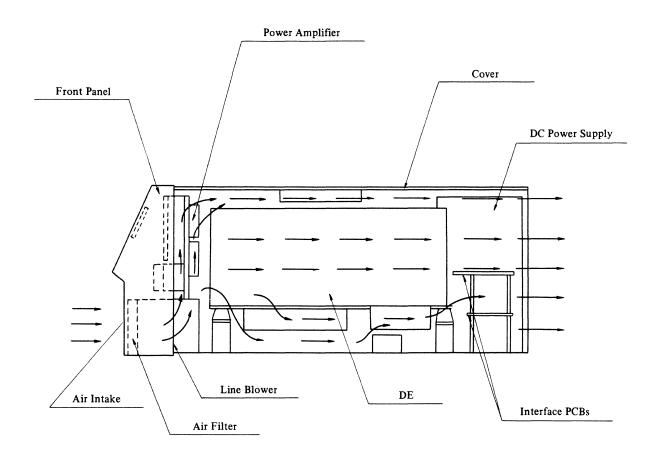

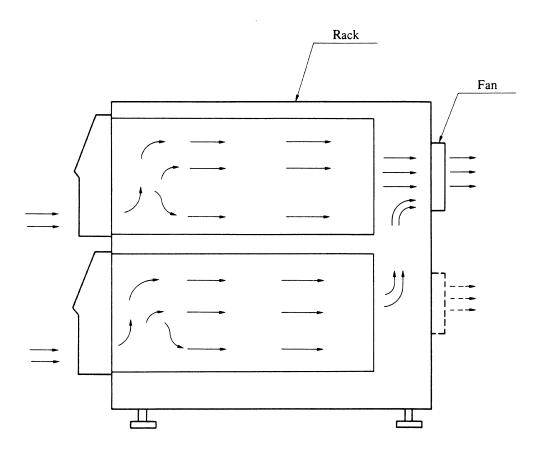

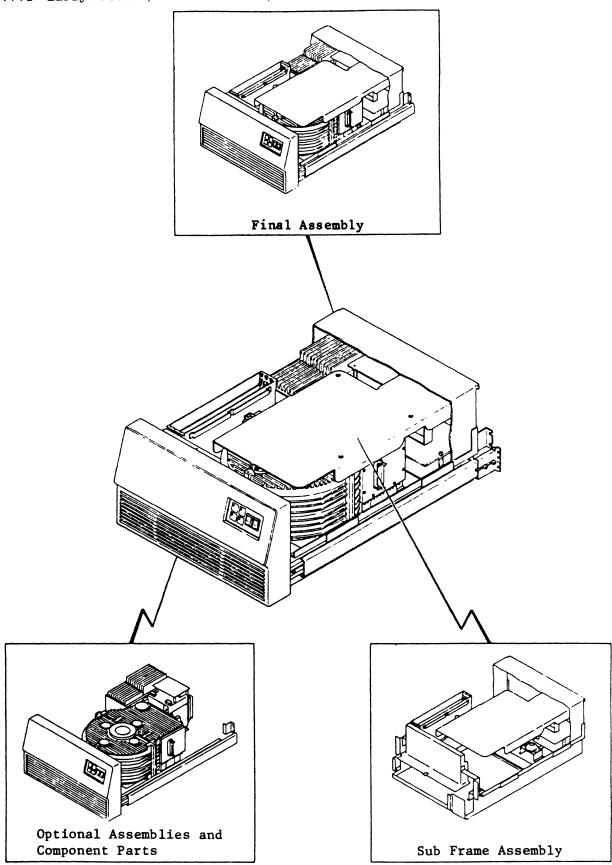

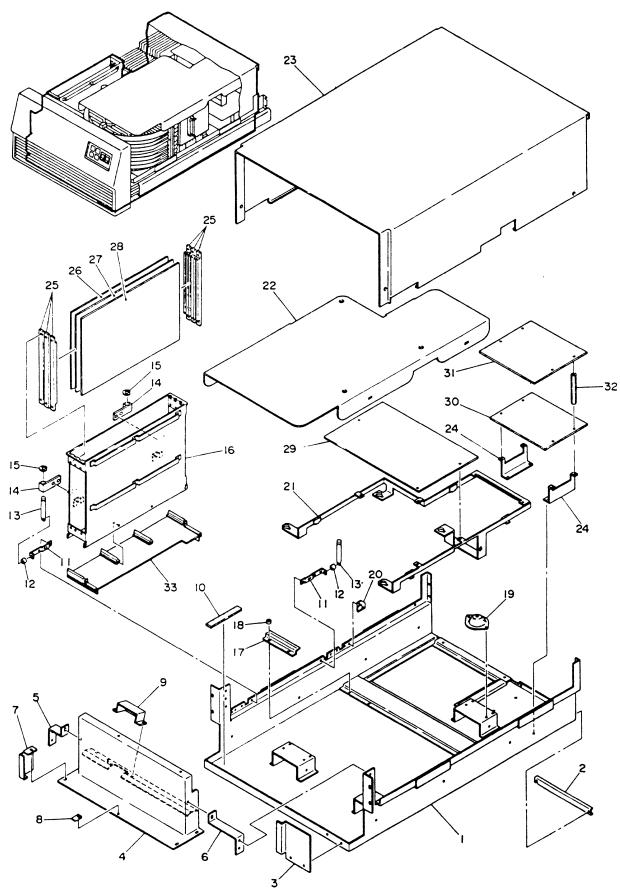

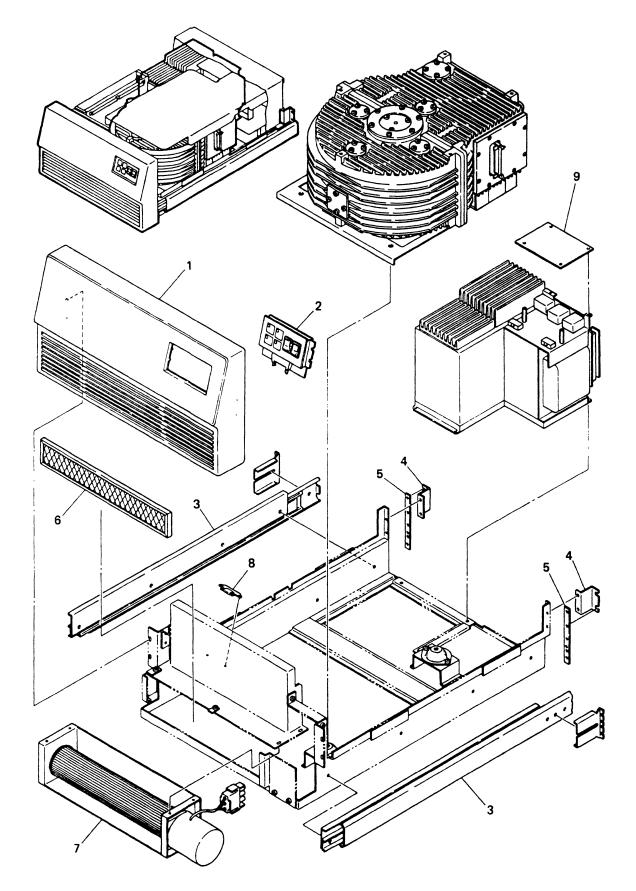

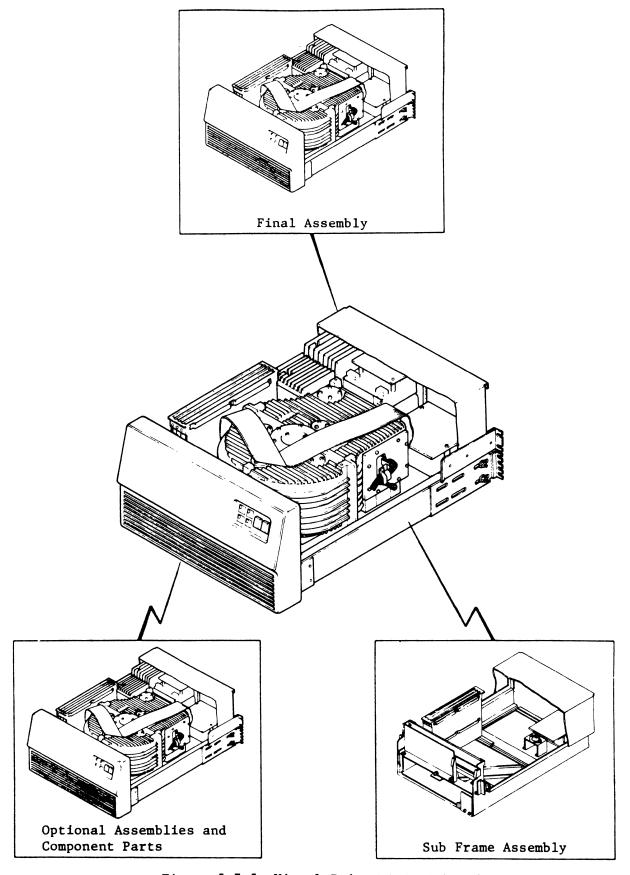

The disk drive is a compact unit containing Disk Enclosure (DE), DC power supply and circuit boards, is designed for mounting in a standard 19-inch rack.

## (3) High Reliability

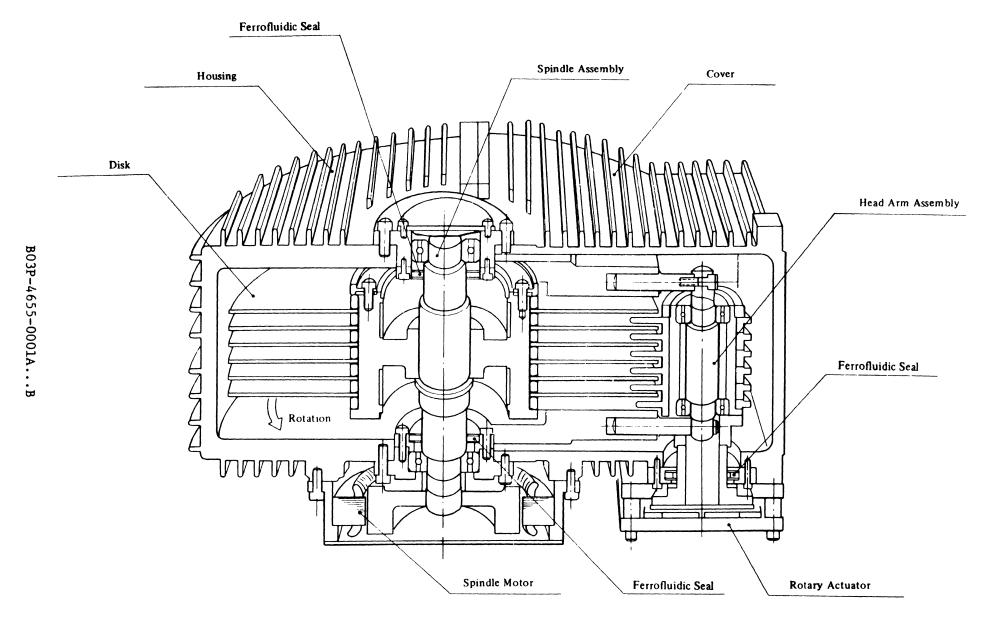

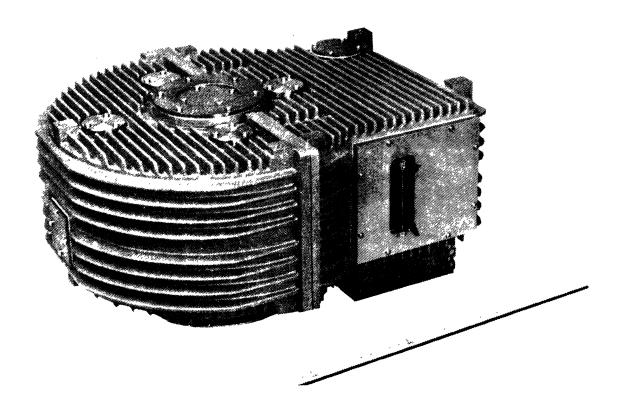

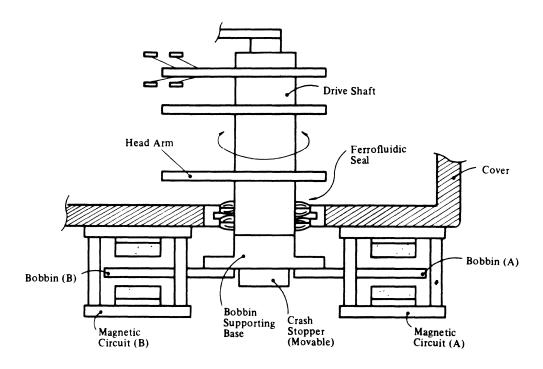

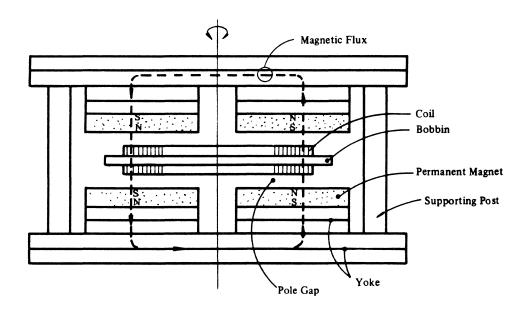

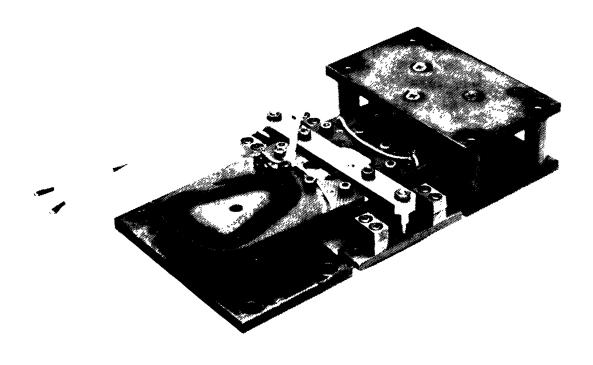

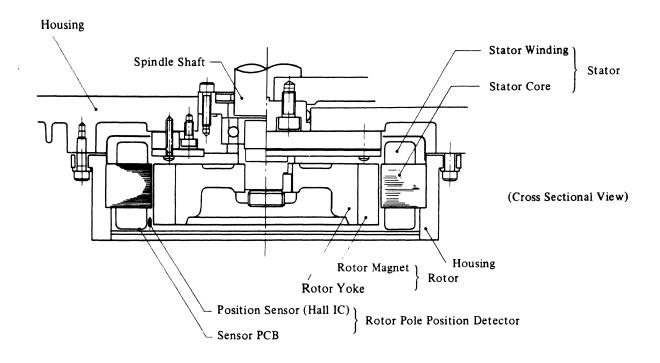

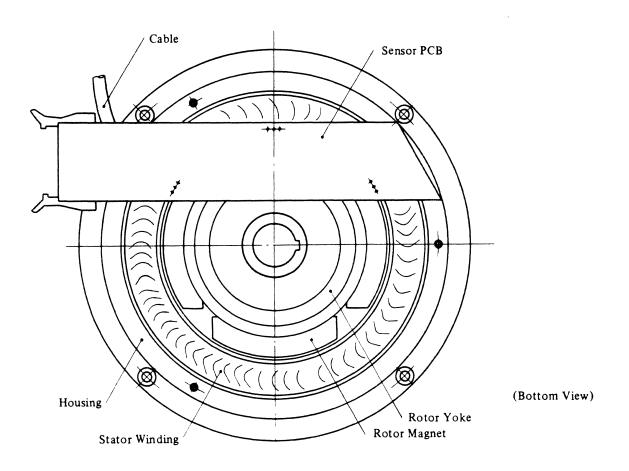

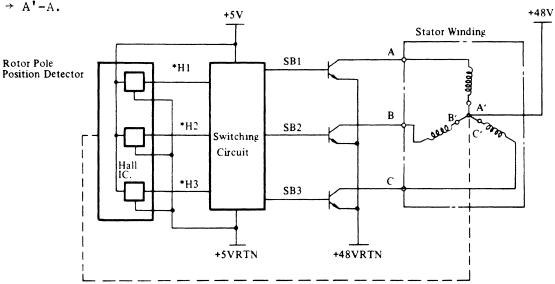

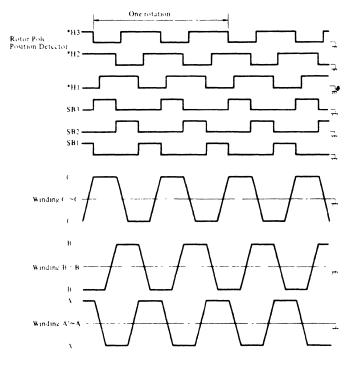

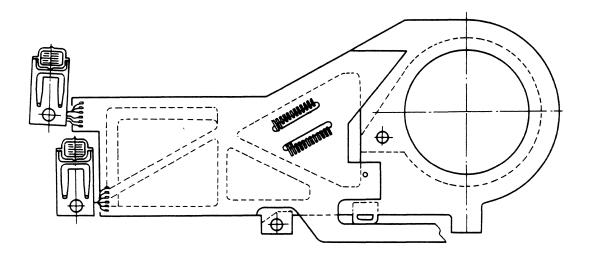

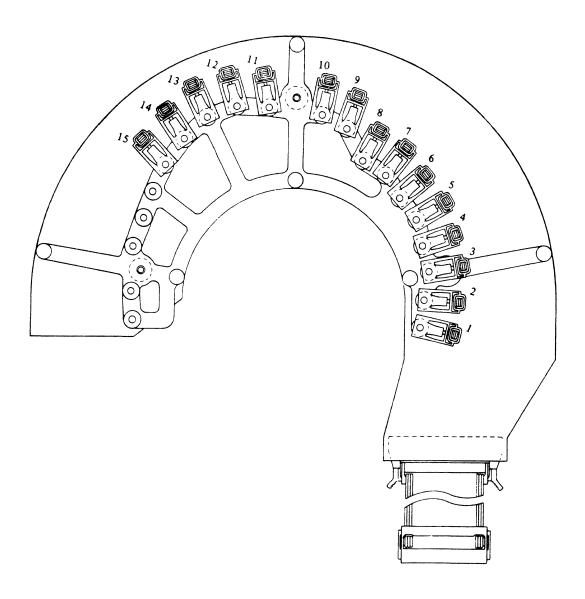

The disk enclosure includes a rotary actuator, a direct-drive spindle motor, the magnetic heads, disks and carriage. A completely sealed self-contained airflow system is used within the DE to assure a clean environment for low-flying heads, thus ensuring very high reliability.

### (4) High Serviceability

- The drive is modular in construction. All major subassemblies are easily removed/replaced in the field.

- Serviceability is further improved by diagnostic information provided on the maintenance-aid display and/or sense information provided by the interface signals.

### (5) Maintenance-free

The M2351 disk drive requires substantially reduced maintenance because of the completely sealed DE, a direct-drive DC Spindle motor and highly reliable printed circuit boards.

### (6) Other Features

High recording density with state-of-the-art technology

A recording density of more than 10<sup>7</sup> bits per square inch is achieved with the advanced head and disk.

- Low power consumption

Less than 0.70 KVA is required despite the large storage capacity.

### - Fixed-head model

The M2351AF has a fixed-head area of 1.69 megabytes (unformatted) capacity. The data in this area can be accessed without positioning time delay but with only latency time delay, thus providing high system throughput.

### - Dual channel feature

This option permits two controllers to access the same disk drive so that a file can be shared by two different systems.

### - Modified SMD Interface

The interface signals between the controller and the disk drive are partially modified from the standard SMD interface to agree with higher track capacity and higher maintainability.

The following are the major modified items.

- (1) Data transfer rate

- (2) Track capacity

- (3) Timing of Read/Write operation

- (4) Addition of Tag 4 and Tag 5

Fig. 1.1-2 Physical Dimensions

## 1.3 PERFORMANCE SPECIFICATIONS

Table 1.3-1 Specifications of M2351A/AF

| Canadity           | /Drive (MB)     | 474.2 (Unformatted)  |  |  |  |

|--------------------|-----------------|----------------------|--|--|--|

| Capacity ———       | /Track (KB)     | 28.160 (Unformatted) |  |  |  |

| Configuration of D | isks and Heads  | Fixed heads  6       |  |  |  |

| Fixed Head         | Tracks          | 60 (3 Cylinders)     |  |  |  |

| (M2351AF Only)     | Capacity (MB)   | 1.69 (Unformatted)   |  |  |  |

| Rotational Speed ( | RPM)            | 3,961                |  |  |  |

| Latency (ms)       |                 | 7.5                  |  |  |  |

| Disk ————          | Diameter (Inch) | 10.5                 |  |  |  |

| DISK -             | Number          | 6                    |  |  |  |

| Heads              | /Drive          | 20 + 1 (Servo)       |  |  |  |

| neaus              | /Surface        | 2                    |  |  |  |

| Cylinders          |                 | 842                  |  |  |  |

| Data Transfer Rate | (MB/sec)        | 1.859                |  |  |  |

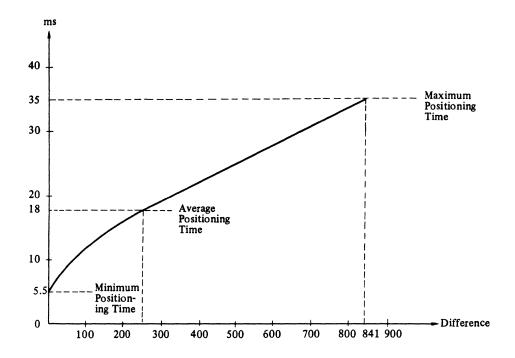

|                    | Maximum         | 35                   |  |  |  |

| Positioning Time   | Average         | 18                   |  |  |  |

| (ms)               | Minimum         | 5.5                  |  |  |  |

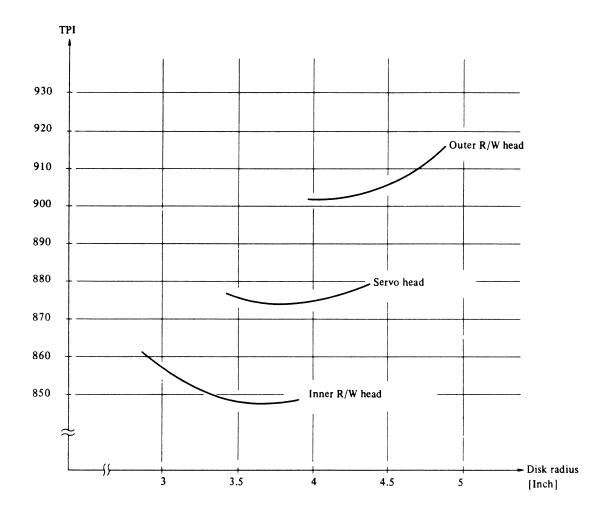

| Track Density (TPI | )               | 880                  |  |  |  |

| Bit Density (BPI)  |                 | 12,800               |  |  |  |

| D . G .W           | on interface    | NRZ                  |  |  |  |

| Data Coding ————   | on disk surface | MFM                  |  |  |  |

Fig. 1.3-1 Positioning Time vs. Difference

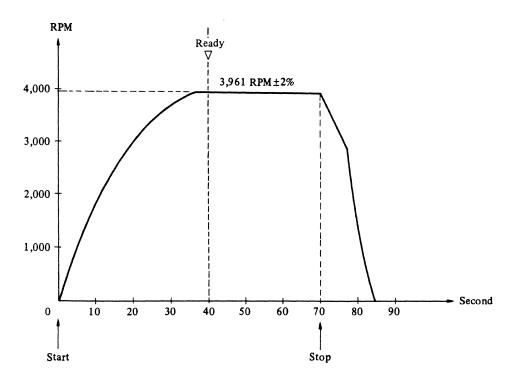

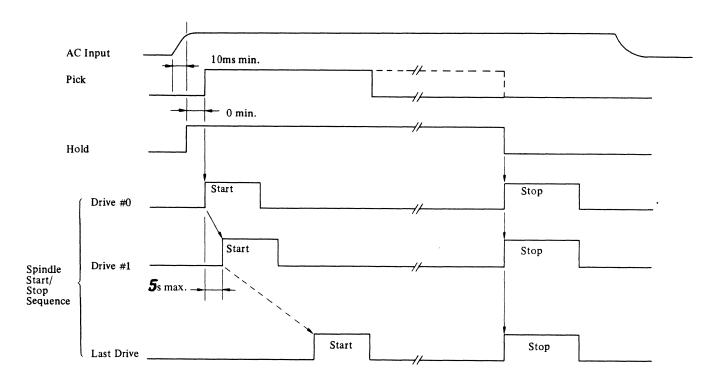

Fig. 1.3-2 Spindle Start/Stop Time

## 1.4 ENVIRONMENTAL SPECIFICATIONS

Table 1.4-1 Environmental Requirements

| Environment  | Storage on<br>in package                                                  |                                                                         | On Site<br>Non-Operating                                | Operating<br>Office<br>Environment                      |  |  |

|--------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|--|--|

| Temperature* | Within 24<br>Hours                                                        | More than 24<br>Hours                                                   | 23°F ∿ 140°F                                            | 50°F ∿ 104°F                                            |  |  |

|              | -40°F ~ 140°F<br>(-40°C ~ 60°C)<br>Max change<br>36°F/Hour<br>(20°C/Hour) | 23°F ∿ 140°F<br>(-5°C ∿ 60°C)<br>Max change<br>18°F/Hour<br>(10°C/Hour) | (-5°C ∿ 60°C)<br>Max change<br>18°F/Hour<br>(10°C/Hour) | (10°C ∿ 40°C)<br>Max change<br>18°F/Hour<br>(10°C/Hour) |  |  |

| Humidity     | 5% ∿ 95% RH<br>Non-condensing                                             |                                                                         | 20% ∿ 80% RH<br>Max change 10%/Hour<br>Non-condensing   |                                                         |  |  |

| Vibration    | 3G (When locked shipment)                                                 | l for                                                                   | 0.2G<br>(10Hz ~ 500Hz)                                  | 0.2G<br>(5Hz ~ 50Hz)<br>1G<br>(50Hz ~ 500Hz)            |  |  |

| Shock        | 5G (Max. 30 ms)                                                           |                                                                         | 3G (Max. 10ms)                                          | 2G (Max. 10ms)                                          |  |  |

| Altitude     | 40,000 FT (12,0                                                           | 000 m)                                                                  | 10,000 FT (3,00                                         | 00 m)                                                   |  |  |

| Dust         | $0.168 \text{ mg/m}^3$ (St                                                | tearic Acid Stan                                                        | dard)                                                   | lard)                                                   |  |  |

| Air flow     |                                                                           | -                                                                       |                                                         | 2.5 m <sup>3</sup> /min.                                |  |  |

| Acoustic     |                                                                           |                                                                         |                                                         | 60 dBA                                                  |  |  |

<sup>\* °</sup>C =  $\frac{5}{9}$ (°F-32)

B03P-4655-0001A...C

## 1.5 POWER SPECIFICATIONS

| Voltage   | Frequency | Current   | (Aac)             | Power Consumption | Heat Dissiptation (K•Cal/ BTU/ |             |             |

|-----------|-----------|-----------|-------------------|-------------------|--------------------------------|-------------|-------------|

| (Vac±10%) | (Hz±2Hz)  | Starting* | Running           | (KVA)             | Hour)                          | Hour        |             |

| 100       |           |           | 5.7/5.4           | 0.57/0.54         | 460/420                        | 1,800/1,600 |             |

| 120       |           |           | 4.8/4.6 0.58/0.55 |                   | 0.58/0.55                      | 470/430     | 1,900/1,700 |

| 200       | 50/60     | 5.3       | 3.1/3.0           | 0.62/0.60         | 510/480                        | 2,000/1,900 |             |

| 220       |           |           | 2.9/2.8           | 0.63/0.62         | 510/500                        | 2,000/1,900 |             |

| 240       |           |           | 2.6/2.5           | 0.62/0.60         | 510/480                        | 2,000/1,900 |             |

Table 1.5-1 Power Requirements (Typical Values)

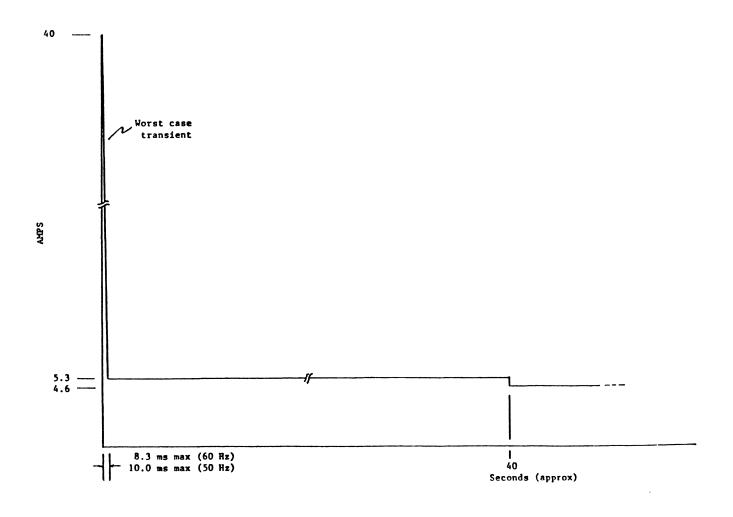

<sup>\*</sup>Worst case transient with a maximum of 40 amps for less than 1/2 cycle of input AC Power. Refer to Figure 1.5-1.

Fig. 1.5-1 AC START/RUN CURRENT CURVE M2351A

## 1.6 CABLE AND CONNECTOR SPECIFICATIONS

Table 1.6-1 Cables and Connectors

|                      | Cab                                 | le                             | Connector (                 | (Supplier)                  |  |  |

|----------------------|-------------------------------------|--------------------------------|-----------------------------|-----------------------------|--|--|

|                      | Specification                       | Supplier                       | Drive Side                  | Cable Side                  |  |  |

| A-Cable<br>(60-Pin)  | Zo = 100±10Ω<br>28 AWG<br>7 Strands | SPECTRA<br>STRIP<br>455-248-60 | FUJITSU<br>FCN-704P060-AU/L | FUJITSU<br>FCN-707J060-AU/B |  |  |

|                      | 100 FT. Max.                        | 433-246-60                     | 3M<br>3472-2303             | 3M<br>3334-6010             |  |  |

| B-Cable (26-Pin)     | $Zo = 100 \pm 10\Omega$ 28 AWG      | ANSLEY<br>174-26               | FUJITSU<br>FCN-705P026-AU/L | FUJITSU<br>FCN-707J026-AU/B |  |  |

|                      | 7 Strands<br>50 FT. Max.            |                                | 3M<br>3429-1303             | 3M<br>3399-6010             |  |  |

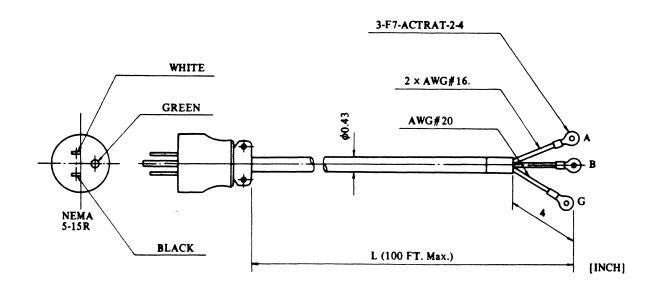

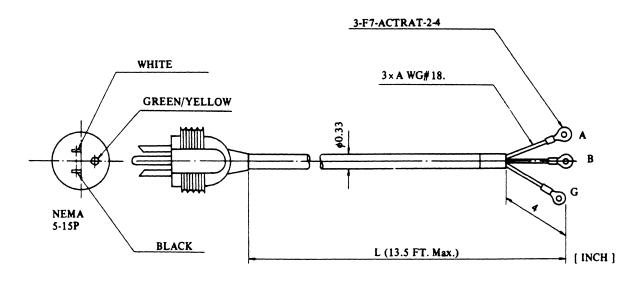

| Power<br>Cable A     |                                     | See Fi                         | gure 1.6-1                  |                             |  |  |

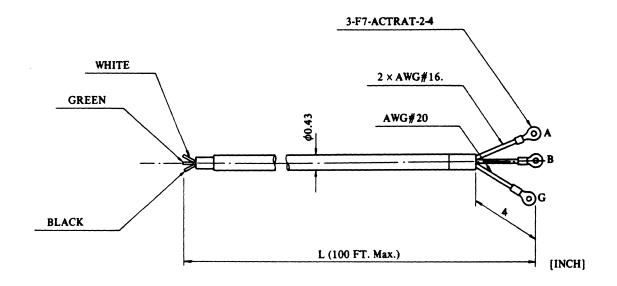

| Power<br>Cable B     |                                     | See Figure 1.6-2               |                             |                             |  |  |

| Power<br>Cable C ∿ D |                                     | See Fi                         | gure 1.6-3                  |                             |  |  |

Fig. 1.6-1 Power Cable A

Fig. 1.6-2 Power Cable B

Fig. 1.6-3 Power Cable C  $\sim$  D

## 1.7 OPTIONS

Table 1.7-1 Option List

| No. | Name                       | Specification             |                                                                                            | Remark                                             |  |  |

|-----|----------------------------|---------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| 1   | A-Cable                    | B660-1065-T006A           | Non-shield                                                                                 | Cable length can be                                |  |  |

| 2   | A-Cable                    | B660-1954-T904A           | Shield                                                                                     | specified from 0.5 m to 30 m in 0.5 m increments * |  |  |

| 3   | B-Cable                    | B660-1065-T008A           | Non-shield                                                                                 | Cable length can be specified from 0.5 m to        |  |  |

| 4   | B-Cable                    | B660-1954-T903A           | Shield                                                                                     | 15 m in 0.5 m increments*                          |  |  |

| 5   | Power Cable A<br>(UL only) | B660-1055-T027A           | Cable length can be specified from 1 m to 30 m in 0.5 m increments. (100/120 Vac only)     |                                                    |  |  |

| 6   | Power Cable B (UL, CSA)    | B660-0620-T387A           | Cable length can be specified from 1 m to 30 m in 0.5 m increments. (200/220/240 Vac only) |                                                    |  |  |

| 7   | Power Cable C<br>(UL, CSA) | B660-1055-T033A           | L = 2.5 m,                                                                                 | (100/120 Vac only)                                 |  |  |

| 8   | Power Cable D (UL, CSA)    | B660-1055-T034A           | L = 3.5  m, (100/120  Vac only)                                                            |                                                    |  |  |

| 9   | Power Cable E (UL, CSA)    | B660-1055-T035A           | L = 4.5 m,                                                                                 | (100/120 Vac only)                                 |  |  |

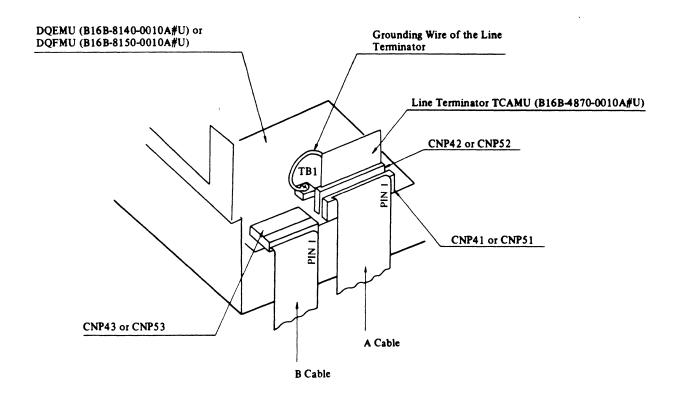

| 10  | Line Terminator (TCAMU)    | B16B-4870-0010A#U         | 1                                                                                          | wo line terminators are dual channel system.       |  |  |

| 11  | Dual Channel<br>Option     | B03B-4655-0100A           |                                                                                            |                                                    |  |  |

| 12  | Slide Guide<br>Option      | B030-4655-V100A           |                                                                                            |                                                    |  |  |

| 13  | Front Panel<br>Option      | B210-1435-X012A           |                                                                                            |                                                    |  |  |

| 14  | Operator Panel<br>Assembly | N860-3346-T001            |                                                                                            |                                                    |  |  |

| 15  | Hour Meter                 | B61L-0140-0011A<br>#10000 | 10,000 hour                                                                                | S                                                  |  |  |

Note: Check with your local sales office for length available

Note that the Fixed-Head is not an option but a model change from the Non Fixed-Head drive.

Non Fixed-Head Drive; M2351A (B03B-4655-B002A)

Fixed Head Drive ; M2351AF (B03B-4655-B003A)

When M2351A or M2351AF is ordered alone, it does not include the front panel, operator panel, etc. listed in Table 1.7-1.

A-, B- and Power Cable A, B length must be specified by adding comment behind the cable specification.

Example: B660-1065-T006A #10.5 m (A-Cable, 10.5 meters)

## 1.8 SPARE PARTS

Table 1.8-1 Recommended Spare Parts List

| No. | Name                       | Specification           | Qua | ntity | MTBF      |   |   | D-                                         | marks                                    |

|-----|----------------------------|-------------------------|-----|-------|-----------|---|---|--------------------------------------------|------------------------------------------|

| No. | Name                       | Specification           | A   | AF    | (K-hours) |   |   | Ke                                         | marks                                    |

| 1   | DE Assembly                | B030-4610-T005A         | 1   | _     | 60        |   |   | Non-fixed                                  | M2351A<br>(#1~#1898)                     |

| 1   | DE Assembly                | B030-4610-T007A         | 1   | _     | 60        |   |   | heads type                                 | M2351A<br>(#1899~)                       |

|     | DE Assembly                | B030-4610-T006A         | -   | 1     | 60        |   |   | Fixed                                      | _                                        |

| 2   | DE Assembly                | B030-4610-T008A         | _   | 1     | 60        |   |   | heads type                                 | M2351AF<br>(#1~)                         |

| 3   | DC Power<br>Supply         | B14L-5105-0073A         | 1   | 1     | 200       |   |   |                                            |                                          |

| 4   | Line Blower                | B90L-1200-0101A         | 1   | 1     | 400       | _ | _ |                                            |                                          |

| 5   | Operator Panel<br>Assembly | N860-3346-T001          | 1   | 1     | 400       |   |   |                                            |                                          |

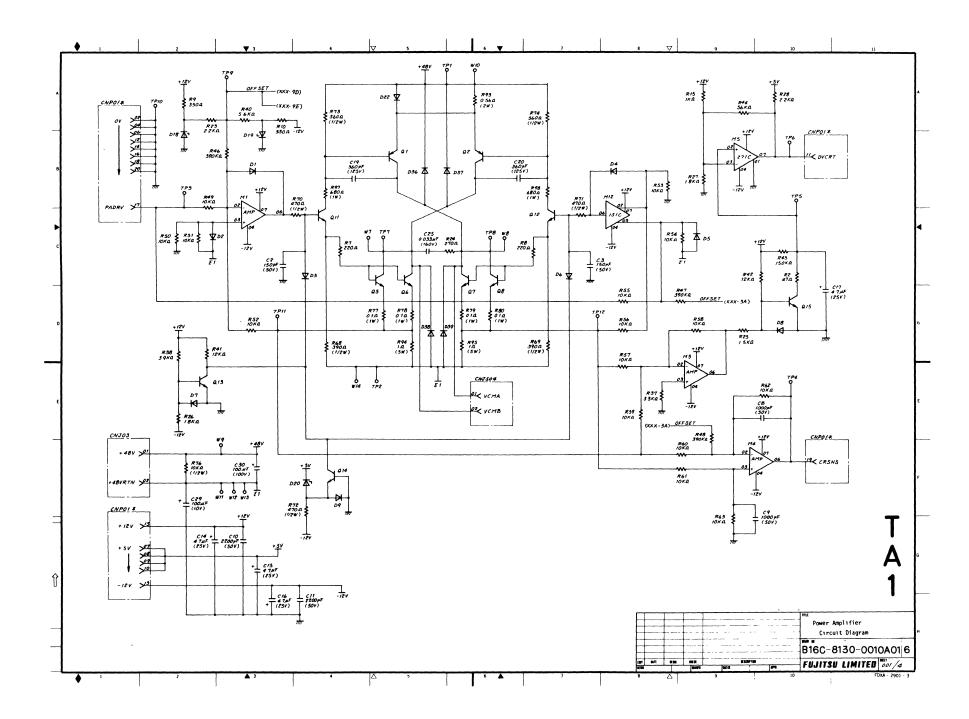

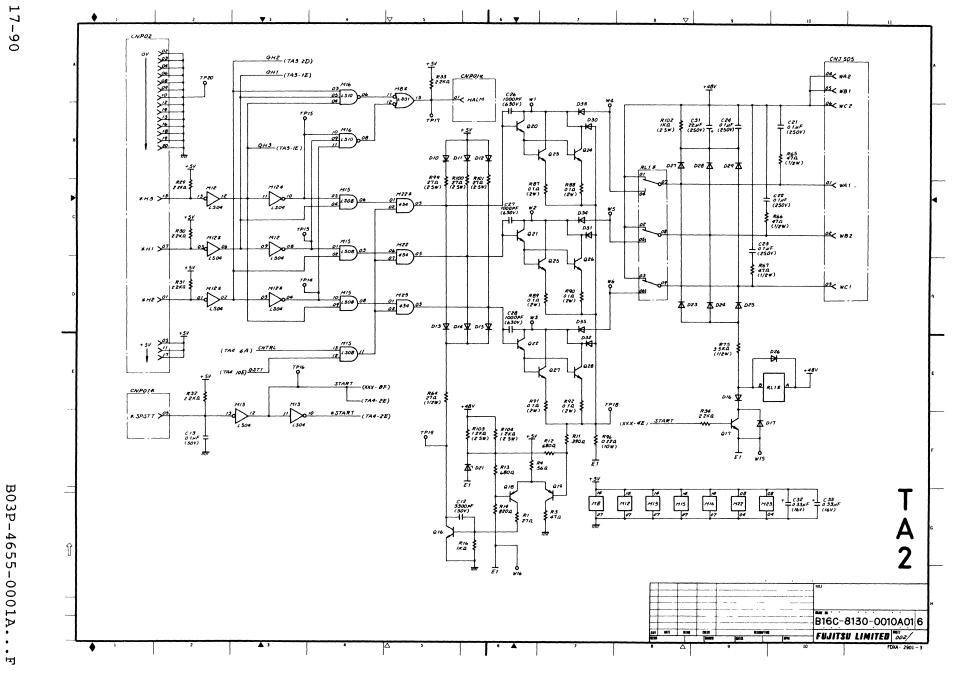

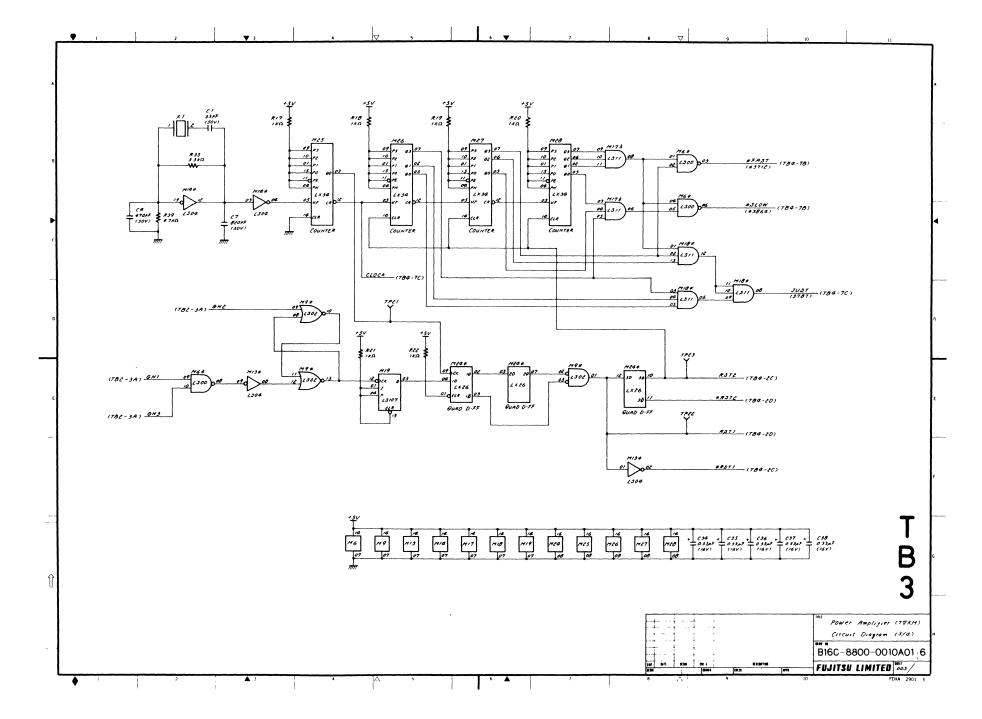

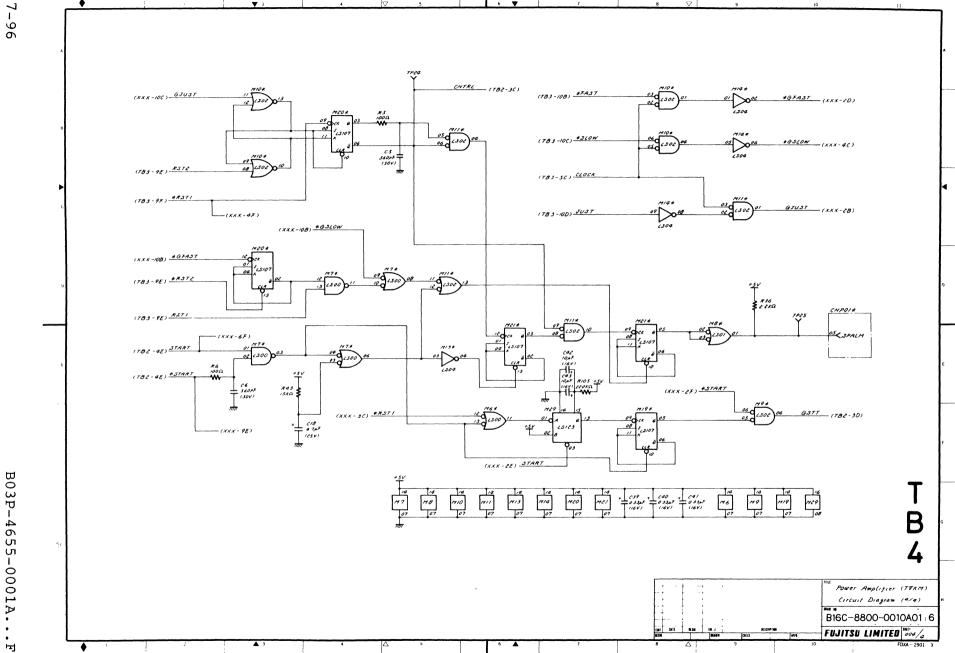

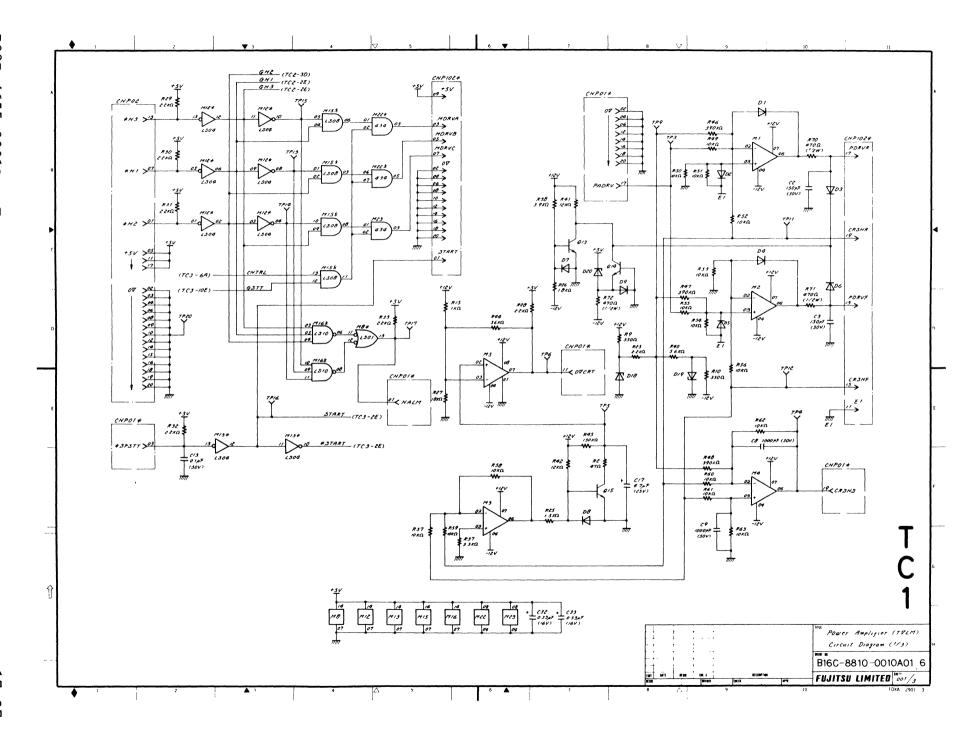

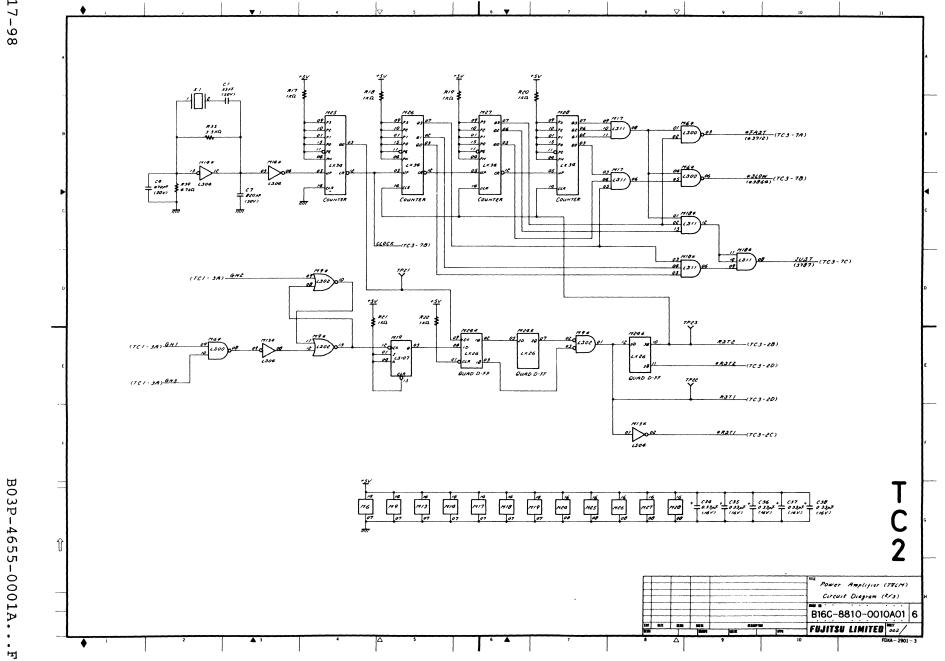

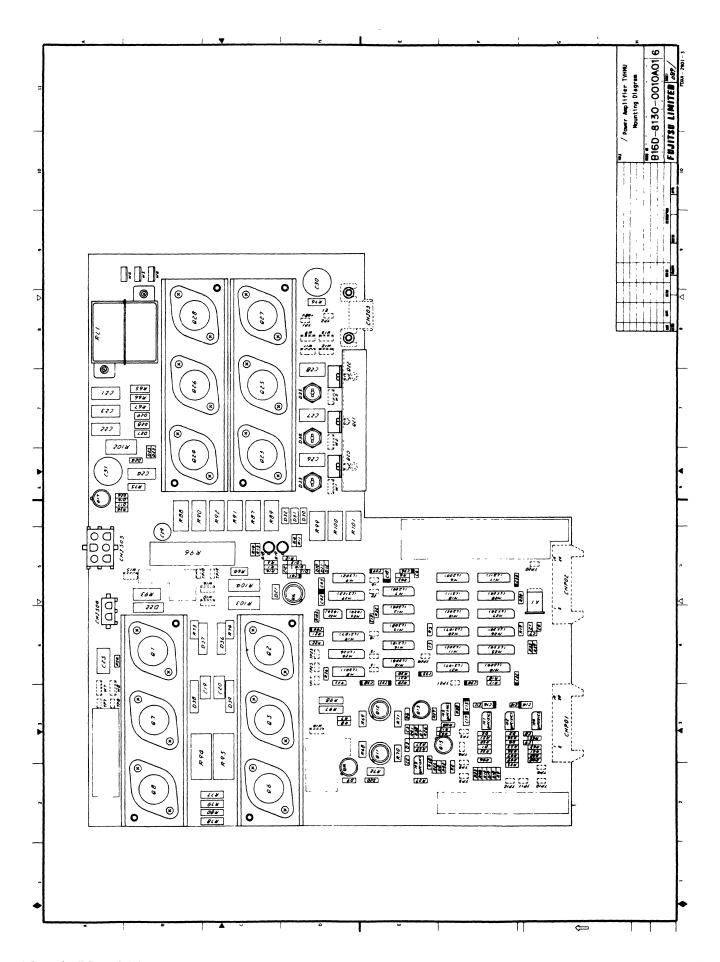

| 6   | PCB TVHMU                  | B16B-8130-0010A#U       | 1   | 1     | 360       |   |   | Power                                      | M2351A<br>(#1~#1898)<br>M2351AF<br>( – ) |

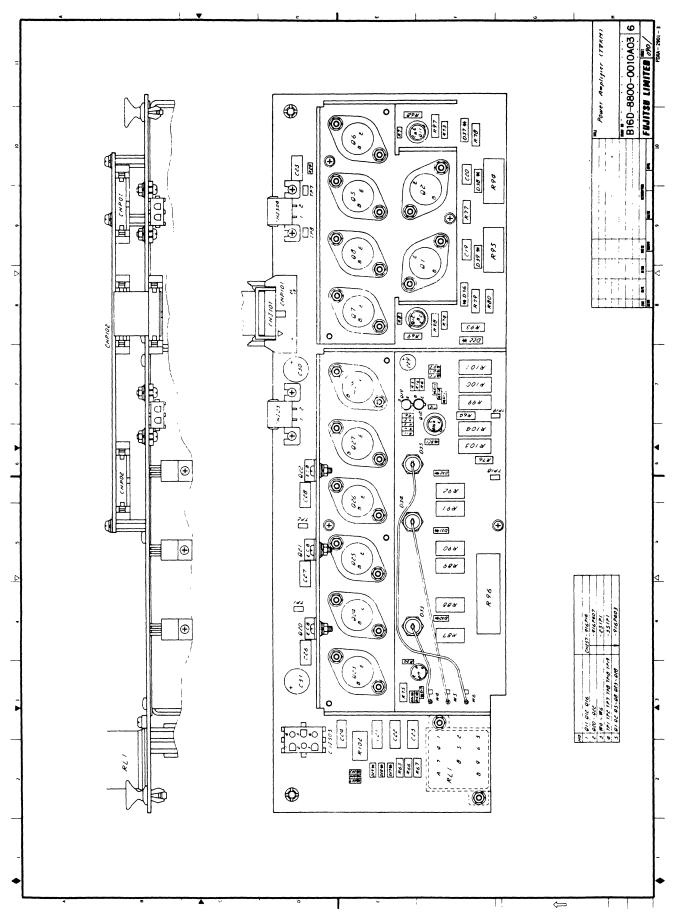

| U   | PCB TVKMU                  | B16B-8800-0010A#U       | 1   | 1     | 360       |   |   | Amplifier                                  | M2351A<br>(#1899~)<br>M2351AF<br>(#1~)   |

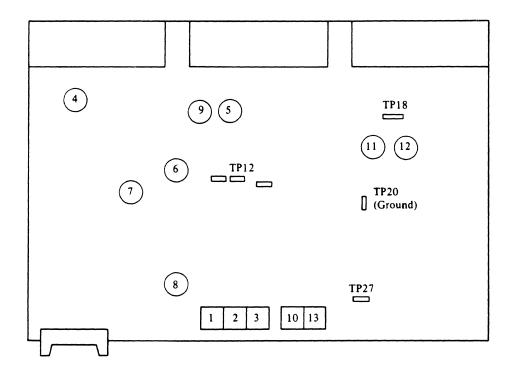

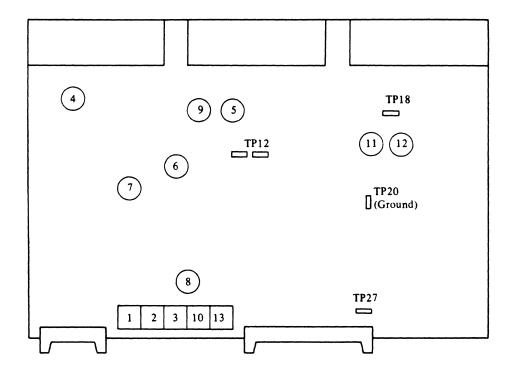

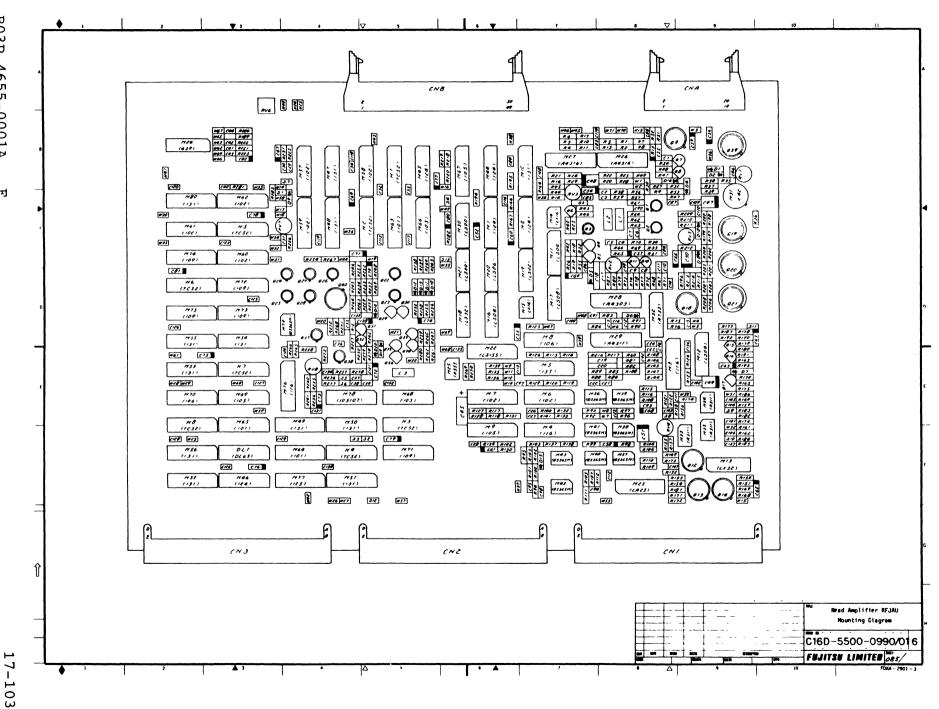

| 7   | PCB RFJAU                  | C16B-5500-0990#U        | 1   | 1     | 220       |   |   | Read Amplif                                | ier                                      |

| 8   | PCB SVIAU                  | C16B-5501-0010#U        | 1   | 1     | 180       |   |   | Servo Circuit                              |                                          |

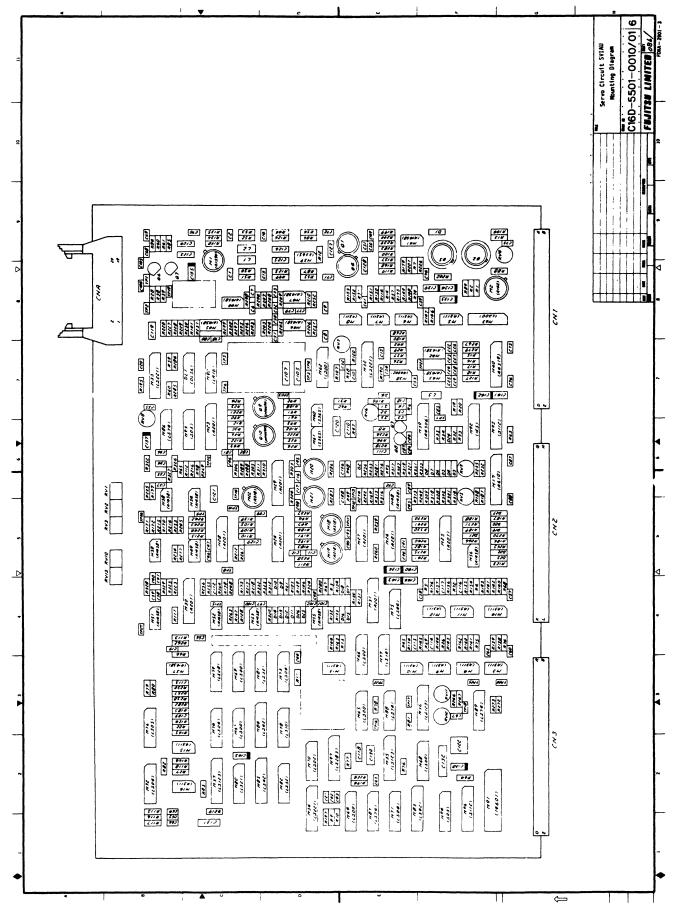

| 9   | PCB 512398                 | C16B-5123-0980#U        | 1   | 1     | 420       |   |   | Logic Circuit                              |                                          |

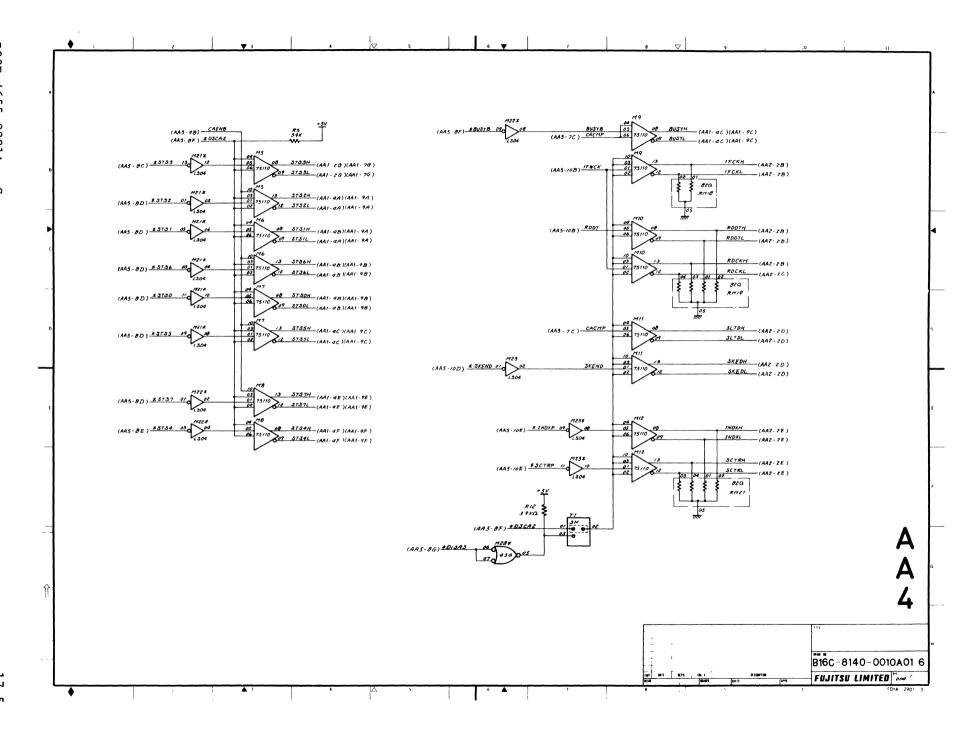

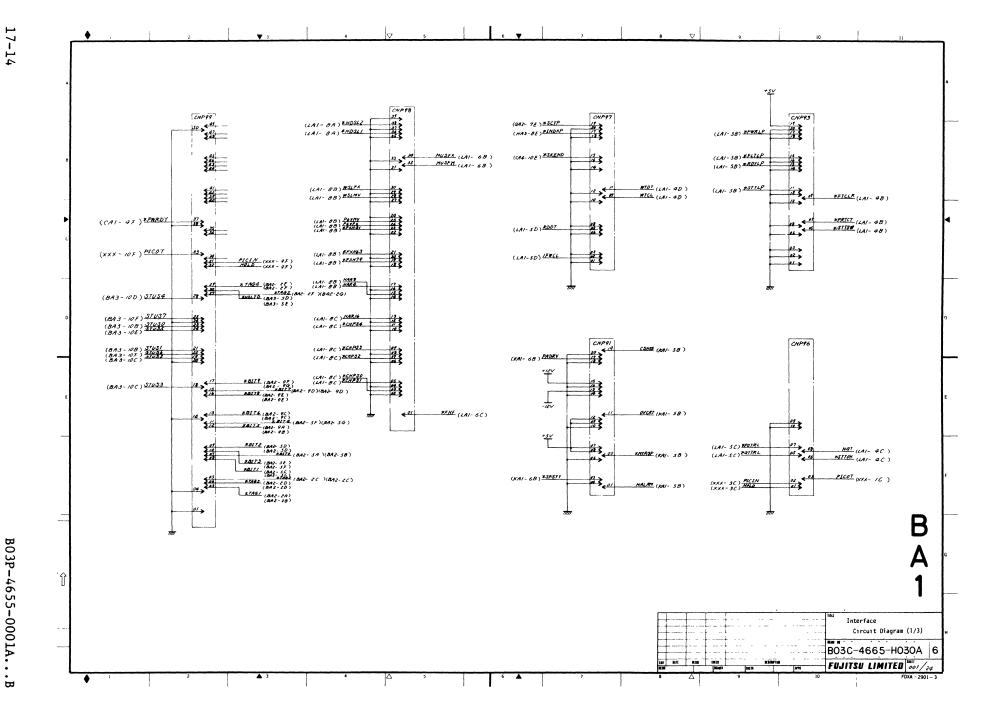

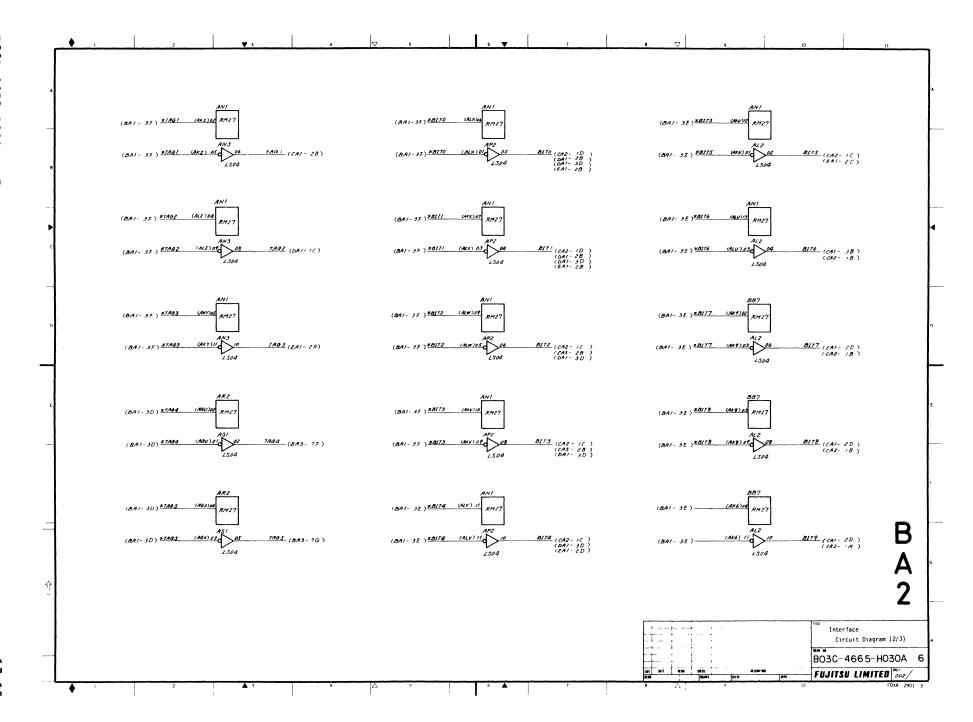

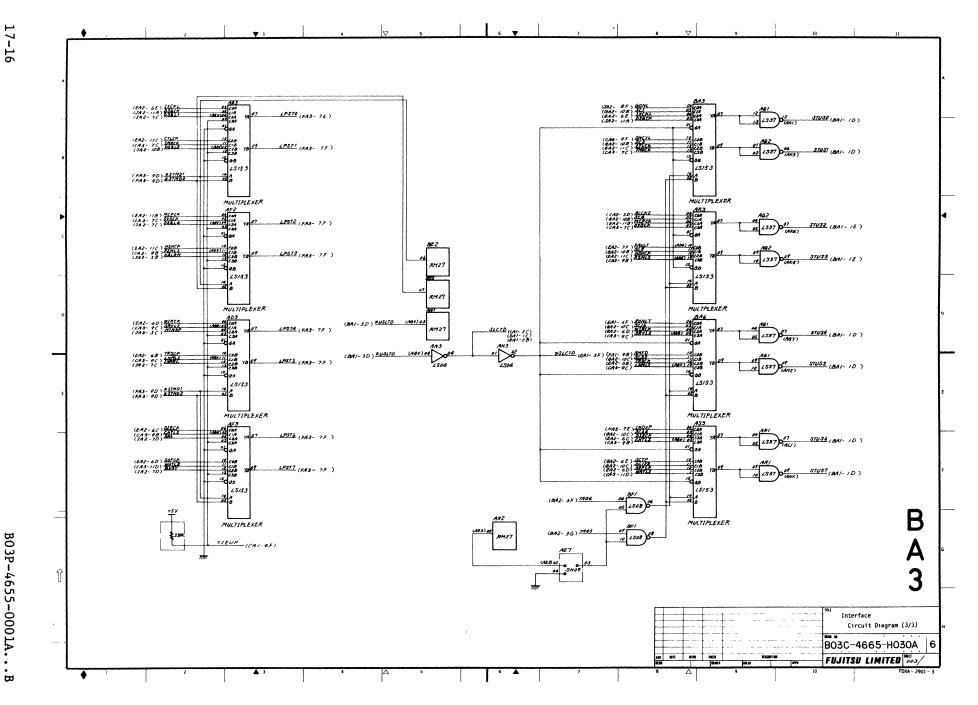

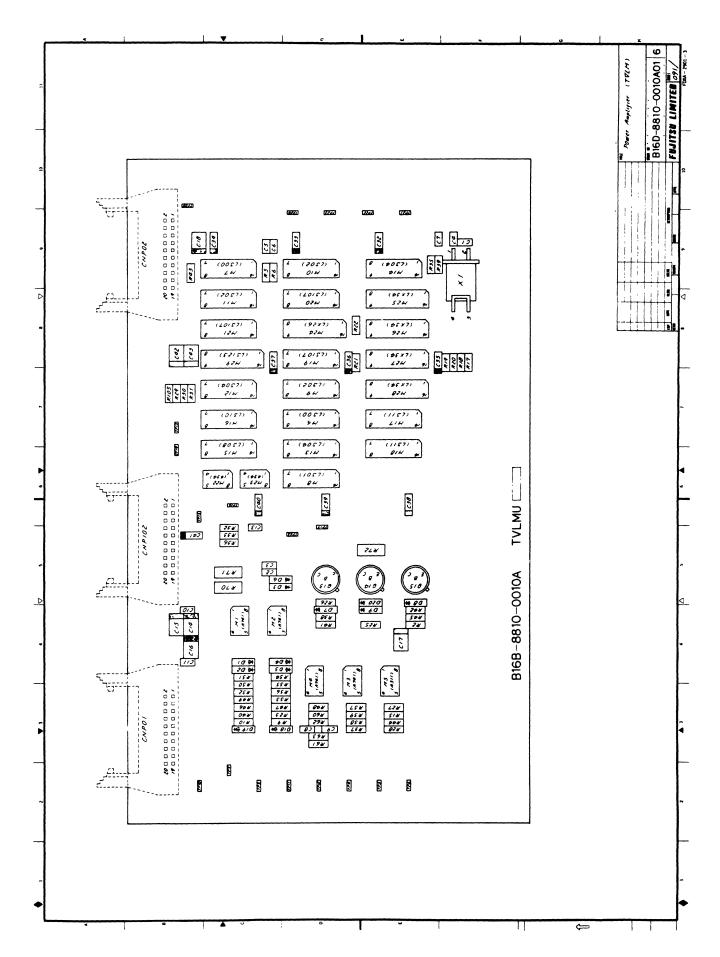

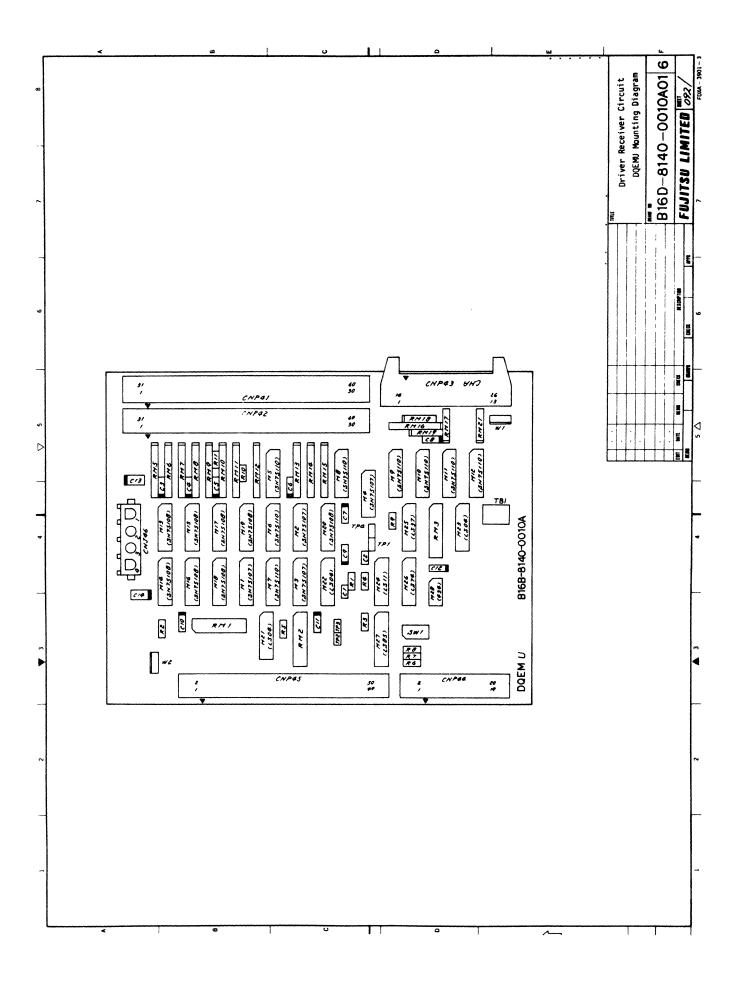

| 10  | PCB DQEMU                  | B16B-8140-0010A#U       | 1   | 1     | 500       |   |   | Interface Circ                             | cuit                                     |

| 11  | PCB HGAMU                  | B16B-7830-0010A#U       | 1   | 1     | 1660      |   |   | Indicator Un                               | it                                       |

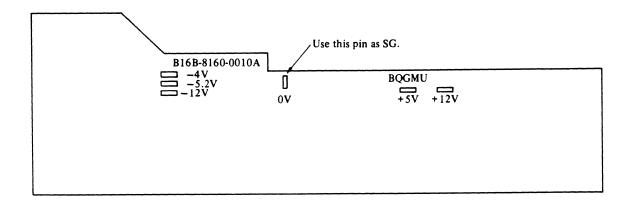

| 12  | PCB BQGMU                  | B16B-8160-0010A#U       | 1   | 1     | 1440      |   |   | Back Panel                                 |                                          |

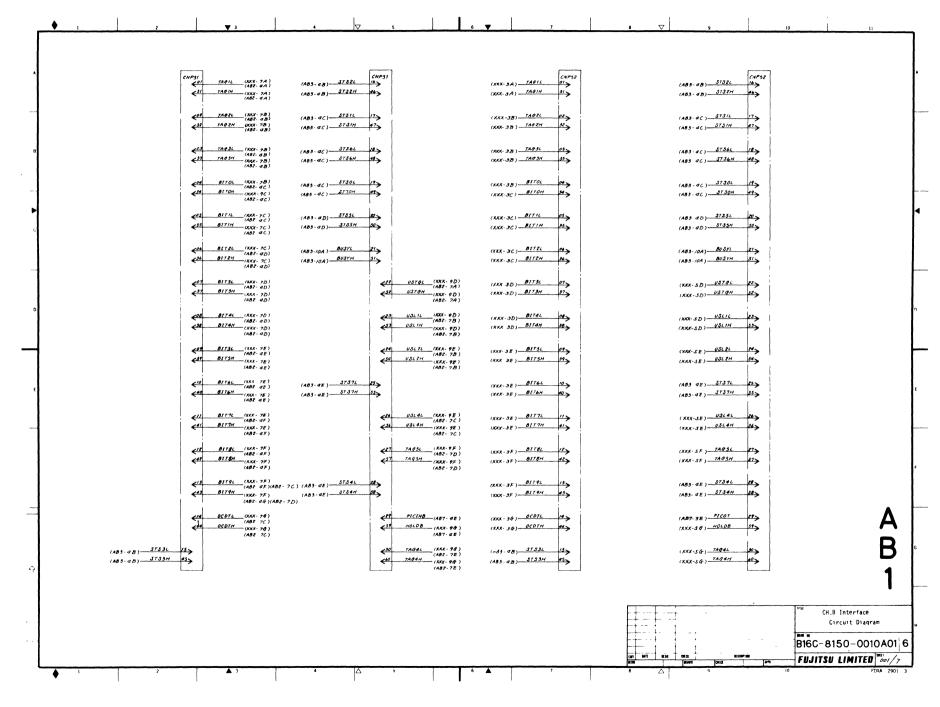

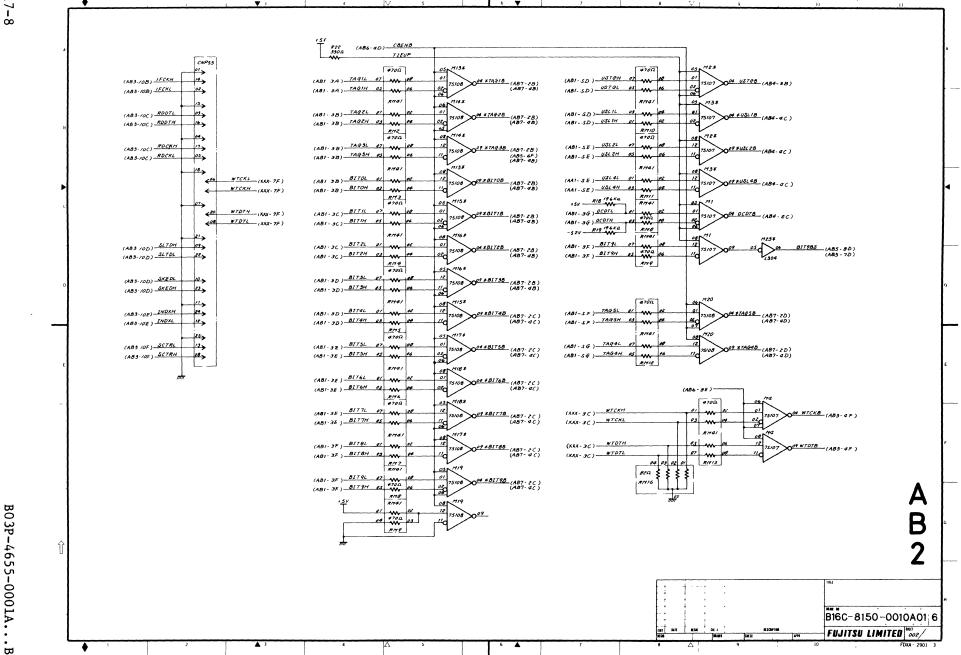

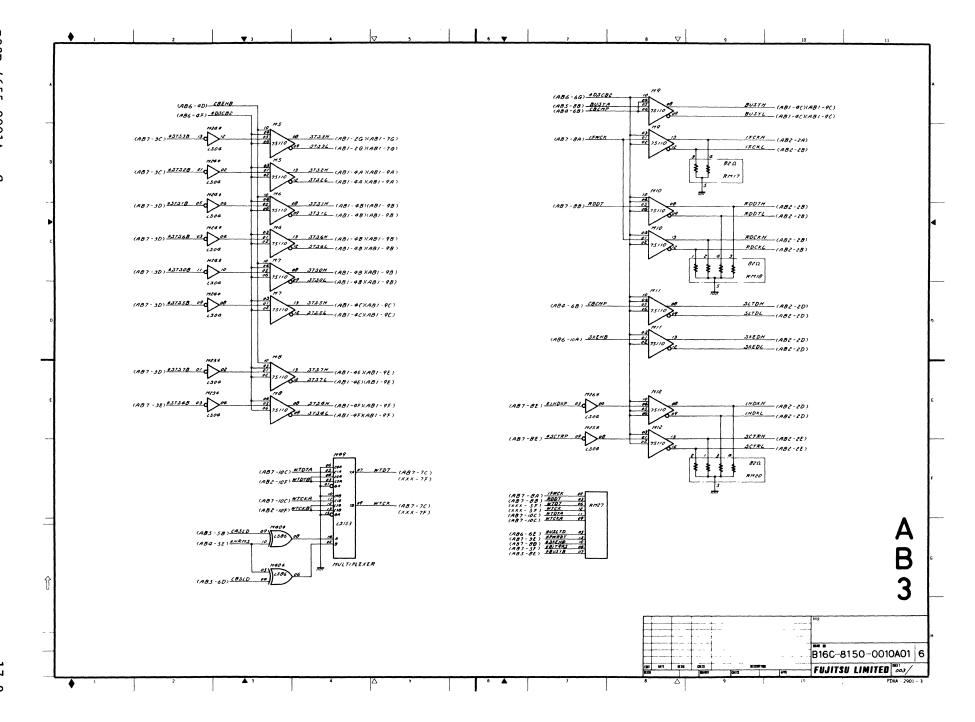

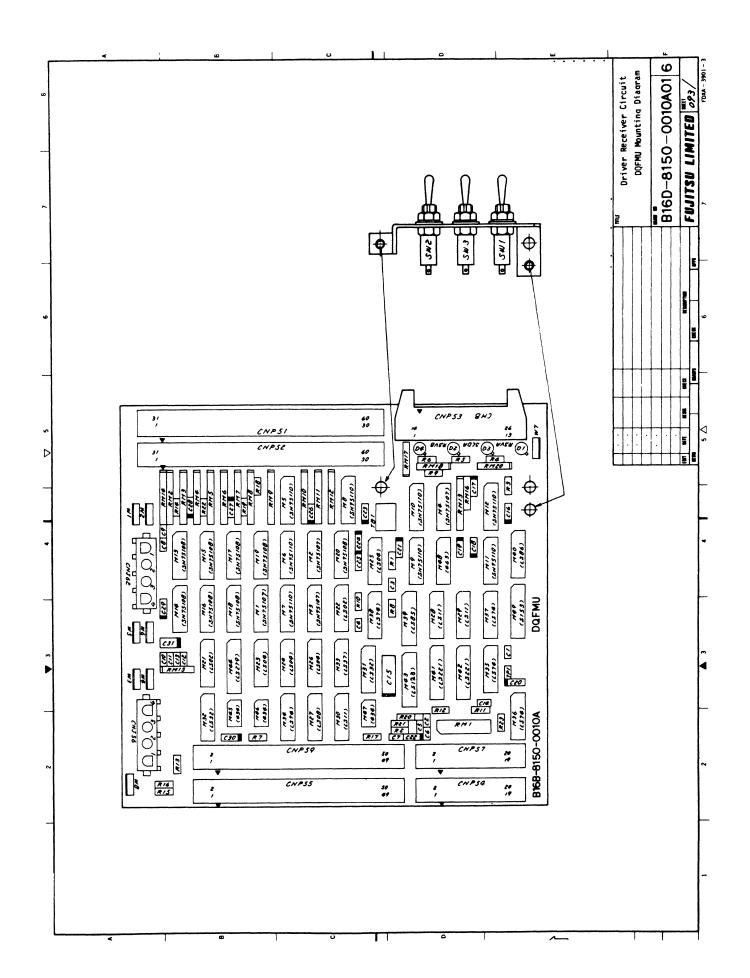

| 13  | PCB DQFMU                  | B16B-8150-0010A#U       | (1) | (1)   | 400       |   |   | Interface Circuit<br>(Dual Channel Option) |                                          |

| 14  | Air Filter                 | B90L-0400-0303A         | 1   | 1     | _         | _ | _ |                                            |                                          |

| 15  | Fuse                       | C60L-0020-0001<br>#MP05 | 1   | 1     |           | - | _ | Used in DC I<br>(0.5 A)                    | ower Supply                              |

Notes: MTBF; Mean Time Between Failures (K•hours)

# 1.9 MAINTENANCE TOOLS AND EQUIPMENT

Table 1.9-1 Maintenance Tools and Equipment

| No. | Tools and Equipment      | Specification                  | Remark               |

|-----|--------------------------|--------------------------------|----------------------|

| 1   | Extension Cable          | B660-1060-T072A#L510R0         | 20 pins              |

| 2   | Extension Cable          | B660-1060-T074A#L510R0         | 50 pins (2 required) |

| 3   | Extension Unit           | С960-0030-Т029                 |                      |

| 4   | Extractor                | C960-0300-T001                 | One required         |

| 5   | Oscilloscope             | TEKTRONIX 475, or equivalent   |                      |

| 6   | Oscilloscope Probe (X10) | TEKTRONIX P6053B or equivalent |                      |

| 7   | Digital Multimeter       |                                |                      |

| 8   | Screwdriver              | #2 Phillips                    |                      |

| 9   | Hexagonal Wrenches       | 6 MM                           | Metric system        |

| 10  |                          |                                |                      |

| 11  |                          |                                |                      |

| 12  |                          |                                |                      |

| 13  |                          |                                |                      |

### 1.10 RELIABILITY AND SERVICE GOALS

### (1) MTBF

MTBF is defined as follows.

MTBF = operating time/the number of failures encountered.

Operating time is the total time duration during which the power is ON except during maintenance work. Failure is defined as a malfunction that requires either repairs, adjustments, or replacement. Mishandling by the operator, power failure, control unit trouble, cable trouble and trouble due to improper environmental conditions are not included.

The MTBF or M2351A/M2351AF is more than 20,000 hours estimated value after an initial period of 200 hours.

### (2) MTTR

MTTR is the average time a trained service mechanic should take to diagnose and repair the failure. The M2351A/M2351AF are designed for an MTTR of 30 minutes or less.

### (3) Preventive Maintenance Time

The front panel air filter should be cleaned or replaced at one year intervals, or as required.

### (4) Component Life

M2351A/M2351AF need not be overhauled for the five first years.

### (5) Power Loss

If AC power to the unit is lost, data stored in the disk is preserved. However, if the power failure occurs during a WRITE operation, that data is not guaranteed.

### (6) Read Error

Prior to determination of the read error rate, the data must be verified as correctly written and all identified media defects must be deallocated or skipped.

- Recoverable Error Rate ....  $10 \times 10^{-11}$  While reading  $10^{11}$  bits of data, less than 10 read errors would be encountered which are recoverable in 4 retries without using the ECC functions and the offset operation.

- Unrecoverable Error Rate ... 10 × 10<sup>-14</sup> While reading 10<sup>14</sup> bits of data, less than 10 read errors would be encountered which are unrecoverable in 5 retries without using the ECC function.

Retry routine; after 4 times of re-reading with and without offset, RTZ must be performed.

- (7) Seek Error Rate .....  $1 \times 10^{-7}$

- (8) Quality Standards of Media at Shipment (Summary)

- The number of defects per DE shall not exceed 500.

- The number of defective tracks per DE shall not exceed 30.

(A track containing two or more defects is defined as a defective track.)

- Head 0 and 1 at cylinder 0 should be perfect tracks.

Refer to Chapter 6.3 for detail.

|  | - |  |

|--|---|--|

|  |   |  |

|  |   |  |

### CHAPTER 2 INSTALLATION

### 2.1 STORAGE

When the drive is stored for a kprolonged period, avoid locations where the environment is extreme. Stored units should be properly packed and can be stored stacked vertically, two high. When the temperature difference between storage (or shipping) and the unpacking environment exceeds 20°C (36°F), the unit should be allowed to remain in packaged form for more than 3 hours to avoid condensation when unpacking.

### 2.2 UNPACKING

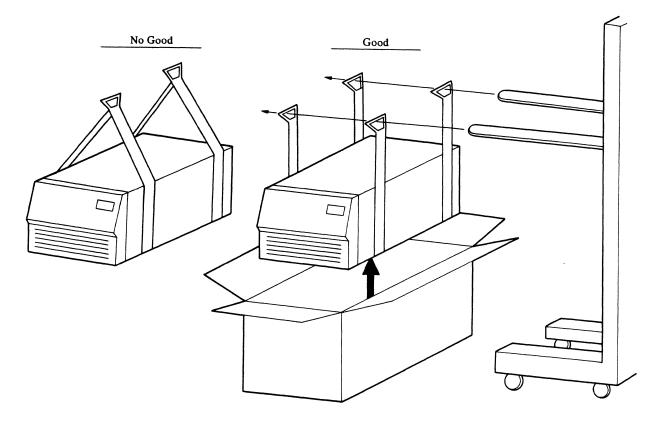

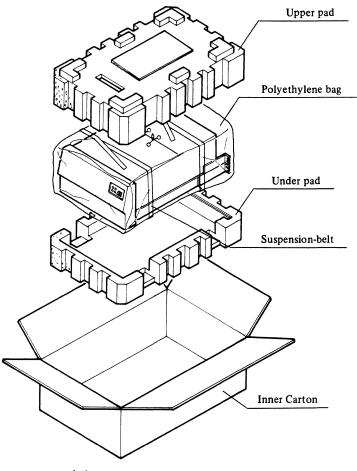

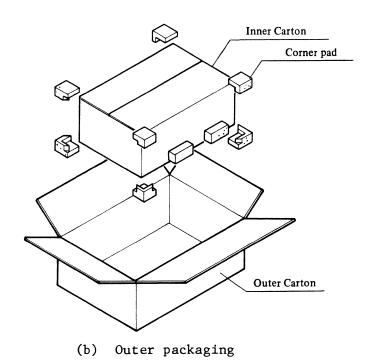

- (1) The M2351 is shipped in a carton surrounded by shock absorber as shown in Figure 2.2-1. (Note: the shipping carton is intended to be reuseable.) To unpack the unit, first the carton flaps to the left and right and then take out the unit. Take the tollowing precautions when removing its packing carton.

- (a) Lift the unit <u>evenly</u> by setting lift forks at 480mm intervals and inserting them at the four suspension-belt ends to remove the drive from its packing carton.

- (b) <u>Do not leave</u> the unit suspended for any length of time. Ensure that it is moved quietly and smoothly.

- (c) If no lift is available:

- Have two or more people carry the unit.

- Lift the unit by the four suspension-belt ends, taking care about the direction in thich pulling is done.

- Lift the unit <u>evenly and gently</u>, and place it onto the floor without exposing it to undue shock or vibration.

- (2) Take care to move the unit carefully to avoid abrute impact or shock, and do not grasp the front panel or cover of the unit to lift use the sub-frame at the bottom to avoid the possibility of sub-assembly damage.

- (3) After unpacking the drive, check for scratches or dents. Remove the cover and visually inspect inside the drive.

(a) Inner packaging

Figure 2.2-1 Exterior View and Construction of Carton

Figure 2.2-2 - Continued

### (2) Locking

This mechanism can be readily viewed from the rear of the drive by looking over the Interface PCB.

Loosen Screw A (by means of a phillips screwdriver, 8 inches or longer), sufficiently to free the screw tip from the hole in the Lock Plate. With the screwdriver, rotate the Locking Lever to the Locked position (Hole A), and secure in that position by gently tightening Screw A. (Refer to Figure 2.3-1)

- (a) Check for loose or missing parts, or foreign matter.

- (b) Check that the PCB's are properly seated in the correct positions.

- (c) Check that all connectors are secure and no cable chafing damage has occurred.

After inspection, (prior to operating the drive), unlock the rotary acutuator and secure in the unlocked position. (Refer to Figure 2.3-1).

### (3) Packing

Prior to packing the drive, insure that the rotary actuactor locking mechanism is secured in the locking position. (Refer to Figure 2.3-1). When reshipping the drive, place it in a polyethelene bag and repack it in the Original carton with shock absorbers. (Refer to Figure 2.2-1)

## (2) Locking

Loosen Screw A (by means of a phillips screwdriver, 8 inches or longer), sufficiently to free the screw tip from the hole in the Lock Plate. With the screwdriver, rotate the Locking Lever to the Locked position (Hole A), and secure in that position by gently tightening Screw A. (Refer to Figure 2.3-1)

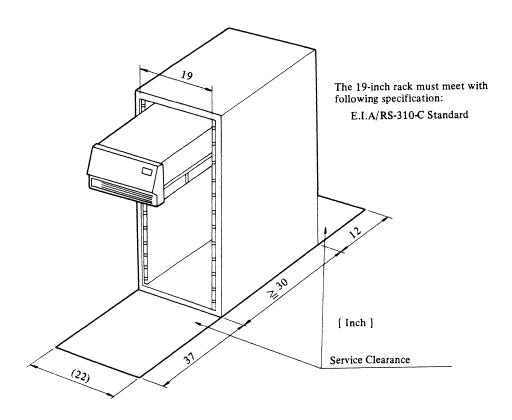

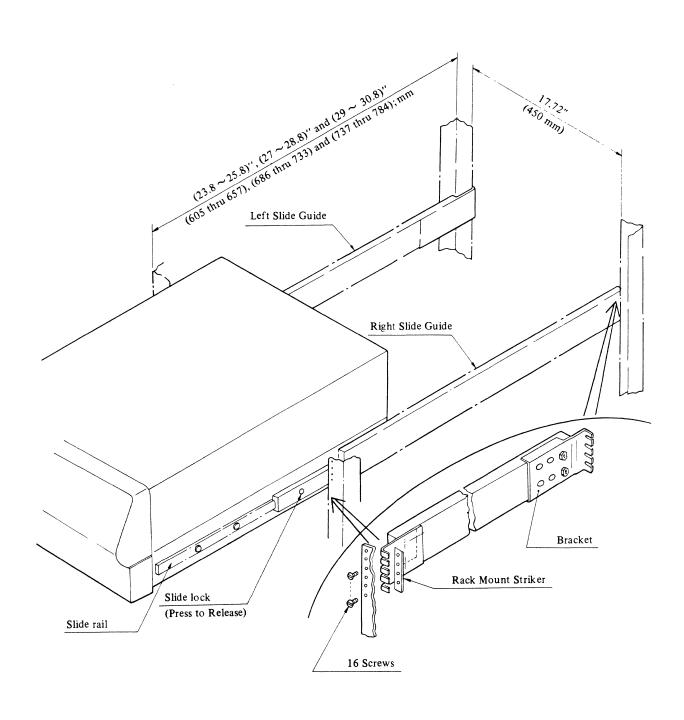

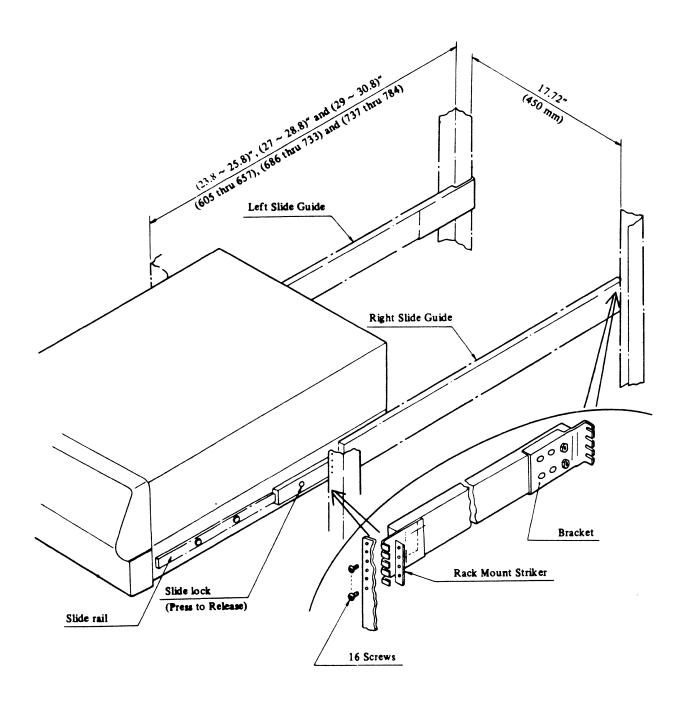

Figure 2.4-1 Rack Mount Installation

Figure 2.4-1 Rack Mount Installation

### 3.1 DC POWER SUPPLY UNIT

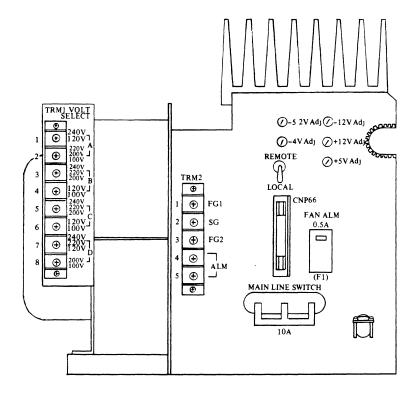

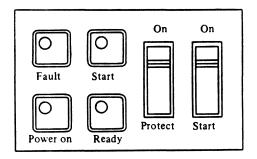

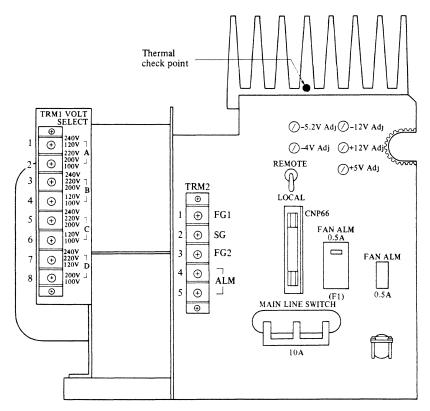

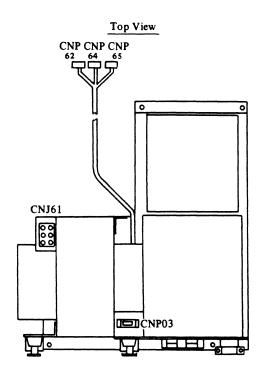

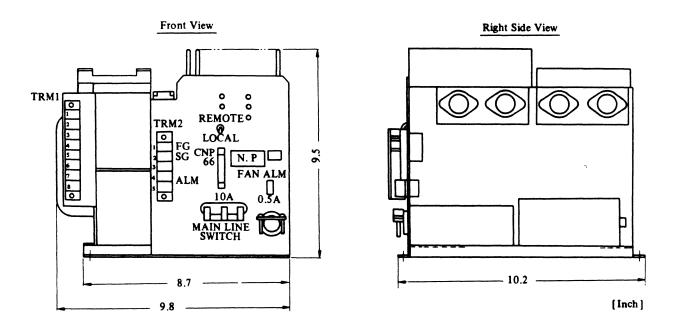

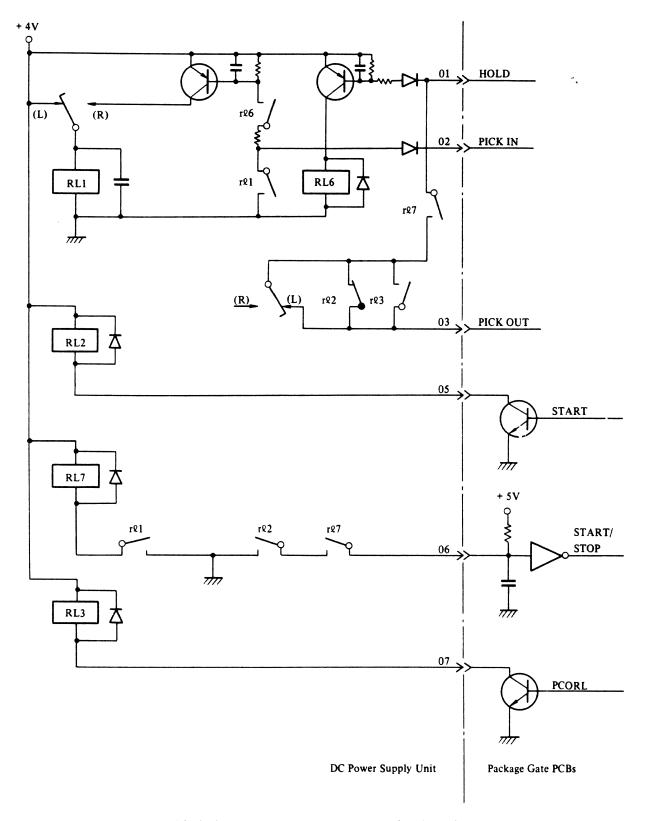

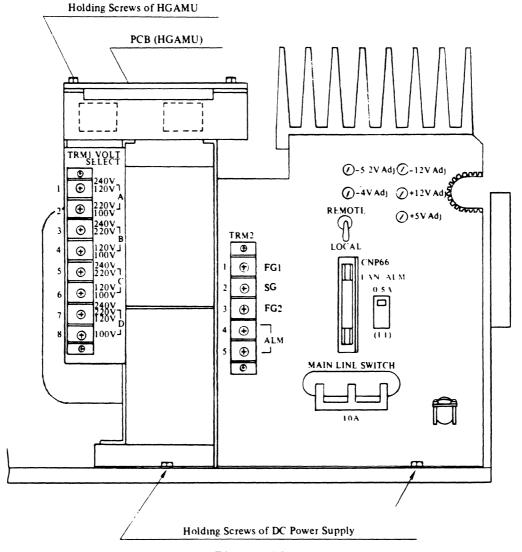

Control panel of the DC power supply unit is shown in Figure 3.1-1.

Figure 3.1-1 Control Panel of DC Power Supply Unit

## (1) Main Line Switch (Non-Fuse Breaker)

Supplies AC power to the unit. If one of following failures occures, it goes off.

- Over current in the AC input

- Over current or voltage in the DC output

- Fan (Line-Blower) Alarm

- Over Temperature of the heat sink or of the transformer in the DC power supply unit.

### (2) Fan ALM (Fuse)

Indicates fan alarm of the line-blower.

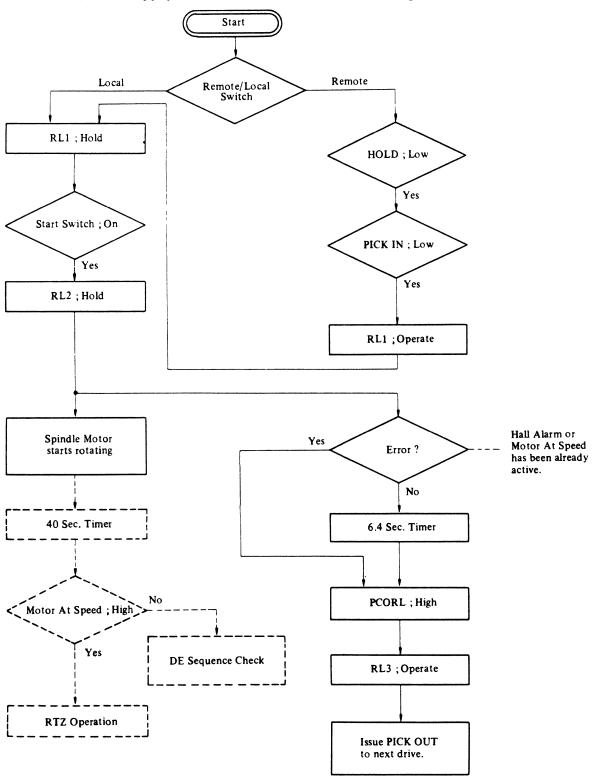

### (3) Remote/Local (Switch)

When this is set to Remote, the spindle motor starts/stops rotating in accordance

with the commands (Power Sequence Pick/Hold) issued from the controller. When set to Local, rotation is under the control of the Start switch on the operator panel.

### (4) TRM 1 (Terminal)

The taps on this terminal must be changed in accordance with the voltage and frequency of AC input power, as shown in Table 3.1-1

|             | Tape Number |     |     |     |  |

|-------------|-------------|-----|-----|-----|--|

| Vac (Hz)    | (A)         | (B) | (C) | (D) |  |

| 100 (50/60) | 2           | 4   | 6   | 8   |  |

| 120 (50/60) | 1           | 4   | 6   | 7   |  |

| 200 (50/60) | 2           | 3   | 5   | 8   |  |

| 220 (50/60) | 2           | 3   | 5   | 7   |  |

| 240 (50/60) | 1           | 3   | 5   | 7   |  |

Table 3.1-1 Tap Number to be shortened

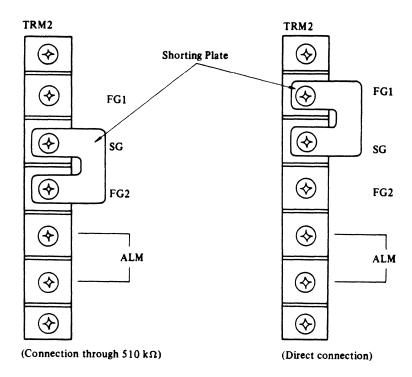

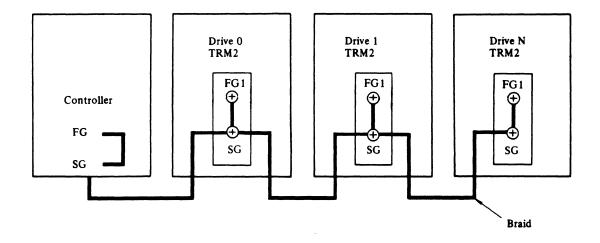

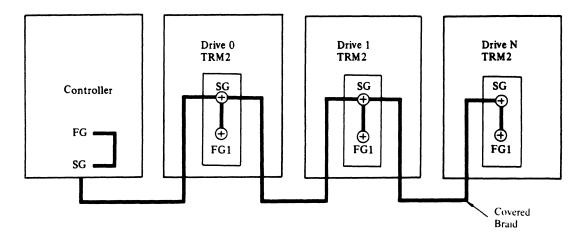

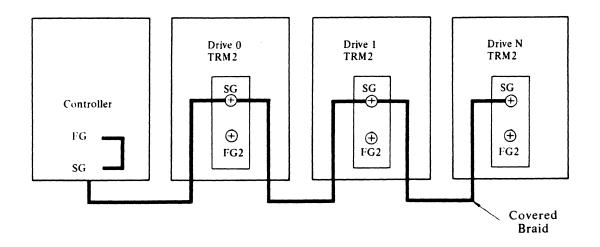

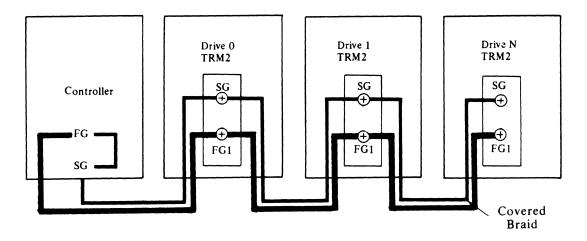

### (5) TRM 2 (Terminal)

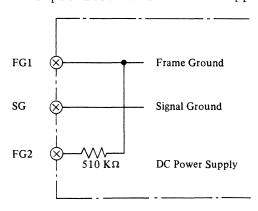

FG1 ..... Frame Ground

SG .... Signal Ground

FG2 ..... Frame Ground with a 510  $k\Omega$  resistor

ALM .... Alarm Output (not used)

The Frame Ground and Signal Ground are completely isolated in the drive, and they are provided as FG1/FG2 and SG on this terminal.

As shown in Figure 3.1-2, FG1 is a frame ground itself, but FG2 is a frame ground to which a 510  $k\Omega$  resistor is provided in DC Power Supply.

Figure 3.1-2 FG1/FG2 and SG

At the time of shipment, SG and FG2 are connected with a shorting plate.

Refer to Chapter 4.3 on the operation.

## (6) Volt ADJ (Variable Resistors)

Although adjustment should not be required, variable resistors are provided to adjust the -5.2, -4,  $\pm 12$ , -5 Vdc output voltages within the tolerance specified, if necessary.

### 3.2 INTERFACE PCBs

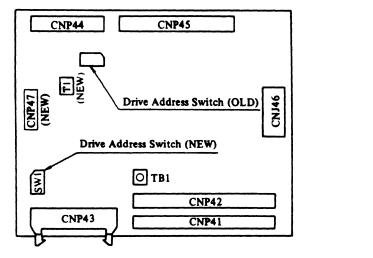

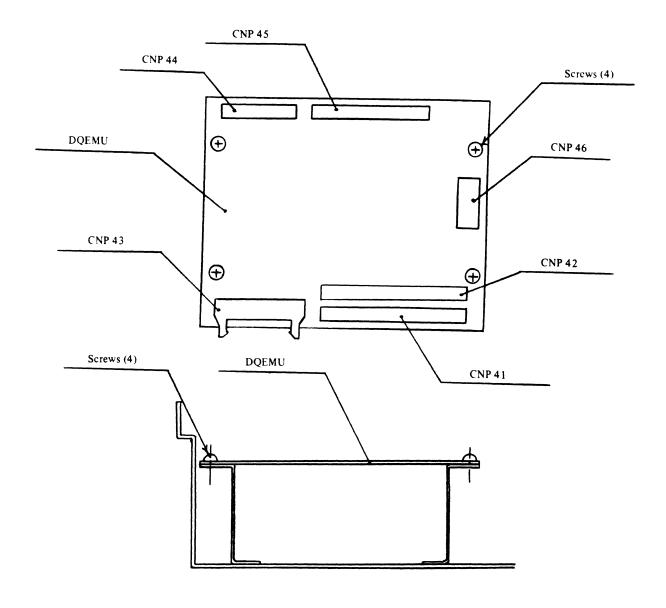

### (1) INTERFACE PCB - DQEMU (B16B-8140-0010A#U)

Drive logical address 0 to 7 can be set with three positions of the switch in binary code as shown in Table 3.2-1.

Figure 3.2-1 Drive Address Switch

Table 3.2-1 Drive Addressing

| Drive Address |     | Switch F | osition |      |  |  |

|---------------|-----|----------|---------|------|--|--|

| Drive Address | 1   | 2        | 3       | 4    |  |  |

| 0             | OFF | OFF      | OFF     |      |  |  |

| 1             | ON  | OFF      | OFF     |      |  |  |

| 2             | OFF | ON       | OFF     |      |  |  |

| 3             | ON  | ON       | OFF     | Not  |  |  |

| 4             | OFF | OFF      | ON      | Used |  |  |

| 5             | ON  | OFF      | ON      |      |  |  |

| 6             | OFF | ON       | ON      |      |  |  |

| 7             | ON  | ON       | ON      | `    |  |  |

Interface Configuration Jumper (T1)

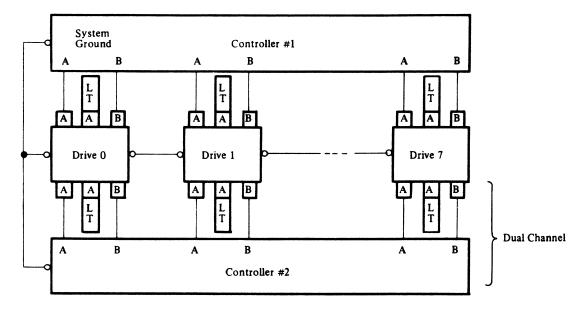

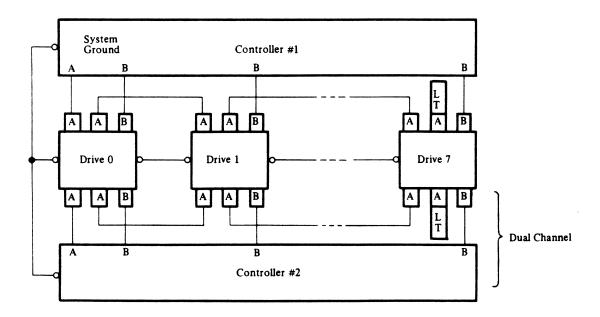

In normal dual port operation, a Priority Select on one port will cause the B Cable Interface on the alternate port to be disabled. Also, a Seek-End response is given for Reserve (Select) and Reserve (Select) Release commands.

Jumper Tl provides the means to inhibit the disabling of the alternate port's B Cable Interface in response to a Priotiy Select. (See also - Table 3.2-3 for DQFMU, Jumpers Tl, T2 & T3)

| Jumper # | Pin Numbers | Option                                            |

|----------|-------------|---------------------------------------------------|

| Tl       | 01-02*      | Disable B cable with<br>Priority Select           |

| (Port A) | 02-03       | Inhibit disabling<br>B cable with Priority Select |

<sup>\*</sup> Jumper position for normal dual port operation

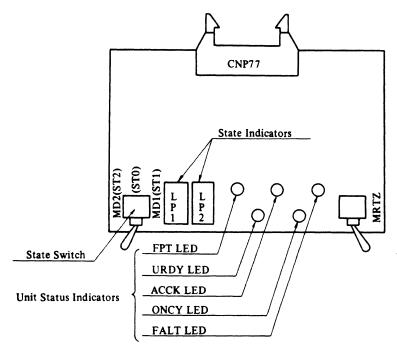

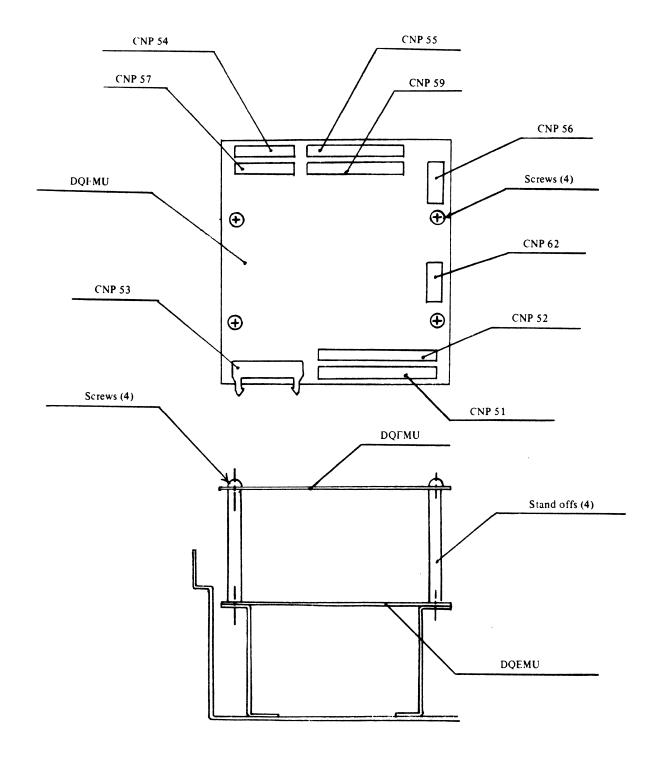

## (2) DUAL CHANNEL INTERFACE PCB ---- DOFMU (B16B-8150-0010A#U)

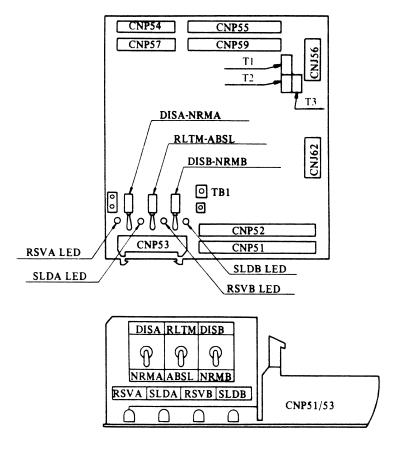

Figure 3.2-2 Switches and Indicators

#### LEDs

- (1) RSVA (Channel A Reserved) Orange Indicates that the drive is reserved by A-channel.

- (2) SLDA (Channel A Selected) Green Indicates that the drive is selected by A-channel.

- (3) RSVB (Channel B Reserved) Orange Indicates that the drive is reserved by B-channel.

- (4) SLDB (Channel B Selected) Green Indicates that the drive is selected by B-channel.

#### Switches

- (1) DISA NRMA (Disable A Normal A). Disconnects or connects the interface signals of A-channel.

- (2) RLTM ABSL (Release Timer Absolute) When the switch is at RLTM side, reserved status will be released 500 ms after Unit Select Command if the Release Command has not already been issued. When the switch is at ABSL side, reserved status can be released only by the Release Command.

- (3) DISB NRMB (Disable B Normal B) Disconnects or connects the interface signals of B-channel.

Interface Configuration Jumpers (Tl. T2, T3)

In normal dual port operation, a Priority Select on one port will cause the B Cable Interface on the alternate port to be disabled. Also, a Seek-end response is given for Reserve (Select) and Reserve (Select) Release commands.

Jumpers T1 and T2 provide a means to inhibit the Seek-end response to Reserve (Select) and Reserve (Select) Release commands.

Table 3.2-3 DQFMU Interface Configuration

Jumper T3 provides the means to inhibit the disabling of the alternate port's B Cable Interface in response to a Priority Select.

| Jumper#  | Pin Numbers | Option                                                 |

|----------|-------------|--------------------------------------------------------|

| Tl       | 01-02*      | Seek-End response for Reserve/Release command.         |

| (Port A) | 02-03       | Inhibit Seek-End response for Reserve/Release command. |

| Т2       | 01-02*      | Seek-End response for reserve/release command.         |

| (Port B) | 02-03       | Inhibit Seek-End response for reserve/release command. |

| Т3       | 01-02*      | Disable B cable with<br>Priority Select                |

| (Port B) | 02-03       | Inhibit disabling B cable with Priority Select         |

<sup>\*</sup> Jumper position for normal dual-port operation.

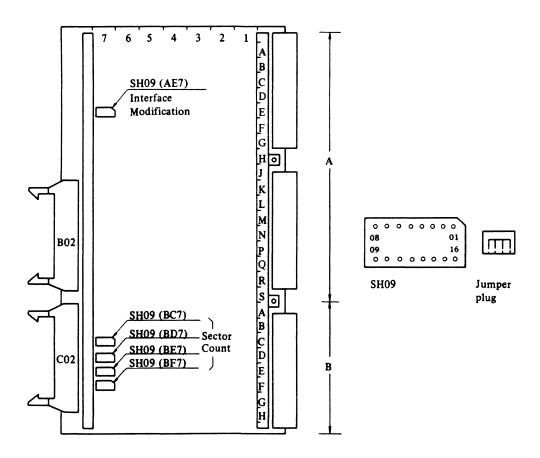

# 3.3 LOGIC PCB ---- (C16B-5123-0980#U)

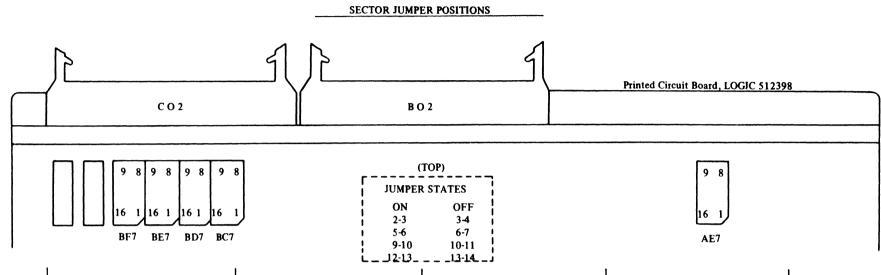

Jumper pins (SH09) and jumper plugs for setting sector count and changing interface requirements are provided.

( ) indicates location of jumper pins on the PCB.

Figure 3.3-1 Sector Count and Interface Selection

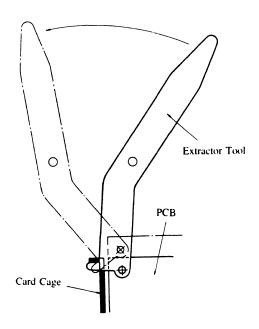

Removal of the Logic PCB is required to set the sector count or change the interface options. This is accomplished with the extractor tools provided with the drive (refer to Table 1.9-1, item 4) as shown below.

Figure 3.3-2 PCB Removal

# (1) Interface Configuration

The interface can be reconfigured by shorting the appropriate pins (Logic PCB, Location AE 7) with jumper plugs, as shown below.

Table 3.3-1 Interface Selection

| Item                            | Pin number to be shortened | Default<br>mode | Function                                                         |

|---------------------------------|----------------------------|-----------------|------------------------------------------------------------------|

| Incorporate * TAG4, 5           | 03 - 02                    | x               | Enable                                                           |

| Status Capability               | 03 - 04                    |                 | Disable                                                          |

| Operation of<br>Seek End status | 06 - 05                    |                 | Seek End is not issued after Offset Command is reset.            |

|                                 | 06 - 07                    | х               | Seek End is issued after<br>Offset Command is reset.             |

| Response of Unit<br>Ready       | 10 - 09                    | х               | Unit Ready is issued even if the drive is in a fault condition.  |

|                                 | 10 - 11                    |                 | Unit Ready is not issued when the drive is in a fault condition. |

<sup>\* (</sup>Note) It is recommended that tag 4 & 5 be disabled if the disk controller does not use the option.

### 3.4 SECTOR COUNT

The number of bytes per sector in Fixed Sector Format is determined by the location of jumper plugs according to the following table and example.

Example; 9 Sectors/Track

Bytes/Sector =

$$\frac{\text{Bytes/Track}}{\text{Sectors/Track}} = \frac{28,160}{9} = 3,128.89$$

If the above calculation results in a remainder, round it up to the next integer, i.e., Bytes/Sector = 3,129

Set this figure minus one with jumper plugs to allow the Byte Counter to start counting from zero.

$$3,129-1 = 3,128 = 2,048 + 1,024 + 32 + 16 + 8$$

BE7

BD7

BC7

Therefore, jumper plugs should be placed on pins 13 - 12 and 10 - 9 of BE7, pins 06 - 05 and 03 - 02 of BD7, and pins 13 - 12 of BC7. However, those pins representing byte-count value not appearing in the calculation must also be jumpered (the complementary position).

In this case, the number of bytes in the last sector is calculated as follows.

$$28,160 - (8 \times 3,129) = 3,128$$

Namely, the last sector is one byte shorter than the others.

Table 3.4-1 Setting of Sector Count

| Sector<br>Count |                  | Location<br>BC7 |       |       |     | Location<br>BD7 | 1     | Location<br>BE7 |     |     |       |       |      | Locatio<br>BF7 |              | Bytes<br>Per Sect/Last Sect |           |

|-----------------|------------------|-----------------|-------|-------|-----|-----------------|-------|-----------------|-----|-----|-------|-------|------|----------------|--------------|-----------------------------|-----------|

| (21             | <sup>n</sup> ) 1 | 2               | 4     | 8     | 16  | 32              | 64    | 128             | 256 | 512 | 1024  | 2048  | 4096 | 8192           | 16384        | spare                       |           |

| 1               | 2-3              | 5-6             | 9-10  | 12-13 | 2-3 | 5-6             | 9-10  | 12-13           | 2-3 | 6-7 | 9-10  | 12-13 | 3-4  | 5-6            | <b>9-1</b> 0 | 13-14                       | 28160     |

| 2               | 2-3              | 5-6             | 9-10  | 12-13 | 2-3 | 5-6             | 9-10  | 12-13           | 3-4 | 5-6 | 9-10  | 13-14 | 2-3  | 5-6            | 10-11        | 13-14                       | 14080     |

| 3               | 3-4              | 5-6             | 10-11 | 12-13 | 3-4 | 5-6             | 10-11 | 12-13           | 3-4 | 6-7 | 9-10  | 13-14 | 3-4  | 5-6            | 10-11        | 13-14                       | 9387/9386 |

| 4               | 2-3              | 5-6             | 9-10  | 12-13 | 2-3 | 5-6             | 9-10  | 13-14           | 2-3 | 5-6 | 10-11 | 12-13 | 2-3  | 6-7            | 16-11        | 13-14                       | 7040      |

| 5               | 2-3              | 5-6             | 9-10  | 12-13 | 2-3 | 5-6 💊           | 9-10  | 12-13           | 2-3 | 6-7 | 9-10  | 13-14 | 2-3  | 6-7            | 10-11        | 13-14                       | 5632      |

| 6               | 2-3              | 6-7             | 9-10  | 13-14 | 2-3 | 6-7             | 9-10  | 13-14           | 3-4 | 5-6 | 10-11 | 13-14 | 2-3  | 6-7            | 10-11        | 13-14                       | 4694/4690 |

| 7               | 3-4              | 5-6             | 9-10  | 13-14 | 2-3 | 5-6             | 10-11 | 12-13           | 2-3 | 5-6 | 9-10  | 12-13 | 3-4  | 6-7            | 10-11        | 13-14                       | 4023/4022 |

| 8               | 2-3              | 5-6             | 9-10  | 12-13 | 2-3 | 5-6             | 10-11 | 12-13           | 2-3 | 6-7 | 9-10  | 12-13 | 3-4  | 6-7            | 10-11        | 13-14                       | 3520      |

| 9               | 3-4              | 6-7             | 10-11 | 12-13 | 2-3 | 5-6             | 10-11 | 13-14           | 3-4 | 6-7 | 9-10  | 12-13 | 3-4  | 6-7            | 10-11        | 13-14                       | 3129/3128 |

|                 |                  |                 |       |       |     |                 |       |                 |     |     |       |       |      |                |              |                             |           |

| Sector<br>Count | int BC7          |     |       | Location<br>BD7 |     |     |       |       | Location<br>BE7 |     |       |       |      | Location<br>BF7 |       |       |           |  |

|-----------------|------------------|-----|-------|-----------------|-----|-----|-------|-------|-----------------|-----|-------|-------|------|-----------------|-------|-------|-----------|--|

| (2 <sup>1</sup> | <sup>n</sup> ) 1 | 2   | 4     | 8               | 16  | 32  | 64    | 128   | 256             | 512 | 1024  | 2048  | 4096 | 8192            | 16384 | spare |           |  |

| 10              | 2-3              | 5-6 | 9-10  | 12-13           | 2-3 | 5-6 | 9-10  | 12-13 | 3-4             | 5-6 | 10-11 | 12-13 | 3-4  | 6-7             | 10-11 | 13-14 | 2816      |  |

| 11              | 2-3              | 5-6 | 9-10  | 12-13           | 2-3 | 5-6 | 9-10  | 12-13 | 2-3             | 6-7 | 10-11 | 12-13 | 3-4  | 6-7             | 10-11 | 13-14 | 2560      |  |

| 12              | 3-4              | 5-6 | 10-11 | 12-13           | 3-4 | 5-6 | 10-11 | 13-14 | 2-3             | 6-7 | 10-11 | 12-13 | 3-4  | 6-7             | 10-11 | 13-14 | 2347/2343 |  |

| 13              | 3-4              | 5-6 | 9-10  | 13-14           | 2-3 | 5-6 | 9-10  | 13-14 | 3-4             | 6-7 | 10-11 | 12-13 | 3-4  | 6-7             | 10-11 | 13-14 | 2167/2156 |  |

| 14              | 2-3              | 5-6 | 10-11 | 12-13           | 2-3 | 6-7 | 9-10  | 12-13 | 2-3             | 5-6 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 2012/2004 |  |

| 15              | 2-3              | 6-7 | 9-10  | 13-14           | 2-3 | 6-7 | 9-10  | 13-14 | 2-3             | 5-6 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1878/1868 |  |

| 16              | 2-3              | 5-6 | 9-10  | 12-13           | 2-3 | 6-7 | 9-10  | 12-13 | 3-4             | 5-6 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1760      |  |

| 17              | 3-4              | 6-7 | 10-11 | 12-13           | 2-3 | 5-6 | 9-10  | 13-14 | 3-4             | 5-6 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1657/1648 |  |

| 18              | 3-4              | 6-7 | 9-10  | 12-13           | 2-3 | 6-7 | 10-11 | 13-14 | 3-4             | 5-6 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1565/1555 |  |

| 19              | 3-4              | 5-6 | 10-11 | 12-13           | 3-4 | 6-7 | 9-10  | 12-13 | 2-3             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1483/1466 |  |

| 20              | 2-3              | 5-6 | 9-10  | 12-13           | 2-3 | 5-6 | 9-10  | 13-14 | 2-3             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1408      |  |

| 21              | 3-4              | 6-7 | 9-10  | 12-13           | 2-3 | 5-6 | 10-11 | 13-14 | 2-3             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1341/1340 |  |

| 22              | 2-3              | 5-6 | 9-10  | 12-13           | 2-3 | 5-6 | 9-10  | 12-13 | 3-4             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1280      |  |

| 23              | 3-4              | 6-7 | 10-11 | 12-13           | 3-4 | 6-7 | 9-10  | 12-13 | 3-4             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1225/1210 |  |

| 24              | 2-3              | 6-7 | 9-10  | 13-14           | 2-3 | 6-7 | 10-11 | 12-13 | 3-4             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1174/1158 |  |

| 25              | 3-4              | 5-6 | 9-10  | 13-14           | 3-4 | 5-6 | 9-10  | 13-14 | 3-4             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1127/1112 |  |

| 26              | 2-3              | 5-6 | 10-11 | 12-13           | 2-3 | 5-6 | 10-11 | 13-14 | 3-4             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1084/1060 |  |

| 27              | 3-4              | 5-6 | 10-11 | 13-14           | 2-3 | 6-7 | 10-11 | 13-14 | 3-4             | 6-7 | 9-10  | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1043/1042 |  |

| 28              | 2-3              | 6-7 | 9-10  | 12-13           | 3-4 | 5-6 | 9-10  | 12-13 | 2-3             | 5-6 | 10-11 | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 1006/998  |  |

| 29              | 2-3              | 5-6 | 10-11 | 12-13           | 3-4 | 6-7 | 9-10  | 12-13 | 2-3             | 5-6 | 10-11 | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 972/944   |  |

| 30              | 3-4              | 5-6 | 10-11 | 12-13           | 3-4 | 5-6 | 10-11 | 12-13 | 2-3             | 5-6 | 10-11 | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 939/929   |  |

| 31              | 3-4              | 6-7 | 9-10  | 12-13           | 3-4 | 6-7 | 10-11 | 12-13 | 2-3             | 5-6 | 10-11 | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 909/890   |  |

| 32              | 2-3              | 5-6 | 9-10  | 12-13           | 3-4 | 5-6 | 9-10  | 13-14 | 2-3             | 5-6 | 10-11 | 13-14 | 3-4  | 6-7             | 10-11 | 13-14 | 880       |  |

| (2 <sup>n</sup> ) 1  33 2-3  34 3-4  35 3-4  36 3-4  37 2-3  38 2-3  39 3-4  40 2-3  41 3-4  42 3-4  43 3-4  44 2-3  45 2-3 | 6-7<br>6-7<br>5-6<br>6-7<br>1<br>6-7<br>5-6<br>1<br>5-6 | 9-10 12 9-10 13 9-10 12 0-11 12 9-10 13 0-11 13 9-10 12 | 8   3-14   3-14   3-13   3-14   3-13   3-14   3-14   3-14   3-14   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13   3-13 | 16<br>2-3<br>2-3<br>3-4<br>3-4<br>2-3<br>3-4<br>2-3<br>2-3 | 32<br>6-7<br>5-6<br>5-6<br>6-7<br>5-6<br>5-6<br>6-7 | 9-10<br>10-11<br>10-11<br>10-11<br>9-10<br>9-10 | 128<br>13-14<br>13-14<br>13-14<br>13-14<br>12-13 | 256<br>2-3<br>2-3<br>2-3<br>2-3<br>3-4<br>3-4 | 512<br>5-6<br>5-6<br>5-6<br>5-6<br>5-6 | 1024<br>10-11<br>10-11<br>10-11<br>10-11 | 2048<br>13-14<br>13-14<br>13-14<br>13-14 | 3-4<br>3-4<br>3-4<br>3-4<br>3-4 | 6-7<br>6-7<br>6-7<br>6-7 | 16384<br>10-11<br>10-11<br>10-11<br>10-11 | 13-14<br>13-14<br>13-14<br>13-14<br>13-14 | 854/832<br>829/803<br>805/790<br>783/755 |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------|--------------------------------------------------|-----------------------------------------------|----------------------------------------|------------------------------------------|------------------------------------------|---------------------------------|--------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------|

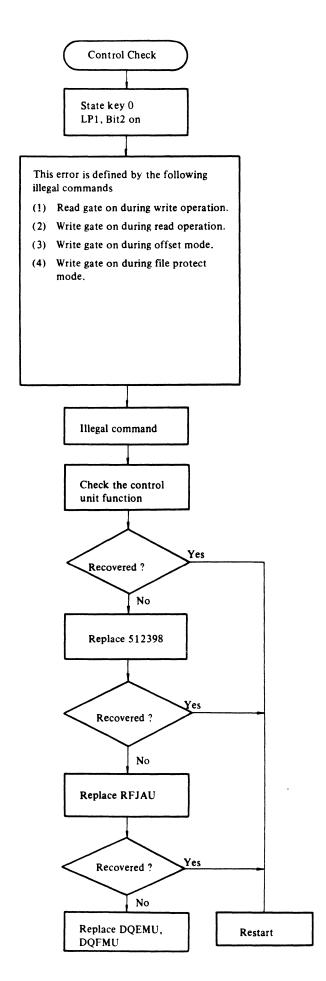

| 34 3-4 35 3-4 36 3-4 37 2-3 38 2-3 39 3-4 40 2-3 41 3-4 42 3-4 43 3-4 44 2-3                                                | 6-7 5-6 6-7 10 6-7 5-6 10 5-6 5-6                       | 9-10 12 9-10 13 9-10 12 0-11 12 9-10 13 0-11 13 9-10 12 | 2-13<br>1-14<br>2-13<br>2-13<br>1-14<br>1-14<br>2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-3<br>3-4<br>3-4<br>2-3<br>3-4<br>2-3                     | 5-6<br>5-6<br>6-7<br>5-6<br>5-6                     | 10-11<br>10-11<br>10-11<br>9-10<br>9-10         | 13-14<br>13-14<br>13-14<br>12-13                 | 2-3<br>2-3<br>2-3<br>3-4                      | 5-6<br>5-6<br>5-6                      | 10-11<br>10-11<br>10-11                  | 13-14<br>13-14<br>13-14                  | 3-4<br>3-4<br>3-4               | 6-7<br>6-7               | 10-11<br>10-11<br>10-11                   | 13-14<br>13-14<br>13-14                   | 829/803<br>805/790<br>783/755            |