| Index |

|-------|

|-------|

# 1 Introduction

2 Installation

3 Hardware User's Manual

4 Appendices to the Hardware User's Manual

5 Copies of Data Sheets

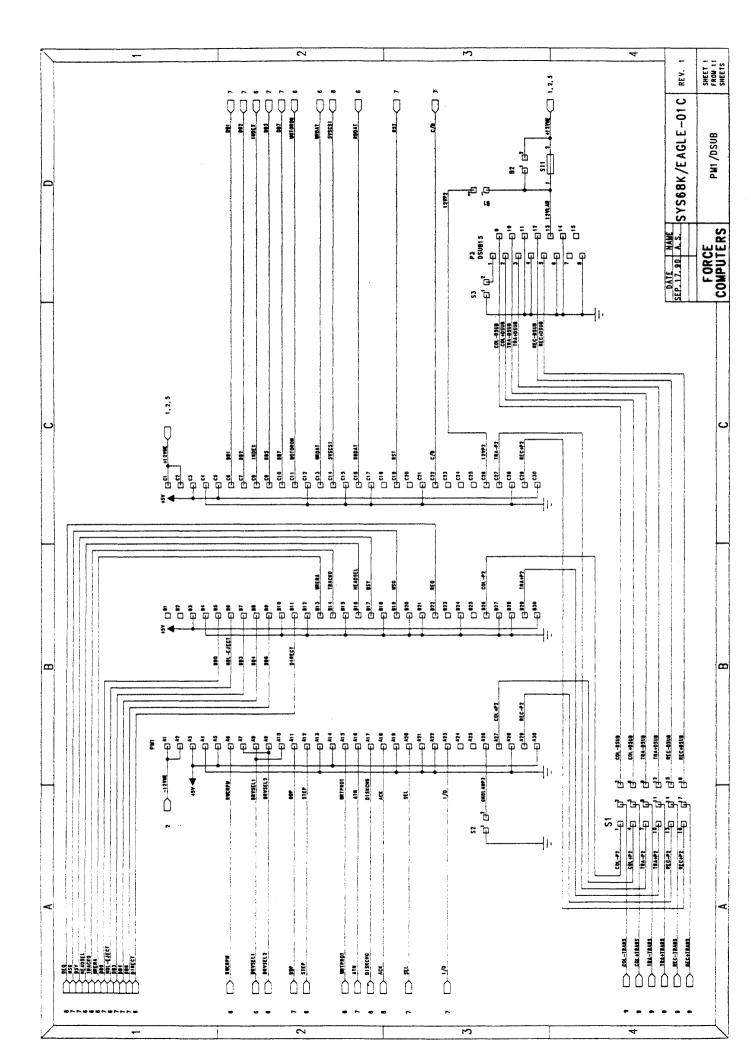

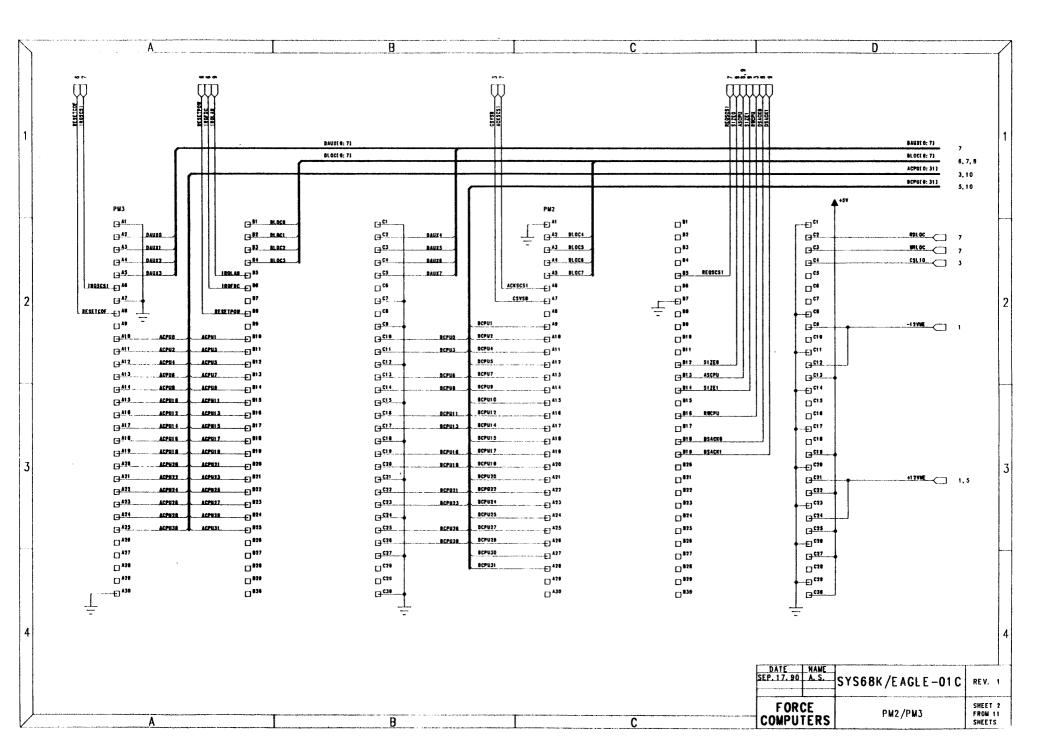

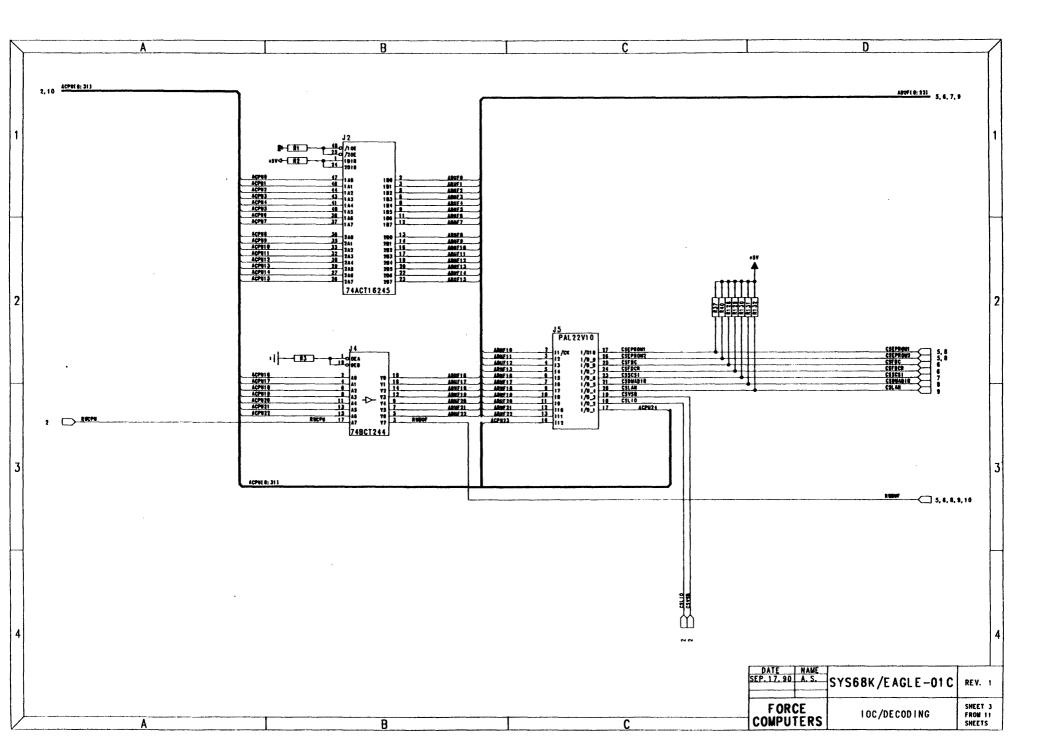

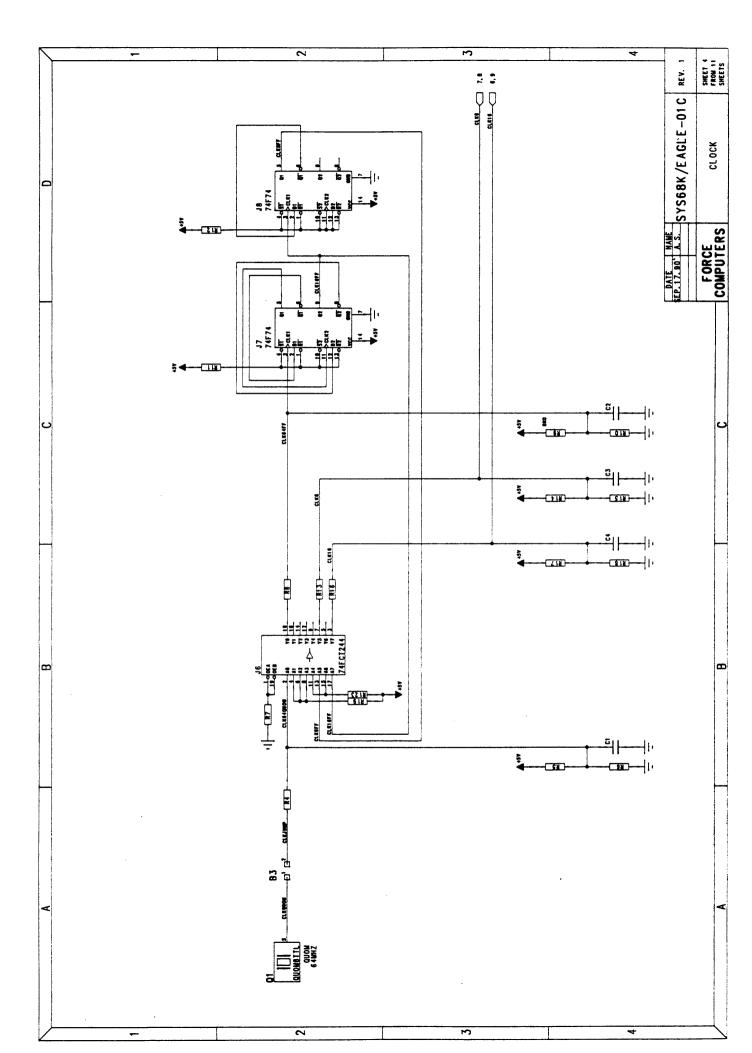

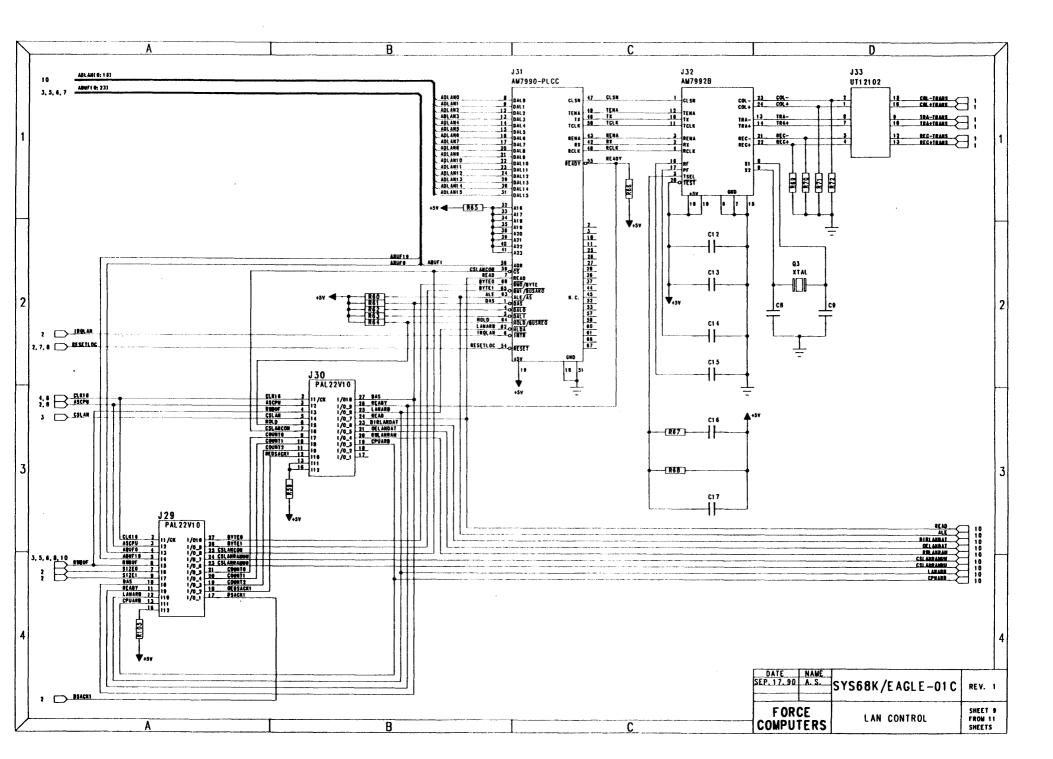

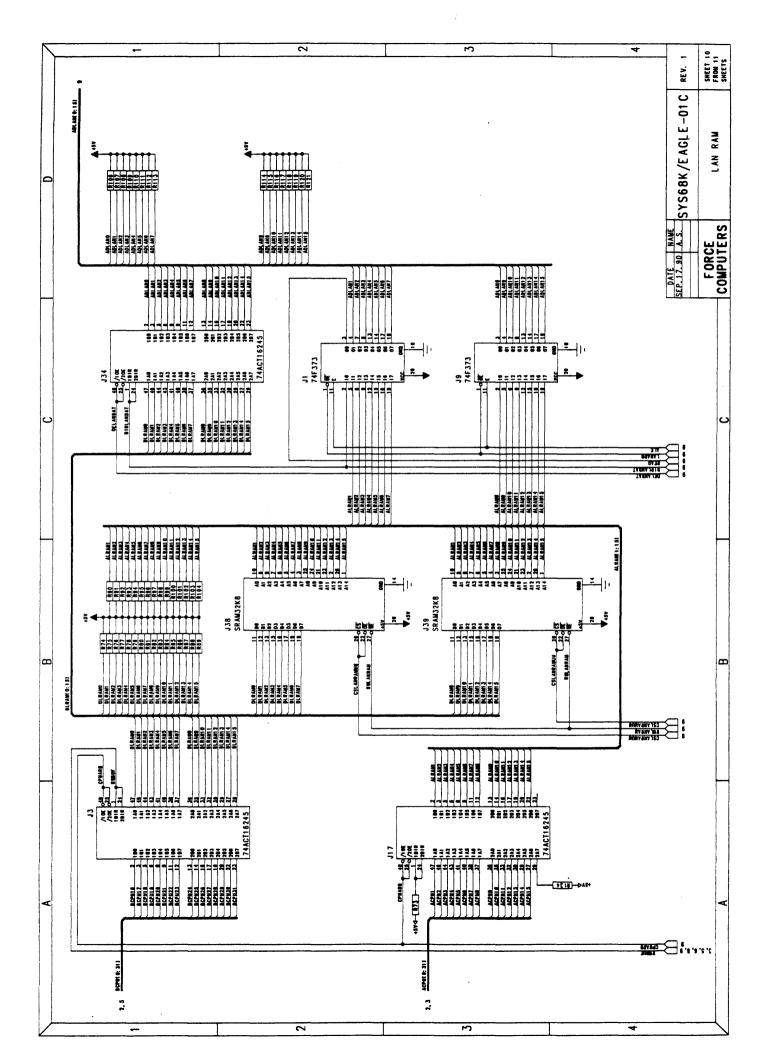

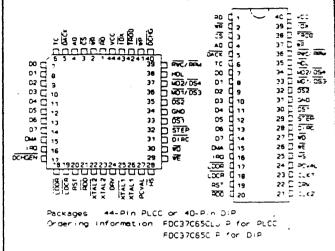

6 Eagle Module

7 Introduction to VMEPROM

8 Appendices to the VMEPROM Introduction

9 Bios Source Code Listing

10 User Notes

11 Options/Applications/ Modifications

н. 1

# SYS68K/CPU-40/41 USER'S MANUAL

Revision No. 2 February 1992

FORCE COMPUTERS Inc./GmbH All Rights Reserved

> This document shall not be duplicated, nor its contents used for any purpose, unless express permission has been granted.

Copyright by FORCE COMPUTERS®

•

# **INTRODUCTION**

This page intentionally left blank

## ΝΟΤΕ

The information in this document has been carefully checked and is believed to be entirely reliable. FORCE COMPUTERS makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors that may appear in this document. FORCE COMPUTERS reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance or design.

FORCE COMPUTERS assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of FORCE COMPUTERS GmbH/Inc.

FORCE COMPUTERS does not convey to the purchaser of the product described herein any license under the patent rights of FORCE COMPUTERS GmbH/Inc. nor the rights of others.

#### FORCE COMPUTERS Inc.

3165 Winchester Blvd. Campbell, CA 95008-6557 U.S.A.

Phone : (408) 370-6300 FAX : (408) 374-1146

#### FORCE COMPUTERS GmbH

Prof.-Messerschmitt-Str. 1 D-8014 Neubiberg/Munich West Germany

Phone : (089) 608 14-0 Telex : 524190 forc-d FAX : (089) 609 77 93

#### FORCE COMPUTERS FRANCE Sarl 11, rue Casteja 92100 Boulogne

France

Phone : (1) 4620 37 37 Telex : 206 304 forc-f FAX : (1) 4621 35 19 FORCE Computers UK Ltd. No. 1 Holly Court 3 Tring Road Wendover Buckinghamshire HP England

Phone : (0296) 625456 Telex : 838033 FAX : (0296) 624027 This page was intentionally left blank

# TABLE OF CONTENTS

| 1.                                      | GENERAL INFORMATION                                                                                                                    | 1-1                             |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1.1                                     | Features of the CPU Board                                                                                                              | 1-4                             |

| 2.                                      | THE PROCESSOR                                                                                                                          | 2-1                             |

| 2.1                                     | The CPU 68040                                                                                                                          | 2-1                             |

| 2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4 | The Shared RAM                                                                                                                         | 2-3<br>2-3<br>2-4<br>2-5<br>2-6 |

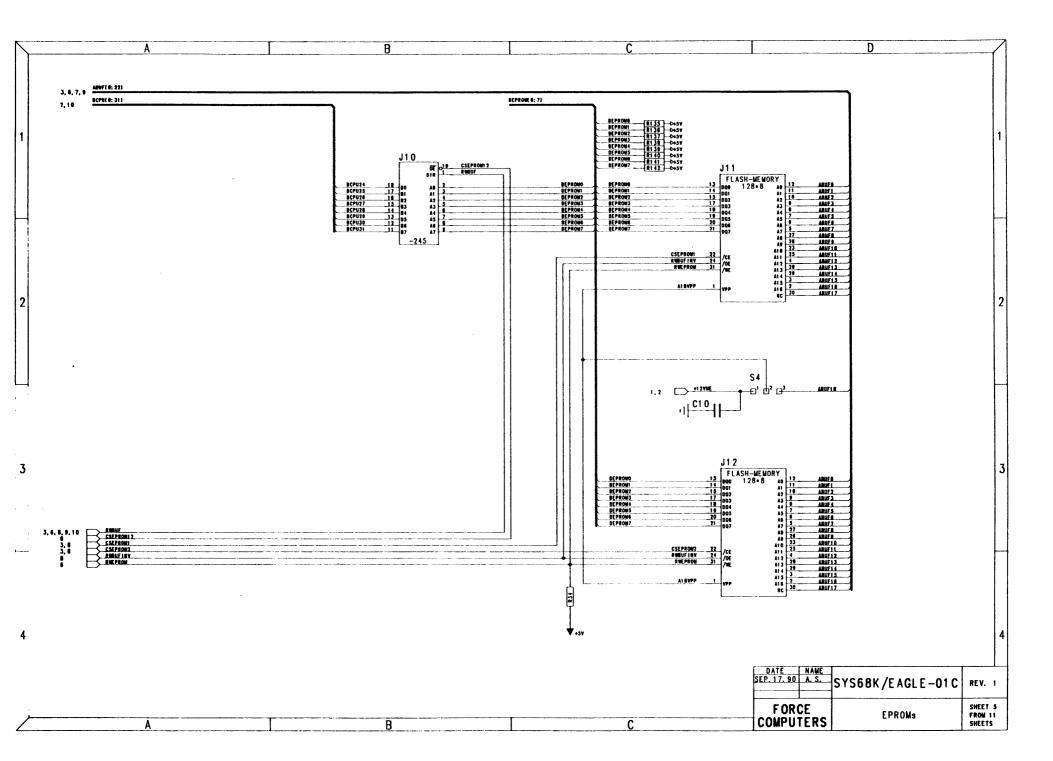

| 2.3                                     | The System EPROM                                                                                                                       | 2-7                             |

| 2.4                                     | The Local SRAM                                                                                                                         | 2-7                             |

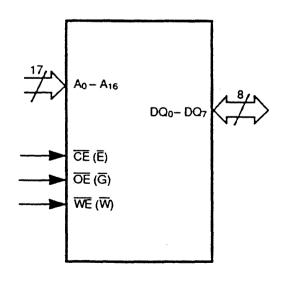

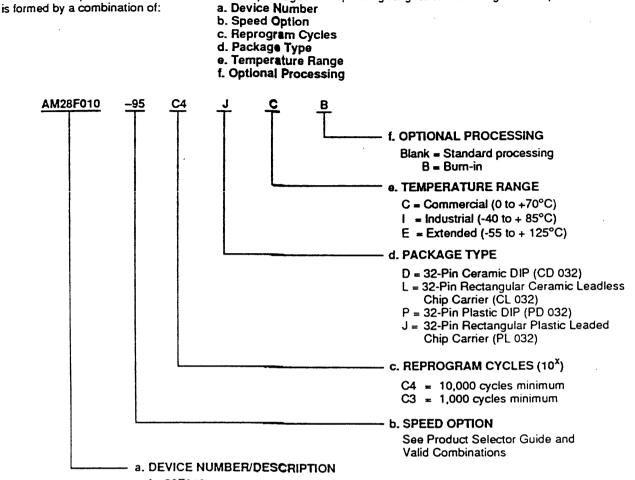

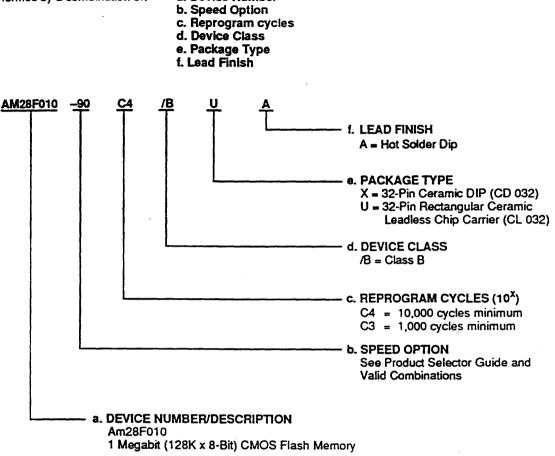

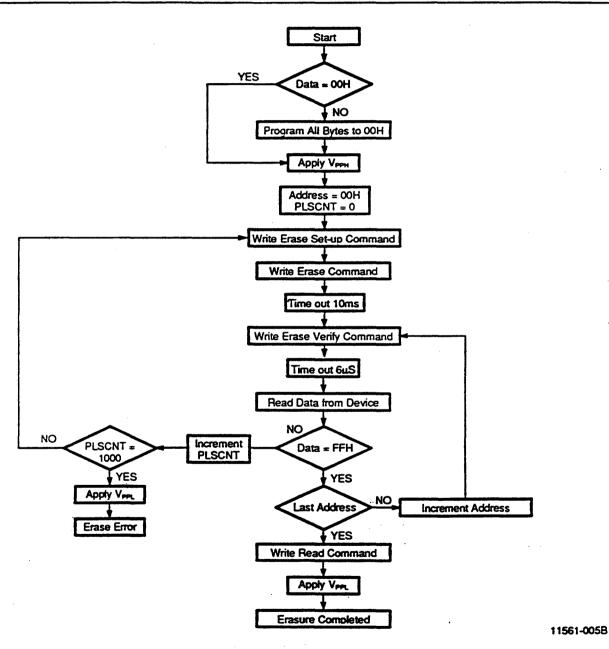

| 2.5                                     | The Local FLASH EPROM                                                                                                                  | 2-7                             |

| 2.6                                     | The Boot EPROM                                                                                                                         | 2-7                             |

| 2.7                                     | The FGA-002                                                                                                                            | 2-8                             |

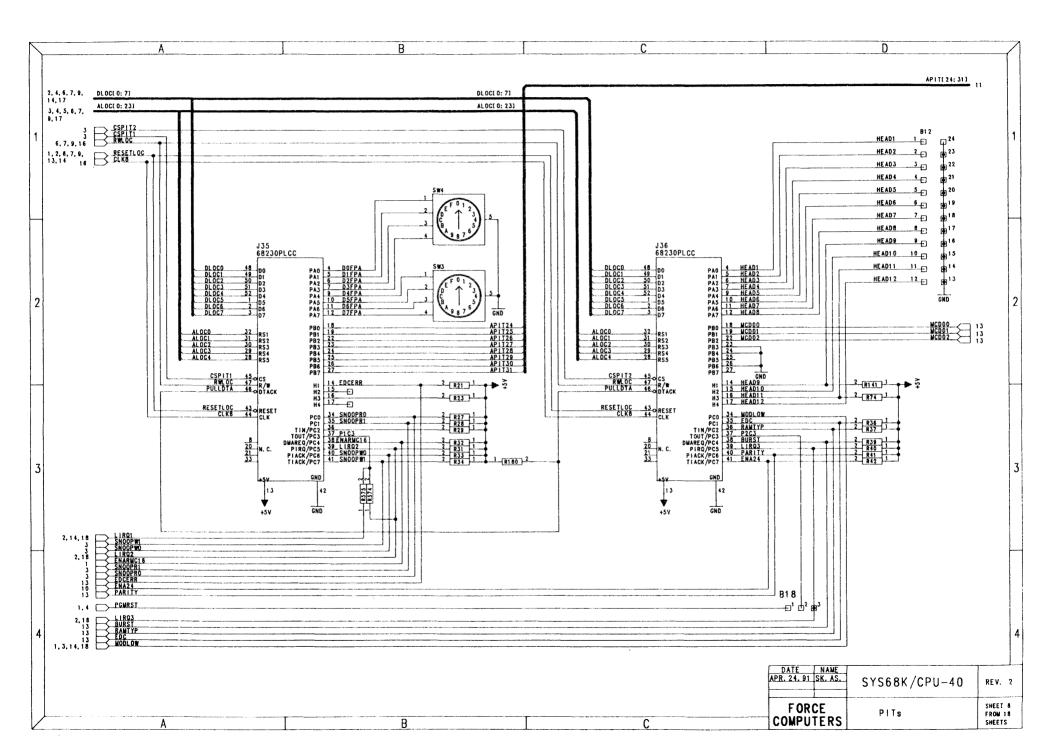

| 2.8<br>2.8.1<br>2.8.2                   | The PI/T 68230The I/O Configuration of PI/T1The I/O Configuration of PI/T2The I/O Configuration of PI/T2The I/O Configuration of PI/T2 | 2-9<br>2-10<br>2-10             |

| 2.9                                     | The Real Time Clock 72423                                                                                                              | 2-11                            |

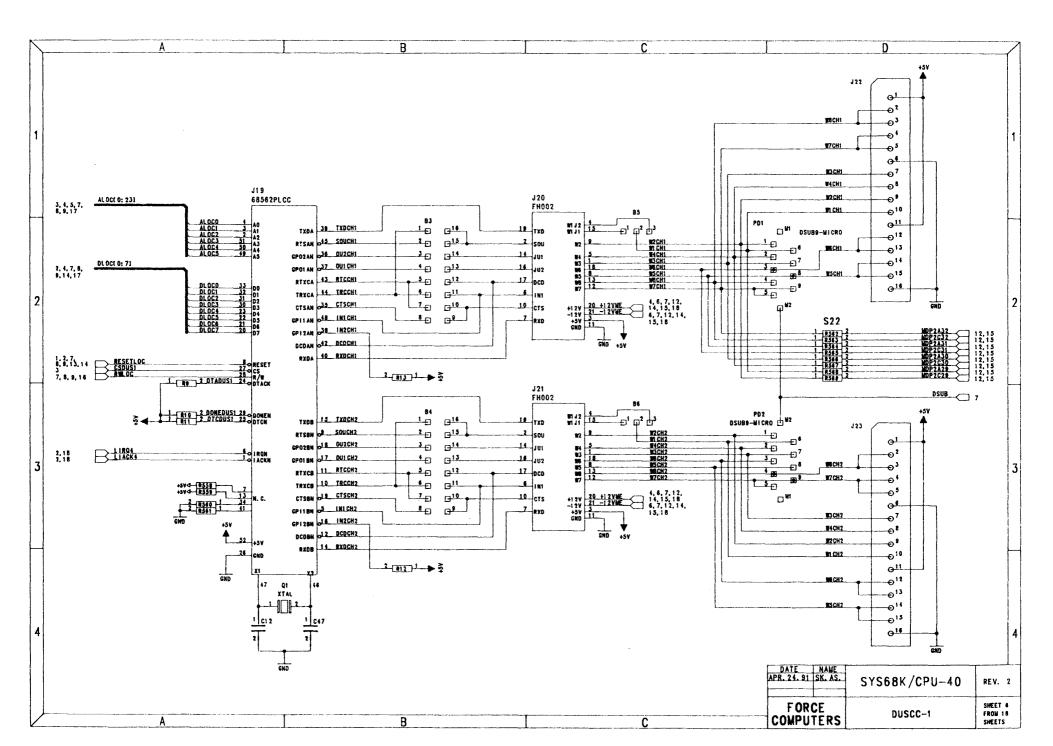

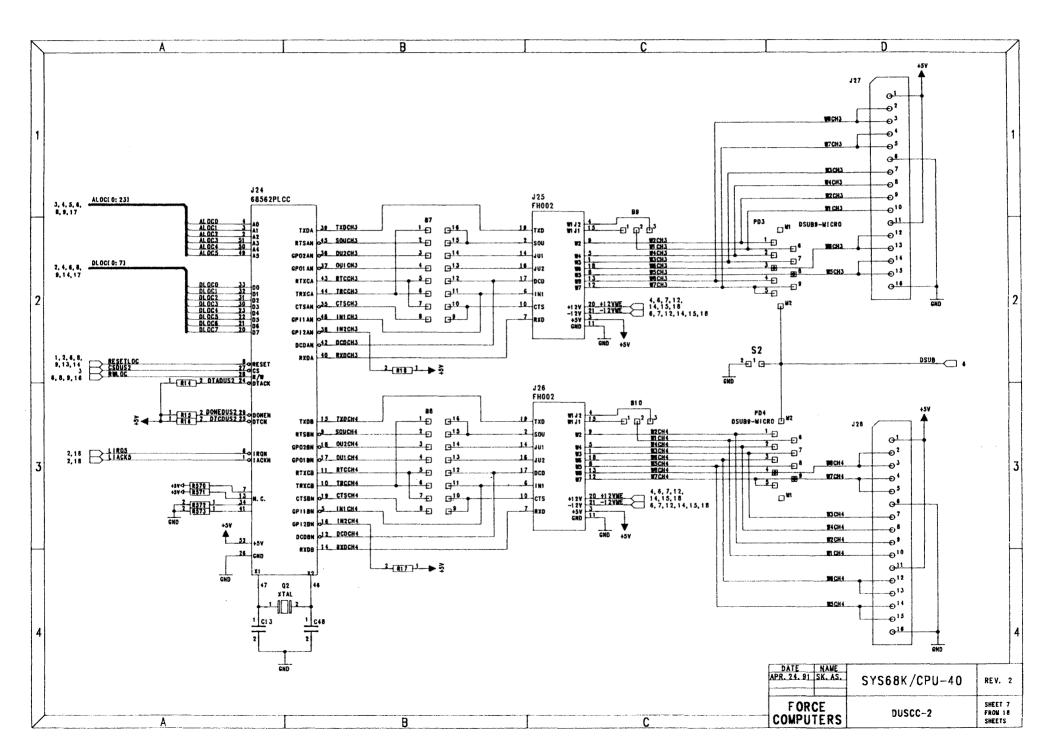

| 2.10<br>2.10.1                          | The DUSCC 68562                                                                                                                        | 2-12<br>2-13                    |

| 2.11                                    | The EAGLE Modules                                                                                                                      | 2-15                            |

| 2.12                                    | The VMEbus Interface                                                                                                                   | 2-15                            |

| 2.13                                    | The Monitor of the CPU board                                                                                                           | 2-17                            |

| 2.14                                    | Default Jumper Settings on the CPU Board                                                                                               | 2-18                            |

| 3.                                      | SPECIFICATIONS OF THE CPU BOARD                                                                                                        | 3-1                             |

| 4.                                      | ORDERING INFORMATION                                                                                                                   | 4-1                             |

| 5.                                      | HISTORY OF MANUAL REVISIONS                                                                                                            | 5-1                             |

## LIST OF FIGURES

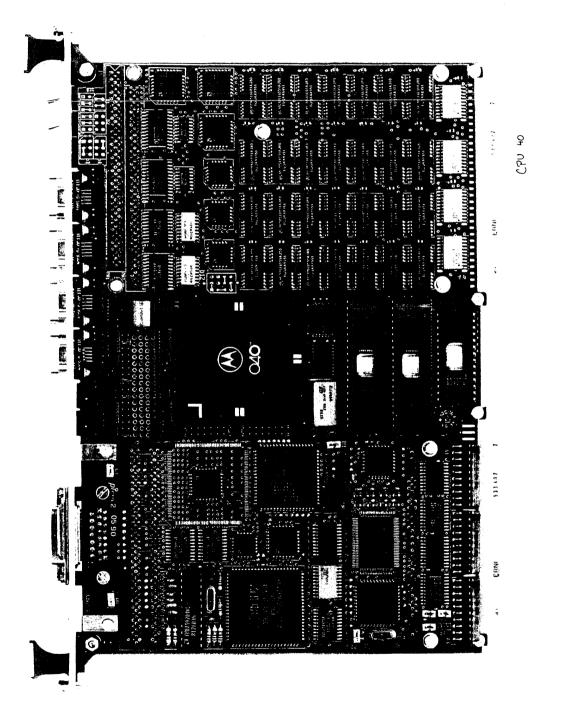

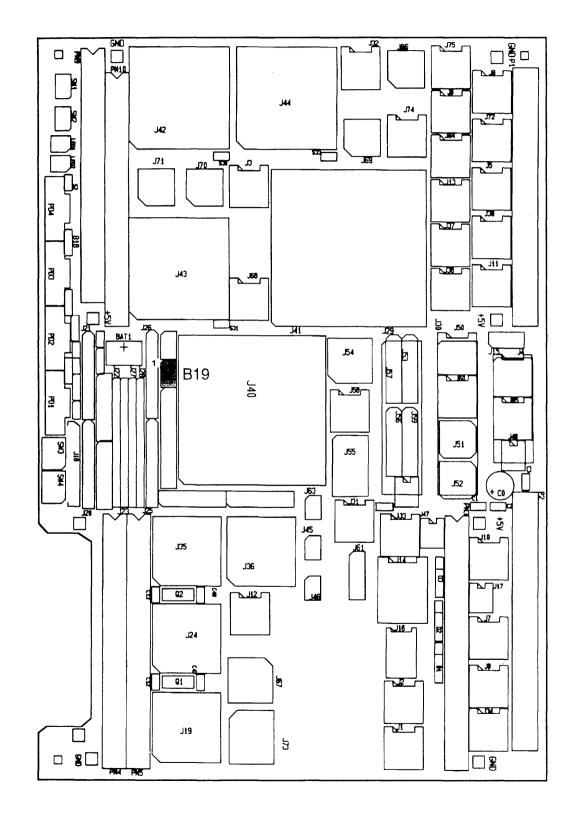

| Figure 1-1: | Photo of the CPU Board                | 1-2  |

|-------------|---------------------------------------|------|

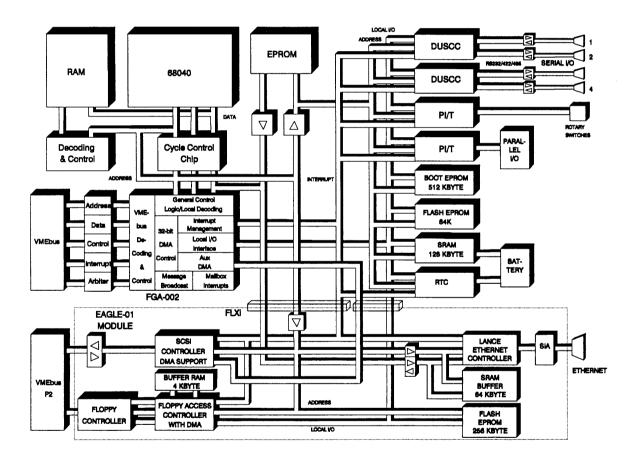

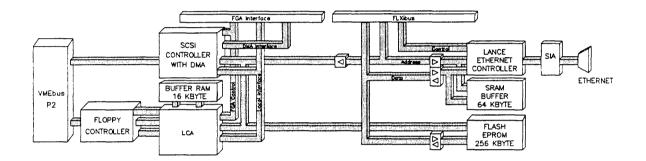

| Figure 1-2: | Block Diagram of the CPU Board        | 1-3  |

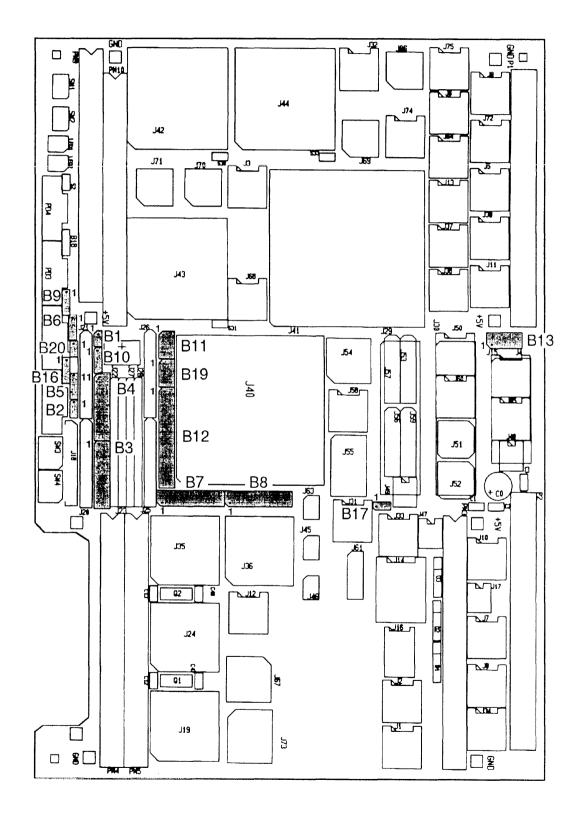

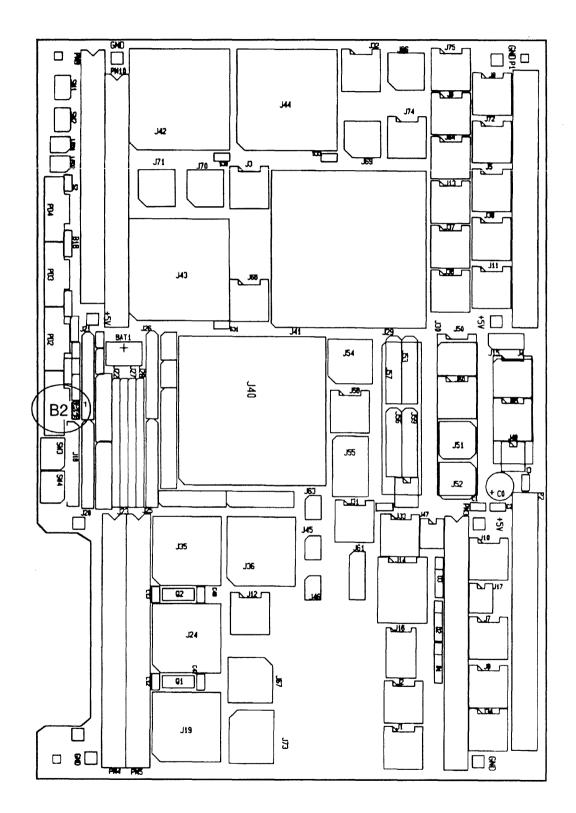

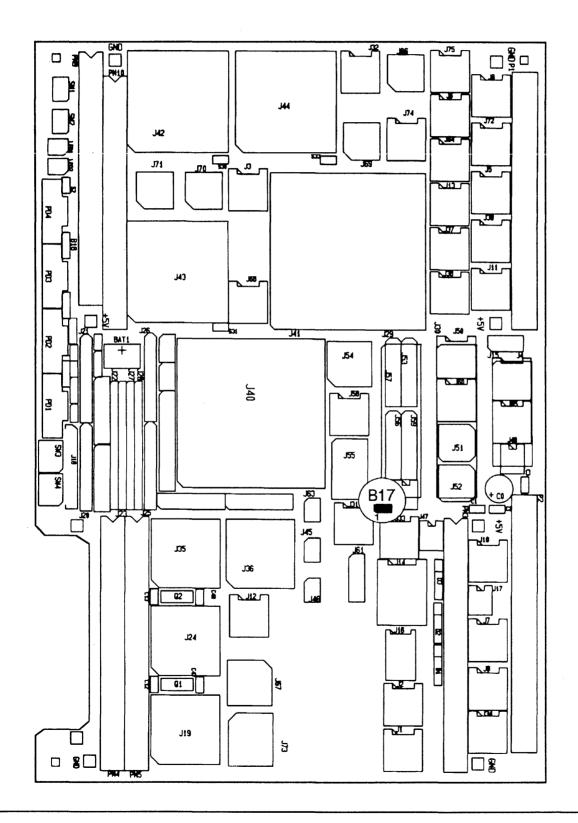

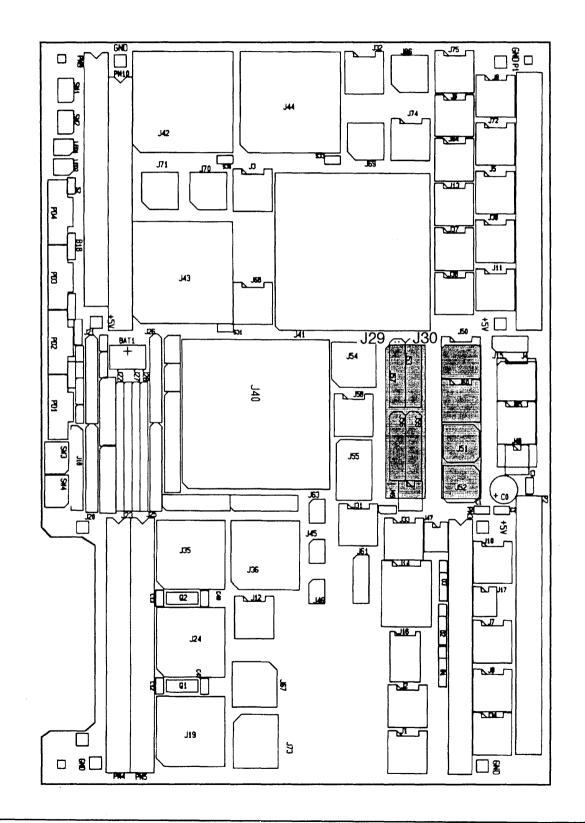

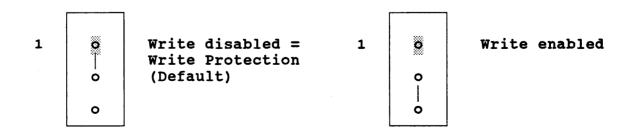

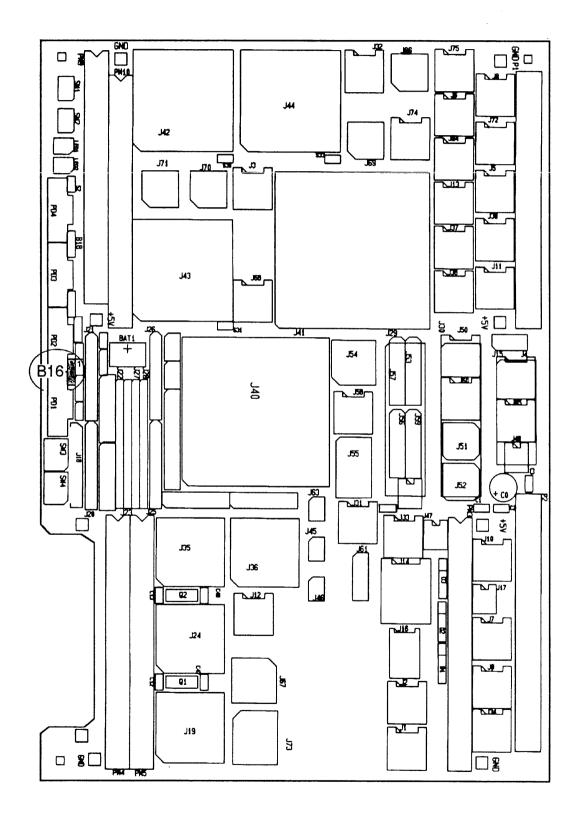

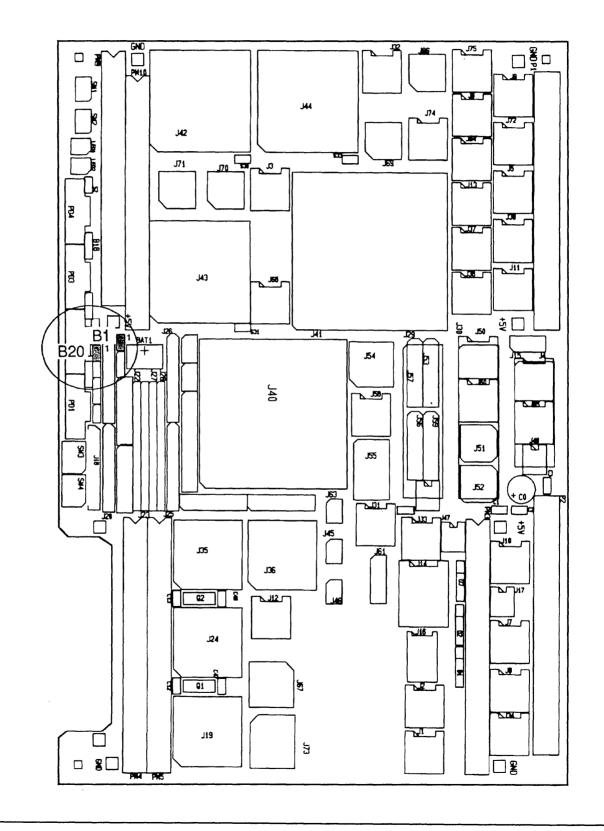

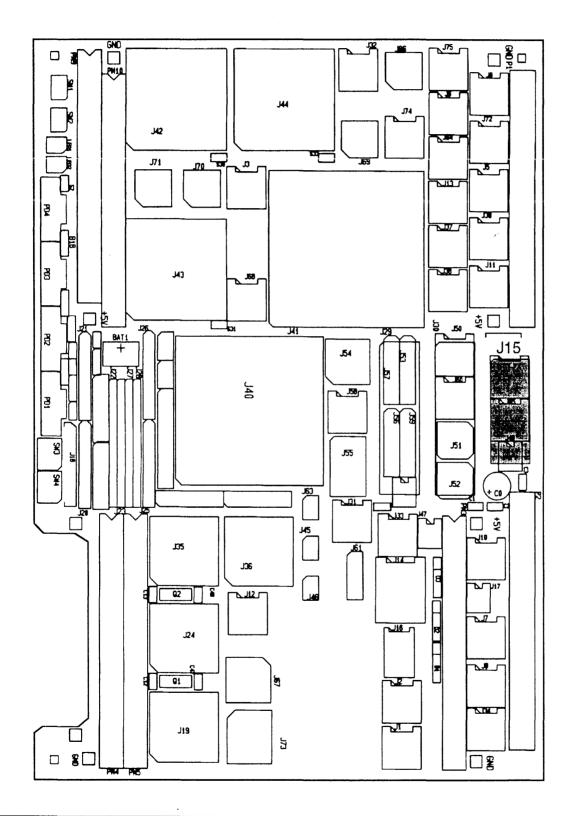

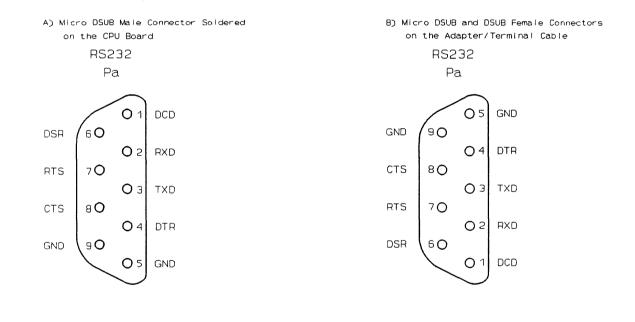

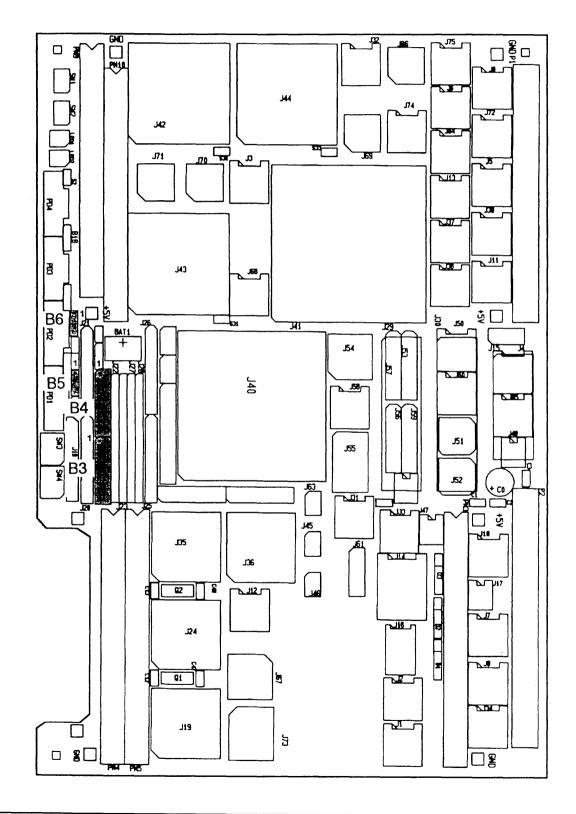

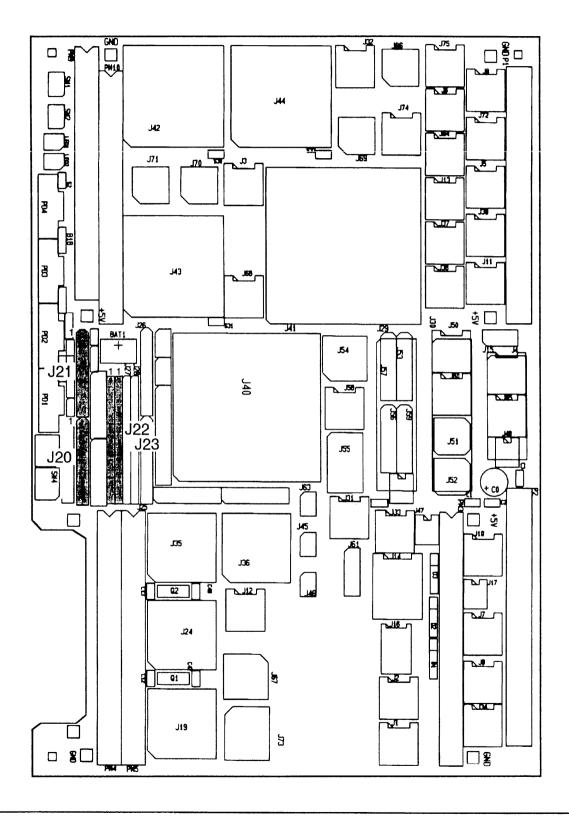

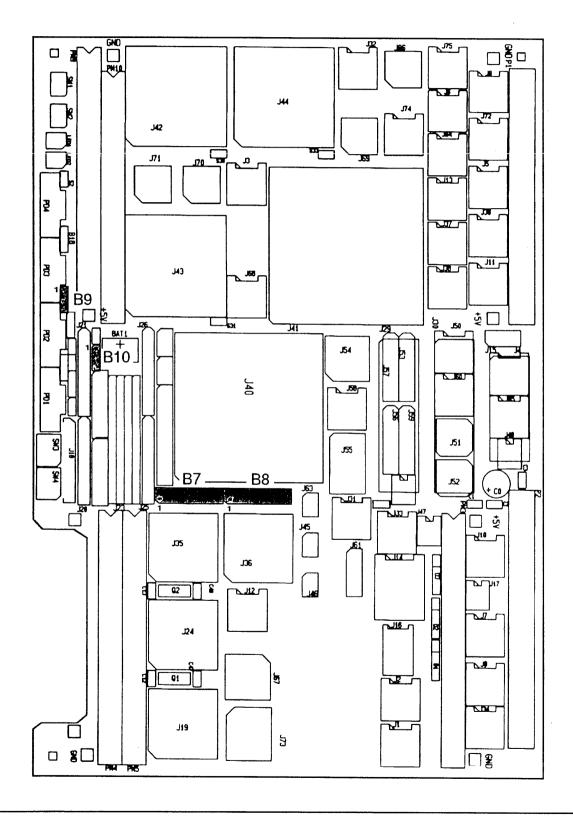

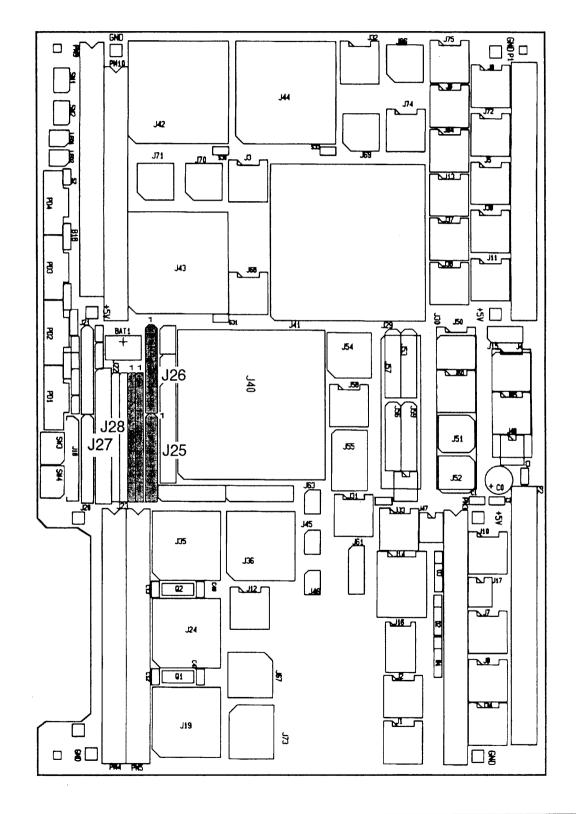

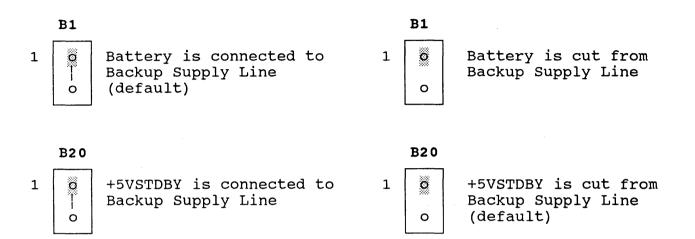

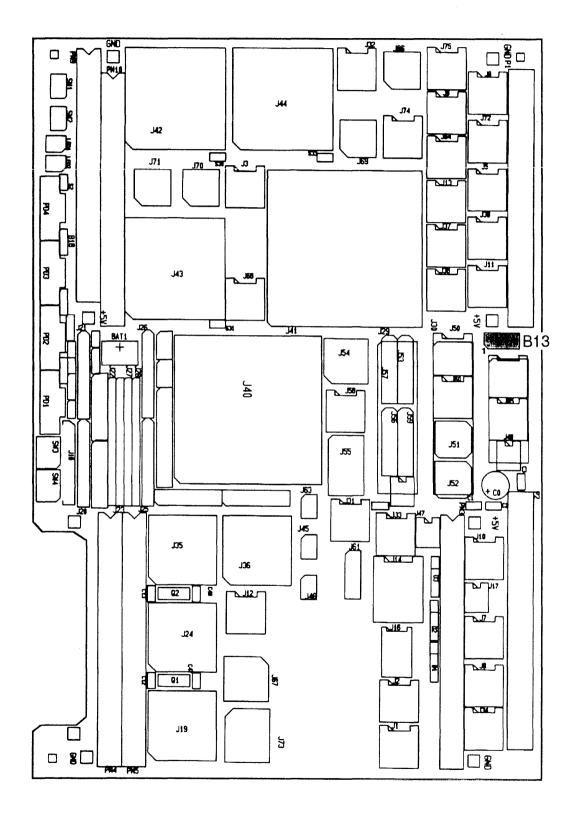

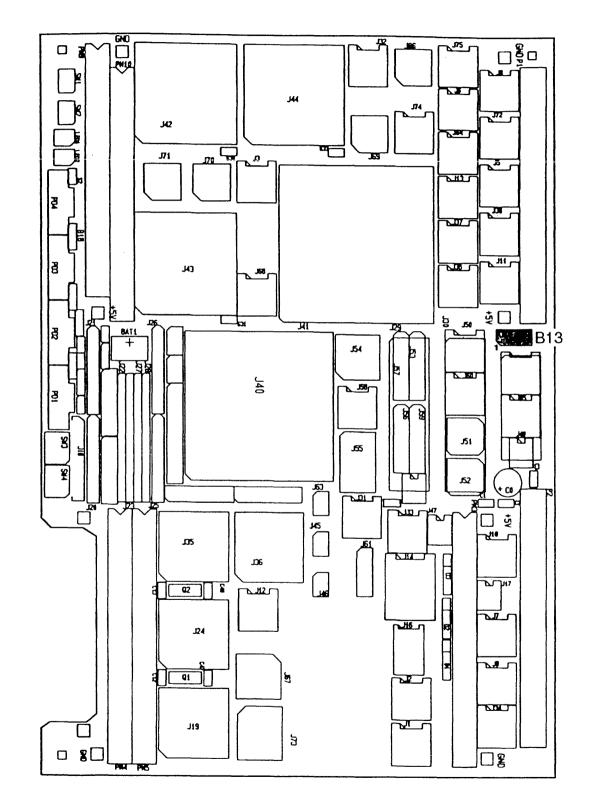

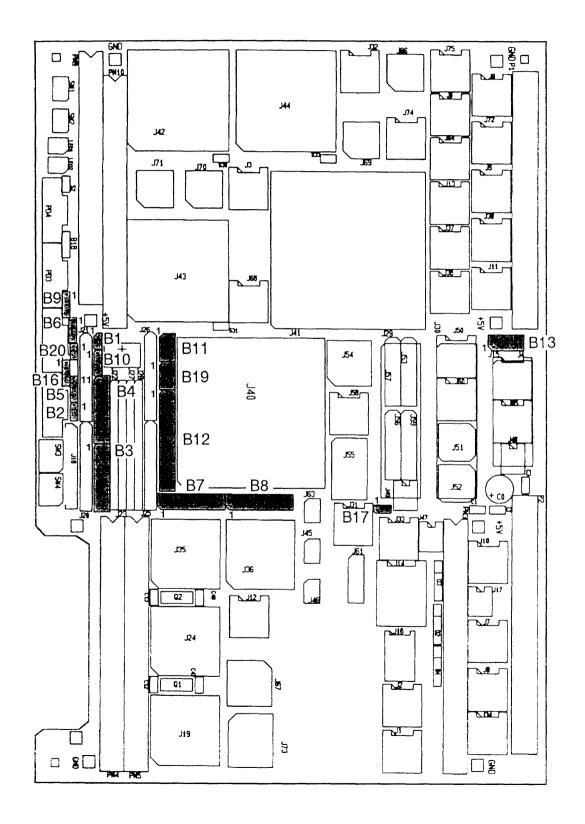

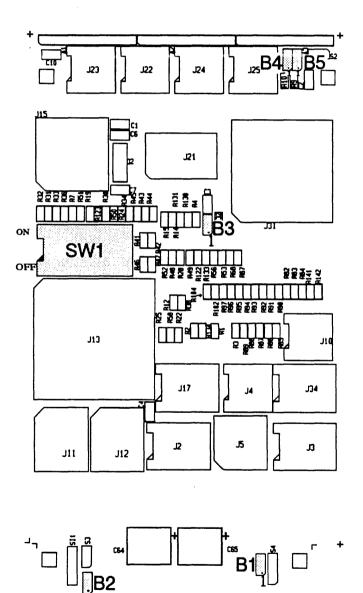

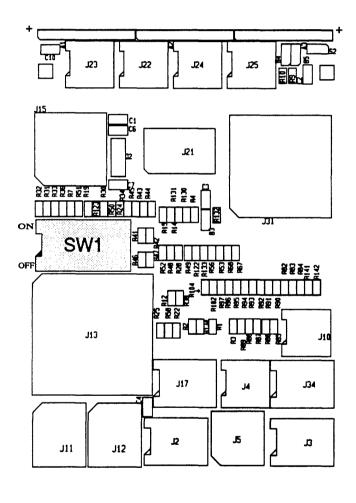

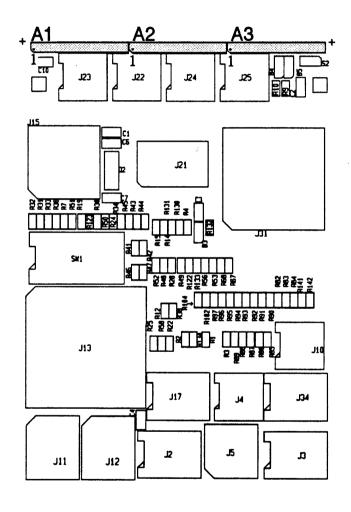

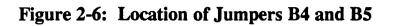

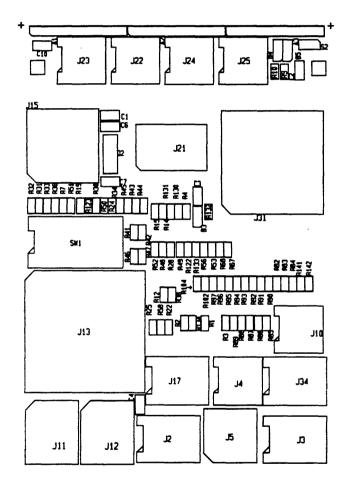

| Figure 2-1: | Location Diagram for All Jumperfields | 2-20 |

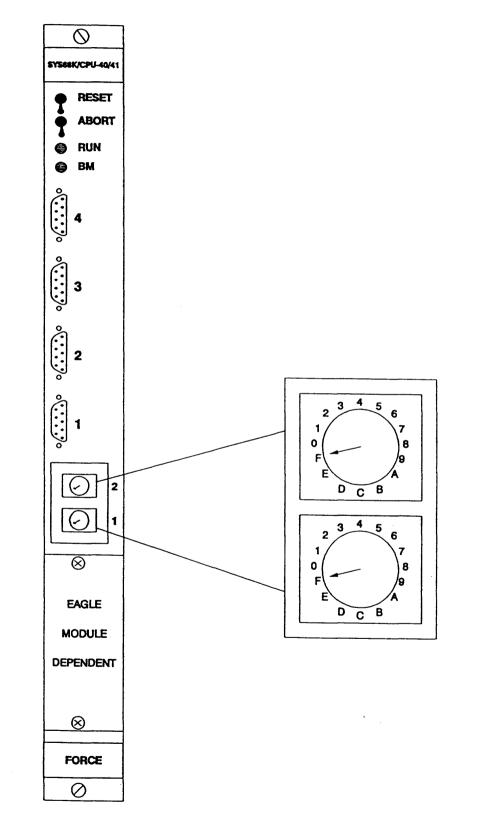

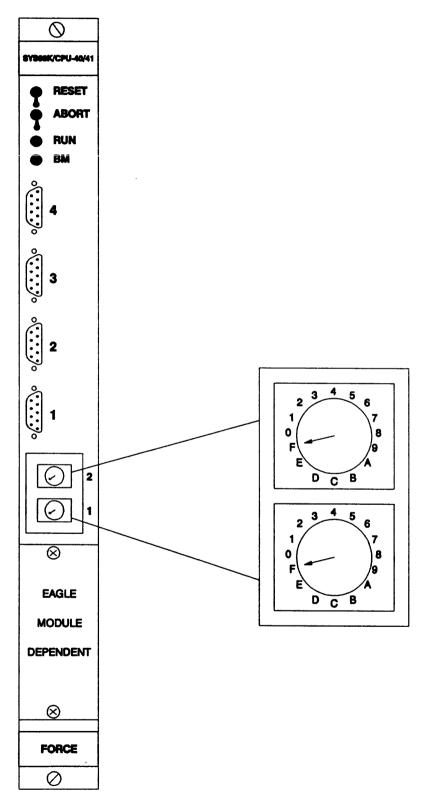

| Figure 2-2: | The Front Panel of the CPU Board      | 2-21 |

# LIST OF TABLES

| Table 1-1: | The Memory Map                              | 1-6 |

|------------|---------------------------------------------|-----|

| Table 1-2: | The Base Addresses of the Local I/O Devices | 1-7 |

## 1. GENERAL INFORMATION

This CPU board is a high performance single board computer based on the 68040 microprocessor and the VMEbus. The board incorporates a modular I/O subsystem which provides a high degree of flexibility for a wide variety of applications. The CPU board can be used with or without an I/O subsystem, called an "EAGLE" module.

The board is able to hold a RAM Module which can be DRAM (CPU-40) or SRAM (CPU-41) based.

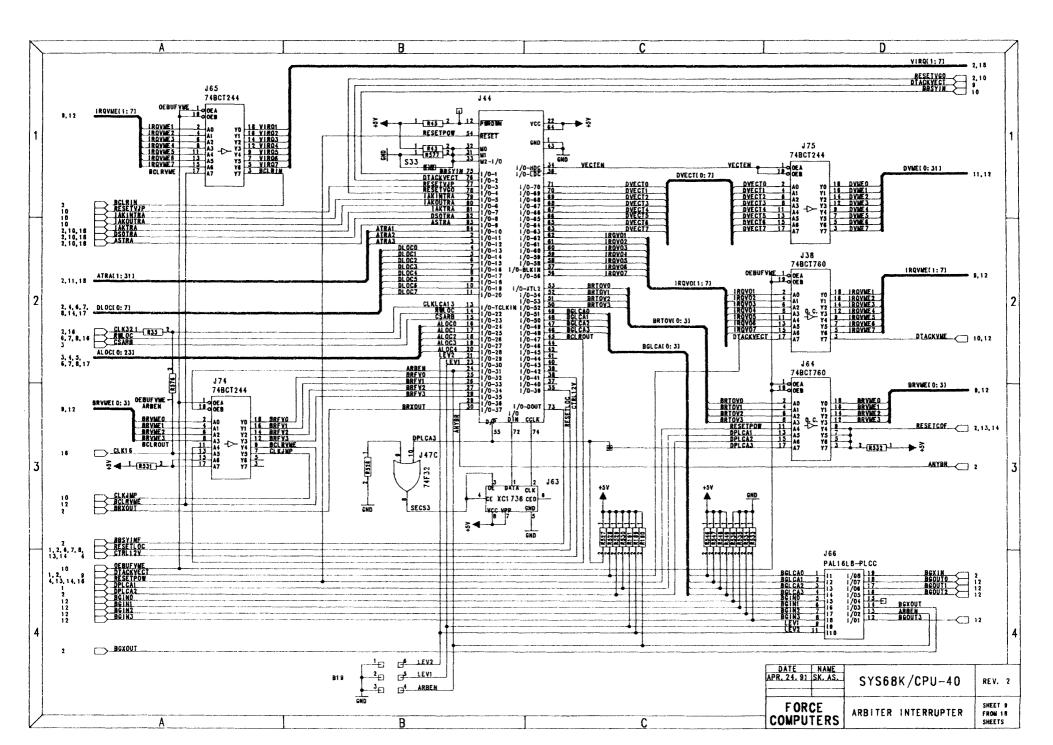

The CPU-40/41 family design utilizes all of the features of the powerful FORCE Gate Array (FGA-002). Among its features is a 32-bit DMA controller which supports local (shared) memory, VMEbus and I/O data transfers for maximum performance, parallel real time operation and responsiveness.

The EAGLE modules are installed on the CPU board via the FLXi (FORCE Local eXpansion interface). This provides a full 32-bit interface between the base board and the EAGLE module I/O subsystem, providing a range of I/O options.

Four multiprotocol serial I/O channels, a parallel I/O channel and a Real Time Clock with on-board battery backup are installed on the base board which, in combination with EAGLE modules, make the CPU board a true single board computer system.

A broad range of operating systems and kernels is available for the CPU board. However, as with all FORCE COMPUTERS' CPU cards, VMEPROM firmware is provided with the board at no extra cost. VMEPROM is a Real Time Kernel and is installed on the CPU board in the two 16-bit wide EPROM sockets, which results in a 32-bit wide System EPROM area. This ensures that the board is supplied ready to use.

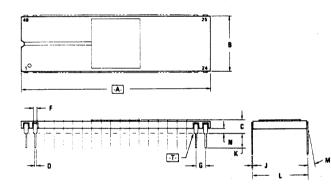

# Figure 1-1: Photo of the CPU Board

#### **1.1 Features of the CPU Board**

- 68040 microprocessor: 25.0 MHz on CPU-40B/41B/x

- 68040 microprocessor: 33.0 MHz on CPU-40D/41D/x

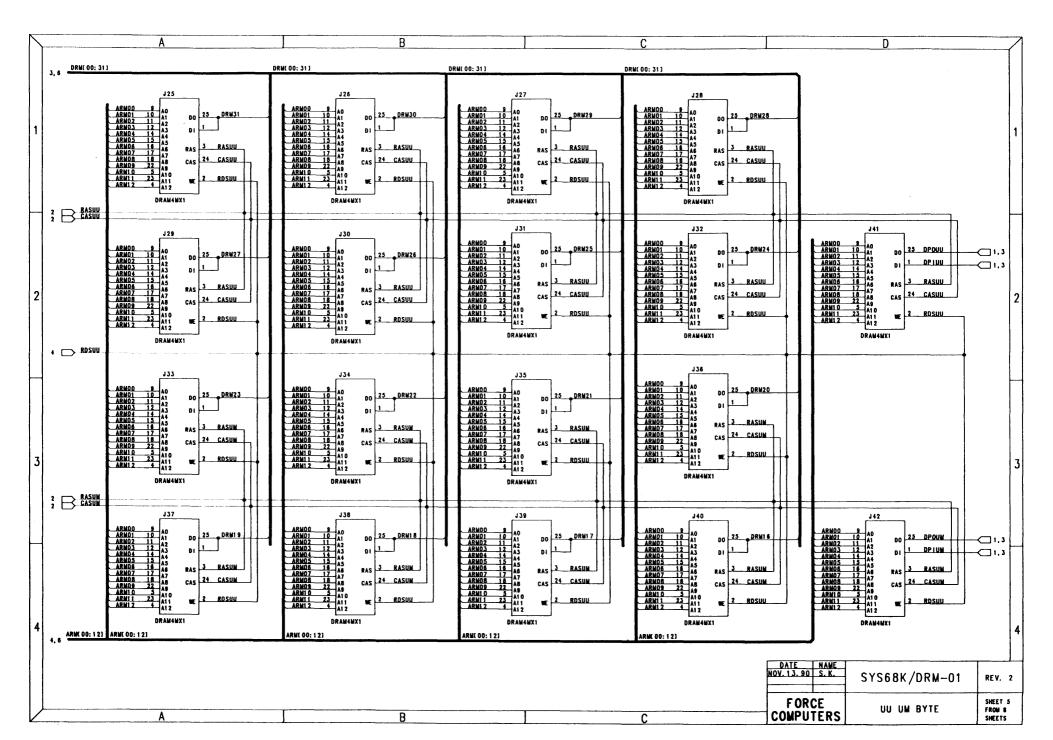

- Shared DRAM Module: 4 Mbyte DRAM with Burst Read/Write and Parity Generation and Checking (DRM-01/4)

16 Mbyte DRAM with Burst Read/Write and Parity Generation and Checking (DRM-01/16)

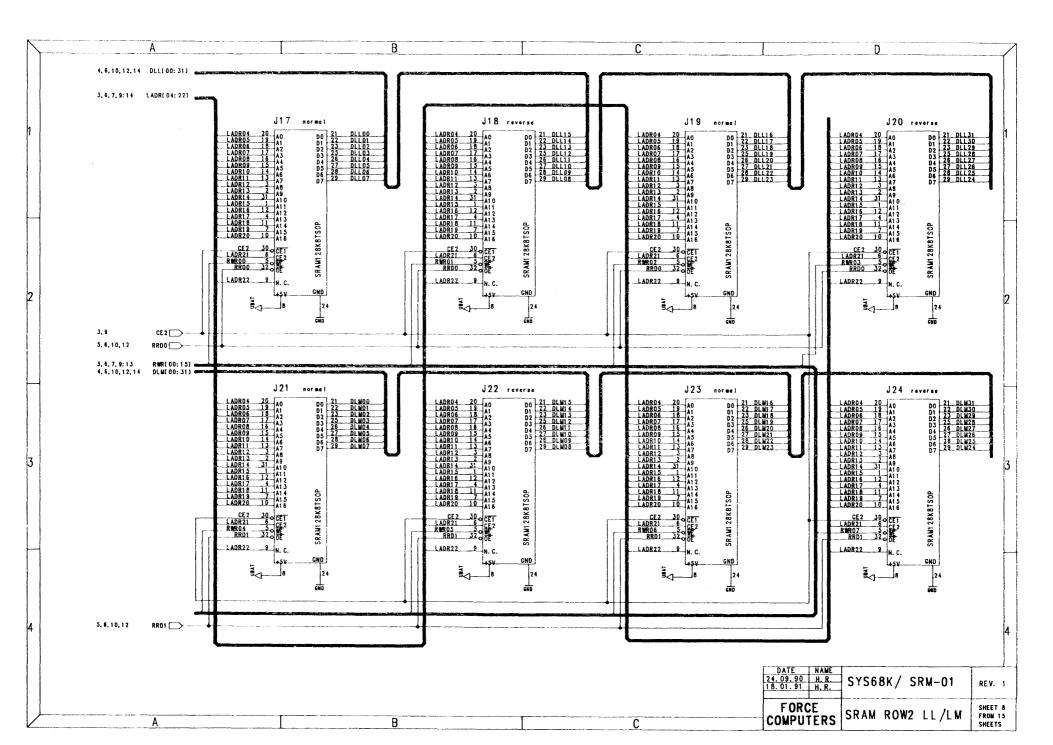

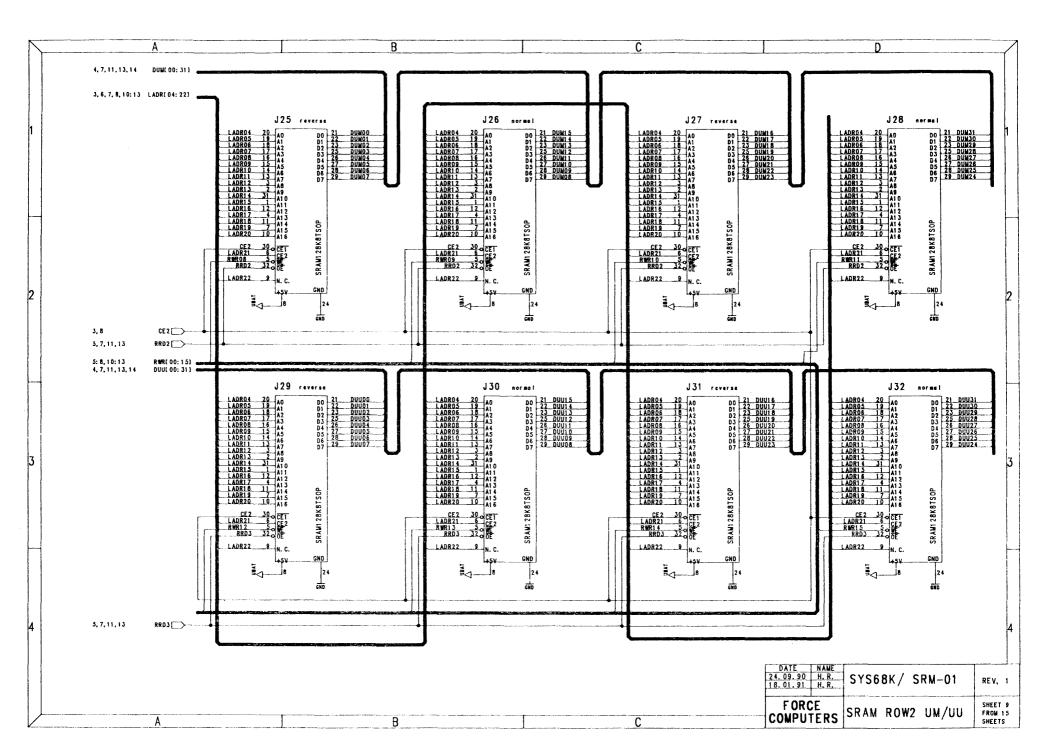

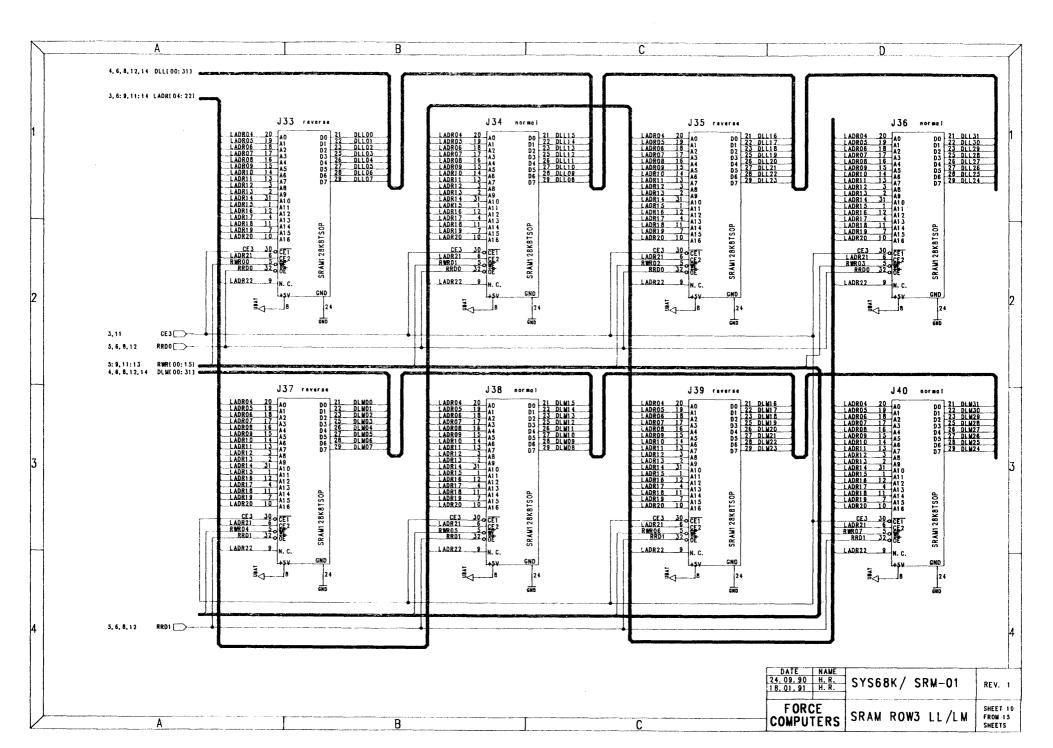

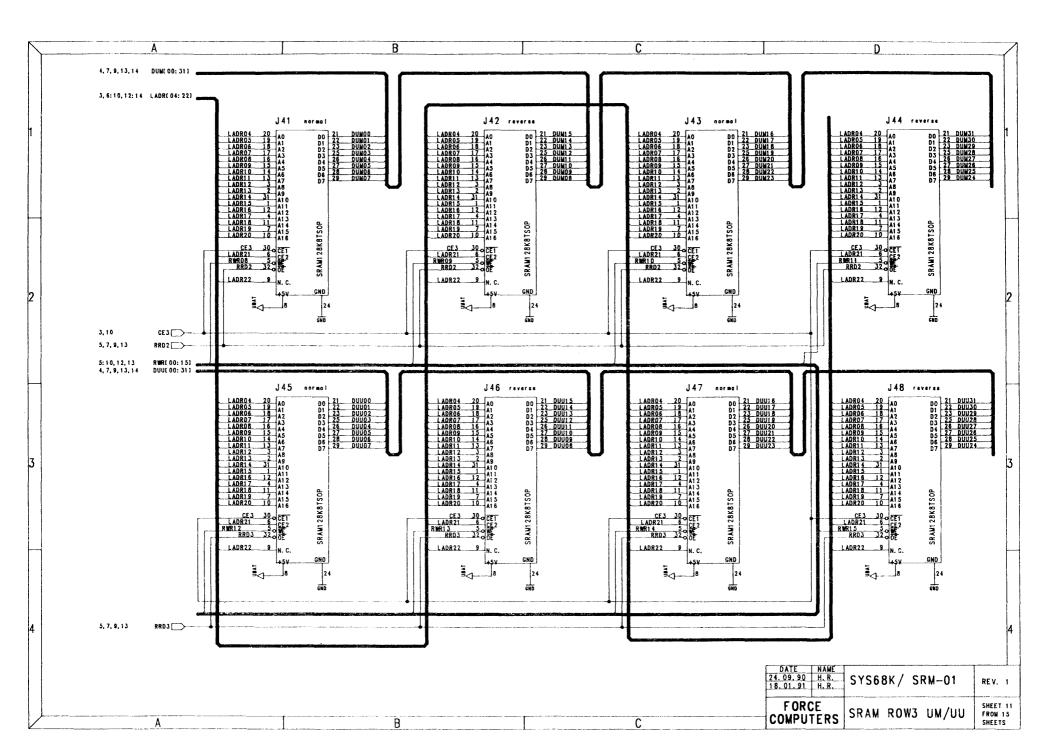

• Shared SRAM Module: 4 Mbyte SRAM with Burst Read/Write (SRM-01/4)

8 Mbyte SRAM with Burst Read/Write (SRM-01/8)

- 32-bit high speed DMA controller for data transfers to/from the shared RAM, VMEbus memory and EAGLE modules; DMA controller is installed in the FGA-002.

- Two system EPROM devices supporting 40-pin devices. Access from the 68040 using a 32bit data path

- One boot EPROM for local booting, initialization of the I/O chips and configuration of the FGA-002

- 128 Kbyte SRAM with on-board battery backup

- 128 Kbyte FLASH EPROM

- FLXi interface for installation of one EAGLE module

- Four Serial I/O interfaces, configurable as RS232/RS422/RS485, available on the front panel

- 8-bit parallel interface with 4-bit handshake

- Two 24-bit timers with 5-bit prescaler

- One 8-bit timer

- Real Time Clock with calendar and on-board battery backup

- Full 32-bit VMEbus master/slave interface, supporting the following data transfer types:

- A32, A24, A16 : D8, D16, D32 Master

- A32, A24 : D8, D16, D32 Slave

- UAT, RMW, ADO

# Features of the CPU Board (cont'd)

- Four-level VMEbus arbiter

- SYSCLK driver

- VMEbus interrupter (IR 1-7)

- VMEbus interrupt handler (IH 1-7)

- Support for ACFAIL\* and SYSFAIL

- Bus timeout counters for local and VMEbus access (15  $\mu$ sec)

- VMEPROM, Real Time Multitasking Kernel with monitor, file manager and debugger

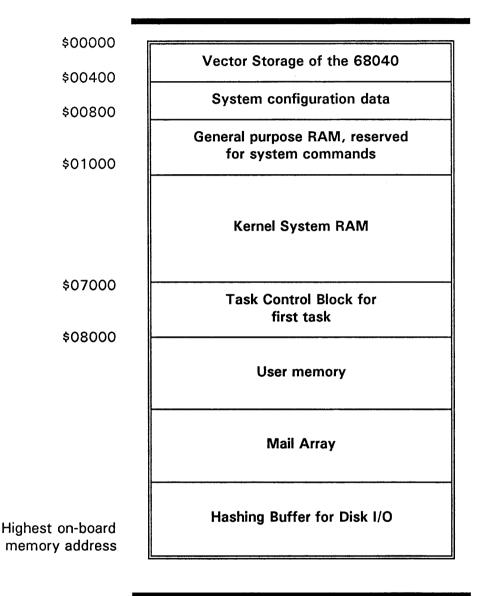

The following table summarizes the memory map of the CPU board.

## Table 1-1: The Memory Map

| Start<br>Address                 | End<br>Address                   | Туре                                                                              |

|----------------------------------|----------------------------------|-----------------------------------------------------------------------------------|

| 00000000<br>00000000<br>00000000 | 003FFFFF<br>007FFFFF<br>00FFFFFF | Shared Memory (4 Mbyte)<br>Shared Memory (8 Mbyte) or<br>Shared Memory (16 Mbyte) |

| 00400000                         | F9FFFFF                          | VMEbus Addresses (4 Mbyte Shared Memory)<br>A32: D32, D24, D16, D8                |

| 00800000                         | F9FFFFF                          | VMEbus Addresses (8 Mbyte Shared Memory)<br>A32: D32, D24, D16, D8                |

| 01000000                         | F9FFFFF                          | VMEbus Addresses (16 Mbyte Shared Memory)<br>A32: D32, D24, D16, D8               |

| FA000000                         | FAFFFFF                          | Message Broadcast Area                                                            |

| FB000000                         | FBFEFFFF                         | VMEbus<br>A24: D32, D24, D16, D8                                                  |

| FBFF0000                         | FBFFFFF                          | VMEbus<br>A16: D32, D24, D16, D8                                                  |

| FC000000                         | FCFEFFFF                         | VMEbus<br>A24: D16, D8                                                            |

| FCFF0000                         | FCFFFFF                          | VMEbus<br>A16: D16, D8                                                            |

| FD000000                         | FEFFFFF                          | Reserved                                                                          |

| FF000000                         | FF7FFFF                          | SYSTEM EPROM                                                                      |

| FF800000                         | FFBFFFFF                         | Local I/O                                                                         |

| FFC00000                         | FFC7FFFF                         | LOCAL SRAM                                                                        |

| FFC80000                         | FFCFFFFF Local FLASH EPROM       |                                                                                   |

| FFD00000                         | FFDFFFF                          | Registers of FGA-002                                                              |

| FFE00000                         | FFEFFFF                          | BOOT EPROM                                                                        |

| FF803E00                         | FF803FFF                         | VMEbus Arbiter                                                                    |

| FFF00000                         | FFFFFFF                          | Reserved                                                                          |

This table gives a brief overview of the local I/O devices and the equivalent base address.

# Table 1-2: The Base Addresses of the Local I/O Devices

| BASE ADDRESS | DEVICE       |

|--------------|--------------|

| \$FF803000   | RTC 72423    |

| \$FF802000   | DUSCC1 68562 |

| \$FF802200   | DUSCC2 68562 |

| \$FF800C00   | PI/T1 68230  |

| \$FF800E00   | PI/T2 68230  |

This page was intentionally left blank

# 2. THE PROCESSOR

## 2.1 The CPU 68040

The 68040 is a third generation full 32 bit enhanced microprocessor. The 68040 is upward object code compatible with the 68030, 68020, 68010 and 68000 line of microprocessors.

The 68040 combines a central processing unit core, an instruction cache, a data cache, a memory management unit, and an enhanced bus controller.

This virtual memory processor utilizes multiple, concurrent execution units and a highly integrated architecture providing a high level of performance.

The 68040 processor combines a 68030 compatible integer unit, a 68881/68882 compatible floating point unit (FPU), memory management units (MMUs), and a 4 Kbyte instruction and data cache. Cache functionality is strengthened by the built-in on-chip bus snooping logic which instantly supports cache logic during multimaster applications.

Instruction administration is routed through both the integer unit and FPU, which link to the fully independent data and instruction memory units. Each memory unit consists of an MMU, an address translation cache (ATC), a main cache, and a snoop controller.

The internal blocks are designed to operate in parallel, allowing instruction execution to be overlapped. In addition, the internal caches, the on-chip memory management unit, and the enhanced bus controller operate parallel to one another.

The 68040 contains an enhanced bus controller that supports both synchronous/ asynchronous bus cycles and burst data transfers. It contains a nonmultiplexed address bus and data bus and supports 32 bits of address and data.

#### Features of the 68040

- Nonmultiplexed 32 bit address and data buses

- 16 general purpose address and data registers (32 bit wide)

- 8 floating point data registers (80 bit wide)

- Two supervisor stack pointers (32 bit wide)

- 19 special purpose control registers

- 4 Kbyte instruction and 4 Kbyte data cache

- On-chip paged memory management unit

- Pipelined architecture with parallelism allowing accesses to internal caches, bus transfers, and instruction execution in parallel

- Synchronous bus cycles and burst read and write data transfers

- Complete floating point support given to the 68882 FPCP subset and software emulation

- 68030 compatible

- Low latency bus accesses to reduce cache miss penalty

- Maximized throughput from the integer unit, FPU, MMU and bus controller

- 4 Gbyte direct addressing range

## 2.2 The Shared RAM

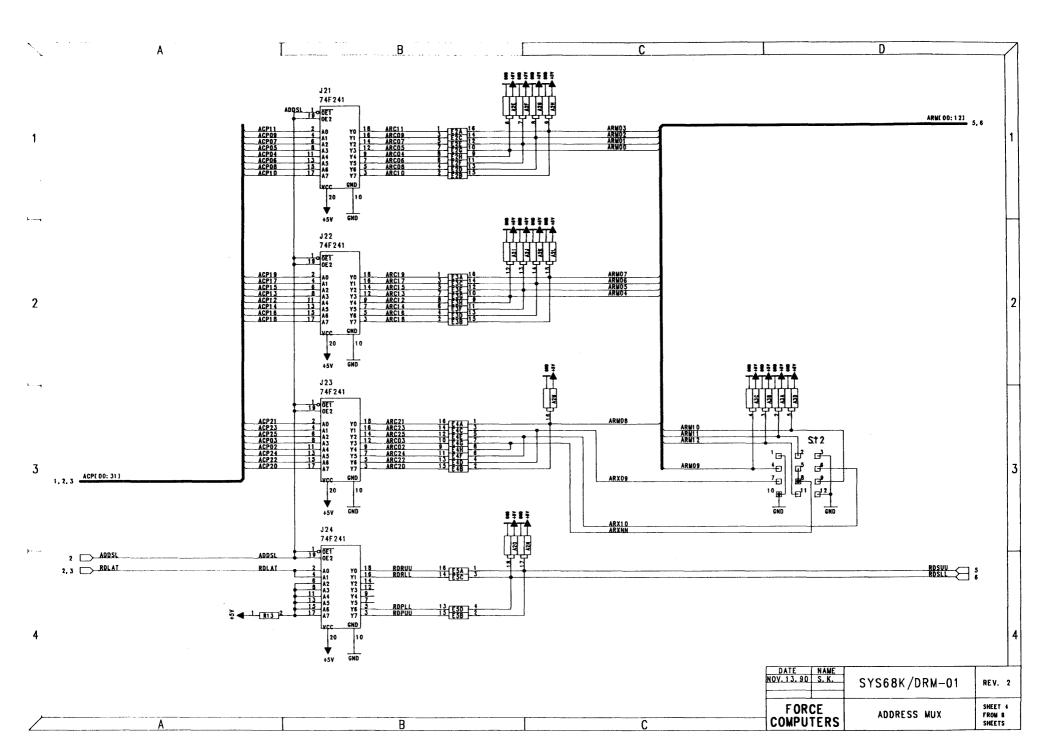

On this CPU board the shared RAM is placed on a module to allow the adaption of DRAM or SRAM to the base board.

All signals which are needed to control the shared RAM are available on the RAM module connector. Therefore RAM devices with different access times can also be used on this CPU board to take advantage of the 68040 with higher frequency if it becomes available.

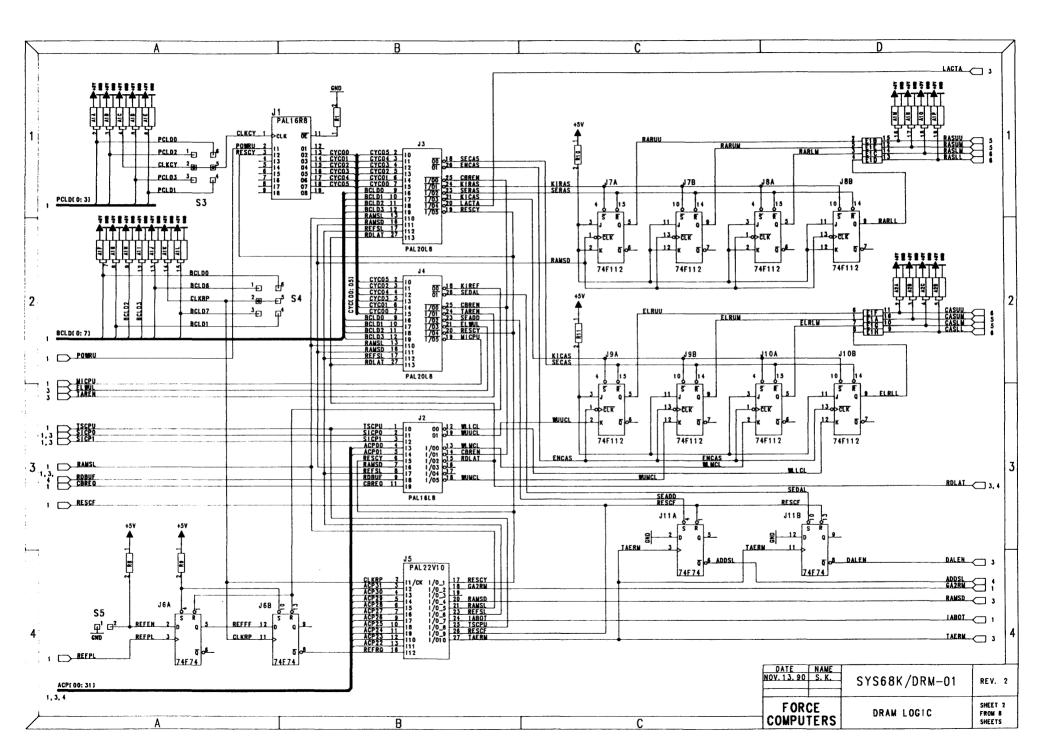

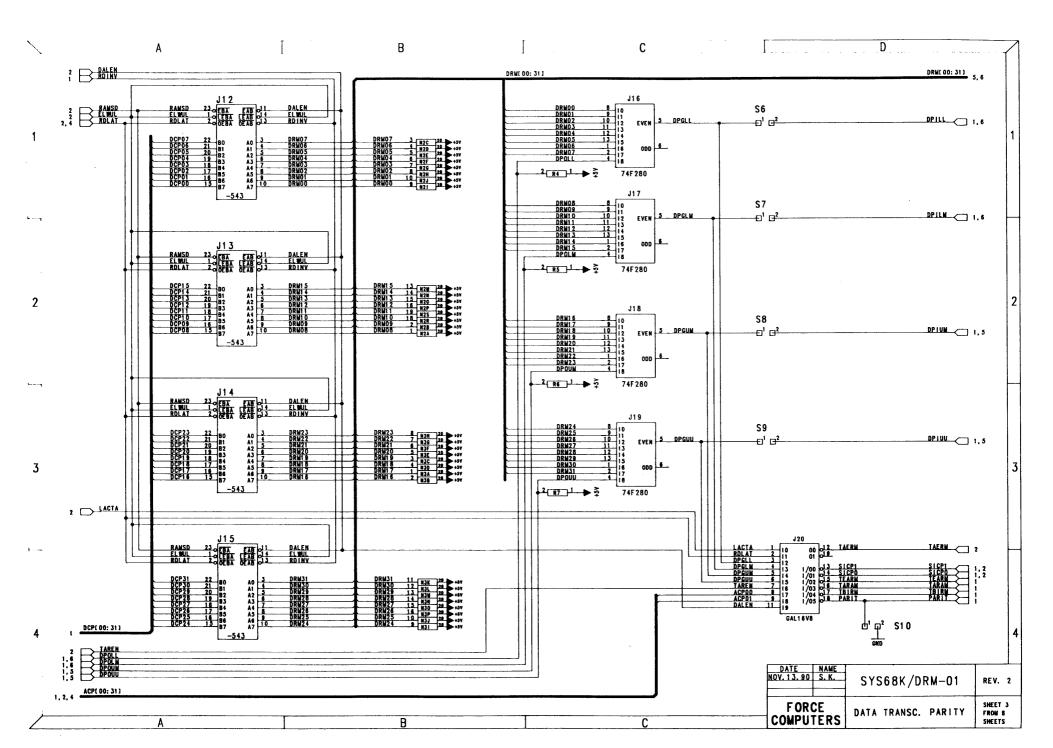

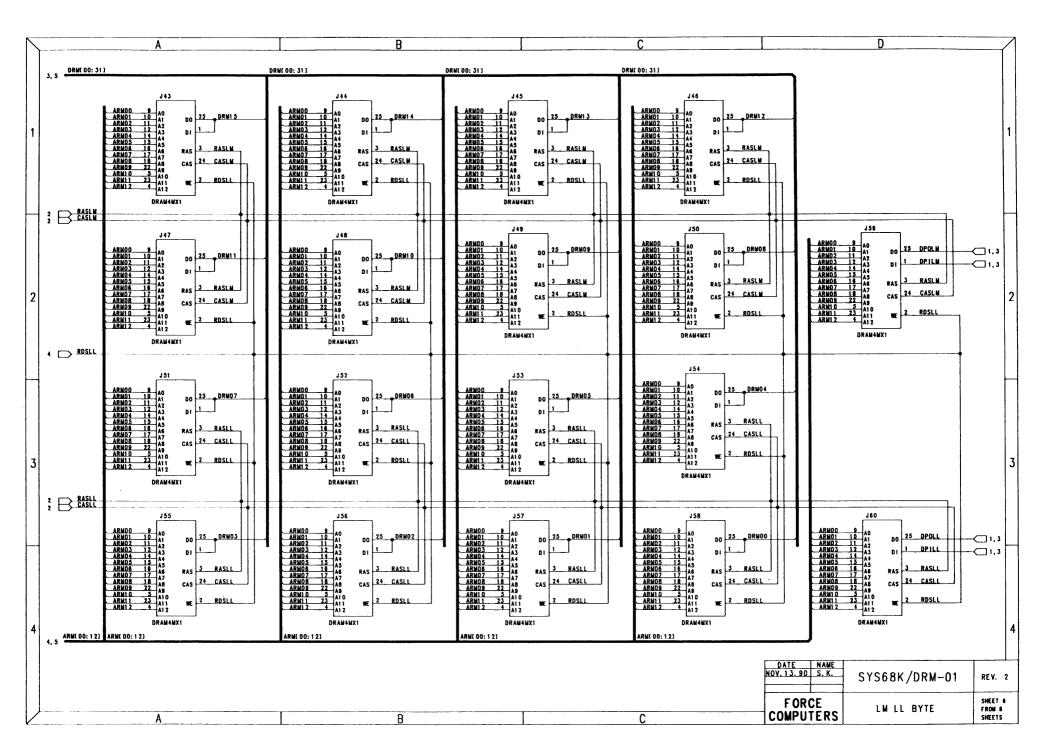

#### 2.2.1 The DRM-01/4

The DRM-01/4 is a 4 Mbyte RAM module which is used on the CPU-40B/4.

#### Features of the DRM-01/4

- 4 Mbyte DRAM

- Burst READ and Burst WRITE capability

- Parity Generation and Checking

- Asynchronous refresh is provided every 14µs

- Accessible via VMEbus

The access address for the 68040 is \$00000000 to \$003FFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined memory range can be write protected in coordination with the address modifier codes. For example, in supervisor mode the memory can be read and written, in user mode memory can only be read.

The DRAM module includes byte parity check for local and VMEbus accesses. If a parity error is detected on a VMEbus cycle, a BERR is forced to the VMEbus informing the requestor that a parity error has occurred. On local accesses, a Transfer Error Acknowledge (TEA) is forced to the processor if a parity error was detected.

The following chart lists the required CPU clock cycles and wait states for accessing the shared RAM.

| Board<br>Type | 68040 Clock<br>Frequency | No. of CPU Clock<br>Cycles Counted<br>From TS to TA<br>for Normal Cycles | No. of CPU Clock<br>Cycles for<br>Burst Cycles | No. of Wait<br>States for<br>Normal Cycles | No. of Wait<br>States for<br>Burst Cycles |

|---------------|--------------------------|--------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-------------------------------------------|

| CPU-40/B      | 25 MHz                   | 4                                                                        | 1                                              | 3                                          | 0                                         |

#### 2.2.2 The DRM-01/16

The DRM-01/16 is a 16 Mbyte RAM module which is used on the CPU-40B/16.

#### Features of the DRM-01/16

- 16 Mbyte DRAM

- Burst READ and Burst WRITE capability

- Parity Generation and Checking

- Asynchronous refresh is provided every 14µs

- Accessible via VMEbus

The access address for the 68040 is \$00000000 to \$00FFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined memory range can be write protected in coordination with the address modifier codes. For example, in supervisor mode the memory can be read and written, in user mode memory can only be read.

The DRAM module includes byte parity check for local and VMEbus accesses. If a parity error is detected on a VMEbus cycle, a BERR is forced to the VMEbus informing the requestor that a parity error has occurred. On local accesses, a Transfer Error Acknowledge (TEA) is forced to the processor if a parity error was detected.

The following chart lists the required CPU clock cycles and wait states for accessing the shared RAM.

| Board<br>Type | 68040-B Clock<br>Frequency | No. of CPU Clock<br>Cycles Counted<br>From TS to TA<br>for Normal Cycles | No. of CPU Clock<br>Cycles for<br>Burst Cycles | No. of Wait<br>States for<br>Normal Cycles | No. of Wait<br>States for<br>Burst Cycles |

|---------------|----------------------------|--------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-------------------------------------------|

| CPU-40/B      | 25 MHz                     | 4                                                                        | 1                                              | 3                                          | 0                                         |

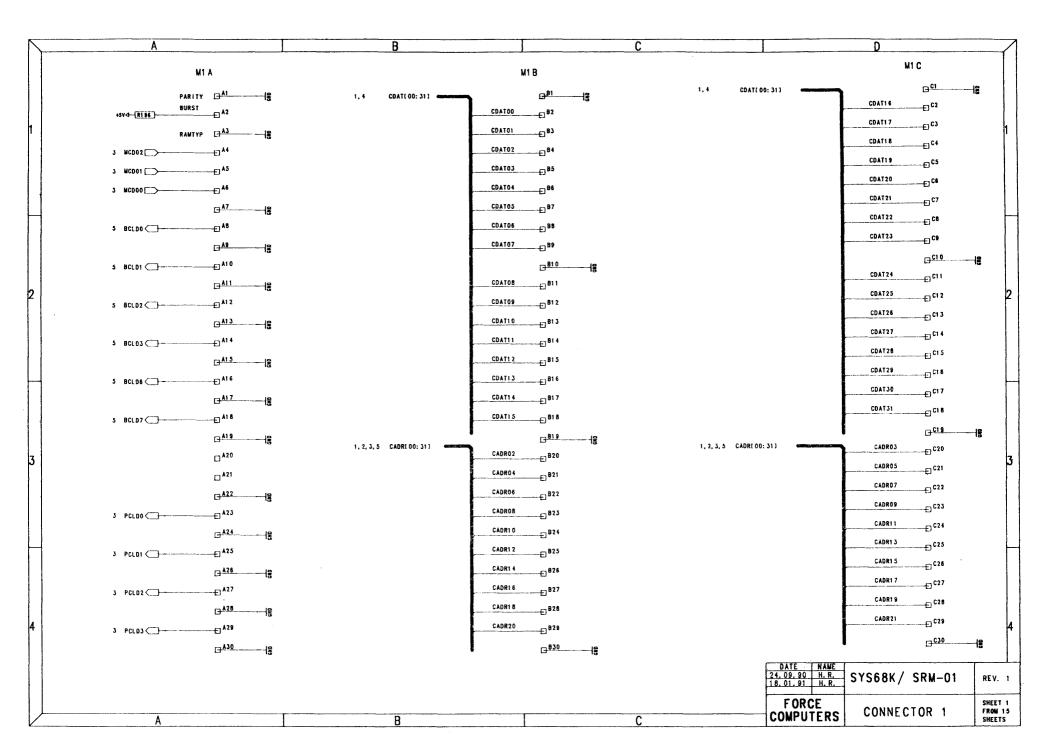

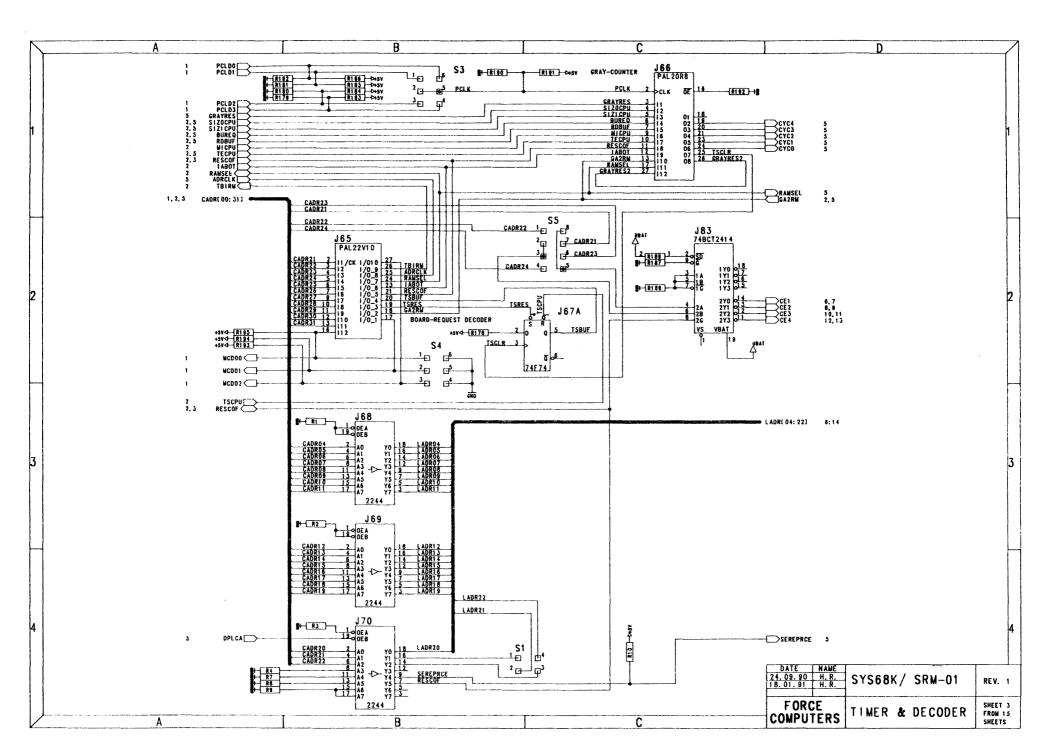

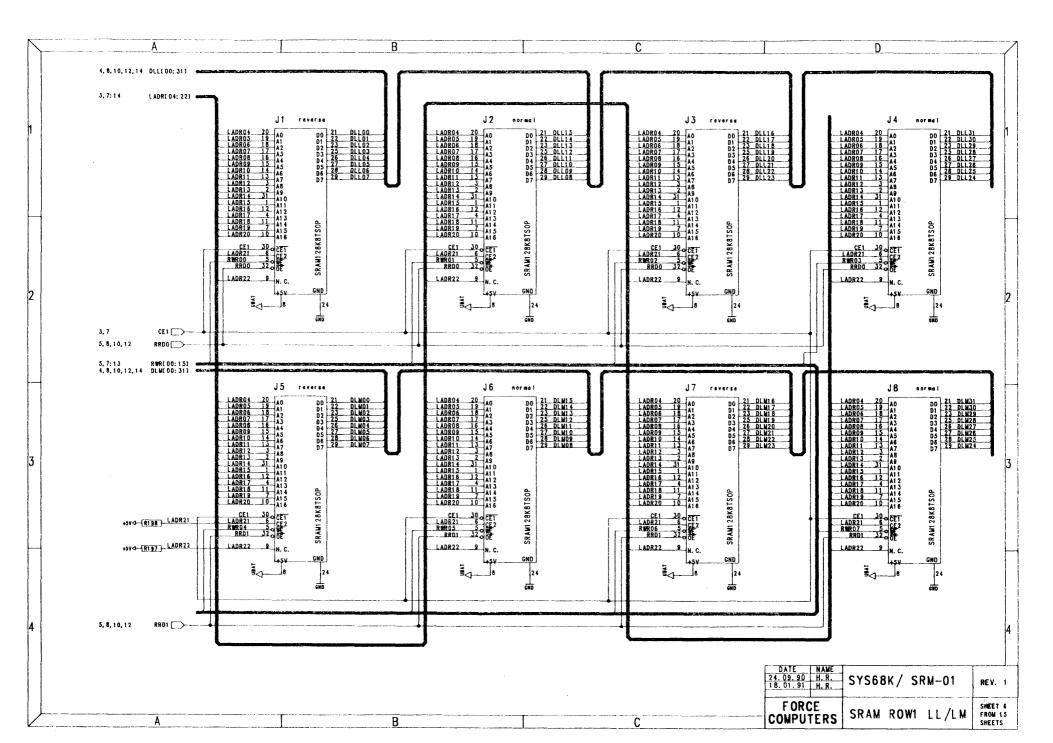

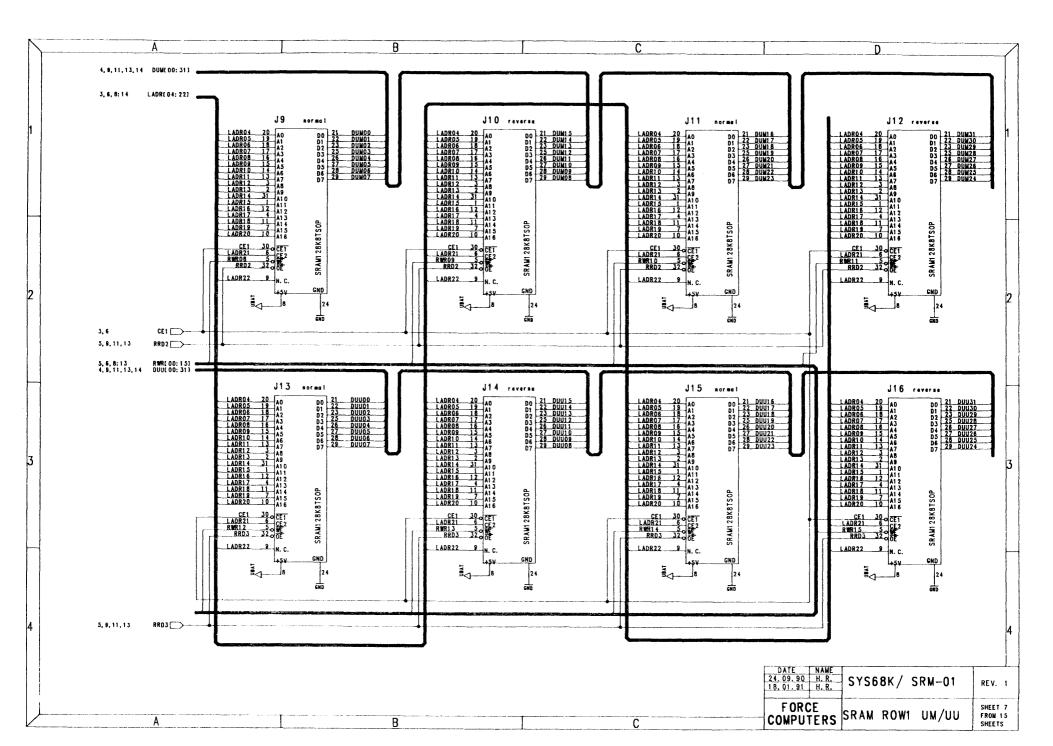

#### 2.2.3 The SRM-01/4

The SRM-01/4 is a 4 Mbyte RAM module which is used on the CPU-41B/4.

#### Features of the SRM-01/4

- 4 Mbyte SRAM

- Burst READ and Burst WRITE capability

- Battery Backup via VMEbus

- Accessible via VMEbus

The access address for the 68040 is \$00000000 to \$003FFFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined memory range can be write protected in coordination with the address modifier codes. For example, in supervisor mode the memory can be read and written, in user mode memory can only be read.

Parity check is not necessary for SRAM devices, because these components are protected against soft errors owing alpha emission. The following chart lists the required CPU clock cycles and wait states for accessing the shared RAM.

| Board<br>Type | 68040 Clock<br>Frequency | No. of CPU Clock<br>Cycles Counted<br>From TS to TA<br>for Normal Cycles | No. of CPU Clock<br>Cycles for<br>Burst Cycles | No. of Wait<br>States for<br>Normal Cycles | No. of Wait<br>States for<br>Burst Cycles |

|---------------|--------------------------|--------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-------------------------------------------|

| CPU-41/B      | 25 MHz                   | 3                                                                        | 1                                              | 2                                          | 0                                         |

#### 2.2.4 The SRM-01/8

The SRM-01/8 is an 8 Mbyte RAM module which is used on the CPU-41B/8.

#### Features of the SRM-01/8

- 8 Mbyte SRAM

- Burst READ and Burst WRITE capability

- Battery Backup via VMEbus

- Accessible via VMEbus

The access address for the 68040 is \$0000000 to \$007FFFF.

The access address for the VMEbus is programmable in 4 Kbyte steps through the FGA-002. The defined memory range can be write protected in coordination with the address modifier codes.

For example, in supervisor mode the memory can be read and written, in user mode memory can only be read.

Parity check is not necessary for SRAM devices, because these components are protected against soft errors owing alpha emission. The following chart lists the required CPU clock cycles and wait states for accessing the shared RAM.

| Board<br>Type | 68040 Clock<br>Frequency | No. of CPU Clock<br>Cycles Counted<br>From TS to TA<br>for Normal Cycles | No. of CPU Clock<br>Cycles for<br>Burst Cycles | No. of Wait<br>States for<br>Normal Cycles | No. of Wait<br>States for<br>Burst Cycles |

|---------------|--------------------------|--------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------|-------------------------------------------|

| CPU-41/B      | 25 MHz                   | 3                                                                        | 1                                              | 2                                          | 0                                         |

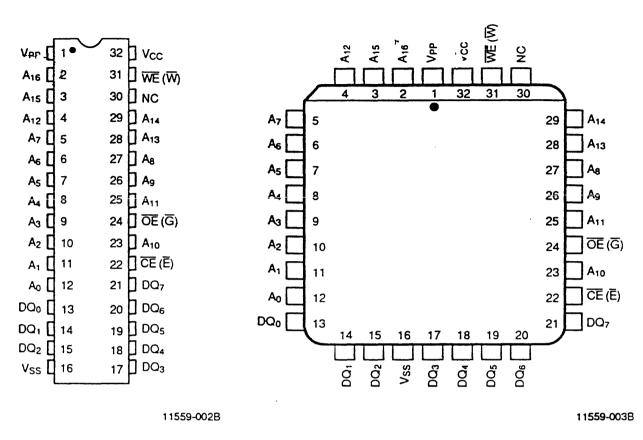

## 2.3 The System EPROM

The CPU board offers two 40-pin EPROM sockets for the installation of two 16-bit wide EPROM devices. The EPROMs present a full 32-bit data path to the processor enabling maximum performance. The following devices are supported in the system EPROM area:

| Organization | Total Memory Capacity |

|--------------|-----------------------|

| 64K x 16     | 256 Kbytes            |

| 128K x 16    | 512 Kbytes            |

| 256K x 16    | 1 Mbyte               |

| 512K x 16    | 2 Mbytes              |

#### Supported Device Types in the System EPROM Area:

#### 2.4 The Local SRAM

The CPU board contains a 128K \* 8 bit SRAM. Battery backup is provided via the on-board battery or the VMEbus + 5VSTDBY line.

# 2.5 The Local FLASH EPROM

A 128 Kbyte FLASH EPROM is included on the base board of the CPU-40 which can be used as additional data backup under conditions of power down for long periods. FLASH EPROM is ideal to hold details of the board status, such as software revision or user data which is to be kept permanently.

# 2.6 The Boot EPROM

The CPU board contains, in addition to the two system EPROMs, a single boot EPROM to boot the local microprocessor, initialize all I/O devices and program the board-dependent functions of the FGA-002. All basic initialization of the I/O devices and the FGA-002 are made through the boot EPROM.

In addition, the boot EPROM contains user utility routines, which may be called out of the user's application program. These routines provide easy software access to the functionality of the FGA-002 (DMA controller, FORCE Message Broadcast, Interrupt Management, etc.).

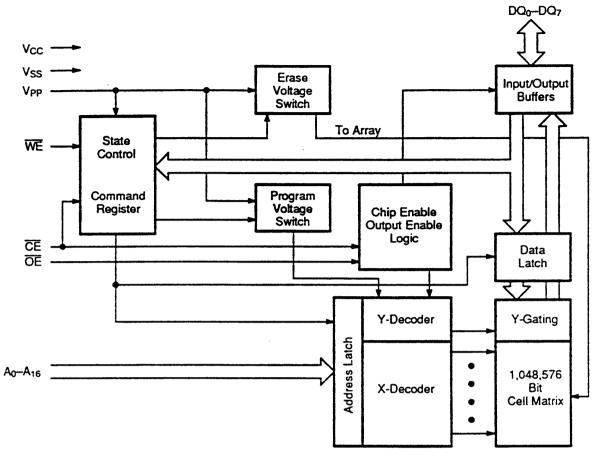

## 2.7 The FGA-002

One of the main features on this CPU board is the FGA-002 Gate Array with 24,000 gates and 281 pins. The FGA-002 controls the local bus and builds the VMEbus interface. It also includes a DMA controller, a complete interrupt handler, message broadcast interface (FMB), timer functions, mailbox locations, and a VMEbus interrupter. This gate array monitors the local bus, which in turn signifies that if any local I/O device is to be accessed, the gate array overrules all control signals, used address signals, and data signals.

The FGA-002 serves as a VMEbus manager. All VMEbus address and data lines are connected to the gate array through the buffers. Additional functions such as the VMEbus interrupt handler are also installed on the FGA-002. The on-chip DMA controller can access the local memory, VMEbus memory, and on-board devices which are able to function in a DMA mode. The start address of the FGA-002 registers is \$FFD00000. All registers of the gate array and associated functions are described in detail in the FGA-002 Users Manual. On the following page you will find a list of features for the FGA-002.

#### Features of the FGA-002

- 32 bit DMA Controller

- 2 Message Broadcast Channels (FMB)

- 8 Mailbox Interrupt Channels

- One 8 bit timer

- Complete Interrupt Management for VMEbus interrupts, ACFAIL, SYSFAIL, Onboard Interrupts and FGA-002 internal interrupts

- VMEbus interface including a single level arbiter

- Decoding logic for accesses to the Shared Memory of the CPU board

A complete functional description of the FGA-002 may be found in the FGA-002 Users Manual.

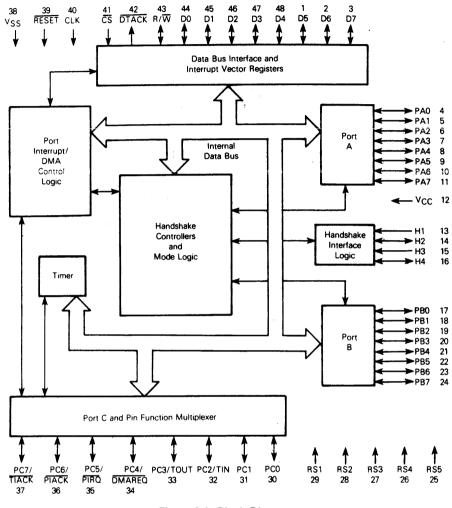

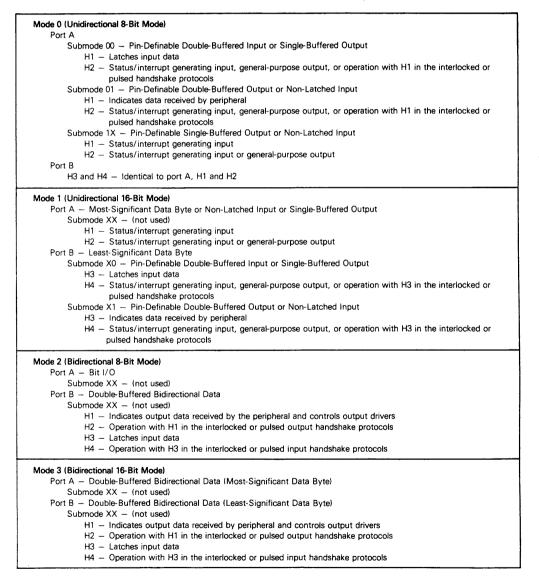

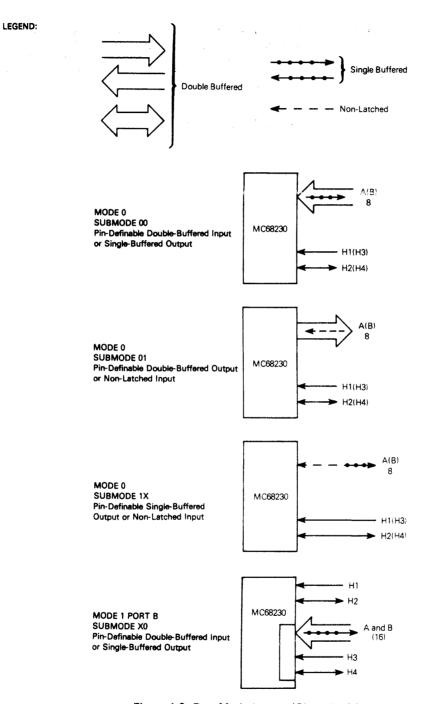

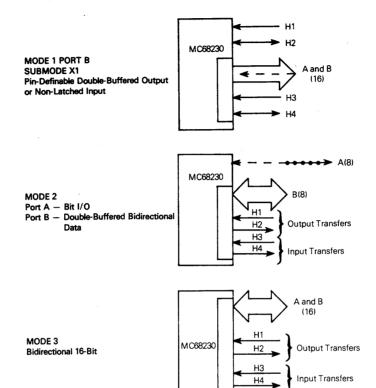

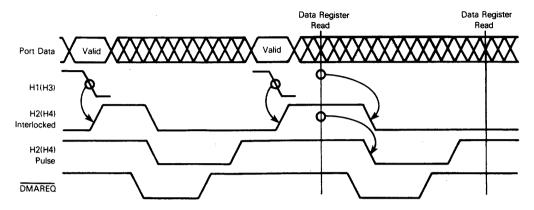

## 2.8 The PI/T 68230

The MC68230 Parallel Interface/Timer (PI/T) provides versatile double buffered parallel interfaces and an operating system oriented timer for MC68000 systems. The parallel interfaces operate in unidirectional or bidirectional modes, 8 or 16 bits wide. The PI/T timer contains a 24 bit wide counter and a 5 bit prescaler.

## Features of the PI/T

- MC68000 Bus Compatible

- Port Modes Include: Bit I/O Unidirectional 8 bit and 16 bit Bidirectional 8 bit and 16 bit

- Selectable Handshaking Options

- 24 bit Programmable Timer

- Software Programmable Timer Modes

- Contains Interrupt Vector Generation Logic

- Separate Port and Timer Interrupt Service Requests

- Registers are Read/Write and Directly Addressable

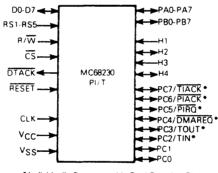

# 2.8.1 The I/O Configuration of PI/T1

Port A is connected to the two 4 bit HEX rotary switches provided on the front panel for application dependent settings.

Port B is used for programming the local base address for A24 accesses from the VMEbus.

Port C is used for port and timer interrupts and to control the RMC behavior of the board.

# 2.8.2 The I/O Configuration of PI/T2

Port A and the handshake lines are routed to a 24-pin header which allows the connection of a flat cable. 8 bits are connected to port A of the PI/T and can be used as inputs or outputs, with the remaining 4 bits being connected to the handshake pins of the PI/T. This port can be used to establish a "Centronics type" interface.

Port B allows the memory capacity of the Shared RAM to be read. Each CPU board of this type contains three readable status bits describing the memory capacity. In addition, the CPU board type can be read through the remaining 5 bits.

Port C grants the RAM type (DRAM/SRAM) burst and parity capability of the Shared RAM to be read.

A "Powerup Reset" can be initiated by software.

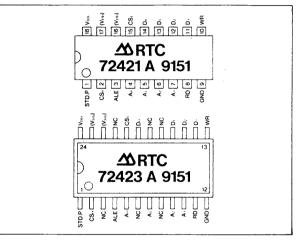

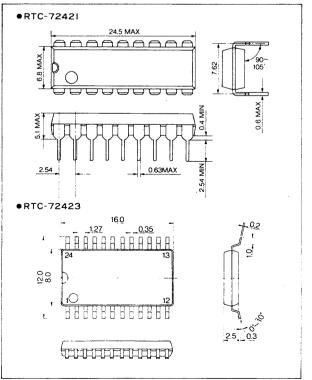

#### 2.9 The Real Time Clock 72423

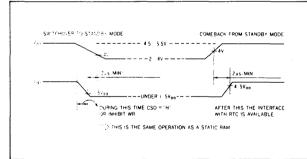

There is a Real Time Clock (RTC) 72423 installed on the CPU board. The CPU board contains a self supportive battery to sustain the RTC during power down.

## Features of the RTC

- Built-in quartz oscillator makes regulation unnecessary and allows easy design

- Direct bus compatibility (120 ns access time)

- Incorporated built-in time (hour, minute, second), and date (year, month, week, day) counters

- 12 hour and 24 hour clock switchover functions and automatic leap year setting

- Interrupt masking

- An error adjustment time function of 30 seconds

- READ, WRITE, HOLD, STOP, RESET, and CHIP SELECT inputs

- The C-MOS IC boasts low current consumption and features a backup function

- A 24-pin *so* package

#### 2.10 The DUSCC 68562

The Dual Universal Serial Communications Controller (DUSCC) 68562 is installed to communicate with terminals, computers, or other equipment.

The DUSCC is a single chip MOS-LSI communications device providing two independent, multiprotocol, full duplex receiver/transmitter channels in a single package. Each channel consists of a receiver, transmitter, 16-bit multifunction counter/timer, digital phaselocked loop (DPLL), parity/CRC generator and checker, and associated control circuits.

#### Features of the DUSCC

- Dual full duplex synchronous/asynchronous receiver and transmitter

- Multiprotocol operation consisting of:

BOP:HDLC/ADCCP, SDLC, SDLC Loop, X.25 or X.75 link levelCOP:BISYNC, DDCMP, X.21ASYNC:5-8 bit plus optional parity

- Programmable data encoding formats: NRZ, NRZI, FMO, FM1, Manchester

- 4 character receiver and transmitter FIFOs

- Individual programmable baud rate for each receiver and transmitter

- Digital phase locked loop

- User programmable counter/timer

- Programmable channel modes full/half duplex, auto echo, local loopback

- Modem control signals for each channel: RTS, CTS, DCD

- CTS and DCD programmable autoenables for Receiver (RX) and Transmitter (TX)

- Programmable interrupt on change of CTS or DCD

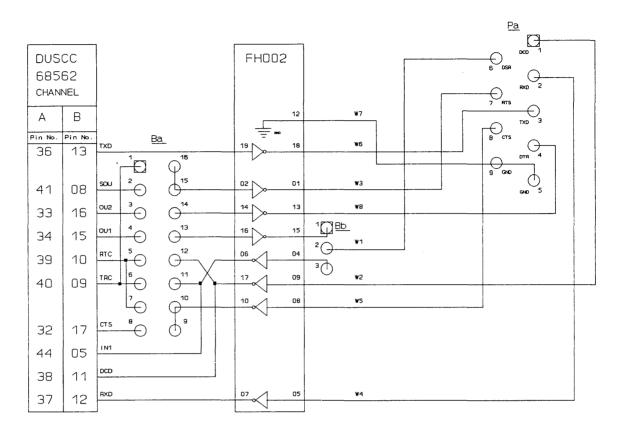

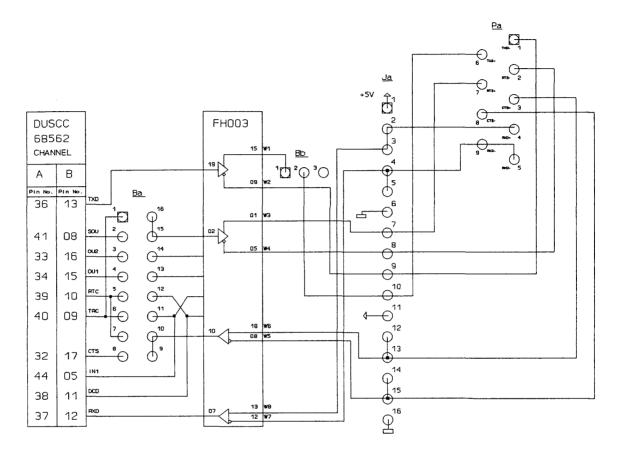

# 2.10.1 The I/O Configuration of DUSCC1 and DUSCC2

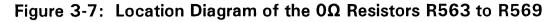

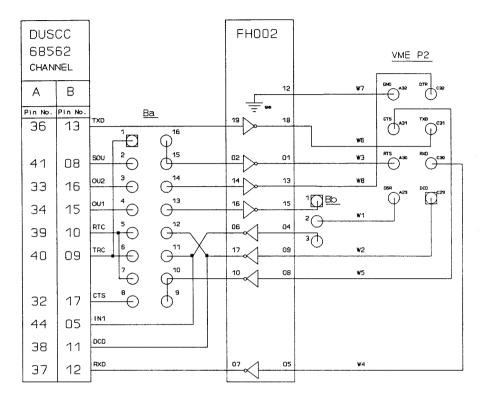

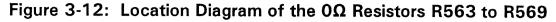

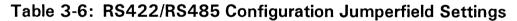

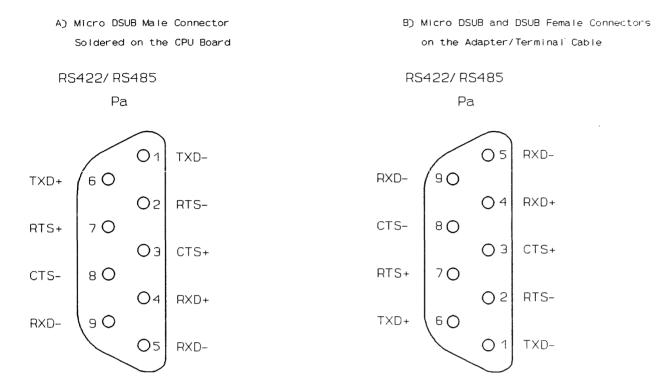

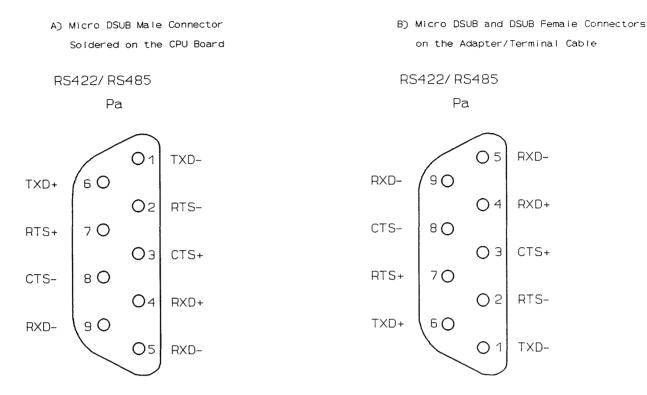

The four channels may be configured to function as a RS232 or RS422/RS485 compatible interface. Termination resistors can be installed to adapt various cable lengths and reduce reflections upon the selection of the RS422/RS485 compatible interface. The DUSCC can interrupt the local CPU at a specified programmable IRQ level.

# I/O Signals for DUSCC1:

The I/O signal assignment of channel 1 to 2 is listed as follows:

| Signal | Input | Output | 9 Pin Micro<br>D-Sub Connector | Description         |

|--------|-------|--------|--------------------------------|---------------------|

| DCD    | Х     |        | 1                              | Data Carrier Detect |

| RXD    | Х     |        | 2                              | Receive Data        |

| TXD    |       | Х      | 3                              | Transmit Data       |

| DTR    |       | Х      | 4                              | Data Terminal Ready |

| GND    |       |        | 5                              | Signal GND          |

| DSR    | X     | X      | 6                              | Data Set Ready      |

| RTS    |       | X      | 7                              | Request to Send     |

| CTS    | Х     |        | 8                              | Clear to Send       |

| GND    |       |        | 9                              | Signal GND          |

The I/O signals of channel 1 can be connected to the VME connector P2 in parallel to the 9-pin Micro D-Sub connector as follows:

| Signal | Input | Output | VME Connector<br>P2 | Description         |

|--------|-------|--------|---------------------|---------------------|

| DCD    | Х     |        | c29                 | Data Carrier Detect |

| RXD    | Х     |        | c30                 | Receive Data        |

| TXD    |       | X      | c31                 | Transmit Data       |

| DTR    |       | X      | c32                 | Data Terminal Ready |

| DSR    | X     | X      | a29                 | Data Set Ready      |

| RTS    |       | X      | a30                 | Request to Send     |

| CTS    | X     |        | a31                 | Clear to Send       |

| GND    |       |        | a32                 | Signal GND          |

#### NOTE

This is only possible if these VMEbus P2 lines are not used by an EAGLE module.

#### I/O Signals for DUSCC2:

The I/O signal assignment of channels 3 and 4 is listed as follows:

| Signal | Input | Output | 9 Pin Micro<br>D-Sub Connector | Description         |

|--------|-------|--------|--------------------------------|---------------------|

| DCD    | Х     |        | 1                              | Data Carrier Detect |

| RXD    | Х     |        | 2                              | Receive Data        |

| TXD    |       | Х      | 3                              | Transmit Data       |

| DTR    |       | Х      | 4                              | Data Terminal Ready |

| GND    |       |        | 5                              | Signal GND          |

| DSR    | Х     | Х      | 6                              | Data Set Ready      |

| RTS    |       | Х      | 7                              | Request to Send     |

| CTS    | Х     |        | 8                              | Clear to Send       |

| GND    |       |        | 9                              | Signal GND          |

#### 2.11 The EAGLE Modules

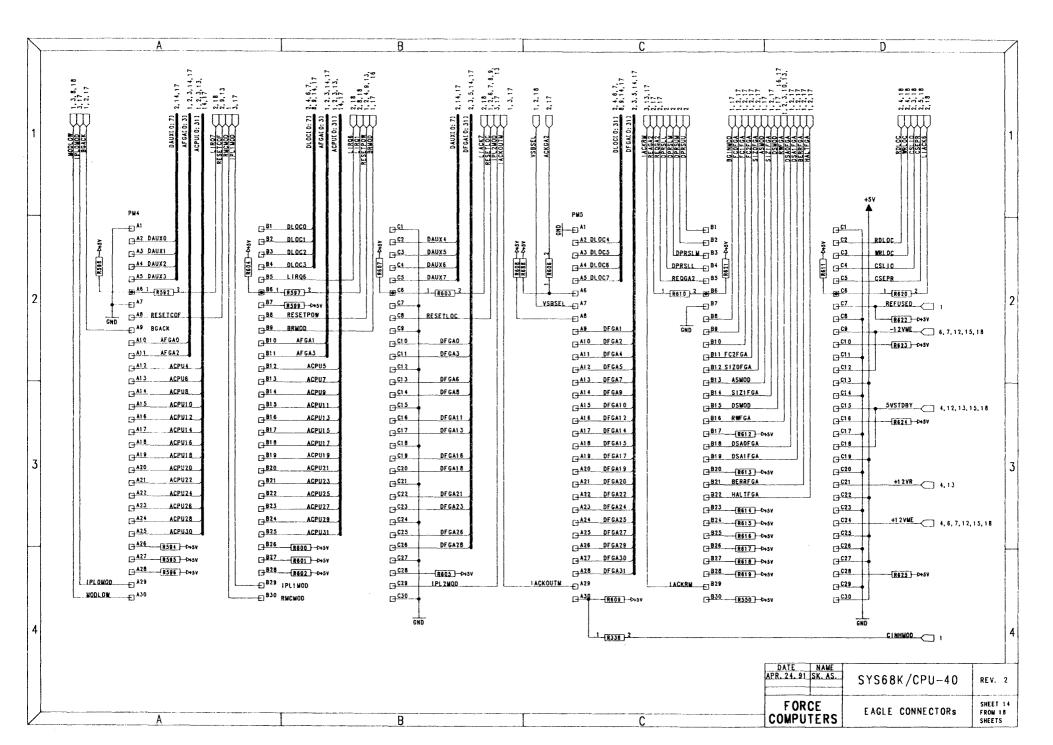

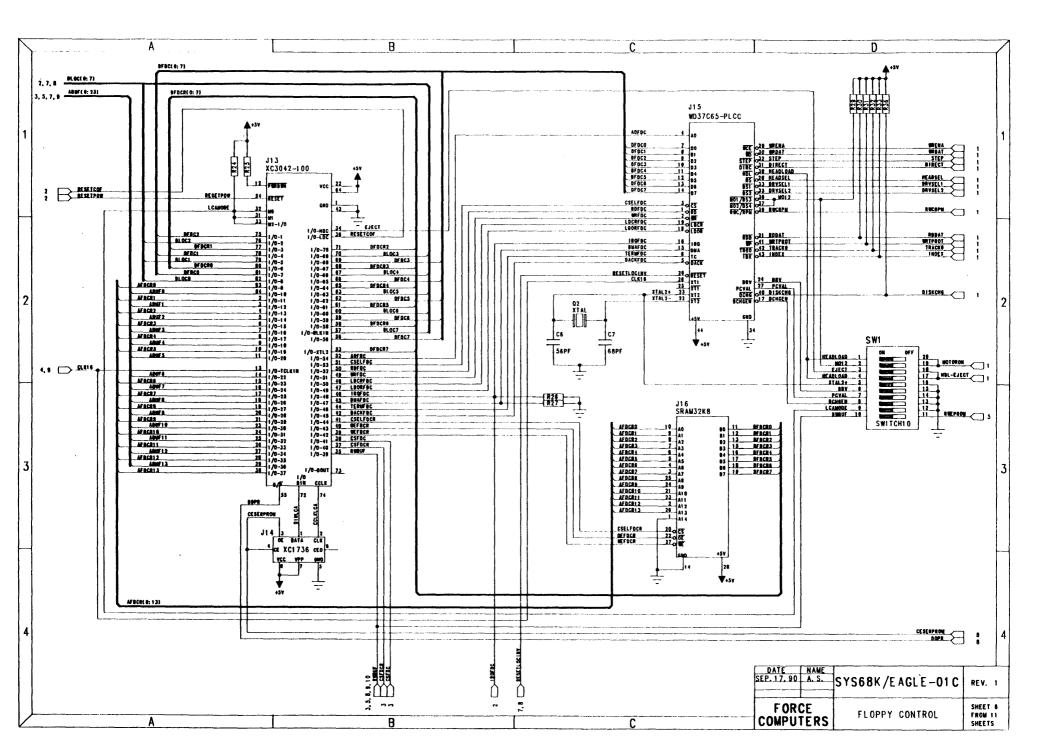

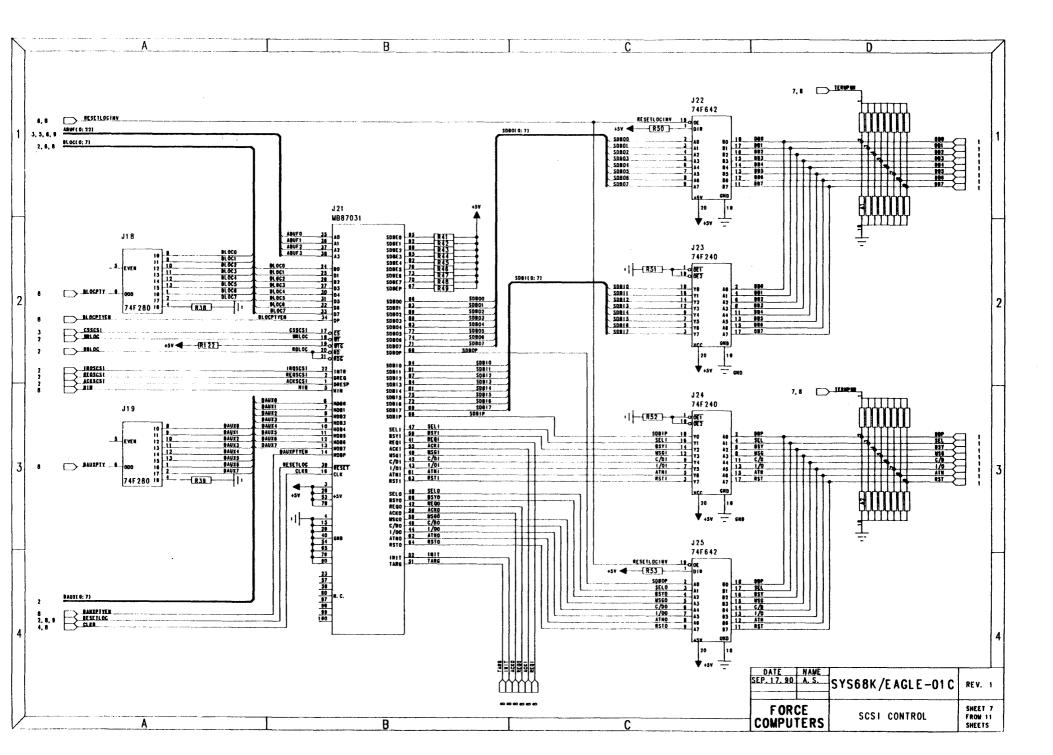

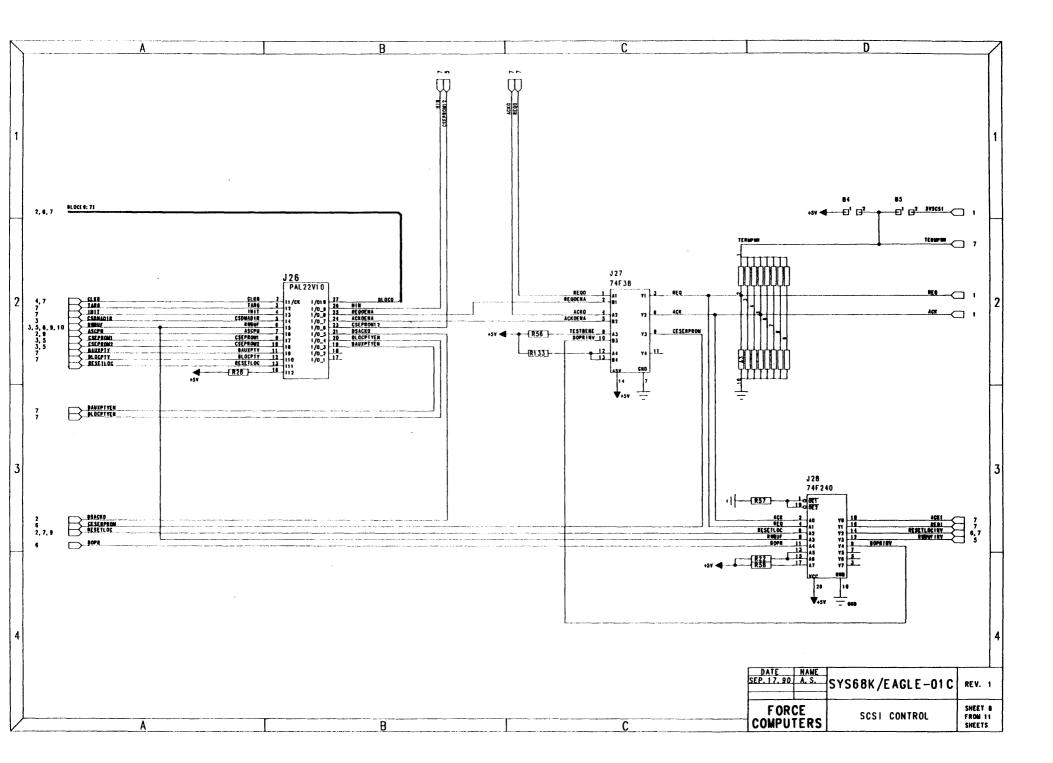

EAGLE modules are I/O subsystems designed not only to increase the functionality of the board but to add the exact I/O features to fit the application requirement. EAGLE modules connect directly onto the FLXi of the base board. FLXi and EAGLE modules will be a feature on future FORCE board generations to ensure continued flexibility.

If your CPU board is assembled with an EAGLE module please refer to the "EAGLE Module" manual which is shipped with this board and should be placed in Section 6 of this manual.

#### 2.12 The VMEbus Interface

The CPU board has a full 32-bit VMEbus interface. The address modifier codes for A16, A24 and A32 addressing are fully supported in master mode. In slave mode, the address modifiers for A32 and A24 are fully supported.

Read-Modify-Write cycles are fully supported to allow multiple CPU boards to be synchronized via the shared RAM. The FGA-002 determines whether or not an access to the shared RAM is allowed and, if allowed, controls the access cycle.

The CPU board provides an interrupt handler capability (IH 1-7) which can be enabled/disabled by programming the FGA-002. The CPU board also provides an interrupter function which enables the board to send interrupts to the VMEbus on seven programmable levels with a software-programmable vector.

The following bus release modes are supported:

| RWD   | = | Release When Done     |

|-------|---|-----------------------|

| ROR   | = | Release On Request    |

| RBCLR | = | Release On Bus Clear  |

| RAT   | = | Release After Timeout |

| REC   | = | Release Every Cycle   |

| ROACF | = | Release On ACFAIL*    |

Each of the listed modes is software programmable inside the gate array. The bus request level of the CPU board is jumper or software selectable (BRO-3).

The DMA controller installed in the FGA-002 on the CPU board is able to access the VMEbus interface independently from the microprocessor, enabling VMEbus communication to take place without impacting the processing capabilities of the rest of the board for number crunching or servicing on-board I/O.

A four level arbiter with round robin and prioritized round robin arbitration modes, a power monitor, a SYSRESET\* generator, IACK\* daisy chain driver and support for ACFAIL\*, SYSFAIL\* and SYSCLK complete the VMEbus interface.

#### 2.13 The Monitor of the CPU board

Every CPU board contains VMEPROM, a real time multitasking monitor debugger. It consists of a powerful real time kernel, file manager and monitor/debugger with 68040 line assembler/disassembler.

The monitor/debugger includes all functions to control the real time kernel and file manager as well as all tools required for program debugging such as breakpoints, tracing, memory display, memory modify and host communication.

VMEPROM supports several memory and I/O boards on the VMEbus to take full advantage of the file manager and kernel functions.

A built-in selftest checks all on-board devices and memory. This allows detection of any failures on the board.

Memory initialization and test commands offer easy installation of global memory in the environment on the local RAM and/or the VMEbus.

The one line assembler/disassembler is 68040 compatible and supports all 68040 commands in the original mnemonic described in the MC 68040 User's Manual.

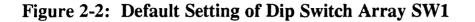

# 2.14 Default Jumper Settings on the CPU Board

The following are the default jumper settings and a location diagram displaying all jumpers.

#### Default Jumper Settings for the CPU

| Jumperfield | Description                                          | Default<br>Connection | Schematics |

|-------------|------------------------------------------------------|-----------------------|------------|

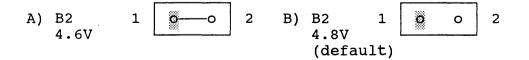

| B2          | Reset Voltage Sensor                                 |                       | SH4<br>B4  |

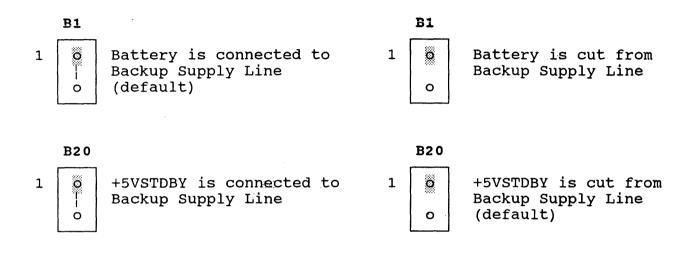

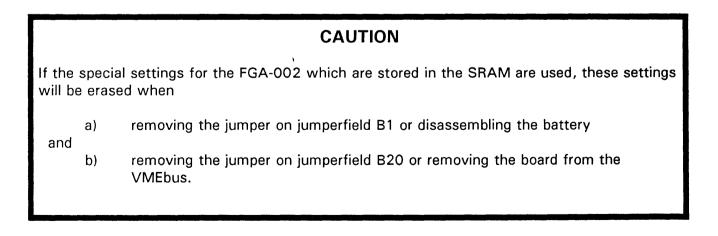

| B20         | Backup Supply for Local SRAM and<br>RTC via +5VSTDBY |                       | SH4<br>B2  |

| B1          | Backup Supply for Local SRAM and RTC via Bat 1       | 1-2                   | SH4<br>B2  |

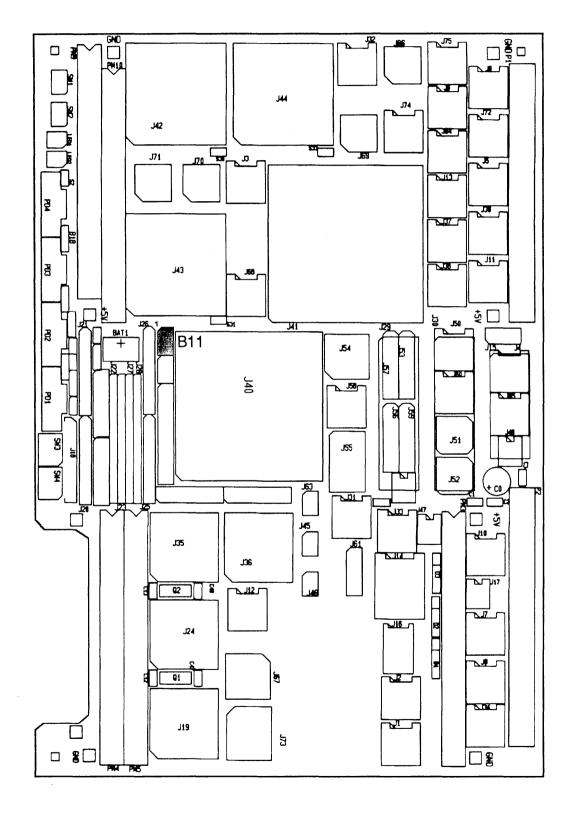

#### Default Jumper Settings for System EPROMs and SRAM/EEPROM

| Jumperfield | Description                   | Default<br>Connection | Schematics |

|-------------|-------------------------------|-----------------------|------------|

| B11         | System EPROM device select    | 1-6                   | SH5<br>A4  |

| B16         | FLASH EPROM write dis-/enable | 1-2                   | SH4<br>C2  |

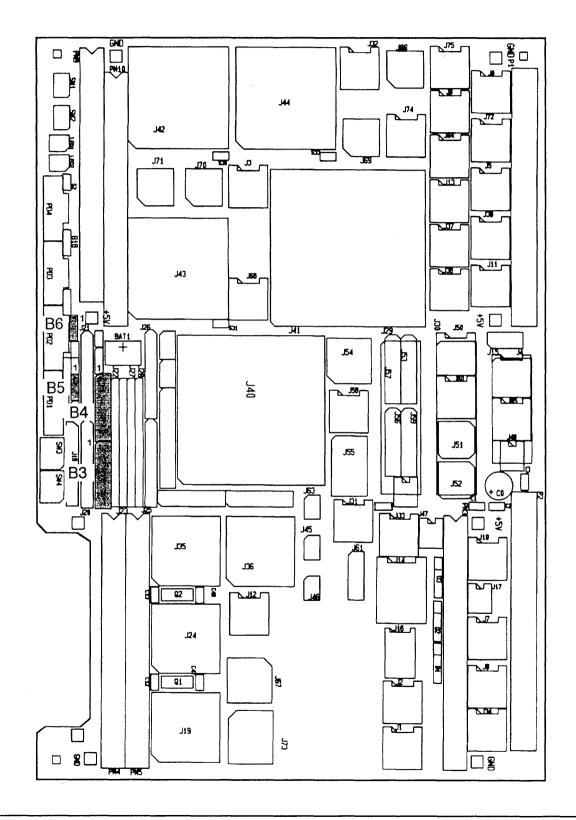

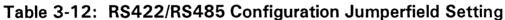

#### Default Jumper Settings for Serial I/O (RS232)

| Jumperfield | Description                               | Default<br>Connection | Schematics |

|-------------|-------------------------------------------|-----------------------|------------|

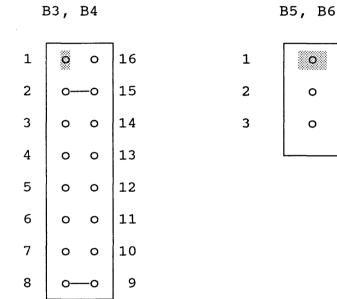

| В3          | Connector 1, PD1<br>(DUSCC1 Port #1)      | 2-15<br>8-9           | SH6<br>B2  |

| В4          | Connector 2, PD2<br>(DUSCC1 Port #2)      | 2-15<br>8-9           | SH6<br>B3  |

| В5          | Connector 1, PD1<br>(DUSCC1 Port #1)      |                       | SH6<br>C2  |

| B6          | Connector 2, PD2<br>(DUSCC Port #2)       |                       | SH6<br>C3  |

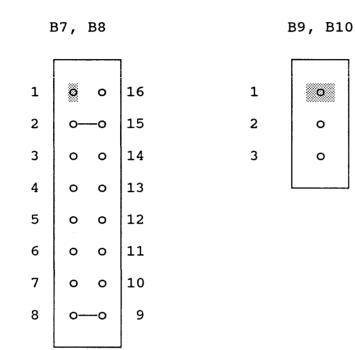

| В7          | Connector 3, PD3<br>(DUSCC2 Port #3)      | 2-15<br>8-9           | SH7<br>B2  |

| B8          | Connector 4, PD4<br>(DUSCC2 Port #4)      | 2-15<br>8-9           | SH7<br>B3  |

| В9          | Connector 3, PD3<br>(DUSCC2 Port #3), PD3 |                       | SH7<br>C2  |

| B10         | Connector 4, PD4<br>(DUSCC Port #4), PD4  |                       | SH7<br>C3  |

## **Default Jumper Settings for VMEbus**

| Jumperfield | Description                                                     | Default<br>Connection    | Schematics |

|-------------|-----------------------------------------------------------------|--------------------------|------------|

| B19         | Four level Arbiter Request Level                                | 1-6<br>2-5<br>3-4        | SH9<br>B4  |

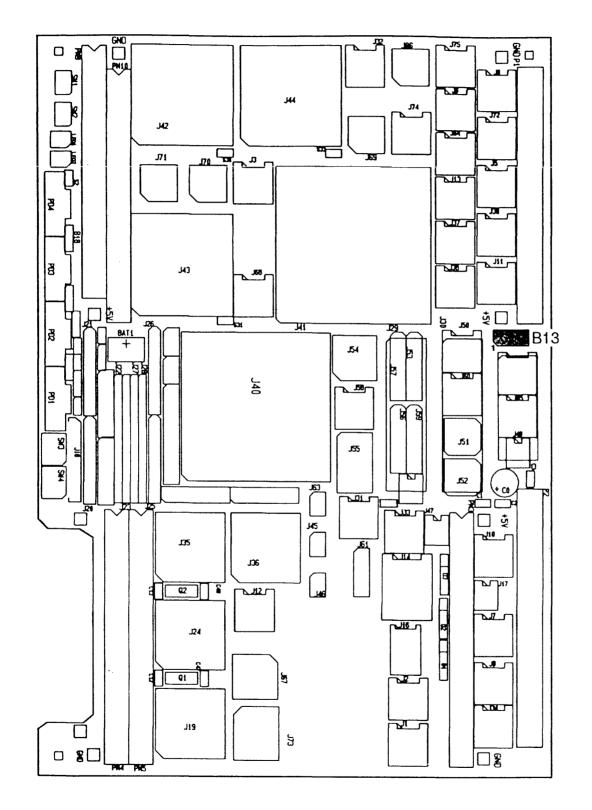

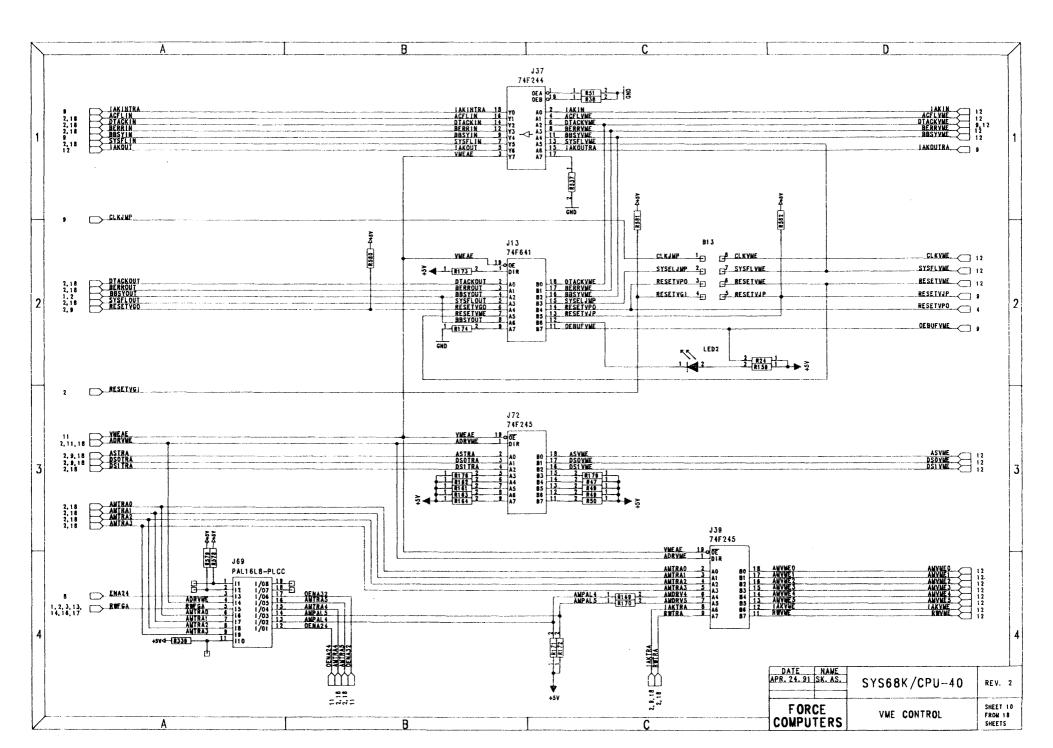

| B13         | SYSCLK<br>SYSFAIL<br>Receive VMEbus RESET<br>Drive VMEbus RESET | 1-8<br>2-7<br>3-6<br>4-5 | SH10<br>C2 |

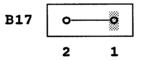

## Default Jumper Settings for Test

| Jumperfield | Description         | Default<br>Connection | Schematics |

|-------------|---------------------|-----------------------|------------|

| B17         | Clock Signal to CPU | 1-2                   | SH16<br>A1 |

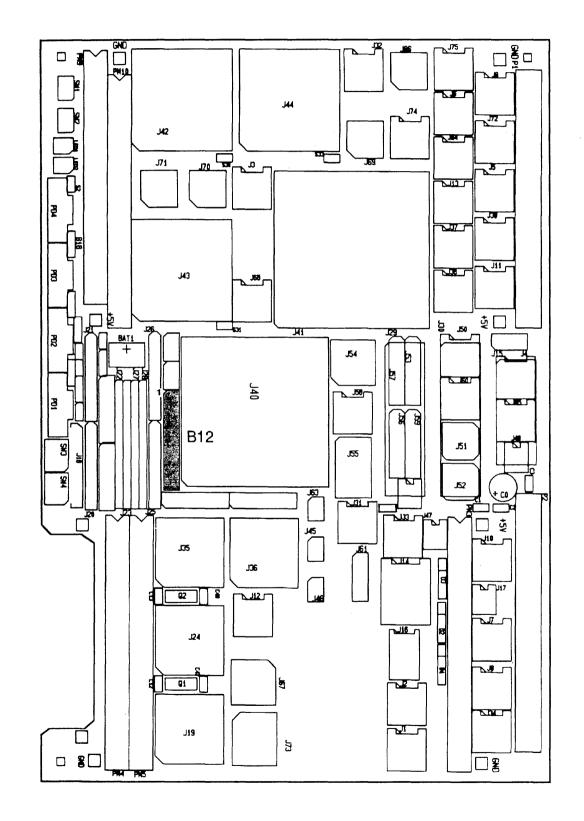

#### Headers for 12 Bit I/O and 8 Bit I/O

| Jumperfield | Description | Default<br>Connection | Schematics |

|-------------|-------------|-----------------------|------------|

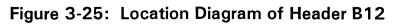

| B12         | User I/O    |                       | SH8<br>D1  |

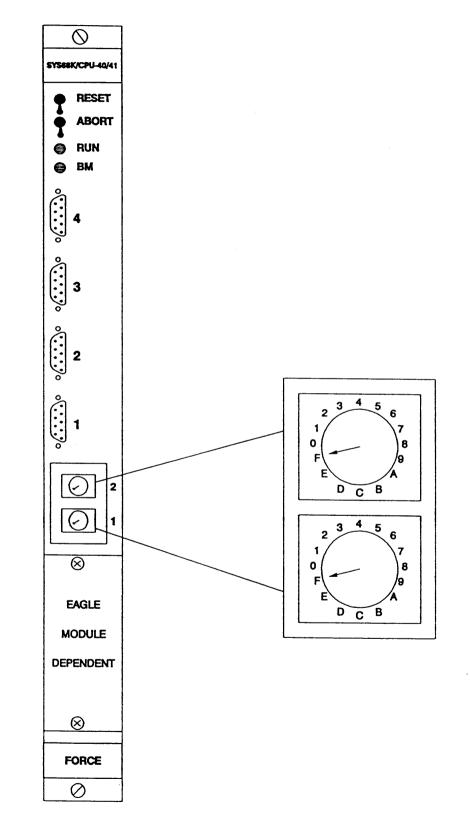

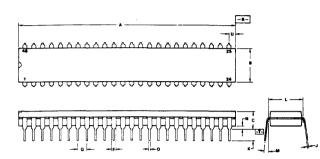

# Figure 2-2: The Front Panel of the CPU Board

This page intentionally left blank

## 3. SPECIFICATIONS OF THE CPU BOARD

| СРИ Туре                                                                                                                                           |                                               | 68040                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------|

| CPU Clock Frequency                                                                                                                                | CPU-40B/x<br>CPU-40D/x                        | 25.0 MHz<br>33.0 MHz                                               |

| Shared DRAM Capacity with Parity                                                                                                                   | CPU-40X/4<br>CPU-40X/16                       | 4 Mbytes<br>16 Mbytes                                              |

| Shared SRAM Capacity                                                                                                                               | CPU-41X/4<br>CPU-41X/8                        | 4 Mbytes<br>8 Mbytes                                               |

| SRAM Capacity with On-board Battery Backup<br>FLASH EPROM                                                                                          |                                               | 128 Kbytes<br>128 Kbytes                                           |

| Number of System EPROM Sockets<br>Data Path                                                                                                        |                                               | 2<br>32-Bits                                                       |

| Serial I/O Interfaces (68562)<br>RS232/RS422/RS485 Compatible                                                                                      |                                               | 4<br>4 of 4                                                        |

| 24-bit Timer with 5-bit Prescaler<br>8-bit Timer                                                                                                   |                                               | 2<br>1                                                             |

| Parallel I/O Interface (68230)                                                                                                                     |                                               | 12 Lines                                                           |

| Real Time Clock with On-board Battery Backup                                                                                                       |                                               | 72423                                                              |

| VMEbus Interface A32, A24, A16:D8, D16, D32, UAT, RMW<br>A32, A24:D8, D16, D32, RMW                                                                |                                               | Master<br>Slave                                                    |

| Four Level Arbiter<br>SYSCLK Driver<br>Mailbox Interrupts                                                                                          |                                               | Yes<br>Yes<br>8                                                    |

| FORCE Message Broadcast                                                                                                                            | FMB FIFO 0<br>FMB FIFO 1                      | 8 Bytes<br>1 Byte                                                  |

| VMEbus Interrupter/VMEbus and Local Interrupt Handler<br>All Sources can be Routed to a Software Programmable IRQ Level                            |                                               | 1 to 7<br>Yes                                                      |

| RESET/ABORT Switch                                                                                                                                 | ······································        | Yes                                                                |

| VMEPROM Firmware Installed on All Board Versions                                                                                                   |                                               | 256 Kbytes                                                         |

| Power Requirements                                                                                                                                 | + 5V min/max<br>+ 12V min/max<br>-12V min/max | 5.2A/6.0A<br>0.1A/0.3A<br>0.1A/0.3A                                |

| Operating Temperature with Forced Air Cooling<br>Storage Temperature<br>Relative Humidity (noncondensing)<br>Board Dimensions<br>No. of Slots Used |                                               | 0 to +50°C<br>-40 to +85°C<br>0 to 95%<br>234x160mm/9.2x6.3in<br>1 |

This page intentionally left blank

## 4. ORDERING INFORMATION

| SYS68K/CPU-40B/4-00  | 25.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared DRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS68K/CPU-40B/4-01  | 25.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared DRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included.  |

| SYS68K/CPU-40B/16-00 | 25.0 MHz 68040 based CPU board with DMA, 16 Mbyte shared DRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                 |

| SYS68K/CPU-40B/16-01 | 25.0 MHz 68040 based CPU board with DMA, 16 Mbyte shared DRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included. |

| SYS68K/CPU-40D/4-00  | 33.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared DRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                  |

| SYS68K/CPU-40D/4-01  | 33.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared DRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included.  |

| SYS68K/CPU-40D/16-00 | 33.0 MHz 68040 based CPU board with DMA, 16 Mbyte shared DRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                 |

| SYS68K/CPU-40D/16-01 | 33.0 MHz 68040 based CPU board with DMA, 16 Mbyte shared DRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included. |

| SYS68K/CPU-41B/4-00  | 25.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared SRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                  |

| SYS68K/CPU-41B/4-01  | 25.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared SRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included.  |

| SYS68K/CPU-41B/8-00  | 25.0 MHz 68040 based CPU board with DMA, 8 Mbyte shared SRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                  |

| SYS68K/CPU-41B/8-01  | 25.0 MHz 68040 based CPU board with DMA, 8 Mbyte shared SRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included.  |

| SYS68K/CPU-41D/4-00  | 33.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared SRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                  |

| SYS68K/CPU-41D/4-01  | 33.0 MHz 68040 based CPU board with DMA, 4 Mbyte shared SRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included.  |

| SYS68K/CPU-41D/8-00  | 33.0 MHz 68040 based CPU board with DMA, 8 Mbyte shared SRAM, 4 serial I/O channels, FLXi, VMEPROM. Documentation included.                                                  |

| SYS68K/CPU-41D/8-01        | 33.0 MHz 68040 based CPU board with DMA, 8 Mbyte shared SRAM, 4 serial I/O channels, EAGLE-01C (SCSI, floppy disk and Ethernet Interface), VMEPROM. Documentation included. |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS68K/IOBP-1              | Backpanel for single board computers providing SCSI and floppy disk drive connectors.                                                                                       |

| SYS68K/CABLE MICRO-9 SET 1 | Set of three adapter cables 9-pin micro D-Sub male connector to 9-pin D-Sub female connector, length 2 m.                                                                   |

| SYS68K/CABLE MICRO-9 SET 2 | Set of four adapter cables 9-pin micro D-Sub male connector to 25-pin D-Sub female connector, length 2 m.                                                                   |

| SYS68K/VMEPROM/40/UP       | VMEPROM update service for the SYS68K/CPU-40 series.                                                                                                                        |

| SYS68K/VMEPROM/UM          | VMEPROM User's Manual excluding the SYS68K/CPU-40 description.                                                                                                              |

| SYS68K/CPU-40/UM           | User's Manual for the SYS68K/CPU-40 product, including VMEPROM User's<br>Manual and EAGLE-01C User's Manual (separately available as<br>EAGLE-01C/UM).                      |

| SYS68K/FGA-002/UM          | User's Manual for the FGA-002 Gate Array.                                                                                                                                   |

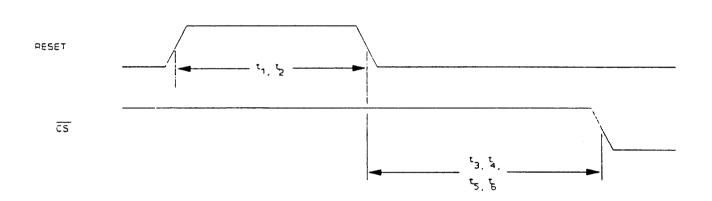

## 6.8 **RESET Generation**

There is an IEEE 1014 compatible SYSRESET\* driver installed on the CPU board. The RESET generator circuitry is operable if the power supply VCC is at least 3 volts. The RESET signal can be asserted (low) on any one of the following conditions:

- Front Panel RESET switch toggled

- Voltage Sensor detects VCC below limit (4.8V)

- Execution of the RESET instruction by the microprocessor on the board

The asserted RESET signal will be held low for at least 200 milliseconds after removing all the above conditions.

When the Reset Switch is toggled twice a Powerup equivalent Reset can be generated. The time lapse immediately after the Reset Switch is released must be 0,2 seconds or less.

## 6.8.1 The Front Panel RESET Switch

The upper switch on the front panel of the CPU board is the RESET switch. Toggling it provides a reset of all on-board devices, independent from the jumper options. With the jumper B13 3-6 connection inserted, the SYSRESET\* signal of the VMEbus backplane will be asserted. When the RUN LED is red, the processor is in the HALT state. For example, this state will be entered if a double bus fault occurs. A reset of the board must be performed by toggling the RESET switch or by asserting the SYSRESET\* backplane signal. The light of the RUN LED is also red while the RESET generator drives the reset. After reset, the red light must change to green.

## 6.8.2 The Voltage Sensor Module FH001

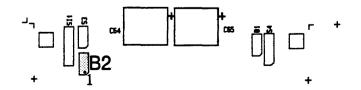

The voltage sensor module FH001 is included with the RESET generator. Power up reset is provided by this sensor, as soon as the supply voltage VCC has reached 3 volts. RESET will be asserted if VCC is less than 4.8 volts on the board, once the jumper B2 pin 1-2 is removed (B). This jumper is removed upon delivery. When the jumper at B2 1-2 is inserted (A), RESET will be asserted if VCC is less than 4.6 volts. RESET will stay asserted at least 200 milliseconds after the supply voltage has passed the threshold. Jumperfield B2 pin 1-2 must be removed for normal operation, and may be inserted for test purposes.

## Figure 6-7: Jumper Settings for Jumperfield B2

## 6.8.3 VMEbus RESET Conditions

## 6.8.3.1 Receive RESET from VMEbus

In order to receive a RESET from the VMEbus on the CPU board, jumper B13, 4-5 must be inserted. If removed, the SYSRESET signal from the VMEbus is not monitored on the CPU board.

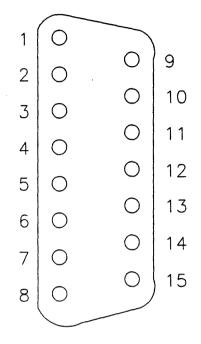

B13

| 8 | 7 | 6 | 5     |  |

|---|---|---|-------|--|

| o | 0 | 0 | 0<br> |  |

| Ö | 0 | 0 | 0     |  |

| 1 | 2 | 3 | 4     |  |

## 6.8.3.2 Drive RESET to VMEbus

To drive the RESET signal on the VMEbus, jumper B13, 3-6 must be inserted on the CPU board. When inserted, the RESET from the front panel switch and voltage monitor are driven to the VMEbus. If not inserted, SYSRESET is not VMEbus driven.

B13

| 8 | 7 | 6 | 5 |

|---|---|---|---|

| 0 | 0 | 0 | ο |

| Ö | 0 | 0 | 0 |

| 1 | 2 | 3 | 4 |

## 6.8.3.3 Default Configuration of Jumperfield B13

By default, SYSCLK and SYSRESET are driven to the VMEbus; SYSRESET and SYSFAIL are monitored by the CPU board.

| B13 |

|-----|

|-----|

| 8 | 7 | 6 | 5 |

|---|---|---|---|

| 0 | 0 | 0 | ο |

|   |   |   |   |

| 0 | 0 | 0 | 0 |

| 1 | 2 | 3 | 4 |

## Figure 6-9: Location Diagram of Jumperfield B13

## 6.8.4 The RESET Instruction

The RESET instruction of the microprocessor is designed to reset peripherals under program control, without resetting the processor itself. This instruction is fully supported by the CPU board. The RESET instruction triggers the RESET generator and resets all peripherals on the board driving RESET to low. At this point the processor on the CPU itself will not be reset. Therefore, program execution will go on with the next operation code. If another board asserts SYSRESET \* before this instruction triggered reset is ended, then the processor will still not be reset because of a lockout logic.

This page was intentionally left blank

•

-

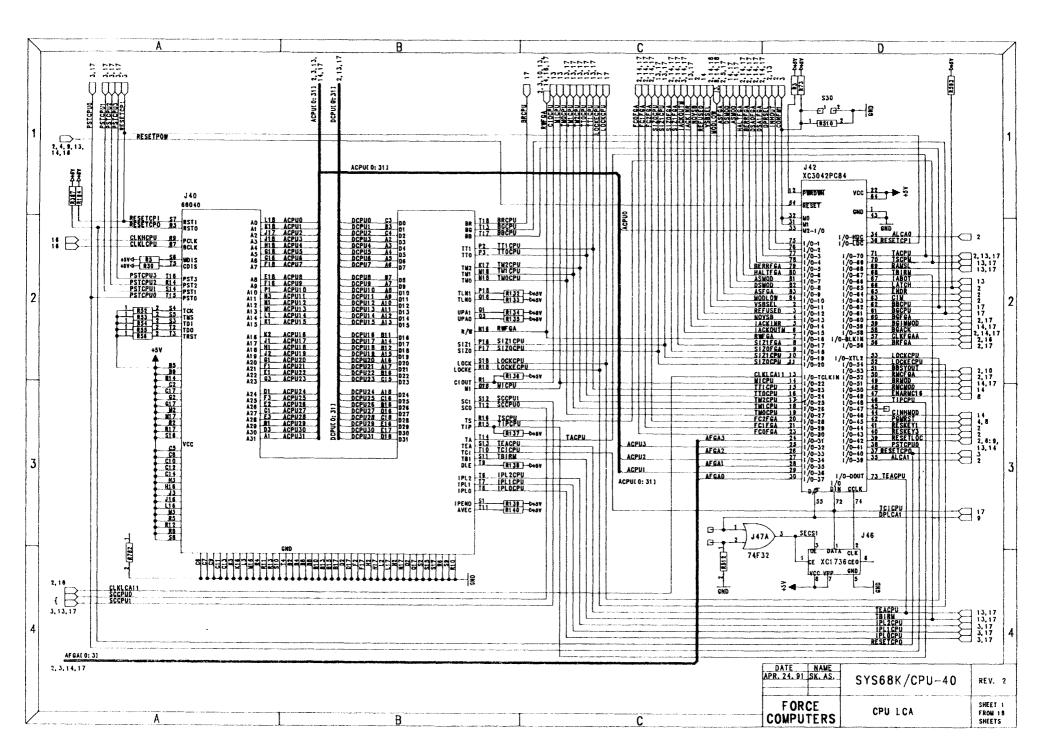

# APPENDIX TO THE HARDWARE USER'S MANUAL

This page was intentionally left blank

- A. SPECIFICATION OF THE CPU BOARD

- B. MEMORY MAP OF THE CPU BOARD

- C. ADDRESS ASSIGNMENT AND REGISTER LAYOUT OF THE I/O DEVICES

- D. PIN ASSIGNMENTS OF THE EPROM SOCKETS D.1 Pin Assignment for EPROM Area

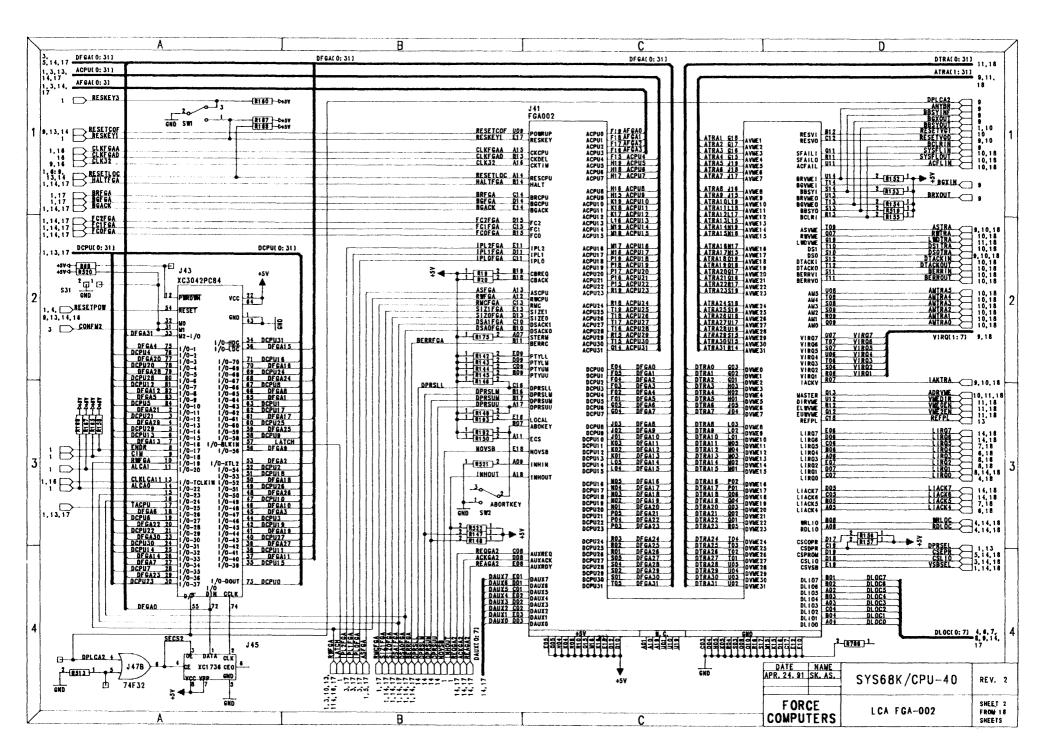

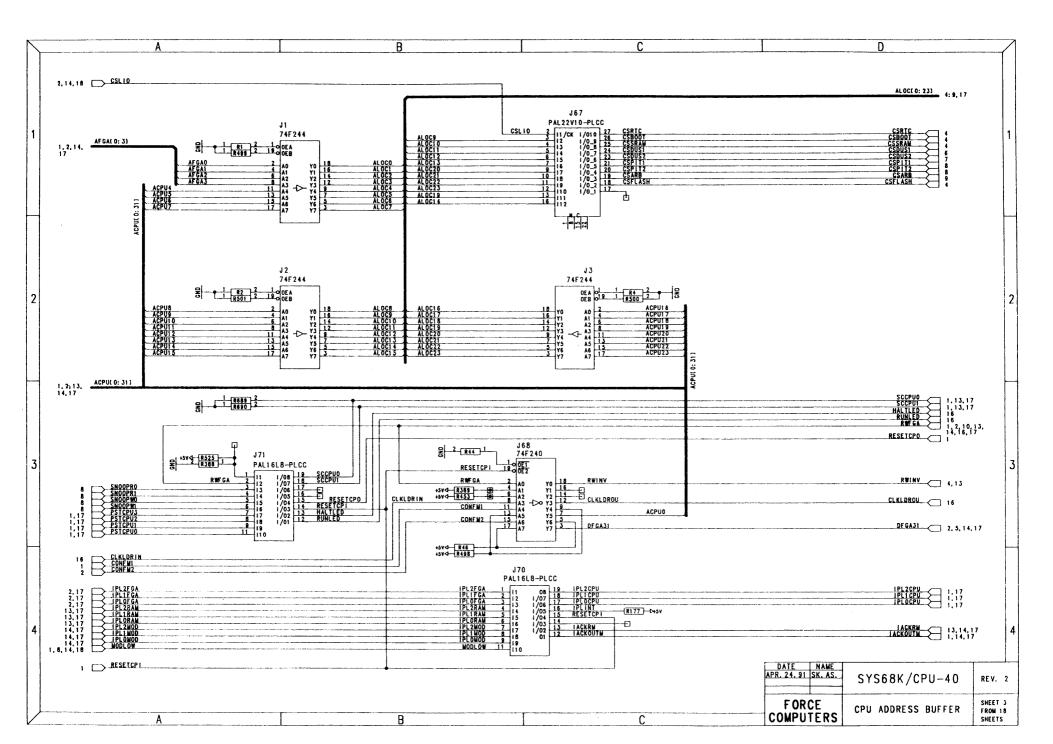

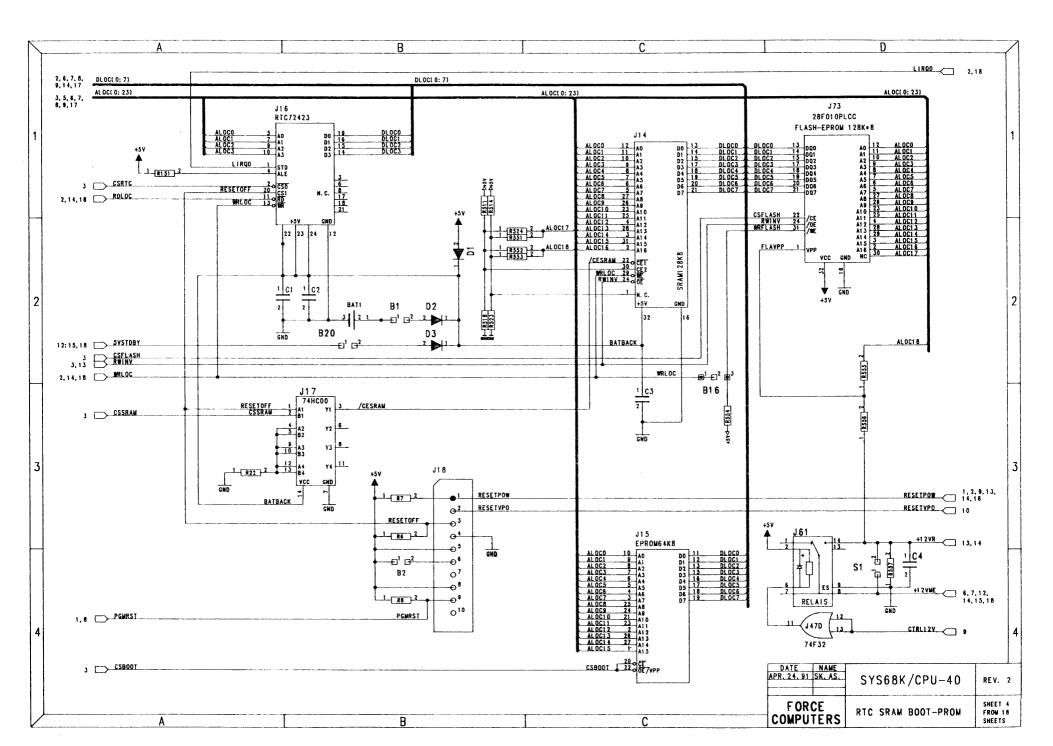

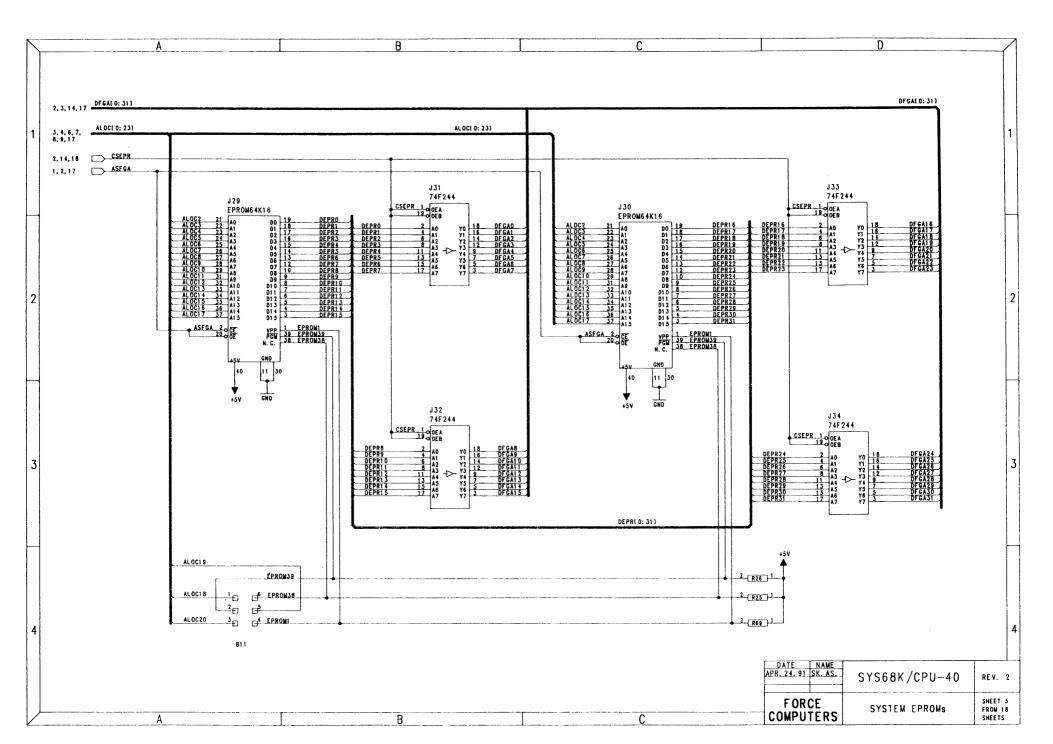

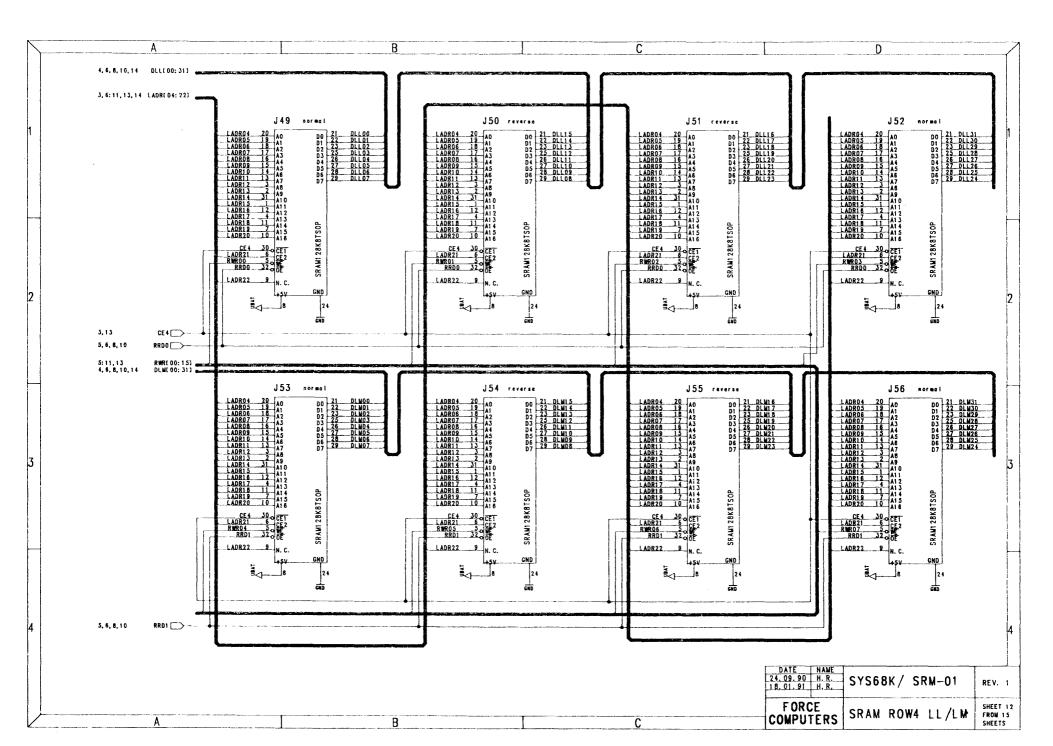

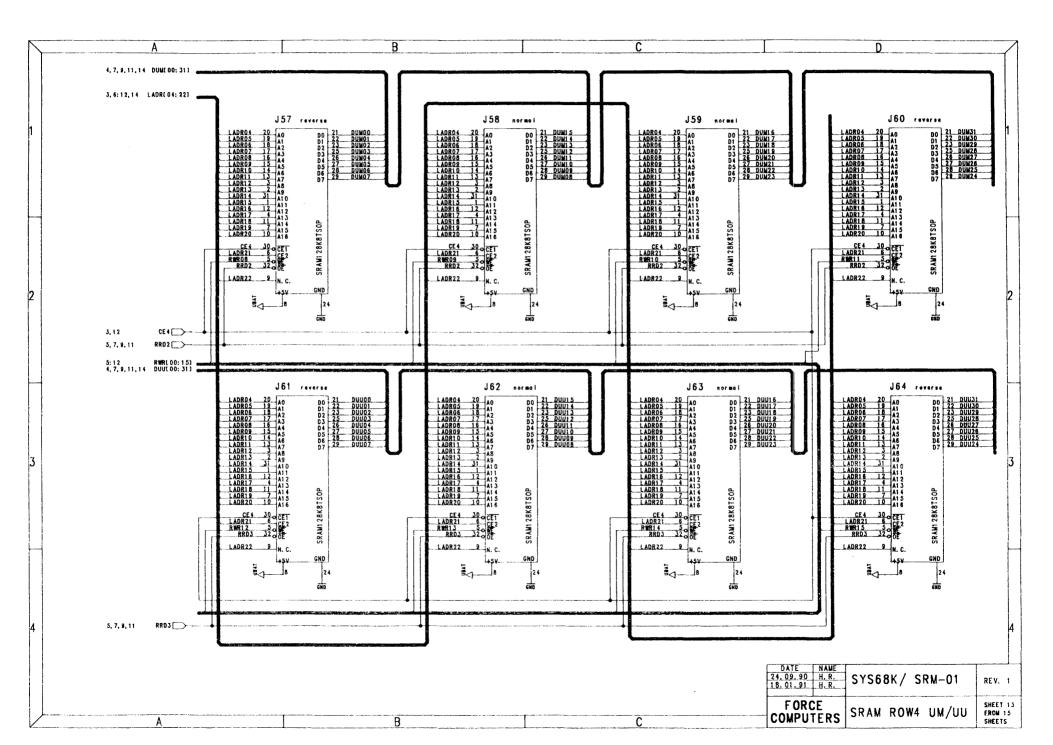

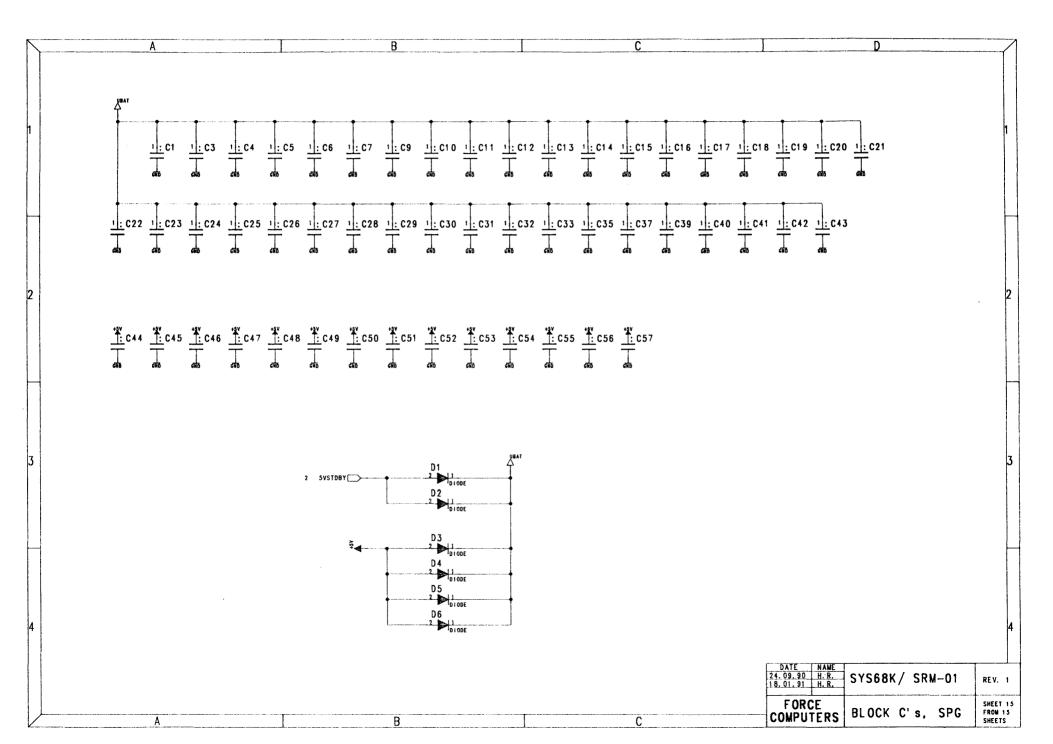

- E. CIRCUIT SCHEMATICS OF CPU BOARD E.1 Circuit Schematics of DRM-01 E.2 Circuit Schematics of SRM-01

- F. DEFAULT JUMPER SETTINGS ON THE CPU BOARD

- G. CONNECTOR PIN ASSIGNMENT G.1 J1/P1 Pin Assignments G.2 J2/P2 Pin Assignments

- H. COMPONENT PART LIST

- I. GLOSSARY OF VME/1014 TERMS

- J. LITERATURE REFERENCE

- K. PRODUCT ERROR REPORT

This page is intentionally left blank.

## APPENDIX A

#### SPECIFICATIONS OF THE CPU BOARD

| СРИ Туре                                                                                                                |                                                                                                                 | 68040                    |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------|

| CPU Clock Frequency                                                                                                     | CPU-40B/x<br>CPU-40D/x                                                                                          | 25.0 MHz<br>33.0 MHz     |

| Shared DRAM Capacity with Parity                                                                                        | CPU-40X/4<br>CPU-40X/16                                                                                         | 4 Mbytes<br>16 Mbytes    |

| CPU Clock Frequency                                                                                                     | CPU-41B/x<br>CPU-41D/x                                                                                          | 25.0 Mhz<br>33.0 MHZ     |

| Shared SRAM Capacity                                                                                                    | CPU-41X/4<br>CPU-41X/8                                                                                          | 4 Mbytes<br>8 Mbytes     |

| SRAM capacity with On-board Battery Backup<br>FLASH EPROM                                                               |                                                                                                                 | 128 Kbytes<br>128 Kbytes |

| Number of System EPROM Sockets<br>Data Path                                                                             |                                                                                                                 | 2<br>32-bits             |

| Serial I/O Interfaces (68562)<br>RS232/RS422/RS485 Compatible                                                           |                                                                                                                 | 4<br>4 of 4              |

| 24-bit Timer with 5-bit Prescaler<br>8-bit Timer                                                                        |                                                                                                                 | 2<br>1                   |

| Parallel I/O Interface (68230)                                                                                          |                                                                                                                 | 12 lines                 |

| Real Time Clock with On-board Battery Backu                                                                             | p                                                                                                               | 72423                    |

| -                                                                                                                       | 4, A16:D8, D16, D32, UAT, RMW<br>4:D8, D16, D32, RMW                                                            | Master<br>Slave          |

| Four Level Arbiter<br>SYSCLK Driver<br>Mailbox Interrupts                                                               |                                                                                                                 | Yes<br>Yes<br>8          |

| FORCE Message Broadcast                                                                                                 | FMB FIFO 0<br>FMB FIFO 1                                                                                        | 8 bytes<br>1 byte        |

| VMEbus Interrupter/VMEbus and Local Interrupt Handler<br>All Sources can be Routed to a Software Programmable IRQ Level |                                                                                                                 | 1 to 7<br>Yes            |

| RESET/ABORT Switch                                                                                                      | ingeneral and an an and an an and an and an and an and an and an and an an and an an and an an an an an an an a | Yes                      |

| VMEPROM Firmware Installed on All Board Ve                                                                              | ersions                                                                                                         | 256 Kbytes               |

#### TO BE CONTINUED

## SPECIFICATIONS OF THE CPU BOARD CONTINUED

| + 5V min/min<br>+ 12V min/max<br>-12V min/max | 5.2A/6.0A<br>0.1A/0.3A<br>1.0A/0.3A |

|-----------------------------------------------|-------------------------------------|

|                                               | 0 to +50°C                          |

|                                               | -40 to +85C<br>0 to 95%             |

|                                               | 234x160mm/9.2x6.3in                 |

|                                               | 1                                   |

|                                               | +12V min/max                        |

## 5. HISTORY OF MANUAL REVISIONS

| Revision No. | Description                                                                                                               | Date of Last Change |

|--------------|---------------------------------------------------------------------------------------------------------------------------|---------------------|

| 0            | First Print.                                                                                                              | FEB/05/1991         |

| 1            | The following sections/pages have been changed:                                                                           | APR/16/1991         |

|              | Section 1:                                                                                                                |                     |

|              | Page 2-16 (EPROM Description)                                                                                             |                     |

|              | Section 3:                                                                                                                |                     |

|              | Pages 3-11, 3-12, 3-14, 3-15 (EPROM Description)                                                                          |                     |

|              | Section 4:                                                                                                                |                     |

|              | Page F-1 (EPROM Description)                                                                                              |                     |

|              | Sections 7, 8, and 9:                                                                                                     |                     |

|              | These have been changed to adapt to VMEPROM Version 2.74                                                                  |                     |

|              | Section 1:                                                                                                                | AUG/23/1991         |

|              | Chapter 3: Power Requirements for + 12V changed from 0.1A/0.5A to 0.1A/0.3A                                               |                     |

|              | Section 3:                                                                                                                |                     |

|              | Chapter 3.9.4 has been eliminated.<br>Chapter 3.9.12: New Board Identification.<br>Chapter 3.9.16: 1 and 0 were switched. |                     |

| 2            | Rework for PCB Revision 2                                                                                                 | FEB/03/1992         |

This page was intentionally left blank

# **INSTALLATION**

This page was intentionally left blank

## WARNING

TO AVOID MALFUNCTIONS AND COMPONENT DAMAGES, PLEASE READ THE COMPLETE INSTALLATION PROCEDURE BEFORE THE BOARD IS INSTALLED IN A VMEBUS ENVIRONMENT. This page was intentionally left blank

.

.

## TABLE OF CONTENTS

| 1.  | GENERAL OVERVIEW              | 1-1 |

|-----|-------------------------------|-----|

| 1.1 | The Rotary Switches           | 1-1 |

| 1.2 | The Function Switch Positions | 1-1 |

| 1.3 | Connection of the Terminal    | 1-3 |

| 1.4 | The Default Hardware Setup    | 1-4 |

| 2.  | INSTALLATION IN THE RACK      | 2-1 |

| 2.1 | Power ON                      | 2-1 |

| 2.2 | Correct Operation             | 2-2 |

| 3.  | ENVIRONMENTAL REQUIREMENTS    | 3-1 |

## LIST OF FIGURES

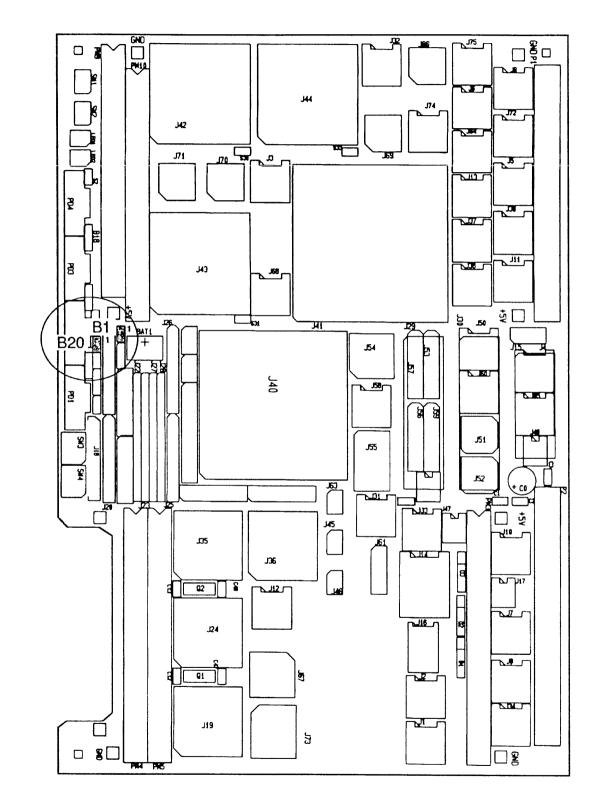

| Figure 1-1: | Front Panel of CPU Board and the Rotary Switch Positions | 1-2 |

|-------------|----------------------------------------------------------|-----|

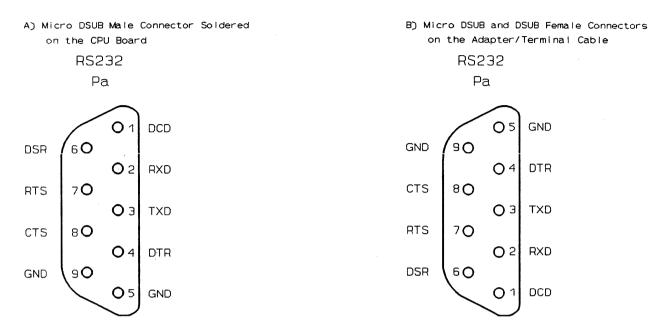

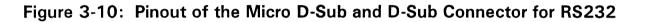

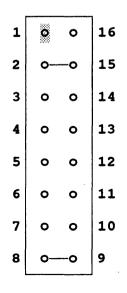

| Figure 1-2: | Pinout of the Micro D-Sub and D-Sub Connector for RS232  | 1-4 |

This page was intentionally left blank

#### 1. GENERAL OVERVIEW

Easy installation of the CPU board is provided since the memory map, the I/O devices, and the interfaces are configured to communicate with a standard terminal containing RS232 interface.

The monitor (VMEPROM) boots up automatically with the setup of the rotary switches on the front panel.

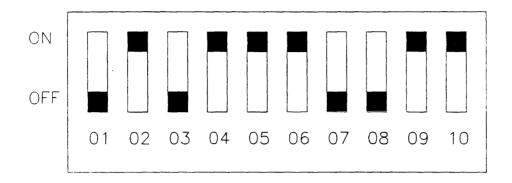

## **1.1 The Rotary Switches**

Two rotary switches are installed on the CPU board to configure the startup of the VMEPROM or a user program.

The following lists the default configuration for bootup.

| Switch | Hex Code |

|--------|----------|

| 2      | \$F      |

| 1      | \$F      |

The different functions of the rotary switches are described in detail in the *Introduction to VMEPROM* as well as in the *Hardware User's Manual* of this particular CPU board.

#### **1.2 The Function Switch Positions**

The CPU board contains two function switches. These two switches are defined as **RESET** and **ABORT**. The **RESET** switch is located in the first and upper position, and the **ABORT** switch is located directly underneath in the second and lower position.

The two moveable positions of these switches are defined as "Up" and "Down".

All function switches must be set to the position "Down" upon performing initial installation.

Please toggle each of the switches before installing the board in the rack in order to detect mechanical damages to the switches during transport.

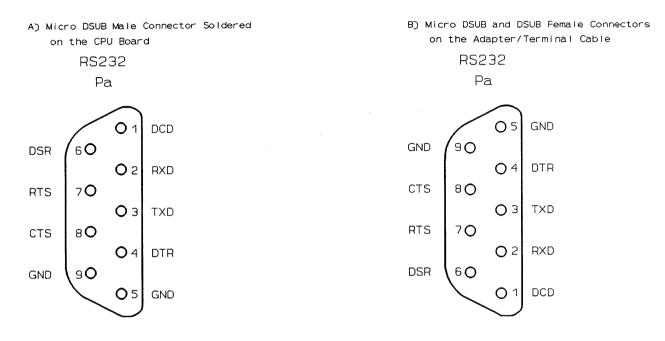

## **1.3** Connection of the Terminal

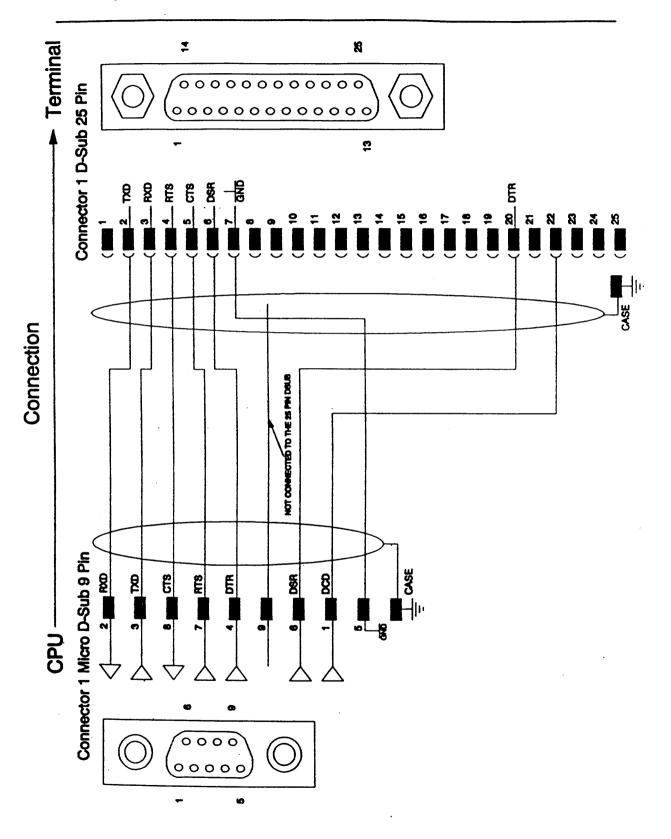

The terminal must be connected to the 9-pin Micro D-Sub connector 1 on the CPU board.

The board is delivered with a 9-pin Micro D-Sub to 9-pin D-Sub adapter cable.

The following communication setup is used for interfacing the terminal. Please configure the terminal to this setup.

No Parity 8 Bits per character 1 Stop Bit 9600 Baud Asynchronous Protocol

The hardware interface is RS232 compatible. The following signals are supported on the 9-pin Micro D-sub connector on the front panel:

| Signal | Input    | Output | Required | 9 Pin Micro<br>D-Sub Connector | Description         | 9 Pin D-Sub of the<br>Adapter Cable |

|--------|----------|--------|----------|--------------------------------|---------------------|-------------------------------------|

| DCD    | x        |        |          | 1                              | Data Carrier Detect | 1                                   |

| RXD    | Х        |        | Х        | 2                              | Receive Data        | 2                                   |

| TXD    |          | X      | Х        | 3                              | Transmit Data       | 3                                   |

| DTR    |          | Х      |          | 4                              | Data Terminal Ready | 4                                   |

| GND    |          |        |          | 5                              | Signal GND          | 5                                   |

| DSR    | X        | Х      |          | 6                              | Data Set Ready      | 6                                   |

| RTS    |          | Х      | Х        | 7                              | Request to Send     | 7                                   |

| CTS    | X        |        | X        | 8                              | Clear to Send       | 8                                   |

| GND    | <u> </u> |        | X        | 9                              | Signal GND          | 9                                   |

## CAUTION

- 1) The terminal used must not drive a signal line which is marked to be an output of CPU board.

- 2) All signals marked as "Required" must be supported from the terminal to enable the transmission.

- 3) If the terminal is configured to the listed setup, please connect the 9-pin Micro D-Sub connector to the terminal with a cable which supports all of the required signals.

12

#### 1-4

## 1.4 The Default Hardware Setup

The VMEbus interface is configured to be used immediately, without any changes.

This results in a default hardware setup which may conflict with other boards installed in the rack.

The following signals are driven/received from the CPU board:

| Signal     | Driven | Received | From               |

|------------|--------|----------|--------------------|

| SYSCLK     | x      |          | FGA-002 Gate Array |

| BR3*       | Х      |          | FGA-002 Gate Array |

| BR[30]*    |        | X        | 4 Level Arbiter    |

| BG[30]OUT* | X      |          | 4 Level Arbiter    |

| ACFAIL*    |        | X        | FGA-002 Gate Array |

| SYSFAIL*   |        | X        | FGA-002 Gate Array |

| SYSRESET*  | Х      | X        | FGA-002 Gate Array |

## CAUTION

1) The on-board four level arbiter is enabled and reacts on every Bus Request\*.

2) The CPU board is configured as a slot 1 controller.

This page intentionally left blank

## 2. INSTALLATION IN THE RACK

The CPU board can immediately be mounted into a VME rack at slot 1.

## CAUTION

- 1) Switch off power before installing the board to avoid electrical damage to the components.

- 2) The CPU board contains a special ejector (the handles). The board must be plugged in, and the screws on the front panel tightened up to guarantee proper installation.

- 3) Unplug every other VMEbus board to avoid conflicts.

## 2.1 Power ON

Power to the VMEbus rack may be switched on when the board is correctly installed, the switches are in the correct positions, and the terminal is correctly configured and under power.

Initially, the green RUN LED will light up, and after one to three seconds the message "Wait until hard disk is up to speed" will be displayed. A few seconds later the VMEPROM banner should appear.

The terminal is now at the user's discretion. At this point, it is advised to make a few carriage returns, to obtain the question mark (?\_) prompt.

## 2.2 Correct Operation

To test the correct operation of the CPU board, the following command must be typed in:

? SELFTEST < cr>

It is a matter of a few seconds until all tests are completed. Once all tests are completed, the following messages will appear on the screen:

#### VMEPROM Hardware Selftest

I/O test .....passed

Memory test .....passed

Clock test . . . . . . . . . passed

Any errors will be reported as they occur.

If an error message is displayed, please refer to *Section 7, "Introduction to VMEPROM*" containing the command description "*SELFTEST*".

#### 3. ENVIRONMENTAL REQUIREMENTS

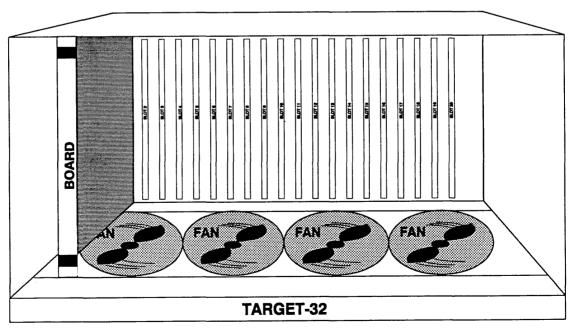

This board was specified and tested for reliable operation under certain environmental conditions. Based on our performance tests, this board is capable of operating within the temperature range of 0°C to 50°C when used inside of a FORCE TARGET-32 chassis. The following chart details the calculated rate of forced air cooling.

| Rate | of | Forced | Air | Cooling |

|------|----|--------|-----|---------|

|------|----|--------|-----|---------|

| Air Cooling per Board                                         | Total Air Cooling - Target-32   |  |  |  |

|---------------------------------------------------------------|---------------------------------|--|--|--|

| 5.5 CFM* = 0.0026 cubic meter/sec                             | 131 CFM = 0.062 cubic meter/sec |  |  |  |

| 275 LFM** = 1.4 meter/sec                                     | 275 LFM = 1.4 meter/sec         |  |  |  |

| * CFM = Cubic Feet per Minute ** LFM = Linear Feet per Minute |                                 |  |  |  |

The TARGET-32 chassis performs forced air cooling using four axial fans. The amount of airflow needed for cooling and normal operation is reflected by certain factors such as ambient temperature, number and location of boards in the system, and outside heat sources. Sufficient air cooling is normally obtained when 5.5 CFM and 275 LFM is circulating around each board at an ambient temperature between 0°C and 50°C. Allowable storage temperatures may range between -40°C and 85°C. The rate of relative humidity (non-condensing) should not be less than 5%, and should not exceed 95%. The following illustration is a pictorial view of the fan placement in the chassis.

20 SLOTS AVAILABLE FOR 20 BOARDS

This page was intentionally left blank

## HARDWARE USER'S MANUAL

.

This page was intentionally left blank

## TABLE OF CONTENTS

| 1.                                                                                                                                               | GENERAL INFORMATION                                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 2.                                                                                                                                               | THE PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1                                                                                               |

| 2.1<br>2.1.1<br>2.1.1.1                                                                                                                          | The CPU 68040Hardware Interface of the 68040General Operation                                                                                                                                                                                                                                                                                                                                                    | 2-1<br>2-1<br>2-1                                                                                 |