# PPC/PowerCore-6750 Reference Guide

P/N 205021 Edition 6.0 August 2000

Force Computers GmbH All Rights Reserved

This document shall not be duplicated, nor its contents used for any purpose, unless written permission has been granted.

Copyright by Force Computers

#### World Wide Web: www.forcecomputers.com

24-hour access to on-line manuals, driver updates, and application notes is provided via SMART, our SolutionsPLUS customer support program that provides current technical and services information.

# **Headquarters**

## The Americas

#### Force Computers Inc.

5799 Fontanoso Way San Jose, CA 95138-1015 U.S.A.

Tel.: +1 (408) 369-6000 Fax: +1 (408) 371-3382 Email: support@fci.com

### Europe

### Force Computers GmbH

Prof.-Messerschmitt-Str. 1 D-85579 Neubiberg/München Germany

Tel.: +49 (89) 608 14-0 Fax: +49 (89) 609 77 93 Email: support@force.de

### Asia

### Force Computers Japan KK

Shiba Daimon MF Building 4F 2-1-16 Shiba Daimon Minato-ku, Tokyo 105-0012 Japan

Tel.: +81 (03) 3437 3948 Fax: +81 (03) 3437 3968 Email: smiyagawa@fci.com

#### NOTE

The information in this document has been carefully checked and is believed to be entirely reliable. Force Computers makes no warranty of any kind with regard to the material in this document, and assumes no responsibility for any errors which may appear in this document. Force Computers reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers assumes no responsibility for the use of any circuitry other than circuitry which is part of a product of Force Computers GmbH. Force Computers does not convey to the purchaser of the product described herein any license under the patent rights of Force Computers GmbH nor the rights of others. All product names mentioned herein are the trademarks or registered trademarks of their respective companies.

Copyright© 2000 by Force Computers. All rights reserved. This document shall not be reproduced, transmitted, or stored in a retrieval system, nor its contents used for any purpose, without the prior written consent of Force Computers GmbH.

# **Table of Contents**

|   | Using | g This M                      | Ianual xi                                         |

|---|-------|-------------------------------|---------------------------------------------------|

| 1 | Safet | y Notes                       | 1                                                 |

| 2 | Intro | duction                       |                                                   |

|   | 2.1   | Specifi                       | cation                                            |

|   | 2.2   | Produc                        | et Nomenclature                                   |

|   | 2.3   | Orderi                        | ng Information                                    |

| 3 | Insta | llation .                     | 9                                                 |

|   | 3.1   | Installa                      | ation Prerequisites and Requirements10            |

|   |       | 3.1.1                         | Requirements                                      |

|   |       | 3.1.2                         | Terminal Connection                               |

|   |       | 3.1.3                         | Location Overview                                 |

|   |       | 3.1.4                         | Upgrading PPC/PowerCore-675015                    |

|   | 3.2   | Autom                         | atic Power Up – Voltage Sensor and Watchdog Timer |

|   | 3.3   | Switch                        | Settings                                          |

|   | 3.4   | Front I                       | Panel                                             |

|   | 3.5   | PPC/P                         | owerCore-6750 Parameters and Timers – CIO19       |

|   | 3.6   | Serial l                      | I/O Ports                                         |

|   | 3.7   | PMC S                         | slots                                             |

|   |       | 3.7.1                         | PMC Voltage Keys                                  |

|   |       | 3.7.2                         | Connector Configuration                           |

|   |       | 3.7.3                         | ISA Connector                                     |

|   | 3.8   | Ethern                        | et Interface                                      |

|   | 3.9   | VMEb                          | us Interface – Universe II                        |

|   | 3.10  | 10 VMEbus P2 Connector Pinout |                                                   |

|   |       |                               |                                                   |

|   | 3.11 | Testing | g the CPU Board Using PowerBoot                   |

|---|------|---------|---------------------------------------------------|

| Ļ | Hard | lware   |                                                   |

|   | 4.1  | PPC/Pe  | owerCore-6750 Address Map 33                      |

|   | 4.2  | PPC/Pe  | owerCore-6750 Interrupt Map                       |

|   | 4.3  | PowerI  | PC CPU                                            |

|   | 4.4  | L2 Cac  | che                                               |

|   | 4.5  | Watch   | dog Timer                                         |

|   |      | 4.5.1   | Watchdog Operation                                |

|   | 4.6  | Shared  | 43 Memory                                         |

|   |      | 4.6.1   | Memory controller                                 |

|   |      | 4.6.2   | Shared Memory Performance                         |

|   |      | 4.6.3   | Shared Memory Capacity                            |

|   |      | 4.6.4   | Shared Memory Organization                        |

|   |      | 4.6.5   | Cache Coherency and Snooping                      |

|   |      | 4.6.6   | Shared Memory Access from the PowerPC CPU         |

|   |      | 4.6.7   | Shared Memory Access via VMEbus                   |

|   |      | 4.6.8   | Shared Memory Access from the Ethernet Controller |

|   |      | 4.6.9   | Shared Memory Access from PMC Modules             |

|   |      | 4.6.10  | Shared Memory Access from the PCI-to-ISA Bridge   |

|   | 4.7  | Boot F  | lash                                              |

|   |      | 4.7.1   | Boot Flash Address Range                          |

|   |      | 4.7.2   | Boot Flash Size and Address Map51                 |

|   |      | 4.7.3   | Boot Flash Devices                                |

|   |      | 4.7.4   | Programming the Boot Flash                        |

|   | 4.8  | User Fl | lash                                              |

|   |      | 4.8.1   | User Flash Address Range                          |

|   |      | 4.8.2   | User Flash Size                                   |

|   |      | 4.8.3   | User Flash Devices                                |

|   |      | 4.8.4   | Programming the User Flash                        |

|   | 4.9  | PPC-to  | -PCI Bridge                                       |

|   | 4.10 | PCI-to- | -VME Bridge – Universe II                         |

|      | 4.10.1             | VMEbus Interface Overview                 | 59        |

|------|--------------------|-------------------------------------------|-----------|

|      | 4.10.2             | VMEbus Master Interface6                  | 50        |

|      | 4.10.3             | VMEbus Slave Interface                    | 52        |

|      | 4.10.4             | DMA-Controller                            | 52        |

|      | 4.10.5             | Exception Signals                         | 53        |

|      | 4.10.6             | VMEbus Slot-1 Functions6                  | 53        |

|      | 4.10.7             | VMEbus Timer                              | 55        |

|      | 4.10.8             | VMEbus Arbitration and VMEbus Requester   | 55        |

| 4.11 | Etherne            | t Interface                               | 67        |

|      | 4.11.1             | Ethernet Controller                       | 58        |

|      | 4.11.2             | Ethernet Interface Adapter6               | 59        |

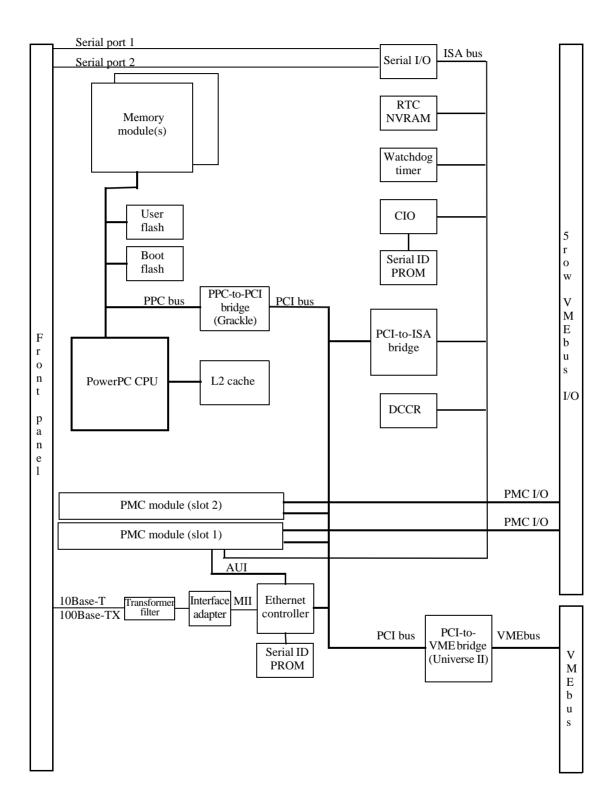

| 4.12 | PCI-to-            | ISA Bridge                                | <u>59</u> |

|      | 4.12.1             | PCI-to-ISA Function                       | 0         |

|      | 4.12.2             | Interrupt Controller                      | 0         |

| 4.13 | Real-Ti            | me Clock / Non-Volatile RAM7              | 1         |

| 4.14 | PPC/Po             | werCore-6750 Parameters and Timers – CIO7 | '3        |

|      | 4.14.1             | Parameters                                | 13        |

|      | 4.14.2             | Timers                                    | '3        |

|      | 4.14.3             | CIO                                       | /4        |

|      | 4.14.4             | CIO Port A Data Register                  | '4        |

|      | 4.14.5             | CIO Port B Data Register                  | '5        |

|      | 4.14.6             | CIO Port C Data Register                  | '5        |

| 4.15 | Serial I/          | O Ports – SCCs                            | 6         |

| 4.16 | PMC SI             | ots                                       | 7         |

|      | 4.16.1             | Busmode                                   | 17        |

| 4.17 | ISA Dev            | vices                                     | /9        |

|      |                    |                                           |           |

|      | erBoot<br>owerBoot | Instruction Set)paginated separately      |           |

|      |                    |                                           |           |

| Powe | erBoot for         | r PPC/PowerCore-6750                      | \$5       |

| 6.1  | PPC/Po             | werCore-6750 Address Map8                 | \$6       |

| 6.2  | PMCPC              | CI – Mapping PMC Modules                  | \$7       |

5

6

| 6.3 | RESET – Restarting the Board                |

|-----|---------------------------------------------|

| 6.4 | SETBOOT – Editing Auto Boot Parameters      |

| 6.5 | USERLED – Setting User LED                  |

| 6.6 | VMEMST – Opening an A32/D32 Master Window   |

| 6.7 | VMESLV – Opening an A32/D32 Slave Window102 |

| 6.8 | VMESYS – Enabling VMEbus System Controller  |

| 6.9 | NETLOAD and NETSAVE – Board Specific Option |

|     |                                             |

**Product Error Report**

Tab./Fig.

Page

# List of Tables and Figures

| History of Manual Publicationxii                                                                                                                                                                     | Tab.         | а        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|

| Fonts, Notations and Conventions                                                                                                                                                                     | Tab.         | b        |

| Specification of the PPC/PowerCore-6750                                                                                                                                                              | Tab.         | 1        |

| Nomenclature of the PPC/PowerCore-6750                                                                                                                                                               | Tab.         | 2        |

| Excerpt from the Data Sheet's Ordering Information                                                                                                                                                   | Tab.         | 3        |

| Typical Power Consumption of the CPU Board                                                                                                                                                           | Tab.         | 4        |

| Qualified Memory Module Configurations                                                                                                                                                               | Tab.         | 5        |

| Max. Power Consumption of the Upper Memory Modules                                                                                                                                                   | Tab.         | 6        |

| Environmental Requirements of PPC/PowerCore-6750 12                                                                                                                                                  | Tab.         | 7        |

| Location Diagram of the PPC/PowerCore-6750 (schematic) 14                                                                                                                                            | Fig.         | 1        |

| Default Switch Settings                                                                                                                                                                              | Tab.         | 8        |

| Front-Panel Features                                                                                                                                                                                 | Tab.         | 9        |

| Pinout of the Front-Panel Serial I/O Port 1 and 2 20                                                                                                                                                 | Tab.         | 10       |

| PN15 Connector Pinout                                                                                                                                                                                | Fig.         | 2        |

| 8-Pin RJ45 Connector                                                                                                                                                                                 | Tab.         | 11       |

| P2 Connector Pinout, Row A and C                                                                                                                                                                     | Fig.         | 3        |

| P2 Connector Pinout, Row Z and D                                                                                                                                                                     | Fig.         | 4        |

| PPC/PowerCore-6750 Block Diagram                                                                                                                                                                     | Fig.         | 5        |

| Buses, Busmodes, and Connected Devices                                                                                                                                                               | Tab.         | 12       |

| Bus Frequencies                                                                                                                                                                                      | Tab.         | 13       |

| PPC/PowerCore-6750 Memory Map seen from the CPU                                                                                                                                                      | Tab.         | 14       |

| PPC/PowerCore-6750 Memory Map seen from the PCI                                                                                                                                                      | Tab.         | 15       |

| PPC/PowerCore-6750 I/O Map seen from the PCI                                                                                                                                                         | Tab.         | 16       |

| PPC/PowerCore-6750 Configuration Base Addresses                                                                                                                                                      | Tab.         | 17       |

| PPC/PowerCore-6750 ISA Bus Ports seen from the CPU                                                                                                                                                   | Tab.         | 18       |

| PPC/PowerCore-6750 PCI I/O Devices seen from the CPU                                                                                                                                                 | Tab.         | 19       |

| Default PPC/PowerCore-6750 Interrupt Map                                                                                                                                                             | Tab.         | 20       |

| PMC Interrupt Routing                                                                                                                                                                                | Tab.         | 21       |

| DCCR, Bits [76]                                                                                                                                                                                      | Tab.         | 22       |

| CIO Port C Data Register, Bit [32]                                                                                                                                                                   | Tab.         | 23       |

| DCCR, Bits [50]                                                                                                                                                                                      | Tab.         | 24       |

| EDO DRAM Capacity                                                                                                                                                                                    | Tab.         | 25<br>26 |

| SDRAM capaCity                                                                                                                                                                                       | Tab.         | 26       |

| Shared Memory Access Address Ranges from the PowerPC CPU                                                                                                                                             | Tab.         | 27       |

| CIO Port A Data Register, Bits [7] and [4]                                                                                                                                                           | Tab.         | 28       |

| Boot Flash Address Range                                                                                                                                                                             | Tab.         | 29<br>20 |

| Boot Flash Address Map52Boot flash factory options, device types, and default configuration52                                                                                                        | Tab.<br>Tab. | 30<br>31 |

| CIO Port A Data Register, Bits [7], [32], and [0]                                                                                                                                                    | Tab.<br>Tab. | 31<br>32 |

| $C_1O_1$ on $\Lambda$ Data (register, Dits [7], [32], and [0] $\ldots \ldots \ldots$ | 1 aU.        | 54       |

| Page                                                            | Tab./Fig. |

|-----------------------------------------------------------------|-----------|

| User Flash Address Map 54                                       | Tab. 33   |

| User Flash Address Range                                        | Tab. 34   |

| User Flash Factory Options and Device Types                     | Tab. 35   |

| CAR and CDR Address Map 58                                      | Tab. 36   |

| VMEbus Master Transfer Cycles Def. for Data Bus Width D32 60    | Tab. 37   |

| VMEbus Master Transfer Cycles Defined for Data Bus Width D16 61 | Tab. 38   |

| Default PCI-to-ISA Bridge Interrupt Structure                   | Fig. 6    |

| Address Space of the RTC/NVRAM                                  | Tab. 39   |

| CIO port A Data Register                                        | Tab. 40   |

| CIO Port B Data Register, Bits [76]                             | Tab. 41   |

| CIO Port C Data Register                                        | Tab. 42   |

| SCC Base Addresses                                              | Tab. 43   |

| CIO Port B Data Register, Bits [51]                             | Tab. 44   |

| CIO Port A Data Register, Bit [6] 79                            | Tab. 45   |

| PPC/PowerCore-6750 Address Map seen from the CPU                | Tab. 46   |

| PCI Addressing Spaces                                           | Tab. 47   |

| PCI I/O Addressing Spaces of the SCSI Controllers               | Tab. 48   |

# **Using This Manual**

This section does not provide information on the product but on common features of the manual itself:

- Structure

- Special layout conventions

- Related documents.

#### Audience of the Reference Guide

The *Reference Guide* is intended for hard- and software developers installing and integrating the PPC/PowerCore-6750 into their systems.

#### **Overview of the Reference Guide**

The *Reference Guide* provides a comprehensive hardware and software guide to the board. It additionally includes the *PowerBoot Instruction Set*.

*Note:* Please take a moment to examine the "Table of Contents" of the *Reference Guide* to see how this documentation is structured. This will be of value to you when looking for information in the future.

#### *Reference Guide* The *Reference Guide* includes:

- Brief overview of the product, the specifications, and the ordering information: see section 2 "Introduction" on page 5

- Installation instructions for powering up the board: see section 3 "Installation" on page 9. It includes the default configuration (switches and the like), initialization, and connector pinouts.

The installation instructions also appear as the product's installation guide -a separate manual delivered together with each shipped product.

- Detailed hardware description: see section 4 "Hardware" on page 29

- Description of the board specific PowerBoot commands: see section 6 "PowerBoot for PPC/PowerCore-6750" on page 85

| Data Sheets                  | They conta                                              | ain information re-                                            | re relevant for the PPC/PowerCore-6750.<br>levant for configuring and inegrating the<br>be found on the respective company's                                                                                                 |

|------------------------------|---------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              | – PCI-te                                                | o-ISA Bridge – W8                                              | 3C553F (http://www.winbond.com)                                                                                                                                                                                              |

|                              | – CIO C                                                 | Counter/Timer – CI                                             | O Z8536 (http://www.zilog.com)                                                                                                                                                                                               |

|                              | – Real-'<br>(http:/                                     | Time Clock and<br>//www.us.st.com)                             | I NVRAM – RTC/NVRAM M48T58                                                                                                                                                                                                   |

|                              | – Serial                                                | I/O Port – TL16C5                                              | 550C (http://www.ti.com)                                                                                                                                                                                                     |

|                              | – Ether                                                 | net Controller – LA                                            | N 21143(http://www.developer,intel.com)                                                                                                                                                                                      |

|                              | – Ethern<br>(http:/                                     | net Interface A<br>//www.level1.com)                           | Adapter – LXT970 and ICS 1890                                                                                                                                                                                                |

|                              |                                                         | bus Interface PCI-t<br>//www.tundra.com)                       | co-VMEbridge – Universe II User's Guide                                                                                                                                                                                      |

|                              | – Grack                                                 | tle NPC106 (http://                                            | www.motorola.com)                                                                                                                                                                                                            |

| PowerBoot<br>Instruction Set | mands whi<br>erBoot cor<br>"PowerBoo<br>The <i>Powe</i> | ch are independent<br>nmands are descril<br>ot for PPC/PowerCo | Set describes only those PowerBoot com-<br>of the CPU board. The board specific Pow-<br>bed in the <i>Reference Guide</i> (see section 6<br>pre-6750" on page 85).<br>Set is packaged separately and always<br>prence Guide. |

|                              | E.                                                      |                                                                | <i>rBoot Instruction Set</i> now: see section 5<br>PowerBoot Instruction Set)".                                                                                                                                              |

| Table a                      | History of                                              | Manual Publicati                                               | on                                                                                                                                                                                                                           |

|                              | Edition                                                 | Date                                                           | Description                                                                                                                                                                                                                  |

|                              | 1.0                                                     | May 1998                                                       | First print                                                                                                                                                                                                                  |

|                              | 2.0                                                     | July 1998                                                      | SDRAM memory module description                                                                                                                                                                                              |

2.1

3.0

December 1998

March 1999

added. Technical Reference Manual

Excerpt from the data sheet's ordering information updated, power requirements and bus frequencies of the 300-MHz and 400-MHz boards included

corrected, revised, and extended.

Edition increased

### Table a

History of Manual Publication

| Edition | Date           | Description                                                                                                                       |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 4.0     | September 1999 | PowerBoot start-up banner changed,<br>SETBOOT extended by Power ON test<br>POT                                                    |

| 5.0     | February 2000  | Changed manual type, changed Power-<br>Boot User's Manual to Instruction Set,<br>removed data sheet section, editorial<br>changes |

| 6.0     | August 2000    | Removed reference to Universe and<br>Grackle Set of Data Sheets, editorial<br>changes                                             |

### Table b

### Fonts, Notations and Conventions

| Notation                | Description                                                                                                                                                                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000.0000 <sub>16</sub> | Typical notation for hexadecimal numbers (digits are<br>0 through F), e.g. used for addresses and offsets.<br>Note the dot marking the 4th (to its right) and 5th (to<br>its left) digit.                        |

| 00008                   | Same for octal numbers (digits are 0 through 7)                                                                                                                                                                  |

| 00002                   | Same for binary numbers (digits are 0 and 1)                                                                                                                                                                     |

| Program                 | Typical character format used for names, values, and<br>the like that should be used typing literally the same<br>word. Also used for on-screen-output.                                                          |

| Variable                | Typical character format for words that represent a<br>part of a command, a programming statement, or the<br>like and that will be replaced by an applicable value<br>when actually applied.                     |

| #                       | A # symbol at the end of a PCI, ISA, or IDE signal<br>name indicates that the signal is active when it is at<br>low voltage. The absence of the # symbol indicates<br>that the signal is active at high voltage. |

| *                       | A * symbol at the end of a VMEbus signal name indi-<br>cates that the signal is active when it is at low voltage.<br>The absence of the * symbol indicates that the signal<br>is active at high voltage.         |

| Register<br>Conventions | Force Computers assumes that the software developer initializes the reg-<br>ister bits which are not described with default settings.                                                                   |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Icons for Ease of Use: Safety Notes and Tips & Tricks                                                                                                                                                   |

|                         | The following three types of safety notes appear in this manual. Be sure to always read and follow the safety notes of a section first – before acting as documented in the other parts of the section. |

| Danger<br>STOP          | Dangerous situation: serious injuries to people or severe damage to objects.                                                                                                                            |

| Caution                 | Possibly dangerous situation: slight injuries to people or damage to objects possible.                                                                                                                  |

*Note:* No danger encountered. Pay attention to important information marked using this layout.

# 1 Safety Notes

|              | This section provides safety precautions to follow when installing, op-<br>erating, and maintaining the PPC/PowerCore-6750. For your protec-<br>tion, follow all warnings and instructions found in the following text.                                                                                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General      | This <i>Reference Guide</i> provides the necessary information to install<br>and handle the PPC/PowerCore-6750. As the product is complex and<br>its usage manifold, we do not guarantee that the given information is<br>complete. In case you need additional information, ask your Force<br>Computers representative.                             |

|              | The PPC/PowerCore-6750 has been designed to meet the standard industrial safety requirements. It must not be used except in its specific area of office telecommunication industry and industrial control.                                                                                                                                           |

|              | Only personnel trained by Force Computers or qualified persons in<br>electronics or electrical engineering are authorized to install, unin-<br>stall or maintain the PPC/PowerCore-6750. The information given in<br>this manual is meant to complete the knowledge of a specialist and<br>must not be taken as replacement for qualified personnel. |

|              | Make sure that contacts and cables of the board cannot be touched<br>while the board is operating.                                                                                                                                                                                                                                                   |

| Installation | Electrostatic discharge and incorrect board installation and uninstal-<br>lation can damage circuits or shorten their life. Therefore:                                                                                                                                                                                                               |

|              | Before installing the board, check:                                                                                                                                                                                                                                                                                                                  |

|              | – section "Power Requirements" on page 10                                                                                                                                                                                                                                                                                                            |

|              | – and section "Thermal Requirements" on page 12                                                                                                                                                                                                                                                                                                      |

|              | • Before touching integrated circuits, ensure that you are working in an electrostatic-free environment.                                                                                                                                                                                                                                             |

|              | • When plugging the board in or removing it, do not press on the front panel but use the handles.                                                                                                                                                                                                                                                    |

|              | • Before installing or uninstalling the board, read section 3 "Instal-<br>lation" on page 9.                                                                                                                                                                                                                                                         |

|              | • Before installing or uninstalling an additional device or module, read the respective documentation.                                                                                                                                                                                                                                               |

|              |                                                                                                                                                                                                                                                                                                                                                      |

• Ensure that the board is connected to the VMEbus via both the P1 and the P2 connectors and that the power is available on both VMEbus connectors. **Operation** While operating the board ensure that the power and environmental requirements as given in table 4 "Typical Power Consumption of the CPU Board" on page 10 and table 7 "Environmental Requirements of PPC/PowerCore-6750" on page 12 are met. • When operating the board in areas of strong electromagnetic radiation ensure that the board is bolted on the VME rack and shielded by closed housing. **EMC** • If boards are integrated into open systems, always cover empty slots. • The front panel of the PPC/PowerCore-6750 provides 2 cutouts for the front panels of the PMC modules. If the board is shipped without the module installed, the front-panel cutouts are covered by blind panels to ensure proper EMC shielding. To ensure proper EMC shielding, always operate the PPC/PowerCore-6750 with the blind panel or with PMC modules installed. Expanding • Check the total power consumption of all components installed (see the technical specification of the respective components). For the total power consumption of the PPC/PowerCore-6750, see table 4 "Typical Power Consumption of the CPU Board" on page 10. • Ensure that any individual output current of any source stays within its acceptable limits (see the technical specification of the respective source). • Only replace components or system parts with those recommended by Force Computers. In case you use components other than those recommended by Force Computers, you are fully responsible for the impact on EMI and the eventually changed functionality of the product. Environment Always dispose used batteries and/or old boards according to your country's legislation.

| Battery            | If a Lithium battery on a board has to be exchanged, observe the fol-<br>lowing safety notes:                                                                                                                                                                                                                       |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | • Incorrect exchange of Lithium batteries can result in a hazardous explosion.                                                                                                                                                                                                                                      |  |

|                    | • Always use the same type of Lithium battery as is already installed.                                                                                                                                                                                                                                              |  |

| RJ-45<br>Connector | If an RJ-45 connector is available on the board, take into account<br>that the RJ-45 connector type is used for telephone connectors and<br>for twisted pair Ethernet (TPE) connectors. Note that mismatching<br>these 2 connectors may destroy your telephone as well as your<br>PPC/PowerCore-6750.<br>Therefore: |  |

|                    | • Make sure that TPE connectors near your working area are clearly marked as network connectors.                                                                                                                                                                                                                    |  |

|                    | • Make sure that TPE bushing of the system is connected only to safety extra low voltage (SELV) circuits.                                                                                                                                                                                                           |  |

|                    | • Verify that the length of an electric cable connected to a TPE bush-<br>ing does not exceed 1 kilometer outside the building.                                                                                                                                                                                     |  |

|                    | • If in doubt, ask your system administrator.                                                                                                                                                                                                                                                                       |  |

# 2 Introduction

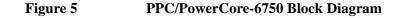

|                 | PPC/PowerCore-6750 is a high performance single-board computer pro-<br>viding a Universe VMEbus interface. It is based on                                                                                                                                                                                                      |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | Microprocessor PowerPC 750                                                                                                                                                                                                                                                                                                     |  |

|                 | • VMEbus                                                                                                                                                                                                                                                                                                                       |  |

| Memory          | Per default PPC/PowerCore-6750 provides a shared memory implement-<br>ed by one (lower) memory module of up to 128 MByte.<br>Depending on the memory module installed on the CPU board, the capac-<br>ity of the shared memory may be increased by installing an upper memo-<br>ry module on top of the (lower) memory module. |  |

|                 | The secondary (L2) cache has a size of up to 1 MByte. The boot flash has a maximum capacity of 2 MByte and the on-board user flash has a maximum capacity of 8 MByte.                                                                                                                                                          |  |

| Interfaces      | PPC/PowerCore-6750 includes VMEbus interface, PCI bus interfaces, Ethernet interface, and 2 serial I/O ports to provide full single-board computer functionality. The serial I/O ports are available at the front panel via two 9-pin Micro D-Sub connectors.                                                                  |  |

| CPU Speed       | The PowerPC CPU runs with a minimum frequency of 233 MHz and pro-<br>vides cache snooping support in order to maintain cache coherency.                                                                                                                                                                                        |  |

| Real-Time Clock | A real-time clock with on-board battery backup is also available.                                                                                                                                                                                                                                                              |  |

#### Specification 2.1

| Table 1              | Specification of the PPC/PowerCore-6750                                                                                    |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Processor            | PowerPC 750                                                                                                                |  |

| Shared memory        | up to 128-MByte (lower) memory module                                                                                      |  |

| PMC slots            | 2 slots for 32-bit PMC modules<br>I/Os for both PMC modules on VME P2 connector                                            |  |

| PCI-to-VME bridge    | Universe II                                                                                                                |  |

| Ethernet interface   | Ethernet controller<br>10Base-T or 100Base-Tx on front panel                                                               |  |

| Two serial I/O ports | RS-232 compatible<br>I/O on front panel                                                                                    |  |

| Counters/timers      | Three 16-bit, programmable                                                                                                 |  |

| Boot flash           | Up to 2 MByte (512 KByte default)<br>On-board programmable<br>Hardware write protection                                    |  |

| User flash           | Up to 8 MByte<br>On-board programmable<br>Hardware write protection                                                        |  |

| RTC/SRAM/battery     | Real-time clock and NVRAM                                                                                                  |  |

| Additional features  | Reset and abort key, status LEDs, serial PROM for board configura-<br>tion, voltage sensors, watchdog timer                |  |

| Firmware             | PowerBoot                                                                                                                  |  |

| Power consumption    | see section 3.1.1 "Requirements" on page 10                                                                                |  |

| Environm. conditions | see subsection"Thermal Requirements" on page 12 and table 7 "Environmental Requirements of PPC/PowerCore-6750" on page 12. |  |

| Standards compliance | ANSI/VITA 1-1994<br>IEEE P1386.1/Draft 2.0                                                                                 |  |

| 1 S | pecification of the | ne PPC/PowerCore-6750 |

|-----|---------------------|-----------------------|

PPC/PowerCore-6750 is available in several memory and speed options. Consult your local sales representative to confirm availability of specific combinations.

# 2.2 Product Nomenclature

| PPC/PowerCore-6750/yyS-ccc-Llll-z |                                   |  |

|-----------------------------------|-----------------------------------|--|

| 750                               | PowerPC processor type 750        |  |

| yyS                               | DRAM size in MByte, S means SDRAM |  |

| ссс                               | Processor clock frequency in MHz  |  |

| LIII                              | L2 cache capacity in KByte        |  |

| Z                                 | User flash capacity in MByte      |  |

### Table 2 Nomenclature of the PPC/PowerCore-6750

# 2.3 Ordering Information

The following table is an excerpt from the PPC/PowerCore-6750 data sheet. Please ask your local Force Computers representative for the current PPC/PowerCore-6750 data sheet.

|                                    | • 0                                                                                                                   |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Product Name                       | Description                                                                                                           |

| PPC/PowerCore-6750/                |                                                                                                                       |

| 16-233-L512-4-SSIO                 | PowerPC 750, 16-MByte EDO DRAM, 233-MHz nominal processor frequency, 512-KByte L2 cache, 4-MByte user flash, and SSIO |

| 128S-400-L1024-8                   | PowerPC 750, 128-MByte SDRAM, 400-MHz nominal processor fre-<br>quency, 1-MByte L2 cache, and 8-MByte user flash      |

| PPC/PowerCore                      |                                                                                                                       |

| MEM/128U                           | user upgradable upper EDO DRAM memory module, 128 MByte                                                               |

| SMEM/128U                          | user upgradable upper SDRAM memory module, 128 MByte                                                                  |

| Accessories PPC/                   |                                                                                                                       |

| PPC/PowerCore-6750-<br>SSIO/AccKit | PPC/IOBP-6750 including cables (see "I/O Panel" on page 25)                                                           |

| PowerCore-6750 RG                  | Reference Guide for PPC/PowerCore-6750 including PowerBoot In-<br>struction Set                                       |

Table 3

Excerpt from the Data Sheet's Ordering Information

# **3** Installation

*Note:* Before powering up or plugging the board in, read section 1 "Safety Notes" on page 1, check section 3.1 "Installation Prerequisites and Requirements" on page 10, check the consistency of the current switch settings (see section 3.3 "Switch Settings" on page 15), and check the consistency of the current switch settings on the PPC/SSIO-6750 if a PPC/SSIO-6750 is installed (see the *PPC/SSIO-6750 Installation Guide*).

To ensure proper functioning of the PPC/PowerCore-6750 board, remove the jumper for IACKIN-IACKOUT- and BGIN-BGOUTbypass on the backplane. This is not necessary on active backplanes.

*Note:* Before installing or uninstalling a PPC/PowerCore memory module, read the respective *Memory Module Installation Guide* packaged together with the memory module. Before installing or uninstalling a PMC module, read the PMC module's documentation.

The CPU board is designed to be maintenance-free. However, note that a Lithium battery is installed on the board. The battery provides a data retention of 7 years summing up all periods of actual battery use. Therefore, Force Computers assumes that there usually is no need to exchange the Lithium battery except for example in the case of long-term spare part handling.

**Observe the following safety notes:**

- Incorrect exchange of Lithium batteries can result in a hazardous explosion.

- Exchange the battery before 7 years of actual battery use have elapsed.

- Exchanging the battery always results in data loss of the devices which use the battery as power backup. Therefore, back up affected data before exchanging the battery.

- Always use the same type of Lithium battery as is already installed.

- When installing the new battery ensure that the marked dot on top of the battery covers the dot marked on the chip.

- Used bateries have to be disposed according to your country's legislation.

# **3.1 Installation Prerequisites and Requirements**

#### 3.1.1 Requirements

The installation requires only

- Power supply

- Fan unit providing an airflow meeting the thermal requirements of the PPC/PowerCore-6750

- VMEbus backplane with P1 and P2 connectors

PowerPPC/PowerCore-6750 provides a limited current at the PMC supply pins.RequirementsThe maximum current depends on:

- CPU type and frequency

- Installed memory modules.

Typical power requirements of the CPU board are given in the following table:

#### Table 4Typical Power Consumption of the CPU Board

| CPU Board with Lower Memory Module<br>but without PMC Module | +5V   |

|--------------------------------------------------------------|-------|

| PPC/PowerCore-6750/16-233-L512-4                             | 3.1 A |

| PPC/PowerCore-6750/64-233-L512-4                             | 3.1 A |

| PPC/PowerCore-6750/64S-300-L1024-8                           | 4.1 A |

| PPC/PowerCore-6750/128S-300-L1024-8                          | 4.2 A |

| PPC/PowerCore-6750/64S-400-L1024-8                           | 4.2 A |

| PPC/PowerCore-6750/128S-400-L1024-8                          | 4.4 A |

| PPC/PowerCore-6750/64S-400-L1024-8-SSIO                      | 4.4 A |

Memory Modules Per default the shared memory of the CPU board is provided by one (lower) memory module directly located on the CPU board. The following two types of memory modules are available:

- EDO DRAM memory module

- SDRAM memory module

If your CPU board is equipped with one of the following lower memory modules, you may increase the capacity of the shared memory by installing an additional appropriate (upper) memory module on top of the lower one:

- 64-MByte EDO DRAM memory module

- 64- or 128-MByte SDRAM memory module

All other memory modules per default installed on the board, for example the 16-MByte EDO DRAM memory module, cannot be upgraded.

When installing or uninstalling a memory module, observe the following safety notes:

- PPC/PowerCore-6750 may be equipped only with memory modules qualified by Force Computers. Otherwise the board or connected components may be damaged.

- On PPC/PowerCore-6750 revision 1.0 only EDO DRAM memory modules may be installed, i.e. it is not allowed to install SDRAM memory modules on boards of revision 1.0.

- Do not place an EDO DRAM memory module on top of an SDRAM memory module or vice versa.

Out of the comprehensive list of possible configurations the memory configurations shown in the following table have been qualified.

| Table 5 | <b>Qualified Memory Module Configurations</b> |

|---------|-----------------------------------------------|

|---------|-----------------------------------------------|

|                         | PPC/PowerCore |                  |

|-------------------------|---------------|------------------|

|                         | MEM/128U      | <b>SMEM/128U</b> |

| PPC/PowerCore-6750/64   | Х             | _                |

| PPC/PowerCore-6750/64S  | _             | Х                |

| PPC/PowerCore-6750/128S | _             | Х                |

The upgrading instructions are shipped together with the memory modules: see the respective *Memory Module Installation Guide*.

When installing an upper memory module on the lower memory module installed per default on the CPU board, you have to consider the power consumption. In this case add

- Power consumption of the CPU board including lower memory module (see table 4 "Typical Power Consumption of the CPU Board" on page 10)

- Max. power consumption drawn by the upper memory module (see table 6 "Max. Power Consumption of the Upper Memory Modules").

Г

Table 6

|                         | <b>PPC/PowerCore</b>                                                                                                                                                                                                          | 3.3 V                                                                                                      |                                                                                                                    |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

|                         | MEM/128U                                                                                                                                                                                                                      | 0.1 A                                                                                                      |                                                                                                                    |

|                         | SMEM/128U                                                                                                                                                                                                                     | 0.2 A                                                                                                      |                                                                                                                    |

| РМС                     | The total maximum permission<br>installed on a CPU board wi<br>If additionally an upper men-<br>ble power consumption valu-<br>max. power consumption va-<br>"Max. Power Consumption of                                       | th a lower memory<br>nory module is in<br>ues of the PMC m<br>lue of the upper m                           | y module is 15 W.<br>Istalled, the max. permissi-<br>nodules are reduced by the<br>nemory module (see table 6      |

| Thermal<br>Requirements | The operating temperature i<br>condensing at $+40\times$ C), when<br>tems providing a minimum<br>minute). The airflow is requi<br>side of the CPU board. The t<br>0°C to $+40$ °C. The followi<br>quirements of the PPC/Power | n operating the PP<br>forced airflow of<br>red at the heat sind<br>ypical operating te<br>ng table summari | C/PowerCore-6750 in sys-<br>300 LFM (linear feet per<br>k of the CPU and at the top<br>emperature of the system is |

### Max. Power Consumption of the Upper Memory Modules

| Table 7 | Environmental Requirements of PPC/PowerCore-6750 |

|---------|--------------------------------------------------|

|---------|--------------------------------------------------|

|                 | Operating                           | Non-Operating                       |

|-----------------|-------------------------------------|-------------------------------------|

| Temperature     | $0^{\circ}$ C to +55°C              | -40°C to +85°C                      |

| Forced Air Flow | 300 LFM (linear feet per minute)    | _                                   |

| Temp. Change    | +/- 0.5°C/min                       | +/- 1°C/min                         |

| Rel. Humidity   | 5% to 95% noncondensing<br>at +40°C | 5% to 95% noncondensing<br>at +40°C |

| Altitude        | -300 m to +3.000 m                  | -300 m to +13.000 m                 |

Backplane The CPU board includes an IACK daisy-chain driver. If the CPU board is Configuration plugged in slot 1 and configured accordingly by SW7-1 (see table 8 "Default Switch Settings" on page 16), the board acts as IACK daisy-chain driver. Plugged in any other slot the board closes the IACKIN-IACK-OUT path. Therefore: If not on an active backplane,

- Remove the jumper on the backplane connecting BG3IN\* and BG3OUT\* for the PPC/PowerCore-6750 slots which actually are connected to the backplane.

- Assemble the jumpers for BG3IN\* and BG3OUT\* on lower and higher slots on the backplane where no board is plugged.

- Slot-1 Function If more than one system controller is active in the VMEbus system, the board or other VMEbus participants can be damaged. Therefore, ensure that only one CPU board is configured to be system controller in the VMEbus system.

#### 3.1.2 Terminal Connection

For the initial power-up, a terminal can be connected to the 9-pin MicroD-Sub connector of the serial port 1, which is located at the front panel (see section 3.6 "Serial I/O Ports" on page 20).

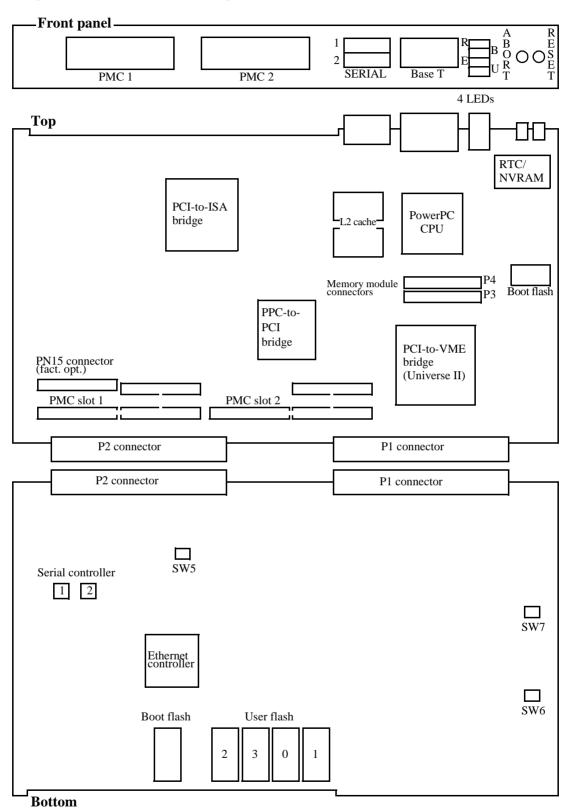

#### 3.1.3 Location Overview

The figure 1 "Location Diagram of the PPC/PowerCore-6750 (schematic)" on page 14 highlights the position of the important PPC/PowerCore-6750 components. Depending on the board type it might be that your board does not include all components named in the location diagram.

#### Figure 1 Location Diagram of the PPC/PowerCore-6750 (schematic)

PPC/PowerCore-6750

### 3.1.4 Upgrading PPC/PowerCore-6750

| Memory Module | Depending on the (lower) memory module, which is per default installed,<br>the memory capacity of the PPC/PowerCore-6750 may be increased by<br>installing an upper memory module on the (lower) memory module.<br>For detailed information on the memory modules, see |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | • section 3.1.1 "Requirements" on page 10                                                                                                                                                                                                                              |

|               | The respective Memory Module Installation Guide                                                                                                                                                                                                                        |

| PMC Module    | PPC/PowerCore-6750 provides 2 PMC slots. The PMC slots can be used to install PMC modules based on the PCI bus architecture. For detailed information on the PMC slots, see                                                                                            |

|               | • section 3.1.1 "Requirements" on page 10                                                                                                                                                                                                                              |

• section 3.7 "PMC Slots" on page 21

# 3.2 Automatic Power Up – Voltage Sensor and Watchdog Timer

- Voltage Sensors If the voltage levels drop below the voltage values given in the VMEbus specification, the voltage sensors generate automatically a reset of the CPU board and proceed with a normal booting procedure.

- Watchdog Timer Per factory default the watchdog timer is disabled. If the watchdog timer is enabled, it generates a non-maskable interrupt (NMI) followed by a reset when it is not retriggered by the software. The watchdog timer can be enabled by SW5-1 (see "SW5-1" on page 16).

# 3.3 Switch Settings

The following table lists the functions and the default settings of all switches shown in figure 1 "Location Diagram of the PPC/PowerCore-6750 (schematic)" on page 14. The switches are located on the bottom side of the CPU board. For switching it is not required to remove any modules.

- Before powering up the board check the current switch settings for consistency.

- SW7-1, SW7-2, and SW7-3 will only be read on a power up.

- Do not switch during operation.

### Table 8

**Default Switch Settings**

| Name and Def<br>Setting | ault         | Description                                                                                                              |

|-------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------|

|                         | SW5-1<br>OFF | Watchdog timer<br>OFF = Timer disabled<br>ON = Timer enabled                                                             |

|                         | SW5-2<br>OFF | Watchdog time ( $\pm\pm\pm\pm$ 8ms)<br>OFF = NMI: 39 ms, RESET: 134 ms<br>ON = NMI: 363 ms, RESET: 1.66 s                |

|                         | SW5-3<br>OFF | VMEbus SYSRESET input<br>OFF = SYSRESET generates power up<br>reset<br>ON = SYSRESET does not generate<br>power up reset |

|                         | SW5-4<br>OFF | Reserved                                                                                                                 |

|                         | SW6-1<br>OFF | RESET key<br>OFF = RESET key enabled<br>ON = RESET key disabled                                                          |

|                         | SW6-2<br>OFF | ABORT key<br>OFF = ABORT key enabled<br>ON = ABORT key disabled                                                          |

|                         | SW6-3<br>OFF | User flash write protection<br>OFF = writing enabled<br>ON = write-protected                                             |

|                         | SW6-4<br>OFF | Boot flash write protection<br>OFF = write-protected<br>ON = writing enabled                                             |

| Name and De<br>Setting | fault        | Description                                                                                                                                                                    |

|------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | SW7-1<br>OFF | VMEbus slot 1 auto-detection<br>OFF = enabled<br>ON = disabled (also called manual mode)                                                                                       |

|                        | SW7-2<br>OFF | System controller (only available if<br>SW7-1 = ON)<br>OFF = disabled<br>ON = enabled                                                                                          |

|                        | SW7-3<br>OFF | Power up detection level<br>OFF = conforms to ANSI/VITA 1-1994<br>ON = below ANSI/VITA 1-1994 (This<br>has the advantage that sudden voltage<br>sags do not generate a reset.) |

|                        | SW7-4<br>OFF | VMEbus SYSRESET output<br>OFF = enabled<br>ON = disabled                                                                                                                       |

#### Table 8

**Default Switch Settings (cont.)**

## 3.4 Front Panel

The features of the front panel are described in the following sections. For a location diagram see figure 1 "Location Diagram of the PPC/PowerCore-6750 (schematic)" on page 14.

| Table 9                             | Front-Panel Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RESET                               | Mechanical reset key: When enabled and toggled it instantaneously affects<br>the CPU board by generating a reset. Depending on SW7-4 the reset gener-<br>ates a VMEbus SYSRESET (see "SW7-4" on page 17).<br>A reset of all on-board I/O devices and the CPU is performed when the re-<br>set key is pushed to the active position. RESET is held active until the key<br>is back in the inactive position, however at least 200 ms are guaranteed by<br>a local timer. Power fail (below approximately 4.7 V) and power up – both<br>lasting at minimum 200 ms to 300 ms – also force a reset to start the CPU<br>board.<br>For information on enabling the key, see "SW6-1" on page 16. |

| ABORT                               | Mechanical abort key: When enabled and toggled it instantaneously affects<br>the CPU board by generating an interrupt request (NMI) via the PCI-to-<br>ISA bridge. This allows to implement an abort of the current program, to<br>trigger a self-test or to start a maintenance program.<br>For information on enabling the key, see "SW6-2" on page 16.                                                                                                                                                                                                                                                                                                                                 |

| LED R                               | RUN/RESET LED indicating the board status:<br>Green: normal operation<br>Red: reset is active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LED B                               | VMEbus master and SYSFAIL LED:<br>Green: when the CPU board accesses the VMEbus as VMEbus master<br>Red: when the CPU board drives SYSFAIL on the VMEbus<br>Off: otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED E                               | Ethernet LED:<br>Green: transmit data<br>Red: receive data<br>Off: no traffic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| LED U                               | User LED: Software programmable by the CIO counter/timer and parallel I/O unit. Bits 0 and 1 of port C are used. Possible status: green, red, or off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 100Base-Tx<br>/10Base-T<br>ETHERNET | An 8-pin RJ45 connector for 100Base-Tx or 10Base-T Ethernet interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SERIAL<br>PORTS                     | Two 9-pin MicroD-Sub connectors for serial interface 1 and 2 (see section 3.6 "Serial I/O Ports" on page 20).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **3.5 PPC/PowerCore-6750 Parameters and Timers – CIO**

| Device: CIO         |                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------|