DATA BOOK

# DATA BOOK 1991 VMEbus Products

© FORCE COMPUTERS 1990 All Rights Reserved First Edition 09.90/30.0/DB/A1/Rev. 1

# **General Information**

## **16-Bit CPU Boards**

## **32-Bit CPU Boards**

**Memory Boards**

**Controller Boards**

I/O Boards

### Accessories

| General Information | Design19Manufacturing23Quality Assurance33                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Bit CPU Boards   | Introduction       40         Overview(s)       41         SYS68K/CPU-4VC       43         SYS68K/CPU-5A       51         SYS68K/CPU-6       59                                                                                                                                                                                                                                                                                                   |

| 32-Bit CPU Boards   | Introduction       68         Overview(s)       69         SYS68K/CPU-22       73         SYS68K/CPU-23       87         SYS68K/CPU-26       101         SYS68K/CPU-26       101         SYS68K/CPU-27       115         SYS68K/CPU-30       137         SYS68K/CPU-31       153         SYS68K/CPU-32       167         SYS68K/CPU-33       177         SYS68K/CPU-386       191         SYS68K/CPU-40       199         SYS68K/CPU-80       215 |

### **Memory Boards**

| Introduction   |  |   |  | • |   |  | • | · | • | 248 |

|----------------|--|---|--|---|---|--|---|---|---|-----|

| Overview(s)    |  |   |  | • |   |  |   |   |   | 249 |

| SYS68K/DRAM-8  |  |   |  |   |   |  |   |   |   | 251 |

| SYS68K/SRAM-3B |  |   |  |   |   |  |   |   |   | 257 |

| SYS68K/SRAM-6  |  |   |  |   |   |  |   |   |   | 263 |

| SYS68K/RR-2    |  | • |  |   | • |  |   |   |   | 269 |

|                |  |   |  |   |   |  |   |   |   |     |

. . . . . . . . . . . . 239

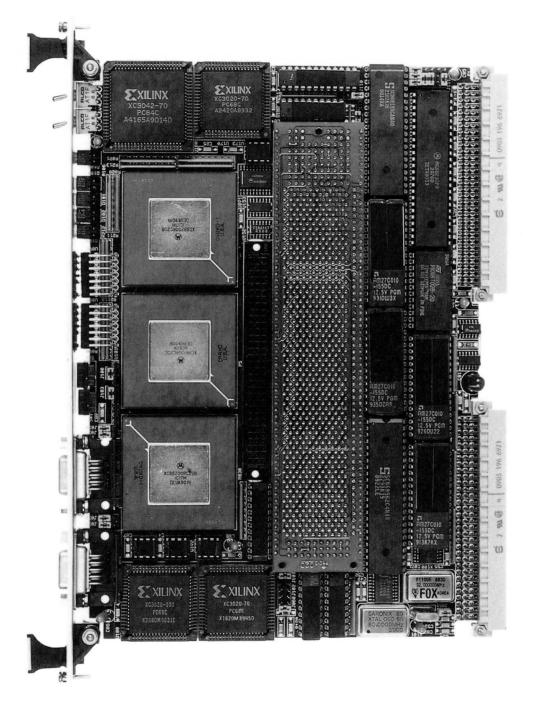

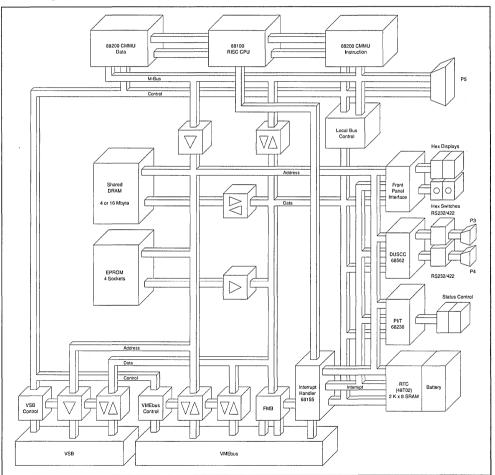

SYS88K/CPU-81

SYS68K/VMEPROM

| <b>Controller Boards</b> | Introduction     |

|--------------------------|------------------|

|                          | Overview(s)      |

|                          | SYS68K/ISCSI-1 ` |

|                          | SYS68K/AGC-2     |

|                          | SYS68K/AGC-3     |

|                          | SYS68K/ASCU-2    |

|                          |                  |

### I/O Boards

| Introduction  |  |  |  | • |  |  |  | 316 |

|---------------|--|--|--|---|--|--|--|-----|

| Overview(s)   |  |  |  |   |  |  |  | 317 |

| SYS68K/IPIO-1 |  |  |  |   |  |  |  | 319 |

| SYS68K/PIO-1  |  |  |  |   |  |  |  | 327 |

| SYS68K/OPIO-1 |  |  |  |   |  |  |  | 333 |

| SYS68K/SIO-2  |  |  |  |   |  |  |  | 339 |

| SYS68K/ISIO-2 |  |  |  |   |  |  |  | 345 |

| SYS68K/ICC-1  |  |  |  |   |  |  |  | 353 |

### Accessories

| TARGET 32 .  |    |    |    |   |   |   |   |   |   |   |   |   |   |   |   |     |

|--------------|----|----|----|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| SYS68K/MOTH  |    | ·  | ·  | • | • | · | • | • | · | · | · | · | · | · | · | 367 |

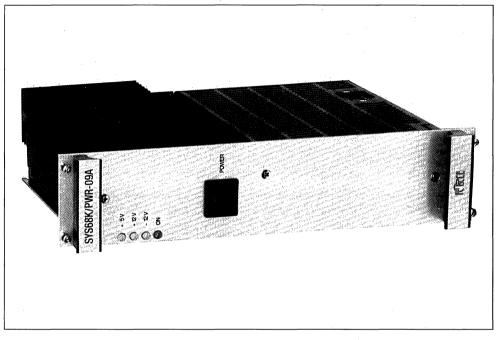

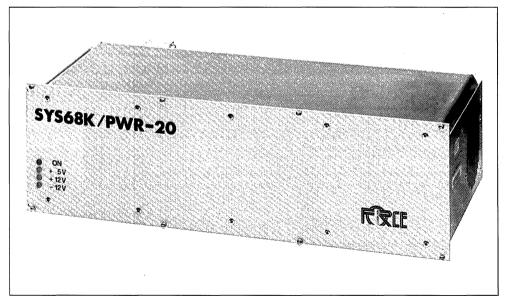

| SYS68K/PWR-0 | 9, | A/ | 20 | ) |   |   |   |   |   |   | • |   |   | • |   | 371 |

| SYS68K/MSM   |    | •  |    |   |   |   |   | • |   |   | • |   |   | • |   | 377 |

| SYS88K/TSM   | •  | •  | •  | · | • | • |   | · | • | • | • | • | • | • |   | 381 |

.

# **General Information**

|                                                         | <u> </u> |

|---------------------------------------------------------|----------|

|                                                         |          |

|                                                         |          |

| n 11 Barrier and an |          |

|                                                         |          |

|                                                         |          |

| etan Staal Baar (K. 1997) Sa                            |          |

|                                                         |          |

|                                                         |          |

|                                                         |          |

|                                                         |          |

|                                                         |          |

|                                                         |          |

|                                                         |          |

Corporate Headquarters FORCE COMPUTERS, INC.

#### European Headquarters FORCE COMPUTERS GmbH

#### For USA and Canada

Corporate Headquarters FORCE COMPUTERS INC. 3165 Winchester Blvd. Campbell, CA 95008 Tel.: (408) 370-6300 US Sales Offices

Northeastern Office FORCE COMPUTERS, INC. 7 Kimball Lane Building E, Suite 1 Lynnfield, MA 01940 Tel.: (617) 245-7977

Southeastern Office FORCE COMPUTERS, INC. 5950 Symphony Woods Road Suite 311 Columbia, MD 21044 Tel.: (301) 964-3377

Central Office FORCE COMPUTERS, INC. 3939 Beltline Road, Suite 570 Dallas, TX 75244 Tel.: (214) 243-1888 Midwestern Office FORCE COMPUTERS, INC. 601 Lakeshore Parkway Suite 1075 Minnetonka, MN 55343 Tel.: (612) 449-5177

Southwestern Office FORCE COMPUTERS, INC. 19800 MacArthur Blvd. Suite 1450 Irvine, CA 92715 Tel.: (714) 724-4576

#### For Europe and Rest of World

European Headquarters FORCE COMPUTERS GmbH Prof.-Messerschmitt-Str. 1 D-8014 Neubiberg/München Tel.: (0 89) 60 81 4-0 **European Sales Offices**

Germany FORCE COMPUTERS GmbH Schulstraße 15a D-2085 Quickborn Tel.: (0 41 06) 50 31

France FORCE COMPUTERS S.A.R.L. 11, Rue Casteja F-92100 Boulogne Tel.: (1) 46 20 37 37

United Kingdom FORCE COMPUTERS (UK) Ltd. No. 1 Holly Court 3 Tring Road Wendover, Bucks. HP22 6PE Tel.: (02 96) 62 54 56 **Commercial Service from Sales Personnel**

**Technical Service from Applications Teams**

#### Commitment to Service

FORCE COMPUTERS believes that service to our customers is as much a product of the company as the VMEbus boards, systems and software we design, manufacture and sell. Accordingly, we commit fully to providing customers with the best possible level of service worldwide. The services we offer are comprehensive, including pre- and post-sales consulting, customer application support, design-in activities, problem diagnosis, field test, Beta-site arrangements, delivery expediting, credit and many more. Our services are provided by fully-trained Field Sales and Technical Support personnel. Authorized FORCE distributors and representatives are also trained by us and are eager to help you with the selection and application of FORCE products.

For further information, please contact FORCE at any of the addresses listed on page 11.

#### Introduction to FORCE COMPUTERS Product Guide

This is the FORCE COMPUTERS product guide, our comprehensive catalog of products and services. For the sake of completeness, the guide includes products that are not recommended for new designs. These products are either obsolete or will become obsolete under FORCE COMPUTERS' controlled End Of Lifetime Buy procedure. This procedure helps provide maximum notice to customers regarding a product's planned obsolescence. In every possible case, FORCE recommends an alternate product. For existing customers, FORCE may continue to produce products not recommended for new designs as long as all component parts are available.

| Part No. | Product            | Description                             | Recom-<br>mended<br>for new<br>Designs | Suggested<br>Alternative           |

|----------|--------------------|-----------------------------------------|----------------------------------------|------------------------------------|

|          | 32-Bit CPU Boards  |                                         | -                                      |                                    |

| 101106   | SYS68K/CPU-22X     | 68020/16.7 MHz/1 Mbyte S-DPR SRAM       | yes                                    |                                    |

| 101102   | SYS68K/CPU-22XA    | 68020/20.0 MHz/1 Mbyte S-DPR SRAM       | yes                                    |                                    |

| 101120   | SYS68K/CPU-23XS    | 68020/12.5 MHz/1 Mbyte Shared SRAM      | yes                                    |                                    |

| 101121   | SYS68K/CPU-23X     | 68020/16.7 MHz/1 Mbyte Shared SRAM      | no                                     | CPU-23XB                           |

| 101122   | SYS68K/CPU-23XB    | 68020/25.0 MHz/1 Mbyte Shared SRAM      | yes                                    |                                    |

| 101134   | SYS68K/CPU-26XS    | 68020/12.5 MHz/1 Mbyte Shared DRAM      | yes                                    |                                    |

| 101130   | SYS68K/CPU-26X     | 68020/16.7 MHz/1 Mbyte Shared DRAM      | no                                     | CPU-26XS,<br>CPU-26XA              |

| 101131   | SYS68K/CPU-26XA    | 68020/20.0 MHz/1 Mbyte Shared DRAM      | yes                                    |                                    |

| 101132   | SYS68K/CPU-26ZA    | 68020/20.0 MHz/4 Mbyte Shared DRAM      | yes                                    |                                    |

| 101171   | SYS68K/CPU-27X     | 68020/16.7 MHz/1 Mbyte DRAM             | no                                     | CPU-27XB                           |

| 101172   | SYS68K/CPU-27XB    | 68020/25.0 MHz/1 Mbyte DRAM             | yes                                    |                                    |

| 101173   | SYS68K/CPU-27XBE   | 68020/25.0 MHz/1 Mbyte DRAM/ETH         | yes                                    |                                    |

| 101152   | SYS68K/CPU-29X     | 68020/16.7 MHz/1 Mbyte SRAM 0WS         | no                                     | CPU-29XB,<br>CPU-29XC,<br>CPU-33XB |

| 101159   | SYS68K/CPU-29XB    | 68020/25.0 MHz/1 Mbyte SRAM 0WS         | yes                                    |                                    |

| 101154   | SYS68K/CPU-29XC    | 68020/30.0 MHz/1 Mbyte SRAM 0WS         | yes                                    |                                    |

| 101302   | SYS68K/CPU-30ZA    | 68030/20.0 MHz/4 Mbyte Shared DRAM      | yes                                    |                                    |

| 101305   | SYS68K/CPU-30ZBE   | 68030/25.0 MHz/4 Mbyte Shared DRAM/ETH  | yes                                    |                                    |

| 101306   | SYS68K/CPU-30BE/16 | 68030/25.0 MHz/16 Mbyte Shared DRAM/ETH | yes                                    |                                    |

| 101312   | SYS68K/CPU-31XA    | 68030/20.0 MHz/1 Mbyte S-DPR SRAM       | yes                                    |                                    |

| 101314   | SYS68K/CPU-31XB    | 68030/25.0 MHz/1 Mbyte S-DPR SRAM       | yes                                    |                                    |

| 101326   | SYS68K/CPU-32XB    | 68030/25.0 MHz/1 Mbyte SRAM 0WS         | yes                                    |                                    |

| 101333   | SYS68K/CPU-32XC    | 68030/30.0 MHz/1 Mbyte SRAM 0WS         | yes                                    |                                    |

| 101340   | SYS68K/CPU-33XN    | CPU-33X without FPU (68882)             | yes                                    |                                    |

| 101341   | SYS68K/CPU-33X     | 68030/16.7 MHz/1 Mbyte Shared DRAM      | yes                                    |                                    |

| 101342   | SYS68K/CPU-33XB    | 68030/25.0 MHz/1 Mbyte Shared DRAM      | yes                                    |                                    |

| 101343   | SYS68K/CPU-33ZB    | 68030/25.0 MHz/4 Mbyte Shared DRAM      | yes                                    |                                    |

| 101427   | SYS68K/CPU-37X     | 68030/16.7 MHz/1 Mbyte DRAM             | no                                     | CPU-30ZA                           |

| 101423   | SYS68K/CPU-37Z     | 68030/16.7 MHz/4 Mbyte DRAM             | no                                     | CPU-30ZA                           |

| 101422   | SYS68K/CPU-37XBE   | 68030/25.0 MHz/1 Mbyte DRAM/ETH         | no                                     | CPU-30ZBE                          |

| 101426   | SYS68K/CPU-37ZBE   | 68030/25.0 MHz/4 Mbyte DRAM/ETH         | no                                     | CPU-30ZBE                          |

| 105001   | SYS68K/CPU-386A    | 80386/16.0 MHz/2 Mbyte DRAM             | yes                                    |                                    |

| 105003   | SYS68K/CPU-386C    | 80386/16.0 MHz/8 Mbyte DRAM             | yes                                    |                                    |

| Part No. | Product              | Description                                  | Recom-<br>mended<br>for new<br>Designs | Suggested<br>Alternative |

|----------|----------------------|----------------------------------------------|----------------------------------------|--------------------------|

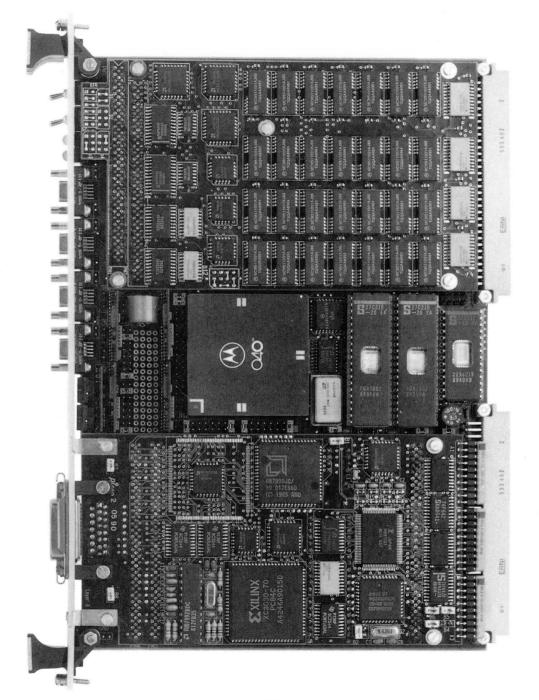

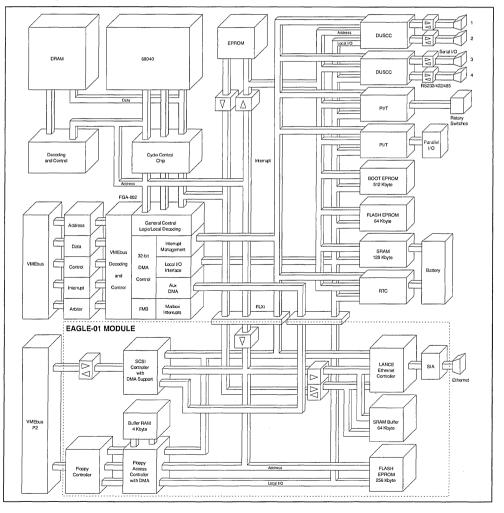

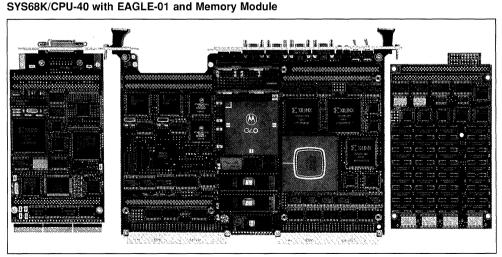

| 102000   | SYS68K/CPU-40B/4-00  | 68040/25.0 MHz/4 Mbyte Shared DRAM           | yes                                    |                          |

| 102001   | SYS68K/CPU-40B/4-01  | 68040/25.0 MHz/EAGLE-01/4 Mbyte Shared DRAM  | yes                                    |                          |

| 102100   | SYS68K/CPU-40B/16-00 | 68040/25.0 MHz/16 Mbyte Shared DRAM          | yes                                    |                          |

| 102101   | SYS68K/CPU-40B/16-01 | 68040/25.0 MHz/EAGLE-01/16 Mbyte Shared DRAM | yes                                    |                          |

| 102200   | SYS68K/CPU-40D/4-00  | 68040/33.0 MHz/4 Mbyte Shared DRAM           | yes                                    |                          |

| 102201   | SYS68K/CPU-40D/4-01  | 68040/33.0 MHz/EAGLE-01/4 Mbyte Shared DRAM  | yes                                    |                          |

| 102300   | SYS68K/CPU-40D/16-00 | 68040/33.0 MHz/16 Mbyte Shared DRAM          | yes                                    |                          |

| 102301   | SYS68K/CPU-40D/16-01 | 68040/33.0 MHz/EAGLE-01/16 Mbyte Shared DRAM | yes                                    |                          |

| 510053   | SYS88K/CPU-80A/4     | 88100/20.0 MHz/ 4 Mbyte Shared DRAM/SCSI     | yes                                    |                          |

| 510054   | SYS88K/CPU-80A/16    | 88100/20.0 MHz/16 Mbyte Shared DRAM/SCSI     | yes                                    |                          |

| 510056   | SYS88K/CPU-80B/16    | 88100/25.0 MHz/16 Mbyte Shared DRAM/SCSI     | yes                                    |                          |

| 510001   | SYS88K/CPU-81A/4     | 88100/20.0 MHz/ 4 Mbyte Shared DRAM/VSB      | yes                                    |                          |

| 510081   | SYS88K/CPU-81A/16    | 88100/20.0 MHz/16 Mbyte Shared DRAM/VSB      | yes                                    |                          |

| 510083   | SYS88K/CPU-81B/16    | 88100/25.0 MHz/16 Mbyte Shared DRAM/VSB      | yes                                    |                          |

|          | 16-Bit CPU Boards    |                                              |                                        |                          |

| 100213   | SYS68K/CPU-2VC       | 68010/10.0 MHz/1024 Kbyte Shared DRAM        | no                                     | CPU-33XN                 |

| 100413   | SYS68K/CPU-4VC       | 68010/12.5 MHz/ 128 Kbyte SRAM               | yes                                    |                          |

| 100501   | SYS68K/CPU-5A        | 68000/16.7 MHz/ 128 Kbyte SRAM 0WS/FPU       | yes                                    |                          |

| 100602   | SYS68K/CPU-6A        | 68000/12.5 MHz/ 512 Kbyte DRAM               | yes                                    |                          |

| 100610   | SYS68K/CPU-6VA       | 68010/12.5 MHz/ 512 Kbyte DRAM               | yes                                    |                          |

|          | 32-Bit Memories      |                                              |                                        |                          |

| 200150   | SYS68K/DRAM-8A       | 2 Mbyte DRAM A32, A24 : D32, D24, D16, D8    | yes                                    |                          |

| 200151   | SYS68K/DRAM-8B       | 4 Mbyte DRAM A32, A24 : D32, D24, D16, D8    | yes                                    |                          |

| 200152   | SYS68K/DRAM-8C       | 8 Mbyte DRAM A32, A24 : D32, D24, D16, D8    | yes                                    |                          |

| 200153   | SYS68K/DRAM-8D       | 16 Mbyte DRAM A32, A24 : D32,D24,D16,D8      | yes                                    |                          |

| 200154   | SYS68K/DRAM-8E       | 32 Mbyte DRAM A32,A24 : D32,D24,D16,D8       | yes                                    |                          |

| 200200   | SYS68K/RR-2          | Naked PROM/EPROM/EEPROM/SRAM/VMX             | yes                                    |                          |

| 200402   | SYS68K/SRAM-3B       | 1 Mbyte SRAM A32 : D32 VME/VMX               | yes                                    |                          |

| 200502   | SYS68K/SRAM-4B       | 1 Mbyte SRAM A32 : D32 VME                   | no                                     | SRAM-6                   |

| 200504   | SYS68K/SRAM-5        | 512 Kbyte SRAM A32 : D32 VME                 | no                                     | SRAM-6                   |

| 200505   | SYS68K/SRAM-6        | 2 Mbyte SRAM A32 : D32 VME                   | yes                                    |                          |

|          | 16-Bit Memories      |                                              |                                        |                          |

| 200010   | SYS68K/RR-1          | Naked ROM/PROM/EPROM/SRAM                    | no                                     | RR-2                     |

|          |                      |                                              |                                        |                          |

| Part No. | Product                 | Description                            | Recom-<br>mended<br>for new<br>Designs | Suggested<br>Alternative |

|----------|-------------------------|----------------------------------------|----------------------------------------|--------------------------|

|          | Controller Boards       |                                        |                                        |                          |

| 400023   | SYS68K/AGC-2            | Graphics Controller                    | yes                                    |                          |

| 400050   | SYS68K/AGC-3            | Advanced Graphics Controller           | yes                                    |                          |

| 700007   | SYS68K/ASCU-2           | Advanced SYS Cont. W GPIB              | yes                                    |                          |

| 300100   | SYS68K/ILANC-1          | Intelligent Ethernet Controller        | no                                     | CPU-30ZBE                |

| 300020   | SYS68K/ISCSI-1          | Intelligent SCSI Controller            | yes                                    |                          |

|          | Input/Output Boards     |                                        |                                        |                          |

| 310050   | SYS68K/IPIO-1           | Intelligent Parallel I/O               | yes                                    |                          |

| 310030   | SYS68K/ISIO-1           | 8 Channel Serial I/O RS232/68010       | no                                     | ISIO-2                   |

| 310031   | SYS68K/ISIO-2           | 8 Channel Serial I/O RS232/RS422/68010 | yes                                    |                          |

| 310004   | SYS68K/SIO-2            | 6 Channel Serial I/O RS232/RS422       | yes                                    |                          |

| 310011   | SYS68K/OPIO-1           | Parallel I/O: Opto Coupled             | yes                                    |                          |

| 310010   | SYS68K/PIO-1            | Parallel I/O: TTL                      | yes                                    |                          |

| 330000   | SYS68K/ICC-1            | Intelligent Communications Controller  | yes                                    |                          |

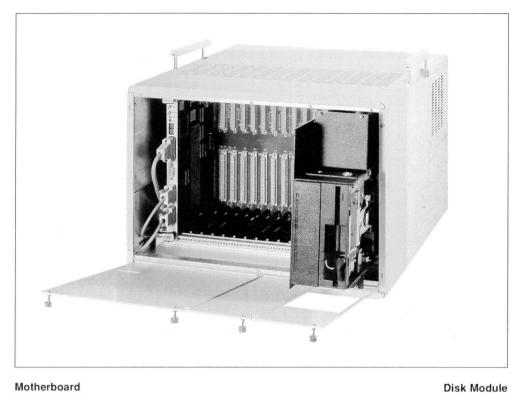

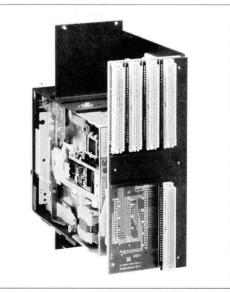

|          | Chassis and Accessories |                                        |                                        |                          |

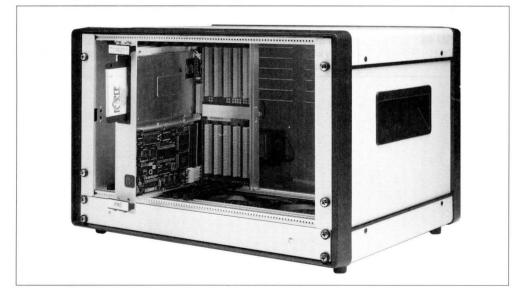

| 610500   | SYS68K/TARGET-32        | TARGET-32 Chassis/20 slots             | yes                                    |                          |

| 610190   | SYS68K/CHAS19-21E/12HE  | 12HE Chassis/21 Slots                  | no                                     | TARGET-32                |

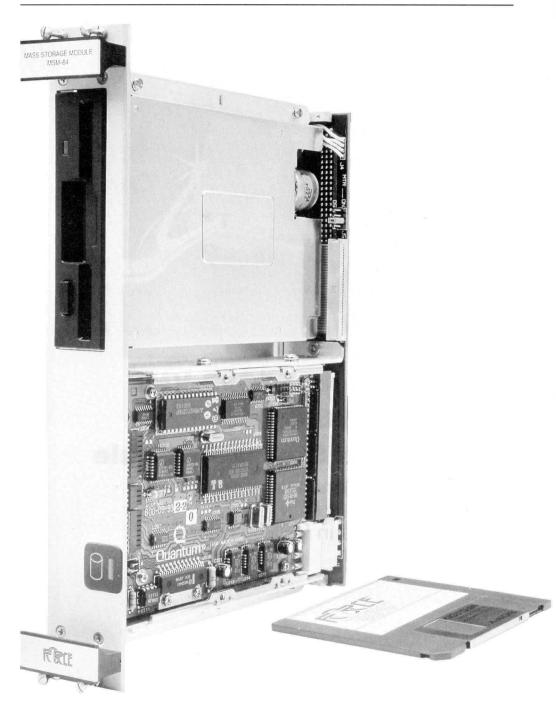

| 510020   | SYS68K/MSM-42           | 42 Mbyte Hard/1 Mbyte Floppy/3.5"      | yes                                    |                          |

| 510021   | SYS68K/MSM-84           | 84 Mbyte Hard/1 Mbyte Floppy/3.5"      | yes                                    |                          |

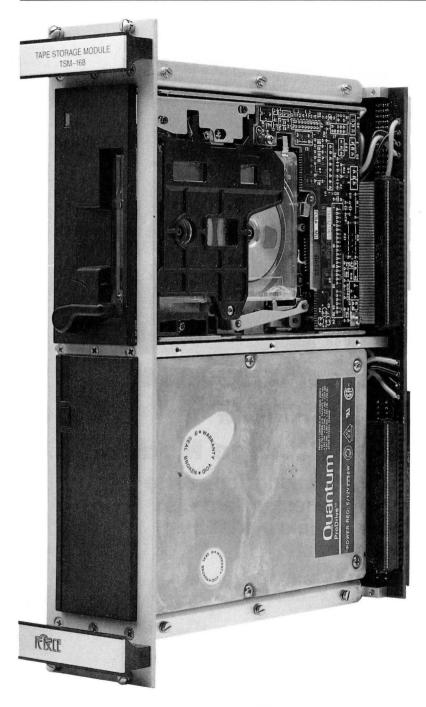

| 510092   | SYS88K/TSM-168          | 155 Mbyte Streamer/168 Mbyte Hard      | yes                                    |                          |

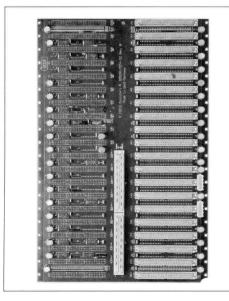

|          | Motherboards            |                                        |                                        |                          |

| 500005   | SYS68K/MOTH-05B         | 5 Slot Motherboard/J1                  | yes                                    |                          |

| 500011   | SYS68K/MOTH-09B         | 9 Slot Motherboard/J1                  | yes                                    |                          |

| 500006   | SYS68K/MOTH-12B         | 12 Slot Motherboard/J1                 | yes                                    |                          |

| 500007   | SYS68K/MOTH-21B         | 21 Slot Motherboard/J1                 | yes                                    |                          |

| 500008   | SYS68K/MOTH-E05A        | 5 Slot 32 Bit Extension/J2             | yes                                    |                          |

| 500012   | SYS68K/MOTH-E09A        | 9 Slot 32 Bit Extension/J2             | yes                                    |                          |

| 500009   | SYS68K/MOTH-E12A        | 12 Slot 32 Bit Extension/J2            | yes                                    |                          |

| 500010   | SYS68K/MOTH-E21A        | 21 Slot 32 Bit Extension/J2            | yes                                    |                          |

|          | Power Supplies          |                                        |                                        |                          |

| 700008   | SYS68K/PWR-09A/220V     | 280 W Power Supply                     | yes                                    |                          |

| 700009   | SYS68K/PWR-20/220V      | 750 W Power Supply                     | yes                                    |                          |

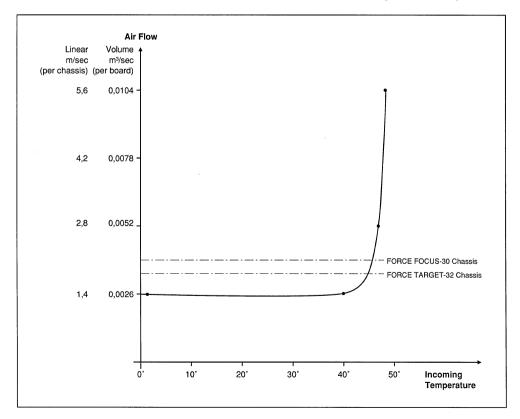

## Environmental conditions for normal board operation

FORCE COMPUTERS' board level products are designed and tested for reliable operation under strictly specified environmental conditions.

The specification of these conditions are:

| Operating temperature | 0 to + 50 °C<br>(with forced air cooling) |

|-----------------------|-------------------------------------------|

| Storage temperature   | – 40 to + 85 °C<br>(non-operating)        |

| Relative humidity     | + 5 to + 95 %<br>(non-condensing)         |

These conditions refer to the environment surrounding the board within the user environment. Operating temperature refers to the temperature of the air circulating around the board and not the actual component temperature. To ensure the operating conditions are met, forced air cooling is required within the chassis environment. This should be achieved by driving air through the air gap between the boards in the chassis. Fans should be installed in the underside of the chassis, evenly placed under the loaded boards. The volume of air required per second is dependent on the number of boards installed in the system. The linear air speed is specified to ensure correct air circulation around the board level components. The other major factor influencing the air-flow requirement is the air temperature at the air inlet to the chassis. The following graph shows the air speed and air volume per board required to ensure correct operation of boards versus external or incoming air temperature. Both of these criteria need to be met to ensure correct, reliable and long-lived board operation.

18

# Design

#### Design

FORCE COMPUTERS has achieved a leadership position in the markets it serves, namely original equipment manufacturers and system integrators who build VMEbus-based computers. FORCE rigorously controls the design phase of our new products. Control is essential to maintain compatibility and ensure continuity of product introductions. At FORCE COMPUTERS we commit to excellence with the objective of designing quality into every product.

#### **Rules and Procedures**

FORCE COMPUTERS designs its products to meet the requirement of the VMEbus specification (IEEE 1014). The electrical and mechanical rules of the VMEbus specification are the baseline conditions for the development of board level products and systems. FORCE uses modern CAD equipment for board layout. We thoroughly check and compare all films with original drawings and circuit schematics.

#### **Component Selections**

FORCE COMPUTERS uses the best commercial grade components (industrial grade where applicable) in the design and manufacture of our products. The availability of second sources is a key criterion in the decision to design-in a particular device. We only consider components with proven reliability and acceptable quality levels. Vendors must supply environmental test data for critical items; we purchase components that have undergone high-temperature burn-in. In addition, we also conduct regular vendor surveys to determine the adequacy of quality programs and production controls.

#### Prototype Development Phase

During the prototype phase of development, engineering and quality assurance work together to assure proper production methods and test procedures for all products. The responsible design and qualification engineers debug products and production methods. Custom test programs exercise new boards according to the design specification, intended functionality and conformance to the VMEbus specification. Full temperature cycling tests precede prototype release. This is often the longest phase of new product development due to the need to debug design, production and test issues. Reiteration of these procedures assures a smooth transition to pre-series production.

#### **Pre-Series Production**

Upon successful completion of the prototype phase, we release the product for pre-series (limited) production. Next, we write in-circuit, functional and burn-in test programs. We also embark on the writing of the VMEbus industry's most detailed and comprehensive product documentation (User's Manual). A limited lot (10-25 boards) is manufactured following documented work instructions, using a prototype board as production master. FORCE Engineering use these pre-series boards to validate the product for series production. Results of the validation effort are fed back to design and produccompleted test programs and tion. The documents form a part of the total release package for manufacturing. Before final release, Quality Assurance tests the product once again for functional compatibility with other products. For example, Quality Assurance tests a new RAM board with all CPU boards to ensure compatibility throughout a product family. Stress testing verifies multi-processor capabilities and simulates worst-case work conditions.

# Manufacturing

#### Manufacturing

#### Manufacturing

The task of manufacturing is to convert the high technology designs developed by Engineering into top quality, long-lived products. The manufacturing system at each working location is defined by considerations of "integrated quality" (see the Quality Assurance section of this book). We design the manufacturing flow flexibly to accommodate demand fluctuation without degradation of efficiency, quality or customer service.

#### **Manufacturing Planning**

Today and in the future the major purposes of manufacturing planning are to ensure timely production and delivery of customer orders and to keep manufacturing capacity in line with market demand. FORCE COMPUTERS' MRP System (Manufacturing Resource Planning) handles manufacturing logistics. This is a company-wide system that monitors orders and sales forecasts at one end and provides order fulfillment data at the other. The FORCE MRP system helps to provide maximum service benefit to our customers by allowing us to establish realistic capabilities for surge capacity. In the future, our MRP system will enable the implementation of just-in-time (JIT) manufacturing procedures. We already accommodate our customer's JIT needs through the MRP system.

#### **Component Purchasing**

In every design, we use only Engineeringapproved vendors for each component. Only components of leading suppliers can be approved. If Manufacturing or Purchasing suggests additional suppliers for specific components, QA Control applies a very strict approval procedure. Our MRP System determines the demand for each component based upon the production schedule and component lead-time information. We negotiate annual delivery contracts with our major suppliers to ensure continued, reliable supply.

#### **Manufacturing Planning**

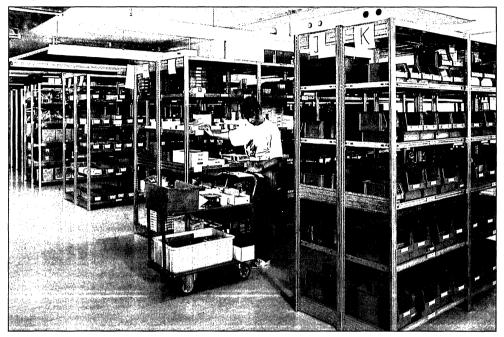

#### Component Warehouse

#### **Component Receiving Quality Control**

Upon arrival at FORCE COMPUTERS, components are immediately subjected to quality control procedures. Besides the outward appearance of incoming components, we also check the internal manufacturer approval, data codes, and revision level. We store approved components in the component warehouse under conditions specified by the manufacturer.

#### Manufacturing Monitor and Control

From the product documentation provided by Engineering, Product Engineering Desian generates the manufacturing documents to enable production to start. Product Engineering uses the MRP System to maintain Components Parts Lists for each FORCE product. Product Engineering is also responsible for the implementation of design revisions within manufacturing to ensure a maximum degree of functional transparency for board and product revision. We coordinate design revision worldwide by the common use of ECO's (Engineering Change Orders); QA monitors implementation of ECO's. When the MRP system calls up a production lot of a particular product in line with demand, the component warehouse provides the lot size of component kits for that product. The programmable devices (PAL, EPROMs etc.) are issued first to be programmed and then returned to the warehouse. This helps to ensure that only complete component kits (or picks) enter the manufacturing flow.

#### **Board Assembly**

FORCE employs state-of-the-art through-hole and surface mount board assembly procedures. Because our VMEbus products are often at the cutting edge of performance, we develop many of our own assembly tools. Regardless of the board assembly technique called for by a product's design, our board assembly procedures adhere to strict quality regulations. Our manufacturing process employs all QA measures that are standard in advanced PCB assembly companies. We monitor and calibrate our assembly equipment following the manufacturer's recommendations. To prevent damage, we transport the assembled products in custom-designed antistatic carriers between all assembly and test locations. We mark each board after assembly with a number that denotes lot number, assembly location, date, revision level and a unique serial number; we also inspect each board before it is passed to In-Circuit test.

#### In-Circuit Test

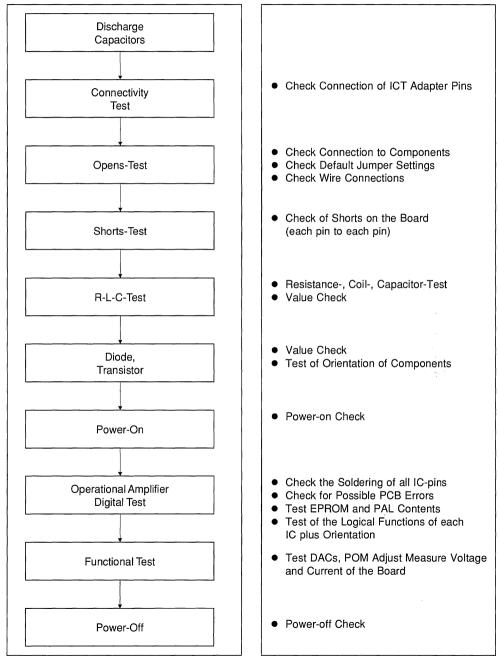

In-circuit testing, using Genrad 2276E test equipment, is the currently approved method. The bed-of-nails and the test program for each procedure are generated, modified and improved at the Design Center that developed the product. All other in-circuit test facilities use adapters and programs from one central source. This helps to ensure uniform testing at FORCE COMPUTERS facilities worldwide. Dedicated software in the test computer generates test reports at the product and component levels. We then provide these reports to the QA and Purchasing departments. Specific component suppliers may be excluded from further delivery if inadequate quality should be detected. Figure 1 shows a flow chart of the In-Circuit Test procedure.

#### In-Circuit Test

#### Figure 1 In-Circuit Test Flow Chart

#### Manufacturing

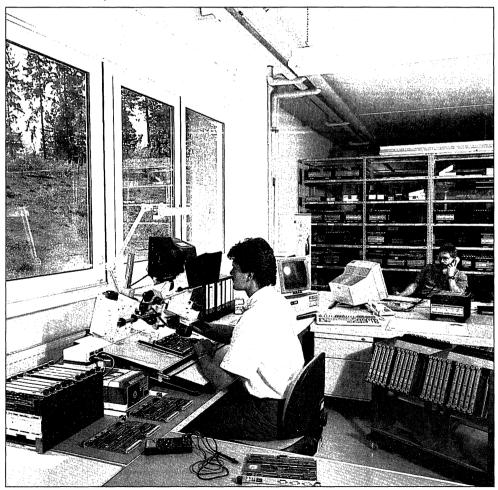

#### **Burn-In Test**

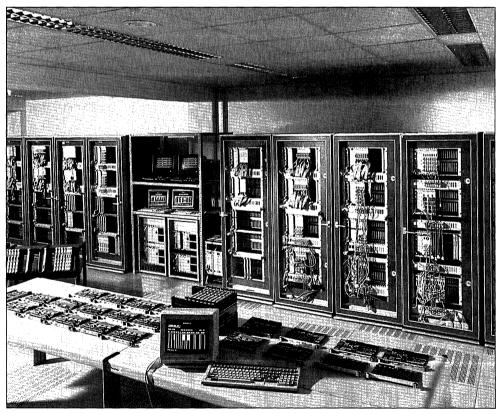

A short functional test of each board follows the In-Circuit Test and precedes the Burn-In Test. The functional test uses a board-specific software routine written simultaneously with the board design. This ensures burn-in time only for functional boards. Burn-in tests are also functional tests that run for 48 hours at a minimum of 50 degrees C. We use test racks that provide a VME operating environment for the boards under test. A high-performance control system operating in a real-time, multi-tasking mode controls and monitors the test racks and the testing tasks. We endeavor to fully exercise all electronic components during the burn-in. All burn-in test departments (worldwide) use these racks with the control unit.

#### **Burn-In Test Racks**

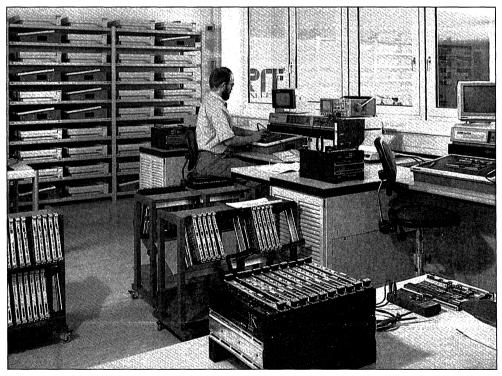

#### **Full Functional Test**

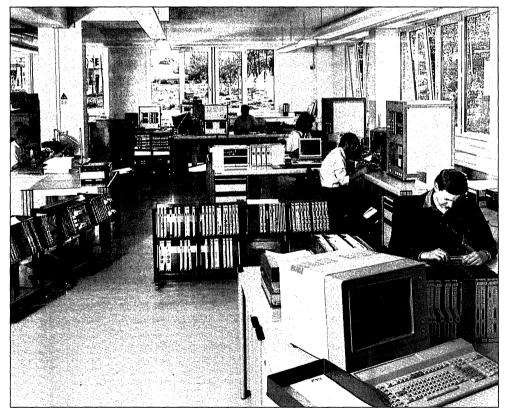

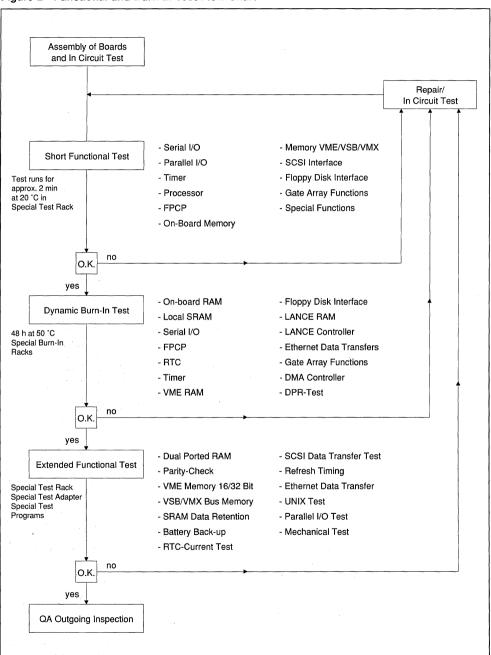

In this part of the manufacturing flow, we check all on-board functions under real-time conditions in a typical or similar user operating environment. Coordinated generation, modification and expansion of these test programs, in our Design Centers, ensures that identical functional tests will be used for a specific product worldwide. For newly introduced products, a team of programmers is constantly developing new program modules to integrate these functional test programs. In addition, we regularly maintain, expand and improve our test programs to increase their utility and accuracy. After passing full functional test, we set each board's factory defaults and submit the boards to QA for outgoing inspection. Figure 2 shows a flow chart of the Functional Test and Burn-In procedure.

**Full Functional Test**

#### Warehouse and Shipping

Following the outgoing inspection, the QA Department transfers the boards and systems to the Finished Goods Warehouse: here, we store the products in anti-static and dust-proof packages. The order schedule determines when the goods are prepared for shipping, when the documentation is included and when they are put into the shipping boxes. We take great care to develop customized shipping containers adequate to protect the product during transport to the customer. The customer will generally specify the shipment procedure. Still, for very urgent orders, FORCE COMPUTERS uses its expertise and connections to provide the optimum means of transportation for timely delivery. Practical packaging, professional documentation and fast delivery are additional features that give the final touch to FORCE COMPUTERS' high-technology products.

#### **Finished Goods Warehouse**

# **Quality Assurance**

#### **Quality Assurance**

The FORCE COMPUTERS quality system incorporates a total quality assurance concept encompassing management, design, purchasing, manufacturing, test, inspection, and documentation. The FORCE Quality Assurance Control program ensures that products conform to published specifications and customer's quality requirements. Records which track the effective operation of FORCE quality systems are available for review at FORCE COMPUTERS by designated purchasing authorities and source inspectors.

#### Organization

Quality is the responsibility of management and it is the policy of management that quality needs to be controlled. A quality assurance organization must be independent of other organizations to function effectively. FORCE COMPUTERS' quality assurance manager reports directly to the general manager and has full authority to resolve matters on quality. FORCE delegates responsibility and authority to those personnel performing quality functions to identify and evaluate quality problems, and to initiate, recommend, or provide solutions. Management regularly reviews the status and adequacy of the quality program.

#### Records

Records are one principal form of objective evidence of quality. FORCE COMPUTERS maintains and uses records for inspection, test, corrective actions, and calibration. Maintained test and inspection records suggest the nature or type of observation, the number of observations made, and number and type of deficiencies found. Corrective actions records detail the nature of the action and effective dates of correction. We also maintain records showing the calibration history and status for test and measurement equipment.

#### **Documentation and Change Control**

In industries where innovation, redesign, and product improvement predominate, control of documentation is of critical importance to product quality and reliability. FORCE COMPUTERS maintains control over documentation relating to the design and manufacture of its products. Current issues of appropriate documents are available at all locations where operations essential to the effective functioning of the quality system are done. All changes to documentation are in writing. We also maintain written records of all changes made.

#### Statistical Quality Control and Analysis

FORCE COMPUTERS uses statistical analysis and tests to maintain the required control of quality. Sampling inspection adheres to MIL-STD-105D. Acceptable quality levels (AQL) apply to both the receiving inspection and final electrical and mechanical/visual inspection. Using modern test equipment, we generate data and analysis on yields as well as product quality trends. Causes of defects or significant variations in manufacturing operations can be identified and the necessary corrective actions quickly carried out.

### Control of Inspection, Measuring and Test Equipment

Proper maintenance and control of test and measurement equipment helps ensure product conformance to specifications and required quality levels. We maintain calibration records and label equipment to show calibration intervals and status. The calibration system conforms to NATO Measurement and Calibration System Requirements for Industry (AQAP-6).

#### **Test Programs and Procedures**

FORCE COMPUTERS has developed sophisticated test programs using state-of-the-art test and measurement equipment for its board level and system products. Board level products are subjected to 100 percent In-Circuit Tests using Genrad 2276E automatic (bed of nails) testers. Data related to yields and product quality trends are collected, analyzed, and used as a basis for product improvement programs. Defect data feedback serves to initiate corrective actions. To screen-out infant mortalities, all boards are subjected to a dynamic burn-in for 48 hours at 50 degrees centigrade. Real-Time software-driven test programs enable board-level products to be tested in functional environments at elevated ambient temperatures. Using proprietary test programs in embedded software, we test all boardlevel products for full functionality in a VME system environment simulating the end use of the product. Processor, memory, and controller chips, for example, are exercised to test performance in the intended application. A post-test electrical and visual sample inspection on all finished products verifies that all tests have been completed as specified.

**Board Test and Inspection**

#### **Standards and Specifications**

The FORCE COMPUTERS' quality system conforms with and applies the following standards and specifications.

| BS5750-Part 1         | Specifications for Design                                            |

|-----------------------|----------------------------------------------------------------------|

| MIL-Q-9858A           | Quality program requirements                                         |

| AQAP-1                | NATO Quality Control System Requirements for Industry                |

| AQAP-6                | NATO Measurement and Calibration System Requirements for Industry    |

| IPC-SM-840            | Qualification and Performance of Permanent Polymer Coatings          |

| MIL-P-55110C          | Military specification printed wiring boards                         |

| IPC-A-600C            | Acceptability of printed wiring boards                               |

| IPC-ML-910A           | Design and end production specification for rigid multi-layer boards |

| MIL-STD-275D          | Printed wiring for electronic equipment                              |

| Workmanship standards | As published by Martin Marietta Aerospace                            |

A complete manufacturing flow chart with QA involvement is shown in Figure 3. A comprehensive description of the FORCE COMPUTERS' quality system is available in handbook form: Quality Assurance and Reliability Handbook.

Figure 3 Quality Assurance Product Connected Target Areas

**16-Bit CPU Boards**

#### FORCE COMPUTERS 16-bit CPU Board Introduction

There are three basic designs in the FORCE family of 16-bit CPU boards. For general purpose flexibility and functionality, the SYS68K/CPU-6 provides all the features that the user could ever need. The CPU-6 family was designed as a functional update for the extremely popular CPU-1 family. It was designed for complete S/W compatibility to the CPU-1 family providing all the same features, whilst conforming fully to the IEEE 1014 VMEbus specification. The CPU-6 includes 512 Kbyte DRAM, 4 EPROM sockets and 2 serial I/O channels as standard. The CPU-6 is the general purpose 16-bit solution.

If your application requires that small to medium sized applications be committed to EPROM, then the SYS68K/CPU-4VC is designed especially for you. With 8 JEDEC compatible sockets, the user has 512 Kbyte of EPROM space. Coupled with the powerful 68010 microprocessor, DMA controller with optional floppy disk controller and serial and parallel I/O, the CPU-4VC is the standalone solution.

For true raw performance, the SYS68K/CPU-5A offers the maximum computing power available with a 16-bit 68000 microprocessor. With the local CPU and floating point co-processor running at 16.67 MHz and with the 128 Kbyte of local RAM inducing no wait states on the CPU, the CPU-5A is the 68000 performance standard.

## 16-Bit CPU Boards (68000/68010-Based)

| FAMILY                                                              | CPU-4VC                                                   | CPU-5A                              | CPU-6A                              | CPU-6VA                             |

|---------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Processor type                                                      | 68010                                                     | 68000                               | 68000                               | 68010                               |

| FPCP type                                                           | no                                                        | 68881                               | no                                  | no                                  |

| Frequency min.<br>max.                                              | 12.5 MHz<br>12.5 MHz                                      | 16.7 MHz<br>16.7 MHz                | 12.5 MHz<br>12.5 MHz                | 12.5 MHz<br>12.5 MHz                |

| DMAC type<br>Frequency max.                                         | 68450<br>8 MHz                                            | 68450<br>8 MHz                      | no<br>no                            | no<br>no                            |

| Main memory type<br>Capacity min.<br>max.<br>No. of wait states     | SRAM<br>(on-board back-up)<br>128 Kbyte<br>128 Kbyte<br>0 | SRAM<br>128 Kbyte<br>128 Kbyte<br>0 | DRAM<br>512 Kbyte<br>512 Kbyte<br>1 | DRAM<br>512 Kbyte<br>512 Kbyte<br>1 |

| RAM function                                                        | local                                                     | local                               | local                               | local                               |

| No. of EPROM sockets<br>Max. capacity<br>Data bus width             | 8<br>512 Kbyte<br>16 Bit                                  | 4<br>256 Kbyte<br>16 Bit            | 4<br>256 Kbyte<br>16 Bit            | 4<br>256 Kbyte<br>16 Bit            |

| Serial I/O (total)<br>RS232<br>RS232/RS422/RS485<br>Controller chip | 1<br>1<br>0<br>68561 (MPCC)                               | 2<br>2<br>0<br>68561 (MPCC)         | 3<br>3<br>0<br>6850 (ACIA)          | 3<br>3<br>0<br>6850 (ACIA)          |

| Parallel I/O                                                        | 20 Bit                                                    | no                                  | 24 Bit                              | 24 Bit                              |

| Timer                                                               | 2×24 Bit                                                  | 1 × 24 Bit                          | 1×24 Bit                            | 1 × 24 Bit                          |

| Real Time Clock                                                     | yes                                                       | no                                  | yes                                 | yes                                 |

| Mass storage interface<br>Floppy<br>SCSI                            | optional<br>no                                            | no<br>no                            | no<br>no                            | no<br>no                            |

| VMEbus arbiter                                                      | Four level                                                | Single level                        | Single level                        | Single level                        |

| Secondary bus interface                                             | no                                                        | VMX                                 | no                                  | no                                  |

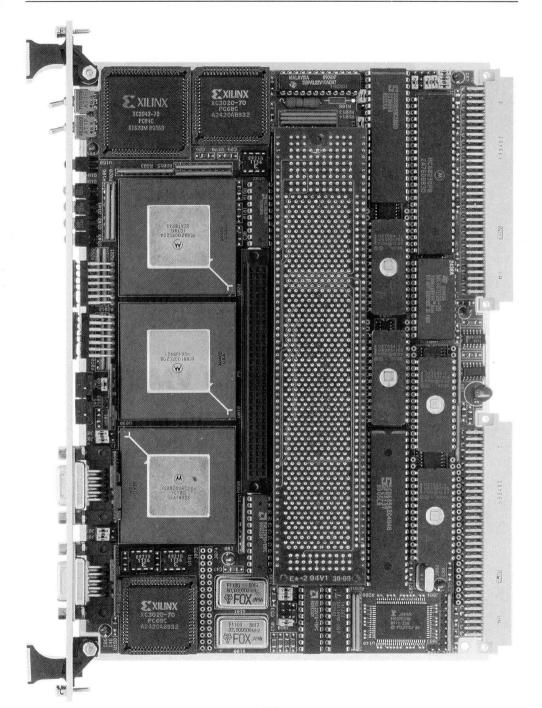

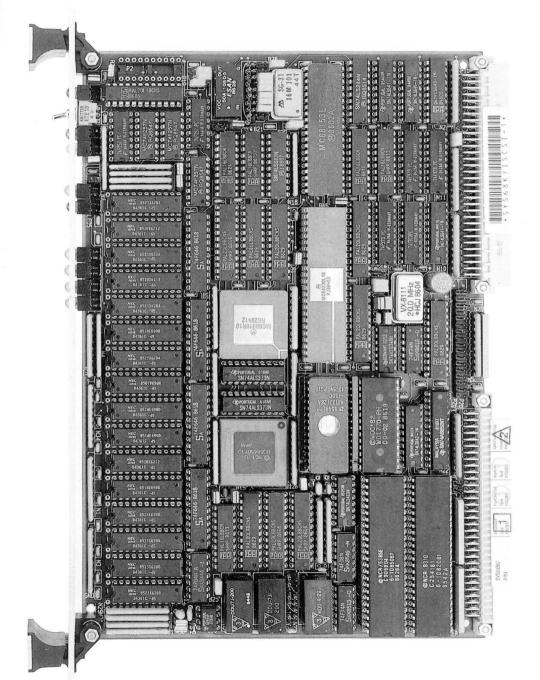

## System 68000 VME SYS68K/CPU-4VC

68010 CPU Board with SRAM and Battery Back-up

#### SYS68K/CPU-4VC

#### General Description

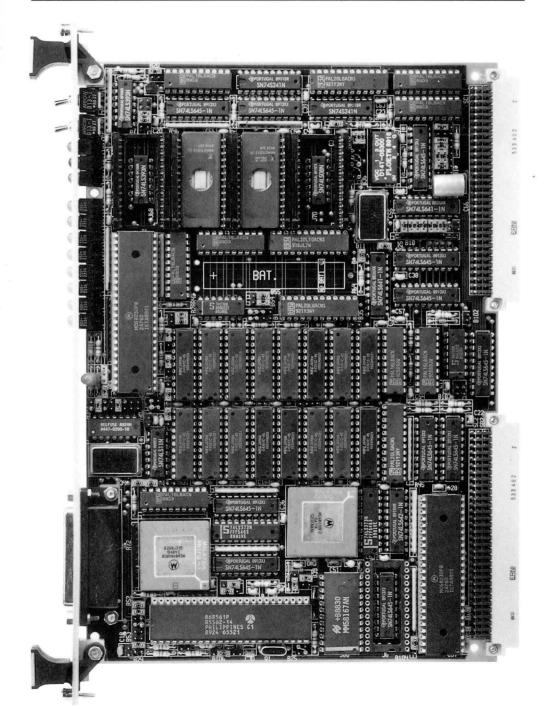

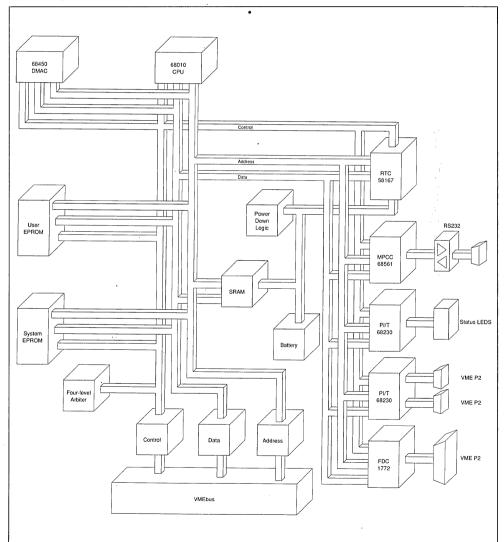

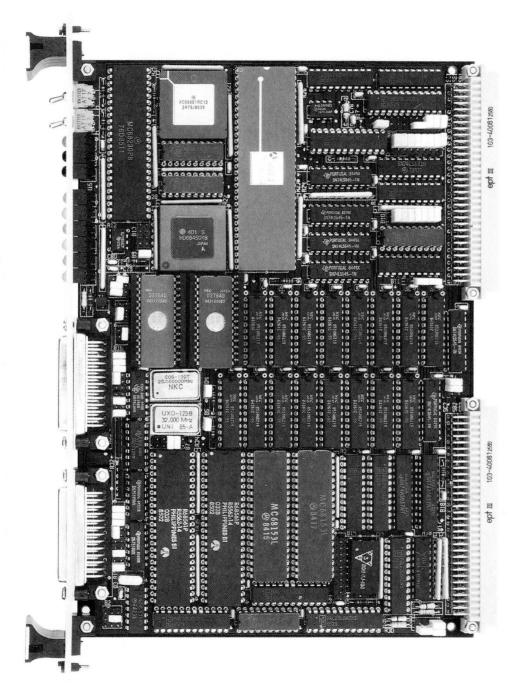

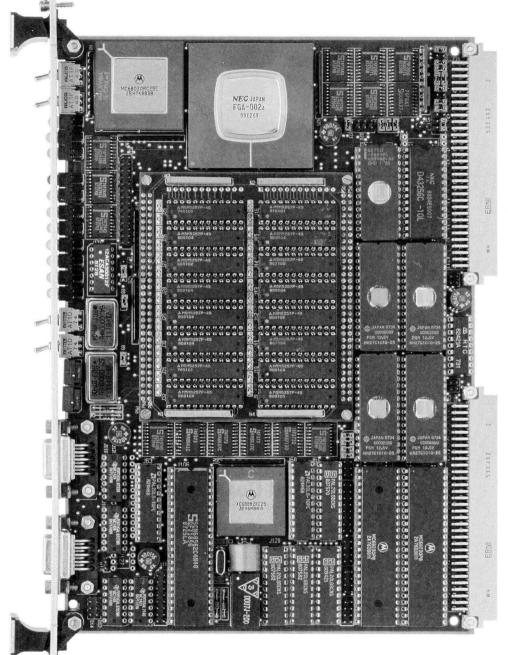

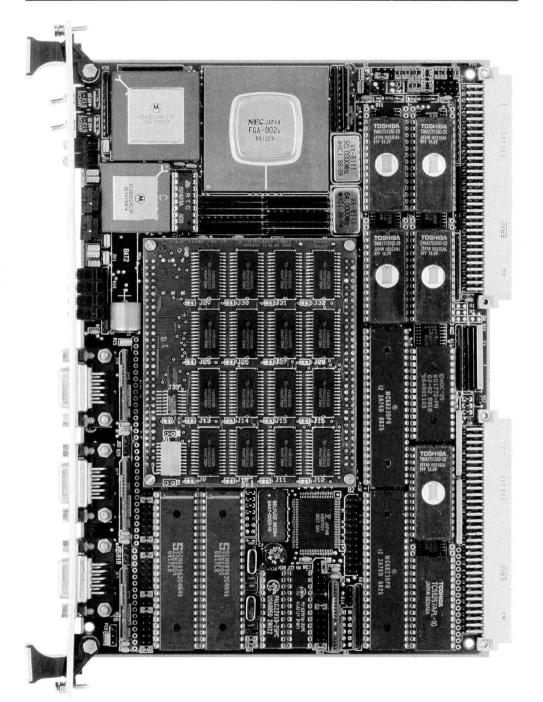

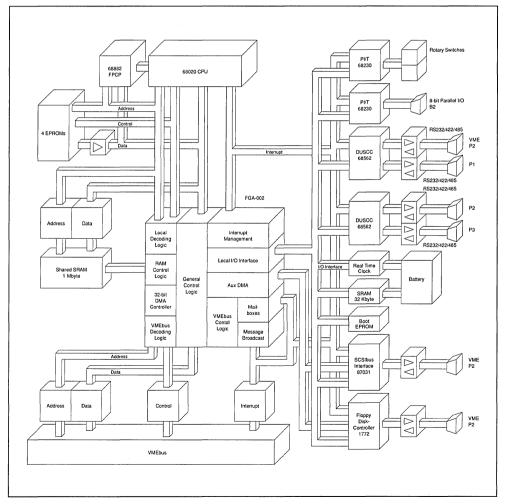

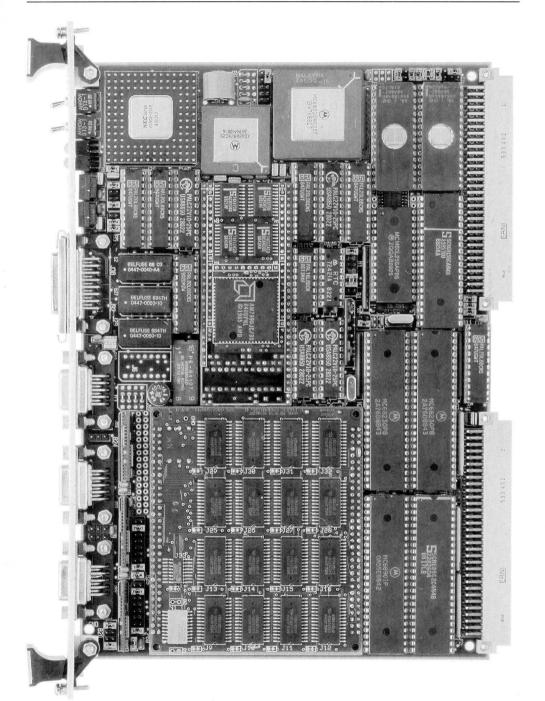

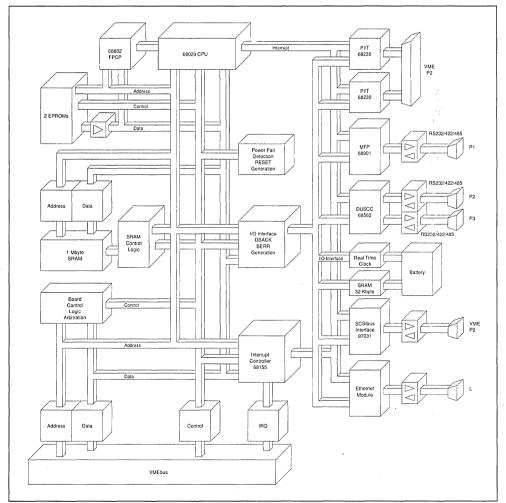

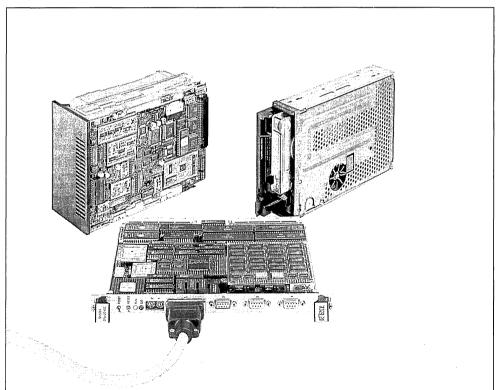

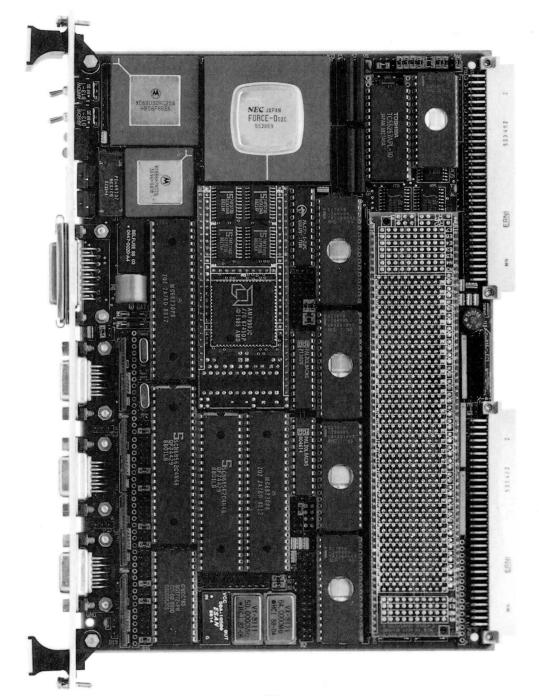

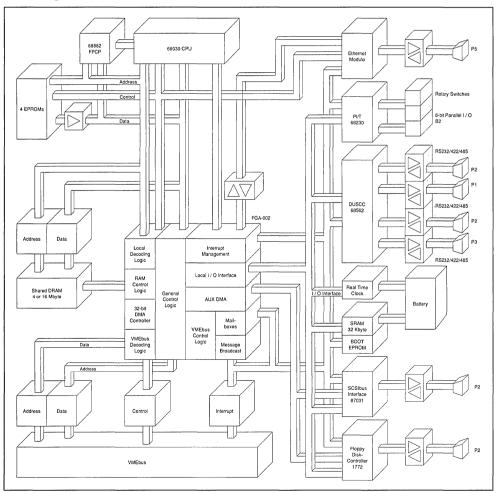

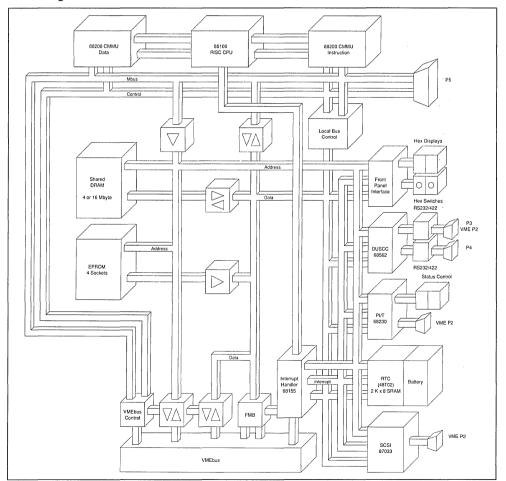

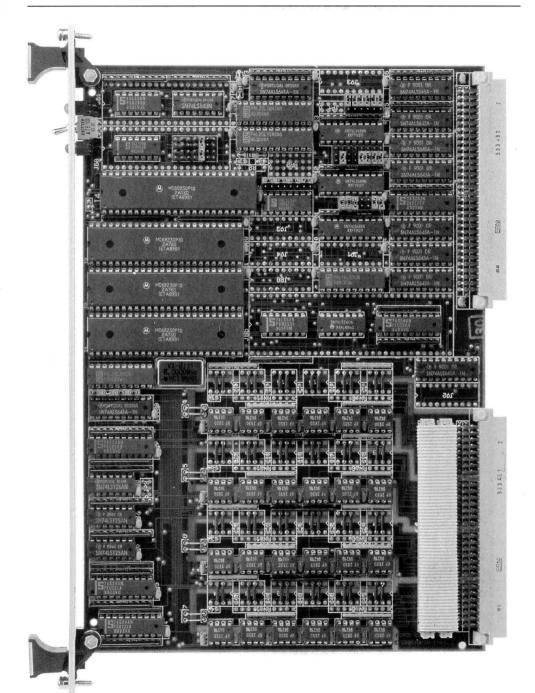

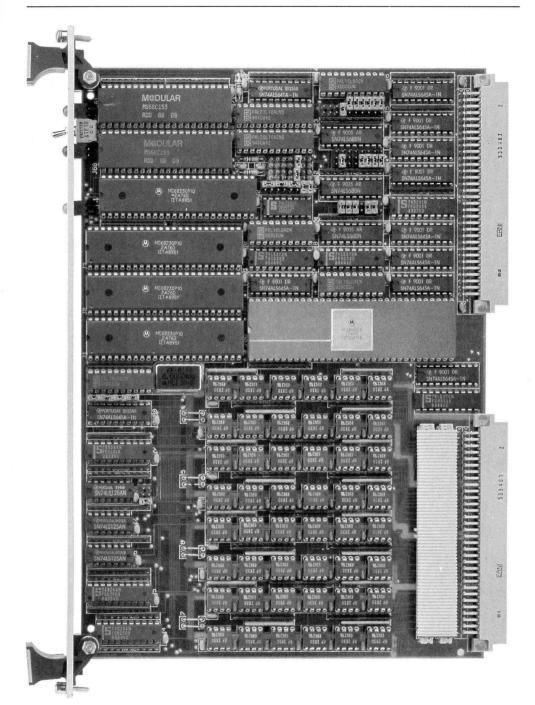

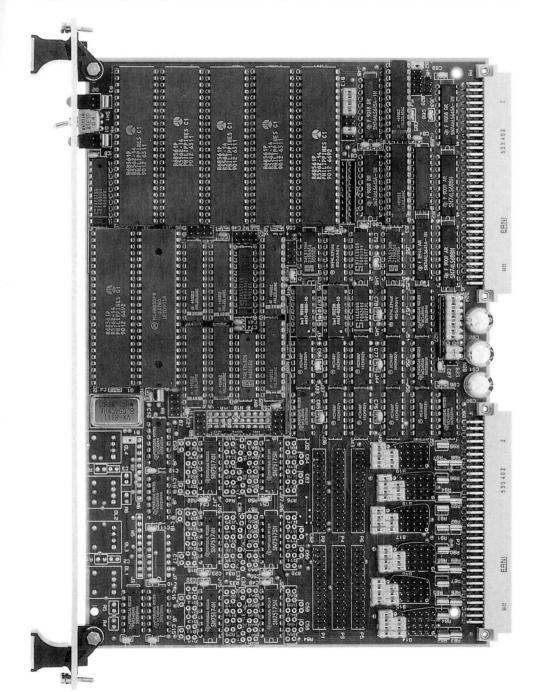

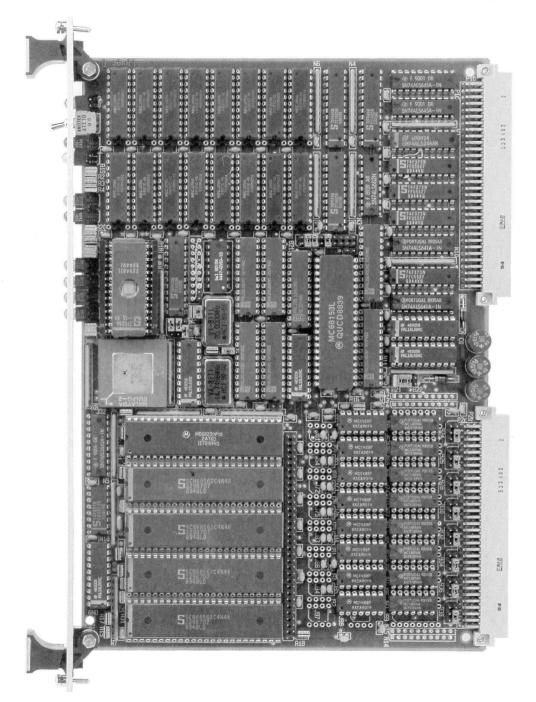

The SYS68K/CPU-4VC board is a high performance multi-processor computer board built around the virtual 68010 CPU and the VMEbus. It contains a Direct Memory Access Controller, 128 Kbyte SRAM, up to 512 Kbyte EPROM and powerful control functions. The implemented VMEbus interface is fully VMEbus and IEEE 1014 Standard compatible and includes a slave bus arbitration as well as a four level prioritized arbiter.

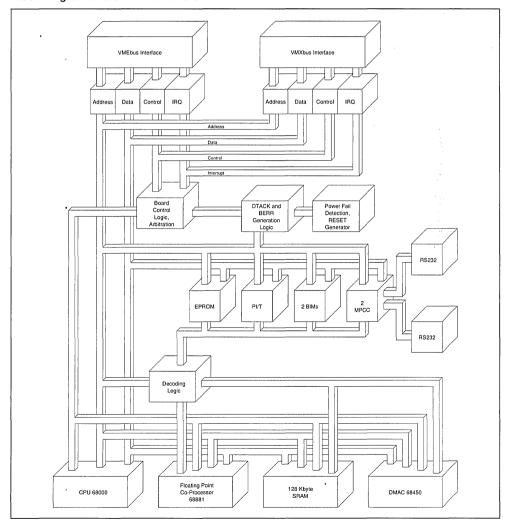

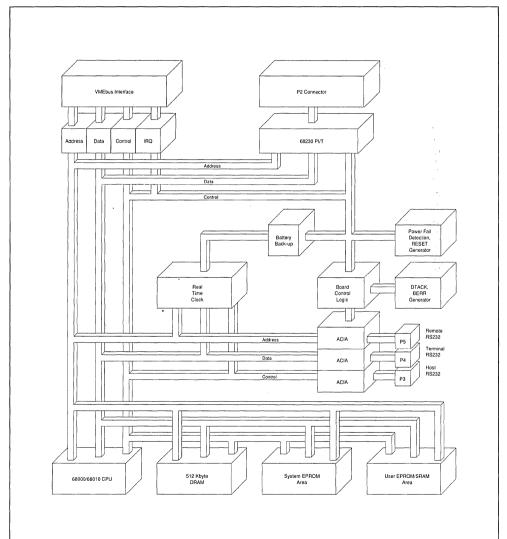

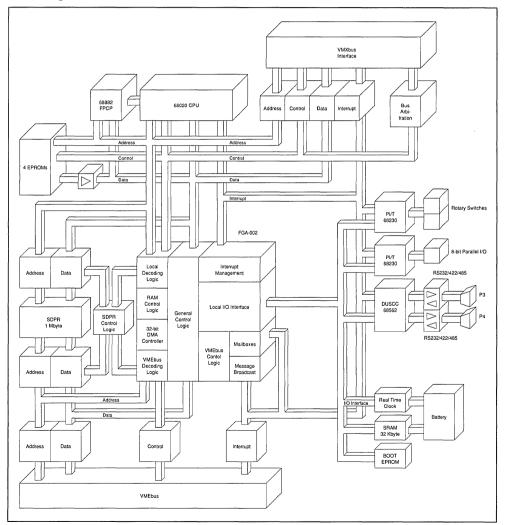

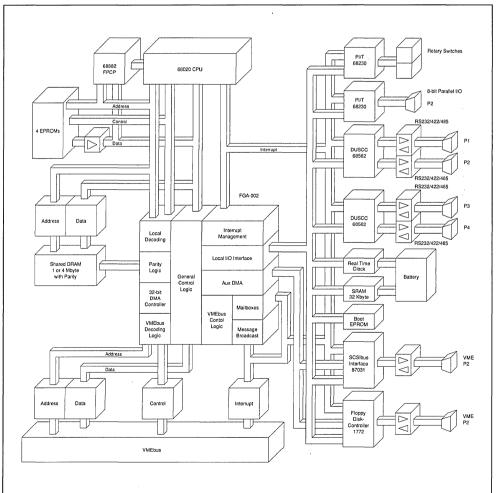

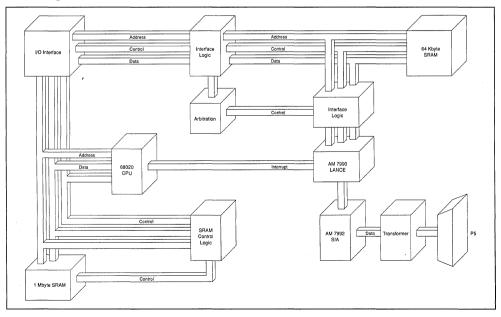

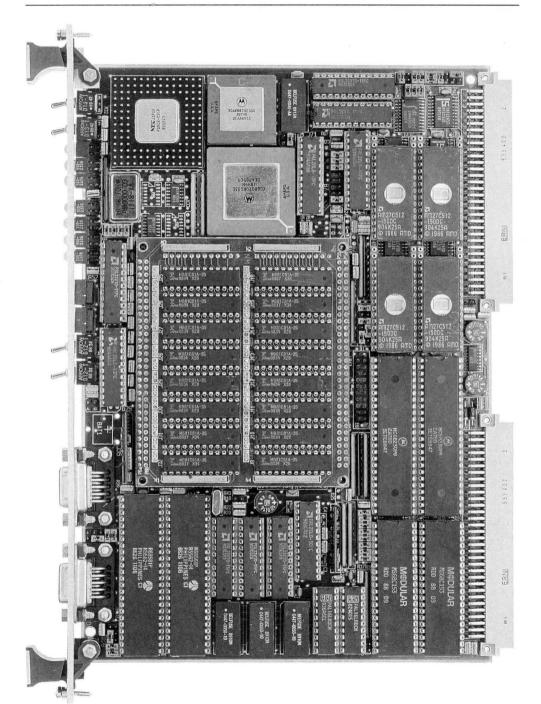

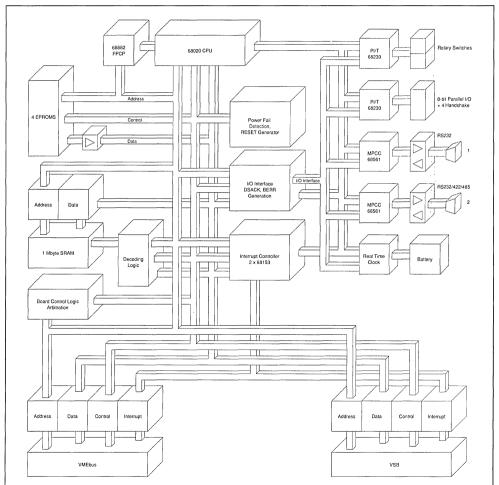

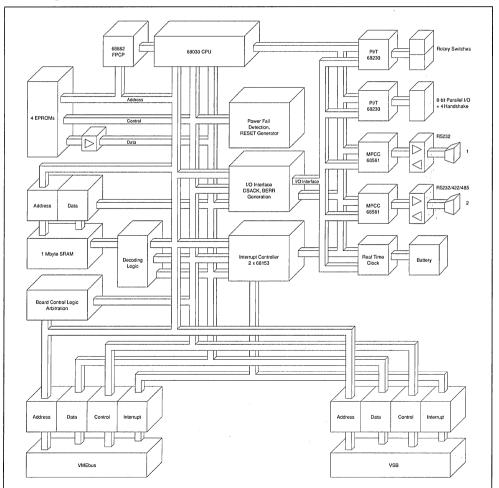

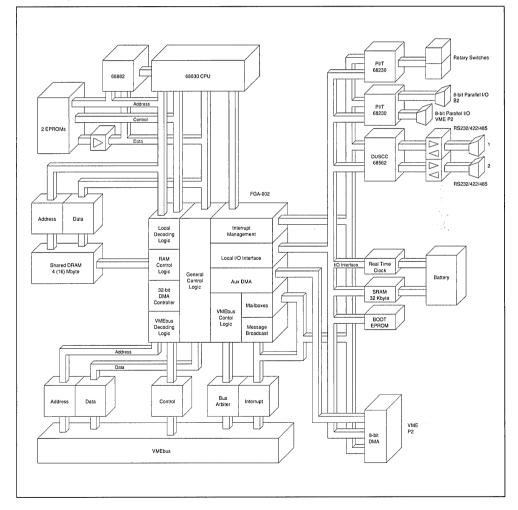

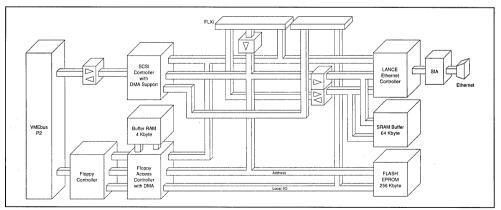

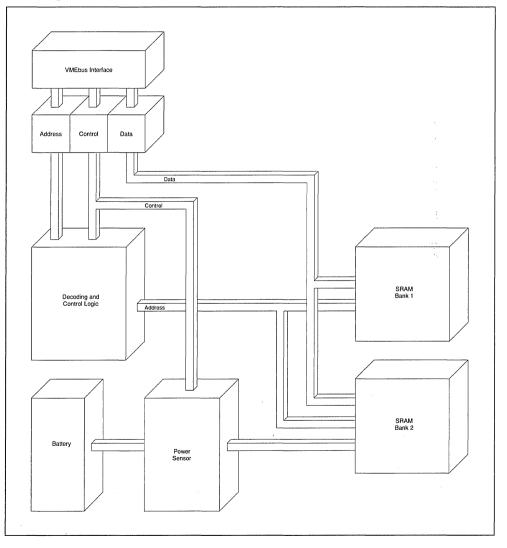

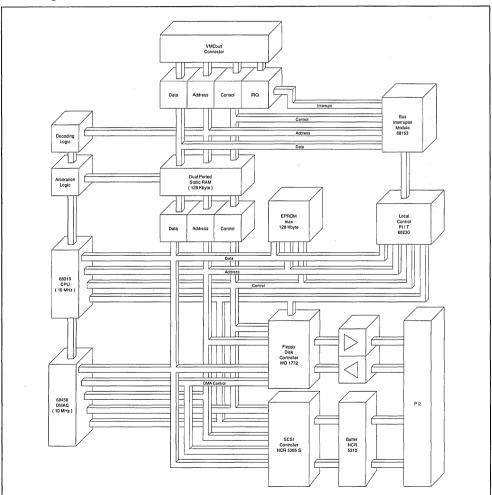

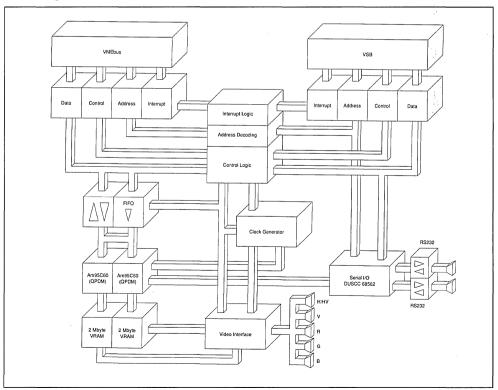

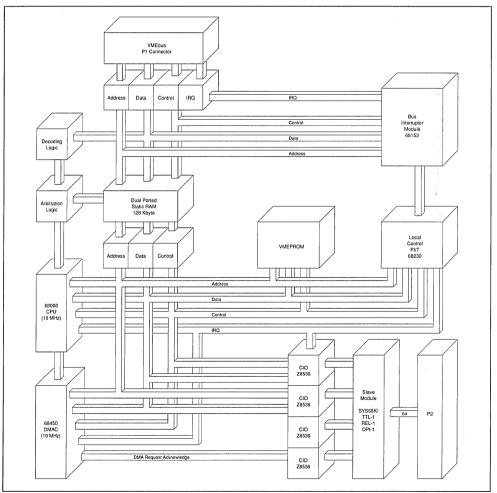

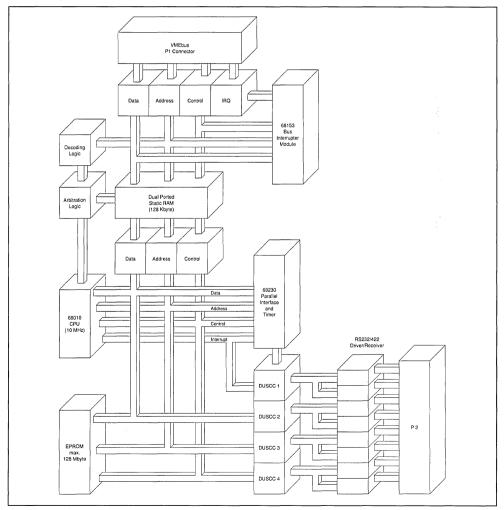

The block diagram shows the SYS68K/CPU-4VC board structure in detail.

Block Diagram of the SYS68K/CPU-4VC

#### Features of the SYS68K/CPU-4VC

- 68010 CPU with 12.5 MHz clock frequency

- 68450 Direct Memory Access Controller with 8 MHz clock frequency

- 68561 Multi-Protocol Communications Controller with an RS232-compatible interface

- 68230 Parallel Interface and Timer Module with 8 MHz clock frequency for local control and status display

- 68230 PI/T with 8 MHz clock frequency for parallel I/O on P2 connector

- 58167 Real Time Clock with battery back-up

- 128 Kbyte of high-speed static RAM with on-board battery back-up

- 8 EPROM sockets for system and/or user programs (max. 512 Kbyte)

- All on-board devices are able to interrupt the CPU

- 4 level bus arbiter (prioritized scheme)

- Bus requestor on a jumper-selectable level (0-3)

- RESET and ABORT function switches

- 8 status LEDs

- Powerful real time monitor/debugger VMEPROM on board

- High level real time operating systems are available for different applications

- Optionally available: 1772 Floppy Disk Controller for up to four 3", 31/2", 51/4" drives

#### **Functional Description**

The DMA Controller and Multi-Protocol Communication Controller communicate with the CPU via the unbuffered address and data bus. The EPROM areas, static RAM, Real Time Clock, Parallel Interface and Timer Module as well as the VMEbus interface communicate with the CPU via the buffered address bus.

Table 1 shows the global memory layout, and the various functional areas of the board are described briefly in the following paragraphs.

#### 1. 68010 Central Processing Unit

The high performance 68010 CPU with its upgraded 68000 instruction set and virtual memory support offers a total of 16 Mbyte of addressable memory through its 24 address signals. The fully asynchronous 16-bit data bus allows high speed data transfers to/from the on-board or VMEbus memory and I/O areas. The SYS68K/CPU-4VC series uses a 12.5 MHz 68010 processor. To provide for fault tolerant systems, the CPU provides excellent exception handling if an error or interrupt occurs. The state and all addresses as well as the fault address are stored on the stack to provide diagnostic and correction as well as re-run functions.

#### **CPU-4VC Memory Layout**

| Address                | Description                     |

|------------------------|---------------------------------|

| 000000<br>to<br>000007 | Start Vectors from System EPROM |

| 000008<br>to<br>01FFFF | Static RAM                      |

| 020000<br>to<br>EFFFFF | VMEbus Addresses                |

| F00000<br>to<br>F7FFFF | System and User EPROM Area      |

| F80000<br>to<br>F8FFFF | Local I/O Devices               |

| F90000<br>to<br>FEFFFF | VMEbus Addresses                |

| FF0000<br>to<br>FFFFFF | Short I/O VMEbus Addresses      |

#### 2. 68450 Direct Memory Access Controller

A high-speed DMA Controller with 8 MHz clock frequency is used on the board to move date to and from the VMEbus. Its four channels can be used from the operating system and/or shared with user programs.

The DMAC has a maximum data transfer speed of 4 Mbyte per second. Data can thus be loaded into the local RAM via the DMAC, giving timecritical number cruncher applications no time overhead through the VMEbus. This also results in a lower VMEbus load.

#### 3. The Static RAM

The SYS68K/CPU-4VC contains a static memory of 128 Kbyte with a maximum access time of 70 nsec. A separate power-down logic on every board is used to disable the SRAM chips when the main power is out of spec. The on-board battery is used for the standby power of the SRAM chips (approx. 1000 h data retention).

Each static RAM access (read and write) of the processor runs without any wait states at 12.5 MHz clock frequency.

#### 4. The System and User Area

The system area consists of two sockets for JEDEC-compatible EPROM devices. The VMEPROM firmware resides with its boot-up and I/O control functions in two EPROM devices (included in the shipment).

The user area (6 sockets) is provided for the use of EPROMs or SRAMs (JEDEC-compatible pin-out).

#### Usable Device Type for Each Area

| Device | Туре  | Organi-<br>zation |   | User<br>Area1–3 | Total<br>Capacity |

|--------|-------|-------------------|---|-----------------|-------------------|

| 2764   | EPROM | 8 K × 8           | х | х               | 64 Kbyte          |

| 27128  | EPROM | 16 K × 8          | х | х               | 128 Kbyte         |

| 27256  | EPROM | 32 K × 8          | х | х               | 256 Kbyte         |

| 27512  | EPROM | 64 K × 8          | х | х               | 512 Kbyte         |

| 6264   | SRAM  | 8 K × 8           |   | х               | 32 Kbyte          |

The access speeds for the system and for the user areas are jumper-selectable from 100 nsec to 400 nsec.

#### 5. 68561 Multi-Protocol Communication Controller (MPCC)

The MPCC contains different protocols to communicate via the RS232-compatible interface to a user-supplied serial communication device.

#### Protocols:

- IBM binary synchronous (ASCII or EBCDIC)

- Character oriented protocols (BSC, DDCMP, X3.38, X.21, ECMA 16 etc.)

- Synchronous bit-oriented protocols (SDLC, HDLC, ADCCP, X.25)

A software-programmable baud rate from 110 to 38400 baud and a local loop-back mode provide maximum flexibility.

The I/O signal assignment of the 4 input and 4 output signals to the 25-pin D-Sub connector on the front panel is jumper-selectable.

The MPCC is able to force an interrupt with 3 different software-programmable vectors to the CPU.

#### 6. The Local Control

The Parallel Interface and Timer Module (PI/T) with its 8 MHz clock frequency allows an optical status display through eight yellow status LEDs on the front panel.

Each interrupt request level (0–7) can be enabled or disabled independently from each other through the CPU. The exception signals ACFAIL\* and SYSFAIL\* are monitored through the third PI/T port. The bus release functions are also software-programmable through the third port.

The PI/T includes a 24-bit programmable timer with a 5-bit prescaler. This timer may be used for measuring time delays or as a watchdog timer. The PI/T timer interrupt request signal is used to force an auto-vectored interrupt to the CPU.

#### 7. The Parallel I/O Port

The second PI/T is used on the board to provide parallel I/O via the P2 connector. Two 8-bit bidirectional ports can be used for bit I/O or special control functions via 4 handshake interface signals.

The port interrupt causes an interrupt request to the on-board CPU on level 4. The 4 different software-programmable IRQ vectors offer maximum flexibility for program handling.

#### 8. 58167 Programmable Real Time Clock

The on-board RTC with its RAM array allows various applications such as time scheduling, time measurement and time-out counters.

Additionally, the RTC may act as an actual time base independent from the main power, providing month, day of month, and day of week. An on-board battery ensures time base operation during power-down.

#### 9. 1772 Floppy Disk Controller Option

The optionally available Single Chip Floppy Disk Controller (FDC) offers the capability of using the SYS68K/CPU-4VC board versions in process control applications without any other mass memory controllers.

The FDC controls up to 4 different drives (3",  $3^{1}/_{2}$ " or  $5^{1}/_{4}$ ") either single or double sided with single or double density (software-programmable).

Additionally, the step-rate is software-programmable from 1 msec to 6 msec.

All drive select signals and status lines from the disk interface are controlled via the PI/T. Easy interface is provided through the P2 I/O pins, which fit into a 1 : 1 connection via a flat cable to the floppy drive edge connector.

An interrupt after operation completion can be generated to the CPU via the PI/T. For high asynchronous use of the floppy, the FDC is connected to the DMAC via its data request signal. The DMA is provided on the board to use the FDC in critical real-time applications. The CPU and the DMAC/FDC work fully asynchronous. The FDC may be ordered as an option for the CPU-4VC.

#### 10. On-Board Exception Handling

The board contains two switches, one for RESET and one for ABORT. During an activated RESET, all on-board devices along with the CPU are reset. Additionally, the reset (SYSRESET\*) can be forced to the VMEbus if this card is used as the system controller (slot 1 functions).

During a pushed ABORT switch, an interrupt (non-maskable) is forced to the CPU.

#### 11. On-Board Interrupt Handling

All on-board devices are able to force interrupts to the CPU on different levels. Table 3 shows the interrupt structure of the SYS68K/CPU-4VC.

| Device | Name   | IRQ<br>Level | Interrupt<br>Auto Vector | Software-prog.<br>Interrupt Vector |

|--------|--------|--------------|--------------------------|------------------------------------|

| SWITCH | ABORT  | 7            | х                        |                                    |

| 58167A | RTC    | 6            | х                        |                                    |

| 68230  | ΡI/T 1 | 5            | х                        |                                    |

| 68230  | PI/T 2 | 4            |                          | х                                  |

| 68561  | MPCC   | 3            |                          | х                                  |

| 68450  | DMAC   | 2            |                          | х                                  |

#### 12. The VMEbus Interface

The implemented VMEbus interface includes 23 address, 16 data, 6 address modifier and different control signals.

A four-level bus arbiter with a prioritized scheme provides fast bus arbitration (if required).

A separate bus arbitration on a jumper-selectable level (0 - 3) provides the bus request/bus busy handshake to the used bus arbiter. Each VMEbus interrupt request level may be enabled or disabled via a jumper to provide multi-processing capabilities. The board supports the Release When Done (RWD), Release on Bus Clear (RBCLR) as well as the Release after Time-out (RAT) function (all software-programmable).

The 16 MHz SYSCLK signal can be driven to the VMEbus (jumper-selectable).

#### 13. Software

It is FORCE COMPUTERS' policy to ensure that as many operating systems and kernels as possible are available to enable the user to select the most appropriate and complete solution. The software is made available and supported either by FORCE COMPUTERS or the third party vendor as outlined in the software availability table. Selection of supply and support source has been made to ensure the highest level of expertise. Since FORCE has an on-going policy to expand its software offering, please contact FORCE regarding availability of any software not listed in this datasheet.

#### **CPU-4 Software Support**

| Operating<br>System/Kernel | Vendor/Support                 |

|----------------------------|--------------------------------|

| PDOS                       | FORCE COMPUTERS                |

| OS-9/9000                  | Contact FORCE for availability |

| VMEPROM                    | FORCE COMPUTERS                |

| VxWORKS                    | Contact FORCE for availability |

| VRTX-32                    | Contact FORCE for availability |

| pSOS                       | Contact FORCE for availability |

As a courtesy, FORCE provides the user with the ability to immediately start a real time application by including VMEPROM on every CPU card, free of charge and free of licensing costs.

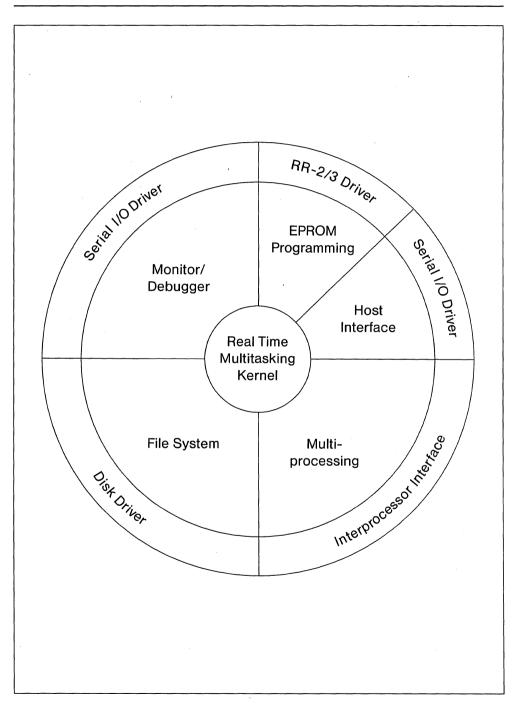

VMEPROM is an EPROM-based Real Time Multi-tasking Kernel/Monitor. The complete package resides in 256 Kbyte of EPROM and uses 32 Kbyte of RAM. VMEPROM fully supports all of the on-board I/O devices.

VMEPROM is composed of a highly sophisticated Real Time Kernel, which is based on the PDOS Real Time Kernel. A file manager supporting sequential, random and shared files is also included.

The user interface contains more than 60 commands perfectly suited for program debugging, host computer communications, as well as task and file management. It includes a powerful debugger, supporting line assembler/disassembler for the microprocessor.

#### Features of VMEPROM

- Real Time Kernel supporting multi-tasking, up to 64 tasks

- File manager, supporting up to 64 open files at the same time

- Line assembler/disassembler with full support of all 680x0 instructions

- Over 20 commands for program debugging, including breakpoints, tracing, processor register display and modify

- S-record up/downloading from any port defined in the system

- Disk support for RAM disk, floppy and Winchester disks

- VMEPROM allows disk formatting and initialization

- Serial I/O support for up to two SIO-2 or ISIO-2 boards in the system; local serial I/O devices are also supported

- EPROM programming utility using the SYS68K/RR-2 board

- Full screen editor

- I/O re-direction to files or ports from the command line

- Over 100 system calls to the kernel

## Specifications

| 68010                                            | <b>F</b>                           | 12.5 MHz                                                            |

|--------------------------------------------------|------------------------------------|---------------------------------------------------------------------|

| 68010                                            | Frequency                          |                                                                     |

| 68450                                            | Frequency                          | 8 MHz                                                               |

| Memory                                           | SRAM<br>Battery back-up<br>EPROM   | 128 Kbyte/0 wait state<br>yes<br>4 JEDEC Sockets<br>512 Kbyte (max) |

| Serial I/O                                       | Channels<br>Controller             | 1 (RS 232)<br>68561                                                 |

| Parallel I/O                                     | Channels<br>Width<br>Controller    | 2<br>8-bit with 2-bit handshake<br>68230                            |

| Real Time Clock Controller                       |                                    | 58167                                                               |

| VMEPROM firmware installed on all board versions |                                    | yes                                                                 |

| VMEbus                                           | Interface<br>Arbiter               | A24, A16 : D16, D8 (master)<br>4 level                              |

| Power requ                                       | irements + 5 V<br>+ 12 V<br>- 12 V | 3.9 A (max)<br>0.2 A (max)<br>0.2 A (max)                           |

| Operating t<br>Relative hu<br>Storage ter        | midity                             | 0 to + 50 °C<br>5 to 95 %<br>− 40 to + 85 °C                        |

| Board dime                                       | nsions                             | $234 \times 160 \text{ mm}$ : 9.2 $\times$ 6.3 in                   |

## Ordering Information

| SYS68K/CPU-4VC<br>Part No. 100413    | 68010 CPU Board with 12.5 MHz CPU and 128 Kbyte SRAM (with battery back-up). VMEPROM and documentation included. |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------|

| SYS68K/CPU-4FDC<br>Part No. 110040   | Floppy Disk Controller option (1772) supporting up to four drives (3", $3^{1}/_{2}$ ", or $5^{1}/_{4}$ ").       |

| SYS68K/VMEPROM/4/UP                  | VMEPROM update service for CPU-4 series.                                                                         |

| SYS68K/CPU-4VC/UM<br>Part No. 800102 | User's Manual for CPU-4VC.                                                                                       |

| SYS68K/VMEPROM/UM<br>Part No. 800140 | VMEPROM User's Manual.                                                                                           |

## System 68000 VME SYS68K/CPU-5A

16 MHz 68000 CPU with Floating Point Co-Processor

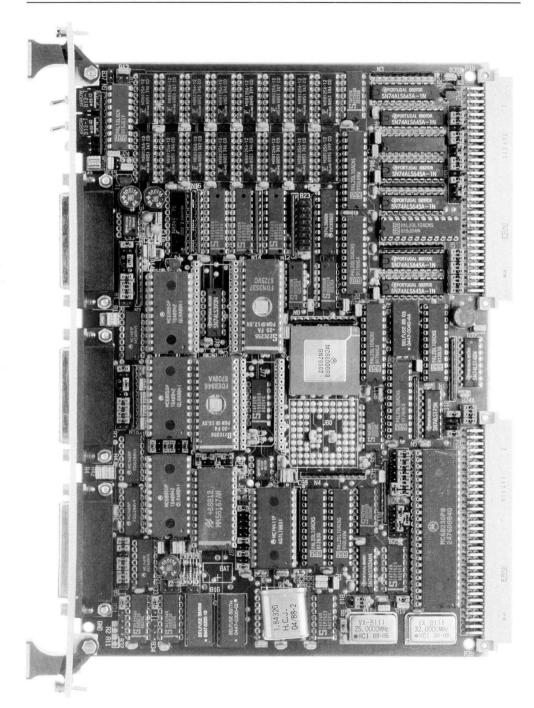

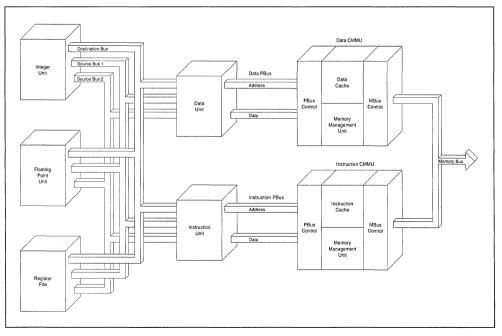

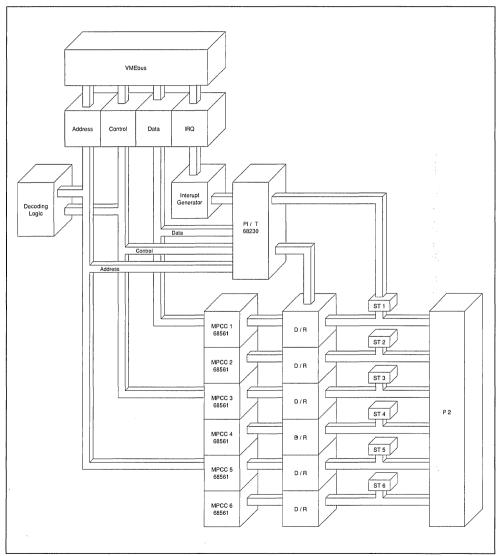

#### General Description

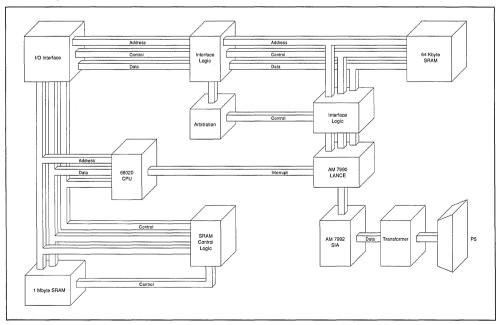

The SYS68K/CPU-5A boards are high speed computer boards built around the 68000 CPU and the Floating Point Co-Processor 68881. Zero wait state operation is performed at 16.7 MHz CPU clock frequency by accessing the 128 Kbyte high speed static RAM.

The installed four channel DMA Controller is capable of transferring data from memory to memory or from the two serial interfaces to memory. One Parallel Interface and Timer Module offers a software-programmable timer as well as VMEbus exception signal handling.

The implemented VMEbus interface is fully VMEbus and IEEE 1014 Standard compatible and includes a one-level arbiter.

The primary VMXbus interface completes the board and offers optimized multi-processing support. The block diagram shows the board structure of the CPU-5 in detail.

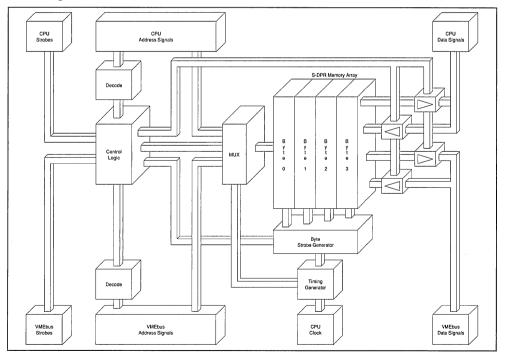

#### Block Diagram of the SYS68K/CPU-5A

#### Features of the SYS68K/CPU-5A

- 68000 CPU with 16.7 MHz clock frequency

- 68881 Floating Point Co-Processor with 16.7 MHz clock frequency

- 68450 DMA Controller with 8 MHz clock frequency

- 68561 Multi-Protocol Communications Controllers with two RS232-compatible interfaces

- 68230 Parallel Interface and Timer Module with 8 MHz clock frequency

- 128 Kbyte of zero wait state static RAM

- 4 EPROM sockets for system and/or user programs

- All on-board interrupt requests are softwareprogrammable (level and vector)

- Each VMEbus IRQ (1 to 7) can be enabled or disabled via software through the PI/T

- Single level arbiter

- VMEbus interface

(A24 + D8, D16); A16 + 5

- (A24 : D8, D16; A16 : D8, D16)

- VMXbus primary master interface (A24 : D16)

- Powerful Real Time Monitor/Debugger VMEPROM on-board

- 9 status LEDs, RESET and ABORT function switch

#### 1. 68000 Central Processing Unit

The high performance 68000 CPU offers a total of 16 Mbyte of addressable memory through its 24 address signals. The fully asynchronous 16-bit data bus allows high speed data transfers to/from the on-board, VME- or VMXbus memory and I/O areas.

The SYS68K/CPU-5A uses a 16.7 MHz 68000 processor and runs constantly without wait states from the 128 Kbyte of static RAM.

The following table shows the global memory layout of the CPU-5A board:

| Address                | Description                     |

|------------------------|---------------------------------|

| 000000<br>to<br>000007 | Start Vectors from System EPROM |

| 000008<br>to<br>01FFFF | On-board Static RAM (128 Kbyte) |

| 020000<br>to<br>xxxxxx | VME or VMXbus Addresses         |

| xxxxxx<br>to<br>EFFFFF | VMX or VMEbus Addresses         |

| F00000<br>to<br>F3FFFF | System and User EPROM Area      |

| F80000<br>to<br>F8FFFF | Local I/O Devices               |

| F90000<br>to<br>FEFFFF | VMEbus Addresses                |

| FF0000<br>to<br>FFFFFF | Short I/O VMEbus Addresses      |

#### 2. The Floating Point Co-Processor:

The 68881 Floating Point Co-Processor is a full implementation of the IEEE Standard 754 for Floating Point Arithmetic.

A set of 8 general Floating Point Data Registers, supporting full 80-bit extended precision are available for arithmetic operations such as:

| Add                     | Sine, cosine, hyperbolic sine and cosine                    |  |

|-------------------------|-------------------------------------------------------------|--|

| Subtract                | Tangent, cotangent, hyperbolic                              |  |

| Multiply                | tangent and cotangent                                       |  |

| Divide                  | e EXP(x)                                                    |  |

| Compare                 | e EXP(x–1)                                                  |  |

| Scale Exponent          | E EXP(xtract (4))                                           |  |

| Modulo                  | ln (x),ln (x + 1)                                           |  |

| Conditional<br>branches | log 10 (x),log2 (x)                                         |  |

| Absolute value          | 2 EXP(x),10 EXP (x)<br>Square root<br>Conditional Trap (32) |  |

The FPCP supports the following data types:

- Byte, word and long integers

- Single, double and extended precision real numbers

- Packed BCD string real numbers

The SYS68K/CPU-5A is fitted with a 16.7 MHz FPCP.

#### 3. The Static RAM

Zero wait state operation for the CPU (16.7 MHz) and the DMAC (8 MHz) is provided by using the 16 static RAMs.

128 Kbyte of SRAM with maximum access time of 55 nsec is provided on each CPU-5A board for program and/or data storage.

#### 4. The System and User Area

The CPU-5A contains four sockets for JEDECcompatible EPROM devices. Two 27512 devices are used for VMEPROM (included in the shipment).

The following table lists the usable EPROM types for each area.

| Device | Organization | Total Capacity |

|--------|--------------|----------------|

| 2764   | 8 K × 8      | 32 Kbyte       |

| 27128  | 16 K×8       | 64 Kbyte       |

| 27256  | 32 K × 8     | 128 Kbyte      |

| 27512  | 64 K × 8     | 256 Kbyte      |

The access time for both areas is jumper-selectable in the range of 100-400 nsec to adapt different EPROM access times.

#### 5. 68450 Direct Memory Access Controller

A high-speed DMA Controller with 8 MHz clock frequency is used on the board to move data on the local, VMX- and the VMEbus. Its four channels can be used from the operating system and/or shared with user programs.

The DMAC has a maximum data transfer speed of 4 Mbyte per second. Time critical programs can thus be loaded into the local RAM via the DMAC, which allows number cruncher applications to run without the time overhead through the VME/VMXbus. This also results in a lower bus load.

#### 6. 68561 Multi-Protocol Communication Controllers (MPCC)

The CPU-5A board contains two serial interfaces for communication to a terminal and/or printer/host computer.

The MPCC offers different protocols to communicate via the RS232-compatible interface to a user-supplied serial communication device.

#### Protocols:

- IBM binary synchronous (ASCII or EBCDIC)

- Character oriented protocols (BSC, DDCMP, X3.28, X.21, ECMA 16 etc.)

- Synchronous bit-oriented protocols (SDLC, HDLC, ADCCP, X.25)

A software-programmable baud rate from 110 to 38400 baud and a local loop-back mode provide maximum flexibility.

The I/O signal assignment of the 4 input and 4 output signals per channel to the 25-pin D-Sub connectors on the front panel is jumper-select-able.

The MPCC is able to force an interrupt with 3 different software-programmable vectors to the CPU.

#### 7. The Local Control

The Parallel Interface and Timer Module (PI/T) with its 8 MHz clock frequency allows an optical status display through six yellow status LEDs mounted on the front panel.

Each interrupt request level from the VMEbus can be enabled or disabled independently from each other through the CPU (dynamically). The VMEbus signals ACFAIL\* and SYSFAIL\* are monitored through the third PI/T port.

The bus release functions described in the VMEbus section are also software-programmable. The PI/T includes a 24-bit programmable timer with a 5-bit prescaler. This timer may be used for measuring time delays or as a watchdog timer.

#### 8. The Interrupt Structure

The CPU-5A contains two Bus Interrupter Modules to provide a flexible interrupt structure for multi-processor applications.

Each on-board interrupt request is software-programmable to one of the IRQ levels of the CPU. The vector is also software-programmable.

The following table lists all the on-board interrupt sources:

| Interrupt    | Device |

|--------------|--------|

| ABORT        | SWITCH |

| TIMER        | PI/T   |

| Serial I/O 1 | MPCC 1 |

| Serial I/O 2 | MPCC 2 |

| DMAC         | DMAC   |

| ACFAIL*      | VMEbus |

| SYSFAIL*     | VMEbus |

| IRQVMX       | VMXbus |

The VMXbus interrupt request is routed into the on-board IRQ structure to offer maximum flexibility (software-programmable level and vector).

The VMEbus interrupt requests can be dynamically enabled or disabled to the CPU through the PI/T device. This allows dynamic adaption for high end multi-processor environments because each of the IRQs (1–7) can be selected separately under run time of the CPU (no jumper settings are required).

#### 9. The VMXbus Interface

The CPU-5A board contains a primary VMXbus interface with a jumper-selectable access address range in the whole address space of 16 Mbyte. 24 address lines and 16 data lines are supported from the VMXbus interface. The early DTACK option can be used to speed up the access cycles.

#### 10. The VMEbus Interface

The implemented VMEbus interface supports 24 address, 16 data, 6 address modifiers and different control signals.

The transfer of 8 and 16 bits of data (A24 : D8, D16) is supported. Software-programmable bus release functions allow flexible adjustment to the various application dependent requirements.

| ROR   | = | Release On Request     |

|-------|---|------------------------|

| RBCLR | = | Release On Bus Clear   |

| RAT   | = | Release After Time-Out |

| RWD   | = | Release When Done      |

The single level arbiter included on the board simplifies installation of the CPU-5A into a VMEbus environment.

#### 11. Software

It is FORCE COMPUTERS' policy to ensure that as many operating systems and kernels as possible are available to enable the user to select the most appropriate and complete solution. The software is made available and supported either by FORCE COMPUTERS or the third party vendor as outlined in the software availability table. Selection of supply and support source has been made to ensure the highest level of expertise. Since FORCE has an on-going policy to expand its software offering, please contact FORCE regarding availability of any software not listed in this datasheet.

#### CPU-5 Software Support

| Operating<br>System/Kernel | Vendor/Support                 |

|----------------------------|--------------------------------|

| PDOS                       | FORCE COMPUTERS                |

| OS-9/9000                  | Contact FORCE for availability |

| VMEPROM                    | FORCE COMPUTERS                |

| VxWORKS                    | Contact FORCE for availability |

| VRTX-32                    | Contact FORCE for availability |

| pSOS                       | Contact FORCE for availability |

As a courtesy, FORCE provides the user with the ability to immediately start a real time application by including VMEPROM on every CPU card, free of charge and free of licensing costs.

VMEPROM is an EPROM-based Real Time Multi-tasking Kernel/Monitor. The complete package resides in 256 Kbyte of EPROM and uses 32 Kbyte of RAM. VMEPROM fully supports all of the on-board I/O devices.

VMEPROM is composed of a highly sophisticated Real Time Kernel, which is based on the PDOS Real Time Kernel. A file manager supporting sequential, random and shared files is also included.

The user interface contains more than 60 commands perfectly suited for program debugging, host computer communications, as well as task and file management. It includes a powerful debugger, supporting line assembler/disassembler for the microprocessor.

#### Features of VMEPROM

- Real Time Kernel supporting multi-tasking, up to 64 tasks

- File manager, supporting up to 64 open files at the same time

- Line assembler/disassembler with full support of all 680x0 instructions

- Over 20 commands for program debugging, including breakpoints, tracing, processor register display and modify

- S-record up/downloading from any port defined in the system

- Disk support for RAM disk, floppy and Winchester disks

- VMEPROM allows disk formatting and initialization

- Serial I/O support for up to two SIO-2 or ISIO-2 boards in the system; local serial I/O devices are also supported

- EPROM programming utility using the SYS68K/RR-2 board

- Full screen editor

- I/O re-direction to files or ports from the command line

- Over 100 system calls to the kernel

## Specifications

| 68000 frequency                                                                    | 16.7 MHz                                               |

|------------------------------------------------------------------------------------|--------------------------------------------------------|

| 68881 frequency                                                                    | 16.7 MHz                                               |