FST-1 Computer Systems Manual

> STOCK NO.: 67095031 RELEASED: October 1970

FAIRCHILD Systems technology

## Warranty\_

Seller warrants equipment of its manufacture against defective materials or workmanship for a period of one year from date on which Seller determines the installation to be complete. The liability of the Seller under this warranty is limited, at Sellers option, solely to repair, replacement with equivalent Fairchild equipment, or an appropriate credit adjustment not to exceed the original equipment sales price, of equipment returned to the Seller provided that (a) Seller is promptly notified in writing by Buyer upon discovery of defects, (b) the defective equipment is returned to Seller, transportation charges prepaid by Buyer, and (c) Seller's examination of such equipment disclosed to its satisfaction that defects were not caused by negligence, misuse, improper installation, accident, or unauthorized repair or alteration by the Buyer. This warranty does not include mechanical parts failing from normal usage nor does it cover limited life electrical components which deteriorate with age such as vacuum tubes, choppers, lamps, etc. In the case of accessories, ie, card punches, typewriters, etc., not manufactured by Seller, but which are furnished with the Seller's equipment. Seller's liability is limited to whatever warranty is extended by the manufacturers thereof and transferable to the Buyer. This warranty is expressed in lieu of all other warranties, expressed or implied, including the implied warranty of fitness for a particular purpose, and of all other obligations or liabilities on the Seller's part, and it neither assumes nor authorizes any other person to assume for the Seller any other liabilities. This warranty should not be confused with or construed to imply free preventative or remedial maintenance, calibration or other service required for normal operation of the equipment.

FAIRCHILD

i

# List of Effective Pages\_\_\_\_\_

## **FST-1 SYSTEMS MANUAL**

The total number of pages of this publication is 68, consisting of the following:

| Page No.         | Issue    |

|------------------|----------|

| Title            | Original |

| i through ix     | Original |

| 1-1 through 1-42 | Original |

| 2-1 through 2-5  | Original |

| 3-1 through 3-5  | Original |

| 4-1 through 4-9  | Original |

| 5-1 through 5-6  | Original |

| 6-1 through 6-8  | Original |

| Al through A2    | -        |

| B1 through B2    | -        |

## TABLE OF CONTENTS

## SECTION I FST-1 SYSTEM DESCRIPTION, FORMATS AND INSTRUCTIONS

| 1.1   | Introduction                                                  | 1_1  |

|-------|---------------------------------------------------------------|------|

| 1.1   |                                                               |      |

| -     | Central Processor Unit                                        |      |

| 1.3   | System Organization                                           |      |

| 1.4   | Central Processor Unit Organization                           |      |

| 1.4.1 | Introduction                                                  |      |

| 1.4.2 | Word Format                                                   | 1-3  |

| 1.4.3 | Instruction Formats                                           | 1-3  |

| 1.4.4 | Registers                                                     | 1-4  |

| 1.4.5 | Reserved Memory                                               | 1-4  |

| 1.5   | Address Modification                                          | 1-6  |

| 1.5.1 | Introduction                                                  | 1-6  |

| 1.5.2 | Indexing                                                      | 1-6  |

| 1.5.3 | Indirect Address Modification                                 | 1-6  |

| 1.6   | Peripheral Interface Organization                             | 1-7  |

| 1.6.1 | Introduction                                                  | 1-7  |

| 1.6.2 | Program Interruption                                          | 1-8  |

| 1.7   | Instruction Repertoire                                        | 1-9  |

| 1.7.1 | Introduction                                                  | 1-9  |

| 1.7.2 | Abbreviations                                                 | 1-9  |

| 1.7.3 | Instruction Format(s)                                         | 1-9  |

| 1.7.4 | Assembler Formats                                             | 1-9  |

| 1.7.5 | Cycles Required                                               | 1-10 |

| 1.7.6 | Arithmetic Instructions (TCA, DTC, ADD, SUB, DADD, DSUB, MUL, |      |

|       | DIV, AOM, SOM)                                                | 1-10 |

|       | TCA, DTC                                                      |      |

|       | ADD, SUB                                                      |      |

|       | DADD, DSUB                                                    |      |

|       | MUL, DIV                                                      |      |

|       |                                                               |      |

|       | AOM, SOM                                                      | 1-10 |

| iii   |                                                               |      |

SECTION I FST-1 SYSTEM DESCRIPTION, FORMATS AND INSTRUCTIONS (Continued)

| 1.7.7  | Data Transfer Instructions (RSR, EXC, STA, STE, LDA, LDE, DLD, DST) | 1-16 |

|--------|---------------------------------------------------------------------|------|

|        | RSR, EXC                                                            |      |

|        | STA, STE                                                            |      |

|        | LDA, LDE                                                            |      |

|        | DLD, DST                                                            |      |

| 1.7.8  | Index Instructions (LDX, LXA, ATX, STX, LAX)                        |      |

|        | LDX, LXA                                                            |      |

|        | ATX, STX                                                            |      |

|        | LAX                                                                 | 1-22 |

| 1.7.9  | Shift Instructions (DSN, SR, LS, SA, SL, DSR, LDS, DSA, DSL)        | 1-22 |

|        | DSN, SR                                                             | 1-23 |

|        | LS, SA                                                              | 1-24 |

|        | SL, DSR                                                             | 1-25 |

|        | LDS, DSA                                                            | 1-26 |

|        | DSL                                                                 | 1-27 |

| 1.7.10 | Logical Instructions (RUM, EOR, AND, OR)                            | 1-27 |

|        | RUM                                                                 | 1-27 |

|        | EOR, AND                                                            | 1-28 |

|        | OR                                                                  | 1-29 |

| 1.7.11 | State Control Instructions (SST, RST)                               | 1-30 |

|        | SST                                                                 | 1-31 |

|        | RST                                                                 | 1-32 |

| 1.7.12 | Compare Instruction (CAM)                                           | 1-33 |

|        | САМ                                                                 | 1-33 |

| 1.7.13 | Transfer of Control Instructions (BAH, BRU, BAT, BOI, BOS, BSM,     |      |

|        | BSZ)                                                                | 1-34 |

|        | ВАН                                                                 | 1-34 |

|        | BRU                                                                 | 1-35 |

|        | BAT                                                                 | 1-36 |

|        | B0I                                                                 | 1-37 |

|        | BOS                                                                 | 1-38 |

|        | BSM                                                                 | 1-39 |

|        | BSZ                                                                 | 1-40 |

Page

SECTION I FST-1 SYSTEM DESCRIPTION, FORMATS AND INSTRUCTIONS (Continued)

| 1.7.14 | <pre>Input/Output Instructions (SPU)</pre> | 1-41 |

|--------|--------------------------------------------|------|

|        | SPU                                        | 1-41 |

| 1.7.15 | No Operation Instruction (NOP)             | 1-42 |

|        | NOP                                        | 1-42 |

## SECTION II CONTROL PANEL

| 2.1     | Introduction 2-1                     |

|---------|--------------------------------------|

| 2.2     | Control Panel Switches 2-1           |

| 2.2.1   | Sense Switches 2-1                   |

| 2.2.2   | Switch Register 2-1                  |

| 2.2.3   | Register Display Select Switches 2-1 |

| 2.2.4   | Manual Command Control 2-1           |

| 2.2.4.1 | LDA (Load A) 2-1                     |

| 2.2.4.2 | LDP (Load P) 2-3                     |

| 2.2.4.3 | LDC (Load C) 2-3                     |

| 2.2.4.4 | CLK (Command Lock) 2-3               |

| 2.2.4.5 | STW (Store Switch Register) 2-3      |

| 2.2.4.6 | EXM (Examine Memory) 2-3             |

| 2.2.4.7 | SMC (Single Memory Cycle) 2-3        |

| 2.2.4.8 | SIC (Single Instruction Cycle) 2-3   |

| 2.2.5   | Operational Controls 2-3             |

| 2.2.5.1 | Start 2-3                            |

| 2.2.5.2 | Stop 2-4                             |

| 2.2.5.3 | Reset 2-4                            |

| 2.2.5.4 | Load CDR 2-4                         |

| 2.2.5.5 | Load MT 2-4                          |

| 2.3     | Control Panel Displays 2-4           |

| 2.3.1   | Status Indicators 2-4                |

| 2.3.2   | State Flip Flop Indicators 2-4       |

| 2.3.3   | Condition Indicators 2-5             |

| 2.3.4   | Program Counter 2-5                  |

| 2.3.5   | Register Indicators 2-5              |

Page

## SECTION III CONSOLE TYPEWRITER

| 3.1     | Introduction               | 3-1 |

|---------|----------------------------|-----|

| 3.2     | System Configuration       | 3-1 |

| 3.3     | Console Typewriter Control | 3-1 |

| 3.3.1   | Reader Commands            | 3-1 |

|         | SPU, STST, RDS, FEED       | 3-2 |

|         | RD, PON, POFF, PCOMP       | 3-3 |

| 3.3.2   | Printer (Punch) Commands   | 3-3 |

|         | STST, RDS, WRIT            | 3-4 |

|         | PON, POFF, PCOMP           | 3-5 |

| SECTION | IV CARD READER             |     |

| / 1     | Introduction               | 4_1 |

| 4.1       | Introduction 4-1                                               |

|-----------|----------------------------------------------------------------|

| 4.2       | System Configuration 4-1                                       |

| 4.3       | Card Reader Instructions 4-1                                   |

| 4.3.1     | Initialization                                                 |

| 4.3.2     | Card Reader Status Transfers 4-2                               |

| 4.3.3     | Card Reader Instructions, Formats and Descriptions             |

|           | STST 4-2                                                       |

|           | RD, ARD, PON 4-3                                               |

|           | POFF, PCOMP, ETST 4-4                                          |

|           | RDS 4-5                                                        |

|           | Card Reader Controller Code Conversions                        |

|           | Card Reader Controller Card To Word Count Conversion Table 4-9 |

|           |                                                                |

| SECTION N |                                                                |

## SECTION V DISC FILE

| 5.1   | Introduction                | 5-1 |

|-------|-----------------------------|-----|

| 5.2   | System Configuration        | 5-1 |

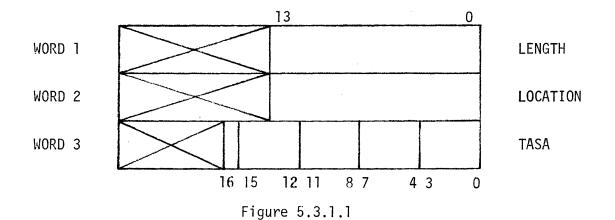

| 5.3   | Disc Subsystem Instructions | 5-1 |

| 5.3.1 | Initialization              | 5-1 |

| 5.3.2 | General Status              | 5-2 |

vi

SECTION V DISC FILE (Continued)

| 5.3.3 | Instruction Format        | 5-3 |

|-------|---------------------------|-----|

|       | STST, ETST, RDST          | 5-3 |

|       | RD, ARD, PON              | 5-4 |

|       | POFF, PCOMP               | 5-5 |

|       | Appendix of Disc Commands | 5-6 |

## SECTION VI MAGNETIC TAPE

| 6.1      | Introduction                   | 6-1         |

|----------|--------------------------------|-------------|

| 6.2      | System Configuration           | 6-1         |

| 6.3      | Tape Command Codes             | 6-1         |

|          | STST, RDS                      | 6-4         |

|          | REWC, ETST, PON, POFF          | 6-5         |

|          | PCOMP, WRIT, SKWR, WRITM       | 6-6         |

|          | RDT, ART, RSKIPF               | 6-7         |

|          | RSKIPB, FSKIPF, FSKIPB, REWIND | 6-8         |

| APPENDIX | A FST-1 ABBREVIATIONS          | A-1         |

| APPENDIX | B FST-1 INSTRUCTION MNEMONICS  | B <b>-1</b> |

Page

## FIGURES

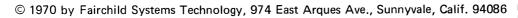

| 1.3.1   | FST-1 system organization with one peripheral interfaced to the accumulator bus and another with DMA interface | Page |

|---------|----------------------------------------------------------------------------------------------------------------|------|

|         | •••••••••••••••••••••••••••••••••••••••                                                                        | 1-2  |

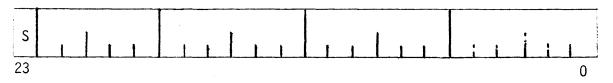

| 1.4.4.1 | FST-1 Main Data Paths                                                                                          |      |

|         |                                                                                                                | 1-3  |

| 2.1.1   | FST-1 Computer Control Panel                                                                                   |      |

|         | •••••••••••••••••••••••••••••••••••••••                                                                        | 2-2  |

| 5.3.1.1 | DCU Data Control Words                                                                                         |      |

|         | •••••••••••••••••••••••••••••••••••••••                                                                        | 5-2  |

viii

| Table 1: | TCU Command Codes                       | Page |

|----------|-----------------------------------------|------|

|          | • • • • • • • • • • • • • • • • • • • • | 6-2  |

| Table 2: | DCB and Data Formats                    |      |

|          |                                         | 6-3  |

## TABLES

## SECTION I

## FST-1 SYSTEM DESCRIPTION, FORMATS AND INSTRUCTIONS

## 1.1 INTRODUCTION

This section discusses the Central Processor Unit, its organization, reserved memory, instruction repertoire, and the accumulator and memory interface system.

Note: Octal notation is used as a convenient shorthand when discussing the binary contents of computer words, registers, etc. Thus operation codes and addresses should always be read as octal values.

## 1.2 CENTRAL PROCESSOR UNIT

The FST-1 Central Processor Unit (CPU) is a high-speed general purpose digital computer, with the following characteristics:

- 24-bit word length.

- Two's complement binary arithmetic.

- 1.75µsec complete cycle time.

- Eight hardware index registers.

- Indirect addressing with most instructions.

- Basic core memory of 4096 words, expandable in modules of 4096 words, up to 16,384 words, all directly addressable.

- Two memory buses for simultaneous access to two memory banks in systems having 8192 or more words of core.

- Direct Memory Access (DMA) on both memory buses.

- The standard DMA interface unit allows data to be either stored or retrieved at a rate of 571,428 words per second per memory bus, or 1,142,856 words per second total.

- The basic system has a capacity of up to 16 DMA channels on each memory bus.

- Sixteen external interrupt channels are also available on the basic system.

- Standard input/output equipment includes a console typewriter with attached paper tape reader and punch, card reader, disk, line printer and magnetic tape.

## 1.3 SYSTEM ORGANIZATION

The FST-1 System is "memory oriented." That is, the memory is the central part of the system, with all other system components interfaced as peripherals to memory. The memory system has two independent memory buses, with each bus having its own priority system. The CPU and all peripherals are assigned access priority when they are interfaced to the memory system.

## Figure 1.3.1

### FST-1 System Organization with one Peripheral Interfaced to the Accumulator Bus and another with DMA Interface

Peripherals may be interfaced to either or both memory buses. The size of core memory can be 4096, 8192, 12,288, or 16,384 words. Any or all of the 4K blocks of memory can be tied to either bus. The CPU has the lowest memory access priority.

The accumulator bus provides a data and control path between the CPU and peripheral controllers. This bus is used by the CPU to select peripheral units and to read either data or status from the peripherals. In addition, it is used to transmit data and control to the peripheral controllers. The accumulator bus is also used when a peripheral requests an interrupt. The bus is used to establish priority between the interrupting devices and to direct the transfer of program control.

## 1.4 CENTRAL PROCESSOR UNIT ORGANIZATION

## 1.4.1 Introduction

This section describes the word and instruction formats and the use of the principal registers in the FST-1.

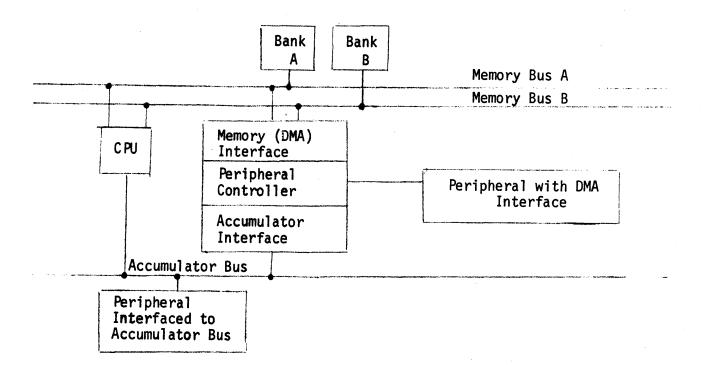

## 1.4.2 Word Format

The FST-1 CPU word is 24 bits. The bit positions are numbered from right to left, beginning with 0. Bit 23 of data words is the sign bit. Negative numbers are stored in two's complement form.

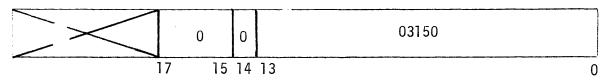

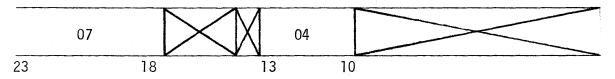

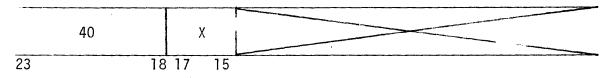

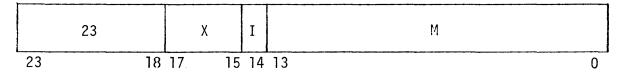

1.4.3 Instruction Formats

Standard Instruction Word

The standard instruction word format consists of a six (6) bit operation code field, a three (3) bit index field, a one (1) bit field used to specify direct (0) or indirect (1) addressing and a fourteen (14) bit address field.

| Operation Code | Index | I  | Operand Address |   |  |

|----------------|-------|----|-----------------|---|--|

| 23 18          | 17 15 | 14 | 13              | 0 |  |

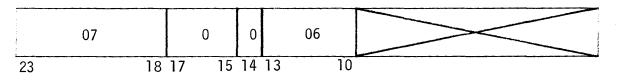

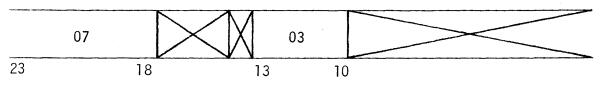

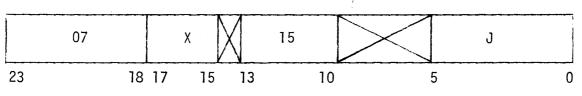

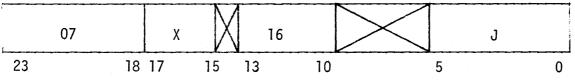

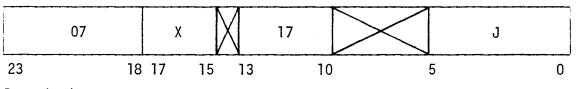

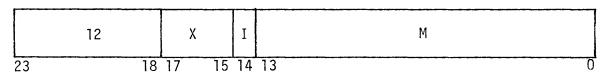

Augmented Instructions

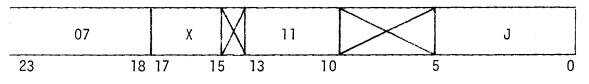

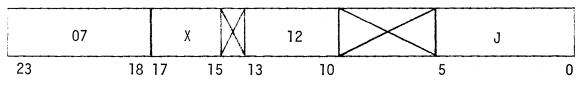

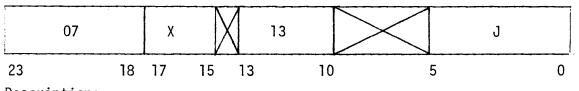

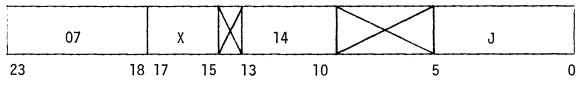

Some instructions do not require a fourteen bit address field, as used in the standard instruction word format. These instructions have operation code 07 and use bits 10 through 13 to 'augment' the 07 operation code. (See also Section 1.7.9.) An example of an augmented operation code is shown below:

Augmented Instruction Word:

|   | 07   |   | Inde | Эх | I  | /  | Augment |     |   | Shift Count |   |

|---|------|---|------|----|----|----|---------|-----|---|-------------|---|

| ź | 23 1 | 8 | 17   | 15 | 14 | 13 | 10      | 9 6 | 5 |             | 0 |

## 1.4.4 Registers

The main registers of the FST-1 CPU are described below:

The Command Register, CR, is a 24-bit register which holds the current instruction for execution.

The A Register or Accumulator (24 bits) is the main arithmetic register.

The <u>E</u> Register is a 24-bit extension of the accumulator. It is used during double precision instructions, such as double-precision additions, multiplications, etc.

The <u>B</u> Register is the memory buffer register (24 bits). Operands are stored in <u>B</u> while the CPU executes arithmetic or data transfer instructions.

The <u>P</u> Register (14 bits) is the program counter. P contains the memory address of the instruction which follows the instruction currently in the command register.

The <u>X</u> Registers (i4 bits each) are eight addressable index registers. Registers XI through X7 may be used for instruction indexing, while X0 may not. X0 is used as the comparison index for both the ADD-TO-INDEX instructions or as a simple counter.

The W Register (24 bits) is the console switch register. It is used for manually loading the accumulator, command register and P counter. The W register can also be loaded into the accumulator under program control.

The <u>R</u> Register. This 6 bit register is the interrupt address director register. It holds one of 63 indirect addresses, to which an external interrupt can cause a program control transfer.

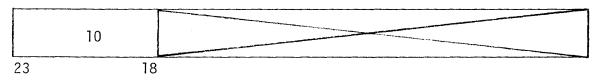

The CPU Registers are interfaced to the memory system buses with the memory interface logic. They are also interfaced to the peripheral controllers on the accumulator bus through the accumulator interface logic. The main data paths are illustrated in Figure 1.4.4.1.

## 1.4.5 Reserved Memory

There are 64 reserved memory locations in the FST-1 memory system. Memory address zero  $(00000_8)$  is reserved as a return address storage location for the BSZ instruction. Memory locations 1 through 63  $(00001_8 - 00077_8)$  are reserved for indirect address storage for the external interrupt system. If the external interrupt system is not in use, these memory locations are available for normal program use.

## Figure 1.4.4.1

FST-1 Main Data Paths

#### 1.5 ADDRESS MODIFICATION

## 1.5.1 Introduction

FST-1 instructions can be address modified by means of either indexing or indirect addressing.

## 1.5.2 Indexing

Address modification by indexing is possible for all memory reference instructions, except those instructions which use bits 15, 16 and 17 for a purpose other than indexing, i.e., BAT, BOI, and BOS. Prior to the execution of an indexable instruction, the contents of the index register specified by bits 15, 16 and 17 of the instruction word are added to the operand address field of the instruction word. The resultant sum replaces the original operand in the command register.

For example, if index register 3 contains 00001 and the command register contains the following instruction:

| 20 |    | 3  |    | 0  | 00403 |   |

|----|----|----|----|----|-------|---|

| 23 | 18 | 17 | 15 | 14 | 13    | 0 |

the 00403 and the 00001 are added together, the sum replacing the 00403, so that the instruction in the command register changes to:

| 1<br>2<br>1 | 20 |    | 0    | 0      | 00404 |   |

|-------------|----|----|------|--------|-------|---|

| 23          |    | 18 | 17 1 | 5 14 1 | 3     | 0 |

The instruction shown immediately above is the instruction actually executed. Note that the index address has been changed to 0. Index address 0 is interpreted as "no indexing" rather than specifying index register 0. It follows then that INDEX REGISTER 0 CANNOT BE SPECIFIED FOR ADDRESS MODIFICATION.

## 1.5.3 Indirect Address Modification

The second technique available in the FST-1 for instruction address modification is indirect address modification. Indirect address modification applies to all memory reference instructions except BAT, BOI, BOS and SPU. Indirect address modification occurs when bit 14 of an instruction word is set. For example:

|    | 20 |    | 0     | 1    | 02000 |   |

|----|----|----|-------|------|-------|---|

| 23 |    | 18 | 17 1! | 5 14 | 4 13  | 0 |

is a typical instruction specifying indirect address modification. The indirect address modification operation occurs as follows:

The instruction operand address is used to fetch a new operand address, indirect flag and index address bits from memory.

For example, if memory location 02000 contained

then the above ADD instruction would be equivalent to:

| 20    | 0     | 0  | 03150 |   |

|-------|-------|----|-------|---|

| 23 18 | 17 15 | 14 | 13    | 0 |

The FST-1 always performs indexing prior to indirect address modification. It is possible to index an instruction, fetch an indirect address word, which, when bits 0-17 are substituted in the instruction, may create another indexing operation and another indirect address modification. This in turn may cause another index operation and another indirect address modification, and so on. There is no theoretical limit to the number of indirect address cycles.

## 1.6 PERIPHERAL INTERFACE ORGANIZATION

#### 1.6.1 Introduction

Peripherals are controlled by the FST-1 CPU via the Accumulator Bus. The accumulator bus is a programmed Input/Output channel. The Select Peripheral Unit (SPU) instruction commands CPU-peripheral communication via the accumulator bus. The accumulator bus is time-shared during the execution of a Select Peripheral Unit instruction to provide a peripheral unit address and command and a 24-bit data transfer either to or from the addressed peripheral. Peripheral status is also transmitted via the accumulator bus during every Select Peripheral Unit instruction execution.

Special synchronization signals allow for the data lines of the accumulator bus to be used as program interruption requests. Sixteen levels of priority interrupt request are available in the FST-1 system. Honored interruptions require the requestor to submit a six-bit interrupt identification code via the accumulator bus. This code is interpreted as an address to one of the 63 low-core memory addresses (location  $00000_8$  excluded) for purposes of interruption servicing.

#### 1.6.2 Program Interruption

The program interruption facilities of the FST-1 computing system provide for the diversion of the CPU from its normal tasks to the processing of a subsidiary task in response to an external request. Sixteen fixed-priority levels of interrupt are available. Each individual request may be enabled or disabled through the Select Peripheral Unit (SPU) command, or, the entire structure of interrupts may be enabled or disabled via the Set State (SST) or Reset State (RST) instructions, respectively.

Interruption of the normal program is allowed at the conclusion of one program step, while its successor is being fetched from memory. At this time, the presence of an interrupt request causes the command register to be loaded with an indirect Branch Store Memory (BSM) command rather than a new instruction word. The Program Counter is inhibited so as to preserve the location of the supplanted instruction. The BSM command word also obtains a six-bit address referencing one of the addresses  $01_8$  through  $77_8$  from the interrupt requestor.

These 63 memory locations constitute a branch table for entry to subroutines designed for processing the various interrupt conditions. This table contains appropriate addresses supplied by the interrupt requestor for the prevailing interrupt condition or conditions.

The address stored in the branch table is used in the normal way by the BSM command; (indexing and further indirection may occur). After tracing through all indirections, the final address receives the contents of the indicators GT, EQ, LT, BE & OV and the contents of the program counter, which locates the return point to the interrupted program. Program control resumes at the next sequential address following the return address.

The requestor of an accepted interrupt maintains its interrupt request until receipt of an acknowledgement. However, at the recognition of the interrupt by the CPU, the Interrupt-Enable flip-flop is cleared, which in turn removes the interrupt synchronizing signal from all peripherals. Therefore, interrupt requests are masked until the Interrupt Enable flip-flop is again set. A Set-State instruction is required for this purpose.

Each interrupt routine must provide for a completion SPU instruction to return the interrupt requestor to its normal state. Furthermore, an SST instruction is needed to re-enable the interrupt system. Return to the main program via an indirect unconditional branch (BRU\*) on the return address, placed at the beginning of the subroutine by the interrupt induced BSM command, will restore the indicators GT, EQ, LT, BE, and OV to their original state.

## 1.7 INSTRUCTION REPERTOIRE

## 1.7.1 Introduction

This section discusses the instruction repertoire of the FST-1. It consists of nine instruction groups, totaling 48 instructions. Accompanying each instruction are examples coded as they would be for the FST-1 assembler.

## 1.7.2 Abbreviations

The appendix contains a list of abbreviations which are used in the description of machine instructions. Any abbreviation which is enclosed in parentheses is a reference to the contents of that particular register or memory location. For example, (M) is a reference to the contents of memory location M; (A) refers to the contents of the accumulator, etc.  $(A) \rightarrow M$  is read, "The contents of A go to memory location M."  $(M) + (A) \rightarrow A$  is read, "The contents of memory location M, plus the contents of A go to A." In the following instruction descriptions, M<sub>e</sub> is used to refer to the effective memory address, i.e., after both indexing and indirection.

Subscripts are used to reference individual bits or groups of bits in the registers. For example,  $A_0$  represents the "0" bit of the accumulator;  $A_{0-7}$  represents the least significant eight bits of the accumulator, etc.

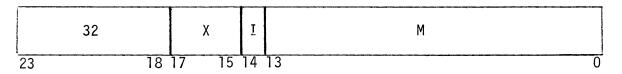

## 1.7.3 Instruction Format(s)

An instruction word generally has four parts: an Operation Code, an Index Address, an Indirect Address Indicator, and an Operand Address. If an insturction can be indexed, the instruction format will include an X, (which designates the index to be used). If an instruction can be indirect address modified, the format will include an I. If the instruction can reference memory, then the M in the instruction format is the memory location of the operand.

#### 1.7.4 Assembler Formats

Each of the instruction descriptions which follow is illustrated with an example of the appropriate FST-1 symbolic assembly code. The FST-1 Assembler manual should be consulted for the details of instruction, formats, conventions, etc. The discussion presented here will clarify the instruction descriptions.

All instructions have an Opcode and most of them also have an Operand, although some others, (such as TCA), do not. "Opcode" is the mnemonic name for the command or Operation Code and "Operand" is the symbolic address of the operand, etc. . .

There are two basic operand formats: indexable and non-indexable, viz:

(1) Indexable instruction: Symbolic address, index

| Examples: |          |          |            |

|-----------|----------|----------|------------|

| STA       | BUFFER,5 | 5        |            |

| LDA       | TABLE (r | no index | specified) |

(2) Non-indexable instruction:

(a) index register, operand address

(b) indicator value, operand address

(c) state flip-flop, operand address

Examples:

BOS 5,L1 BOS PASSL,L232 BOI 3,LEQ LDX 6,5 LDX PNTRX,TABLE-2

Indirect addressing is noted by an asterisk (\*) immediately following the opcode mnemonic, viz:

LDE\* TEMP1,3 MUL\* FACTOR

1.7.5 Cycles Required

In each of the instruction descriptions which follow, the number of machine cycles required to execute the instruction is given - exclusive of indexing and indirection. A memory cycle is 1.75 microseconds in duration.

### 1.7.6 Arithmetic Instructions

This section contains the following 10 arithmetic instructions: TCA, DTC, ADD, SUB, DADD, DSUB, MUL, DIV, AOM and SOM.

## TCA TWO'S COMPLEMENT A REGISTER

Definition: Two's Complement of  $(A) \rightarrow A$

Cycles Required: 1

Instruction Format (Augmented):

|    | 07 |    | 0     | 0    | 01 |    |  |

|----|----|----|-------|------|----|----|--|

| 23 |    | 18 | 17 15 | 5 14 | 13 | 10 |  |

Description: The contents of the accumulator are two's complemented and placed in the accumulator.

Assembler Format: TCA

DTC DOUBLE TWO'S COMPLEMENT

Definition: Two's Complement of (A and E)  $\rightarrow$  A and E

Cycles Required: 2

Instruction Format (Augmented):

Description: The contents of A and E are two's complemented and the result is placed in A and E.

Assembler Format: DTC

ADD ADDITION

Definition: (A) + (M<sub>e</sub>) $\rightarrow$ A

Cycles Required: 2

Instruction Format:

| 20    | Х     | I    | М  |   |

|-------|-------|------|----|---|

| 23 18 | 17 15 | 14 1 | 13 | 0 |

Description: The contents of memory location, M, are added algebraically to the contents of the accumulator, with the sum being stored in the accumulator. The contents of memory are not changed. An overflow from the accumulator will set the overflow flag OV, indicating the result is incorrect.

Assembler Format: ADD\* TABLE+1,2

SUB SUBTRACTION

Definition: (A) -  $(M_{\rho}) \rightarrow A$

Cycles Required: 2

Instruction Format:

| 22    | Х     | I  | М  |   |

|-------|-------|----|----|---|

| 23 18 | 17 15 | 14 | 13 | 0 |

Description: The contents of memory location,  $M_e$ , are subtracted algebraically from the contents of the accumulator, with the difference being stored in the accumulator. The contents of memory are not changed. An overflow from the accumulator will set the overflow flag OV, indicating the result is incorrect.

Assembler Format: SUB\* TABLE+1,7

DADD DOUBLE ADDITION

Definition: (A and E) + ( $M_e$  and  $M_e$  + 1)  $\rightarrow$  A and E, where  $M_e$  is an even numbered address.

Cycles Required: 4

Instruction Format:

|    | 30 |    | Х     | I  | · M |   |

|----|----|----|-------|----|-----|---|

| 23 |    | 18 | 17 15 | 14 | 13  | 0 |

Description: The contents of memory locations,  $M_{e}$  and  $M_{e}$  + 1 are added algebraically to the contents of A and E. Bits 23 of  $(M_{e})$  and (A) are the operand signs. The sum is stored in A and E as a 47 bit signed number with A containing the most significant half of the sum. The sign of the sum is stored in A<sub>23</sub>. Two's complement is used for negative numbers. The contents of memory are unchanged by the operation. An overflow will set the overflow flag OV, indicating the result is incorrect.

Assembler Format: DADD\* TABLE+1

DSUB DOUBLE SUBTRACTION

Definition: (A and E) - ( $M_e$  and  $M_e$  + 1)  $\rightarrow$  A and E, where  $M_e$  is an even numbered address.

Cycles Required: 4

Instruction Format:

Description: The contents of  $M_e$  and  $M_e + 1$  are subtracted algebraically from the contents of A and E. Bits 23 of  $(M_e)$  and (A) are the signs of the operands. The difference is stored in A and E as a 47 bit signed number, with A containing the most significant half. The sign of the difference is stored in A<sub>23</sub>. Two's complement notation is used for negative numbers. The contents of memory are unchanged by the operation. An overflow will set the overflow flag OV, indicating the result is incorrect.

Assembler Format: DSUB\* TABLE+1

MUL MULTIPLY

Definition:  $(M_{\rho}) \times (A) \rightarrow A$  and E

Cycles Required: 25

Instruction Format:

|    | 34 |    | Х  |    | I  |    | Μ |   |

|----|----|----|----|----|----|----|---|---|

| 23 |    | 18 | 17 | 15 | 14 | 13 |   | 0 |

Description: The contents of memory location,  $M_e$ , are multiplied by the contents of the accumulator. The product is stored in A and E, with A containing the most significant half. A and  $M_e$  are assumed to be positive numbers. The contents of memory are not changed.

Assembler Format: MUL\* ALPHA

DIV DIVISION

Definition: (A and E)/(M<sub>e</sub>)  $\rightarrow$  E Remainder  $\rightarrow$  A

Cycles Required: 25

Instruction Format:

|    | 35      |    |    | Х  | I  |    | М  |   |

|----|---------|----|----|----|----|----|----|---|

| 23 | <b></b> | 18 | 17 | 15 | 14 | 13 | P. | 0 |

Description: The contents of A and E are divided by the contents of memory location  $M_{\rho}$ . The quotient is left in E and the remainder in A. The original contents of A, E and  $M_{\rho}$  are assumed to be positive. The contents of memory are not changed. A divide overflow will occur if  $(A) \geq (M_{\rho})$ . For this condition, the divide is terminated and the overflow flip flop is set. In the event of an overflow, A and E remain shifted left one place.

Assembler Format: DIV\* ROGER,2

AOM ADD ONE TO MEMORY

Definition:  $(M_e) + 1 \rightarrow M_e$

Cycles Required: 4

Instruction Format:

|    | 36 | X     | I     | M | <br>,<br>,<br>,<br>, |

|----|----|-------|-------|---|----------------------|

| 23 | 18 | 17 15 | 14 13 |   | <br>0                |

Description: The contents of memory location,  $M_e$ , are incremented by one (1). An overflow condition will cause the OV flag to be set. In the event of an overflow, the result of the operation is incorrect.

Assembler Format: AOM\* BETA

SOM SUBTRACT ONE FROM MEMORY

Definition:  $(M_e) - 1 \rightarrow M_e$

Cycles Required: 4

Instruction Format:

|    | 37 | X     | I     | М |   |

|----|----|-------|-------|---|---|

| 23 | 18 | 17 15 | 14 13 |   | 0 |

Description: The contents of memory location,  $M_e$ , are decremented by one (1). An overflow condition will cause the OV flag to be set. In the event of an overflow, the result of the operation is incorrect.

Assembler Format: SOM TEM1

## 1.7.7 Data Transfer Instructions

This section contains the following 8 data transfer instructions: RSR, EXC, STA, STE, LDA, LDE, DLD and DST.

RSR READ SWITCH REGISTER

Definition:  $(W) \rightarrow A$

Cycles Required: 1

Instruction Format (Augmented):

Description: The contents of the console switch register, W, are loaded in the A register.

Assembler Format: RSR

EXC EXCHANGE A AND E

Definition:  $(A) \rightarrow E$ ,  $(E) \rightarrow A$

Cycles Required: 1

Instruction Format (Augmented):

Description: The contents of the A register and the contents of the E register are exchanged.

Assembler Format: EXC

STA STORE A

Definition:  $(A) \rightarrow M_{\rho}$

Cycles Required: 2

Instruction Format:

|    | 14 | Х     | I  | М    |  |

|----|----|-------|----|------|--|

| 23 | 18 | 17 15 | 14 | 13 0 |  |

Description: The contents of the A register are stored in memory location,  $\rm M_{e}.$  The contents of A are not changed.

Assembler Format: STA\* ALP1,2

STE STORE E

Definition: (E)  $\rightarrow M_{e}$

Cycles Required: 2

Instruction Format:

|    | 15 | Х     | I  | М |   |

|----|----|-------|----|---|---|

| 23 | 18 | 17 15 | 14 |   | 0 |

Description: The contents of the E register are stored in memory location  $\rm M_{e}.$  The contents of E are not changed.

Assembler Format: STE\* TEMP5

LDA LOAD A Definition: (M<sub>e</sub>)→ A Cycles Required: 2 Instruction Format:

| 24                                       | Х              | I            | м                                                                   | i         |

|------------------------------------------|----------------|--------------|---------------------------------------------------------------------|-----------|

| 23 18                                    | 17 15          | 14           | 13                                                                  | 0         |

| Description: The c<br>lator A. The conte | contents of mo | of m<br>emor | emory location, M <sub>e</sub> , are copied into y are not changed. | the accum |

| Assembler Format:                        | LDA* TABI      | LE,X         | PNTR                                                                |           |

| LDE LOAD E (The Ac                       | cumulato       | r Ex         | tension)                                                            |           |

| Definition: (M <sub>e</sub> )→           | E              |              |                                                                     |           |

| Cycles Required: 2                       | 2              |              |                                                                     |           |

| Instruction Format:                      |                |              |                                                                     |           |

|                                          | <b></b>        | <b>-</b> 1   |                                                                     |           |

| 25                                       | Х              | Ι            | М                                                                   |           |

| 23 18                                    | 17 15          | 14           | 13                                                                  | 0         |

Description: The contents of memory location,  $\rm M_{e},$  are copied into the accumulator extension E. The contents of memory are not changed.

Assembler Format: LDE\* TABLE+1

### DLD DOUBLE E LOAD A AND E

Definition:  $(M_e \text{ and } M_e + 1) \rightarrow A$  and E, where  $M_e$  is an even numbered address. Cycles Required: 3

Instruction Format:

|    | 31 | х     | I     | М |

|----|----|-------|-------|---|

| 23 | 18 | 17 15 | 14 13 | 0 |

Description: The contents of memory location,  $\rm M_{e}$  and  $\rm M_{e}$  + 1, are loaded into A and E respectively. The contents of memory are not changed.

Assembler Format: DLD\* TABLE+5,2

DST DOUBLE STORE

Definition: (A and E)  $\rightarrow$  M<sub>e</sub> and M<sub>e</sub> + 1, where M<sub>e</sub> is an even numbered address.

Cycles Required: 3

Instruction Format:

| 3: | 3  | Х     | I  | Μ    | • |

|----|----|-------|----|------|---|

| 23 | 18 | 17 15 | 14 | 13 0 | - |

Description: The contents of the A and E registers are stored in memory locations,  $M_e$  and  $M_e$  + 1 respectively. The contents of A and E are not changed.

Assembler Format: DST TEMP2+2

### 1.7.8 Index Instructions

This section contains the following 5 instructions: LDX, LXA, ATX, STX and LAX.

Note on Index Register Usage: It is standard practice to use the index registers in the FST-1 in adjacent pairs, viz: X7 with X6, X5 with X4, X3 with X2 and X1 with X0. When so used, the odd index is the active, working index while the even index is the limit index for comparison purposes.

LDX LOAD INDEX

Definition:  $M_{\rho} \rightarrow X_{n}$

Cycles Required: 1

Instruction Format:

|    | 05 |    | Х  |    | I  |    | М |   |

|----|----|----|----|----|----|----|---|---|

| 23 |    | 18 | 17 | 15 | 14 | 13 |   | 0 |

Description: The effective address,  $M_e$  is loaded into the addressed index register. Index address modification does not occur, but a special form of indirect addressing does take place: bits 14-0 are replaced in the command register from memory address M, bits 17-15 being obtained from the current instruction word and not from memory address M. (See also ATX and STX)

Assembler Format: LDX\* 7,200

LXA LOAD INDEX FROM A

Definition:  $(A_{0-13}) \rightarrow X_n$

Cycles Required: 1

Instruction Format (Augmented):

|    | 07 |    | Х     | 0  | 00 |    |  |

|----|----|----|-------|----|----|----|--|

| 23 |    | 18 | 17 15 | 14 | 13 | 10 |  |

Description: The addressed index register,  $X_n$ , is loaded from the contents of the accumulator bits,  $A_0$  through  $A_{13}$ . Index address modification does not occur.

Assembler Format: LXA INDX3

ATX ADD TO INDEX

Definition:  $M_e + (X) \rightarrow X$

Cycles Required: 2

Instruction Format:

|    | 11 | Х  | I     | M  |   |

|----|----|----|-------|----|---|

| 23 | 18 | 17 | 15 14 | 13 | 0 |

Description: The contents of the addressed index register are added to the effective address (after indirect address modification) and the sum is placed back in the addressed index register. Then the GT, EQ, and LT indicators are set by comparing  $X_n$  (the addressed index register) to  $X_{n-1}$  ('n' must be odd). Index address modification does not occur.

Note that only bits 14-0 are replaced in the command register from memory address M under indirection. (See also LDX and STX).

Assembler Format: ATX\* 5, TABLE1

STX STORE

Definition:  $(X_n) \rightarrow M_e$

Cycles Required: 2

Instruction Format:

| <u></u> , | 16 | Х     | I     | М |   |

|-----------|----|-------|-------|---|---|

| 23        | 18 | 17 15 | 14 13 |   | 0 |

Description: The contents of the addressed index register X are stored in memory location  $M_e$ . The contents of X are unchanged. Bits 14-23 of  $M_e$  are zeroed. Index address modification does not occur, but a special form of indirect addressing does take place: bits 14-0 are replaced in the command register from memory address M, bits 17-15 being obtained from the current instruction word and not from memory address M. (See also ATX and LDX).

Assembler Format: STX 5,TEMP1

LAX LOAD A FROM INDEX

Definition:  $(X_n) \rightarrow A$

Cycles Required: 1

Instruction Format:

Description: The contents of the specified index register are transferred to A. Bits 23-14 of A are zeroed.

Assembler Format: LAX 2

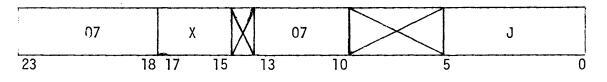

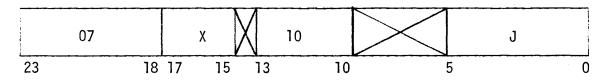

### 1.7.9 Shift Instructions

This section consists of the following 9 augmented instructions: DSN, SR, LS, SA, SL, DSR, LDS, DSA and DSL. The execution time depends upon the number of bit positions to be shifted.

The following table illustrates the execution time versus the number of shifts:

2 cycles for  $J_e < 9$ 3 cycles for  $9 < J_e < 14$ 4 cycles for  $14 < J_e < 19$ 5 cycles for  $19 < J_e < 24$ 6 cycles for  $24 < J_e < 29$ 7 cycles for  $29 < J_e < 34$ 8 cycles for  $34 < J_e < 39$ 9 cycles for  $44 < J_e < 49$

Expressed as a formula:

$T = 2 + [(J_e-9)/5]$  cycles.

DSN DOUBLE SHIFT NORMALIZE

Definition: Normalize A and E

Cycles Required: 2 + [(J-9)/5]

integer

Instruction Format:

Description:

The contents of A and E are shifted left  $J_e$  bit positions, or until the information in bit position  $A_{23}$  differs from that in  $A_{22}$ .  $E_{23}$  shifts into  $A_0$  and zeros are entered into  $E_0$ . At the termination of the shifting, the contents of the shift counter are stored in Index register zero. DSN may use indexing; the contents of X are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: DSN 10

SR SHIFT RIGHT

Definition: Shift (A) Right Arithmetical

Cycles Required: 2 + [(J-9)/5]

integer

Instruction Format:

### Description:

The contents of the A register are shifted right  $J_e$  bit positions. The sign bit, bit 23, of the A register is copied into bit position 22 as the register is shifted. Bits shifted from  $A_0$  are lost. SR may use indexing; the contents of  $X_n$  are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: SR 5

LS LOGICAL SHIFT Definition: Shift (A) Right Logical Cycles Required: 2 + [(J-9)/5] integer

Instruction Format:

Description:

The contents of the A register are shifted right  $J_e$  bit positions, zeros being entered into A from the left (A23). LS may use indexing; the contents of X are added to J to obtain the modified shift count,  $J_e$ .

Assembler Format: LS 5

SA SHIFT AROUND

Definition: Shift (A) Left Around

Cycles Required: 2+ [(J-9)/5]

integer

Instruction Format:

Description:

The contents of the A register are shifted left around  $J_e$  bit positions, with A<sub>23</sub> shifting into A<sub>0</sub>. SA may use indexing; the contents of the X are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: SA 4,5

SL SHIFT LEFT

Definition: Shift (A) Left End Off

Cycles Required: 2 + [(J-9)/5]

integer

Instruction Format:

Description:

The contents of the A register are shifted left  $J_e$  bit positions, with zeros being entered into  $A_0$ . SL may use indexing; the contents of X are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: SL 0,3

DSR DOUBLE SHIFT RIGHT

Definition: Shift A and E Right Arithmetical

Cycles Required: 2 + [(J-9)/5] integer

Instruction Format:

Description:

The contents of the A and E registers are shifted right (A<sub>0</sub> shifting into E<sub>23</sub>)  $J_e$  bit positions. The sign of A (A<sub>23</sub>) does not change during this shift operation and is repeatedly copied into A<sub>22</sub> during the shift. DSR may use indexing; the contents of X are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: DSR 25

LDS LOGICAL DOUBLE SHIFT

Definition: Logical Shift A and E Right

Cycles Required: 2 + [(J-9)/5] integer

Instruction Format:

Description:

The contents of A and E are shifted right  $J_e$  bit positions. Zeros are entered into A<sub>23</sub>. In addition, A<sub>0</sub> is shifted into E<sub>23</sub>, while bits shifted out of E<sub>0</sub> are lost. LDS may use indexing; the contents of X<sub>n</sub> are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: LDS 0,5

DSA DOUBLE SHIFT AROUND

Definition: Shift A and E Around Left

Cycles Required: 2+[(J-9)/5]

integer

Instruction Format:

Description:

The contents of A and E are shifted left around J<sub>e</sub> positions, (A<sub>23</sub> going to E<sub>0</sub> and E<sub>23</sub> going to A<sub>0</sub>). DSA may use indexing; the contents of X are added to J to obtain the modified shift count, J<sub>e</sub>.

Assembler format: DSA 24

# DSL DOUBLE SHIFT LEFT

Definition: Shift A and E Left

Cycles Required: 2 + [(J-9)/5]

integer

Instruction Format:

Description:

The contents of A and E are shifted left  $J_e$  bit positions;  $E_{23}$  is shifted into  $A_0$ . Zeros are entered into  $E_0$  and the bits shifted out of  $A_{23}$  are lost. DSL may use indexing; the contents of X are added to J to obtain the modified shift count,  $J_e$ .

Assembler format: DSL 20

1.7.10 Logical Instructions

This section contains the following 4 logical instructions; RUM, EOR, A ND and OR.

RUM REPLACE UNDER MASK

Definition:  $(M_e) \land (E) \lor (A) \land (\overline{E}) \rightarrow A$

on a bit by bit basis.

Cycles Required: 2

Instruction Format:

| 17    | х     | I  | М  |   |

|-------|-------|----|----|---|

| 23 18 | 17 15 | 14 | 13 | 0 |

Description:

The contents of  $M_e$  are masked into A under the control of E. For each "l" bit in E, the corresponding bit in A is replaced by the corresponding bit in  $M_e$ . Neither ( $M_e$ ) nor (E) change.

Assembler format: RUM\* 2020

EOR EXCLUSIVE OR

Definition: (A)  $\forall$  (M<sub>e</sub>)  $\rightarrow$  A

Cycles Required: 2

Opcode Format:

| 21                                                                                                                                   | х                     | I        |    | Μ |   |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|----|---|---|

| 23 18                                                                                                                                | 17 15                 | 14       | 13 |   | 0 |

| Description:                                                                                                                         |                       |          |    |   |   |

| The contents of M <sub>e</sub> are "Exclusively ORed," with the contents of A on a bit<br>by bit basis, and the results stored in A. |                       |          |    |   |   |

| Assembler format:                                                                                                                    | EOR TEN               | 4P1-     | +] |   |   |

| AND LOGICAL AND                                                                                                                      |                       |          |    |   |   |

| Definition: (A) A                                                                                                                    | $(M_e) \rightarrow A$ |          |    |   |   |

| Cycles Required:                                                                                                                     | 2                     |          |    |   |   |

| Instruction Format:                                                                                                                  |                       |          |    |   |   |

|                                                                                                                                      |                       | <b>.</b> |    |   |   |

| 26                                                                                                                                   | х                     | I        |    | М |   |

23 18 17 15 14 13

Description:

The contents of  ${\rm M}_{\rm e}$  and the A register are "ANDed" on a bit by bit basis and the results stored in A.

Assembler format: AND TEMP1

0

OR LOGICAL OR (INCLUSIVE OR)

Definition: (A)  $(M) \rightarrow A$

Cycles Required: 2

Instruction Format:

|    | 27 | х     | I  | М  |   |

|----|----|-------|----|----|---|

| 23 | 18 | 17 15 | 14 | 13 | 0 |

Description:

The contents of  $\rm M_{\rm e}$  and the A register are "ORed" on a bit by bit basis and the results stored in A.

Assembler Format: OR\* 1000

### 1.7.11 State Control Instructions

This section consists of 2 instructions: "SET STATE" and "RESET STATE", both of which are augmented instructions. The state flip flops affected by these instructions are defined by  $C_e$ , the least significant 10 bits of the instruction, modified by the contents of X. The ten state flip flops which are affected by these instructions are: SWO, SW1, SW2, SW3, SW4, SW5, SW6, and SW7, the interrupt enable flip flop IE, and the overflow indicator OV.

The individual controls for these indicators are the set state and reset state instruction bits,  $0_0$  through  $0_9$ , respectively.

If the effective address of the set state (or reset state) instruction has a logical one in the least significant bit, bit  $0_0$ , SWO will be set (or reset) by the instruction.

If  $0_0$  is a logical zero, SWO will not be changed. SWI will be set (reset) if a logical one exists in bit  $0_1$  of the effective address of the instruction.

Any number of the state flip flops can be set (or reset) with one instruction execution.

| Operand Address Bit | State Flip Flop Affected |

|---------------------|--------------------------|

| 00                  | SWO                      |

| 01                  | SW1                      |

| 0 <sub>2</sub>      | SW2                      |

| 03                  | SW3                      |

| 04                  | SW4                      |

| 0 <sub>5</sub>      | SW5                      |

| 06                  | SW6                      |

| 07                  | SW7                      |

| 08                  | IE                       |

| 0 <sub>9</sub>      | Ον                       |

# SST SET STATE

Definition: Set States Defined by C

Cycles Required: 1

Instruction Format:

|    | 07 |   | 02 |      | С |   |

|----|----|---|----|------|---|---|

| 23 | 18 | } | 13 | 10 9 |   | 0 |

Description:

Execution of the SET STATE instruction will cause any of ten state flip flops to be set.

Assembler Format: SST, SWO, SW1, SW4, OV

Note: A special assembler mnemonic exists for setting bit  $O_8$  (IE). This is IEN for Interrupt Enable.

Assembler Format: IEN

# RST RESET STATE

Definition: Reset States Defined by C

Cycles Required: 1

Instruction Format:

Description:

The execution of the Reset State instruction will cause the state flip flops addressed to be reset.

Assembler Format: RST, SW2, SW3, IE, OV

Note: A special assembler mnemonic exists for resetting bit  ${\rm O}_8$  (IE). This is IDA for Interrupt Disable.

Assembler Format: IDA

1.7.12 Compare Instruction (1 instruction).

CAM COMPARE A WITH MEMORY

Definition: The contents of A, (A), are compared with the contents of  $M_e$ ,  $(M_e)$ . The indicators GT, EQ, LT and BE are set accordingly.

Cycles Required: 2

Instruction Format:

Description:

The contents of A are compared with the contents of memory location  $M_e$ . The greater than (GT), equal (EQ), less than (LT), or bit equal (BE) indicators are set in accordance with the outcome of the comparison as described below:

- 1. If (A) >  $(M_{\rho})$  the GT indicator is set,

- 2. If (A) =  $(M_e)$  the EQ indicator is set,

- 3. If (A) <  $(M_{\rho})$  the LT indicator is set,

- 4. BE is set if a logical one exists in any corresponding bit positions of both A and  $M_e$ . For example, if the fifth bit of A is a one, and the fifth bit position of  $M_e$  is also a one, BE will be set when the comparison is complete.

The contents of  $\mathrm{M}_{\mathrm{p}}$  are not changed.

Assembler Format: CAM TEMP5

# 1.7.13 Transfer of Control Instructions

This section consists of 7 instructions which effect transfer of control (or branching). They are: BAH, BRU, BAT, BOI, BOS, BSM and BSZ.

BAH BRANCH AND HALT

Definition: Branch to  $M_{\rho}$  and Halt

Cycles Required: 1

Instruction Format:

|   | 00    | . X     | I  | 11   |   |

|---|-------|---------|----|------|---|

| 2 | 23 18 | 3 17 15 | 14 | 13 0 | ¥ |

Description:

Program Control is transferred to  $M_e$ , after which program execution is halted. The next instruction, which will be executed if the start switch is actuated, is displayed in the command register indicators.

Assembler Format: BAH START2

# BRU BRANCH UNCONDITIONALLY

Definition: Branch Unconditionally to  $M_{\rho}$

Cycles Required: 1

Instruction Format:

|    | 01 | x  | I     |    | М |   |

|----|----|----|-------|----|---|---|

| 23 | 18 | 17 | 15 14 | 13 |   | 0 |

Description:

The BRU instruction will transfer program control unconditionally to  $\rm M_{e}.~BRU$  can be indexed and indirect address modified.

An Indirect Address modification of BRU will set the five indicators OV, GT, LT, EQ, and BE from bit positions 23, 22, 21, 20 and 19 of the memory location containing the effective address word. For example, if bit position 23 of the memory location containing the  $M_e$  for BRU contains a one-bit, OV will be set during execution of the BRU instruction. Bit 22, containing a one, will cause GT to be set, etc.

An indirect BRU is generally used as a return branch for either a BSM (branch, store return at location M") or a BSZ ("branch store return at location zero") instruction. Note that this restores the five indicators to the states which existed when either a BSM or BSZ instruction was executed.

Assembler Format: BRU\* START+5

#### BAT BRANCH A REGISTER TEST

Definition: Branch to M on A Register Test

Cycles Required: 1

Instruction Format:

| Γ | · · · · · · · · · · · · · · · · · · · |         |      |

|---|---------------------------------------|---------|------|

|   | 02                                    | К       | М    |

| 2 | 3 18                                  | 3 17 14 | 13 0 |

Description:

The BAT instruction will transfer program control to M, dependent upon the contents of the accumulator. The accumulator contents are tested for positive, zero, negative or odd states.

BAT can neither be indexed nor address modified. The K-field (bits 17-14) specifies the state of A to be tested. If bit 17 is a one, program control will be transferred to M, providing the contents of A are positive ( $A_{23}$ =0). If bit 16 is a one, program control will be transferred to M, providing the contents of A are zero, etc. Combinations of states are allowed. For example, if both bits 17 and 14 are ones, program control will be transferred to M if A is positive or if A is odd ( $A_0$ =1).

Note: Zero is an exclusive state and is neither positive nor negative.

Assembler Format: BAT K,TEST2

Note: Seven special assembler mnemonics exist to aid the programmer. These are: BP, BPZ, BZ, BNZ, BN, BNEZ and BO for K = 10, 14, 4, 6, 2, 12 and 1, respectively, (i.e. Branch Positive, Positive or Zero, Zero, Negative or Zero, Negative, Not Equal to Zero and Odd, respectively).

Assembler Format: BPZ TEST2

#### BOI BRANCH ON INDICATOR

Definition: Branch to M if tested Indicator(s) set

Cycles Required: 1

Instruction Format:

| Γ  | 03 | К     | М    |          |

|----|----|-------|------|----------|

| 23 | 18 | 17 14 | 13 ( | <u>]</u> |

#### Description:

The BOI instruction will transfer program control to M, dependent upon the state of the four indicators GT, EQ, LT, or BE. BOI can neither be indexed nor indirect address modified. The value, K, is defined by bits 17-14 of the BOI instruction word. Bit 17 tests the state of the GT indicator, while bits 16, 15 and 14, respectively, test the states of the EQ, LT and BE indicators. If one or more of the tests is true, program control will be transferred to M. For example, if bits 17 or 16 are set in the BOI instruction word, then program control will be transferred to M, if either GT or EQ is set.

Assembler Format: BOI K, TEST2

Note: Seven special assembler mnemonics exist to aid the programmer. These are: BG, BGE, BE, BLE, BL, BNE and BBC for K = 10, 14, 4, 6, 2, 12 and 1, respectively, (i.e. Branch Greater, Greater or Equal, Equal, Less Than or Equal, Less Than, Not Equal and Bit Compare, respectively).

Assembler Format: BGE TEST2

# BOS BRANCH ON STATE

Definition: Branch to M if State K Set

Cycles Required: 1

Instruction Format:

| 2  |    |       |    |   |

|----|----|-------|----|---|

|    | 04 | K     | M  | 1 |

| 23 | 18 | 17 14 | 13 | 0 |

Description:

Program control is transferred to M, providing the switch or indicator defined by K is set. BOS can neither be indexed nor indirect address modified. Bits 17, 16, 15 and 14 of the BOS instruction word are decoded into sixteen values of K. The table below defines the appropriate switch or indicator tested for each value of K (expressed octally):

| K <sub>8</sub>                       | State Tested                                                                                                                                                 |                                        |                     |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Switch Flip Flop<br>Switch Flip Flop |                                        |                     |

| 10<br>11                             | Interrupt Enable<br>Overflow Indicator                                                                                                                       |                                        | testing,<br>reset.) |

| 12<br>13<br>14<br>15<br>16<br>17     | Console Switch<br>Console Switch<br>Console Switch<br>Console Switch<br>Console Switch<br>Console Switch                                                     | CSO<br>CS1<br>CS2<br>CS3<br>CS4<br>CS5 | <br>                |

Assembler format: BOS K,ALPHA

1-38

# BSM BRANCH STORE RETURN AT M

Definition: Branch to  $M_{\rho}$  + 1, Store Return at  $M_{e}$

Cycles Required: 2

Instruction Format:

Description:

Program control is unconditionally transferred to  $M_e$  + 1. The contents of the Program Counter, (current program address + 1) are stored in  $M_e$ , bits 0 - 13. The states of the five indicators OV, BT, EQ, LT, and BE, are stored in memory location  $M_e$  in bit positions 23, 22, 21, 20, and 19, respectively. These states are restored to the indicators when an indirect BRU instruction is used as a subroutine exit (see BRU description).

Assembler format: BSM PRTCH

# BSZ BRANCH STORE RETURN AT ZERO

Definition: Branch to  $M_{e}$ , Store Return at Memory Location Zero

Cycles Required: 2

Instruction Format:

| 13   | Х      | Ι      | М   |

|------|--------|--------|-----|

| 23 1 | 3 17 1 | 5 14 1 | 3 0 |

Description:

Program control is unconditionally transferred to  $M_{\rm e}$ . The contents of the Program Counter, (current program address + 1) are stored in memory location zero, bits 0 - 13.

The states of the five indicators OV, GT, EQ, LT, and BE, are stored in memory location zero, in bit positions 23, 22, 21, 20 and 19, respectively. These states are restored to the indicators when an indirect BRU instruction is used as a subroutine exit (see BRU description).

Assembler format: BSZ\* TEST3

1.7.14 Input/Output Instructions

This section consists of 1 multifunction instruction: SPU.

SPU SELECT PERIPHERAL UNIT

Definition: Select Peripheral Unit "U"

Cycles Required: 1

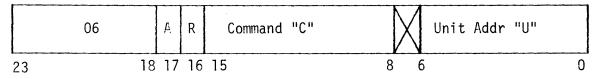

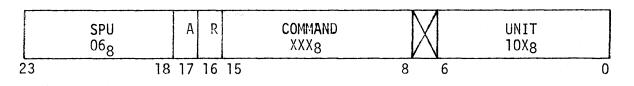

Instruction Format:

The Select Peripheral Unit is a multifunction instruction. These functions are:

- (1) the addressing of a peripheral unit for selection;

- (2) the transfer of a command to the addressed unit;

- (3) the transfer of up to 24 bits of information in either direction between the addressed unit and the CPU's accumulator;

- (4) the transfer of the unit's status to the CPU.

"U" defines the unit to be selected by the SPU command. The seven bits in this field allow the selection of up to 128 unique units.

"C" defines the command to the addressed peripheral unit. During the SPU execution, this command field is gated to the peripheral unit, where it is decoded and used to initiate a peripheral operation. (For a description of the commands for each peripheral unit, refer to the sections describing the particular peripheral unit.)

The "A" and "R" bits define a transfer between the addressed peripheral and the CPU accumulator. If the A bit is a "1", there will be an information transfer. If R = 0, the transfer will be from the CPU accumulator to the peripheral unit; if R = 1, the transfer will be from the peripheral unit to the CPU accumulator. If the A bit is a "0", no transfer will occur. During each SPU execution, the addressed peripheral will send status to the CPU. This status is stored in the GT, EQ, LT and BE indicators. Refer to the section devoted to peripheral controllers for interpretation of indicators following an SPU command.

1.7.15 No Operation Instruction

NOP NO OPERATION

Definition: No operation

Cycles Required: 1

Instruction Format:

Description:

No Operation of any kind will occur on the instruction. Its main use is in debugging so as to provide spare instruction slots in assembly programs.

Assembler format: NOP

#### SECTION II

#### CONTROL PANEL

#### 2.1 INTRODUCTION

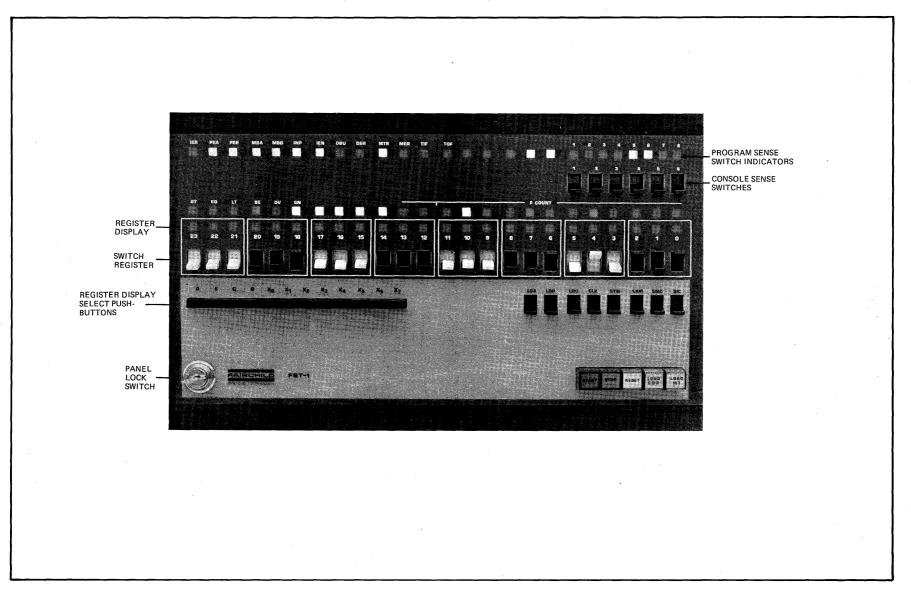

This section describes the manual controls and displays of the FST-1 control panel. A photograph of the control panel is shown in Figure 2.1.1. These controls and displays provide for data entry, single step control and monitoring of the principal components of the FST-1 CPU.

### 2.2 CONTROL PANEL SWITCHES

#### 2.2.1 Sense Switches

These six switches, located on the upper right corner of the control panel are used to control the response of the Branch On State (BOS) instruction.

# 2.2.2 Switch Register $(W_{23}-W_{00})$

These 24 switches, located across the center of the control panel allow manual entry of data to the A Register, the Program Counter, and the Command Register, using the LDA, LDP and LDC switches, respectively, (described below). The setting of these switches may also be loaded into the A register by execution of the Read Switch Register (RSR) instruction.

#### 2.2.3 Register Display Select Switches

These 12 push buttons, located at the left below the switch register, select one of 12 registers for display in the indicator lights immediately above the Switch Register. They are labeled A (accumulator), E (extension), C (command), B (buffer), and  $X_0$  through  $X_7$  (indexes 0 through 7).

#### 2.2.4 Manual Command Control

The following eight switches, located at the right below the switch register, are enabled only when the keyswitch (lower left corner) is turned clockwise.

# 2.2.4.1 LDA (Load A)

Loads the A register from the switch register.

Figure 2.1.1. FST-1 Computer Control Panel

2-2

# 2.2.4.2 LDP (Load P)

Loads the P counter from the switch  $(W_0 - W_{14} \text{ only})$ .

# 2.2.4.3 LDC (Load C)

Loads the Command Register from the switch register.

# 2.2.4.4 CLK (Command Lock)

Locks the current command in the command register. The effective memory address is formed by joining bits 12 and 13 from the command register with bits 0 thru 11 from the Program counter. The P counter advances by one after each execution of the command.

# 2.2.4.5 STW (Store Switch Register)

Loads the B register from the switch register and initiates a write memory cycle to store the contents of B at the memory location specified by the contents of the Program Counter. The P-counter advances by one for each actuation of the STW switch.

# 2.2.4.6 EXM (Examine Memory)

Initiates a read memory cycle from the memory location specified by the contents of the Program Counter and loads the read data into the B register. The P-counter advances by one for each actuation of the EXM switch.

#### 2.2.4.7 SMC (Single Memory Cycle)

Causes a Halt of the CPU following each memory cycle.

#### 2.2.4.8 SIC (Single Instruction Cycle)

Causes a Halt of the CPU following the execution of each instruction.

# 2.2.5. Operational Controls

The following five push buttons, located at the lower right corner of the control panel are the operational controls for the FST-1 CPU.

### 2.2.5.1 Start

Causes execution to commence with the instruction which occupies the Command Register and to continue with the instruction at the location specified by the contents of the Program Counter.

# 2.2.5.2 Stop

Causes execution to halt with the next instruction in the Command Register and the address of the next instruction plus one in the Program Counter.

### 2.2.5.3 Reset

Sets the Program Counter to  $00100_8$  and prepares the CPU for an instruction fetch. The CPU must be halted for the reset push button to be effective.

#### 2.2.5.4 Load CDR

Causes card reader to read a single card and store the resulting data in 40 consecutive memory locations beginning with address  $00100_8$ .

# 2.2.5.5 Load MT

Pushing this button causes one record of magnetic tape to be read and stored in 40 consecutive memory locations beginning with address  $00100_8$ .

### 2.3 CONTROL PANEL DISPLAYS

### 2.3.1 Status Indicators

Thirteen indicators along the upper left edge indicate system status. They are:

| IER | Instruction ERror                           |

|-----|---------------------------------------------|

| PEA | Parity Error A memory bank                  |

| PEB | Parity Error B memory bank                  |

| MBA | Memory Busy A bank                          |

| MBB | Memory Busy B bank                          |

| INP | INput Pending                               |

| IEN | Interrupt ENable                            |

| DBU | Disc BUsy                                   |

| DER | Disc ERror                                  |

| MTB | Magnetic Tape Busy                          |

| MER | Magnetic Tape ERror                         |

| TIF | Time of Instruction Fetch                   |

| TOF | <u>Time</u> of <u>O</u> perand <u>Fetch</u> |

# 2.3.2 State Flip-Flop Indicators

At the upper right, the condition of eight state flip-flops is displayed. They are controlled by program using the <u>Set STate</u> (SST) and <u>Reset STate</u> (RST) instructions.

# 2.3.3 Condition Indicators

Upper center on the left are six condition indicators:

GT <u>Greater Than</u> EQ <u>EQ</u>ual LT <u>Less Than</u> BE <u>Bit Equal</u> OV <u>OVerflow</u> SN Sign

# 2.3.4 Program Counter

The contents of the Program Counter is displayed at the right center.

# 2.3.5 Register Indicators

Immediately above the switch register is the selectable register display. Any one of the registers A (accumulator), E (extension), C (command), B (buffer), or  $X_0$  through  $X_7$  (index) may be selected for display by depressing the appropriate pushbutton at the lower left of the control panel. These pushbuttons are mechanically interlocked such that depressing one releases all others.

# SECTION III

## CONSOLE TYPEWRITER

### 3.1 INTRODUCTION

A console typewriter is provided as standard equipment with the FST-1. This unit has a keyboard, a printer, and may optionally have a paper tape punch and paper tape reader. The typewriter can be used either off-line or on-line.

The characteristics of the typewriter are given below;

| Input/Output Speed   | 10 characters per second |

|----------------------|--------------------------|

| Code                 | ASCII                    |

| Printable Characters | 63                       |

| Characters per Line  | 73                       |

#### 3.2 SYSTEM CONFIGURATION

The typewriter is interfaced to the FST-1 on the Accumulator Bus. The typewriter controller contains two character buffers, one for input and one for output. With both the input and output buffered, input and output data transfers can be performed simultaneously at the maximum mechanism speed.

The typewriter controller utilizes the FST-1 interrupt system. When enabled, either a reader or a printer interrupt is generated at the completion of a reader or printer operation. Either of these interrupts will cause program control to be transferred to an appropriate service program in memory.

#### 3.3 CONSOLE TYPEWRITER CONTROL

#### 3.3.1 Reader Commands

Seven commands are available for testing and control of the paper tape reader. These commands are variations of the Select Peripheral Unit (SPU) instruction. They differ only in the command code. The unit address remains constant. Each paper tape reader command causes the general status of the controller to be signalled. General status is stored in the CPU indicators GT, EQ, LT, BE, where program tests may be conducted on the status. These indicators convey the following information when set:

| GT | Idle            |

|----|-----------------|

| EQ | Idle with error |

| LT | Busy            |

| BE | Not available   |

3-1

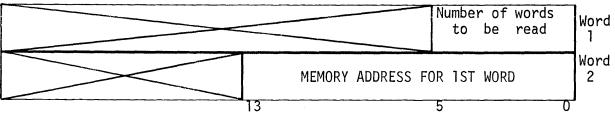

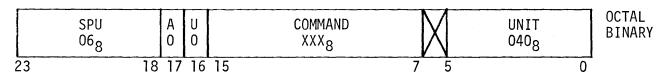

# SPU SELECT PERIPHERAL UNIT

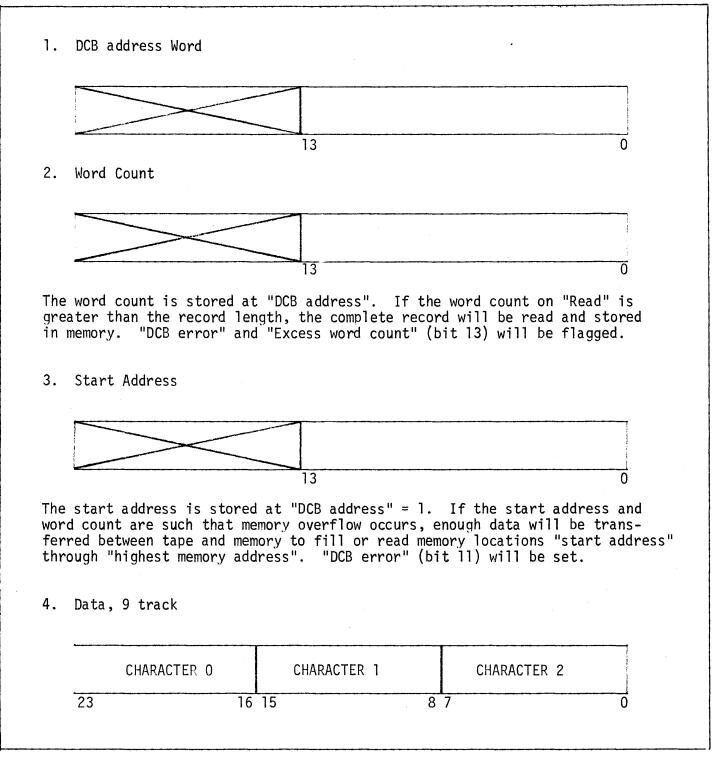

Instruction Format:

|     | SPU<br>06 <sub>8</sub> | A<br>0 | R<br>O | COMMAND<br>XXX <sub>8</sub> | X | UNIT<br>020 <sub>8</sub> |

|-----|------------------------|--------|--------|-----------------------------|---|--------------------------|

| - 1 | 23 18                  | 3 17   | 16     | 15 8                        | 3 | 6 0                      |

Note: Commands which the paper tape reader controller is unable to accept are ignored.

STST STATUS TEST

Description: Command Code 000<sub>8</sub>

The Status Test command is a null command used to obtain the reader status without changing the condition of the reader controller.

Assembler Format: STST 20B

RDS READ STATUS

Description: Command Code 0238

The Read Status instruction execution returns controller status to the CPU Accumulator  $(A_{n-3})$ , as indicated below:

| Bit | 0 | set: | Read Error;                |

|-----|---|------|----------------------------|

| Bit | 1 | set: | Read Interrupt In Process; |

| Bit | 2 | set: | Read Interrupt Enabled;    |

| Bit | 3 | set: | SPU Command Code Error.    |

Assembler Format: RDS 20B (Read Status, Reader)

FEED CHARACTER FEED

Description: Command Code 0418

The Character Feed instruction execution transfers the ASCII code for the character presently in the read station of the paper tape reader to the Input buffer. It also advances the paper tape one character position.

Assembler Format: FEED 20B (Character Feed)

#### RD READ INPUT BUFFER

Description: Command Code 003<sub>o</sub>

The Read Input Buffer instruction execution transfers the contents of the Reader's Character Buffer into the CPU's Accumulator  $(A_{0-7})$ , providing: