# TTL MEMORY 93400 • 93400B • 93401

## 256-BIT READ/WRITE MEMORY & DECODER/DRIVER

FORMERLY 4100 • 4100B • 4101

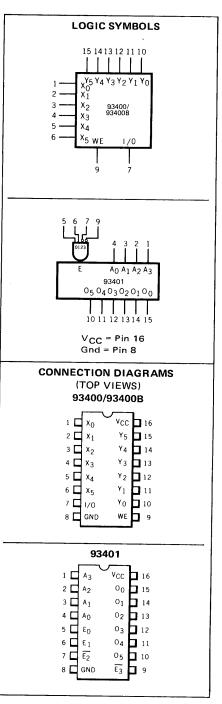

DESCRIPTION — The 93400 256-Bit Read/Write Memory and the 93401 Decoder/Driver are components for use in high speed memory systems. The 93400 is a fast 256 x 1 random access read/write memory which is addressed with a partially decoded x-y coincident selection scheme. There are two device grades, with the 93400B having a slower access time than the 93400. The companion decoder and buffer driver, 93401, converts binary addresses into the partially decoded form required by the 93400, and provides sufficient drive to connect to 32 93400's. Both devices are supplied in 16-lead Dual In-Line Packages.

#### 93400/93400B

- TTL COMPATIBLE

- 16-LEAD PACKAGE

- OUTPUT WIRED—OR CAPABILITY

- 70 ns TYPICAL ACCESS TIME (93400)

- 125 ns TYPICAL ACCESS TIME (93400B)

- LOW INPUT LOADING

#### 93401

- TTL COMPATIBLE

- 16-LEAD PACKAGE

- 20 ns TYPICAL THROUGH DELAY

- LOW INPUT LOADING

- 4 ENABLE INPUTS FOR CHIP SELECTION

- DRIVES UP TO 32 93400's

### ABSOLUTE MAXIMUM RATINGS

V<sub>CC</sub> Pin Potential to Ground Pin Input Voltage Voltage Applied to Output when Output is HIGH Current into Output when Output is LOW Storage Temperature -0.5 V to +7.0 V -0.5 V to +5.25 V -0.5 V to +V<sub>CC</sub> +25 mA -65°C to +150°C

#### **FUNCTIONAL DESCRIPTIONS**

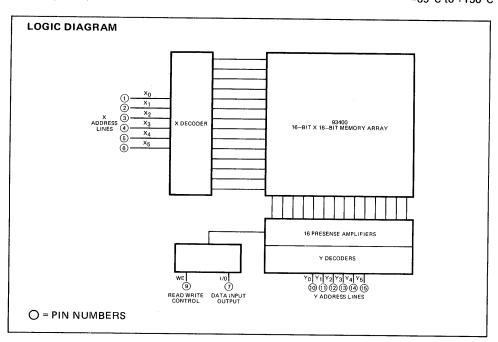

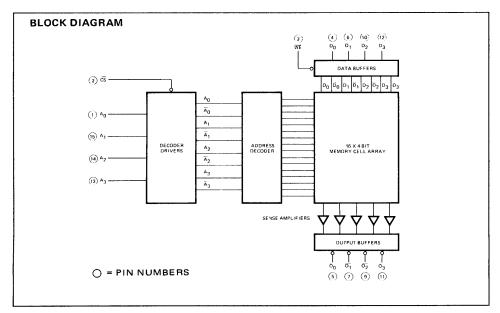

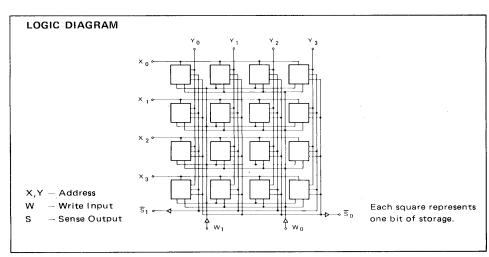

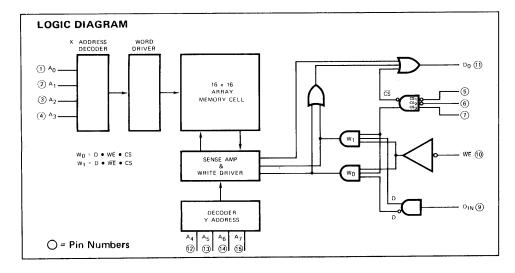

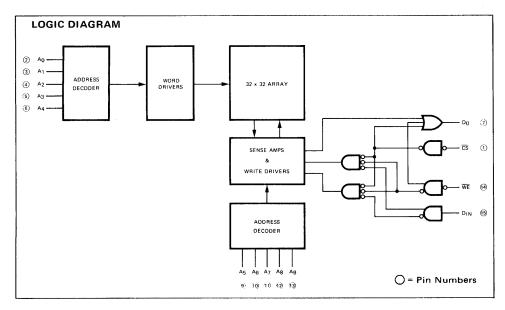

The 93400 and 93400B contain 256 bipolar storage cells arranged in a 16 by 16 format. Any one of the 256 cells may be accessed by supplying an address code on the X address inputs and the Y address inputs. Internal decoders decode the X and Y addresses into one of 16 rows and one of 16 columns in the matrix of storage cells. Data may be written into or read out from the cell lying at the intersection of the selected row and

The X and Y addresses supplied to the 93400 and 93400B are partially decoded in a "3 of 6" code. Of the six X address lines and the six Y address lines there are always three lines HIGH and three lines LOW. There are 20 such combinations, 16 are decoded by the internal row and column decoders. The four unused combinations of 3 of 6 will not select any row or column. If there are more than three lines HIGH in either the X or Y address, then multiple row or column selection will occur. The sixteen 3 of 6 codes used by the 93400 and 93400B are generated by the 93401 decoder/driver.

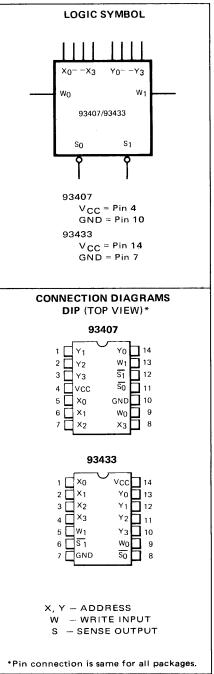

Data enters and leaves the memory on a single input/output (I/O) line (pin 7). The I/O line is an open collector output, so many 93400 I/O lines can be connected together in a wired-OR configuration. Input data must be applied to the I/O lines through an open collector gate. Each I/O line requires a pull-up resistor to V<sub>CC</sub>. The magnitude of the pull-up resistor is determined by the number of 93400 I/O lines tied together. The I/O of a 93400 which is not addressed will be HIGH.

Read/Write selection is determined by the state of pin 9, the active HIGH write enable. When WE is HIGH, the data on the I/O line will be written into the selected address in the 93400. When the Write Enable line is LOW, data will be read out of the addressed location.

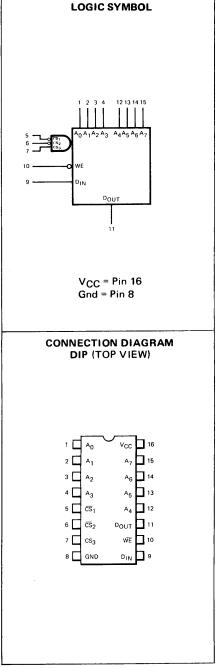

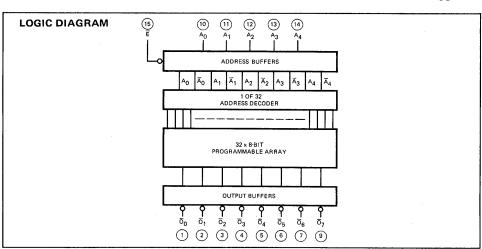

The 93401 is a partial decoder and driver for the 93400. It accepts a 4-bit binary code on the address inputs  $(A_0-A_3)$  and produces a 3 of 6 code on the six output-pins  $(O_0-O_5)$ . The decoder also features four separate enables, two active HIGH and two active LOW. All four enables must be active before the decoder will produce a 3 of 6 code. Since two of the enables are HIGH and two are LOW, it is possible to route two binary coded lines to four different 93401's to get two additional bits of decoding with no extra packages.

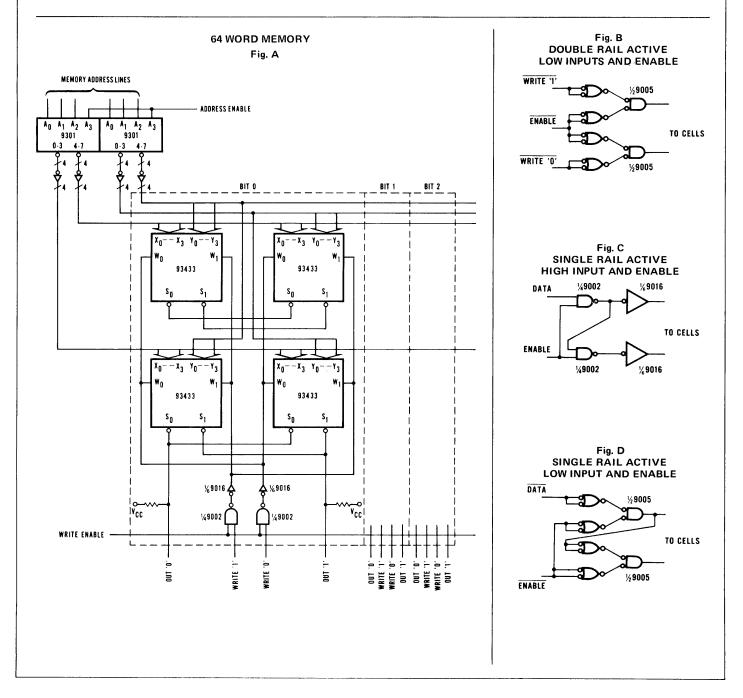

Ordinarily in memory systems, 93400 memory devices will be arranged in a matrix of rows and columns. Each column will store a particular bit and each row of 93400's will be 256 words. A 93401 driver will be used for each row and each column in the matrix. One 93401 can drive up to 32 93400 X or Y address lines. The usual driving scheme is to connect the four LSB's of address to each of the column decoders. The next four bits of address are connected to each of the row decoders. Additional address bits are decoded to the chip selects on the row decoders. Each column decoder drives the Y address lines on up to 32 93400's in a column. Each row decoder drives the address lines on up to 32 93400's in a row.

#### THE THREE OF SIX CODE

The "3 of 6" code used in the 93400 and produced by the 93401 is a tradeoff between memory chip complexity and pin count. The simplest 256-bit memory chip would be a 16 by 16 matrix of storage cells, with all 16 rows and 16 column select lines brought off chip. The lowest pin count for a 256-bit memory chip would be achieved by fully decoded X and Y select lines reducing the 32 lines of the simple scheme to only 8 lines. However, full binary decoding of the X and Y lines on chip significantly increases to complexity of the memory chip. The 93400 and 93401 are designed to gain the good features of both alternatives. The 16 X and Y lines are decoded into 6 lines each, allowing the memory to fit into a 16-lead package and still keeping the memory chip fairly simple, since the 3 of 6 code does not require a complex decoder. The table on the right below shows the conversion of 4-bit binary to 3 of 6 code by the 93401, and also the internal column or row selected by the 3 of 6 to 1 of 16 decoder inside the 93400.

### TTL LOAD AND DRIVE FACTORS

93400 • 93400B

INPUT

X Lines

Y Lines

WE

OUTPUT

Output

1/0

| Ç | 93 | 4 | O | 1 |

|---|----|---|---|---|

INPUT

$E_0, E_1$

E2, E3

A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>, A<sub>3</sub>

00, 01,

OUTPUT

02, 03, 04, 05

0.33/0.25

DRIVE FACTOR

Numerator = HIGH level load (1 load = 0.06 mA) Denominator = LOW level load

(1 load = 1.6 mA)

CODE CONVERSION EQUATIONS

LOAD

0.33/0.125

DRIVE FACTOR

Open Collector

3.1

$\begin{aligned} &O_0 = \overline{A_3} \\ &O_1 = (\overline{A_1} + \overline{A_0}) \ (\overline{A_3} + \overline{A_1}) \ (\overline{A_2} + \overline{A_0}) \\ &O_2 = (\overline{A_1} + \overline{A_0}) \ (\overline{A_3} + \overline{A_0}) \ (\overline{A_2} + \overline{A_1}) \\ &O_3 = (\overline{\overline{A_1}} + \overline{A_0}) \ (\overline{A_3} + \overline{A_0}) \ (\overline{A_2} + \overline{A_1}) \\ &O_4 = (\overline{\overline{A_1}} + \overline{A_0}) \ (\overline{A_3} + \overline{A_1}) \ (\overline{A_2} + \overline{A_0}) \\ &O_5 = \overline{A_2} \end{aligned}$

### TRUTH TABLE

| вп       | NAR'<br>TO 9 | Y INF<br>93401 | PUT            | 3 OF 6 CODE<br>OUTPUT OF 93401;<br>INPUT TO 93400<br>(L = O OR X OR Y) |                |                |    |    |                | 93400<br>93400B<br>INTERNAL<br>X OR Y ADDRESS |  |  |

|----------|--------------|----------------|----------------|------------------------------------------------------------------------|----------------|----------------|----|----|----------------|-----------------------------------------------|--|--|

| A3       | A2           | Α1             | A <sub>0</sub> | L <sub>0</sub>                                                         | L <sub>1</sub> | L <sub>2</sub> | Lз | L4 | L <sub>5</sub> | Row or Column                                 |  |  |

| L        | L            | L              | L              | Н                                                                      | Н              | L              | L  | L  | н              | 0                                             |  |  |

| L        | ī            | Ĺ              | н              | н                                                                      | L              | Н              | L  | L  | Н              | 1                                             |  |  |

| ار       | ī            | Н              | L              | Н                                                                      | L              | L              | н  | L  | Н              | 2                                             |  |  |

| ۱ī       | ī.           | н              | н              | н                                                                      | L.             | L              | L  | н  | Н              | 3                                             |  |  |

| ١ī       | H            | Ł              | L              | н                                                                      | Н              | Н              | L  | L  | L              | 4                                             |  |  |

| l ī      | н            | L              | н              | н                                                                      | L              | н              | L  | н  | L              | 5                                             |  |  |

| l ī      | н            | н              | L              | н                                                                      | н              | L              | Н  | L  | L              | 6                                             |  |  |

| ١ī       | н            | н              | н              | н                                                                      | L              | L              | Н  | Н  | L              | 7                                             |  |  |

| lн       | L            | L              | L              | L                                                                      | н              | L              | H  | L  | Н              | 8                                             |  |  |

| Н        | L            | L              | Н              | L                                                                      | Н              | Н              | L  | L  | Н              | 9                                             |  |  |

| Н        | Ē            | н              | L              | L                                                                      | L              | L              | н  | Н  | Н              | 10                                            |  |  |

| Н        | L            | Н              | Н              | L                                                                      | L              | Н              | L  | Н  | H              | 11                                            |  |  |

| Н        | н            | L              | L              | L                                                                      | Н              | н              | Н  | L  | L              | 12                                            |  |  |

| l H      | н            | L              | н              | L                                                                      | Н              | Н              | L  | Н  | L              | 13                                            |  |  |

| н        | Н            | н              | L              | L                                                                      | н              | L              | Н  | Н  | L              | 14                                            |  |  |

| Н        | Н            | н              | Н              | L                                                                      | L              | н              | н  | Н  | L              | 15                                            |  |  |

| <u> </u> |              |                |                |                                                                        |                |                |    |    |                | L                                             |  |  |

NOTE: Enables on 93401 must be LLHH. Any other state on the enable inputs causes 93401 outputs to go LOW, and addresses no internal row or column in the 93400 memory matrix.

### FAIRCHILD TTL MEMORY 93400 • 93400B • 93401

93400 • 93400B ELECTRICAL CHARACTERISTICS ( $T_C = 0^{\circ}C$  to  $75^{\circ}C$  in operation;  $V_{CC} = 5.0 \text{ V } \pm 5\%$ ) (Part No. 93400XC/93400BXC)\* LIMITS SYMBOL **PARAMETER** 0°C 25°C 75°C UNITS CONDITIONS AND COMMENTS MIN. MAX MIN. TYP. MA'X MIN. MAX  $\overline{v}_{OL}$ Output LOW Voltage 0.45 0.20 0.45 Volts 0.45  $I_{OL} = 5 \, \text{mA}$  $V_{CC} = 4.75 V$ , I<sub>OL</sub> = 10 mA See Figure 3. 0.55 CE Output Leakage Current 100 100 100 μΑ  $V_{CC}$  = 5.25 V,  $V_{CE}$  = 4.5 V All Inputs Grounded VIL Address, Write Guaranteed LOW Input 0.85 0.85 0.85 Volts Input LOW Voltage Threshold  $\overline{V_{1H}}$ Address, Write Guaranteed HIGH Input 2.0 2.0 2.0 Volts Input HIGH Voltage Threshold I<sub>F</sub>1 Data Input Forward -250 -250 Current -250  $V_{CC}$  = 5.25 V,  $V_F$  = 0.45 V μΑ X Address Input V<sub>F</sub> = 0.45 V, V<sub>CC</sub> = 5.25 V 2 other X Lines. 3 Y Lines @ 4.5 V FX -250 -250 -250 μΑ Forward Current Remaining X and Y Lines @ .45 V V<sub>F</sub> = 0.45 V, V<sub>CC</sub> = 5.25 V 2 other Y Lines. 3 X Lines @ 4.5 V IFY Y Address Input -250 -250 -250 μΑ Forward Current Remaining X and Y Lines @ .45 V Address Input 20 <sup>I</sup>RX 20 20  $V_{CC}$  = 5.25 V,  $V_R$  = 4.5 V μΑ Leakage Current 20 20 20 IRY Other X and Y inputs grounded Write Input FW  $V_{CC} = 5.25 \text{ V}, V_F = 0.45 \text{ V}$ -250 μΑ -250 -250 Forward Current Write Input IRW 20 20 20 μΑ  $V_{CC}$  = 5.25 V,  $V_{R}$  = 4.5 V Leakage Current

### 93401 ELECTRICAL CHARACTERISTICS (T<sub>C</sub> = 0°C to 75°C in operation; V<sub>CC</sub> = 5.0 V ±5%) (Part No. 93401XC)\*

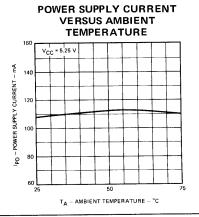

100

140

mΑ

V<sub>CC</sub> = 5.0 V, all inputs at ground

|                                  |                           | _         |           |      | -    |      |       |                                                                                                  |  |  |  |

|----------------------------------|---------------------------|-----------|-----------|------|------|------|-------|--------------------------------------------------------------------------------------------------|--|--|--|

|                                  |                           |           | LIMITS    |      |      |      |       |                                                                                                  |  |  |  |

| SYMBOL                           | PARAMETER                 | 0°C       | + 25°C    |      | + 7  | 5°C  | UNITS | CONDITIONS                                                                                       |  |  |  |

|                                  |                           | MIN. MAX. | MIN. TYP. | MAX. | MIN. | MAX. |       |                                                                                                  |  |  |  |

| v <sub>OH</sub>                  | Output HIGH Voltage       | 2.4       | 2.4 3.0   |      | 2.4  |      | Volts | $V_{CC}$ = 4.75 V, $I_{OH}$ = 1.0 mA<br>V <sub>IL</sub> = value indicated below on this<br>table |  |  |  |

| v <sub>oL</sub>                  | Output LOW Voltage        | 0.45      | 0.3       | 0.45 |      | 0.45 | Volts | V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 10 mA                                                |  |  |  |

| V <sub>IH</sub>                  | Input HIGH Voltage        | 2.0       | 2.0       |      | 2.0  |      | Volts | Guaranteed input HIGH threshold for all inputs                                                   |  |  |  |

| VIL                              | Input LOW Voltage         | 0.85      |           | 0.85 |      | 0.85 | Volts | Guaranteed input LOW threshold for all inputs                                                    |  |  |  |

| <sup>I</sup> FA                  | Add. Input Load Current   | -0.4      |           | -0.4 |      | -0.4 | mA    | V <sub>CC</sub> = 5.25 V V <sub>F</sub> = 0.45 V, V <sub>R</sub> =                               |  |  |  |

| <sup>I</sup> FE                  | Enable Input Load Current | -0.4      |           | -0.4 |      | -0.4 | mA    | V <sub>CC</sub> = 5.25 V 4.5 V on other input                                                    |  |  |  |

| I <sub>RA</sub> &I <sub>RE</sub> | Input Leakage Current     | 20        |           | 20   |      | 20   | μΑ    | $V_{CC}$ = 5.25 V, $V_R$ = 4.5 V, Gnd. on other inputs                                           |  |  |  |

| <sup>1</sup> cc                  | Power Supply Current      | 140       | 120       | 140  |      | 140  | mA    | $V_{CC} = 5.25 \text{ V}$ , all inputs at ground                                                 |  |  |  |

<sup>\*</sup>X = package type; F for Flatpak, D for Ceramic Dip, P for Plastic Dip. See Packaging Information Section for packages available on this product.

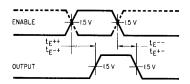

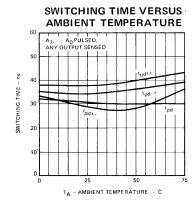

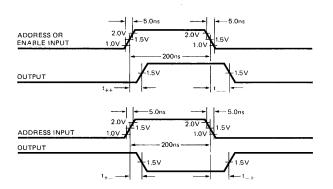

### 93401 SWITCHING CHARACTERISTICS ( $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$ ) (See Fig. 2)

1cc

Power Supply Current

|                                                                           |                                                                        | LIMITS |                           |      |                        |       |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------|--------|---------------------------|------|------------------------|-------|--|--|

| SYMBOL                                                                    | YMBOL PARAMETER                                                        |        | oF (Equiv. to<br>( Lines) |      | F (Equiv. to<br>Lines) | UNITS |  |  |

|                                                                           |                                                                        | TYP.   | MAX.                      | TYP. | MAX.                   |       |  |  |

| t <sub>A</sub> ++, t <sub>A</sub> +-<br>t <sub>A</sub> -+, t <sub>A</sub> | Delay from address going LOW or HIGH to output going LOW or HIGH       | 20     | 25                        | 30   | 40                     | ns    |  |  |

| t <sub>E</sub> ++, t <sub>E</sub> +-<br>t <sub>E</sub> -+, t <sub>E</sub> | Delay from enable going active or inactive to output going HIGH or LOW | 20     | 25                        | 30   | 40                     | ns    |  |  |

### FAIRCHILD TTL MEMORY 93400 • 93400B • 93401

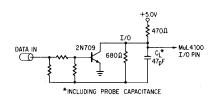

93400 ● 93400B SWITCHING CHARACTERISTICS (V<sub>CC</sub> = 5.0 V, T<sub>A</sub> = 25°C.) C<sub>L</sub> = 47 pF; Equivalent to eight OR—tied 4100 outputs

|                 |                                                                                                                |        | 93400 |                     |     | 934008 | 3              |    |

|-----------------|----------------------------------------------------------------------------------------------------------------|--------|-------|---------------------|-----|--------|----------------|----|

| SYMBOL          | PARAMETER                                                                                                      | LIMITS |       |                     |     | UNITS  |                |    |

|                 |                                                                                                                | MIN    | TYP   | MAX                 | MIN | TYP    | MAX            |    |

| <sup>t</sup> AX | Read Access Time. Time from good X address to good data at output                                              | 30     | 70    | 100                 | 30  | 100    | 200            | ns |

| <sup>t</sup> AY | Read Access Time. Time from good Y address to good data at output                                              | 15     | 45    | 65                  |     | 45     | 100            | ns |

| <sup>t</sup> RR | Read Recovery Time. Time for output to go HIGH after removal of address.                                       |        |       | 100                 |     |        | 150            | ns |

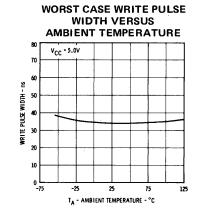

| <sup>t</sup> WP | Write Pulse Width. Width of pulse on WE required to write data into memory.                                    | 80     |       |                     | 100 |        |                | ns |

| t <sub>SH</sub> | Data Setup Time. Time HIGH or LOW data must be                                                                 |        |       | t <sub>WP</sub> +10 | •   |        | 100            | ns |

| t <sub>SL</sub> | present before end of write pulse to write proper data into memory.                                            |        |       | 70<br>(Note 2)      |     |        | 70<br>(Note 3) | ns |

| <sup>t</sup> RH | Data Release Time. This is the minimum set-up time.                                                            | 0      |       |                     | 0   |        |                | ns |

| tRL             | Removal of data after the release time will not affect the data written into the memory. See note 1.           | 10     |       |                     | 10  |        |                | ns |

| СО              | Output Capacitance                                                                                             |        | 7.0   |                     |     | 7.0    |                | pF |

| C <sub>AX</sub> | Input Capacitance for X address line                                                                           |        | 3.0   |                     |     | 3.0    |                | pF |

| CAY             | Input Capacitance for Y address line                                                                           |        | 15    |                     |     | 15     |                | pF |

| <sup>t</sup> AS | Address Set Up Time. Time address must be good before end of write pulse during write operation. (See Fig. 3b) | 80     |       |                     | 80  |        |                | ns |

| <sup>t</sup> AP | Address Pulse Width. Time that address must remain good for write operation. (See Fig. 3b)                     | 100    |       |                     | 100 |        |                | ns |

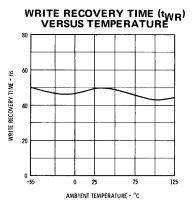

| <sup>t</sup> WR | Write Recovery Time. Time in write-read cycle from end of write pulse to valid output data.                    |        |       | 120                 |     |        | 120            | ns |

#### NOTES

- (1) The set up and release times define a window during which devices are responding to the data and/or address. Inputs must remain good at all times in between the set up and release time limits.

- (2) Applies for write pulse less than 150 ns.

- (3) Applies for write pulse more than 160 ns.

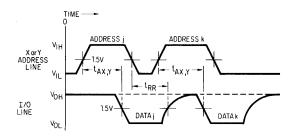

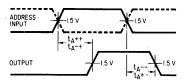

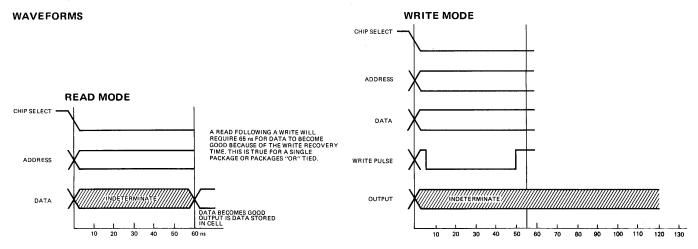

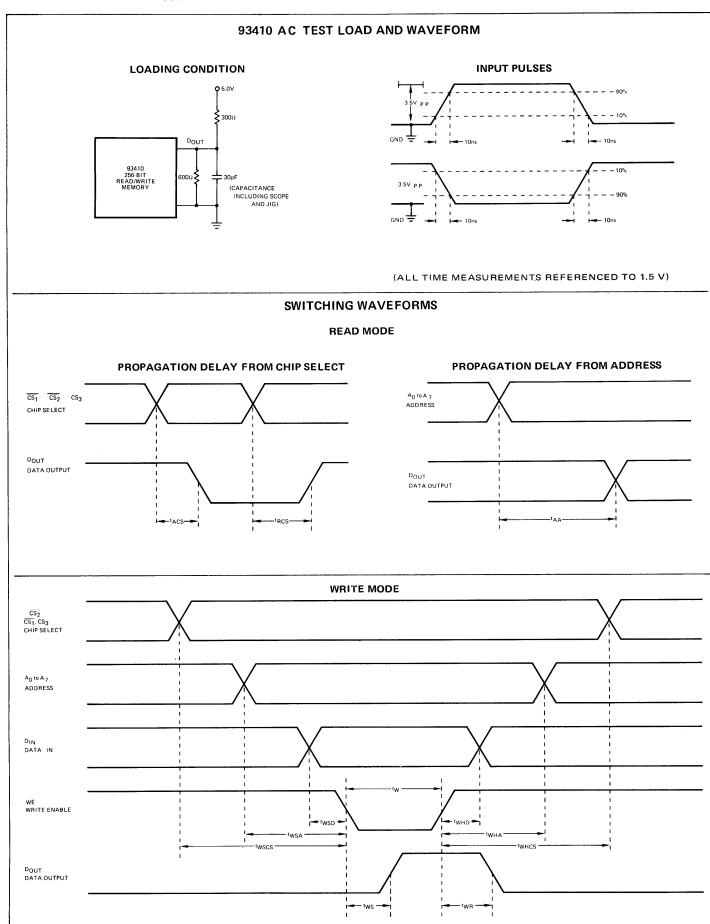

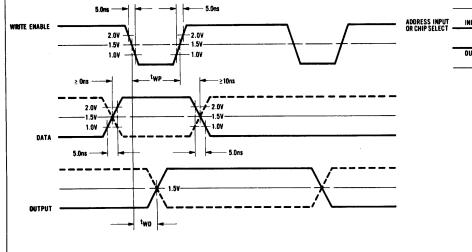

Fig. 1a-93400 TYPICAL READ CYCLE

$t_{\mbox{AX}}$ ,  $\gamma$  is the time from a good address to good data on the output. Note that the access time may be overlapped with the recovery time to improve speed on consecutive read operations.

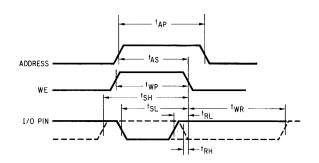

Fig. 1b-93400 WRITE CYCLE

The address must be maintained for 100 ns. The simplest write cycle is achieved by applying the data, then simultaneously raising the address and write pulses for 100 ns. If the write pulse width is less than 100 ns, then the address should come up at about the same time as the write pulse and should be held on after the write pulse. The address should not be applied more than 25 ns before the write pulse, because an early address will cause a read operation to begin disrupting data on the I/O lines (see  $t_{RR}$ ). For a longer write pulse the address pulse may appear anytime as long as it starts before  $t_{AS}$  and lasts at least  $t_{AP}$ .

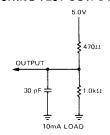

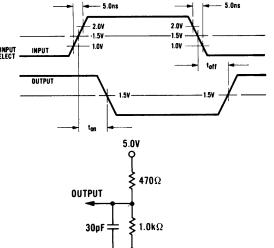

Fig. 2-93401 SWITCHING WAVEFORMS AND TEST LOAD CONDITIONS

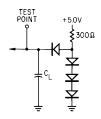

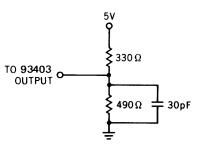

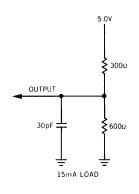

Fig. 3 93400 **TEST LOAD CONDITIONS**

tr=5 Ons ±1 Ons=1<sub>f</sub>

Fig. 4

93400 STANDARD

**INPUT PULSE**

LOW Level  $\leq$  0.45 V HIGH Level  $\geq$  3.0 V Rise, Fall Time = 10 ±5 ns

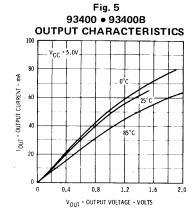

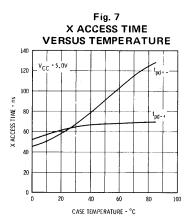

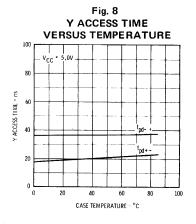

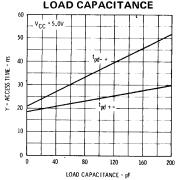

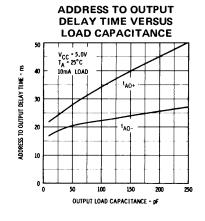

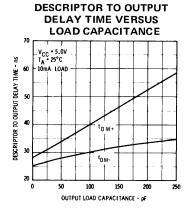

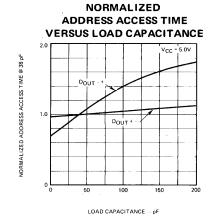

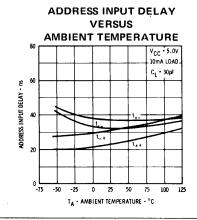

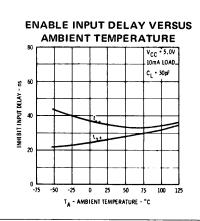

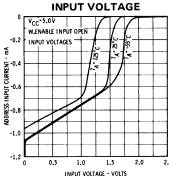

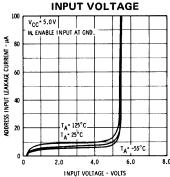

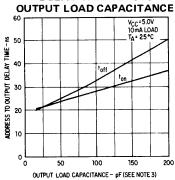

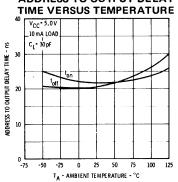

The timing curves in Figures 8 through 13 are obtained using the pulse shape in Figure 6 and the loading in Figure 5. In Figures 12 and 13 the C<sub>L</sub> value in the load is varied.

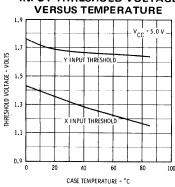

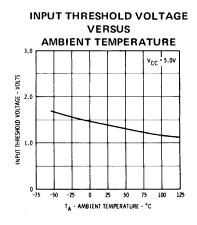

Fig. 6 INPUT THRESHOLD VOLTAGE **VERSUS TEMPERATURE**

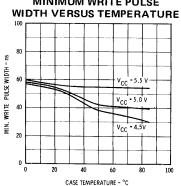

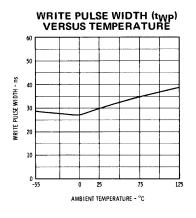

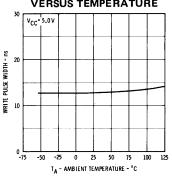

Fig. 9 MINIMUM WRITE PULSE

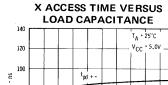

Fig. 10

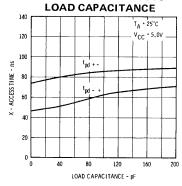

Fig. 11 Y ACCESS TIME VERSUS LOAD CAPACITANCE

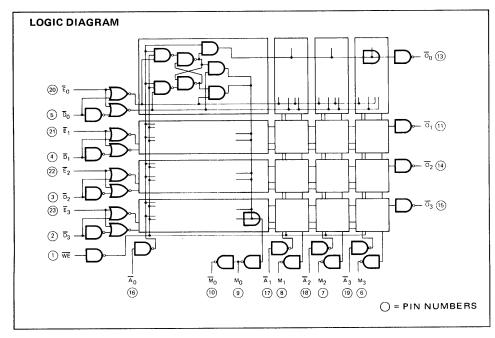

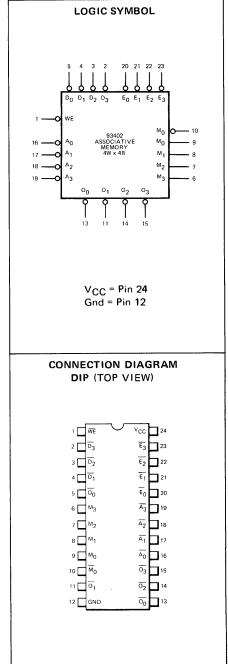

## 16-BIT ASSOCIATIVE/CONTENT ADDRESSABLE MEMORY

FORMERLY 4102

**DESCRIPTION** – The 93402 is a high speed 16-Bit Associative Random Access Memory. It is a linear select 4-word by 4-bit array which performs the equality search on all bits in parallel. The 93402 is TTL compatible.

With the bit enable lines  $(\overline{\mathbb{E}}_0-\overline{\mathbb{E}}_3)$  LOW, the outputs  $(M_0-M_3)$  go HIGH if associated stored data matches the descriptor bits  $(\overline{\mathbb{D}}_0-\overline{\mathbb{D}}_3)$ . If a bit enable line is held HIGH, a match is forced on the corresponding bit in all the words regardless of the state of the descriptor bit  $(\overline{\mathbb{D}}_0-\overline{\mathbb{D}}_3)$ . An inverter is connected to the match output  $M_0$  to give its negation  $\overline{M}_0$ .

A word is addressed by having an active LOW on the appropriate address line  $(\overline{A_0} - \overline{A_3})$ . Any number of words may be addressed simultaneously.

Data can be written into the memory through the data inputs  $(\overline{D}_0-\overline{D}_3)$  under control of the address inputs and the appropriate bit enable  $(\overline{E}_0-\overline{E}_3)$  when the write enable  $(\overline{W}E)$  is LOW.

Reading can occur either during an equality search or a write operation. If a single word is addressed that word will appear at the data outputs  $(\overline{O}_0-\overline{O}_3)$ . If multiple addressing is used, the word appearing at the data output is the AND (positive logic) or the OR (negative logic) of the addressed words.

All outputs are uncommitted collectors allowing maximum flexibility in output connection. In many applications such as memory expansion, the outputs of many 93402's can be tied together. In other applications, the wired-OR is not used. In either case an external pull up resistor must be used to attain a HIGH at an output.

- 25 ns TYPICAL MATCH TIME

- MULTIPLE MATCHING AND ADDDRESSING

- UNCOMMITTED COLLECTOR OUTPUTS FOR WIRED-OR CAPABILITY

- LINEAR SELECT ADDRESSING

- BIT MASKING

### FAIRCHILD TTL MEMORY • 93402

### **LOADING RULES**

|              | HIGH LEVEL<br>(TTL Unit Loads) | LOW LEVEL<br>(TTL Unit Loads) |

|--------------|--------------------------------|-------------------------------|

| Address      | 1.0                            | 1.0                           |

| Bit Enable   | 1.5                            | 1.5                           |

| Write Enable | 1.5                            | 1.5                           |

| Data Input   | 1.0                            | 1.0                           |

| Data Output  | Open Collector                 | 6.2                           |

| Match Outpus | Open Collector                 | 6.2                           |

1 Unit Load (U.L.) = 60  $\mu$ A HIGH/1.6 mA LOW.

The external pull-up resistor R is selected to lie in the range as shown.

$$\frac{5.1}{10-F.O.\,(1.6)} \,\,\leq\,\, R \,\,\leq \frac{2.1}{NL+F.O.\,(0.06)}$$

R is in  $k\Omega$

N = number of wired-OR outputs

F.O. = number of TTL loads driven

$L = Sum of all I_{CEX} of wired-OR outputs$

The minimum value of R is limited by output current sinking ability. The maximum value of R is determined by the output and input leakage current (ICEX and IR) which must be supplied to hold the output at 2.4 V.

| F.O. | Maximum number of Wired-OR's |

|------|------------------------------|

| 1    | 66                           |

| 2    | 52                           |

| 3    | 38                           |

| 4    | 24                           |

| 5    | 10                           |

| 5.7  | 0                            |

### ABSOLUTE MAXIMUM RATINGS (above which the useful life may be impaired)

Storage Temperature

Temperature (Ambient) Under Bias

VCC Pin Potential to Ground

Input Pin Voltage

Current into Output Terminal

Output Voltage

-65°C to +150°C -55°C to +125°C -0.5 V to +7.0 V -0.5 V to +5.5 V 50 mA -0.5 V to +8.0 V

ELECTRICAL CHARACTERISTICS (T<sub>A</sub> =  $0^{\circ}$ C to 75°C, V<sub>CC</sub> = 5.0 V ±5%) (units are pulse tested) (Part No. 93402XC)\*

| 0.4450.         | _                                         |                  | LIMITS             |                    |          |                                                                                     |  |  |

|-----------------|-------------------------------------------|------------------|--------------------|--------------------|----------|-------------------------------------------------------------------------------------|--|--|

| SYMBOL          | PARAMETER                                 | 0°C<br>MIN. MAX. | +25°C<br>MIN. MAX. | +75°C<br>MIN. MAX. | UNITS    | CONDITIONS                                                                          |  |  |

| <sup>l</sup> FA | Address Input Load Current                | -1.6             | -1.6               | -1.6               | mA       | V <sub>CC</sub> = 5.25 V, V <sub>A</sub> = 0.45 V                                   |  |  |

| I <sub>FB</sub> | Bit Enable Load Current                   | -2.4             | -2.4               | -2.4               | mA       | V <sub>CC</sub> = 5.25 V, V <sub>CS</sub> = 0.45 V                                  |  |  |

| FWE             | Write Enable Load Current                 | -2.4             | -2.4               | -2.4               | mA       | V <sub>CC</sub> = 5.25 V, V <sub>W</sub> = 0.45 V                                   |  |  |

| lFI             | Data Input Load Current                   | -1.6             | -1.6               | -1.6               | mA       | V <sub>CC</sub> = 5.25 V, V <sub>D</sub> = 0.45 V                                   |  |  |

| RA              | Address Input Leakage Current             | 60               | 60                 | 60                 | μΑ       | V <sub>CC</sub> = 5.25 V, V <sub>A</sub> = 4.5 V                                    |  |  |

| RBE             | Bit Enable Input Leakage Current          | 90               | 90                 | 90                 | μΑ       | V <sub>CC</sub> = 5.25 V, V <sub>CS</sub> = 4.5 V                                   |  |  |

| RWE             | Write Enable Leakage Current              | 90               | 90                 | 90                 | μΑ       | V <sub>CC</sub> = 5.25 V, V <sub>W</sub> = 4.5 V                                    |  |  |

| RI              | Data Input Leakage Current                | . 60             | 60                 | 60                 | μΑ       | V <sub>CC</sub> = 5.25 V, V <sub>D</sub> = 4.5 V                                    |  |  |

| CEX             | Output Leakage Current (Note 4)           | 50               | 50                 | 50                 | μΑ       | V <sub>CC</sub> = 5.25 V, V <sub>CEX</sub> = 5.25 V                                 |  |  |

| CEX MO          | Output Leakage Current for M <sub>0</sub> | 110              | 110                | 110                | μΑ       | V <sub>CC</sub> = 5.25 V, V <sub>CEX</sub> = 5.25 V                                 |  |  |

| VOL             | Output LOW Voltage (Note 5)               | 0.45             | 0.45               | 0.45               | ٧        | V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 10 mA One Word Addressed                |  |  |

| VIL             | Input LOW Voltage (Note 6)                | 0.85             | 0.85               | 0.85               | ٧        | V <sub>CC</sub> = 5.0 V, Monitor Appropriate Output<br>To Guarantee This Test Limit |  |  |

| V <sub>IH</sub> | Input HIGH Voltage (Note 6)               | 2.0              | 2.0                | 2.0                | <b>V</b> | V <sub>CC</sub> = 5.0 V, Monitor Appropriate Output<br>To Guarantee This Test Limit |  |  |

| ICC .           | Supply Current                            | 125              | 125                | 125                | mA       | V <sub>CC</sub> = 5.25 V, Worst Case                                                |  |  |

<sup>\*</sup>X = package type; F for Flatpak, D for Ceramic Dip, P for Plastic Dip. See Packaging Information Section for packages available on this product.

### NOTES:

- (4) For all outputs except M<sub>0</sub>.

- (5) For all outputs.

- (6) For all inputs

### FAIRCHILD TT!. MEMORY • 93402

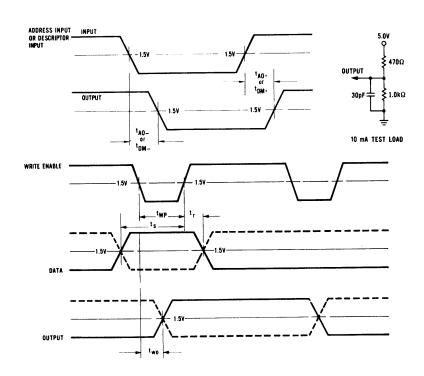

### SWITCHING CHARACTERISTICS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

|                                                         |                                                                                                                                    | LIMI                 | T (ns)               | LOAD                             | CONDITIONS                       | NOTE  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------------------|----------------------------------|-------|

| SYMBOL                                                  | PARAMETER                                                                                                                          | TYP.                 | MAX.                 | LUAD                             | С                                | 10.12 |

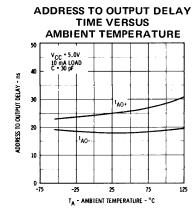

| tAO-                                                    | Address to Output Turn-On Delay Address to Output Turn-Off Delay                                                                   | 20<br>25             | 30<br>35             | 10 mA<br>10 mA                   | 30 pF<br>30 pF                   | 1 1   |

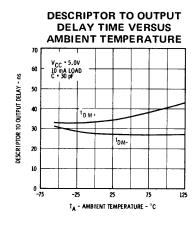

| t <sub>DM+</sub><br>t <sub>DM-</sub><br>t <sub>WP</sub> | Descriptor to Output Match Turn-On Delay Descriptor to Output Match Turn-Off Delay Write Pulse Width Required to Write Write Delay | 25<br>30<br>33<br>50 | 35<br>40<br>40<br>80 | 10 mA<br>10 mA<br>10 mA<br>10 mA | 30 pF<br>30 pF<br>30 pF<br>30 pF | 2 2   |

| t <sub>S</sub>                                          | Maximum Set-up Time on Data Input<br>Release Time (Minimum Set-up Time) on Data Input                                              | 33<br>0              | 40<br>19             | 10 mA<br>10 mA                   | 30 pF<br>30 pF                   | 3 3   |

(1) To test t<sub>AO+</sub> and t<sub>AO</sub> a LOW must be stored in the cell under test.

(2) To test t<sub>DM-</sub> and t<sub>DM+</sub>, a mismatch must occur in at least one bit of the word under test

(3) Setup and release times are measured with respect to the rising edge of the Write enable. To guarantee writing in the correct data, the data input must be good by t<sub>s</sub> and remain good until after t<sub>r</sub>.

The typical capacitance of one 93402 output is 7.0 pF.

### **SWITCHING WAVEFORMS**

### 9

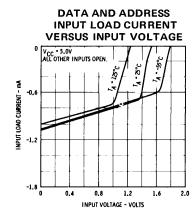

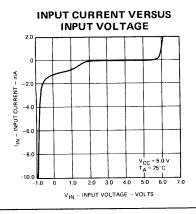

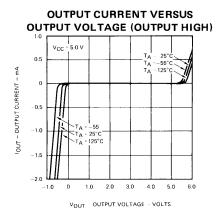

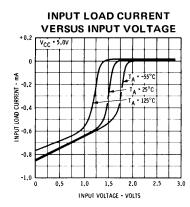

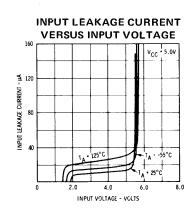

### TYPICAL ELECTRICAL CHARACTERISTICS

## 64-BIT FULLY DECODED READ/WRITE MEMORY

FORMERLY 4103

**DESCRIPTION** — The 93403 is a high speed 64-Bit Read/Write Memory organized 16 words by four bits. Four address lines are buffered and decoded "on chip" for word selection. The 93403 is made with TTL circuitry and all inputs are equivalent to one TTL load.

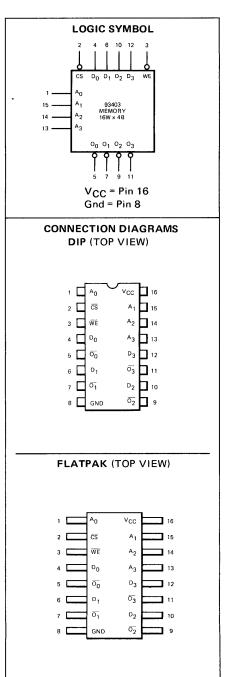

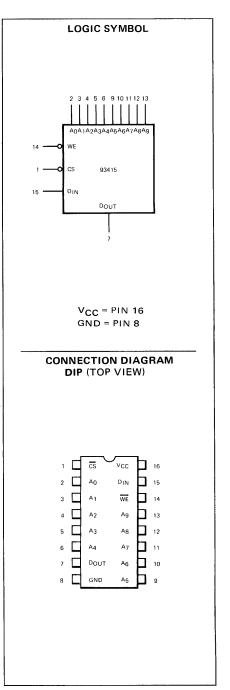

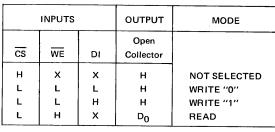

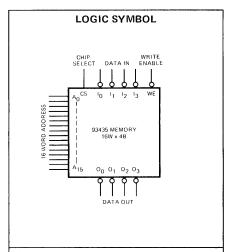

**OPERATION** — When the 93403 receives a LOW at the Chip Select  $(\overline{CS})$  input, the binary address  $(A_0, A_1, A_2 \text{ and } A_3)$  is decoded to select one of sixteen 4-bit words. If the Write Enable  $(\overline{WE})$  is at a HIGH level, the contents of the selected word are non-destructively read out and the sense amplifier outputs  $(\overline{O_0}, \overline{O_1}, \overline{O_2} \text{ and } \overline{O_3})$  reflect the state of the stored data in the four bits of the selected word. If the Write Enable is LOW, the data present on the Data Input lines  $(D_0, D_1, D_2 \text{ and } D_3)$  is written into the four bits of the selected word. Note that there is inversion through the device in a read operation.

- OUTPUT WIRED-OR CAPABILITY

- ON CHIP DECODING

- NON-DESTRUCTIVE READOUT

- CHIP SELECT FOR SYSTEM WORD EXPANSION

- TTL COMPATIBLE

### ABSOLUTE MAXIMUM RATINGS (above which the useful life may be impaired)

### FAIRCHILD TTL MEMORY • 93403

**ELECTRICAL CHARACTERISTICS** ( $T_{case} = 0^{\circ} C$  to  $75^{\circ} C$ ,  $V_{CC} = 5.0 V \pm 5\%$ ) (units are pulse tested) (Part No. 93403XC)

|                  |                                   |                  | LIMITS              |                     |       |                                                                                                    |

|------------------|-----------------------------------|------------------|---------------------|---------------------|-------|----------------------------------------------------------------------------------------------------|

| SYMBOL           | TEST                              | 0°C<br>MIN. MAX. | + 25°C<br>MIN. MAX. | + 75°C<br>MIN. MAX. | UNITS | CONDITIONS                                                                                         |

| 1 <sub>FA</sub>  | Address Input Load Current        | -1.6             | -1.6                | -1.6                | mA    | V <sub>CC</sub> = 5.25 V, V <sub>A</sub> = 0.45 V                                                  |

| 1 <sub>FCS</sub> | Chip Select Load Current          | -1.6             | -1.6                | -1.6                | mA    | V <sub>CC</sub> = 5.25 V, V <sub>CS</sub> = 0.45 V                                                 |

| FWE              | Write Enable Load Current         | -1.6             | -1.6                | -1.6                | mA    | V <sub>CC</sub> = 5.25 V, V <sub>W</sub> = 0.45 V                                                  |

| I <sub>FD</sub>  | Date Input Load Current           | -1.6             | -1.6                | -1.6                | mA    | $V_{CC} = 5.25 \text{ V}, V_D = 0.45 \text{ V}$                                                    |

| I <sub>RA</sub>  | Address Input Leakage Current     | 60               | 60                  | 60                  | μΑ    | V <sub>CC</sub> = 5.25 V, V <sub>A</sub> = 4.5 V                                                   |

| <sup>I</sup> RCS | Chip Select Input Leakage Current | 60               | 60                  | 60                  | μΑ    | V <sub>CC</sub> = 5.25 V, V <sub>CS</sub> = 4.5 V                                                  |

| IRWE             | Write Enable Leakage Current      | 60               | 60                  | 60                  | μΑ    | V <sub>CC</sub> = 5.25 V, V <sub>W</sub> = 4.5 V                                                   |

| <sup>I</sup> RD  | Data Input Leakage Current        | 60               | 60                  | 60                  | μΑ    | V <sub>CC</sub> = 5.25 V, V <sub>D</sub> = 4.5 V                                                   |

| ICEX             | Output Leakage Current            | 100              | 100                 | 100                 | μΑ    | V <sub>CC</sub> = 5.25 V, V <sub>CEX</sub> = 5.25 V<br>3.0 on Chip Select                          |

| v <sub>oL</sub>  | Output LOW Voltage                | 0.45             | 0.45                | 0.45                | V     | $V_{CC} = 4.75 \text{ V}, I_{OL} = 16 \text{ mA}$ $\overline{CS} = V_{IL}, \overline{WE} = V_{IH}$ |

| VIL              | Input LOW Voltage                 | 0.85             | 0.85                | 0,85                | V     | V <sub>CC</sub> = 5.0 V,<br>Monitor Appropriate Output<br>To Guarantee This Test Limit             |

| V <sub>IH</sub>  | Input HIGH Voltage                | 2.0              | 2.0                 | 2.0                 | V     | V <sub>CC</sub> = 5.0 V,  Monitor Appropriate Output To Guarantee This Test Limit                  |

| <sup>I</sup> CC  | Supply Current                    | 110              | 110                 | 110                 | mA    | V <sub>CC</sub> = 5.25 V,<br>Write Enable = 3.0 V, other<br>inputs Grounded                        |

| V <sub>CD</sub>  | Clamp Diode Voltage, All Inputs   | -1.0             | -1.0                | -1.0                | V     | I <sub>CD</sub> = -5.0 mA                                                                          |

| вV <sub>X</sub>  | Breakdown Voltage, All Inputs     | 5.5              | 5.5                 | 5.5                 | V     | I <sub>X</sub> = 1.0 mA                                                                            |

X = package type; F for Flatpak, D for Ceramic Dip, P for Plastic Dip. See Packaging Information Section for packages available on this product.

### SWITCHING CHARACTERISTICS

|                |                     |                                                              |      | LIMIT | S    |       |

|----------------|---------------------|--------------------------------------------------------------|------|-------|------|-------|

| SYMBOL         | CHARACTERISTIC      | DEFINITION                                                   |      | 25° C |      | UNITS |

|                |                     |                                                              | MIN. | TYP.  | MAX. |       |

| <sup>t</sup> A | Read Access Time    | Time From Switching Address Or Chip Select To Data At Output |      | 45    | 60   | ns    |

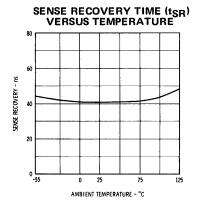

| tSR            | Sense Recovery Time | Time From Switching Address Or Chip Select To Output HIGH    |      | 45    | 60   | ns    |

| tWP            | Write Pulse         | Write Pulse Width - Width of Pulse Guaranteed to Write       | 45   | 30    |      | ns    |

| tWR            | Write Recovery Time | Time From Write Pulse Going HIGH to Output LOW               |      |       | 65   | ns    |

| tDH            | Data Hold Time      | Time From Write Pulse Going HIGH to Change Data Or Address   |      |       | 5.0  | ns    |

| tDS            | Data Set-Up Time    | Time Data Must Be Present Before Write Pulse                 | 5.0  | 0     |      | ns    |

| tAS            | Address Strobe Time | Time Address Must Be Present in Order to Write               | 5.0  | 10    | 45   | ns    |

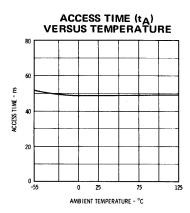

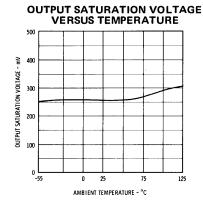

### TYPICAL ELECTRICAL CHARACTERISTICS

## INPUT THRESHOLD VOLTAGE **VERSUS TEMPERATURE** 2.0 THRESHOLD VOLTAGE - VOLTS 1.5 1.0 0.5

AMBIENT TEMPERATURE - °C

### **TTL LOADING RULES**

|              | HIGH LEVEL     | LOW LEVEL |

|--------------|----------------|-----------|

| Address      | 1 U. L.        | 1 U. L.   |

| Chip Select  | 1 U. L.        | 1 U. L.   |

| Write Enable | 1 U. L.        | 1 U. L.   |

| Data Input   | 1 U. L.        | 1 U. L.   |

| Data Output  | Open Collector | 10 U. L.  |

- 1 LOW Level TTL Unit Load (U.L.) = 1.6 mA

- 1 HIGH Level TTL Unit Load (U.L.) = 60 µA

Uncommitted collector outputs are provided on the 93403 to allow maximum flexibility in output connection. In many applications such as memory expansion, the outputs of many 93403 can be tied together. In other applications the wired-OR is not used. In either case an external pullup resistor of value R1 must be used to provide a HIGH at the output when it is off. Any value of  ${\rm R}_{\rm L}$  within the range specified below may be used.

$$\frac{5.05}{16 - F.O. (1.6)} \le R_L \le \frac{2.1}{N (0.1) + F.O. (0.06)}$$

RL is in  $k\Omega$ N = number of wired-OR outputs F.O. = number of TTL loads driven  $V_{CC}$  = 5.0 V  $\pm 10\%$

The minimum value of  $R_L$  is limited by output current sinking ability. The maximum value of R<sub>L</sub> is determined by the output and input leakage current (ICEX and IR) which must be supplied to hold the output at 2.4 V.

### **TRUTH TABLE**

| WE | cs | OUTPUT                                | MODE         |

|----|----|---------------------------------------|--------------|

| Ξ  | Ι  | HIGH<br>No Glitches                   | Not<br>Read  |

| L  | н  | Indeterminate<br>Output               | Not<br>Write |

| н  | L  | Function of<br>Data Stored<br>in Cell | Read         |

| L  | L  | Indeterminate<br>Output               | Write        |

### **SWITCHING TEST CIRCUIT** 15 mA LOAD

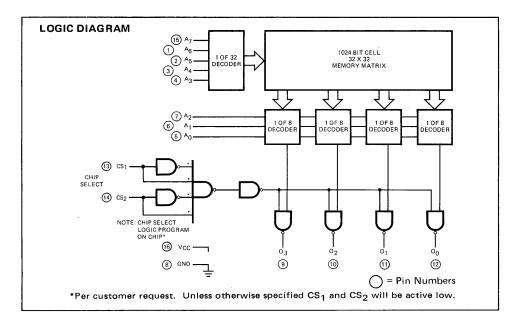

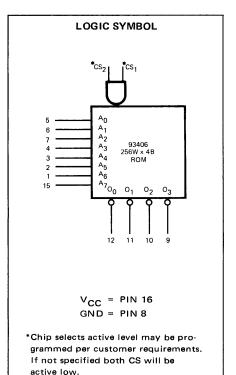

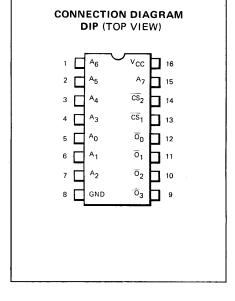

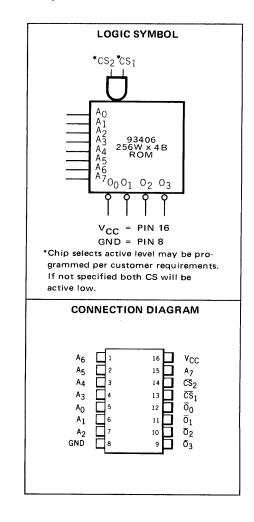

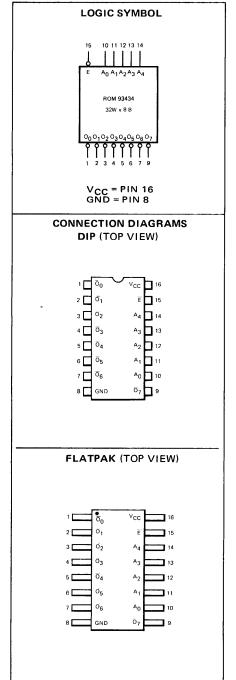

## TTL MEMORY 93406 1024-BIT READ ONLY MEMORY

DESCRIPTION — The Fairchild 93406 is a 1024-bit Bipolar Read Only Memory organized 256 words by four bits. An 8-bit binary address is used to select the desired word. The four outputs are uncommitted collectors which permit "OR" tying of the outputs for expanding the memory in the word direction. The customer can specify the active level of the 2-input chip select gate. CS₁ and CS₂ both will be active LOW unless otherwise specified by the customer. The programmable enable feature allows expansion of the memory to 1024 words without any external gates.

The contents of the memory are mask programmed to the customers specification. The customer can specify the desired ROM code on either the 93406 Coding Form(s) or by punched cards using the 93406 Data Card Format.

- DTL AND TTL COMPATIBLE

- ACCESS TIME 50 ns MAX

- FULLY DECODED ON CHIP ADDRESS DECODER AND BUFFER

- 2 CHIP SELECT INPUTS PROVIDING EASY MEMORY EXPANSION

- PROGRAMMABLE CHIP SELECTS

- OR-TIE CAPABILITY

- STANDARD 16-LEAD DUAL IN-LINE PACKAGE

### PIN NAMES

$\begin{array}{c} \underline{A_0} \text{ to } \underline{A_7} \\ \underline{CS_1}, \underline{CS_2} \\ \overline{O_0} \text{ to } \overline{O_3} \end{array}$

Address Inputs Chip Select Inputs Data Outputs

### 93406 DATA CARD FORMAT

The most efficient method of ordering the 93406 is to punch the desired truth table on a punched card in the format described below. Fairchild will generate mask and test program data directly from these inputs. This eliminates the chance of error when transcribing inputs from a hand written truth table.

Data should be provided on a deck of 34 standard 80 column cards containing the following information.

### CARD NO. 1 - Customer Identification

| Column | Content                                                                                                         |

|--------|-----------------------------------------------------------------------------------------------------------------|

| 1      | Blank                                                                                                           |

| 2-28   | Customer Name, Drawing or Specification control number.                                                         |

| 29-32  | Blank                                                                                                           |

| 33–39  | FAIRCHILD PART NUMBER. This part number is supplied by the factory through your Fairchild sales representative. |

| 40-64  | Blank                                                                                                           |

| 65-72  | Date                                                                                                            |

| 73-80  | Blank                                                                                                           |

### CARD NO. 2 - Chip Select Option

| Column | Content                                                                                                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–11   | Punch "Chip Select"                                                                                                                                                              |

| 12     | Blank                                                                                                                                                                            |

| 13, 14 | Punch Charts '00', '01', '10' or '11', depending on the chip select code option. (First bit represents $CS_1$ input, second bit represents $CS_2$ input. '0' = LOW, '1' = HIGH.) |

| 15-32  | Blank                                                                                                                                                                            |

| 33-39  | Repeat FAIRCHILD PART NUMBER (This is used for positive identification).                                                                                                         |

| 40-80  | Blank                                                                                                                                                                            |

### CARDS NO. 3 through 34 - Truth Table Deck

Each card will contain instructions for the output levels for 8 input words.

| Column | Content                                                                                                                                                                                                  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1–7    | Punch the numerals representing the first and last words on that card (i.e.: 000-007, 008-015, 016-023248-255). Word order is determined by the value of the binary address $-A_7 = MSB$ , $A_0 = LSB$ . |

| 8-9    | Blank                                                                                                                                                                                                    |

| 10–13  | Punch the desired combination of "1's" and "0's" representing the output levels for outputs $O_3$ , $O_2$ , $O_1$ and $O_0$ (in that order), for the first word on the card, '0' = LOW, '1' = HIGH.      |

| 14     | Blank                                                                                                                                                                                                    |

| 15-18  | Punch the desired combination of "1's" and "0's" representing the output levels for the second word on the card.                                                                                         |

| 19     | Blank                                                                                                                                                                                                    |

| 20-23  | Punch the desired combination of "1's" and "0's" representing the output levels for the third word on the card.                                                                                          |

| 24     | Blank                                                                                                                                                                                                    |

| 25-28  | Punch the desired combination of "1's" and "0's" representing the output levels for the fourth word on the card.                                                                                         |

| 29     | Blank                                                                                                                                                                                                    |

| 30-33  | Punch the desired combination of "1's" and "0's" representing the output levels for the fifth word on the card.                                                                                          |

| 34     | Blank                                                                                                                                                                                                    |

### FAIRCHILD TTL MEMORY • 93406

### CARDS NO. 3 through 34 - Truth Table Deck (cont'd)

| io. 3 through 34 — Truth Table Deck (cont'd)                                                                      |

|-------------------------------------------------------------------------------------------------------------------|

| Content                                                                                                           |

| Punch the desired combination of "1's" and "0's" representing the output levels for the sixth word on the card.   |

| Blank                                                                                                             |

| Punch the desired combination of "1's" and "0's" representing the output levels for the seventh word on the card. |

| Blank                                                                                                             |

| Punch the desired combination of "1's" and "0's" representing the output levels for the eighth word on the card.  |

| Blank                                                                                                             |

| Repeat chip select code option as in columns 13 and 14 of card number 2.                                          |

| Blank                                                                                                             |

| Repeat FAIRCHILD PART NUMBER (this number is used for positive identification).                                   |

| Blank                                                                                                             |

| Use optional.                                                                                                     |

|                                                                                                                   |

### 93406 Address Scheme

The 93406 is organized 256 words by 4-bits. The words are numbered 0 through 255 and are addressed using sequential addressing of address inputs  $A_0$  through  $A_7$ , with  $A_0$  as the least significant digit.

|          |                |                |                | INPL           | JTS            |                |                |                |

|----------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| WORD     | Pin 15         | Pin 1          | Pin 2          | Pin 3          | Pin 4          | Pin 7          | Pin 6          | Pin 5          |

| •        | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |

| WORD 0   | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 0              |

| WORD 1   | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1              |

| WORD 2   | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 0              |

| WORD 3   | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1              |

|          |                |                |                |                |                |                |                |                |

| WORD 255 | 1              | 1              | 1              | 1              | 1              | 1              | 1              | 1              |

**ABSOLUTE MAXIMUM RATINGS**

Storage Temperature

Temperature (Ambient) Under Bias

V<sub>CC</sub> Pin Potential to Ground

Input Pin Voltage

Current into Output Terminal

Output Voltages

-65°C to +150°C 0°C to +75°C -0.5 V to +8.0 V -1.5 V to +5.5 V 100 mA -0.5 V to V<sub>CC</sub> Value

DC ELECTRICAL CHARACTERISTICS (T<sub>A</sub> =  $0^{\circ}$ C to  $+75^{\circ}$ C,  $V_{CC}$  =  $5.0 \text{ V} \pm 5\%$ )

|                           | LIMITS                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                      | HINITS                                                                                                                                                                                                                                                                                    | CONDITIONS                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHARACTERISTIC            | MIN.                                                                                                                                                                                                                                         | TYP.                                                                                                                                                                                                                                                                 | MAX.                                                                                                                                                                                                                                                                                      | ONTIS                                                                                                                                                                                                                                                                                  | 30.02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Output Leakage Current    |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      | 40                                                                                                                                                                                                                                                                                        | μΑ                                                                                                                                                                                                                                                                                     | $V_{CC}$ = 5.25 V, $V_{CEX}$ = 5.25 V<br>Address any HIGH output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Output LOW Voltage        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      | 0.45                                                                                                                                                                                                                                                                                      | Volts                                                                                                                                                                                                                                                                                  | V <sub>CC</sub> = 4.75 V, I <sub>OL</sub> = 15 mA<br>Address any LOW output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Input HIGH Voltage        | 2.0                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                           | Volts                                                                                                                                                                                                                                                                                  | Guaranteed Input HIGH Voltage for All Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input LOW Voltage         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      | 0.85                                                                                                                                                                                                                                                                                      | Volts                                                                                                                                                                                                                                                                                  | Guaranteed Input LOW Voltage for All Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Input LOW Current         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                           | mA                                                                                                                                                                                                                                                                                     | V <sub>CC</sub> = 5.25 V, V <sub>F</sub> = 0.45 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IFA (Address Inputs)      | Ì                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                      | 0.8                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      | 0.8                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Input HIGH, Current       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                           | μΑ                                                                                                                                                                                                                                                                                     | V <sub>CC</sub> = 5.25 V, V <sub>R</sub> = 4.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

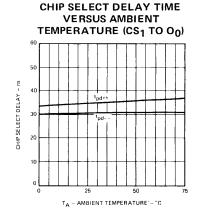

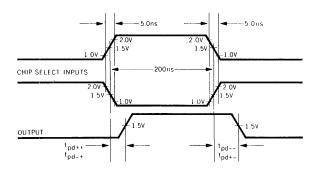

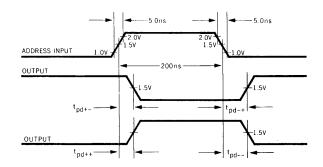

| IRA (Address Inputs)      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                      | 40                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |