DUAL SYSTEMS CONTROL CORPORATION 2530 San Pablo Avenue Berkeley, CA. 94702 415/549-3854 • TELEX 172029 SPX

CPU/68000

USER'S MANUAL

### 68000-BASED

CENTRAL PROCESSING UNIT BOARD

FOR THE I.E.E. 696/S-100 BUS

Dual Systems Control Corp. 2530 San Pablo Avenue Berkeley, CA 94702

Rev. B

COPYRIGHT

C 1982 BY DUAL SYSTEMS CONTROL CORP. ALL RIGHTS RESERVED

# Table of Contents

| Introduction                  | 2                    |

|-------------------------------|----------------------|

| Specifications                | 3                    |

| Booting with the Monitor      | 4                    |

| On-Board ROM                  | 8                    |

| Address Bus                   | 12                   |

| Data Bus                      | ····· 1 <sup>2</sup> |

| TMA Control                   | 12                   |

| Interrupt Modes               | 15                   |

| Appendix A. Selecting ROMs    | 16                   |

| Appendix B. Details of S-100  | interface 17         |

| Appendix C. Special Configura | tions 18             |

| Appendix D. A Few Programs    | 19                   |

## INTRODUCTION

The Dual Systems CPU/68000 is a high-performance CPU board combining the Motorola MC68000 chip, the logic circuitry necessary for interfacing to the S-100 bus in full compliance with the IEEE-696 specification, and ROMs containing a powerful monitor. Among its highlights are:

- o 8 MHz 68000 microprocessor

- o 4 MHz S-100 bus operation

- o 24 bit extended address bus

- o 16 bit data transfers

- o 8 bit transfers for compatibility with older peripherals

- o On chip interrupt controller

- o Operation with up to 16 DMA devices

- o Up to 8 Kilobytes of on board ROM

- o Supports I/O mapped peripherals

The **Dual Systems** CPU/68000 board is based on the Motorola 68000 processor, a high-performance microprocessor with 32-bit internal architecture and a large, uniform memory space. The 68000 features 16 32-bit registers, eight for addresses and eight for data. Data can be accessed in byte, word, and long word (32 Bit) quantities.

The board is designed to take full advantage of new IEEE-696 S-100 features. 16 bit memory accesses double the effective transfer rate of the 4 MHz S-100 bus. The processor fully complies with IEEE specifications for a permanent bus master and supports temporary bus master operation. Twenty-four address lines allow direct access to 16 Megabytes of memory. Processor: Motorola MC68000-L8

Clock Speed: 8 Megahertz

Bus: Meets all requirements of IEEE-696 (S-100)

- Address Bus: 24 bits; conforms to S-100 extended addressing specifications (16 Megabytes)

- Data Bus: 16 bit bidirectional data transfers. Also supports byte data transfers to eight-bit peripherals.

- ROM: Two sockets are provided on board for up to 8K of ROM. This ROM can be used for program storage or exception vectors or both.

- Control: Configured as bus master, provides TMA protocol per IEEE-696. Provides automatic 8/16 bit data path selection. (requires 16 bit memory for program execution). Provides 64k programmable I/O space.

- Machine Cycle Time:Standard S-100 cycle: 750nS (min) Fast Mode: 500nS (min)

- Memory Speed: Memory must have data on the bus no later than 450 nS after address is valid on bus.

- Status Indicators: RUN (Green LED) HALT (Red LED) HOLD (Yellow LED)

- PC board: High quality epoxy, solder masked both sides, screened component legend, plated through holes, gold plated edge connector fingers.

Sockets: Provided for all IC's

Power Consumption: 950 mA nominal at 5 V.

User-Selectable

Options: Hardware relocatable boot and exception vectors.

A0 line of address bus may be asserted for high byte or low byte.

Phantom line asserted while in USER mode. (for example disk controller may be disabled while not in SYSTEM mode.)

### Booting the CPU/68000 with Macsbug<sup>1</sup>

The CPU/68000 comes with the Macsbug<sup>1</sup> monitor installed in the on-board ROM sockets. The monitor is factory configured for use with a Godbout Interfacer I serial I/O board. If the CPU/68000 is ordered with the Interfacer<sup>2</sup> and CMEM memory cards, then the system can be brought up immediately.

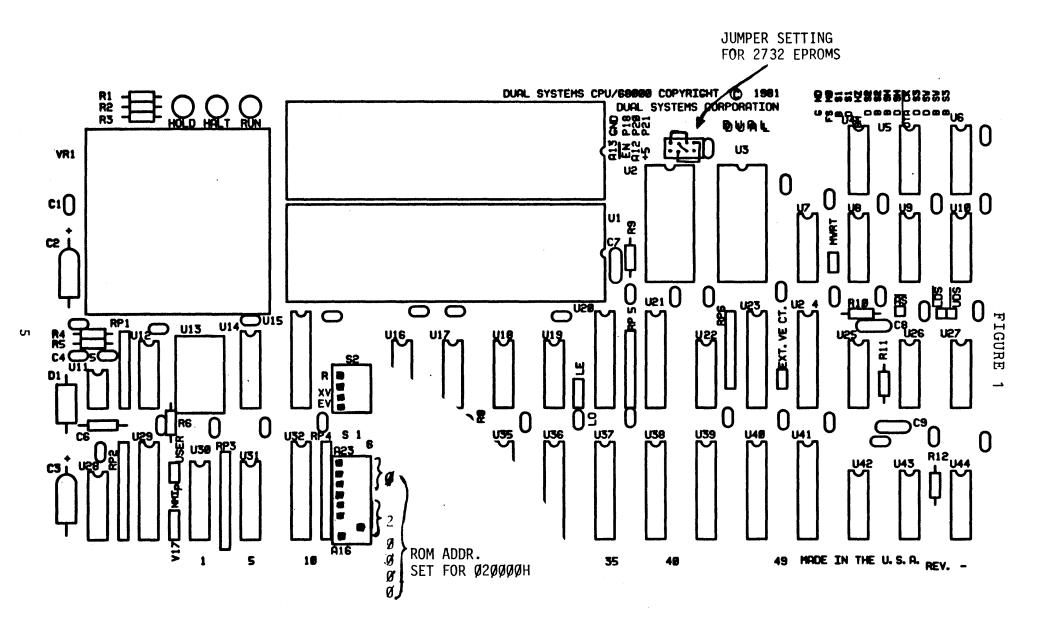

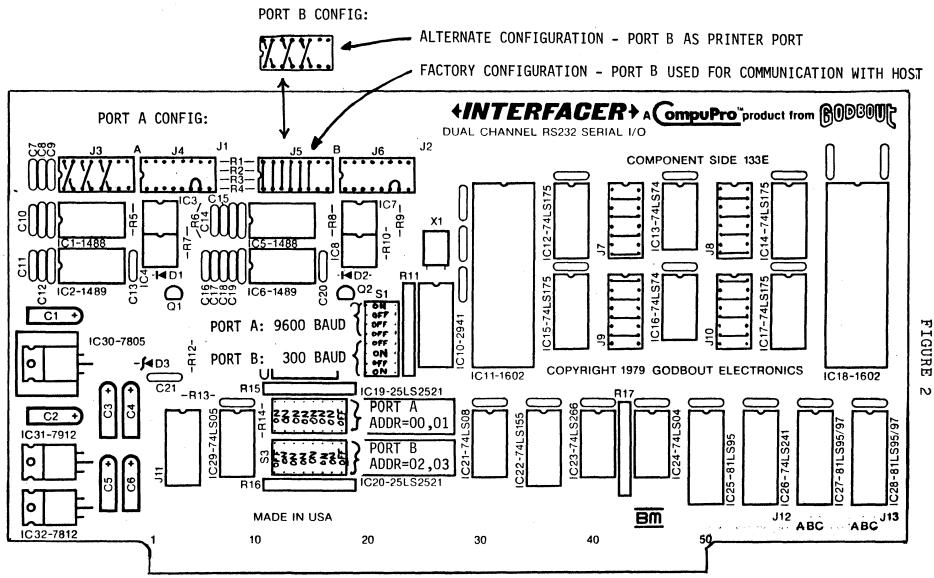

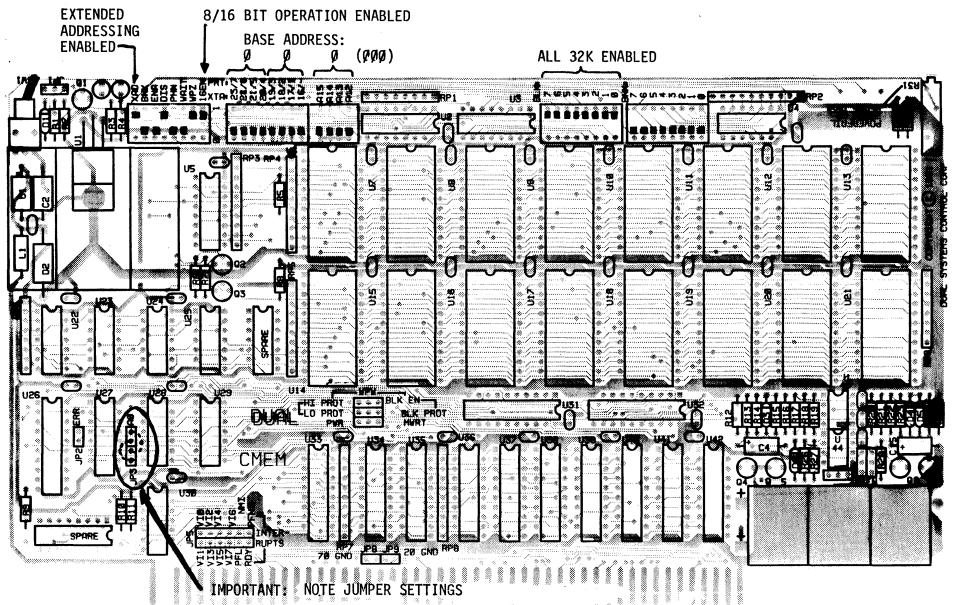

Set the dip-switches on the CPU/68000, Interfacer<sup>2</sup>, and CMEM cards as shown in figures 1, 2, and 3.

After the dip-switches have been set properly, insert the CPU/68000, the Interfacer, and the CMEM boards into the S-100 card cage. Then connect the serial I/O cables between the Interfacer card and the terminal. Be sure to connect pin 1 on the ribbon cable by the index on the edge connector. Set the terminal for 9600 BAUD and upper case only. Now apply power. If everything was done properly, you should see the Macsbug prompt on the terminal:

# MACSBUG 1.31

If this does not appear, turn off the power and recheck all connections and dip-switch settings. Be sure the Interfacer and the terminal are set for identical BAUD rates. Try again. If there is still no response please call Dual Systems.

The dip-switch settings on the CPU/68000 map the monitor program to location 020000H and provide for the boot vectors to be read from the ROMs. These switches are described fully in this manual.

The Interfacer<sup>2</sup> switch setting define the first port to be at I/O location OH and the second port (for printer or host computer) at I/O location 2H.

In order to configure the board for use with your terminal and printer, the port 1 baud rate must be set for the speed of the console terminal and the Port 2 baud rate must match the speed of the printer or the connection to the host computer. In the figure these rates are 9600 and 300 respectively. Parity and stop bits are set for use with an ADM 3A or ADM 5 terminal. For more information regarding baud rates, stop bits, parity etc., refer to the Godbout Interfacer I manual.

The CMEM is set to span memory locations OH to 7FFFH. The stacks reside in the top 1 Kbyte of this memory, the exeption vectors in the low 1 Kbytes and the middle is available for user programs. The remaining switches are set to enable extended addressing, initially enable the board, and to allow writing to the board. For more details refer to the CMEM manual.

<sup>1</sup> Macsbug is a trademark of Motorola.

<sup>2</sup> Interfacer is a trademark of Godbout Electronics

Figure 1. Factory settings for switches S1 and S2, and jumpers on CPU/68000 board.

Figure 2. Factory configuration of serial I/O board for operation with CPU/68000.

δ

FIGURE 3

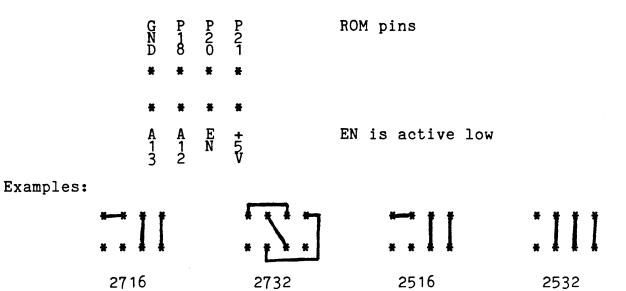

Two ROM sockets are available on the CPU board to store up to 8K bytes of data. The ROMs can be used to store programs, interrupt vectors, or both. A variety of five volt only, 8 bit EPROMs or ROMs may be used. The CPU/68000 is factory configured for use with 2732 EPROMs, see Appendix A for jumper installation for alternate EPROMs.

Switches S1 and S2 determine the ROMs base address and their mode of operation. Either one of two conditions may enable the ROMs:

#### Using the ROMs to Store Programs:

The ROMs may be selected on any read from the address space starting at the address specified by S1. This mode is selected if S2-3 is on. Since only the most significant 8 address bits are decoded the ROMS occupy a full 64 kilobytes of memory.

#### Hardware relocation of the Exception Vectors:

The ROMs can be enabled on memory reads to the exception vector address space. The MC68000 expects to find the exception vectors stored in the first 1024 bytes of memory. Typically it is desirable to store most vectors in RAM to allow software control of traps, interrupts etc. However, the power on sequence requires two 32 bit vectors for the initial stack pointer and program counter. The 68000 expects these 8 bytes at memory locations zero (0) through 7 and they should be stored in ROM to ensure their validity on power up.

Switch S2-1 ("EV", Enable for Vectors) determines whether the vectors are read from on-board ROM or off-board memory (usually ROM). If switch S2-1 is ON the on-board ROMs will be accessed on a read from the exception vector space. If switch S2-1 is OFF, the vectors will be read from off-board memory.

Switch S2-2 ("XV", eXception Vectors) determines which exception vectors enable the ROMs. S2-2 in an ON position enables the ROMs only for the two reset vectors. S2-2 in an OFF position enables the ROMs for the first 64 exception vectors. Normally S2-2 is kept in an on position. However, for some dedicated applications it may be desirable to store the many system exception vectors (divide by zero, trap, interrupt etc.) in ROM.

If one desires to store exception vectors in an off-board ROM (i.e. S2-1 off) S1 determines the new starting address of the vectors.

If the address translation feature is not desired, S1 should be set to all zeros. In this case the address appearing on the bus is identical to the processor's address lines. The user must not disable this feature unless non-volatile (and previously set) memory resides in the first 8 bytes of memory.

#### Switch 2

| OF | ਜ |  |

|----|---|--|

| Ur | г |  |

ON

| 1) "EV"         | Read vectors from<br>OFF-BOARD memory<br>at S1 address | Read vectors from<br>ON-BOARD ROMS                           |

|-----------------|--------------------------------------------------------|--------------------------------------------------------------|

| 2) <b>"</b> XV" | Enable for ALL<br>system vectors.                      | Enable ONLY for reset vectors.                               |

| 3) "R"          | ROMs for vectors only.                                 | Enable ROMs when reading from address space set by switch 1. |

| 4)              | Unused.                                                | Unused.                                                      |

#### Summary

The possible configurations are:

| <u>S2-1</u> | <u>S2-3</u> | Effect                                                                                    |

|-------------|-------------|-------------------------------------------------------------------------------------------|

| OFF         | OFF         | Read exception vectors from off-board memory starting at S1 address.                      |

| OFF         | ON          | Read exception vectors from off board memory and program starting at S1 address from ROM. |

| ON          | OFF         | Read vectors only from ROM.                                                               |

| ON          | ON          | Read vectors and programs from ROM. Program starts at S1 address.                         |

For each of these configurations, if S2-2 is ON then "vectors" only means the first two boot vectors, otherwise all the system vectors (the first 64) are referred to.

Note that even though the program address space starts at the S1 address, you must not overlap the program with the exception vectors. If S2-2 is ON then the program can start at location 08H, if S2-2 is OFF then the program must start after location OFFH.

| Vector    |      | Address |       | ]                            |

|-----------|------|---------|-------|------------------------------|

| Number(s) | Dec  | Hex     | Space | Assignment                   |

| 0         | . 0  | 000     | SP    | Reset: Initial SSP           |

|           | 4    | 004     | SP    | Reset: Initial PC            |

| 2         | 8    | 008     | SD    | Bus Error                    |

|           | 12   | 00C     | SD    | Address Error                |

| 4         | 16   | 010     | SD    | Illegal Instruction          |

| 5         | 20   | 014     | SD    | Zero Divide                  |

| 6         | 24   | 018     | SD    | CHK Instruction              |

| 7         | 28   | 01C     | SD    | TRAPV Instruction            |

| 8         | 32   | 020     | SD    | Privilege Violation          |

| 9         | 36   | 024     | SD    | Trace                        |

| 10        | 40   | 028     | SD    | Line 1010 Emulator           |

| 11        | 44   | 02C     | SD    | Line 1111 Emulator           |

| 12*       | 48   | 030     | SD    | (Unassigned, reserved)       |

| 13*       | 52   | 034     | SD    | (Unassigned, reserved)       |

| 14*       | 56   | 038     | SD    | (Unassigned, reserved)       |

| 15*       | 60   | 03C     | SD    | (Unassigned, reserved)       |

| 16-23*    | 64   | 040     | SD    | (Unassigned, reserved)       |

|           | 95   | 05F     |       | _                            |

| 24        | 96   | 060     | SD    | Spurious Interrupt           |

| 25        | 100  | 064     | SD    | Level 1 Interrupt Autovector |

| 26        | 104  | 068     | SD    | Level 2 Interrupt Autovector |

| 27        | 108  | 06C     | SD    | Level 3 Interrupt Autovector |

| 28        | 112  | 070     | SD    | Level 4 Interrupt Autovector |

| 29        | 116  | 074     | SD    | Level 5 Interrupt Autovector |

| 30        | 120  | 078     | SD    | Level 6 Interrupt Autovector |

| 31        | 124  | 07C     | SD    | Level 7 Interrupt Autovector |

| 32-47     | 128  | 080     | SD    | TRAP Instruction Vectors     |

|           | 191  | OBF     |       |                              |

| 48-63*    | 192  | 0C0     | SD    | (Unassigned, reserved)       |

|           | 255  | OFF     |       |                              |

| 64-255    | 256  | 100     | SD    | User Interrupt Vectors       |

|           | 1023 | 3FF     |       | —                            |

# **Exception Vector Assignment**

\*Vector numbers 12 through 23 and 48 through 63 are reserved for future enhancements by Motorola. No user peripheral devices should be assigned these numbers.

Figure 4. Exception Vector Assignment

| Level | 1 | interrupt | autovector: | V15 |

|-------|---|-----------|-------------|-----|

| Level | 2 | interrupt | autovector: | VI4 |

| Level | 3 | interrupt | autovector: | VI3 |

| Level | 4 | interrupt | autovector: | VI2 |

|       |   |           | autovector: |     |

| Level | 6 | interrupt | autovector: | VIO |

| Level | 7 | interrupt | autovector: | NMI |

The SYSTEM vectors are vector numbers 0 through 63, at addresses 0 through OFF (255).

#### What happens on Power Up

After power up the 68000 loads the system stack pointer and program counter from the first two exception vectors. These two 32 bit vectors are stored in the least significant eight bytes of memory. Since these vectors are required when power is first applied, they should be stored in ROM. In this example, the program counter vector points to location 020008H which is the first instruction in the program in ROM, (after the boot vectors).

If you wish to modify the monitor, you could copy the contents of the ROMS into another memory board, preferably non-volatile RAM. (To read the ROMS, simply read from locations 20000 through 21FFF.) Then you can modify the copy in RAM. To execute the new version you must relocate the RAM to location 20000 and set S2-1 and S2-3 to OFF, so the monitor and the boot vectors are read from the RAM. A sample program for a block move is listed in Appendix D.

#### Format of Data Stored in ROMs

Since the ROMs support word transfers, sequential addresses are stored in alternate ROMs. That is, one ROM (U2) holds the low byte of each word and the other (U1) holds the high byte of each word.

#### NOTE:

If S2-3 is ON (so that the S1 address is mapped to the ROMS) you must make sure that no other memory lies in the address space of the 64K block of memory starting at the S1 address.

#### ADDRESS BUS

The processor board supports an extended 24 bit address bus. This allows the CPU to directly address up to 16 megabytes of memory. Such a vast address space eliminates the need for cumbersome bank select schemes. Older boards responding to only the 16 bit address bus may be used with this CPU but this would restrict the total system address space to 64 kilobytes.

#### I/O Space vs. Memory Space

The 68000 instruction set does not have an explicit Input/Output instruction. Motorola architects intended for all 68000 I/O to be memory mapped. Memory mapped I/O takes advantage of the many powerful addressing modes for fast, efficient I/O routines.

To support S-100 I/O mapped peripherals the processor board dedicates the most significant 64 kilobytes of memory to I/O. As a result, any memory access to hex address FF0000 through FFFFF results in an I/O bus cycle. That is, such an access asserts status outputs SINP or SOUT. This configuration allows efficient memory mapped software while maintaining full compatibility with existing I/O devices.

For example, hex address FF0002 corresponds to I/O port with address 02. So the 68000 instruction:

#### MOVE.B OFF0002H,D0

is similar to the 8080 instruction:

#### IN 02H

Note that 64 kilobytes of address space are dedicated to I/O devices. This allows over 64 thousand input and output ports. To support this many ports requires that I/O devices decode the least significant 16 address bits. The IEEE specification allows extended I/O addressing but does not require it.

The majority of current I/O boards decode only the least significant 8 address bits. This gives 256 input and output ports. The processor board can be used with such an I/O device. Since the I/O board does not decode the full 16 bit I/O address its ports address is replicated throughout the 64 kilobyte I/O address space. The processor board functions quite well with existing I/O boards and is capable of fully supporting future extended I/O address boards as well.

If you are using an I/O board which only decodes the low eight bits of the address then you can use the 16-bit word addressing mode of the 68000. Since to the I/O board address OFF0002 is indistinguishable from OFFFF02, and the 68000 sign extends the word long address, you can also use the address OFF02. So the above example could also be coded: MOVE.B OFF02.W,D0

A0

The 68000 address bus directly drives A1 through A23. The CPU/68000 comes factory jumpered for the updated IEEE-696 standard. That is, the most significant byte of each word is stored at an even address and the least significant byte is stored at the next odd address. Note that instructions, operands, stack data, address vectors etc. are all stored at even addresses.

The definition of AO may be reversed by **carefully** cutting the trace marked LO (Low Odd) and installing a jumper to the pad marked LE (Low Even).

#### DATA BUS

The 68000 transfers data over a single 16 bit bidirectional bus. Programs must reside in 16 bit memory, however, data bytes may be accessed from byte wide memory. Long words must be transferred in sequential 16 bit bus cycles. Byte data is transferred over the corresponding data lines; high order (even address) bytes on D15-D8, low order (odd address) bytes on D7-D0.

The S-100 bus has two 8 bit data paths, Data Odd and Data Even). For byte transfers data is sent over the Data Even bus for write operations and over the Data Odd bus for read operations. For word transfers Data Even and Data Odd are ganged, forming a 16 bit bidirectional bus. During word bus cycles the even (A0=0) byte is transferred over the Data Even bus and the odd (A0=1) byte over the Data Odd bus. On the 68000 the even byte is most significant (D15-D8). If you have changed the A0 jumper on the CPU board then these definitions are reversed.

#### TEMPORARY BUS MASTER INTERFACE (TMA CONTROL)

The 68000 processor board functions as a permanent bus master as specified in the IEEE proposed S100 standard. Temporary bus masters (DMA devices) request the bus by asserting control input HOLD. They receive control of the bus when the bus master (68000 CPU) asserts control output hold acknowledge (pHLDA).

Upon receipt of HOLD the 68000 completes the current bus cycle and then asserts pHLDA. The 68000 suspends all processing until HOLD is released. A temporary master may now disable the permanent bus masters address, data, status and control buses by asserting the four disable lines ADSB, DODSB, SDSB and CDSB. The temporary master now has complete control of the bus for as long as it wishes. When the bus is no longer needed control is returned to the permanent master by releasing the bus disable signals and finally, releasing HOLD.

The method of transferring the bus from the permanent bus master to a temporary master is explicitly specified in the IEEE bus standard section 2.8. Of significance is the method used to transfer ownership of the control output bus. To ensure glitch free transfer, both the permanent and temporary master drive the control output bus during the transfer period. Except for pHLDA, all lines are driven at their non-asserted levels. After a specified time (125 nanoseconds) the temporary master asserts CDSB, disabling the permanent master,s control output bus drivers and acquiring control of the bus.

Up to 16 temporary masters may coexist in a system. A distributed arbitration scheme determines the highest priority device which then takes control of the bus upon assertion of pHLDA.

In general, the 68000 will relinquish control of the bus after the current bus cycle. However, if HOLD is received just before the start of a bus cycle, the 68000 will go ahead with the bus cycle, relinquishing control after its completion.

The 68000 instruction TAS (Test And Set) results in different CPU timing than other instructions. Motorola defines it as a read-modify write cycle. The instruction results in sequential read and write cycles on the S-100 bus. The two cycles are indivisible, that is, the write cycle must follow the read cycle. This type of instruction allows meaningful communications within a multiprocessor or multiprocessing environment. TAS is designed to prevent transfer of bus control until the entire instruction has completed execution. Note that two distinct S-100 cycles are completed, but no interrupts or bus requests will be accepted until the second cycle has completed.

#### INTERRUPTS

The 68000 has a powerful internal interrupt controller. There are seven levels of interrupt priority. All except the non-maskable interrupt are software maskable via the system status word.

The processor board is configured to accept seven of the S-100 interrupt signals, VI5 through VI0 and NMI, where VI5 has the lowest priority. Note that NMI will always generate an interrupt when asserted. VI6 and VI7 are not supported. The S-100 interrupt signals correspond to the MC68000 IPL interrupt levels as follows:

| S-100 definition:   | VI5 | VI4 | VI3 | VI2 | VI1 | VIO | NMI |

|---------------------|-----|-----|-----|-----|-----|-----|-----|

| 68000 CPU notation: | IP1 | I₽2 | IP3 | IP4 | IP5 | IP6 | IP7 |

After receiving an interrupt with priority greater than that specified by the system status word, the 68000 loads the program counter from the appropriate exception vector (a 32-bit address) and begins execution of the interrupt routine. The seven autovectors are vector numbers 25 through 31 (decimal) and reside at locations 100 through 124 (hex). No interrupt acknowledge cycle is needed.

# Appendix A

# Selecting ROMS

The ROM type is selected by jumpers on H1. ROMs supported are the 2716, 2732, 2516, and 2532. The CPU comes configured for use with 2732 ROMs. Following is a diagram of H1:

16

#### Appendix B

# Details of the S-100 bus Interface for the 68000

### FUNCTION OF M1

Status signal sM1 is asserted during any program (as opposed to data) fetch. Historically, sM1 indicated that the current bus cycle would require four clock periods instead of three clock periods. The extra clock period, required for instruction decode, allowed time to refresh dynamic memory. With the 68000, no assumption can be made about the length of a bus cycle based on the level of sM1.

# SIXTN Line

The CPU/68000 does not support sequential byte operations to implement a sixteen-bit data transfer. Therefore it has no need for the SIXTN line on the S-100 bus and it is ignored.

### Appendix C

#### Special Configurations

#### Faster Memory Access When Used with Dual Systems Memories

When the CPU/68000 is used with the Dual Systems line of FAST CMEM (Rev. B and later) memories, memory cycle time is decreased by 25%. This allows the CPU/68000 to run at absolutely full speed with no CPU wait states. This increased speed is possible through the use of an asynchronous bus transfer protocol. When the CPU commences a memory cycle, the CMEM memories respond to a valid address on the bus by asserting a manufacturer-definable line (#66) called FASTACK\* and either gates data onto or latches the data from the data bus. Immediately after the CPU detects that FASTACK\* has been asserted, the processor completes the cycle.

If the memories being accessed do not respond with FASTACK\* a standard S-100 bus cycle is completed. Thus, both Dual FAST CMEM and regular 16 bit S-100 memories may be used in the same system.

The CPU/68000 must have the pins labled "FAST" and "66" jumpered together to enable fast mode.

#### Using the Phantom Line for System Protection

The 68000 is always in one of two modes: system mode or user mode. When in user mode, it is usually desirable to not allow the user access to anything which might impair the integrity of the operating system or file system.

The CPU/68000 is capable of supporting a simple protection scheme. Install a jumper between the pads marked "USER" and "P" (Phantom). When this jumper is installed, the Phantom line will be asserted whenever the CPU is in user mode. Then any I/O (especially disks) which should only be accessed when in system mode can be set to disable themselves when the Phantom line is asserted. In addition, memory that should only be seen read or changed by the operating system directly, can also be set to be disabled when the phantom line is asserted.

# Appendix D

A Few Utility Programs

This program performs a block move, enter it with: A0 Starting address of source A1 Starting address of destination A2 Last address to move + 1

| 0000 | 32D8      | LP1: | MOVW A0@+,A2@+ | MOVE A | WORD       |

|------|-----------|------|----------------|--------|------------|

| 0002 | B1CA      |      | CMPL A2,AÓ     | DONE?  |            |

| 0004 | 6dfa      |      | BLTS LP1       | REPEAT |            |

| 0006 | 4EF9 0002 | 00D8 | JMP /200D8     | RETURN | TO MACSBUG |

This fills a block with a word. AO ADDRESS of word to fill with A1 Starting address of block A2 Last address of block + 1

| 0000 | 32D0      | LP2: M | WVON | A00,A10+ | MOVE A WORD       |

|------|-----------|--------|------|----------|-------------------|

| 0002 | B3CA      | C      | CMPL | A2,Å1    | DONE?             |

| 0004 | 6dfa      | B      | BLTS | LP2      | REPEAT            |

| 0006 | 4EF9 0002 | 00D8 J | JMP  | /200D8   | RETURN TO MACSBUG |

For testing hardware with a scope, this repeatedly sends a byte to any address (could be an I/O port). Sends the byte in D0 to the address pointed to by A0.

| 1080 | LP3: | MOVB | D0,A00 |

|------|------|------|--------|

| 60FC |      | BRAS | LP3    |

This reads from the address in AO and puts the result in DO.

| 1010 | LP4: | MOVB | AO@,DO |

|------|------|------|--------|

| 60FC |      | BRAS | LP4    |

All of these routines are relocatable. They can be entered into any free area of memory (such as 2000) with the MACSBUG OP command. The entry parameters can be directly placed in the registers, and the routine executed with the G command.

#### 1. INTRODUCTION

This document describes the operation of the MACSbug monitor after it has been installed. It includes a complete description of all the commands and examples of its use.

#### 2. OPERATIONAL PROCEDURE

After the CPU/68000 board has been installed, as per the manual, the user should perform the following:

a. Turn power ON to the system.

b. Depress the RESET (black) button.

The system should initialize and print:

MACSBUG 1.31

If these two lines do not print out, go back and check the CPU/68000 manual. Check especially that the terminal and I/O board have the same BAUD rates.

#### 3. COMMAND LINE FORMAT

Commands are entered the same as in most other buffer organized computer systems. A standard input routine controls the system while the user types a line of input. The delete (RUBOUT) key or control 'H' will delete the last character entered. A control 'X' will cancel the entire line. Control 'D' will redisplay the line. Processing begins only after the carriage return has been entered.

During output to the console the control 'W' will suspend the output until another character is entered. The BREAK key will abort most commands.

The format of the command line is:

\*COmmand parameters; options

\*

where:

is the prompt from the monitor. The user does not enter this. In the examples given, the lines beginning with this character are lines where the user entered a command.

- CO is the necessary input for the command. Each command has one or two <u>upper case letters</u> necessary in its syntax. In the <u>examples</u>, the entire command may be used, but only those letters in upper case in the syntax definition are necessary.

- mmand is the unnecessary part of the command. It is given in the syntax definition only to improve readability. If this part of the command was actually entered on the command line, it would be ignored.

- parameters depends upon the particular command. Data is usually in hex but most printable ASC11 characters may be entered if enclosed in single quotes. The system also supports a limited symbolic feature allowing symbols to be used interchangeably with data values.

- ;options modifies the nature of the command. A typical option might be to disregard the checksum while reading a file.

Message put out by MACSbug to indicate user is

Note: MACSbug requires all commands to be entered in upper case letters. If lower case letters are used, MACSbug will respond with WHAT?

4. EXAMPLE OF COMMAND PROCEDURES

MACSBUG 1.0 \*P2 \*TRANSPARENT\* User may now communicate directly with the host system User may now communicate directly with the host system. Typing a control A at any time will exit to MACSbug.

```

(Control A)

*MACSBUG*

```

|                                | now in MACSbug command mode                 |

|--------------------------------|---------------------------------------------|

| *READ ;=COPY FILE.MX,#CN       | Download from EXORciser host                |

| *DM 1000                       | Display memory                              |

| 001000 70 01 70 02 70 03 70 04 | 70 05 4E F8 10 00 FF FF p.p.p.p.N           |

| *PC 1000                       | Set program counter to START                |

| *TD CLEAR                      | Clear the trace display                     |

| *TD PC.22 DO.1                 | Specify which registers to print in display |

| *TD                            | Print the trace display                     |

| PC≑1000 DO=00                  |                                             |

| *BR 1004                       | Set a breakpoint                            |

| *T TILL O                      | Trace command                               |

| PC=1002 DO=01                  |                                             |

| PC=1004 DO=02                  | Stopped at breakpoint                       |

| :*GO                           |                                             |

| PC=1004 DO=02                  | Stopped at breakpoint                       |

| *                              | Program is ready to run                     |

# 3.6 MACSbug COMMAND SUMMARY

.

| COMMAND           | DESCRIPTION                                                  | PAGE    |

|-------------------|--------------------------------------------------------------|---------|

| reg#              | Print a register                                             | 3.5     |

| reg# hexdata      | Put a hex value in the register                              |         |

| reg# 'ASCII'      | Put hex-equivalent characters in register                    |         |

| reg#:             | Print the old value and request new value                    |         |

| class             | Print all registers of a class (A or D)                      |         |

| class:            | Sequence through print old value request new                 |         |

| DM start end      | Display memory, hex ASCII memory dump                        | 3-6     |

| SM address data   | Set memory with data                                         |         |

| OPen address      | Open memory for read/change                                  | 3.7     |

| SYmbol NAME value | Define and print symbols                                     | 3-8     |

| W#                | Print the effective address of the window                    | 3.9     |

| ₩#. 1en EA        | Define window length and addressing mode                     |         |

| M# data           | Memory in window, same syntax as register                    |         |

| Go                | Start running from address in program counter                | 3-10    |

| Go address        | Start running from this address                              |         |

| Go TILL add       | Set temporary breakpoint and start running                   |         |

| BReakpoint        | Print all breakpoint addresses                               |         |

| BR add: count     | Set a new breakpoint and optional count                      |         |

| BR —address       | Clear a breakpoint                                           |         |

| BR CLEAR          | Clear all breakpoints                                        |         |

| TD                | Print the trace display                                      | 3.11    |

| TD reg#. format   | Put a register in the display                                |         |

| TD Clear          | Take all registers out of the display                        |         |

| TD ALI            | Set all registers to appear in the display                   |         |

| TD A. 1 D. 1 L. c | Set register blocks or line separator                        | 3.12    |

| T                 | Trace one instruction                                        | 3.13    |

| T count           | Trace the specified number of instructions                   |         |

| T TILL Address    | Trace until this address                                     |         |

| :*(CR)            | Carriage return trace one instruction                        |         |

| OFfset address    | Define the global offset                                     | 3.14    |

| CV decimal        | Convert decimal number to hex                                | 3-15    |

| CV \$hex          | Convert hex to decimal                                       |         |

| CV value,value    | Calculate offset or displacement                             |         |

| REad ; =text      | Expect to receive 'S' records                                | 3-16    |

| VErify; =text     | Check memory against 'S' records                             |         |

| PUnch start end   | Print 'S' records (tape image)                               |         |

| FOrmat hex        | Program/initialize an ACIA                                   | 3-17    |

| NUII hex          | Set character null pads                                      |         |

| CR hex            | Set carriage return null pads                                |         |

| TErminal baud     | Set terminal null pads to default values                     |         |

| CAll address      | JSR to user utility routine                                  | 3-18    |

| P2                | Enter transparent mode                                       | 3-19    |

| *data             | Transmit command to host                                     |         |

| Break             | The BREAK key will abort most commands                       |         |

| CTL-A             | The control A key ends transparent mode                      |         |

| CTL-D             | The control D key redisplays the line                        |         |

| CTL-H             | The control H key deletes the last character entered         |         |

| CTL-W             | The control W key suspends output until another character is | entered |

| CTL-X             | The control X key cancels the entire line                    |         |

| Rubout            | The RUBOUT key deletes the last character entered            |         |

| Del               | The DEL key deletes the last character entered               |         |

|                   |                                                              |         |

#### 3.6.1 Set and Display Registers

### 68000 REGISTER MNEMONICS

D0,D1,D2,D3,D4,D5,D6,D7 A0,A1,A2,A3,A4,A5,A6,A7 PC SR SS US

#### COMMAND FORMATS

reg# hexdata reg# 'ascii data' reg#: reg# class (where class=D or A) class:

### **EXAMPLES**

\*A5 123 \*A5 A5=00000123 Computer response \*D4 FFFFFF Set a data register \*D0: D0=0000000=?45FE \*D: D0=000045FE=? 9EAB3 D1 = 00000000 = ? (CR)D2=00000000=? (CR) D3=00000000=? (CR) D4=00FFFFF=? (CR) D5=0000000=?55555 D6=0000000=?(CR)D7=00000000=? (CR) \*D Display all data registers D0=0009EAB3 D1=00000000 D2=00000000 D3=00000000 D4=00FFFFFF D5=00055555 D6=0000000 D7=0000000 Display and request input for program counter \*PC: Set the program counter to new value PC=0008B3=? 2561 Set status register to zero (user mode) \*SR 0 \*A7 4321 Set address register (same as US now) Display user stack pointer \*US US=00004321 Set supervisor stack pointer \*SS 7FFF Set status register to supervisor mode \*SR 2000 Print A7 which is now the SS register \*A7 A7=00007FFF

### DESCRIPTION

Data registers Address registers Program counter Status register (condition codes) Supervisor stack pointer (A7 in supervisor mode) User stack pointer (A7 in user mode)

### DESCRIPTION

Put a hex value into register 'reg#' Put ASCII value into register 'reg#' Print register value and take in new value Print register value Print values of all registers in the class Cycle through all registers in the class printing old value and requesting new value

# COMMENTS

Set address register A5 to hex value 123 Command to print the value of register A5 Command to print old value and take in new value Computer prompts with old value; new value entered Command to cycle through all data registers Change value of register D0 from 45FE to 9EAB3 Carriage return (null line) means the value remains the same.

Change register D5 to a new value

**REGISTER DISPLAY**

### COMMAND FORMAT

DESCRIPTION

| FYA  |                | COMMENTS                                                                                              |

|------|----------------|-------------------------------------------------------------------------------------------------------|

| SM a | ddress data N  | The 'N' as the last character means start a new line; the system will prompt with the current address |

|      | ddress 'ASCII' | Set Memory to ASCII                                                                                   |

|      | ddress data    | Set Memory to hex                                                                                     |

|      | start end      | Send output to PORT 2                                                                                 |

|      | start count    | Where start > count                                                                                   |

| DM   | start end      | Display Memory in hex and ASCII where start $<$ end                                                   |

### EXAMPLES

\*DM 2003 12

COMMENIS

| *SM 2000 'ABC'       | Set memory to some ASCII data |

|----------------------|-------------------------------|

| *SM 2003 4445 46 'G' | Set some more locations       |

| *DM 2000 2010        | Command to dump memory        |

002000 41 42 43 44 45 46 47 00 00 00 00 00 00 00 00 00 ABCDEFG.

> In this version of the command the second number is smaller than the first so it is decoded as a count.

\*SM 1000 1 23 456 7890 ABCDE 12345678 Size can be up to 8 characters \*DM 1000 001000 01 23 04 56 78 90 0A BC DE 12 34 56 78 00 00 00 .....

\*SM 1000 TABLE ' 00005678 N Use of the 'N' parameter to start a new line

0000100C? 'START ' 00023456

\*DM 1000 20

001000 54 41 42 4C 45 20 20 20 00 00 56 78 53 54 41 52 TABLE . . . . VxSTAR 001010 54 20 20 20 00 02 34 56 00 00 00 00 00 00 00 00 T.....4V.....

\*OFFSET 2030 Global offset will be added to command parameters \*DM 1000 . . . . . . . . . . . . . . . . .

\*SM 1005 1234 N Global offset added to address 1005 00003037 ? AB \*DM 1000 003030 FF FF FF FF FF 12 34 AB FF .....

| *SM 20000 AB CD EF | Trying to set ROM |

|--------------------|-------------------|

| ERROR              | Error message     |

| *                  |                   |

# 3.6.3 Open Memory for Read/Change

# COMMAND FORMAT

DESCRIPTION

# OPen address

Open memory at specified address and enter subcommand mode

A

# SUBCOMMAND FORMAT

| ADDRESS     | CON | ITENT | USER<br>ENTERS | COMMENTS                                          |

|-------------|-----|-------|----------------|---------------------------------------------------|

| *OP 1000    |     |       |                | Open memory location 1000                         |

| 001000      | -   | FF?   | 12             | User enters data and system goes to next location |

| 001001      | -   | AB?   | (CR)           | Carriage return means go to the next location     |

| 001002      | =   | 44 ?  | 34†            | Up arrow means go to previous location            |

| 001001      | =   | AB?   | 1              | Can be entered without data                       |

| 001000      | -   | 12 ?  | 77=            | Equal sign means stay at same address             |

| 001000      | =   | 77 ?  | =              | Can be used without any data                      |

| 001000      | =   | 77?   |                | Period means return to MACSbug                    |

| *           |     |       |                | Returns to command level                          |

| *OP 1234    |     |       |                |                                                   |

| 021234      | =   | FF?   | 99=            | Example of trying to change ROM                   |

| **NO CHANGE | **  |       |                | Warning message                                   |

| 021234      | =   | FF?   |                | Does not abort command                            |

| CON | IMAN | D FOR | MAT |

|-----|------|-------|-----|

|     |      |       |     |

DESCRIPTION

| SYml | ool name hex value | Put a symbol in the symbol table with a hex value or assign a new value to a previously defined one. NAME can be 8 characters long, consisting of: A-Z, O-9, (period), and \$ (dollar sign). It must begin with letter (A-Z) or period. |

|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SY   | -name              | Remove a symbol from the symbol table                                                                                                                                                                                                   |

| SY   | name               | Print the current value of the symbol (absolute)                                                                                                                                                                                        |

| SY   | value              | Print the first symbol with the given value                                                                                                                                                                                             |

| SY   |                    | Print the sorted symbol table                                                                                                                                                                                                           |

#### NOTE

Offset is not used by this command. Some commands recognize the words TILL, ALL, and CLEAR as key words and will not interpret them as symbols.

Puts the symbol in the table

#### EXAMPLES

COMMENTS

\*SY XYZ 5000 \*SY XYZ XYZ =5000 \*SY XYZ 123 \*SY ABC34 2500 \*SY Z17.RT5 XYZ \*SY 123 XYZ =123 \*SY B\$67ABC 4300 \*SY RFLAG 2300 \*SY MVP2 9990 \*SY ABC34 00002500 RFLAG 00002300

Change a symbol's value Define another symbol Define a symbol with value from another symbol Print first symbol with value of 123

Command prints out the symbol's current value

Define some more symbols

| Print the sorted symbol table |          |         |          |

|-------------------------------|----------|---------|----------|

| B\$67ABC                      | 00004300 | MVP2    | 00009990 |

| XYZ                           | 00000123 | Z17.RT5 | 00000123 |

\*SY TTT T IS NOT A HEX DIGIT \*SY 567 00000567=567 Print a value for symbol not in table, when not found, it tries to convert parameter to number Attempt to print value for symbol not in table

### SYNTAX EXAMPLES

### <u>COMMENTS</u>

\*BR MVP2 \*CALL RFLAG \*PC ABC34 \*DM MVP2 10 Set a symbolic breakpoint User defined routine Set a register Display some memory

# **EXAMPLES OF KEY WORDS IN COMMANDS**

| *BR CLEAR        | The word CLEAR is not considered a symbol here |

|------------------|------------------------------------------------|

| *GO TILL Z17.RT5 | The word TILL is part of the command           |

| *T TILL ABC34    | The word TILL is part of the command           |

#### 3.6.5 Displaying and Accessing Memory through Windows

#### WINDOWS

A "window" is an effective address through which the user can "see" memory. The windows are labeled W0 to W7 and are defined using the syntax listed below. The windows address corresponding memory locations labeled M0 to M7 which use the same syntax as registers. These memory locations can be examined, set or defined in the display the same as a register.

#### **COMMAND FORMAT** DESCRIPTION **W**# Print the effective address of a given window W#. len EA Define a window size and effective address # is the window number 0 to 7 len is the length in bytes 1=byte; 2=word; 3=3 bytes; 4=long word O=close a window (undefine it) EA is Effective Addressing mode (see EA SYNTAX EXAMPLES in table below) M# data or 'ASCII' Pseudo registers have same syntax as registers EA SYNTAX EXAMPLES DESCRIPTION **FE84** Absolute address (A6) Address register indirect 100(A6) Indirect with displacement -10(A6.D2)Indirect with index and displacement -100(\*)Program counter with displacement 10(\*.A4) Program counter with index and displacement **EXAMPLES** COMMENTS \*W3.4 (A6) Define a window \*A6 2000 Enter a value for the address register \*W3 Print the effective address of a window W3.4(A6) = 2000\*M3 87342 Set memory through the window \*M3 Command to print memory through the window M3=00087342 \*DM 2000 Display a line of memory 002000 00 08 73 42 00 00 00 00 00 00 00 00 00 00 00 00 . . sB ..... **\*TD CLEAR** Clear all registers from the trace display \*TD PC. 2 A6. 3 M3. 1 Define some registers for the display \*TD Command to print the trace display PC=00A2 A6=002000 M3=42 NOTE: W3. 4 and M3. 1 only lowest byte displayed \*W3.2 (A6) Change width of window \*TD M3.2 Change width of display \*TD PC=00A2 A6=002000 M3=0008 \*W0.110(\*,A6) Define a new window: PC+A6+10 \*W0 Print effective address of window WO W0.110(\*,A6)=20B2 \*W3.0 Close window W3. undefine it \*TD

**Closed/undefined windows are not in the display**

PC=00A2 A6=002000

# **GO, BREAKPOINT**

#### COMMAND FORMAT

Go Go address Go TILL address

#### BR

BR address BR –address BR address;count BR CLEAR

#### **EXAMPLES**

# COMMENTS

DESCRIPTION

Begin execution at address in PC register

Print the address of all breakpoints (8 maximum)

Set a breakpoint at this address with a count

Set a temporary breakpoint at the address and run until a break-

Begin execution at this address

Set a breakpoint at this address

Remove the breakpoint at this address

point is encountered

Remove all breakpoints

(see example program on page 3-3)

| *PC 1000                        | Set program counter to starting address                        |

|---------------------------------|----------------------------------------------------------------|

| *TD CLEAR                       |                                                                |

| *TD PC. 2 DO. 1                 | Set trace display format                                       |

| *TD                             | Print trace display                                            |

| PC=1000 D0=00                   |                                                                |

| *G TILL 1008                    | Run until address                                              |

| PC=1008 D0=04                   | System displays when it stops                                  |

| *BR 1002                        | Set a breakpoint                                               |

| *G                              | Run until breakpoint                                           |

| PC=1002 D0=01                   | Trace display                                                  |

| *BR 1008: 4                     | Set a breakpoint with a count                                  |

| *BR                             | Print the breakpoints                                          |

| BRKPTS= 1002 1008: 4            |                                                                |

| *G                              | Run                                                            |

| PC=1000 D0=4                    | Decrements count, prints display, continues                    |

| PC=1002 D0=1                    | Stops at breakpoint with zero count                            |

| *BR                             | Print the breakpoints                                          |

| BRKPTS= 1002 1008: 3            | Count has been decremented by one                              |

| *BR -1002                       | Remove a breakpoint                                            |

| *G                              | Run                                                            |

| PC=1000 D0=4                    | Count from 3 to 2                                              |

| PC=1008 D0=4                    |                                                                |

| PC=1008 D0=4                    | 1 to 0 and it stops here                                       |

| *BR                             | Print the breakpoints                                          |

| BRKPTS=1008                     | No count for this breakpoint                                   |

| *BR 1000                        | Set another breakpoint                                         |

| *G 1000                         | Start running from 1000, bypass breakpoint at starting address |

| PC=1008 D0=4                    | and stop at next breakpoint                                    |

| *SY JUMPER 100A                 | Define a symbol                                                |

| *BR JUMPER: 5                   | Set a breakpoint at a symbolic address                         |

| *BR 123456: 7897 11 22 33 44 55 |                                                                |

|                                 | D 100A: 5 123456: 7897 11 22 33 44                             |

| *OFFSET 3000                    |                                                                |

| *BR CLEAR                       |                                                                |

| *BR 50                          | When setting breakpoints the global offset is added to the     |

| *BR                             | parameter but all addresses printed are absolute               |

| BRKPTS = 3050                   |                                                                |

## 3.6.7 Set the Trace Display Format (Individual Registers)

#### COMMAND FORMAT DESCRIPTION TD Print the trace display **TD CLear** Take everything out of the display TD ALI Put all registers in display (see page 3-12) TD reg#. format Add or delete registers in display where reg# is D0.D7, A0.A7, W0.W7, MO-M7, PC, SR, US, SS, A, D, or L (see page 3-12 for A,D,L). format can be 0,1,2,3,4,Z,D,R, or S O=remove the item from the display 1,2,3,4=print this number of bytes as hex characters, include all leading zeros Z=signed long word hex with zero suppress D=signed long word decimal with zero suppress R=subtract offset (see OFfset command) then print with Z format with letter 'R' at end S=search symbol table for 4 byte value, if found print symbol name as 8 characters. if not found print hex value as 8 characters EXAMPLES COMMENTS **\*TD CLEAR** Turn off all the registers in display \*TD PC. 3 D1. 1 Define PC as 3 bytes and D1 as one \*TD Command to display PC=000000 D1=05 This is the trace display \*TD PC. 0 A6 Remove PC and add A6 which defaults to 4 bytes \*TD Display D1=05 A6=000008F Display with two new registers \*W3. 2 2000 Define a window \*M3 20 Set value of memory pseudo register \*TD M3. 2 Add a memory pseudo register to the display \*TD Display D1=05 A6=000008F M3=0020 New display \*TD A6. 1 D1. 3 M3. Z Change length of registers already in display \*TD Display D1=000005 A6=8F M3=20 New display, M3 now suppresses leading zeroes \*TD D1. R M3. D D1 is relative and M3 is decimal \*OFFSET 12345 Set the offset (see OFfset command) \*TD Display D1=-12340R A6=8F M3=32 5-offset=-12340R; 20 hex = 32 decimal \*SY TABLE 8F Define a symbol (see SYmbol command) \*TD A6. S M3. 0 Make A6 print symbol if value is in table \*TD D1 = -12340RA6 = TABLEPrints symbolic value \*A6 123 Set A6 to a value NOT in symbol table \*TD

A6 prints value with 4 byte format

D1 = -12340RA6 = 00000123

| TD CLear       Take everything out of the display         TD D. 1       Put all data registers in display as a block         TD A. 1       Put all address registers in display as a block (for D. 1 and A. 1 the format is fixed at 4 bytes)         TD L character       Define a line separator at the end of display (0 will reverse A. 1, D. 1, and L char commands)         TD ALI       Same as keying in:         *TD PC. 3 SR. 2US. 4 SS. 4 D 1 A 1 L – does not affect other registers and windows that have been previously defined to display <b>EXAMPLES</b> COMMENTS         *TD CLEAR       Clear the display         *TD CLEAR       Clear the display         *TD CLEAR       Print the trace display         *TD CLEAR       Print the trace display         *TD CLEAR       Define all address registers in a block         *TD A. 1       Define all address registers in a block         *TD A. 1       Define all address registers in a block         *TD A. 1       Define all ine separator (a row of '@')         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A5=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A0=00000000 A1=00000000 A2=000000000 A3=00000000                                                    | COMMAND FORMAT                               | DESCRIPTION                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------|

| TD A. 1       Put all address registers in display as a block (for D. 1 and A. 1 the format is fixed at 4 bytes)         TD L character       Define a line separator at the end of display (0 will reverse A. 1, D. 1, and L. char commands)         TD ALI       Same as keying in:         *TD PC. 3 SR. 2 US. 4 SS. 4 D. 1 A. 1 L –       does not affect other registers and windows that have been previously defined to display         EXAMPLES       COMMENTS         *TD D. 1       Define all data registers in a block         *TD       Print the trace display         *TD A. 1       Define all data registers in a block         *TD       Print the trace display         000000000 D1=00000000 D2=00000000 D7=00000000         04=00000000 D5=00000000 D2=00000000 D7=00000000         04=00000000 D5=00000000 A2=00000000 A3=00000000         04=00000000 A1=00000000 A2=0000000 A3=00000000         A4=00000000 A1=0000000 A2=00000000 A3=00000000         A4=00000000 A1=0000000 A2=00000000 A3=00000000         A4=00000000 A1=0000000 A2=00000000 A3=00000000         A4=00000000 A1=0000000 A2=00000000 A3=00000000         A4=000000000 A1=00000000 A2=00000000 A3=000000000           | TD CLear                                     | Take everything out of the display                                    |

| TD L. character       Define a line separator at the end of display (.0 will reverse A. 1,<br>D. 1, and L. chara commands)         TD ALI       Same as keying in:<br>*TD PC. 3 SR. 2 US. 4 SS. 4 D. 1 A. 1 L. –<br>does not affect other registers and windows that have been<br>previously defined to display <b>EXAMPLES</b> COMMENTS         *TD CLEAR       Clear the display         *TD D. 1       Define all data registers in a block         *TD       Print the trace display         *TD D. 1       Define all datres registers in a block         *TD       Print the trace display         *TD ALI       Define all address registers in a block         *TD       Print the trace display         *TD A. 1       Define all address registers in a block         *TD       Print the trace display         *TD A. 1       Define all address registers in a block         *TD       Print the trace display         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A5=00000000 A2=00000000 A3=00000000         A4=000000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=000000000 A1=00000000 A2=00000000 A3=000000000         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A5=00000000 A2=00000000 A7=00007FFE         &&&& & & & & & & & & & & & & & & & & &                                                    | TD D. 1                                      | Put all data registers in display as a block                          |

| TD L character       Define a line separator at the end of display (.0 will reverse A. 1,<br>D. 1, and L. char commands)         TD ALI       Same as keying in:<br>*TD PC. 3 SR. 2 US. 4 SS. 4 D. 1 A. 1 L. –<br>does not affect other registers and windows that have been<br>previously defined to display         EXAMPLES       COMMENTS         *TD CLEAR       Clear the display         *TD D. 1       Define all data registers in a block         *TD       Print the trace display         00000000 D1=00000000 D2=00000000 D3=00000000         04=00000000 D5=00000000 D7=00000000         04=00000000 A1=0000000 A2=0000000 A3=00000000         *TD A. 1       Define all address registers in a block         *TD       A0=00000000 A1=0000000 A2=0000000 A3=0000000         A4=00000000 A1=00000000 A2=0000000 A3=00000000         A4=00000000 A1=00000000 A2=0000000 A3=00000000         A4=00000000 A1=0000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=000000000 A1=00000000 A2=000000000 A3=00000000         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=000000000 A1=000000000 A2=000000000 A3=000000000         A | TD A. 1                                      | Put all address registers in display as a block (for D. 1 and A. 1 $$ |

| D. 1, and L. char commands)         TD ALI       Same as keying in:         *TD PC. 3 SR. 2 US. 4 SS. 4 D. 1 A. 1 L. –         does not affect other registers and windows that have been previously defined to display         EXAMPLES       COMMENTS         *TD 0.1       Define all data registers in a block         *TD 0       Print the trace display         00000000 D1=00000000 D2=0000000 D3=00000000       D4=00000000 D5=00000000 D5=00000000 D7=00000000         *TD CLEAR       TD CLEAR         *TD 1       Define all address registers in a block         *TD 4.1       Define all address registers in a block         *TD 4.1       Define all address registers in a block         *TD 4.1       Define all ine separator (a row of '@')         *TD 4.2       Define a line separator (a row of '@')         *TD 4.3       Define a line separator (a row of '@')         *TD 4.4       Define a line separator (a row of '&')         *TD 4.4       Define a line separator (a row of '&')         *TD 4.4       Define a line separator (a row of '&')         *TD 4.4       Define a line separator (a row of '&')         *TD 4.4       Define a line separator (a row of '&')         *TD 4.4       Define a line separator (a row of '&')         *TD 4.5       Define a line separator (a row of '&') <td></td> <td>the format is fixed at 4 bytes)</td>                                                 |                                              | the format is fixed at 4 bytes)                                       |

| *TD PC. 3 SR. 2 US. 4 SS. 4 D. 1 A. 1 L. –<br>does not affect other registers and windows that have been<br>previously defined to displayEXAMPLESCOMMENTS*TD CLEARClear the display*TD D. 1Define all data registers in a block*TDPrint the trace display00=0000000 D1=00000000 D2=00000000 D3=0000000004=00000000 D5=00000000 D6=00000000 D7=0000000004=00000000 D5=00000000 D6=00000000 D7=0000000004=00000000 A1=00000000 A2=00000000 A3=0000000004=00000000 A1=00000000 A2=00000000 A7=00007FFE*TD L @Define a line separator (a row of '@')*TD L @Define a line separator (a row of '@')*TD L &Define a line separator (a row of '@')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Define a line separator (a row of '&')*TD L &Turn on commonly used registers                                                                                                                                                                                                                                                                                                                                                                                | TD L. character                              |                                                                       |

| does not affect other registers and windows that have been<br>previously defined to displayEXAMPLESCOMMENTS*TD D. 1Define all data registers in a block*TDPrint the trace display*TD 0Print the trace displayD0=00000000 D1=00000000 D2=00000000 D3=00000000D4=00000000 D5=00000000 D6=00000000 D7=00000000PTD CLEAR*TD A. 1Define all address registers in a block*TDA0=0000000 A1=0000000 A2=0000000 A3=00000000A4=00000000 A1=0000000 A2=0000000 A7=00007FFE*TD LDefine a line separator (a row of '@')*TDA0=0000000 A1=0000000 A2=0000000 A3=00000000A4=00000000 A1=0000000 A2=0000000 A3=00000000A4=00000000 A1=0000000 A2=0000000 A3=00000000A4=00000000 A1=00000000 A2=0000000 A3=00000000A4=00000000 A1=00000000 A2=00000000 A3=00000000A4=00000000 A1=00000000 A2=00000000 A3=00000000A4=00000000 A1=00000000 A2=00000000 A3=00000000A4=00000000 A1=00000000 A2=00000000 A3=00000000A0=00000000 A1=00000000 A2=00000000 A3=00000000A0=00000000 A1=00000000 A2=00000000 A7=00007FFE&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&&                                                                                                                                                                                                                                                                                                                                                                                                          | TD ALI                                       |                                                                       |

| EXAMPLES         COMMENTS           *TD CLEAR         Clear the display           *TD D. 1         Define all data registers in a block           *TD         Print the trace display           D0=0000000 D1=00000000 D2=00000000 D3=00000000         D4=00000000 D5=00000000 D7=00000000           04=00000000 D5=00000000 D2=00000000 D7=00000000         TD           *TD D         Print the trace display           D0=00000000 D5=00000000 D7=00000000         TD           *TD CLEAR         *TD A           *TD A         Define all address registers in a block           *TD A         Define all address registers in a block           *TD A         Define all address registers in a block           *TD L         @           A0=00000000 A1=00000000 A2=00000000 A3=00000000           A4=00000000 A1=00000000 A2=00000000 A3=00000000           A4=00000000 A1=00000000 A2=00000000 A3=00000000           A4=00000000 A1=00000000 A2=00000000 A3=00000000           *TD L         Define a line separator (a row of '&')           *TD         A           A0=00000000 A1=00000000 A2=00000000 A3=00000000           A0=00000000 A1=00000000 A2=00000000 A7=00007FFE           &&& Define a line separator (a row of '&')           *TD                                                                                                                                                                              |                                              |                                                                       |

| *TD CLEAR       Clear the display         *TD D.1       Define all data registers in a block         *TD       Print the trace display         D0=00000000 D1=00000000 D2=00000000 D3=000000000       D4=00000000 D5=00000000 D7=00000000         D4=00000000 D5=00000000 D6=00000000 D7=00000000       *TD         TD A.1       Define all address registers in a block         *TD       A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A5=00000000 A2=00000000 A7=00007FFE         *TD L @       Define a line separator (a row of '@')         *TD       A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A7=00007FFE       @@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                              | -                                                                     |

| *TD D. 1       Define all data registers in a block         *TD       Print the trace display         D0=0000000 D1=0000000 D2=0000000 D3=0000000       D4=0000000 D5=0000000 D6=0000000 D7=0000000         PTD CLEAR       *TD A.1         *TD A       Define all address registers in a block         *TD       A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A5=00000000 A6=00000000 A7=00007FFE         *TD L       @         Define a line separator (a row of '@')         *TD         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A3=00000000         A4=000000000 A1=00000000 A2=00000000 A3=00000000         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A0=00000000 A1=00000000 A2=00000000 D3=000000000         A0=00000000 A1=00000000 D2=000000000                                                        | EXAMPLES                                     | COMMENTS                                                              |

| *TD       Print the trace display         D0=00000000 D1=00000000 D2=00000000 D3=00000000         D4=00000000 D5=00000000 D6=00000000 D7=00000000         *TD CLEAR         *TD A. 1       Define all address registers in a block         *TD         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A5=00000000 A6=00000000 A7=00007FFE         *TD L       @         Define a line separator (a row of '@')         *TD         A0=00000000 A1=00000000 A2=00000000 A3=00000000         A4=00000000 A1=00000000 A2=00000000 A7=00007FFE         @@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | *TD CLEAR                                    | Clear the display                                                     |

| D0=00000000 D1=00000000 D2=00000000 D3=00000000<br>D4=00000000 D5=00000000 D6=00000000 D7=00000000<br>*TD CLEAR<br>*TD A. 1 Define all address registers in a block<br>*TD<br>A0=00000000 A1=00000000 A2=00000000 A3=00000000<br>A4=00000000 A1=00000000 A2=00000000 A7=00007FFE<br>*TD L @ Define a line separator (a row of '@')<br>*TD<br>A0=00000000 A1=00000000 A2=00000000 A3=00000000<br>A4=00000000 A1=00000000 A2=00000000 A7=00007FFE<br>@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | *TD D. 1                                     |                                                                       |

| D4=0000000 D5=0000000 D6=0000000 D7=0000000<br>*TD CLEAR<br>*TD A. 1 Define all address registers in a block<br>*TD<br>A0=00000000 A1=0000000 A2=0000000 A3=0000000<br>A4=00000000 A1=0000000 A2=0000000 A7=0007FFE<br>*TD L @ Define a line separator (a row of '@')<br>*TD<br>A0=00000000 A1=0000000 A2=0000000 A3=0000000<br>A4=00000000 A1=0000000 A2=0000000 A7=0007FFE<br>@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | *TD                                          | Print the trace display                                               |

| *TD CLEAR         *TD A. 1       Define all address registers in a block         *TD         A0=00000000 A1=0000000 A2=0000000 A3=0000000         A4=00000000 A5=00000000 A6=0000000 A7=00007FFE         *TD L.@       Define a line separator (a row of '@')         *TD         A0=00000000 A1=0000000 A2=0000000 A3=0000000         A4=00000000 A1=00000000 A2=00000000 A7=00007FFE         @@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@@                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D0=0000000 D1=0000000 D2=                    | 0000000 D3=0000000                                                    |