₹.÷ .

# MODEL DU686

# DISK CONTROLLER

# **REVISION F**

# INSTALLATION AND OPERATION MANUAL

# 3 November 1987

DISTRIBUTED LOGIC CORPORATION 1555 S. Sinclair Street P.O. Box 6270 Anaheini, California 92806 Telephone: (714) 937-5700 Telex: 6836051

# TABLE OF CONTENTS

|         |    |     |                                         | PAGE  |

|---------|----|-----|-----------------------------------------|-------|

| SECTION | 1  |     | DESCRIPTION                             | 1-1   |

|         |    |     | CHARACTERISTICS                         | 1-1   |

|         |    |     | Data Buffer                             | 1-1   |

|         |    |     | Command Buffering                       | 1-1   |

|         |    |     | Elevator Seek Ordering Algorithm        |       |

|         |    |     | Overlapped Seeks                        |       |

|         |    |     | Inhibit DMA Incomponent                 | 1-3   |

|         |    |     | Inhibit DMA Increment                   | 1-3   |

|         |    |     | Modio Elou Componention                 | 1-3   |

|         |    |     | Media Flaw Compensation                 | 1-3   |

|         |    |     | Hardware Bootstrap                      | 1-3   |

|         |    |     | Automatic Self Test                     | 1-4   |

|         |    |     | Unibus Interface                        | 1 11  |

|         |    |     | Disk Drives Supported                   | 1 - 4 |

|         |    |     | Disk Drives Supported                   | 1 7   |

|         |    |     |                                         | 1-9   |

|         |    |     |                                         |       |

| SECTION | 2  |     | INSTALLATION                            | 2-1   |

|         |    |     | PRE-INSTALLATION CHECKS                 | 2-3   |

|         |    |     | RECOMMENDED DRIVE SETUP                 |       |

|         |    | -   | INSTALLATION                            | 2-4   |

| SECTION | R  |     | OPERATIONFORMAT, DIAGNOSTICS, AND ERROR |       |

| SECTION | J  |     |                                         | 3-1   |

|         |    |     |                                         | ) – 1 |

|         |    |     | COMMUNICATION WITH CRT OR HARD COPY     |       |

|         |    |     | -                                       | 3-1   |

|         |    |     |                                         | 3-1   |

|         |    |     |                                         | 3-3   |

|         |    |     | VAX-11/750 COMMUNICATIONS PROCEDURE     | 3-3   |

|         |    | · • |                                         | 3-5   |

|         |    |     |                                         | 3-7   |

|         |    |     | MAIN MENU                               | 3-8   |

|         |    |     |                                         | 3-8   |

|         |    |     |                                         | 3-9   |

|         |    |     | DRIVE CONFIGURATION                     | 3-10  |

|         |    |     |                                         | 3-10  |

|         |    |     |                                         | 3-12  |

|         |    |     |                                         | 3-13  |

|         |    |     |                                         | 3-14  |

|         |    |     |                                         | 3-14  |

|         |    |     |                                         | 3-20  |

|         |    | •   |                                         | 3-21  |

|         |    |     |                                         | 3-22  |

|         |    |     |                                         | -22   |

|         | ٠. |     | · · · · · · · · · · · · · · · · · · ·   | 3-24  |

|         |    |     | ERROR LOGGING                           | 3-28  |

# TABLE OF CONTENTS (Continued)

# LIST OF ILLUSTRATIONS

| Figure 1-1<br>Figure 1-2 | Disk System, Simplified  | 1-2<br>1-8 |

|--------------------------|--------------------------|------------|

| Figure 2-1               | Controller Configuration | 2-1        |

.

-

-

·

# LIST OF TABLES

| Table 1-1<br>Table 1-2<br>Table 1-3 | Controller/Unibus Interface Lines<br>Controller Cable J1 - Controller to Drive<br>Data Cables J2, J3, J4, J5 - Controller | 1-5<br>1-7                   |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                                     | to Drive                                                                                                                  | 1-7                          |

| Table 2-1<br>Table 2-2              | Switch and Jumper Setting                                                                                                 | 2-2<br>2-6                   |

| Table 3-1<br>Table 3-2              | VAX-11/750 IP/SA Addresses                                                                                                | 3 <b>-</b> 4<br>3 <b>-</b> 6 |

#### SECTION 1

#### DESCRIPTION

This manual describes the installation and operation of Distributed Logic Corporation (DILOG) Model DU686 Disk Controller. The controller interfaces up to four ESDI, 5-1/4-inch Winchester disk drives to DEC\* VAX or PDP-11 Unibus based computer systems. Transfer rates of the system are up to 15 MHz.

The controller is software compatible with DU drivers, MSCP, in MUMPS, VMS, RT-11, RSTS/E, and RSX-11 operating systems. The controller is programmable by the host software driver to transfer from 1 to 8 words per DMA request.

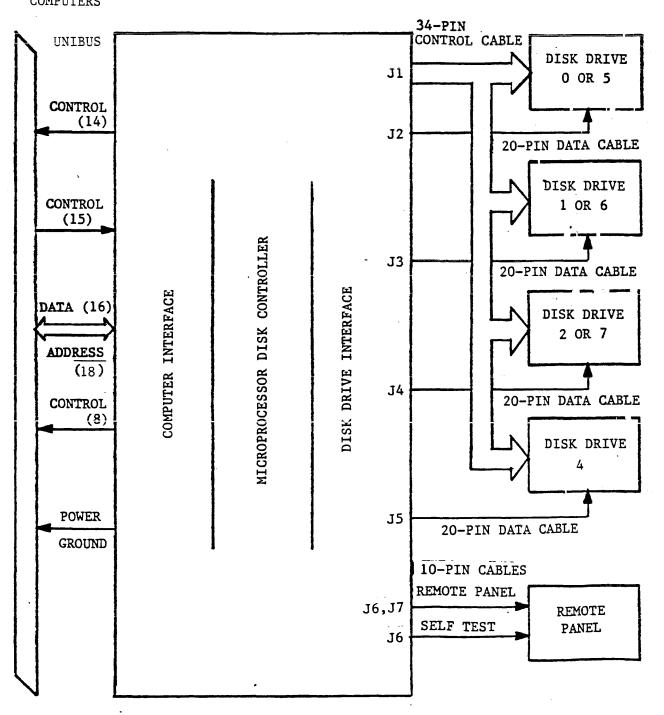

Figure 1-1 is a simplified diagram of a disk system.

CHARACTERISTICS

Characteristics of the controller are as follows:

. Data Buffer

The controller contains a 28-sector FIFO data buffer to support a 1 to 1 sector interleave and reduce software-generated latencies between the Unibus and disk drive.

. Command Buffering

The controller contains a command queue buffer capable of storing up to 16 commands. The buffer stores all commands received by the controller and queues the command for proper order of execution on each drive.

. Elevator Seek Ordering Algorithm

The controller uses an elevator seek ordering algorithm to determine the execution order for commands in the command buffer. This algorithm reduces drive seek latencies.

. Overlapped Seeks

The controller supports overlapped seeks for up to four (4) drives and will start a transfer on the drive whose seek completes first. This feature reduces multiple drive seek latencies.

\* DEC PDP-11, VAX, RT-11, MSCP, and DU Driver are registered trademarks of Digital Equipment Corporation.

UNIVERSAL FORMATTING is a trademark of Distributed Logic Corporation.

PDP-11 AND VAX COMPUTERS

Figure 1-1. Disk System, Simplified

# CHARACTERISTICS (Continued)

#### Parameter Passing Commands

With these ESDI commands, drive parameters are no longer stored in programmable components on the controller or recorded on the surface of the drive(s) attached to the controller. The drive(s) now communicates configuration information to the controller every time power is applied to the system.

Inhibit DMA Increment

The controller contains the ability to move blocks of data in or out of a specific memory of I/O address location. This function is software selectable for applications that require both incremental and non-incremental applications to run concurrently on the same controller.

Onboard Formatting

The controller onboard formatter is accessible through the system processor to provide interactive terminal access to the controller. The formatter is menu driven and also provides controller and drive test options.

Media Flaw Compensation

The following functions compensate for media defects:

FIRST, at format time one sector per track is reserved as an alternate. DILOG'S UNIVERSAL FORMATTING system has the ability to reassign reserved sectors for defective sectors. Also at format time the controller has the ability to read the manufacturer's defect map (if recorded per ESDI specification) and replace the sectors found bad by the drive manufacturer.

SECOND, if an error is encountered after the drive is formatted the controller will try to reread the sector with ECC disabled.

THIRD, if the error still exists, ECC is used to recover the data. This enhanced 32-bit ECC polynomial is capable of correcting one error per sector that is 11 bits or less in length. Error packets are generated by the controller every time an error recovery operation is performed.

FOURTH, if the error still exists, reassignment of defective sectors is accomplished through a dynamic replacement scheme controlled by the host software.

Hardware Bootstrap

The controller contains an onboard bootstrap support for RPO2, RLO1/02, RMO3, RMO5, RM80, RKO6/07, RXO2, TS11, TSVO5, TM11 and DU driver devices. Onboard jumpers allow selectable bootstrap addresses, in addition to enabling/disabling the bootstrap. When the bootstrap is disabled, the controller will boot from the standard DEC module.

# Automatic Self Test

The controller is supplied with an automatic self test function that is initiated each time power is applied. The controller performs additional tests each time it is brought online. A green card-edge LED is lit and remains lit after each successful completion. Should self test fail, the controller isolates the disk drive from the system and the LED is extinguished.

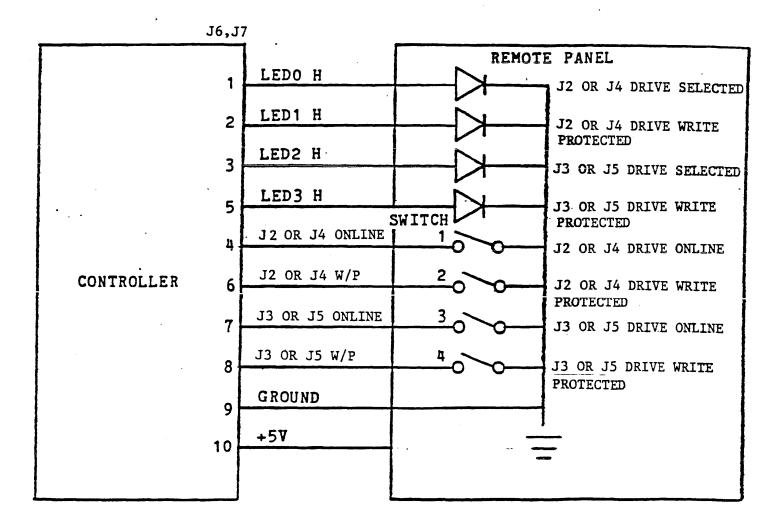

#### Remote Panel Interface

Two interface connectors are supplied for remote panels. The panels are user-supplied. Each panel contains four LEDs and four switches for drive selection and write protection. Error codes are also displayed on one of the remote panels.

Unibus Interface

Commands, data and status transfers between the controller and the computer are executed via the parallel I/O bus of the computer. Data transfers are direct to memory via the DMA facility of the bus; commands and status are under programmed I/O. Controller/Unibus\_interface lines are listed in Table 1-1.

Disk Drives Supported

The controller is compatible with disk drives from the following manufacturers. Contact the factory for additional drive support.

| Control | Data | Corporation | Micropolis |

|---------|------|-------------|------------|

| Fujitsu |      | -           | NEC        |

| Hitachi |      |             | Priam      |

| Maxtor  |      |             | Siemens    |

# Table 1-1. Controller/UNIBUS Interface Lines

.

| BUS PIN | MNEMONIC | IC DESCRIPTION Non-Processor Grant In—Generated by the processor in response to NPR whenever the pro- cessor is not using the bus. NPG is daisy-chained through the devices connected to the bus and is received and regenerated by each device until it reaches the requested device. |  |  |  |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CA1     | NPG INH  |                                                                                                                                                                                                                                                                                        |  |  |  |

| CB1     | NPG OUTH | Non-Processor Grant Out                                                                                                                                                                                                                                                                |  |  |  |

| CC1     | PAL      | Parity Bit A                                                                                                                                                                                                                                                                           |  |  |  |

| CD2     | D15L     | Data Line Bit 15—These 16 lines DXXL, are used to transfer data and register control/status information to and from the controller.                                                                                                                                                    |  |  |  |

| CE2     | D14L     | Data Line Bit 14                                                                                                                                                                                                                                                                       |  |  |  |

| CF2     | D13L     | Data Line Bit 13                                                                                                                                                                                                                                                                       |  |  |  |

| CH1     | D11L     | Data Line Bit 11                                                                                                                                                                                                                                                                       |  |  |  |

| CH2     | D12L     | Data Line Bit 12                                                                                                                                                                                                                                                                       |  |  |  |

| CJ2     | D10L     | Data Line Bit 10                                                                                                                                                                                                                                                                       |  |  |  |

| CK2     | D09L     | Data Line Bit 9                                                                                                                                                                                                                                                                        |  |  |  |

| CL2     | DOBL     | Data Line Bit 8                                                                                                                                                                                                                                                                        |  |  |  |

| CM2     | D07L     | Data Line Bit 7                                                                                                                                                                                                                                                                        |  |  |  |

| CN1     | DCLOL    | DC Power Low                                                                                                                                                                                                                                                                           |  |  |  |

| CN2     | D04L     | Data Line Bit 4                                                                                                                                                                                                                                                                        |  |  |  |

| CP2     | DOSL     | Data Line Bit 5                                                                                                                                                                                                                                                                        |  |  |  |

| CR2     | D01L     | Data Line Bit 1                                                                                                                                                                                                                                                                        |  |  |  |

| CS1     | PBL      | Bus Parity Bit B                                                                                                                                                                                                                                                                       |  |  |  |

| CS2     | DOOL     | Data Line Bit 0                                                                                                                                                                                                                                                                        |  |  |  |

| CT2     | DO3L     | Data Line Bit 3                                                                                                                                                                                                                                                                        |  |  |  |

| CU2     | D02L     | Data Line Bit 2                                                                                                                                                                                                                                                                        |  |  |  |

| CV1     | ACLOL    | AC Power Low                                                                                                                                                                                                                                                                           |  |  |  |

| CV2     | DOGL     | Data Line Bit 6                                                                                                                                                                                                                                                                        |  |  |  |

| DD2     | BR7L     | Bus Request 7—One of these lines BPXL, will be asserted by the controller to request control of the bus for the purpose of transferring data.                                                                                                                                          |  |  |  |

| DE2     | BRGL     | Bus Request 6                                                                                                                                                                                                                                                                          |  |  |  |

| DF2     | BR5L     | Bus Request 5                                                                                                                                                                                                                                                                          |  |  |  |

| DH2     | BR4L     | Bus Request 4                                                                                                                                                                                                                                                                          |  |  |  |

| DK2     | BGI7H    | Bus Grant Bit 7 In—These daisy-chained Bus Grant lines are asserted by the processor after completing the instruction in progress. Issued in response to the corresponding Bus Request line, the Bus Grant will be generated by each device until it reaches the requested device.     |  |  |  |

| DL1     | INITL    | INITIALIZE—This signal is asserted by the processor to initialize or clear all devices con-<br>nected to the bus.                                                                                                                                                                      |  |  |  |

| DL2     | BGO7H    | Bus Grant Bit 7 Out                                                                                                                                                                                                                                                                    |  |  |  |

| DM2     | BGI6H    | Bus Grant Bit 6 In                                                                                                                                                                                                                                                                     |  |  |  |

| DN2     | вдоен    | Bus Grant Bit 6 Out                                                                                                                                                                                                                                                                    |  |  |  |

| DP2     | BGI5H    | Bus Grant Bit 5 In                                                                                                                                                                                                                                                                     |  |  |  |

| DR2     | BGO5H    | Bus Grant Bit 5 Out                                                                                                                                                                                                                                                                    |  |  |  |

| DS2     | BGI4H    | Bus Grant Bit 4 In                                                                                                                                                                                                                                                                     |  |  |  |

| DT2     | BGO4H    | Bus Grant Bit 4 Out                                                                                                                                                                                                                                                                    |  |  |  |

# Table 1-1. Controller/UNIBUS Interface Lines (Continued)

| BUS PIN MNEMONIC |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| EC1              | A12L  | Address Bit 12-These lines are the 18-bit address bus over which memory and peri<br>register address information is communicated. Address information is placed on the to<br>the bus master device and received and decoded by the selected slave device. The m<br>device then either receives input data from, or outputs data to the addressed slave device<br>(memory) over the data bus lines. |  |  |  |  |

| ED1              | A17L  | Address Bit 17                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| ED2              | A15L  | Address Bit 15                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| EE1              | MSYNL | Master Sync—This control signal is issued by the master device to indicate that Address and Control information is present on the bus,                                                                                                                                                                                                                                                             |  |  |  |  |

| EE2              | A16L  | Address Bit 16                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| EF1              | A02L  | Address Bit 2                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EH1              | A01L  | Address Bit 1                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EH2              | AOOL  | Address Bit 0                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EJ1              | SSYNL | Slave Sync—This control signal is issued by the slave device in response to the signals (MSYN or INTR) generated by the master device.                                                                                                                                                                                                                                                             |  |  |  |  |

| EK1              | A14L  | Address Bit 14                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| EK2              | A13L  | Address Bit 13                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| EL1              | A11L  | Address Bit 11                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| EN2              | A08L  | Address Bit 8                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EP1              | A10L  | Address Bit 10                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| EP2              | A07L  | Address Bit 7                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| ER1              | A09L  | Address Bit 9                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EU1              | AOGL  | Address Bit 6                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EU2              | A04L  | Address Bit 4                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EV1              | A05L  | Address Bit 5                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EV2              | AO3L  | Address Bit 3                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| EJ2              | COL   | Control Bit Zero—These two control lines are coded by the master device to describe the type of transfer.                                                                                                                                                                                                                                                                                          |  |  |  |  |

|                  |       | C1 C0 OPERATION                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                  |       | 0 0 DATI-Data In (to master)                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|                  |       | 1 0 DATO—Data Out (from master)                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|                  |       | 1 1 DATOB—Data Out, Byte (from master)                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| EF2              | C1L   | Control Bit One                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| FD1              | BBSYL | Bus Busy—This signal is asserted by the bus master to indicate the bus is in use. When BBSY goes faise, control of the bus is passed to the new bus master.                                                                                                                                                                                                                                        |  |  |  |  |

| FJ1              | NPRL  | Non-Processor Request—This signal is asserted by the controller to request control of the bus for the purpose of transferring data directly to or from memory.                                                                                                                                                                                                                                     |  |  |  |  |

| FM1              | INTRL | Interrupt Request—The controller asserts this signal after becoming bus master to indicate that the desired interrupt Vector information is present on the bus.                                                                                                                                                                                                                                    |  |  |  |  |

| FT2              | SACKL | Selection Acknowledge—This signal is asserted by the controller in response to the proces-<br>sor's NPG or Bus Grant signal, indicating that control of the bus will pass to the controller<br>when the current bus master completes its operation.                                                                                                                                                |  |  |  |  |

#### Disk Interface

The controller interfaces up to four disk drives through 34- and 20-pin cables. If more than one drive is used, the 34-pin control cable is daisy-chained. The 20-pin cables are connected separately from the controller to each drive. Table 1-2 lists the 34-pin interface signals, and Table 1-3 lists the 20-pin interface signals.

| Signal Name                                                                                                                                                                                                                                                                                                                                                                                                                                             | Signal<br>Pin | Ground<br>Pin | Source     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------------|

| <ul> <li>Head Select 2<sup>3</sup></li> <li>Head Select 2<sup>2</sup></li> <li>Write Gate</li> <li>Configuration Status Data</li> <li>Transfer Acknowledge</li> <li>Attention</li> <li>Head Select 2<sup>0</sup></li> <li>Sector</li> <li>Head Select 2<sup>1</sup></li> <li>Index</li> <li>Ready</li> <li>Transfer Request</li> <li>Drive Select 1</li> <li>Drive Select 2</li> <li>Drive Select 3</li> <li>Read Gate</li> <li>Command Data</li> </ul> | 2             | 1             | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4             | 3             | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6             | 5             | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8             | 7             | Drive      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10            | 9             | Drive      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12            | 11            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14            | 13            | Drive      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16            | 15            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18            | 17            | Drive      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20            | 19            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22            | 21            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24            | 23            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26            | 25            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28            | 27            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30            | 29            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32            | 31            | Controller |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34            | 33            | Controller |

Table 1-2. Control Cable J1 - Controller to Drive

Table 1-3. Data Cables J2, J3, J4, J5 - Controller to Drive

| Signal Name                                                                                                                                                                                                                                                              | Signal<br>Pin                                                      | Ground<br>Pin          | Source                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------|

| <ul> <li>Drive Selected</li> <li>Sector</li> <li>Command Complete</li> <li>Address Mark Enable</li> <li>Reserved</li> <li>+/- Write Clock</li> <li>Reserved</li> <li>+/- Read/Reference Clock</li> <li>+/- NRZ Write Data</li> <li>+/- DR Data</li> <li>Index</li> </ul> | 1<br>2<br>3<br>4<br>5<br>7/8<br>9<br>10/11<br>13/14<br>17/18<br>20 | 6<br>12<br>15/16<br>19 | Drive<br>NOT USED<br>Drive<br>Controller<br>Controller<br>Drive<br>Controller<br>Drive<br>Drive |

Figure 1-2 shows the interface for the customer-supplied remote panels. There are two panels; one connects from J6 and one from J7. The switches and LED connections depend on which drives are connected to J2, J3, J4 and J5. Error codes are displayed from J6 connectors. These codes are listed in Section 2.

Figure 1-2. Remote Panel Interface

• 0

# CONTROLLER SPECIFICATIONS \*

#### MECHANICAL

The controller is completely contained on a quad-height module 26.4 cm (10.44 in.) wide by 22.8 cm (8.88 in.) deep and plugs into one standard Unibus SPC quad-height slot.

### BASE ADDRESSES

8 choices, switch selectable:

| IP-772150 | IP-760334 | IP-760340 | IP-760344 |

|-----------|-----------|-----------|-----------|

| SA-772152 | SA-760336 | SA-760342 | IP-760346 |

| IP-760354 | IP-760360 | IP-760374 | IP-760400 |

| SA-760356 | SA-760362 | SA-760376 | SA-760402 |

#### INTERRUPT VECTOR ADDRESS

Programmable by software.

#### PRIORITY LEVEL

BR5 in etch; BR4, BR6, and BR7 by jumpers.

#### DMA BURST SIZE

Preprogrammed for 4-word transfers.

#### DISK TRANSFER RATES

Up to 15 MHz per second.

# DISK DRIVE I/O

One 34-pin flat ribbon cable and four 20-pin flat ribbon cables (one for each drive).

#### POWER

+5 volts at 2.5 amps.

### ENVIRONMENT

Operating temperature 50 degrees F. (10 degrees C.) to 104 degrees F. (40 degrees C.); Humidity 10-90% non-condensing.

# SHIPPING WEIGHT

5 pounds, including documentation and cables.

### MTTR

Less than 0.5 hours.

\* SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE.

#### SECTION 2

#### INSTALLATION

The padded shipping carton contains the controller board, a 34-pin control cable to the drive, and if specified on the sales order, four optional 20-pin data cables to the drives. Inspect the controller board and its components and the cables for damage.

#### NOTE

If damage to the board, components on the board, or cables is noted, do not install. Immediately inform the carrier and DILOG.

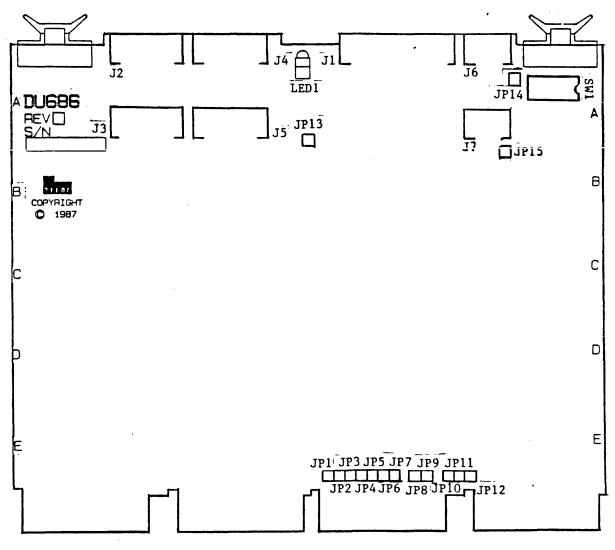

Figure 2-1 shows the locations of the switch and jumpers.

Table 2-1 describes the switch and jumper settings. Some jumper connections may be etched or cut on the board and are referred to in the table as installed or removed.

Figure 2-1. Controller Configuration

Table 2-1. Switch and Jumper Setting

Switch SW1 Slave Address Select (IP/SA Register) SW1-2 SW1-3 ADDRESS SELECT SW1-1 \_ \_ \_ \_ \_ \_\_\_\_ \_\_\_\_ OFF OFF OFF = 772150 OFF = OFF 760334 ON = OFF ON OFF 760340 ON ON OFF = 760344 OFF ON = 760354 OFF OFF ON = 760360 ON OFF ON ON = 760374 ON ON ON = 760400 Switch SW1-4 - MUST BE OFF Switch SW1-5 - MUST BE OFF Switch SW1-6 - MUST BE OFF Switch SW1-7 EXTENDED DWELL TIME ON = Extends the dwell time between DMA bursts (12.8 usec) if pending interrupt requests OFF = Normal dwell time between DMA bursts Switch SW1-8 PARITY ENABLE ON = Checks and reports parity to host OFF = Parity disabled Jumpers JP1 through JP12 - FACTORY SET Jumper JP13 - Installed (Factory Etch) When removed, indicates a future hardware revision. Jumper JP14/JP15 - Removed (Factory Set) These jumpers may be installed for +5V Remote Panel power. PRE-INSTALLATION CHECKS Before the controller is installed, it may be necessary to check

the operating system for device addresses. The drives are designated DUX except in VAX/VMS where they are designated DUAX. The "X" represents drive number and drives may be any number from 0 to 6. The numbering of drives is described in Section 3 under Main Menu, Select Drive. The ESDI drive numbering system is 1-7; the DEC numbering system is 0-6. Consult the drive manufacturer's documentation for selecting the ESDI configuration of the drive. The controller on-board formatting program lists both numbers; for example, "ESDI DRIVE 01 (DU00) SELECTED."

From the operating system, determine and select the address of the controller to be installed. Available addresses are listed in Table 2-1. Examples of controller names for the first controller for some operating systems are as follows:

| OPERATING SYSTEM | CONTROLLER |

|------------------|------------|

| RSTS/E           | RU 1       |

| RSX-11M-PLUS     | DUA        |

| RT-11            | Port0      |

| VAX/VMS          | DUA        |

- 2. Determine and select the drive name. The first drive may be DUO, except for VAX/VMS, which is DUAO. Set the switches and jumpers in the controller and drive for the selected addresses.

- 3. Remove power from the system and install the controller as described below.

#### RECOMMENDED DRIVE SETUP

The switches and jumpers on the disk drive need not be set up to accommodate the controller. The controller interrogates the drive for the status and configuration and selects the optimum format. However, where there are choices for selecting drive options (for example, hard/ soft sectoring), for the most efficient use of the system, DILOG reccommends the following:

| OPTION                                   | RECOMMENDATION/REQUIREMENT                                                                                                                                     |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Hard/Soft Sector                         | Hard Sector - The controller can accept<br>both, but hard sectoring is the most<br>efficient use of drive capacity.                                            |  |  |  |

| Motor Control Enable/<br>Disable         | Enabled - With motor control enabled,<br>the controller can sequence the drive,<br>requiring less power consumption.                                           |  |  |  |

| Drive Cabling From<br>J2, J3, J4, and J5 | No recommendation - J2, J3, J4 and J5<br>cables may be connected to any drive.<br>The remote panel connections depend on<br>the J2, J3, J4 and J5 connections. |  |  |  |

2-3

Step or Serial Mode

SERIAL MODE REQUIRED - Few drives offer a step mode option, but these must be set for serial mode. (With the step mode, the controller must know where the head is and where the next Seek must go. With the serial mode, a single command causes a Seek to a given track.)

#### INSTALLATION

To install the controller module, proceed as follows:

#### CAUTION

Remove DC power from computer chassis before inserting or removing controller module.

Damage to the backplane assembly and the controller module will occur if the controller module is plugged in backwards!

- 1. Select the backplane Small Peripheral Controller (SPC) location into which the controller is to be inserted. SPC locations are connectors C, D, E, and F of a UNIBUS backplane assembly.

- 2. To use the DMA (NPR) facility required with the controller, the backplane wiring of the SPC slot must be modified. The modification is as follows:

Remove the wire on the connector C between A1 and B1 of the slot into which the controller is to be plugged. This allows the nonprocessor grant priority line to be carried through the controller. If the controller is removed, replace this wire.

Note that any connector rows which do not have a card installed, must have a bus grant jumper card installed in the D slot to continue the bus grants to other devices in the UNIBUS.

On older PDP-11 backplanes, the following additional wiring changes may be necessary if slot 1 AU1 is directly connected to slot 4 AU1 of the system unit into which the controller is to be installed.

- A. Remove wire between 1 AU1 and 4 AU1.

- B. At the controller slot, connect 1 AU1 to CA1 and 4 AU1 to CB1.

Additional consideration of the slot into which the controller is to be plugged is required. The interrupt request and NPR request levels are selected by the position of the controller on the backplane bus. Remember that devices closest to the processor have highest priority.

When selecting the backplane slot, NPR request priority should be considered first, then priority of interrupt requests.

- 3. Perform this step if the remote panel switch/indicators are to be connected. Connect the cables from J6 and J7 on the controller to the remote panels (not supplied by DILOG). Refer to Figure 1-2 for pinouts and descriptions.

- 4. Install J1 and J2 into the connectors on the controller and J3, J4 and J5, if four drives are used. Ensure pin 1 on each cable is matched with the triangle on each connector as indicated on Figure 2-1.

- 5. Ensure the controller is oriented with the components facing row one, the processor, and gently press both handles until the module connectors are firmly seated in the backplane.

- 6. Connect J1 to the drive or drives if daisy=chained. Ensure the terminator is installed in the last drive. Connect the J2, J3, J4 and J5 cables to the appropriate drive as described in Section 3 under Drive Select.

- 7. Refer to the disk drive manual for operating instructions, and apply power to the drive(s) and the computer.

- 8. Power up the system. If the green LED lights, self test passed. If the green LED does not light, self test failed. If the remote panels (J6 and J7) are used, the remote panel LEDs will display the self test error code on J6 only. (See Table 2-2 for self test error code definitions.) If the green LED does not light, perform the following steps:

- A. Power down the system.

- B. Remove all drive cables.

- C. Power up the system.

- D. If the green LED lights, the cabling is probably wrong. Install the cables into the proper connector.

- 9. The system is now ready to operate. Format the disks as described in Section 3.

# Table 2-2. Test in Error--Remote Panel

Self test is entered upon initialization (Reset or Write IP Register). If self test fails, an error code is displayed on the Remote Panel LEDs (J6 only) and self test LED is off. Upon self test failure, report status to DILOG Customer Service.

| LED3<br>J3 or J5<br>Drive<br>Write<br>Protected | LED2<br>J3 or J5<br>Drive<br>Selected | LED1<br>J2 or J4<br>Drive<br>Write<br>Protected | LEDO<br>J2 or J4<br>Drive<br>Selected | DESCRIPTION                                                  |

|-------------------------------------------------|---------------------------------------|-------------------------------------------------|---------------------------------------|--------------------------------------------------------------|

| 0                                               | 0                                     | 0                                               | 1                                     | Test Drive Status A<br>Register                              |

| 0                                               | 0                                     | 1                                               | 0                                     | Test Drive Status B<br>Register                              |

| 0                                               | 0                                     | 1                                               | 1                                     | Test Controller Status<br>Register<br>(Remote Write Protect) |

| 0                                               | 1                                     | 0                                               | 0                                     | Request QBIC Status<br>Register and Test Status<br>Bits      |

| 0                                               | 1                                     | 0                                               | 1                                     | Test QBIC DMA LSB Byte<br>Count Register                     |

| 0                                               | 1                                     | 1                                               | 0                                     | Test QBIC DMA MSB Byte<br>Count Register                     |

| 0                                               | 1                                     | 1                                               | 1                                     | Test QBIC DMA MSB Byte<br>Count Register                     |

| 1                                               | 0                                     | 0                                               | 0                                     | Clear QBIC DMA Byte Count<br>Register                        |

| 1                                               | 0                                     | 0                                               | 1                                     | Test QBIC DMA Control<br>Register (Enable Zero<br>Fill)      |

| 1                                               | 0                                     | 1                                               | 0                                     | Test Z80 Working RAM<br>Address Test (only on<br>power up)   |

| 1                                               | 0                                     | 1                                               | 1                                     | Test Z80 Working RAM<br>Pattern (5AH) (only on<br>power up)  |

|                                                 |                                       |                                                 |                                       |                                                              |

2-6

| LED3<br>J3 or J5<br>Drive<br>Write<br>Protected | LED2<br>J3 or J5<br>Drive<br>Selected | LED1<br>J2 or J4<br>Drive<br>Write<br>Protected | LEDO<br>J2 or J4<br>Drive<br>Selected | DESCRIPTION                                                           |

|-------------------------------------------------|---------------------------------------|-------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------|

| 1                                               | 1                                     | 0                                               | 0                                     | Test Z80 Working RAM<br>Pattern (A5H) (only on<br>power up)           |

| 1                                               | 1                                     | 0                                               | 1                                     | Test Disk Data RAM<br>Address/Pattern (only on<br>power up) First 8K  |

| 1                                               | 1                                     | 1                                               | 0                                     | Test Disk Data RAM<br>Address/Pattern (only on<br>power up) Second 8K |

| 1                                               | 1                                     | 1                                               | 1                                     | Zero Fill Data RAM and<br>test for zeros (16K)<br>(only on power up)  |

|                                                 |                                       |                                                 |                                       |                                                                       |

# Table 2-2. Test in Error--Remote Panel (Continued)

.

#### SECTION 3

OPERATION -- FORMAT, DIAGNOSTICS, AND ERROR LOGGING

The operation of the controller includes interrogating the drive, formatting the disc, running diagnostics, and checking the disk subsystem error log. Interrogating the ESDI drive is simply determining the drive parameters for formatting.

The method for establishing communications with the formatting program is the DILOG Boot procedure. This method is described below. Diagnostic procedures and error log messages are listed at the end of this section.

COMMUNICATION WITH CRT OR HARD COPY CONSOLE

If using the optional Dilog Format Paddle Card, the system console must be set up as follows:

- . 9600

- $\cdot$  8 bit .

- no parity

- . 1 stop bit

If the system console is attached directly to the host, the setup is as follows:

- 9600, 4800, 2400, 1200

- . 8 bit

- . no parity

- . 1 stop bit

# DILOG PDP-11 BOOTSTRAP PROCEDURE

The controller not only supports standard DEC devices, but also allows the use of the onboard formatter. When DU is used, the standard DEC emulation is called. When FT is used, the onboard formatter is enabled for use through the system console.

The following assumes the system is in ODT mode. Note that the bootstrap can be used under processor Power Up Mode 2 conditions. Refer to the appropriate DEC manual for a discussion of the Power Up modes. Further note that the disc drive does not need to be READY to enter the bootstrap.

Reset the system by pressing RESET (Break) or enter the following (characters underlined are output by the system; characters not underlined are input by the operator):

- <u>@</u> <IP>/0

- € <SA>/77777

- € 2000G

The values for the IP and SA addresses and switch settings are as follows:

| SW1-1 | SW1-2 | SW1-3 |   | IP     | SA     |

|-------|-------|-------|---|--------|--------|

|       |       |       |   |        |        |

| OFF   | OFF   | OFF   | = | 772150 | 772152 |

| ON    | OFF   | OFF   | = | 760334 | 760336 |

| OFF   | ON    | OFF   | = | 760340 | 760342 |

| ON    | ON    | OFF   | = | 760344 | 760346 |

| OFF   | OFF   | ON    | = | 760354 | 760356 |

| ON    | OFF   | ON    |   | 760360 | 760362 |

| OFF   | ON    | ON    | = | 760374 | 760376 |

| ON    | ON    | ON    | = | 760400 | 760402 |

Enter one of the following: DMO, DPO, DLO, DRO, MSO, MTO, DYO, DU, or FT <CR>.

Definitions are as follows:

DM = RK06/07 Disc DP = RP02/03 Disc DL = RL01/02 Disc DR = RM03/05/80 MS = TS11 Tape MT = Tape MU = (TMSCP) Tape DY = RX02 Floppy Disc DU = DU emulation (see below) FT = Enable onboard formatter through system console

Booting can be executed from logical units other than "0" shown above by entering the desired logical unit number, i.e., 1, 2, 3, ... or 7.

# VAX-11/730 COMMUNICATIONS PROCEDURE

- 1. On the VAX-11/730, press the Restart switch.

- 2. Enter the code below. (Underlined values are outputs to the terminal.) The values of the IP and SA registers are listed in Table 3-1.

>>> D/P/L F26804 80000001 <CR>

>>> D/P/W <IP> O <CR>

>>> D/P/W <SA> 3FFF <CR>

>>> D/G F 200 <CR>

$\rightarrow \rightarrow \rightarrow$  C <CR>

#### VAX-11/750 COMMUNICATIONS PROCEDURE

- 1. On the VAX-11/750, press the Restart switch.

- 2. Enter the code below. (Underlined values are outputs to the terminal.) The values of the IP and SA registers are listed in Table 3-1.

>>> D/P/L F30804 8000001 <CR>

If the controller is plugged into the <u>second</u> Unibus adapter in the VAX-11/750, enter the following line; otherwise, omit this entry and proceed to the next entry:

>>> D/P/L F32804 80000001 <CR>

>>> D/P/W <IP> 0 <CR>

>>> D/P/W <SA> 3FFF <CR>

If the controller is plugged into the <u>second</u> Unibus adapter in the VAX-11/750, enter the following line; otherwise, omit this entry and proceed to the last two entries.

>>> D/P/L 230 F80000 <CR>

>>> D/G F 200 <CR>

$\geq \geq \geq$  C <CR>

.

# Table 3-1. VAX-11/750 IP/SA Addresses

|                                                  |                                            |                                                  | First Unibus Adapter                                                                   |                                                                              |                                                                              |

|--------------------------------------------------|--------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Switch SW1                                       |                                            |                                                  | IP (Octal)                                                                             | <ip><br/>IP Hex Address<br/>Entered</ip>                                     | <sa><br/>SA Hex Address<br/>Entered</sa>                                     |

| SW1-1                                            | SW1-2                                      | SW 1-3                                           |                                                                                        |                                                                              | <br>                                                                         |

| OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON | OFF<br>OFF<br>ON<br>OFF<br>OFF<br>ON<br>ON | OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>ON<br>ON  | 772150<br>760334<br>760340<br>760344<br>760354<br>760354<br>760360<br>760374<br>760400 | FFF468<br>FFE0DC<br>FFE0E0<br>FFE0E4<br>FFE0EC<br>FFE0F0<br>FFE0FC<br>FFE100 | FFF46A<br>FFE0DE<br>FFE0E2<br>FFE0E6<br>FFE0EE<br>FFE0F2<br>FFE0FE<br>FFE102 |

|                                                  |                                            |                                                  | Second Unibus Adapter                                                                  |                                                                              |                                                                              |

| SW 1 - 1                                         | SW1-2                                      | SW1-3                                            |                                                                                        |                                                                              |                                                                              |

| OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON | OFF<br>OFF<br>ON<br>OFF<br>OFF<br>ON<br>ON | OFF<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>ON | 772150<br>760334<br>760340<br>760344<br>760354<br>760360<br>760374<br>760400           | FBF468<br>FBEODC<br>FBEOE0<br>FBEOE4<br>FBEOEC<br>FBEOF0<br>FBEOFC<br>FBE100 | FBF46A<br>FBE0DE<br>FBE0E2<br>FBE0E6<br>FBE0EE<br>FBE0F2<br>FBE0FE<br>FBE102 |

#### VAX 11/780 COMMUNICATIONS PROCEDURE

1. On the VAX-11/780, press the Restart switch.

Enter the code below. (Underlined values are outputs to the terminal.) The values of the IP and SA registers are listed in Table 3-2.

$\rightarrow \rightarrow \rightarrow$  I <CR>

>>> D/P/L 20006804 8000001 <CR>

If the controller is plugged into a <u>second</u>, <u>third</u>, or <u>fourth</u> Unibus adapter in the VAX-11/780, enter the following; otherwise, proceed to the next entry:

Second UB: >>> D/P/L 20008804 80000001 <CR> Third UB: >>> D/P/L 2000A804 80000001 <CR> Fourth UB: >>> D/P/L 2000C804 80000001 <CR>

>>> D/P/W <IP> O <CR>

>>> D/P/W <SA> 3FFF <CR>

If one Unibus adapter is used, enter the first line of code. If more than one are used, enter the appropriate code as follows:

First UB: >>> D/P/L 227 20100000 <CR> Second UB: >>> D/P/L 227 20140000 <CR> Third UB: >>> D/P/L 227 20180000 <CR> Fourth UB: >>> D/P/L 227 20180000 <CR>

>>> D/G F 200 <CR>

$\rightarrow \rightarrow \rightarrow$  C <CR>

|                                                              |                                                              |                                                             |                                                                              | First Unibus Adapter                                                                         |                                                                                                          |  |

|--------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| Switch SW1                                                   |                                                              | IP (Octal)                                                  | <ip><br/>IP Hex Address<br/>Entered</ip>                                     | <sa><br/>SA Hex Address<br/>Entered</sa>                                                     |                                                                                                          |  |

| SW1-1<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF          | SW1-2<br>OFF<br>OFF<br>ON<br>ON<br>OFF<br>OFF<br>ON          | SW1-3<br>OFF<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON         | 772150<br>760334<br>760340<br>760344<br>760354<br>760360<br>760374           | 2013F468<br>2013E0DC<br>2013E0E0<br>2013E0E4<br>2013E0EC<br>2013E0F0<br>2013E0FC             | 2013F46A<br>2013E0DE<br>2013E0E2<br>2013E0E6<br>2013E0E6<br>2013E0EE<br>2013E0F2<br>2013E0F2<br>2013E0FE |  |

| ON                                                           | ON                                                           | ON                                                          | 760400                                                                       | 2013E100<br>Second Unit                                                                      | 2013E102<br><br>ous Adapter                                                                              |  |

| SW 1 - 1                                                     | SW1-2                                                        | SW1-3                                                       |                                                                              |                                                                                              |                                                                                                          |  |

| OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON             | OFF<br>OFF<br>ON<br>ON<br>OFF<br>OFF<br>ON<br>ON             | OFF<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>ON            | 772150<br>760334<br>760340<br>760344<br>760354<br>760360<br>760374<br>760400 | 2017F468<br>2017E0DC<br>2017E0E0<br>2017E0E4<br>2017E0EC<br>2017E0FC<br>2017E0FC<br>2017E100 | 2017F46A<br>2017E0DE<br>2017E0E2<br>2017E0E6<br>2017E0E6<br>2017E0EE<br>2017E0F2<br>2017E0FE<br>2017E102 |  |

|                                                              |                                                              |                                                             |                                                                              | Third Unibus Adapter                                                                         |                                                                                                          |  |

| SW 1 - 1<br>======<br>OFF                                    | SW1-2<br>======<br>OFF                                       | SW1-3<br>======<br>OFF                                      | 772150                                                                       | ======================================                                                       | 201BF46A                                                                                                 |  |

| ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON                    | OFF<br>ON<br>OFF<br>OFF<br>ON<br>ON                          | OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>ON                   | 760334<br>760340<br>760344<br>760354<br>760360<br>760374<br>760400           | 201BE0DC<br>201BE0E0<br>201BE0E4<br>201BE0EC<br>201BE0F0<br>201BE0FC<br>201BE100             | 201BE0DE<br>201BE0E2<br>201BE0E6<br>201BE0EE<br>201BE0EE<br>201BE0F2<br>201BE0FE<br>201BE102             |  |

|                                                              |                                                              |                                                             |                                                                              | Fourth Unit                                                                                  | ous Adapter                                                                                              |  |

| SW1-1<br>=====<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF | SW1-2<br>=====<br>OFF<br>OFF<br>ON<br>OFF<br>OFF<br>ON<br>ON | SW1-3<br>=====<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>ON<br>ON | 772150<br>760334<br>760340<br>760344<br>760354<br>760360<br>760374<br>760400 | 201FF468<br>201FE0DC<br>201FE0E0<br>201FE0E4<br>201FE0EC<br>201FE0FC<br>201FE0FC<br>201FE100 | 201FF46A<br>201FF0DE<br>201FE0E2<br>201FE0E6<br>201FE0EE<br>201FE0F2<br>201FE0FE<br>201FE0FE<br>201FE102 |  |

# Table 3-2. VAX-11/780 IP/SA Addresses

3-6

#### FORMATTING PROGRAM

After communication is established, the program is ready to format the disk.

#### NOTE

Inputs or outputs to or from the program may be in either decimal or Hexadecimal. In the upper right hand corner of the screen after the header, either "DECIMAL" or "HEX" will be shown. To change values, use the CONTROL and B keys. When these keys are pressed an audible alarm will sound, and outputs will toggle immediately. Exceptions are listed below:

The following outputs are fixed, and will not change:

- . SA/IP Registers Always Octal

- . Firmware Version Always Decimal

- . Date Always Decimal

- . Drive Capacity and Transfer Rate Always Decimal

- . Correction Pattern and Vector Always Hexadecimal

The first display of the program will be:

NO DRIVE SELECTED

ARE YOU USING A (P)RINTER OR (C)RT?

If a CRT is used, the program will display rolling cylinder addresses. If a printer is used, the addresses will not be printed unless an error is detected. If an address is needed when a printer is used, use the CONTROL and P keys and the address will be printed.

Each display on the screen will list the program name, the version, and the controller model, followed by either "NO DRIVE SELECTED" or "DRIVE 0 (or 1) SELECTED." The main formatter menu will appear next. The logo is shown in the first example, below, but is omitted in the subsequent examples after the Main Formatter Menu. The ESDI convention of numbering drives is 1-7; the DU driver convention is 0-6.

# MAIN MENU