214690 1926

## guong left gib ent

po box 6528 denver, colorado 80206 (303) 777-7133

# DOUBLE DENSITY DISC CONTROLLER SYSTEM MANUAL

#### THE DIGITAL GROUP

#### DOUBLE DENSITY DISC CONTROLLER SYSTEM MANUAL

#### (C) 1979 BY

#### THE DIGITAL GROUP

"Reproduction in any part or form of the contents of this document or its accompanying cassette tape or disk, except for the personal use of the original purchaser, is strictly forbidden without the expressed written consent and permission of The Digital Group, Inc."

### TABLE OF CONTENTS

|   | Section    |                                                     | Page |

|---|------------|-----------------------------------------------------|------|

|   |            |                                                     |      |

|   | CHAPTER    | 1 INTRODUCTION                                      | 1    |

|   |            | 2 ASSEMBLING THE CONTROLLER                         |      |

|   | 2.1        | INTRODUCTION                                        |      |

| • | 2.2        | PRELIMINARY INSPECTION                              |      |

|   | 2.3        | RESISTOR INSTALLATION                               |      |

|   | 2.4        | INTEGRATED CIRCUIT SOCKET INSTALLATION              |      |

|   | 2.5<br>2.6 | CAPACITOR INSTALLATION                              | _    |

|   | 2.7        | BOARD ADDRESS JUMPER INSTALLATION                   |      |

|   | 2.8        | HEAD LOAD MOTOR-ON JUMPER                           | -    |

|   | 2.9        | FINAL INSPECTION AND CLEANING                       | -    |

|   | 2.5        | TAND INDICITOR AND CHERRING CONCERNMENT CONCERNMENT | ,    |

|   | CHAPTER    | 3 TESTING/TROUBLESHOOTING                           | 10   |

|   | 3.1        | INTRODUCTION                                        | 10   |

|   | 3.2        | GENERAL- POWER SUPPLIES AND CAPACITORS              |      |

|   | 3.3        | THE POWER-ON RESET AND LOW VOLTAGE CIRCUIT          |      |

|   | 3.4        | USING HMON/2 FOR TESTING                            |      |

|   | 3.5        | BOARD SELECT AND GATING CIRCUITS                    |      |

|   | 3.6        | DEVICE ATTRIBUTE, VCO AND CLOCK CIRCUITS            |      |

|   | 3.7        | TIMING ELEMENT AND DISC I/O BUFFER CIRCUITS         |      |

|   | 3.8        | BRINGING UP THE 1791 IC                             | 20   |

|   | CHAPTER    | 4 THEORY OF OPERATION                               | 26   |

|   | 4.1        | INTRODUCTION                                        |      |

|   | 4.2        | PORT LABEL DEFINITIONS                              |      |

|   | 4.3        | POWER-ON RESET AND LOW VOLTAGE CIRCUIT              |      |

|   | 4.4        | ADDRESS DECODE AND CPU I/O BUFFERS                  |      |

|   | 4.5        | WAIT LOGIC                                          |      |

|   | 4.6        | SEL PORT LOGIC                                      |      |

|   | 4.7        | WRITE PRECOMPENSATION CIRCUIT                       | 35   |

|   | 4.8        | DELAY AND READY LOGIC                               |      |

|   | 4.9        | CONTROLLER CLOCK CIRCUIT                            |      |

|   | 4.10       | VCO PHASE LOCKED LOOP                               |      |

|   | 4.11       | DISC I/O BUFFERING                                  |      |

|   | 4.12       | POWER SUPPLIES                                      |      |

|   | 4.13       | INTERRUPTS                                          | 45   |

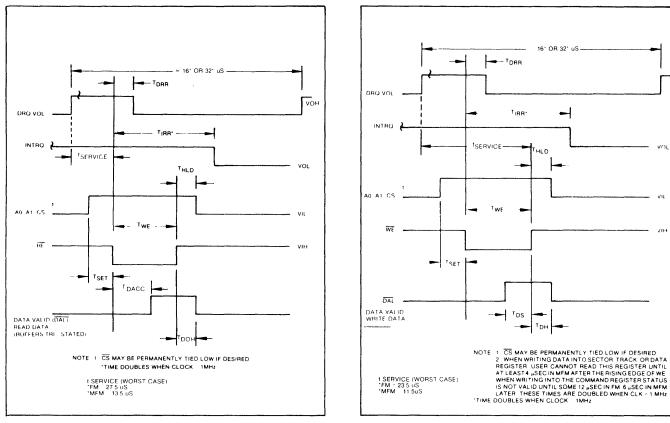

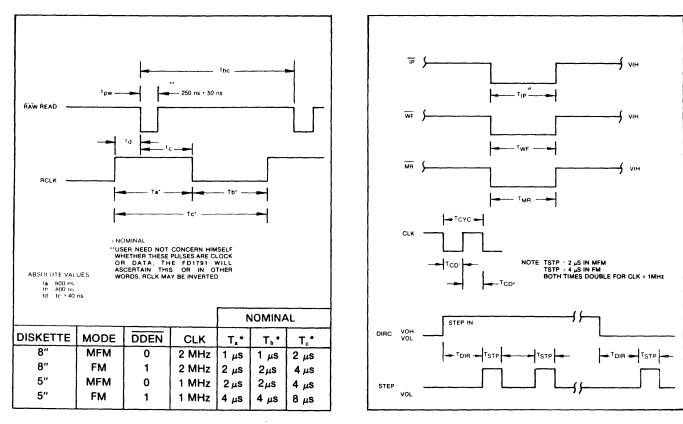

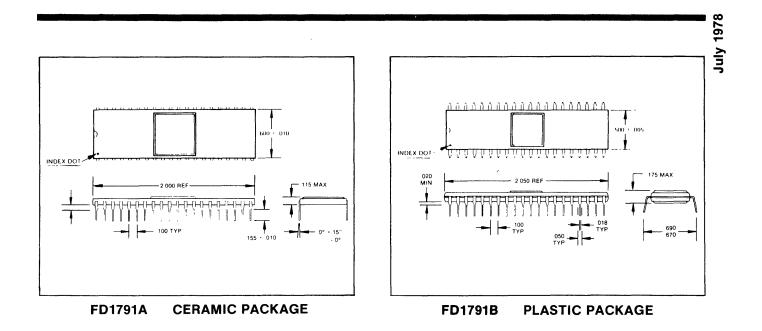

|   | CHAPTER    | 5 1791 PRODUCT SPECIFICATION                        | 46   |

|   | 5.1        | INTRODUCTION TO WD1791 PRODUCT SPECIFICATION        |      |

|   | 5.2        | 1791 PRODUCT SPECIFICATION                          | 49   |

|   |            |                                                     |      |

|   | CHAPTER    |                                                     | 50   |

|   | 6.1        | INTRODUCTION                                        |      |

|   | 6.2        | SAMPLE DRIVER CODE                                  | 51   |

|   | CHAPTER    | 7 SAMPLE FORMAT PROGRAM                             | 60   |

|   | - 7.1      | INTRODUCTION                                        |      |

|   | 7.2        | FORMAT CODE                                         | 60   |

|   |            |                                                     |      |

| Section  |   |                                                            | Page |

|----------|---|------------------------------------------------------------|------|

| APPENDIX | A | PARTS LIST BY VALUE                                        | 61   |

| APPENDIX | В | PARTS LIST BY LABEL                                        | 69   |

| APPENDIX | С | DRIVE ATTRIBUTE SOCKET DEFINITION                          | 72   |

| APPENDIX | D | BOARD ADDRESSING                                           | 73   |

| APPENDIX | Е | ONE SHOT TIMINGS                                           | 74   |

| APPENDIX | F | WRITE PRECOMPENSATION TIMING DIAGRAM                       | 75   |

| APPENDIX | G | WAIT LOGIC TIMING DIAGRAM                                  | 76   |

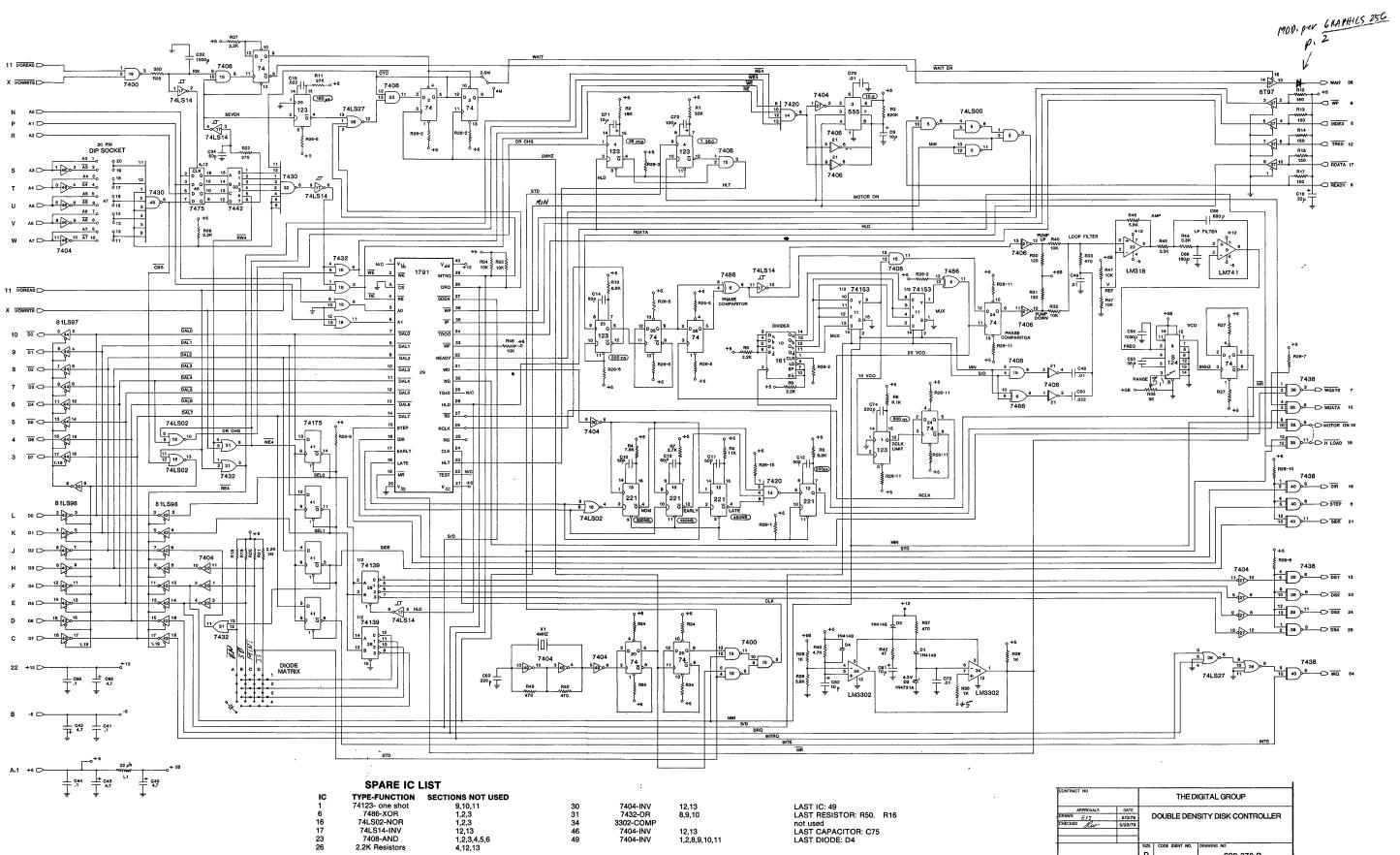

| APPENDIX | H | SCHEMATIC                                                  | 77   |

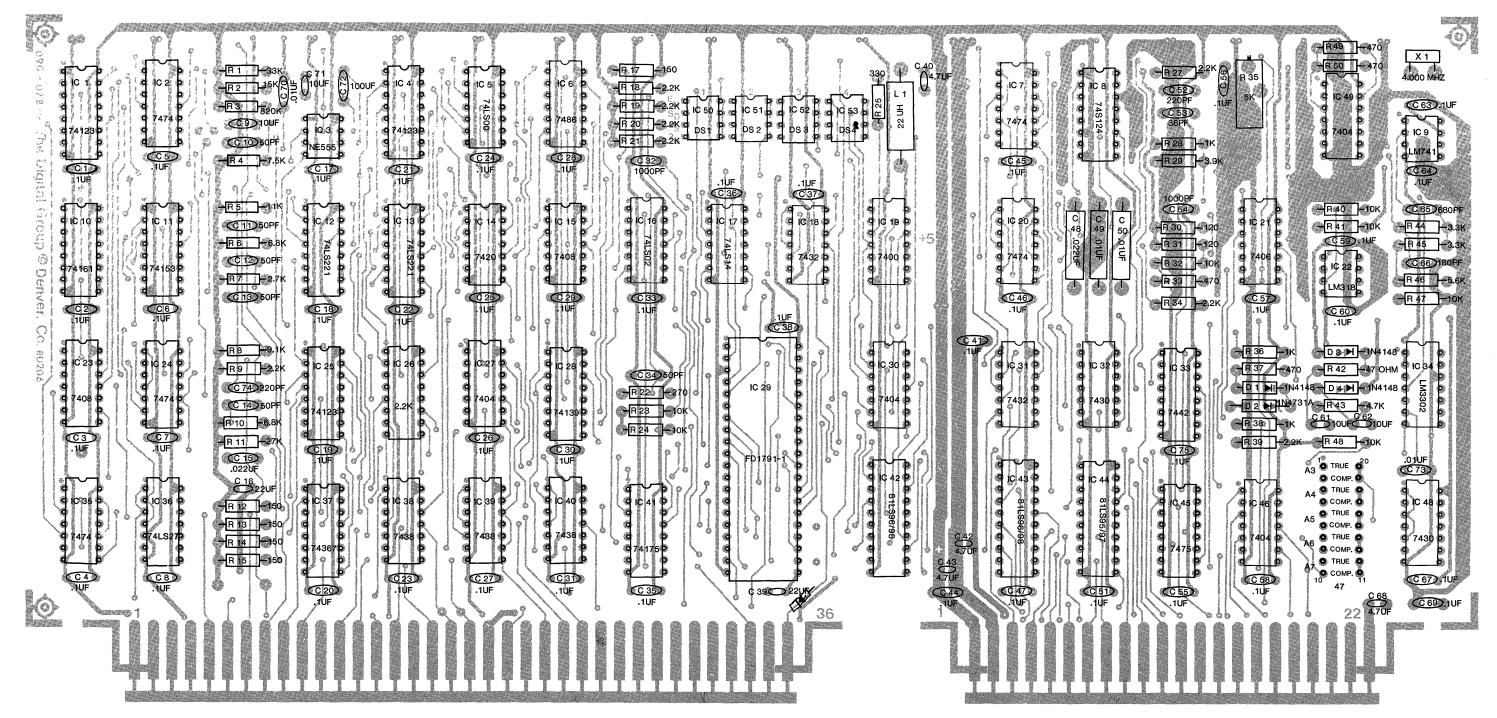

| APPENDIX | I | PARTS PLACEMENT DIAGRAM                                    | 78   |

| APPENDIX | J | SOFTWARE COMPATIBILITY (OLD VS NEW)                        | 79   |

| APPENDIX | K | APPLICATION NOTE #1 . Using Intermpts                      | 80   |

| APPENDIX | L | APPLICATION NOTE #2 Optimizing Timing Volumy               | 81   |

| APPENDIX | М | APPLICATION NOTE #3 3 Logicol to 2 Physicol Orives         | 82   |

| APPENDIX | N | APPLICATION NOTE #4 Multi Hole Oisketter                   | 83   |

| APPENDIX | 0 | APPLICATION NOTE #5 Bringing Out the Drive Attribute Duday |      |

| APPENDIX | Р | APPLICATION NOTE #6 . Using More + man 4 Brives            | 85   |

| APPENDIX | Q | APPLICATION NOTE #7 2.5 Mb2 US 4 Mb2                       | 86   |

| APPENDIX | R | APPLICATION NOTE #8 . Prazmic Manay and Ketush             |      |

| APPENDIX | S | APPLICATION NOTE #9 . Sungert Drive Symmetry Adjust        | 88   |

| APPENDIX | Т | APPLICATION NOTE #10 Innover Drives                        | 90   |

.

#### CHAPTER 1

#### INTRODUCTION

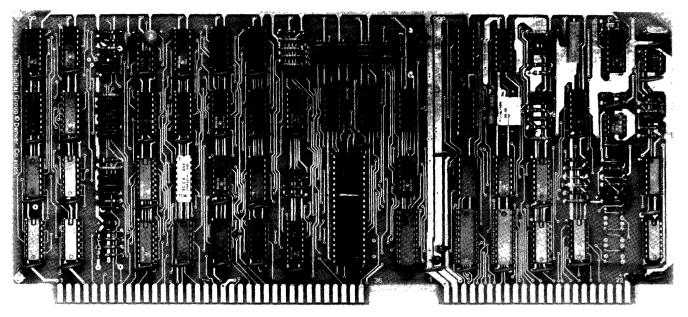

The DIGITAL GROUP DOUBLE DENSITY CONTROLLER MANUAL is a comprehensive set of documentation that allows the user to Assemble, Test, Troubleshoot, and Install the Board in his system. Each section of the manual contains ordered concise instructions for getting the user up fast and reliably.

An Installation Manual is included for the user who bought the board assembled. All he needs to do is consult the Installation Manual for getting the board up.

For the kit builder, the Assembly and Testing sections are provided. Along with the Installation Manual, the kit builder will find the Controller board easy to build.

Also included in the documentation is the Hardware Monitor Manual and Cassette. This Monitor is very powerful in aiding the user to Test and Diagnose problems that might occur in assembly and testing. The Assembled Board purchaser might wish to perform some of the Diagnostics provided in HMON to continue to monitor the reliability of the System. You might think of the Diagnostics in HMON as a "Memory Test" for the Controller.

#### CHAPTER 2

#### ASSEMBLING THE CONTROLLER

2.1 INTRODUCTION

Estimated Construction Time: 4-8 Hours

To build the Digital Group Dual Density Floppy Card, you will need the following tools and equipment:

Fine tipped low wattage soldering iron (25 watt is ideal) Solder 60/40 RESIN core wire solder, 20-30 gauge DO NOT USE ACID CORE SOLDER (SEE OUR WARRANTY POLICY) Diagonal cutters, small micro-shear preferred Long-nosed pliers flux remover or Alcohol small brush

Volt-Ohmmeter (20K Ohms per VOLT or better) 15 Mhz Dual Trace Triggered Sweep Oscilloscope

Before you start to assemble the board, take a little time to inspect the P.C. board. Check to see if there are any shorts on the top side of the board under where the Integrated Circuit sockets will be placed. Once the Sockets are in place, it will be very difficult to find shorts in this area. Also, read through the entire assembly procedure before starting to familiarize yourself with the proceedure.

2.2 PRELIMINARY INSPECTION

() Remove all parts from their bags and plastic rails.

- () Sort the components into individual values. (cupcake trays are good for this)

- ( ) Verify that all parts are there by checking them off of the PARTS LIST in APPENDIX A

- () Remove the Parts Placement Diagram from APPENDIX I and place it conveniently in front of you.

- 2 -

2.3 RESISTOR INSTALLATION

NOTE: All resistors are mounted on .4 inch centers. (If you have a lead bender, by all means use it.) ( // Insert the following Resistors into the board: () R42 47 Ohm (yel-vio-blk) () R30,R31 120 Ohm (brn-red-brn) () R12, R13, R14 150 Ohm (brn-grn-brn) () R15,R17 150 Ohm () R22 270 Ohm (red-vio-brn) () R25 330 Ohm (org-org-brn) ( ) Turn the board over at this time and solder in these Resistors. ( / Insert the following Resistors into the board: 470 Ohm () R33,R37 (yel-vio-brn) () R49, R50 470 Ohm () R28,R36 (brn-blk-red) 1k Ohm () R38 1 K Ohm () R9,R18,R19 2.2K Ohm (red-red-red) () R20,R21 2.2K Ohm ( ) Turn the board over at this time and solder in these Resistors. ( /) Insert the following Resistors into the board: 2.2K Ohm (red-red-red) () R27,R34,R39 () R7 2.7K Ohm (red-vio-red) () R44,R45 3.3K Ohm (org-org-red) () R29 3.9K Ohm (org-whi-red)

- 3 -

( ) R43 4.7K Ohm (yel-vio-red)

( ) R46 5.6K Ohm (grn-blu-red)

() R6,R10 6.8K Ohm (blu-gry-red)

( ) R4 7.5K Ohm (vio-grn-red)

- () R8 9.1K Ohm (whi-brn-red)

- ( ) Turn the board over at this time and solder in these Resistors.

( $^{\prime}$ ) Insert the following Resistors into the board:

() R23, R24, R32 10K Ohm (brn-blk-org)

() R40,R41,R47 10K Ohm

() R48 10K Ohm

- () R5 11K Ohm (brn-brn-org)

- () R2 15K Ohm (brn-grn-org)

() R11 27K Ohm (red-vio-org)

- () R1 33K Ohm (org-org-org)

- () R3 820K Ohm (gry-red-yel)

- ( ) Turn the board over at this time and solder in these Resistors.

2.4 INTEGRATED CIRCUIT SOCKET INSTALLATION

If you received SAE sockets with your kit, DO NOT REMOVE the white strips located on the bottom of the socket.

$(\/)$  Install the following IC Sockets at this time by inserting the socket and SLIGHTLY bending two diagonally opposing corner pins outwards to hold the socket onto the board.

- ( ) IC3,IC9,IC22 8 Pin Socket

- () IC50,51,52 8 Pin Socket

- () IC53 8 Pin Socket

- 4 -

Turn the board over at this time and solder in the 8 Pin Sockets.

( Install the following IC Sockets at this time by inserting the socket and SLIGHTLY bending two diagonally opposing corner pins outwards to hold the socket onto the board.

- () IC2, IC5, IC6, IC7 14 Pin Socket

- () IC14, IC15, IC16 14 Pin Socket

- () IC17, IC18, IC19 14 Pin Socket

- () IC20, IC21, IC23 14 Pin Socket

- () IC24, IC27, IC30 14 Pin Socket

- () IC31,IC32,IC34 14 Pin Socket

- () IC35, IC36, IC38 14 Pin Socket

- () IC39, IC40, IC46 14 Pin Socket

- () IC48,49 14 Pin Socket

- ( ) Turn the board over at this time and solder in the 14 Pin Sockets.

$(\checkmark)$  Install the following IC Sockets at this time by inserting the socket and SLIGHTLY bending two diagonally opposing corner pins outwards to hold the socket onto the board.

- () IC1, IC4, IC8 16 Pin Sockets

- () IC10, IC11, IC12 16 Pin Sockets

- () IC13, IC25, IC26 16 Pin Sockets

- () IC28, IC33, IC37 16 Pin Sockets

- () IC41,IC45 16 Pin Sockets

- ( ) Turn the board over at this time and solder in the 16 Pin Sockets.

(') Install the following IC Sockets at this time by inserting the socket and SLIGHTLY bending two diagonally opposing corner pins outwards to hold the socket onto the board.

() IC42, IC43, IC44 20 Pin Sockets

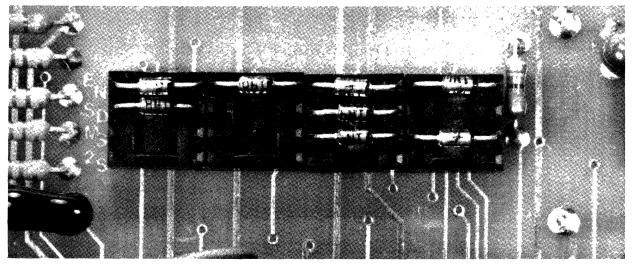

NOTE: No 20 Pin Socket will be installed in IC Position 47.

() IC29 40 Pin Socket

( Turn the board over at this time and solder in the 20 and 40 Pin Sockets.

2.5 CAPACITOR INSTALLATION

Insert the following Capacitors into the board and then bending the leads slightly enough to hold the Capacitor in place.

( ) Insert the following Capacitors into the board:

() C10,C11,C12 50pf Silver Mica () C13,C14,C34 50pf Silver Mica ( Y C53 36pf Silver Mica C,66 180pf Silver Mica (could be marked 181) C52.C74 220pf Silver Mica (could be marked 221) ( 1 65 680pf Silver Mica (could be marked 681) ( </ C32, C54 1000pf Silver Mica (could be marked 102) (  $\checkmark$  Turn the board over at this time and solder in these Capacitors. Insert the following Capacitors into the board: ( / C70, C73 .01 Disc Ceramic (-) C49.C50 .01 10% Mylar ( **C**48 .022 10% Mylar (X C15 .022 10% Disc Ceramic ) Turn the board over at this time and solder in these Capacitors.

( ) Insert the following Capacitors into the board. Be sure to check the Parts Placement Diagram and PC board for the correct orientation of the + end of the capacitors. (*X* C40, C42, C43 4.7uf Tantalum (Observe Polarity) (X C68 4.7uf Tantalum (Observe Polarity) ( *J* C9, C61, C62 10uf Tantalum (Observe Polarity) ( C71 10uf Tantalum (Observe Polarity) ( ) C16,C39 22uf Tantalum (Observe Polarity) ( *X* C72 100uf Tantalum (Observe Polarity) ( $\checkmark$ ) Turn the board over at this time and solder in these Capacitors. ( ) Insert the following Capacitors into the board: (~) C1-C8 .1uf Disc Ceramic (人 C17-C31 .1uf Disc Ceramic ( $\checkmark$ ) Turn the board over at this time and solder in these Capacitors. () Insert the following Capacitors into the board: ( 1 c33, c35-c38 .1uf Disc Ceramic ( / C41,C44-47 .1uf Disc Ceramic C51.C55-C60 .1uf Disc Ceramic ( / C63.C64.C67 .1uf Disc Ceramic ( / C69.C75 .1uf Disc Ceramic (  $\checkmark$  Turn the board over at this time and solder in these Capacitors. 2.6 REMAINING COMPONENT INSTALLATION

( / Insert the remaining components into the board:

- 7 -

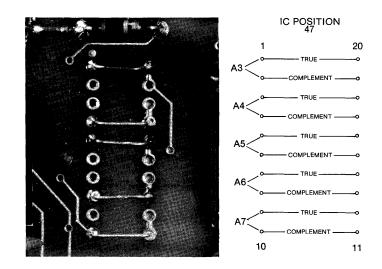

( D1.D3.D4 1N4148 Diode (save the leads for later) ( D2 1N4731A Zener Diode (.5 in. Centers) 22uh Choke (red-red-blk) looks like 2W resistor ( **R**35 5K Ohm 10 Turn Trim-Pot  $(\mathbf{y}_{\mathbf{X}1})$ 4.000 Mhz Crystal ( ) Turn the board over at this time and solder in the LEFT To Do last of the components. By the solder in the last of the components. Be sure to solder the Last of the components. Be sure to solder the crystal as quickly as possible to minimize heat 1, (IC 48 SockET) 2. (6-50pf Mica) 2. (C10-14 C34) 3. (L1 22uh CHOKE) buildup. 2.7 BOARD ADDRESS JUMPER INSTALLATION < 4. (DA PIN 36 WAIT) ( / Using the leads saved from the 1N4148 Diodes: < ( / Form five jumper wires bent on .3 in. spacing. ( /) Install the Port Addressing jumpers into the jumper pads at IC Position 47 as follows: ( $\cdot$ ) Pin 1 to Pin 20 ( ) Pin 4 to Pin 17 () Pin 5 to Pin 16 () Pin 8 to Pin 13 ( ) Pin 10 to Pin 11 () Solder in these jumpers and trim the excess leads.

2.8 HEAD LOAD MOTOR-ON JUMPER

If you intend to use the Disc Controller on Mini Drives with the DSM-INT1 cabling installed OR you intend to run both Mini and Standard drives with the DSS-INT1 cabling, install the following:

() Install a small jumper wire between the pads near the 36 Pin edge connector pins 18 and 19.

#### 2.9 FINAL INSPECTION AND CLEANING

All components that are to be soldered onto the board have been soldered in. The only parts that should be left over at this time should be the Integrated Circuits and 7 1N4148 Diodes. These parts will be installed during testing. You should now look over your work and check for obvious shorts, solder splashes and unsoldered pins. After you are satisfied that no glaring shorts or opens exist, clean the board in commercial board cleaner or alcohol.

- () Inspect the board for obvious solder shorts, solder splashes, and unsoldered pins.

- () Clean the board in commercial board cleaner or alcohol.

- () Re-inspect the board for shorts and unsoldered pins again.

- ( ) Be sure that all solder joints are clean and SHINY.

- () RE-SOLDER any joints that appear dull in finish.

- () Reclean the board if joints needed retouching.

You have completed the assembly phase of construction. Go to the Installation Manual now and perform any CPU modifications that are required. If you presently have a single density Controller (DSS-INT1 or DSM-INT1) and you have a spare slot on the I/O Bus, you should parallel the connections on Pins 34 and 36 of the 36 Pin edge connector to this spare slot. Some of the testing could be done with your old controller installed along with the new Double Density Controller. If this is the first Disc Controller to be installed in your system, perform all required cabling at this time. You don't need to parallel a slot if this is your first disc system. After you have installed all required modifications and cabling you should take a break. The next thing we will do is test the Double Density Controller. Proceed to the next chapter.

- 9 -

#### CHAPTER 3

#### TESTING/TROUBLESHOOTING

#### 3.1 INTRODUCTION

The Double Density Disc Controller is not a difficult board to troubleshoot. The board was designed to be modular. The following tests check out each section to the degree that the section should work. Each test will also give the user the ability to check further into the circuitry should the test results be negative.

In general, if there is a problem in one section, the user should consult the theory of operation for that section to get a better idea as to where the problem lies.

3.2 GENERAL- POWER SUPPLIES AND CAPACITORS

Before power is applied to the disc controller board all of the power supply traces should be tested. This is to ensure that shorts or reversed Tantalum capacitors will not destroy the computers power supplies. NO integrated circuits should be installed on the disc controller board for this test.

- (1). With an Ohmmeter, check the +5, +12, and -5 volt power supplies with respect to ground and the other supplies. There should be no direct shorts (resistance less than 25 Ohms) to ground or any other supply. Be sure to check these measurements by reversing the leads of the Ohmmeter.

- (2). If the above test was successful, recheck the polarity of all Tantalum and Electrolytic capacitors. If there was a short between any power supply and ground or between any supply find the cause of this short before proceeding.

- (3). Insert the disc controller (less Integrated Circuits) into the computer and apply power. Check to see that there are no power supply failures. Now, just leave the disc controller inserted and the power on for about five minutes. If a capacitor was installed incorrectly it will probabily fail in this time period (it's better for it to fail now rather than when all the Integrated Circuits are installed).

3.3 THE POWER-ON RESET AND LOW VOLTAGE CIRCUIT

- The Power-on reset circuit will now be tested. This circuit holds the 1791 IC and the write gate inactive during power up and during a power loss. If this circuit fails to operate the controller board will not function at all. The controller board may be inserted into any I/O slot for this test.

- (1). Install the following IC: IC34 (LM3302). Insert the disc controller board in the computer and apply power. Adjust the Computer +5 Volt supply for +5 Volts at the top of the Disc Controller card. The tolerance is + or - 5%. Do NOT use the extender cards for this setting.

- (2). Now, place the disc controller up on extender boards if you have them. Apply power again and see if the output of IC34 pins 1 and 2 are high. If not, check the +12 volt power supply and then recheck the +5 volt supply. If the +12 volt supply failed (crow-barred) check all components associated with that supply. If the +5 volt supply was low, readjust that supply and start the test all over again. Correct polarity of diodes D1 through D4 are critical to the operation of this circuit. Check to see if these diodes are installed correctly.

- (3). Observe the output of IC34 pins 1 and 2 with an oscilloscope. During powerup, IC34 pin 2 will hold low for approximately 50 milliseconds. If this level is not present, check for shorts or bad polarity of capacitor C62. Also, the LM3302 could be bad.

- (4). Now with the oscilloscope in place reduce the computer +5 volt supply until IC34 pin 1 goes low. Note that this voltage should be arround 4.3 volts. If this voltage is above 4.3 volts replace Zener D2 or Diode D1. If the voltage is below 4.3 volts, check or replace the Zener D2, or the LM3302. Retest if necessary. (above or below means 10% either way)

- (5). Readjust the computer +5 Volt power supply to +5 volts as in Step 1. Now, attach one probe to the +5 Volt supply and the other to IC34 Pins 1 or 2, then cycle the AC power on and off. AC trigger the scope to when the +5 Volt supply starts to go low. Observe that the output of IC34 Pins 1 and 2 go low prior to the total loss of the +5 volt power supply. (Note that IC34 Pins 1 and 2 output goes low when the +5 Volt supply passes through 4.3 Volts.)

- (6). Now, place one scope probe on the +12 Volt power supply. Place the other on the +12 Volt supply Pin 3 of IC34. Cycle the AC power again and note that the +12 Volt "storage" circuit comprised of C61, R42 and D4 remains charged after the standard +12 Volt supply discharges. then remove the scope probe from the +12 Volt supply and place it on the +5

Volt supply. Note also that while cycling the AC power the +5 Volt supply discharges to 0 while the voltage on IC34 Pin 3 is still above +5 Volts. The +5 Volt supply discharge rate is a function of the load of your particular system, but it should discharge in less than one second. If this is not the case, check the polarity of D4 and C61. Also be sure that the value of R42 is correct.

#### 3.4 USING HMON/2 FOR TESTING

Most of the following tests will use the HMON/2 Hardware monitor for exercising the controller board. The user should read the HMON/2 Manual and familiarize himself with the operation of this monitor. HMON/2 has been used to adjust all the sections of the Dual Density Controller board. The only secton that the monitor can't diagnose is the Phase locked loop. It should be noted that using the INP-<port>:CON function, the user can generate a single repetitive pulse train that any "good" scope can sync to. These pulses occur at approximately a 10 millisecond rate. Use of the DELay function can extend these pulses to allow the user to trigger all of the timing elements on the board. In one of the sections we will use this technique to check all the controller to disc buffers and timing elements. When an example is given there will be no explanation of the command or how to terminate it. The user should read the rest of the test procedure and then go back to the HMON/2 Manual and reread the functions used exclusively for testing. Be sure that you know how to STOP any function that we will be using.

We will be reloading the HMON/2 cassette three or four times. If you presently have a Single density disc system or a Phideck system, you may want to load in HMON/2 at this time and save it on disk or cassette. The Double Density Controller board may be tested in the slot next to the intended slot for most of the tests. This can be accomplished by installing temporary motherboard jumpers from the intended slot to this new slot for both the Int and Wait lines. Remember, you can load HMON/2 through any operating system except for the last test, which requires you to connect the Double Density Controller to the actual disc drives.

#### 3.5 BOARD SELECT AND GATING CIRCUITS

In this section we will test all of the address gating and port select logic. We will also test the wait logic here. The first test will check to see if any shorts exist in the output data enable and the wait enable lines. If there is a problem here, the computer will not function as the controller board will either interfear with the computers I/O bus or the Wait line. Should the user have dynamic memory, the holding of the Wait line will cause memory loss. We will next test the Input/Output gating logic to see if the board can be accessed. Then, the wait logic will be tested to see if the wait timeout timer and the entire wait circuit functions properly.

- (1). Install all IC's EXCEPT the following: IC8, IC9, IC22, IC29, IC37, and IC44.

- (2). Insert the disc controller and apply power. Check to see that all of the power supplies are operating and that no IC is getting excessively hot to the touch.

- (3). With either a scope or a voltmeter, check the following:

- (a). Pins 1 and 19 of IC44 are at a constant high level.

- (b). Pin 15 of IC37 is also at a constant high level.

If either of these signals is low, there is a problem in the address select or wait logic. At this point the user should start back tracking from these pins to find the source of the problem.

- (4). Now remove power from the system and install IC's 37 and 44.(Be sure that the Wait jumper and Int jumper on the motherboard are in place)

- (5). Read in the disc diagnostic tape using the "ZE" ROM and execute the HMON/2 with option 6.

The following tests will establish whether the address decoding and wait generation logic are functioning properly.

Most of the tests will have visual outputs to the screen. You should stop with the testing and start scoping the board when your outputs do not agree with the examples.

(6). First we will see if the board responds to the computer. Execute the following program:

:OUT-54,0:INP-54:OUT-54,377:INP-54 (cr)

The computer should respond with:

**INPUT PORT 054 = 304 INPUT PORT 054 = 307**

If this is the result you received, go on to step 7. If both inputs resulted in a 000, the board was not selected. Check IC's 16, 31, 33, 45. This test should have generated the strobe pulse labeled RE4 on the schematic. To aid in testing this section, re-execute the above test but place a "CON" statement at the end. This will cause the test to be repeated

1

at speeds a scope will sync to. If the result of the test was not 000 but something else, check the problem bits in IC's 30, 41, 42, 43 and 44.

(7). Now we'll see if the wait logic is operable. Temporarily short pins 38 and 39 of the IC29 to ground. (Jumper IC29-39 to IC29-3 and IC29-38 to IC29-20.) (Use the hookup wire supplied.) Then try the following:

> :SET-.10000 (cr) :OUT-57,0:NEX:MES-/DONE/ (cr)

Time the length of the second line above.(app 25 sec) Th

:SET-.10000 (cr) :OUT-53,0:NEX:MES-/DONE/ (cr)

The second test should execute about 1.5 seconds faster. If this was true proceed to step 8. If the tests ran at the same speed, there is a problem with the wait logic. Check to see if the CPU mods have been installed and their associated jumpers on the motherboard are there. If this is not the problem then read the theory of operation of the wait logic and check IC's 2, 7, 15, 17, 25, 36.

(8). We apparently have some communication with the controller board at this time. Remove power and insert all the IC's EXCEPT IC29, the 1791.

3.6 DEVICE ATTRIBUTE, VCO AND CLOCK CIRCUITS

In this section we will check out the Attribute selection circuts, the Phase locked loop and the Basic 1791 clock circuit. The attribute circuit will also test some of the input/output buffer lines. Any shorts on these lines could cause problems for the 1791 IC. We will also set the free running frequency of the Phase locked loop. This adjustment is the most critical adjustment to be made and should be done carefully. Once the adjustment has been made, we will change the attributes for device 0 and check the switching of different sections of the loop. If a problem arises in this circuit, a careful examination of the rest of this circuit is in order. Finally, we will check the Basic clock frequency of the 1791 and check to see if it switches properly for each attribute.

- (1). Install the controller board on its extender boards again and reload HMON/2.

- (2). Get two of the 1N4148 diodes that were supplied and bend the leads to fit the .3" spaced socket.

- (3). Please refer to APPENDIX C on DEVICE ATTRIBUTES for the

following:

(a). Start HMON/2 with option 6.

(b). The following program will be run for all 4 drives. This is done by replacing the word "DATA" in the OUT-54,"DATA" with the following: 0, 1, 2, 3. In each case the user should place a diode in each of the 4 possible positions for that drive and observe the results on the screen.

(c). Run the following program for each drive:

:OUT-54, DATA: INP-54: CON (cr)

The results obtained should conform to the following table:

| DATA<br> | POSITION | POSITION | POSITION | POSITION |  |

|----------|----------|----------|----------|----------|--|

| 0        | 300      | 344      | 324      | 314      |  |

| 1        | 301      | 345      | 325      | 315      |  |

| 2        | 302      | 346      | 326      | 316      |  |

| 3        | 303      | 347      | 327      | 317      |  |

|          |          |          |          |          |  |

If any of the above results were incorrect, study the data pattern for all tests and check the associated bits on the controller board.

Now we will set and check out the VCO basic free running frequency.

- (2). The VCO free running frequency is set as follows:

- (a). Place a diode in the Single/Double density position for device 0.

- (b). Select this device by executing a OUT-54,0 (cr) instruction.

- (c). Observe the clock period at IC29 Pin 26 with an oscilloscope.

- (d). Adjust Pot R35 for a square wave with a period of 2 usec high and 2 usec low. Tolerance is: +5% -0%.

(e). With a voltmeter, measure the DC voltage at Pin 3 of

- 15 -

IC8. Make a note of this voltage on the schematic for later reference.

(3). Now we will check the operation of the loop.

- (a). Remove the diode installed in the Single/Double density position for device 0. Observe that the clock period at IC29 Pin 26 just halved. (1 usec high and 1 usec low)

- (b). Now install the diode in the Mini/Standard position for device 0. Observe that the period doubled to 2 usec high and 2 usec low.

- (c). Install the second diode in the Single/Double density position for device 0. Observe that the clock period doubled again to 4 usec high and 4 usec low.

If any of the above observations didn't occur, back track from IC29 Pin 26 to where the problem exists.

- (3). We will now test the fixed clock frequency for the 1791 IC. This is either a 1 Mhz or 2Mhz clock applied to Pin 24 of IC29.

- (a). With the 2 diodes still installed from the above test, observe that the period of the clock on IC29 Pin 24 is 500 nsec high and 500 nsec low.

- (b). Now remove the 2 diodes and observe that the period of the clock on Pin 24 of IC29 just halved to 250 nsec high and 250 nsec low.

If you didn't observe the 2 different periods as above, check IC's 19, 20 and 49.

3.7 TIMING ELEMENT AND DISC I/O BUFFER CIRCUITS

In the following section we will check to see that all the timing elements are operating properly. For example, if the drive change one-shot fails to function, all disc copying may fail due to improper settle time. Other timing element failures could cause: loss of input data, improper write timing, no motor startup delay or excessive wait states. We will use the strobe feature mentioned above to "fire" the timing elements and also to see if a clear path exists for other Disc I/O Buffers.

(1). For all the tests we will use the input strobe of IC29 Pin4. Use the hookup wire supplied to form jumpers for these

tests. If any of these tests fail, trace through the logic from IC29 Pin 4 to the source of the problem. Now let's generate the repeatable strobe by executing the following:

OUT-54,0 (cr) INP-50:CON (cr)

(2). First let's test the lines to the disc:

(a). Jumper IC29 Pins 4 and 15.

- (b). Observe that the signal at IC40 Pin 5 Is the same as IC29 Pin 15.

- (c). Now jumper IC29 Pins 4 and 16.

- (d). Observe that the signal at IC40 Pin 2 is the same as IC29 Pin 16.

- (e). Jumper IC29 Pins 4 and 28.

- (f). Observe that the signal at IC39 Pin 5 is the same as the signal on IC29 Pin 28.

- (g). Observe that the signal at IC38 Pin 13 is the same as the signal on IC29 Pin 28.

- (h). Jumper IC29 Pins 4 and 30.

- (i). Observe that the signal at IC38 Pin 2 is the same as The signal on IC29 Pin 30.

- (3). Next we will test the head load delay timer. There are two ways this timer may be fired, we will test both.

- (a). Reinstall the jumper from IC29 Pins 4 and 28.

- (b). Stop the program presently running and type the following:

INP-50:DEL-.100:CON (cr)

- (c). Observe that the negative going pulse at IC4 Pin 4 is between 35 and 45 milliseconds.

- (d). Now Stop the program that is executing and type the following:

OUT-54,20:DEL-.100:CON (cr)

(e). Jumper IC29 Pins 28 and 39.

- 17 -

- (f). Observe that the pulse on IC4 Pin 4 is the same as in (c).

- (4). We will now check the wait timeout timer. This may be done, without the use of jumpers. Jumper 16-29 plus 38 and 39 to ground,

- (a). Stop the program that is presently running and type the following:

INP-57:CON (cr)

- (b). Observe that there is a positive going 160 to 170 micro second pulse on IC37 PIN 13.

- (5). The next timer to check out is the mini motor startup timer.

- (a). Install a diode in the Mini/Standard position for device 0.

- (b). Temporarily remove IC3 and jumper IC3 Pins 2 and 3.

- (c). Stop the program that is presently running and type the following:

OUT-50,0:DEL-.1500:CON (cr)

- (d). Observe that the negative going pulse at IC4 Pin 12 is low for about .8 to 1.1 seconds. (Sweep: .2sec/cm, Trigger: negative DC, normal trigger, not auto.)

- (e). Remove the jumper on IC3 and reinstall IC3.

- (6). The mini motor timeout timer is easy to test. Try the following:

- (a). Place a scope probe on IC38 Pin 10.

- (b). Stop the present program.

- (c). Type in the following:

0UT-50

- (d). Use a stopwatch or sweep hand on your non-digital watch and:

- (e). Wait for a convenient time then depress (cr).

- (f). The signal on IC38 Pin 2 should go high. Measure the time it takes for the signal to return low. This time

.

should be in the range of 10 seconds.

- (g). Retime this signal a few times to be sure it is consistant. If the time varies by more that 20%, check to see if capacitor C72 is installed correctly.

- (7). The last timer test is to see if the write precompensation circuit functions properly. There are 3 timers associated with this circuit that generate the compensation and one that generates the actual write data pulse. If your oscilloscope does not have the 15Mhz bandwidth to measure the following pulses accurately, just observe their presence for now.

- (a). Jumper the following on IC29:

- (1). Pin 4 to Pin 31.

- (2). Pin 18 to 20.

- (3). Pin 17 to 3.

- (b). Type in the following:

INP-50:CON (cr)

- (c). Observe the following:

- (1). IC13 Pin 4 has 300 nanosecond negative pulse.

- (2). IC13 Pin 12 is always high.

- (3). IC12 Pin 4 is always high.

- (4). IC12 Pin 5 has 250 nanosecond positive pulse.

- (d). Jumper IC29 Pins 17 and 39 then observe the following:

- (1). IC 13 Pin 4 is always high

- (2). IC13 Pin 12 has 150 nanosecond negative pulse.

- (3). IC12 Pin 4 is always high.

- (4). IC12 Pin 5 has 250 nanosecond positive pulse.

- (e). Jumper IC29 Pins 17 to 3 and 18 to 38. Then observe the following:

- (1). IC13 Pin 4 is always high.

- (2). IC13 Pin 12 is always high.

(3). IC12 Pin 4 has 450 nanosecond negative pulse.

(4). IC12 Pin 5 has 250 nanosecond positive pulse.

(f). Remove all jumpers installed on socket IC29.

- (8). The last Disc I/O Buffers to be checked are the disc status lines. To do this test we will need a shorting wire. Each of the input disc signals should be shorted to ground at the 36 Pin edge cnnector while the user observes the voltage level at IC29. To enable the READY line one jumper must be used on IC29. The diode installed for the motor tests is to be removed.

- (a). Remove the diode installed in the Mini/Standard position for device 0.

- (b). Jumper IC29 Pins 28 and 39.

- (c). Observe the following:

- (1). When Pin 9 of the edge is shorted IC29 Pin 36 goes low.

- (2). When Pin 5 of the edge is shorted IC29 Pin 35 goes low.

- (3). When Pin 12 of the edge is shorted IC29 Pin 34 goes low.

- (4). When Pin 8 of the edge is shorted IC29 Pin 32 goes HIGH.

- (5). When Pin 17 of the edge is shorted IC25 Pin 9 goes low.

3.8 BRINGING UP THE 1791 IC

The last item to be tested is the 1791 itself. The previous tests have given us a 99% chance that the board will now work. We have checked all the circuitry associated with the 1791 IC except the operation of the Phase locked loop and the data lines. This will be done in this last section.

If you have been loading HMON/2 with the old Disc controller board, you will now have to load it a last time using the audio cassette.

At this time the user should go to the INSTALLATION portion of the manual to connect a drive to the Controller board. Be sure that all the proper

- 20 -

terminators have been installed at the disc drive.

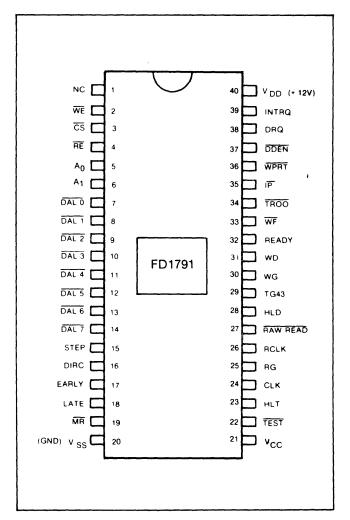

- (1). Remove the controller board from the system and check to see that Pin 1 of IC29 is NOT SHORTED to anything else.

- (2). Reinstall the controller board and check to see if:

(a). Pin 21 of IC29 has +5 Volts to it.

(b). Pin 40 of IC29 has +12 Volts to it.

(c). Pin 20 of IC29 is at ground potential.

- NOTE: IF THE 1791 IC IS INSTALLED UPSIDE DOWN, THE CHIP WILL BE DESTROYED. WE WILL TEST THE IC AT THE FACTORY AND NO WARRANTY REPLACEMENT WILL BE ALLOWED IF THIS HAS HAPPENED.

- (3). Install the 1791 IC WITH PIN 1 AWAY FROM THE EDGE CONNECTORS.

- Note: We will test the drive in the single density mode. If you wish, you may retest the drive in the double density mode using the procedures in this section.

- (4). Place a Diode in the following positions:

- (a). The select position for DSO.

- (b). The single density position for DSO.

- (c). If you have a Mini drive Install a diode in the mini position for DSO.

- (5). Install the controller board into the computer in the slot assigned it.

- (6). Reload HMON/2 .

- (7). Begin execution at Option S. 5 Ou to use ( have ,

- (8). Select device 0 by executing the following::OUT-54,0 (cr)

- (9). Now see if the data lines are ok. Try:

:OUT-51,0:INP-51:OUT-51,377:INP-51 (cr)

- 21 -

The computer should respond with:

PORT 051 = 000 PORT 051 = 377

If your results are not the same, you have a shorted or open data line to/from the 1791 IC.

(10). Let's try to get the head over track 0. First, manually position the drive read/write head to the center of the disc by turning the shaft at the end of the steper lead screw by hand. Do not install the media at this time. But, close the door. Now try:

:LOA-0 (cr)

the computer responds with the prompt:

Enter Macro Instruction >

Now enter:

INP-51:CON (cr)

OUT-50,013:MAC-0 (cr)

The user should hear the drive step to track 0 while the screen displays a desending sequence of numbers from 377 to 000.

If you did not get these results, first be sure the device select light on the drive came on. If it did, again, manually spin the stepper motor shaft to force the head to the center of the disc. Try the test again. If the numbers do appear desending on the screen but the drive does not step, check all lines corresponding to DIR STEP TK00 DS0 and HLOAD. If the numbers are not decending on the screen, check the TK00 line first. If this line is low while the device select light is on, we still don't have good communication with the 1791 IC. Check IC29 Pin 24 for a 2Mhz signal if Standard drive or a 1Mhz signal for a Mini drive. If the clock line is ok then the problem is still in the data or port select logic. Remove the drive from the system and then remove the 1791 IC and return to the addressing section of this manual.

- (11). Assuming that all is well so far, its time to format a diskette.

- (a). Place an "expendable" diskette in the drive and close the door.

- (b). Carefully place a scope probe on Pin 2 of IC38. (Write Gate)

(c). By now the drive select light should have gone out. If it hasn't, check the INDEX line for problems.

(d.) Start H-mon at option 5 (FOR- vill not vark on option b.)

(d.). Here we GO ! Type the following:

FOR-0 (cr)

The head should have loaded and the drive should be stepping. If there was no responce, check the HLT logic and its associated IC's.

If the drive IS stepping, check to see that the signal on IC 38 Pin 2 Is a square wave of 166/200 ms up 166/200 ms down (std/mini). If that is so, we're probably formatting the disc. To be sure:

- (e). Wait for the format to finish and the head to unload.

- (f). Carefully place the scope probe on Pin 5 of IC38. (Write Data)

(g). Retype the FOR-O (cr) instruction.

See that the signal on Pin 5 of IC38 is a series of 250ns pulses occuring at a 2/4us rate (std/mini). If these pulses are absent check the Write Precompensation circuit, IC's 12, 13, 14, 16 and 30.

(12). Seems we can format. let's see if the controller can read.

(a). Type the following command:

RAT-3:RET (cr)

- (b). You are now back in the Suding Operating System.

- (c). Now enter HMON/2 at Option 5.

- (d). You should hear the drive restore to track 0 and see the introduction message.

- (e). Let's see if it can read. Type:

GED-0,1 (cr)

(f). The system should respond with a screen (128 bytes) full of 345's.

If the system went away, check the Interrupt lines you installed on the CPU and Motherboard plus the wait logic. If the system came back with an error (CRC RNF IDF ), check the data separator in the following way:

Issue the following command:

- 23 -

TRK-0 (cr)

Place one scope lead on IC25 Pin 12 and the other on IC29 Pin 26. Trigger on the IC25 pin first. You should see a series of 200ns pulses on IC25 separated by 2/4us (std/mini). The other trace should be a overlapping square wave 180 Degrees out of phase with the pulses. There is a 250ns allowable "jitter" in the Square wave with respect to the pulses. Now switch triggering and see that the square wave stops overlapping and measures 2/4us up and 2/4us down (std/mini). There is an allowable error here but the timing should be within 5%. If the square wave has a severe "accordian" appearance to it the loop is not locking. Remove the diskette and readjust the VCO Free Running Frequency, (as done before in Sec 1.7-(2)), if incorrect. Tolerance is +5% and -0%. Reinstall the diskette and see if the problem clears itself. If not, there is a problem in some part of the loop. Go read the theory of operation of the VCO Phase locked loop and check IC's 6, 7, 8, 9, 10, 11, 15, 17 21, 24, 35 and 25.

(13). If you received a screen full of 345's, it looks as if the controller reads. But, let's be sure. Type:

RES:VER (cr)

Allow the drive to step through all tracks and return with:

DONE

Now type:

DEC:ERA:STA (cr)

The screen should erase and the Disc Status Table should be displayed. There should be 01001/00720 (std/mini) reads with no errors logged.

(14). The last test will be to see if the controller can read and write successfully. Type the following:

RES:ERA:RND (cr)

HMON/2 will now do 100 random read/writes. Wait for:

DONE

Now let's look at the Disc Log Table again by typing:

ERA:STA (cr)

The table should now show 100 reads and 100 writes with no errors.

If the above tests were successfull, The Board is in operating condition and you should read the Theory of Operation and the rest of the documentation. You might want to test the board further at this time. Read the tests available in the HMON/2 Manual and try some of them. The Disc Log Table

will keep track of the performance of the hardware and signals can be examined as these tests execute.

- 25 -

\* / \*

#### CHAPTER 4

#### THEORY OF OPERATION

#### 4.1 INTRODUCTION

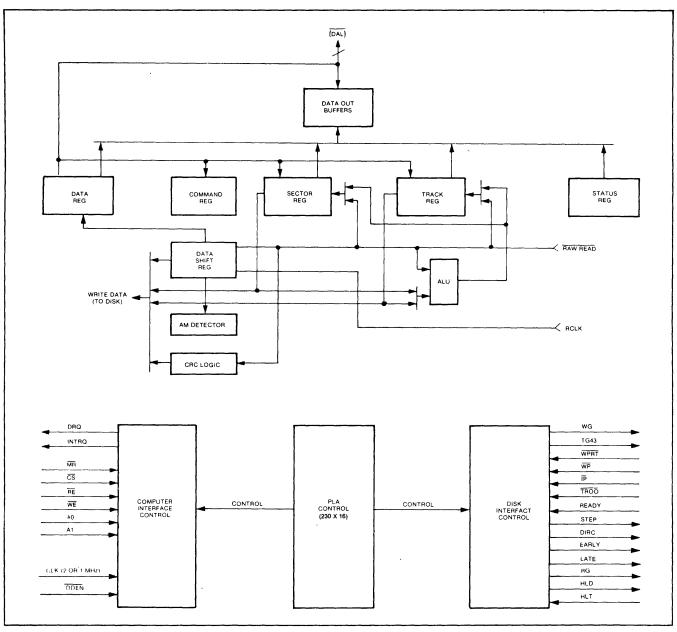

The Theory of Operation is broken into 13 sections, each covering a different portion of the circuitry. There is a partial schematic next to each section so that the user may view that section as he reads the theory.

As far as terminology is concerned, points on the schematic that are labelled with a signal name, will be called by that name. For points on the schematic that are not labelled, the IC and its associated pin number will be used (IC29 Pin 4 will be written as IC29-4). If an IC has more than one function the IC will be broken into parts, ie, IC13a.

There are many inputs and outputs of gates that require pullups. When a pullup resistor in used to pull up gates in different areas on the schematic, that pullup resistor appears in both areas. Don't be confused when you see numerous resisitor numbers repeated. Also, all resistors in the RPACK labeled IC26 are called out on the schematic as R26-(Pin Number).

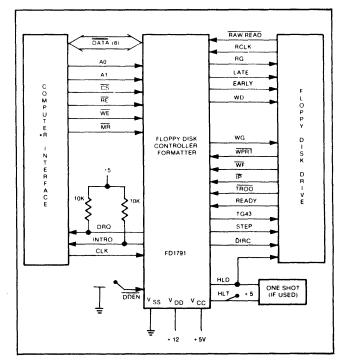

4.2 PORT LABEL DEFINITIONS

The controller occupies eight consecutive I/O addresses. Of these, six are used. The base address must start on an address that is a multiple of eight. There are 32 such locations that the controller board can occupy. For the Theory of Operation and for the Software Listings, we will fix this base address as 050Q or 028H. All references to these ports could be either numeric or by their software label. The following table should aid the user in determining the ports.

| PORT                                          | INPUT DESCRIPTION                                                                                                                        | OUTPUT DESCRIPTION                                                                                                                    |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 050<br>051<br>052<br>053<br>054<br>055<br>056 | STAT- 1791 STATUS<br>TRACK- CURRENT TRACK<br>SECTOR- DESIRED SECTOR<br>AVAIL BUT NOT USED<br>SEL- NUMEROUS FLAGS<br>NOT USED<br>NOT USED | CMND- 1791 COMMAND<br>TRACK- CURRENT TRACK<br>SECTOR- DESIRED SECTOR<br>DATA- SEEK DATA<br>SEL- DEVICE SELECT<br>NOT USED<br>NOT USED |

| 057                                           | WAIT- USER DATA PORT                                                                                                                     | WAIT- USER DATA PORT                                                                                                                  |

|                                               |                                                                                                                                          |                                                                                                                                       |

FIGURE 1.

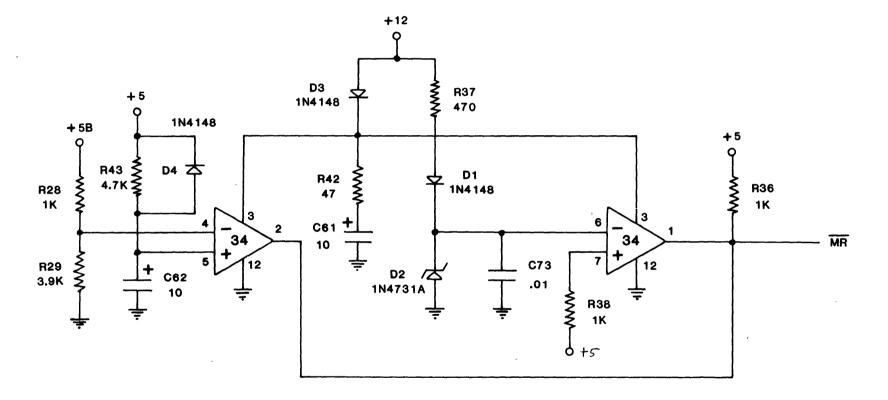

4.3 POWER-ON RESET AND LOW VOLTAGE CIRCUIT

The Power-On Reset and Low Voltage Circuit monitors the computer's +5 Volt line. It forces the 1791 into Master Reset on powerup and during any other time that the +5 Volt line decays below +4.3 Volts.

This circuitry also inhibits Write Gate during these occasions. This prevents the controller from accidentally writing over portions of the diskette.

This circuit consists of IC34, a Quad Comparator (2 used), and its associated resistors, capacitors and diodes.

During powerup the output IC34-2 has control of the circuit. The sequence of events are as follows: DS' has allowed C62 to discharge rapidly, insuring that on the initial (or subsequent) powerup, C62 will be discharged. When power is applied, C62 begins to charge through R37. At this time IC34-5 (the positive input) tracks the capacitor. R28 and R29 form a voltage divider that sets the negative compare voltage at approximately 4.0 Volts. Until this voltage is exceeded on the positive input IC34-5, the output IC34-2 remains low. The Capacitor, C62 takes approximately 50 milliseconds to charge to a voltage above 4.0 Volts. This keeps the output IC34-2 low for this time which forces a Master Reset into the 1791 IC. It also keeps the Write gate IC38-3 inactive.

During a voltage fluctuation on the +5 Volt supply that falls below +4.3 Volts, comparator output IC34-1 becomes active. The sequence of events is as follows: The positive input of the comparator IC34-7 tracks the +5 volt supply through R38. The negative comparator input, IC34-6, Has a fixed reference voltage of +4.3 Volts set by the Zener diode D2. R37 provides constant current through the Zener. When +12 Volts is lost, blocking diode D2, along with capacitor C73, temporarily provide the current for the reference Zener, D2. When the +5 Volt supply drops below the reference voltage on IC34-6, the comparator output IC34-1 goes low, again forcing the 1791 IC into Master Reset and inhibiting the Write Gate.

To insure that the outputs of the comparators remain active during a normal system power down, capacitor C61, along with blocking diode,  $D\#_{2}^{2}$ , combine to supply the voltage and current for IC34. Resistor R42 insures a constant charging rate for C61.

FIGURE 2

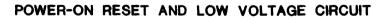

4.4 ADDRESS DECODE AND CPU I/O BUFFERS

The Address Decode and I/O Buffer circuit enables the computer to pass information to and from the Double Density Disc Controller board.

In order for the board to be accessed, the following conditions must be met:

00101 +++

1. The upper five address lines must match the selected base address.

2. The three lower address lines must be in the range of 0 through 4 or 7. 3. Either I/O READ or I/O WRITE must be active low.

When these conditions are met the board can be accessed for read or write.

#### ADDRESS GATING

The addressing operation happens as follows: The upper five address lines are presented to IC46 where the user selects which section in the I/O address space he wishes the board to occupy. This is done by selectively inverting the proper lines in IC46. Once this has been done, when the computer sends this address to the board, IC48-8 will go low. This line is the Conditional Board Select (CBS) signal and is gated to the following: 1. To the I/O Buffer Control Gate IC16-12. 2. To the enable input of IC33, the Port Select Decoder. The lower three addresses are presented to the port decoder through Latch IC45. Also the lower two address lines are buffered in IC18c,d and presented to the Controller IC29. IC33 generates all the conditional port select gating. If the lower three address lines are between 0 and 3, IC33 gates on IC32-8 which in turn is inverted in IC17. This inverted Controller Select(CS) signal partially enables IC's 18a and 18b. If the lower three address lines were decoded in IC33 to be equal to 4, The RW4 signal is generated which partially enables IC's 31a and 31b. If the lower three address lines were decoded to be 7, The SEVEN signal is generated. This SEVEN signal is passed to the Wait logic.

We have at the present selected one of three things. We have generated the CS signal or the RW4 signal or the SEVEN signal. We have also partially enabled the I/O buffer control gate.

#### I/O READ

Now, if this is a I/O READ operation, the computer will lower the I/O READ line. This line is presented to four gates. First it will fully enable the I/O buffer control gate IC16-13 which will cause the input buffer IC43 to turn off and then the output buffer IC44 to turn on. Second it is combined with RW4 in IC31a. Third, it will combine with CS in IC18a.

If the RW4 signal was active, I/O READ combines with RW4 to generate the RE4 signal at the output of IC31a. This signal enables octal buffer IC42 onto the I/O bus allowing the computer to read the data in the D Latches IC41, the drive attribute bits, and the two status signals from the

controller IC29.

If the CS signal was active, I/O READ combines with CS to form RE at the output of IC18a, which when generated, will gate the controller register, selected by the lower two address lines, onto the I/O data bus for the computer to read.

The I/O READ signal is also presented to IC19a, to be gated with the SEVEN signal, but this is in the Wait logic and will be discussed later.

#### I/O WRITE

Now, if this is an I/O WRITE operation, the computer will lower the I/O WRITE line. This line is presented to three gates. First, it is combined with RW4 in IC31b. Second, it is combined with CS in IC18b.

If the RW4 signal was active, I/O WRITE combines to form WE4 at the output of IC31b. This signal provides the strobe pulse to the Device Select, Side Select, and Interrupt Enable D type Latch IC41. It also conditionally enables the Drive Change signal(DR CHG) at IC16c. If Data bit 4 is low true at the time, the DR CHG signal is generated at the output of IC16c.

If the CS line was active, I/O Write combines to form WE at the output of IC18b. This signal enables the Controller register, selected by the lower two address lines, to be written into by the computer.

The I/O WRITE signal is also presented to IC19a, to be gated with the SEVEN signal. This is in the Wait circuit and will be discussed later.

#### **I/O BUFFERS**

The computer data interface to the controller is through three Octal buffer IC's 42, 43, 44. The controller's internal data bus is a low true bidirectional bus. When the board is not being accessed, the normal state of the internal bus is recieve. This normal state only changes to transmit when the computer has presented the proper port address and the I/O READ signal is active low. Since the computer I/O input bus is inverted, the Octal buffer IC44 is noninverting so that the controllers internal low true bus is gated to the computers low true I/O input bus. Octal buffer IC42 converts the high true data on its inputs to low true data for the controllers low true data bus. 4.5 WAIT LOGIC

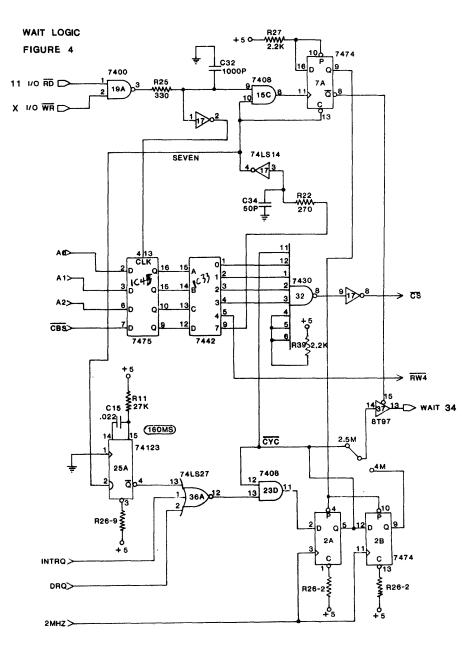

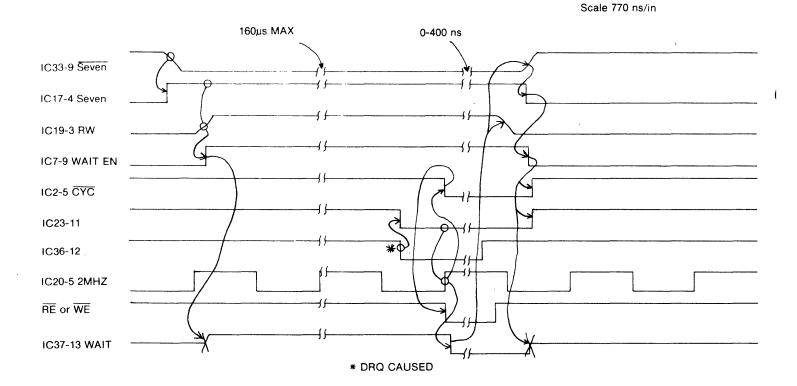

The Wait logic enables the computer to wait for the data coming from the disc without the fear of waiting "forever". This is accomplished by the wait timeout timer.

If data is already present when the computer enters wait, a maximum of two extra wait states is added to the I/O cycle.

The Wait logic is conditioned by three signals. These are, I/O READ, I/O WRITE and SEVEN. When the computer executes an I/O instruction, either I/O READ or I/O WRITE will become active low. This Combination is NANDed in IC19a and then filtered by the RC network of R25 and C32. This cleaned up signal is used to latch the Conditional Board Select signal(CBS) and the lower three address lines in Latch IC44. If the decoder IC33 detects a 7, this signal is filtered by RC network of R22 and C34. The SEVEN signal removes the CLEAR input to IC7a and allows the ANDed signals of SEVEN and RW to clock IC7-11 through IC15-8. The SEVEN signal also triggers (or retriggers) the wait timeout timer, IC25a, at this time. Once IC7a has been clocked it should not be clocked again until the wait cycle finishes. The Q output of IC7a also removes the PRESET of IC2a,b. This allows IC2 to function. IC2-5 places a high on the input of IC37a forcing the computer into the Wait State.

To remove the wait, one of three events occur. First, the wait timeout timer can timeout. This causes a high level to be presented to IC36-13. Second, a Completion Interrupt can occur from the controller IC29. This causes a high level on IC36-1. Third and most common, a Data Request could be generated by the Controller IC29. This causes IC36-2 to go high. Any of these High levels at IC36a will cause the output IC36-12 to go low. Since we just removed the PRESET from IC2, the output of IC2-5 is high. This, along with the former high of IC36a, kept IC23-11 high. Now that IC36-12 is low, IC23-11 will go low. At the next 2Mhz clock rising edge, the Q output IC2-5 will go low. This signal now enables one input to IC32 (CYC) and causes the CS signal to be generated. This along with the lower two address lines being one, causes the fourth register in the controller to either be read or written. The signal from IC2-5 also disables the D input to itself through IC15-12. This forces the Q output IC2-5 to remain low until IC7a is CLEARed.

The controller IC29 was selected and we are still in wait. When the next 2Mhz rising edge comes along, the low at the D input IC2-12 is clocked to the Q output. This signal is gated to the CPU through IC37-13 and removes the wait request. Now we are waiting on the CPU to release from the wait state and remove either the I/O READ or I/O WRITE that started this wait state. When the computer removes this signal, Latch IC45 is opened and the next address on the address bus sets up. This in turn removes the SEVEN signal which forces IC7a into the CLEARed state. The Q outputof IC7a now

PRESETS IC2 while the  $\overline{Q}$  output three states IC37a again. The wait Circuitry is now ready to start another cycle.

Note that when any one of the conditions to remove us from wait occurs, we must wait for the 2Mhz clock to occur. Then we must wait for the computer to acknowledge our request for wait state exit. If these first two events occur at their worst case times, (fastest) we could cycle so fast that we don't meet the access time of the controller IC29. There is a jumper removing the second period of wait if the CPU is running at 2.5Mhz. If the system were to be run at 4Mhz without the trace broken and the jumper installed to add this second 500ns delay (IC2-9) the access time of the controller IC29 would be exceeded. Therefore if the system is to be run at 2.5Mhz, no modifications need be done. However, if the system is to be run at 4Mhz, the user should cut the trace butween IC2-5 and IC37-14 and jumper IC2-9 to IC37-14. NOTE that The Digital Group does NOT support a 4Mhz system (4/79).

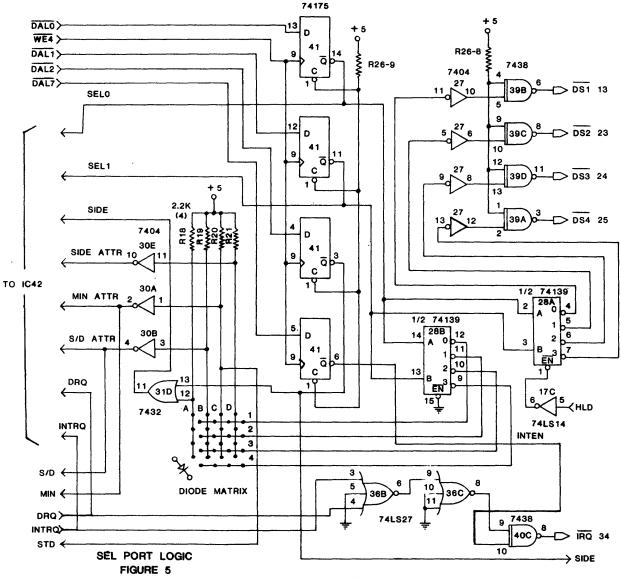

4.6 SEL PORT LOGIC

The SEL Port logic contains all drive select, side select, board interrupt enable, and drive change logic. The drive select bits are read/write. The side select bit is read/write only if that particular drive is jumpered as present. The board interrupt enable bit and the drive change bit are write only. All bits except the drive change bit are stored in D type Latch IC41.

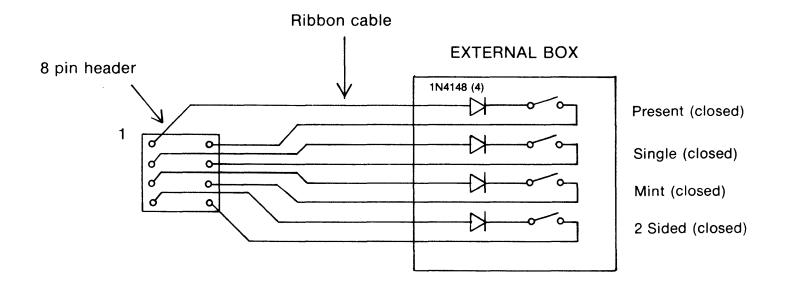

There are three drive attribute bits associated with the SEL Port. These bits set up the drive's attributes according to the diode matrix. This matrix allows each drive to be of a different size or density or number of sides.

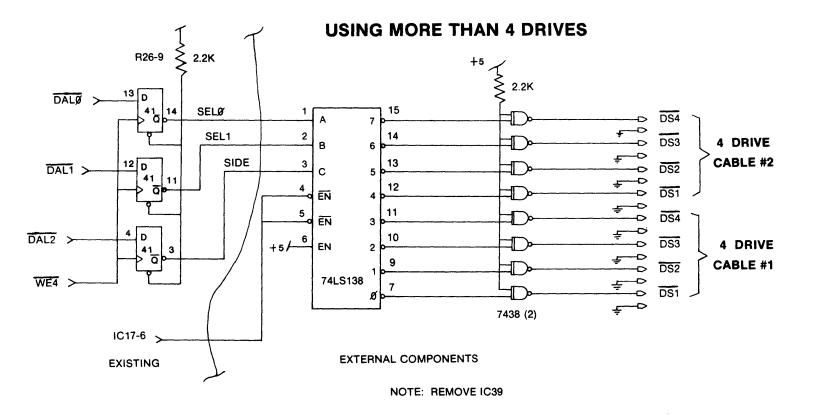

#### DRIVE SELECT CIRCUITRY

The lower two bits of the SEL port are the Drive Select bits. These bits are presented to the drive select decoder, IC28, where a Two Line to Four Line decode takes place twice. The first, in IC28a, is used to select the correct drive when the head is loaded. This decoder provides the drives with the Drive Select signal through inverter IC27 and Open Collector Driver IC39. The second set of decoding, IC28b, is active all the time and provides the diode matrix with one crosspoint per drive. These crosspoints are labeled 1 through 4 on the schematic and correspond to drives 1 through 4 that may be attached to the controller. The crosspoints provide a ground for the diodes that would be installed to select certain attributes.

### SIDE SELECT CIRCUITRY

The Side Select bit is the third bit. This bit is sent to the drives through Open Collector Driver IC40d. The Side Select line, IC41-3, is logically ORed in IC31d with the "A" column of the diode matrix before being read back by the computer through Octal buffer IC42. Placing a diode in the "A" column for the selected drive causes resistor R18 to be pulled low by an output of IC28b. This low allows the output of IC31d to track the input IC31-13. If no diode was installed in the "A" column for the selected drive, resistor R18 presents a constant one to the output of IC31d regardless of the condition of the Side Select D Latch IC41.

The software selects the bottom side of a particular drive by writing a zero to the side select bit. If upon reading back this bit, the software finds that it has changed to a one, it can be assumed that no drive is present for this particular drive number.

#### DRIVE CHANGE CIRCUITRY

The Drive Change signal is generated by the combination of WE4 and the fifth bit of the SEL Port in IC16-10. This signal is a one microsecond positive strobe and is Write only. The drive change strobe triggers the

head load delay one shot IC4-4 if the head was already loaded. (See Figure  $\not(f_{\star})$

BOARD INTERRUPT CIRCUITRY

The top output bit is the Board Interrupt Enable bit. This bit is write only. When set to a one, this signal allows the interrupt generated by INTRQ or DRQ in IC36b,c to be gated through Open Collector driver IC40c. Specific causes for interrupts are discussed in the 1791 section.

#### ATTRIBUTE SELECT LOGIC

The Drive Attribute Logic performs all logic switching to convert the controller board from different densities and different size diskettes. There are four attributes that are selected by the diode matrix for each drive. These are:

- A. Drive Present (explained in Side Circuitry).

- B. Single or Double Density.

- C. Mini or Standard Drive.

- D. One or Two Sided.

Three of these attributes are presented to the computer on bits three through five of the SEL Port through IC42.

The first of these attributes is the Single/Double Density attribute. To generate the Double attribute, no diode is placed in the "B" column for the selected drive. This causes resistor R19 to pull up the "B" crosspoint for the selected drive. In turn, IC30b inverts this high to generate a low S/D signal. The S/D signal is gated with other portions of the circuit to select Double density. This signal is also presented to Octal buffer IC42. If a diode is installed in the "B" column in the matrix for the selected drive, the line from IC28b pulls down resistor R19, which is then inverted through IC30b to produce a high S/D signal. This high S/D signal is then gated to other portions of the circuit to select Single Density.

The second of these attributes is the Mini/Standard attribute. To generate the Standard attribute, no diode is placed in the "C" column for the selected drive. This causes resistor R20 to pull up the "C" crosspoint for the selected drive. This in turn generates a high STD signal attached to R20. IC30a invert this high level to generate a low MIN signal. Both of these signals are gated with other portions of the circuit to select a Standard drive. The output of IC30a is presented to Octal buffer IC42. If a diode is installed in the "C" column in the matrix for the selected drive, the line from IC28b pulls down resistor R20, which generates a low STD signal. Both these signals are gated to other portions of the circuit to select a Standard drive.

The third attribute is the Side attribute. To select a single sided

### CHAPTER 4: THEORY OF OPERATION

drive, no diode is installed in the "D" column for the selected drive. This causes resistor R21 to pull up the input of inverter IC30e. The low output of IC30e is passed to Octal buffer IC42 to be read by the computer as single sided. If a diode was placed in the "D" column of the selected drive, the output of IC28b will pull down resistor R21. This low is inverted by IC30e and passed to Octal buffer IC42 to be read by the computer as double sided.

### OTHER SEL PORT SIGNALS

Two other read only signals are accessable by reading the SEL port. These are status outputs of the controller IC29. The INTRQ output IC29-39 is passed to the top bit of Octal buffer IC42 while the DRQ output IC29-38 is presented to the sixth bit  $\mathfrak{W}$  of Octal buffer IC42. These two signals will be explained in the 1791 section.

- 34 -

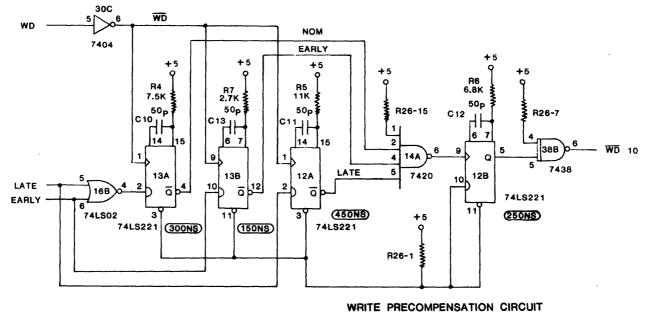

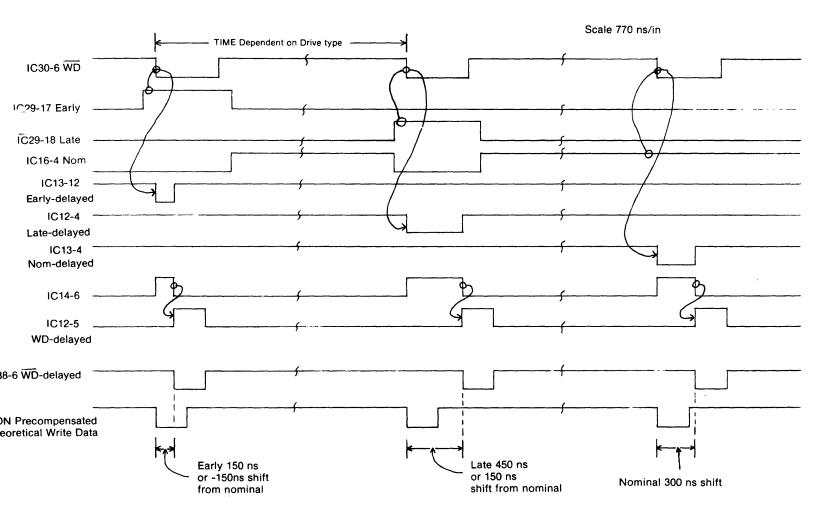

#### 4.7 WRITE PRECOMPENSATION CIRCUIT

The Write Precompensation Circuit generates the proper amount of compensation to the Write Data pulse for reliable Double Density operation. This is done by selecting one out of the three one-shots to be fired for the correct length of time. The original Write Data pulse is delayed a fixed amount of time for Nominal Data timing. For an Early Write data pulse, the original Write Data pulse is generated 150 nanoseconds earlier than a Nominal Data pulse. For a Late Write data pulse, the original Write Data pulse is delayed 150 nanoseconds after the Nominal Data pulse.

Three signals from the controller IC29 are required to operate the Write Precompensation Circuit. These are Early, Late and Write Data. The Early and Late signals are valid prior to the leading edge of each Write Data The Early signal IC29-17 is passed directly to the negative edge pulse. enable input of the Early one shot IC13b. The Late signal IC29-18 is passed directly to the negative edge enable input of the Late one shot IC12a. Both the Early and Late signals are NORed in IC16b to produce the negative edge enable signal for the Nominal one shot IC13a. Note that under normal operating conditions, the combination of Early and Late being high at the same time is not possible. The Write Data pulses are inverted by IC30c to produce a negative pulse. This negative pulse is presented to the negative edge trigger input of Early, Nominal and Late one shots IC13b, IC13a, and IC12a. Whichever oneshot has its negative edge enable input high will fire at this time. This pulse in NANDed in IC14 to trigger the Write Data one shot IC12b on the falling edge. This one shot produces a positive going 250 nanosecond Write Data pulse that is presented to the drives through Open Collector Inverting Driver IC38b.

FIGURE 6

- 35 -

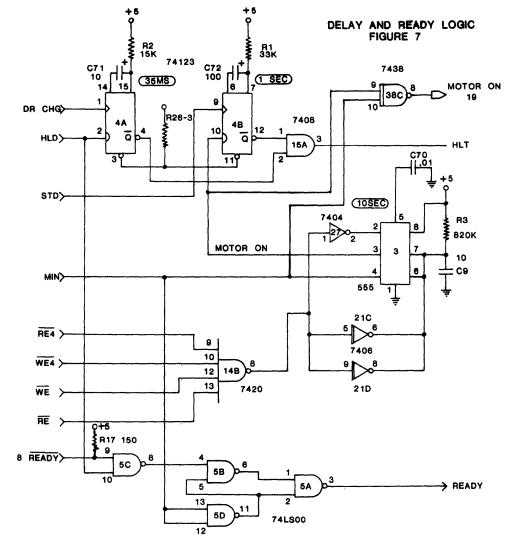

4.8 DELAY AND READY LOGIC

The delay logic performs three delay functions. The READY logic is also included in this section.

#### MINI MOTOR DELAY TIMER

The first delay is the motor timeout timer for Mini drives. This timer IC3 acts as a retriggerable one shot. The timer is enabled by the MIN signal on Pin 4. The timer is triggered by one of the four port enable strobes RE, WE, RE4, WE4 through IC14. Once triggered, capacitor C9 charges through resistor R3. When further accesses are made to the board, IC14 pulses high. These high pulses are used to partially discharge capacitor C9 through two Open collector Inverters IC21c,d. This discharge pulse is one micro second in duration and many of these pulses are required to maintain a low voltage on capacitor C9. It should be noted then, that the motor on timer requires HEAVY board usage to maintain the mini motors in the on state.

### MINI MOTOR STARTUP DELAY TIMER

The second timer is the mini motor startup timer IC4b. This timer inhibits the controller IC29 from reading or writing until the mini motors are up to speed. The only time this timer fires is when a rising edge is generated by the mini motor timer starting. If the selected drive is a Mini drive, the STD signal is low. This signal is presented to the positive edge trigger enable input IC4-9. The rising edge of IC3-3 generates a negative going pulse out of IC4-12. This negative going pulse is ANDed with the Head load delay timer in IC15a to produce a low on IC29-23 whenever a delay in reading or writing to the disc is required.

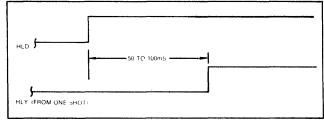

### HEAD LOAD DELAY TIMER

The third timer is the head load delay timer. This timer inhibits reading or writing to the disc whenever the head has been loaded and the head settling time has not expired. The head load delay timer can be triggered in one of two ways. The first way is when the controller IC29-28 (HLD) goes high signifing that the head is to be loaded. On this occasion, IC4-1 is low. The rising edge HLD into IC4-2 causes the one shot to trigger. This generates a low output pulse on IC4-4 which is ANDed with the mini motor startup timer in IC15a. The output of IC15a generates a low on IC29-23 causing reading or writing to the disc to be inhibited.

The second way the head load timer may be triggered is when the head is loaded and a drive change pulse is issued. When the head is loaded, HLD presents a high to IC4-2. This high level is also equivalent to the negative edge enable required by the negative edge trigger input to trigger. When a drive change pulse is generated in IC16c (DR CHG), the negative edge of this pulse triggers the Head load timer. The drive change pulse only will trigger the head load timer when the HLD signal is active high.

#### READY LOGIC

The Ready logic performs three tasks. It allows the Ready line from a Standard drive to be inverted and gated to the controller IC29-32 whenever the head is loaded. It prevents the Ready line to the controller IC29-32 from going Not Ready whenever the head is not loaded. It also presents a constant Ready to the controller whenever the controller is using Mini drives.

IC5 performs all the Ready logic functions. IC5a,b,d combine to form an AND OR circuit. One input to the AND OR is through IC5c. The two inputs to IC5c are the high true head load (HLD) signal and the low true Drive Ready signal from 36 Pin edge connector Pin 8. Resistor R17 terminates the Drive Ready signal. The only time a Not Ready signal is Presented to the IC5-4 input to the AND OR circuit is when the drive is Not Ready (IC5-9 high) and the HLD signal to IC5-10 is high. This causes the output of the AND OR gate to go low if IC5-5 was high. In order for IC5-5 to be high, IC5d must have a low on its input, which is the MIN signal. This case would be true if the STD signal has high (selecting Standard drives). If the MIN signal was high, its inversion through IC5d disables the Standard drive ready line and produces a constant high on the output of the AND OR gate by placing a low on IC5-2.

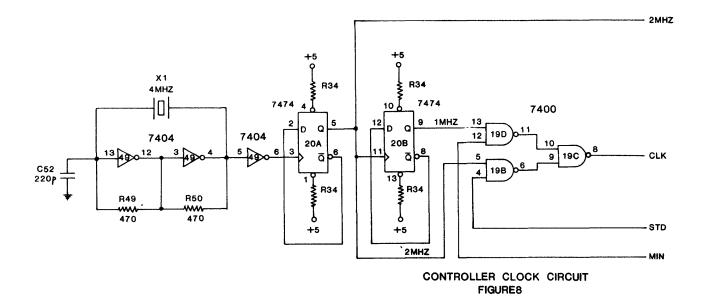

4.9 CONTROLLER CLOCK CIRCUIT

The controller clock circuit generates and switches the system clock between the two frequencies required for Mini and Standard drives. The clock frequency for Standard drives is 2 Mhz and the the clock frequency for Mini drives is 1 Mhz.

A 4 Mhz clock signal is generated by the TTL oscillator IC49. D type Flip Flop IC20a divides this 4Mhz clock by 2 before it is presented to D Flip Flop IC20b where it is divided by 2 again. The Q output of IC20a is presented to IC19b which is acting as a two to one line decoder. The Q output of IC20a is presented to IC19d. The 2 Mhz clock is passed to the controller IC29-24 through IC19b,c when the STD signal is high. The 1 Mhz clock is passed through IC19d,c when the MIN signal is high.

The 2 Mhz signal from IC20a is also presented to the Wait logic for the clocking of IC2.

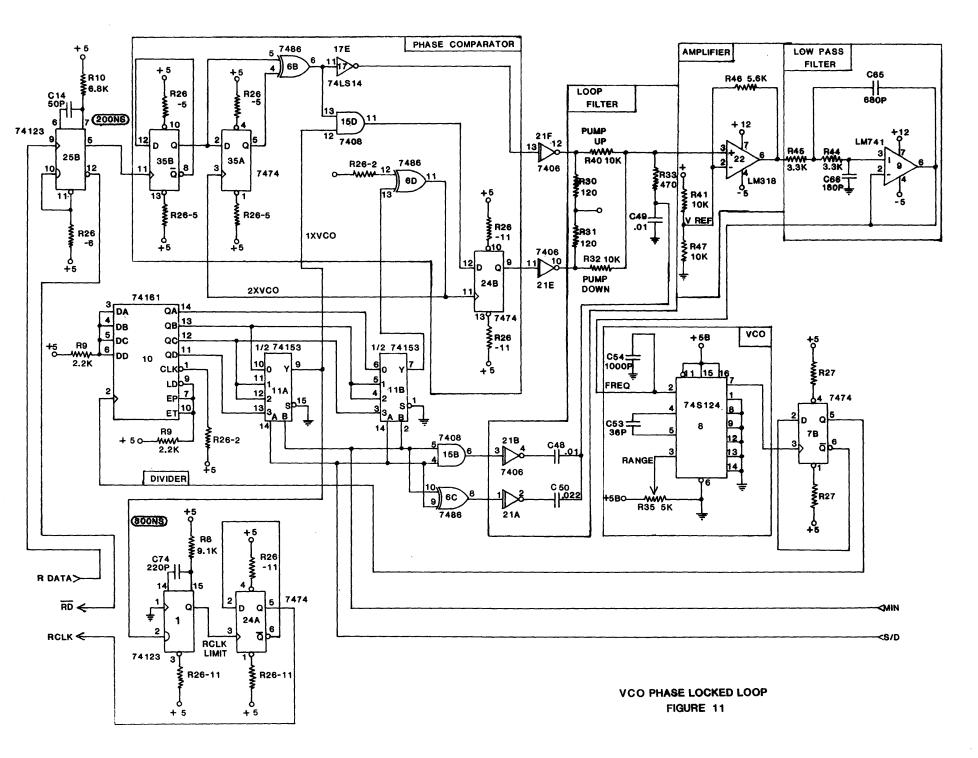

4.10 VCO PHASE LOCKED LOOP

The VCO Phase Locked Loop is comprised of six sections. These are:

- 1. Phase Comparator

- 2. Loop Filter (switchable)

- 3. Amplifier

- 4. Low Pass Filter

- 5. Voltage Controlled Oscillator

- 6. Divider Chain

#### PHASE COMPARATOR

The Phase Comparator determines the phase error of the input frequency (Data) against the present VCO frequency and generates a difference voltage used to change the frequency of the VCO towards the incoming Read Data frequency.

Read Data from the disc is buffered by IC37d. The Read Data line is terminated by resistor R15. The buffered Read Data is presented to IC25b where the input pulse is shortened to 200 nanoseconds. The Q output of IC25b is sent to the controller IC29-27 as the RD pulses. The Q output of IC25b is presented to the clock input of IC35b. IC35b, a D type Flip Flop performs a divide by two on the data. This converts the input data from a pulse to either a rising edge or a falling edge. This divided by two data is presented to D type Flip Flop IC35a. Here the Data is clocked with the 2X VCO frequency. A phase comparison is made between the 2X VCO and the input data in IC6b. This comparison is inverted in IC17e and then reinverted in IC21f to produce the Pump Up signal. The Pump Up signal is also ANDed with the 1X VCO signal in IC15d and then presented to the D input Of D type Flip Flop IC24b. This Flip Flop is clocked by the 2X VCO signal. The Q output of IC24b is inverted in IC21e to produce the Pump Down signal.

#### LOOP FILTER

The Loop Filter generates the lock, range and steady state Phase error constants of the system. It has two extra capacitors that are switched into operation to change the characteristics of the loop for different data rates.

The Pump Up and Pump Down signals are combined at the junction of resistors R40, R32, and R33. The steady state bias point of this junction is 2.5 Volts. The Pump Up and Pump Down signals vary this voltage in proportion to the frequency difference between the incoming data pulses and the 1X VCO frequency. Loop filtering is done in resistor R33 and Capacitors C48, C49 and C50. In Double Density Standard mode, both C48 and C50 are gated off by the two lows presented to the inputs of IC's 15b and 6c. The two lows are the MIN and S/D signals produced in the diode matrix. In the Single Density Standard and Double Density Mini mode, only capacitor C48 is gated off. In this case, one of the two signals MIN or S/D is low. One of these lows inhibits one input of AND gate IC15b. Capacitor C50 is gated on by one of these signals also through IC6c. The last case is the Single Density Mini. Here, capacitor C48 is gated on and capacitor C48 is gated off. In Single Density Mini, both MIN and S/D are active high. This enables AND gate IC15b and disables XOR gate IC6c. These capacitors modify the natural frequency of the loop to accomodate the different data rates of the above types of drives.

### LOOP AMPLIFIER

The Amplifier is used to adjust overall loop gain. This Amplifier must have a high slew rate.

The Loop Amplifier is a noninverting high slew rate Operational Amplifier with a gain of +2.1. The input resistance is the parallel combination of R41 and R47. The feedback resistor is R46. The negative input is biased at 2.5 Volts to adjust for the steady state input bias from the Loop Filter. This steady state bias is passed to the next stage.

#### LOW PASS FILTER

The Low pass filter is used to remove high frequencies introduced by the digital phase comparitor. It is also used to reduce the response of the loop to instantanious variations in the input data stream.

The Low Pass Filter is a 2 Pole Butterworth Active filter. The cutoff frequency of this filter is approximately 150 Khz. The Low Pass Filter consists of IC9 a LM741, capacitors C65 and C66, plus resistors R44 and R45. It is a noninverting type filter.

#### VCO

The VCO is the basic clock for the loop. It has a Range input to set the Mhz/Volt constant and a Frequency input to vary the output frequency to achieve lock.

The VCO is a Texas Instruments 74S124 Dual VCO IC. Its free running frequency is set by the Range input and capacitor C53. The output frequency is 8Mhz. Capacitor C54 filters the Frequency control input to remove any high frequency noise generated by the TTL circuits nearby. The 8Mhz output

on IC8-7 is sent to the Divider Chain to provide the 1X and 2X VCO signals required for the Phase Comparitor. The second VCO section of IC8 is disabled.

#### DIVIDER CHAIN

The Divider Chain provides different divide rates for the different data rates used in the controller. It also provides the controller IC29 with the 180 degree out of phase bit rate clock required for data separation.

The Divider Chain receives its input from IC8-7 the VCO. This 8Mhz signal is first divided by two in D type Flip Flop IC7b. The output of IC7b is a 4 Mhz signal presented to the Binary divider IC10. IC10 divides this 4 Mhz signal into the different 1X and 2X VCO signals required. IC11 is a Dual four line to one line multiplexer. The output of IC11b is the 1X VCO signal. The output of ICN1b is the 2X VCO signal. The multiplexer is switched by the S/D and MIN diode matrix signals. The output periods of IC11 for different S/D and MIN signals are tabulated below.

| S/D | MIN | DRIVE TYPE | İC11a | IC11b |

|-----|-----|------------|-------|-------|

| 0   | 0   | D.D. STD   | 1 us  | .5 us |

| 0   | 1   | D.D. MIN   | 2 us  | 1 us  |

| 1   | 0   | S.D. STD   | 2 us  | 1 us  |

| 1   | 1   | S.D. MIN   | 4 us  | 2 us  |

|     |     |            |       |       |

|     |     |            |       |       |

The output of IC11b is first limited to a period of 800 ns low and 800 ns high by IC1. This prevents exceeding the limits imposed by the controller IC29 on its RCLK input IC29-26 (see 1791 operating specs). This signal is then divided by two to generate the 180 degree out of phase RCLK signal in IC24a. The RCLK signal is presented to the controller IC29-26. 4.11 DISC I/O BUFFERING

The Disc I/O signals and the IRQ signal buffering will be discussed here.

There are three Status signals from the drive that are buffered by parts of IC37. These are:

.

The Write Protect Signal enters the controller board on 36 Pin edge connector Pin 9. This line is terminated by resistor R12. The Write Protect signal is buffered in IC37a and is presented to the WP controller input IC29-36.

The Index signal enters the controller board on 36 Pin edge conector Pin 5. This line is terminated by resistor R13. The Index signal is buffered in IC37b and then presented to the IP controller input IC29-33.