# VAX 8800 System Technical Description

Volume 2

FOR INTERNAL USE ONLY

## VAX 8800 System Technical Description

Volume 2

FOR INTERNAL USE ONLY

Prepared by Educational Services of Digital Equipment Corporation

## Copyright Digital Equipment Corporation 1986 All Rights Reserved

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

### Printed in U.S.A.

### Class A Computing Devices

Notice: This equipment generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference in which case the user at his own expense may be required to take measures to correct the interference.

The following are trademarks of Digital Equipment Corporation:

| logo         | DECwriter    | RSX            |

|--------------|--------------|----------------|

| logo         | DIBOL        | Scholar        |

| DEC          | MASSBUS      | ULTRIX         |

| DECmate      | PDP          | UNIBUS         |

| DECset       | P/OS         | VAX            |

| DECsystem-10 | Professional | VMS            |

| DECSYSTEM-20 | Rainbow      | VT             |

| DECUS        | RSTS         | Work Processor |

## CONTENTS

| SECTION 6          | INSTRUCTION BOX (IBOX)                         |

|--------------------|------------------------------------------------|

| CHAPTER 1          | INTRODUCTION                                   |

| 1.1                | OVERVIEW                                       |

| 1.1.1              | Dual-Processor Configuration                   |

| 1.2                | LOGIC ELEMENTS                                 |

| 1.2.1              | Physical Implementation                        |

| 1.2.2              | Instruction Buffer (IB)                        |

| 1.2.2.1            | Writing the IB 1-5                             |

| 1.2.2.2            | Reading the IB 1-5                             |

| 1.2.3              | IB Manager 1-6                                 |

| 1.2.3.1            | IB Read/Write Control 1-6                      |

| 1.2.3.2            | Computing Amount of IB Data Consumed 1-6       |

| 1.2.4              | Decoder Logic                                  |

| 1.2.4.1            | Decoder RAMs                                   |

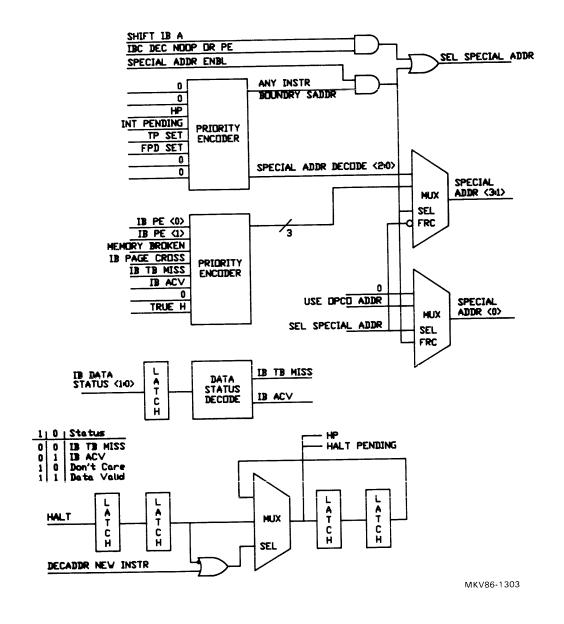

| 1.2.4.2            | Special Address Encoder                        |

| 1.2.5              | Microsequencer Logic 1-8                       |

| 1.2.6              | Control Store                                  |

| 1.2.7              | Condition Code and Macrobranch Logic 1-9       |

| 1.2.7.1            | PSL CC Bits 1-9                                |

| 1.2.7.2            | CPU State Flags 1-10                           |

| 1.2.8              | Interrupt and Processor Register Logic 1-10    |

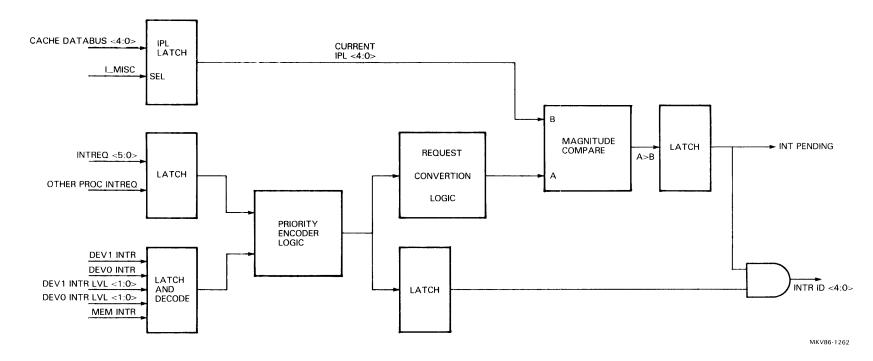

| 1.2.8.1            | Interrupt Logic                                |

| 1.2.8.2            | Processor Register Logic 1-10                  |

| 1.2.9              | File Address Generator                         |

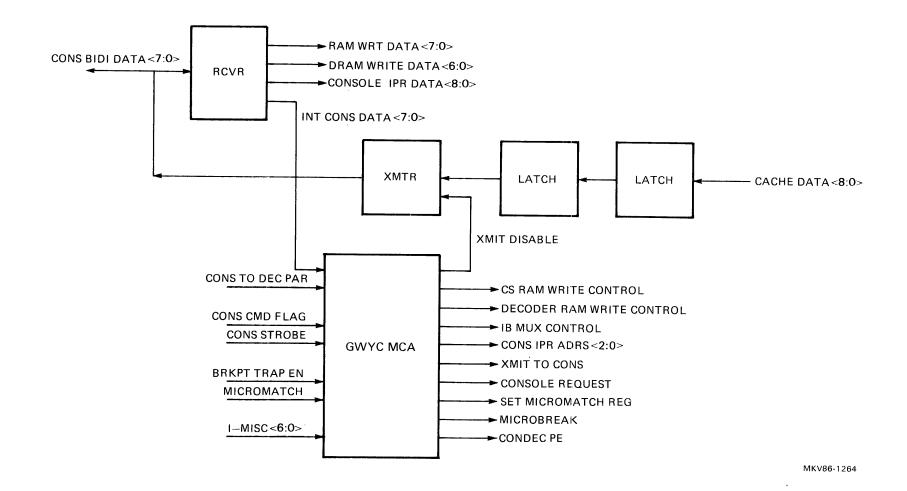

| 1.2.10             | Gateway Control Logic 1-11                     |

| 1.2.10.1           | Primary Functions 1-11                         |

| 1.3                | IBOX BUSES                                     |

| 1.3.1              | Cache Data Bus 1-12                            |

| 1.3.2              | IB Data Bus 1-12                               |

| 1.3.3<br>1.4       | Cons Bidi Data Bus                             |

| 1.4                | IBOX RESIDENT INTERNAL PRIVILEGED REGISTERS    |

| 1.4.1              | (IPRs)                                         |

| 1.4.2              | VAX Architecture IPRs                          |

| 1.4.2.1            | VAX 8800-Specific IPRs                         |

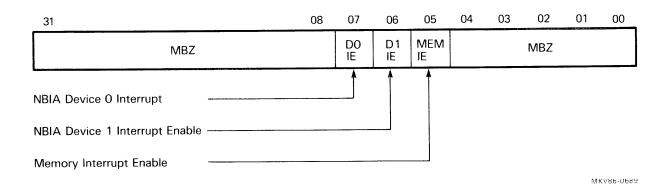

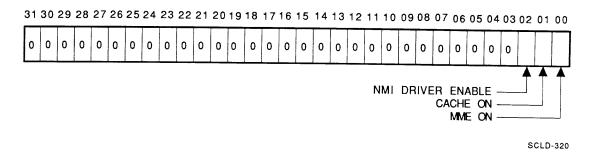

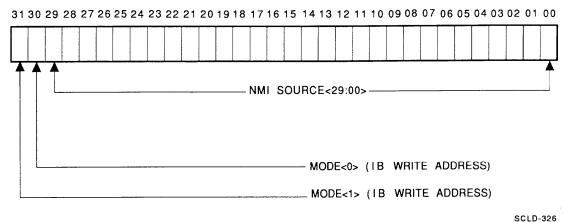

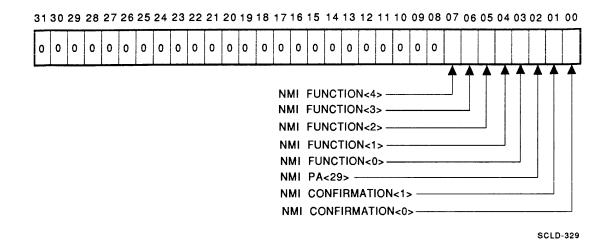

| 1.4.2.2            | NMI Interrupt Control Register (NICTRL) 1-14   |

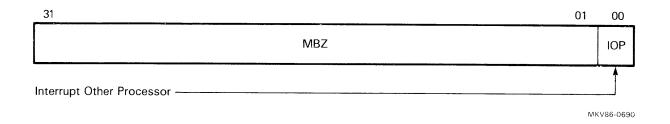

| 1.4.2.2            | Interrupt Other Processor Register (INOP) 1-15 |

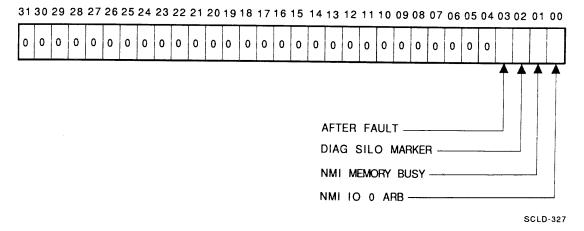

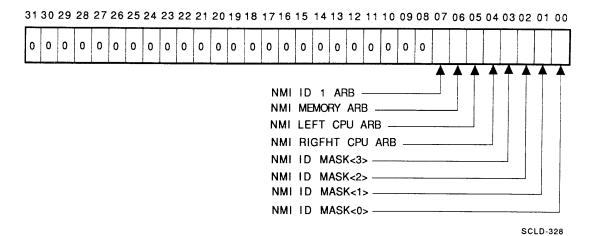

| 1.5.1              | IBOX MICROCODE VISIBLE ONLY REGISTERS 1-16     |

| 1.5.2              | Clear Interrupt Other Processor (CIOP) 1-16    |

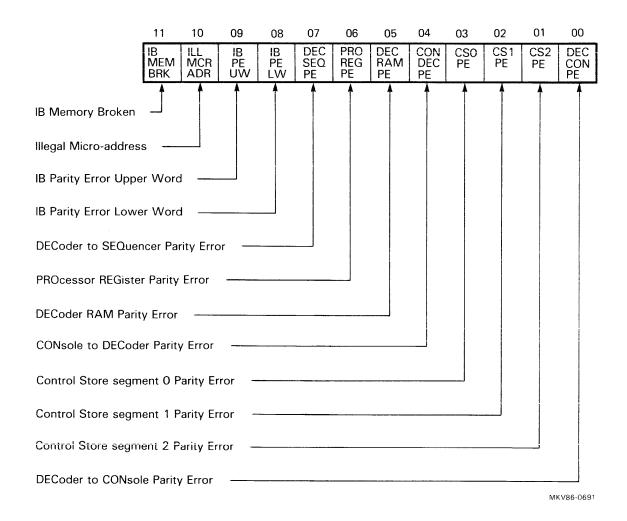

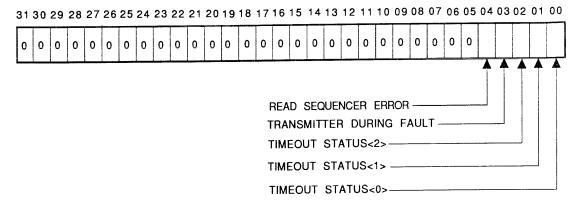

|                    | IBox Error Register (IBER) 1-16                |

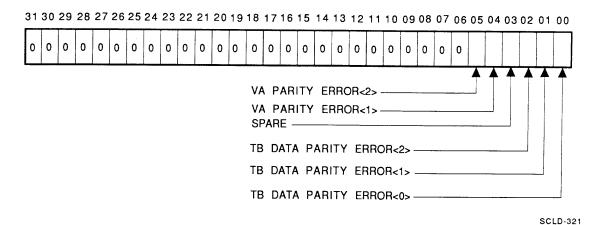

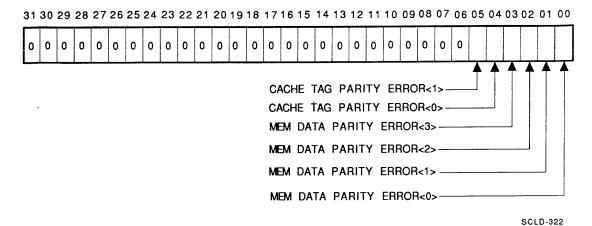

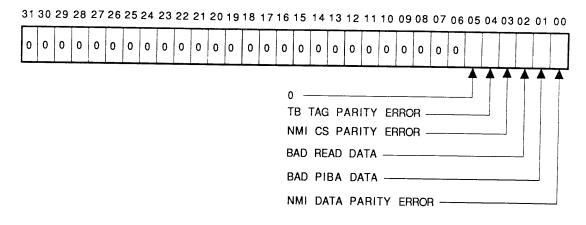

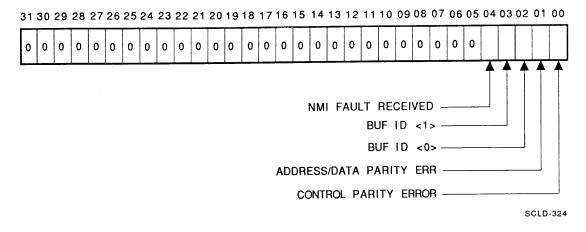

| 1.5.2.1<br>1.5.2.2 | IBER Usage                                     |

|                    | IBER Bits <7:0>                                |

| 1.5.2.3            | IBER Bits <11:08>                              |

| 1                  | Clear Error Register (CEP)                     |

| CHAPTER 2 | MICROCODE OVERVIEW AND PIPELINE CONCEPTS    |

|-----------|---------------------------------------------|

| 2.1       | CHAPTER SCOPE                               |

| 2.2       | VAX 8800 MAIN CONTROL STORE OVERVIEW 2-1    |

| 2.2.1     | Microcode Size and Allocation 2-1           |

| 2.2.2     | Microcode File Structure 2-1                |

|           | Microcode Assembly                          |

| 2.2.3     | Other Loadable Binary Files                 |

| 2.2.3.1   | Other Loadable Billary Files                |

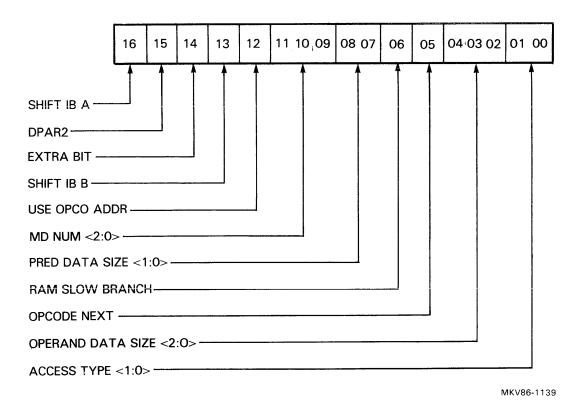

| 2.2.4     | Microword Format                            |

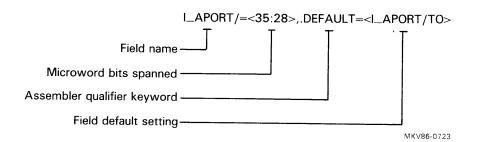

| 2.2.4.1   | Field Naming Convention                     |

| 2.2.4.2   | Field Functionality                         |

| 2.2.5     | Microcode Definition Files 2-11             |

| 2.2.5.1   | Field Definition File - DEFIN.MIC 2-11      |

| 2.2.5.2   | Macrodefinition File - MACRO.MIC 2-13       |

| 2.2.6     | Microcode Related Documentation 2-15        |

| 2.3       | MICROCODE PIPELINING CONCEPTS 2-20          |

| 2.3.1     | Pipelining Rationale 2-20                   |

| 2.3.2     | Pipelined Versus Nonpipelined Machines 2-20 |

| 2.3.2.1   | Performance Factors 2-22                    |

| 2.4       | VAX 8800 PIPELINE CHARACTERISTICS 2-23      |

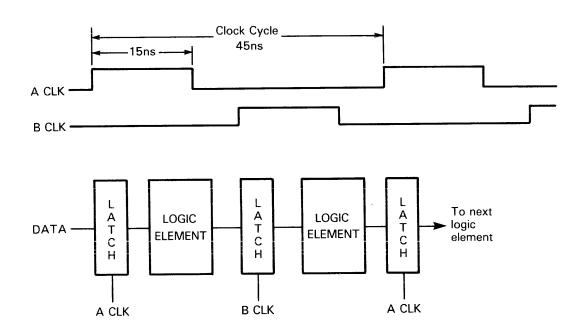

| 2.4.1     | CPU Clock Cycle                             |

| 2.4.1     | CPU Hardware Design                         |

|           | Relationship Between Microcycles and CPU    |

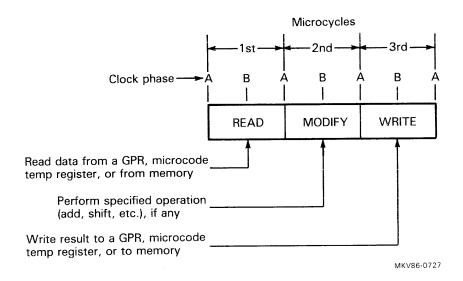

| 2.4.3     | Functions                                   |

| 0 4 4     | Tunectons.                                  |

| 2.4.4     | ib becode cycle                             |

| 2.4.5     | Canonical lime ocacoo.                      |

| 2.4.5.1   | DCITITCION OF a canonizada zima             |

| 2.4.5.2   | Overtupping 11ms beacost                    |

| 2.4.6     | Time State Events 2-29                      |

|           | IBOX FUNCTIONAL DESCRIPTION                 |

| CHAPTER 3 | IBOX FUNCTIONAL DESCRIPTION                 |

| 3.1       | CHAPTER SCOPE                               |

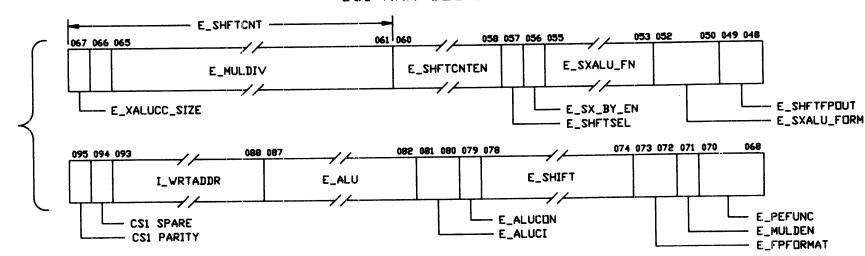

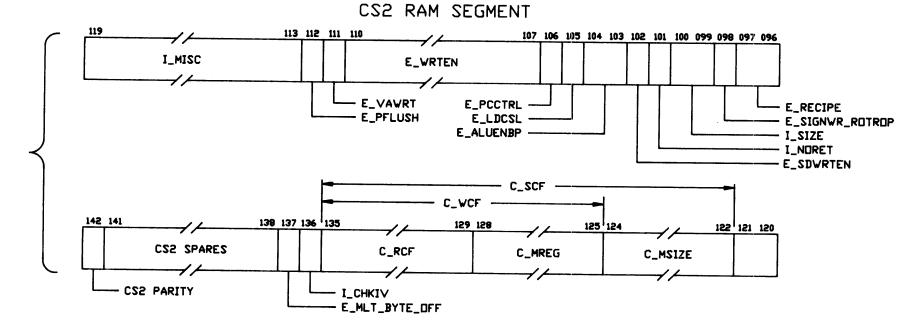

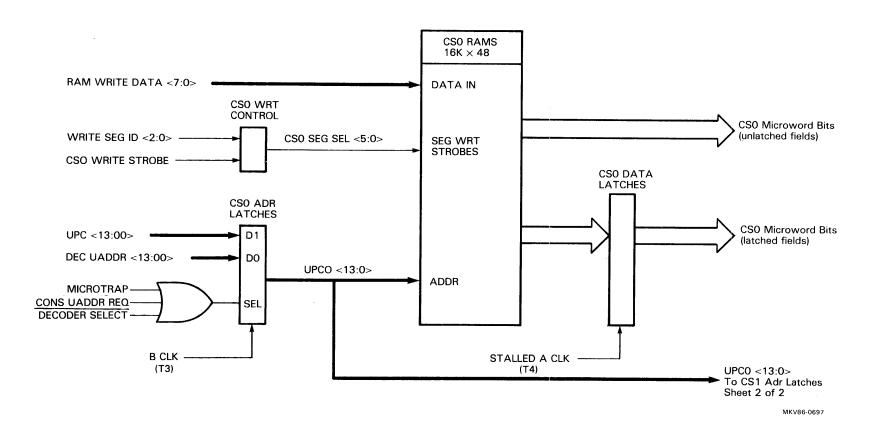

| 3.2       | CONTROL STORE LOGIC                         |

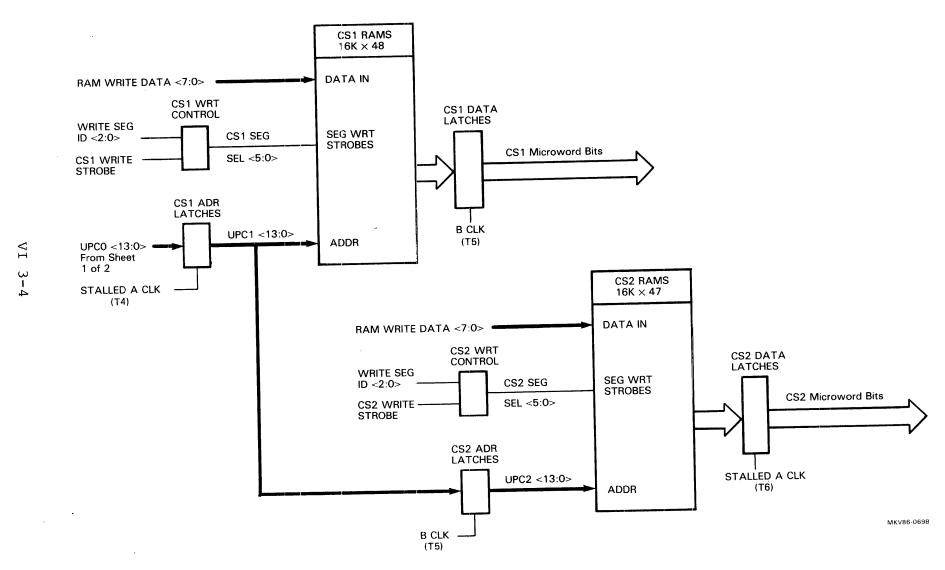

| 3.2.1     | Control Store RAM Segments 3-2              |

| 3.2.2     | Control Store RAM Addressing 3-5            |

| 3.2.3     | Control Store RAM Data Latches 3-5          |

| 3.2.4     | Loading the Control Store RAMs 3-6          |

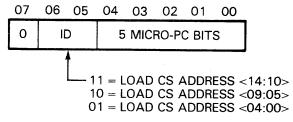

| 3.2.4.1   | Load Control Store Microaddress 3-6         |

| 3.2.4.2   | Write Data to Selected Address 3-7          |

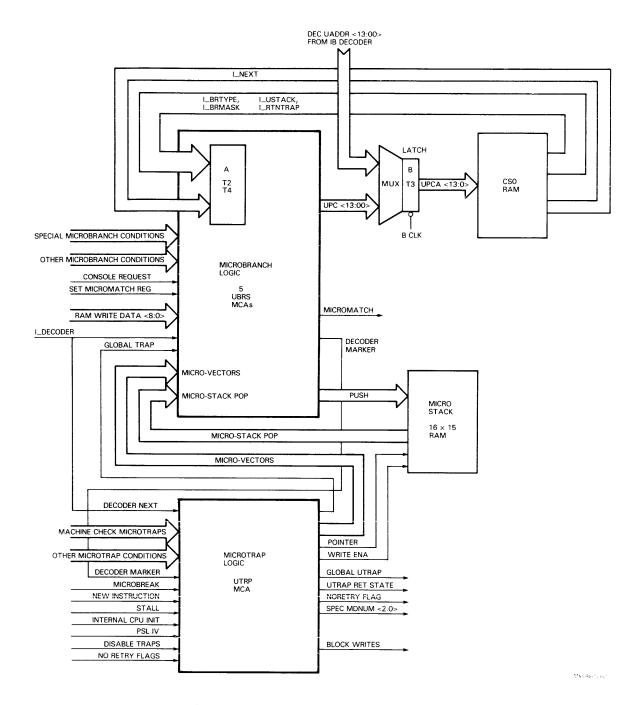

| 3.3       | MICROSEQUENCING                             |

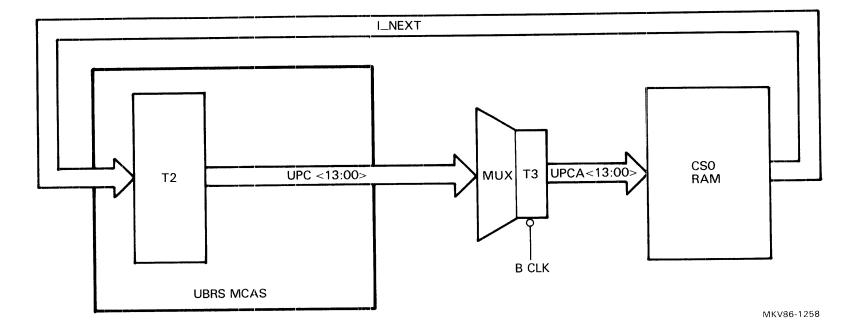

| 3.3.1     | Microsequencer Hardware 3-9                 |

| 3.3.1.1   | Microbranch Slice (UBRS) MCAs 3-9           |

| 3.3.1.2   | Microtrap (UTRP) MCA                        |

| 3.3.1.3   | Microstack                                  |

| 3.3.1.3   | Normal Microcode Flow                       |

|           | IB Decoder Supplied Microaddress            |

| 3.3.3     | Microbranching                              |

| 3.3.4     | Microbranch Conditions                      |

| 3.3.4.1   | Microbranch Latency                         |

| 3.3.4.2   | nicion Laconor                              |

| 3.3.5     | MICEOSabloacino cario and moderni           |

| 3.3.5.1   | NOT mai hiciosedon operación.               |

| 3.3.5.2   | Microsubroutine Calls 3-21                  |

| 3.3.5.3 | Microsubroutine Returns 3-23                     |

|---------|--------------------------------------------------|

| 3.3.6   | Microtraps                                       |

| 3.3.6.1 | Microtrap Servicing                              |

| 3.3.6.2 | Disabling Microtraps                             |

| 3.3.7   | Console Supplied Microaddresses                  |

| 3.4     | MACROINSTRUCTION DECODING                        |

| 3.4.1   | Initializing the IB (IB Flush)                   |

| 3.4.1.1 | Full IB Flush                                    |

| 3.4.1.2 | IB Flush Logic                                   |

| 3.4.1.3 | Partial IB Flush                                 |

| 3.4.2   | I-Stream Prefetching                             |

| 3.4.2.1 | General Description                              |

| 3.4.2.2 | Refilling Cache                                  |

| 3.4.3   | Loading the IB                                   |

| 3.4.3.1 | IB Write Control                                 |

| 3.4.3.2 | Cache Monitor Logic                              |

| 3.4.3.3 | IB Full Logic                                    |

| 3.4.3.4 | IB Load Example                                  |

| 3.4.4   | Reading The IB                                   |

| 3.4.4.1 | Pipeline Timing                                  |

| 3.4.4.2 | TR Pond Ports                                    |

| 3.4.4.3 | IB Read Ports                                    |

| 3.4.4.4 | IB Data Aligner                                  |

| 3.4.4.5 |                                                  |

| 3.4.5   | IB Read Example                                  |

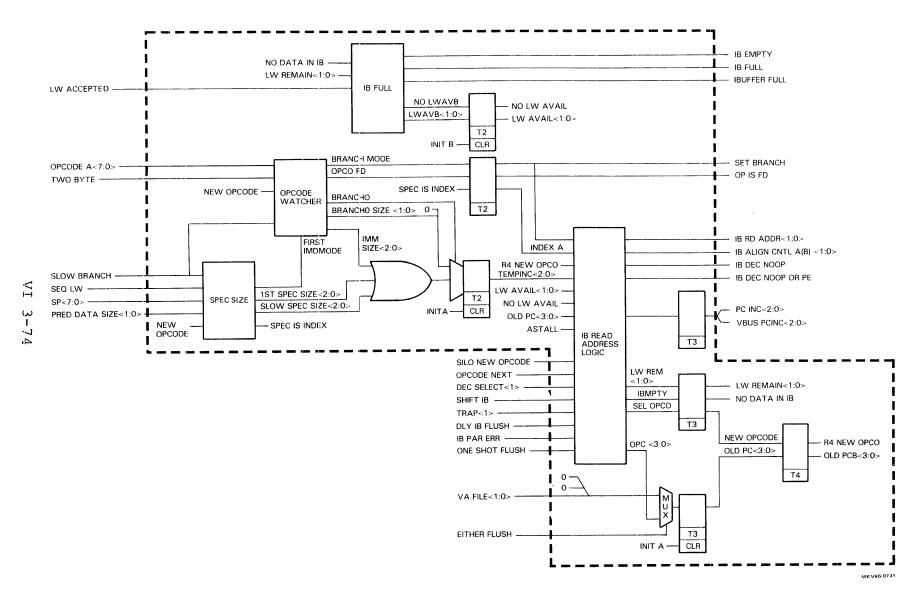

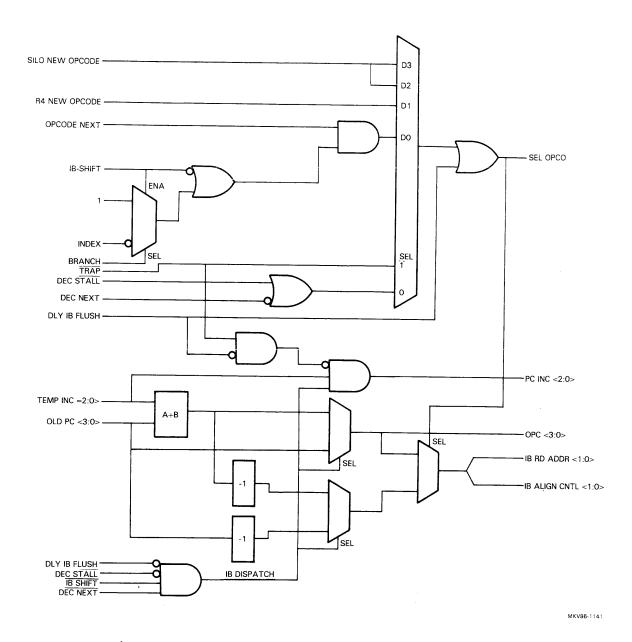

| 3.4.5.1 | IB Manager Operations                            |

| 3.4.5.2 | IB Read Address Logic                            |

| 3.4.5.3 | Opcode Watcher Logic                             |

| 3.4.5.4 | Specifier Size Logic                             |

| 3.4.5.5 | Checking TEMPINC <2:0> Validity 3-81             |

| 3.4.5.6 | Decoder Stall                                    |

| 3.4.5.7 | Modifying the IB Pointer                         |

| 3.4.5.8 | IB Read Address Logic Control Signals 3-85       |

| 3.4.6   | Computing Number of IB Longwords Consumed 3-91   |

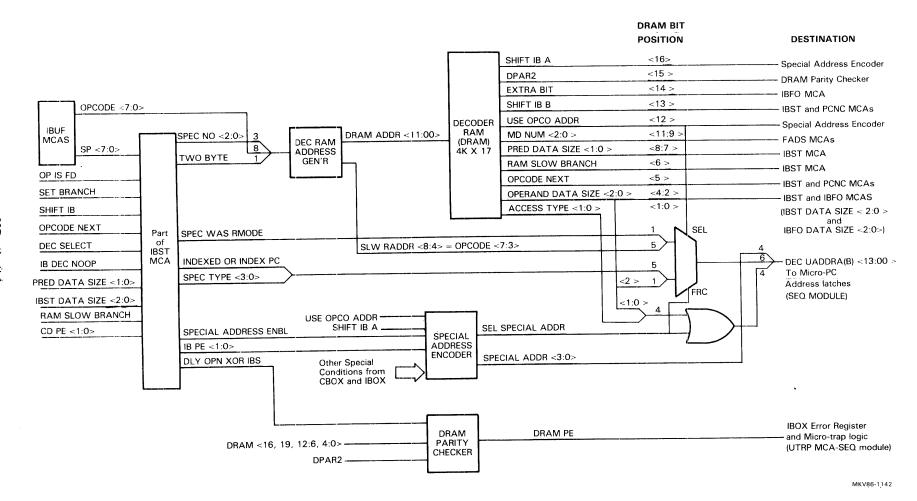

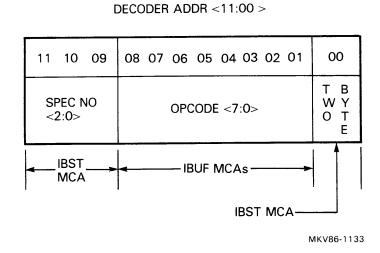

| 3.4.6.1 | Instruction Decoder Operation                    |

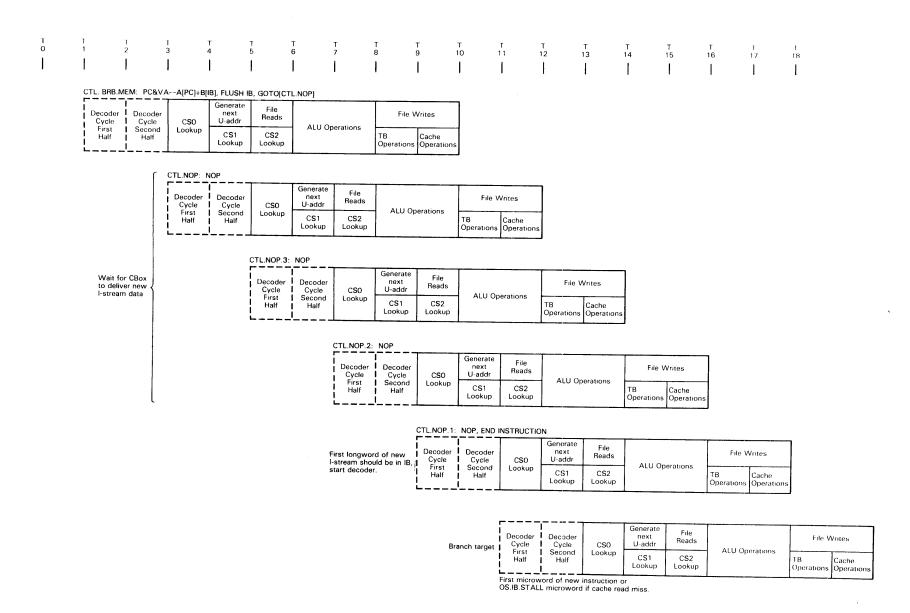

| 3.4.6.2 | Pipeline Timing Considerations 3-93              |

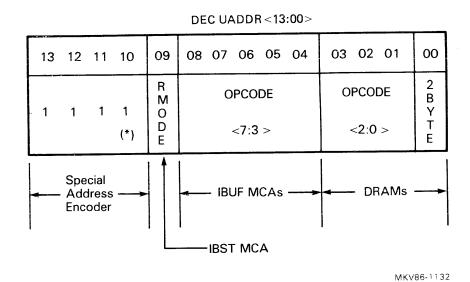

| 3.4.6.3 | Operand Specifier Entry Point Addresses 3-96     |

| 3.4.6.4 | Opcode Entry Point Microaddresses 3-104          |

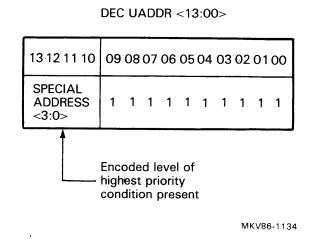

| 3.4.6.5 | Special Microaddresses                           |

| 3.4.0.3 | IBST MCA Signals Related to Instruction Decoding |

| 3.4.6.6 |                                                  |

| 3.4.7   | Decoder RAM (DRAM)                               |

| 3.4.7.1 | Optimized Instructions                           |

| 3.4.7.2 | Simple Move Instructions                         |

| 3.5     | Simple Branch Instructions                       |

|         | MACROBRANCH INSTRUCTIONS                         |

| 3.5.1   | Branch Instruction Basics                        |

| 3.5.2   | Branch Instruction Classes                       |

| 3.5.3   | Unconditional Branches                           |

| 3.5.4   | Short Conditional Branches                       |

| 3.5.5   | Long Conditional Branches                        |

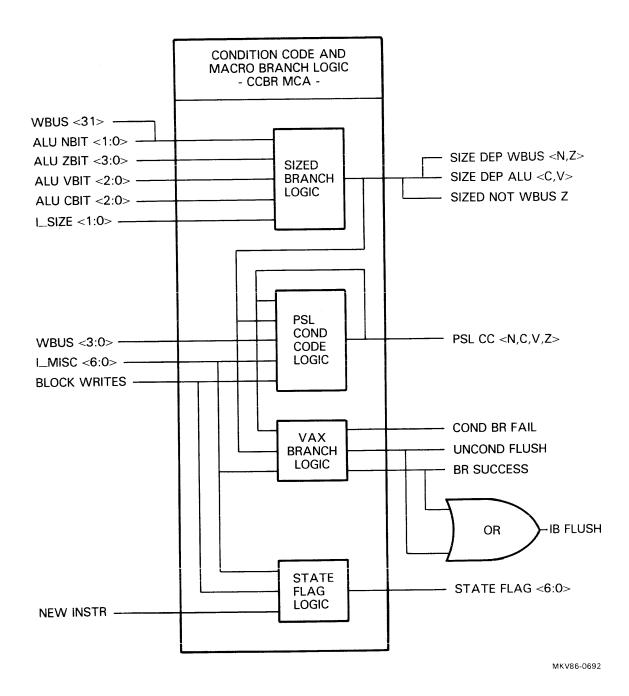

| 3.5.6   | Condition Code and Macro Branch Logic 3-147      |

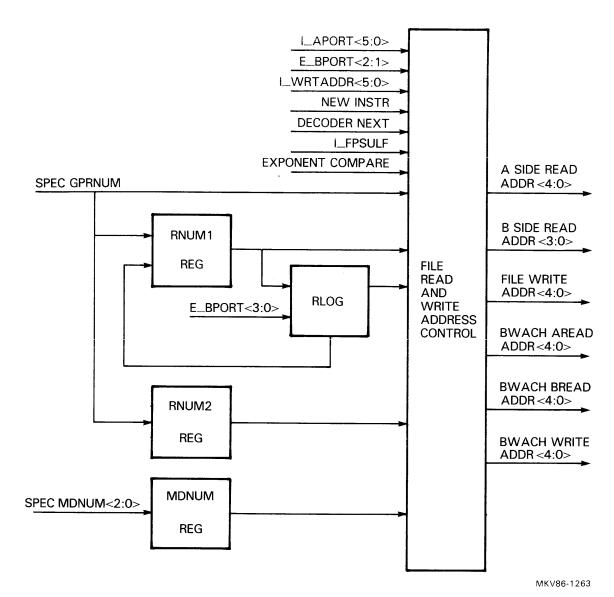

| 3.6.2<br>3.6.3<br>3.7<br>3.7.1<br>3.7.2<br>3.8<br>3.8.1<br>3.8.2<br>3.8.3<br>3.8.4<br>3.8.5 | RLOG Register                                                                                    |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|                                                                                             | FIGURES                                                                                          |

| No.                                                                                         | Title Page                                                                                       |

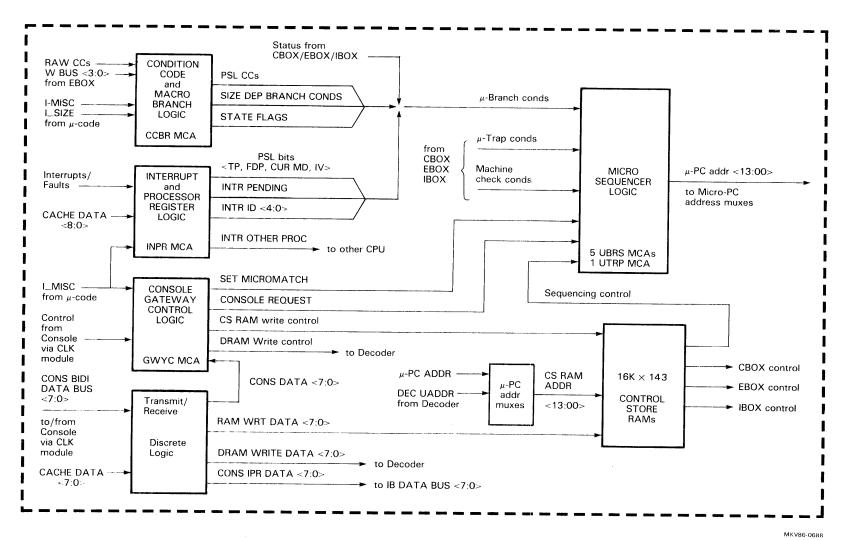

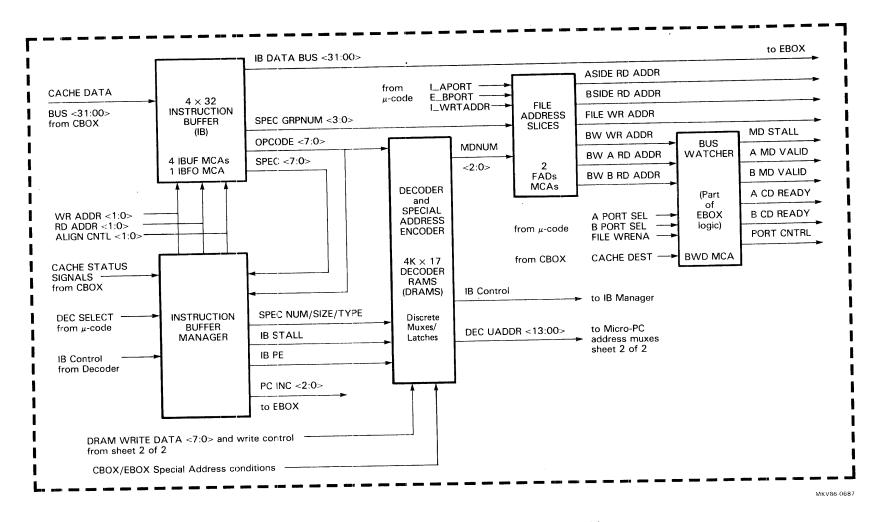

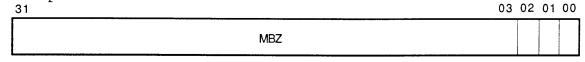

| 1-1<br>1-2                                                                                  | <pre>IBox Block Diagram 1-3 NMI Interrupt Control (NICTRL) Register</pre>                        |

| 1-3                                                                                         | Bit Map                                                                                          |

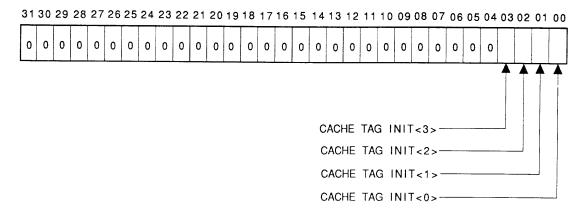

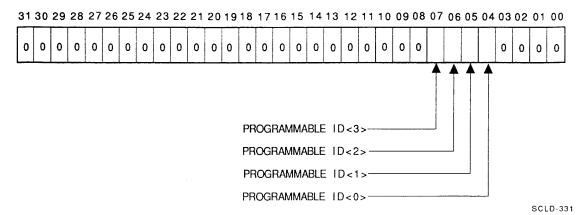

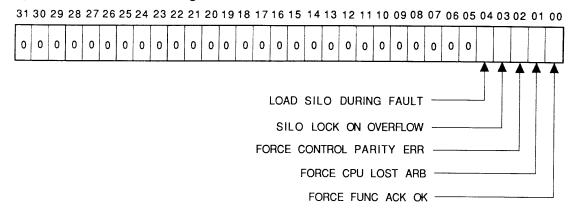

| 1-4                                                                                         | Bit Map                                                                                          |

| 2-1<br>2-2                                                                                  | Microword Bit Format                                                                             |

| 0 0                                                                                         | I APORT Field                                                                                    |

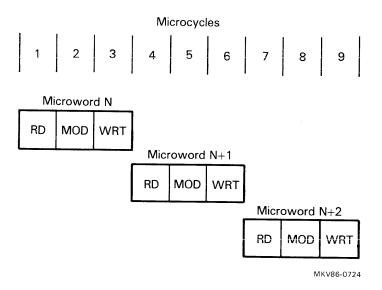

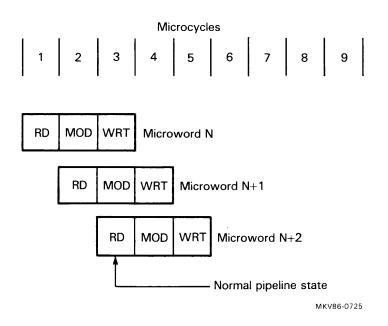

| 2-3<br>2-4                                                                                  | Basic Time State Diagram - Nonpipelined CPU 2-21 Basic Time State Diagram - Pipelined CPU 2-21   |

| 2-5                                                                                         | Basic CPU Timing                                                                                 |

| 2-6                                                                                         | Microcycles/CPU Functions 2-26                                                                   |

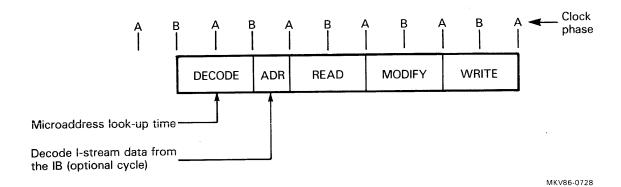

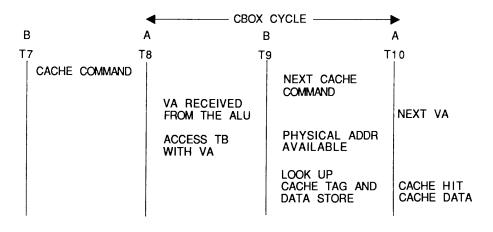

| 2-7                                                                                         | IB Decode Cycle                                                                                  |

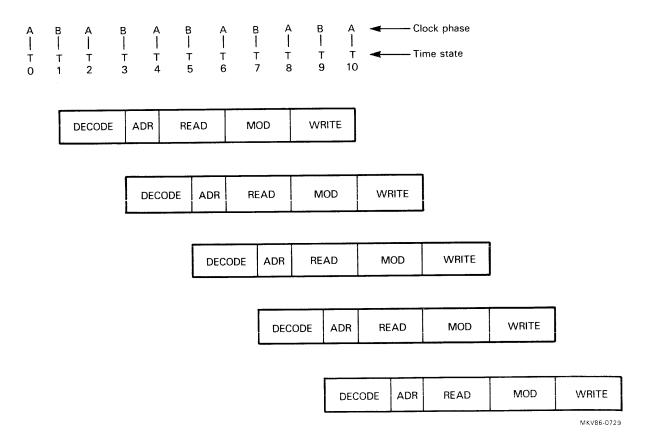

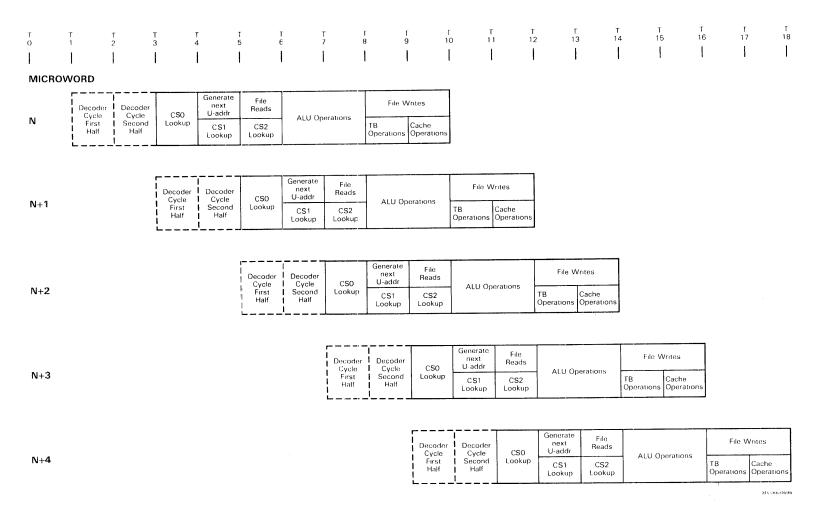

| 2-8                                                                                         | Canonical Time States 2-28                                                                       |

| 2-9                                                                                         | VAX 8800 Pipeline Time State Diagram 2-30                                                        |

| 3-1<br>3-2                                                                                  | Control Store Logic Simplified Block Diagram 3-3 Microaddress Bit Slices for Micromatch Register |

|                                                                                             | Loading                                                                                          |

| 3-3                                                                                         | Control Store RAM Load Path                                                                      |

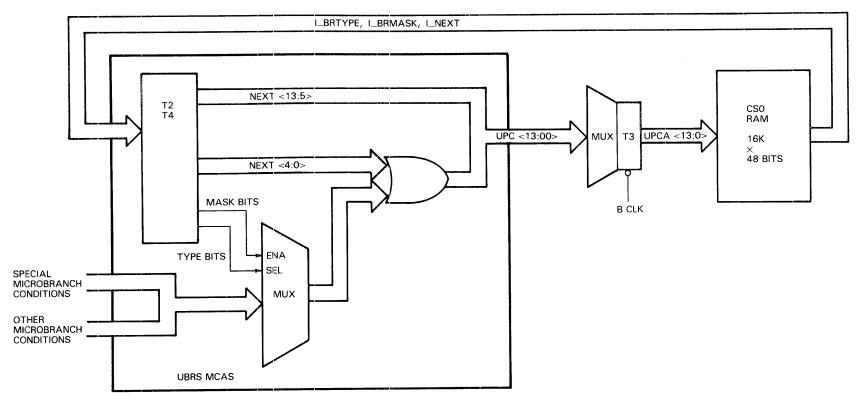

| 3-4                                                                                         | Microsequencer Logic                                                                             |

| 3-5<br>3-6                                                                                  | Normal INEXT Field Addressing                                                                    |

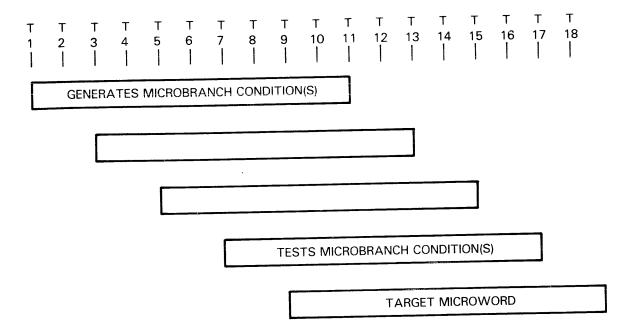

| 3-7                                                                                         | Microbranch Latency                                                                              |

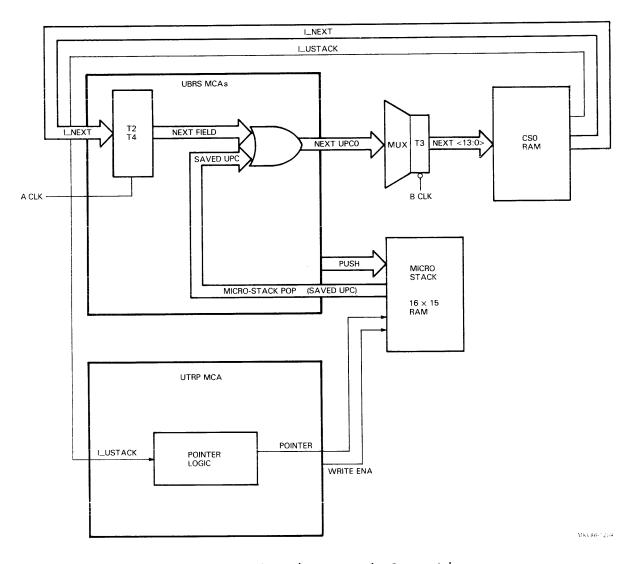

| 3-8                                                                                         | Microstack Operation                                                                             |

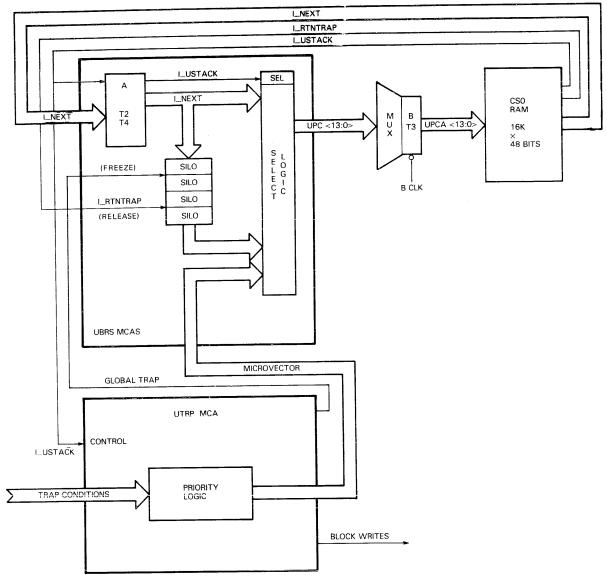

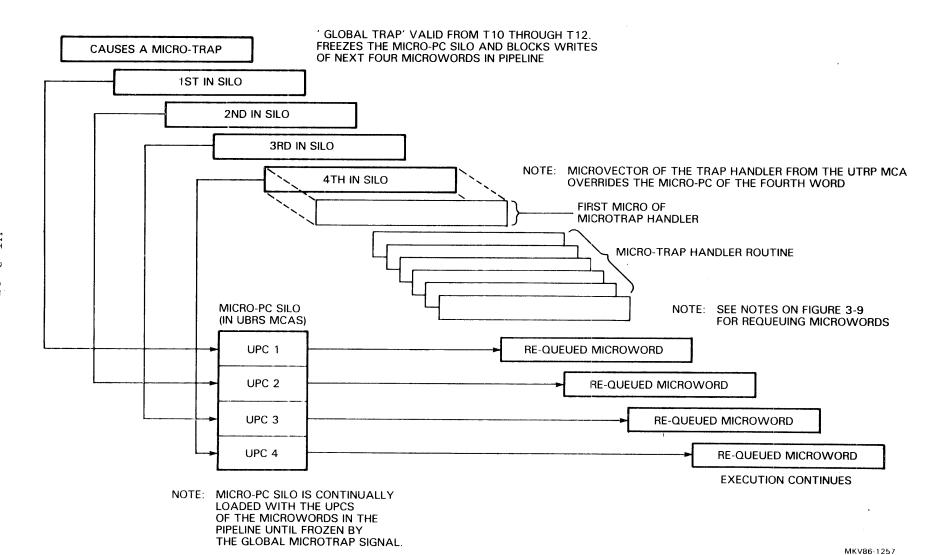

| 3-9                                                                                         | Microtrap Servicing 3-26                                                                         |

| 3-10                                                                                        | Microtrap Latency                                                                                |

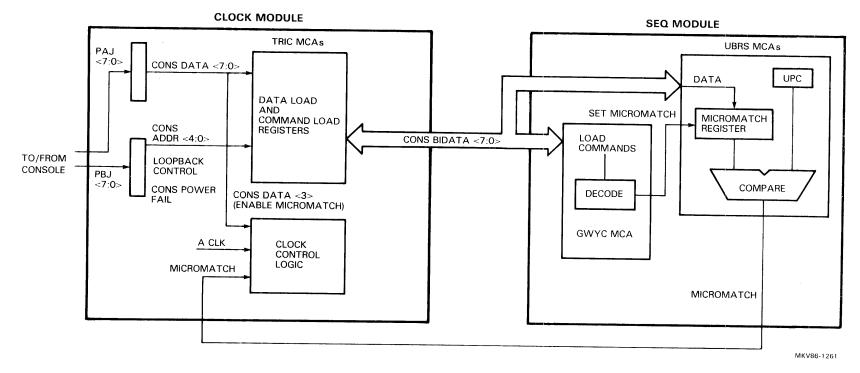

| 3-11                                                                                        | Console Supplied Microaddress                                                                    |

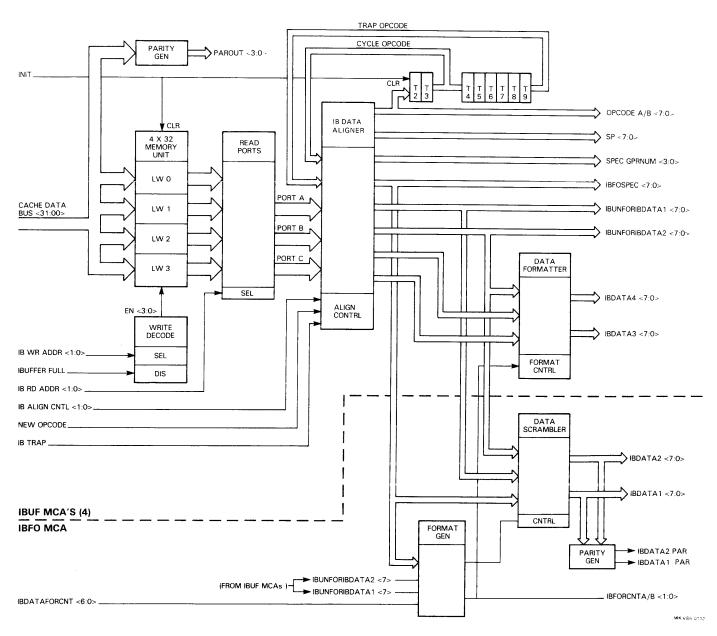

| 3-12                                                                                        | Instruction Buffer Logic                                                                         |

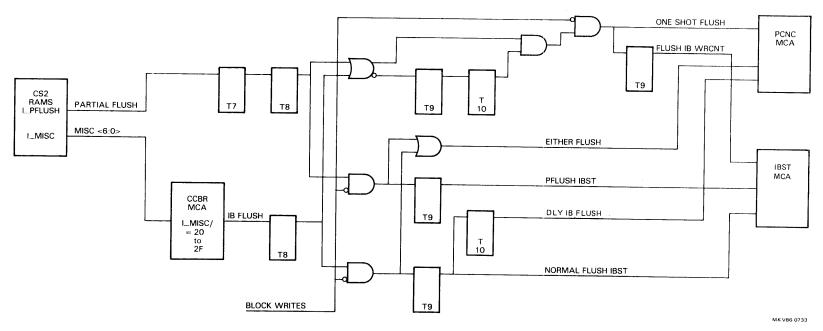

| 3-13                                                                                        | IB Flush Logic                                                                                   |

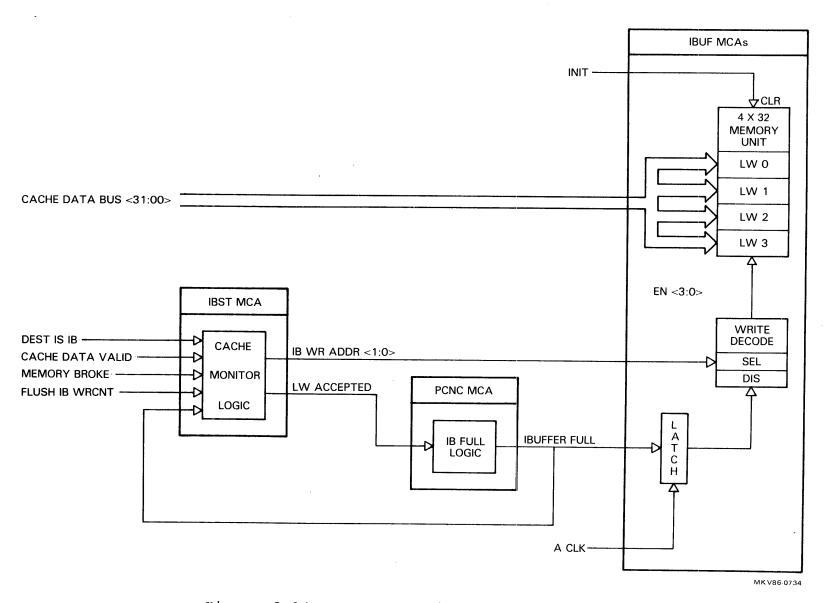

| 3-14                                                                                        | IB Load Logic                                                                                    |

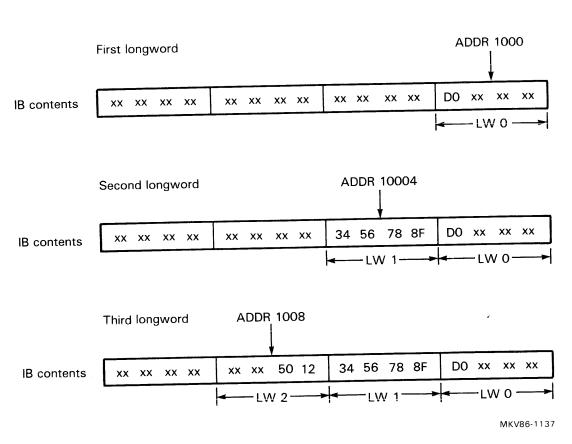

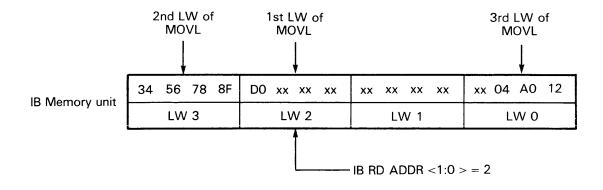

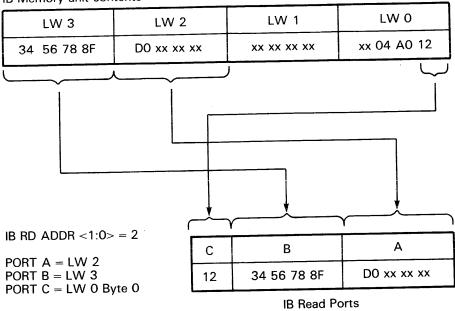

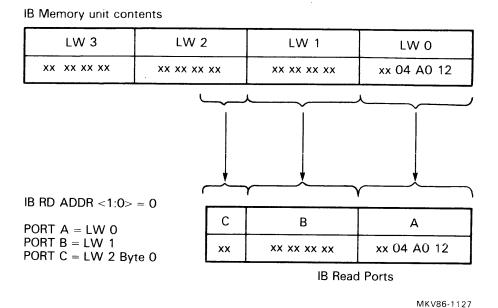

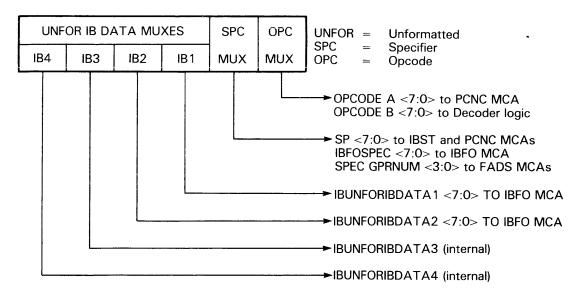

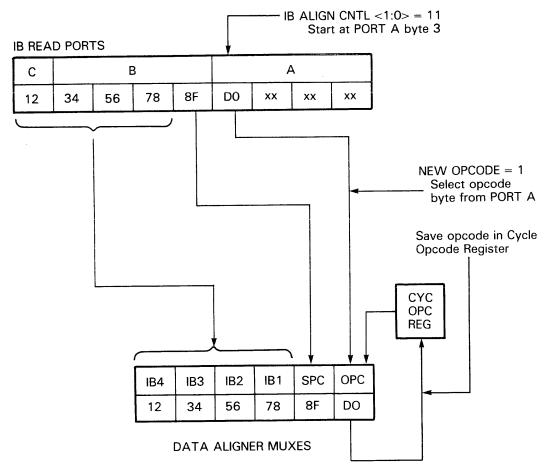

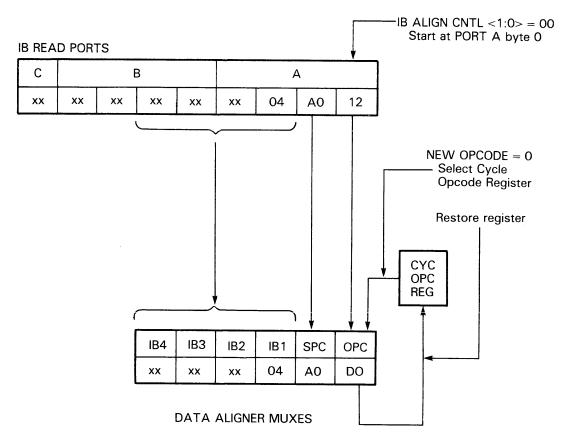

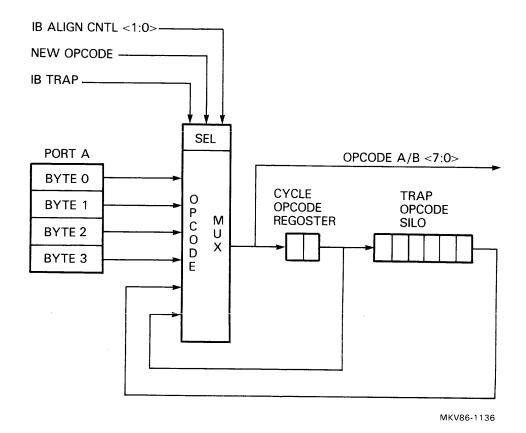

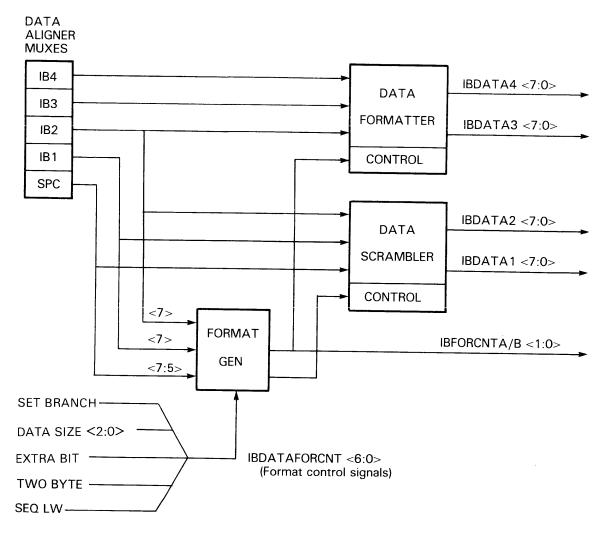

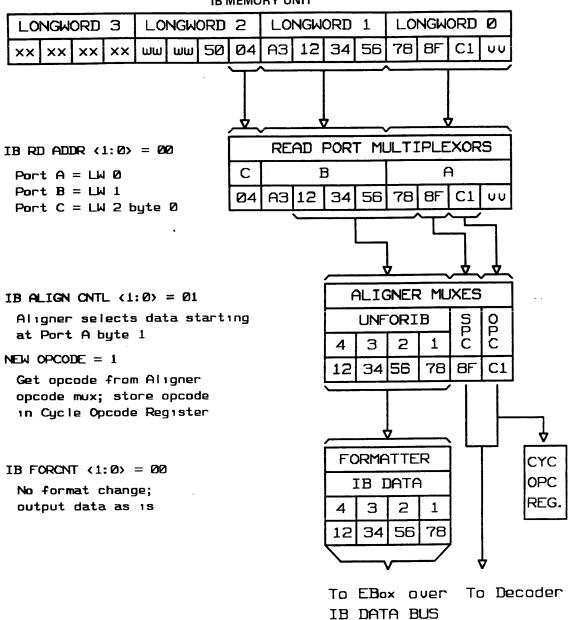

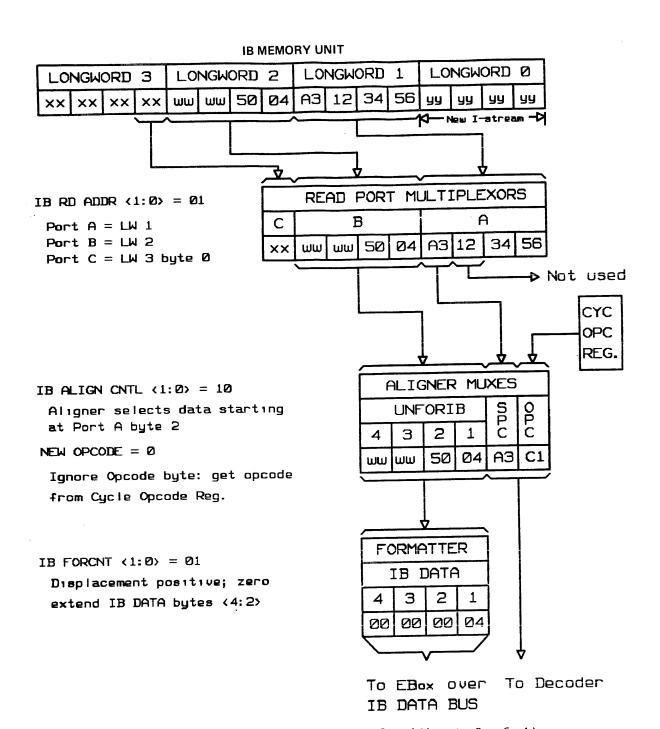

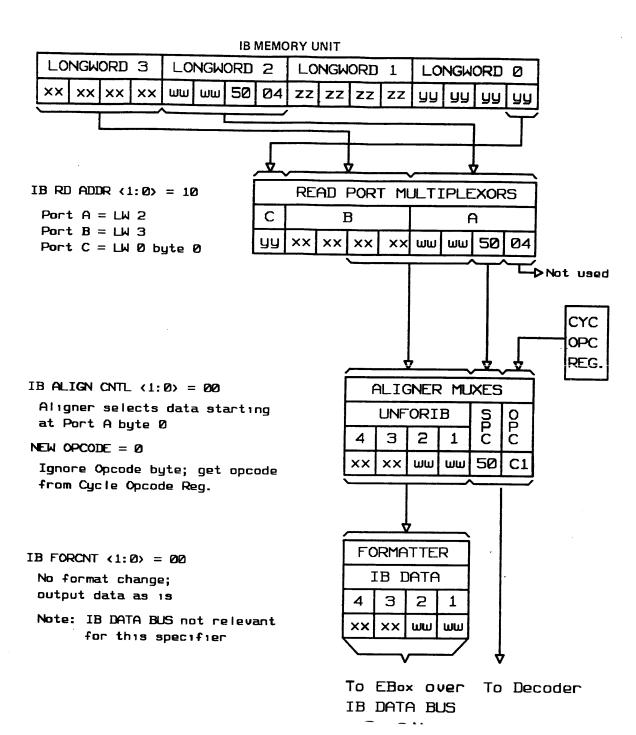

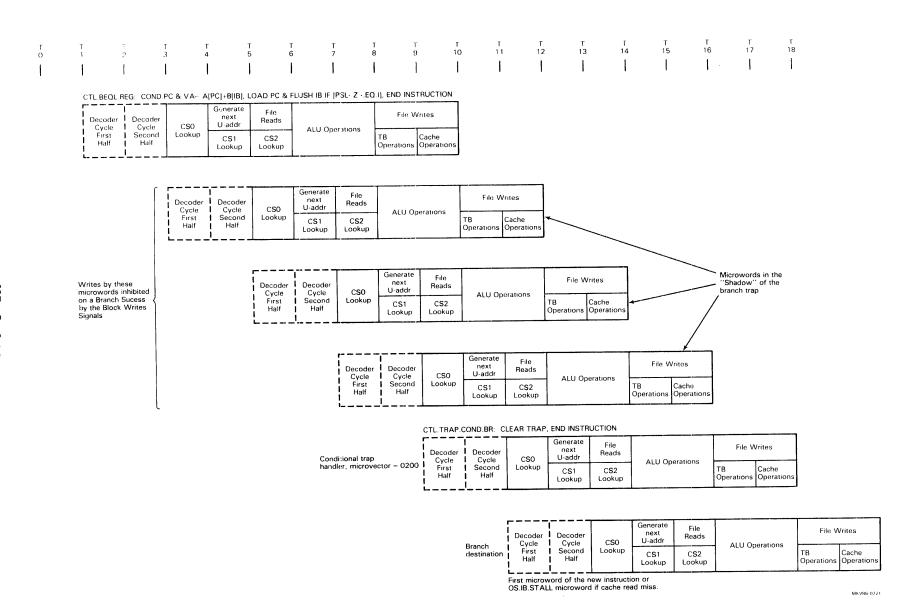

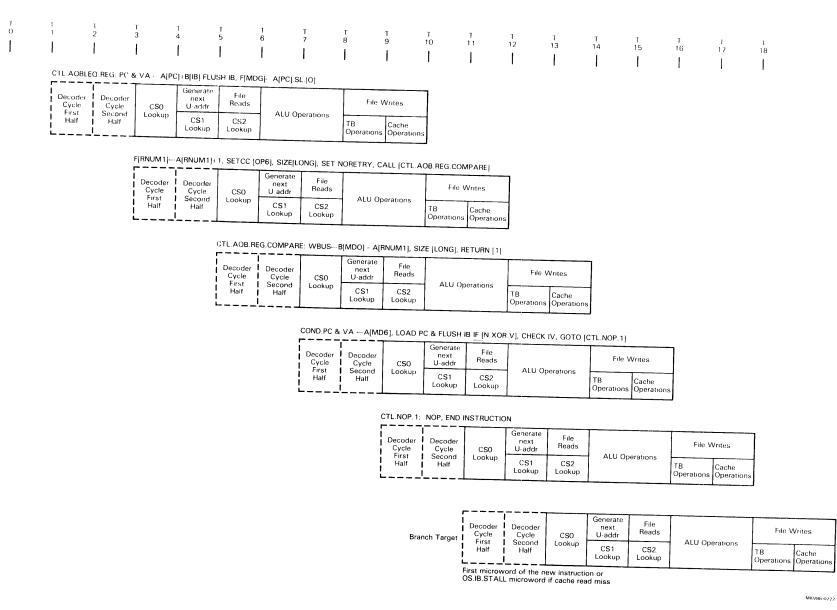

| 3-15 3-16 3-17 3-18 3-19 3-20 3-21 3-22 3-23 3-24 3-25 3-26 3-27 3-28 3-29 3-30 3-31 3-32 3-33 3-34 3-35 3-36 3-37 3-38 3-39 3-40 | I-Stream Data Entering the IB.  IB Memory Unit Contents for MOVL Example  3-47 IB Read Port Example - Part 1 |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|                                                                                                                                   | TABLES                                                                                                       |

| No.                                                                                                                               | Title                                                                                                        |

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5                                                                                                   | Microcode Features                                                                                           |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10                                                               | VAX 8800 Microcode Files                                                                                     |

| 3-1          | Control Store RAM Segment Functionality 3-2        | 2 |

|--------------|----------------------------------------------------|---|

| 3-2          | Next Microaddress Sources 3-5                      | ) |

| 3-3          | IBRTYPE/IBRMASK Microword Field Relationship 3-15  | ) |

| 3-4          | Microbranch Conditions 3-16                        | ) |

| 3 <b>-</b> 5 | Special Microbranch Condition Bit Usage 3-18       |   |

| 3-6          | Microtrap Conditions and Vectors 3-24              |   |

| 3-7          | Machine Check Microtrap Conditions 3-25            |   |

| 3-8          | IBST and PCNC MCA Outputs After an IB Flush 3-37   | ! |

| 3-9          | IB Flush Relative State Changes - IBST and PCNC    |   |

|              | MCAs                                               |   |

| 3-10         | IB Read Address/IB Read Port Source 3-46           |   |

| 3-11         | Data Aligner Control Signals/Data Selection 3-52   |   |

| 3-12         | IB Data Format Control Signals/Functions 3-62      |   |

| 3-13         | IB Format Control Signals/Specifier Data Type 3-63 |   |

| 3-14         | IB Data Formatter and Data Scrambler Output 3-67   |   |

| 3-15         | Floating Point Short Literal Formats 3-68          |   |

| 3-16         | Specifier Size Logic Control Signals 3-79          |   |

| 3-17         | Slow Spec Size <2:0> Values 3-80                   |   |

| 3-18         | IB Pointer Source                                  | 4 |

| 3-19         | Operand Specifier Entry Address Bit                |   |

|              | Descriptions                                       |   |

| 3-20         | Operand Data Size/Access Type Correlation 3-98     | 3 |

| 3-21         | Operand Specifier Entry Address Symbolic           |   |

|              | Labels                                             | J |

| 3-22         | Opcode Entry Address Bit Descriptions 3-103        | ) |

| 3-23         | Special Microaddress Conditions 3-11               | 4 |

| 3-24         | Special Conditions Serviced During IB Decode       |   |

|              | Cycles                                             | 6 |

| 3-25         | Decoder RAM Output Signal Descriptions 3-124       | 4 |

| 3-26         | Execute Code for a BRB Instruction 3-133           | 2 |

| 3-27         | Microword CTL.BRB.MEM Event Timing 3-13            | 4 |

| 3-28         | IMISC Field Settings for Macrobranch Recipes 3-130 | б |

| 3-29         | IMISC Field Settings for PSL Condition Code        | _ |

|              | Recipes                                            | 3 |

| 3-30         | Execute Code for a AOBLEQ Instruction 3-14         | 6 |

| 3-31         | IMISC Field Settings for State Flag Control 3-14   | 9 |

| 3-32         | Hardware Interrupt Priority Levels 3-15            | 4 |

| 3-33         | Interrupt ID Codes/IPLs                            | 7 |

|              |                                                    |   |

|              | EXAMPLE                                            |   |

| No.          | Title                                              | е |

| 2-1          | Sample Field Value Assignments - I APORT 2-1       | 2 |

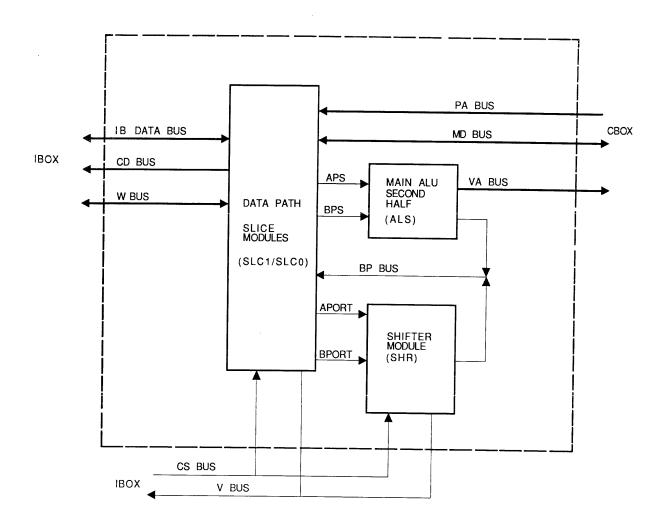

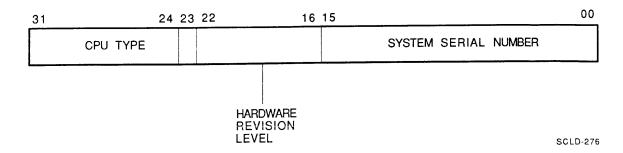

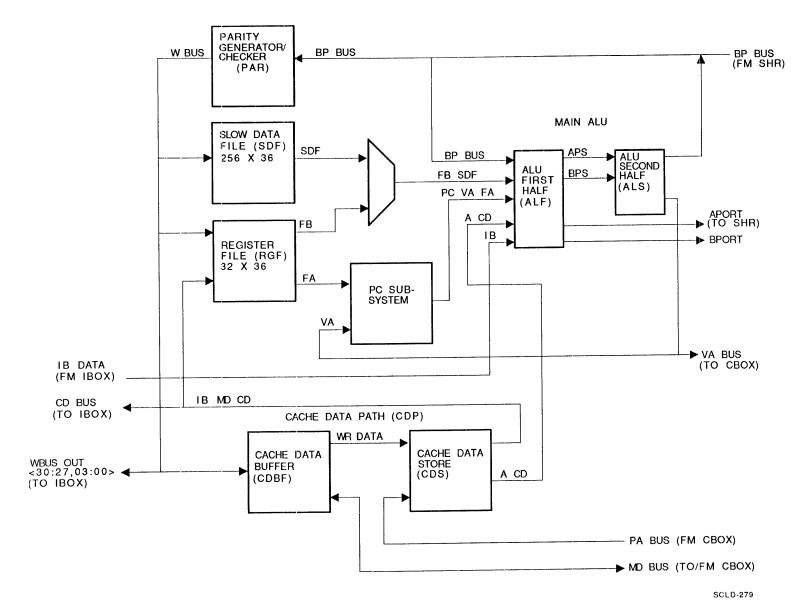

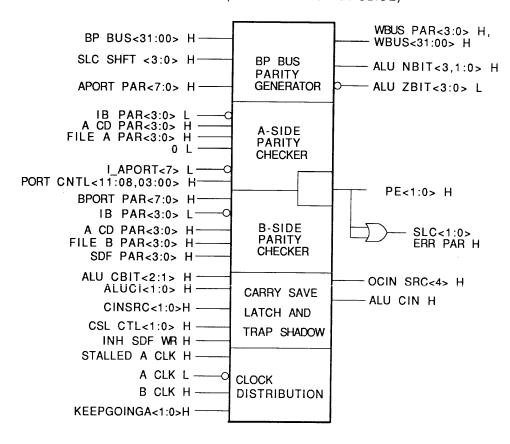

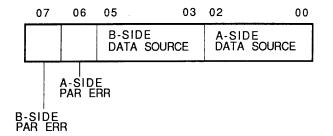

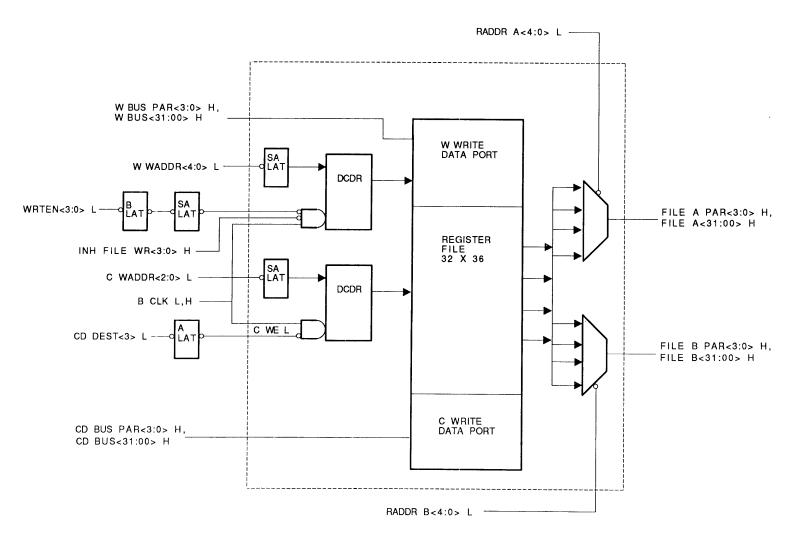

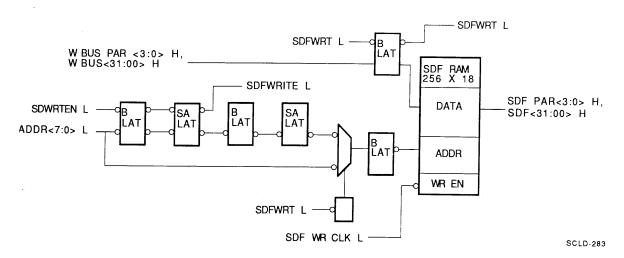

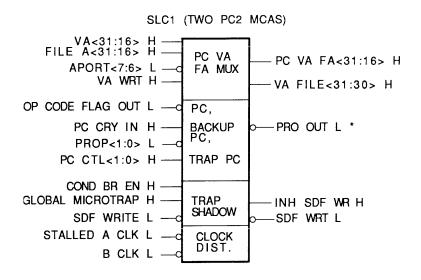

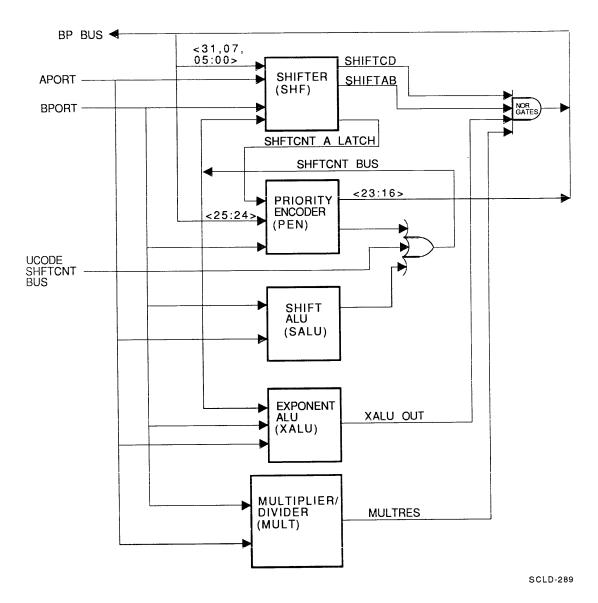

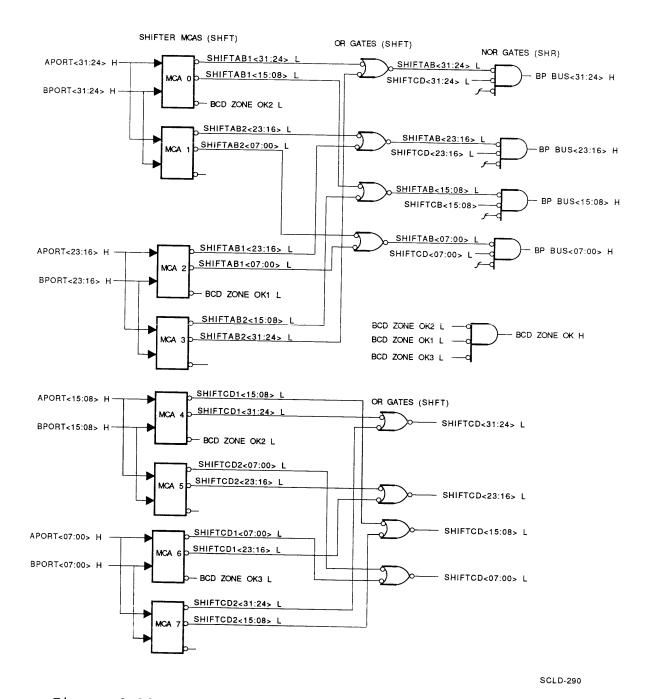

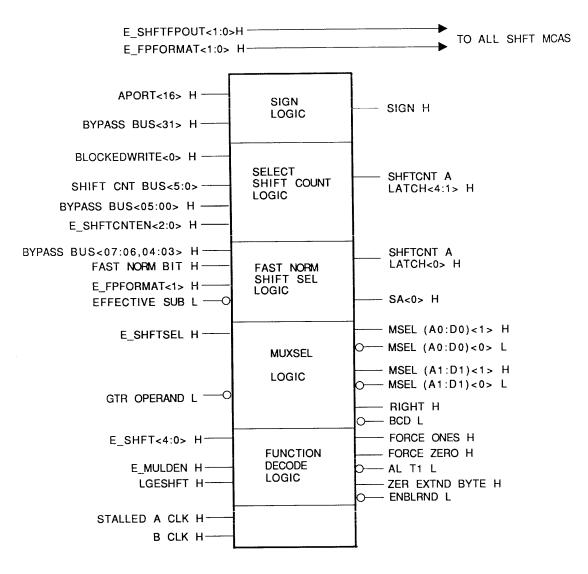

#### SECTION 7 EXECUTION BOX LOGIC (EBOX) CHAPTER 1 INTRODUCTION 1.1 EBox Organization. . . . . . . . . . . . . . . . . . 1-2 1.1.1 1.1.2 1.1.2.1 1.1.2.2 Cache Data Path (CDP) and Bus 1.2 1.2.1 Parity Generator/Checker (PAR) . . . . . . . 1-5 1.2.2 Register File (RGF). . . . . . . . . . . . . . . 1-6 1.2.3 Slow Data File (SDF) . . . . . . . . . . . . . 1-6 Program Counter (PC) Subsystem . . . . . . . . 1-7 1.2.4 1.2.5 Cache Data Path (CDP). . . . . . . . . . . . . . . . 1-7 1.2.6 Main Arithmetic Logic Unit (Main ALU). . . . . 1-8 1.2.7 1.3 SHIFTER MODULE (SHR) FUNCTIONS . . . . . . . . 1-9 1.3.1 Shifter (SHF). . . . . . . . . . . . . . . . . . 1-9 1.3.1.1 1.3.1.2 1.3.1.3 1-10 1.3.2 1-10 1.3.2.1 1-10 1.3.2.2 1-11 1.3.2.3 1-11 Multiplier/Divider (MULT)....... 1.3.3 1-11 1.4 1-12 1.4.1 POLR, PlLR, and SLR Internal Bit Formats . . . 1 - 131.4.2 1-13 Machine Check Status Register (MCSTS). . . . 1.4.2.1 1-13 1.4.2.2 System Identification (SID) Register . . . . 1-14 1.4.2.3 Revision Registers (REVRl and REVR2) . . . 1-15 1.4.2.4 EBox Parity Error Register (EBER). . . . . . 1-17 CHAPTER 2 FUNCTIONAL DESCRIPTION 2.1 SLICE MODULE (SLC1/SLC0) DESCRIPTION . . . . . . 2-1 2.2 2.2.1 Parity Generator/Checker (PAR) . . . . . . . . 2-1 Parity Generator . . . . . . . . . . . . . . . . 2-8 2.2.1.1 2.2.1.2 Parity Checker . . . . . . . . . . . . . . . . . . 2-8 2.2.1.3 EBox Parity Error Register (EBER). . . . . . 2.2.1.4 Carry Save Logic . . . . . . . . . . . . . . . . 2-12 Register File (RGF)........ 2.2.2 2 - 142.2.2.1 2 - 142.2.2.2 Memory Data (MD) Registers . . . . . . . . . . . . 2-16 2.2.2.3 2-16 2.2.3 2-18 2.2.3.1 2 - 192.2.3.2 2 - 192.2.3.3 2 - 19

| 2.2.4.1 2.2.4.2 2.2.4.3 2.2.4.4 2.2.5 2.2.5.1 2.2.5.2 2.2.6 2.2.6.1 2.2.6.2 2.3 2.3.1 2.3.1.1 2.3.1.2 2.3.1.3 2.3.1.4 2.3.1.5 2.3.2 2.3.2.1 2.3.2.2 2.3.2.3 2.3.3 2.3.3.1 2.3.3.1 2.3.3.1 2.3.3.2 2.3.3.3 2.3.3.1 | PC VA FA Multiplexer                                                    | 2234113331114411555588802088665<br>77866655588802088665 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|

|                                                                                                                                                                                                                   | FIGURES                                                                 |                                                         |

| No.                                                                                                                                                                                                               | Title                                                                   | је                                                      |

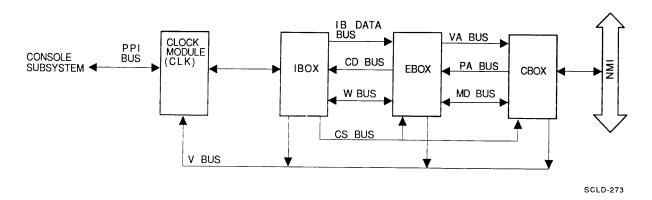

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5                                                                                                                                                                                   | VAX 8800 CPU Kernel Block Diagram 1 Execution Unit (EBox) Block Diagram | -3<br>13<br>14<br>15                                    |

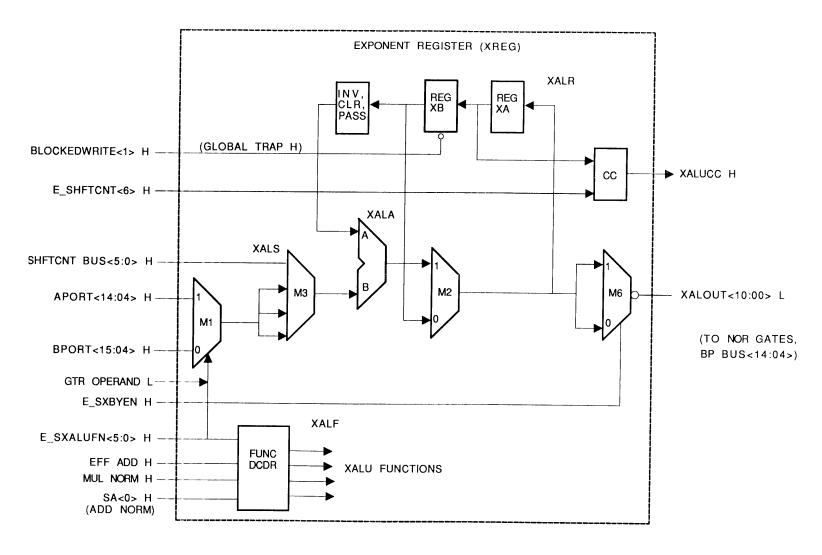

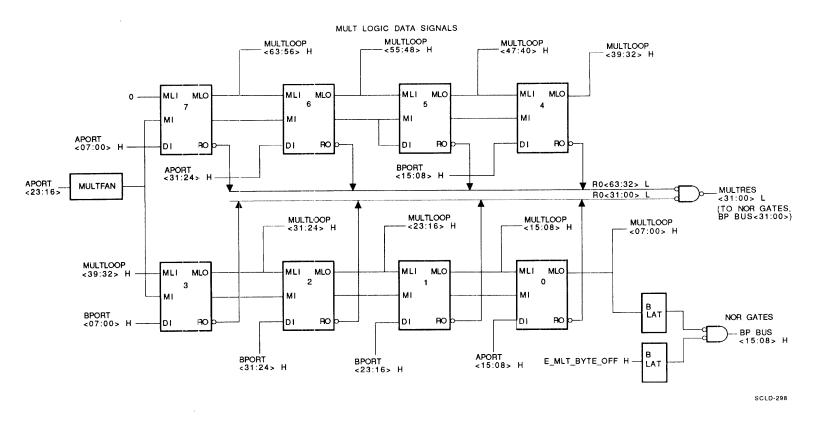

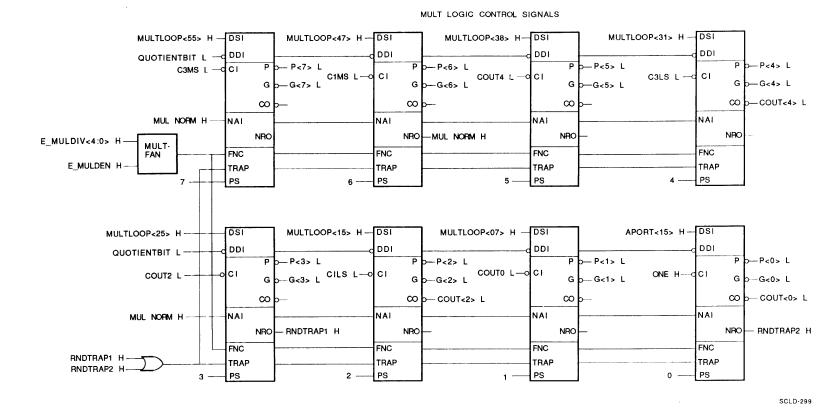

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10                                                                                                                                               | Slice Module (SLC1/SLC0) Block Diagram                                  | -3<br>11<br>15<br>19<br>23<br>32<br>43                  |

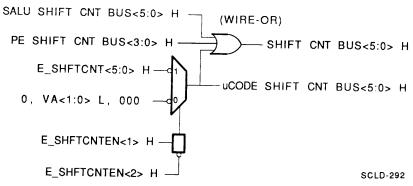

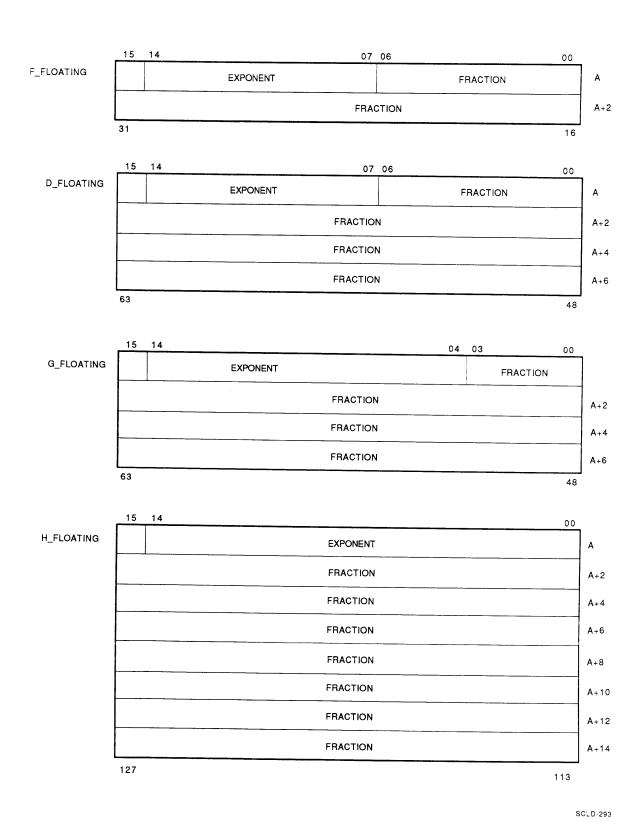

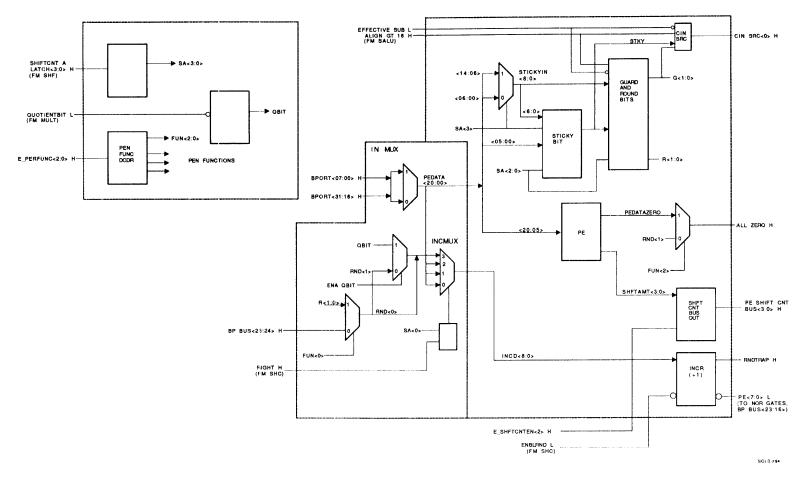

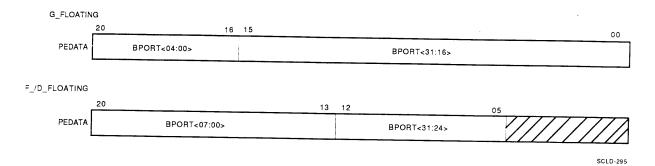

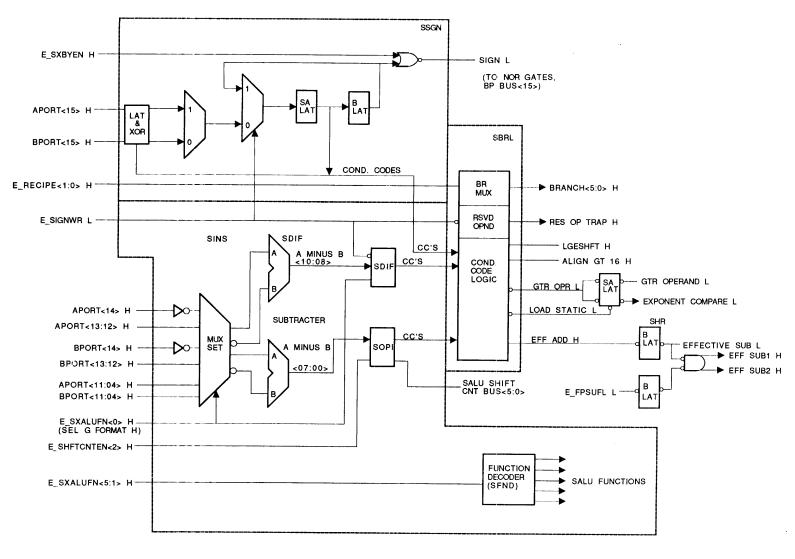

| 2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>2-16<br>2-17<br>2-18 | Shift Control MCA (SHC) Block Diagram. 2-Shift Count Bus Signal and Gating Block Diagram. 2-VAX-11 Floating-Point Formats. 2-VAX-11 | 55<br>61<br>64<br>65<br>73 |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                              | TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| No.                                                          | Title Pag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | је                         |

| 1-1<br>1-2<br>1-3                                            | Privileged IPRs Maintained by the EBox 1-1<br>POLR, PlLR, and SLR Internal Formats 1-1<br>Machine Check Status Register (MCSTS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

| 1-4                                                          | Bit Descriptions 1-1 System Identification (SID) Register Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 4                        |

| 1-5                                                          | Revision Register 1 (REVR1) Bit Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                          |

| 1-6                                                          | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| 2-1                                                          | Parity Generator/Checker (PAR) Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ′                          |

| 2-2<br>2-3<br>2-4<br>2-5                                     | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0<br>0                     |

| 2-6                                                          | E_SHFT<4:0> Control of the EBox Parity Error Register (EBER)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                          |

| 2-7<br>2-8<br>2-9<br>2-10                                    | Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6<br>7                     |

| 2-11                                                         | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                          |

| 2-12                                                         | PC Multiplexer Input Selection 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| 2-13<br>2-14<br>2-15<br>2-16<br>2-17                         | Select Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4<br>8<br>0<br>5           |

| 2-18<br>2-19<br>2-20                                         | ALU Second Half (ALS) Signal Descriptions. 2-48 A-Side Select (ASEL) Input Control Signals . 2-49 B-Side Select (BSEL) Input Control Signals . 2-49 Keepgoing/Stall Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9<br>9                     |

| 2-21                                                         | EALU(5:0) Field Control of the Main ALU. 2-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| 2-22                                                            | Shift Count Bus Signals and Source ESHFT<4:0> Field Selection of Shifter | 2-55                            |

|-----------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------|

| 2-23                                                            | (SHF) MCA Logic Functions                                                | 2-56                            |

| 2-24                                                            | ESHFTSEL Selection of a Result Output to the BP Bus                      | 2-57                            |

| 2-25                                                            | EFPFORMAT(1:0) Field Control of Decimal                                  |                                 |

|                                                                 | all the bala conversion is a second second                               | 2-59                            |

| 2-26                                                            | EPEFUNC Field Selection of PEN Functions                                 | 2-65                            |

| 2-27                                                            | Priority Encoder (PE) Results Passed                                     |                                 |

| ,                                                               | to the Shift Count Bus                                                   | 2-67                            |

| 2-28                                                            | Increment Multiplexer Data (INCD) Selection                              |                                 |

| 2 20                                                            | to the Incrementer (INCR)                                                | 2-68                            |

| 2-29                                                            | Sticky Bit Logic Input and Test Selection                                | 2-68                            |

| 2-29<br>2-30                                                    | G<1:0> Guard Bit Input Selection                                         | 2-69                            |

|                                                                 | Round Bit R<1:0> Input Selection                                         | 2-69                            |

| 2-31                                                            | SALU and XALU Control Signals                                            |                                 |

| 2-32                                                            | from the Microcode                                                       | 2-71                            |

|                                                                 | Trom the preceded.                                                       | 2-72                            |

| 2-33                                                            | ESYMPOLIN LIGIT CONCLOS OF CHA CHIEF LINES                               | 2-74                            |

| 2-34                                                            | KESHILLING DIGHT OF CHO LEGGETON                                         |                                 |

| 2-35                                                            | SALU Selection of the APORT and BPORT Inputs                             | 2-74                            |

| 2-36                                                            | A-Latched Condition Code Inputs to the Branch                            |                                 |

|                                                                 | MULTIPLEMEN                                                              | 2-76                            |

| 2-37                                                            | Microbranch Condition Code Description                                   | 2-77                            |

| 2-38                                                            | ESXALUFN<5:3) Control of the General XALU                                |                                 |

| 2 30                                                            | Functions                                                                | 2-80                            |

| 2.0                                                             | XALU Functions with E_SXALUFN<5:3> Equal                                 |                                 |

| 2-39                                                            | to 000                                                                   | 2-81                            |

| 0 40                                                            | XALU Functions with ESXALUFN<5:3> Not Equal                              |                                 |

| 2-40                                                            |                                                                          | 2-81                            |

|                                                                 | to 000                                                                   | 2-82                            |

| 2-41                                                            | XALU Condition Code (XALUCC) Tests                                       | 2-83                            |

| 2-42                                                            | Ml Inputs Passed to M3                                                   |                                 |

| 2-43                                                            | M3 Inputs Passed to the Adder B-side                                     | 2-84                            |

| 2-44                                                            | M2 Outputs to M6 or the XREG                                             | 2-85                            |

| 2-45                                                            | M2 Data Passed to the BP Bus by M6                                       | 2-85                            |

| 2-46                                                            | Multiplier/Divider (MULT) Control Signals                                |                                 |

| 2-40                                                            | from the Microcode                                                       | 2-90                            |

| ^ 4 <b>7</b>                                                    | E MULDIV Field Control of the MULT Functions                             | 2-91                            |

| 2-47                                                            | MULT Logic Signal Port Function Description                              |                                 |

| 2-48                                                            | MULT Logic Signal Port Function Description                              | <b>L</b> 9 <b>3</b>             |

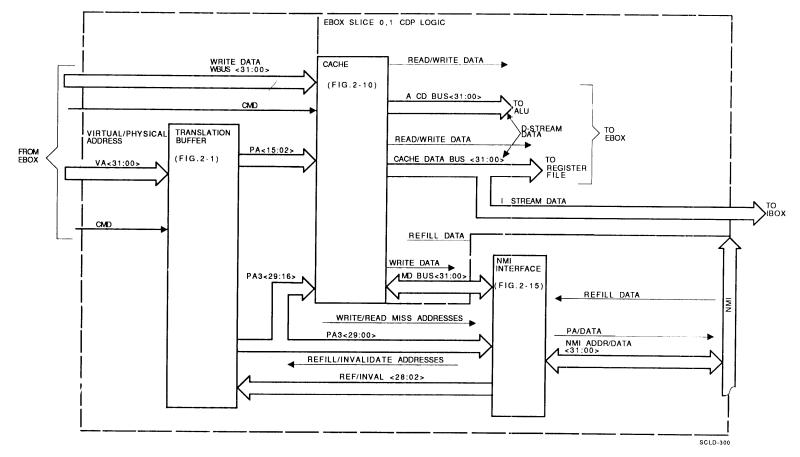

| SECTION 8                                                       | CACHE BOX LOGIC (CBOX)                                                   |                                 |

| CHAPTER 1                                                       | INTRODUCTION                                                             |                                 |

| 1.1<br>1.2<br>1.2.1<br>1.2.1.1<br>1.2.1.2<br>1.2.1.3<br>1.2.1.4 | CACHE BOX SYSTEM DESCRIPTION                                             | 1-5<br>1-6<br>1-7<br>1-8<br>1-8 |

| 1.2.1.5<br>1.2.1.6<br>1.2.1.7<br>1.2.2                                                                                                                                                                            | TB Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 2                                                                                                                                                                                                         | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

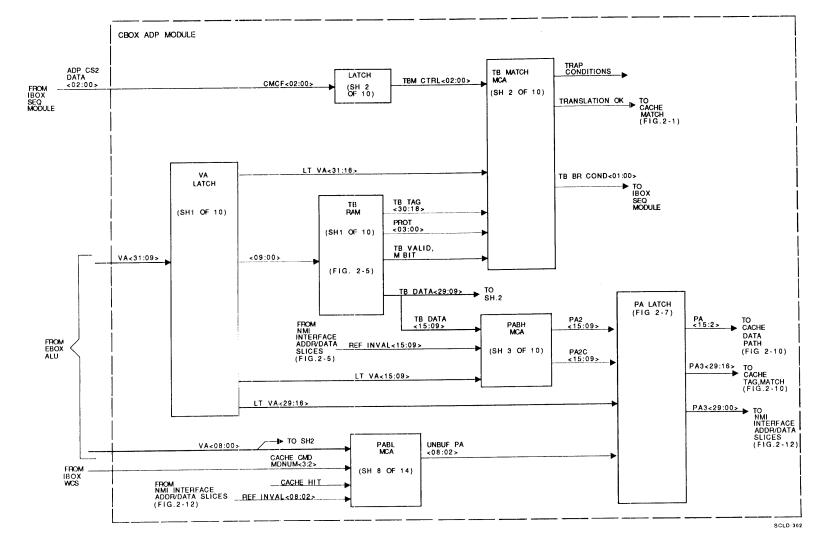

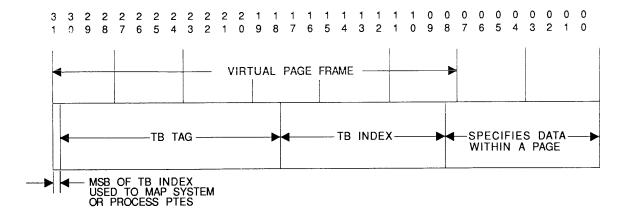

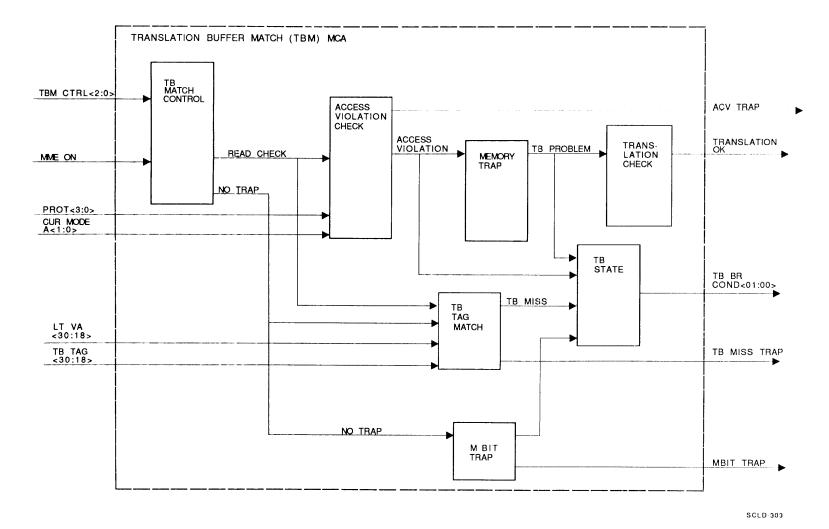

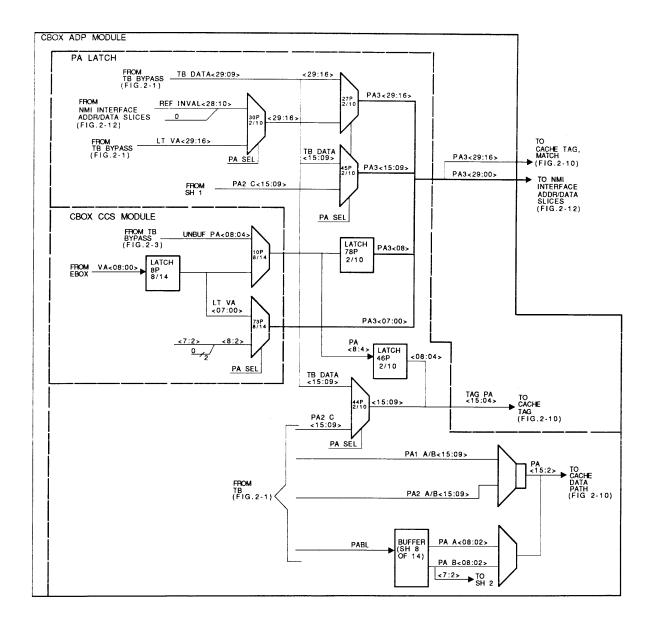

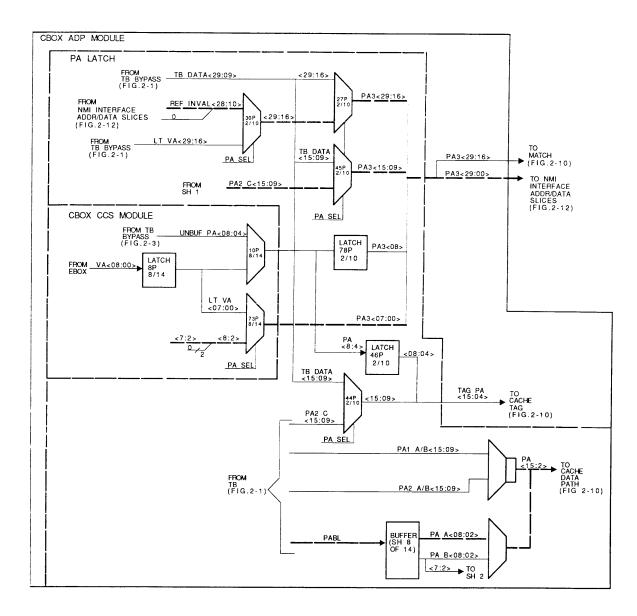

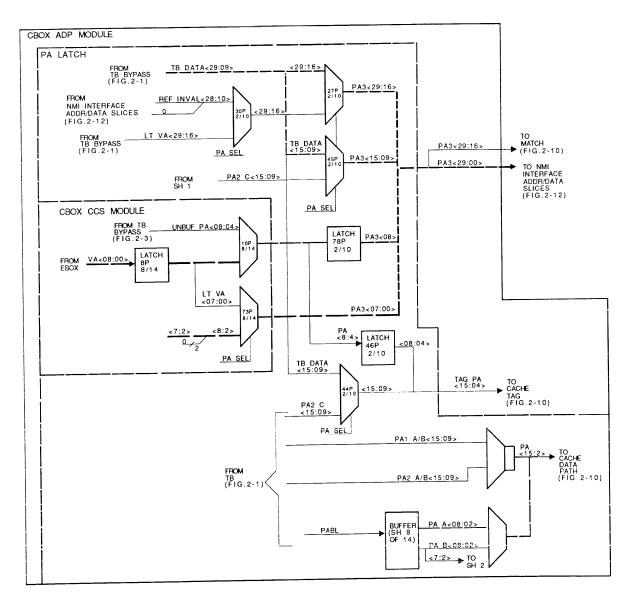

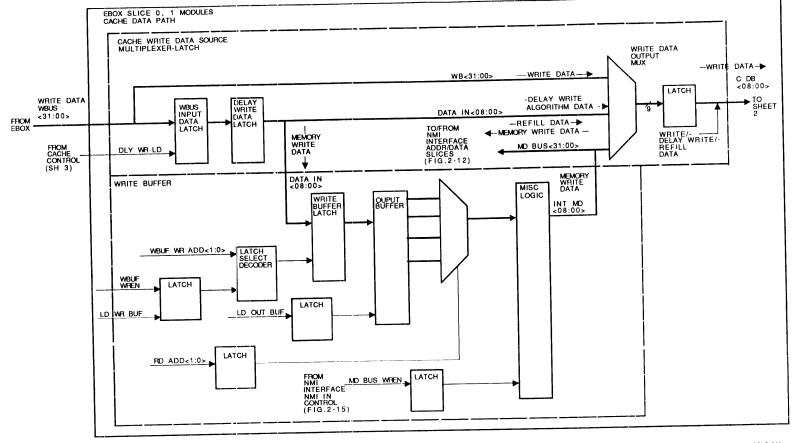

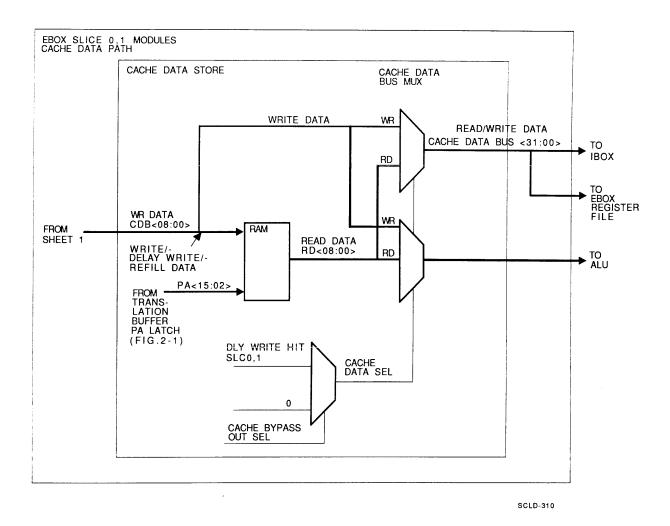

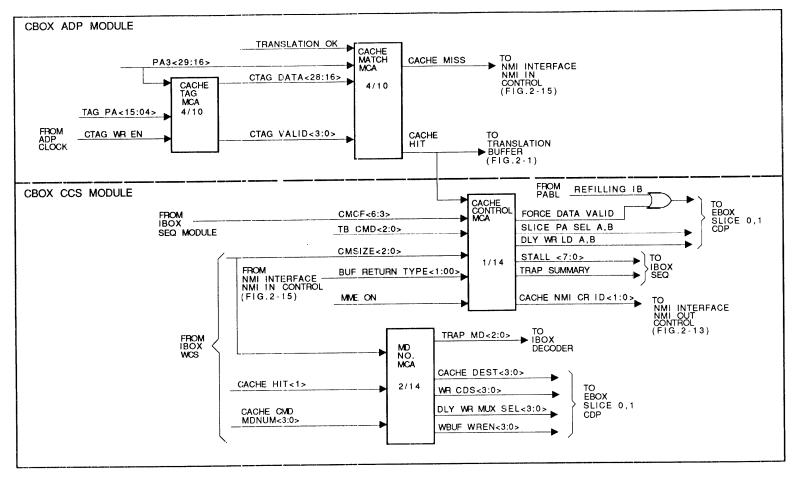

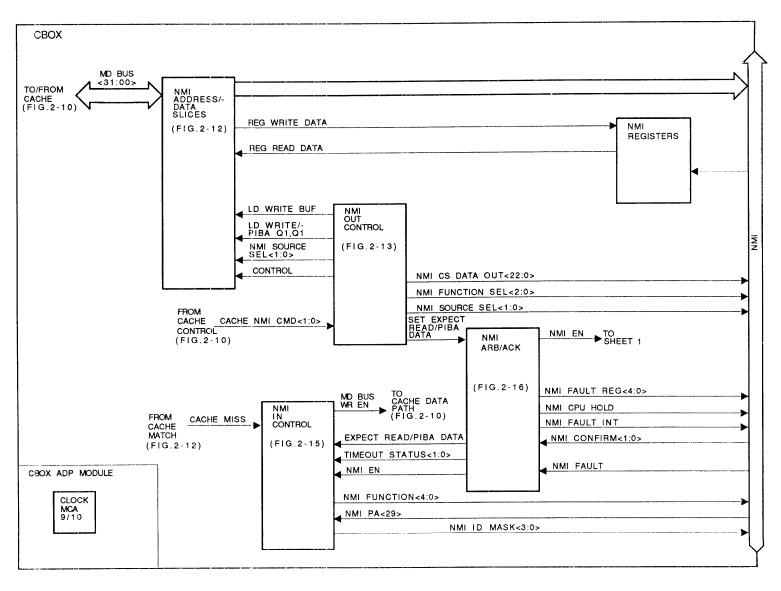

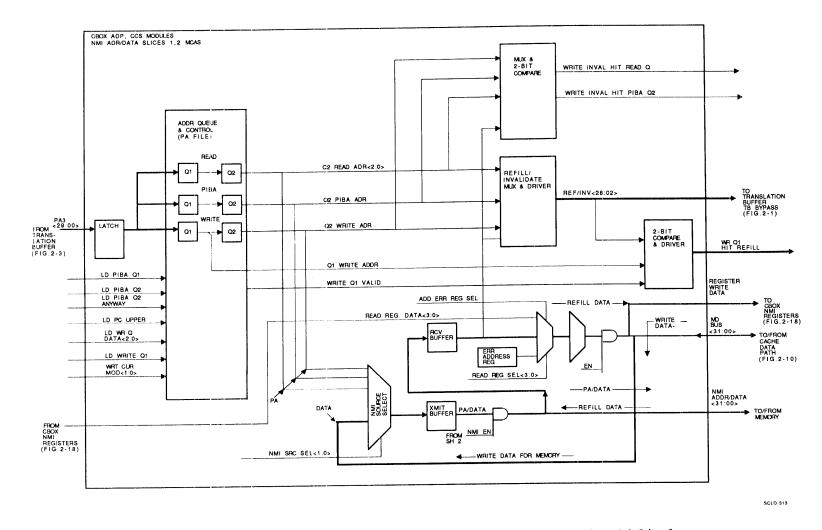

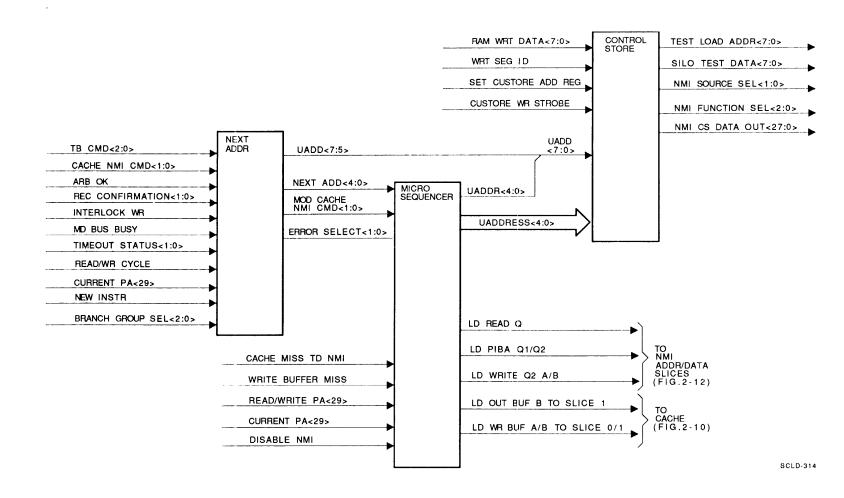

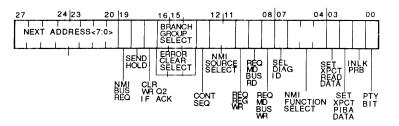

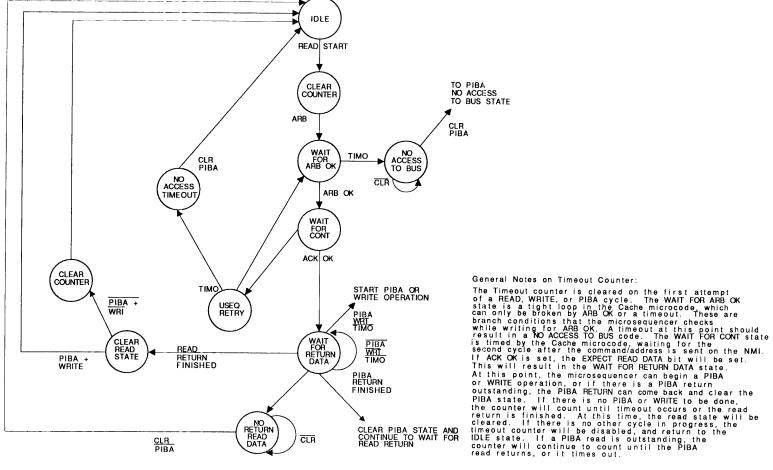

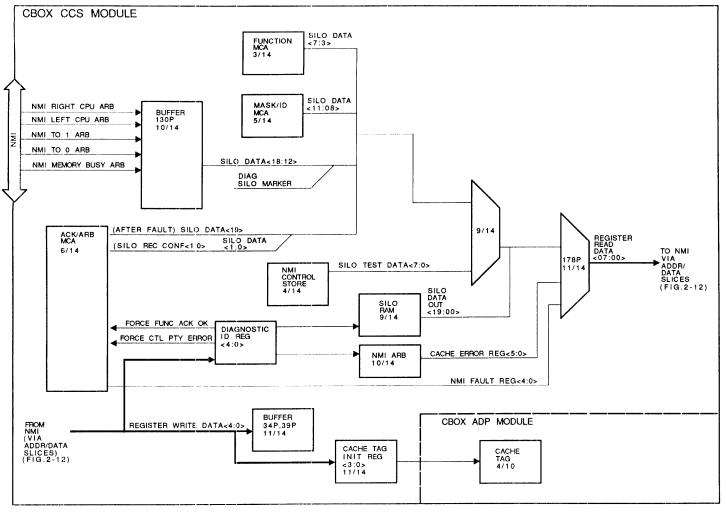

| 2.1<br>2.1.1<br>2.1.1.1<br>2.1.1.2<br>2.1.1.3<br>2.1.1.4<br>2.1.1.5<br>2.2<br>2.2.1<br>2.2.1.1<br>2.2.1.2<br>2.2.1.3<br>2.2.1.4<br>2.2.1.5<br>2.3<br>2.3.1<br>2.3.1.1<br>2.3.1.2<br>2.3.1.3<br>2.3.1.4<br>2.3.1.5 | CBOX SUBSYSTEMS DESCRIPTION       2-1         Translation Buffer       2-1         VA Latch       2-4         TB RAM       2-5         TB Match MCA       2-8         TB RAM Bypass       2-10         PA Latch       2-14         CBOX SUBSYSTEMS DESCRIPTION       2-19         Cache       2-19         Cache Data Path Logic       2-19         Cache Tag MCA       2-25         Cache Match MCA       2-25         Cache Control MCA       2-27         MD Number MCA       2-28         CBOX SUBSYSTEMS DESCRIPTION       2-28         CBOX SUBSYSTEMS DESCRIPTION       2-29         NMI Interface       2-29         NMI Address/Data Slices       2-31         NMI Out Control       2-36         NMI In Control       2-42         NMI Arbitration/Acknowledgment       2-47         CBox NMI Registers       2-52 |

| No.                                                                                                                                                                                                               | FIGURES Title Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1-1<br>1-2                                                                                                                                                                                                        | CBox Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

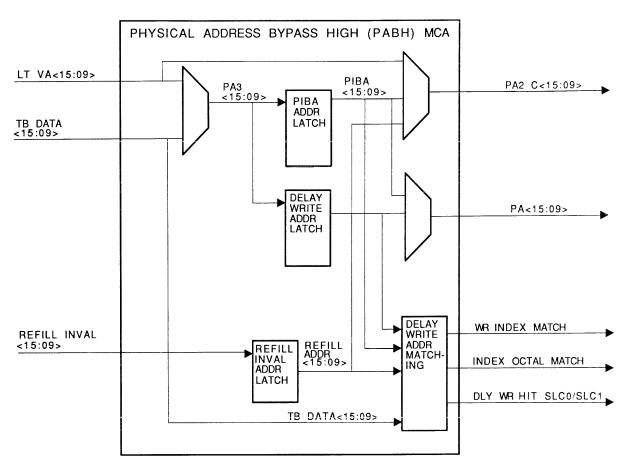

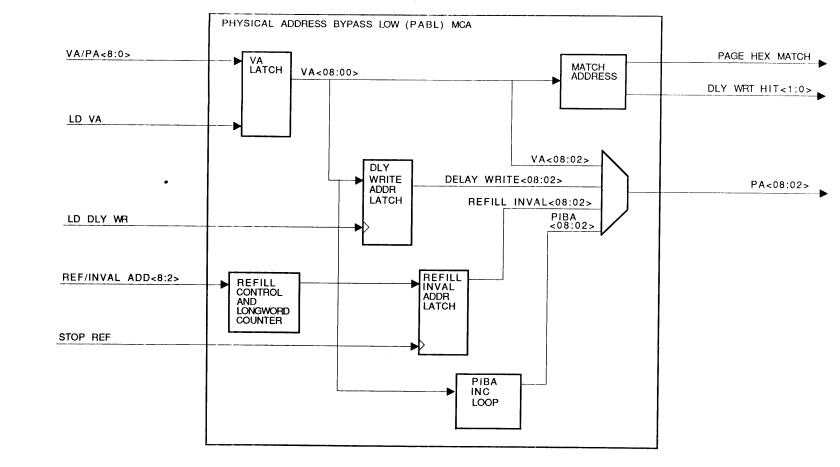

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12                                                                                                                               | Translation Buffer Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2-14                                                                                                                                                                                                              | Control Store Microword Format Diagram 2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2-15                                                                                                                                                                                                              | NMI In Control Block Diagram 2-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

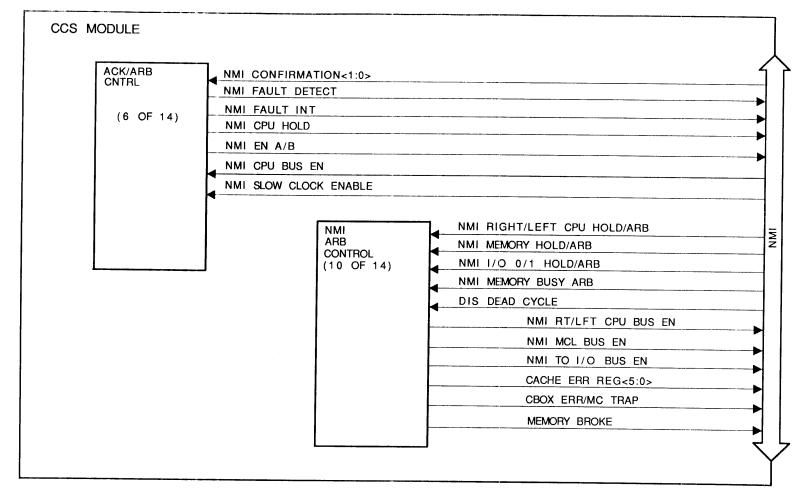

| 2-16  2-17 2-18 2-19 2-20 2-21 2-22 2-23  2-24  2-25 2-26 2-27 2-28 2-29  2-30 2-33 | NMI Arbitration/Acknowledgment Control Simplified Block Diagram | 123567<br>8 01356<br>78 |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|

|                                                                                     | TABLES                                                          |                         |

| No.                                                                                 | Title                                                           | е                       |

| 1-1                                                                                 | CBox Cycles                                                     | 7                       |

| 2-1                                                                                 | PROTection Field <03:00> Coding and Access                      |                         |

|                                                                                     | Allowed                                                         |                         |

| 2-2                                                                                 | TB Match MCA Operation Coding                                   |                         |