PDP-15 Systems Maintenance Manual

# **AD15 Analog Subsystem**

# AD15 ANALOG SUBSYSTEM MAINTENANCE MANUAL

Copyright © 1971 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

COMPUTER LAB

# CONTENTS

|         |                                    | Page |

|---------|------------------------------------|------|

| CHAPTER | R 1 BASIC DESCRIPTION              |      |

| 1.1     | Purpose of Equipment               | 1-1  |

| 1.2     | System Functional Description      | 1-1  |

| 1.2.1   | Interface                          | 1-4  |

| 1.2.2   | Multiplexer                        | 1-4  |

| 1.2.3   | Analog-to-Digital Converter        | 1-5  |

| 1.3     | Physical Description               | 1-5  |

| 1.3.1   | AD15 Minimum System Configuration  | 1-5  |

| 1.3.1.1 | Frame and Wired Assembly           | 1-5  |

| 1.3.1.2 | Amphenol Connector Assembly        | 1-7  |

| 1.3.1.3 | H929B Filler Plates                | 1-8  |

| 1.3.1.4 | Analog Power Supply                | 1-10 |

| 1.3.1.5 | I/O Bus Cable Assembly             | 1-10 |

| 1.3.2   | System Expansion                   | 1-10 |

| 1.4     | Specifications                     | 1-11 |

| CHAPTER | R 2 DETAILED THEORY OF OPERATION   |      |

| 2.1     | Modes of Operation                 | 2-1  |

| 2.1.1   | Program Control                    | 2-1  |

| 2.1.2   | PDP-15 Data Channel                | 2-1  |

| 2.1.3   | Add-to-Memory                      | 2-2  |

| 2.2     | Program Interrupt                  | 2-2  |

| 2.3     | Automatic Priority Interrupt       | 2-3  |

| 2.4     | Latency                            | 2-3  |

| 2.5     | Detailed Block Diagram Description | 2-4  |

| 2.5.1   | Power Supplies                     | 2-4  |

| 2.5.2   | Sync Logic                         | 2-4  |

| 2.5.3   | Analog Multiplexing                | 2-4  |

| 2.5.4   | Gain Selection                     | 2-4  |

| 2.5.5   | Sample and Hold Amplifier          | 2-7  |

| 2.5.6   | Analog-to-Digital Conversion       | 2-7  |

| 2.5.7   | Flag Status and IOT Decoding       | 2-7  |

| 2.6     | Detailed Logic Analysis            | 2-7  |

# CONTENTS (Cont)

|         |                                                     | Page |

|---------|-----------------------------------------------------|------|

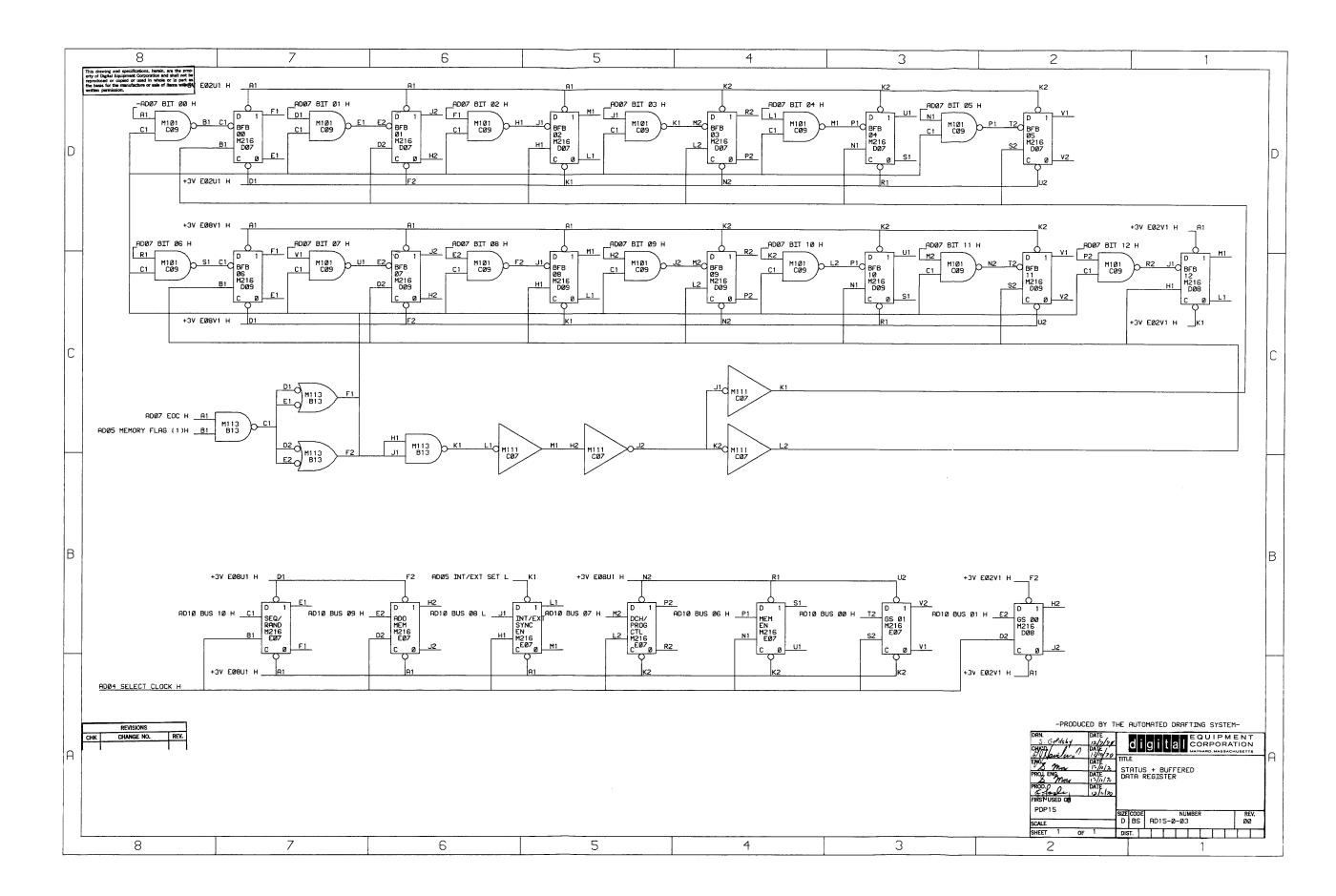

| 2.6.1   | Status Register and Buffered Data Register          | 2-8  |

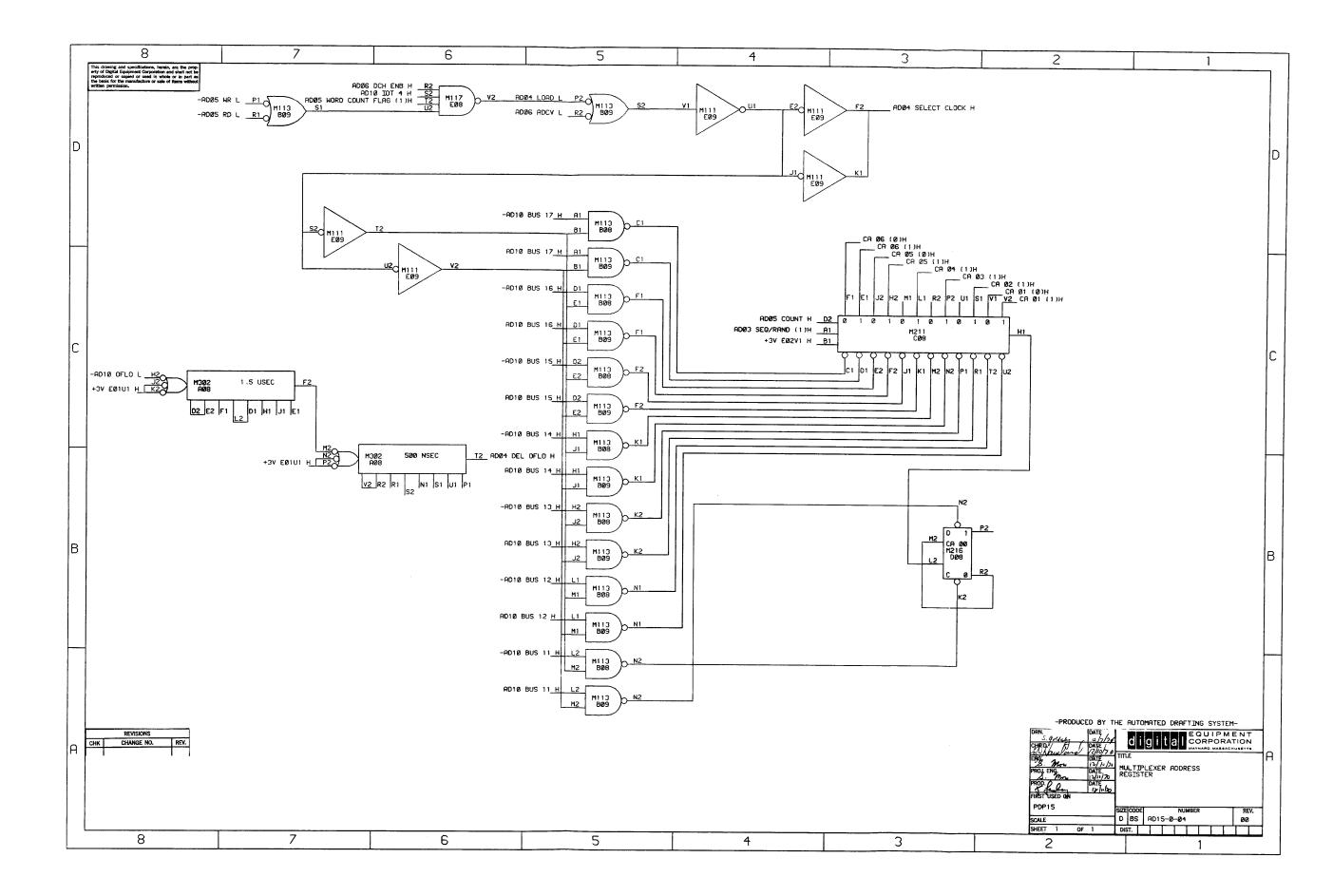

| 2.6.2   | Multiplexer Channel Address Register                | 2-8  |

| 2.6.3   | Flag Logic                                          | 2-9  |

| 2.6.3.1 | Word Count Flag                                     | 2-9  |

| 2.6.3.2 | API Flag                                            | 2-10 |

| 2.6.3.3 | Memory Flag                                         | 2-10 |

| 2.6.3.4 | Read/Write Logic                                    | 2-10 |

| 2.6.3.5 | DONE Flag                                           | 2-11 |

| 2.6.3.6 | DCH Flag                                            | 2-11 |

| 2.6.3.7 | Flag Testing                                        | 2-11 |

| 2.6.4   | Device Decoders, API and Data Channel Logic         | 2-12 |

| 2.6.5   | Analog Subsection                                   | 2-12 |

| 2.6.5.1 | Gain Switching                                      | 2-13 |

| 2.6.5.2 | Sample and Hold Amplifier                           | 2-13 |

| 2.6.5.3 | Analog-to-Digital Converter                         | 2-13 |

| 2.6.6   | Binary-Octal Decoder and Analog Multiplexer         | 2-14 |

| 2.6.7   | I/O Bus Drivers                                     | 2-15 |

| 2.6.8   | Bus Receivers, Analog Inputs, and I/O Bus Interface | 2-16 |

| 2.6.9   | Expansion Unit AM01                                 | 2-16 |

| CHAPTER | R 3 IOT INSTRUCTION FORMAT                          |      |

| 3.1     | Equipment Turn-On/Turn-Off Procedures               | 3-1  |

| 3.2     | Instruction and Data Formats                        | 3-1  |

| 3.2.1   | IOT Timing                                          | 3-1  |

| 3.2.2   | IOT Instruction Format                              | 3-1  |

| 3.2.2.1 | ADCV (convert) Octal Code 701304                    | 3-2  |

| 3.2.2.2 | ADRB (read data buffer) Octal Code 701302           | 3-2  |

| 3.2.2.3 | ADRS (read status register) Octal Code 701342       | 3-2  |

| 3.2.2.4 | ADCF (clear all AD15 flags) Octal Code 701362       | 3-2  |

| 3.2.2.5 | ADSF (skip on A/D DONE flag) Octal Code 701301      | 3-2  |

| 3.2.3   | Output Status Word Format                           | 3-2  |

| 3.2.4   | Data Word Format                                    | 3-3  |

| 3.2.4.1 | WCSF (skip on word count overflow flag) Octal       | 3-3  |

# CONTENTS (Cont)

|         |                                                       | Page         |

|---------|-------------------------------------------------------|--------------|

| 3.2.4.2 | MSSF (skip on memory overflow flag) Octal Code 701321 | 3-3          |

| 2 2 5   |                                                       | 3 <b>-</b> 3 |

| 3.2.5   | Input Status Word                                     |              |

| 3.3     | Programming Examples                                  | 3-4          |

| 3.3.1   | Program Control Mode                                  | 3-4          |

| 3.3.2   | Data Channel Mode - Sequential Operation              | 3-5          |

| 3.3.3   | Data Channel Mode - Random Operation                  | 3-7          |

| CHAPTER | 4 INSTALLATION AND ADJUSTMENTS                        |              |

| 4.1     | Installation Planning                                 | 4-1          |

| 4.2     | Environmental Requirements                            | 4-1          |

| 4.3     | Installation Procedure                                | 4-1          |

| 4.4     | Adjustments                                           | 4-3          |

| CHAPTER | 5 MAINTENANCE                                         |              |

| 5.1     | AD15 MAINDEC-15-D6GA-D(D) Diagnostic Program          | 5-1          |

| 5.2     | Preventive Maintenance                                | 5-2          |

| 5.2.1   | Preventive Maintenance Tasks                          | 5-2          |

| 5.3     | Corrective Maintenance                                | 5 <b>-</b> 3 |

| 5.3.1   | Preliminary Investigation                             | 5-4          |

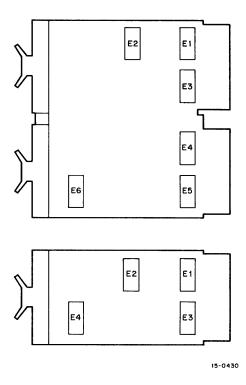

| 5.3.2   | System Troubleshooting                                | 5-4          |

| 5.3.3   | Logic Troubleshooting                                 | 5-4          |

| 5.3.4   | Circuit Troubleshooting                               | 5 <b>-</b> 5 |

| 5.3.5   | Validation Tests                                      | 5-7          |

| 5.3.6   | Recording                                             | 5-7          |

| 5.4     | Test Equipment                                        | 5 <b>-</b> 7 |

| 5.5     | Module Handling and Repair                            | 5-9          |

| 5.6     | Spare Parts                                           | 5-9          |

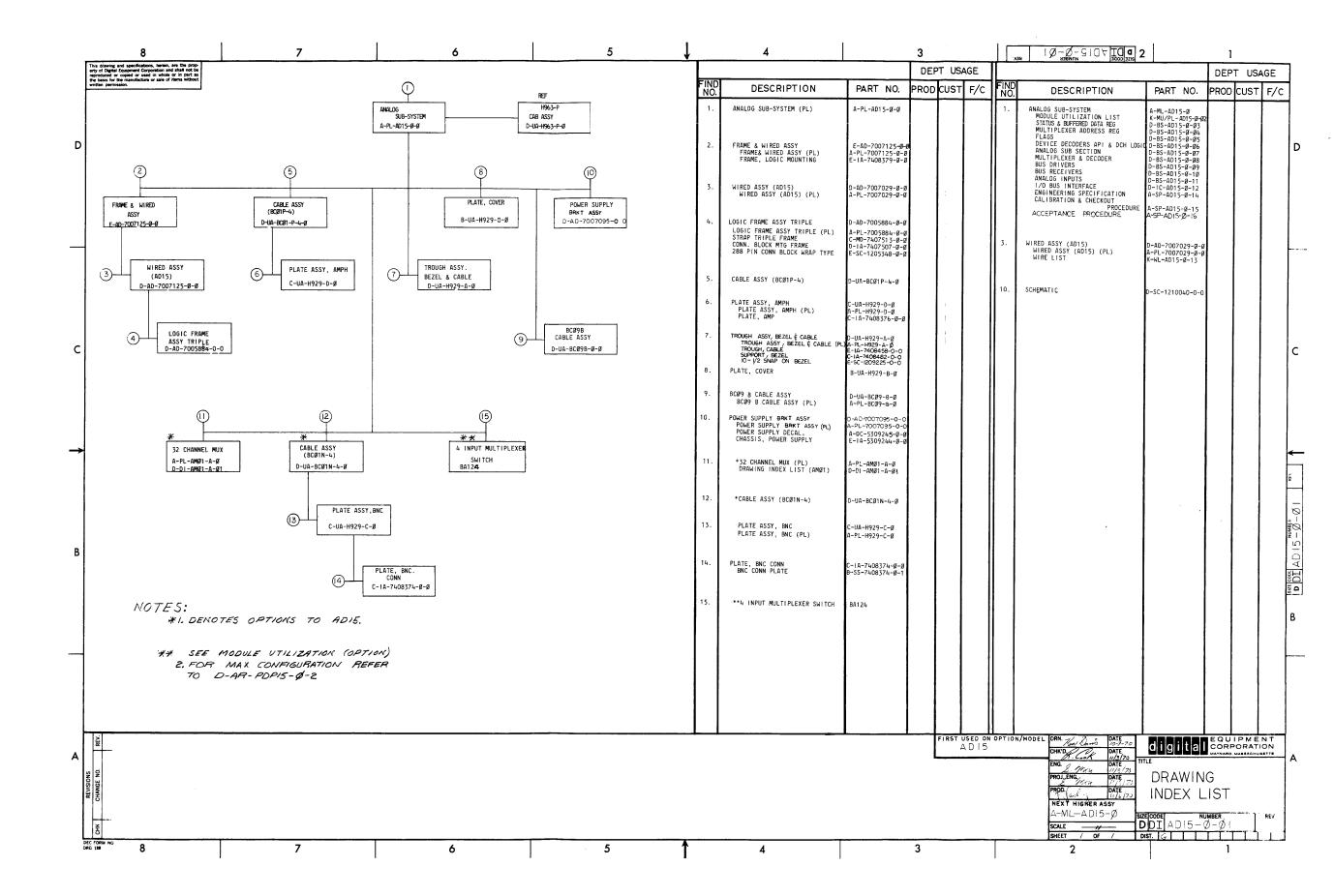

| CHAPTER | 6 Engineering Drawings                                |              |

| 6.1     | Drawing Codes                                         | 6-1          |

| 6.2     | Drawing Number Index                                  | 6-1          |

| 6.3     | Signal Glossary                                       | 6-2          |

# ILLUSTRATIONS

Title

Figure No.

Art No. Page

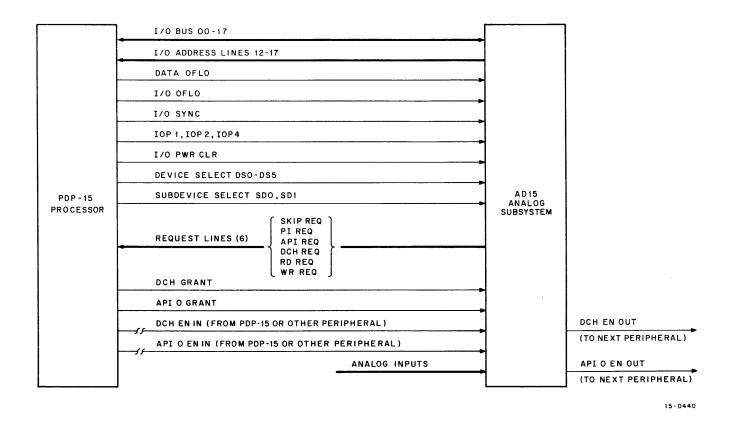

| 1-1       | AD15 Signal Interface Diagram 15-0440             |         | 1-2  |

|-----------|---------------------------------------------------|---------|------|

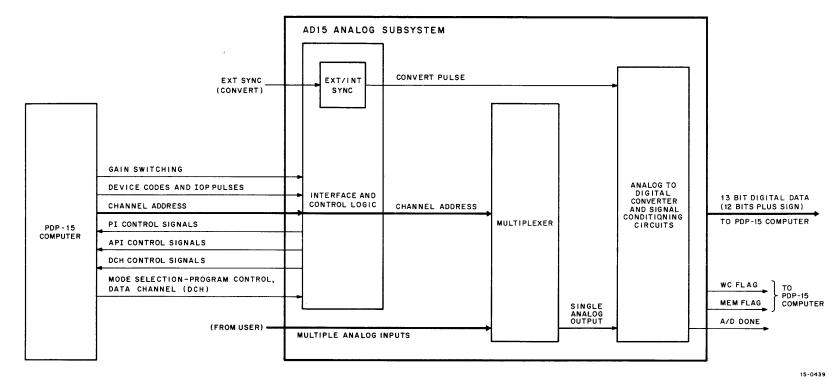

| 1-2       | AD15 System Block Diagram                         | 15-0439 | 1-3  |

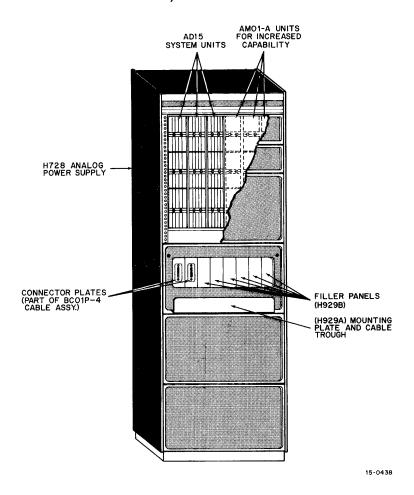

| 1-3       | Analog Cabinet H963-P                             | 15-0438 | 1-7  |

| 1-4       | BC01P-4 Cable Assembly                            | 5316-2  | 1-8  |

| 1-5       | BC01N-4 Cable Assembly                            | 5316-1  | 1-9  |

| 1-6       | Wiring of User Inputs                             | 15-0437 | 1-9  |

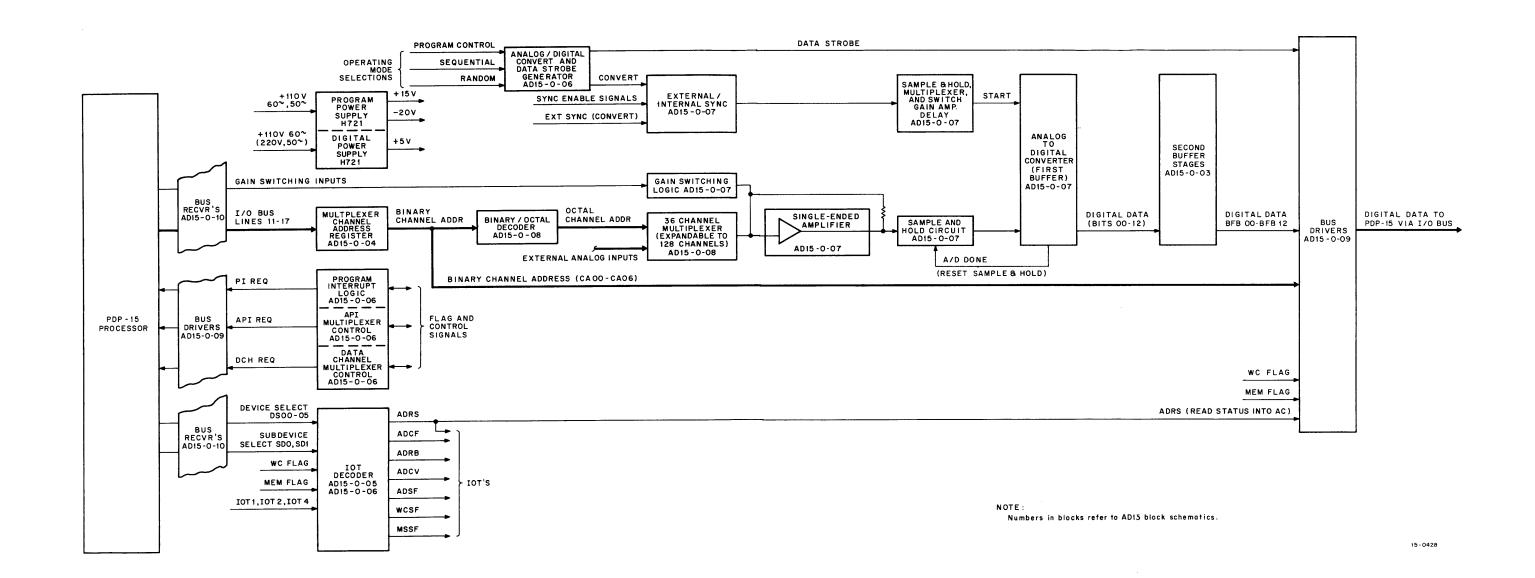

| 2-1       | AD15 Analog Subsystem Functional<br>Block Diagram | 15-0428 | 2-5  |

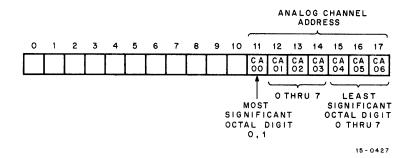

| 2-2       | Analog Addressing                                 | 15-0427 | 2-7  |

| 2-3       | External Sync Timing Diagram                      | 15-0426 | 2-13 |

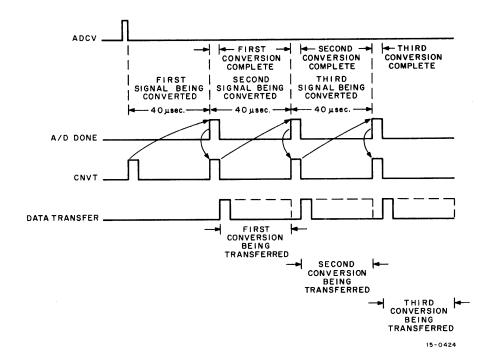

| 2-4       | Sequential Mode Timing Relationships              | 15-0424 | 2-14 |

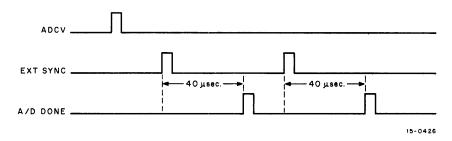

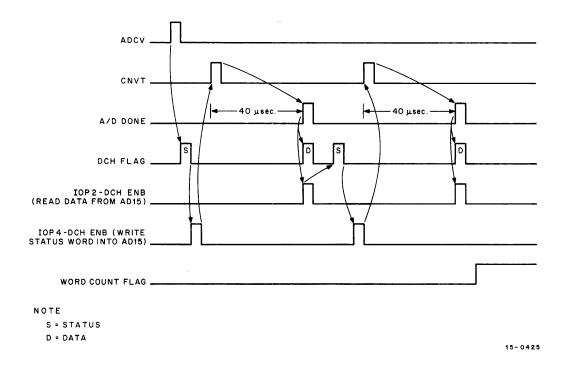

| 2-5       | Random Mode Timing Relationships                  | 15-0425 | 2-15 |

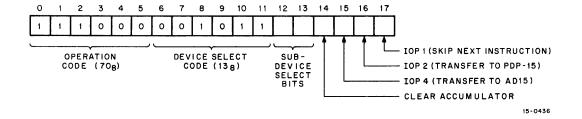

| 3-1       | IOT Instruction Format                            | 15-0436 | 3-2  |

| 3-2       | Output Status Word Format                         | 15-0433 | 3-3  |

| 3-3       | Data Word Format                                  | 15-0434 | 3-3  |

| 3-4       | Input Status Word Format                          | 15-0435 | 3-4  |

| 3-5       | Example of Program Control Input Status<br>Word   | 15-0431 | 3-5  |

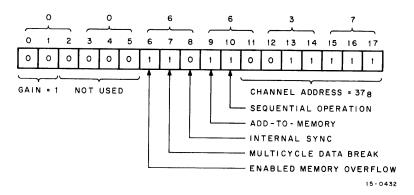

| 3-6       | Example of Sequential Mode Status<br>Word         | 15-0432 | 3-6  |

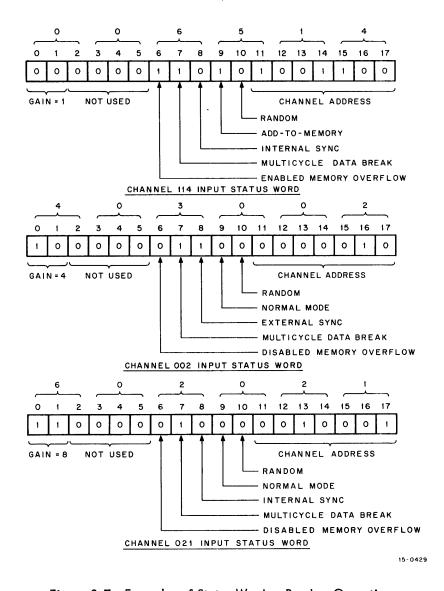

| 3-7       | Examples of Status Words – Random<br>Operation    | 15-0429 | 3-7  |

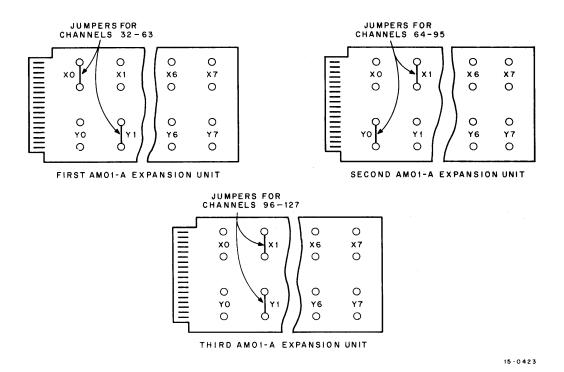

| 4-1       | Jumper Connections for G729 Card                  | 15-0423 | 4-3  |

| 5-1       | IC Location                                       | 15-0430 | 5-6  |

| 5-2       | IC Pin Location                                   | 15-0430 | 5-6  |

|           | TABLES                                            |         |      |

| Table No. | Title                                             |         | Page |

| 1-1       | AD15 Equipment and Module Complement              |         | 1-6  |

| 1-2       | AM01-A Equipment and Module Complemen             | nt      | 1-10 |

| 1-3       | System Expansions                                 |         | 1-11 |

| 1-4       | General Specifications                            |         | 1-11 |

| 4-1       | Adjustments                                       |         | 4-3  |

|           |                                                   |         |      |

# TABLES (Cont)

| Table No. | Title                 | Page |

|-----------|-----------------------|------|

| 5-1       | Maintenance Equipment | 5-7  |

| 5-2       | Spare Parts List      | 5-9  |

| 6-1       | List of AD15 Drawings | 6-2  |

| 6-2       | Signal Glossary       | 6-3  |

# **FOREWORD**

The AD15 Analog Subsystem Maintenance Manual consists of six chapters that cover the following general topics:

Chapter 1 contains a functional and physical description of the AD15 Analog Subsystem. It also describes system expansion capabilities, options, and accessories. A list of pertinent system parameters and specifications is included at the end of the chapter.

Chapter 2 contains a detailed block diagram description of the AD15 Analog Subsystem. Logic descriptions of complicated circuitry are also provided at the end of the chapter.

Chapter 3 describes the AD15 IOT instructions, input status word and output status word formats. Several programming examples are provided to illustrate the capabilities of the AD15 Analog Subsystem.

Chapter 4 contains the installation and adjustment procedures for the AD15.

Chapter 5 provides a description of the procedures required to maintain and troubleshoot the AD15 Analog Subsystem.

Chapter 6 contains the engineering drawing set and complete signal glossary for the AD15.

The reader should be familiar with and have access to the following documentation:

| DEC-15-GR1A-D    |

|------------------|

| DEC-15-MR2A-D    |

| DEC-15-H2BB-D    |

| DEC-15-H2EA-D    |

| DEC-15-H0AB-D    |

| 042D 00370 AKO   |

| A-SP-AD15-0-14   |

| A-SP-AD15-0-15   |

| DEC-15-D6GA-D(D) |

|                  |

# CHAPTER 1 BASIC DESCRIPTION

#### 1.1 PURPOSE OF EQUIPMENT

The AD15 Analog Subsystem is a computer-controlled device capable of multiplexing a maximum of 128 analog channels onto a common bus for analog-to-digital conversion. A maximum of 25,000 conversions per second can be handled by the system. The analog input voltage range is ±10V. Typical sources of analog input are: biomedical research, data accumulation on patients, and psychological and scientific investigation. The system can detect analog inputs as low as ±300 µV increments. The AD15 is designed to operate with the 18-bit PDP-15 computer. Both analog channel and gain selection are under control of the PDP-15. Figure 1-1 illustrates all interface signals between the PDP-15 and the AD15.

# 1.2 SYSTEM FUNCTIONAL DESCRIPTION

The AD15 Analog Subsystem consists of an interface, a single-ended multiplexer, and an analog-to-digital converter. Figure 1-2 shows the functional relationship of these units.

To initiate an analog-to-digital conversion, the accumulator in the PDP-15 is initially loaded with a status word containing gain selection, analog channel selection, and certain designated control functions (refer to Chapter 3). This status word is transferred to the AD15, using the input-output transfer (IOT) instructions. Other IOT instructions allow the analog inputs, which have been converted to digital data, to be transferred to the PDP-15 accumulator, or allow status information such as channel and flag selection to be transferred to the accumulator. The IOT instructions consist of an operation code (70<sub>8</sub>), a device and subdevice select code, and IOP pulses used for determining program skips and direction of transfer. The IOT instruction uniquely addresses the AD15 with a device select code of 13<sub>8</sub>.

There are two basic operating modes in the AD15 subsystem: program-controlled transfers and data channel (DCH) transfers. When operating in program control mode, data transfers occur between the PDP-15 accumulator and the AD15 under IOT control. When operating in the DCH mode, data transfers are made directly to and from memory under control of the PDP-15 I/O processor. Both sequential

Figure 1-1 AD15 Signal Interface Diagram

Figure 1-2 AD15 System Block Diagram

and random operations are possible in DCH mode. In sequential operation, analog channels are converted successively; while, in random operation, preselected analog channels can be converted without regard for any specific sequence.

An add-to-memory feature is employed in the AD15 whereby a converted value can be added to the contents of an existing memory location. The add-to-memory feature is desirable for signal averaging techniques.

#### 1.2.1 Interface

The AD15 interface provides an address and data interface between the PDP-15 and the AD15; the interface also contains additional control logic, which includes selection of external or internal sync. When internal sync is selected, a convert pulse that initiates the conversion is internally generated within the AD15. When external sync is selected, the convert pulse is supplied from an external source.

The AD15 interface also provides additional logic to initiate program interrupts (PI), automatic priority interrupts (API), or data channel activity (DCH). The PI and API logic give the AD15 the capability to interrupt the PDP-15 computer to request servicing. The data channel logic interrupts the PDP-15 on a cycle-stealing basis and allows direct data transfers between the AD15 and the PDP-15 memory. For a detailed description of PI, API, or DCH, refer to the PDP-15 Maintenance Manual (DEC-15-H2BB-D).

Moreover, the interface logic decodes the IOT device code of 13<sub>8</sub> (which is used to uniquely address the AD15), decodes the IOP pulses to determine if a skip is to be made, or determines the direction of data transfer (to or from the AD15). The status word is also decoded by the interface logic to determine the gain selected, the analog input channel selected, and the operating mode.

# 1.2.2 Multiplexer

The analog channel address supplied to the AD15 from the PDP-15 is a 7-bit code capable of addressing a maximum of 128 analog channels. The analog input signal, uniquely addressed by this 7-bit code from the computer, is multiplexed onto a common output line. This signal is subsequently amplified by a single-ended operational amplifier. A gain factor of 1, 2, 4 or 8 can be selected for increased dynamic range with unchanged accuracy. For example, if signals are in the range of ±1.25V, a gain of 8 is selected to provide a full-scale deflection of ±10V, as seen by the A/D converter. A sample and hold circuit is provided in the multiplexer to allow sufficient time for analog-to-digital conversion when sampling rapidly fluctuating voltages.

# 1.2.3 Analog-to-Digital Converter

The amplified analog input is applied to an analog-to-digital converter module along with a start pulse. The module produces 13 output bits corresponding to a 2's complement, right-justified digital value of the input voltage. When the digital value of the 13 output bits has been determined, an A/D DONE pulse is generated, indicating completion of the conversion. The digital data from the output of the analog-to-digital converter is then transferred to the PDP-15 where it is used for further processing (such as signal analysis).

The input voltage range of the analog-to-digital converter is  $\pm 10V$  with an input resistance of  $28 \text{ k}\Omega$ . Greater accuracy of small signals can be obtained by increasing the gain; consequently, these signals approximate the maximum input voltage to the converter, i.e., the gain should be selected to maximize the reading as a percentage of full-scale.

# 1.3 PHYSICAL DESCRIPTION

A physical description of the AD15 Analog Subsystem is provided in the following paragraphs. A minimum system 32-channel configuration is described first, followed by a description of increased system capability in increments of 32 channels. The user can purchase any number of channels in increments of four; however, based on the modular design, the most economical configurations are in increments of 32 channels.

# 1.3.1 AD15 Minimum System Configuration

When an AD15 subsystem is ordered, the user receives the items listed in Table 1-1. The frame and wired assembly include all the modules necessary for operation, including one A124 Multiplexer Module for the switch gain amplifier. Multiplexer modules intended for use with the analog channels must be ordered separately. Each multiplexer module handles four channels; thus, if a user desires a 32-channel subsystem, he must order an AD15 and eight BA124 Multiplexer Modules. He will receive the items listed in Table 1-1, and also the eight BA124 Multiplexer Modules specified. The following paragraphs describe each of the items shipped with the AD15.

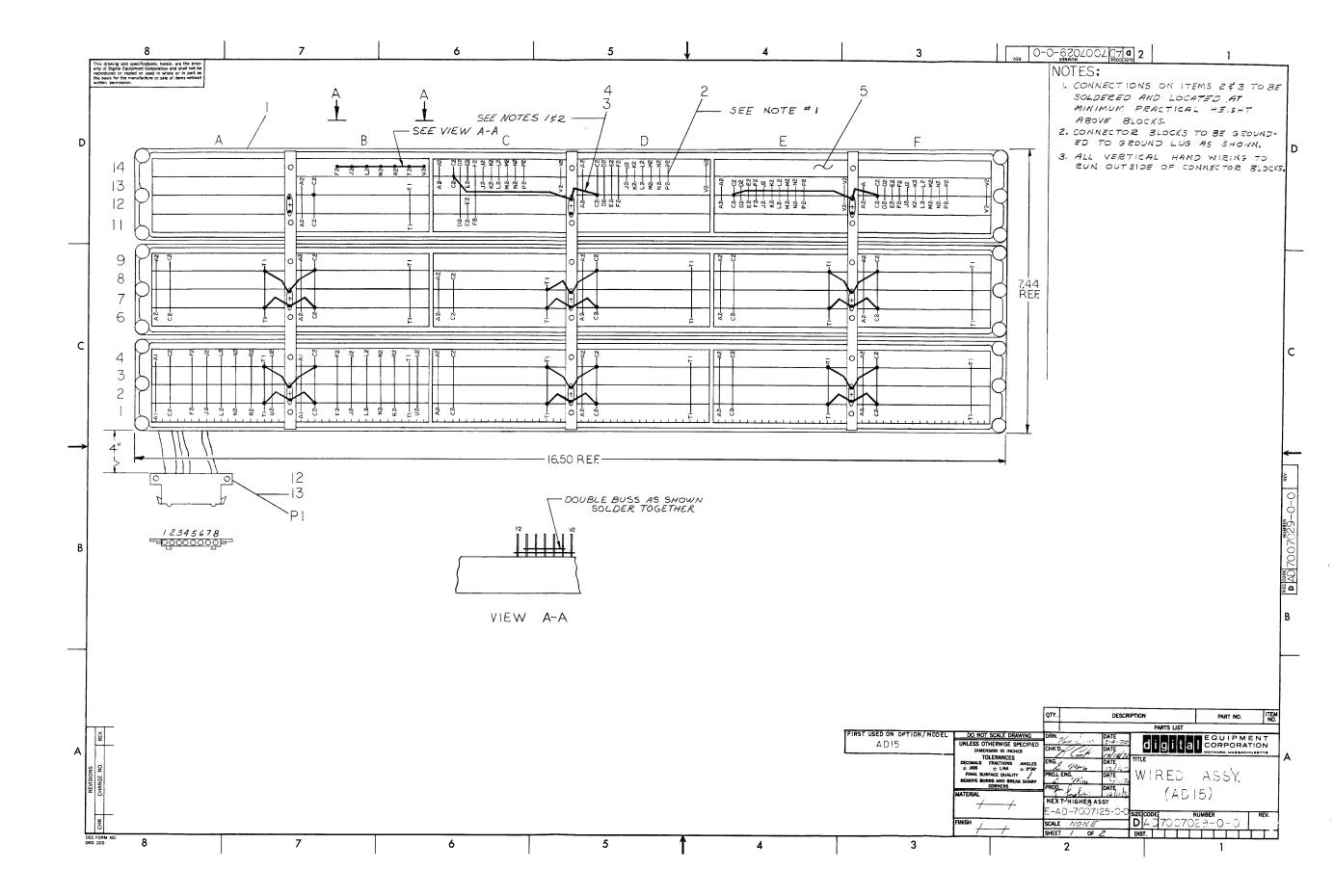

1.3.1.1 Frame and Wired Assembly – The frame and wired assembly is the mounting frame used to house all the modules and connector boards. The assembly includes all the modules listed in Table 1–1. The modules are housed on H803 Connector Blocks (see <u>DEC Logic Handbook</u> for pin assignments); each connector block has receptacles for eight single-height, single-width modules.

NOTE

Certain modules are double or quadruple height and correspondingly take up two or four module slots.

Table 1–1

AD15 Equipment and Module Complement

| Quantity | Nomenclature                        | Part Number/Module | Module Locations                                  |

|----------|-------------------------------------|--------------------|---------------------------------------------------|

| 1        | Frame and Wired Assembly            | D-AD-7007029-0-0   | -                                                 |

| 2        | Amphenol Connector Cable Assemblies | BC01P-4            | -                                                 |

| 1        | Mounting Plate                      | H929A              | -                                                 |

| 6        | Filler Plates                       | H929B              | -                                                 |

| 1        | Analog Power Supply and Chassis     | H728               | -                                                 |

| 1        | I/O Bus Cable Assembly              | BC09B              | _                                                 |

| 9†       | Multiplexer                         | BA124              | C13, C14, D12,<br>D13, D14, E12,<br>E13, F12, F13 |

| 1        | Switch Gain Amplifier               | A222               | C12                                               |

| 1        | Sample and Hold Amplifier           | A405               | A <u>1</u> 2                                      |

| 1        | Voltage Regulator                   | A708               | A10                                               |

| 1        | Analog-to-Digital Converter         | A877               | C10                                               |

| 1        | Bus Data Interface                  | M101               | C9                                                |

| 1        | Device Selector                     | M103               | В6                                                |

| 2        | I/O Bus Multiplexer                 | M104               | A6, A7                                            |

| 2        | Inverter                            | MIII               | C7, E9                                            |

| 5        | 2-Input NAND Gates                  | M113               | B8, B9, B13, E1, E2                               |

| 2        | 3-Input NAND Gates                  | M115               | E3, E4                                            |

| 2        | 4-Input NAND Gates                  | M117               | B7, E8                                            |

| 1        | Binary-Octal Decimal Decoder        | M161               | F9                                                |

| 1        | Binary Counter                      | M211               | C8                                                |

| 5        | Six D-Type Flip-Flops               | M216               | D7, D8, D9, E6, E7                                |

| 3        | Dual Delay Multivibrator            | M302               | A8, A9, F8                                        |

| 4        | I/O Bus Receiver                    | M510               | C1, C2, D3, C4                                    |

| 5        | Data Bus Driver                     | M621               | D1, D2, D3, D4,<br>D6                             |

| ו        | 8-Bit Positive Input/Output Driver  | M622               | C6                                                |

| 2        | Ribbon Connector                    | M908               | E14, F14                                          |

| 4        | I/O Bus Connector                   | M912               | A1, A2, A3, A4                                    |

| 1        | Bus Connector Module                | M935               | A14                                               |

One A124 Module is supplied with the AD15 and is used by the Switch Gain Amplifier. For 32-channel operation, eight additional BA124 Modules must be ordered.

Three connector blocks strapped together constitute a system unit (see Figure 1-3). The 32-channel minimum configuration AD15 contains three system units as shown.

Figure 1-3 Analog Cabinet H963-P

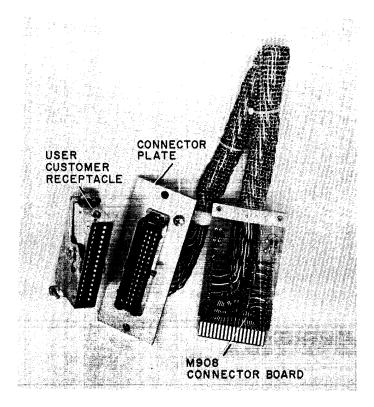

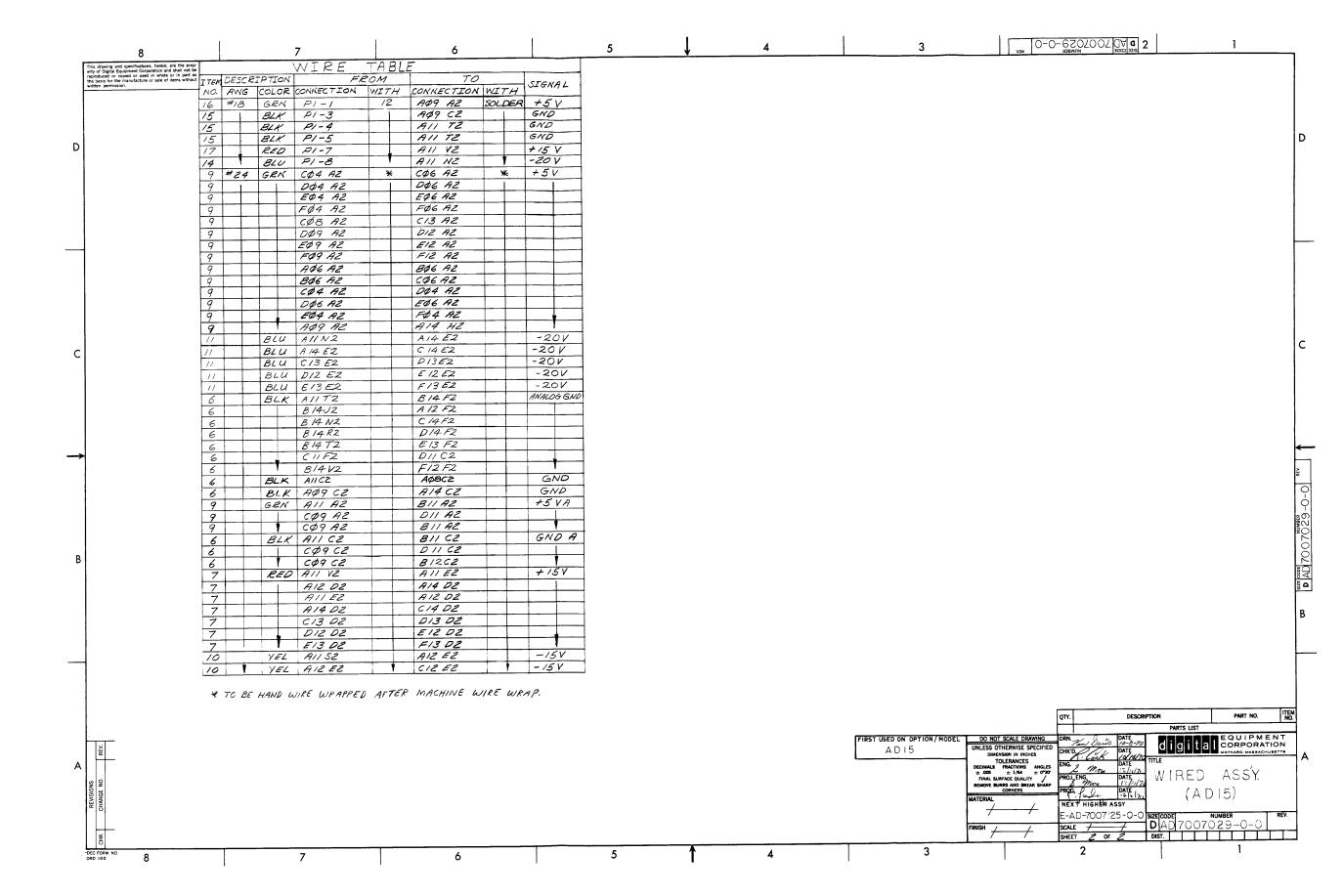

1.3.1.2 Amphenol Connector Assembly – Two BC01P–4 Amphenol Connector Assemblies are supplied with the AD15 subsystem. Each cable assembly handles 16 channels. The cable assembly consists of a user receptacle (Amphenol Series 26), a connector plate that is mounted in a 10–1/2 in. high connector panel, a woven twisted–pair cable, and an M908 Connector Board (see Figure 1–4). User inputs are soldered to the user receptacle and are routed to the AD15 via the M908 Connector Board, which plugs into module slots E14 and F14 (see Drawing D–AD–7007029–0–0).

Figure 1-4 BC01P-4 Cable Assembly

# NOTE

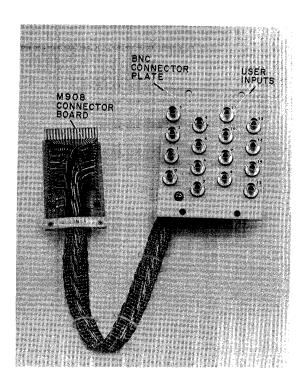

If the user installation employs BNC connectors, two BC01N-4 Cable Assemblies (see Figure 1-5) must be ordered, because they are not supplied with the basic system. The BC01N-4 assembly is similar to the BC01P-4; it differs in that the panel houses the BNC connectors rather than the 32-pin ribbon-type connectors. Customer inputs are routed to the AD15 via the BNC connector panel and the M908 Connector Card, which also plugs into slots E14 and F14. The BNC connector panel is clearly marked by channel number for wiring of customer inputs.

The user analog inputs can be wired to the AD15, using the Amphenol Series 26 connectors (see Figure 1-6). Each connector contains 32 pins (one analog signal pin and one ground for each channel).

1.3.1.3 H929B Filler Plates – For the 32-channel minimum configuration AD15, six H929B Filler Plates are included on the connector panel adjacent to the BC01P-4 Cable Assembly Connector Plates. As the system configuration is expanded, the required H929B Filler Plates are removed to allow the added BC01P-4 Cable Assembly Connector Plates to be installed.

Figure 1-5 BC01N-4 Cable Assembly

PART OF BCOIP-4 CABLE ASSEMBLY

#### 32-PIN RIBBON CONNECTOR - CHANNEL O - CHANNEL 16 PINS 1-16 ANALOG SIGNALS FOR CHANNELS 16 THROUGH 31 PINS 1-16 ANALOG SIGNALS FOR CHANNELS O THROUGH 15 PINS 17 - 32 ANALOG GROUNDS PINS 17-32 ANALOG GROUNDS CHANNEL 15 CHANNEL 31 OTHER END OF CABLE ASSEMBLY PLUGS INTO SLOT F14 OTHER END OF CABLE ASSEMBLY PLUGS INTO MODULE SLOT E14

Figure 1-6 Wiring of User Inputs

15-0437

1.3.1.4 Analog Power Supply – The AD15 subsystem contains an H728 Analog Power Supply. This power supply operates with 110V input and provides regulated outputs of 15 Vdc at 2A and 20 Vdc at 1.2A.

1.3.1.5 I/O Bus Cable Assembly – A BC09B I/O Bus Cable is supplied with the AD15 to interface the AD15 to the PDP-15 computer. The BC09B Cable Assembly comprises two multiconductor cables with two M912 Connectors at each end and associated hardware. The M912 is a double-height board and connects to module slots A1, A2 and B1, B2. Module slot A3 is jumpered to A1, A4 is jumpered to A2, B3 is jumpered to B1, and B4 is jumpered to B2 to provide a receptacle for another BC09B cable that is daisy-chained to the next device. For a more detailed description of the BC09B Cable Assembly, refer to the PDP-15 Interface Manual.

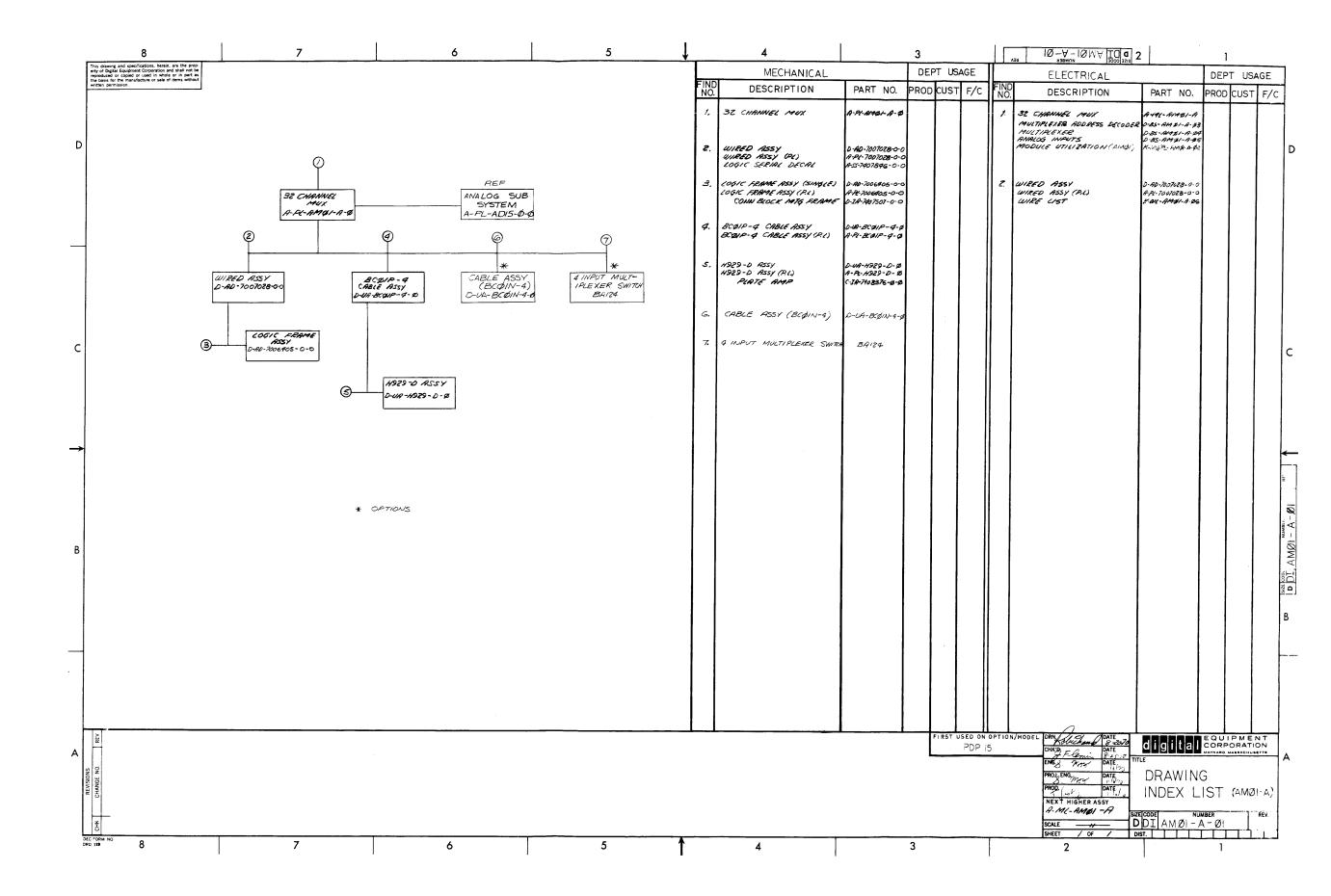

# 1.3.2 System Expansion

The addition of an AM01-A system unit is required to expand the AD15 from 32 to 64 channels. The AM01-A comprises two BC01P-4 Cable Assemblies and the modules listed in Table 1-2. The required number of BA124 Multiplexer Modules must be ordered, as with the AD15 subsystem. Thus, to expand a system from 32 to 64 channels, an AM01-A system unit and eight additional BA124 Multiplexer Modules must be ordered. The BC01P-4 Cable Assemblies connect the user's 32 analog channels to the AD15. Two of the H929B Filler Plates are removed, and the 32-pin Amphenol Connector Plates (part of the BC01P-4) are mounted in place. If the user employs BNC connectors at his site, he must procure two BC01N-4 Cable Assemblies for each 32 channels; they are not supplied with the system.

Table 1-2

AM01-A Equipment and Module Complement

| Quantity               | Nomenclature                                                                      | Part Number/Module                    | Module Locations                             |

|------------------------|-----------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------|

| 2                      | Amphenol Connector Cable Assemblies                                               | BC01P-4                               | -                                            |

| 8†<br>1<br>1<br>1<br>2 | Multiplexer<br>Jumper Card<br>Octal Decoder<br>Bus Receiver<br>Bus Connector Card | BA124<br>G729<br>M161<br>M510<br>M935 | C1 - C4, D1 - D4<br>B3<br>B2<br>E1<br>A1, A4 |

<sup>†</sup>BA124 Multiplexer Modules are not supplied with the AM01-A and must be ordered separately. For an additional 32 channels beyond the 32 channels in the AD15, eight modules must be ordered.

Table 1-3 lists different system configurations and the equipment provided with each. The user can tailor the system to his own individual needs using the examples provided.

Table 1-3

System Expansions

| Channel                                                    | AD15                                 | BA124 Modules†                                        | AM01-A                                              |

|------------------------------------------------------------|--------------------------------------|-------------------------------------------------------|-----------------------------------------------------|

| 28<br>32<br>36<br>60<br>64<br>68<br>92<br>96<br>100<br>124 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 7<br>8<br>9<br>15<br>16<br>17<br>23<br>24<br>25<br>31 | 0<br>0<br>1<br>1<br>2<br>2<br>2<br>2<br>3<br>3<br>3 |

$<sup>^\</sup>dagger \text{Excluding the A124 Multiplexer Module used with the Switch Gain Amplifier and supplied with the System.}$

# 1.4 SPECIFICATIONS

Table 1-4 lists the specifications of the AD15 Analog Subsystem.

Table 1-4

General Specifications

| Specification                              | Description                                          |

|--------------------------------------------|------------------------------------------------------|

| PHYSICAL SPECIFICATIONS                    |                                                      |

| Frame Dimensions                           | Height – 17 in.<br>Depth – 1.5 in.<br>Width – 19 in. |

| environmental specifications               |                                                      |

| Cooling                                    | Ambient air (forced)                                 |

| Temperature range – operating<br>– storage | 0° to 50°C<br>-25° to +85°C                          |

| Humidity                                   | To 90% without condensation                          |

# Table 1-4 (Cont) General Specifications

| Specification                                                                                | Description                                          |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| POWER REQUIREMENTS                                                                           |                                                      |  |

| Input voltage and frequency                                                                  | 105 – 125 Vac<br>47 to 420 Hz single-phase           |  |

| AC current                                                                                   | Less than 1A                                         |  |

| Power dissipation                                                                            | Less than 100W                                       |  |

| ACCURACY                                                                                     |                                                      |  |

| System                                                                                       | ±0.04%                                               |  |

| Temperature coefficient                                                                      | ±30 PPM/°C                                           |  |

| Sample and Hold                                                                              | ±0.02%                                               |  |

| Multiplexer and Switch Gain Amplifier                                                        | ±0.02%                                               |  |

| Analog-to-Digital Converter                                                                  | ±0.015% ±1/2 LSB                                     |  |

| 30 day long term stability Temperature coefficient                                           | ±20 PPM/°C                                           |  |

| range of input signals                                                                       |                                                      |  |

| ±10V full-scale<br>± 5V full-scale<br>±2.5V full-scale<br>±1.25V full-scale                  | (gain = 1)<br>(gain = 2)<br>(gain = 4)<br>(gain = 8) |  |

| SAMPLING RATE                                                                                |                                                      |  |

| Sample and Hold                                                                              | 25 kHz                                               |  |

| SYSTEM SPEED                                                                                 |                                                      |  |

| ADC conversion                                                                               | <35 μs                                               |  |

| ADC conversion, multiplexer, sample and hold and amplifier settling                          | <40 μs                                               |  |

| Switch Gain Amplifier setting time including 100% overload recovery (x8 gain with 10V input) | <3 µs                                                |  |

| number of channels                                                                           |                                                      |  |

| Expandable in groups of 4 Basic system is 32 channels                                        | To a maximum of 128                                  |  |

# Table 1-4 (Cont) General Specifications

| Specification                    | Description                                       |  |

|----------------------------------|---------------------------------------------------|--|

| INPUT SPECIFICATION              |                                                   |  |

| Single-ended input<br>Impedance  | <br>Greater than 100 MΩ in<br>parallel with 20 pf |  |

| NOISE                            |                                                   |  |

| Less than ±4 mV peak-to-peak RTO | ±3 sigma confidence level                         |  |

| CROSSTALK                        | 78 db (32 channels, 180 Hz)                       |  |

| RESOLUTION                       | One part in 4096 full-scale                       |  |

# CHAPTER 2 DETAILED THEORY OF OPERATION

#### 2.1 MODES OF OPERATION

The AD15 has two basic modes of operation: program control and data channel. All transfers made in program control mode occur through the PDP-15 accumulator, while all transfers made using the data channel are made directly to memory.

# 2.1.1 Program Control

In program control mode, each analog input to be converted and stored requires a new set of instructions. Consequently, this method is not advantageous in the case of many conversions.

#### 2.1.2 PDP-15 Data Channel

Two types of operation are possible using the PDP-15 data channel facility: sequential or random. In sequential operation, only one set of instructions is required to convert successive analog channels and store the results in sequential memory locations. To accomplish this, the programmer must load two memory locations (26 and 27) in the PDP-15. Location 26 is loaded in 2's complement notation with the desired number of words to be converted (word count). Location 27 is loaded with the starting address minus one, where the first converted analog input is stored (current address). After each analog input is converted, the word count is incremented. The incremented word count, in turn, causes the current address to be incremented. This ensures that the next analog input to be converted will be stored in the next sequential memory location. When the desired number of conversions have been completed, a word count overflow flag is raised, because sensing all 0s in word count location 26 causes I/O OFLO to be generated and supplied to the AD15. I/O OFLO causes the word count flag to be raised. This flag causes an interrupt, indicating completion of the required number of conversions. Bit 10 of the input status word must be a logic 1 for sequential operation.

#### NOTE

When employing sequential operation, only one status word is employed, and the data words are converted one after the other automatically. Therefore, it is necessary to use the same fixed-gain for all channels in this mode.

Random operation is similar to sequential operation except that a separate status word (channel address, gain, etc.) is associated with each analog channel. The status words are retrieved from one memory table and the converted data words are stored in a second memory table. Memory locations 24 and 25 are reserved for the status words, and memory locations 26 and 27 are reserved for the data words.

Location 24 is loaded with one less than the 2's complement of the number of words to be converted, and location 25 is loaded with the starting address minus one where the first status word is stored. Location 26 is loaded with the 2's complement of the word count value; location 27 is loaded with the memory location minus one where the first converted data word is to be stored. Although random channels may be converted in this manner, note that the status words are sequentially stored in memory, and the data words are also stored in successive memory locations. In this way, the word count and current address cycles of the three-cycle data channel facility are utilized (refer to the PDP-15 Maintenance Manual for a more detailed description of the three-cycle data channel). Bit 10 of the input status word must be a logic 0 for random operation.

#### NOTE

In sequential operation, one three-cycle data break is required for each data word to be transferred into PDP-15 memory. In random operation, however, two three-cycle data breaks are required for each data word. The first three-cycle break transfers the status word to the AD15, and the second three-cycle break transfers the converted data word to PDP-15 memory. When word count overflow occurs, it is a result of location 26 overflowing indicating that all data words have been transferred.

## 2.1.3 Add-to-Memory

The add-to-memory feature of the PDP-15 computer allows an analog input (after it is converted to digital) to be added to the contents of a memory location. If the value added to memory is sufficient to cause a sign change in the result, a data overflow pulse is generated. If the programmer desires to cause an interrupt when a change of sign occurs, it is necessary for him to set the add-to-memory bit (bit 9) of the input status word to a logic 1 and to also set bit 6 of the status word to a logic 1. Bit 6, when set, enables the memory flag to cause a program interrupt. The add-to-memory feature is discussed in greater detail in the PDP-15 Maintenance Manual.

# 2.2 PROGRAM INTERRUPT

There are three sources of program interrupts: A/D DONE, data overflow (DATA OFLO), or word count overflow (WC OFLO). A/D DONE causes an interrupt under program control operation, data overflow causes an interrupt during add-to-memory, if enabled, and word count overflow causes an

interrupt during the data channel mode. When the desired number of conversions have been accomplished, the PDP-15 senses word count overflow (all 0s in location 26) and issues an OFLO signal that raises the word count flag in the AD15. This flag raises the API flag, which is fed to the M104 API Multiplexer Control Module. An output, designated API, is supplied to the PDP-15 via two I/O bus drivers. One bus driver yields PROG INT RQ and the other yields API 0 RQ. If the PDP-15 does not have the API option installed, only the PROG INT RQ is recognized. The main program traps to location 000000<sub>8</sub> as a result of the program interrupt, and the current contents of certain PDP-15 registers is stored in this location. The instruction in location 000001<sub>8</sub> is fetched and executed. This instruction is an entry to a skip chain that determines the peripheral device causing the interrupt. When this is ascertained, the program enters a service routine to service the device. On completion of servicing, control is returned to the main program.

#### 2.3 AUTOMATIC PRIORITY INTERRUPT

If the AD15 is connected to the Automatic Priority Interrupt (API) System, it is assigned the trap address of  $57_8$ . Conversions are done on a cycle stealing basis, similar to that described in the program interrupt section (see Paragraph 2.2). When the required number of conversions have been accomplished, the PDP-15 senses word count overflow in location 26 and generates an OFLO signal, causing the word count flag to be raised in the AD15. This signal causes the API flag to be raised which, in turn, causes API to be generated at the output of the M104 API Multiplexer Control Module. This signal is applied to two bus drivers to yield PROG INT RQ and API 0 RQ. With the API option installed and enabled in the PDP-15, the API 0 RQ overrides PROG INT RQ and the main program in the PDP-15 traps to location 57 (AD15 trap address). Location 57 contains a JMS to a service routine. The first location of the service routine stores the contents of certain PDP-15 registers. Each device associated with API has its own unique trap address; thus, it is not necessary to enter a skip chain to determine the device that caused the interrupt. A small skip chain is necessary to determine the internal source (A/D DONE, WC OFLO or MEM OFLO) of the interrupt. On completion of the servicing, a JMP \* instruction returns control to the main program.

#### 2.4 LATENCY

If there are many devices of higher priority than the AD15 operating on the data channel, the programmer should be concerned with I/O Latency Time. The I/O Latency Time must be considered because a data word that has been converted to digital is available in the AD15 buffer register for a maximum of approximately 40 µs. If this data word is not transferred to the PDP-15 memory within this time, the initial data word is lost as a result of the next data word being strobed into the buffer register.

# 2.5 DETAILED BLOCK DIAGRAM DESCRIPTION

The following paragraphs describe the AD15 power supplies, modes and types of AD15 operation, and a detailed block diagram description.

# 2.5.1 Power Supplies

The AD15 operates at 110V, 60 cycle input, and includes an analog power supply (designated H728) operating with input power of 110V at 60 cycles. The power supply provides outputs of +15V and -20V for the A877 Analog-to-Digital Converter, the A405 Sample and Hold Amplifier, the A222 Gain-Switching Amplifier, and the A124 Multiplexer Modules. In addition to the H728 Power Supply, the H721 Power Supply, housed in the H963-P Analog Equipment Cabinet, provides +5 Vdc for all the digital modules.

# 2.5.2 Sync Logic

In either program control or data channel mode, a convert pulse is generated (see Figure 2-1). This pulse is coupled with a sync enable signal to generate internal sync. Internal sync initiates the timing for the analog-to-digital conversion. This timing can also be initiated externally by an external sync signal that serves as the convert pulse. With internal or external sync, a delay of 3.0 µs is timed out before allowing the analog-to-digital conversion to take place. This delay provides sufficient time for amplifier settling and for stabilizing of circuit elements. At the end of the delay, a start pulse is developed and applied to the analog-to-digital converter.

# 2.5.3 Analog Multiplexing

The computer-specified 7-bit address of the analog input to be converted is loaded in the AD15 channel address register via I/O bus lines 11 through17. The 7-bit address is then converted to octal format as shown in Figure 2-2. The octal addresses range from 000 to 177 in the maximum system configuration.

The channel address is then supplied to a 32-channel multiplexer (minimum system configuration) along with the external analog inputs. The multiplexer logic selects the analog input specified by the channel address. The selected analog input is then multiplexed onto a common output line.

#### 2.5.4 Gain Selection

The selected analog signal, after being multiplexed, is supplied to a single-ended gain switching amplifier with selectable gain of 1, 2, 4 or 8. The gain is selected on the basis of the voltage range of the analog inputs. For voltages in the range of 10V, unity gain is selected, whereas voltages in the range of 1.25V require a gain of 8 for full-scale deflection.

Figure 2-1 AD15 Analog Subsystem Functional Block Diagram

Figure 2-2 Analog Addressing

# 2.5.5 Sample and Hold Amplifier

From the gain-switching amplifier, the amplified analog signal is supplied to a sample and hold amplifier that stores rapidly fluctuating analog signals to allow sufficient time for analog-to-digital conversion. The input is continually tracked in the sample mode and is stored in the hold mode for the length of time needed to convert the signal from analog to digital. This time is approximately 35 µs. The sample and hold amplifier is common to all analog channels and can sample any desired input.

# 2.5.6 Analog-to-Digital Conversion

The analog-to-digital converter provides a 12-bit digital equivalent of the analog input with a 13th sign bit used to distinguish between positive and negative voltages. After conversion, the digital word is supplied to a series of bus drivers. On coincidence of the digital word and a data strobe, the data is strobed onto the I/O bus and transferred into the PDP-15 computer.

# 2.5.7 Flag Status and IOT Decoding

The PDP-15 computer can monitor the analog channel address and the status of word count overflow and memory overflow flags by issuing an ADRS instruction, one of the seven IOT instructions used in the AD15. This instruction is normally used for diagnostic purposes. The IOT instructions are decoded from the I/O bus device and subdevice select lines, the IOP pulses, and word count and memory flag status.

# 2.6 DETAILED LOGIC ANALYSIS

The following paragraphs provide additional detailed descriptions concerning the applicable logic schematics. These paragraphs, with the system description, functional description, and signal glossary, provide the user with adequate knowledge of system orientation and detailed theory of operation.

# 2.6.1 Status Register and Buffered Data Register

The upper half of block schematic AD15-0-03 represents the 13-bit buffer register (12 bits plus sign bit) that receives the 13-bit digital data from the output of the analog-to-digital converter (see block schematic AD15-0-07). This second stage of buffering stores the converted data word while waiting for the PDP-15 to accept it and allows a second conversion to be started without destroying the contents of the first conversion. The buffer register is strobed by A/D DONE at the end of each conversion. If a memory overflow flag is raised (add-to-memory), the buffer register cannot be loaded because MEM FLAG (1) H inhibits A/D DONE from strobing the register. This allows the programmer the capability of preserving the contents of the buffer register. By preserving the contents of the buffer register, the original value in memory before add-to-memory can be reconstructed. For example, assume the memory location contained the value X and the value Y was added to it, resulting in the sum of Z with a sign change. When overflow occurred, the original value (X) in memory is lost but by preserving Y in the buffer register and knowing the value of Z it is possible to reconstruct the value X.

The lower portion of block schematic AD15-0-03 shows the various control flip-flops that are set or reset by the control bits of the input status word. The flip-flops include sequential/random, add-to-memory, external/internal sync, data channel/program control, memory enable/disable, and the two gain switching flip-flops (G\$01 and G\$02). The control flip-flops are strobed by SELECT CLOCK, which is generated during data channel, when no word count overflow occurs or when an ADCV IOT instruction is issued under program control.

# 2.6.2 Multiplexer Channel Address Register

Block schematic AD15-0-04 shows the seven-stage channel address register employed. The register is preset with the starting address and is incremented on completion of each conversion in sequential mode. Note that the register uses jam transfer. Either the true (set) or complement (reset) version of each address bit is present at the input to the register. Consequently, the input address can be properly loaded into the register regardless of the previous contents.

#### NOTE

The input bits are inverted on the I/O bus and inverted a second time through the channel address register, restoring the bits to their original value.

The SEQ input to the register enables the register during sequential operation, and the COUNT signal causes the register to increment after each conversion. The COUNT signal is generated on block schematic AD15-0-05 as a result of A/D DONE, the DCH/PRG CTRL flip-flop in DCH mode, and WC FLAG (1) H.

The input address to the channel address register is strobed by SELECT CLOCK, which occurs as a result of an ADCV instruction or a LOAD signal. LOAD occurs during direct memory access if no word count flag is present and if IOP4 (PDP-15 to AD15 transfer) is present. During add-to-memory, it is necessary to inhibit IOP4 from affecting certain logic in the AD15. This is accomplished when both write (WR) and read (RD) signals are present; these signals occur only during add-to-memory.

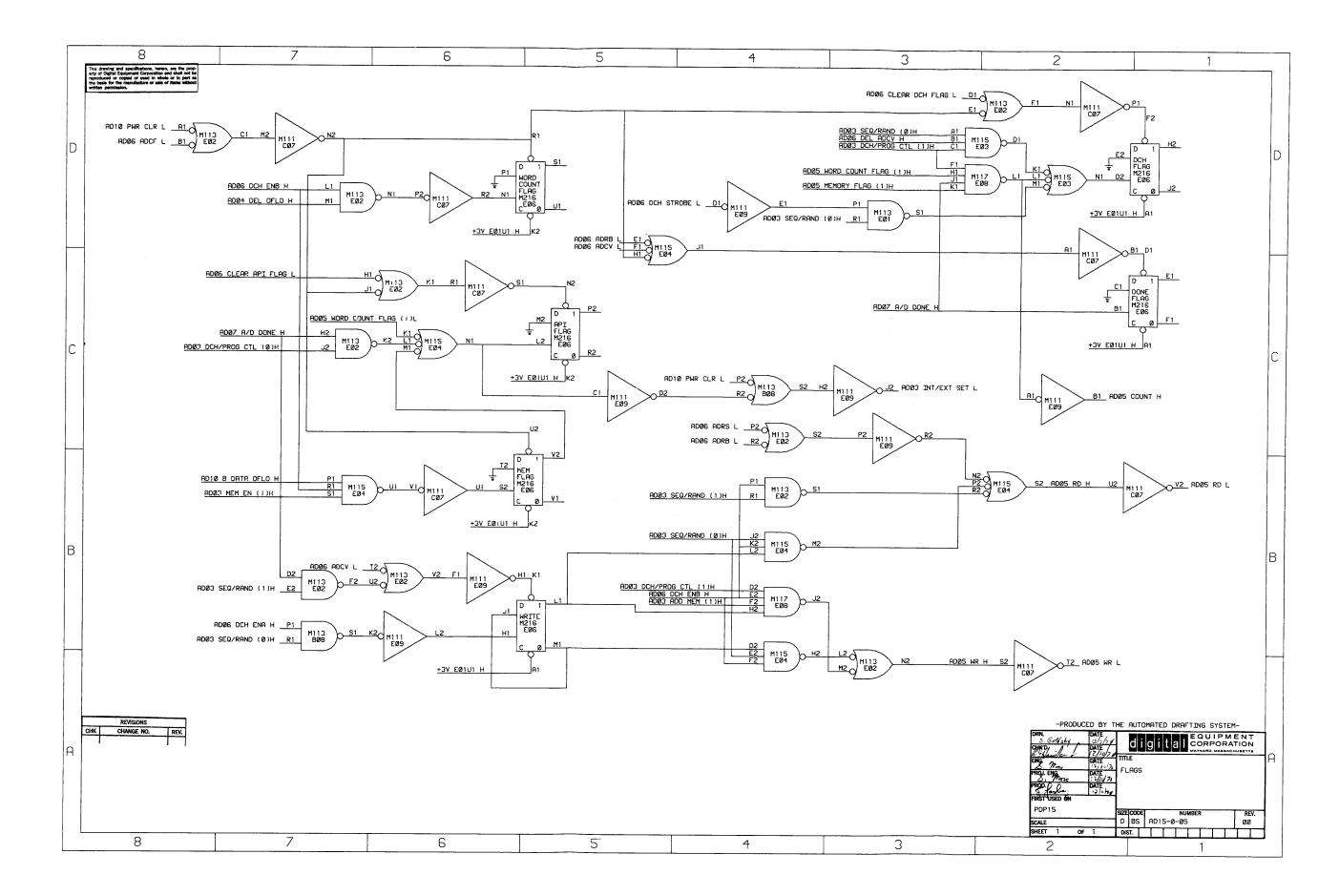

# 2.6.3 Flag Logic

Block schematic AD15-0-05 shows the logic necessary to implement the following flags:

- a. Word count flag

- b. API flag

- c. Memory flag

- d. DCH flag

- e. Done flag

In addition, the block schematic contains the read and write logic necessary to implement transfers to and from the PDP-15.

2.6.3.1 Word Count Flag - The word count flag is employed during sequential and random operation. In sequential mode, a word count location in PDP-15 memory (location 26) is preset with the 2's complement of the number of data words to be transferred. This location is incremented each time a word is converted to digital. In random mode, memory location 24 is also preset with the 2's complement of the number of data words to be transferred. In addition, however, memory location 24 is preset with one less than the 2's complement of the number of data words to be transferred. Each time a data word is transferred, location 26 is incremented; each time a status word is transferred to the AD15, location 24 is incremented. When location 26 increments from all 7s to all 0s, an overflow signal is generated indicating that the desired number of words have been converted. In addition to the overflow signal, a data channel enable signal (DCH ENB) is required to raise the word count flag indicated by WORD COUNT FLAG (0) H. The flag flip-flop can be reset by a power clear or ADCF IOT instruction, which clears all flags. The word count flag, when raised, is supplied to the PDP-15 and to the IOT decoding logic to enable a program skip, when executed. It is also supplied as an inhibit to the API, DCH, and select clock logic.

# NOTE

The word count flip-flop is delayed by 2  $\mu$ s due to the delay multivibrators shown on block schematic AD15-0-04 (see DEL OFLO). The flip-flop is delayed by 2  $\mu$ s to enable IOP2 to allow the last data word in a series of conversions to be transferred.

- 2.6.3.2 API Flag The API flag is designed to cause an API interrupt if the API option is installed in the PDP-15. When the interrupt occurs, the program traps to location 57<sub>8</sub>. This location normally contains a jump-to-subroutine (JMS), which stores the contents of the PDP-15 program counter in the first address of the subroutine. The next instruction is the start of the AD15 service routine. On completion of the routine, a JMP \* (jump indirect) returns control to the main program at the point where the interrupt occurred. The API flag can be raised under any of the following three conditions:

- a. Word count overflow indicated by WORD COUNT FLAG (1) L.

- b. Under program controlled transfers, when a data word has been converted (A/D DONE), and

- c. Under add-to-memory operation, when overflow occurs (MEM FLAG (0) H).

The API flag, when raised, is indicated as API FLAG (0) H and can be cleared by power clear, ADCF, or clear API flag signals. The API flag is supplied to the M104 API Multiplexer Control Module to initiate an API request (API RQ 00), which is supplied to the PDP-15 via the I/O bus.

2.6.3.3 Memory Flag - The memory flag is raised when data overflow occurs during add-to-memory operation only. Data overflow occurs when the contents of an existing memory location is added to a data word in the PDP-15 adder and the sum results in a change of sign. To raise the memory flag, bit 6 (memory enable overflow) must be set, and bit 9 (add-to-memory) of the input status word must be set. These bits set the memory enable and add-memory flip-flops, respectively (see block schematic AD15-0-03). The add-memory flip-flop must be set to initiate a write request during add-to-memory operation. The write request sent to the PDP-15 causes the contents of the specified memory location to be strobed into the PDP-15 adder, where it is added with the converted data word. If overflow (change of sign) occurs, a DATA OFLO signal is generated in the PDP-15 and transferred to the AD15.

This signal and the memory enable (MEM EN) signal, generated by bit 6 of the input status word, cause the memory flag to be raised. The flag can be lowered by power clear or the ADCF IOT instruction. The memory flag is supplied to the PDP-15 computer via the I/O bus and is also applied to the IOT decoding logic to enable a program skip if memory overflow occurs.

- 2.6.3.4 Read/Write Logic The read/write logic on block schematic AD15-0-05 is used to request a read (transfer to memory) or write (transfer from memory) cycle from the PDP-15. A read request is generated under any of the following condition:

- a. Issuance of ADRS or ADRB IOT instructions,

- b. Operating in sequential mode, or

- c. Operating in random mode for a read operation.

A write request is generated under any of the following conditions:

- a. In add-to-memory mode, under sequential operation or when doing a read operation.

- b. In random mode, when doing a write operation.

The WRITE flip-flop (M216-E05) is wired with a toggle input and is enabled when in random mode. When the flip-flop is in the write state (reset) a status word is transferred to the AD15. When the flip-flop toggles to the read state (set) on the next DCH ENA pulse, a data word is transferred to the PDP-15.

- 2.6.3.5 DONE Flag The DONE flag is raised by A/D DONE, which occurs at the end of a conversion. It is used in conjunction with the skip logic on block schematic AD15-0-06. The flag can be cleared by ADRB, ADCV, or ADCF IOT instructions or by the PWR CLR signal.

- 2.6.3.6 DCH Flag The data channel (DCH) flag can be raised as a result of A/D DONE during data channel activity, providing word count overflow has not occurred. This flag is raised to allow the data word to be transferred to PDP-15 memory. A second method of raising the DCH flag occurs during data channel random operation. In this operation, it is necessary to transfer the first status word to the AD15 by means of the ADC instruction. Subsequent status word transfers occur as a result of IOP2 of the preceding data word transfer. The DCH flag can be lowered by PWR CLR or CLEAR DCH FLAG signals or by the ADCF IOT instruction. The DCH flag is first applied to the M104 Data Channel Multiplexer Control Module and then to the PDP-15 via the I/O bus as DCH REQ to initiate a data channel request to the PDP-15.

# 2.6.3.7 Flag Testing - The following flags generated in the AD15 can be tested by the programmer:

| Flag      | Raised by                                                     | Lowered by                           |

|-----------|---------------------------------------------------------------|--------------------------------------|

| WC Flag   | I/O OFLO                                                      | ADCF or PWR CLR                      |

| API Flag  | WC Flag or A/D DONE<br>(under program control) or<br>MEM Flag | PWR CLR or ADCF or<br>CLEAR API FLAG |

| MEM Flag  | DATA OFLO<br>(MEM EN Bit must be set)                         | PWR CLR or ADCF                      |

| DONE Flag | A/D DONE                                                      | ADRB or ADCV or<br>PWR CLR or ADCF   |

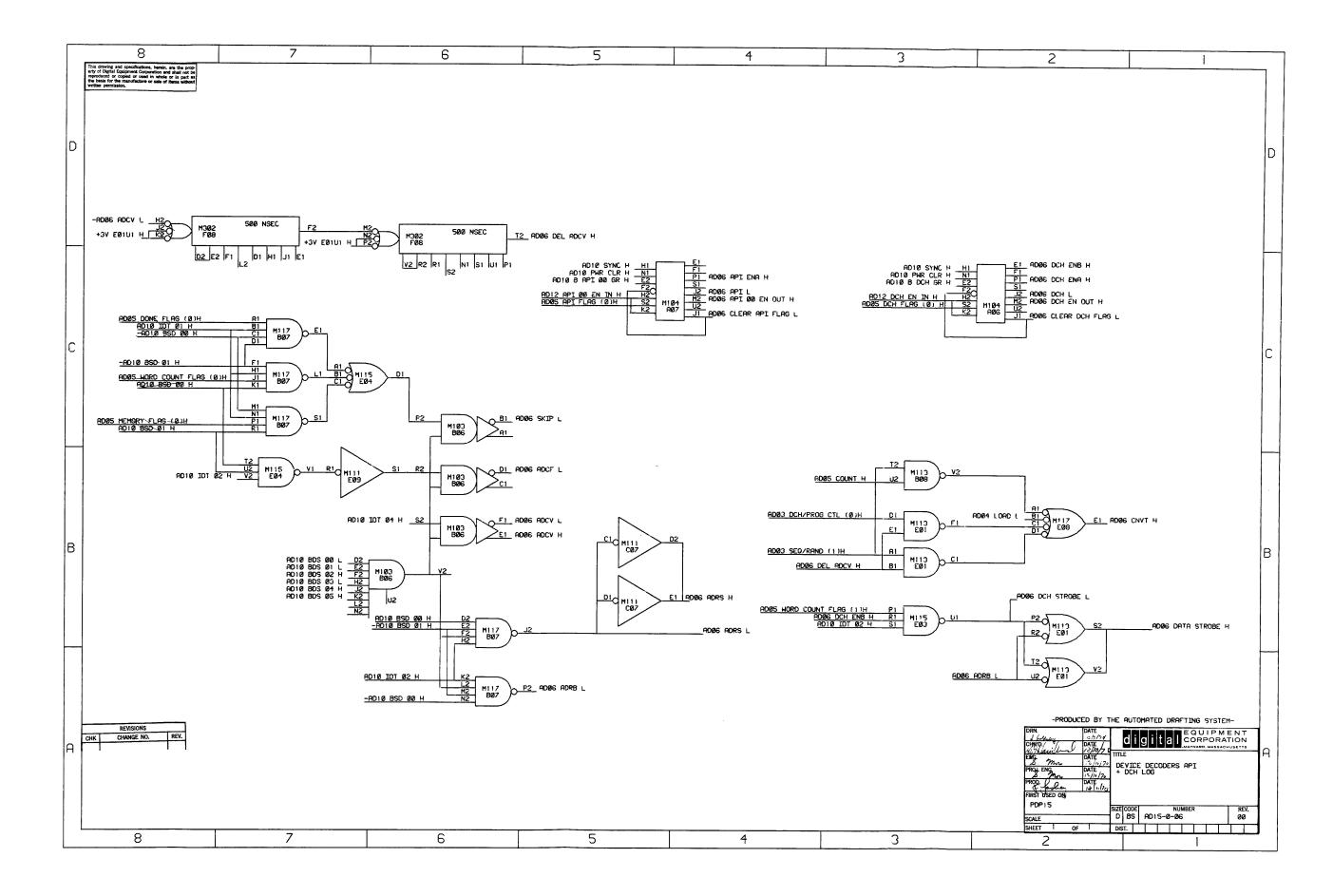

# 2.6.4 Device Decoders, API and Data Channel Logic

Block schematic AD15-0-06 contains the logic used to decode the various IOT instructions. Three of the IOTs (ADSF, WCSF, and MSSF) cause a SKIP signal to be generated. This signal is supplied to the PDP-15 to cause a skip of the next sequential instruction in the main PDP-15 program.

#### NOTE

The IOT instructions associated with transferring status to the AD15 are enabled by an IOT 04 signal (bit 15 of status word), and the IOT instructions associated with transferring data to the PDP-15 are enabled by the IOT 02 signal (bit 16 of the status word).

A complete description of the M104 API and data channel multiplexer control modules can be found in the PDP-15 Interface Manual or the PDP-15 Module Manual.

The convert (CNVT) pulse is applied to the analog-to-digital converter when internal sync is employed. The convert pulse logic, shown on block schematic AD15-0-06, permits the convert pulse to be generated under any of the conditions below:

- a. In sequential mode, the first convert pulse is generated as a result of SEQ (1) H and DEL ADCV H. All other convert pulses in this mode are generated as a result of A/D DONE, the DCH flip-flop being set, absence of the word count flag, and absence of the memory flag.

- b. In random mode, the convert pulse is generated as a result of the LOAD signal (see block schematic AD15-0-06).

- c. In program control mode, DEL ADCV (delayed from ADCV by 1.0 μs) causes the convert pulses to be generated.

A signal, designated DCH STROBE, is generated on AD15-0-06 and is used to raise the DCH flag (see AD15-0-05) in random mode. This signal allows input status words to be transferred to the AD15.

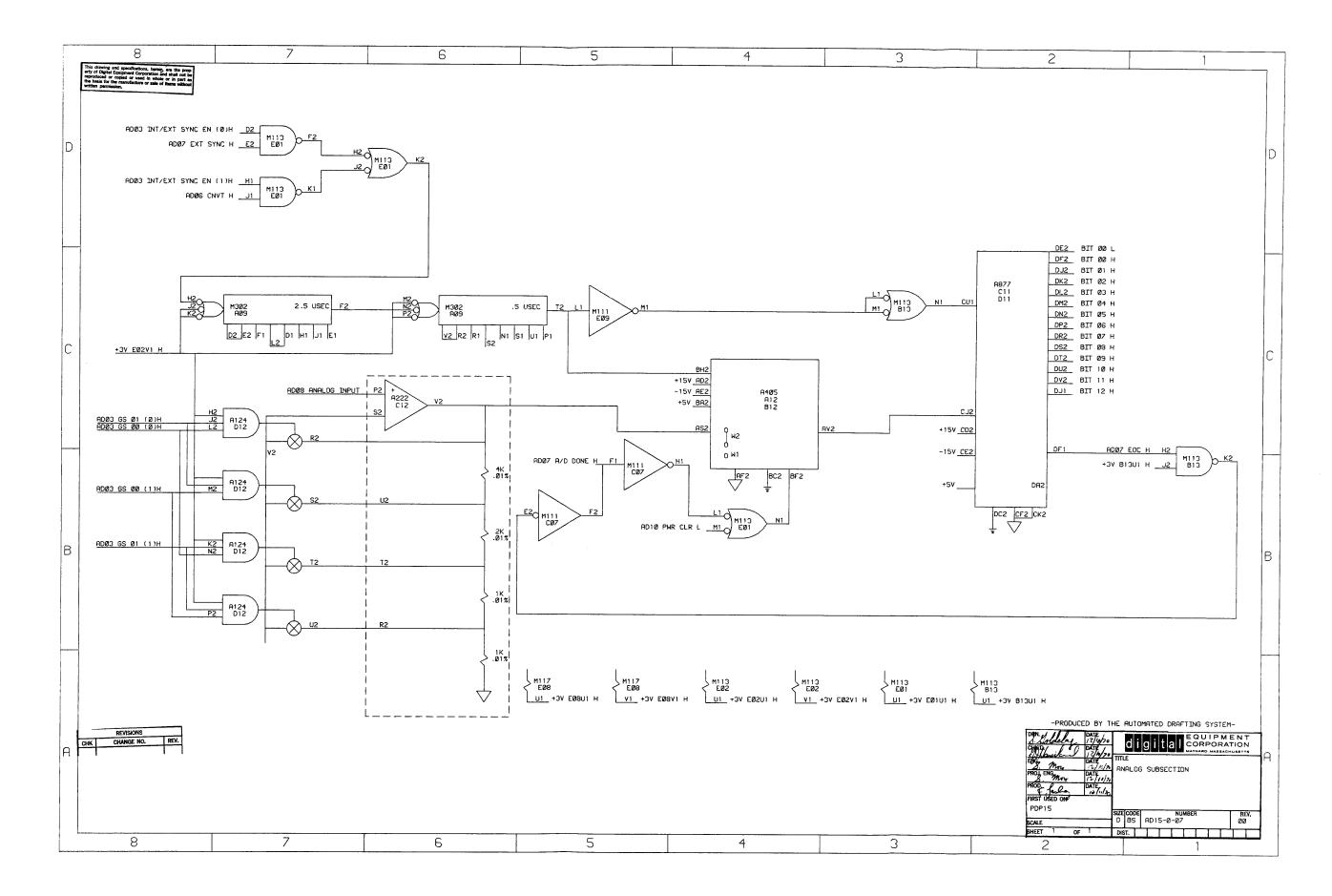

# 2.6.5 Analog Subsection

Block schematic AD15-0-07 contains the internal/external sync logic, gain switching logic, sample and hold amplifier, and analog-to-digital converter. Either internal or external sync is required to initiate the timing for the analog-to-digital conversion. If internal sync is used, the convert pulse, internally generated on AD15-0-06, initiates the timing. A delay of 4.5 µs is necessary, before the conversion is started, to allow for amplifier, multiplexer switch, and sample and hold settling. Two M302 Dual Delay Multivibrators provide this function. If external sync is employed, the conversion is not started until an external sync pulse is received (see Figure 2-3).

Figure 2-3 External Sync Timing Diagram

2.6.5.1 Gain Switching - Gain switching is accomplished by the A124 Multiplexer, which selects one of four possible gains (1, 2, 4 or 8) for the A222 Operational Amplifier. The gain switching bits (GS00 and GS01 of the input status word) specify the selected gain, as shown.

| <u>Gain</u> | <u>G\$00</u> | GS01 |  |

|-------------|--------------|------|--|

| 1           | 0            | 0    |  |

| 2           | 0            | 1    |  |

| 4           | 1            | 0    |  |

| 8           | 1            | 1    |  |

#### NOTE

When an interrupt is issued, the EXT SYNC/INT SYNC flip-flop is forced to INT SYNC to prevent undesired conversions from occurring without the programmer's knowledge. External sync pulses will cause conversions as long as the EXT/INT SYNC flip-flop is on EXT SYNC. Therefore, it is necessary to have this flip-flop on INT SYNC for the last conversion. This is accomplished by the EXT/INT SET L signal generated on drawing AD15-0-05.

- 2.6.5.2 Sample and Hold Amplifier The amplified analog signal is then applied to sample and hold amplifier A405, which samples and stores the input at 25 kHz, minimum. The sample and hold amplifier provides the capability of sampling and storing extremely rapid analog fluctuations, which could not otherwise be accurately measured.

- 2.6.5.3 Analog-to-Digital Converter The output from the sample and hold amplifier is applied to the A877 Analog-to-Digital Converter, where the analog signal is converted to a 13-bit digital word (12 bits plus sign bit). Conversion time is approximately 35 µs, and at the completion of this period, an A/D DONE signal is generated indicating the conversion is complete. In sequential mode, while the first conversion is waiting to be transferred to the PDP-15 memory, the second analog signal is being converted as a result of A/D DONE, which enables the next convert pulse to initiate a

conversion. After the conversion, which takes approximately 35  $\mu$ s, A/D DONE is issued which, in turn, enables another convert pulse to be issued. The timing relationships for this interaction are shown on Figure 2-4.

Figure 2-4 Sequential Mode Timing Relationships

In random or program controlled mode, a new status word must be loaded prior to another conversion. The timing relationships for this mode of operation are shown in Figure 2-5. The A/D DONE signal, in addition to being supplied to the circuits previously described, is also applied to the sample and hold amplifier as a reset to allow new analog inputs to be sampled and stored.

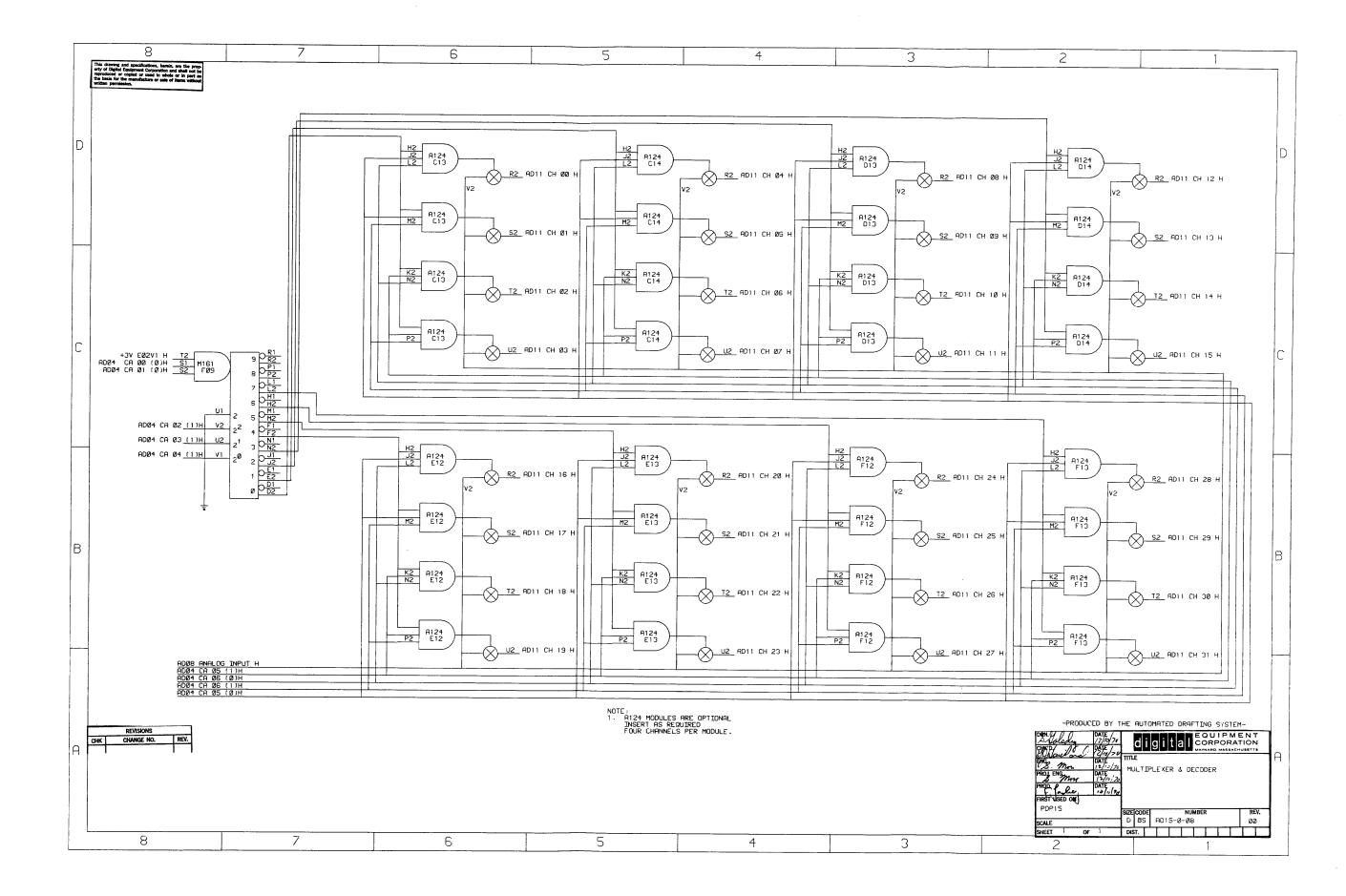

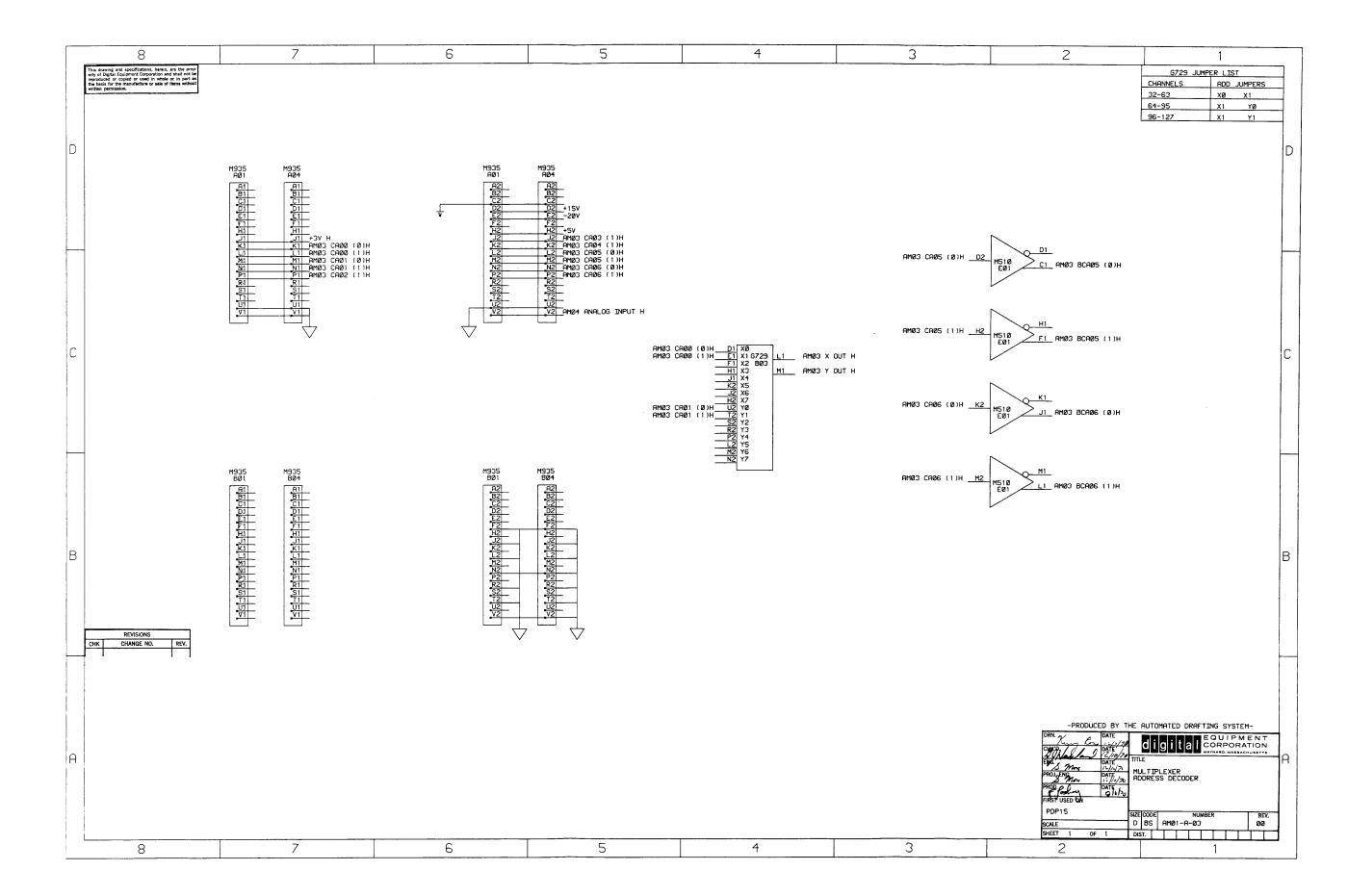

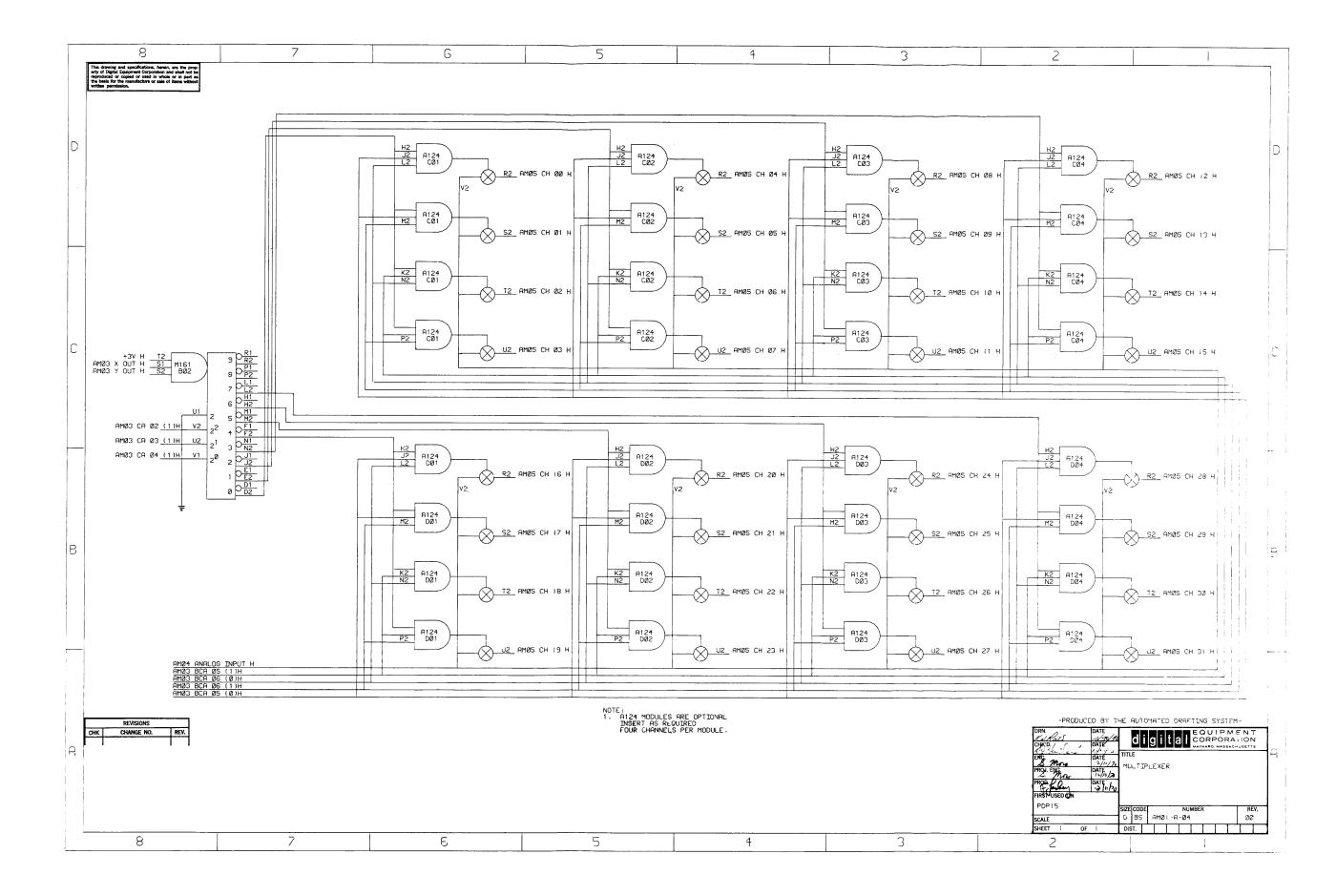

### 2.6.6 Binary-Octal Decoder and Analog Multiplexer

Block schematic AD15-0-08 shows the binary-to-octal decoder and a 32-channel multiplexer designated A124. This logic is necessary for a 32-channel system. For each additional 32 channels added to the system, an additional multiplexer is required; thus, 128 channels (maximum system configuration) requires four multiplexers. The multiplexers are specified by bits 0 and 1 of the analog channel address, as follows.

| 0–31 channels   | CA00=0, CA01=0 |

|-----------------|----------------|

| 32–63 channels  | CA00=0, CA01=1 |

| 64–95 channels  | CA00=1, CA01=0 |

| 96–127 channels | CA00=1, CA01=1 |

Figure 2-5 Random Mode Timing Relationships

Bits 2 through 6 of the analog channel address specify one of 32 channels within the multiplexer designated by CA00 and CA01. For example, in the minimum 0- to 32-channel system, channel 19 is addressed when bits 2, 5, and 6 are logic 1s, and bits 3 and 4 are logic 0s.

# NOTE

The channel numbers shown by 32, with each new AM01-A multiplexer added.

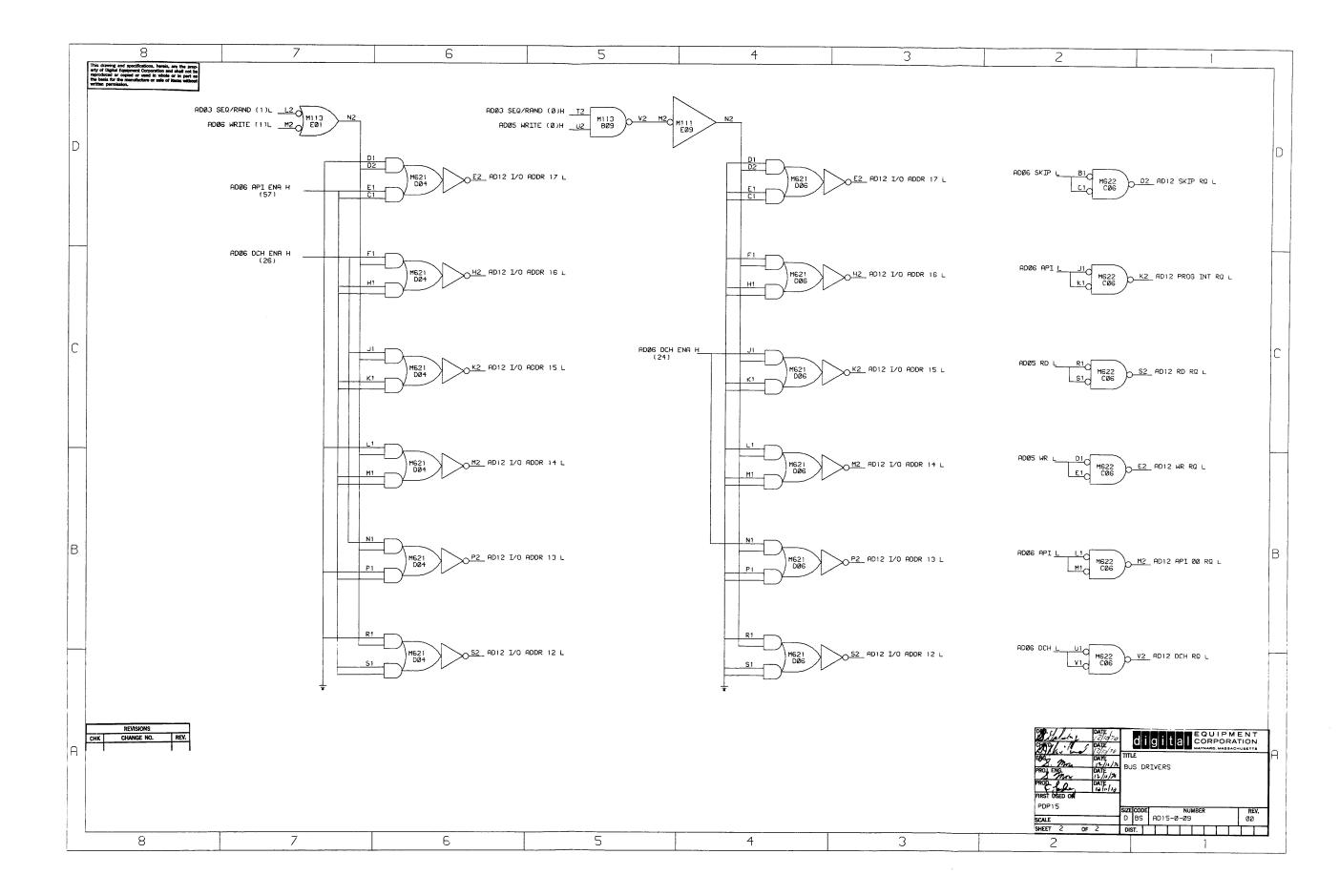

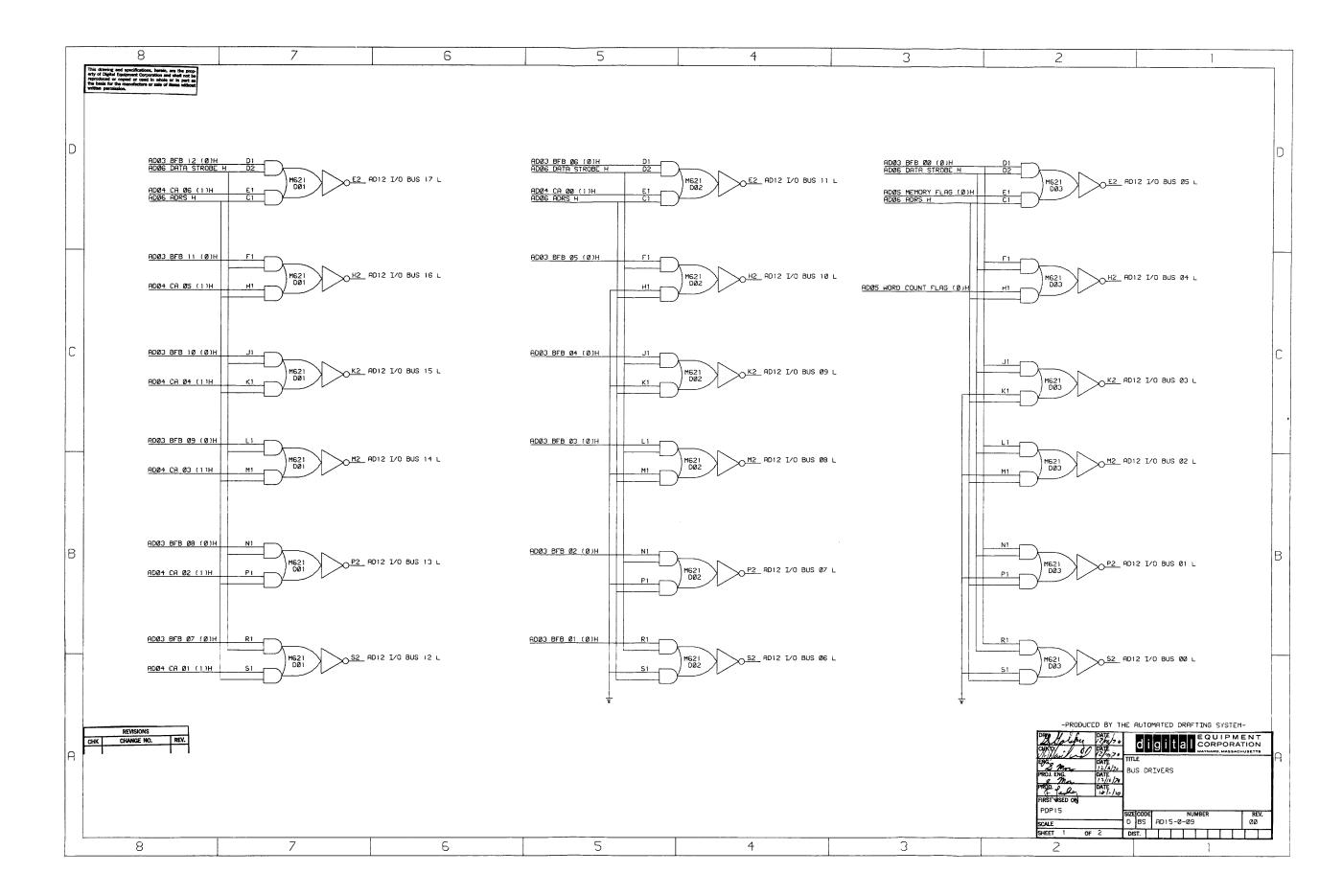

### 2.6.7 I/O Bus Drivers

Block schematic AD15-0-09 (sheets 1 and 2) contain the I/O bus drivers that provide the drive necessary to transmit signals down the I/O bus to the PDP-15 computer. The contents of the 13-stage buffer register is strobed on the I/O bus when DATA STROBE occurs, while the analog channel address is strobed on the I/O bus when the ADRS IOT instruction is issued. The ADRS also enables the PDP-15 to monitor the status of the word count and memory flags.

Sheet 2 of block schematic AD15-0-09 contains the drivers for the API Trap address, the word count addresses (status and data words), and the various request signals. The API Trap address causes lines 12 and 14 through 17 to go low, and 13 to remain high. This represents the complement of the trap address, which is inverted by the I/O bus receivers in the PDP-15 to yield the true address.

The data word count address (26) is enabled by a READ signal indicating a request to transfer information to the PDP-15. The information in this case is the data word count address. I/O address lines 13, 15, and 16 are driven low and 12, 14, and 17 remain high, representing the complement of the word count address of 26. This complement is again inverted in the I/O bus receivers to yield the true version of the address. The status word count address (24) is enabled during a write operation if the AD15 is in random mode. I/O address lines 13 and 15 are driven low and 12, 14, 16, and 17 remain high, representing the complement of the word count address of 24. The complement is inverted by the I/O bus receivers to yield the true version of the address.

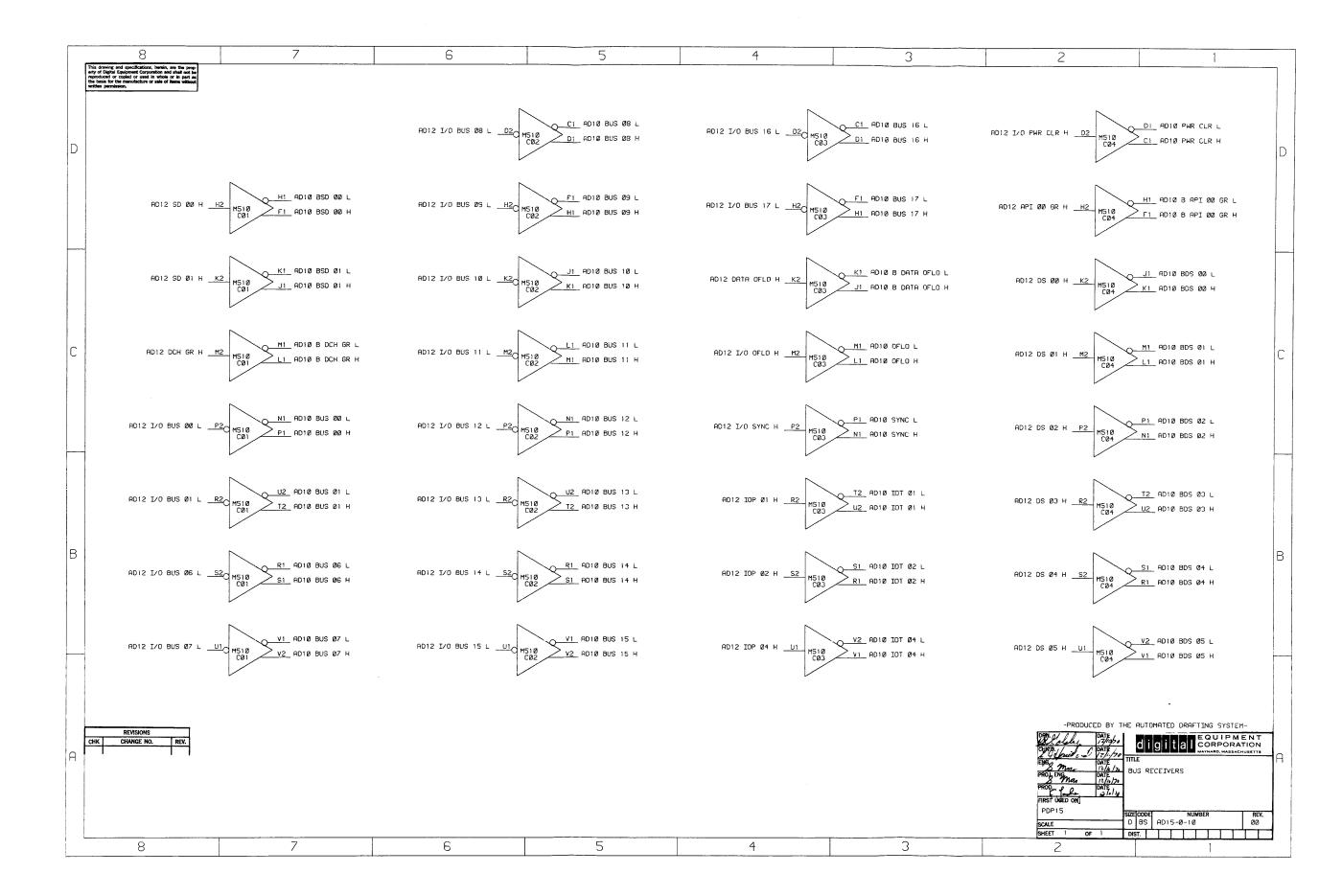

# 2.6.8 Bus Receivers, Analog Inputs, and I/O Bus Interface

Block schematic AD15-0-10 shows the I/O bus receivers that receive signals from the PDP-15 I/O bus drivers. Both the true and complement versions of the signals are available at the receiver outputs.

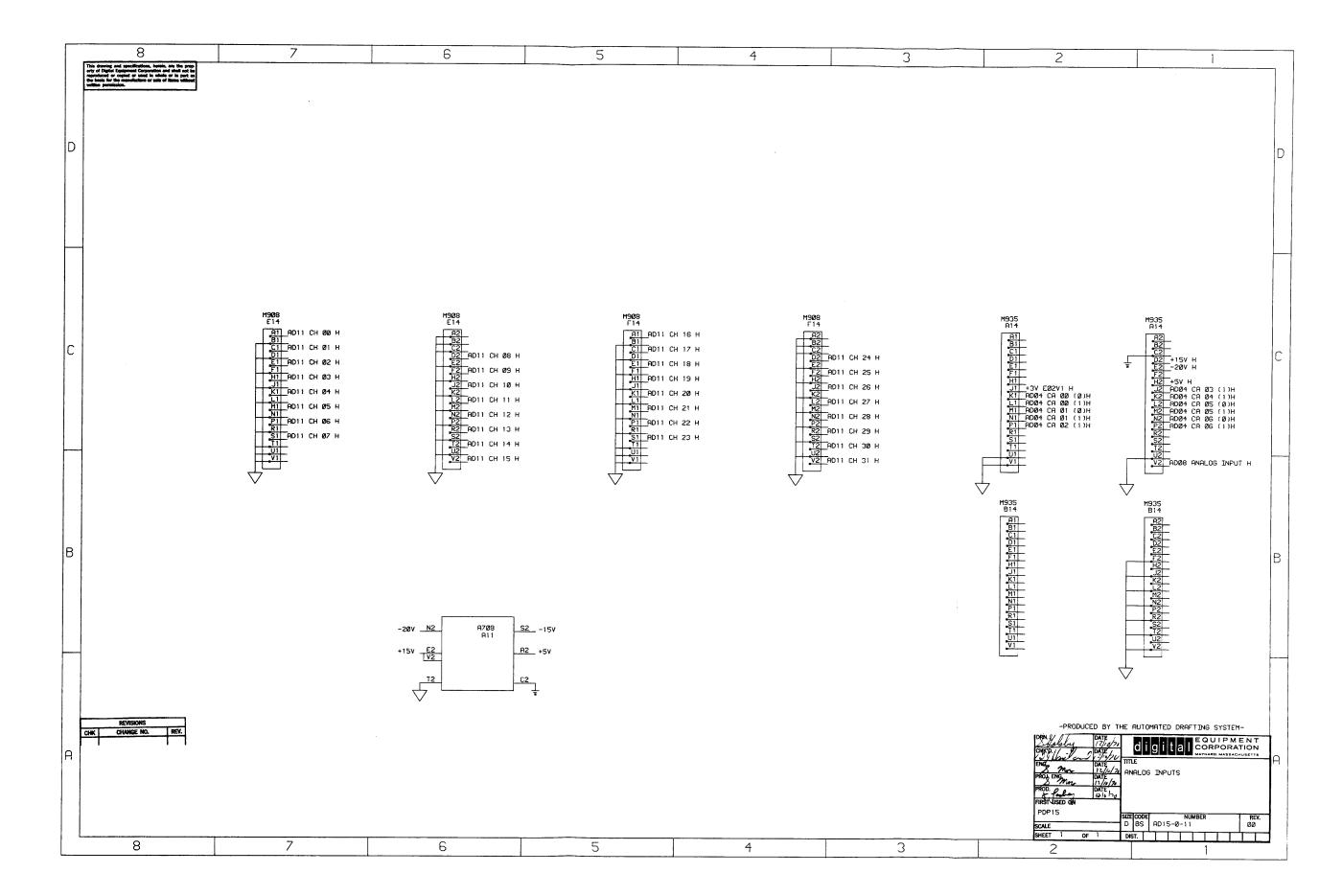

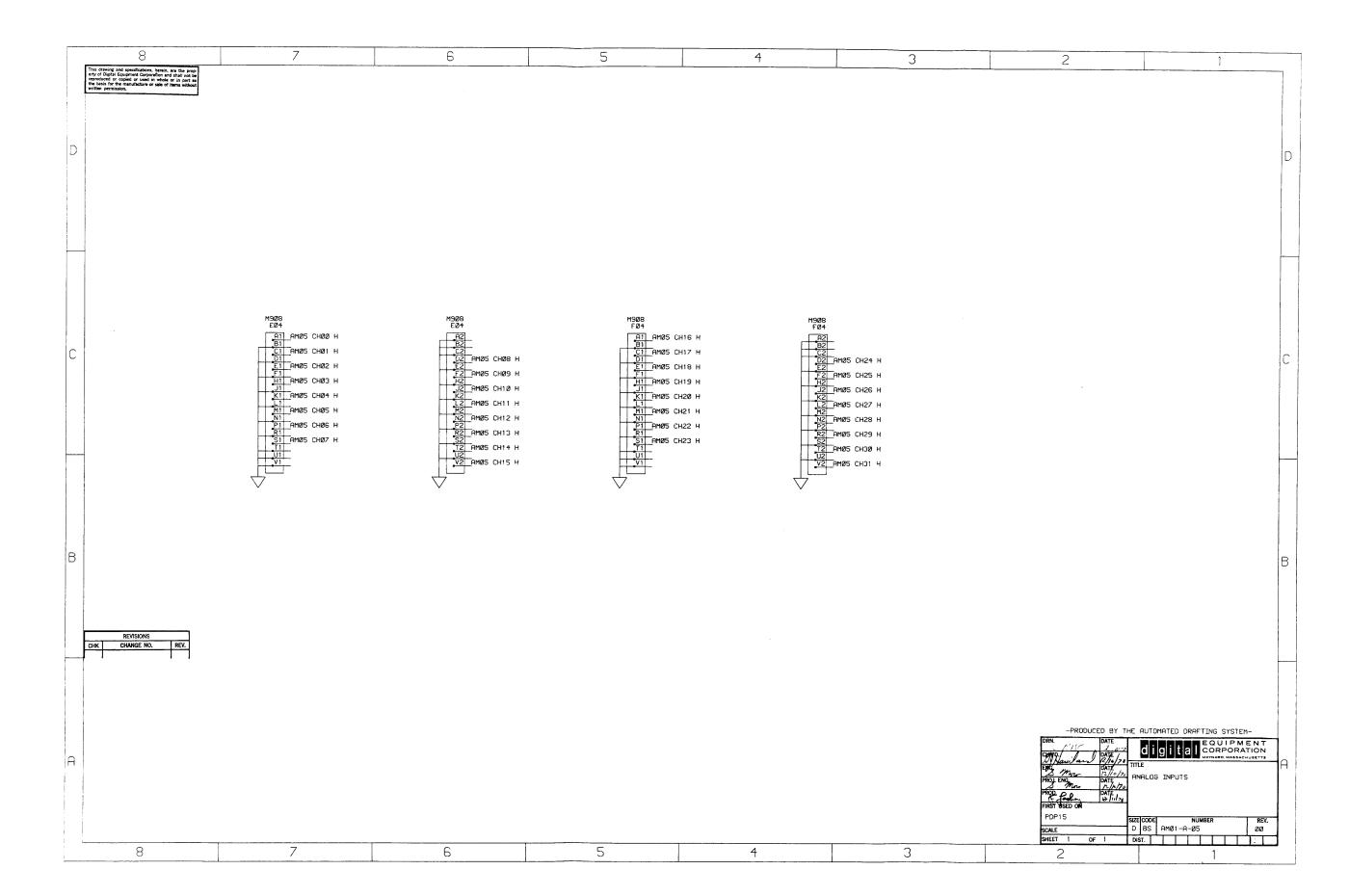

Block schematic AD15-0-11 shows the connections from the external analog inputs to the AD15 subsystem. A more detailed description of these connections can be found in the physical description in Chapter 1 of this manual.

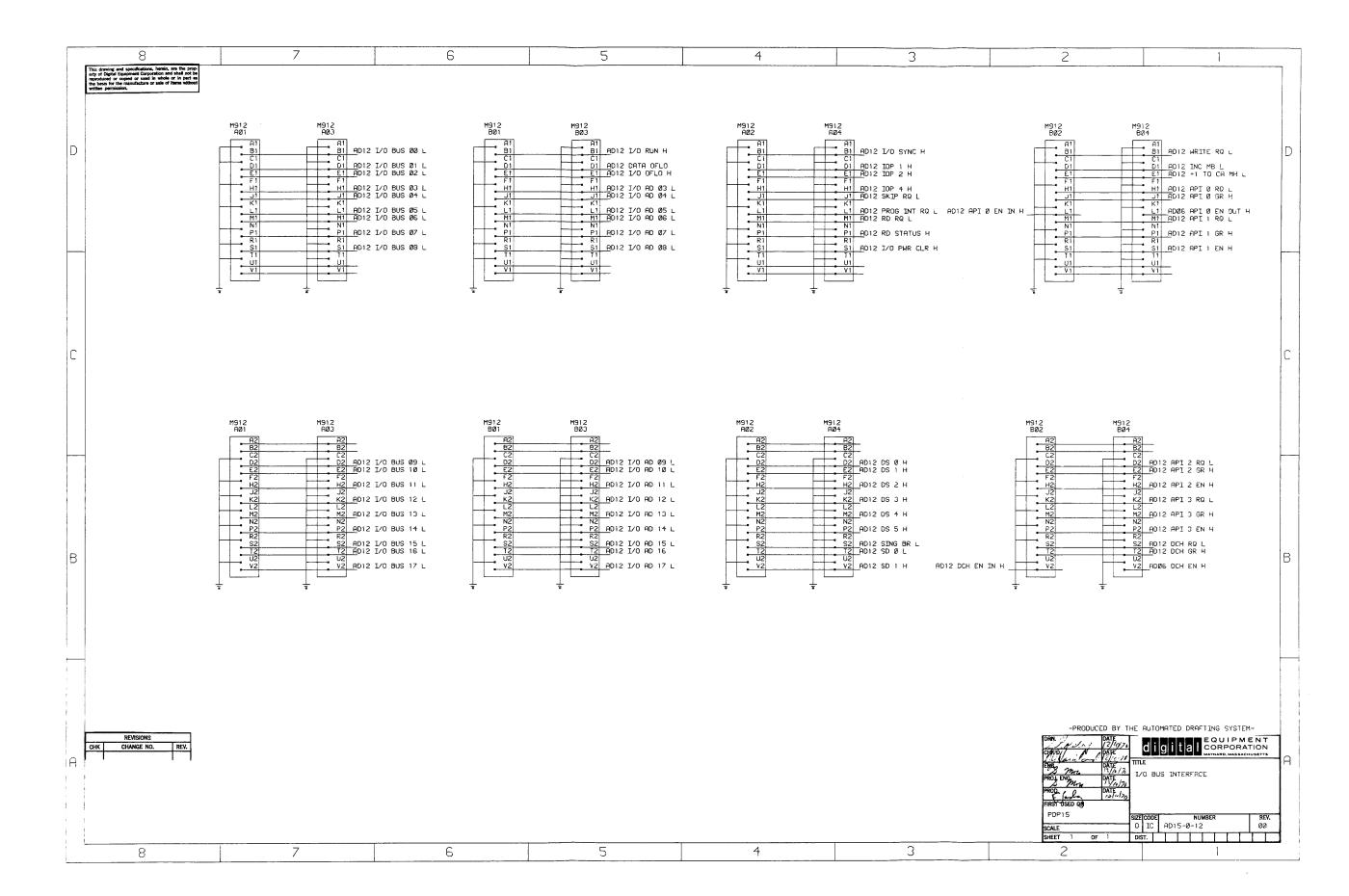

Block schematic AD15-0-12 shows the I/O bus interface containing all the signals between the PDP-15 computer and the AD15 subsystem. Some of the signals shown are not used with the AD15. Figure 1-1 of this manual depicts the signals that are used and do interface between the PDP-15 and the AD15.

#### 2.6.9 Expansion Unit AM01

Each AM01 (a maximum of three) provides the AD15 with 32 additional channels for increasing the system configuration. Block schematics AM01-A-03 through AM01-A-05 show the AM01 circuitry. Block schematic AM01-A-03 shows the M908 Card that provides connections for 32 additional channels. Thus, each AM01 contains a M908 Connector to interface the PDP-15 to the external analog sources. Block schematic AM01-A-04 contains an A124 Multiplexer that provides multiplexer capability for an additional 32 channels. Block schematic AM01-A-05 shows the M935 Bus Extender Card, which is provided to jumper the operating voltages and the appropriate channel address bits to the AM01. The right-hand section of the drawing shows the M510 I/O Bus Receivers used to increase the fan-out capability for channel address bits CA05 and CA06.

# CHAPTER 3 IOT INSTRUCTION FORMAT

# 3.1 EQUIPMENT TURN-ON/TURN-OFF PROCEDURES

There are no special turn-on or turn-off procedures associated with the AD15 subsystem. The normal PDP-15 turn-on procedure is all that is required to initiate AD15 operation.

#### 3.2 INSTRUCTION AND DATA FORMATS

The AD15 Analog Subsystem uses a total of seven IOT instructions for system operation. These instructions provide transfer of status information and data between the PDP-15 computer and the AD15 subsystem. The IOTs also provide clearing of flags and force program skips when certain flags are raised. The IOTs are described in the following paragraphs and are followed by a description of the input status word (from the PDP-15 to the AD15), output status word (from the AD15 to the PDP-15), and the converted data word (from the AD15 to the PDP-15).

#### 3.2.1 IOT TIMING

For a description of IOT Timing, refer to the PDP-15 Maintenance Manual.

#### 3.2.2 IOT INSTRUCTION FORMAT

The format for the IOT instruction is shown in Figure 3-1. Bits 0 through 5 specify the IOT operation code of 70g; bits 6 through 11 are device select bits, and bits 12 and 13 are subdevice select bits. The device select bits specify an octal code of 13g to uniquely address the AD15. These bits are also used in conjunction with the subdevice select bits to decode the various IOT instructions. Bit 14 is a microprogrammable bit that is used to clear the PDP-15 accumulator. Bits 15, 16, and 17 are the IOP4, IOP2, and IOP1 pulses, respectively. These bits are also microprogrammable. IOP4 is employed in the transfer of information from the PDP-15 to the AD15. IOP2 is employed in the transfer of information from the PDP-15. IOP1 is used for I/O skip instructions to test a device flag. For transfers between the PDP-15 and the AD15, the first 12 bits (operation code and device select code) are fixed (7013--8). Bits 12 through 17 can be altered depending on the type and direction of transfer.

Figure 3-1 IOT Instruction Format

- 3.2.2.1 ADCV (convert) Octal Code 701304 This IOT instruction transfers the contents of the PDP-15 accumulator (containing the input status word) to the AD15 Analog Subsystem, clears the A/D DONE flag, and initiates timing for the analog-to-digital conversion.

- 3.2.2.2 ADRB (read data buffer) Octal Code 701302 This IOT instruction transfers the converted data from the AD15 data buffer to the PDP-15 accumulator and clears the A/D DONE flag.

- 3.2.2.3 ADRS (read status register) Octal Code 701342 This IOT instruction transfer certain contents of the AD15 status register to the PDP-15 accumulator (see Paragraph 3.2.3). The status register contains selected gain data, analog channel address, and designated control functions, such as mode, type of operation, sync selection, memory overflow, etc.

- 3.2.2.4 ADCF (clear all AD15 flags) Octal Code 701362 This IOT instruction clears all AD15 flags. These flags include word count overflow, memory, A/D DONE and DCH flags.

- 3.2.2.5 ADSF (skip on A/D DONE flag) Octal Code 701301 This IOT instruction is a skip instruction that causes a program skip of the next sequential instruction if the A/D DONE flag is raised.

#### 3.2.3 Output Status Word Format

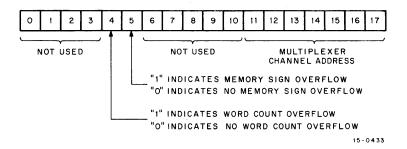

The output status word is a word in the AD15 containing information regarding analog channel selection, and word count and memory sign overflow (see Figure 3-2). The AD15 status can be monitored by transferring the output status word to the PDP-15 accumulator via an ADRS IOT instruction. Bits 0 through 3 of the output status word are not used. A logic 1 in bit 4 indicates a word count overflow, and a logic 1 in bit 5 indicates a memory sign overflow. Bits 6 through 10 are not used, and bits 11 through 17 represent the analog channel address.

Figure 3-2 Output Status Word Format

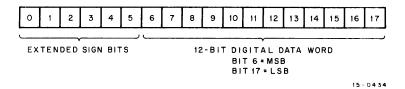

#### 3.2.4 Data Word Format

The format of the converted data word is shown in Figure 3-3. The converted word is a 12-bit, right-justified, 2's complement, data word with extended sign bit (bits 0 through 5). This data word represents the digital value of the analog word after conversion.

Figure 3-3 Data Word Format

- 3.2.4.1 WCSF (skip on word count overflow flag) Octal Code 701341 This IOT skip instruction causes a program skip of the next sequential instruction, if the word count overflow flag is raised. The raising of the word count overflow flag signifies that the desired number of words have been transferred.

- 3.2.4.2 MSSF (skip on memory overflow flag) Octal Code 701321 This IOT skip instruction causes a program skip of the next sequential instruction, if the memory overflow flag is raised. This flag is raised during an add-to-memory operation where the value added to memory was of sufficient magnitude to cause a sign change.

# 3.2.5 Input Status Word

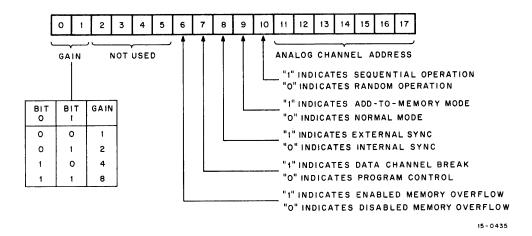

The input status word is the word that is initially loaded in the PDP-15 accumulator prior to the IOT instruction. The IOT instruction causes the contents of the accumulator containing this word to be transferred to the AD15 subsystem. The format of the input status word is shown in Figure 3-4. Bits 0 and 1 determine the gain selected. Bits 2 through 5 are not used. Bits 6 through 10 are control bits and the function of each is defined in Figure 3-4. Bits 11 through 17 comprise the seven-bit analog channel address which specifies one of 128 possible addresses.

Figure 3-4 Input Status Word Format

# 3.3 PROGRAMMING EXAMPLES

The following paragraphs describe several programming examples that illustrate the capabilities of the AD15 in the various modes and types of operation. These examples are described for illustrative purposes and are not intended to replace existing software.

# 3.3.1 Program Control Mode

The following program is an example of a program controlled transfer, where channel 74<sub>8</sub> is to be converted from analog-to-digital, a gain of 4 is to be selected, and external sync is to be employed. The results of the conversion are read into the accumulator.

| 000200/200210 | LAC 210           |

|---------------|-------------------|

| 000201/701304 | ADCV              |

| 000202/701301 | ADSF              |

| 000203/600202 | JMP1              |

| 000204/701312 | CLA! ADRB         |

| 000205/740040 | HLT               |

| 000210/401074 | INPUT STATUS WORD |

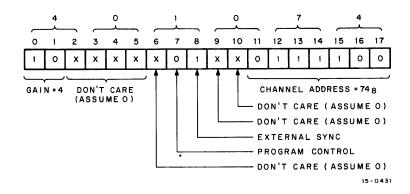

The first instruction (LAC 210) loads the accumulator with the contents of location 210, which is the input status word. The format of the input status word for this example (401074) is shown in Figure 3–5. For those bits which are not used or are "don't cares", logic 0s have been assumed. The results are the same if logic 1s are assumed; the only difference is the octal value of the status word.

The computer has set up the status word specifying the various parameters for the conversion (see Figure 3-5). The ADCV instruction then transfers the status word in the accumulator to the AD15, clears the A/D DONE flag, and initiates timing for the conversion. The ADSF (skip on A/D flag) and

JMP. -1 instructions form a waiting loop that allows time for the conversion to be completed. On completion of the conversion, the A/D flag is raised and the ADSF instruction causes a program skip of the JMP. -1 instruction. The CLA! ADRB instruction clears the accumulator and transfers the converted data word of channel 74<sub>8</sub> to the PDP-15 accumulator. The next sequential instruction (HLT) halts the program. Thus, the analog signal in channel 74<sub>8</sub> has been converted to digital and transferred to the PDP-15 accumulator.

Figure 3-5 Example of Program Control Input Status Word

# 3.3.2 Data Channel Mode - Sequential Operation

The following program uses the sequential feature of the data channel mode of operation. The analog inputs from 16<sub>8</sub> successive channels starting at location 37<sub>8</sub> are to be converted to digital data. The converted data is to be stored in successive locations, starting at location 400. The following parameters are to be selected:

Gain = 1 Add-to-memory feature Enable memory sign overflow Internal sync

Initially, it is necessary to preload the word count and current address locations (26, and 27, respectively). The word count location is loaded with 777762<sub>8</sub> (2's complement of 16<sub>8</sub>). The current address location is loaded with one less than the starting address or 000377<sub>8</sub>, because the current address is incremented before the first conversion takes place. Consequently, the first converted word is transferred to location 400, the second to location 401, etc.

Figure 3-6 shows the format of the status word associated with this example; this status word is initially stored in location 000170.

The following sample program, starting at location 100, accomplishes the successive conversions previously stated.

| 000100/200170 | LAC 170           |

|---------------|-------------------|

| 000101/701304 | ADCV              |

| 000102/701341 | WCSF              |

| 000103/600102 | JMP1              |

| 000104/600350 | JMP 350           |

| 000170/006637 | Input Status Word |

The first instruction loads the status word stored in location 000170 (006637) into the accumulator. The ADCV instruction transfers the status word to the AD15, clears the A/D DONE flag, and initiates the timing for the conversion.

Figure 3-6 Example of Sequential Mode Status Word

The next two instructions (WCSF and JMP. -1) form a waiting loop for the conversion to be completed. The PDP-15 can be programmed to execute normal program sequences during this time. At the conclusion of the conversion, the AD15 issues an A/D DONE signal and requests a data channel break. When the PDP-15 grants this request, the word count is incremented to 777763, the current address is incremented to 400, and the converted data word is transferred to the PDP-15 and stored in location 400. While the AD15 is converting the next data word, the PDP-15 is free to operate normal program sequences. After the data word is converted, another A/D DONE signal is generated and a second data channel request is initiated. When the request is granted, word count is incremented to 777764, current address is incremented to 401, and the data word is then transferred to memory location 401. The process continues until the word count transitions change from all 7s to all 0s. The PDP-15 senses this as word count overflow and generates an overflow signal. This signal is then sent to the AD15 to raise the word count flag. This flag causes a program interrupt, or automatic priority interrupt to occur if these systems are enabled. The interrupt, when acknowledged, indicates that the required number of data words have been converted and stored in the PDP-15 memory. In the preceding example, when the word count flag is raised, the WCSF instruction causes a program skip of the JMP. -1 instruction and allows execution of the JMP 350 instruction to occur.

## 3.3.3 Data Channel Mode - Random Operation

The following program illustrates random operation in the data channel mode. Convert the following three channels using the control functions indicated:

- a. Channel 114 (octal) gain of 1, add-to-memory mode, enabled memory overflow, internal sync