1st Edition March, 1970 2nd Edition July, 1972

Copyright © 1970, 1972 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

COMPUTER LAB

# CONTENTS

|           |                                    | Page |                    |                                                                  | Page       |

|-----------|------------------------------------|------|--------------------|------------------------------------------------------------------|------------|

| CHAPTER   | 1 GENERAL INFORMATION              |      | 2.3.2              | Input and Output Organization                                    | 2-6        |

| 1 1       | Comment                            | 1.1  | 2.3.3              | Input and Output Assignment Tables                               | 2-6        |

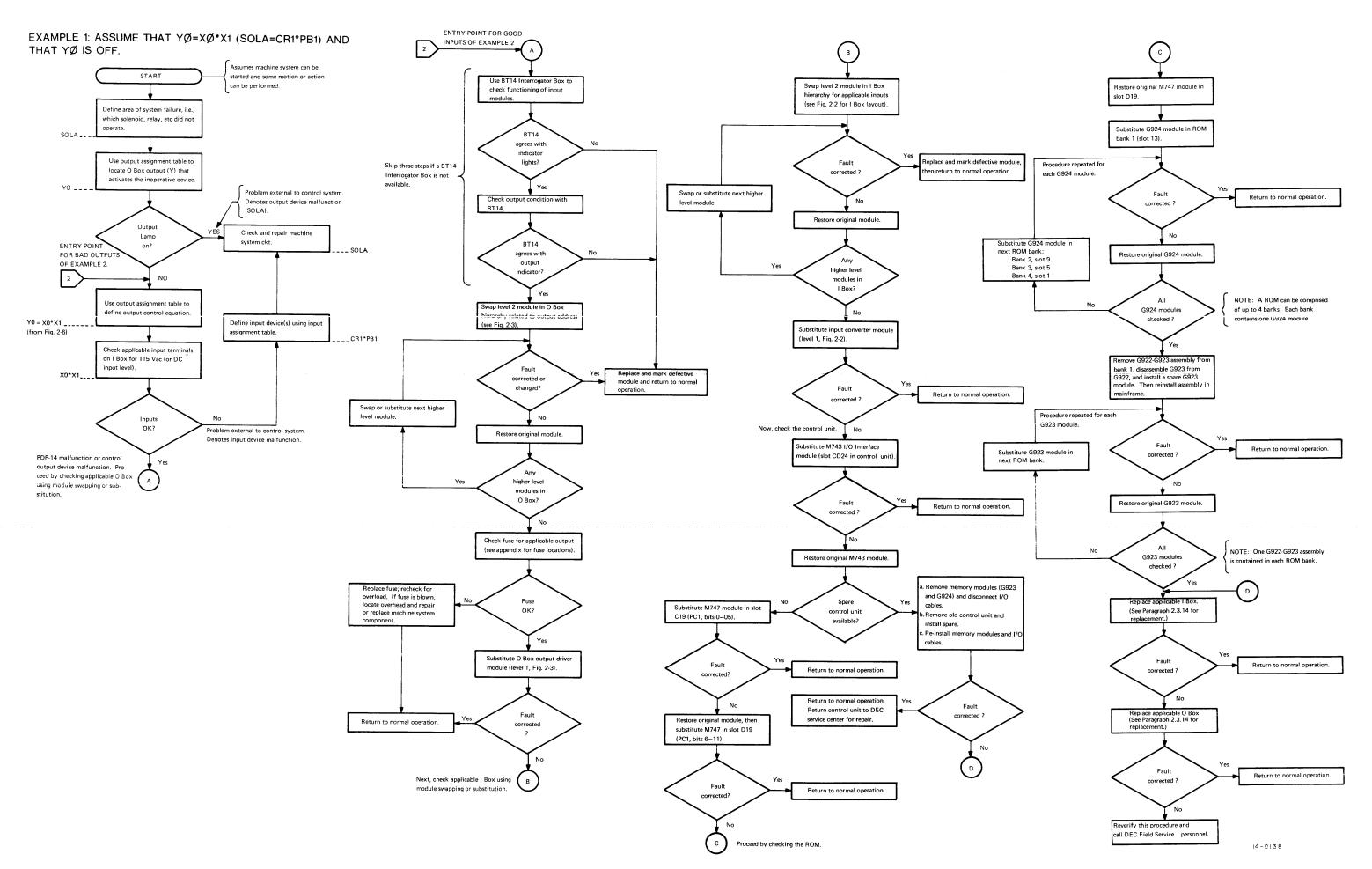

| 1.1       | General                            | 1-1  | 2.3.4              | Fault Isolation Example Number 1                                 | 2-9        |

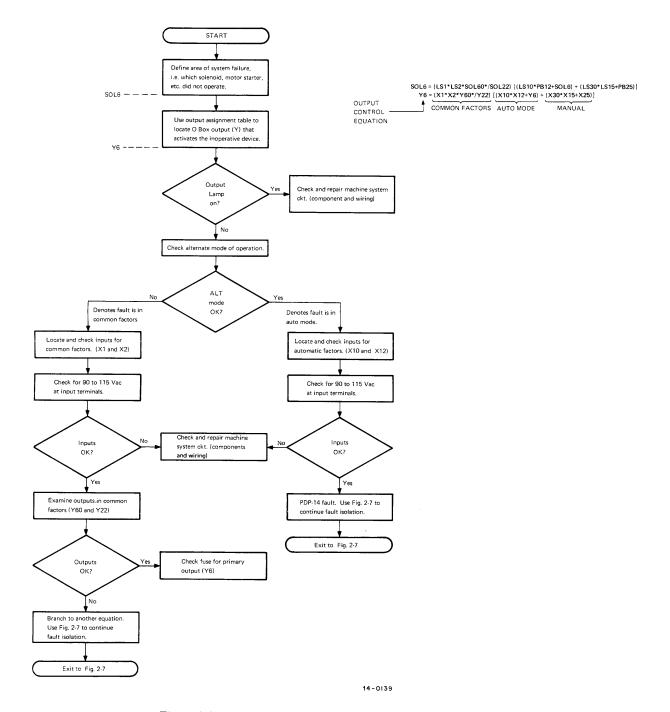

| 1.2       | System Description                 | 1-1  | 2.3.5              | Fault Isolation Example Number 2                                 | 2-9        |

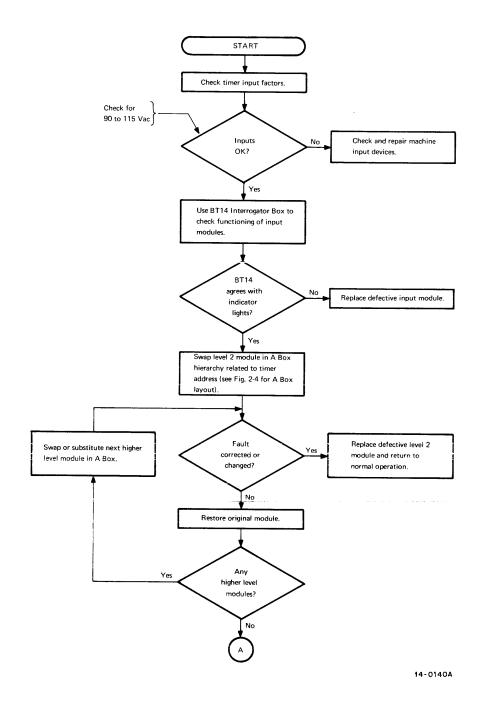

| 1.2.1     | Purpose and Use                    | 1-1  | 2.3.6              | Fault Isolation For Equations Involving Timer Functions          | 2-9        |

| 1.2.2     | Stand-Alone Applications           | 1-1  | 2.3.7              | Fault Isolation For Equations Involving Retentive Memory Factors | 2-9        |

| 1.2.3     | Monitoring Applications            | 1-1  | 2.3.8              | Fault Isolation For Equations Involving A Box Storage Functions  | 2-11       |

| 1.2.4     | Interactive Applications           | 1-1  | 2.3.9              | Fault Isolation For Major System Failure                         | 2-11       |

| 1.2.5     | Operating Concepts                 | 1-2  | 2.3.10             | Troubleshooting Hints and Kinks                                  | 2-11       |

| 1.3       | Equipment Description              | 1-2  | 2.3.11             | Module Substitution and Replacement Notes                        | 2-11       |

| 1.3.1     | General                            | 1-2  | 2.3.12             | Mainframe Replacement                                            | 2-11       |

| 1.3.2     | Control Unit Mainframe             | 1-4  | 2.3.13             | Power Supply Replacement                                         | 2-11       |

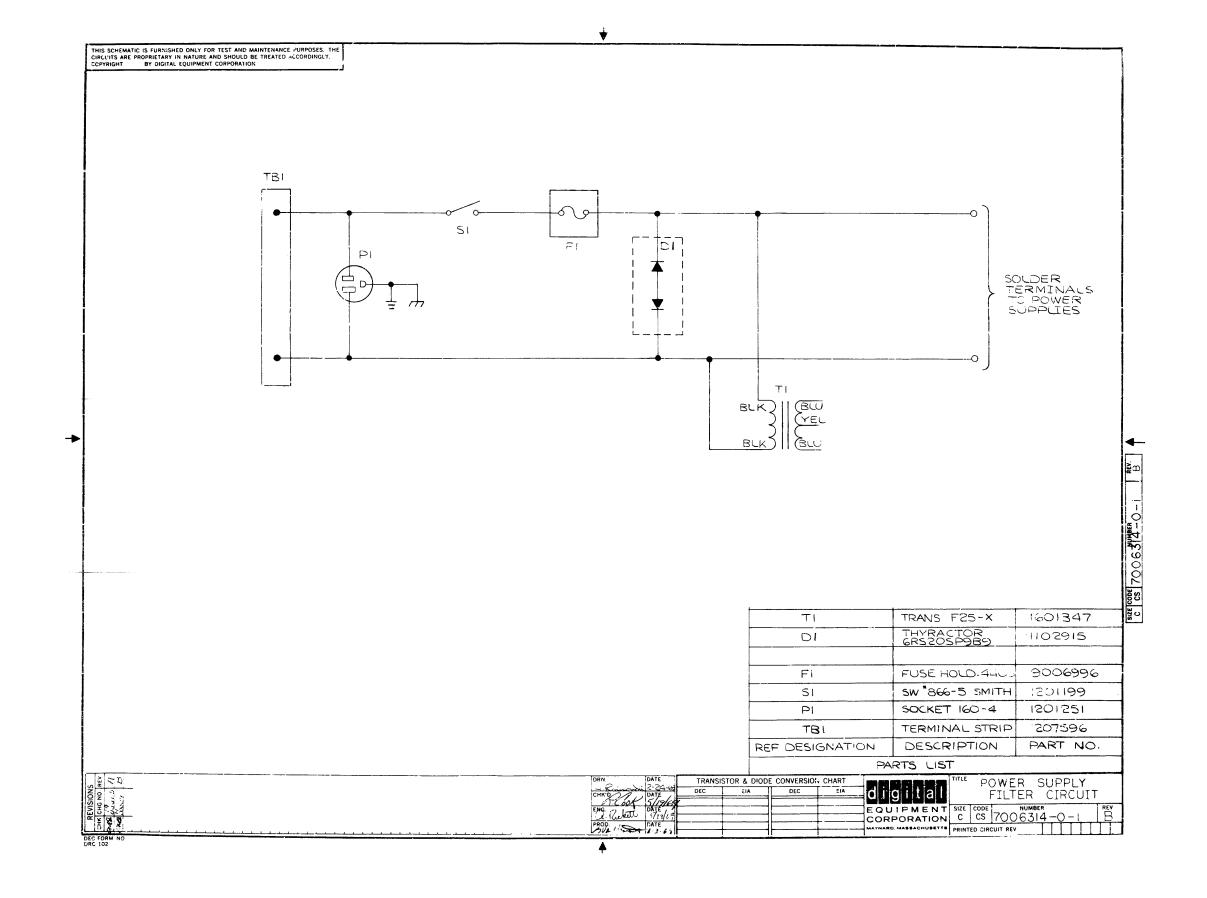

| 1.3.2.1   | Power Supply Filter Assembly       | 1-4  | 2.3.14             | I, O, and A Box Replacement                                      | 2-11       |

| 1.3.2.2   | Power Supply                       | 1-4  | 2.3.15             | A Box Replacement                                                | 2-11       |

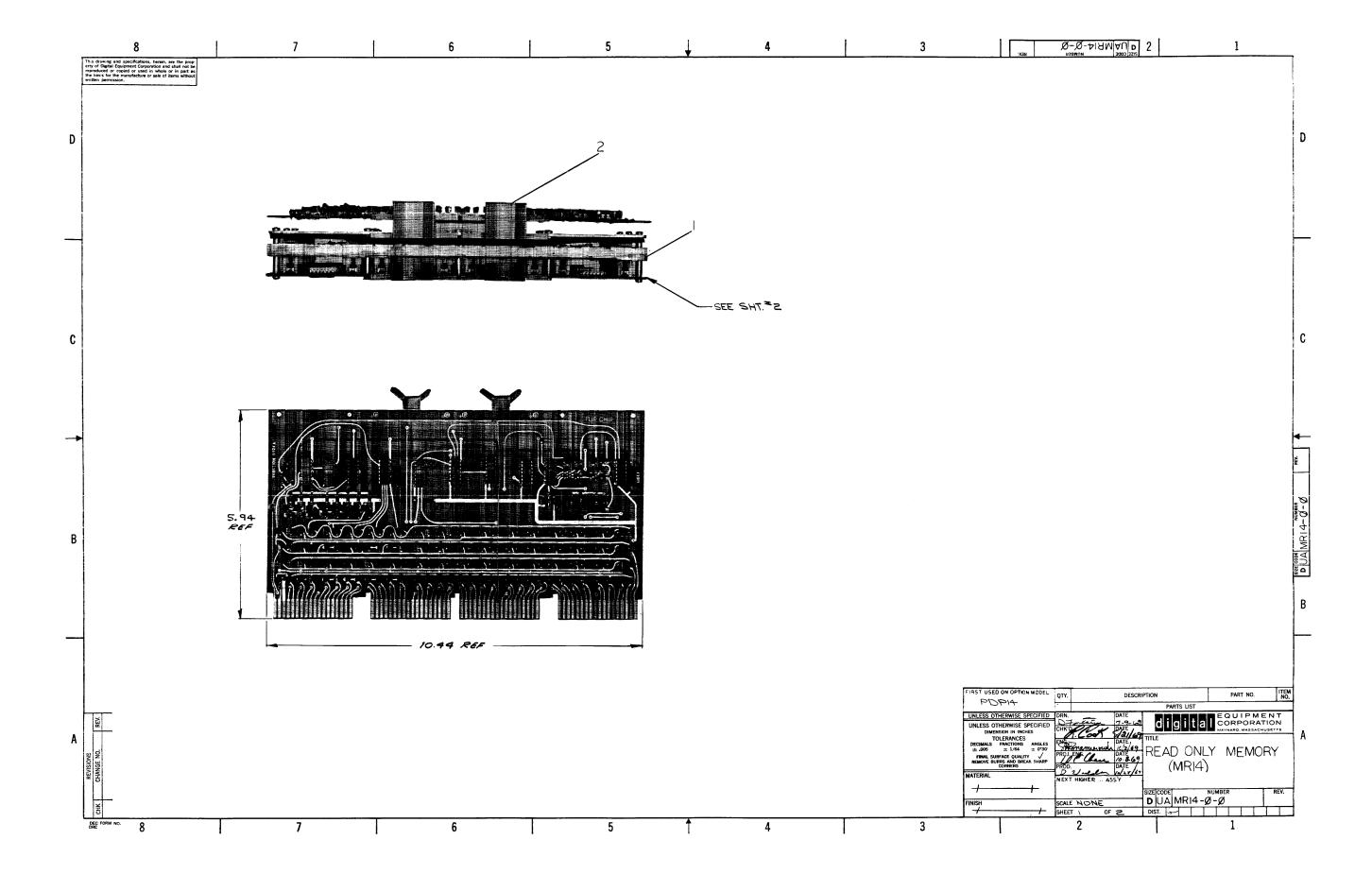

| 1.3.2.3   | Read-Only Memory                   | 1-4  | 2.4                | Fault Isolation With A Computer                                  | 2-11       |

| 1.3.2.4   | Control Unit                       | 1-4  | 2.4.1              | Fault Isolation Approach                                         | 2-11       |

| 1.3.3     | I Boxes                            | 1-4  | 2.4.2              | Connecting a Computer                                            | 2-13       |

| 1.3.4     | O Boxes                            | 1-5  | 2.4.3              | Loading of Binary (BIN) Loader Tape (DEC-08-LBAA-PM)             | 2-16       |

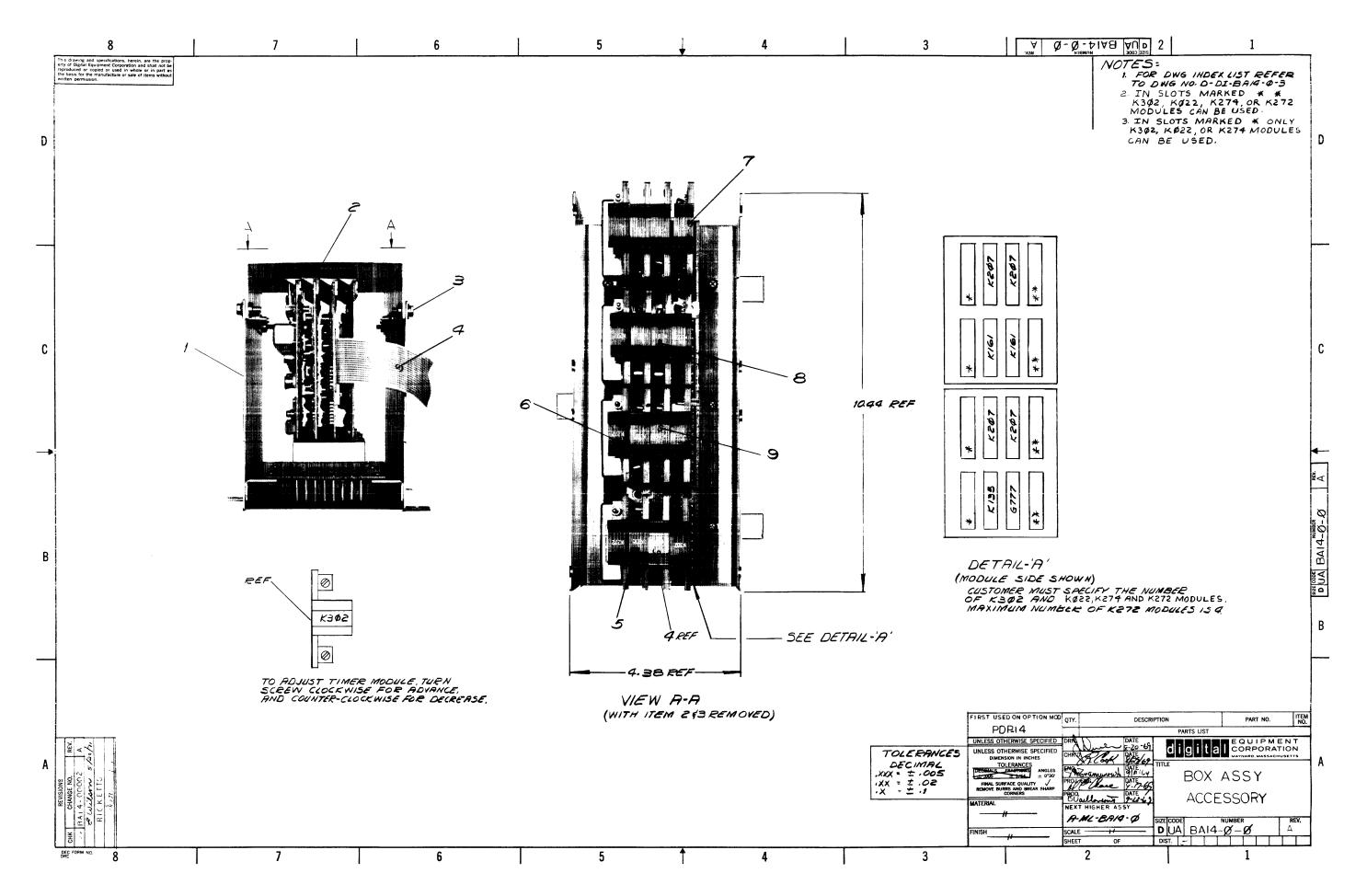

| 1.3.5     | A Boxes                            | 1-5  | 2.4.4              | Loading of Diagnostic Tapes                                      | 2-16       |

| 1.3.6     | Storage Module                     | 1-5  | 2.4.5              | Control Unit Fault Isolation Using TEST-14                       | 2-16       |

| 1.3.7     | Operating Summary                  | 1-5  | 2.4.6              | Control Unit I/O Interface Fault Isolation Using TEST-14         | 2-19       |

| 1.4       | Specifications                     | 1-5  | 2.4.7              | Output Fault Isolation Using TEST-14                             | 2-19       |

| CILL PEED | A VOED MARKETANA                   |      | 2.4.8              | ROM Fault Isolation Using VER-14 (MAINDEC-14-D1AB-D)             | 2-20       |

| CHAPTER   | 2 USER MAINTENANCE                 |      | 2.4.9              | Accessory Box Fault Isolation Using ABE-14 (MAINDEC-14-D8AB-D)   | 2-21       |

| 2.1       | General                            | 2-1  | 2.4.10             | Fault Isolation Using ROL-14                                     | 2-22       |

| 2.2       | Maintenance Information            | 2-1  |                    |                                                                  |            |

| 2.2.1     | Maintenance Philosophy             | 2-1  | CHAPTER 3          | THEORY OF OPERATION                                              |            |

| 2.2.2     | Controller Description             | 2-1  | •                  |                                                                  |            |

| 2.2.2.1   | ROM                                | 2-1  | 3.1                | General                                                          | 3-1        |

| 2.2.2.2   | Control Unit                       | 2-1  | 3.2                | System Relationships                                             | 3-1        |

| 2.2.2.3   | I Boxes BX14-DA and BX14-DD        | 2-3  | 3.2.1              | Operating Configurations and Modes                               | 3-1        |

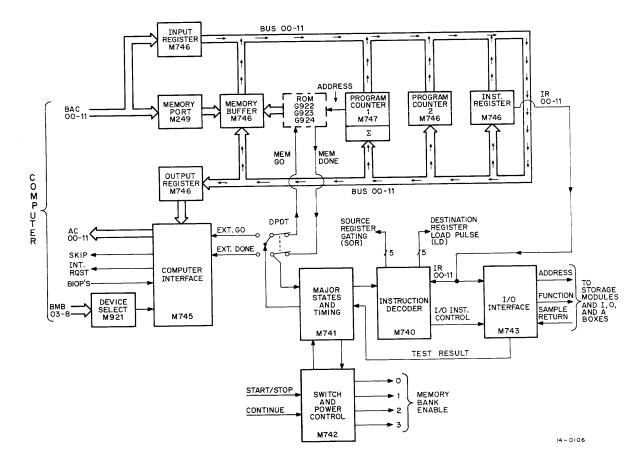

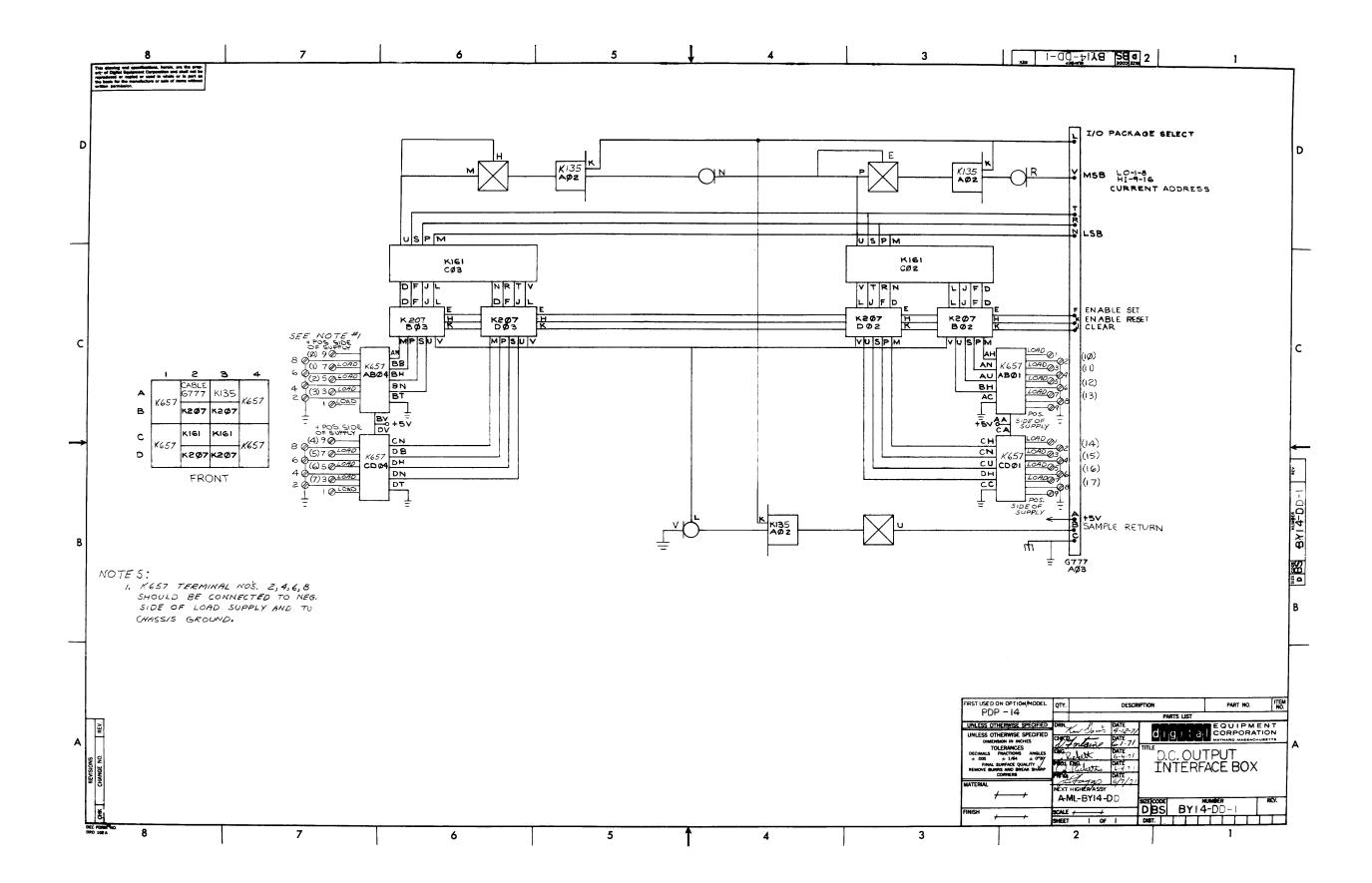

| 2.2.2.4   | O Boxes BX14-DA and BY14-DD        | 2-3  | 3.2.2              | Control Unit Block Diagram Description                           | 3-1        |

| 2.2.2.5   | A Box                              | 2-4  | 3.2.2.1            | General                                                          | 3-1        |

| 2.2.3     | Recommended Test Equipment         | 2-5  | 3.2.2.2            | Bus Arrangement and Internal Transfers                           | 3-1        |

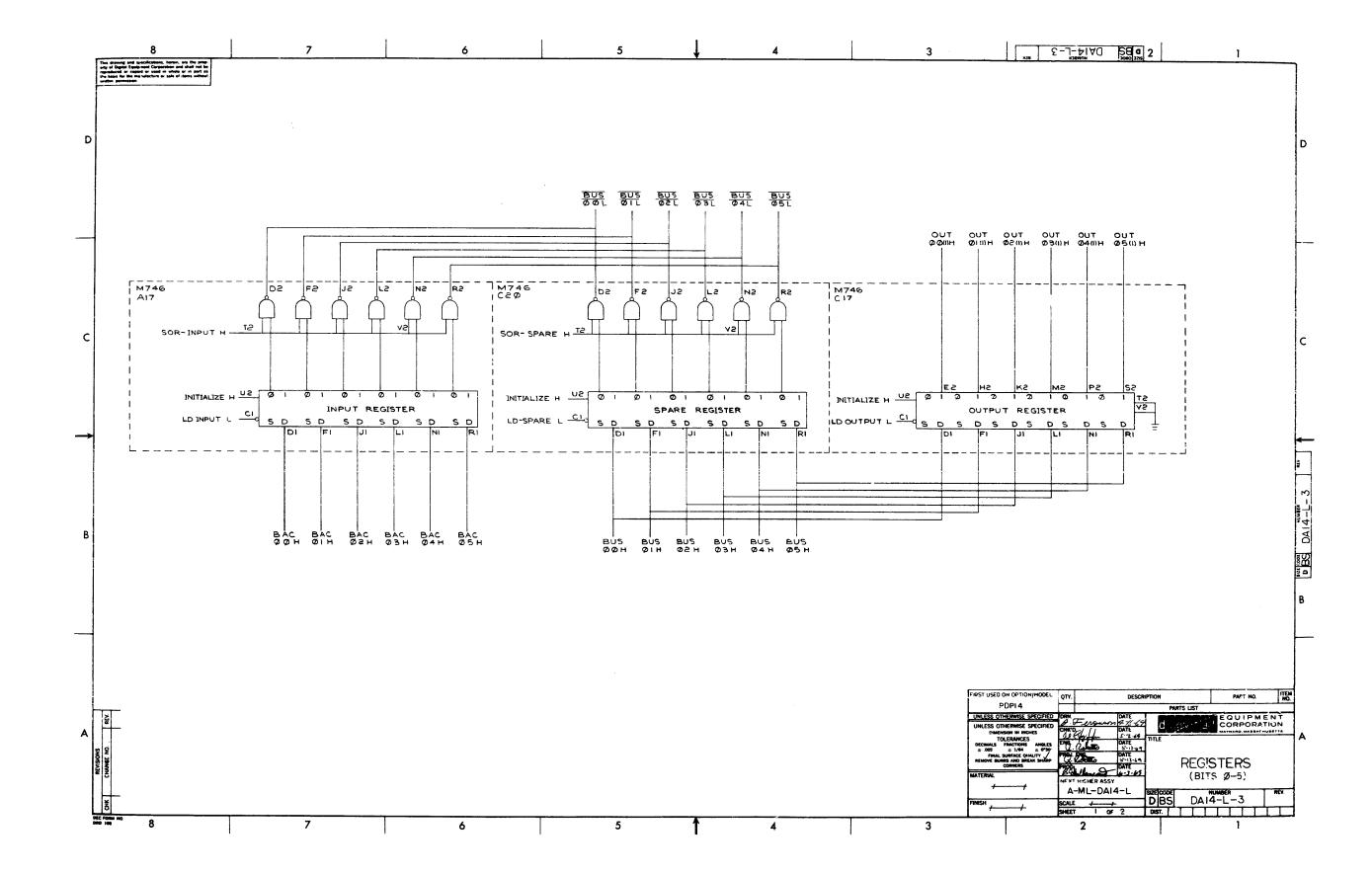

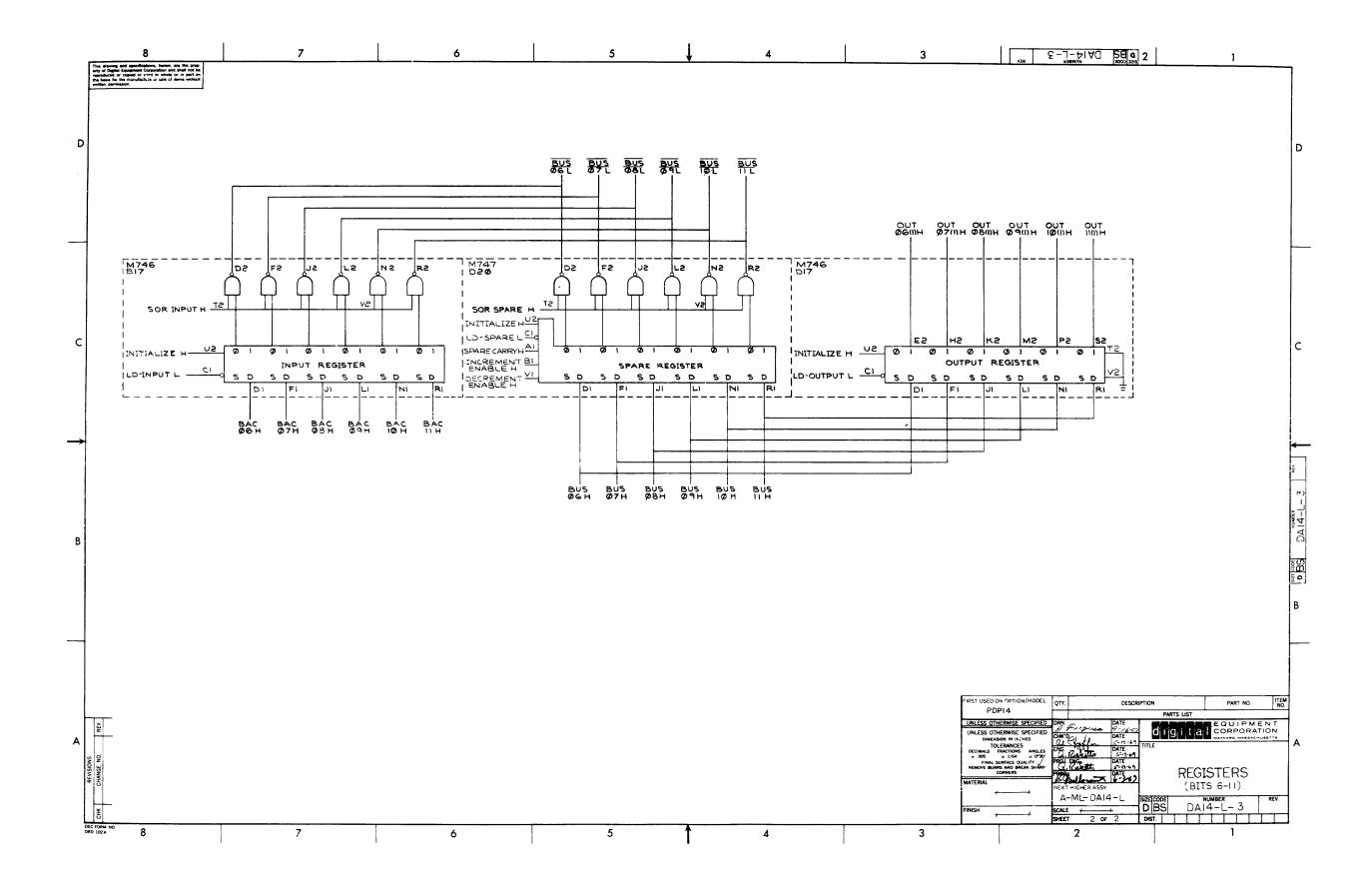

| 2.2.4     | Recommended Spare Parts            | 2-5  | 3.2.2.3            | Registers                                                        | 3-2        |

|           | recommended Spare 1 arts           |      |                    |                                                                  |            |

| 2.3       | Fault Isolation Without a Computer | 2-5  | 3.2.2.4<br>3.2.2.5 | I/O Interface Computer Interface                                 | 3-2<br>3-2 |

# CONTENTS (Cont)

|                     |                                         | Page |           |                                                         | Page |

|---------------------|-----------------------------------------|------|-----------|---------------------------------------------------------|------|

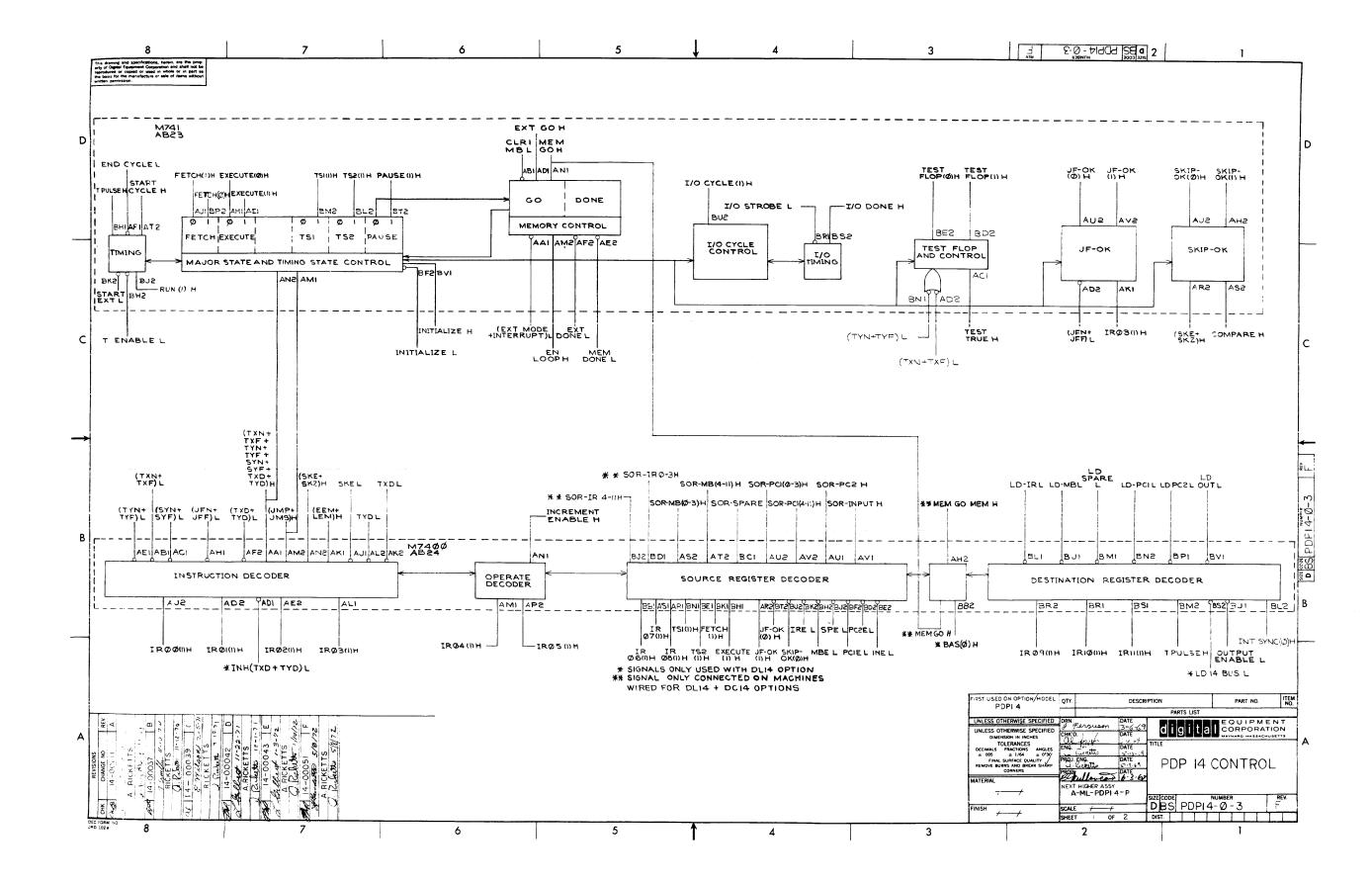

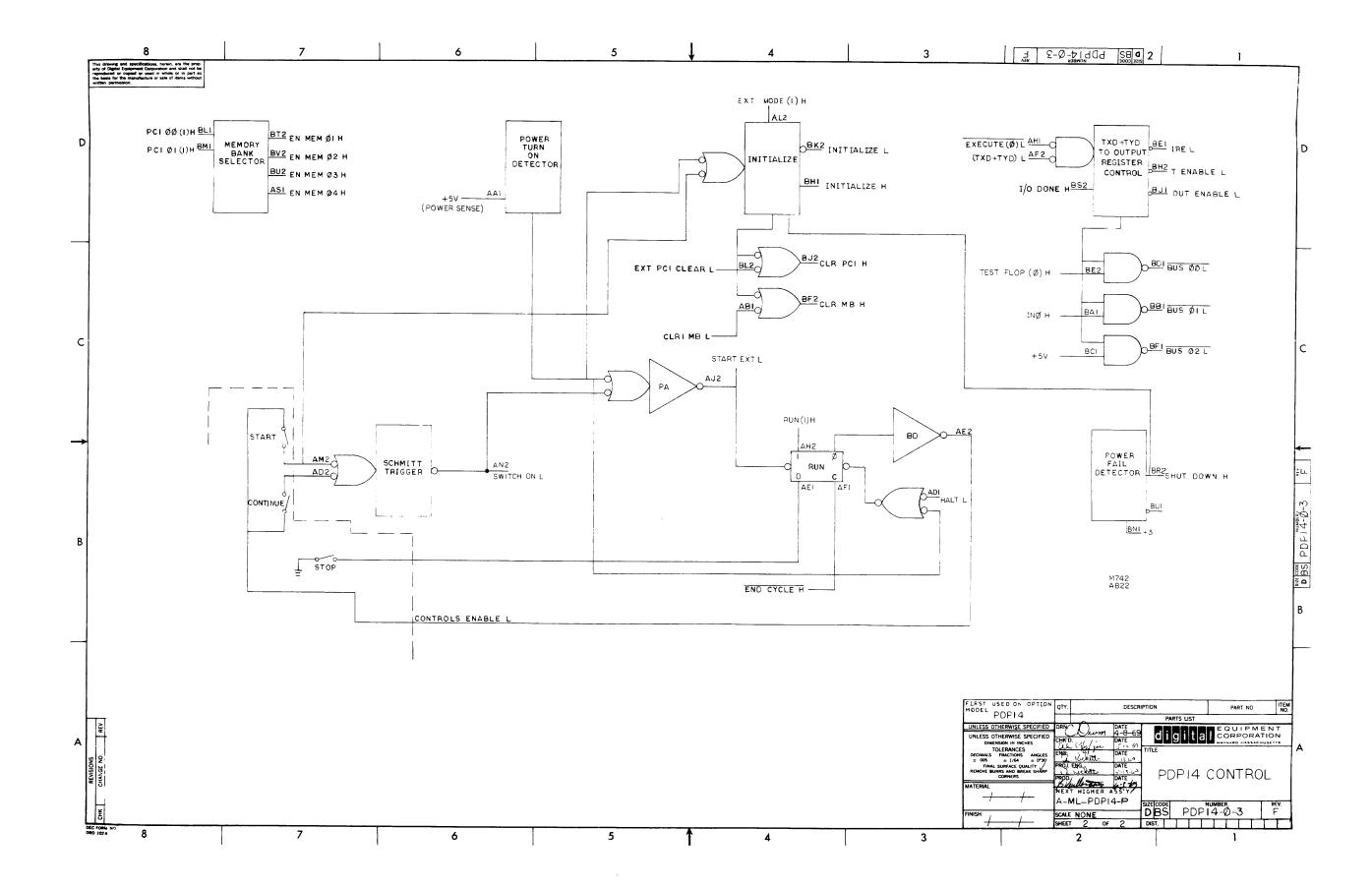

| 3.2.2.6             | Control                                 | 3-2  | 3.5.7     | Instruction Decoding and Register Control               | 3-15 |

| 3.2.3               | ROM Block Diagram Description           | 3-2  | 3.5.8     | I/O Interface Circuits                                  | 3-15 |

| 3.2.4               | I Box Block Diagram Description         | 3-2  | 3.5.8.1   | General                                                 | 3-15 |

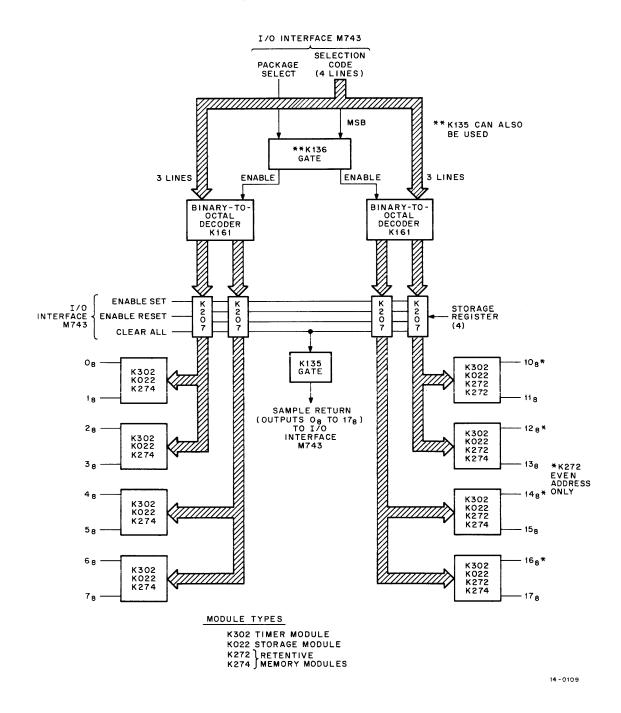

| 3.2.5               | O Box Block Diagram Description         | 3-3  | 3.5.8.2   | Input Tests                                             | 3-16 |

| 3.2.6               | A Box Description                       | 3-4  | 3.5.8.3   | Output Tests                                            | 3-16 |

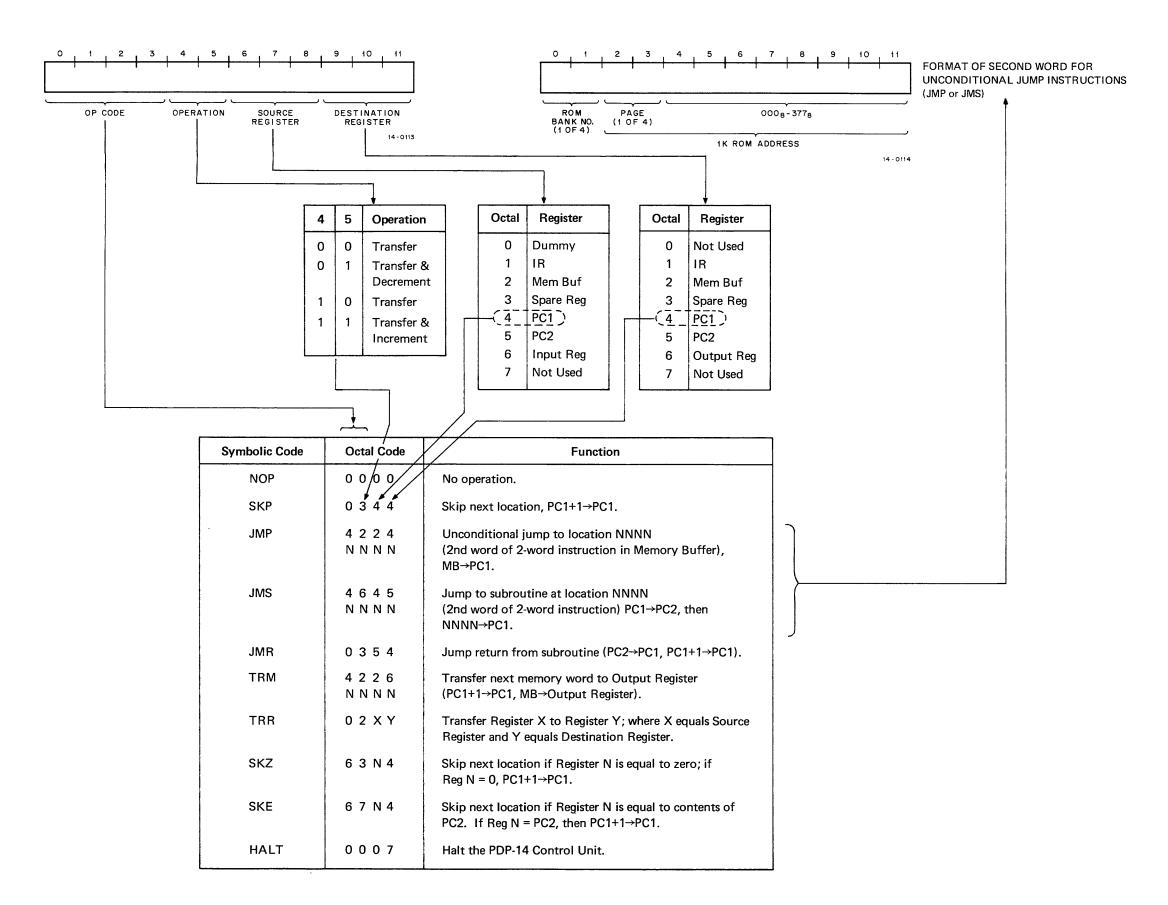

| 3.3                 | Instruction Set                         | 3-4  | 3.5.8.4   | Output Functions                                        | 3-16 |

| 3.3.1               | General                                 | 3-4  | 3.5.9     | Conditional Jump Circuits                               | 3-16 |

| 3.3.2               | Internal Mode Instruction Set           | 3-4  | 3.5.10    | Computer Interface                                      | 3-16 |

| 3.3.2.1             | General                                 | 3-4  | 3.5.10.1  | General                                                 | 3-16 |

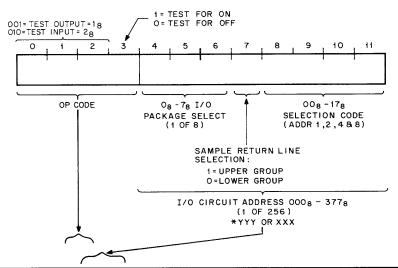

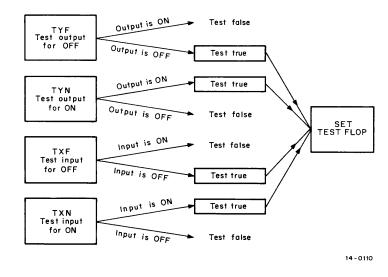

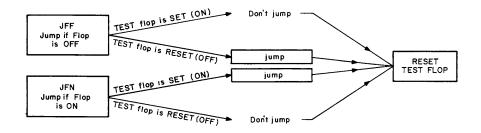

| 3.3.2.2             | Test Instructions                       | 3-4  | 3.5.10.2  | Device Selector Logic                                   | 3-17 |

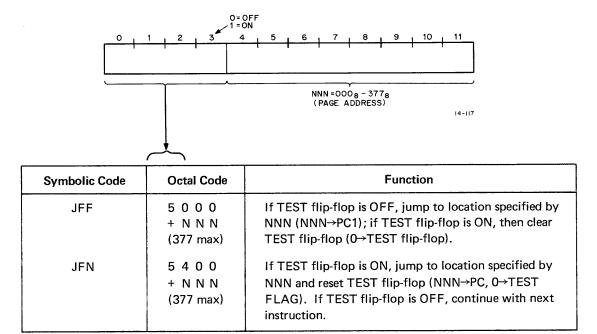

| 3.3.2.3             | Decision Instructions                   | 3-5  | 3.5.10.3  | Skip Bus                                                | 3-17 |

| 3.3.2.4             | Operate Instructions                    | 3-6  | 3.5.10.4  | Interrupt Operation                                     | 3-17 |

| 3.3.2.5             | Monitoring Instructions                 | 3-6  | 3.5.10.5  | External Mode Operation                                 | 3-18 |

| 3.3.2.6             | Housekeeping Instructions               | 3-6  | 3.6       | I, O, and A Box Circuit Description                     | 3-19 |

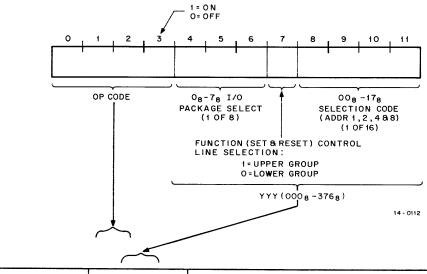

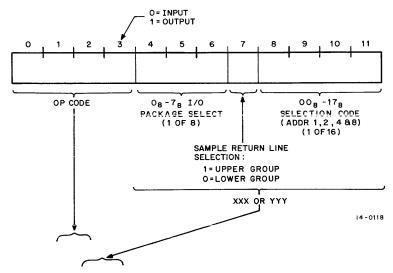

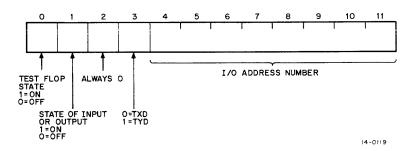

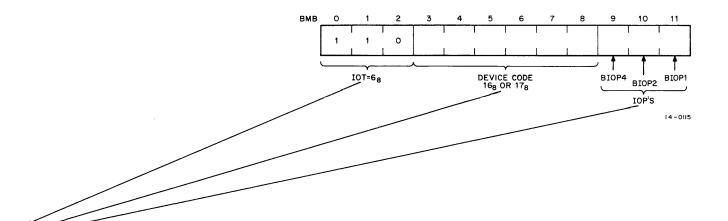

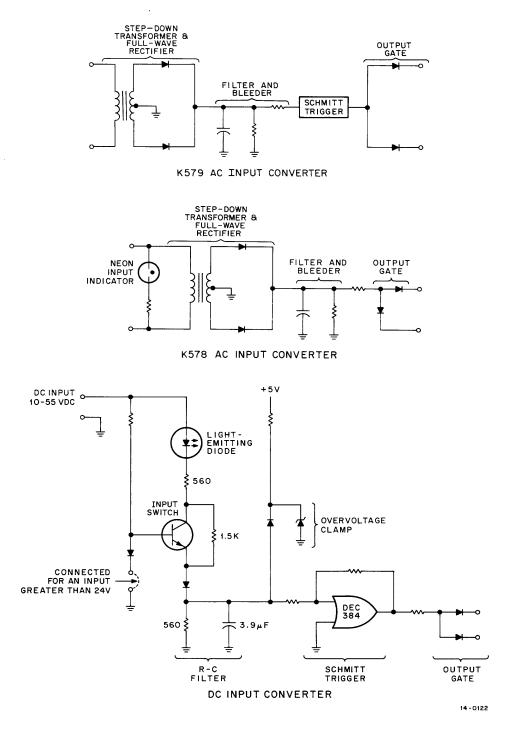

| 3.3.3               | IOT Instructions                        | 3-6  | 3.6.1     | Input Circuits                                          | 3-19 |

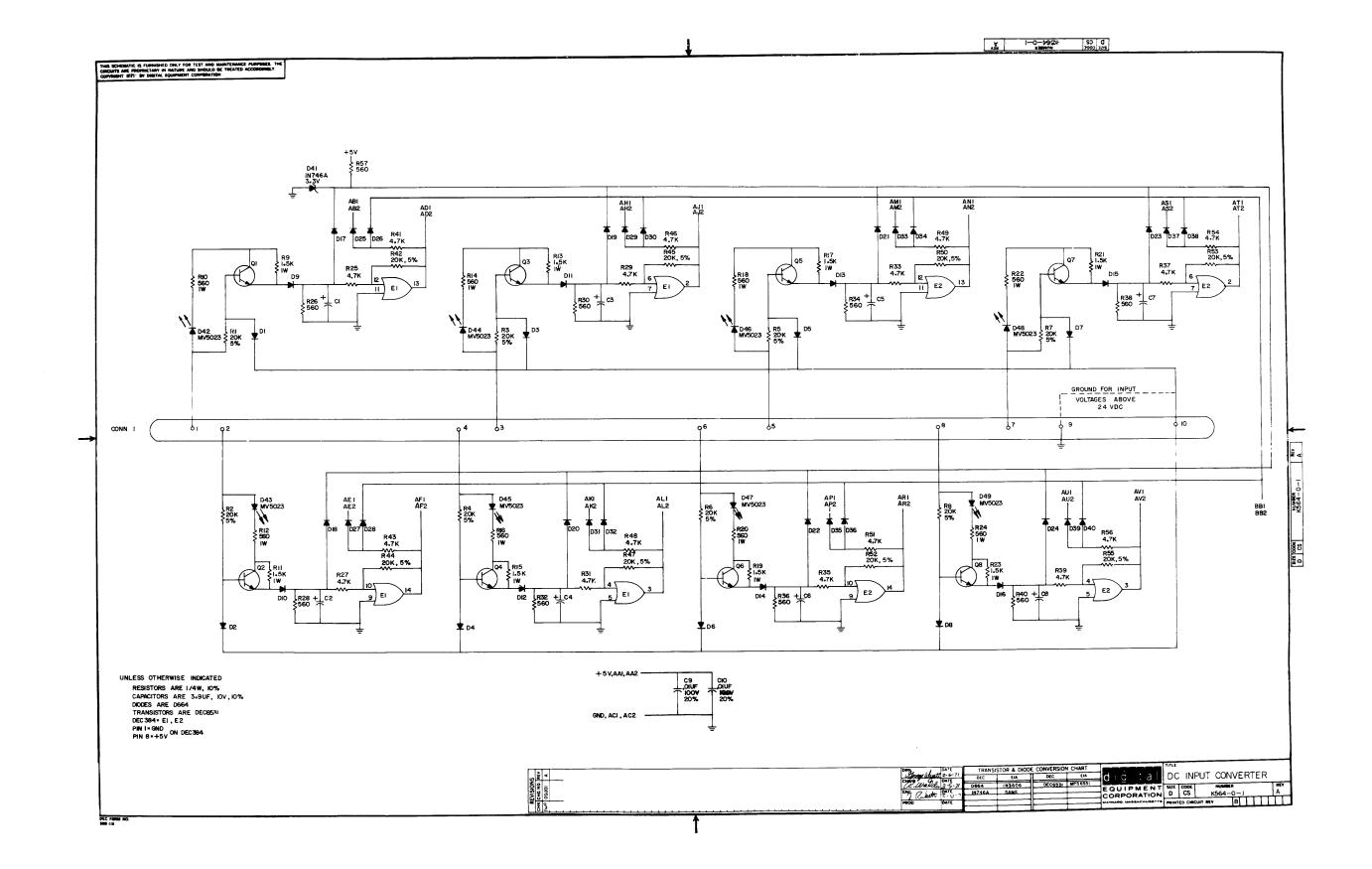

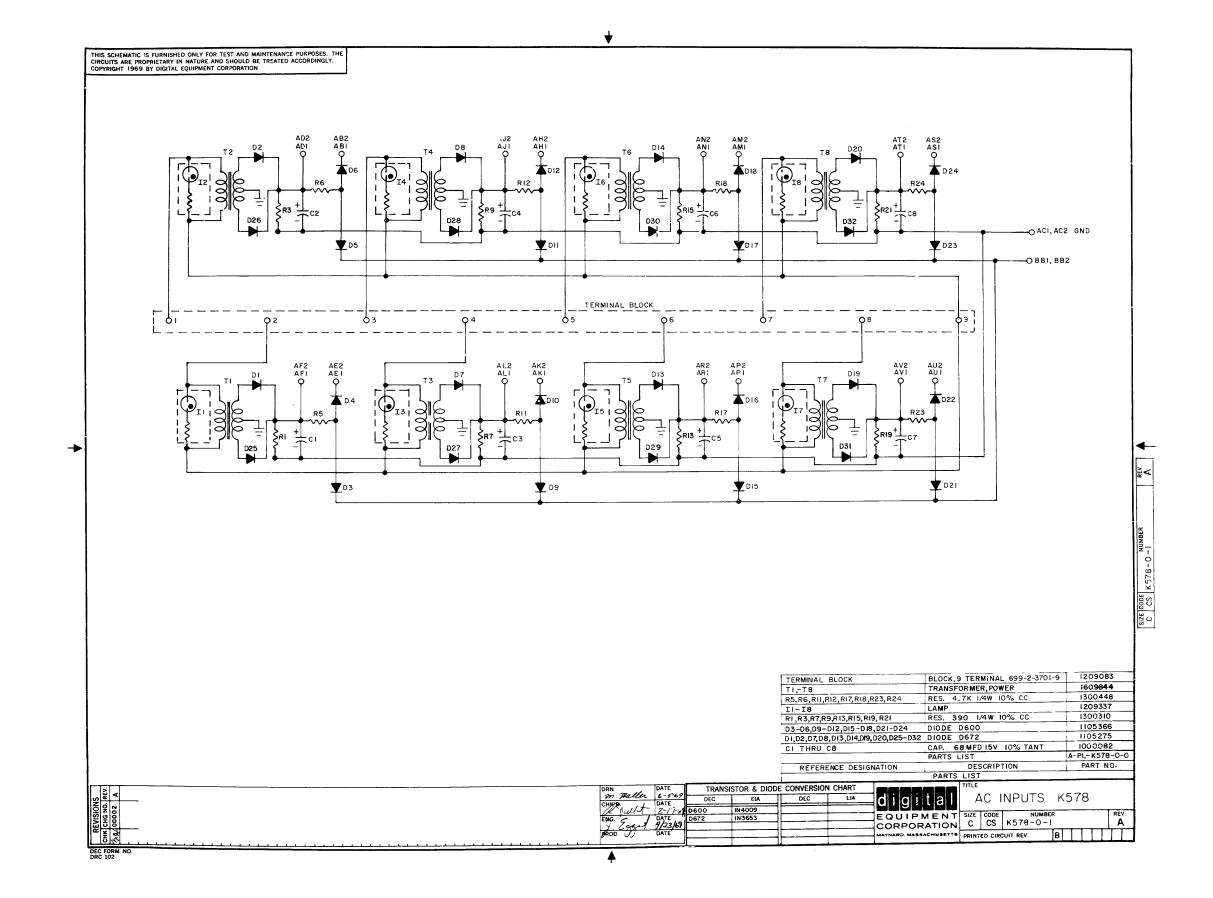

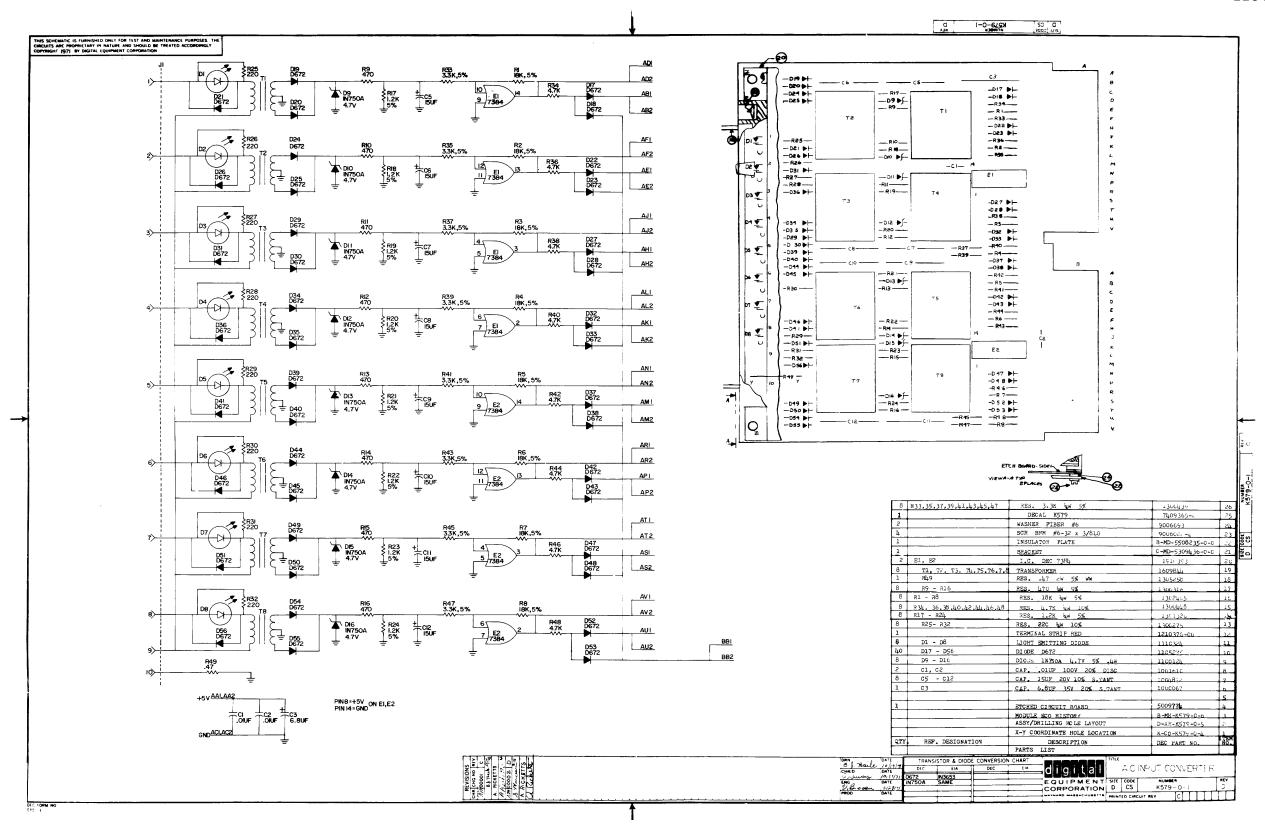

| 3.3.4               | External Mode Instructions              | 3-9  | 3.6.1.1   | AC Input Converter                                      | 3-19 |

| 3.4                 | Instruction Flow                        | 3-9  | 3.6.1.2   | DC Input Converter                                      | 3-19 |

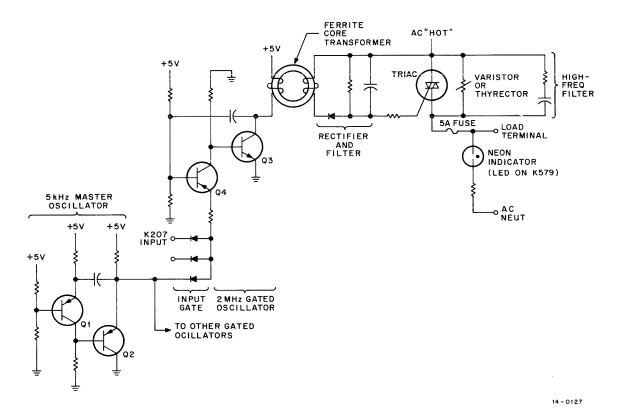

| 3.4.1               | General                                 | 3-9  | 3.6.2     | Output Circuits                                         | 3-19 |

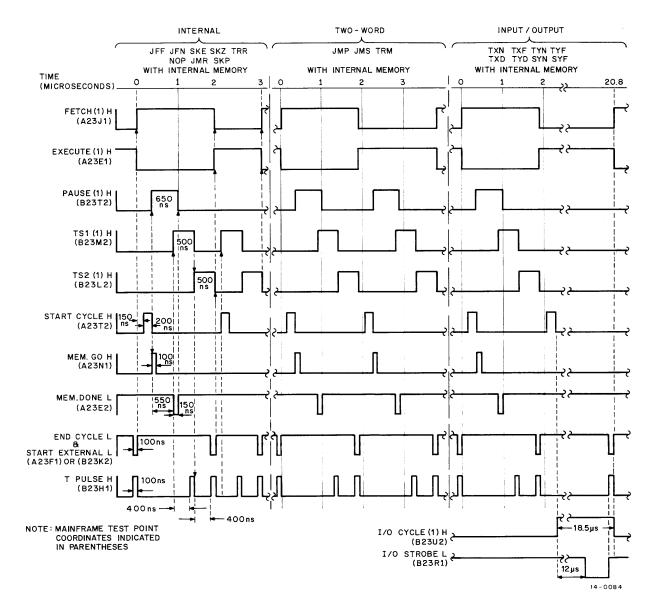

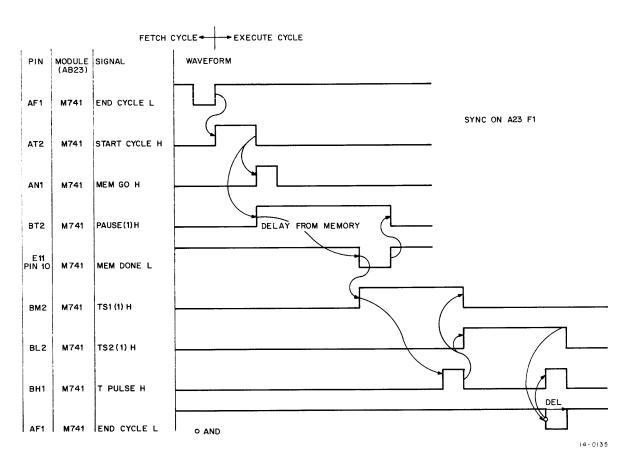

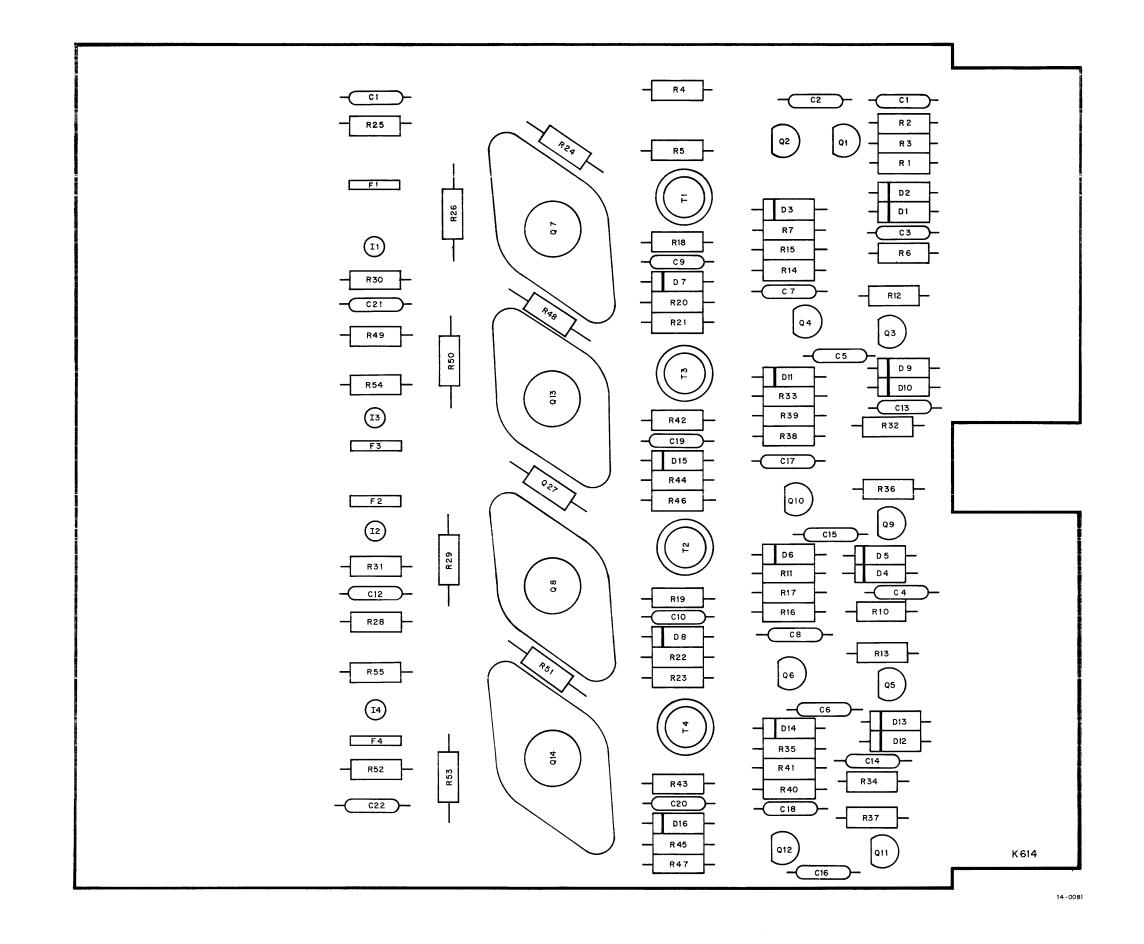

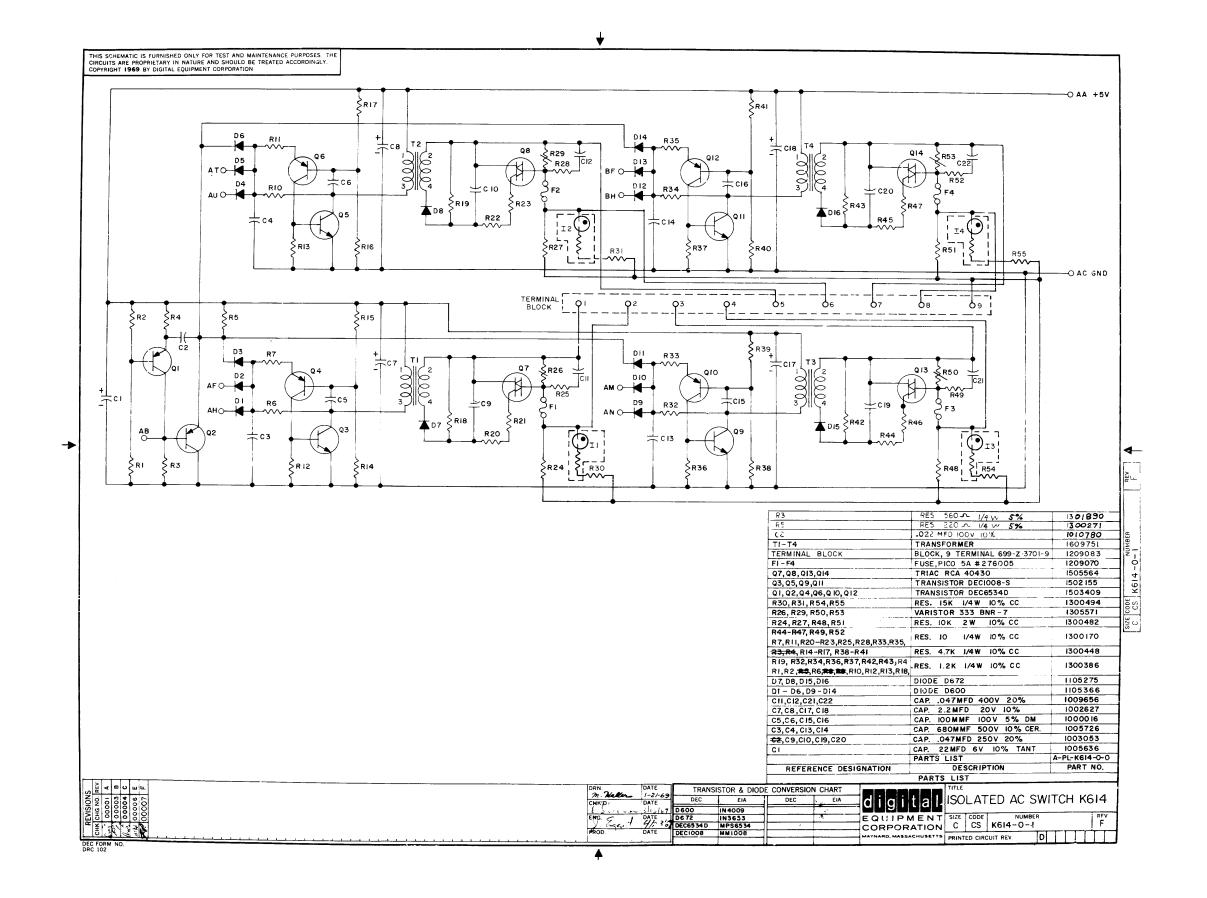

| 3.4.2               | FETCH Cycle for Internal Mode           | 3-9  | 3.6.2.1   | Isolated AC Switch                                      | 3-19 |

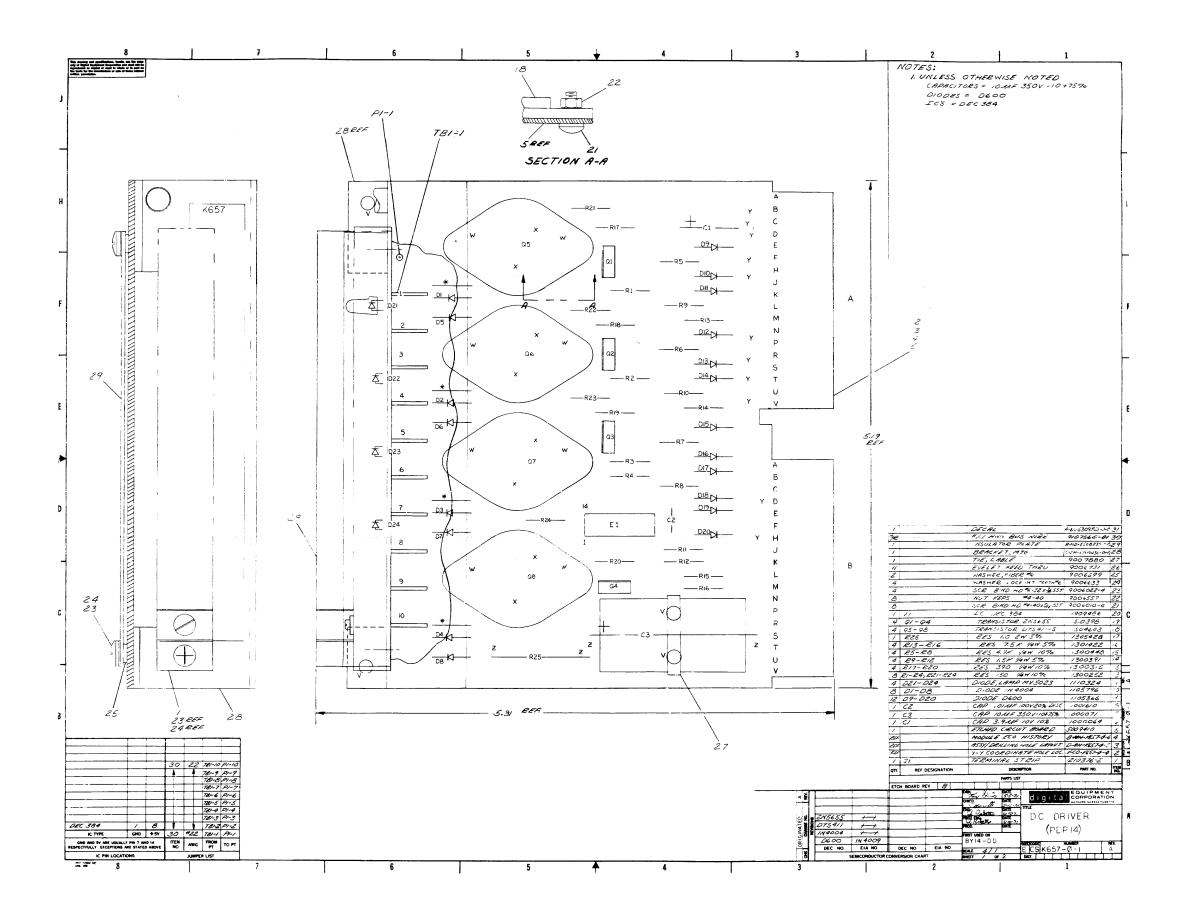

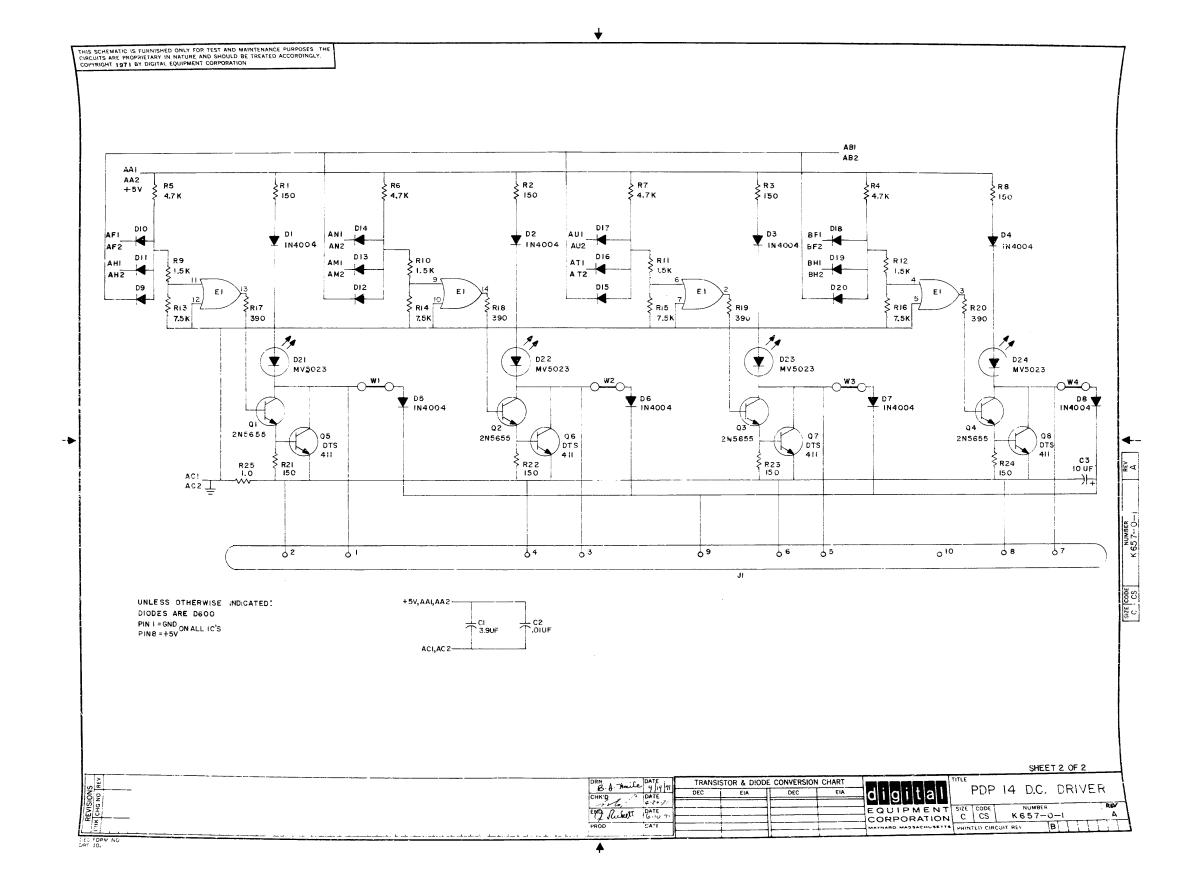

| 3.4.3               | FETCH Cycle for Interrupt Mode          | 3-9  | 3.6.2.2   | DC Output Driver                                        | 3-20 |

| 3.4.4               | FETCH Cycle for External Mode Operation | 3-9  | 3.6.3     | Accessory Box Circuits                                  | 3-20 |

| 3.4.5               | EXECUTE Cycle                           | 3-9  | 3.6.3.1   | Timer Circuits                                          | 3-20 |

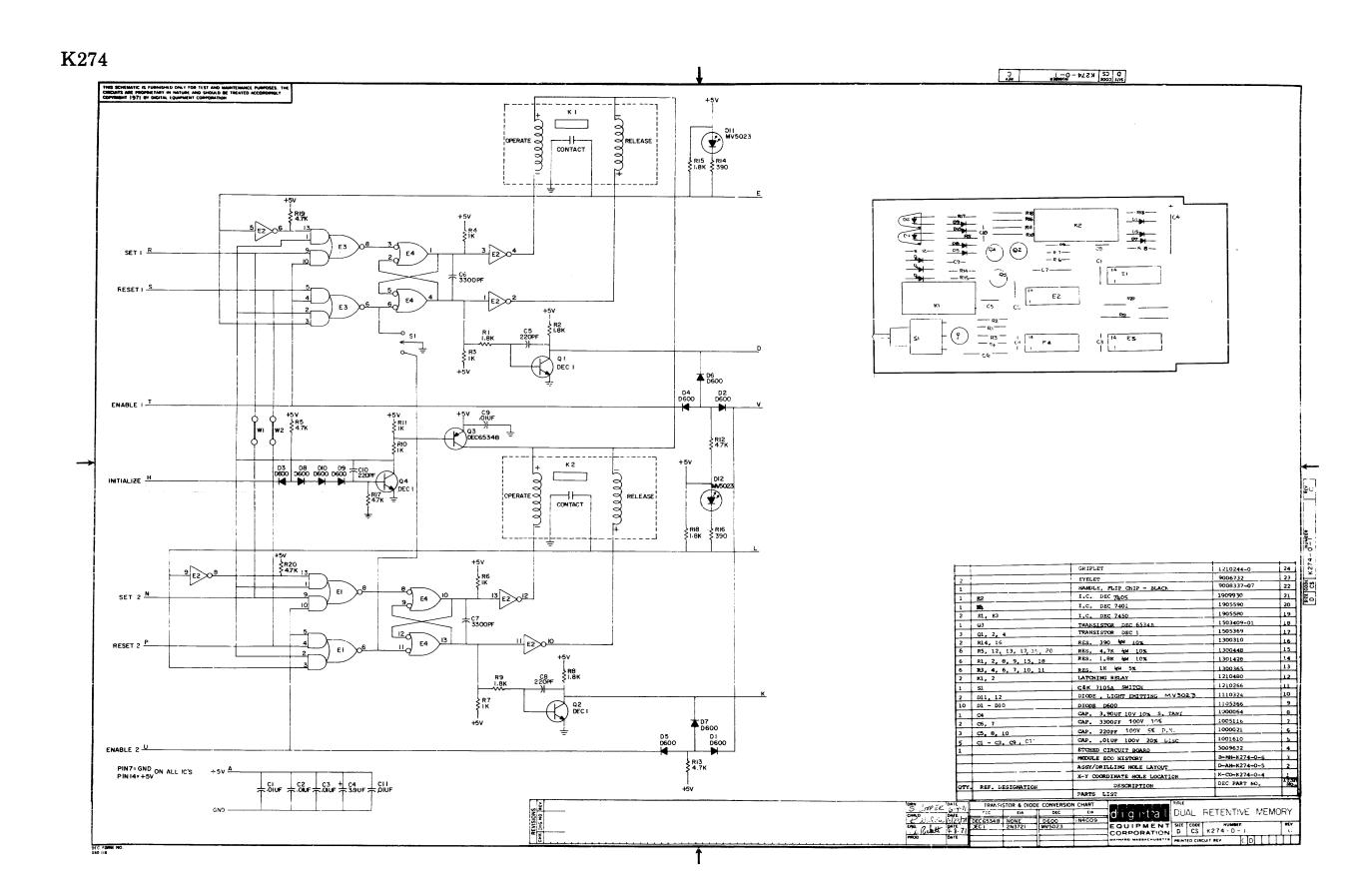

| 3.5                 | Logic and Circuit Description           | 3-10 | 3.6.3.2   | K274 Retentive Memory                                   | 3-21 |

| 3.5.1               | General                                 | 3-10 |           | ·                                                       |      |

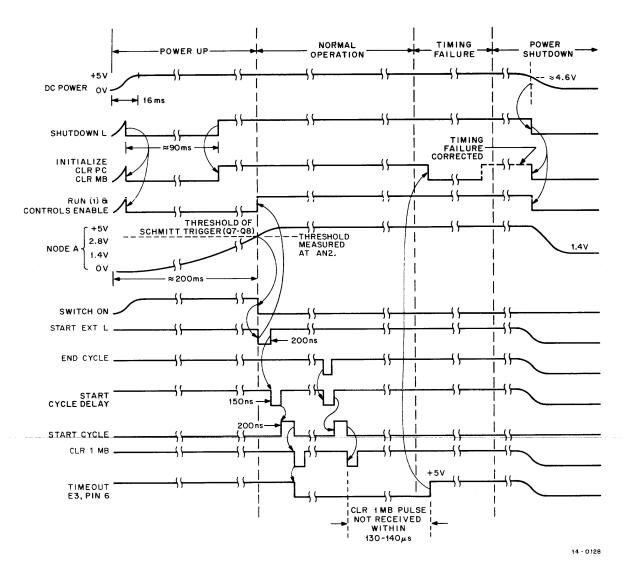

| 3.5.2               | Initialization                          | 3-10 | CHAPTER 4 | DETAILED MAINTENANCE                                    |      |

| 3.5.3               | Manual Controls                         | 3-11 |           |                                                         |      |

| 3.5.4               | Major States and Timing                 | 3-11 | 4.1       | General                                                 | 4-1  |

| 3.5.4.1             | General                                 | 3-11 | 4.2       | Level of Maintenance                                    | 4-1  |

| 3.5.4.2             | FETCH Cycle                             | 3-11 | 4.2.1     | Personnel Intended to Use This Chapter                  | 4-1  |

| 3.5.4.3             | EXECUTE Cycle                           | 3-12 | 4.2.2     | Relationship to Other Chapters                          | 4-1  |

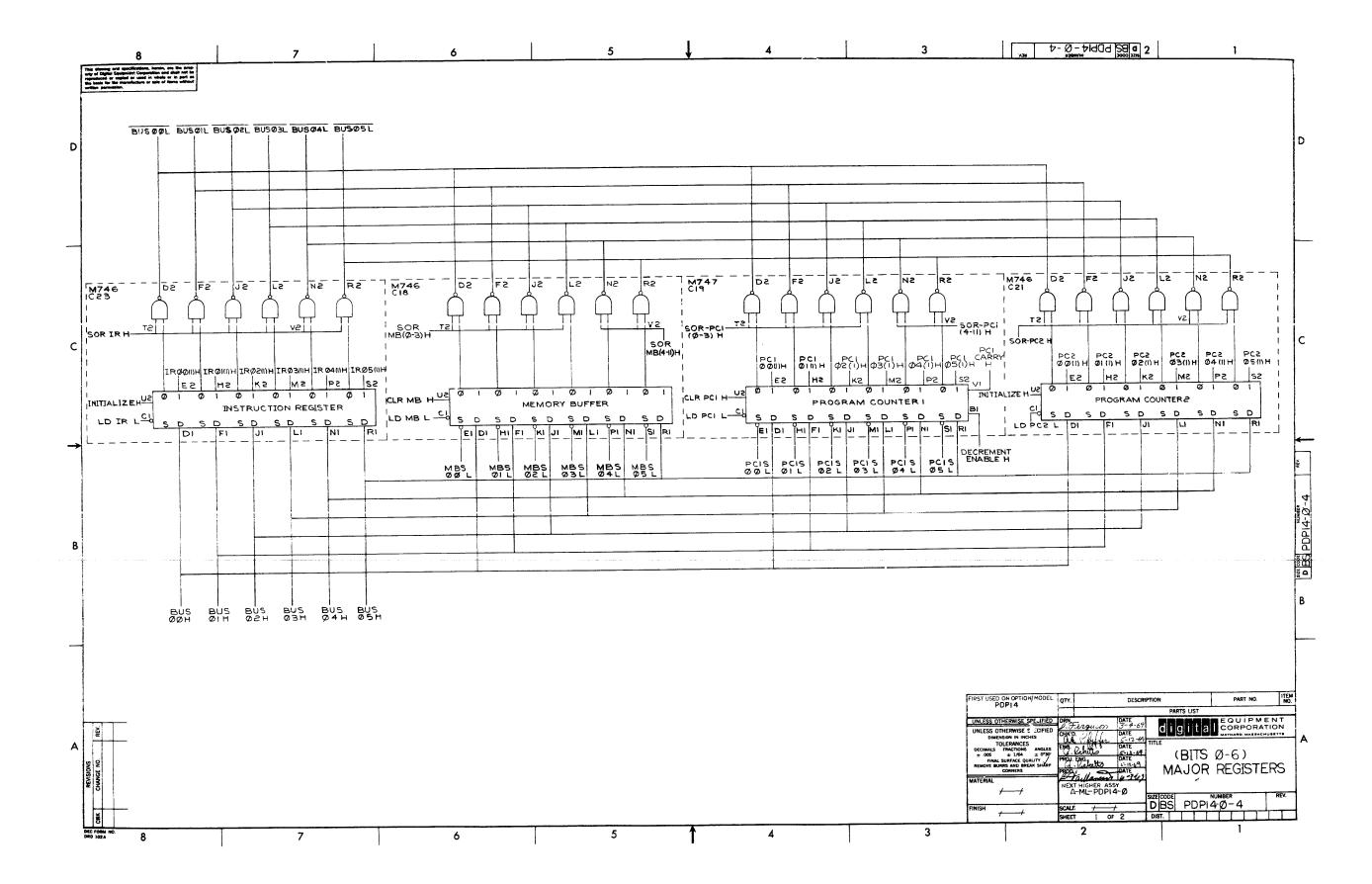

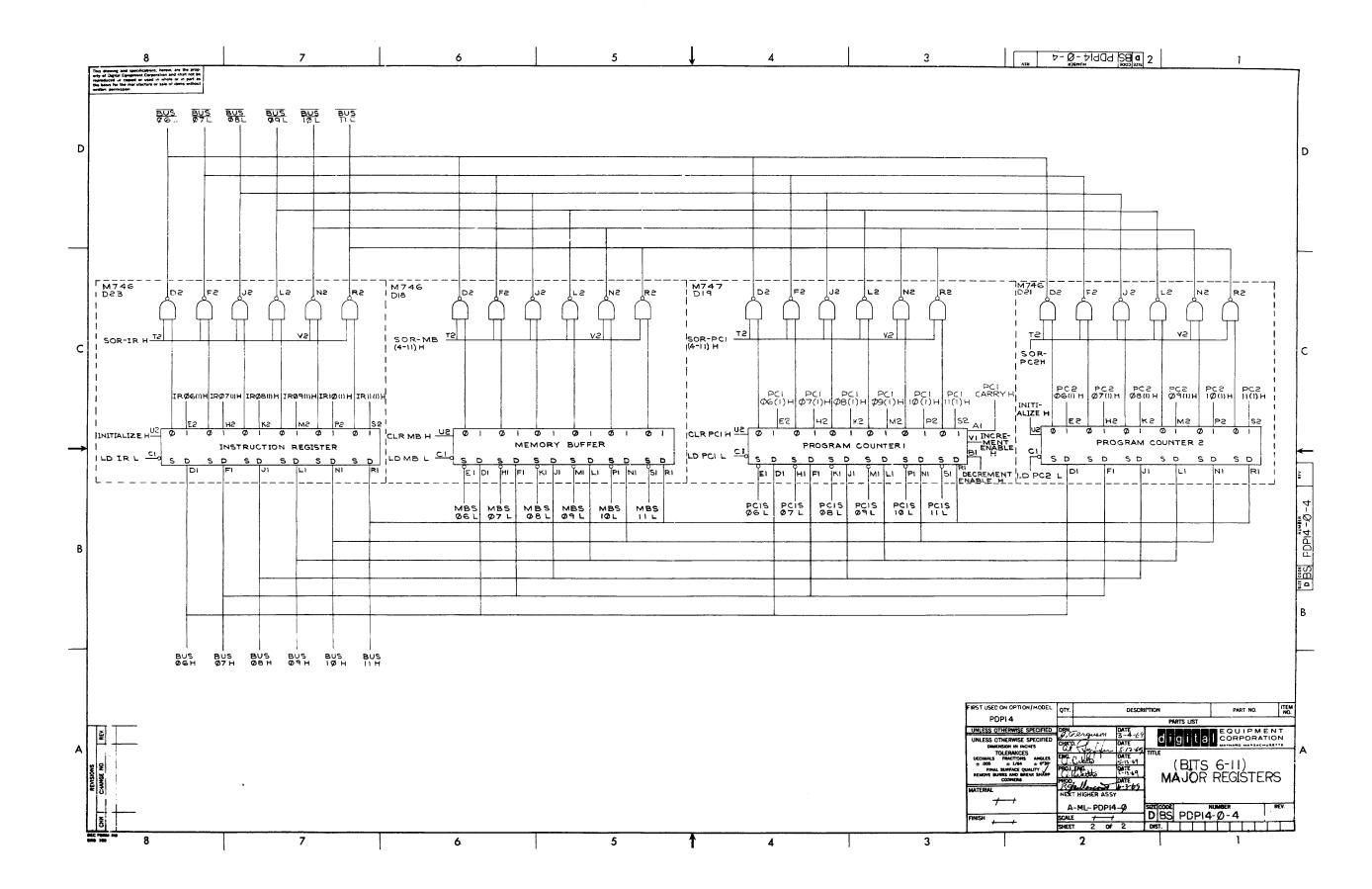

| 3.5.5               | Major Registers                         | 3-12 | 4.3       | Tools and Test Equipment                                | 4-1  |

| 3.5.5.1             | General                                 | 3-12 | 4.4       | System Checkout                                         | 4-1  |

| 3.5.5.2             | Program Counter 1 (PC1)                 | 3-12 | 4.4.1     | Power Voltage Checks                                    | 4-1  |

| 3.5.5.3             | Program Counter 2 (PC2)                 | 3-13 | 4.4.2     | Power Supply Ripple Check                               | 4-1  |

| 3.5.5.4             | Memory Buffer                           | 3-13 | 4.4.3     | Power-up Sequence and Manual Controls                   | 4-1  |

| 3.5.5.5             | Instruction Register (IR)               | 3-13 | 4.4.3.1   | Power-up Sequence                                       | 4-1  |

| 3.5.5.6             | Input Register                          | 3-13 | 4.4.3.2   | Manual Controls Check                                   | 4-2  |

| 3.5.5.7             | Output Register                         | 3-13 | 4.4.4     | Processor Timing Checks                                 | 4-2  |

| 3.5.5.8             | Memory Port Buffer                      | 3-13 | 4.4.4.1   | General                                                 | 4-2  |

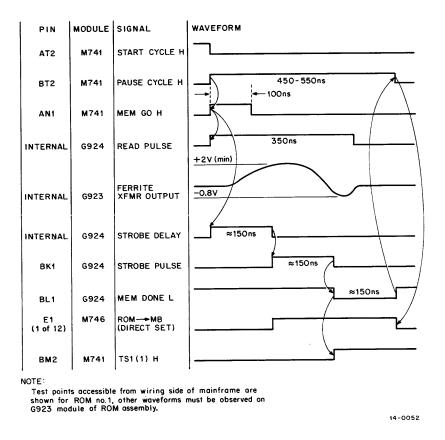

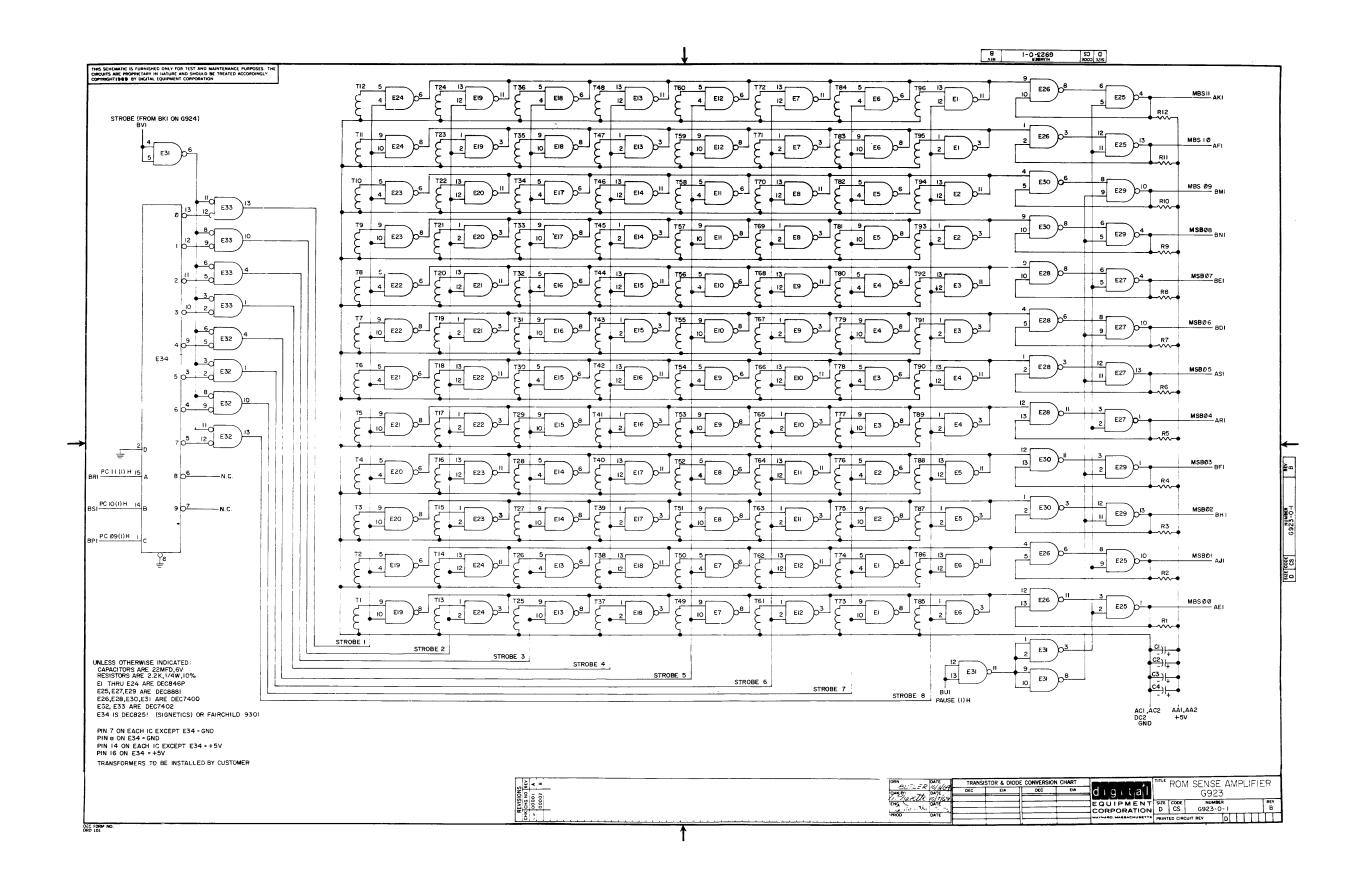

| 3.5.6               | ROM Circuits                            | 3-13 | 4.4.4.2   | Processor Timing Assumptions                            | 4-2  |

| 3.5.6.1             | General                                 | 3-13 | 4.4.4.3   | Detailed Timing Analysis (FETCH Cycle)                  | 4-3  |

| 3.5.6.2             | Address Selection                       | 3-13 | 4.4.4.4   | Detailed Timing Analysis (EXECUTE Cycle: JFF, JFN, SKE, |      |

| 3.5.6.3             | Timing Circuits                         | 3-13 |           | SKZ, TRR, NOP, JMR, and SKP)                            | 4-3  |

| 3.5.6.4             | Data Sense Circuits                     | 3-13 | 4.4.4.5   | Detailed Timing Analysis (Two-word EXECUTE Cycle: JMP,  |      |

| J.J.U. <del>4</del> | Data Selise Circuits                    | 5-15 |           | JMS, and TRM Instructions)                              | 4-4  |

# CONTENTS (Cont)

|         |                                                            | Page |            |                                                                 | Pag         |

|---------|------------------------------------------------------------|------|------------|-----------------------------------------------------------------|-------------|

| 4.4.4.6 | Detailed Timing Analysis (I/O Execution: TXD, TYD, SYF,    |      | APPENDIX   | A PDP-14 SIGNAL GLOSSARY                                        | <b>A</b> -1 |

|         | SYN, TXF, TXN, TYF, and TYN)                               | 4-4  |            |                                                                 |             |

| 4.4.5   | Memory Timing Checks                                       | 4-5  | APPENDIX   | B REFERENCE DRAWINGS                                            | B-1         |

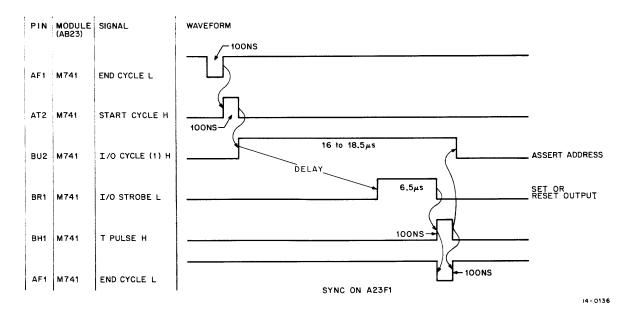

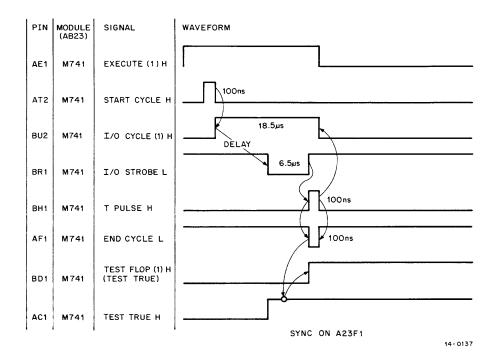

| 4.4.6   | I/O Timing Checks and Notes                                | 4-5  |            |                                                                 |             |

| 4.4.7   | Computer Interface Check                                   | 4-5  |            |                                                                 |             |

| 4.4.7.1 | Running Standard DEC Software on the Serial-Line Interface | 4-6  |            |                                                                 |             |

| 4.4.8   | Scope Loops and How You Get Them                           | 4-7  |            |                                                                 |             |

| 4.4.8.1 | General                                                    | 4-7  | ILLUSTR    | ATIONS                                                          |             |

| 4.4.8.2 | Procedure                                                  | 4-7  |            |                                                                 |             |

| 4.5     | I/O Troubleshooting                                        | 4-7  | E: NI.     | Title                                                           | Doc         |

| 4.5.1   | Test True                                                  | 4-7  | Figure No. | Title                                                           | Pag         |

| 4.5.2   | Sample Return Troubleshooting                              | 4-7  | 1-1        | Stand-Alone Application                                         | 1-1         |

| 4.5.3   | Address Line Troubleshooting                               | 4-8  | 1-2        | Monitored Application                                           | 1-1         |

| 4.5.3.1 | Address Line 1                                             | 4-8  | 1-3        | Interactive Application                                         | 1-1         |

| 4.5.3.2 | Address Line 2                                             | 4-8  | 1-4        | PDP-14 Program Execution Cycle                                  | 1-2         |

| 4.5.3.3 | Address Line 4                                             | 4-8  | 1-5        | Typical PDP-14 Control System                                   | 1-3         |

| 4.5.3.4 | Address Line 8                                             | 4-8  | 1-6        | PDP-14 Control System                                           | 1-4         |

| 4.5.4   | Package Select Lines                                       | 4-8  | 1-7        | Power Supply Connections                                        | 1-4         |

| 4.5.5   | Only One Address Fails                                     | 4-8  | . 2-1      | PDP-14 Mainframe Showing Module Locations                       | 2-2         |

| 4.5.6   | Set and Reset Lines                                        | 4-8  | 2-2        | I Box Layout and Hierarchy                                      | 2-3         |

| 4.5.7   | Clear Lines                                                | 4-9  | 2-3        | O Box Layout and Hierarchy                                      | 2-4         |

| 4.5.8   | A Box                                                      | 4-9  | 2-4        | A Box Layout and Hierarchy                                      | 2-5         |

| 4.6     | Timer Adjustment                                           | 4-9  | 2-5        | User Maintenance Steps                                          | 2-6         |

| 4.6.1   | Timer Adjustment With a Computer                           | 4-9  | 2-6        | Input/Output Relationships                                      | 2-7         |

| 4.6.2   | Timer Adjustment Without a Computer                        | 4-9  | 2-7        | Decision Diagram, Fault Isolation Example Number 1              | 2-8         |

| 4.7     | Memory Troubleshooting                                     | 4-9  | 2-8        | Decision Diagram, Fault Isolation Example Number 2              | 2-9         |

| 4.7.1   | General                                                    | 4-9  | 2-9        | Decision Diagram, Fault Isolation for Equations Involving Timer |             |

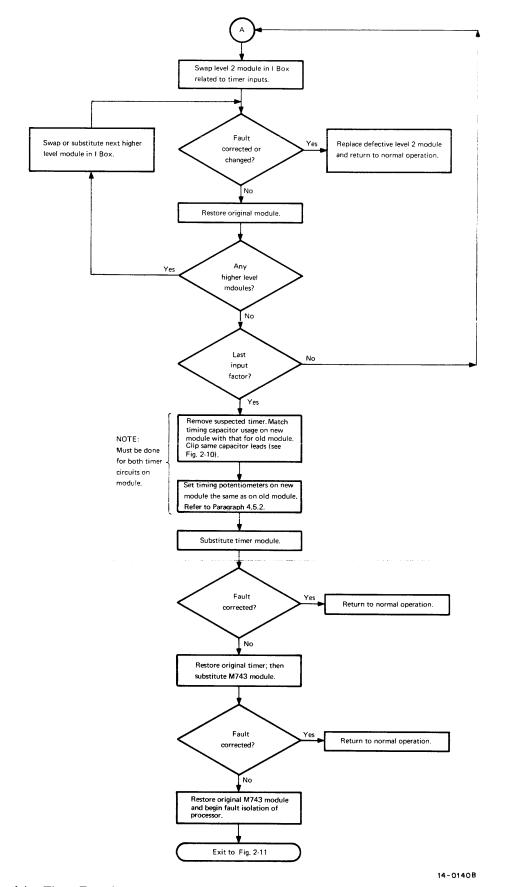

| 4.7.2   | No Memory Output                                           | 4-10 |            | Functions                                                       | 2-1         |

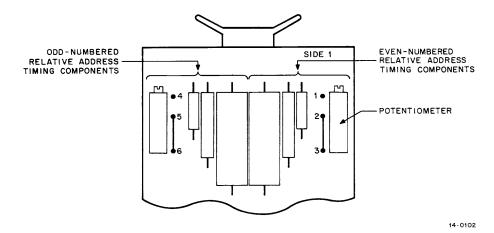

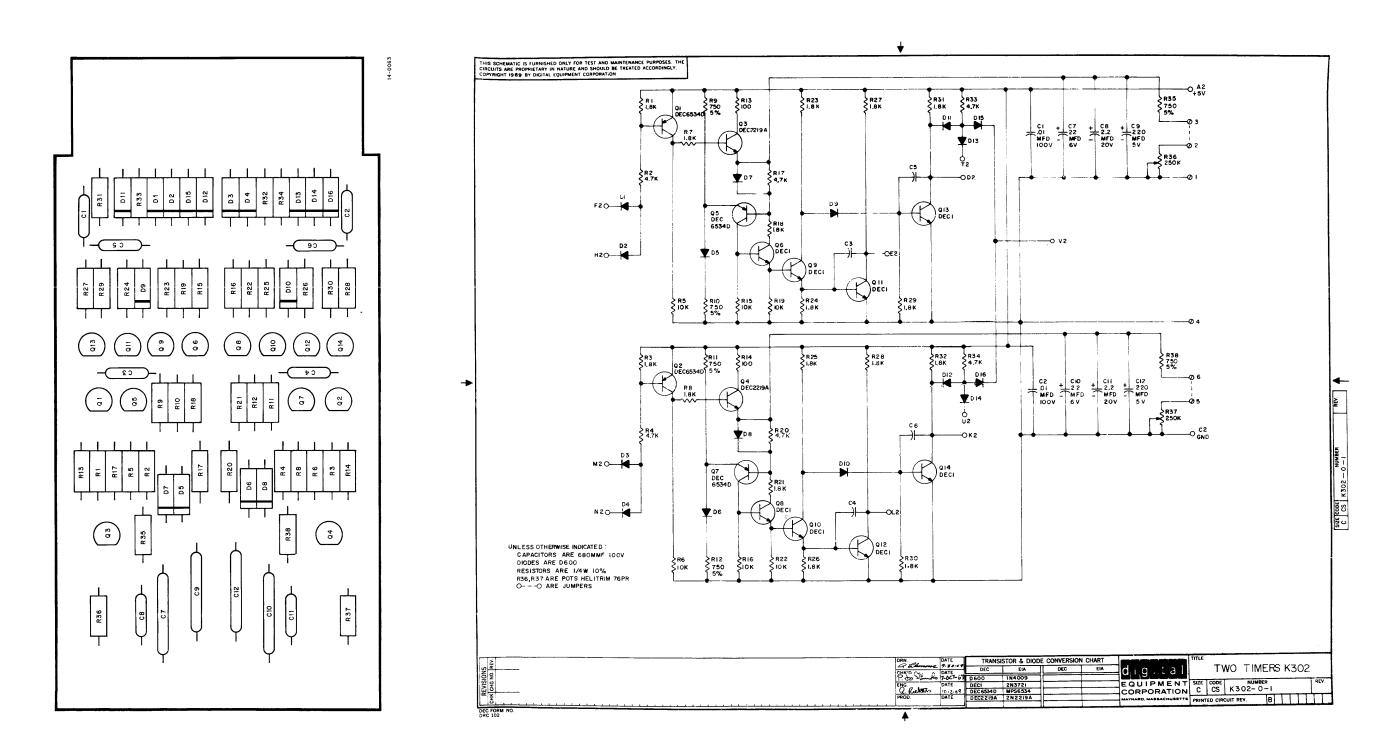

| 4.7.2.1 | No Memory Output and Processor is Halting                  | 4-10 | 2-10       | K302 Timer Components                                           | 2-1         |

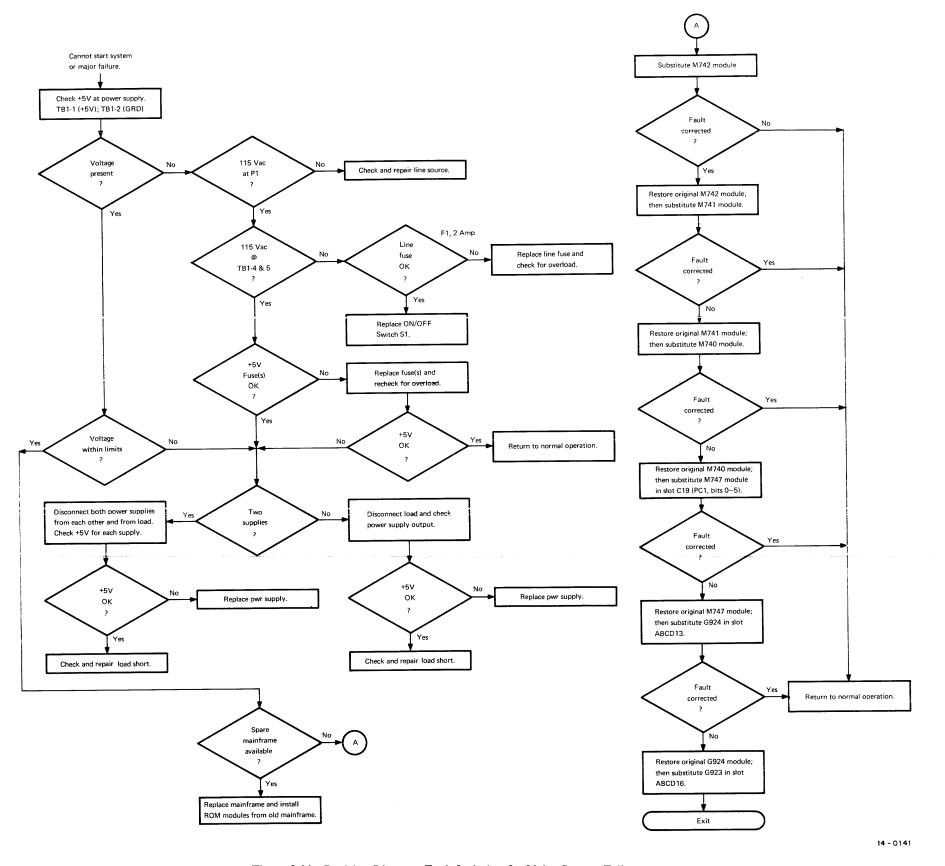

| 4.7.2.2 | No Memory Output and the Processor Continues to Run        | 4-10 | 2-11       | Decision Diagram, Fault Isolation for Major System Failure      | 2-1         |

| 4.7.3   | One Bit in Every Word Set or Cleared                       | 4-10 | 2-12       | Diagnostic Test Usage                                           | 2-1         |

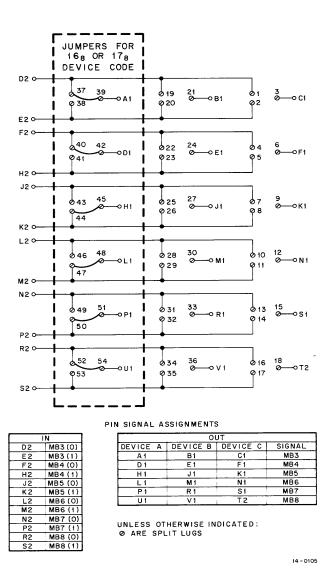

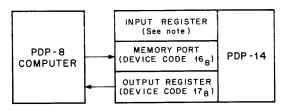

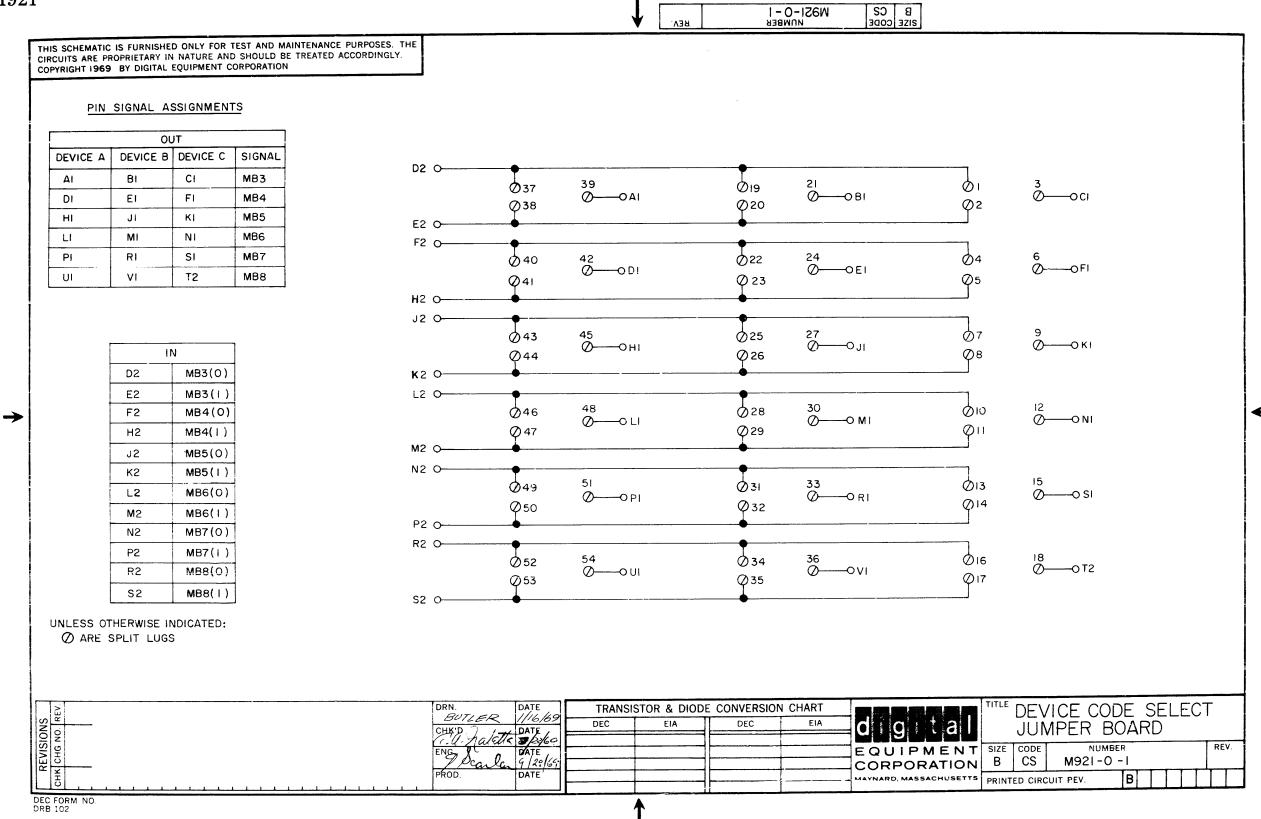

| 4.7.4   | One Bit in Every Eighth Word is Bad                        | 4-10 | 2-13       | M921 Connections for a Device Code of 168 or 178                | 2-1         |

| 4.7.5   | Groups of Eight Words Bad                                  | 4-10 | 2-14       | PDP-14 Cabling                                                  | 2-1         |

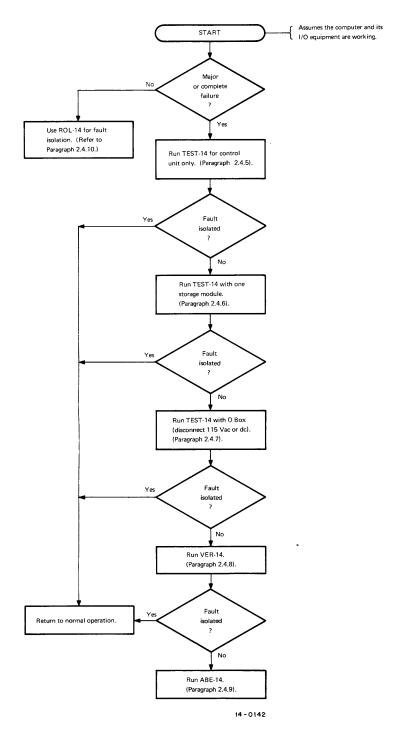

| 4.7.6   | STROBE 1 to STROBE 8                                       | 4-10 | 3-1        | PDP-14 Control Unit, Block Diagram                              | 3-1         |

| 4.7.7   | Current Switches                                           | 4-11 | 3-2        | I Box Block Diagram                                             | 3-3         |

| 4.7.8   | Matrix-Base Driver Transistors                             | 4-11 | 3-3        | O Box Block Diagram                                             | 3-3         |

| 4.7.9   | One-Half Memory Select                                     | 4-11 | 3-4        | A Box Block Diagram                                             | 3-4         |

| 4.7.10  | Field Select                                               | 4-11 | 3-5        | Test Instructions                                               | 3-5         |

| 4.8     | Troubleshooting and Repair Techniques                      | 4-11 | 3-6        | Decision Instructions                                           | 3-5         |

| 4.8.1   | Logic Troubleshooting                                      | 4-11 | 3-7        | Operate Instructions                                            | 3-6         |

| 4.8.2   | Module (Circuit) Troubleshooting                           | 4-11 | 3-8        | TXD and TYD Instructions and Display Words                      | 3-6         |

| 4.8.3   | Repairs and Replacements                                   | 4-12 | 3-9        | Housekeeping Instructions                                       | 3-          |

| 4.8.4   | Validation Tests                                           | 4-12 | 3-10       | IOT Instructions                                                | 3-8         |

|         |                                                            |      |            |                                                                 |             |

V

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                          | Page                                  | Figure No.   | Title                                                                | Page |

|------------|----------------------------------------------------------------|---------------------------------------|--------------|----------------------------------------------------------------------|------|

| 3-11       | Power Control Timing                                           | 3-10                                  | 4-8          | Memory Timing Checks (Paragraph 4.4.5)                               | 4.5  |

| 3-12       | Control Logic Timing                                           | 3-11                                  | 4-9          |                                                                      | 4-5  |

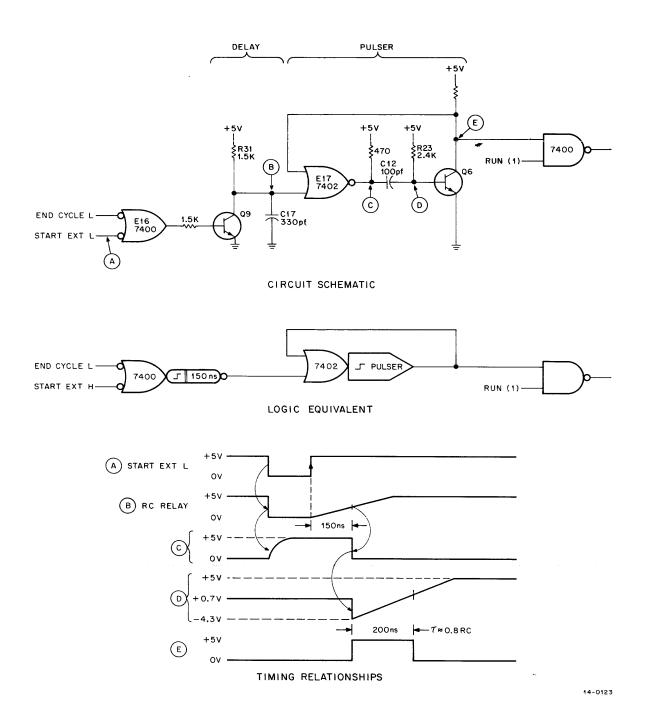

| 3-13       | Delay and Pulser Operation                                     | 3-12                                  | 4-10         | I/O Timing Checks (Paragraph 4.4.6) PDP-8/PDP-14 Interface           | 4-5  |

| 3-14       | ROM Functional Diagram                                         | 3-14                                  | 4-10<br>4-11 | ·                                                                    | 4-6  |

| 3-15       | ROM Timing Relationships                                       | 3-15                                  | 4-12         | Tape Flag for Counting Screwdriver Turns Integrated Circuit Location | 4-9  |

| 3-16       | ROM Data Sense Circuits, Simplified Logic Diagram              | 3-15                                  | 4-13         | •                                                                    | 4-12 |

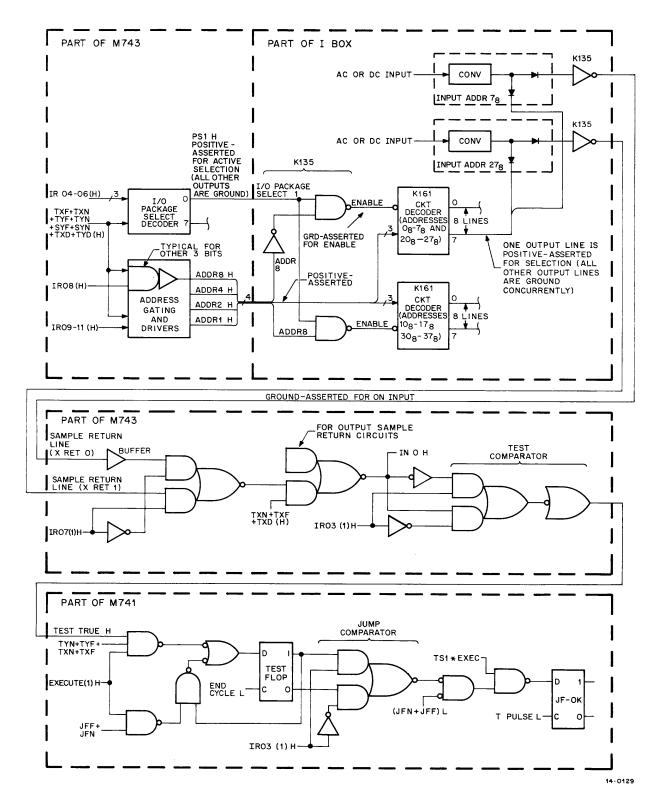

| 3-17       | Input Test Functional Diagram                                  | 3-17                                  | 4-13         | Integrated Circuit Pin Locations — Top View                          | 4-12 |

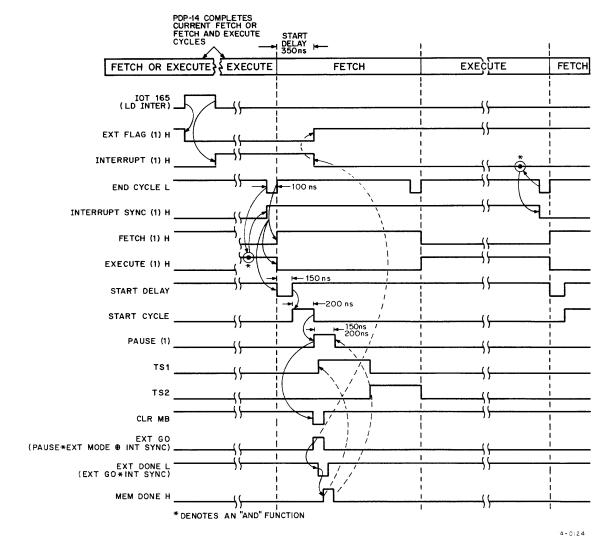

| 3-18       | PDP-14 Interrupt Mode Timing                                   | 3-18                                  |              |                                                                      |      |

| 3-19       | Input Converter Circuits                                       | 3-19                                  | TABLES       |                                                                      |      |

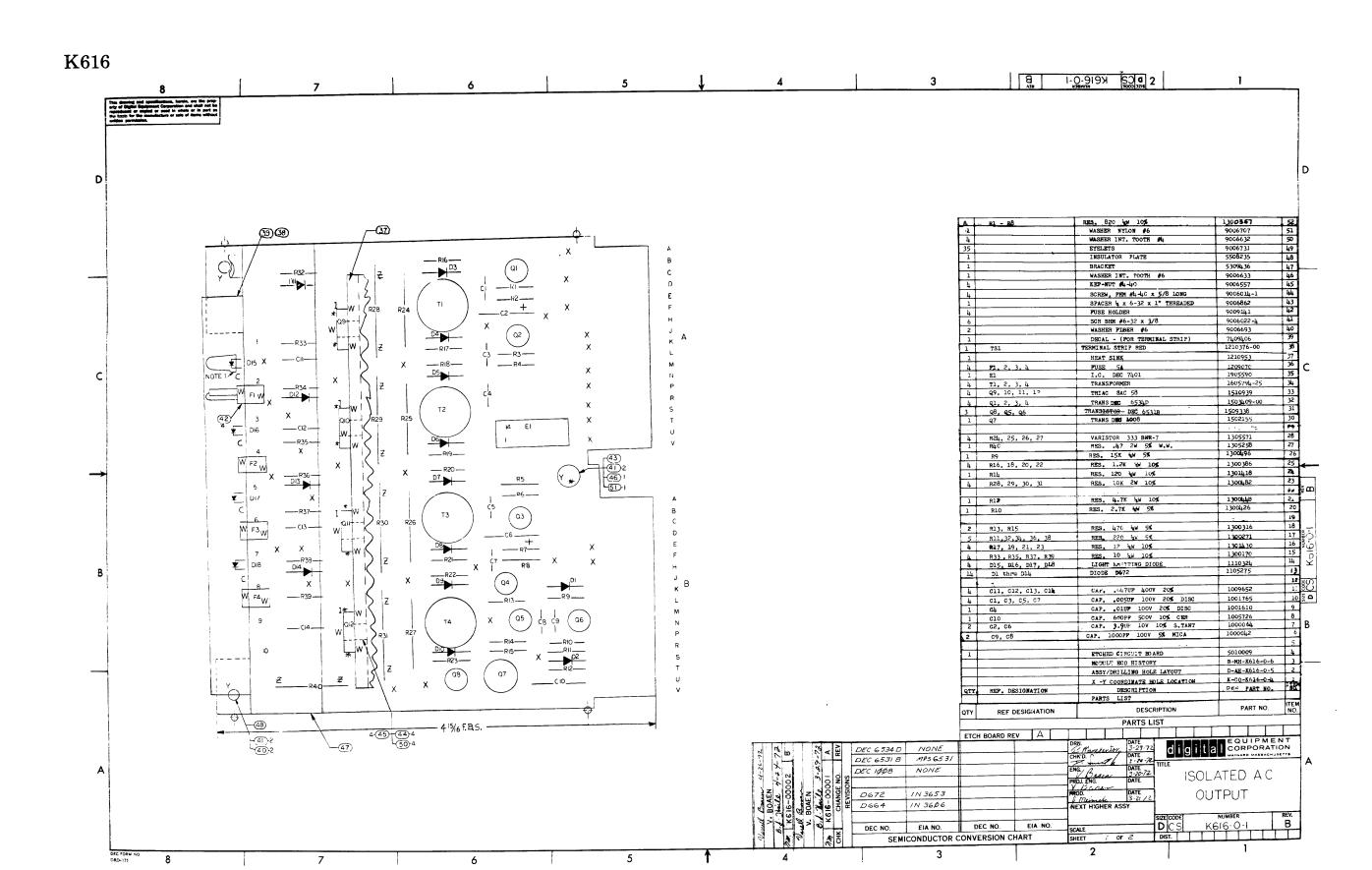

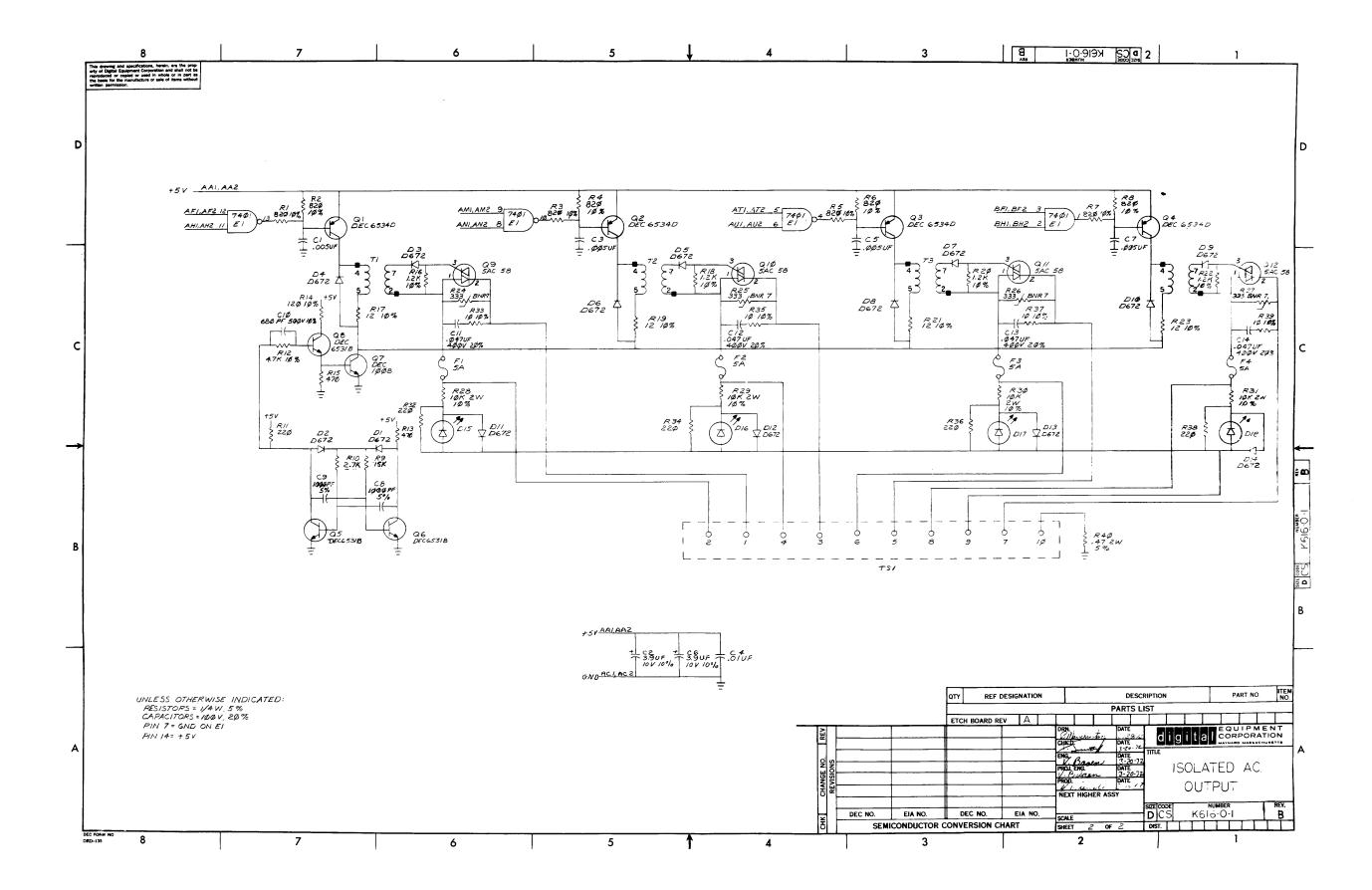

| 3-20       | AC Isolated Switch                                             | 3-20                                  | TABLES       |                                                                      |      |

| 3-21       | DC Driver                                                      | 3-20                                  |              |                                                                      |      |

| 3-22       | Timer Module, Time Delay Circuit, Simplified Schematic Diagram |                                       | Table No.    | Title                                                                | Page |

|            | and Equivalent Logic Diagram                                   | 3-21                                  | 2-1          | Recommended Spare Parts by Major Units                               | 2-5  |

| 3-23       | Timer Relationships                                            | 3-21                                  | 2-2          | Spare Parts Recommended for a Typical Configuration                  | 2-6  |

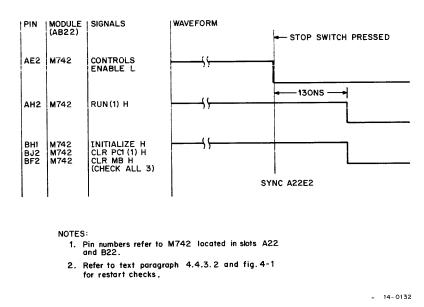

| 4-1        | Startup Timing                                                 | 4-2                                   | 2-3          | RIM Loader                                                           | 2-16 |

| 4-2        | Manual Controls Check                                          | 4-2                                   | 2-4          | Test Program Error Code/Module Location Cross Reference              | 2-18 |

| 4-3        | Free-Running Multivibrator                                     | 4-2                                   | 2-5          | Accessory Box Module/ABE-14 Error Code Cross Reference               | 2-22 |

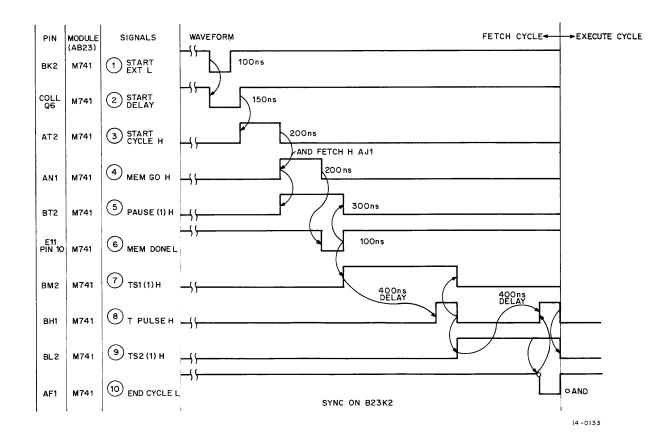

| 4-4        | FETCH Cycle Timing Analysis (Paragraph 4.4.4.3)                | 4-3                                   | 3-1          | PDP-14 Major Registers                                               | 3-2  |

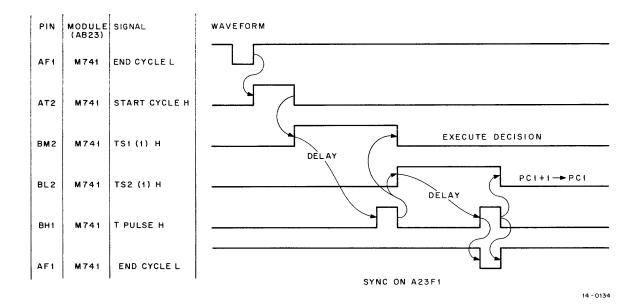

| 4-5        | Internal Execution (JFF, JFN, SKE, SKZ, TRR, NOP, JMR, and     |                                       | 3-2          | External Mode Instructions                                           | 3-9  |

|            | SKP) (Paragraph 4.4.4.4)                                       | 4-4                                   | 4-1          | Recommended Tools and Test Equipment                                 | 4-1  |

| 4-6        | Two-Word Instruction Execution (JMS, JMP, and TRM)             |                                       | 4-2          | Short Patch for Computer Interface Checkout                          | 4-6  |

|            | (Paragraph 4.4.4.5)                                            | 4-4                                   | 4-3          | I/O Fault Identification                                             | 4-7  |

| 4-7        | I/O Execution Cycle (TXN, TXF, TYN, TYF, TXD, TYD, SYN, and    |                                       | 4-4          | Scope Loop Program for Testing an Input or Output                    | 4-8  |

|            | SYF) (Paragraph 4.4.4.6)                                       | 4-4                                   | 4-5          | ROM Fault Isolation                                                  | 4-10 |

|            | · · · · · · · · · · · · · · · · · · ·                          | * * * * * * * * * * * * * * * * * * * | T 2          | NOM I dult isolation                                                 | 7-10 |

vi

## INTRODUCTION

This manual contains instructions and drawings for maintaining the PDP-14 Programmable Controller manufactured by Digital Equipment Corporation, Maynard, Massachusetts. The manual is organized into four chapters for various levels of maintenance personnel.

Chapter 1 provides a brief description and specifications for the PDP-14 and is designed to give the reader a first level introduction to the system.

Chapter 2 presents the first level maintenance philosophy and procedures to be used by maintenance personnel assigned to the machine. The techniques described are those of module swapping which, when systematically performed, will correct most problems.

Chapters 3 and 4 are intended to be used by highly trained and qualified maintenance personnel. Chapter 3 explains the theory of operation and Chapter 4 outlines techniques to be used for fault isolation on a particular module.

#### **REFERENCES**

For additional information concerning the PDP-14, the PDP-14/L, or system-related equipment, refer to the following DEC publications:

PDP-14 Reference Card PDP-14 User's Manual Control Handbook Small Computer Handbook

#### SOFTWARE DOCUMENTATION

The following diagnostic documentation is also provided by DEC:

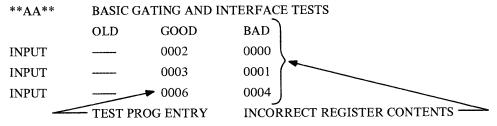

TEST-14, MAINDEC-14-D7AB-D: This document contains the program listing for TEST-14 plus instructions for using the diagnostic program and interpreting its results. TEST-14 performs a comprehensive test of the PDP-14 Processor, Input Boxes, and Output Boxes.

TEST-14/L, MAINDEC-14-D7LA-D-(D): Same as TEST-14 except for PDP-14/L.

ABE-14, MAINDEC-14-D8AB-D: This document contains the program listing and instructions for loading, running, and interpreting the results of ABE-14. ABE-14 is a diagnostic program for testing PDP-14 and PDP-14/L Accessory Boxes.

VER-14, MAINDEC-14-D1AB-D: This document contains the program listing and instructions for using VER-14. VER-14 is a program that verifies the contents and operation of a Read-Only Memory (ROM).

LOAD-14, DEC-14-LZPB-D: This document contains the program listing and instructions for LOAD-14. LOAD-14 is used to enter a ROM program into the computer memory for verification by VER-14.

ROL-14, DEC-14-MWZC-PB: This document contains the program listing and instructions for using the ROL-14 program. ROL-14 is an interrogation and control program that can be used with an on-line system for diagnostic tests.

#### MAINTENANCE PHILOSOPHY

This manual contains two levels of maintenance instructions. The first level, designated User Maintenance, is presented in Chapter 2 and is intended primarily for end user maintenance personnel. However, it should also be used as the first level of maintenance for DEC Field Service personnel. This level of maintenance assumes the user is familiar with industrial control systems and basic electrical repair techniques but may not be familiar with programmable controllers.

There are two primary divisions of user maintenance; one for fault isolation using module substitution techniques and a second for using computer diagnostics. In either case, only module replacement is recommended; repair of the modules should only be attempted by qualified personnel.

Detailed Maintenance is the second level of maintenance and is intended only for DEC Field Service personnel or user personnel thoroughly trained in electronic repair (and solid-state digital repair techniques). This level is intended primarily for module repair and is presented in Chapter 4.

vii

|  | - |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

# CHAPTER 1 GENERAL INFORMATION

#### 1.1 GENERAL

This chapter defines the purpose of the PDP-14 Controller, lists typical system applications, and describes the major elements of the controller. A summary of equipment specifications is also included at the end of the chapter.

#### 1.2 SYSTEM DESCRIPTION

#### 1.2.1 Purpose and Use

The PDP-14 Controller replaces conventional relay control systems in virtually all types of industrial applications requiring high-reliability control operations. Typical uses include the PDP-14 as the controller for:

- Transfer and assembly lines

- Machine tool systems

- Packaging and materials handling systems

- Chemical mixing systems

- Elevator control systems

The PDP-14 can control any operation or process sequence that comprises discrete steps and involves on/off status inputs and on/off control outputs. The controller can be used in a stand-alone application or can be used with a computer in a monitoring application or an interactive application.

#### 1.2.2 Stand-Alone Applications

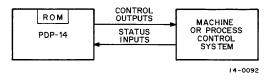

When used in a stand-alone or independent application (Figure 1-1), the PDP-14 controls the machine or process system operating sequence using a program in its Read-Only Memory (ROM). This program establishes the control relationships between status inputs and control outputs.

Status inputs are provided as on/off inputs from machine system pushbutton switches, limit switches, etc. The program continually tests the status inputs (and outputs) and, based upon the results, advances the control sequence by turning outputs (to solenoids, motor starters, etc.) on or off.

In a stand-alone application, the PDP-14 can accept up to 256 status inputs and can control up to 255 outputs.

Figure 1-1 Stand-Alone Application

#### 1.2.3 Monitoring Applications

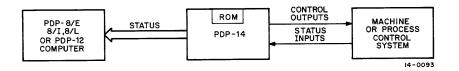

The PDP-14 can be connected to a small, general purpose computer such as the PDP-8/E for monitoring (Figure 1-2). The PDP-14 still performs control functions as described in Paragraph 1.2.2; however, it also reports status information to the PDP-8/E. The PDP-8/E analyzes this data to determine if the machine is working properly and/or stores production information (e.g., piece counts, cycle times, scheduled tool changes, etc.).

Figure 1-2 Monitored Application

In other applications, the PDP-14 does not control machine operation (this function is provided by relays or other control systems). Instead, the PDP-14 acts as an interface for the computer and tests inputs from the machine in an order defined by a ROM program (or by the computer) and provides the test results to the computer. Since the PDP-14 does not control any outputs in this application, it can be configured to accept up to 512 discrete status inputs.

#### 1.2.4 Interactive Applications

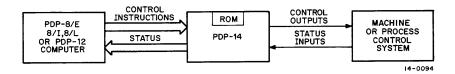

The PDP-14 can also be used with a small, general purpose computer in an interactive application (Figure 1-3). In this application, the PDP-14 can provide the fundamental control for the machine and return status information to the computer. The computer can then direct the control in the PDP-14 based upon the status information provided by the PDP-14 or upon other information available to the computer (such as analog signals from a measuring device).

Figure 1-3 Interactive Application

#### 1.2.5 Operating Concepts

The controller directs the machine or process system sequence by solving input/output relationships, using a program (a method or procedure for solving a problem) stored in its memory. Basically, this program defines what outputs are to be turned on or off (and in what order or sequence) and what combinations of inputs (and outputs) are to effect an output. In other words, the controller controls the machine or process system sequence by solving input/output equations.

The controller cannot directly react to an input (or output) change of state (on-to-off or off-to-on). Therefore, it must test the pertinent inputs (and outputs) many times a second and it must define the pertinent state of the test. With each test, the controller must decide whether to turn an output on or off before continuing the testing procedure. Following a valid test decision, the controller turns the output on or off, then continues testing.

The above operations are all performed as discrete steps of a program. The smallest part of a program is called an instruction. The instruction is stored in a discrete memory location called an address. It defines a single step or action to be performed. The controller uses three basic types of instructions: Test, Decision, and Operate. A Test instruction defines the input (or output) to be tested and the applicable state (on or off). A Decision instruction links the Test instructions with other Test instructions or with the Operate instructions. That is, for a valid decision, either an Operate instruction can be performed to turn an output on or off, or another Test instruction can be performed.

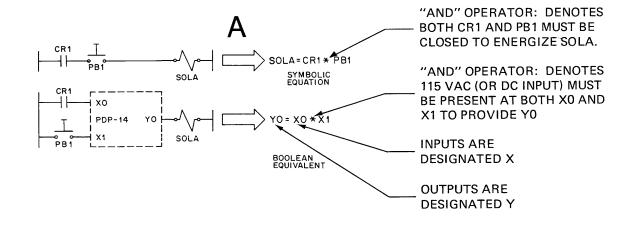

The basic logic operators (AND and OR) for solving input/output equations are inherent in the arrangement of the Test, Decision, and Operate instructions. The following example defines one way the controller might solve an input/output equation.

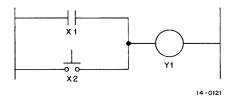

Assume a machine motion requires two inputs; for example, POWER ON and START. If POWER ON is represented as X1 (input 1), START as X2 (input 2), and the machine motion as Y1 (output 1), then:

Y1 = X1 \* X2, where \* signifies both inputs are needed concurrently; i.e., a logical AND function.

The "ladder diagram" for the above example is shown at the right.

For solution of this equation, the controller could test input X1 for an on condition. It could then examine the test result with a Decision instruction. If X1 is off, there is no need to test input X2; therefore, the controller can continue the program by testing other equations. Input X1 would then be tested again on the next complete cycle through memory. If, however, X1 is on, the Decision instruction could link the program to a Test instruction for X2. This Test instruction could then be followed with another

Decision instruction. If X2 is off, the controller returns to other testing. If X2 is on, however, the program is linked to an Operate instruction that turns on output Y to cause machine motion.

#### NOTE

Inputs are always identified with the letter X; outputs are always identified with the letter Y.

1-2

A logical OR function could be represented as follows:

Y1 = X1 + X2, where + signifies that either input (or both) can activate an output; i.e., a logical OR function.

The "ladder diagram" for the above example is shown at the right.

For solution of this equation, both inputs need be tested only if the one checked first is off. Each Test instruction could be linked to an Operate instruction (using a Decision instruction) if either input is on.

The PDP-14 Controller has the capabilities for checking inputs (or outputs) for either an on or off state. In addition, there are other instructions to control sequences. Therefore, the control programs can be written in a number of ways.

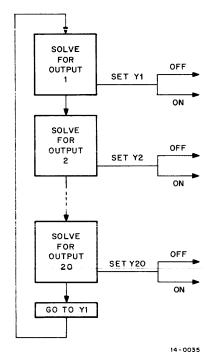

To summarize, a typical PDP-14 control program is made up of a series of instructions that are stored in a Read-Only Memory (ROM). These instructions can be arranged in groups as shown in Figure 1-4. Each group of instructions solves a Boolean equation by testing specific PDP-14 inputs and outputs and, at the end of the test, turns an output either on or off.

The final instruction in the program is an unconditional jump instruction. This instruction returns the PDP-14 to the first instruction in the program and the program execution cycle is repeated. Thus, the PDP-14 control program consists of a closed loop of instructions which are executed every 15 to 60 milliseconds (the actual execution time is dependent on the number of instructions in the program).

#### 1.3 EQUIPMENT DESCRIPTION

#### 1.3.1 General

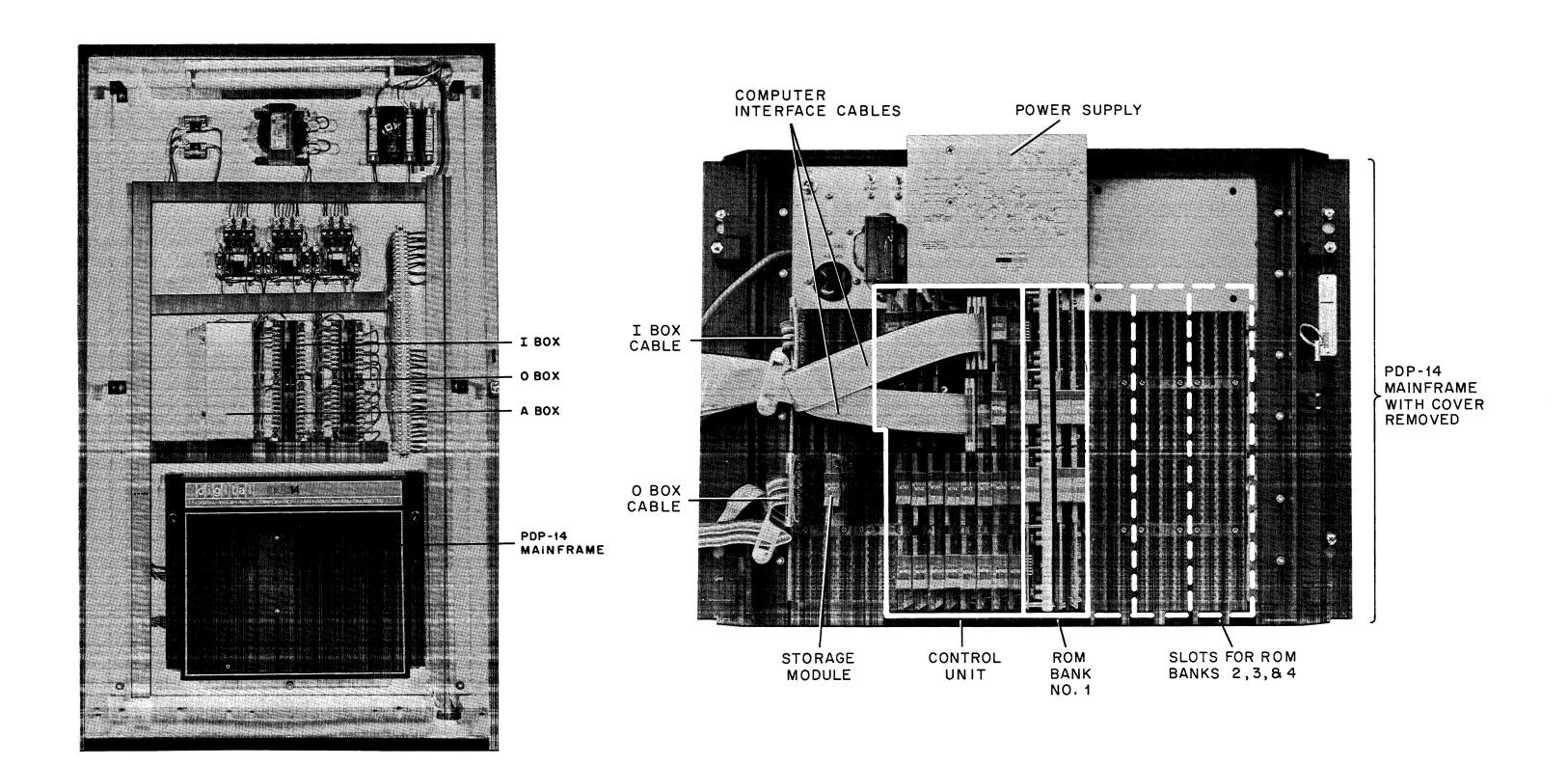

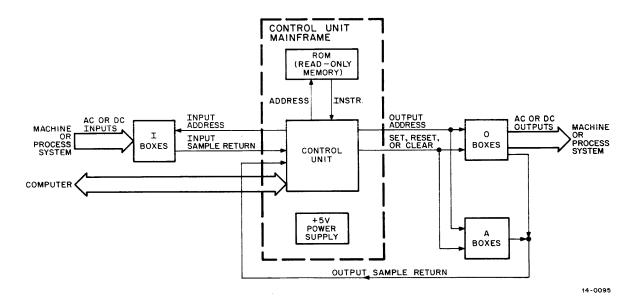

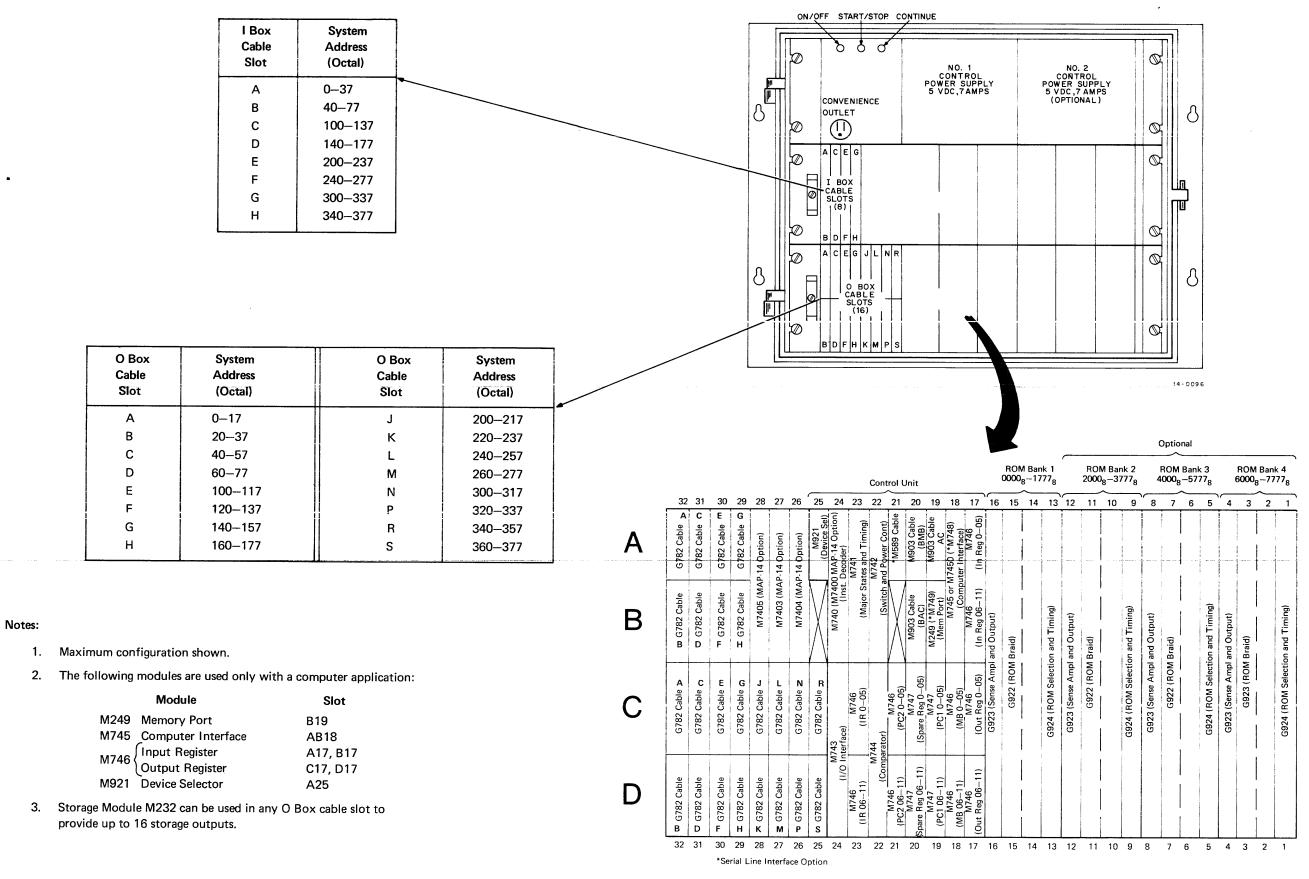

A PDP-14 Controller comprises the four major assemblies that are identified in Figure 1-5. Figure 1-6 depicts the functional relationships of the major assemblies that are described in subsequent paragraphs.

In a typical control application, the PDP-14 Controller consists of a Control Unit, a Read-Only Memory (ROM), Input (I), Output (O), and Accessory (A) Boxes. The Control Unit is fundamentally the heart of the controller. It directs and coordinates the overall operation from manual control inputs, the stored program, input (or output) test

Figure 1-4 PDP-14 Program Execution Cycle

results, or information supplied by a computer. The ROM stores the program for evaluating status inputs and controlling a machine or process system. An I Box converts machine or process system inputs into signals usable by the controller. Similarly, O Boxes convert controller outputs into signals usable by the machine or process system. Accessory (A) Boxes provide timer functions, storage functions during normal operation, and special storage functions during power-off conditions.

Figure 1-5 Typical PDP-14 Control System

Figure 1-6 PDP-14 Control System

#### 1.3.2 Control Unit Mainframe

The control unit mainframe consists of a heavy steel frame that is hinged to a mounting base frame (Figure 1-5). The mainframe contains a low-voltage power supply (or supplies), module sockets for Control Unit and Read-Only Memory (ROM) logic, and module sockets for Input (I) Box, Output (O) Box, and Accessory (A) Box connectors.

- 1.3.2.1 Power Supply Filter Assembly This assembly contains an input power terminal strip, a utility receptacle, an ON/OFF switch, and a 2A line fuse. The assembly also contains two manual control switches. The START/STOP switch, as the name implies, starts or stops the controller's timing circuits. The CONTINUE switch allows the controller to resume operation at the point it was stopped. In contrast, a start operation causes the program to begin at its initial step. These manual switches are not used during normal operation or trouble-shooting.

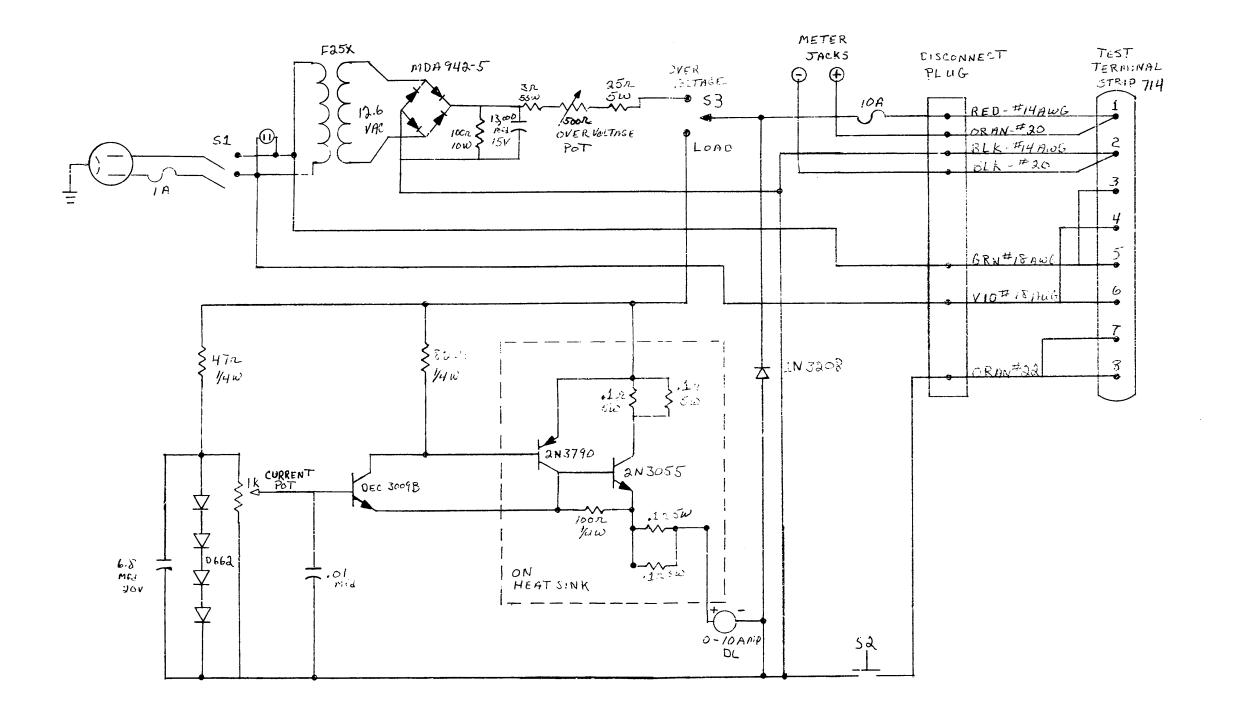

- 1.3.2.2 Power Supply The +5V power supply provides the operating potential for logic circuit operation. The supply operates from a 105 to 125 Vac (or 210 to 250 Vac), 47 to 500 Hz source. It provides a nominal +5 Vdc at 7A. The power supply is short-circuit proof and provides over-load protection for logic circuits.

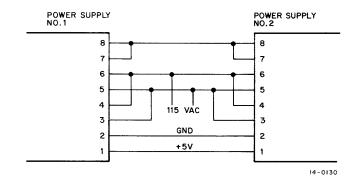

Two power supplies are required for controller configurations having load currents in excess of 7A. These supplies are connected in parallel as shown in Figure 1-7.

1.3.2.3 Read-Only Memory – The PDP-14 Memory stores a program that defines the machine system operating sequence. The memory is termed "read-only" because it cannot be altered electrically (i.e., written on).

A machine program consists of many discrete steps called instructions. Each instruction is stored in a discrete ROM location called an address and is retrieved (fetched) from memory by Control Unit action. When executed by the Control Unit, an instruction causes the controller to perform a single action such as testing an input or turning on an output.

Figure 1-7 Power Supply Connections

The ROM is a passive device; i.e., it provides an instruction only when requested by the Control Unit. In its maximum configuration, the ROM provides the capability for storing up to 4096 instructions; therefore the Control Unit must be capable of addressing 4096 locations.

The ROM is not interchangeable with ROM units used in other PDP-14 control systems. It is functionally equivalent to the interconnections in a relay control system, and as such, is specifically programmed (wired) for each application.

1.3.2.4 Control Unit – The Control Unit directs the operation of the controller based upon manual inputs, program instructions, test results, or information provided by a computer. It interfaces with the ROM, all I, O, and A Boxes, and the computer.

The Control Unit begins operation by initializing the controller (placing its circuits in a state for starting operation). Next, it addresses the first ROM location and fetches an instruction. The Control Unit interprets (decodes) then performs (executes) the instruction.

Instruction execution can entail testing an input or output, making a decision, or turning an output on or off. After executing an instruction, the Control Unit repeats the cycle by fetching another instruction.

For a Test Input instruction, the Control Unit addresses the input circuit. The input circuit responds by providing the on/off state of the input to the Control Unit on the input sample return line. The Control Unit temporarily stores this information. It then fetches another instruction to evaluate the input.

An identical operation is performed for a Test Output instruction. For an Operate instruction, however, the Control Unit also specifies the function to be performed; i.e., whether an output is to be turned on (SET) or off (RESET), or whether all outputs are to be turned off (CLEARED).

#### 1.3.3 I Boxes

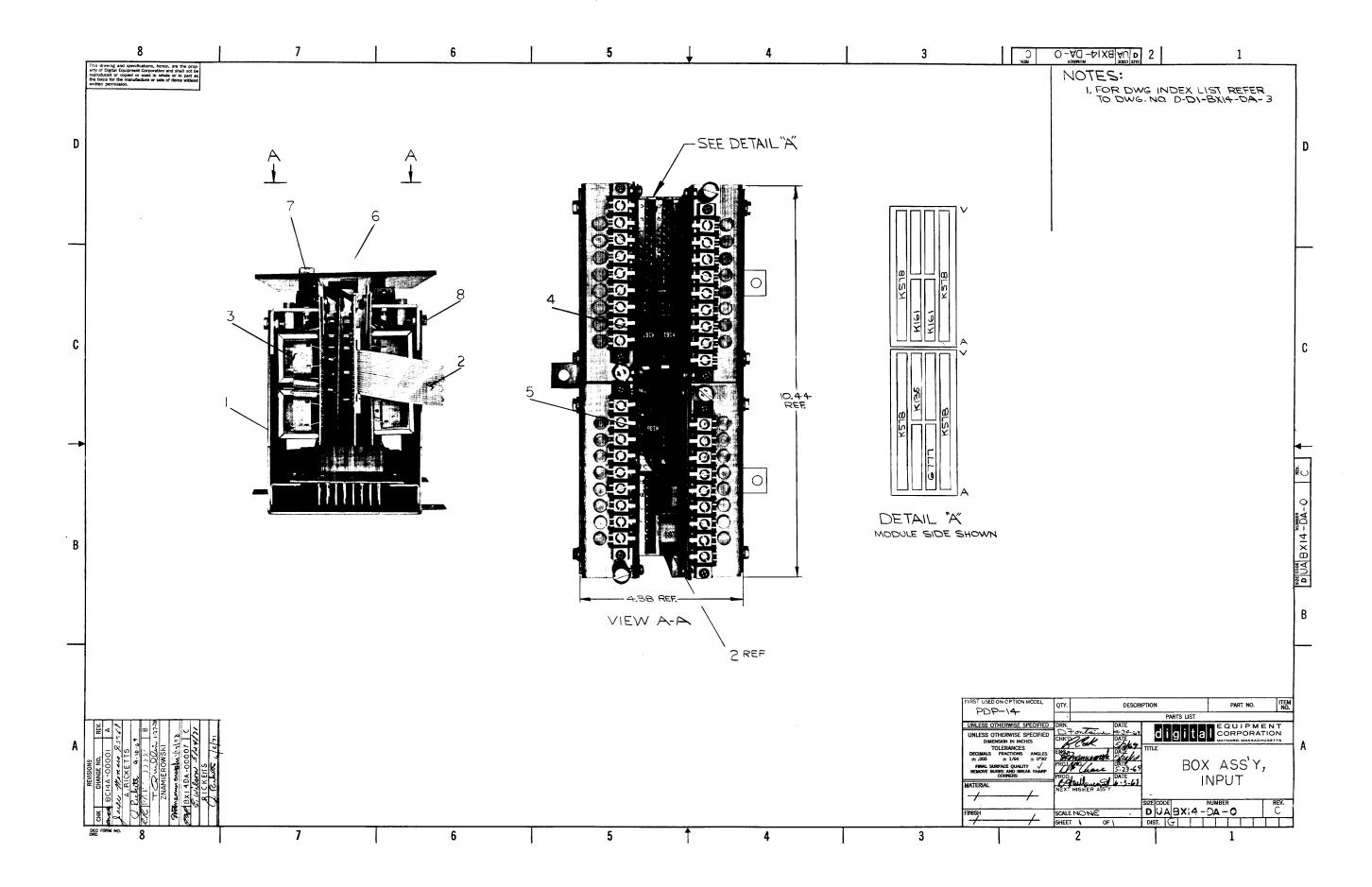

An I Box accepts on/off status inputs from the machine or process system and converts them into logic levels usable by the controller. Each I Box is capable of accepting up to 32 ac or dc inputs (but not both). Up to eight I Boxes can be used in a typical control application for a total of 256 inputs. Machine inputs are connected to screw terminals on the front of I Box modules. Control cables (one from each I Box) connect the I Boxes with the Control Unit.

A Test Input instruction defines the input to be tested and the state (on or off). When the controller executes one of these instructions, the Control Unit sends an input address (for selecting one of 32 inputs) to the I Boxes

and selects one of eight possible I Boxes. The selected I Box, in turn, decodes the address and selects two input circuits. Information from the selected input circuits is then provided on two sample return lines and the PDP-14 Control Unit must determine which sample return is valid.

#### 1.3.4 O Boxes

An O Box converts controller logic levels into outputs used by machine or process system load circuits (such as indicators, solenoids, motor starters, etc.). Up to sixteen outputs can be handled by one O Box. These outputs can be either ac or dc (but not both). Up to sixteen O Boxes can be used in an application for a total of 255 outputs (the last output address, 256, is reserved for a special function). Output connections are provided by screw terminals on the output modules. Control cables (one from each O Box) connect the O Boxes to the Control Unit.

An output can be turned on or off or tested for an on or off state by the program instructions. These instructions define the output and the function to be executed. When the controller executes one of these instructions, the Control Unit addresses the output and defines the function. An output is turned on by a SET function and remains on until turned off by a RESET or CLEAR function. For testing of an output, the Control Unit simply addresses the output. In return, the O Box provides the state of the addressed output to the Control Unit on the output sample return line.

#### 1.3.5 A Boxes

An A Box is a special purpose assembly that provides timer, retentive memory, and storage functions. An A Box requires one O Box cable slot in the mainframe and thus precludes the use of 16 output drivers. The A Box uses the same addressing logic and instructions as the O Box.

Up to 16 timer (or delay) circuits can be used in an A Box. The circuits are packaged two per board. Each timer circuit can provide a delay interval from 0.01 seconds to approximately 3 minutes. Each timer has an associated storage register (flip-flop) that is turned on (SET) or off (RESET) by program instructions. When set, this flipflop starts the delay interval. After the timeout interval, the timer is considered on with respect to testing. A timer must be turned off (RESET) before it can be used again. A program instruction or an initialize operation resets the associated flip-flop to implement this action.

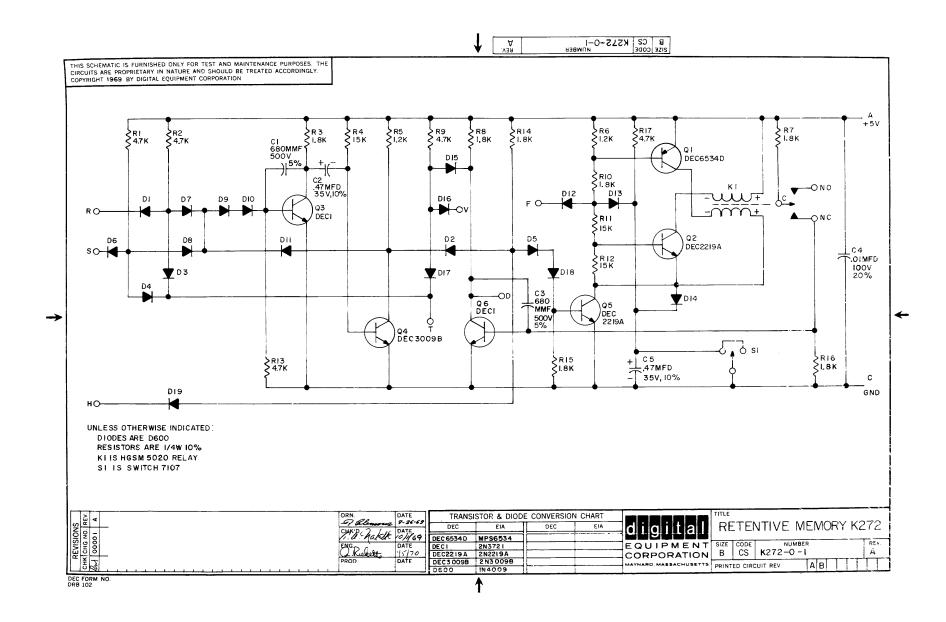

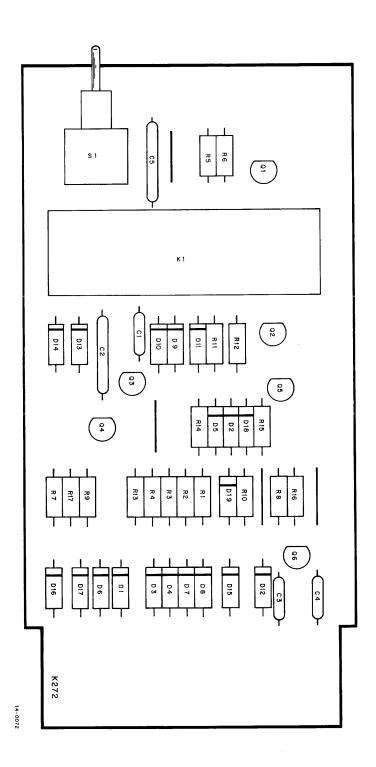

A retentive memory is a device that retains its state during power shutdown, power-off, or power-up conditions. Its principal use is to record a critical action or event and to retain the state corresponding to the event even though power is lost. Thus, its output can be used as a reference point when power is restored.

Two types of retentive memory modules are available. The K274 module provides two retentive memories (with indicator lights). The retentive memories are addressed in the same manner as outputs. Up to 16 retentive memories can be accommodated in one A Box by using K274 modules. The K272 module provides one retentive memory and only uses the even-numbered addresses on the right side of the A Box. Therefore, up to four retentive memories can be accommodated in an A Box by using K272 modules.

Each retentive memory has an associated control flip-flop. Each memory is turned on (SET) or off (RESET) by program instructions and is unaffected by an initialize operation.

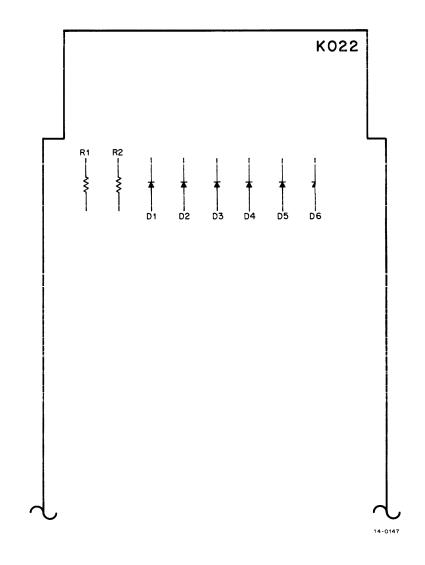

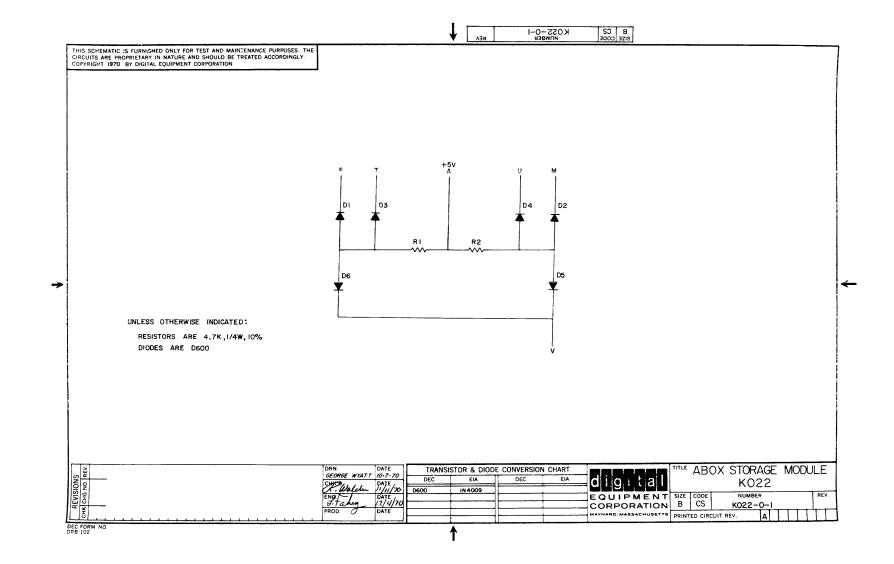

Unused timer or retentive memory module slots can be used for storage outputs. A storage module is inserted in the vacant slots to connect the output of two storage register flip-flops to the output sample return line.

#### 1.3.6 Storage Module

Storage functions can be provided by elements in the Control Unit as well as the A Box. A storage module can be installed in the Control Unit O Box connector slots. It provides 16 storage outputs but precludes the use of 16 "real" outputs. The storage module is addressed in the same manner as "real" outputs.

#### 1.3.7 Operating Summary

A Test instruction defines whether an input or output is to be tested, the state (on or off) to be checked, and which input or output (address). For a Test Input instruction, the Control Unit provides the input address selection code to the I Boxes. The state of the applicable input is then provided to the Control Unit on the input sample return line. The Control Unit temporarily stores this state, then fetches another instruction from the ROM.

A Test Input instruction can be followed by a Decision instruction. This instruction compares the test result with a programmed state (on or off). Based upon the comparison, the program can branch to: 1) turn an output on; 2) turn an output off; or 3) continue testing. This branching defines the next ROM address.

Following the above action, the Control Unit fetches the next instruction from the specified ROM address and decodes the instruction. An Operate instruction defines the output function and the output address. For an Operate instruction, the Control Unit provides the output address selection code to the O and A Boxes. It also specifies a turn-on (SET) or turn-off (RESET) function. If a "real" output is specified, an output is provided to the machine or process system.

As the above operation continues, only pertinent portions of the ROM program are used (as determined by program branching). When the end of a ROM cycle is reached, the operation recycles. If no input (or output) states have changed since the last test, the program will follow the same memory path. If, however, input or output conditions have changed, program branching will cause a different path through the ROM, thereby changing the output states.

As mentioned previously, A Boxes permit the use of timers, retentive memories, or storage elements. Outputs provided by these elements do not directly control system outputs and are not considered "real" outputs. Accessory (A) Boxes use the same instruction and address selection scheme as O Boxes.

#### 1.4 SPECIFICATIONS

#### Overall System

Number of Inputs: Up to 256 (eight I Boxes with 32 inputs each). Further

expansion in units of 32 is possible up to a maximum of

512 inputs by decreasing output capability accordingly.

Type of Inputs: ac or dc

Number of Outputs: Up to 255 (sixteen O Boxes with sixteen outputs each;

output address 256 is reserved for clearing all outputs).

Type of Outputs: ac or dc

Average Instruction Execution Time:  $20 \, \mu s \pm 20\%$

ROM Capacity: 1024 to 4096 12-bit instruction words in increments of

1024 words.

\*Average ROM Program Execution Times 1K 2K 3K 4K for Program Usage: 15 ms 30 ms 45 ms 60 ms

Environmental:

Operating Temperature 0° to 70°C (32° to 160°F) at controller; 0° to 55°C

(32° to 130°F) ambient (outside enclosure).

Relative Humidity 10 to 85%

Vibration 1.25 g's (maximum); 0 to 100 Hz (sinusoidal) in each of

three normal axes.

Other Designed for NEMA 12 enclosure.

Power Requirements:

Voltage 105 to 125 Vac or 210 to 250 Vac

Frequency 47 to 500 Hz

Wattage 86W (average power dissipation for maximum system

using ac inputs and outputs)

BX14-DA Input (I) Box

Number of Inputs: 32 (with indicators)

Input Voltage and Loading: 115 Vac @ 1.5 VA

Input Threshold: 100 Vac (minimum)

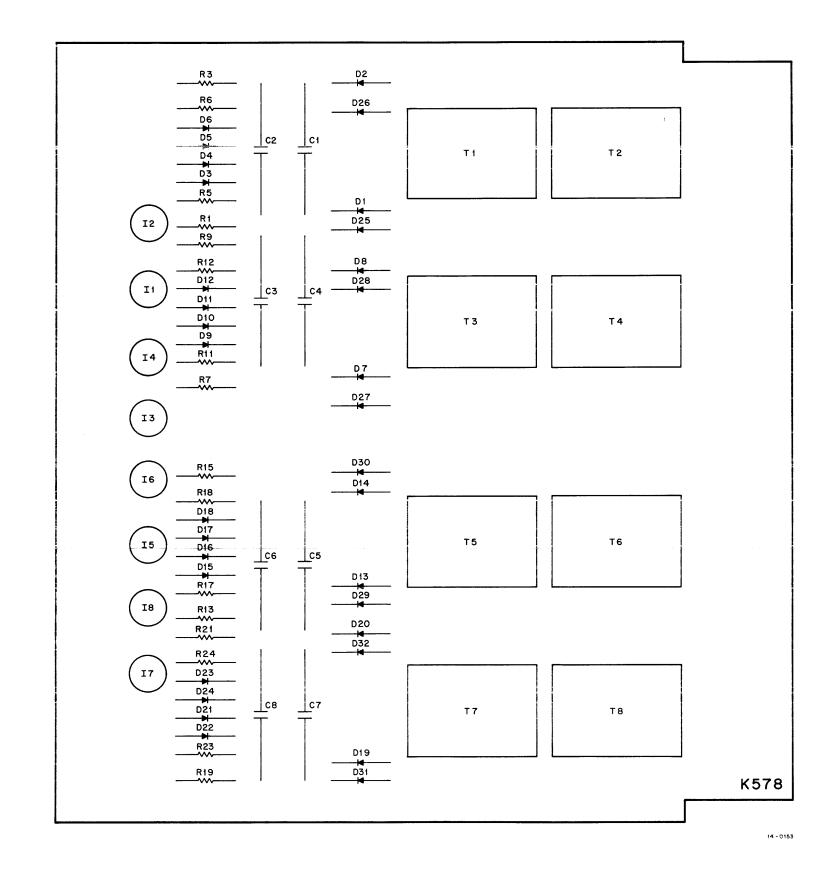

Response: 16 to 32 ms for K578A usage; 8 ms (minimum) for

K578B usage.

BX14-SA Input (I) Box

Number of Inputs: 32 (with LED indicators)

Input Voltage and Loading: 115 Vac @ 1.5 VA

Input Threshold: 80 Vac (minimum)

Response: 8 to 12 ms

BX14-DD Input (I) Box

Number of Inputs: 32 (with indicators)

Input Voltage Range: 10 to 55 Vdc (above 55 Vdc with external series resistor

at 50 ohms per volt)

Input Voltage and Current (typical): 12 Vdc @ 10 mA

$24\ Vdc\ @\ 10$  or  $30\ mA$

48 Vdc @ 20 mA

Response Time:

2 ms excluding contact bounce

Bounce Rejection:

will reject up to a 3-ms bounce

\*Based upon a 20-µs instruction execution time and 75% usage of program instructions.

BY14-DA Output (O) Box

Number of Outputs: 16 (with indicators)

Output Voltage and Drive: 115 Vac; 500 VA (maximum) per output or a distributed

maximum of 1000 VA per 1/4 O Box.

BY14-DD Output (O) Box

Number of Outputs: 16 (with indicators)

Output Voltage: 10 to 250 Vdc (dc switched to ground)

Output Current: 1A (maximum) for each circuit

Output Saturation Voltage: 2.5V (maximum)

BA14 Accessory (A) Box

\*Number of Retentive Memories: 16 maximum using the K274 module (2 memories per

module)

4 maximum using the K272 module (1 memory per

module)

\*Number of Timers: 16 maximum (2 timers per K302 module)

Timer Intervals: 0.01 to 30 sec (standard). Up to 4 min, 45 sec with

additional resistance.

\*Storage Outputs: 16 maximum (2 outputs per K022 module)

BF14-M Storage Module

Storage Outputs: 16 non-active outputs. Plugs into PDP-14 mainframe in

place of an ac or dc Output Box.

<sup>\*</sup>One A Box can accommodate various combinations of up to eight retentive memory, timer, and storage modules (Figure 2-4).

# CHAPTER 2 USER MAINTENANCE

#### 2.1 GENERAL

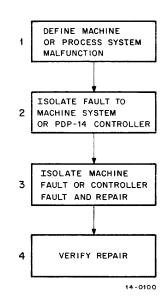

This chapter contains instructions that enable user personnel to maintain the PDP-14 Controller; they are also intended as the first level of maintenance for field service personnel. The chapter has three primary divisions:

- a. Maintenance Information 1) defines the maintenance philosophy; 2) briefly describes the controller units and functional relationships; and 3) lists the recommended test equipment and spares.

- b. Fault Isolation and Repair Without A Computer provides the recommended approach and procedures for isolating and repairing the PDP-14.

- Fault Isolation and Repair With A Computer provides the procedure for using computer diagnostics and for repair of the PDP-14.

#### 2.2 MAINTENANCE INFORMATION

#### 2.2.1 Maintenance Philosophy

The PDP-14 requires no periodic maintenance or adjustments and, therefore, no scheduled downtime. From a maintenance standpoint, it is operated continually until a system malfunction occurs.

For the user, the recommended level of repair is module replacement. If the PDP-14 cannot be fixed by module replacement, replace the next larger assembly or contact your DEC Field Service representative. Module repair should only be attempted by personnel thoroughly trained in electronics and digital repair techniques.

#### 2.2.2 Controller Description

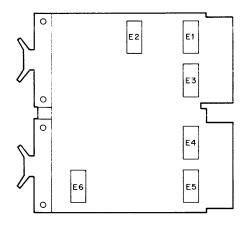

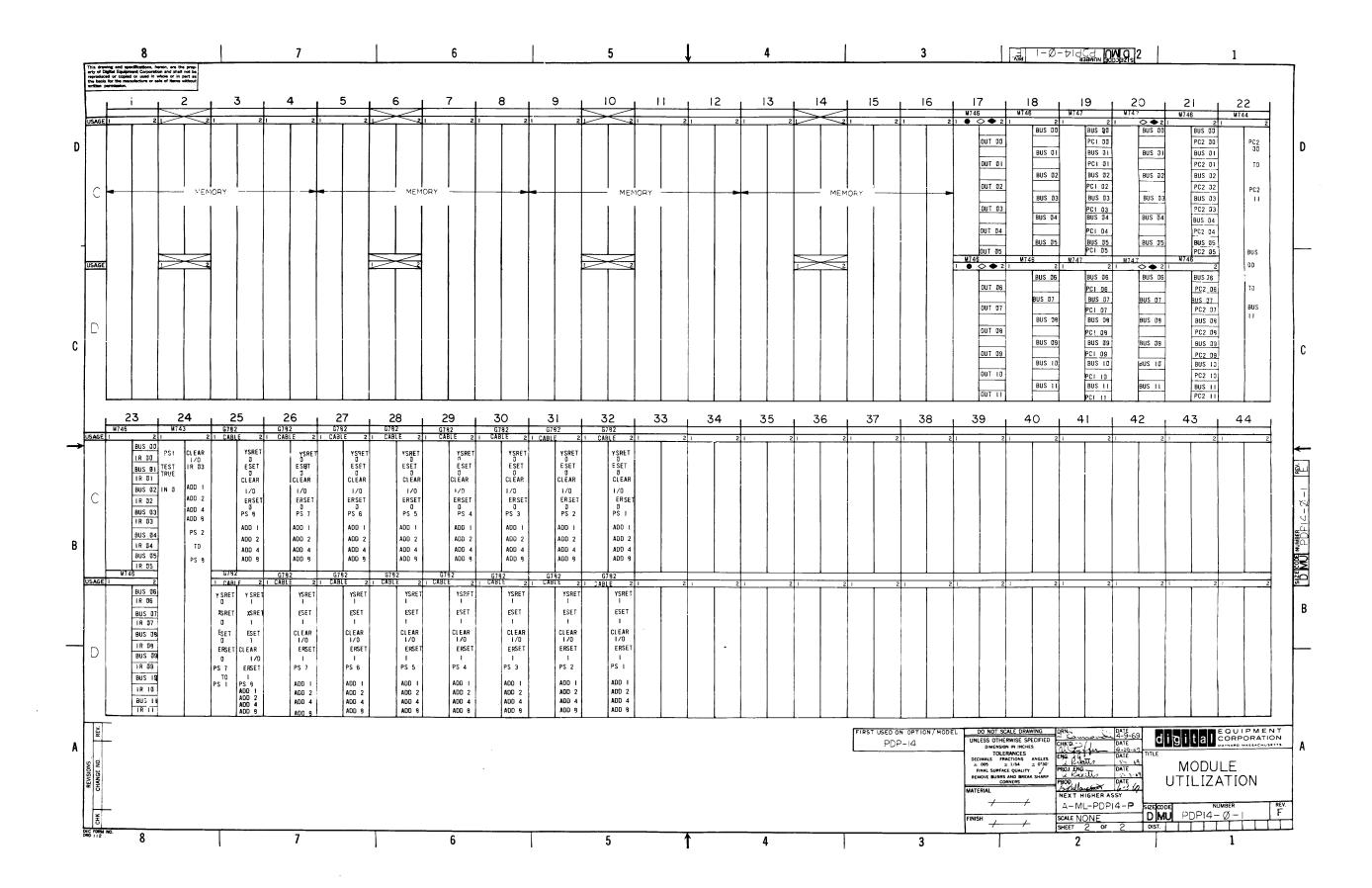

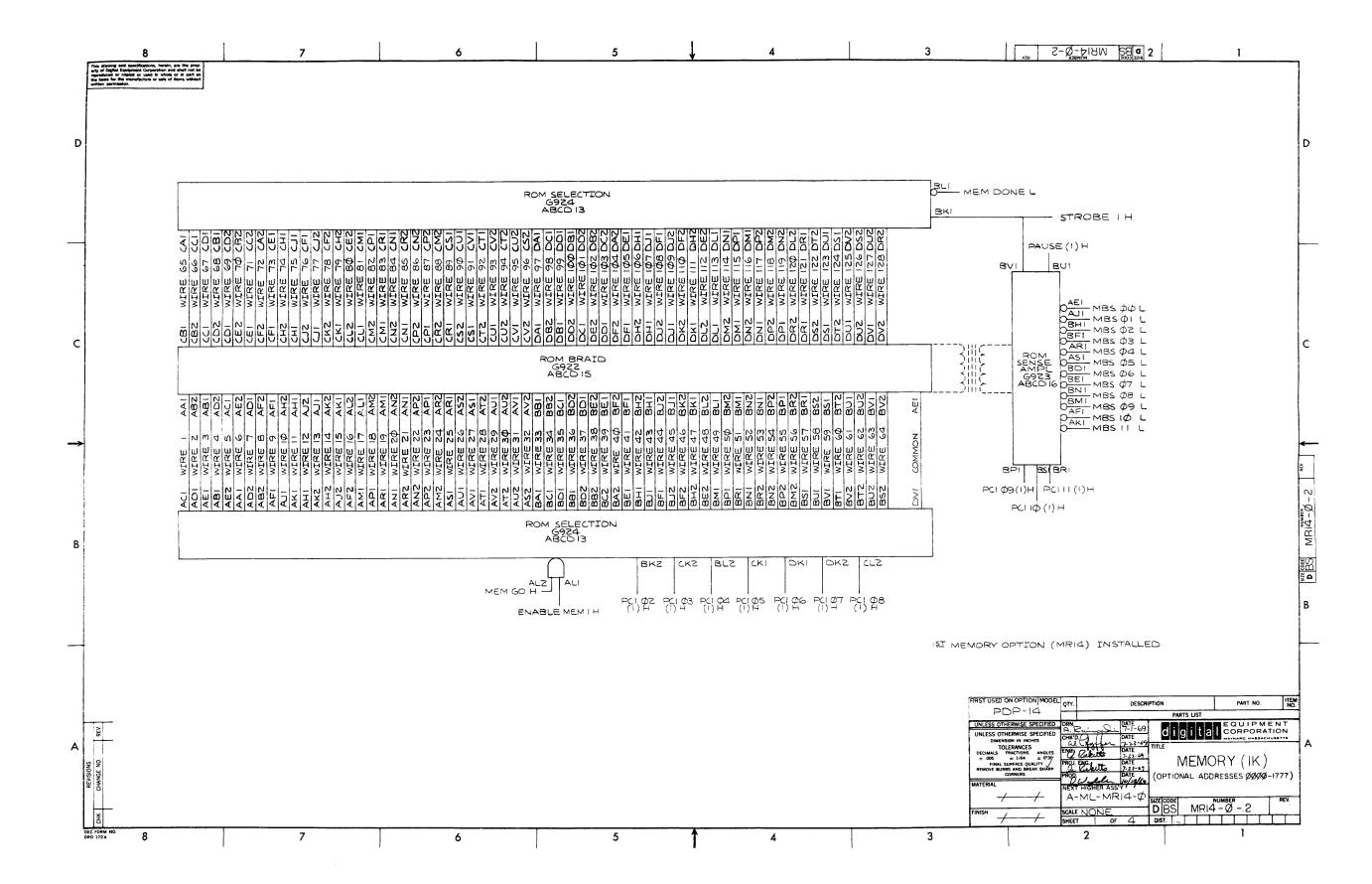

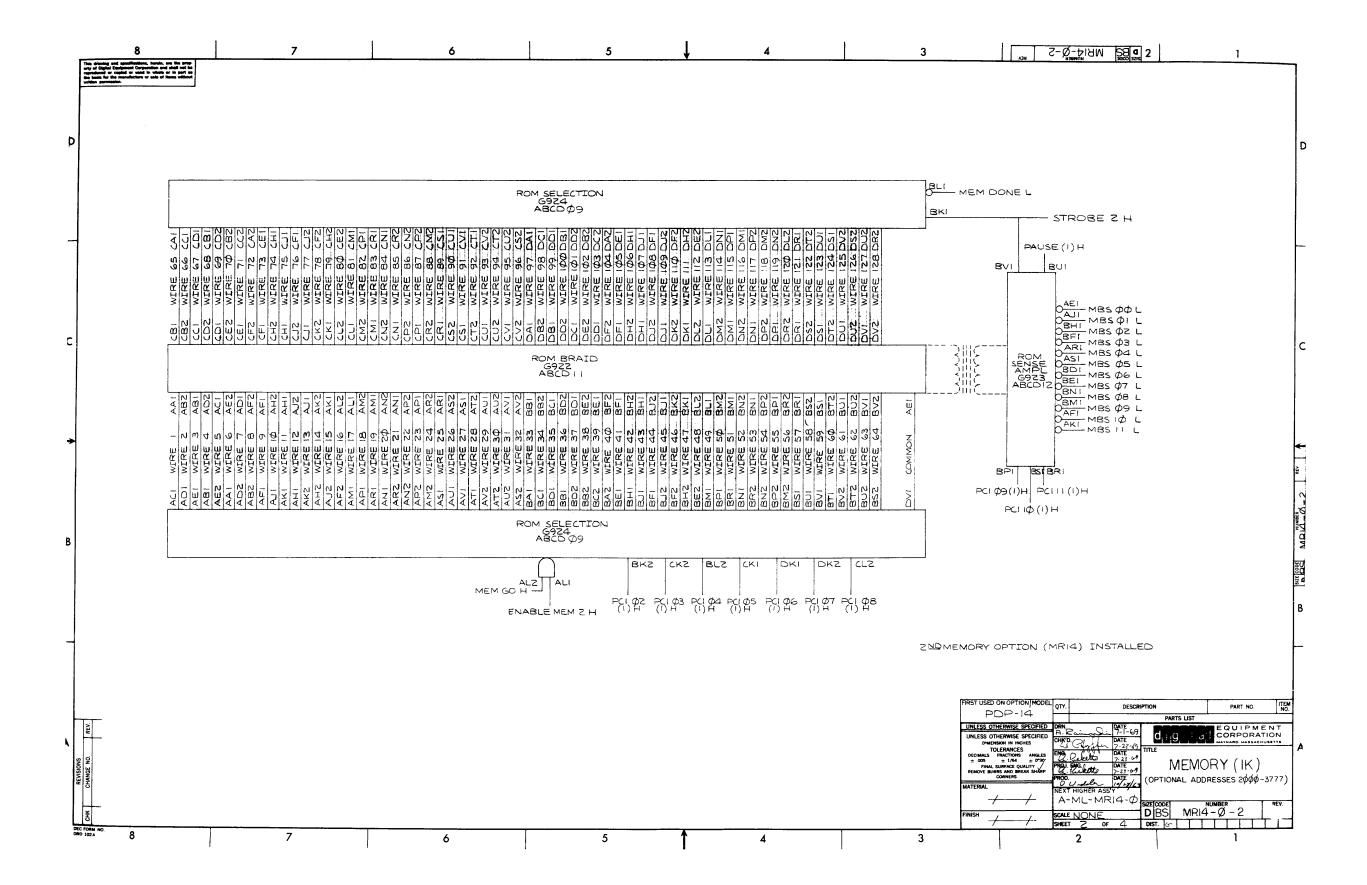

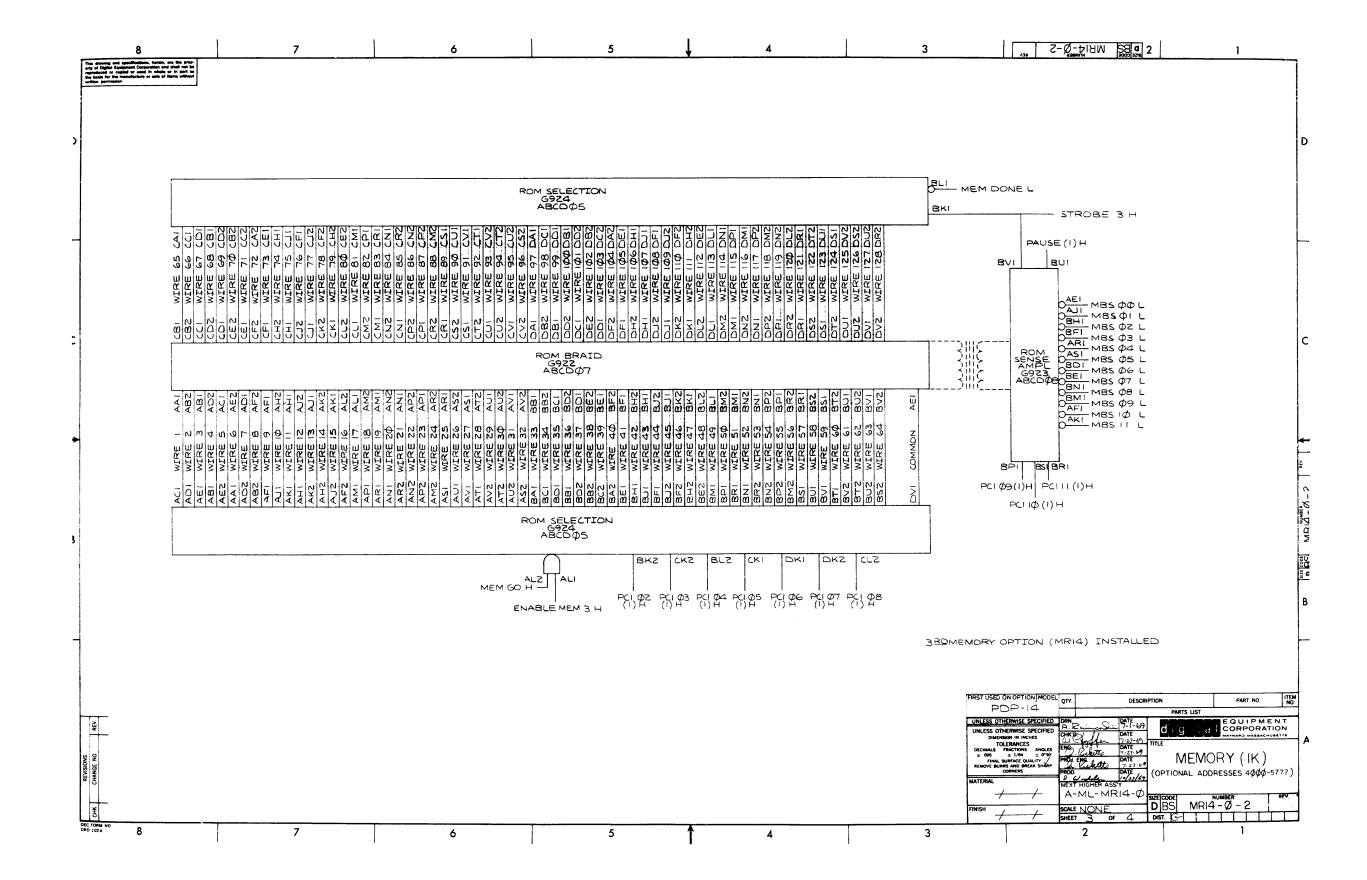

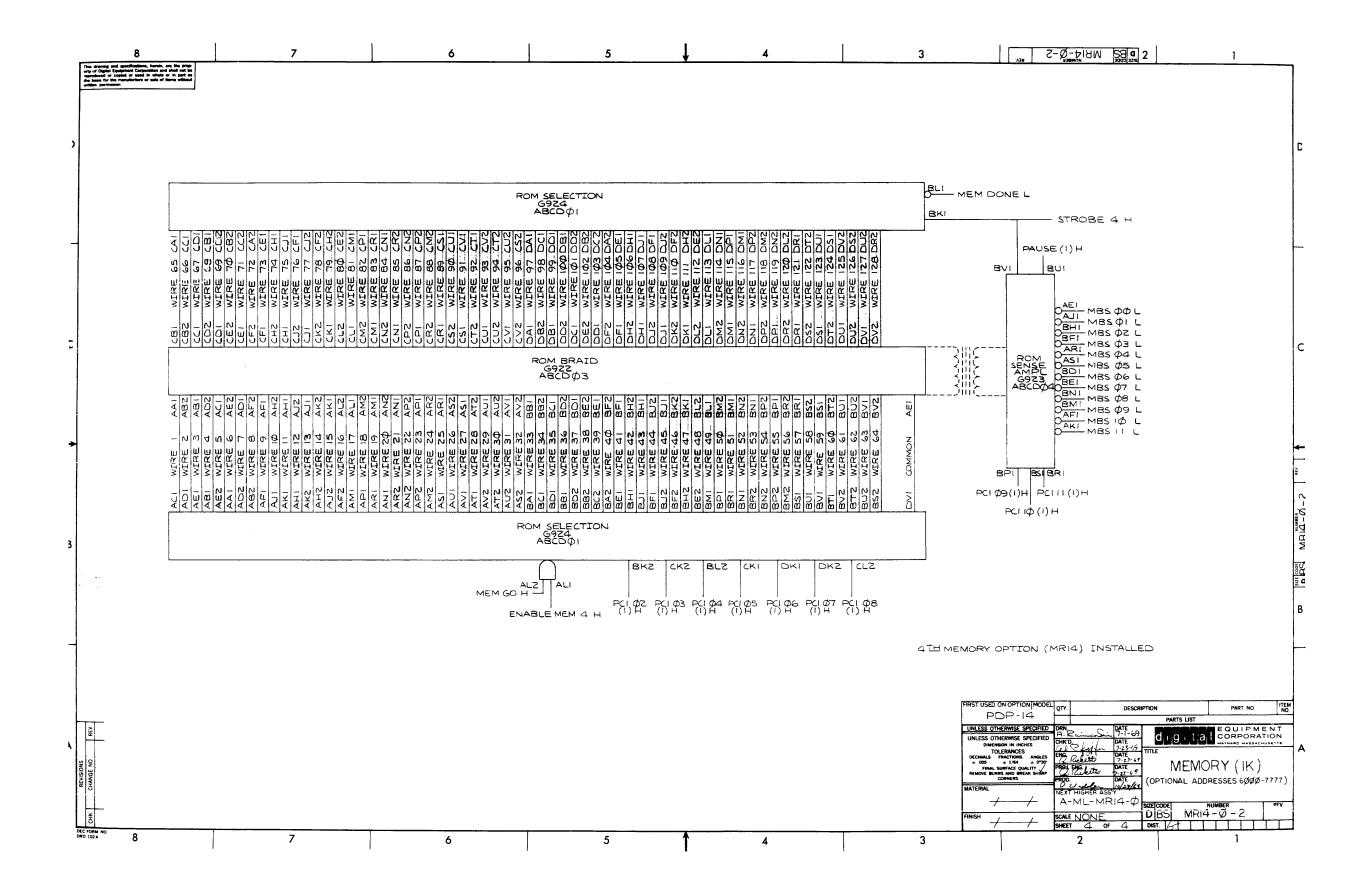

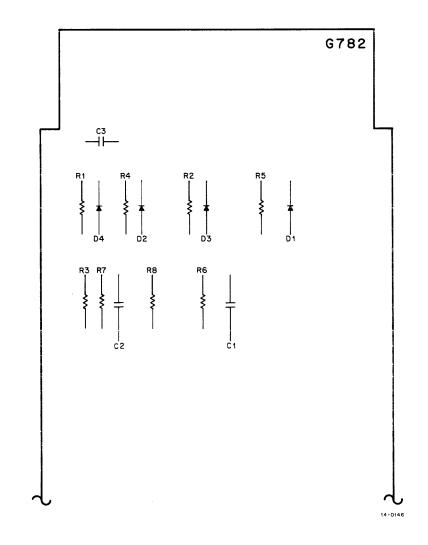

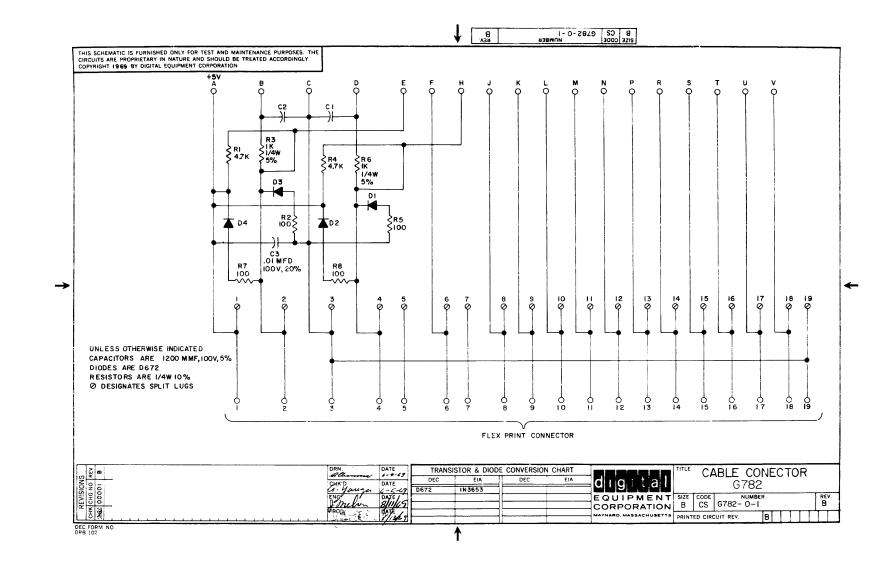

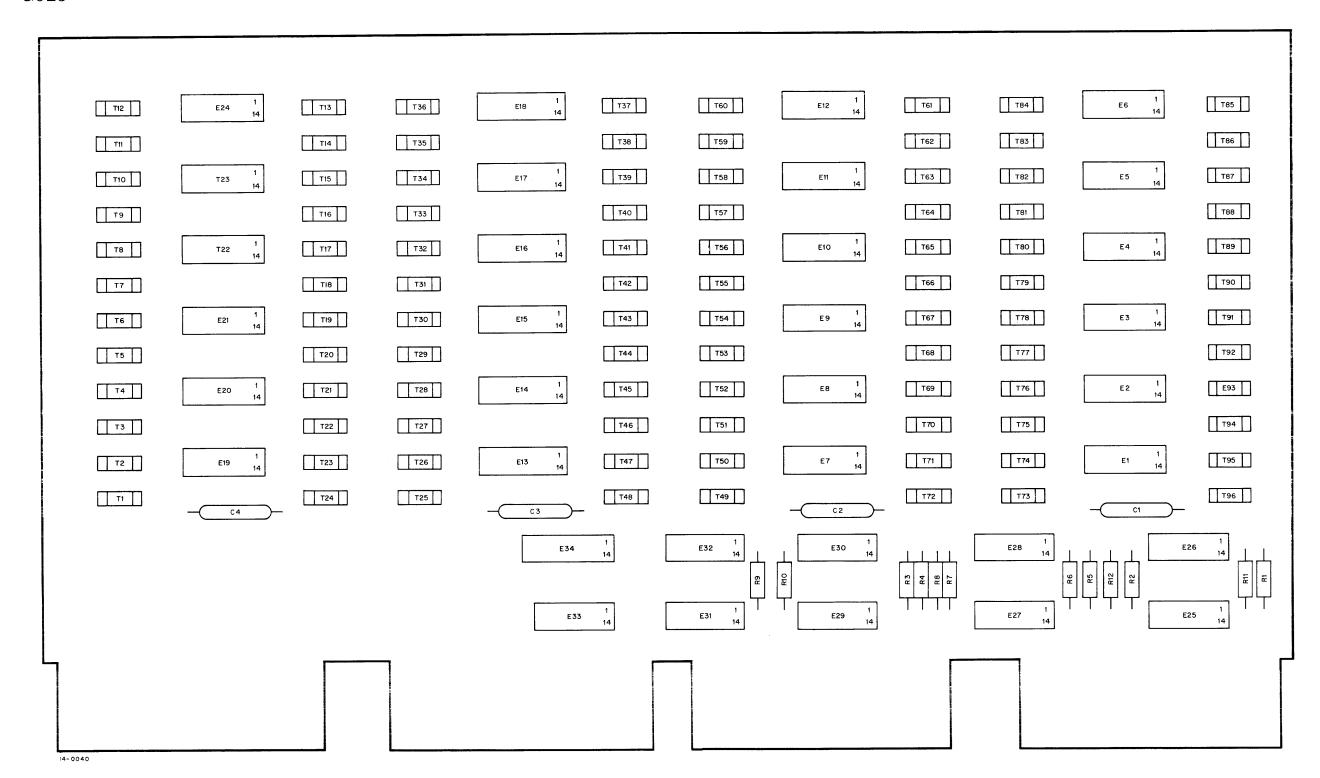

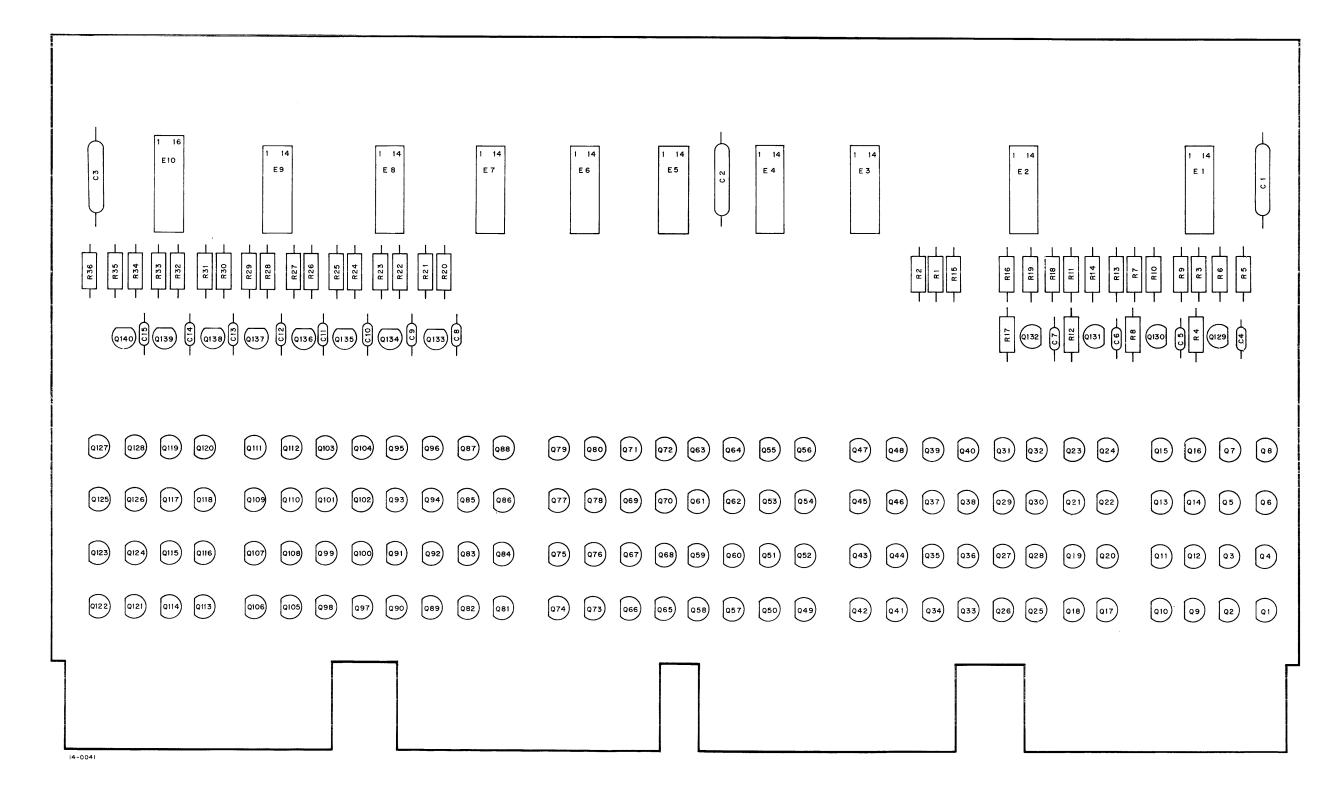

- 2.2.2.1 ROM A ROM (Read-Only Memory) stores the program instructions for implementing a machine or process system sequence. A ROM can be comprised of up to four banks as shown in Figure 2-1. Each ROM bank consists of three modules, two of which (the G922 and G923) form one plug-in assembly. Each bank can store up to 1024 12-bit instructions. The functions provided by each module are described below:

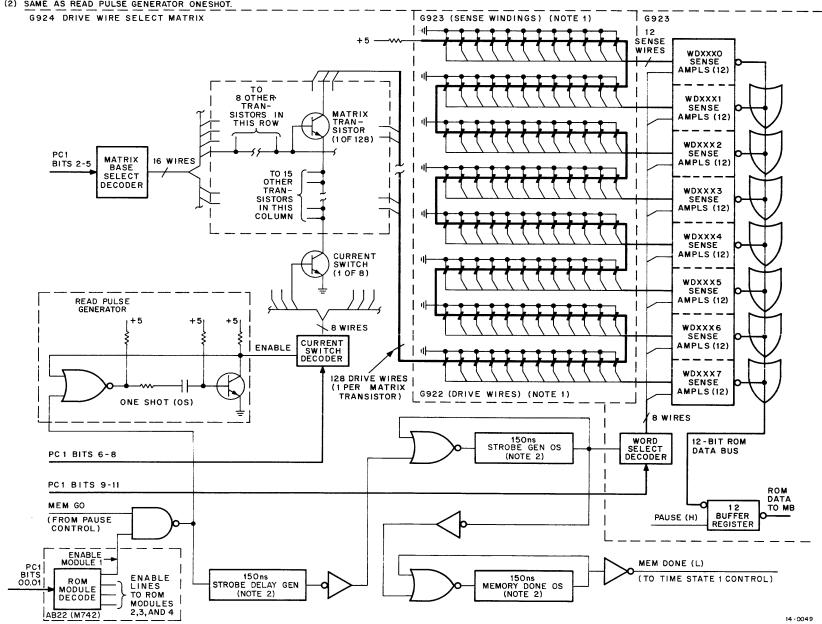

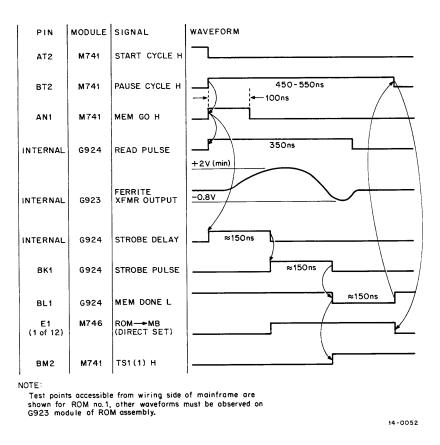

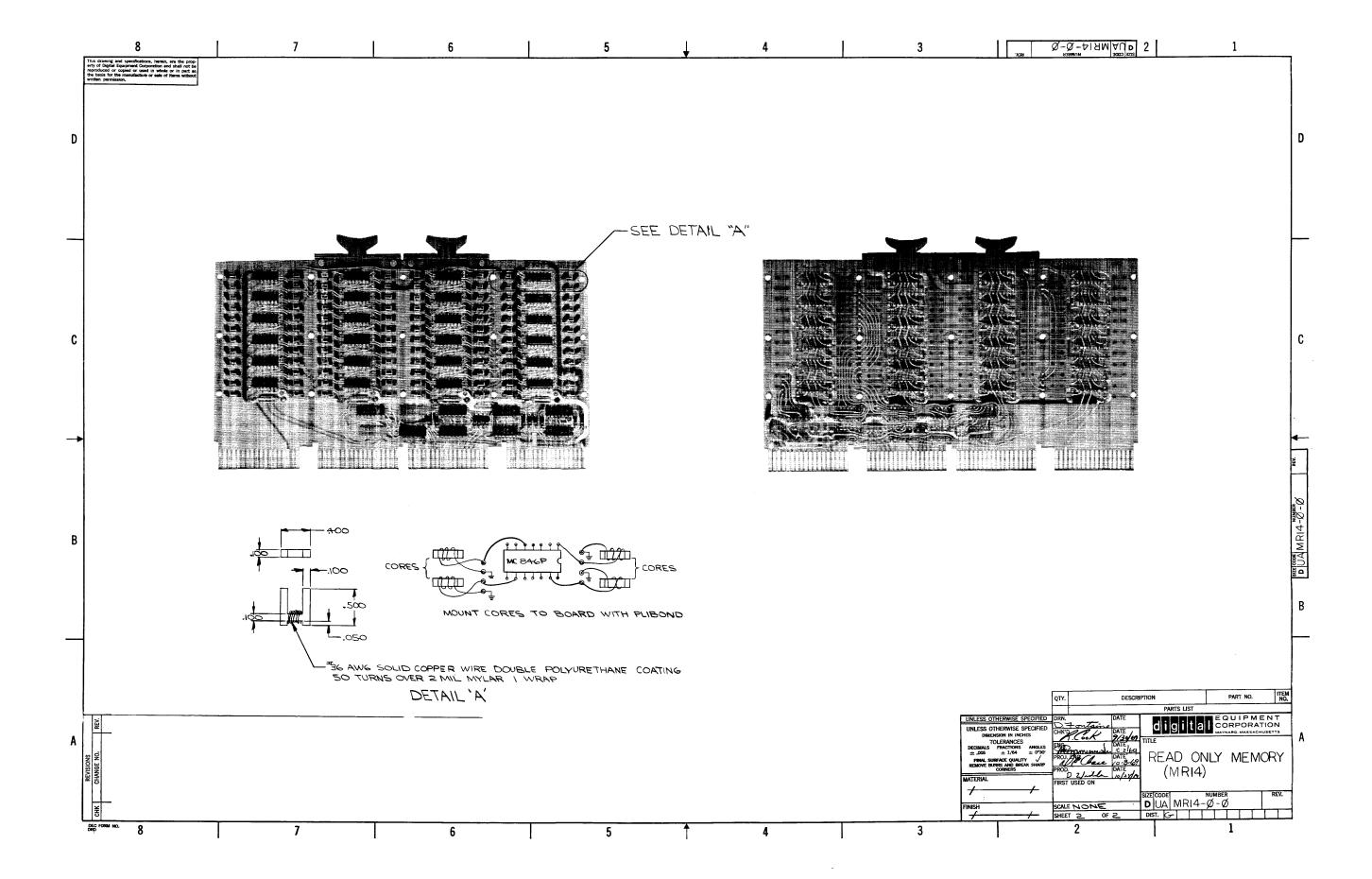

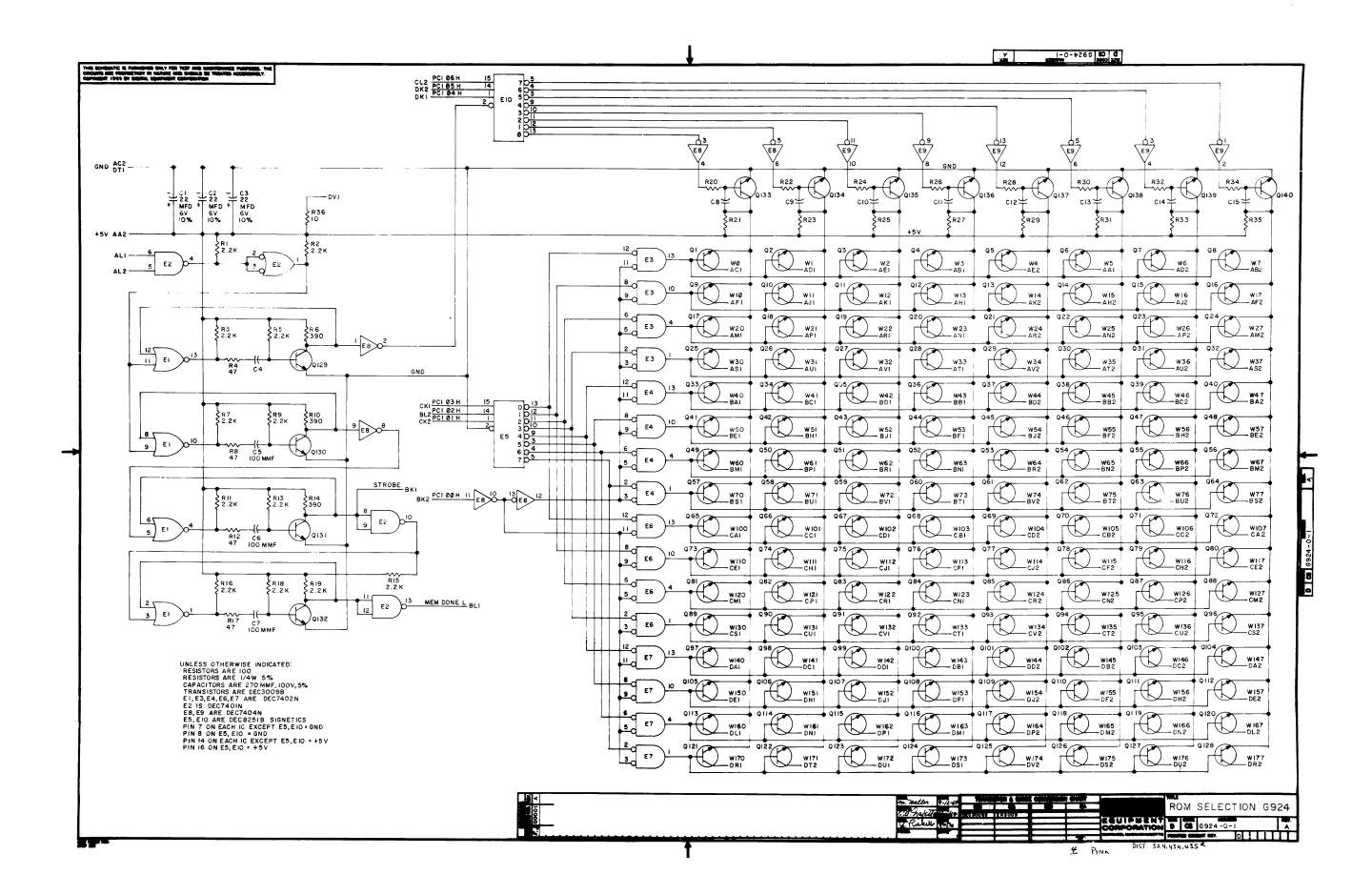

- a. G924 ROM Selection This module selects the instructions stored in the ROM as specified by the control unit. This module also contains the timing circuits for controlling ROM operation. For an address selection, the Control Unit enables one memory bank and provides a 10-bit address and a timing pulse to start the operation. The G924 module receives seven of these address bits and selects one of 128 braid wires. The three remaining bits select one out of eight rows of sense amplifiers on the G922-G923 assembly. After a short interval allotted for circuit settling, the G924 module pulses the selected group of sense amplifiers to load an instruction in its output buffer. It then notifies the Control Unit that the memory cycle is complete.

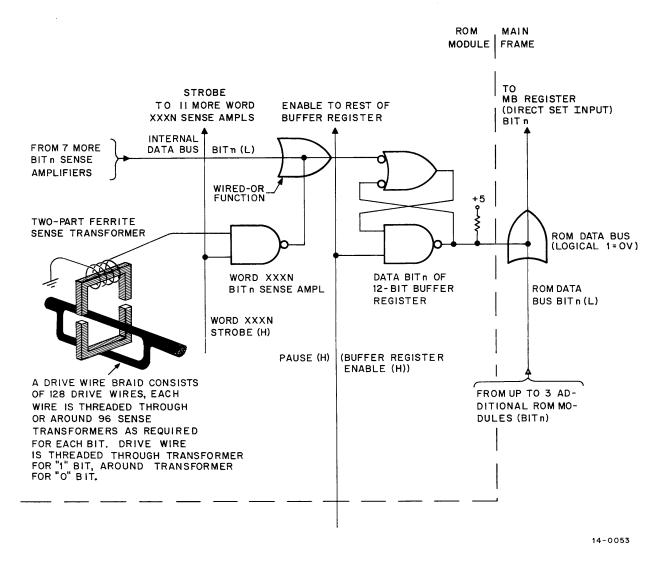

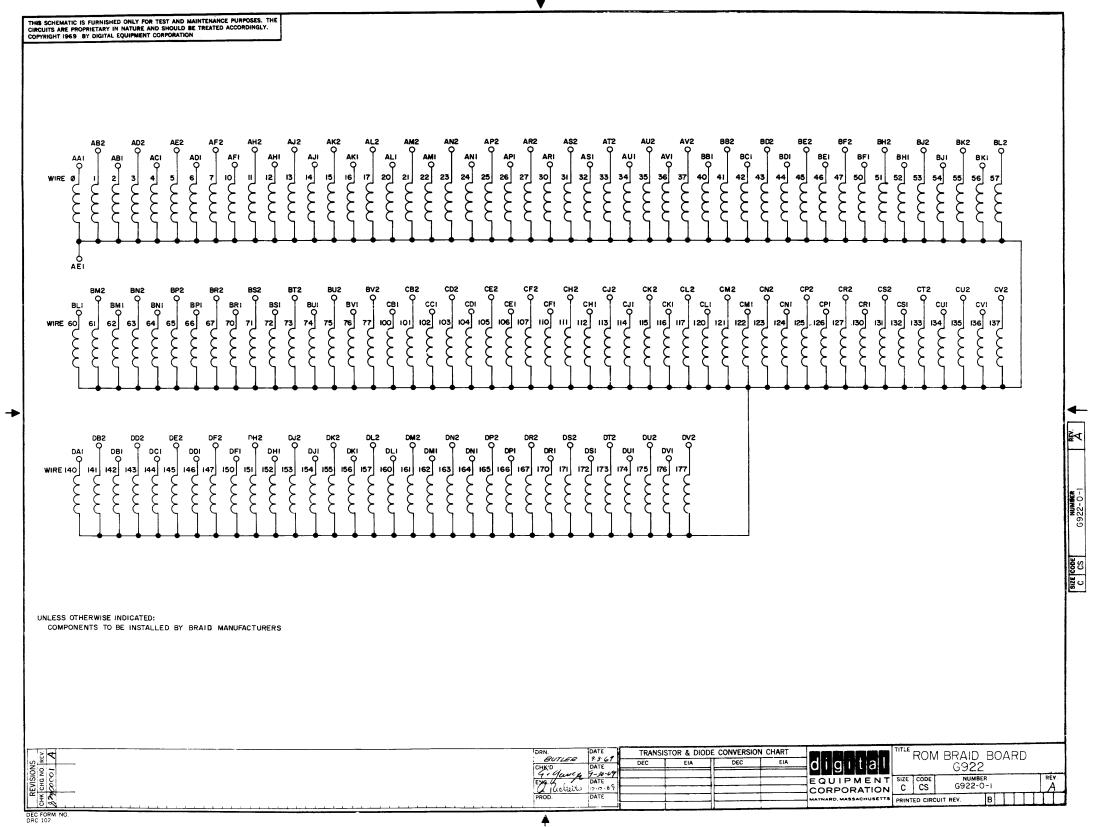

- b. G922 ROM Braid and G923 Sense Amplifier The G922 module contains a pattern or braid of 128 wires. Each wire is routed either through or around 96 (8 sets of 12) Ferrite-core transformers to form

the binary content of eight 12-bit instructions. (If the wire is routed through the transformer, it results in a logical 1 for the pertinent bit when the wire is pulsed; if the wire is routed around, it results in a logical 0 bit). The braid arrangement is functionally equivalent to the wiring in a conventional control system; i.e., it forms a list of permanently wired instructions that define the control operation. Once the braid is formed, it is encapsulated for immunity to accidental change. The module is then attached to the G923 module to form one plug-in assembly.

The G923 module decodes three bits of address to select one of eight groups of sense amplifiers. Each group consists of 12 sense amplifiers or one for each bit in an instruction. This selection (in conjunction with that of the G924) selects one 12-bit instruction out of 1024 possible instructions (128 wires x 8 instructions per wire). The selected instruction is made available to the Control Unit when the G924 module notifies the Control Unit that an instruction cycle is completed.

#### NOTE

The information content of each G922 module is unique; therefore, do not substitute this plug-in assembly.

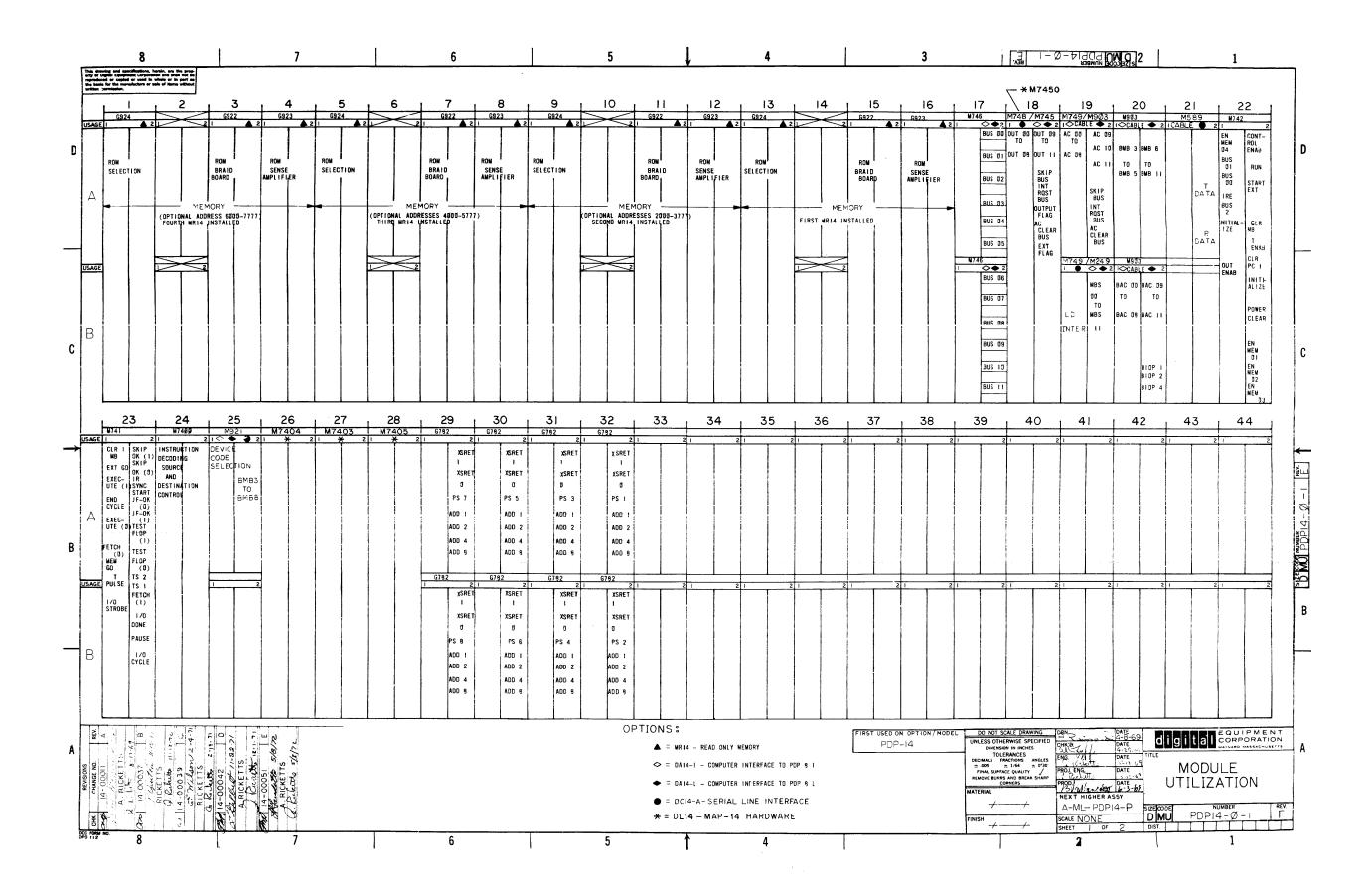

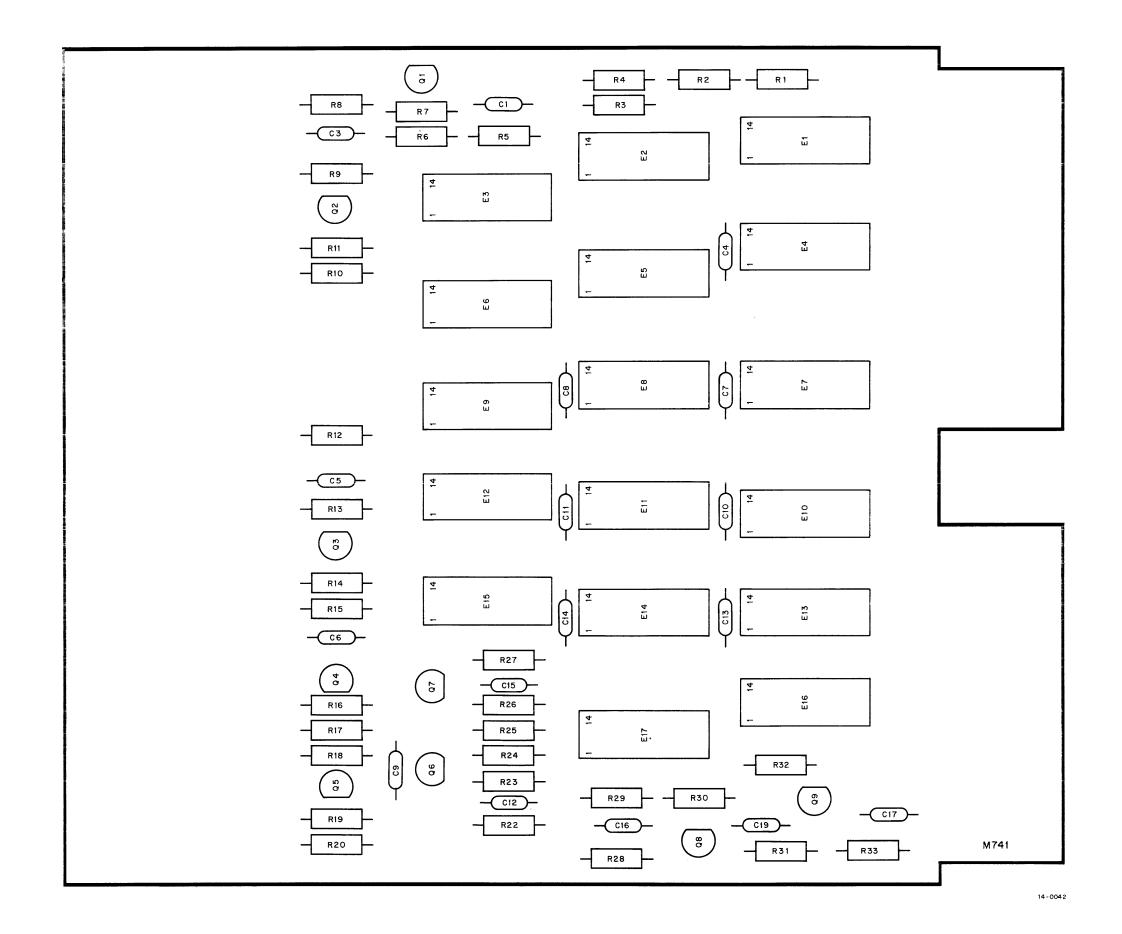

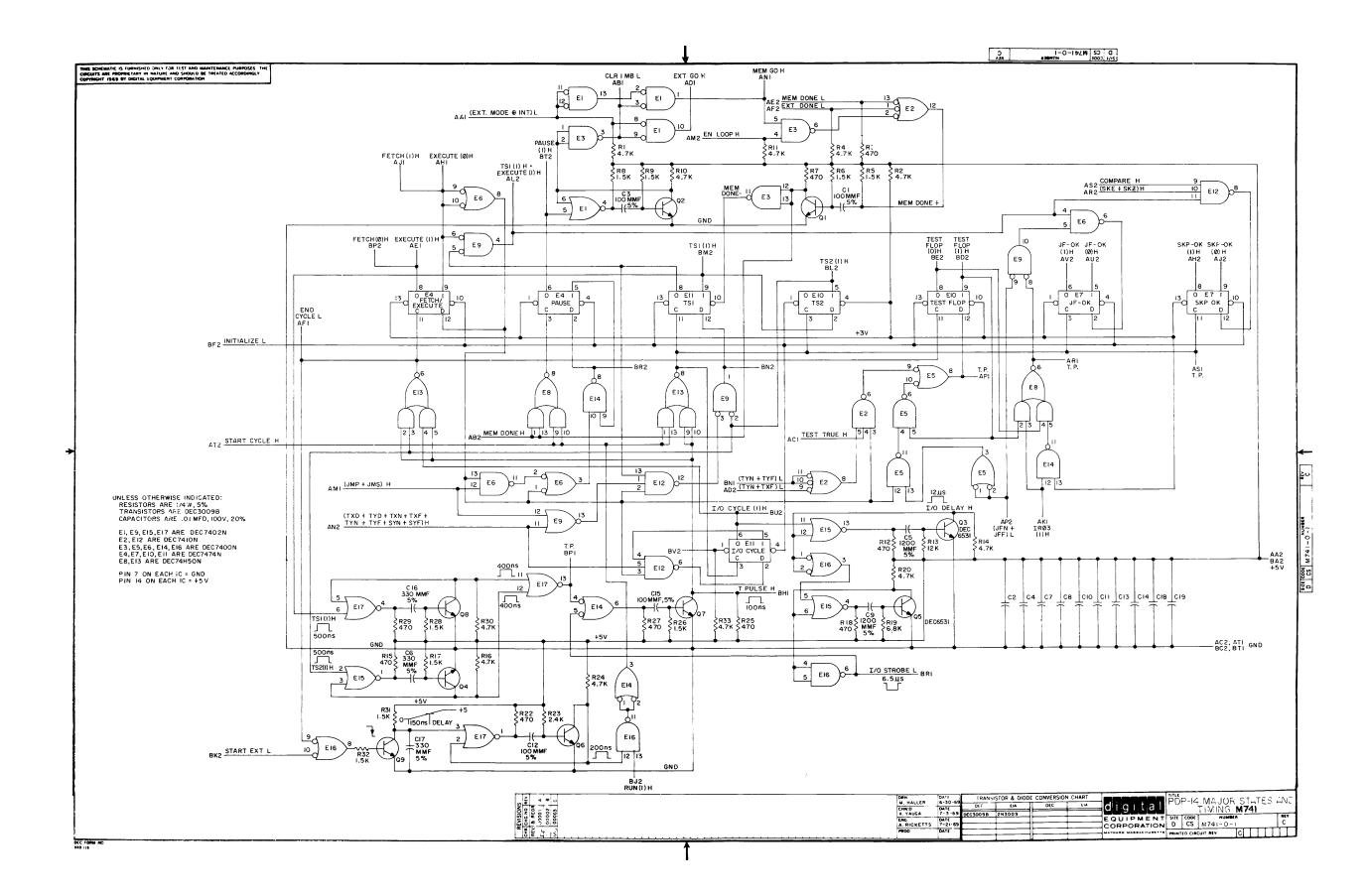

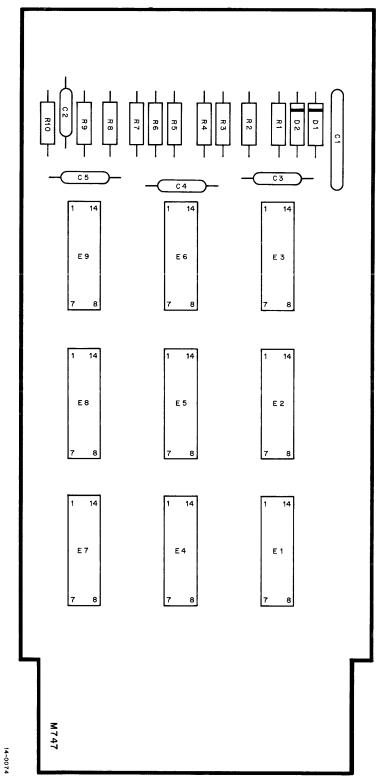

2.2.2.2 Control Unit — As mentioned previously, the Control Unit is fundamentally the heart of the PDP-14 Controller. It consists of a number of modules with perhaps the most complex interrelationships of the system. Figure 2-1 shows the Control Unit modules and includes a brief title that defines their function. Note that the maximum configuration is shown; a number of the modules (and connectors) are required only if the controller interfaces with a computer. A brief functional description of the modules follows:

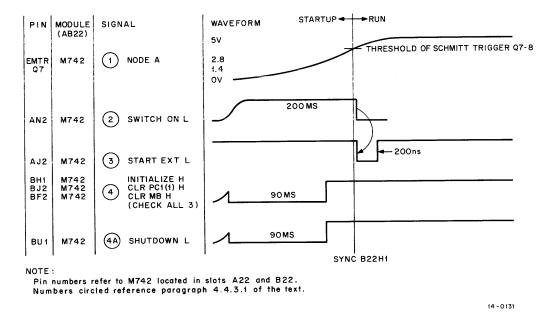

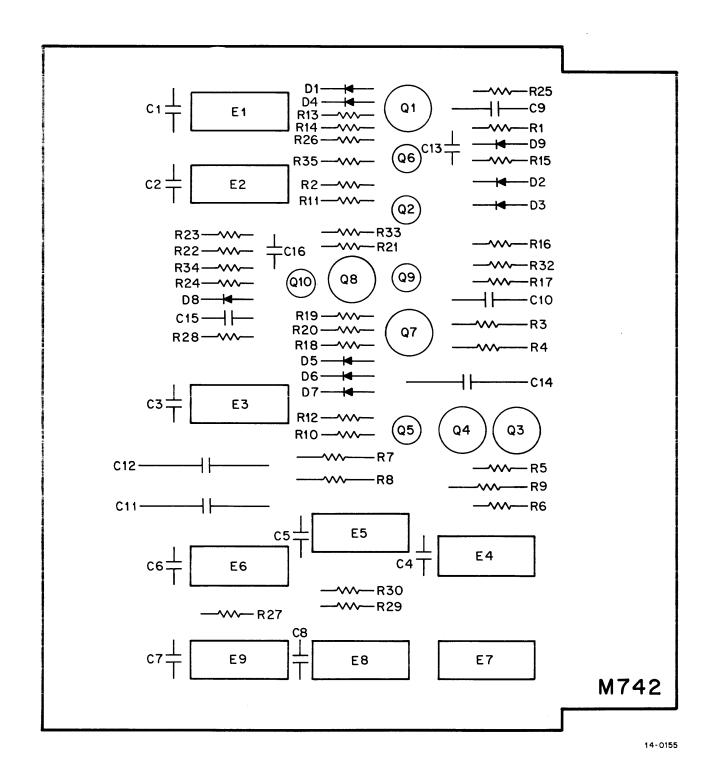

- a. M742 Switch and Power Control This module:

- 1) Senses power-up and power-down conditions, initializes the system, and starts system timing.

- 2) Interfaces with the START/STOP and CONTINUE switches to provide manual control.

- 3) Detects timing failures and holds the system in an initialize state.

- 4) Decodes two bits of the memory address to enable one out of four possible ROM banks.

- 5) Provides control (and three bits) for Test and Display instructions used for computer monitoring.

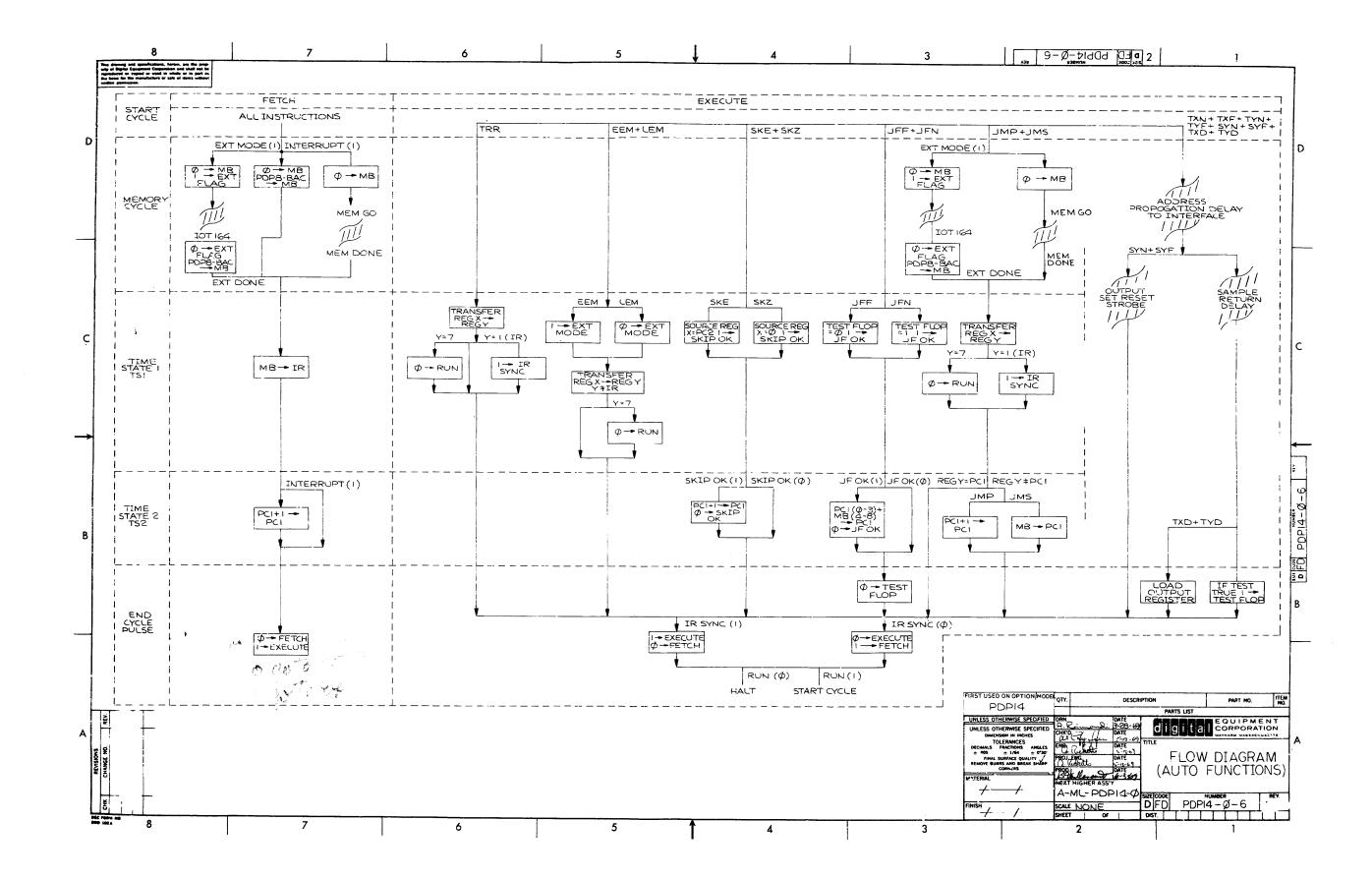

- b. M741 Major States and Timing This module provides the timing relationships and control signals for:

- 1) Fetching of instructions

- 2) Decoding of instructions

- 3) Execution of instructions

- 4) Sampling and storing input or output test results

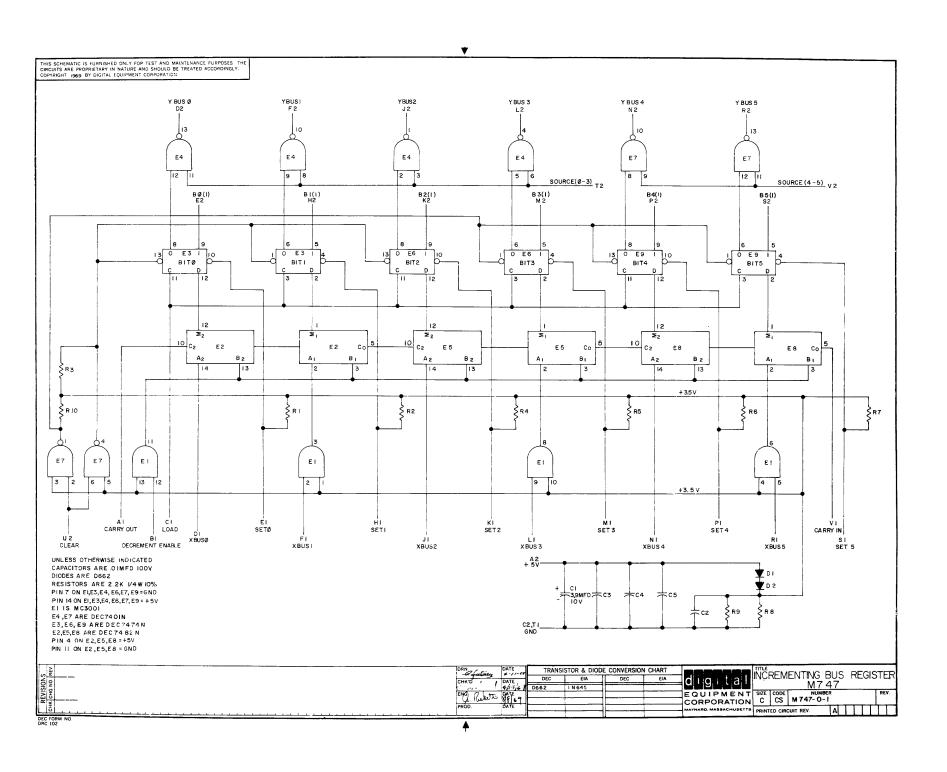

- c. M747 Program Counter 1 (PC1) Two M747 modules comprise PC1. This register addresses the ROM to fetch an instruction. It is an incrementing type register; i.e., its count can be incremented by one.

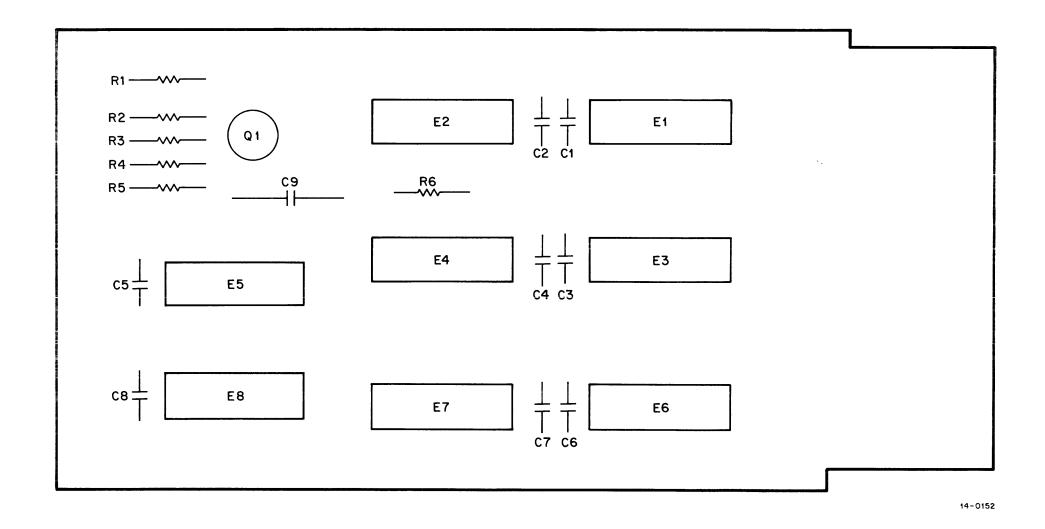

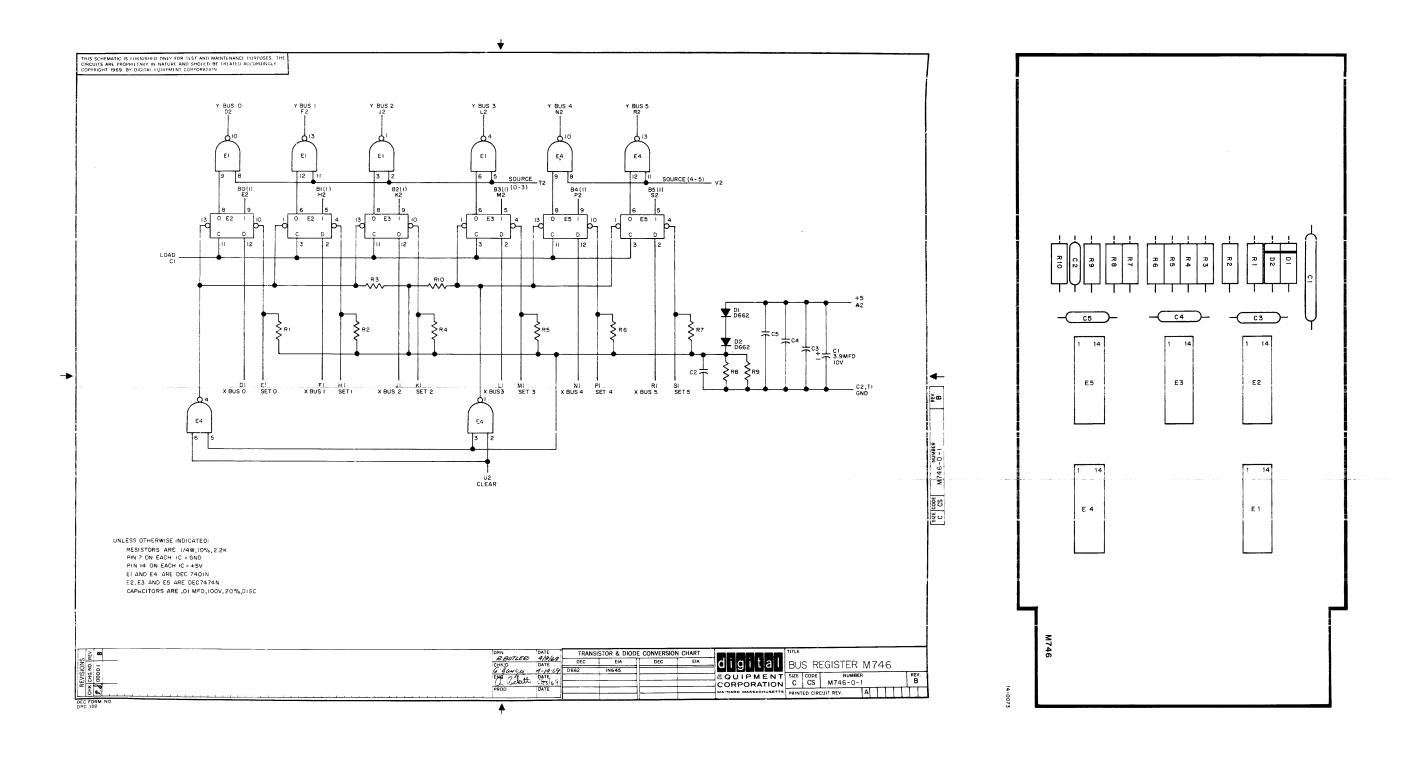

- d. M746 Memory Buffer (MB) Register Two M746 modules comprise the MB Register. This register temporarily stores instructions provided by the ROM or computer.

- e. M746 Instruction Register (IR) Two M746 modules comprise the IR. This register accepts the instructions from the MB Register and stores them for decoding and execution.

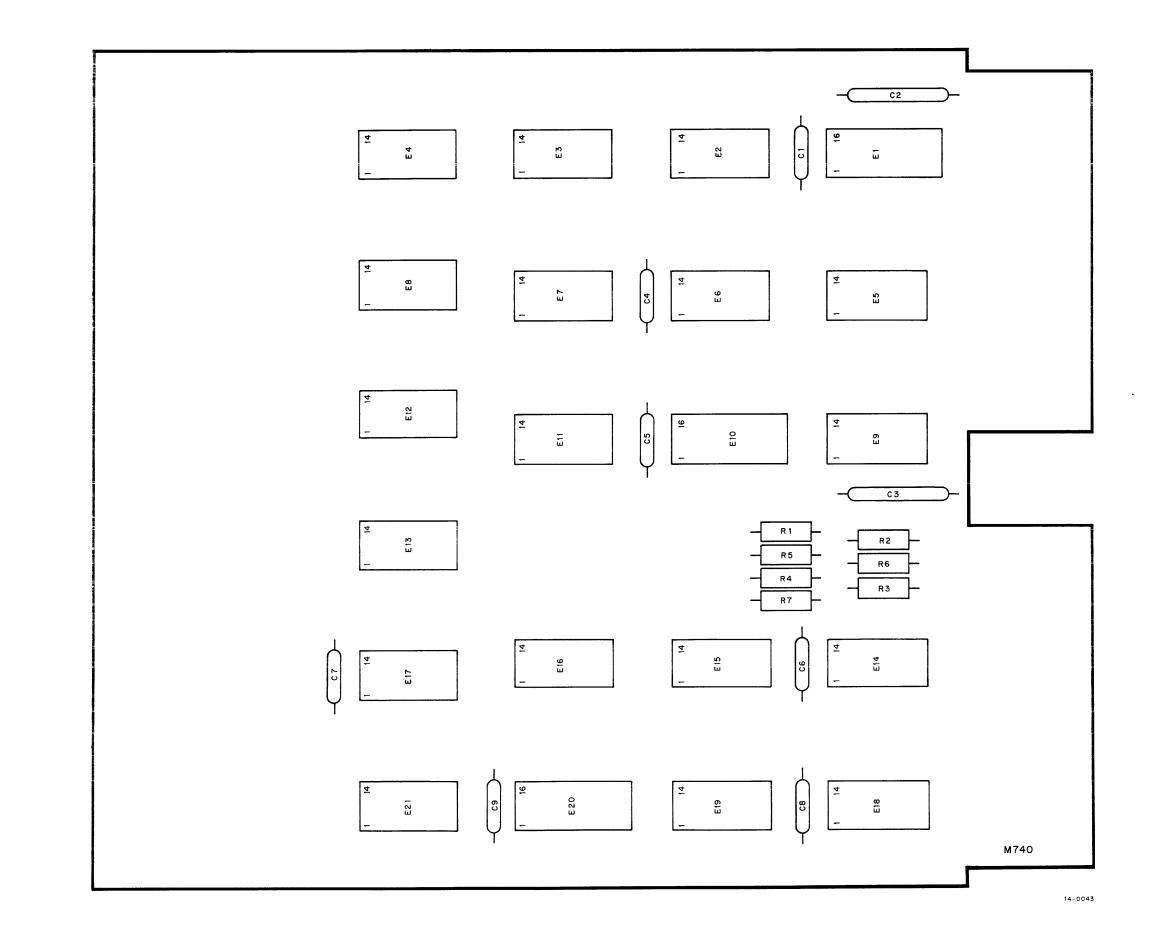

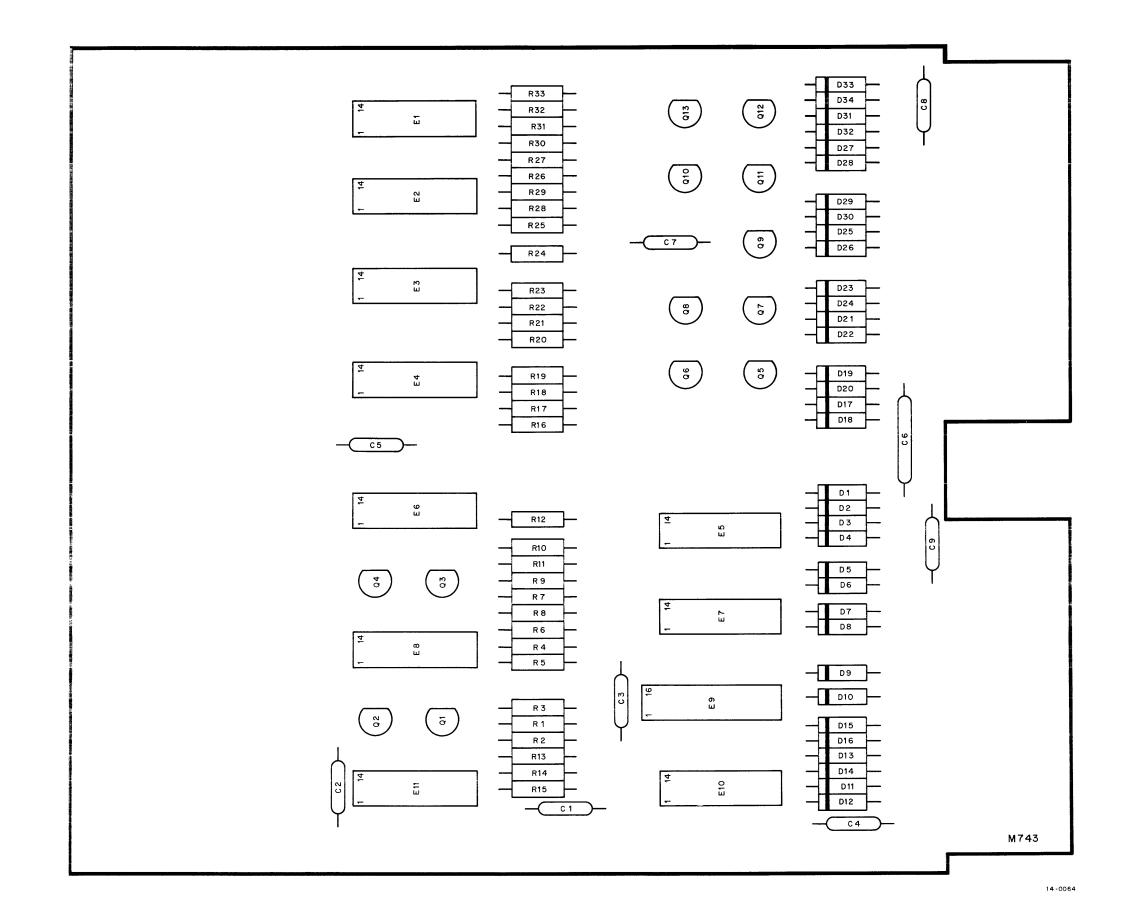

Figure 2-1 PDP-14 Mainframe Showing Module Locations

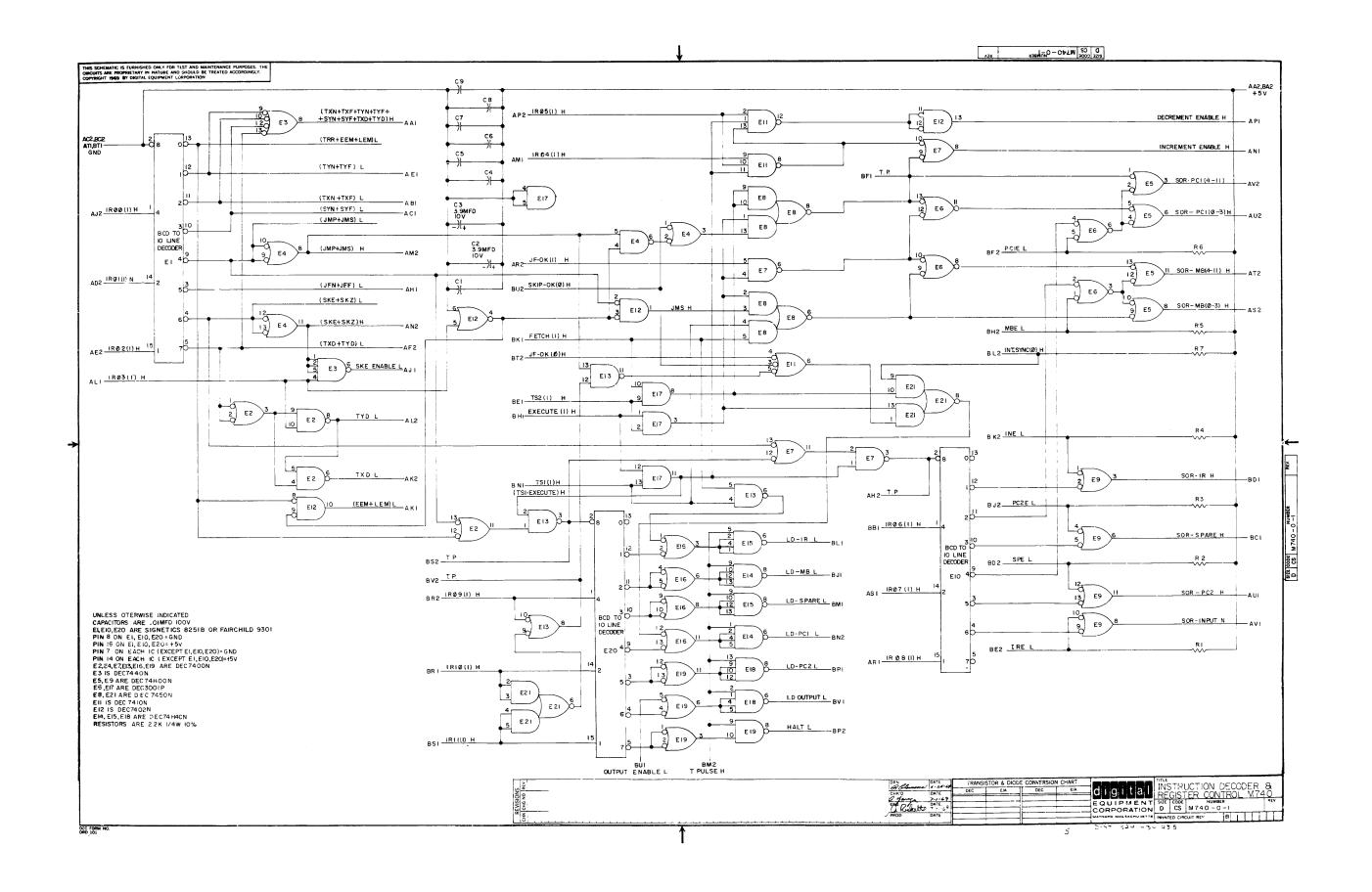

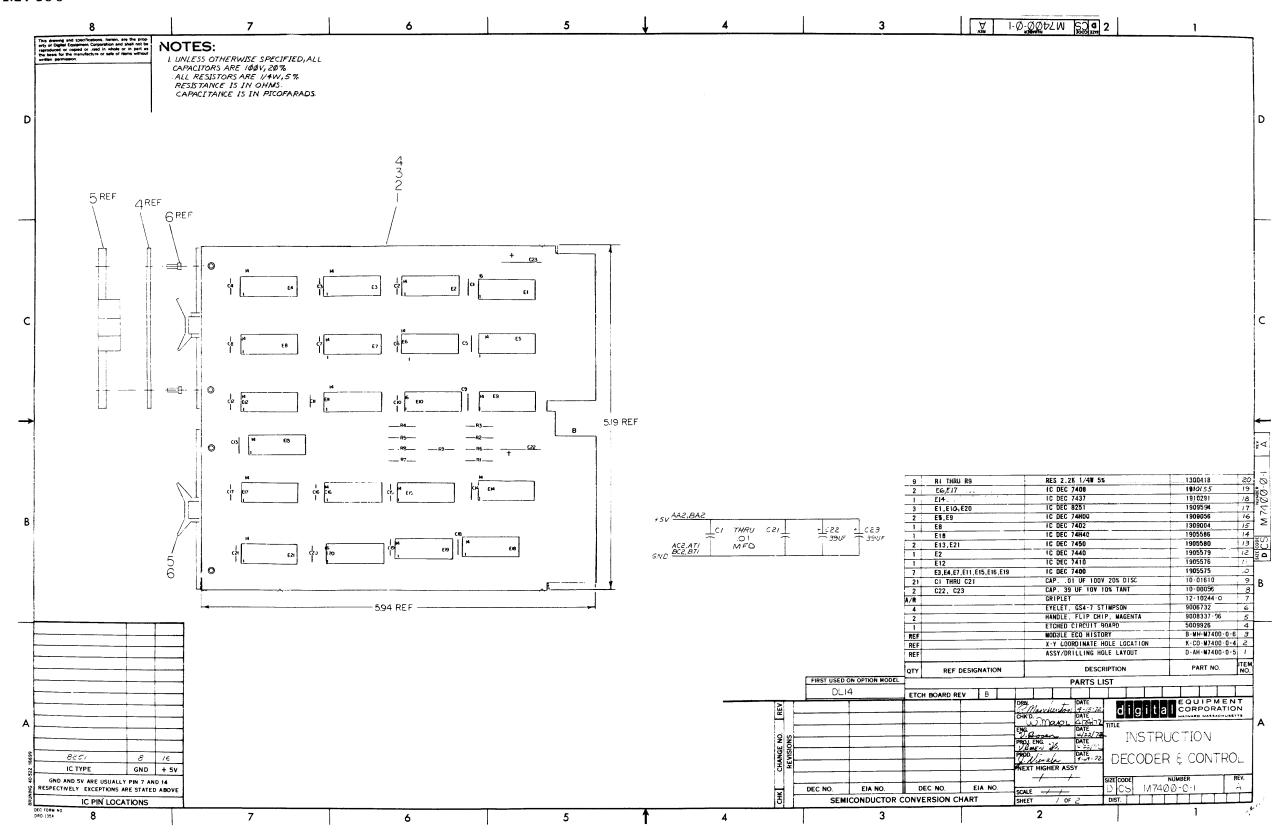

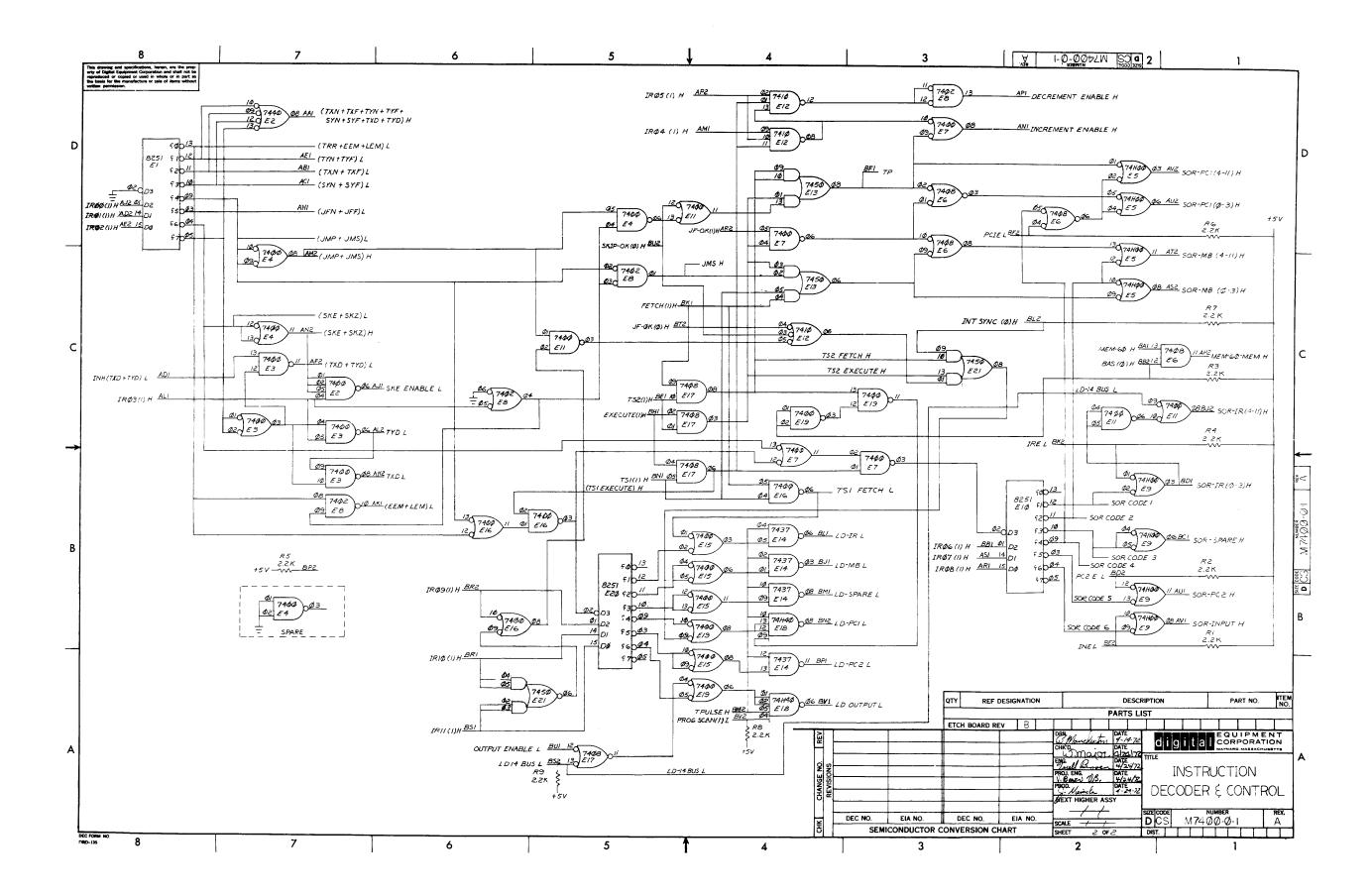

- f. M740 (or M7400) Instruction Decoder This module examines each instruction and provides unique control signals for instruction execution. (The M7400 module must be used with MAP-14.) This module decodes parts of the instruction to:

- 1) Define the type and specific instruction to be executed

- 2) Select the source register for internal transfers

- 3) Select the destination register for internal transfers

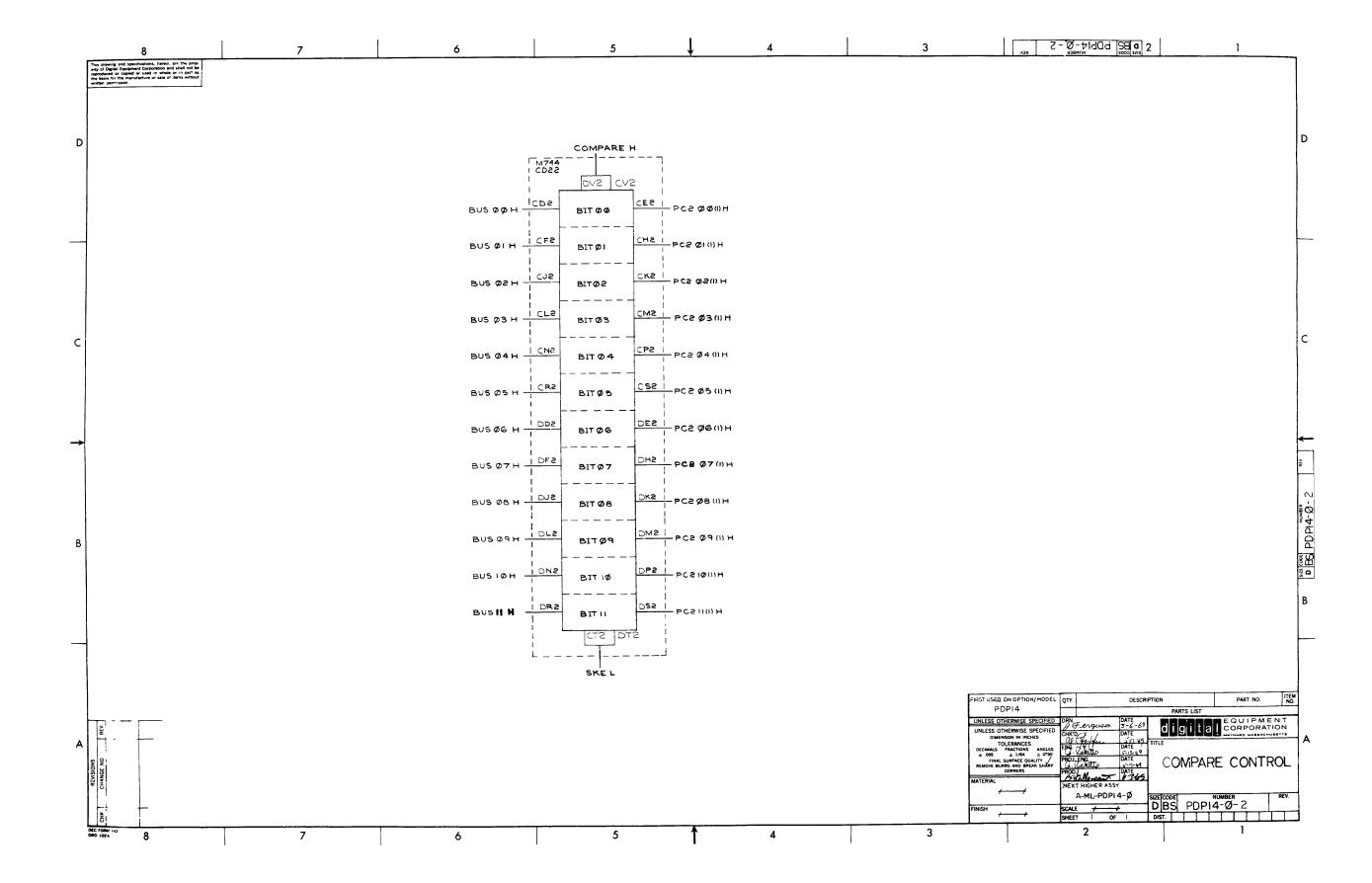

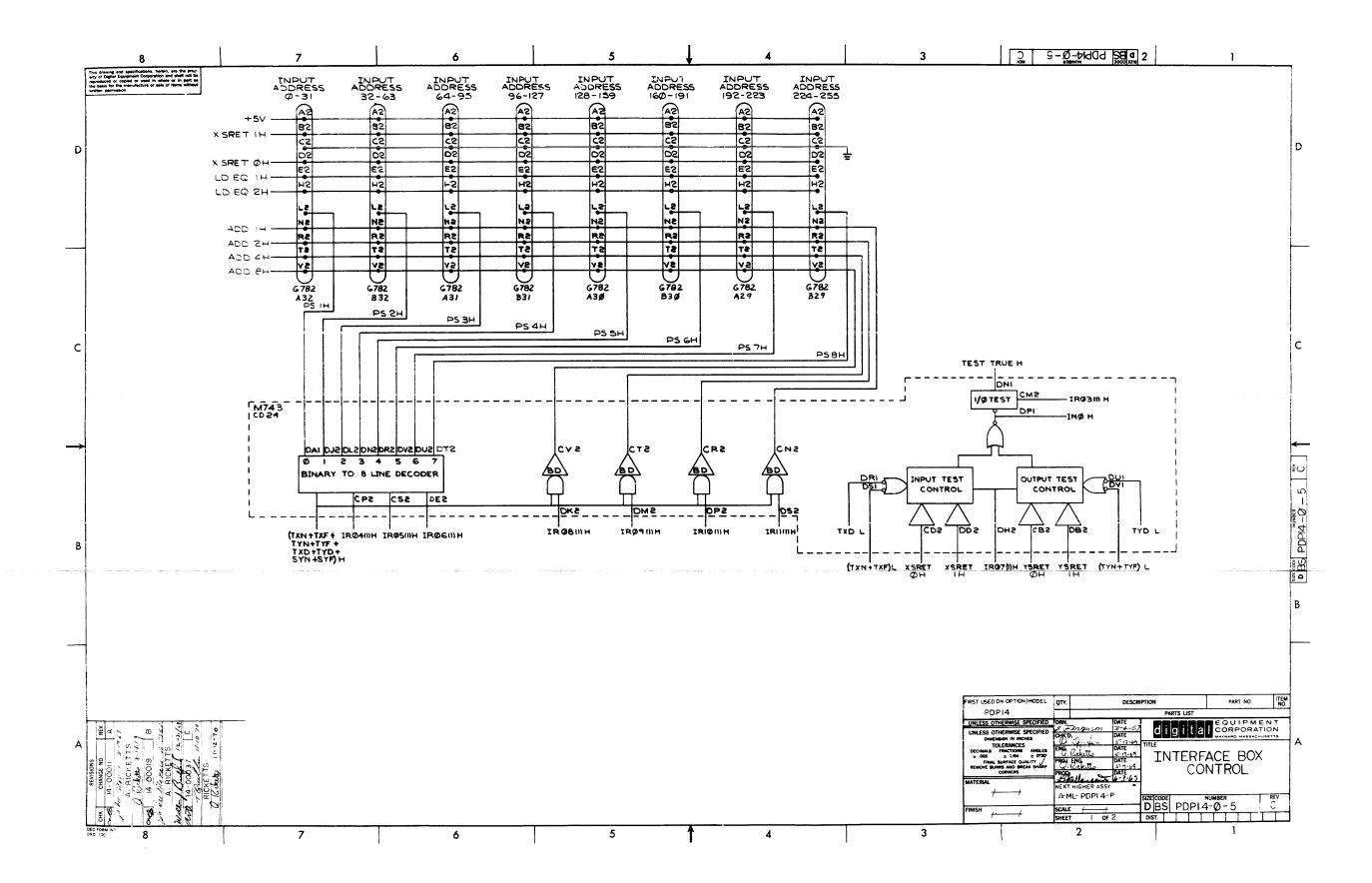

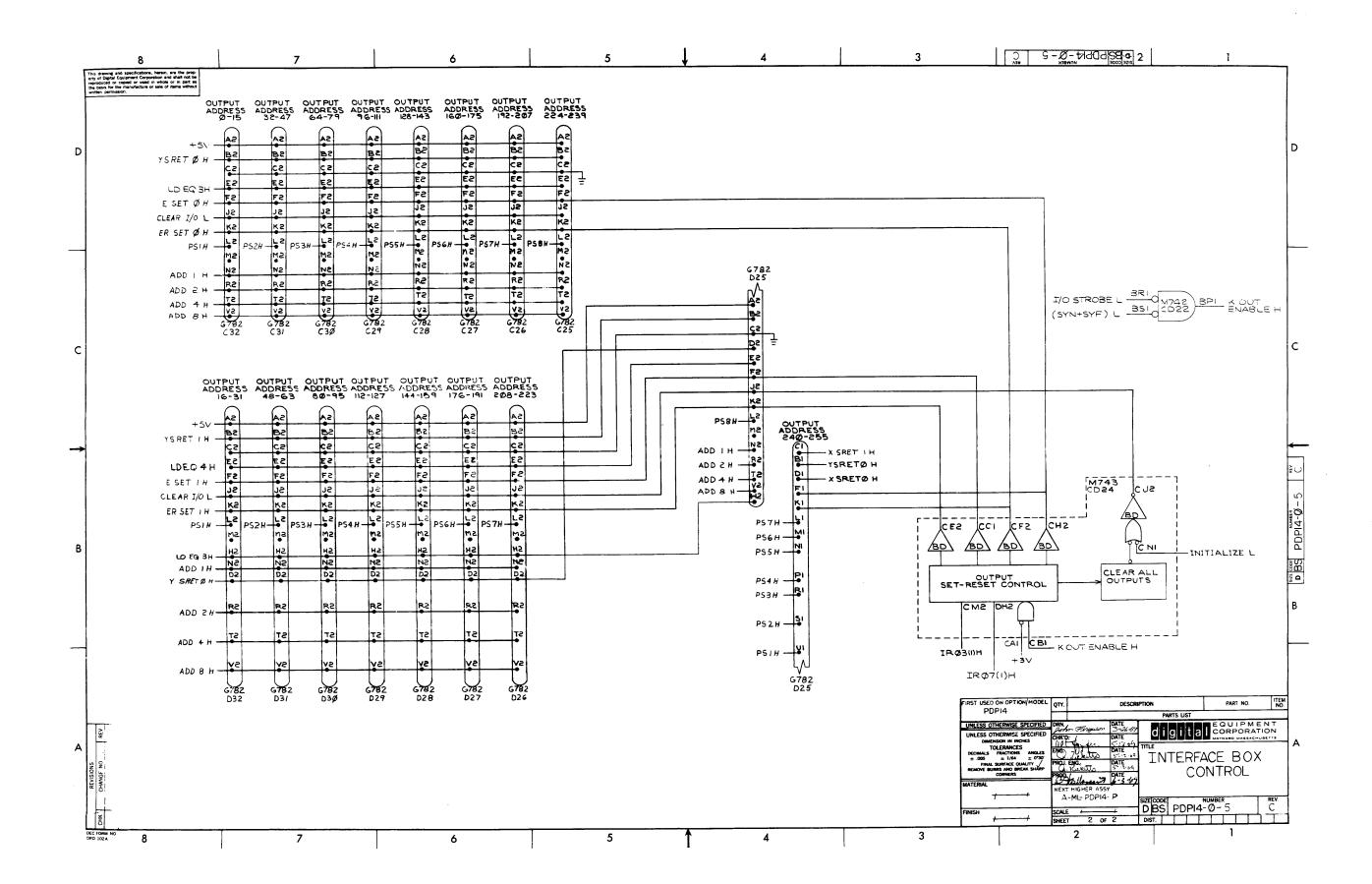

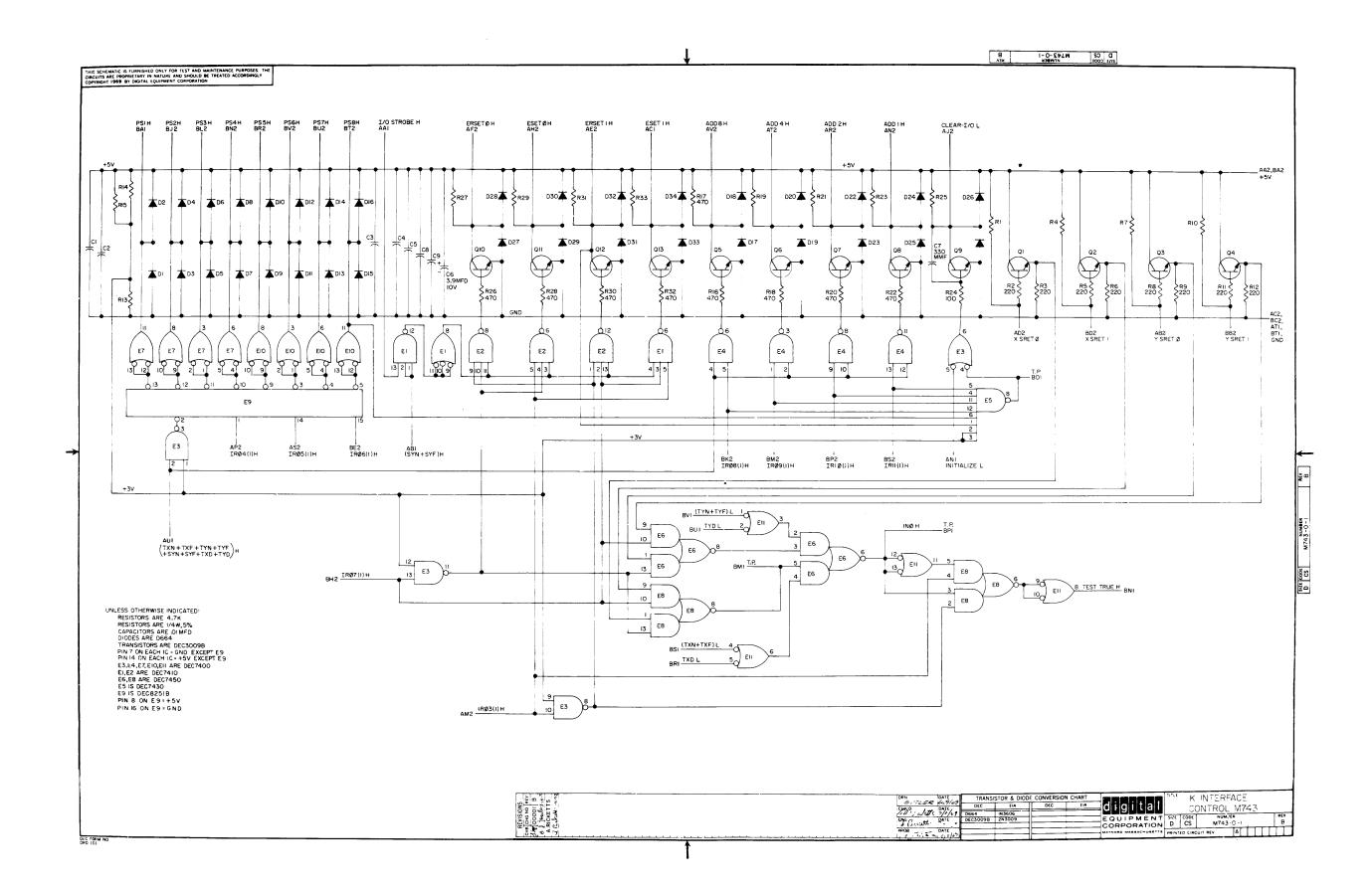

- g. M743 I/O Interface This module interfaces the Control Unit with the I, O, and A Boxes. It provides the input or output circuit address and designates the required function for outputs. It also compares the test result with the program-expected result and provides this comparison result to the M741 module.

- h. M746 Program Counter 2 (PC2) Two M746 modules comprise PC2. This register is used only for program subroutines. It stores the program return address for subroutines.

- i. M747 Spare Register Two M747 modules comprise the Spare Register. This register is not normally included in the PDP-14 and is not required. If included, this register is used as a utility register.

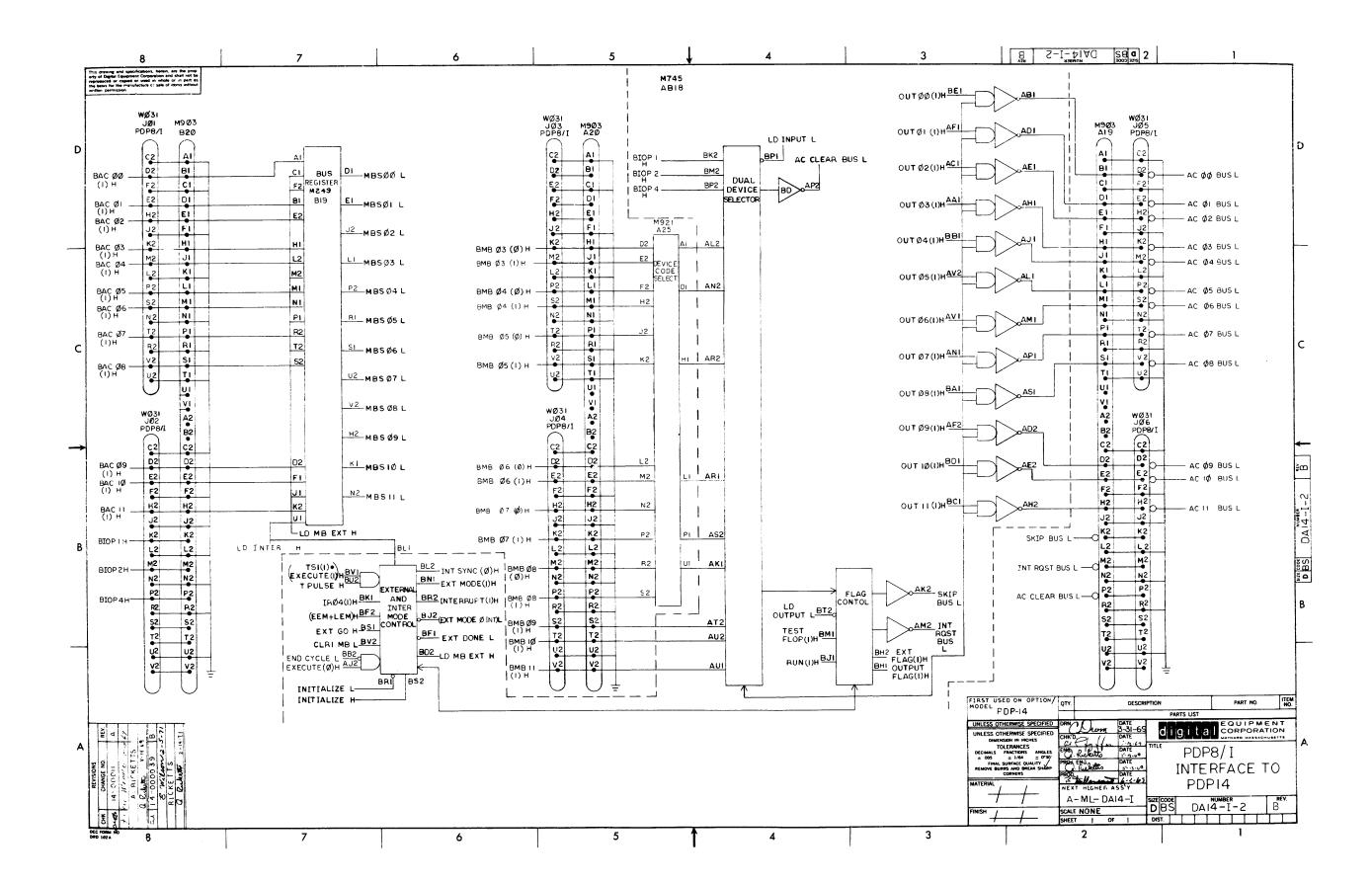

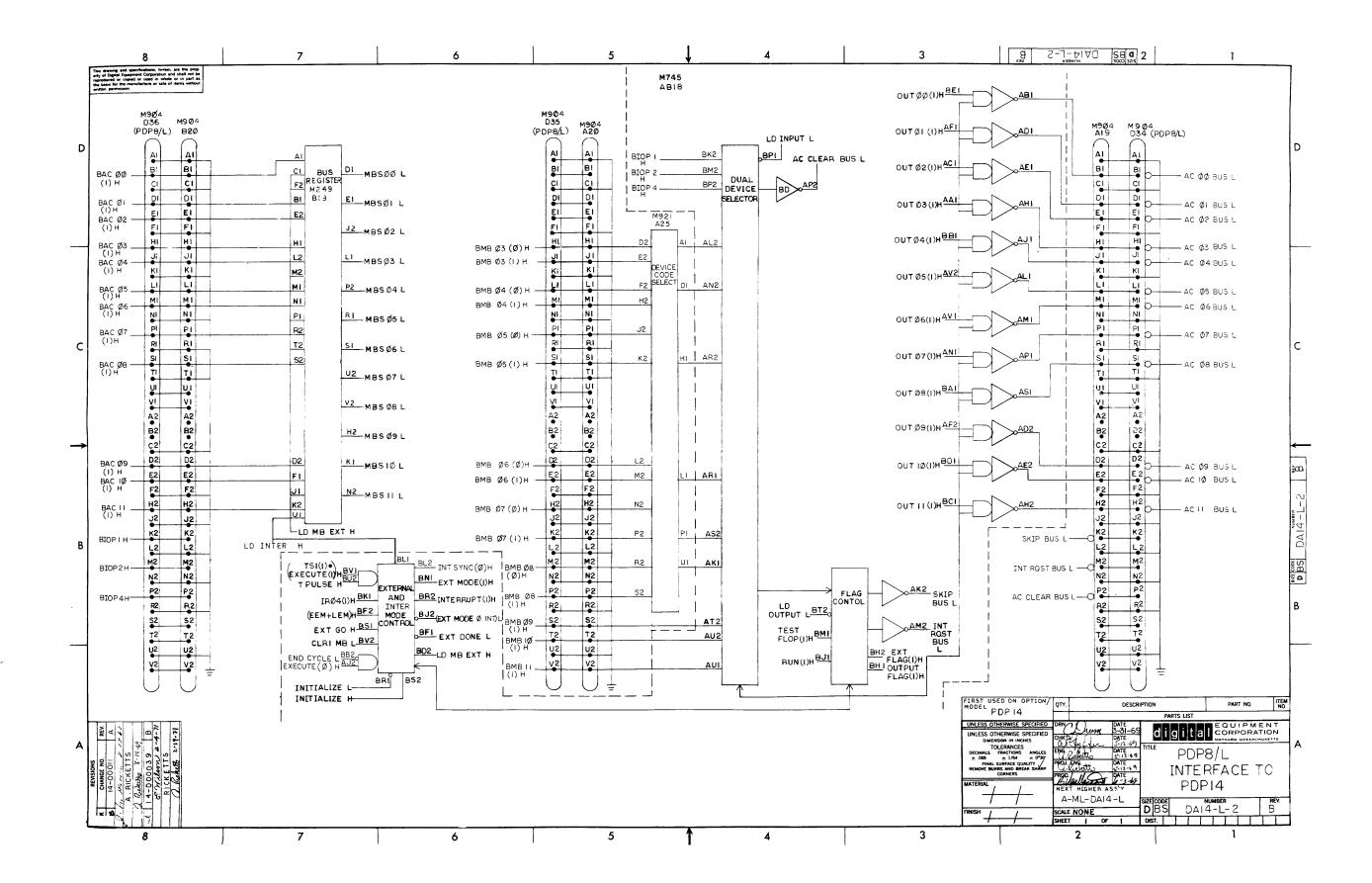

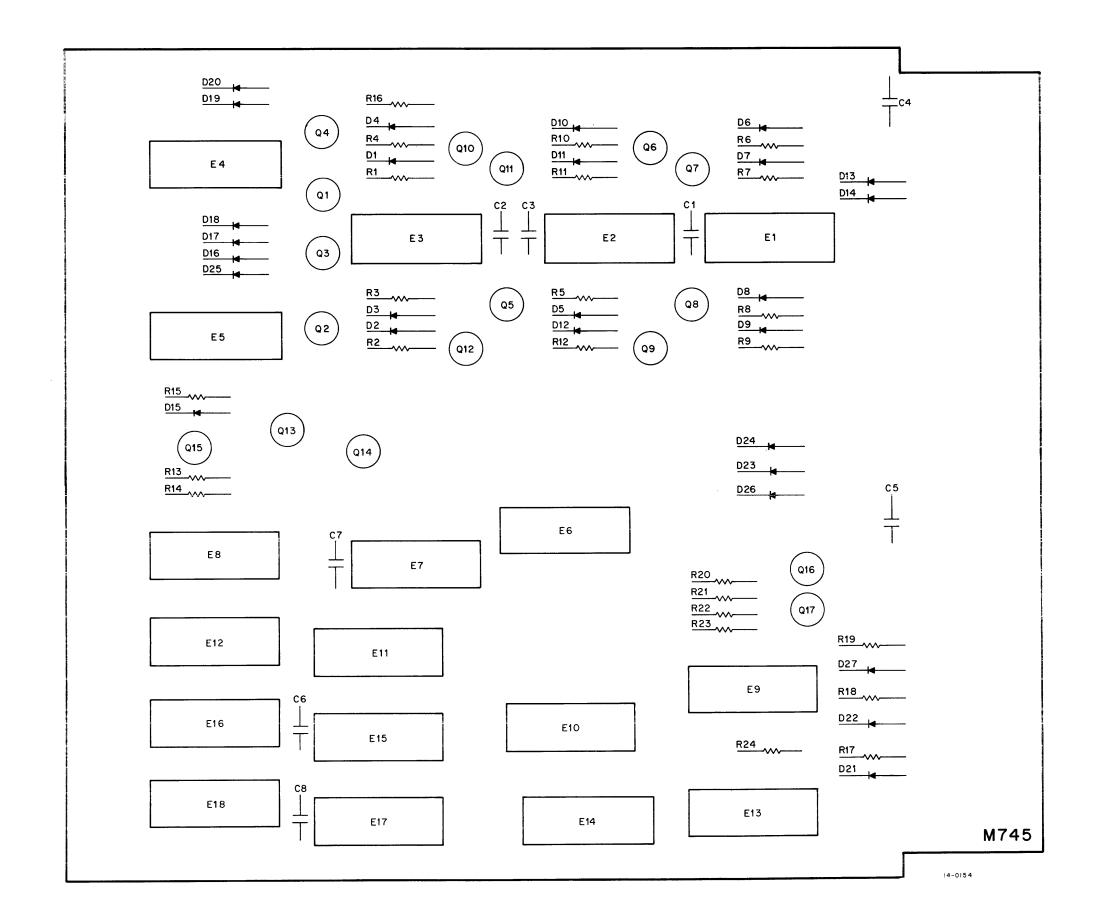

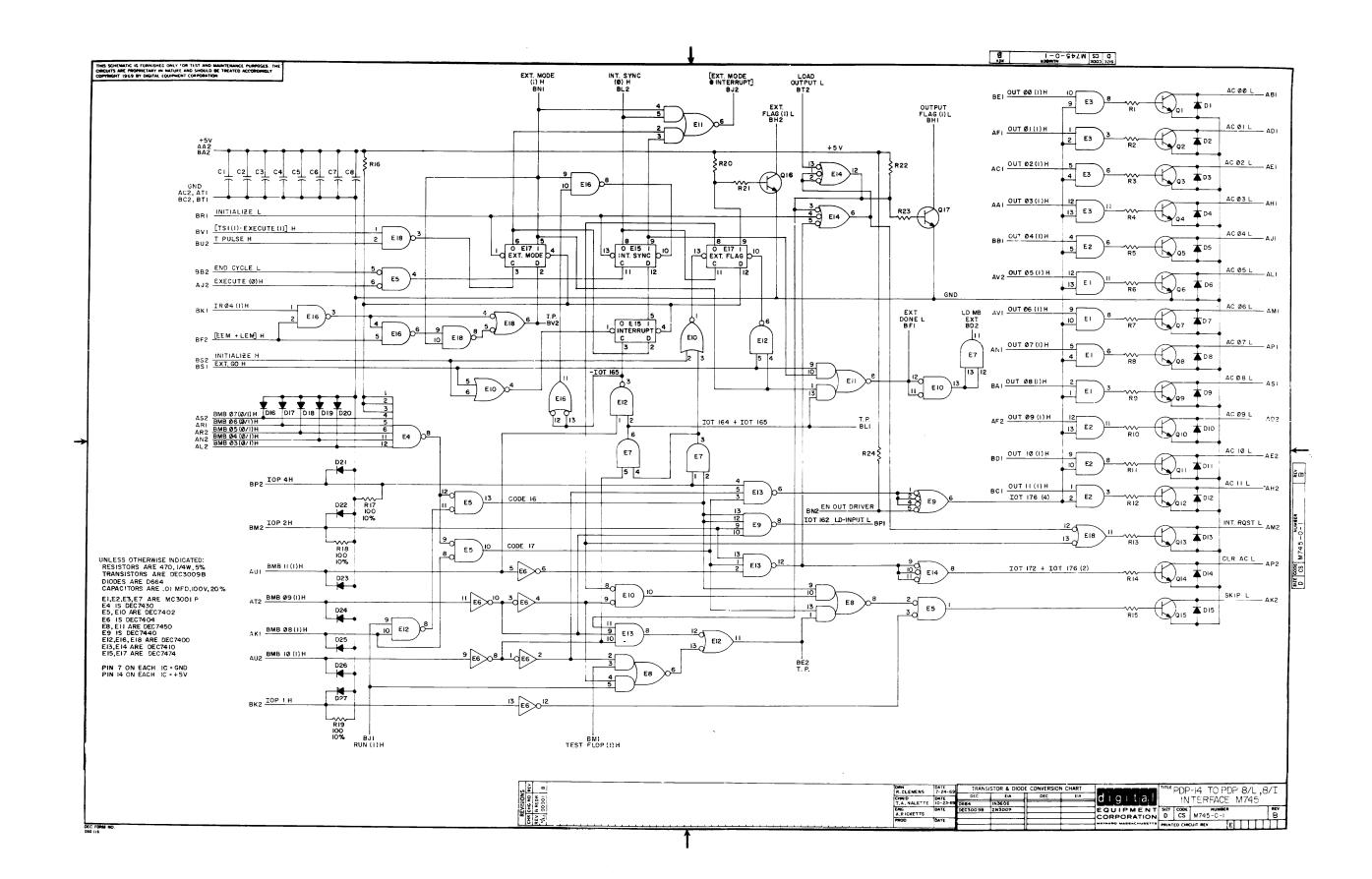

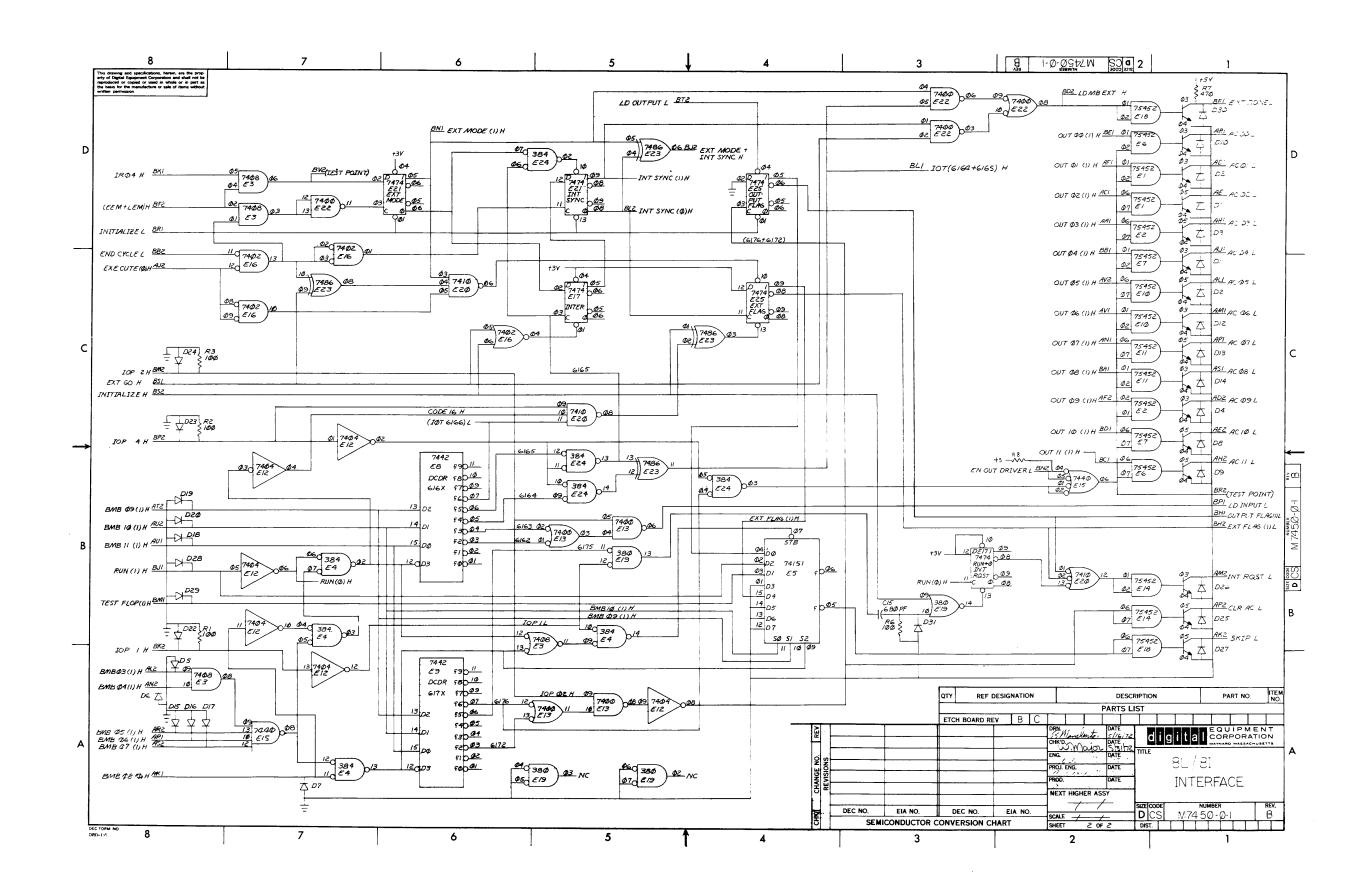

- j. M745 Computer Interface This module interprets computer input/output transfer (IOT) instructions and synchronizes controller operations with the computer.

- k. M746 Input Register Two M746 modules comprise the Input Register. The register is only used for computer operations. The register accepts and buffers 12-bit data from the computer for internal register transfer instructions.

- 1. M746 Output Register Two M746 modules comprise the Output Register. The principal use for this register is to return test results to a computer.

- m. M921 Device Selector This module is only used for computer operations. It establishes a device code for the PDP-14 Controller so that the computer can communicate with the controller.

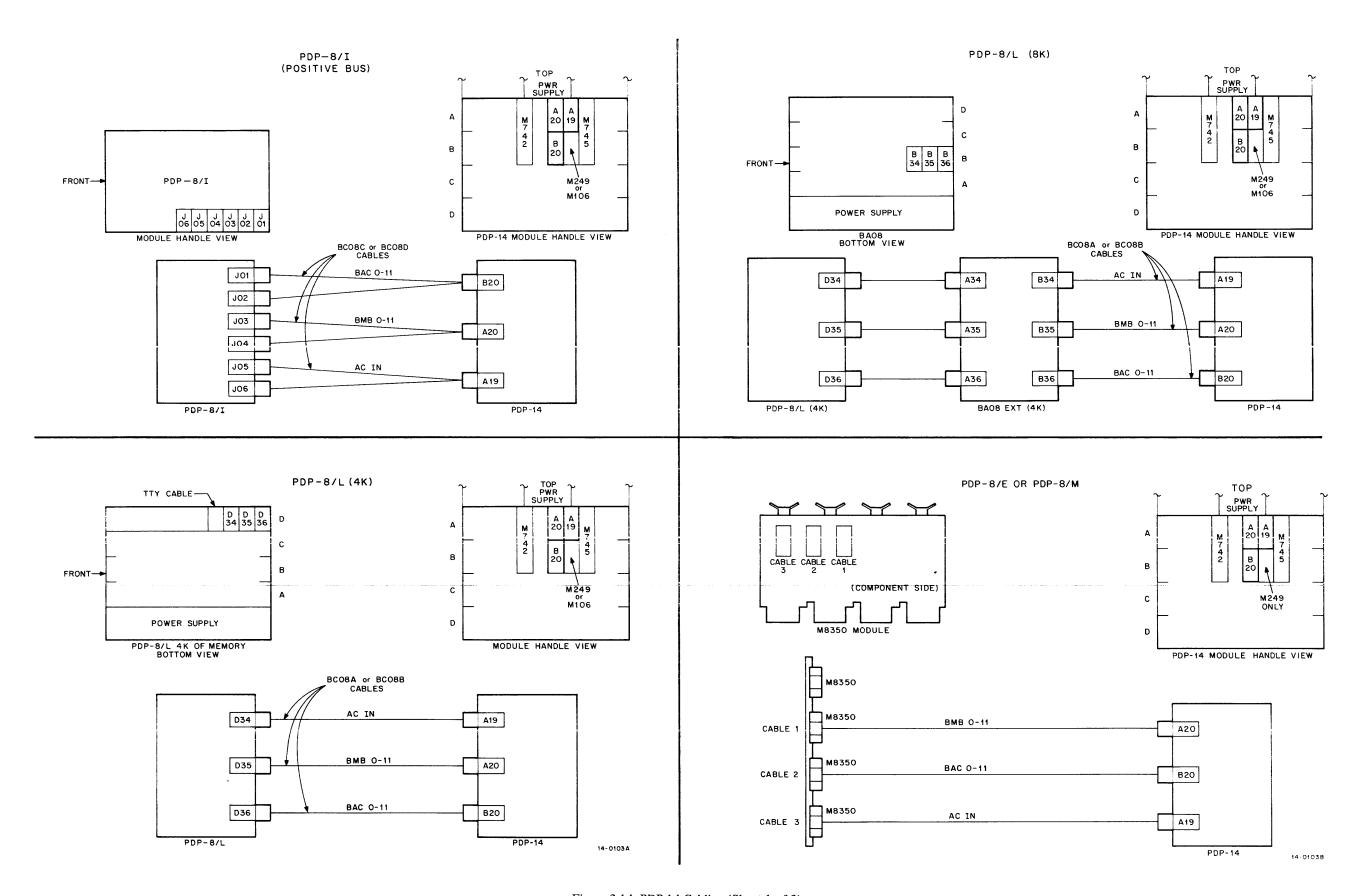

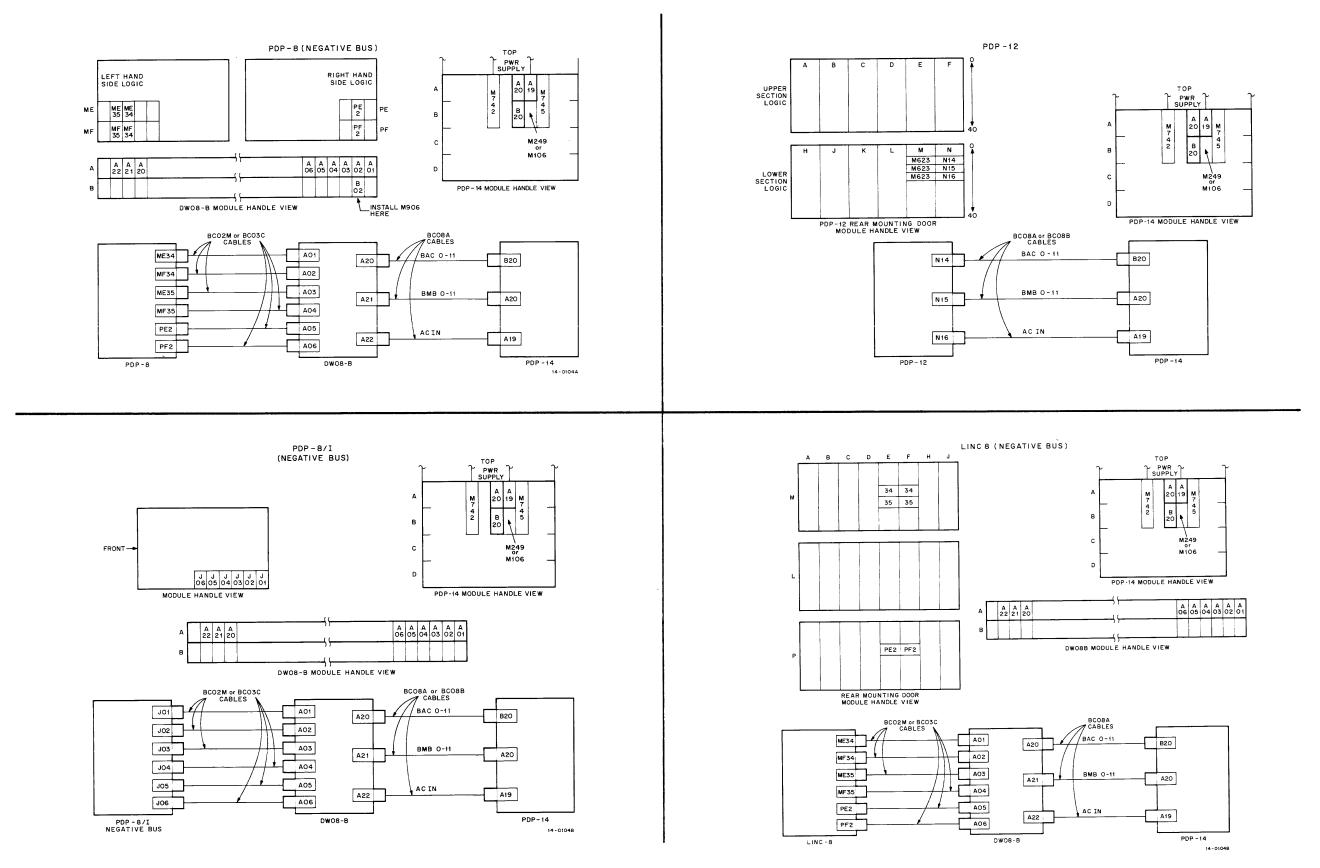

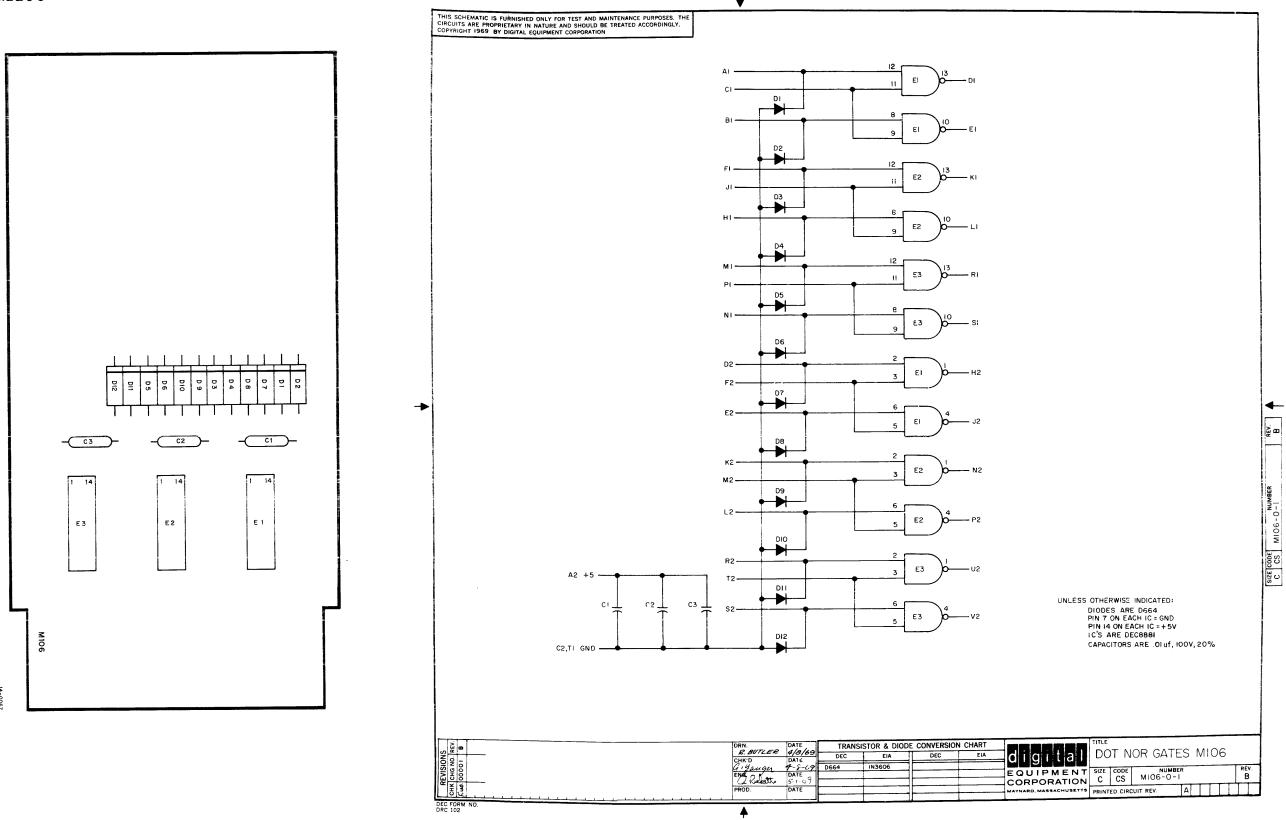

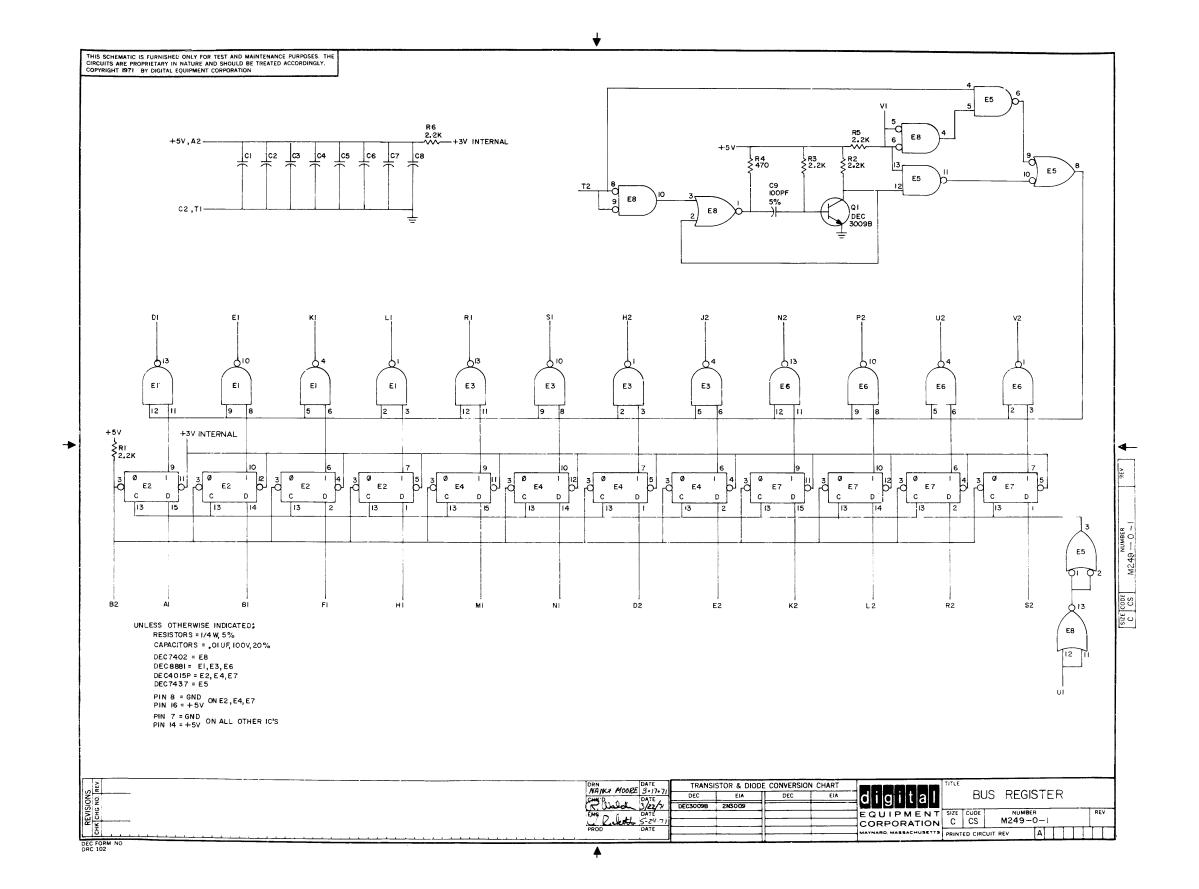

- n. M249 (or M106) Memory Port This module is only used for computer operations. The register accepts and buffers 12-bit instructions from the computer and provides them to the MB register for execution. The M249 Memory Port must be used with the PDP-8/E computer. PDP-14s used with the PDP-8/I or PDP-8/L computer may also use the M106 Memory Port in place of M249 if the proper ECO is installed.

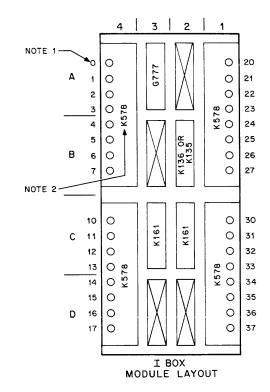

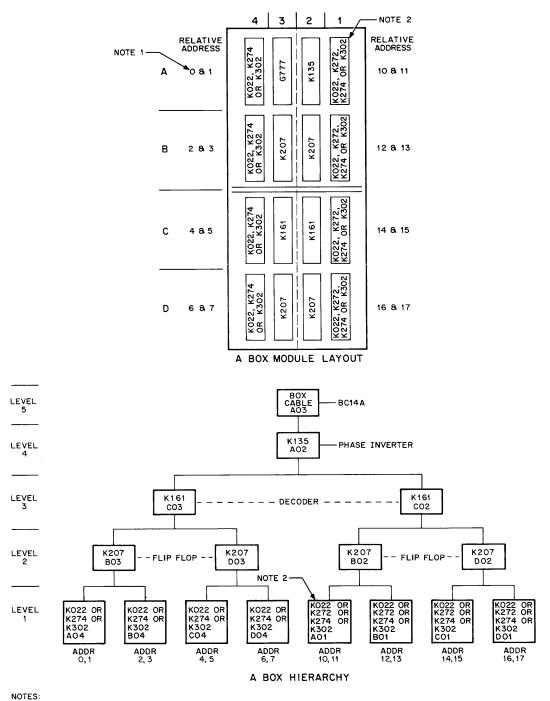

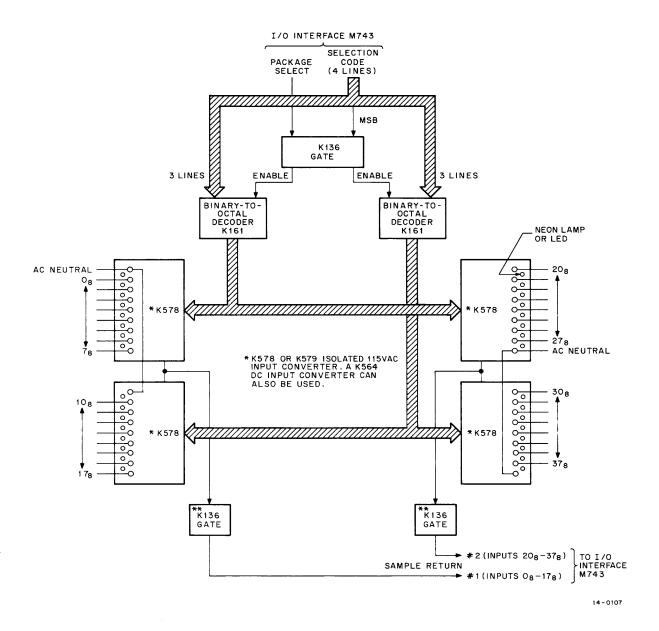

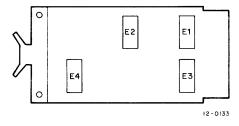

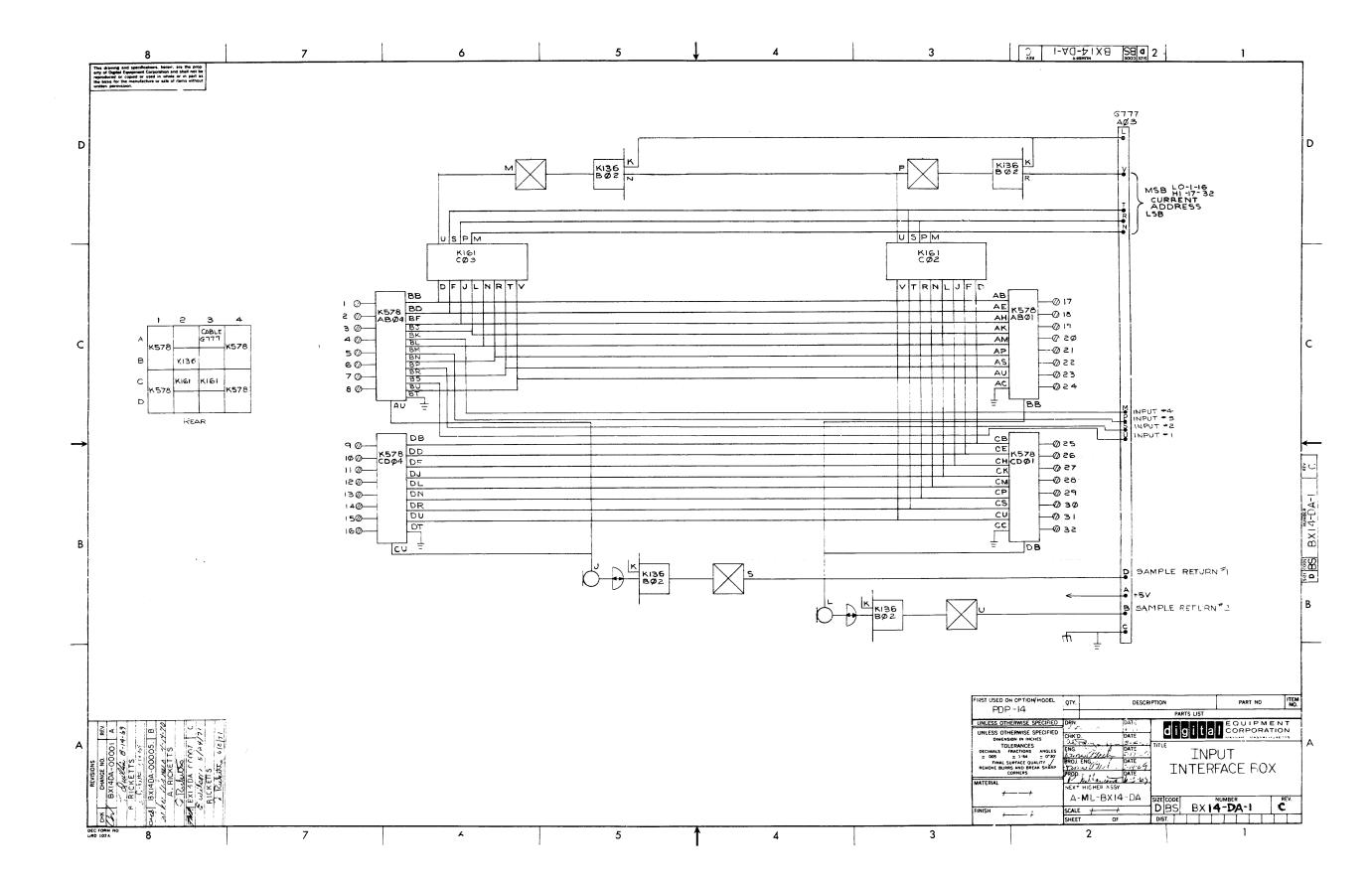

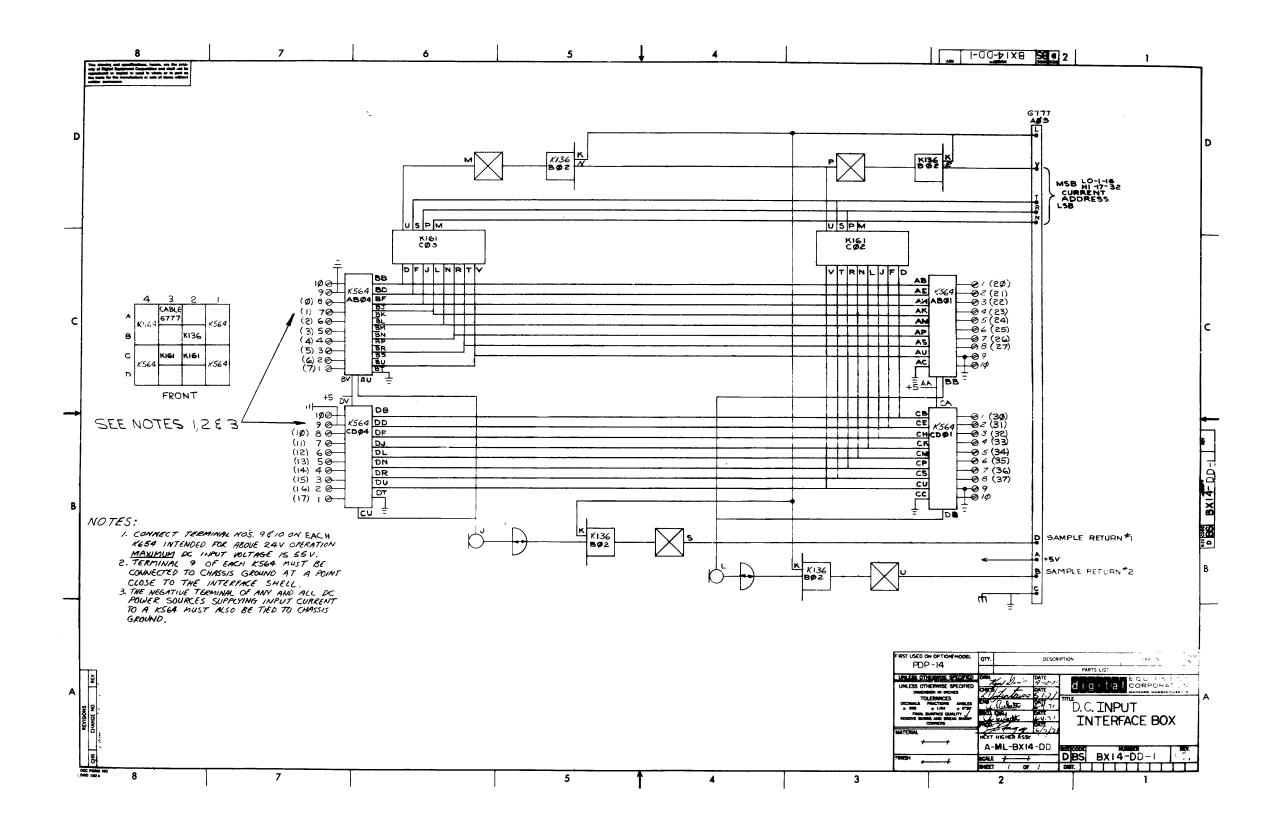

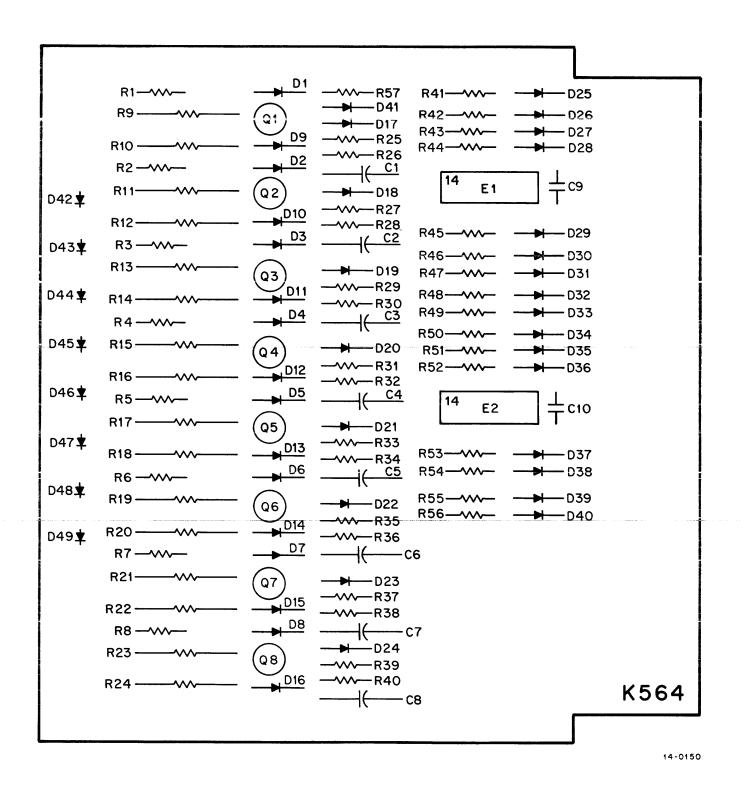

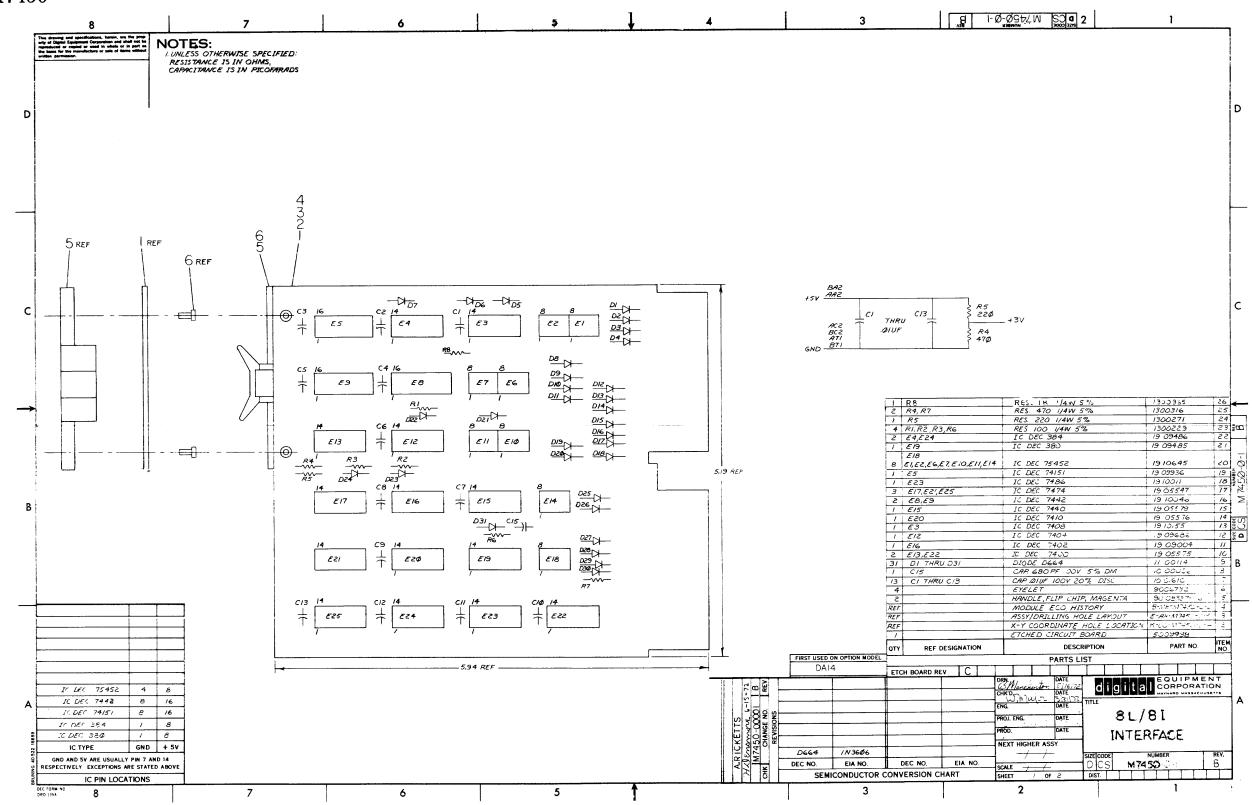

- 2.2.2.3 I Boxes BX14-DA and BX14-DD As mentioned previously, each I Box provides the capability for handling 32 status inputs. These inputs can be either ac or dc (but not both). For ac inputs, a system uses I Box BX14-DA. For dc inputs, a system uses I Box BX14-DD. These I Boxes differ only in the input converter module used. Figure 2-2 depicts the module layout for an I Box and the hierarchy of modules as related to fault isolation. The modules are described in subsequent paragraphs.

- a. K578 AC Input Converter This module accepts up to eight ac inputs and converts them into logic levels. Inputs are connected to a terminal strip on the front of the module. A neon indicator is provided for each input; this indicator lights when 115 Vac is present at the input.

- b. K564 DC Input Converter This module accepts up to eight dc inputs and converts them into logic levels. This module accepts inputs having a range from 10 to 55 Vdc (or above 55 Vdc with an external series resistor at 50 ohms per volt). Inputs are connected to a terminal strip on the front of the module. A light-emitting diode (LED) is provided for each input. This indicator lights when voltage is present at the input terminal.

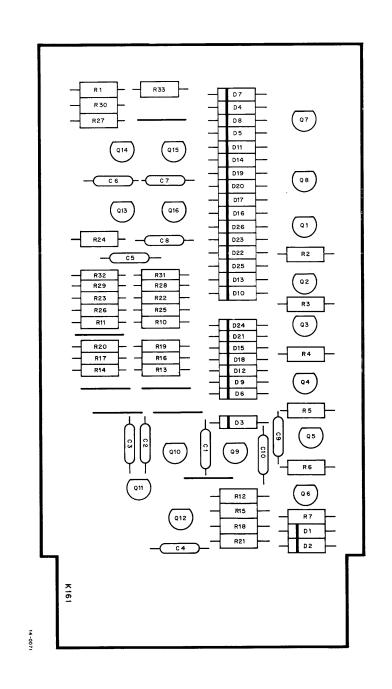

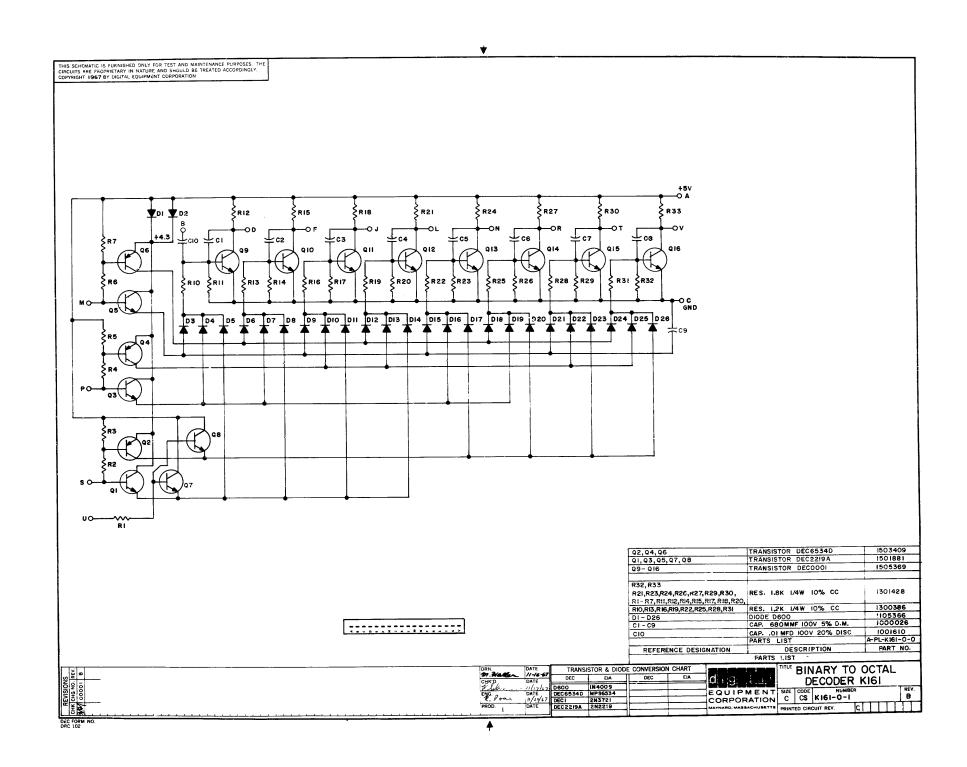

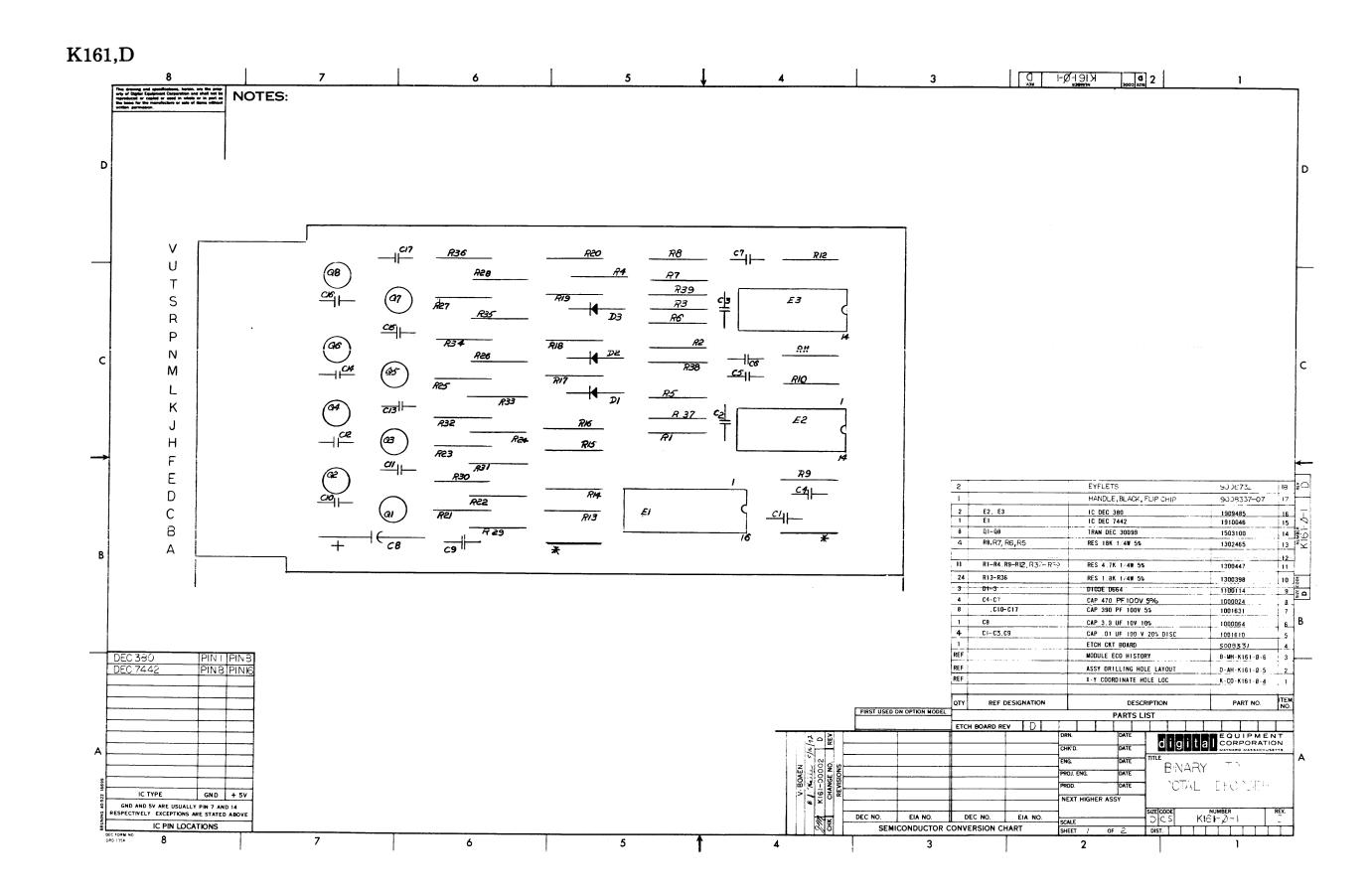

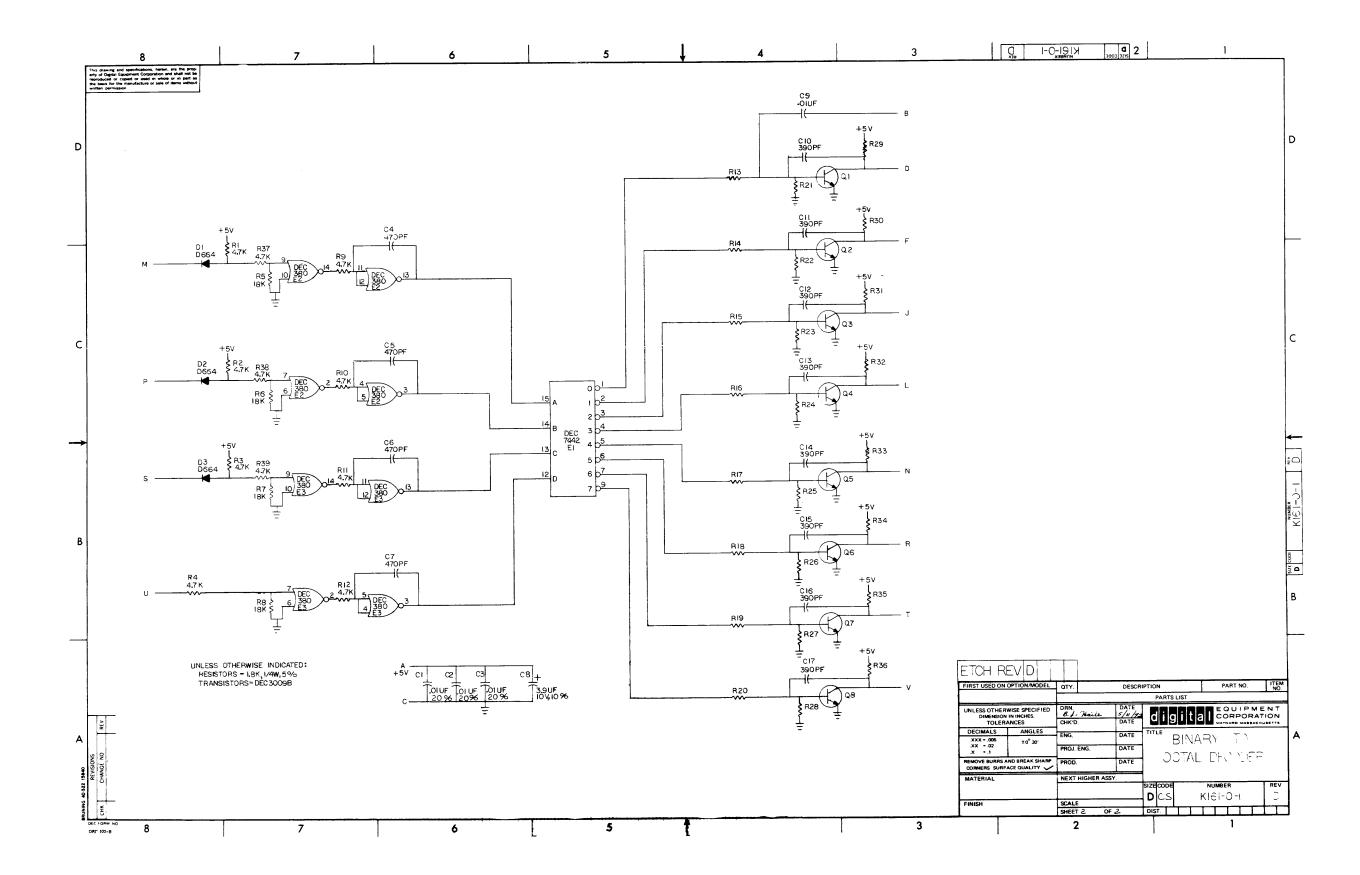

- c. K161 Decoder This module is used in the addressing (or selection) of inputs. It decodes three bits of address from the Control Unit to select one of the eight input circuits on a K578 or K564 Input Converter.

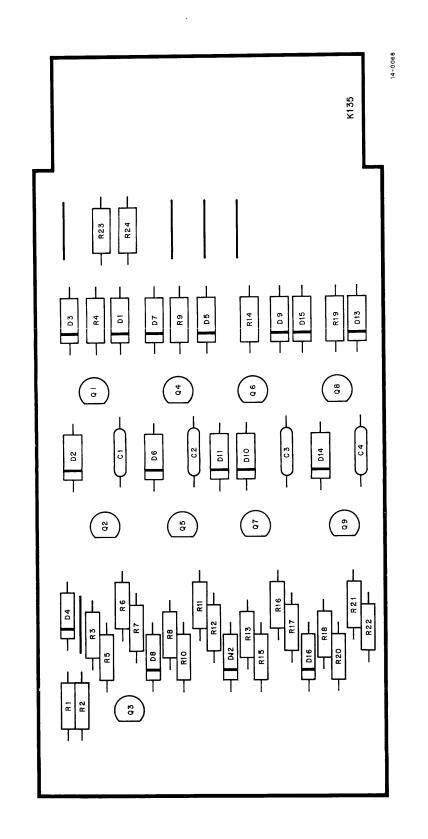

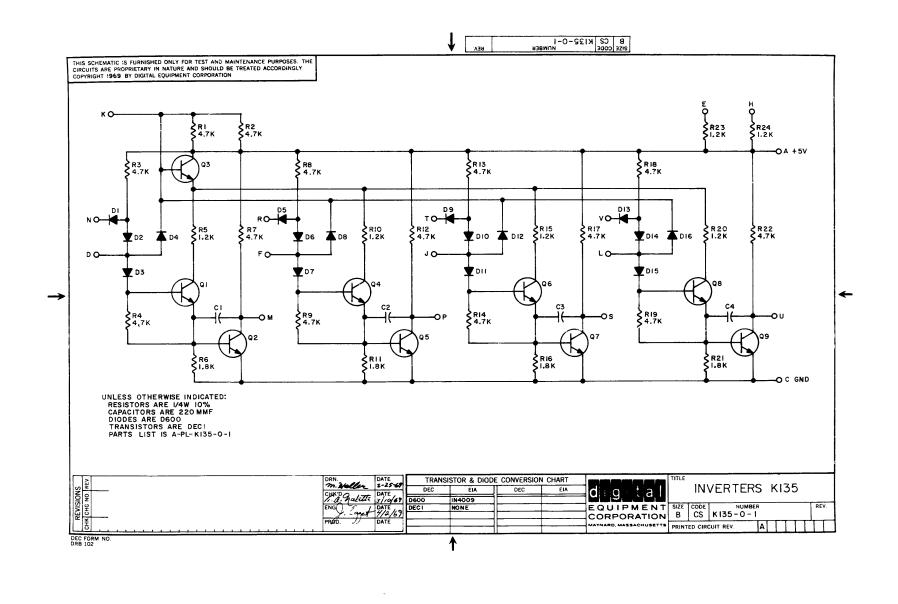

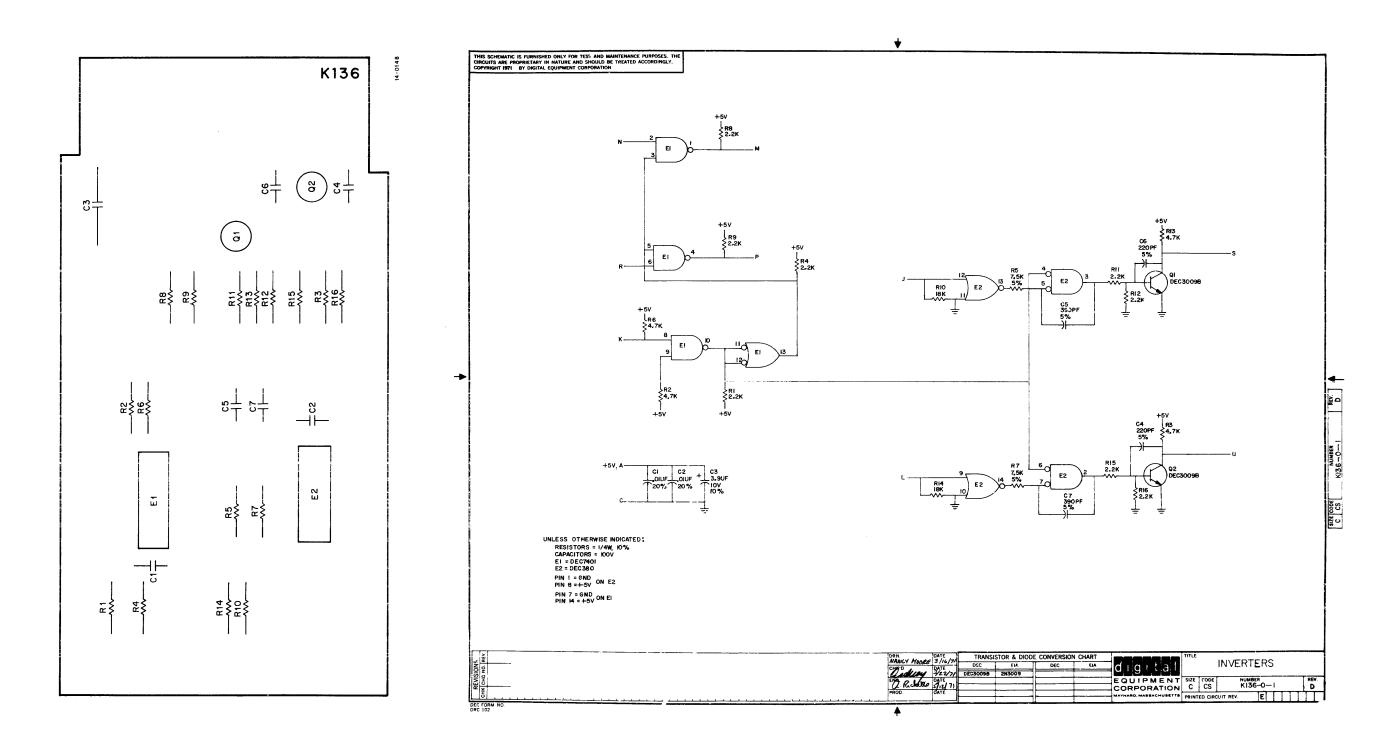

- d. K136 (or K135) Inverter This module contains four independent inverter circuits used in the addressing of input circuits and in input test return circuits. Each inverter circuit performs a logical NOT function.

Figure 2-2 I Box Layout and Hierarchy

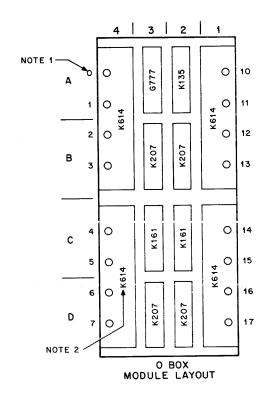

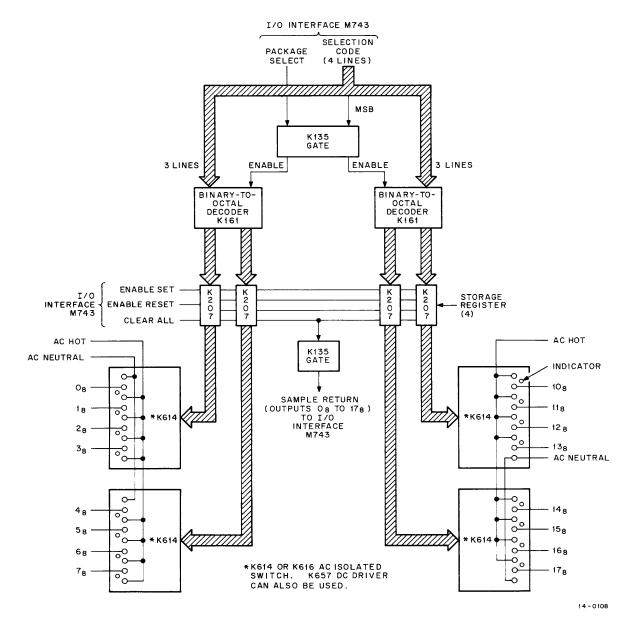

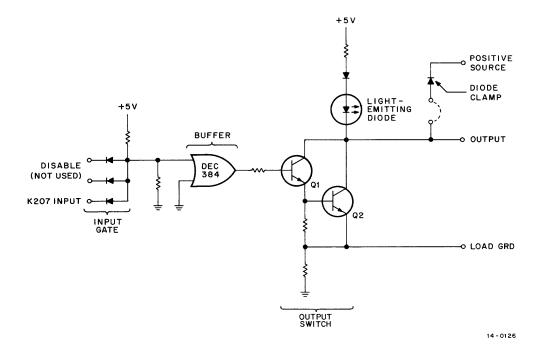

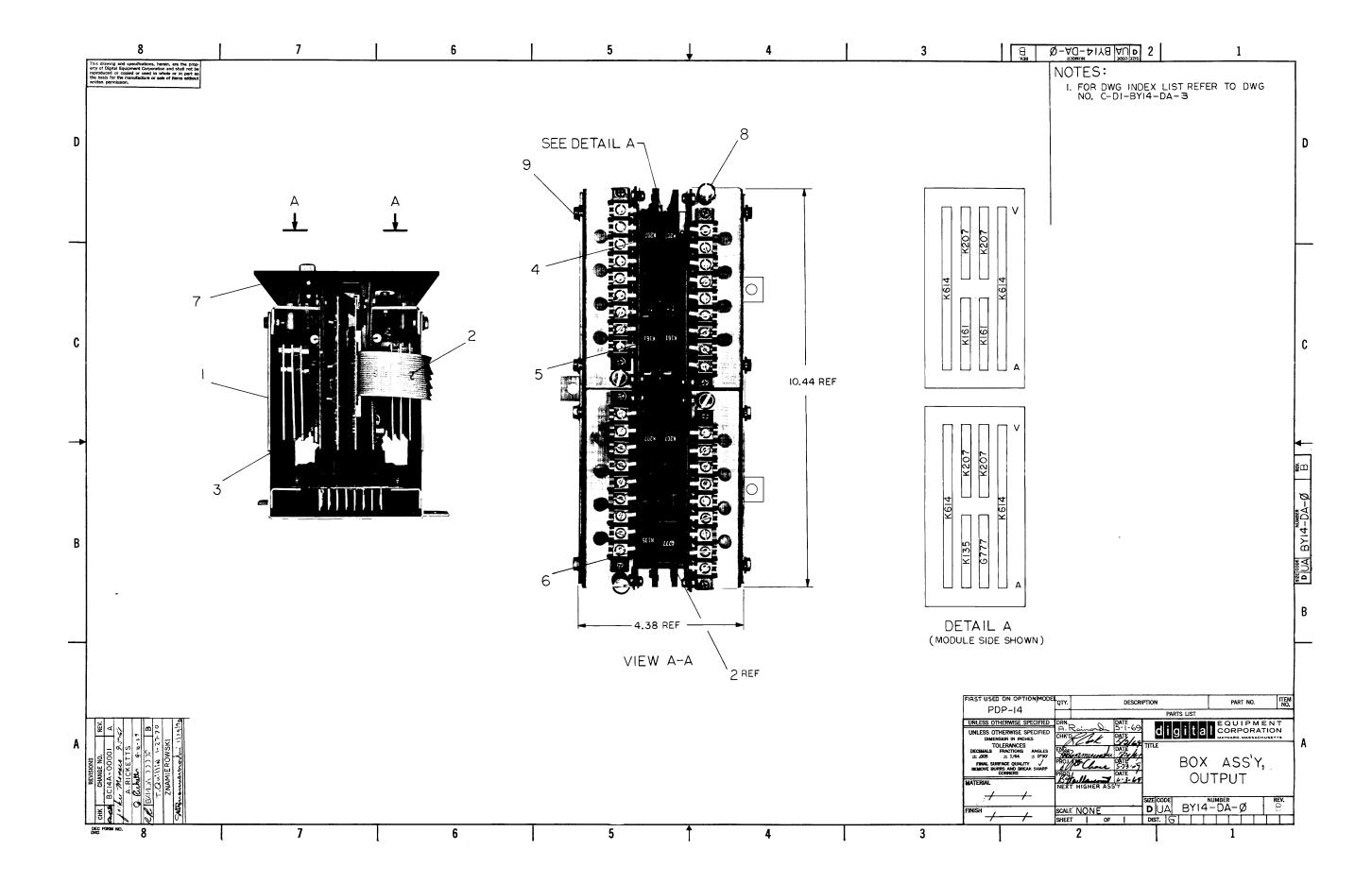

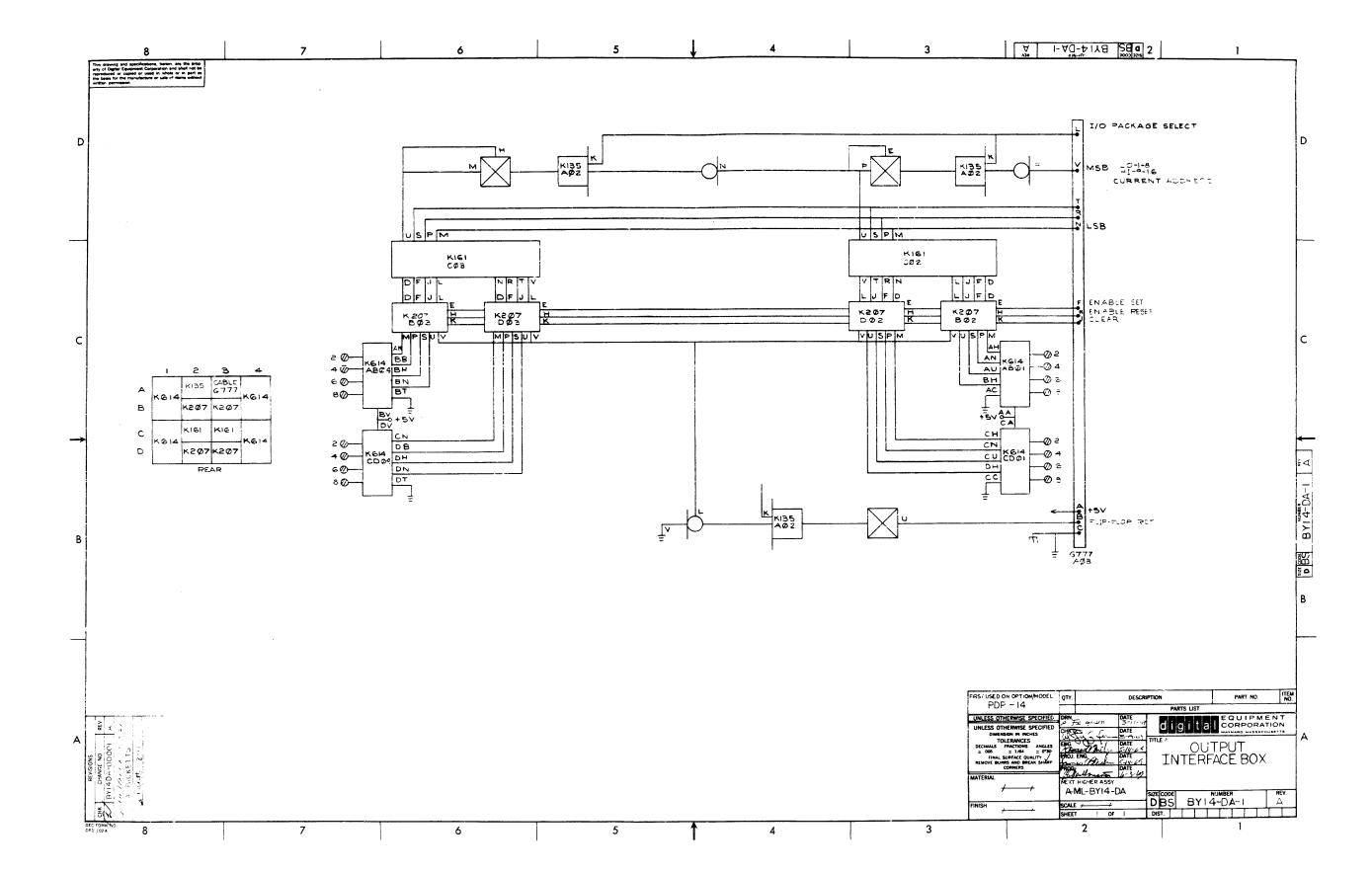

2.2.2.4 O Boxes BY14-DA and BY14-DD — Each O Box contains 16 independent output circuits that drive machine or process system devices. The outputs can be either ac or dc (but not both) depending upon system usage. A BY14-DA O Box provides ac outputs; a BY14-DD O Box provides dc outputs. These boxes differ only in the output driver modules used.

Figure 2-3 depicts the module layout for an O Box and the hierarchy of modules as related to fault isolations. The modules are briefly described in the following paragraphs.

Figure 2-3 O Box Layout and Hierarchy

14-0098

- a. K614 Isolated AC Switch Four of these modules can be used in a BY14-DA O Box. Each module contains four independent ac driver circuits. Each circuit is independently rated at 500 VA, however, the collective total power rating for a module is 1000 VA. Each circuit is equipped with a neon indicator. This indicator lights when 115 Vac is being provided to the load.

- b. K657 DC Driver Four of these modules can be used in a BY14-DD O Box. Each module contains four dc driver circuits. Each circuit can be used to switch a dc load (having a source voltage from 10 to 250 Vdc) to ground. Each driver circuit is rated at 1A (maximum). Each output has an LED that indicates when the output path is completed.

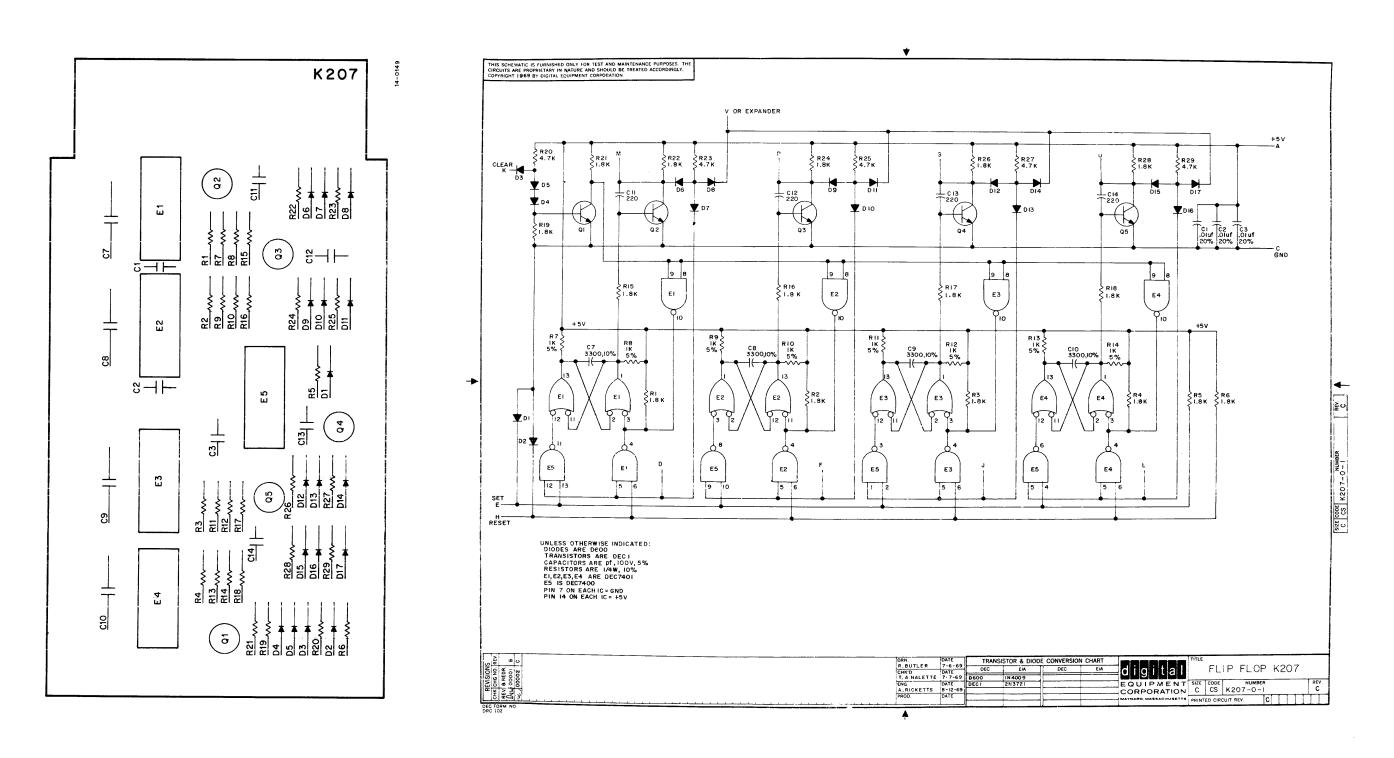

- c. K207 Flip-Flop This module contains four storage registers (flip-flop circuits) that control the output circuit on a K614 or K657 module. When turned on (SET) by a program instruction, a flip-flop causes the output circuit path to be completed. The flip-flop remains in this state until turned off (RESET) by a program instruction or an initialize operation. The state of the K207 flip-flop is tested by the control program to determine if an output is on or off.

- d. K161 Decoder This module is used in the addressing (or selection) of outputs. It decodes three bits of address from the Control Unit for selection of one of eight flip-flop circuits contained in two K207 modules

- e. K135 Inverter This module contains four independent inverter circuits used in the addressing of output circuits and in the output test return circuits. Each inverter circuit performs a logical NOT function.

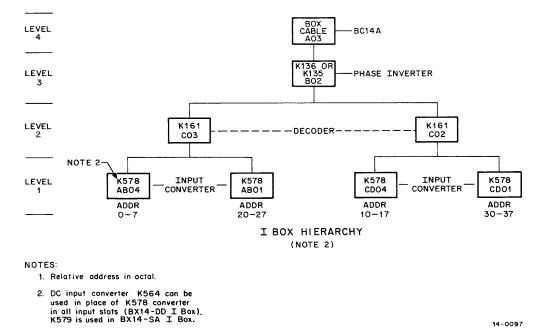

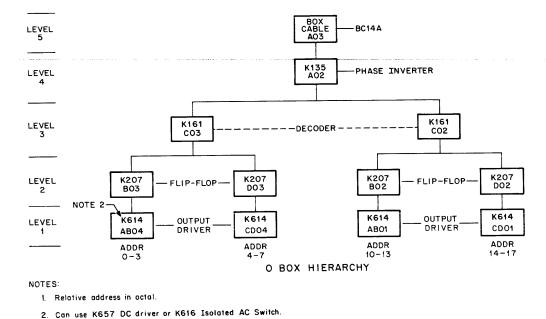

- 2.2.2.5 A Box An A Box can be used to provide timer (delay), retentive memory (event storage during power-off states), or normal storage functions. Each A Box requires one O Box cable slot. In most instances, A Boxes are assigned an upper system address to differentiate from "real" outputs. An A Box can be configured in a number of ways. Figure 2-4 depicts the module location and hierarchy for an A Box. A brief description of the modules is provided in subsequent paragraphs. (For additional details concerning A Box functions and relationships, refer to Chapter 1).

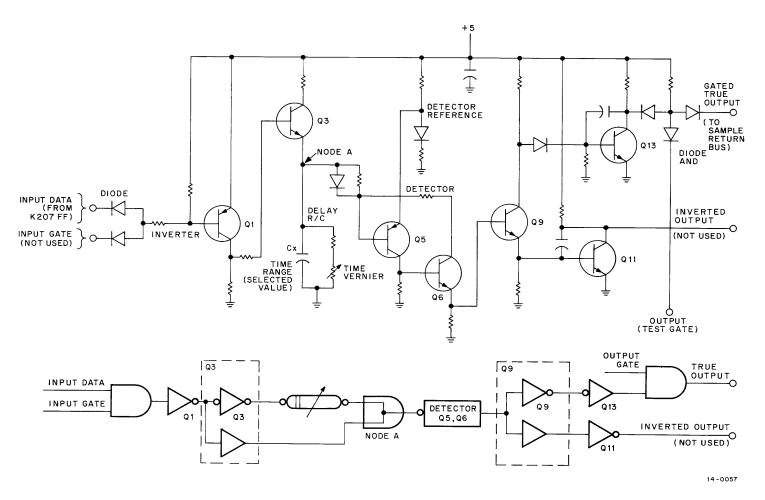

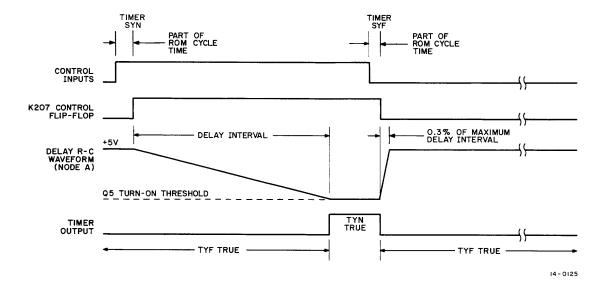

- a. K302 Timer A K302 Timer module contains two timer circuits. Each circuit is capable of providing standard delay intervals from 0.01 to 30 seconds. With the additional resistance, a timer can also provide delay intervals up to 4 minutes, 45 seconds. A timer circuit is addressed in the same manner as O Box modules, except the sample return is generated on this module and not on the K207. Up to eight K302 Timer modules (16 timer circuits) can be accommodated in one A Box.

- b. K272 Retentive Memory A retentive memory retains its state during power off and is unaffected by an initialize operation. Up to four K272 Retentive Memory modules can be used in an A Box, each providing one retentive memory circuit. These modules are addressed in the same manner as "real" outputs but only even-numbered relative addresses on the right-hand side of the A Box can be used.

- c. K274 Retentive Memory This module functions in the same manner as the K272 module, but contains two retentive memory circuits per board. Up to eight K274 modules can be accommodated in one A Box to provide a total of 16 retentive memory circuits.

- d. K022 Storage Module This module can be inserted in the unused timer or retentive memory slot to provide two storage outputs. The module connects the outputs from two K207 flip-flops to the output test return circuits in an A Box. The storage outputs provided by the K022 use the relative addresses of the module slot.

- e. K207 Flip-Flops This module contains four flip-flops. Each flip-flop can be independently set and reset or all can be collectively reset. Each flip-flop can control one timer or one retentive memory or can be used with a K022 Storage module to provide one storage output. Unlike the O Box, the sample return in an A Box is not generated from this module.

- f. K161 Decoder This module is used in the addressing of A Box circuits. It decodes three bits of address from the Control Unit to select one of eight K207 flip-flops.

(continued on next page)

K135 Inverter - This module contains four independent inverter circuits used in the addressing of A Box circuits. Each inverter circuit performs a logical NOT function.

- 1 Relative address in octal

- K272 retentive memory contains one memory and uses only even numbered relative addresses. K274 retentive memory contains two memories and uses both addresses.

14-0099

Figure 2-4 A Box Layout and Hierarchy

#### 2.2.3 Recommended Test Equipment

A VOM (such as Simpson, Model 260 or Triplett, Model 630NA) is recommended for user maintenance. An oscilloscope (such as Tektronix, Model 453) is considered optional.

#### 2.2.4 Recommended Spare Parts

Table 2-1 lists the recommended spare parts by major units. Table 2-2 lists the spare parts recommended for a typical PDP-14 configuration.

Table 2-1 Recommended Spare Parts by Major Units

| Recommended Spare Parts by Major Units               |                                                                                                                                     |                                         |                                         |                                                                                                |                                  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------|

|                                                      | CONTROL UNIT SPAR                                                                                                                   | ES                                      |                                         | INPUT (I) BOX SPARES                                                                           |                                  |

| M740<br>M741<br>M742<br>M743<br>M744<br>M746<br>M747 | Instruction Decoder Major States and Timing Switch and Power Contro I/O Interface Comparator Bus Register Incrementing Bus Register | three control units                     | K136<br>K161<br>K564<br>or<br>K578/K579 | Inverter Binary-To-Octal Decoc DC Input Converter or AC Input Converter  DUTPUT (O) BOX SPARES | one for<br>every<br>two<br>boxes |

| BC14A-15                                             | I/O Cable                                                                                                                           |                                         |                                         | OUTIOT (O) BOX STAKES                                                                          |                                  |

|                                                      | OMPUTER INTERFACE S                                                                                                                 | PARES                                   | K135<br>K161<br>K207                    | Inverter Binary-To-Octal Decoder Flip-Flop                                                     | one for every                    |

| M249<br>M745<br>M746<br>M921                         | Memory Port Computer Interface Bus Register Device Selector                                                                         | one for every three computer interfaces | K614/K616<br>or<br>K657                 | Isolated AC Switch or DC Driver  CCESSORY (A) BOX SPAR                                         | two<br>boxes<br>ES               |

|                                                      | MEMORY SPARES                                                                                                                       | c                                       | K135<br>K161                            | Inverter Binary-To-Octal Decoder                                                               |                                  |

| G923<br>G924                                         | ROM Sense Amplifier ROM Selection and Timin                                                                                         | one for every four ROMs                 | K207<br>K302<br>K022<br>K272            | Flip-Flop Timer A Box Storage Module Retentive Memory or                                       | one for every two boxes          |

|                                                      | FUSES                                                                                                                               |                                         | K274                                    | Retentive Memory                                                                               | J                                |

| Littelfuse 5<br>Switch                               | A type 276005 for K614 I                                                                                                            | solated AC                              |                                         |                                                                                                |                                  |

#### 2.3 FAULT ISOLATION WITHOUT A COMPUTER

### 2.3.1 General Approach

Fault isolation of a machine system malfunction can be analogous to isolating faults in the automobile. That is, the same general principles apply. First, we try to analyze the fault in major categories; whether the entire system is inoperative or, if it works, what part works and what part does not work.

Table 2-2

Spare Parts Recommended for a Typical Configuration

| G C                     | Recommended Spares |                                                                |  |

|-------------------------|--------------------|----------------------------------------------------------------|--|

| Configuration           | Quantity           | Spare                                                          |  |

| One PDP-14 Control Unit | 1                  | BC14A-15 I/O Cable                                             |  |

| One Computer Interface  | 1                  | G923 ROM Sense Amplifier                                       |  |

| Two 1K ROMs             | 1                  | G924 ROM Selection and Timing                                  |  |

| Four I Boxes            | 1                  | K022 A Box Storage Module                                      |  |

| Four O Boxes            | 5                  | K135 Inverters                                                 |  |

| One A Box               | 5                  | K161 Binary-To-Octal Decoders                                  |  |

| Two Storage Modules     | 3                  | K207 Flip-Flops                                                |  |

|                         | 1                  | K274 Retentive Memory                                          |  |

|                         | 1                  | K302 Timer                                                     |  |

|                         | 2                  | K578 or K579 AC Input Converters (or K564 DC Input Converters) |  |

|                         | 2                  | K614 or K616 Isolated AC Switches (or K657 DC Drivers)         |  |

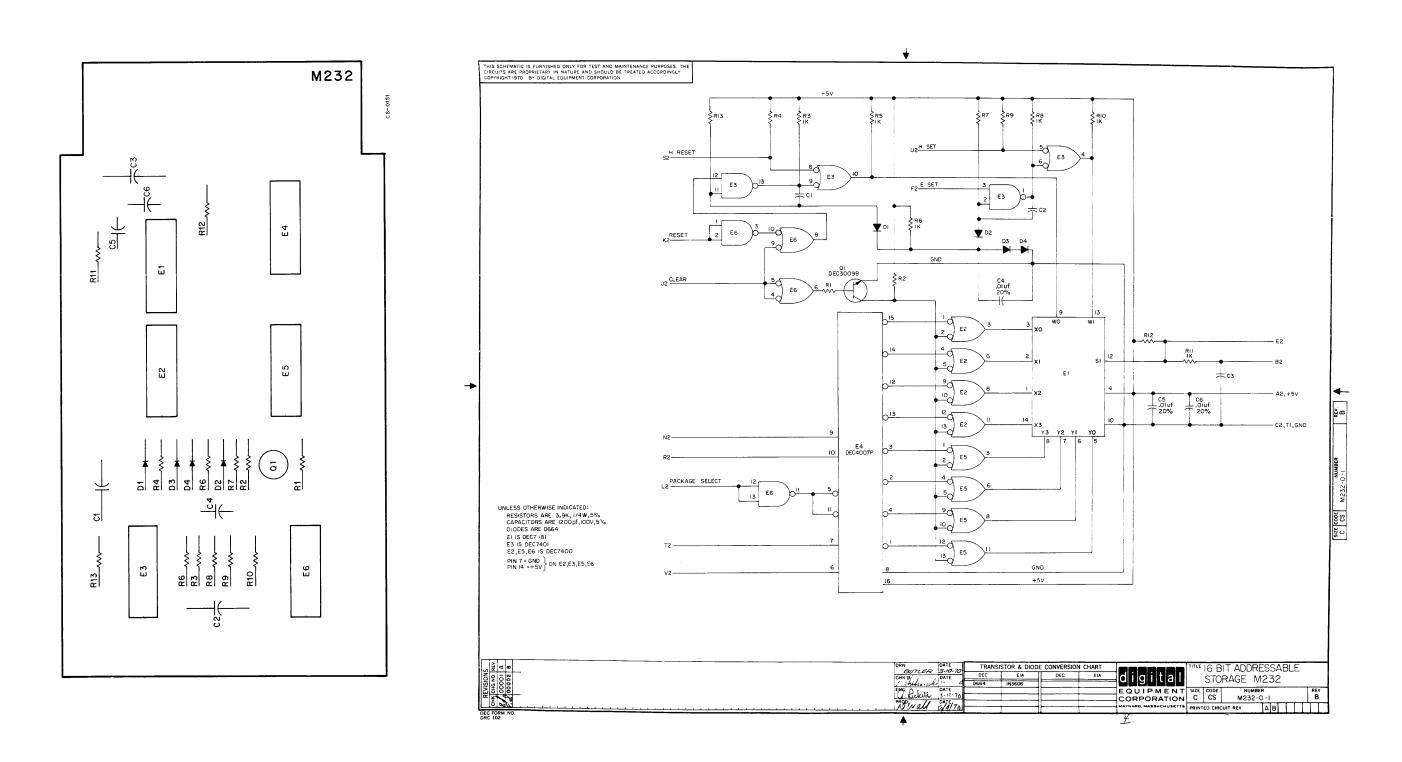

|                         | 1                  | M232 Storage Module (BF14-M)                                   |  |

|                         | 1                  | M249 Memory Port                                               |  |

|                         | 1                  | M740 Instruction Decoder                                       |  |

|                         | 1                  | M741 Major States and Timing                                   |  |

|                         | 1                  | M742 Switch and Power Control                                  |  |

|                         | 1                  | M743 I/O Interface                                             |  |

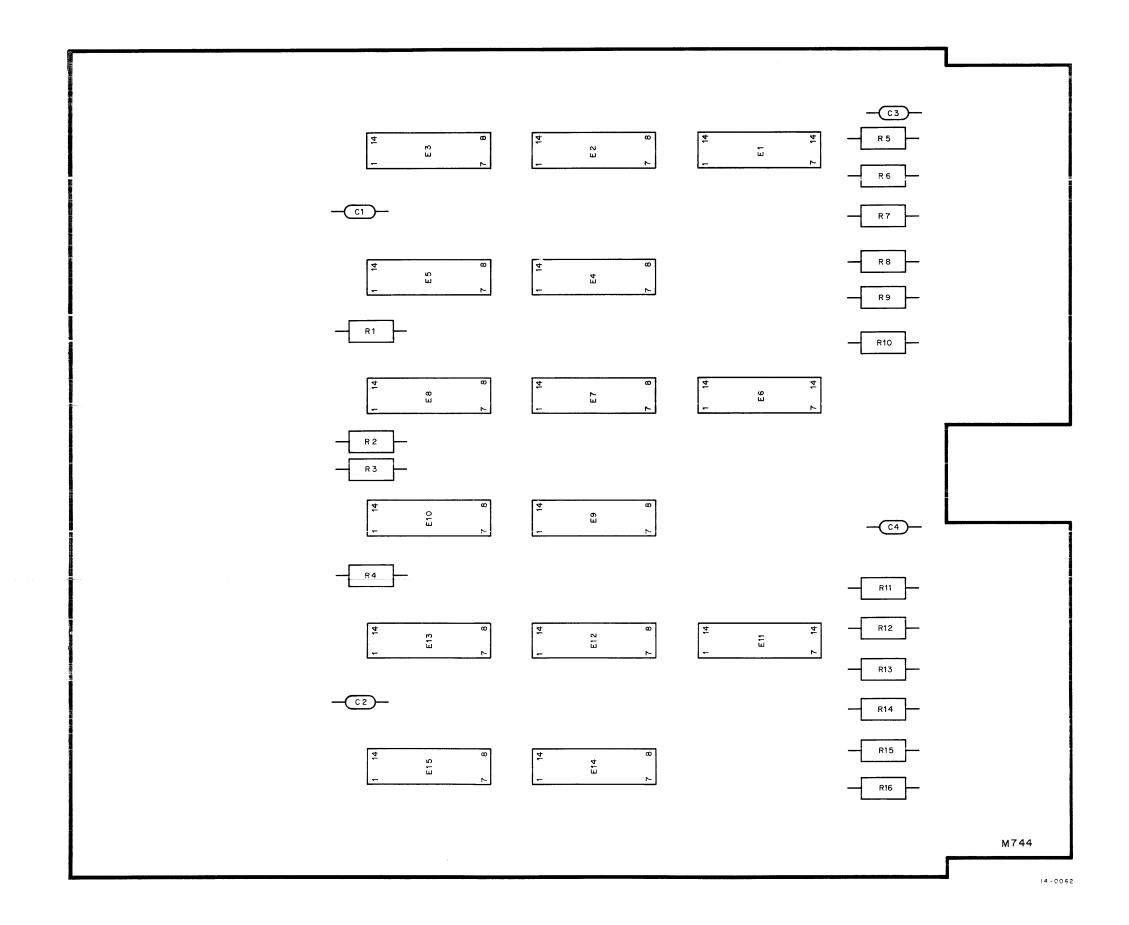

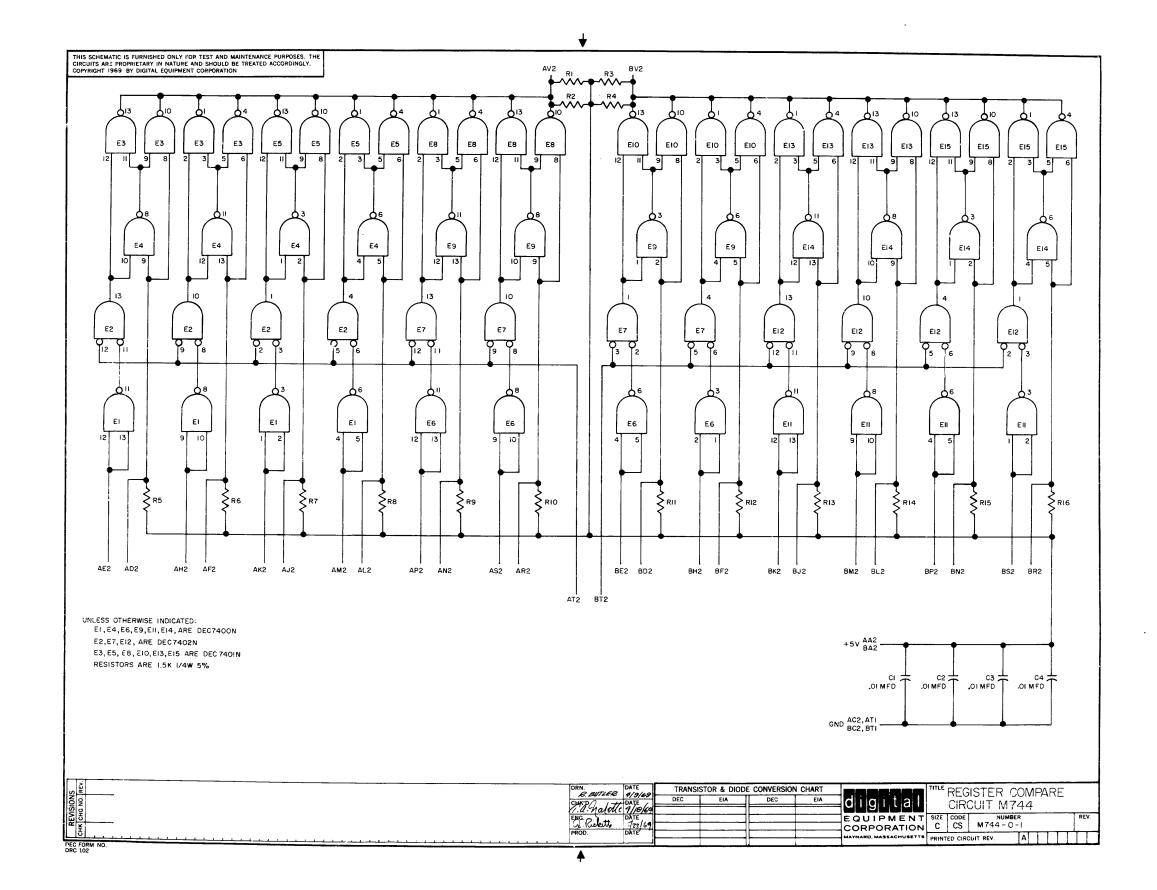

|                         | 1                  | M744 Comparator                                                |  |

|                         | 1                  | M745 Computer Interface                                        |  |

|                         | 2                  | M746 Bus Registers                                             |  |

|                         | 1                  | M747 Incrementing Bus Register                                 |  |

|                         | 1                  | M921 Device Selector                                           |  |

For example, if someone told you that your car won't run, you'd probably begin by finding out if the starting system will turn over the engine. If it did not, you'd probably suspect the starting system (battery, starter motor, solenoid, etc.). From this point, you can continue the investigation or begin substitution of components. If, however, the engine can be rotated but fails to start, you'd suspect a different set of components (possibly the carburetor, distributor, etc.) and would begin isolation from this point.