Cypress Semiconductor is a trademark of Cypress Semiconductor Corporation.

Cypress Semiconductor 3901 North First St. San Jose, CA 95134 (408) 943-2600, Telex: 821032, TWX: 910 997 0753

## How To Use This Book

This book has been organized by product type, beginning with Product Information. The products then follow, beginning with RAMs, then PROMS, PALs, and finally LOGIC. FIFO products are included in the LOGIC section. The Appendix A covers Packages, and Thermal Data. Appendix B covers Cypress Quality and Reliability aspects, and Appendix C is a compilation of various Application Briefs. A Numeric Device Index is included after the Table of Contents that identifies products by numeric order, rather than by device type which is how the manual is set up. To further help you in identifying parts, a Product Line Cross Reference is in Product Information. Use it to find the Cypress part number that is comparable to another manufacturer's part number.

| PRODUCT ==================================== |

|----------------------------------------------|

| STATIC RAMS 2                                |

| PROMS 3                                      |

| PALS4                                        |

| LOGIC 5                                      |

| APPENDICES6                                  |

- -

\_

## **General Product Information**

## **Page Number** Cypress Semiconductor Background ......1-1

## Static RAMs (Random Access Memory)

\_

| Device Number | Description                      |      |

|---------------|----------------------------------|------|

| CY2147        | 4096 x 1 Static RAM              |      |

| CY2148        | 1024 x 4 Static RAM              |      |

| CY21L48       | 1024 x 4 Static RAM              |      |

| CY2149        | 1024 x 4 Static RAM              |      |

| CY21L49       | 1024 x 4 Static RAM              |      |

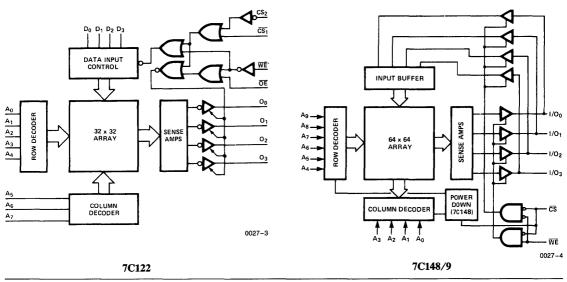

| CY7C122       | 256 x 4 Static RAM Separate I/O  | 2-10 |

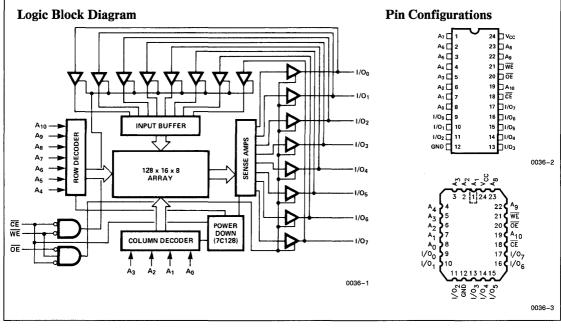

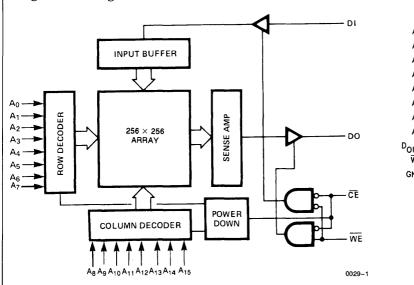

| CY7C128       | 2048 x 8 Static RAM              |      |

| CY7C129       | 2048 x 8 Static RAM              |      |

| CY7C147       | 4096 x 1 Static RAM              |      |

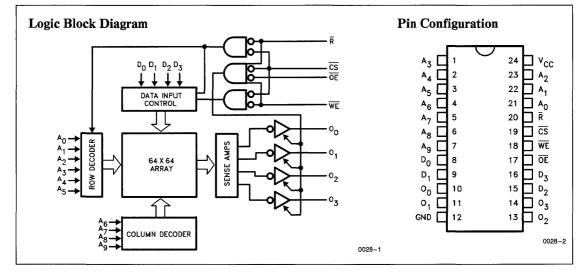

| CY7C148       | 1024 x 4 Static RAM              | 2-28 |

| CY7C149       | 1024 x 4 Static RAM              | 2-28 |

| CY7C150       | 1024 x 4 Static RAM Separate I/O |      |

| CY7C167       | 16,384 x 1 Static RAM            | 2-40 |

| CY7C168       | 4096 x 4 Static RAM              |      |

| CY7C169       | 4096 x 4 Static RAM              |      |

| CY7C170       | 4096 x 4 Static RAM              |      |

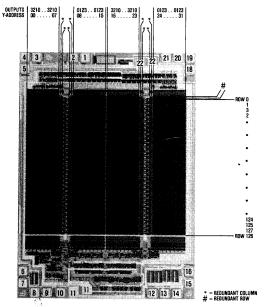

| CY7C187       | 65,536 x 1 Static RAM            |      |

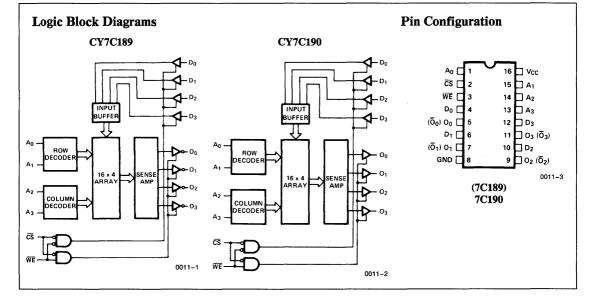

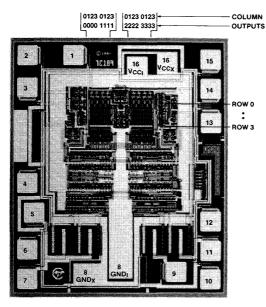

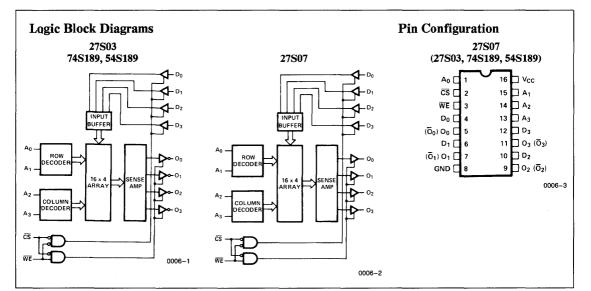

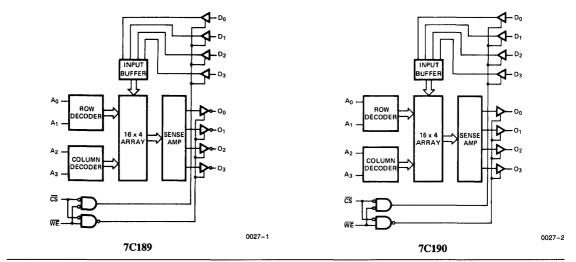

| CY7C189       | 16 x 4 Static RAM                |      |

| CY7C190       | 16 x 4 Static RAM                |      |

| CY74S189      | 16 x 4 Static RAM                |      |

| CY54S189      | 16 x 4 Static RAM                |      |

| CY27S03       | 16 x 4 Static RAM                |      |

| CY27S07       | 16 x 4 Static RAM                |      |

| CY93422A      | 256 x 4 Static RAM Separate I/O  |      |

| CY93L422A     | 256 x 4 Static RAM Separate I/O  | 2-69 |

| CY93422       | 256 x 4 Static RAM Separate I/O  |      |

| CY93L422      | 256 x 4 Static RAM Separate I/O  |      |

## **PROMs (Programmable Read Only Memory)**

| PROM Introduction            |                          | -1         |

|------------------------------|--------------------------|------------|

| Device Number                | Description              |            |

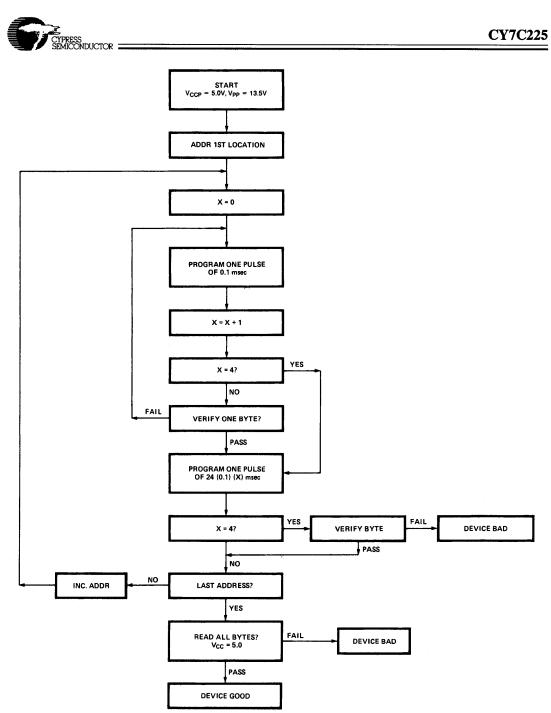

| CY7C225                      | 512 x 8 Registered PROM  | -3         |

| CY7C235                      | 1024 x 8 Registered PROM |            |

| CY7C245                      | 2048 x 8 Registered PROM | 23         |

| CY7C281                      | 1024 x 8 PROM            | 34         |

| CY7C282                      | 1024 x 8 PROM            | 34         |

| CY7C291                      | 2048 x 8 PROM            | 12         |

| CY7C292                      | 2048 x 8 PROM            | <b>i</b> 2 |

| <b>PROM</b> Programming Info | rmation                  | 50         |

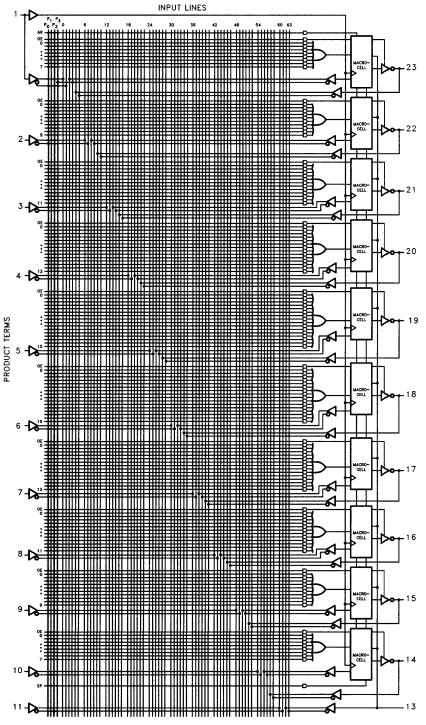

## PALs (Programmable Array Logic)

## Page Number

| 4-3 |

|-----|

|     |

|     |

|     |

## LOGIC

| Device Number | Description                   |

|---------------|-------------------------------|

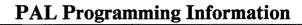

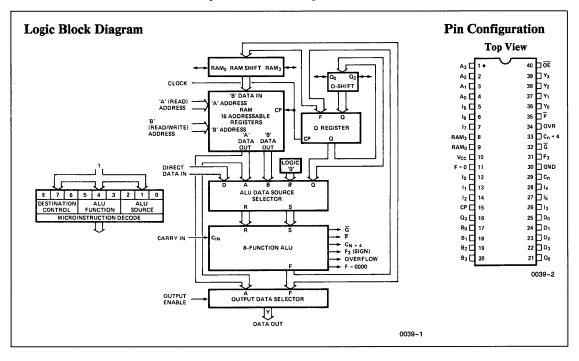

| CY2901B       | CMOS Four Bit Slice           |

| CY2901C       | CMOS Four Bit Slice           |

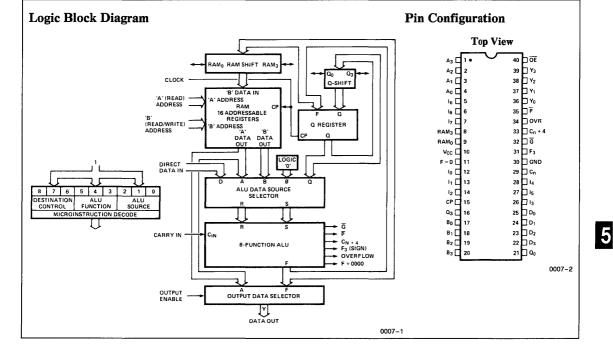

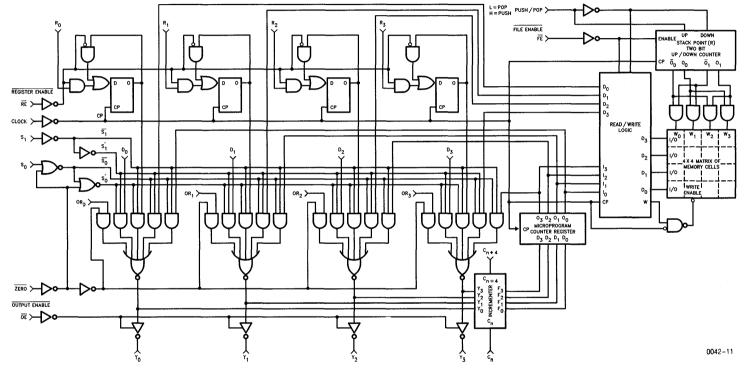

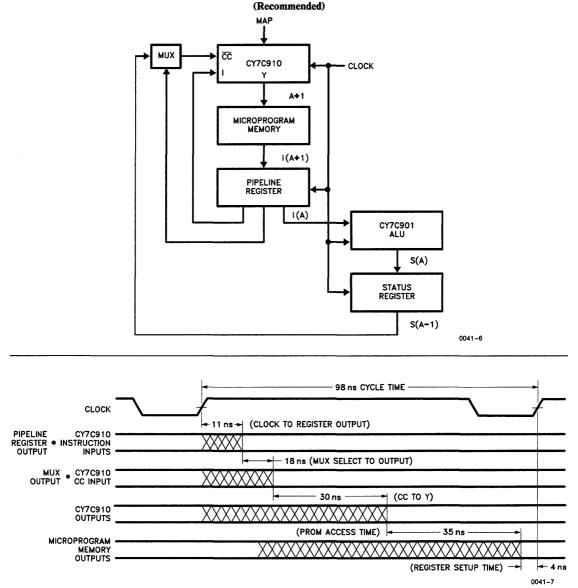

| CY2910        | CMOS Microprogram Controller  |

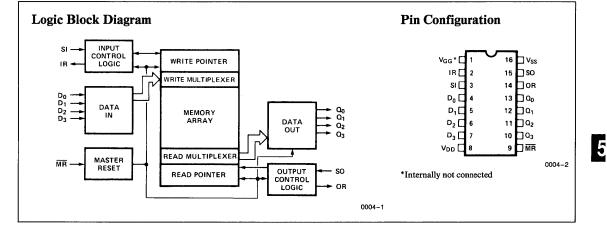

| CY3341        | 64 x 4 FIFO Serial Memory     |

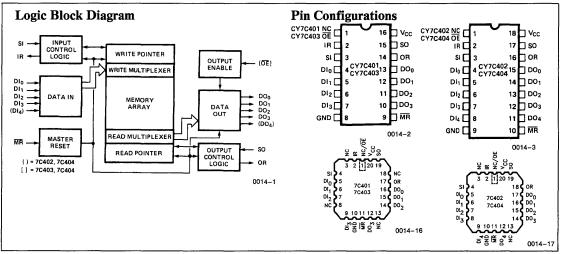

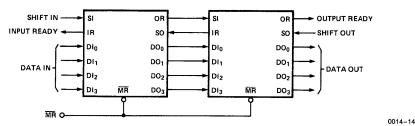

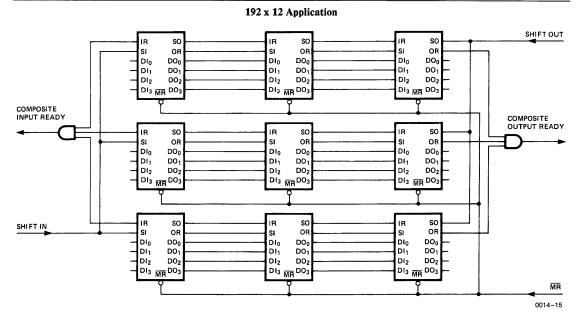

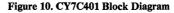

| CY7C401       | Cascadeable 64 x 4 FIFO       |

| CY7C402       | Cascadeable 64 x 5 FIFO       |

| CY7C403       | Cascadeable 64 x 4 FIFO       |

|               | with Output Enable            |

| CY7C404       | Cascadeable 64 x 5 FIFO       |

|               | with Output Enable            |

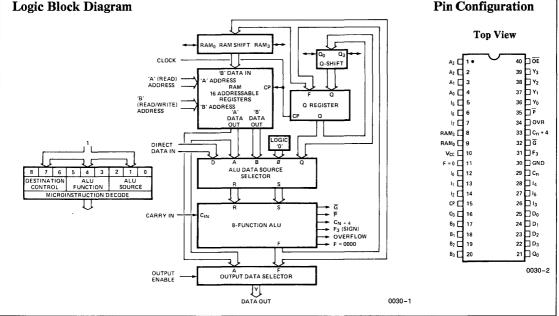

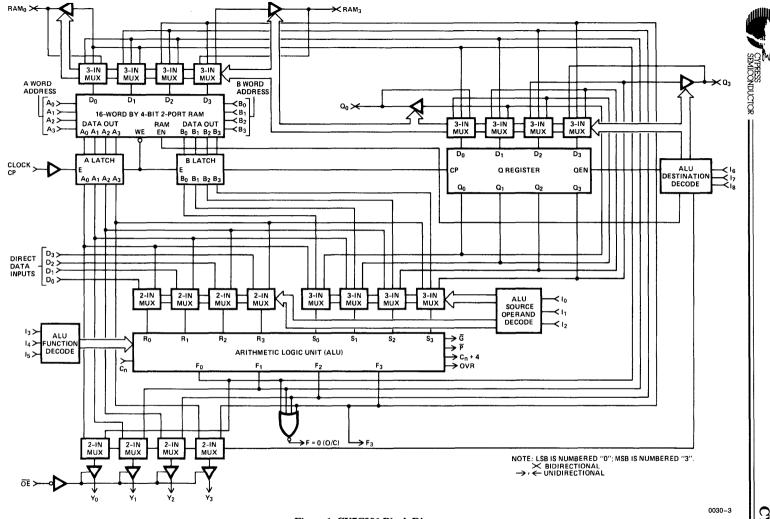

| CY7C901       | CMOS Four-Bit Slice           |

| CY7C909       | Micro Programmed Sequencer    |

| CY7C911       | Micro Programmed Sequencer    |

| CY7C910       | Micro Programmed Controller   |

| CY8C901       | Low Power CMOS Four-Bit Slice |

## APPENDICES

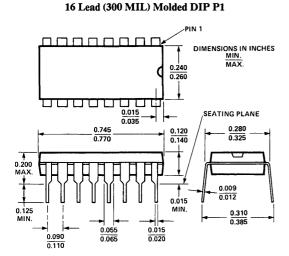

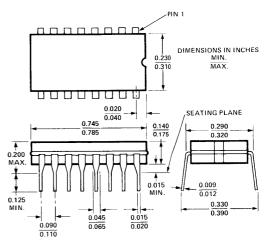

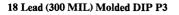

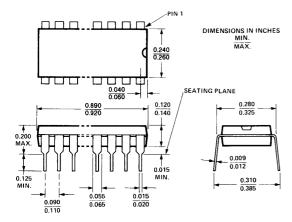

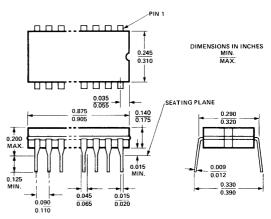

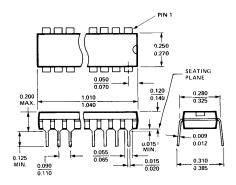

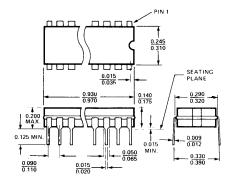

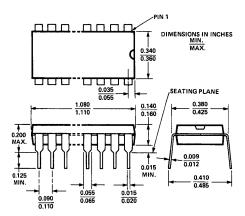

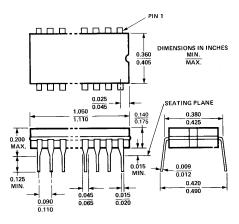

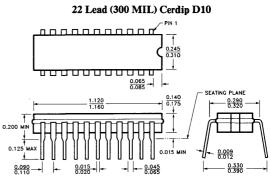

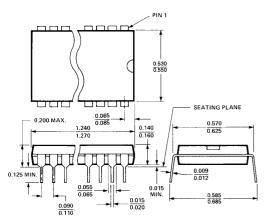

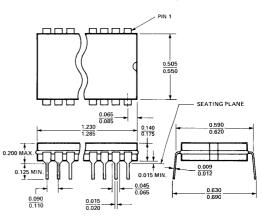

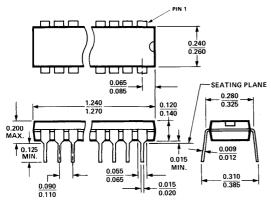

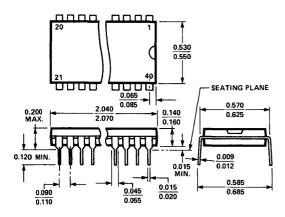

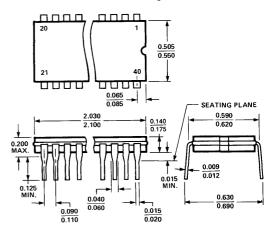

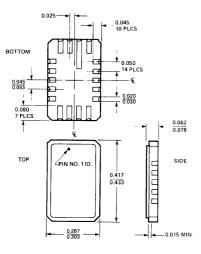

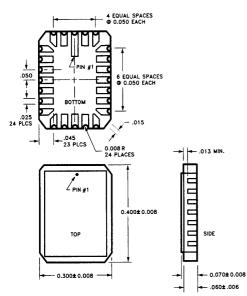

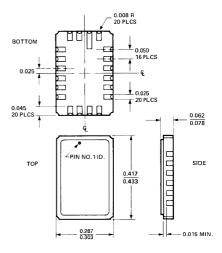

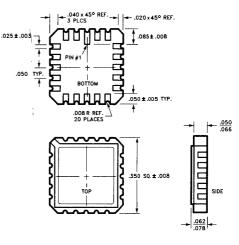

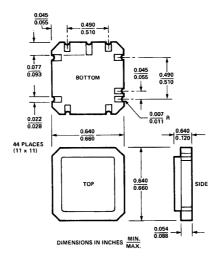

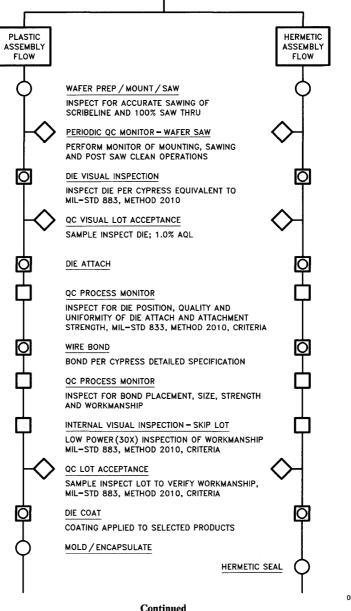

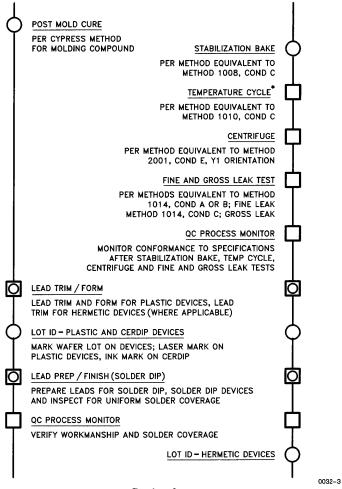

| Appendix A: Packages                                | . 6-1          |

|-----------------------------------------------------|----------------|

| Package Diagrams                                    | . 6-1<br>. 6-7 |

| Appendix B: Quality, Reliability, and Process Flows | . 6-8          |

| Appendix C: Application Briefs                      | 6-16           |

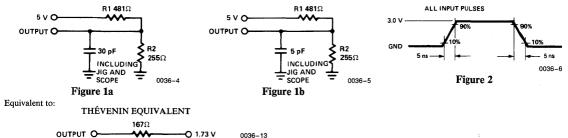

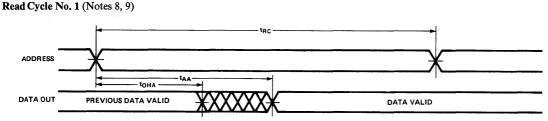

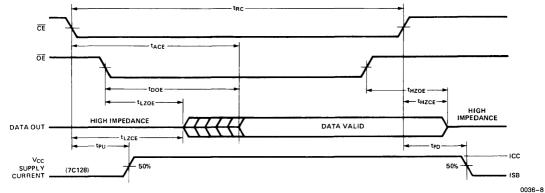

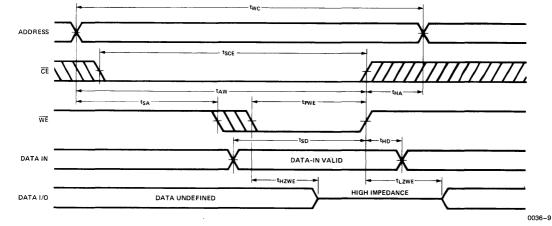

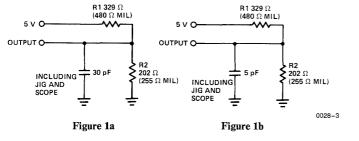

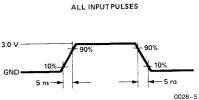

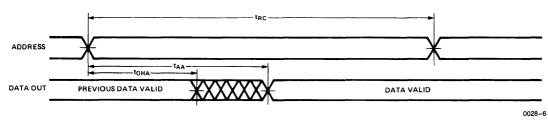

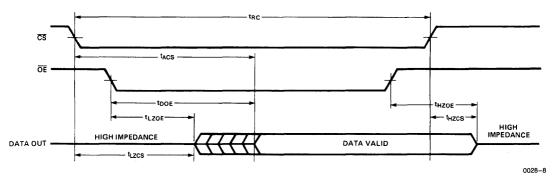

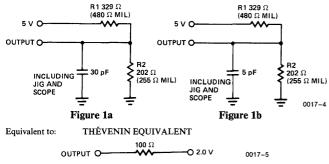

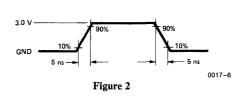

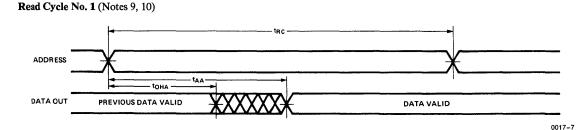

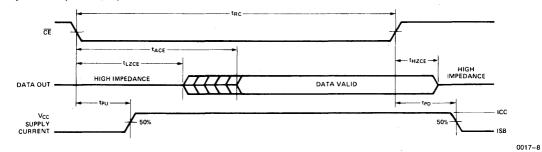

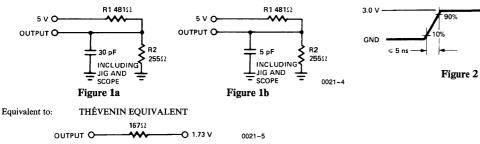

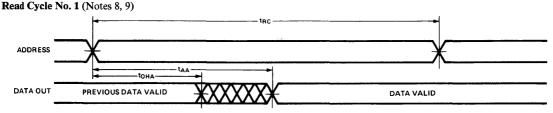

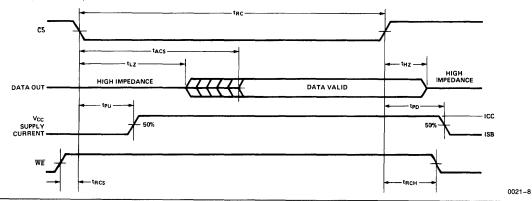

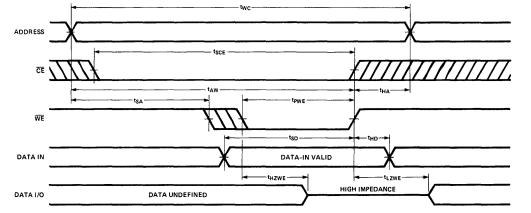

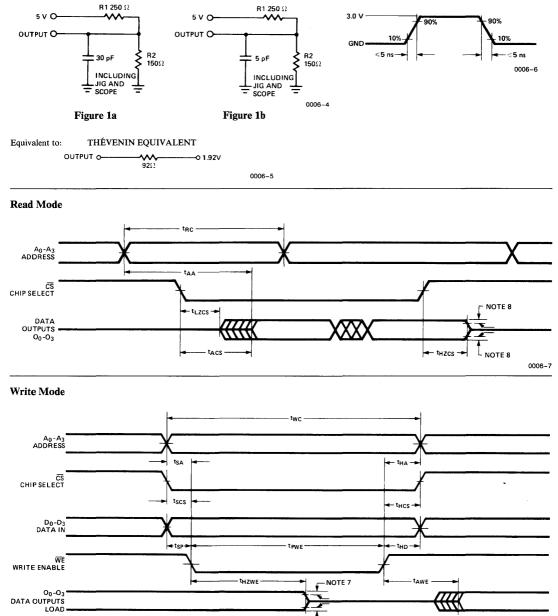

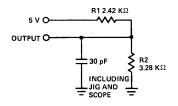

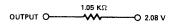

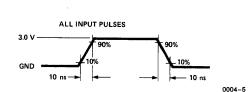

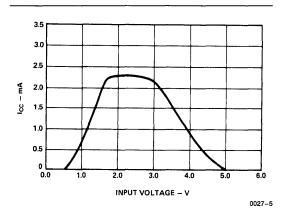

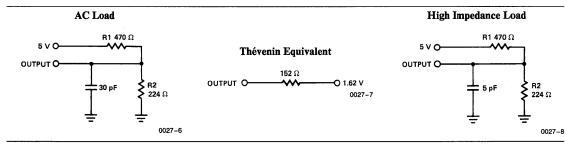

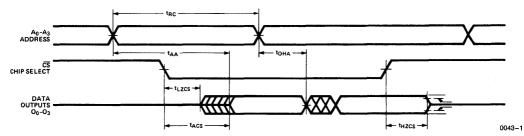

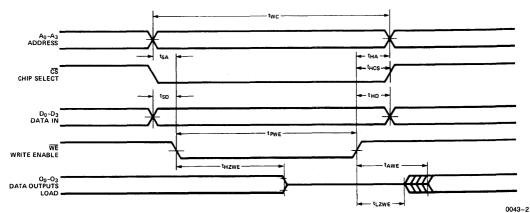

| RAM Input and Output Characteristics                | 6-23           |

| SEMICONDUCIOR     |                                            |              |

|-------------------|--------------------------------------------|--------------|

| Device Number     | -                                          | age Number   |

| 2147              | 4096 x 1 Static RAM                        |              |

| 2148              | 1024 x 4 Static RAM                        |              |

| 21L48             | 1024 x 4 Static RAM                        |              |

| 2149              | 1024 x 4 Static RAM                        |              |

| 21L49             | 1024 x 4 Static RAM                        |              |

| 27803             | 16 x 4 Static RAM                          |              |

| 27807             | 16 x 4 Static RAM                          |              |

| 2901B             | CMOS Four Bit Slice                        |              |

| 2901C             | CMOS Four Bit Slice                        |              |

| 2910              | CMOS Microprogram Controller               |              |

| 3341              | 64 x 4 FIFO Serial Memory                  |              |

| 54S189            | 16 x 4 Static RAM                          |              |

| 74F189            | 16 x 4 Static RAM                          |              |

| 74S189            | 16 x 4 Static RAM                          |              |

| 7C122             | 256 x 4 Static RAM Separate I/O            |              |

| 7C128             | 2048 x 8 Static RAM                        |              |

| 7C129             | 2048 x 8 Static RAM                        |              |

| 7C147             | 4096 x 1 Static RAM                        |              |

| 7C148             | 1024 x 4 Static RAM                        |              |

| 7C149             | 1024 x 4 Static RAM                        |              |

| 7C150             | 1024 x 4 Static RAM Separate I/O           |              |

| 7C167             | 16,384 x 1 Static RAM                      |              |

| 7C168             | 4096 x 4 Static RAM                        |              |

| 7C169             | 4096 x 4 Static RAM                        |              |

| 7C170             | 4096 x 4 Static RAM                        |              |

| 7C187             | 65,536 x 1 Static RAM                      |              |

| 7C189             | 16 x 4 Static RAM                          |              |

| 7C190             | 16 x 4 Static RAM                          |              |

| 7C225             | 512 x 8 Registered PROM                    |              |

| 7C235             | 1024 x 8 Registered PROM                   |              |

| 7C245             | 2048 x 8 Registered PROM                   |              |

| 7C281             | 1024 x 8 PROM                              |              |

| 7C282             | 1024 x 8 PROM                              |              |

| 7C291             | 2048 x 8 PROM                              |              |

| 7C292             | 2048 x 8 PROM                              |              |

| 7C401             | Cascadeable 64 x 4 FIFO                    |              |

| 7C402             | Cascadeable 64 x 5 FIFO                    |              |

| 7C403             | Cascadeable 64 x 4 FIFO                    |              |

|                   | with Output Enable                         | 5-7          |

| 7C404             | Cascadeable 64 x 5 FIFO                    |              |

|                   | with Output Enable                         | 5-7          |

| 7C901             | CMOS Four-Bit Slice                        |              |

| 7C909             | Micro Programmed Sequencer                 |              |

| 7C910             | Micro Programmed Controller                | 5_35         |

| 7C911             | Micro Programmed Sequencer                 | 5_07         |

| 8C901             | Low Power CMOS Four-Bit Slice              | 5-27<br>5_47 |

| 93422             | 256 x 4 Static RAM Separate I/O            |              |

| 93422A            | 256 x 4 Static RAM Separate I/O            |              |

| 93L422            | 256 x 4 Static RAM Separate I/O            |              |

| 93L422<br>93L422A | 256 x 4 Static RAM Separate I/O            |              |

| / <b>51722</b> A  | $250$ x + Static MAN Separate 1/O $\cdots$ |              |

## CYPRESS SEMICONDUCTOR

## Numeric Device Index (Continued)

| <b>Device Number</b> | Description                             | Page Number |

|----------------------|-----------------------------------------|-------------|

| PAL 20A Series       | CMOS PAL Device                         |             |

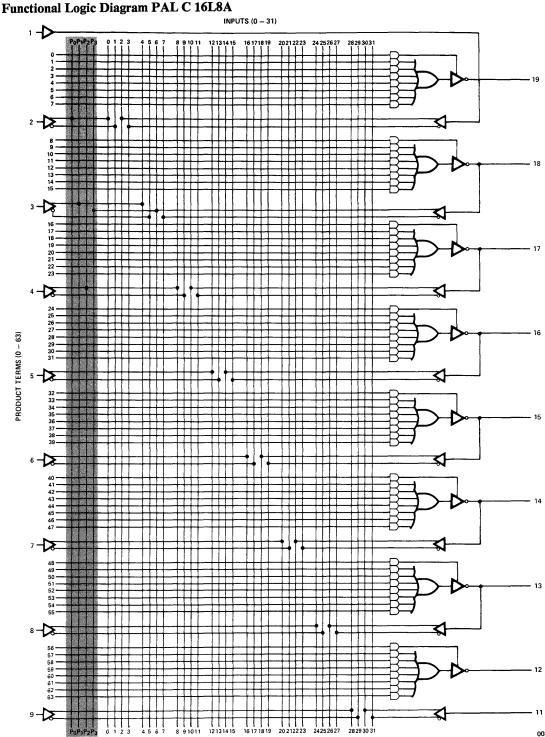

| 16L8A                |                                         |             |

| 16L8A-2              | • • • • • • • • • • • • • • • • • • • • |             |

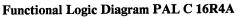

| 16R4A                |                                         |             |

| 16R4A-2              |                                         |             |

|                      |                                         |             |

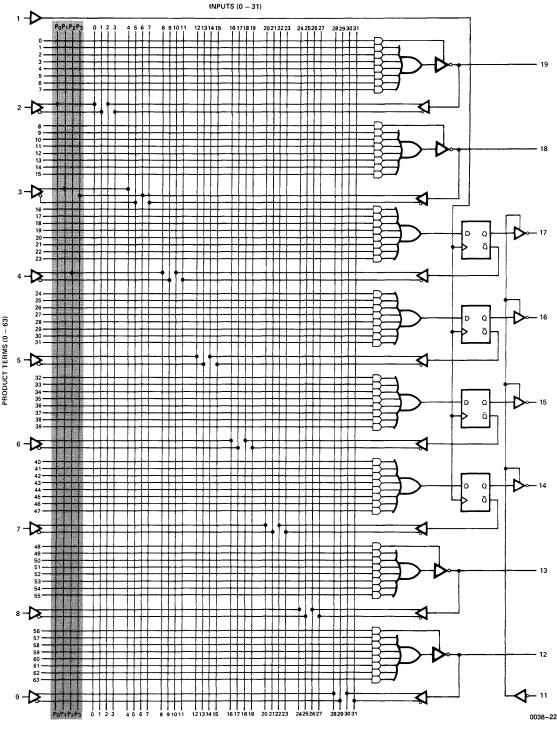

| 16R6A-2              |                                         |             |

|                      |                                         |             |

|                      | • • • • • • • • • • • • • • • • • • • • |             |

| PAL C 20A Series     | CMOS PAL Device                         |             |

| PAL C 16L8A          |                                         |             |

|                      |                                         |             |

|                      |                                         |             |

|                      |                                         |             |

| PAL C 22V10          | CMOS PAL Device                         |             |

| PAL C 32V10          | CMOS PAL Device                         |             |

| PRODUCT         | =1         |

|-----------------|------------|

| <br>STATIC RAMS | 2          |

| PROMS           | 3          |

| PALS            | <b>■</b> 4 |

| LOGIC           | <b>5</b>   |

| APPENDICES      | 6          |

## **General Product Information**

## **Page Number** Cypress Semiconductor Background .....1-1

## **Cypress Semiconductor Background**

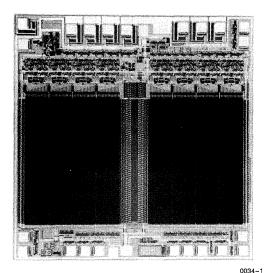

Cypress Semiconductor was founded in April of 1983 and has quickly emerged as a leader of high performance CMOS products. The Cypress CMOS product line is targeted to replace slower bipolar and NMOS products with reliability, high speed and low power.

Cypress products fall into three families: High Speed Static RAMs, Programmable Products, and Logic. Initial members of the Static RAM family include devices in densities of 64 bits to 16K bits and performance from 15 to 35 ns. The various organizations from 16 x 4, 256 x 4 through 16K x 1, 2K x 8, and 4K x 4 provide field applications in large mainframes, high speed controllers, communications, and graphics display.

Cypress Programmable Products consist of high speed CMOS PROMs and Programmable Array Logic (PAL), both employing an EPROM programming element. Like the High Speed Static RAM family, these products are the natural choice to replace older devices manufactured in bipolar technology because they provide superior performance at one half of the power consumption.

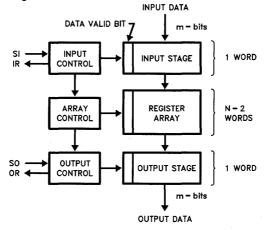

Logic products beginning with the 7C901 Four Bit Slice, include a family of FIFO's (First In First Out buffers). FIFOs provide the interface between digital information paths of widely varying speeds. This allows the information source to operate at its own intrinsic speed while the results may be processed or distributed at a speed commensurate with need.

Cypress's semiconductors are 100% "Made in USA". Situated in California's Silicon Valley, Cypress houses R&D, design, wafer fabrication, assembly, and administration. The facilities are designed to the most demanding technical and environmental specifications in the industry. In many other semiconductor facilities, wafers are fabricated in Class 100 environments, often under laminar flow hoods only. At Cypress the entire wafer fabrication area is a Class 10 environment. This means that the ambient air has less than 10 particulates of greater than 0.2 micron in diameter per cubic foot of air. Other environmental considerations are carefully insured: temperature is controlled to a  $\pm 0.2$ degree Fahrenheit tolerance; filtered air is completely exchanged 10 times each minute throughout the fab; critical equipment is situated on isolated slabs to minimize vibration.

Attention to assembly is just as critical. Assembly is done in a Class 100 clean room until the silicon die is sealed in a package. Lead frames are handled in carriers or cassettes through the entire operation. Automated robots remove and replace parts into cassettes. Using sophisticated automated equipment, parts are assembled and tested in less than five days. The Cypress assembly line is the most flexible, automated line in the United States.

The Cypress motto has always been "only the best". The best facilities, the best equipment, the best employees ... all striving to make the best CMOS product. Cypress has grown very quickly to become "the best".

## **Cypress CMOS Technology**

In the last decade, there has been a tremendous need for high performance semiconductor products manufactured with a balance of SPEED, RELIABILITY, and POWER. Cypress Semiconductor has overcome the classically held perceptions that CMOS is a moderate performance technology. That places its product lines ahead of its bipolar competitors in all three areas.

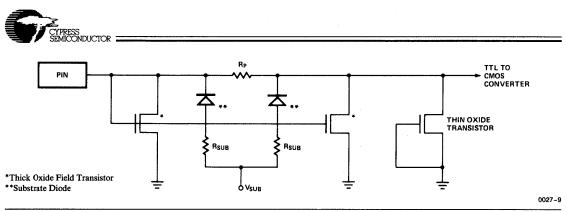

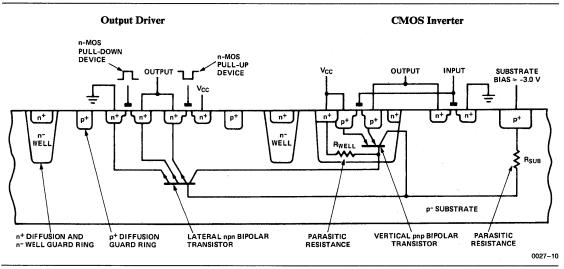

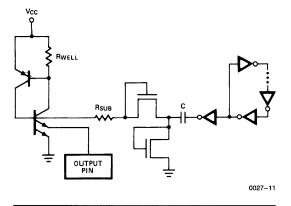

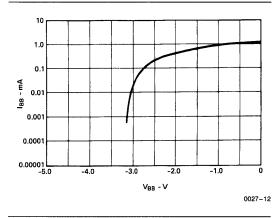

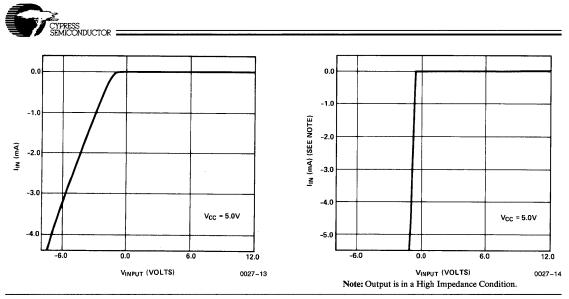

The Cypress process is a 1.2 micron "N" well technology with double layer poly, single layer metal and an EPROM capability. The process employs lightly doped extensions of the heavily doped source and drain regions for both "N" and "P" channel transistors for significant improvement in gate delays. Further improvements in performance, through the use of substrate bias techniques, have added the benefit of eliminating the input and output latchup characteristics associated with the older CMOS technologies.

To further enhance the technology from the reliability direction, improvements have been incorporated in the process and design minimizing electrostatic discharge and input signal clipping problems.

Finally, although not a requirement in the high performance arena, CMOS technology substantially reduces the power consumption for any device. This improves reliability by allowing the device to operate at a lower die temperature. Now higher levels of integration are possible without trading performance for power. For instance, devices may now be delivered in plastic packages, without any impact on reliability.

While addressing the performance issues of CMOS technology, Cypress has not ignored the quality and reliability aspects of technology development. Rather, the traditional failure mechanisms of electrostatic discharge (ESD) and latchup have been addressed and solved through process and design technology innovation.

ESD-induced failure has been a generic problem for many high performance MOS and bipolar products. Although in its earliest years MOS technology experienced oxide reliability failures, this problem has largely been eliminated through improved oxide growth techniques and a better understanding of the ESD problem. The effort to adequately protect against ESD failures is perturbed by circuit delays associated with ESD protection circuits. Focusing on these constraints, Cypress has developed ESD protection circuitry specific to 1.2 micron CMOS process technology. All Cypress products are designed to withstand voltage and energy levels in excess of 2000 volts and 0.4 milli-joules, more than twice the energy level specified by MIL STD 883C.

Latchup, a traditional problem with CMOS technologies, has been eliminated through the use of substrate bias generation techniques, the elimination of the "P" MOS pullups in the output drivers, the use of guardring structures, and care in the physical layout of the products.

The Cypress CMOS technology has been carefully designed, creating products that are "only the best" in high speed, excellent reliability, and low power.

## **Product Line Cross Reference**

| CYPRESS          | CYPRESS    | CYPRESS   | CYPRESS                | CYPRESS     | CYPRESS     | AMD              | CYPRESS     |

|------------------|------------|-----------|------------------------|-------------|-------------|------------------|-------------|

| 2147-35C         | 7C147-35C  | 2901CM    | 2901BM                 | 7C901-69C   | 7C901-31C   | 2147-45M         | 2147-45M    |

| 2147-45C         | 2147-35C   | 3341C     | 7C401-10C              | 7C901-88M   | 7C901-32M   | 2147-55C         | 2147-55C    |

| 2147-45C         | 7C147-45C  | 54S189M   | 27S03M                 | 9122-25C    | 7C122-15C   | 2147-55M         | 2147-55M    |

|                  |            |           |                        |             |             |                  |             |

| 2147-45M         | 7C147-45M  | 74S189C   | 27S03C                 | 9122-25C    | 91L22-25C   | 2147-70C         | 2147-55C    |

| 2147-55C         | 2147-45C   | 7C122-35C | 7C122-25C              | 9122-35C    | 9122-25C    | 2147-70M         | 2147-55M    |

| 2147-55 <b>M</b> | 2147-45M   | 7C122-35M | 7C122-25M              | 9122-35C    | 91L22-35C   | 2148-35C         | 2148-35C    |

| 2148-35C         | 7C148-35C  | 7C128-45C | 7C128-35C              | 9122-45C    | 93L422-C    | 2148-35M         | 2148-35M    |

| 2148-35C         | 21L48-35C  | 7C128-55C | 7C128-45C+             | 91L22-25C   | 7C122-25C   | 2148-45C         | 2148-45C    |

| 2148-35C         | 7C148-35M  | 7C128-55M | 7C128-45M              | 91L22-35C   | 7C122-25C   |                  |             |

|                  |            |           |                        |             |             | 2148-45M         | 2148-45M    |

| 2148-45C         | 2148-35C   | 7C129-45C | 7C129-35C              | 91L22-45C   | 93L422AC    | 2148-55C         | 2148-55C    |

| 2148-45C         | 21L148-45C | 7C129-55C | 7C129-45C+             | 93422AC     | 9122-35C    | 2148-55 <b>M</b> | 2148-55M    |

| 2148-45M         | 7C148-45M  | 7C129-55M | 7C129-45M+             | 93422AC     | 7C122-35C   | 2148-70C         | 2148-55C    |

| 2148-45M         | 2148-35M   | 7C147-35C | 7C147-25C              | 93422AM     | 7C122-35M   | 2148-70M         | 2148-55M    |

| 2148-55C         | 21L48-55C  | 7C147-45C | 7C147-35C              | 93422C      | 93L422AC    | 2149-35C         | 2149-35C    |

| 2148-55C         | 2148-45C   | 7C147-45M | 7C147-35M              | 93422M      | 93422AM     | 2149-45C         | 2149-45C    |

| 2148-55M         | 2148-45M   | 7C148-45C | 7C147-35M              | 93422M      | 93L422AM    | 2149-45M         |             |

|                  |            |           |                        |             |             |                  | 2149-45M    |

| 2149-35C         | 7C149-35C  | 7C148-45M | 7C148-35M              | 93L422AC    | 7C122-35C   | 2149-55C         | 2149-55C    |

| 2149-35C         | 21L49-35C  | 7C149-45C | 7C149-35C              | 93L422AC    | 91L22-45C   | 2149-55M         | 2149-55M    |

| 2149-35M         | 7C149-35M  | 7C149-45M | 7C149-35M              | 93L422AM    | 7C122-35M   | 2149-70C         | 2147-55C    |

| 2149-45C         | 21L49-45C  | 7C150-35C | 7C150-25C              | 93L422C     | 93L422AC    | 2149-70M         | 2147-55M    |

| 2149-45M         | 7C149-45M  | 7C167-45C | 7C167-35C              | 93L422M     | 93L422AM    | 2167-35C         | 7C167-35C   |

| 2149-45M         | 2149-35M   | 7C167-45M | 7C167-35M              | PAL16L8A-2C |             | 2167-35M         | 7C167-35M   |

|                  |            |           |                        |             | PALC16L8AM  | 2167-45C         |             |

| 2149-55C         | 21L49-55C  | 7C168-35C | 7C168-25C              |             |             |                  | 7C167-45C   |

| 2149-55C         | 2149-45C   | 7C168-45C | 7C168-35C              | PAL16L8AC   | PALC16L8AC  | 2167-45M         | 7C167-45M   |

| 2149-55M         | 2149-45M   | 7C168-45M | 7C168-35M              | PAL16L8AM   | PALC16L8AM  | 2167-55C         | 7C167-45C   |

| 21L48-35C        | 7C148-35C  | 7C169-35C | 7C169-25C              | PAL16R4A-2C | PALC16R4AC  | 2167-55M         | 7C167-45M   |

| 21L48-45C        | 21L48-35C  | 7C169-40C | 7C169-35C              | 1           | PALC16R4AM  | 2167-70C         | 7C167-45C   |

| 21L48-45C        | 7C148-45C  | 7C169-40M | 7C169-35M              | PAL16R4AC   | PALC16R4AC  | 2167-70M         | 7C167-45M   |

| 21L48-55C        |            |           | 7C170-25C              |             |             |                  |             |

|                  | 21L48-45C  | 7C170-35C |                        | PAL16R4AM   | PALC16R4AM  | 2168-45C         | 7C168-45C   |

| 21L49-35C        | 7C149-25C  | 7C170-40C | 7C170-35C              | PALI6R6A-2C | PALC16R6AC  | 2168-55C         | 7C168-45C   |

| 21L49-45C        | 7C149-45C  | 7C170-40M | 7C170-35M              | PAL16R6A-2M | PALC16R6AM  | 2168-55M         | 7C168-45M   |

| 21L49-45C        | 21L49-35C  | 7C187-35C | 7C187-25C              | PAL16R6AC   | PALC16R6AC  | 2168-70C         | 7C168-45C   |

| 21L49-55C        | 21L49-45C  | 7C187-45C | 7C187-35C              | PAL16R6AM   | PALC16R6AM  | 2168-70M         | 7C168-45M   |

| 27S03AC          | 7C189-18C  | 7C187-45M | 7C187-35M              |             | PALC16R8AC  | 2169-40C         | 7C169-40C   |

| 27S03AC          | 7C189-25C  | 7C225-40C | 7C225-30C              |             | PALC16R8AM  | 2169-40M         | 7C169-40M   |

| 27S03AM          | 7C189-25M  | 7C225-40C | 7C225-35M              | PAL16R8AC   | PALC16R8AC  | 2169-50C         | 7C169-40C   |

|                  |            |           |                        |             |             |                  |             |

| 27S03C           | 27S03AC    | 7C235-40C | 7C235-30C              | PAL16R8AM   | PALC16R8AM  | 2169-50M         | 7C169-40M   |

| 27S03C           | 74S189C    | 7C245-45C | 7C245-35C              | PALC22V10C  | PALC22V10AC | 2169-70C         | 7C169-40C   |

| 27S03M           | 27S03AM    | 7C281-45C | 7C281-30C              | PALC22V10M  | PALC22V10AM | 2169-70M         | 7C169-40M   |

| 27S03M           | 54S189M    | 7C282-45C | 7C282-30C              | PALC32V10C  | PALC32V10AC | 21L47-45C        | 7C147-45C   |

| 27S07AC          | 7C190-18C  | 7C291-50C | 7C291-35C              | PALC32V10M  | PALC32V10AM | 21L47-55C        | 7C147-45C   |

| 27S07AM          | 7C190-25M  | 7C292-50C | 7C292-35C              |             |             | 21L47-70C        | 7C147-45C   |

| 178070           | 27507 + 0  | 70401 100 | 70401 150              | 41470       | CURRECC     | 01T 40 450       | 211 49 450  |

| 27S07C           | 27S07AC    | 7C401-10C | 7C401-15C              | AMD         | CYPRESS     | 21L48-45C        | 21L48-45C   |

| 27S07C           | 7C190-25C  | 7C401-10M | 7C401-15M              | PREFIX: Am  | PREFIX: CY  | 21L48-55C        | 21L48-55C   |

| 27S07AC          | 7C190-25C  | 7C402-10C | 7C402-15C              | PREFIX: SN  | PREFIX: CY  | 21L48-70C        | 21L48-55C   |

| 27S07M           | 27S07AM    | 7C402-10M | 7C402-15M              | SUFFIX: B   | SUFFIX: B   | 21L49-45C        | 21L49-45C   |

| 27S07M           | 7C190-25M  | 7C403-10C | 7C403-15C              | SUFFIX: D   | SUFFIX: D   | 21L49-55C        | 21L49-55C   |

| 2901BC           | 7C901-31C  | 7C403-10M | 7C403-15M              | SUFFIX: F   | SUFFIX: F   | 21L49-70C        | 21L49-55C   |

| 2901BM           | 7C901-32C  | 7C403-15C | 7C403-25C              | SUFFIX: L   | SUFFIX: L   | 22V10AC          | PALC22V10AC |

| 2901CC           | 79901-69C  | 7C404-10C | 7C403-25C<br>7C404-15C | SUFFIX: P   | SUFFIX: P   | 22V10AC          | PALC22V10AC |

| 2901CC<br>2901CC |            |           |                        |             |             |                  |             |

|                  | 2901BC     | 7C404-10M | 7C404-15M              | 2147-35C    | 2147-35C    | 22V10C           | PALC22V10C  |

| 2901CM           | 7C901-88M  | 7C404-15C | 7C404-25C              | 2147-45C    | 2147-45C    | 22V10M           | PALC22V10M  |

Note: Unless otherwise noted, product meets all performance specs and is within 10 mA on I<sub>CC</sub> and 5 mA on I<sub>SB</sub>;

+ = meets all performance specs but may not meet  $I_{CC}$  or  $I_{SB}$ ; \* = meets all performance specs except 2V data retention—may not meet  $I_{CC}$  or  $I_{SB}$ ;

- = functionally equivalent

## Product Line Cross Reference (Continued)

|                    |                          | r                        |                   |                  |                  | ·····       |                                       |

|--------------------|--------------------------|--------------------------|-------------------|------------------|------------------|-------------|---------------------------------------|

| AMD                | CYPRESS                  | AMD                      | CYPRESS           | AMD              | CYPRESS          | FUJITSU     | CYPRESS                               |

| 27PS181AC          | 7C282-45C                | 27845M                   | 7C245-45M         | PAL16R8LM        | PAL16R8A-2M      | 2149-55L    | 21L49-55C                             |

| 27PS181AM          | 7C282-45M+               | 2841AC                   | 3341C+            | PAL16R8AC        | PAL16R8AC        | 2149-70L    | 21L49-55C                             |

| 27PS181C           | 7C282-45C                | 2841C                    | 3341C+            | PAL16R8AM        | PAL16R8AM        | 7132E       | 7C282-45C                             |

| 27PS181M           | 7C282-45M+               | 3341C                    | 3341C+            | PAL16R8C         | PAL16R8A-2C      | 7132E-SK    | 7C281-45C                             |

| 27PS191AC          | 7C292-50C                | 54S189M                  | 54S189M           | PAL16R8M         | PAL16R8A-2M      | 7132E-W     | 7C282-45M                             |

| 27PS191AM          | 7C292-50C                | 74S189C                  | 74S189C           | IALIOKOW         | TALIOROA-2M      | 7132H       | 7C282-45C                             |

| 2/F5191AW          | 7C292-JUIVI +            | /431090                  | 743109C           |                  |                  | /15211      | /0202-430                             |

| 27PS191C           | 7C292-50C                | 9122-25C                 | 9122-25C          | FAIRCHILD        | CYPRESS          | 7132H-SK    | 7C281-45C                             |

| 27PS191M           | 7C292-50M +              | 9122-25M                 | 7C122-25M         | PREFIX: F        | PREFIX: CY       | 7132Y       | 7C282-30C                             |

| 27PS281AC          | 7C281-45C                | 9122-25M                 | 9122-35C          | SUFFIX: D        | SUFFIX: D        | 7132Y-SK    | 7C281-30C                             |

| 27PS281AC          | 7C281-45C<br>7C281-45M+  | 9122-35C<br>9122-35M     | 7C122-35M         | SUFFIX: F        | SUFFIX: F        | 7138E       | 7C291-50C                             |

| 27PS281C           |                          | 9122-35M                 | 7C150-25C         | SUFFIX: L        | SUFFIX: L        | 7138E-SK    | 7C292-50C                             |

|                    | 7C281-45C                |                          |                   |                  |                  |             |                                       |

| 27PS281M           | 7C281-45M+               | 9150-35C                 | 7C150-35C         | SUFFIX: P        | SUFFIX: P        | 7138E-W     | 7C292-50M                             |

| 27PS291AC          | 7C291-50C                | 9150-35M                 | 7C150-35M         | SUFFIX: QB       | SUFFIX: B        | 7138H       | 7C292-35C                             |

| 27PS291AC          | 7C291-50C<br>7C291-50M + | 9150-45C                 | 7C150-35C         | 3341AC           | 3341C+           | 7138H-SK    | 7C292-35C<br>7C291-35C                |

|                    |                          |                          |                   | 3341C            | 3341C+           | 7138Y       | 7C291-35C<br>7C292-35C                |

| 27PS291C           | 7C291-50C                | 9150-45M                 | 7C150-35M         | 1                |                  |             |                                       |

| 27PS291M           | 7C291-50M+               | 91L22-35C                | 91L22-35C         | 54F189           | 7C189-25M-       | 7138Y-SK    | 7C291-35C                             |

| 27S03AC            | 27S03AC                  | 91L22-35M                | 7C122-35M         | 54F219           | 7C190-25M-       | 8167A-45    | 7C167-45C                             |

| 27S03AM            | 27S03AM                  | 91L22-45C                | 91L22-45C         | 54F413           | 7C401-15M        | 8167A-55    | 7C167-45C                             |

| 27S03C             | 27S03C                   | 91L22-45M                | 7C122-35M         | 54S189M          | 54S189M          | 8167A-70    | 7C167-45C                             |

| 27S03M             | 27S03C<br>27S03M         | 91L22-45101<br>91L22-60C | 7C122-35C+        | 74F189           | 7C189-25C-       | 8168-55     | 7C168-45C                             |

| 27S07AC            | 27SO7AC                  | 93422AC                  | 93422AC           | 74F219           | 7C189-25C        | 8168-70     | 7C168-45C                             |

| t                  |                          | 93422AC                  | 93422AC<br>93422M | 74F413           | 7C401-15C        | 8108-70     | /0108-450                             |

| 27S07AM            | 27807AM                  |                          |                   |                  |                  | ILADDIC     | CVDDECC                               |

| 27S07C             | 27S07C                   | 93422C                   | 93422C            | 74S189           | 74S189C          | HARRIS      | CYPRESS                               |

| 27S07M             | 27S07M                   | 93422M                   | 93422M            | 93422AC          | 93422AC          | PREFIX: 1   | SUFFIX: D                             |

| 27S181AC           | 7C282-30C                | 93L422AC                 | 93L422AC          | 93422AM          | 93422M           | PREFIX: 3   | SUFFIX: P                             |

| 27S181AC           | 7C282-45M                | 93L422AC                 | 93L422AC          | 93422C           | 93422C           | PREFIX: 4   | SUFFIX: L                             |

| 27S181AM           | 7C282-45C                | 93L422C                  | 93L422C           | 93422C<br>93422M | 93422C<br>93422M | PREFIX: 9   | SUFFIX: F                             |

|                    |                          |                          |                   | 93422M           |                  |             |                                       |

| 27S181C            | 7C282-45C                | 93L422M                  | 93L422M           |                  | 2149-45C         | PREFIX: HM  | PREFIX: CY                            |

| 27S181M            | 7C282-45M                | 99[L]68-45C              | 7C168-45C*        | 93L422AC         | 93L422AC         | PREFIX: HPL | PREFIX: CY                            |

| 27S191AC           | 7C292-35C                | 99[L]68-55C              | 7C168-45C*        | 93L422AM         | 93L422AM         | SUFFIX: -8  | SUFFIX: B                             |

| 27S191AM           | 7C292-50M                | 99[L]68-55M              | 7C168-45M*        | 93L422C          | 93L422C          | 6-76161-2   | 7C291-50M                             |

| 27S191AM           | 7C292-50C                | 99[L]68-70C              | 7C168-45C*        | 93L422M          | 93L422M          | 6-76161-5   | 7C291-50C                             |

| 27S191C            | 7C292-50M                | 99[L]68-70M              | 7C168-45M*        | 93Z451AC         | 7C282-30C        | 6-76161A-5  | 7C291-50C                             |

| 27S25AC            | 7C225-30C                | PAL16L8C                 | PAL16L8A-2C       | 93Z451AC         | 7C282-30C        | 6-76161B-5  | 7C291-35C                             |

|                    |                          |                          |                   |                  |                  |             |                                       |

| 27S25AM            | 7C225-35M                | PAL16L8M                 | PAL16L8A-2M       | 93Z451C          | 7C282-45C        | 6-7681-5    | 7C281-45C                             |

| 27S25C             | 7C225-40C                | PAL16L8AC                | PAL16L8AC         | 93Z451M          | 7C282-45M        | 6-7681A-5   | 7C281-45C                             |

| 27S25M             | 7C225-40M                | PAL16L8AM                | PAL16L8AM         | 93Z511C          | 7C292-35C        | 76161-2     | 7C292-50M                             |

| 278281AC           | 7C281-30C                | PAL16L8LC                | PAL16L8A-2C       | 93Z511M          | 7C292-50M        | 76161-5     | 7C292-50C                             |

| 27S281AM           | 7C281-45M                | PAL16L8LM                | PAL16L8A-2M       | <b>352511</b> 11 | CEPE Som         | 76161A-5    | 7C292-50C                             |

| 27S281AW           | 7C281-45C                | PAL16R4LC                | PAL16R4A-2C       | FUJITSU          | CYPRESS          | 76161B-5    | 7C292-35C                             |

| 27S281C            | 7C281-45C                | PAL16R4LC                | PALI6R4A-2C       | PREFIX: MB       | PREFIX: CY       | 7681-2      | 7C292-35C<br>7C282-45M                |

| 27S291AC           | 7C291-35C                | PAL16R4LM                | PAL16R4A-2M       | PREFIX: MB       |                  | 7681-5      | 7C282-45C                             |

| 2/02/IAC           | 10271-330                | I ALIONAAC               | I ALIONAAC        | I KEFIA: MDM     | I ADPIA: UI      | ,001-5      | , 0202-730                            |

| 27S291AM           | 7C291-50M                | PAL16R4AM                | PAL16R4AM         | SUFFIX: F        | SUFFIX: F        | 7681A-5     | 7C282-45C                             |

| 278291C            | 7C291-50C                | PAL16R4C                 | PAL16R4A-2C       | SUFFIX: M        | SUFFIX: P        | 77209-2     | PAL16L8A-2M                           |

| 27S291M            | 7C291-50M                | PAL16R4M                 | PAL16R4A-2M       |                  | SUFFIX: D        | 77209-5     | PAL16L8A-2C                           |

| 27S35AC            | 7C235-30C                | PAL16R6AC                | PAL16R6AC         | 2147H-35         | 2147-35C         | 77210-2     | PAL16R4A-2M                           |

| 27835AM            | 7C235-40M                | PAL16R6AM                | PAL16R6AM         | 2147H-45         | 2147-45C         | 77210-5     | PAL16R4A-2C                           |

| 27835AM            | 7C235-40C                | PAL16R6C                 | PAL16R6A-2C       | 2147H-55         | 2147-55C         | 77211-2     | PAL16R6A-2M                           |

|                    |                          |                          | 1.12101001120     | 211/11/00        |                  |             |                                       |

| 27S35M             | 7C235-40M                | PAL16R6M                 | PAL16R6A-2M       | 2147H-70         | 2147-55C         | 77211-5     | PAL16R6A-2C                           |

| 27S45AC            | 7C245-35C                | PAL16R6LC                | PAL16R6A-2C       | 2148-55L         | 21L48-55C        | 77212-2     | PAL16R8A-2M                           |

| 27S45AM            | 7C245-45M                | PAL16R6LM                | PAL16R6A-2M       | 2148-70L         | 21L48-55C        | 77212-5     | PAL16R8A-2C                           |

| 27S45C             | 7C245-45C                | PAL16R8LC                | PAL16R8A-2C       | 2149-45          | 2149-45C         |             |                                       |

| Note: Unless other |                          |                          |                   |                  |                  |             | · · · · · · · · · · · · · · · · · · · |

Note: Unless otherwise noted, product meets all performance specs and is within 10 mA on I<sub>CC</sub> and 5 mA on I<sub>SB</sub>;

+ = meets all performance specs but may not meet I<sub>CC</sub> or I<sub>SB</sub>;

\* = meets all performance specs except 2V data retention—may not meet  $I_{CC}$  or  $I_{SB}$ ;

- = functionally equivalent

# RESS

## Product Line Cross Reference (Continued)

|                                                                                                                                           |                                                                                                                                                                               |                                                                                                                                                            | - 14                                                                                                                                                            |                                                                                                                |                                                                                                                                |                                                                                                                                    |                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HITACHI                                                                                                                                   | CYPRESS                                                                                                                                                                       | HITACHI                                                                                                                                                    | CYPRESS                                                                                                                                                         | IDT                                                                                                            | CYPRESS                                                                                                                        | INTEL                                                                                                                              | CYPRESS                                                                                                                                                               |

| PREFIX: HM                                                                                                                                | PREFIX: CY                                                                                                                                                                    | 6287L-55                                                                                                                                                   | 7C187-45C*                                                                                                                                                      | 6168585                                                                                                        | 7C168-45C                                                                                                                      | PREFIX: L                                                                                                                          | SUFFIX: L                                                                                                                                                             |

| PREFIX: HN                                                                                                                                | PREFIX: CY                                                                                                                                                                    | 6287L-70                                                                                                                                                   | 7C187-45C*                                                                                                                                                      | 6168S85B                                                                                                       | 7C168-45M                                                                                                                      | PREFIX: P                                                                                                                          | SUFFIX: P                                                                                                                                                             |

| SUFFIX: CG                                                                                                                                | SUFFIX: L                                                                                                                                                                     |                                                                                                                                                            |                                                                                                                                                                 | 7187L45                                                                                                        | 7C187-45C*                                                                                                                     | SUFFIX: /B                                                                                                                         | SUFFIX: B                                                                                                                                                             |

| SUFFIX: G                                                                                                                                 | SUFFIX: D                                                                                                                                                                     | IDT                                                                                                                                                        | CYPRESS                                                                                                                                                         | 7187L55                                                                                                        | 7C187-45C*                                                                                                                     | 2147 <b>H</b>                                                                                                                      | 2147-55C                                                                                                                                                              |

| SUFFIX: P                                                                                                                                 | SUFFIX: P                                                                                                                                                                     | PREFIX: IDT                                                                                                                                                | PREFIX: CY                                                                                                                                                      | 7187L55B                                                                                                       | 7C187-45M*                                                                                                                     | 2147H-1                                                                                                                            | 2147-35C                                                                                                                                                              |

| 25089                                                                                                                                     | 7C282-45C                                                                                                                                                                     | SUFFIX: B                                                                                                                                                  | SUFFIX: B                                                                                                                                                       | 7187L70                                                                                                        | 7C187-45C*                                                                                                                     | 2147H-2                                                                                                                            | 2147-45C                                                                                                                                                              |

| 25005                                                                                                                                     | /0202-450                                                                                                                                                                     | 50111A, D                                                                                                                                                  | 50111A. D                                                                                                                                                       | 101210                                                                                                         | /010/-450                                                                                                                      | 214/11-2                                                                                                                           | 2147-450                                                                                                                                                              |

| 25089S                                                                                                                                    | 7C282-45C                                                                                                                                                                     | SUFFIX: D                                                                                                                                                  | SUFFIX: D                                                                                                                                                       | 7187L70B                                                                                                       | 7C187-45M*                                                                                                                     | 2147 <b>H</b> -3                                                                                                                   | 2147-55C                                                                                                                                                              |

| 25169S                                                                                                                                    | 7C292-50C                                                                                                                                                                     | SUFFIX: F                                                                                                                                                  | SUFFIX: F                                                                                                                                                       | 7187L85B                                                                                                       | 7C187-45M*                                                                                                                     | 2147 <b>HL</b>                                                                                                                     | 7C147-45C                                                                                                                                                             |

| 4847                                                                                                                                      | 2147-55C                                                                                                                                                                      | SUFFIX: L                                                                                                                                                  | SUFFIX: L                                                                                                                                                       | 7187S45                                                                                                        | 7C187-35C                                                                                                                      | 2148H                                                                                                                              | 2148-55C                                                                                                                                                              |

| 4847-2                                                                                                                                    | 2147-45C                                                                                                                                                                      | SUFFIX: P                                                                                                                                                  | SUFFIX: P                                                                                                                                                       | 7187S55                                                                                                        | 7C187-45C                                                                                                                      | 2148H-2                                                                                                                            | 2148-45C                                                                                                                                                              |

| 4847-3                                                                                                                                    | 2147-55C                                                                                                                                                                      | 6116L120T                                                                                                                                                  | 7C128-45C*                                                                                                                                                      | 7187S55B                                                                                                       | 7C187-45M                                                                                                                      | 2148H-3                                                                                                                            | 2148-55C                                                                                                                                                              |

| 6116ALS-12                                                                                                                                | 7C128-45C*                                                                                                                                                                    | 6116L120TB                                                                                                                                                 | 7C128-45M*                                                                                                                                                      | 7187870                                                                                                        | 7C187-45C                                                                                                                      | 2148HL                                                                                                                             | 21L48-55C                                                                                                                                                             |

| 6116ATS 15                                                                                                                                | 70109 450*                                                                                                                                                                    | 61161 150T                                                                                                                                                 | 70109 450*                                                                                                                                                      | 71975700                                                                                                       | 70107 4514                                                                                                                     | 2140111 2                                                                                                                          | 211 49 550                                                                                                                                                            |

| 6116ALS-15                                                                                                                                | 7C128-45C*                                                                                                                                                                    | 6116L150T                                                                                                                                                  | 7C128-45C*                                                                                                                                                      | 7187S70B                                                                                                       | 7C187-45M                                                                                                                      | 2148HL-3                                                                                                                           | 21L48-55C                                                                                                                                                             |

| 6116ALS-20                                                                                                                                | 7C128-45C*                                                                                                                                                                    | 6116L150TB                                                                                                                                                 | 7C128-45M*                                                                                                                                                      | 7187S85B                                                                                                       | 7C187-45M                                                                                                                      | 2149H                                                                                                                              | 2149-55C                                                                                                                                                              |

| 6116AS-12                                                                                                                                 | 7C128-45C+                                                                                                                                                                    | 6116L90T                                                                                                                                                   | 7C128-45C*                                                                                                                                                      |                                                                                                                |                                                                                                                                | 2149H-1                                                                                                                            | 2149-35C                                                                                                                                                              |

| 6116AS-15                                                                                                                                 | 7C128-45C+                                                                                                                                                                    | 6116L90TB                                                                                                                                                  | 7C128-45M*                                                                                                                                                      | INMOS                                                                                                          | CYPRESS                                                                                                                        | 2149H-2                                                                                                                            | 2149-55C                                                                                                                                                              |

| 6116AS-20                                                                                                                                 | 7C128-45C+                                                                                                                                                                    | 6116S120T                                                                                                                                                  | 7C128-45C                                                                                                                                                       | PREFIX: IMS                                                                                                    | PREFIX: CY                                                                                                                     | 2149H-3                                                                                                                            | 2149-55C                                                                                                                                                              |

| 6147                                                                                                                                      | 7C147-45C*                                                                                                                                                                    | 6116S120TB                                                                                                                                                 | 7C128-45M                                                                                                                                                       | SUFFIX: B                                                                                                      | SUFFIX: B                                                                                                                      | 2149HL                                                                                                                             | 21L49-55C                                                                                                                                                             |

| 6147-3                                                                                                                                    | 7C147-45C*                                                                                                                                                                    | 6116S150TB                                                                                                                                                 | 7C128-45M                                                                                                                                                       | SUFFIX: P                                                                                                      | SUFFIX: P                                                                                                                      | 51C67-35                                                                                                                           | 7C167-35C                                                                                                                                                             |

| 6147H-35                                                                                                                                  | 7C147-35C                                                                                                                                                                     | 6116S70T                                                                                                                                                   | 7C128-45C                                                                                                                                                       | SUFFIX: S                                                                                                      | SUFFIX: D                                                                                                                      | M2147H                                                                                                                             | 2147-55M                                                                                                                                                              |

| 6147H-45                                                                                                                                  | 7C147-45C                                                                                                                                                                     | 6116S90T                                                                                                                                                   | 7C128-45C                                                                                                                                                       | SUFFIX: W                                                                                                      | SUFFIX: L                                                                                                                      | M2147H-3                                                                                                                           | 2147-55M                                                                                                                                                              |

| 6147H-55                                                                                                                                  | 7C147-45C                                                                                                                                                                     | 6116S90TB                                                                                                                                                  | 7C128-45C                                                                                                                                                       | 1400-35                                                                                                        | 7C167-35C                                                                                                                      | M2148H                                                                                                                             | 2147-55M                                                                                                                                                              |

| 6148                                                                                                                                      | 7C148-45C                                                                                                                                                                     | 6167L45                                                                                                                                                    | 7C128-45101<br>7C167-45C*                                                                                                                                       | 1400-35M                                                                                                       | 7C167-35C                                                                                                                      | M2149H                                                                                                                             | 2148-55M                                                                                                                                                              |

|                                                                                                                                           |                                                                                                                                                                               |                                                                                                                                                            |                                                                                                                                                                 | 1400-45                                                                                                        |                                                                                                                                |                                                                                                                                    |                                                                                                                                                                       |

| 6148-6                                                                                                                                    | 7C148-45C                                                                                                                                                                     | 6167L45B                                                                                                                                                   | 7C167-45M*                                                                                                                                                      | 1400-45                                                                                                        | 7C167-45C                                                                                                                      | M2149H-2                                                                                                                           | 2149-45M                                                                                                                                                              |

| 6148H-35                                                                                                                                  | 21L48-35C                                                                                                                                                                     | 6167L55                                                                                                                                                    | 7C167-45C*                                                                                                                                                      | 1400-45M                                                                                                       | 7C167-45M                                                                                                                      | M2149H-3                                                                                                                           | 2149-55M                                                                                                                                                              |

| 6148H-45                                                                                                                                  | 7C148-45C                                                                                                                                                                     | 6167L55B                                                                                                                                                   | 7C167-45M*                                                                                                                                                      | 1400-55                                                                                                        | 7C167-45C                                                                                                                      |                                                                                                                                    |                                                                                                                                                                       |

| 6148H-55                                                                                                                                  | 7C148-45C                                                                                                                                                                     | 6167L70                                                                                                                                                    | 7C167-45C*                                                                                                                                                      | 1400-55M                                                                                                       | 7C167-45M                                                                                                                      | MMI                                                                                                                                | CYPRESS                                                                                                                                                               |