### CONVEX Computer Corporation 3000 Waterview Parkway P.O. Box 833851 Richardson, TX 75083-3851 United States of America (214)497-4000

د معودمان. در ایر شاهه در

EDTX 2-04-CV-120 51056DOC065301

# CONVEX C-Series Acrhitecture

Order No. DSW-300

Seventh Edition March 1994

CONVEX Press Richardson, Texas United States of America

## CONVEX C-Series Architecture

Order No. DSW-300

Copyright © 1994 CONVEX Computer Corporation All rights reserved.

This document is copyrighted. This document may not, in whole or part, be copied, duplicated, reproduced, translated, electronically stored, or reduced to machine readable form without prior written consent from CONVEX Computer Corporation.

Although the material contained herein has been carefully reviewed, CONVEX Computer Corporation does not warrant it to be free of errors or omissions. CONVEX reserves the right to make corrections, updates, revisions or changes to the information contained herein. CONVEX does not warrant the material described herein to be free of patent infringement.

CONVEX and the CONVEX logo ("C") are registered trademarks of CONVEX Computer Corporation. UNIX is a registered trademark of UNIX System Laboratories, Inc., a wholly owned subsidiary

of Novell, Inc.

و ب ا ا ا

Printed in the United States of America

4

# Revision information for CONVEX C-Series Architecture

ţ

| Edition | Document No.   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Seventh | 081-011830-001 | Released March 1994. Documents C4600 Series as part of the C-Series architecture. Changes the document name to <i>C-Series Architecture</i> .                                                                                                                                                                                                                                                                                                                                                |

| Sixth   | 081-011830-000 | Released March 1993. Separates the assembly language<br>instruction set to the new CONVEX Assembly Language Reference<br>Manual (C Series), from the CONVEX Architecture Reference Manual<br>(C100, C200 Series), renamed the CONVEX Assembly Language<br>Reference Manual (C Series). Documents C3400 and C3800 Series<br>CPUs as part of the C Series architecture and clarifies the<br>separation of C100 Series CPUs (single-processor operation) from<br>multiprocessing CPU operation. |

| Fifth   | 081-000050-203 | Released May 1990. Updates the fourth edition of CONVEX<br>Architecture Reference Manual (C100, C200 Series). Documents the<br>addition of the load cache bypass instruction.                                                                                                                                                                                                                                                                                                                |

| Fourth  | 081-000050-202 | Released May 1989. Updates the third edition of CONVEX<br>Architecture Reference Manual (C100, C200 Series). Documents the<br>addition of the memory instruction duals.                                                                                                                                                                                                                                                                                                                      |

| Third   | 081-000050-201 | Released October 1988. Updates the version 2.0 of CONVEX C1/C120/C210 Architecture Reference Manual. Changes document name to CONVEX Architecture Reference Manual (C100, C200 Series). Documents the C100 Series architecture (C1 and C120 CPUs) and the C200 Series architecture (C201, C202, C210, C220, C230, and C240 CPUs).                                                                                                                                                            |

| Second  | 081-000050-200 | Released February 1988, version 2.0. Updates version 1.2 of<br>CONVEX Architecture Handbook. Changes document name to<br>CONVEX C1/C120/C210 Architecture Reference Manual. Documents<br>the expansion of the original instruction set, transparent changes<br>to the interrupt structure, and changes to the C210A architecture<br>and generic C1 Series architecture.                                                                                                                      |

| First   | 080-000120-000 | Released 1984. Version 1.0 (initial release) of the CONVEX<br>Architecture Handbook.                                                                                                                                                                                                                                                                                                                                                                                                         |

•

# Contents

## Using this manual xix Purpose and audience xix

| Notational conventions        | xix   |

|-------------------------------|-------|

| Text notation                 | xix   |

| Command syntax                | xxii  |

| Data notation                 | xxiii |

| Notes, cautions, and warnings | xxv   |

| Associated documents          |       |

| Ordering documents            | xxvi  |

| Technical assistance          | xxvi  |

| 1 | Introduction                     | 1   |

|---|----------------------------------|-----|

|   | The CONVEX C-Series architecture |     |

|   | Chapter summaries                | 4   |

|   | Data representations             |     |

|   | Register sets                    |     |

|   | Memory management                |     |

|   | Multiprocessor management        |     |

|   | Exceptions and interrupts        | . 7 |

|   | Implementation-specific features | . 8 |

|   | Instruction set                  | . 9 |

|   |                                  |     |

#

| Basic data representations                    | 12 |

|-----------------------------------------------|----|

| Data representation memory alignment          | 12 |

| Virtual addresses                             | 13 |

| Mixed mode arithmetic                         | 13 |

| Signed fixed-point integer representations    | 14 |

| Unsigned fixed-point integer representations  | 16 |

| Floating-point representations                | 17 |

| Native floating-point implementation          | 18 |

| Native single-precision floating-point format | 18 |

| Native double-precision floating-point format | 20 |

| Native reserved operands                      | 21 |

| Native floating-point zero                    | 21 |

| Native rounding                               | 21 |

| Native operations                             | 23 |

Contents v

EDTX 2-04-CV-120 51056DOC065305

**.** . . . . .

| Native compare operations                                                                                        |                  |

|------------------------------------------------------------------------------------------------------------------|------------------|

| Native add or subtract                                                                                           |                  |

| Native multiply operations                                                                                       |                  |

| Native divide operations                                                                                         |                  |

| Native square root operations                                                                                    |                  |

| Native square root operations<br>Native min/max operations                                                       |                  |

| Native conversion operations                                                                                     |                  |

| IEEE floating-point implementation                                                                               |                  |

| IEEE single-precision floating-point format                                                                      |                  |

| IEEE double-precision floating-point format                                                                      |                  |

| IEEE special operands                                                                                            | 32               |

| IEEE floating-point zero                                                                                         | 32               |

| IEEE rounding                                                                                                    |                  |

| IEEE operations                                                                                                  | 34               |

| IEEE compare operations                                                                                          | 34               |

| IEEE add or subtract operations                                                                                  | 34               |

| IEEE multiply operations                                                                                         | 34               |

| IEEE divide operations                                                                                           | 24               |

| IEEE min/max operations                                                                                          |                  |

| IEEE square root operations                                                                                      |                  |

| IEEE conversion operations                                                                                       |                  |

| Native and IEEE floating point algorithms                                                                        |                  |

| Native and IEEE floating-point algorithms<br>Add or subtract                                                     |                  |

|                                                                                                                  |                  |

| Multiply                                                                                                         |                  |

|                                                                                                                  | 47               |

| Divide                                                                                                           |                  |

| Divide<br>Conversions                                                                                            |                  |

|                                                                                                                  |                  |

| Conversions                                                                                                      |                  |

| Conversions Register sets                                                                                        | 47<br><b>4</b> 7 |

| Conversions                                                                                                      |                  |

| Conversions<br>Register sets<br>Address registers<br>Scalar registers                                            |                  |

| Conversions                                                                                                      |                  |

| Conversions<br>Register sets<br>Address registers<br>Scalar registers<br>Vector registers<br>Vector accumulators |                  |

| Conversions                                                                                                      |                  |

vi CONVEX C-Series Architecture

3

112.1

.

| 4 | Memory management                           |

|---|---------------------------------------------|

|   | Physical address space                      |

|   | Virtual address space                       |

|   | Addressing modes                            |

|   | Process structures                          |

|   | Process control                             |

|   | Stacks and stack frames                     |

|   | Stack operations 77                         |

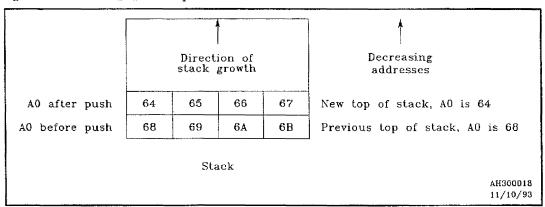

|   | Process return blocks                       |

|   | Stack frame structures 83                   |

|   | Stack switching                             |

|   | Resource structures                         |

|   | Shared resource structures                  |

|   | Stack resource structures 89                |

|   | System resource structures 91               |

|   | Virtual memory management                   |

|   | Multiprocessing extensions                  |

|   | Shared and unshared memory                  |

|   | Segment descriptor register 98              |

|   | SDR format - C100                           |

|   | SDR format - C3200/C3400/C3800 99           |

|   | SDR format - C4600 100                      |

|   | Page table entries 101                      |

|   | PTE format - C100 101                       |

|   | PTE format - C3200/C3400/C3800 103          |

|   | PTE format - C4600                          |

|   | Thread-level PTE Operation                  |

|   | Virtual-to-physical address translation 110 |

|   | C100                                        |

|   | C3200/C3400/C3800/C4600                     |

|   | Referenced and modified bits                |

|   | Virtual memory protection                   |

|   | Ring maximization                           |

|   | Access Validation                           |

|   | Memory protection notes                     |

|   | Inter-ring procedure call and return 121    |

|   | Corrupted pointers                          |

|   | Reserved virtual memory                     |

|   | Page 0 - C100                               |

|   | Page 0 - C3200/C3400/C3800/C4600            |

|   | Power up addressing mode 131                |

Contents vii

-

### EDTX 2-04-CV-120 51056DOC065307

| 5 | Multiprocessor management                    | .133 |

|---|----------------------------------------------|------|

|   | Tightly-coupled symmetric multiprocessing    |      |

|   | Automatic self-allocating processors         |      |

|   | Communication registers                      |      |

|   | Communication index register                 | 137  |

|   | CIR - C3200                                  | 138  |

|   | CIR - C3400/C3800/C4600                      |      |

|   | Communication register virtual addressing    |      |

|   | Communication register physical addressing   | 145  |

|   | Communication register address translation   | 148  |

|   | CMR address translation - C3200              | 148  |

|   | CMR address translation - C3400/C3800/C4600  | 149  |

|   | Communication register modified bits - C3200 | 151  |

|   | Hardware communication registers             | 154  |

|   | Hardware communication registers - C3200     |      |

|   | Hardware communication registers - C3400/C38 |      |

|   | Hardware communication registers - C4600     |      |

|   | Fork event communication registers           |      |

|   | Segment descriptor registers                 |      |

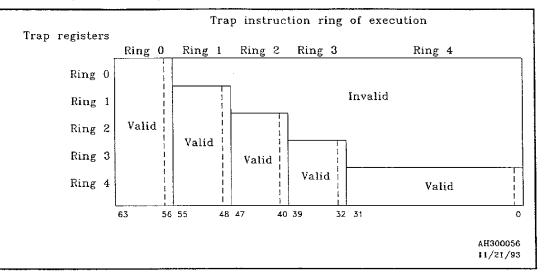

|   | Trap instruction registers                   | 161  |

|   | Thread allocation mask and count             |      |

|   | CPU execution clock registers                | 163  |

|   | Hardware reserved CMR - C3200                |      |

|   | Control registers - C3400                    |      |

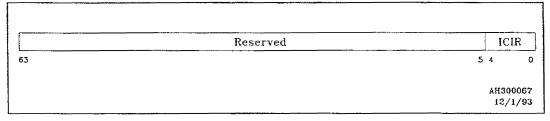

|   | Interrupt control register                   |      |

|   | Time of century register                     | 168  |

|   | Time of century delta time register          |      |

|   | Interval timers                              |      |

|   | Interval timer indicators                    |      |

|   | Process trap mail box                        |      |

|   | Interval timer interrupt indicators          |      |

|   | CPU exist indicators                         |      |

|   | Realtime indicators                          |      |

|   | Deadlock indicators                          |      |

|   | Global enable register                       |      |

|   | Local enable registers                       |      |

|   | Broadcast enable registers                   |      |

|   | Interrupt/trap source indicators             |      |

|   | Interrupt/trap acknowledge indicators        | 174  |

|   | Interrupt/trap request indicators            | 174  |

|   | SIB interrupt request indicators             |      |

|   | ION bit                                      |      |

|   | RT_ION bit                                   |      |

|   | Interval status register                     |      |

|   | Idle indicators                              | 176  |

|   | Communication interrupt registers            | 176  |

viii CONVEX C-Series Architecture

L.,

.

| TOC surite energlate                        | 1.77 |

|---------------------------------------------|------|

| TOC write complete                          |      |

| Post bit register                           |      |

| TER trap enable register                    | 170  |

| Control registers - C3800/C4600             | 100  |

| Lockbit shift register                      | 100  |

| Time of century register                    | 100  |

| Trap command register                       |      |

| Posted thread CIR                           |      |

| Next ITC register                           |      |

| Interval timer counter                      |      |

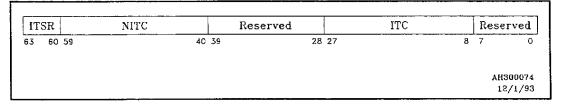

| ITC status register                         |      |

| ITC interrupt channel register              | 181  |

| IO INSTALL register                         | 181  |

| CPU INSTALL register                        |      |

| Communication index registers               |      |

| IDLE registers                              |      |

| Globally pending interrupt register         |      |

| Global enable register                      | 182  |

| Memory base pointer register                |      |

| Local enable registers                      | 182  |

| Broadcast enable registers                  |      |

| Traps and interrupts                        | 183  |

| Communication register primitive operations |      |

| Locking memory structures                   | 186  |

| Multithreaded execution                     |      |

| CPU states                                  |      |

| CPU scheduling                              | 189  |

| CPU allocation and deallocation             |      |

| ConvexOS/Secure                             |      |

| Parallel processing                         | 193  |

| Symmetric parallel processing               |      |

| Asymmetric parallel processing              | 195  |

| Privileged CPU control operations           |      |

| Forking operations                          |      |

| Forking commands                            |      |

| Idle CPU allocation                         |      |

| CPU deadlock detection                      |      |

| Process deadlock                            | 206  |

|                                             |      |

# 6 Exceptions and interrupts......209

·····ba....

| Exception system       | 209 |

|------------------------|-----|

| Process exceptions     |     |

| Arithmetic trap        |     |

| Instruction trace trap |     |

| Sequential execution   |     |

| Breakpoints            |     |

| System exceptions      |     |

. · · .

Contents ix

| Error exit trap                                                              | 220    |

|------------------------------------------------------------------------------|--------|

| Undefined op code trap                                                       |        |

| Vector valid trap                                                            |        |

| Ring violation traps and faults                                              | 222    |

| Page table entry violation faults                                            | 223    |

| Nonresident page faults                                                      | 224    |

| Process deadlock traps                                                       |        |

| Invalid communication address exception                                      |        |

| Process traps and process breakpoints                                        |        |

| System exception processing                                                  |        |

| Global hard error trap                                                       |        |

| CXBASE registers                                                             |        |

| Machine exceptions                                                           |        |

| Interrupt system                                                             |        |

| Interrupt processing - C100                                                  | 242    |

| Base-level processing                                                        |        |

| Interrupt-level processing                                                   |        |

| Common interrupt processing sequence                                         |        |

| General interrupt processing notes - C100                                    |        |

| Interrupt Processing - Multiprocessing CPUs                                  |        |

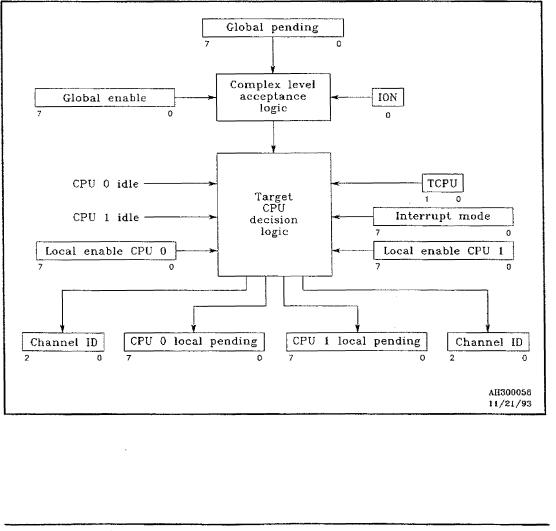

| Interrupt flow - C3200                                                       |        |

| Interrupt flow - C3400                                                       |        |

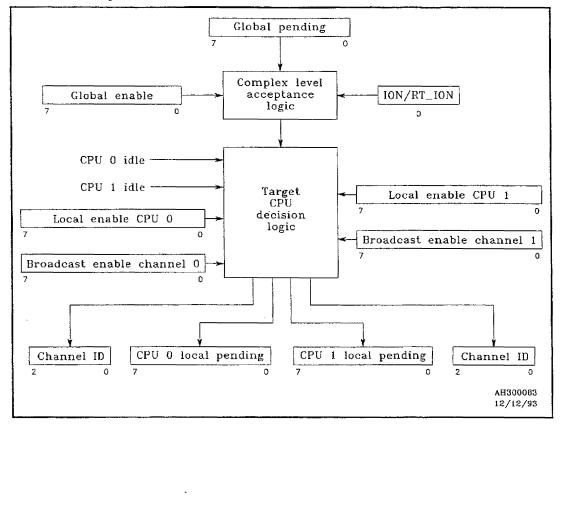

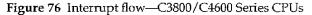

| Interrupt flow - C3800/C4600                                                 |        |

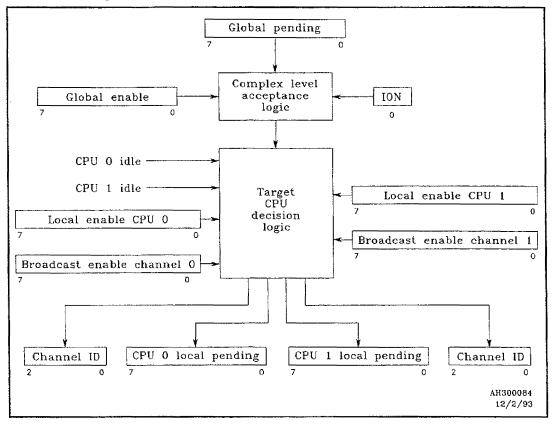

| Interrupt context blocks                                                     |        |

| Servicing interrupts                                                         | 256    |

| Virtual memory restrictions                                                  | 257    |

| Idle CPU interrupt processing                                                | 257    |

| Active CPU interrupt processing                                              | 259    |

| Returning from a base-level interrupt                                        | 261    |

| General interrupt notes - multiprocessing CPL                                | Js 262 |

| 7 Implementation-specific features.                                          |        |

| Physical address space                                                       |        |

| Power-up addressing mode - C100                                              |        |

| Physical address space - C100                                                |        |

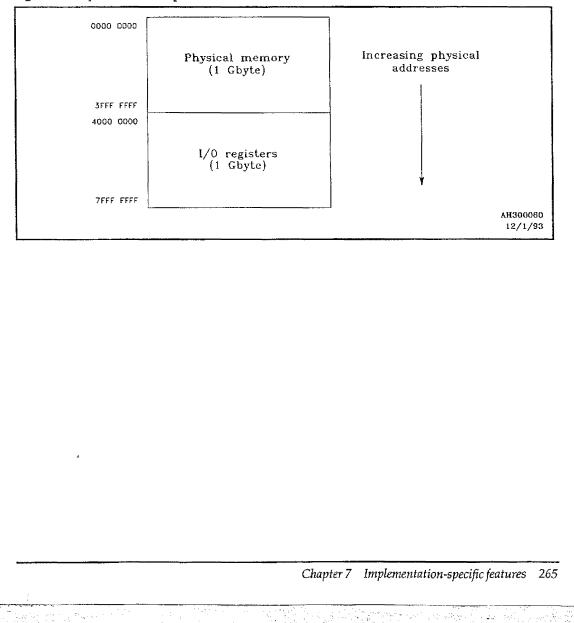

| Physical address space - C100<br>Physical address space - C3200              |        |

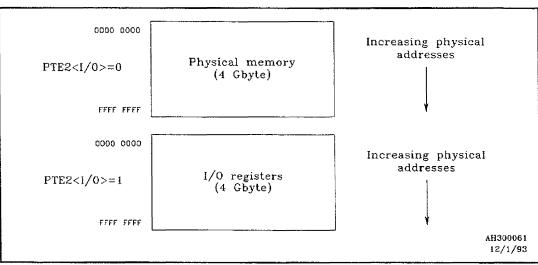

| Physical address space - C3200<br>Physical address space - C3400/C3800/C4600 |        |

| I/O address space                                                            |        |

| I/O address space - C100                                                     |        |

| I/O address space - C100                                                     |        |

| Referenced and modified bits                                                 |        |

|                                                                              |        |

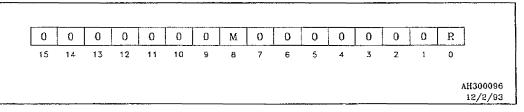

| R&M bits - C100                                                              |        |

| R&M bits - C3200                                                             |        |

| R&M bits - C3400/C3800                                                       |        |

| R&M bits - C4600                                                             |        |

*x* CONVEX C-Series Architecture

ļ

| Physical configuration map - C3200             | 276 |

|------------------------------------------------|-----|

| Physical configuration map - C3400/C3800/C4600 |     |

| Timers                                         |     |

| Interval timers                                |     |

| Interval timers - C100                         |     |

| Interval timers - C3200                        | 281 |

| Interval timers - C3800/C4600                  |     |

| Interval timers - C3400                        | 284 |

| Time of century clocks                         | 287 |

| TOC - C3200                                    | 287 |

| TOC - C3400/C3800/C4600                        | 288 |

| CPU execution timer                            |     |

| Thread timer                                   |     |

| CTR and TTR manipulation                       | 292 |

| Event counter - C4600                          | 294 |

| Memory and cache management                    | 295 |

| Cache management - Č100                        |     |

| Cache management - C3200/C3400/C3800           | 296 |

| PTE cache management                           | 296 |

| Instruction cache management                   | 297 |

| Data cache management                          |     |

| Cache management - C4600                       | 301 |

| PTE cache management                           | 301 |

| Instruction cache management                   | 302 |

| Data cache management                          | 302 |

| Cache coherency                                | 303 |

| Memory interleave                              | 305 |

| Interleave - C100                              |     |

| Interleave - C3200/C3400                       |     |

| Interleave - C3800                             | 310 |

|                                                |     |

Contents xi

EDTX 2-04-CV-120 51056DOC065311

EDTX 2-04-CV-120 51056DOC065312

# **Figures**

· · · · · ·

| Figure 1  | Memory longword structure xxiii                     |

|-----------|-----------------------------------------------------|

| Figure 2  | Memory longword structure                           |

| Figure 3  | Virtual address format                              |

| Figure 4  | Signed fixed-point integer representations          |

| Figure 5  | Unsigned fixed-point integer representations 16     |

| Figure 6  | Native single-precision floating-point format       |

| Figure 7  | Native double-precision floating-point format 20    |

| Figure 8  | IEEE single-precision floating-point format         |

| Figure 9  | IEEE double-precision floating-point format         |

| Figure 10 | Internal floating-point format                      |

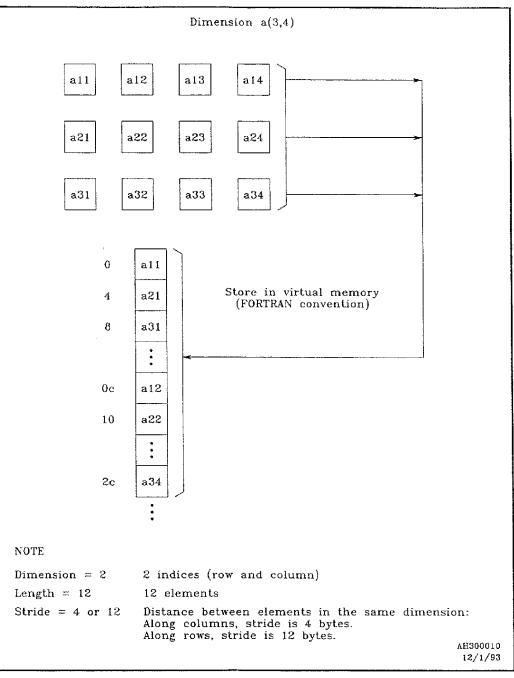

| Figure 11 | Vector terminology 55                               |

| Figure 12 | Program counter format                              |

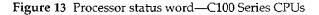

| Figure 13 | Processor status word—C100 Series CPUs 59           |

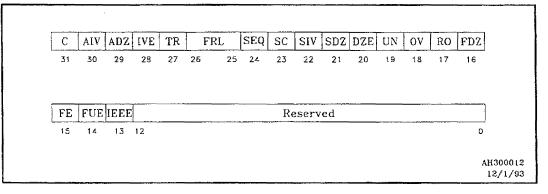

| Figure 14 | Processor status word—C3200, C3400, C3800,          |

| Ŭ         | C4600 Series CPUs                                   |

| Figure 15 | Ring structure of the virtual address space         |

| Figure 16 | Virtual address format                              |

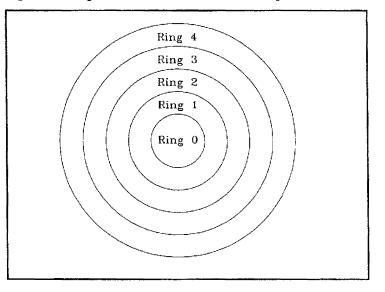

| Figure 17 | Process, system, and ring structures75              |

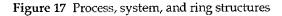

| Figure 18 | Push and pop stack operations                       |

| Figure 19 | Short return block                                  |

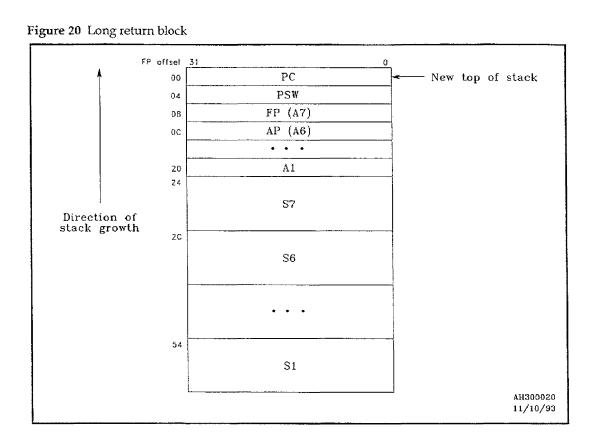

| Figure 20 | Long return block                                   |

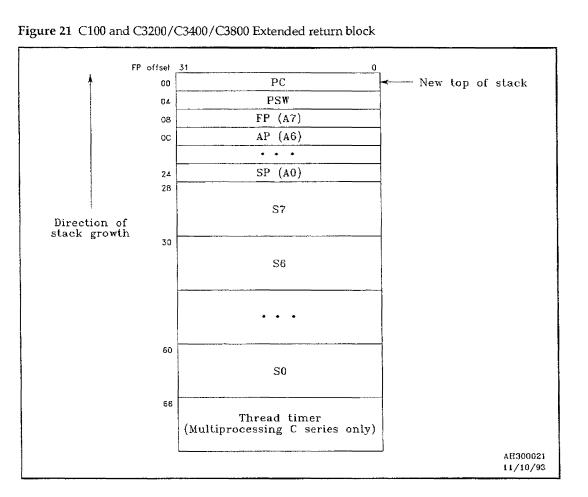

| Figure 21 | C100 and C3200/C3400/C3800 Extended return          |

| U         | block                                               |

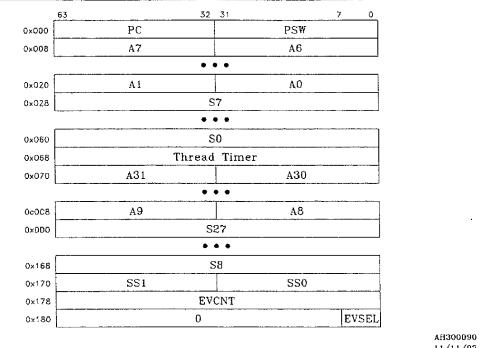

| Figure 22 | C4600 Extended return block 82                      |

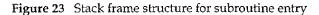

| Figure 23 | Stack frame structure for subroutine entry          |

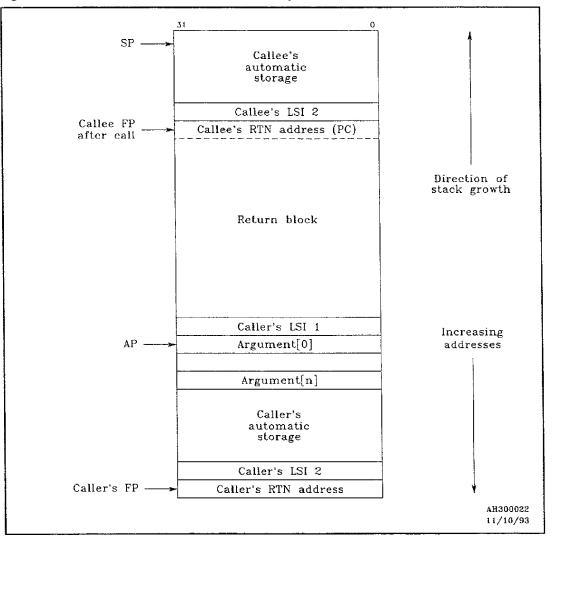

| Figure 24 | Stack structure after a short call                  |

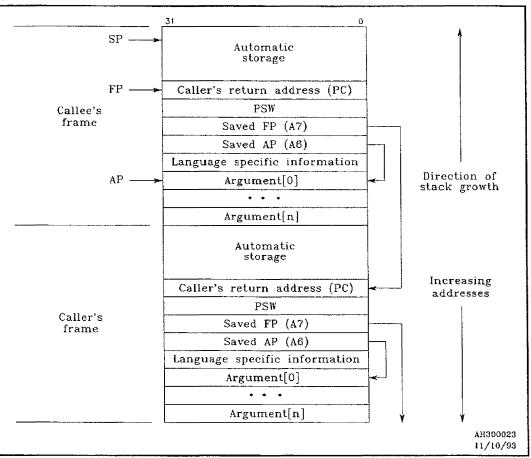

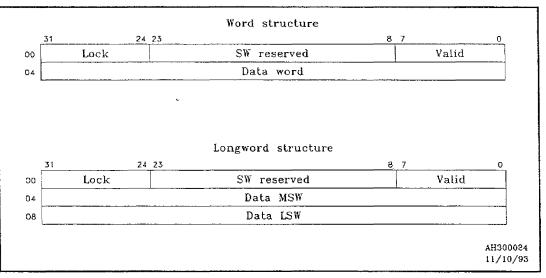

| Figure 25 | Word and longword shared resource structures 88     |

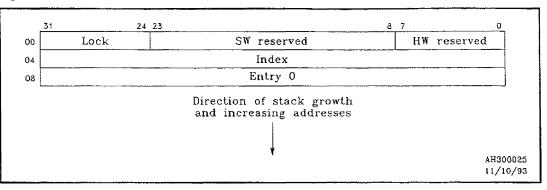

| Figure 26 | Stack resource structure                            |

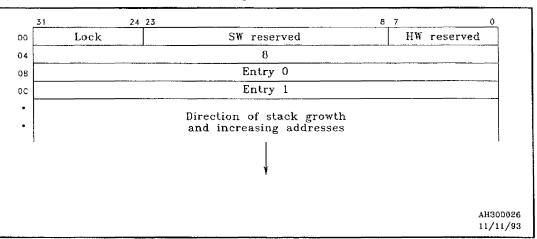

| Figure 27 | Stack resource structure with two pushed entries 90 |

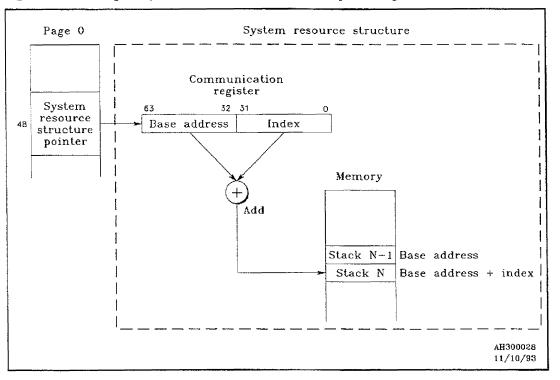

| Figure 28 | System resource structure                           |

| Figure 29 | Accessing the system resource structure for         |

| Q         | multiprocessing C-Series CPUs 92                    |

| Figure 30 | SDR Format—Č100 Series CPUs                         |

| Figure 31 | SDR format-C3200/C3400/C3800 Series CPUs 99         |

| Figure 32 | SDR format—C4600 series CPUs 100                    |

| Figure 33 | Resident PTE format—C100 Series CPUs 101            |

| Figure 34 | Nonresident PTE format-C100 Series CPUs 103         |

| Figure 35 | Resident PTE format-C3200/C3400/C3800               |

| 0         | Series CPUs104                                      |

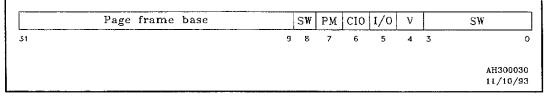

|           |                                                     |

Figures xiii

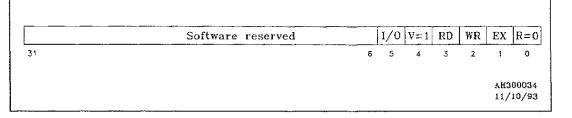

| Figure 36             | Nonresident PTE format—C3200/C3400/C3800<br>Series CPUs104 |

|-----------------------|------------------------------------------------------------|

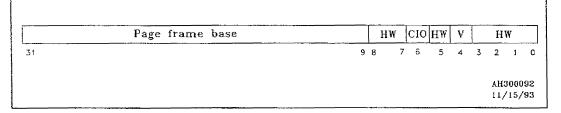

| Figure 37             | Resident PTE formatC4600 Series CPUs                       |

| Figure 38             | Virtual-to-physical address translation-                   |

| rigule 30             |                                                            |

| T: 20                 | C100 Series CPUs                                           |

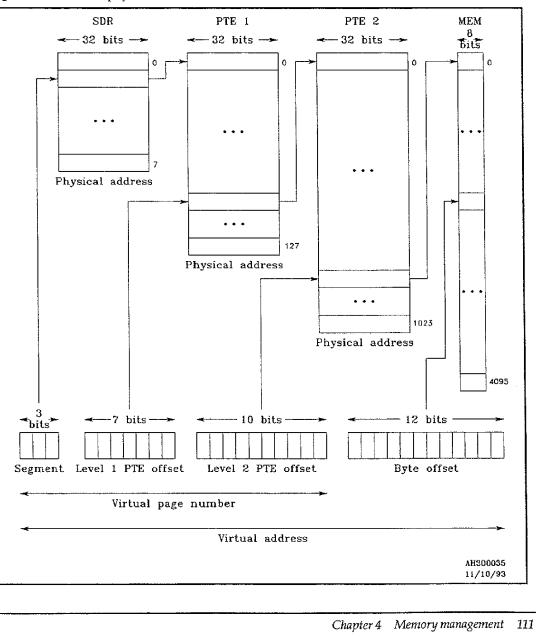

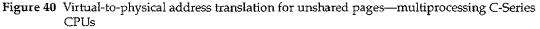

| Figure 39             | Address translation step for unshared                      |

|                       | pages-multiprocessing C-Series CPUs                        |

| Figure 40             | Virtual-to-physical address translation for                |

|                       | unshared pages—multiprocessing C-Series CPUs 115           |

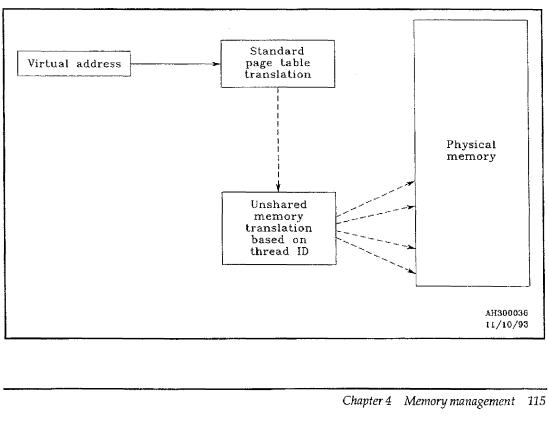

| Figure 41             | Gate array structure 121                                   |

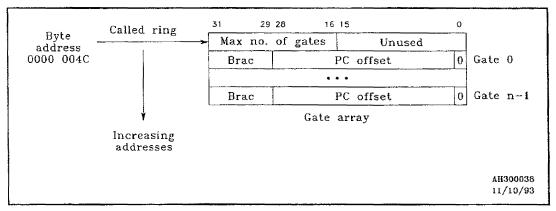

| Figure 42             | Page 0 virtual memory organization                         |

|                       | C100 Series CPUs125                                        |

| Figure 43             | Page 0 virtual memory                                      |

| -                     | organization-multiprocessing C-Series CPUs128              |

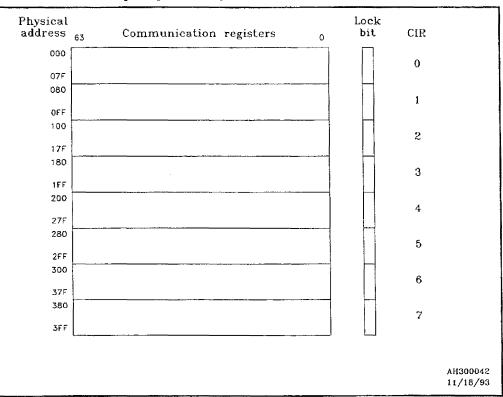

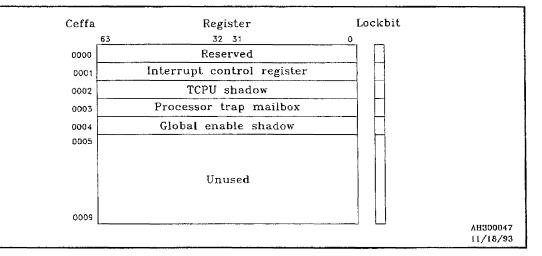

| Figure 44             | Communication register partitions by CIR                   |

| 0                     | index—C3200 Series CPUs 139                                |

| Figure 45             | Communication register partitions by CIR                   |

| 0                     | indexC3400/C3800/C4600 Series CPUs                         |

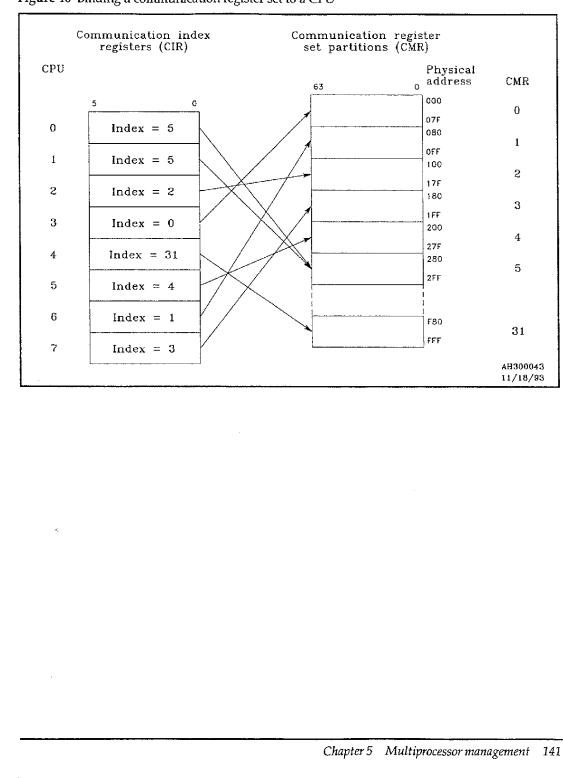

| Figure 46             | Binding a communication register set to a CPU 141          |

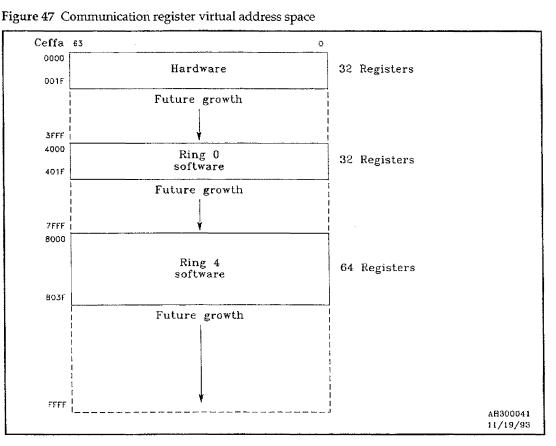

| Figure 47             | Communication register virtual address space 143           |

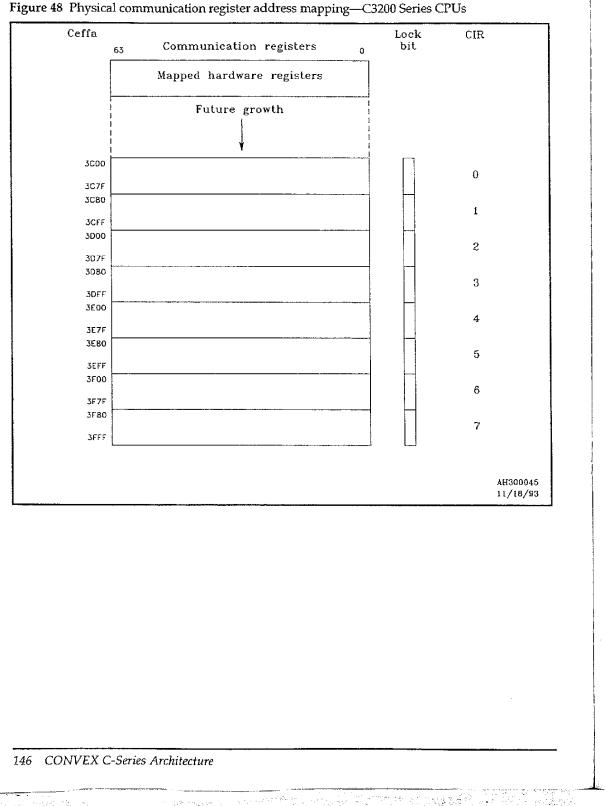

| Figure 48             | Physical communication register address                    |

| 116uic 40             | mapping—C3200 Series CPUs                                  |

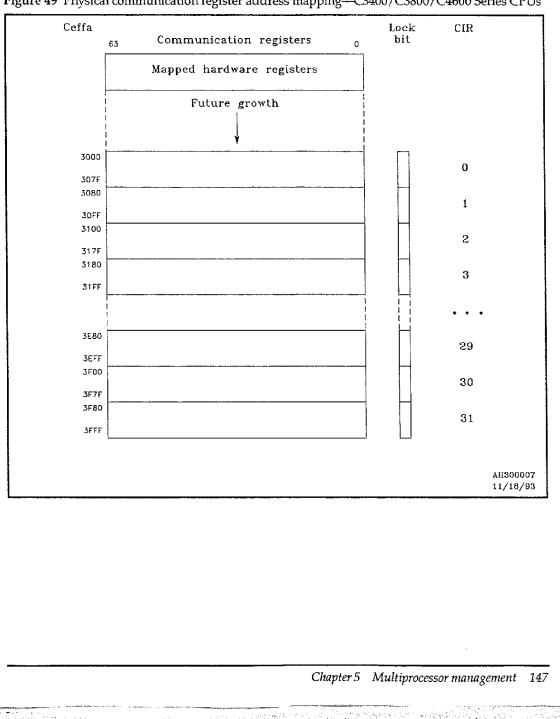

| Figure 49             | Physical communication register address                    |

| Figure 49             | mapping—C3400/C3800/C4600 Series CPUs 147                  |

| Eigene 50             |                                                            |

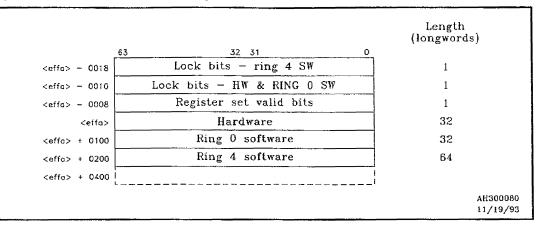

| Figure 50             | ldcmr/stcmr memory map                                     |

| Figure 51             | Hardware communication registers-                          |

| F: FO                 | C3200 Series CPUs                                          |

| Figure 52             | Hardware communication registers-                          |

| <b>D</b> - <b>C</b> 0 | C3400/C3800 Series CPUs                                    |

| Figure 53             | Hardware Communication Registers-                          |

|                       | C4600 Series CPUs                                          |

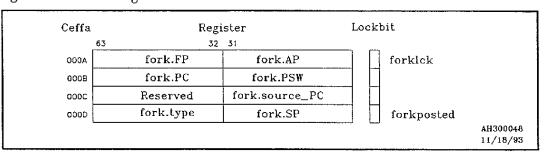

| Figure 54             | Fork event registers-C3200 Series CPUs 158                 |

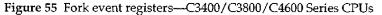

| Figure 55             | Fork event registers—C3400/C3800/C4600                     |

|                       | Series CPUs                                                |

| Figure 56             | Segment descriptor registers-C3200 Series CPUs 160         |

| Figure 57             | Segment descriptor registers—                              |

|                       | C3400/C3800/C4600 Series CPUs                              |

| Figure 58             | Trap instruction registersC3200 Series CPUs 161            |

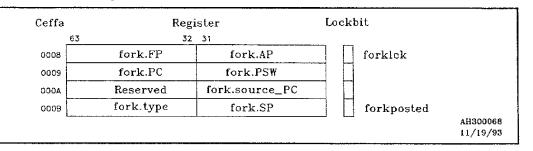

| Figure 59             | Trap instruction registers—C3400/C3800/C4600               |

| Ū                     | Series CPUs                                                |

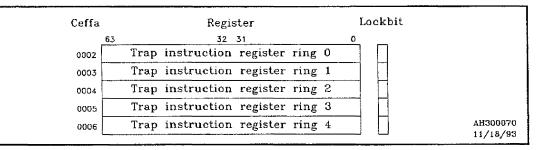

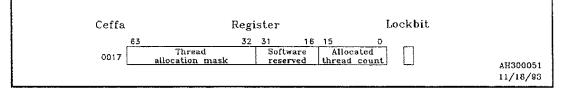

| Figure 60             | Thread allocation register-C3200 Series CPUs 162           |

| Figure 61             | Thread allocation register and CPU                         |

| 0                     | mask—C3400/C3800/C4600 Series CPUs                         |

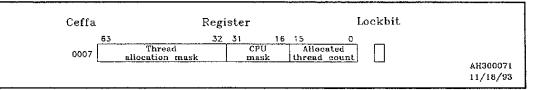

| Figure 62             | CPU execution clock registers—                             |

|                       | C3200 Series CPUs                                          |

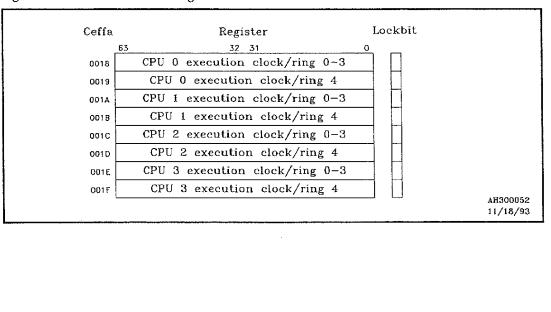

| Figure 63             | CPU execution clock registers-                             |

| rigute 05             | C3400/C3800 Series CPUs                                    |

|                       | CUTUU/ CUUU DELIES CE US                                   |

: -

. .

xiv CONVEX C-Series Architecture

2

÷ .

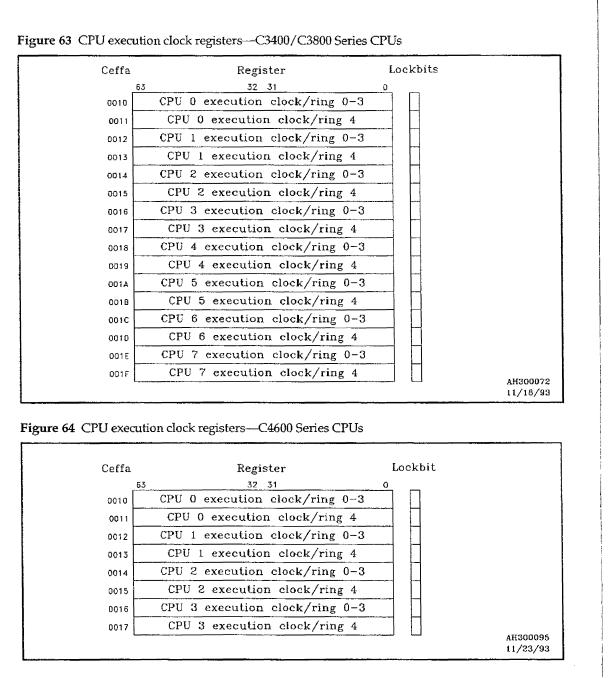

| Figure 64 | CPU execution clock registers—                   |

|-----------|--------------------------------------------------|

|           | C4600 Series CPUs164                             |

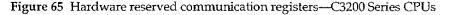

| Figure 65 | Hardware reserved communication registers        |

|           | C3200 Series CPUs 165                            |

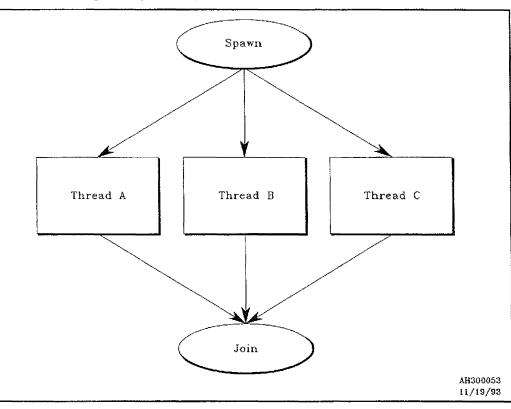

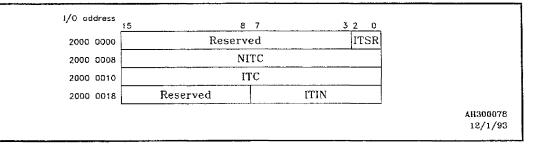

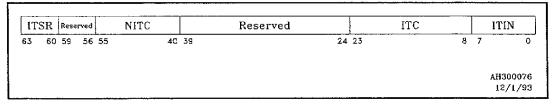

| Figure 66 | Control register mapping-C3400 Series CPUs 166   |

| Figure 67 | Control register layout-C3400 Series CPUs 167    |

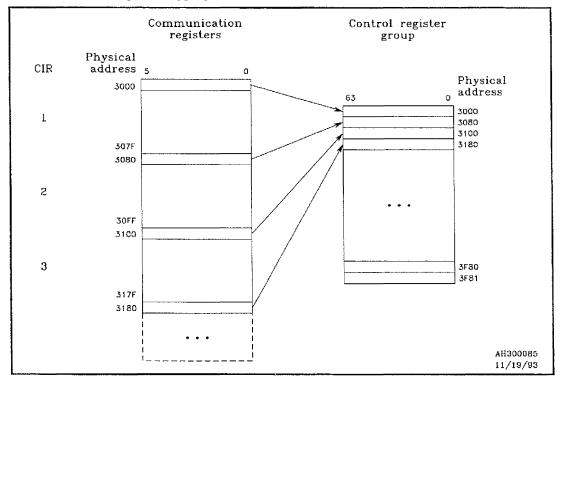

| Figure 68 | Symmetric parallel processing                    |

| Figure 69 | Example of a multithreaded symmetric process 194 |

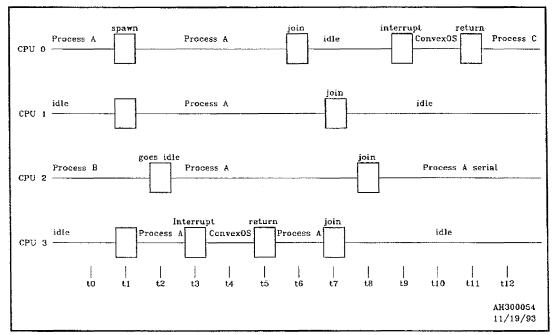

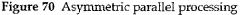

| Figure 70 | Asymmetric parallel processing 196               |

| Figure 71 | Trap instruction register partitioning           |

| Figure 72 | Interrupt control register (ICR)—                |

| õ         | C3200 Series CPUs 248                            |

| Figure 73 | Interrupt control register (ICR)—                |

| Ũ         | C3400/C3800/C4600 Series CPUs                    |

| Figure 74 | Interrupt flow—C3200 Series CPUs                 |

| Figure 75 | Interrupt flow—C3400 Series CPUs                 |

| Figure 76 | Interrupt flowC3800/C4600 Series CPUs 255        |

| Figure 77 | Interrupt context block                          |

| Figure 78 | Physical address space—C120 CPUs                 |

| Figure 79 | Physical address space-C3200 Series CPUs 266     |

| Figure 80 | Physical address space—C3400/C3800/C4600         |

| Ŭ         | Series CPUs                                      |

| Figure 81 | Memory page referenced and modified bits—        |

| 0         | C3200 Series CPUs 271                            |

| Figure 82 | Referenced and modified bit addresses—           |

| Ū.        | C3400/C3800 Series CPUs272                       |

| Figure 83 | Referenced/Modified Bits                         |

| Figure 84 | Physical configuration map entry 275             |

| Figure 85 | Interval timer registers—C100 Series             |

| Figure 86 | Interval timer registers—C3200 Series            |

| Figure 87 | Interval timer registers—C3800/C4600             |

| Ý         | Series systems                                   |

| Figure 88 | 64-bit TOC clock—C3200 Series CPUs 287           |

.....

·· · · ·

Figures xv

# **Tables**

| Table 1            | Notivo cinale presision input operando 10              |

|--------------------|--------------------------------------------------------|

| Table 1<br>Table 2 | Native single-precision input operands                 |

|                    | Native single-precision dynamic range                  |

| Table 3            | Native double-precision input operands                 |

| Table 4            | Native double-precision dynamic range                  |

| Table 5            | Native floating-point nomenclature                     |

| Table 6            | Native operation results-add or subtract               |

| Table 7            | Native operation results—multiply 25                   |

| Table 8            | Native operation results-divide                        |

| Table 9            | Native operation results—square root                   |

| Table 10           | Native operation results-min/max operations 27         |

| Table 11           | Native operation results-float-to-fixed conversions 27 |

| Table 12           | Native operation results-fixed-to-float conversions 28 |

| Table 13           | Native operation results—float-to-float conversions 28 |

| Table 14           | IEEE single-precision input operands                   |

| Table 15           | IEEE single-precision dynamic range                    |

| Table 16           | IEEE double-precision input operands 31                |

| Table 17           | IEEE double-precision dynamic range                    |

| Table 18           | IEEE floating-point nomenclature                       |

| Table 19           | IEEE operation results—add or subtract                 |

| Table 20           | IEEE operation results—multiply                        |

| Table 21           | IEEE operation results—divide                          |

| Table 22           | IEEE operation results—min/max 40                      |

| Table 23           | IEEE operation results—square root                     |

| Table 24           | IEEE operation results-float-to-fixed conversions 42   |

| Table 25           | IEEE operation results—fixed-to-float conversions 42   |

| Table 26           | IEEE operation results-float-to-float conversions 43   |

| Table 27           | Intermediate result rounding - add, subtract,          |

|                    | multiply                                               |

| Table 28           | Intermediate result rounding - divide                  |

| Table 29           | C-Series architecture virtual address space            |

| Table 30           | C-Series addressing modes                              |

| Table 31           | Ring maximization for source and target 118            |

| Table 32           | Communication register address mapping—                |

|                    | C3200 Series CPUs 148                                  |

| Table 33           | C3200CIR physical address base assignment—             |

|                    | C3200                                                  |

| Table 34           | Communication register address                         |

|                    | mapping—C3400/C3800/C4600 Series CPUs 150              |

| Table 35           | CIR physical address base—C3400/C3800/C4600 150        |

|                    |                                                        |

Tables xvii

•

| Table 36 | MBOX action codes-C3400 Series CPUs 169               |

|----------|-------------------------------------------------------|

| Table 37 | Bit assignments-global and local enable registers 171 |

| Table 38 | Bit assignment—Interrupt/trap source registers 173    |

| Table 39 | TER operations diag instruction subcodes              |

| Table 40 | C3800/C4600 Series control registers in X space 179   |

| Table 41 | Deadlock detection instructions                       |

| Table 42 | Arithmetic exceptions and corresponding               |

|          | PSW bits 214                                          |

| Table 43 | Trace trap class codes and qualifiers                 |

| Table 44 | Process deadlock class codes and qualifiers           |

| Table 45 | System exception class codes and qualifiers—          |

|          | C100 Series CPUs                                      |

| Table 46 | System exception class codes and qualifiers—          |

|          | C3200/C3400/C3800 Series CPUs                         |

| Table 47 | System exception class codes and qualifiers           |

|          | C4600 Series CPUs233                                  |

| Table 48 | Machine exceptions 238                                |

| Table 49 | Realtime interrupt channels-C3400 Series CPUs. 240    |

| Table 50 | Realtime virtual channels—C3400 Series CPUs 247       |

| Table 51 | Full and overflow bit values and events—              |

|          | C100 Series                                           |

| Table 52 | Values for EVSEL register 294                         |

| Table 53 | Icache, Dcache, and ATUcache purges                   |

|          | C100 Series CPUs                                      |

| Table 54 | Instruction and PTE cache management—                 |

|          | C3200/C3400/C3800 Series CPUs                         |

| Table 55 | C4600 cache summary                                   |

| Table 56 | C4600 cache management 304                            |

| Table 57 | Memory interleave—C100 Series CPUs 306                |

| Table 58 | Memory subsystem bandwidth and                        |

|          | interleaving—C3200/C3400 Series CPUs                  |

| Table 59 | Memory subsystem bandwidth and                        |

|          | interleaving—C3800 Series CPUs                        |

xviii CONVEX C-Series Architecture

# Using this manual

**Purpose and** The CONVEX C-Series Architecture describes the architecture of the CONVEX C-Series supercomputers. It is a companion to the audience CONVEX Assembly Language Reference Manual (C Series). This document applies to all CONVEX C-Series architecture CPUs, including the C100, C3200, C3400, C3800, and C4600 Series CPUs. It serves as a tool to help engineers and software developers make maximum use of any CONVEX processor's facilities. Notational Notational conventions are those characters, symbols, terminology, or abbreviated expressions used in this manual. conventions Text notation Text notation conventions set apart special items. Monospace type represents computer output, binary or hexadecimal numbers, commands, instructions or mnemonics. Example: ERROR: Unknown command. Reenter. Using this manual xix Bold monospace type represents your response to a program or utility prompt.

#### Example:

Do you really want to exit? y

Bold uppercase names designate keycap names.

#### Example:

#### RETURN

If two keycap names are separated by a space, they are pressed sequentially.

#### Example:

#### ESC Q

If two keycap names are separated by a hyphen, they are pressed simultaneously.

#### Example:

#### CTRL-C

- The word "enter" followed by a command, means to type the command and then press **RETURN**.

- Italicized words in an example command sequence are representative of a user-supplied name, such as a file name.

#### Example:

#### command filename

Angle brackets (< >) designate unprintable ASCII characters.

#### Example:

<197> is an em dash

xx CONVEX C-Series Architecture

. . . .

• Angle brackets (< >) are used to designate bits as fields in a byte, word, register, and so forth.

#### Example:

PSW <6...0>

Square brackets ([]) in a command sequence designate optional letters, characters, subcommands or other command elements. Brackets may be nested, indicating optional subelements. If there are two or more options, they are separated by vertical slashes or pipe symbols.

#### Example:

#### com[mand] [filename] devicename]

Braces ( { } ) in a command sequence designate mandatory input, which must be one of two or more possible options. These options are separated by vertical slashes or pipe symbols.

#### Example:

com[mand] {a|b|c}

A vertical slash (1), also known as the pipe symbol, in a command sequence indicates "or," giving you a choice between optional elements of a command.

#### Example:

conf[igure] [command | alias]

• Horizontal ellipses (...) in a command sequence show that the element immediately preceding them can be repeated.

#### Example:

ad[d] [ [[board] ...] | all]

Using this manual xxi

Vertical ellipses in a command sequence show that lines of an example have been left out.

#### Example:

```

Verifying image 99

Verifying image 199

.

.

.

Verifying image 999

```

#### Command syntax

The previous conventions are used in the example that follows to define the commands in the user interface.

#### Example:

com[mand]{.t|.f] [-a|-b] input\_file [...] [output\_file]

In the example:

- command is required and may be abbreviated to com (square brackets indicate optional portion).

- If a command option (indicated by a list in braces, separated by a vertical slash) is used, then either .t or .f, if required.

- If a command option (indicated by a list in square brackets, separated by a vertical slash) is used, then either -a or -b is optional.

- input\_file, indicated by italics with no square brackets, is a required file name supplied by the user.

- Additional *input\_file* names, indicated by ellipses in square brackets, may optionally be supplied by the user.

- output\_file, indicated by square brackets and italics, is an optional file name supplied by the user.

xxii CONVEX C-Series Architecture

## Data notation

The following data notation conventions identify specific definitions in CONVEX supercomputer architecture:

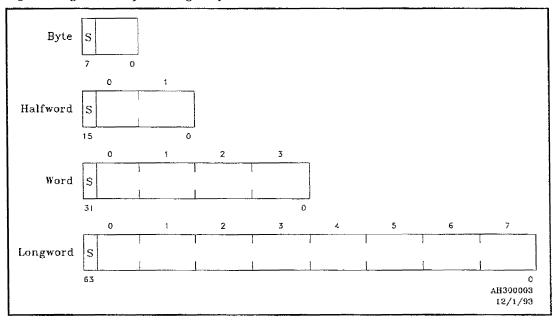

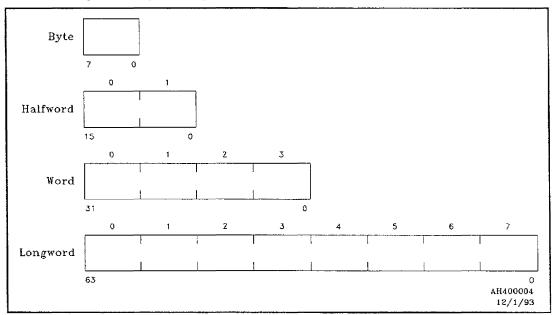

- A *bit* is a single binary value or entity.

- A nibble is 4 bits.

- A byte is 8 bits.

- A halfword is 16 bits.

- A word is 32 bits.

- A longword is 64 bits.

- Single-precision is a 32-bit floating-point word.

- Double-precision is a 64-bit floating-point longword.

- An *instruction* is a multi-halfword operand.

- A bit is set when it contains a binary value of 1.

- A bit is clear when it contains a binary value of 0.

- Bit numbering is from left to right, *n*-1 through 0. The most significant numerical bit is *n*-1, the least-significant is 0. The bit numbering represents the binary weight of a position.

- Byte numbering is from left to right, 0 through *n*-1.

- Byte order in a 64-bit longword is interpreted with increasing byte addresses associated with higher order bytes within a longword. The most-significant bit is associated with the least significant byte number.

Figure 1 represents the ordering of each addressable entity within a 64-bit longword.

#### Figure 1 Memory longword structure

| 63   | 56 | 55   | 48 | 47   | 40 | 39   | 32 | 31   | 24 | 23   | 16 | 15   | 8 | 7                     | 0    |

|------|----|------|----|------|----|------|----|------|----|------|----|------|---|-----------------------|------|

| Byte | 0  | Byte | 1  | Byte | 2  | Byte | 3  | Byte | 4  | Byte | 5  | Byte | 6 | Byte                  | 7    |

| 7    | 0  | 7    | 0  | 7    | 0  | 7    | 0  | 7    | o  | 7    | 0  | 7    | 0 | 7                     | 0    |

| Addr | 0  | Addr | 1  | Addr | 2  | Addr | 3  | Addr | 4  | Addr | 5  | Addr | 6 | Addr<br>AH300<br>12/1 | 0001 |

• A *register* is a programmer-visible hardware storage element internal to the CPU.

Using this manual xxiii

- All register contents are written in hexadecimal notation, unless explicitly stated otherwise.

- · Bit fields are specified with decimal numbers as

reg\_name<x..y>

where the bit field is reg\_name from bits x through y.

- Individual bit positions within a register are specified as

- \* reg\_name<15,4,0>

where 15, 4, and 0 are bits within reg\_name.

- An instruction is a group of halfwords.

- For C100 Series CPUs, only the standard instruction can be used. In the standard instruction, the first halfword is an op code and the remaining halfwords are operands.

- For multiprocessing C-Series CPUs (C3200, C3400, C3800, and C4600 Series CPUs), either the standard or the extended instruction can be used. In the extended instruction, the first halfword is an op code prefix, another halfword is an op code, and the remaining halfwords are operands.

- All memory and I/O addresses are written in hexadecimal notation unless explicitly stated otherwise.

- Physical memory is the physical storage (main memory) actually installed with the CPU.

- Virtual memory is the perceived amount of main memory as seen by the application programmer.

- The symbol *k* is an abbreviation for *kilo* or 1,024.

- The symbol *M* is an abbreviation for *mega* or 1,048,576.

- The symbol *G* is an abbreviation for *giga* or 1,073,741,824.

- A *stack* is a data structure in which memory is allocated and deallocated from one end, usually called the top, on a last-in, first-out basis (LIFO).

- A *return block* is a collection of register contents that are pushed on or popped off a stack in response to an instruction or other event.

- Reserved or undefined indicate what, if anything, to expect from unused fields in registers, reserved memory, or reserved I/O space. Algorithm implementation based on the use of reserved fields is not recommended.

xxiv CONVEX C-Series Architecture

έ, τ

## Notes, cautions, and warnings

This document presents notes, cautions, and warnings in the following formats.

A Note highlights supplemental information.

| Note |

|------|

|------|

Ξ.

Caution

A Caution highlights information necessary to avoid damage to the system.

Warning highlights information necessary to avoid injury to personnel.

Using this manual xxv

| Associated<br>documents | The following is a partial list of other manuals or books that may<br>provide more detailed information on the topics presented in<br>this manual:                                                                                                                                                                                                                                 |  |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                         | <ul> <li>CONVEX Assembly Language Reference Manual (C Series),<br/>Order No. DSW-301—This manual is a reference guide for<br/>developing software for CONVEX C-Series processors. It<br/>contains the formats for the CONVEX C-Series instruction set.</li> </ul>                                                                                                                  |  |  |  |  |  |

|                         | <ul> <li>CONVEX Processor Diagnostics Manual (C Series), Order<br/>No. DSW-302—This manual documents the service<br/>processor unit (SPU)-based processor diagnostics for<br/>CONVEX supercomputers.</li> </ul>                                                                                                                                                                    |  |  |  |  |  |

|                         | • CONVEX System Manager's Guide, Order No. DSW-004—<br>This manual is written for system managers who are<br>responsible for administering resources on CONVEX<br>systems. Included are descriptions for configuring devices,<br>authorizing users, setting up mail and communications,<br>performing backups and system accounting functions, and<br>monitoring system resources. |  |  |  |  |  |

| Ordering<br>documents   | To order the current edition of this or any other CONVEX document, send requests to:                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|                         | CONVEX Computer Corporation                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                         | Customer Service<br>PO Box 833851                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                         | Richardson, TX 75083-3851<br>USA                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                         | Include the order number or exact title with the request. The order number is on the title page of the manual and begins with the letters "DSW-" or "DHW"                                                                                                                                                                                                                          |  |  |  |  |  |

|                         | The order number for the <i>CONVEX C Series Architecture</i> is DHW-300.                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Technical<br>assistance | Hardware and software support can be obtained through the CONVEX Technical Assistance Center (TAC).                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 03313101100             | <ul> <li>From all locations in the United States, customers call<br/>(800)952-0379.</li> </ul>                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                         | <ul> <li>From all locations in the United States, CONVEX employee</li> </ul>                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

74,....

1

٠.

EDTX 2-04-CV-120 51056DOC065327

# Introduction

This document is a reference for the CONVEX C-Series architecture. As new model numbers are added to any series, the material in this document may apply in whole or in part. These lists should not be considered exclusive.

The C100 Series includes the C1 and C120 CP Us.

The implementation of the C-Series architecture on the C200 Series and C3200 Series CPUs is identical, therefore references in this book are written for the C3200 Series CPUs. The C3200 Series includes the C210, C220, C230, C240, C3210, C3220, C3230, C3240 CPUs.

The C3400 Series includes the C3410ES, C3420ES, C3410, C3420, C3430, C3440, C3460, and C3480 CPUs.

The C3800 Series includes the C3810, C3820, C3830, C3840, C3460, and C3880 CPUs.

The C4600 Series includes the C4610, C4620, C4630, and C4640 CPUs

All C100 Series CPUs are single processors. Multiprocessing C-Series CPUs include the C3200, C3400, C3800, and C4600 Series CPUs.

Chapter 1 Introduction 1

| The CONVEX<br>C-Series<br>architecture | The architecture presented in this manual defines the specifications of the central processing unit (CPU) of the CONVEX supercomputers.                                                                                                                                                                                                                                                                                                     |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| archilecidie                           | The term <i>architecture</i> is defined as the attributes of a system as<br>seen by the programmer (the conceptual structure and functional<br>behavior), as distinct from the organization of the data flow and<br>controls, the logical design, and the physical implementation.<br>Within this context, an architectural specification defines the<br>following attributes, as perceived by the programmer and the<br>hardware designer: |

|                                        | Data representations                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        | Register sets                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                        | - General registers                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                        | - Communication registers                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        | Instruction set                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                        | Memory management                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        | <ul> <li>Physical address space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                        | <ul> <li>Virtual address space</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        | <ul> <li>Process structure and control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        | <ul> <li>Virtual memory management</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

|                                        | <ul> <li>Virtual memory protection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

|                                        | – Caches                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | <ul> <li>Multiprocessor management</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                               |

|                                        | <ul> <li>Automatic self-allocating processors</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                    |

|                                        | <ul> <li>Parallel processing mechanisms</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        | <ul> <li>Forking and spawning mechanism</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

|                                        | <ul> <li>Memory protection mechanisms</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        | <ul> <li>Exception and interrupt mechanisms</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                      |

|                                        | The instruction set is described in the CONVEX Assembly Language Reference Manual (C Series).                                                                                                                                                                                                                                                                                                                                               |

|                                        | The CONVEX C-Series architecture incorporates the following features:                                                                                                                                                                                                                                                                                                                                                                       |

|                                        | <ul> <li>An integrated vector processor incorporated within the<br/>system for high-speed operation</li> </ul>                                                                                                                                                                                                                                                                                                                              |

|                                        | <ul> <li>A full range of fixed and floating-point data types</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

2 CONVEX C-Series Architecture

- A total capacity of four Gbytes of virtual memory two Gbytes available to support large user programs and data, and two Gbytes to support the operating system

- Large, high-speed register sets (address, scalar, and vector) that support high-performance operation for address calculations in parallel with scalar and vector calculations

- Communication registers and multiprocessing structures (in the multiprocessing C-Series CPUs)

- Multilevel protection systems that support and separate users, thereby enhancing system reliability and increasing the performance of operating system functions

All CONVEX C-Series CPUs share a common architecture, in most respects. However, some software, such as the ConvexOS operating system, use features whose implementation varies among different CONVEX CPUs. Although not immediately visible to the user, the fine detail and construction of these features are visible to the ConvexOS software.

Chapter 1 Introduction 3

## Chapter summaries

This section contains brief summaries of the chapters that follow. In addition, a brief summary of the instruction set is found in the CONVEX Assembly Language Instruction Set (C Series).

- Data representations and operations

- General registers

- Memory management

- Multiprocessor management

- Exceptions and interrupts

- Implementation-specific features

#### Data representations

There are three binary numeric data representations:

- Signed fixed point integer

- Unsigned fixed point integer

- Floating point

The CONVEX processors support four fixed-point integer precisions. Signed fixed-point numbers are interpreted as two's complement representations. Integer quantities exist in four lengths:

- Byte—8 bits

- Halfword—16 bits

- Word-32 bits

- Longword—64 bits

The CONVEX CPUs support both native and IEEE standard floating point number representations in two formats: single-precision word (32 bits) and double-precision longword (64 bits). Both formats are interpreted as binary, normalized fractions with an implicit value of "1" in the most-significant bit of the fraction. The exponent is a biased power of two, scale factor.

An address or logical value is treated as an unsigned 32-bit integer usually contained in the address registers. For numeric purposes, an address register may be treated as a signed or unsigned 32-bit integer.

Virtual addresses are byte-granular. Instruction operands in memory may begin on any byte boundary that allows all byte locations within a given data type to be used, even though the operands may be unrelated. Operations are performed in integer and floating-point. Floating-point operations are performed in native and IEEE modes. The differences are delineated for add, subtract, multiply, divide, square root, compare, and conversion operations.

### **Register sets**

There are three general register sets and several status registers. The three register sets are partitioned according to the type of operand to be manipulated:

- Address registers

- Scalar registers

- · Vector register

There are four general status registers and three privileged flags. The four status registers are:

- Program counter (PC)

- · Processor status word (PSW)

- Scalar stride zero (SS0 C4600 Series CPUs only)

- Scalar stride one (SS1 C4600 Series CPUs only))

The three privileged flags are:

• Interrupt on (ION)

÷. 4. . .

- Realtime interrupt on (RT\_ION C3400 Series CPUs only)

- Vector valid flag (VV)

### Memory management

The memory management unit (MMU) supports the operating system in providing a versatile and reliable virtual memory programming environment. The CONVEX C-Series architecture provides 4 Gbytes of virtual memory in its virtual address space partitioned into eight 512-Mbyte segments. Four segments are allocated to the operating system and four segments to the user. The maximum size of a user program (instructions and data) is limited to 2 Gbytes. The operating system data structures and instructions necessary to manage the user program occupy the remaining 2 Gbytes of virtual storage.

Because the address space of the CONVEX system architecture is virtual, an address may be a valid logical address, but the referenced data may or may not be in physical memory. Memory is managed as pages on a fixed-size basis.

Since the operating system is embedded within the user-virtual address space, it must be protected from the user. The memory protection system protects the user's programs from other users' programs, while supporting time-sharing and operating system structures.

This system is based on hierarchical structures called rings and

- supports embedding the operating system in the user's virtual address space,

- contains certain access violations to the user's process,

- permits implementing the operating system efficiently, and

- enhances operating system call processing by reducing the time for context switching.

6 CONVEX C-Series Architecture

÷., , ,

### Multiprocessor management

*Multiprocessing* is the creation and scheduling of individual processes on any subcomplex. The multiprocessor management hardware incorporated in each C-Series architecture CPU provides the operating system and user a simple and flexible set of instructions for dynamic allocation, deallocation, and communication. Each CPU in a C-Series architecture complex operates independently as a 64-bit supercomputer. The multiprocessor management hardware binds these CPUs into a tightly coupled set with shared memory. This implements a multi-instruction multi-data (MIMD) architecture that provides a parallel execution environment for user applications.

### **Exceptions and interrupts**

Exceptions occur when a currently executing program encounters event such as arithmetic inconsistencies, address translation faults, or some asynchronous event (such as an interrupt). When an exception occurs, control is transferred to a predetermined address whose value is a function of the exception.

Interrupts are the result of events that occur asynchronously and belong to the system, not to the executing process. When an interrupt occurs, the processor jumps to a particular interrupt handler determined by the interrupt source.

All I/O data references by the CPU are memory mapped. There are no explicit I/O instructions. The I/O registers and memory status bits are referenced through the appropriate logical-to-physical address mapping.

EDTX 2-04-CV-120 51056DOC065335

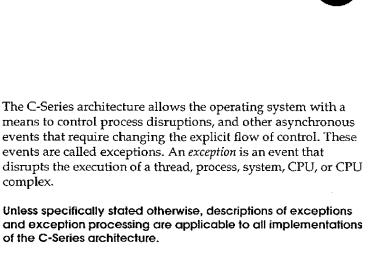

# Implementation-specific features