A PennWell Publication

AUGUST 1984

## COMPUTER DESIGN

THE MAGAZINE OF COMPLITER BASED SYSTEMS

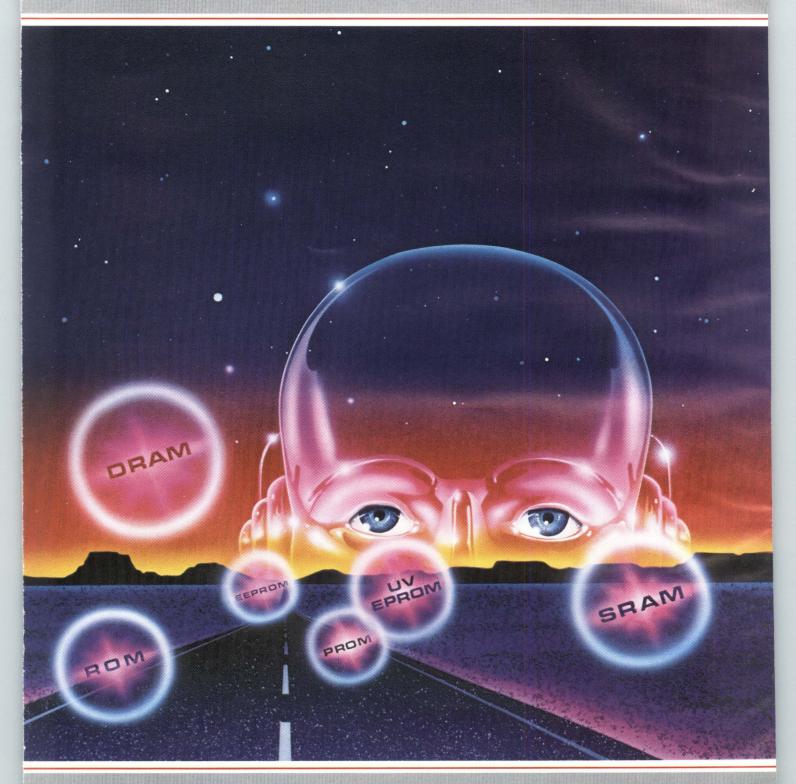

SEMICONDUCTOR MEMORIES

## INOUR MEMORIES.

NEC Electronics

## THERESNOIA

#### AT NEC, YOU'LL FIND QUALITY MEMORIES IN EVERY CATEGORY.

All in one place.

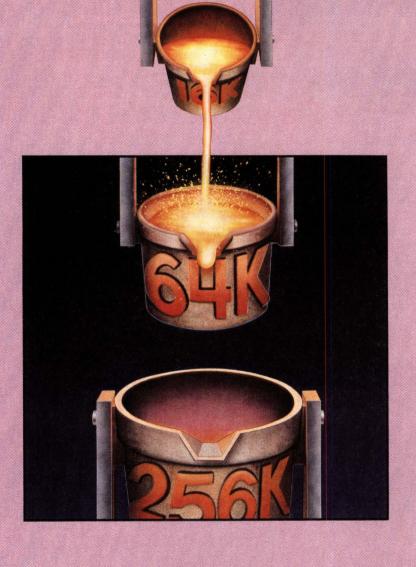

Chances are, we have the exact memories you're looking for. Leading-edge 25ns 4K static RAMs. 64K static RAMs. 128K UV EPROMs. New 256K DRAMs. And our remarkable one megabit ROM-the highest density ROM in the world.

These aren't promises of things to come. They're here. Now. And ready for your next design.

You can trust our memories.

At NEC, quality is understood. Fact is, you can expect 100% burn-in, standard. And a guaranteed AQL of 0.1%. Which means, with NEC, your memories will be worry-free.

A complete package deal.

Be reminded, our memory devices come in a variety of packages. Standard and skinny. Plastic and ceramic DIPs. Flat packages and leadless chip carriers.

So if you have designs on the future, remember NEC. For a never-ending line of quality memories.

#### NEC Memory Products

|                         | Tec  | chn  | olo  | gies | Densities |    |    |    |     |     |     |      |      |    |  |  |

|-------------------------|------|------|------|------|-----------|----|----|----|-----|-----|-----|------|------|----|--|--|

| Type of Memory          | CMOS | MMOS | NMOS | B/P  | 1K        | 2K | 4K | 8K | 16K | 32K | 64K | 128K | 256K | IM |  |  |

| Static RAM <sup>2</sup> |      |      | •    |      |           |    | •  |    | •   |     | •   |      |      |    |  |  |

| Dynamic RAM             |      | •    |      |      |           |    | •  |    | •   |     | •   |      | •    |    |  |  |

| ROM                     |      |      | •    |      |           |    |    |    |     | •   | •   | •    | •    | •  |  |  |

| PROM                    |      |      |      | •    | •         |    |    | •  |     |     |     |      |      |    |  |  |

| <b>EEPROM</b>           |      |      | •    |      |           |    |    |    | •   |     |     |      |      |    |  |  |

| <b>UV EPROM</b>         |      |      | •    |      |           |    |    |    |     | •   | •   | •    |      |    |  |  |

<sup>1</sup>MMOS refers to Mixed-MOS technology (CMOS and NMOS). <sup>2</sup>High speed 4K and 16K devices available.

#### WE'RE TAKING ON THE FUTURE.

Ror a fast response about NEC Electronics' complete line of memory products, call TOLL FREE 1-800-556-1234, ext. 188. In California, call 1-800-441-2345, ext. 188. NEC sales offices: Woburn, MA (617) 935-6339 - Melville, NY (516) 423-2500 - Poughkeepsis, NY (94) 452-4747 - Pompano Beach, FL (305) 785-8250 - Columbia, MD (301) 730-8600 - Norcross, GA (404) 447-4409 - Arlington Heights, IL (312) 577-9090 - Southfield, MI (313) 559-24242 - Bloomington, MN (612) 854-4443 - Dallas, TX (214) 931-0641 - Orange, CA (714) 937-5244 - Cupertino, CA (408) 446-0650

© 1983, NEC Electronics

MEMORIES OF THE FUTURE

#### PIONEER FAMILIE

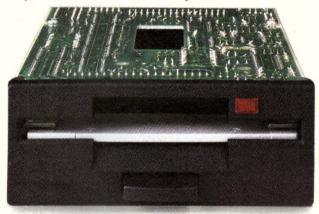

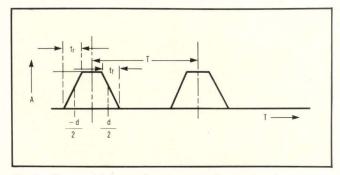

Kennedy didn't just pioneer the 1/4" cartridge field — it started it, with the first practical recorder using the new 1/4" 3M cartridge.

Model 6470 continues the tradition with the usual package of new features, such as:

- High Capacity Model 6470 can store up to 54 MBYTES of formatted data on one cartridge.

- Start/Stop with data streamings at 37.5 ips.

- · Full Command Repertoire, utilizing either the Pico Bus or

- · Automatic Read Thresholds during read retry three different thresholds are automatically selected, a feature usually found only on large 9 track tape transports.

- Backward Compatibility Model 6470 will read tapes written by Model 6455.

These are but a few of Model 6470's many features. Write or give us a call today for the complete story of the newest member of this oldest family.

Pertec interface. 1600 Shamrock Ave., Monrovia, CA 91016 357-8831 • ITT TELEX 472-0116 KENNEDY KENNEDY 646

KENNEDY · QUALITY · COUNT ON IT

### **COMPUTER DESIGN®**

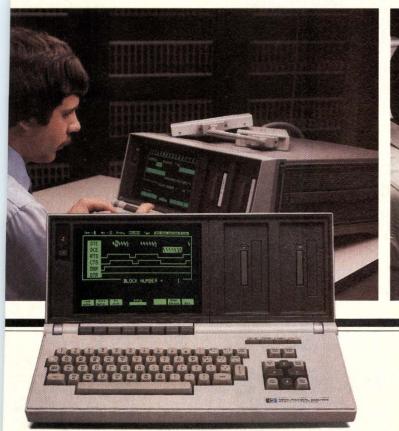

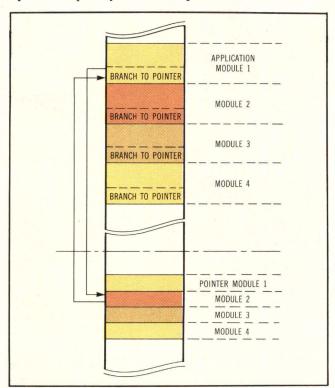

#### System technology

Page 29

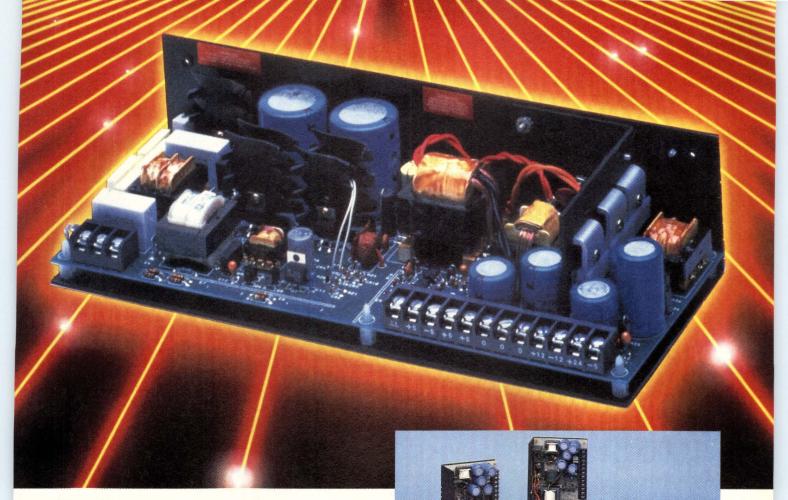

- 29 Packaging & power: Power and logic devices are merging on the same chip

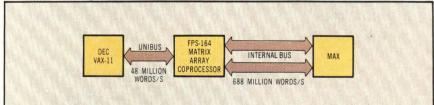

- 38 Computers:

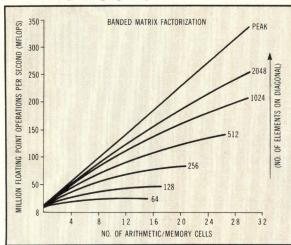

Matrix array processor breaks through supercomputer barrier

- 44 Software:

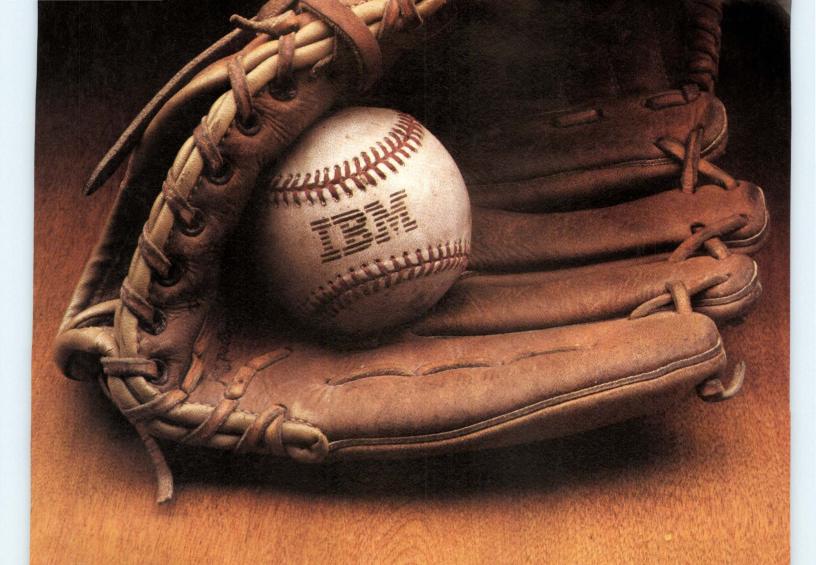

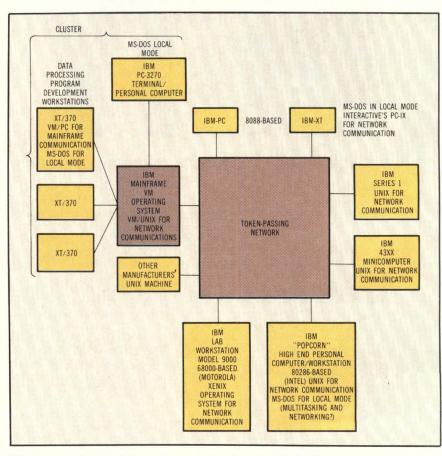

Big Blue makes a major move to link computers

- 53 Software:

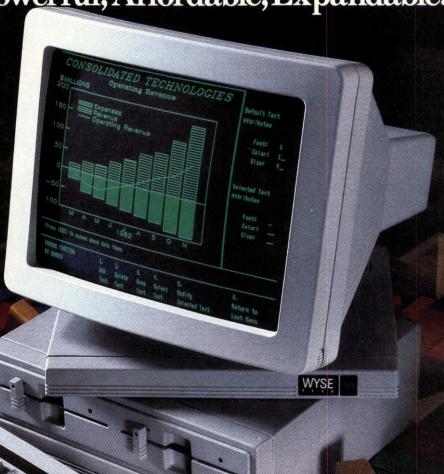

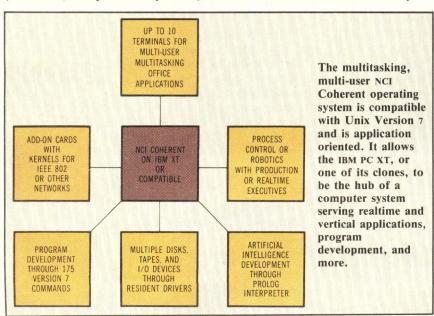

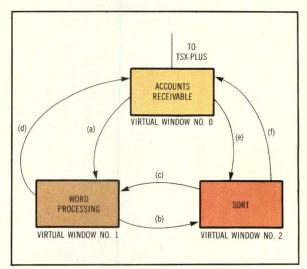

Multitasking Unix look-alike supports 11 IBM XT users

- 60 Peripherals:

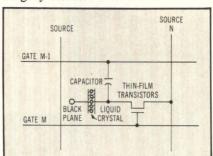

Flat panels approach monochrome CRT specifications

#### System design

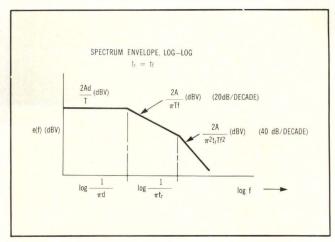

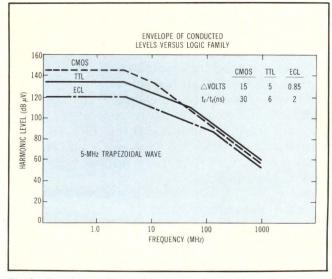

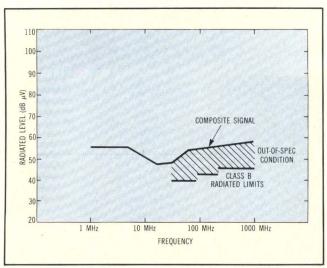

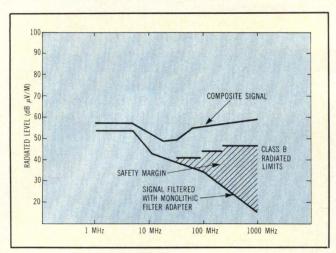

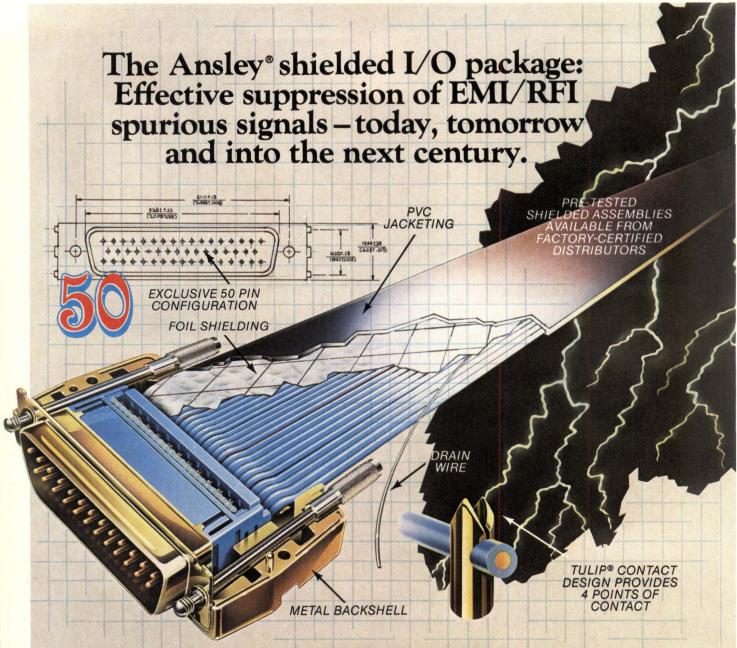

- Packaging & power: Connectors—the missing link in EMI suppression by Frank Drzymkowski and Dave Goodman—Computer equipment must meet stringent FCC restrictions on rf emissions. Although the first line of defense for designers is proper packaging, electromagnetic interference can occur between units if attention is not paid to connector design.

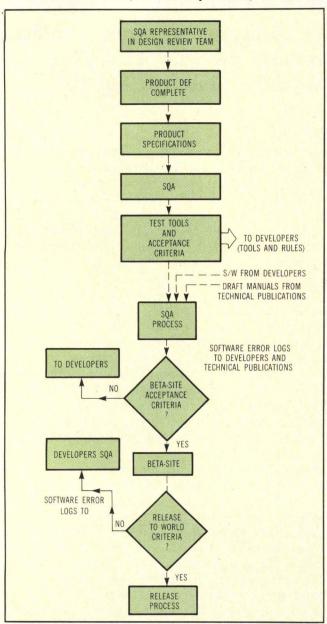

- 91 Software: Software quality: design it in from the start by M. Ghiassi—A comprehensive software quality assurance program should be an integral part of the development process. This program ensures not only that functions work as planned, but that planned functions are useful.

#### Midcon/84 and Mini/Micro Southwest

65 Midcon and Mini/Micro Southwest, two major southwest OEM electronics and computer conferences, are being held concurrently this year in Dallas, Texas on September 11-13. Keynote speaker Admiral "Bobby" Inman, CED of the Microelectronics and Computer Technology Group, will lead off the two programs of technical sessions. Of specific interest to computer system designers are the technical sessions at Mini/Micro as well as many at Midcon.

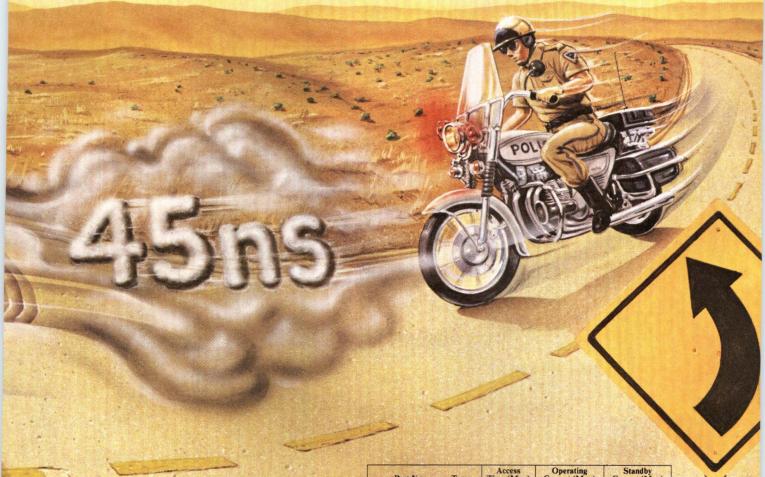

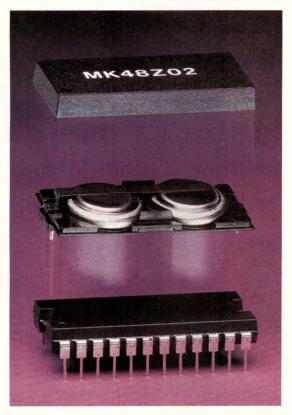

#### Special report on semiconductor memories

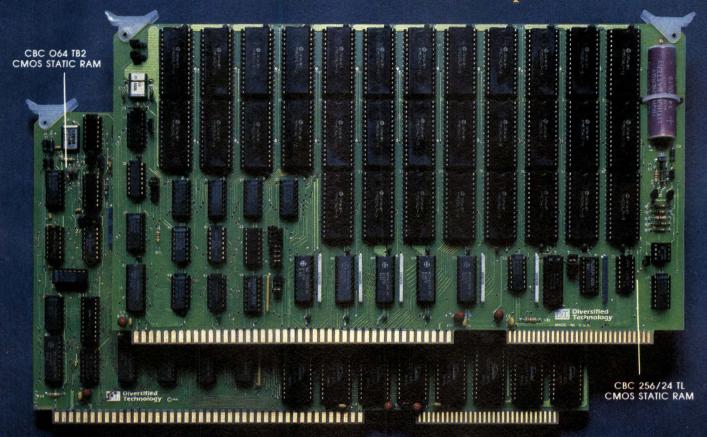

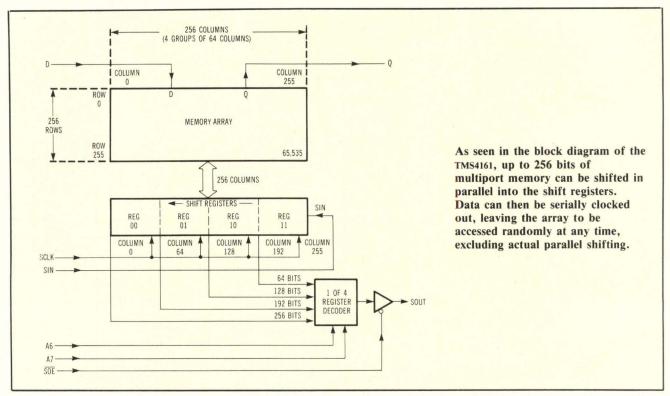

101 Fed by breakthroughs in CMOS and the insatiable demand of modern systems for memory, semiconductor memory technology is branching beyond mere "by 1" density increases. VLSI memories are providing system solutions and breaking down performance bottlenecks. In addition to more efficient, denser main memories, RAMS, EPROMS, and EEPROMS are appearing in the parts of the system where their special features are most needed and offering new design possibilities.

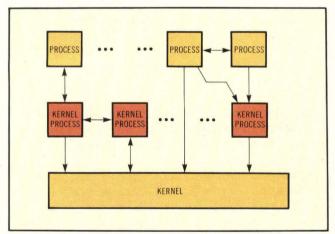

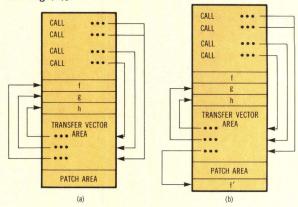

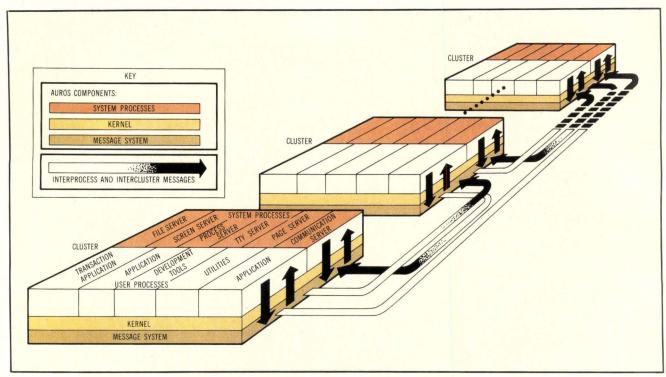

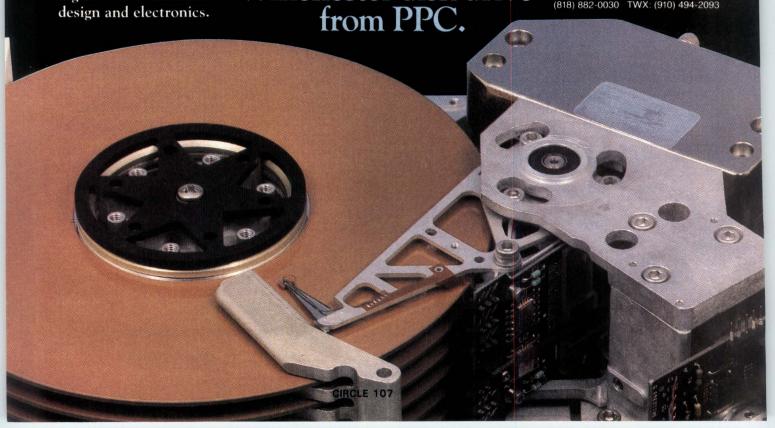

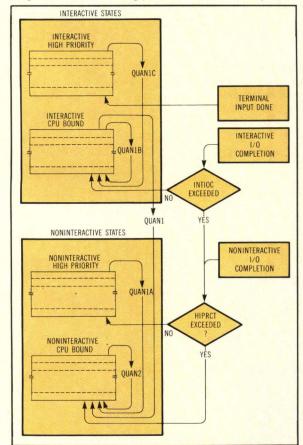

#### Special report on minicomputer operating systems

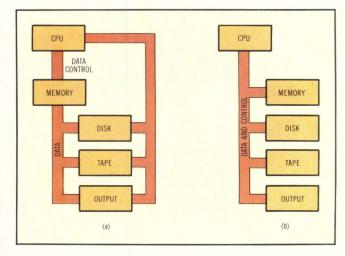

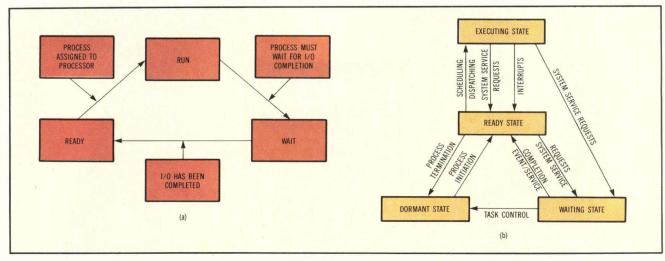

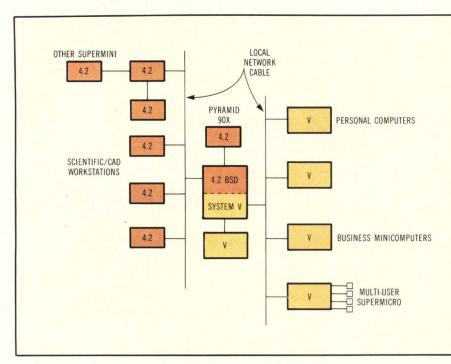

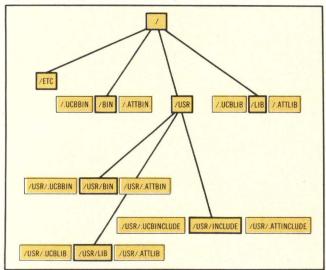

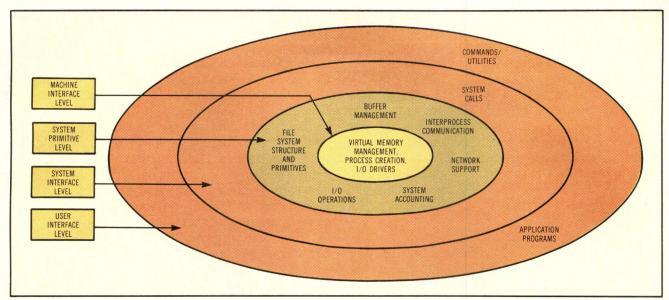

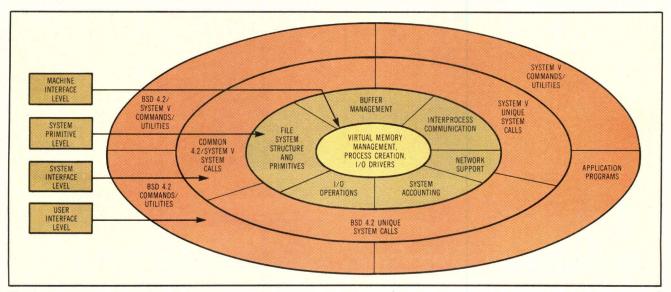

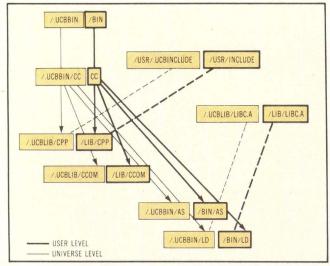

Minicomputer system designers will find a Unix operating system or a Unix look-alike often meets their needs for increased operating system functionality. In fact, the latest minicomputer operating systems for the past five years are more like operating environments and sport both realtime capabilities and fault-tolerant features—whether or not they are Unix based. Computer system designers opting for minicomputers need to know how minicomputer operating systems determine their computer's behavior.

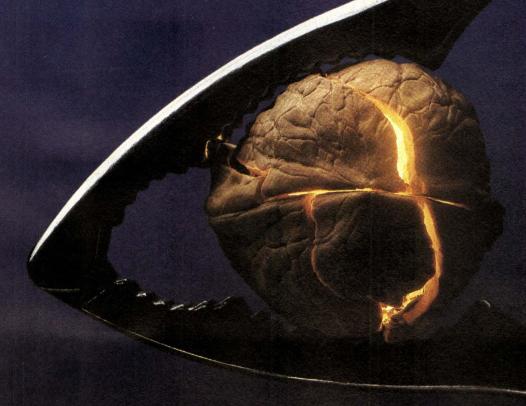

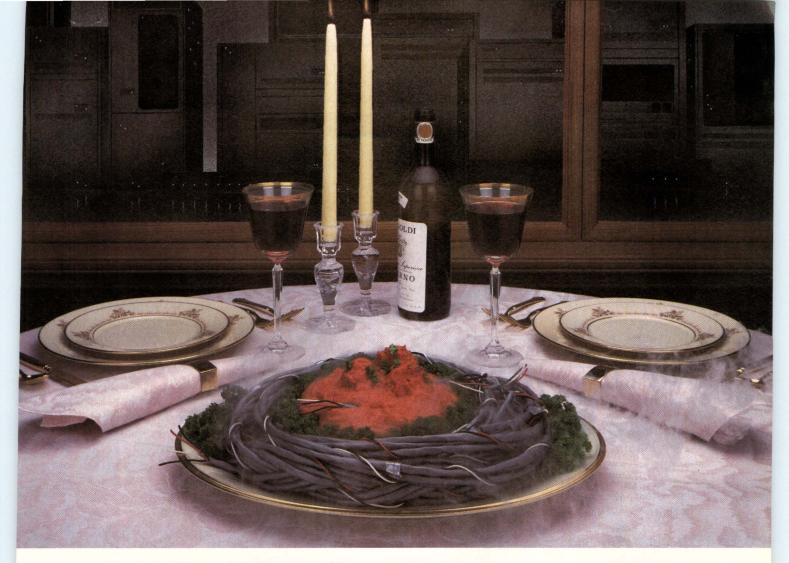

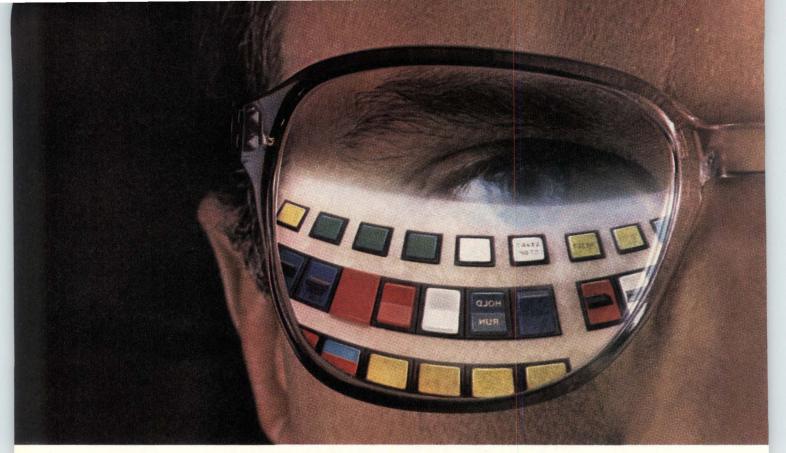

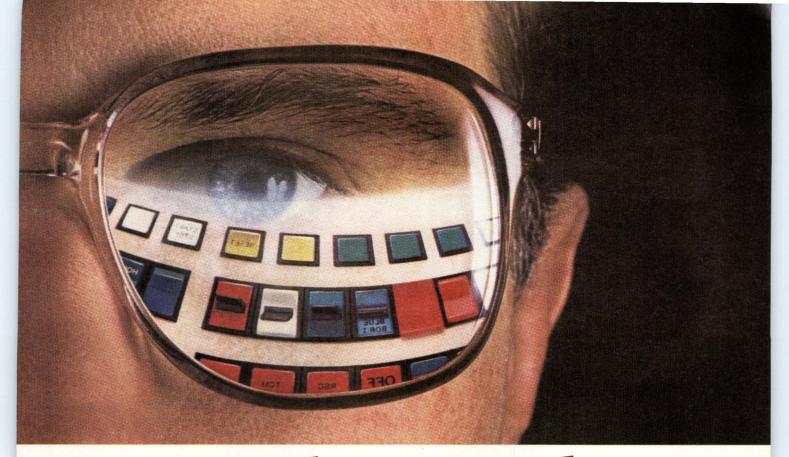

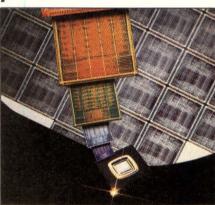

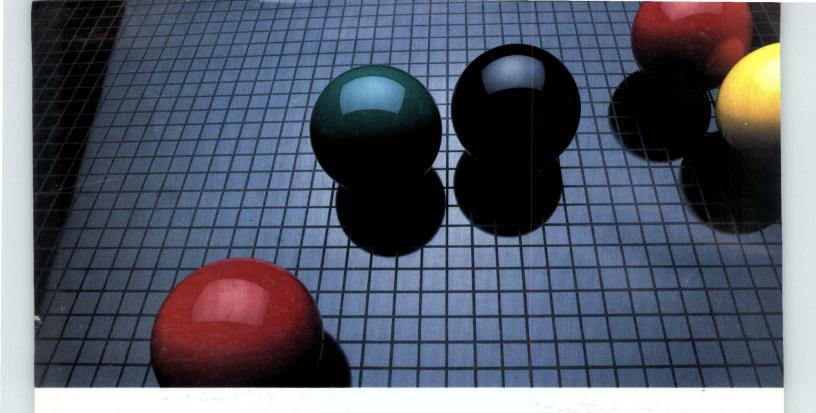

This month's cover was prepared by Mark Lindquist on the Digital Effects Video Palette III and D-48 high resolution camera system. The data base was constructed by Joe Pasquale. The cover was based upon material supplied by United Technologies Mostek.

#### System components

233 Test & development:

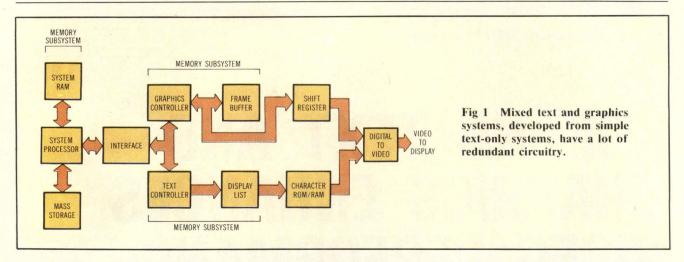

Workstation graphics architecture lightens programming load

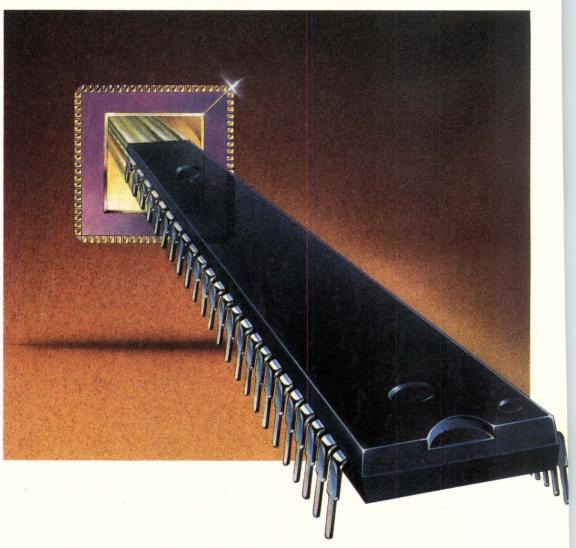

234 Integrated circuits:

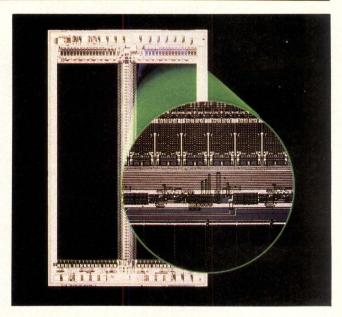

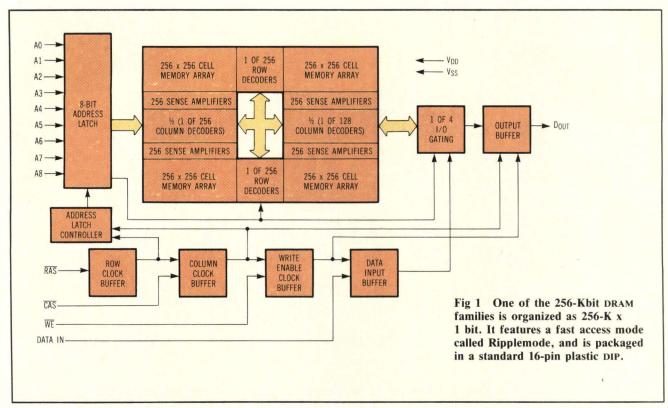

Dynamic RAMs deliver 256-Kbit power using CMOS process

234 Computers:

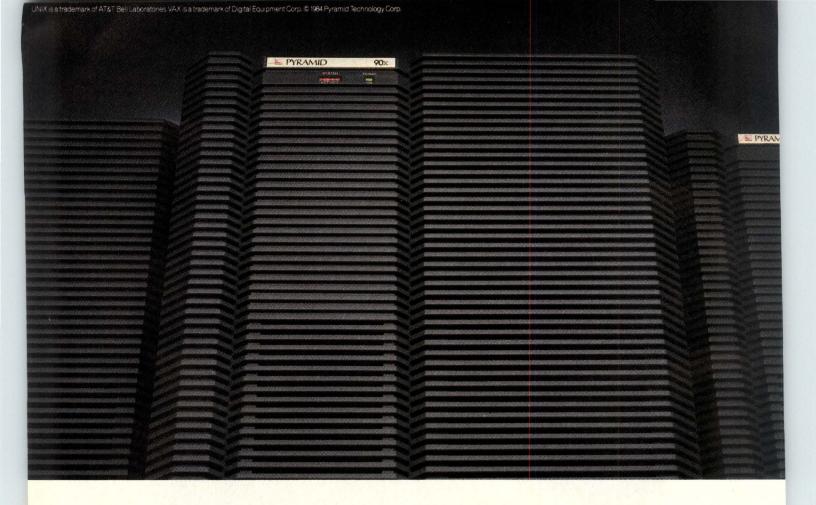

High end supermini melds Unix with marked speed

236 Software:

Structured analysis eases project specification

236 Computers:

Unix systems provide long-term solutions with upgradeability

237 Memory systems:

Winchester merges with controller for single-board integration

237 Integrated circuits:

Gate array series reaches 11,000-circuit density

#### **Departments**

5 Up front 277 Designer's bookcase

13 Editorial 279 System showcase

23 Letters to the editor 280 Advertisers' index

273 Literature 283 Reader inquiry card

274 Calendar 283 Change of address card

COMPUTER DESIGN © 1984 (ISSN-0010-4566) is published monthly, with a thirteenth and fourteenth issue respectively in June and October by PennWell Publishing Company, Advanced Technology Group, 119 Russell Street, Littleton, MA 01460. Second-class postage paid at Littleton, MA 01460 and additional mailing offices. COMPUTER DESIGN is distributed without charge to U.S. and W. Europe-based engineers and engineering managers responsible for computer-based equipment and systems design. Subscription rate for others is \$50 in U.S.A. and \$75 elsewhere. Single copy price is \$5.00 in U.S.A. and \$7.50 elsewhere. Microfilm copies of COMPUTER DESIGN are available and may be purchased from University Microfilms, a Xerox Company, 300 North Zeeb Road, Ann Arbor, Michigan 48106. POSTMASTER: CHANGE OF ADDRESS-FORM 3579 to be sent to COMPUTER DESIGN, Circulation Department, P.O. Box 593, Littleton, MA 01460 (USPS 127-340).

Officers of PennWell Publishing Company, 1421 S. Sheridan, Tulsa, OK 74101: P. C. Lauinger, Chairman; Philip C. Lauinger, Jr., President; Joseph A. Wolking, Senior Vice President; H. Mason Fackert, Group Vice President; Carl J. Lawrence, Group Vice President; V. John Maney, Vice President, Finance; L. John Ford, Vice President.

WBPA KABP

<sup>©</sup> COMPUTER DESIGN is a registered trademark. All rights reserved. No materials may be reprinted without permission. Phone (617) 486-9501.

## It's easy to make points when you're a pro.

**POINT...** The Houston Instrument DMP-41 plotter meets the needs of the serious or professional user, yet it's easy to operate.

point . . . C/D size format, comprehensive front-panel controls and sophisticated firmware are all tailored to the needs of the surveyor, drafter, oceanographer, geophysicist and land developer . . . to name but a few. You can generate superior architectural elevations, contour maps, circuit-board layouts and assembly drawings quickly and accurately on bond, vellum or synthetic media.

POINT . . . The DMP-41 is configured to work with micros and minis, and has the capacity to take advantage of a mainframe's increased capability. RS-232-C interfacing is standard, with alternate protocols available. The DMP-41 is easy to live with, adhering to FCC Class B requirements. UL listing pending.

**POINT** . . . Minutely defined step size and high-resolution logic—combined with robust drives and optimized pen ballistics enable you to create plots of high precision and surpassing quality.

POINT . . . The Houston Instrument DMP-41 is one of your most cost effective considerations.\*

For the name, address and phone number of your nearest representative, write Houston Instrument, P.O. Box 15720, Austin, TX 78761. Phone 512-835-0900, or

800-531-5205 if outside Texas. In Europe contact Houston Instrument Belgium NV., Rochesterlaan 6, 8240 Gistel, Belgium. Tel 059-27-74-45, tlx 846-81399.

\*suggested US retail \$2,995

#### **UP FRONT**

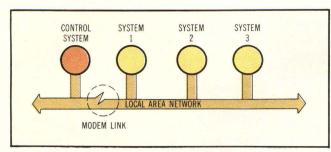

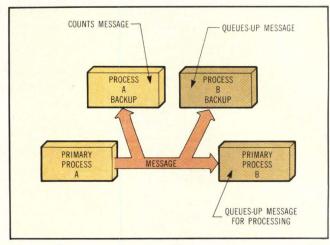

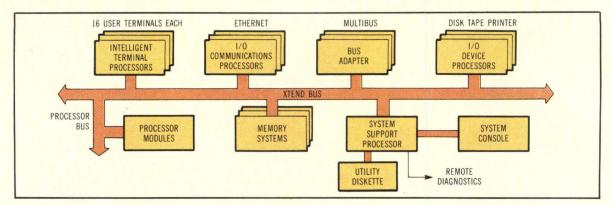

#### System will attack fault-tolerant price barrier

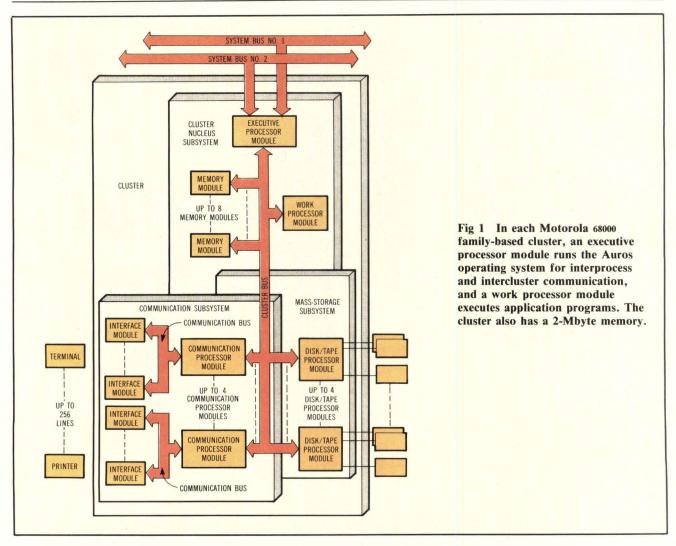

Founded less than a year ago, EnMasse Computer Corp (Acton, Mass) is in the late stages of developing a 32-bit Unix-based multiprocessor system with fault-tolerant features. The system is currently scheduled for introduction during the first quarter of 1985 and is list priced below \$50,000 for a basic configuration that will support up to 32 users. Customers will be able to expand on the basic hardware to build a single system that can support up to 768 user terminals while handling multiple tasks simultaneously, all with no sacrifice in processing speed. Incremental cost for adding each new user is claimed to be reduced to as low as \$500. The computer runs under Unix System V, the emerging de facto standard operating system for program portability. EnMasse Link architecture creates a high speed network of file processors and distributed application processors. The system will have gateways to other EnMasse computers, IBM and DEC hosts, and IBM PC and compatible workstations. The system is designed for distributed online transactions, office, communications, and other multi-user applications.—J.H.

#### Low cost PC video imaging system performs at less than 1 s

A single-board, high performance frame grabber-based subsystem to be released within the next month or two by Data Translation (Marlboro, Mass) fits into any expansion slot of an IBM PC or PC/XT and provides realtime video digitization and display. The DT2803 hardware will sell for about \$1500 and operates with realtime video I/O software called Videolab. Comparison benchmark tests for the board alone in a PC indicate a required time of 10 min for a 3 x 3 convolution pixel operation. With a math coprocessor board in place, the operation required only 50 s. However, the frame grabber board is designed to operate optionally with an array processor board, to be supplied by Sky Computers (Lowell, Mass). With that board, the operation requires 1 s or less.—S.F.S.

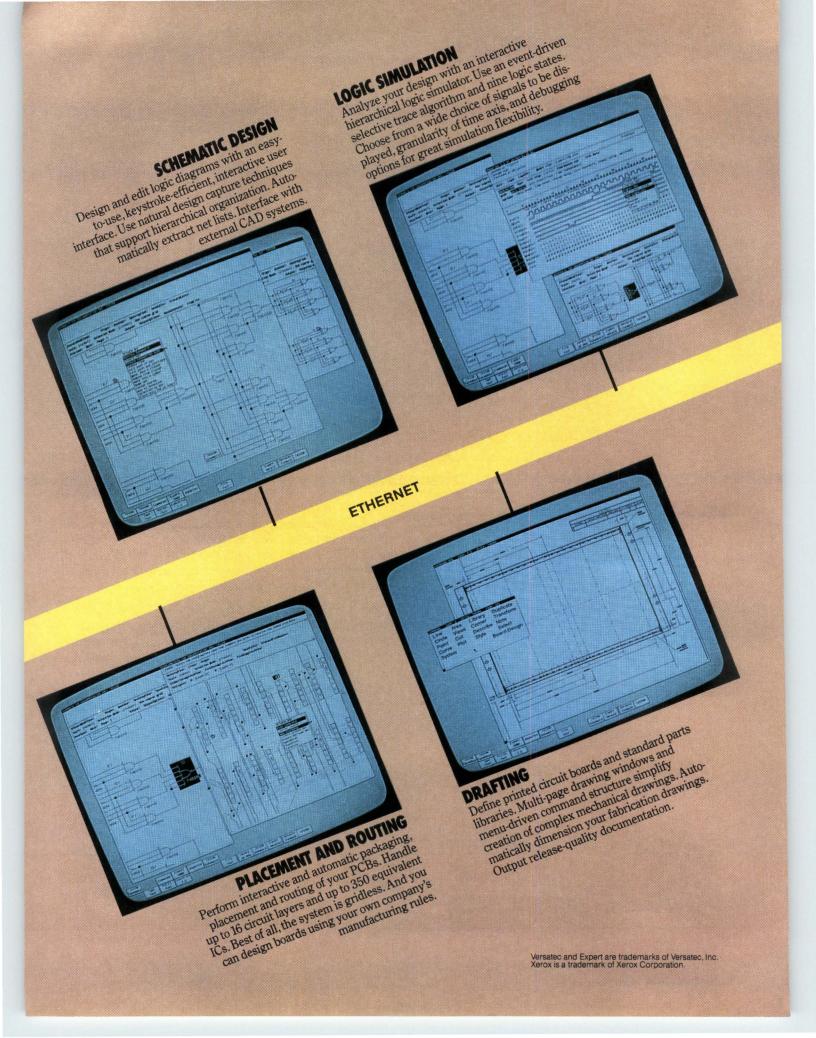

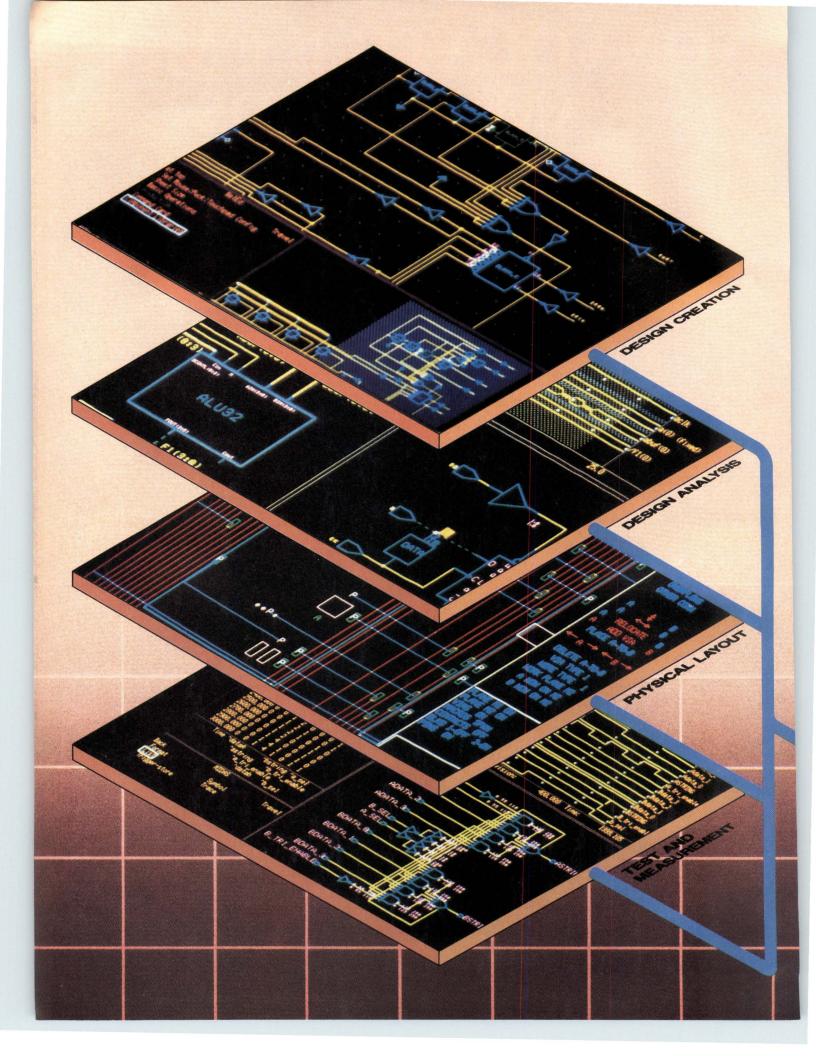

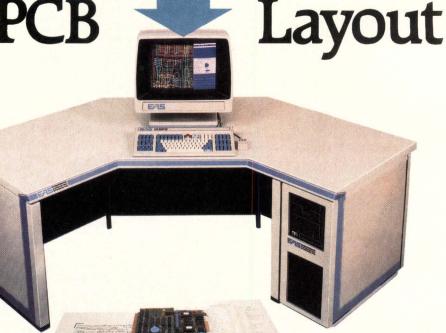

#### Automated design processes—heading toward complete integration?

In the CAD/CAE/CAM environment, some equipment offers only schematic capture, while others will not only help you with the design, but will carry the process all the way through to production. The most apparent trend, as noted at the recent Design Automation Conference, is that the industry is heading for total integration of the design process, from chip to system level. Even such ATE firms as GenRad (Concord, Mass) and Teradyne (Boston, Mass) are becoming links in the design chain and offer entries that provide logic design simulation throughout an entire design evolution, as well as the test generation to improve all testing efficiencies. These procedures include program generation testing, prototype testing, and digital IC manufacturing testing. While integration seemed to be the main theme of the conference, the wide range of available hardware and software indicates that everyone can become involved in design automation. The low end process, usually running on the IBM PC, offers the potential to speed the design cycle at minimum cost. At the high end, Control Data Corp provides complex software that includes an integrated data base and engineering data library. The power behind this approach is that it allows simulation of complete systems rather than of individual components.—M.B.

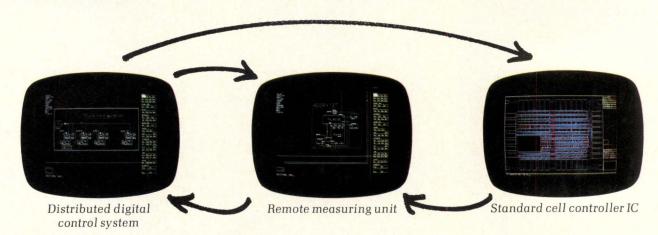

#### Design tools simulate entire system

Design tools that Control Data (Minneapolis, Minn) engineers used internally to design ICs for the CYBER 200 series supercomputers are now available as commercial products. The company's Modular Integrated Design Automation System (MIDAS) consisting of logic simulation, fault simulation, and layout has been developed and continually enhanced by Control Data for the past 10 years. MIDAS operates on the company's CYBER computers and uses the Cybernet data services network to transfer integrated data bases and engineering data beween stations. Designers can thus simulate complete systems rather than being limited to simulating individual components. Control Data engineers have designed boards with 120,000 logic gates using MIDAS, a hundred-fold increase over current densities. MIDAS' shared data base allows the designer to make numerous design and layout changes before a board is committed to fabrication. Control Data claims that its engineers routinely perform system-level simulation following completion of the physical design steps for system complexities up to 300,000 gates. A minimum, fully configured system based on the CYBER 810, with all the necessary hardware and MIDAS software applications, costs \$500,000.—N.M.

#### NCC '84 melts away in Vegas

Although the American Federation of Information Processing Societies was eager to predict a large attendance in its promotion for NCC '84, no one at that organization will now release even an estimate of the final attendance figures. Preconference estimates from AFIPS, the central organization among the several sponsors of all National Computer Conferences, were for a minimum of 100,000 attendees. Whether it was the expected oppressive heat of Las Vegas in July or any of a seemingly endless number of reasons offered by those persons who did attend, that original figure was not even nearly met. Estimates from among a number of press and exhibitor personnel who have been to many National, Spring Joint, and Fall Joint Computer Conferences agreed that the final attendance was probably not over 60,000—and even that may be a generous figure. Additionally, lastminute cancellations left several booth spaces unfilled, a true novelty for NCC in the past several years. Whatever the true reasons were for this year's ultralow attendance, NCC '85 will be in Chicago—and although it again will occur in July, no one presumably will be able to logically blame the heat if people or exhibitors stay away—S.F.S.

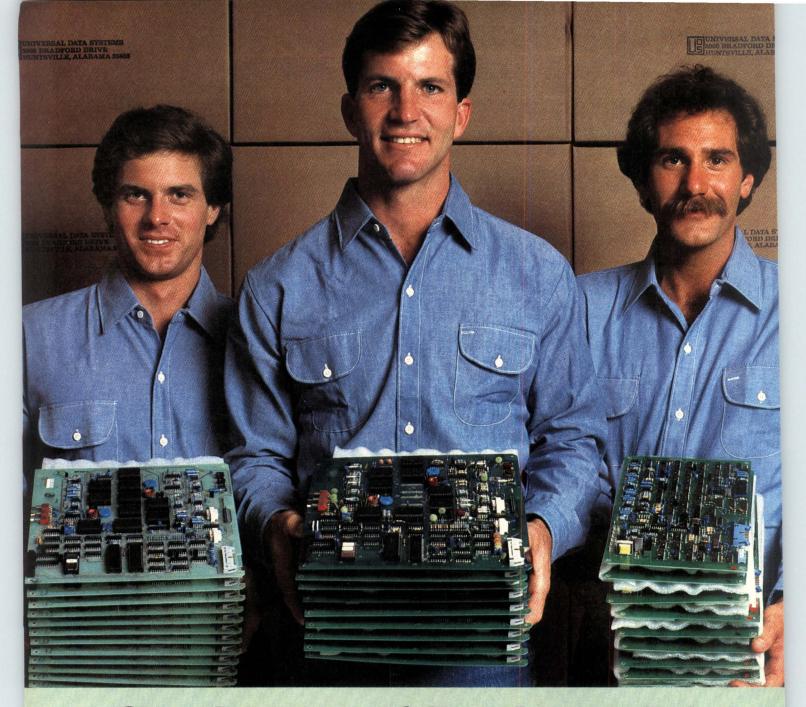

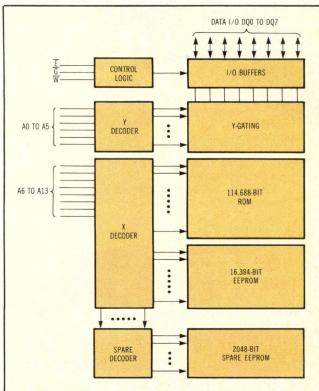

#### Semicustom IC design—a movable service

In what amounts to taking the semicustom IC design business to the customer instead of having the customer seek out a semicustom chip vendor, RCA Solid State (Somerville, NJ) has signed an agreement with distributor Hamilton-Avnet (Culver City, Calif) to both design and sell RCA's COSMOS gate array and standard cell ICs. H-A plans to open 12 design centers across the United States over the next year to assist users in the logic design of semicustom chips. Customers will be able to implement the completed logic design and debug the chip at workstations set up at the design centers and then forward the MIMIC data base to RCA's manufacturing facilities for fabrication. In this way, the customer will be spared the necessity of learning the rest of the design automation tools and will only need to learn the MIMIC software. This market is expected to reach a \$2 billion volume for gate arrays and standard cell ICs by 1987, according to Integrated Circuit Engineering Corp, a research firm based in Phoenix, Ariz.—N.M.

## Like DEC's.

\$8,845 system price\*

256 KB minimum... up to 4 MB!

Media and software compatibility with DEC's RX02 8" floppy (vs. Micro/PDP-11's non-compatible 51/4" floppy)

8-quad slot Q-BUS card cage

Supports RT-11, RSTS, RSX-11M-PLUS, UNIX, and TSX-PLUS

> Two fans in card cage area (vs. one in Micro/PDP-11)

> > Cartridge tape capability

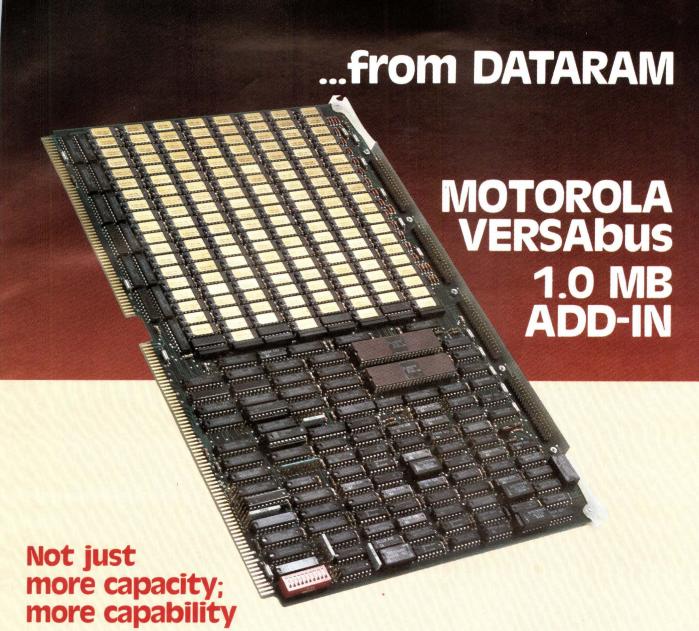

DATARAM

1.0 MB floppy disk back-up (vs. 2 x 400 KB for Micro/PDP-11)

RL02-compatible 51/4" Winchester disk; 10 MB, 20 MB, or

40 MB capability

Only better.

You can buy DEC's Micro/PDP-11 with its impressive You can buy DEC's Micro/PDP-11 with its impressive array of features...or you can get Dataram's A22 —an LSI-11/23 based minicomputer that gives you a whole lot more...for a lot less dollars! Like an 8" RX02-compatible floppy. 40 MB 5½" Winchester and ½" cartridge tape capability. And two fans that provide push-pull air flow in the card cage area. For more information, forward this coupon to us, or, for faster response, call (609) 799-0071.

☐ Send information.

☐ Contact me immediately.

Name

Company

Address

State

Phone

Dataram Corporation, Princeton Road, Cranbury, NJ 08512

\*\$8,845 is single-quantity domestic price for A22 with LSI-11/23, 256 KB, 10 MB Winchester and RX02-compatible 8" floppy.

DEC, LSI-11, Micro/PDP, PDP, RSTS, RSX, and RT-11 are trademarks of Digital Equipment Corporation. TSX-PLUS is a trademark of s&h computer systems, inc. UNIX is a trademark of Bell Laboratories.

CIRCLE 4

#### AI development tools available for the professional personal computer

An expert system development package using the Professional Computer from Texas Instruments (Dallas, Tex) incorporates all necessary features for a designer to prototype and develop sophisticated commercial applications. The Personal Consultant development tools are aimed at users who are interested in developing rule-based expert systems at their desktops without the need to learn the popular AI Lisp language. TI researchers have coded their program using a similar data file format to the EMYCIN developed at Stanford University. As opposed to programming MYCIN in Lisp, users of the Personal Consultant can write their rules in a Basic-like rule specification language. The tools will be available in the last quarter of 1984 for \$3000 a copy. A 3-day training course is also available for \$1500. In addition, the package can be obtained bundled with the Professional Computer for \$15,500. Creating end-user knowledge bases from the tools can be done for a one-time license fee of \$25,000 and a royalty fee of \$25 for each application copy.—N.M.

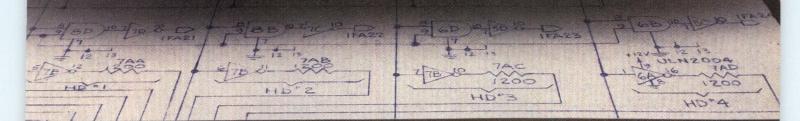

#### PDI handles data transfer PDO

A new twist in the standard interface situation, the Parallel Device Interface (PDI) promises to bridge the gap between high and low level devices. To accomplish this, PDI, a level 2 definition of the Intelligent Peripheral Interface (IPI) specification, will support data transfers occurring at rates between 15 and 80 Mbits/s. Promoted by Control Data Corp (Minneapolis, Minn) and supported by Emulex (Costa Mesa, Calif), the specification provides for maximum transfer rate over a maximum cable length, simplifies controller design, and promotes future compatibility. In addition to supporting the specification, Emulex is managing the development of a chip to implement PDI and thus ensure compatibility to controllers. PDI is expected to see red line print this month and to achieve blue line by the end of this year. First products should be forthcoming by mid-1985.—P.K.

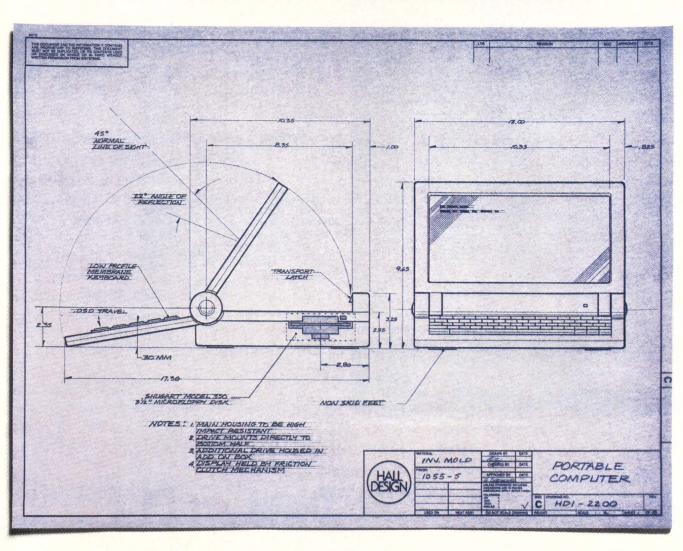

#### Scuttlebutt heard in dark corners

Rumors and general data wafting around the environs of the recent NCC '84 hint that a major manufacturer is readying a featherweight portable computer—so light, in fact, that it needs no handle. Details are sparse, save that it is said to incorporate an LCD, two sub-51/4-in. disk drives, and the obligatory keyboard. There's also no handle as to price and delivery. Keep tuned—J.H.

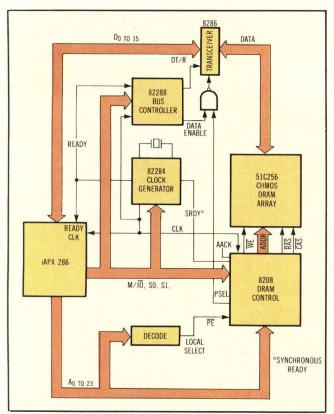

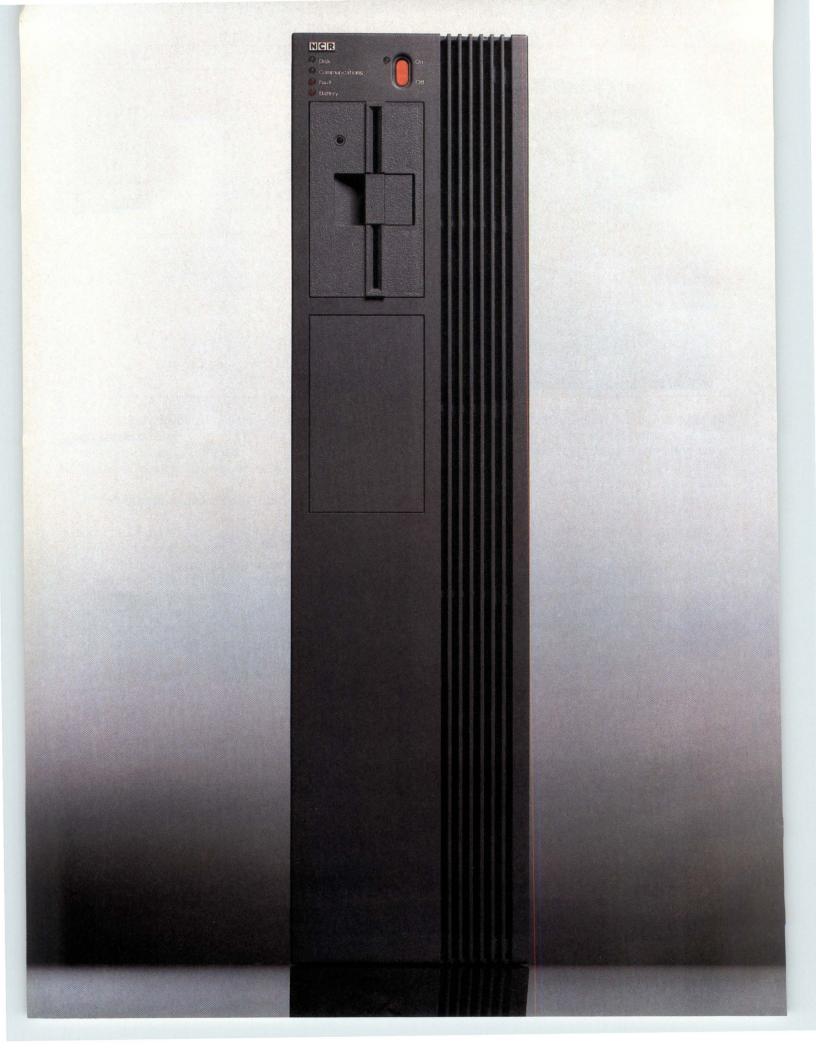

#### Unix starts to appear in smaller packages

Efforts to provide real Unix environments to an ever-increasing community of users are meeting with some success, thanks to some of the newer microprocessors and advances in memory technology. At the same time, this push is spurring developments in other areas. Unix means disk storage, so developments in half-height, large capacity Winchester drives are rising to meet the challenge. Advanced Storage Technology and Qume Corp (both of San Jose, Calif) have announced half-height 5½-in. Winchesters using plated media. The Qume line ranges in capacity from 13 to 40 Mbytes, and the AST from 61 to 220 Mbytes. Processors such as the Intel iAPX 256 and the Motorola 68010, which support virtual memory, are making it possible to build a range of multi-user, Unix-based systems that can support different numbers of users but that aim for a per-user cost of about \$2500. With the small, high capacity drives becoming available, these systems should appear in even smaller packages as well.—T.W.

## Crack the Nut.

The LAN nut.

When you're developing a LAN-based computer system, you're faced with a tough nut to crack. You need to know what's going on in your Local Area Network system. Many computers are carrying on many conversations. Simultaneously. And at speeds 10,000 times faster than traditional data communications. How do you test it? How do you debug it? How does

the system really perform? Excelan can help you crack that nut with the Nutcracker $^{TM}$ , the world's only comprehensive analyzer/simulator for Ethernet systems. Packaged as an integrated workstation, the Nutcracker provides advanced

LAN instrumentation hardware capable of making real-time diagnostic decisions at 10 million bits per second. Also included is an 8086-based CPU, about 1 MB of RAM, a 20 MB disk, a 600 KB floppy, keyboard, 12" CRT and 100 cps external printer, and complete menudriven software that brings the power of the Nutcracker to you.

With the Nutcracker connected to the Ethernet cable, you're in control. You can create

"Excellence in Local Network Technology"

2180 Fortune Drive San Jose, California 95131 (408) 945-9526 TELEX 176610 and detect pathological conditions for shake-down testing. Powerful filtering facilities allow you to extract precise packet substreams for triggering and tracing functions to find those elusive bugs. You can generate traffic for simulation of various load conditions. And high resolution time-stamping means you can track system performance against this regulated traffic load.

Increase your productivity, speed development time, and get your network system up and running — with confidence in it's performance and integrity.

Join computer industry leaders. Crack the LAN nut with the Excelan Nutcracker.

CIRCLE 5

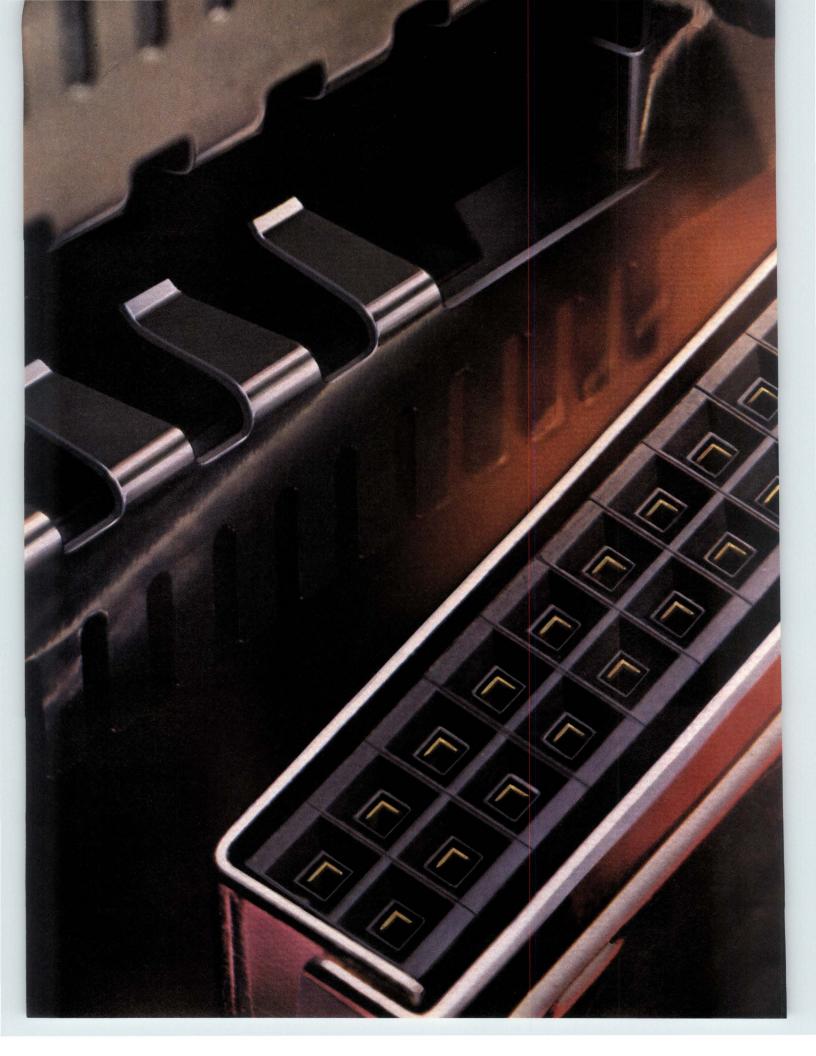

## HERE'S A TANDON DISK DRIVE WITHOUT TANDON-BUILT PARTS.

As you can see, the Tandon theory of vertical integration doesn't leave much room for outside manufacturers. That's precisely what we liked about it from the start. And we've been right about our hunch.

We're the leading manufacturer of microcomputer random access disk drives in the world. We didn't get here by following in the paths of our competitors.

Instead of piecing together someone else's parts, we manufacture our own. We know every detail about every part in all our drives. From manufacturing the button head for the recording head assembly, to producing our own plated media, we're involved with it all. As a consequence, Tandon-built parts comprise 80% of the cost of our drives. There's a lot to be said for that.

Quality, for one thing, is a lot easier to control. The toughest Tandon specifications are met every step of the way. Revisions and improvements can be implemented when they're needed, where they're most effective, resulting in higher reliability.

That tight control makes it easier for us to keep our costs down, and manufacturing yields high. Per unit savings mean the lowest overall prices available. Which is obviously to your advantage.

And since we're a supplier as well as a manufacturer, we'll get your order to you quickly. We'll always deliver the drives you need when you need them.

We've recently made a move to expand our vertical integration even further. Our new \$5 million facility produces plated disks for use in all of our Winchester drives. In keeping with Tandon quality, cost-effectiveness, and advanced technology.

All this is what we're calling vertical integration. A strategy we initiated before many of our competitors even existed. But what it comes down to for you is a reliable, high-performance disk drive at the lowest of possible costs.

And, all theory aside, you just won't find a better combination than that.

## The Driving Force Behind the SMALL COMPUTER INDUSTRY.

Tandon Corporation, 20320 Prairie, Chatsworth, CA 91311. (818) 993-6644, TWX: 910-494-1721, Telex: 194794. Regional Sales Offices: Boston (617) 938-1916 • New York (201) 851-2322 • Atlanta (404) 934-0620 • Chicago (312) 530-7401 • Dallas (214) 423-6260 • Irvine (714) 669-9622 • Santa Clara (408) 727-4545 • Frankfurt, West Germany 6107-2091, Telex: 411547 • London, England (0734) 664-676, Telex: 848411. Distributors: Hall-Mark, Kierulff, Schweber.

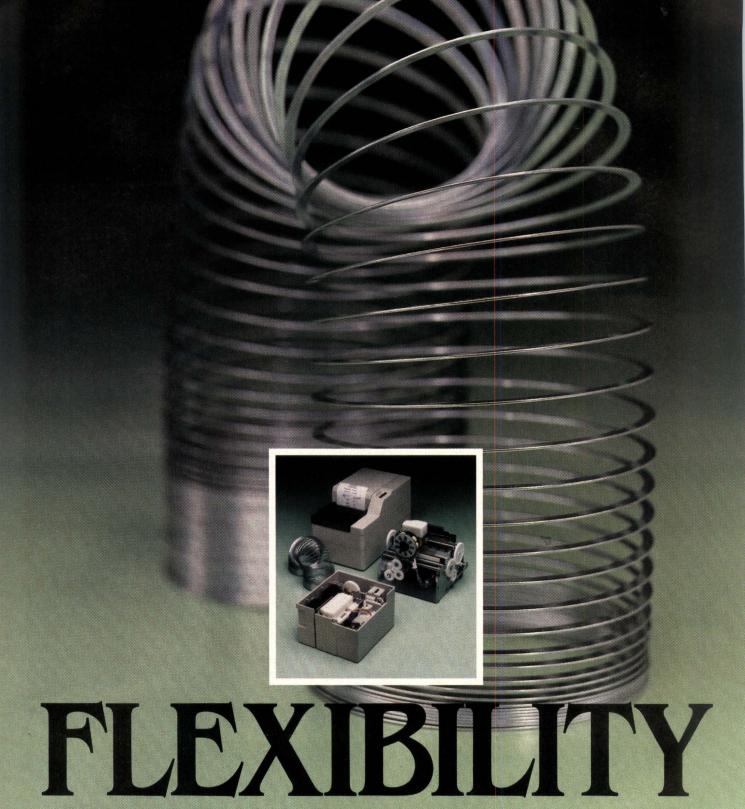

## UNIX IS A DINOSAUR CP/M & MS-DOS ARE TOYS

**MULTI SOLUTIONS PRESENTS**

## THE WORLD'S FIRST 4th GENERATION

**OPERATING SYSTEM**

A SERIOUS OPERATING SYSTEM SI

#### FOR TODAY AND TOMORROW

- PORTABLE

- MODULAR

- MULTIUSER

- MULTITASKING

- MULTI PROCESSING

- PARALLEL PROCESSING

- 64 CHARACTER NAMES

- 3 COMMAND PROCESSORS

- REAL TIME

- NETWORKING

- DISTRIBUTED PROCESSING

- HIERARCHICAL DIRECTORIES

- KEYED FILES

- · ISAM

- · VSAM

- B-tree

- RECORD LOCKING

- UNIX SOURCE COMPATIBLE

- WINDOWING

- BIT MAPPED DISPLAYS

- FULL SCREEN MANAGEMENT

- FULL SCREEN EDITING

- FULL MEMORY MANAGEMENT

- VIRTUAL MEMORY

- SEMAPHORES & LOCKS

- EXTENSIVE UTILITIES

- AND MUCH, MUCH MORE

S1 IS THE ONLY OPERATING SYSTEM WORTHY OF THE TITLE:

"THE NEXT WORLD STANDARD."

#### **ONLY S1 DOES IT ALL.**

NO OTHER OPERATING SYSTEM COMES CLOSE. CUTS DEVELOPMENT TIME FROM MAN YEARS TO MAN MONTHS.

MULTI SOLUTIONS INC. Multi Solutions, Inc.

Multi Solutions, Inc. 123 Franklin Corner Rd. Lawrenceville, N.J. 08648 609-896-4100 Telex: 821073

Please send for our FREE S1 Book or Call 609-896-4100

IN TIME, ONLY THE BEST WILL SURVIVE: S1

<sup>\*</sup>Reg. Trademarks: CP/M of Digital Research; Unix of Bell Laboratories Trademarks: MS-DOS of Microsoft, Inc.

#### SHOWTIME IN LAS VEGAS

As I write this, it is July and I am at the National Computer Conference in Las Vegas. The people at our office in Massachusetts tell me my editorial is late and that I have to rush it to them today. But, the temperature hit 110 degrees today, and my usual problem of technostress has been replaced by a new problem—heat stress.

This town appears to be controlled by its cab fleet owners. Because parking facilities are inadequate for major conventions, conventioneers are forced to the streets in search of cabs. This week, people waited an hour or more for cabs, and then were jammed, four at a time, into cabs without air conditioning. As if this weren't enough, some of the drivers had the nerve to collect the full fare from each rider. Any city that is serious about attracting convention business should have corrected its transpor-

tation problems long ago. But then, as we heard today from some of the casino owners, Las Vegas doesn't like conventioneers—especially those from our industry—because they don't gamble enough. Did the casino people honestly believe that otherwise-intelligent engineers came to Las Vegas in July to have fun? How could they really believe that entrepreneurs and salespeople in the fiercely competitive computer industry would need the extra risk and excitement of the crap tables to spice up their lives?

Besides, physical survival in Las Vegas can be quite a gamble. In fact, if you have ever wondered what happens if the power fails here, I can now give you a first-hand account. When the subject is under discussion, the standard response is "Don't worry, they have backup power." Well, after 60 mph winds downed some city power lines, I was able to see "Plan B" in action.

Yes, the hotels do have backup power; but that doesn't begin to supply the total need. So, with a characteristically inverted set of priorities, the gaming tables and slot machines took precedence over "less important" things like air conditioning and elevators.

I think it's obvious that we don't need this city and this city doesn't need us. So, why are we here? Unfortunately, Las Vegas is one of the few cities with convention and hotel facilities extensive enough to accommodate a show the size of NCC. An added problem is that this year NCC is competing with other events such as the Olympic games and the national political conventions. As a result, Las Vegas grabbed most of the big computer shows this year. Thus, we were here in March for Interface, we are here now for NCC, and some of us will be here again in November for Comdex.

There are no easy solutions to the problems posed by trade shows and conferences. There are too many of them and they are becoming too large. Ironically, some of the better organized ones are already being strangled by their own success. We can't expect the organizers or exhibitors to voluntarily cut back on their activities. That would be conceding victory to their competitors. The shakeout will be precipitated only by a market boycott—and we are the market. We have to vote with our feet and start attending only those conferences that are vitally important to us—and at the best times and in those locations where the conditions are most tolerable. Therefore, I hereby serve notice that, although I will be attending Wescon in Anaheim, I will not be attending Comdex in Las Vegas. Other editors will represent our magazine, but I won't be one of them—we are cutting back on our coverage.

Michael Elphick Editor in Chief

In Elephia

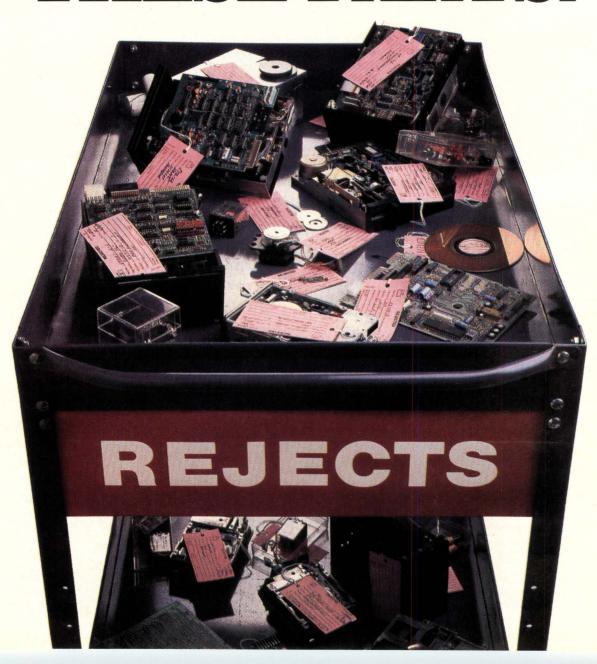

# YOU WON'T FIND MANY SHUGART DRIVES AROUND THESE PARTS.

You find Shugart new generation drives where they were built to be. In all kinds of systems. Under all kinds of conditions. Running. And running and running.

Setting a world standard for quality. A standard that doesn't allow room for failure. Because

you don't.

To insure the reliability of your system, we begin with our suppliers. They go through a lot. Learning and qualifying, even building drives themselves.

We also involve our manufacturing engineers. And our quality control experts. From the very beginning. The design stage.

With their full collaboration, every new drive is designed for top quality. Unbeatable reliability. And ease of assembly. Using the fewest number of parts possible.

In other words, the same uncompromising quality you design into your system is designed and built into every new Shugart drive. Right from the start. So you can count on consistent reliability. For example, 20,000 hours MTBF for new generation Winchesters.

Of course, every Shugart drive is subject to the most stringent testing and inspection at every stage. But inspection doesn't insure quality. At Shugart, we believe there's only one way to insure a reliable product. By eliminating the cause of failure from the product design.

At Shugart, quality is designed

in. Not inspected in.

Let us prove it. Write for our white paper on quality to Shugart Corporation, 475 Oakmead Parkway, M/S 3-5, Sunnyvale, CA 94086. Or call, (408) 737-4360.

**Shugart**Right from the start.

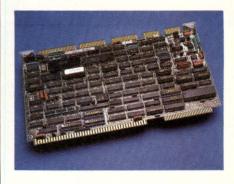

#### UNFORGETABLE MEMORIES MULTIBUS — QBUS

#### **MULTIBUS MEMORY** 512KB TO 2MB EDC

- Error Detecting and Correcting (EDC)

- Faster Access Times

#### SINGLE QTY. PRICE

W/EDC Without/EDC 512KB 895.00 1495.00 2MB 4775.00 5775.00

#### **O-BUS MEMORY** 256KB TO 4MB

- Battery Backup Mode

- Block Mode DMA, ECC or Parity

- Works with LSI-11, J-11, MicroVAX SINGLE OTY. PRICE

| 1MB   |   |  |  |  |  |  |  |  |  |  | 1 | 975.00 |

|-------|---|--|--|--|--|--|--|--|--|--|---|--------|

| 256KB | , |  |  |  |  |  |  |  |  |  |   | 525.00 |

OFFERING QUALITY WITH AFFORDABLE PRICING

J-11, LSI-11, MicroVAX, Q-BUS are trademarks of Digital Equipment Corporation. MULTIBUS is a trademark of Intel Corporation.

CIRCLE 9

KELTRON has the answers in High Voltage Power Supplies for the color or monochrome OEM ...

Custom design HVPS for the OEM **KELTRON CORPORATION**

See what Keltron has to offer!

225 Crescent Street, Waltham, MA 02154 • (617) 894-8700

#### **COMPUTER DESIGN**

The PennWell Building, Littleton, MA 01460, Tel: (617) 486-9501 Editorial/Executive Offices

Editor in Chief, Michael S. Elphick

Managing Editor, Sydney F. Shapiro Senior Editor, John Bond Senior Editor, Peg Killmon Special Features Editor, James W. Hughes Senior Associate Editors. Malinda E. Banash, Deb Highberger Associate Editor, Jack Vaughan Assistant Managing Editor, Leslie Ann Wheeler

Copy Editors,

Helen McElwee, Leah A. Rappaport, Nancy E. Purcell, Jane E. Shattuck Editorial Assistants, Julia E. Cote,

Lisa M. Stephens New York Field Office: 230 Park Ave, Suite 907 New York, NY 10169, Tel: (212) 986-4310 Senior Editor, Nicolas Mokhoff Special Features Editor, Harvey J. Hindin Western Field Office: 540 Weddell Dr, Suite 8 Sunnyvale, CA 94089, Tel: (408) 745-0715 West Coast Managing Editor, Tom Williams

Senior Editor, Bill W. Furlow Field Editor, Joseph A. Aseo Editorial Assistant, Robin Mock

Production Director, Linda M. Wright Production Manager, Philip Korn Art Director, Lou Ann Morin Technical Art, Designline Ad Traffic Coordinator, Debra Friberg Printing Services, Padraic Wagoner

Marketing Director, Robert A. Billhimer Circulation Director, Robert P. Dromgoole Promotion Director, Steve Fedor Marketing Services/PR Manager, Linda G. Clark

Publisher, Frederic H. Landmann

#### **PennWell**

Advanced Technology Group 119 Russell St, Littleton, MA 01460 Tel: (617) 486-9501

H. Mason Fackert, Group Vice President Saul B. Dinman, Editorial Director John M. Abernathy, MIS/DP Director Patricia M. Armstrong, Administrative Services Manager

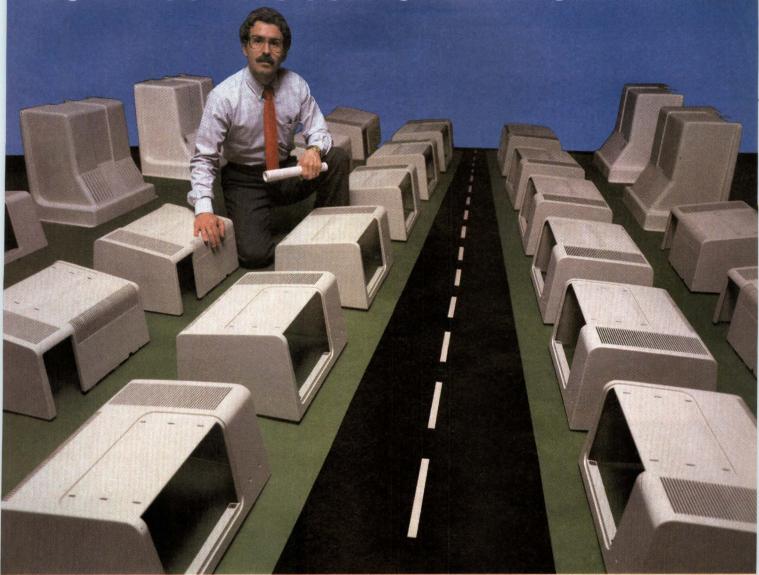

# Before TEMPLATE, graphics software that ran on mainframes and minis and micros all looked like this.

Which is to say, nonexistent. Some manufacturers make graphics software packages for main-

frames. Others for minis. Still others make it for micros. But no one made high-level graphics software that ran on all three.

TEMPLATE just changed all that. By becoming the *only* high-level graphics software available on micros, minis and mainframes. And it took our extensive experience in graphics software to do it.

Now all computer-using design engineers and scientists can utilize the industry's finest software. And bring mainframe applications right to the bench. Or vice versa. Which means TEMPLATE's device-intelligence and computer-independence is even further enhanced. And you get the graphics functionality for mechanical and electrical CAD,

scientific analysis, seismic work, VLSI, and molecular modeling that puts TEMPLATE in a class by itself. In

any environment, whether it's batch or interactive, 2D or 3D.

TEMPLATE features table-driven architecture, 3D software display lists, metafile capability over 250 user-callable FORTRAN routines, workstation model, post processing capability, run-time selection, and complete support functions.

So when you're looking for graphics software that'll run on *all* your computers, call Megatek.

And find out all about TEMPLATE.

The product that just gave micros, minis, and mainframes a

new computer graphics image.

Making History out of State-of-the-Art

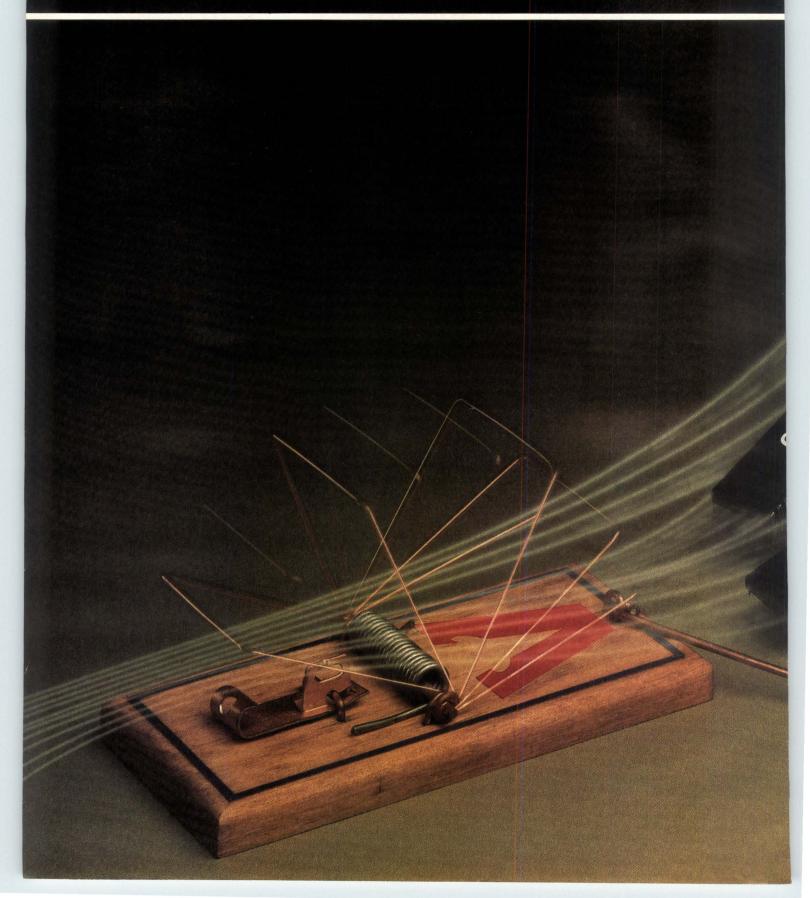

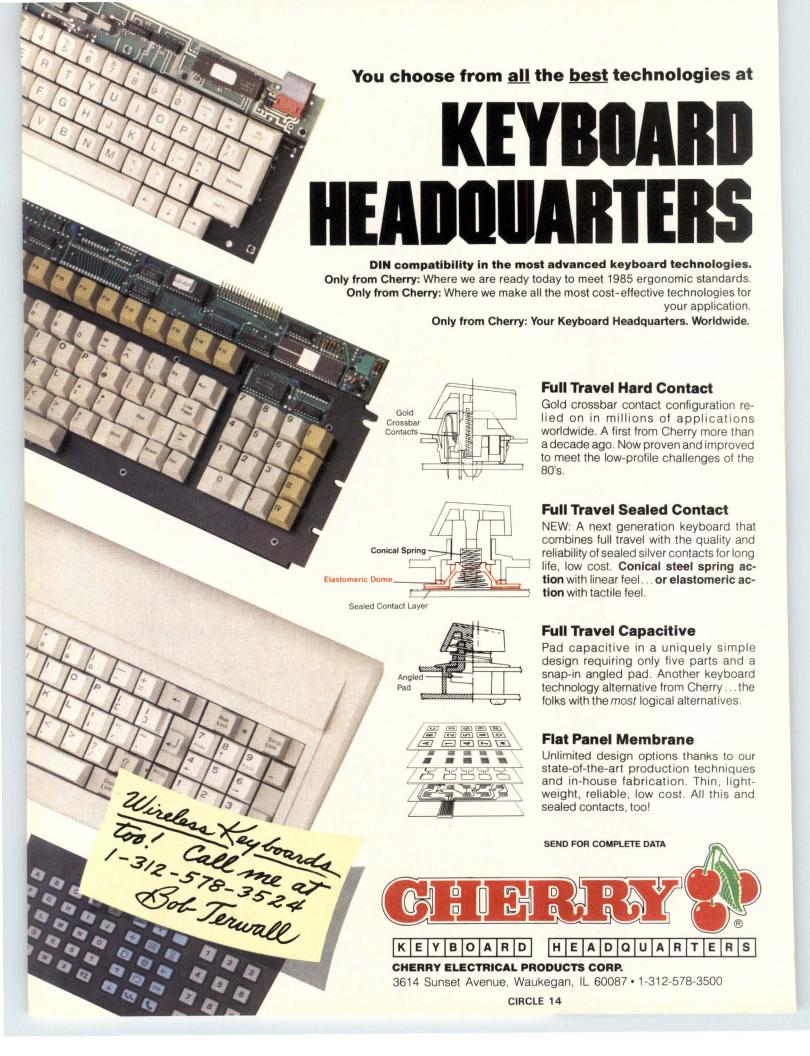

#### You'll never get trapped into dead-end designs with

#### Zilog's high-speed Z80B CPU's and Peripherals.

Here's more proof that nobody does more to extend the life of your 8-bit designs than Zilog. Because now you can increase 8-bit Z80\* performance up to 6 MHz with the high-speed Z80B CPU and its family of peripherals. You can join the hundreds of design engineers that have already tested this claim with winning results. Or wonder...

Is there something here they know that you don't? Like the fact that the Z80B CPU has the same 158 instruction set and the elegant registers and interrupts that you're used to working with, but runs them 50 percent faster than the Z80A chip?

That the Z80B processor is completely software compatible with the rest of the Z80 family, permitting you to upgrade to higher performance without getting trapped into software redevelopment? That software compatibility also means you can use the Z80B device in co-processing and/or multi-processing environments along side our other Z80 processors?

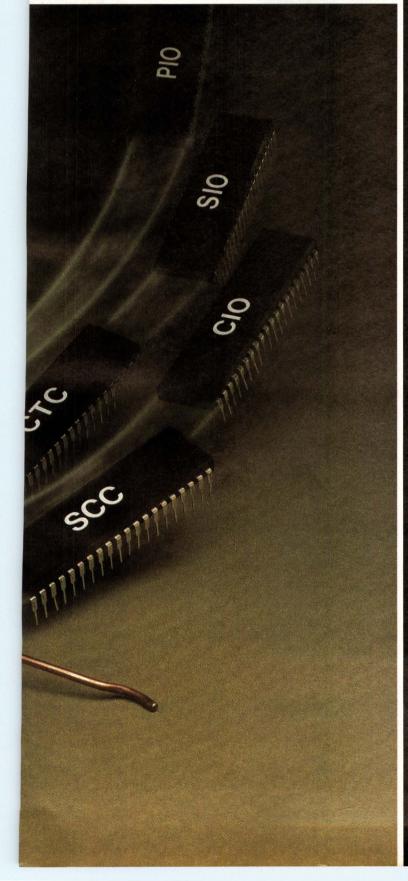

And consider the fact that you can surround our Z80B CPU's with a complete family of Z8400 and Z8500 peripherals and really boost system performance. They help you keep your parts and space requirements to a minimum and increase system throughput because we build more functions into every device. The peripherals include a PIO, a CTC, an SIO, an SCC, an FIO, an FIFO, a CIO, and a UPC.

For complete specifications and applications data on the Z80B and peripherals, fill out the coupon and mail to: Zilog, Inc., Components Tech. Publications, 1315 Dell Avenue, MS C2-6, Campbell, CA 95008. Or call our TOLL FREE Literature Hot Line at 800-272-6560. For information on Zilog's other components, call (408) 370-8000.

Z80 is a registered trademark of Zilog, Inc.

| ☐ I'd like more inform☐ Please have a salesm |       |            |       |

|----------------------------------------------|-------|------------|-------|

| Name                                         |       | STATE SALE |       |

| Title                                        |       |            |       |

| Company                                      |       |            |       |

| Address                                      |       |            | 10000 |

| City                                         | State | Zip        |       |

| Phone//<br>Z80B/Peripherals                  |       | CD-8/      | 84    |

Zilog

an affiliate of

EXON Corporation

Pioneering the Microworld

CIRCLE 12

## MICROSOFT STRIKES GOLD.

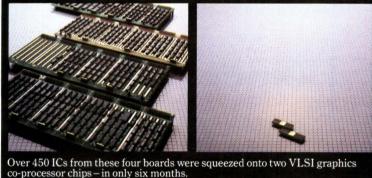

This is what paydirt looks like when it's turned into silicon.

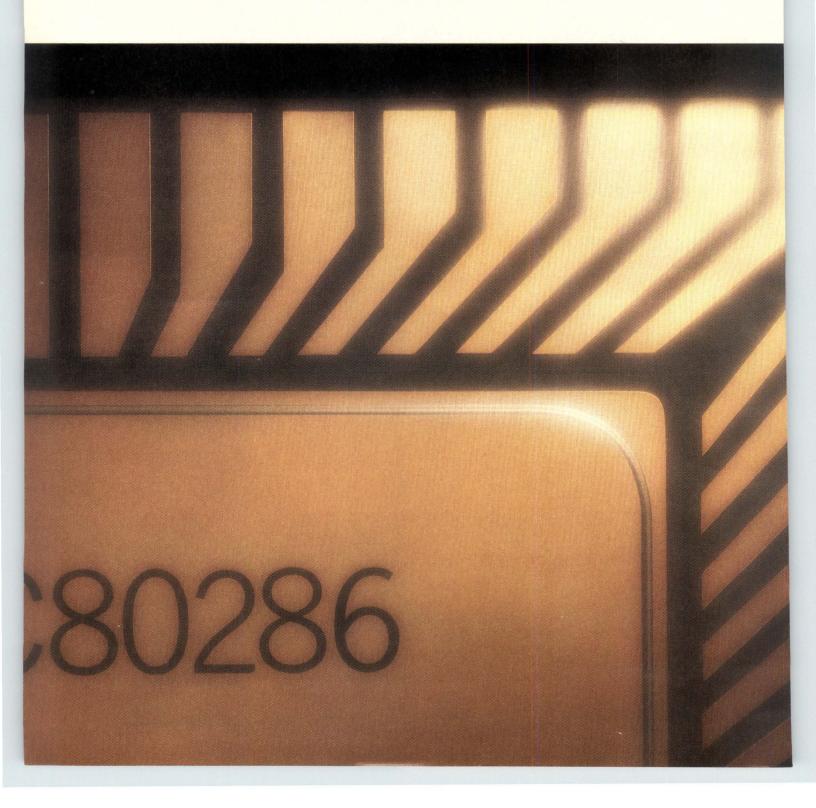

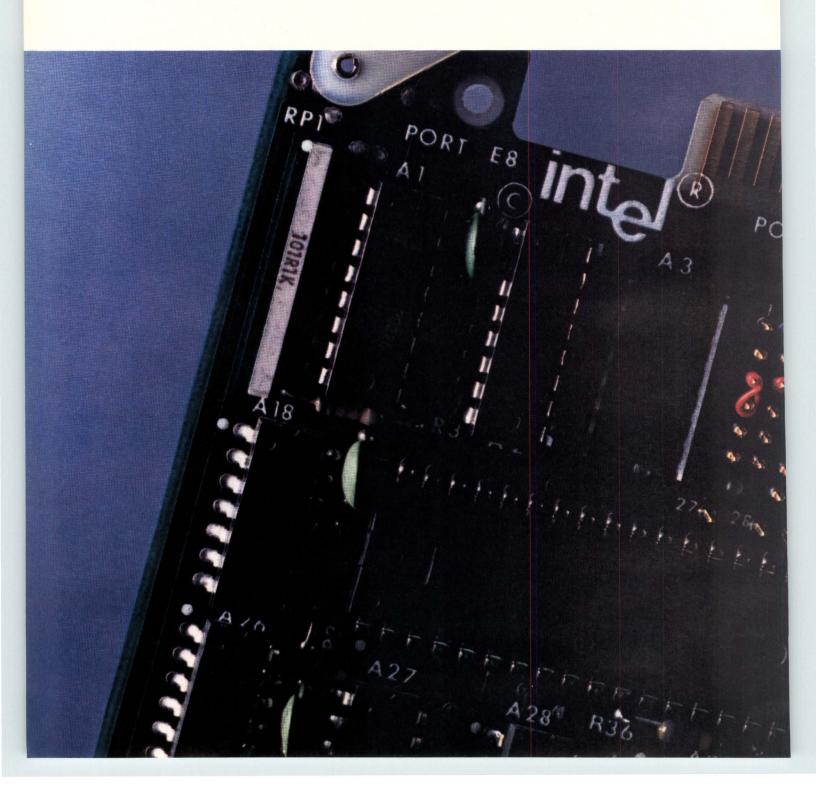

Intel's iAPX 80286

microprocessor.

Together, Microsoft and Intel used this gem to create another: the XENIX\* 286 Operating System. The most powerful implementation of UNIX\* on the market today for any micro-

processor. And the most reliable, functional, commercial enhancement of the UNIX operating system ever created.

The XENIX 286 Operating System includes UNIX enhancements available from both AT&T™ and U.C. Berkeley. But Microsoft has also added loads of other commercial enhancements to make your life richer, in more ways than one. For instance, there are record and file locks, semaphores to help manage multiuser/multitasking

data, and automatic disk recovery for better reliability.

Which makes XENIX 286 an ideal Operating System for applications software development. Over

opment. Over Chairman of Microsoft Corp.

one hundred and fifty in the volume of Microsoft Corp.

one hundred and fifty in the volume of the ware packages have been developed for XENIX, making it one of the most useable multiuser Operating Systems available today.

Chairman of Microsoft Corp.

One of

For Microsoft, the unique advantages of Intel's 80286 microprocessor were most appealing. As Bill Gates, chairman of Microsoft, said, "On-chip memory management and protection offered by the 286 ensures code compat-

ability and makes it easy to port XENIX between different OEM systems."

In addition, its ability to run in fast 8086 mode makes the 286 the only processor that can support both XENIX 286 and MS-DOS without additional hardware. "With this ability, users get the best of both worlds in one piece of hardware," said Gates.

What's more, it's the only microprocessor architecture with the flexibility to offer you entry at whatever level of inte-

gration you choose: chips, boards, or complete systems (including, of course, our new 286/310 supermicro system.) So you get to market when you want,

in the way you want.

Why not dig a little deeper, and call us toll-free at (800) 538-1876. In California, (800) 672-1833. Or write Intel, Lit.Dept.#S9,3065 Bowers Avenue, Santa Clara, CA 95051.

And don't be surprised if you hear shouts of "Eureka!" coming from your product development team.

\*XENIX and MS-DOS are trademarks of Microsoft Corporation. UNIX is a trademark of Bell Labs, Inc. AT&T is a trademark of American Telephone & Telegraph. © 1984 Intel Corporation.

Bill Gates.

#### Unix: a closer look

I have enjoyed reading the April issue, especially the items concerning the Unix operating system. Sam Bassett's article, "Operating Systems Contend for Position as Industry Standard" (p 42), reflects a good grasp of the matter. His description of Unix as "endlessly modifiable" highlights a strength of its modular design. OEMs are using Unix as a metaenvironment (an environment for building specific environments) to develop vertical market applications such as CAE systems, fault-tolerant systems, secure systems, business systems, and realtime SCADA systems. When desirable, it has been straightforward to add demand-paged virtual memory, record locking, and bitmapped windowing.

Naturally, Bassett would be remiss if he did not point out the flaws in the Unix operating system. Its user interface was designed over 10 years ago for low baud rate teletypewriters and dumb CRTs. Until five years ago, it was lauded as a paradigm of user-friendliness. But the advent of microcomputers for the masses, with software designed for a whole new class of users, has changed that.

Hence, the article contains a few unfortunate statements concerning the Unix operating system, such as "nobody can be expected to understand [Unix] in a finite period of time." Because understanding is a qualitative abstraction, the same statement can be made of any operating system whose code will not fit on the back of an envelope.

In addition, "[Unix] is written in Ca far cry from Cobol, in which most applications are written," and "The whole system has a bad habit of changing completely every time a new system programmer works on it." First, microcomputer software applications written in Cobol are rare. They are almost exclusively written in Pascal, Basic, or assembler. Now, C is becoming the language of choice. Ask Digital Research, Microsoft, Lotus, or VisiCorp. Second, the system changes fault lies with system administrators, not Unix. Uncontrolled change is risky regardless of the operating system involved.

Bassett went on to say that "the supplied documentation, by its sheer weight and incomprehensibility, is guaranteed to give an English major a hernia and hysterics," and that "when [a program] must be halted for some reason, the entire pro-

gram and data are swapped out to disk. When it can run again, it must be reloaded from disk and reconnected to the operating system."

In reality, large operating systems perforce have extensive documentation. Look at the number of manuals supplied with Multics or AOS. Technical manuals are notorious for misjudging their audience. The Unix System v manuals are a marked improvement over the past. And, now that AT&T has a desktop micro, the 3B2, I suspect we will see manuals that satisfy the needs of microcomputer users. In the interim, there are numerous books that will fill this gap.

Also, multitasking systems must either swap or limit the size and number of tasks that can be executed concurrently. Swapping definitely degrades performance in the face of low performance drives. But, the situation is not as dark as Bassett paints it. Unix System v swaps a waiting program only when there is insufficient memory to load the current program. Since text (instructions) is shared, this segment of program may not get swapped at all.

Fred Christiansen Motorola Microsystems 2900 S Diablo Way Tempe, AZ 85282

#### Don't ignore a good chip

I can understand Surendar Magar's desire to push TI's TMS320 in his article, "Signal Processing Chips Invite Design Comparisons" (Apr 1984, p 179). It is a very nice chip and I use it. However, I cannot understand how one can ignore, in an informative article, the existence of a high performance chip such as the Fujitsu MB8764, with such features as a 100-ns cycle, microprogramming, and a 256-word memory. This chip has been available for some time and can hardly be overlooked.

Gideon Keydar Scitex Corp Ltd PO Box 330 43103 Herzlia B, Israel I must applaud your use of computer graphics techniques to create cover art for *Computer Design*. However, I feel that you are giving computer graphics a bad name by continuing to allow your artists to use equipment that produces output with severe spatial aliasing. I am sure many of your readers are becoming disenchanted with computer graphics as an output medium because of the "jaggies" in your cover art.

There are many anti-aliasing techniques available and, undoubtedly, one of them would be appropriate for your system. I would encourage you to explore these techniques as they could significantly improve the quality of your covers without incurring excessive cost. Also, computer graphics neophytes will not get a negative impression before they have a chance to experience higher quality displays.

L. Jay Bass Burroughs Corp 11010 Roselle St San Diego, CA 92121

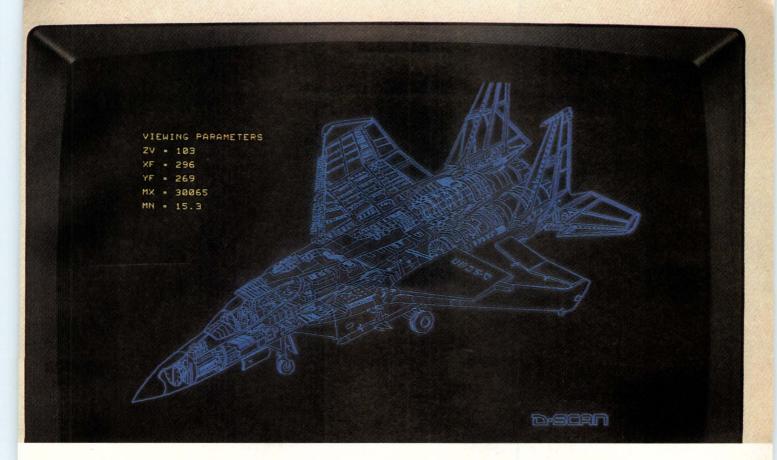

Other readers have questioned our use of relatively low quality graphics techniques when today's most advanced equipment allows much higher resolution. For this reason, beginning in September our covers will be created using a wider range of computer graphics techniquesincluding three-dimensional effects. One problem, of course, is that computer graphics can now create pictures that are almost indistinguishable from hand drawings or photographs of solid objects. Our dilemma, therefore, is to show textually that we are using computer graphics, while also availing ourselves of the full potential of the technology. For this reason, we may sometimes deliberately introduce "jaggies" into our cover art, even though the equipment is capable of eliminating them. Thus, we would be creating the high-tech equivalent of brush marks in an oil painting.

Michael Elphick Editor in Chief

(continued on page 24)

(continued from page 23)

#### They don't have to be whiz kids

I read with great interest the editorial in the February issue (p 11) on Computer Literacy. [The following are excerpts from a short article Mr Eisenberg sent to members of his local school board.]

"The time has come the walrus said..." With this phrase Alice was swept into Wonderland. Today, we are all being swept into a different Wonderland-Microland. Computers will continue to pervade many facets of our lives. Our children are exposed to them before they enter grade school (remember the video game hooked to your living room TV).

In our grade schools, "computer literacy" is the new buzz phrase all educators are striving for. Everyone wants it—but how many know what it is? I have heard people at all levels of our educational system echo the theme "Computer literacy is necessary to survive in our technological society." Without it, they fear that our kids will be somehow left out. My question is, left out of what?

Are we forgetting the primary purpose, perhaps the only purpose, of our schools is to teach our children the skills necessary to live in the world they will see when they graduate? Now, I know that most of us do not understand computers; we feel threatened by them, and we see them as invading our workplace and our homes. But does that mean that we need to raise a generation of programming wizards? Or does it really mean we must teach our children to function in a world that will use computers much the way we use TV's today?

I have been working with computers for over 20 years; I have been using a TV for longer than that. I am fully willing to admit that I have no real understanding of how a TV works, but this lack of knowledge has not proved a significant handicap to watching what I want, when I want. The TV is a tool—one designed to provide entertainment.

The computer is also a tool, a multifunctional tool perhaps, but a tool nonetheless. For most of us, knowing how to use a tool is both necessary and sufficient. Understanding how it works from the inside out, or how to program it is unnecessary. Providing this functional understanding of how to use computers is what I mean by "computer literacy."

I think there is a problem in assuming that all children need to know how to program computers to survive in the world of 1988 to 1995. That kind of perception leads us into wanting to train all our kids in computer programming. What is the role of the computer in our schools? What functions can it serve? How can we provide the right form of "computer literacy"? And, perhaps most importantly, how can we use its power to augment the educational process? Clearly, turning our children into a generation of hack programmers is not the answer to these questions!

Just as Alice strayed into Wonderland and experienced both exciting and frightening adventures, so too can the novice wander in Microland with equal delight and profit. How good or how bad the experience is depends only on the quality of the planning done beforehand and the understanding of the real needs of the organization.

A. M. Eisenberg E. I. DuPont de Nemours & Co Wilmington, DE 19898

#### Another view on reliability

In response to Michael Hordeski's letter in the June 1 issue, my point is that reliable designs require a lot of careful work. There are many potential problems, and some of them are quite obscure. I do not think reliable microprocessor design is a lost cause-far from it. Many of them are very good.

The use of normal MTBF (MIL STD 217) reliability prediction simply takes into account the reliability of each individual component. This does not account for race conditions, noise problems, or even designs that don't work. The MTBF method of reliability prediction is simplistic and is only one small part of a truly reliable design. If we could only use this method as Mr Hordeski suggests, anyone could beat us.

Carl Oppenheimer 12 Depot Rd Kingston, NH 03848

DISPLAY ☐ Bright 1" high display system

Progress indicated during programming □ Error messages

**KEYBOARD** □ Full travel entry keys

Auto repeat

Illuminated function indicators

INTERFACE □ RS-232C for data transfer

110-19.2K baud

X-on X-off control of serial data

FUNCTIONS - Fast and standard programming algorithms ☐ Single key commands ☐ Search finds data strings up

to 256 bytes long

Electronic signatures for easy data error I.D.

"FF" skipping for max programming speed

User sets memory boundaries

15 commands including move, edit, fill, search, etc. functions Extended mode reads **EPROM** sets

GENERAL Stand alone operation, external terminal not needed for full command set 🗆 Total support 🗆 28 pin sockets Taulty EPROMS indicated at socket Programs 1 to 128K devices

Built in diagnostics 🗆 No calibration required \( \subseteq \text{No personality} \) modules to buy Complete with 128K buffer Only

Dealer inquiries welcome

SOUTHERN COMPUTER CORPORATION 3720 N. Stratford Rd., Atlanta, GA 30342, 404-231-5363

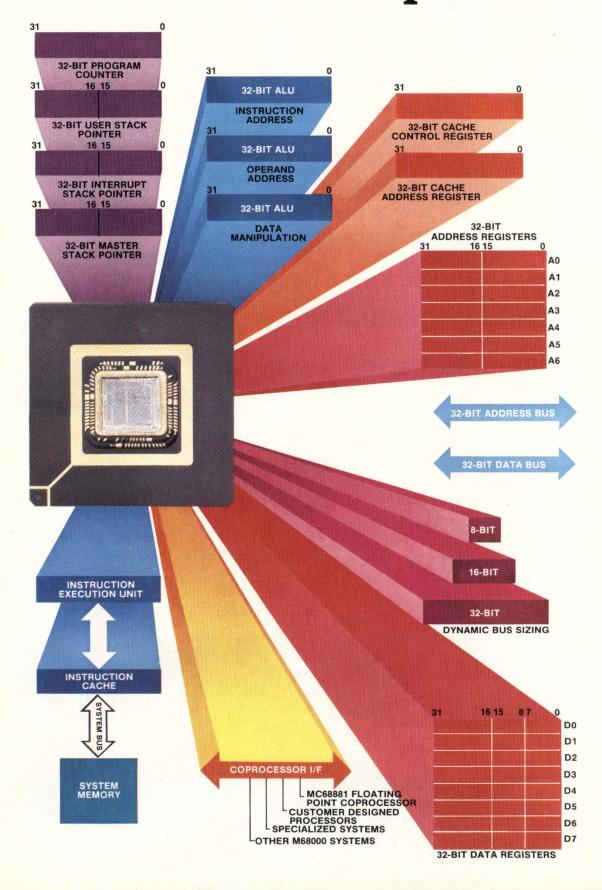

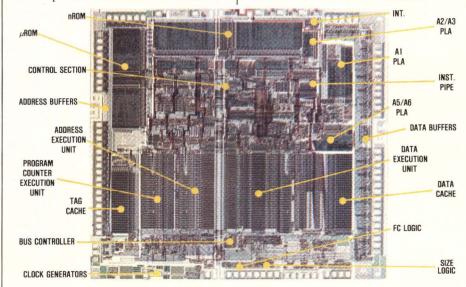

## Once in a generation:

introducing the 32-bit microprocessor performance standard.

## Unleash the potential of your the complete 32-bit

## new system with the MC68020: microprocessor.

#### The new performance standard.

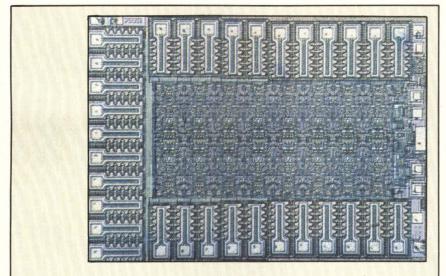

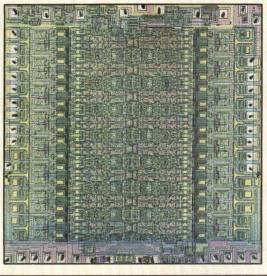

Motorola's new MC68020 performs at speeds typically 400% of the established standard of comparison, the MC68000. It's up to ten times faster in dedicated 32-bit applications.

No other 32-bit MPU makes this extensive a leap in performance improvement. At 16.67 MHz the MC68020 typically runs at 2.5 MIPS for integer processing. MIPS rates several times typical are achievable in dedicated 32-bit applications.

The advanced two-micron HCMOS manufacturing technology which allows this unparalleled performance also results in very low power dissipation. In fact, the MC68020 consumes less power in a system than the original MC68000.

The MC68020 creates opportunities you've never had before--opportunities to unleash the full potential in your 32-bit MPU-based systems because it sets the standard for 32-bit microprocessors. And, because it's the first complete 32-bit microprocessor available, more than just a 16-bit design on a data bus stretched to 32 bits. A detailed look at the architecture reveals this totality.

#### A fully compatible M68000 Family member.

Yes, the MC68020 has features new to the M68000 Family to maximize its true 32-bit capabilities.

Yes, it's an all new design built with advanced, highly manufacturable HCMOS technology.

And, yes, it's a fully-compatible member of the M68000 Family of MPUs and peripherals. All user object code written for previous M68000 Family MPUs executes without revision. In fact, MC68020 enhancements allow it to run more than three times faster.

Family compatibility is further enhanced by dynamic bus sizing, which supports the use of 8-, 16- and 32-bit ports in 68020-based systems. In fact, the MC68020 can be used in existing 8- or 16-bit systems.

#### New features enhance 32-bit architecture.

The MC68020 design is new, however its architecture is based on the proven M68000 Family 32-bit register set. And, the MC68020 is highly enhanced.

On-board instruction cache speeds operation and provides increased multiprocessing efficiency. The coprocessor interface allows direct expansion of the architecture off the MC68020 chip to coprocessors or customer-specified processing systems.

New addressing modes, new instructions and a 32-bit barrel shifter support new capabilities. Operating system efficiency is improved with a 32-bit program counter.

These enhancements and more optimize the MC68020 for 32-bit operations.

#### Design support brings projects together, fast.

Making the most of your new 32-bit design opportunities with the MC68020 is simple and effective with the backing of powerful new hardware and software support from Motorola.

The Benchmark 20<sup>™</sup> evaluation system has been developed as a maximum environment testbed for resultant software. For initial software development, cross-support packages under both the UNIX<sup>™</sup>-derived System V/68<sup>™</sup> and the real-time VERSAdos<sup>™</sup> operating systems run on standard Motorola VME/10<sup>™</sup> and EXORmacs\* hosts

You'll find MC68020 designs a breeze with Motorola's advanced development tools--real time emulation and bus-state analysis with the HDS400 development system.

#### Move up to the MC68020.

The opportunity to design new-generation systems around the MC68020 and the M68000 Family is yours today. Marketplace attention will be focused directly on the growth-oriented companies that take advantage of this opportunity. Motorola's sales engineers and field applications specialists are available and equipped to assist you in moving up to the new 32-bit microprocessor performance standard. Contact one of them today.

Additional technical information is available by writing or sending the completed coupon to Motorola Semiconductor Products Inc., P.O. Box 20912, Phoenix, AZ 85036.

Benchmark 20, SYSTEM V/68, VME/10 and VERSAdos are trademarks of Motorola

EXORmacs is a registered trademark of Motorola UNIX is a trademark of AT&T Bell Laboratories.

## Because You need to run FORTRAN programs 10X to 100X faster...

Mini-MAP makes it practical to apply array processing to general-purpose scientific and engineering computing.

Practical in terms of use: Mini-MAP's compiler allows you to program the array processor directly in FOR-TRAN. An assembler, a linker, and a debugger are also part of the package. Plus you can use our library of over 250 highly optimized scientific subroutines.

Practical in terms of throughput: Because it is an array processor, Mini-

MAP increases the computing speed of a mini or supermini computer as much as 10 to 100 times. Where it takes a typical minicomputer minutes to perform tasks such as image rotation, Mini-MAP reduces interactive response times to seconds. Your computer may require hours to perform each step of a trial-and-error-process such as simulation, but Mini-MAP, can zip through in mere minutes. DEC, PDP-11, LSI-11, and VAX-11 are trademarks of Digital Equipment Corp. Mini-MAP is a trademark of CSPI.

Practical in terms of cost:

Mini-MAP is available as an economical, four-board set or as a packaged system. Now, with Mini-MAP, OEMs can offer their customers a better product at lower costs. Mini-MAP's low power demands, small size, and high reliability make the package extremely attractive. And end users will find our FORTRAN compiler and other software tools minimize program development costs.

Some practical things to know about Mini-MAP:

32-bit DEC™ floating point format ☐ Interfaces to DEC PDP-11, LSI-11, and VAX-11 series ☐ Up to 16 MBytes of data memory ☐ 1024 x 1024 2-D FFT in 8.8 seconds ☐ Extensive software tools plus dedicated applications assistance including training, convenient parts depots, and field service staff support our worldwide installations. To find out how Mini-MAP can work for you, call toll free 1 800 325-3110.

We built Mini-MAI

THE ARRAY PROCESSORS

40 Linnell Circle, Billerica, Massachusetts 01821 • 617/272-6020 • TWX 710-347 0176

#### Power and logic devices are merging on the same chip

A revolution is brewing in the field of power semiconductors. Sheer brawn is giving way to brawn and brain, as power semiconductor devices gain greater intelligence in the form of logic on the same chip holding the power transistor(s). Advances in merging bipolar and MOS technologies have made this possible. Although the technology of joining logic and power on the same chip is still very young, it holds immense implications for circuit and system

designers. With decentralized microprocessor power already widely available, the next step is likely to be truly intelligent power devices with microprocessors on the same chip holding the power device, leading to distributed power control.

Much of the success of intelligent power IC technology rests on the ability of process engineers to merge such unlikely partners as CMOS devices, generally used for logic functions, with high speed and high power

bipolar and double-diffused MOS (DMOS) devices. Until a few years ago, such merged technologies were difficult to master and uneconomical to use. However, with the advent of improved lithographic etching and ion-implantation equipment, as well as greater experience in making merged processes work, intelligent power ICs made with mixed technologies are looking economically more attractive.

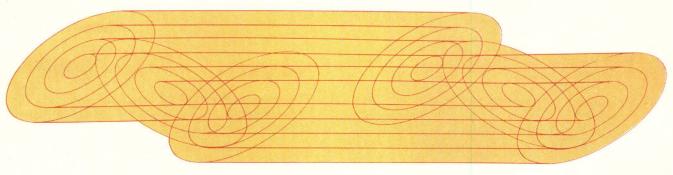

Designers are discovering that not only does the merger of logic and power technologies on one chip produce smaller size ICs than if two separate devices are used, it also means lower overall costs, increased performance levels, and higher reliability. Moreover, circuit designs are simplified considerably.

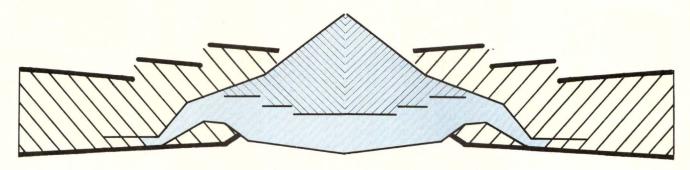

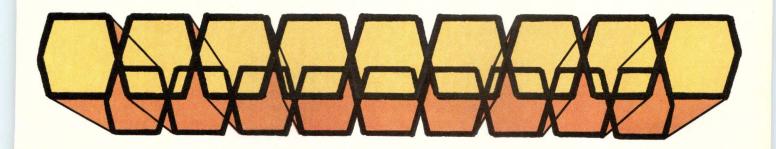

The ultimate goal is to create intelligent power devices with the fastest possible switching speeds and the most efficient operation, at the lowest possible cost. This pursuit of theoretical performance limits has MOSFET power device designers chasing after all sorts of cell layout geometries, to get the most performance from the least amount of silicon area. The goal is to achieve maximum packing densities and the lowest MOSFET on resistance. The larger the ratio of the FET's source width to area, the more active silicon in the form of individual cells that can be achieved on a given chip.

#### The shape of things to come

Thus, it is not surprising to see a plethora of MOSFET cell shapes emerging, with square and hexagonal cells predominating. The square cell is the choice of such device manufacturers as Motorola Semiconductor Products Inc. Siemens Inc. and Siliconix Inc. Japanese manufacturers like Hitachi Ltd, Nippon Electric Corp, Toshiba, and Matsushita are also opting for the square-cell

(continued on page 30)

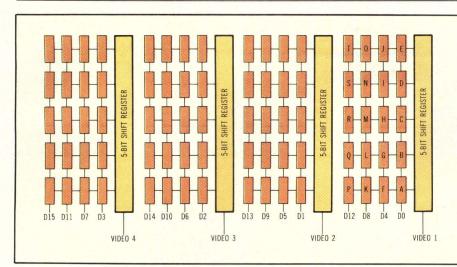

BIDFET row (top) and column (bottom) driver ICs can drive up to 32 electrodes each. Each device has its own 32-bit shift register and drives thin-film, flat-panel electroluminescent displays. The row driver withstands up to 225 V and supplies a 50-mA current output. The column driver provides a 60-V output swing, a 15-mA output source, and sink current.

Power and logic devices (continued from page 29)

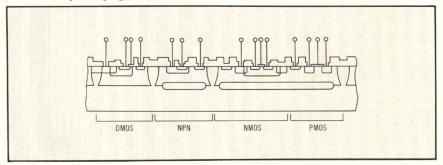

The BIDFET process brings together on one chip double-diffused MOS (DMOS), npn, NMOS, and PMOS transistors. It allows the merging of precision-control and self-isolated CMOS logic devices with high voltage interface circuitry through the use of standard junction-isolation techniques.

approach. International Rectifier Corp, on the other hand, feels that the hexagonal cell it pioneered is superior; so does General Electric Co, Unitrode Inc, and RCA Semiconductor Inc. Others, like Texet Corp, are using triangular cells, while Supertex Inc uses an interdigitated approach. Besides the square cell, Siliconix also uses the interdigitated approach.

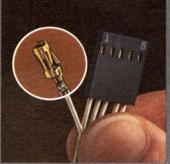

Regardless of what cell shape is used, all are achieving record levels of silicon-area utilization, record high voltage capabilities, and new lows in MOSFET on resistance. And, they are doing it while successfully mixing with other process technologies. The Texas Instruments, Inc (PO Box 225012, Dallas, TX 75265) BIDFET driver ICs for electroluminescent flatpanel displays are but one example.

The SN7551/7552 row drivers and SN7553/7554 column drivers are made by the BIDFET process that mixes bipolar, DMOS, and FET transistors on the same chip, hence its BIDFET name. The BIDFET process merges precision-control, self-isolated CMOS logic with high voltage interface circuitry on a common monolithic substrate, by using standard junctionisolation techniques. It solves the high voltage limitation problems of conventional ICs while retaining their logic capabilities. BIDFET devices have been produced with working voltages of up to 250 V and breakdowns of more than 300 V. This is achieved by replacing the conventional bipolar output stage with a DMOS transistor.

Driving 32 electrodes, the row drivers can withstand up to 225 V and provide a 50-mA output current. Input is CMOS compatible. The column driver IC also drives 32 electrodes with a 60-V output swing, and a 15-mA output source and sink current. It features high speed serially shifted data, and totem-pole latched outputs.

The junction-isolated process TI uses in making the BIDFET drivers is gaining in popularity over another process known as self isolation. The former process provides higher onchip current (about 10 to 20 vs 2 to 4 A), and lower on resistances. The trade-off is a lower maximum voltage rating (about 150 vs 400 V), and an additional processing step for an epitaxial layer.

Yet another mixed process yielding intelligent power devices is the Bi-MOS process used by Motorola. This process not only allows power devices with minimum power dissipation, high efficiency, and direct interfacing with external digital circuits, but also the ability to block both negative and positive high voltage transients.

In this power process, a vertical pnp bipolar transistor is used at the output of a power device. As a result, die area is minimized through the presence of a substrate collector that eliminates both the top collector contact area and the lateral spacing needed to maintain high breakdown voltages. Collector series resistance is decreased by using the package header as the output. With this type of structure, better gain is possible than with lateral transistors having the same die area. There is a price, however. Latching is more common due to the forward biasing of the epitaxial-substrate junction during device operation, leaving the transistor's output collector at a high potential. This can be alleviated using MOS transistors that are less susceptible to latching than bipolar ones.

Motorola has made a high side driver with the Bimos process. The

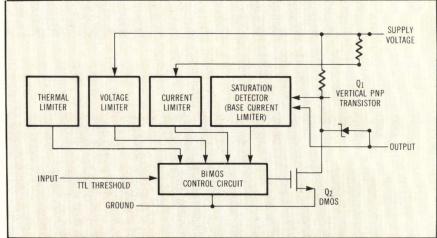

A high side driver IC merges bipolar and MOS transistors with a BiMOS process. The driver, with TTL-compatible inputs, can drive loads to within a few hundred millivolts of the supply voltage, and features voltage and thermal shutdown capability, current limiting, and a saturation detector. Lateral pnp transistors and laterally diffused MOS transistors within the device block negative, as well as positive, 125-V transients.

circuit has TTL-compatible inputs and can drive loads to within a few hundred millivolts of the supply voltage. The device features thermal and voltage shutdown capability, current limiting, and a saturation detector. Lateral pnp bipolar transistors and laterally diffused MOS transistors block negative and positive transients of up to 125 V.

#### Intelligent regulators too

Motorola Semiconductor Products. Inc (5005 E McDowell Rd, Phoenix, AZ 85008) makes an entire family of intelligent power devices appropriately named SMARTpower. One such device is the MPC100, a 5-V fixed regulator with an 80-W output transistor. The device can deliver up to 10 A, has internal thermal protection and short-circuit protection, overcurrent limiting, and, thanks to the regulator's low saturation voltage, features a low differential-voltage operation of just 1.5 V at the maximum output current of 10 A. The device is intelligent enough that it becomes a variable voltage regulator when a pair of external resistors are added to it.

Yet another SMARTpower device is the MPC2005, an overvoltage and temperature-protection circuit made of a combined CMOS and TMOS process. (TMOS is so named because drain current is split into a T formation.) The device, which combines the best of CMOS and bipolar transistor characteristics, discharges up to 150-A peak currents and operates at up to 15 A of continuous anode current. It trips when voltage exceeds 6.2 V or when the junction temperature rises over 125 °C, to remove the voltage supply from the system to which it is connected.

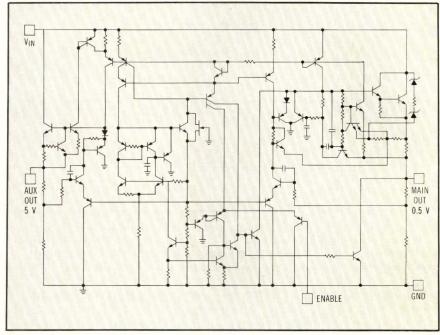

One of the most intelligent monolithic voltage regulators is the LT1005 from Linear Technology Corp (1360 McCarthy Blvd, Milpitas, CA 95035). The dual output device has two independent 5-V regulators and is logic controlled by a TTL- or CMOScompatible enable signal. Its 5-V output can be switched to near zero by a logic low signal. The auxiliary output is unaffected by the logic control

One of the most intelligent monolithic voltage regulators is the LT1005. This dual-output IC has two independent 5-V regulators and is logic controlled. The main regulator's output can be logically controlled by a TTL- or CMOS-compatible enable signal, with its 5-V output switchable to near zero by a logic LOW signal. Meanwhile, the other regulator works without being affected by the logic control signal or by any fault condition at the main regulator.

signal, as well any fault condition at the main regulator circuit, and will continue to deliver its 5-V output. Such a dual structure allows a system to be designed such that the main 5-V supply can be shut down for power savings or protected in the event of failure, while the auxiliary supply continues to apply power to other critical circuits.

Fault protection is what distinguishes the IM2925 monolithic regulator from National Semiconductor Corp (2900 Semiconductor Dr, Santa Clara, CA 95050). The 5-V, 750-mA device with a small I/O differential of just 600 mA, automatically shuts down in case of a short circuit, thermal overload, or the presence of input transients anywhere from -50 to 60 V. Not only that, but it automatically resets itself and restarts after a delay that can be set by the user. That delay can range from milliseconds to seconds, depending on the value of an external capacitor that is connected to one of the IC's pins. The regulator continues operating with an input as high as 31 V. When a fault

occurs, the regulator's pin 5 shows a normally high reset flag, which can be sensed by a microprocessor for switching over to another voltage regulator.

TI has used its BIDFET process to make an intelligent and adjustable monolithic voltage regulator supplying up to 1 A over a range of 5.25 to 200 V all in a TO-220 package. Unlike the firm's display drivers, most of the regulator's transistors are bipolar, and the output stage is a lateral DMOS transistor.

Intelligence also lends a hand in making monolithic voltage regulators more versatile, as can be seen in the Unitrode Corp (580 Pleasant St, Watertown, MA 02172) UC1834 threeterminal regulator. It includes many features that would normally require external circuitry for other threeterminal regulator ICs. For example, besides its high gain error amplifier and output-driver stage, the unit has onchip provisions for current sensing, remote-voltage sensing, and thermal protection. The regulator's output (continued on page 32)

#### Power and logic devices (continued from page 31)

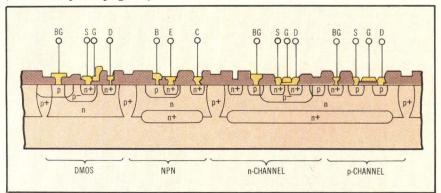

CMOS logic devices (right) may share the same substrate space with high current DMOS transistors (left). Siliconix has used this process to build a controller IC with exclusive-OR logic to switch 12-A peak currents at 120 V and at 200-kHz rates. The process can handle 150-V potentials and 20-A peak currents.

transistor can serve as a sink or a source, allowing one device to serve as either a positive or a negative output supply. The chip furnishes 200 mA over ambient temperatures from -55 to 125 C.

#### Smarter power transistors

Thanks to a Bimos process that General Electric Corp, Semiconductor Division (W Genesee St, Auburn, NY 13021) perfected, 500-V power transistors have been teamed with 20-V CMOS logic devices, on a single junction-isolated IC. There is only one drawback to such devices—the emitters of the bipolar transistors and the sources of the MOSFETs must be connected to ground for operation. This slightly limits the devices' flexibility.

GE achieved the 500-V breakdown rating by a technique known as lateral charge control. The technique permits lateral high voltage devices to be built in 7- $\mu$ m, lightly doped n – epitaxial layers grown on a p substrate. Unlike standard processes where the voltage breakdown of a transistor is a function of the thickness of the epitaxial layer, the breakdown voltage for the GE BiMOS devices is a function of the length of the chargecontrol drift region and the depth of the implanted impurity ions. The longer the drift region, the less the charge per unit area for a given voltage.

Until recently, if designers wanted to control power MOS transistors with 5-V logic signals, they not only needed special level shifting circuits, but also an additional supply voltage to drive those circuits. This is because it takes at least 10 V between a power MOSFET's gate and source terminals to get it into full saturation. The logic-level FET (LLFET) family of MOSFETS from RCA Corp, Solid State Division (Rte 202, Somerville, NJ 08876) has done away with all this. They can be driven into saturation with just 5 V between their source and gate terminals, sacrificing no speed, resistance or current-handling capability.

Teledyne Semiconductor Inc (1300 Terra Bella Ave, Mountain View, CA 94043) also makes level-shifting devices. Three dual power CMOSFET drivers translate a low level TTL or CMOS input signal into an ouput voltage swing within 25 mV of the power supply rails. The TCS426 has two inverting drivers, the TCS427 is a noninverting driver, and the TCS428 has one inverting and one noninverting driver. Without external capacitors to speed their operation, each device can swing a 1000-pF load to 18 V in just 30 ns. This combination of high speed and a wide voltage swing ensures that power MOSFETs are fully turned on or off, minimizing conduction power dissipation. At low supply voltages and with high threshold

power devices, the rail-to-rail swing is particularly useful in minimizing power loss in switch-mode power supplies, motor-control systems, and dc-to-dc converters.

Because the gate-drive requirements of power MOSFETS have been reduced, the FETs are becoming attractive candidates as output devices for smart power ICs. For example, International Rectifier Corp, Semiconductor Division (233 Kansas St, El Segundo, CA 90245) takes a LED, illuminates a pile of photovoltaic cells with the LED's output, and triggers the gate of a MOSFET with the resultant electrical output of the photovoltaic cells. All of these functions are on one chip, and allow switching up to 1000 V. The device includes a bidirectional MOSFET known as bidirectional output-switch FET (BOSFET) and control logic on one chip.

The company also uses the photovoltaic principle in its solid-state switch with zero crossing (S3X) solidstate relay chip. The IC contains an optical receiver, signal conditioner, zero-crossing detector, and a high power thyristor, all on one substrate.

Another example of a smart power switch is the experimental XPC1500 logic-to-power switch for Motorola, for switching up to 16 A, on command signals received from CMOS logic or TTL inputs. The firm is also developing the XPC1600, a pulsewidth-modulated power IC that can handle 150-V potentials at a maximum current drain of 10 A. The MOSFET device is designed for switching-regulator and motorcontrol applications.

Siliconix Inc (2201 Laurelwood Rd, Santa Clara, CA 95054) has developed a controller chip to handle up to 150-V potentials and peak currents as high as 20 A. This chip combines DMOS and CMOS devices on one substrate for greater intelligence in power devices. The junction-isolation process employed uses n + channel power devices implanted in an n - epitaxial layer, and CMOS devices built in a p

## Tek software sheds new light on your VAX.

Turn your VAX™ computer into a powerful microprocessor development system.

Tektronix software. The same powerful tools that set the standard for high-level programming on Tek's 8500 series of microprocessor development systems are now available for use on your VAX. Get the sophistication of Pascal and C Language Development Systems (LANDS). Plus real-time emulation and debug

when you integrate Tek's 8540 emulation unit to your system. Add 4105 Color Graphics terminals to access Colorkey+, Tek's single-key interactive user interface. All fully integrated with VAX-specific communications software.

Support from the first line of source code to the last line of debug.

Call your Tektronix sales engineer. With your VAX, we'll help you create a system that suits your engineering environment, and show you how Tek and your VAX have met the challenge of microprocessor software design.

Tektronix Microprocessor Development Systems.

Lookat Us how!

Call 1-800-547-1512

VAX is a registered trademark of Digital Equipment Corporation.

U.S.A., Asia, Austrália, Central & South America, Japan: Tektronix, Inc., P.O. Box 1700. Beaverton, OR 97075. For additional literature, or the address and phone number of the Tektronix Sales Office nearest you, contact. Phone: (800) 547-1512, Oregon only: (800) 452-1877. TWX. (910) 467-8708, TLX: 151754, Cable: TEKWSGT

Europe, Africa, Middle East; Tektronix Europe B.V. European Headquarters, Postbox 827, 1180 AV Amstelveen, The Netherlands, Phone: (20) 471146, Telex: 18312-18328

Canada: Tektronix Canada Inc., P.O. Box 6500, Barne, Ontario L4M 4V3, Phone: (705) 737-2700 Tektronix COMMITTED TO EXCELLENCE

Copyright ©1984, Tektronix, Inc. All rights reserved. MIA-131

Circle 18 for Literature Circle 19 for Sales Contact

## It's easy to see why our new CRT series is an improvement down the line.